Staggered heterojunction tunneling field effect transistor based on InAsN-GaAsSb material

A tunneling field effect and transistor technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of inability to form staggered heterojunctions, difficulty in meeting performance requirements, and small conduction current, so as to improve conduction current, increase tunneling probability, and improve device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

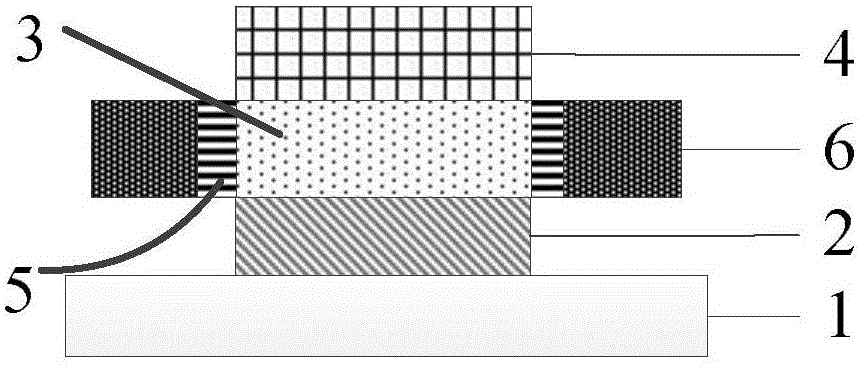

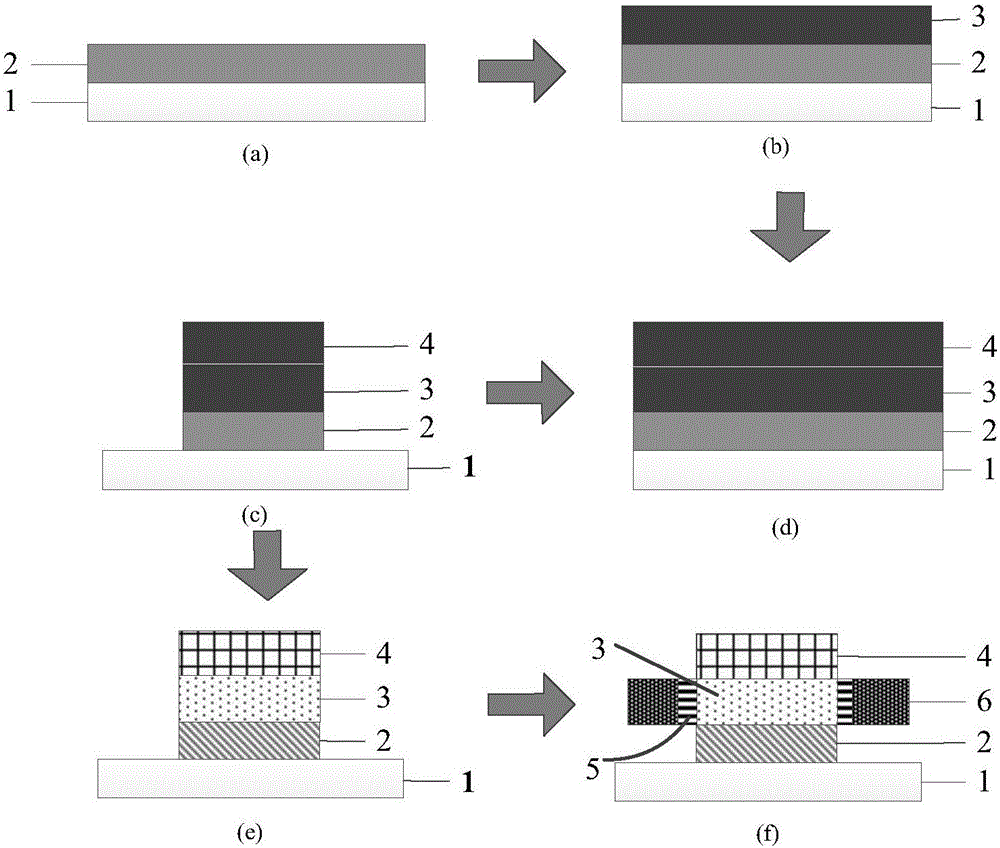

[0031] Embodiment 1: Making InAs-based 0.95 N 0.05 -GaAs 0.35 Sb 0.65 Materials for staggered heterojunction n-channel tunneling field effect transistors.

[0032] Step a: Using molecular beam epitaxy, on the InAs substrate 1, using solid In, As and N as evaporation sources, at a temperature of 725°C and a pressure of 10 -4 Pa conditions, grow the InAsN composite material with N composition of 0.05 to form the source layer, such as figure 2 a.

[0033] Step b: Using molecular beam epitaxy, on the source layer, using solid Ga, As and Sb as evaporation sources, at a temperature of 725°C and a pressure of 10 -4 Pa condition, grow GaAsSb composite material with Sb composition of 0.65 to form a channel layer, such as figure 2 b;

[0034] Step c: Using molecular beam epitaxy, on the channel layer, using solid Ga, As and Sb as evaporation sources, at a temperature of 725°C and a pressure of 10 -4 Pa condition, grow the GaAsSb composite material with Sb composition of 0.65 t...

Embodiment 2

[0041] Embodiment 2: Making InAs-based 0.97 N 0.03 -GaAs 0.5 Sb 0.5 Materials for staggered heterojunction p-channel tunneling field effect transistors.

[0042] Step 1: Using molecular beam epitaxy, on an InAs substrate 1, using solid In, As and N as evaporation sources, at a temperature of 725°C and a pressure of 10 -4 Pa condition, grow the InAsN composite material with N composition of 0.03 to form the source layer, such as figure 2 a;

[0043] Step 2: Using molecular beam epitaxy, on the source layer, use solid Ga, As and Sb as evaporation sources at a temperature of 725°C and a pressure of 10 -4 Pa conditions, grow GaAsSb composite material with Sb composition of 0.5 to form a channel layer, such as figure 2 b;

[0044] Step 3: Using molecular beam epitaxy, on the channel layer, use solid Ga, As and Sb as evaporation sources at a temperature of 725°C and a pressure of 10 -4 Pa condition, grow the GaAsSb composite material with Sb composition of 0.5 to form the dr...

Embodiment 3

[0052] Embodiment 3: Making InAs-based 0.99 N 0.01 -GaAs 0.65 Sb 0.35 Staggered Heterojunction P-Channel Tunneling Field-Effect Transistor Based on Materials

[0053] The first step: using molecular beam epitaxy, on the InAs substrate 1, using solid In, As and N as evaporation sources, at a temperature of 725°C and a pressure of 10 -4 Pa conditions, grow the InAsN composite material with N composition of 0.01 to form the source layer, such as figure 2 a;

[0054] The second step: using molecular beam epitaxy, on the source layer, using solid Ga, As and Sb as evaporation sources, at a temperature of 725 ° C and a pressure of 10 -4 Pa conditions, grow GaAsSb composite material with Sb composition of 0.35 to form a channel layer, such as figure 2 b;

[0055] The third step: using molecular beam epitaxy, on the channel layer, using solid Ga, As and Sb as evaporation sources, at a temperature of 725°C and a pressure of 10 -4 Pa condition, grow the GaAsSb composite materia...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More