Amorphous silicon film transistor with double grid structure and mfg. method thereof

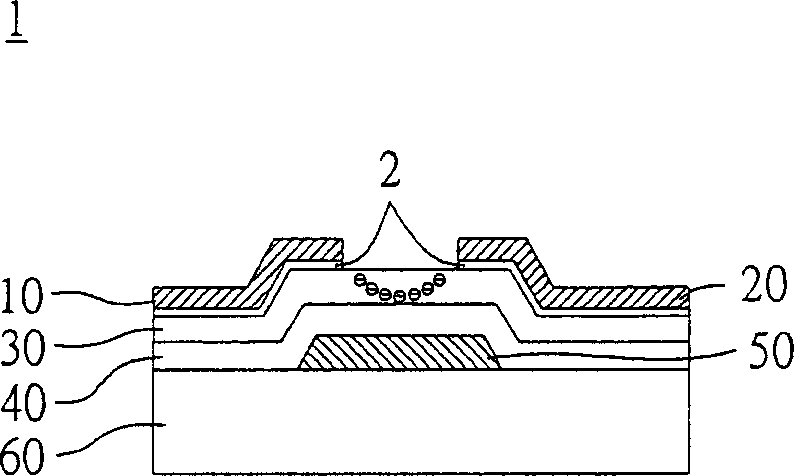

A technology of an amorphous silicon thin film and a manufacturing method, which is applied in the directions of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of reducing the reliability of amorphous silicon thin film transistors 1, insufficient current conduction capability, large operating voltage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

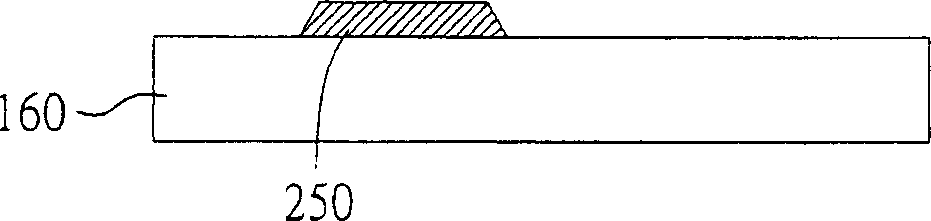

[0035] Please refer to Figure 2A-2F , which shows a process cross-sectional view of an amorphous silicon thin film transistor with a double-gate structure according to Embodiment 1 of the present invention. First, in Figure 2A Among them, a substrate 160 is provided, and a first gate 250 is formed on the substrate 160 . Wherein, the substrate 160 includes a glass substrate, a plastic substrate or an insulating substrate, and the first gate 250 includes a metal or a metal alloy.

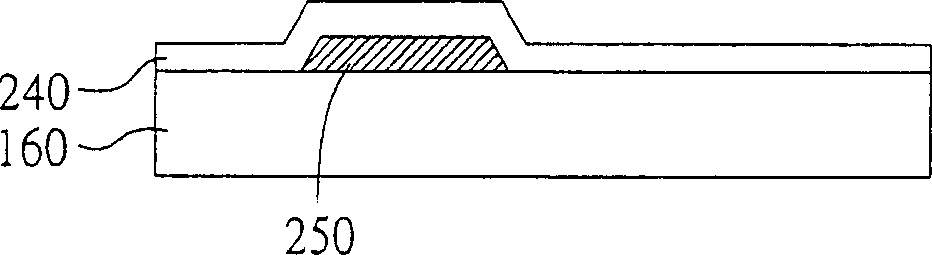

[0036] Next, if Figure 2B As shown, a first insulating layer 240 is formed on the substrate 160 and covers the first gate 250 . Wherein, the first insulating layer 240 includes silicon nitride (silicon nitride, SiN), silicon oxynitride (silicon oxynitride, SiON), nitride, oxynitride or oxide.

[0037] Then, if Figure 2C As shown, an amorphous silicon channel layer 130 is formed on the first insulating layer 240 . Wherein, the amorphous silicon channel layer 130 is formed corresponding to the...

Embodiment 2

[0045] Please refer to Figures 3A-3H , which shows a process cross-sectional view of a thin film transistor with a double-gate structure according to Embodiment 2 of the present invention. First, if Figure 3A As shown, a substrate 360 is provided, and a first gate 350 is formed on the substrate 360 . Wherein, the substrate 360 includes a glass substrate, a plastic substrate or an insulating substrate, and the first gate 350 includes a metal or a metal alloy.

[0046] Next, if Figure 3B As shown, a first insulating layer 340 is formed on the substrate 360 and covers the first gate 350 . Wherein, the first insulating layer 340 includes silicon nitride, silicon oxynitride, nitride, oxynitride or oxide.

[0047] Then, if Figure 3C As shown, an amorphous silicon layer 330 is formed on the first insulating layer 340 .

[0048] Next, if Figure 3D As shown, an etch-stop layer 380 is formed on a portion of the amorphous silicon layer 330 , and the etch-stop layer 38...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More