Patents

Literature

114results about How to "Improve the coupling rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

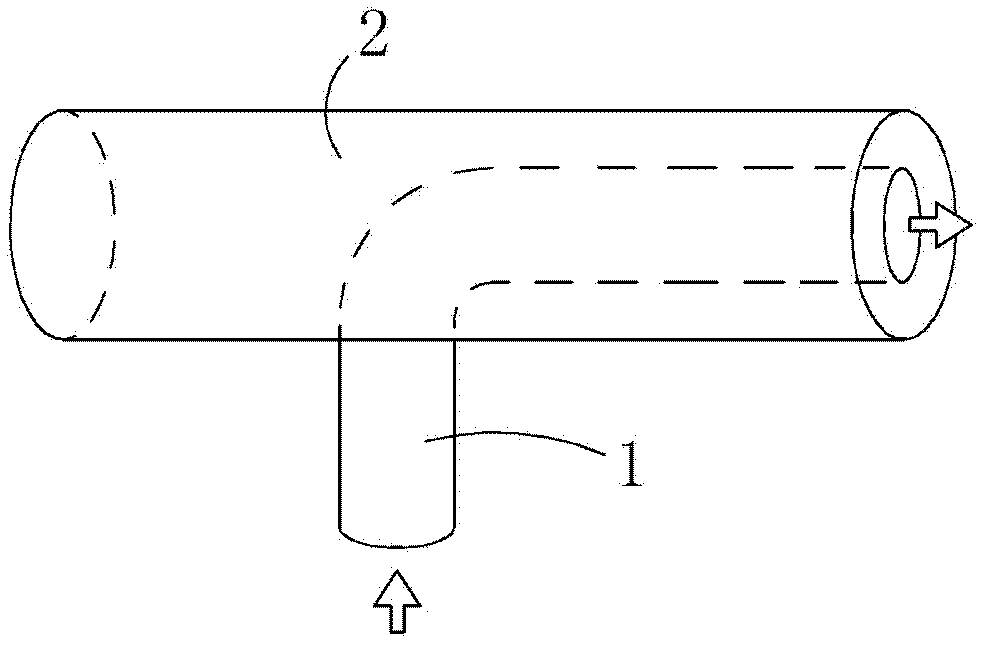

Non-contact type power feeder system for mobile object and protecting apparatus thereof

InactiveUS20080129246A1Enhanced strengthEasy to manufactureRail devicesBatteries circuit arrangementsMobile objectConductor Coil

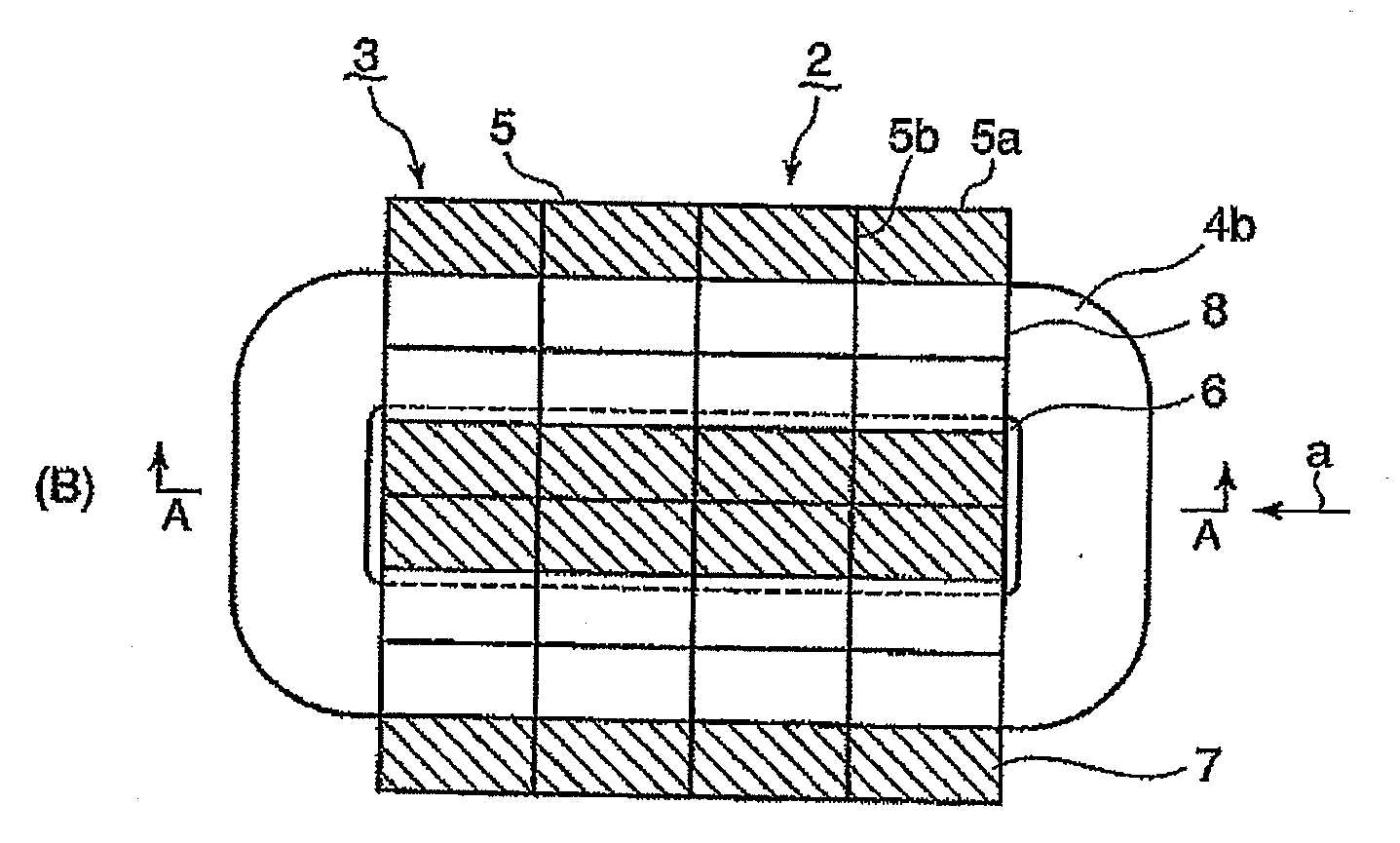

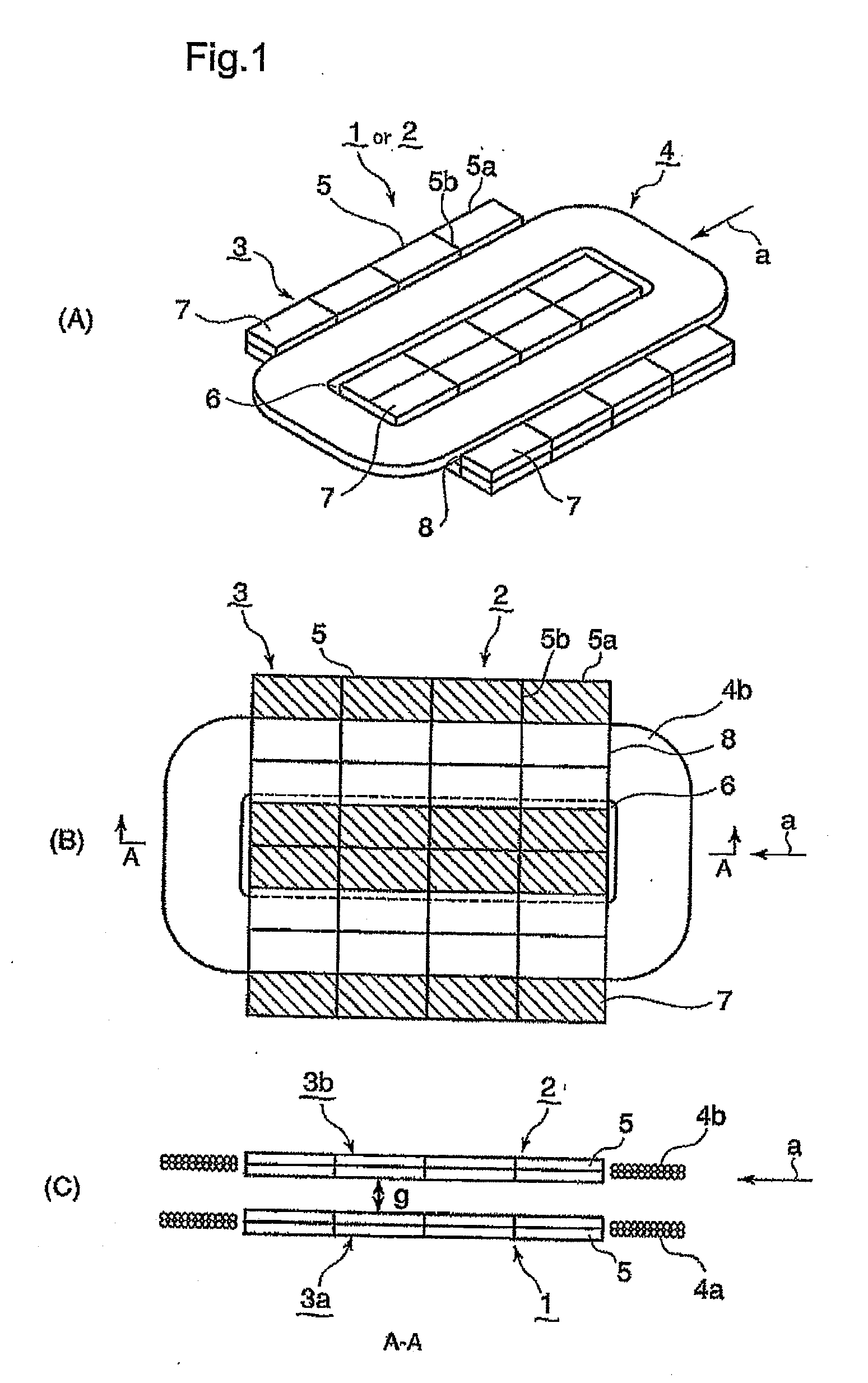

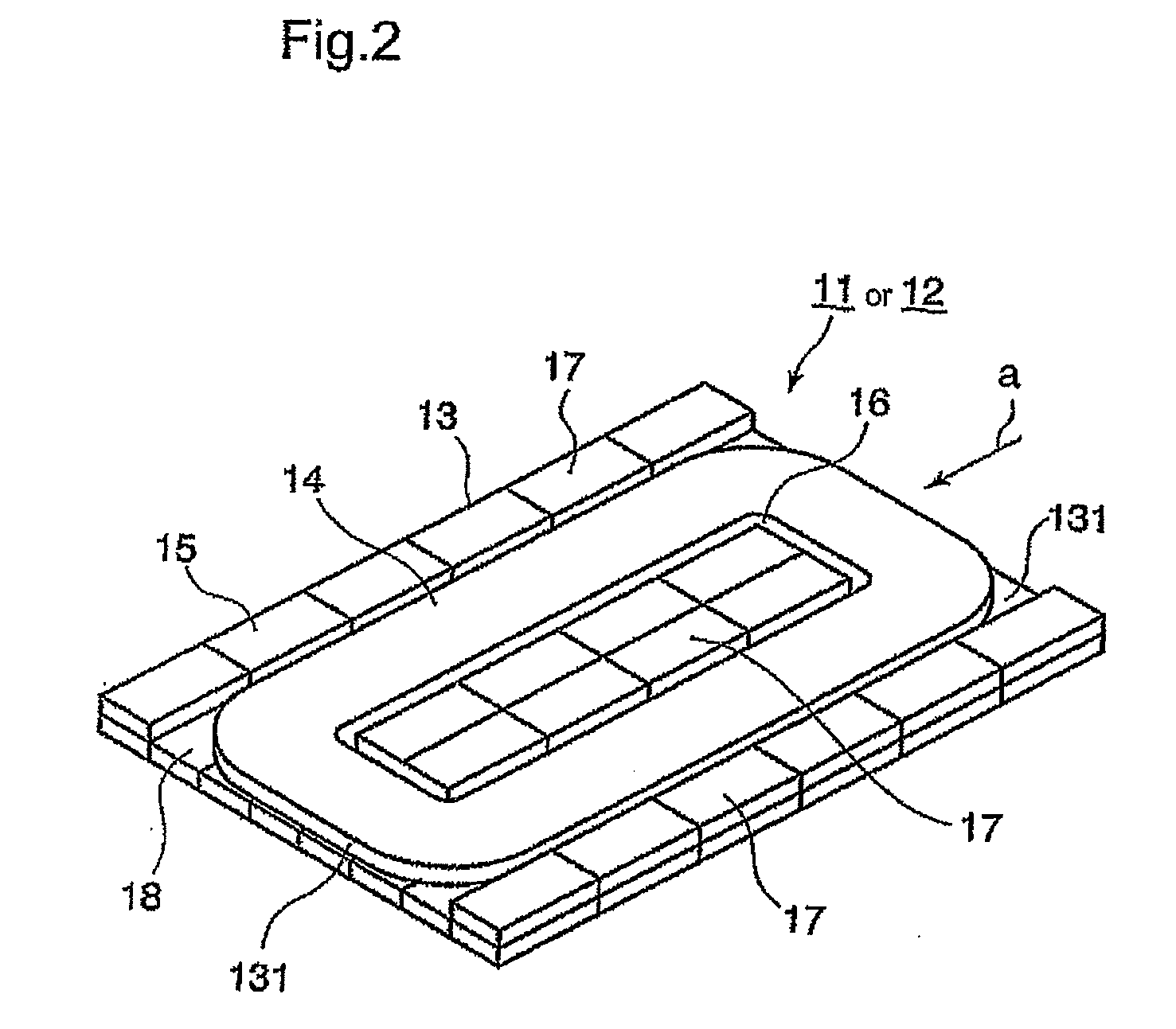

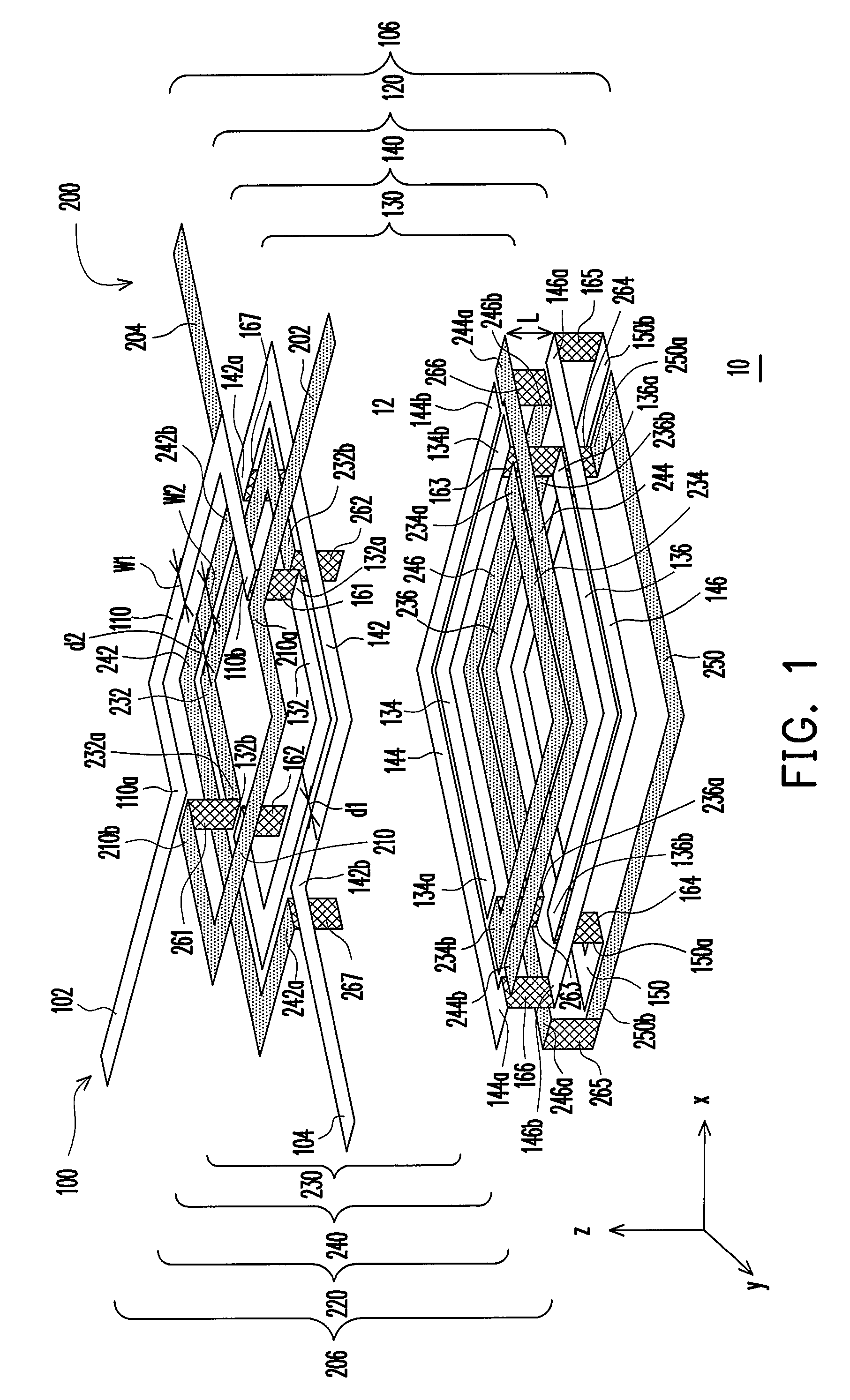

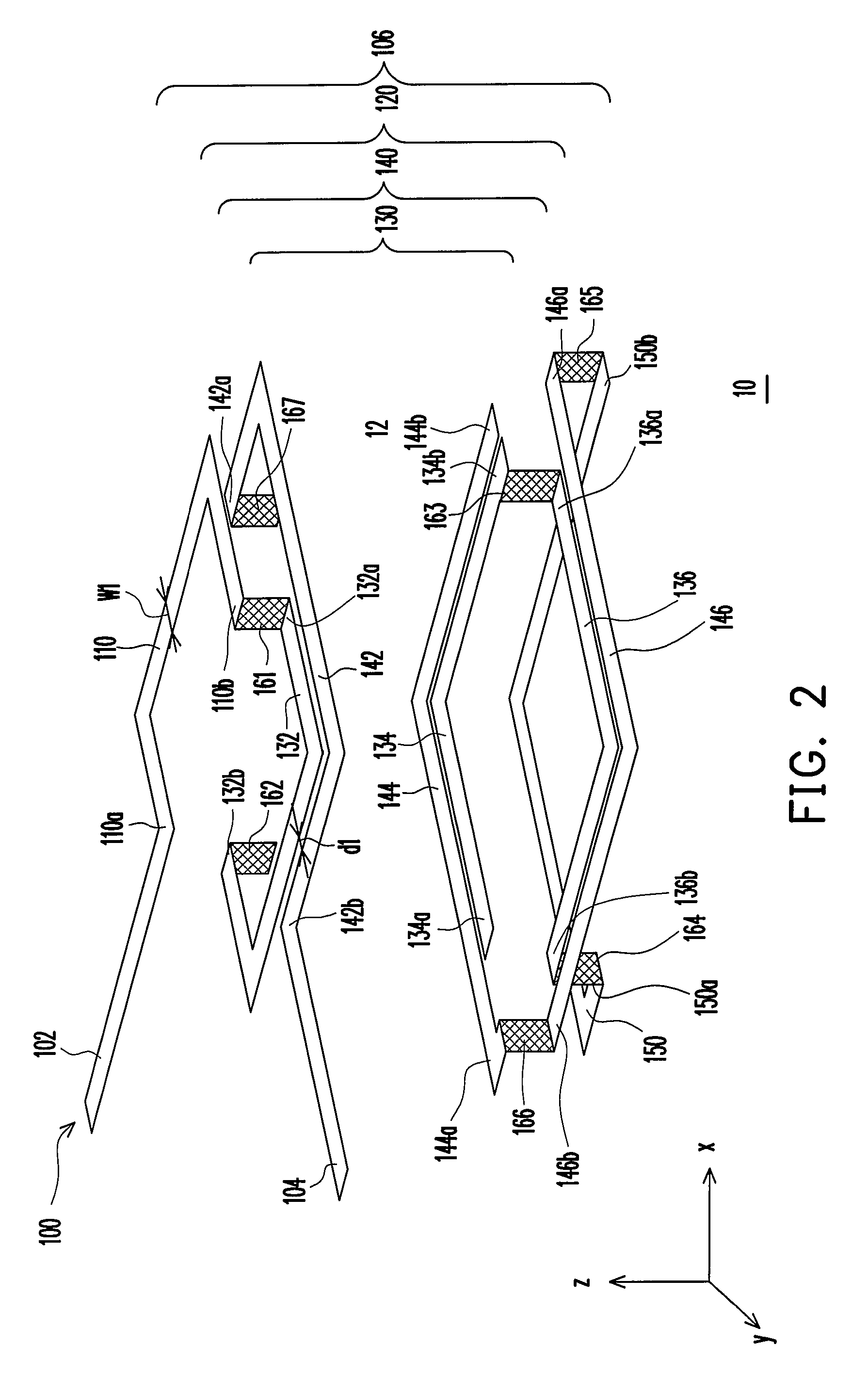

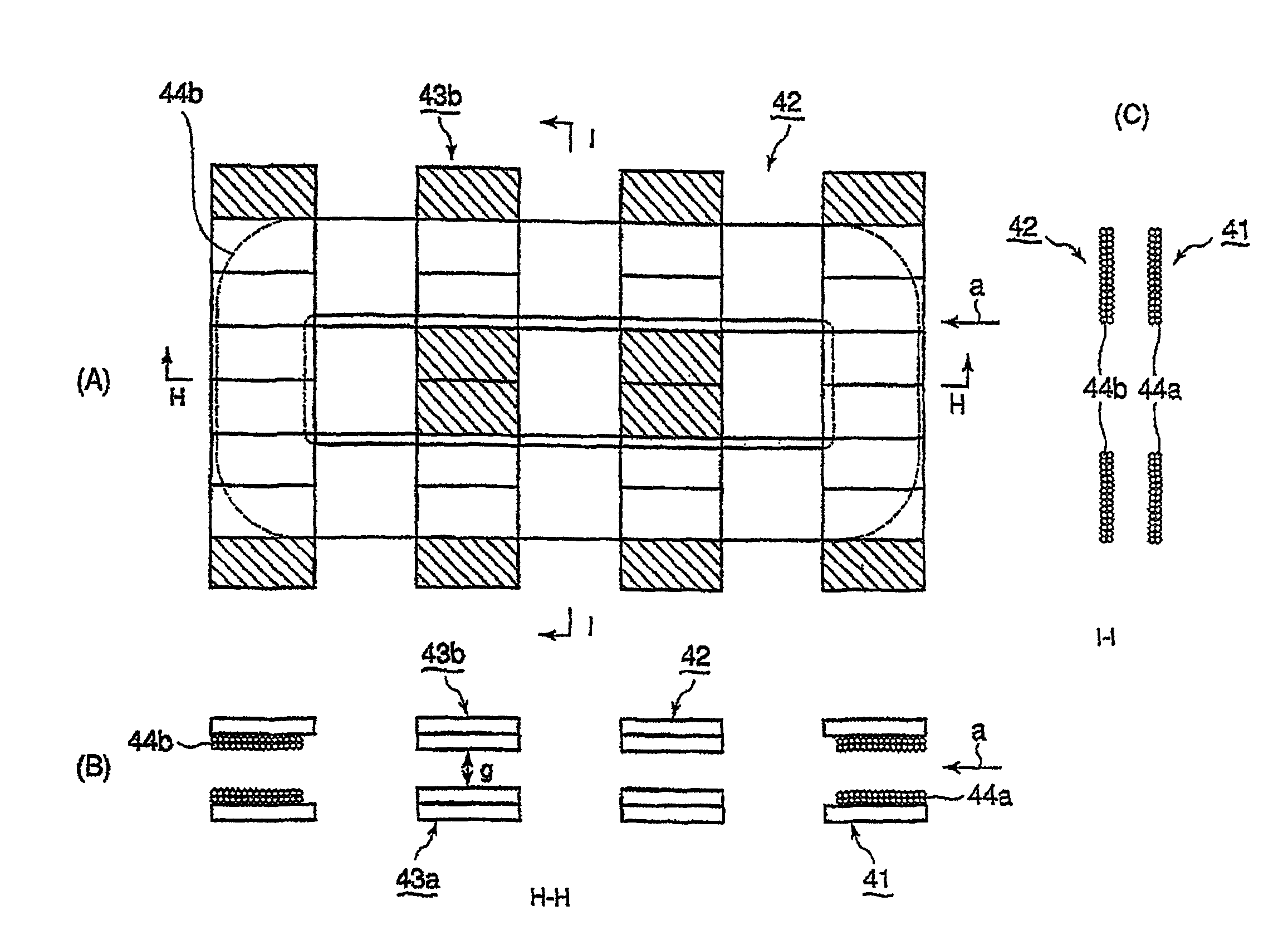

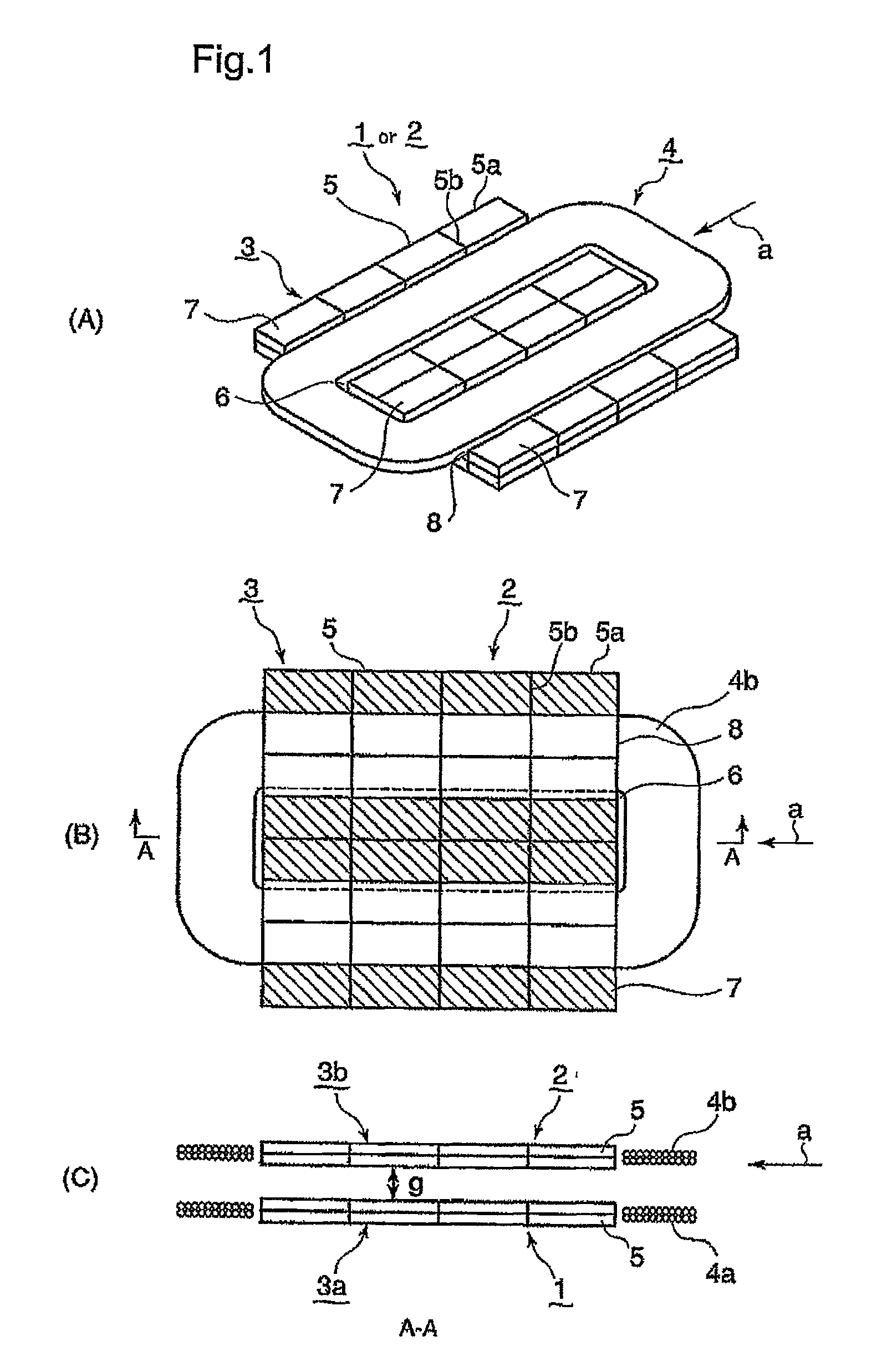

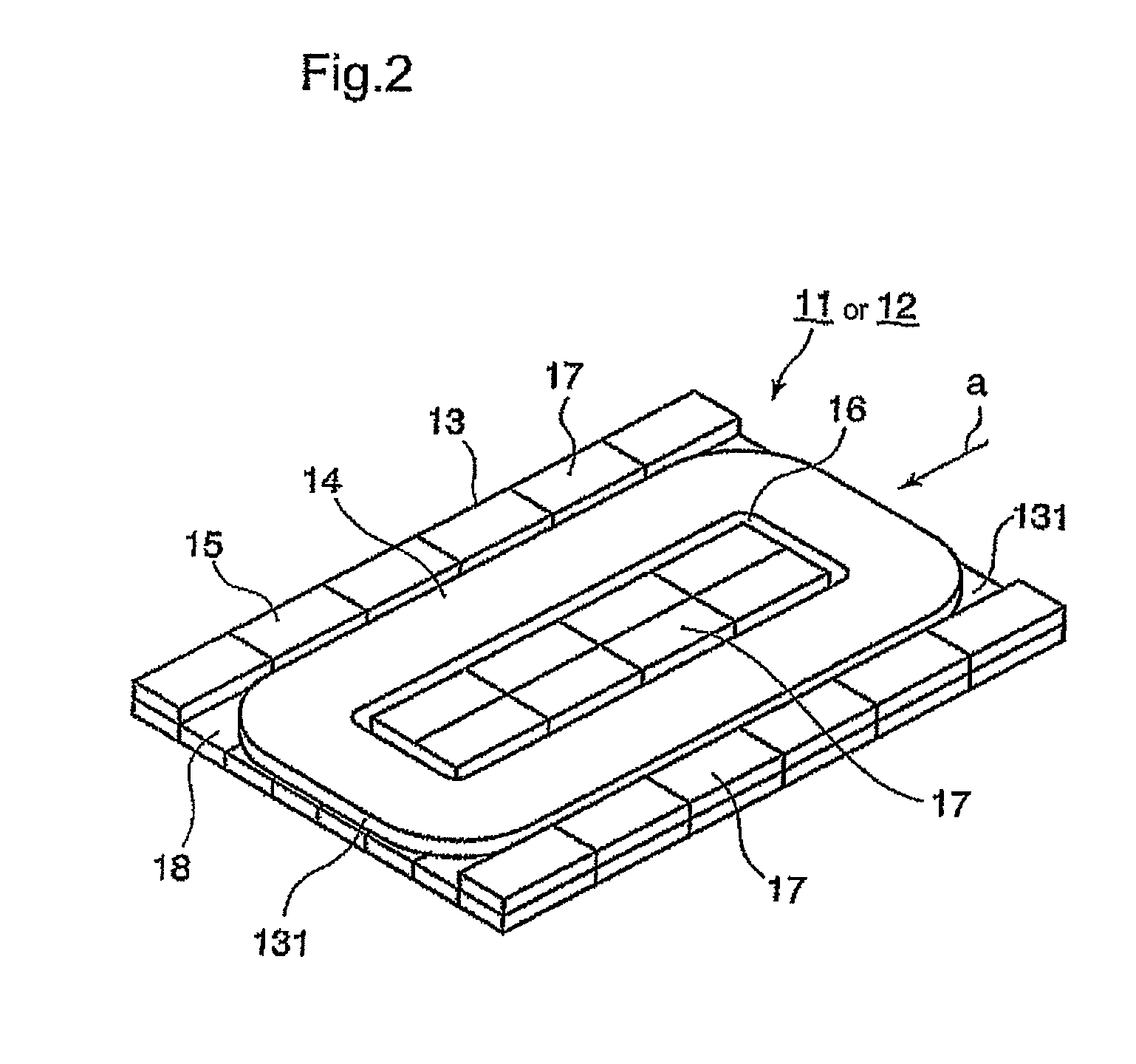

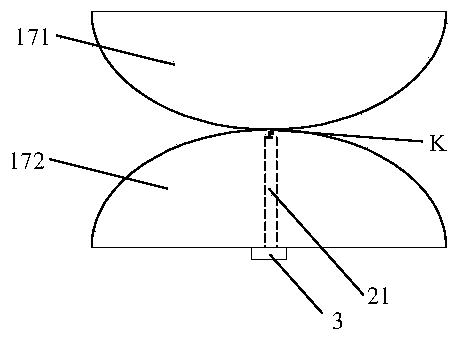

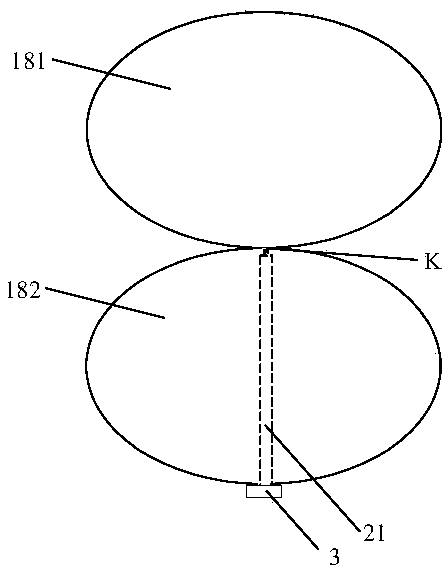

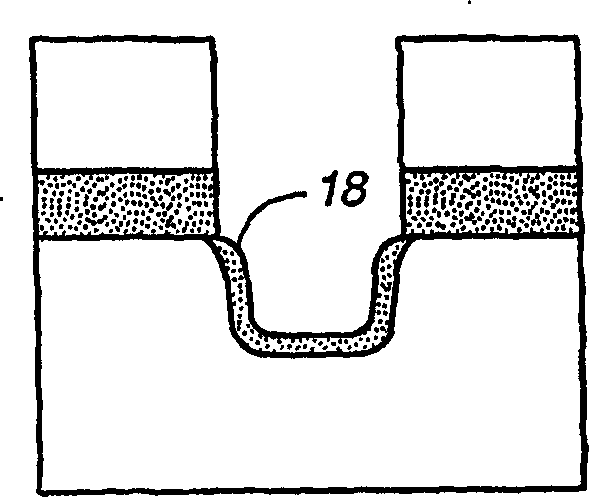

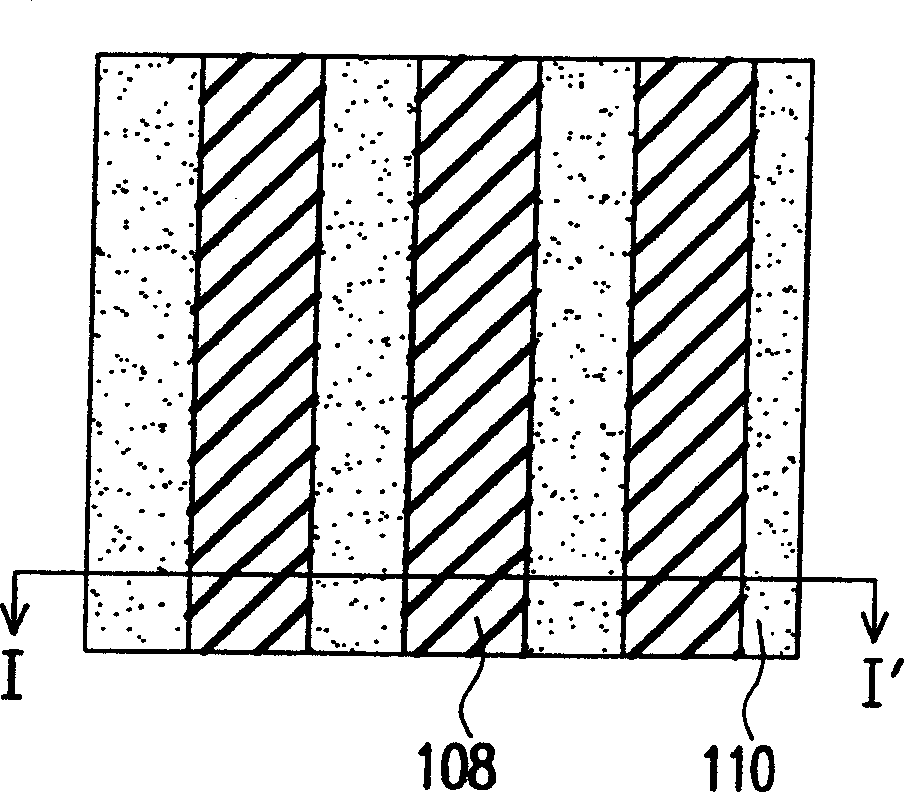

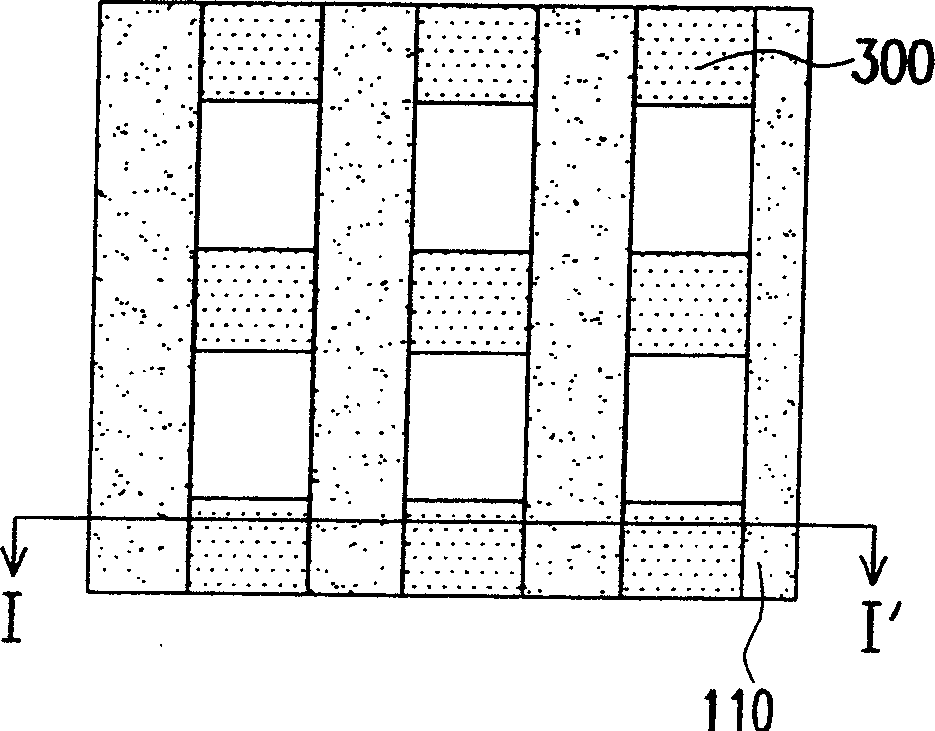

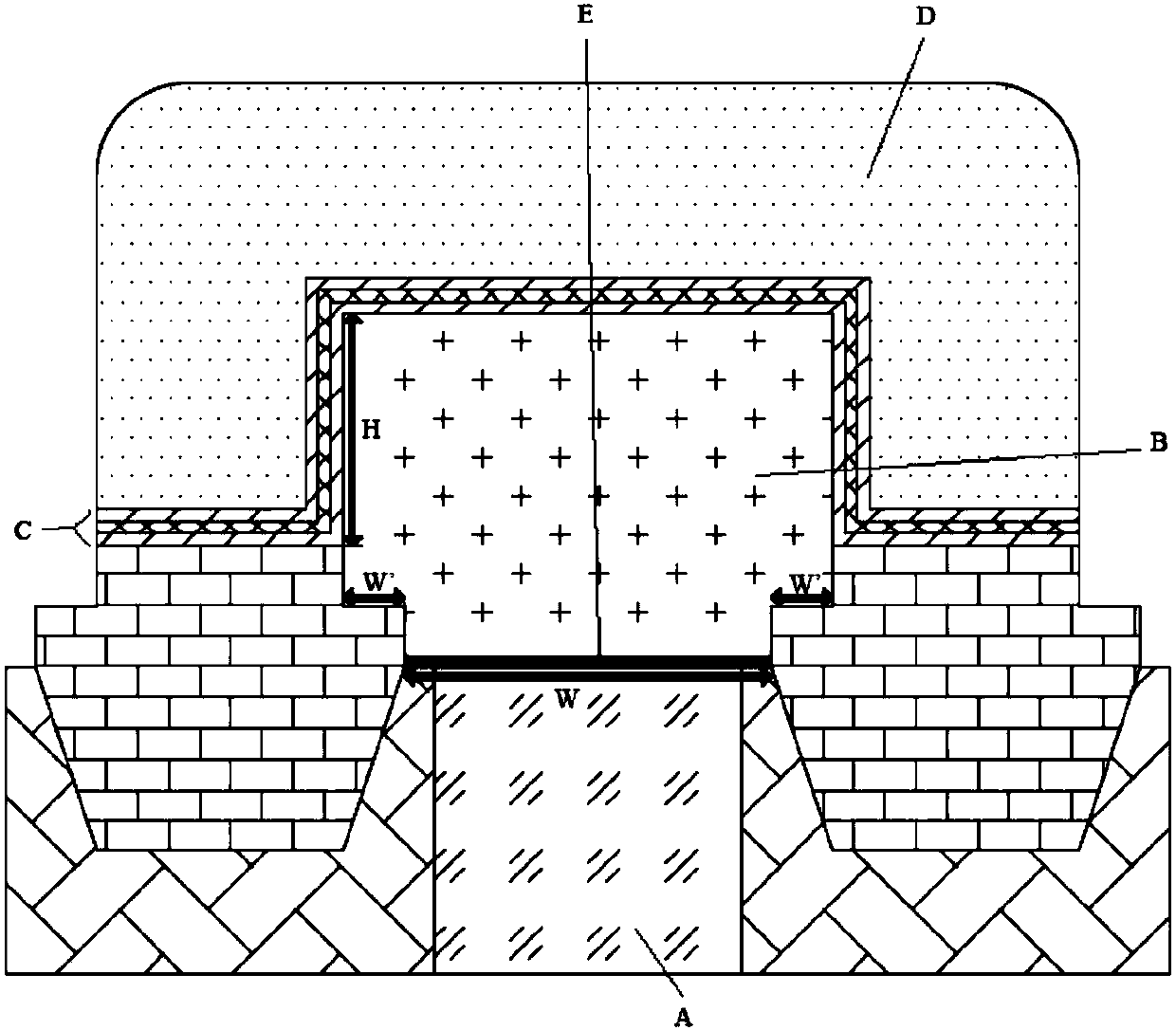

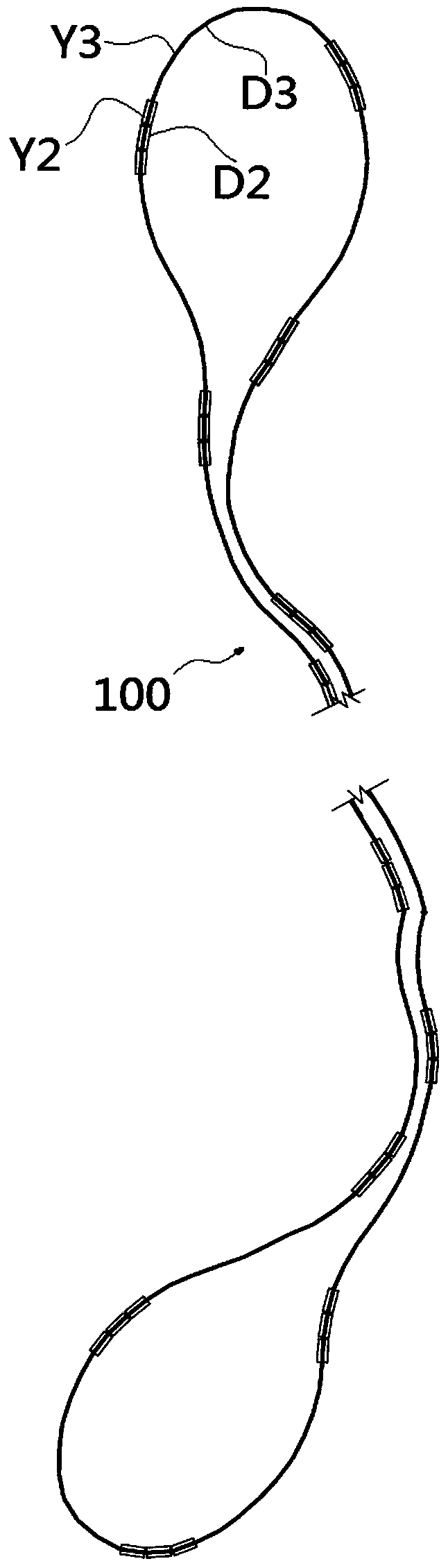

A noncontact type power feeder system for feeding a power to a mobile object, in which a power feeding portion and a power receiving portion can be easily manufactured at low costs and which can transmit a high power. The noncontact type power feeder system for a mobile object, comprises a power feeding portion provided in a surface on which the mobile object runs, and a power receiving portion provided in the lower part of the mobile object at a position facing to the power supply portion, the each of the power feeding portion and the power receiving portion is composed of windings formed in an oval shape, and a magnetic planar core formed therein with a recess in which the windings are accommodated so that the longitudinal direction of the oval shape of the windings is extended along the travel direction of the mobile object, the planer core is composed of several planar blocks each having a rectangular surface, several blocks being laid so that long sides of the rectangular surfaces are extended in the travel direction of the mobile object, in which several blocks are also laid in the direction orthogonal to the travel direction, and several blocks being superposed one upon another, the recess of the planar core is defined by thick wall parts in which the planar cores are superposed on the surface of the planar core, outside and inside of the oval shape part of the windings.

Owner:MITSUBISHI HEAVY IND ENG LTD

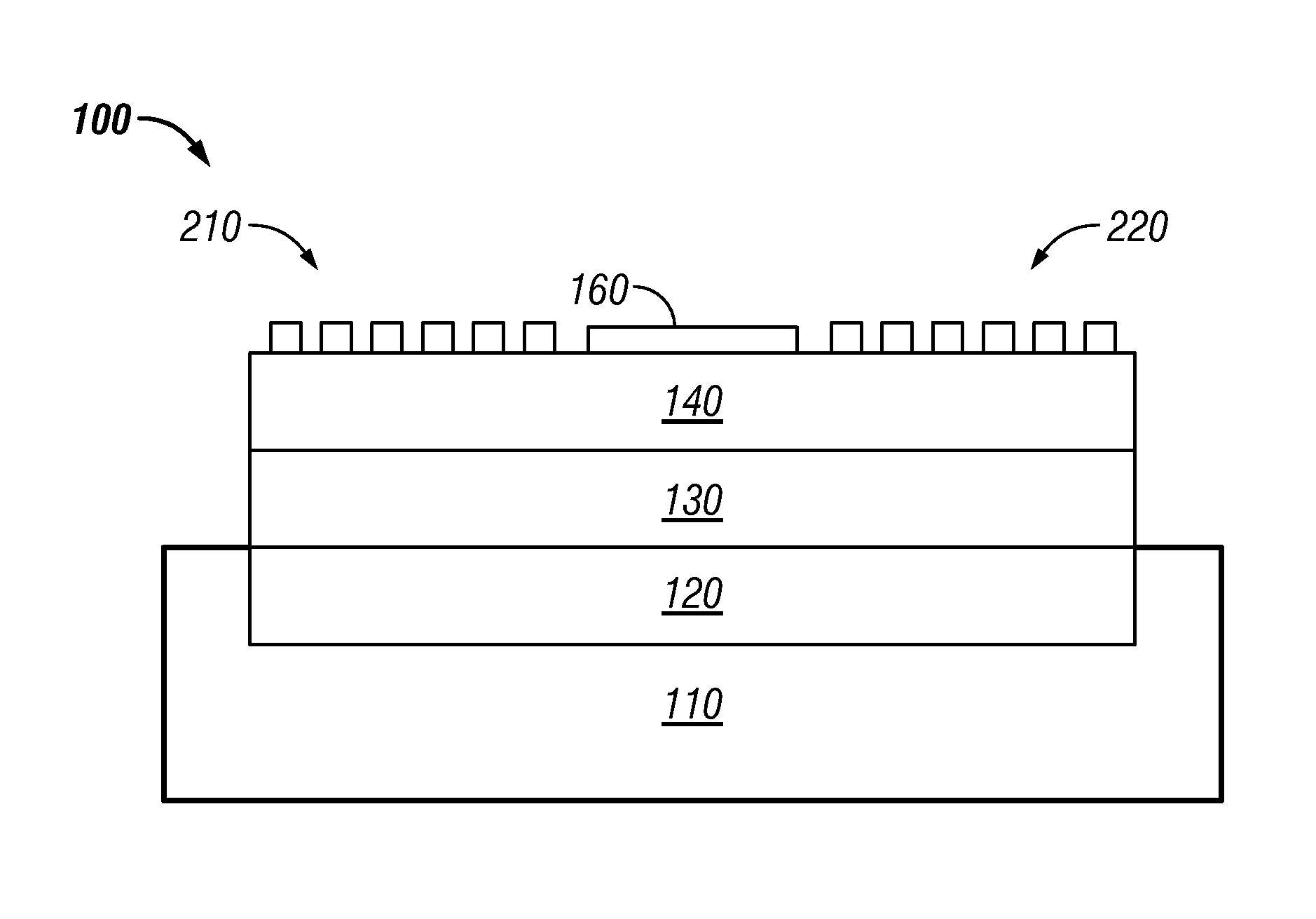

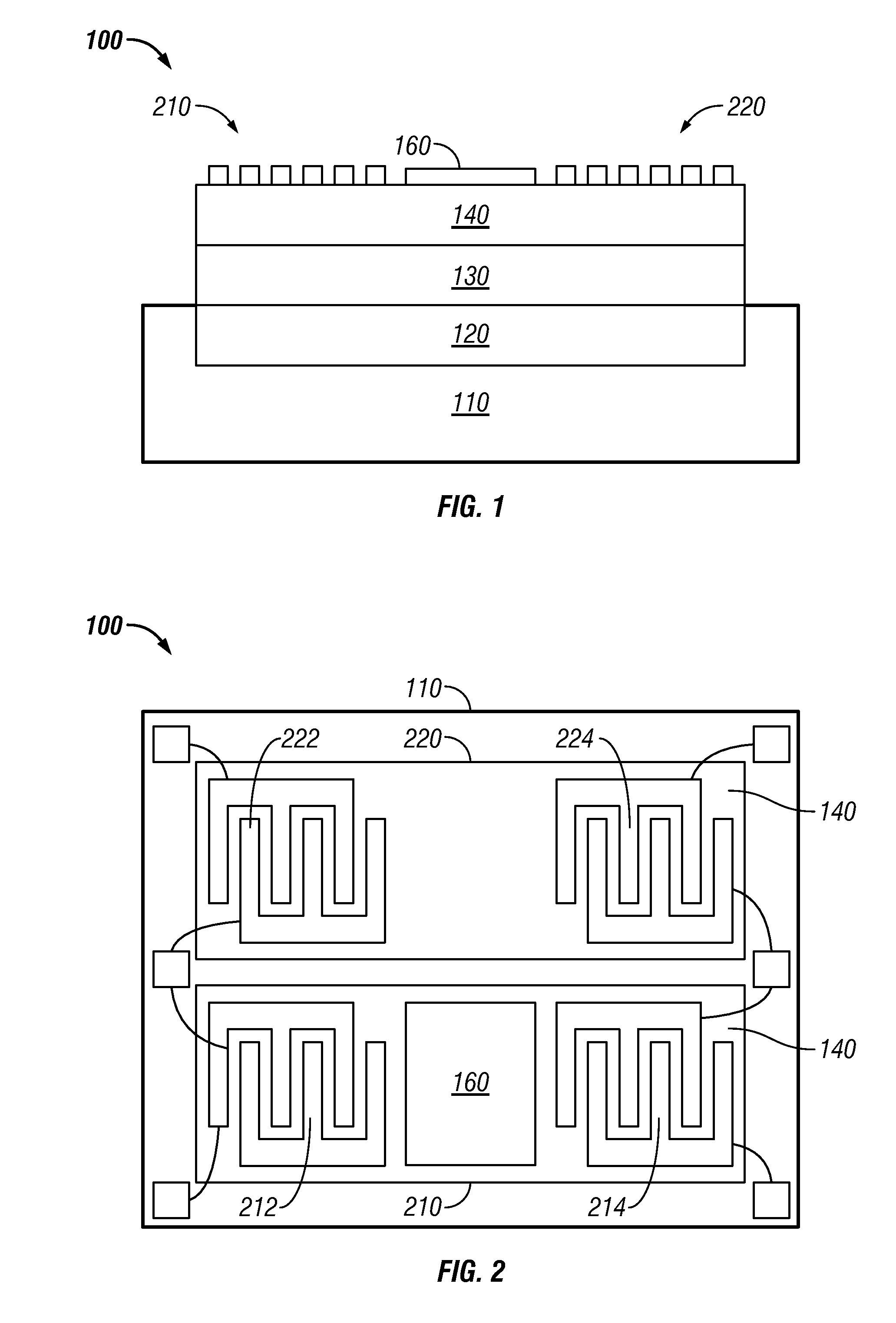

Three dimensional transformer

ActiveUS7405642B1Improve the coupling rateChip area is preservedTransformers/inductances coils/windings/connectionsFixed transformers or mutual inductancesInter layerTransformer

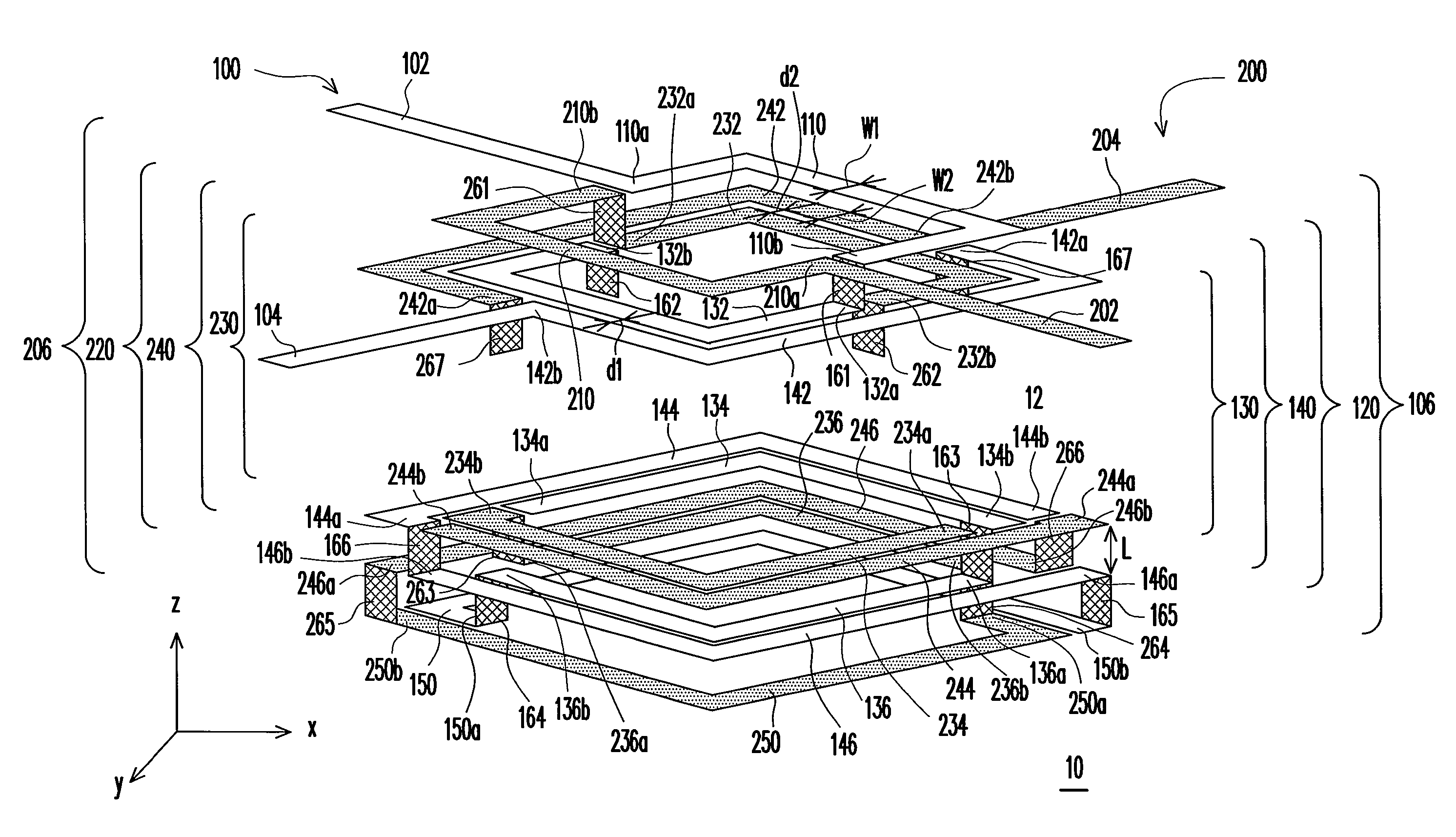

A three dimensional (3D) transformer includes a first coil and a second coil. Each coil includes a first port, a second port, a top layer metal line, inter-layer inner metal lines, inter-layer outer metal lines and a bottom layer metal line. Each metal line of the first coil and that of the second coil are correspondingly arranged to the opposite side of each other. Each of the first port is electrically connected to each of the top metal line. Each coil is arranged clockwise from the top metal line, the inter layer inner metal line down to the bottom layer metal line and arranged clockwise from the bottom layer metal line, the inter layer outer metal line up to the upper metal line of the inter layer outer metal line. Each upper metal line of the inter layer outer metal line is electrically connected to each second port.

Owner:NATIONAL CHUNG HSING UNIVERSITY

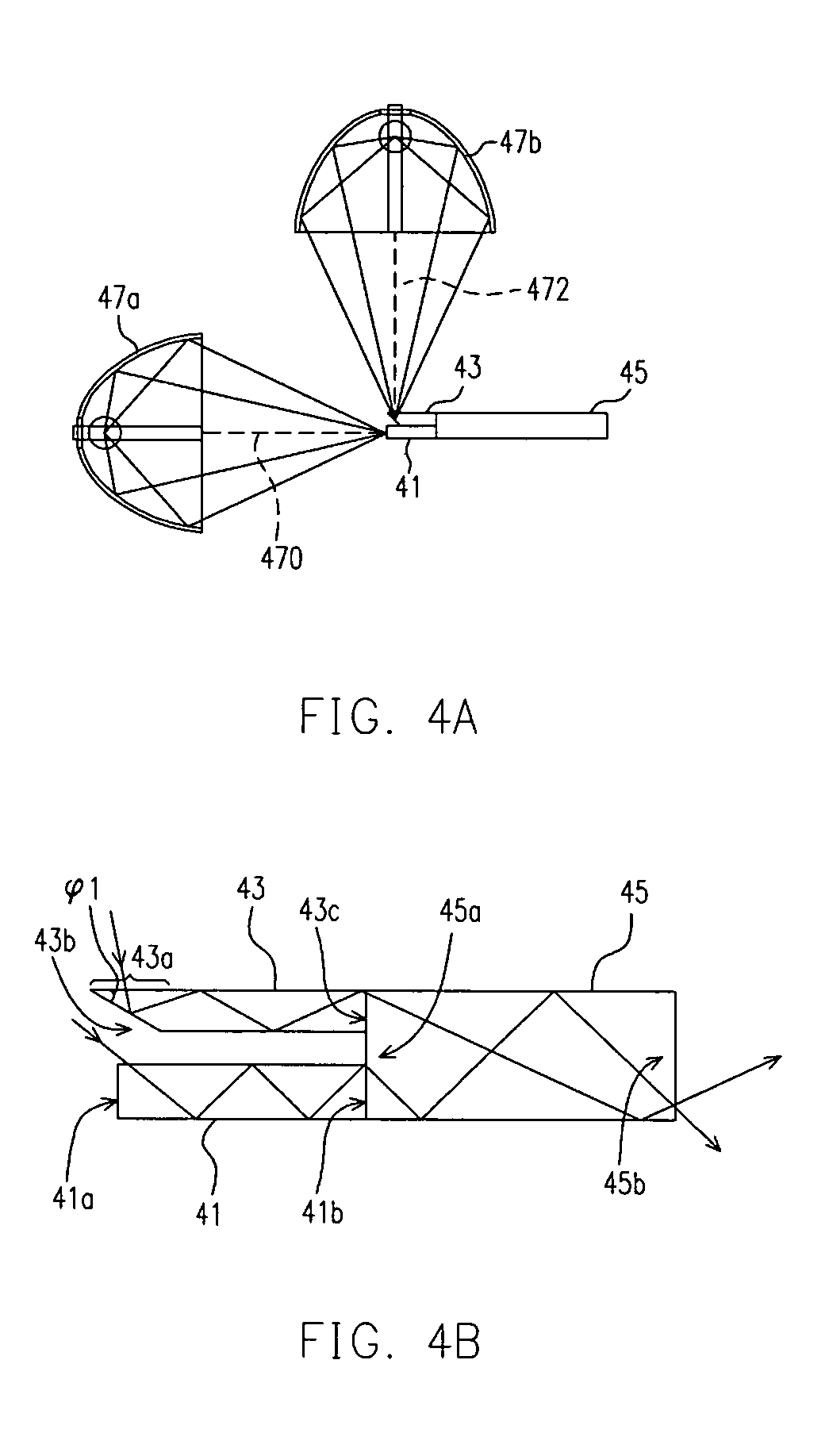

Illumination structure with multiple light sources and light integration device in a projection system

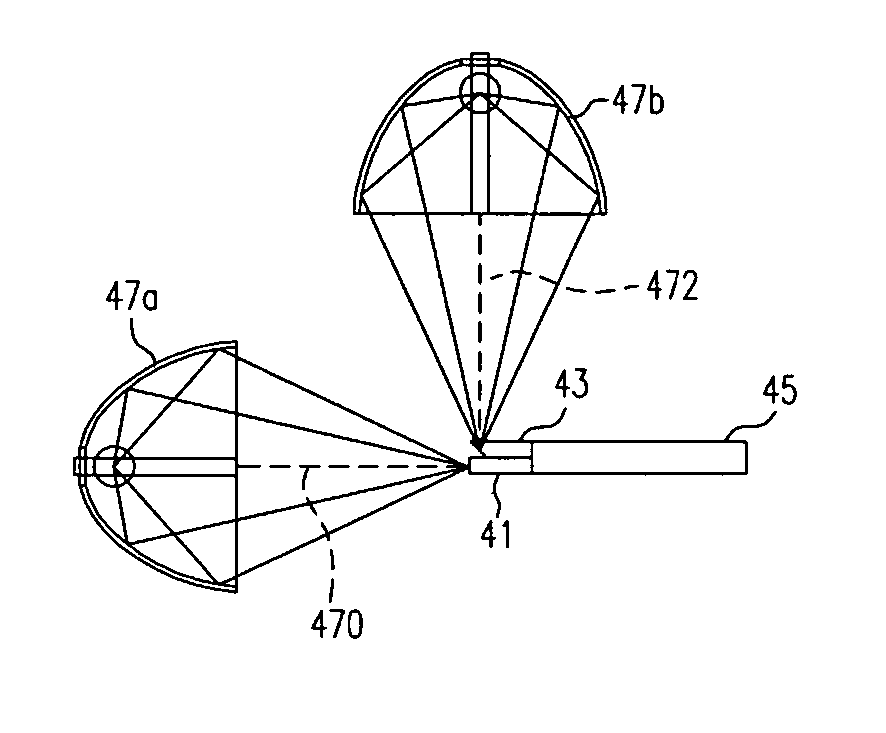

InactiveUS20050083685A1Lower the volumeImprove the coupling rateMechanical apparatusStatic indicating devicesProjection systemLight source

An illumination structure with multiple light sources in projector has first, second, third integration rods, first and second light sources. The second integration rod having a light incident surface, a light outgoing surface and a light reflection surface, is placed along the first integration rod. The light incident surface is parallel to the second integration rod, forming an angle between the light incident surface and light reflection surface. The first light source is vertically placed with respect to the second light source. The light emitted from the first light source is focused to the light incident surface of the first integration rod. The light emitted from the second light source is incident to the light incident surface of the second integration rod, and then reflected by the light reflection surface. The light reflected by the light reflection surface propagates forward the light outgoing surface of the second integration rod.

Owner:DELTA ELECTRONICS INC

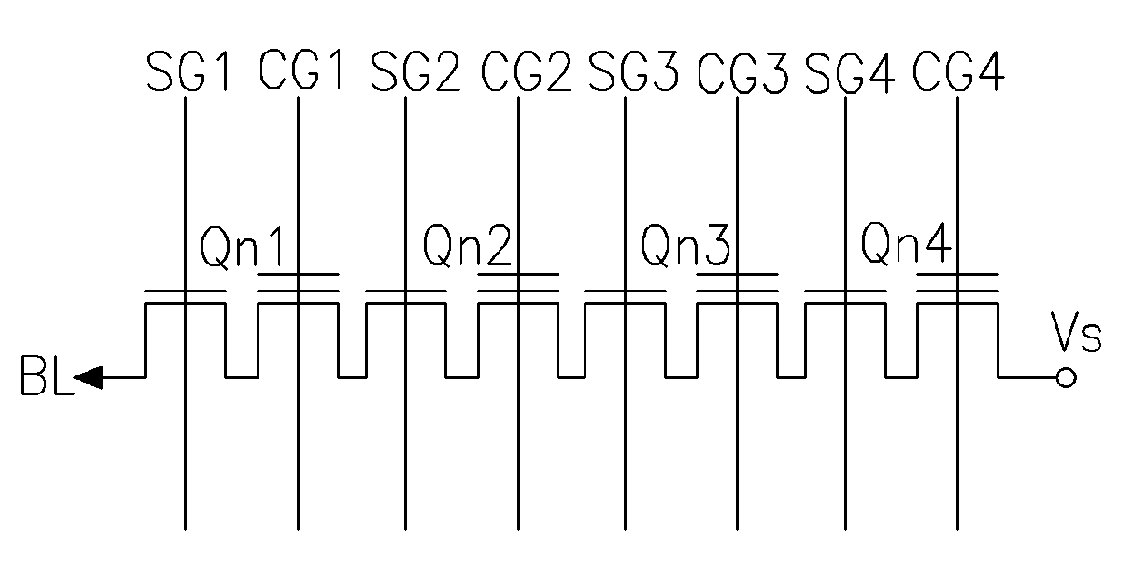

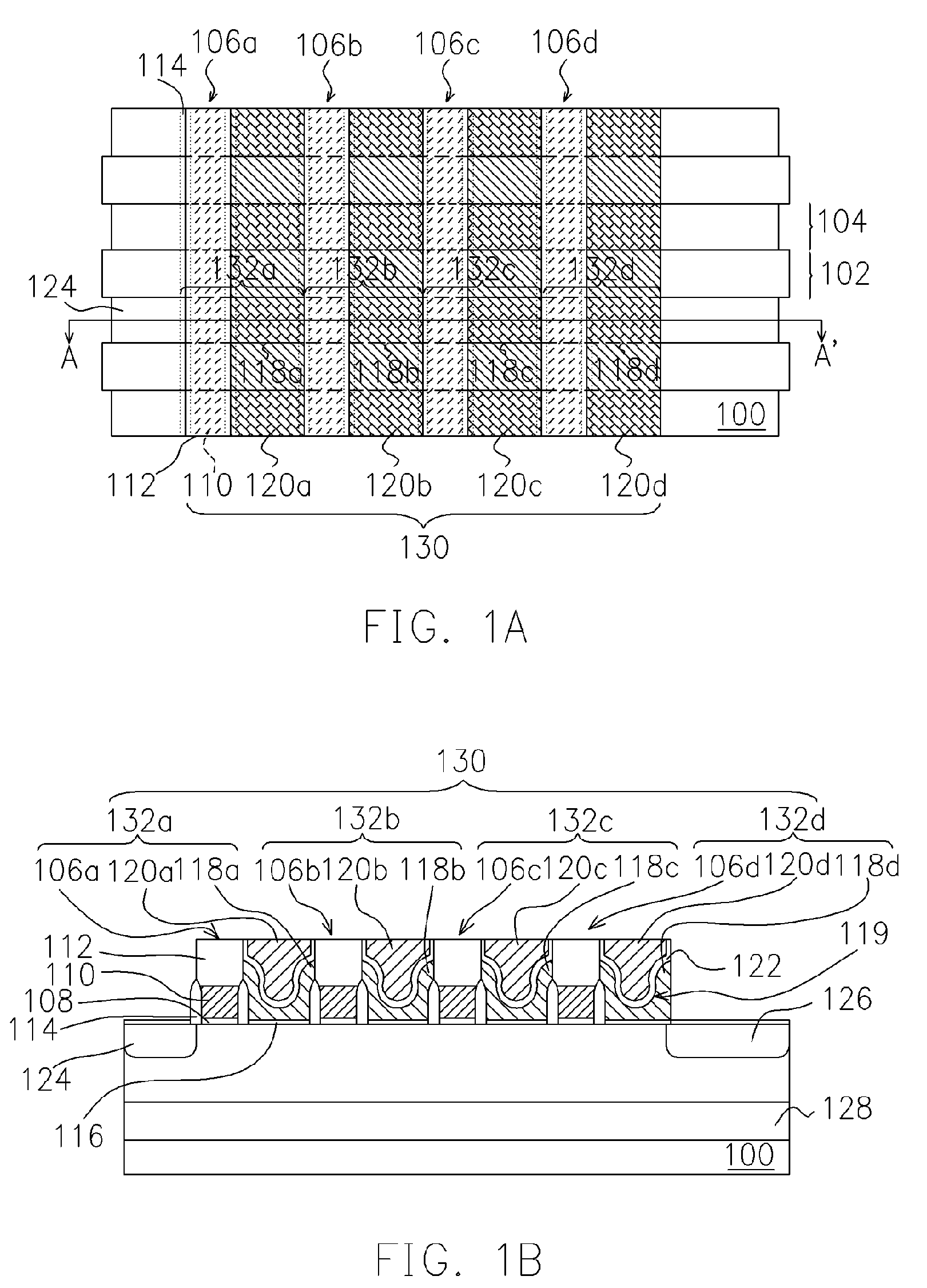

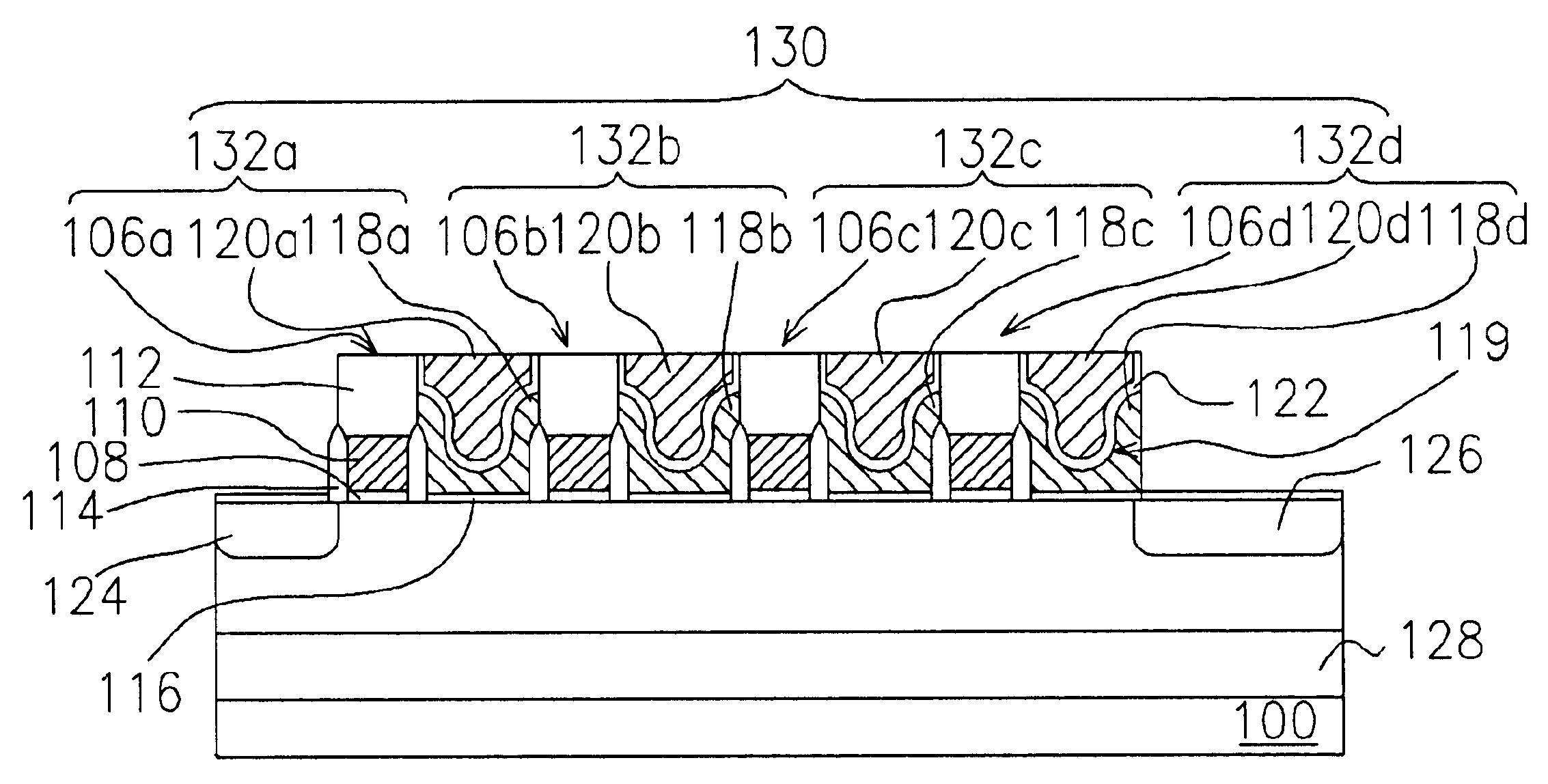

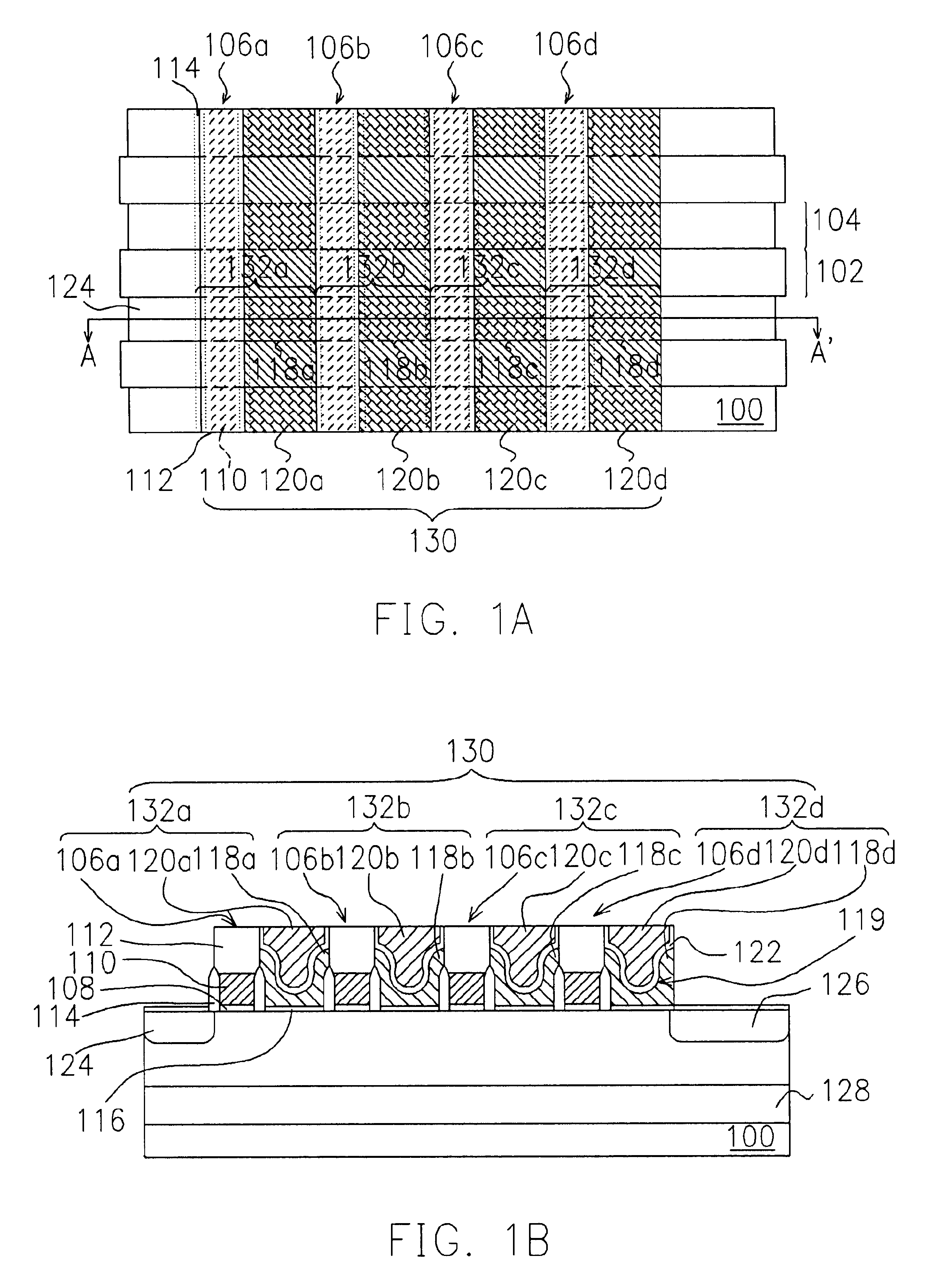

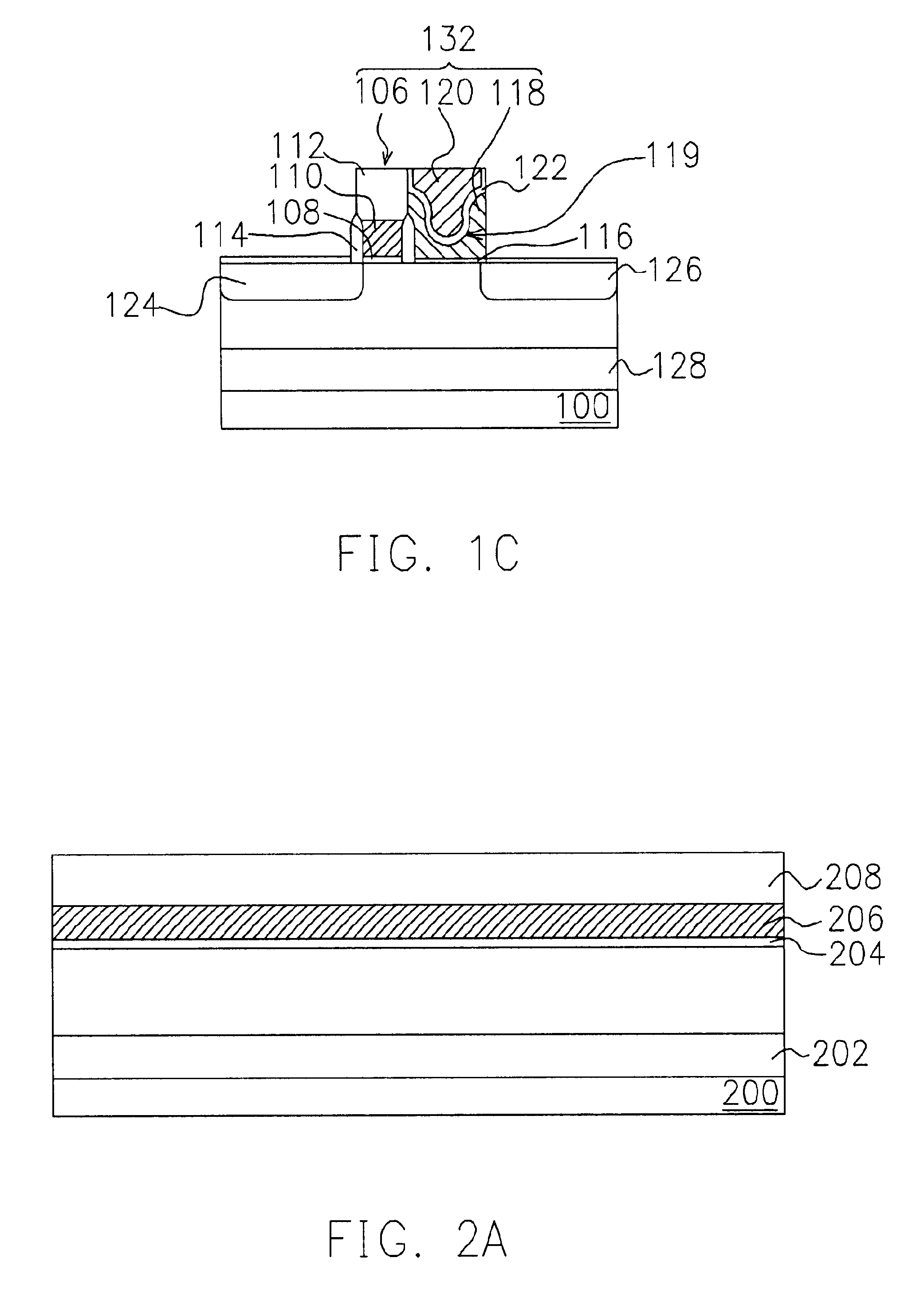

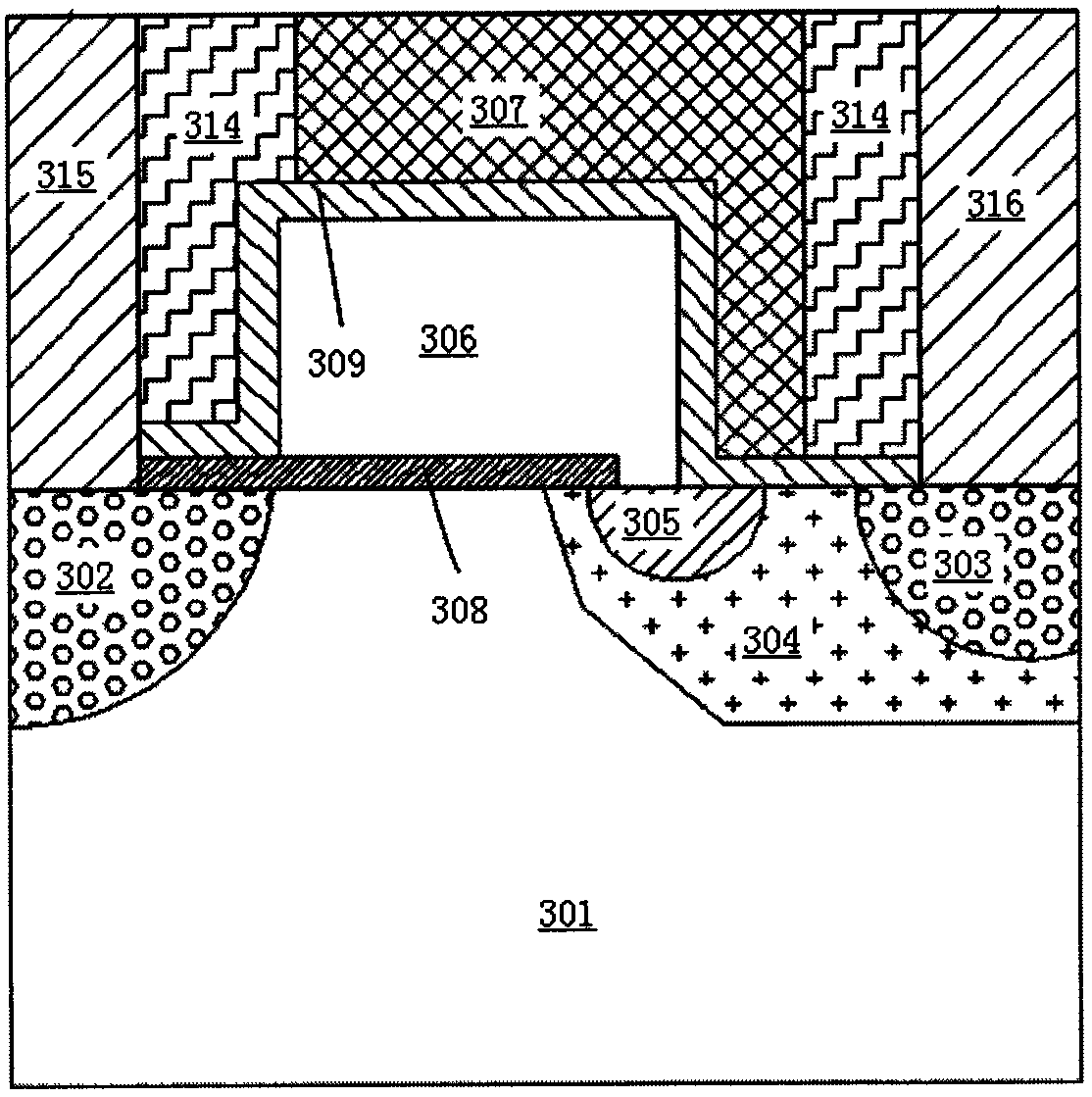

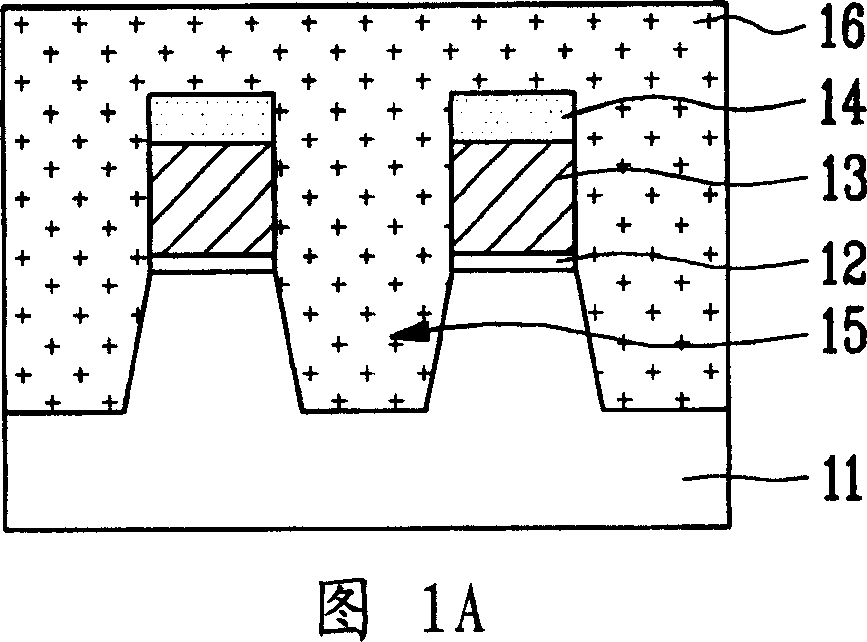

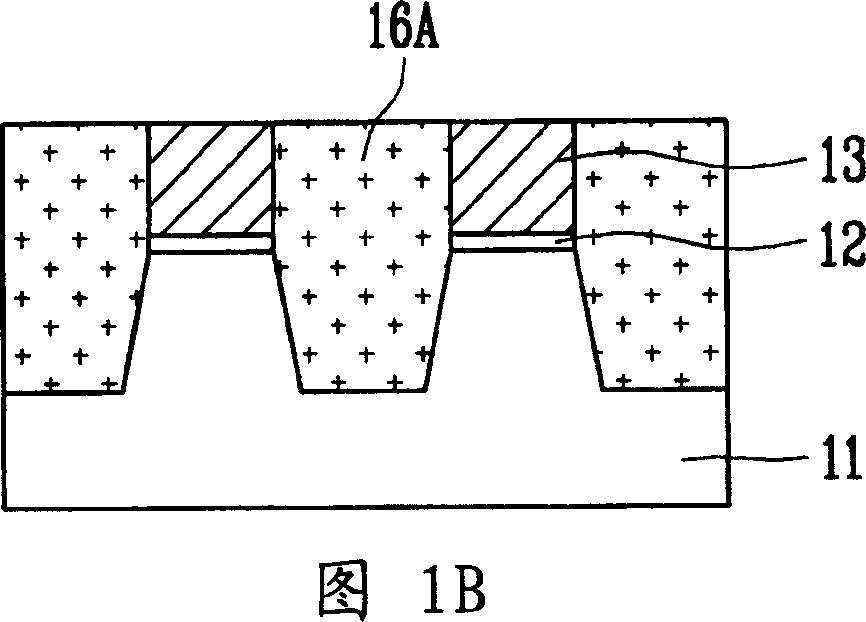

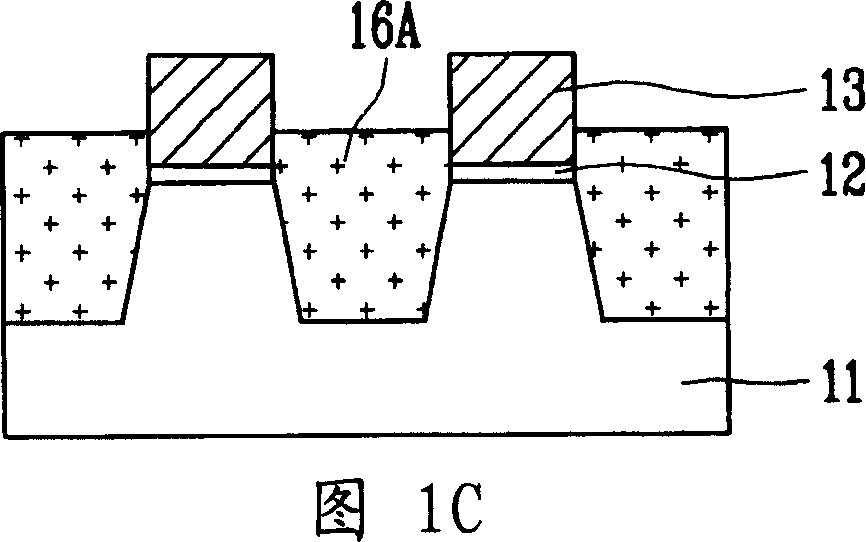

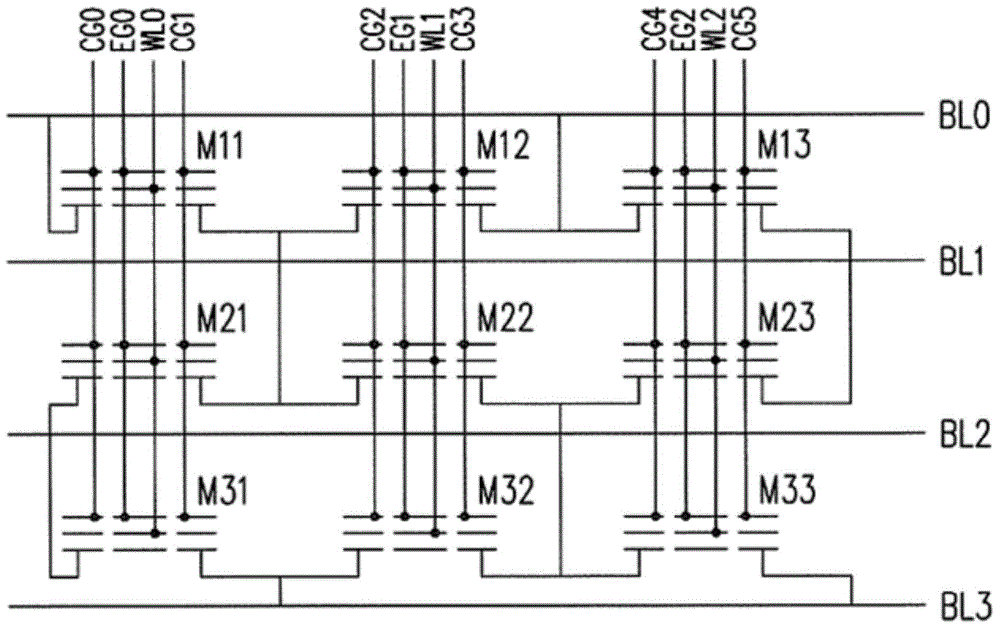

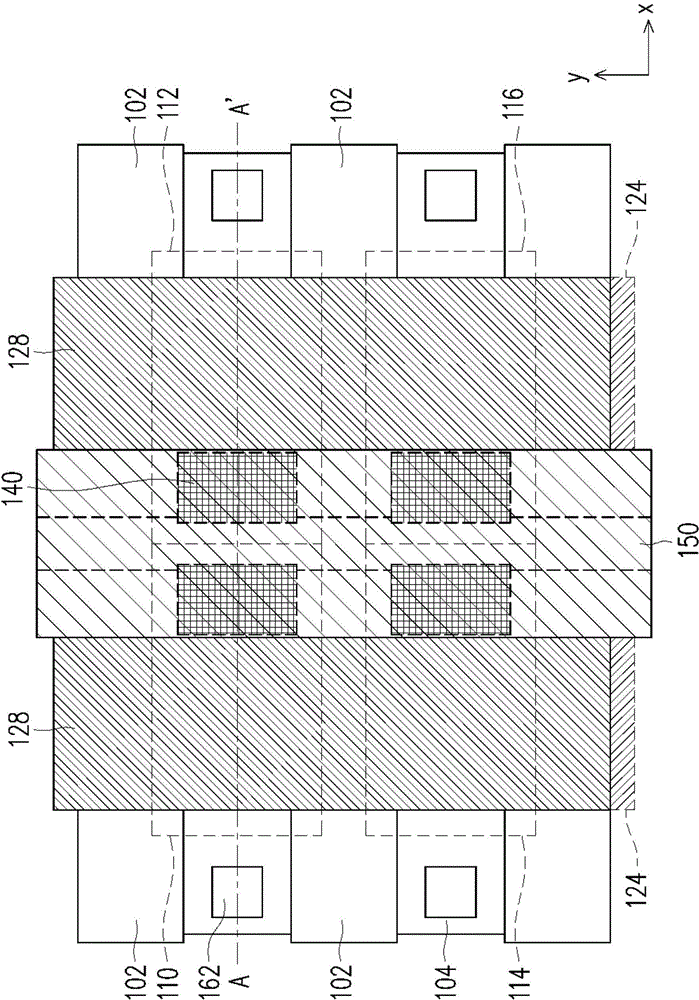

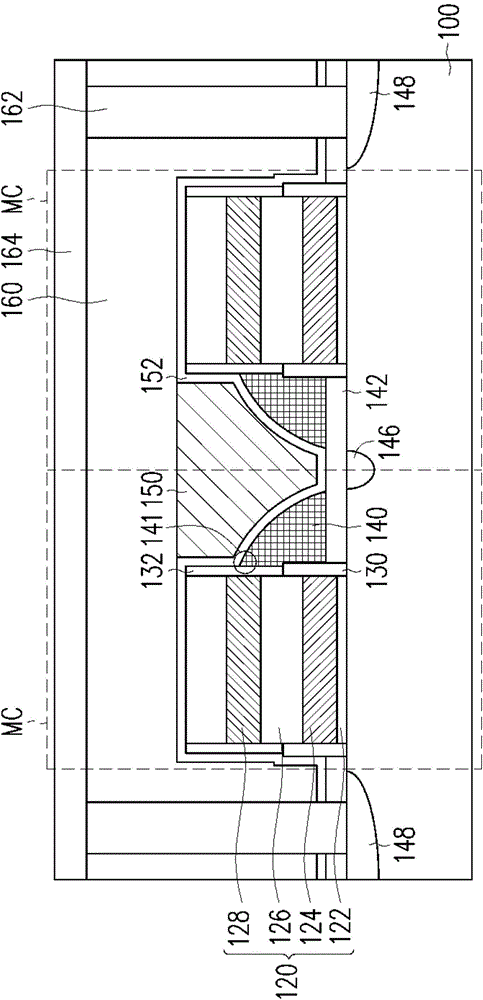

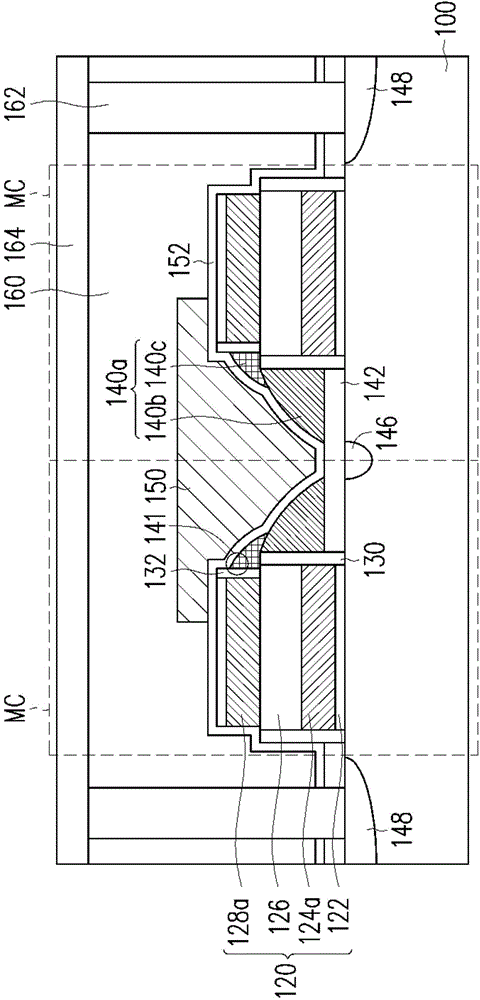

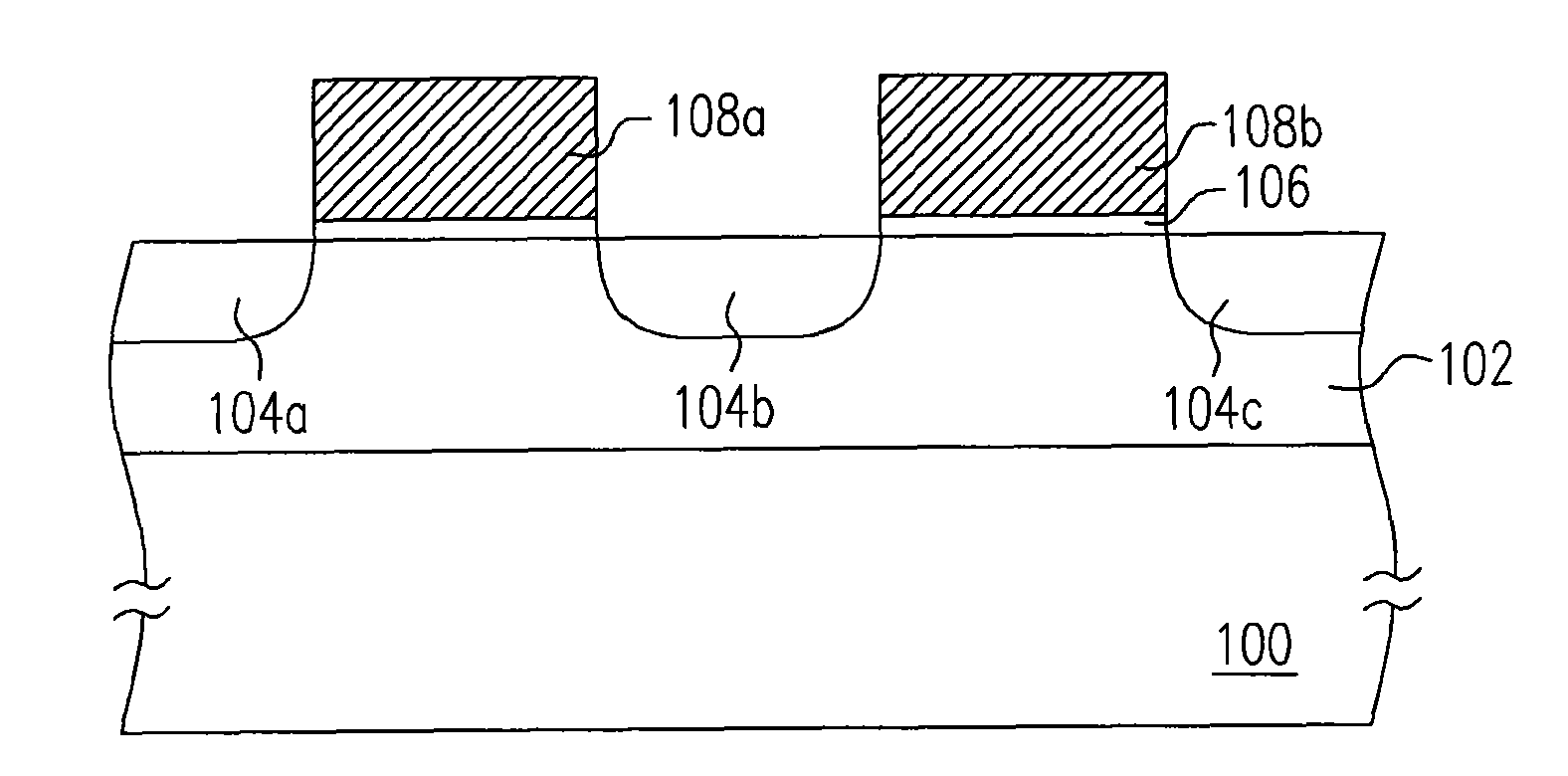

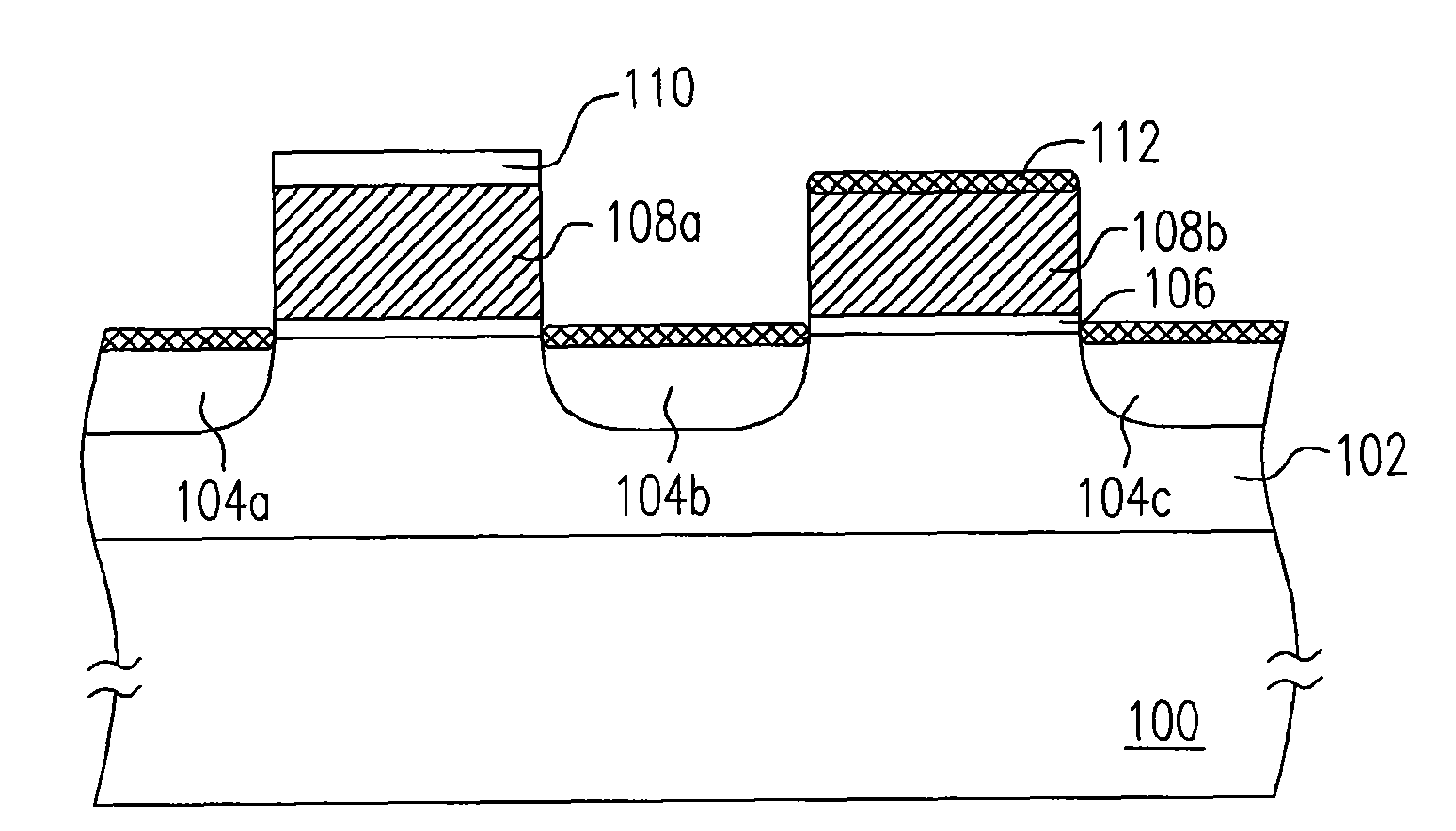

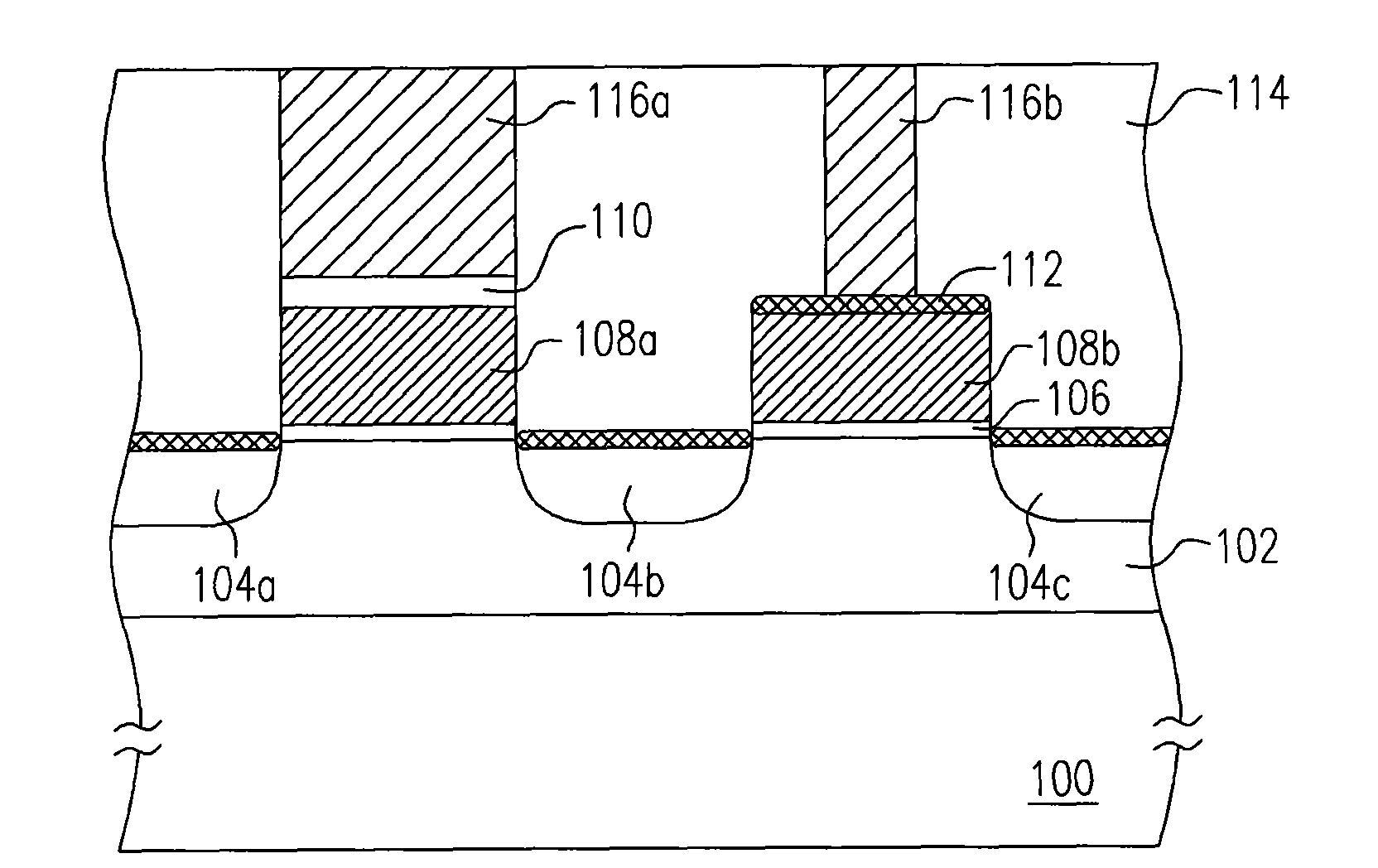

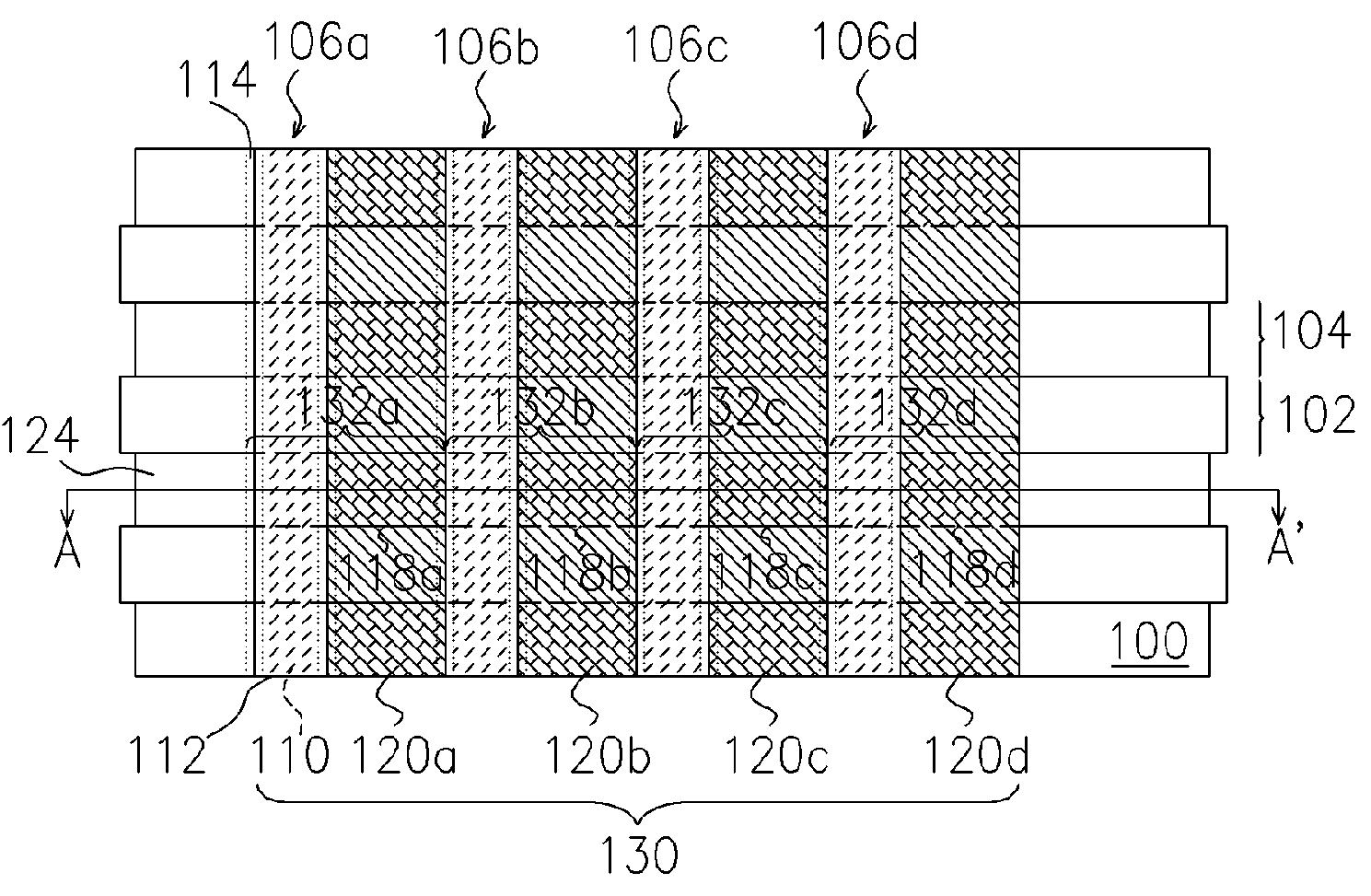

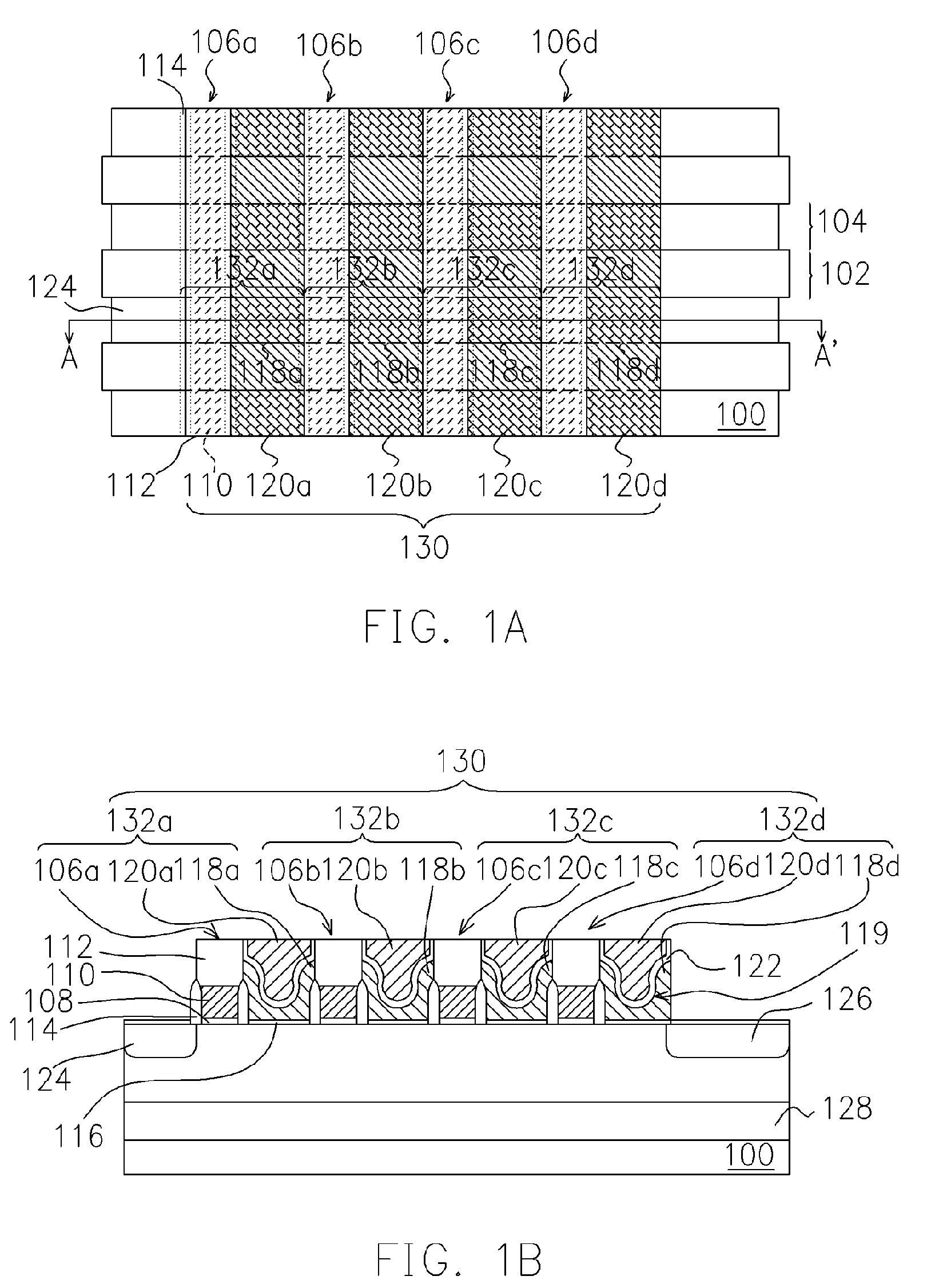

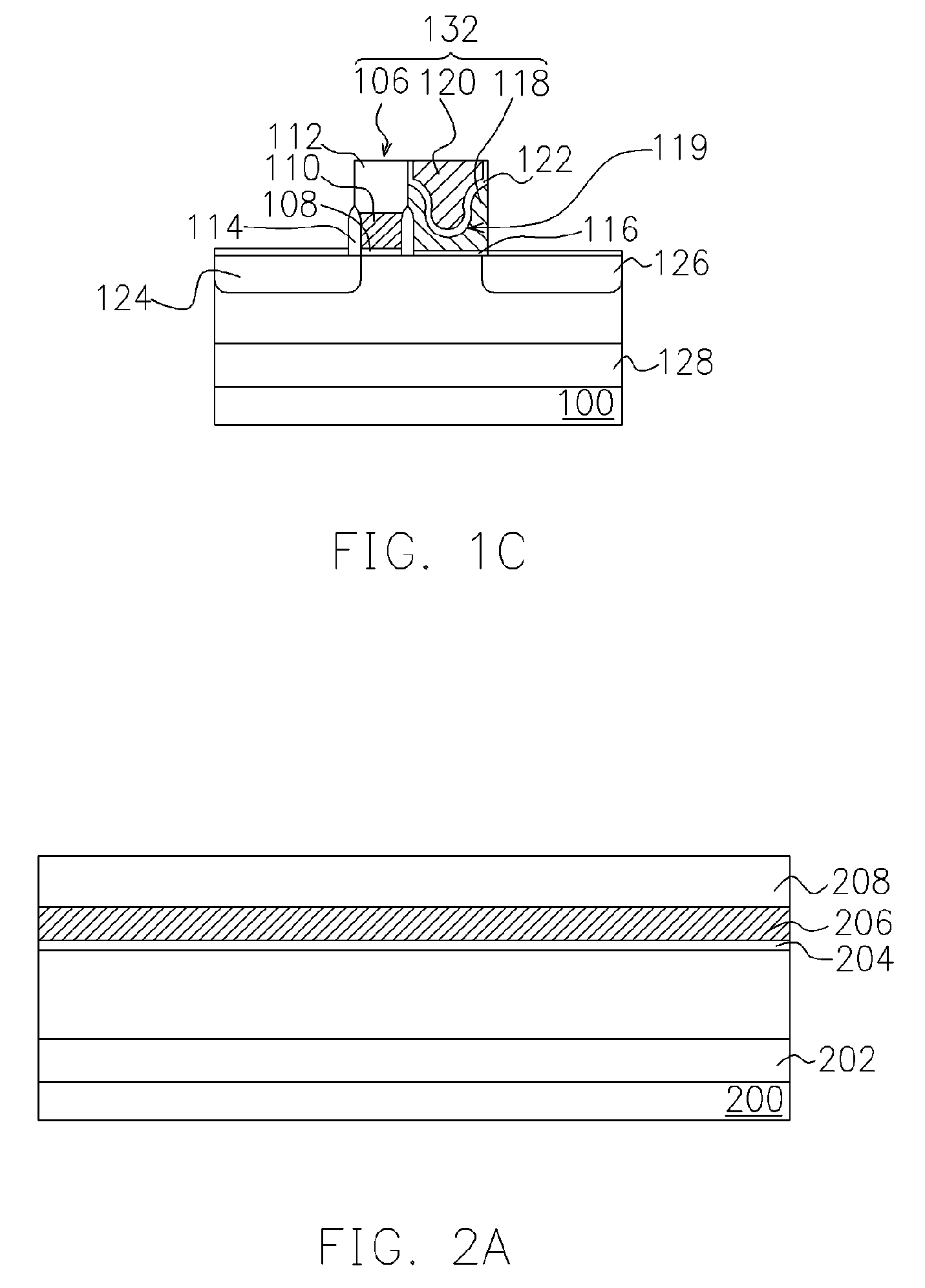

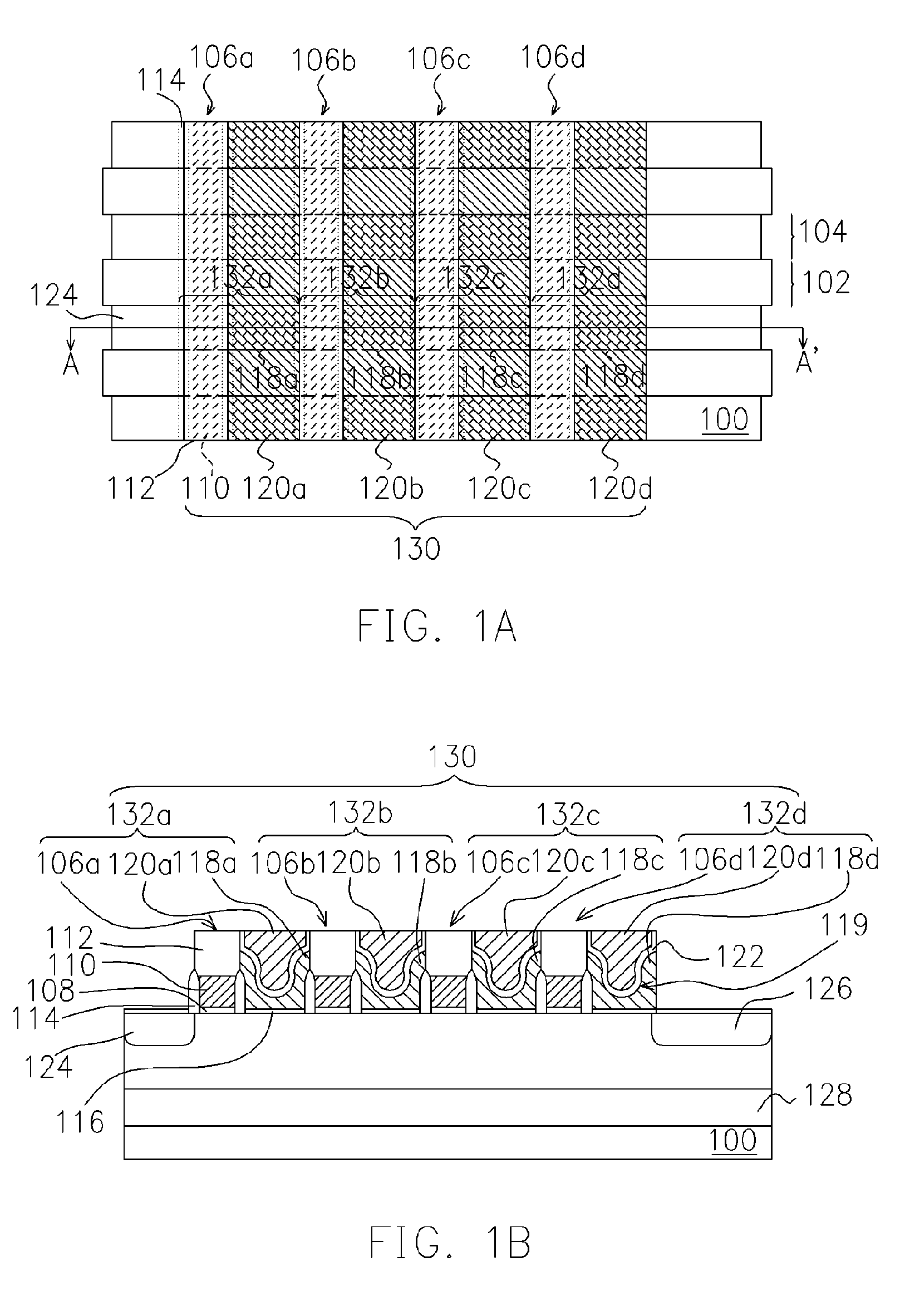

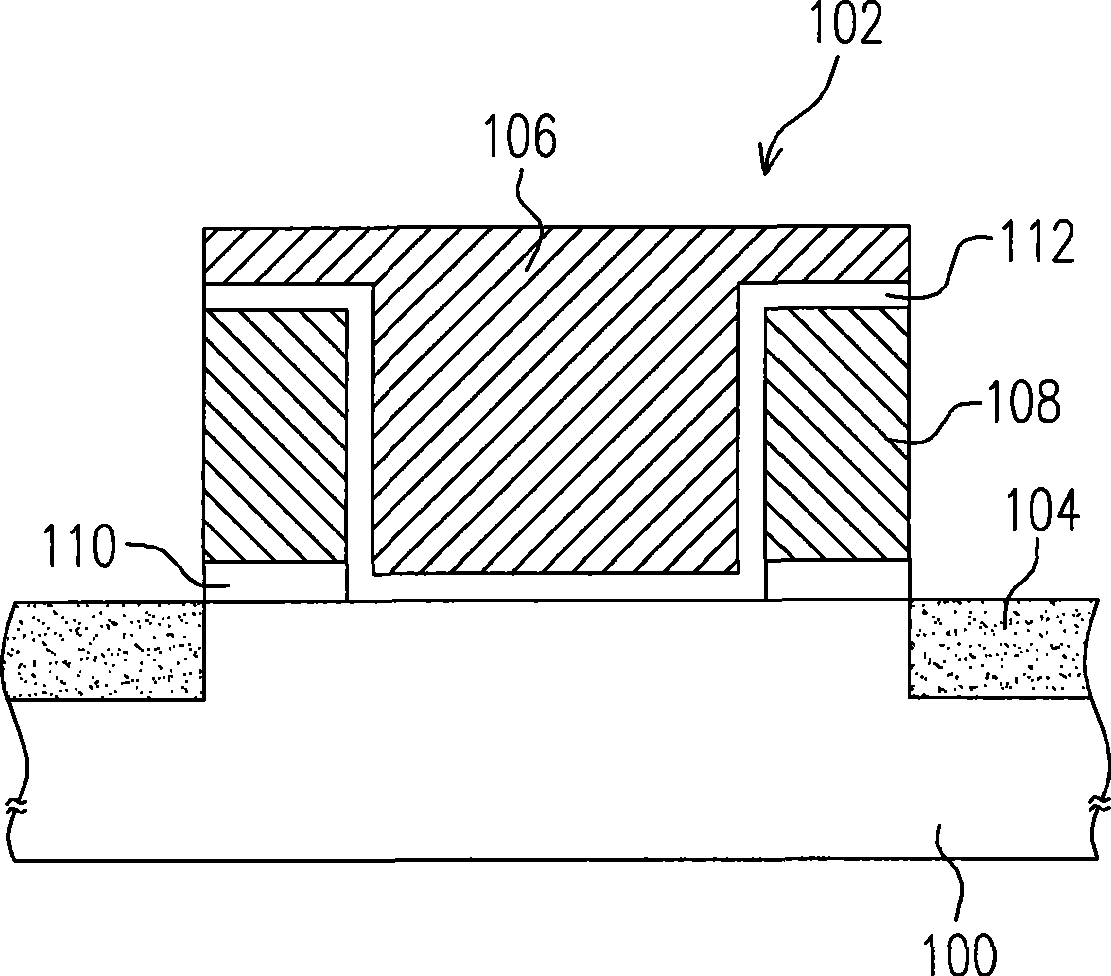

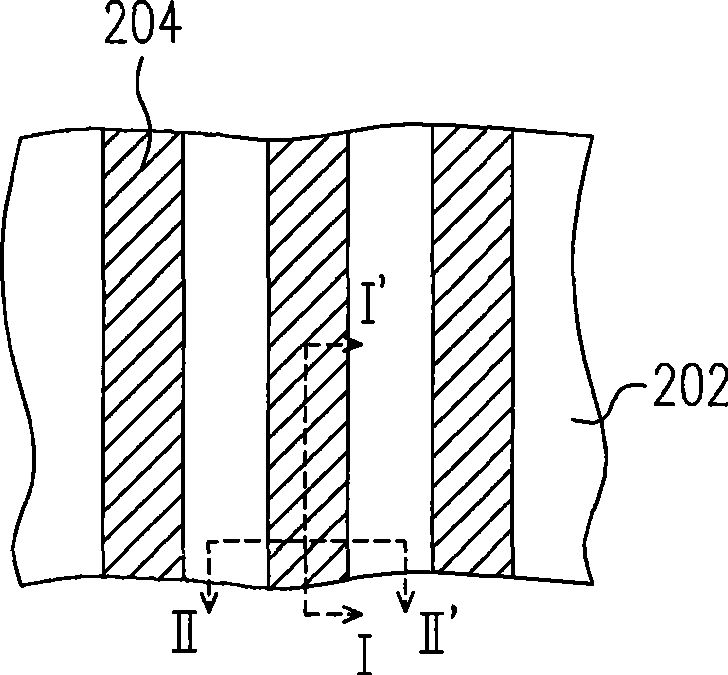

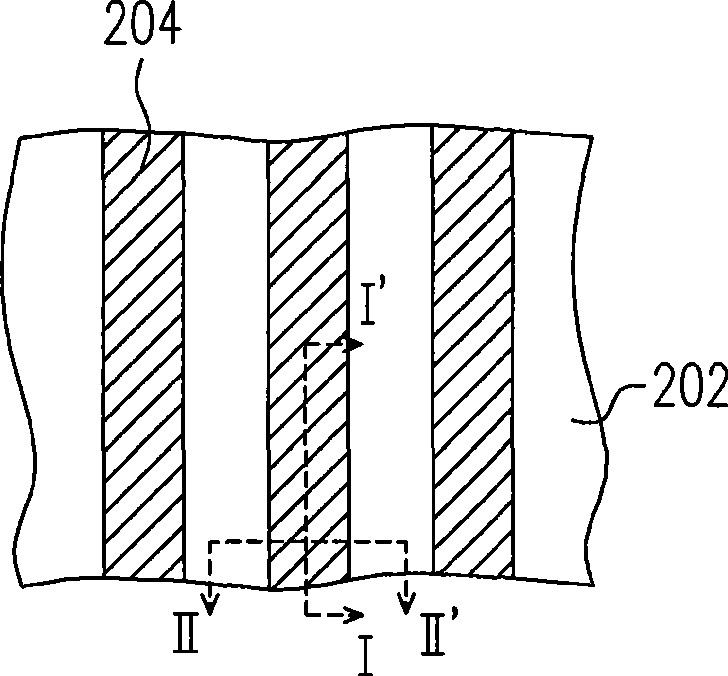

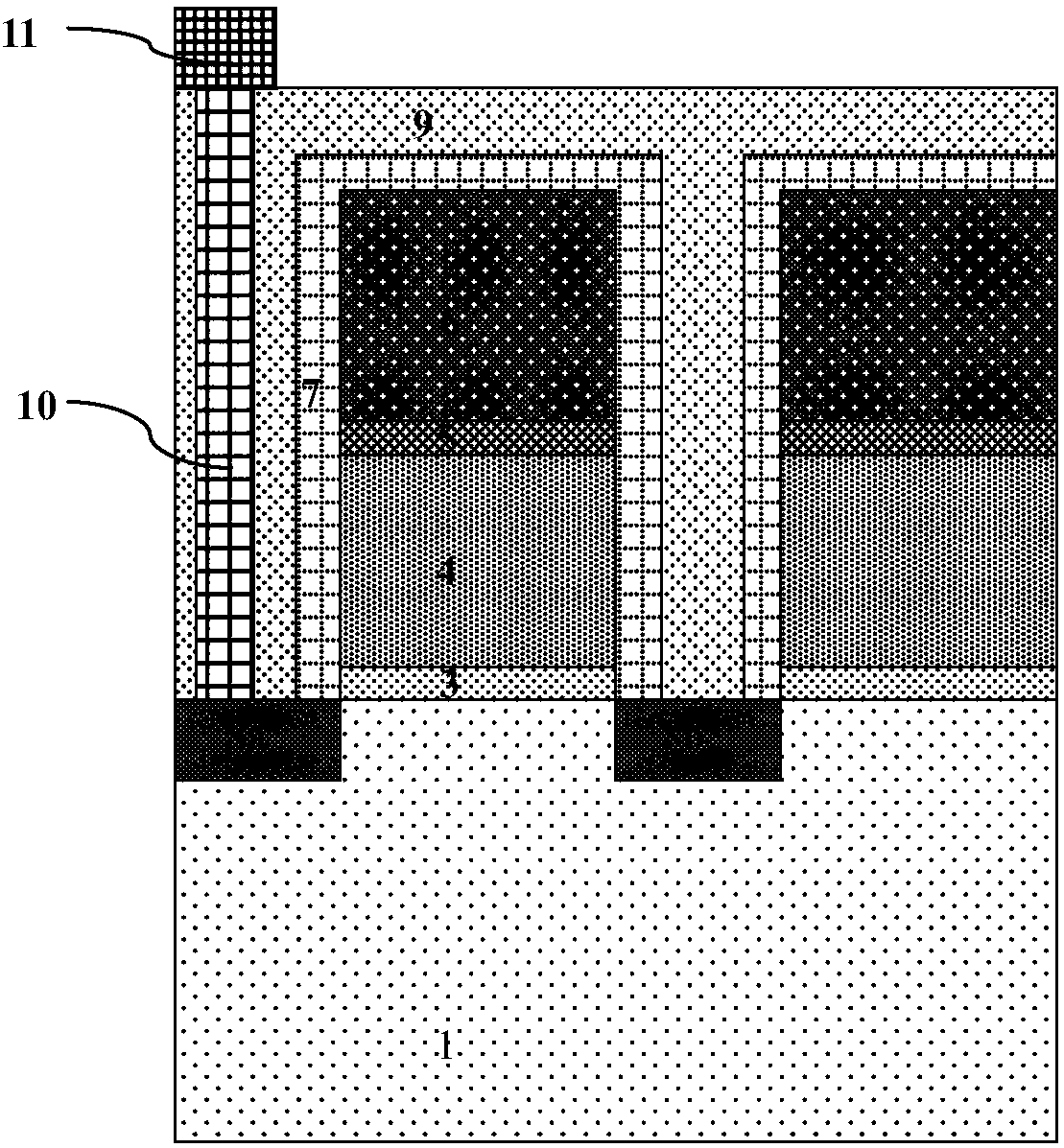

Flash memory cell, flash memory cell array and manufacturing method thereof

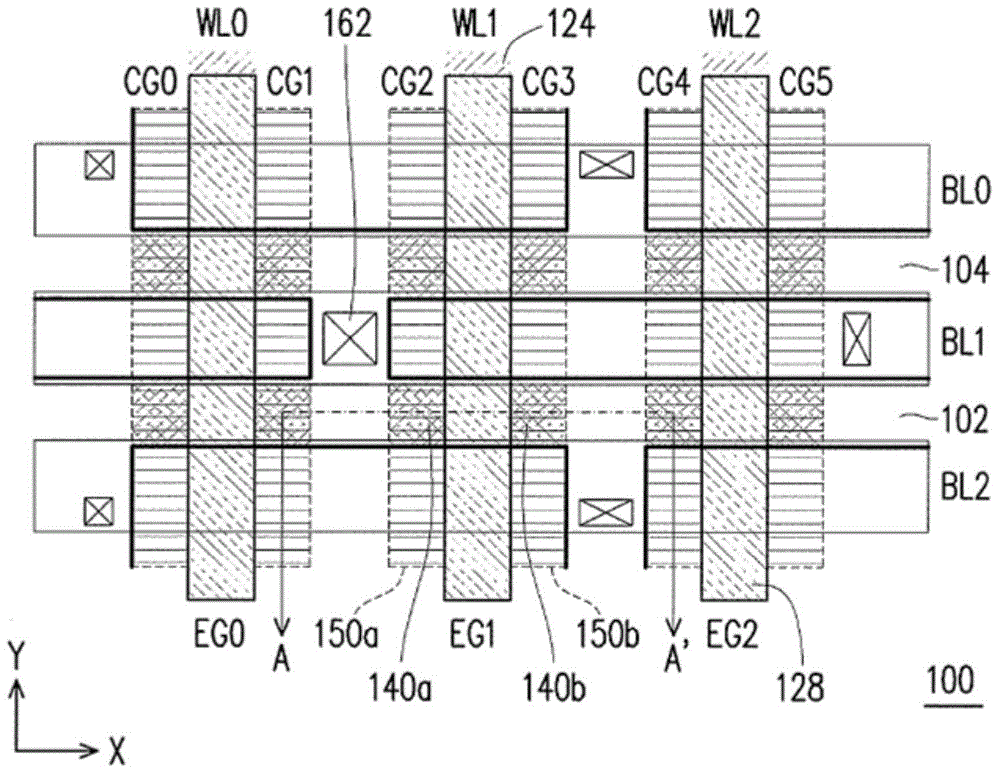

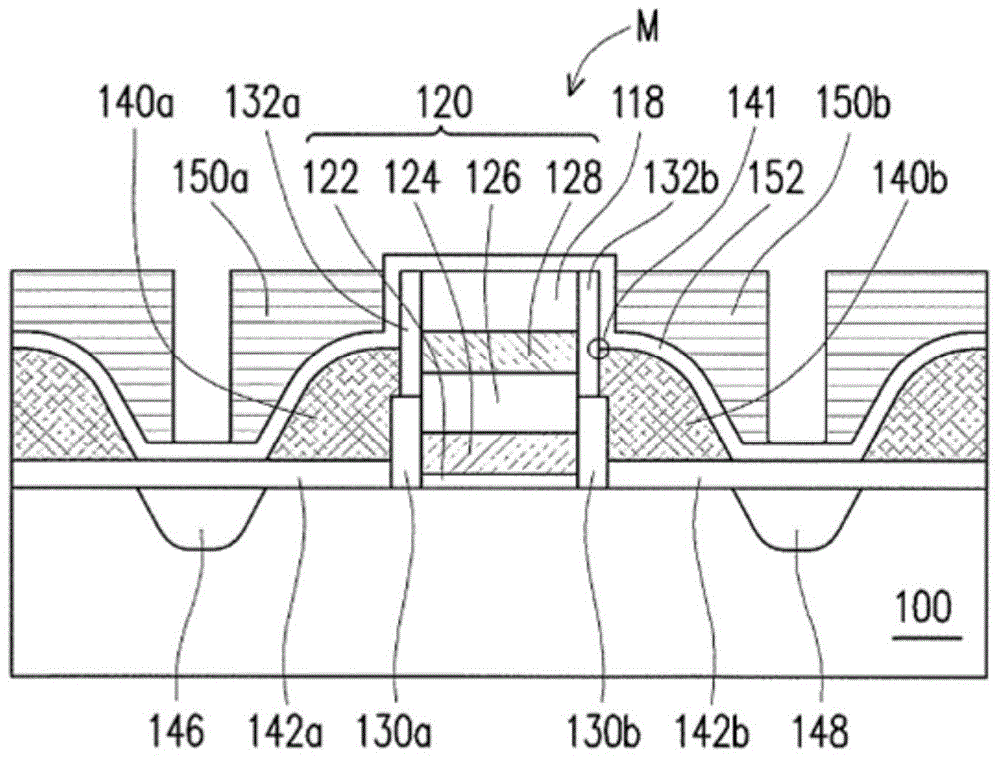

InactiveUS7057940B2Enhance programming speed and efficiencyImprove performanceSolid-state devicesRead-only memoriesGate dielectricUnit structure

A flash memory cell array comprises a substrate, a string of memory cell structures and source region / drain region. Each of memory cell structures includes a stack gate structure including a select gate dielectric layer, a select gate and a gate cap layer formed on the substrate; a spacer is set on the sidewall of the select gate; a control gate connected to the stack gate structure is set on the one side of the stack gate structure; a floating gate is set between the control gate and the substrate; an inter-gate dielectric layer is set between the control gate and the floating gate; and a tunneling dielectric layer is set between the floating gate and the substrate. The source region / drain region is set in the substrate near outer control gate and stack gate structure of the flash memory cell array.

Owner:POWERCHIP SEMICON MFG CORP

Non-contact type power feeder system for mobile object and protecting apparatus thereof

InactiveUS7804272B2Easy to manufactureLow costRail devicesBatteries circuit arrangementsContact typeEngineering

A noncontact type power feeder system for feeding a power to a mobile object, in which a power feeding portion and a power receiving portion can be easily manufactured at low costs and which can transmit a high power. The noncontact type power feeder system for a mobile object, comprises a power feeding portion provided in a surface on which the mobile object runs, and a power receiving portion provided in the lower part of the mobile object at a position facing to the power supply portion, the each of the power feeding portion and the power receiving portion is composed of windings formed in an oval shape, and a magnetic planar core formed therein with a recess in which the windings are accommodated so that the longitudinal direction of the oval shape of the windings is extended along the travel direction of the mobile object, the planer core is composed of several planar blocks each having a rectangular surface, several blocks being laid so that long sides of the rectangular surfaces are extended in the travel direction of the mobile object, in which several blocks are also laid in the direction orthogonal to the travel direction, and several blocks being superposed one upon another, the recess of the planar core is defined by thick wall parts in which the planar cores are superposed on the surface of the planar core, outside and inside of the oval shape part of the windings.

Owner:MITSUBISHI HEAVY IND ENG LTD

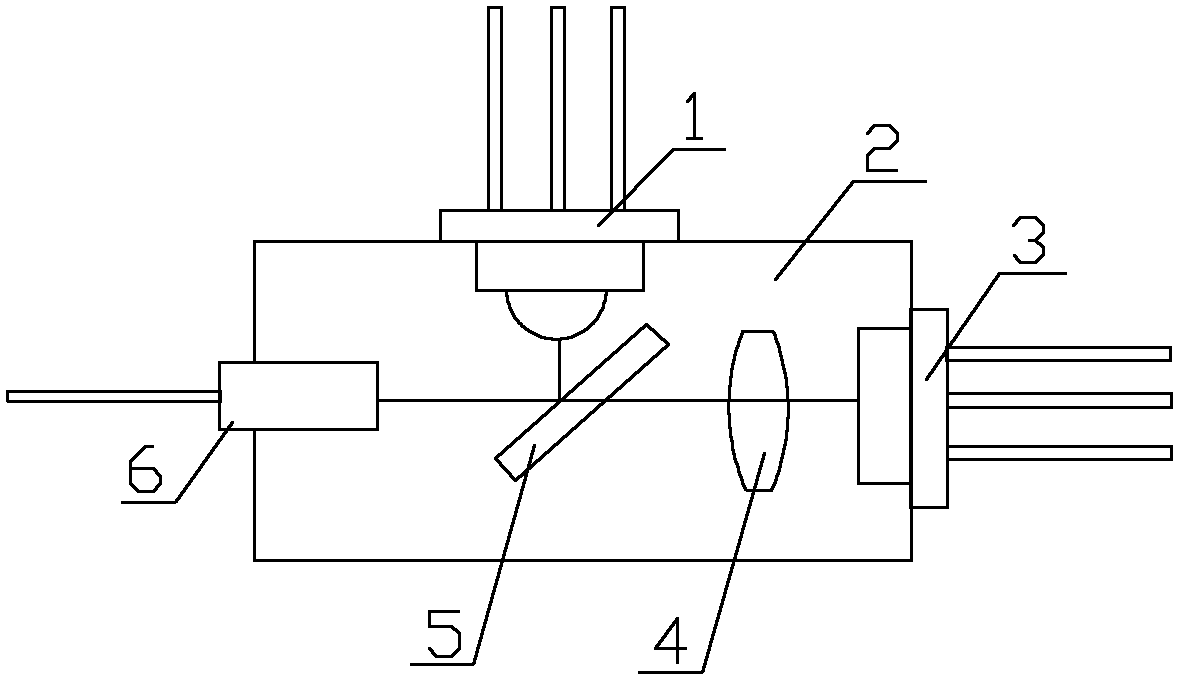

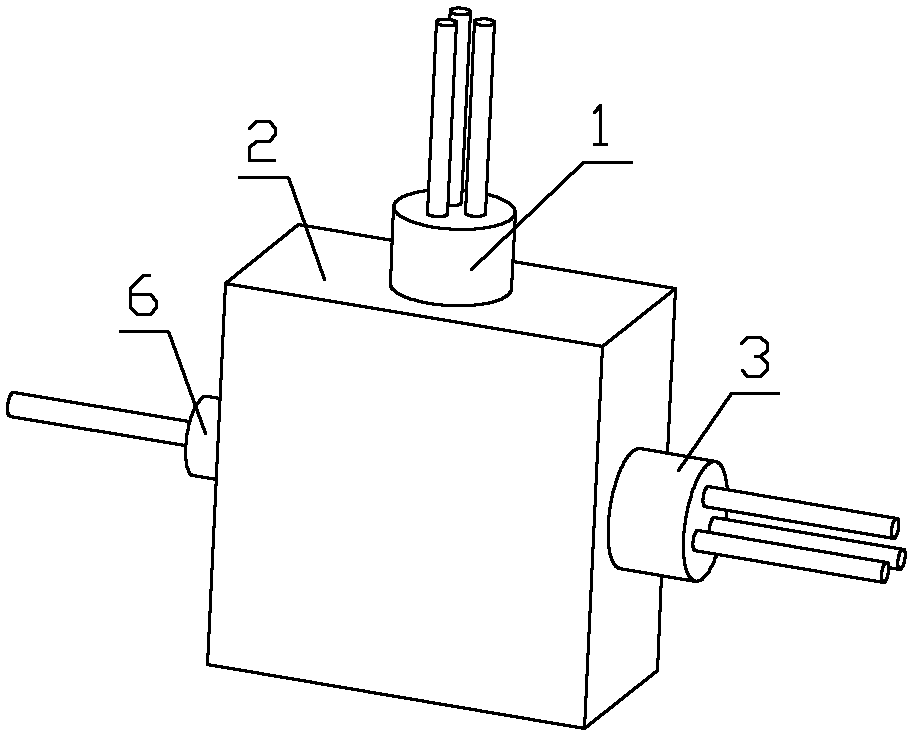

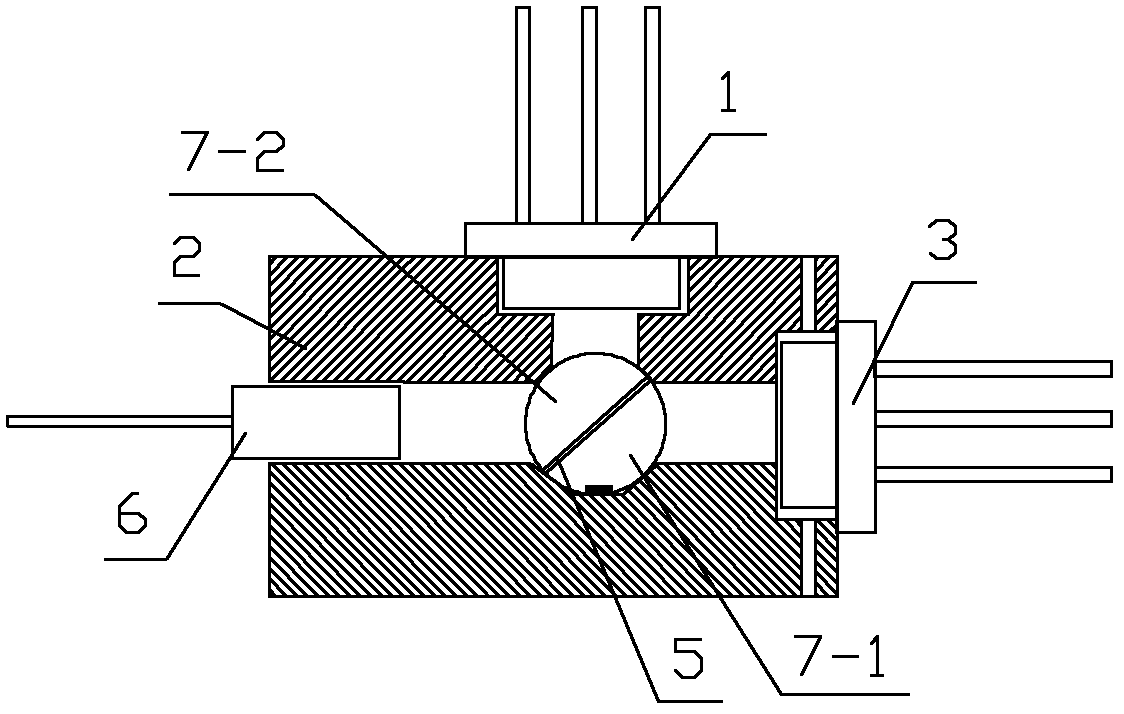

Single-fiber bidirectional transceiver module and capsulation thereof

The invention discloses a single-fiber bidirectional transceiver module which comprises a laser diode, a photodiode, a first lens and a second lens, wherein an optical splitter is arranged between the first lens and the second lens; the optical splitter is plated with an anti-reflection film and an anti-incidence film; and the first lens, the second lens, the laser diode and the photodiode have the same optical axis, and the optical axis is a straight line. The invention further discloses the capsulation for the module and an application method thereof. In the invention, the lens in the prior art and the hemispherical end surface of the photodiode are improved into the hemispherical lens or spherical lens in the direction of the laser diode, thereby reducing the dimension of an optical module in the direction of the laser diode and ensuring that multiple optical transceivers can be arranged on the circuit board with the same dimension or the same optical transceivers can be arranged; and the area of the circuit board is small, thereby enabling the dimension of the whole optical device to be reduced. In the invention, the focusing is carried out on optical signals by adopting the hemispherical lens or the spherical lens, thereby greatly enhancing the coupling ratio of the photodiode, the optical fiber and the optical path of the laser diode.

Owner:SOURCE PHOTONICS CHENGDU

Flash memory cell, flash memory cell array and manufacturing method thereof

InactiveUS6911690B2Improve programming speedImprove efficiencyTransistorRead-only memoriesGate dielectricDielectric layer

A flash memory cell array comprises a substrate, a string of memory cell structures and source region / drain region. Each of memory cell structures includes a stack gate structure including a select gate dielectric layer, a select gate and a gate cap layer formed on the substrate; a spacer is set on the sidewall of the select gate; a control gate connected to the stack gate structure is set on the one side of the stack gate structure; a floating gate is set between the control gate and the substrate; an inter-gate dielectric layer is set between the control gate and the floating gate; and a tunneling dielectric layer is set between the floating gate and the substrate. The source region / drain region is set in the substrate near outer control gate and stack gate structure of the flash memory cell array.

Owner:POWERCHIP SEMICON MFG CORP

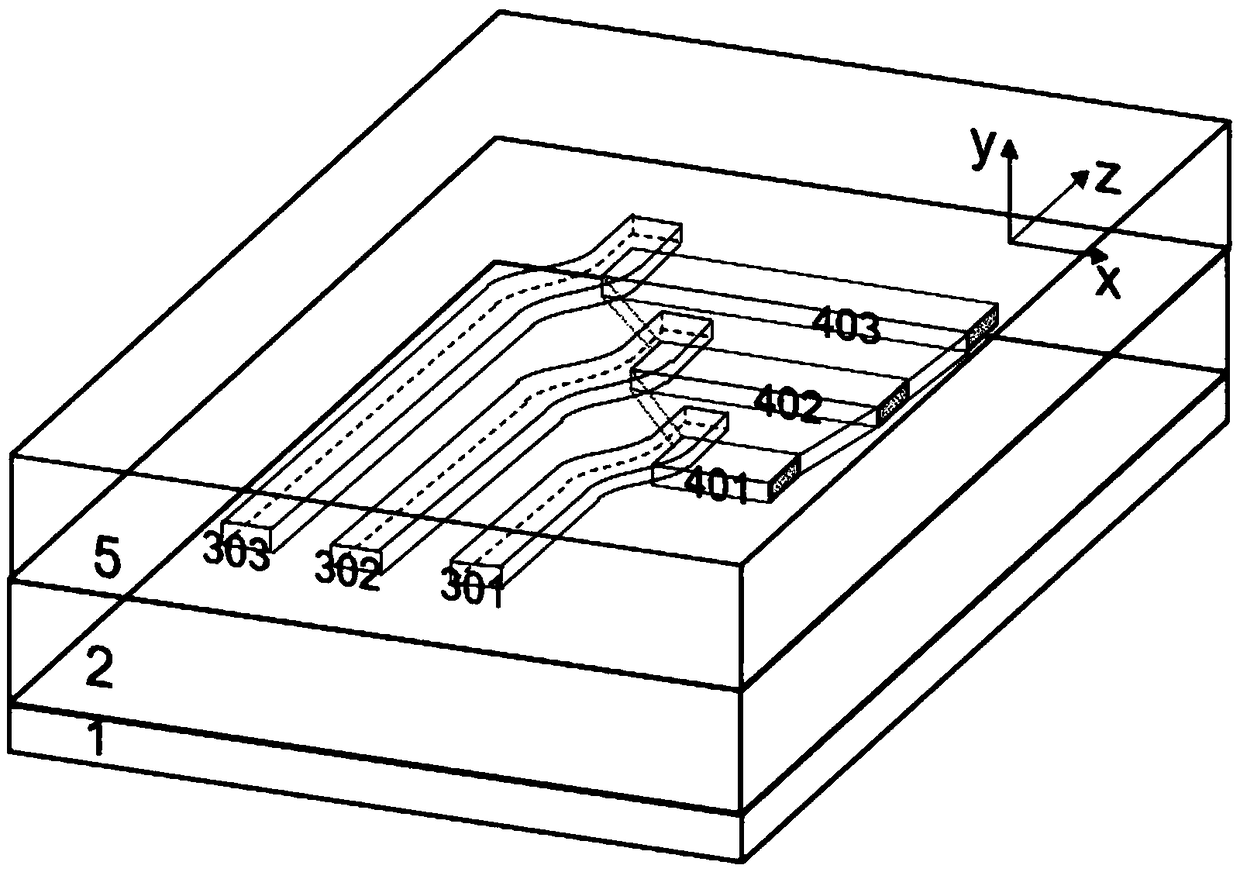

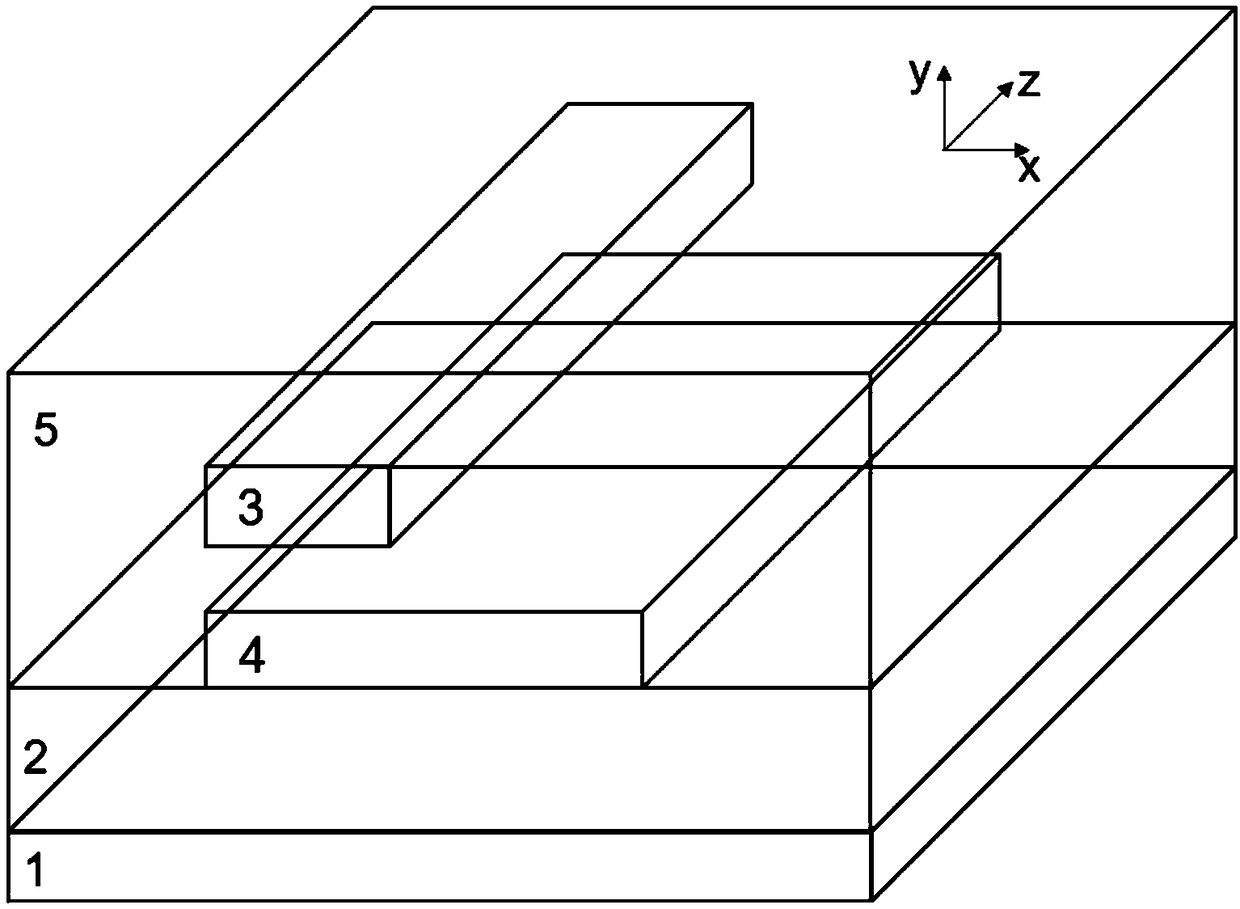

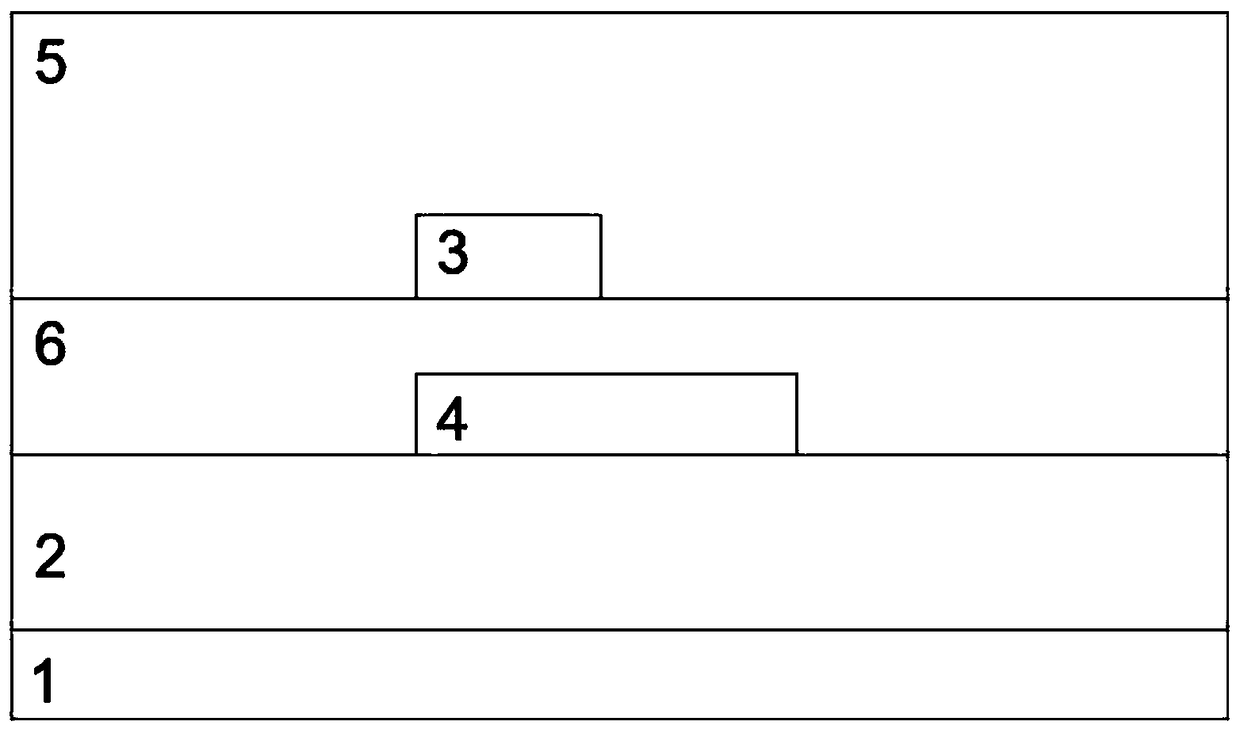

Three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and preparation method thereof

PendingCN108761637AIncrease the dimension of integrationHighly integratedOptical waveguide light guideMultiplexerDirect coupling

The invention relates to a three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and a preparation method thereof and belongs to the optical communication device technical field, in particular, a mode division multiplexing system. According to the three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and the preparation method thereof ofthe invention, a three-dimensional multilayer waveguide integrated structure is adopted, and therefore, the limitations of a traditional two-dimensional planar waveguide structure can be eliminated, the integration dimensions of the device can be increased, the integration and flexibility of the device can be enhanced, and the communication capacity of a system can be improved. The boundary of anyone side of the upper-layer waveguide of the three-dimensional waveguide is aligned with the boundary of any one side of the lower-layer waveguide of the three-dimensional waveguide, so that the direct three-dimensional coupling of a fundamental mode and a high-order mode is realized, and therefore, a defect that a traditional three-dimensional mode multiplexer fails to realize direct coupling ofmodes can be eliminated, and the structure and complexity of the device can be simplified. The device of the invention is prepared based on a mature CMOS process, so that high efficiency, low cost and mass production of the device can be realized. With the three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and the preparation method thereof of the invention adopted, the flexible three-dimensional coupling of the modes can be realized, a solid foundation is laid for on-chip mode multiplexing technology. The three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and the preparation method thereof can be further applied to the flexible mode routing of a mode division multiplexing network.

Owner:NANJING UNIV OF POSTS & TELECOMM

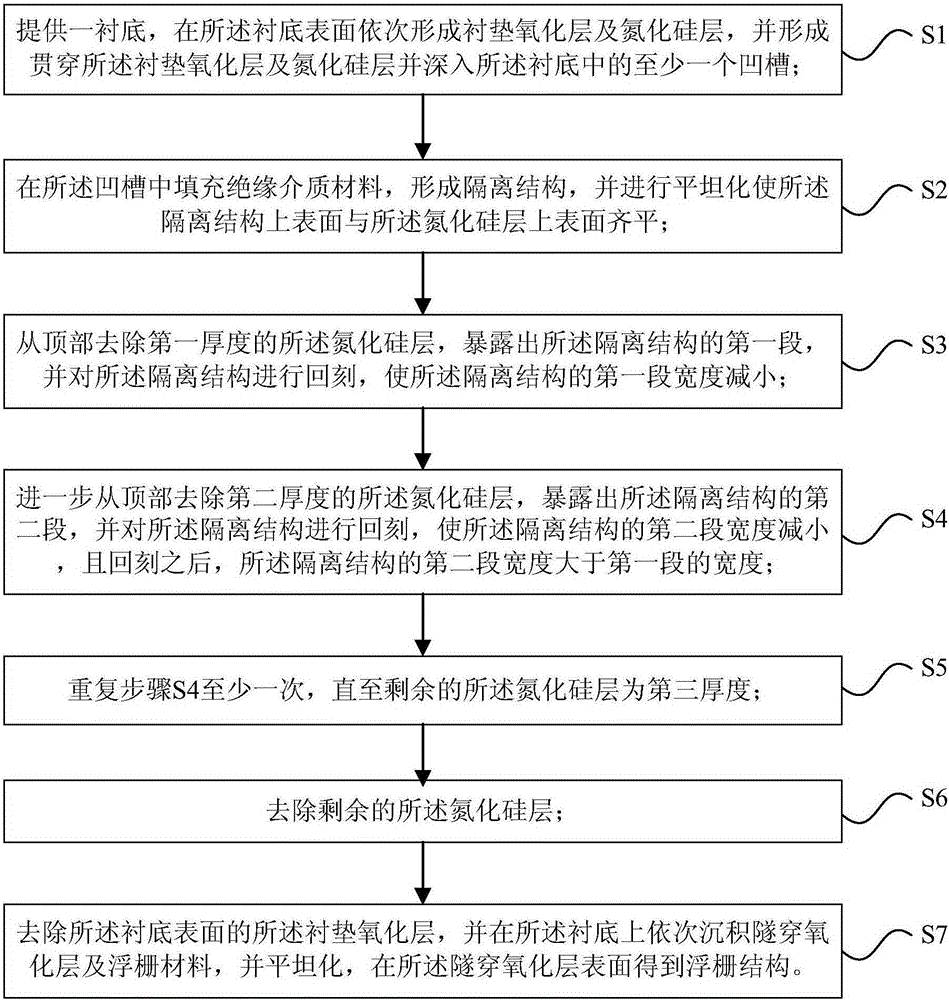

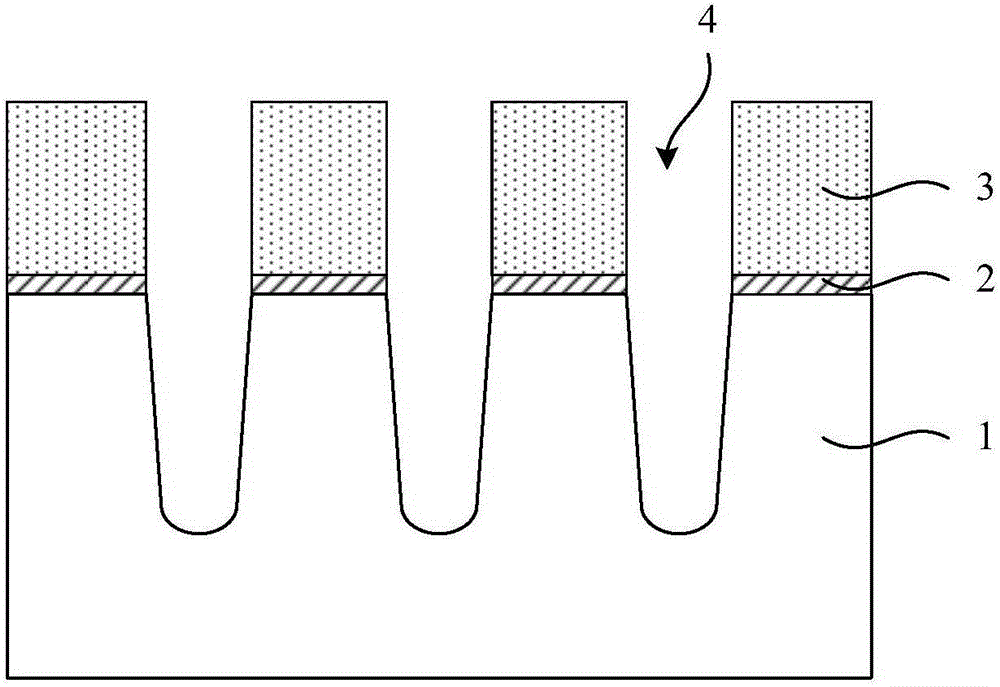

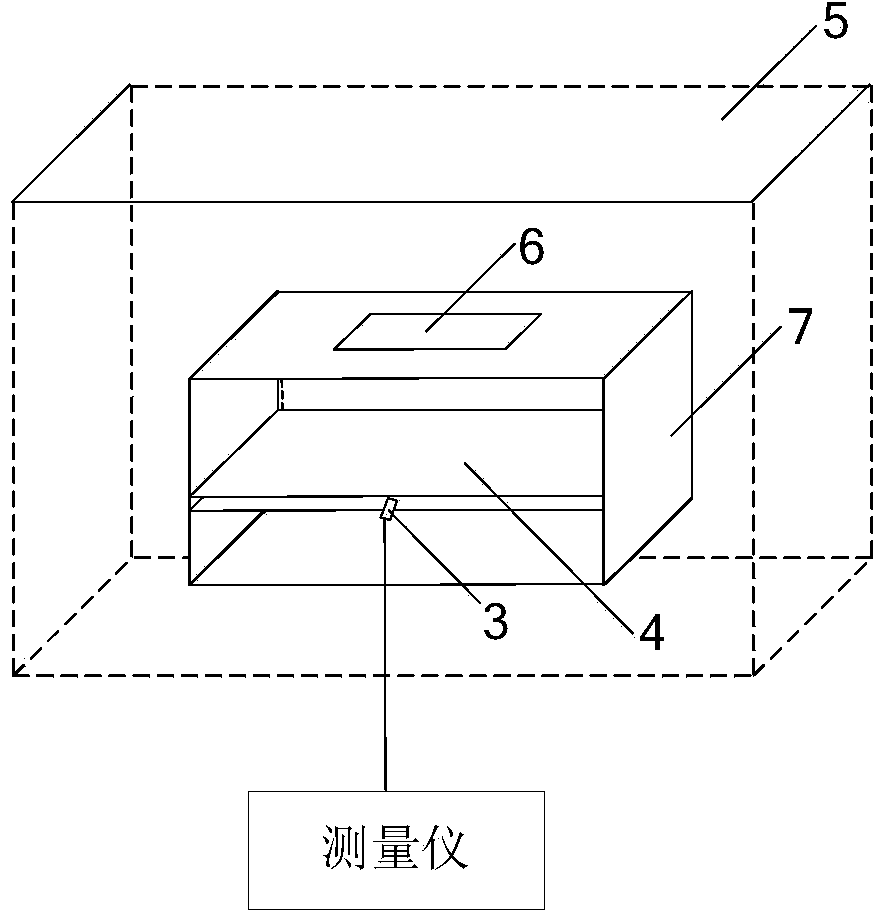

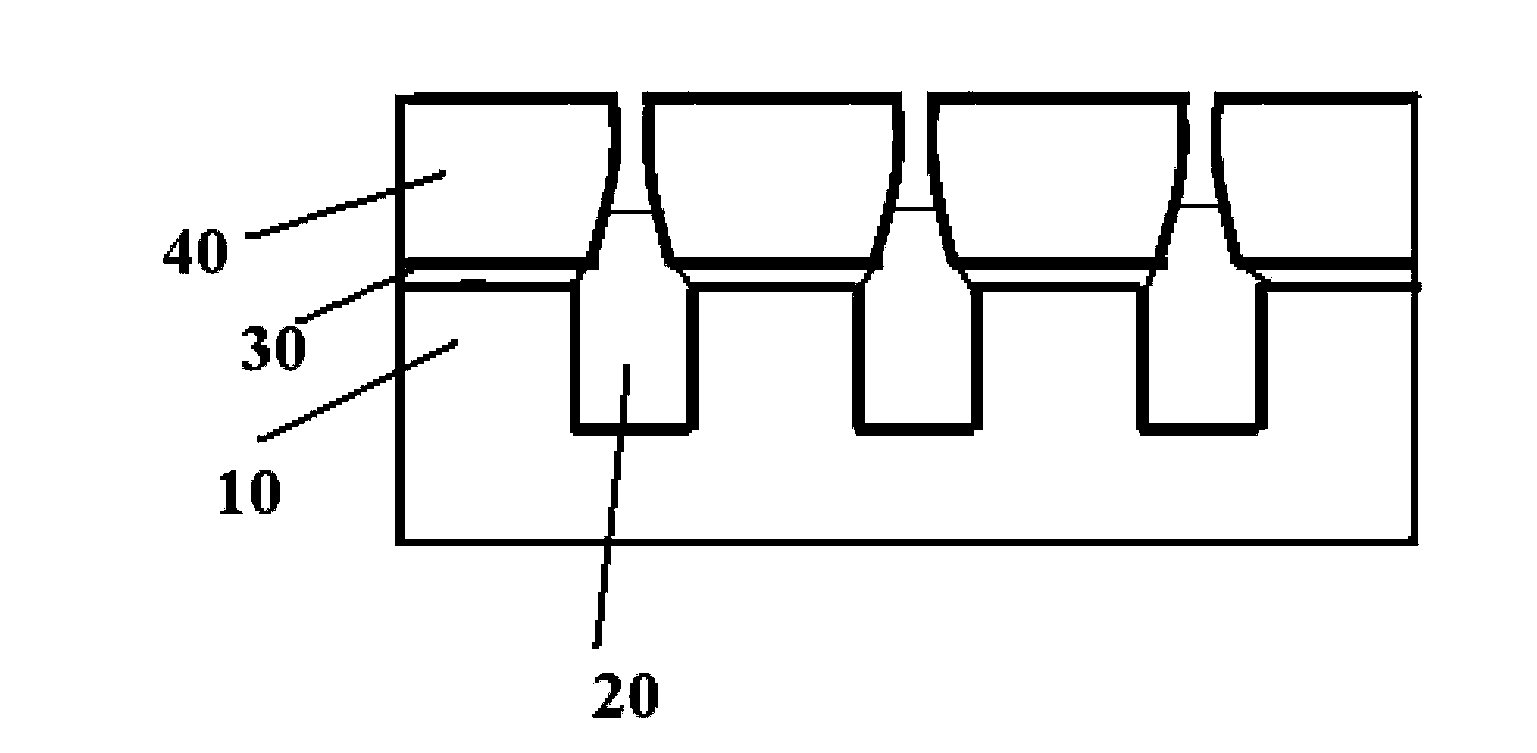

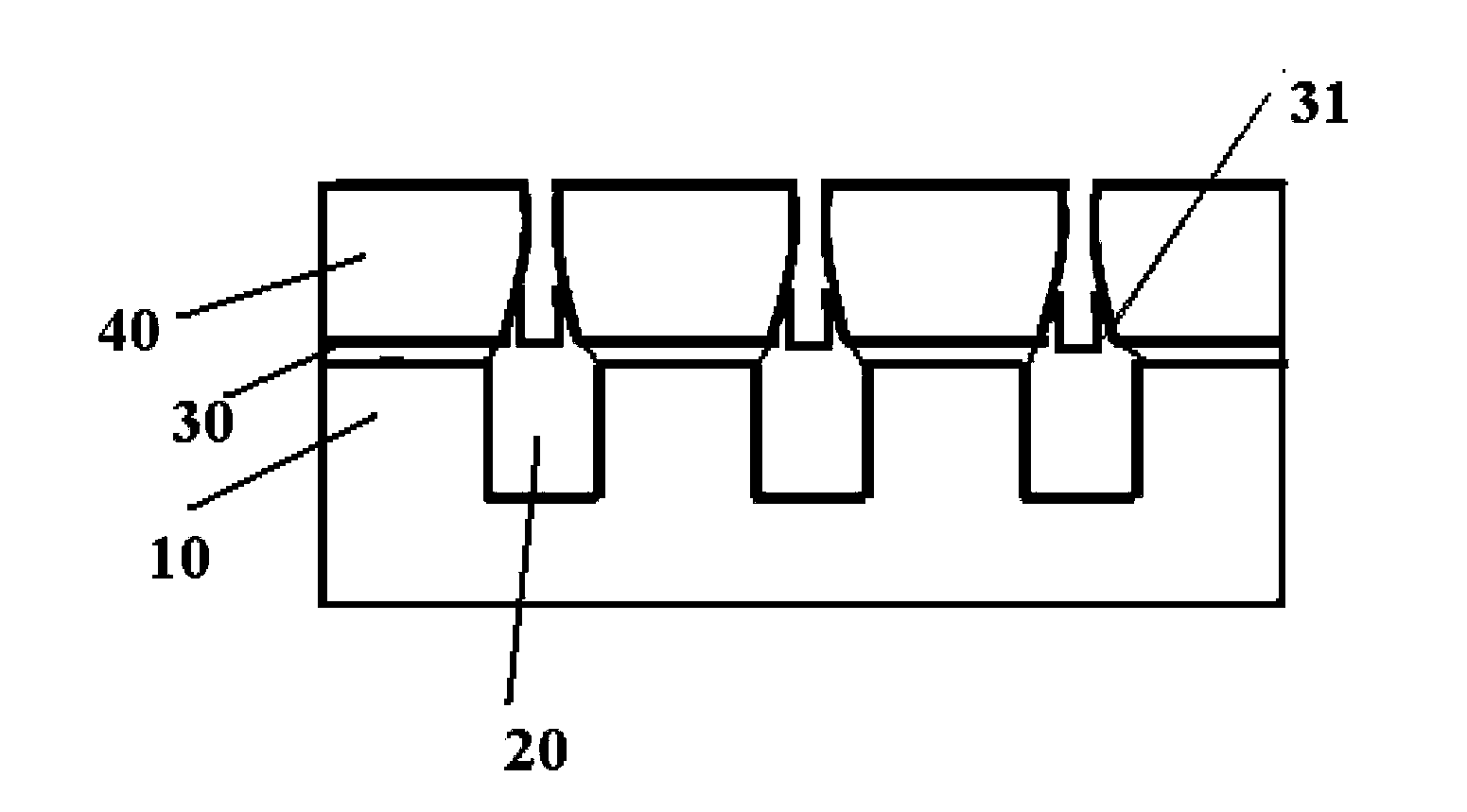

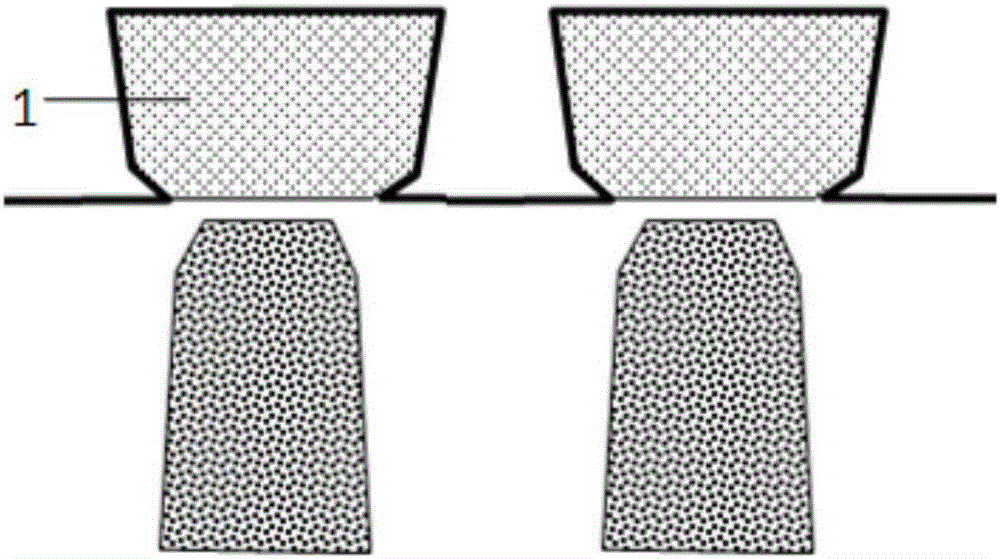

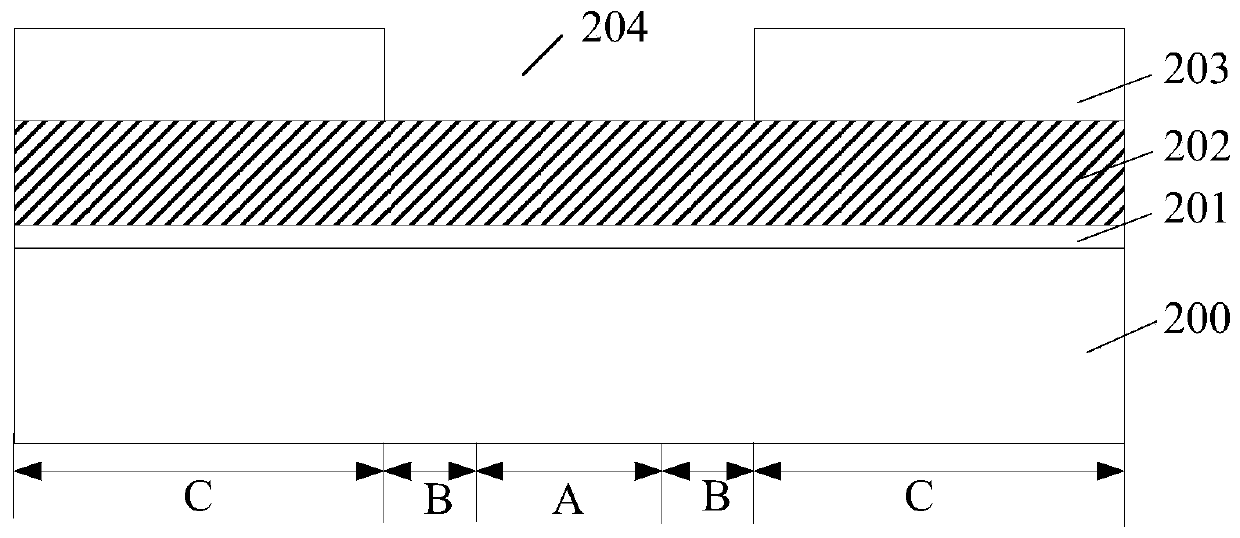

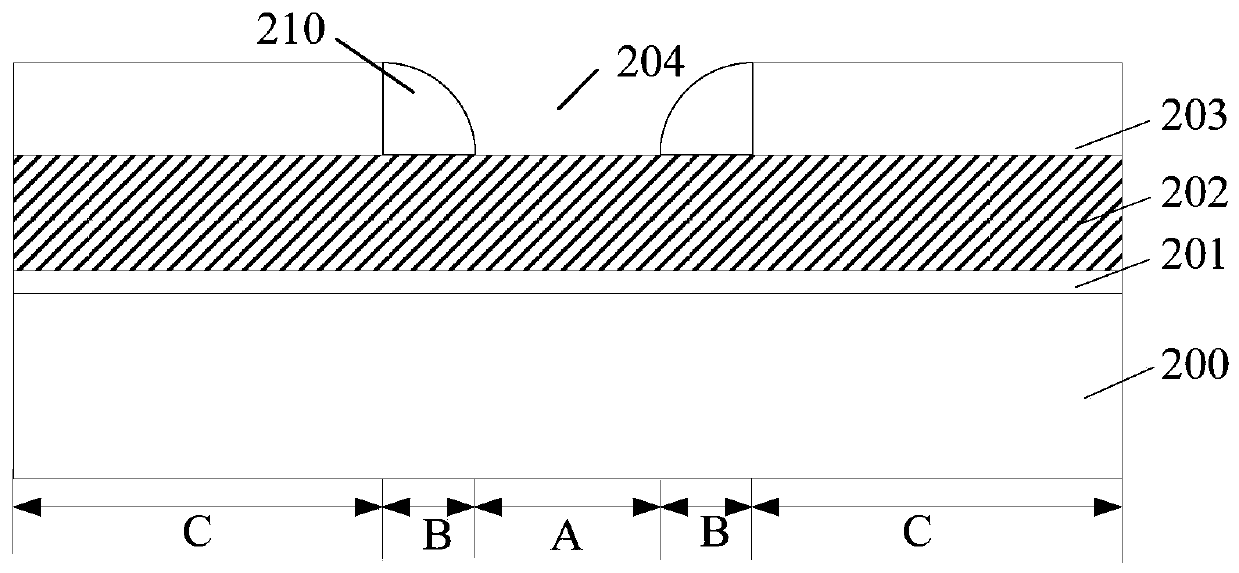

Semiconductor structure manufacturing method

ActiveCN106469730ARegulatory TopographyEasy to fillSolid-state devicesSemiconductor devicesSemiconductor structureEngineering

The invention discloses a semiconductor structure manufacturing method, which comprises the following steps: 1) forming at least one concave groove that penetrates a silicon nitride layer and goes deep into a substrate; 2) forming an isolation structure; 3) removing from the top a first thickness silicon nitride layer so as to expose the first section of the isolation structure; and conducting an etchback to the isolation structure to reduce the width of the first section; 4) further removing a second thickness silicon nitride layer so as to expose the second section of the isolation structure; and conducting an etchback to the isolation structure to reduce the width of the second section; 5) repeating the step 4 at least one time until the remaining silicon nitride layer is provided with a third thickness; 6) removing the remaining silicon nitride layer; and 7) depositing and obtaining a floating gate structure. According to the invention, in the manufacturing process of the floating gate, the floating gate is gradually enlarged to fill the upper opening while the active region CD at the bottom does not have to be enlarged. In this way, it is possible to enlarge the processing window and effectively avoid the appearance of holes in the floating gate. And it is also possible to better regulate the shape and appearance of the floating gate, increase the coupling rate of components and improve the breakdown performance between the active region and the control gate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

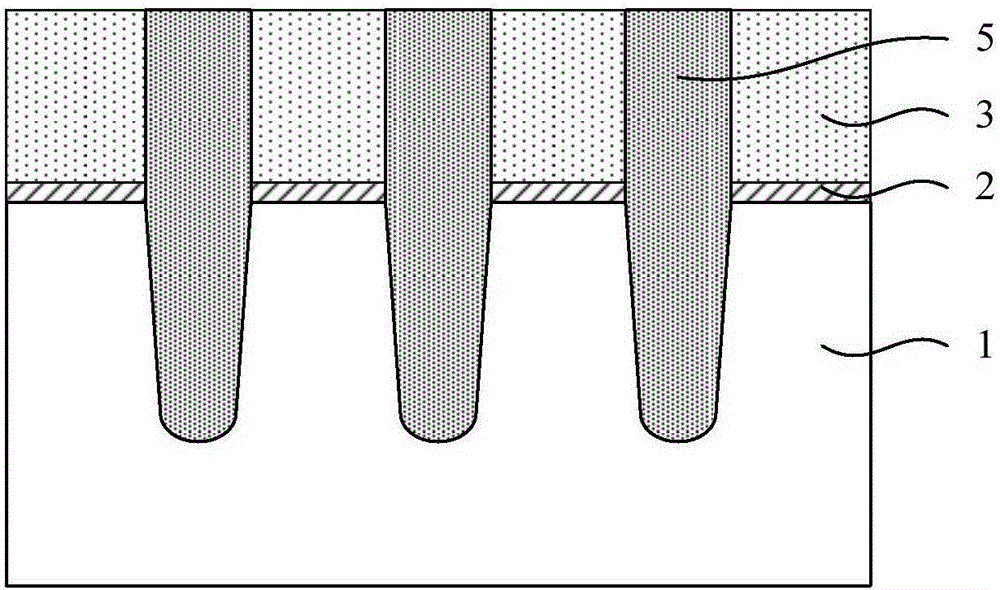

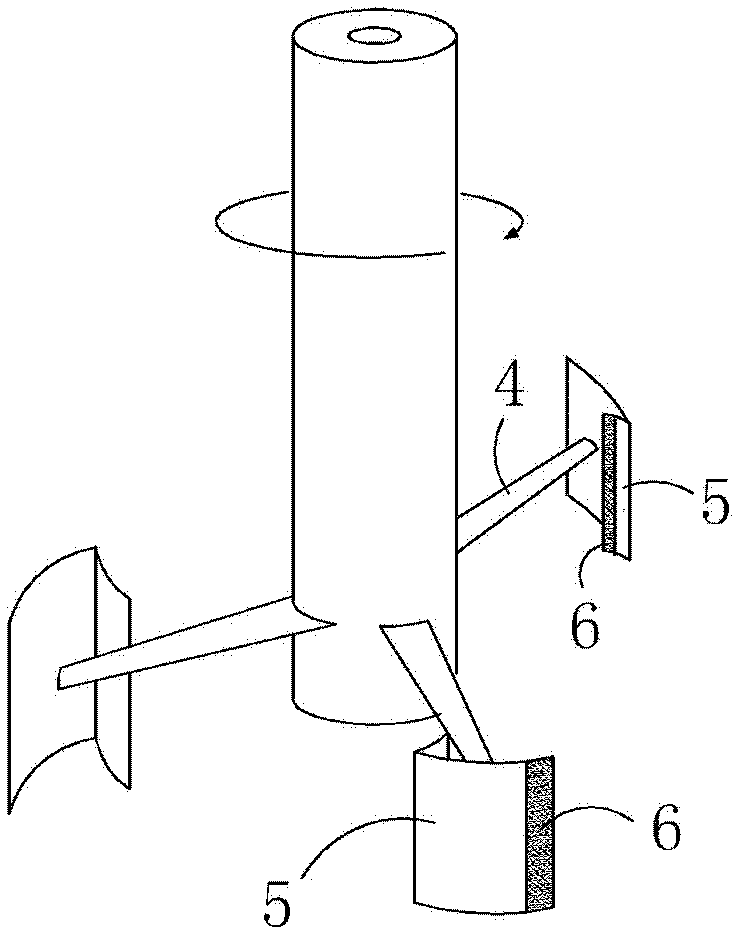

Coupled antenna and complete machine testing system

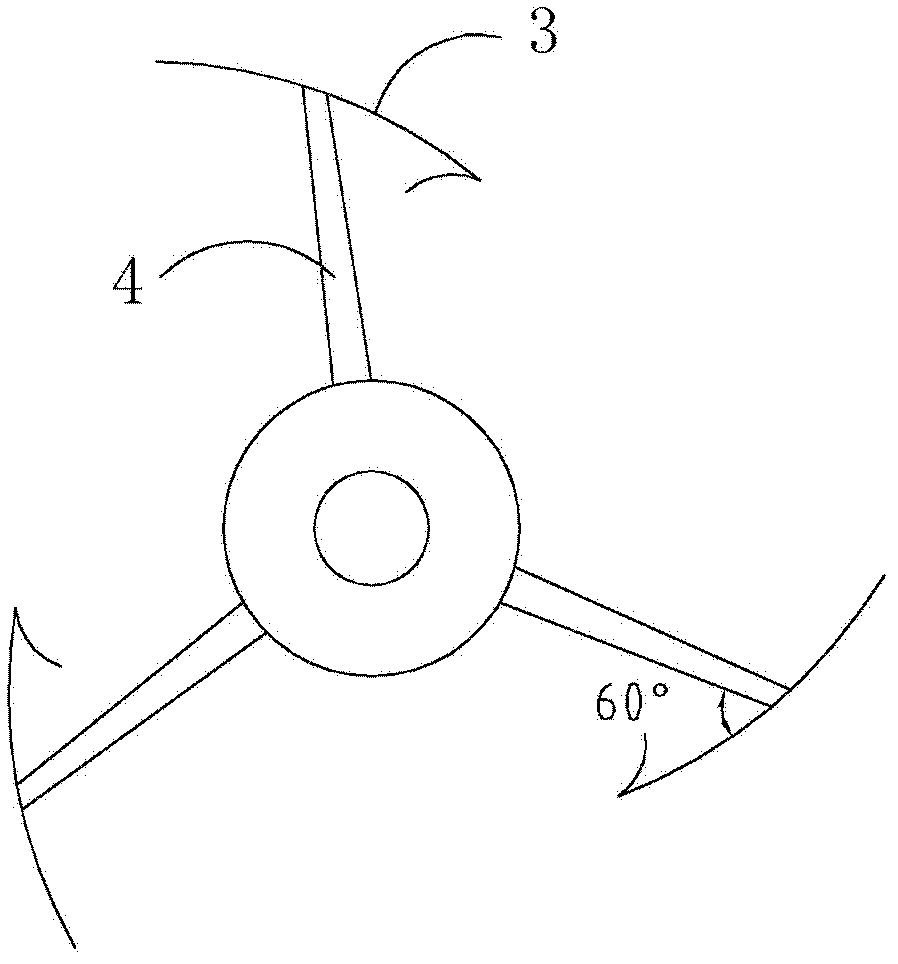

ActiveCN103682599AImprove the coupling rateTest accurateRadiating elements structural formsAntennas earthing switches associationFrequency bandPhysics

The invention belongs to the field of coupling testing and provides a coupled antenna and a complete machine testing system. The coupled antenna comprises a dipole used for coupling radio-frequency signals of a preset frequency band, a feeder line and a coupling testing interface. The dipole comprises two symmetric antenna elements and one of the symmetric antenna elements is grounded; one end of the feeder line is connected to a connecting point on the symmetric axis of the dipole and used for transmitting the radio-frequency signals received by coupling of the dipole to the coupling test interface; the coupling test interface is arranged at the other end of the feeder line and used for being externally connected with a gauge so as to accomplish whole machine testing. Thus, in the complete machine testing system, the coupled antenna is used for replacing a traditional coupling board and the coupling efficiency of the radio-frequency signals sent by the antenna of a coupling terminal device is improved, so that complete machine testing is accurately conducted through the radio-frequency signals coupled by the coupled antenna.

Owner:HONOR DEVICE CO LTD

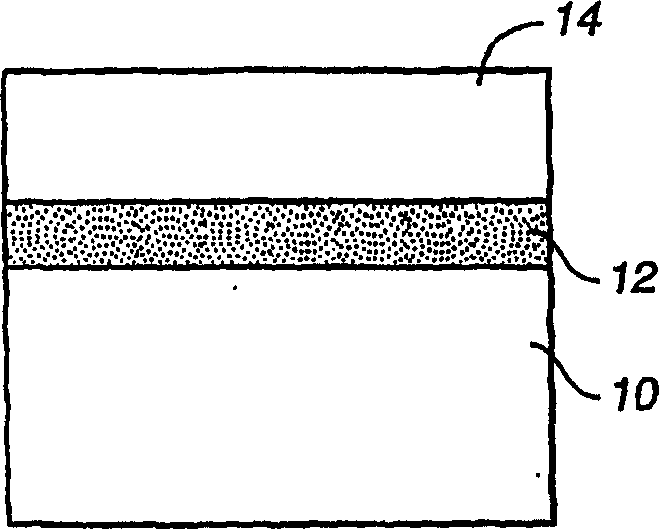

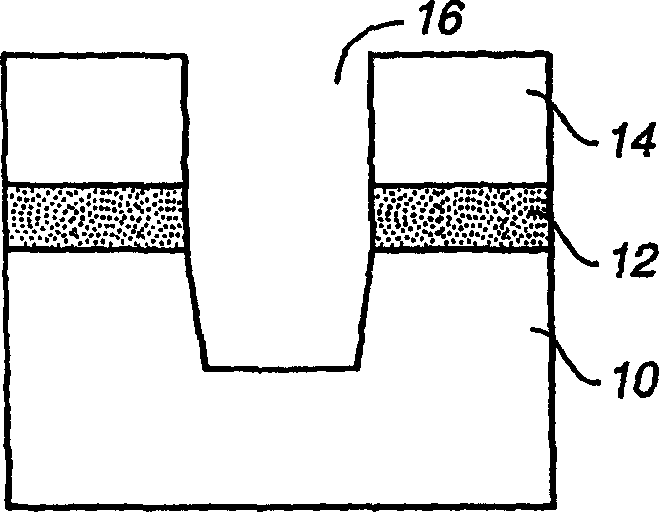

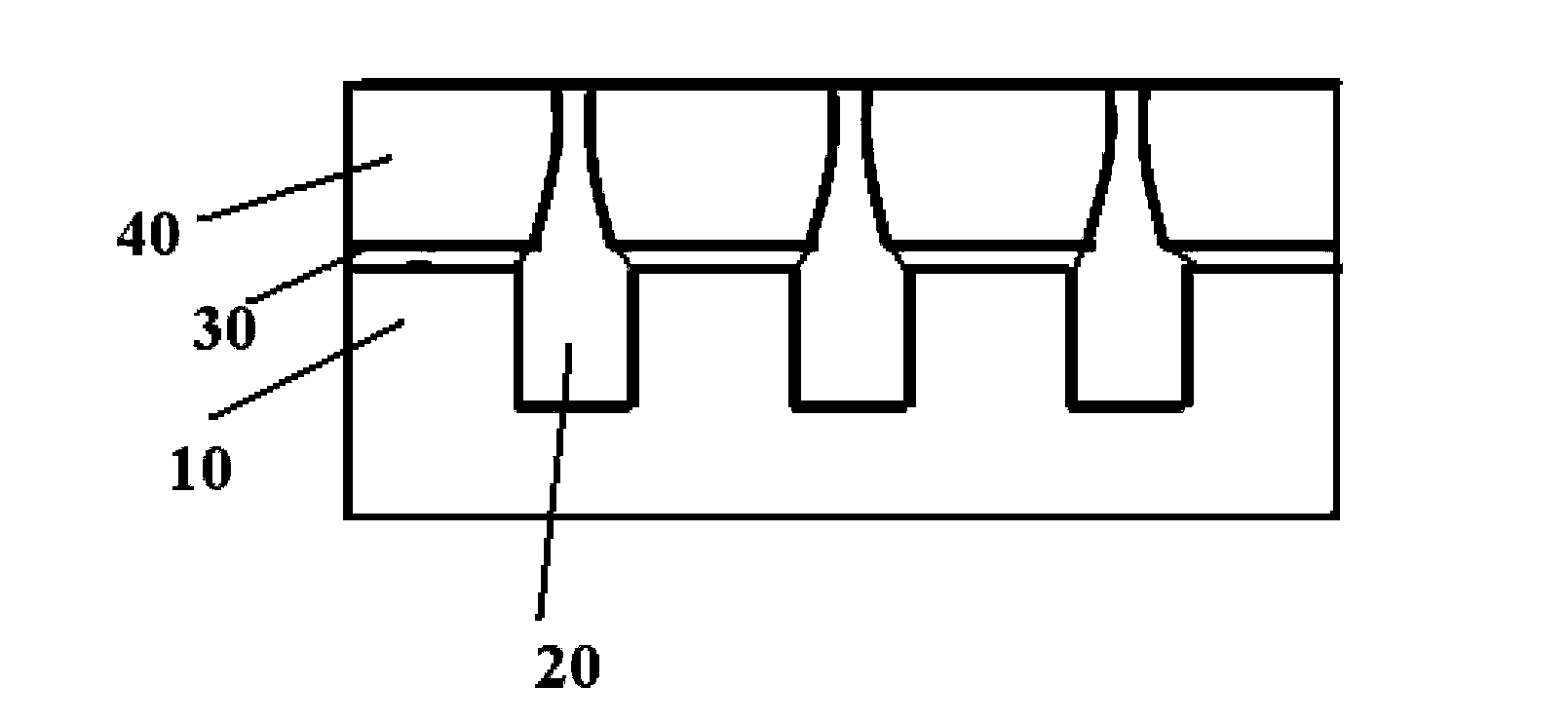

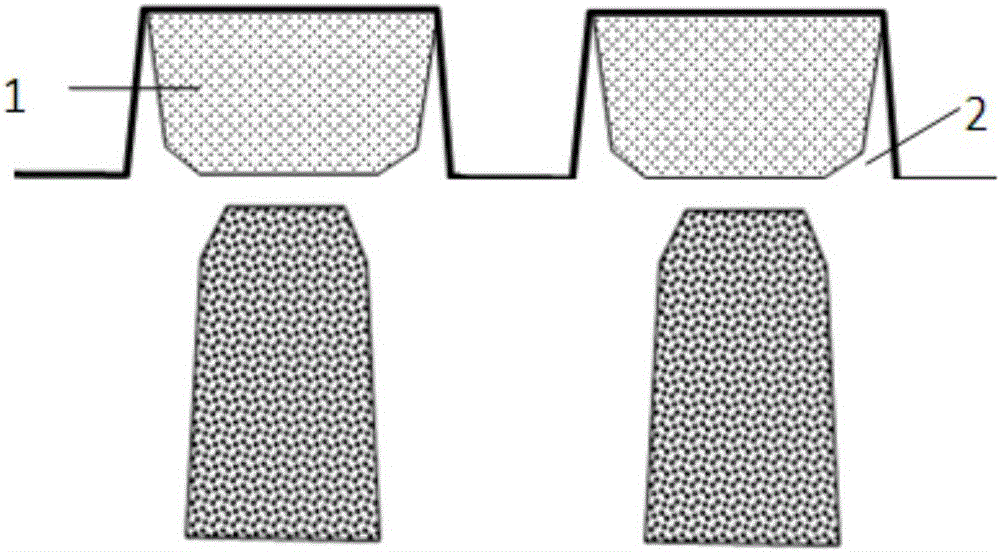

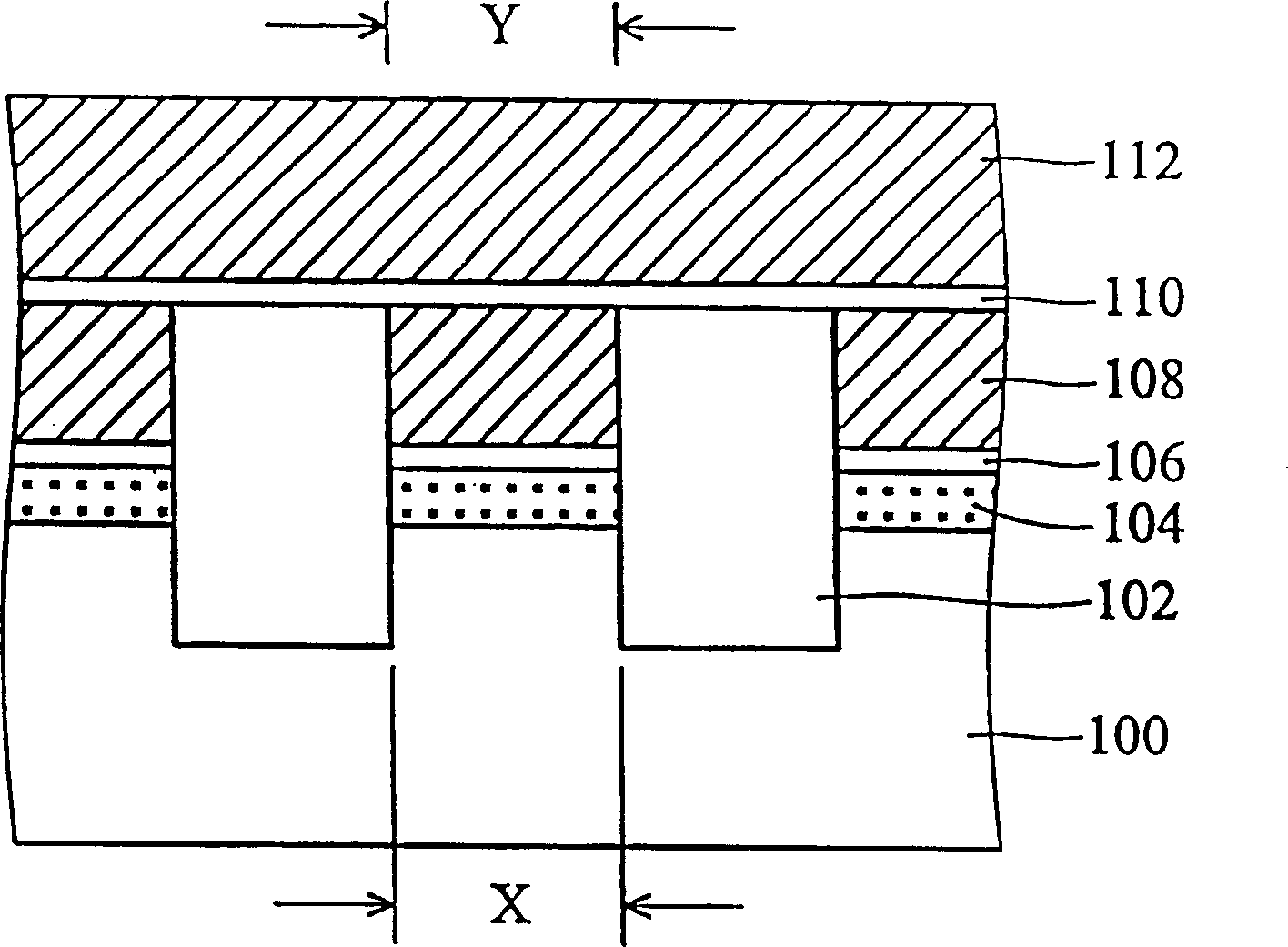

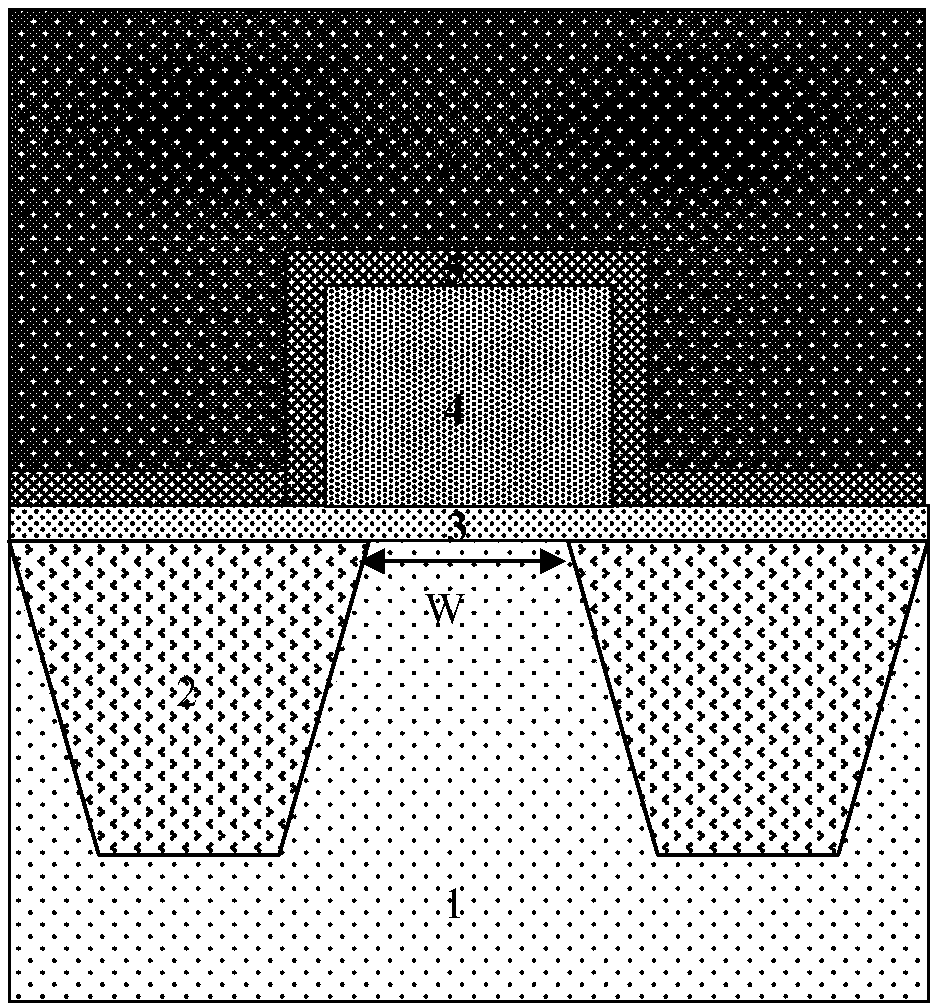

Method of forming shallow trench isolation structure in a semiconductor device

InactiveCN1701433AExtend etch timeImprove the coupling rateSolid-state devicesSemiconductor/solid-state device manufacturingAnisotropic etchingNitride

A method (Figs. 3A-3I) for fabricating a shallow trench isolation structure (Fig. 4) is described, in which a bottom pad oxide layer (62), a middle silicon nitride layer (64), a middle oxide layer (66) and a top silicon nitride layer (68) are sequentially formed on a silicon substrate (60). Photo-lithographic masking and anisotropic etching are then conducted to form a trench (70) in the substrate. An oxide material (80) is then deposited on top of the top silicon nitride layer, filling up the trenches at the same time (Fig. 3E). The top silicon nitride layer is then removed, followed by an isotropic etch of the oxide layer below. With the middle nitride layer acting as a natural etch stop, the oxide material is sculpted to a desirable shape. The middle nitride layer and the pad oxide layer are subsequently removed to complete the fabrication of a shallow trench isolation structure.

Owner:ATMEL CORP

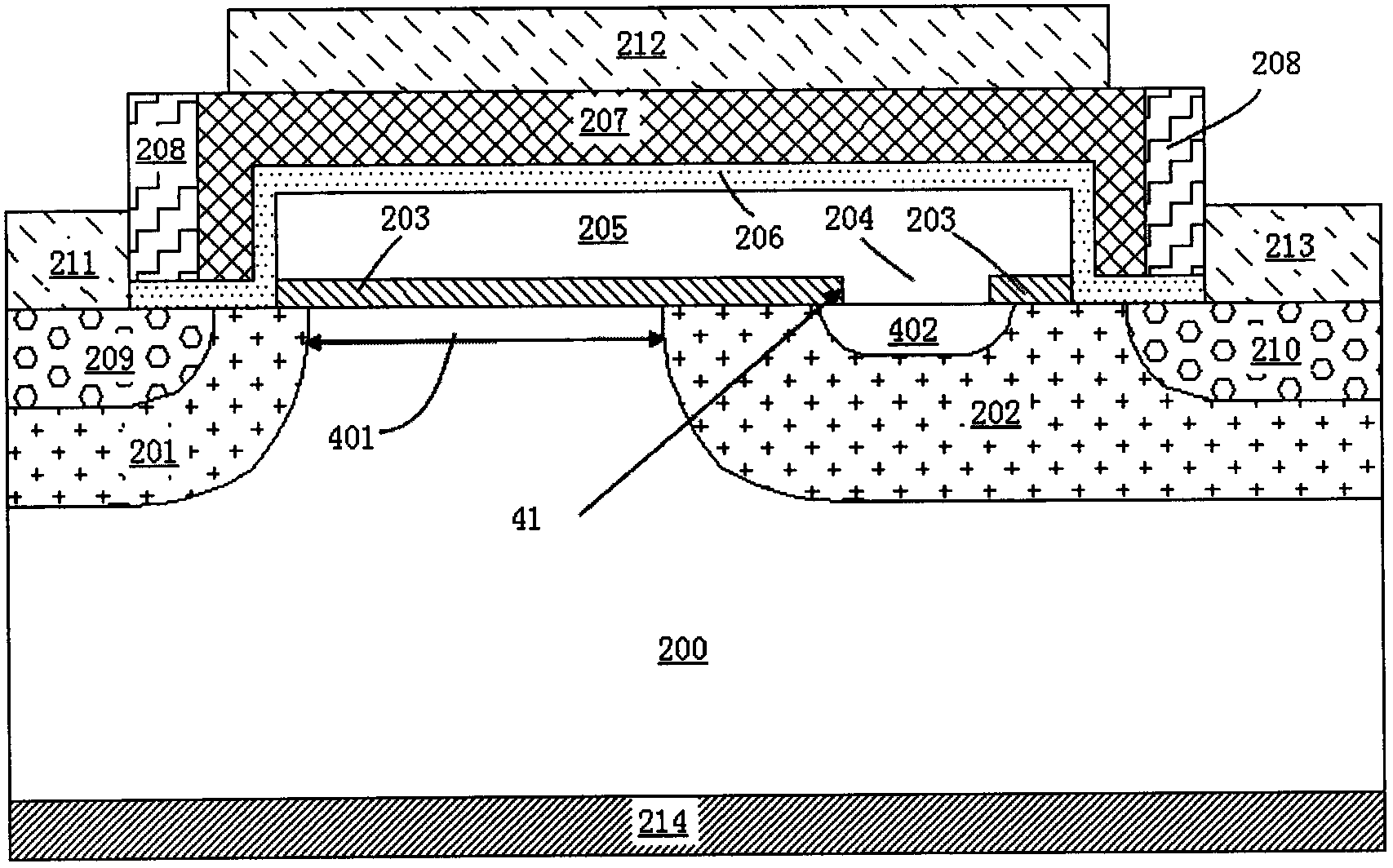

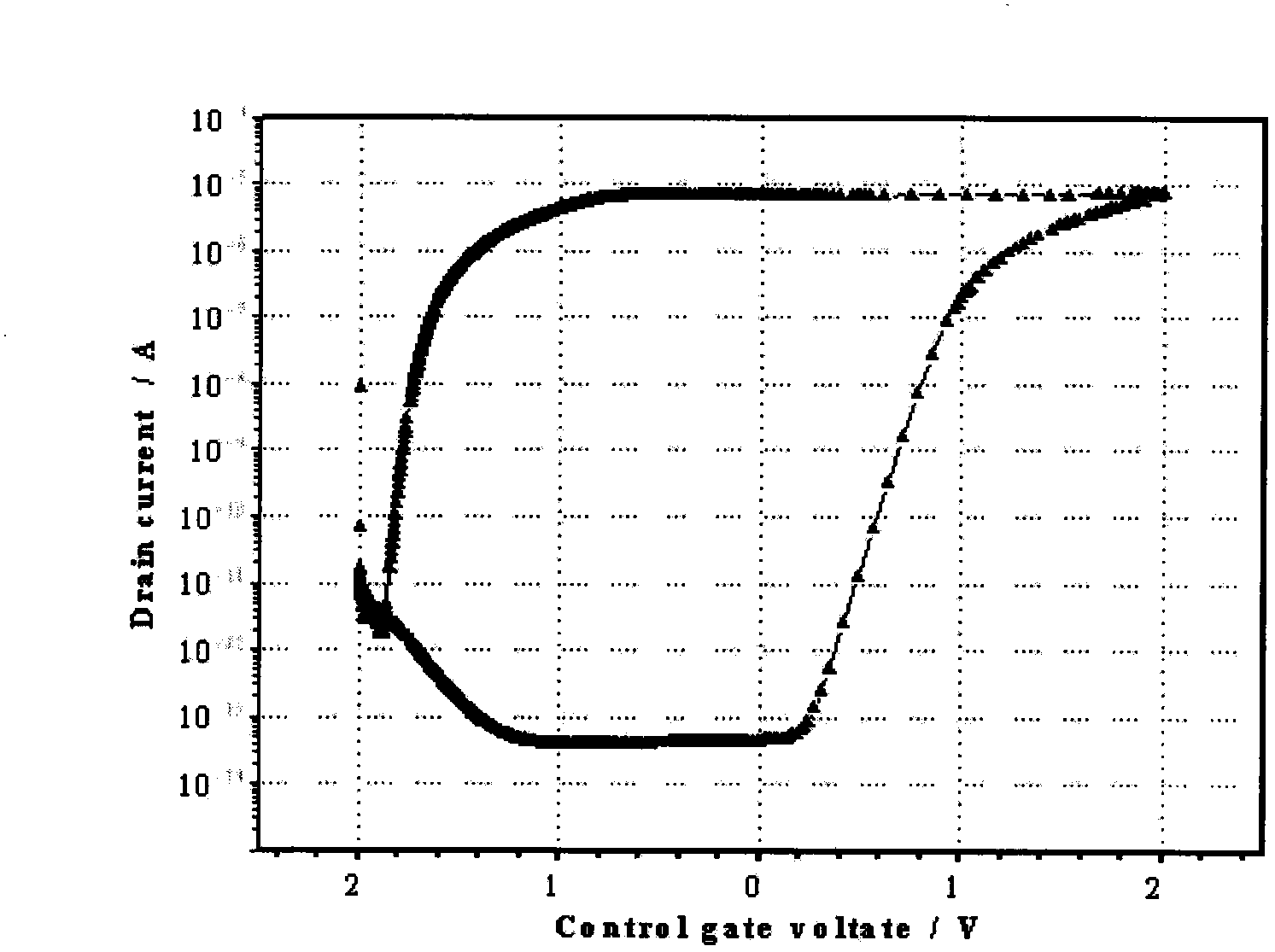

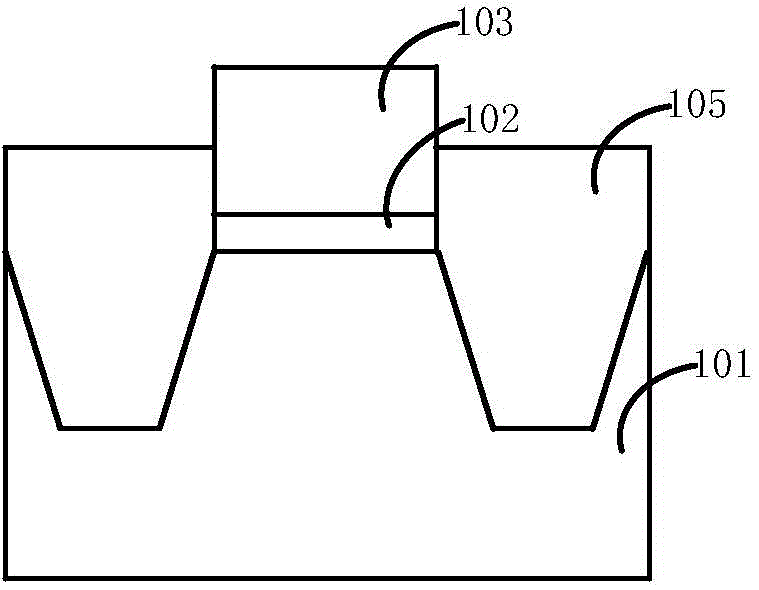

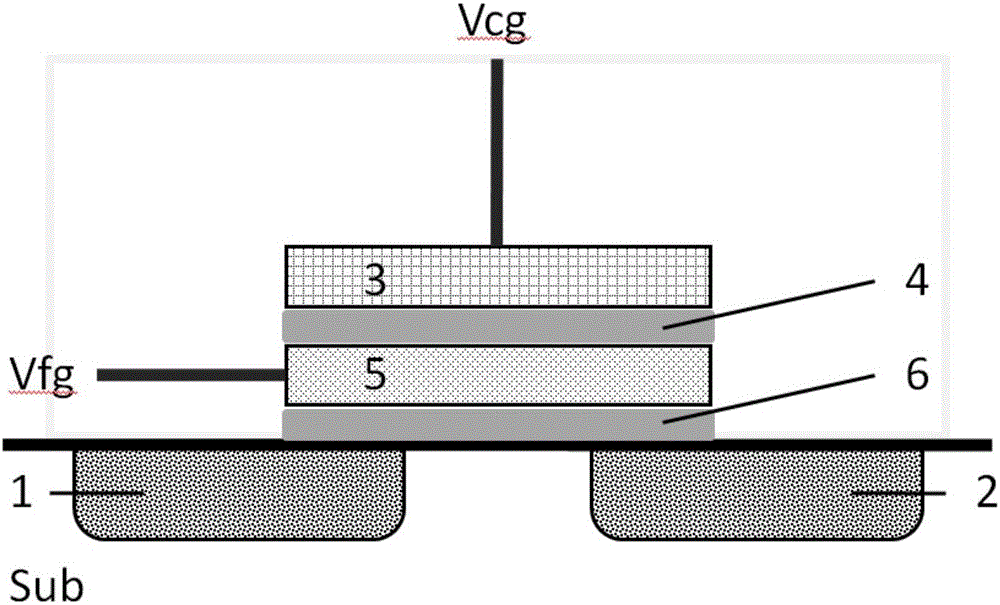

Semiconductor device and manufacturing method thereof

InactiveCN103915439AImprove the coupling rateReduce operating voltageSolid-state devicesSemiconductor/solid-state device manufacturingCoupling efficiencyCharge and discharge

The invention belongs to the technical field of semiconductor memories, and particularly relates to a semiconductor device which comprises at least one semiconductor substrate, a source region, a drain region, a floating gate, a control gate and a grid-control p-n junction diode used for connecting the floating gate and the substrate. The semiconductor device is used for storing information of the floating gate and charging and discharging the floating gate through the grid-control p-n junction diode, and has the advantages that coupling efficiency of the control gate is high, and operation voltage in storage of data is low. By means of the semiconductor device, quick storage and compatible manufacturing of logic devices and flash memory devices can be achieved.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

Method of manufacturing flash memory device

ActiveCN1992231AImprove the coupling rateAvoid damageSemiconductor/solid-state device manufacturingResistCoupling ratio

A method of manufacturing a flash memory device. According to the invention, a floating gate can be formed and a distance between cells can be secured sufficiently by using one conductive layer without using a SA-STI process that cannot be applied to the manufacture process of high-integrated semiconductor devices. It is therefore possible to minimize an interference phenomenon between neighboring cells. Furthermore, an isolation film is etched after a photoresist film covering only a high-voltage transistor region is formed, or a gate oxide film is formed after a semiconductor substrate is etched at a thickness, which is the same as that of the gate oxide film of the high-voltage transistor region, so that a step between the cell region and the high-voltage transistor region is the same. Accordingly, the coupling ratio can be increased even by the gate oxide film of the high-voltage transistor region, which is thicker than the tunnel oxide film of the cell region. In addition, damage to a tunnel oxide film, a semiconductor substrate or a floating gate while an isolation film is etched at a predetermined depth in order to control the EFH can be prevented by controlling the EFH in such a manner than conductive layer spacers are formed on sidewalls of the floating gate and the isolation film is further etched.

Owner:SK HYNIX INC

Manufacturing method of flash memory

InactiveCN1571146ALower the altitudeIncrease the overlapping areaSemiconductor/solid-state device manufacturingElectrical conductorEngineering

The invention is a flash memory manufacturing method, in turn forming tunneled dielectric layer, conductor layer and mask layer on a substrate, then patternizing the conductor layer and the mask layer, forming vertically-arranged sticks on the substrate, then forming a buried drain region in the substrate between two adjacent sticks, successively patternizing the sticks, and forming floating grid structure on the substrate, then forming insulating layer around the floating grid structure, where the surface of the insulating layer is lower than the top surface of the patternized conductor layer in the floating grid structure to expose partial surface of side wall around the patternized conductor layer, successively removing the mask layer, forming grid-grid dielectric layer on the conductor layer and then forming control grid on the grid-grid dielectric layer.

Owner:MACRONIX INT CO LTD

Nonvolatile memory

ActiveCN106206588APromote accumulationThe overall thickness is thinSolid-state devicesSemiconductor devicesGate dielectricInsulation layer

The invention provides a nonvolatile memory. The nonvolatile memory is provided with a storage unit, wherein the storage unit is provided with a stack structure, a first floating gate, a second floating gate, erase gate dielectric layers, auxiliary gate dielectric layers, a first doping region, a second doping region, a first control gate and a second gate, wherein the stack structure comprises a gate dielectric layer, an auxiliary gate, an insulation layer and an erase gate which are sequentially arranged, the first floating gate and the second floating gate are respectively arranged on side walls of two sides of the stack structure, the erase gate dielectric layers are arranged between the erase gate and the first floating grid and between the erase gate and the second floating grid, the auxiliary gate dielectric layers are arranged between the auxiliary gate and the first floating gate and between the auxiliary gate and the second floating gate, the first doping region and the second doping region are respectively arranged at two sides of the stack structure, the first floating gate and the second floating gate, and the first control gate and the second gate are respectively arranged on the first floating gate and the second floating gate. By the nonvolatile memory, low-voltage operation can be performed, and the reliability of a semiconductor component is further improved.

Owner:IOTMEMORY TECH +1

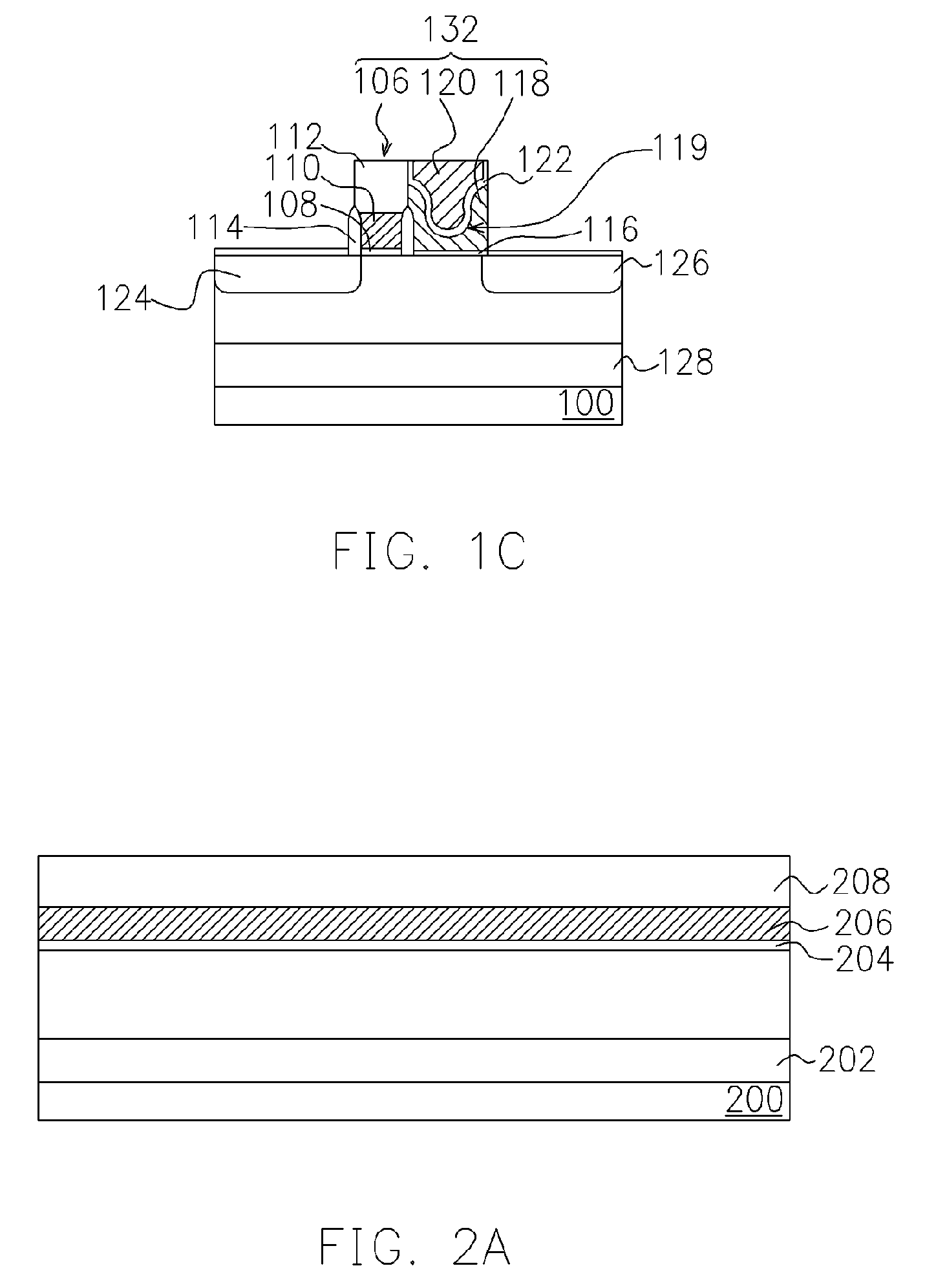

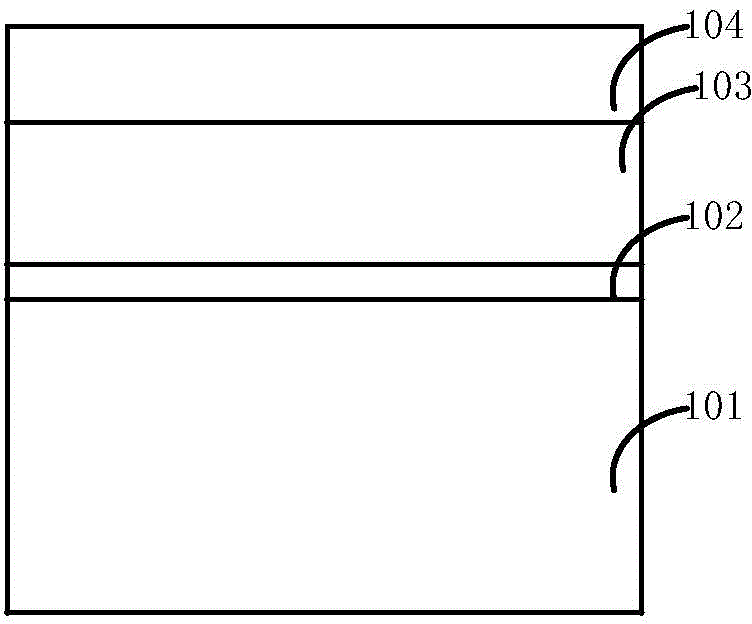

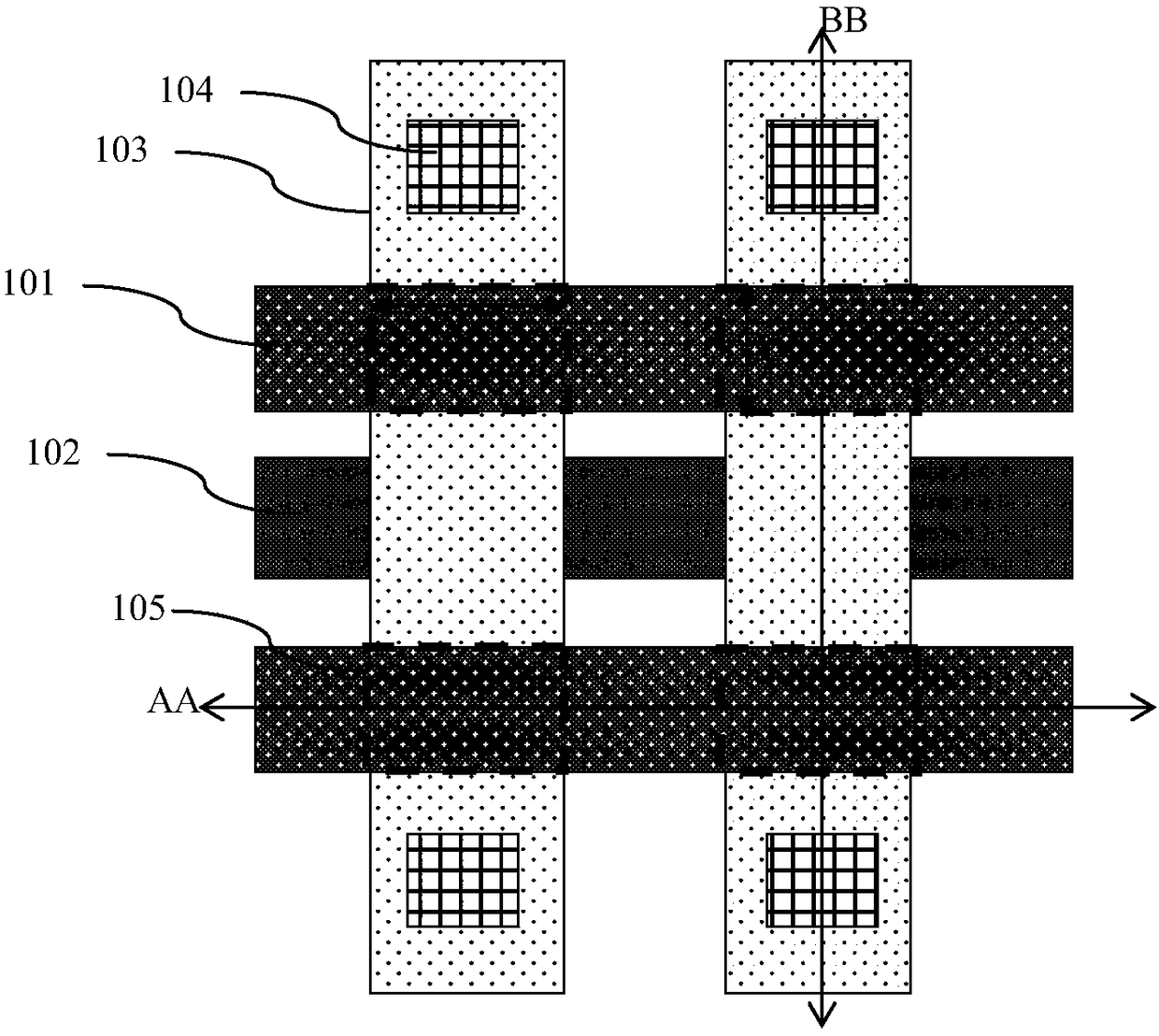

Semiconductor memory device and preparation method thereof

InactiveCN104681494AImprove the coupling rateImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingOxideSemiconductor memory

The invention relates to a semiconductor memory device and a preparation method thereof. The method comprises the following steps: providing a semiconductor substrate and forming a tunneling oxide layer, a floating gate layer and a mask layer on the semiconductor substrate; patterning the mask layer, the floating gate layer, the tunneling oxide layer and the semiconductor substrate to form shallow trenches in the semiconductor substrate on the two sides of a floating gate laminate while the floating gate laminate is formed; selecting an isolation material to fill the shallow trenches so as to form a shallow trench isolation structure; removing the mask layer to form a groove on the upper side of the floating gate layer; etching back the isolation material on the two sides of the groove to increase the critical size of the groove; depositing a semi-spherical floating gate film at the bottom and on the side wall of the groove with the increased critical size to form a floating gate structure. The floating gate structure comprises a semi-spherical floating gate film, so the surface area of the floating gate structure is increased, the electric capacity formed by the floating gate is increased, and the performance of the device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Nonvolatile memory manufacturing method thereof

ActiveCN105990360AHighly integratedThe overall thickness is thinSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

The invention provides a nonvolatile memory. The nonvolatile memory is provided with a storage unit, wherein the storage unit is provided with a stacked structure, floating gates, a tunneling dielectric layer, an erasing gate dielectric layer, an auxiliary gate dielectric layer, a source electrode region, a drain electrode region, control gates and an inter-gate dielectric layer; the stacked structure is provided with successively arranged gate dielectric layer, auxiliary gates, insulating layer and erasing gates; the floating gates are arranged at the side wall of the first side of the stacked structure; the tunneling dielectric layer is arranged below the floating gates; the erasing gate dielectric layer is arranged between the erasing gates and the floating gates; the auxiliary gate dielectric layer is arranged between the auxiliary gates and the floating gates; the source electrode region and the drain electrode region are respectively arranged at two sides of the stacked structure and the floating gates; the control gates are arranged on the source electrode region and the floating gates; and the inter-gate dielectric layer is arranged between the control gates and the floating gates.

Owner:IOTMEMORY TECH +1

Floating gate preparation method

ActiveCN103903969AImprove the coupling rateAvoid the risk of short circuitsSolid-state devicesSemiconductor devicesIon implantationSemiconductor

The invention discloses a floating gate preparation method. The method comprises steps: S1, a shallow trench isolation structure whose upper surface is higher than the first height H1 of the upper surface of a semiconductor substrate is formed on a semiconductor substrate; S2, an active region is formed on the semiconductor substrate through ion implantation; S3, a tunnel oxide layer is formed on the semiconductor substrate; S4, a floating gate material layer is deposited on the tunnel oxide layer; S5, the floating gate material layer is flattened to enable the upper surface of the shallow trench isolation structure to be exposed; and S6, part of the shallow trench isolation structure is removed by etching to form the floating gate. S6 further comprises steps of adopting wet etching to remove the shallow trench isolation structure with a second height H2 to enable coupling efficiency between the floating gates and control gates formed subsequently to be high, and adopting dry etching to remove the shallow trench isolation structure with a third height H3 to form the floating gates. When the technical scheme of the invention is applied, the coupling efficiency between the floating gate and control gates formed subsequently is high, and the risk of short circuit between the active region and the control gates can be avoided.

Owner:GIGADEVICE SEMICON (BEIJING) INC

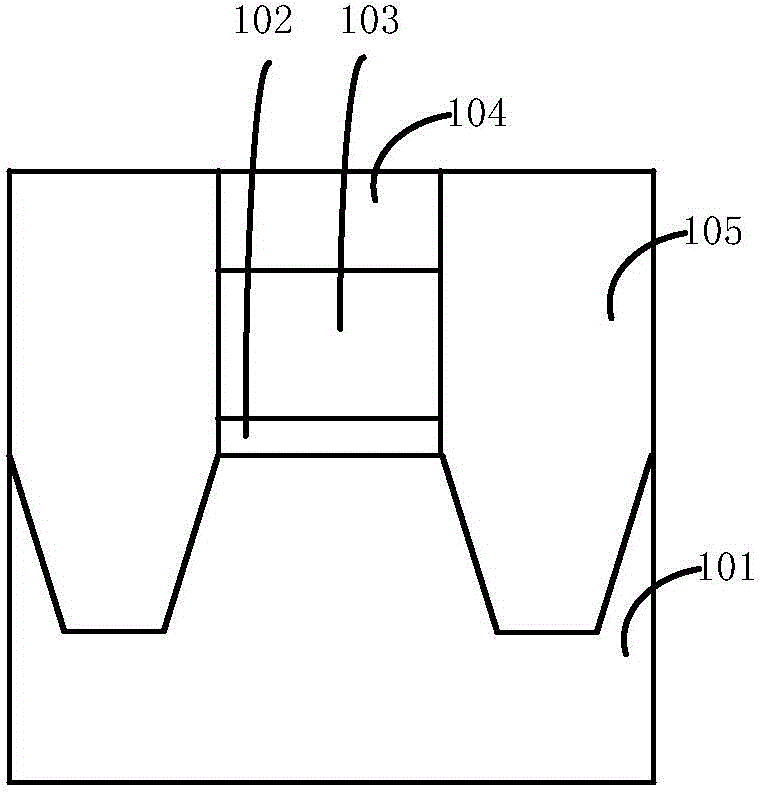

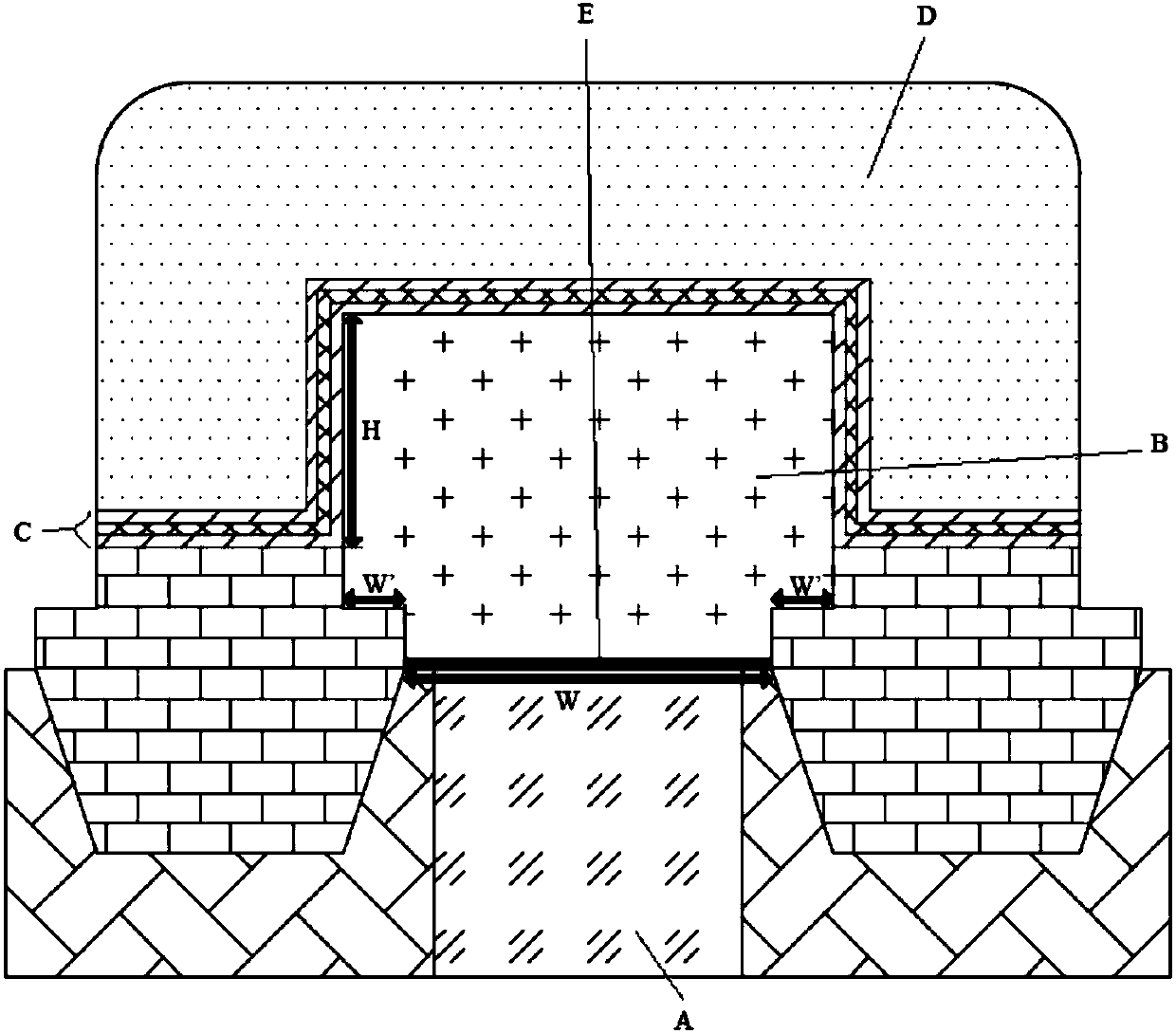

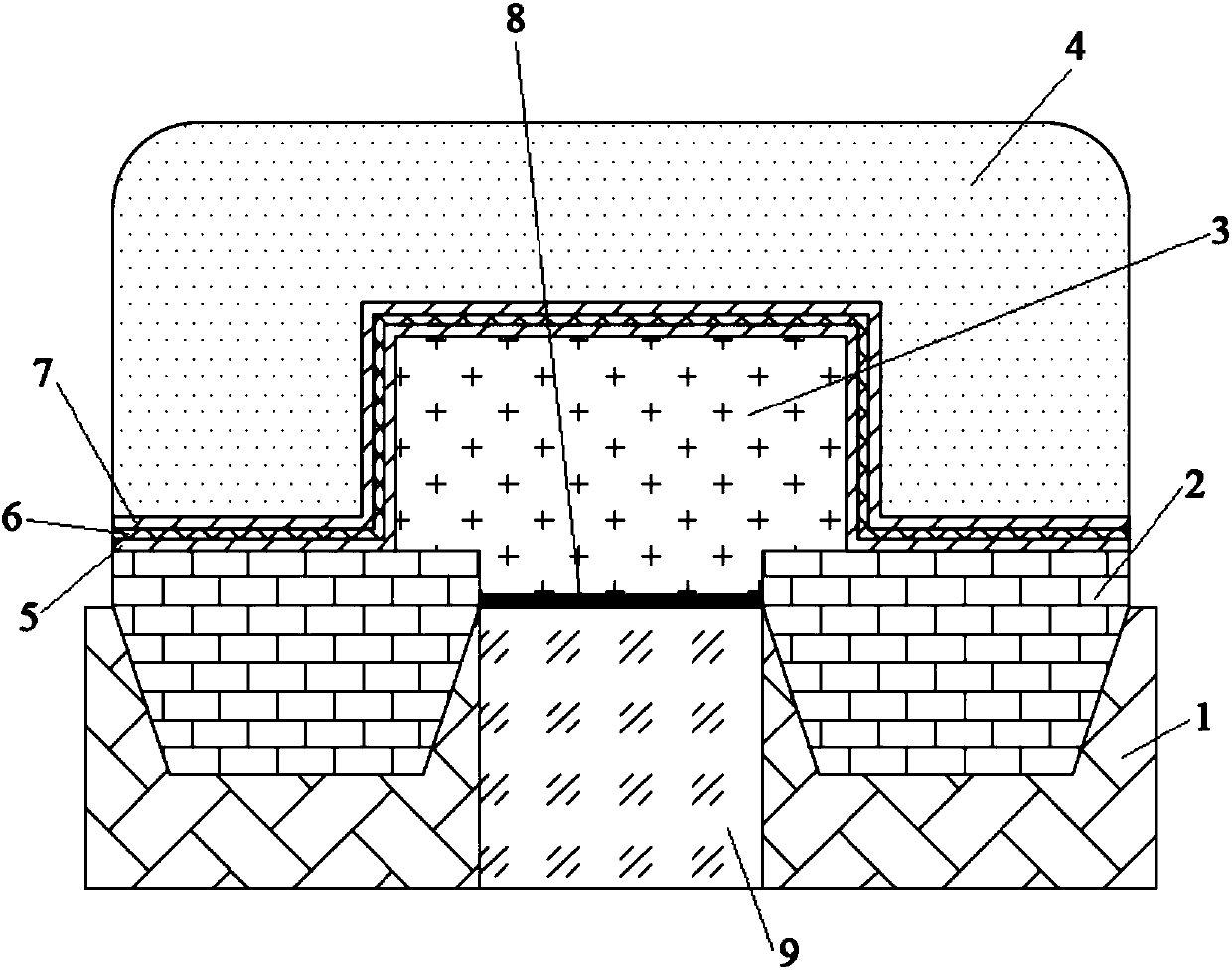

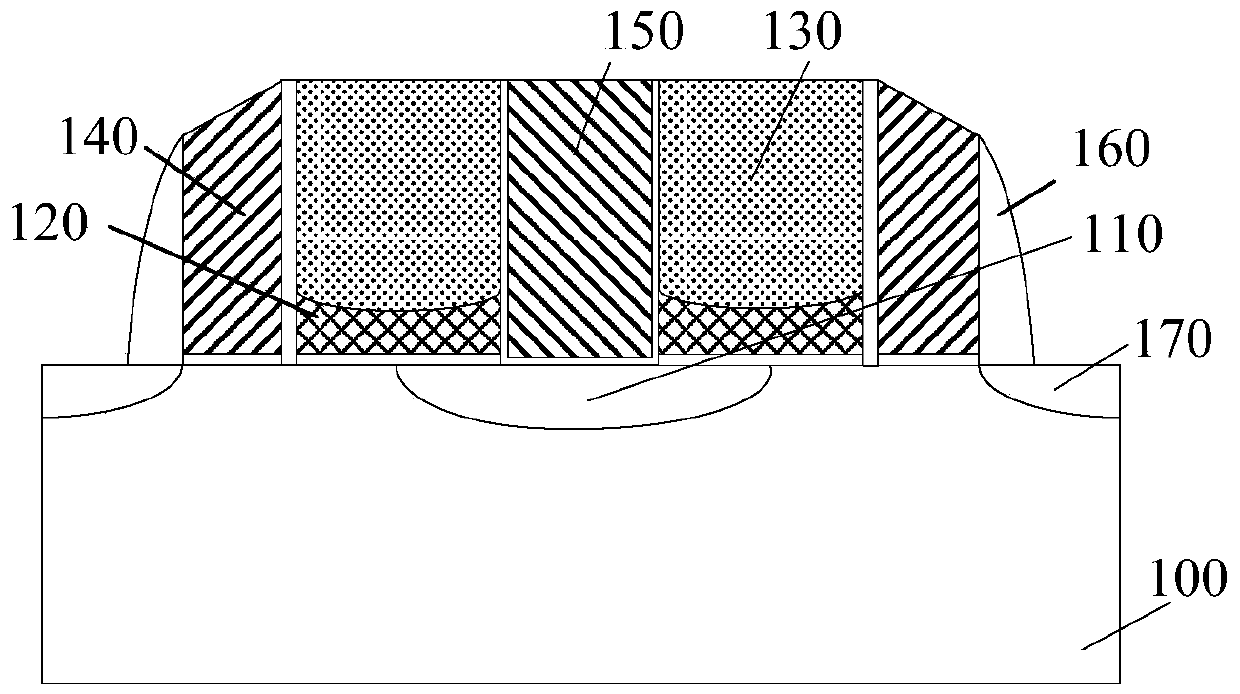

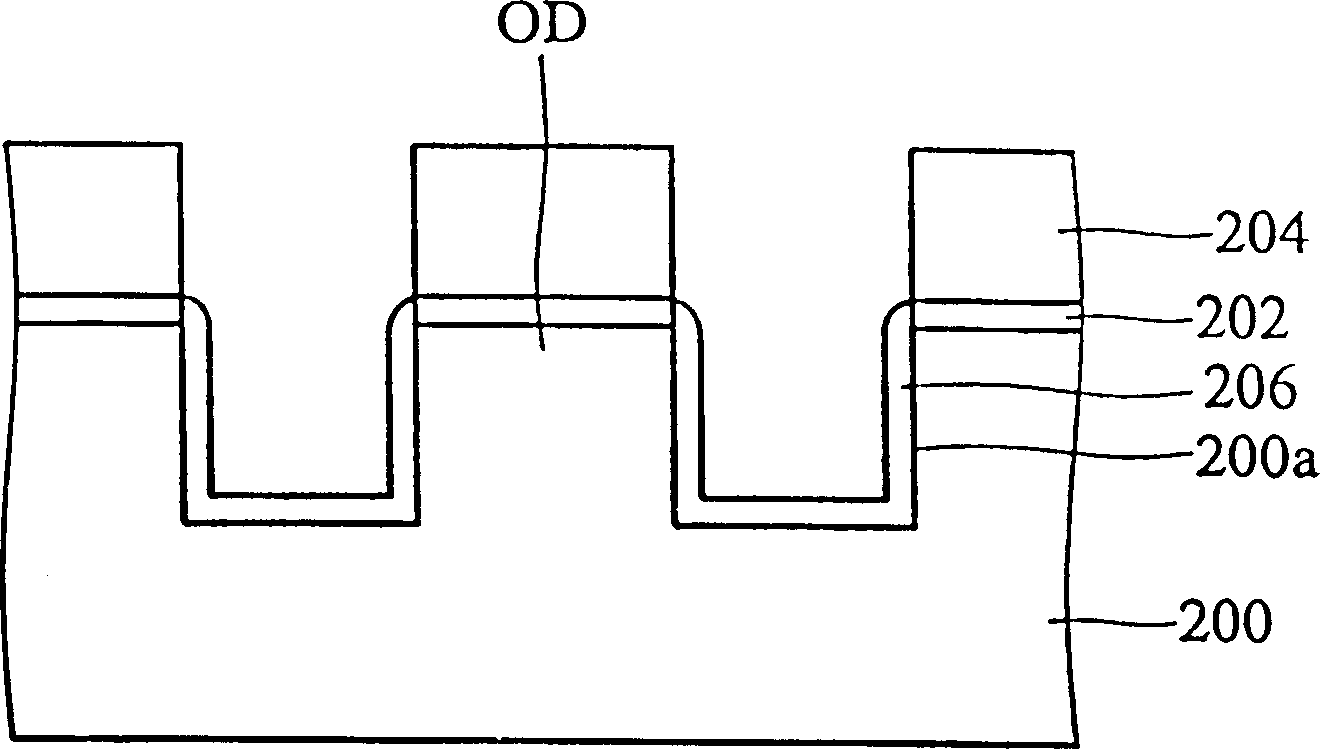

Flash memory unit structure with high coupling ratio and preparation method thereof

InactiveCN107946370AImprove the coupling rateReduce capacitanceTransistorSemiconductor/solid-state device manufacturingCapacitanceCoupling ratio

The present invention relates to a flash memory unit structure with a high coupling ratio and a preparation method thereof. The flash memory unit structure comprises: a semiconductor substrate, wherein the semiconductor substrate comprises two shallow trench isolations and an active area, and the active area is located in the semiconductor substrate between the two shallow trench isolations; a tunneling oxide layer; a floating gate; a dielectric layer; and a control gate, wherein the dimensions of the top portions of the two shallow trench isolations are equal to the dimension of the top portion of the active area, and the dimension of the tunneling oxide layer is equal to the dimension of the top portion of the active area. A silicon nitride reduction resistance amount prior to depositionof the shallow trench isolations is increased to increase the dimensions of the top portions of the shallow trench isolations; and moreover, in the subsequent technology process, the top portions ofthe shallow trench isolations can be consumed, the dimensions of the top portions of the shallow trench isolations after consumption are equal to the actual dimension of the top portion of the activearea to allow the width of the bottom portion of the floating gate to be equal to the dimension of the top portion of the active layer when a subsequent floating gate process is performed so as to reduce the capacitance of the floating gate to the substrate and increase the coupling ratio of a flash unit.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

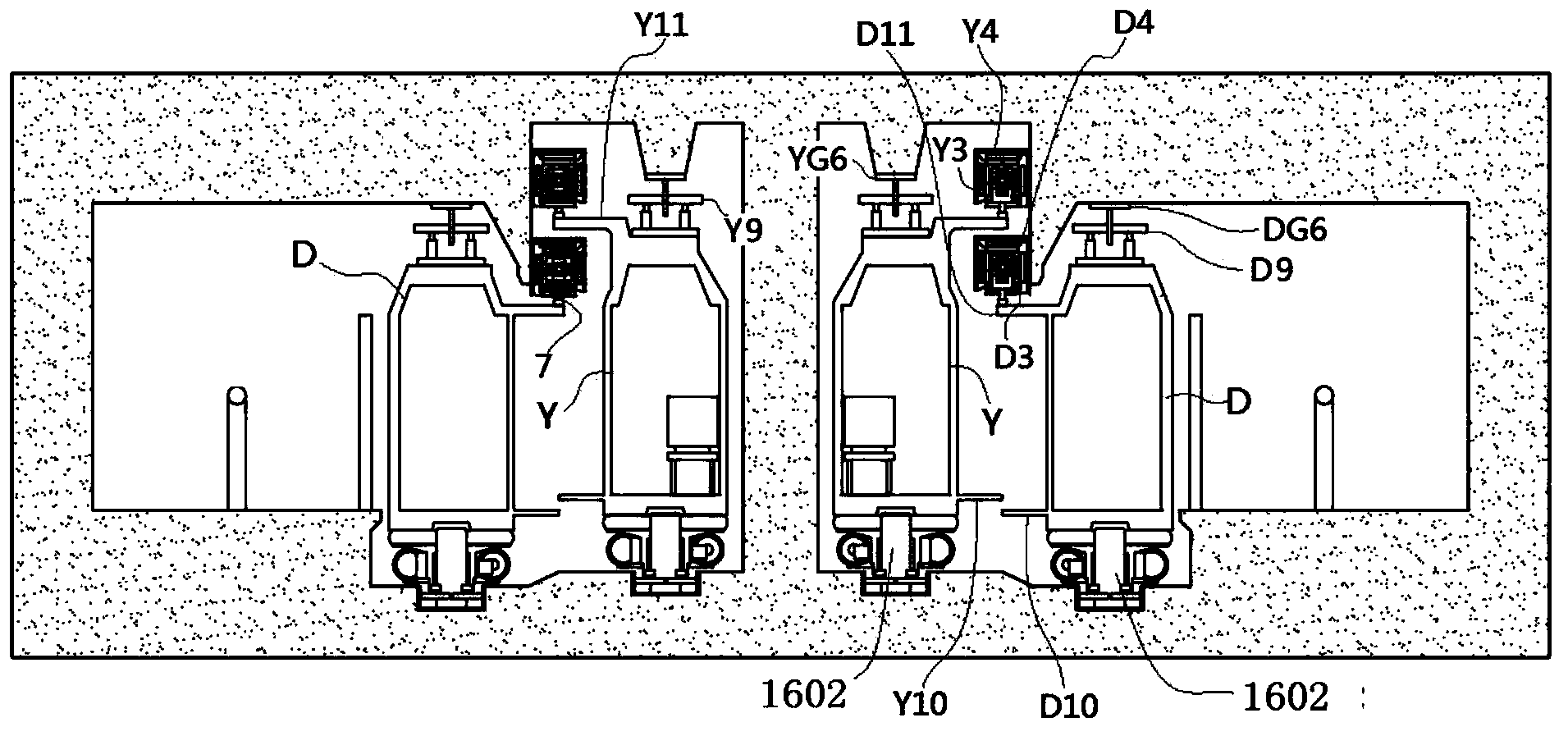

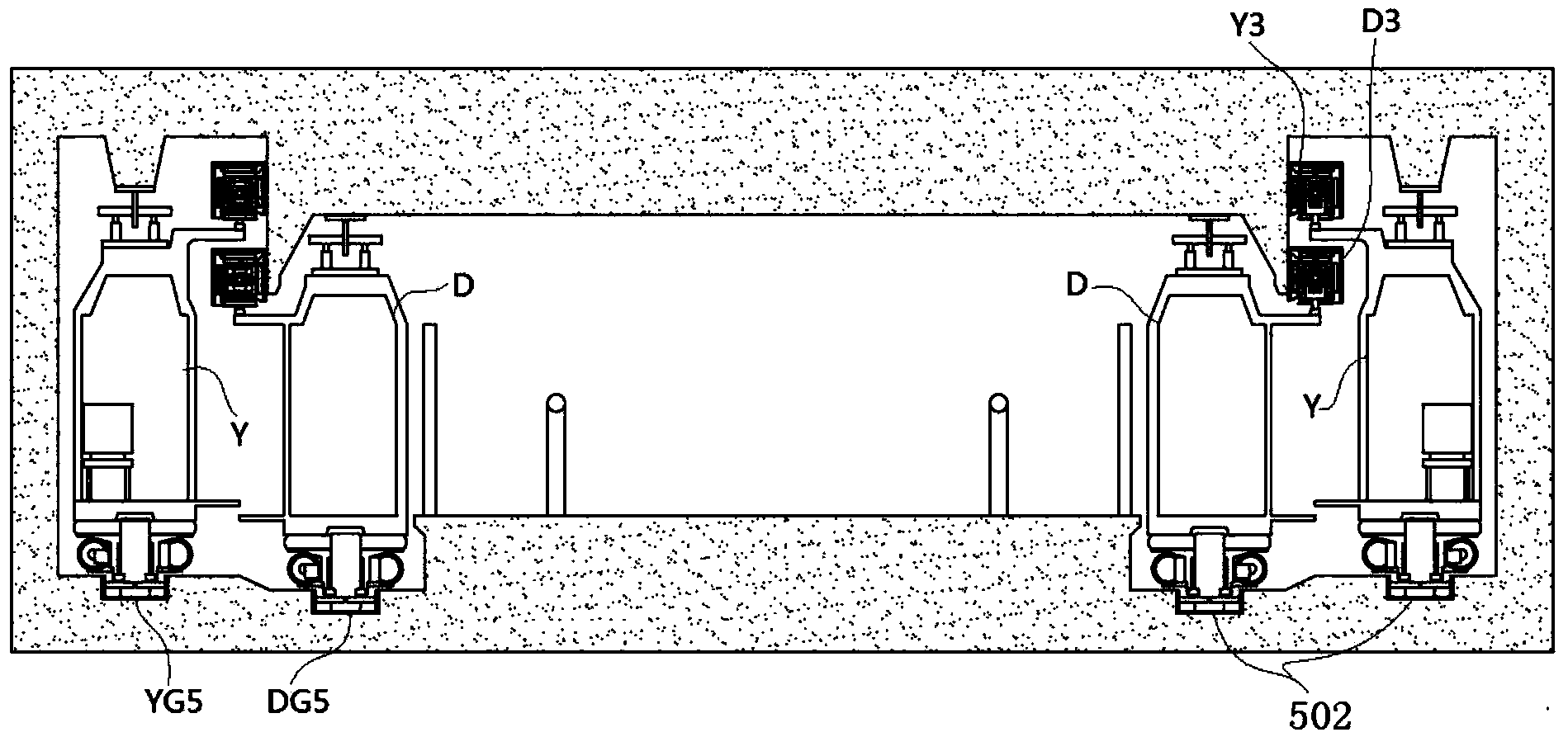

Parallel connection type descending operation track train and transporting method thereof

InactiveCN104386066AAchieve the desired effectGet the desired effectRailway componentsRailway stationCarrying capacityConnection type

The invention discloses a parallel connection type descending operation track train and a transporting method thereof. The parallel connection type descending operation track train comprises a return closed descending track line, an operation track line, descending trains running on the descending track line, and operation trains running on the operation track line, wherein the two track lines are both provided with descending segments and curve rotation segments, and the descending segments of the descending track line and the descending segments of the operation track line are in equidistant and parallel arrangement; and the descending trains and the operation trains respectively operate in an equidirectional and independent manner on the descending track line and the operation track line, and the descending trains and the operation trains are connected in parallel and operate at an equal speed periodically at the descending segment of the operation track line. According to the invention, getting on and off the trains in an intensive and partitioned manner at all lines are realized, the carrying capacity is large, the interval time between trips is short, the average travelling speed is high, each long-range passenger of whom the range is more than two thousands of meters directly reaches destinations without stopping halfway, the problems that the passengers travel inconveniently and uncomfortably, the travelling is crowded and the time is consumed are solved in a centralized manner, and at the same time, the load factor of the trains is increased at time periods and road segments with fewer flows of passengers.

Owner:周新华

Nonvolatile memory and manufacturing method thereof

ActiveCN101593753AAvoid electrical connectionsIncrease the capacitance contact areaSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorDielectric layer

The invention discloses a nonvolatile memory which comprises a substrate, a plurality of doped regions, a first grid, a conductor layer, a first contact window plug and a dielectric layer, wherein the doped regions are arranged in the substrate; the first grid is arranged on the substrate between two adjacent doped regions; the conductor layer is arranged above the first grid; the first contact window plug is arranged between the first grid and the conductor layer; and the dielectric layer is arranged between the first grid and the first contact window plug.

Owner:HEJIAN TECH SUZHOU

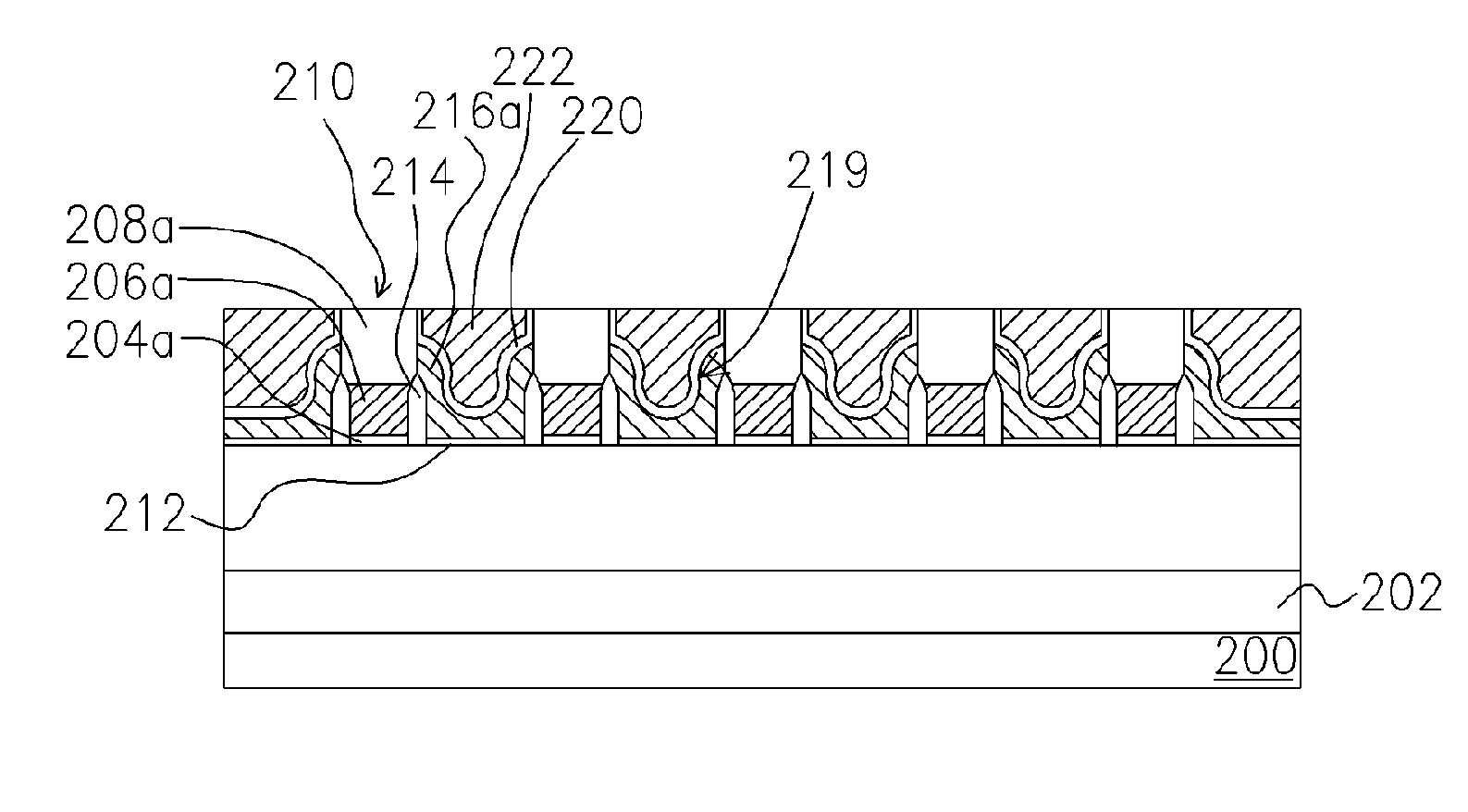

Flash memory cell, flash memory cell array and manufacturing method thereof

ActiveUS20050169035A1Improve programming speedImprove efficiencySolid-state devicesRead-only memoriesGate dielectricDielectric layer

A flash memory cell array comprises a substrate, a string of memory cell structures and source region / drain region. Each of memory cell structures includes a stack gate structure including a select gate dielectric layer, a select gate and a gate cap layer formed on the substrate; a spacer is set on the sidewall of the select gate; a control gate connected to the stack gate structure is set on the one side of the stack gate structure; a floating gate is set between the control gate and the substrate; an inter-gate dielectric layer is set between the control gate and the floating gate; and a tunneling dielectric layer is set between the floating gate and the substrate. The source region / drain region is set in the substrate near outer control gate and stack gate structure of the flash memory cell array.

Owner:POWERCHIP SEMICON MFG CORP

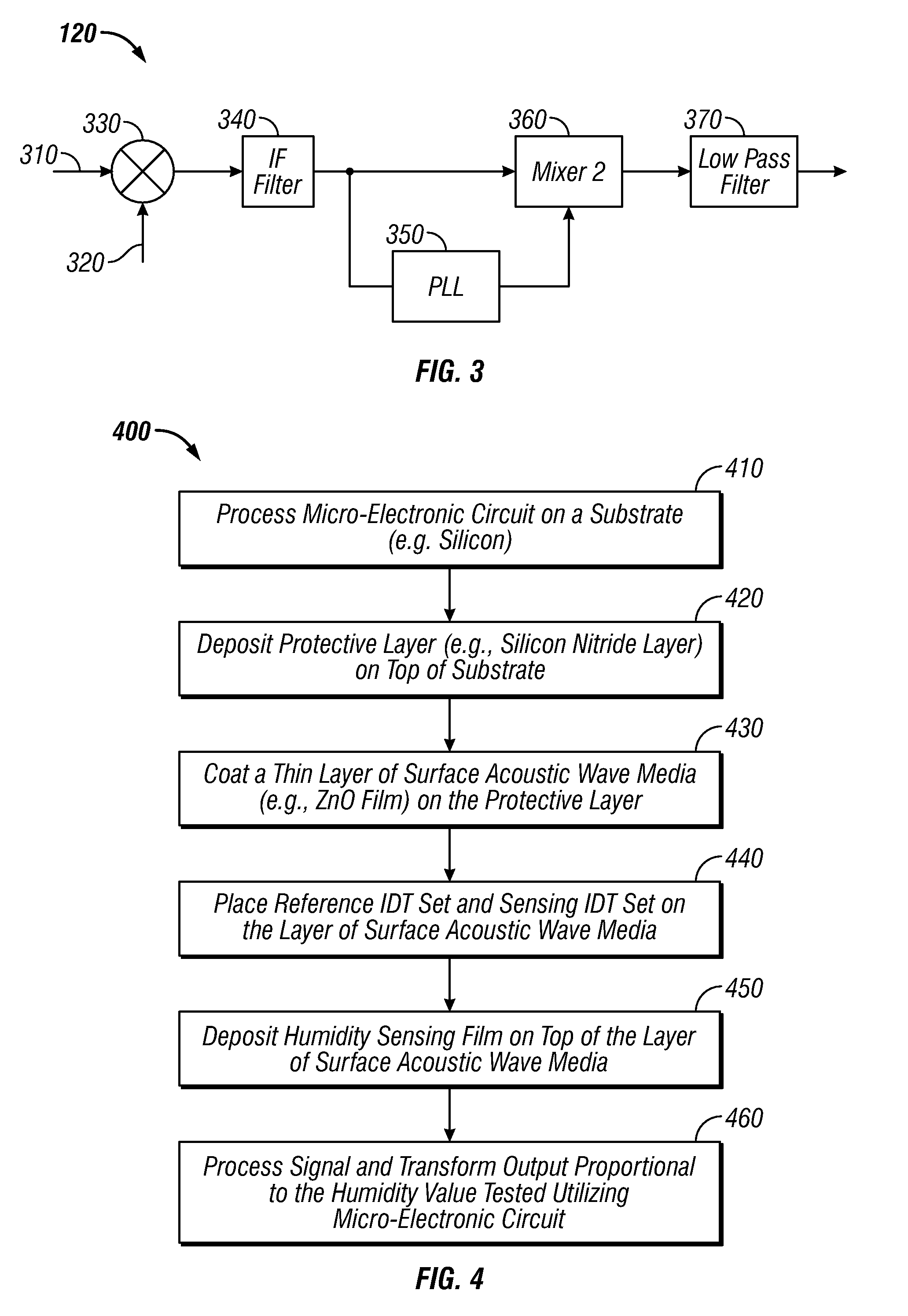

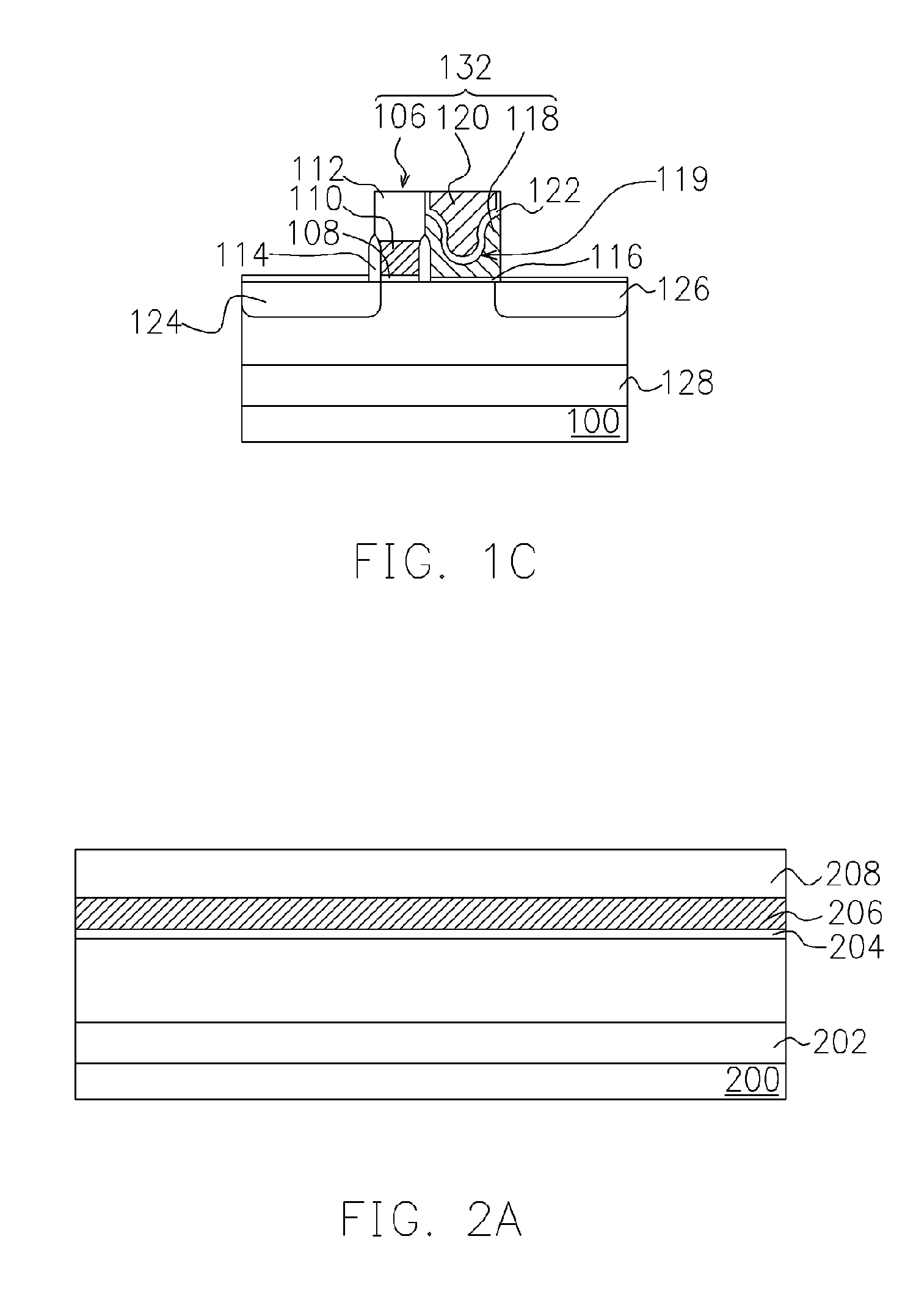

Surface acoustic wave based humidity sensor apparatus with integrated signal conditioning

InactiveUS8015872B2Eliminate common mode noiseProtection from damageMaterial analysis using sonic/ultrasonic/infrasonic wavesUsing mechanical meansSignal conditioningSurface acoustic wave sensor

Owner:HONEYWELL INT INC

Flash memory cell, flash memory cell array and manufacturing method thereof

InactiveUS20050170579A1Enhance programming speed and efficiencyImprove performanceTransistorRead-only memoriesGate dielectricEngineering

A flash memory cell array comprises a substrate, a string of memory cell structures and source region / drain region. Each of memory cell structures includes a stack gate structure including a select gate dielectric layer, a select gate and a gate cap layer formed on the substrate; a spacer is set on the sidewall of the select gate; a control gate connected to the stack gate structure is set on the one side of the stack gate structure; a floating gate is set between the control gate and the substrate; an inter-gate dielectric layer is set between the control gate and the floating gate; and a tunneling dielectric layer is set between the floating gate and the substrate. The source region / drain region is set in the substrate near outer control gate and stack gate structure of the flash memory cell array.

Owner:POWERCHIP SEMICON MFG CORP

Cell recess oxide etching method of improving deep-submicron flash memory device coupling rate

ActiveCN105826326AOvercoming the characteristics of uneven densityUniform densitySolid-state devicesSemiconductor/solid-state device manufacturingCouplingDry etching

The present invention provides a cell recess oxide etching method of improving a deep-submicron flash memory device coupling rate. The method is characterized by combining a first dry etching step, a wet etching step and a second dry etching step; the dry etching effectively overcomes the characteristic that the density of the filling oxides is uneven, and the oxides in a density loose area at an opening in a cell recess are removed by the first dry etching step, so that the subsequently etched oxide interfaces are same in height and even and consistent in density; then, the oxide side walls at the side walls of the polycrystalline floating gates caused by the first dry etching are removed by the wet etching, so that the side walls are totally not covered by the oxides; and then, the cell recess oxide bottoms of consistent height and the oxide side walls at the bottoms of the side walls of the polycrystalline floating gates of uniform morphology and protecting the tunneling oxide layers are realized by the second dry etching, and then the ONO deposition is carried out to form the consistent ONO capacitors formed by the contact of the ONO and the polycrystalline floating gates, thereby achieving the purposes of improving the coupling rate of a deep-submicron flash memory device and improving the product qualified rate and service life.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Flash memory and forming method thereof

ActiveCN109742076AImprove the coupling rateReduce the coupling rateSolid-state devicesSemiconductor devicesEngineeringSemiconductor

The invention provides a flash memory and a forming method thereof. The flash memory comprises: a semiconductor substrate, wherein the semiconductor substrate comprises a source line region and a floating gate region, and the floating gate region is adjacent to the source line region and is located on both sides of the source line region; a source region located in the source line region of the semiconductor substrate; a source line layer located on the source region, wherein the source line layer is electrically connected with the source region; floating gate structures respectively located on the floating gate region of the semiconductor substrate, wherein the heights of the floating gate structures are greater than the height of the source line layer; and an erase gate structure locatedon the source line layer. The performance of the flash memory is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method for manufacturing fast flash memory with coupling rate increased

InactiveCN1445839AImprove the coupling rateSemiconductor/solid-state device manufacturingElectrical conductorCapacitive coupling

The prewent invention discloses a manufacture method for flash memory to increasethe coupling ratio, which first defines two isolation structures projected above the surface of semiconductor substrate and then executes ion implanting so as to form adoping region on the semiconductor substrate at two sides of the isolation structure as well as forms dielectric isolation part at the side wall of two projected isolation structures, and at least, forms tunnelling dielectric layer and floating grid between the dielectric isolation parts in sequence to make the lower surface area of the floating grid smaller than the upper surface area of it for increasing the capacity coupling ratio.

Owner:TAIWAN SEMICON MFG CO LTD

Non-volatile memory and preparation thereof

ActiveCN101388363AImprove the coupling rateIncrease the areaTransistorSolid-state devicesGate dielectricEngineering

The invention relates to a nonvolatile memory, which comprises a gate structure and a source electrode / drain region, wherein the gate structure is arranged on a base, and comprises floating gates, a tunneling dielectric layer, a control gate and a gate dielectric layer, wherein the floating gates are arranged on the base, the tunneling dielectric layer is arranged between each floating gate and the base, the control gate is arranged on the base between the pair of the floating gates, and covers the top surface and at least side walls of each floating gate, the gate dielectric layer is arranged between the control gate and each floating gate and between the control gate and the tunneling dielectric layer, and is arranged between the control gate and the base, and the source electrode-drain region is arranged in the base on the two sides of the gate structure. Therefore the invention increases the covered area of the floating gate by the control gate, and further increases the coupling rate between the control gate and the floating gate.

Owner:NAN YA TECH

Flash memory and manufacturing method thereof

ActiveCN108336087AControl thicknessSimple processSolid-state devicesSemiconductor devicesCouplingEngineering

The invention discloses a flash memory. Each flash memory is formed in the same active region, poly-silicon control gates at the same line are connected to form a poly-silicon line, N+ diffusion regions are symmetrically formed at two sides of each poly-silicon floating gate, each N+ diffusion region at the same row is connected to form an N+ diffusion region row, channel regions are arranged among the N+ diffusion region rows and are covered by the poly-silicon floating gates, each poly-silicon floating gate is formed by laminating a bottom poly-silicon floating gate and a top poly-silicon floating gate, the length of the top poly-silicon floating gate is smaller than the length of the bottom of the bottom poly-silicon floating gate, the length of the channel region is defined by the bottom poly-silicon floating gate in an alignment way, a third dielectric layer covers a surface of each N+ diffusion region, and a surface of the third dielectric layer is lower than or equal to a surface of the bottom poly-silicon floating gate. The invention also discloses a manufacturing method of the flash memory. By the flash memory, the coupling rate between the poly-silicon control gate and the poly-silicon floating gate can be improved, and meanwhile, the mutual interference between adjacent poly-silicon floating gates can be reduced.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Preparation method of liposome with functions of fat reduction and calcium supplement

InactiveCN102204867AGood for dissolution processingFunction increasePowder deliveryMetabolism disorderFreeze-dryingLiposome

The invention discloses a preparation method of a liposome with functions of fat reduction and calcium supplement. The preparation method is characterized in that: on the basis of defining the therapeutic and health-care mechanism of a folk recipe, namely vinegar egg liquid, an ethanol injection method, an original sleeve dual-ejection technology and a homogenizing device with smeared sealing function are combined to reinforce the formation of the liposome of lecithin and the package of calcium acetate; the calcium acetate packaged by the liposome is transformed into ionic calcium hydroxide by transferring the liposome with the acetic acid through a calcium acetate gradient method; the liposome rich in the ionic calcium hydroxide is processed into an oral solution or freeze-dried powder. Compared with the traditional folk recipe, namely the vinegar egg liquid, the biological product developed by the method contributes more to massive production and long-term preservation and is more easy to absorb by a human body; the utilization of the calcium ions by the human body is greatly improved; the acidity of the human body is reduced; a healthy alkalescent environment is created in the human body; the fat-reducing function of the human body is enhanced; the target characteristic of softening blood vessels is more outstanding; and the therapeutic and health-care effect is more obvious.

Owner:ANHUI FINDSHE BIOLOGICAL PHARMA CO LTD +1