Method for manufacturing fast flash memory with coupling rate increased

A manufacturing method and memory technology, applied in the direction of semiconductor/solid-state device manufacturing, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

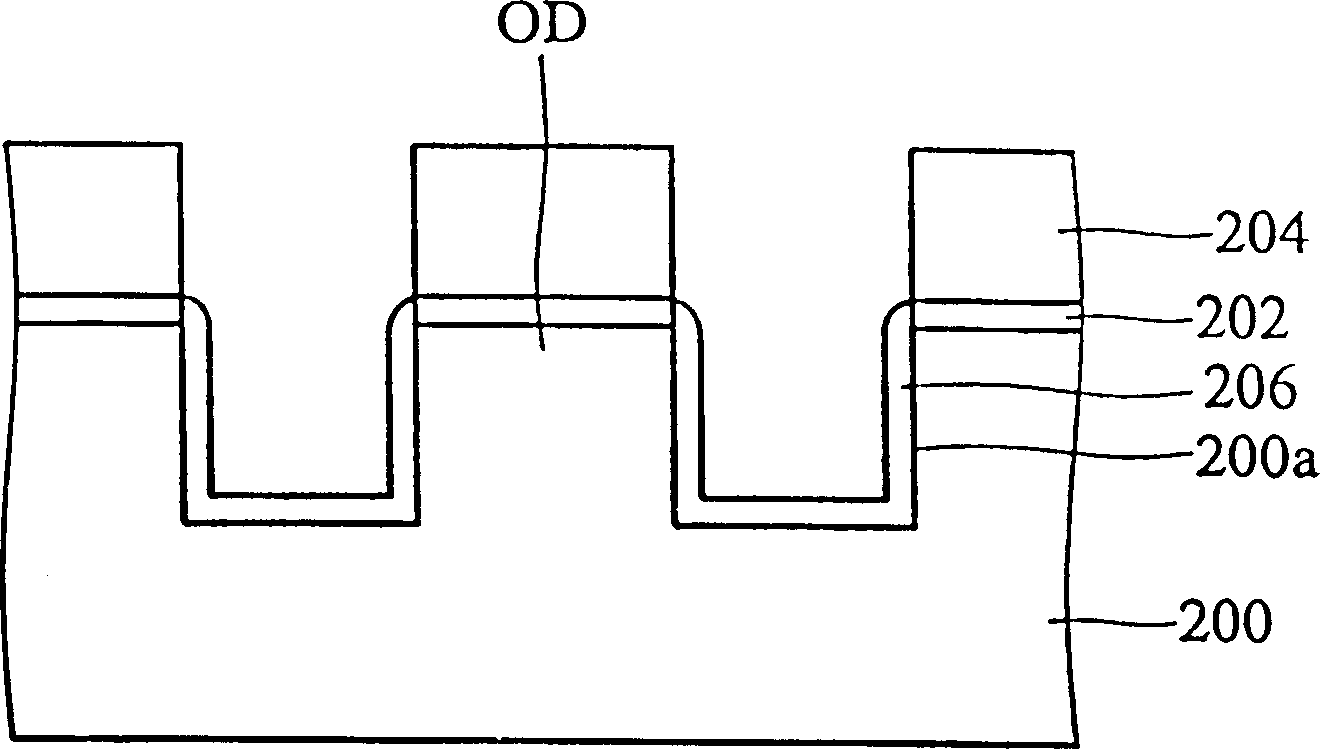

[0016] Figure 2a to Figure 2g And the manufacturing method of the flash memory with increased coupling ratio according to the first embodiment of the present invention is described. First, please refer to Figure 2a , provide a semiconductor substrate 200, such as a silicon wafer, on the substrate 200, deposit and form an insulating layer 202, such as an oxide layer, and a hard mask layer (hardmask) 204, such as a silicon nitride layer, with a thickness of about 110 Angstroms () and 1600.

[0017] Next, please refer to Figure 2b , in order to define the active region OD, first define and etch the hard mask layer 204 to expose the insulating layer 202, and then use the patterned hard mask layer 204 as a mask to etch the exposed oxide layer 202 and the semiconductor substrate 200 surface below. The semiconductor substrate 200 is formed with two trenches 200a as isolation structures. Then, a pad oxide layer 206 with a thickness of about 200 Å is formed on the inner wall o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More