Patents

Literature

40results about How to "Extend etch time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

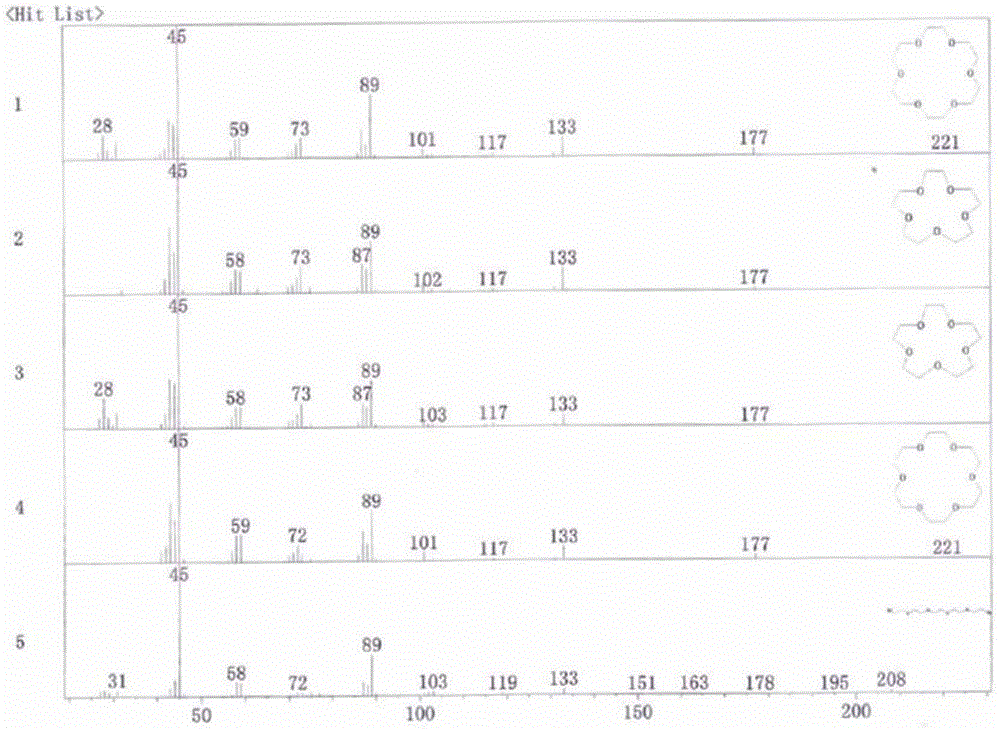

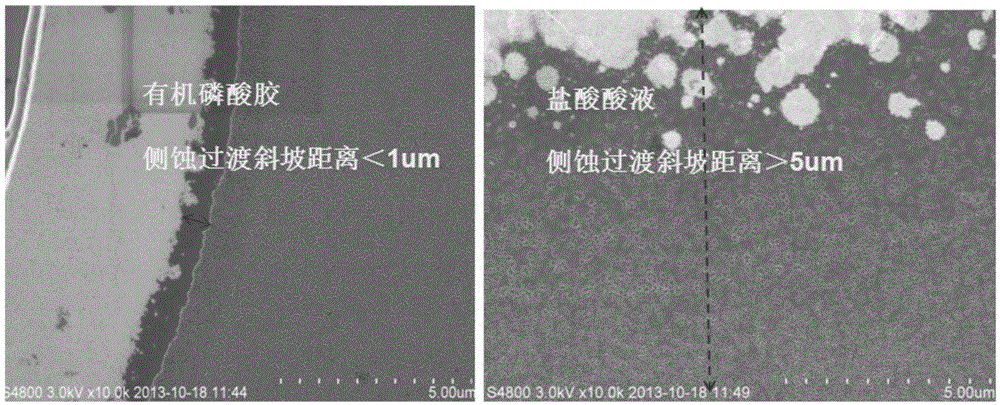

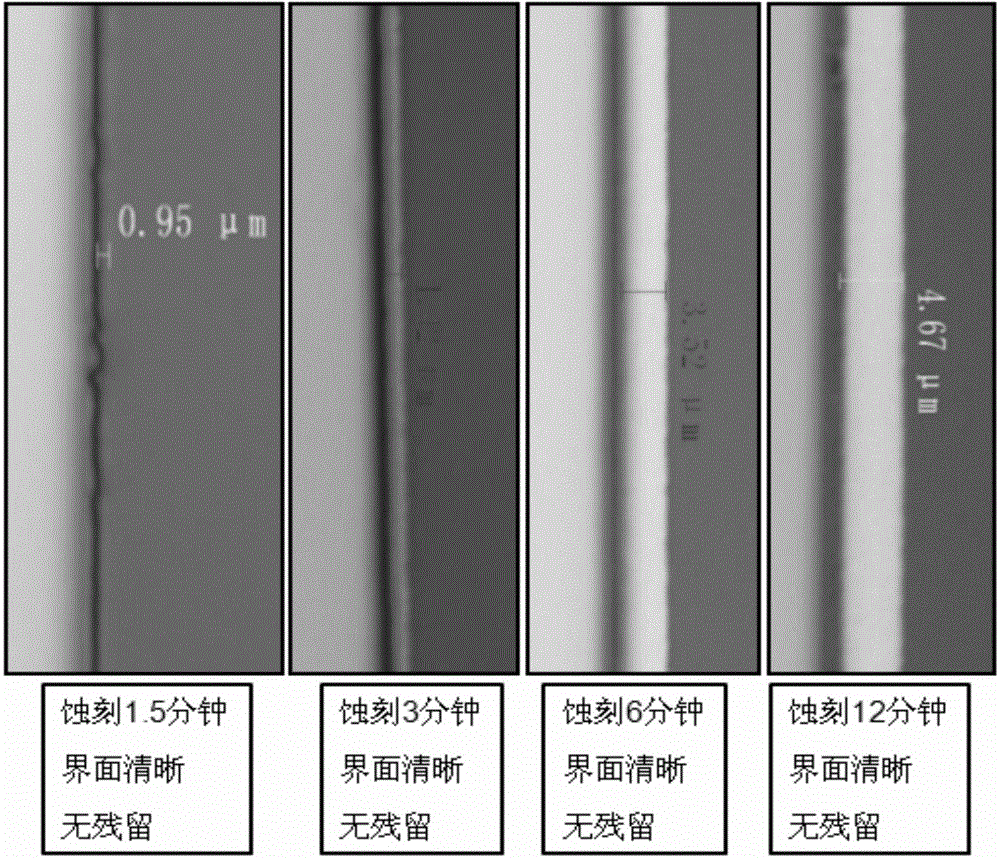

Novel etching solution used in oxide material system, and etching method and application thereof

ActiveCN103980905AControl thicknessReduce liquidityCable/conductor manufactureSurface treatment compositionsAlloySolar cell

The invention discloses a novel etching solution used in an oxide material system. The novel etching solution comprises an oxide etching solution, an adjustment agent for adjusting the thickness, and water. The invention also discloses an etching method and an application of the novel etching solution. The novel etching solution and the etching method are generally suitable for etching film materials based on Sn, Zn, Al, Ga and In and alloy oxides thereof, especially oxide materials of ZnO, AZO, GZO, IGZO and IZO, and can also be widely used for etching oxide materials for making fine electronic components, such as semiconductor photoelectric devices, solar cells, TFT film transistors, semiconductor integrated circuits and transparent electrodes. Compared with traditional etching solutions, the novel etching solution has the advantages of lateral etching inhibition, uneven etching prevention and etching residual prevention.

Owner:FOSHAN INST SUN YAT SEN UNIV

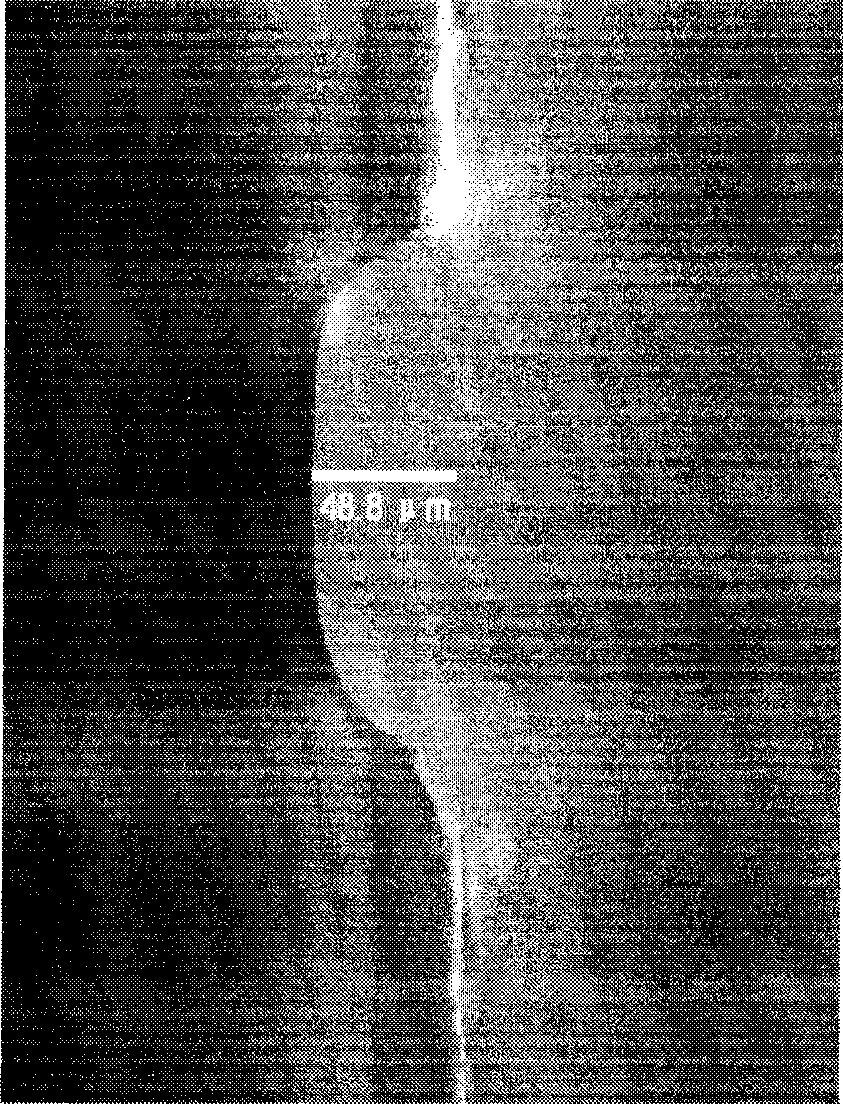

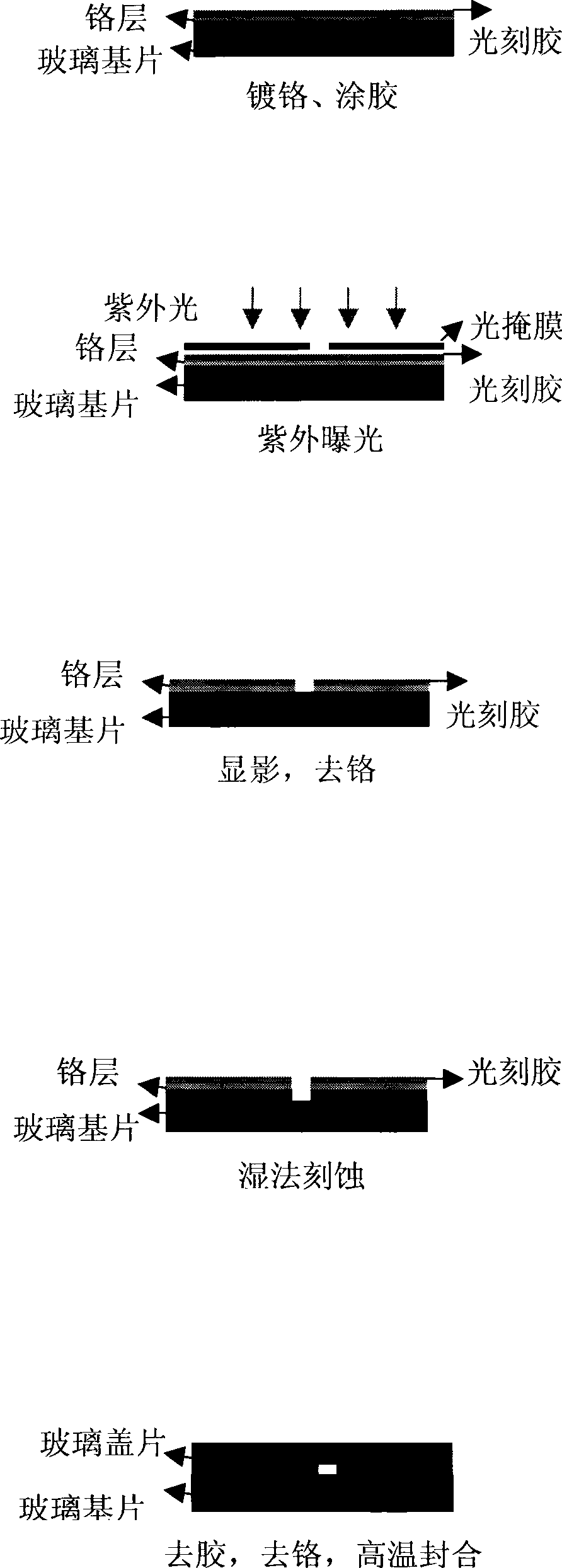

Method for preparing protective film playing a role in protecting glass micro-fluidic chips in etching process

InactiveCN101544349AAddressing Insufficient ProtectionQuality improvementDecorative surface effectsChemical vapor deposition coatingCross-linkPhotoresist

The invention relates to a method for preparing protective film playing a role in protecting glass micro-fluidic chips in etching process. The method comprises the steps of plating a glass substrate with a chromium sacrificial layer, smearing glue, baking the glue, performing UV exposure, developing, removing the chromium sacrificial layer, performing wet etching, removing the glue, removing the chromium sacrificial layer and sealing at high temperature when a glass micro-fluidic chip is conventionally manufactured. The method is characterized in that positive photoresist containing linear phenolic resin is taken as a basis; after the developing step and before the follow-up step of removing the chromium sacrificial layer, by taking a formaldehyde monomer aqueous solution or a glutaraldehyde aqueous solution with a certain concentration and pH value as a cross-linking agent, formaldehyde or glutaraldehyde and the linear phenolic resin in the positive photoresist containing the linear phenolic resin are subjected to cross-linking reaction; and the photoresist is cross-linked to be the protective film of which the body type is in a network structure so as to enable the photoresist protective film to prolong the time of tolerating the corrosion of hydrofluoric acid glass etching liquid and increase the etching depth of micro-fluidic channels. The method is applicable to the glass substrates plated with other metal sacrificial layers.

Owner:INST OF CHEM CHINESE ACAD OF SCI

UV gravure RFID printing ink and preparation method thereof

The invention discloses UV gravure RFID printing ink and a preparation method thereof; the UV gravure RFID printing ink comprises, by weight:10-30 parts of petroleum resin, 10-30 parts of acrylic acid prepolymer, 0.1-1 part of a polymerization inhibitor, 5-12 parts of a photoinitiator, 5-10 parts of pigment, 1-5 parts of a dispersant, and 20-50 parts of acrylic acid monomers. The UV gravure RFID printing ink of the invention has the following beneficial effects: the printing ink is suitable for gravure press and flexo-graphic machines, is instantly dried by an ultraviolet lamp, which greatly increases the working efficiency. After dried, the printing ink can resist strong acid etching; the concentration of the etching acid can be adjusted at will; the etching solution temperature can be increased; the etching time can be increased; and thus processing of various RFID labels can be met. After drying and etching, the printing ink is easy to be washed by alkalis, and a 3% NaOH solution can remove the ink within 5-20 seconds. The line surface is effectively maintained to be clean and free of printing ink residues, and thus the final product quality is ensured.

Owner:杭华油墨股份有限公司

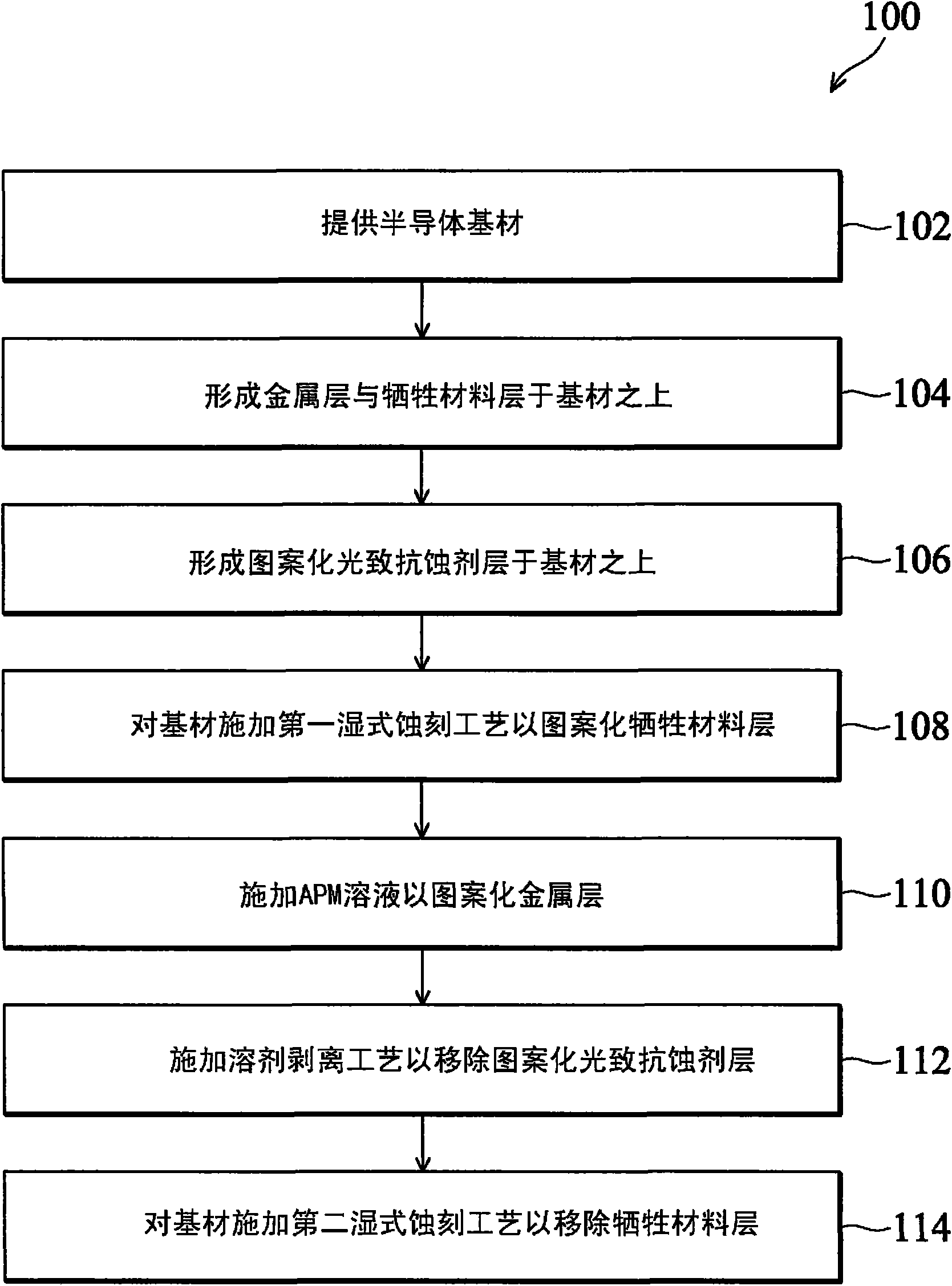

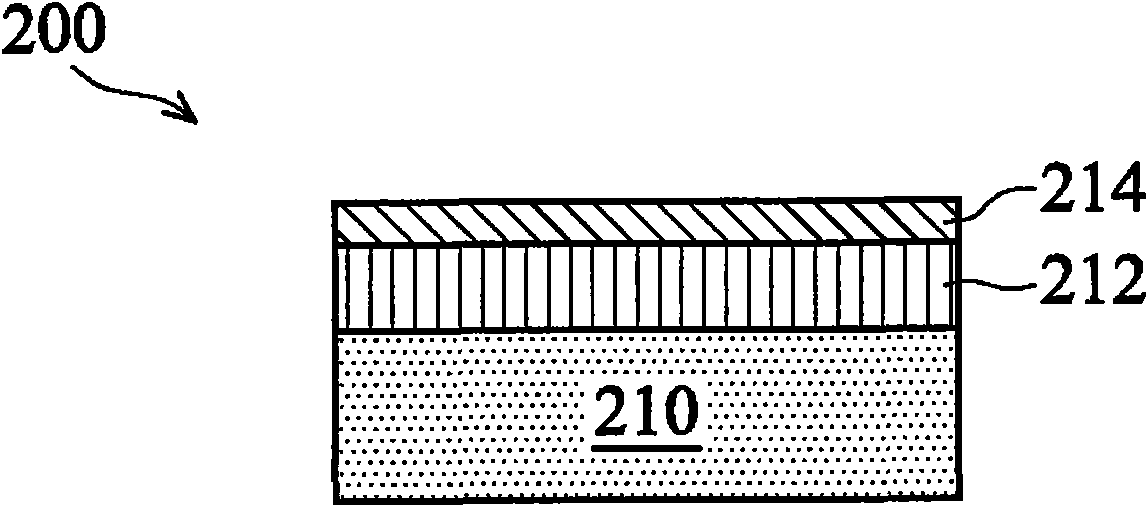

A method for making a semiconductor device

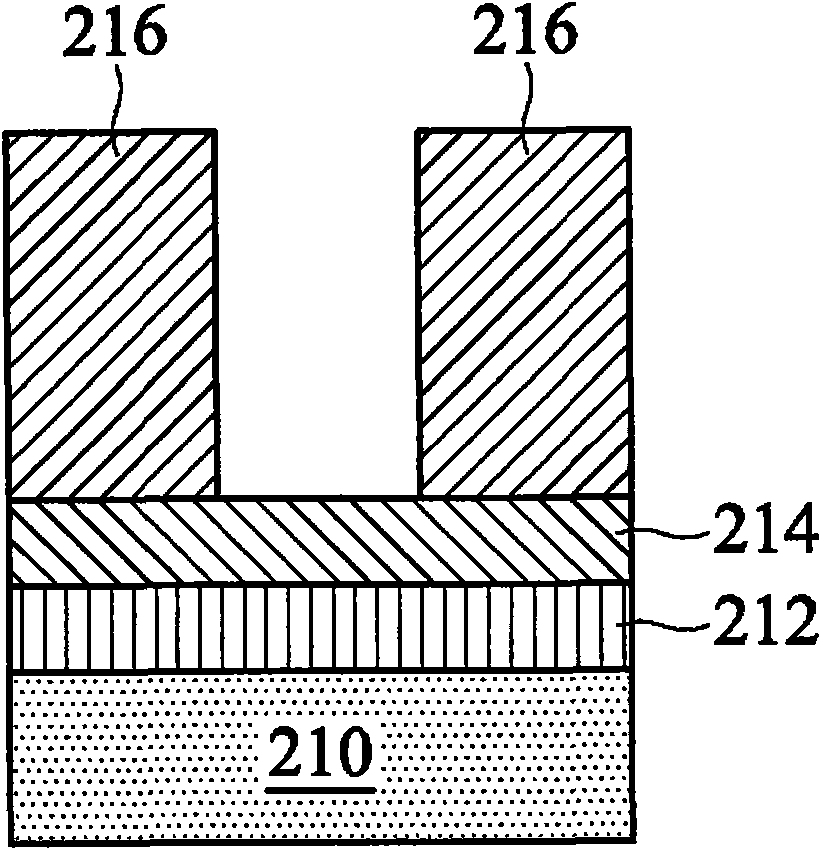

InactiveCN101789367ANo peeling problemPeeling (peeling) problem solvingPhotomechanical apparatusSemiconductor/solid-state device manufacturingEtchingTitanium nitride

The present disclosure provides a method for making a semiconductor device. The method includes forming a material layer on a substrate; forming a sacrificial layer on the material layer, where the material layer and sacrificial layer each as a thickness less than 100 angstrom; forming a patterned photoresist layer on the sacrificial layer; applying a first wet etching process to etch the sacrificial layer to form a patterned sacrificial layer using the patterned photoresist layer as a mask; applying a second wet etching process to etch the first material layer; and applying a third wet etching process to remove the patterned sacrificial layer. The invention prolongs the etching time without photoresist peeling problem; or reduces the wet etching time of the second material layer to solve the photoresist peeling problem; or solves the problem that the photoresist is remained on the surface of the titanium nitride.

Owner:TAIWAN SEMICON MFG CO LTD

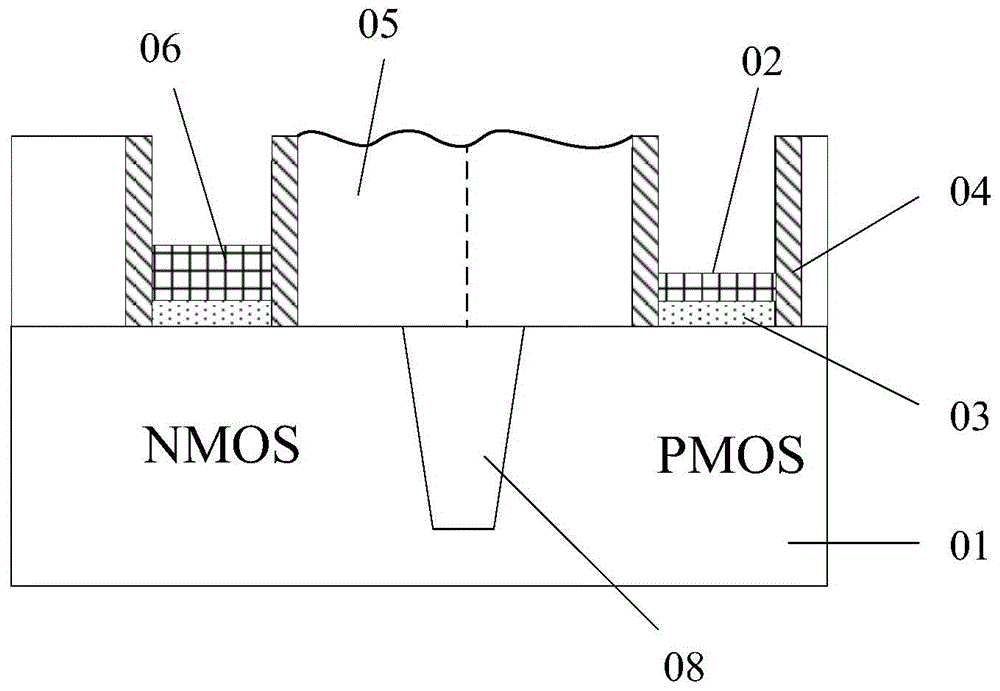

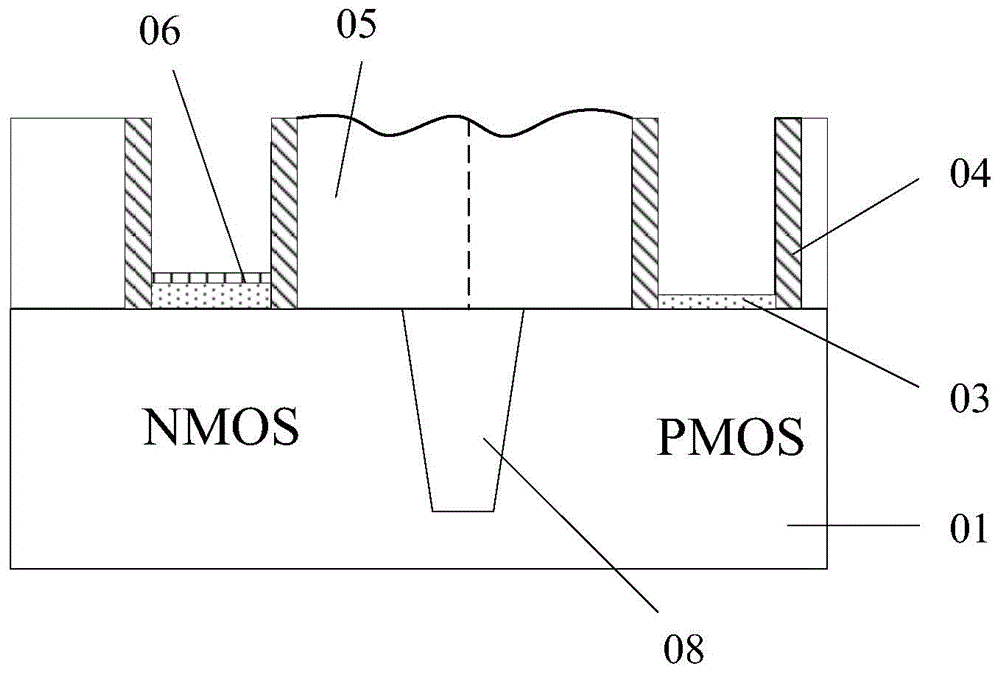

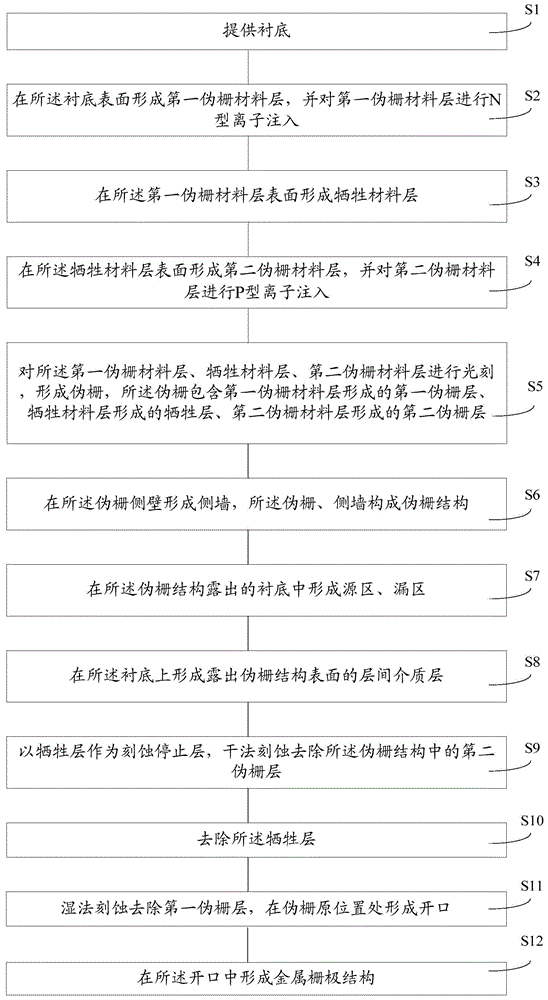

Transistor forming method

ActiveCN104701167AImprove performanceReduce the impactSemiconductor/solid-state device manufacturingMedia layerDry etching

The invention provides a transistor forming method. The method includes forming a first false grid layer, a sacrificial layer and a second false grid layer on a substrate from bottom to top; forming a side wall on the side wall of a false grid, and obtaining a false grid structure comprising the false grid and the side wall; forming a source region and a leak region in the substrate; forming an interlayer medium layer exposing the surface of the false grid structure; allowing the sacrificial layer to serve as an etching stop layer, and removing the second false grid layer of the false grid structure by dry etching; removing the sacrificial layer; removing the first false grid layer by wet etching, and forming an opening; forming a metal grid electrode structure in the opening. The method has the advantages that the influence of the substrate during false grid removal is small, and the quality of a formed transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

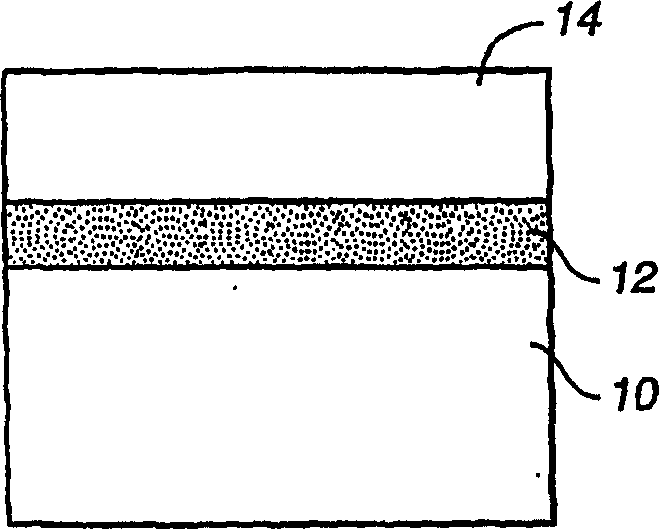

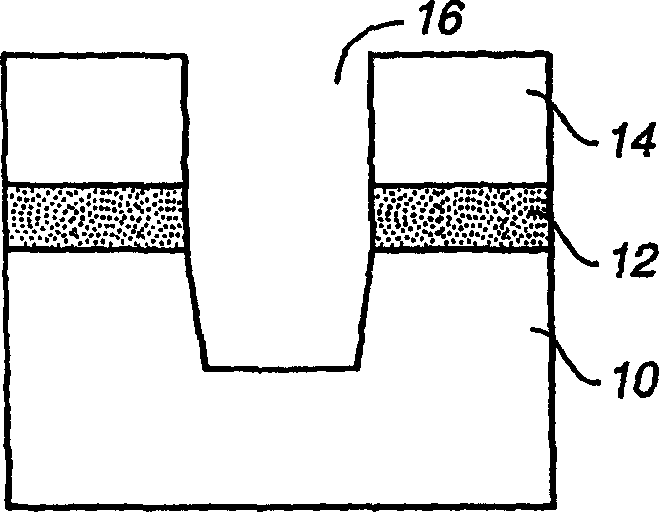

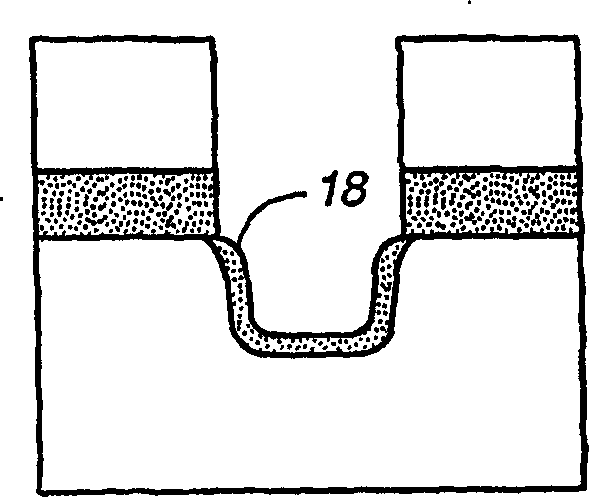

Method of forming shallow trench isolation structure in a semiconductor device

InactiveCN1701433AExtend etch timeImprove the coupling rateSolid-state devicesSemiconductor/solid-state device manufacturingAnisotropic etchingNitride

A method (Figs. 3A-3I) for fabricating a shallow trench isolation structure (Fig. 4) is described, in which a bottom pad oxide layer (62), a middle silicon nitride layer (64), a middle oxide layer (66) and a top silicon nitride layer (68) are sequentially formed on a silicon substrate (60). Photo-lithographic masking and anisotropic etching are then conducted to form a trench (70) in the substrate. An oxide material (80) is then deposited on top of the top silicon nitride layer, filling up the trenches at the same time (Fig. 3E). The top silicon nitride layer is then removed, followed by an isotropic etch of the oxide layer below. With the middle nitride layer acting as a natural etch stop, the oxide material is sculpted to a desirable shape. The middle nitride layer and the pad oxide layer are subsequently removed to complete the fabrication of a shallow trench isolation structure.

Owner:ATMEL CORP

Etching method for silver-copper solder

The invention relates to an etching method for silver-copper solder. The etching method comprises the following steps of (1) alkaline oil removal, specifically, a brazed semi-finished product outer shell is put into an alkaline oil removal solution to be cleaned up; (2) water washing, specifically, the brazed semi-finished product outer shell is washed by tap water firstly and then washed by usingdeionized water; (3) pickling, specifically, the water-washed outer shell is put into a pickling liquid to be washed; (4) drying, specifically, a high-temperature blast drying box is used for high-temperature drying the water-washed outer shell; (5) etching, specifically, the outer shell is placed in an etching solution; and (6) final processing, specifically, the outer shell is taken out after etching is finished, the step (2) water washing and the step (4) drying are repeated. The etching method has the advantages that (1) the silver-copper solder is etched without any corrosion damage, thecoverage of outer shell brazing appearance, size, solder and subsequent plating reliability are high; (2) the etching process is slowed down, and the etching time range is increased; (3) environmental pollution is relieved; (4) the etching method is low in cost, simple and easy to operate; and (5) the problem of silver displacement of radio frequency power device outer shells is solved, and the effect is remarkable.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

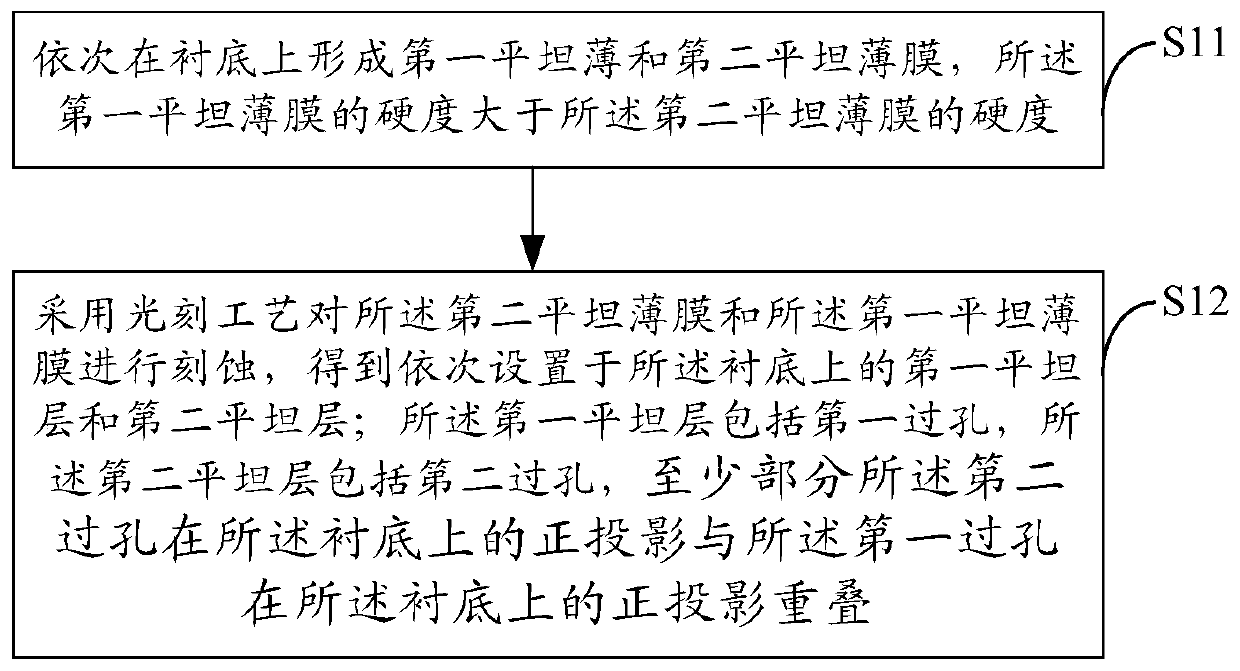

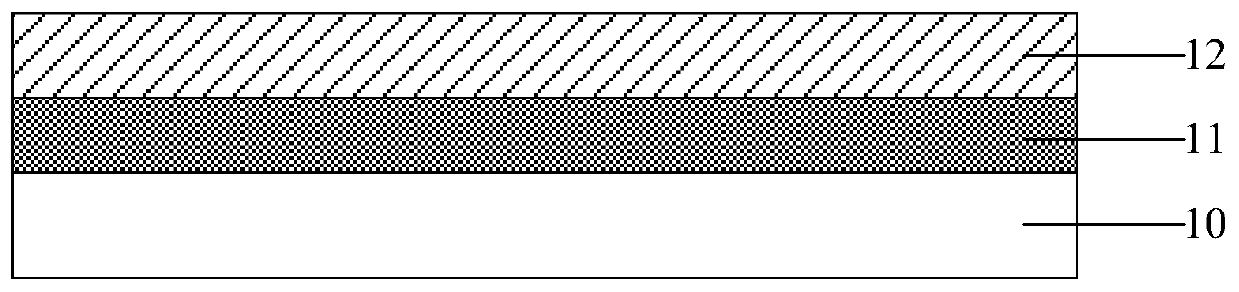

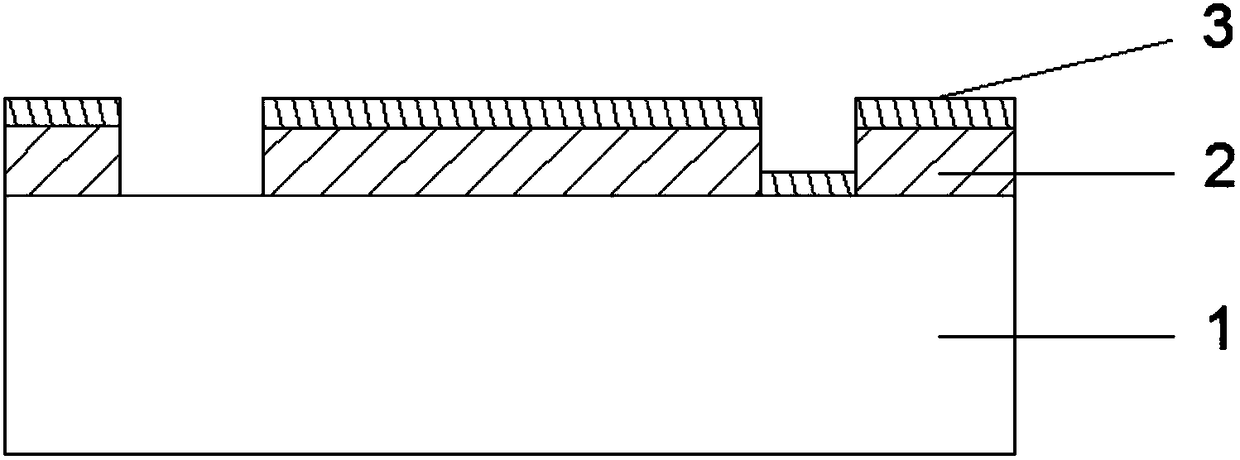

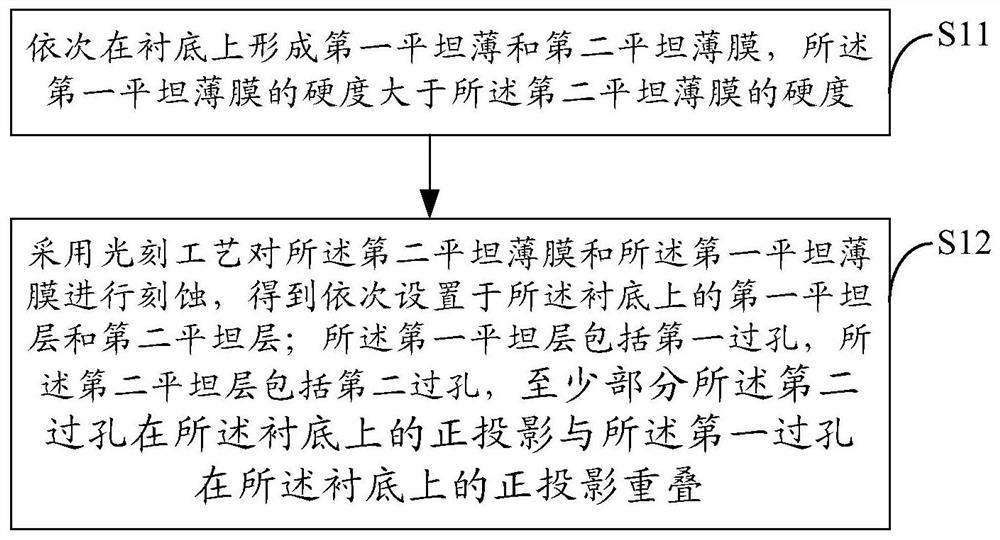

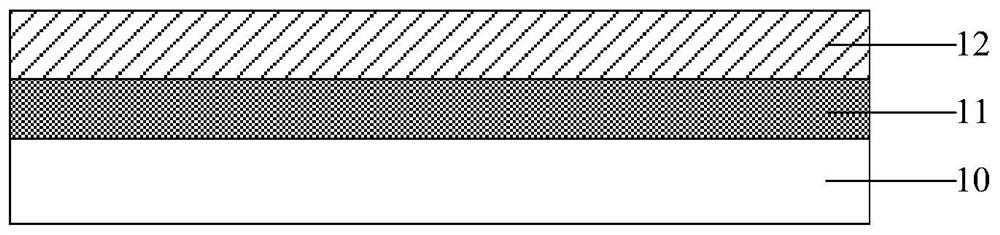

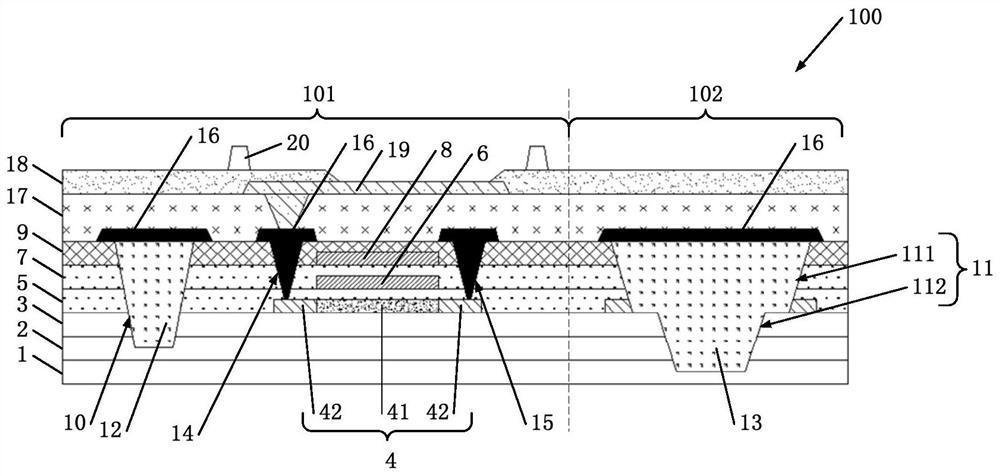

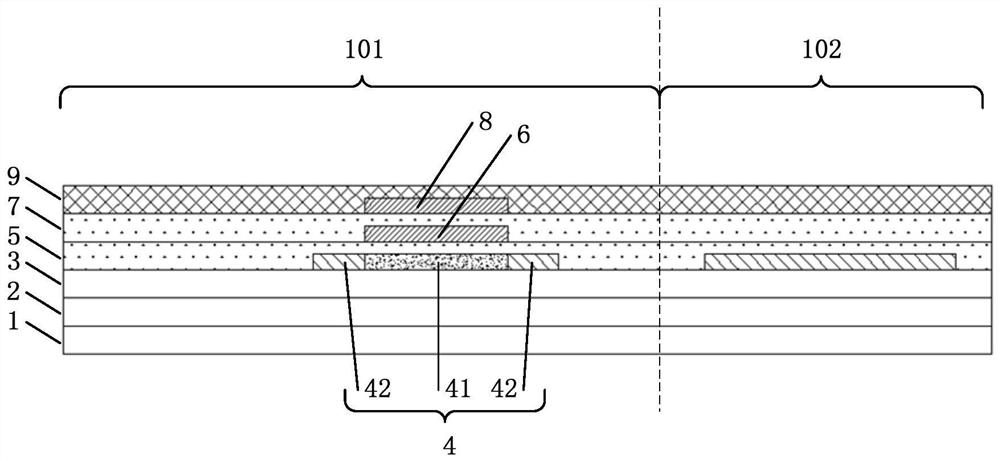

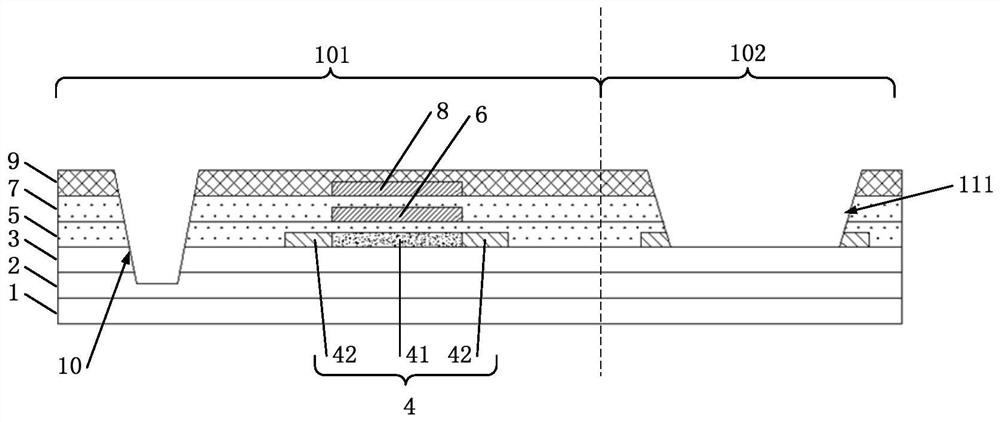

Base plate and preparation method thereof and display device

ActiveCN110797303AImprove the display effectExtend etch timeSolid-state devicesSemiconductor/solid-state device manufacturingLithography processDisplay device

The embodiment of the invention provides a base plate and a preparation method thereof and a display device, and relates to the technical field of display. The slope angle of a second via hole can bereduced so as to improve the display effect of the display device. The preparation method of the base plate comprises the following steps: a first flat film and a second flat film are sequentially formed on a substrate, and the hardness of the first flat film is larger than that of the second flat film; the second flat film and the first flat film are etched by adopting a photo-etching process toobtain a first flat layer and a second flat layer which are sequentially arranged on the substrate; and the first flat layer comprises a first via hole, the second flat layer comprises a second via hole, and the orthographic projection of at least part of the second via hole on the substrate is overlapped with the orthographic projection of the first via hole on the substrate.

Owner:BOE TECH GRP CO LTD +1

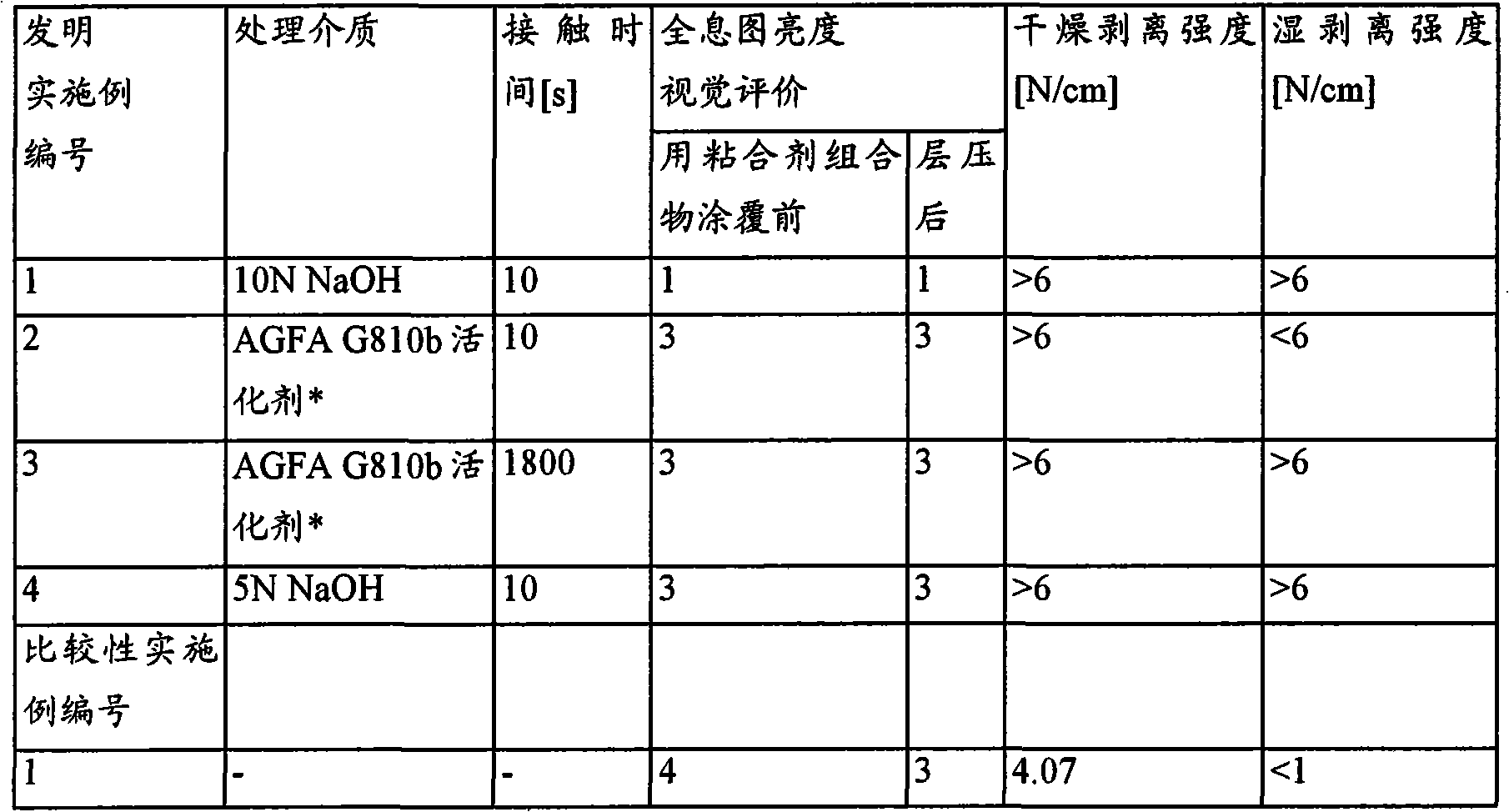

Security laminates with interlaminated transparent embossed polymer hologram

InactiveCN101815610AImprove adhesionAvoid delaminationStampsOther printing matterRefractive indexPolymer thin films

Owner:AGFA GEVAERT AG

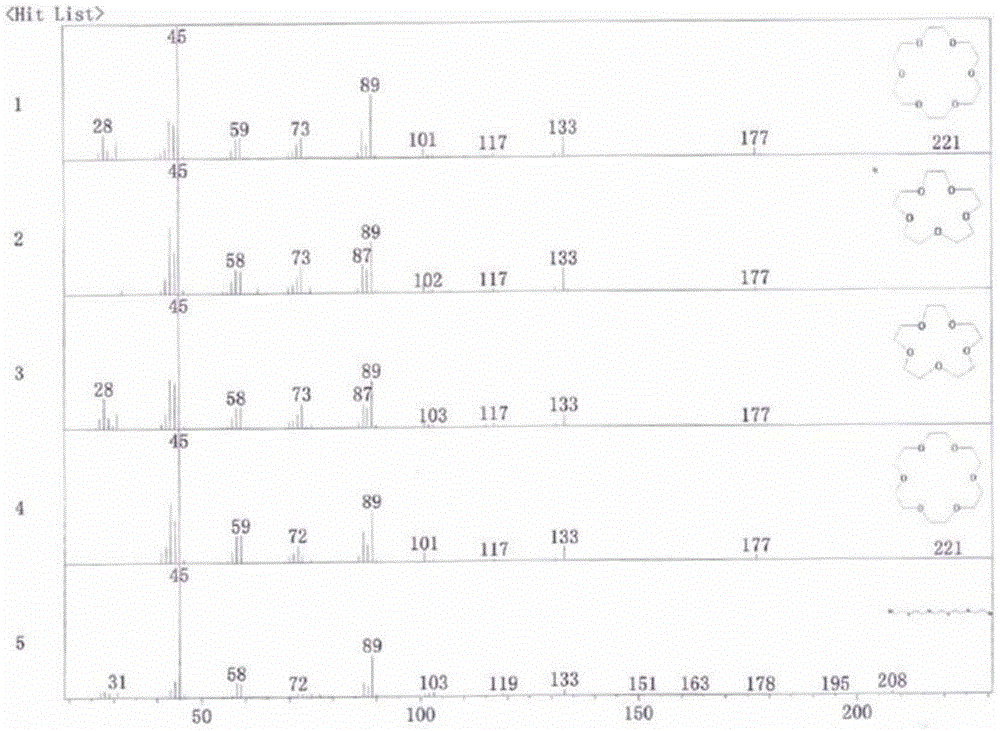

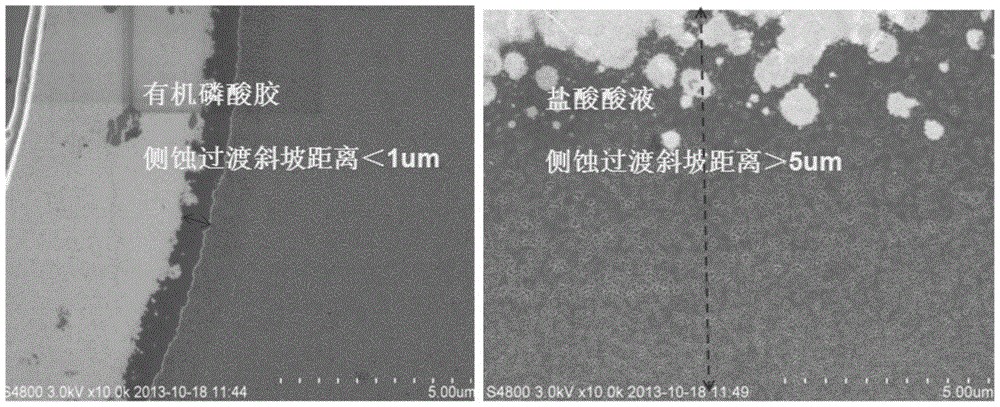

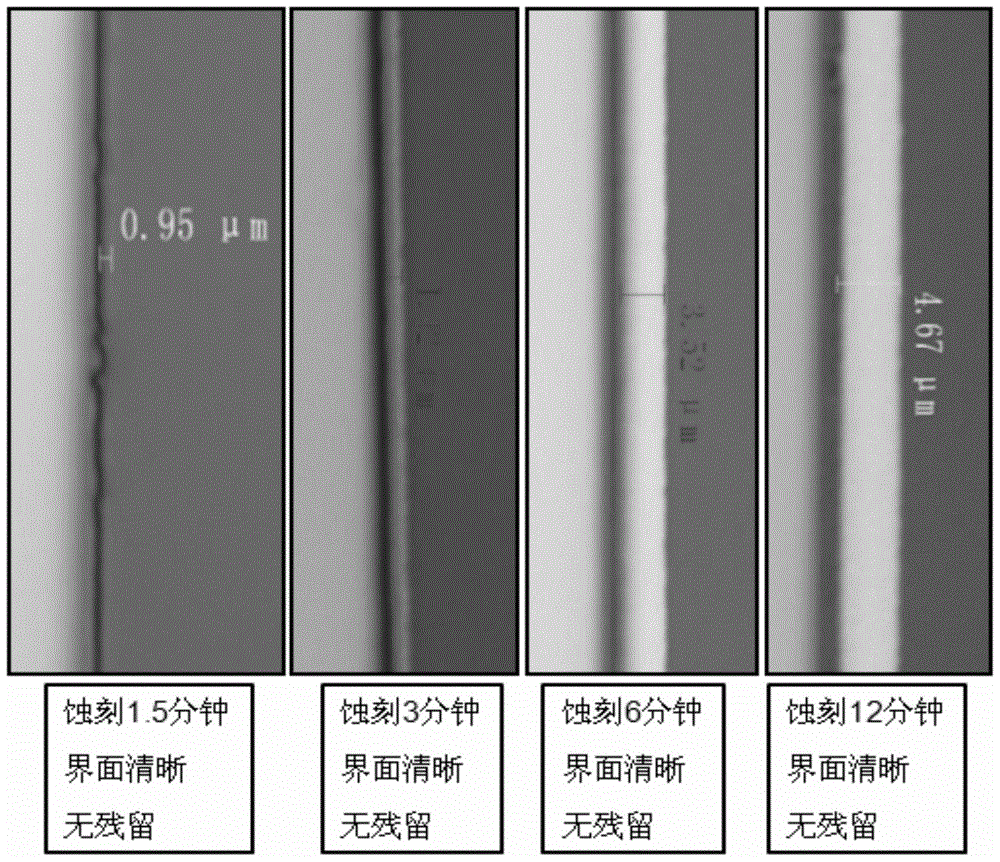

A kind of etching solution for oxide material system and its etching method and application

ActiveCN103980905BControl thicknessReduce liquidityCable/conductor manufactureSurface treatment compositionsAlloySolar cell

The invention discloses a novel etching solution used in an oxide material system. The novel etching solution comprises an oxide etching solution, an adjustment agent for adjusting the thickness, and water. The invention also discloses an etching method and an application of the novel etching solution. The novel etching solution and the etching method are generally suitable for etching film materials based on Sn, Zn, Al, Ga and In and alloy oxides thereof, especially oxide materials of ZnO, AZO, GZO, IGZO and IZO, and can also be widely used for etching oxide materials for making fine electronic components, such as semiconductor photoelectric devices, solar cells, TFT film transistors, semiconductor integrated circuits and transparent electrodes. Compared with traditional etching solutions, the novel etching solution has the advantages of lateral etching inhibition, uneven etching prevention and etching residual prevention.

Owner:FOSHAN INST SUN YAT SEN UNIV

High-efficiency environment-protective acidic etching solution and etching method thereof

The invention discloses a high-efficiency environment-protective acidic etching solution. The acidic etching solution comprises an etching solution base solution, an acid etching solution I and an acid etching solution II, wherein in the etching solution base solution, the content of hydrogen ions is 0. 5g / L-1.5 g / L, the content of chloride ions is 230 g / L-260 g / L, the content of the copper ions is 120 g / L-150 g / L, and the redox potential difference of the copper ions and cuprous ions is 450-550 millivolt, the content of chlorate ions in the acidic etching solution I is 80 g / L-180 g / L, and thecontent of the hydrogen ions in the acid etching solution II is 100 g / L-200 g / L. The invention further discloses an etching method of the high-efficiency environment-protective acidic etching solution. The method has the advantages of being high in etching efficiency, small in pollution and the like, the etching efficiency is effectively improved, the pollution is reduced, the production cost issaved, and the production efficiency of a circuit board is improved.

Owner:惠州市鸿宇泰科技有限公司

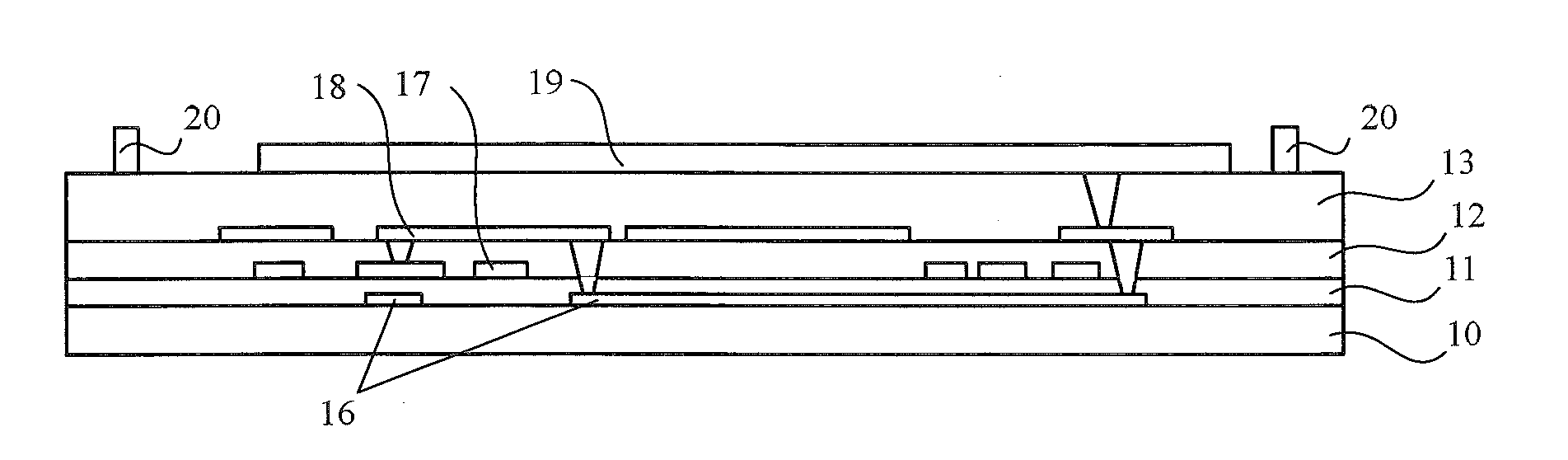

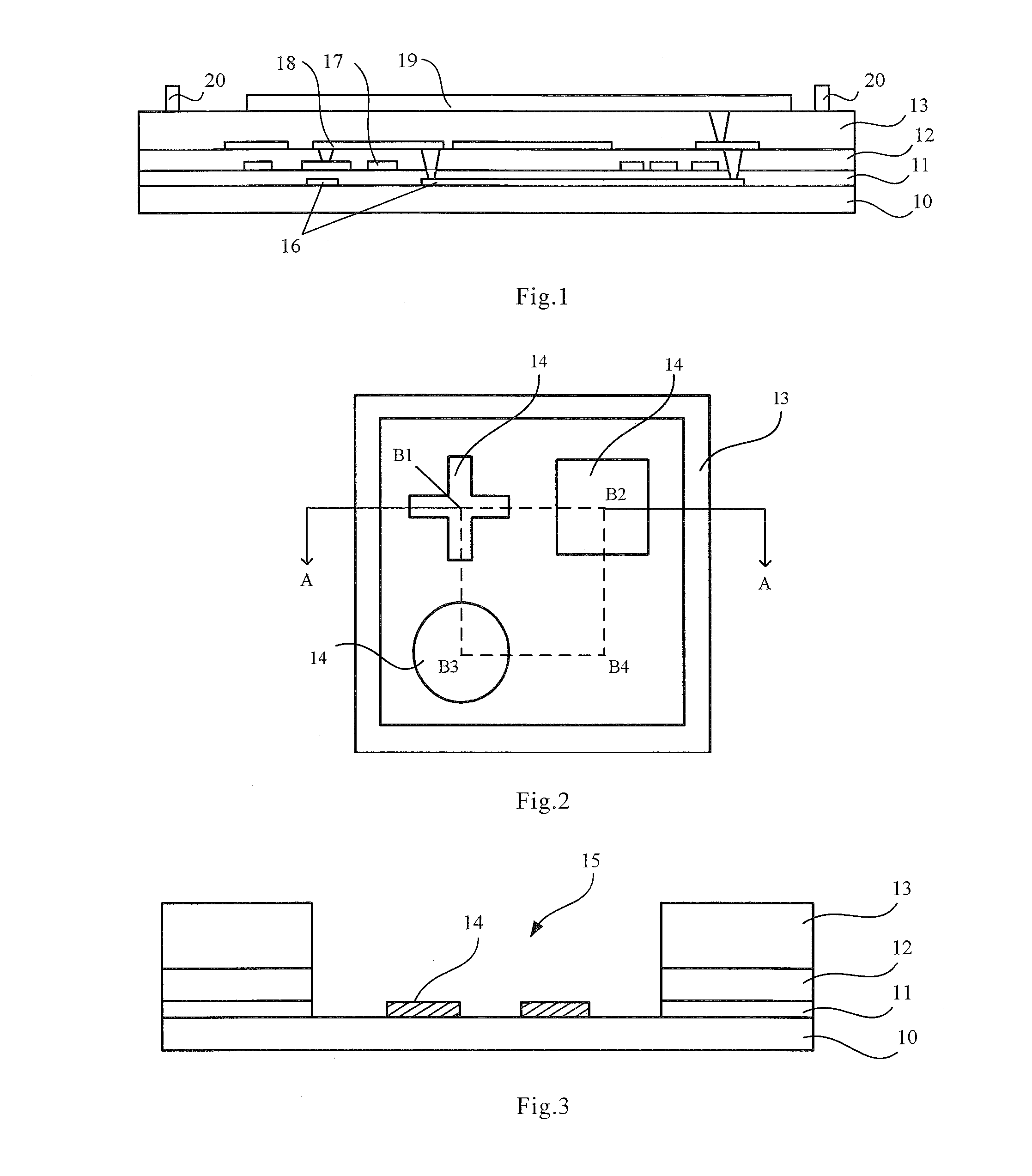

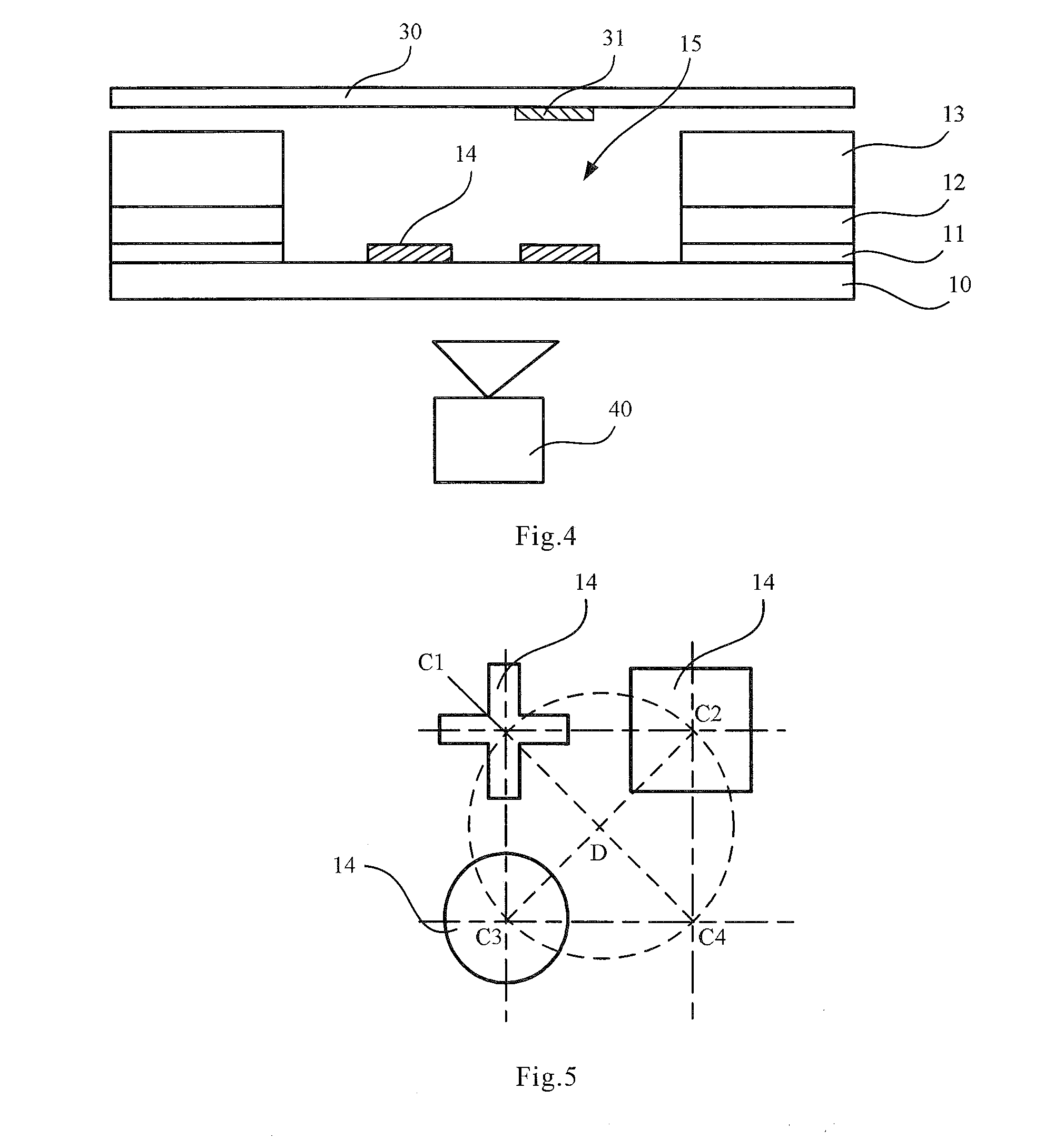

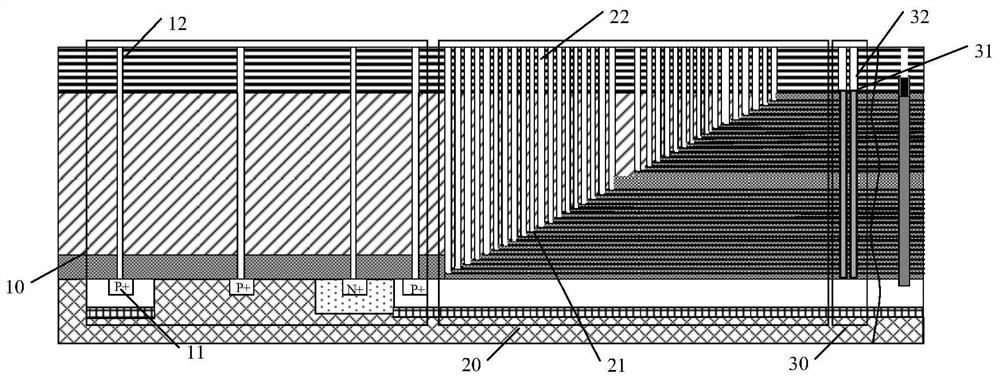

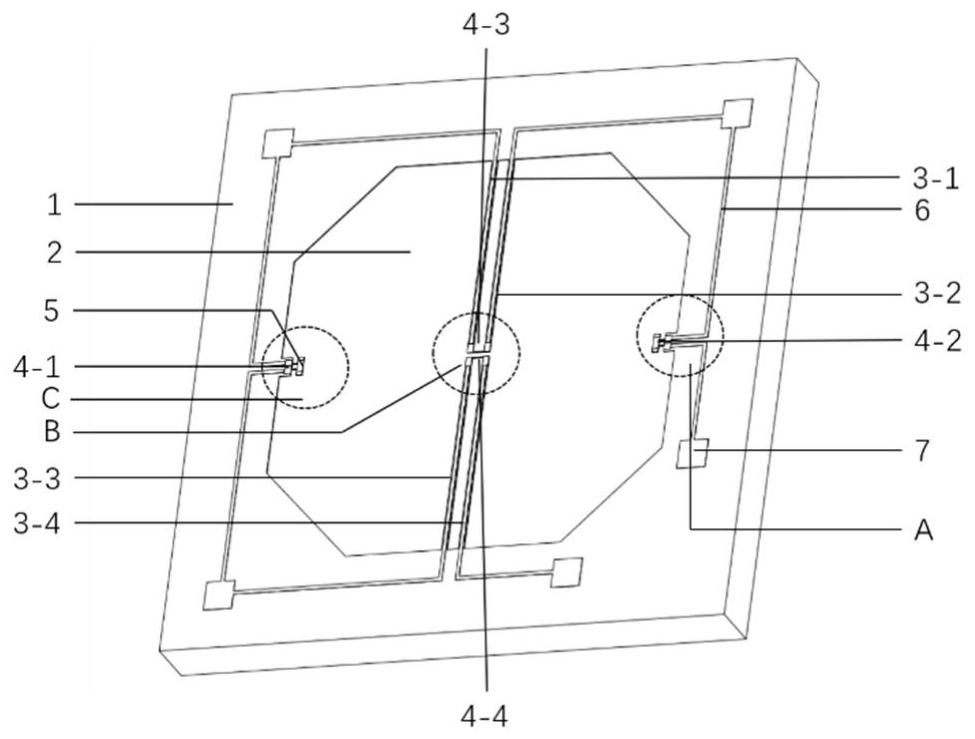

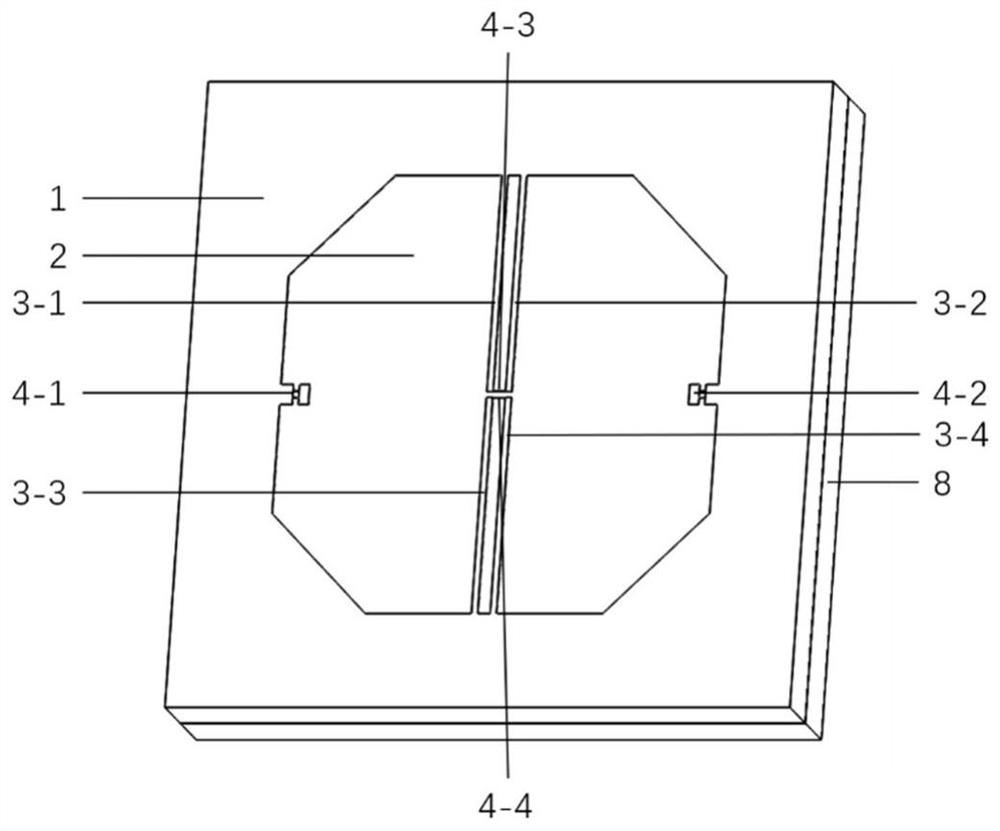

OLED Backboard, Method of Manufacturing the same, Alignment System and Alignment Method thereof

ActiveUS20160254321A1Improve efficiencyTime of alignmentTelevision system detailsImage enhancementOLEDMaterials science

The present disclosure relates to a technical field of OLED display and discloses an OLED backboard, a method of manufacturing the same, an alignment system and an alignment method thereof, which aims to solve a problem of low efficiency in forming an organic light-emitting material layer on the OLED backboard. The OLED backboard comprises: a transparent substrate; at least two functional layers disposed on the upper surface of the transparent substrate and stacked on each other; at least two via holes formed in predefined areas of the at least two functional layers and extending through at least the upper one of the at least two functional layers; and at least two alignment modules located in the at least two via holes respectively, wherein each of the at least two alignment modules comprises at least three first alignment structures arranged in a predefined trace, and a virtual alignment point is allowed to be determined based on the relative position among all the first alignment structures in each of the alignment modules. The efficiency of forming the organic light-emitting material layer on the OLED backboard is thus increased by using the above OLED backboard.

Owner:BOE TECH GRP CO LTD +1

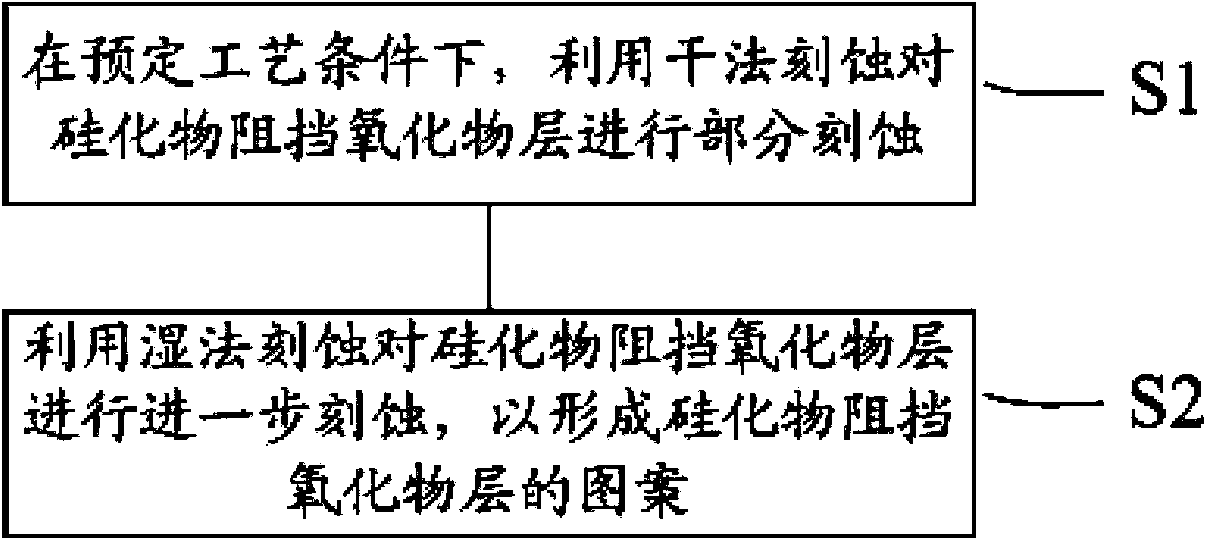

Method for etching silicide-blocked oxide layer

InactiveCN103441072AControl thicknessControl UniformitySemiconductor/solid-state device manufacturingSalicideDry etching

The invention provides a method for etching a silicide-blocked oxide layer. The method includes the steps that in predetermined technological conditions, partial etching is performed on the silicide-blocked oxide layer through dry etching; further etching is performed on the silicide-blocked oxide layer through wet etching so as to form patterns of the silicide-blocked oxide layer. The predetermined technological conditions are that etching power is 150W-250W, pressure is 50mT-100mT, and etching time is not less than 10 seconds.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Manufacturing method for composite of aluminum alloy and plastic

The invention provides a manufacturing method for a composite of an aluminum alloy and plastic. The composite is obtained by covering the outer surface of the aluminum alloy with the plastic. The manufacturing method comprises the following steps: S1, carrying out oil-removing, dust-removing and coarse etching treatment on the surface of the aluminum alloy; step 2, immersing the aluminum alloy prepared by the step S1 into an etching solution to be finely etched to prepare an aluminum alloy with fine lines or fine holes on the surface, wherein a coating formed by an etching solution solvent covers the prepared fine lines or fine holes; S3, washing the etched aluminum alloy with water; S4, drying the aluminum alloy washed with the water; and S5, integrally molding by injecting the aluminum alloy and the plastic to obtain the composite. In the step S2, the etching solution is a mixed solution of cyclohexanone and fine gloss oil containing a nitrogen element. The etching solution is mixed with the fine gloss oil so that the fine gloss oil is attached on the surface of the aluminum alloy to form the coating when the aluminum alloy is etched; and the fine lines can be prevented from expanding and being recovered due to the self tension of the aluminum alloy, the widths and the depths of the fine lines and the fine holes are kept, and the aluminum alloy is conveniently combined with the plastic by injection molding.

Owner:GUANGDONG SUNRISE ELECTRONICS TECH

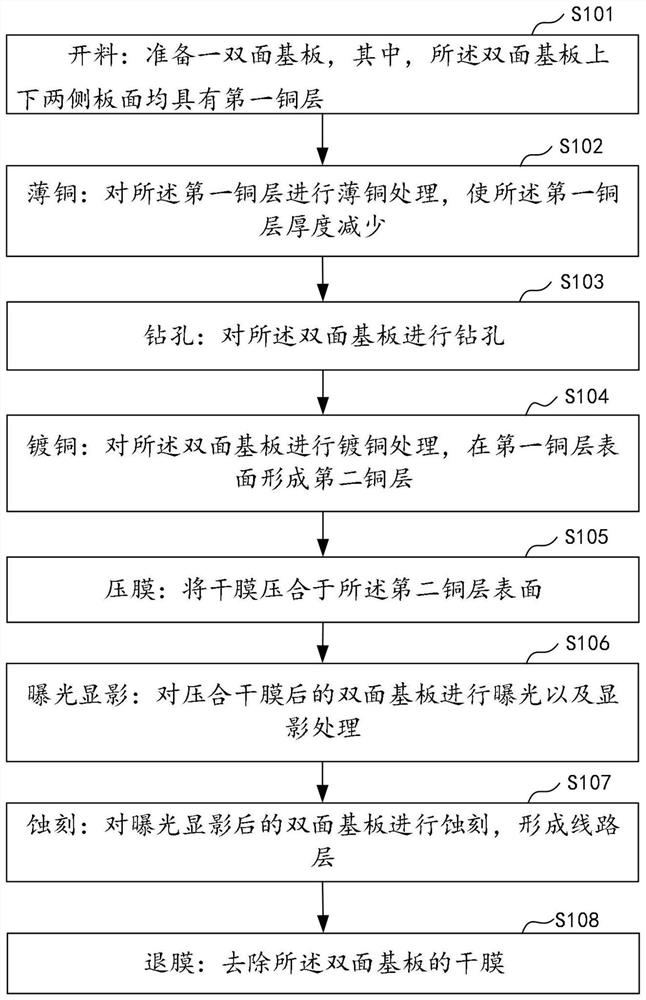

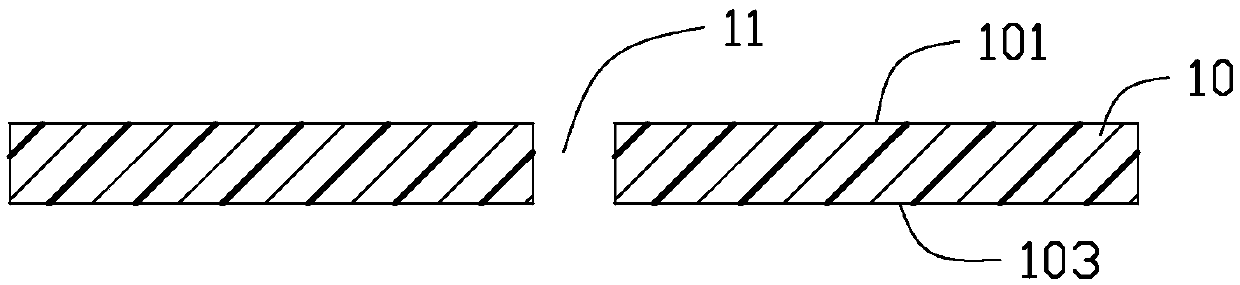

PCB micro-etching process of micro circuit and circuit board

PendingCN113766747AReduce thicknessReduce etch rateConductive material chemical/electrolytical removalConductive pattern reinforcementMetallurgyElectrical and Electronics engineering

The embodiment of the invention discloses a PCB micro-etching process of a micro circuit and a circuit board. The PCB micro-etching process comprises the following steps: cutting: preparing a double-sided substrate, and the upper and lower side plate surfaces of the double-sided substrate being respectively provided with a first copper layer; copper thinning: carrying out copper thinning treatment on the first copper layer to reduce the thickness of the first copper layer; drilling: specifically, performing drilling on the double-face substrate; copper plating: performing copper plating treatment on the double-sided substrate, and forming a second copper layer on the surface of the first copper layer; film pressing: pressing a dry film on the surface of the second copper layer; exposing, developing, etching and stripping the film. According to the embodiment of the invention, the first copper layer is subjected to copper thinning treatment, so that the thickness of the first copper layer is reduced to be within the preset thickness range, the etching rate of the circuit board is reduced, namely, the etching time of the circuit board is prolonged, the circuit layer of the circuit board is accurately controlled, and the yield and the production efficiency of the circuit board are effectively improved.

Owner:江西景旺精密电路有限公司

Quick-drying environmental-protection ink preparation method

The invention discloses a quick-drying environmental-protection ink preparation method, wherein the ink comprises, by weight, 10-30 parts of a hydrocarbon resin, 10-30 parts of an acrylic acid prepolymer, 0.1-1 part of a polymerization inhibitor, 5-12 parts of a photoinitiator, 5-10 parts of a pigment, 1-5 parts of a dispersant, and 20-50 parts of an acrylic monomer. According to the present invention, the ink is suitable for flexographic printing machines, and is instantaneously dried by an ultraviolet lamp so as to greatly improve the working efficiency; the ink can resist strong acid etching after being dried, wherein the concentration of the etching acid can be freely increased, the temperature of the etching liquid can be increased, and the etching time can be increased so as to meetthe processing requirements of various RFID tags; the ink is easily subjected to alkali washing after being dried and etched, and the deinking can be achieved within 5-20 s with a 3% NaOH solution; and with the quick-drying environmental-protection ink, the clean circuit surface with no ink residue can be effectively achieved so as to ensure the quality of the final product.

Owner:任洋

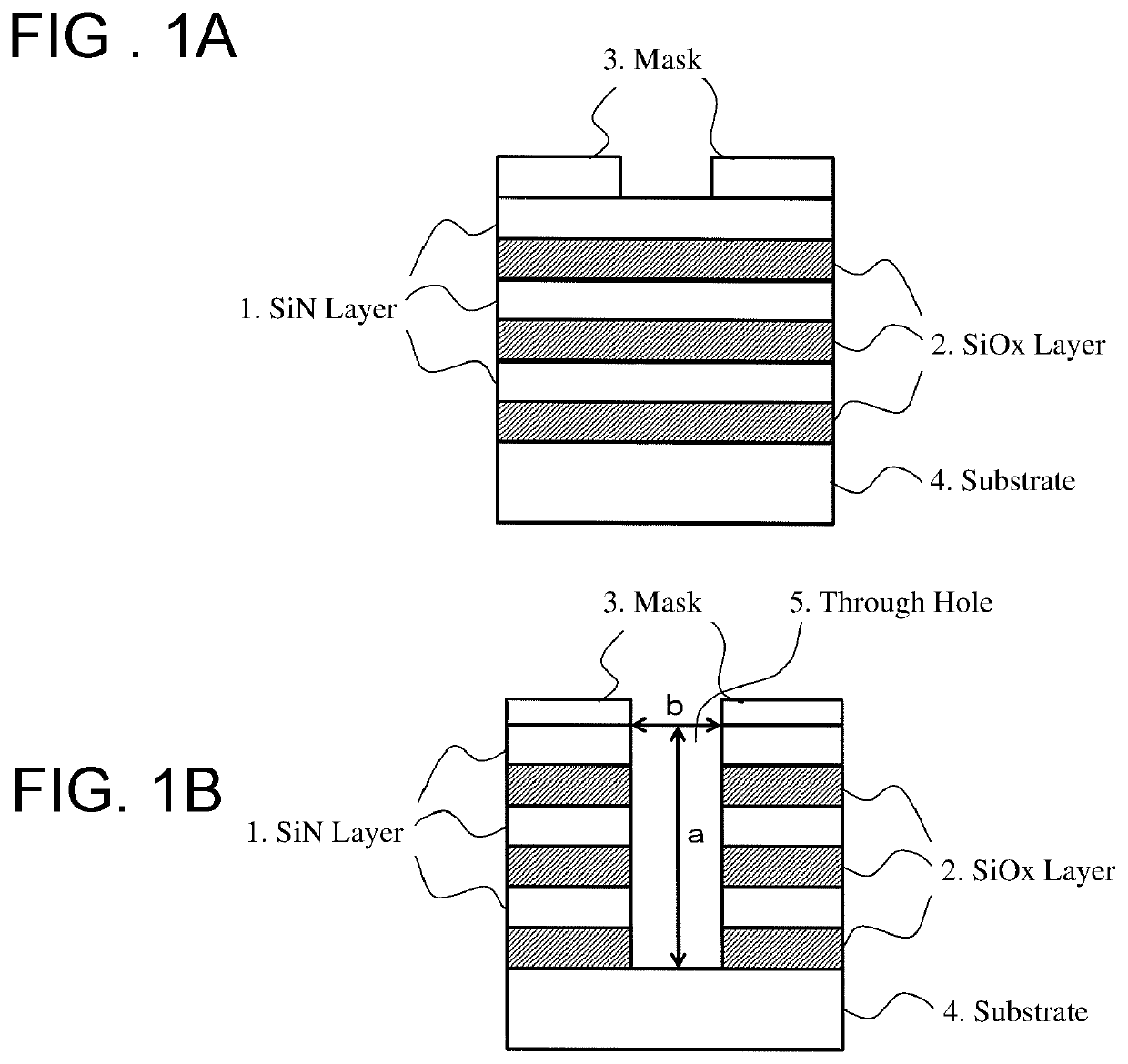

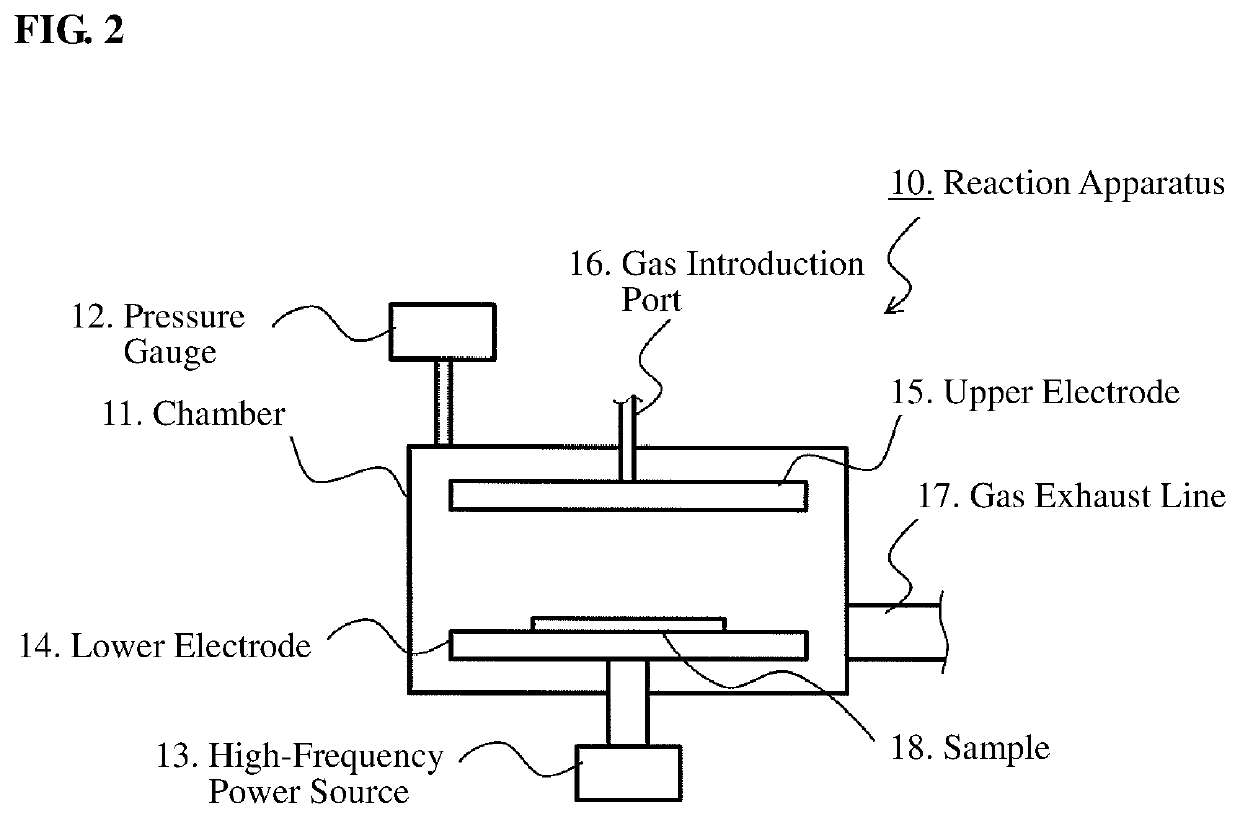

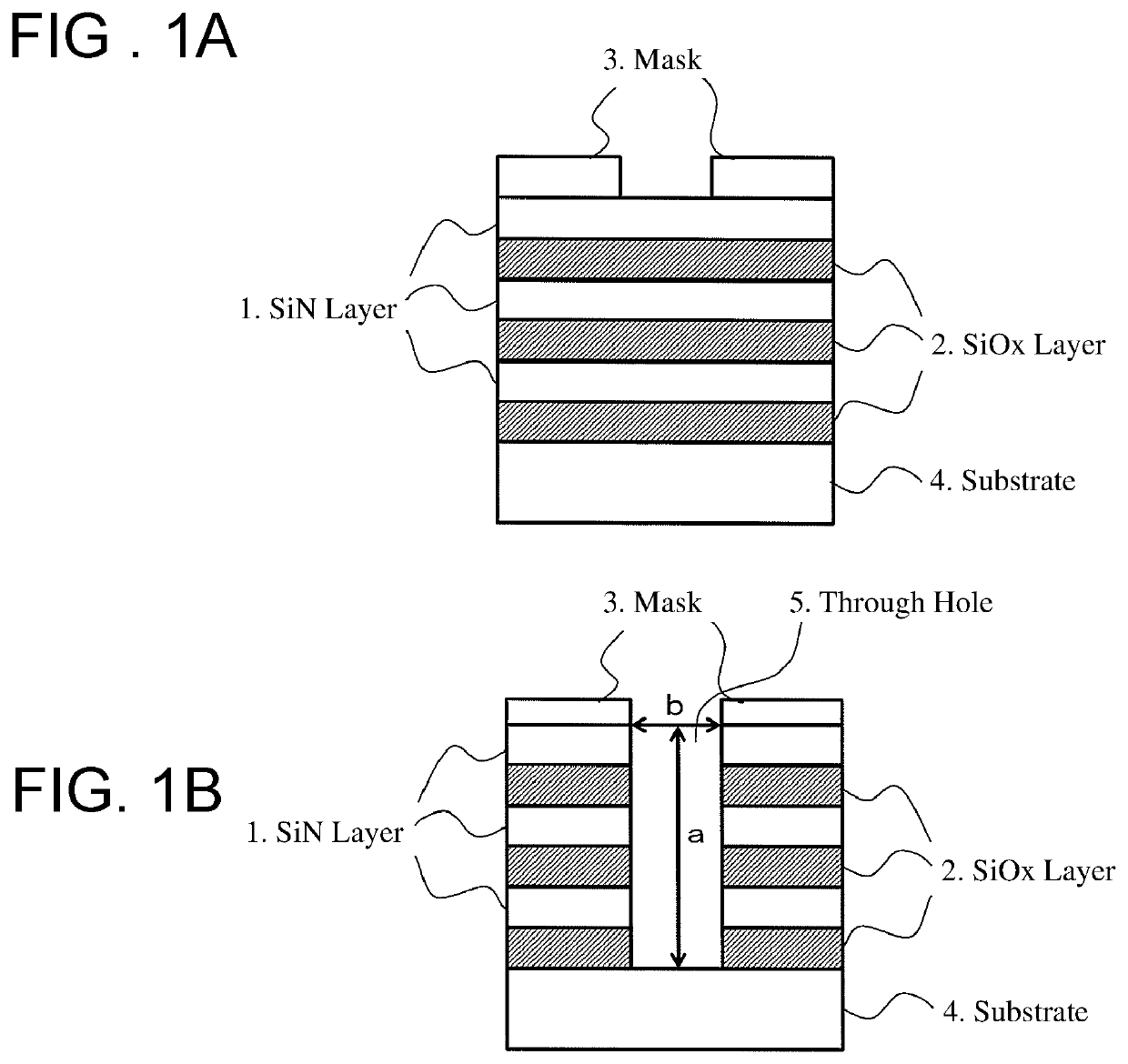

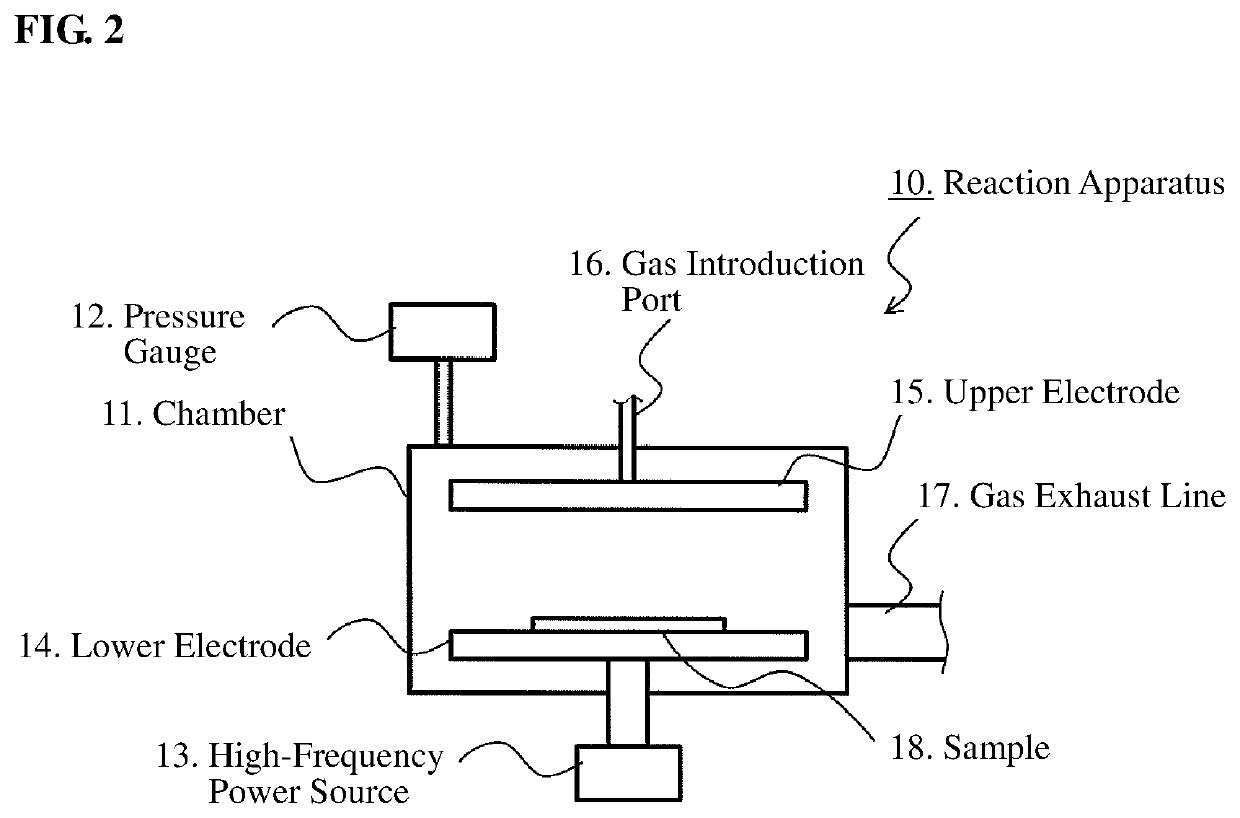

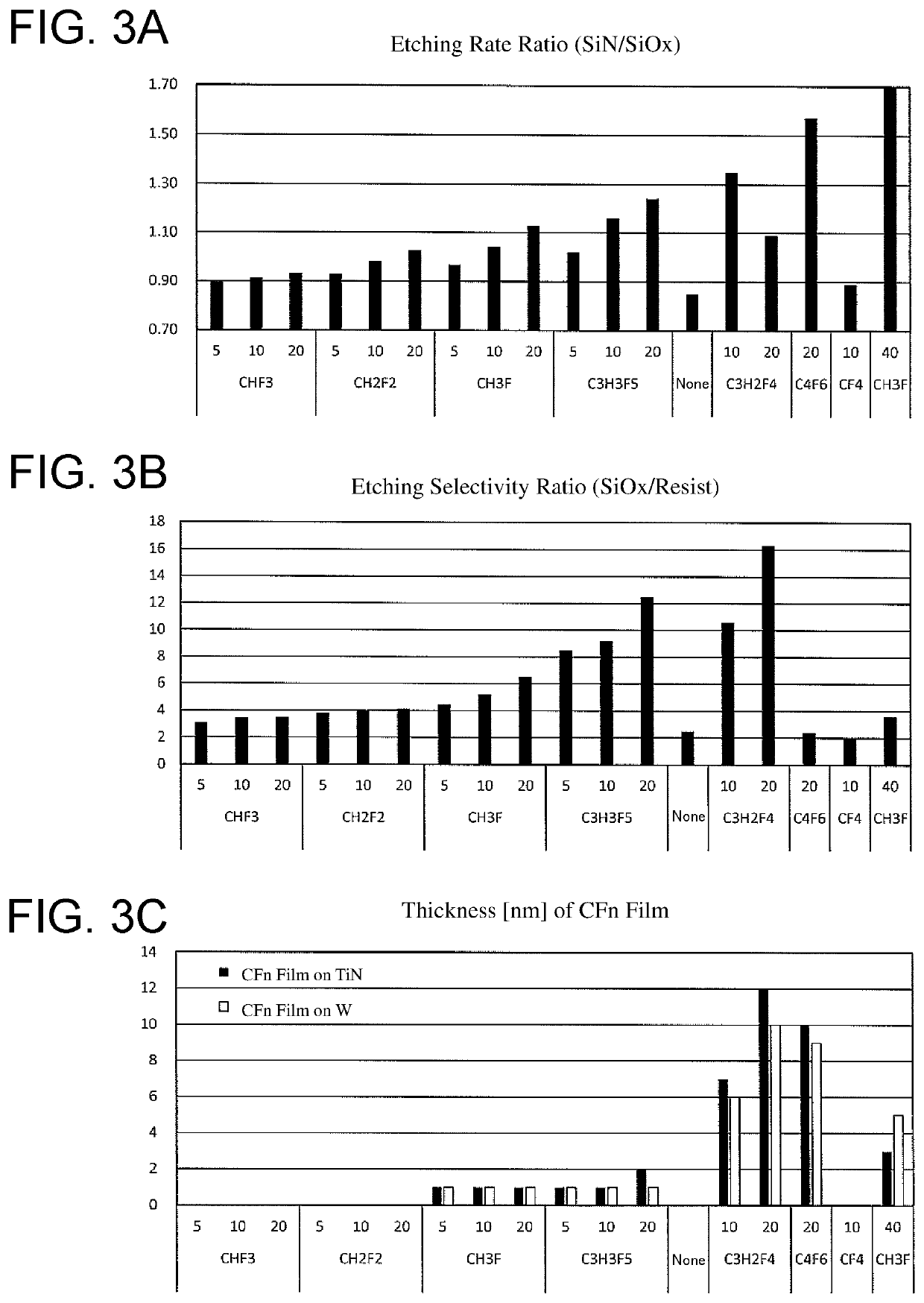

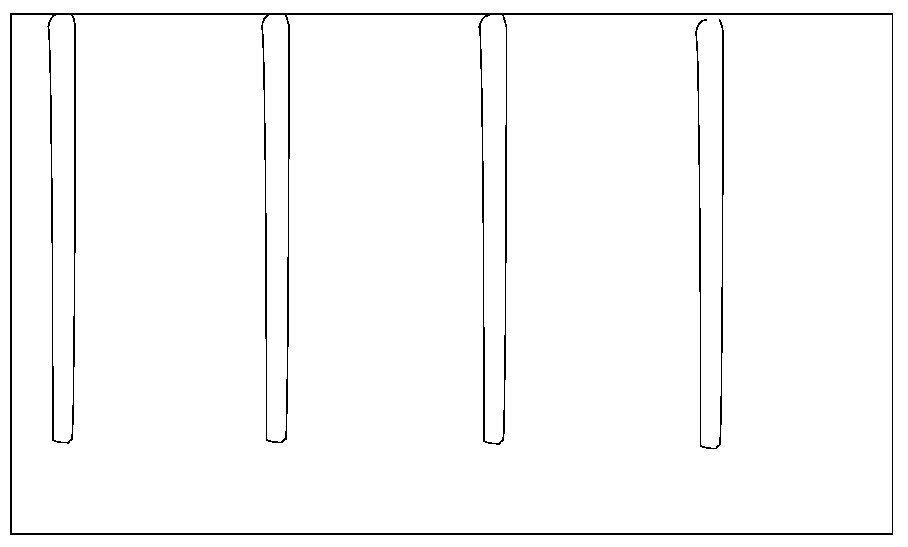

Dry Etching Method

ActiveUS20210358762A1Excessive depositionControl rateSemiconductor/solid-state device manufacturingSurface treatment compositionsSilicon oxideFluorocarbon

A dry etching method according to the present disclosure is for forming a through hole in a laminated film of silicon oxide layers and silicon nitride layers on a substrate in a direction vertical to the laminated film by plasmatizing a dry etching agent to generate a plasma and etching the laminated film by the plasma through a mask having a predetermined opening pattern under a negative direct-current self-bias voltage whose absolute value is 500 V or greater, wherein the dry etching agent contains at least C3F6, a hydrogen-containing saturated fluorocarbon represented by CxHyFz and an oxidizing gas, and wherein the volume of the hydrogen-containing saturated fluorocarbon contained in the dry etching agent is in a range of 0.1 to 10 times the volume of C3F6 contained in the dry etching agent.

Owner:CENT GLASS CO LTD

Method for manufacturing circuit board

ActiveCN109673111ANo additional compensationImprove bindingInsulating substrate metal adhesion improvementPrinted circuit aspectsCopper platingMaterials science

The present invention provides a method for manufacturing a circuit board. The method comprises the following steps of: providing an insulation substrate, and arranging at least one through hole penetrating the two opposite surfaces of the insulation substrate on the insulation substrate; forming silver layers respectively on the two opposite surfaces, and forming a silver conductive structure connected with the two silver layers in the through hole; performing copper plating for the insulation substrate with the silver layers and the silver conductive structure to form a copper circuit layer,wherein the copper circuit layer covers the silver conductive structure and the part area of the silver layers; and etching the silver layers by employing first etching liquid to silver circuit layers corresponding to the copper circuit layer, wherein the first etching liquid does not corrode the copper circuit layer.

Owner:HONGQISHENG PRECISION ELECTRONICS (QINHUANGDAO) CO LTD +1

UV gravure RFID printing ink and preparation method thereof

The invention discloses UV gravure RFID printing ink and a preparation method thereof; the UV gravure RFID printing ink comprises, by weight:10-30 parts of petroleum resin, 10-30 parts of acrylic acid prepolymer, 0.1-1 part of a polymerization inhibitor, 5-12 parts of a photoinitiator, 5-10 parts of pigment, 1-5 parts of a dispersant, and 20-50 parts of acrylic acid monomers. The UV gravure RFID printing ink of the invention has the following beneficial effects: the printing ink is suitable for gravure press and flexo-graphic machines, is instantly dried by an ultraviolet lamp, which greatly increases the working efficiency. After dried, the printing ink can resist strong acid etching; the concentration of the etching acid can be adjusted at will; the etching solution temperature can be increased; the etching time can be increased; and thus processing of various RFID labels can be met. After drying and etching, the printing ink is easy to be washed by alkalis, and a 3% NaOH solution can remove the ink within 5-20 seconds. The line surface is effectively maintained to be clean and free of printing ink residues, and thus the final product quality is ensured.

Owner:杭华油墨股份有限公司

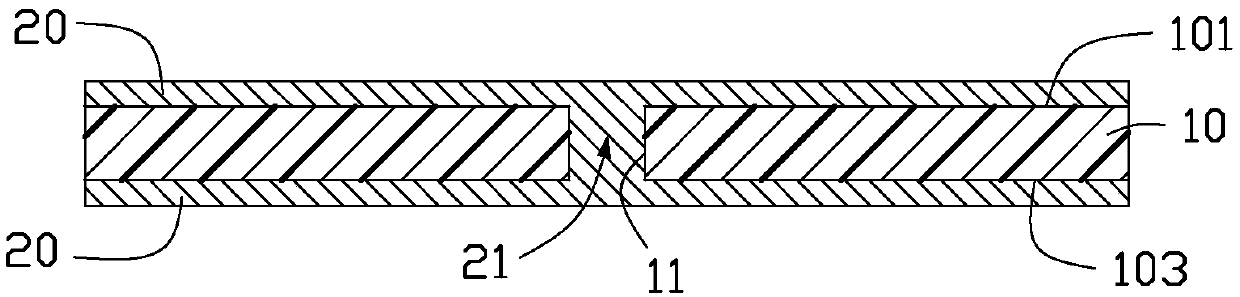

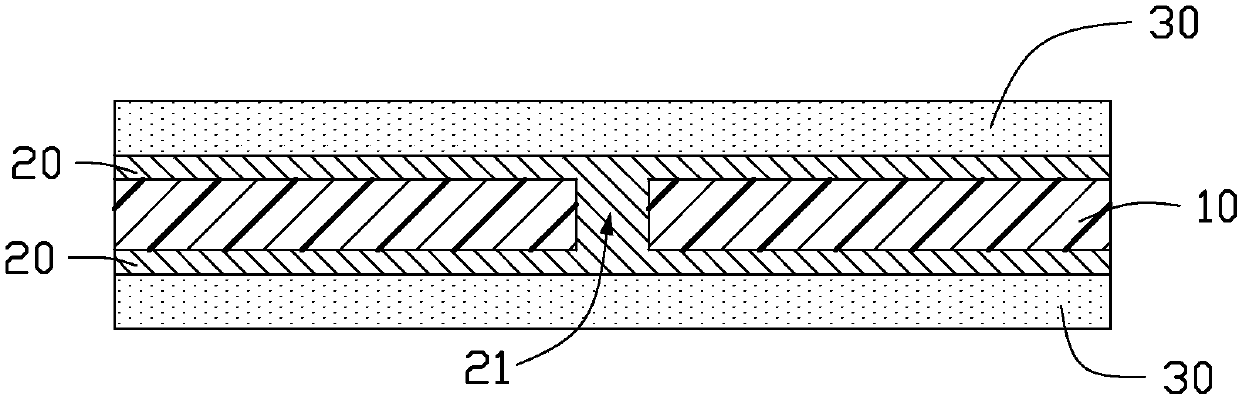

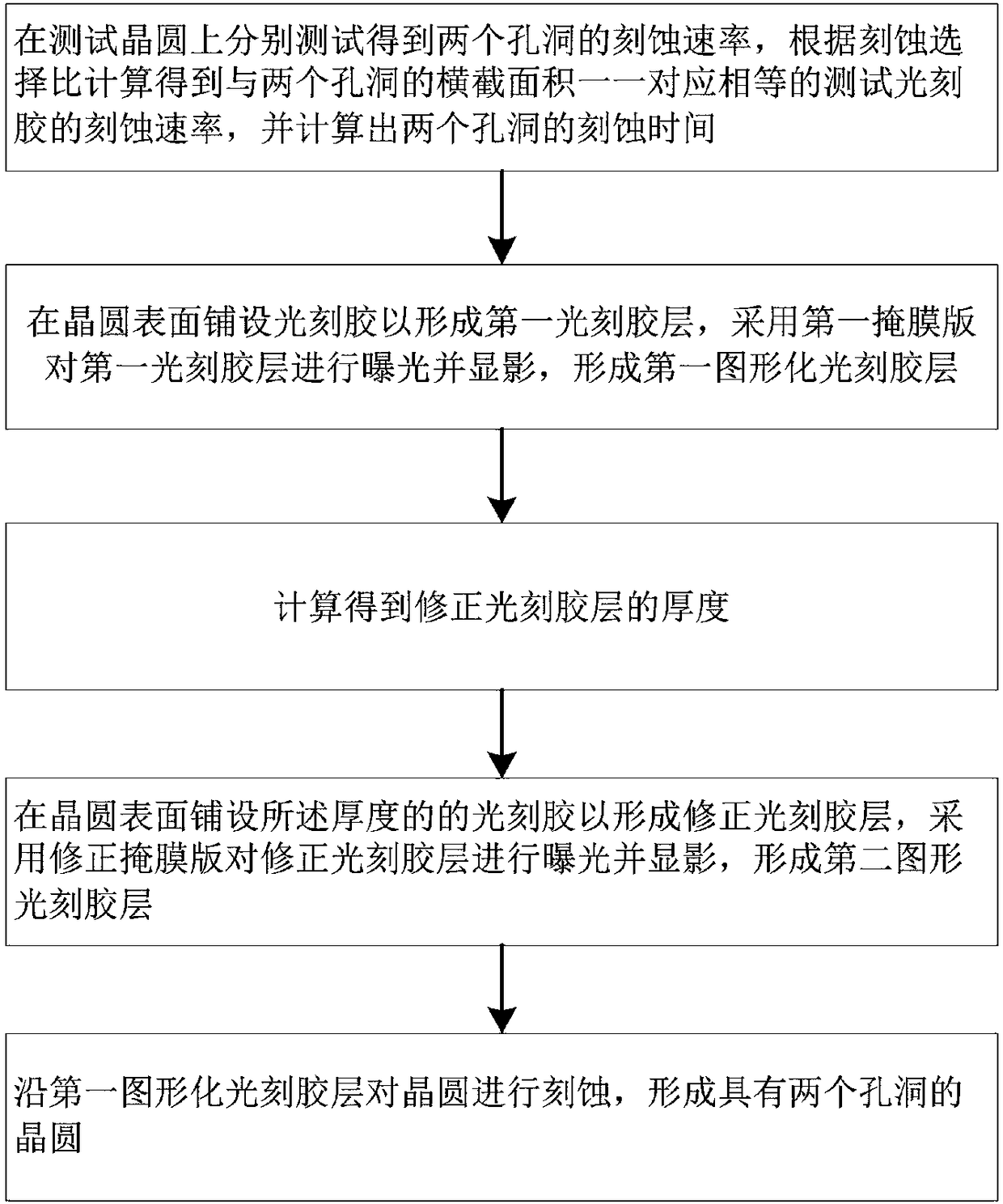

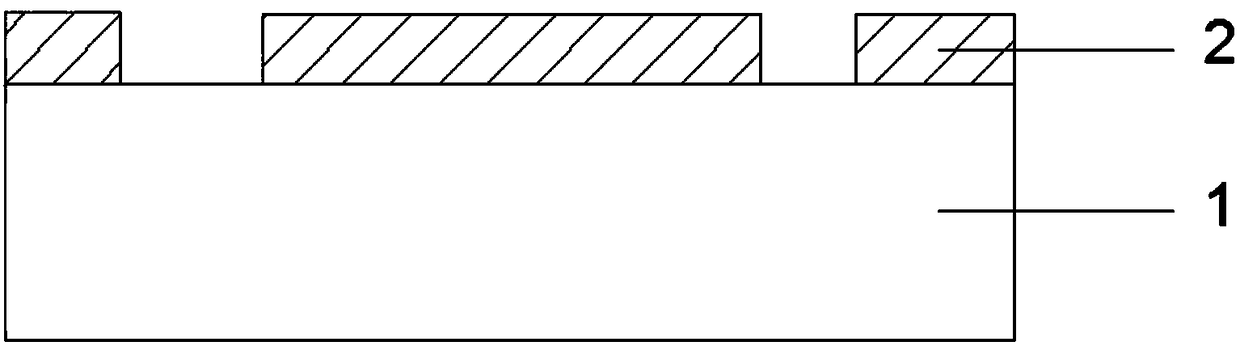

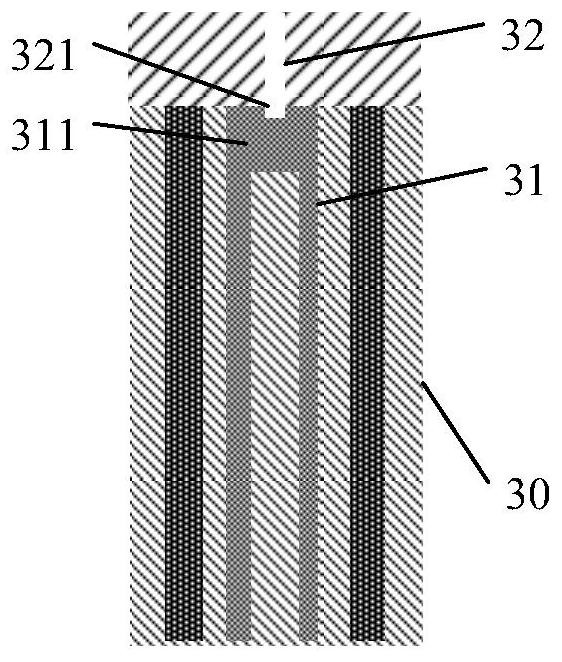

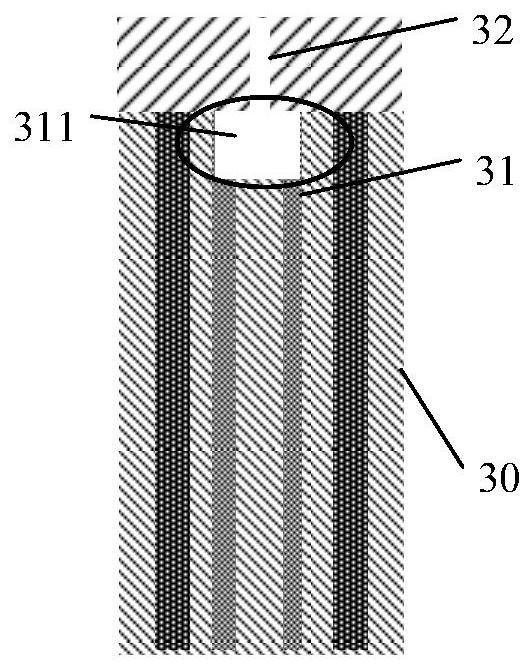

Semiconductor wafer hole manufacturing method

ActiveCN108376644AExtend etch timeAvoid damage to the waferSemiconductor/solid-state device manufacturingMicrowaveRadio frequency

The invention relates to the radio frequency microwave semiconductor making technology field and particularly relates to a semiconductor wafer hole manufacturing method. The method comprises steps that etching rates of two holes are acquired through the test on a test wafer, and the equal etching rate of the test photoresist and the etching time of the two holes in one-to-one correspondence with cross-sectional areas of the two holes are acquired through calculation; a first photoresist layer is laid on a surface of a wafer, the first photoresist layer is exposed and developed to form a firstgraphic photoresist layer; thickness of the correction photoresist layer is acquired through calculation; the correction photoresist layer with the thickness is laid on the surface of the wafer, and the correction photoresist layer is exposed and developed to form a second graphic photoresist layer; the wafer is etched along the first graphic photoresist layer, and the wafer having the two holes is formed. The method is advantaged in that the relatively long etching time is taken as reference, the etching time of another hole is extended through laying the correction photoresist layer, and theetching depth beyond a preset value or damage to the wafer is avoided.

Owner:CHENGDU HIWAFER SEMICON CO LTD

Method for forming contact groove and semiconductor

ActiveCN111261636BLow costReduce time consumptionSolid-state devicesSemiconductor devicesEngineering physicsSemiconductor

The embodiment of the present application discloses a method for forming a contact groove and a semiconductor. The method includes: providing a semi-finished semiconductor, the semiconductor includes a first structure using a first material corresponding to different regions, and a second material using a second structure. The second structure of the second structure, and at least the third structure with the second material on the top; through the same first etching process, using the different etching rates of the first material and the second material, the first structure, the second structure and the third structure are etched to form grooves of a specific depth; wherein, the etching rate of the first material is greater than the etching rate of the second material, so that using the The top of the third structure of the second material acts as an etch stop layer.

Owner:YANGTZE MEMORY TECH CO LTD

A kind of etching method of silver-copper solder

The invention relates to an etching method for silver-copper solder, which comprises the following steps: (1) Alkaline degreasing: put the brazed semi-finished shell into an alkaline degreasing solution for cleaning; (2) Washing: first rinse with tap water, and then Clean it with deionized water; (3) pickling: put the washed shell into the pickling solution to clean; (4) dry; use a high-temperature blast drying box to dry the washed shell at high temperature; (5) ) Etching: Put the casing into the etching solution; (6) After the etching is completed, take out the casing and repeat the process step (2) washing with water, and step (4) drying. Advantages: 1) There is no corrosion damage to the etching of silver-copper solder, and the shell brazing shape, size, solder coverage and subsequent plating reliability are high. 2) Slow down the etching process, increase the range of etching time, 3) reduce environmental pollution; 4) low cost, simple and easy to implement; 5) solve the "silver migration" problem of the RF power device casing, the effect is remarkable.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

Dry etching method

ActiveUS11251051B2Control rateExtend etch timeSemiconductor/solid-state device manufacturingSurface treatment compositionsPhysical chemistrySilicon oxide

A dry etching method according to the present disclosure is for forming a through hole in a laminated film of silicon oxide layers and silicon nitride layers on a substrate in a direction vertical to the laminated film by plasmatizing a dry etching agent to generate a plasma and etching the laminated film by the plasma through a mask having a predetermined opening pattern under a negative direct-current self-bias voltage whose absolute value is 500 V or greater, wherein the dry etching agent contains at least C3F6, a hydrogen-containing saturated fluorocarbon represented by CxHyFz and an oxidizing gas, and wherein the volume of the hydrogen-containing saturated fluorocarbon contained in the dry etching agent is in a range of 0.1 to 10 times the volume of C3F6 contained in the dry etching agent.

Owner:CENT GLASS CO LTD

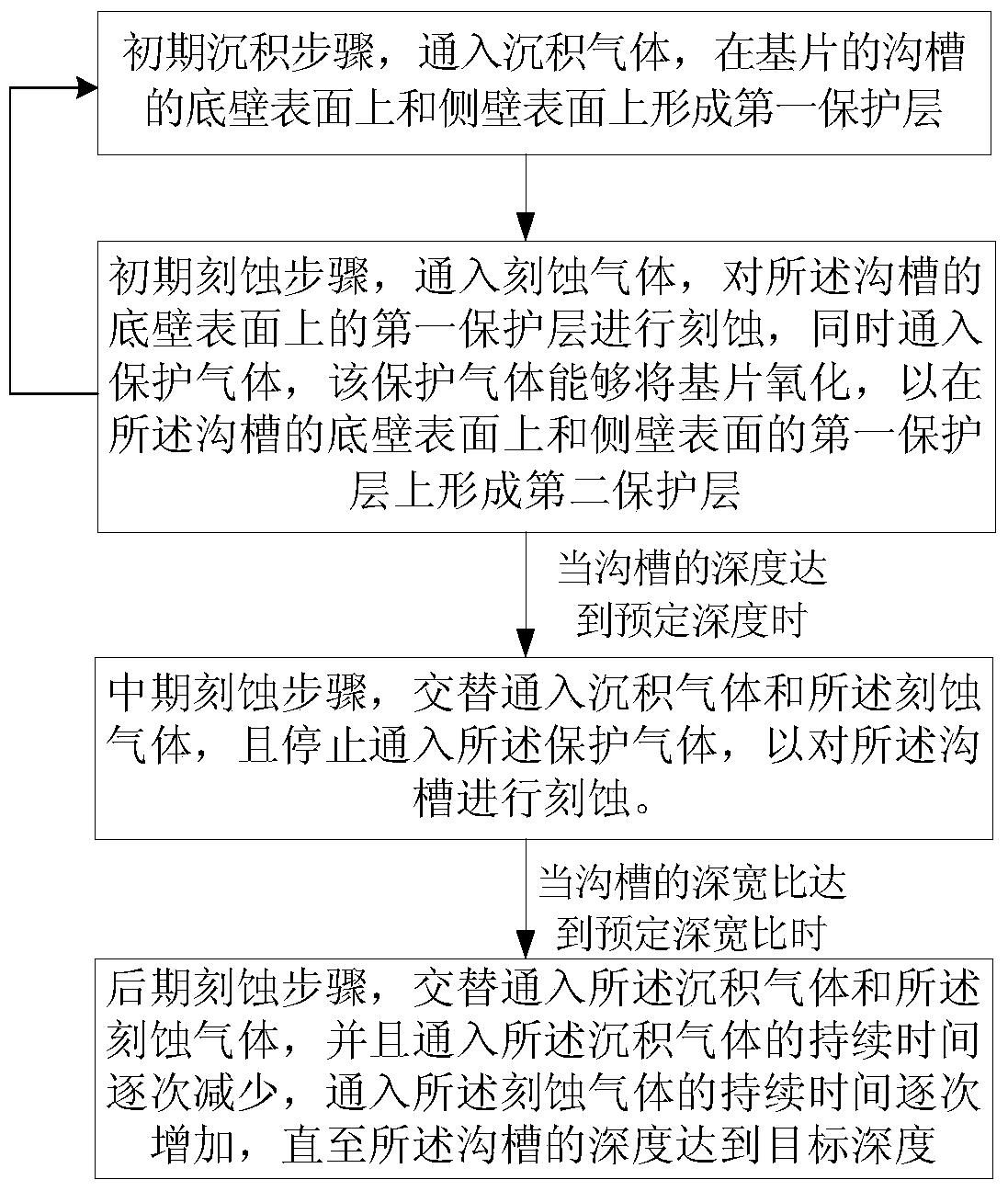

Etching method

ActiveCN105097494BLess bendingLow shrinkageSemiconductor/solid-state device manufacturingShielding gasMaterials science

The present invention provides a kind of etching method, and this etching method comprises the following steps of carrying out alternately: Initial deposition step, pass into deposition gas, form the first protective layer on the bottom wall surface and the side wall surface of the groove of substrate In the initial etching step, an etching gas is introduced to etch the first protective layer on the bottom wall surface of the groove, and a protective gas is introduced at the same time, and the protective gas can oxidize the substrate to form a A second protection layer is formed on the bottom wall surface of the trench and on the first protection layer on the side wall surfaces. In the present invention, the etching method can form the first protective layer and the second protective layer on the sidewall surface of the trench. Compared with the prior art, the etching method provided by the present invention can reduce the lateral etching speed , so that the occurrence of side wall bending can be effectively reduced, thereby improving product quality.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

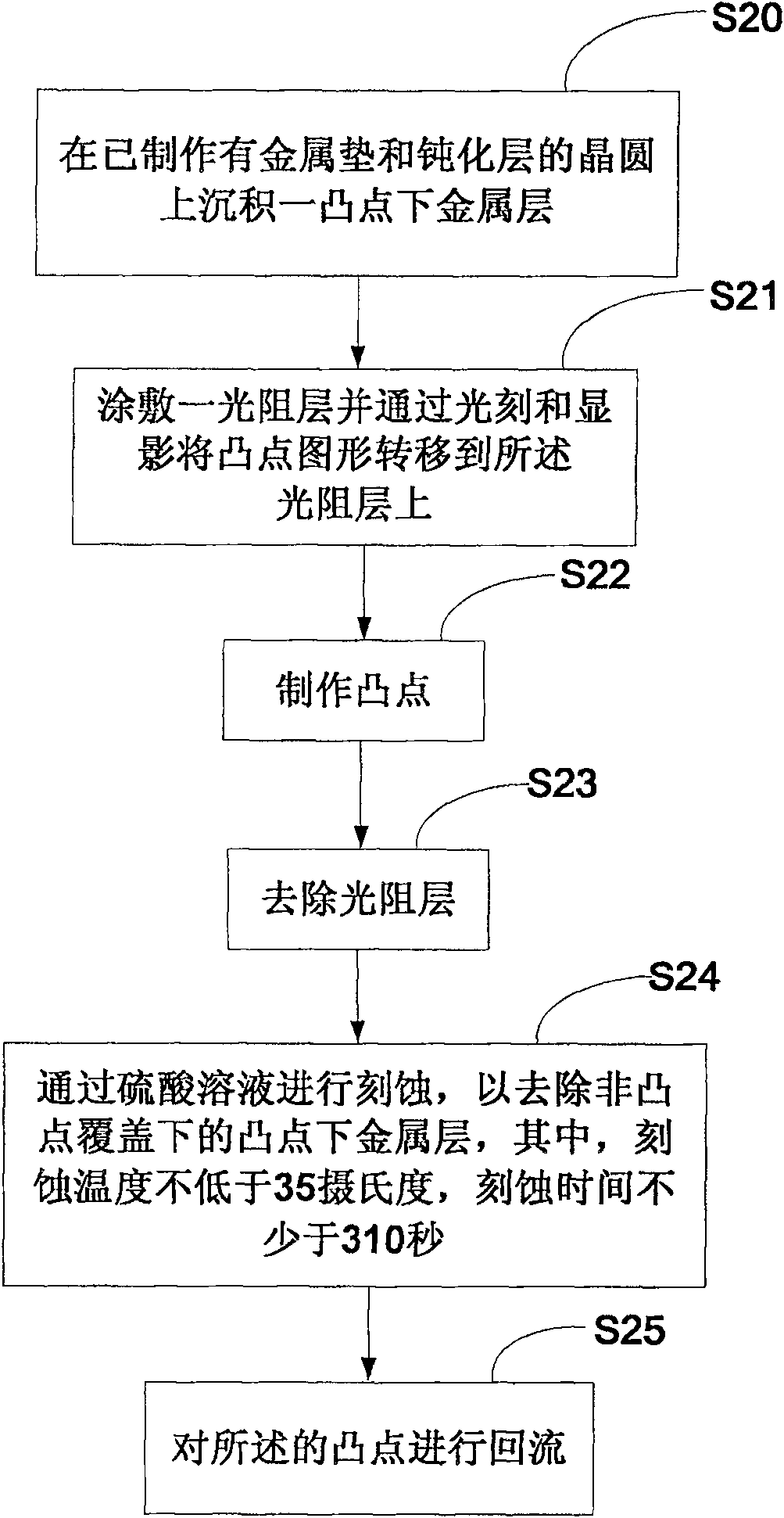

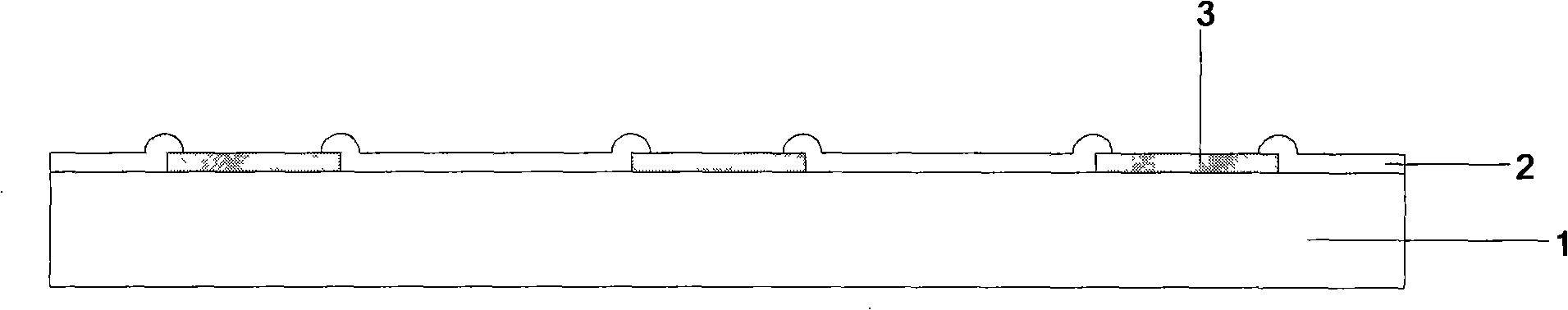

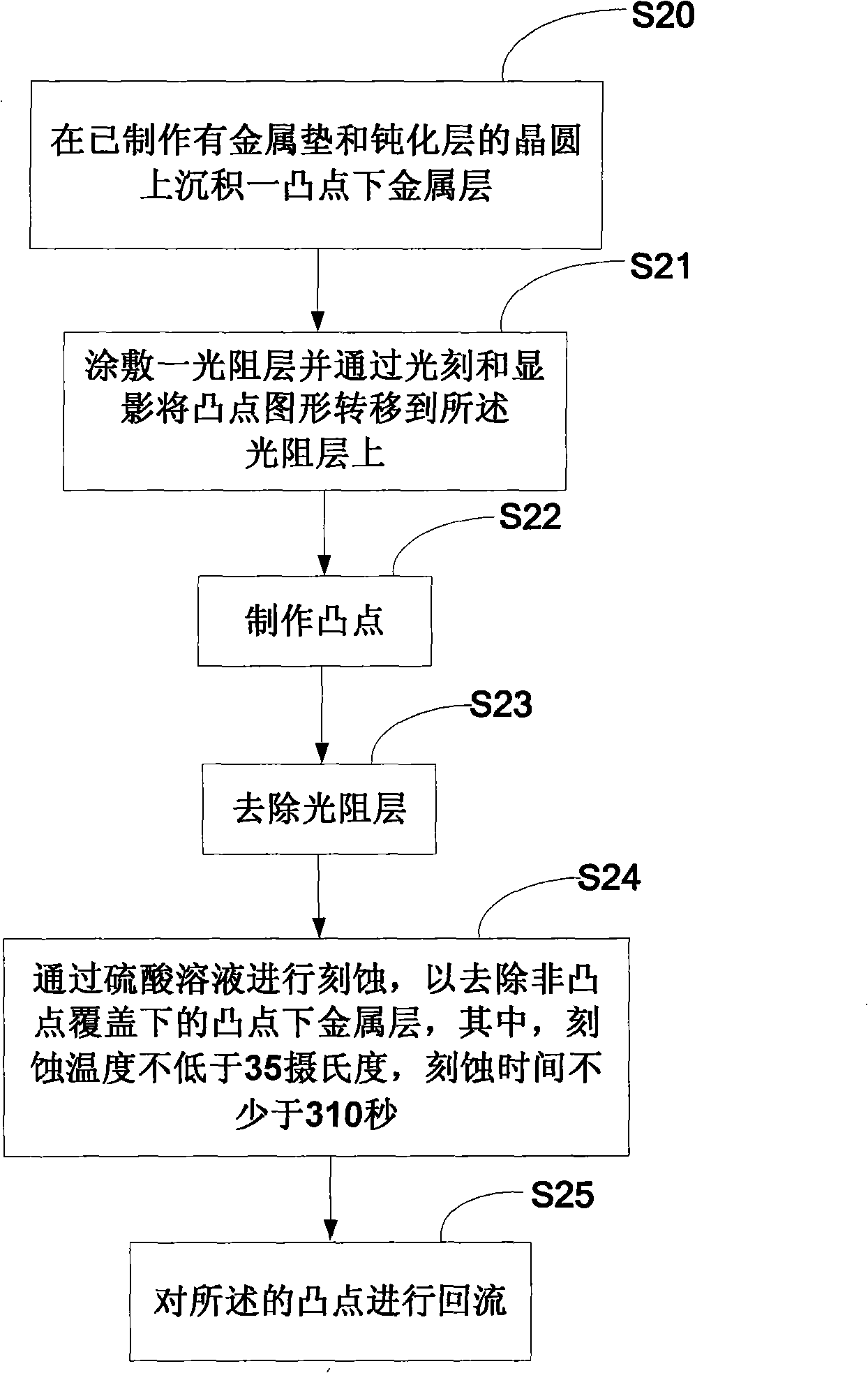

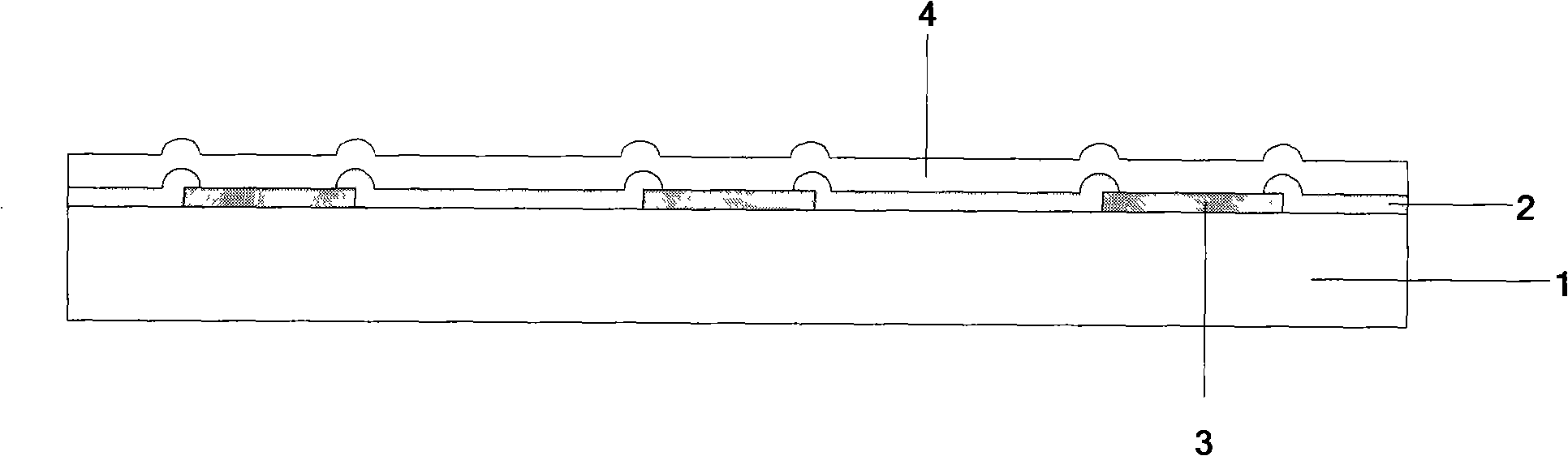

Convex point production method capable of preventing blue film

InactiveCN100570845CAvoid generatingEtching temperature increasedSolid-state devicesSemiconductor/solid-state device manufacturingEtchingLithographic artist

The invention provides a convex point fabrication method which can avoid blue membrane appearance. The existing convex point fabrication method uses low-temperature sulfuric acid solution for carrying out the etching, so as to remove a metal layer below the convex point; the metal layer below the convex can be removed, but the blue membrane is easy to be generated. In the convex point fabrication method of the invention which can avoid the blue membrane appearance, a metal layer below the convex point is firstly deposited on the existing wafers with a metal pad and a passivation layer fabricated, a light resistance layer is plated on the metal layer and the convex point images are transferred on the light resistance layer by lithography and development; the convex point is then fabricated and the light resistance is removed then; the sulfuric acid solution is then used for carrying out the etching, so as to remove the metal layer below the convex point which is covered by non-convex point; the convex point is finally refluxed; wherein, in the step that the metal layer below the convex point under the coverage of non-convex point is removed by carrying out the etching with the sulfuric acid solution, the etching temperature is not lower than 35 DEG C and the etching time is not less than 310 seconds. Blue membranes can be avoided by adopting the method of the invention when the convex point is fabricated.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

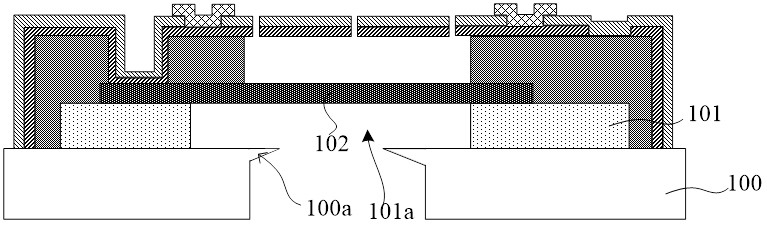

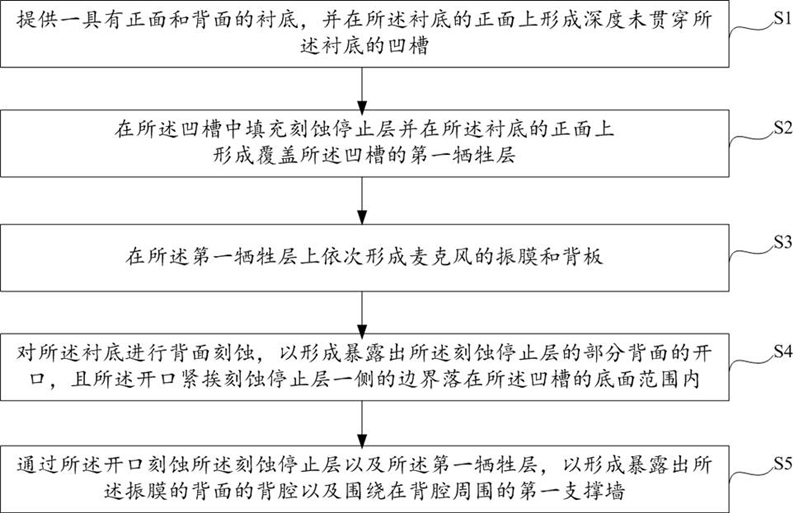

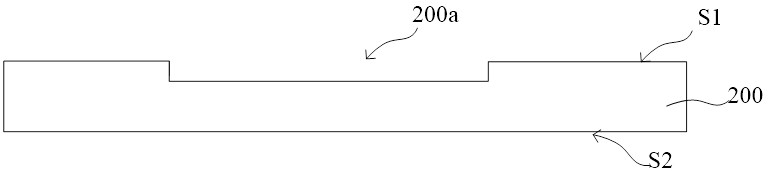

Microphone and its manufacturing method

Owner:SEMICON MFG ELECTRONICS (SHAOXING) CORP

A kind of substrate and its preparation method, display device

ActiveCN110797303BImprove the display effectExtend etch timeSolid-state devicesSemiconductor/solid-state device manufacturingLithography processDisplay device

Owner:BOE TECH GRP CO LTD +1

A display panel and method of making the same

ActiveCN111106149BExtend etch timeMeet the depthSolid-state devicesPhotovoltaic energy generationActive layerMaterials science

The present invention relates to a display panel and a preparation method thereof. In the present invention, a first groove is formed in the display area from the surface of the interlayer insulating layer in the display area away from the substrate to the barrier layer and from the curved surface through the first mask at the same time. The surface of the interlayer insulating layer of the folded region away from the substrate penetrates to the first groove body of the second groove in the active layer, which saves the cost of the mask. On the other hand, the present invention retains the active layer in the bending area, thereby prolonging the etching time of the first groove body, so that the first mask can satisfy the depth of the first groove and the first groove of the second groove at the same time. body depth requirements.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

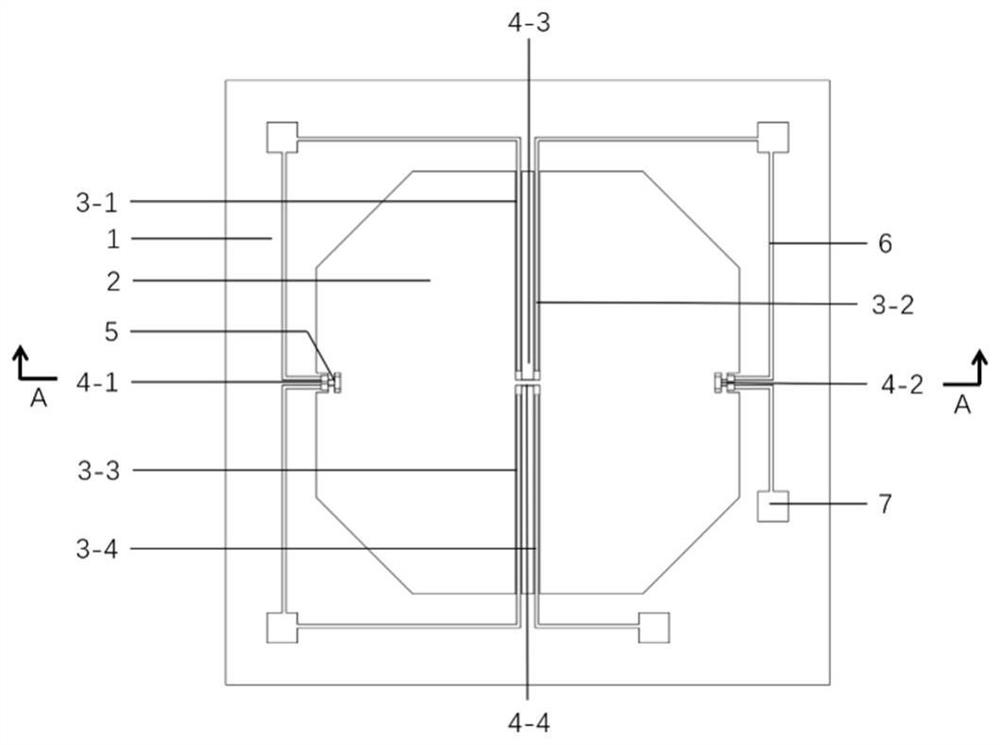

Piezoresistive beam stress concentration micro-pressure sensor chip and preparation method thereof

ActiveCN113295306ASolving problems that cannot be narrowedSolve the problem that the width must be greater than the length of the varistor stripTelevision system detailsImpedence networksThin membraneSilicon

The invention discloses a piezoresistive beam stress concentration micro-pressure sensor chip and a preparation method thereof, the sensor chip comprises a silicon substrate and a glass substrate, the back surface of the silicon substrate is etched with a back cavity, the bottom surface of the back cavity is a pressure-bearing film, and the front surface of the pressure-bearing film is provided with a first piezoresistive beam, a second piezoresistive beam, a third piezoresistive beam and a fourth piezoresistive beam; the first piezoresistive beam, the second piezoresistive beam, the third piezoresistive beam and the fourth piezoresistive beam are respectively provided with piezoresistor strips respectively, the length direction of each piezoresistor strip is the same as the length direction of the piezoresistive beam where the piezoresistor strip is located, and the piezoresistor strips are connected through metal leads and metal bonding pads to form a Wheatstone bridge. The problem that the beam structure cannot be narrower because the width of the beam structure must be larger than the width of the piezoresistor strips due to the fact that the piezoresistor strips on a traditional beam structure are arranged perpendicular to the straight line where the beam structure is located is solved.

Owner:XI AN JIAOTONG UNIV +2

Convex point production method capable of preventing blue film

InactiveCN101271852AAvoid generatingEtching temperature increasedSolid-state devicesSemiconductor/solid-state device manufacturingEtchingLithographic artist

The invention provides a convex point fabrication method which can avoid blue membrane appearance. The existing convex point fabrication method uses low-temperature sulfuric acid solution for carrying out the etching, so as to remove a metal layer below the convex point; the metal layer below the convex can be removed, but the blue membrane is easy to be generated. In the convex point fabrication method of the invention which can avoid the blue membrane appearance, a metal layer below the convex point is firstly deposited on the existing wafers with a metal pad and a passivation layer fabricated, a light resistance layer is plated on the metal layer and the convex point images are transferred on the light resistance layer by lithography and development; the convex point is then fabricated and the light resistance is removed then; the sulfuric acid solution is then used for carrying out the etching, so as to remove the metal layer below the convex point which is covered by non-convex point; the convex point is finally refluxed; wherein, in the step that the metal layer below the convex point under the coverage of non-convex point is removed by carrying out the etching with the sulfuric acid solution, the etching temperature is not lower than 35 DEG C and the etching time is not less than 310 seconds. Blue membranes can be avoided by adopting the method of the invention when the convex point is fabricated.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1