Transistor forming method

A transistor, wet etching technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems affecting transistor performance, and achieve the effect of improving performance, flattening the surface, and reducing the etching rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

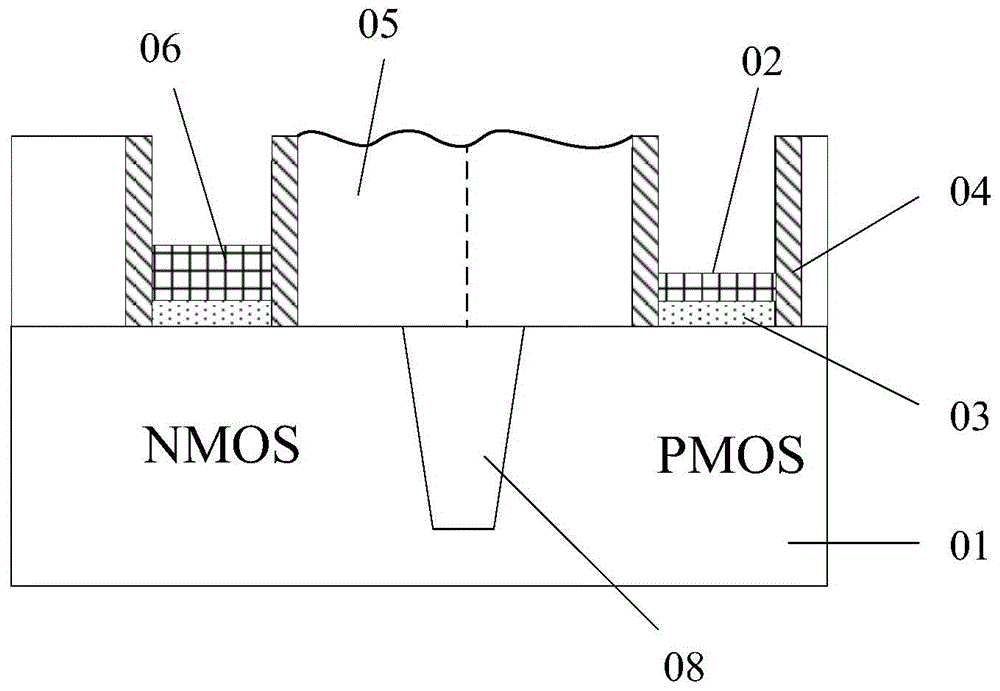

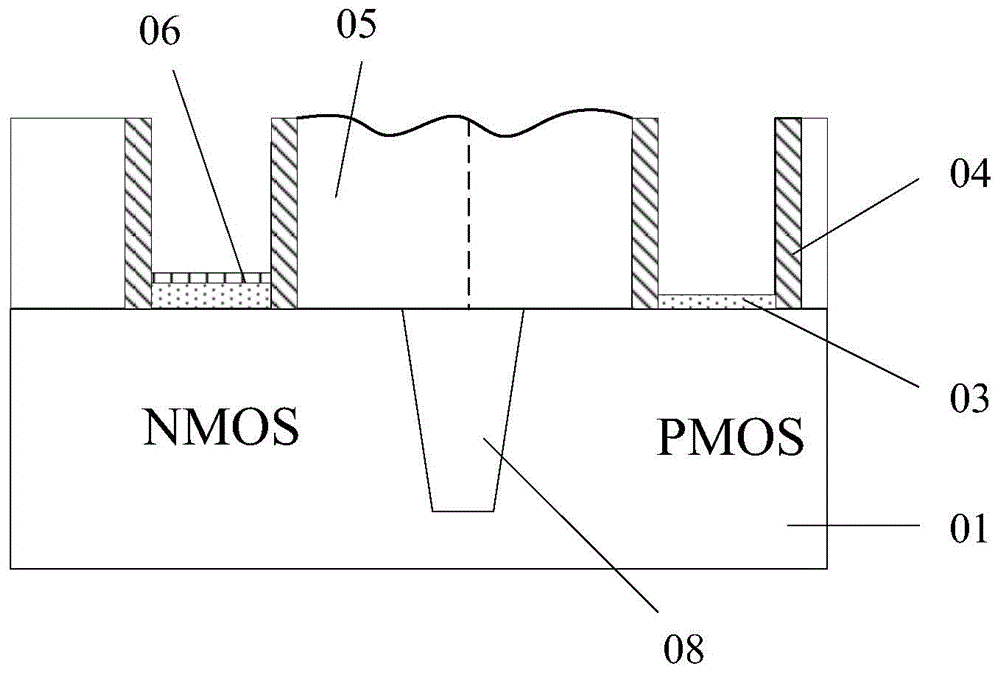

[0037] In the step of removing dummy gates in the metal gate formation process of transistors in the prior art, the dummy gates have different heights in areas where dummy gates are densely packed and where dummy gates are loose. The top surface of the gate is also uneven, so that after the dry etching of the dummy gate, the thickness of the remaining dummy gate is not uniform, and the residual dummy gate in the thicker part is The etching may not be clean, or the substrate under the dummy gate in the thinner part is damaged by wet etching.

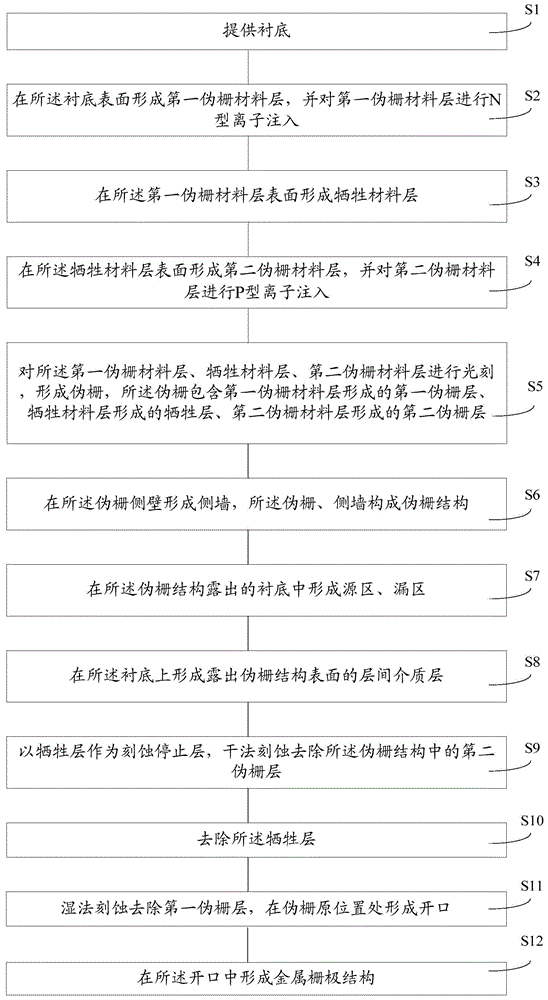

[0038] In order to solve the above technical problems, the present invention provides a method for forming a transistor. In the process of forming a dummy gate, a three-layer transistor consisting of a first dummy gate layer, a sacrificial layer and a second dummy gate layer is formed from bottom to top. The dummy gate, wherein the sacrificial layer is used as an etch stop layer of the second dummy gate layer, can make the surface thickne...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More