Semiconductor wafer hole manufacturing method

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of prolonging etching time, difficult photolithography, wafer damage, etc., and achieve the effect of prolonging etching time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the purpose, technical solution and advantages of the present application clearer, the present application will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. For simplicity, some technical features known to those skilled in the art are omitted from the following description.

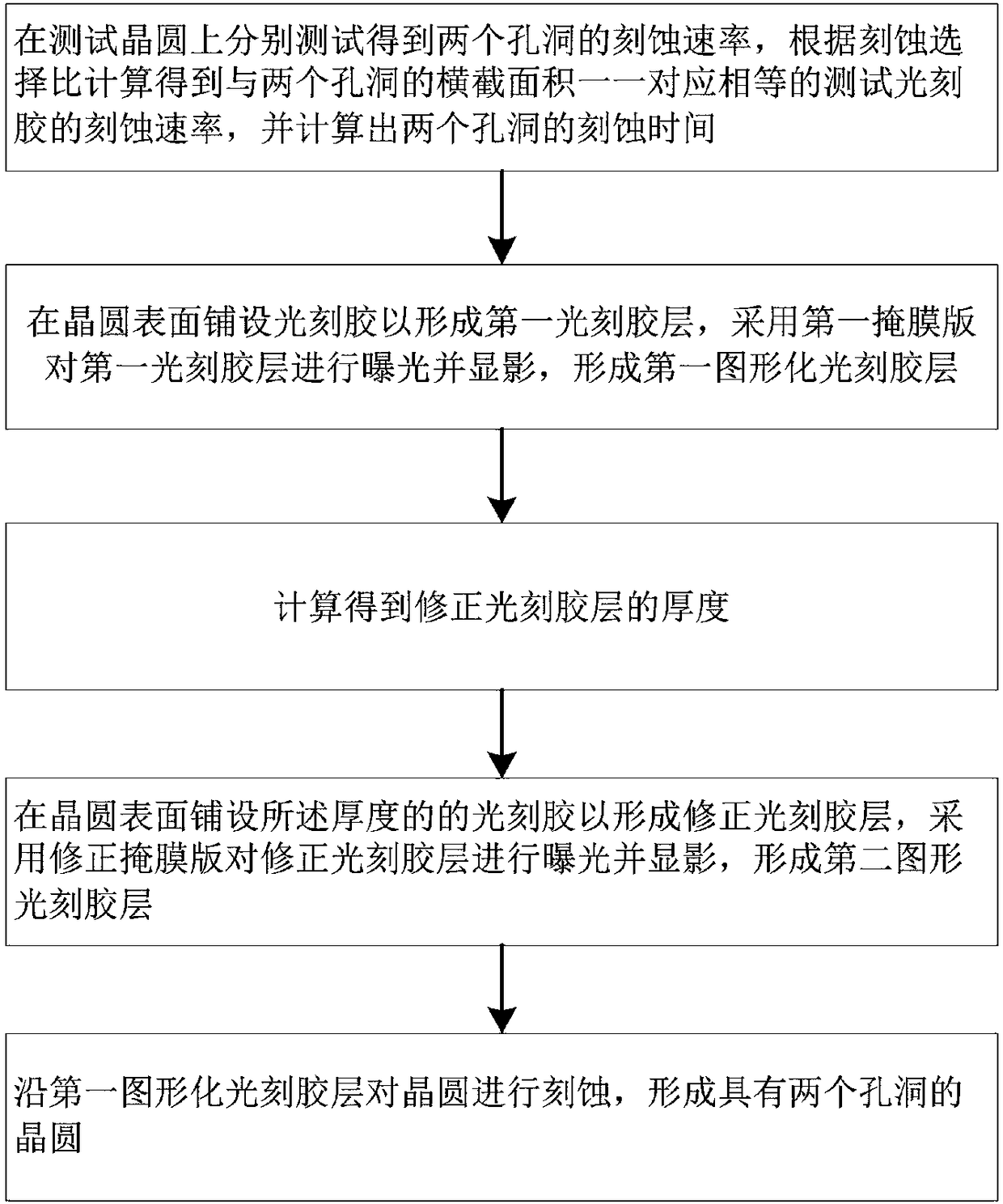

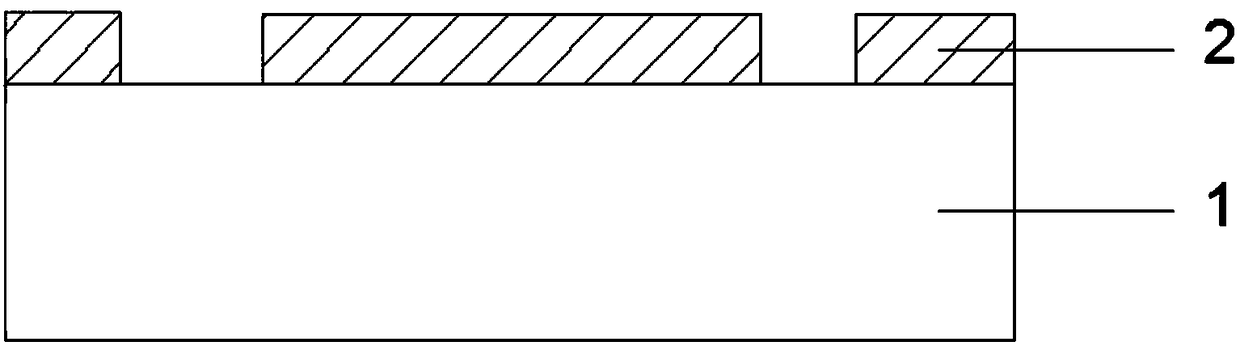

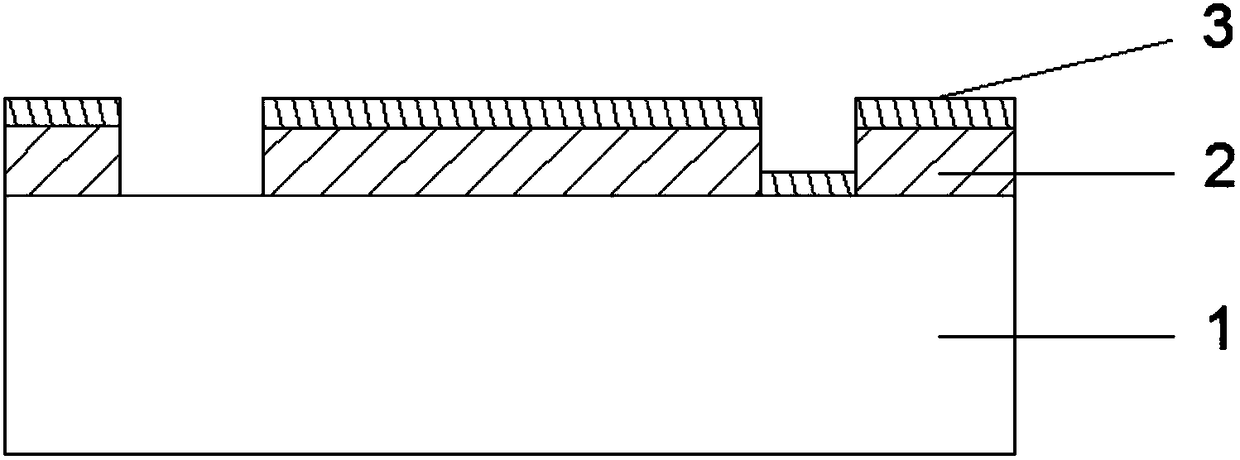

[0023] Such as Figure 1-5 As shown, the present embodiment provides a semiconductor wafer hole manufacturing method, including:

[0024] Basic parameter calculation steps:

[0025] Separately test 2 holes to be etched on the same test wafer as the product wafer, that is, measure the etching time required for each hole when etching the same depth, and divide the depth value by the etching of each hole time so as to obtain the etching rate E of the first hole 4 and the second hole 5 1 ,E 2 According to the etching selection ratio of the test wafer 1 and the test photoresist, the etching rate E of the photoresist cor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More