Patents

Literature

19122results about "Cable/conductor manufacture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

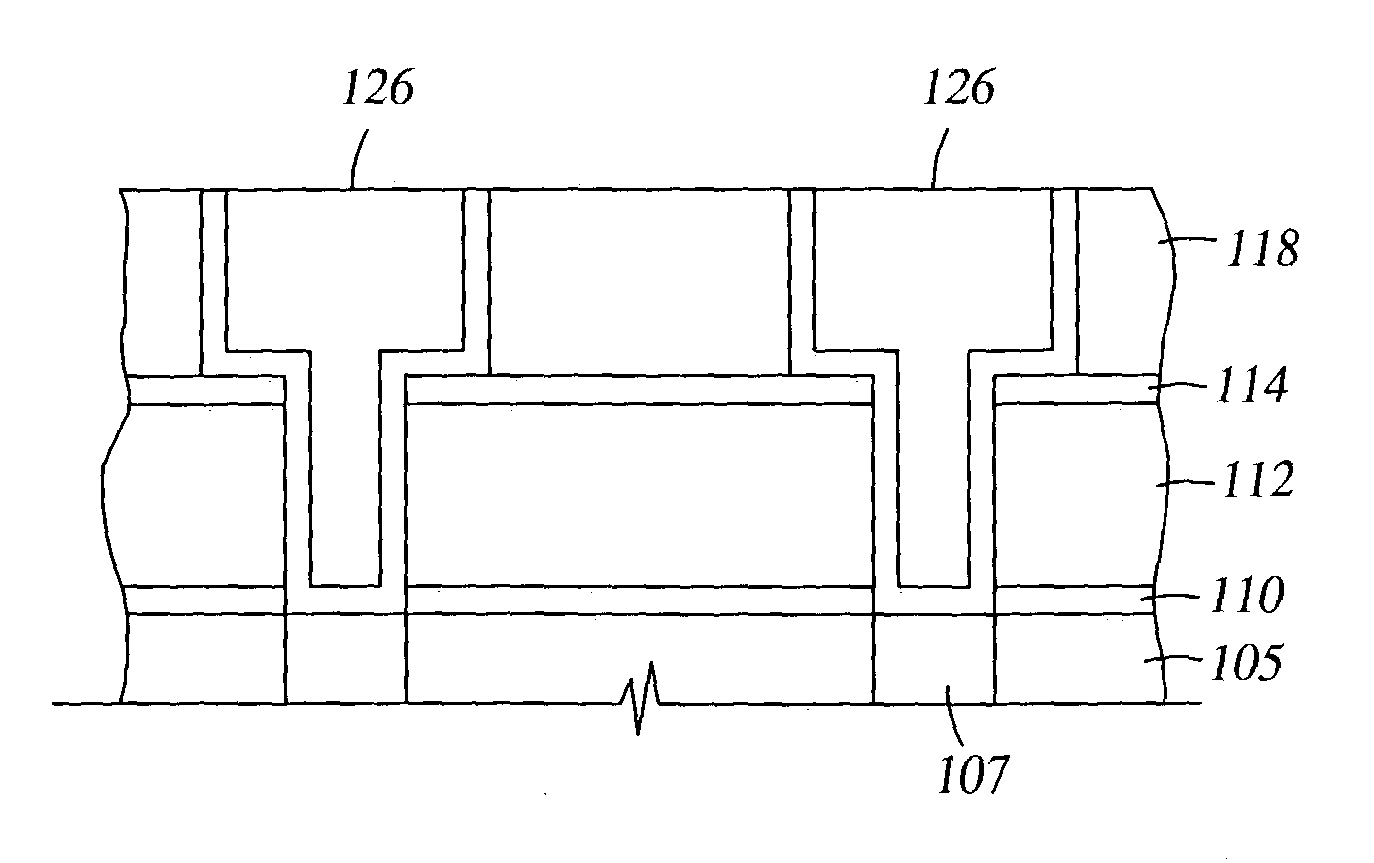

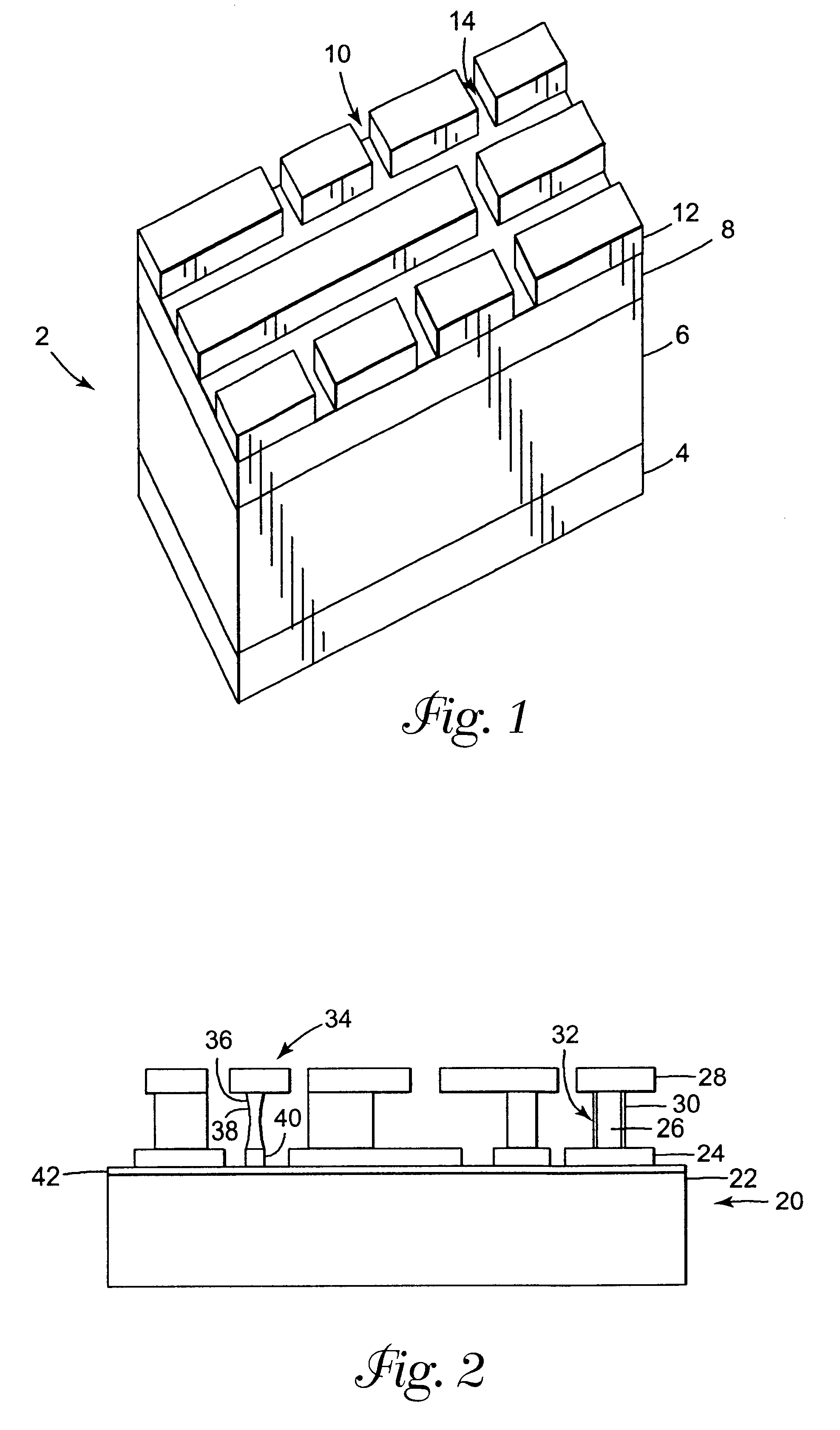

Integrated low K dielectrics and etch stops

InactiveUS6340435B1Decorative surface effectsSemiconductor/solid-state device detailsHydrogenFluorocarbon

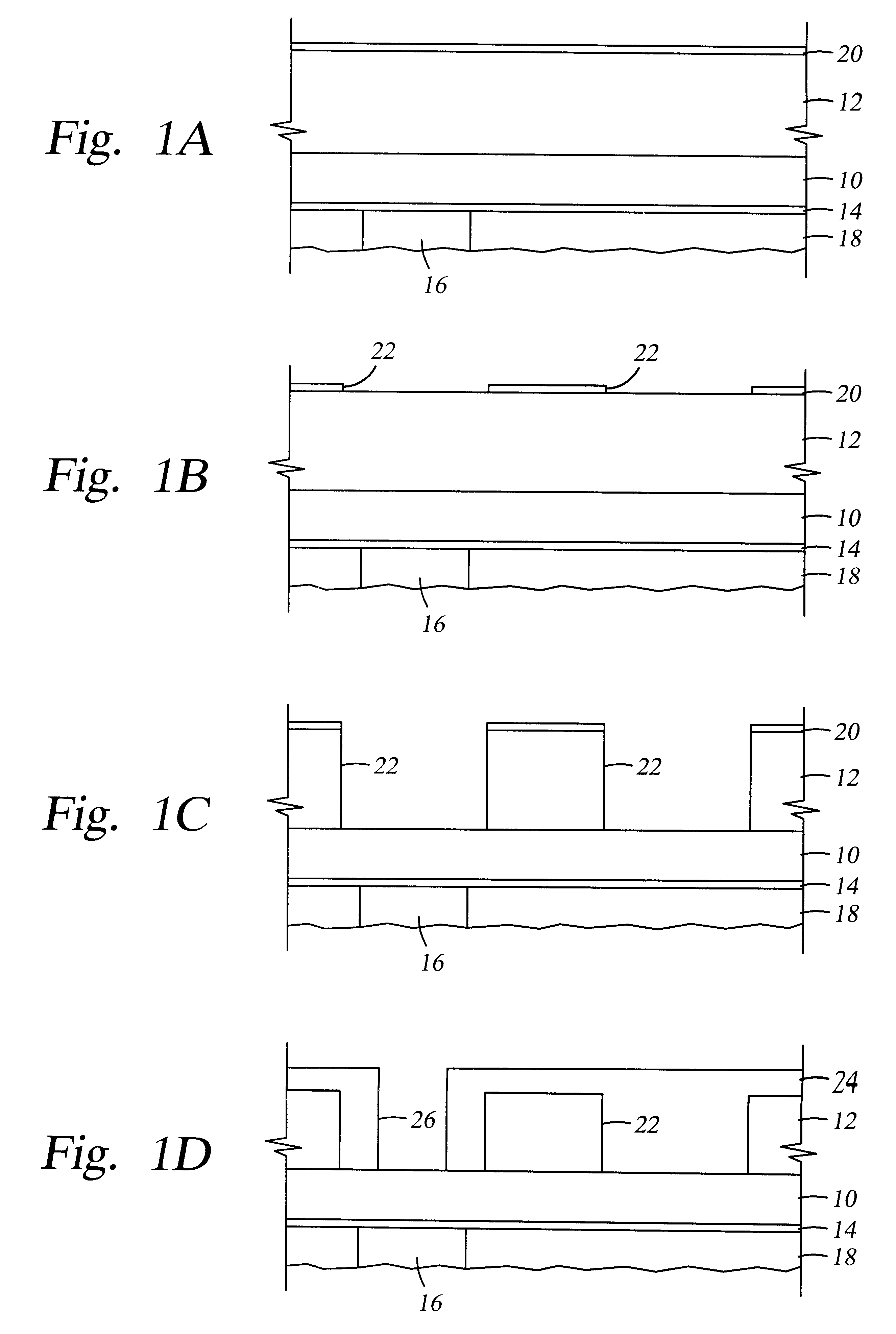

A method of depositing and etching dielectric layers having low dielectric constants and etch rates that vary by at least 3:1 for formation of horizontal interconnects. The amount of carbon or hydrogen in the dielectric layer is varied by changes in deposition conditions to provide low k dielectric layers that can replace etch stop layers or conventional dielectric layers in damascene applications. A dual damascene structure having two or more dielectric layers with dielectric constants lower than about 4 can be deposited in a single reactor and then etched to form vertical and horizontal interconnects by varying the concentration of a carbon:oxygen gas such as carbon monoxide. The etch gases for forming vertical interconnects preferably comprises CO and a fluorocarbon, and CO is preferably excluded from etch gases for forming horizontal interconnects.

Owner:APPLIED MATERIALS INC

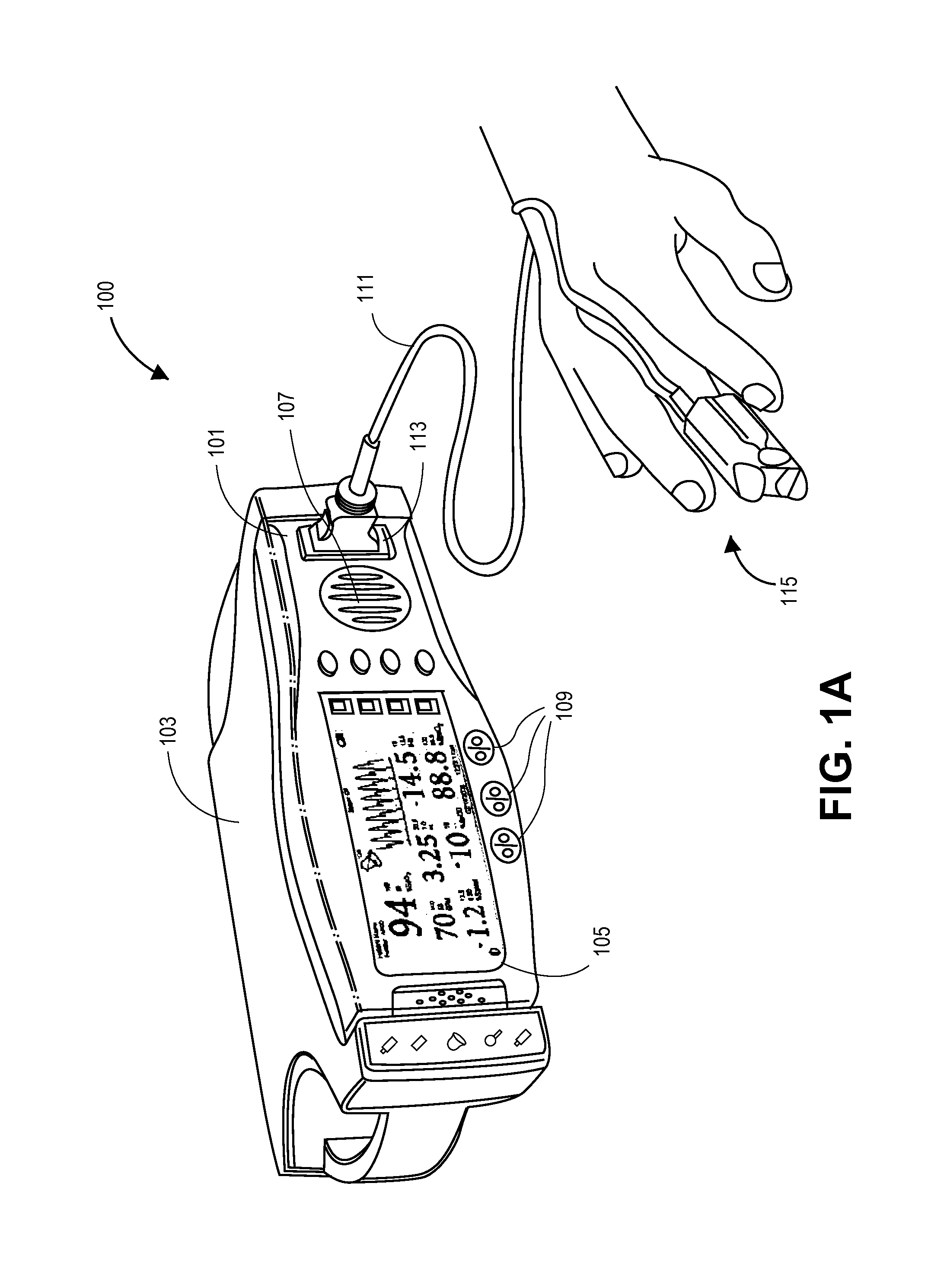

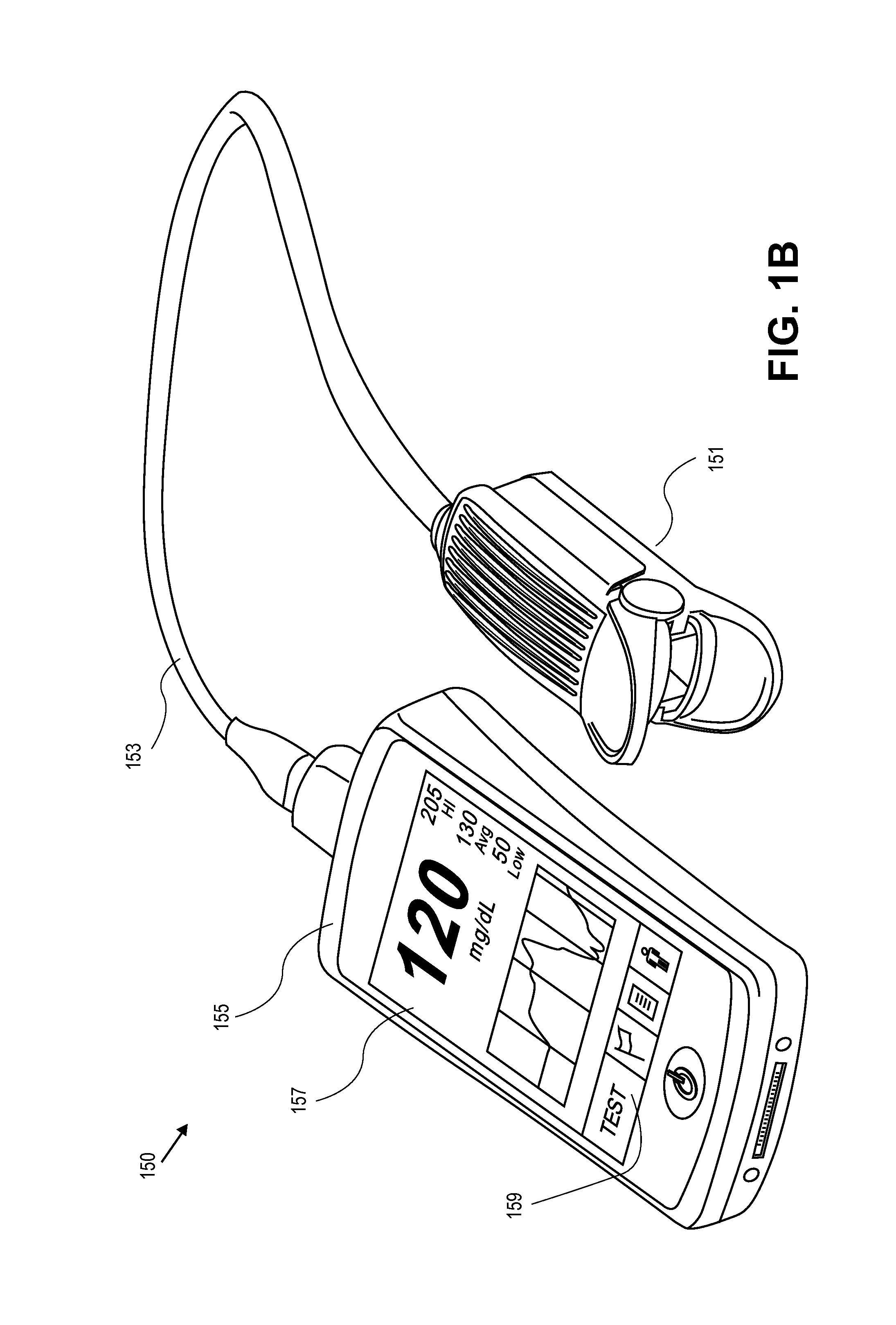

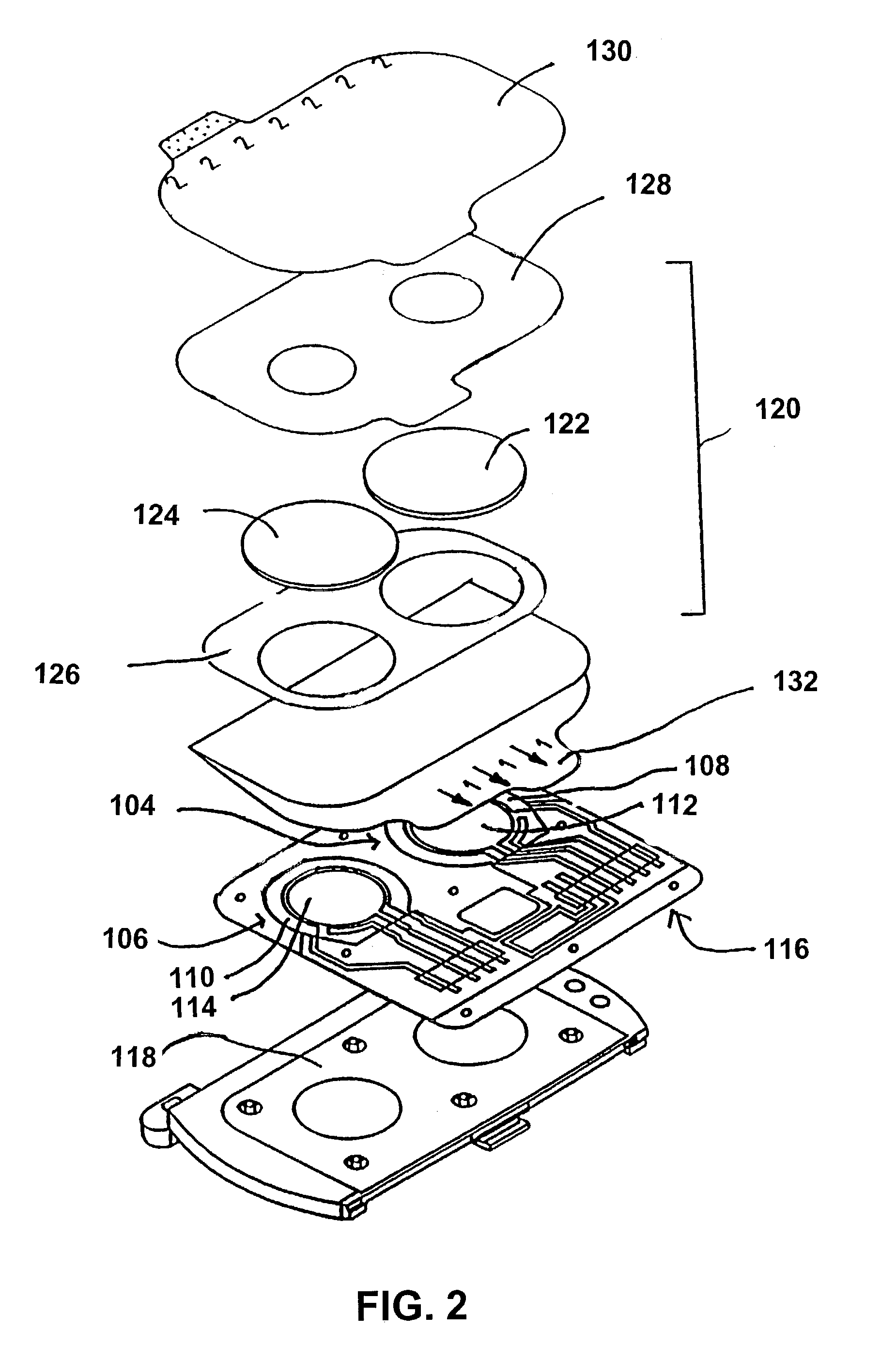

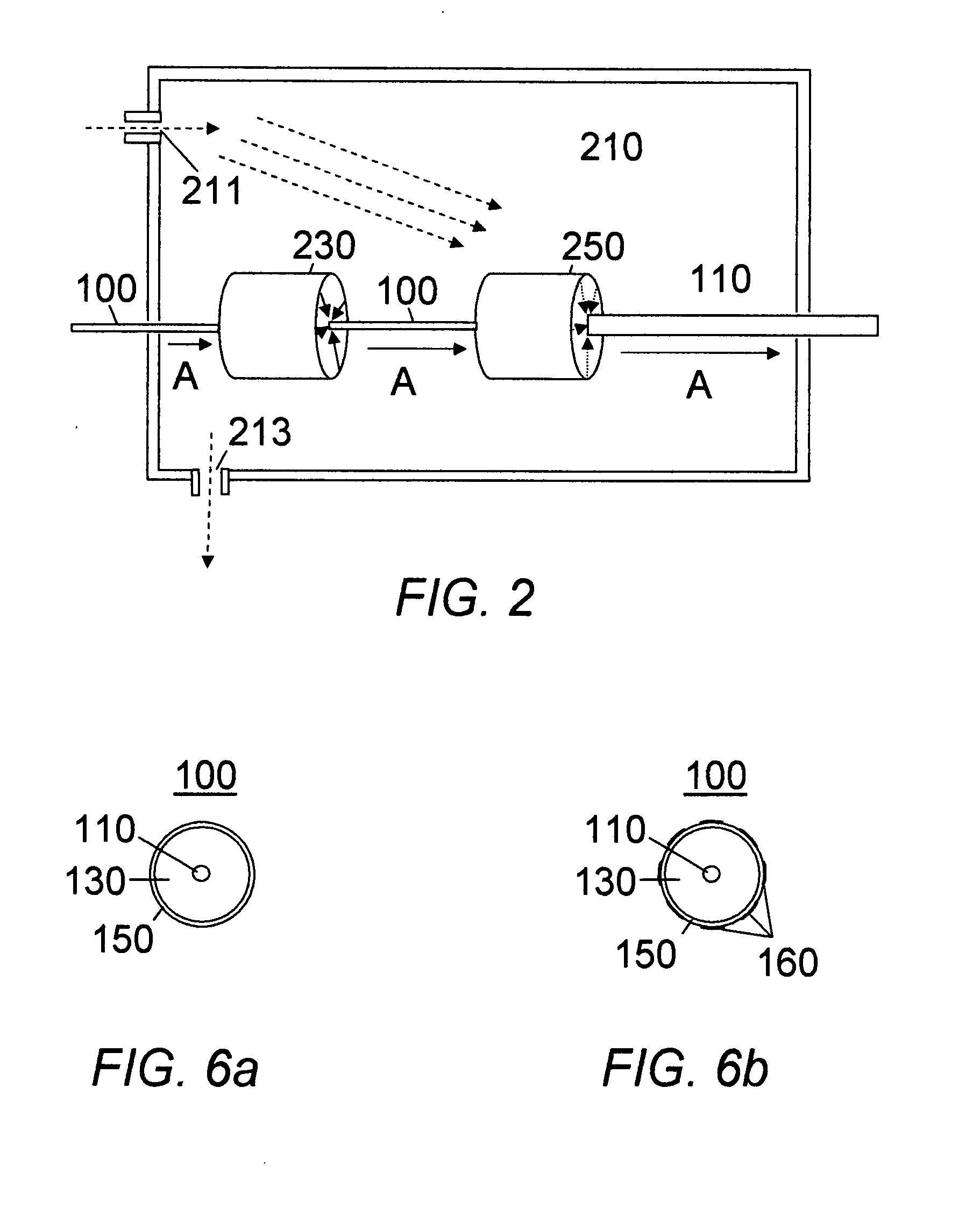

Low noise cable providing communication between electronic sensor components and patient monitor

ActiveUS9245668B1Reduce crosstalkNot hindering sensor placementDiagnostics using lightConductive materialLow noiseEngineering

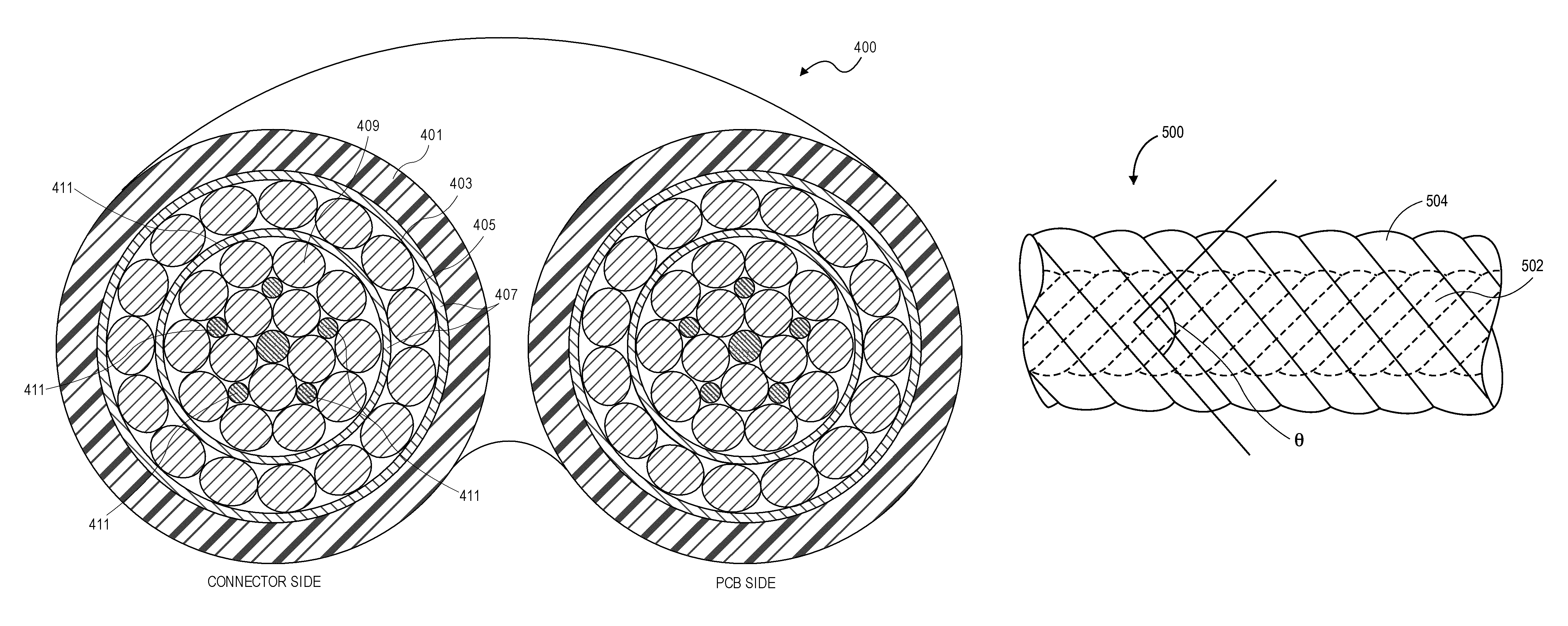

A physiological measurement system can include a low noise patient cable that connects a monitor and a noninvasive optical sensor. The cable has a plurality of emitter wires configured to communicate a drive signal between the monitor and at least one emitter. The cable also has a plurality of detector wires configured to communicate a physiological signal between at least one detector responsive to the emitter and the monitor. The emitter and detector wires are orthogonally disposed so that crosstalk between the two functionally different wires is mitigated.

Owner:MASIMO CORP

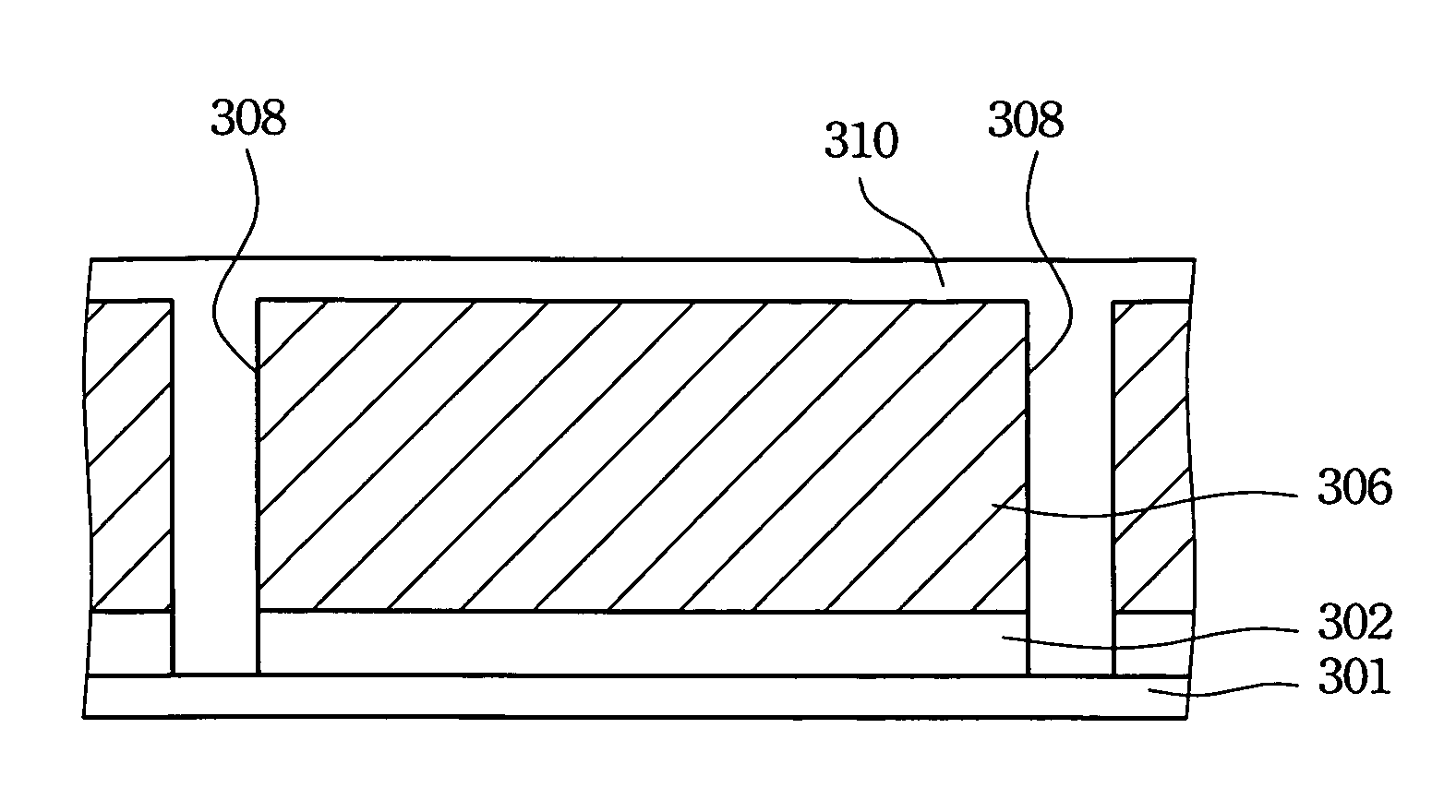

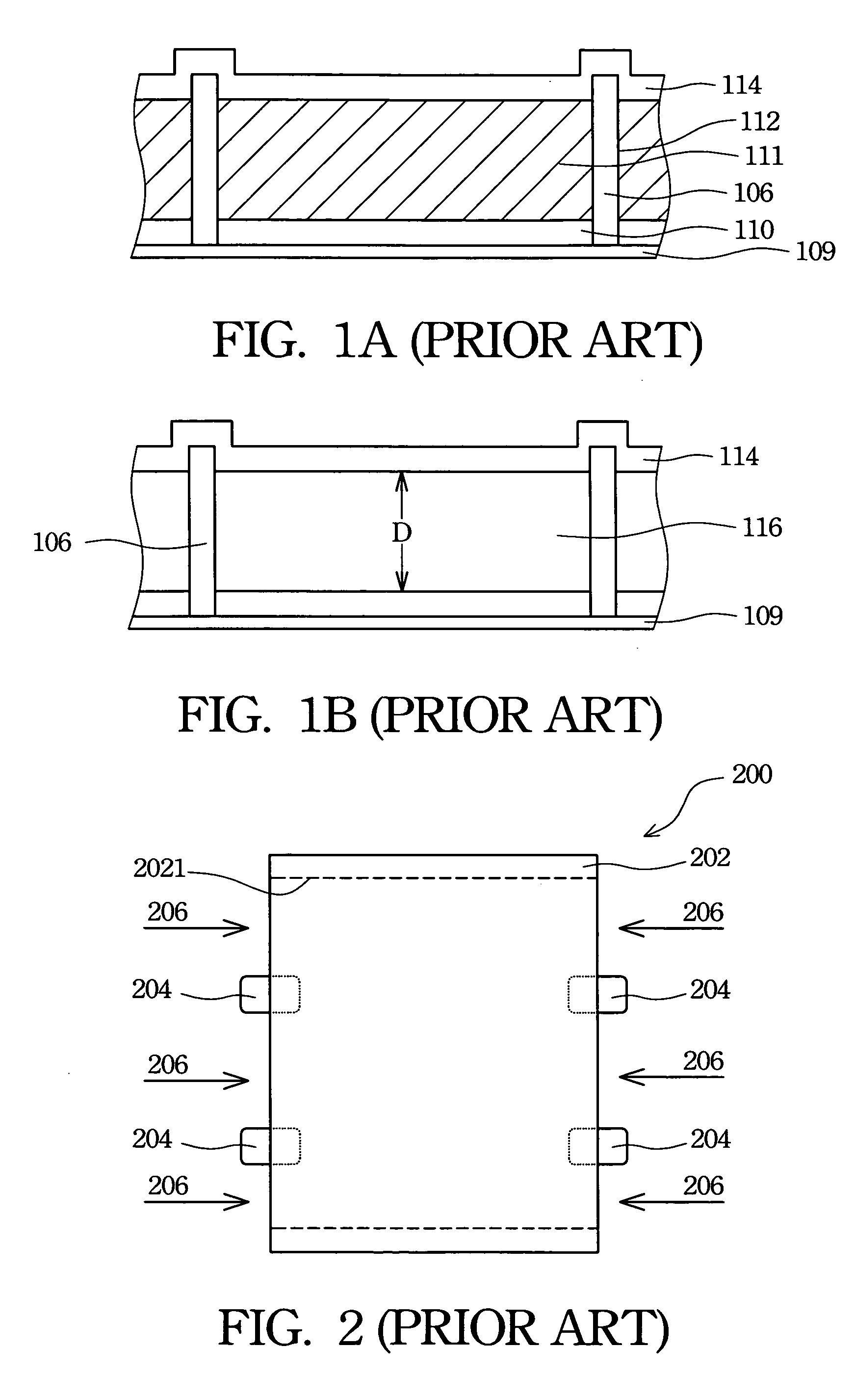

Method for fabricating optical interference display cell

InactiveUS20050003667A1Easily reorganized and consolidatedLow costDecorative surface effectsSolid-state devicesRemote plasmaOptoelectronics

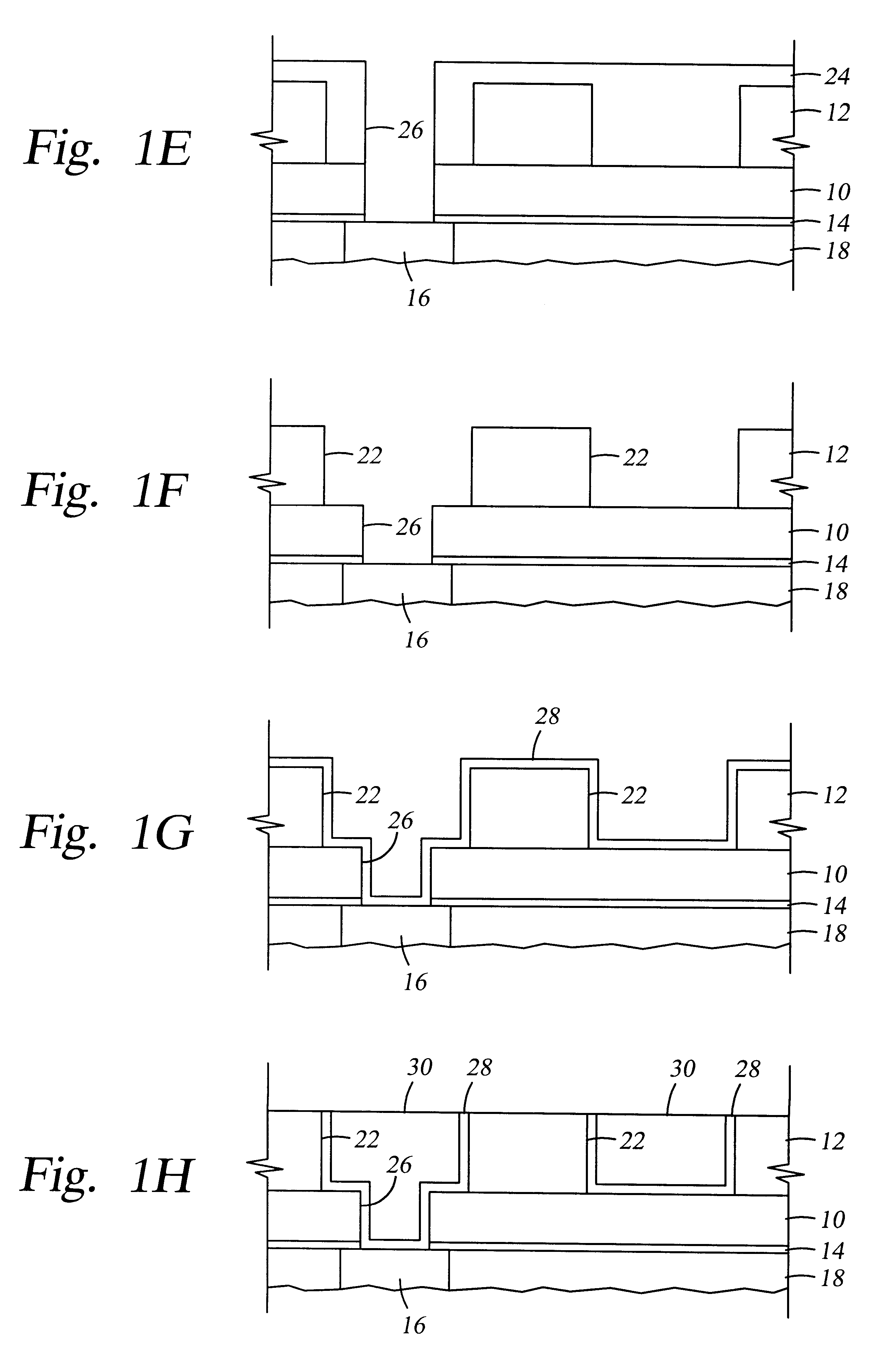

A method for fabricating an optical interference display cell is described. A first electrode and a sacrificial layer are sequentially formed on a transparent substrate and at least two openings are formed in the first electrode and the sacrificial layer to define a position of the optical interference display cell. An insulated heat-resistant inorganic supporter is formed in each of the openings. A second electrode is formed on the sacrificial layer and the supporters. Finally, a remote plasma etching process is used for removing the sacrificial layer.

Owner:SNAPTRACK

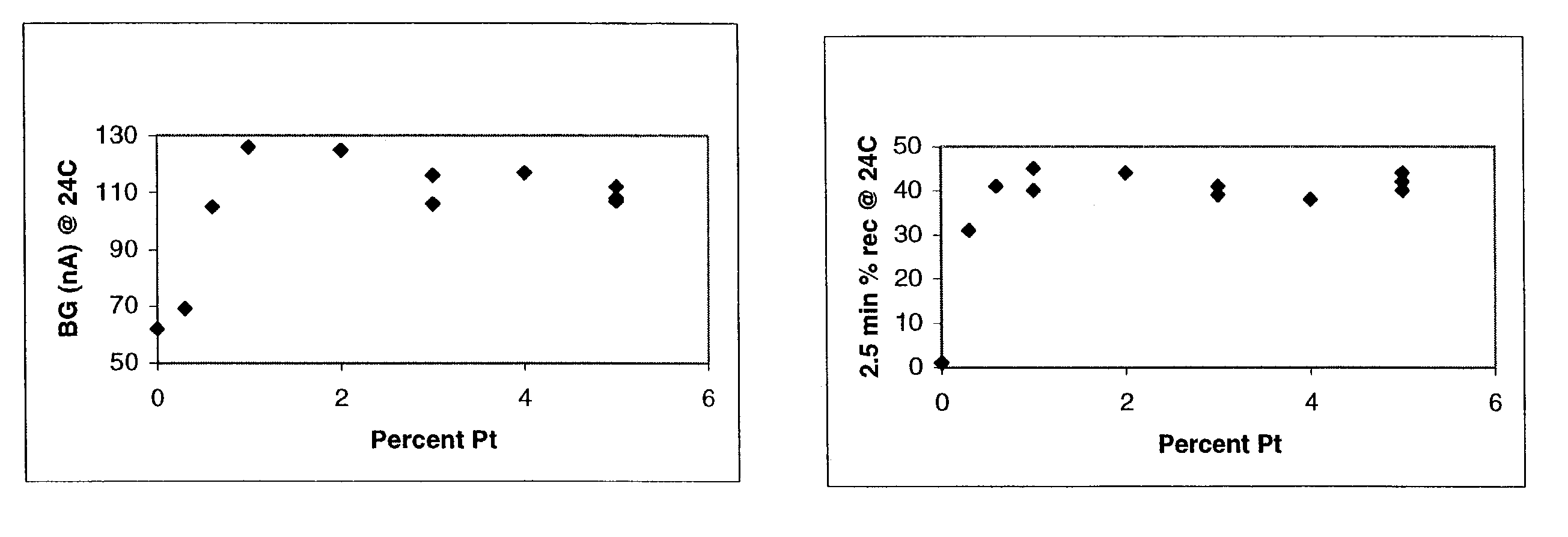

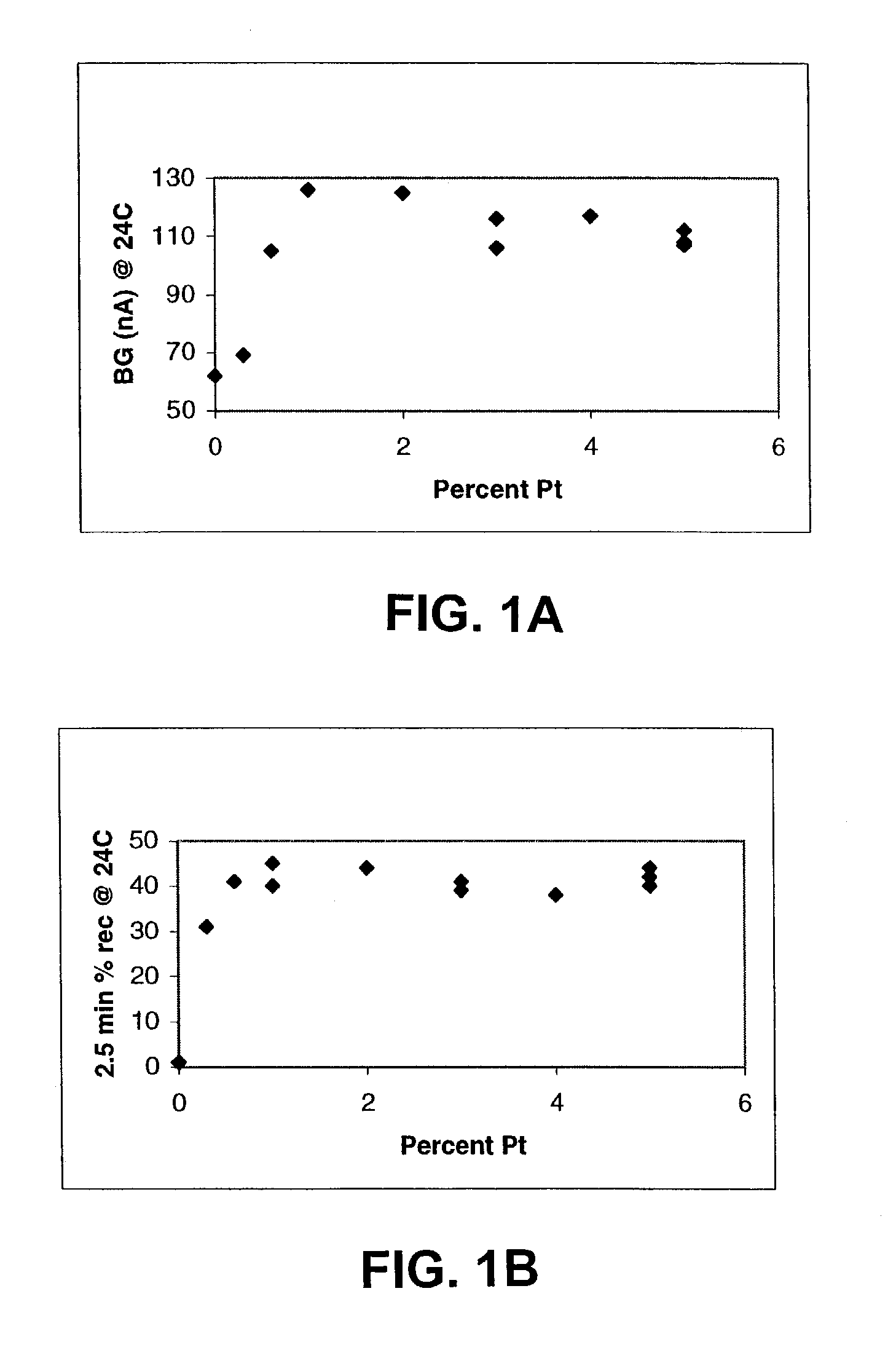

Highly catalytic screen-printing ink

ActiveUS7018568B2Easy to produceConductive layers on insulating-supportsConductive materialConductive polymerPrinting ink

The invention is directed to conductive polymer compositions, catalytic ink compositions (e.g., for use in screen-printing), electrodes produced by deposition of an ink composition, methods of making, and methods of using thereof. An exemplary ink material comprises platinum black and / or platinum-on-carbon as the catalyst, graphite as a conducting material, a polymer binding material, and an organic solvent. The polymer binding material is typically a copolymer of hydrophilic and hydrophobic monomers. The conductive polymer compositions of the present invention can be used, for example, to make electrochemical sensors. Such sensors can be used in a variety of analyte monitoring devices to monitor analyte amount or concentrations in subjects, for example, glucose monitoring devices to monitor glucose levels in subjects with diabetes.

Owner:LIFESCAN IP HLDG LLC +1

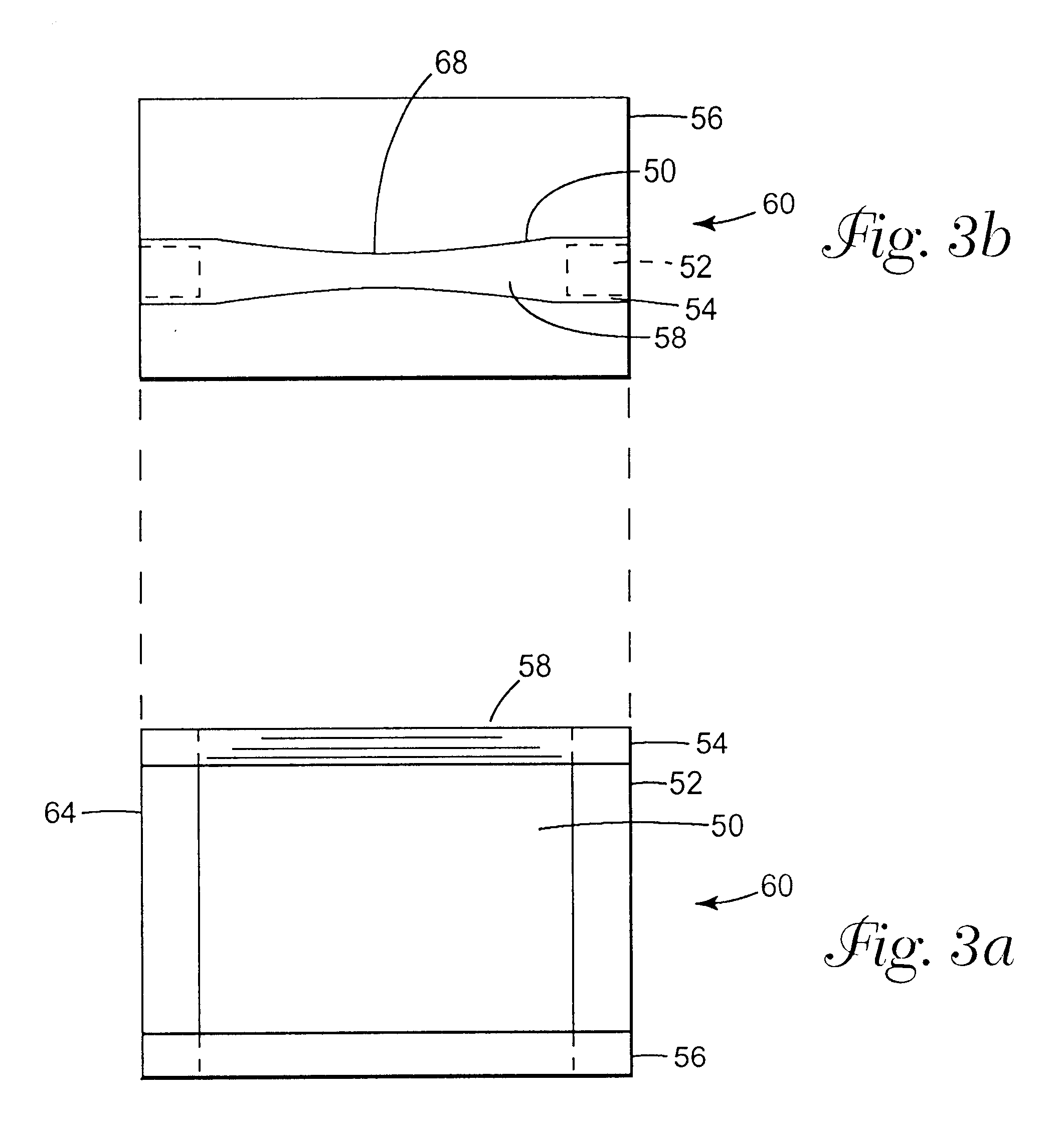

Remotely-excited fluorine and water vapor etch

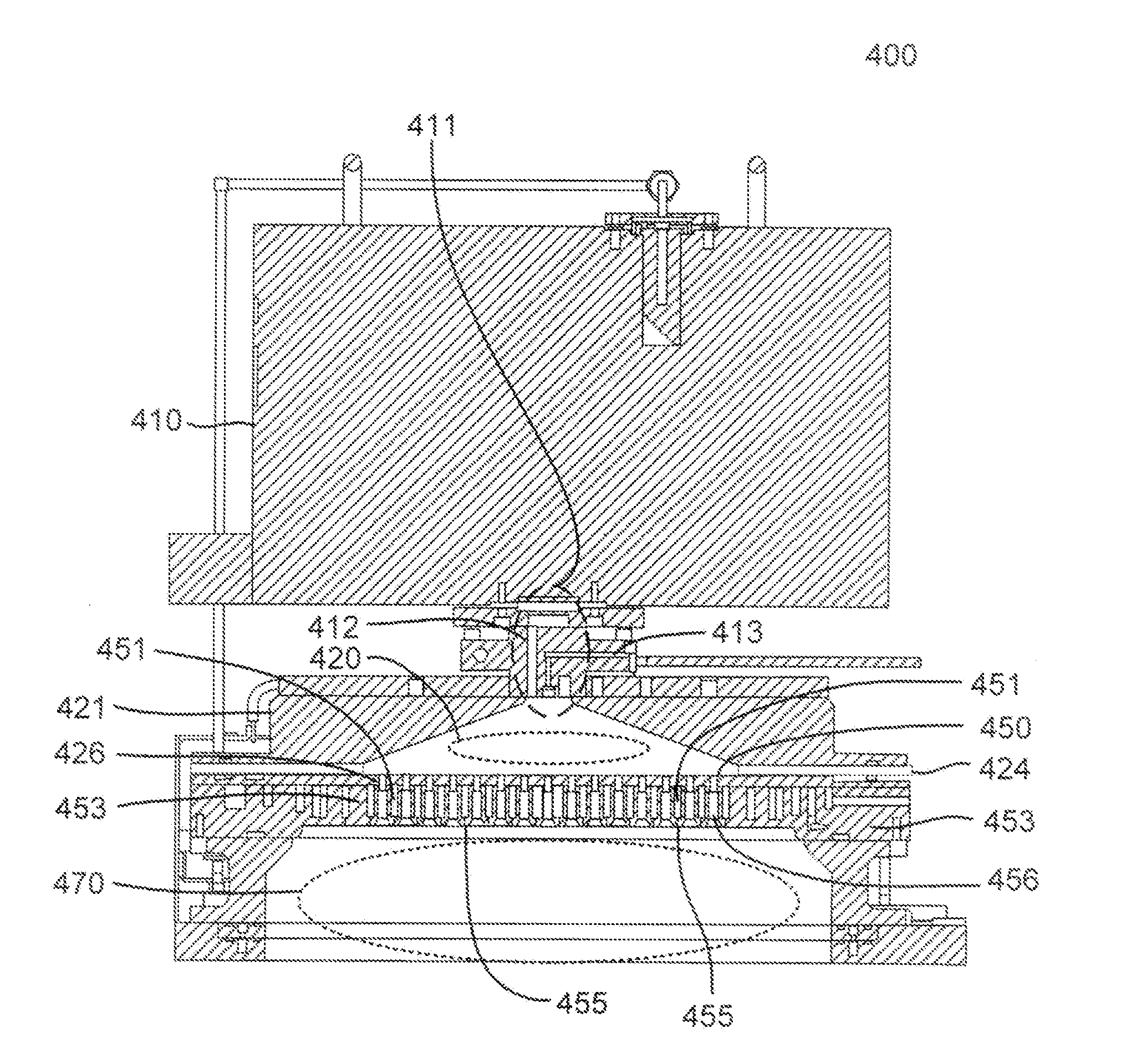

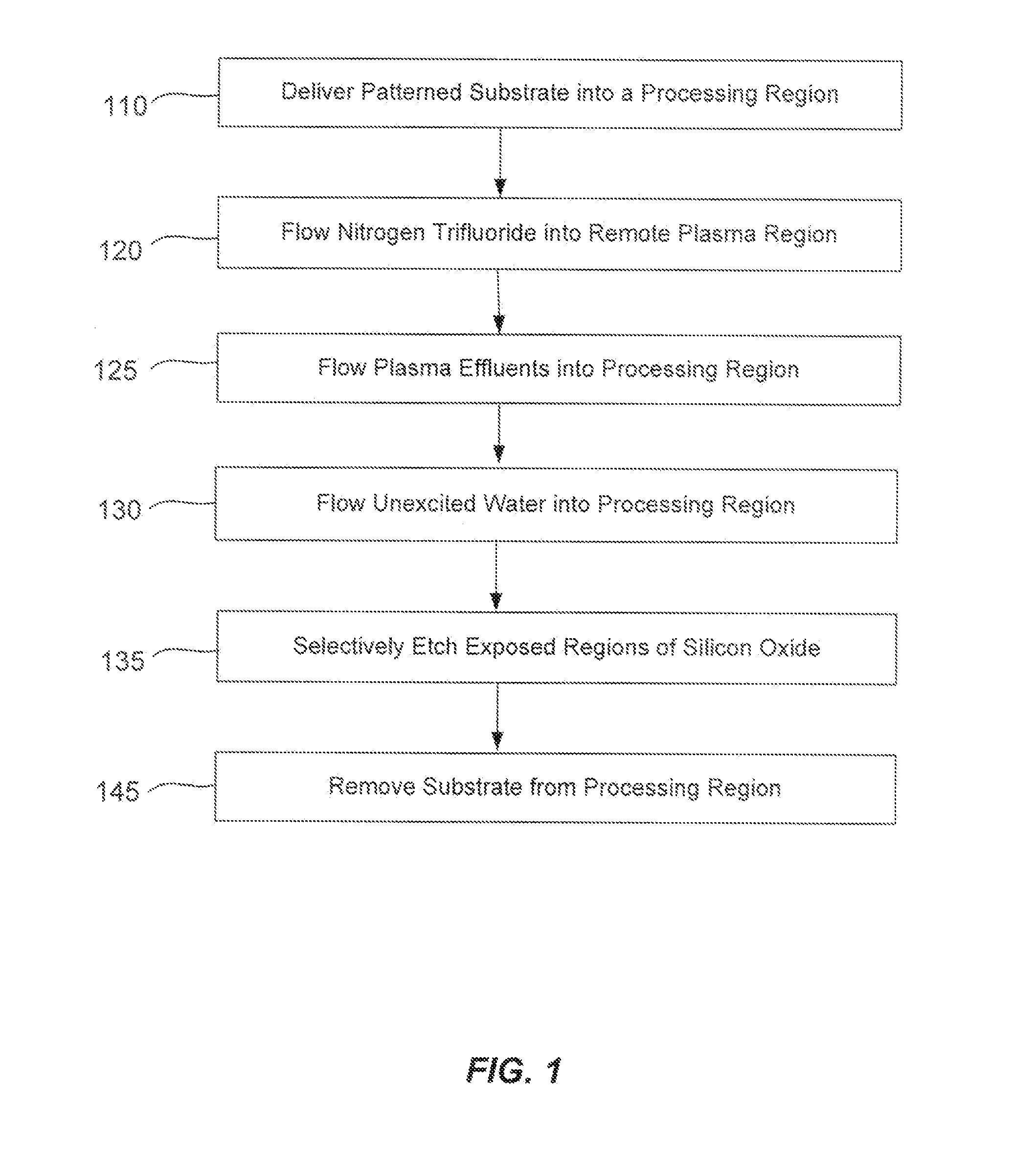

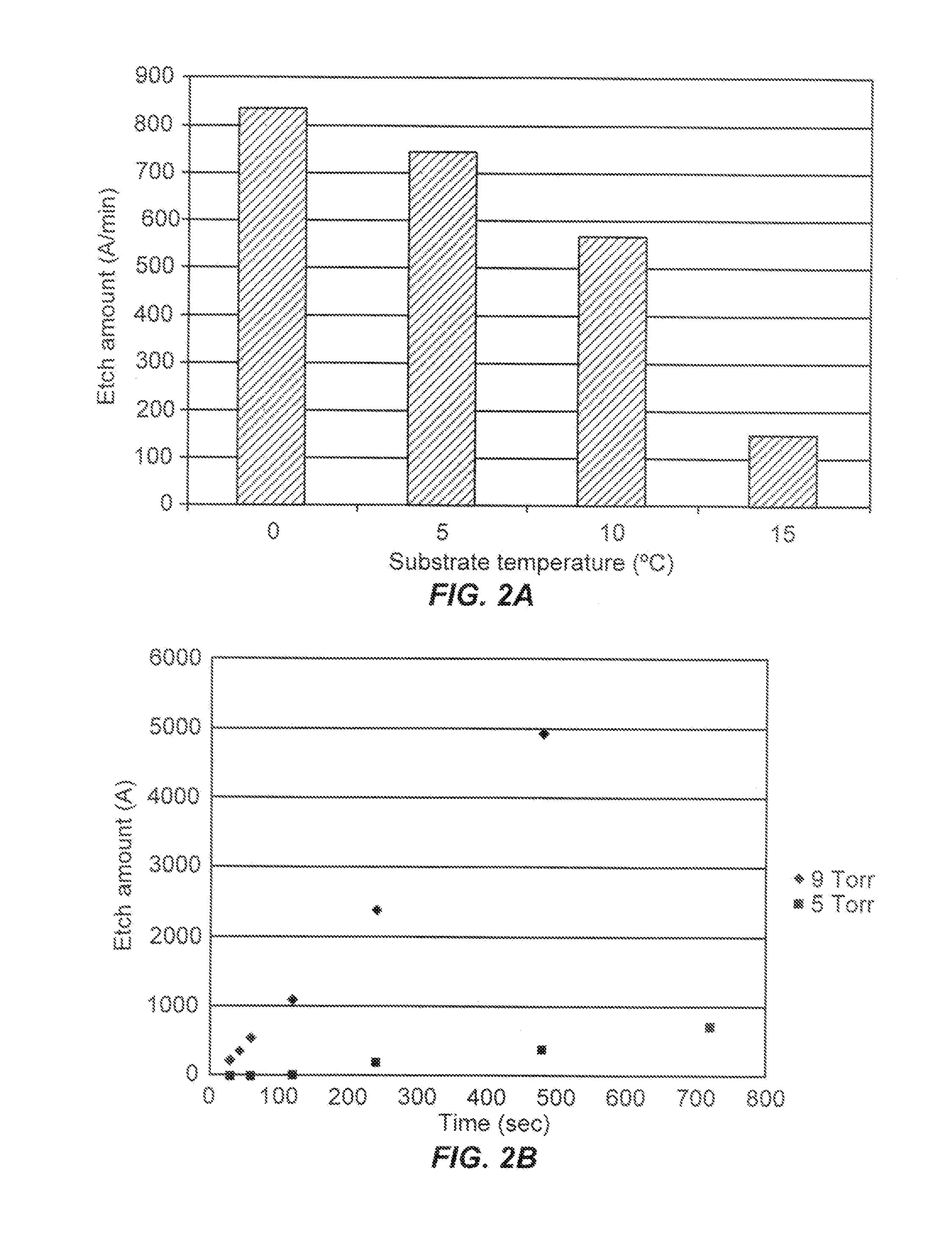

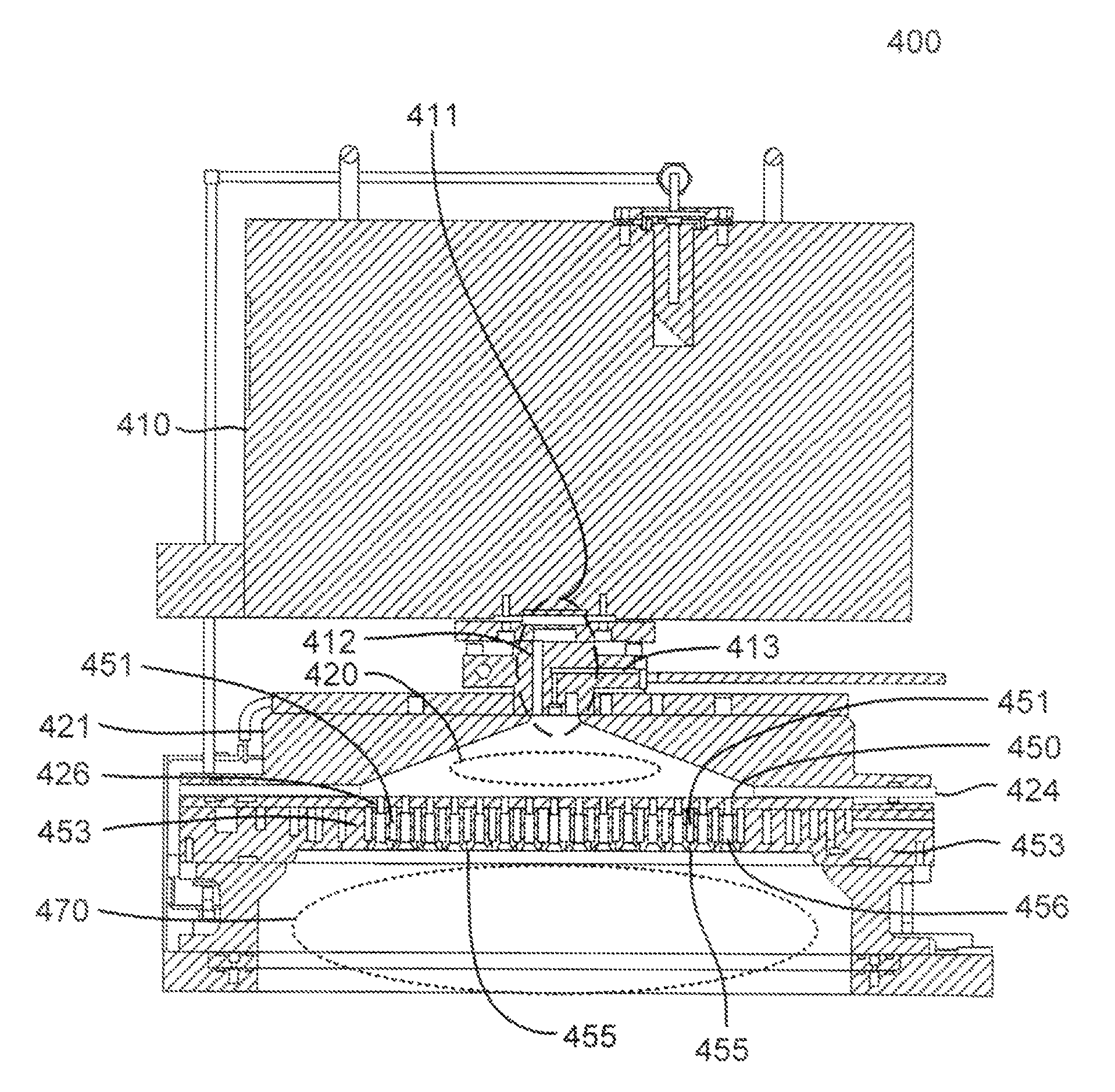

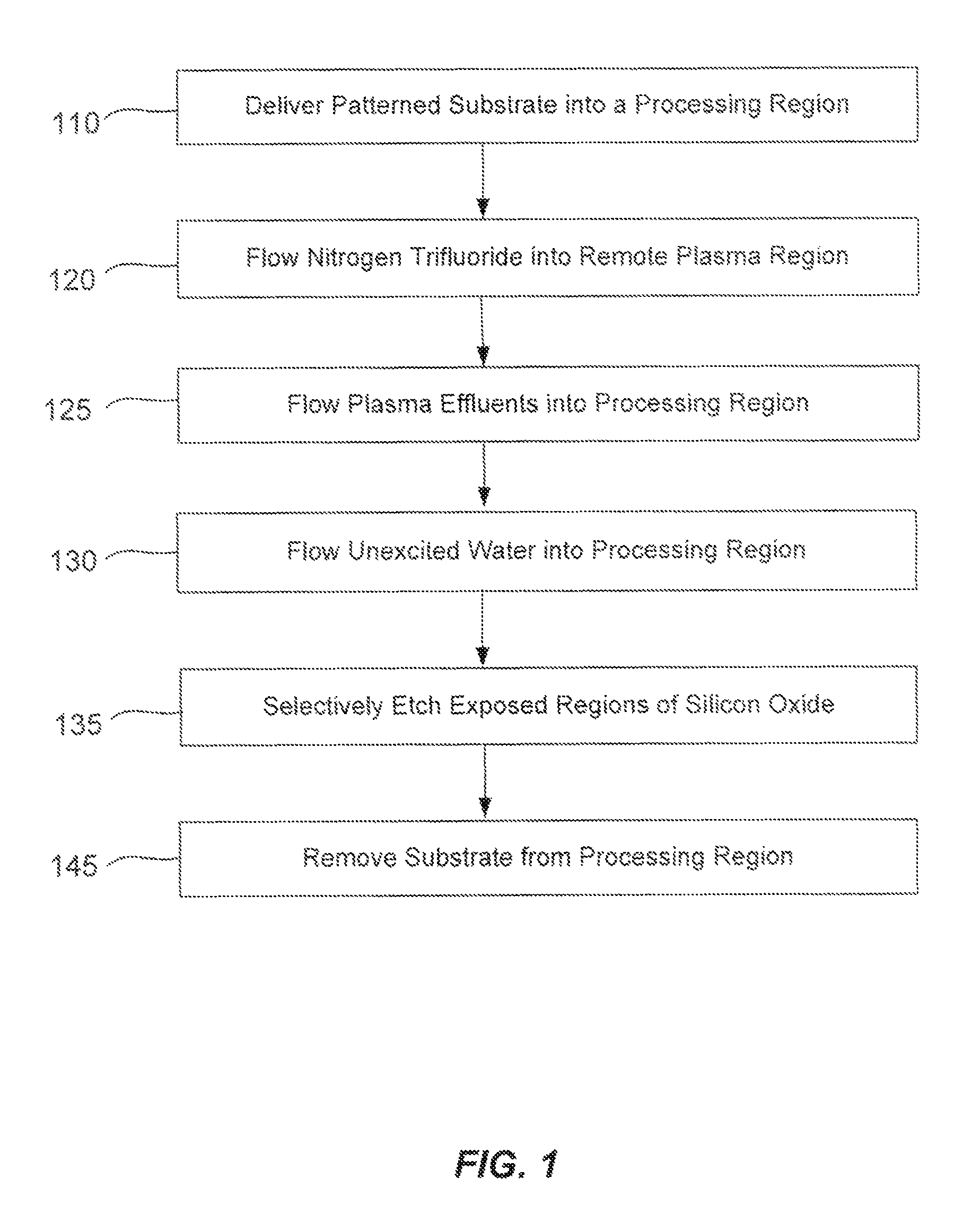

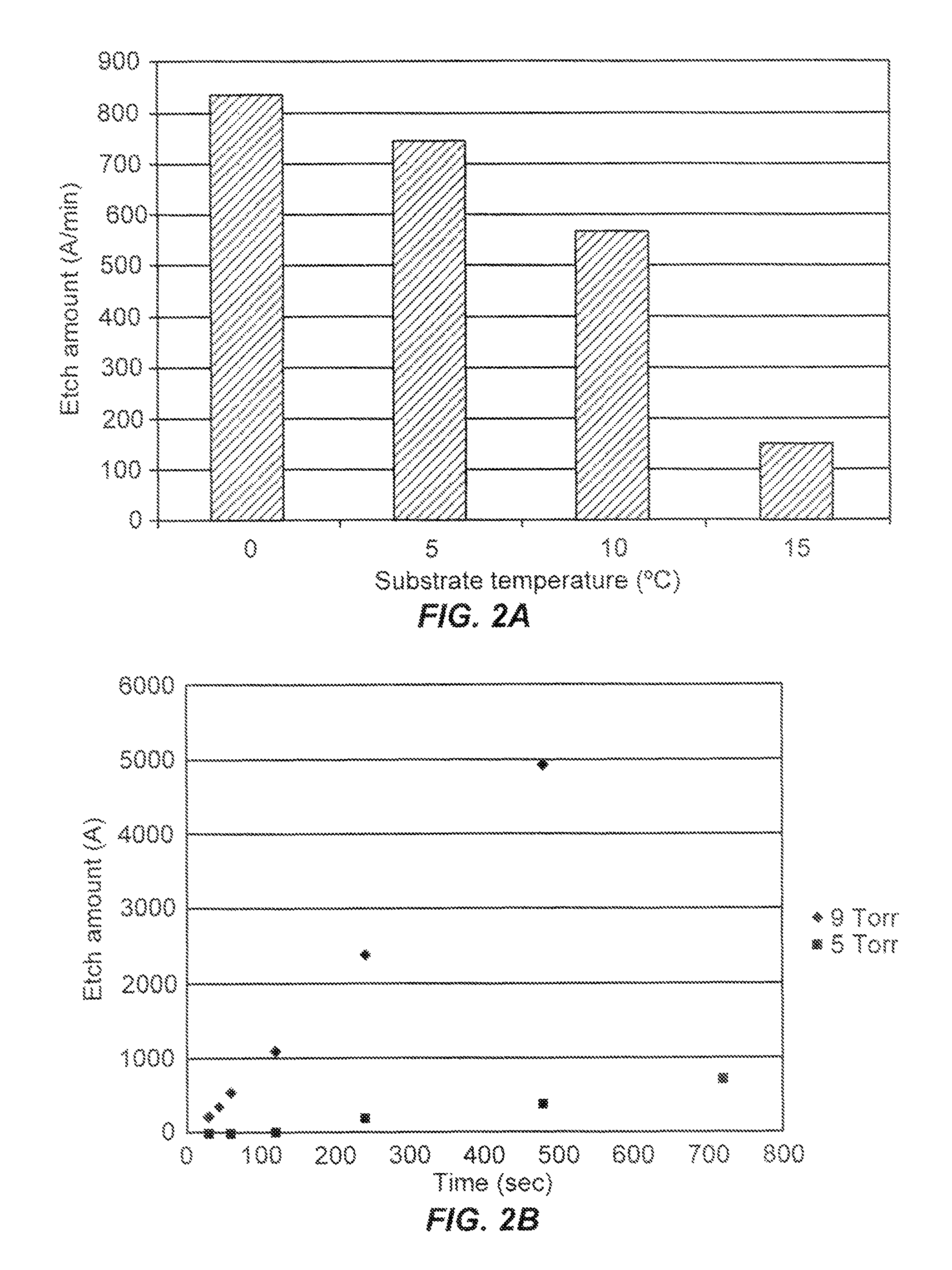

ActiveUS20120211462A1Small overall deformationElectric discharge tubesDecorative surface effectsChemical reactionRemote plasma

A method of etching exposed silicon oxide on patterned heterogeneous structures is described and includes a remote plasma etch formed from a fluorine-containing precursor. Plasma effluents from the remote plasma are flowed into a substrate processing region where the plasma effluents combine with water vapor. The chemical reaction resulting from the combination produces reactants which etch the patterned heterogeneous structures to produce, in embodiments, a thin residual structure exhibiting little deformation. The methods may be used to conformally trim silicon oxide while removing little or no silicon, polysilicon, silicon nitride, titanium or titanium nitride. In an exemplary embodiment, the etch processes described herein have been found to remove mold oxide around a thin cylindrical conducting structure without causing the cylindrical structure to significantly deform.

Owner:APPLIED MATERIALS INC

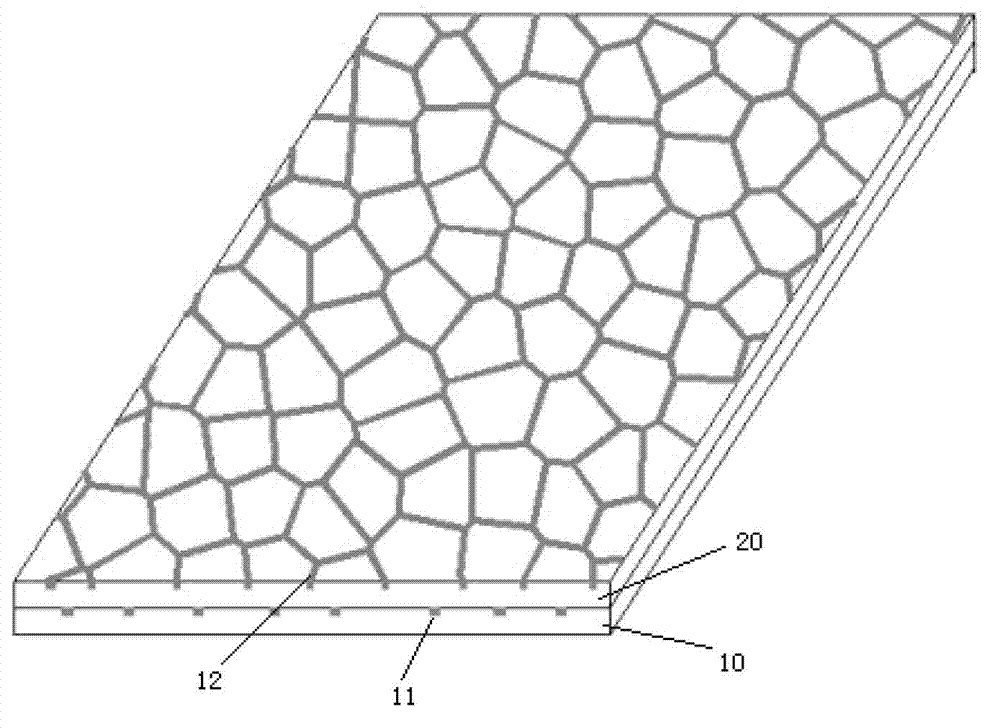

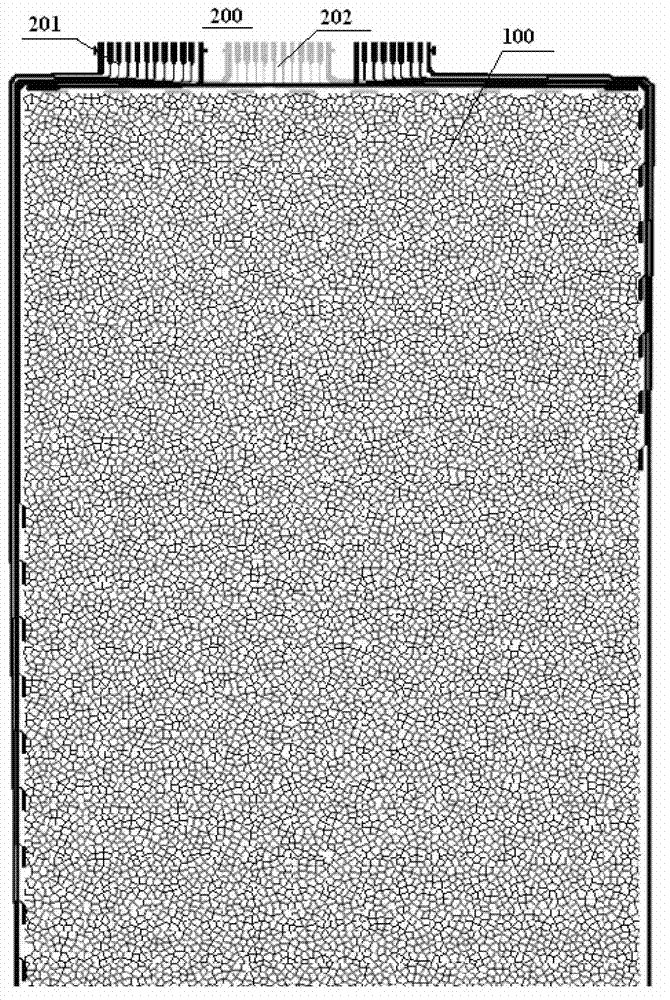

Conduction structure in transparent conduction film, transparent conduction film and manufacture method thereof

ActiveCN102903423AConductive layers on insulating-supportsTransparent dielectricsTransmittanceConductive materials

The invention discloses a transparent conduction film, a conduction structure thereof and a preparation method of the transparent conduction film. The transparent conduction film is of a single-sided dual-layer conduction structure. The conduction structure comprises a first metal embedding layer and a second metal embedding layer, wherein the first metal embedding layer is formed by impressing on a substrate or impressing on a polymer layer on the surface of the substrate; and the second metal embedding layer is formed by coating the polymer layer on the surface of the first metal embedding layer through impressing, the first layer of conduction structure and the second layer of conduction structure have a grid groove structure, and conductive materials are filled in grooves. The single-sided graphical transparent conduction film provided by the invention has the advantages of high resolution and transmittance, independent and adjustable sheet resistance, and the like. According to the transparent conduction film, the cost can be reduced, and the weight and the thickness of a manufactured touch panel can be reduced.

Owner:ANHUI JINGZHUO OPTICAL DISPLAY TECH CO LTD

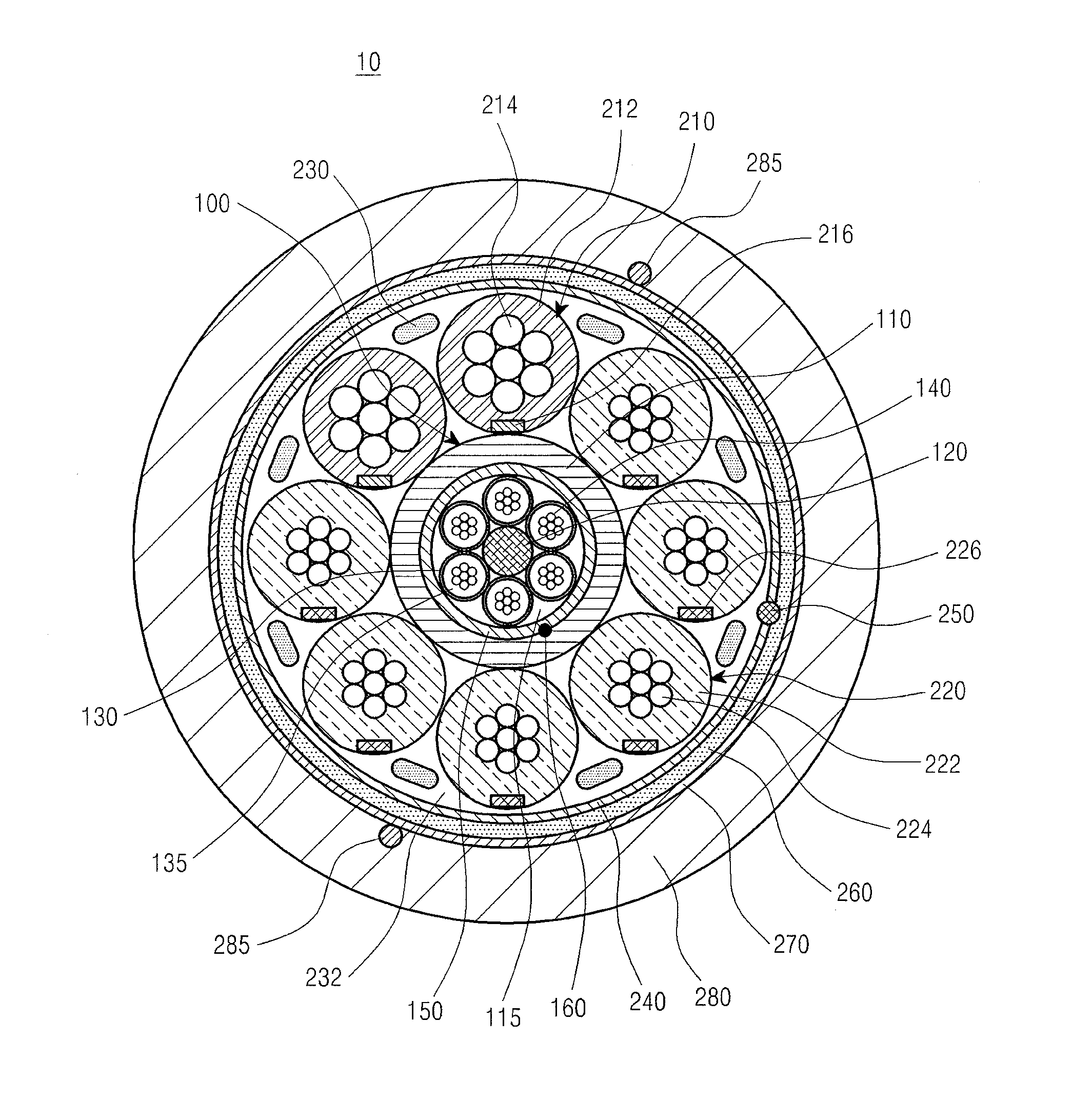

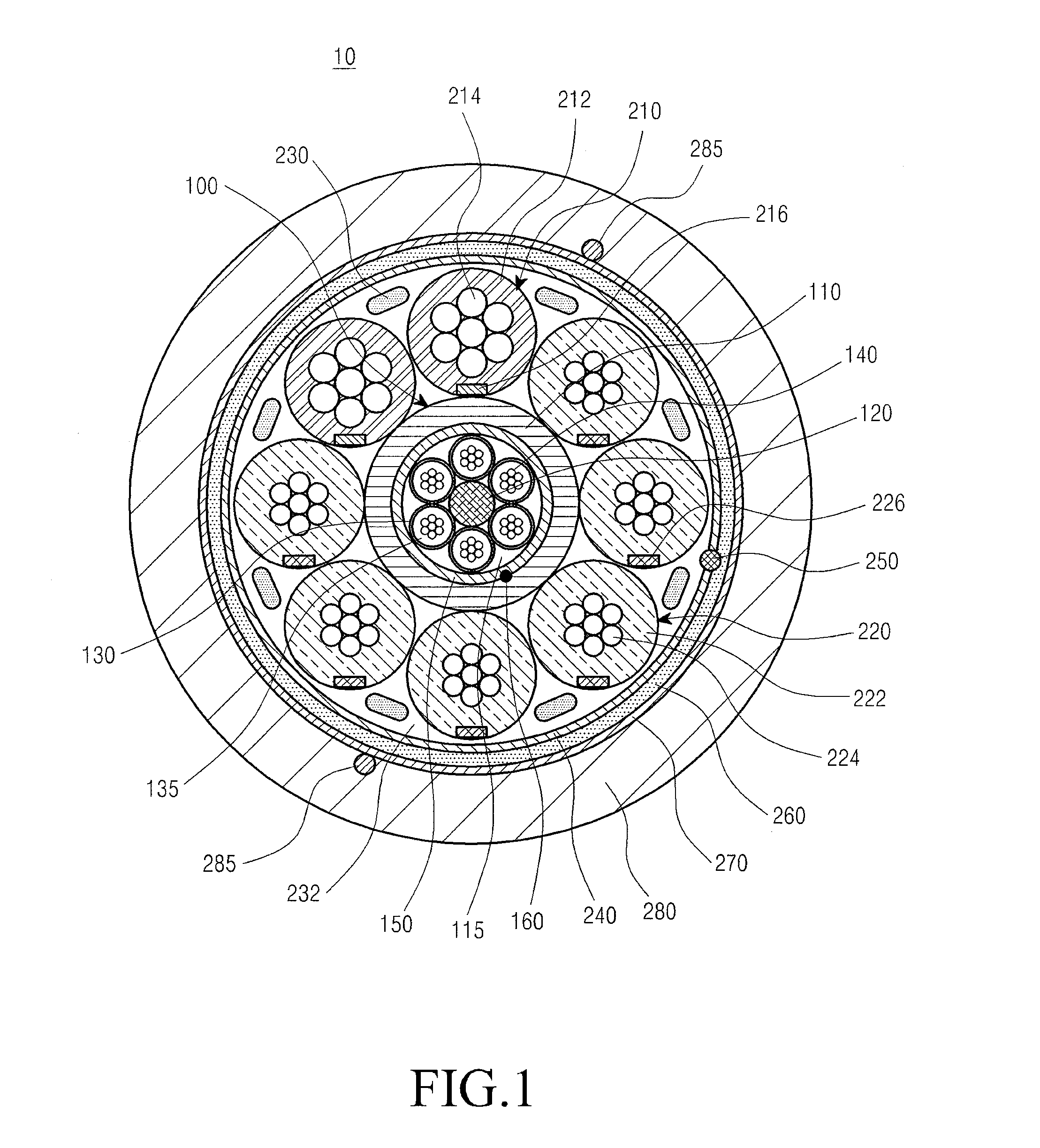

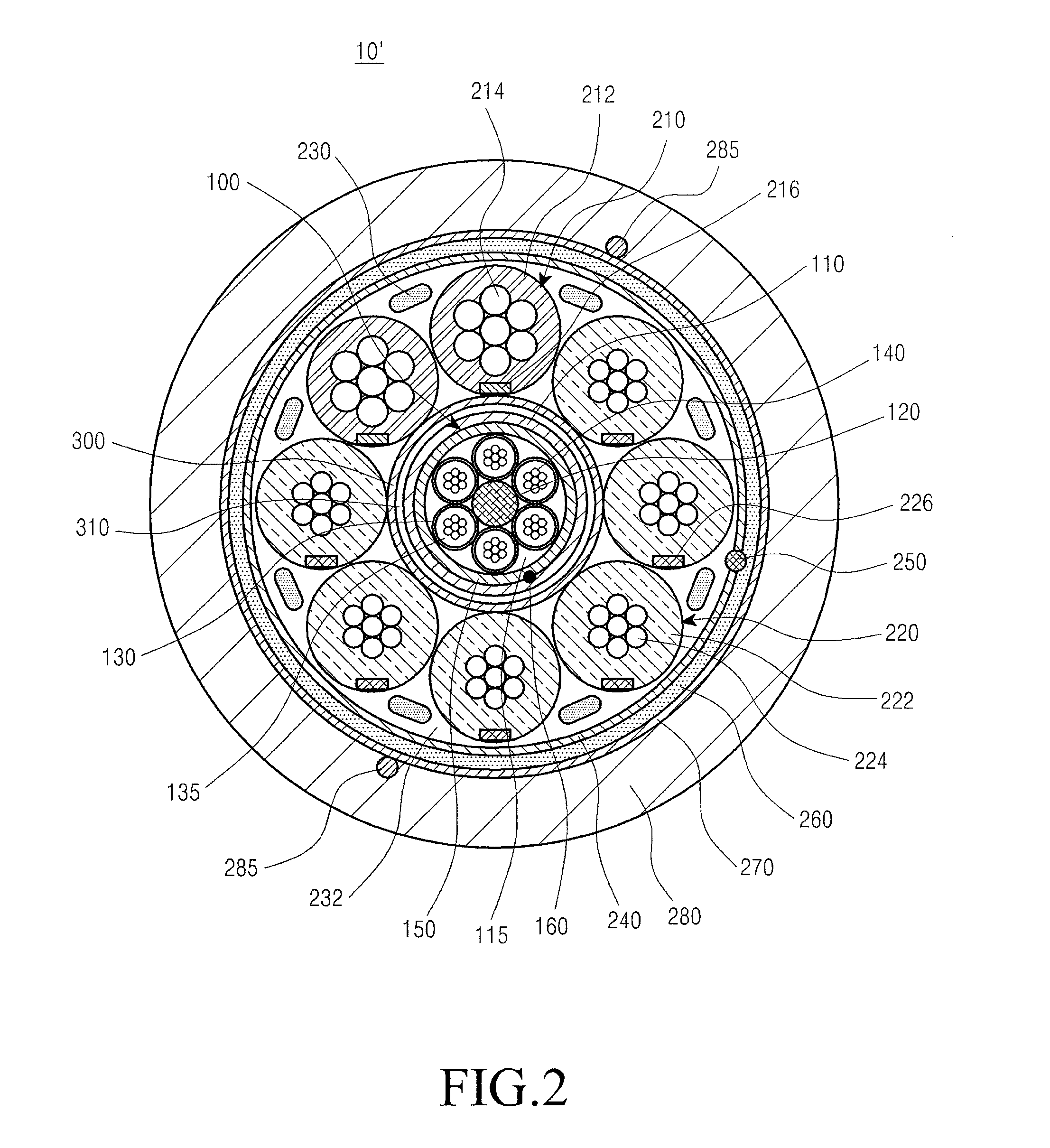

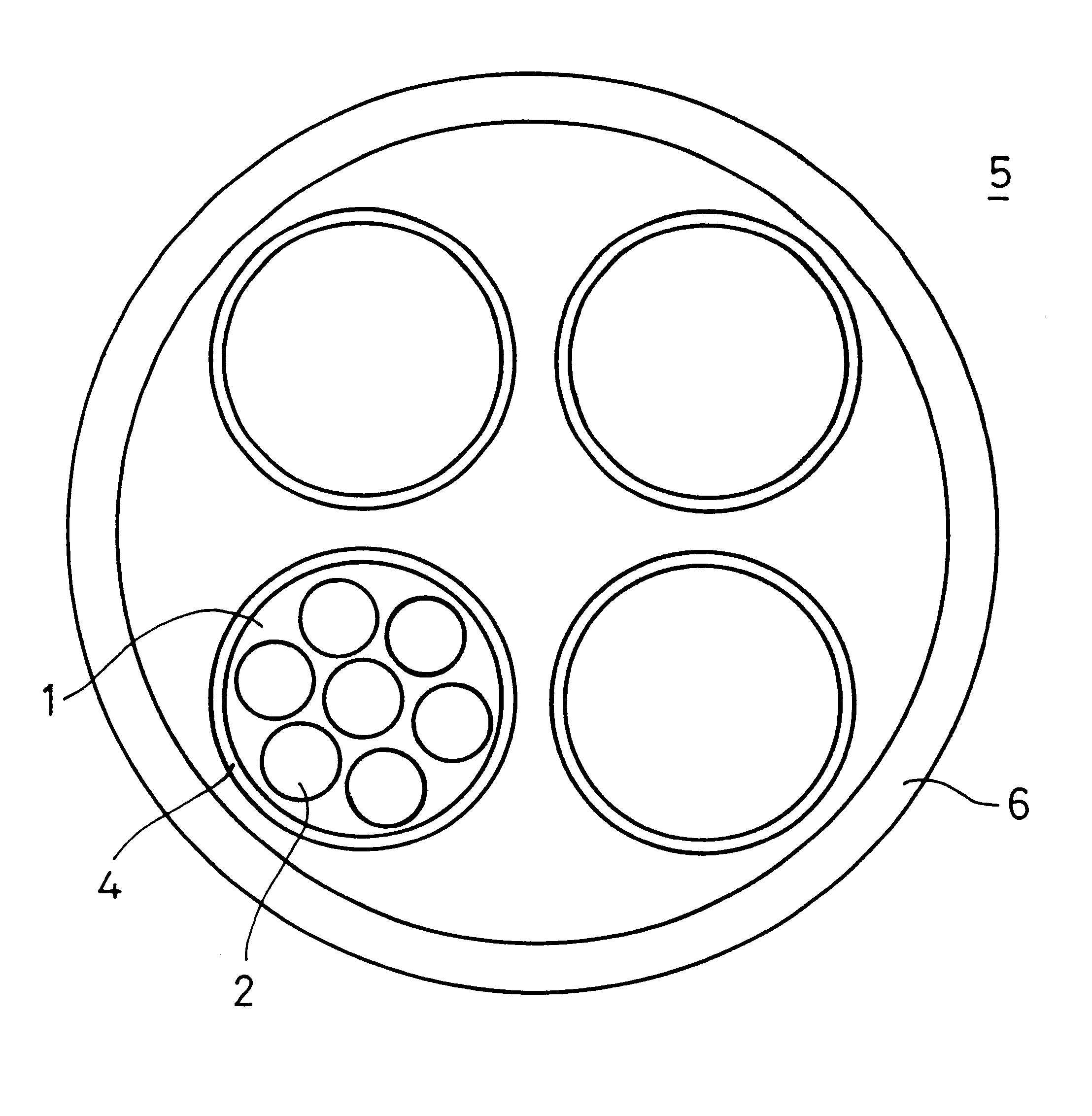

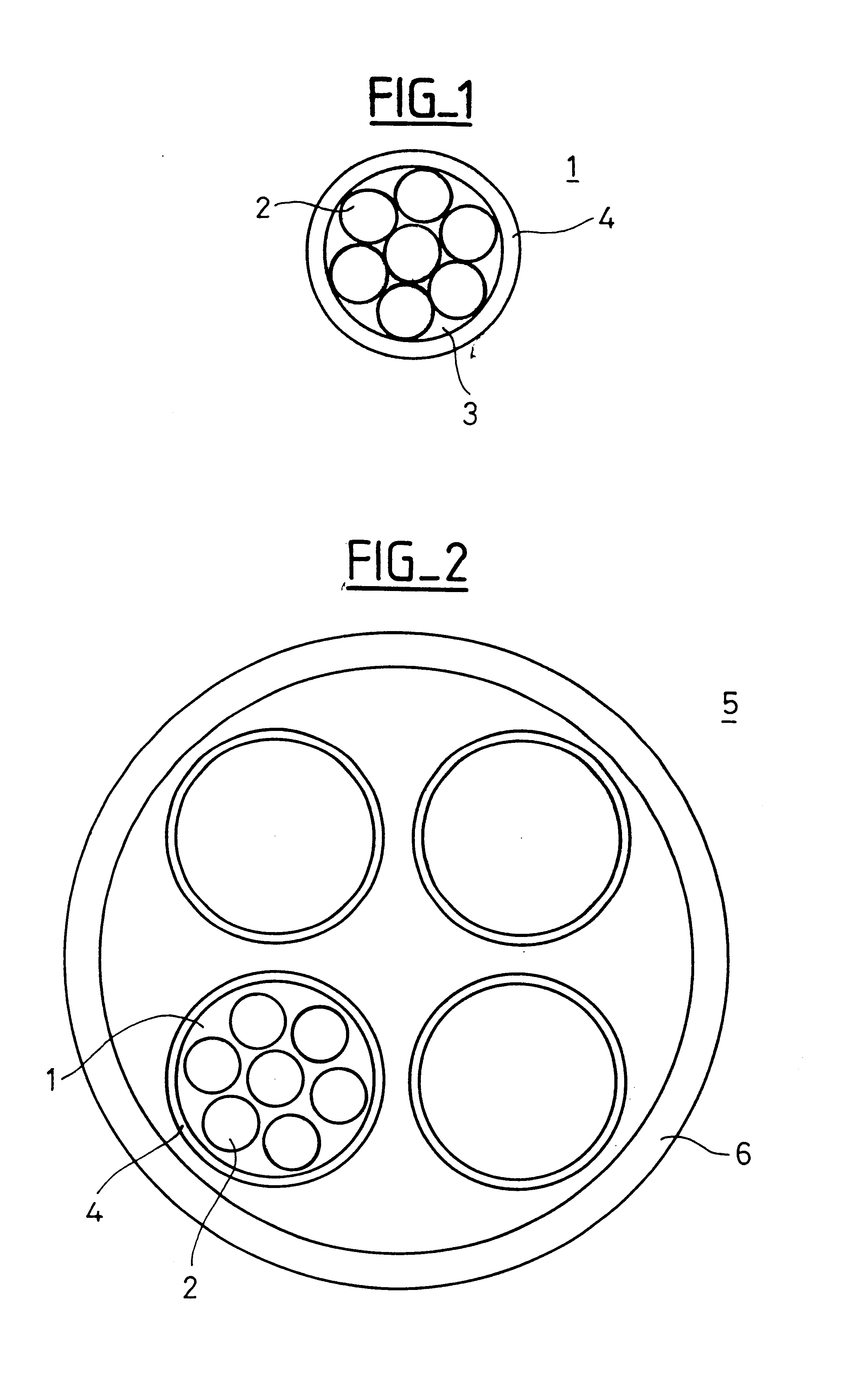

Optical electrical hybrid cable

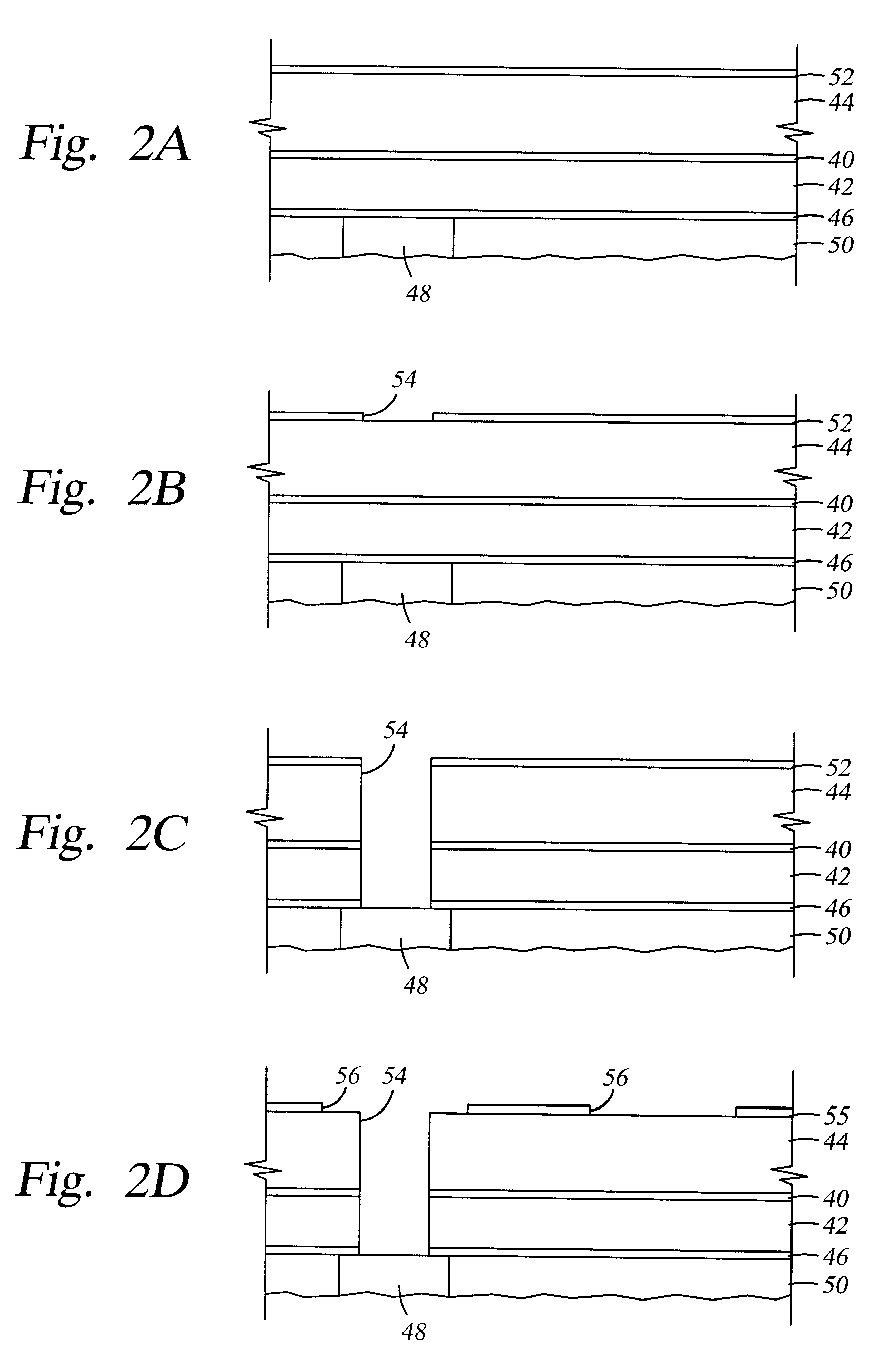

InactiveUS8792760B2Reduce the overall diameterThe process is stable and efficientCommunication cablesCoupling light guidesFiberElectric force

An optical electrical hybrid cable for transmitting an optical signal and an electrical signal simultaneously is provided. The optical electrical hybrid cable includes a fiber-optic cable disposed in the center of the optical electrical hybrid cable, and including a plurality of tubes each of which comprises a plurality of optical fibers operatively mounted in an inner space thereof, and a first binder disposed around the plurality of tubes, a plurality of power cables disposed around the fiber-optic cable, each of the power cables comprising a plurality of conducting wires, and a second binder disposed around the plurality of power cables.

Owner:SAMSUNG ELECTRONICS CO LTD

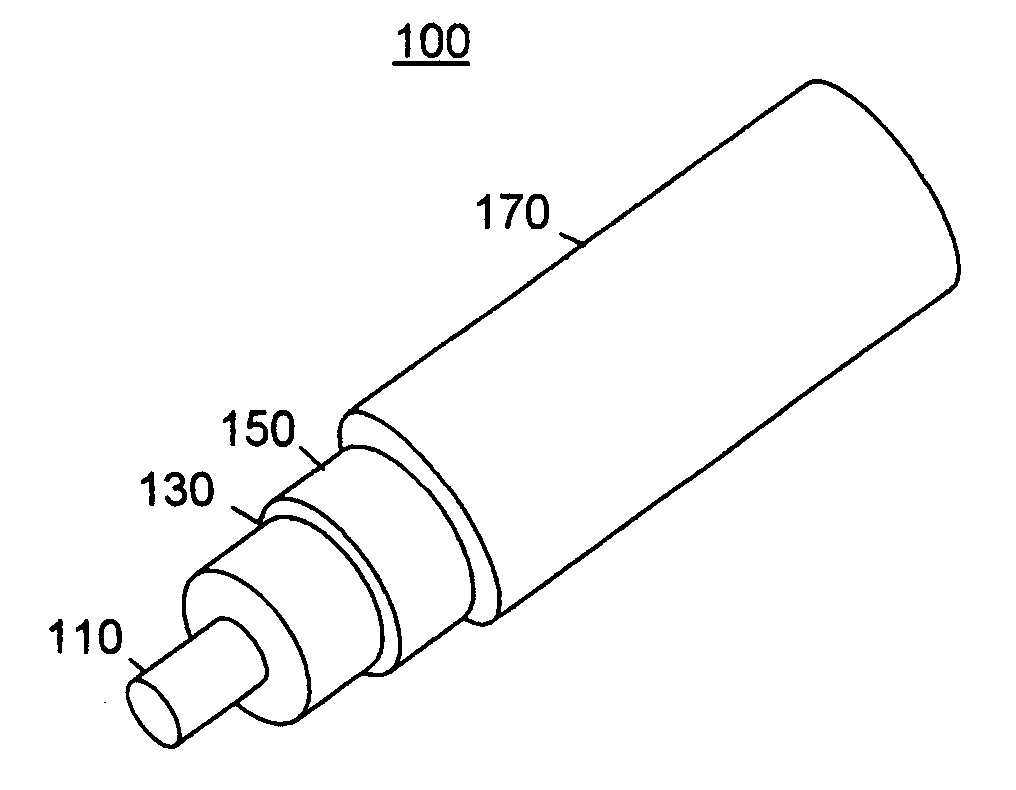

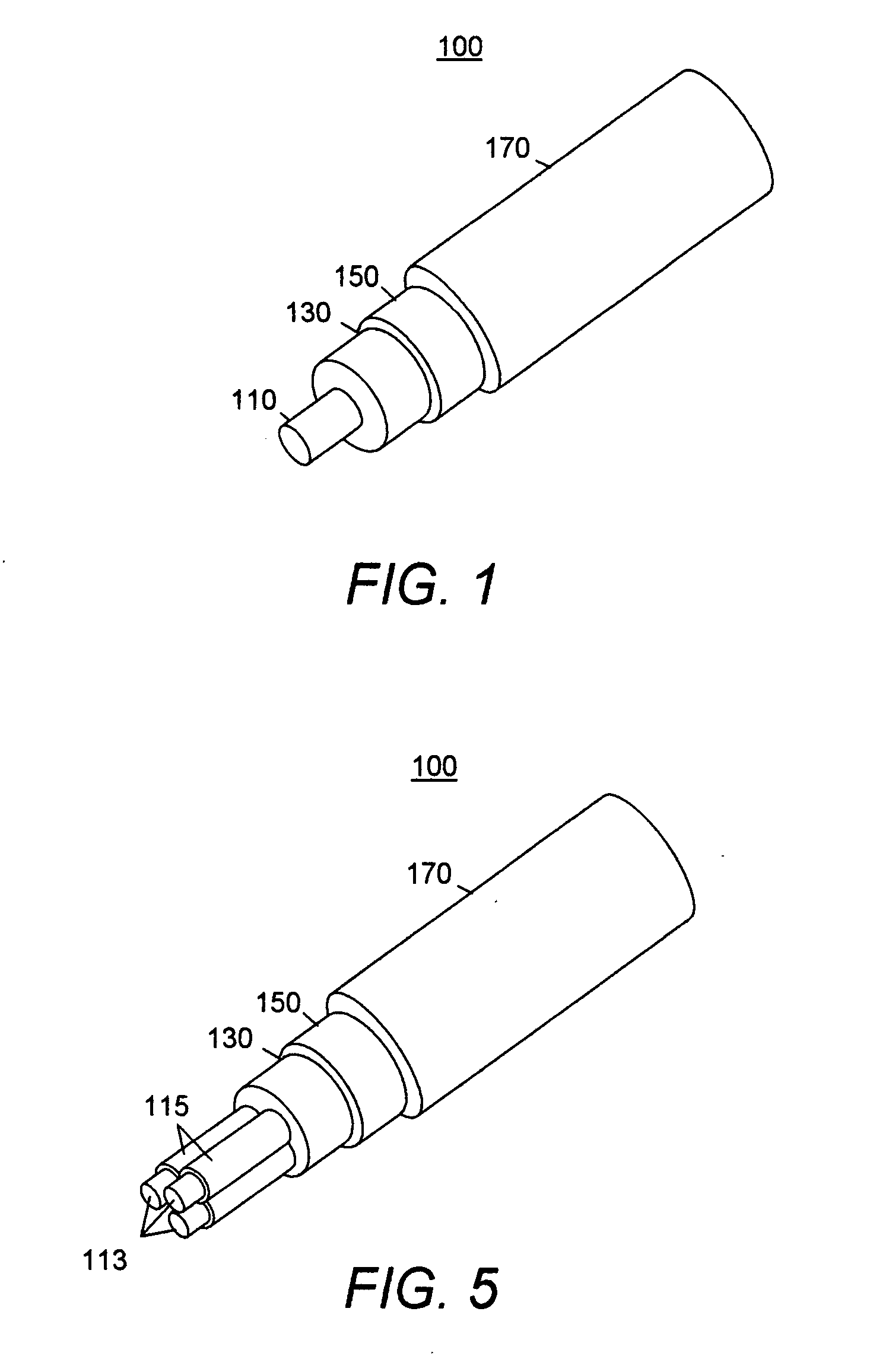

Multi-layer cable design and method of manufacture

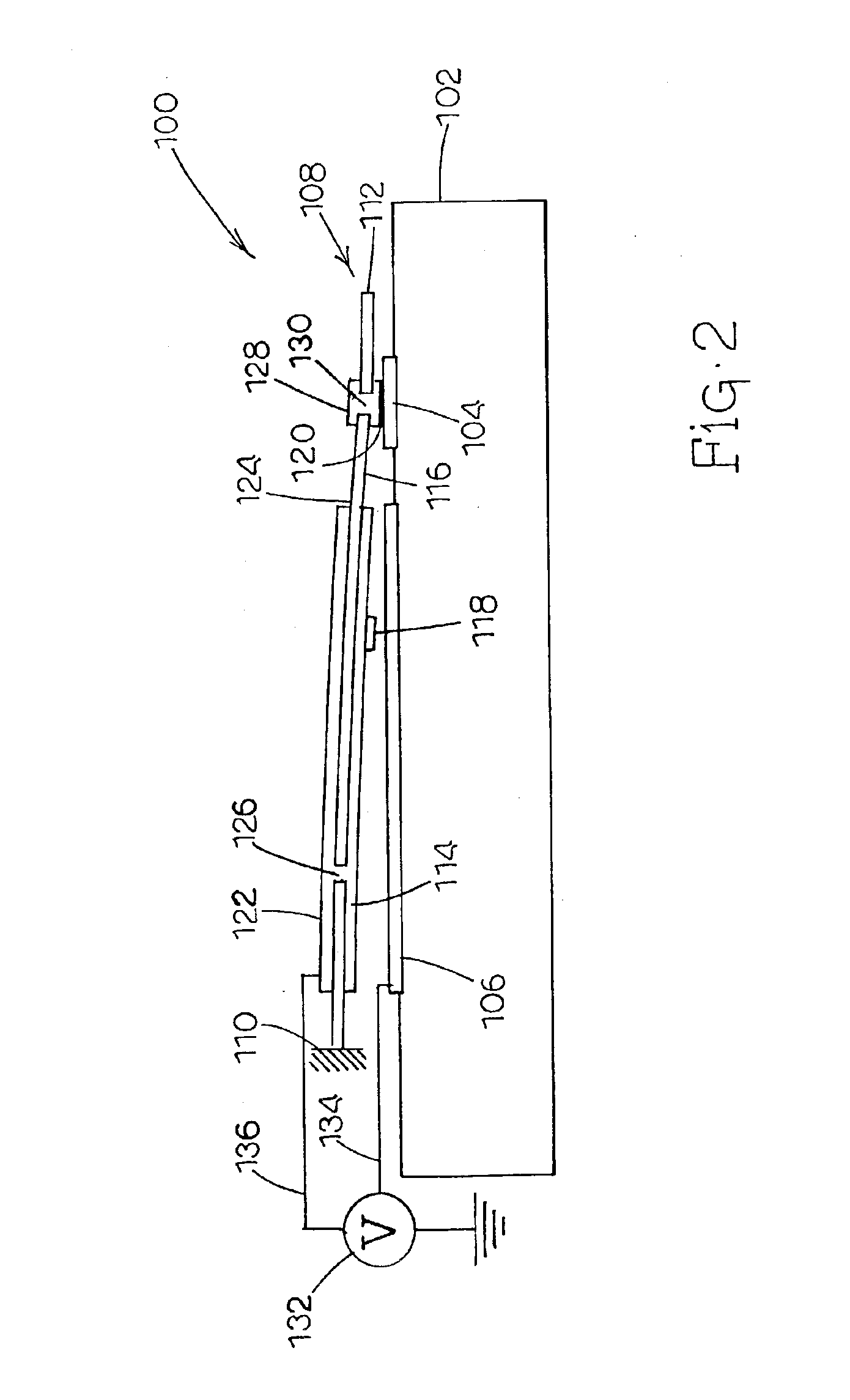

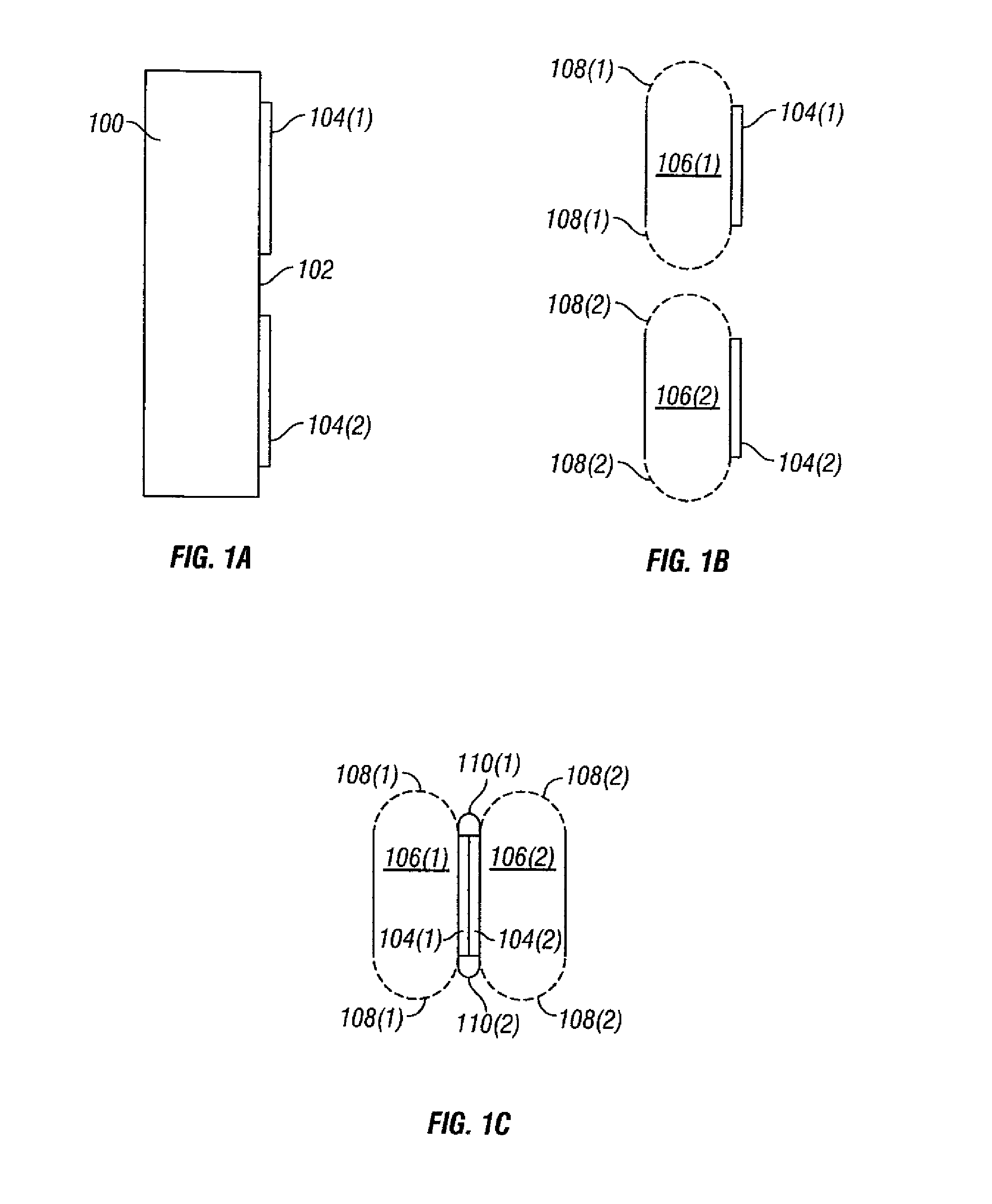

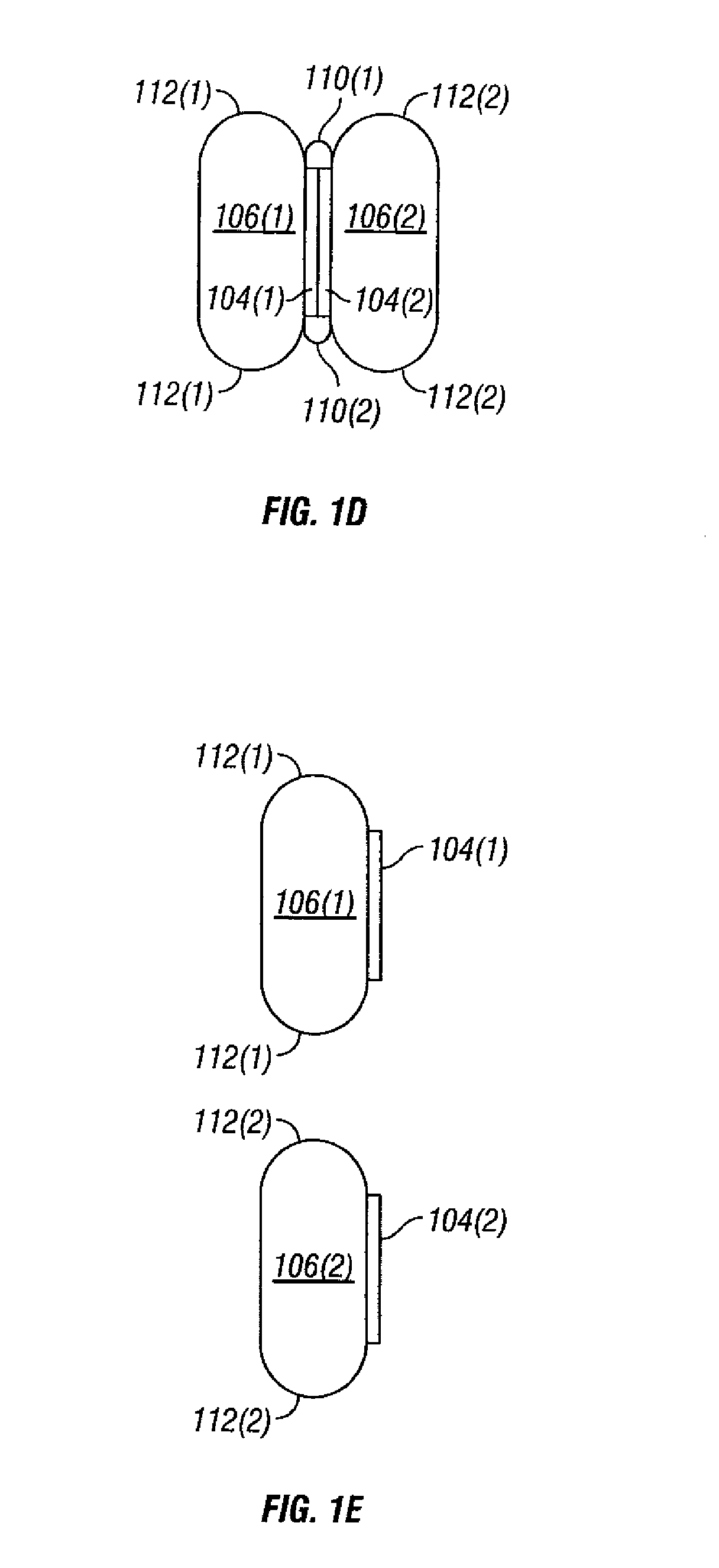

InactiveUS20080060832A1Economically manufacturedVolume/mass flow measurementFluid pressure measurement by electric/magnetic elementsCathodic arc depositionFiber

A novel method of designing and fabricating flexible and lightweight cable [100] having a central conductor [110], a dielectric layer [130], an outer conductor [150] and an insulation coating [170] using thin film technology is disclosed. The dielectric layer [130] is ‘grown’ on dielectric layer [130] using electrophoretic deposition to a specified thickness, based upon its intended use. It may include nano-diamonds. Ion beam assisted deposition is used to metalize the cable dielectric layer [130]. This may be ion beam assisted sputtering, ion beam assisted evaporative deposition or ion beam assisted cathodic arc deposition. In an alternative embodiment, the outer conductor may be etched to provide greater flexibility, or to add a piezoelectric layer. The central conductor [110] may be created from dielectric fibers [113] which are metalized as described above. The piezoelectric layer added to create ultrasonic transducer cables.

Owner:RAZAVI ALI

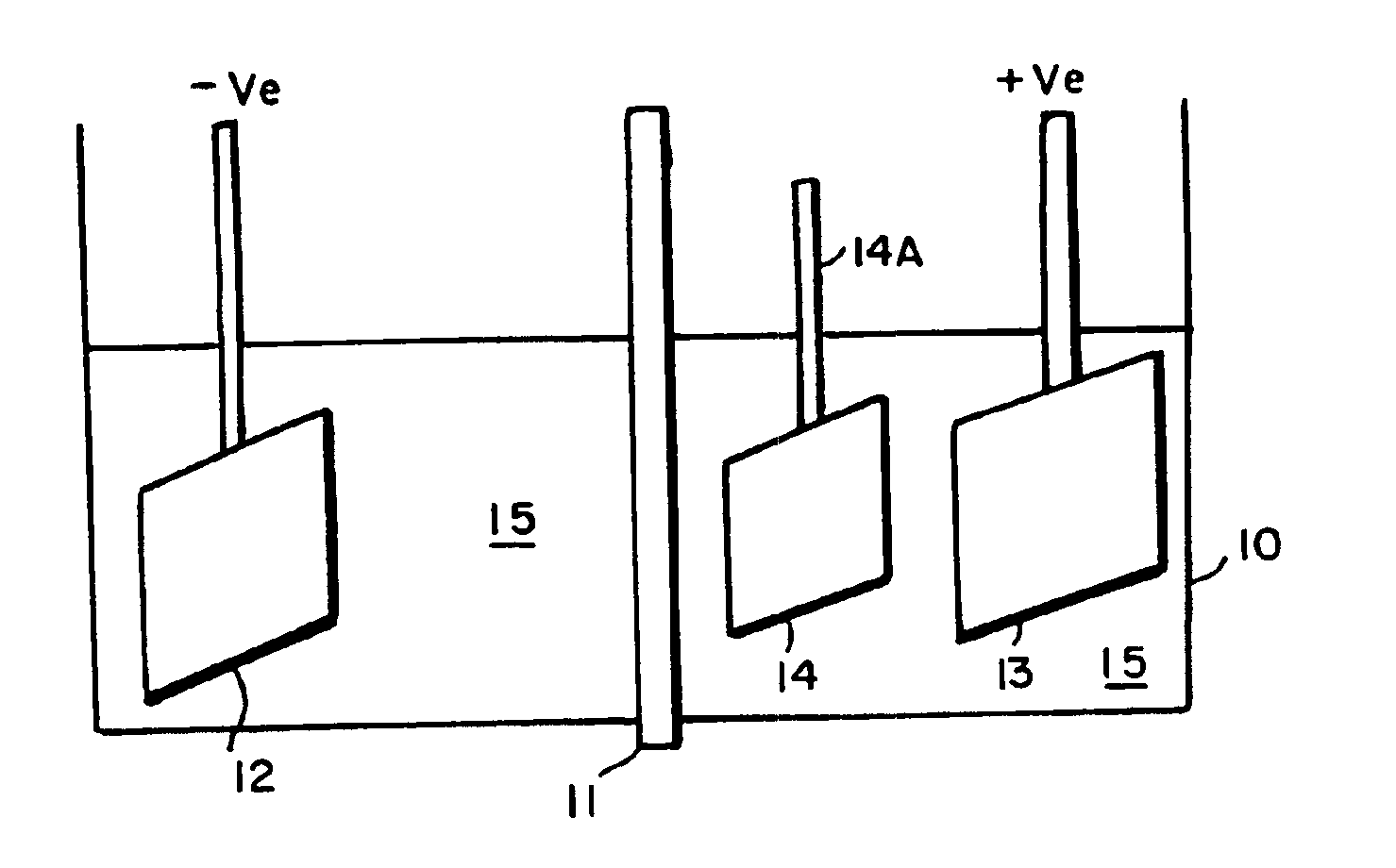

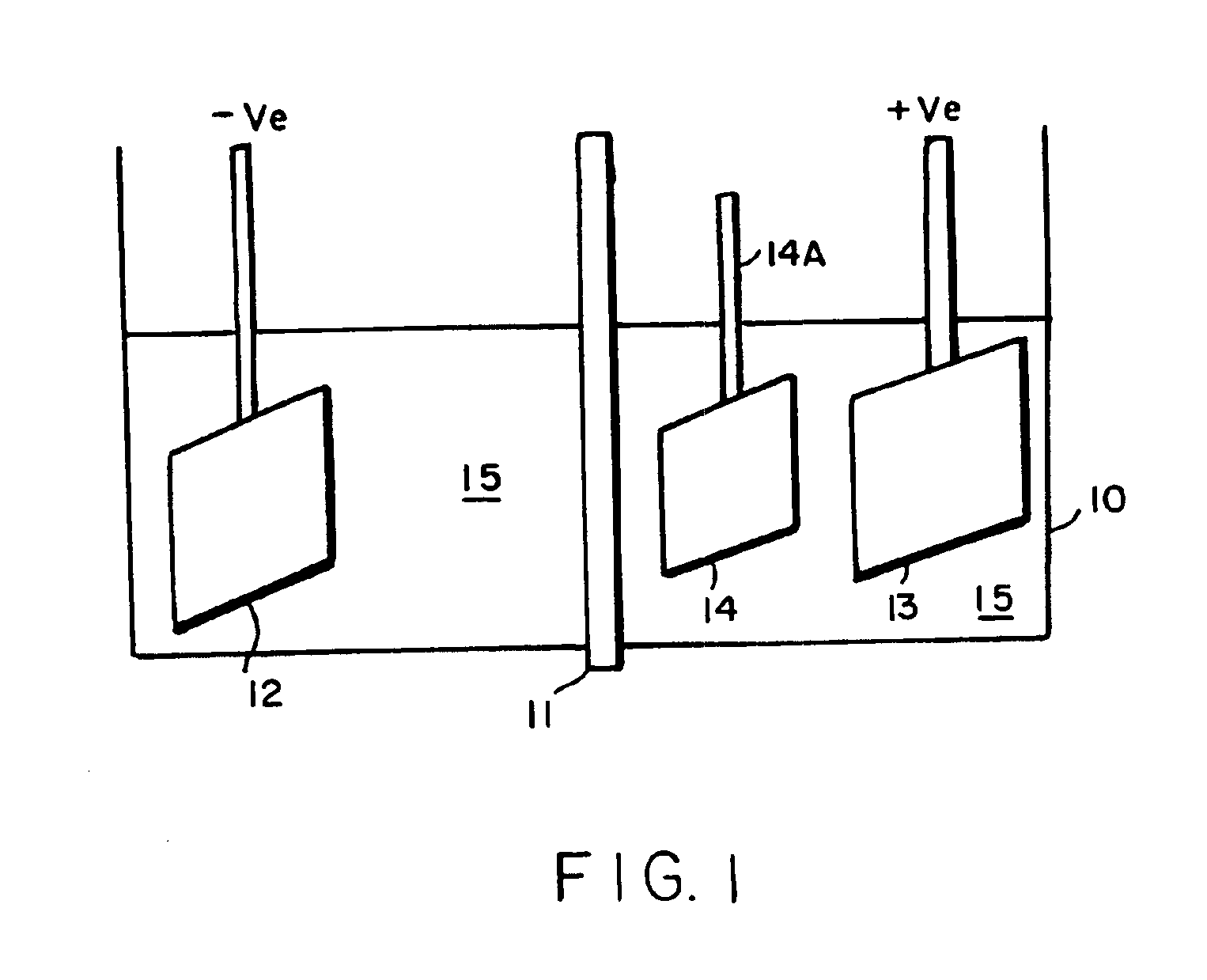

Electroless plating processes

InactiveUS6861097B1Reducing problem encounteredSimple methodPaper/cardboard articlesDecorative surface effectsPolymeric surfaceOxidation state

The invention includes processes for combined polymer surface treatment and metal deposition. Processes of the invention include forming an aqueous solution containing a metal activator, such as an oxidized species of silver, cobalt, ruthenium, cerium, iron, manganese, nickel, rhodium, or vanadium. The activator can be suitably oxidized to a higher oxidation state electrochemically. Exposing a part to be plated (such as an organic resin, e.g. a printed circuit board substrate) to the solution enables reactive hydroxyl species (e.g. hydroxyl radicals) to be generated and to texture the polymer surface. Such texturing facilitates good plated metal adhesion. As part of this contacting process sufficient time is allowed for both surface texturing to take place and for the oxidized metal activator to adsorb onto said part. The part is then contacted with a reducing agent capable of reducing the metal activator to a lower ionic form, or a lower oxidation state. That reduction can result in the formation of metallic catalytic material over the surface of the part. The reduced metal activator can then function to catalyze the electroless deposition of metal such as copper from solution by contacting the part with the plating solution.

Owner:SHIPLEY CO LLC

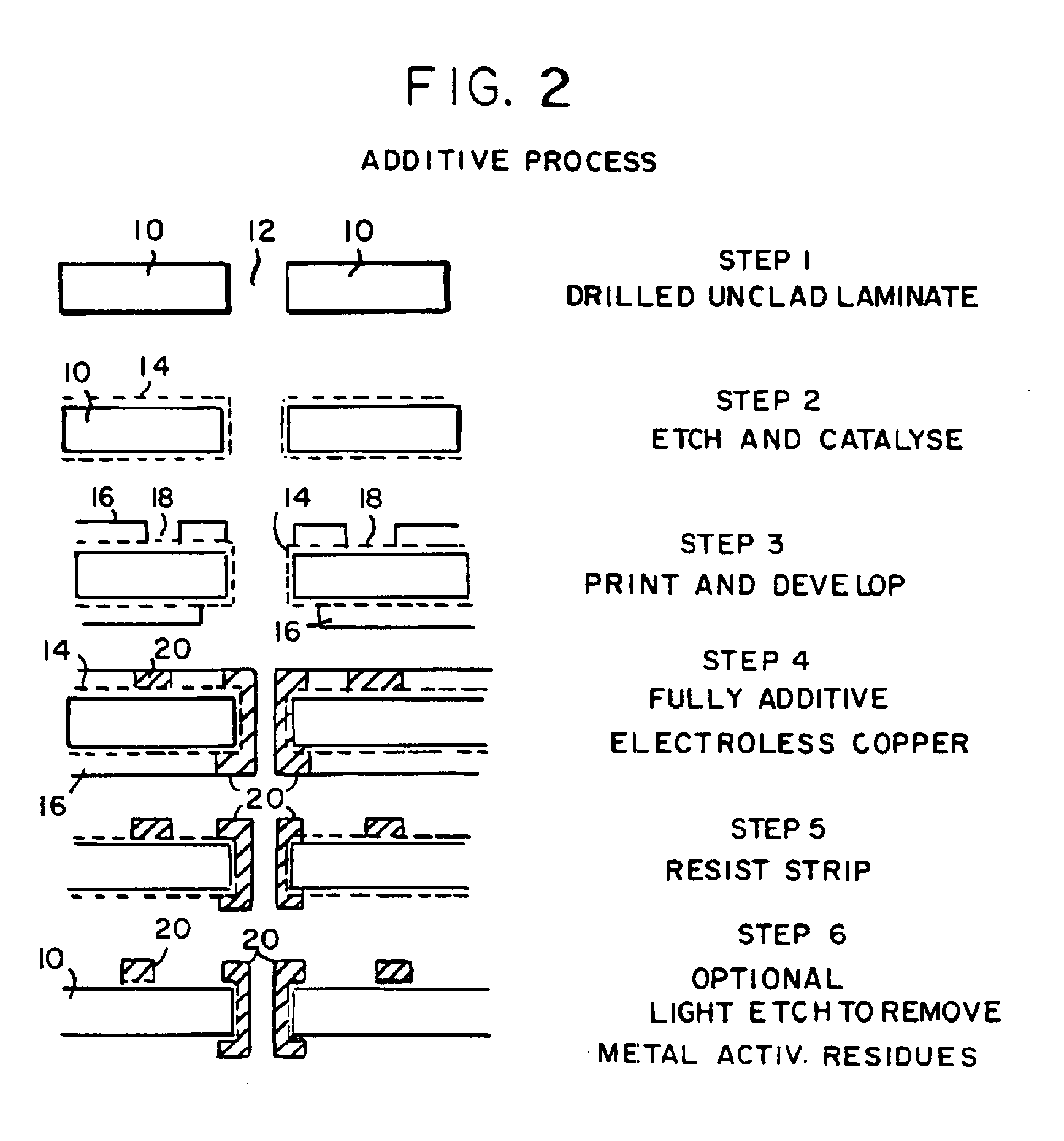

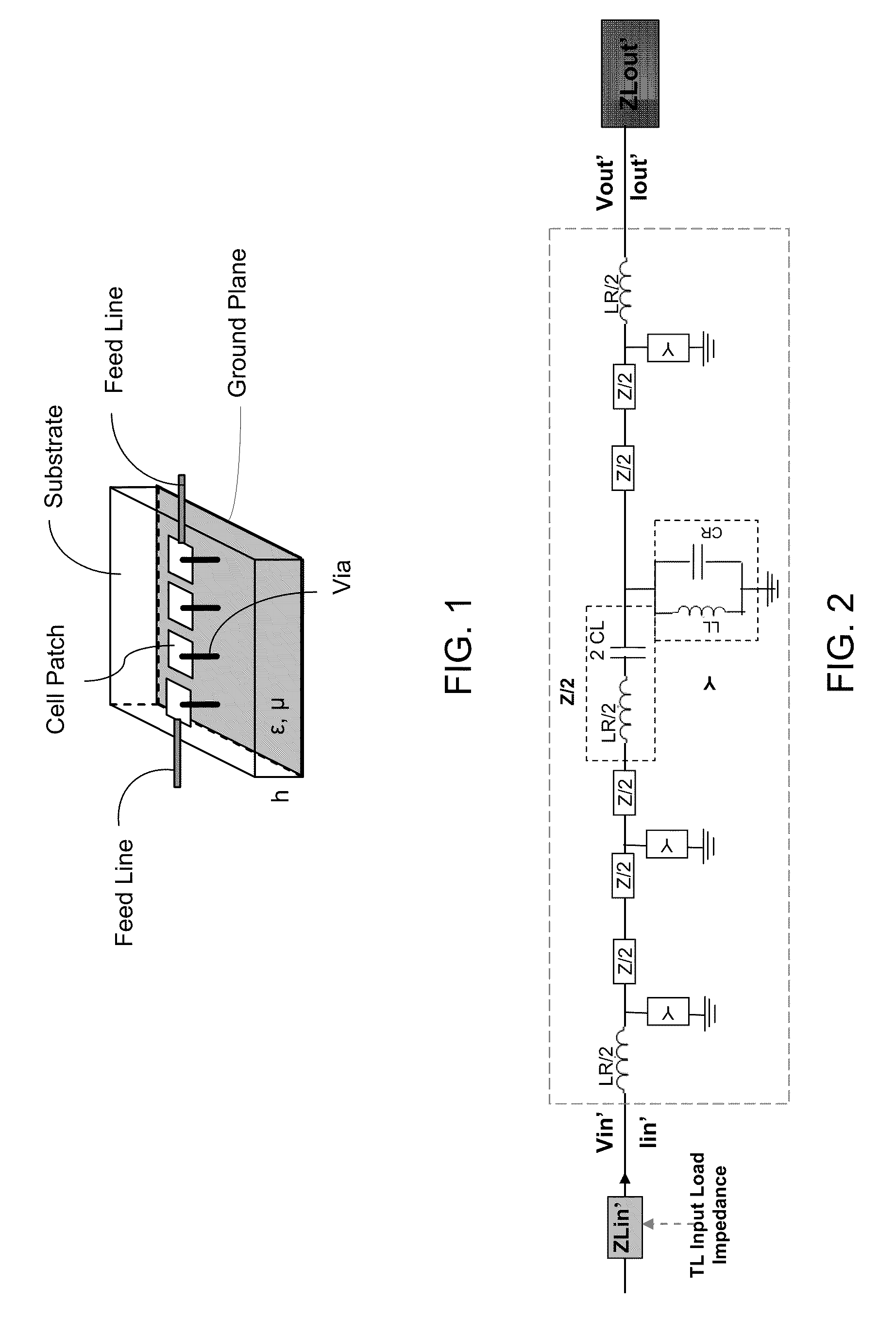

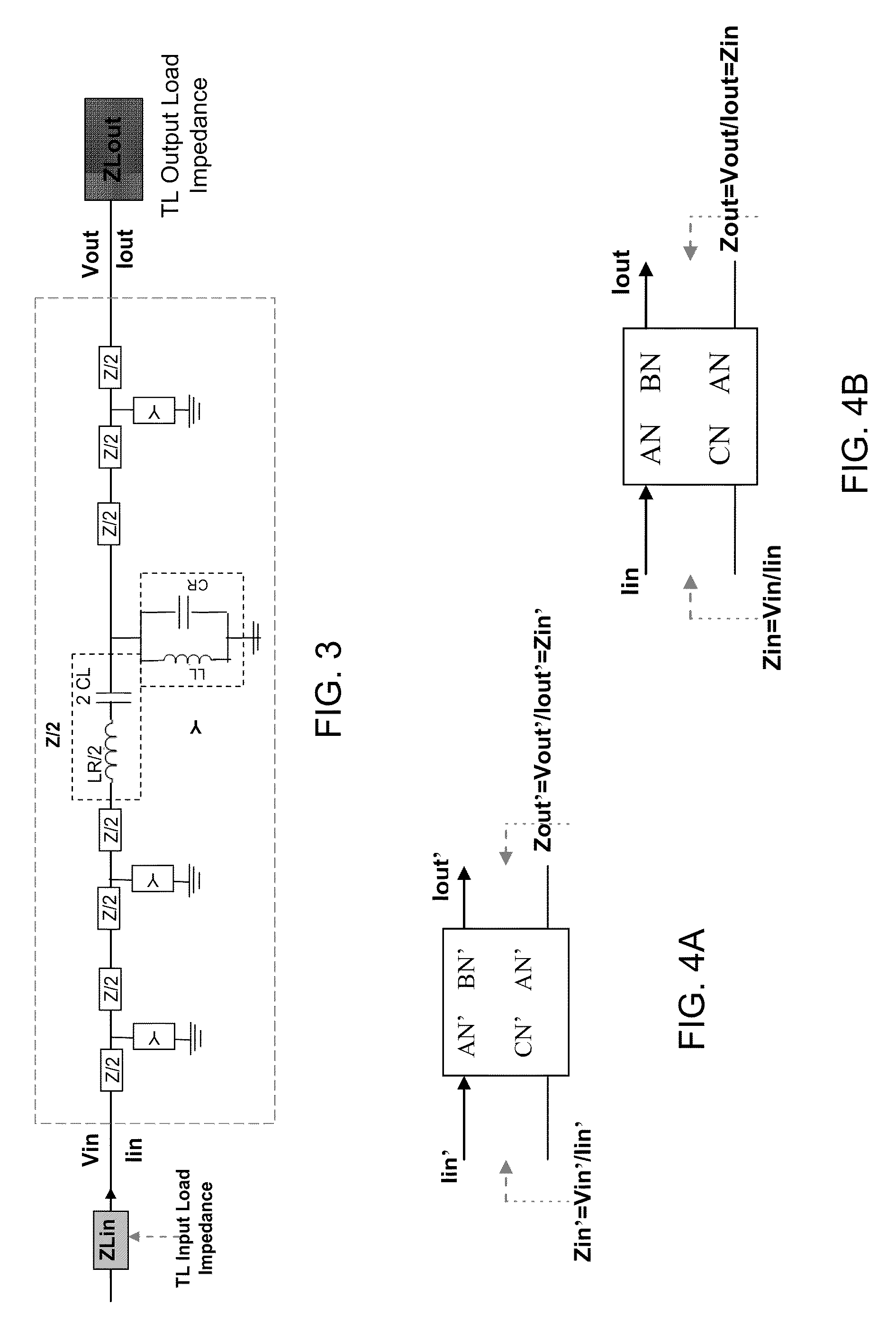

Multiband composite right and left handed (CRLH) slot antenna

This application relates to slot antenna devices based on Composite Right and Left Handed (CRLH) metamaterial (MTM) structures.

Owner:TYCO ELECTRONICS SERVICES GMBH

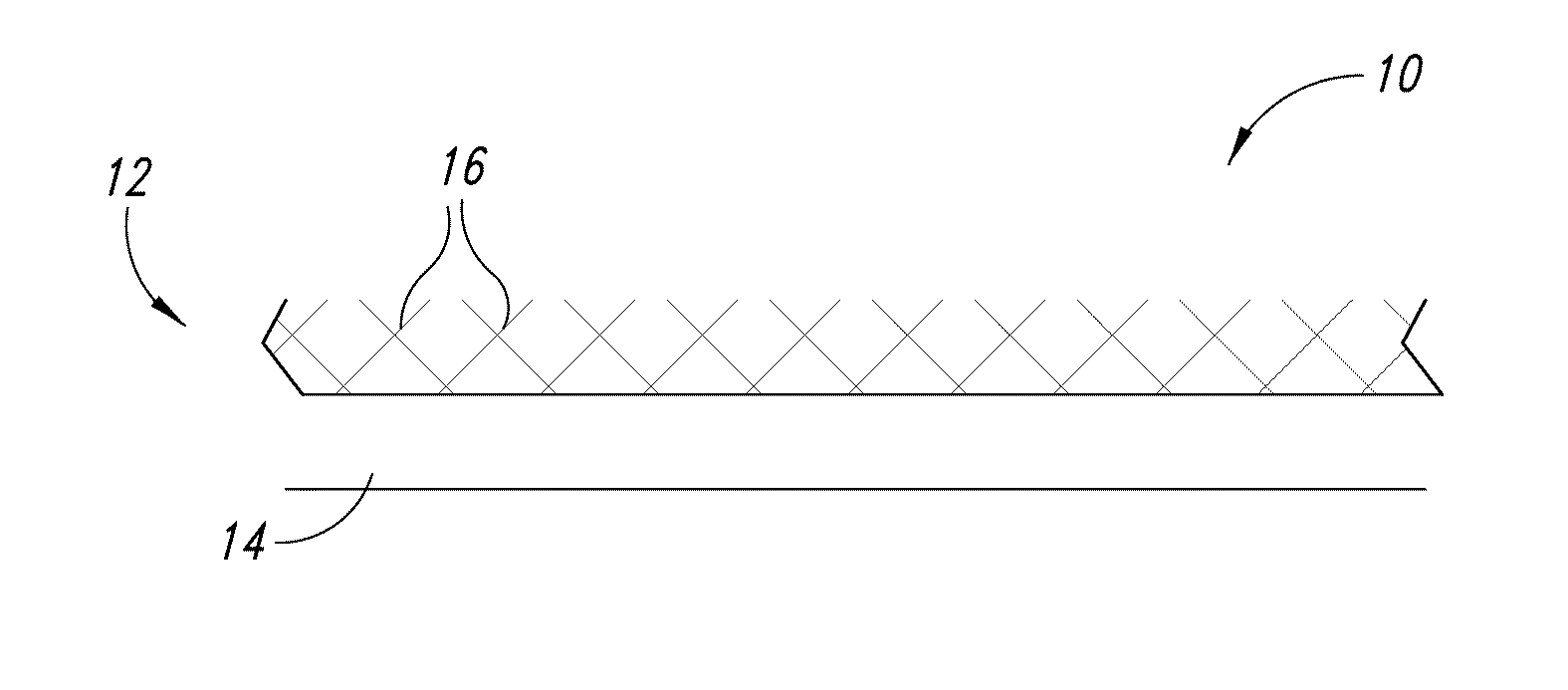

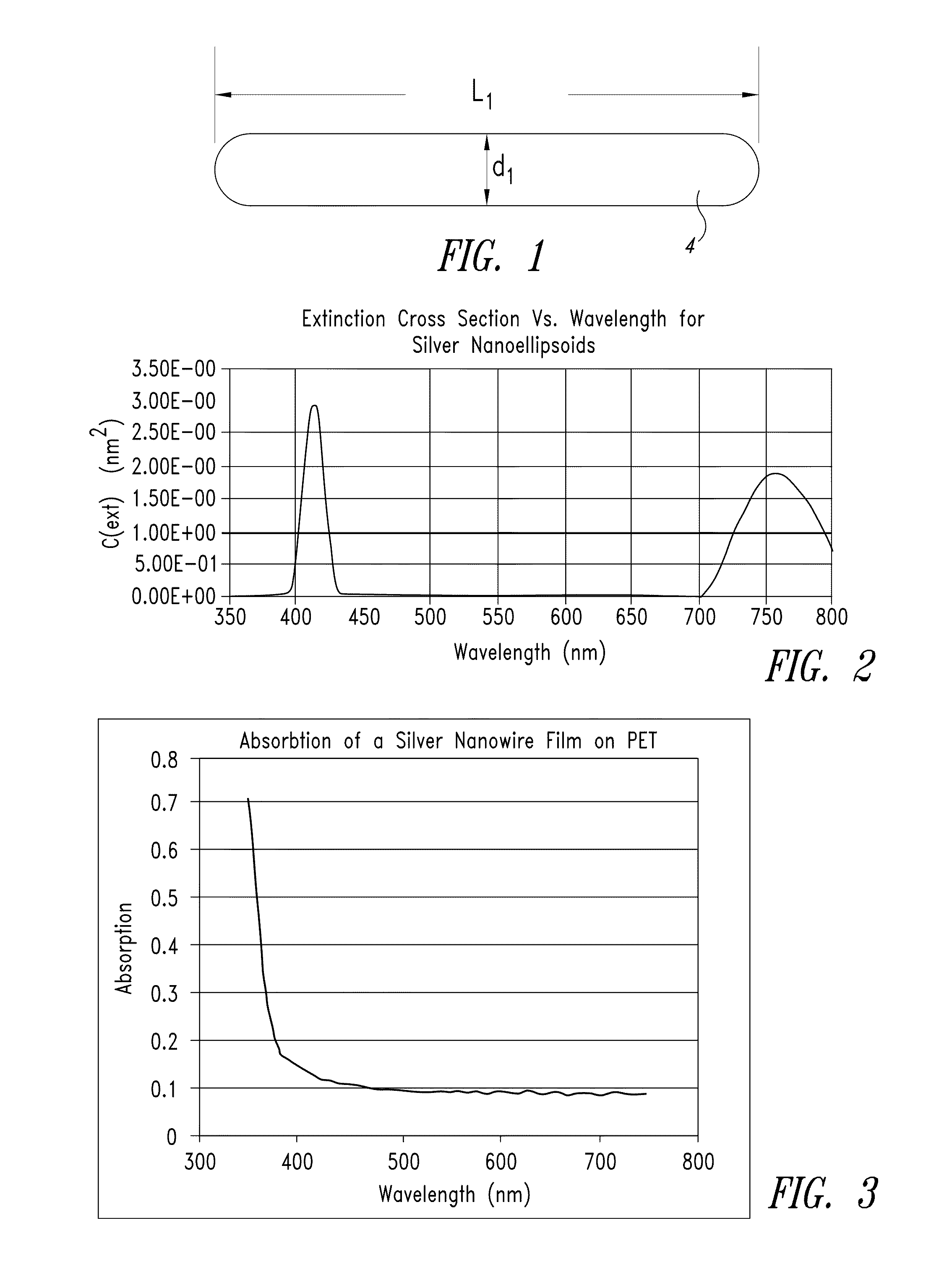

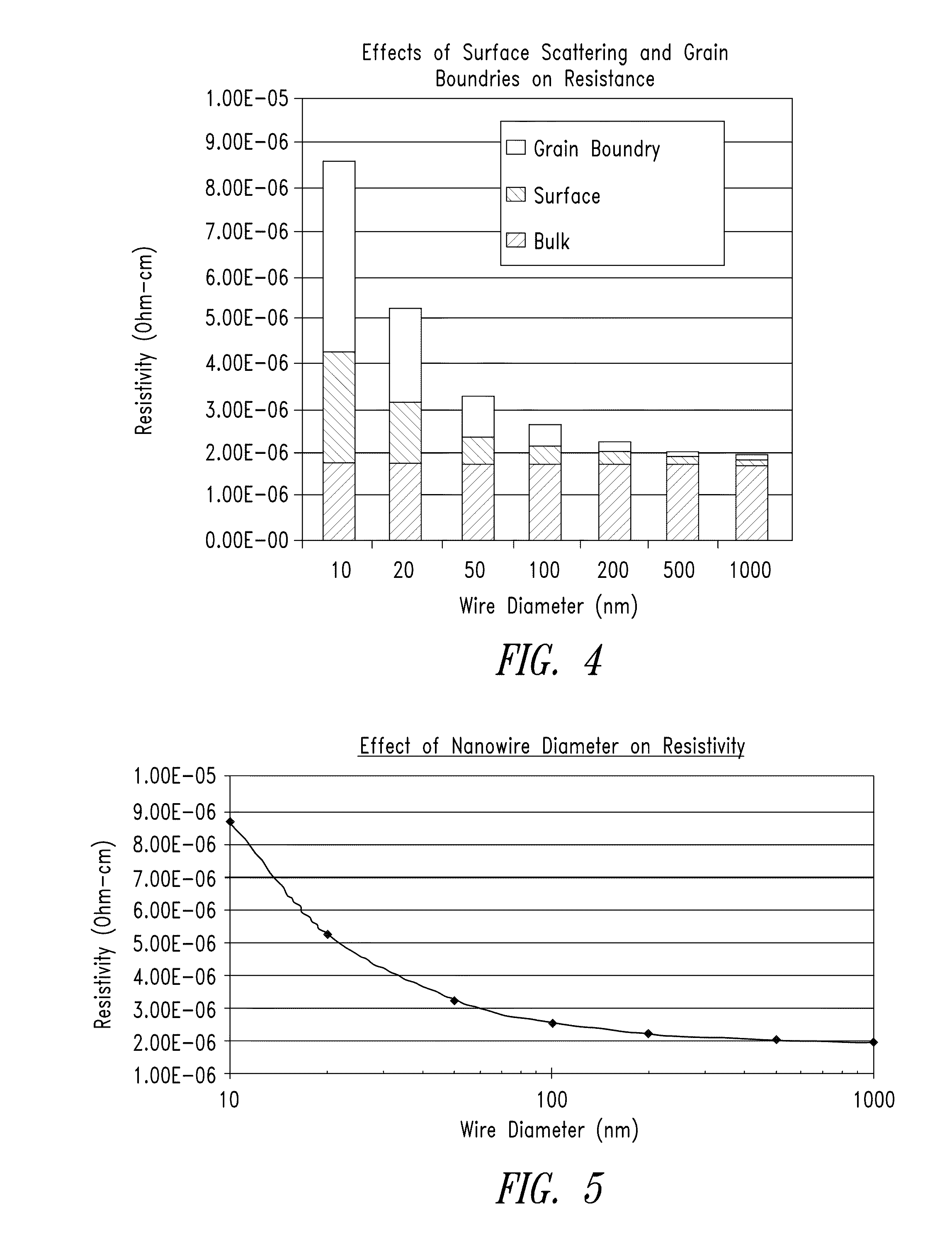

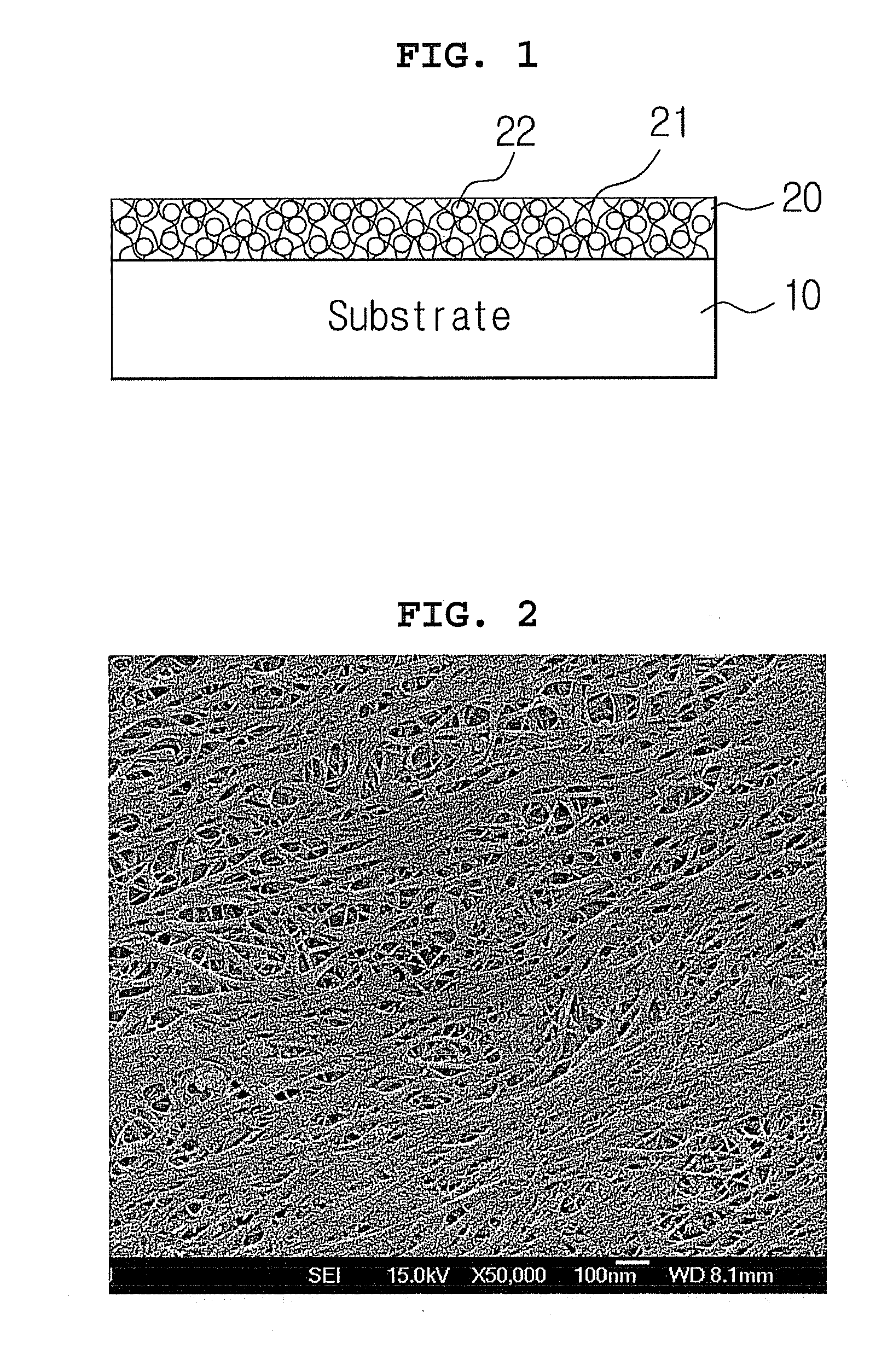

Nanowire-based transparent conductors and applications thereof

A transparent conductor including a conductive layer coated on a substrate is described. More specifically, the conductive layer comprises a network of nanowires that may be embedded in a matrix. The conductive layer is optically clear, patternable and is suitable as a transparent electrode in visual display devices such as touch screens, liquid crystal displays, plasma display panels and the like.

Owner:CHAMP GREAT INTL

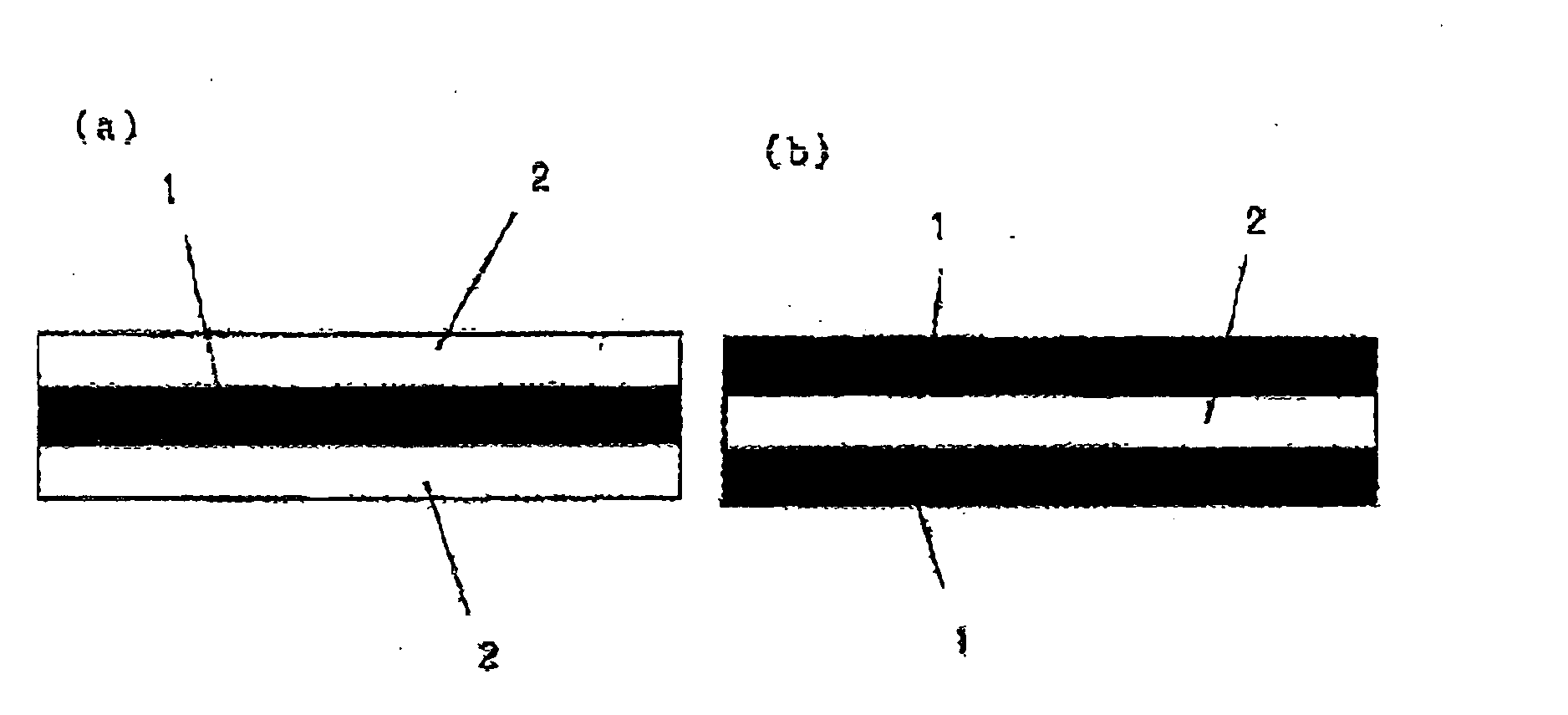

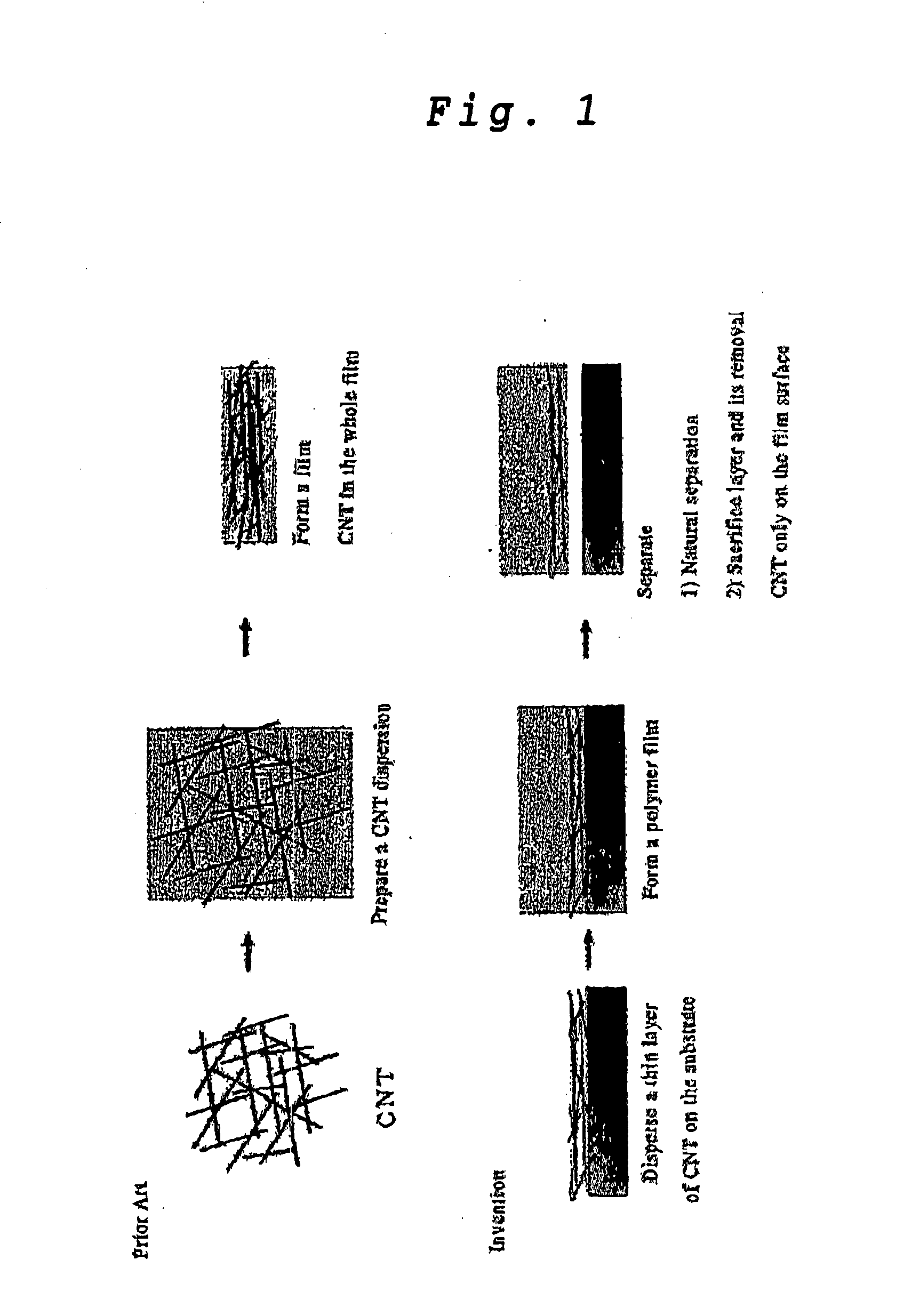

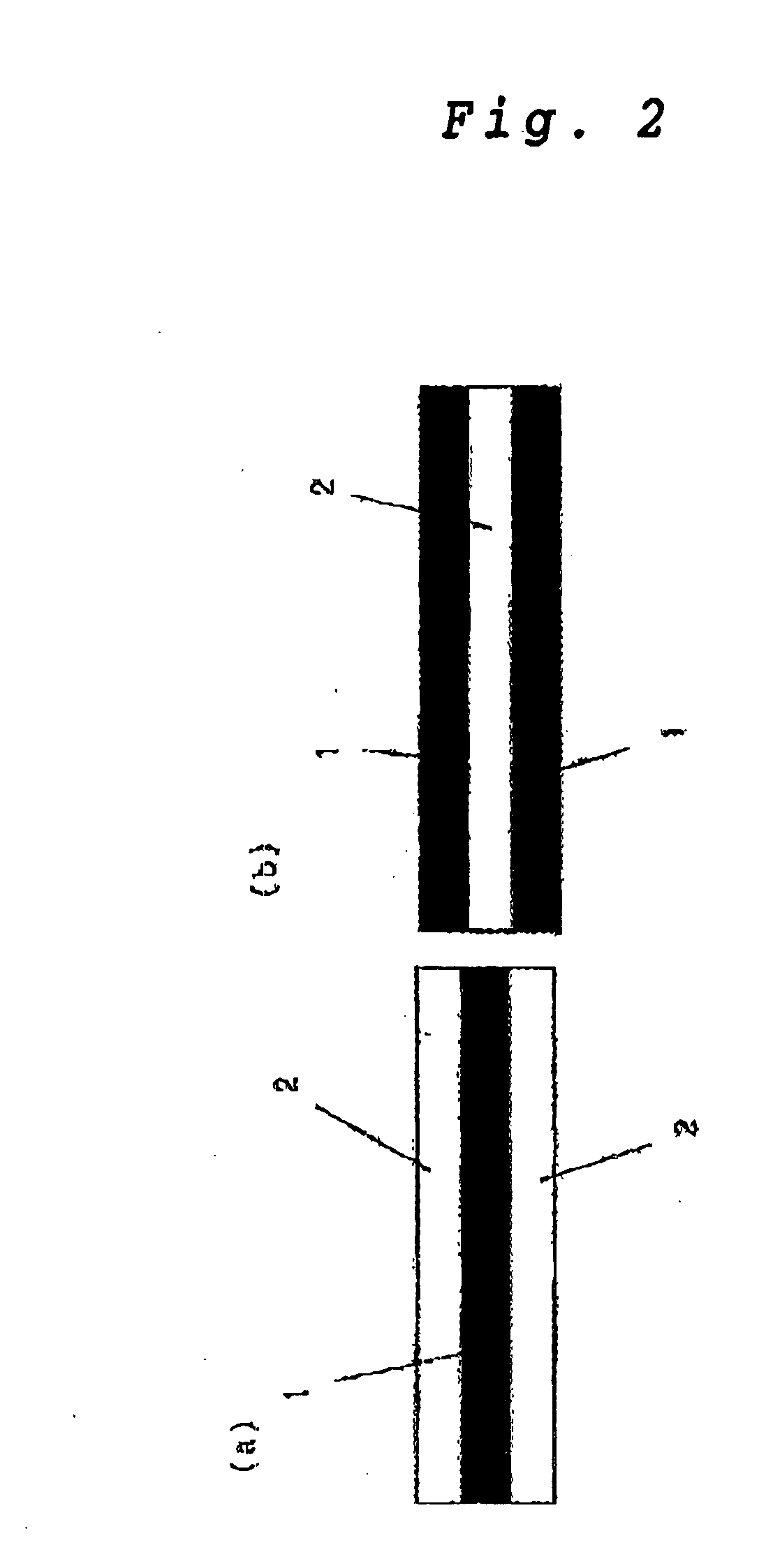

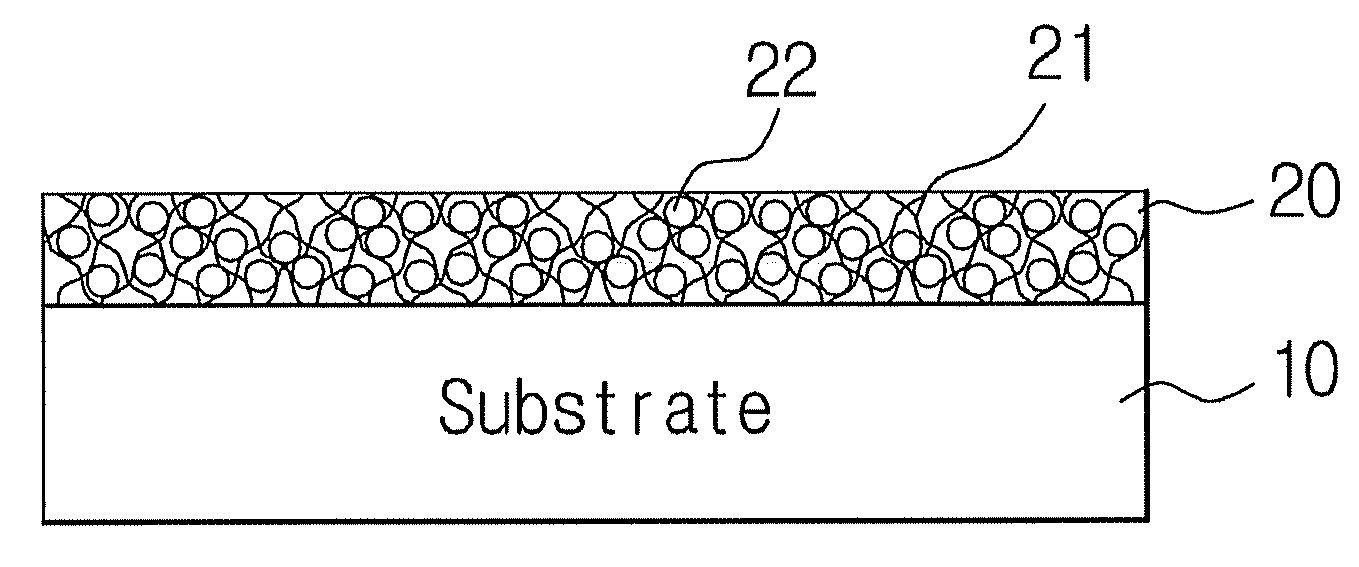

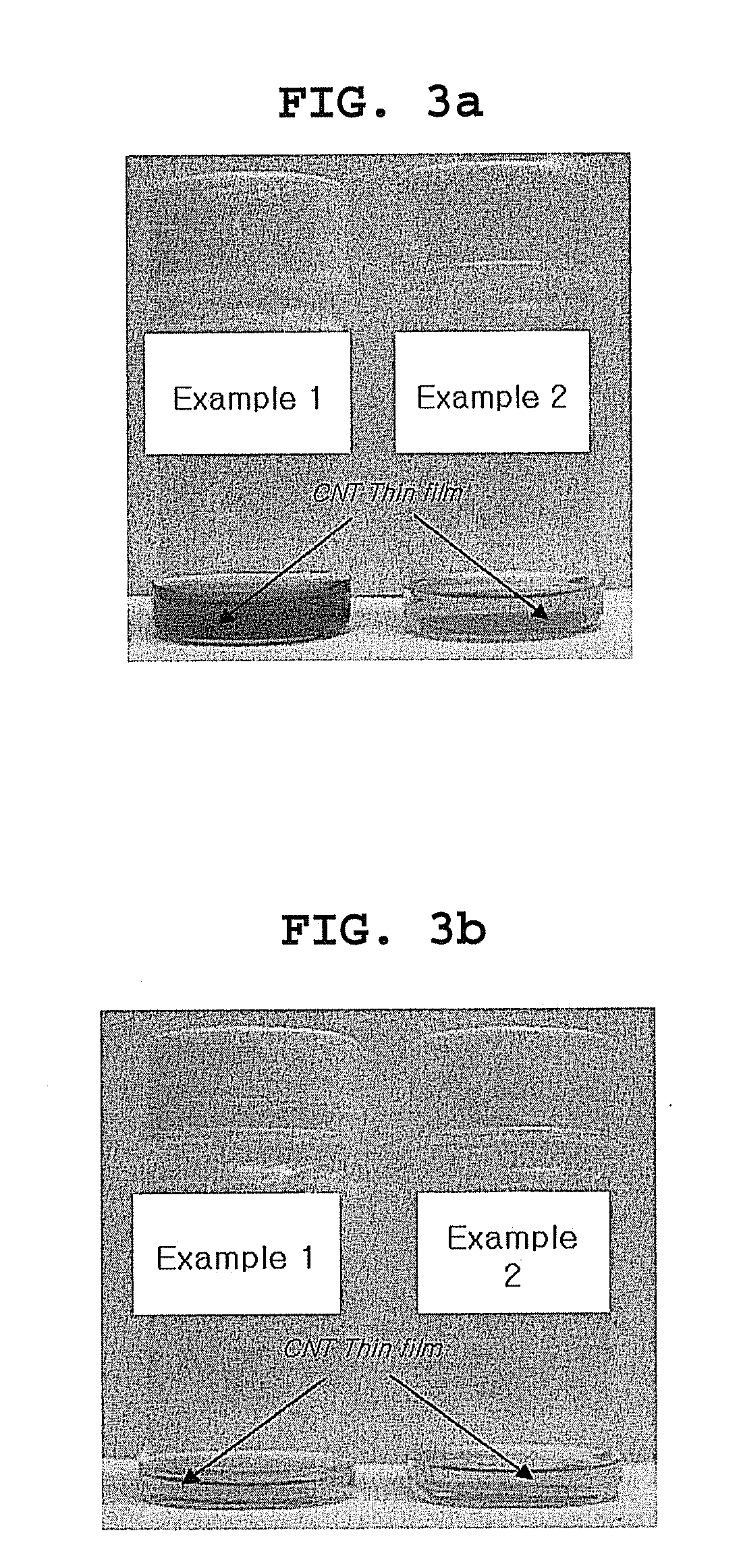

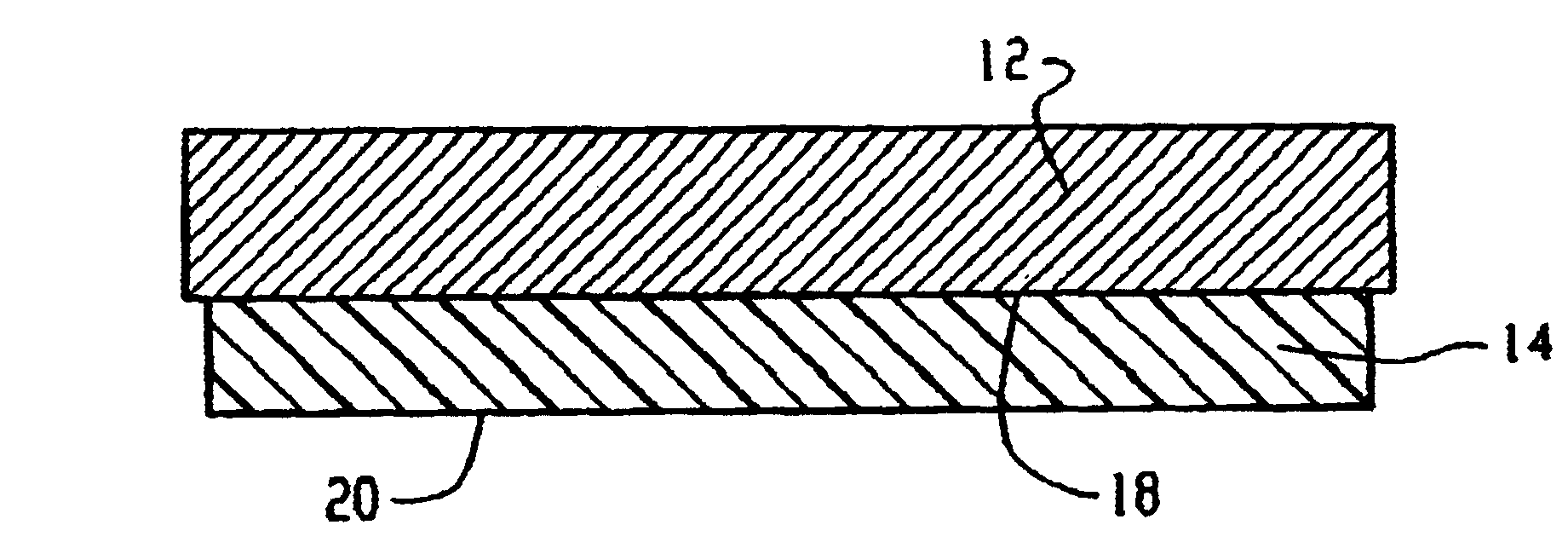

Transparent Conductive Carbon Nanotube Film and a Method for Producing the Same

InactiveUS20070298253A1Conductive and soft and flexibleImprove conductivityMaterial nanotechnologyConductive layers on insulating-supportsCarbon nanotubeTransparent conducting film

A transparent conductive film wherein carbon nanotubes are discursively embedded in the surface portion of a resin film is produced by (A) dispersing carbon nanotubes on a substrate surface, (B) forming a transparent resin film over the substrate on which the carbon nanotubes are dispersed, and then (C) separating the thus-formed resin film. This is a novel technique for realizing a highly transparent conductive film which is flexible and highly conductive even when amount of carbon nanotubes used therefor is small.

Owner:NAT INST OF ADVANCED IND SCI & TECH

Protective skin for optical fibers

Owner:ALCATEL LUCENT SAS

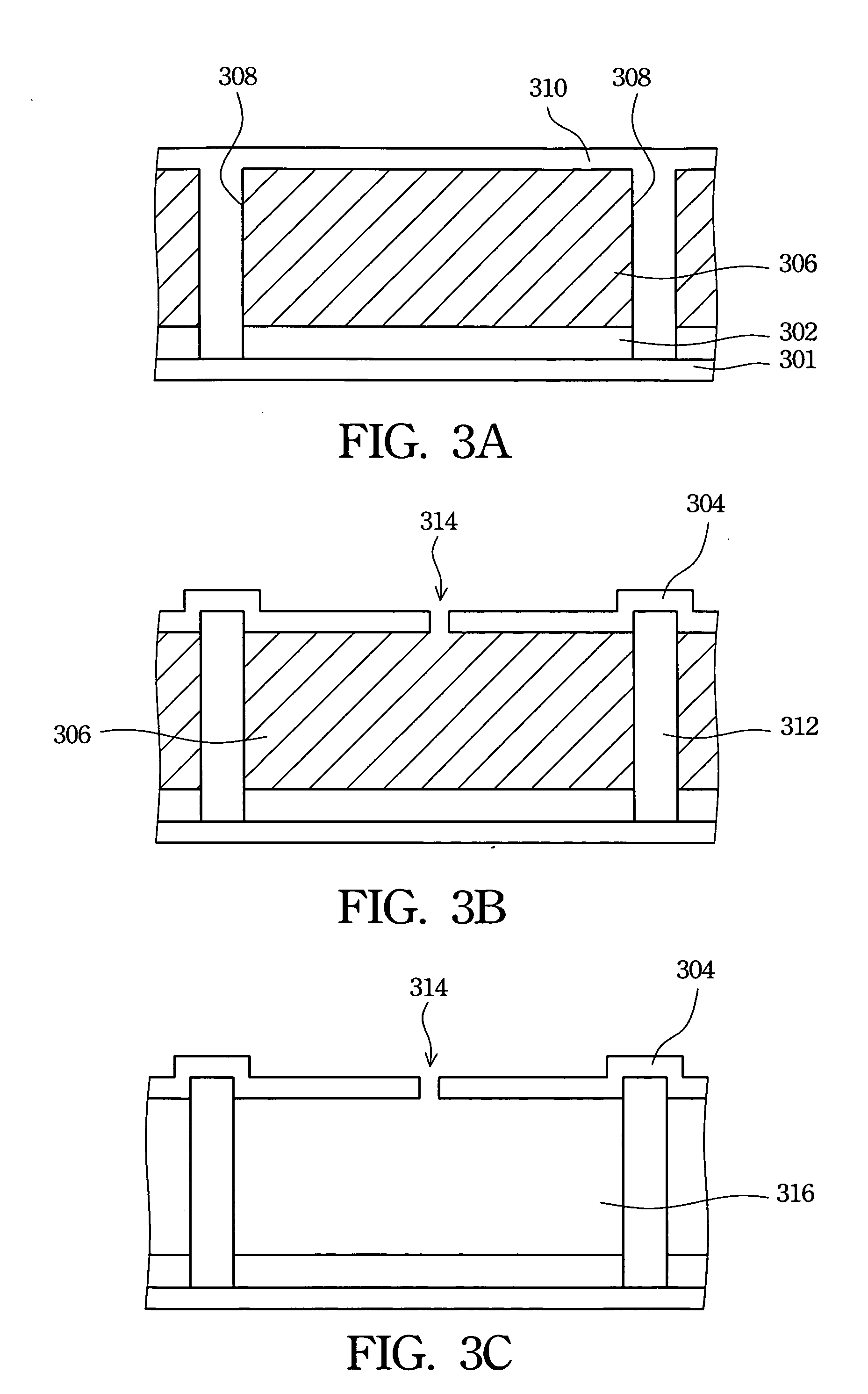

MEMS device having contact and standoff bumps and related methods

InactiveUS6876482B2Avoid contactOptical radiation measurementSolid-state devicesConductive materialsElectrical and Electronics engineering

MEMS Device Having Contact and Standoff Bumps and Related Methods. According to one embodiment, a movable MEMS component suspended over a substrate is provided. The component can include a structural layer having a movable electrode separated from a substrate by a gap. The component can also include at least one standoff bump attached to the structural layer and extending into the gap for preventing contact of the movable electrode with conductive material when the component moves.

Owner:AAC TECH PTE LTD

Remotely-excited fluorine and water vapor etch

A method of etching exposed silicon oxide on patterned heterogeneous structures is described and includes a remote plasma etch formed from a fluorine-containing precursor. Plasma effluents from the remote plasma are flowed into a substrate processing region where the plasma effluents combine with water vapor. The chemical reaction resulting from the combination produces reactants which etch the patterned heterogeneous structures to produce, in embodiments, a thin residual structure exhibiting little deformation. The methods may be used to conformally trim silicon oxide while removing little or no silicon, polysilicon, silicon nitride, titanium or titanium nitride. In an exemplary embodiment, the etch processes described herein have been found to remove mold oxide around a thin cylindrical conducting structure without causing the cylindrical structure to significantly deform.

Owner:APPLIED MATERIALS INC

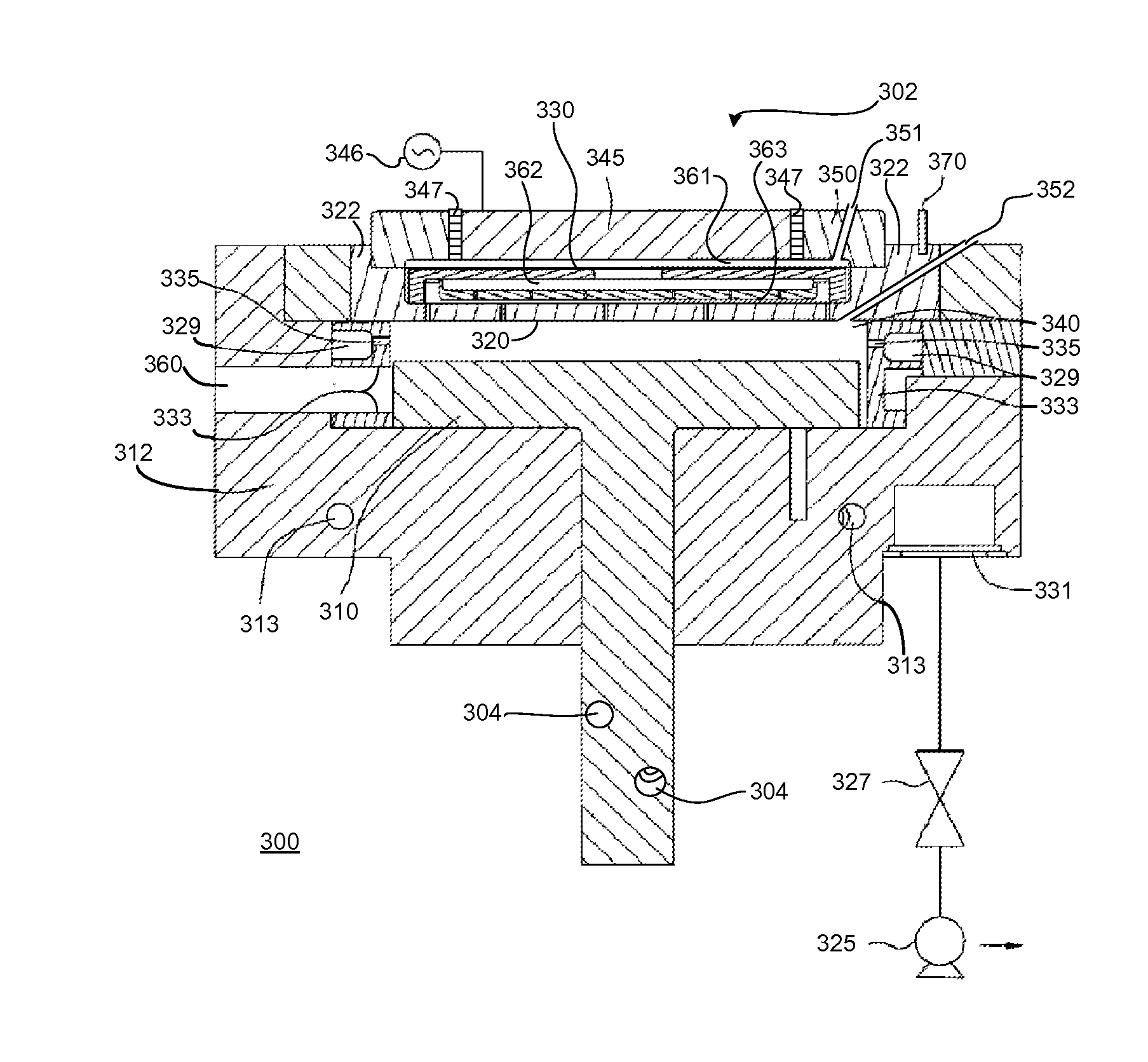

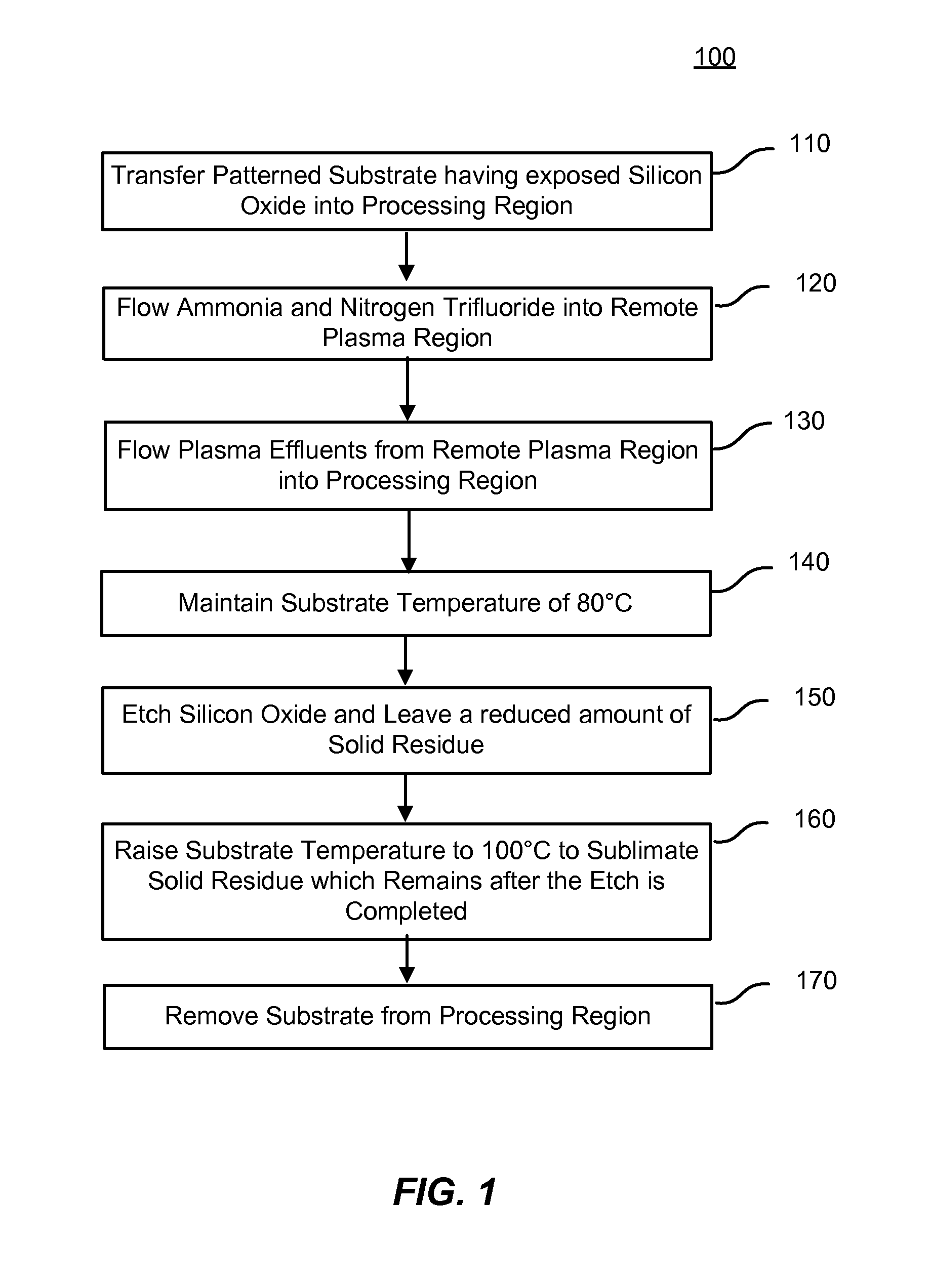

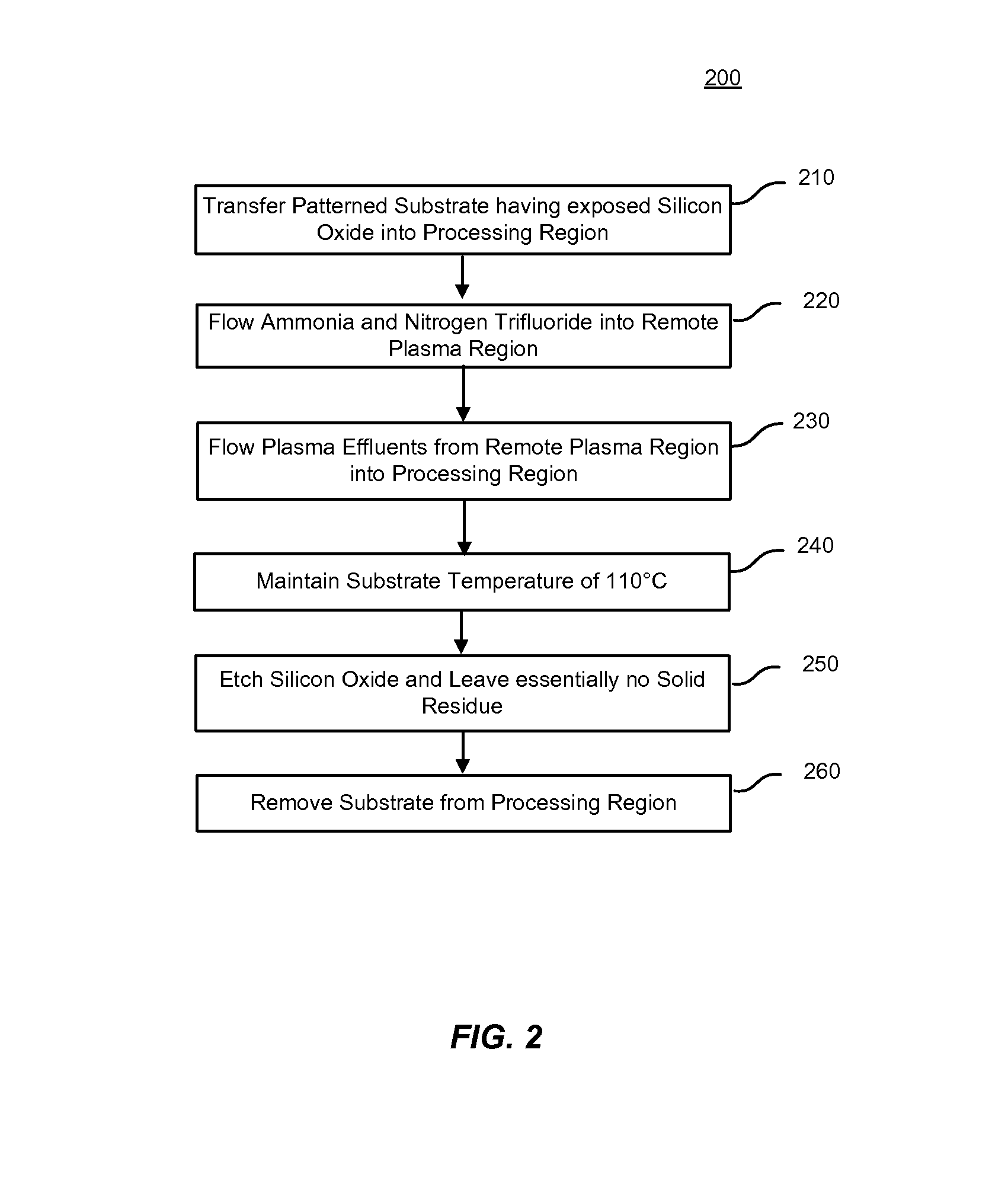

High-temperature selective dry etch having reduced post-etch solid residue

ActiveUS8475674B2Residue reductionHigh temperature of the dielectric filmsElectric discharge tubesDecorative surface effectsDielectricDry etching

Methods of dry etching silicon-containing dielectric films are described. The methods include maintaining a relatively high temperature of the dielectric films while etching in order to achieve reduced solid residue on the etched surface. Partially or completely avoiding the accumulation of solid residue increases the etch rate.

Owner:APPLIED MATERIALS INC

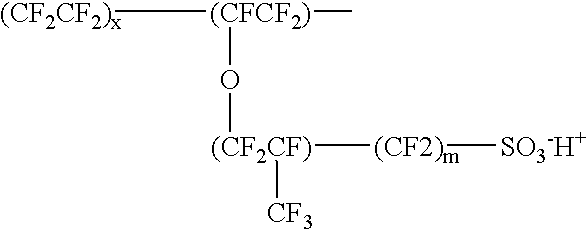

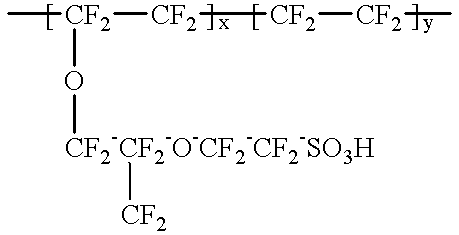

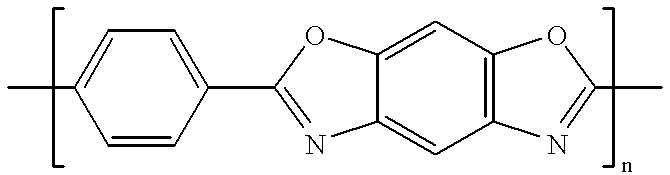

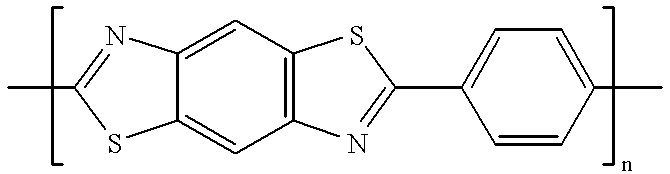

Proton-selective conducting membranes

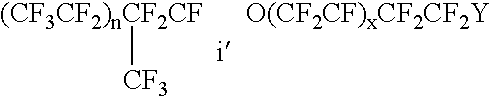

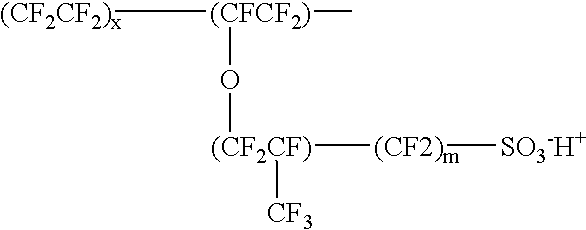

InactiveUS20020127474A1Easy to operateSelective operationIon-exchanger regenerationSolid electrolyte cellsHydrophobic polymerProton

A membrane comprising: (a) a hydrophobic matrix polymer, and (b) a hydrophilic non-ionic polymer, wherein the hydrophobic polymer and the hydrophilic polymer are disposed so as to form a dense selectively proton-conducting membrane. The microstructure of such a membrane can be tailored to specific functionality requirements, such as proton conductivity vs. proton selectivity, and selectivity to particular species.

Owner:E C R ELECTRO CHEM RES

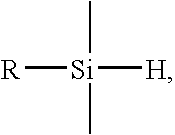

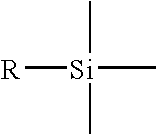

Method of improving stability in low k barrier layers

InactiveUS20040137756A1Decorative surface effectsSemiconductor/solid-state device detailsHydrogenPhenyl group

A method is provided for processing a substrate including providing a processing gas comprising hydrogen gas and an organosilicon compound comprising a phenyl group to the processing chamber, and reacting the processing gas to deposit a low k silicon carbide barrier layer useful as a barrier layer in damascene or dual damascene applications with low k dielectric materials.

Owner:APPLIED MATERIALS INC

Composite solid polymer elecrolyte membranes

InactiveUS20020045085A1Optimize swellingOptimize fuel crossover resistanceElectrolyte holding meansFinal product manufacturePolymer electrolytesPolymer science

The present invention relates to composite solid polymer electrolyte membranes (SPEMs) which include a porous polymer substrate interpenetrated with an ion-conducting material. SPEMs of the present invention are useful in electrochemical applications, including fuel cells and electrodialysis.

Owner:FOSTER-MILLER

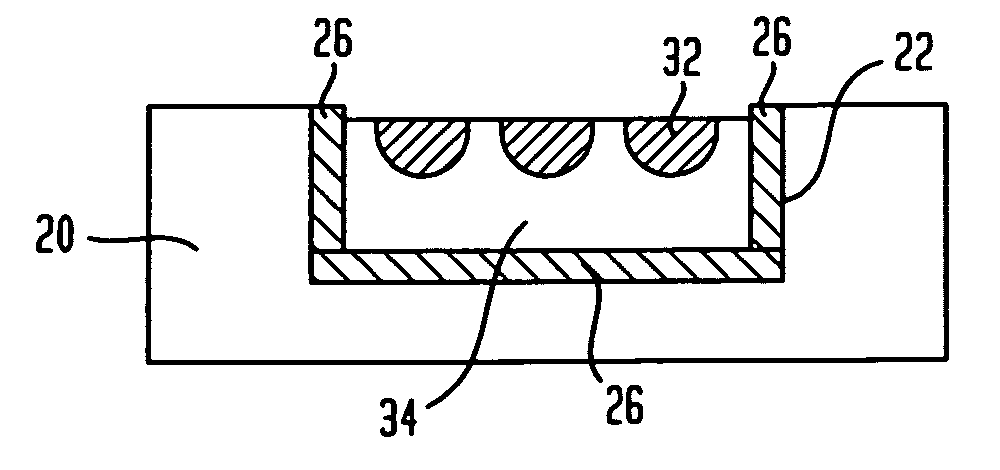

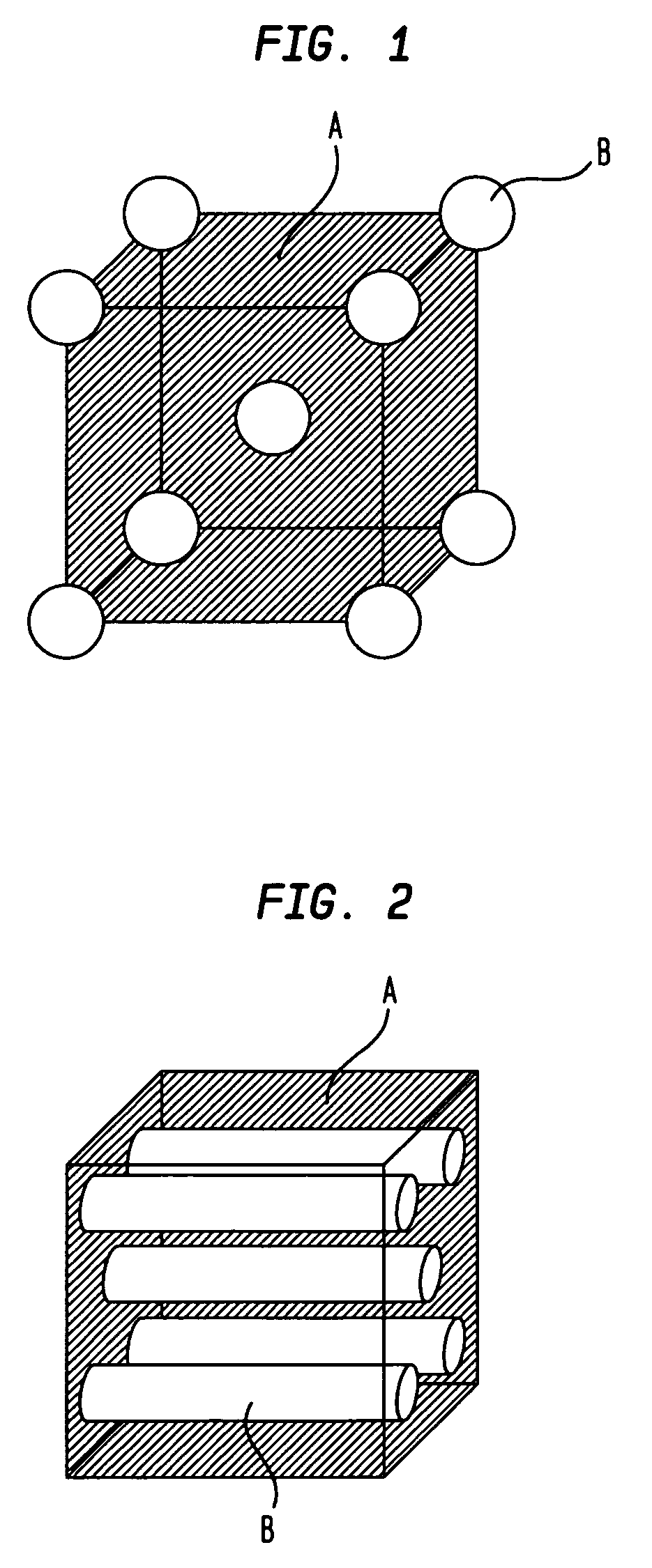

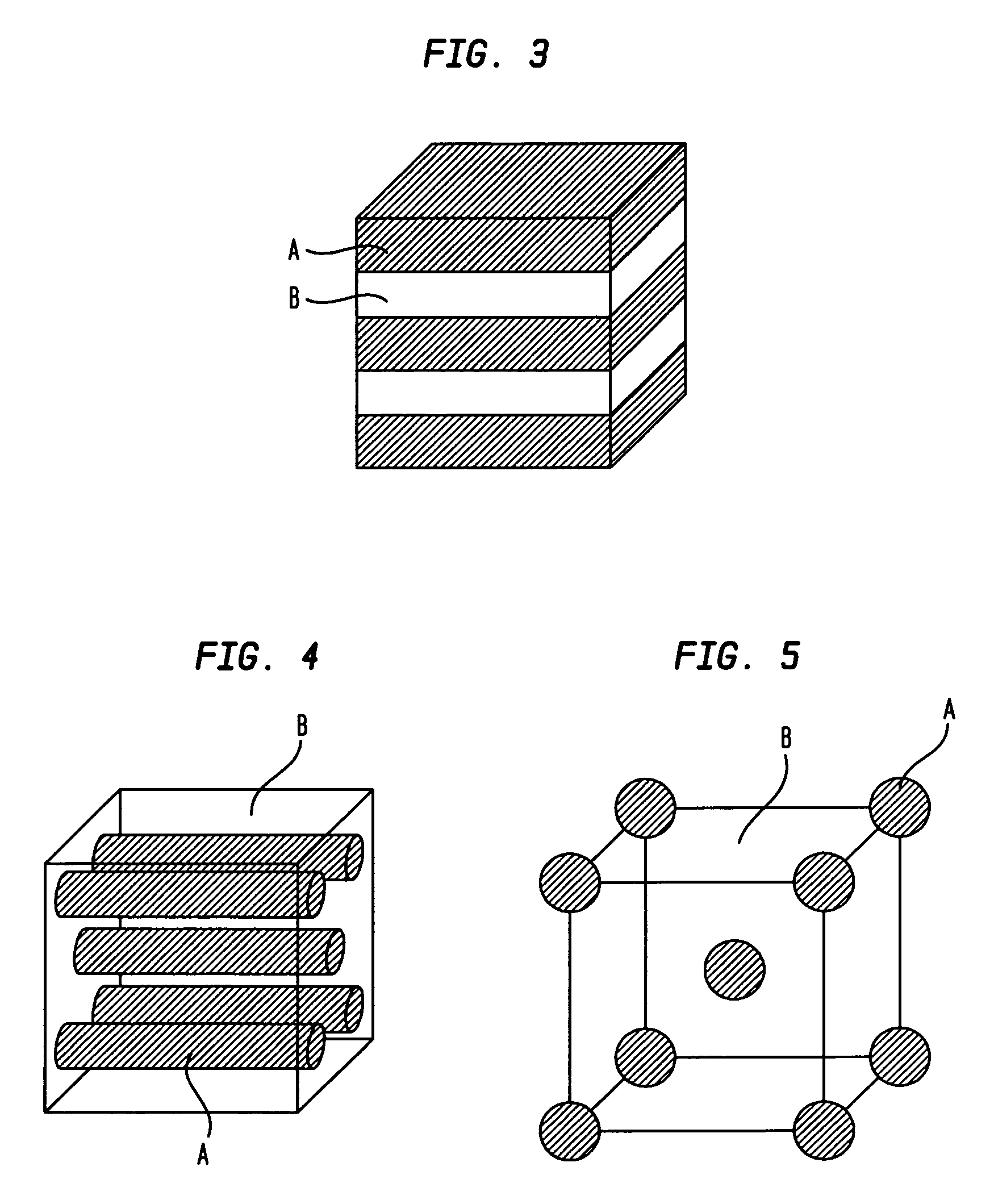

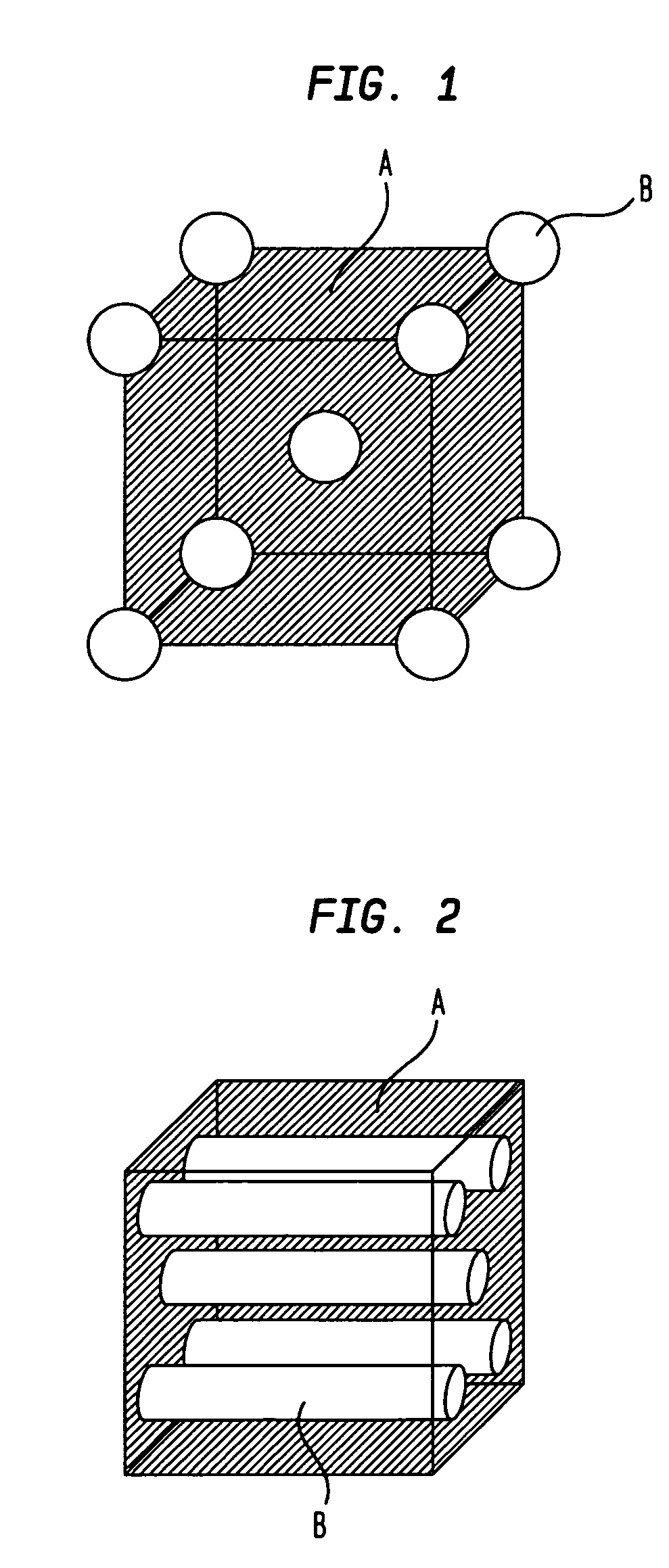

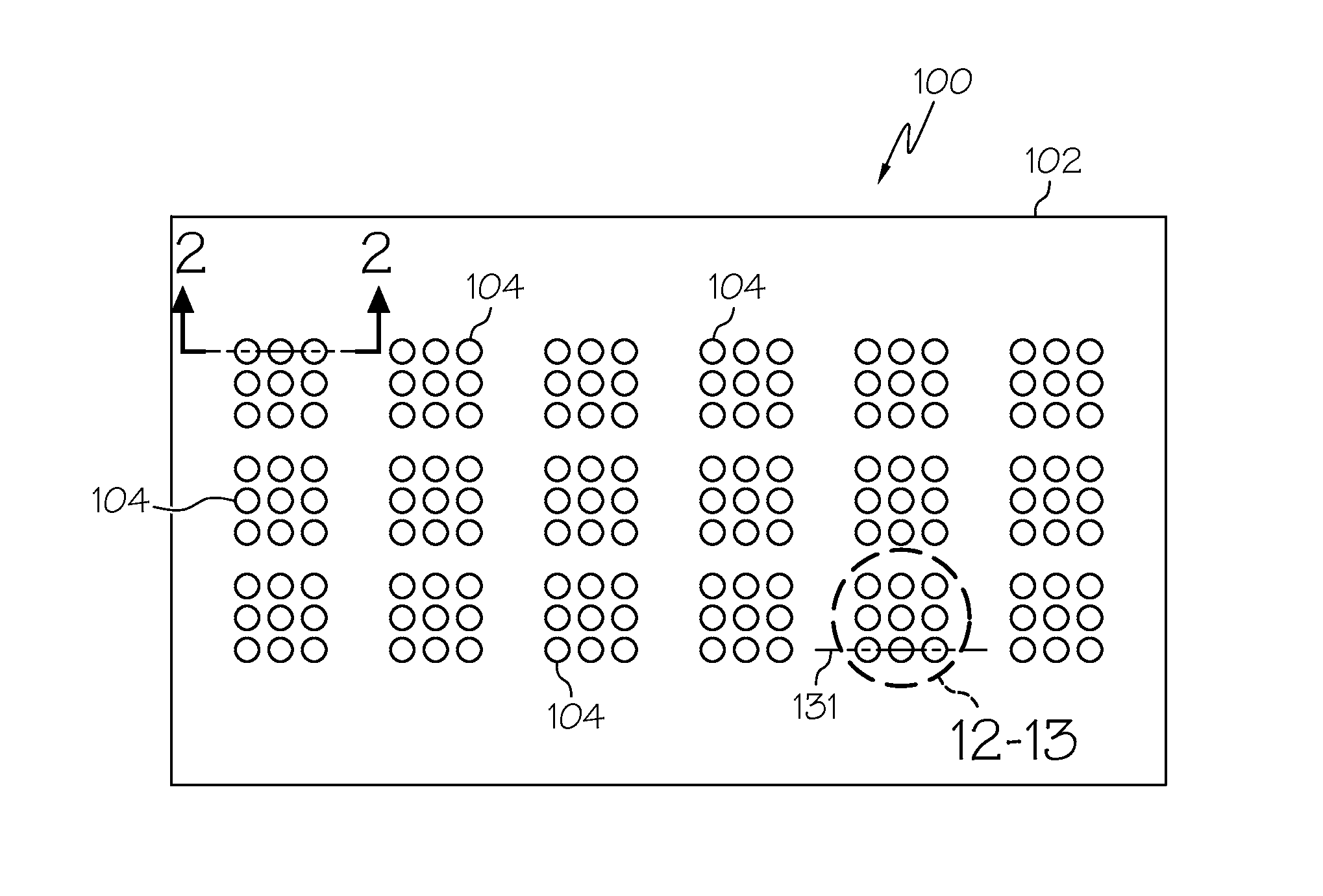

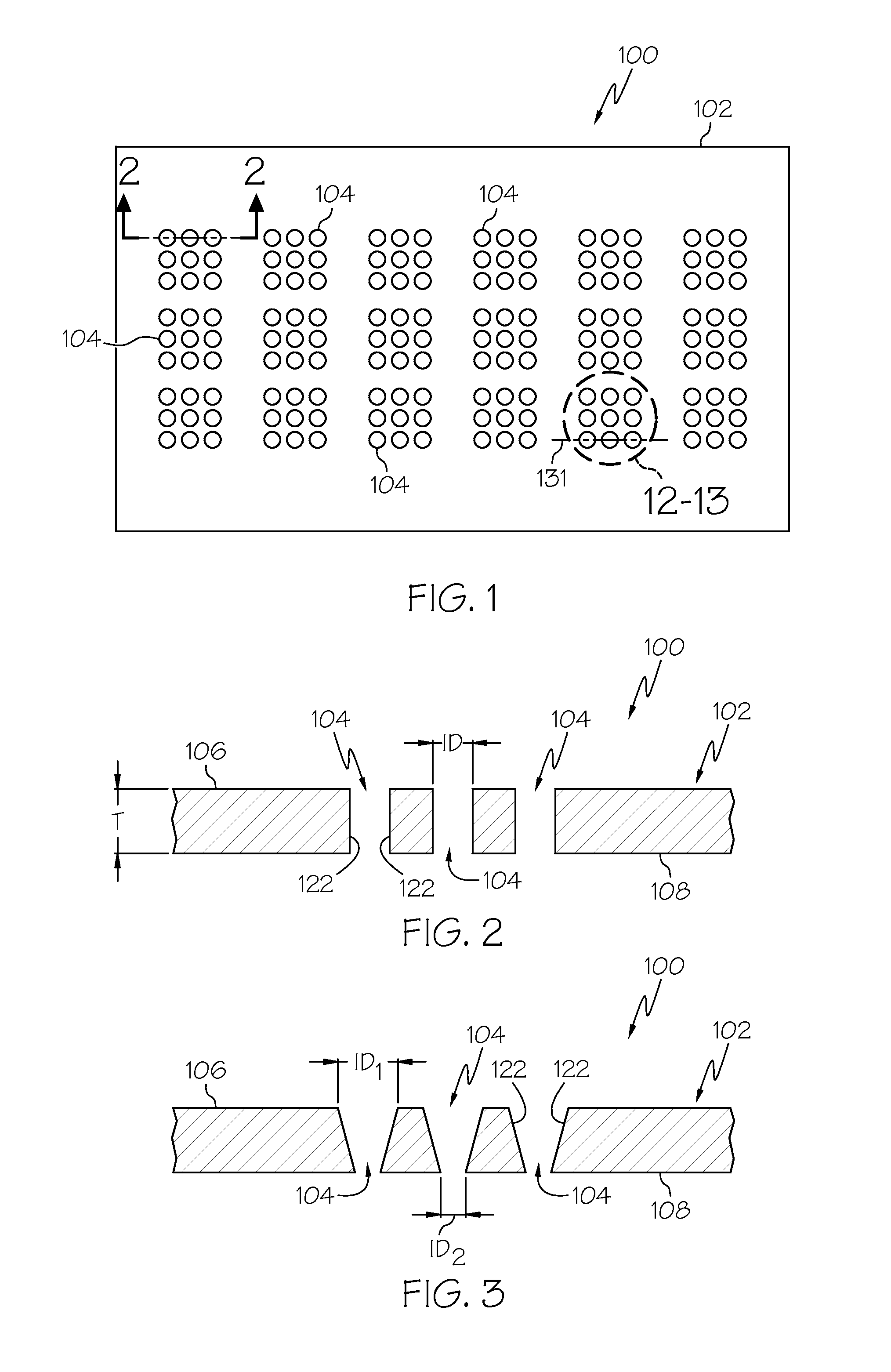

Methods for forming improved self-assembled patterns of block copolymers

ActiveUS7347953B2Easy alignmentReduce defectsMaterial nanotechnologyRadiation applicationsSemiconductor structureStructural unit

A method for forming self-assembled patterns on a substrate surface is provided. First, a block copolymer layer, which comprises a block copolymer having two or more immiscible polymeric block components, is applied onto a substrate that comprises a substrate surface with a trench therein. The trench specifically includes at least one narrow region flanked by two wide regions, and wherein the trench has a width variation of more than 50%. Annealing is subsequently carried out to effectuate phase separation between the two or more immiscible polymeric block components in the block copolymer layer, thereby forming periodic patterns that are defined by repeating structural units. Specifically, the periodic patterns at the narrow region of the trench are aligned in a predetermined direction and are essentially free of defects. Block copolymer films formed by the above-described method as well as semiconductor structures comprising such block copolymer films are also described.

Owner:GLOBALFOUNDRIES US INC

Methods for forming improved self-assembled patterns of block copolymers

ActiveUS20070175859A1Easy alignmentReduce defectsMaterial nanotechnologyRadiation applicationsSemiconductor structureStructural unit

A method for forming self-assembled patterns on a substrate surface is provided. First, a block copolymer layer, which comprises a block copolymer having two or more immiscible polymeric block components, is applied onto a substrate that comprises a substrate surface with a trench therein. The trench specifically includes at least one narrow region flanked by two wide regions, and wherein the trench has a width variation of more than 50%. Annealing is subsequently carried out to effectuate phase separation between the two or more immiscible polymeric block components in the block copolymer layer, thereby forming periodic patterns that are defined by repeating structural units. Specifically, the periodic patterns at the narrow region of the trench are aligned in a predetermined direction and are essentially free of defects. Block copolymer films formed by the above-described method as well as semiconductor structures comprising such block copolymer films are also described.

Owner:GLOBALFOUNDRIES US INC

Nanoscale electronic devices & frabrication methods

InactiveUS20050064618A1Raise the possibilityConductive layers on insulating-supportsNanostructure manufactureNanowireElectric devices

The invention relates to a method of forming a conducting nanowire between two contacts on a substrate surface wherein a plurality of nanoparticles is deposited on the substrate in the region between the contacts, and the single nanowire running substantially between the two contacts is formed by either by monitoring the conduction between the contacts and ceasing deposition at the onset of conduction, and / or modifying the substrate to achieve, or taking advantage of pre-existing topographical features which will cause the nanoparticles to form the nanowire. The resultant conducting nanowires are also claimed as well as devices incorporating such nanowires.

Owner:UNIVERSITY OF CANTERBURY

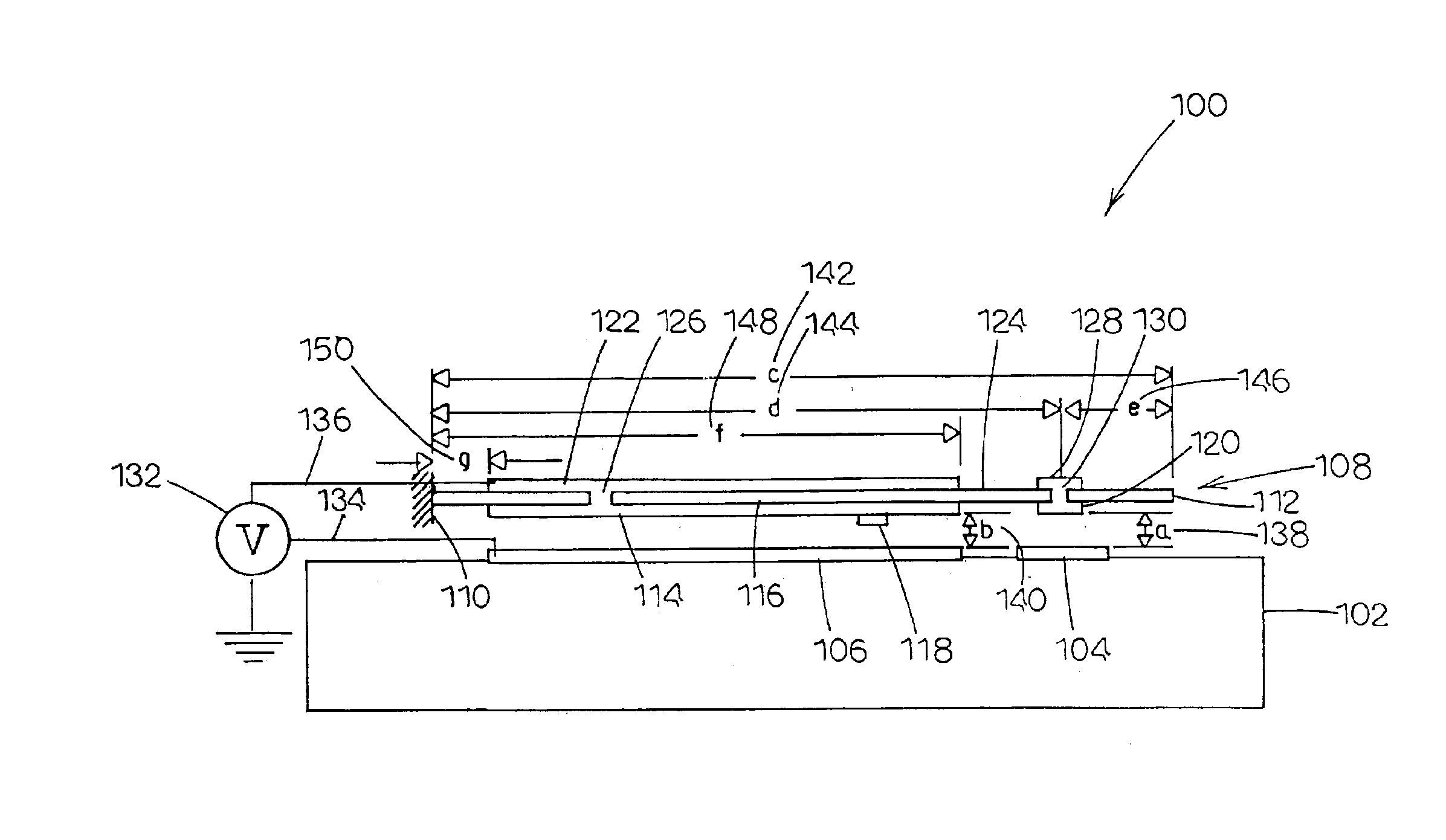

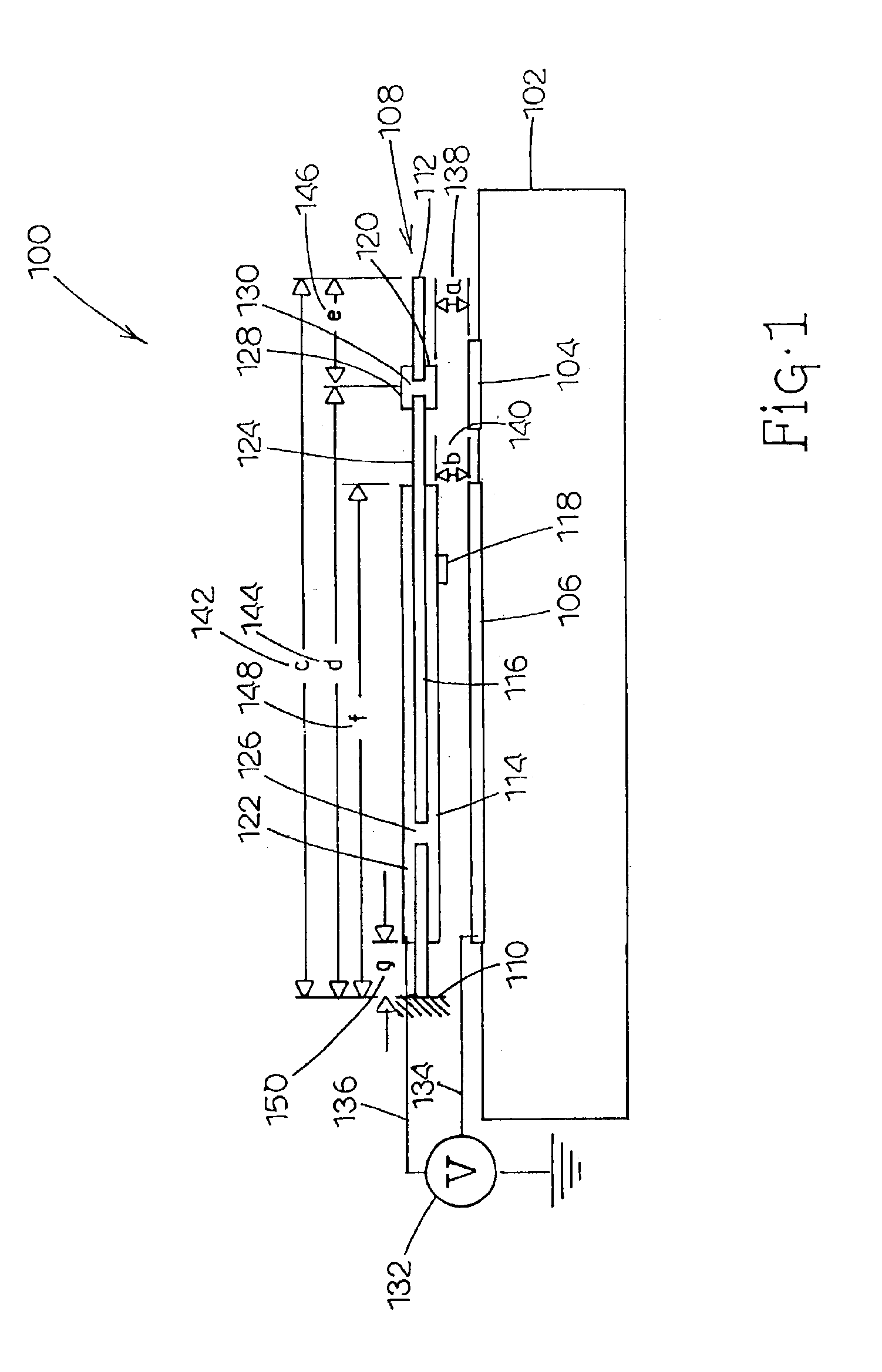

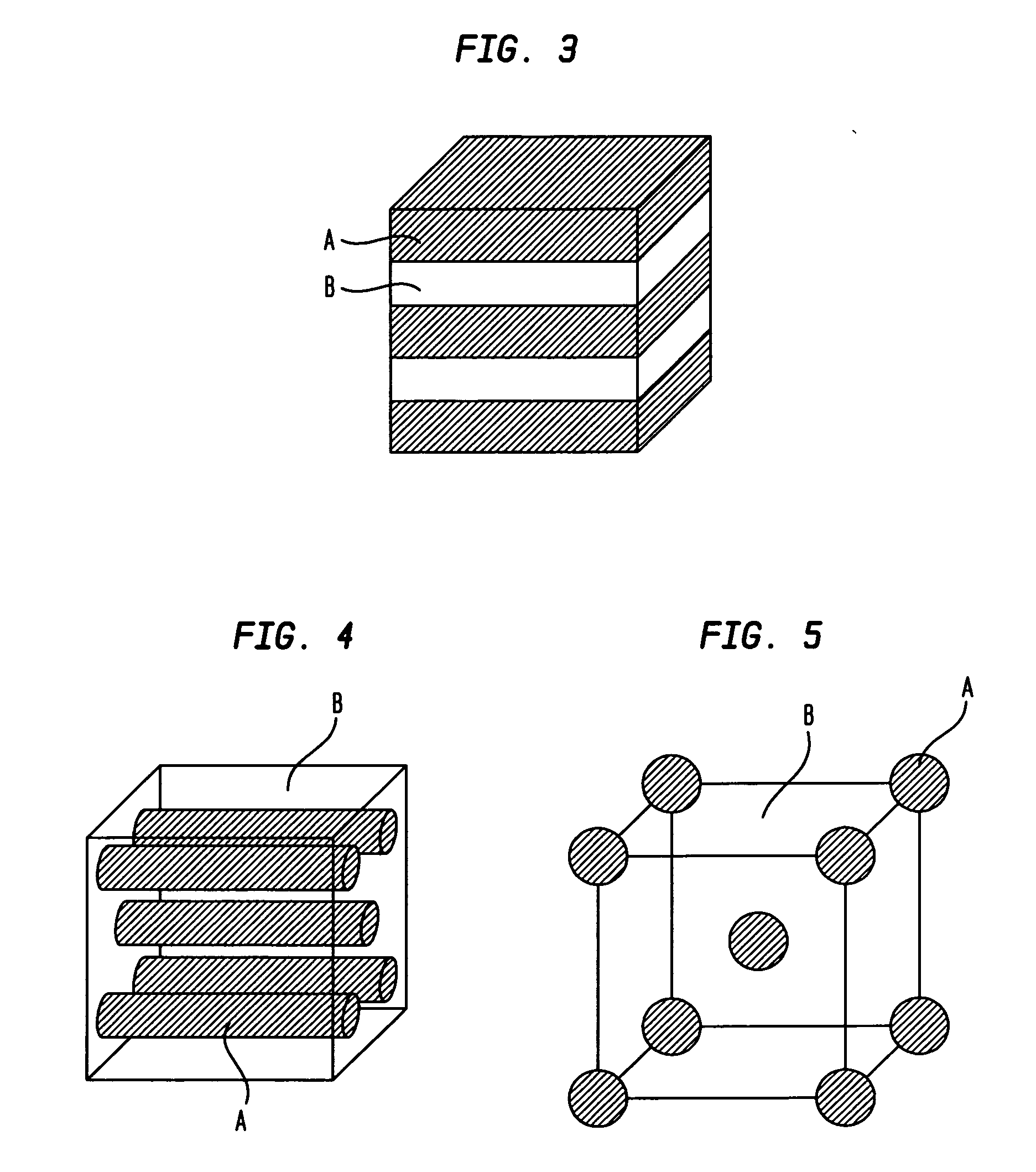

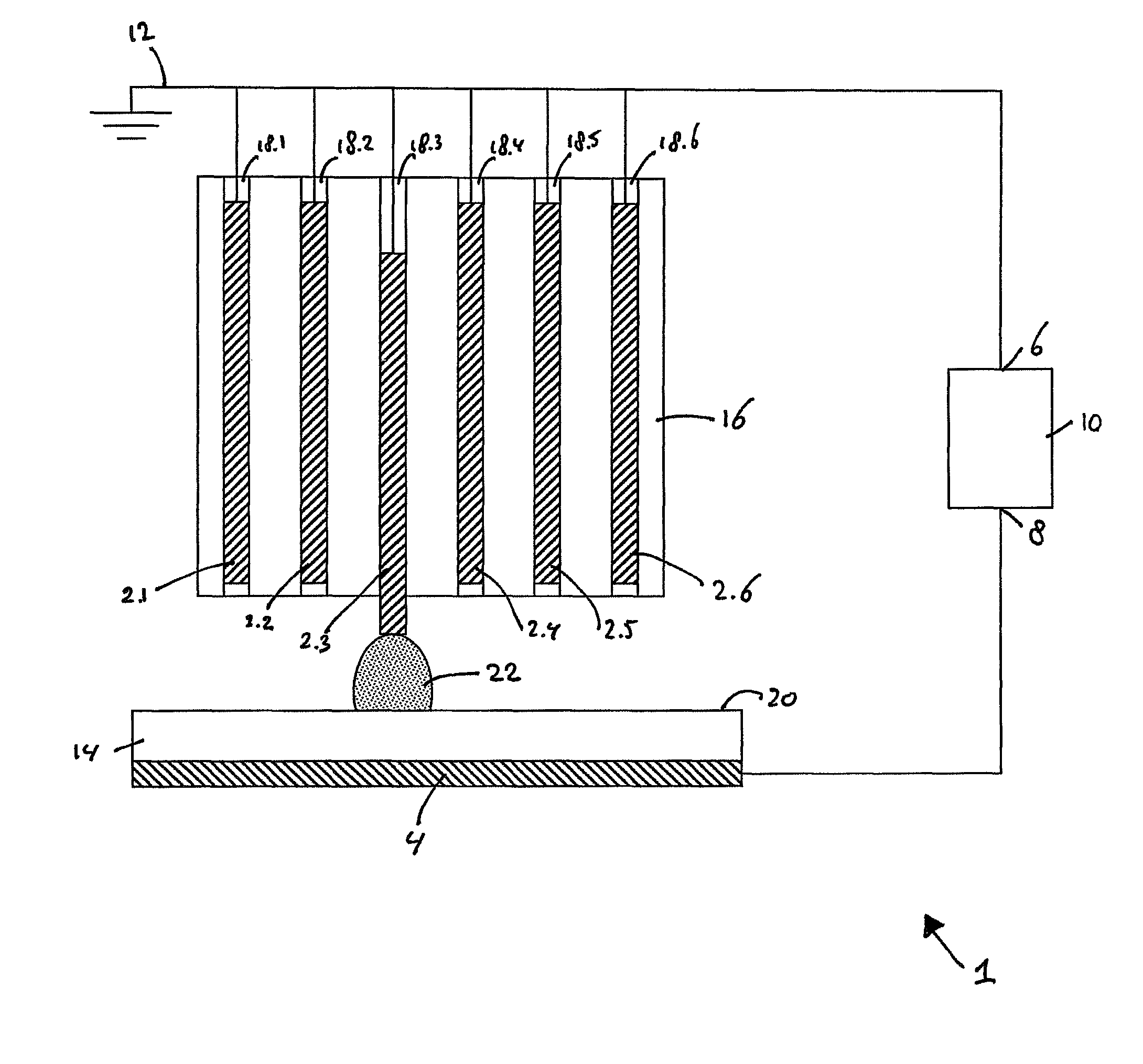

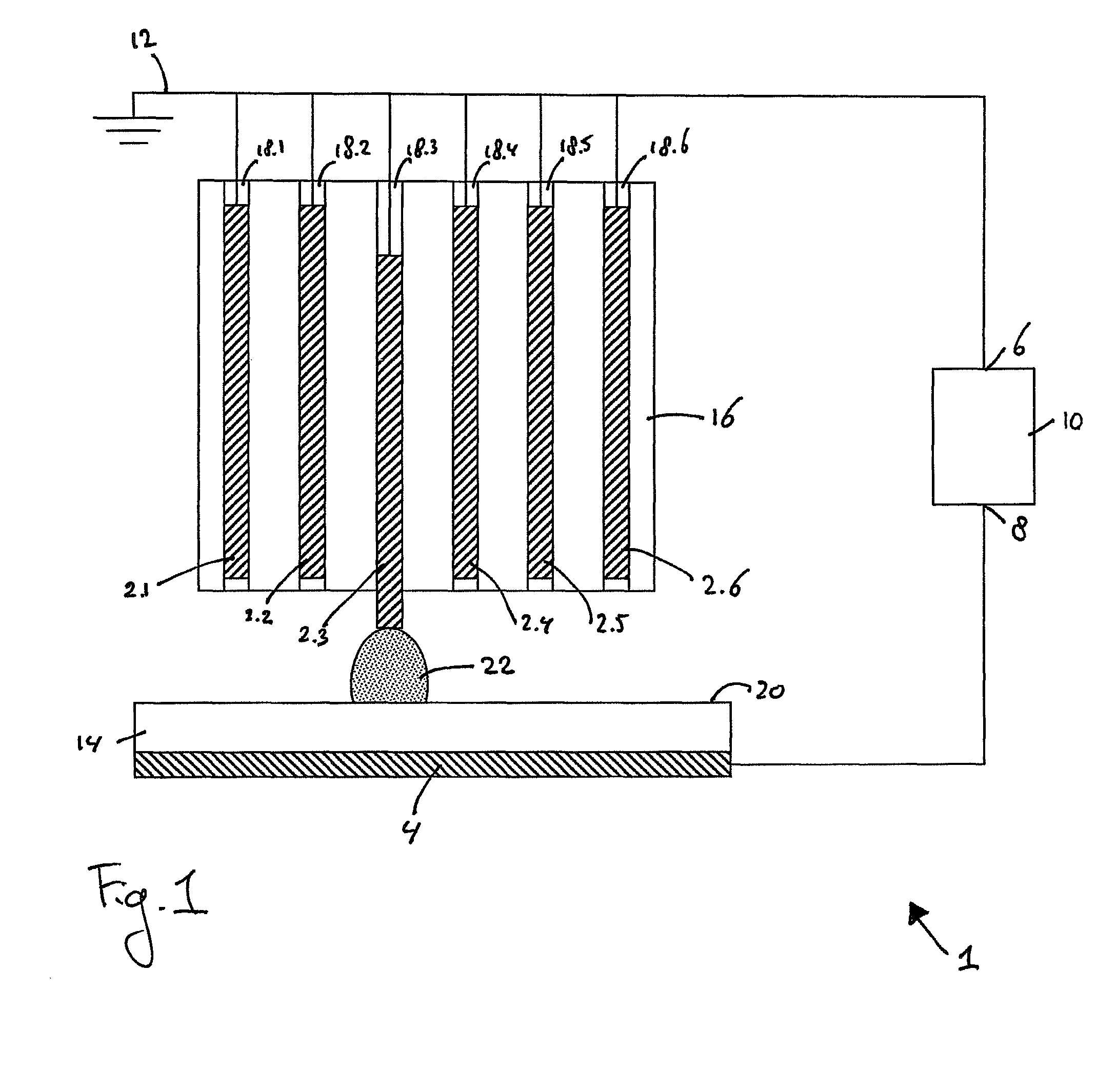

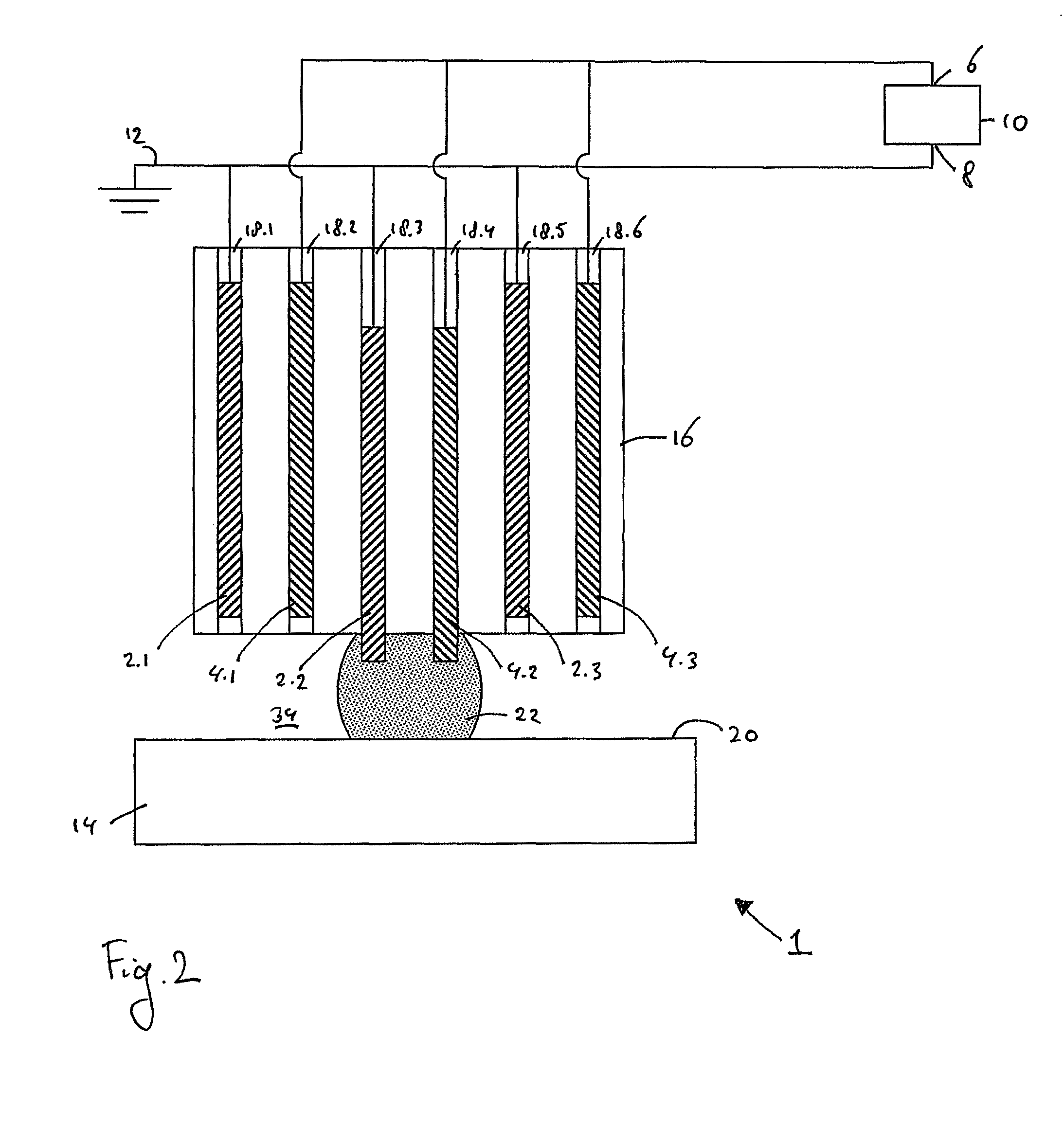

Device for generating a plasma discharge for patterning the surface of a substrate

InactiveUS8702902B2Easy to controlLong electrode lifeDecorative surface effectsSemiconductor/solid-state device manufacturingHigh pressureHigh voltage source

Device for generating a plasma discharge for patterning the surface of a substrate, comprising a first electrode having a first discharge portion and a second electrode having a second discharge portion, a high voltage source for generating a high voltage difference between the first and the second electrode, and positioning means for positioning the first electrode with respect to the substrate, wherein the positioning means are arranged for selectively positioning the first electrode with respect to the second electrode in a first position in which a distance between the first discharge portion and the second discharge portion is sufficiently small to support the plasma discharge at the high voltage difference, and in a second position in which the distance between the first discharge portion and the second discharge portion is sufficiently large to prevent plasma discharge at the high voltage difference.

Owner:VISION DYNAMICS HLDG

Full perimeter chemical strengthening of substrates

Owner:APPLE INC

Transparent carbon nanotube electrode using conductive dispersant and production method thereof

ActiveUS20080088219A1Improve conductivityMaterial nanotechnologyConductive layers on insulating-supportsSolar cellTouchscreen

Disclosed is a transparent carbon nanotube (CNT) electrode using a conductive dispersant. The transparent CNT electrode comprises a transparent substrate and a CNT thin film formed on a surface the transparent substrate wherein the CNT thin film is formed of a CNT composition comprising CNTs and a doped dispersant. Further disclosed is a method for producing the transparent CNT electrode.The transparent CNT electrode exhibits excellent conductive properties, can be produced in an economical and simple manner by a room temperature wet process, and can be applied to flexible displays. The transparent CNT electrode can be used to fabricate a variety of devices, including image sensors, solar cells, liquid crystal displays, organic electroluminescence (EL) displays and touch screen panels, that are required to have both light transmission properties and conductive properties.

Owner:SAMSUNG ELECTRONICS CO LTD

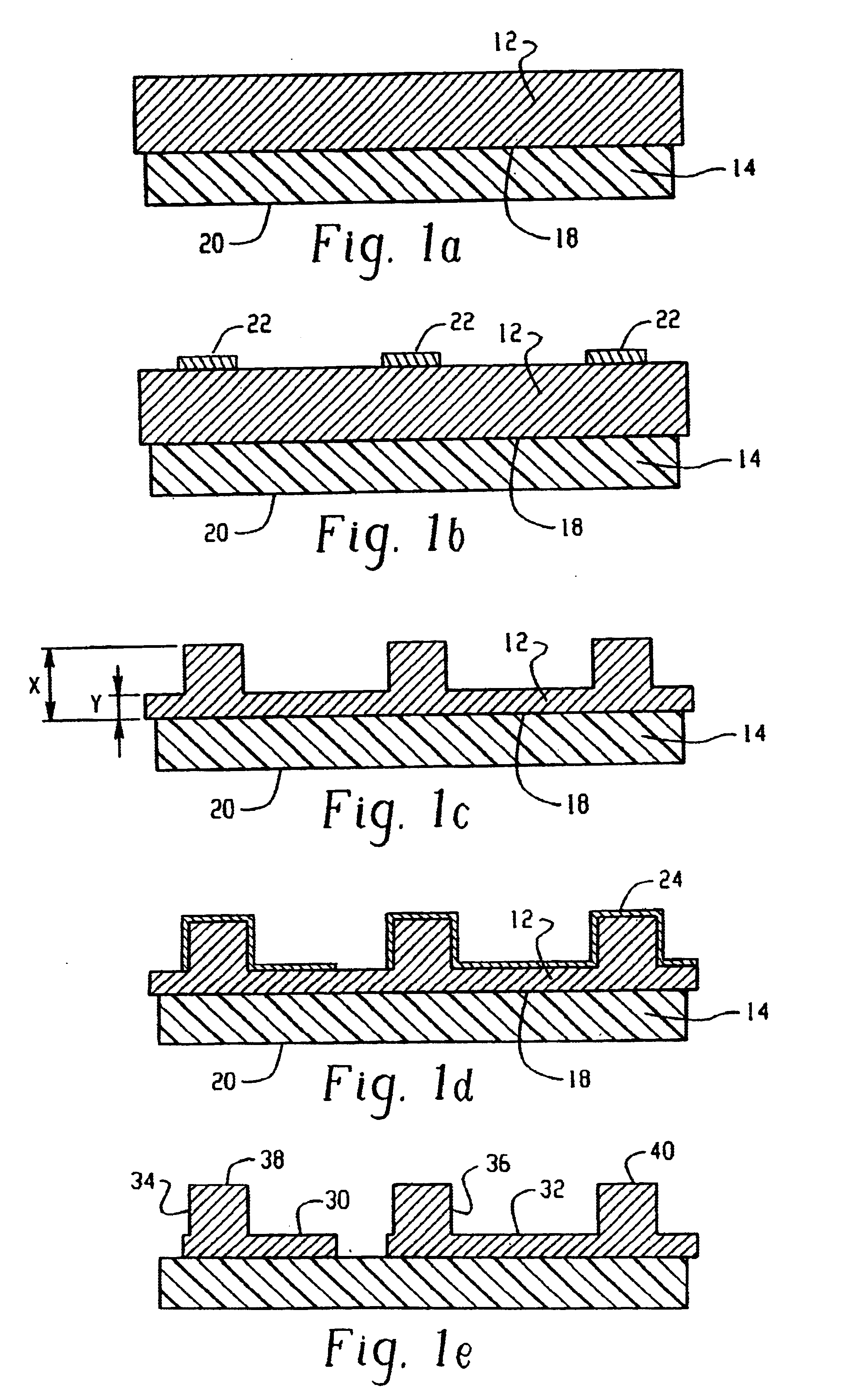

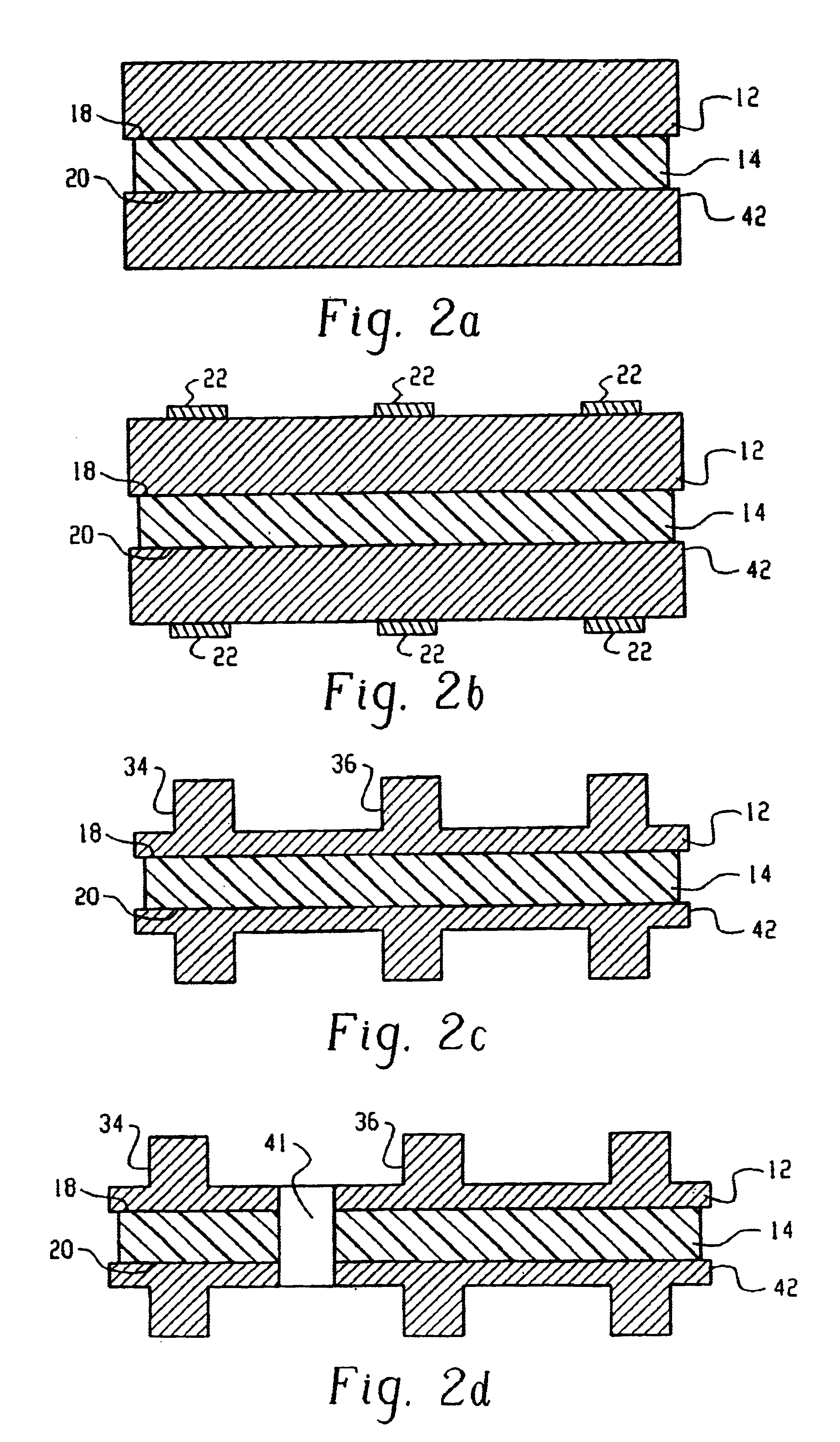

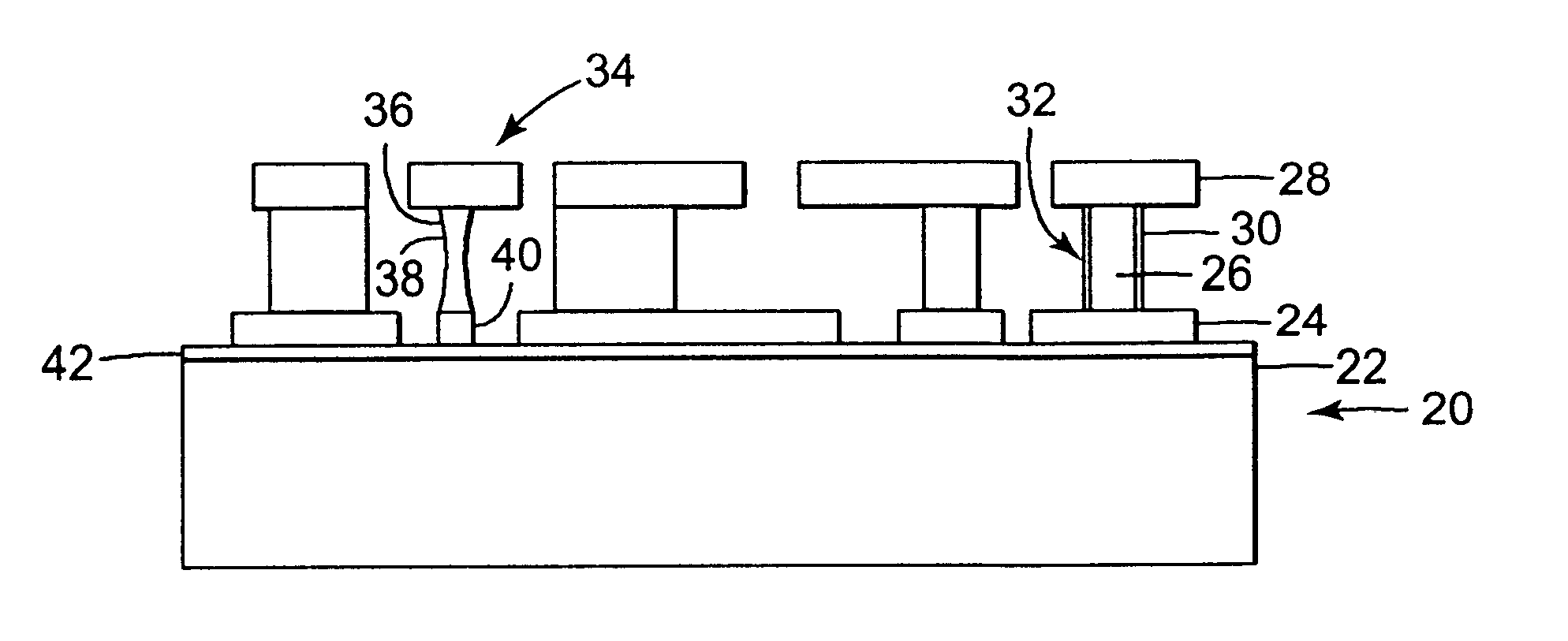

Manufacturing methods for printed circuit boards

InactiveUS6902869B2Improve rigidityEasy to handleLine/current collector detailsWave amplification devicesDielectric substratePhotoresist

A method of forming a plurality of solid conductive bumps for interconnecting two conductive layers of a circuit board with substantially coplanar upper surfaces. The method comprises the steps of applying a continuous homogenous metal layer onto a dielectric substrate, applying a first photoresist and exposing and developing said first photoresist to define a pattern of conductive bumps; etching the metal layer exposed by said development to form said plurality of conductive bumps; removing said first photoresist; applying a second photoresist onto the metal layer; exposing and developing said second photoresist to define a pattern of conductive bumps and circuit lines; etching the metal layer exposed by said development to form a pattern of circuit lines in said metal layer; and removing said second photoresist. The methods of the present invention also provides for fabricating a multilayer circuit board and a metallic border for providing rigidity to a panel.

Owner:GLOBALFOUNDRIES INC

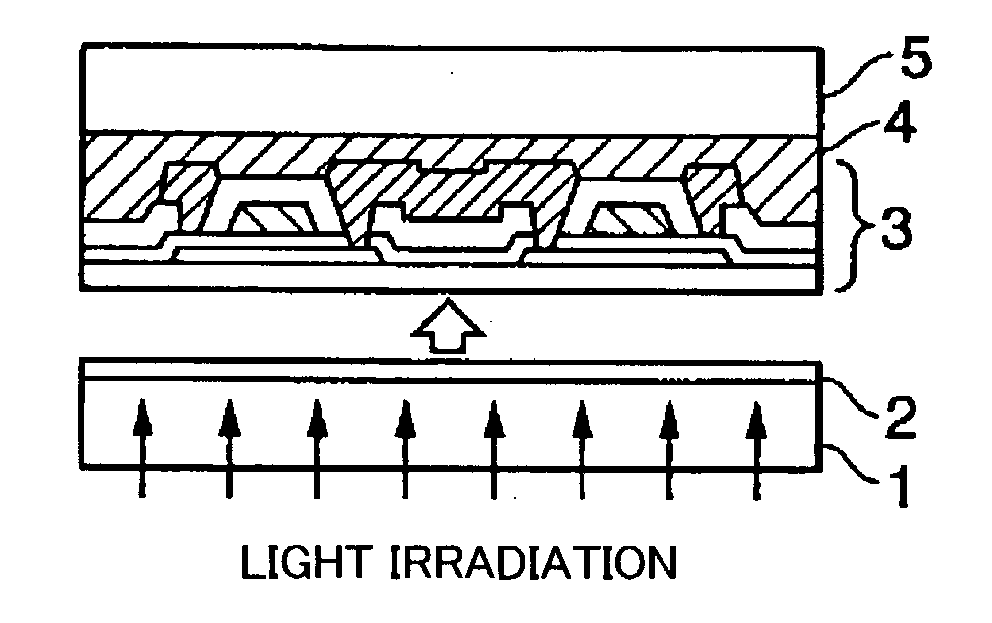

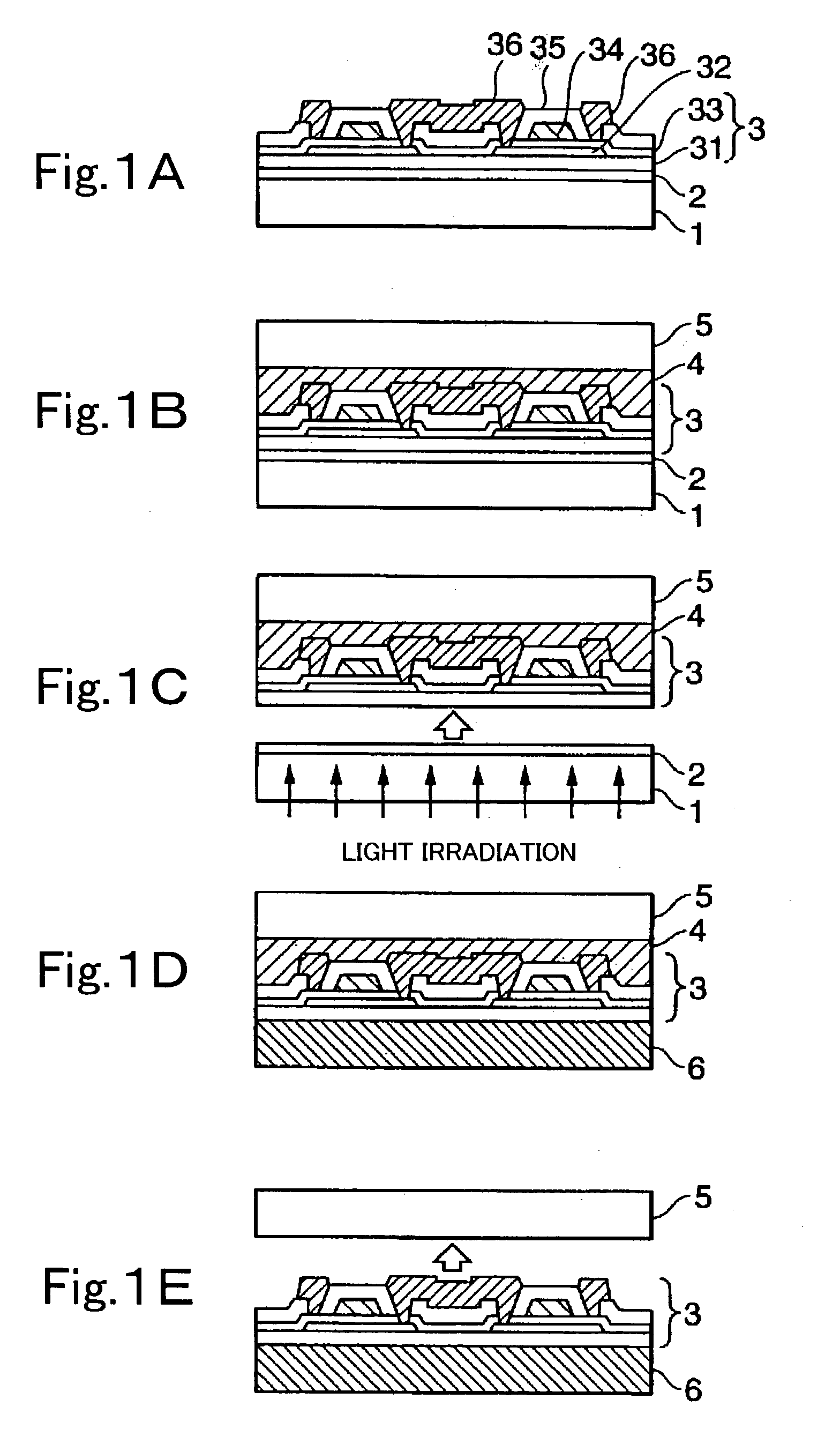

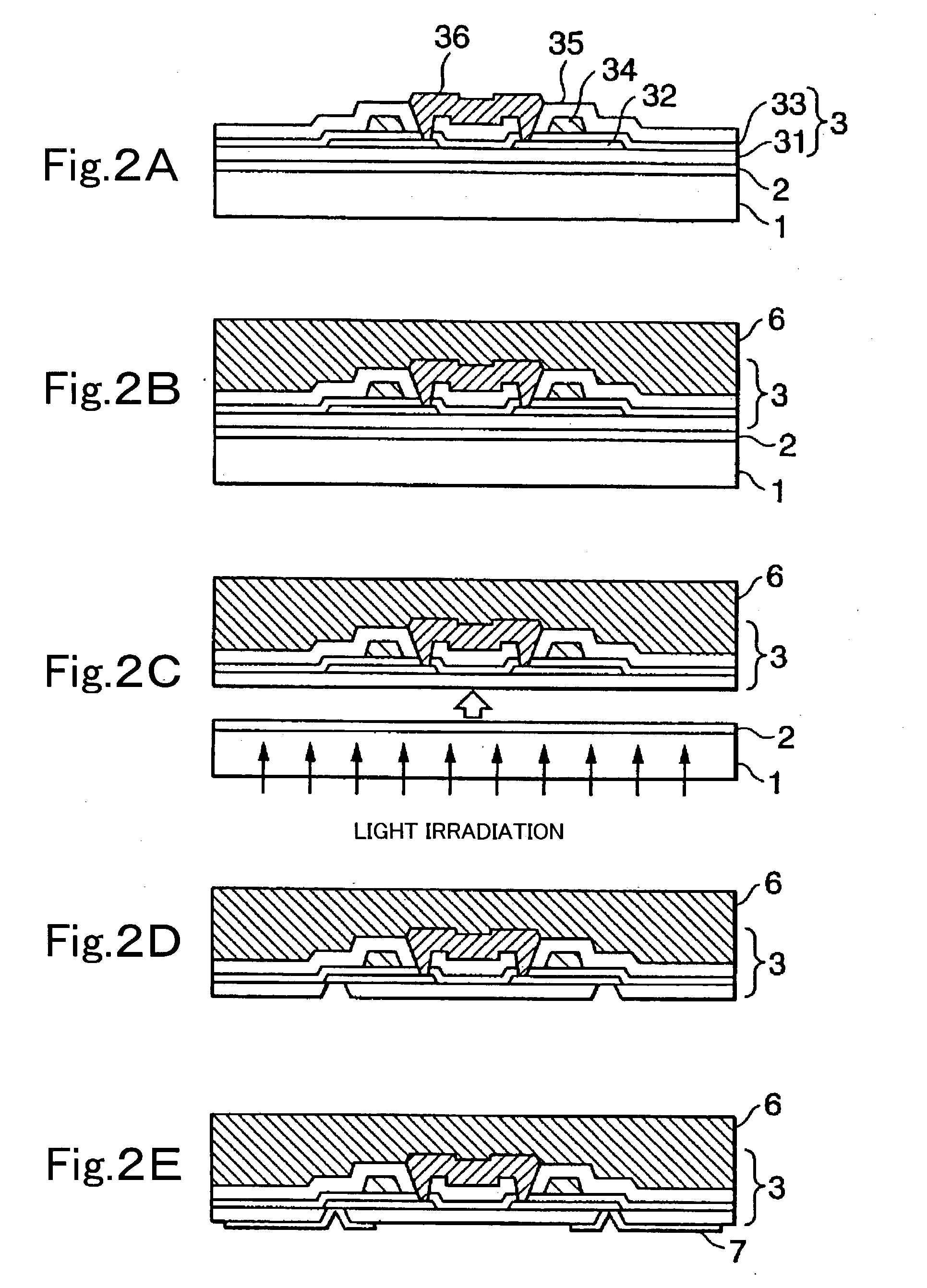

Method for transferring element, method for producing element, integrated circuit, circuit board, electro-optical device, IC card, and electronic appliance

InactiveUS20030024635A1Thinner semiconductor deviceMinimize cracksLamination ancillary operationsDecorative surface effectsDevice materialEngineering

A peeling layer 2 is formed on an element-forming substrate 1, an element-forming layer 3 including an electrical element is formed on the peeling layer, the element-forming layer is joined by means of a dissolvable bonding layer 4 to a temporary transfer substrate 5, the bonding force of the peeling layer is weakened to peel the element-forming layer from the element-forming substrate, the layer is moved to the temporary transfer substrate 5 side, a curable resin 6 is applied onto the element-forming layer 3 which has been moved onto the temporary transfer substrate 5, the resin is cured to form a transfer substrate 6, and the bonding layer 4 is dissolved to peel the temporary transfer substrate 5 from the transfer substrate 6, resulting in a structure in which a transfer substrate is formed directly on the element-forming layer 3. The separation and transfer technique can be used to form a substrate with better flexibility and impact resistance directly on a semiconductor element, without an adhesive layer on the semiconductor device that is produced.

Owner:SAMSUNG ELECTRONICS CO LTD

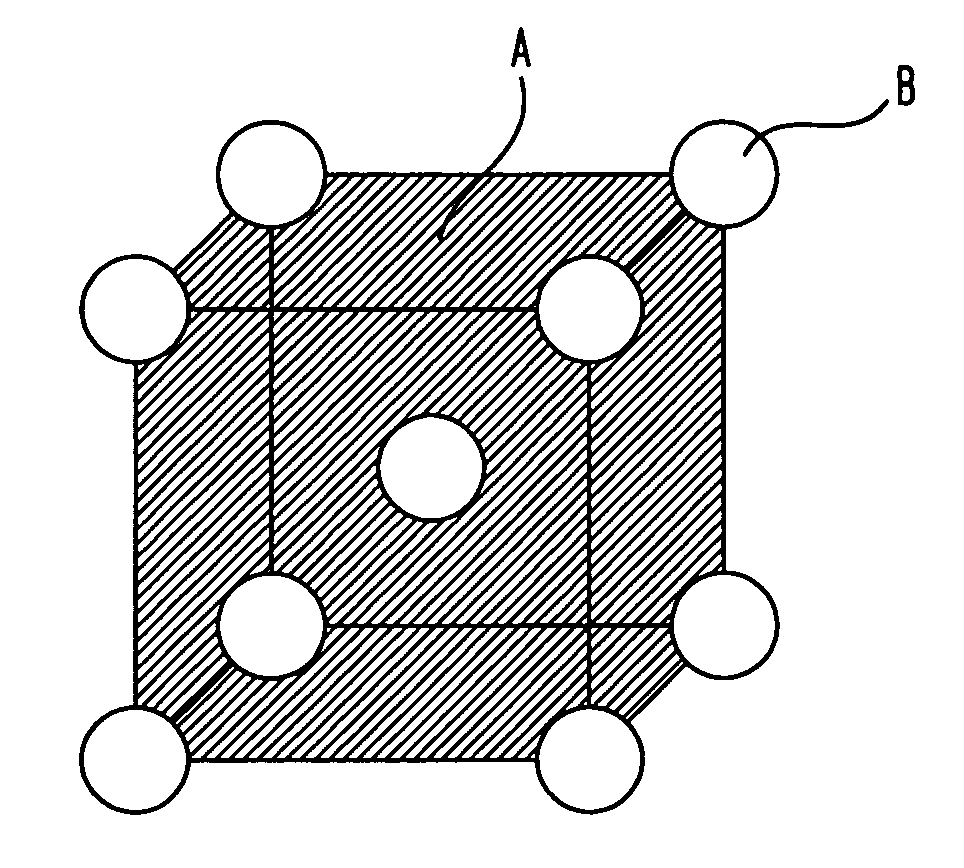

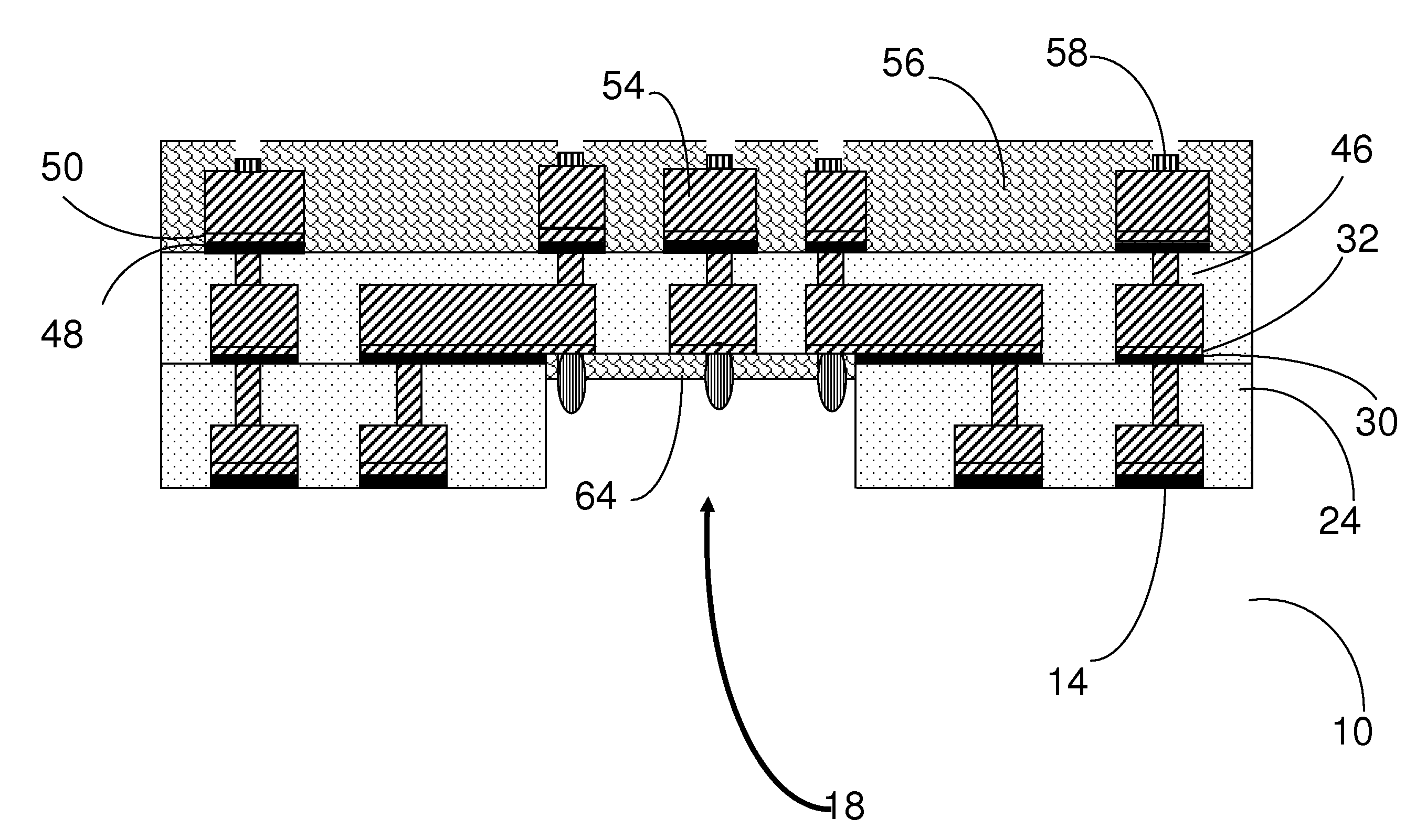

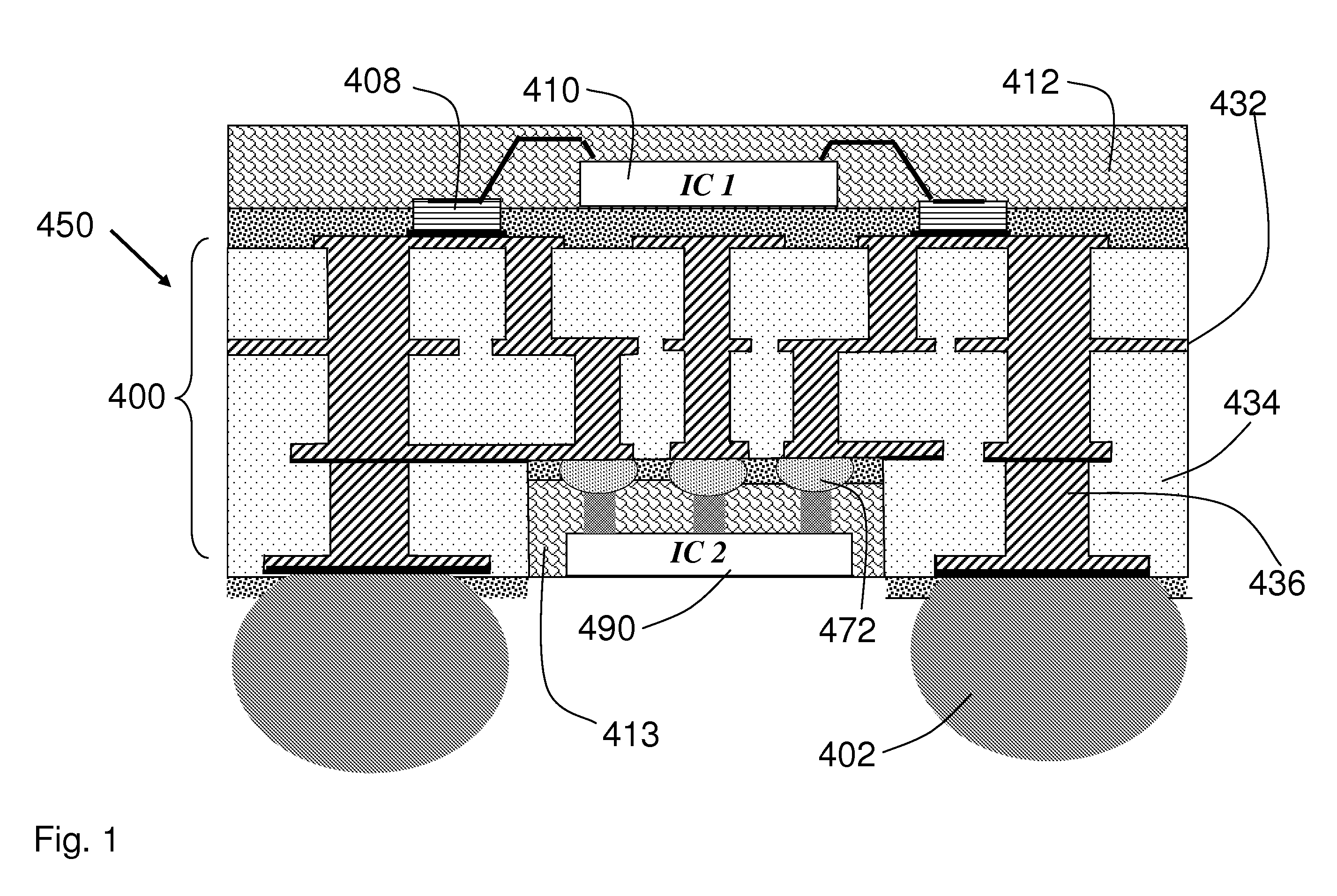

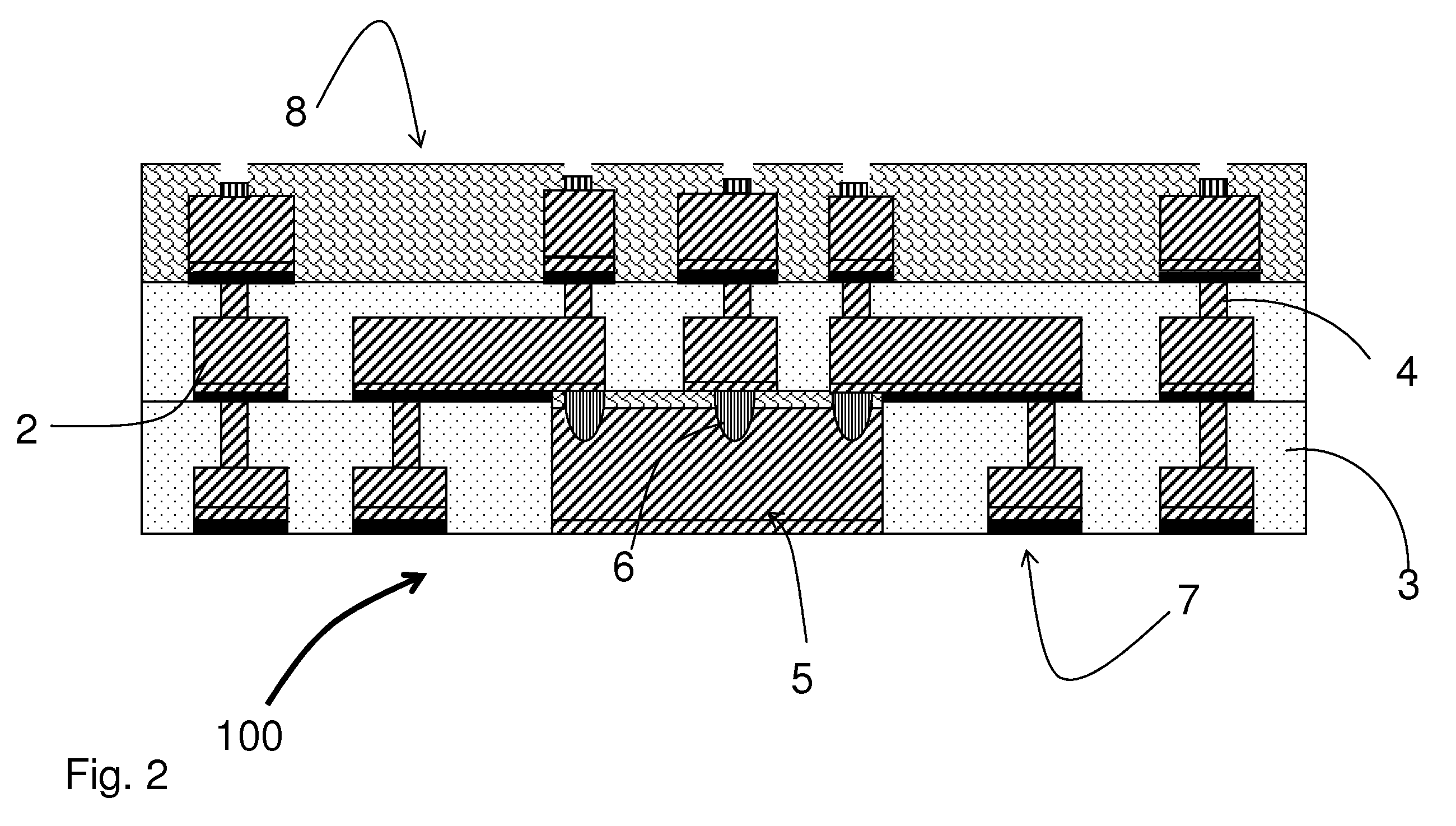

Coreless cavity substrates for chip packaging and their fabrication

ActiveUS7669320B2High yieldSuitable for mass productionDecorative surface effectsSemiconductor/solid-state device detailsCopperElectrical and Electronics engineering

A method for fabricating an IC support for supporting a first IC die connected in series with a second IC die; the IC support comprising a stack of alternating layers of copper features and vias in insulating surround, the first IC die being bondable onto the IC support, and the second IC die being bondable within a cavity inside the IC support, wherein the cavity is formed by etching away a copper base and selectively etching away built up copper.

Owner:ZHUHAI ADVANCED CHIP CARRIERS & ELECTRONICS SUBSTRATE SOLUTIONS TECH

Etching of metallic composite articles

A process for the etching of multiple layers of at least two different metals comprisies:forming a resist pattern over a first layer of metal, said resist pattern having a pattern of openings therein, applying a first etch solution onto said resist pattern so that at least some etch solution contacts exposed areas of the first layer of metal, etching away the majority of the depth of the first metal in exposed areas of metal in the first layer of metal, applying a second etch solution onto the resist pattern the second etch solution having a rate of etch towards the first metal as compared to the first etch solution that is at least 20% less than the millimeter / minute rate of etch of the first etch solution at the same etch solution temperature, removing the second etch solution from said resist pattern after at least the first metal layer has been etched sufficiently to expose areas of a second metal layer underlying the first metal layer by forming an etched first metal layer, and applying a third etch solution to said etched first metal layer, the third etch solution having a faster rate of etch towards the second metal than towards the first metal to etch into said second metal layer without destroying the etched first metal layer.

Owner:BMC INDS

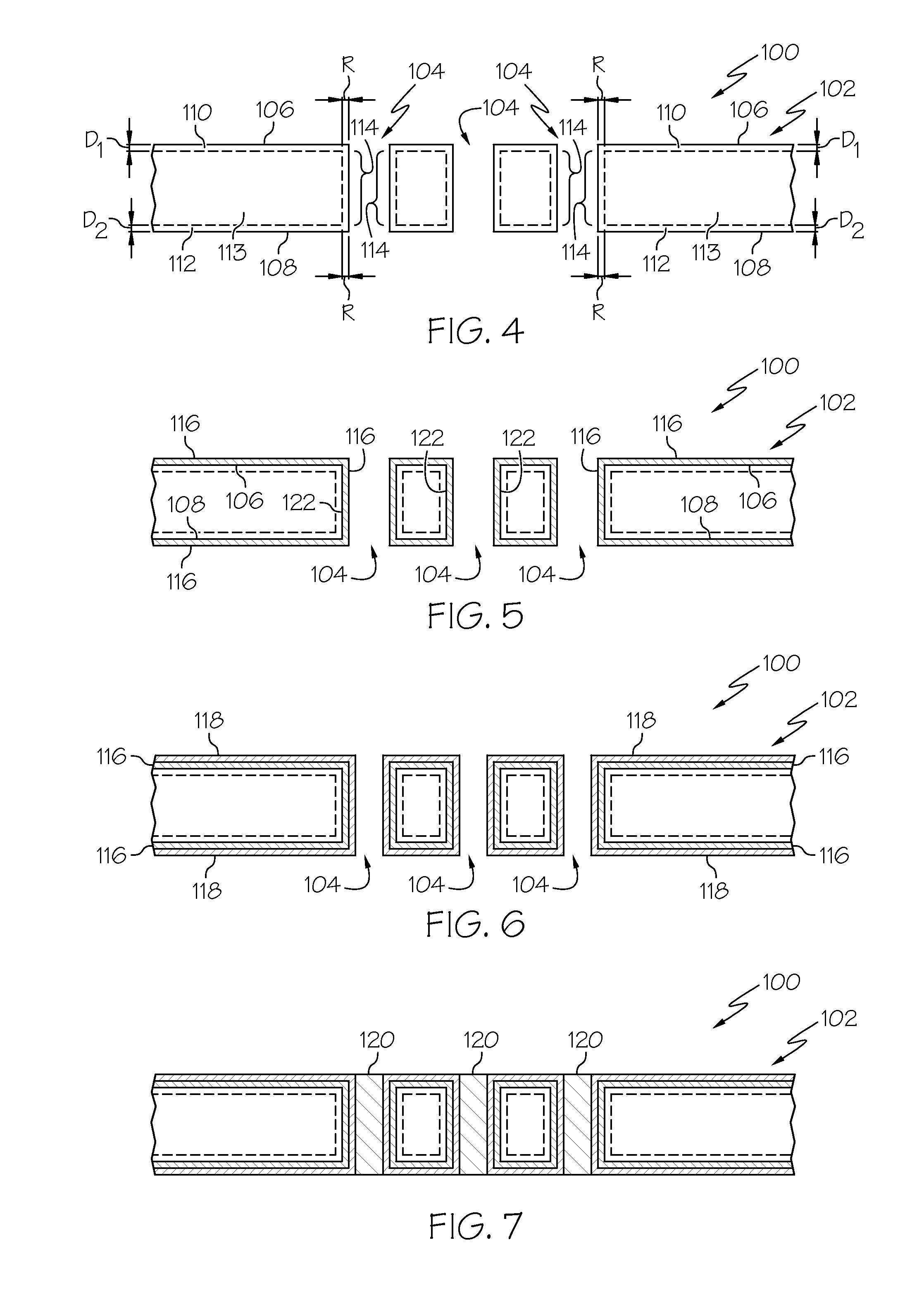

Glass Interposer Panels And Methods For Making The Same

InactiveUS20120048604A1Line/current collector detailsPrinted circuit detailsInterposerSecondary layer

Glass interposer panels and methods for forming the same are described herein. The interposer panels include a glass substrate core formed from an ion-exchangeable glass. A first layer of compressive stress may extend from a first surface of the glass substrate into the thickness T of the glass substrate core to a first depth of layer D1. A second layer of compressive stress may be spaced apart from the first layer of compressive stress and extending from a second surface of the glass substrate core into the thickness T of the glass substrate core to a second depth of layer D2. A plurality of through-vias may extend through the thickness T of the glass substrate core. Each through-via is surrounded by an intermediate zone of compressive stress that extends from the first layer of compressive stress to the second layer of compressive stress adjacent to a sidewall of each through-via.

Owner:CORNING INC