Semiconductor memory device and preparation method thereof

A technology of storage devices and semiconductors, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., and can solve problems such as high power consumption, reduced coupling rate, and high operating voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

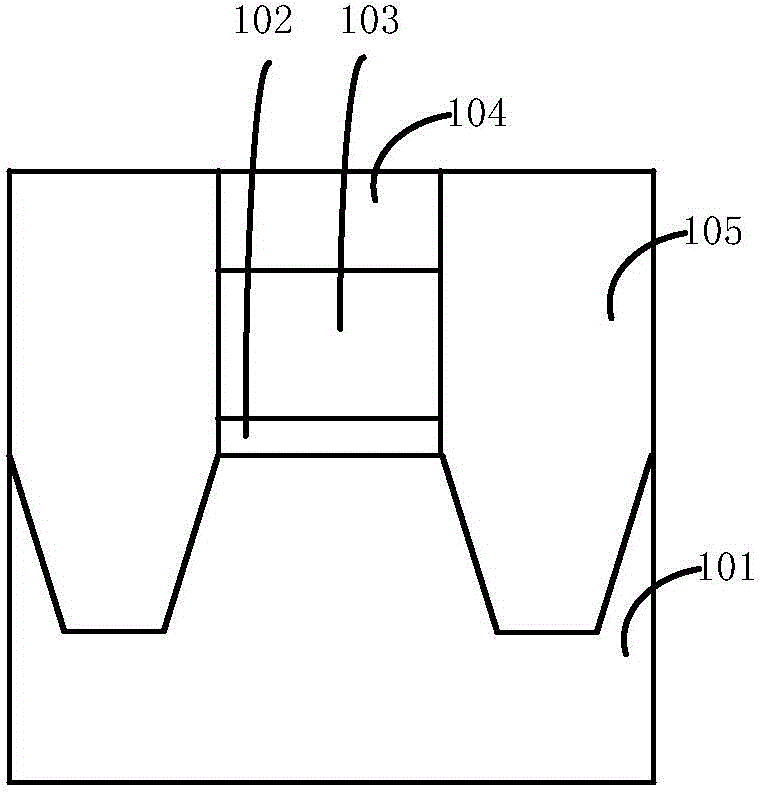

[0042] Attached below Figure 2a-2d A specific embodiment of the present invention will be described.

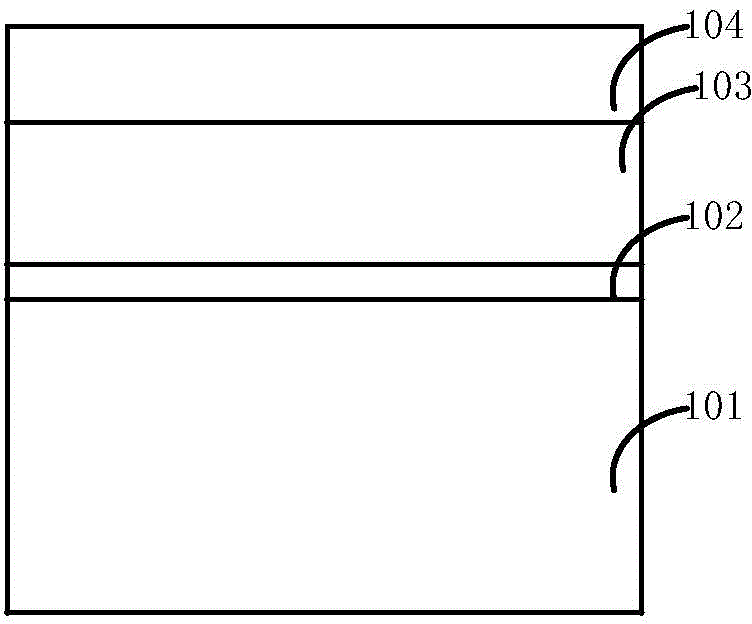

[0043] First, step 201 is performed to provide a semiconductor substrate 201 on which a tunnel oxide layer (tunnel oxide) 202 , a floating gate layer 203 and a mask layer 204 are formed.

[0044] Specifically, please refer to Figure 2a, first provide a semiconductor substrate 201, wherein the semiconductor substrate 201 can be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), germanium-on-insulator Silicon-on-insulator (S-SiGeOI), silicon-germanium-on-insulator (SiGeOI), and germanium-on-insulator (GeOI). In addition, an active region may be defined on the semiconductor substrate 201 . Other active devices may also be included on the active area, which are not marked in the shown figures for convenience.

[0045] The semiconductor substrate 201 can be selected as P-type, and a tunnel oxide layer is deposited...

Embodiment 2

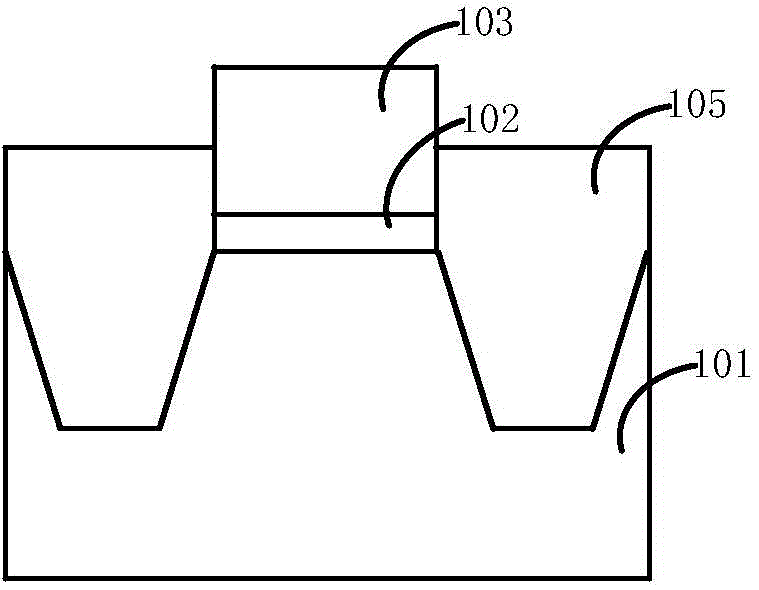

[0082] The present invention also provides a floating gate structure, including:

[0083] semiconductor substrate 201;

[0084] a tunnel oxide layer 202 located on the semiconductor substrate;

[0085] The floating gate, located on the tunnel oxide layer 202 , includes a floating gate layer 203 and a hemispherical floating gate film 206 located on the floating gate layer 203 .

[0086] Wherein, the critical dimension of the hemispherical floating gate film 206 is greater than the critical dimension of the floating gate layer 03, the hemispherical floating gate film 206 is concave overall, and its inner surface has hemispherical floating gate crystal grains to increase The surface area of the floating gate structure.

[0087] Further, the floating gate structure also includes:

[0088] ONO material layer, located above the hemispherical floating gate film 206;

[0089] a control gate layer located above the ONO material layer;

[0090] A shallow trench isolation structur...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More