Patents

Literature

51results about How to "Reduce Switching Power Consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

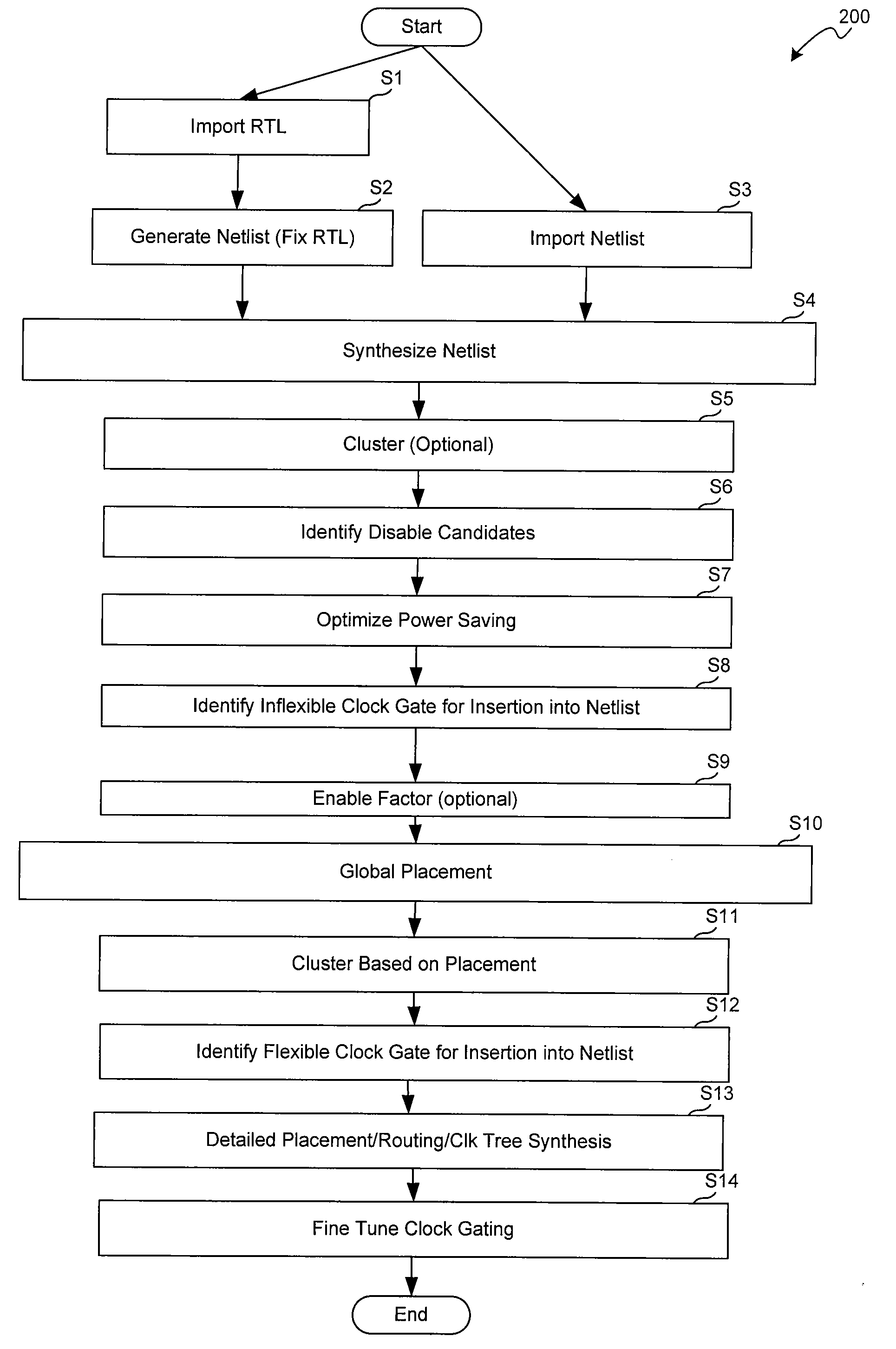

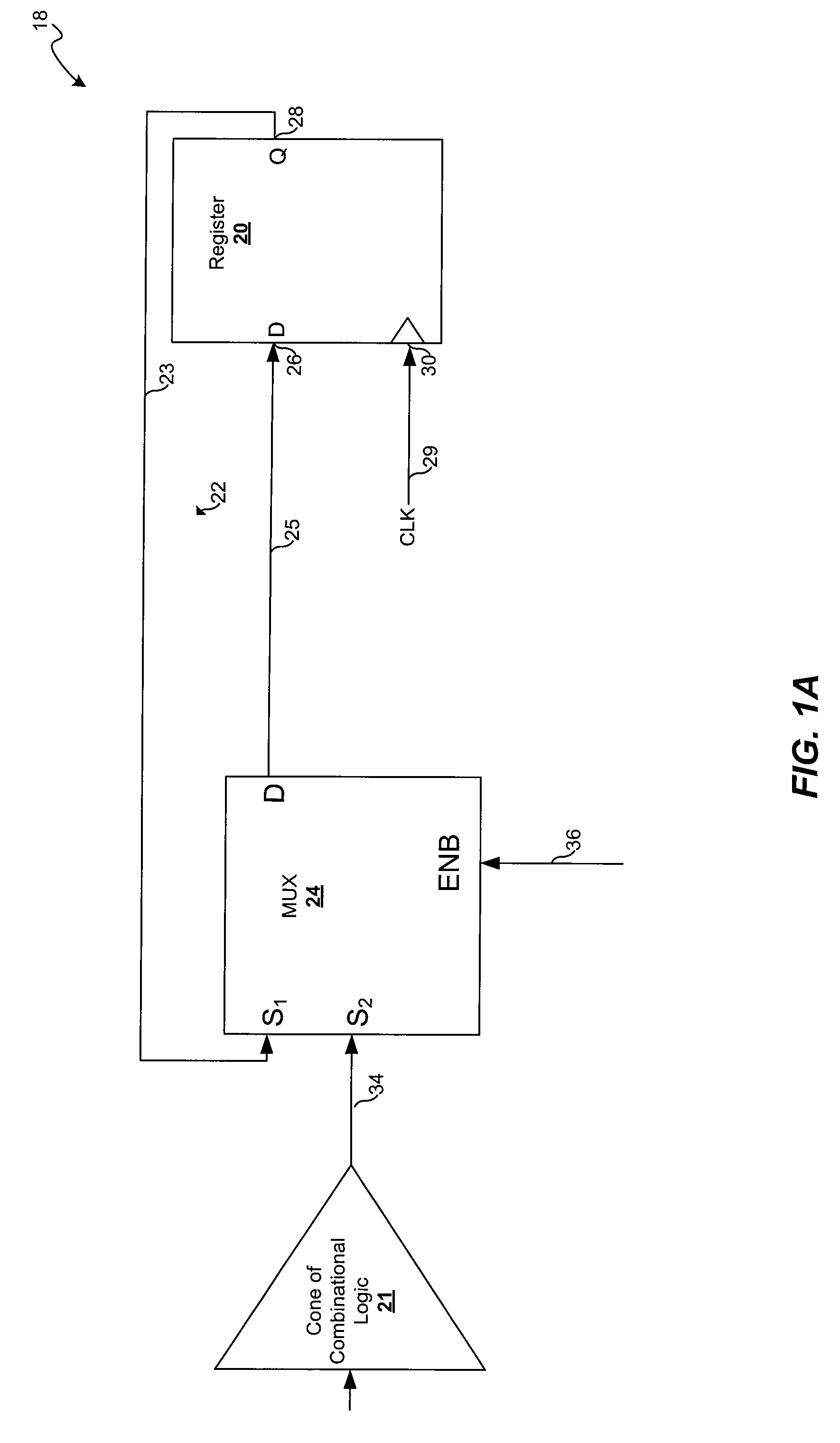

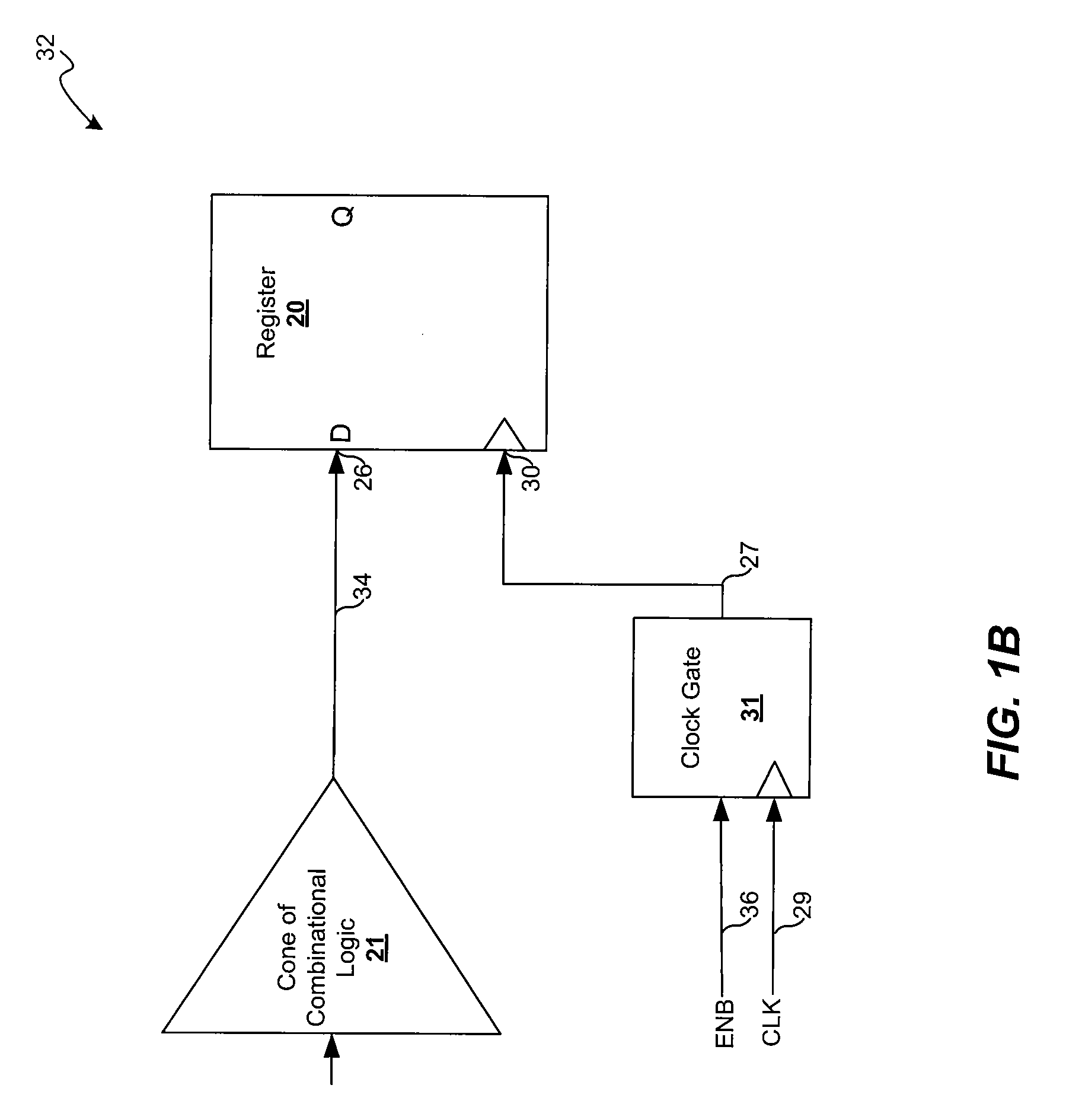

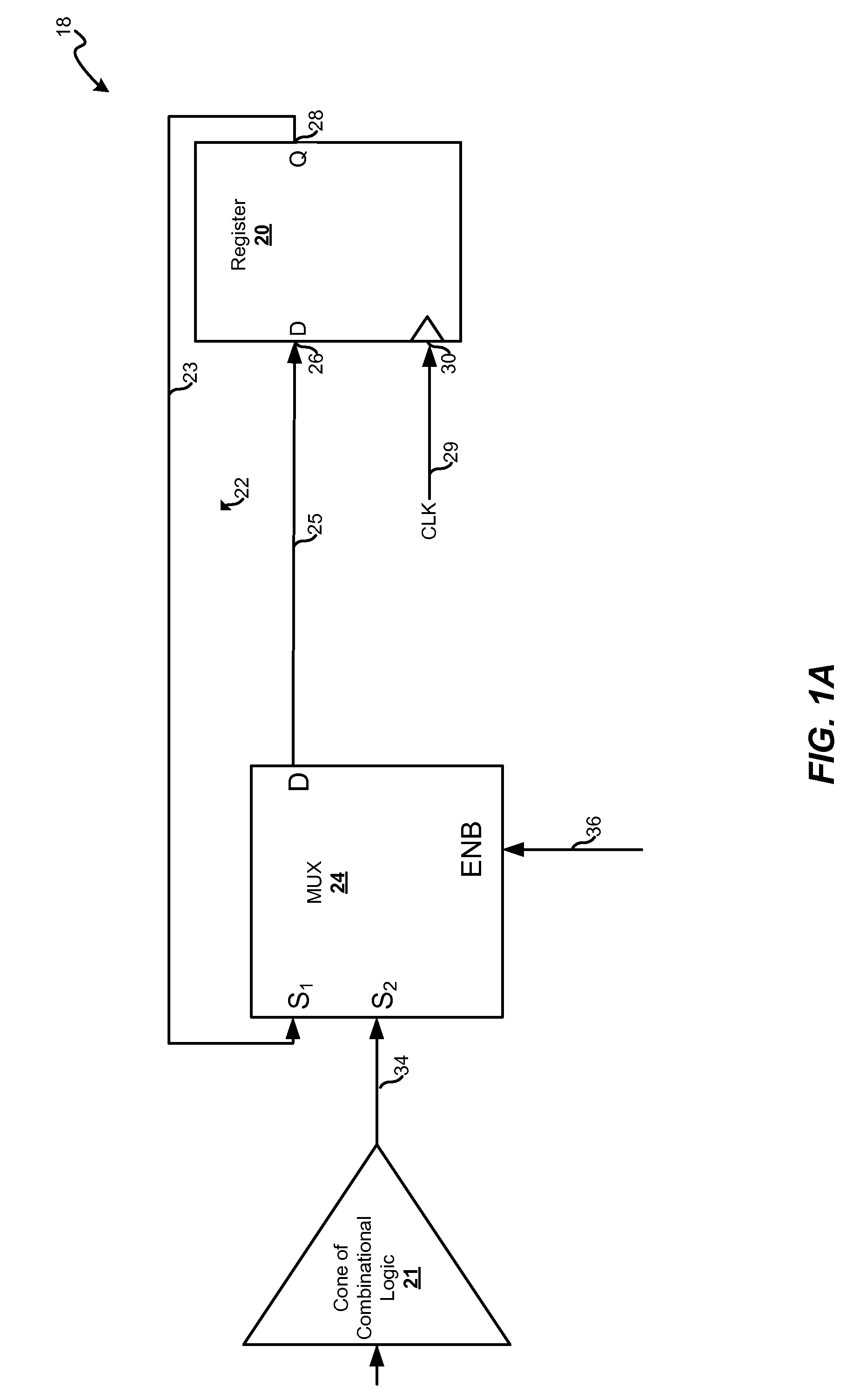

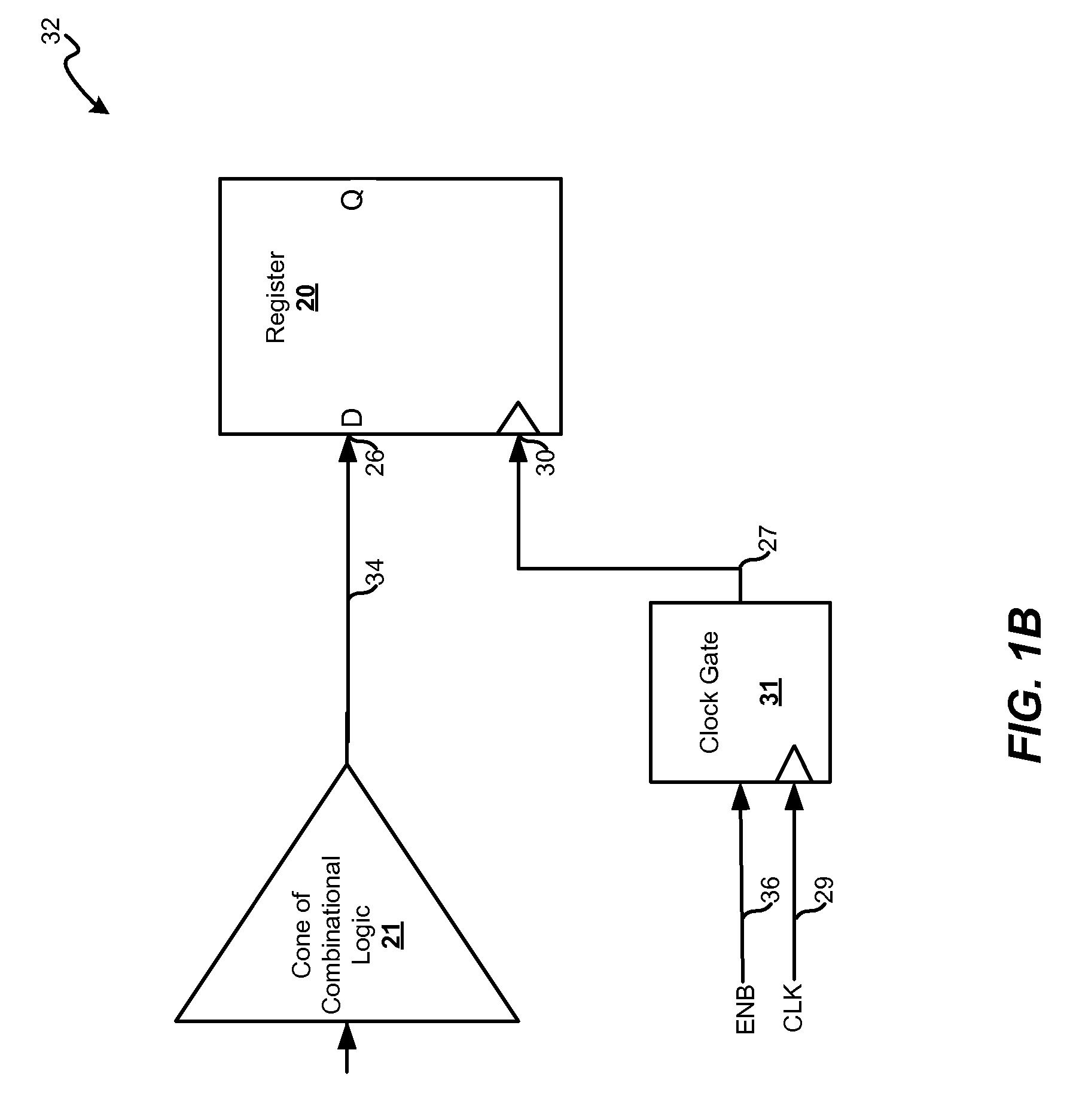

Method For Optimized Automatic Clock Gating

ActiveUS20080301594A1Reduce Switching Power ConsumptionConsumes less powerCAD circuit designMulti-objective optimisationComputer architectureCombinational logic

A method of optimizing clock-gated circuitry in an integrated circuit (IC) design is provided. A plurality of signals which feed into enable inputs of a plurality of clock gates is determined, where the clock gates gate a plurality of sequential elements in the IC design. Combinational logic which is shared among the plurality of signals is identified. The clock-gated circuitry is transformed into multiple levels of clock-gating circuitry based on the shared combinational logic.

Owner:SYNOPSYS INC

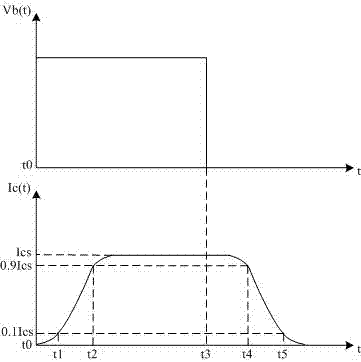

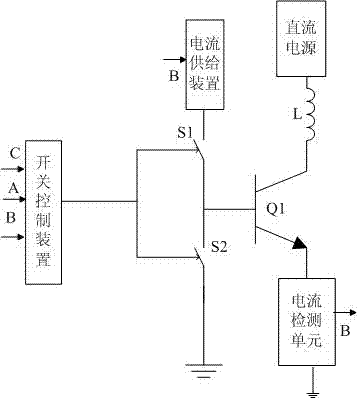

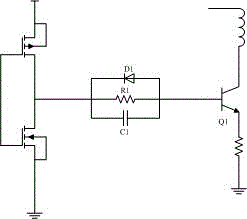

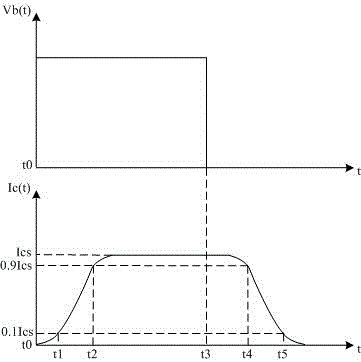

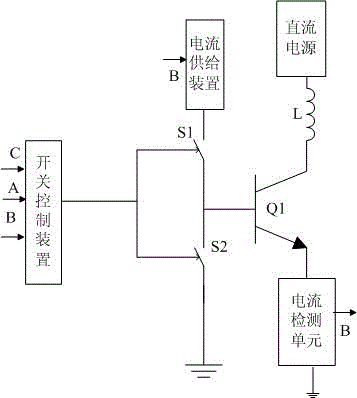

Driving circuit of triode and driving method thereof

The invention relates to a driving circuit of a triode. The circuit comprises a current supply device, a first switch device, a second switch device, a switch control device, an inductor, a direct-current power supply and a current detection unit, wherein the current supply device is grounded after being sequentially connected with the first switch device and the second switch device; the triode is connected between the first switch device and the second switch device, the direct-current power supply is connected with the collecting electrode of the triode, and an emitting electrode of the triode is grounded; the switch control device receives a detection voltage provided by the current detection unit and an externally supplied control voltage to control the on-off states of the first switch device and the second switch device so as to control the on-off state of the triode; and the current supply device supplies a direct current which reflects the changing of the current of the collecting electrode to the base electrode of the triode. By utilizing the driving circuit of the triode, the turn-off time of the switch is shortened, and the power dissipation is reduced; and meanwhile, the invention discloses a driving method of the driving circuit of the triode and a switch power supply.

Owner:BYD SEMICON CO LTD

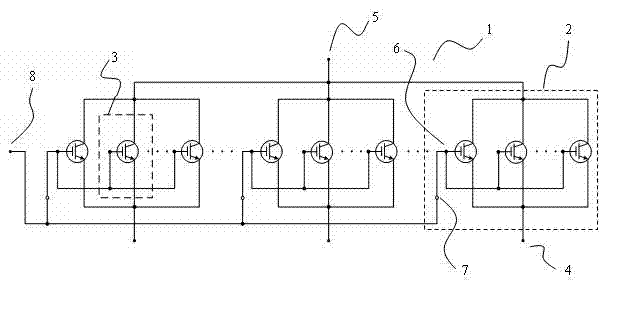

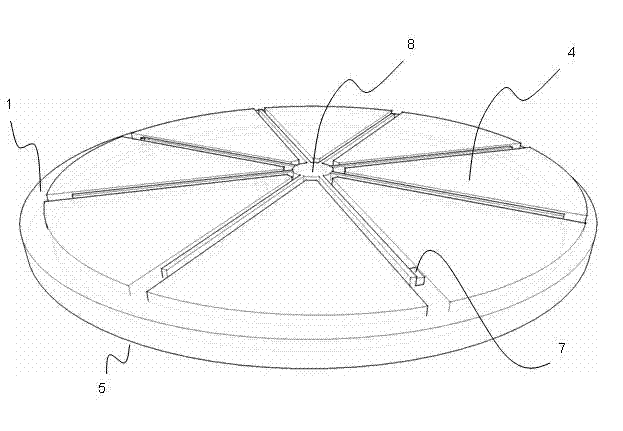

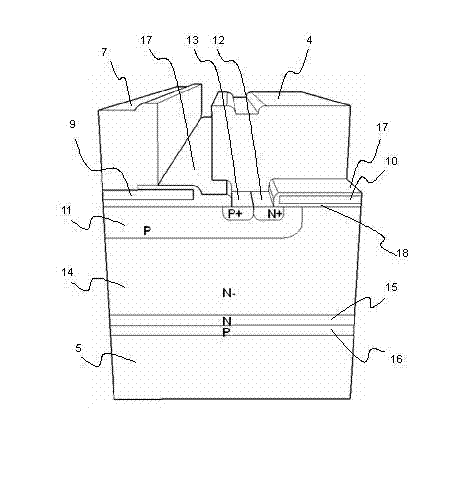

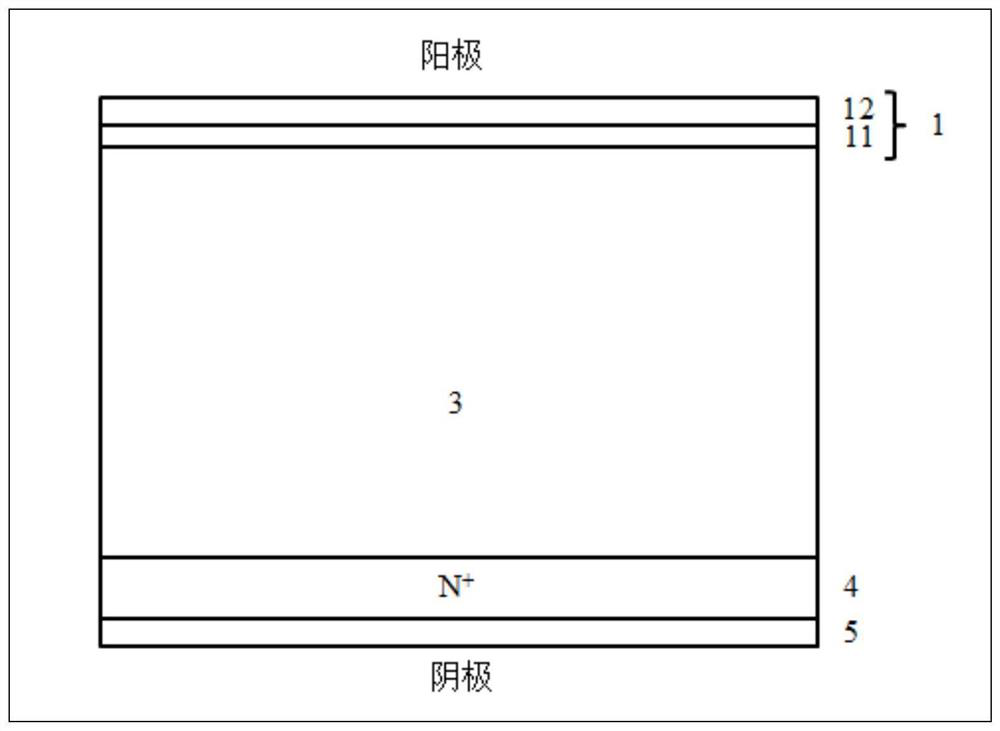

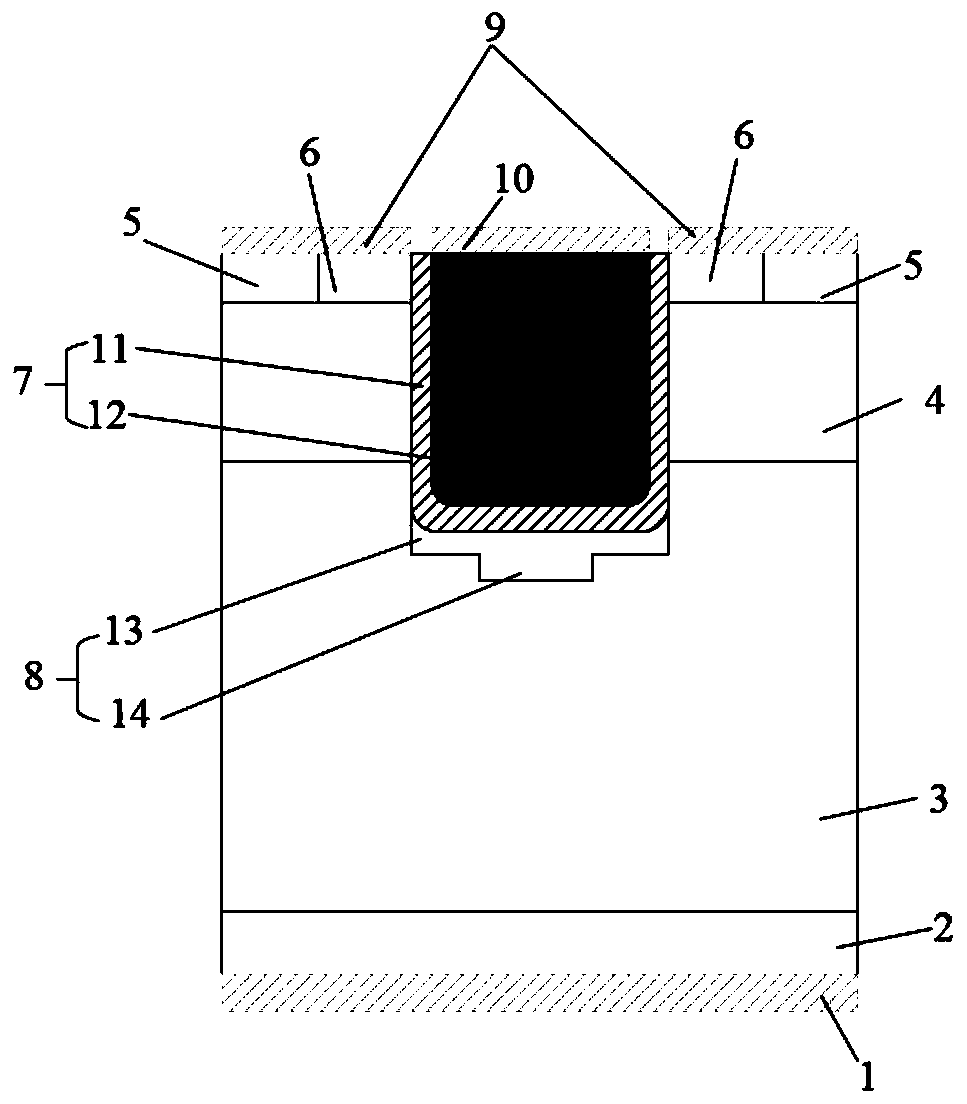

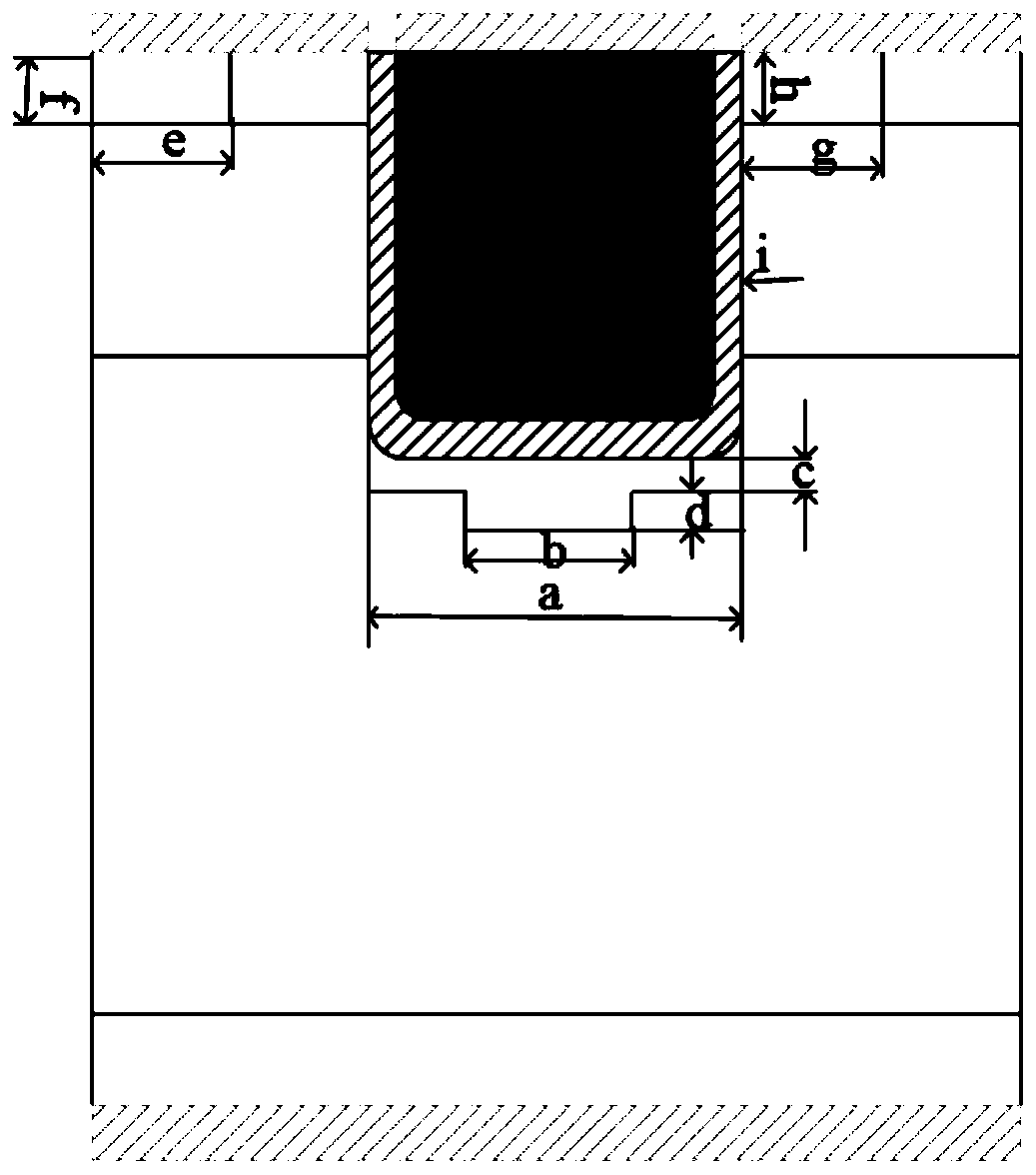

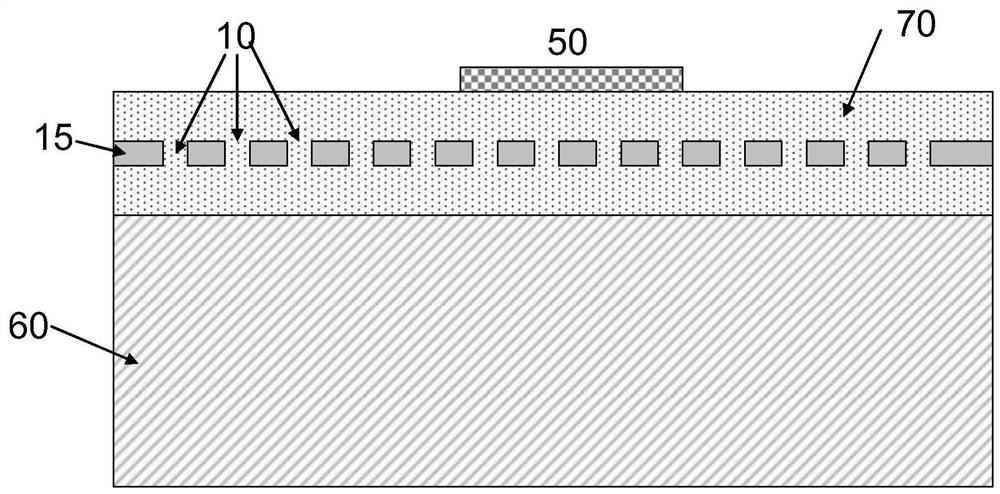

High-current full-wafer full-crimp flat-pack IGBT and manufacturing method thereof

ActiveCN102270640AIncrease working voltageReduce Switching Power ConsumptionTransistorSemiconductor/solid-state device manufacturingEngineeringMetal electrodes

The invention discloses a heavy-current whole-wafer total-pressure-contact flat-plate encapsulated IGBT (Insulated Gate Bipolar Transistor) and a manufacturing method thereof. The heavy-current whole-wafer total-pressure-contact flat-plate encapsulated IGBT comprises an IGBT whole wafer and a total-pressure-contact flat-plate encapsulation, the whole wafer comprises multiple independent IGBT device regions, each IGBT device region is composed of multiple IGBT units which are connected in parallel, collectors of all the IGBT device regions are connected in parallel to form a total collector, atransmitter is led from each IGBT device region independently, gate poles of all the IGBT device regions in a normal operating state are connected to a total gate pole arranged in the center of the wafer by using an interconnecting line, and the transmitter of each IGBT device region is connected with a metal electrode plate of a total transmitter in parallel by virtue of a metal gasket of the transmitter. According to the invention, a heavy-current IGBT whole wafer device is realized, the advantages of high working voltage, low switching power consumption and simple voltage control of the gate pole are maintained, current carrying capacity, heat-conducting property, heat shock resistance and long-term reliability of the device are improved, and the problem of property matching between IGBT units is solved.

Owner:HUNAN UNIV

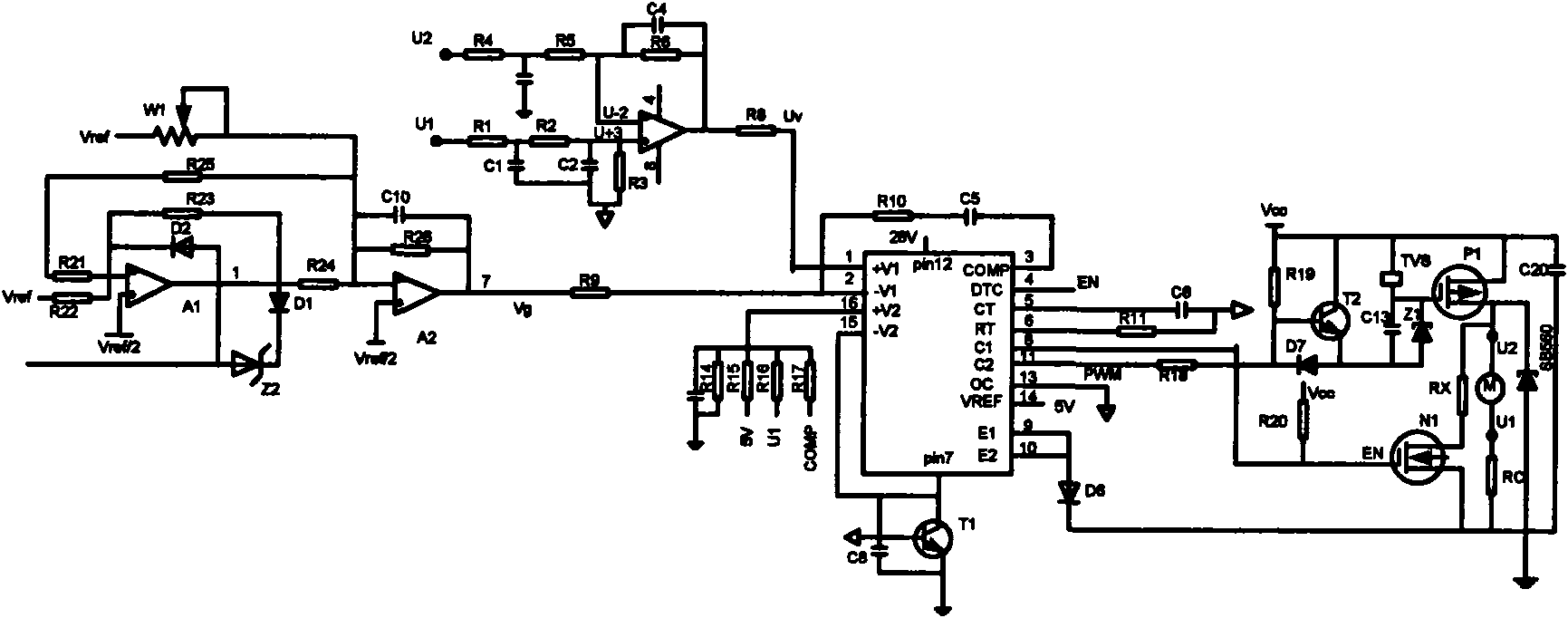

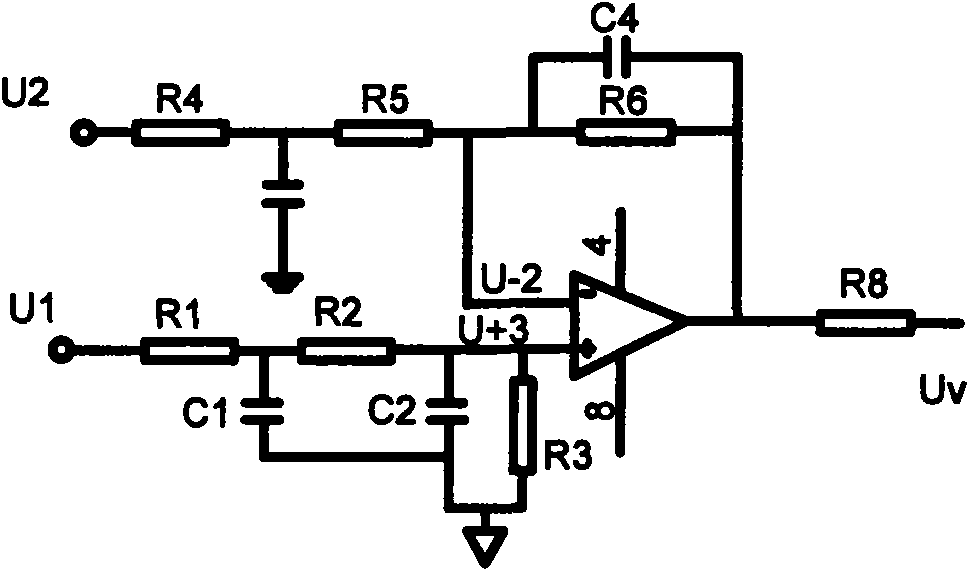

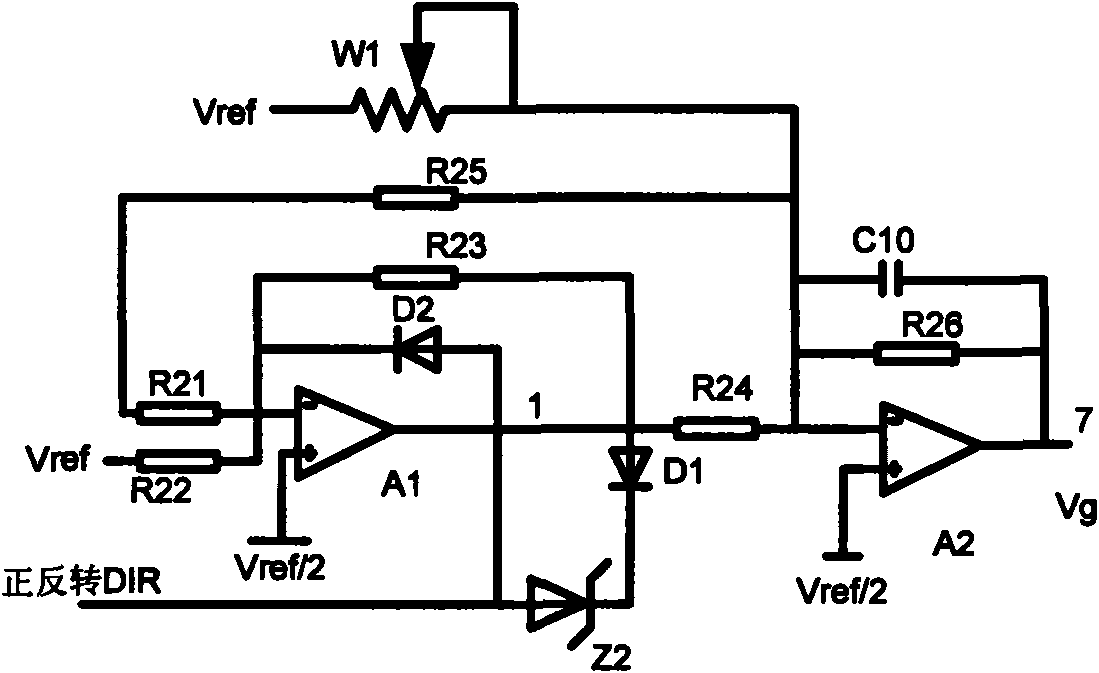

Compensation control circuit of direct current motor

InactiveCN101615878AEliminate common ground coupling interferenceFast switching speedDC motor speed/torque controlAudio power amplifierControl signal

The invention discloses a compensation control circuit of a direct current motor, comprising a speed-measuring circuit, a speed instruction conditioning circuit, a speed instruction control circuit and a driving buffering brake circuit. The speed-measuring circuit acquires signals U1 and U2 of voltage to ground of two ends of the direct current motor, and generates a speed-measuring signal Uv. The speed instruction conditioning circuit rectifies the voltage of the speed instruction signal into unipolar level, outputs a control signal of positive and negative rotation of the motor and biased-amplifying the rectified speed instruction signal into a speed instruction signal Vg conforming the range specification of the speed-measuring signal Uv. The speed instruction control circuit comprises an error amplifier and a proportional integral circuit; the error amplifier amplifies error comparison between the speed-measuring signal Uv and the speed instruction signal Vg, and generates a pulse signal for controlling a semiconductor switch device; and the proportional integral circuit controls the error amplifier. The semiconductor switch device of the driving buffering brake circuit is controlled by the pulse signal and is used for driving buffering brake direct current motor.

Owner:漳州维德焊接技术开发有限公司

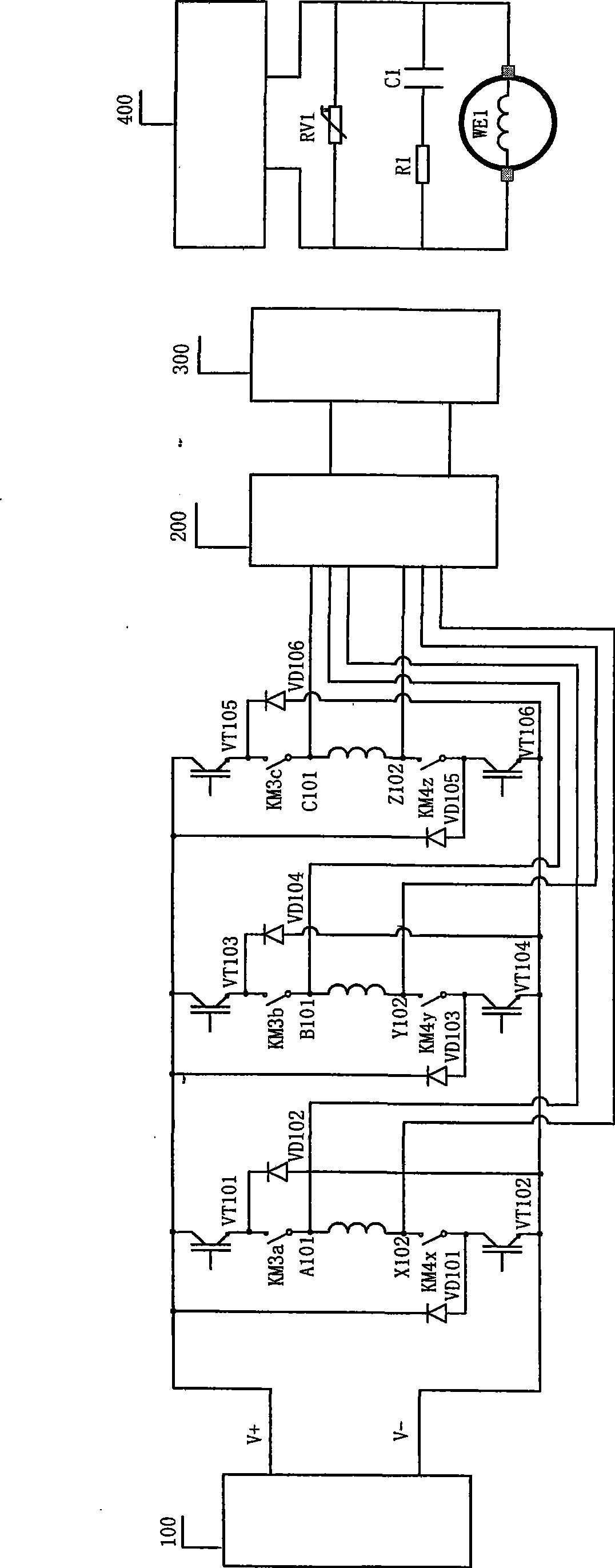

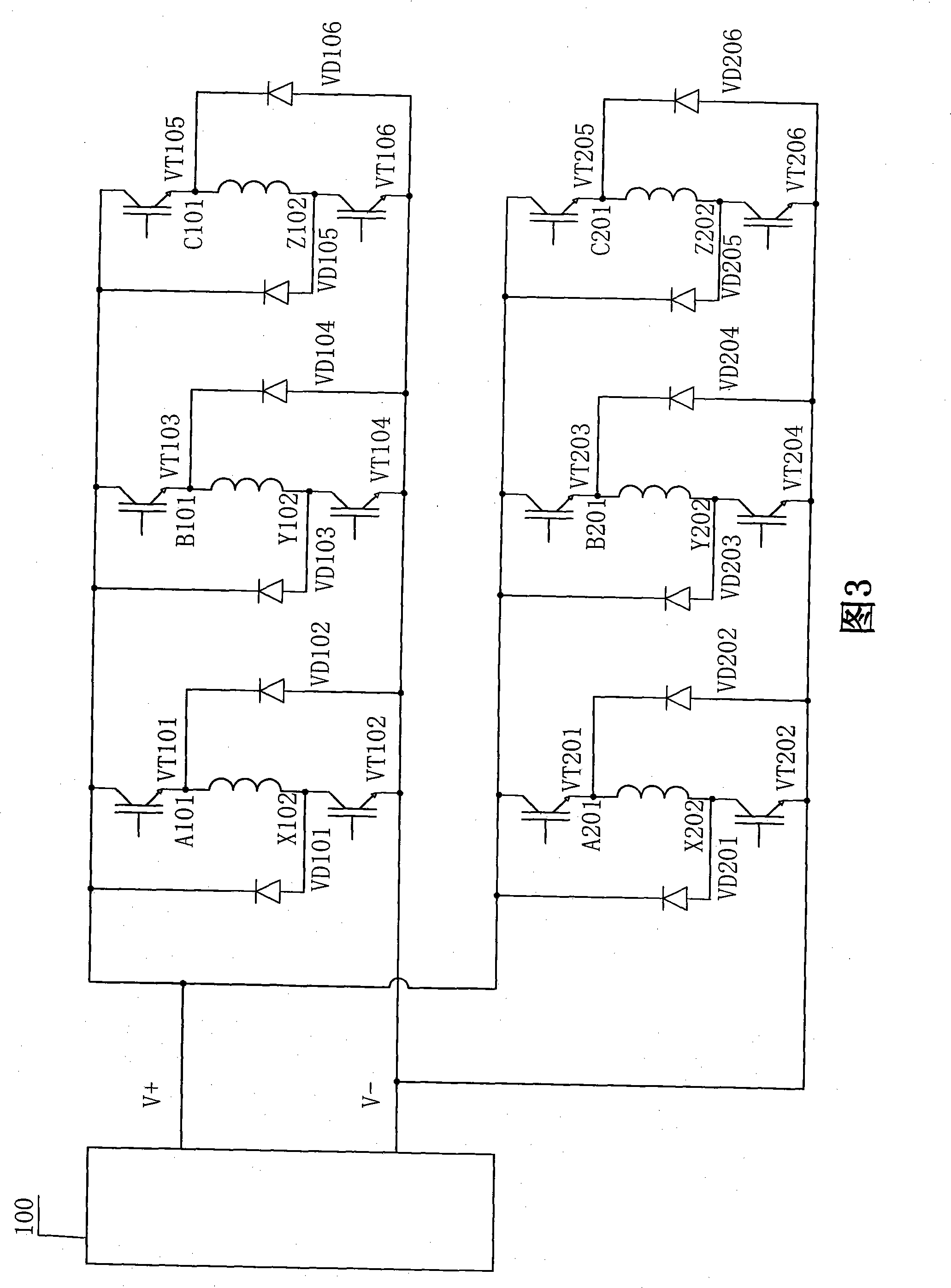

Power generation machine for switched reluctance motor

InactiveCN101483374AElectronically controlled reductionIncrease profitMechanical energy handlingElectricityElectric machine

The present invention relates to a switch reluctance motor electricity generator, which comprises stator, rotor and driving device in salient pole structure pressure-superposed by silicon steel sheet, wherein tooth of the stator is provided with centralized armature winding; the armature winding are connected in series or in parallel to constitute a phase on two tooth of same windings phase, characterized in that the rotor is provided with windings. The driving device of the electricity generator can adopt either electronic sensor or mechanical driving device or combining both. The present invention breaks adding exciter winding on electric machine rotor in normal way, which enhances performance and efficiency of power generation.

Owner:张世清

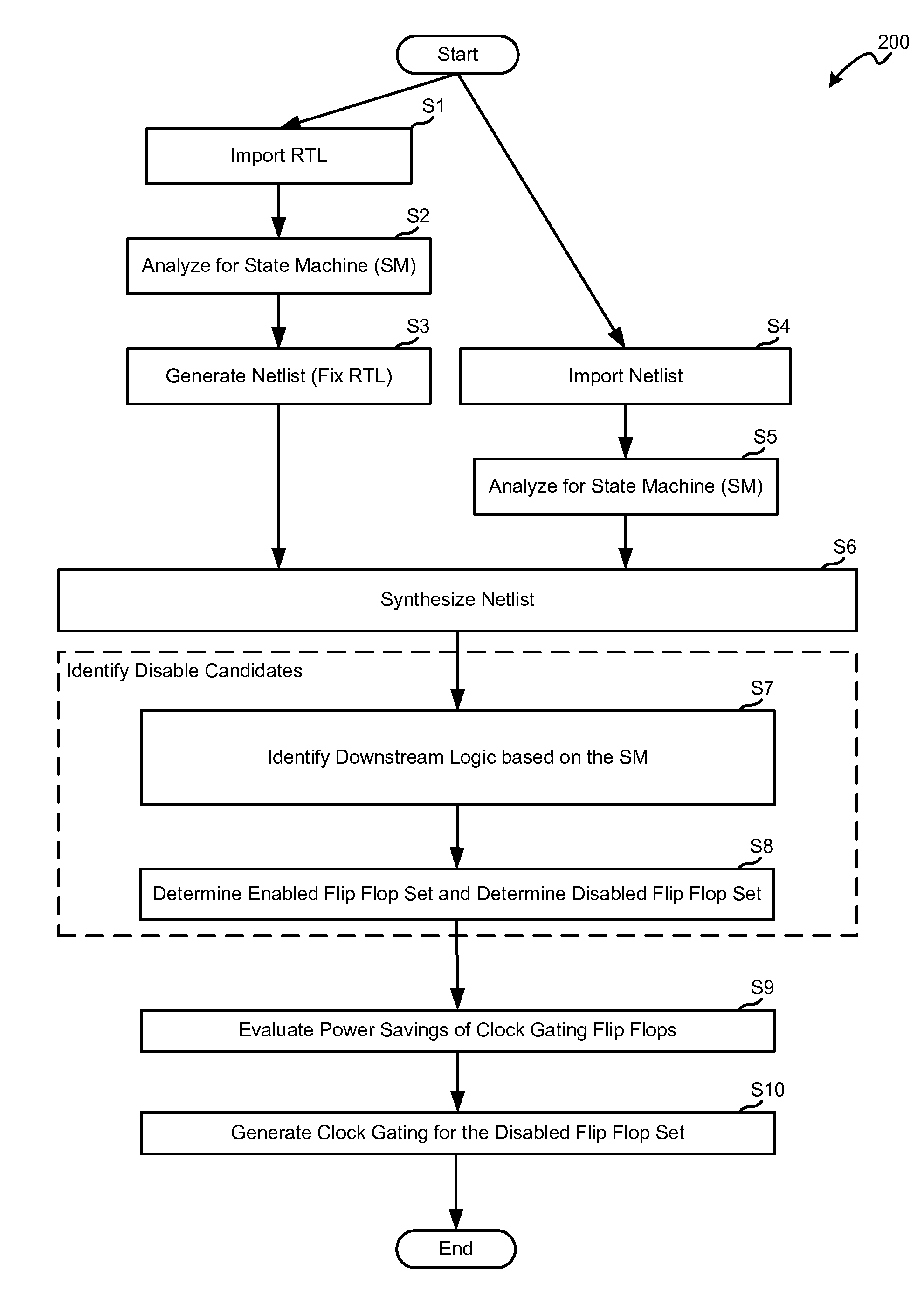

Method for multi-cycle path and false path clock gating

ActiveUS7958476B1Reduce Switching Power ConsumptionConsumes less powerVolume/mass flow measurementPower supply for data processingEngineeringFalse path

A power optimization method of deriving gated circuitry in an integrated circuit (IC) is provided. A design description of the IC is received and analyzed. A state machine is identified based on the analysis. One or more candidate blocks are determined to be capable of being disabled. At least one of the candidate blocks is selected based on one or more states of the state machine. A gating circuit is inserted for gating the selected candidate block(s). In another embodiment of power optimization, one or more state machines are identified and a synthesized netlist is generated. One or more candidate blocks in the synthesized netlist are determined to be capable of being disabled. At least one of the candidate blocks is selected based on one or more states in the state machine, and a gating circuit is inserted for gating the selected candidate block(s).

Owner:SYNOPSYS INC

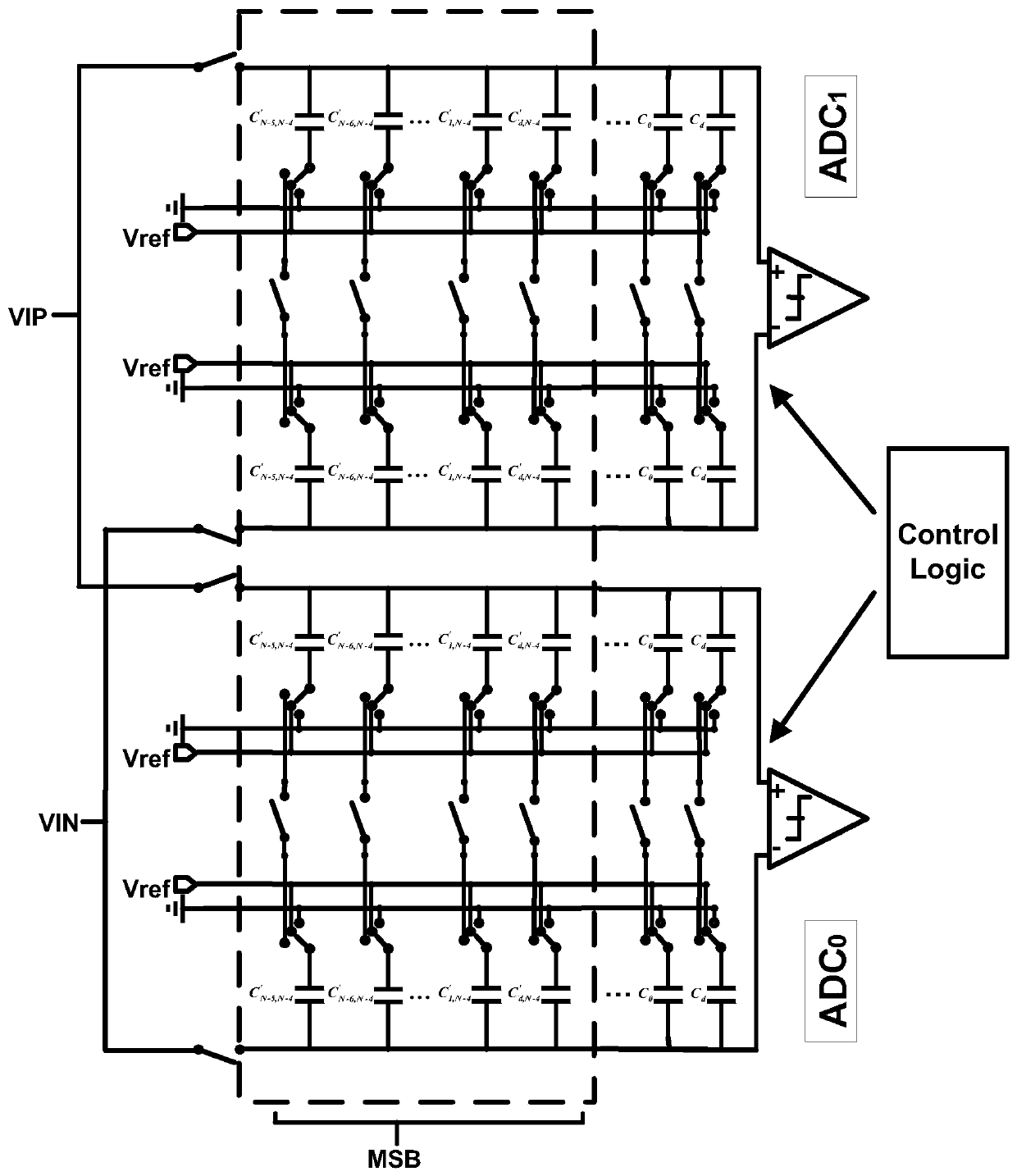

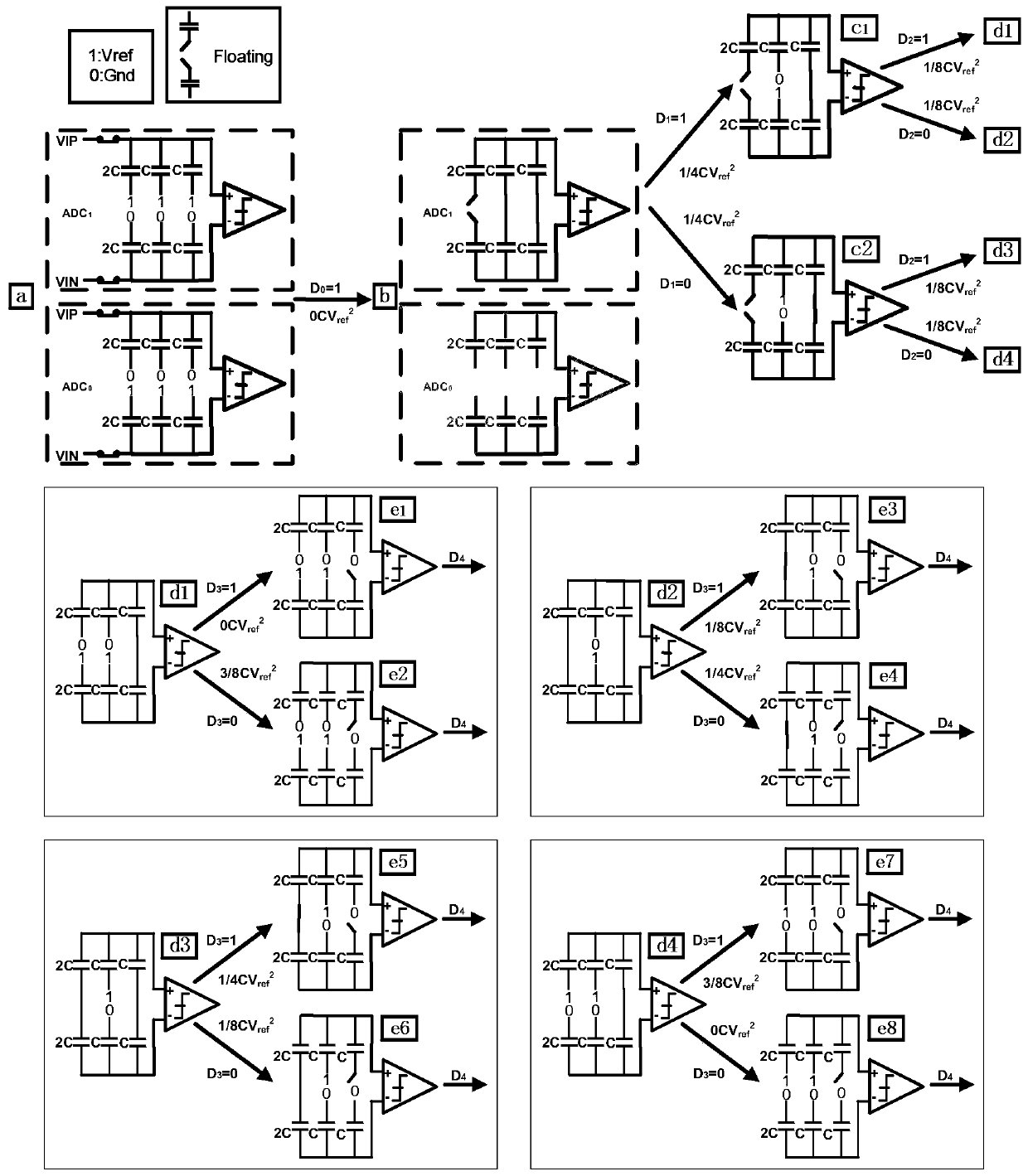

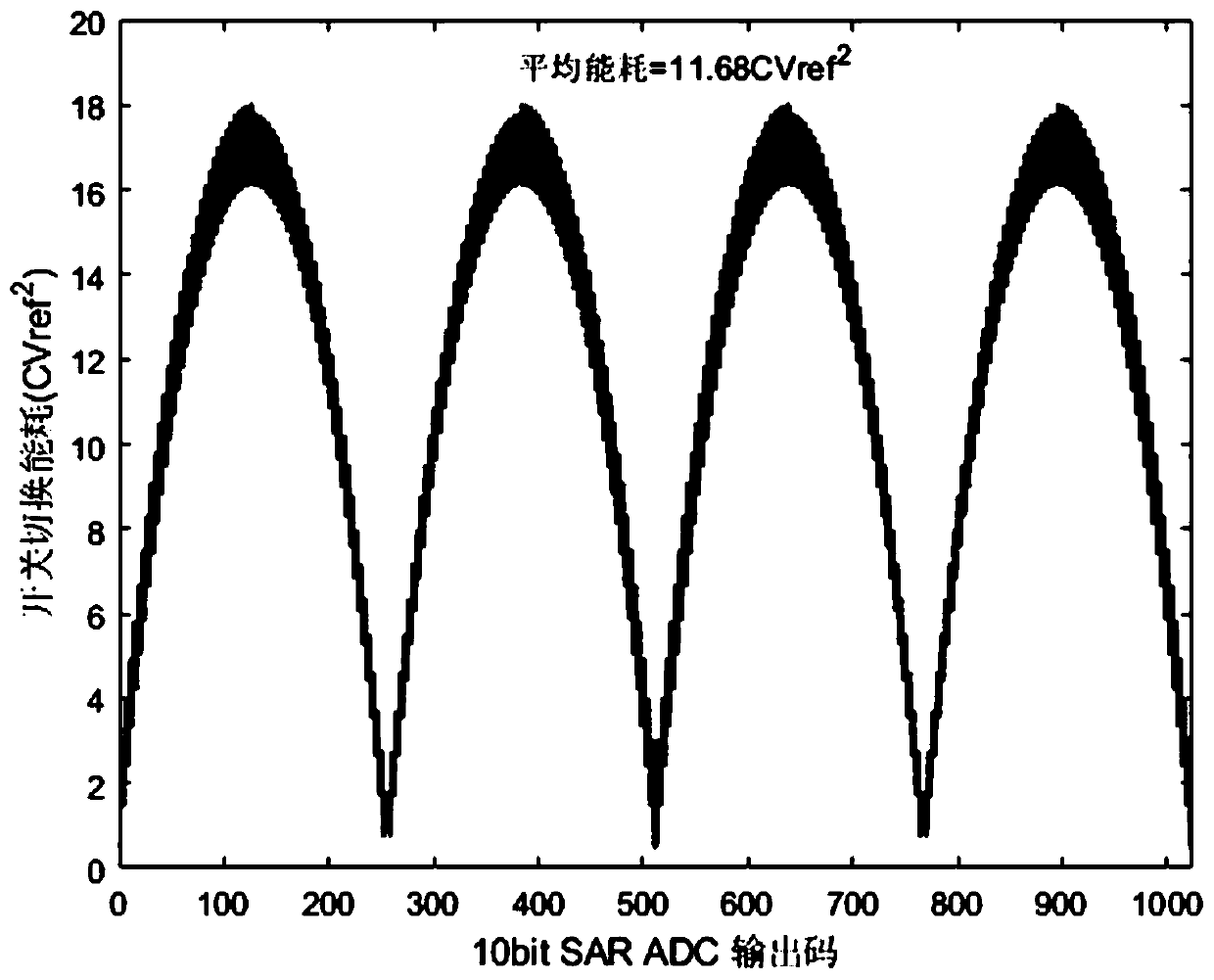

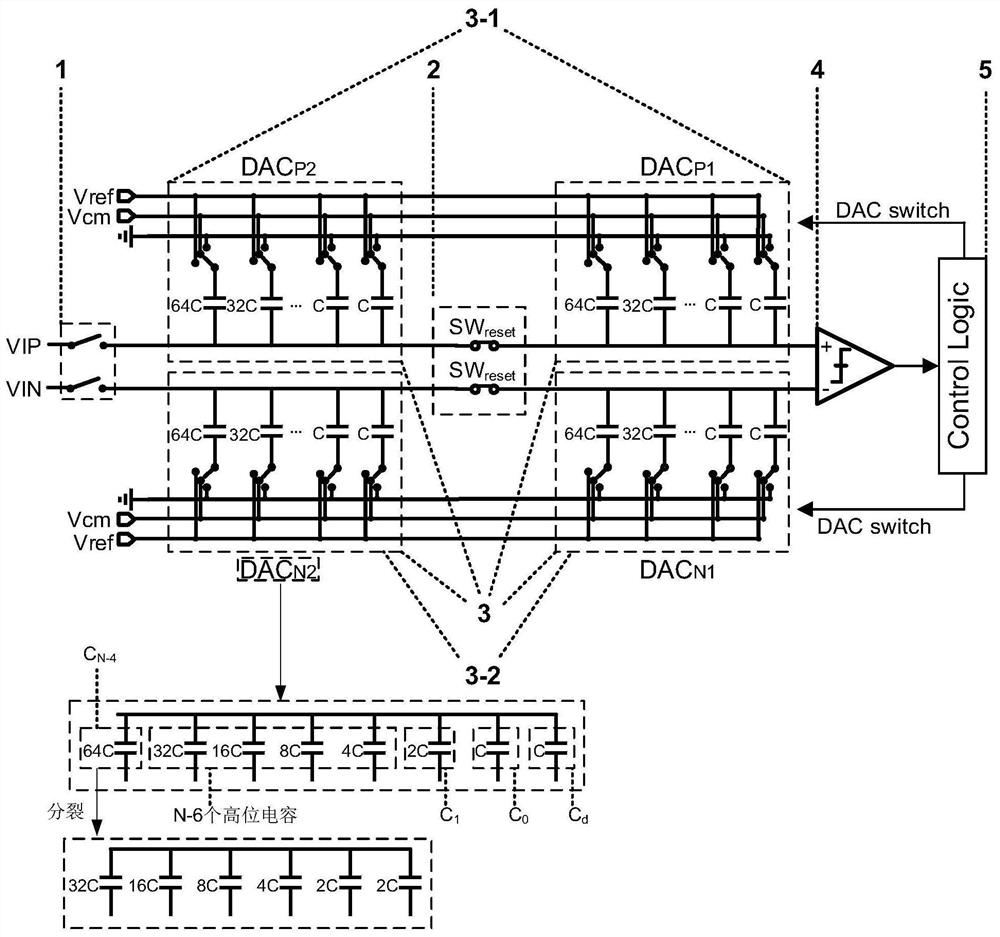

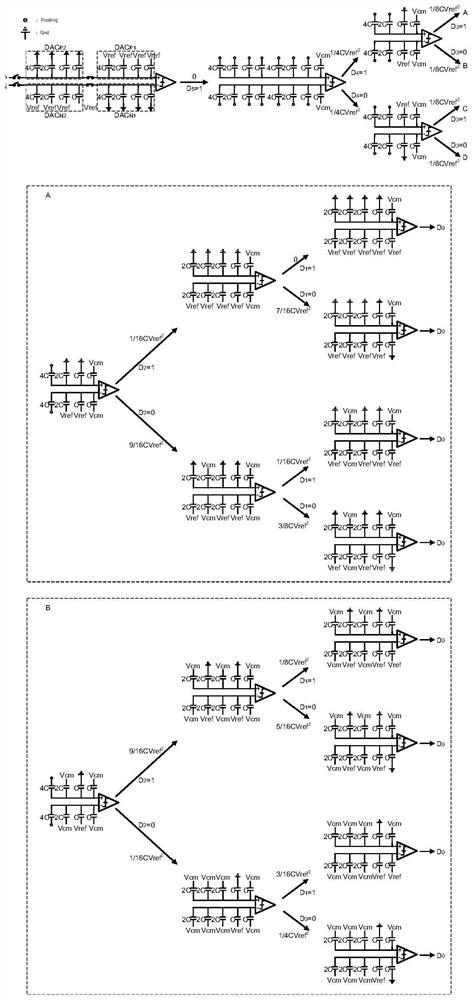

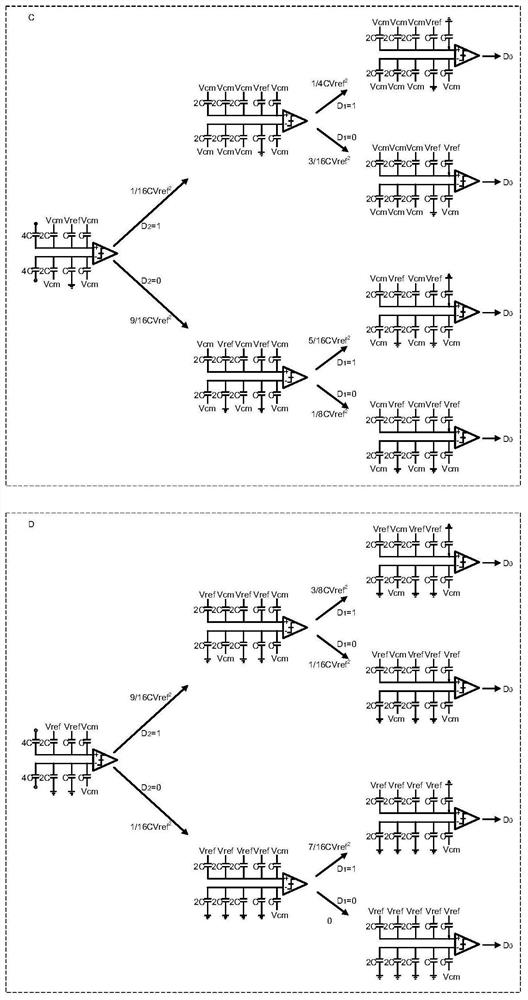

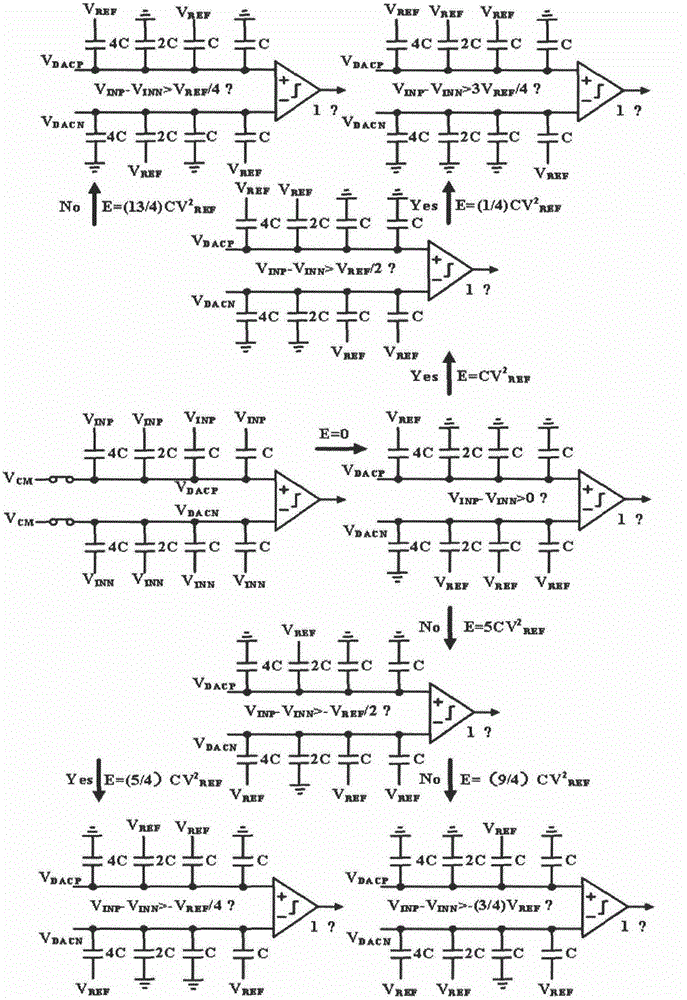

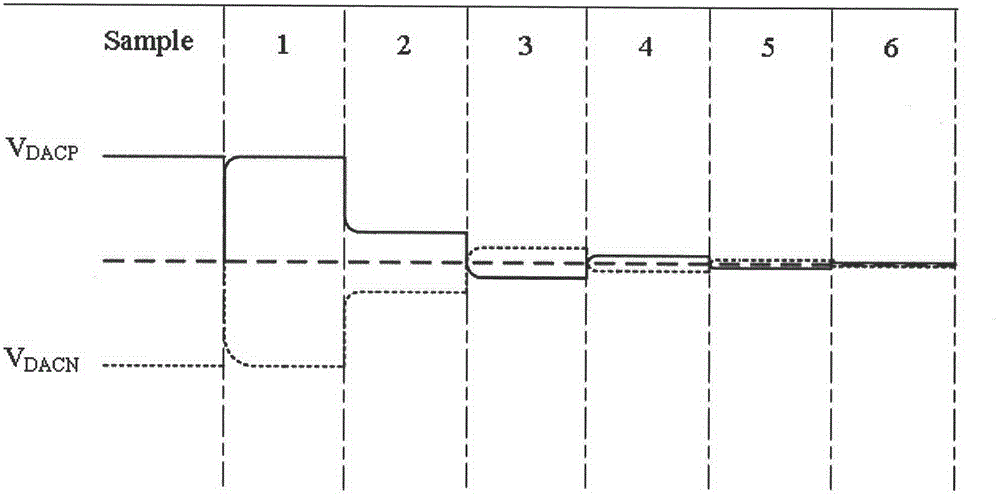

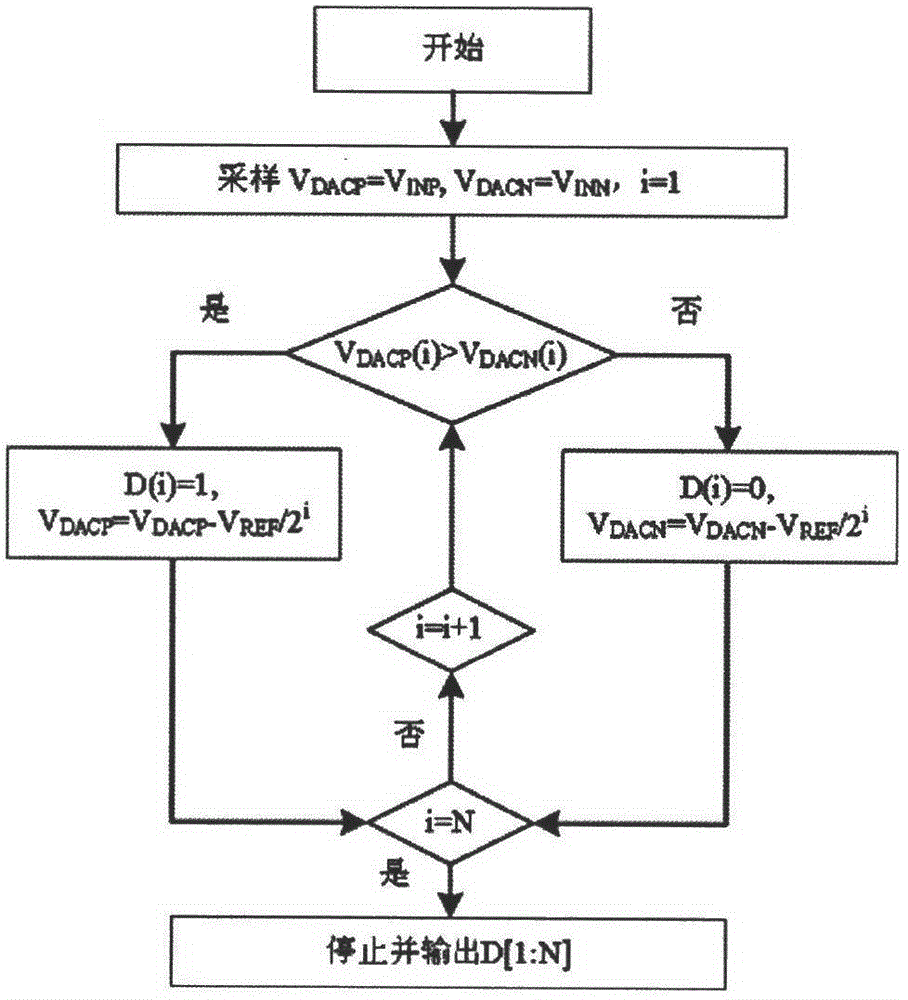

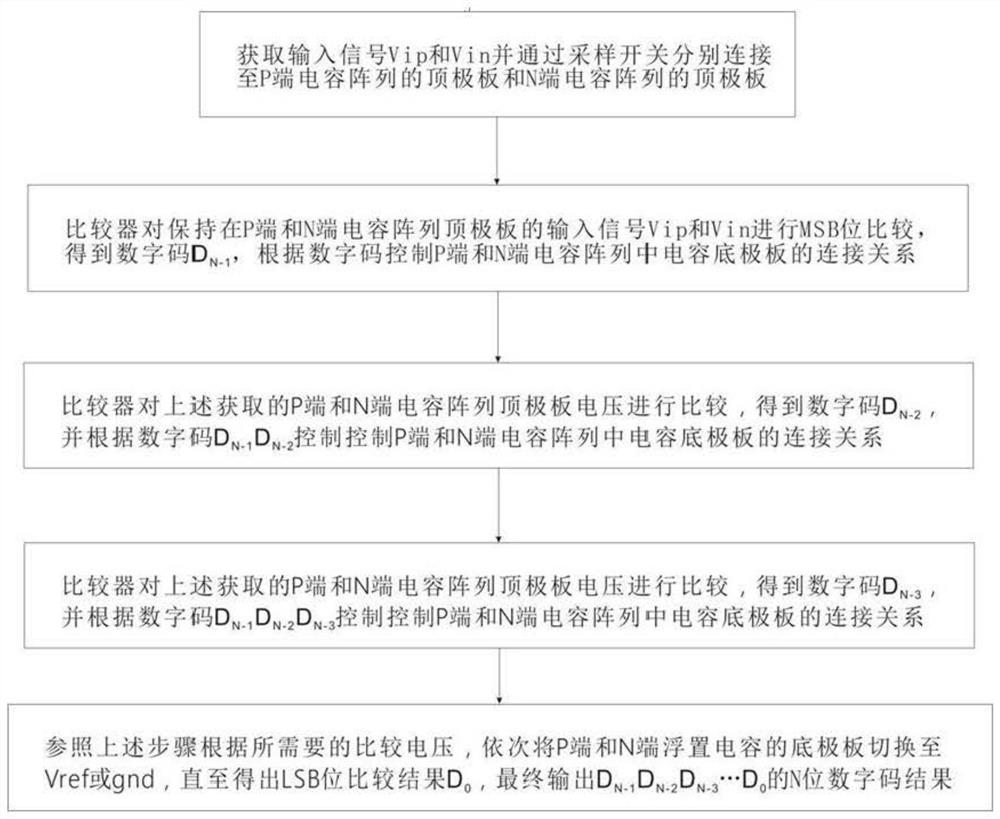

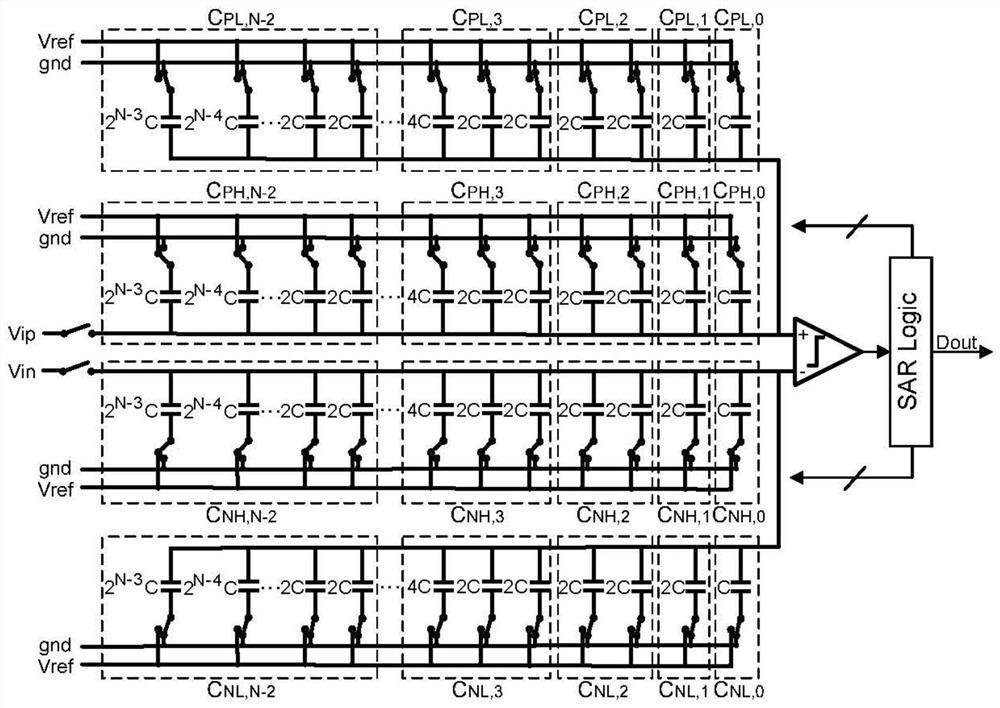

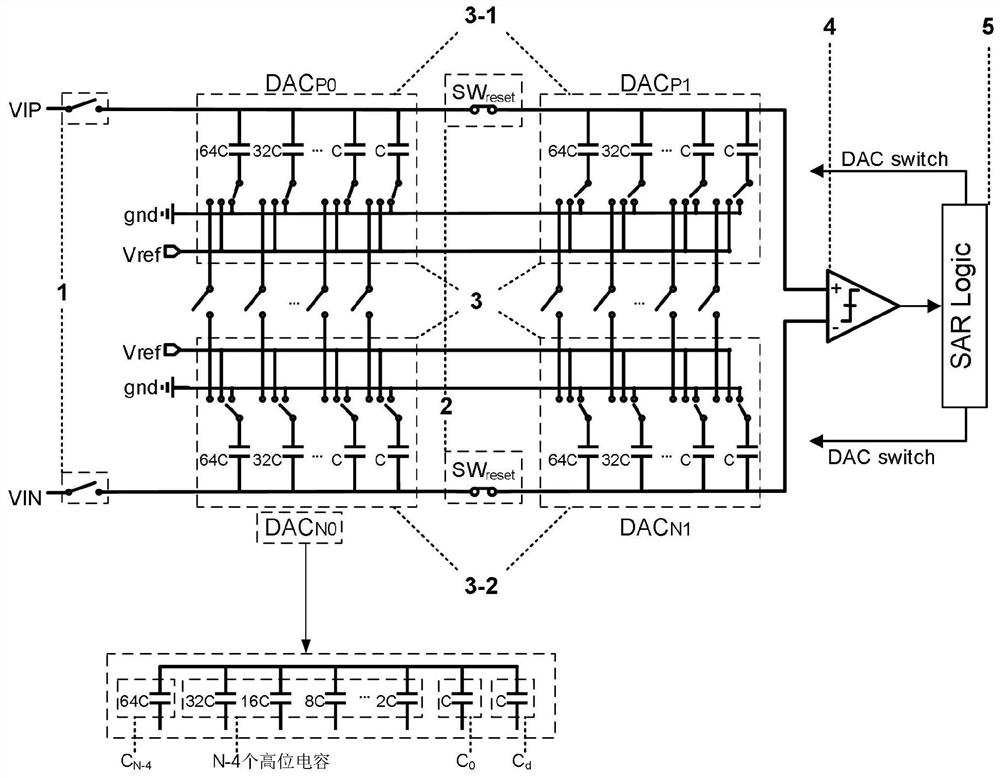

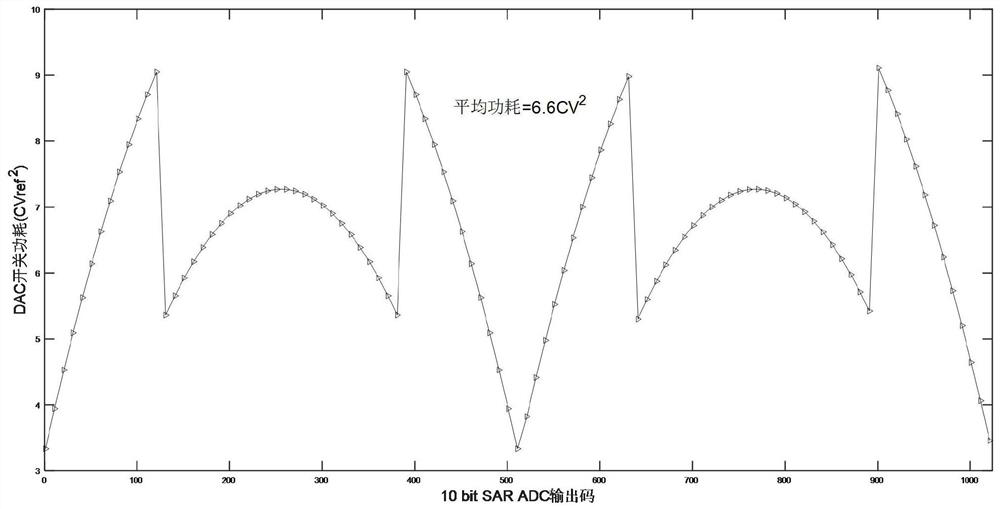

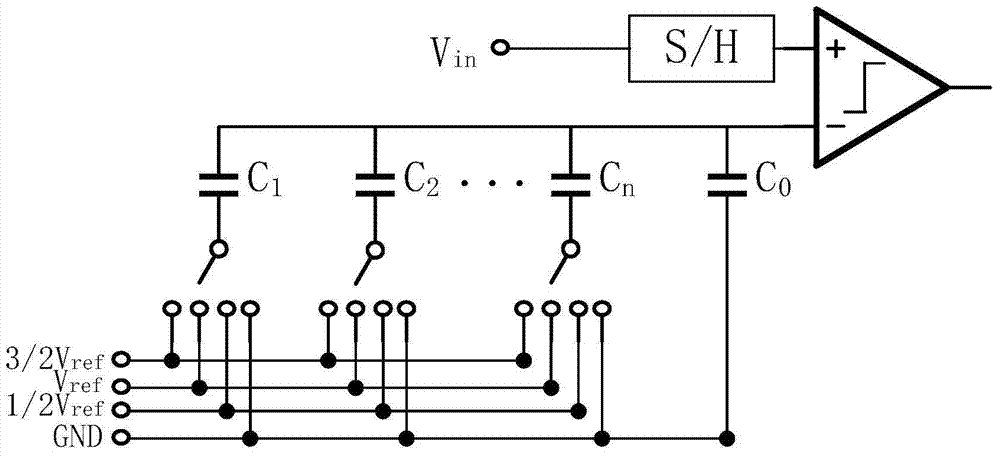

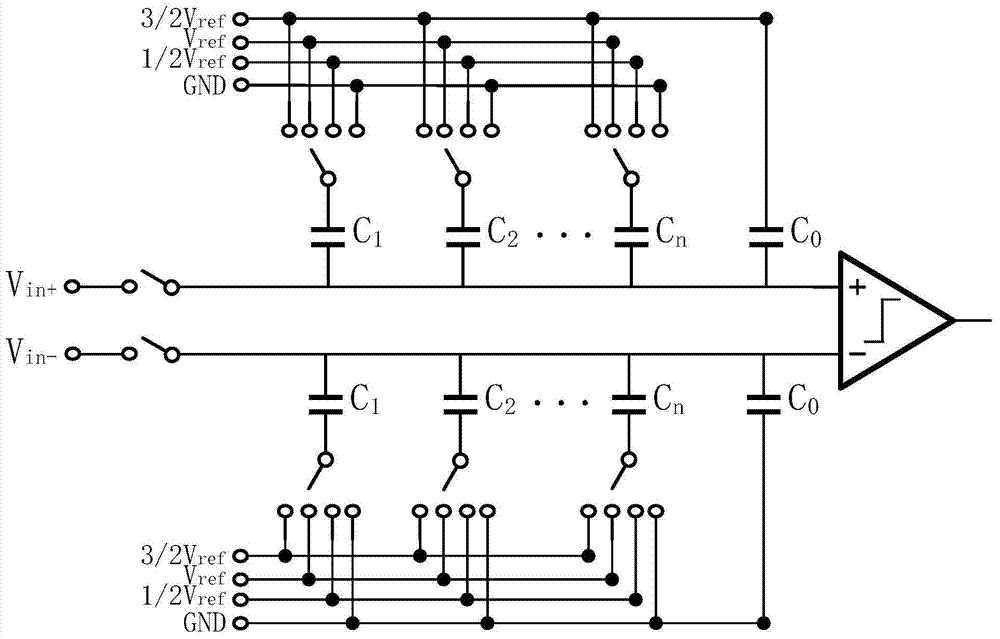

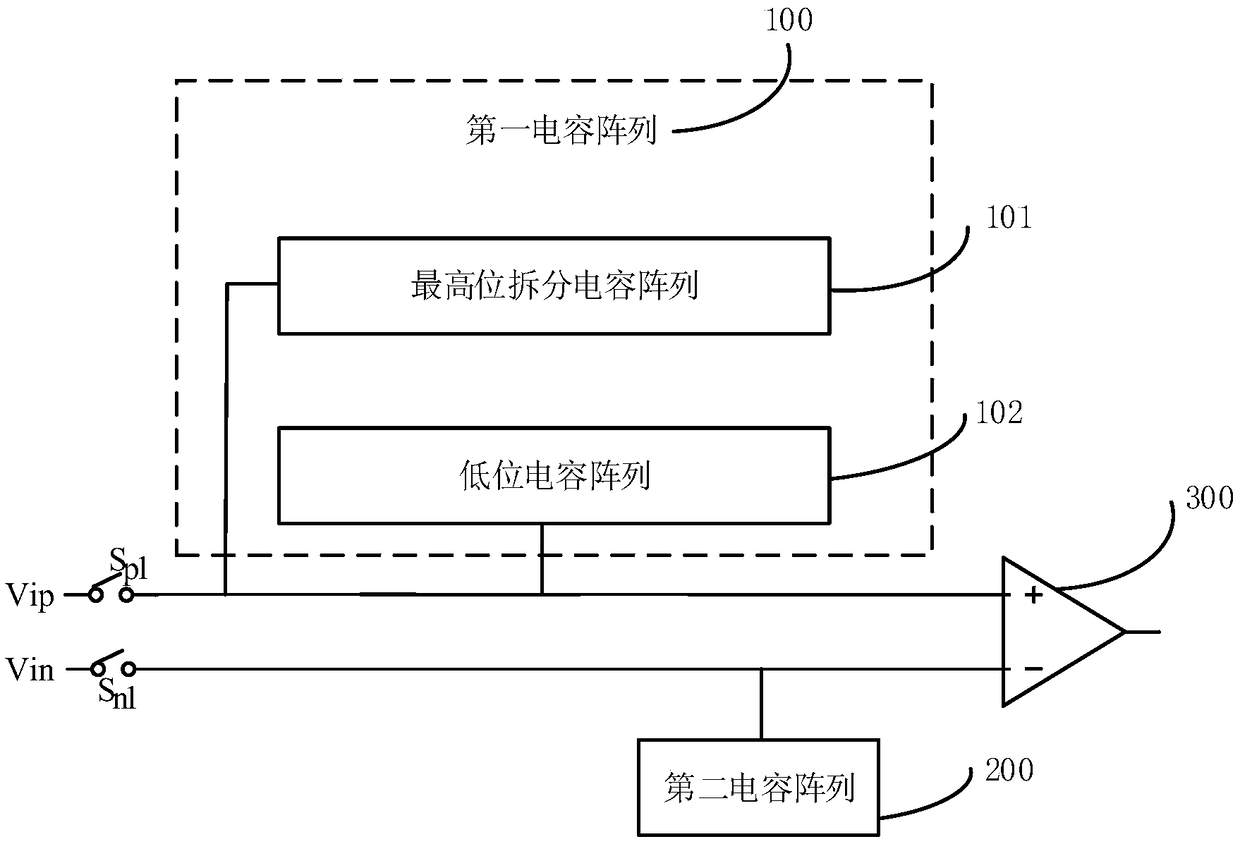

Capacitor array switching method applied to low-voltage SAR ADC

ActiveCN110380730AImprove signal-to-noise ratioReduce Switching Power ConsumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceLow voltage

The invention discloses a capacitor array switching method applied to a low-voltage SAR ADC. An analog-to-digital converter based on the method comprises two N-bit sub analog-to-digital converters with the same structure, the method comprises the following steps: for the input signals VIP and VIN, after N comparisons, obtaining N-bit digital output codes, which are divided into a sampling stage and a conversion stage, wherein, in the sampling stage, the input signals VIP and VIN are respectively connected to top polar plates of an upper capacitor array and a lower capacitor array through sampling switches, and bottom polar plates of all capacitors of the upper capacitor array and bottom polar plates of all capacitors of the lower capacitor array are connected to corresponding voltages; and, in the conversion stage, the comparator performs MSB bit-to-LSB bit comparison on the voltages of the top polar plates of the upper and lower capacitor arrays to obtain corresponding digital codes,and the connection relationship of the capacitor bottom polar plates in the upper and lower capacitor arrays are controlled according to the digital codes, and the N-bit digital output codes are obtained through N times of comparison. According to the invention, the power consumption of the DAC part in the conversion process can be greatly reduced, only two reference levels are adopted, and the method is suitable for the design under the near threshold voltage.

Owner:SOUTHEAST UNIV

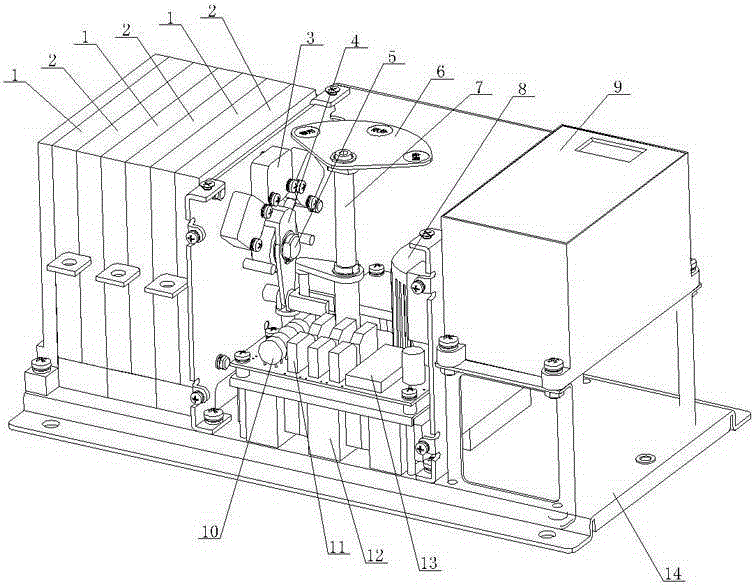

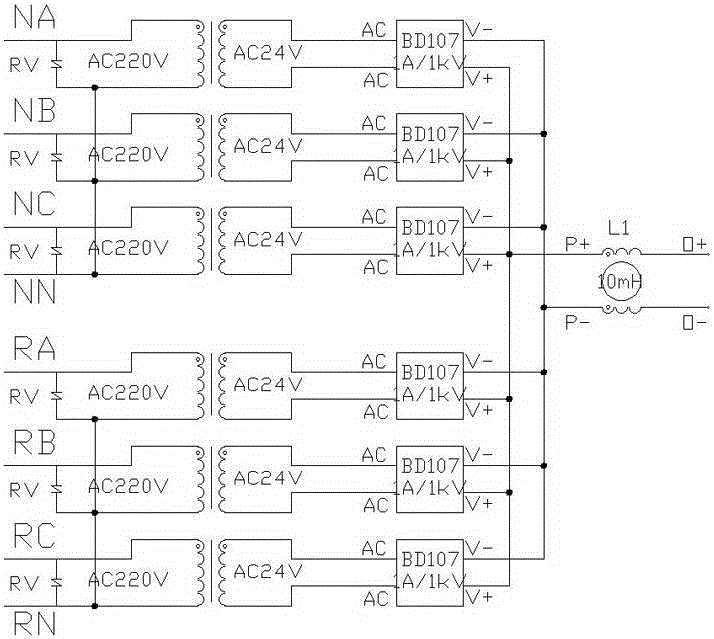

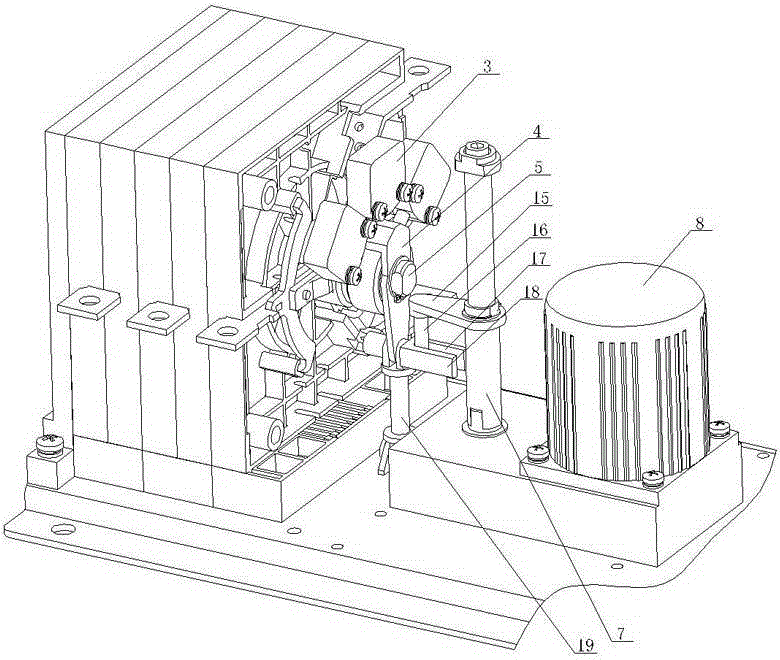

PC-level dual-power source automatic change-over switch

InactiveCN105225861AReliable short-circuit making capacityEnsure safetyContact driving mechanismsPower network operation systems integrationElectricityTransformer

The invention discloses a PC-level dual-power source automatic change-over switch. The PC-level dual-power source automatic change-over switch is characterized in that the PC-level dual-power source automatic change-over switch includes a bottom plate as well as a contact system, a transmission device, a rectifying device and an intelligent controller which are installed on the bottom plate; a plurality of single-phase contact units are stacked in a front-and-back manner so as to from the contact system; the transmission mechanism is arranged between the contact system and the intelligent controller; the transmission mechanism is driven under the control of a motor; the rectifying device is arranged at one side of the transmission mechanism; and the rectifying device includes an one-way transformer, a rectifier bridge and a common-mode suppression coil. The PC-level dual-power source automatic change-over switch of the invention has the advantages of simple structure and convenient assembly. The normal work of the PC-level dual-power source automatic change-over switch can be guaranteed as long as any one phase of two power sources is switched on, and the safety of electricity utilization can be ensured; a commonly-used power source and a standby power source share one load end, and the power consumption of the switch can be decreased; the accuracy of the position of the switch in the switching of the two power sources can be greatly ensured; the possibility of simultaneous switching off of the two power sources under any circumstances can be eliminated, and the reliability of power supply and the safety of electrical equipment can be greatly improved.

Owner:WENZHOU POPP ELECTRIC

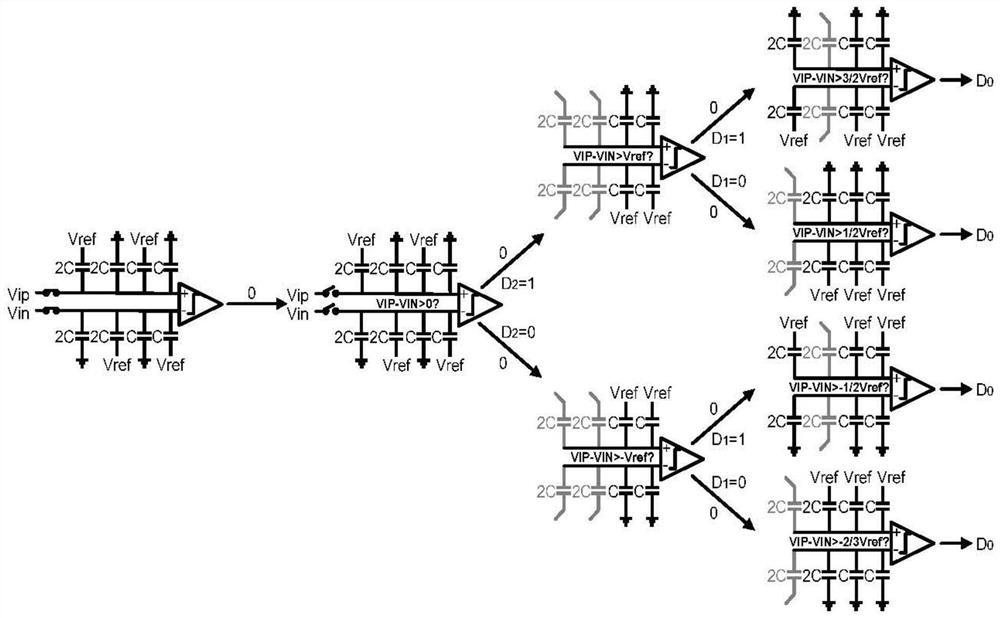

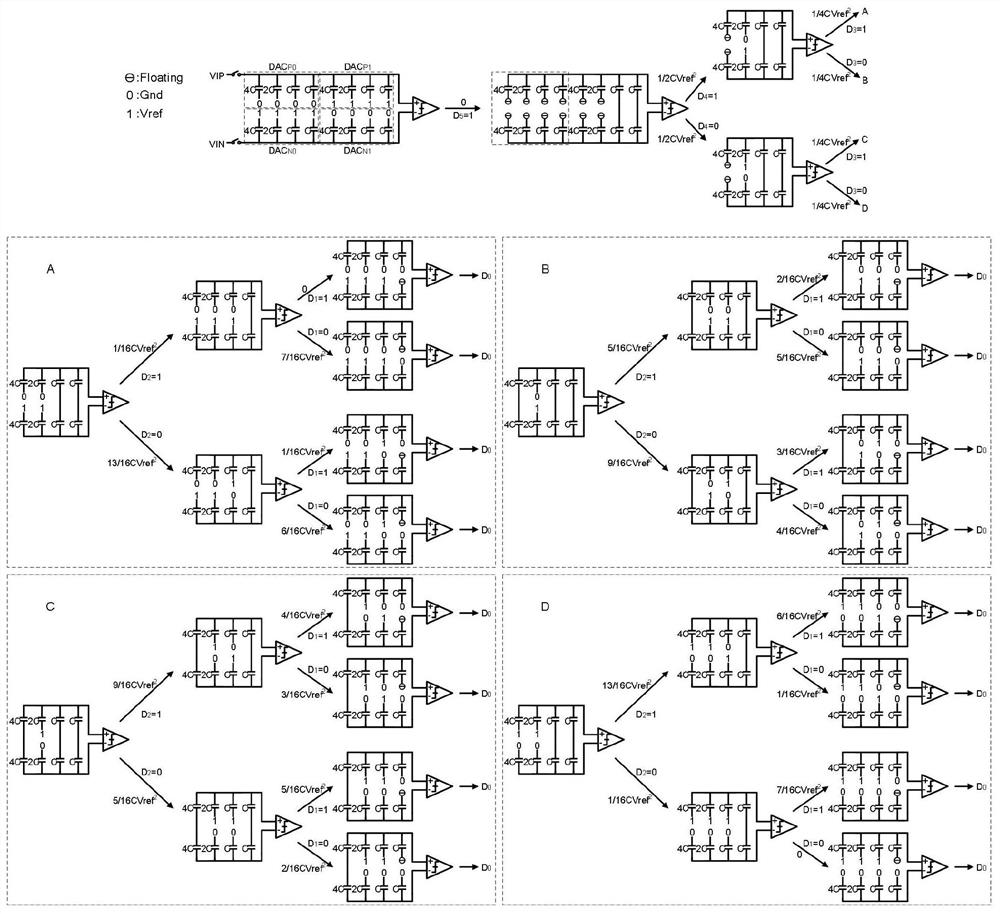

Successive approximation type analog-to-digital converter and three-level switching method thereof

PendingCN112583409AReduce Switching Power ConsumptionReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceA d converter

The invention discloses a successive approximation type analog-to-digital converter and a three-level switching method thereof. The method comprises the steps that input signals VIP and VIN are compared N times to obtain an N-bit digital code, the N-bit digital code is divided into a sampling stage and a conversion stage, and in the sampling stage, the input signals VIP and VIN are connected to top polar plates of an upper capacitor array and a lower capacitor array through sampling switches respectively, and the bottom polar plate of each capacitor is connected to a corresponding voltage; inthe conversion stage, the comparator performs MSB bit-to-LSB bit comparison on the voltages of the top electrode plates of the upper capacitor array and the lower capacitor array to obtain corresponding digital codes, and the connection relation of the capacitor bottom electrode plates in the capacitor arrays is controlled according to the digital codes; and comparing for N times is performed to obtain an N-bit digital code. According to the invention, the voltage change of + / -Vref is generated on the top plate of the capacitor for the first time, so that the reference voltage Vref of the capacitor array is reduced to half of the reference voltage Vref of a common method. Compared with a traditional switching algorithm, the method has the advantages that 99.79% of DAC power consumption isreduced, 75% of capacitance area is saved, common-mode level offset is only 0.5 LSB, and compromise of energy efficiency, area and common-mode level is achieved.

Owner:SOUTHEAST UNIV

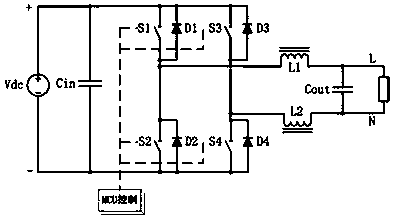

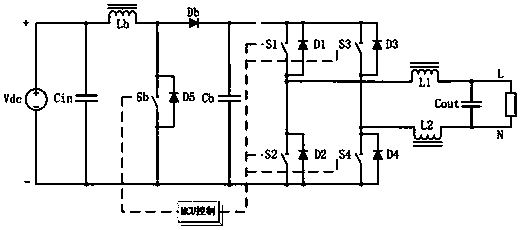

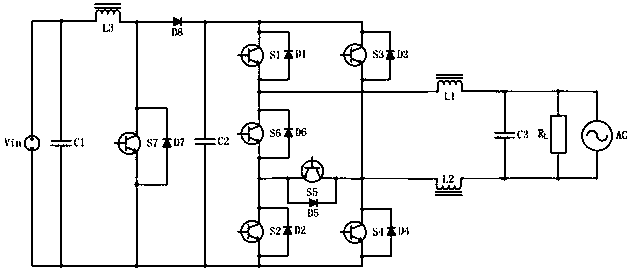

Two-stage single-phase inverter

The invention discloses a two-stage single-phase inverter, including a DC input power supply, a DC-DC booster circuit, a single-phase multi-level inverter circuit and a control circuit. The input endof the DC-DC booster circuit is connected with the DC input power supply, and the output end is connected with the input end of the single-phase multi-level inverter circuit; when a voltage of the DCinput power supply is lower than a voltage peak of AC output of the single-phase multi-level inverter circuit, the two-stage single-phase inverter works in a Boost mode, the DC-DC booster circuit works in an SPWM high-frequency switch state, and the single-phase multi-level inverter circuit works in a power frequency commutation state; and when the voltage of the DC input power supply is higher than the voltage peak of AC output of the single-phase multi-level inverter circuit, the two-stage single-phase inverter works in a Buck mode, the DC-DC booster circuit works in a bypass working state,and the single-phase multi-level inverter circuit works in an SPWM high-frequency switch state. The front stage and the rear stage of the two-stage single-phase inverter work in a partial-power mode,a relatively small DC bus capacitor can be used, and switch power consumption is small.

Owner:胡炎申

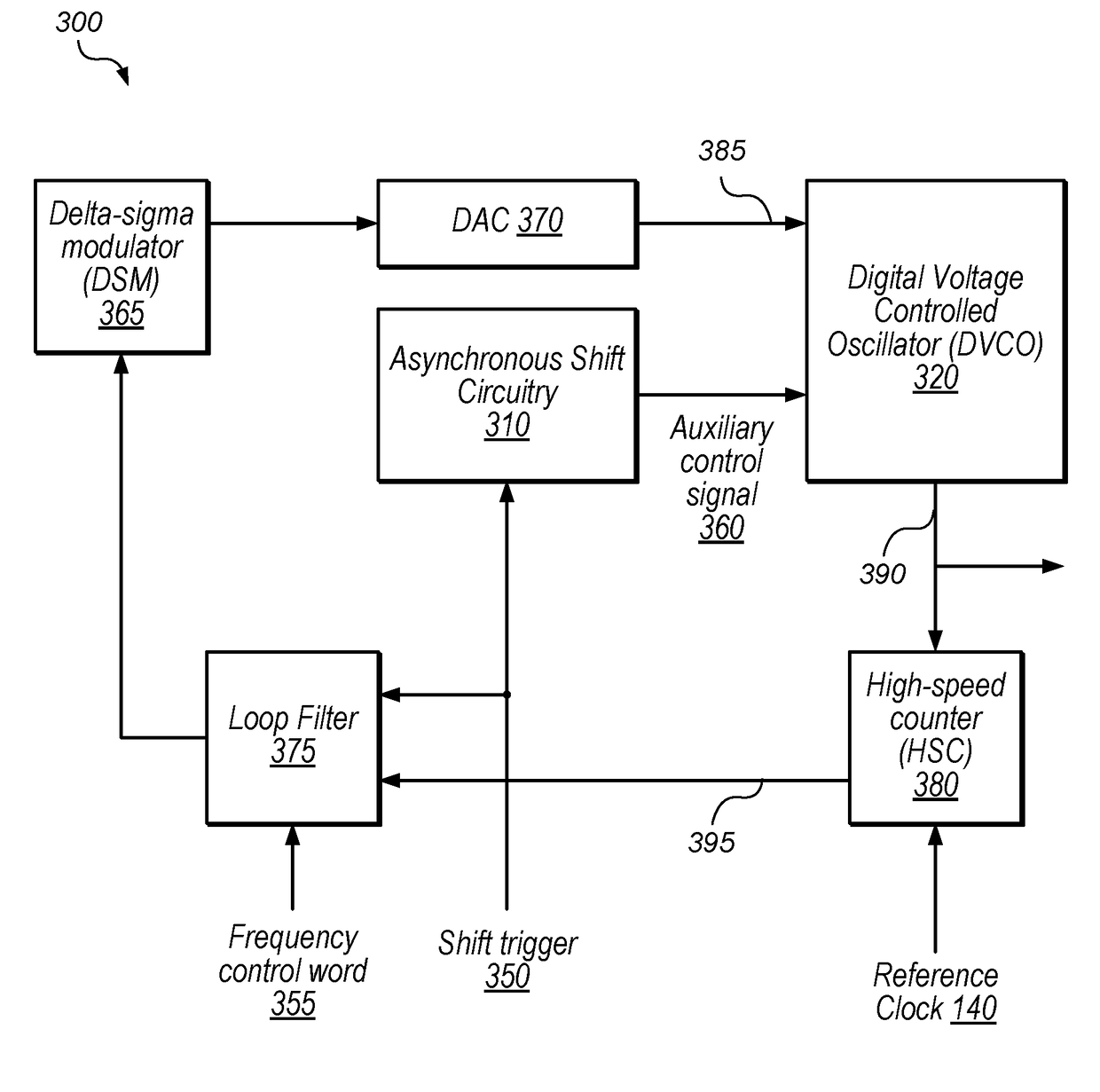

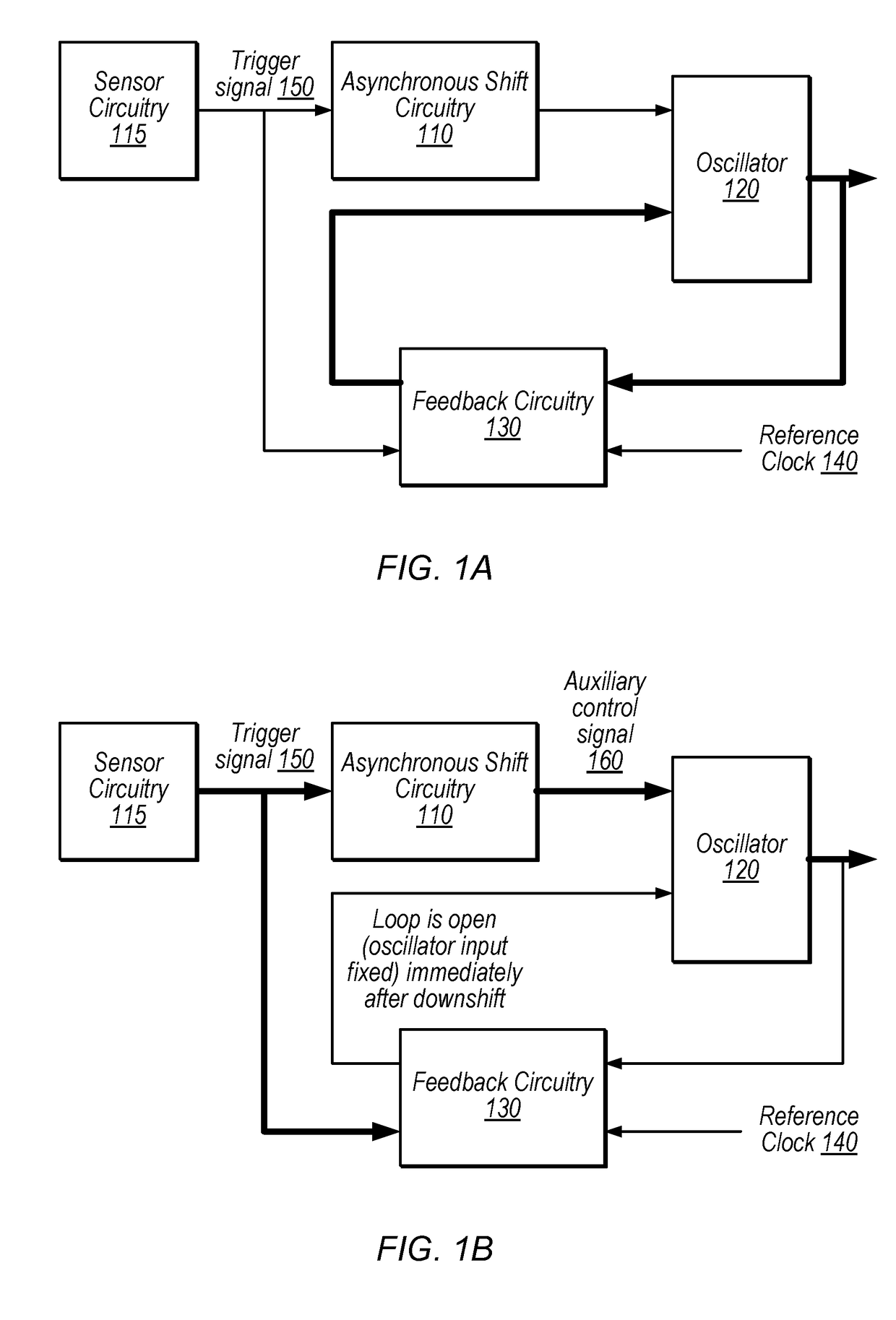

Downshift Techniques for Oscillator with Feedback Loop

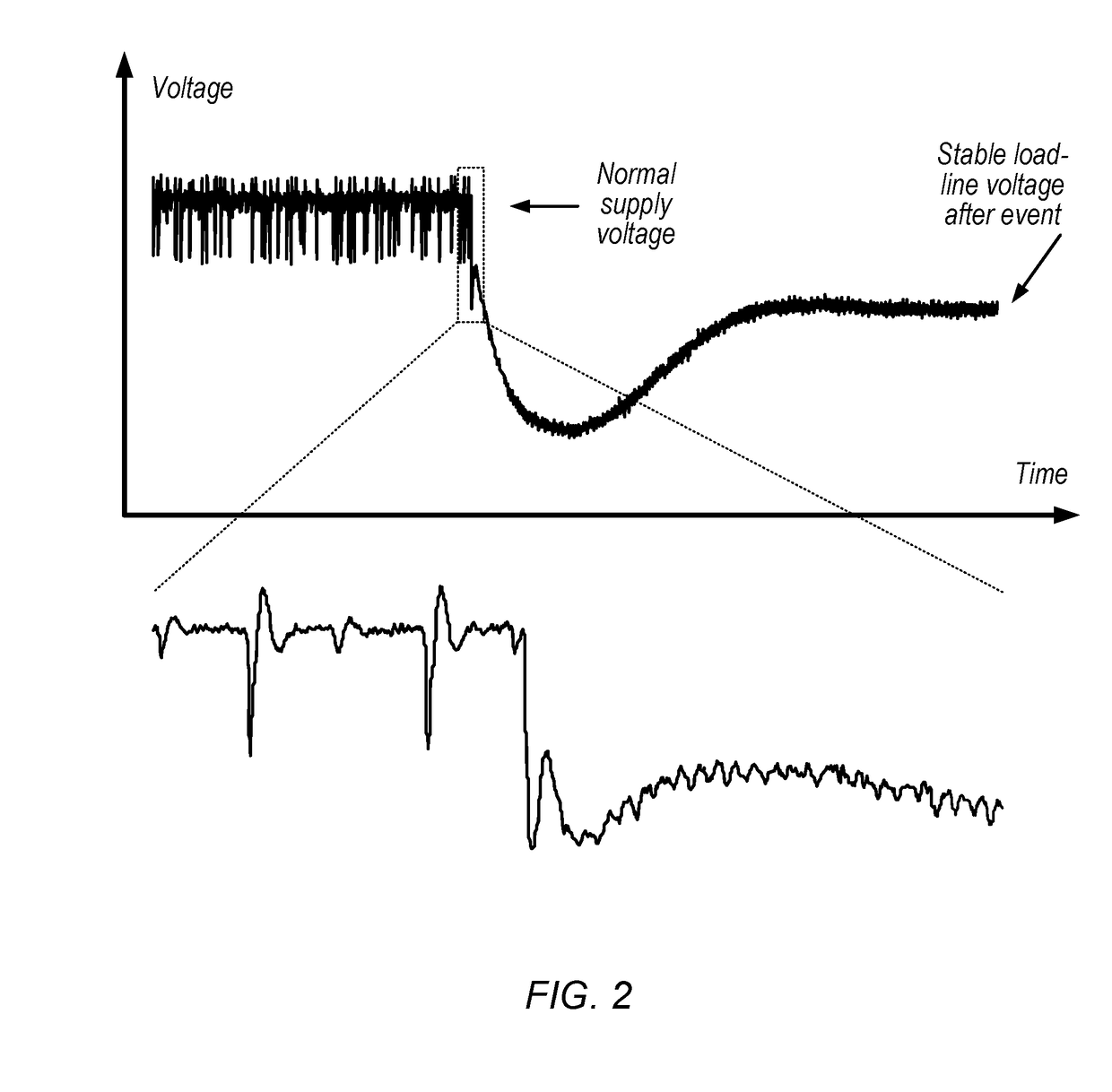

ActiveUS20170324417A1Quickly downshiftReduce Switching Power ConsumptionPulse automatic controlOscillations generatorsNegative feedbackClosed loop

Techniques are disclosed relating to rapidly downshifting the output frequency of an oscillator. In some embodiments, the oscillator is configured to operate in a closed-loop mode in which negative feedback is used to maintain a particular output frequency (e.g., in a phase-locked loop (PLL)). In some embodiments, the negative feedback loop is configured to maintain the output of the oscillator at a particular frequency based on a reference clock signal and the output of the oscillator. The nature of a negative feedback loop may render rapid frequency changes difficult, e.g., because of corrections by the loop. Therefore, in some embodiments, the loop is configured to switch to an open-loop mode in which a control input to the oscillator is fixed. In some embodiments, the loop switches to open-loop mode in response to a trigger signal and control circuitry forces the oscillator to a new target frequency.

Owner:APPLE INC

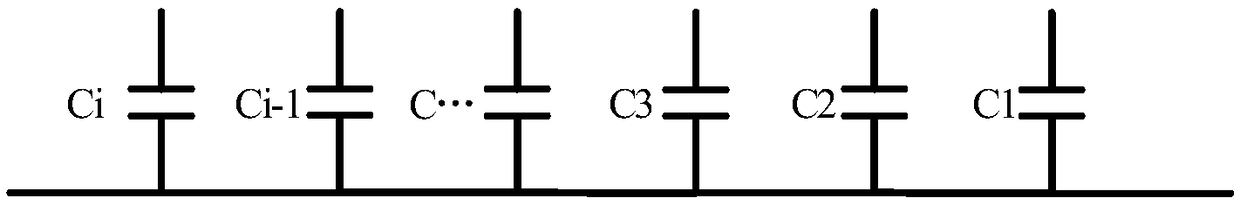

Monotonic switching method and circuit for successive approximation type analog-digital converter

InactiveCN104485961AQuantity halvedNo energy consumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceDigital down converter

The invention relates to a monotonic switching method and circuit for a successive approximation type analog-digital converter. The monotonic switching method and circuit are used for n-bit analog-digital conversion. The monotonic switching circuit comprises a comparator and (n-1) bits of binary system switching capacitors, an upper electrode plate of the first capacitor in each pair of capacitors is connected with a positive phase input end of the comparator and a difference input signal end VINP, an upper electrode plate of the second capacitor in each pair of capacitors is connected with a negative phase input end of the comparator and a difference input signal end VINN, and a lower electrode plate of each pair of capacitors is selectively connected with reference voltage VREF or a ground end GND. Sampling is carried out through the upper electrode plates, primary power consumption is avoided, the unit capacitor number is reduced, switching power consumption is greatly reduced through the monotonic switching method, and the circuit is simple and reliable in structure.

Owner:WUJIANG SHENGBORUI INFORMATION TECH

Low-voltage SAR ADC switch switching method based on charge recovery

ActiveCN112332846AEfficient and flexible switching algorithmReduce Switching Power ConsumptionElectric signal transmission systemsAnalogue-digital convertersCapacitanceSynthetic aperture radar

The invention discloses a low-voltage SAR ADC (Synthetic Aperture Radar Analog-to-Digital Converter) switch switching method based on charge recovery, which comprises the following steps: sampling stage differential input signals Vip and Vin are connected to top polar plates of P-end and N-end capacitor arrays through sampling switches, reference voltages Vref and gnd are connected to bottom polarplates of P-end and N-end corresponding capacitors, the capacitor arrays are pre-charged; and the sampling switches are disconnected in the transforming stage. the comparator compares the voltages ofthe top electrode plates of the P-end capacitor array and the N-end capacitor array from the MSB bit to the LSB bit in sequence to obtain digital codes of corresponding bits, floating and voltage switching of corresponding capacitors of the P-end capacitor array and the N-end capacitor array are controlled according to the digital codes, and a binary search algorithm is completed. According to the invention, 100% capacitor array switching energy can be saved, extra third reference voltage does not need to be generated, the circuit is suitable for design under near threshold voltage, in a conversion stage, common-mode voltage of top polar plates of the P-end capacitor array and the N-end capacitor array is always kept constant, and the design difficulty of a comparator is reduced.

Owner:SOUTHEAST UNIV

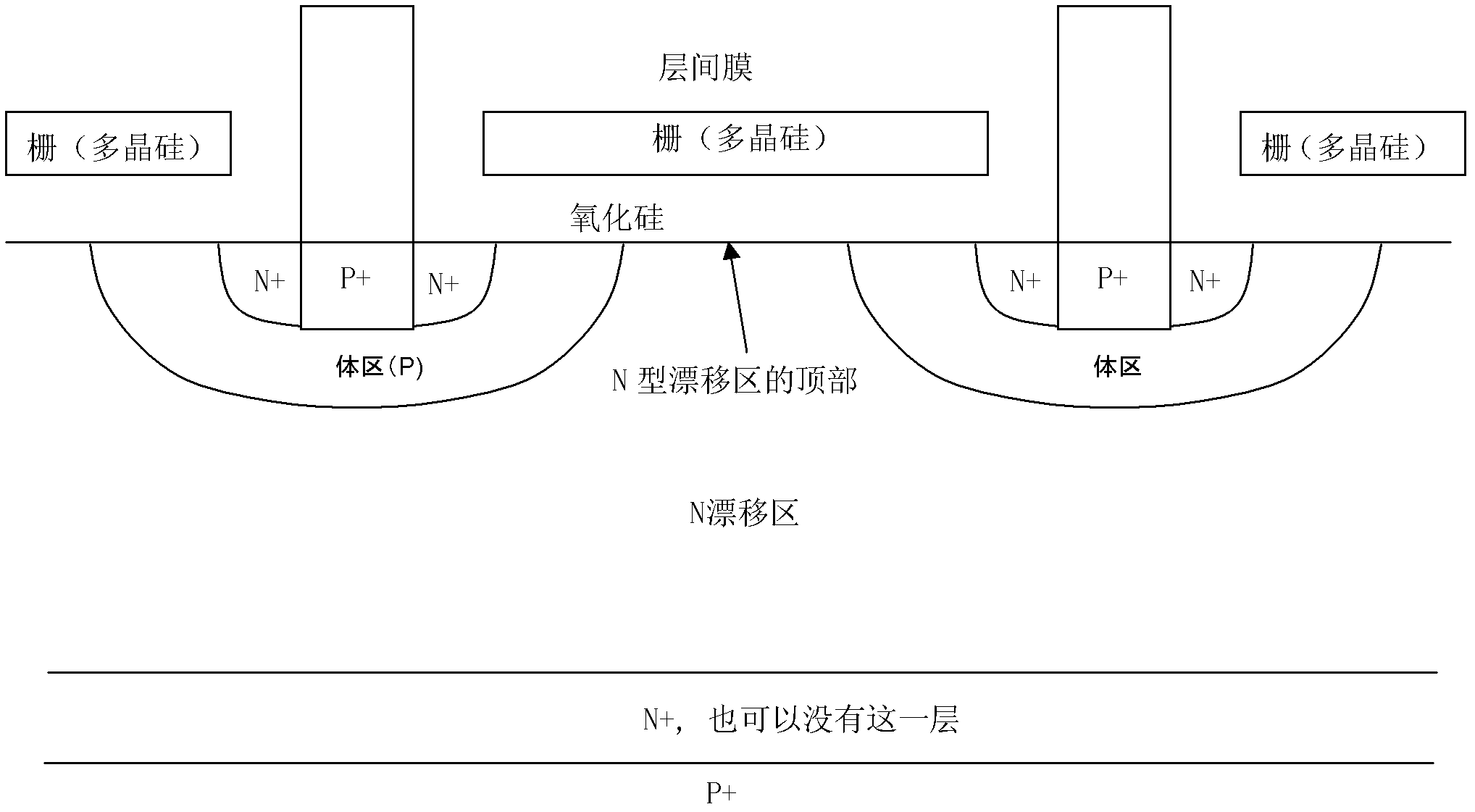

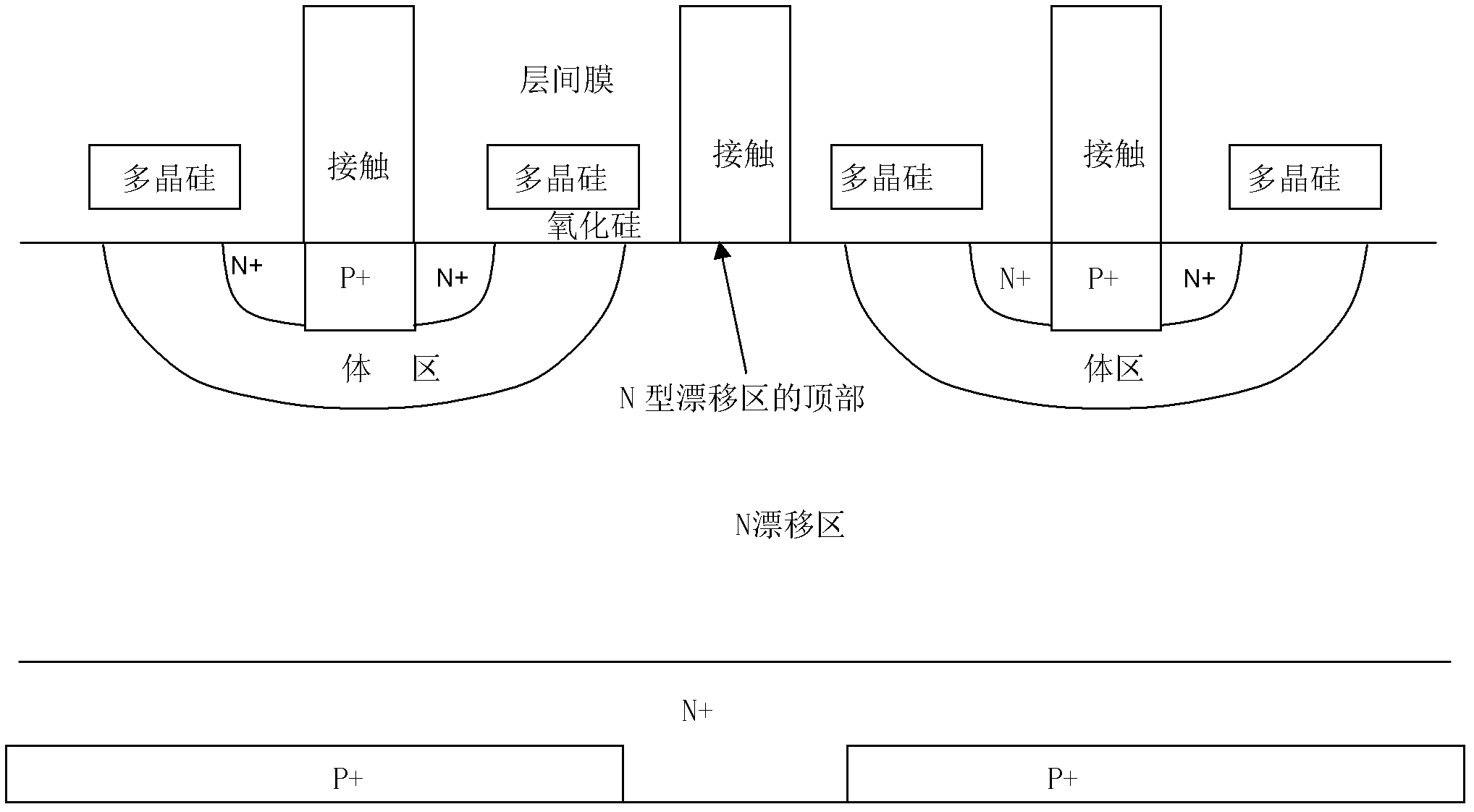

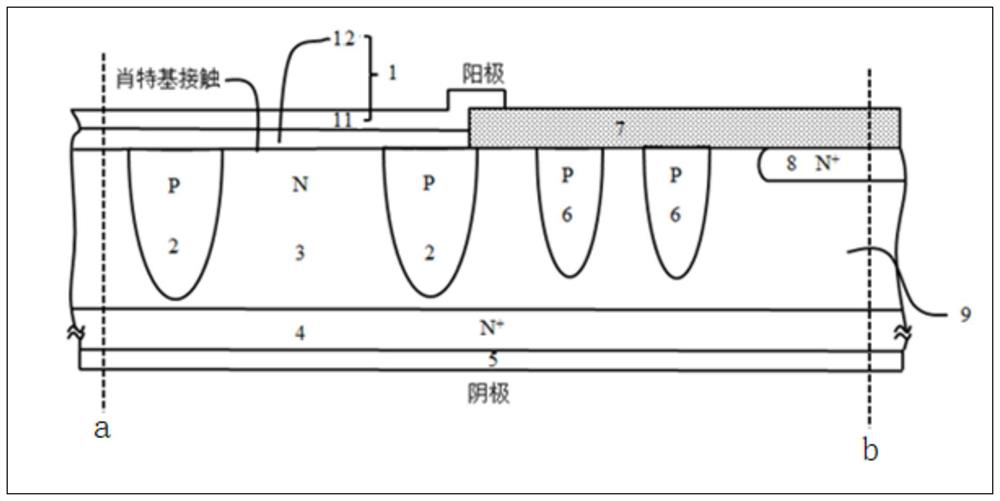

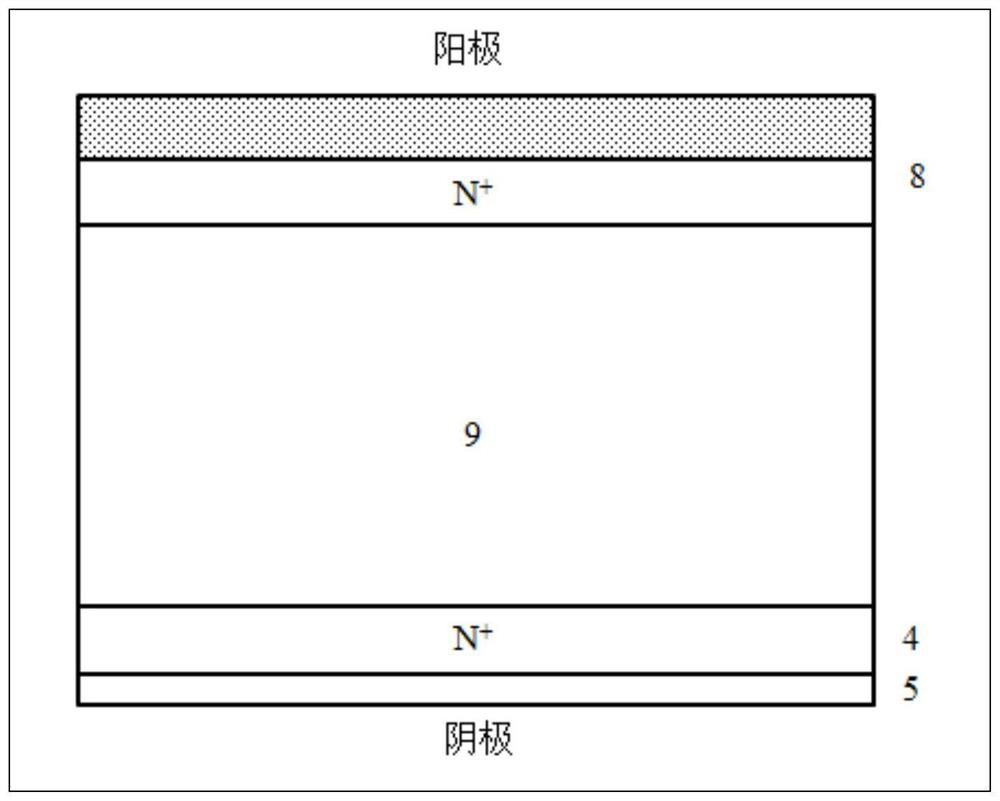

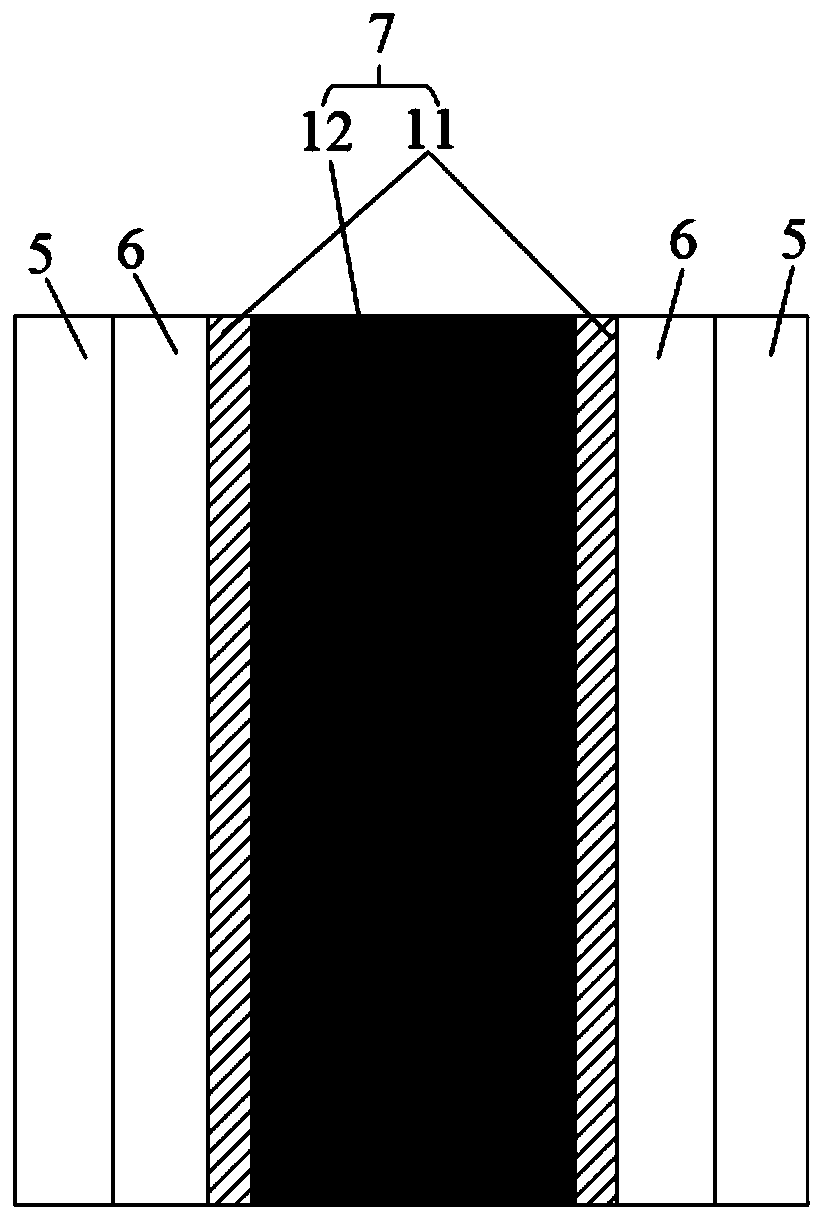

Insulated gate bipolar transistor structure integrated with Schottky diode and preparation method thereof

ActiveCN102931216AFast switching speedReduce Switching Power ConsumptionSemiconductor/solid-state device manufacturingSemiconductor devicesInsulated-gate bipolar transistorReverse recovery

The invention discloses an insulated gate bipolar transistor structure integrated with a Schottky diode. The insulated gate bipolar transistor structure comprises an IGBT (Insulated Gate Bipolar Transistor), wherein the top parts of N-type drift regions of the IGBT comprise regions covered by polysilicon gates and regions not covered by the polysilicon gates; the regions not covered by the polysilicon gates and metal arranged at the upper parts thereof form Schottky contact, so that a Schottky diode is integrated with the IGBT and are connected with a collecting electrode and an emitting electrode of the IGBT in parallel. According to the invention, the Schottky diode is integrated in the IGBT, when current of the IGBT is conducted from the emitting electrode to the collecting electrode, freewheeling function can be achieved, so that the switching speed is improved, and the switching power consumption is reduced; and when the conduction of current of the IGBT from the collecting electrode to the emitting electrode is turned off, a bypass can be additionally provided for reverse recovery of minority carriers, so that the reverse recovery time for freewheeling turn-off is greatly reduced and the switching speed is improved. The invention further discloses a method for preparing the insulated gate bipolar transistor structure integrated with the Schottky diode.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Two-level switching method applied to successive approximation type analog-to-digital converter

PendingCN112332847AImprove energy efficiencyReduce Switching Power ConsumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceControl engineering

The invention discloses a two-level switching method applied to a successive approximation type analog-to-digital converter, which comprises the following steps of: comparing input signals VIP and VINfor N times to obtain an N-bit digital code, dividing the N-bit digital code into a sampling stage and a conversion stage, connecting the input signals VIP and VIN to top polar plates of an upper capacitor array and a lower capacitor array through a sampling switch in the sampling stage, and connecting each capacitor bottom polar plate to a corresponding voltage; in the conversion stage, enablingthe comparator to perform comparison from MSB bits to LSB bits on the voltages of the top polar plates of the upper and lower capacitor arrays to obtain corresponding digital codes so as to control the state of the bottom polar plate of each capacitor; and comparing for N times to obtain an N-bit digital code. The voltage change of + / -Vref is generated by switching for the first time, and the reference voltage Vref of the capacitor array is reduced to half of the reference voltage Vref of a common method; the introduced floating state is released within three-step conversion so as to simplifythe control logic; and only the LSB bit introduces a common mode level offset of 0.5 LSB. Compared with a traditional switching algorithm, the method has the advantages that the power consumption ofthe DAC is reduced by 99.51%, the capacitance area is saved by 75%, and the requirements on other modules of the ADC are not improved.

Owner:SOUTHEAST UNIV

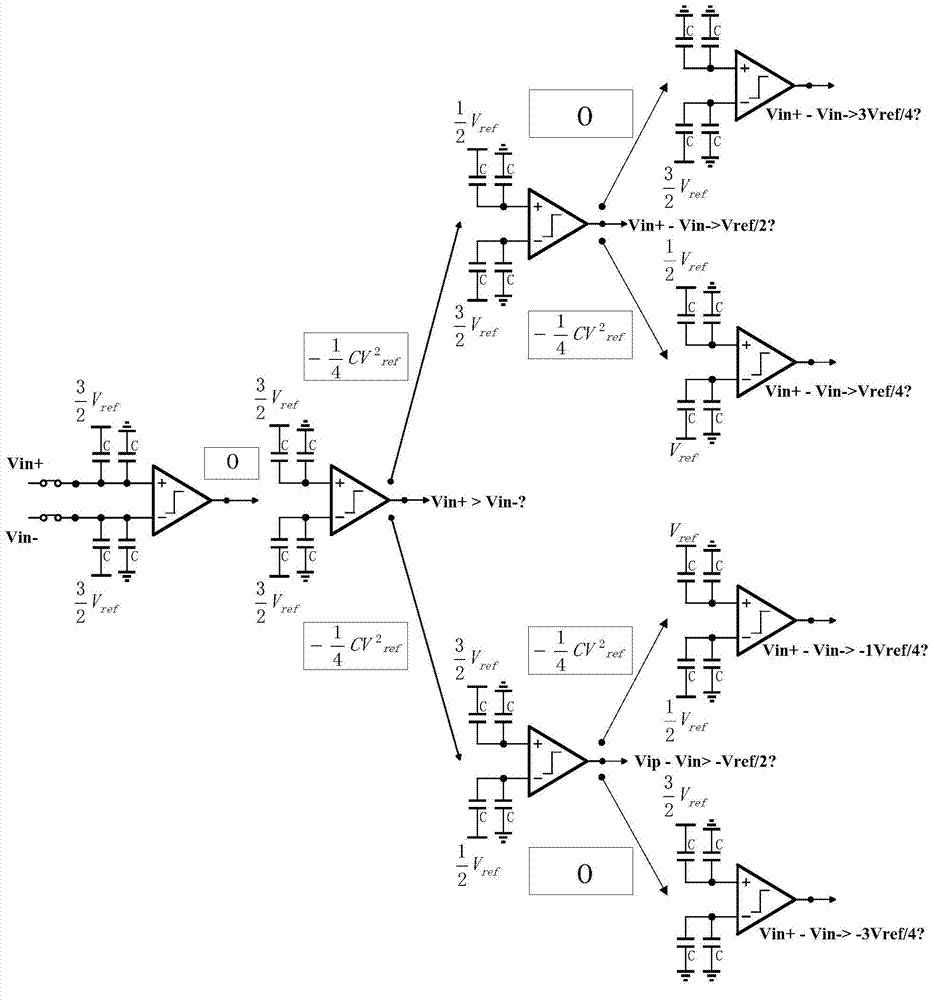

Low-power-consumption Radix-4 charge weight distributed type DAC and switching technology

ActiveCN104734721AReduce switching power consumptionReduce capacitanceDigital-analogue convertorsCapacitanceVoltage reference

The invention discloses a low-power-consumption Radix-4 charge weight distributed type DAC and switching technology. The low-power-consumption Radix-4 charge weight distributed type DAC comprises a capacitor array, reference voltage generators and a toggle switch controlled by digital signals for making the reference voltage generators connect or disconnect with capacitors; the weight express circuits showing sizes of various capacitors in the capacitor array are quaternary circuits, and the number of the reference voltage generators is three; the switching technology comprises a common-mode level switchover downward type and a successive approximation method; according to the low-power-consumption Radix-4 charge weight distributed type DAC and the switching technology, the toggle switch is controlled by the digital signals for making the reference voltage generators connect or disconnect with capacitors, so that charges on polar plates of the various capacitors are redistributed, and analog signals are output from an output end; due to that the weights of the sizes of various capacitors in the capacitor array are quaternary, and the number of the reference voltage generators is three, so that digital-to-analogue conversion is achieved through less switching times, the switching power consumption of the DAC is reduced, needed capacitor is less, and thereby the circuit area of the DAC is reduced.

Owner:STATE GRID CHONGQING ELECTRIC POWER CO ELECTRIC POWER RES INST +2

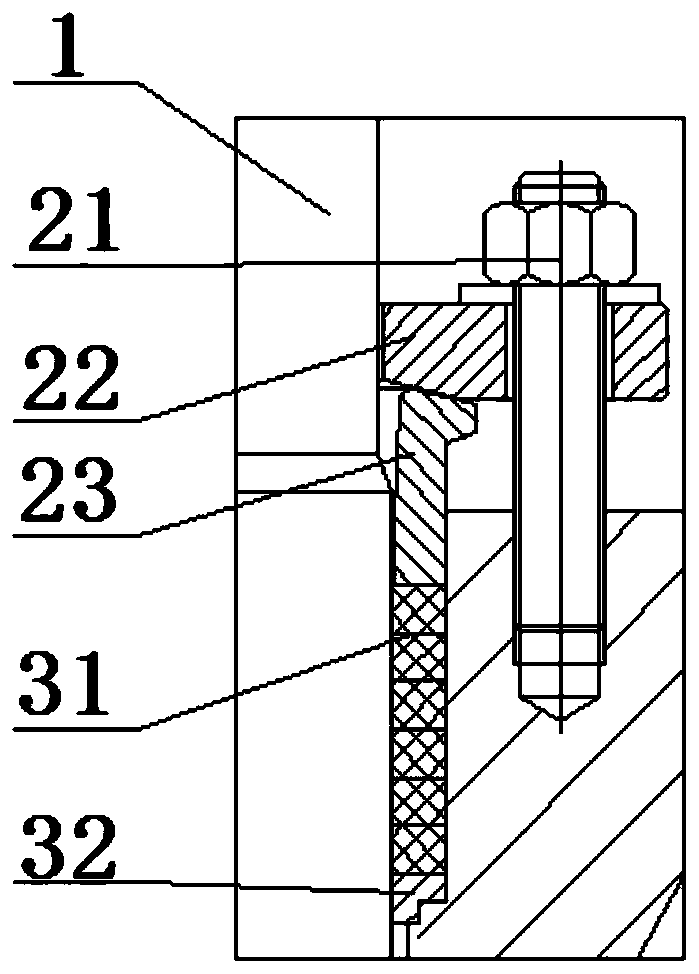

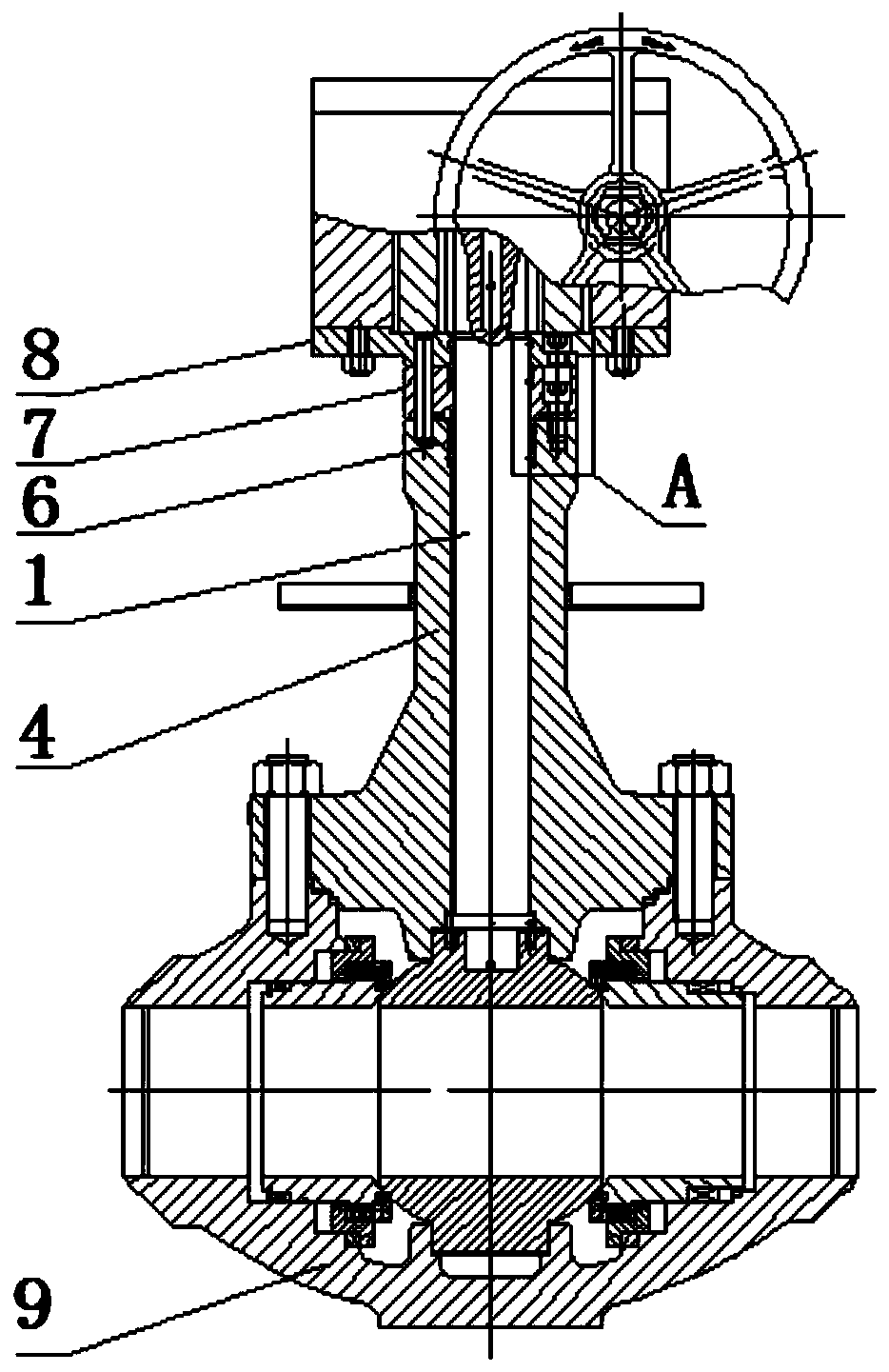

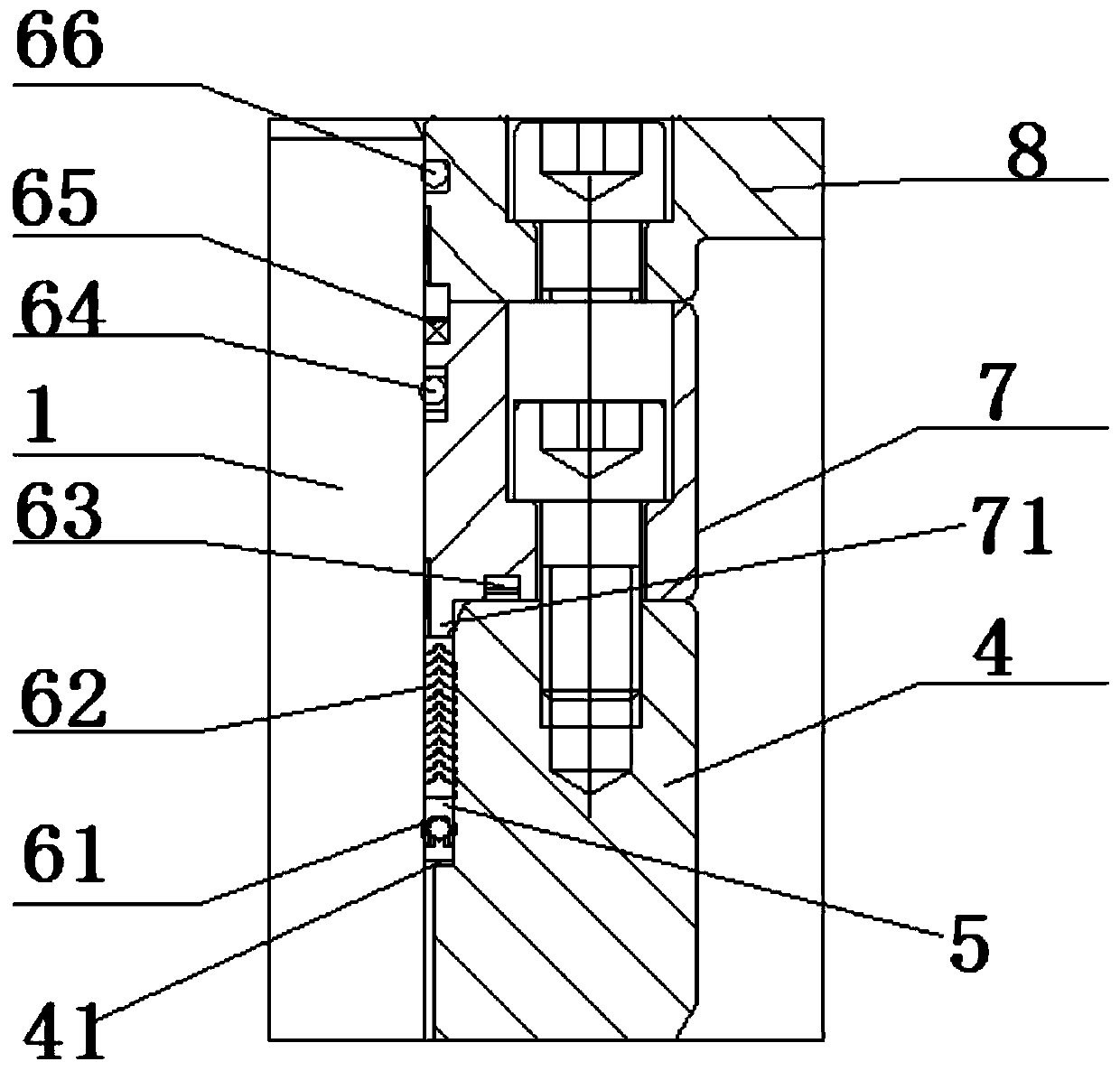

Valve rod sealing structure and valve

PendingCN111255945ASimple structureCompact structureSpindle sealingsPlug valvesLinear motionFriction torque

The invention provides a valve rod sealing structure and a valve. The valve rod sealing structure comprises a valve rod, a valve cover and a spring ring, wherein the valve comprises the valve rod sealing structure; the valve cover sleeves the valve rod; a first annular groove is formed in the inner wall surface of the valve cover; a filler groove is formed between the outer wall of the valve rod and the inner wall of the valve cover; and the spring ring sleeves the valve rod, and is positioned in the filler groove. The valve rod sealing structure with the structure is applied to the valve without needing to arrange a pressing plate and a pressing sleeve, is simple in structure, saves the space, and is compact in structure; the spring ring is deformed by medium force, and the inner side andthe outer side are correspondingly bonded on the valve rod and the valve cover to realize sealing between the valve rod and the valve cover; when the valve rod sealing structure is mounted, pretightening force is not needed to be applied to fillers; when the valve rod performs a rotating motion or a linear motion, the friction torque of the valve rod is low, so that the torque of the valve duringopening and closing is reduced, and the opening and closing power consumption of the valve is reduced; the medium force is high, so that the spring ring is high in stress deformation, and the sealingof the spring ring is more reliable; and the valve rod sealing structure can be used on various valves.

Owner:NEWAY VALVE SUZHOU

Low-power-consumption high-performance super-junction JBS diode and manufacturing method thereof

PendingCN112289848AGood reverse blocking propertiesReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceReverse recovery

The invention belongs to the field of power semiconductor devices, and particularly relates to a low-power-consumption high-performance super-junction JBS diode and a manufacturing method thereof. Thelow-power-consumption high-performance super-junction JBS diode is manufactured by using a traditional silicon-based process technology, so that the manufacturing cost is low; a P heavily doped cylindrical region and an N cylindrical drift region which have the characteristics of large area, high concentration and large junction depth are adopted, so that the forward conduction resistance is reduced; a super junction is formed, and good reverse blocking characteristics are achieved by optimizing electric field distribution; by optimizing parameters of the super junction, higher blocking withstand voltage can be realized, and the on-state and off-state power consumption of the device is reduced; and optimal two-dimensional electric field distribution is obtained by optimizing the doping concentration and width of the P column region and the N column region, unification of high blocking voltage and low on-resistance and unification of high blocking voltage and rapid switching are achieved, compromise between forward on-state voltage drop and reverse blocking characteristics and compromise between reverse recovery characteristics and reverse blocking voltage are optimized, and the limit of a traditional silicon material is broken through.

Owner:SHENYANG POLYTECHNIC UNIV

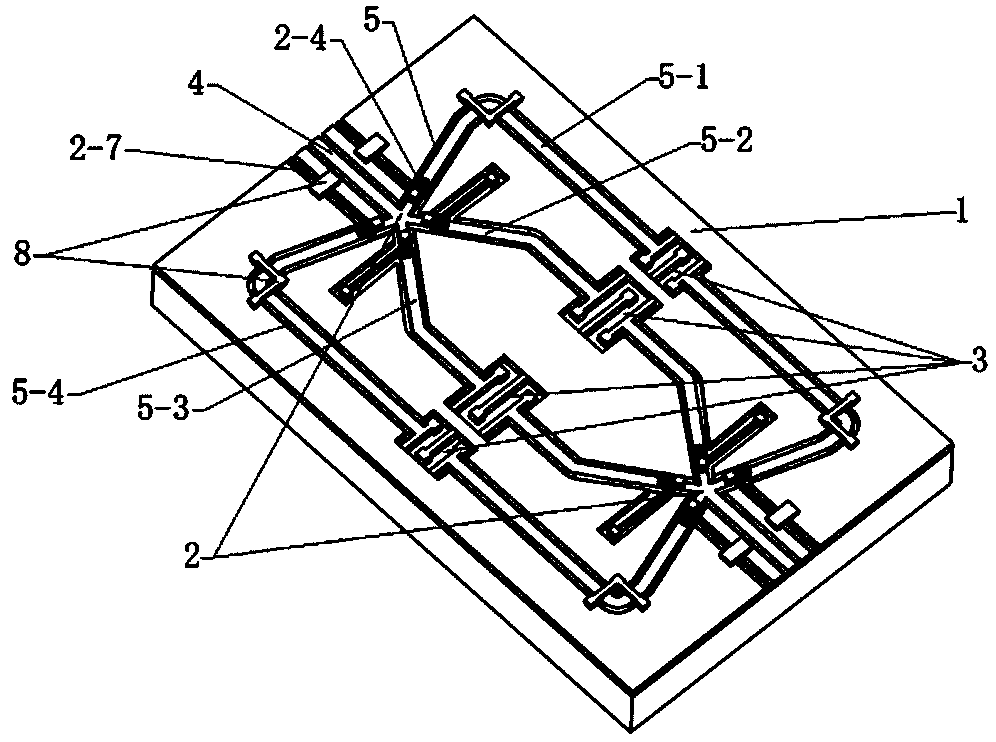

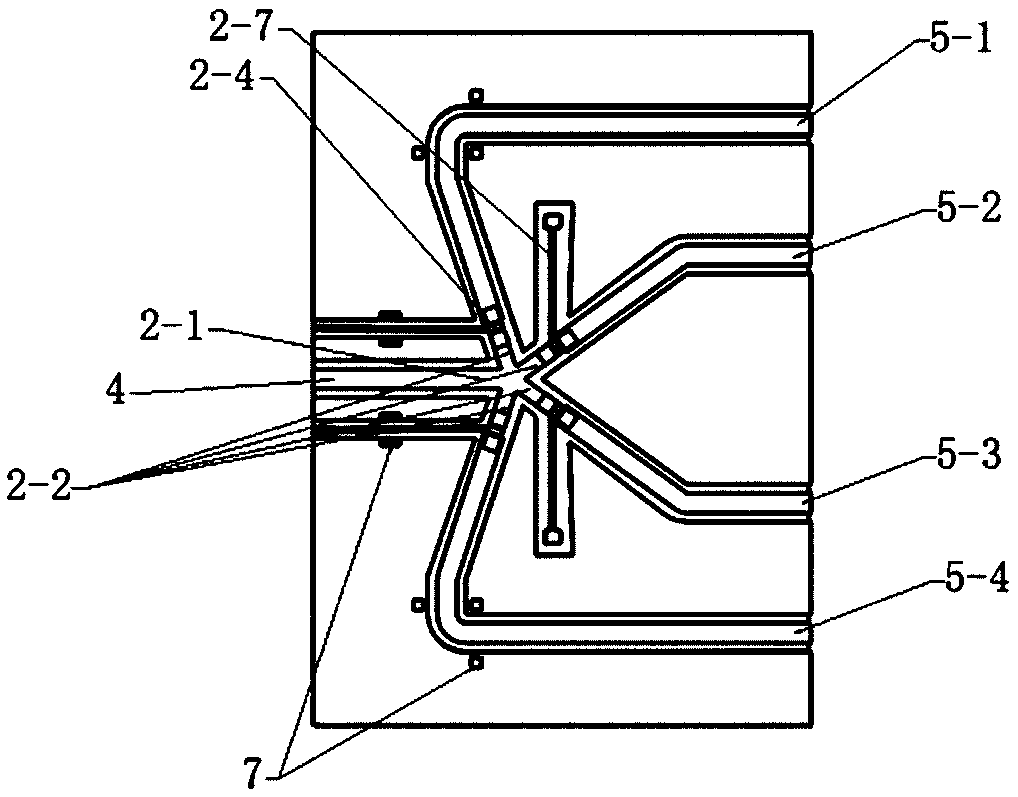

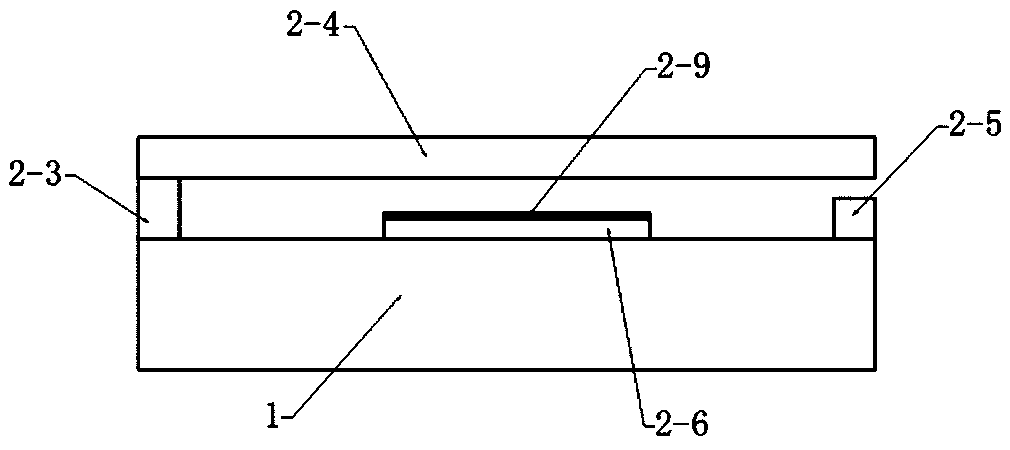

Multichannel interdigital tunable filter based on MEMS switch

InactiveCN110783673AReduce system sizeReduce Switching Power ConsumptionWaveguide type devicesPhysicsChannel gating

The invention belongs to the technical field of tunable filters, and in particular relates to a multichannel interdigital tunable filter based on a MEMS switch. The multichannel interdigital tunable filter comprises a substrate, wherein two single-pole multi-throw switches are fixed to the substrate in a mirrored manner. Each single-pole multi-throw switch includes an input end and at least two output ends. An input signal line is connected to the input end of the single-pole multi-throw switch. An interdigital filter is arranged between the output ends of the two single-pole multi-throw switches. The output ends of the single-pole multi-throw switches are connected with the interdigital filter through output signal lines. Ground wires are arranged on both sides of the input signal line and the output signal lines. The multichannel interdigital tunable filter can reduce an overall system size and switching power consumption, has a high Q value, low insertion loss, low power consumption, high linearity, easy integration, and the like, and has superior practicability in the range of 0-20GHz. The multichannel interdigital tunable filter can realize the multichannel gating of DC-20GHz,and realizes the high integration of the MEMS switch and the filter. The multichannel interdigital tunable filter is used for filtering different frequencies.

Owner:ZHONGBEI UNIV

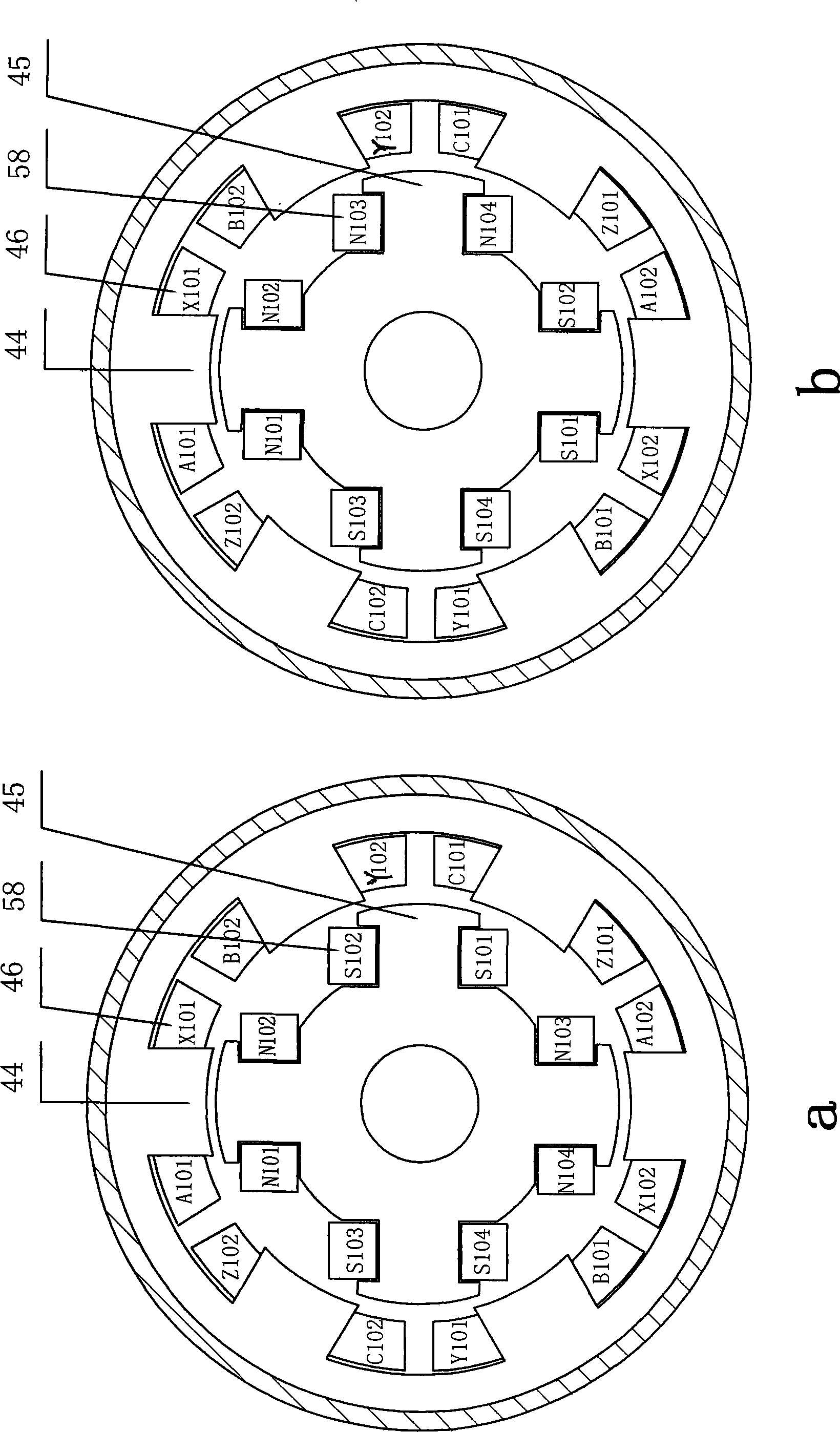

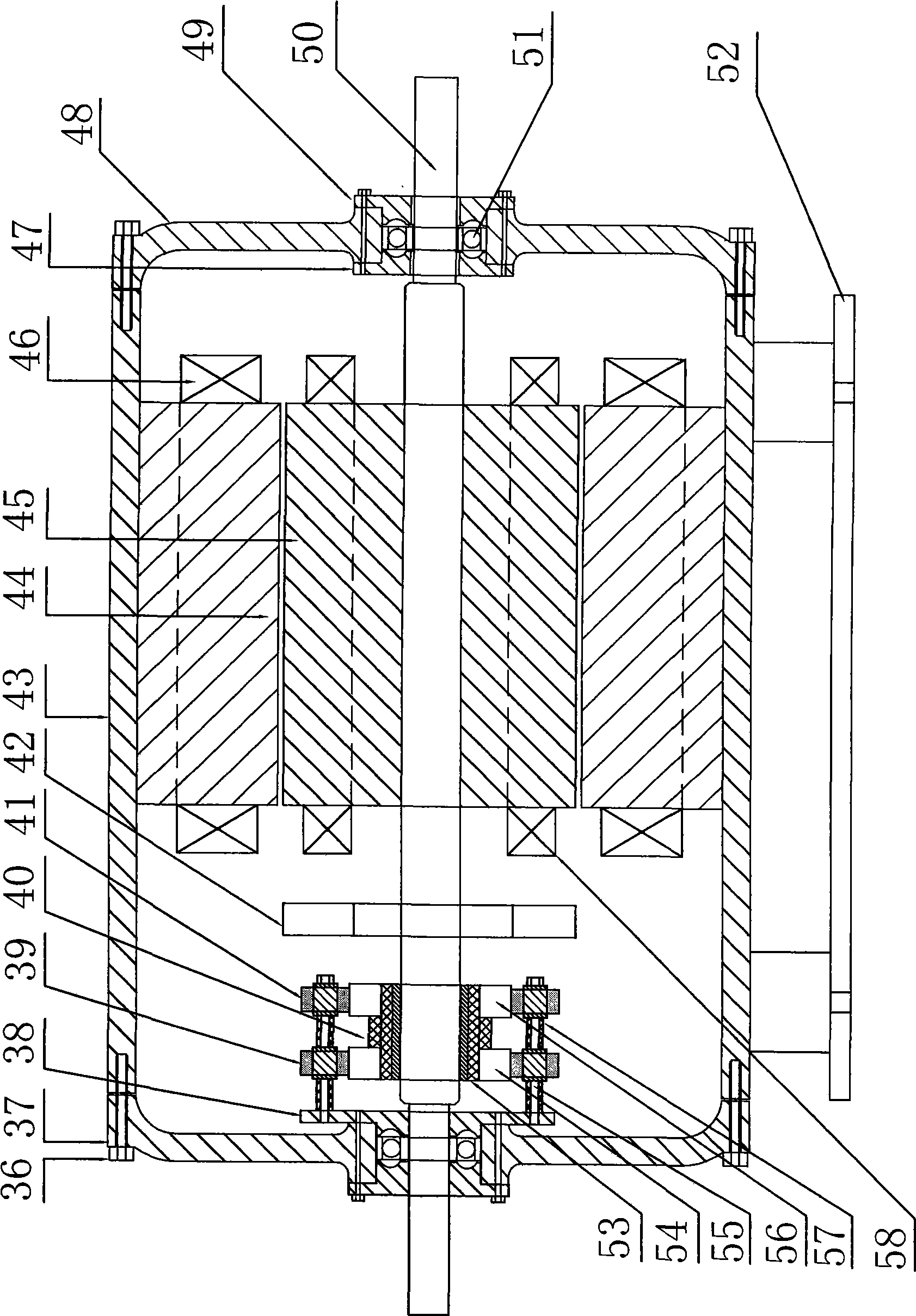

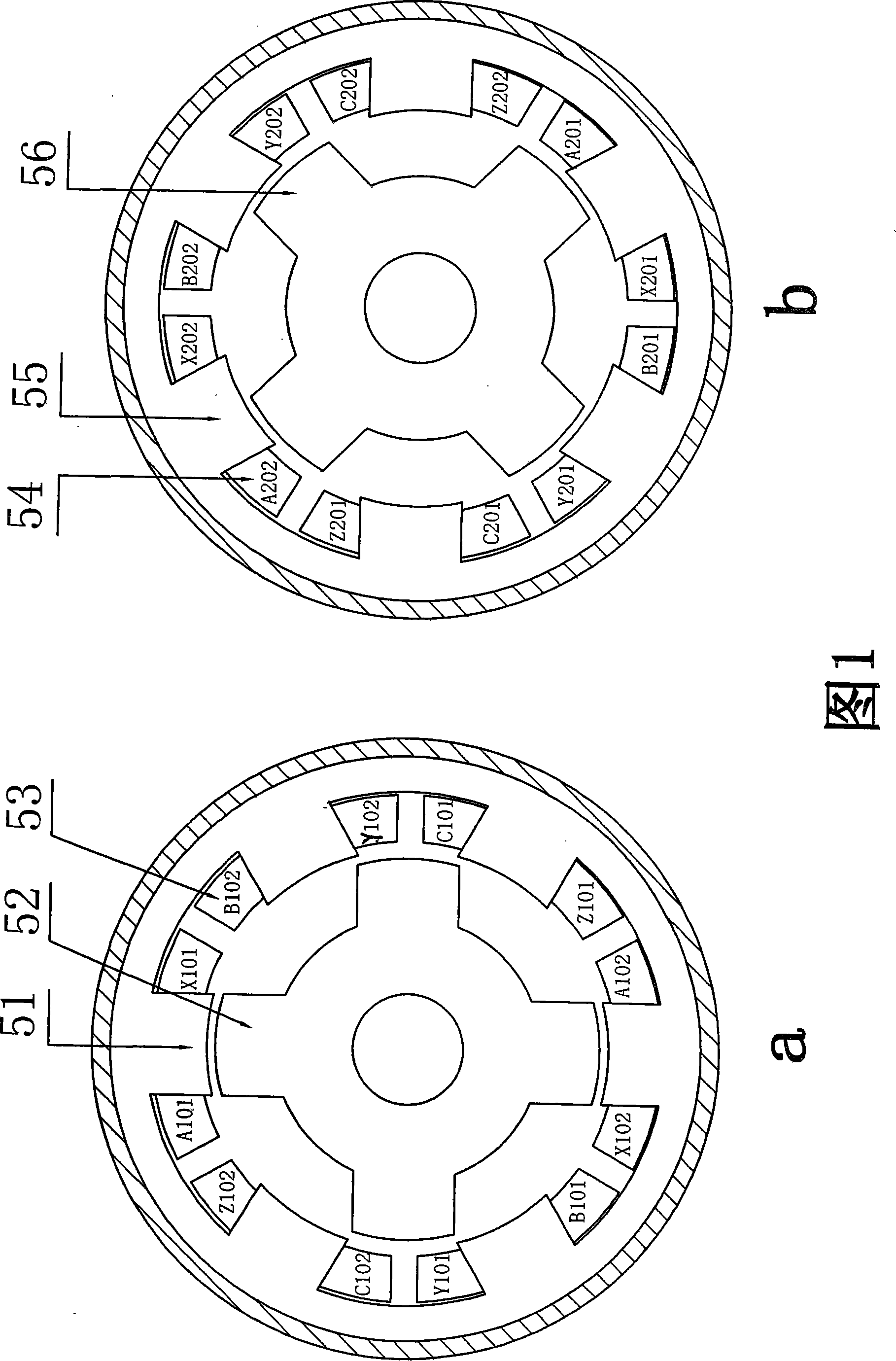

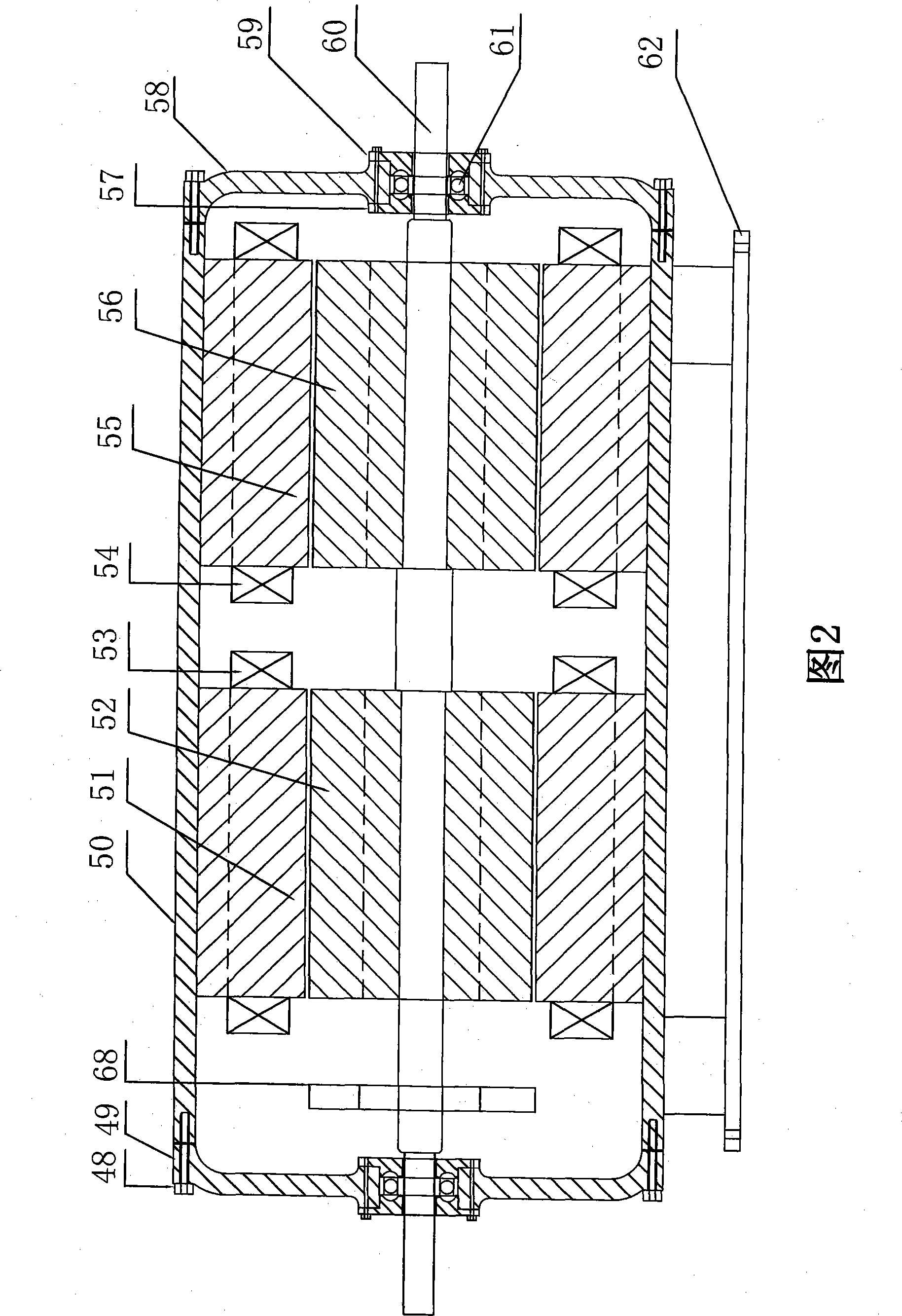

Switched reluctance motor with double stators and double rotors

InactiveCN101483370BImprove startup performanceGuaranteed uptimeMagnetic circuit stationary partsLow noiseMagnetic poles

The present invention relates to a dual stator and rotor switch reluctance motor, which comprises stator and rotor that stacked and pressed into salient pole structure by silicon steel sheet, wherein core of the stator and rotor are composed by two segments, and length of core of the two-segment stator and rotor equal to diameter; the stator tooth is provided with two set of centralized armature winding respectively while two teeth of same phase in each set of windings are provided with armature winding that connected in series or in parallel to constitute a phase, characterized in that: the two-segment stator is staggered 360p / 2Ns degree electrical angle for mounting, wherein p is number of pole-pairs of stator magnetic pole, Ns is stator magnetic pole number; the two-segment rotor staggered 360 / 2Nr degree electrical angle for mounting, wherein Nr is rotor magnetic pole number. The present invention can reach purpose of high starting torque, low swinging motion and low noise operation.

Owner:张世清

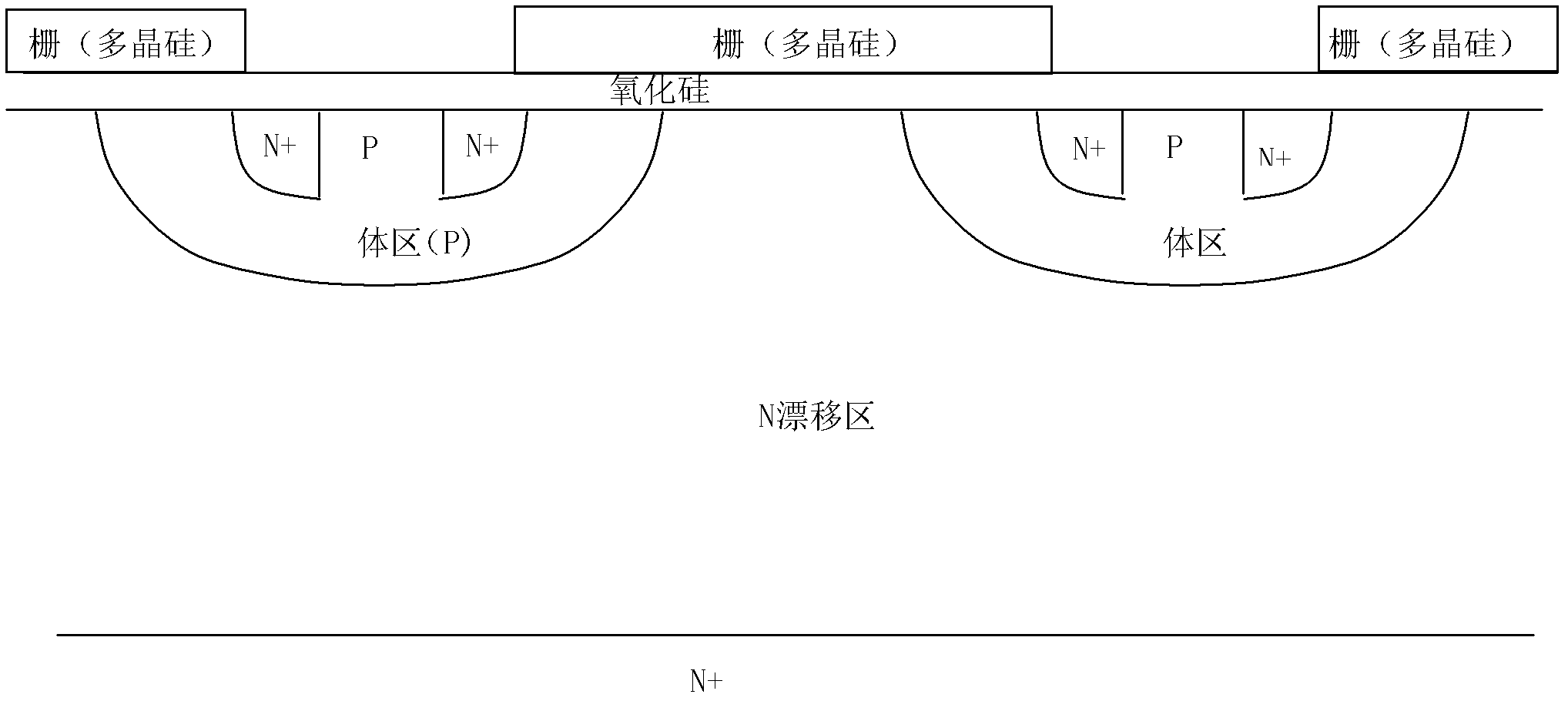

Silicon carbide MOSFET device with T-type masking layer structure

InactiveCN110212019AFast switching speedReduce Switching Power ConsumptionSemiconductor devicesMOSFETBreakdown voltage

The invention relates to a silicon carbide MOSFET device with a T-type masking layer structure. The silicon carbide MOSFET device comprises a drain electrode, an N-type doped substrate layer, an N-type drift region and a P-type base region which are sequentially arranged from bottom to top; P-type source regions and N-type source regions are arranged on the P-type base region; a groove gate structure is arranged in the P-type base region; the bottom of the groove gate structure extends into the interior of the N-type drift region, and the top of the groove gate structure extends out of the upper surface of the P-type base region; the T-shaped masking layer structure is arranged below the groove gate structure, and the upper surface of the T-shaped masking layer structure is in contact withthe lower surface of the groove gate structure; source electrodes are arranged on the P-type source regions and the N-type source regions; and a gate electrode is arranged on the groove gate structure. According to the silicon carbide MOSFET device, the T-shaped masking layer structure is added at the bottom of the groove gate structure, so that the breakdown voltage of the device is improved, the switching speed of the device is increased, and meanwhile, the switching power consumption of the device is reduced.

Owner:XIDIAN UNIV

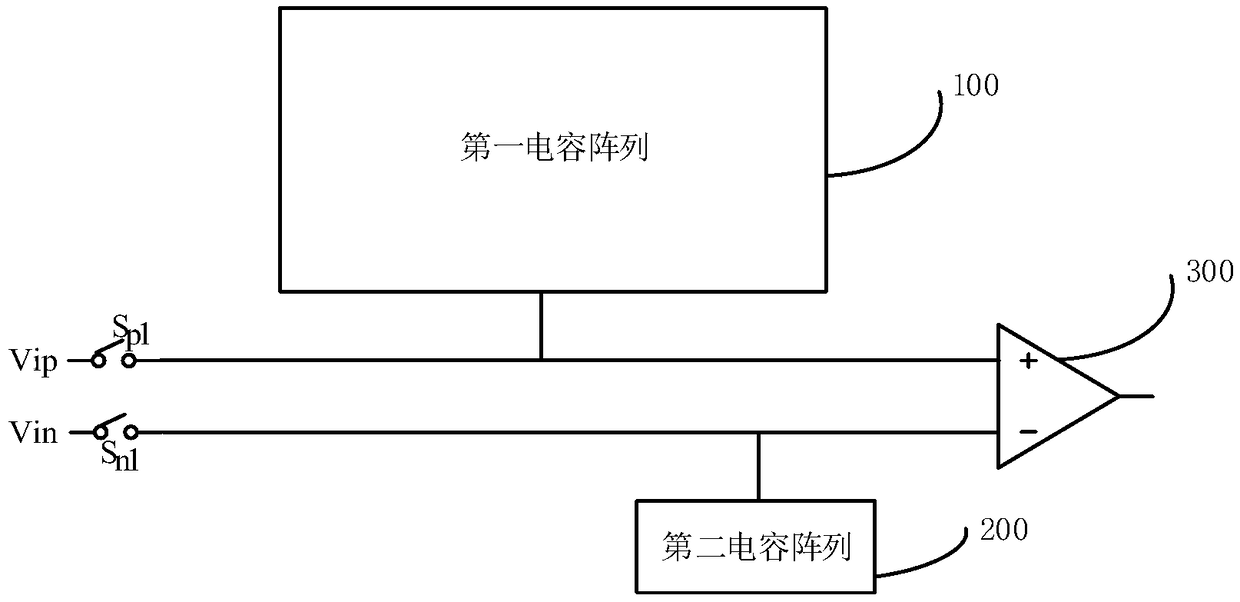

Digital-analog converter of successive approximation type

ActiveCN109245771AReduce Switching Power ConsumptionReduce areaAnalogue/digital conversionElectric signal transmission systemsCapacitanceNon symmetric

The invention relates to a digital-analog converter of a successive approximation type, and the digital-to-analog converter includes a first input terminal, a second input terminal and a first capacitor array; a second capacitor array, a first switch, a second switch, and a comparator, wherein the first input terminal is electrically connected to the non-inverting input end of the comparator through the first switch, and the first capacitor array is electrically connected to the non-inverting input end of the comparator. The second input terminal is electrically connected to the inverting input end of the comparator through the second switch, and the second capacitor array is electrically connected to the inverting input end of the comparator. The invention solves a power consumption problem caused by the excessive area of a switch capacitor array in the conventional time sequence. In addition, the highest bit capacitance splitting and the characteristics of the asymmetric structure itself stabilize the linearity. Meanwhile, the application of a dummy capacitor enables the capacitor area and power consumption to be further reduced.

Owner:XIDIAN UNIV

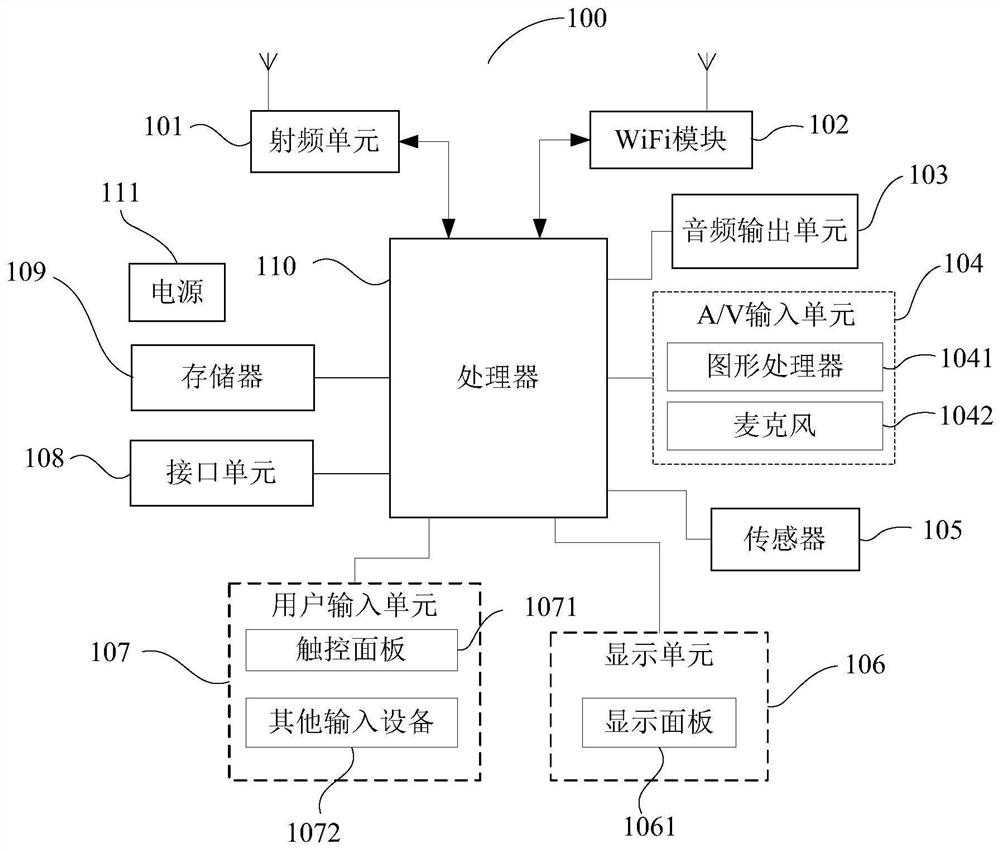

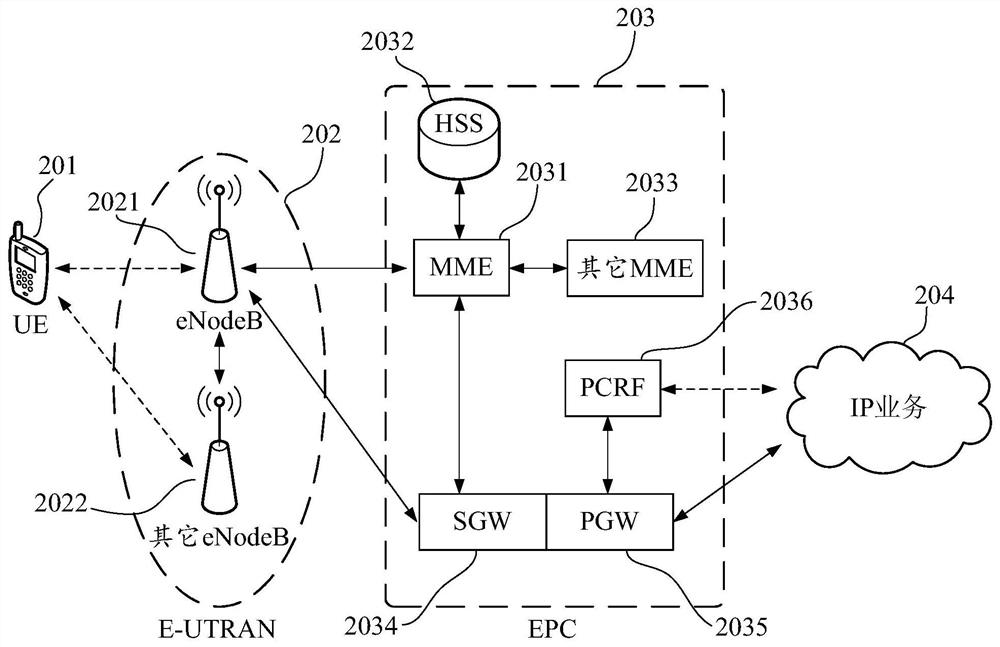

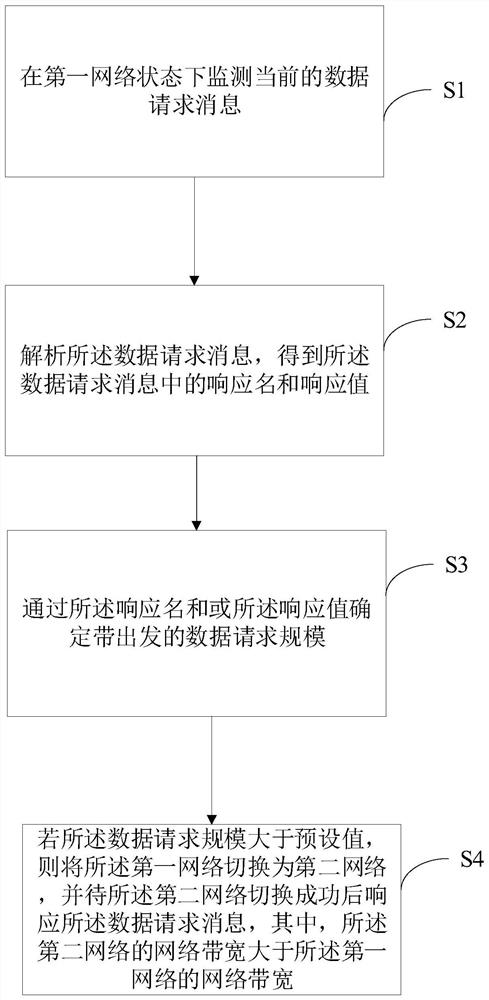

Network switching control method and device and computer readable storage medium

PendingCN111970738AReduce network switching power consumptionImprove accuracyHigh level techniquesWireless communicationEngineeringReal-time computing

The invention discloses a network switching control method and device and a computer readable storage medium, and the method comprises the steps: monitoring a current data request message in a first network state; then, analyzing the data request message to obtain a response name and a response value in the data request message; then, determining the scale of a data request to be sent through theresponse name and / or the response value; and finally, if the data request scale is greater than a preset value, switching the first network to a second network, and responding to the data request message after the second network is successfully switched, the network bandwidth of the second network being greater than the network bandwidth of the first network. According to the invention, a humanized network switching control scheme is realized, so that the opportunity of switching the 4G network to the 5G network better meets the network requirements of users, the network switching power consumption is reduced, the network switching accuracy is improved, and the user experience is improved.

Owner:NUBIA TECHNOLOGY CO LTD

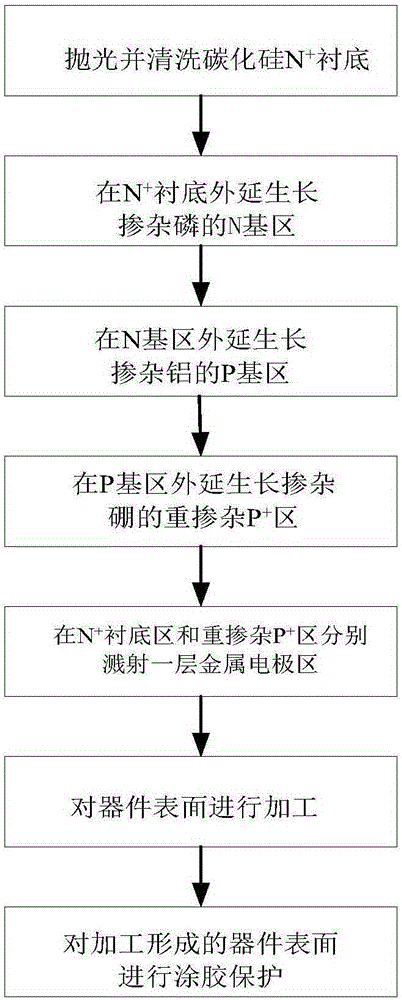

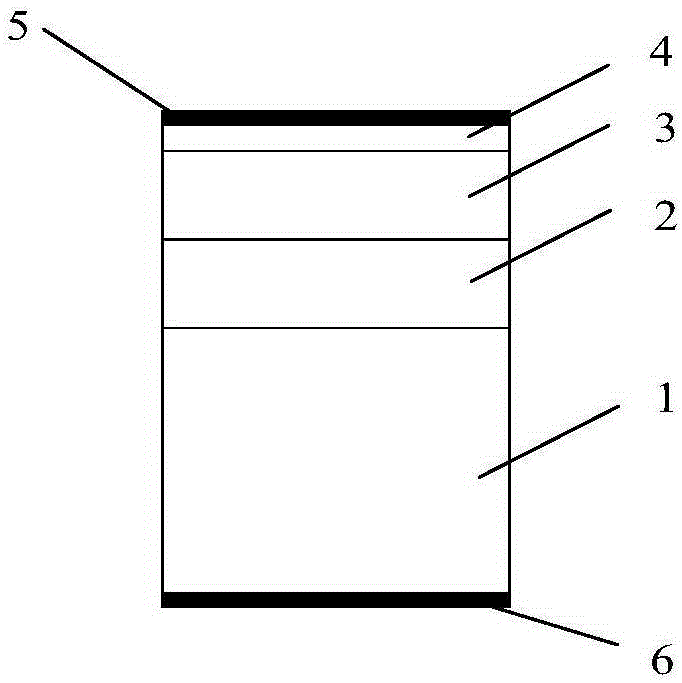

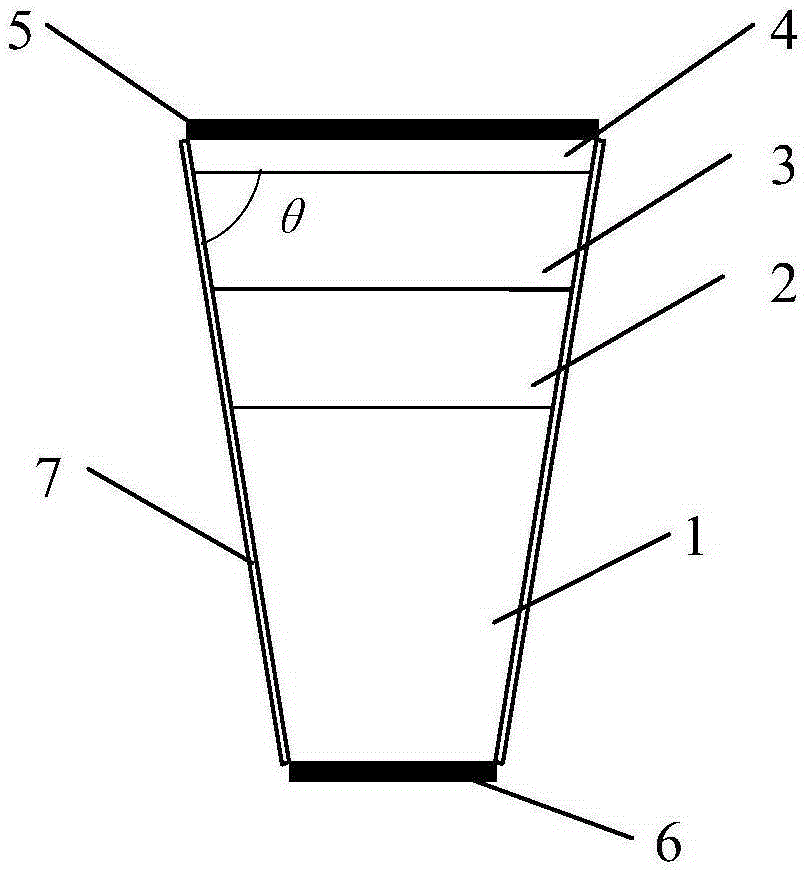

Semiconductor cut-out switch based on silicon carbide, and manufacturing method thereof

ActiveCN105185820AOptimize terminal structureHigh thermal conductivitySemiconductor devicesOblique angleBoron

The invention discloses a manufacturing method for a semiconductor cut-out switch based on silicon carbide. The method comprises the following steps: using silicon carbide as an N+ substrate, a phosphorus-doped N base region, an aluminum-doped P base region, and a boron-doped heavy-doping P+ region epitaxially growing in sequence on the substrate; respectively processing two ends of the formed device to form a cathode electrode and an anode electrode; using a mechanical cutting oblique angle method to execute platform modeling and gumming protection, so as to complete a manufacturing process of the semiconductor cut-out switch. The invention also discloses a semiconductor cut-out switch based on silicon carbide, the switch being manufactured by the method. The semiconductor cut-out switch manufactured by the manufacturing method has larger compromise among pumping, switching, and switching characteristics, heat radiation requirement under a high-frequency condition is reduced, and reliability under high-temperature condition is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

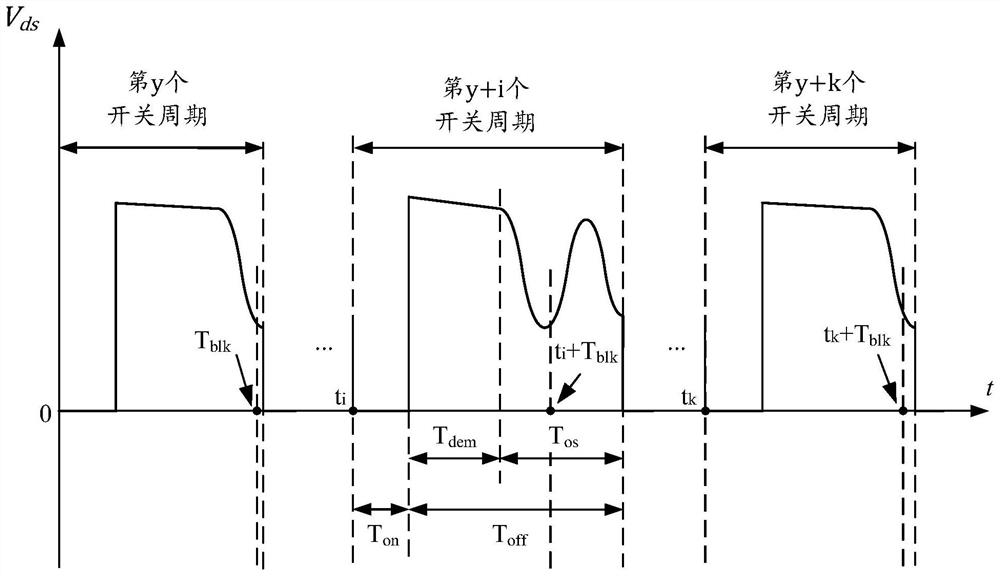

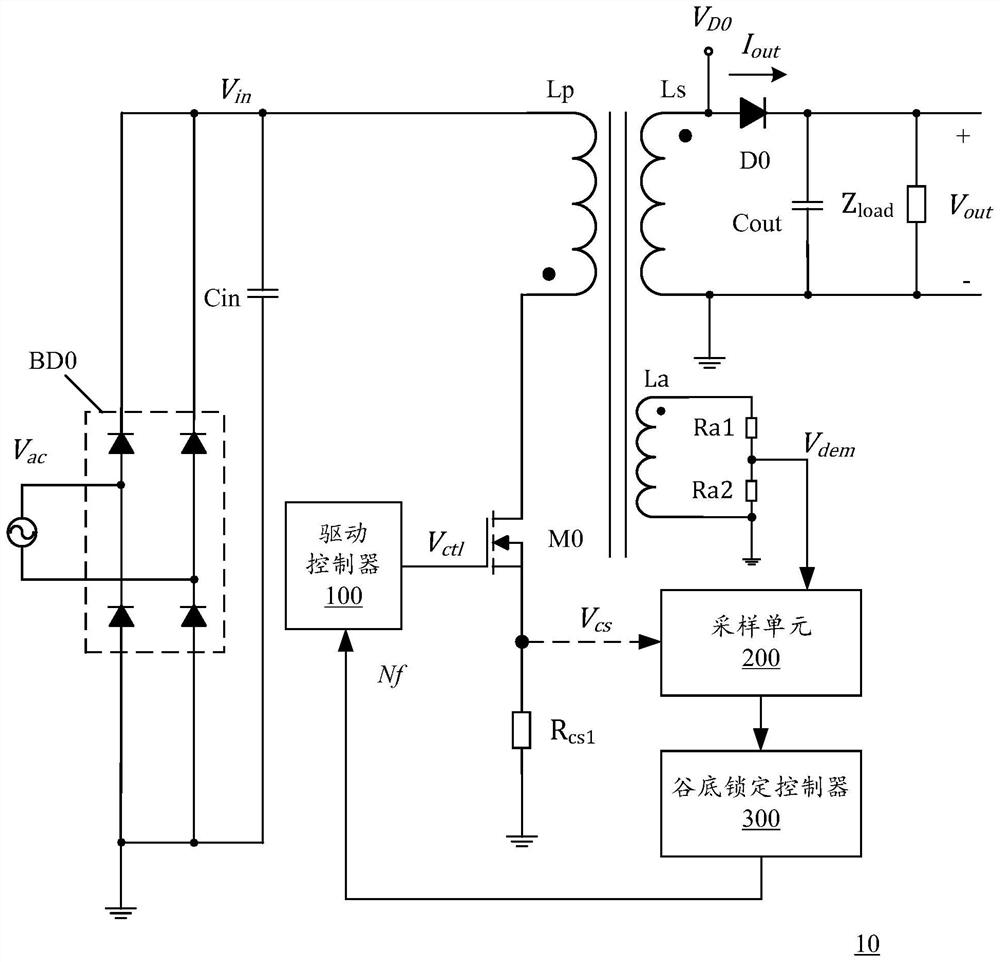

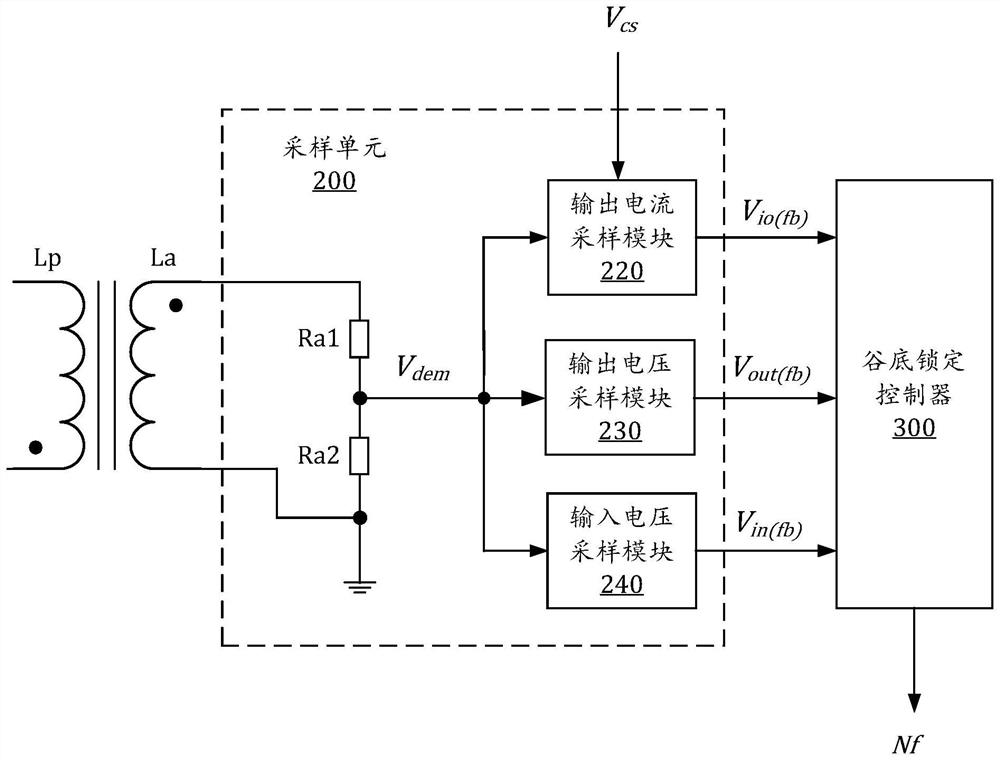

Control circuit, switching power supply circuit and control method

PendingCN114374327AAchieving AdaptivenessReduce Switching Power ConsumptionEfficient power electronics conversionDc-dc conversionConvertersControl engineering

The invention discloses a control circuit of a power converter, a control method of the control circuit, a switching power supply circuit and a driving control method. The control circuit comprises a sampling unit used for sampling an input voltage, an output voltage and an output current of the power converter to obtain a plurality of sampling signals; the valley bottom locking controller is electrically connected with the sampling unit and adaptively selects the most adaptive valley bottom matched with the current input and output specification according to the plurality of sampling signals; and the driving controller is used for conducting the power tube at the most adaptive valley bottom after the demagnetization of the power converter is finished. The invention provides a new quasi-resonance control technology which can realize valley bottom locking and adaptive adjustment of each input and output specification, thereby avoiding the phenomenon of'valley bottom jumping 'while adapting to various input and output specifications, and improving the efficiency and the anti-electromagnetic interference performance.

Owner:HANGZHOU SILAN MICROELECTRONICS

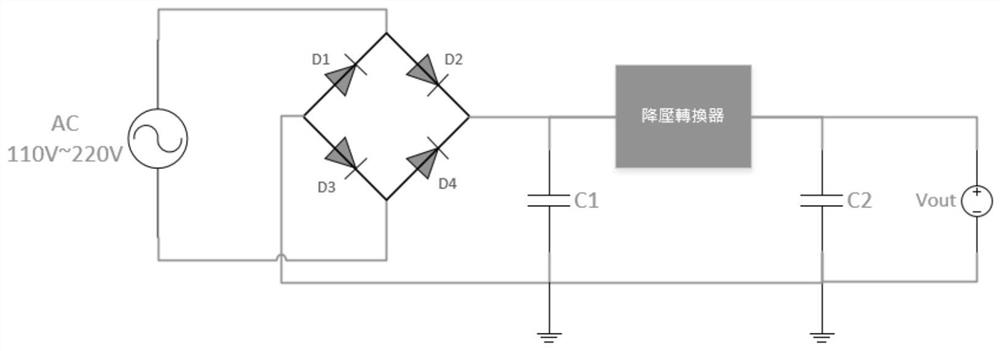

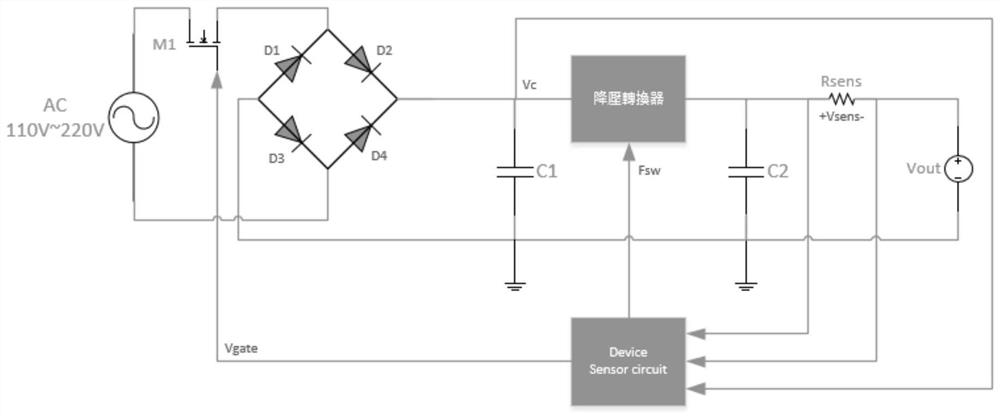

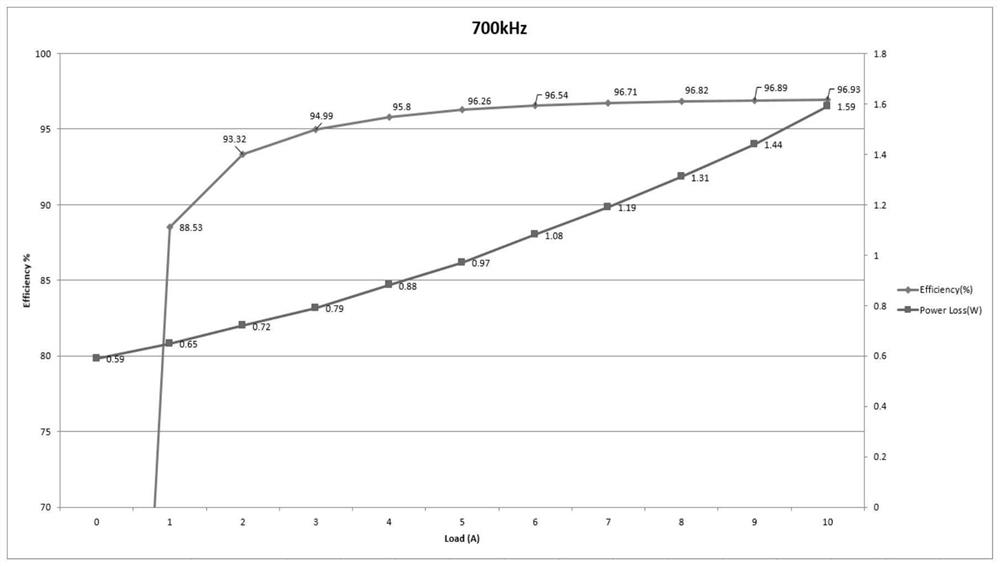

Circuit for realizing power saving of power supply and power supply method

InactiveCN112290810AReduce switching power consumptionAvoid Buck Converter DamageAc-dc conversion without reversalEfficient power electronics conversionPower savingConverters

The invention discloses a circuit for realizing power saving of a power supply and a power supply method, and aims to achieve the purpose of instantly detecting the voltage of a sensor by using an equipment sensor circuit and simultaneously respond to a switching circuit to control switching of an AC input power supply. The voltage difference of a sensor voltage end is received through an equipment sensor circuit end detection circuit device, the smaller the sensor voltage is, the smaller the load current is, the larger the sensor voltage is, the larger the load current is, and when no load exists, a switching circuit is informed to be closed through an equipment sensor circuit, so that the power consumption of the rectifier is effectively reduced, and the efficiency is improved. When theload is light, a buck converter is informed through the equipment sensor circuit, so that the frequency reduction effect is achieved, and the switching power consumption of the buck converter is effectively reduced; when a rectifier is damaged to cause capacitor voltage abnormity, the equipment sensor circuit informs the switch circuit of closing, thereby preventing capacitor voltage abnormity from causing damage to the buck converter.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

A kind of driving circuit and driving method of triode

The invention relates to a driving circuit of a triode. The circuit comprises a current supply device, a first switch device, a second switch device, a switch control device, an inductor, a direct-current power supply and a current detection unit, wherein the current supply device is grounded after being sequentially connected with the first switch device and the second switch device; the triode is connected between the first switch device and the second switch device, the direct-current power supply is connected with the collecting electrode of the triode, and an emitting electrode of the triode is grounded; the switch control device receives a detection voltage provided by the current detection unit and an externally supplied control voltage to control the on-off states of the first switch device and the second switch device so as to control the on-off state of the triode; and the current supply device supplies a direct current which reflects the changing of the current of the collecting electrode to the base electrode of the triode. By utilizing the driving circuit of the triode, the turn-off time of the switch is shortened, and the power dissipation is reduced; and meanwhile, the invention discloses a driving method of the driving circuit of the triode and a switch power supply.

Owner:BYD SEMICON CO LTD

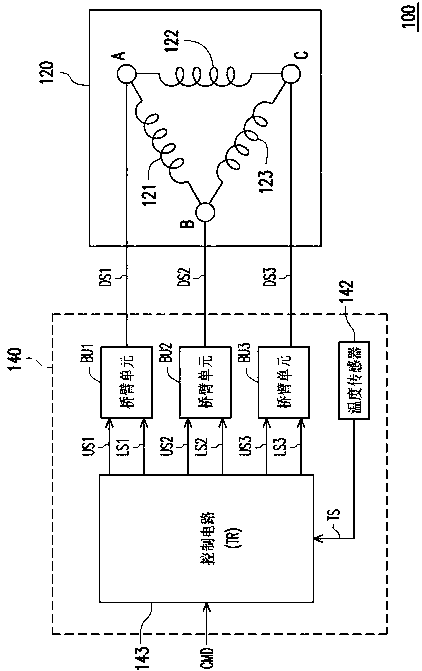

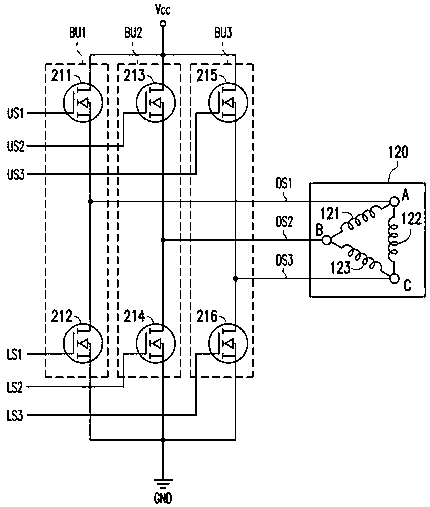

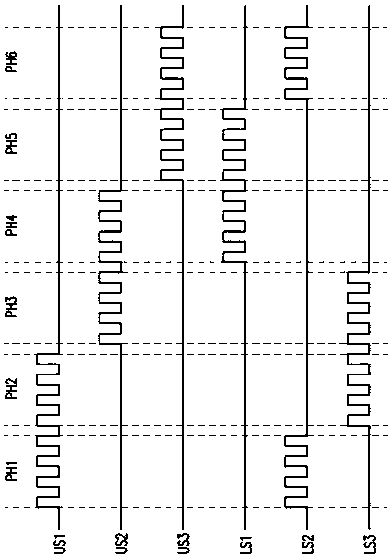

Motor apparatus and motor driving circuit

InactiveCN108418352AReduce the temperatureHigh speedElectric motor controlStructural associationWork cycleDrive motor

The invention provides a motor apparatus and a motor driving circuit. The motor apparatus includes a motor module and the motor driving circuit. The motor driving circuit includes a plurality of bridge arm units, a temperature sensor, and a control circuit. Each of the bridge arm units is controlled by one of the first PWM signals and one of the second PWM signals generated by the control circuitand outputs a driving signal to drive the motor module. The temperature sensor senses a temperature of the bridge arm units and provides a temperature sensing value to the control circuit. When the temperature sensing value is greater than or equal to a threshold temperature value, the control circuit increases a duty cycle of the first PWM signal of one bridge arm unit and a duty cycle of the second PWM signal of the other bridge arm units, thereby reducing switching power consumption and temperature of the brige arm units.

Owner:FAIRWAY ELECTRONICS

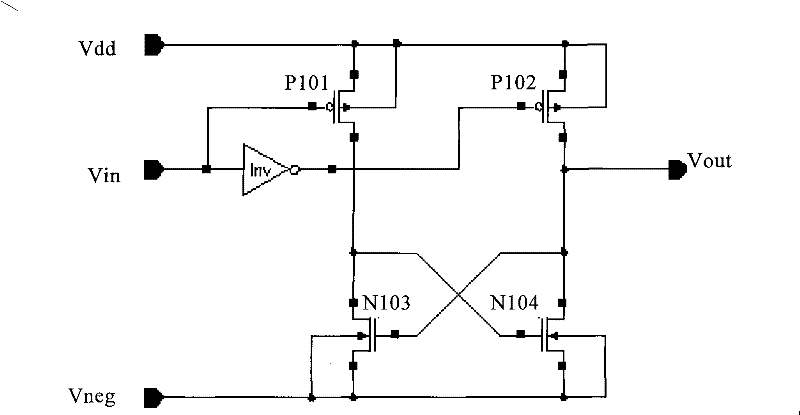

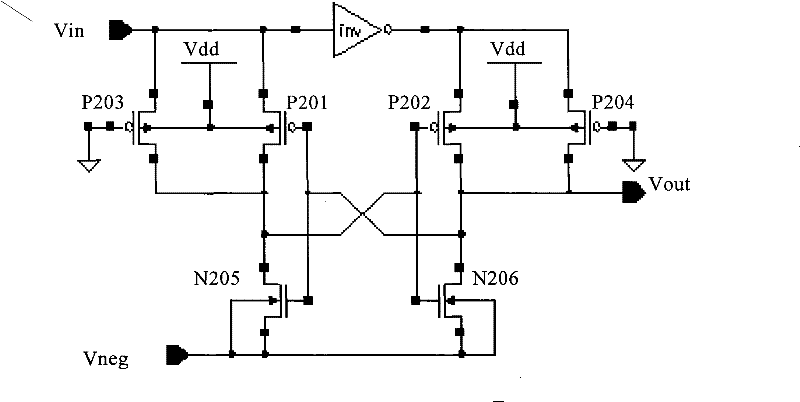

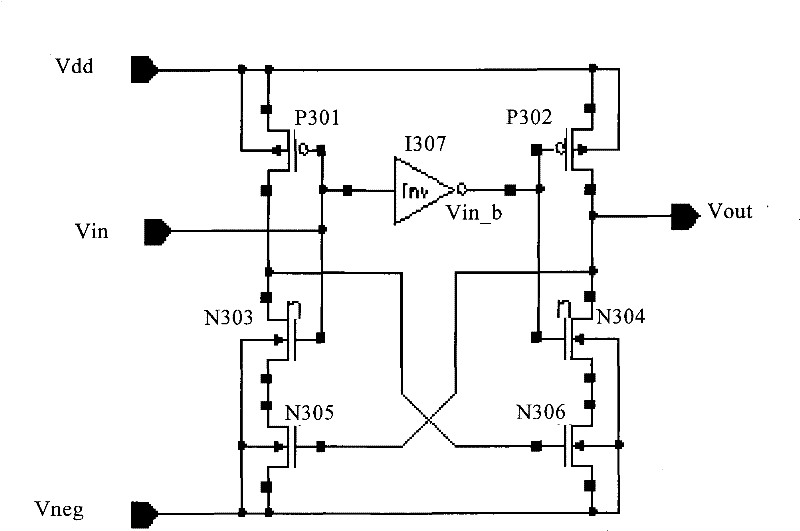

Negative voltage level switching circuit

ActiveCN101764605BSmall conduction currentSmall sizeLogic circuits coupling/interface using field-effect transistorsPositive feedbackSwitching power

A negative voltage level switching circuit, including: 2 inserted N tubes; 2 pull-up P tubes, the sources of which are connected to the forward voltage Vdd, and the drains are respectively connected to the drains of the inserted N tubes; 2 positive feedback The source of the N tube is connected to the negative voltage Vneg, and the drains are respectively connected to the sources of the two inserted N tubes; the node between the second inserted N tube and the second pull-up P tube is the output Vout, and the first inserted The gates of the N tube and the first pull-up P tube are connected to the input signal Vin, the gate of the first positive feedback N tube is connected to the output voltage Vout; the second insertion N tube and the second pull-up P tube gate are connected to The output end of the inverter and the input end of the inverter are connected to the input signal Vin; the gate of the second positive feedback N transistor is connected to the node between the first insertion N transistor and the drain of the first pull-up P transistor. The conduction current required by the P tube can be reduced under the same conduction condition, and the area of the P tube can be reduced; and the voltage switching speed can be accelerated and the switching power consumption can be reduced.

Owner:GIGADEVICE SEMICON (BEIJING) INC

A photonic crystal digital optical switch

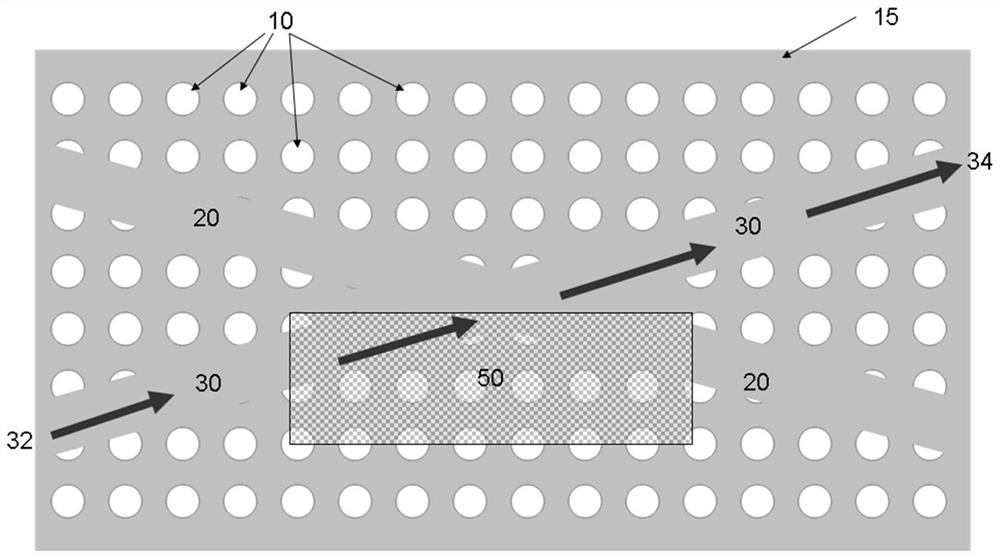

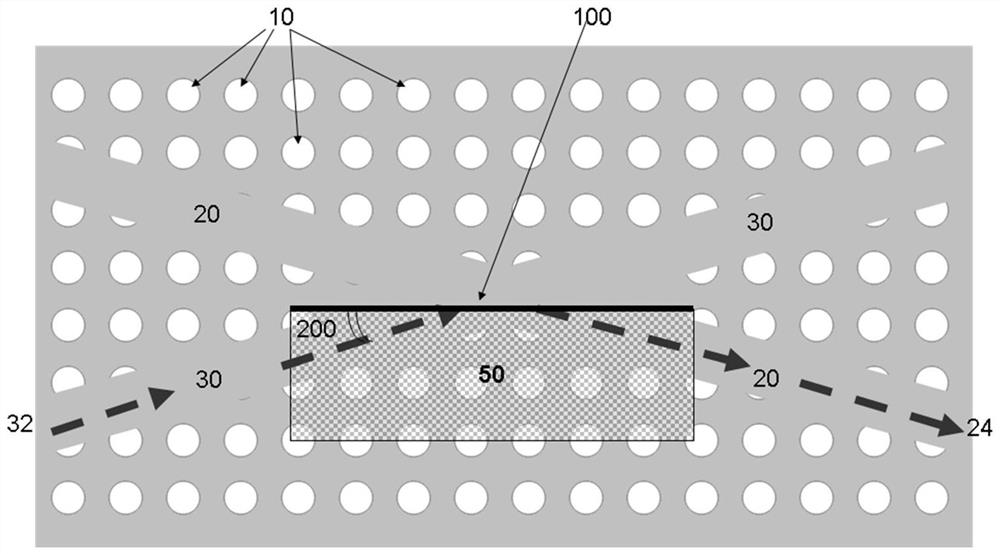

ActiveCN111290144BImprove performanceGood refractive indexOptical light guidesNon-linear opticsPhotonic crystalControl signal

The invention discloses a photonic crystal digital optical switch, which comprises a heater and a cladding layer, a hole-shaped layer is arranged in the cladding layer, and more than two photonic crystal waveguides are arranged on the hole-shaped layer, and the The intersection between the photonic crystal waveguides; the heater is used to heat the area around the intersection of the photonic crystal waveguides, and one side of the heating area is located between the two intersecting photonic crystal waveguides. The photonic crystal waveguide propagates through; when the heater is working, a refractive index interface is formed on the side of the heating area between the photonic crystal waveguides. Optical signals are output from another intersecting photonic crystal waveguide. The extinction ratio and crosstalk of the optical switch of the invention change monotonously with the control signal, and meanwhile, the performance of the device is high.

Owner:江苏长实基业电气科技有限公司