Patents

Literature

100 results about "Binary search algorithm" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, binary search, also known as half-interval search, logarithmic search, or binary chop, is a search algorithm that finds the position of a target value within a sorted array. Binary search compares the target value to the middle element of the array. If they are not equal, the half in which the target cannot lie is eliminated and the search continues on the remaining half, again taking the middle element to compare to the target value, and repeating this until the target value is found.

Frequency correction method and system of phase-locked loop

ActiveCN104052474AEffective control of counting timeReduce calibration timeTransmitters monitoringReceivers monitoringMulti bandEngineering

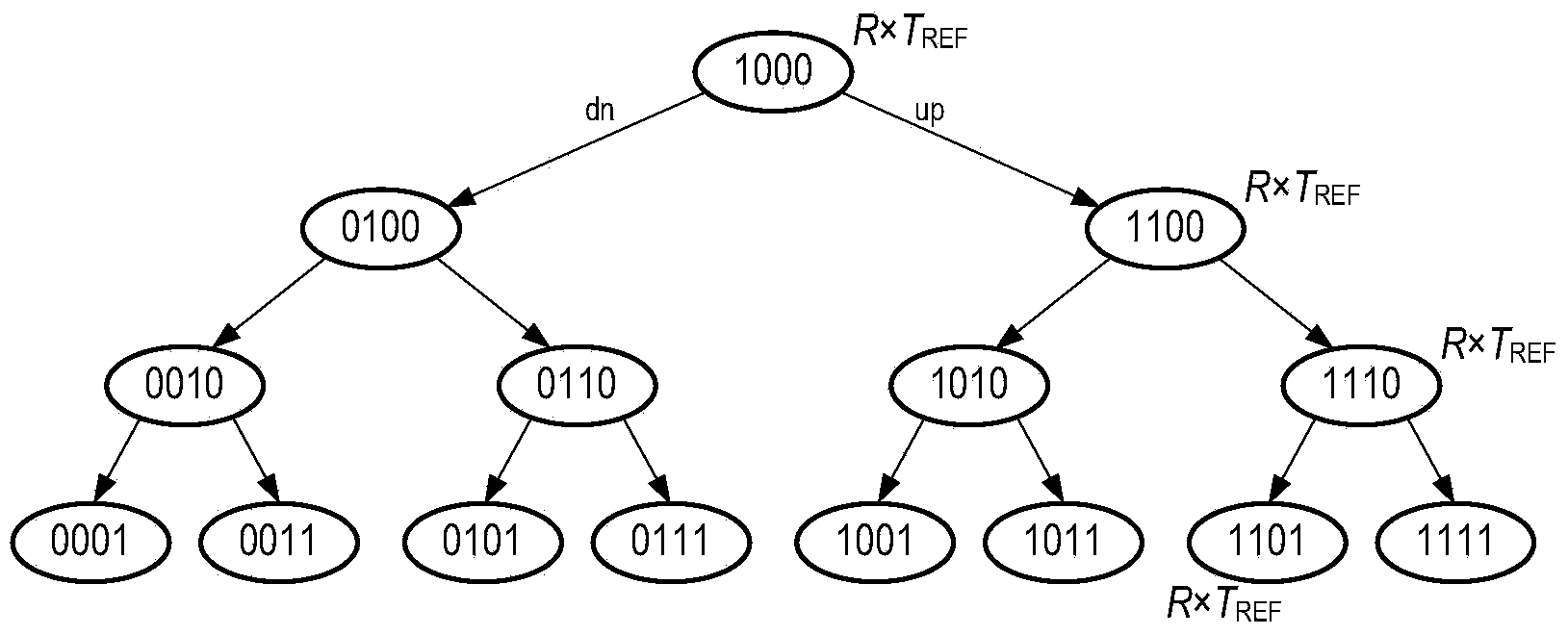

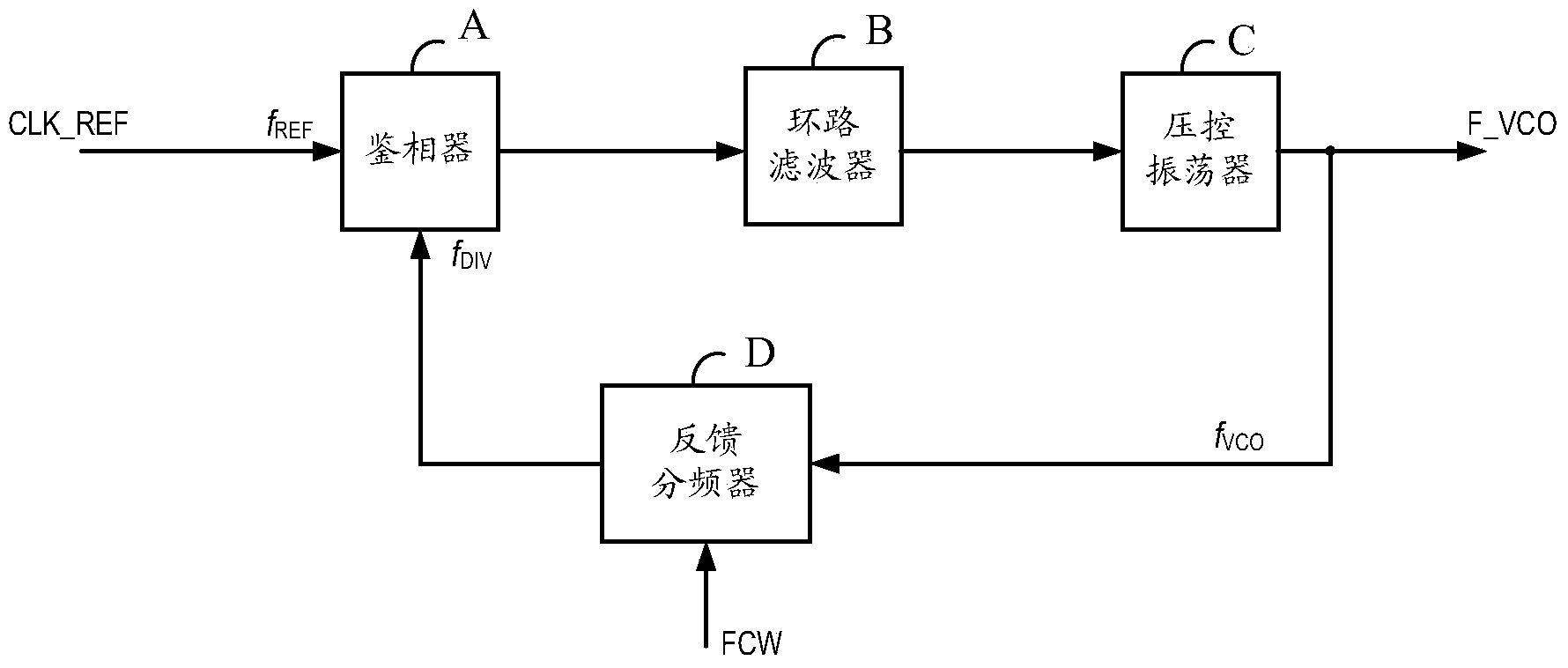

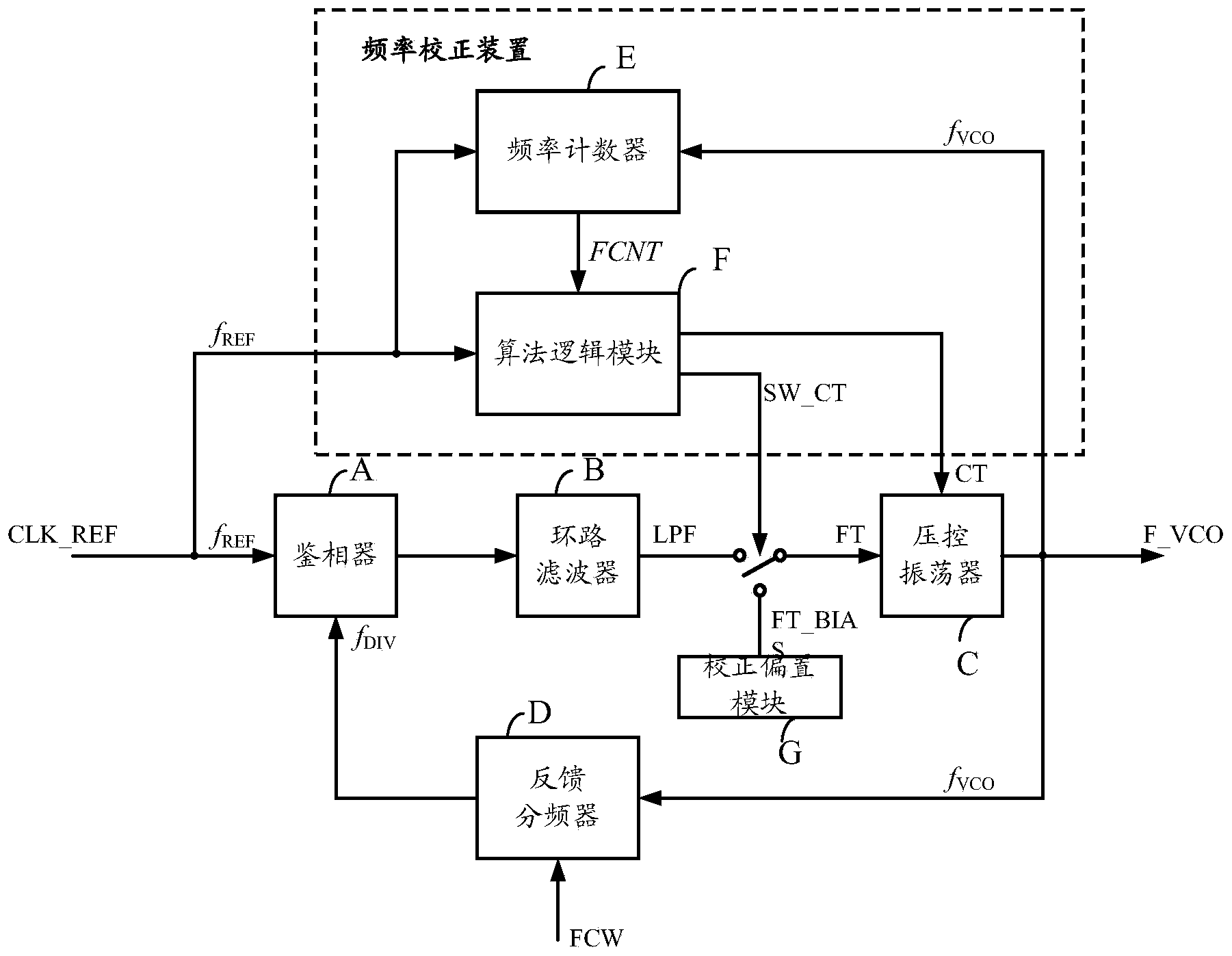

The invention provides a frequency correction method and system of a phase-locked loop. The frequency correction method and system of the phase-locked loop are applied to selection of sub-bands of multi-band voltage-controlled oscillators. The method includes the steps that in the counting time TCNT [k], frequency counting is conducted on frequency signals output by a voltage-controlled oscillator at the current working sub-band, and a frequency count value FCNT[k] is obtained, wherein the current working sub-band corresponds to a binary value of a current node in a binary search tree; the error between the FCNT [k] and a target frequency count value FCNTTARGET [k] is calculated, the absolute value of the error is compared with a predetermined value, the TCNT [k] is adjusted dynamically in value range of the TCNT [k] according to a comparison result, and a target working sub-band of the voltage-controlled oscillator is determined by combining the binary search algorithm. According to the method, the measurement error is compared with the predetermined value, and therefore whether a counting time reference is increased or not is controlled; a correct choice is made between correction time and correction accuracy, and therefore the correction time is effectively controlled; the dynamic correction method can effectively shorten the correction time on the whole.

Owner:HUAWEI TECH CO LTD

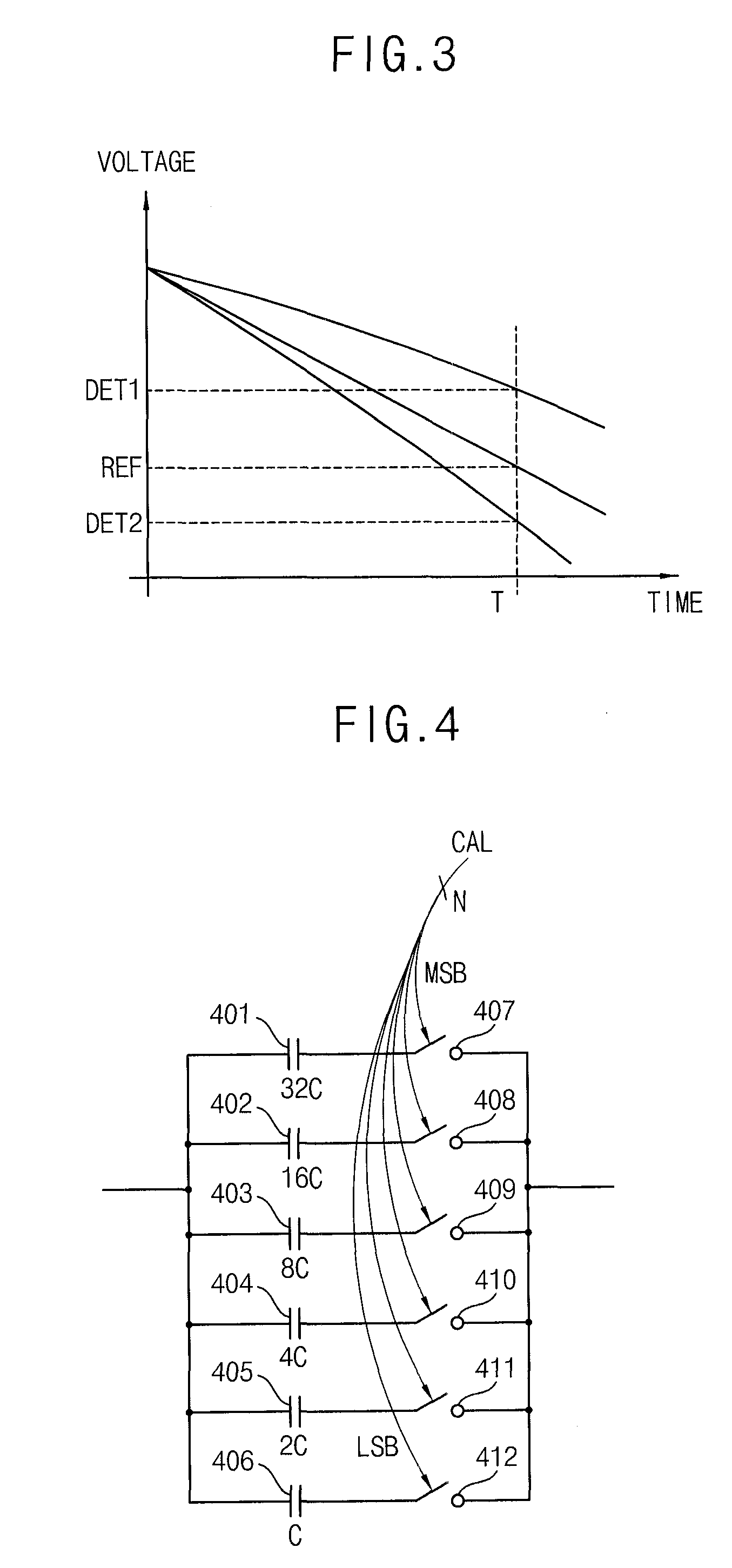

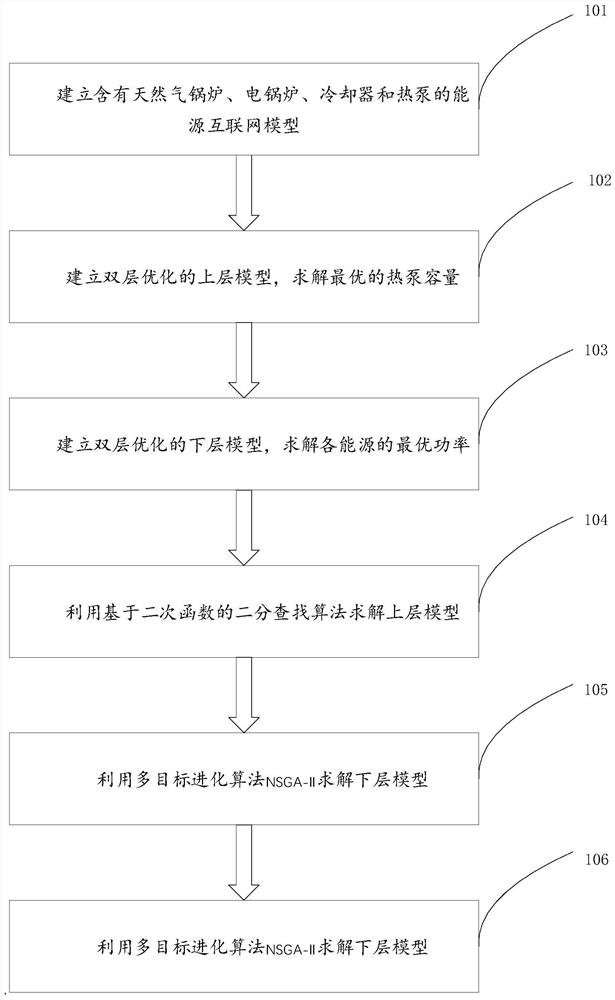

Advanced frequency calibration

ActiveUS20080158179A1Resistance/reactance/impedenceFault locationLocal oscillatorBinary search algorithm

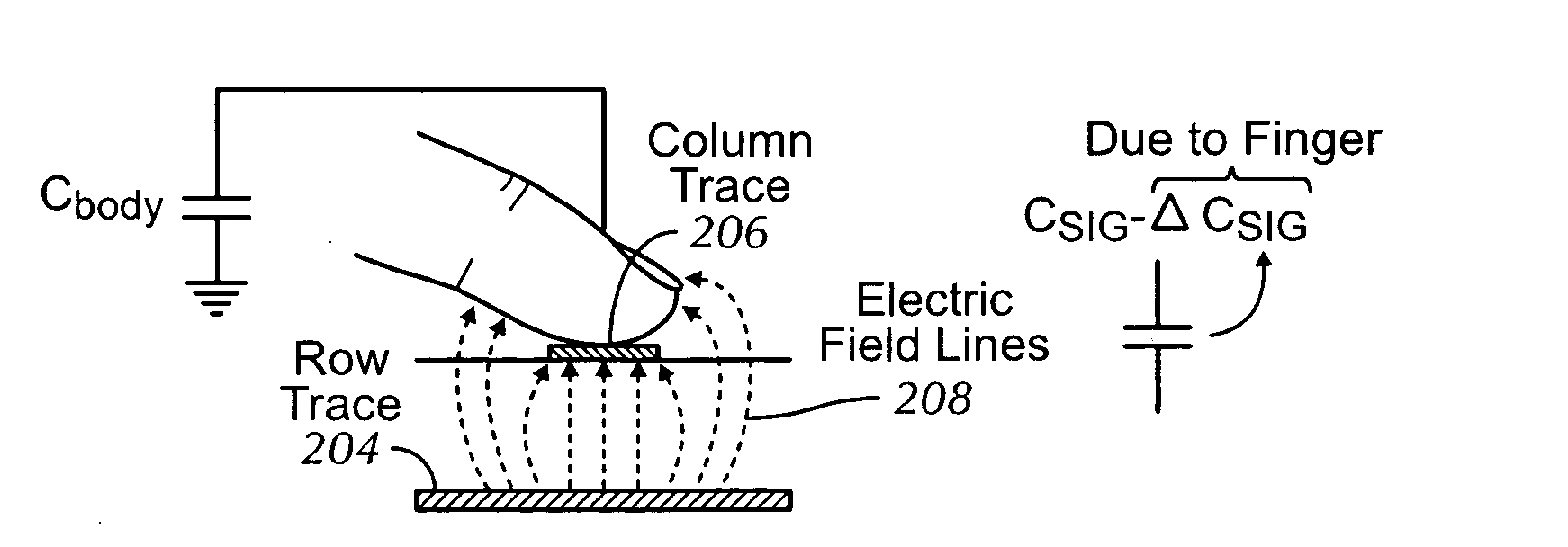

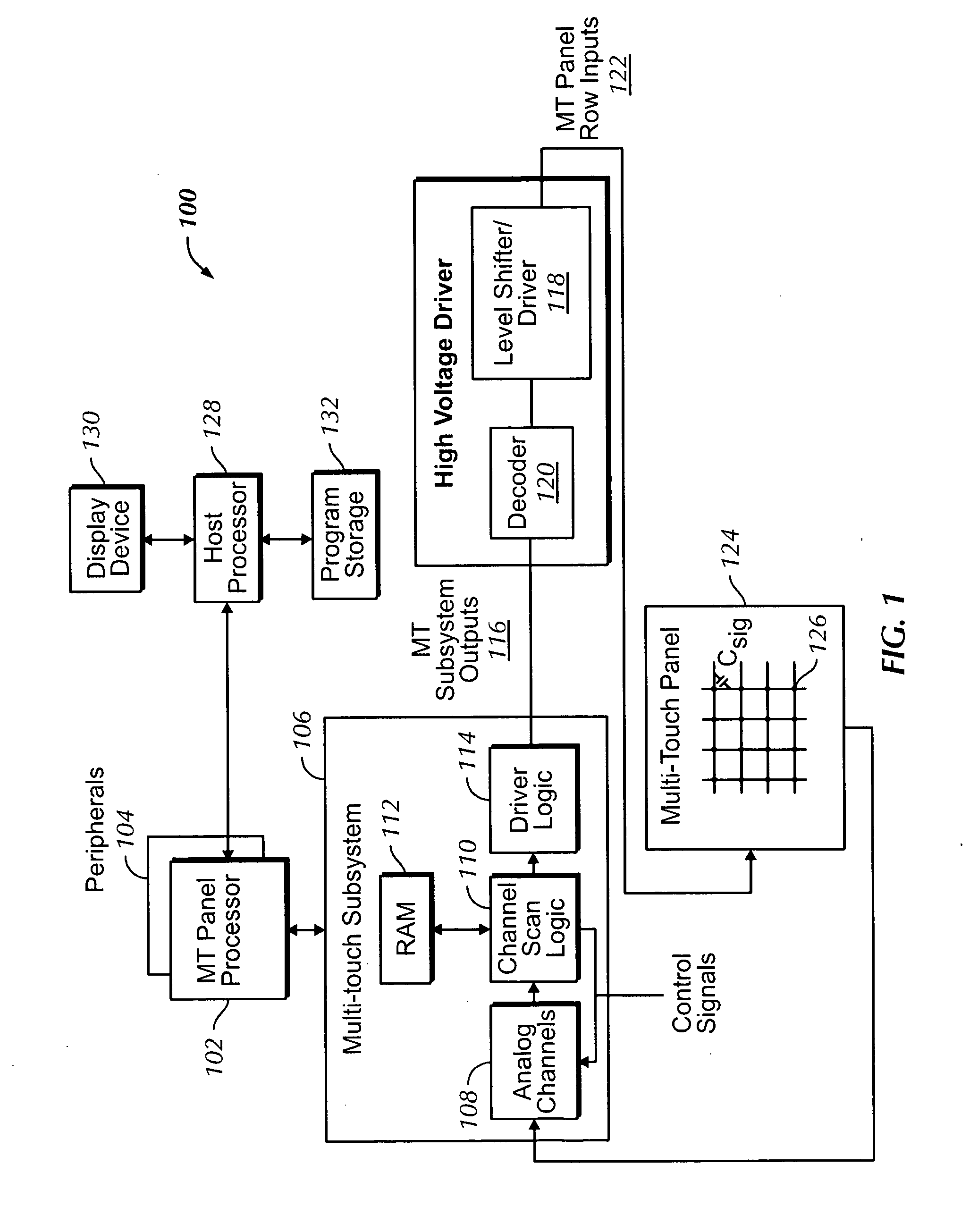

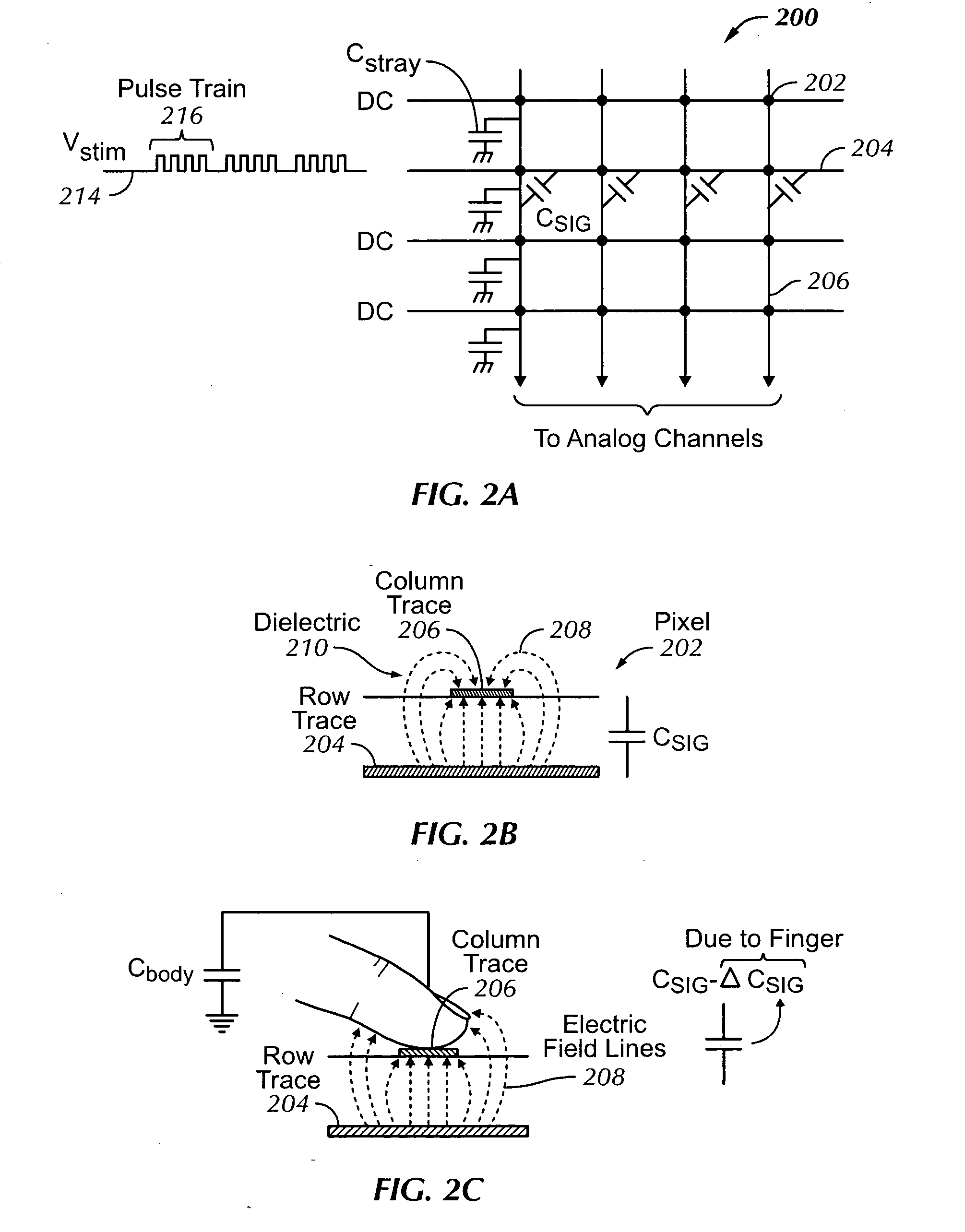

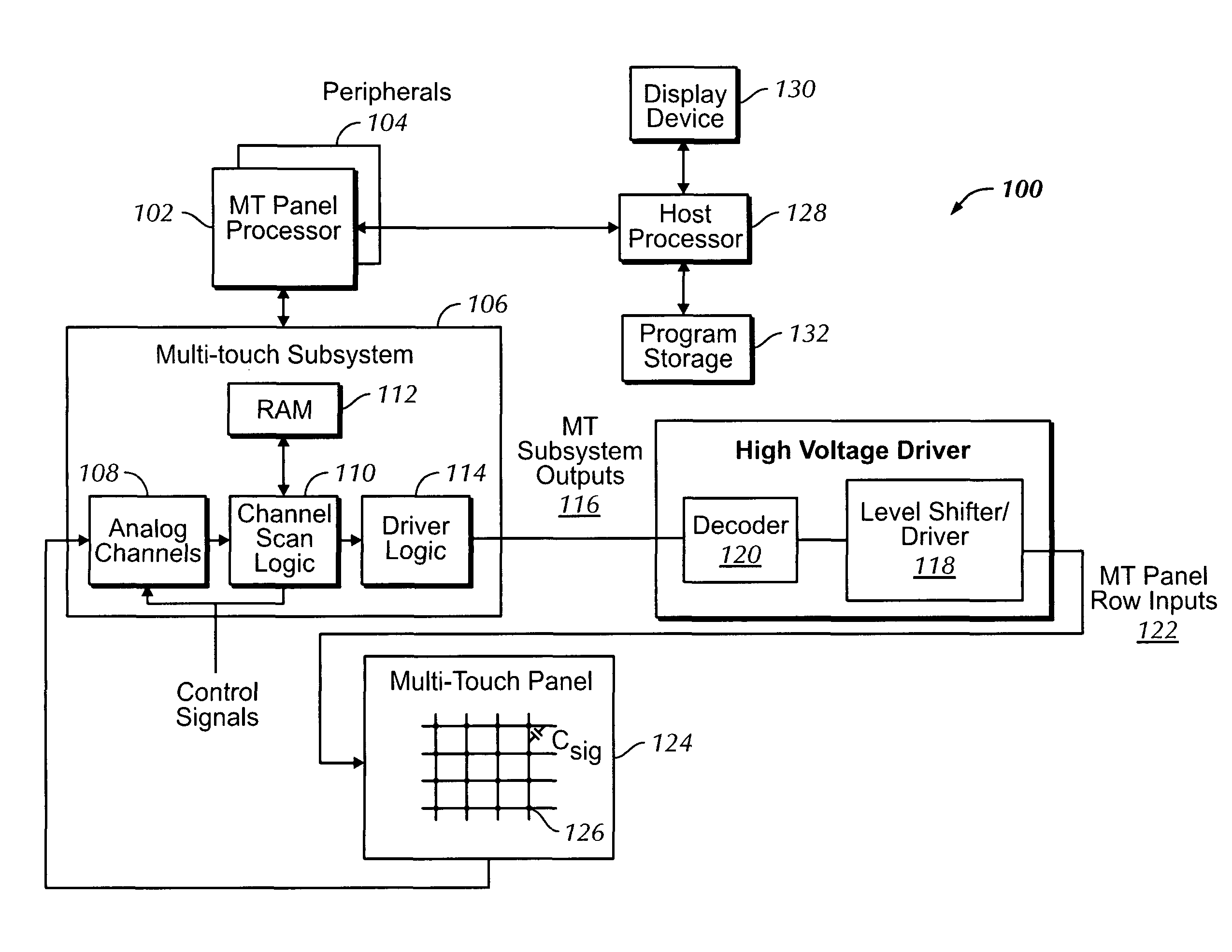

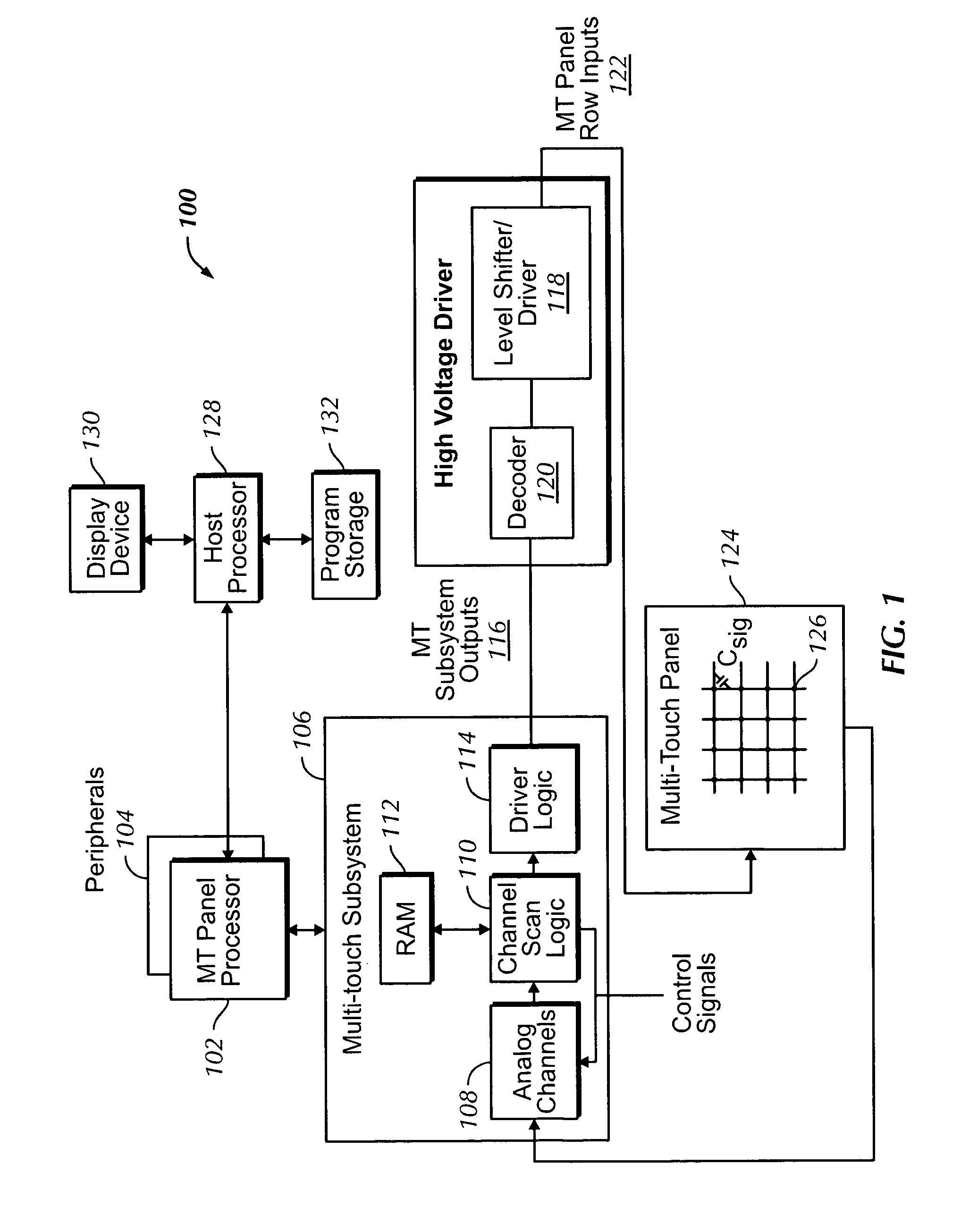

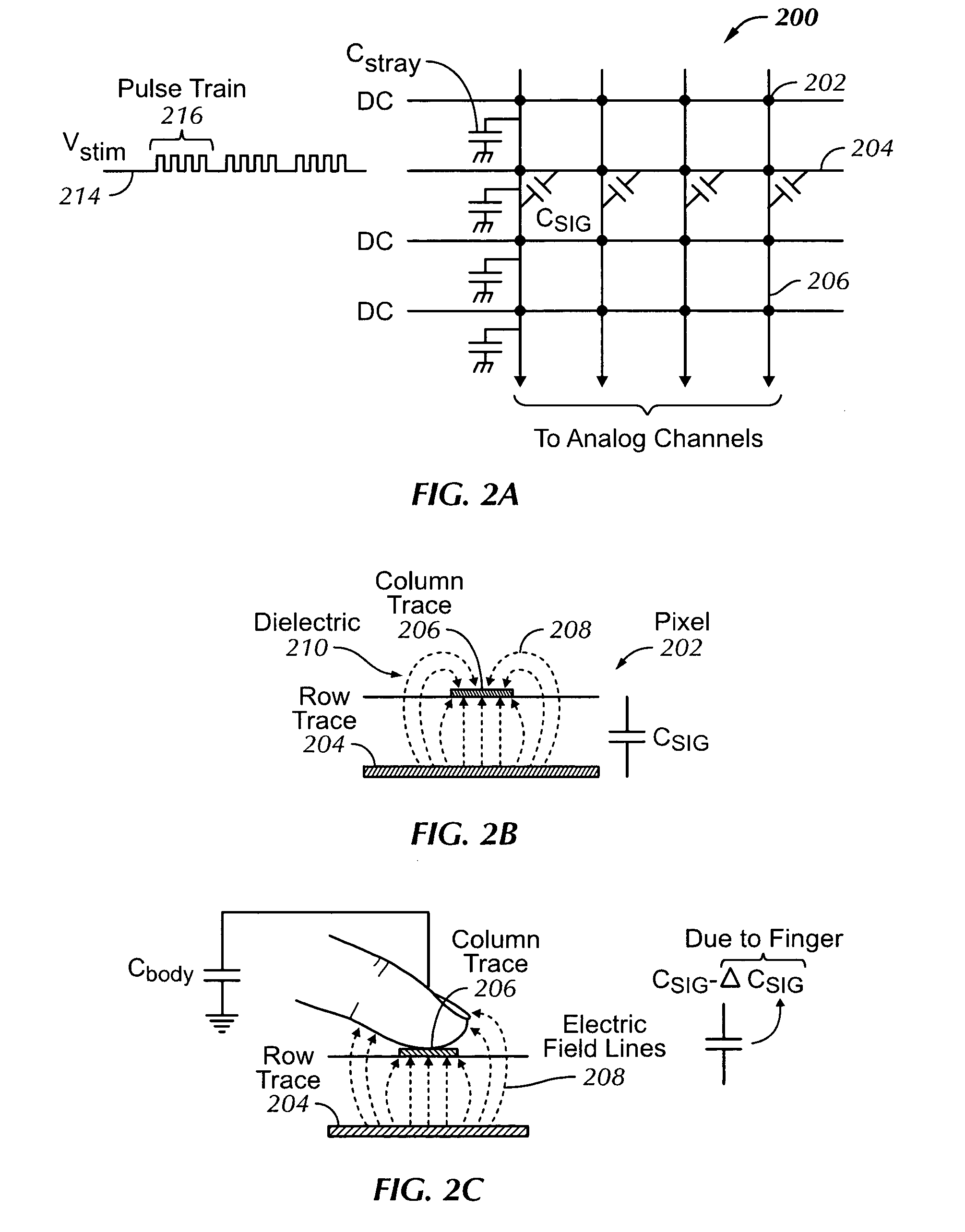

An oscillating signal of relatively precise frequency is generated by tuning an oscillator using an external stable oscillating source as a reference. Calibration logic is included to compare a signal from the local oscillator to the reference signal and vary the local signal to a desired frequency. In one embodiment, a binary search algorithm is used to tune the local oscillator. The local oscillating signal can be sent to one or more circuits including at least one sensor of a touch sensitive panel for detecting touch events.

Owner:APPLE INC

Advanced frequency calibration

ActiveUS8085247B2Transmission systemsResistance/reactance/impedenceLocal oscillatorBinary search algorithm

An oscillating signal of relatively precise frequency is generated by tuning an oscillator using an external stable oscillating source as a reference. Calibration logic is included to compare a signal from the local oscillator to the reference signal and vary the local signal to a desired frequency. In one embodiment, a binary search algorithm is used to tune the local oscillator. The local oscillating signal can be sent to one or more circuits including at least one sensor of a touch sensitive panel for detecting touch events.

Owner:APPLE INC

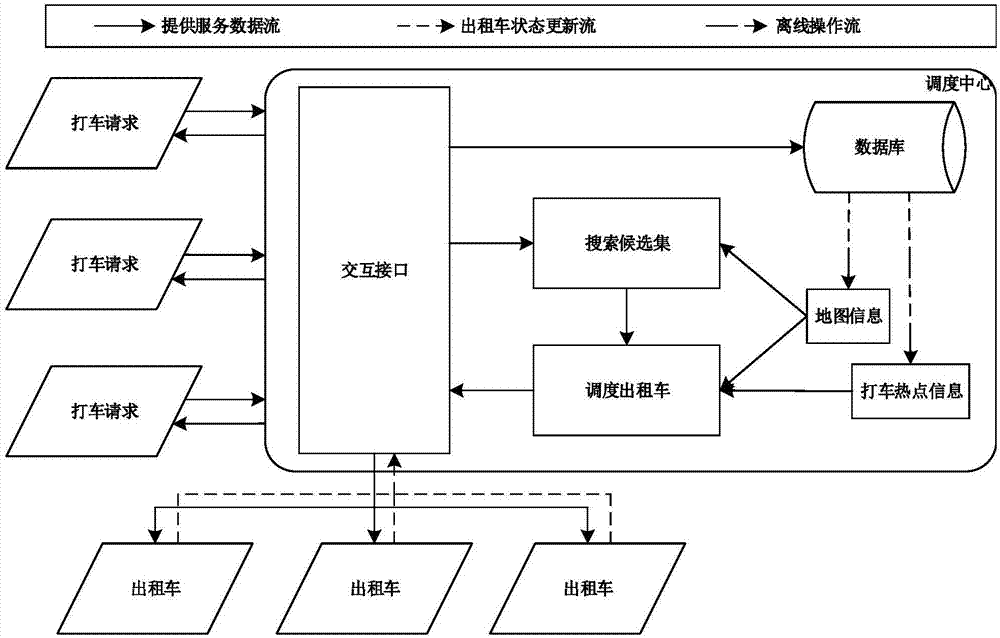

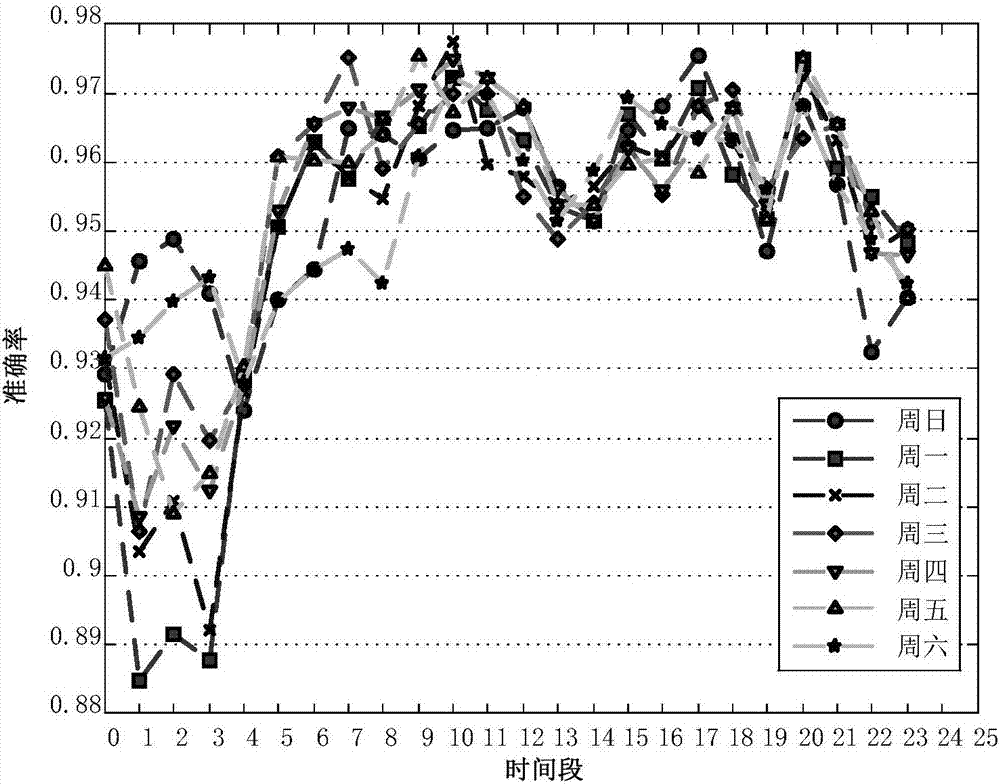

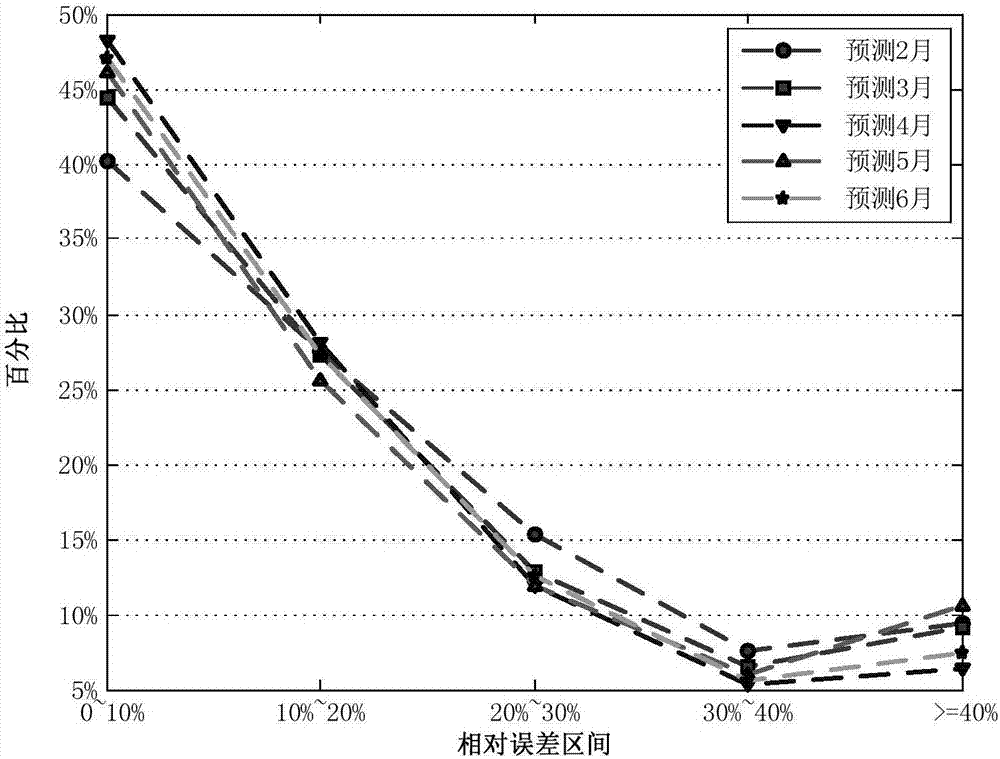

Dynamic carpooling scheduling method based on taxi-hailing hot spot

The invention belongs to the computer application technology field and discloses a dynamic carpooling scheduling method based on a taxi-hailing hot spot. The method is performed mainly through two stages: a searching stage and a scheduling stage. In the searching stage, a time-based binary search algorithm is used to quickly and efficiently retrieve taxi candidate sets that may serve passengers. In the scheduling stage, according to the given definition of dynamic carpooling scheduling problem, the conditions for each taxi in the candidate taxi sets are determined so that the taxis with the largest average satisfaction are selected to provide service for passengers, and in view of the empty car scheduling, and an optimal scheduling strategy based on hot spot is provided. This method can realize the personalized dispatching service for passengers, and it is simple and efficient, and has very strong expansibility. This provides important reference value for the study of dynamic carpooling scheduling.

Owner:DALIAN UNIV OF TECH

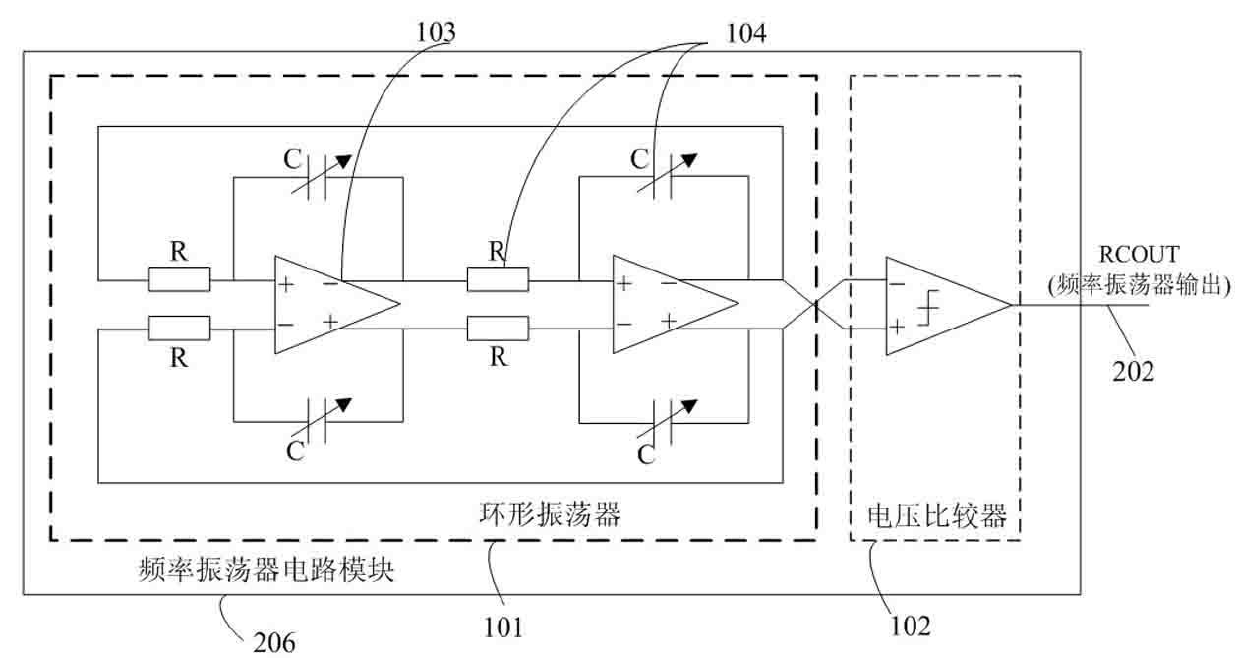

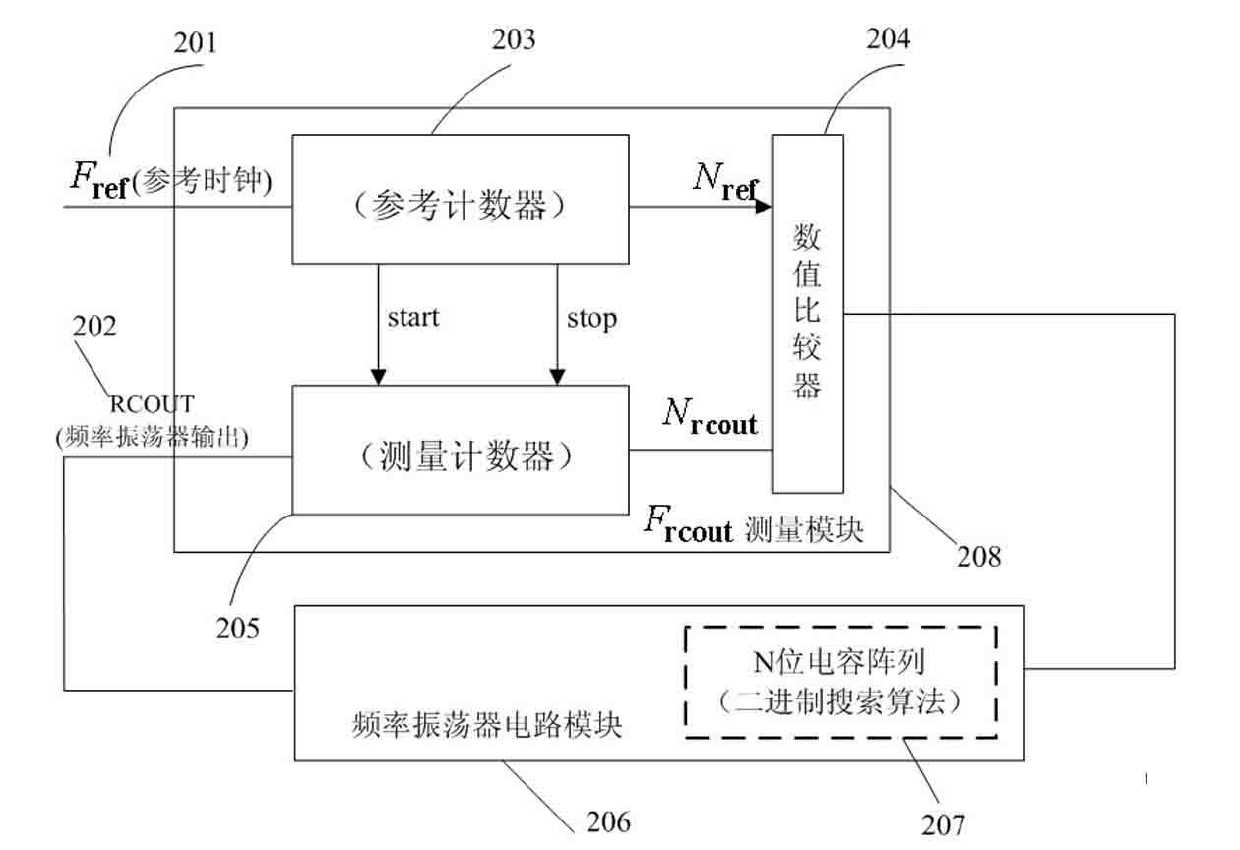

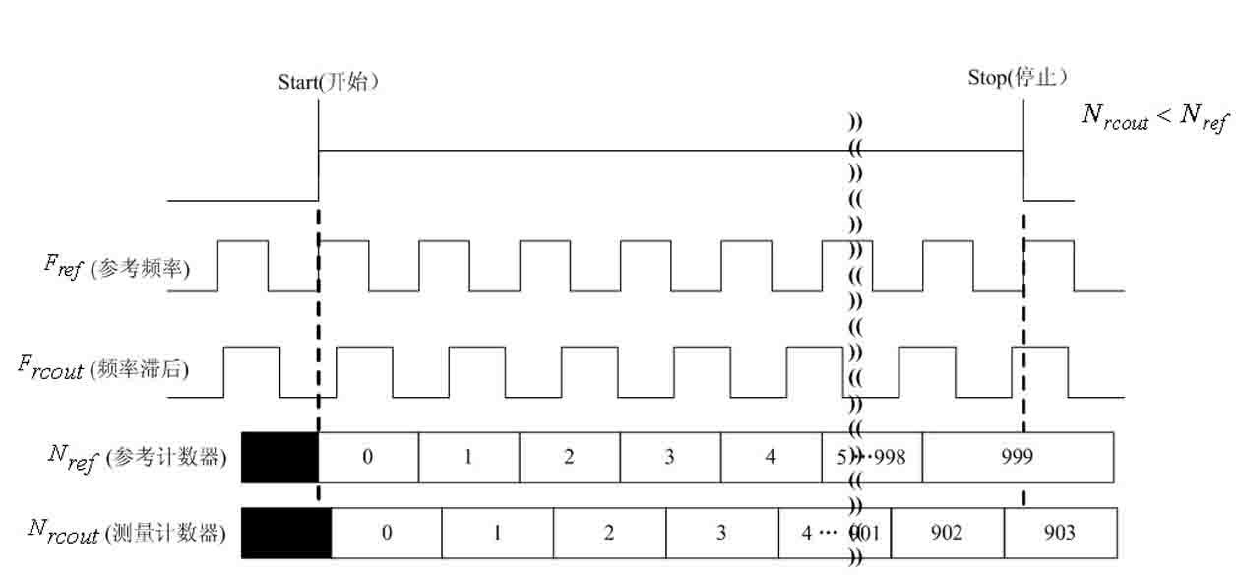

Resistance capacitance (RC) constant measuring method based on frequency measurement

ActiveCN102207522AAchieve correctionImplement correction applicationResistance/reactance/impedenceResistance capacitanceFrequency measurements

The invention discloses a resistance capacitance (RC) constant measuring method based on frequency measurement. Based on the output frequency measurement and the RC constant design, and the relationship between an output frequency of an oscillator and an RC constant in the frequency oscillator, the RC constant measurement based on the frequency measurement and the application of RC constant measurement in correction of a frequency oscillating circuit are realized. A measurement modular circuit effectively realizes the frequency oscillating circuit according to the fact that the RC constant setting and the output frequency have a definite inverse proportional relationship, and provides preconditions for the digital circuit measurement and correction adjustment. A digital circuit is convenient and flexible to measure an oscillating frequency and the RC constant; and a correction speed is greatly improved by a binary search algorithm.

Owner:GUANGZHOU RUNXIN INFORMATION TECH

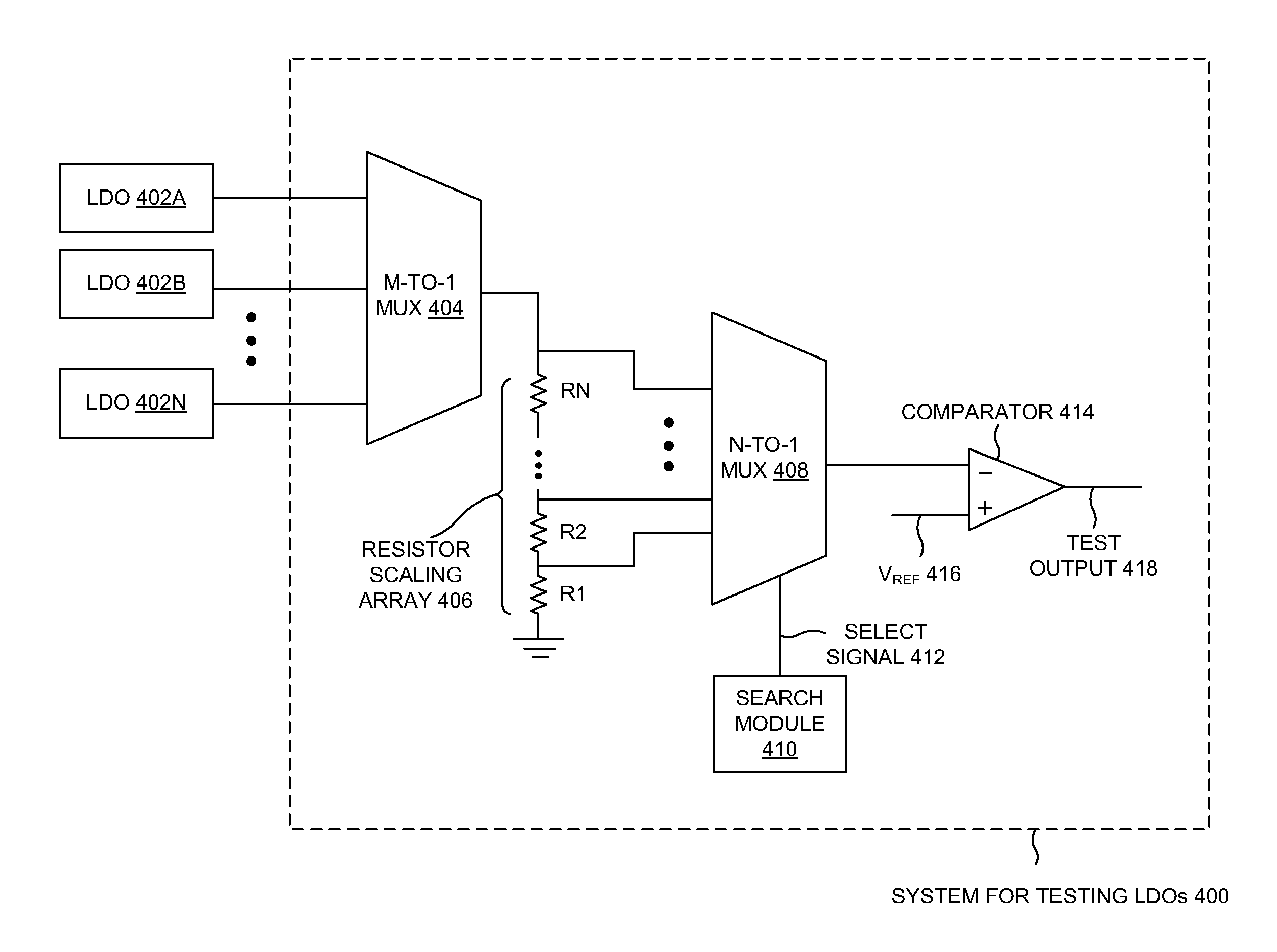

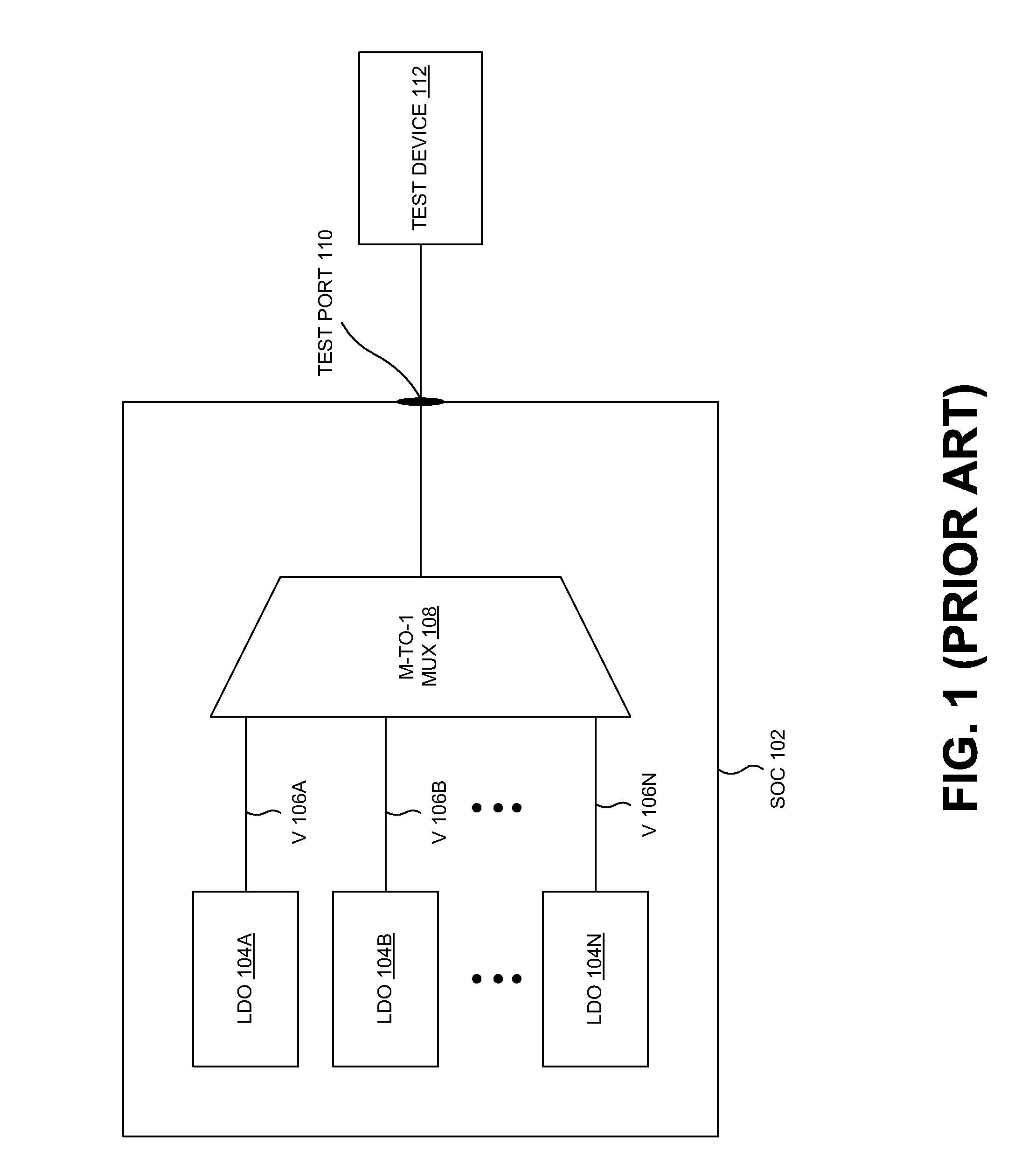

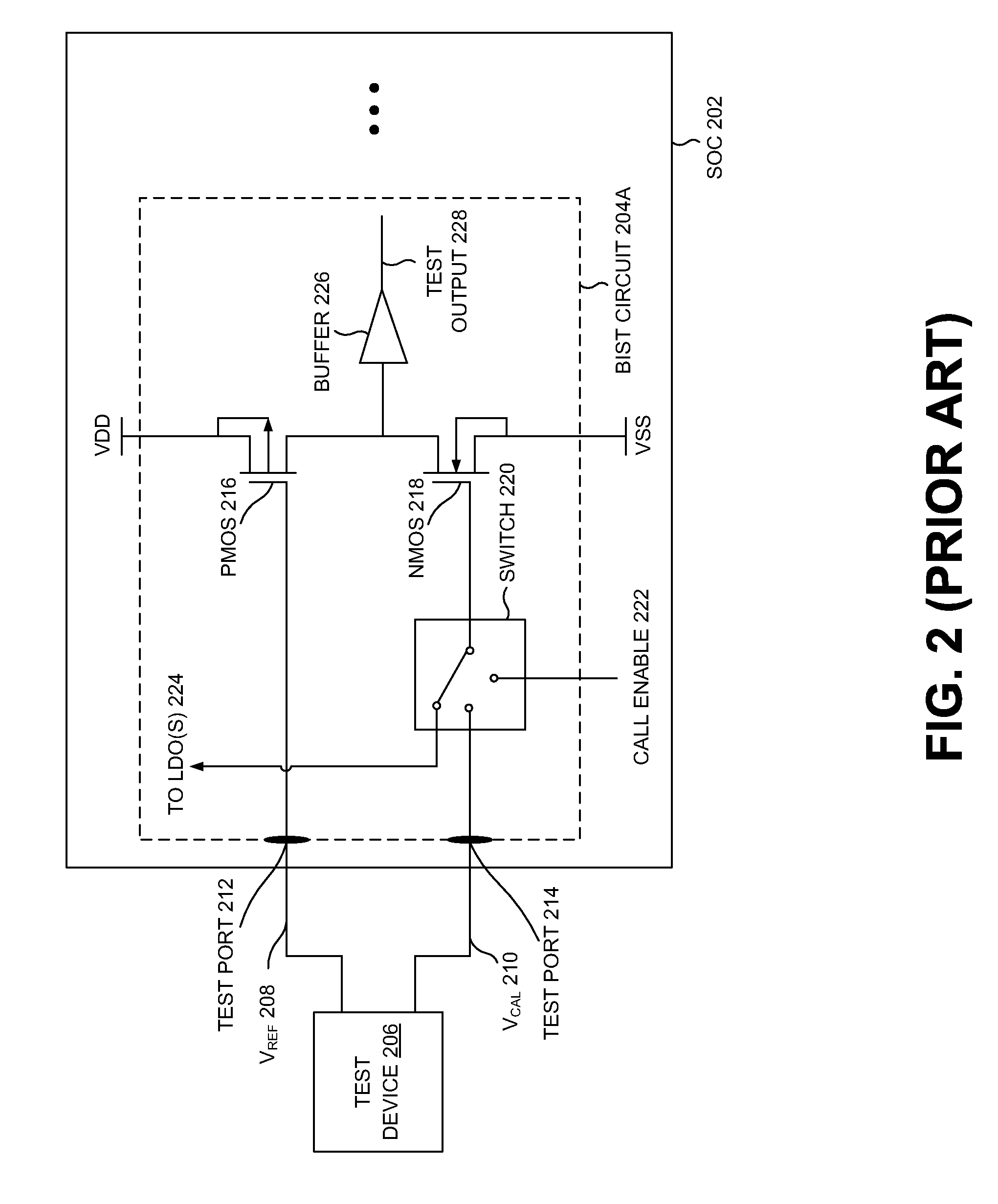

Low dropout regulator testing system and device

A device for testing low dropout (LDO) regulator is disclosed. In one embodiment, a device for testing LDO regulators includes an absolute value measurement module for measuring absolute output voltages of the LDO regulators including a resistor scaling array for generating candidate voltages based on a first output voltage of the LDO regulators, a multiplexer for forwarding one of the candidate voltages selected by a binary search algorithm, and a comparator for generating a first test output by comparing the candidate voltage with an external reference voltage, and a DC load regulation measurement module for measuring corresponding DC regulation voltages of the LDO regulators including a switch for applying an internal test load to a second output voltage of the LDO regulators, and the comparator for generating a second test output by comparing a reference voltage with the second output voltage modified by the internal test load.

Owner:TEXAS INSTR INC

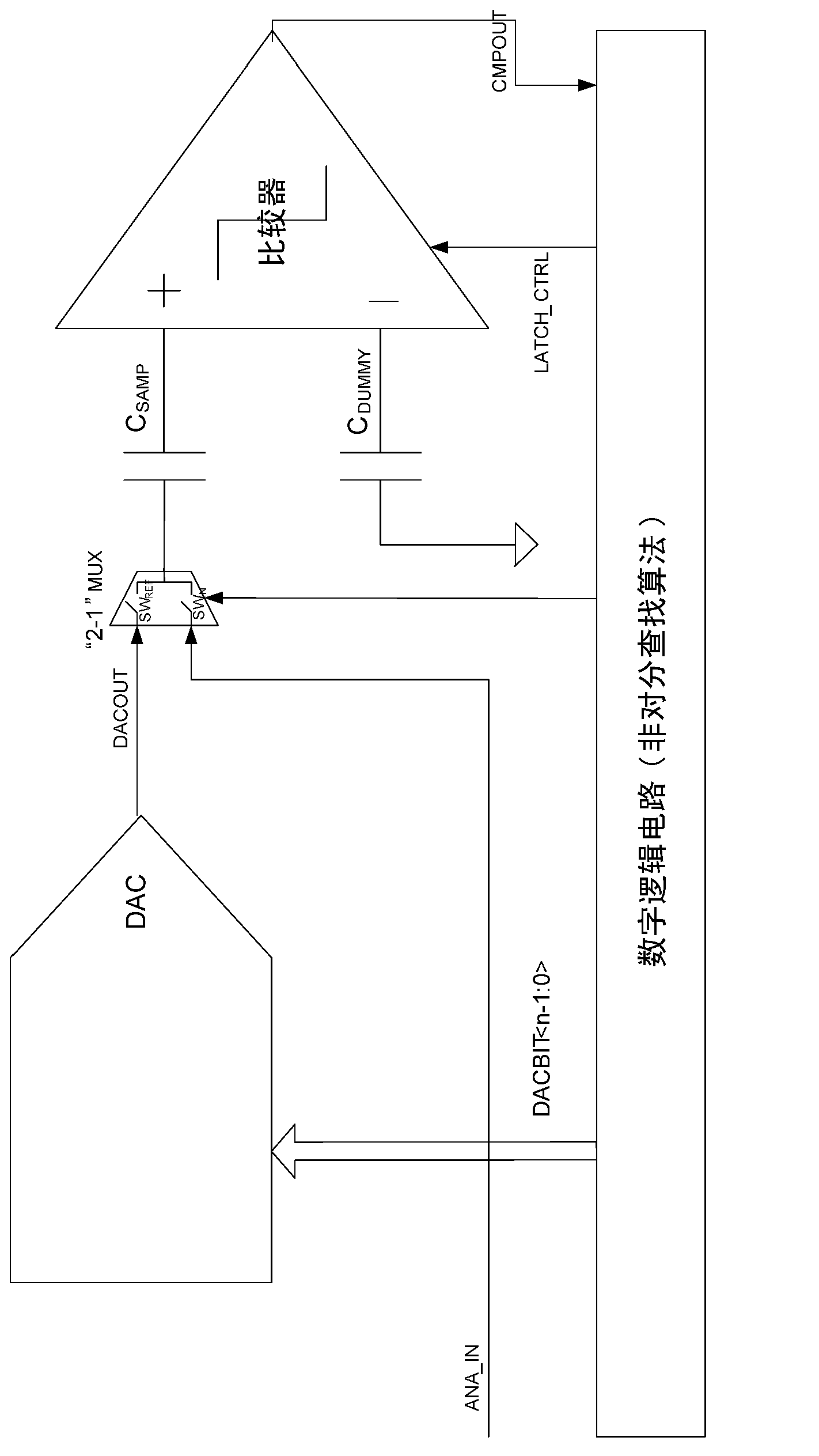

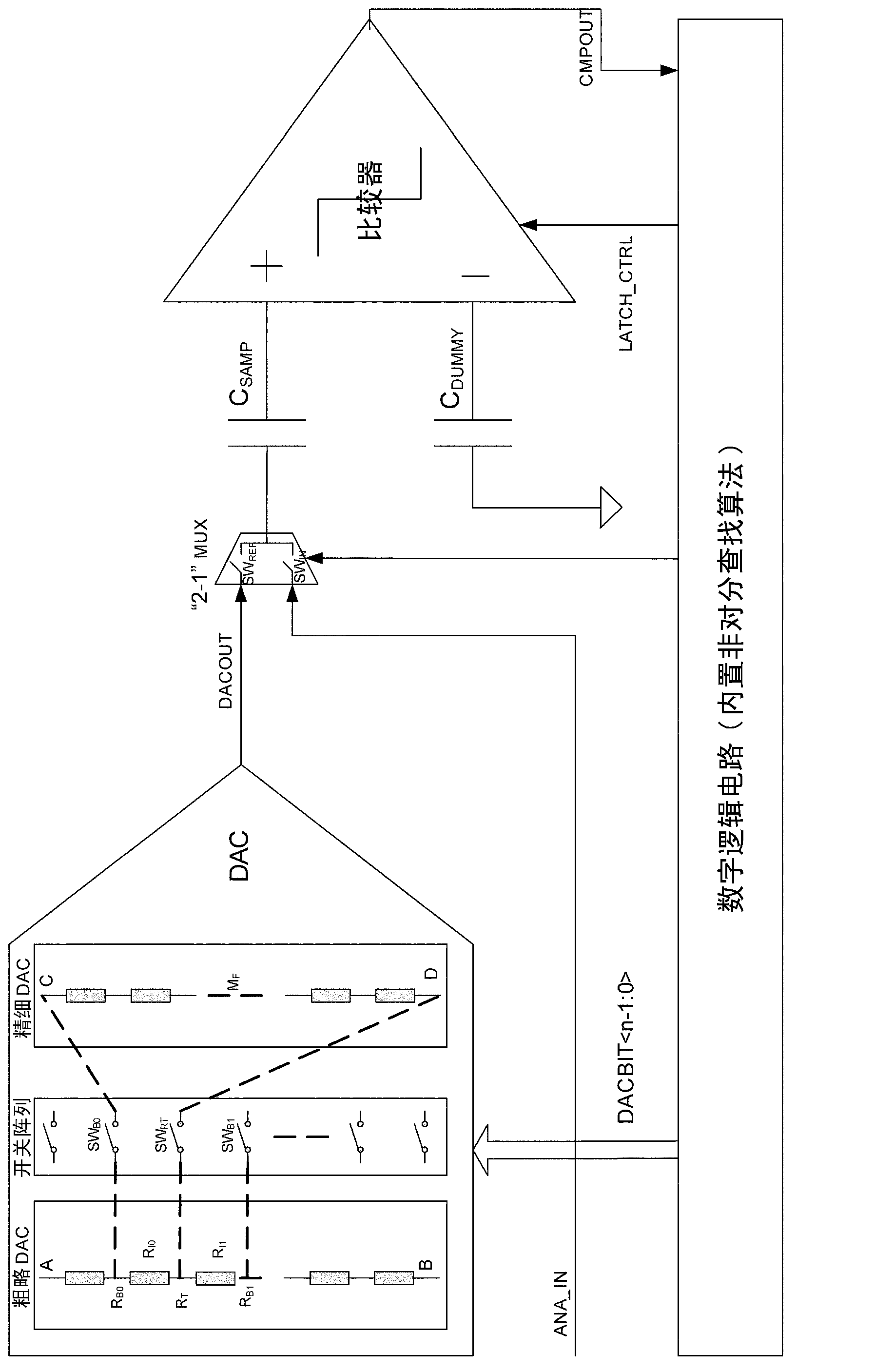

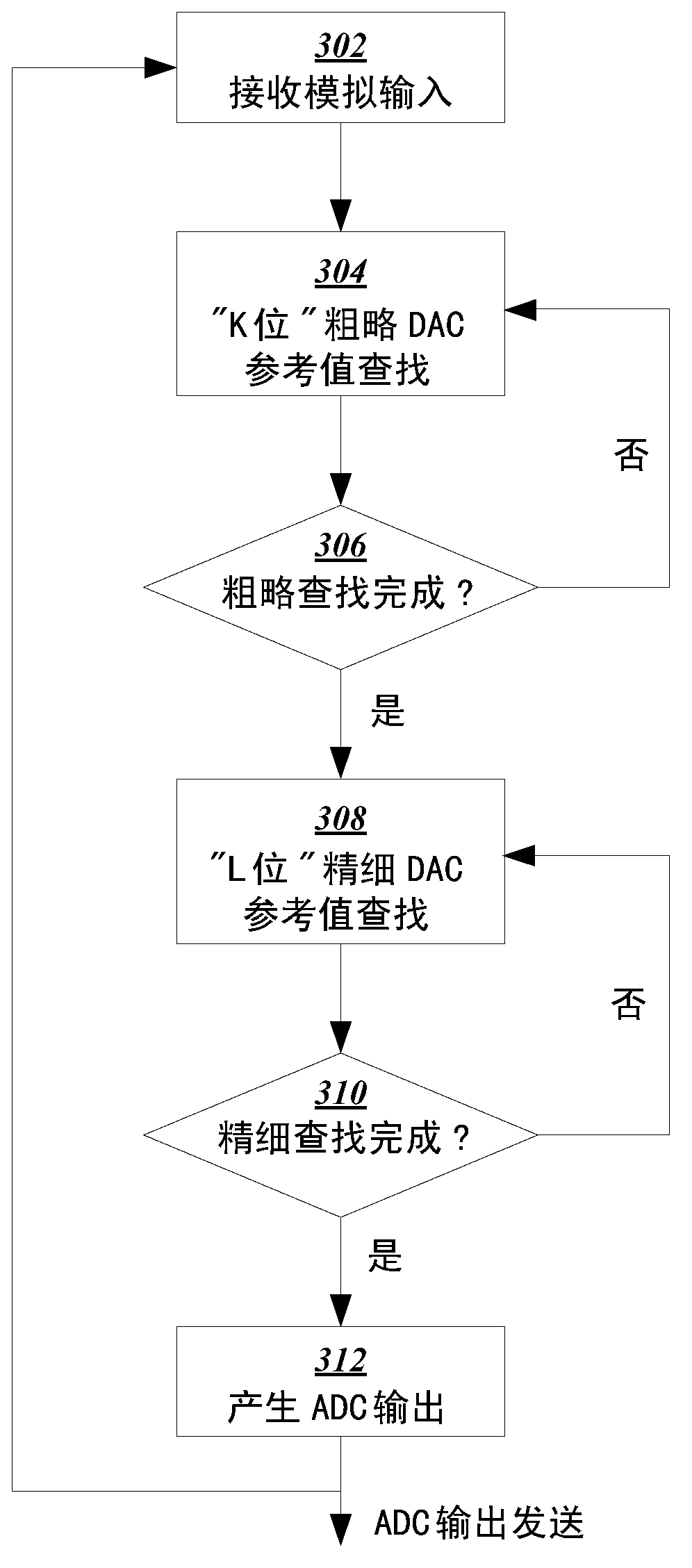

Successive approximation register analog to digital converter

InactiveCN103227642AAnalogue/digital conversionElectric signal transmission systemsDigital down converterDigital control

An apparatus implements analog-to-digital conversion with released requirement on the reference settling errors and improved immunity to the noise originated from the power supply, ground and the positive and negative references. It includes a comparator comparing the specified reference levels with the analog input, multi DAC sub-circuits with separate non-binary search schemes applied to and a digital control logic controlling the reference search process. No cross-talk occurs among the different non-binary search algorithms. Each redundancy scheme is localized in a respective DAC sub-circuit and covers the reference levels only in the current DAC. The non-binary search algorithms are fulfilled in the digital domain and trade the non-binary search step sizes with the number of the search steps to introduce redundancy to the reference levels.

Owner:NXP BV

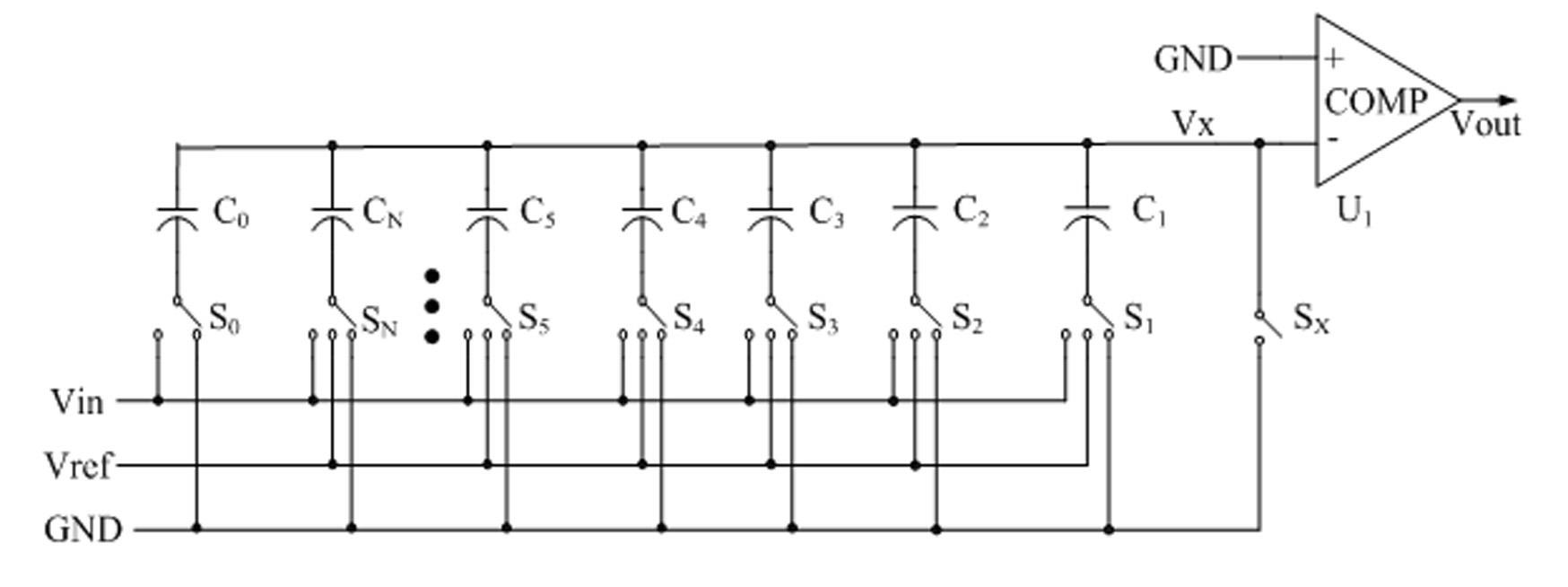

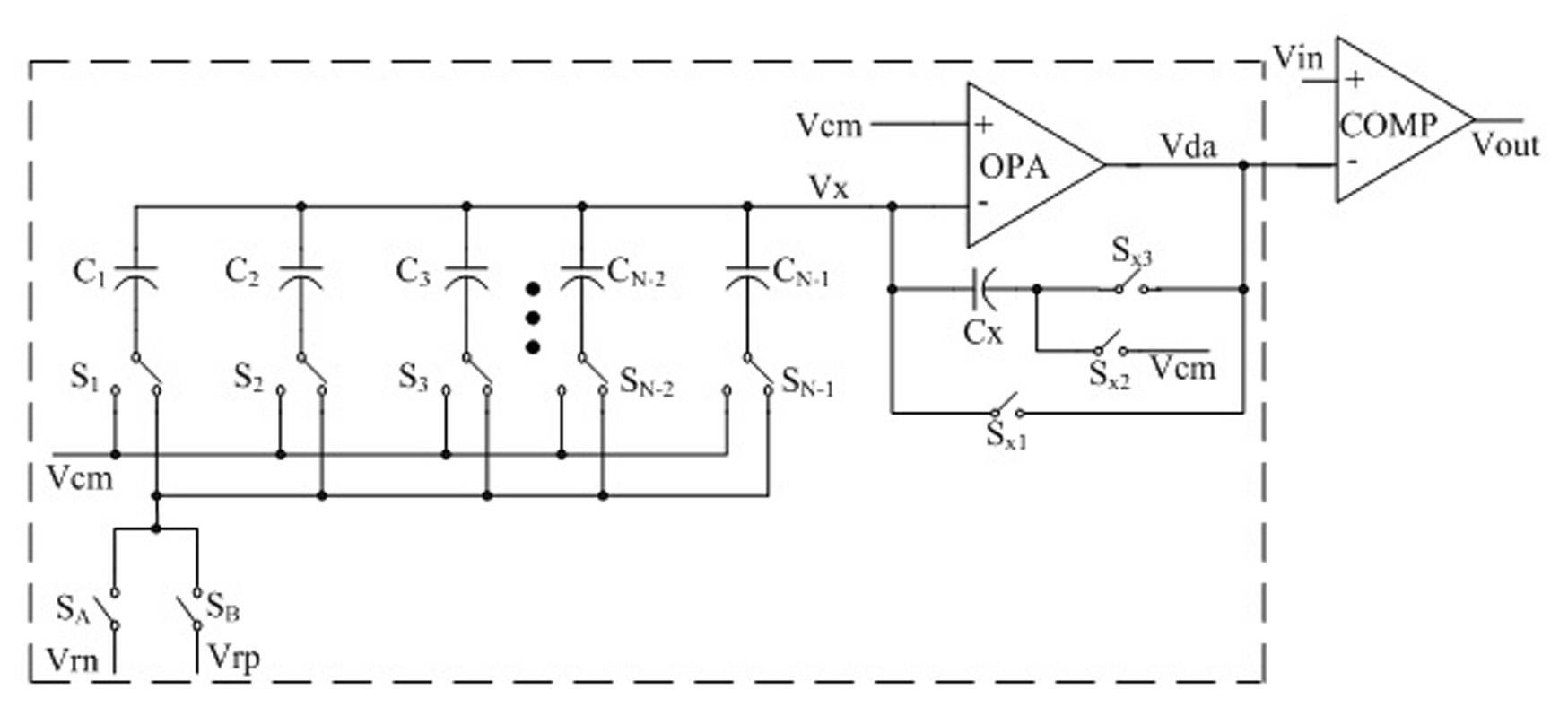

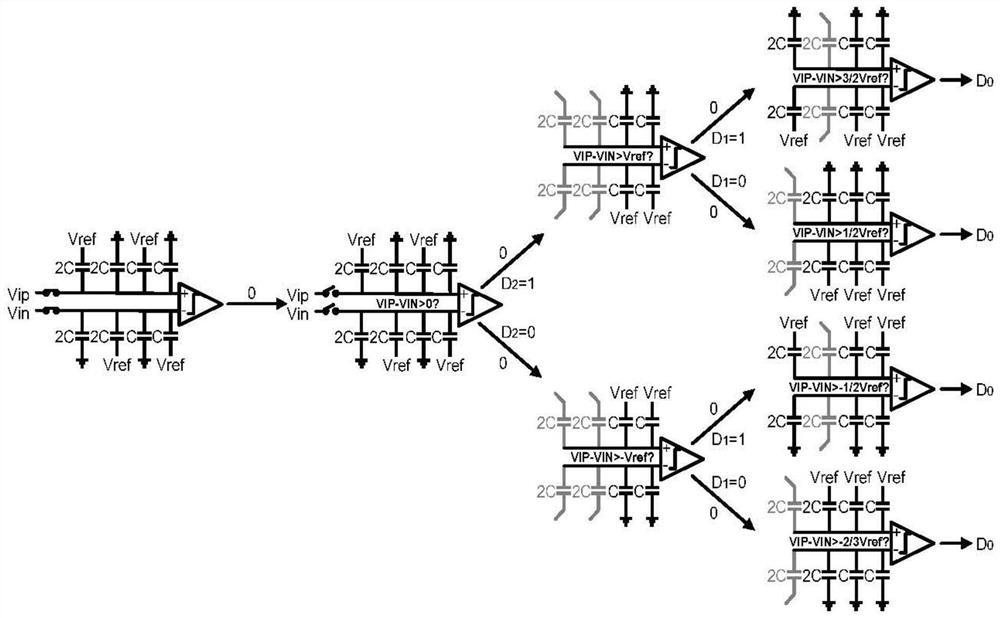

Successive approximation register analog-to-digital conversion circuit for realizing minimal dynamic range

ActiveCN102111156ADynamic range is not wastedLow costAnalogue/digital conversionElectric signal transmission systemsIntegratorVoltage reference

The invention provides a successive approximation register analog-to-digital conversion circuit for realizing minimal dynamic range, comprising a simulation input signal, a successive approximation register integrator and a comparator, wherein the simulation input signal has simulation input voltage Vin, wherein the input signal of the successive approximation register integrator are three reference voltages comprising Vrp, Vrn and Vcm, and the output voltage Vda at an output end of the successive approximation register integrator is driven according to a binary search algorithm; the positiveinput end of the comparator is connected with the simulation input signal and the negative input end of the comparator is connected with the output voltage Vda of the integrator, the output end of the comparator gradually outputs N-bit digital signals. The requirement of the actual application can be effectively satisfied by the SARADC (successive approximation register analog-to-digital conversion) circuit within the minimal dynamic range by regulating the input reference voltage of the successive approximation register integrator; thus, the dynamic range of the SARADC circuit is not wasted;and besides, the cost of the actual circuit is saved.

Owner:SHENZHEN RENERGY TECH

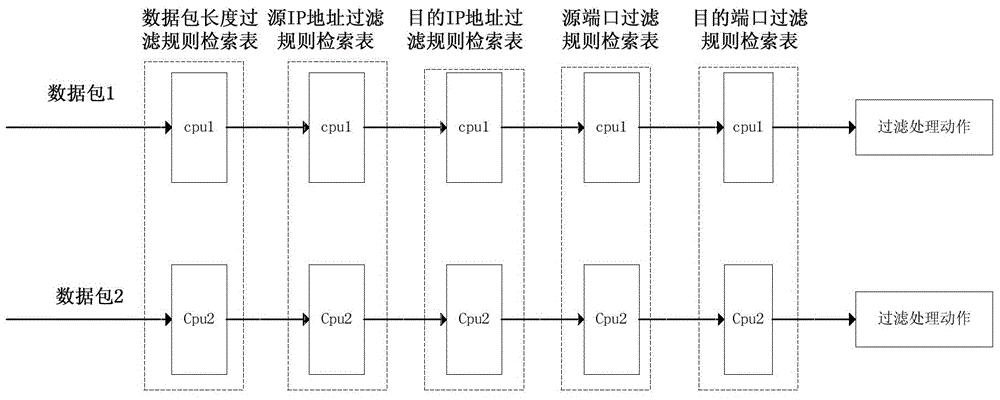

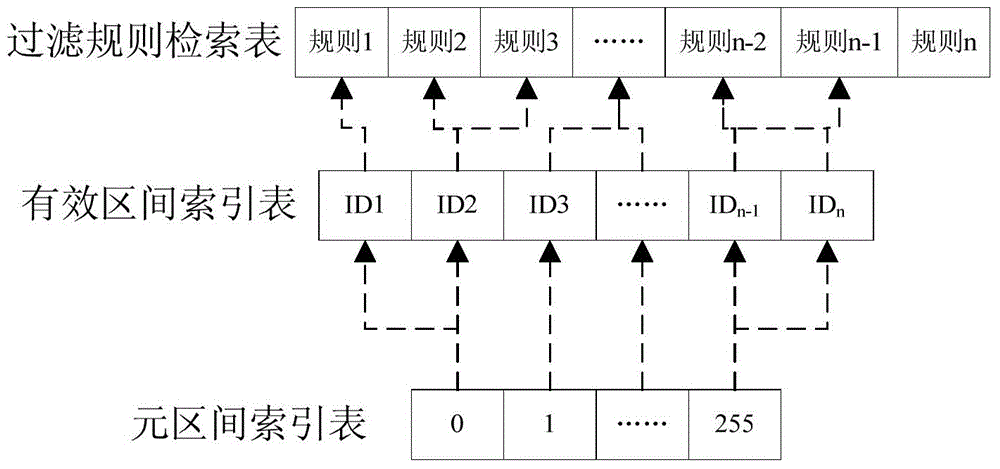

High-efficiency filtering method for data packets

ActiveCN103338155AImprove the speed of matching filter rulesImprove filtration efficiencyData switching networksFiltering rulesData mining

The invention discloses a high-efficiency filtering method for data packets. The method comprises the steps as follows: firstly, preprocessing all filtering rules to obtain a filtering rule retrieval table and a mapping relation table of the field type filtering rules with the same number as CPU (central processing unit) cores; secondly, obtaining the filtered field information of the data packets to be processed by the CPU cores and determining the filtering rules corresponding to the filtered field information through a dextroposition operation and a binary search algorithm; thirdly, processing the filtered field information in the data packets according to the corresponding filtering rules so as to finish filtering of the data packets. According to the method, the filtering rules can be quickly and accurately matched, so that the filtering speed is greatly increased, the data throughput performance is greatly improved, and the data packet filtering efficiency is improved.

Owner:ANHUI ZHONGXIN SOFTWARE

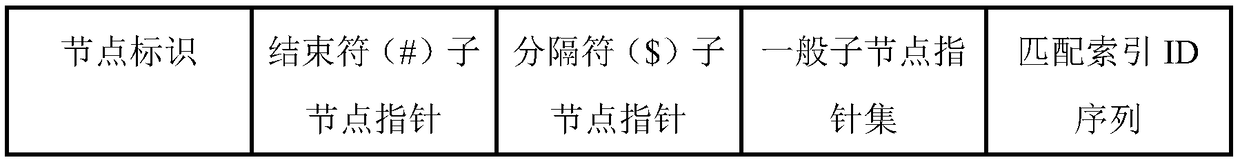

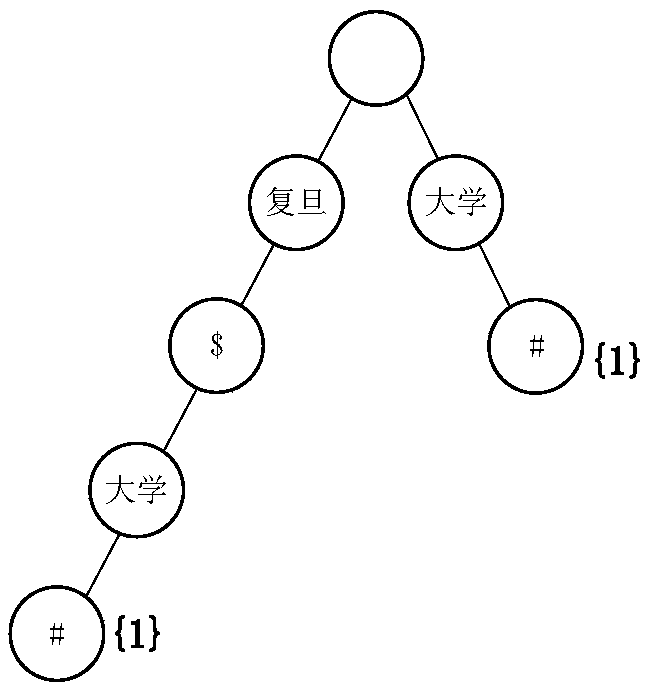

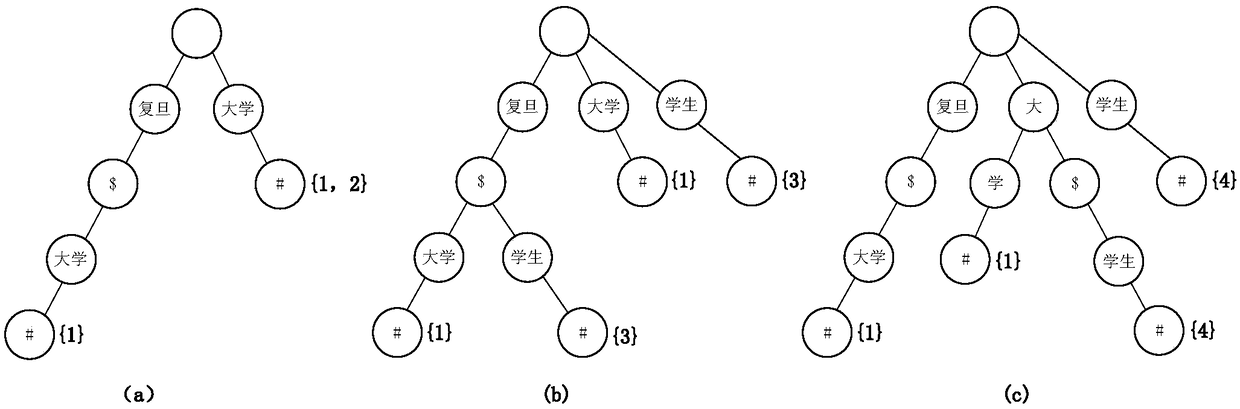

Search algorithm for Chinese word segmentation

ActiveCN108846016AImprove search efficiencyLess build timeNatural language data processingSpecial data processing applicationsTheoretical computer scienceChinese word

The invention belongs to the technical field of text search engines and specifically relates to a search algorithm for Chinese word segmentation. The algorithm is mainly divided into two phases including an offline indexing phase and an online searching phase. In the offline indexing phase, firstly suffix string sets of all original string sets are extracted, and then an improved suffix tree is generated by the suffix string sets. In the online searching phase, firstly query results of a keyword are obtained according to an index model based on the suffix tree, then a matching degree between the keyword and the query result is quantified, and finally, the query results are sorted from high to low according to a matching program followed by return. According to the search algorithm, an index construction time and an occupation space are balanced through an improved index structure based on the suffix tree, thus the search efficiency of the index structure with the search algorithm is much higher than the efficiency of violently calculating the matching degree and sorting efficiency of a result set.

Owner:FUDAN UNIV

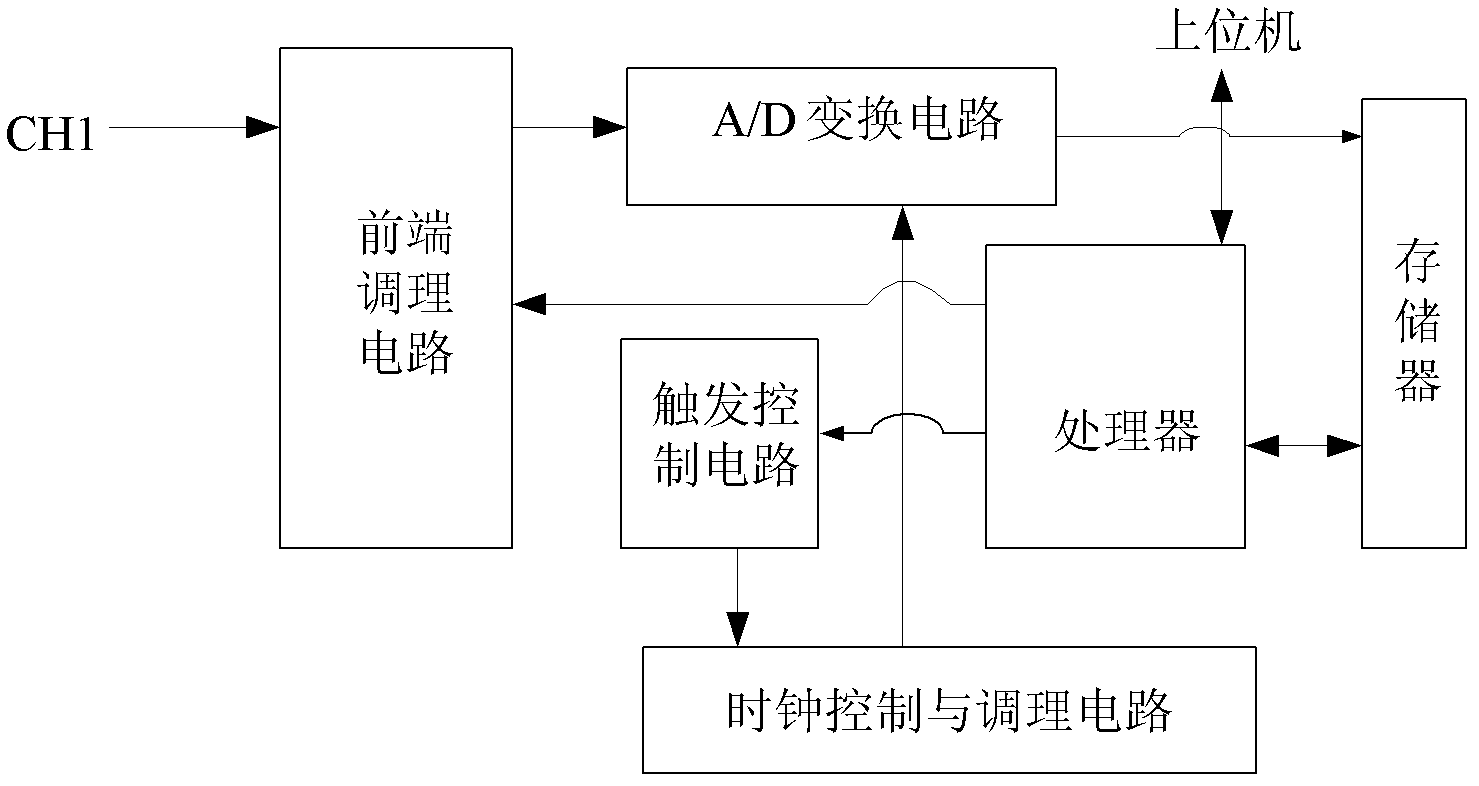

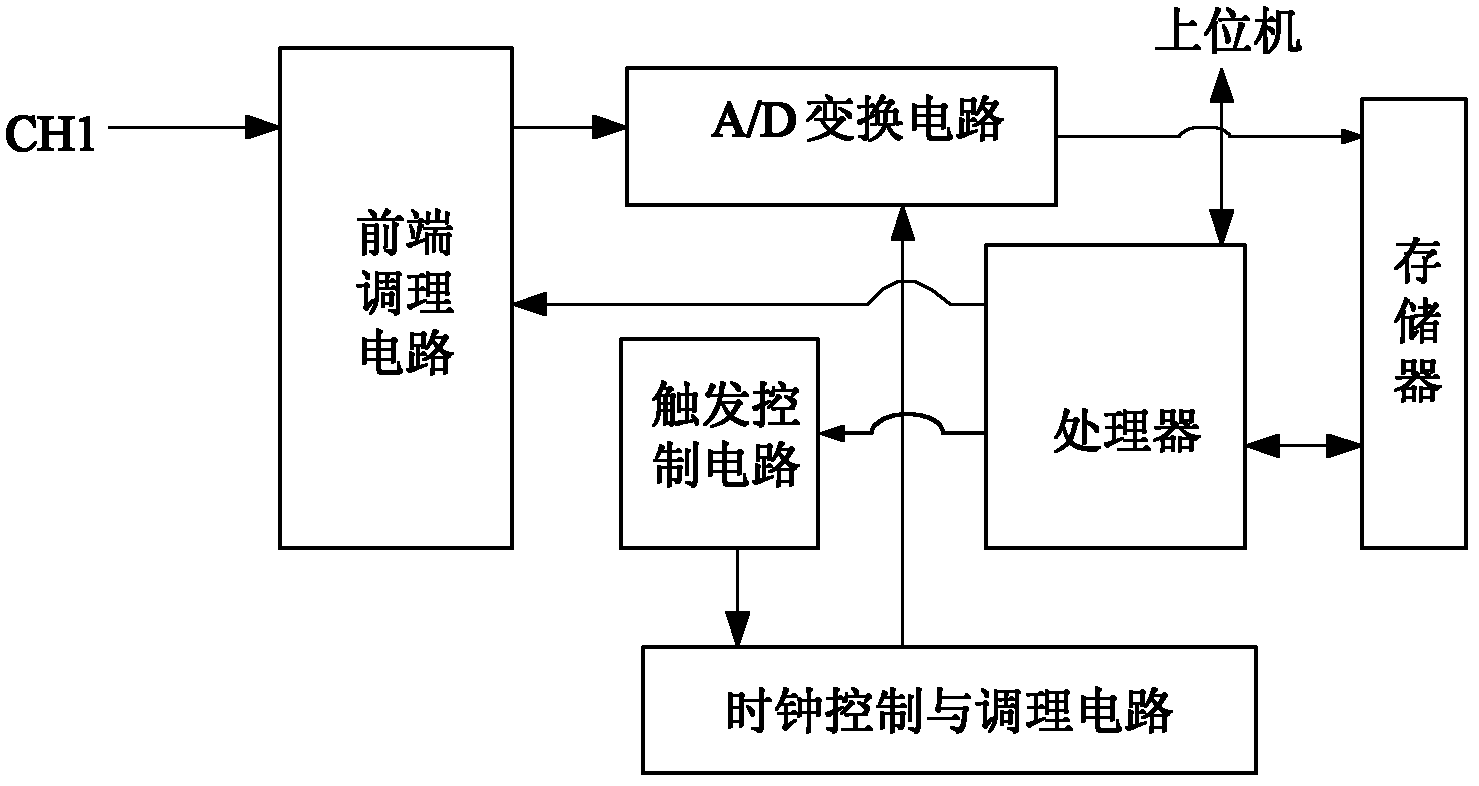

Method for automatically calibrating direct current accuracy of digital oscilloscope on basis of binary search

ActiveCN102495387AImprove calibration accuracyIncrease production capacityElectrical measurementsVoltage amplitudeGreek letter epsilon

The invention discloses a method for automatically calibrating the direct current accuracy of a digital oscilloscope on the basis of the binary search. After the method is adopted, the aims of reducing the calibrating time of the digital oscilloscope and improving the calibrating accuracy can be fulfilled. Specifically, the method comprises the following steps: a user sets a corrected value of anadder of a front-end conditioning circuit, a channel and a range of the digital oscilloscope, a calibration error limit epsilon and a voltage amplitude Dexp of a calibration target analog voltage signal; when the corrected value of the adder is set into Vmin, the digital oscilloscope starts to acquire to obtain an average value Dmin corresponding to the Vmin; likewise, the corrected value of the adder is set into Vmax, an average value Dmax corresponding to the Vmax is obtained; an upper computer carries out data processing by adopting a binary search algorithm and generates a calibrating result Vexp according to the Dmin, the Dmax, the Dexp and the epsilon; the upper computer sends the Vexp to a storage and resets the digital oscilloscope; and when the user restarts the upper computer, the upper computer reads the calibrating result from the storage and writes the calibrating result into the adder in the front-end conditioning circuit, wherein the calibrating result is used for correcting a direct current error generated by the front-end conditioning circuit.

Owner:BEIJING AEROSPACE MEASUREMENT & CONTROL TECH

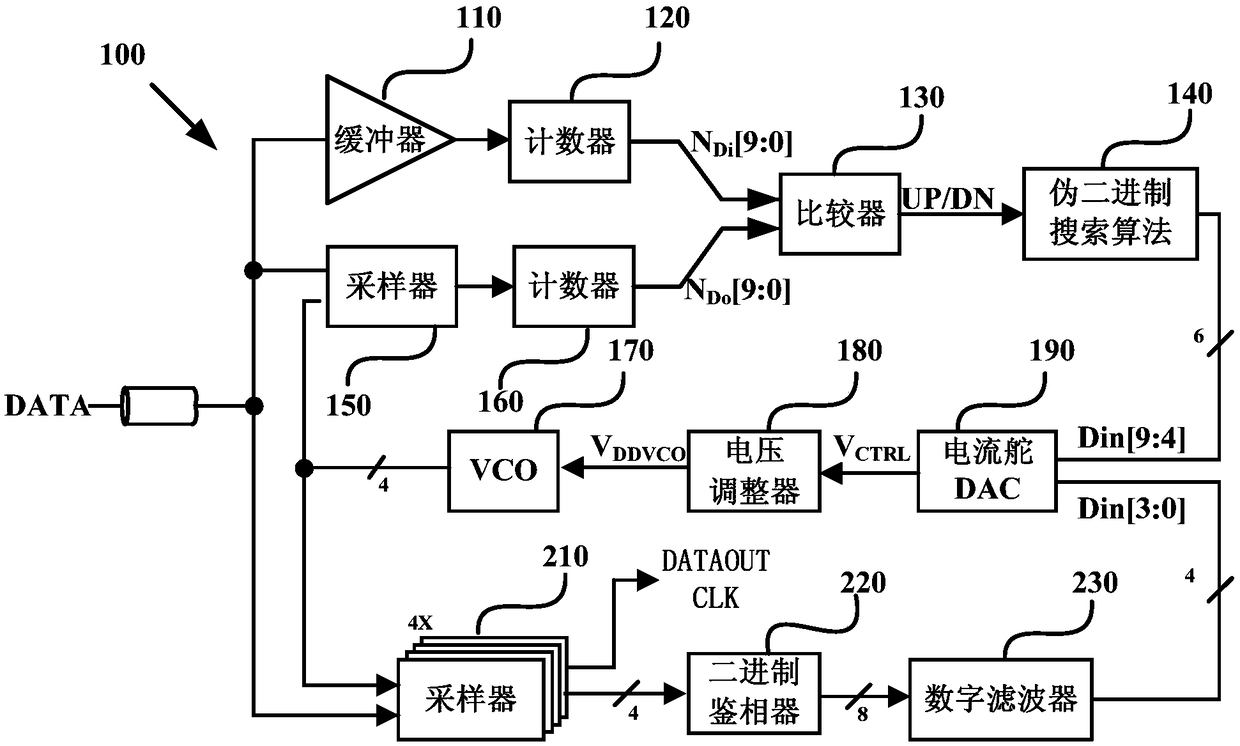

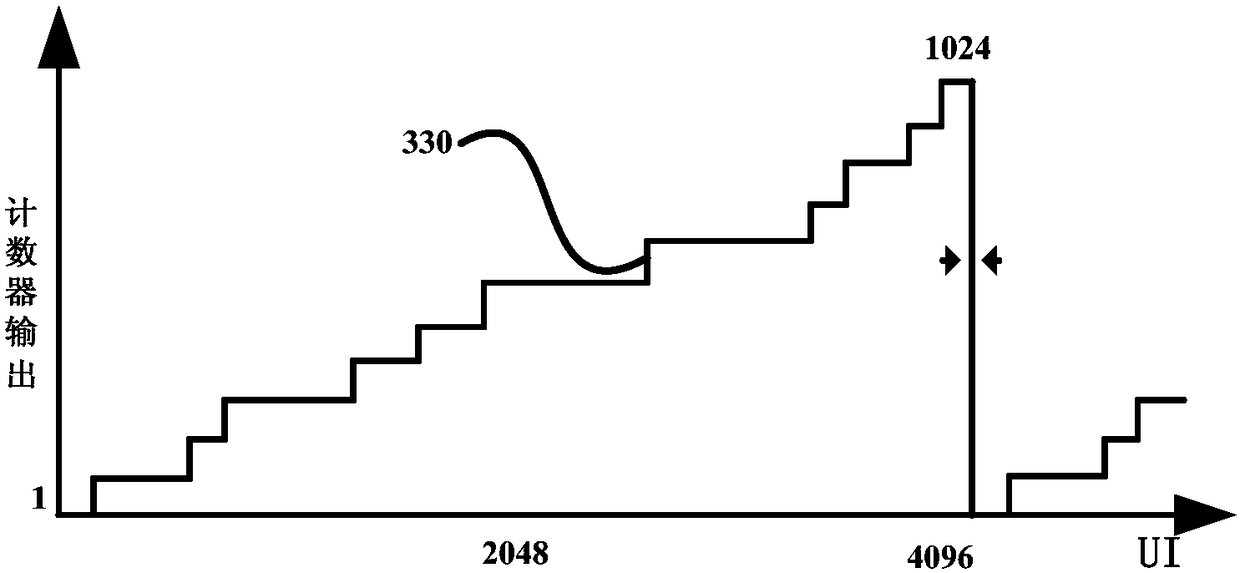

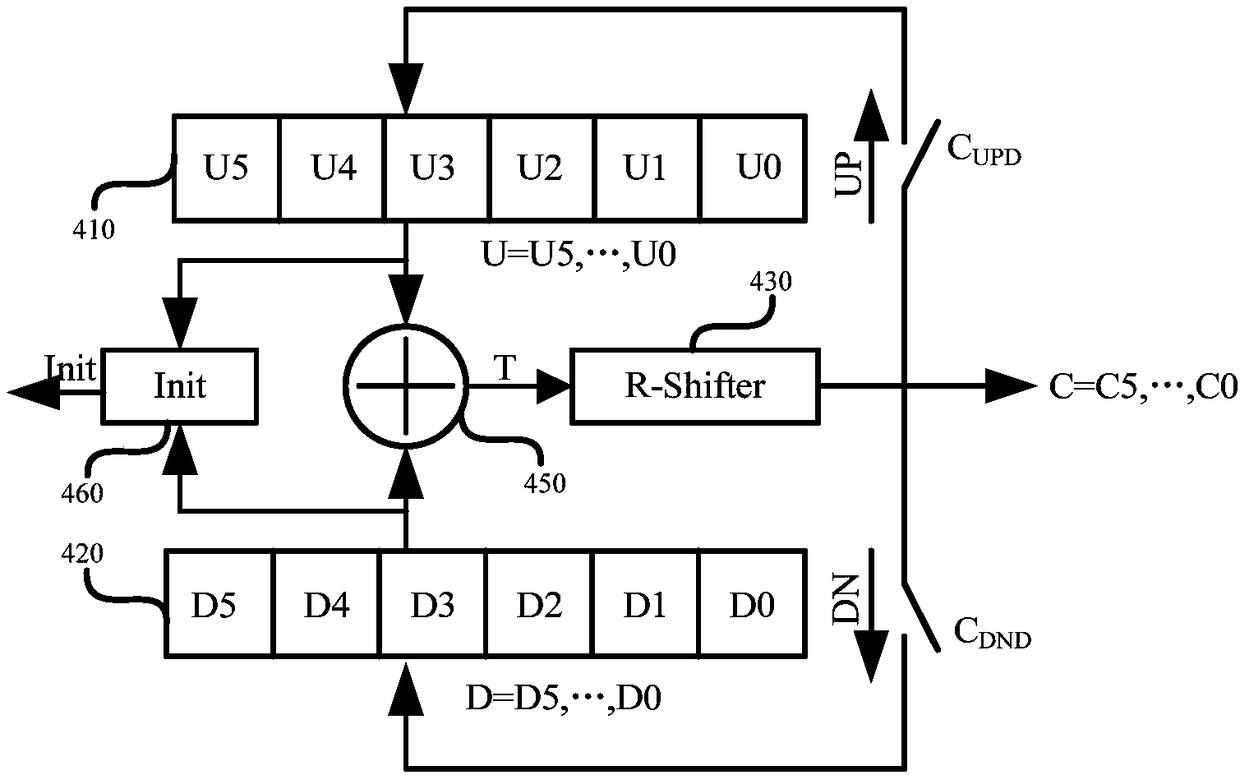

Clock and data recovery circuit without reference clock input

The invention relates to a clock and data recovery circuit without reference clock input. The circuit comprises a high-speed sampler, a binary phase discriminator, a counter, a comparator, a pseudo-binary searching algorithm, a digital filter, a voltage regulator, a current steering DAC and a low-phase noise width frequency VCO; the clock and data recovery circuit adopts dual-ring architecture, the quick locking of the frequency is performed by coarsely regulating a frequency-locking loop to guarantee that the sampling clock frequency is approximately equal to the rate of inputting data; afterthe frequency-locking loop regulation is finished, the circuit can realize the phase locking by finely regulating a phase-locking loop to guarantee that the sampling clock is located at the middle location of the data, thereby accurately recovering the clock and data information. Through the control way disclosed by the invention, the wide rate range work can be realized without requiring an external reference clock, and the circuit has strong jittering tolerance capacity and quick locking capacity.

Owner:BEIJING MXTRONICS CORP +1

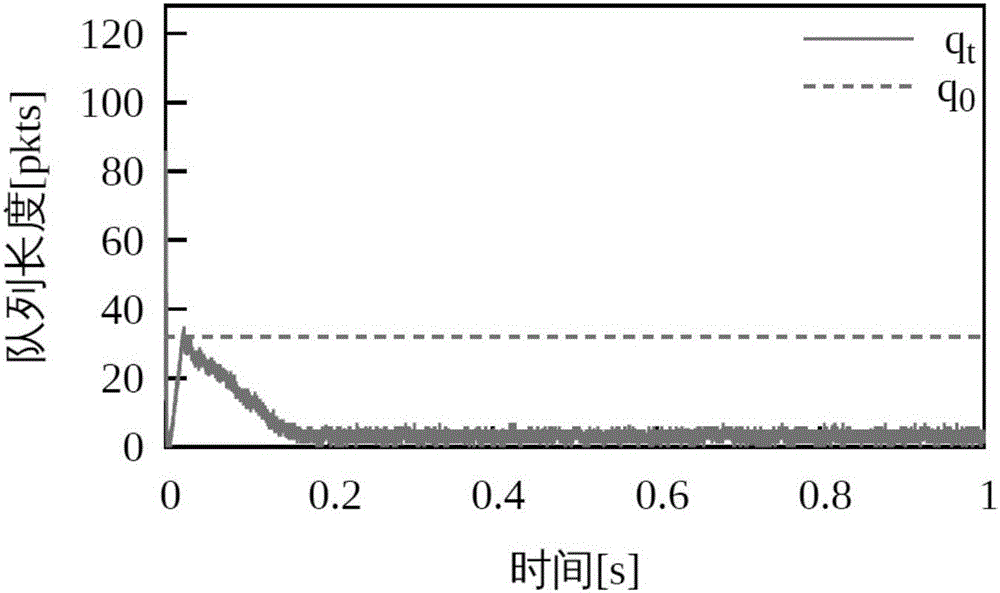

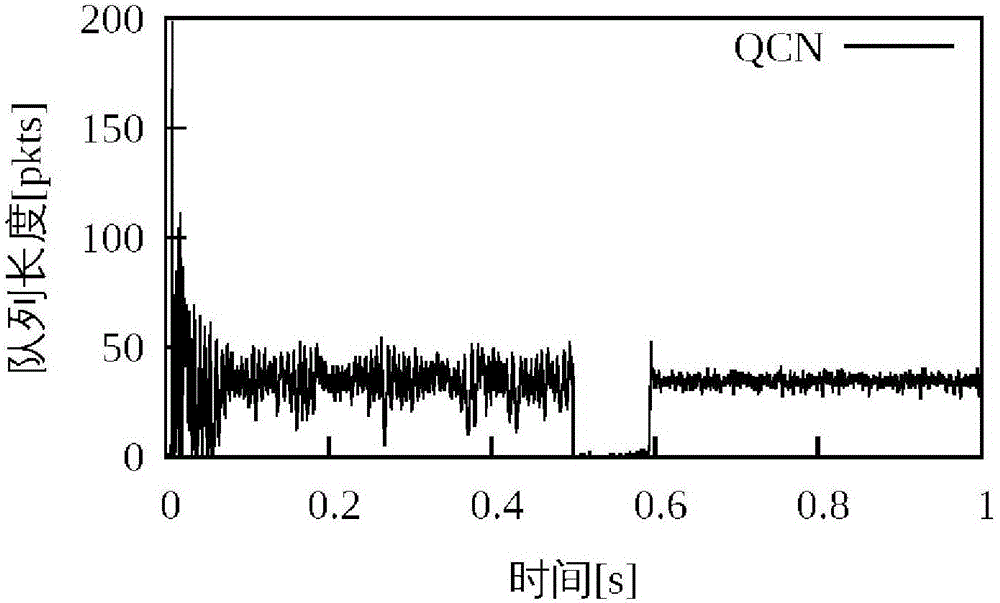

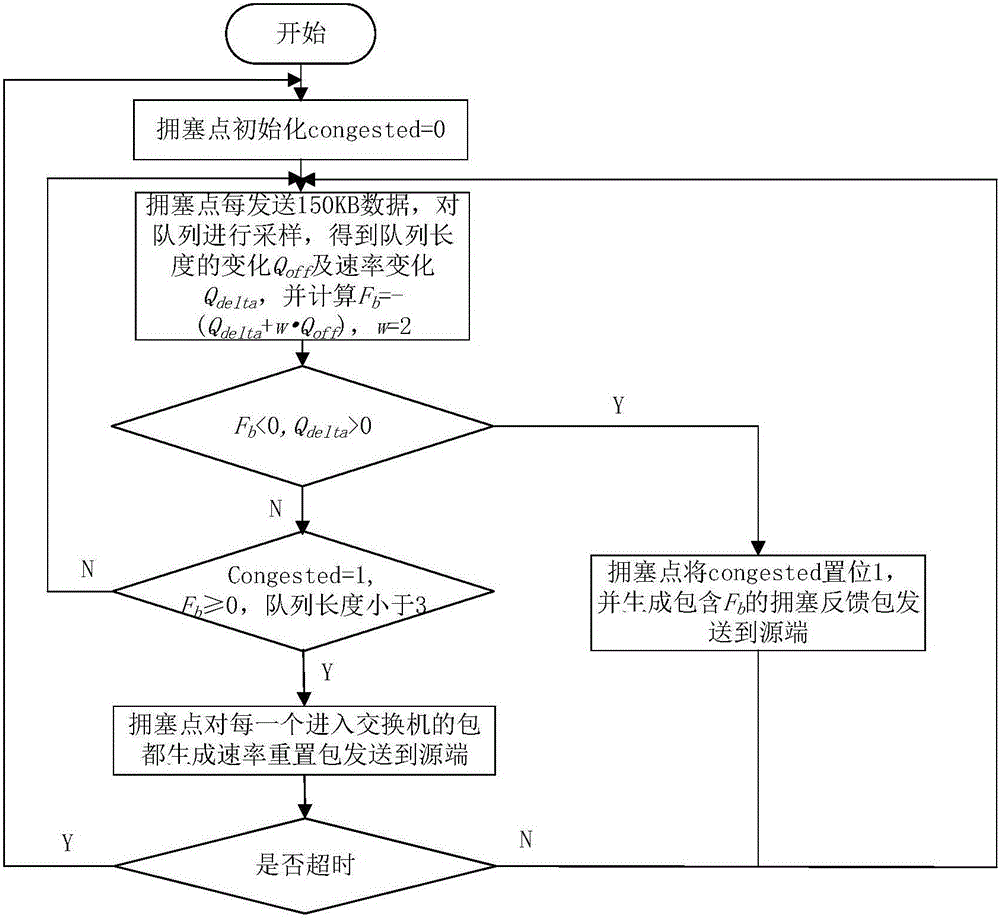

Rapid and simple quantitative congestion notification method

ActiveCN105915464AAvoid wastingProper sending rateData switching networksData centerBinary search algorithm

The invention discloses a rapid and simple quantitative congestion notification method. The method is cooperatively completed by a congestion point and a response point; the response point (namely a source end) initializes the sending rate into the link rate, determines whether to decrease the speed and reset the sending rate according to the type of a feedback packet received by self, or adjusts the sending rate by adopting a binary searching algorithm while not receiving the feedback packet; and the congestion point (namely a switch) initializes a variable congested to identify whether the switch is congested, samples to generate the feedback packet according to the queue length and the variable quantity of the queue length in a sampling period, and sends the feedback packet to the response point. According to the rapid and simple quantitative congestion notification method disclosed by the invention, the quantitative congestion notification (QCN) of a link layer congestion control standard protocol established by an IEEE 802.1Qau working team is simplified and improved; the spare bandwidth can be rapidly obtained; and thus, the rapid and simple quantitative congestion notification method is particularly applied to a data centre network environment.

Owner:CENT SOUTH UNIV

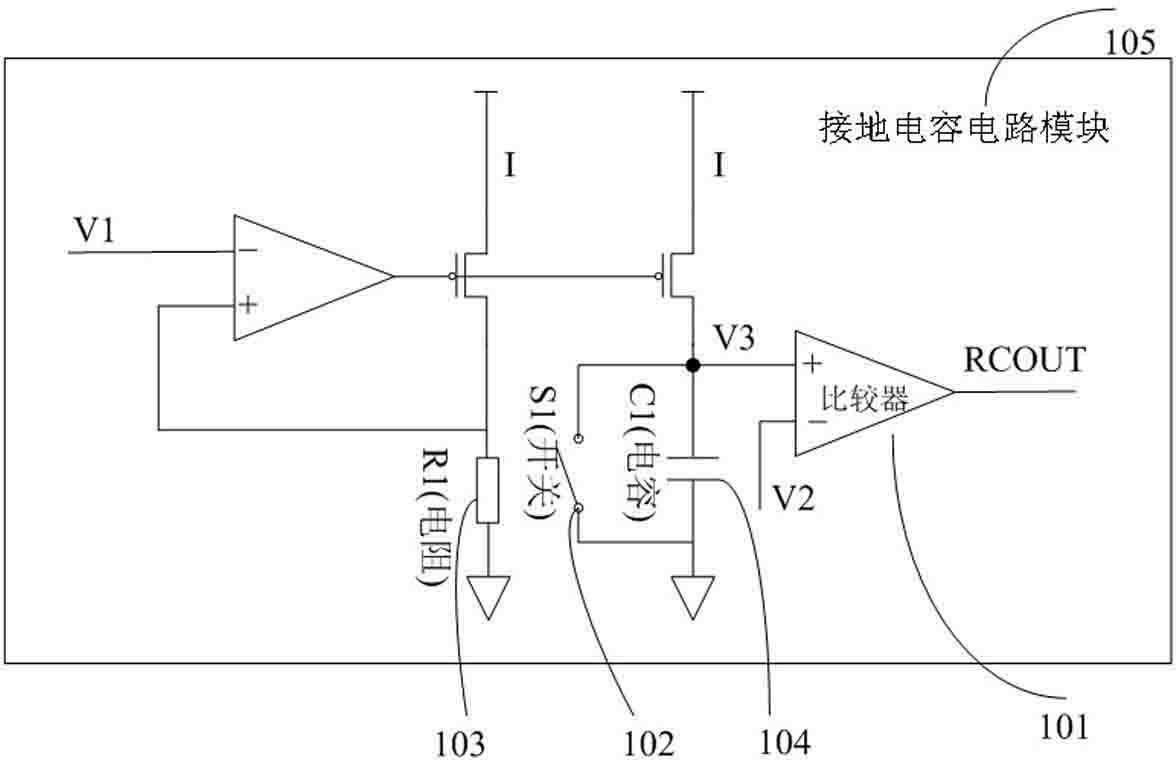

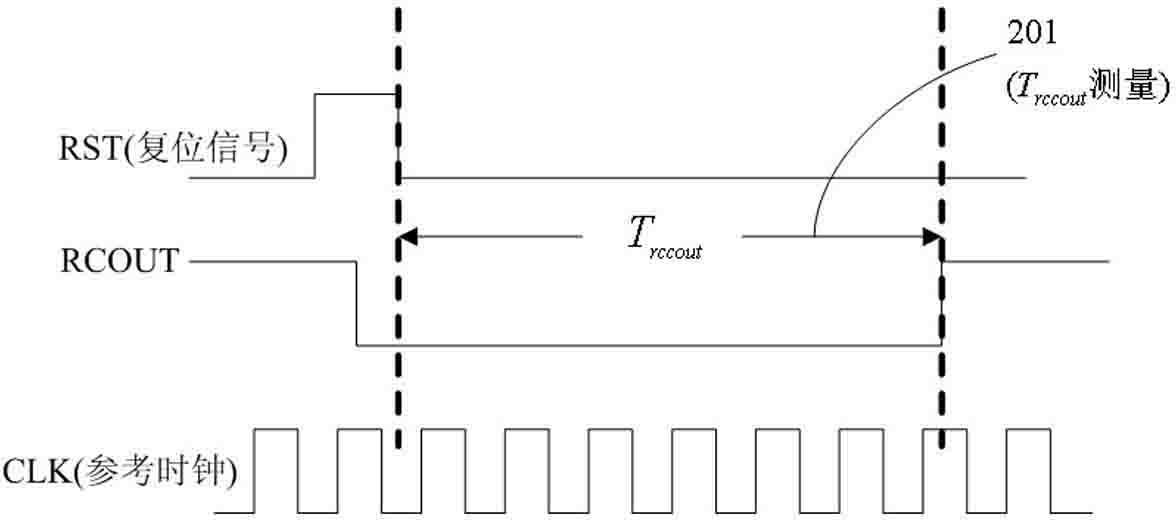

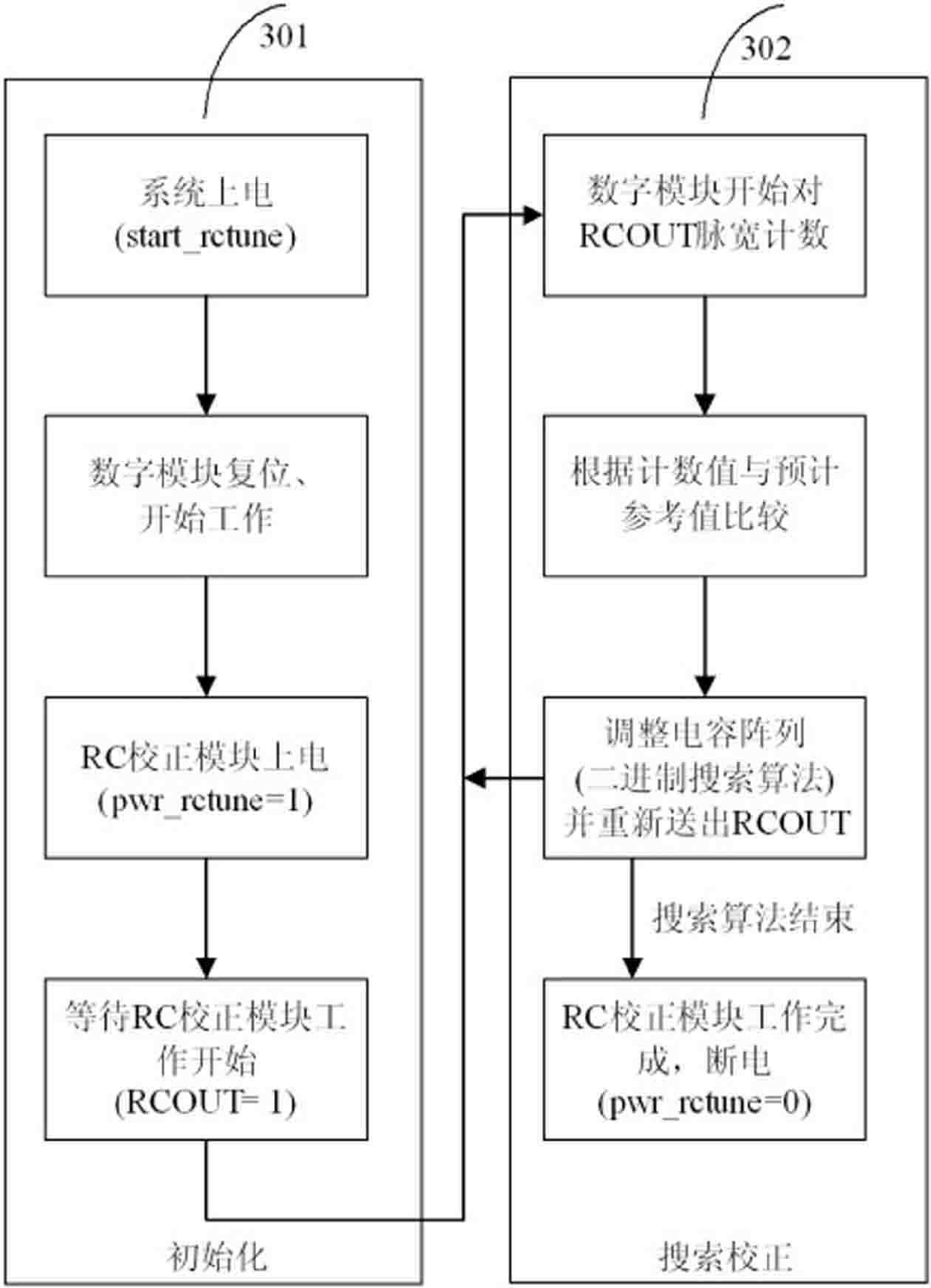

Measuring method of RC constant of ground capacitance

InactiveCN102226823AEasy and flexible calibrationFast calibrationResistance/reactance/impedenceCapacitanceRC time constant

The invention discloses a measuring method of a RC constant of a ground capacitance. According to the invention, on the basis of a circuit structure that takes a RC constant as a ground capacitance, the RC constant is converted to a pulse width and a digital circuit is employed, so that a measuring method aiming at the RC constant as the ground capacitance is realized. The method enables the measurement of the RC constant as the ground capacitance and correction of the RC constant in the circuit to be realized. A ground capacitance circuit module enables the conversion of the RC constant and a time constant to be realized easily, thereby providing a condition for measurement and correction by employing the digital circuit. The correction of the RC constant of the digital circuit can be carried out conveniently and agilely; and the binary search algorithm enables the correction speed to be enhanced substantially. Therefore, the method can be better applied to measurement and correction of a RC constant in a circuit structure of a ground capacitance.

Owner:GUANGZHOU RUNXIN INFORMATION TECH

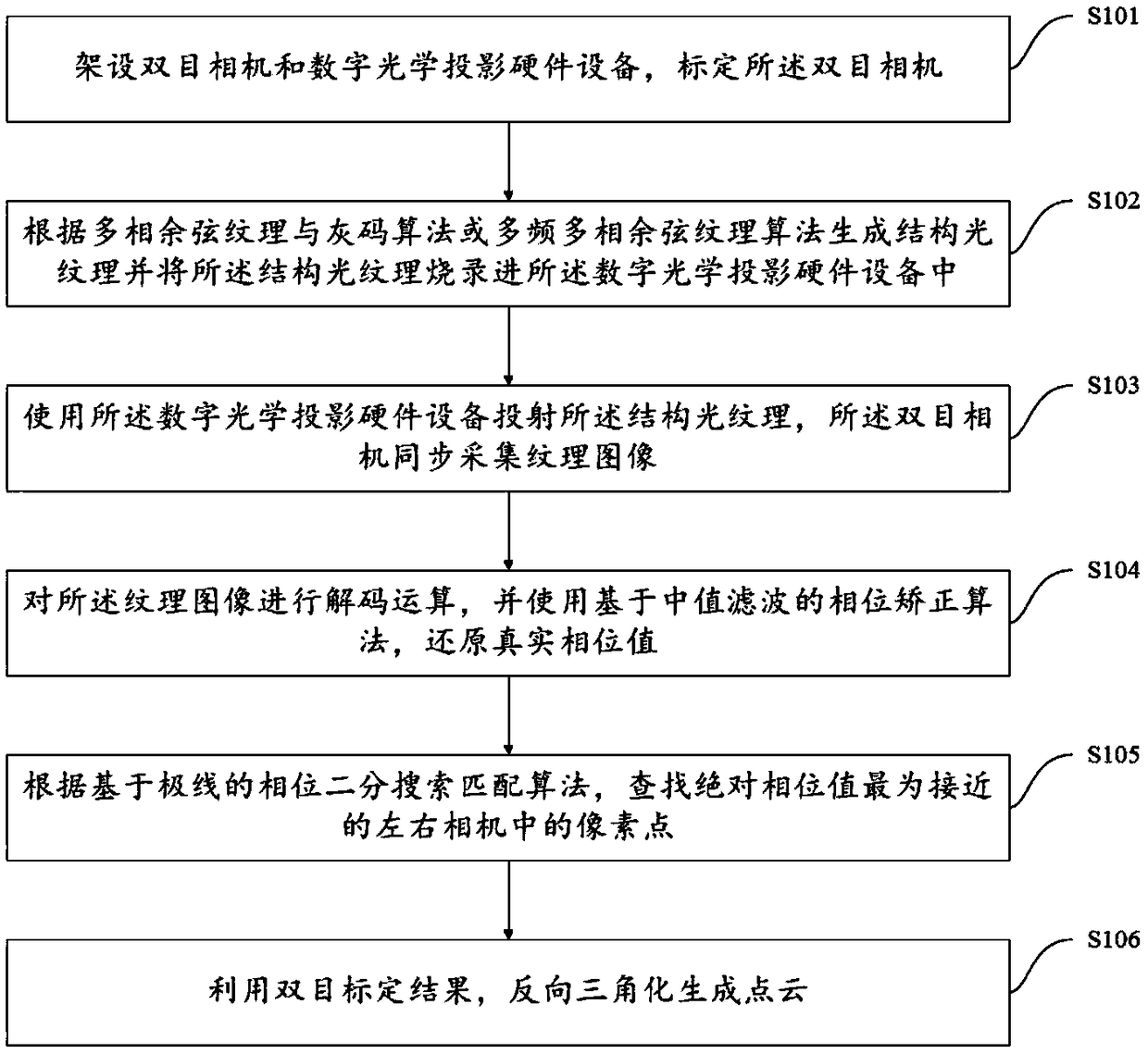

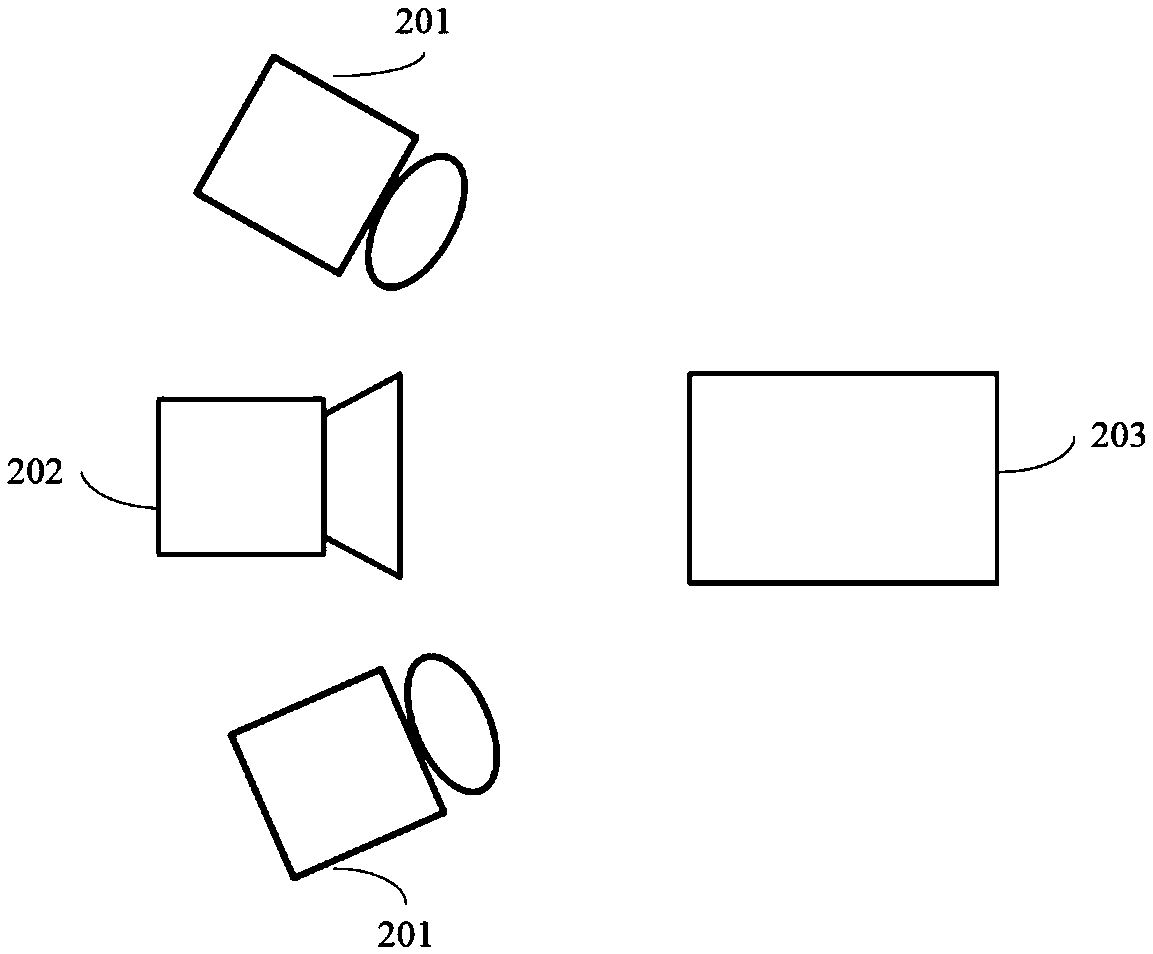

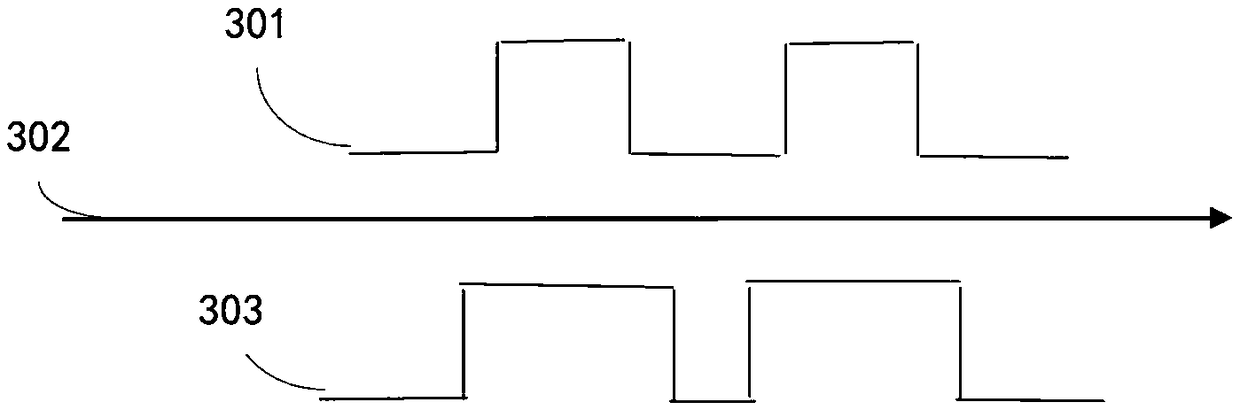

Precision three-dimensional vision measurement method based on binocular camera and structured light projection

The invention relates to the field of three-dimensional scanning and measuring technology and calculating stereo vision, in particular to a precise three-dimensional vision measuring method based on binocular camera and structured light projection; the method comprises: setting up a binocular camera and a digital optical projection device, and calibrating a binocular camera; generates a structuredlight texture according to a multiphase cosine texture and gray code algorithm or a multi-frequency multiphase cosine texture algorithm and burns it into a digital optical projection device; projectsa structured light texture using a digital optical projection device, and simultaneously acquires a texture image by a binocular camera; Decodes the texture image, and restore the true phase value byusing the median filtering based phase correction algorithm; according to the polar line based phase binary search algorithm, locate the pixel points in the a stereo cameras having the closest absolute phase values; use the binocular to demarcate the result, and generate a point cloud by the inverse triangulation. The invention combines the structured light projection with the binocular camera, and uses a plurality of algorithms to realize precise measurement of the image with high precision.

Owner:深圳市艾视铂智能技术有限公司

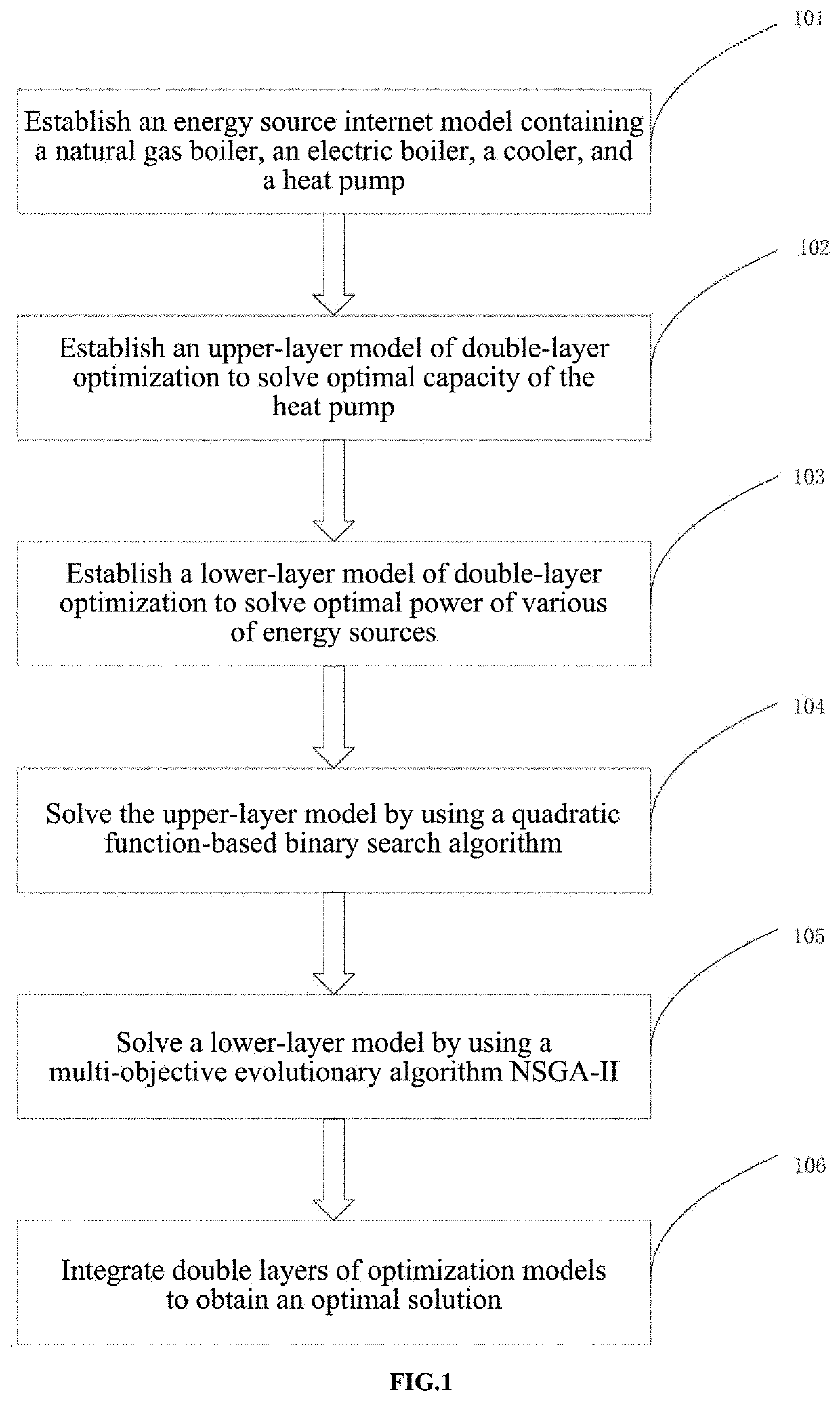

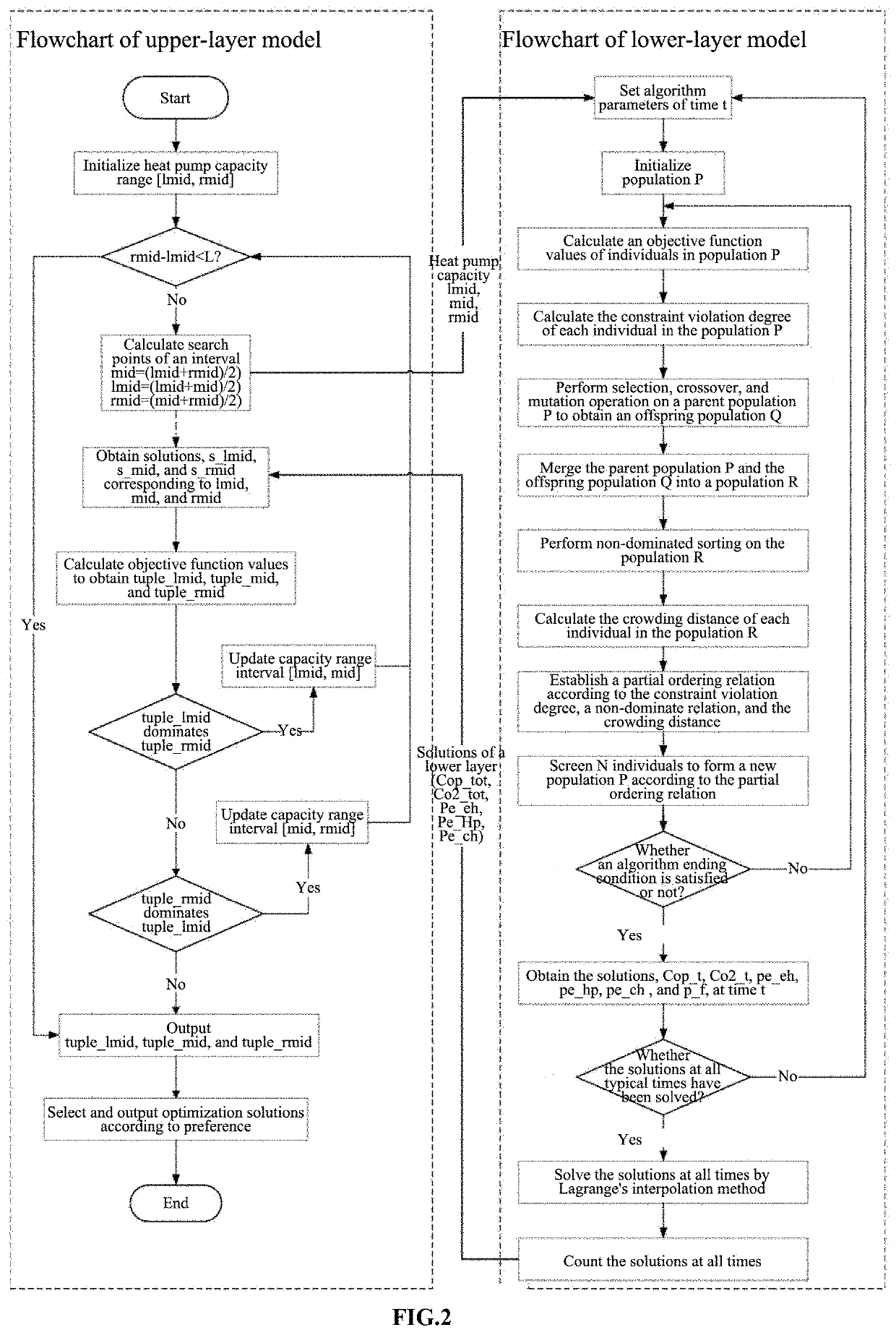

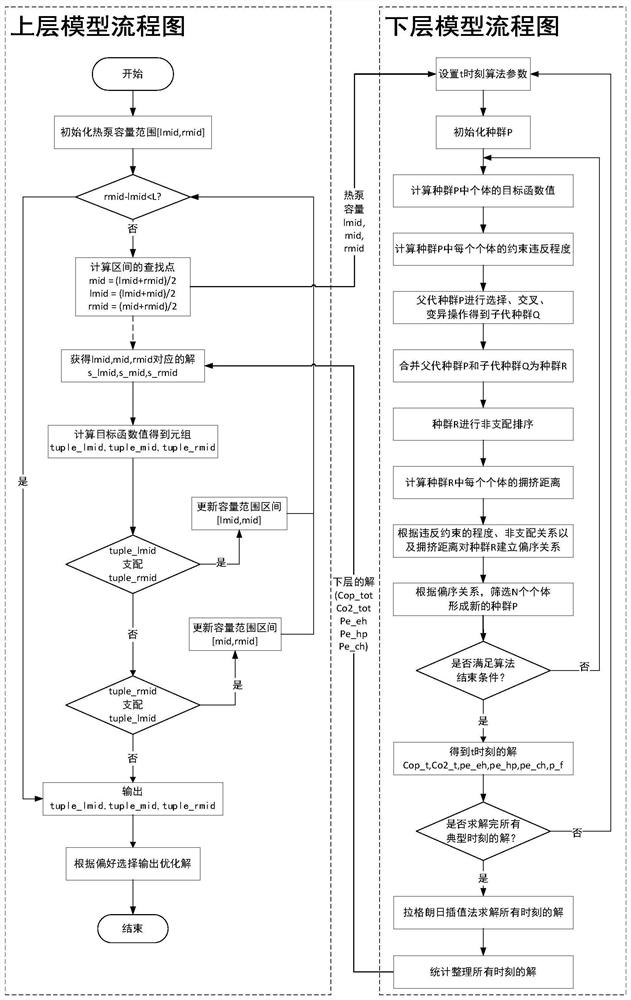

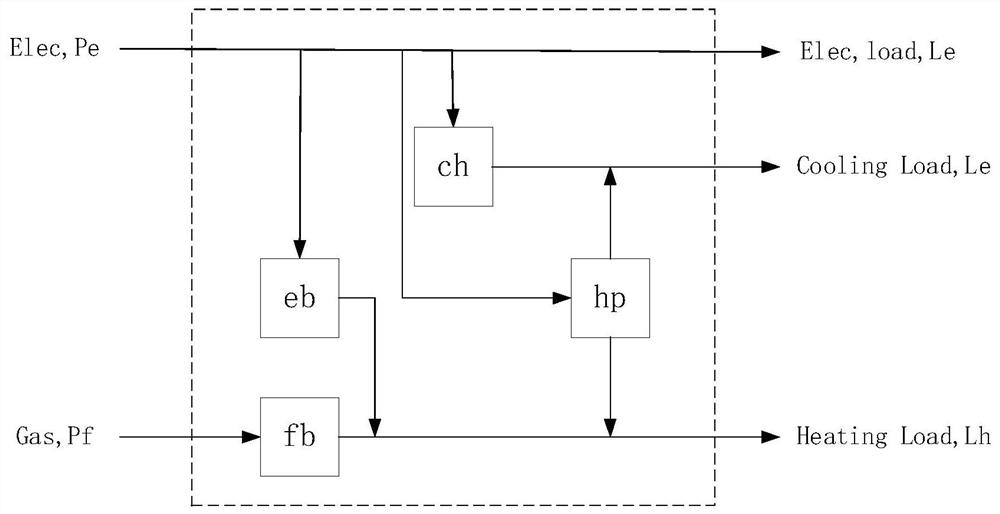

Optimization method for capacity of heat pump and power of various sets of energy source equipment in energy hub

PendingUS20210376605A1Avoid complex analysisEasy to solveGeometric CADGeneration forecast in ac networkExhaust gas emissionsIndustrial engineering

The present disclosure discloses a method for optimizing equipment capacity and equipment power of an energy hub system. The method includes establishing an energy hub model containing natural gas boilers, electric boilers, coolers and heat pumps, establishing a bilevel optimized upper model to solve the optimal heat pump capacity, and establishing a bilevel optimized lower model to solve the optimal power utilization of each energy device based on the binary search algorithm of the quadratic function solves the upper model by using the multi-objective evolutionary algorithm NSGA-II to solve the lower model. The optimization method of the present invention can solve the multi-objective bilevel model problem without the help of commercial optimization software. Obtaining a reasonable, efficient and green planning scheme makes the total operating cost and total exhaust gas emissions of the energy hub relatively optimal.

Owner:XIANGTAN UNIV

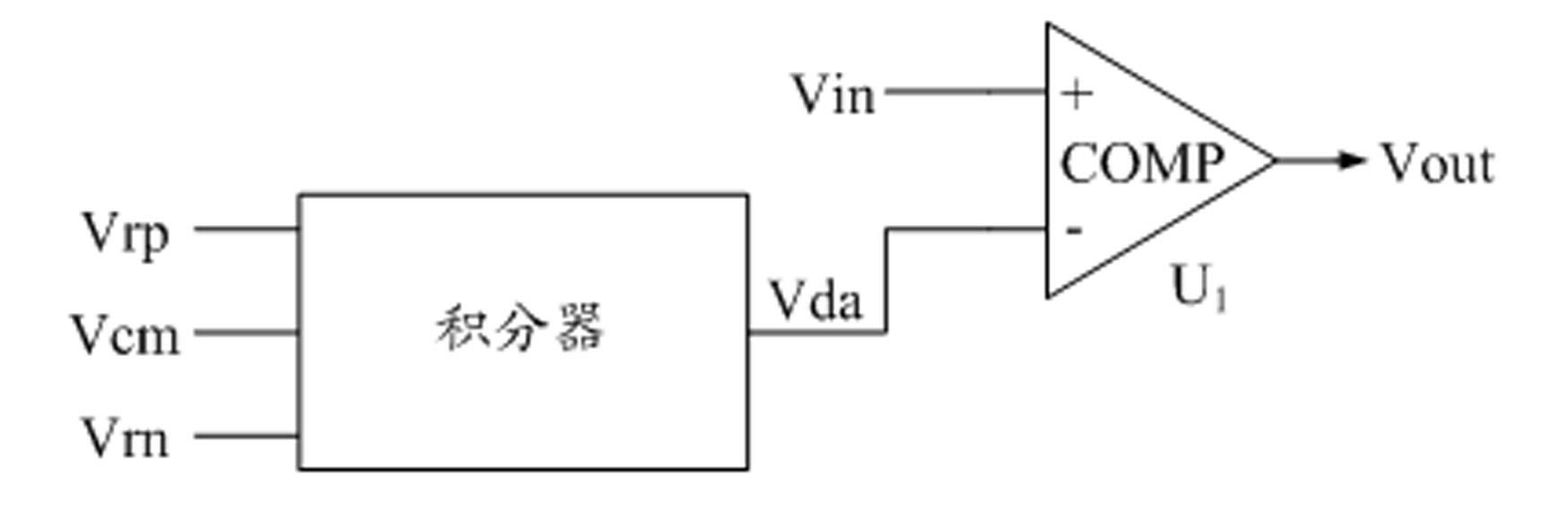

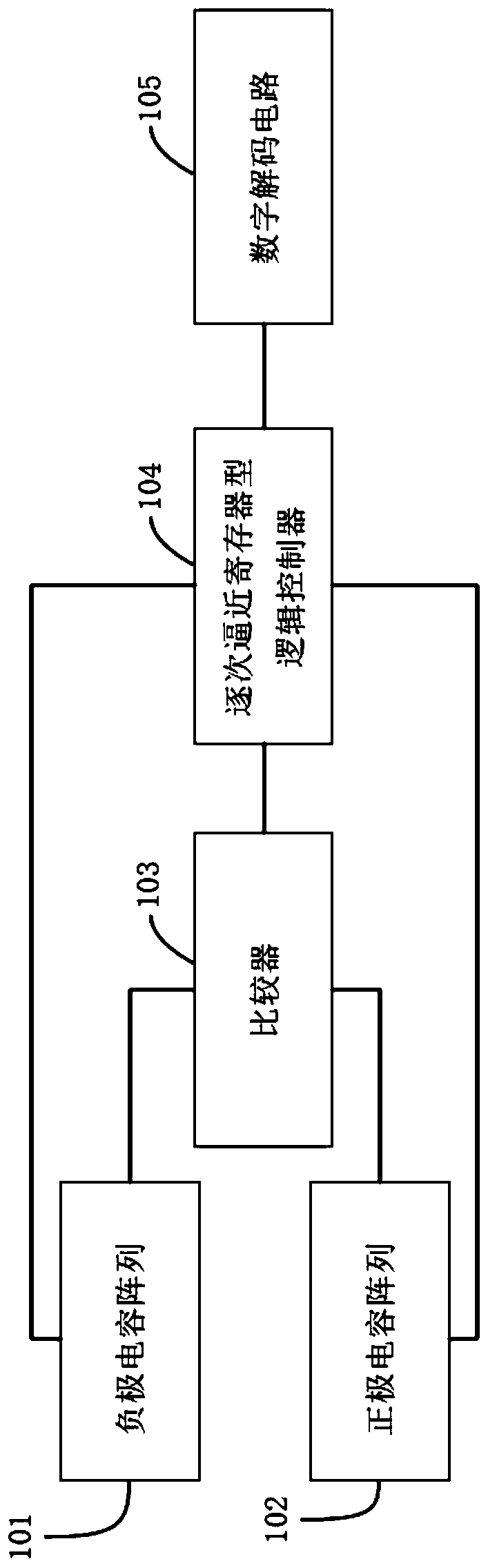

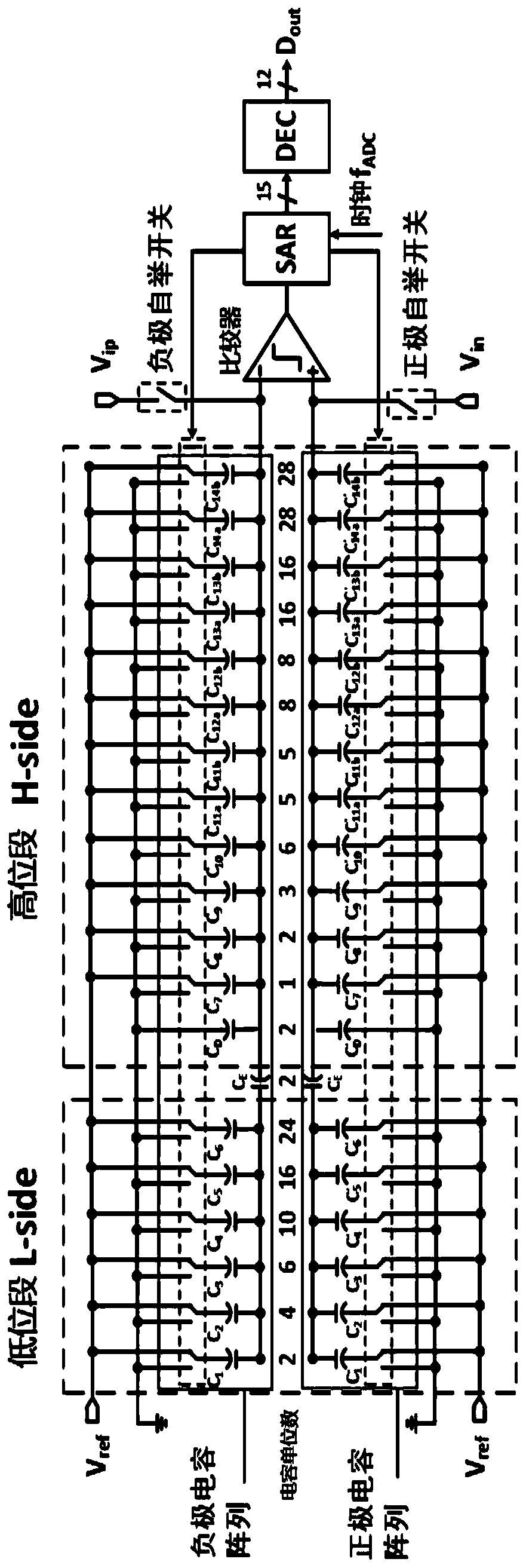

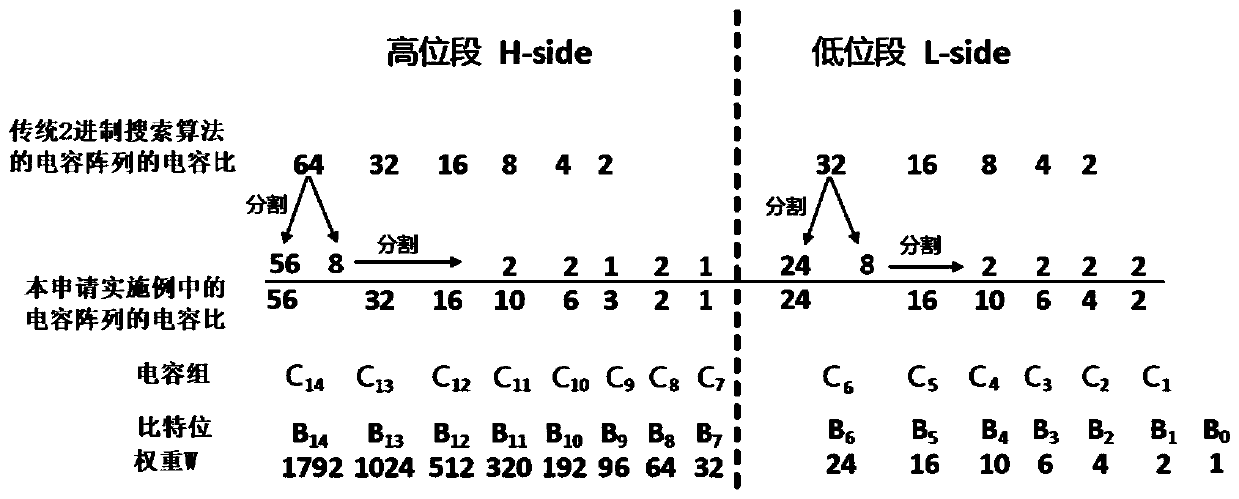

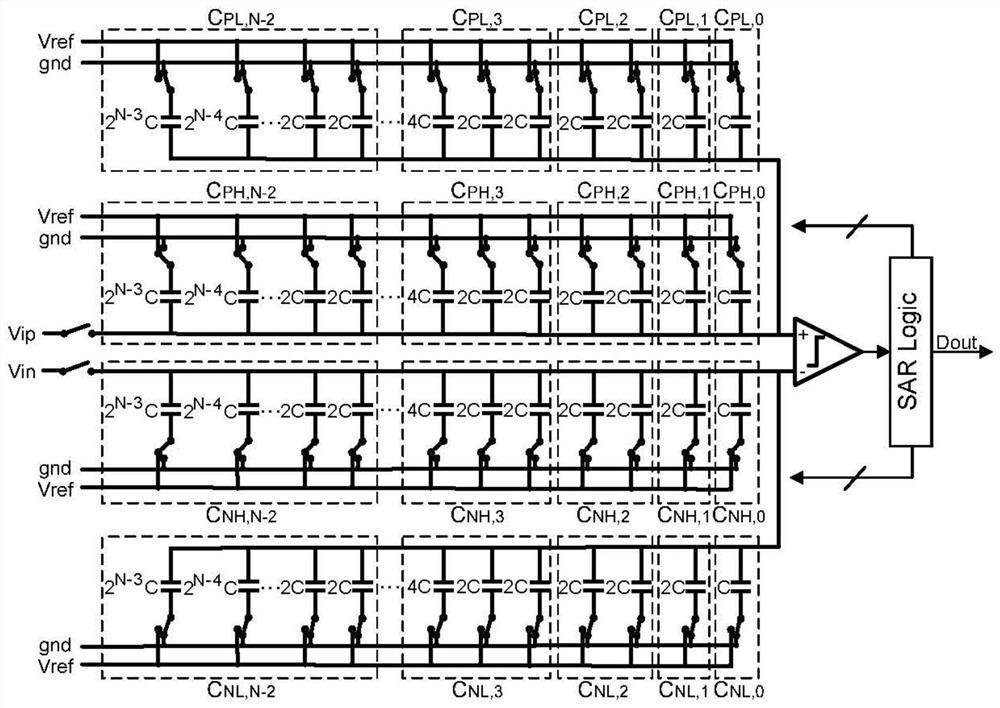

Successive approximation register type analog-to-digital converter and signal conversion method thereof

ActiveCN111130550AReduce design requirementsReduce usagePower saving provisionsElectric signal transmission systemsCapacitanceEngineering

The invention discloses a successive approximation register type analog-to-digital converter and a conversion method thereof. The successive approximation register type analog-to-digital converter comprises a negative capacitor array, a positive capacitor array, a comparator, a successive approximation register type logic controller and a digital decoding circuit, wherein the negative input end ofthe comparator is connected with the negative capacitor array, the positive input end of the comparator is connected with the positive capacitor array, and the successive approximation register typelogic controller is connected with the output end of the comparator and the digital decoding circuit. Decision errors generated in early steps can be effectively suppressed by using a redundant structure. Compared with a traditional structure based on a binary search algorithm, the most important difference is that the sum of the weights of low-order capacitor banks of the redundant structure is higher than the weights of the adjacent capacitor banks. By redistributing the capacitors in the negative capacitor array and the positive capacitor array and inserting a new capacitor bank, the weightcorresponding to the high-order capacitor bank is less than the sum of the weights of the low-order capacitor banks, and a redundant structure is achieved. The number of the used capacitors can be reduced by adopting a segmented structure for the capacitor array, and the power consumption is reduced.

Owner:TSINGHUA UNIV

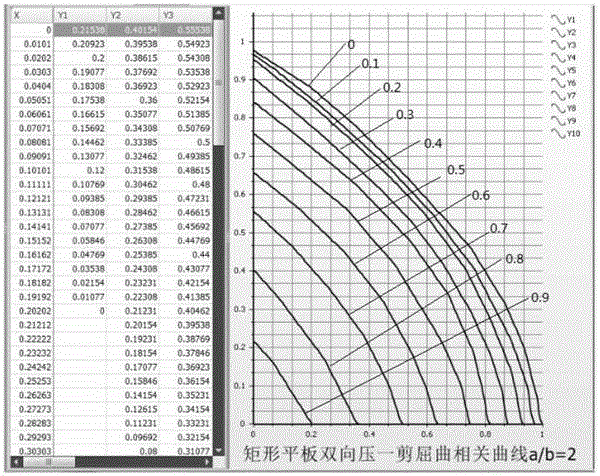

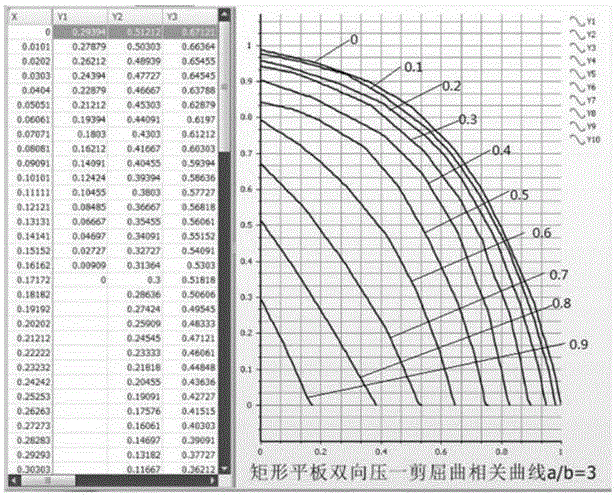

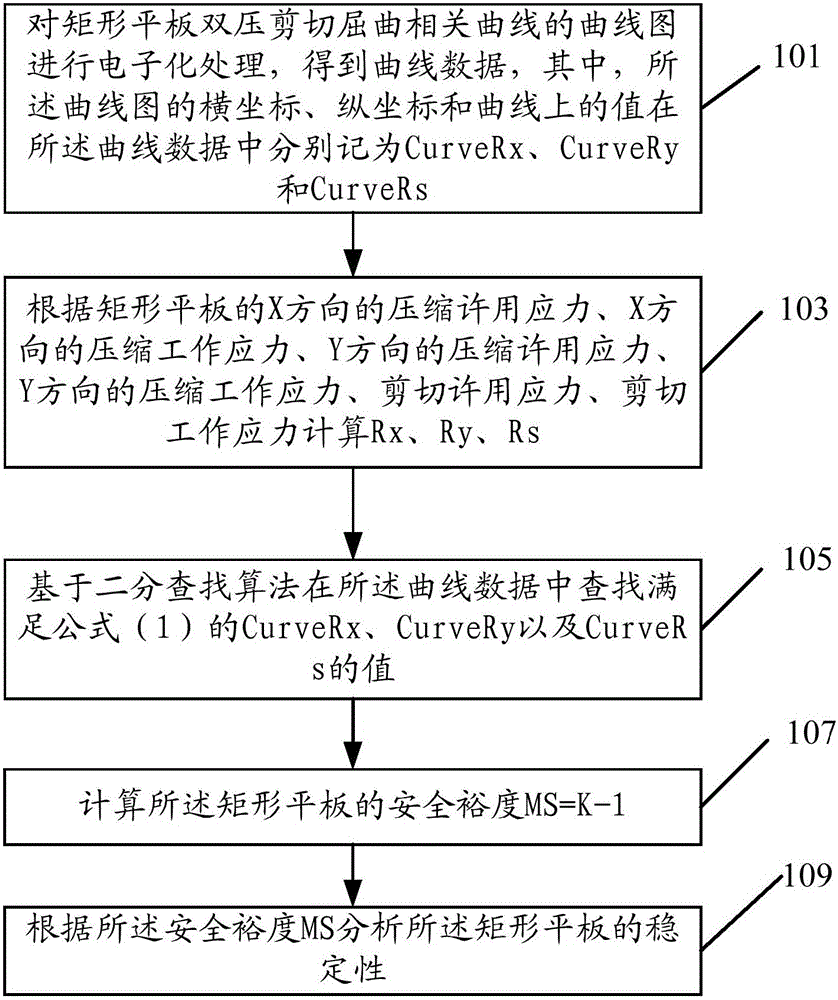

Stability analysis method and device for airplane structure rectangular flat plate

ActiveCN106021770AThe stability analysis results are reasonable and reliableStrong reliabilityGeometric CADSpecial data processing applicationsClassical mechanicsStructural engineering

The embodiment of the invention provides a stability analysis method and device for an airplane structure rectangular flat plate. The method comprises the steps that electronization is carried out on a curve chart of dual-pressure shearing and buckling related curves of the rectangular flat plate, and curve data is obtained, wherein the x-coordinates, the y-coordinates and values on the curves of the curve chart are marked as CurveRx, CurveRy and CurveRs in the curve data respectively; Rx, Ry and Rs are calculated according to the compression allowable stress sigma ccrx of the rectangular flat plate in the X direction, the compression allowable stress sigma ccry of the rectangular flat plate in the Y direction, the shearing allowable stress tau cr, the compression working stress sigma cx in the X direction, the compression working stress sigma cy in the Y direction and the shearing working stress tau; the CurveRx value, the CurveRy value and the CurveRs value meeting formula (I) are sought in the curve data based on a binary search algorithm; the safety margin MS=K-1 of the rectangular flat plate is calculated; the stability of the rectangular flat plate is analyzed according to the safety margin MS. By means of the method and device, the worked out safety margin is high in scientificity and reliability, and therefore the stability analysis result of the airplane structure rectangular flat plate is more reasonable and reliable.

Owner:SHANGHAI GONGFANG SOFTWARE CO LTD

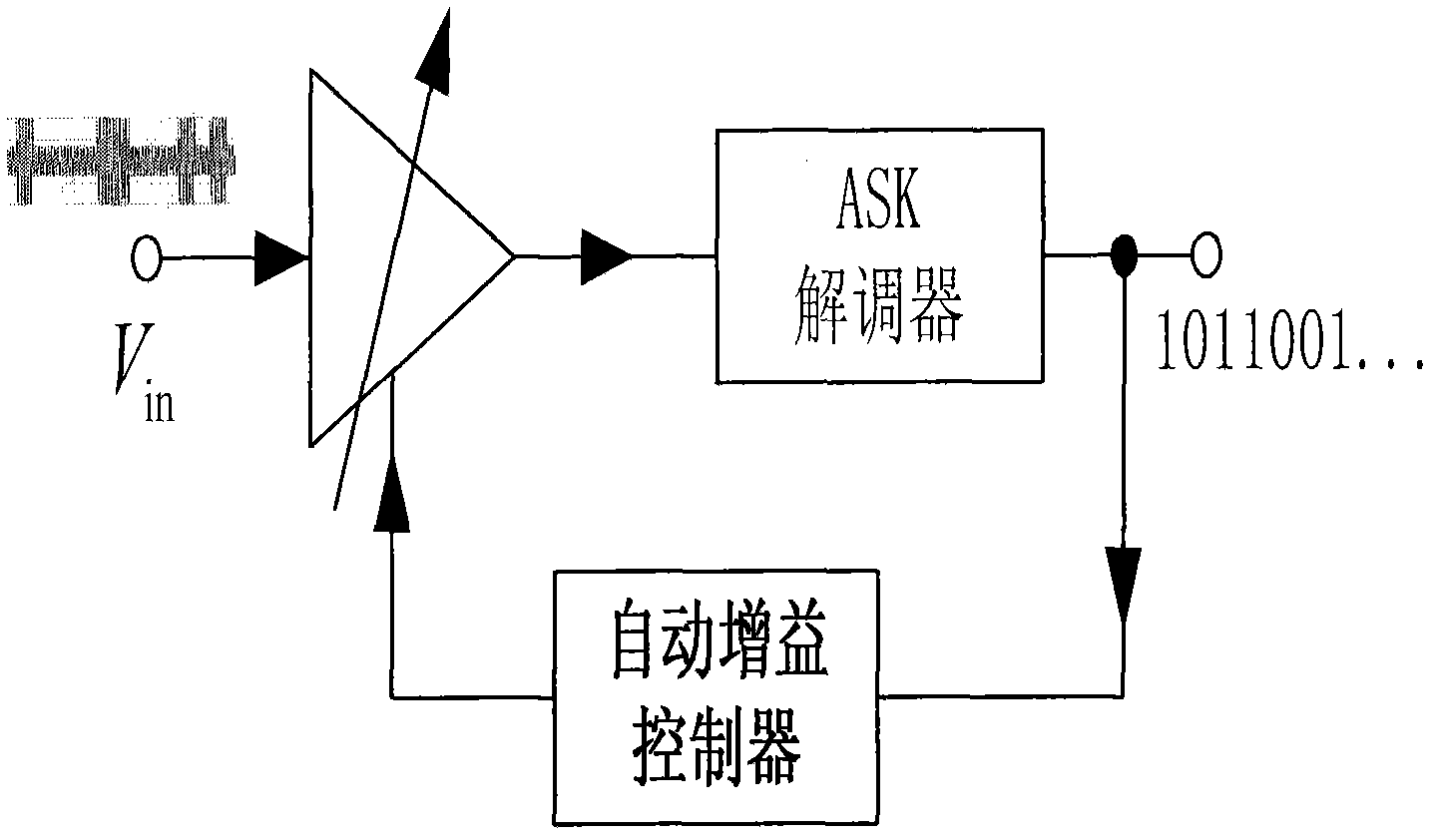

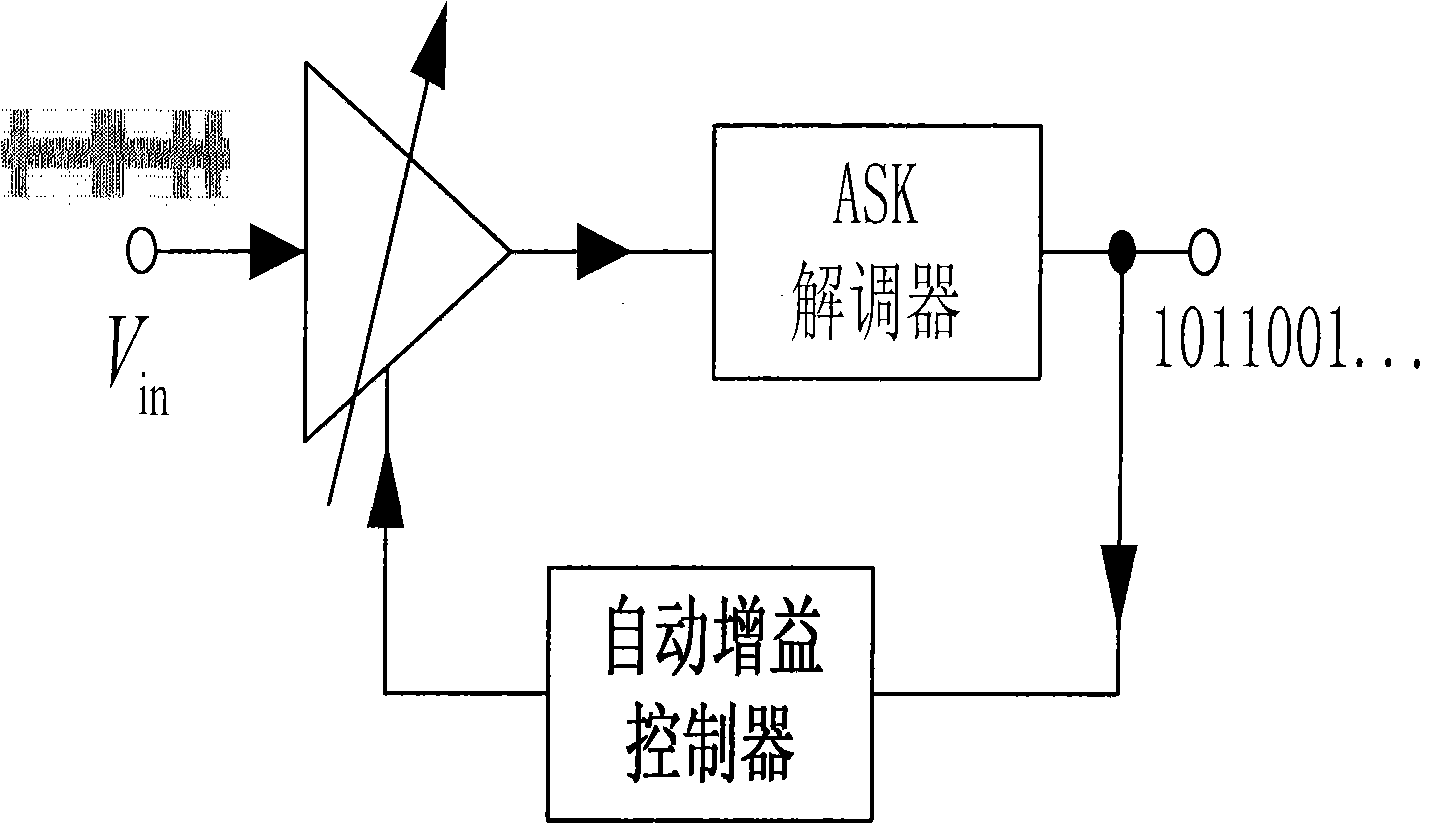

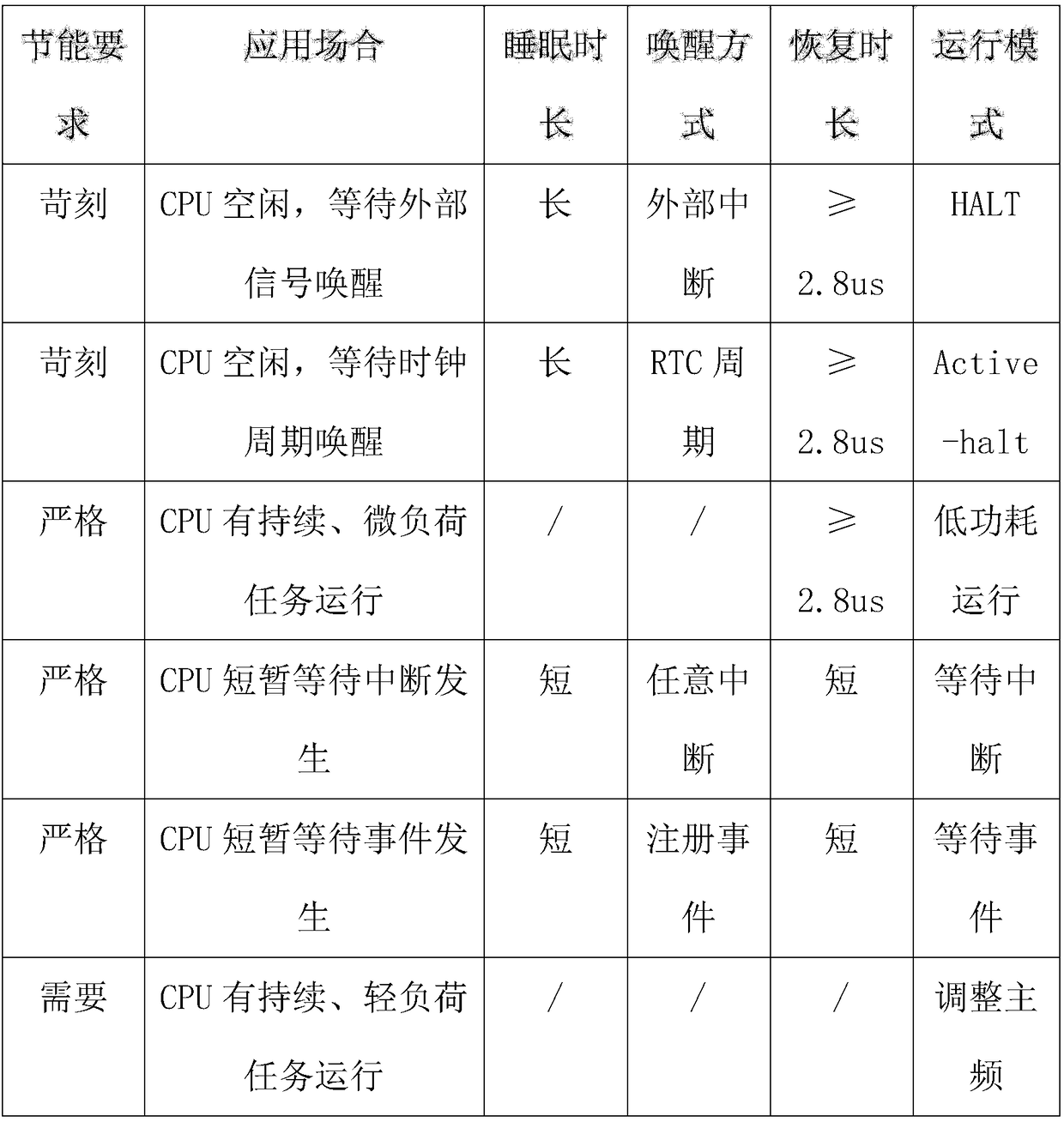

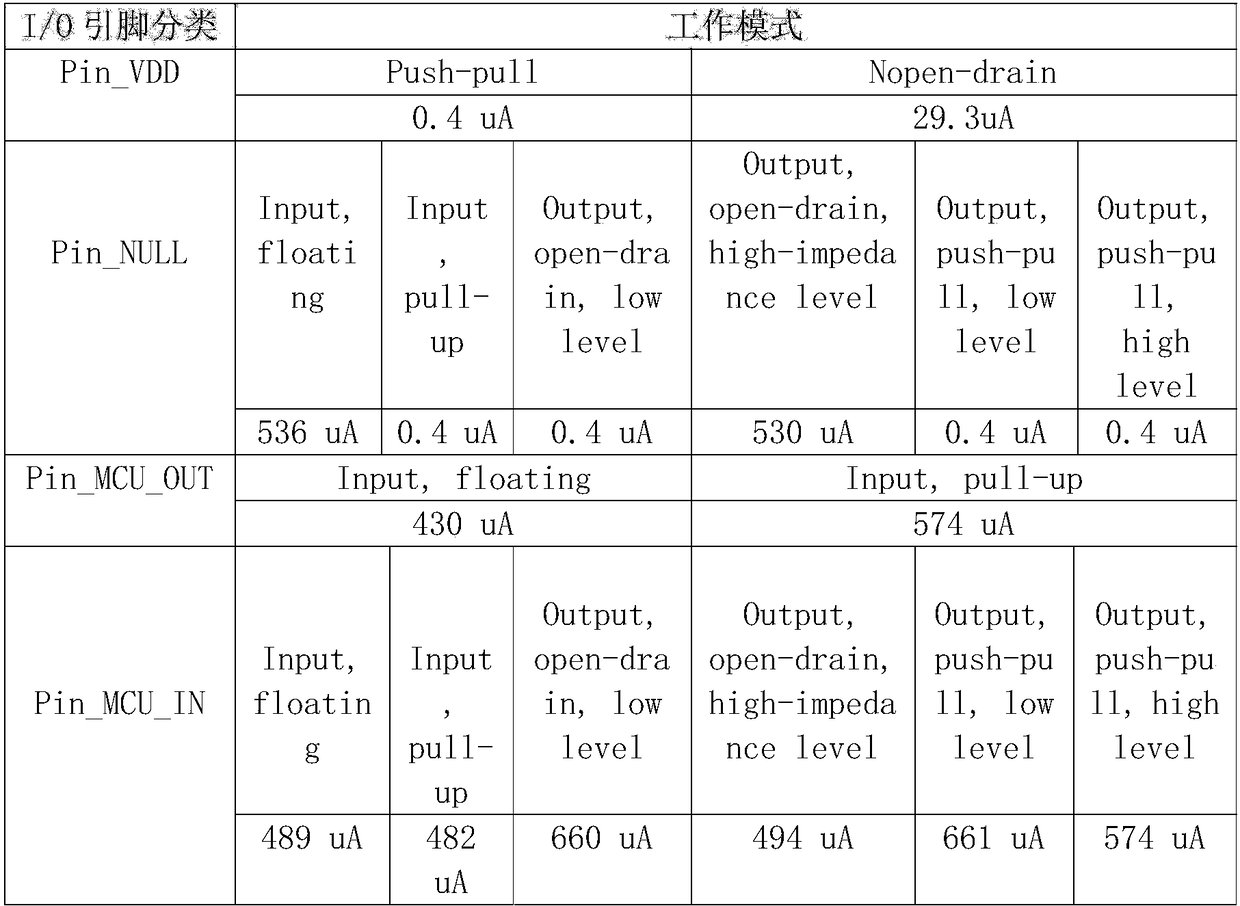

Low power consumption automatic gain control method suitable for ASK analog receiver

InactiveCN101958694AIncrease data rateReduce power consumptionGain controlTransmissionAuto regulationAudio power amplifier

The invention discloses a low power consumption automatic gain control method suitable for an ASK analog receiver, belonging to the wireless communication field. The method comprises the following steps: utilizing a principle of a scrambler in a digital communication system; and judging that the gain of a forward link of the current receiver is too high or too low according to binary code stream information output by the ASK analog receiver, thus automatically regulating the gain in a programmable gain amplifier (PGA) in the forward link, and realizing the automatic gain control function of the ASK analog receiver. In order to shorten the gain regulation time, the method of the invention also adopts a method for improving the gain regulation based on a binary search algorithm. The automatic gain control method does not need to use a multi-bit analog to digital converter, and does not introduce an analog closed loop, thus the automatic gain control scheme can support higher data rate, has low power consumption, and can be applied in the ASK receiver with low power consumption and high data rate.

Owner:RESEARCH INSTITUTE OF TSINGHUA UNIVERSITY IN SHENZHEN

Non-sample point monitoring method aiming at AQI (air quality index) sparse monitoring

The invention discloses a non-sample point monitoring method aiming at AQI (air quality index) sparse monitoring. The method comprises the following steps: building an extension field intensity single-parameter model, and introducing a parameter as shown in the specification to control the field intensity attenuation degree; obtaining a relational graph between the parameter and a mean-square error on the basis of sample data; solving the optimal value as shown in the specification by virtue of a binary search algorithm; building an extension field intensity dual-parameter model, adding a parameter as shown in the specification to adjust the field intensity influence range, and obtaining a relational graph between the parameters and the mean-square error on the basis of the sample data; solving the optimal combination of the parameters by virtue of an iterative bilinear interpolation algorithm; and carrying out spatial interpolation calculation of AQI spare monitoring data by virtue of a single-parameter or dual-parameter extension field intensity model aiming at the region corresponding to the sample data. The method disclosed by the invention has the advantages of simple model and high interpolation precision, and is easily popularized and applied to different regions and other types of spatial data except for AQI.

Owner:WUHAN UNIV

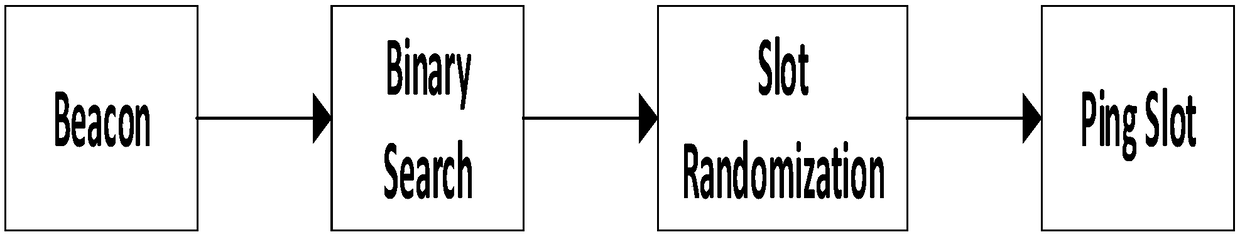

Lora terminal energy-saving method based on binary search time slot randomization communication mechanism

ActiveCN108934063AShorten communication timeSave energyPower managementHigh level techniquesStart timeCommunications system

The invention discloses a Lora terminal energy-saving method based on a binary search time slot randomization communication mechanism, which comprises an algorithm adopted by a Lora terminal, an MCU used by a terminal, and a Lora radio frequency module. The algorithm adopted by the Lora terminal Class B includes the following steps: S1: using the binary search algorithm to select and set an appropriate PingNb when a node receives a Beacon; S2: obtaining the offset PingOffset of a start time point of a Ping Slot of each node through time slot randomization; S3: entering the Ping Slot for data reception. The terminal algorithm uses the binary search algorithm to select and set the appropriate PingNb. Each time, the selection range can be reduced by half, and the set PingNb can be quickly andaccurately selected, which greatly shortens the communication time and saves more energy. The time slot randomization is adopted to obtain a cheap amount, it can be ensured that only one node in thePing Slot performs data, and additional energy consumption due to communication system collision or monitoring overload cannot be caused. The Lora terminal energy-saving method can effectively reducepower consumption and achieve energy saving.

Owner:FOSHAN SHUNDE SUN YAT SEN UNIV RES INST +2

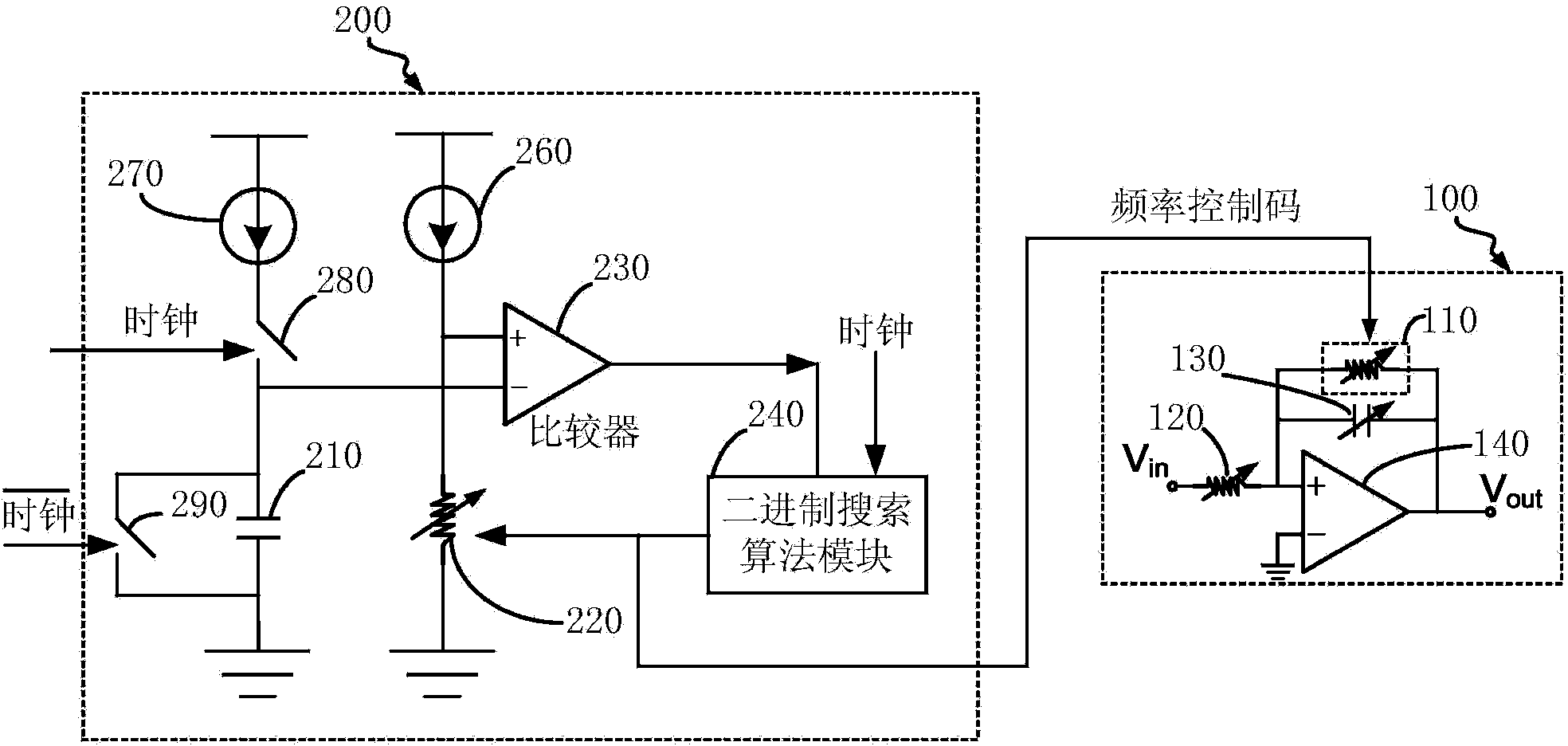

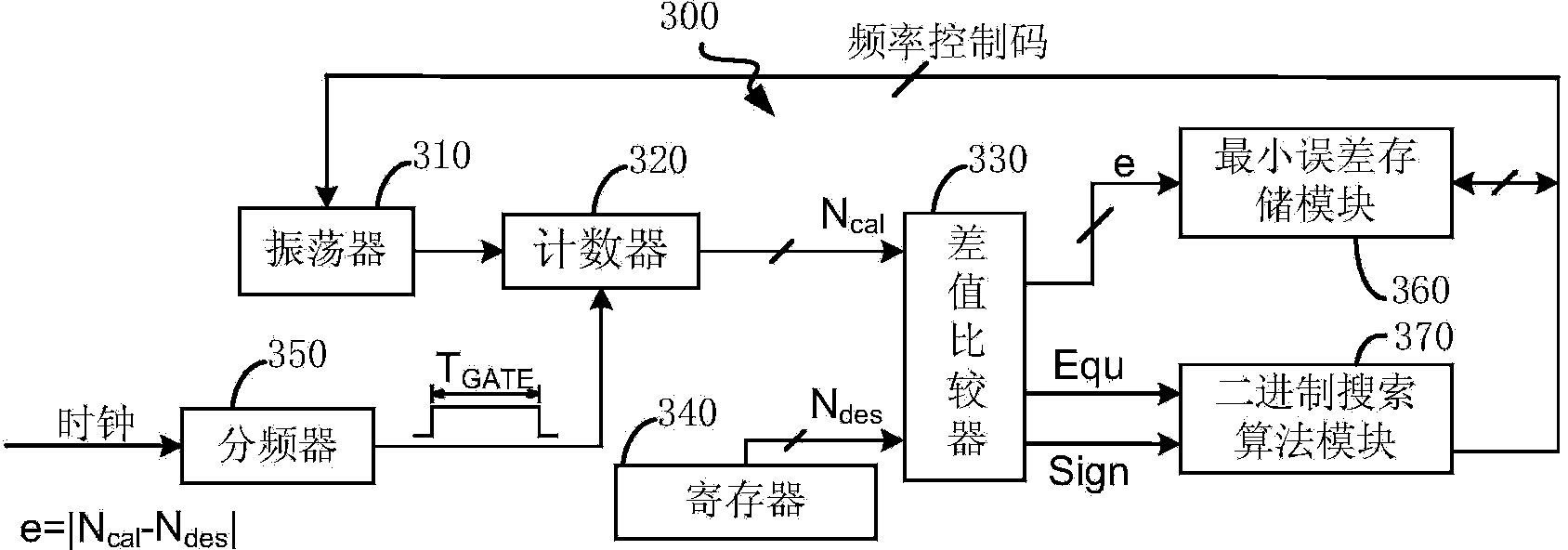

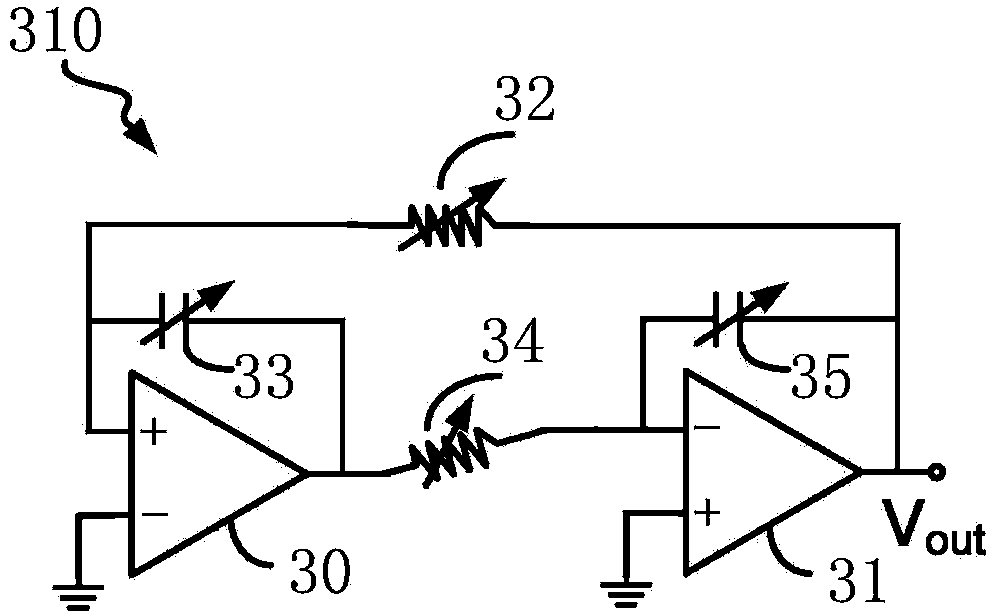

Wave filter bandwidth calibrating circuit

InactiveCN103716040AHigh Bandwidth AccuracyBandwidth Accuracy GuaranteedGenerator stabilizationCapacitanceBand width

The invention provides a wave filter bandwidth calibrating circuit. According to the technical scheme, the wave filter bandwidth calibrating circuit comprises an oscillator, a counter, a differential comparator, a register, a frequency divider, a minimum error storage module and a binary search algorithm module, wherein the binary search algorithm module is used for generating a frequency control code and outputting the frequency control code into the oscillator and the minimum error storage module; the oscillator is used for generating a corresponding oscillation signal and outputting the oscillation signal into the counter; the minimum error storage module is used for storing the frequency control code; the counter is used for mounting the numbers of rising edges of the oscillation signal generated by the oscillator and outputting a counting result into the differential comparator; the differential comparator is used for outputting an error absolute value obtained in a comparison mode into the minimum error storage module and outputting an error symbol into the binary search algorithm module; the minimum error storage module is used for storing the error absolute value. Compared with a wave filter designed by an existing wave filter bandwidth calibrating circuit, as the wave filter bandwidth calibrating circuit provided by the invention is used, the numbers of capacitors or resistors required by the wave filter are greatly decreased, the area is saved and the design complexity is reduced.

Owner:NAT UNIV OF DEFENSE TECH +1

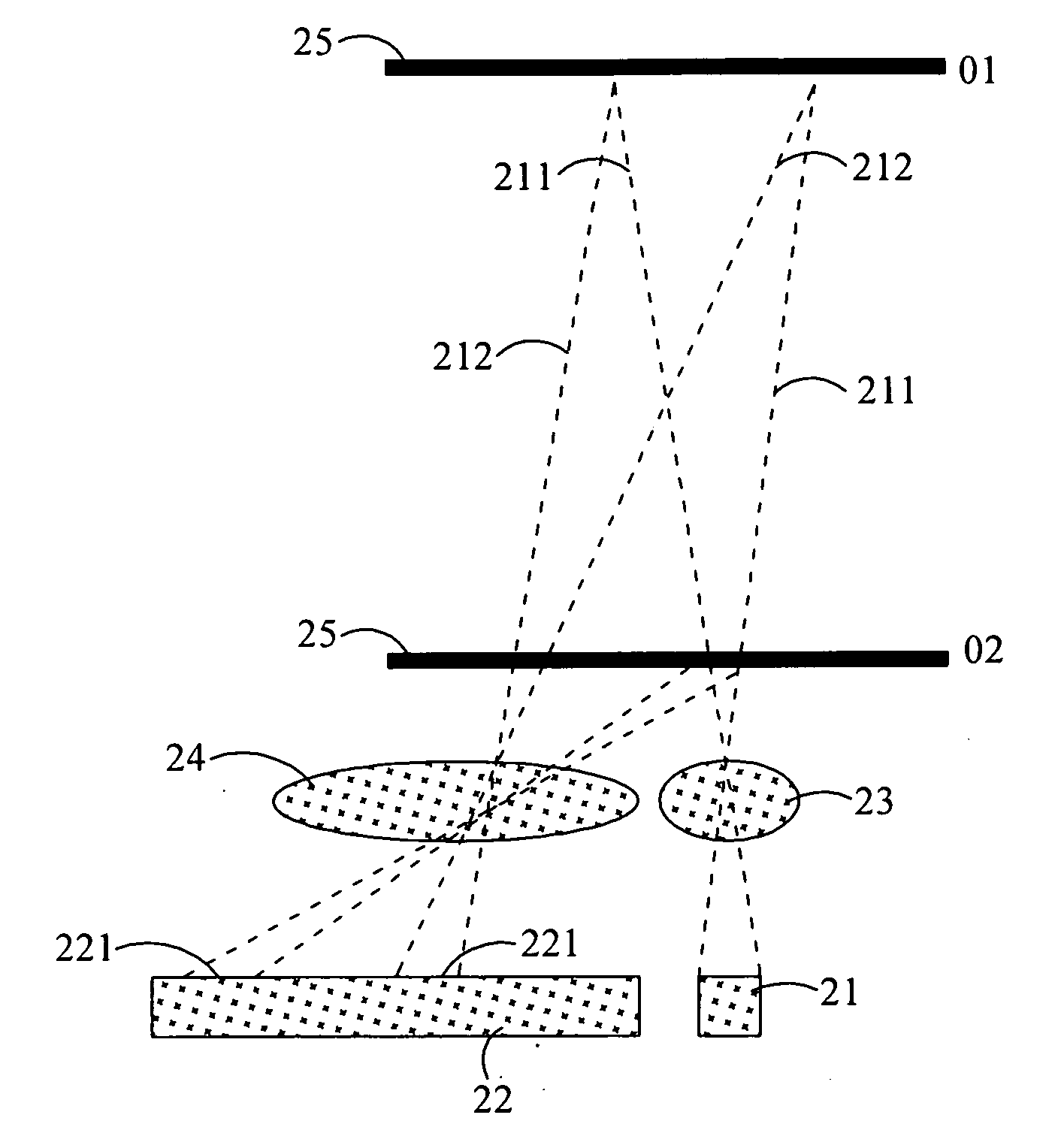

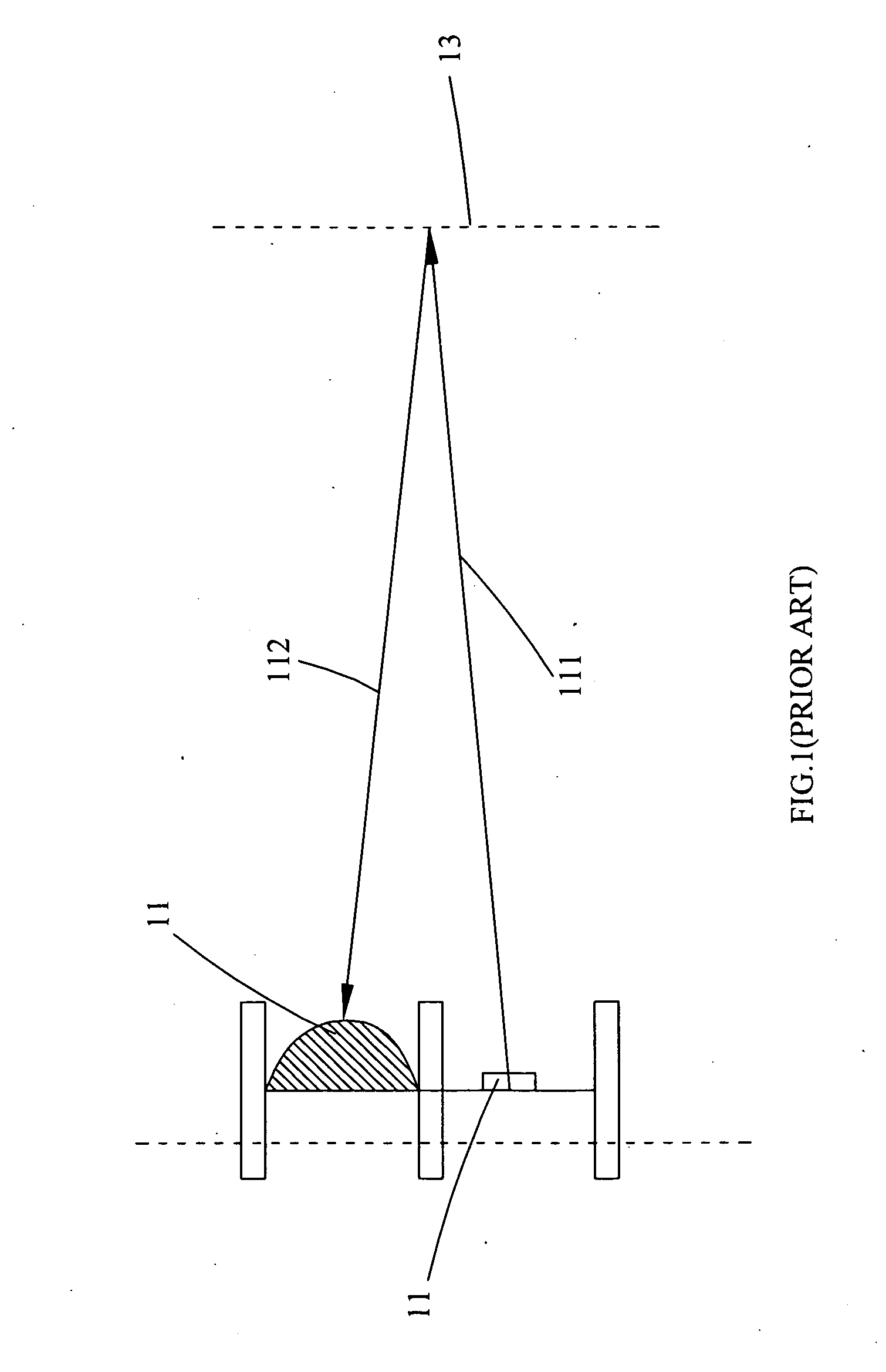

Optical quantized distance measuring apparatus and method thereof

InactiveUS20100277711A1Accurate measurementOptical rangefindersMeasurement deviceBinary search algorithm

The present invention discloses an optical quantized distance measuring apparatus and a method thereof. The optical distance quantized measuring apparatus comprises an illuminating module, a sensing component array and a processing module. The illuminating module projects a light source onto an object to generate a reflecting light. The sensing component array receives the reflecting light, which generates a light source location on the sensing component array. The processing module determines the light source location, and determines an interval between the object and the sensing component array according to the light source location. The processing module determines the light source location with the binary search algorithm.

Owner:CAPELLA MICROSYSTEMS (TAIWAN) INC

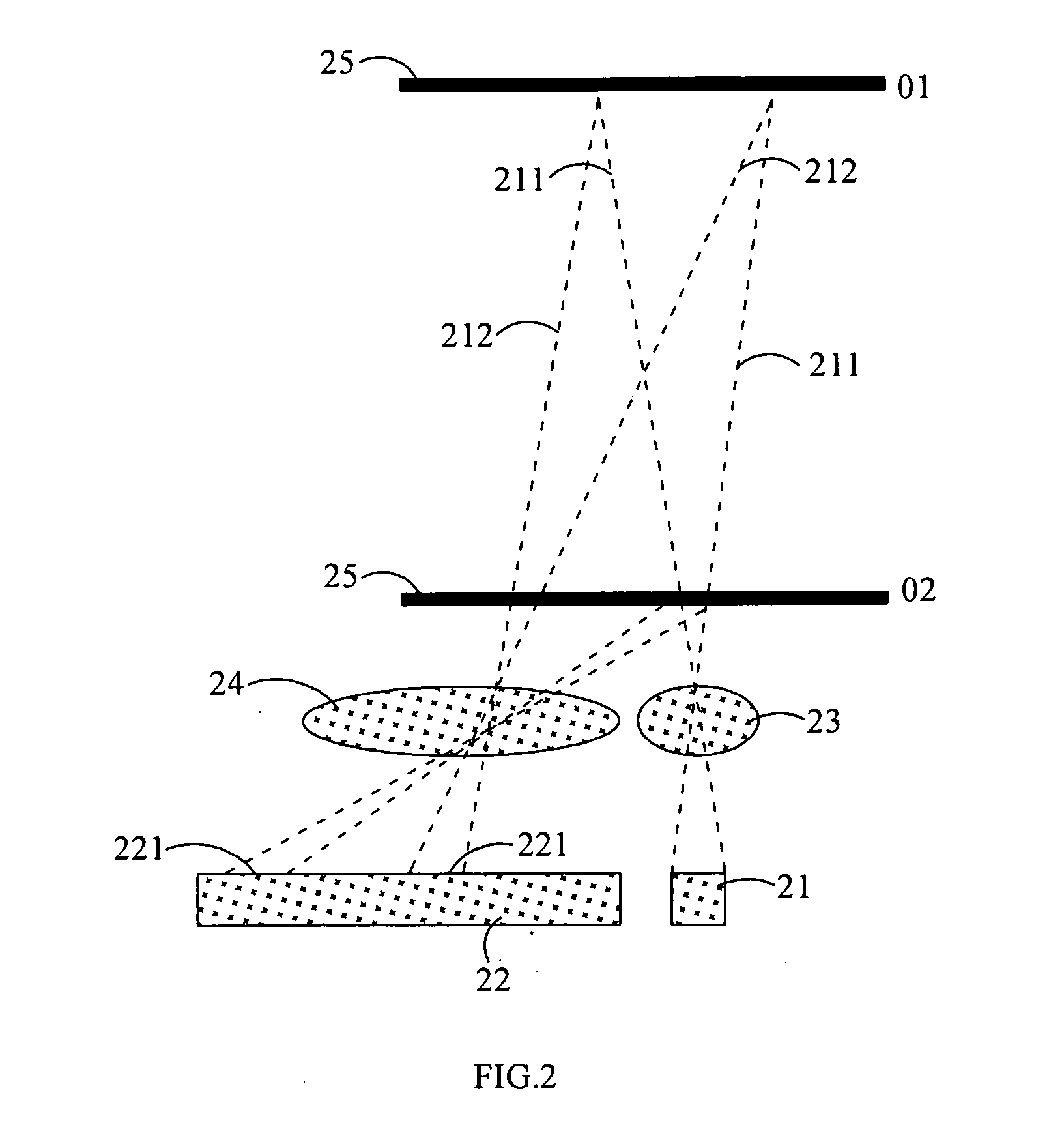

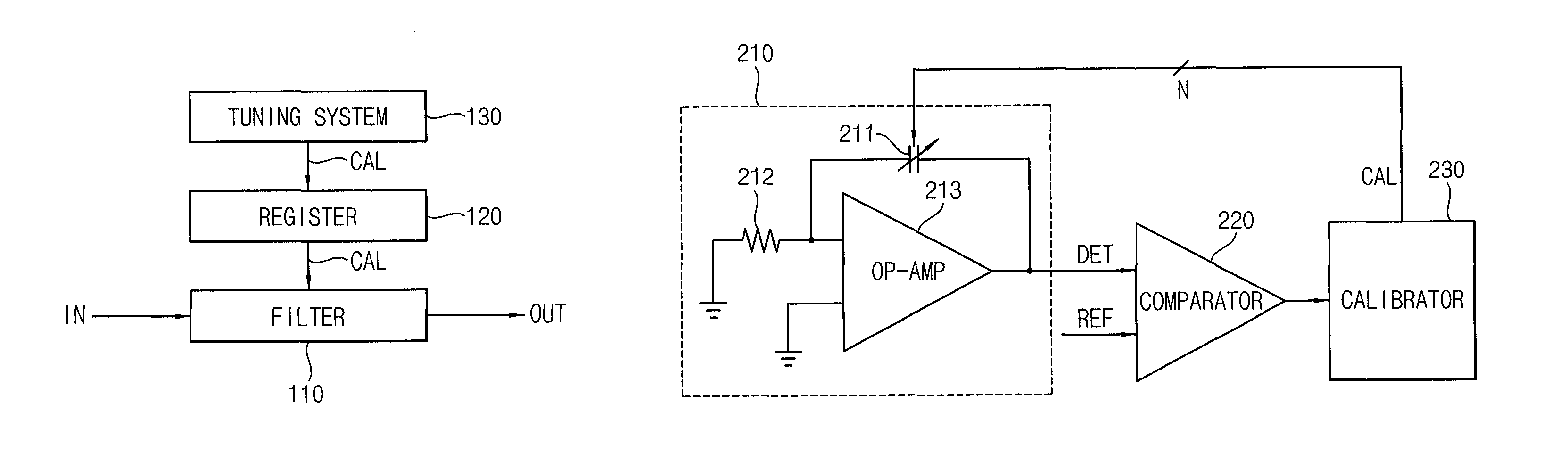

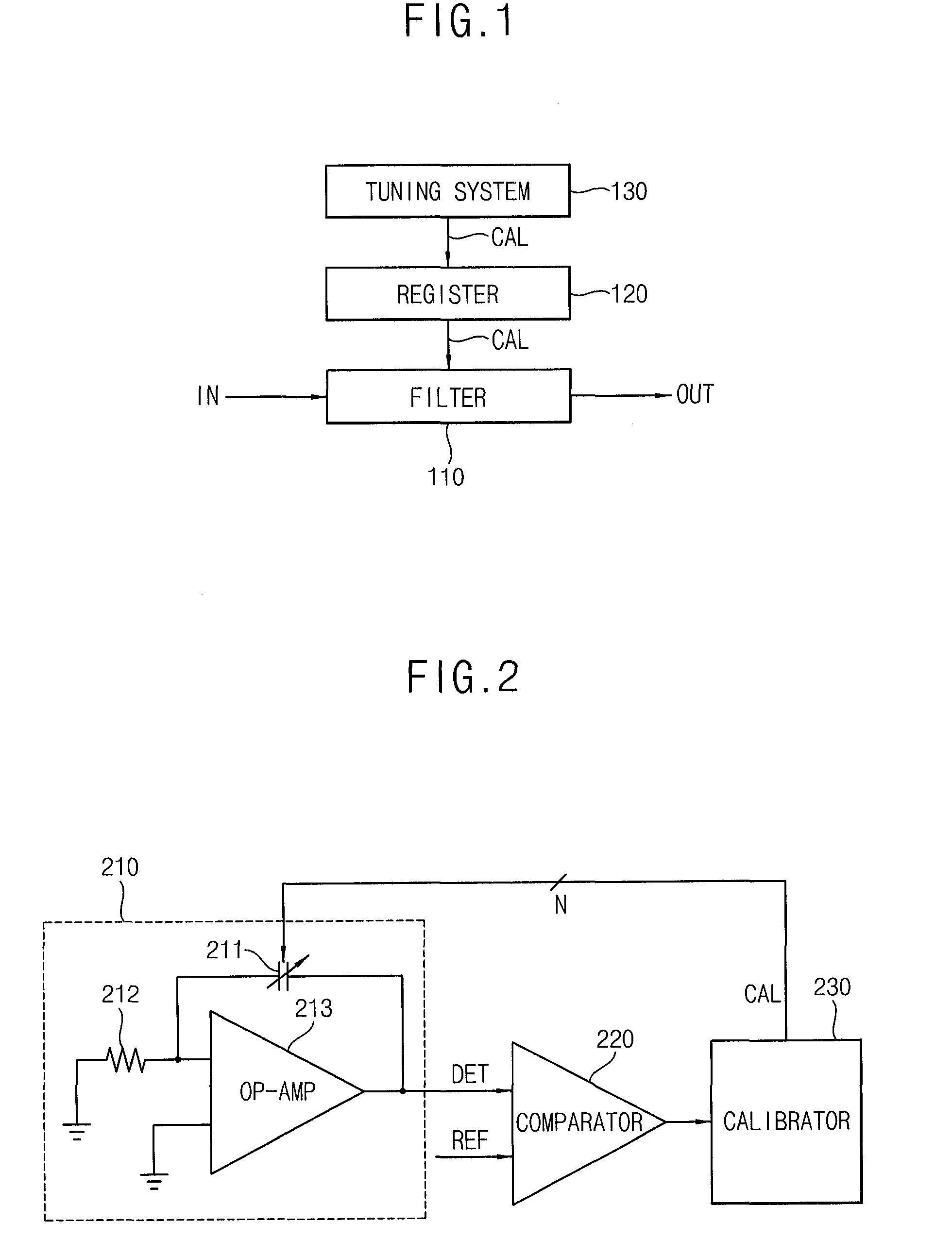

Systems and methods for filter tuning using binary search algorithm

InactiveUS7944286B2Quick compensationOvercoming inefficienciesMultiple-port networksElectronic switchingFilter tuningIntegrator

Owner:I&C TECH

Method for optimizing heat pump capacity and power of each energy device in energy hub

PendingCN111881540AAvoid complex analysisGeometric CADGeneration forecast in ac networkBilevel optimizationExhaust gas emissions

The invention discloses a method for optimizing heat pump capacity and energy equipment power in an energy hub. The method comprises the following steps: establishing an energy hub model containing anatural gas boiler, an electric boiler, a cooler and a heat pump; establishing a double-layer optimized upper-layer model, and solving the optimal heat pump capacity; establishing a double-layer optimized lower-layer model, and solving the optimal power of each energy device; solving the upper-layer model by utilizing a binary search algorithm based on a quadratic function; and solving a lower-layer model by using a multi-objective evolutionary algorithm NSGAII. By adopting the optimization method provided by the invention, the problem of a multi-target double-layer model can be solved withoutthe help of commercial optimization software. And a reasonable, efficient and green planning scheme is obtained, so that the total operating cost and the total exhaust emission of the energy hub arerelatively optimal.

Owner:XIANGTAN UNIV

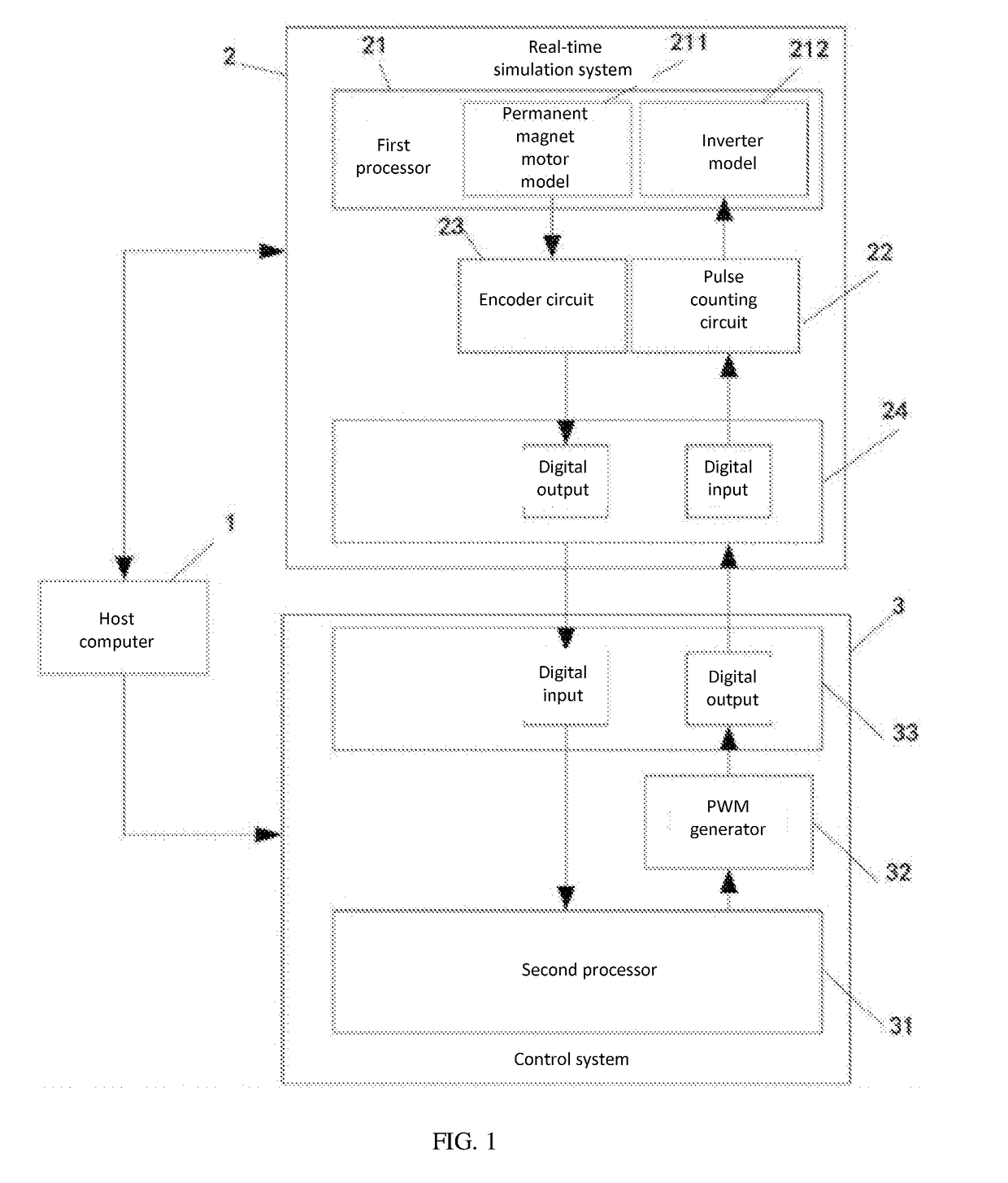

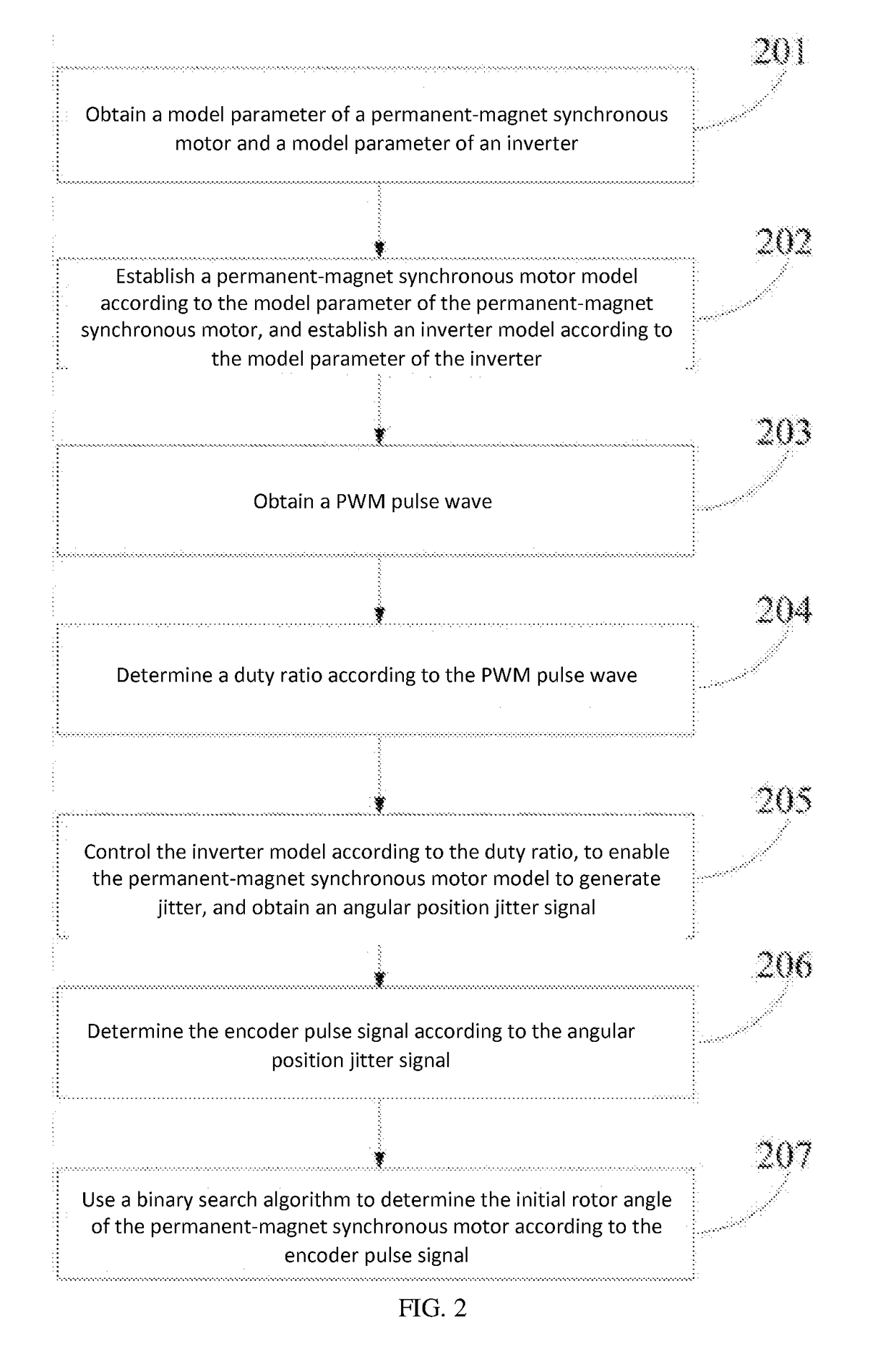

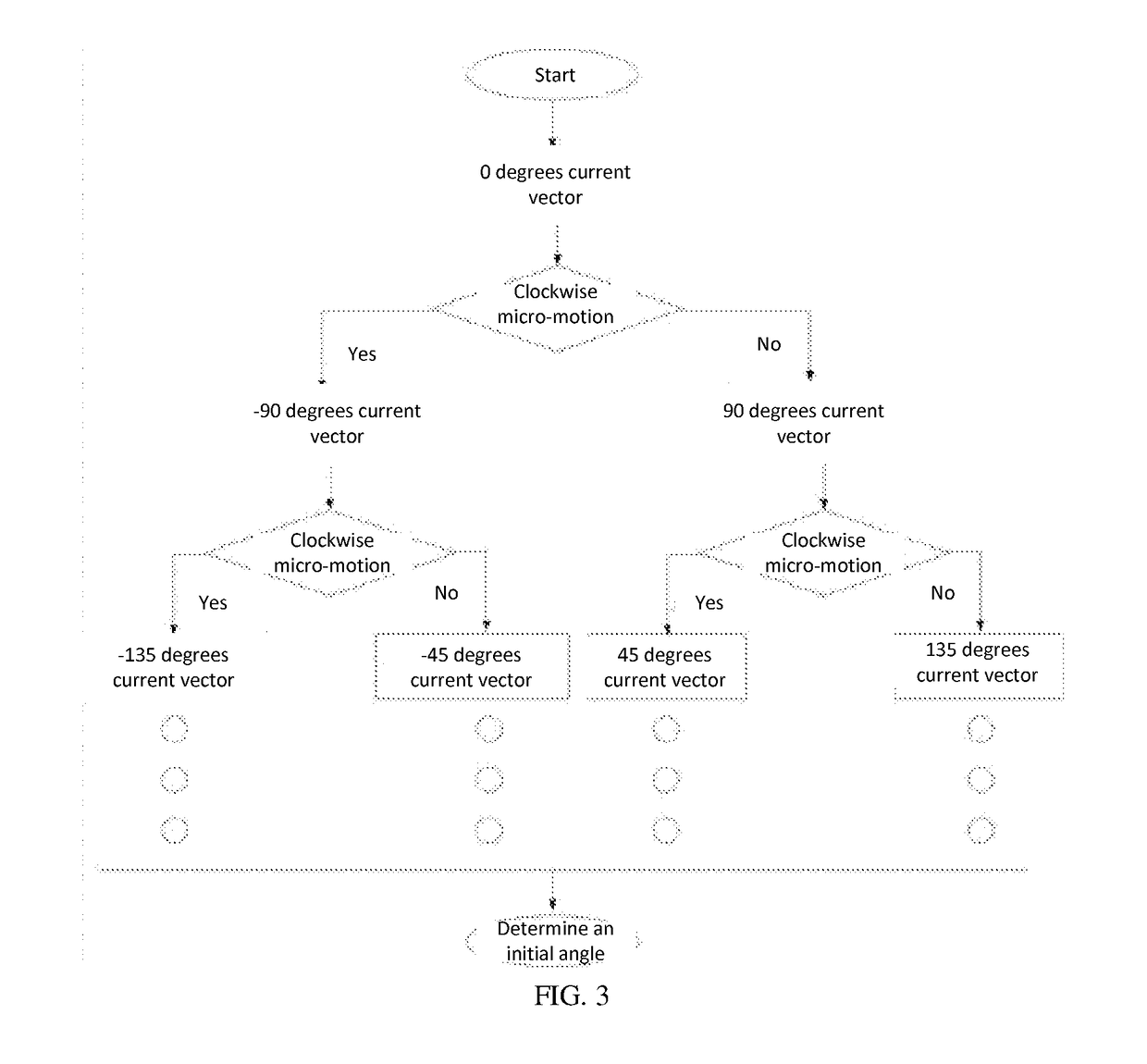

Initial Rotor Position Detection Device and Method Based on Permanent-Magnet Synchronous Motor

ActiveUS20190036469A1Effectively and quickly detect an initial rotor positionReduce testing costsVector control systemsDynamo-electric converter controlReal-time simulationSynchronous motor

An initial rotor position detection device based on a permanent-magnet synchronous motor, including a host computer, a real-time simulation system, and a control system, where the real-time simulation system is connected to the control system, for determining an encoder pulse signal according to the model parameter of the permanent-magnet synchronous motor, the model parameter of the inverter, and a PWM pulse wave generated by the control system; and the control system is connected to the real-time simulation system, for using a binary search algorithm to determine an initial rotor angle of the permanent-magnet synchronous motor according to the encoder pulse signal sent by the real-time simulation system. A comprehensive closed-loop test circuit can be achieved by setting a host computer, a real-time simulation system, and a control system, and a used binary search algorithm can effectively and quickly detect an initial rotor position of a permanent-magnet synchronous motor.

Owner:SHENZHEN JINGQUANHUA ELECTRONICS

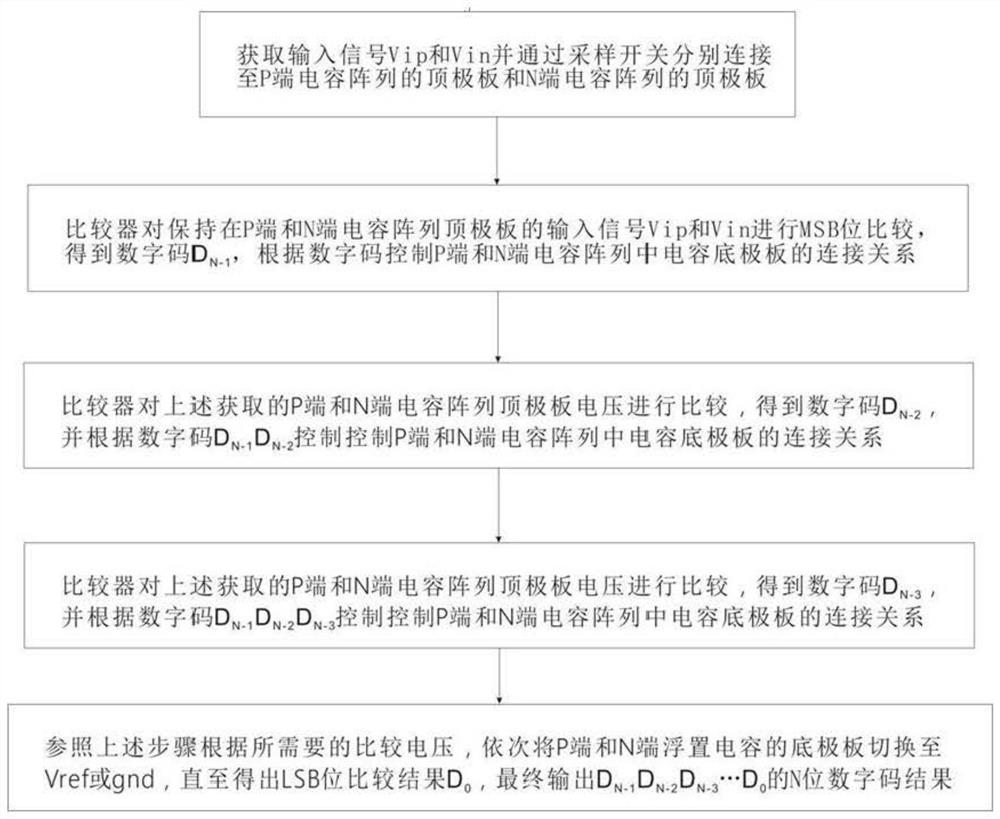

Low-voltage SAR ADC switch switching method based on charge recovery

ActiveCN112332846AEfficient and flexible switching algorithmReduce Switching Power ConsumptionElectric signal transmission systemsAnalogue-digital convertersCapacitanceSynthetic aperture radar

The invention discloses a low-voltage SAR ADC (Synthetic Aperture Radar Analog-to-Digital Converter) switch switching method based on charge recovery, which comprises the following steps: sampling stage differential input signals Vip and Vin are connected to top polar plates of P-end and N-end capacitor arrays through sampling switches, reference voltages Vref and gnd are connected to bottom polarplates of P-end and N-end corresponding capacitors, the capacitor arrays are pre-charged; and the sampling switches are disconnected in the transforming stage. the comparator compares the voltages ofthe top electrode plates of the P-end capacitor array and the N-end capacitor array from the MSB bit to the LSB bit in sequence to obtain digital codes of corresponding bits, floating and voltage switching of corresponding capacitors of the P-end capacitor array and the N-end capacitor array are controlled according to the digital codes, and a binary search algorithm is completed. According to the invention, 100% capacitor array switching energy can be saved, extra third reference voltage does not need to be generated, the circuit is suitable for design under near threshold voltage, in a conversion stage, common-mode voltage of top polar plates of the P-end capacitor array and the N-end capacitor array is always kept constant, and the design difficulty of a comparator is reduced.

Owner:SOUTHEAST UNIV

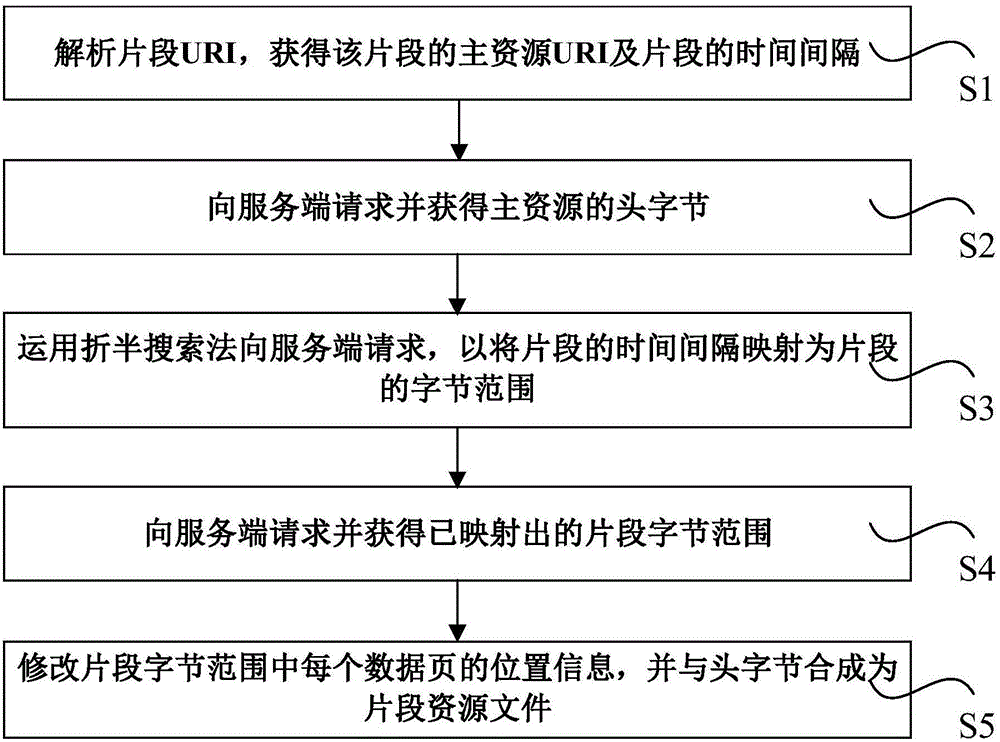

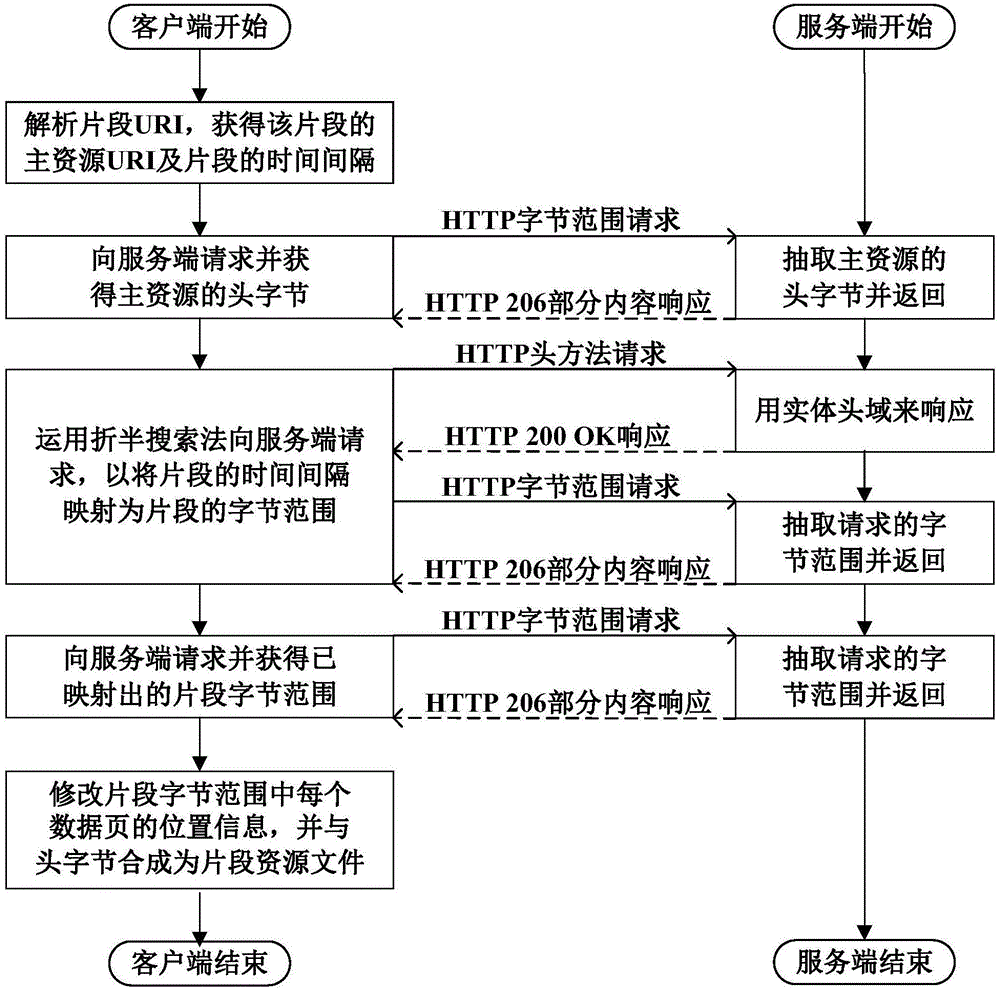

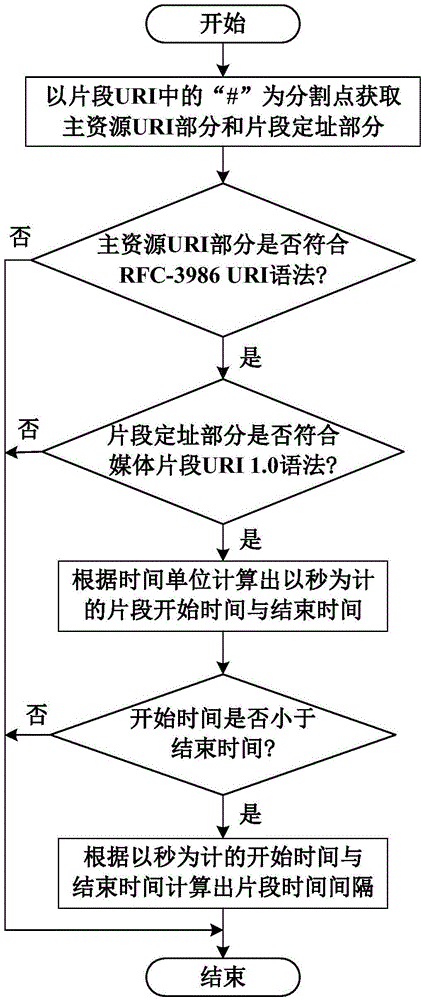

Client HTTP retrieval method for Ogg format time slices of URI

ActiveCN104580389ASave communication bandwidthReduce communication delayTransmissionSpecial data processing applicationsMultiplexingUniform resource identifier

The invention discloses a client HTTP (Hyper Text Transport Protocol) retrieval method for Ogg format time slices of URI (Uniform Resource Identifier), which comprises the following steps: parsing a fragment URI, and acquiring a primary resource URI of the fragment and a time interval of the fragment; requesting a sever and acquiring a header byte of the primary resource; applying a binary search algorithm to send a request to the server, so that the time interval of the fragment is mapped into a byte range of the fragment; requesting the server and acquiring the mapped byte range of the fragment; and modifying the position information of each data page within the byte range of the fragment, and combining with the header byte to form a fragment resource file. The disclosed client HTTP retrieval method for Ogg format time slices of URI can support the W3C media fragment URI 1.0 standard; the client applies the binary search algorithm to requesting a small amount of bytes from the traditional server and then completes the mapping of the time slice URI to the corresponding byte range in the primary resource, and generates a media fragment file (to support a variety of multiplexing of the fragment) after acquiring the byte range from the traditional server, so as to greatly save the network communication bandwidth and shorten the communication latency.

Owner:HOHAI UNIV

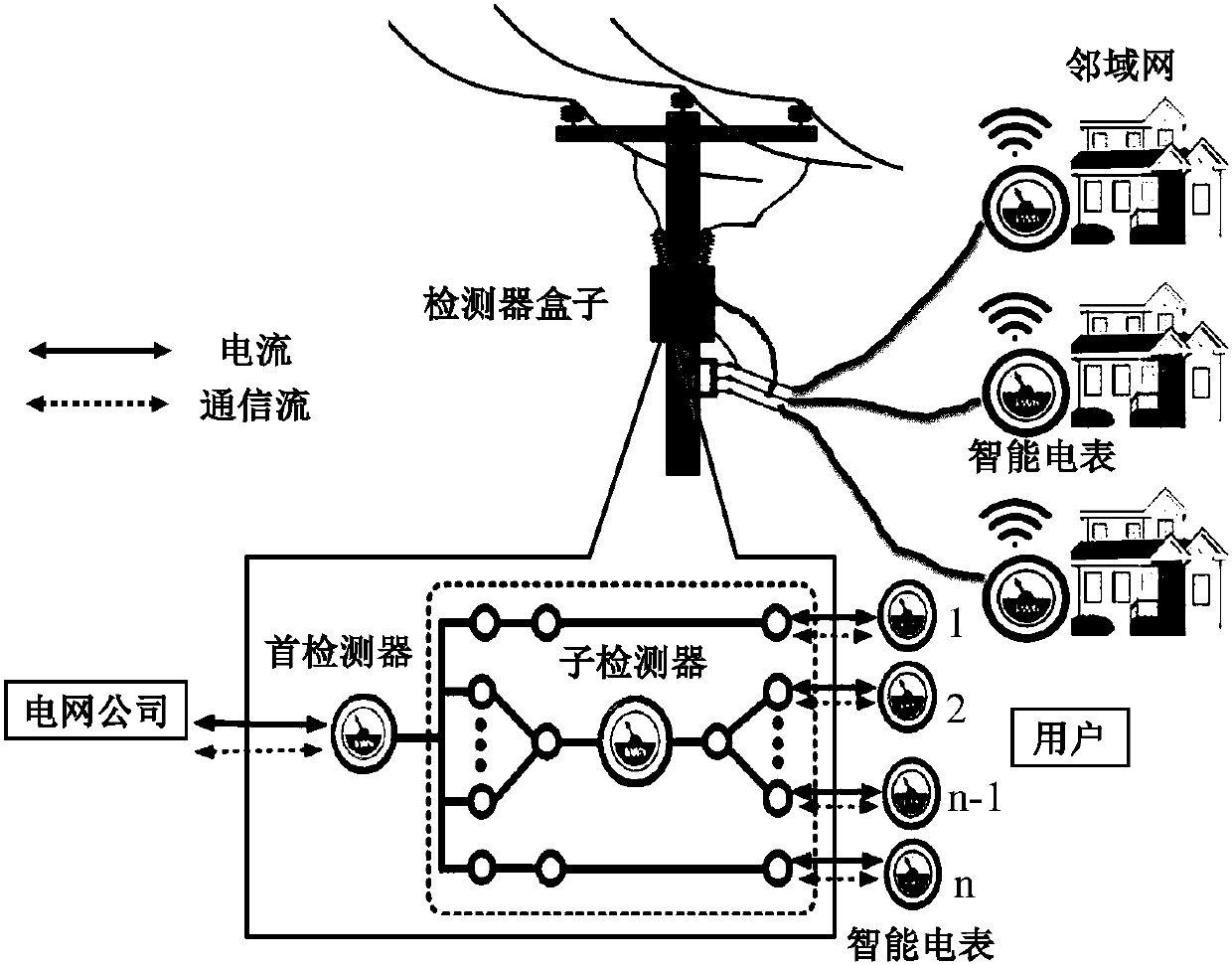

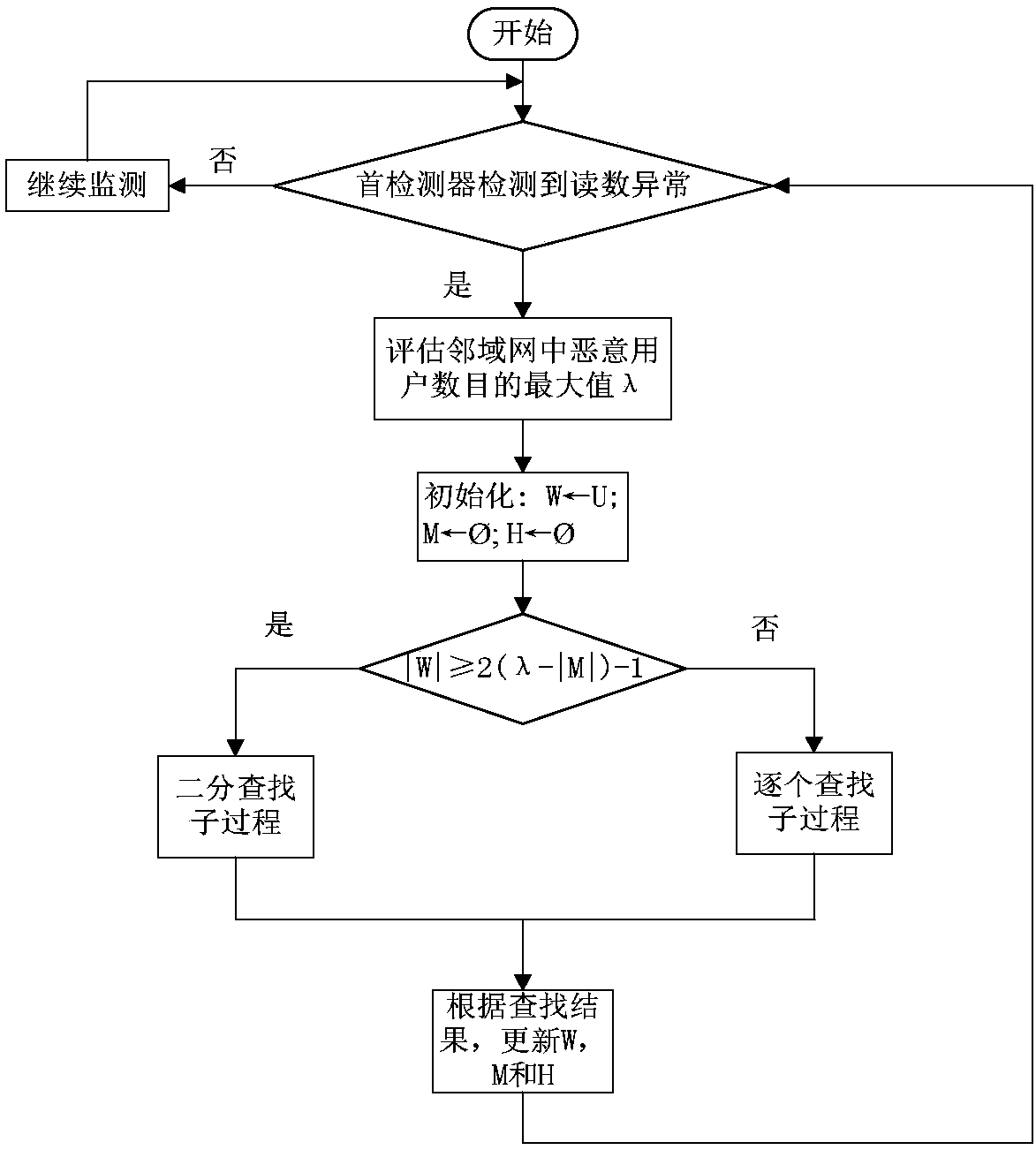

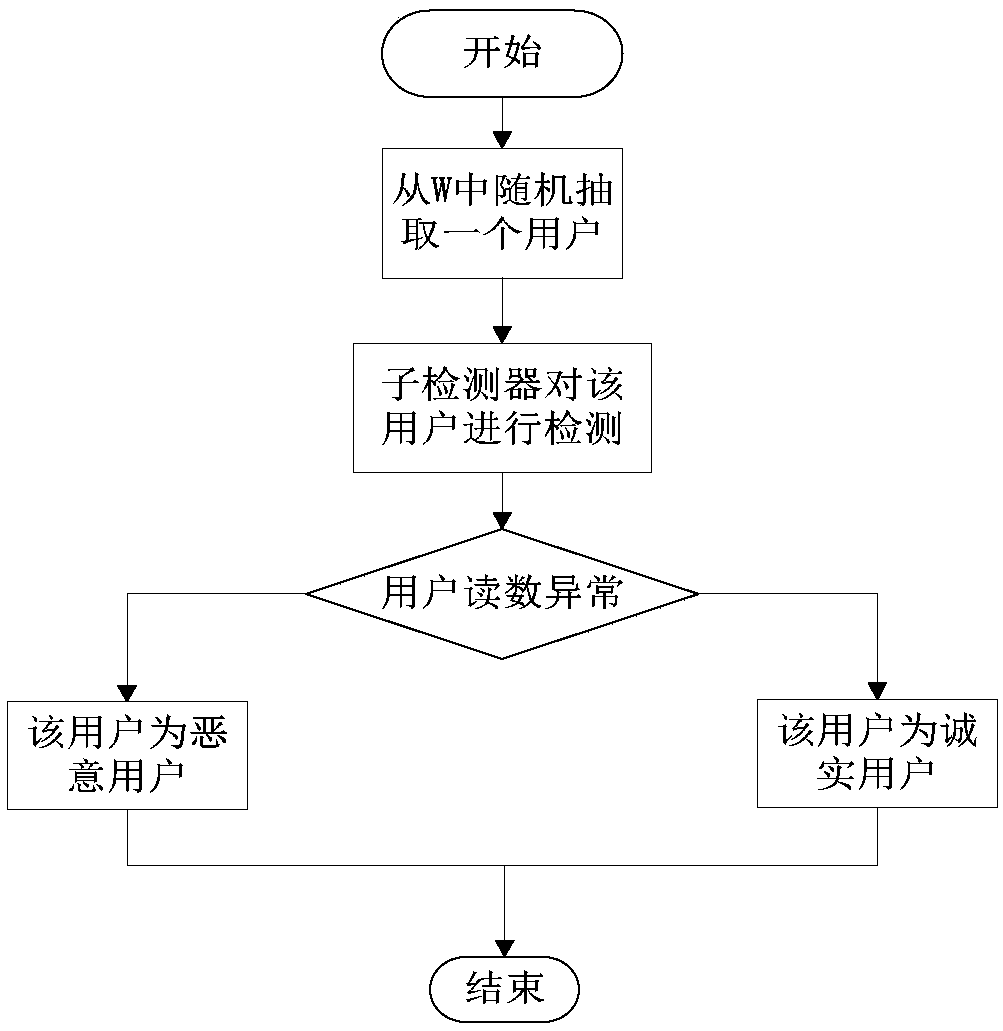

Adaptive binary search algorithm for malicious user positioning in smart grid neighboring network

The invention relates to a smart grid technology, and in particular relates to an adaptive binary search algorithm for malicious user positioning in a smart grid neighboring network. The method comprises the steps that first the maximum value of malicious users in the neighboring network is estimated; in a searching process, a detector adaptively adjusts a search strategy according to the relationship between the number of detected malicious users and the total number of users still needing to be detected; when a one-by-one search strategy is used, the detector detects only one user at a time;when a binary search strategy is adopted, the detector detects multiple users at the same time; and the number of detected users is determined by the number of detected malicious users and the numberof users still needing to be detected together. According to the invention, the adaptive binary search method for malicious user positioning in the smart grid neighboring network is proposed under the premise of reducing the deployment cost of detectors; and the algorithm can adaptively adjust the search strategy during a detection process and shorten the detection time of malicious users.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

Method, terminal and computer-readable recording medium for deblurring barcode image

InactiveUS8320695B2Shorten the timeThe solution function is relatively simpleImage enhancementCharacter and pattern recognitionBarcodeComputer terminal

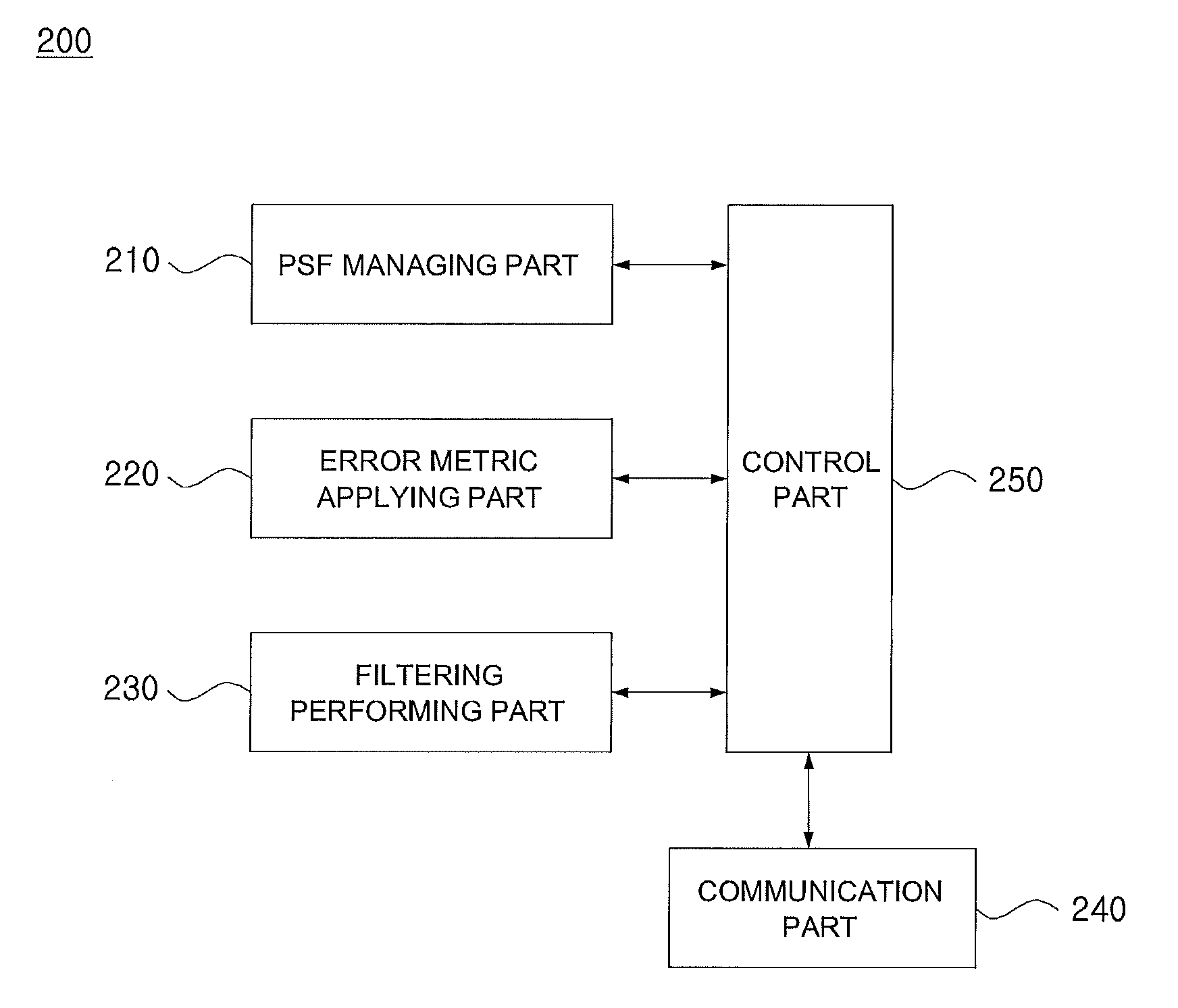

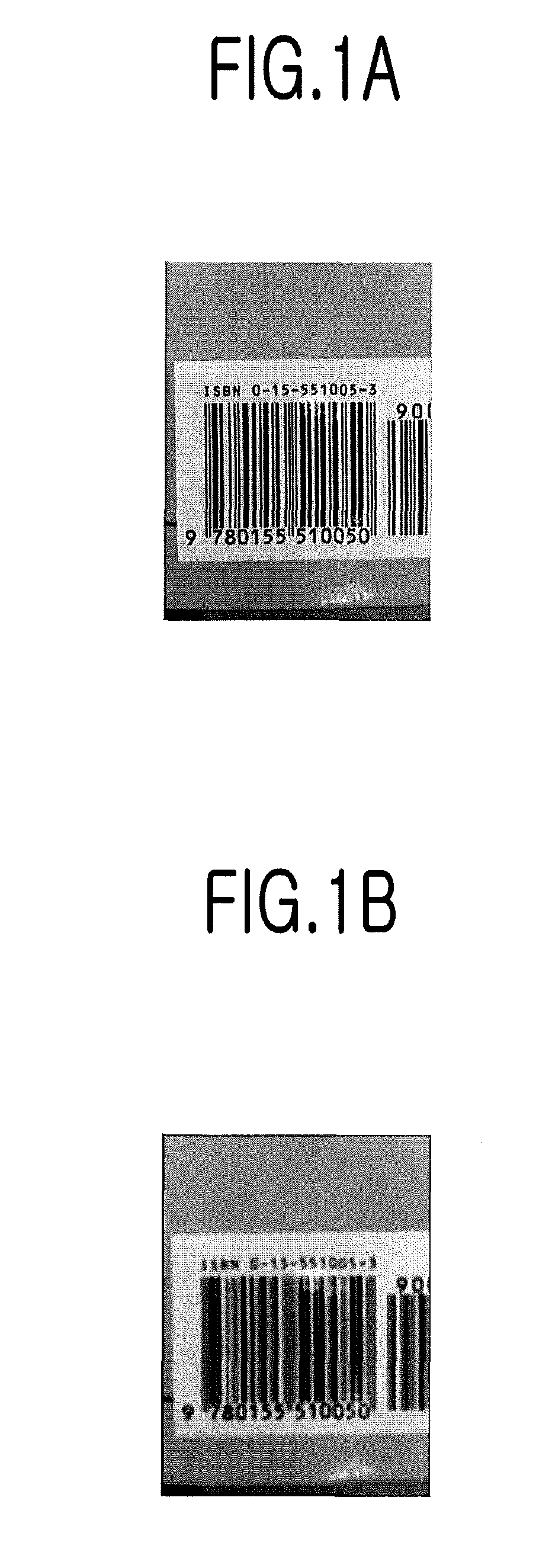

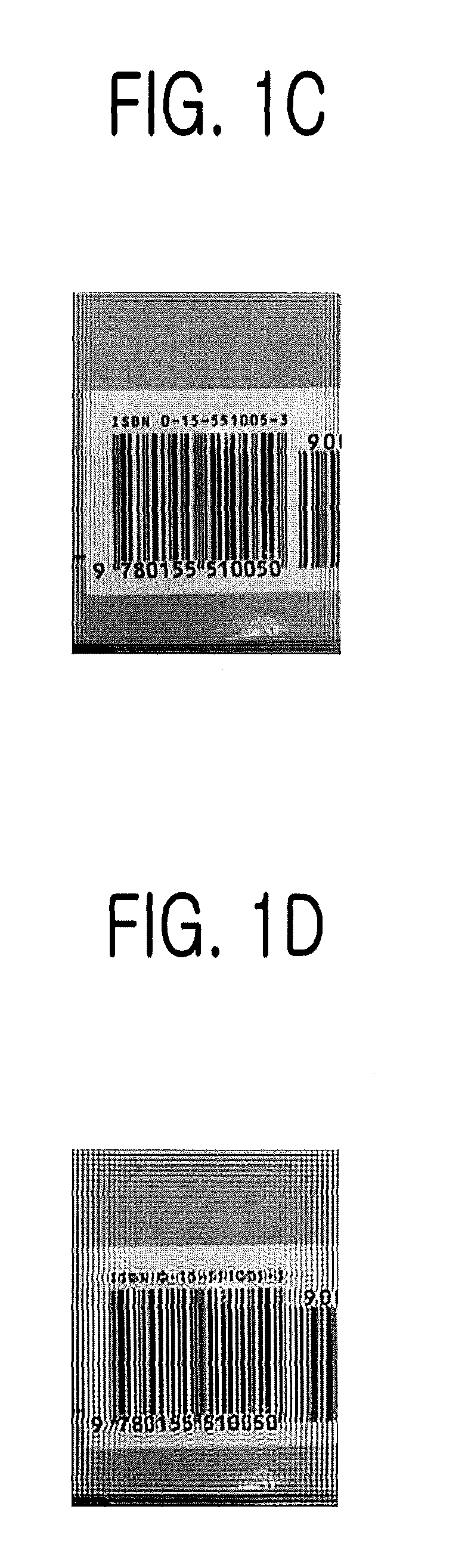

The present invention relates to a method for deblurring a barcode image. The method includes the steps of: acquiring the terminal's n OTFs calculated by varying focal lengths for a subject; if a barcode image is inputted through the mobile terminal, fixing a specific value among NSRs as a value to be applied to an error metric of Wiener filtering, applying n PSFs calculated from the n OTFs to the error metric by a binary search algorithm and determining whether the result of the application to the error metric is not exceeding the pre-set threshold or not; and selecting a PSF value and an NSR value as values of Wiener filtering if the result of the application to the error metric is not exceeding the pre-set threshold and then performing the Wiener filtering to the inputted barcode image by using the selected PSF value and the selected NSR value.

Owner:INTEL CORP