Patents

Literature

46 results about "Near threshold" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In addition, by definition, near-threshold design means the design is close to not being functional at all, and so monitoring of process, voltage, and temperature become critical to ensure that adjustments can be made in the supplies to take changes in process and temperature into account.”.

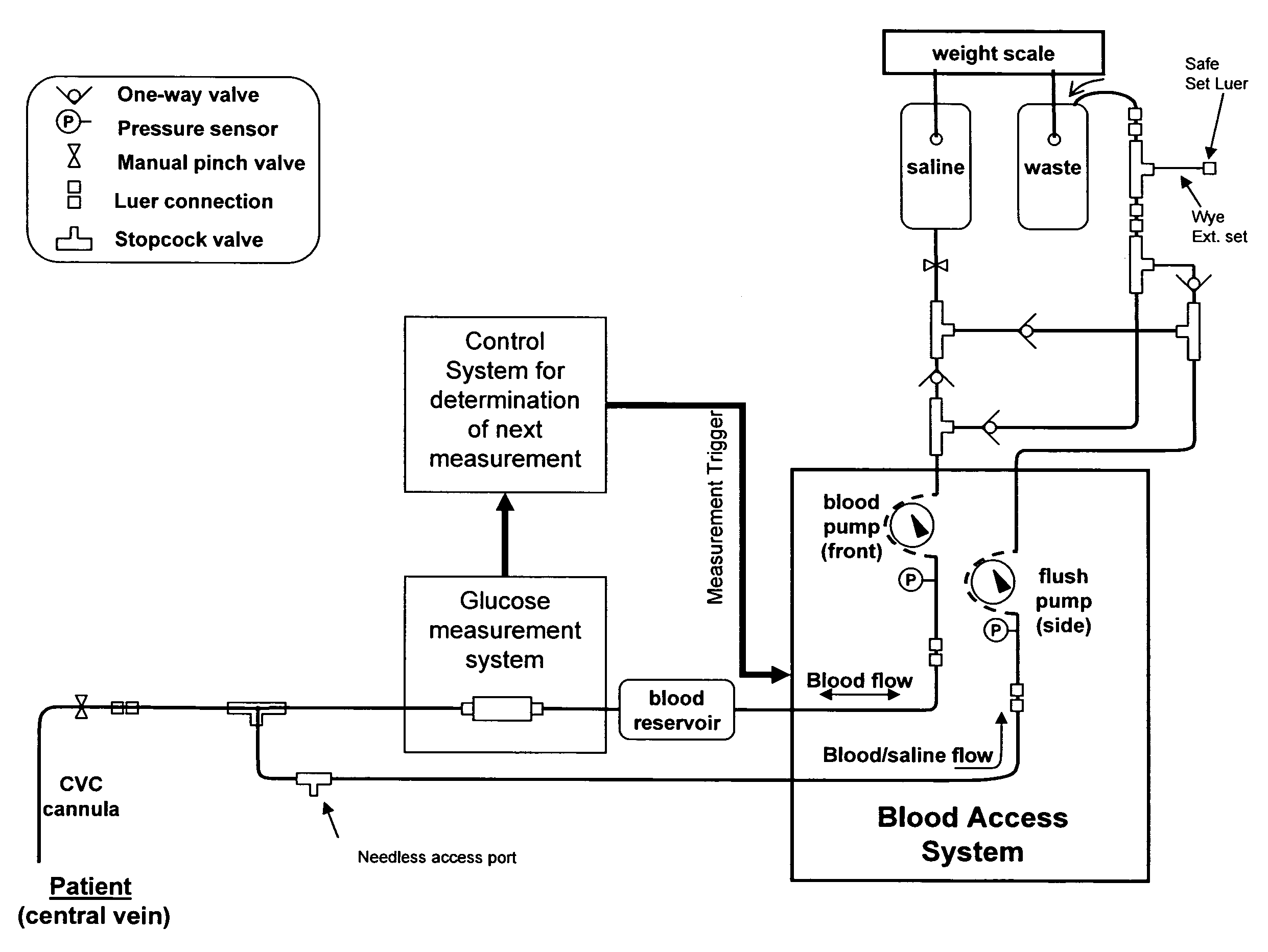

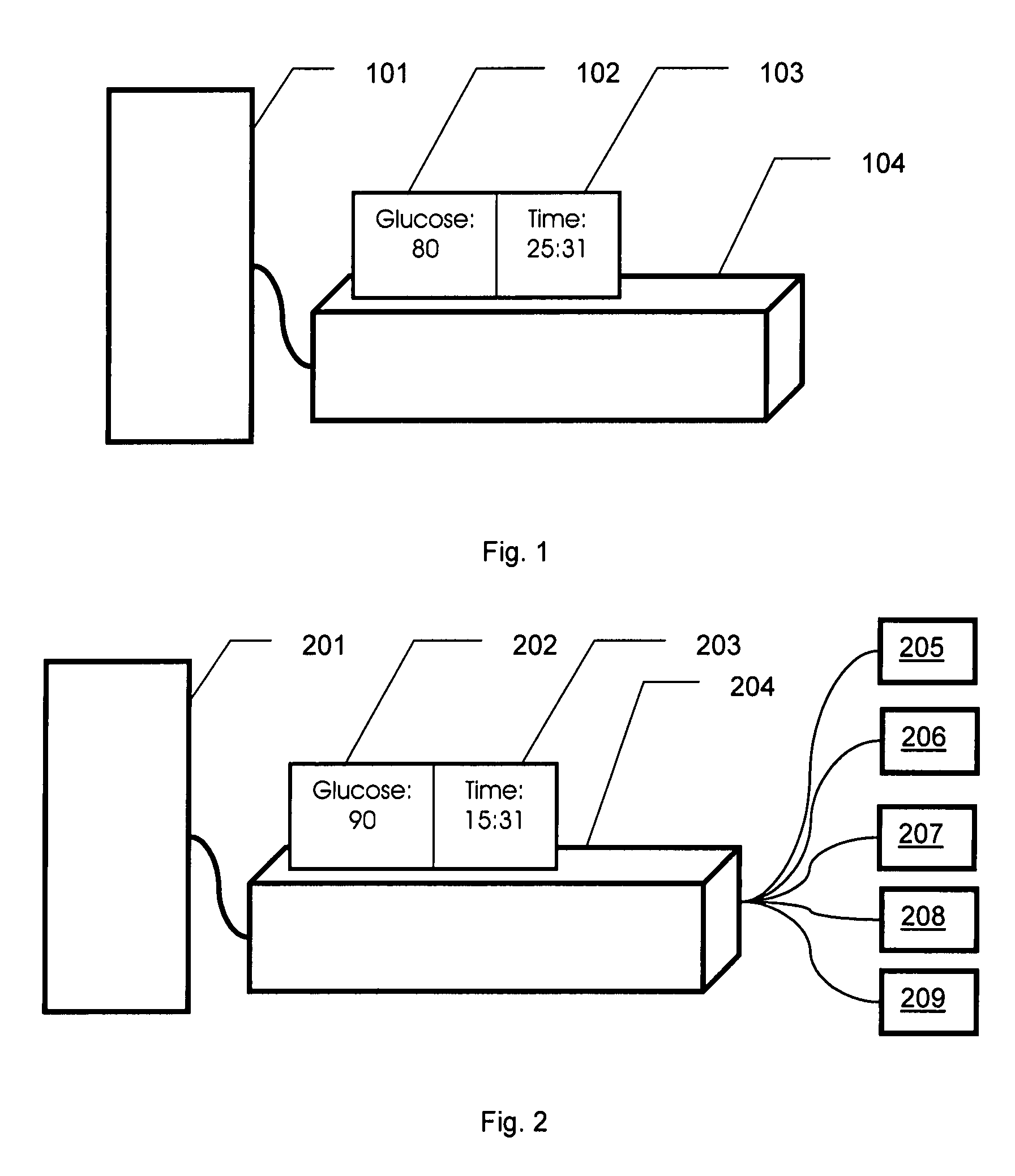

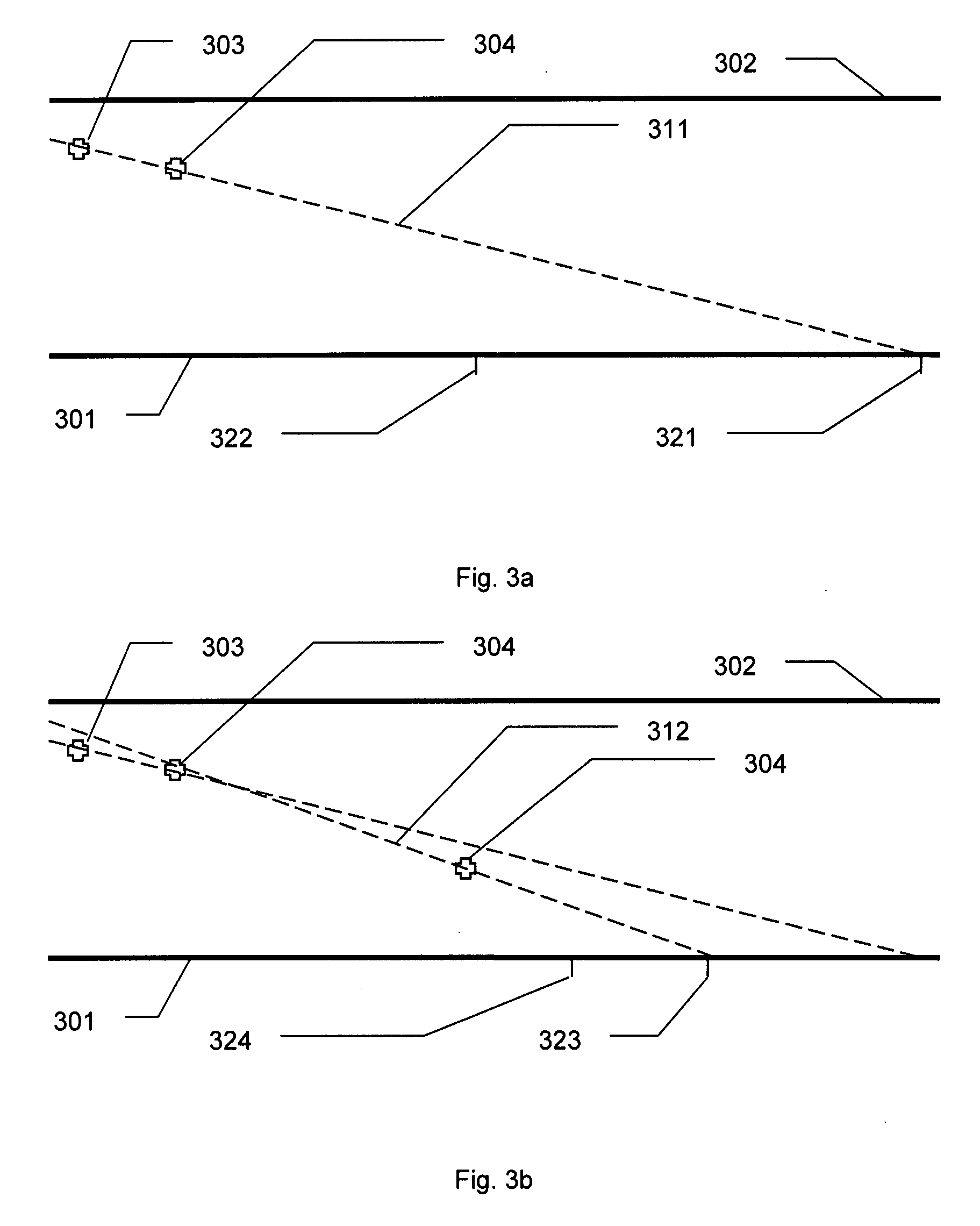

Variable Sampling Interval for Blood Analyte Determinations

InactiveUS20090054753A1Efficient measurementGreat patient safetyMedical simulationLocal control/monitoringAnalyteMedicine

The present invention provides methods and apparatuses that can provide measurement of glucose with variable intervals between measurements, allowing more efficient measurement with greater patient safety. A method according to the present invention can comprise measuring the value of an analyte such as glucose at a first time; determining a second time from a patient condition, an environmental condition, or a combination thereof; then measuring the value of the analyte at the second time (where the second time can be expressed as an interval after the first time, an absolute time, or a time indicated when certain patient or environmental conditions, or both, are reached or detected). The second time can be determined, as an example, from a comparison of the analyte value at the first time with a threshold. The interval between the first time and the second time can be related to the difference between the analyte value at the first time and the threshold; e.g., the closer to the threshold, the closer the two measurement times. The invention can be used with automated measurement systems, allowing the system to determine measurement times and automatically make measurements at the determined times, reducing operator interaction and operator error.

Owner:ROBINSON MARK RIES +2

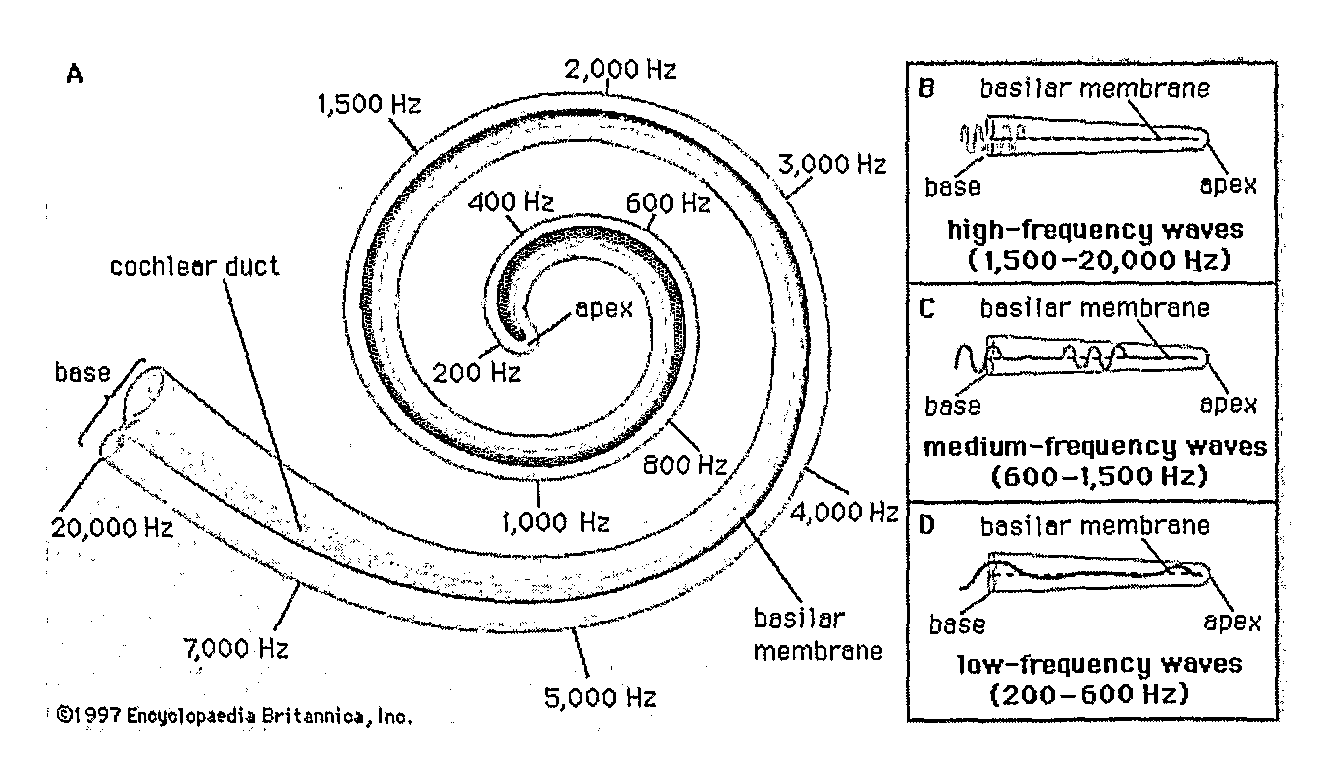

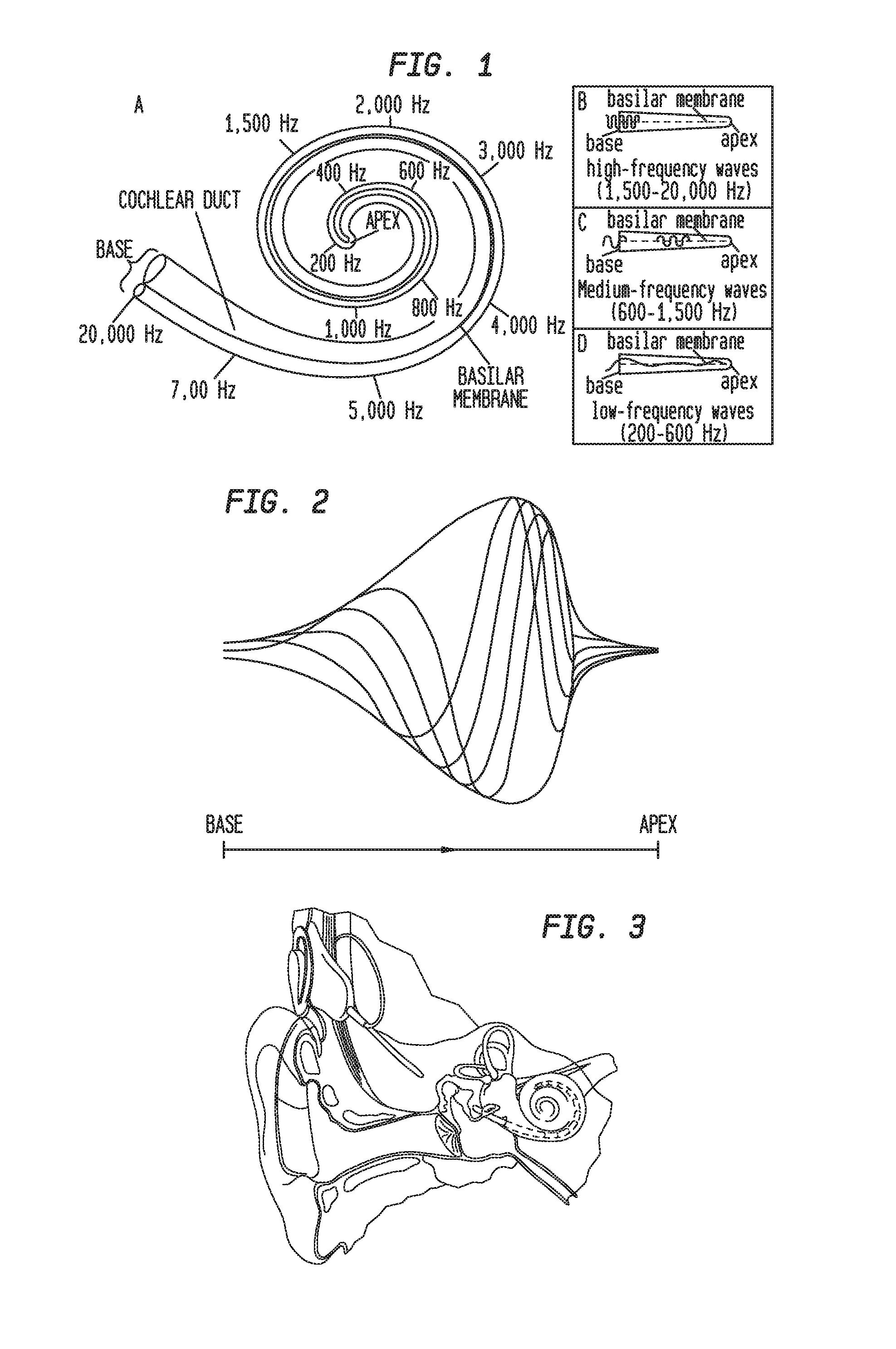

Sound processing method and system

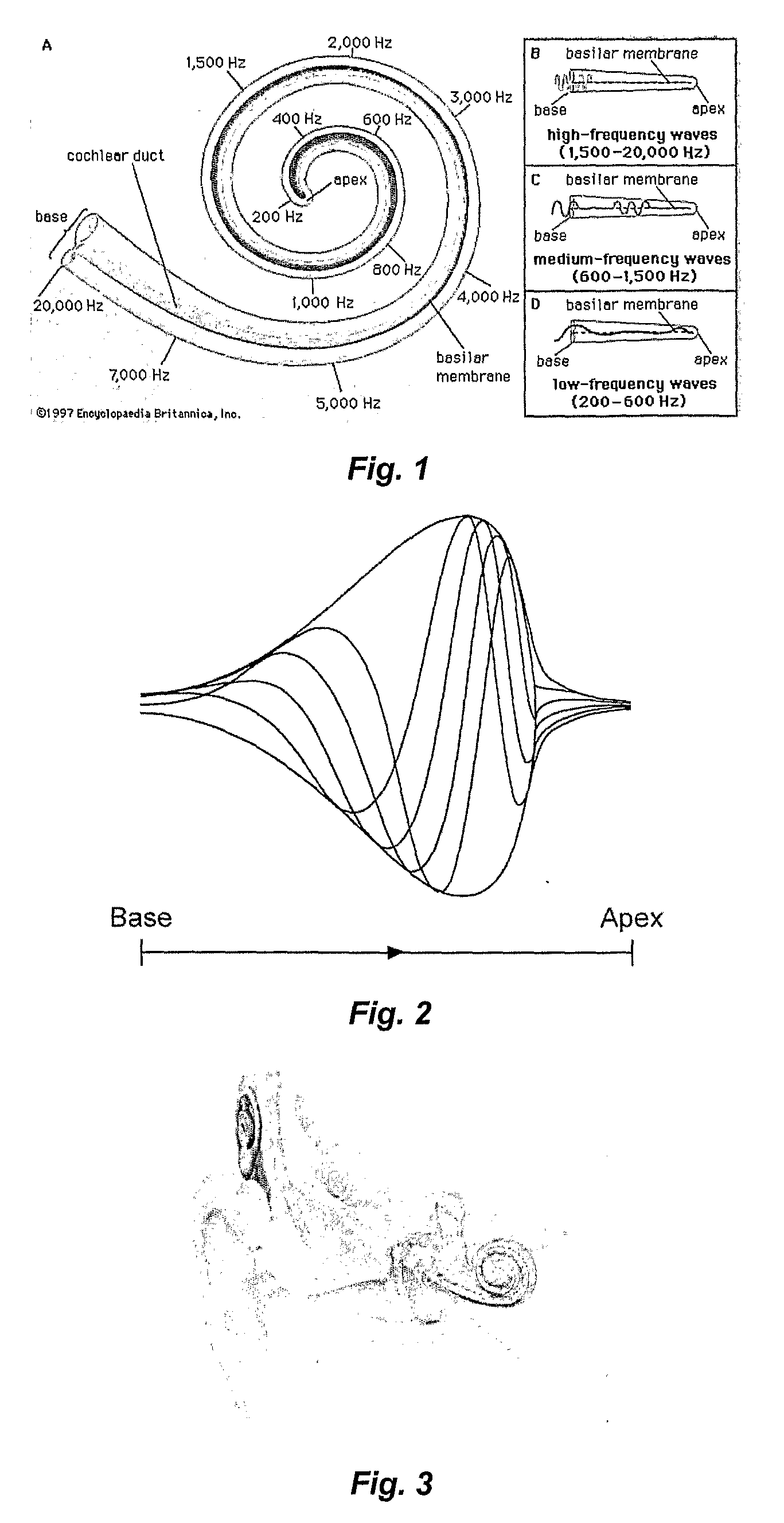

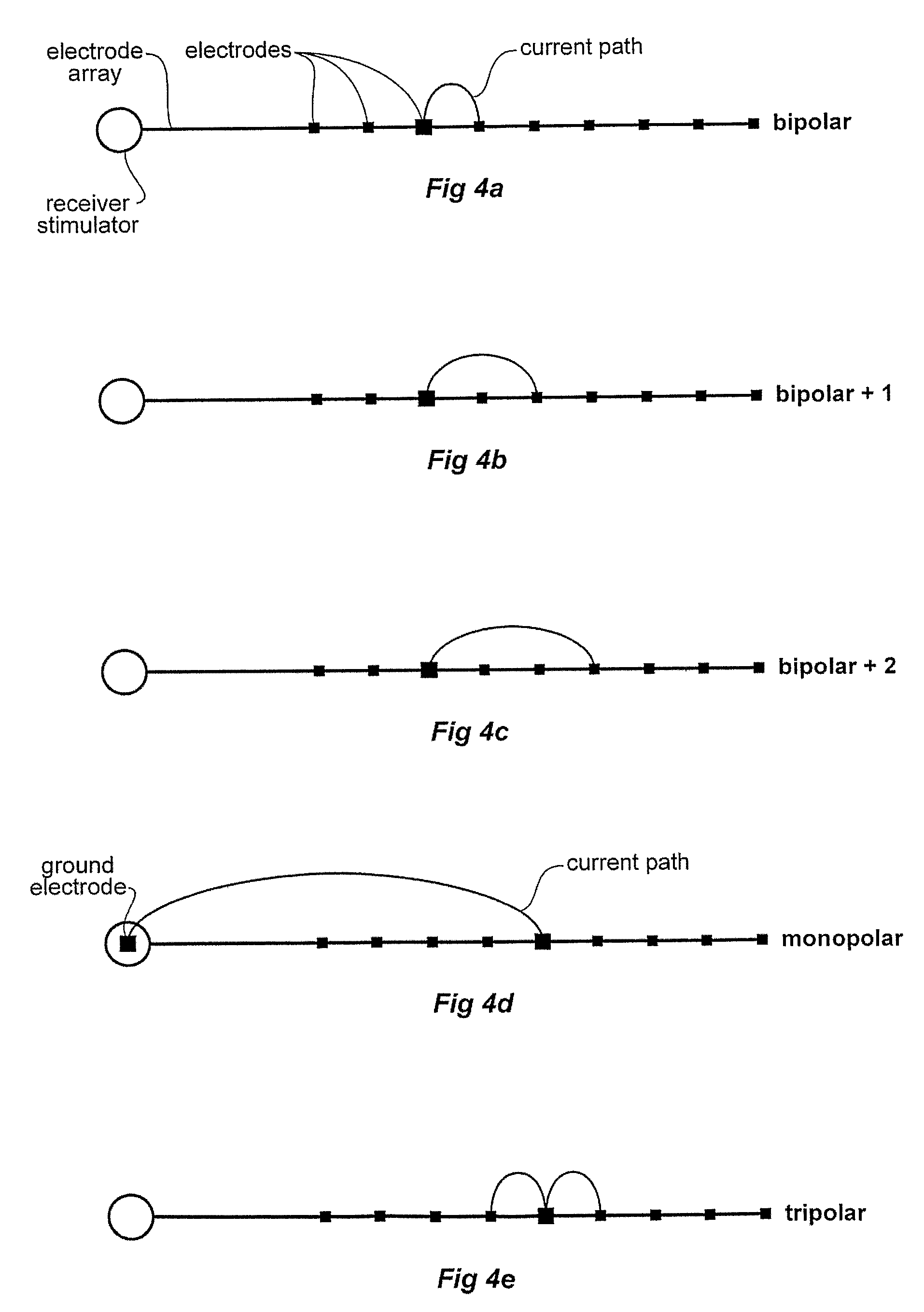

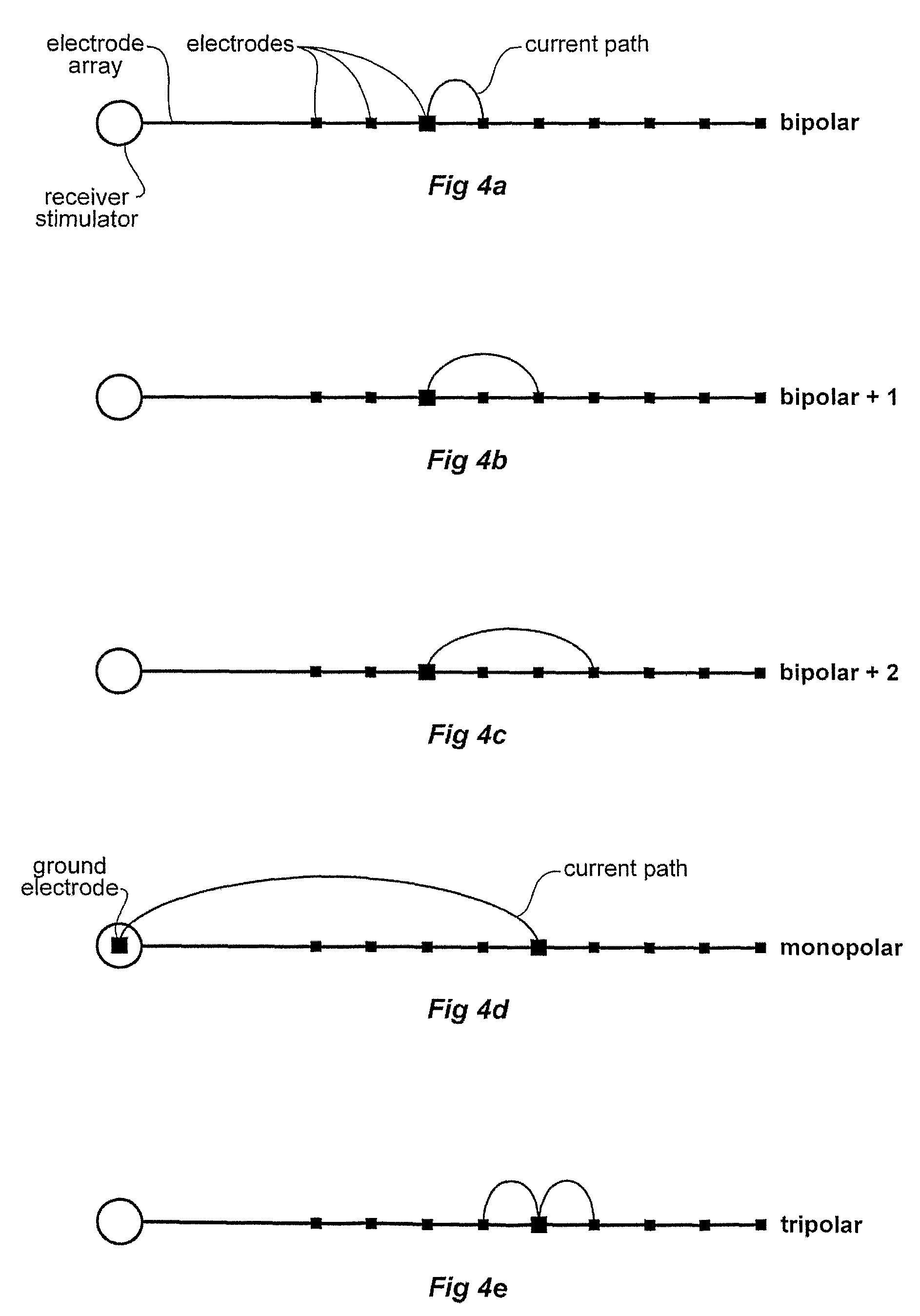

Coding of received audio signals and the resulting application of electrical stimuli applied to electrodes used in a cochlear implant system are disclosed together with a method of fitting this new coding strategy. One of the aims is to place specific stimulation representing pitch by applying near threshold electrical stimuli with limited and focussed excitation fields. A range of stimulation rates and a minimal range of current levels above threshold are used for creation of a dynamic loudness percept for a cochlear implant recipient. Another aim is to disclose a coding scheme based on a model of physiological measures (i.e. refractoriness, adaptation, spread of activation field, spatiotemporal acoustical cochlear activation patterns and spontaneous activity) to estimate the proportions of available excitable auditory neurons close to the electrodes available for stimulation. The spectral bands formed from the pre-processing of incoming audio signals are weighted by these proportions of excitability to control place, timing, rate and current level of electrical stimuli applied to the electrodes available in the array.

Owner:COCHLEAR LIMITED

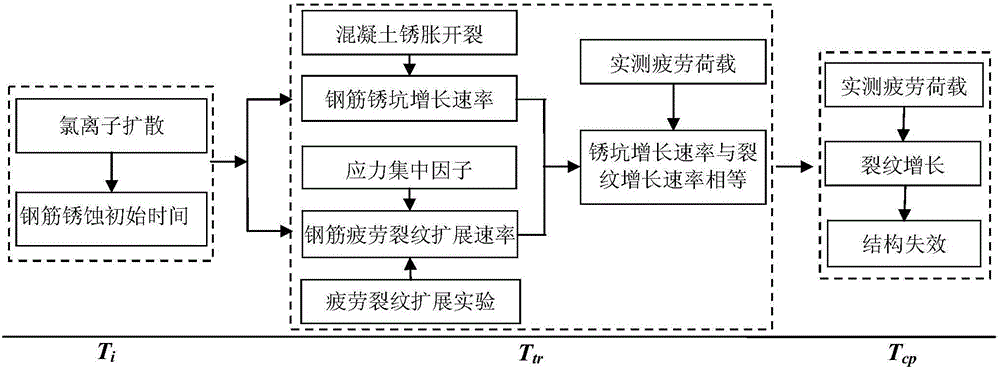

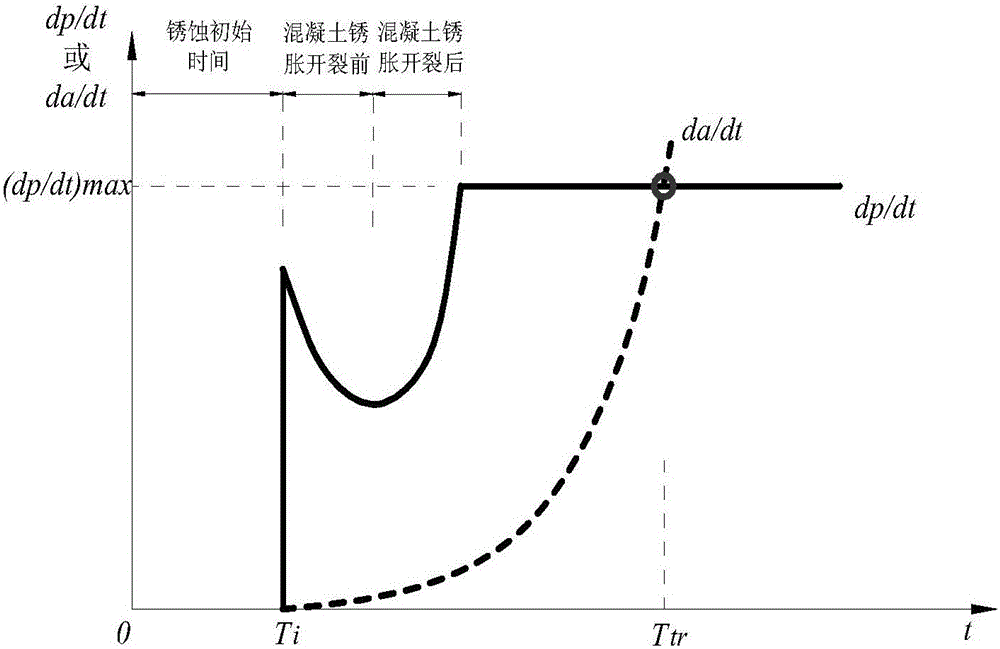

Method for evaluating fatigue life of aged reinforced concrete bridge

ActiveCN105825030AThe prediction method is reasonableGeometric CADForecastingStress concentrationCrazing

The invention discloses a method for evaluating the fatigue life of an aged reinforced concrete bridge. The method comprises the following steps of obtaining initial corrosion time of reinforcement in concrete based on the second diffusion law of Fick, and considering the influence of concrete cracking due to corrosion expansion in a corrosion rate model; adopting a small crack growth and near threshold growth analysis and determining relevant parameters of fatigue crack propagation rate of materials by developing a fatigue crack propagation test of reinforced concrete materials; performing a corrosion fatigue test or finite element analysis on corroded reinforcement to obtain stress concentration factors at different corrosion levels, and integrating into a stress intensity factor model to obtain the fatigue crack propagation rate of the reinforcement under the influence of corrosion; comparing the magnitude of a corrosion pit growth rate and the fatigue crack propagation rate and gradually converting into a single growth analysis on fatigue cracks of the reinforcement; meanwhile, combining with vehicle load observing information to realize life evaluation of a bridge at different service stages. The prediction method disclosed by the invention is reasonable and high in popularization, and can provide technical support for evaluating the life of the concrete bridges.

Owner:CHANGSHA UNIVERSITY OF SCIENCE AND TECHNOLOGY

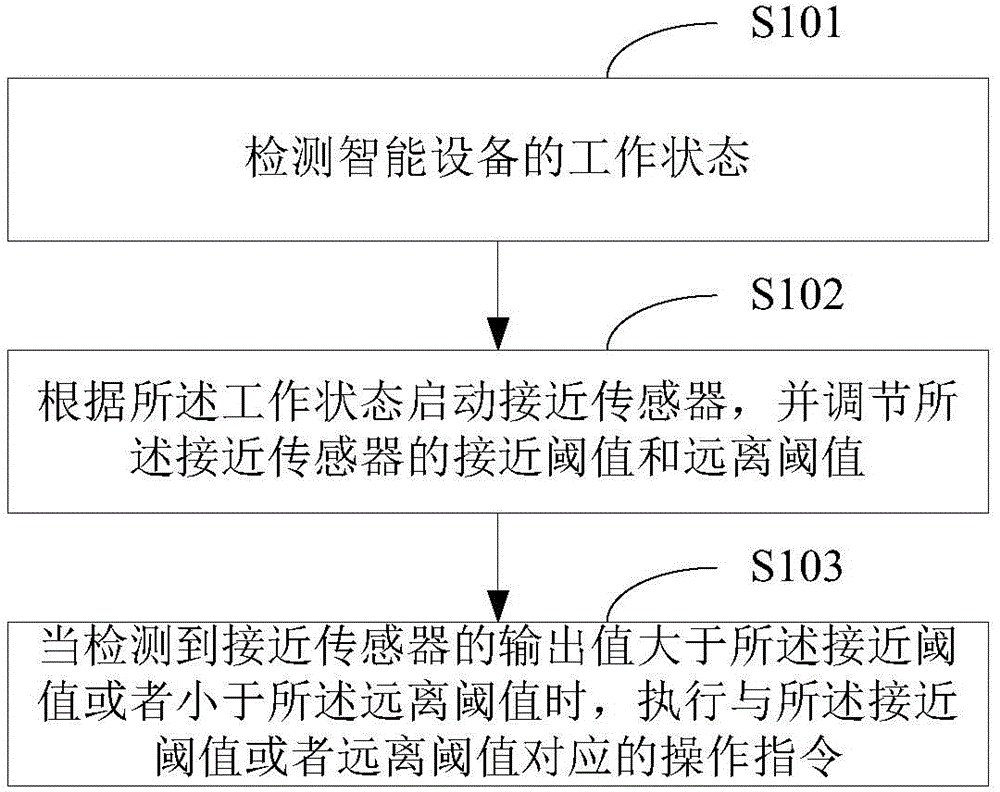

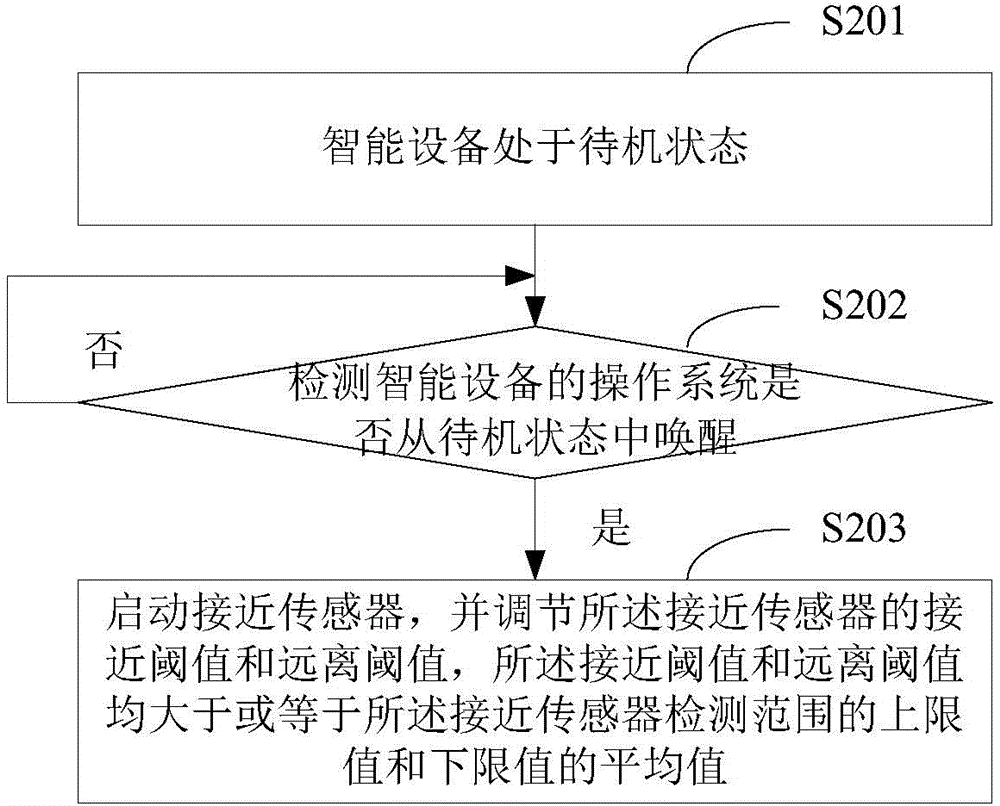

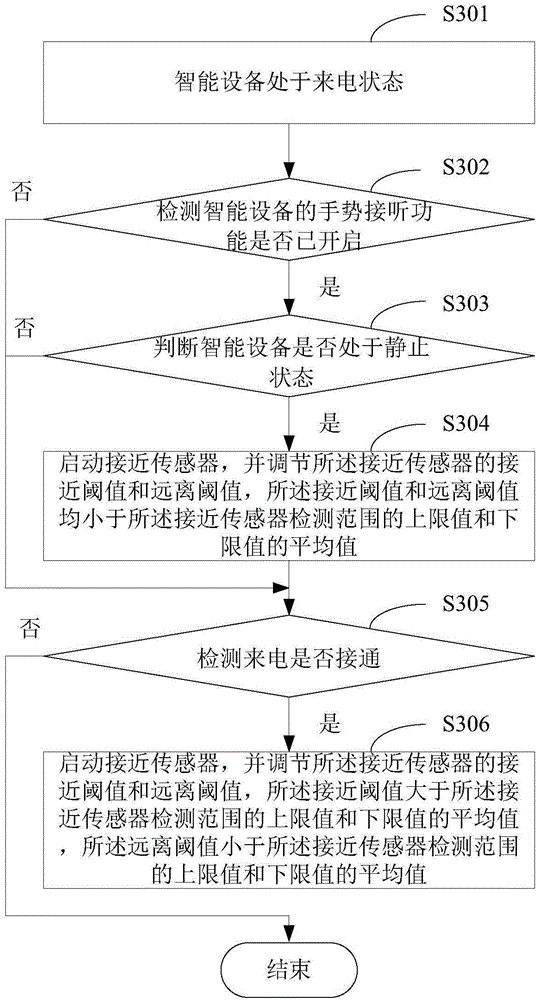

Proximity sensor threshold adjusting method and device and intelligent device

ActiveCN104683598AImprove accuracyReduce false recognition rateSubstation equipmentProximity sensorSomatosensory system

The invention applies to the technical field of intelligent equipment, and provides a proximity sensor threshold adjusting method and device and an intelligent device. The method comprises the following steps: detecting the working state of an intelligent device; starting a proximity sensor according to the working state, and adjusting the proximity threshold and leave-away threshold of the proximity sensor; performing an operation instruction corresponding to the proximity threshold or the leave-away threshold if the detected output value of the proximity sensor is more than the proximity threshold or less than the leave-away threshold, wherein the proximity value is more than the leave-away threshold, and the proximity threshold and the leave-away threshold are respectively corresponding to the working state of the intelligent device. With the adoption of the method, the proximity threshold and the leave-away threshold of the proximity sensor can be dynamically adjusted according to different working states of the intelligent device, so that the accuracy of intelligent motion recognizing in different application scenes can be increased, and the probability of inaccurate or invalid intelligent motion recognizing can be reduced.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

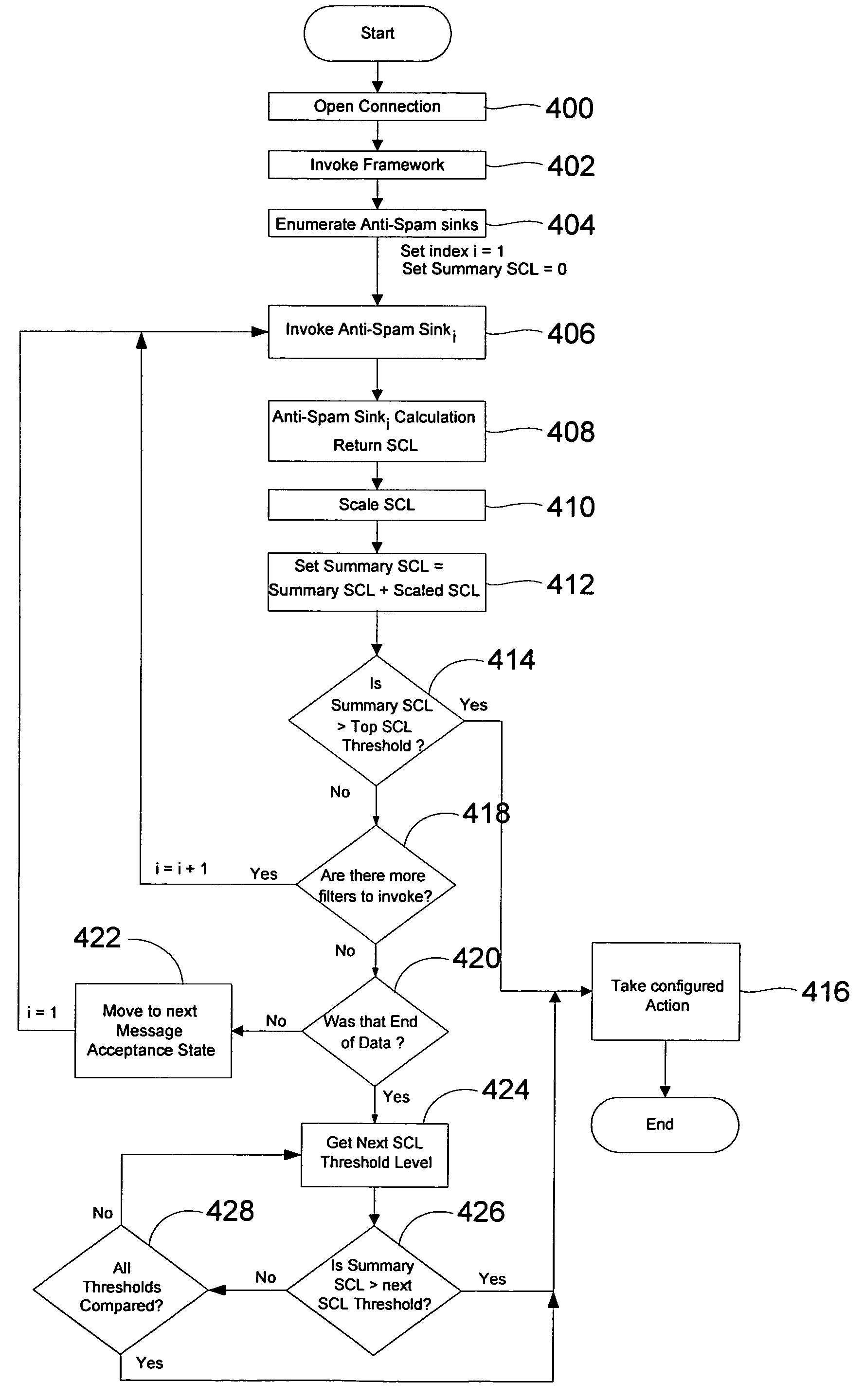

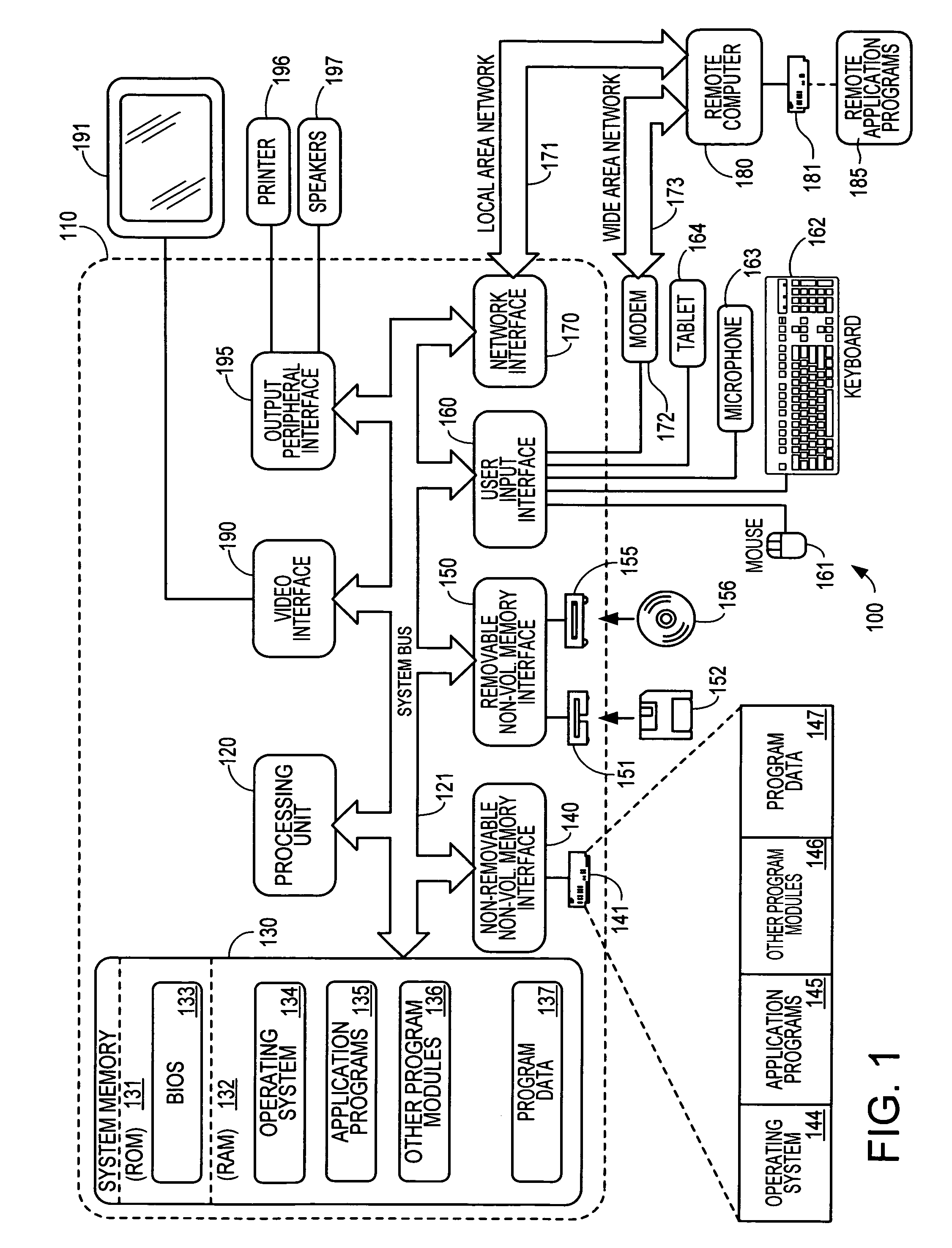

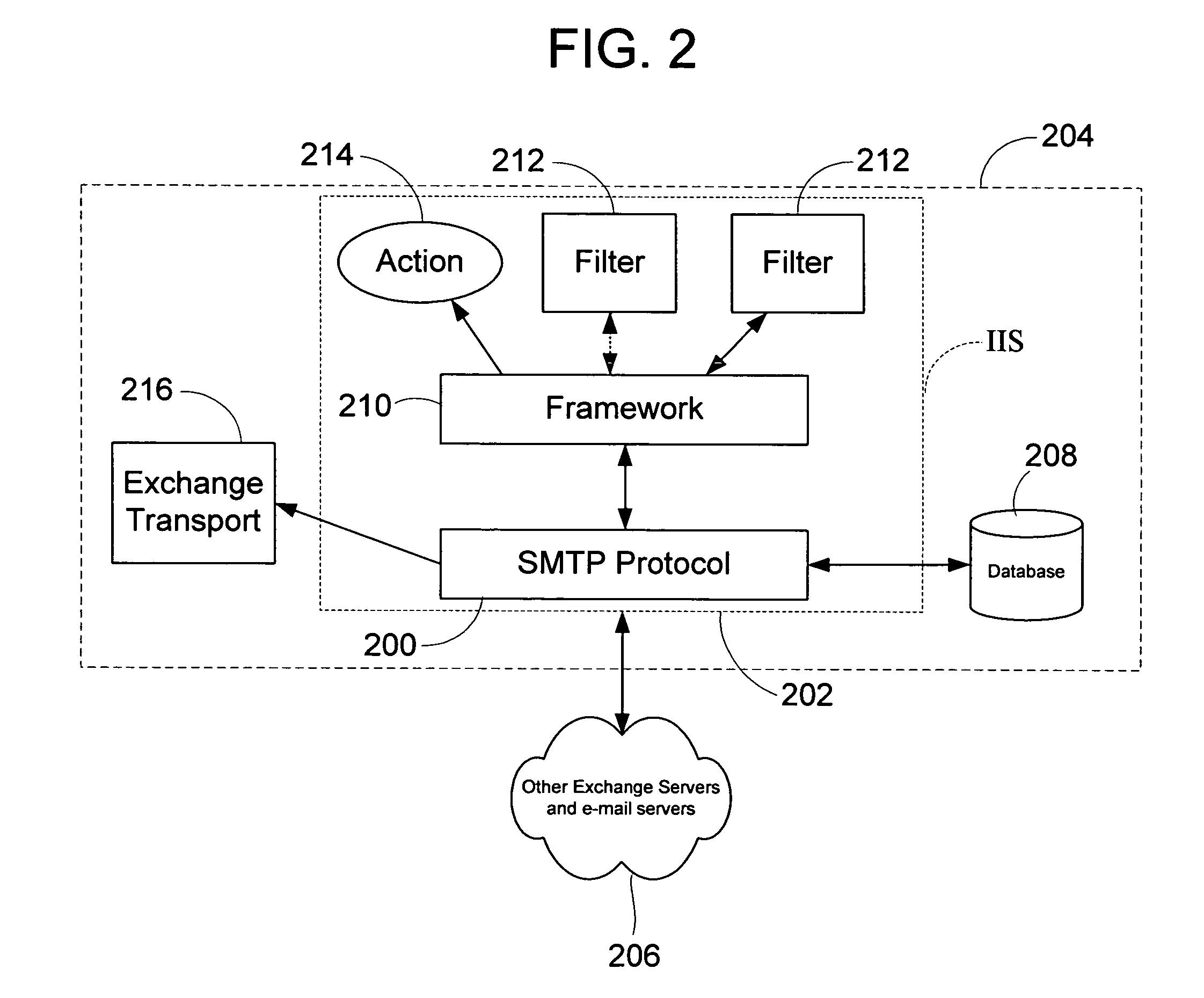

Framework to enable integration of anti-spam technologies

InactiveUS7533148B2Rapid deploymentData processing applicationsMemory loss protectionAnti-spam techniquesConfidence metric

Owner:MICROSOFT TECH LICENSING LLC

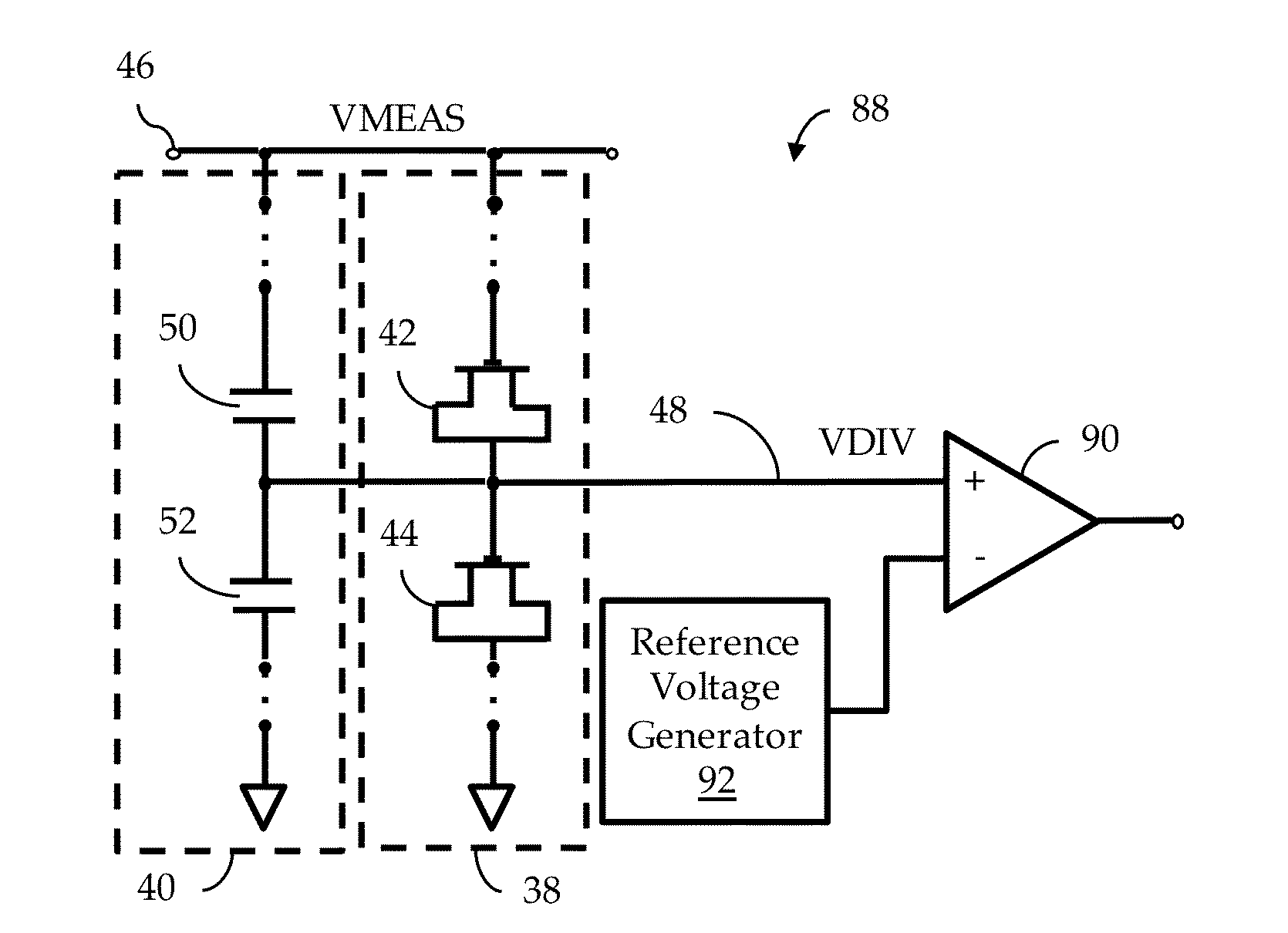

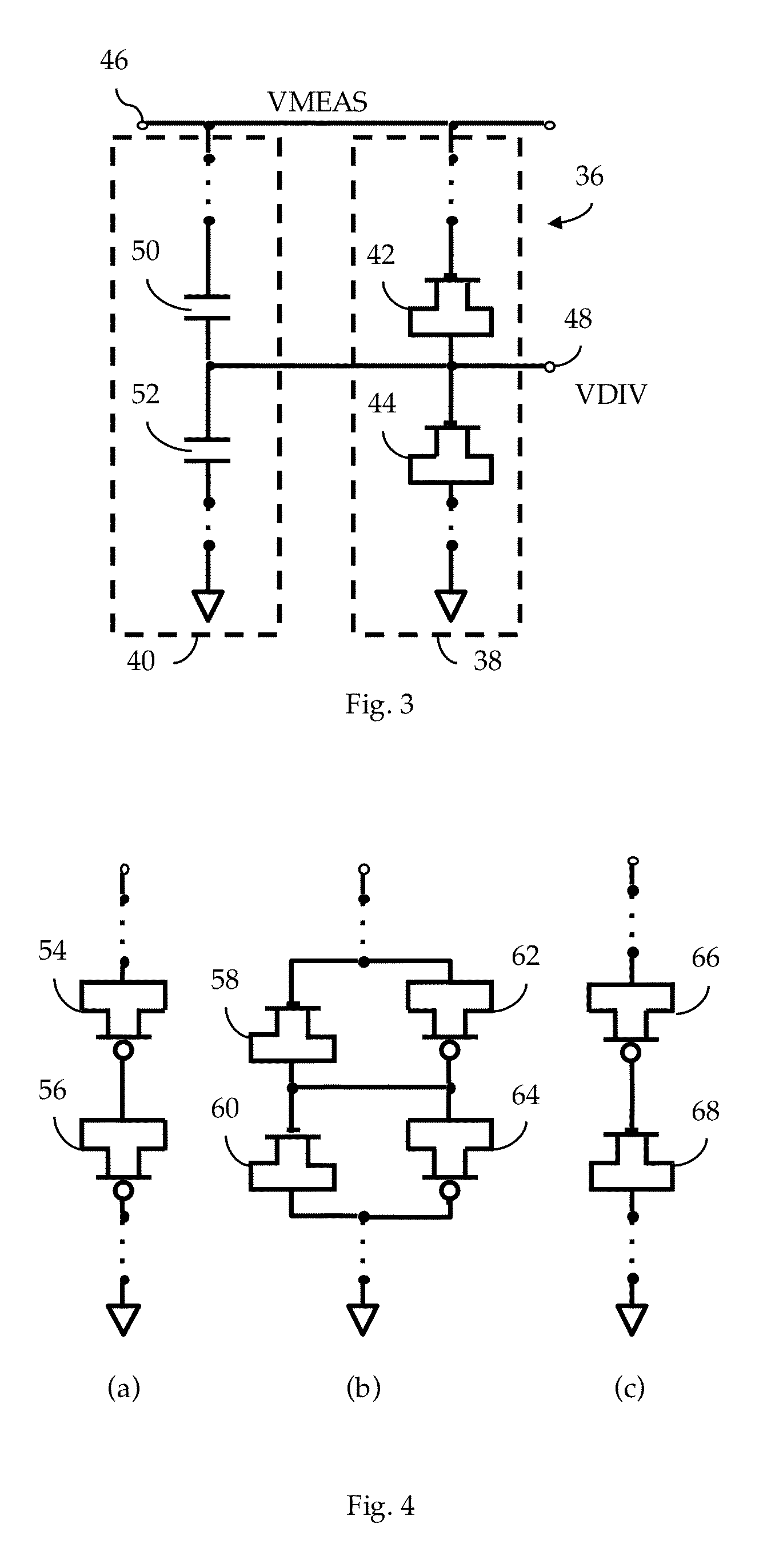

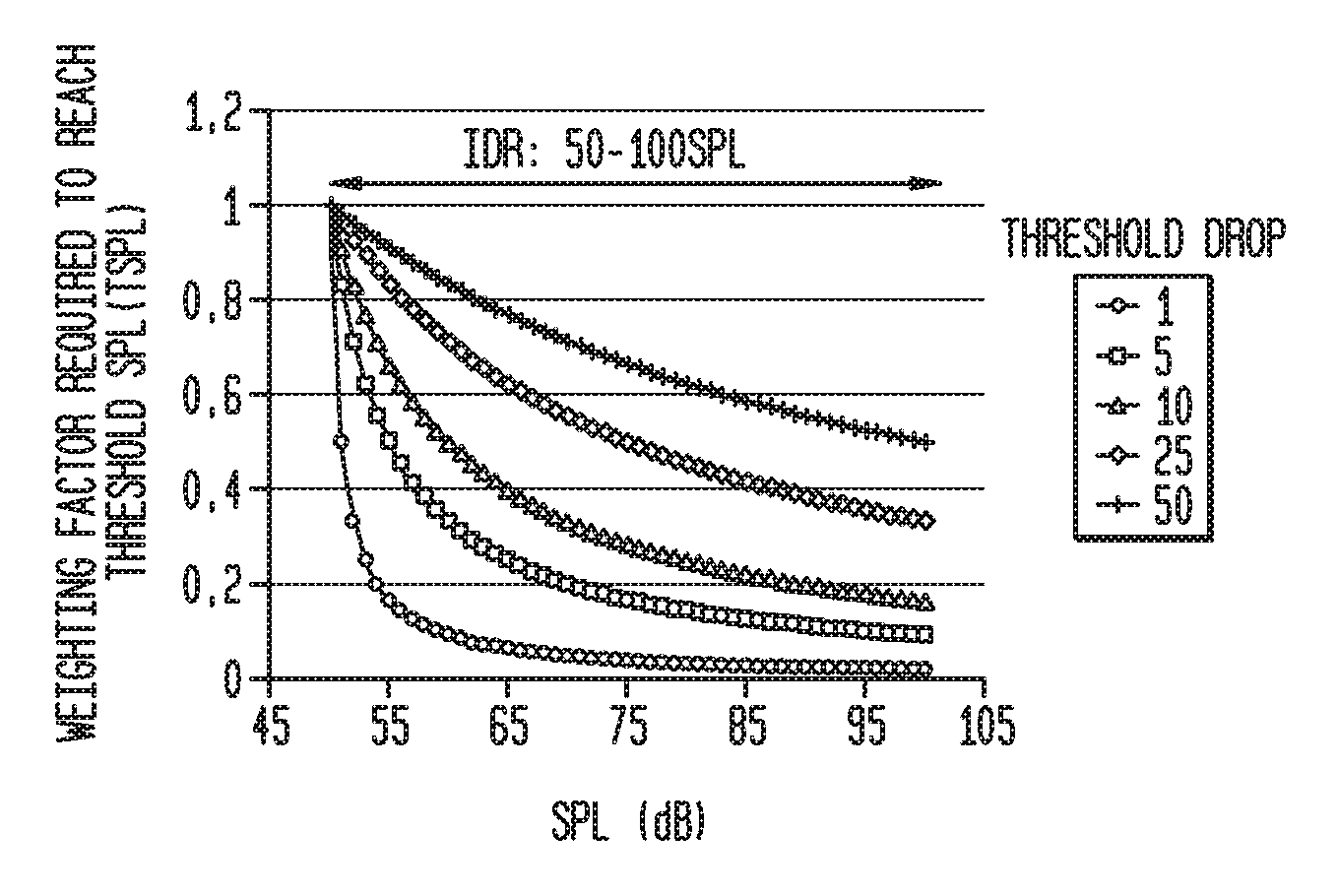

Gate Leakage Based Low Power Circuits

InactiveUS20160112042A1Pulse automatic controlEfficient power electronics conversionSub thresholdCapacitive divider

A low power voltage divider facility using gate leakage characteristics to divide voltage levels of sub-threshold and near-threshold circuits. The divider comprises a gate leakage based divider facility, and, optionally, a capacitive divider facility.

Owner:AMBIQ MICRO

Sound processing method and system

Coding of received audio signals and the resulting application of electrical stimuli applied to electrodes used in a cochlear implant system are disclosed together with a method of fitting this new coding strategy. One of the aims is to improve place specific stimulation representing pitch by applying near threshold electrical stimuli with limited and focused excitation fields. A range of stimulation rates and a minimal range of current levels above threshold are used for creation of a dynamic loudness percept for a cochlear implant recipient. Another aim is to disclose a coding scheme based on a model of physiological measures (i.e. refractoriness, adaptation, spread of activation field, spatiotemporal acoustical cochlear activation patterns and spontaneous activity) to estimate the proportions of available excitable auditory neurons close to the electrodes available for stimulation. The spectral bands formed from the pre-processing of incoming audio signals are weighted by these proportions of excitability to control place, timing, rate and current level of electrical stimuli applied to the electrodes available in the array.

Owner:COCHLEAR LIMITED

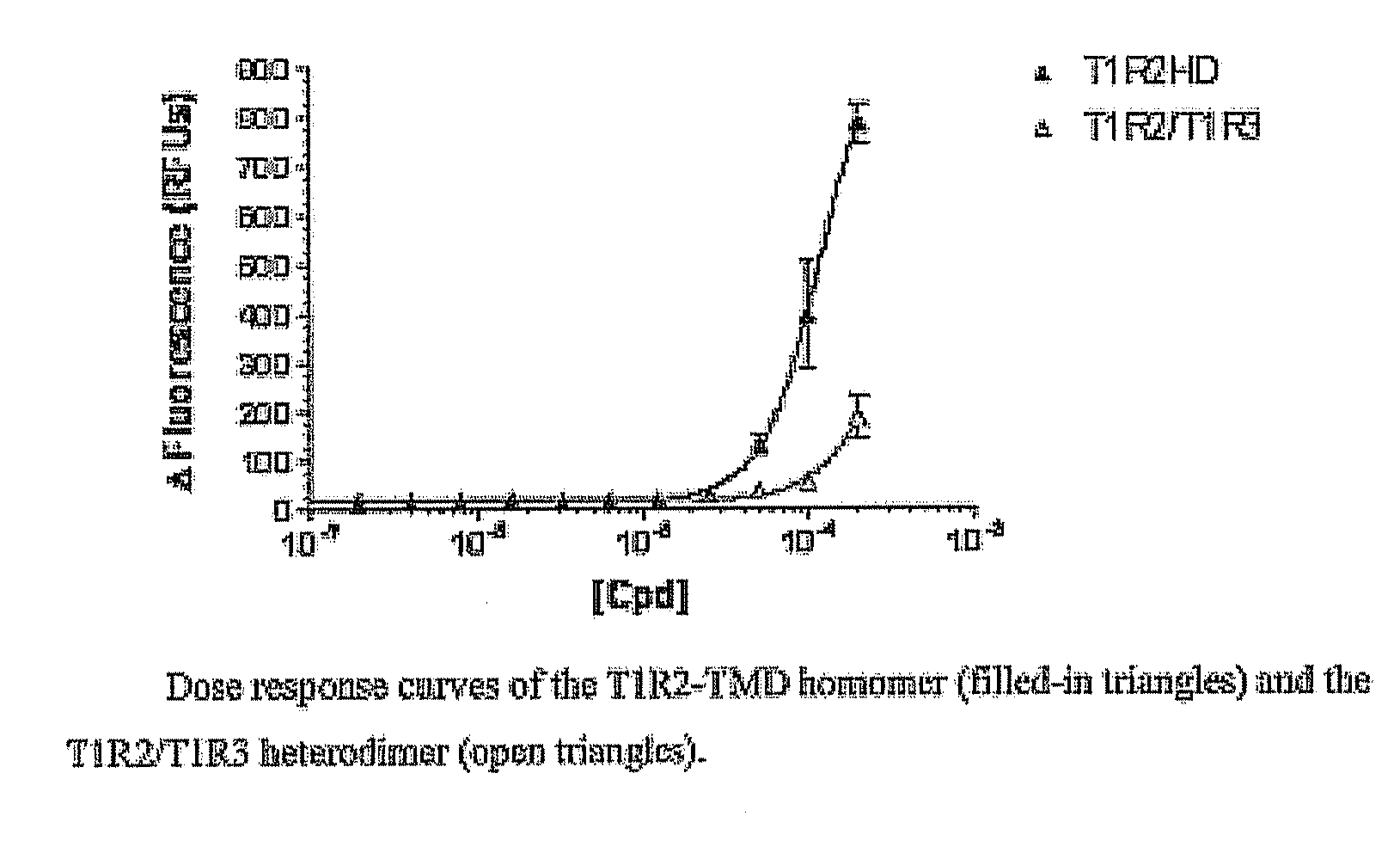

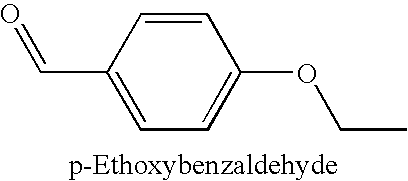

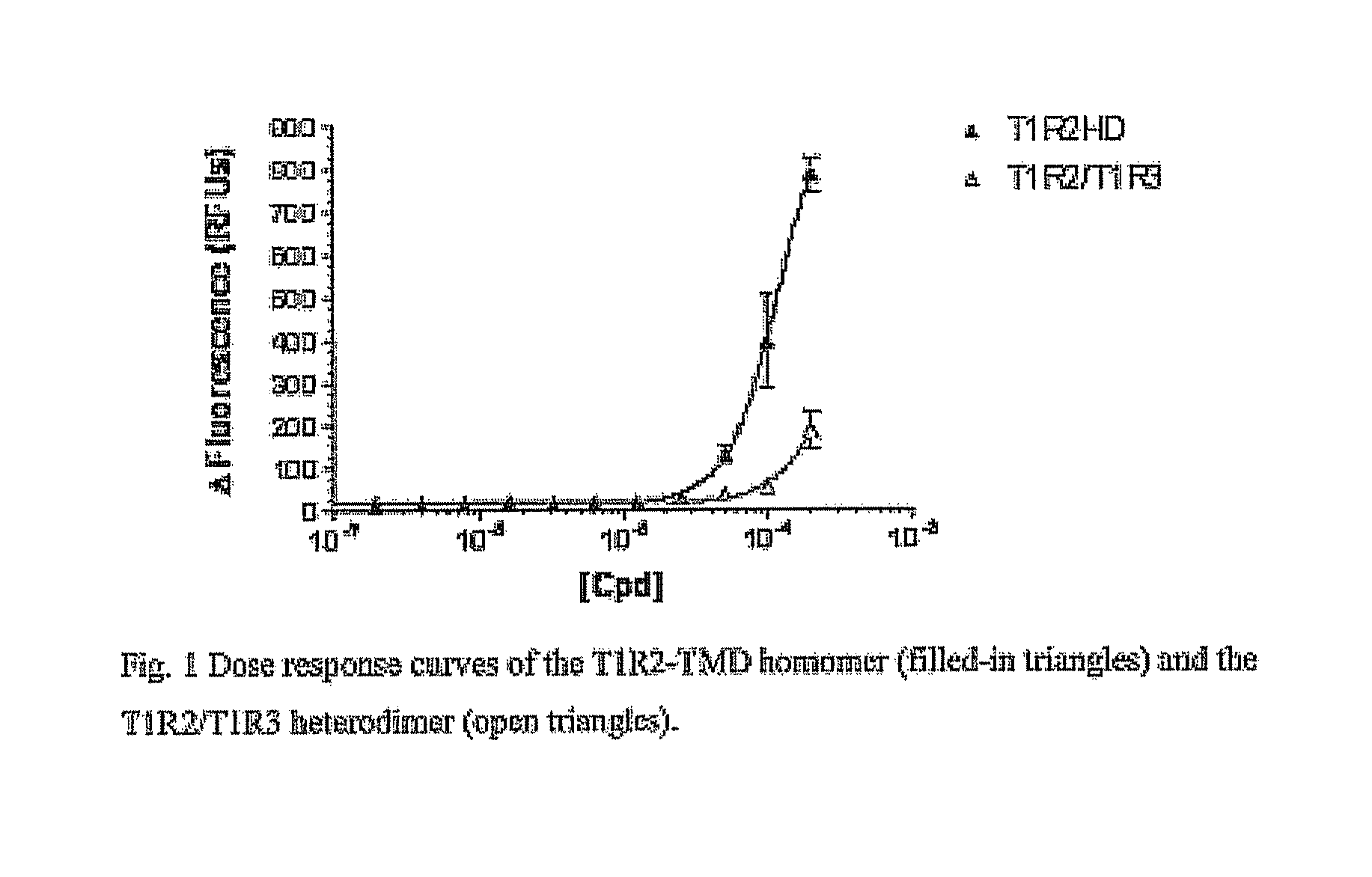

Method relating to sweetness enhancement

ActiveUS20090311686A1Microbiological testing/measurementBiological material analysisBinding siteSweetness

We have discovered a method to enhance sweetness comprising the use of a sweetener at a sub- to near-threshold concentration which is used in combination with a suprathreshold concentration of another sweetener. The sweetener used at the near-threshold concentration is selected based on its likely binding site in the human sweet taste receptor. The invention relates to the identification of agents that can modulate the taste response in humans (such as sweet taste enhancers) through assays based on a novel sweet receptor protein, heterologous expression systems containing nucleic acid constructs forming said novel sweet receptor protein, and the use of the novel sweet receptor protein in screening.

Owner:GIVAUDAN SA

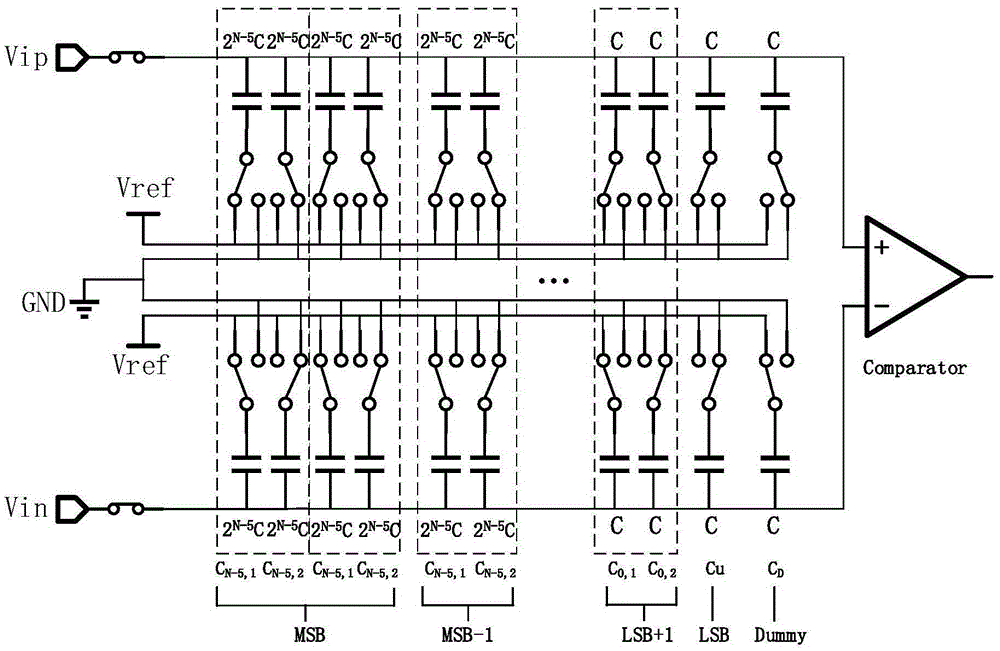

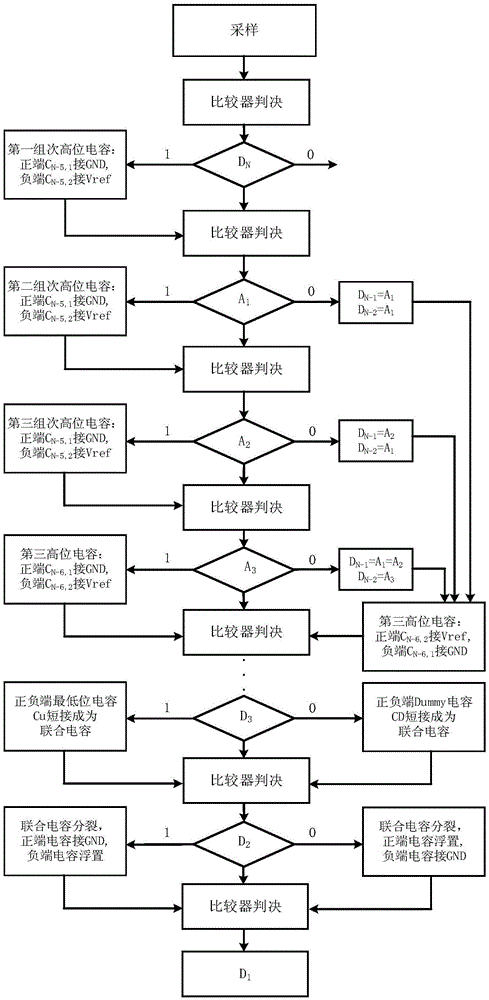

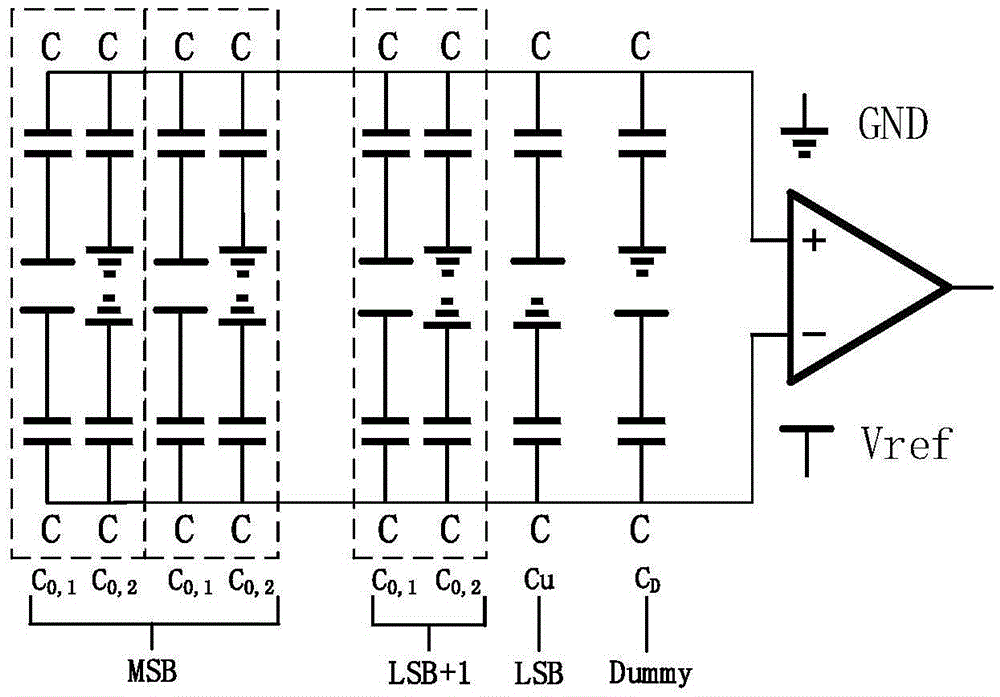

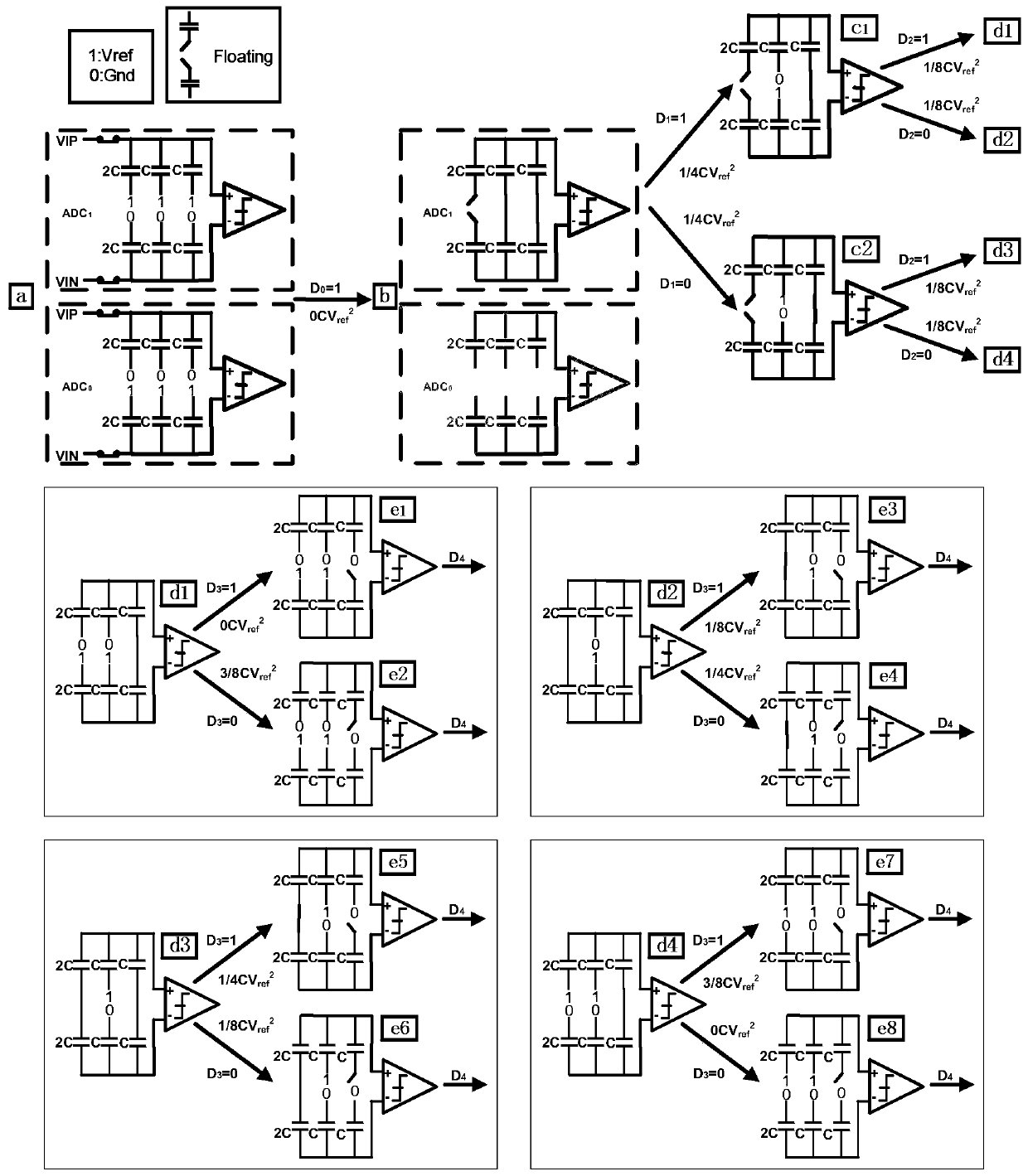

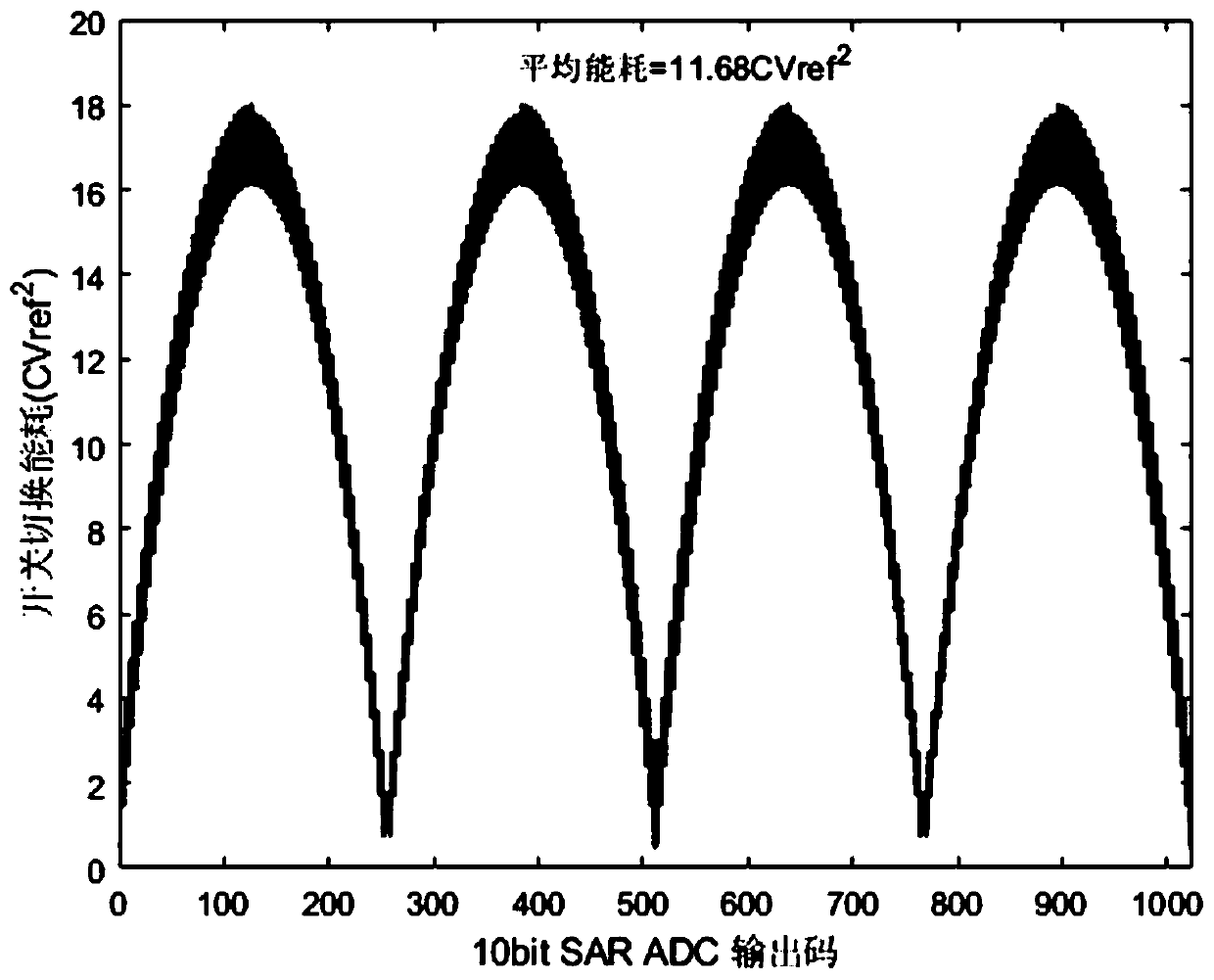

Binary capacitor array applied to near-threshold SARADC and switching method with low power consumption thereof

ActiveCN105553479AImprove performanceMitigate the deterioration of linearityAnalogue/digital conversionElectric signal transmission systemsCapacitanceEngineering

The invention discloses a binary capacitor array applied to a near-threshold SARADC and a switching method with low power consumption thereof. By means of special construction of a core module thereof, namely a DAC capacitor array, the power consumption of the DAC part in the conversion process of the SARADC can be greatly reduced in combination with a provided new switching algorithm. Only two reference levels are adopted in the algorithm, such that the algorithm is applied to designing the SARADC under near-threshold voltage. Compared with the area of the capacitor array required by the ordinary two-level capacitor switching technology, by means of flexible application of united, split and floating capacitor switching technologies, the total area of the capacitor array is reduced by 50%.

Owner:SOUTHEAST UNIV

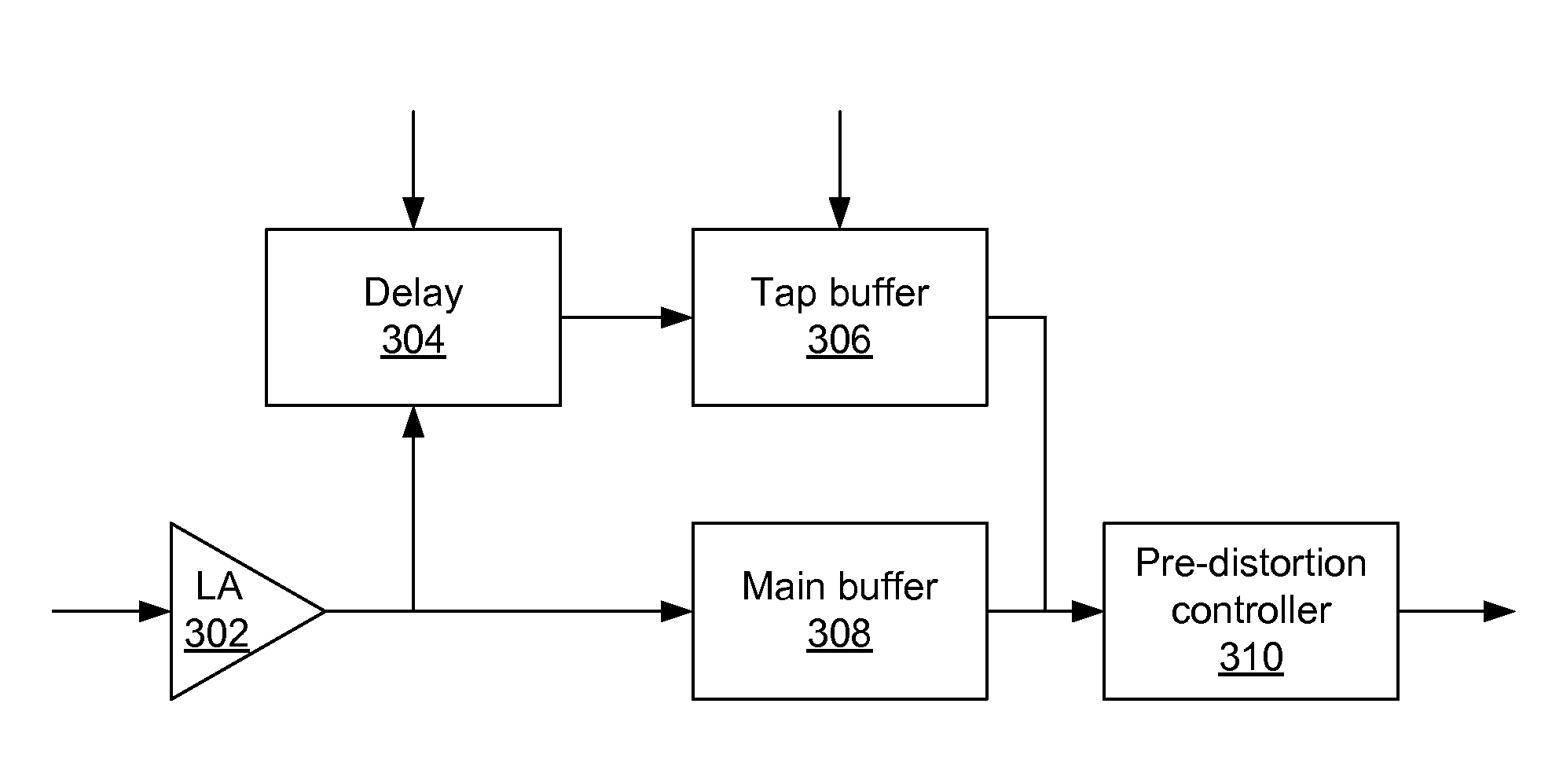

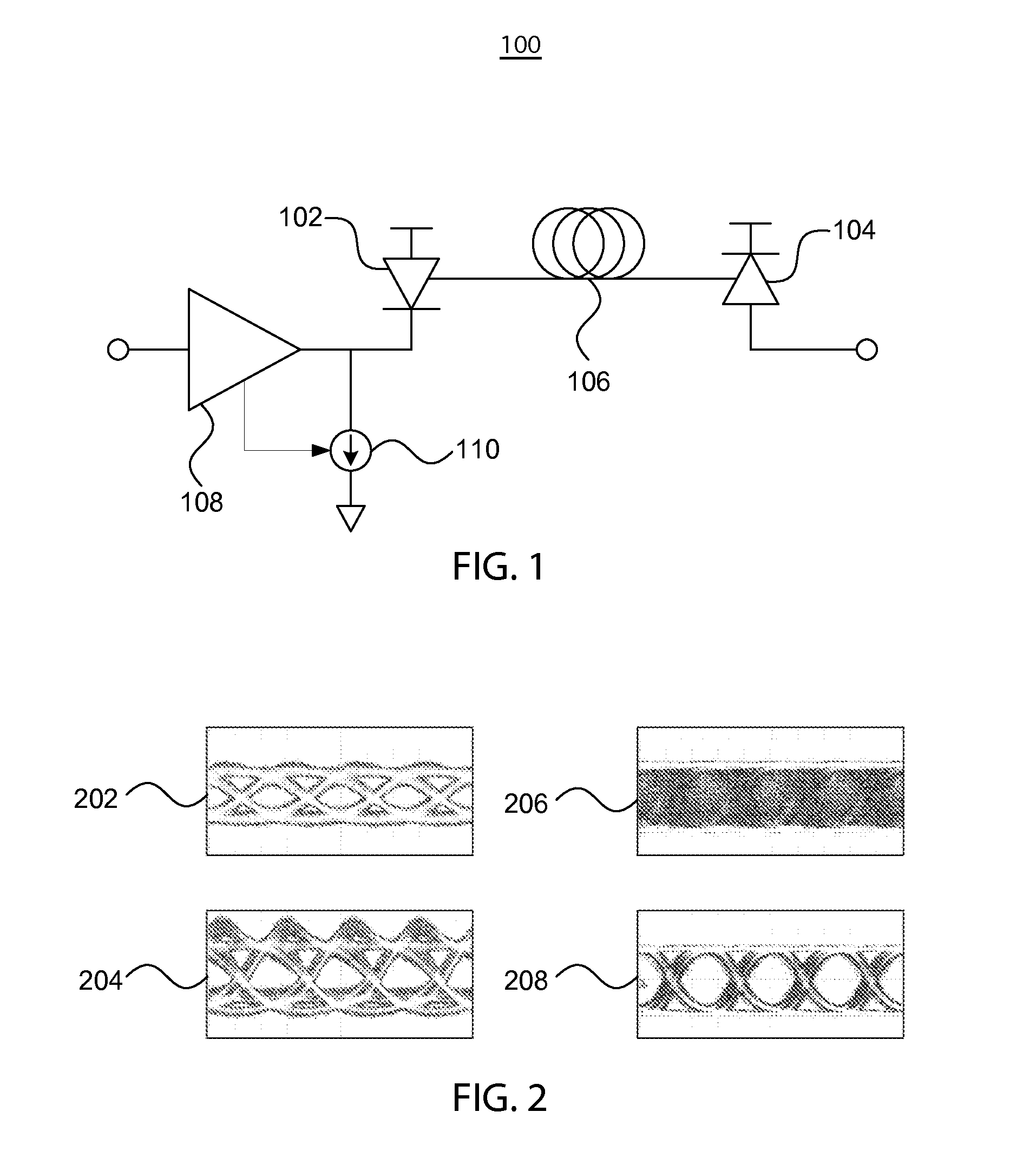

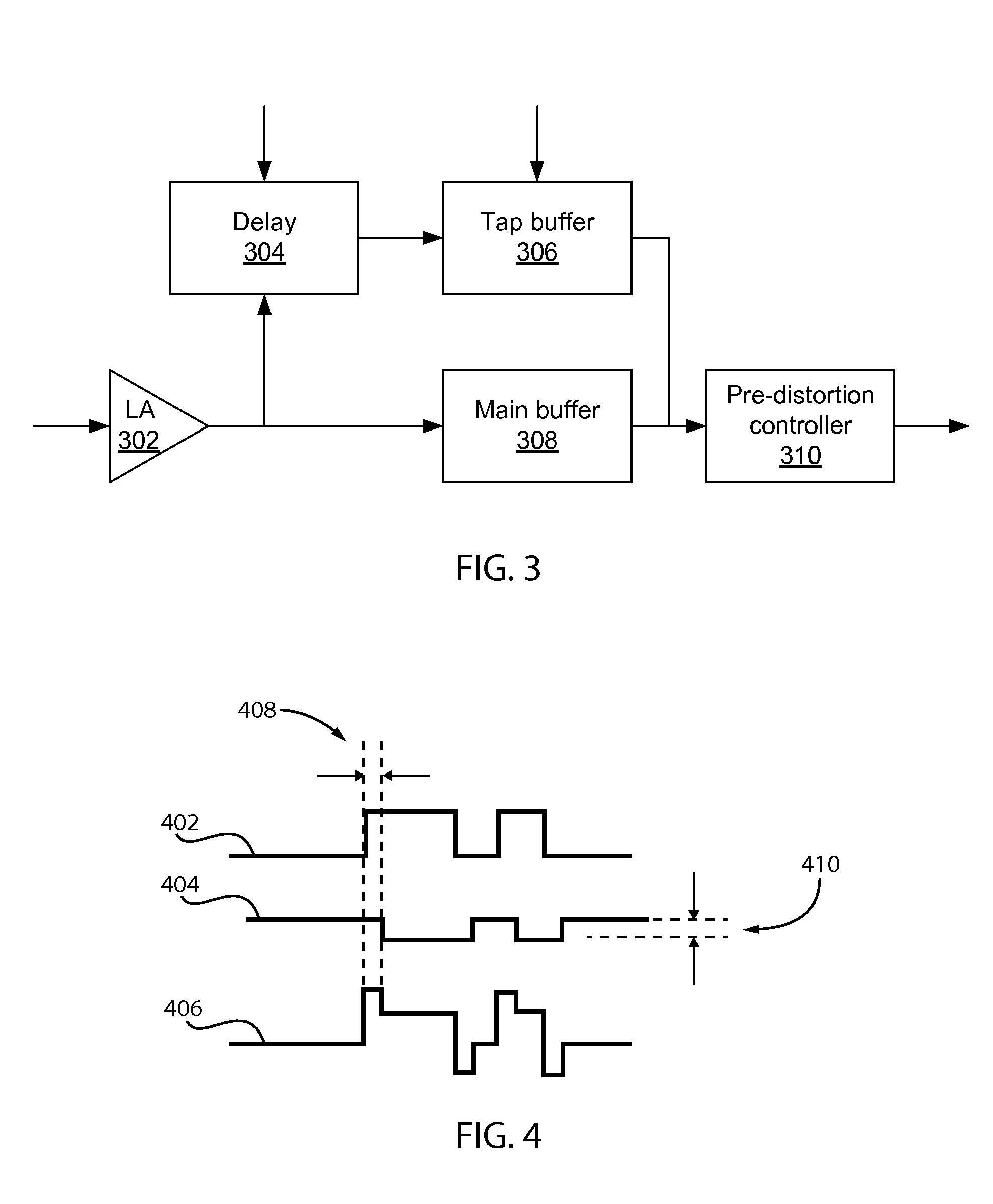

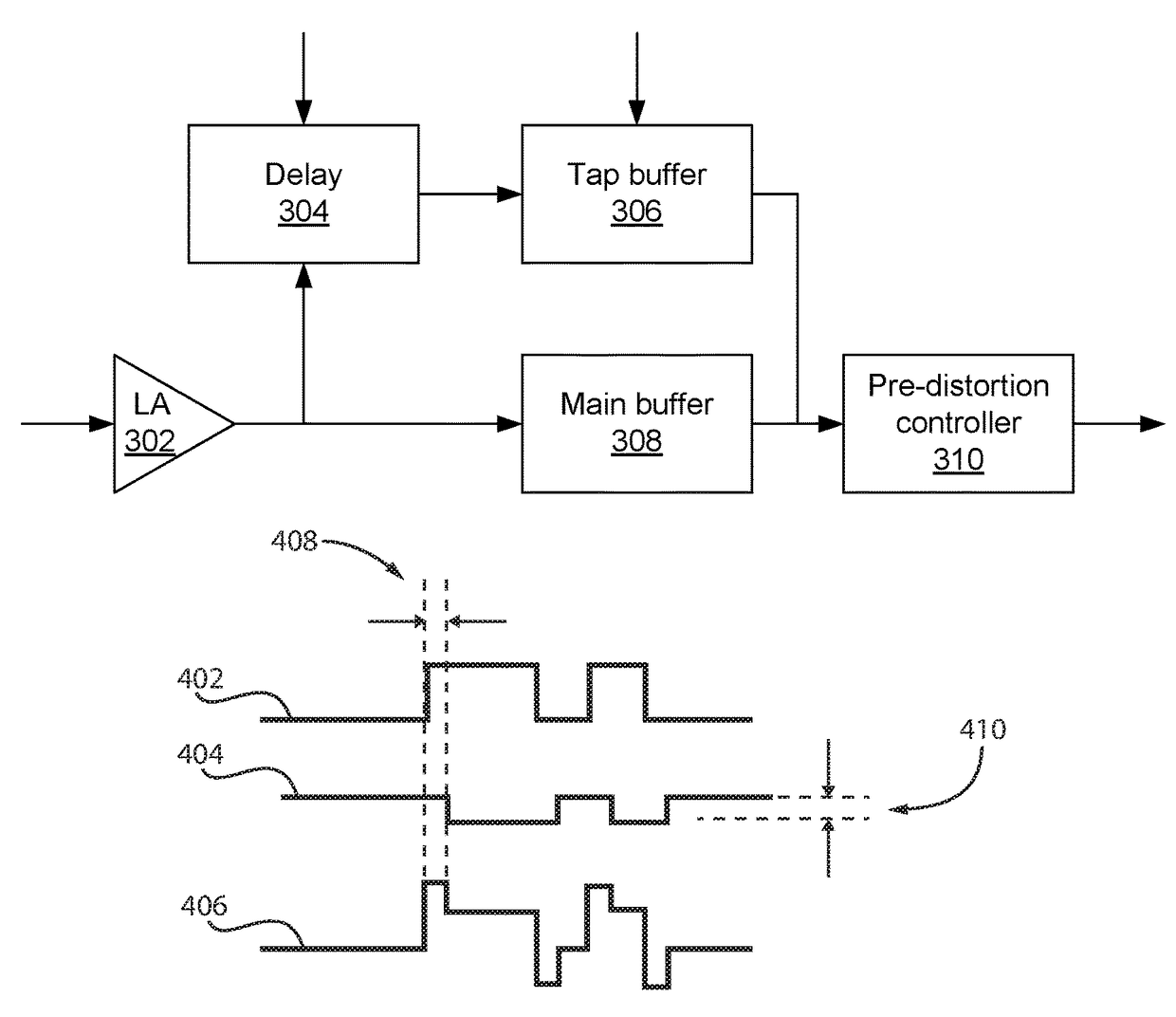

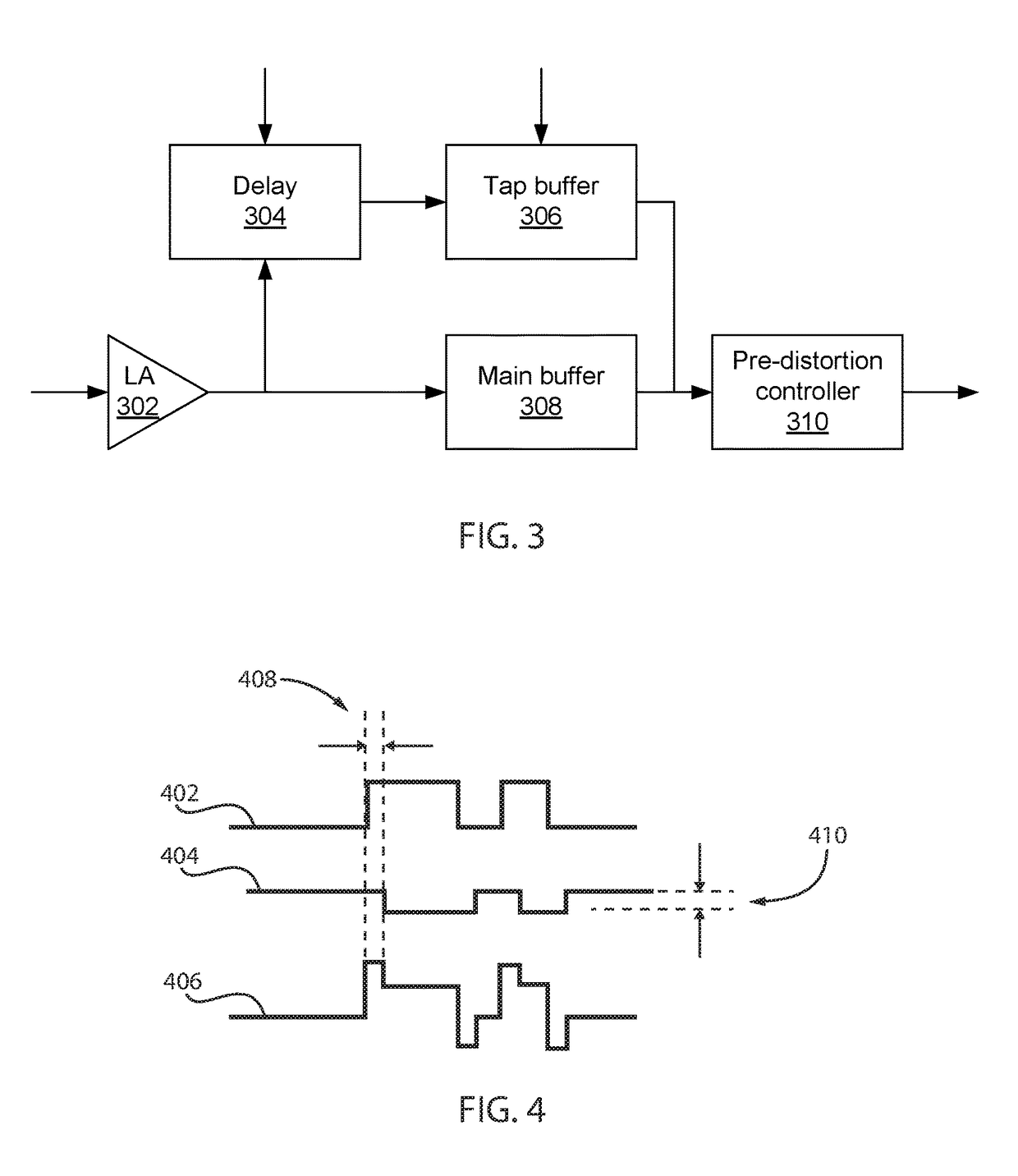

Near-threshold optical transmitter pre-distortion

ActiveUS20160094295A1Quickly bring the emitter into a linear operating rangeDistortion/dispersion eliminationElectromagnetic transmittersData signalNear threshold

Methods an systems for low-power transmission include biasing an emitter in a non-linear operating range of the emitter near a threshold current of the emitter. A data signal is distorted to add a precursor pulse to a rising edge of a data waveform to quickly bring the emitter into a linear operating range. The distorted data signal is transmitted at the emitter.

Owner:IBM CORP

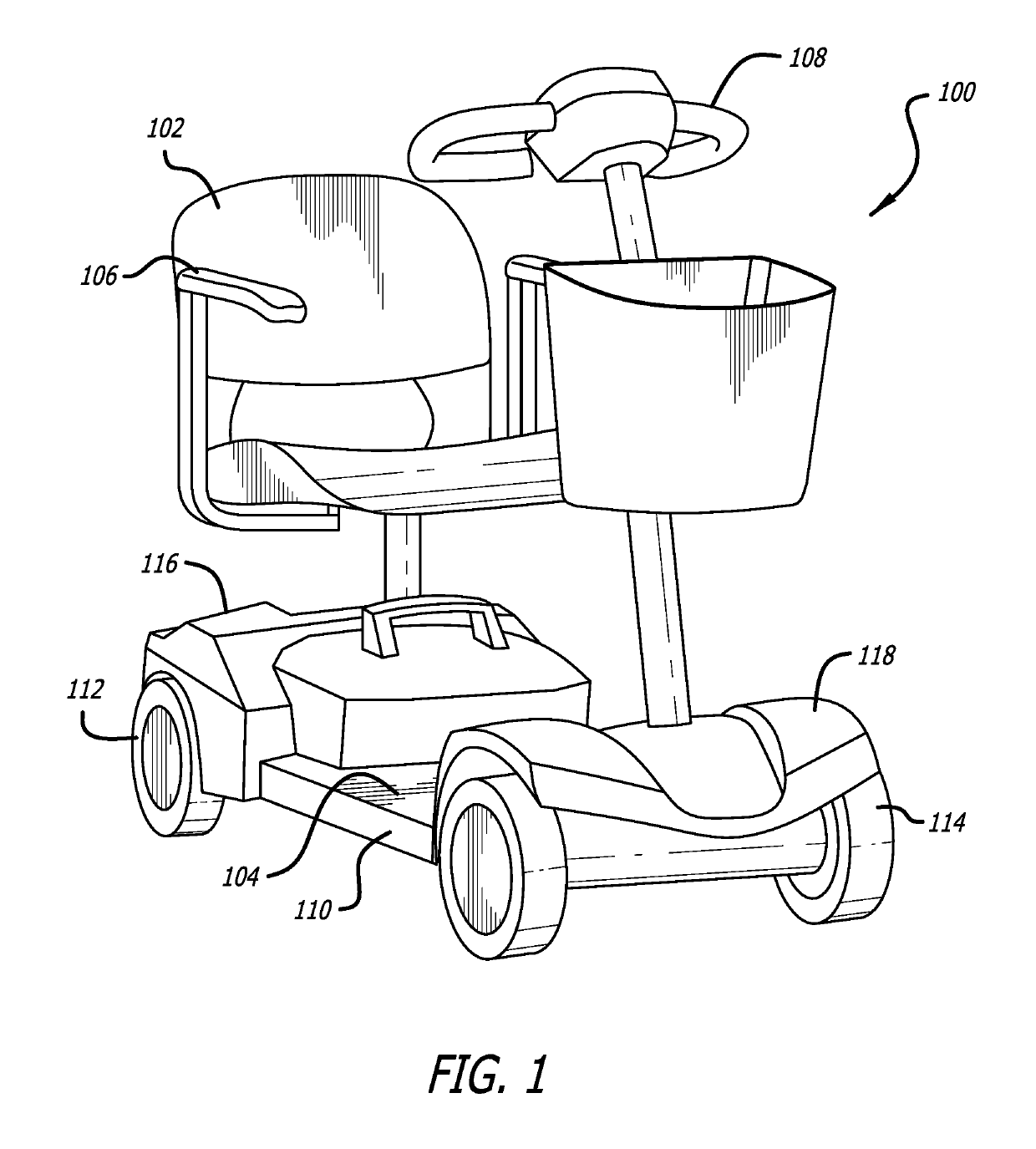

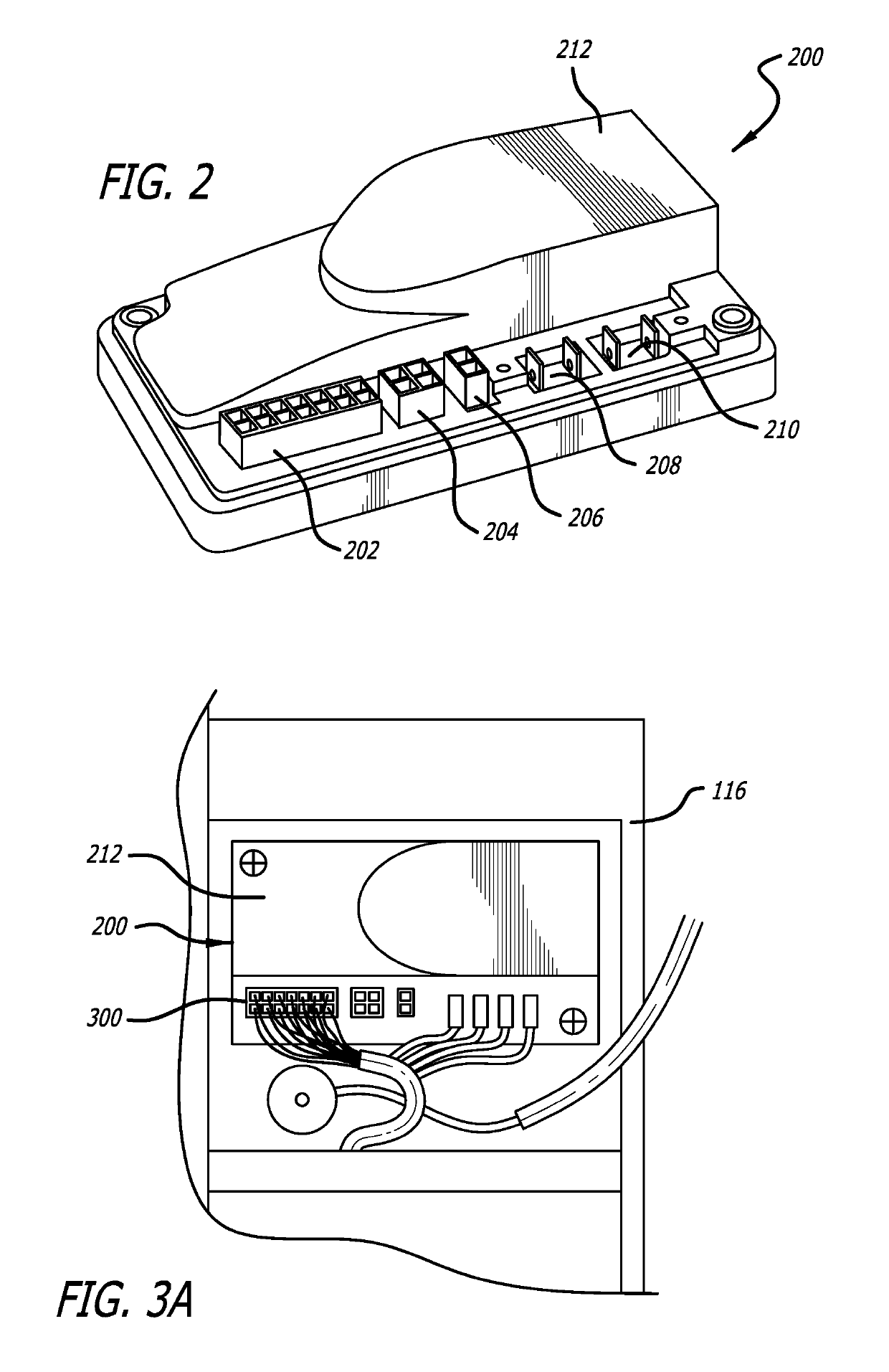

Anti-collision system for personal mobility scooters

ActiveUS10426675B1Reduce collisionEasy to installWheelchairs/patient conveyanceExternal condition input parametersCommunication interfaceProximity sensor

An anti-collision system for use by a mobility scooter to reduce collisions between the mobility scooter and objects or ledges is disclosed. The system comprising an input / output communication interface and an anti-collision circuitry configured to: receive a movement signal from the mobility scooter, the movement signal signaling a movement variable and a direction, receive proximity data from one or more proximity sensors through the input / output communication interface, perform a determination as to whether the received proximity data indicates the mobility scooter is within a proximity threshold, wherein the proximity threshold corresponds to the movement variable, and in response to determining the received proximity data indicates the mobility scooter is within the proximity threshold, provide one or more control signals to a controller, the controller in communication with at least a motor or a brake of the mobility scooter.

Owner:ERICKSON KEVIN

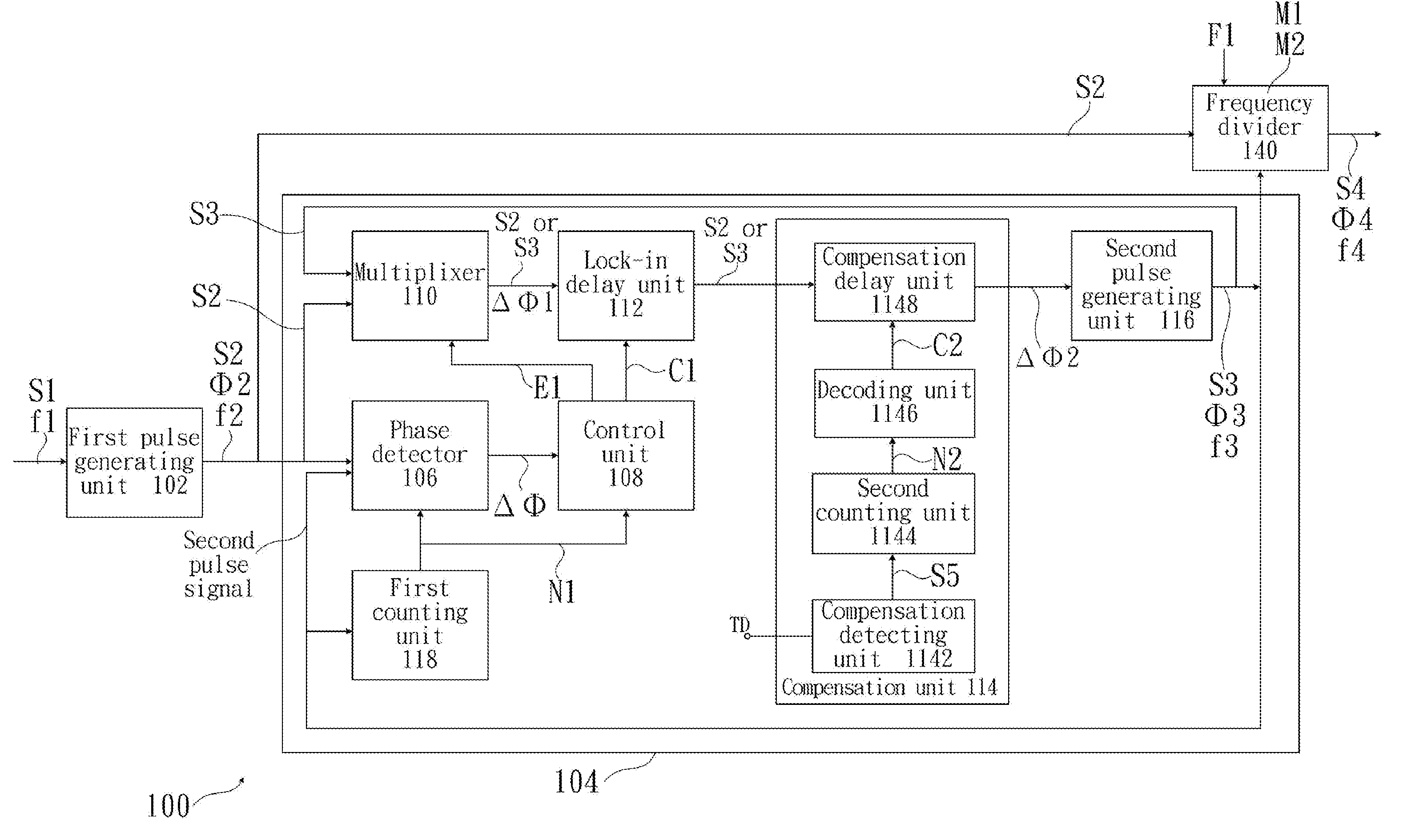

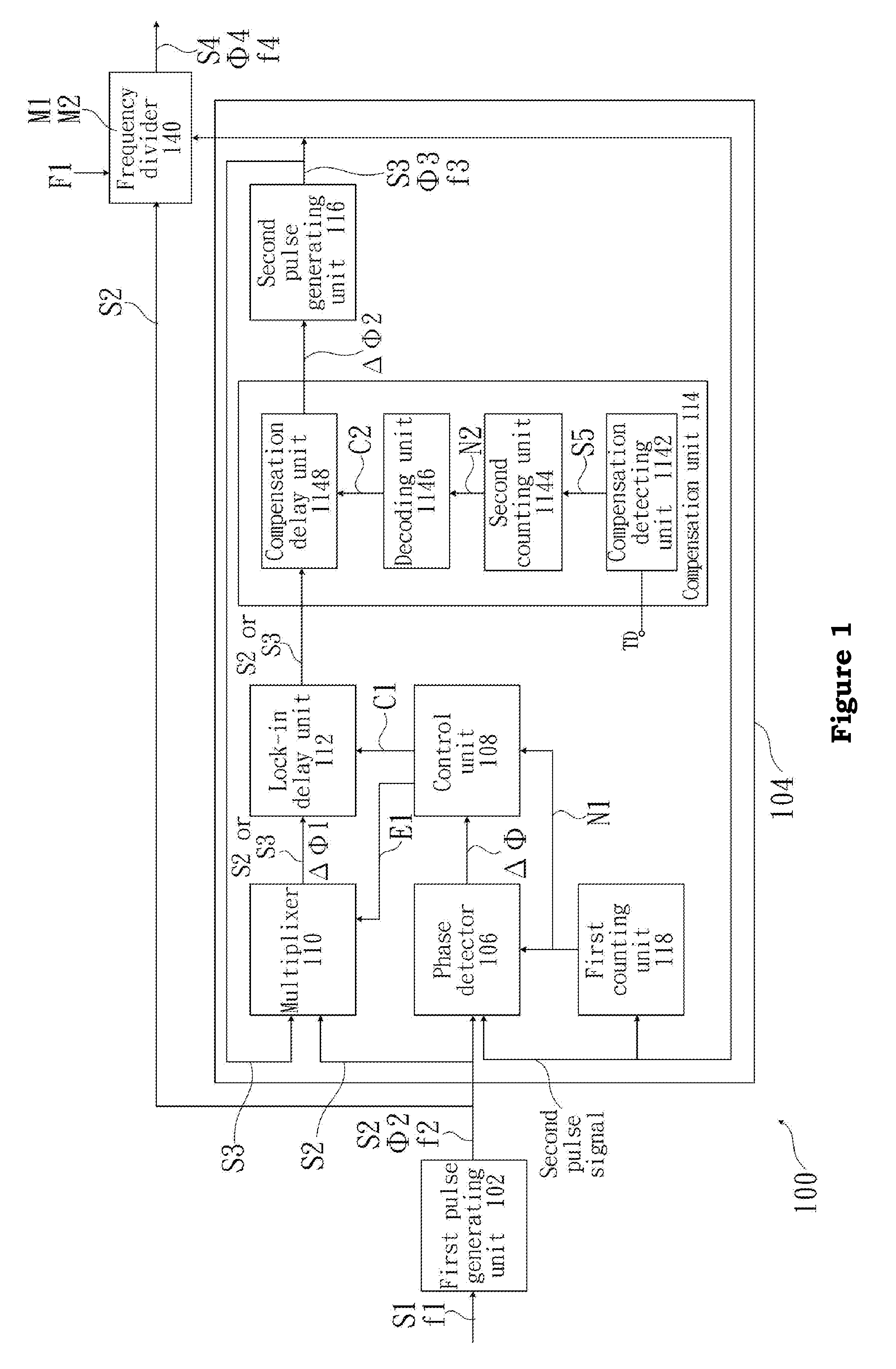

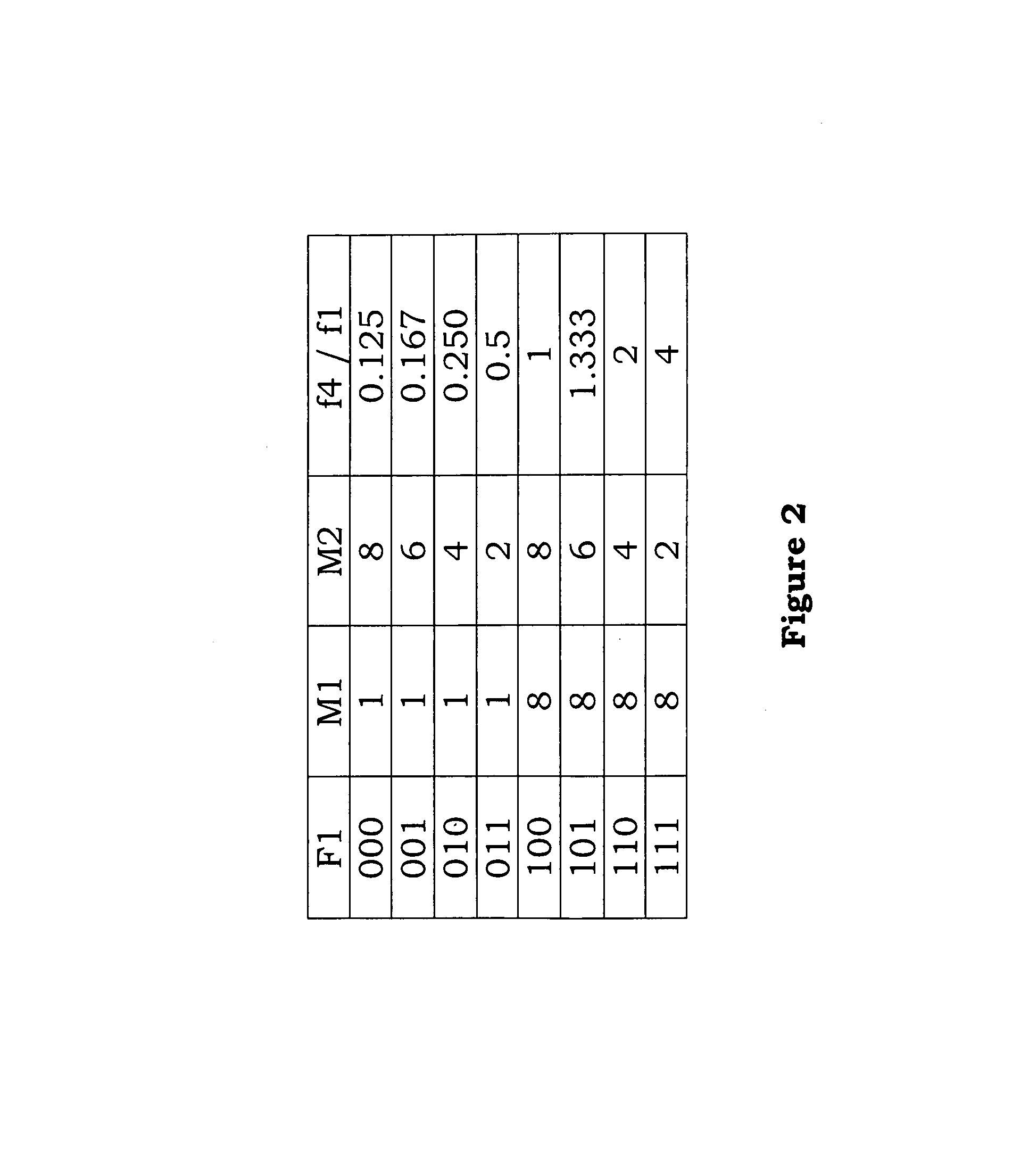

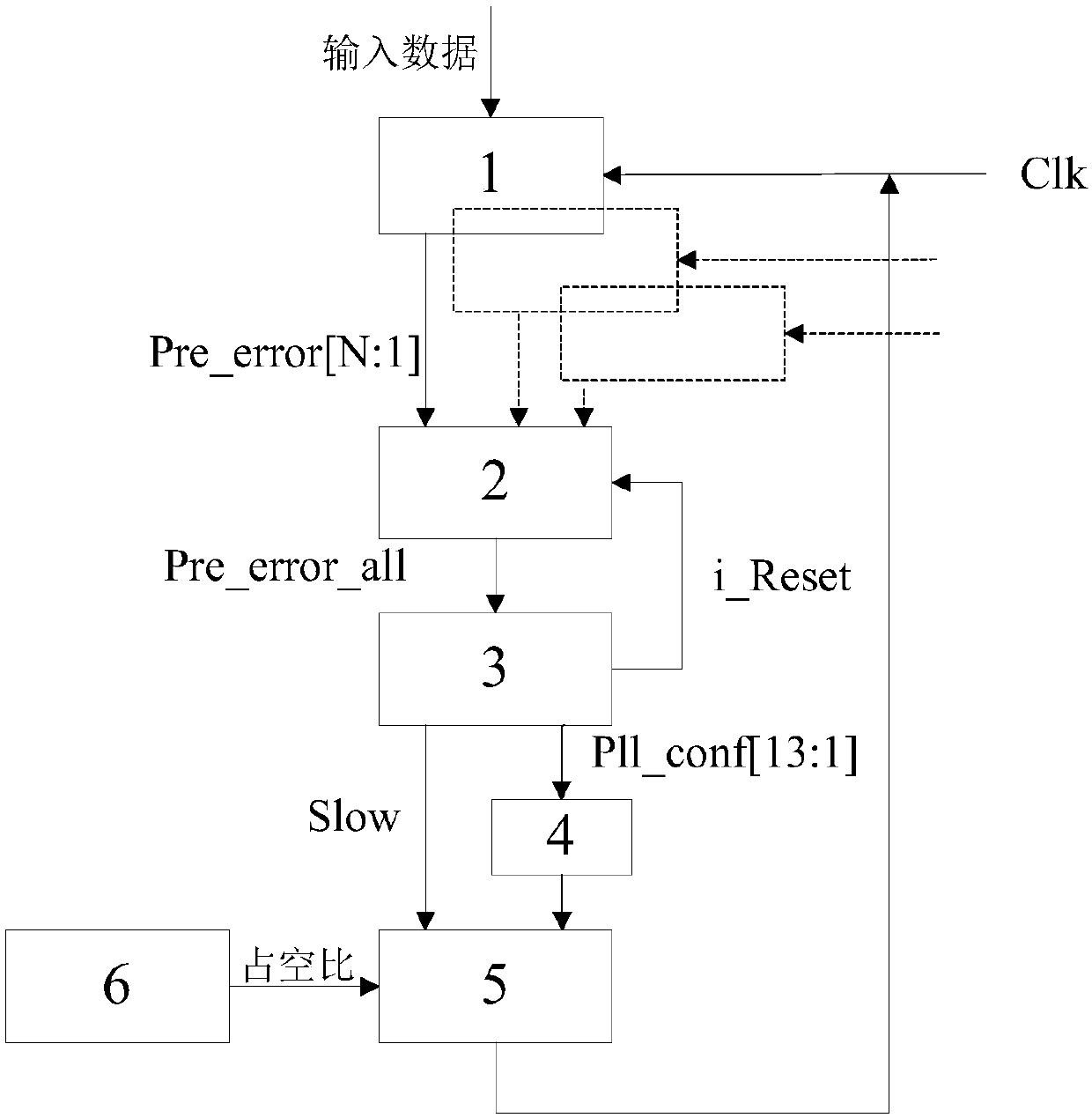

Programmable clock generator used in dynamic-voltage-and-frequency-scaling (DVFS) operated in sub- and near- threshold region

A programmable clock generator, which is used in dynamic-voltage-and-frequency-scaling (DVFS) operated in Sub- and Near-Threshold region. The programmable clock generator includes first pulse generating unit and a pulse multiplier. A first counter is configured to generate a first counting signal, so as to control the phase detector comparing the phase difference between a first pulse signal and a second pulse signal. A first control signal is transmitted by a control unit in accordance with a phase difference signal, and the phase of the second pulse signal is adjusted by a lock-in delay unit, so that a predetermined phase is generated between the first pulse signal and the second pulse signal. The PVT variation may be compensated by the programmable clock generator during the sub threshold region. Therefore, the period of reference clock is in the locking range of lock-in delay line.

Owner:NAT CHIAO TUNG UNIV

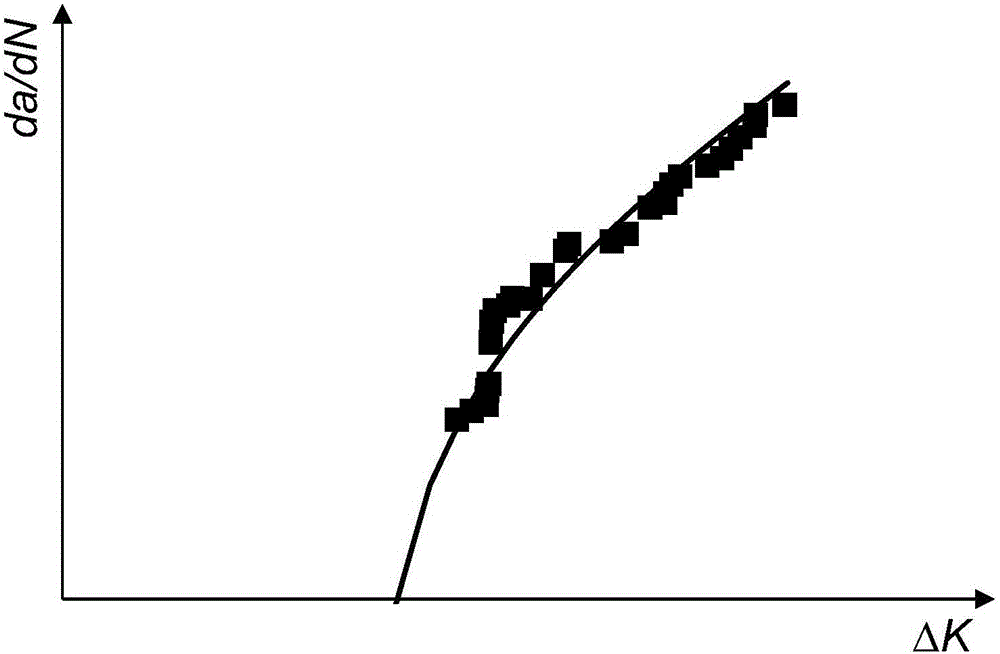

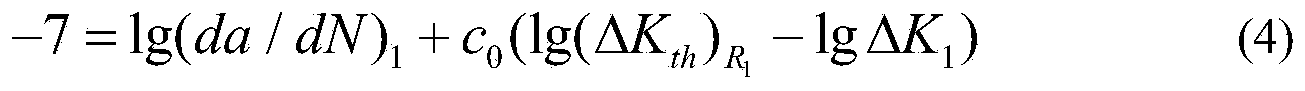

Method for predicting fatigue crack expanding threshold value under different stress ratios

The invention relates to a method for predicting a fatigue crack expanding threshold value under different stress ratios. The method comprises the steps of solving a linear fitting slope and a cross-over point of fatigue crack stable expanding area and near-threshold area data points on a log-log coordinate through the test data of the fatigue crack expanding threshold value under a known stress ratio, i.e. the relation between the fatigue crack expanding rate da / dN and a stress intensity factor range delta K, and executing the calculation under the condition that the maximal stress intensity factor Kmax is equal to delta K / R on the cross-over point of a stable expanding area and a near-threshold area under different stress ratios, so that the fatigue rack expanding threshold value of the unknown stress ratio R can be predicted, and R is more than zero. Compared with the traditional study, the method is not subjected to the limitation of the specific material, and is applicable to the material with uniform tissues and good in universality; moreover, the test workload of the threshold value can be effectively alleviated, and the cost is lowered.

Owner:TSINGHUA UNIV +1

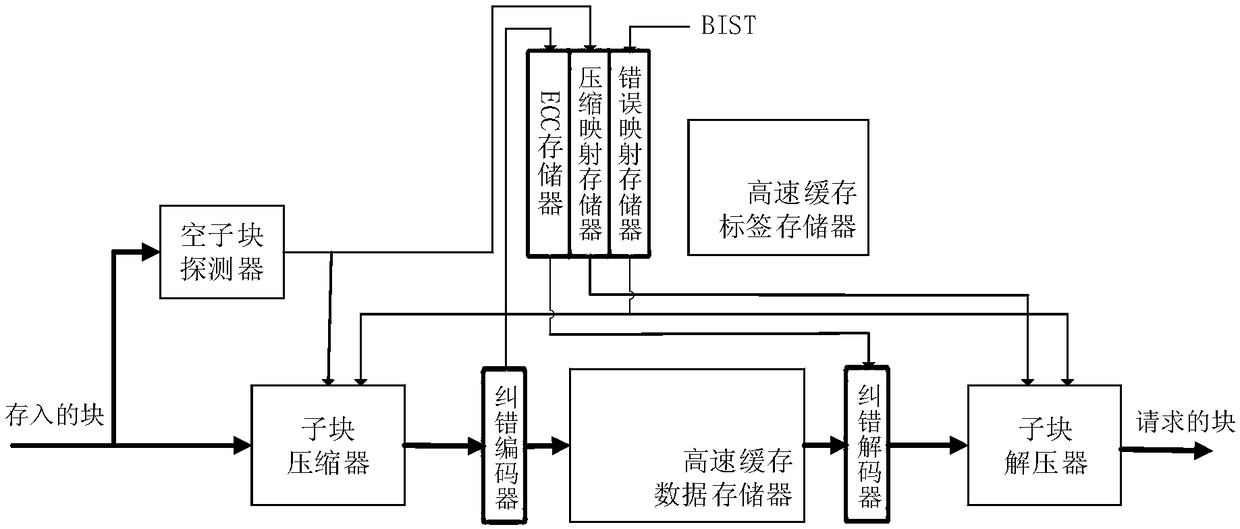

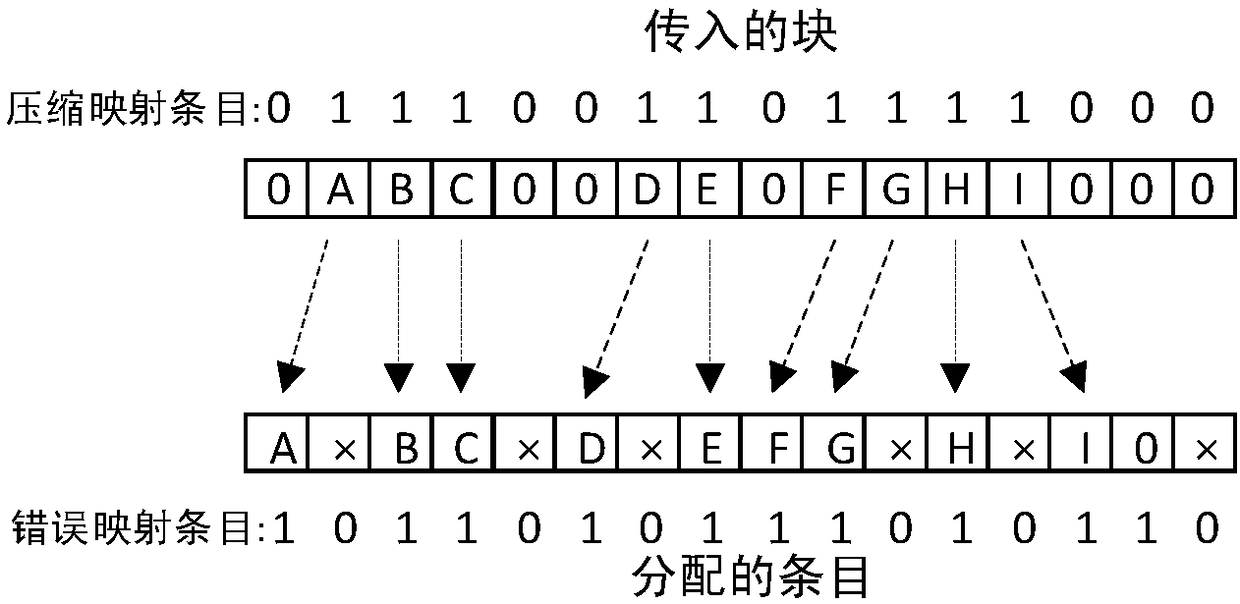

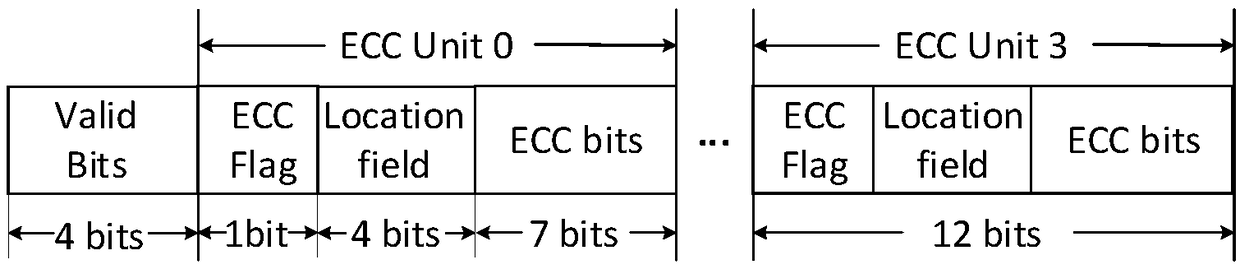

Caching multi-bit hard error detection and fault tolerance device and method under near threshold voltage

The invention relates to a caching multi-bit hard error detection and fault tolerance device and method under a near threshold voltage. The detection and fault tolerance device comprises a Cache datamemory, a Cache tag memory, a BIST circuit, an ECC memory, an error correction encoder, an error correction decoding, an error map memory, a compression map memory, an empty sub-block detector, a sub-block compressor and a sub-block decompressor, and ECC error correction codes and empty sub-block data compression methods of single-error correction double-error detection (SECDED) are used for detecting and conducting fault tolerance on multi-bit hard errors occurring in the Cache data memory according to a selected Cache management strategy. A microprocessor is achieved by the device and method, the multi-bit hard errors caused by fluctuations of process parameters in a cache memory can be detected in the microprocessor, fault tolerance can be conducted, and reliability when the microprocessor is under a low power consumption environment and uses a near threshold voltage technology is improved.

Owner:WUHAN UNIV OF TECH

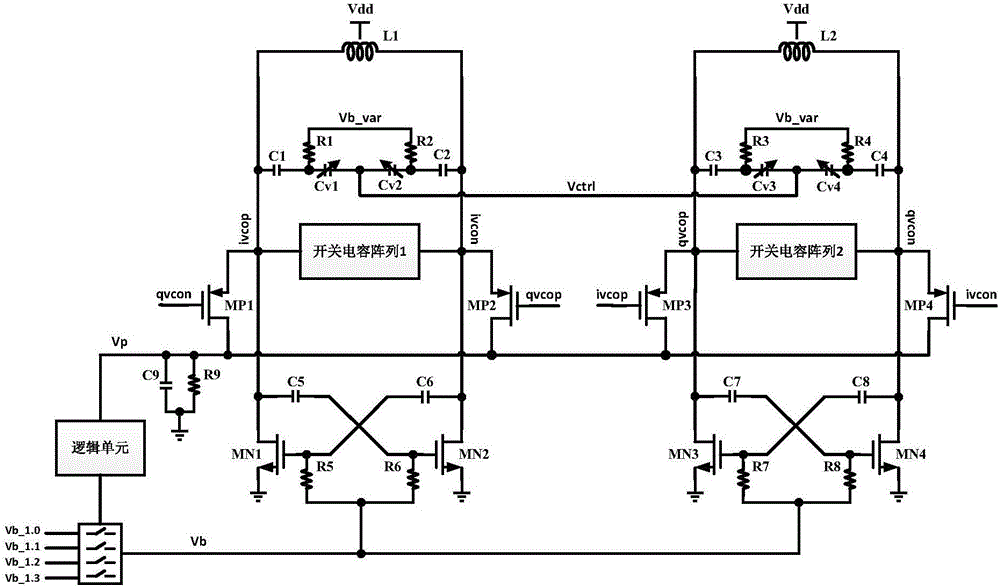

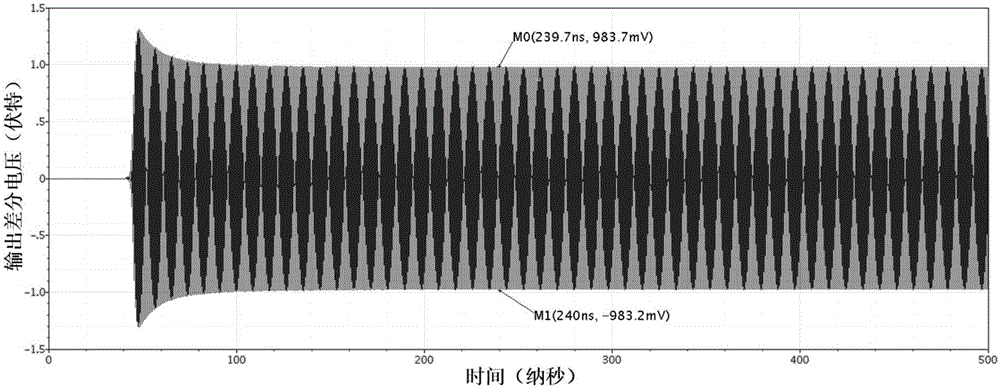

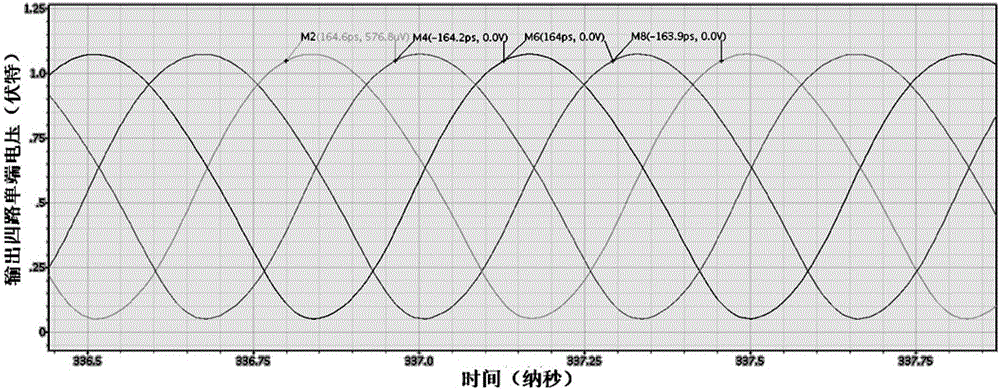

Near-threshold low-power-consumption quadrature voltage controlled oscillator

ActiveCN106026923AFast start-upReduce power consumptionOscillations generatorsPhase differenceDetection bias

The invention discloses a near-threshold low-power-consumption quadrature voltage controlled oscillator. The voltage controlled oscillator comprises an oscillator main body circuit and a self-detection bias circuit, wherein a phase coupling circuit in the oscillator main body circuit and a peak value detection circuit in the self-detection bias circuit are combined, so that current is multiplexed, and the power consumption is lowered. The near-threshold low-power-consumption quadrature voltage controlled oscillator works under a relatively high bias voltage at the beginning of oscillation start, and oscillation of the circuit can be started rapidly under large current. After oscillation start, four PMOS (P-channel Metal Oxide Semiconductor) transistors limit phase differences among four paths of oscillation signals at 90 degrees, detect a peak voltage and control the bias circuit to lower a bias point, so that the power consumption is lowered, and the noise performance is optimized.

Owner:SOUTHEAST UNIV

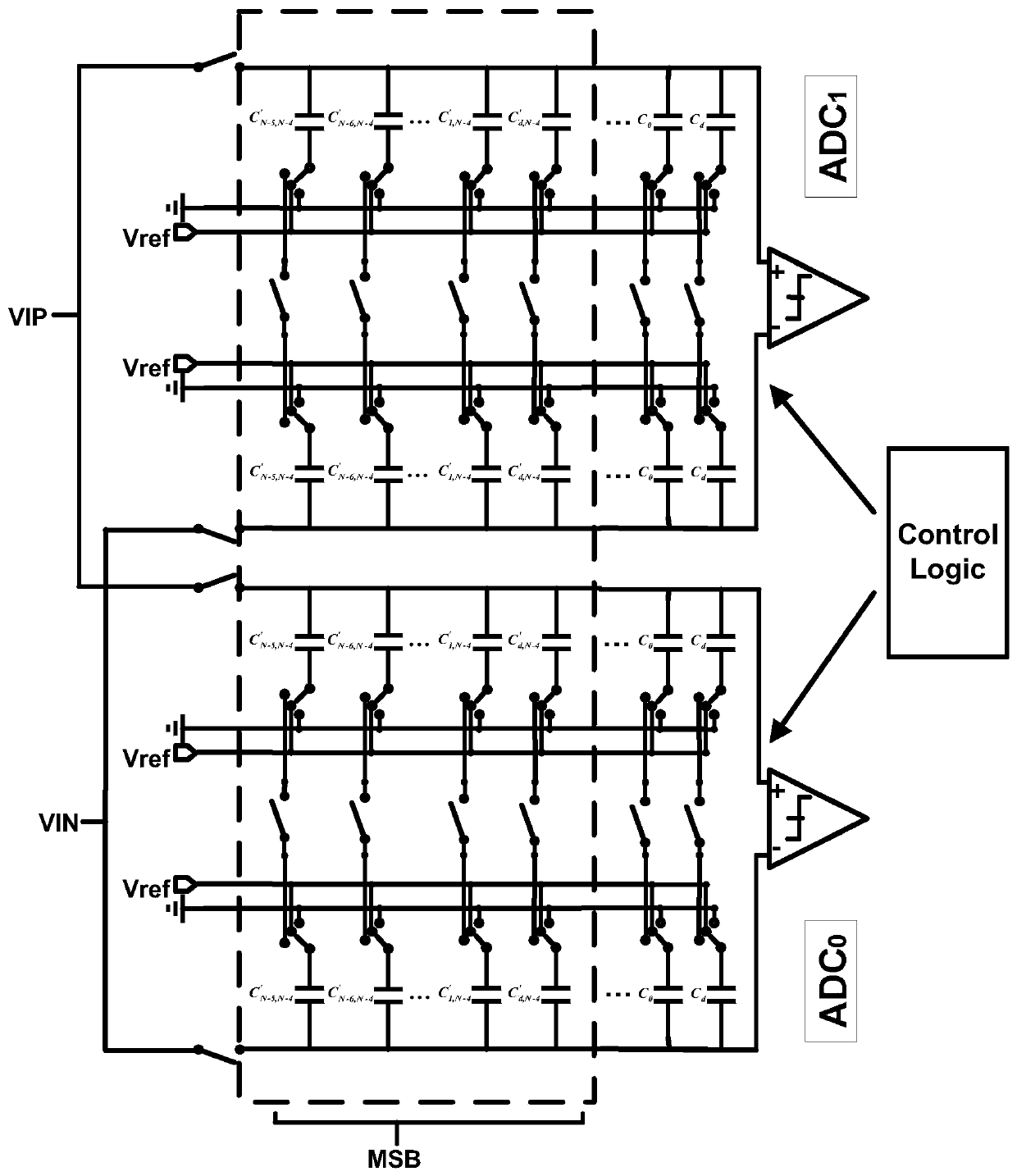

Capacitor array switching method applied to low-voltage SAR ADC

ActiveCN110380730AImprove signal-to-noise ratioReduce Switching Power ConsumptionAnalogue/digital conversionElectric signal transmission systemsCapacitanceLow voltage

The invention discloses a capacitor array switching method applied to a low-voltage SAR ADC. An analog-to-digital converter based on the method comprises two N-bit sub analog-to-digital converters with the same structure, the method comprises the following steps: for the input signals VIP and VIN, after N comparisons, obtaining N-bit digital output codes, which are divided into a sampling stage and a conversion stage, wherein, in the sampling stage, the input signals VIP and VIN are respectively connected to top polar plates of an upper capacitor array and a lower capacitor array through sampling switches, and bottom polar plates of all capacitors of the upper capacitor array and bottom polar plates of all capacitors of the lower capacitor array are connected to corresponding voltages; and, in the conversion stage, the comparator performs MSB bit-to-LSB bit comparison on the voltages of the top polar plates of the upper and lower capacitor arrays to obtain corresponding digital codes,and the connection relationship of the capacitor bottom polar plates in the upper and lower capacitor arrays are controlled according to the digital codes, and the N-bit digital output codes are obtained through N times of comparison. According to the invention, the power consumption of the DAC part in the conversion process can be greatly reduced, only two reference levels are adopted, and the method is suitable for the design under the near threshold voltage.

Owner:SOUTHEAST UNIV

Near-threshold optical transmitter pre-distortion

ActiveUS9735879B2Quickly bring the emitter into a linear operating rangeDistortion/dispersion eliminationElectromagnetic transmittersPower flowData signal

Methods an systems for low-power transmission include biasing an emitter in a non-linear operating range of the emitter near a threshold current of the emitter. A data signal is distorted to add a precursor pulse to a rising edge of a data waveform to quickly bring the emitter into a linear operating range. The distorted data signal is transmitted at the emitter.

Owner:IBM CORP

Methods of screening for sweet taste modulators

ActiveUS8124361B2Cell receptors/surface-antigens/surface-determinantsSugar derivativesBinding siteSweetness

Owner:GIVAUDAN SA

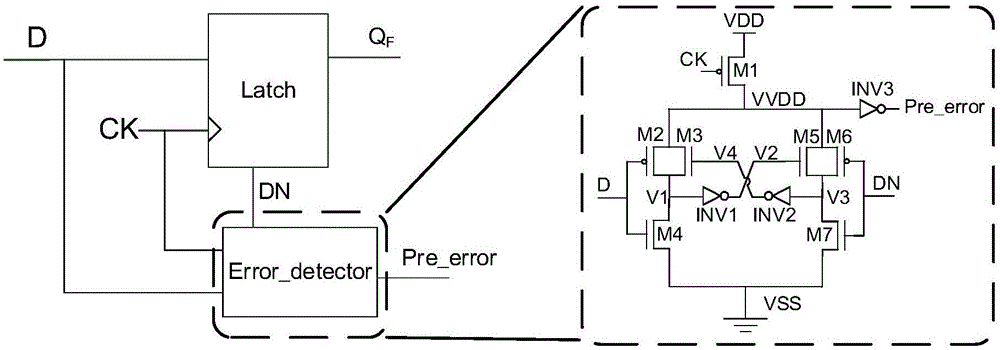

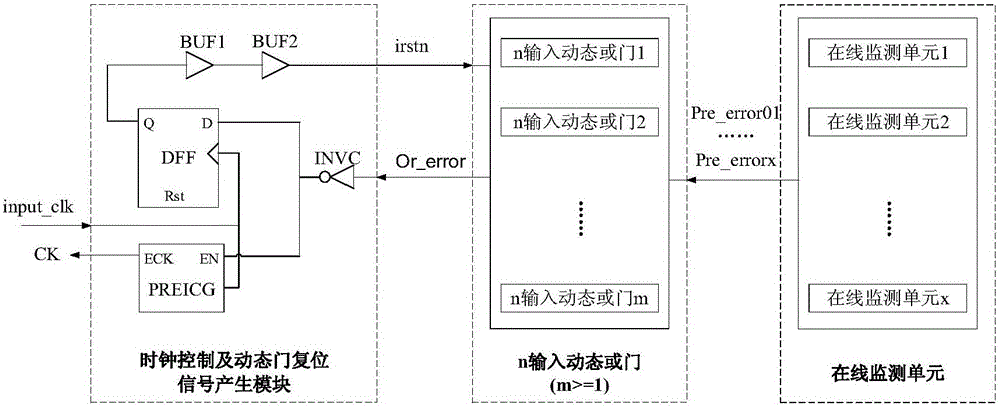

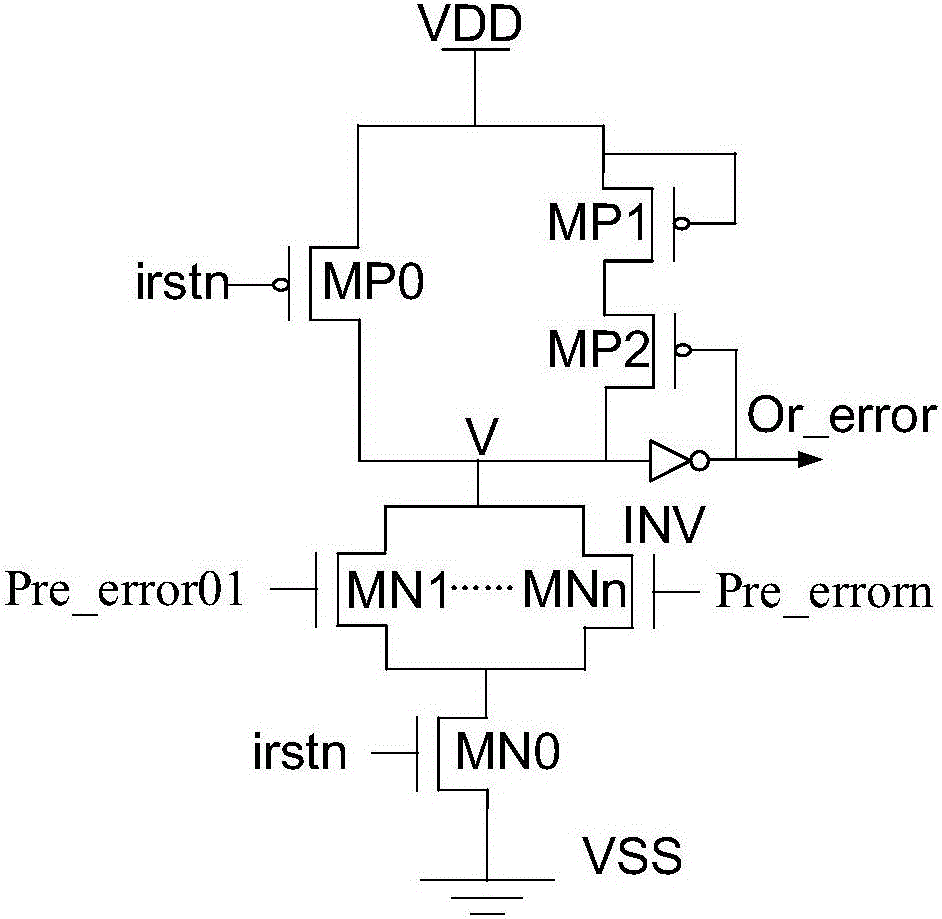

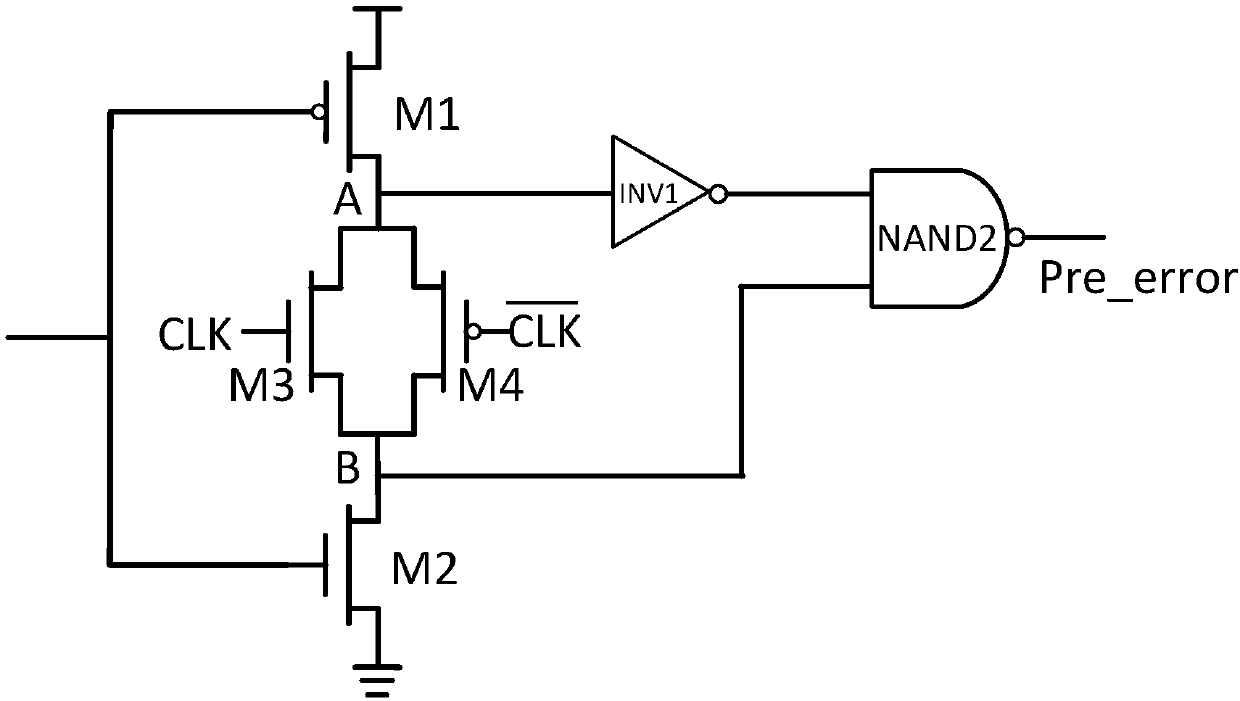

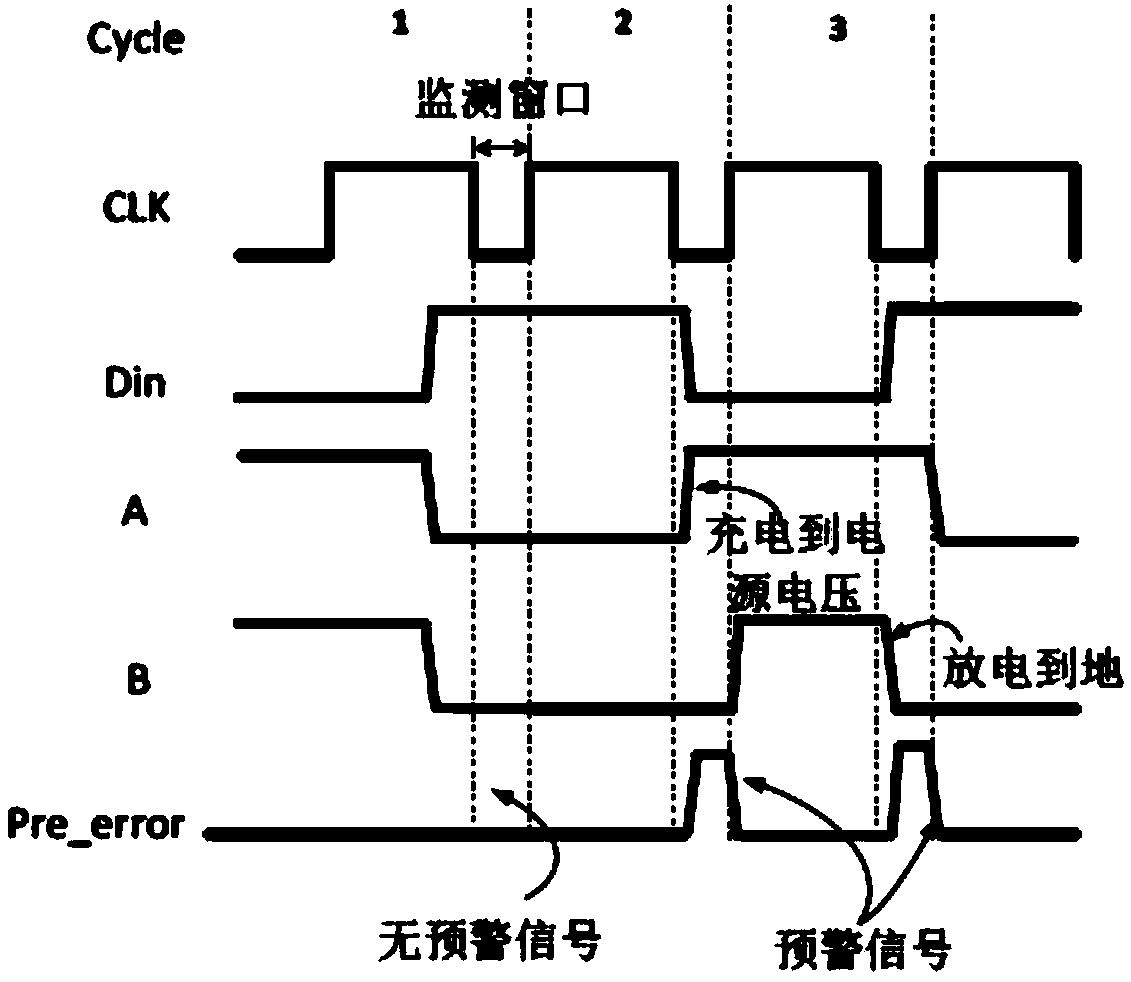

Fully symmetrical online monitoring unit capable of stable working within near-threshold region and control circuit

InactiveCN106603042AReduce areaReduce power consumptionHardware monitoringArchitecture with single central processing unitTime delaysControl system

The invention discloses a fully symmetrical online monitoring unit capable of stable working within a near-threshold region and a control circuit. Compared with common online monitoring units, according to the invention, the online monitoring unit does not need to reserve a time delay unit and replaces an original trigger in the common online monitoring unit with a latch, and designs a data jump monitor which has fewer transistors than a shadow latch in the common online monitoring unit. The data jump monitor can work stably within the near-threshold region, has a time delay of inverter magnitudes, has the characteristics of fastness and stability which enable the control system to rapidly respond to alerts, avoids actual time-sequence errors, and finally reduces the area and power consumption of the online monitoring unit maximumly. In addition, according to the invention, since the online monitoring unit uses the latch of which the time borrowing characteristics enable the online monitoring unit to resist errors of circuit time-sequence caused by PVT deviation under near-threshold, the online monitoring unit completely eliminates the time-sequence residual reserved when designed, and has ensured higher power consumption. Also, the invention discloses a control circuit which is in cooperation to the online monitoring unit so as to better achieve functions of the entire system.

Owner:SOUTHEAST UNIV

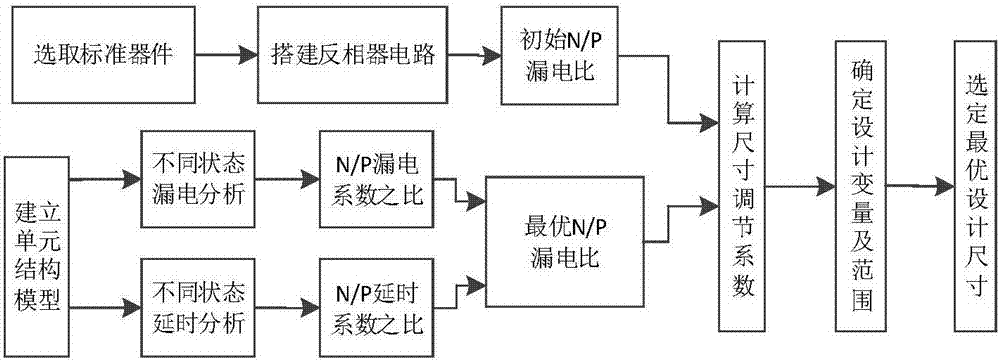

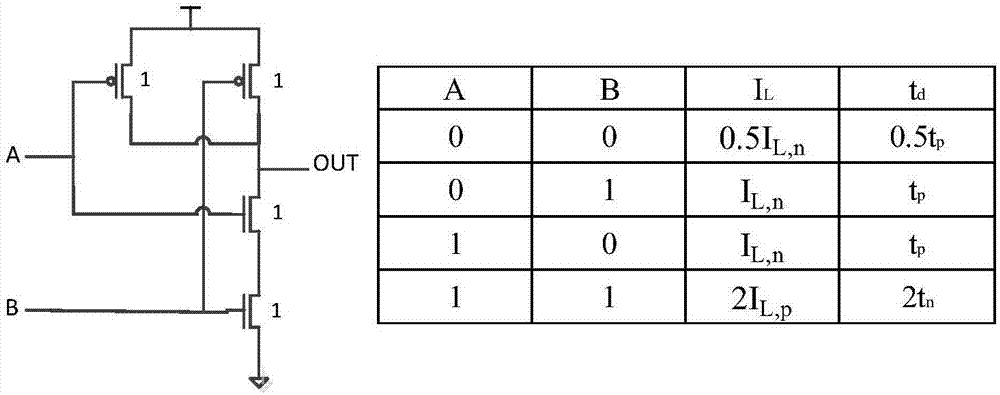

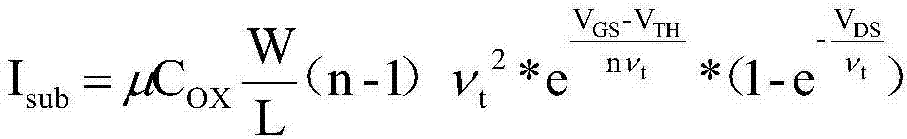

Design method suitable for near-threshold and sub-threshold low electric leakage standard cell

ActiveCN107403052AReduce leakageRealize the designCAD circuit designSpecial data processing applicationsSub thresholdDrain current

The invention discloses a design method suitable for a near-threshold and sub-threshold low electric leakage standard cell, and belongs to the technical field of digital integrated circuits. The design method comprises selecting standard devices of predetermined dimensions to build an inverter and calculating N / P electric leakage ratios of the standard devices; building a standard cell circuit and dividing leakage current and time delay of the standard cell circuit from sources thereof, calculating and obtaining N / P electric leakage coefficient ratios and N / P time delay coefficient ratios of the standard cell circuit, and therefore obtaining the optimal N / P electric leakage ratio of the standard cell circuit with minimum electric leakage energy consumption; and calculating adjusting parameters according to the N / P electric leakage ratios of the standard devices and the optimal N / P electric leakage ratio of the standard cell circuit, designing dimensions according to the adjusting parameters, and obtaining the optimal dimensions of NMOS transistors and PMOS transistors forming the standard cell circuit when the electric leakage energy consumption is minimum. The standard cell designed according to the method has low electric leakage characteristics, and therefore low-power digital circuits can be designed.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

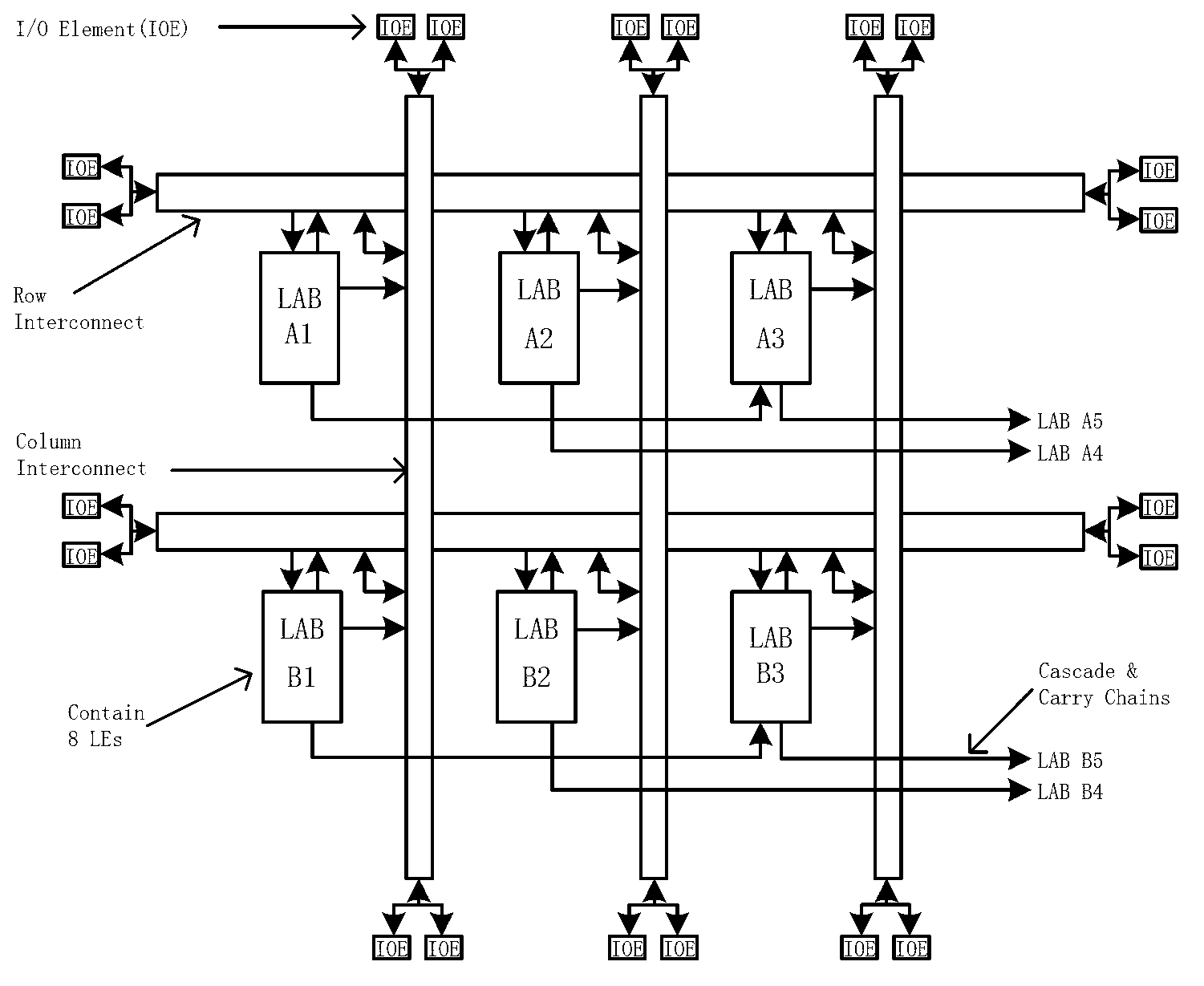

Low-power dissipation static random access memory (SRAM) type field programmable gate array (FPGA) design method

InactiveCN103066993AReduce power consumptionHigh power consumptionLogic circuits using elementary logic circuit componentsStatic random-access memorySub threshold

Provided is a low-power dissipation static random access memory (SRAM) type field programmable gate array (FPGA) design method. A level shifter is used for at least reducing working voltage of a two-dimensional logical block array of the FPGA to a near-threshold, the Schmidt trigger type SRAM is adopted in a look up table (LUT) in the two-dimensional logical block array, a sub-threshold D latch is adopted in a programmable D-flip flop, the LUT and the programmable D-flip flop work under reduced low supply voltage, and therefore the FPGA works normally under ultra-low supply voltage. The invention provides the novel method. According to the method, the level shifter is used for reducing the working voltage of the two-dimensional logical block array of the FPGA to be in a near-threshold or even a sub-threshold area, the FPGA can work normally under the ultra-low supply voltage, and therefore the FPGA can further achieve work of ultra-low power dissipation.

Owner:SOUTHEAST UNIV

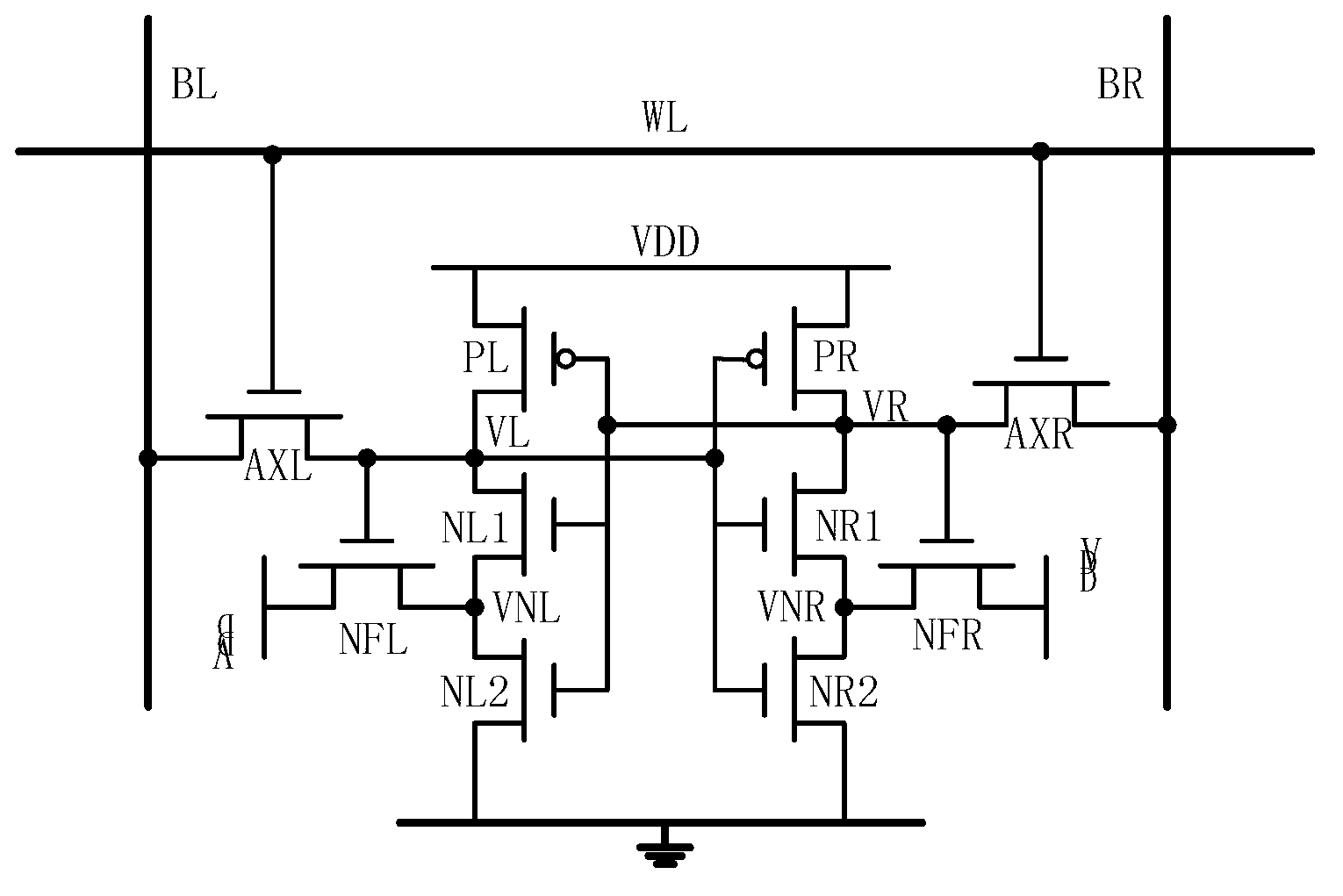

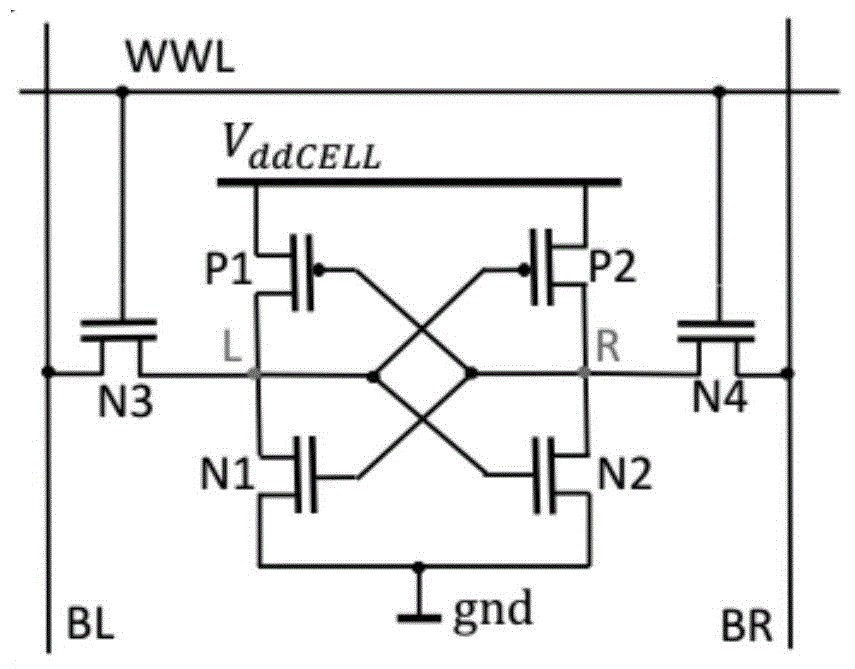

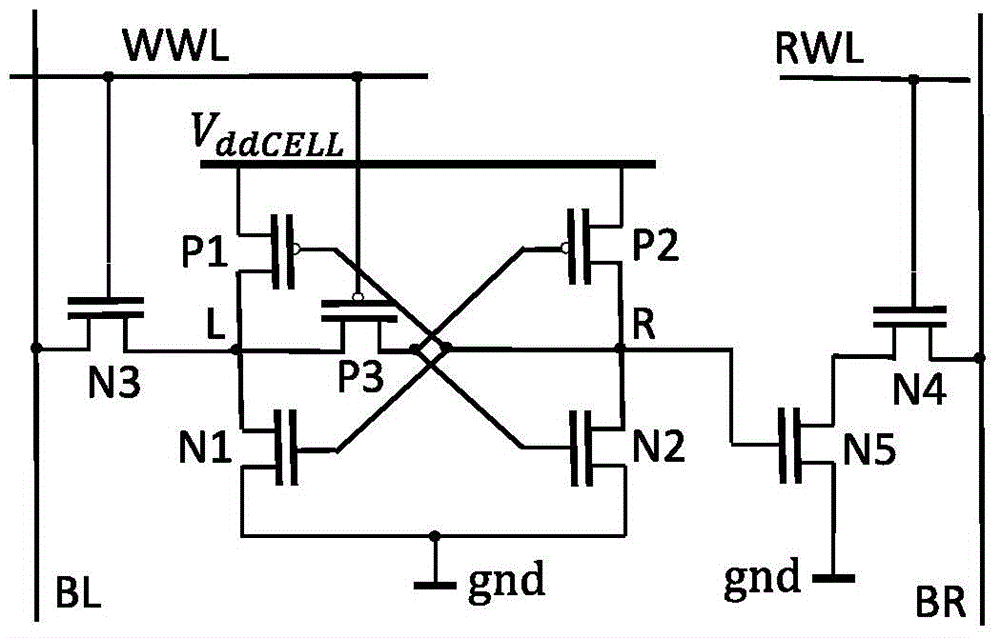

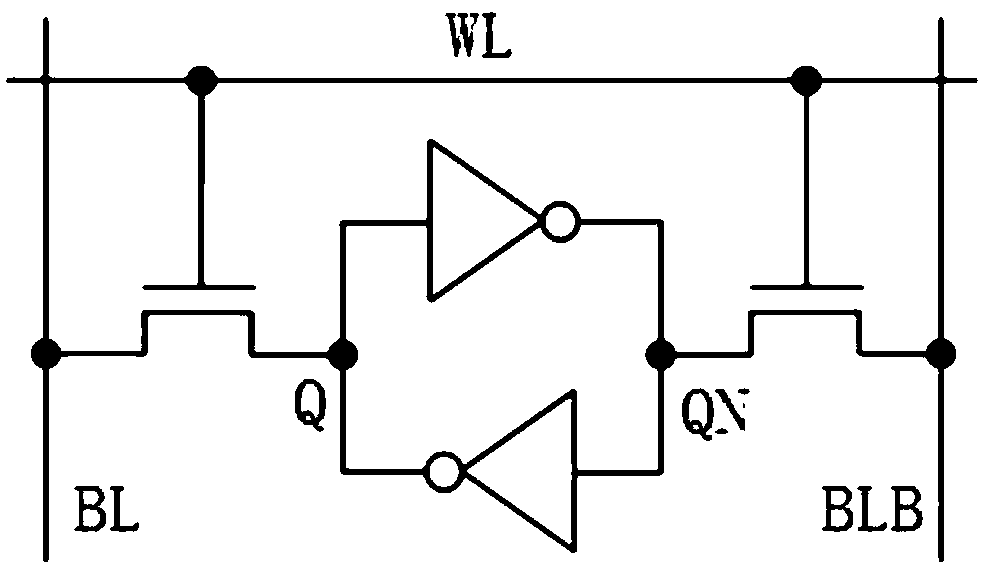

Near-threshold 8-tube static random memory unit

InactiveCN104882159AEliminate Data Retention CapabilitiesEasy to writeDigital storageBit lineEngineering

The invention relates to a near-threshold 8-tube static random memory unit, and belongs to the field of design of integrated circuits. The unit structurally comprises a first phase inverter consisting of a first NMOS transistor and a first PMOS transistor, and a second phase inverter consisting of a second NMOS transistor and a second PMOS transistor; the input ends and output ends of the two phase inverters in serial connection are respectively connected with a source electrode and a drain electrode of a third PMOS transistor so as to form a latch structure; the source electrode and drain electrode of the third PMOS transistor are respectively connected with a bit line BL and a data storage point L; a grid electrode of the second NMOS transistor and a grid electrode of the third PMOS transistor are both connected to a write line WWL; a drain electrode and a source electrode of a fourth NMOS transistor are respectively connected with a bit line BR and a source electrode of a fifth NMOS transistor; a grid electrode of the fourth NMOS transistor is connected to a read line RWL; a grid electrode of the fifth NMOS transistor is connected to a data storage point R; the drain electrode of the fifth NMOS transistor is connected to ground gnd. The structure can be used for reinforcing the stability and the read and write capabilities of a near-threshold working voltage, and further reducing the power consumption, has no size construction of pull-down ratio and the like, is capable of simplifying the design difficulty further, and has no cost of area sacrifice.

Owner:TSINGHUA UNIV

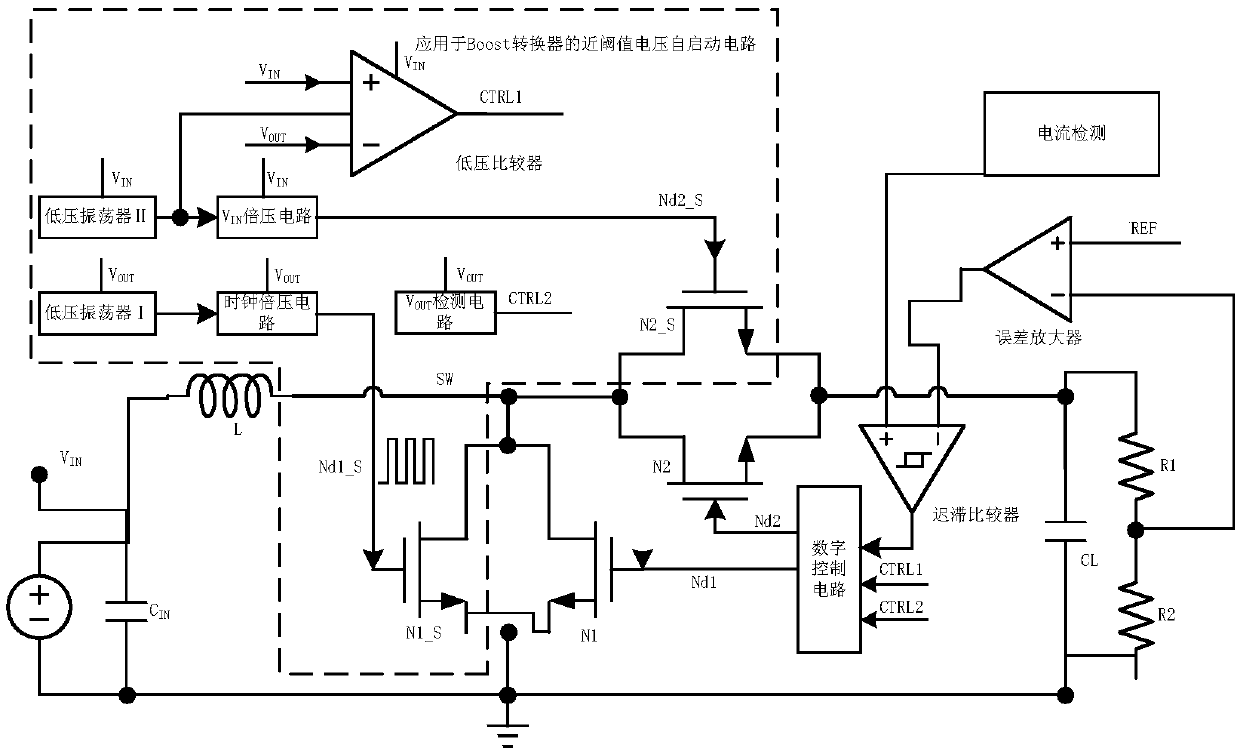

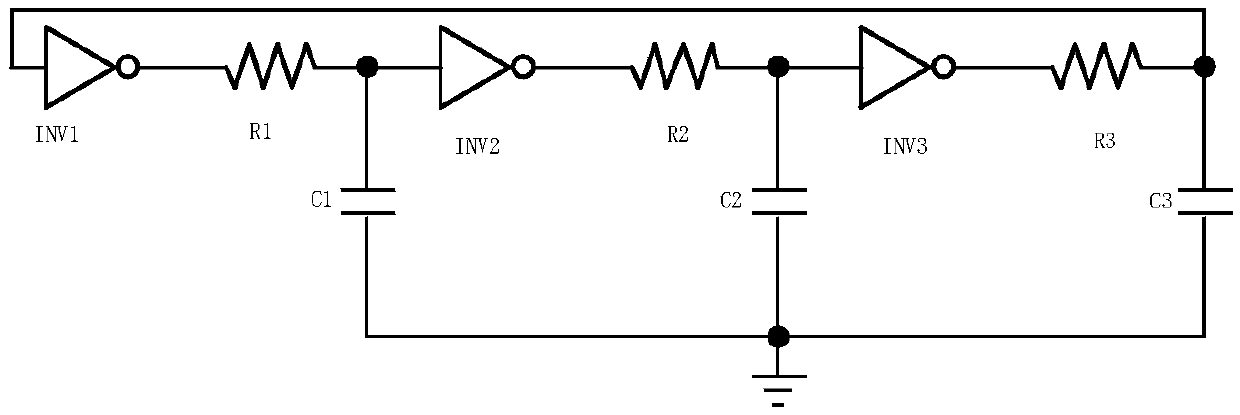

Near-threshold-voltage automatic starting circuit applied to Boost converter

The invention relates to a near-threshold-voltage automatic starting circuit applied to a Boost converter. The near-threshold-voltage automatic starting circuit applied to the Boost converter comprises a low-voltage oscillator I, a low-voltage oscillator II, a VIN voltage doubling circuit, a low-voltage comparator, a VOUT detection circuit, a clock voltage doubling circuit, an auxiliary starting tube N1_S and an auxiliary starting tube N2_S. The output end of the low-voltage oscillator I is connected with the input end of the clock voltage doubling circuit. The output end of the low-voltage oscillator II is connected with the input end of the VIN voltage doubling circuit and the input end of the low-voltage comparator. The input end of the clock voltage doubling circuit is connected with the output end of the low-voltage oscillator I, and the output end of the clock voltage doubling circuit is connected to a grid electrode of the auxiliary starting tube N1_S. The input end of the VIN voltage doubling circuit is connected to the output end of the low-voltage oscillator II, and the output end of the VIN voltage doubling circuit is connected to a grid electrode of the auxiliary starting tube N2_S.

Owner:XIDIAN UNIV

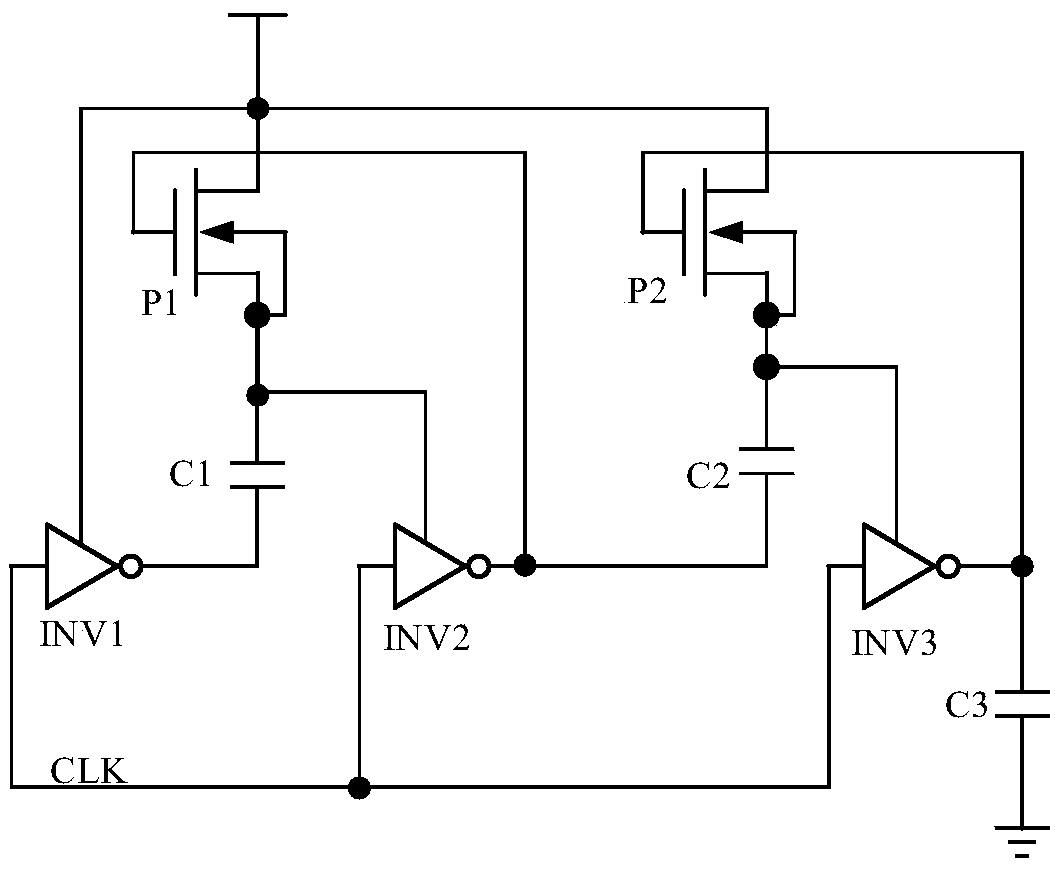

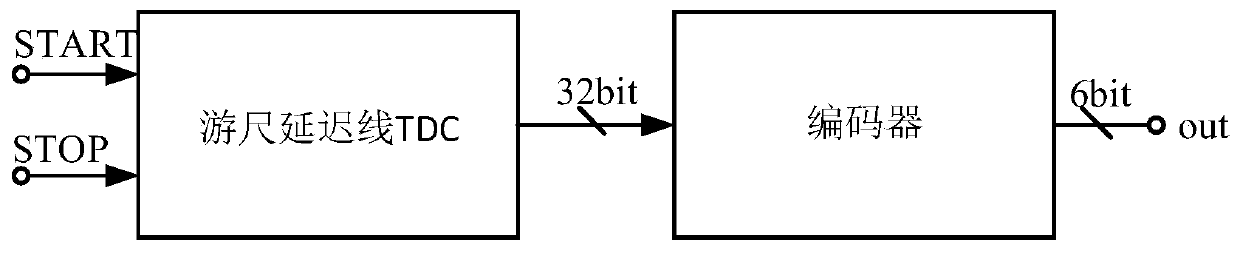

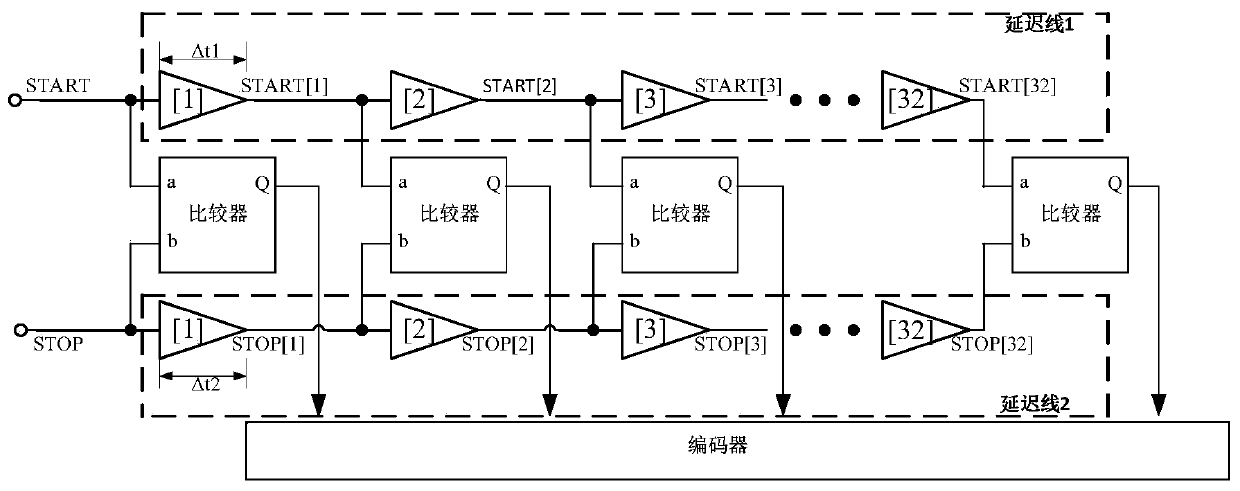

Time-to-digital converter adopting dynamic threshold technology

ActiveCN109884873AOverdrive voltage increasesHigh speedElectric unknown time interval measurementDigital down converterEngineering

The invention relates to a time-to-digital converter adopting a dynamic threshold technology, which is suitable for a near-threshold supply voltage environment and comprises a vernier delay line TDC circuit and an encoder circuit, wherein the vernier delay line TDC circuit judges the time difference of START and STOP signals and outputs corresponding results in a binary form. Due to the fact thatthe lower supply voltage is adopted, the overdrive voltage of the transistor is insufficient, the current of circuit operation can be reduced, and therefore the working time of the vernier delay lineTDC is greatly prolonged. According to the invention, the substrate of the transistor is connected with a gate end by adopting the dynamic threshold technology, so that the potential of the substratecan be changed along with the change of the gate voltage, the threshold voltage of the transistor can be greatly reduced, the source-drain current can be increased, the generation of leakage current can be avoided to the maximum extent, and the speed and the reliability of the circuit are improved.

Owner:NANJING UNIV OF POSTS & TELECOMM +1

Timing sequence monitoring unit and monitoring system oriented to near-threshold low voltage

ActiveCN107733402ALow area costSimple structurePulse automatic controlContinuous to patterned pulse manipulationLow voltageMonitoring system

The invention discloses a timing sequence monitoring unit and a monitoring system oriented to near-threshold low voltage, relates to an adaptive frequency adjustment technology based on on-chip timingsequence detection, and belongs to the technical field of integrated circuit low-power consumption design. The monitoring unit provided by the invention realizes timing monitoring oriented to near-threshold voltage with relatively lower circuit cost, realizes adaptive adjustment of system frequency through establishment of the monitoring system comprising a frequency control state machine, a phase-locked loop and a fast clock adjustment module, and solves a technical problem that a timing sequence monitoring circuit which is designed in a manner of being oriented to a normal voltage can hardly work correctly in a near-threshold region and rare timing sequence monitoring units which can work in a manner of being oriented to the near-threshold voltage region have large area and needs high cost.

Owner:SOUTHEAST UNIV +1

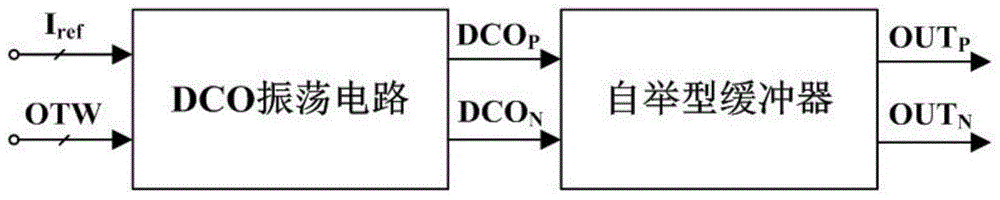

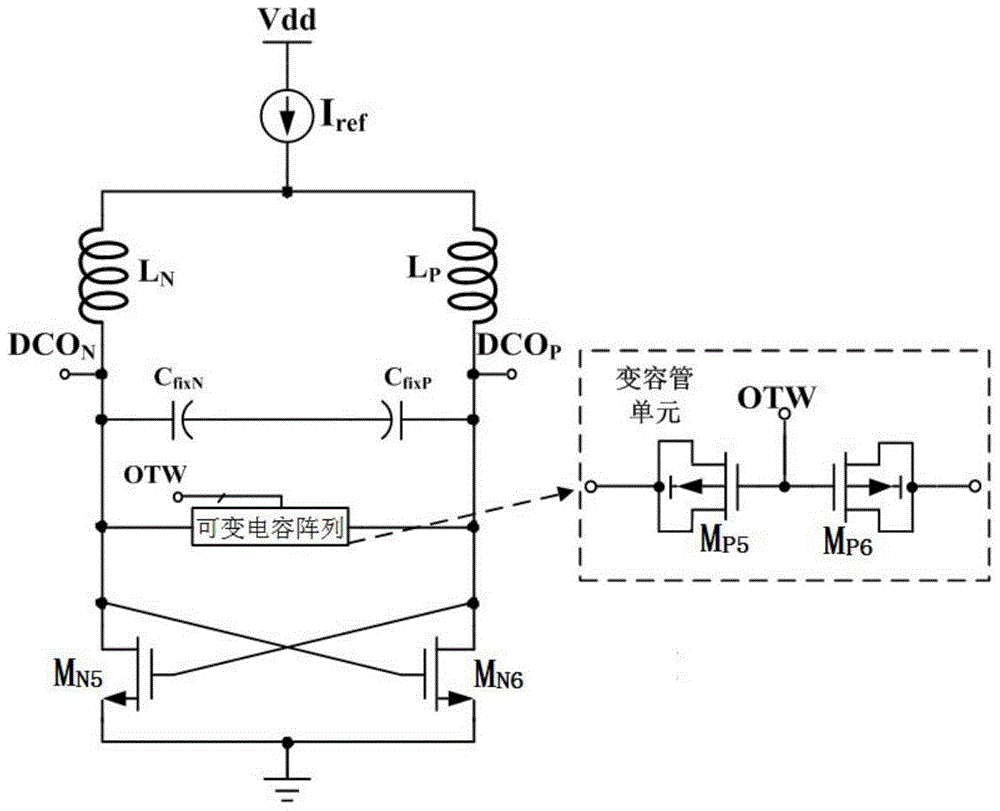

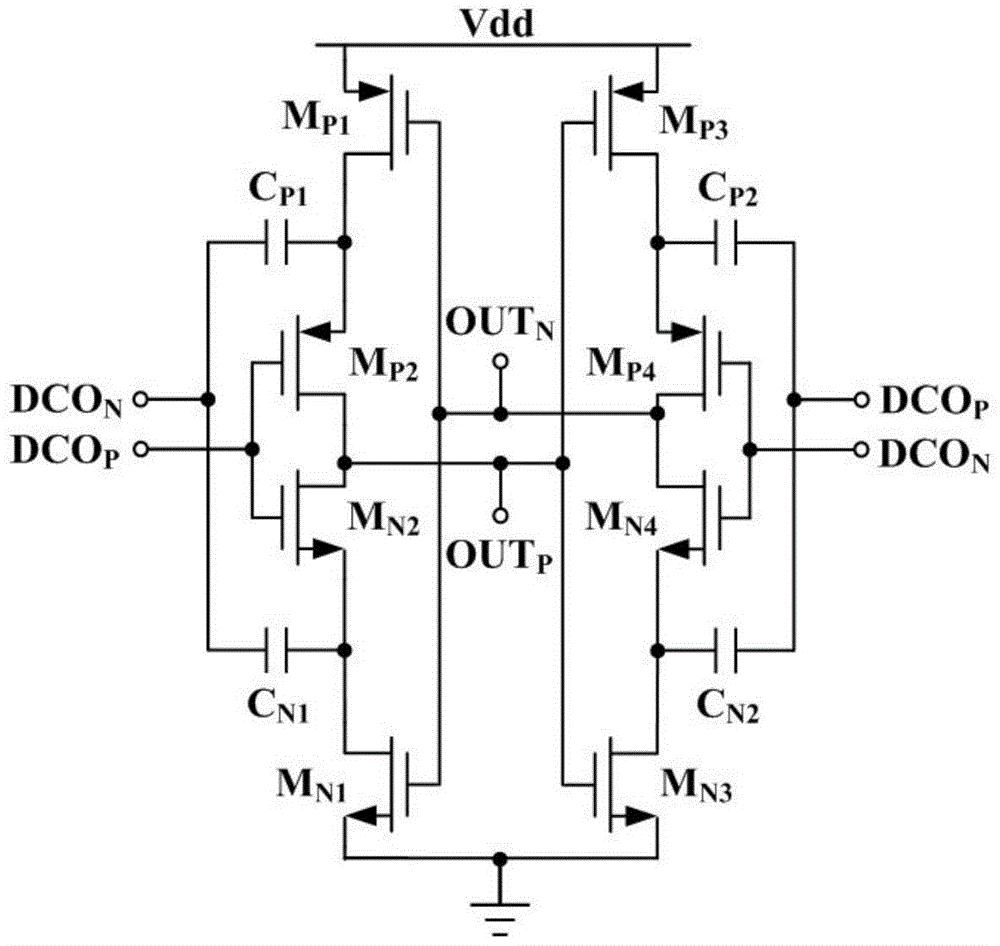

Numerically controlled oscillator working under near-threshold power voltage

ActiveCN105743496AImprove Phase Noise PerformanceSolve power consumptionPulse automatic controlCapacitancePhase noise

The invention relates to a numerically controlled oscillator working under near-threshold power source voltage. An LC cross coupling structured oscillator having high phase noise performance and a bootstrap type buffer based on a differential structure are adopted; the principle of a bootstrap circuit is utilized; bootstrap capacitors are charged and discharged through charging transistors; voltage superposition is carried out on the basis of the power source voltage; therefore, an output signal of a DCO oscillation circuit is amplified, so that the output oscillation amplitude reaches more than two times that of a power source voltage value; on the premise that low power consumption is ensured, the phase noise performance of the DCO oscillation circuit is improved; and the contradictory relation between the power consumption and the phase noise of the DCO oscillation circuit under the near-threshold power voltage can be solved.

Owner:NANJING LOW POWER IC TECH INST CO LTD

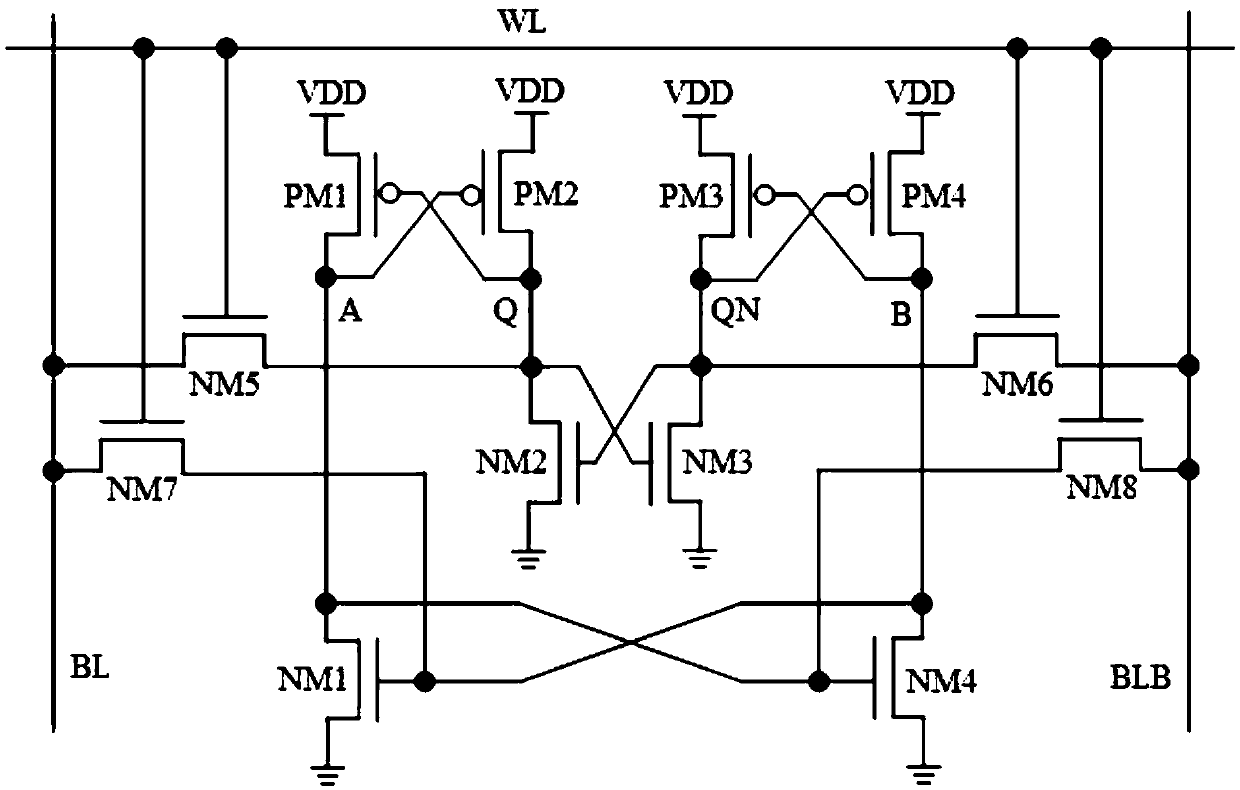

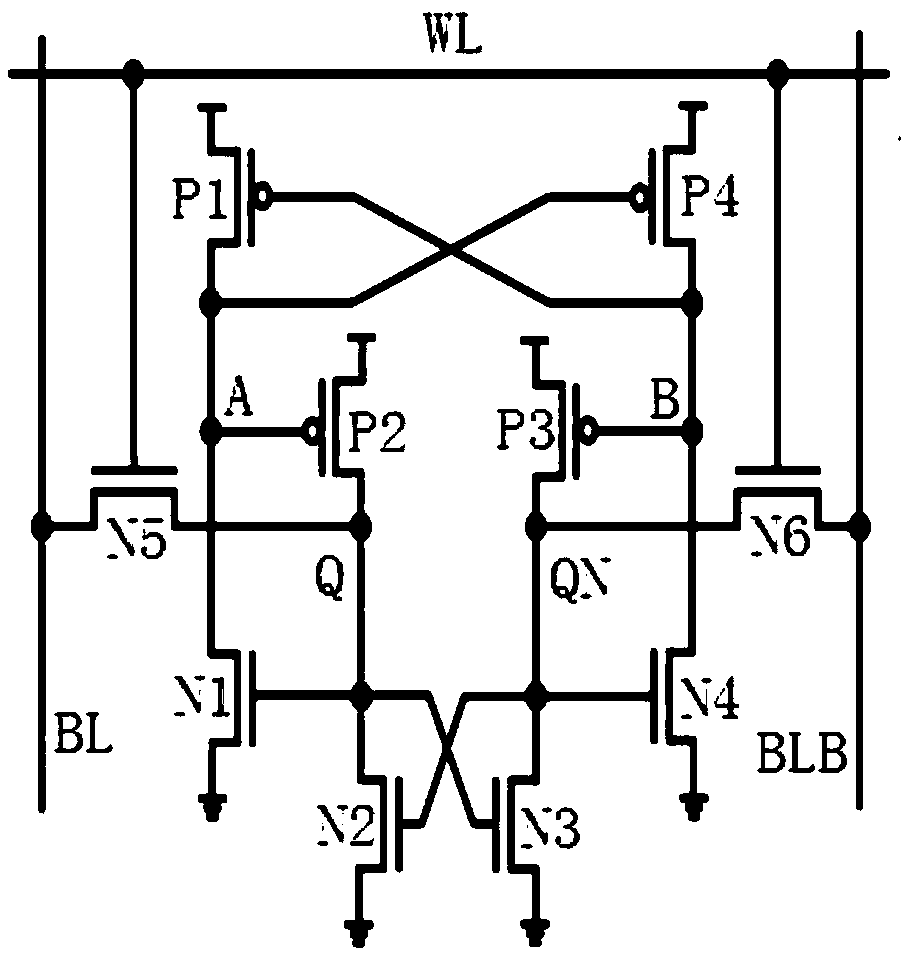

SRAM memory cell

The invention discloses an SRAM memory cell, which is composed of two groups of P-type cross-coupling latch structures, two groups of N-type cross-coupling latch structures and four N-type transfer tubes. The invention not only can realize the function of resisting soft error, but also can work under the near threshold voltage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

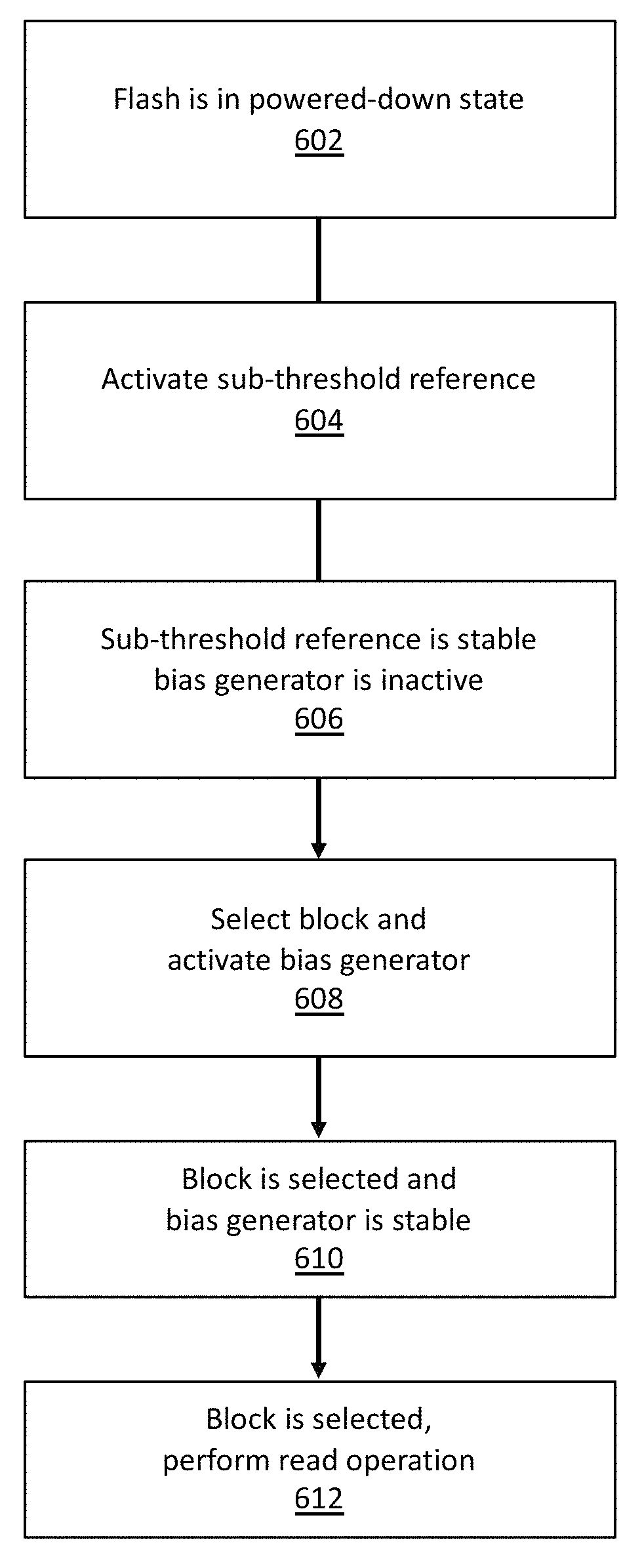

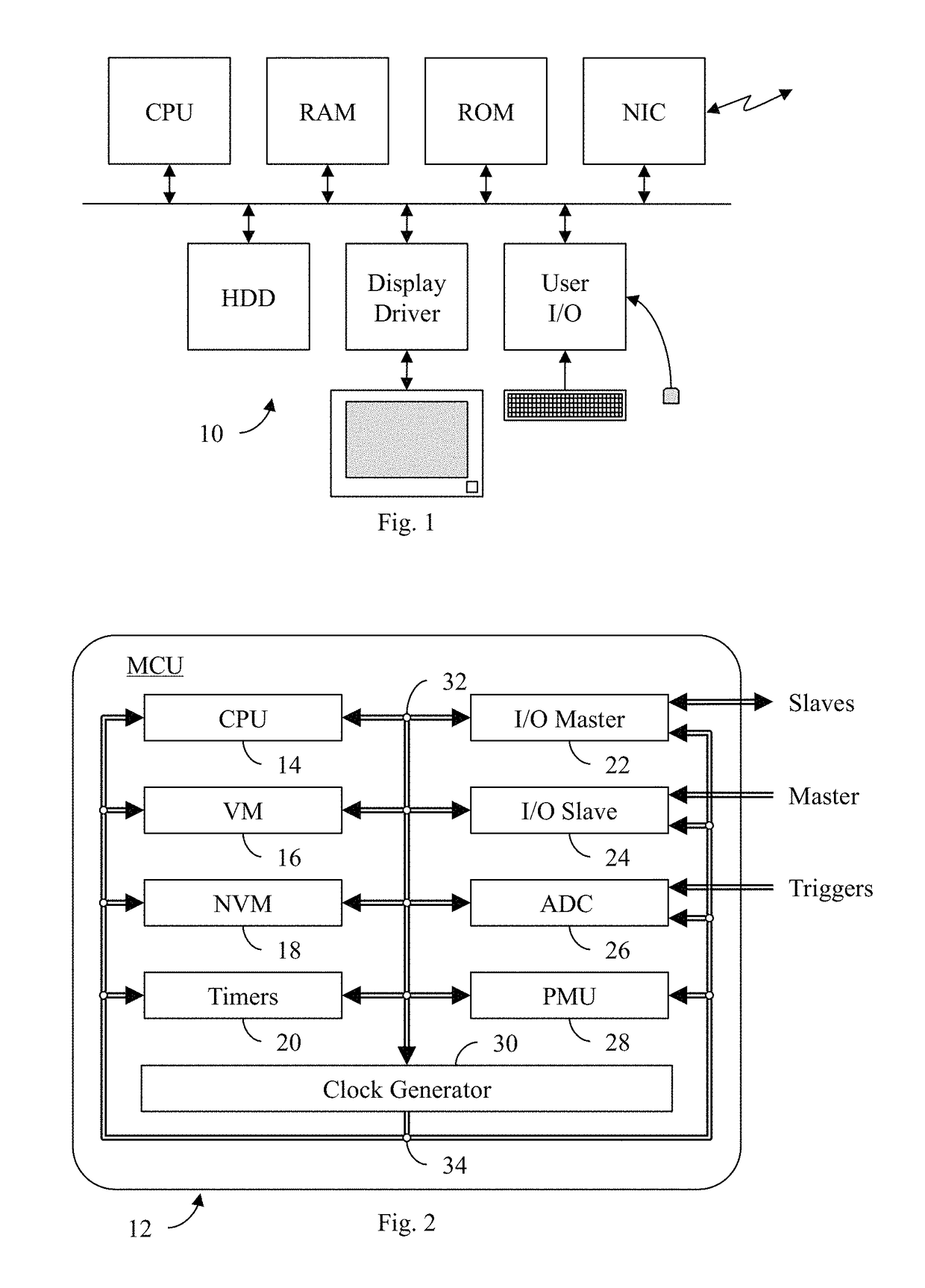

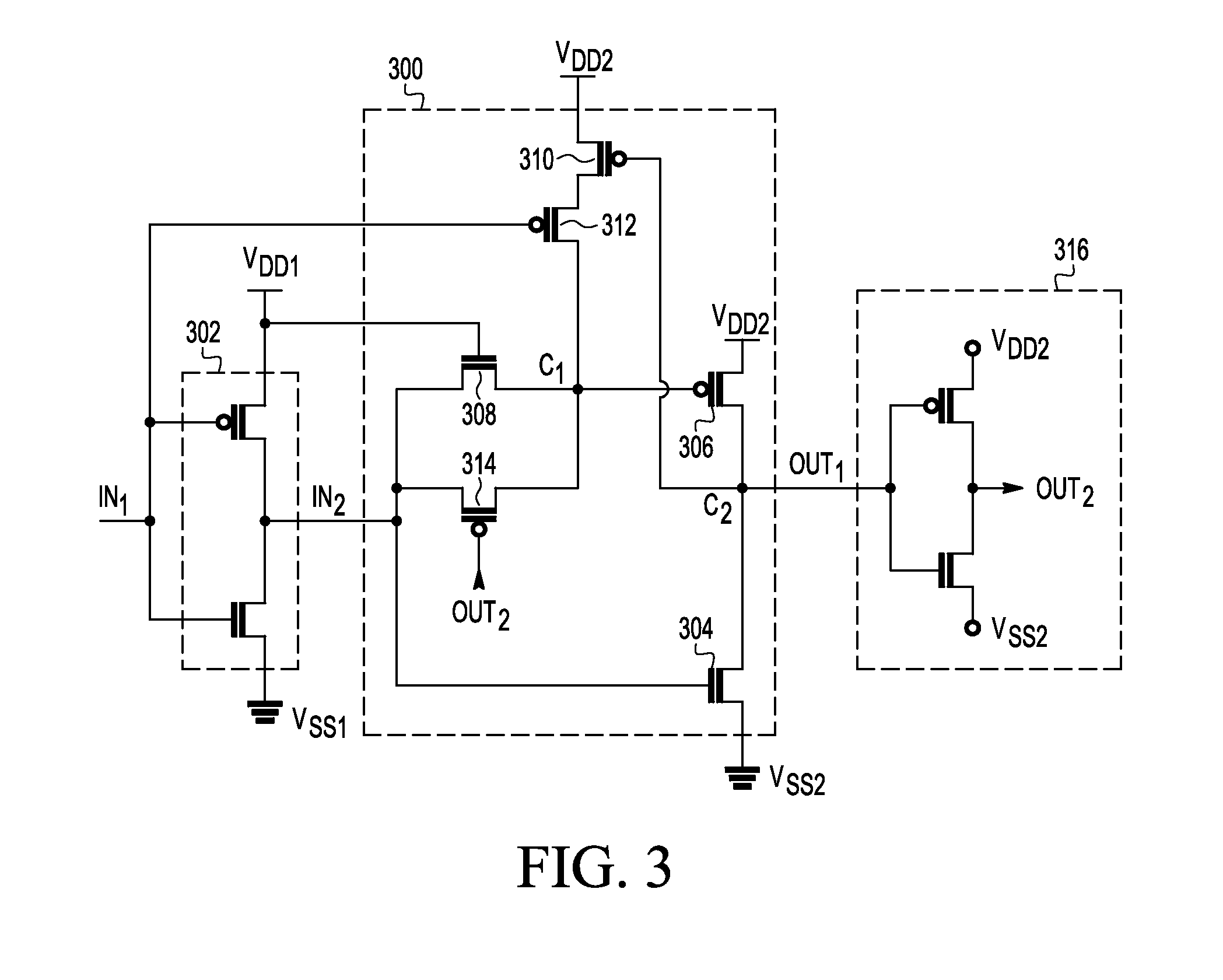

Sub-threshold enabled flash memory system

A flash memory system for use in an electronic system comprising an integrated circuit such as a microcontroller. The flash memory system embodies one or more circuits adapted to operate at sub- or near-threshold voltage levels. These low-power circuits are selectively activated or de-activated to balance power dissipation with the response time of the memory system required in particular applications.

Owner:AMBIQ MICRO

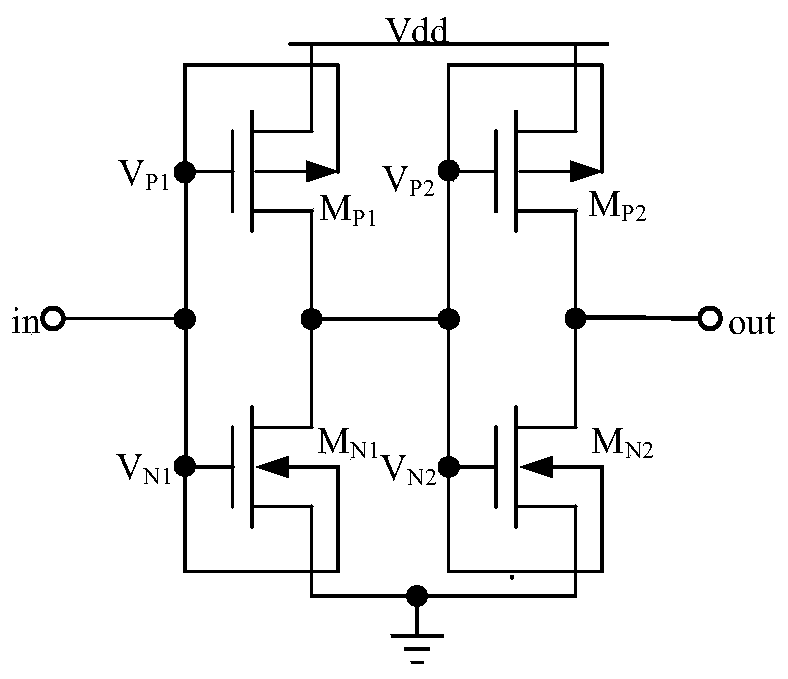

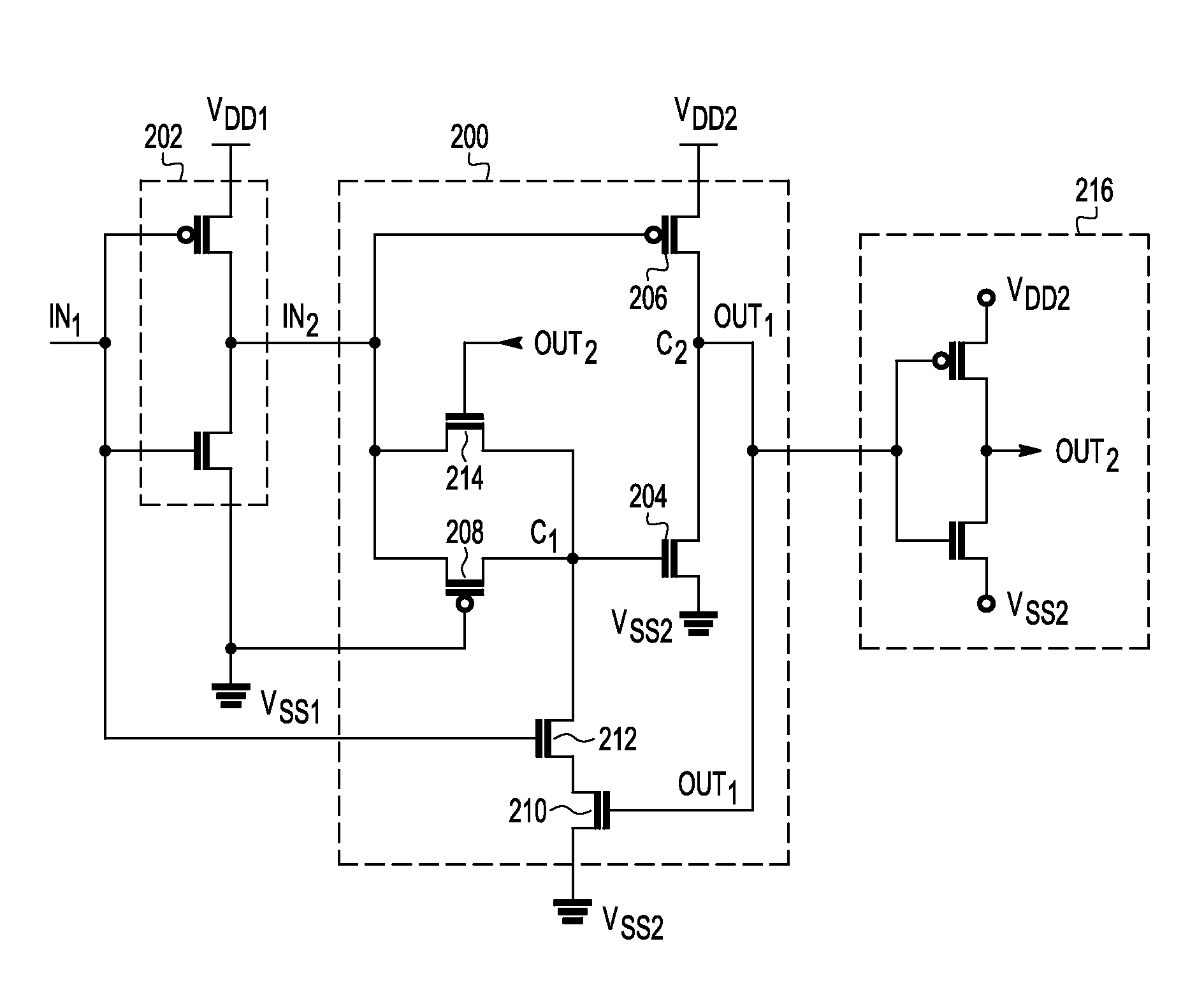

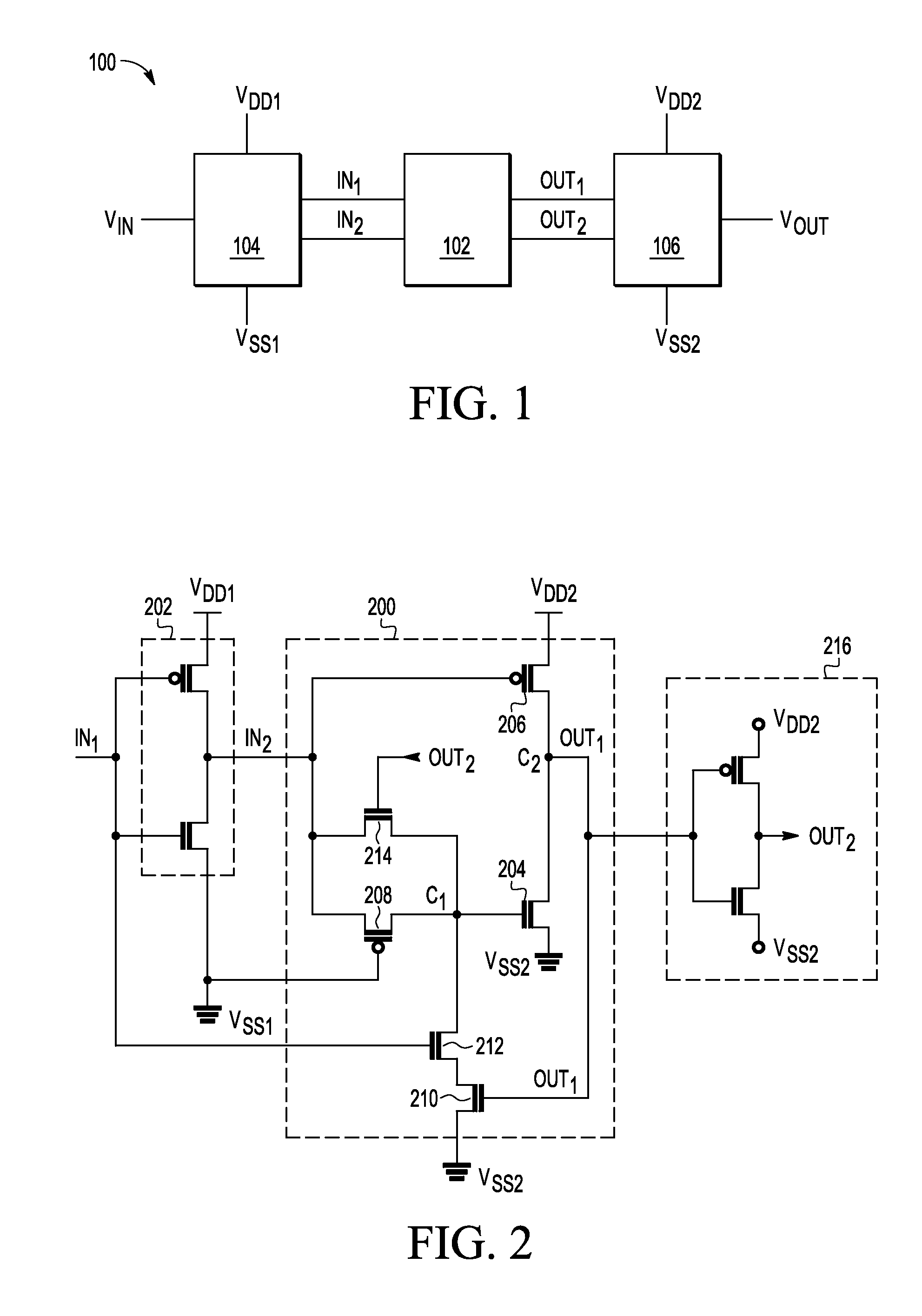

Ratioless near-threshold level translator

ActiveUS20150303923A1Pulse automatic controlLogic circuits coupling/interface using field-effect transistorsEngineeringLogic state

Owner:NXP USA INC

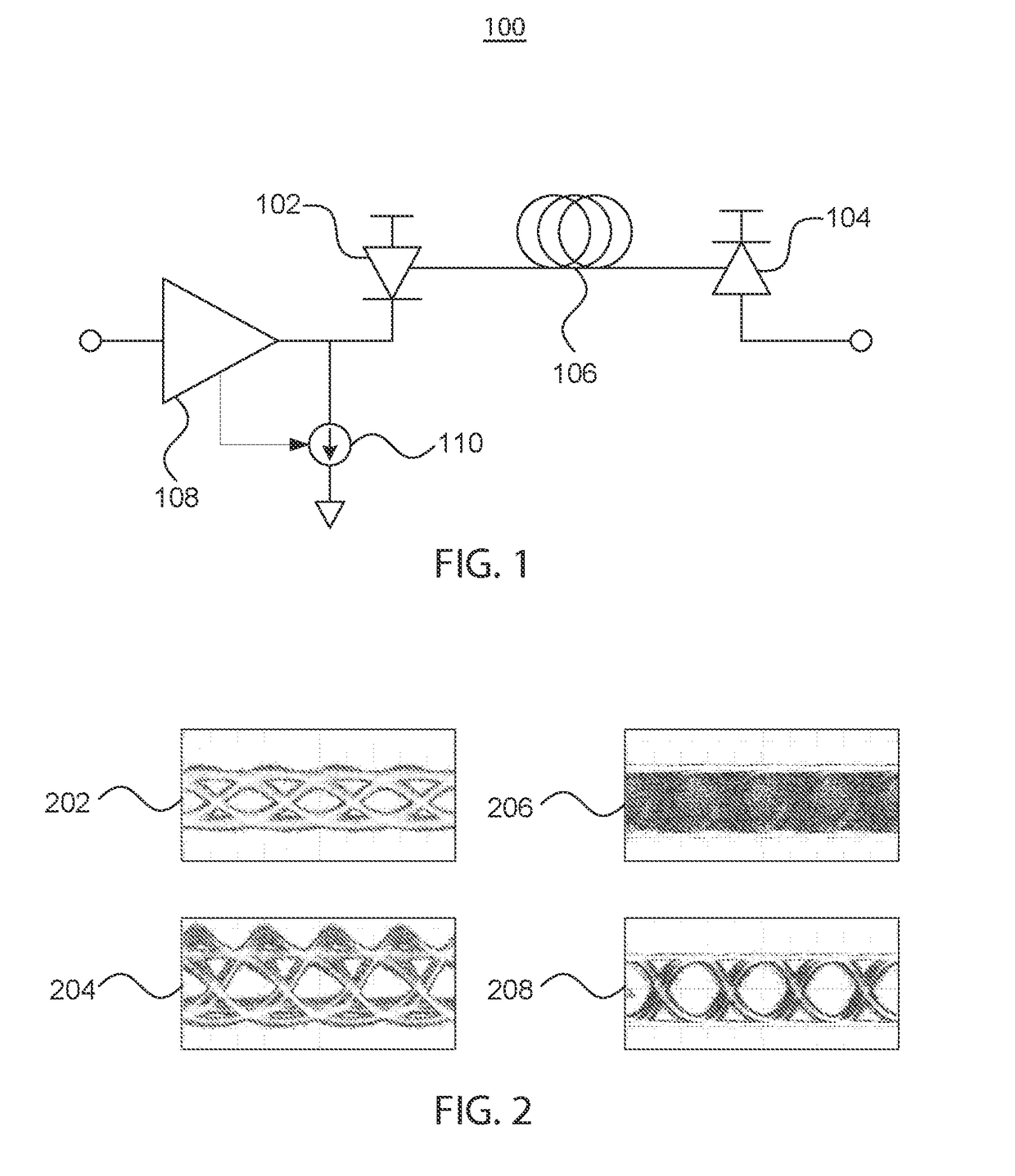

Systems and methods for real-time compensation for non-linearity in optical sources for analog signal transmission

ActiveUS7505496B2Gain of the feedback loopEasy to operateLaser detailsUsing optical meansRelative intensity noiseLinearization

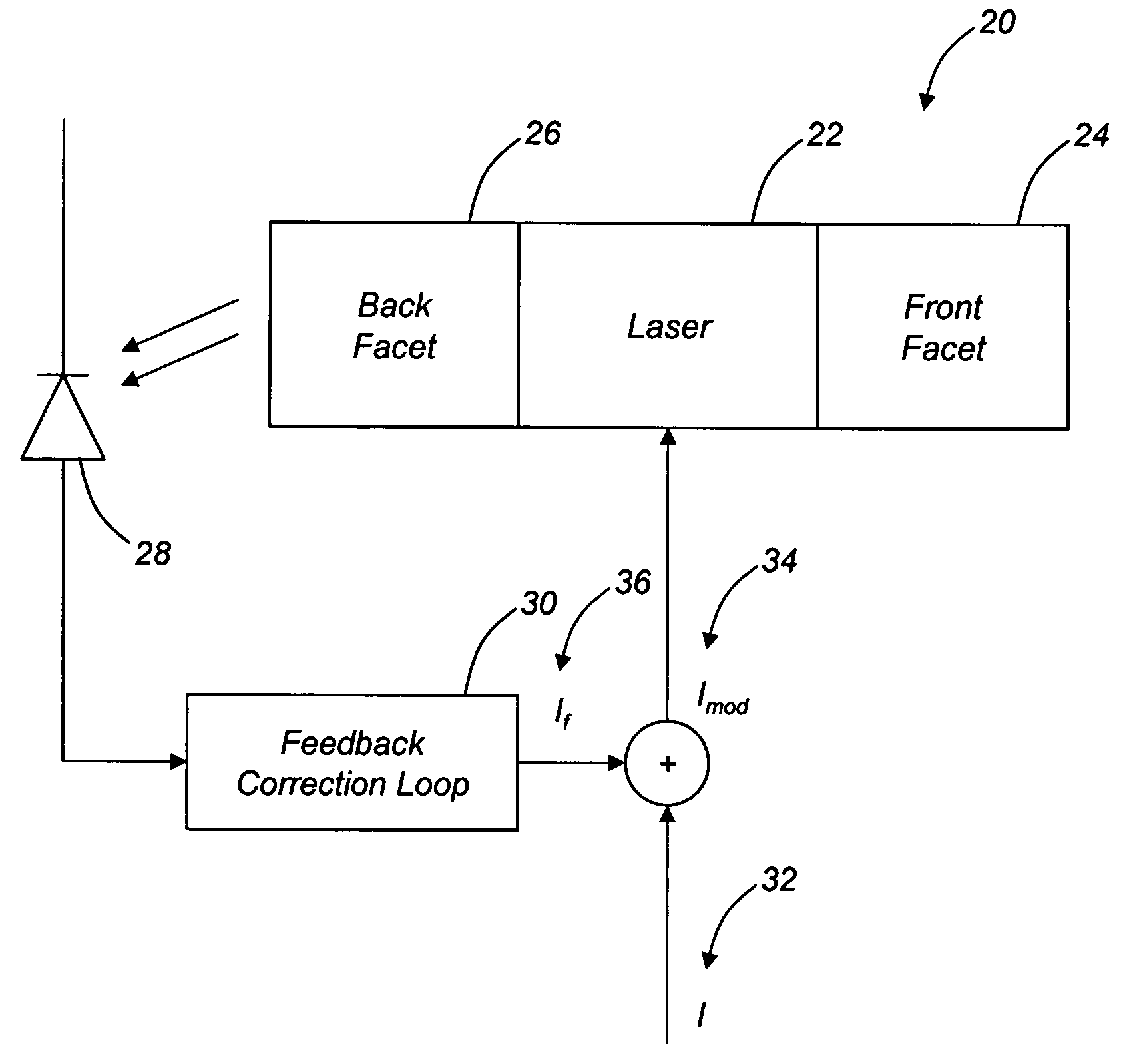

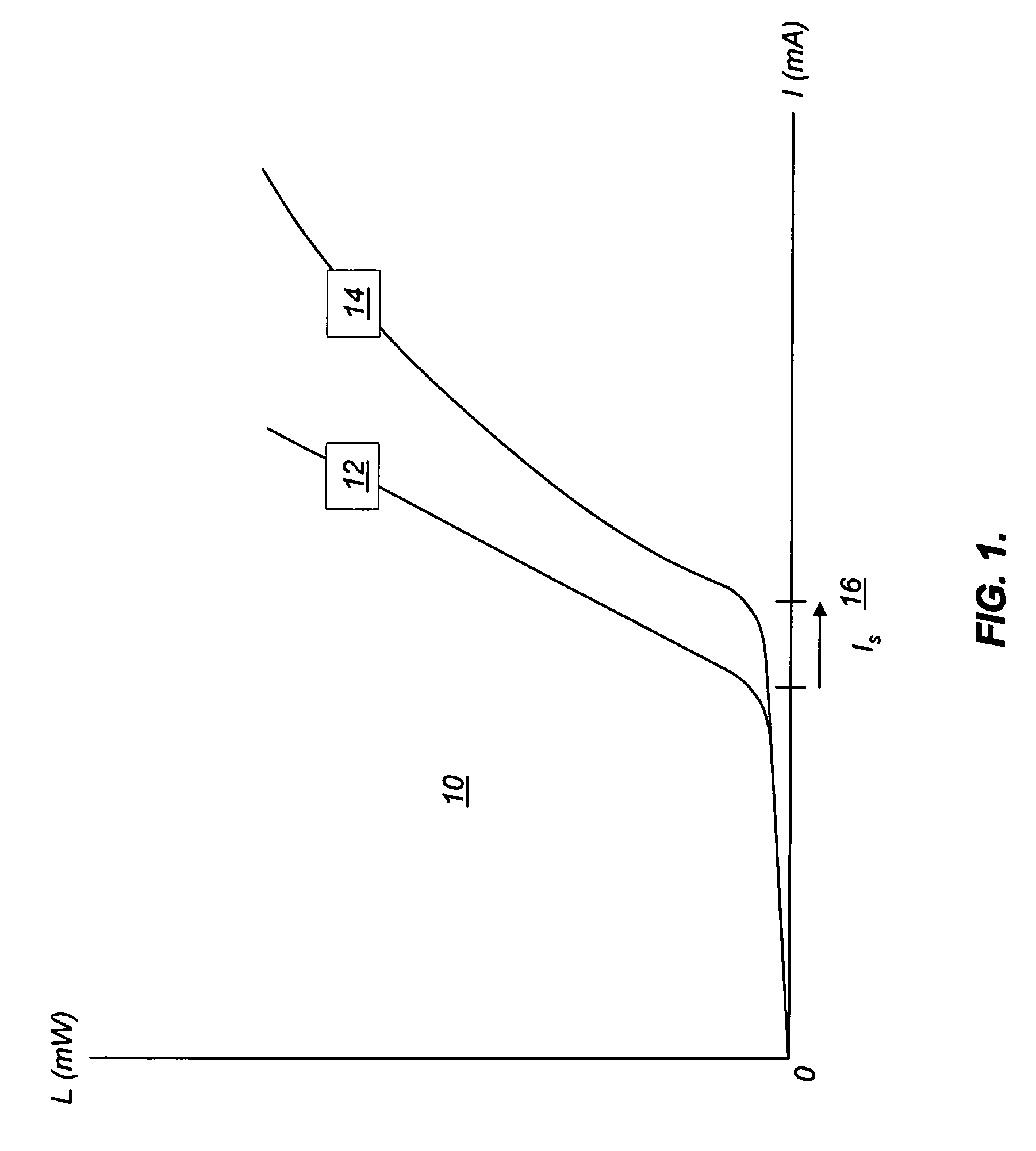

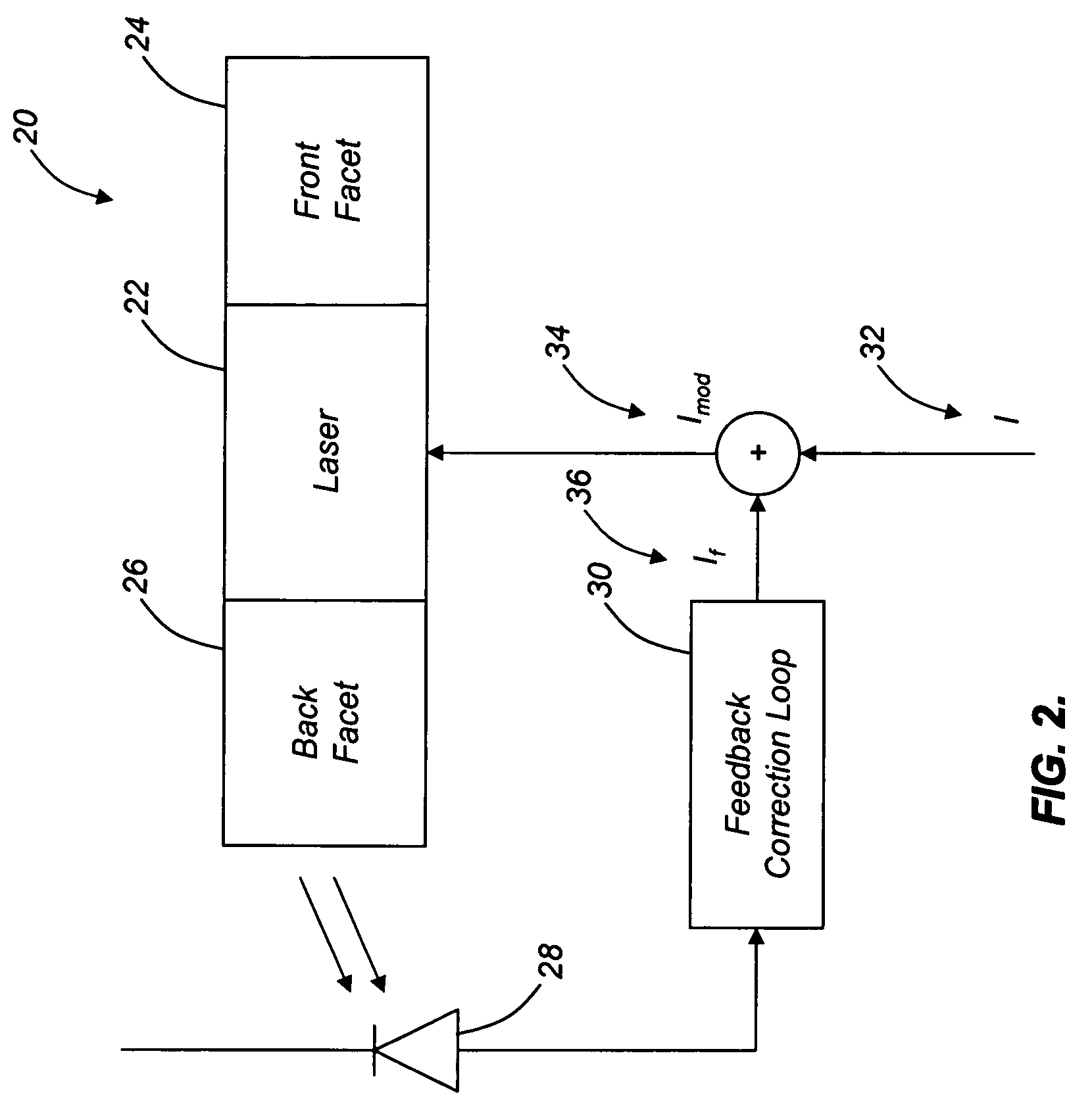

The present invention provides a compact analog directly modulated laser configuration that is suitable for use in the field that uses electrical feedback to compensate for non-linearity in real time, such that no matter how the LI curve changes, the electrical feedback compensates for non-linearity by amplifying a portion of the output analog optical signal and combining it with the input analog electrical signal using the standard control method of negative feedback. When the gain of the feedback loop is relatively high, the overall transfer function of the system is primarily dependent on the feedback loop gain block, which is substantially linear. This is accomplished by incorporating a relatively large bandwidth photo-detector at the back facet of the laser that both monitors the output power of the system and provides a feedback signal to the linearization control circuit, as well as an amplifier. The amplified signal from the relatively large bandwidth photo-detector is used to correct for various undesirable effects, such as non-linearity and relative intensity noise (RIN) of the laser. The signal from the relatively large bandwidth photo-detector also allows the laser to operate effectively close to threshold.

Owner:CIENA