Low-power dissipation static random access memory (SRAM) type field programmable gate array (FPGA) design method

A design method and low power consumption technology, applied in the direction of logic circuits using specific components, logic circuits using basic logic circuit components, etc., to achieve the effects of reduced read and write power consumption, good anti-interference ability, and reduced power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

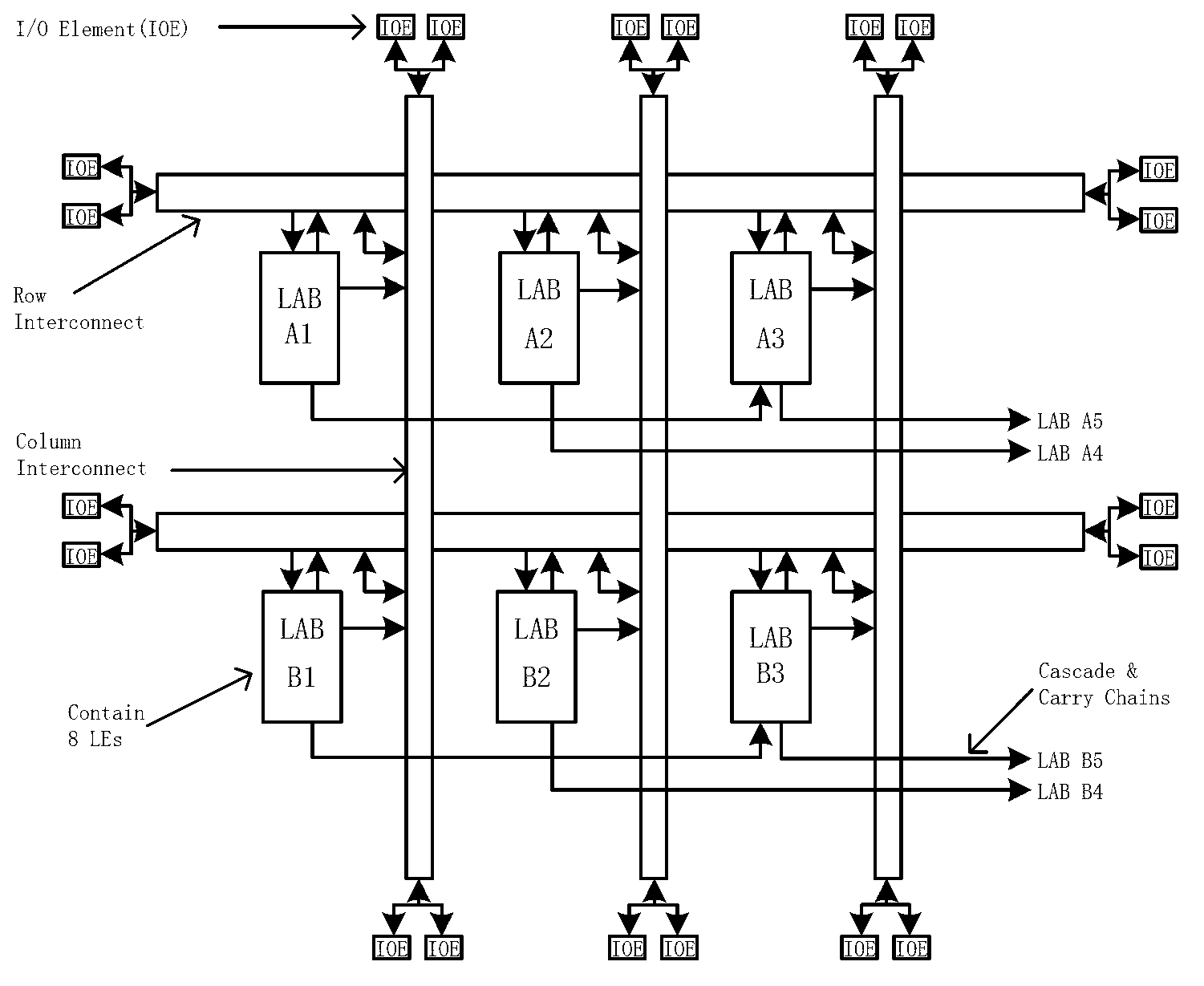

[0018] Although the structure of FPGA, CPLD and other types of PLD has its own characteristics and strengths, in general, they are composed of three major parts, such as figure 1 As shown, it includes:

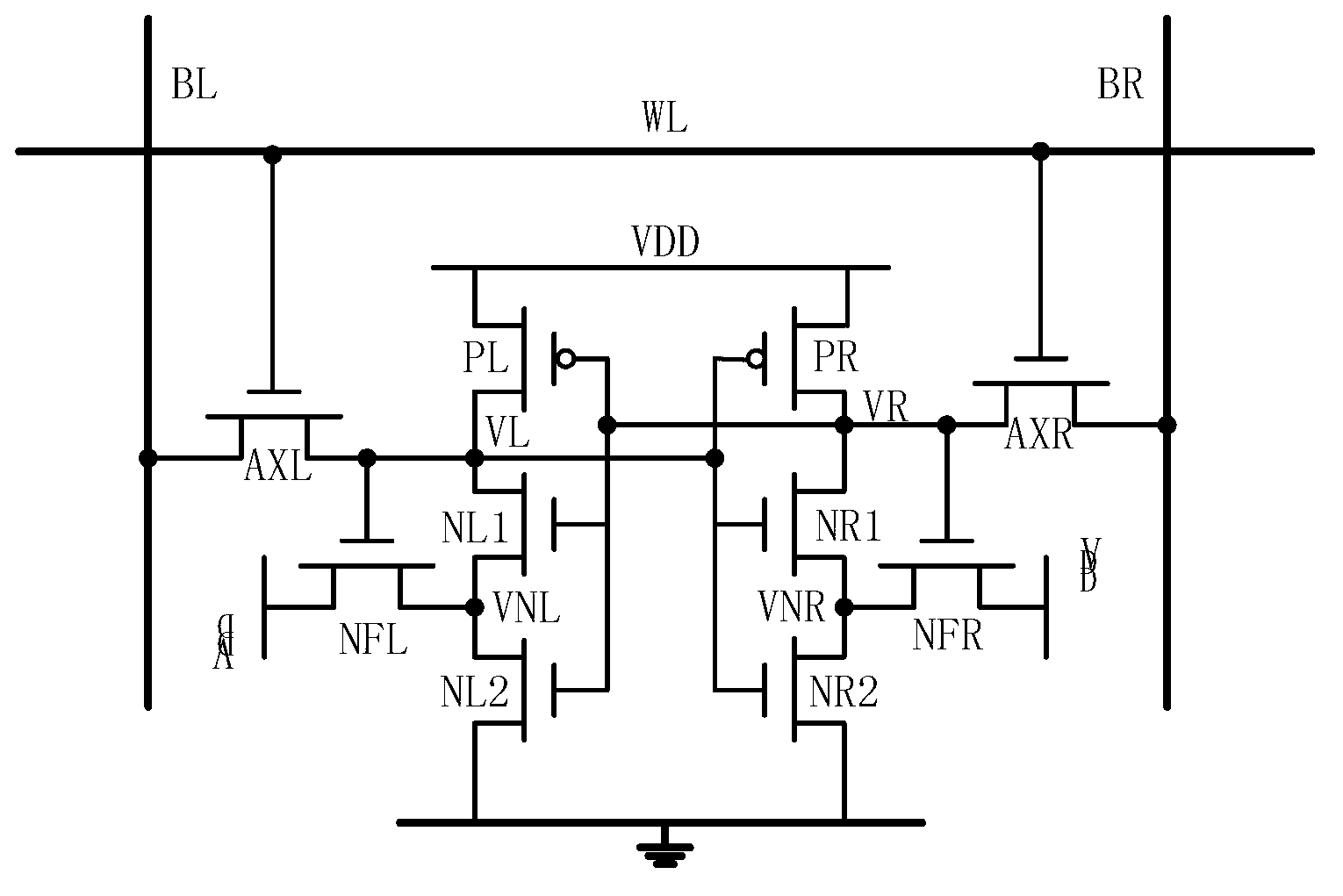

[0019] (1) A two-dimensional logic block array LAB constitutes the logic composition core of the SRAM type FPGA, and each LAB is composed of 8 logic units LE (Logic Element), and LE is the circuit to be discussed in the present invention. figure 1 The cascade and carry chain signals in LE are also derived from LE, see figure 2 ;

[0020] (2) Input / output block IOE (I / O Element);

[0021] (3) The interconnection resources connecting the logic blocks are composed of wire segments of various lengths, and there are also some programmable connection switches, which are used for the connection between logic blocks, between logic blocks and input and output blocks.

[0022] Logic unit LE is the smallest logic unit in FPGA, which can effectively implement logic functions. Each LA...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More