Design method suitable for near-threshold and sub-threshold low electric leakage standard cell

A technology of standard unit and design method, applied in CAD circuit design, calculation, electrical and digital data processing, etc., can solve the problems of increasing total energy consumption and leakage energy consumption, and achieve the effect of realizing design and low design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

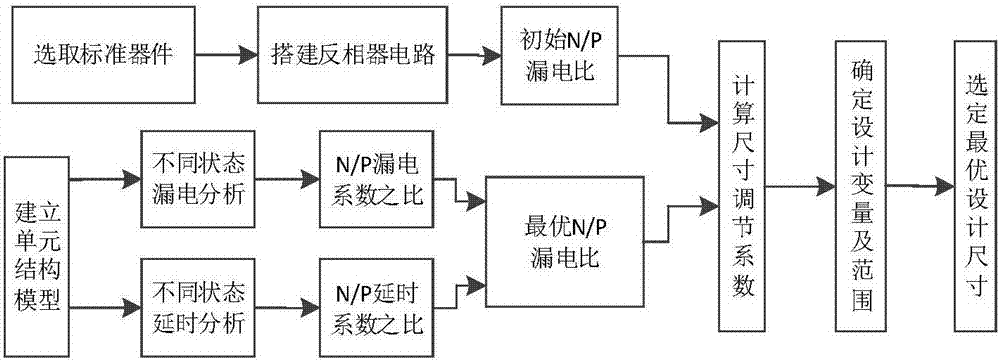

Method used

Image

Examples

Embodiment

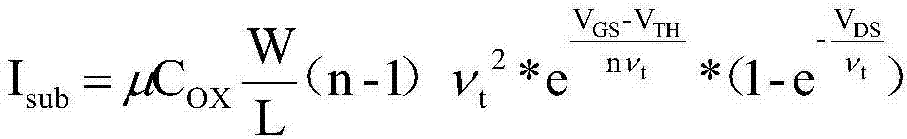

[0047] Taking the standard CMOS 0.18 micron process, power supply voltage VDD=0.4V, two-input NAND gate NAND2 unit as an example, the steps of unit size design are described in detail below:

[0048] 1. Select the minimum size tube W / L=220n / 180n as the standard size tube, and build an inverter based on the standard size tube, and obtain the leakage current when the input is low level and high level respectively I L,normn = 9.519p and I L,normp =0.7511p, then (I L,n / I L,p ) init =12.67.

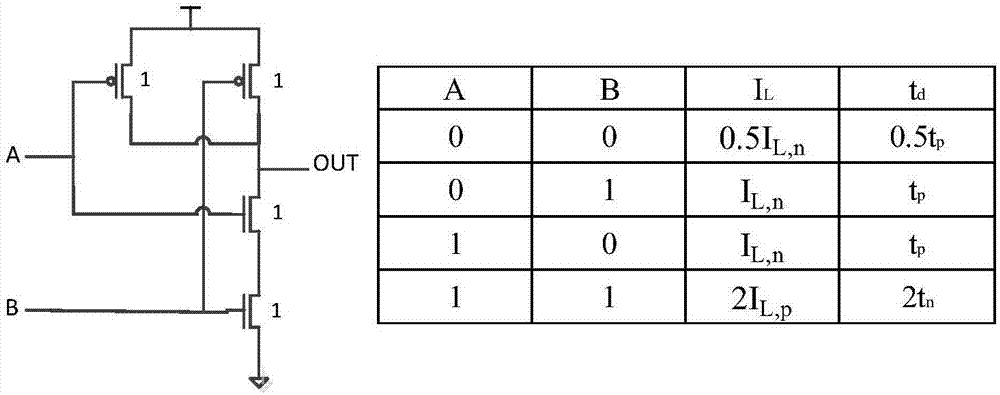

[0049] 2. Use the NMOS and PMOS of the standard size to build the NAND2 structure, such as figure 2 shown. Let "0" represent a low level, and "1" represent a high level, then the leakage current of the two-input NAND gate NAND2 unit in the four states of input AB=00, 01, 10, and 11 is 0.5I respectively L,n , I L,n , I L,n and 2I L,p , then I L =0.25(0.5I L,n +I L,n +I L,n +2I L,p ) = 0.625I L,n +0.5I L,p , get λ n =0.625,λ p = 0.5, so λ n / λ p =1.25; when the two-input NA...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More