Patents

Literature

58 results about "Full custom" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Full-custom design is a methodology for designing integrated circuits by specifying the layout of each individual transistor and the interconnections between them. Alternatives to full-custom design include various forms of semi-custom design, such as the repetition of small transistor subcircuits; one such methodology is the use of standard cell libraries (standard cell libraries are themselves designed using full-custom design techniques).

Real-time receipt, decompression and play of compressed streaming video/hypervideo; with thumbnail display of past scenes and with replay, hyperlinking and/or recording permissively intiated retrospectively

InactiveUS6154771AEfficient multicastingEasy to seeTelevision system detailsDigital data information retrievalFull customSoftware system

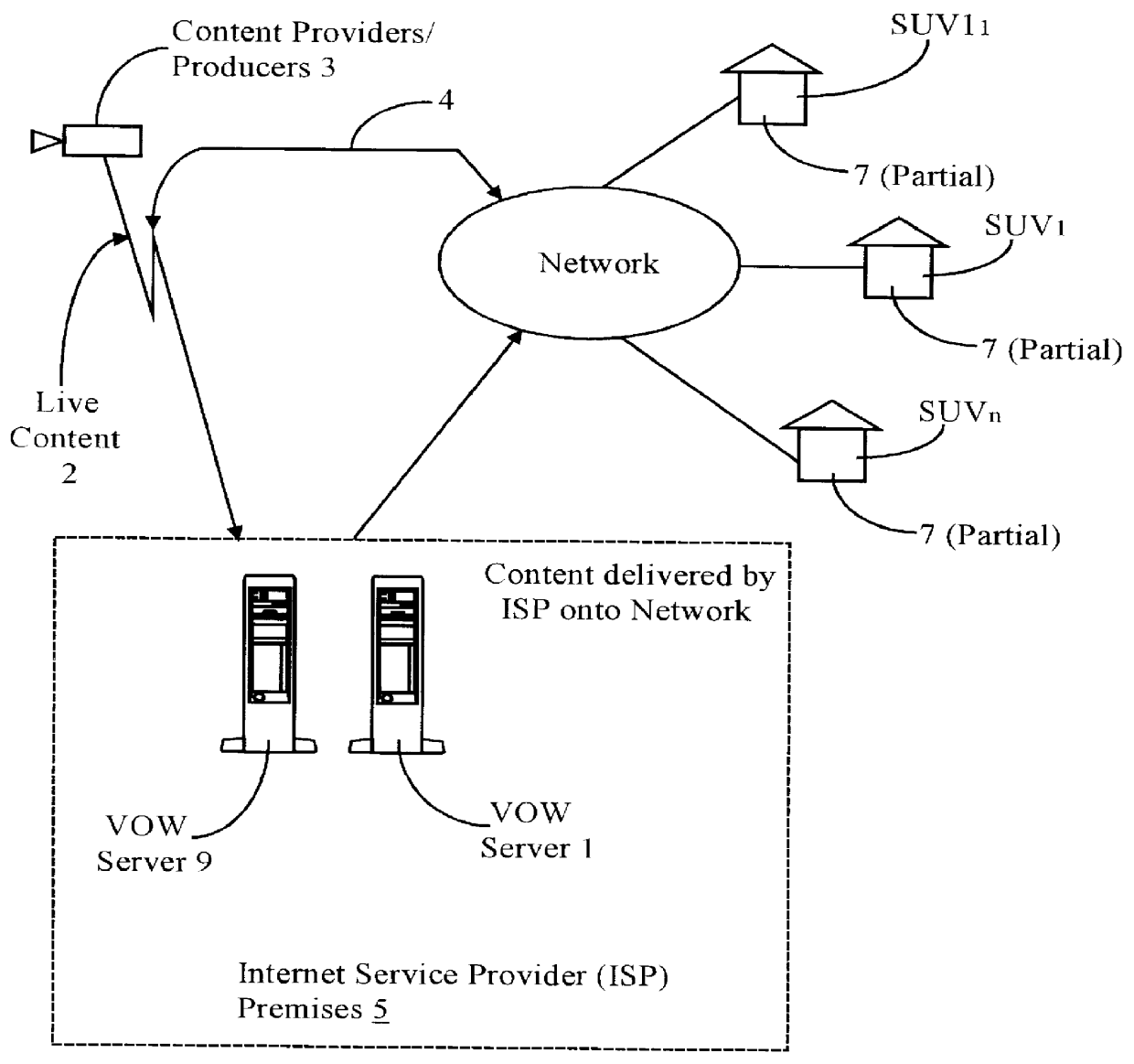

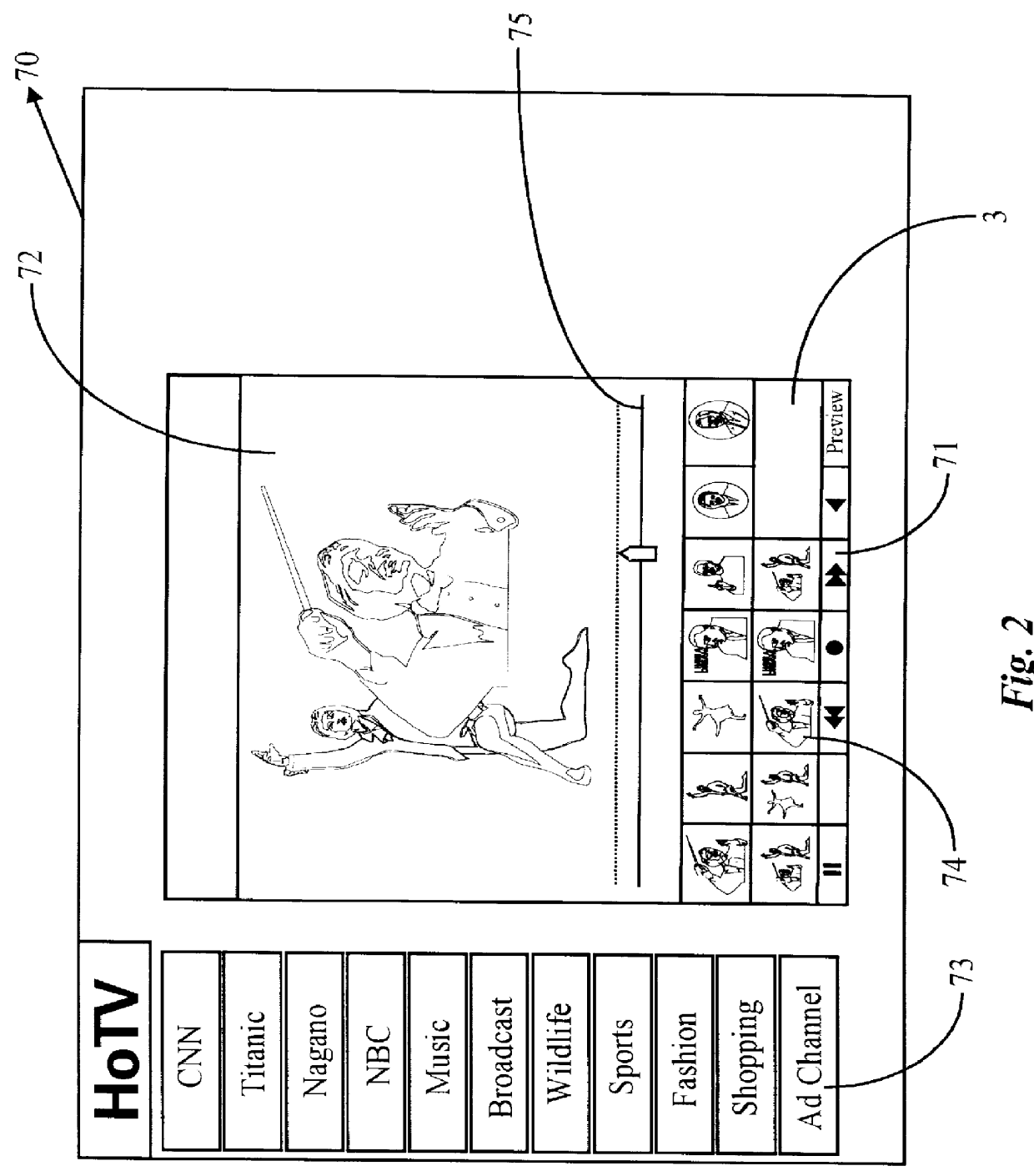

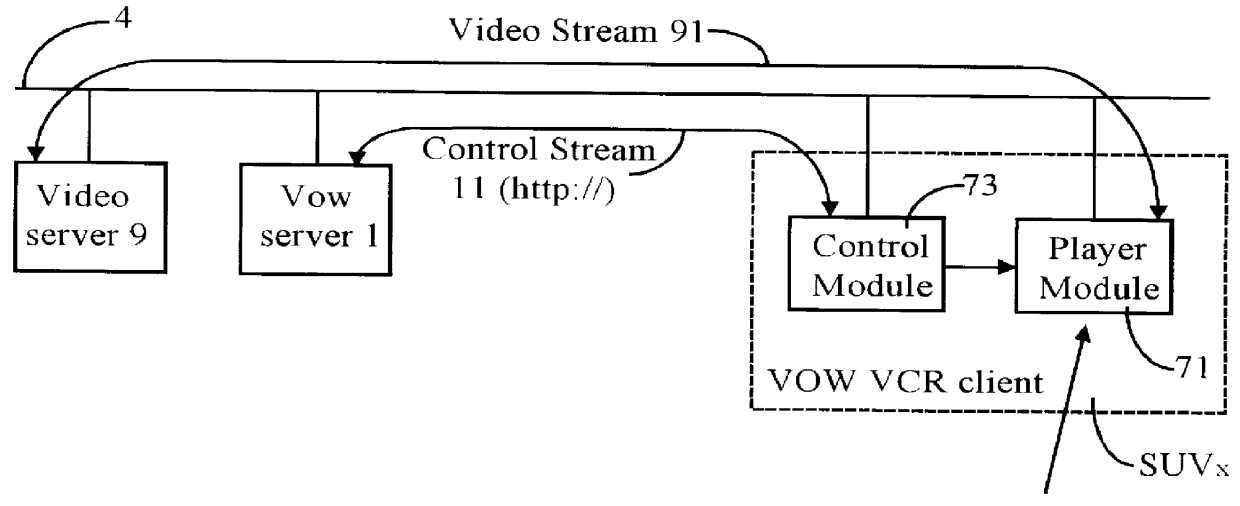

Streaming compressed digital hypervideo received upon a digital communications network is decoded (decompressed) and played in a client-computer-based "video on web VCR" software system. Scene changes, if not previously marked upstream, are automatically detected, and typically twenty-one past scenes are displayed as thumbnail images. Hyperlinks within the main video scene, and / or any thumbnail image, show as hotspots, with text annotations typically appearing upon a cursor "mouse over". All hyperlinks-as are provided and inserted by, inter alia, the upstream network service provider (the "ISP")-may be, and preferably are, full-custom dynamically-resolved to each subscriber / user / viewer ("SUV") upon volitional "click throughs" by the SUV, including retrospectively on past hypervideo scenes as appear within the thumbnail images. Hyperlinking permits (i) retrieving information and commercials, including streaming video / hypervideo, from any of local storage, a network (or Internet) service provider ("ISP"), a network content provider, and / or an advertiser network site, (ii) entering a contest of skill or a lottery of chance, (iii) gambling, (iv) buying (and less often, selling), (v) responding to a survey, and expressing an opinion, and / or (vi) sounding an alert.

Owner:TATA AMERICA INT

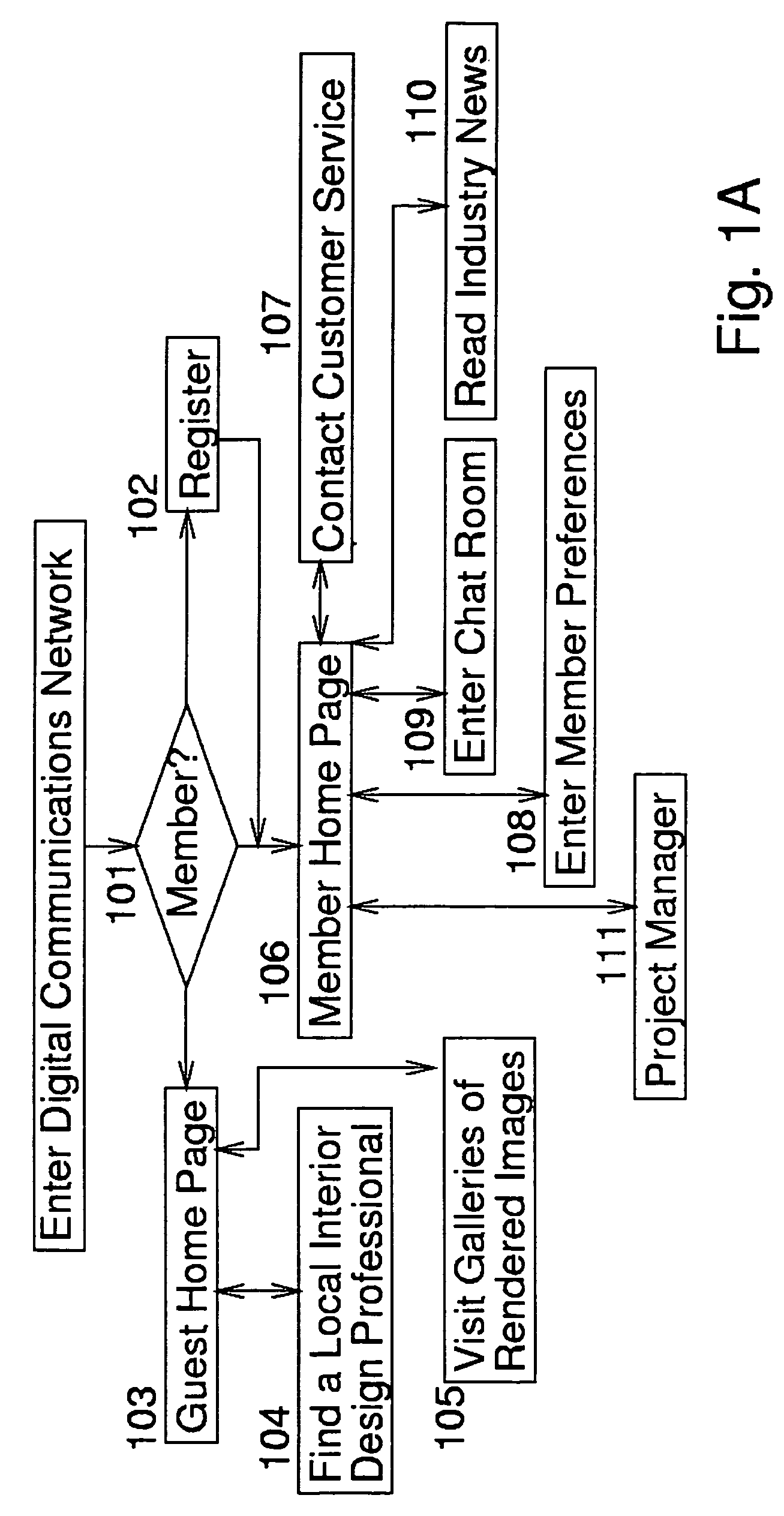

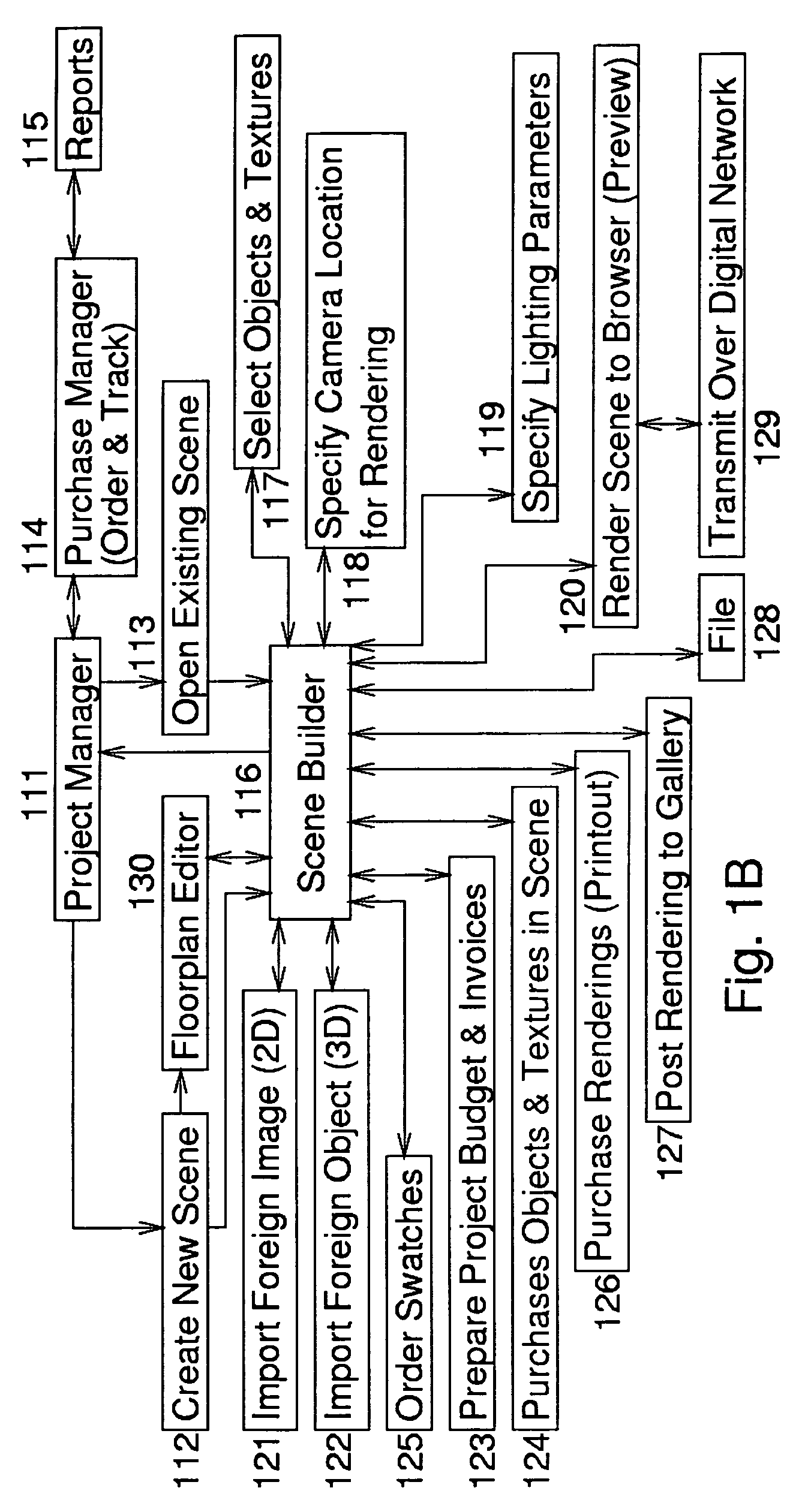

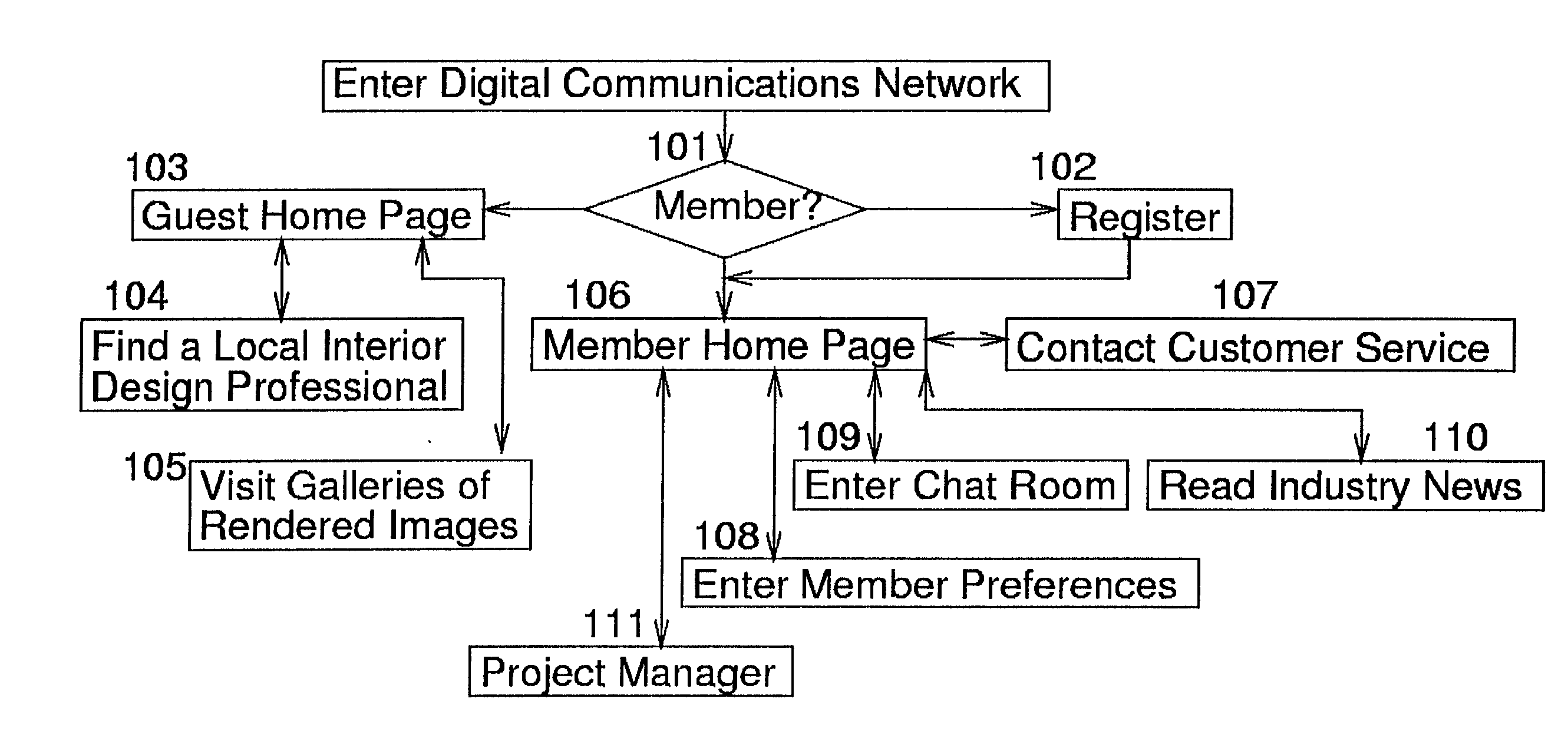

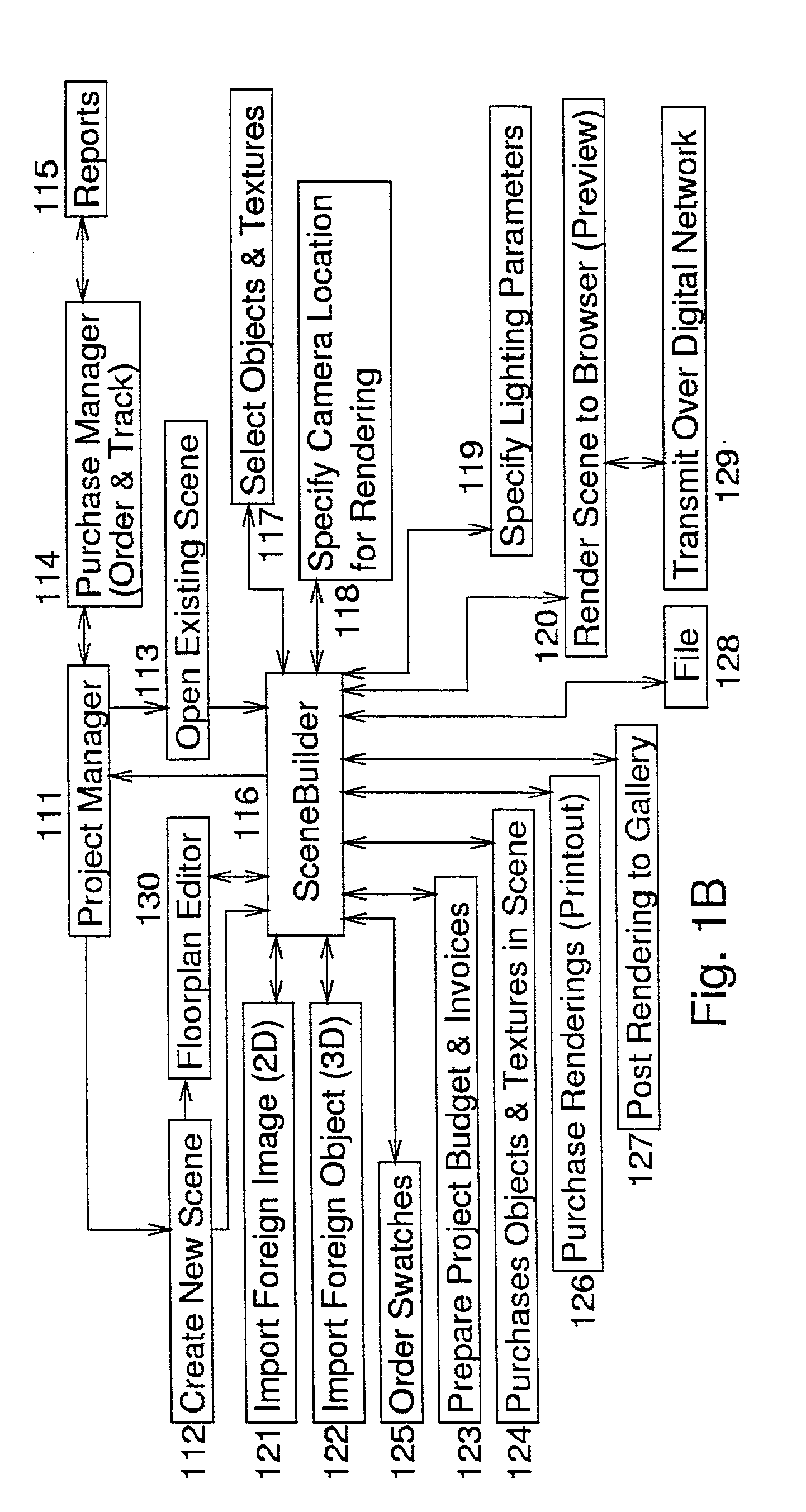

Network-linked interactive three-dimensional composition and display of saleable objects in situ in viewer-selected scenes for purposes of promotion and procurement

InactiveUS7062722B1Sufficiently accurateSufficiently appealingSpecial data processing applicationsMarketingFull custom3d image

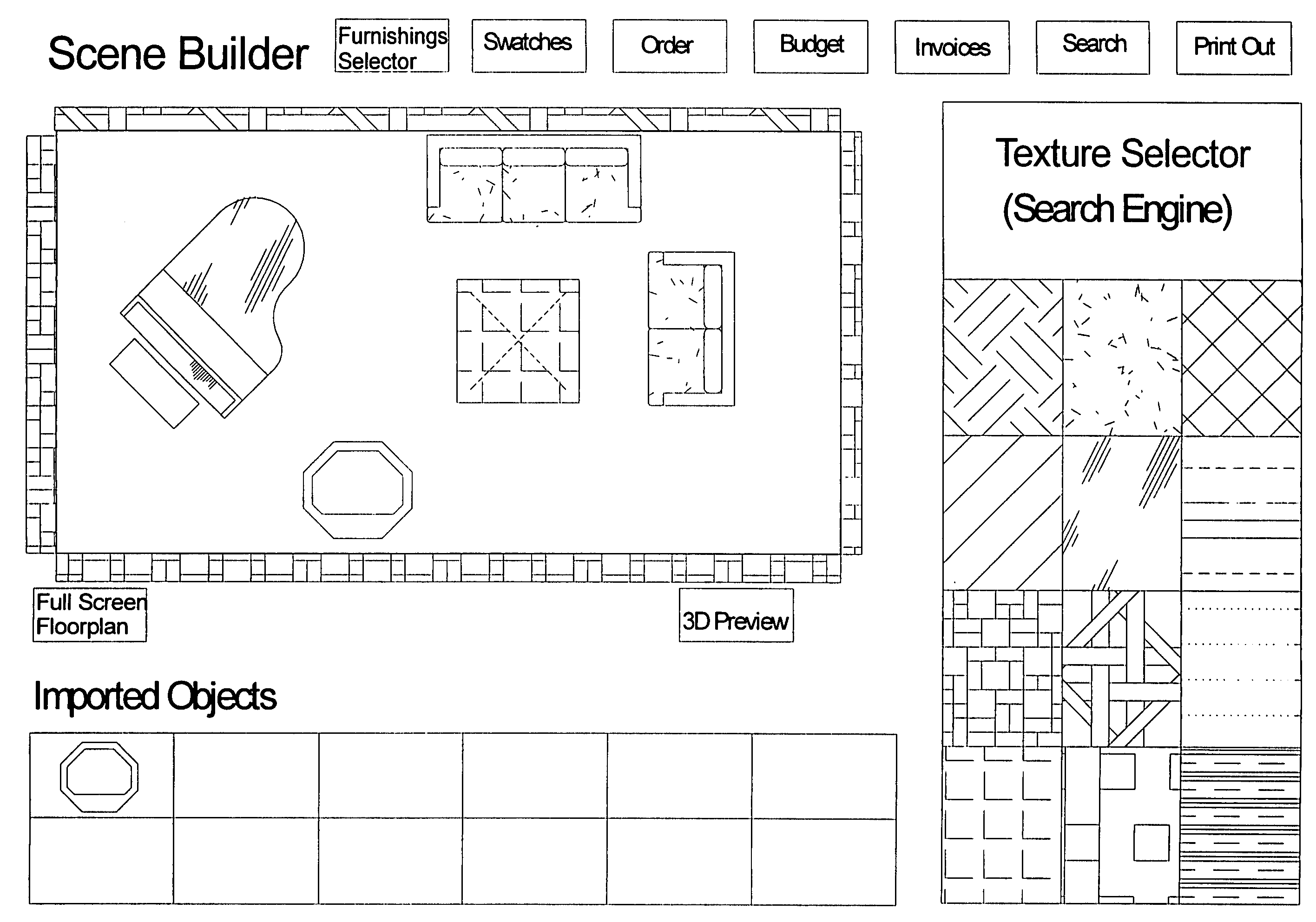

A design professional such as an interior designer running a browser program at a client computer (i) optionally causes a digital image of a room, or a room model, or room images to be transmitted across the world wide web to a graphics server computer, and (ii) interactively selects furnishings from this server computer, so as to (iii) receive and display to his or her client a high-fidelity high-quality virtual-reality perspective-view image of furnishings displayed in, most commonly, an actual room of a client's home. Opticians may, for example, (i) upload one or more images of a client's head, and (ii) select eyeglass frames and components, to (iii) display to a prospective customer eyeglasses upon the customer's own head. The realistic images, optionally provided to bona fide design professionals for free, promote the sale to the client of goods which are normally obtained through the graphics service provider, profiting both the service provider and the design professional. Models of existing objects are built as necessary from object views. Full custom objects, including furniture and eyeglasses not yet built, are readily presented in realistic virtual image.Also, a method of interactive advertising permits a prospective customer of a product, such as a vehicle, to view a virtual image of the selected product located within a customer-selected virtual scene, such as the prospective customer's own home driveway. Imaging for all purposes is supported by comprehensive and complete 2D to 3D image translation with precise object placement, scaling, angular rotation, coloration, shading and lighting so as to deliver flattering perspective images that, by selective lighting, arguably look better than actual photographs of real world objects within the real world.

Owner:CARLIN BRUCE +3

Network-linked interactive three-dimensional composition and display of saleable objects in situ in viewer-selected scenes for purposes of object promotion and procurement, and generation of object advertisements

A design professional such as an interior designer, furniture sales associate or advertising designer running a browser program at a client computer (i) uses the world wide web to connect to a graphics server computer, and (ii) interactively selects or specifies furnishings or other objects from this server computer and previews the scene and communicates with the server, so as to (iii) receive and display to his or her client a high-fidelity high-quality virtual-reality perspective-view photorealistic image of furnishings or other objects displayed in, most commonly, a virtual representation of an actual room of a client's home or an advertisement scene. The photorealistic images, optionally provided to bona fide design professionals and their clients for free, but typically paid for by the product's manufacturer, promote the sale to the client of goods which are normally obtained through the graphics service provider's customer's distributor, profiting both the service provider and the design professional. Models, textures and maps of existing objects are built as necessary from object views or actual objects. Full custom objects, including furniture and other products not yet built, are readily presented in realistic virtual image. Also, a method of interactive advertising permits a prospective customer of a product, such as furniture, to view a virtual but photorealistic, image of a selected product located within a customer-selected scene, such as the prospective customer's own home, to allow in-context visualization.

Owner:CARLIN BRUCE

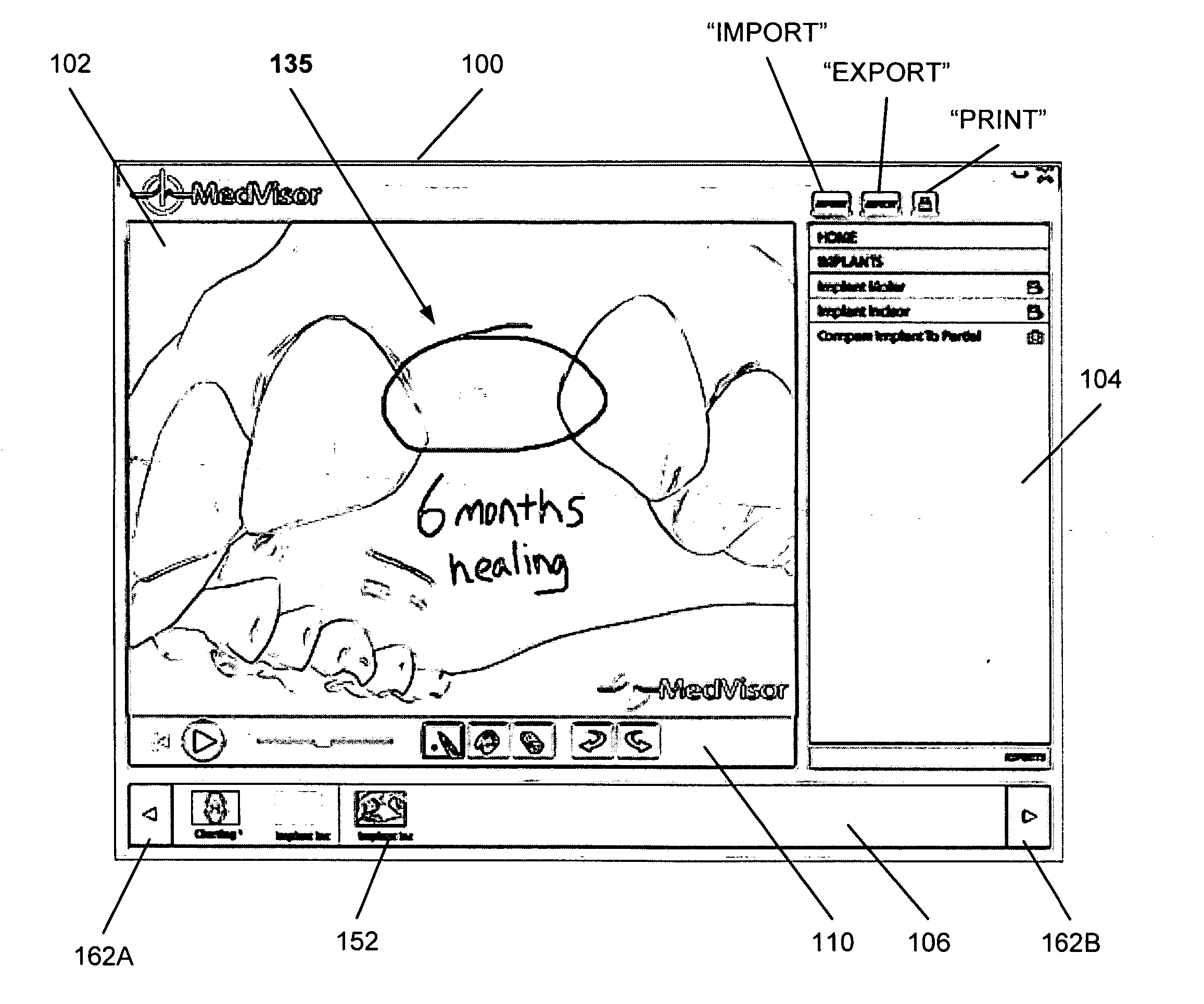

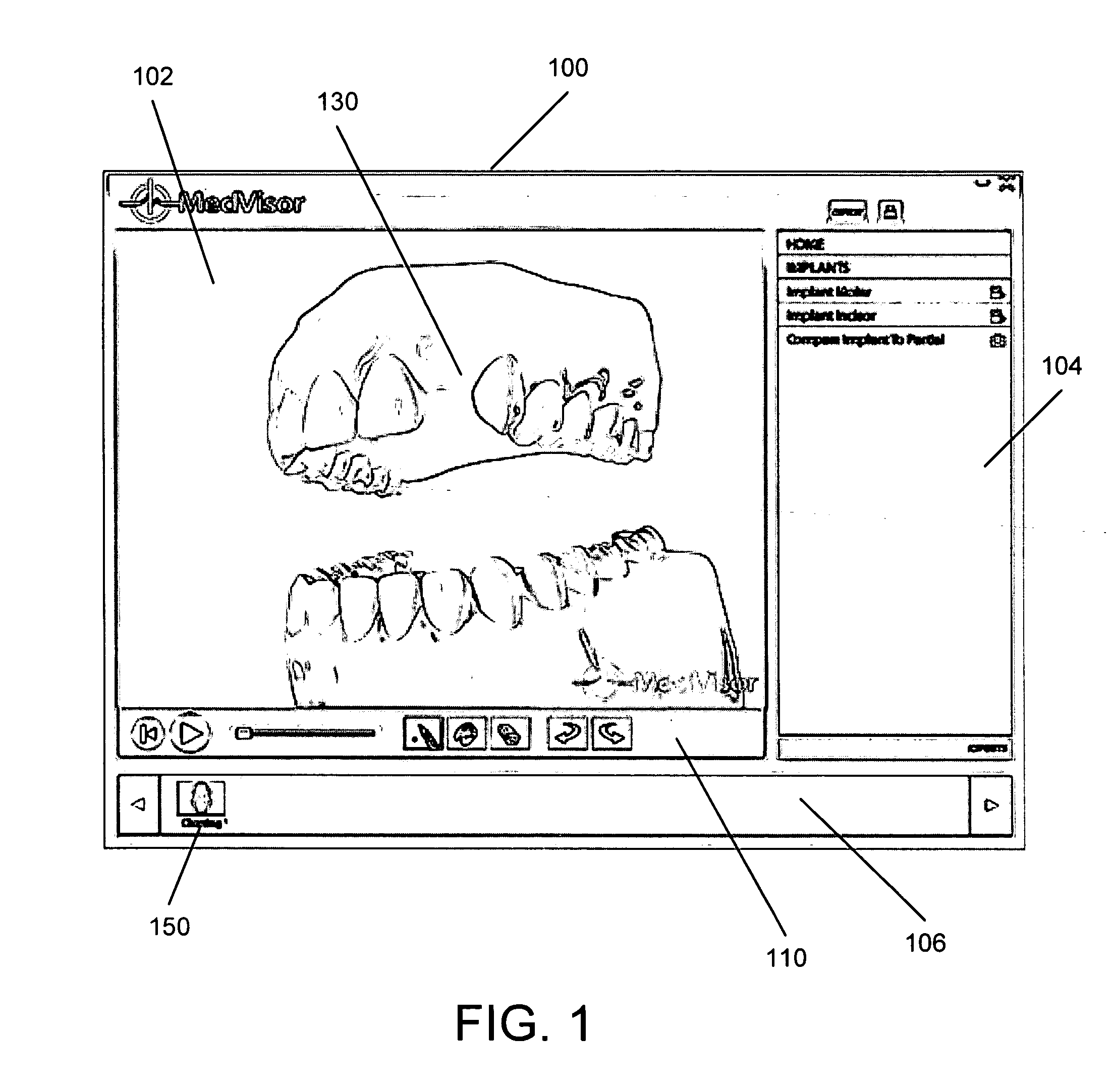

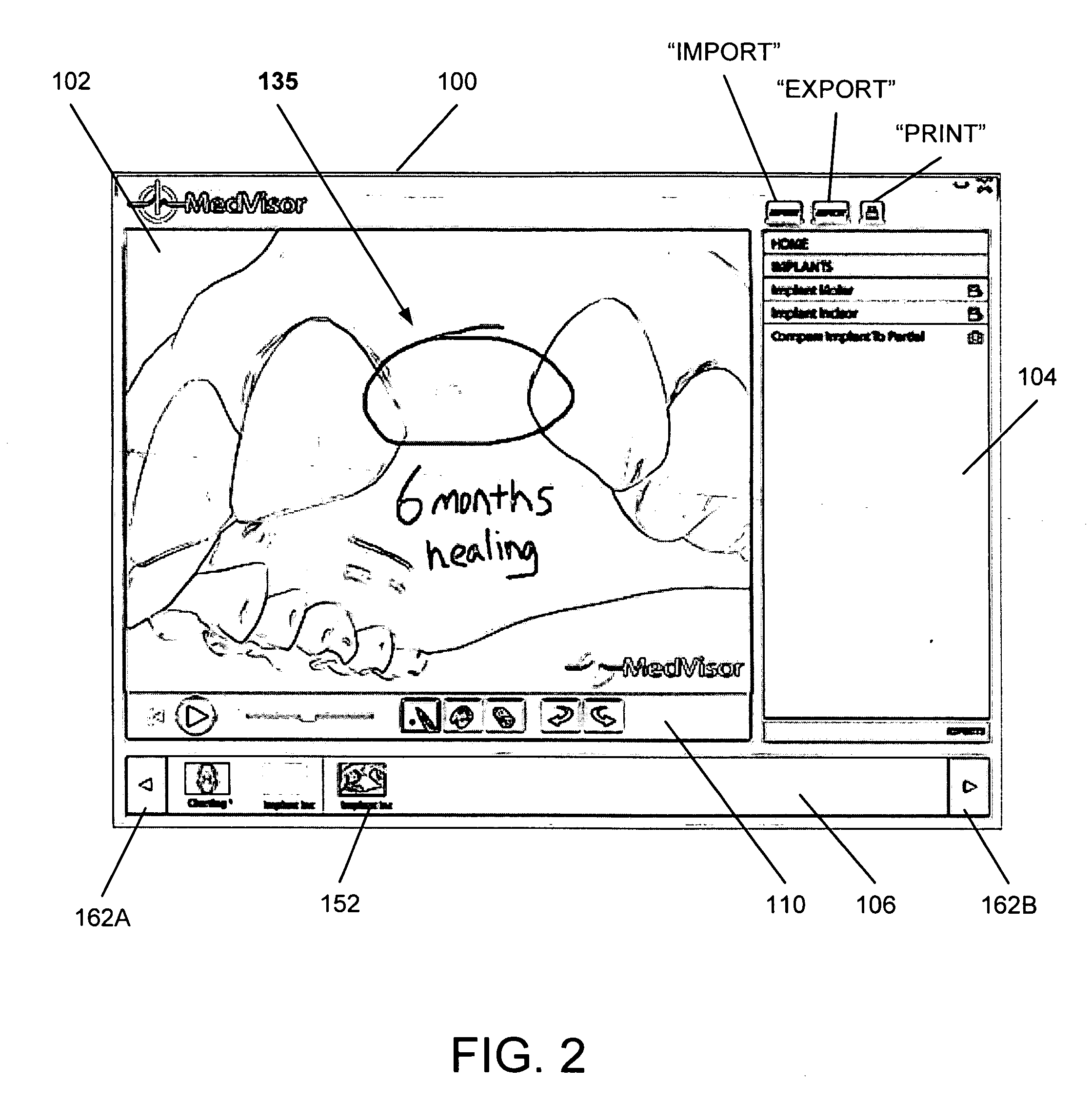

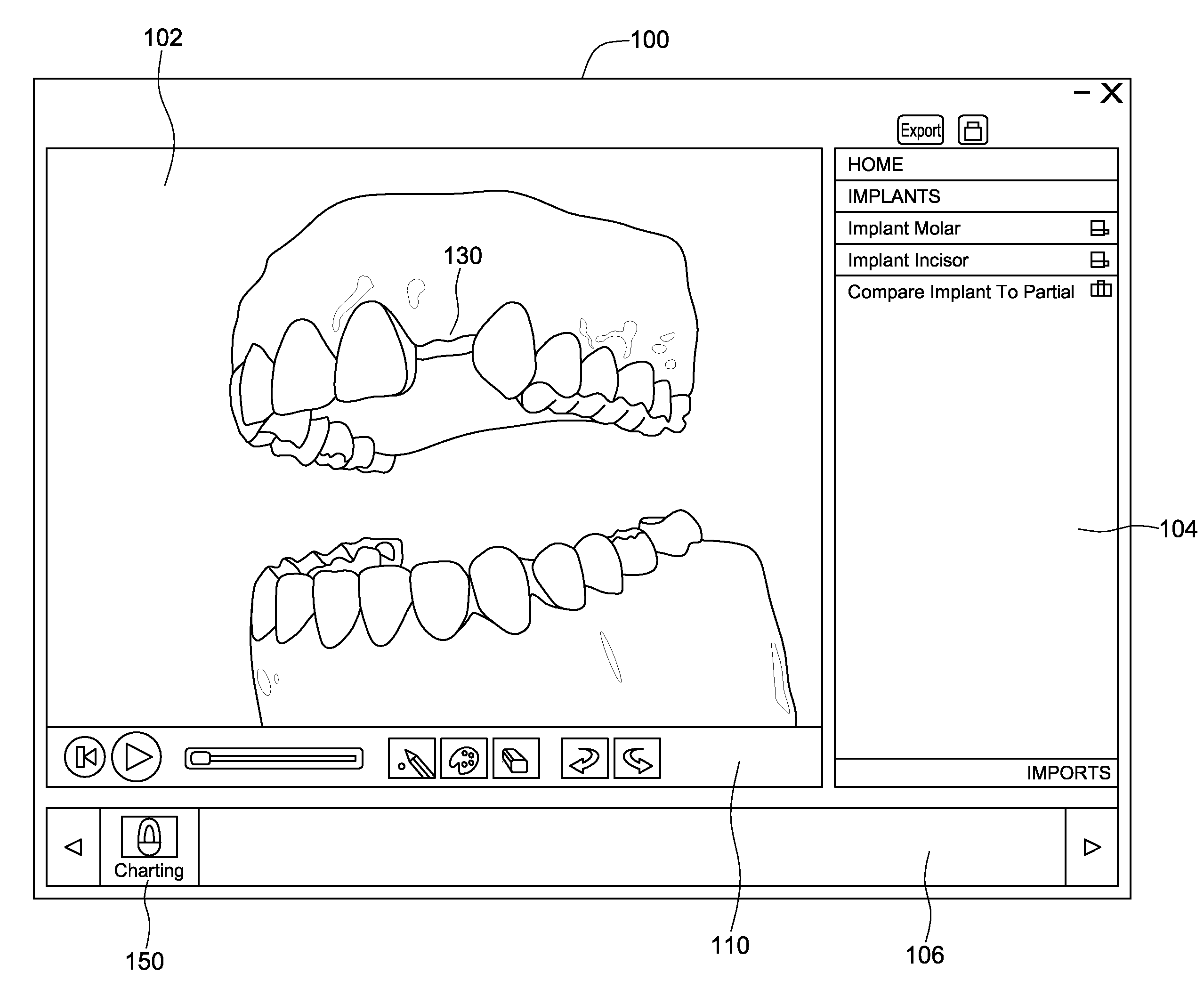

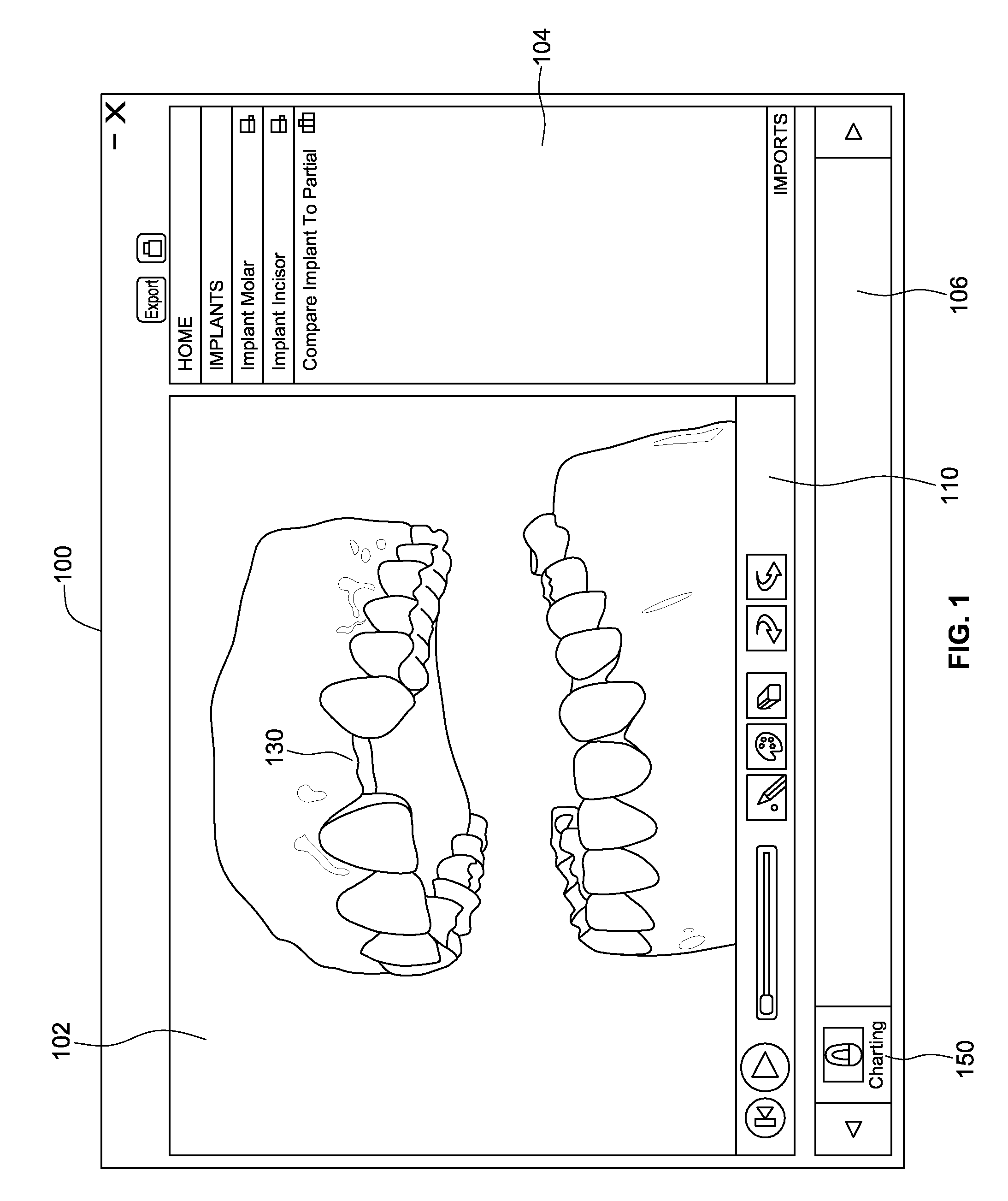

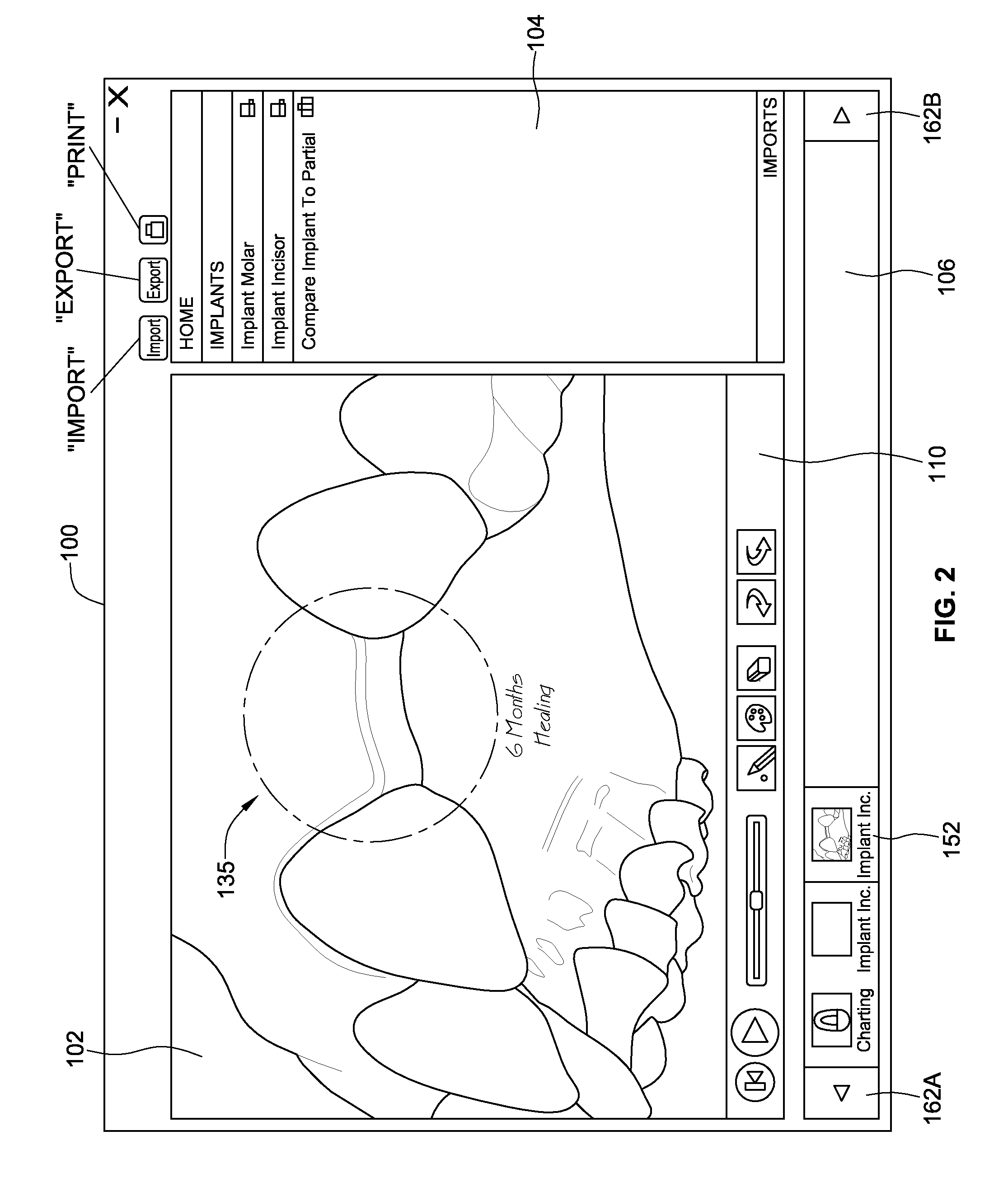

Interactive patient education system

Interactive patient education system for use in operatory or office settings, provides interactive 3-D animations, graphics and other media, enabling real-time markup and customization to better illustrate and communicate not only generic information, but the individual patient's physiology, treatment options, and anticipated outcomes. Preferred embodiments are portable, computer-implemented, interactive multimedia educational tools. Import of patient-specific graphics, video and audio contributes to full-custom educational content to optimize patient understanding.

Owner:REALITY ENG

Method and system for the design of an enclosure to house internal components

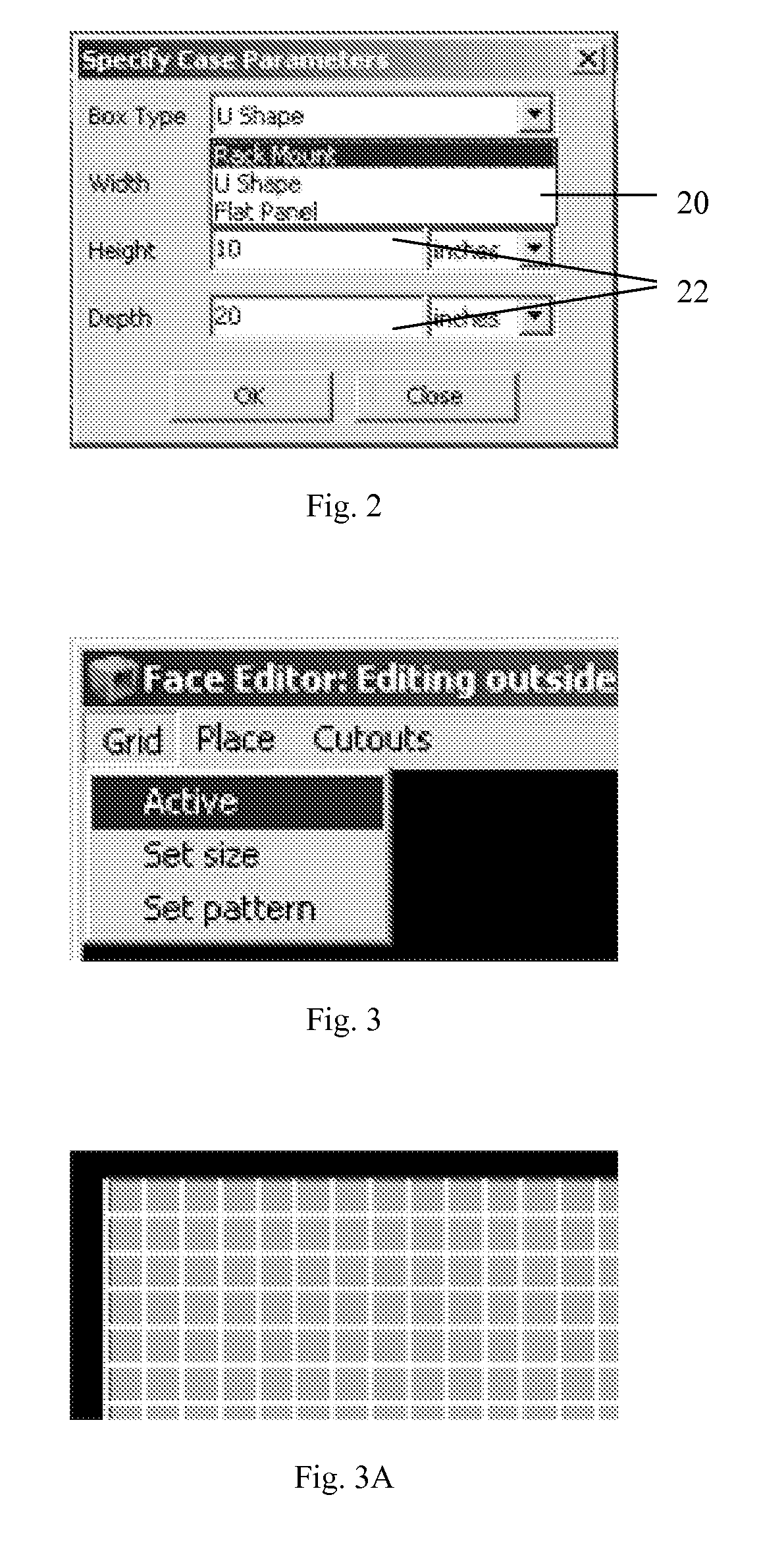

ActiveUS20080120086A1Simple to useSimple to learnRack/frame constructionSupport structure mountingComputer basedManufacturing engineering

Disclosed are a method, a computer-based system and a computer-readable medium having computer-readable code embodied therein for creating the specifications for the fabrication of a fully customized enclosure housing internal components. First a suitable three dimensional template representing a basic form of the enclosure is chosen from a plurality of predetermined three dimensional templates and sized. Each face of the enclosure is selected and customized by selecting specific design features from a range of predetermined design options as necessary until a complete set of specifications for the enclosure is obtained.

Owner:PROTOCASE

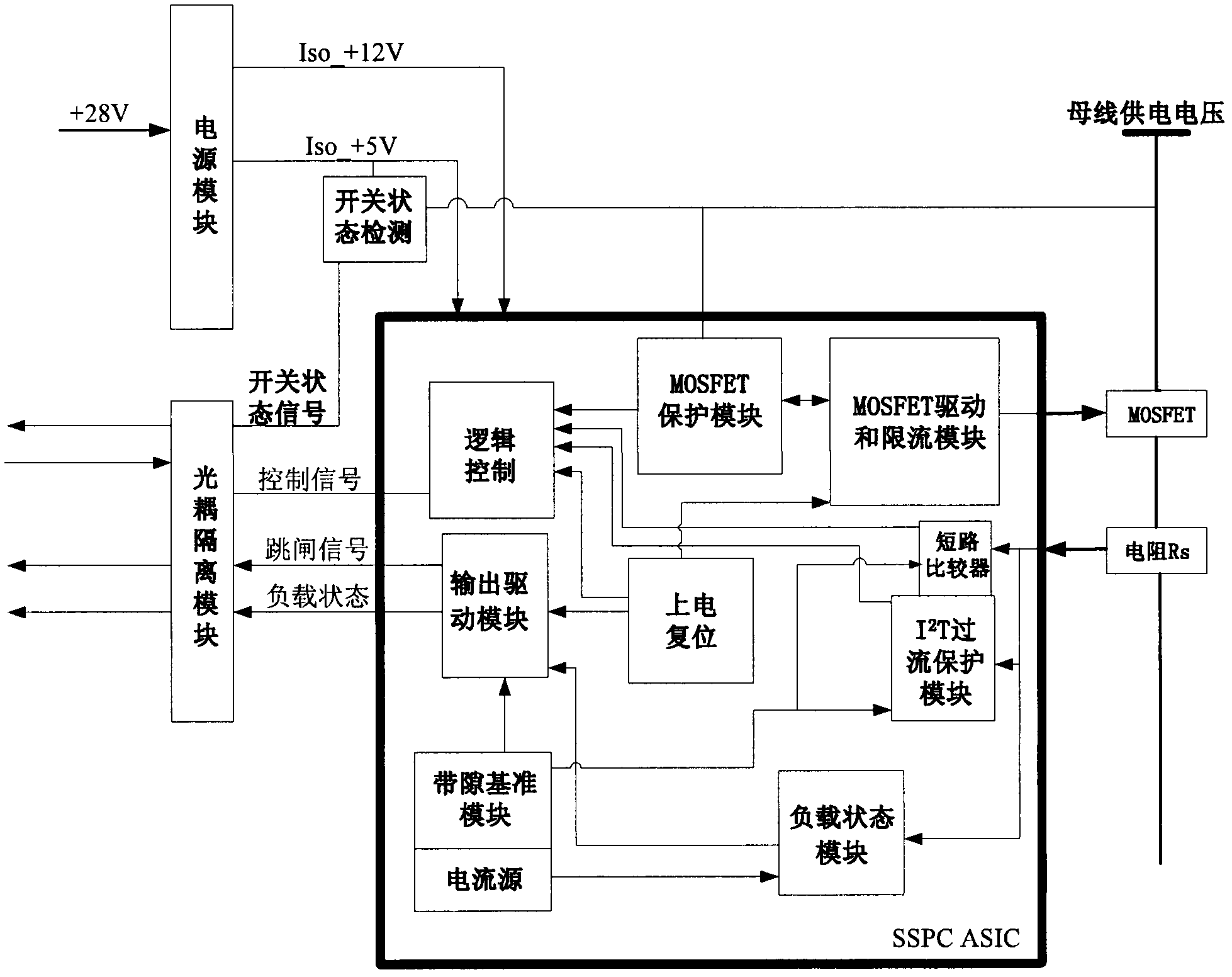

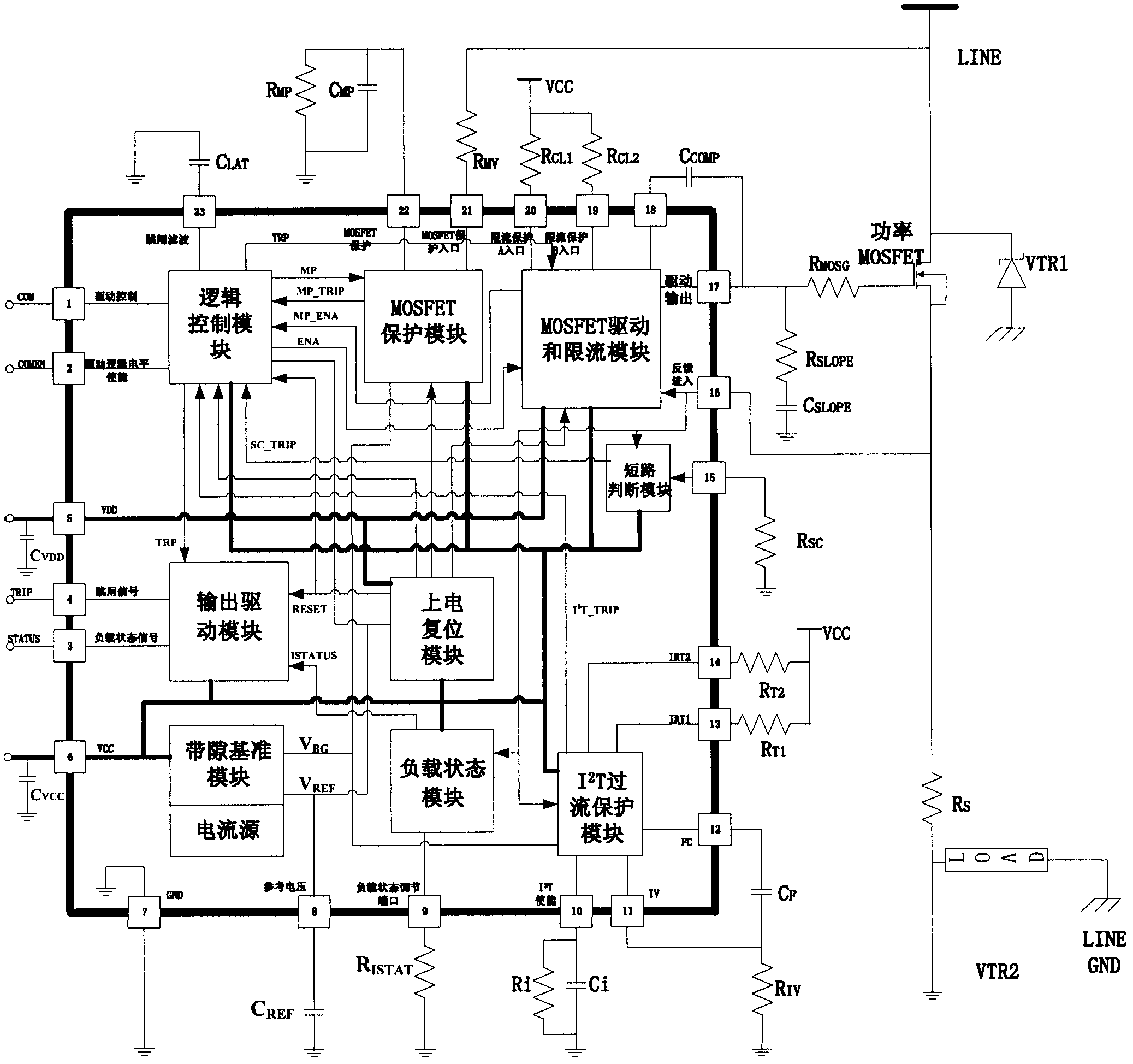

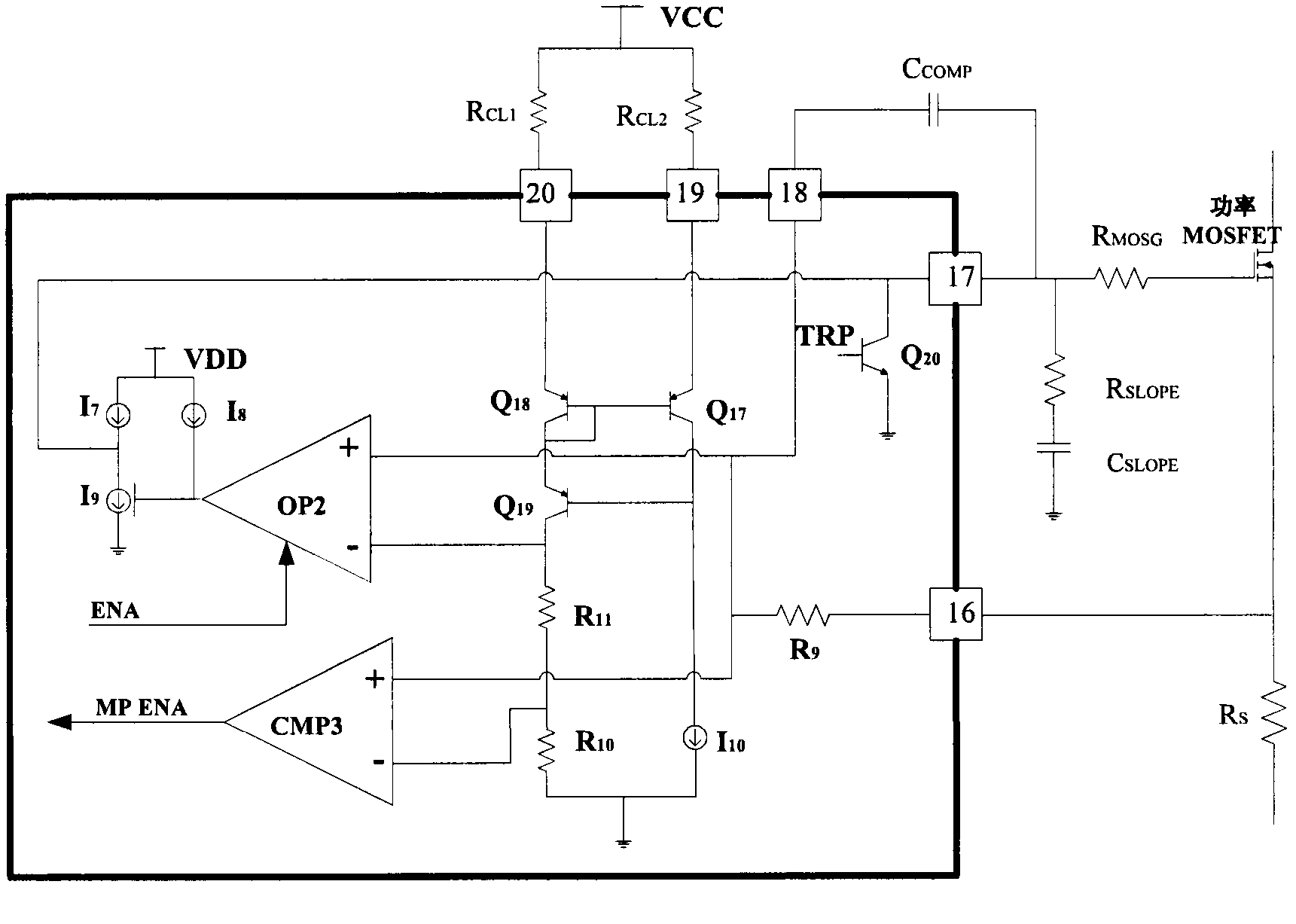

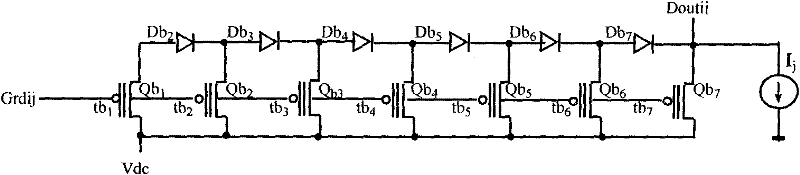

DC solid-state power controller

ActiveCN102570412AImprove environmental adaptabilityMiniaturizationEmergency protective circuit arrangementsFull customShort circuit protection

The invention relates to a DC solid-state power controller, which is suitable for power distribution networks with different power levels. The DC solid-state power controller consists of a signal processing unit based on and taking a full-custom special integrated-circuit chip as the core, a power supply isolation unit, a signal isolation unit, a power MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) and a resistor connected in series with a bus. The DC solid-state power controller receives a driving switching signal to achieve on / off of the MOSFET connected in series to the bus, can serve the functions of bus load detection, current-limiting protection, overcurrent protection, short-circuit protection and self protection, and can achieve a plurality of protection parameters through change of a hardware circuit. All functions of the solid-state power controller are served by the internal hardware circuit, and the MOSFET driving signals and the protection signals are all generated by a full-custom integrated circuit. Therefore, the DC solid-state power controller has the characteristics of strong anti-interference performance, short reaction time, simple structural design, high reliability, low power consumption, compactness and the like.

Owner:CHINA AEROSPACE TIMES ELECTRONICS +1

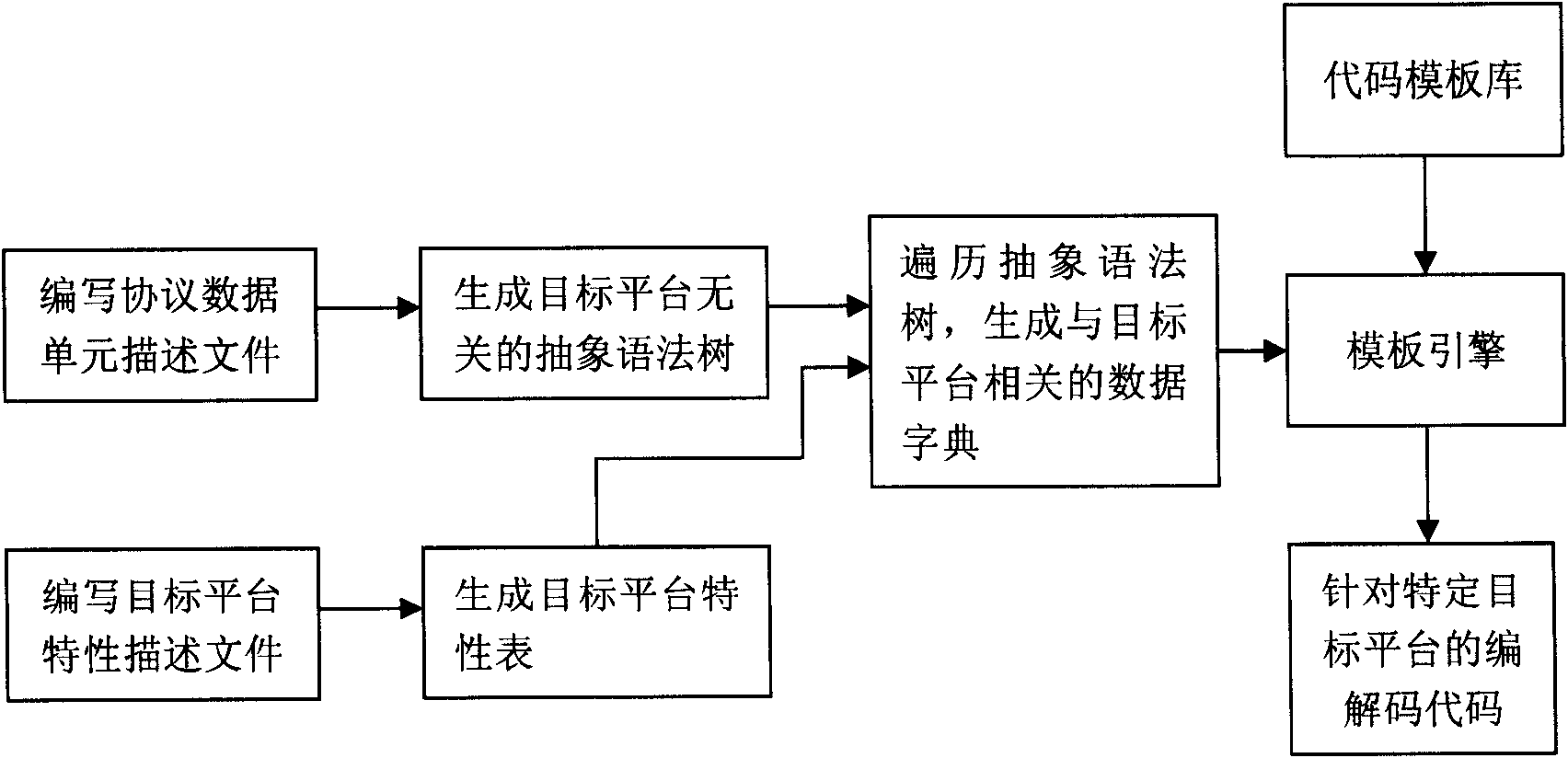

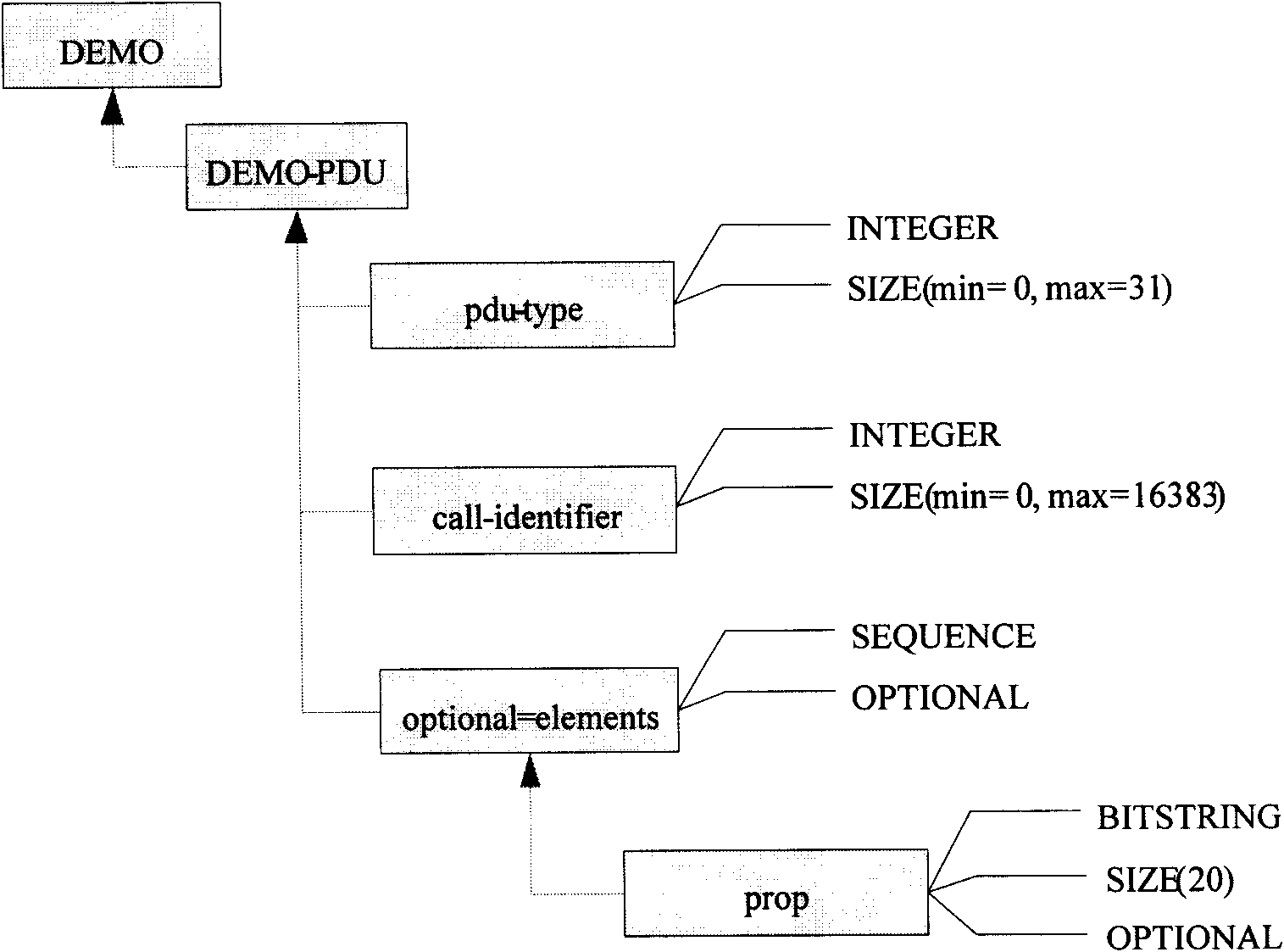

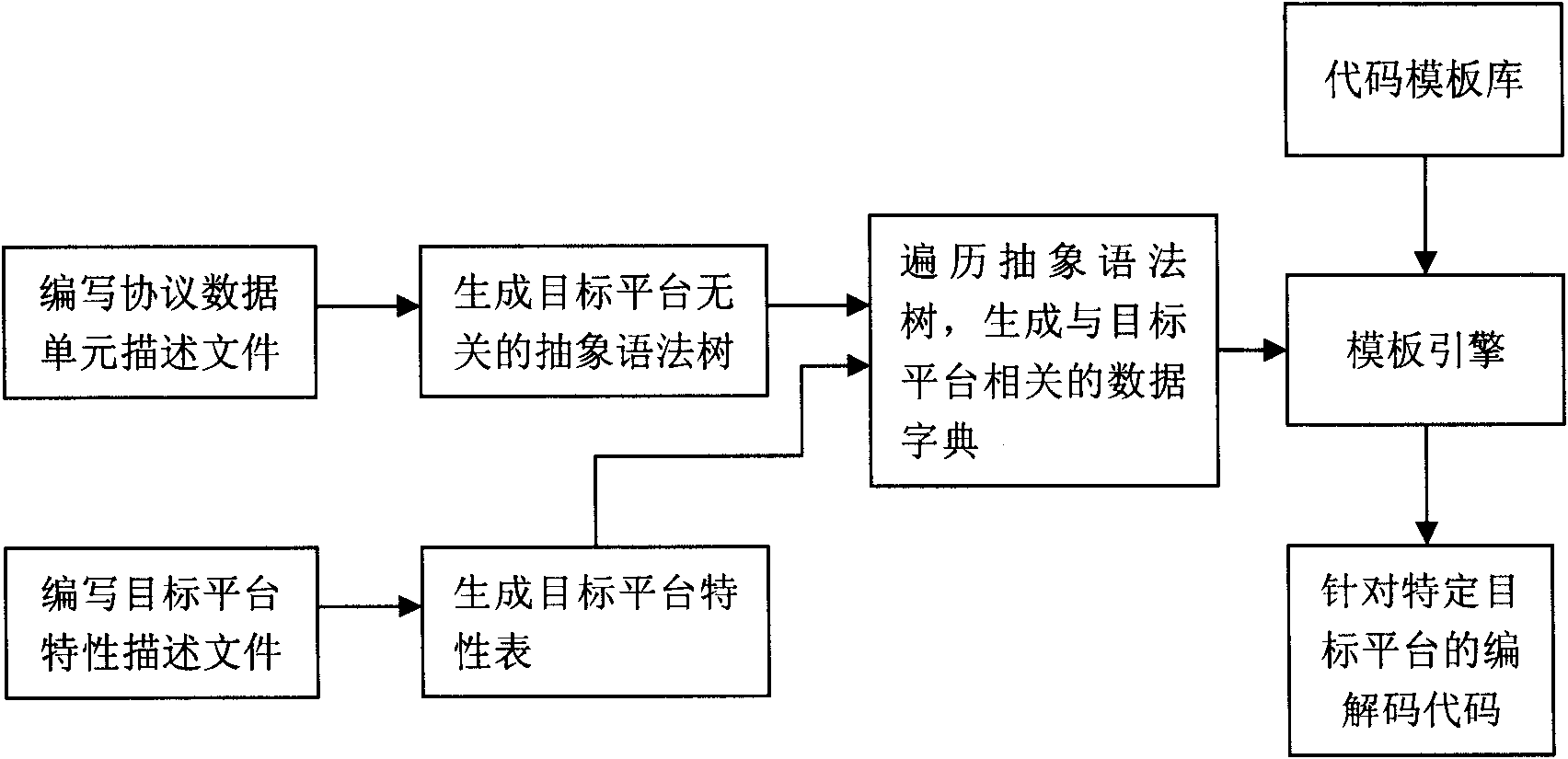

Target variable protocol data unit codec code automatic generation implementation method

ActiveCN101841515AOvercoming scalabilityOvercome target platformTransmissionSpecific program execution arrangementsTemplate basedAbstract syntax tree

The invention discloses a target variable protocol data unit codec code automatic generation implementation method. Firstly, a target platform characteristic description file is written, the file describes the basic conventional characteristics of the specific target platform, then a PDU description file is written to describe composition of inner elements of PDU, a system automatically analyzes the PDU description file and generates an abstract syntax tree irrelevant to the target platform according to the content thereof, and then the system traverses the abstract syntax tree and generates a data dictionary relevant to the target platform by utilizing the characteristic of the target platform, and finally a code template base is written and PDU codec code directing to the specific target platform is generated. The system applying the method can conveniently generate PDU codec code supporting various target platforms, and especially the target platform and template to generate code can be completely customized without modifying the code generation system.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

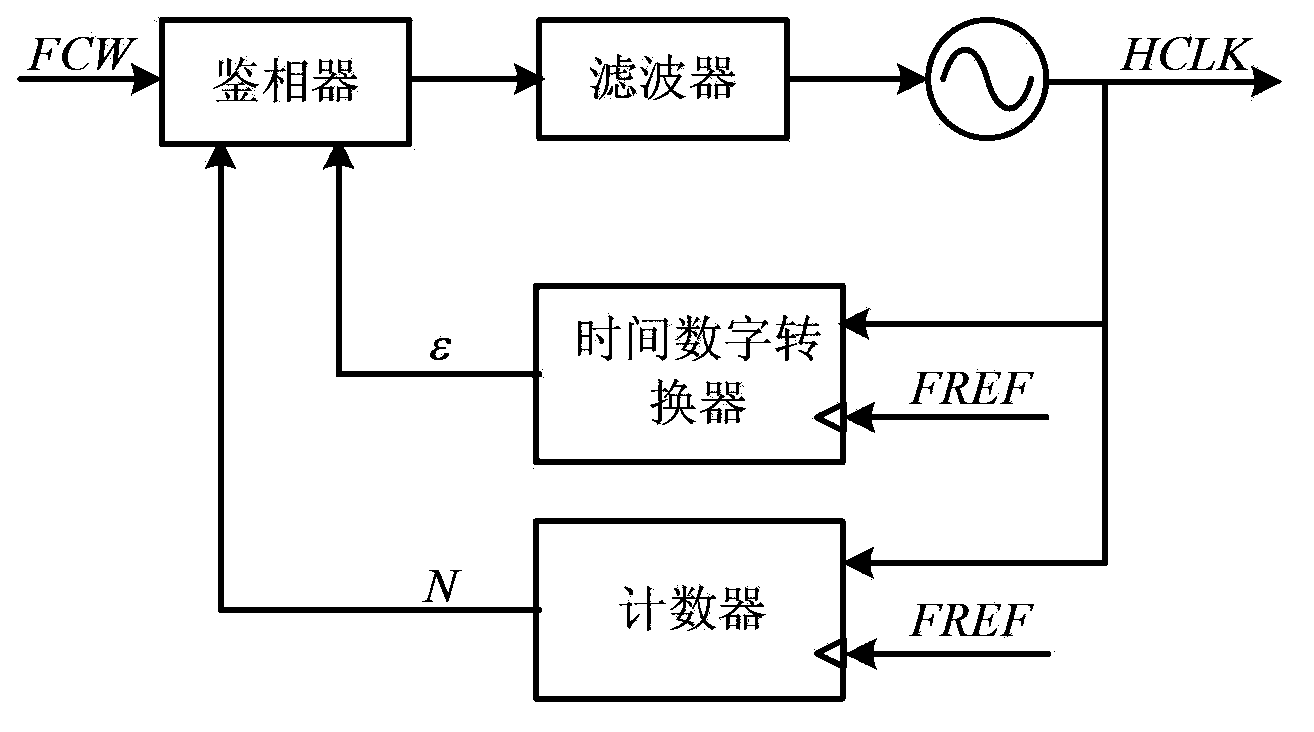

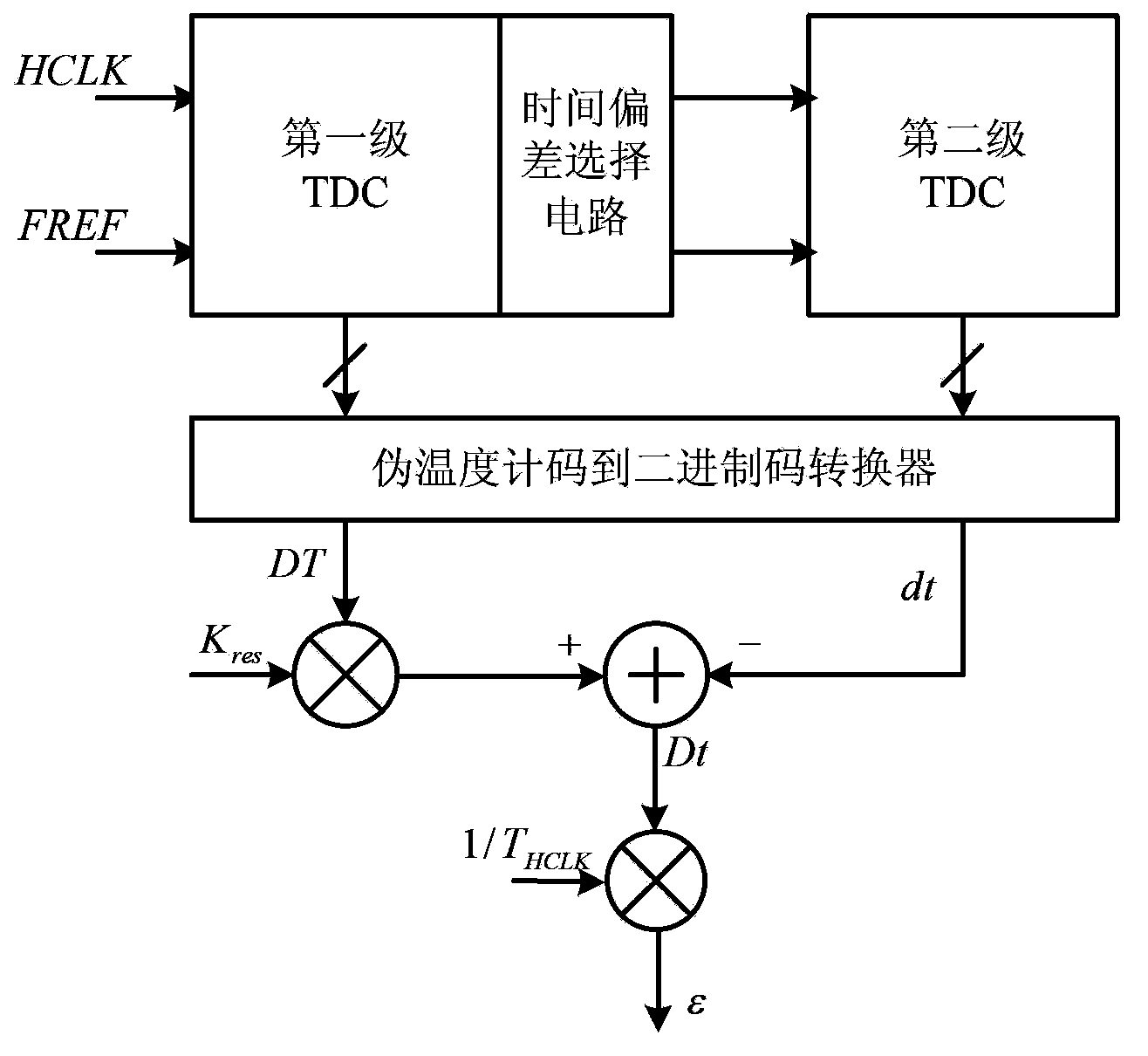

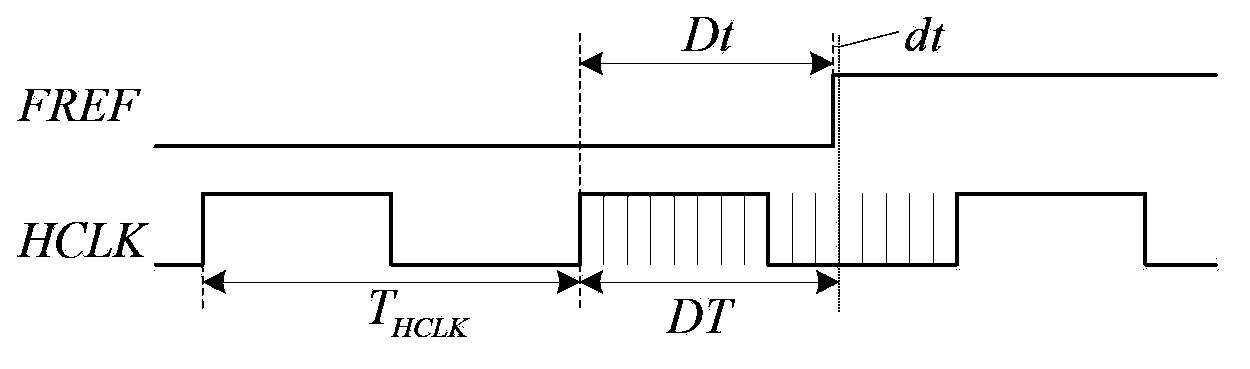

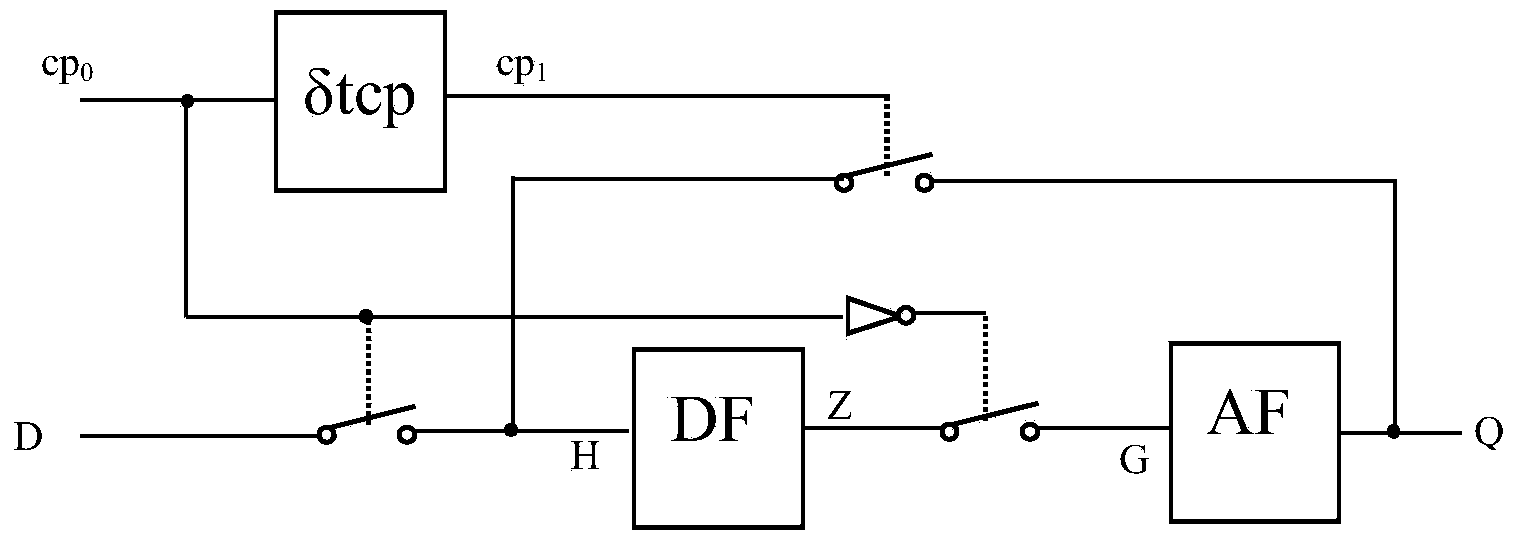

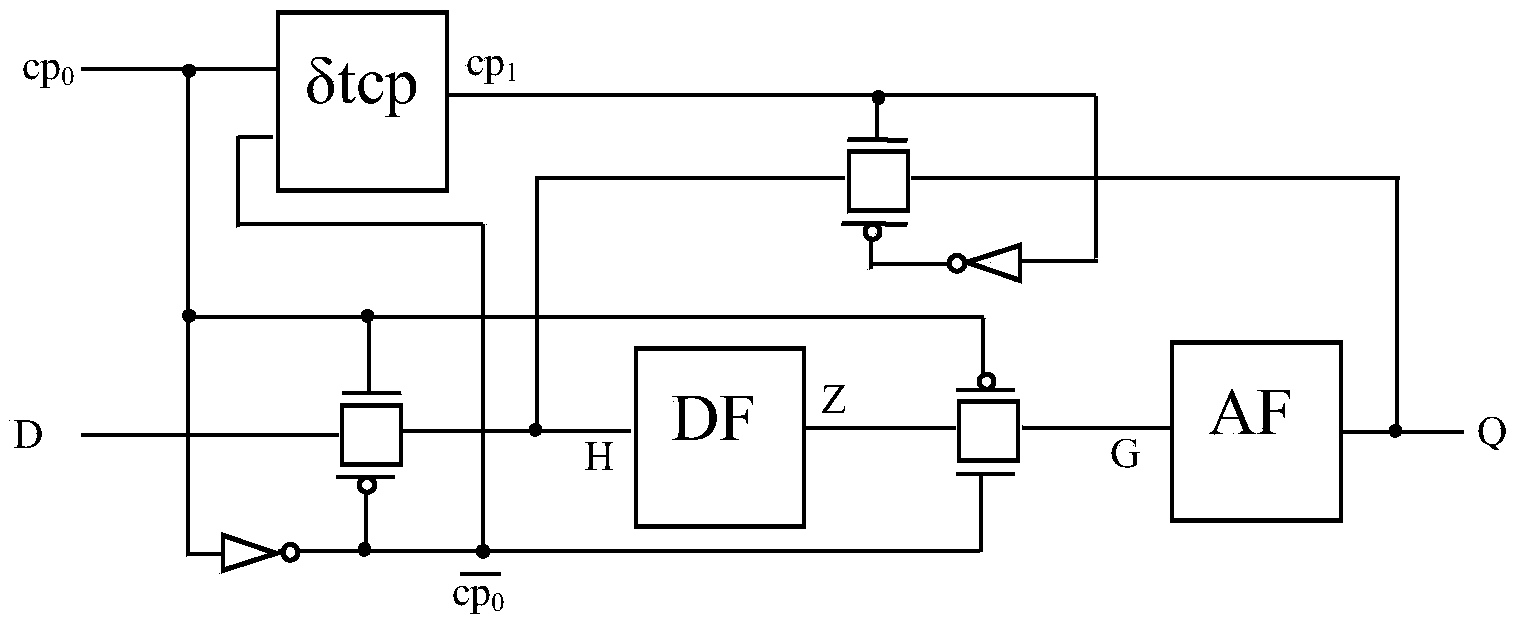

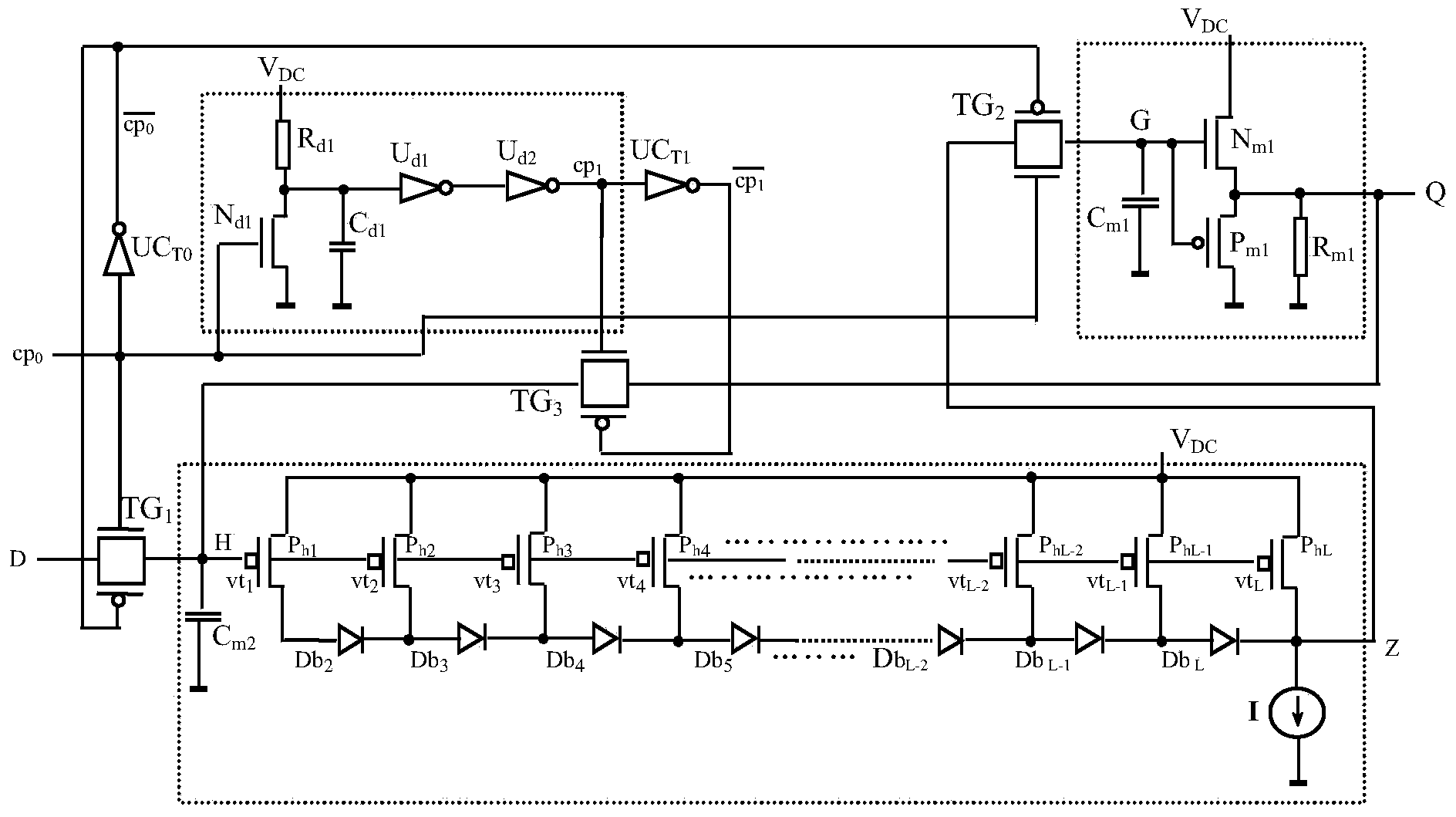

Two-stage time-to-digital converter

InactiveCN103684467AAdapt to needsHigh resolutionAnalogue/digital conversionElectric signal transmission systemsDigital down converterFull custom

The invention belongs to the field of microelectronics and time measurement, and particularly relates to a two-stage time-to-digital converter. The circuits of the converter can be applied to all digital phase-locked loops (ADPLL) with high frequency wide bands. According to the two-stage time-to-digital converter of the invention, the combination of semi custom and full custom is adopted, and two-stage time-to-digital converter comprises a first-stage quantizing structure, a time deviation selection circuit, a second-stage quantizing structure and a decoding circuit, wherein the first-stage quantizing structure adopts a buffer delay chain for coarse quantization; the time deviation selection circuit is composed of a selective signal generator, a delay chain and a multiplexer; the second-stage quantizing structure adopts a Vernier delay chain using a buffer as a basic unit to carry out fine quantization, and a duplication chain comprising a first-stage buffer chain simultaneously multiplexes the Vernier delay chain for measurement of a resolution ratio; the decoding circuit corresponds to a quantization scheme to realize transformation from pseudo thermometer codes to binary codes; the selective signal generator and the decoding circuit are realized by Verilog semi-custom, and the rest are realized by full-custom. The two-stage time-to-digital converter of the invention can be applied to ADPLL with the high frequency wide bands so as to realize time-to-digital conversion with high resolution and linearity.

Owner:FUDAN UNIV

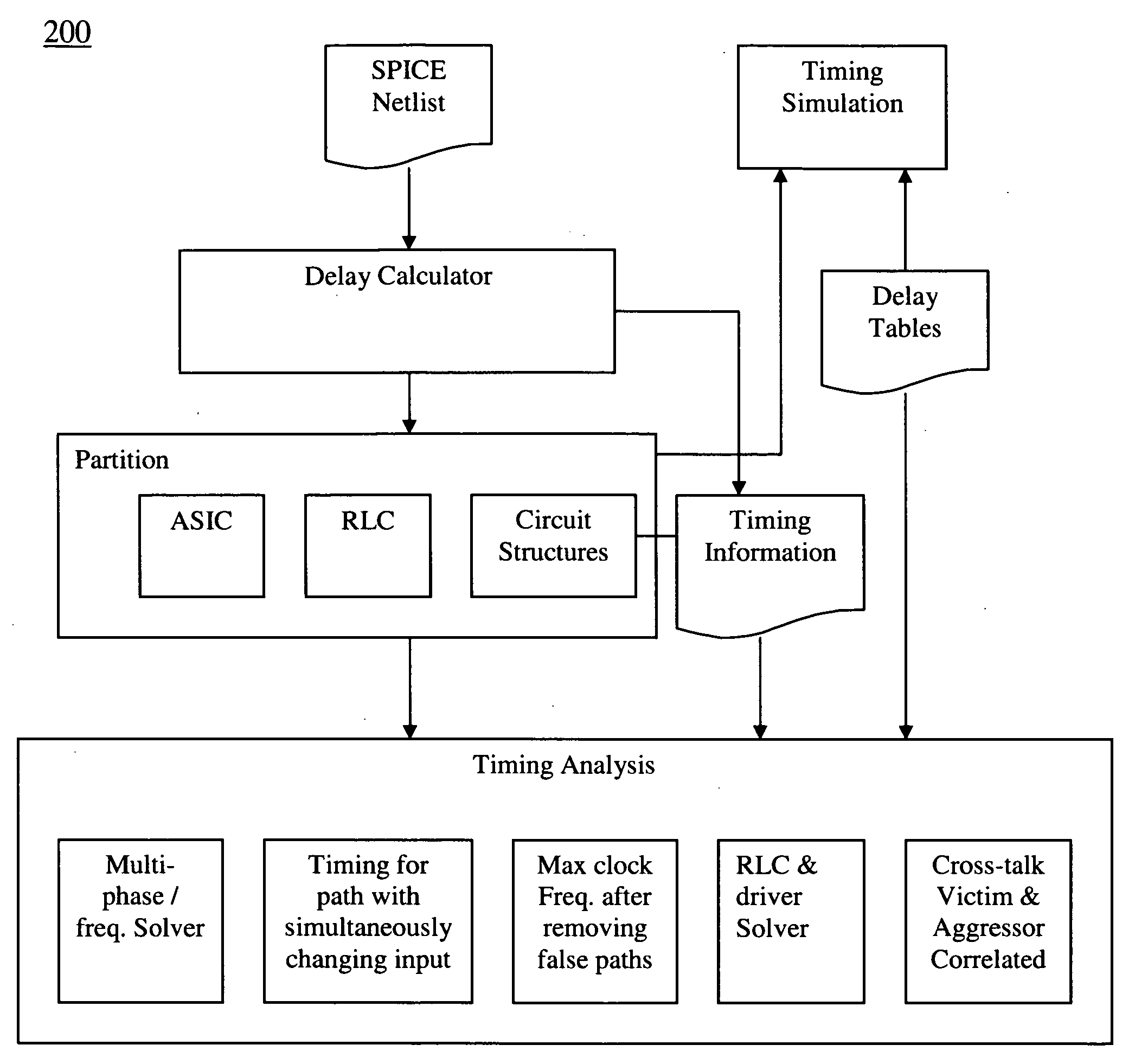

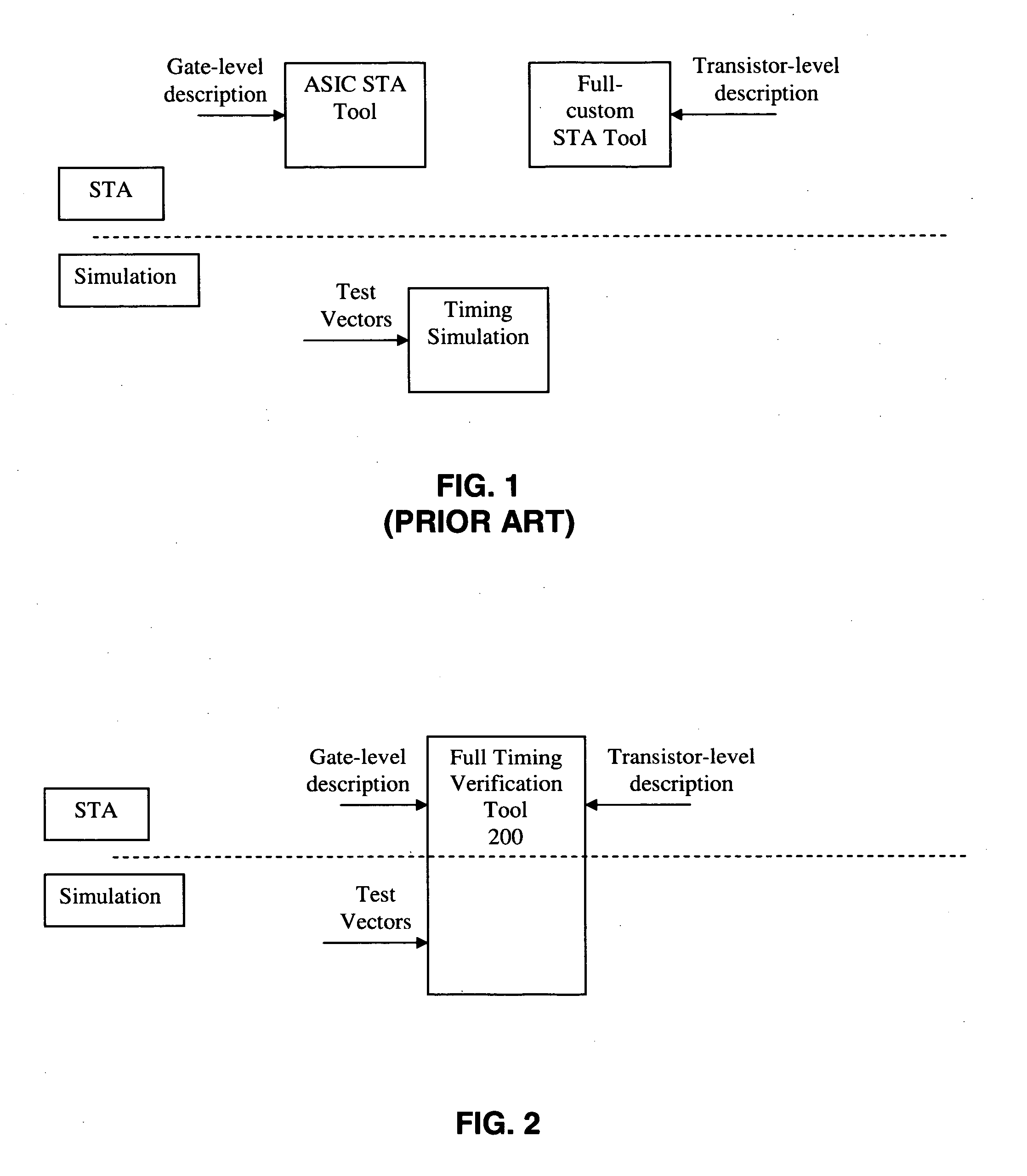

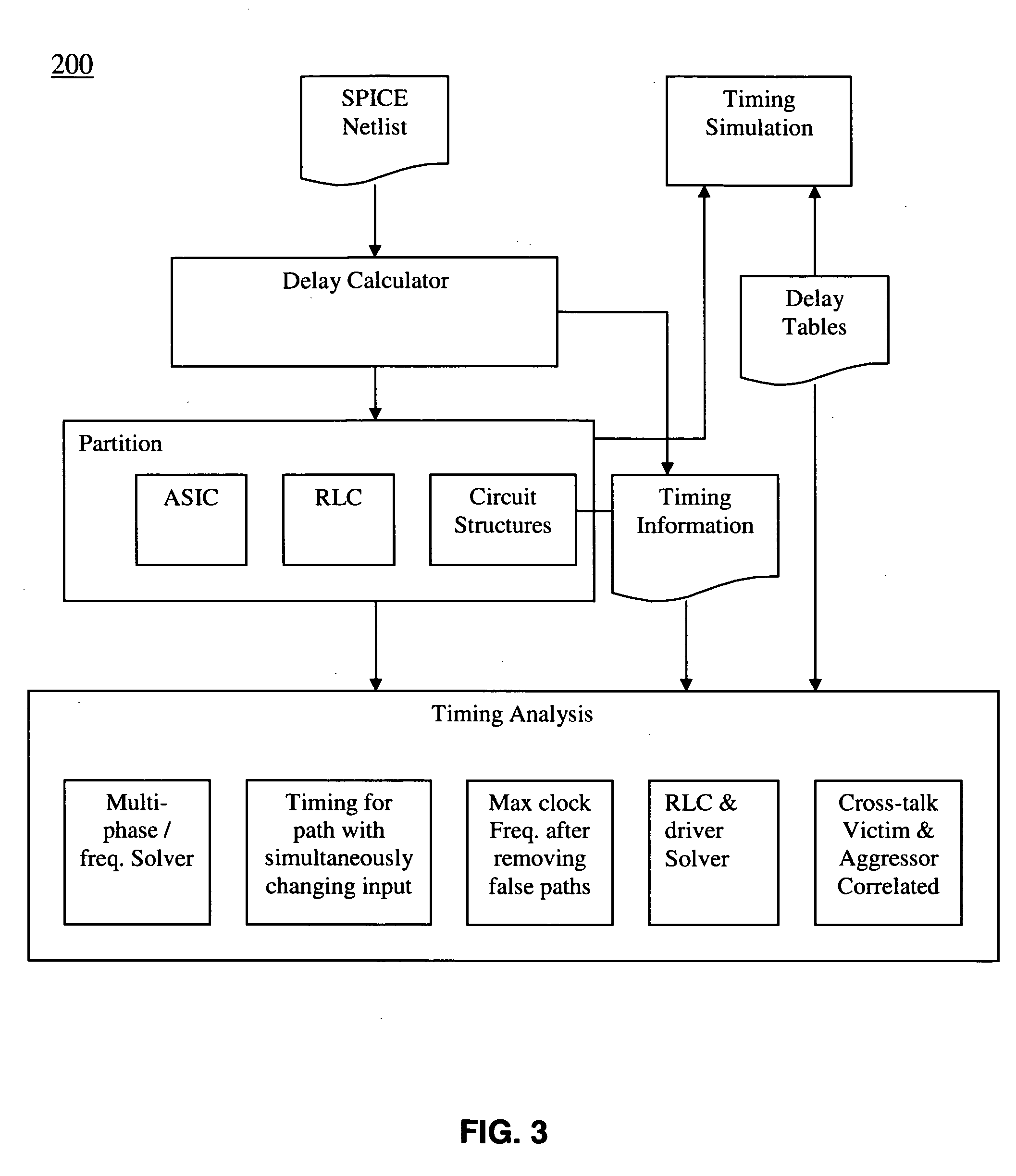

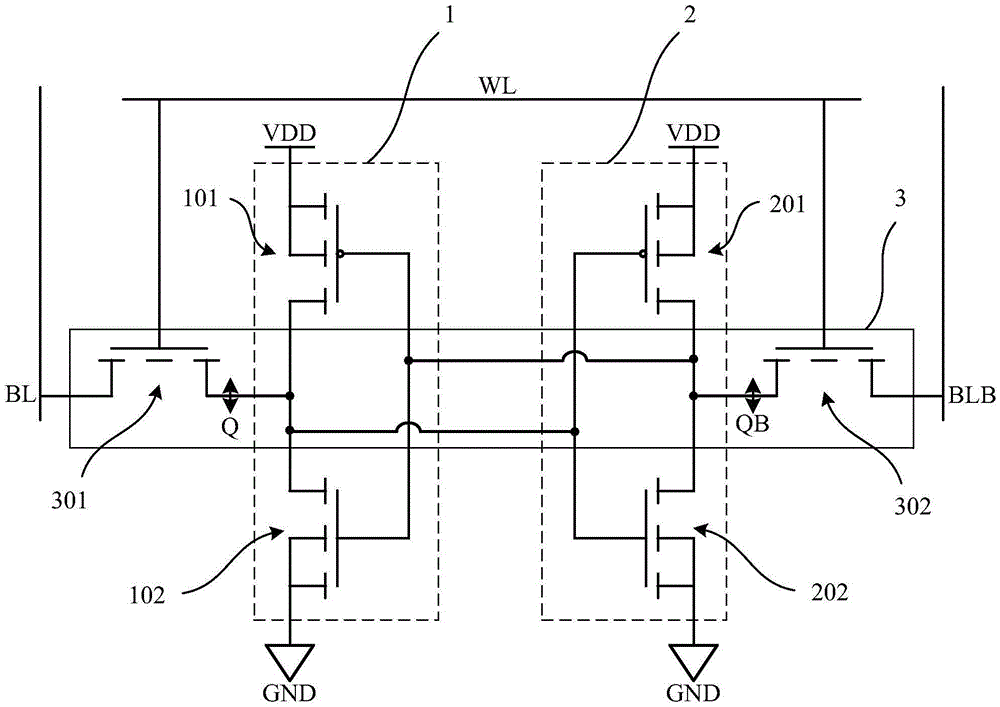

Static timing analysis and dynamic simulation for custom and ASIC designs

ActiveUS20060200786A1CAD circuit designSoftware simulation/interpretation/emulationFull customFalse path

A single verification tool provides both static timing analysis and timing simulation capabilities targeted at both full-custom and ASIC designs in a unified environment. In various embodiments the verification tool includes the following features: (a) Integrating both static timing analysis and dynamic simulation tools into a single tool, (b) Efficient path search for multi-phase, multi-frequency and multi-cycle circuit in the presence of level sensitive latch, (c) Automatically identifying circuit structure, e.g. complex gate, for timing characterization, (d) Circuit structures at transistor level solved by incorporating function check, (e) Carrying out functional check to filter out failing path and identifying gate with simultaneously changing inputs, (f) Finding maximum operation frequency in the presence of level sensitive latches after filtering out false paths, (g) Crosstalk solver by utilizing the admittance matrix and voltage transfer of RLC part in frequency domain coupled with the non-linear driver in time domain implemented in spice-like simulator, (h) Making use of the correlation between inputs of aggressors and victim to determine switching time at victim's output iteratively.

Owner:SAGE SOFTWARE

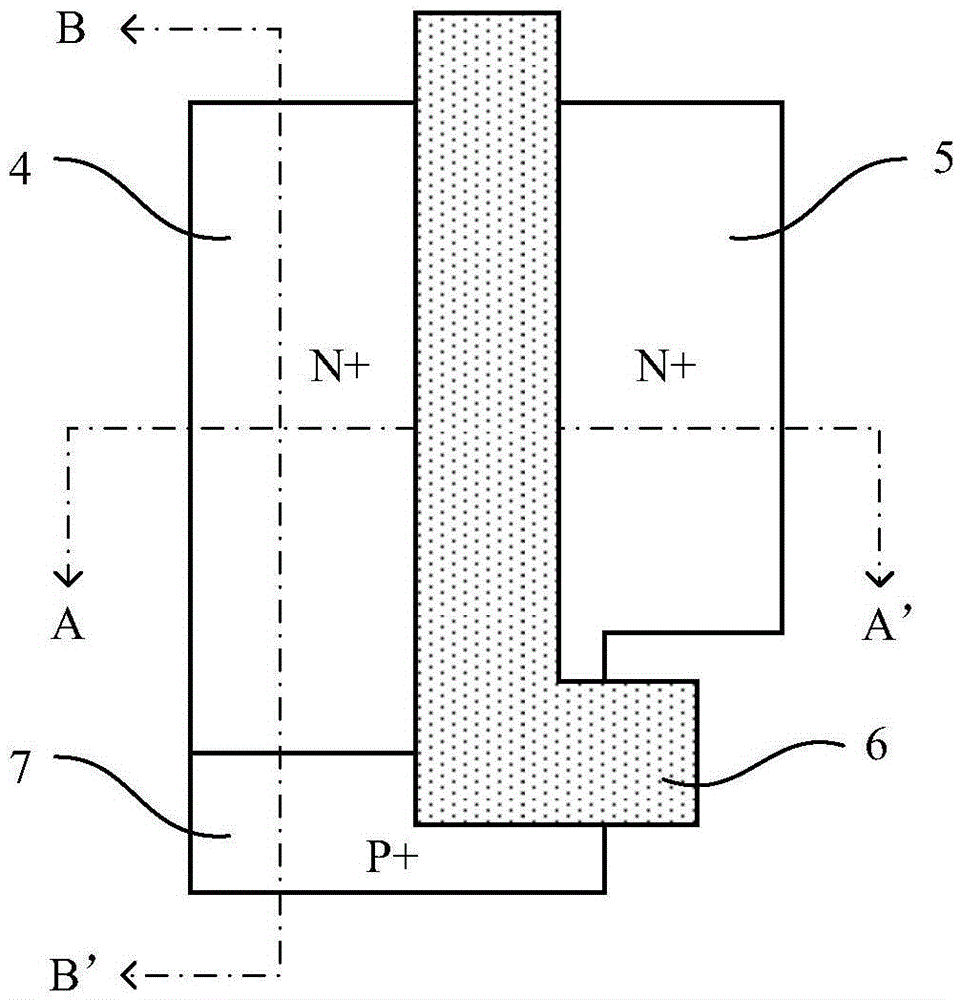

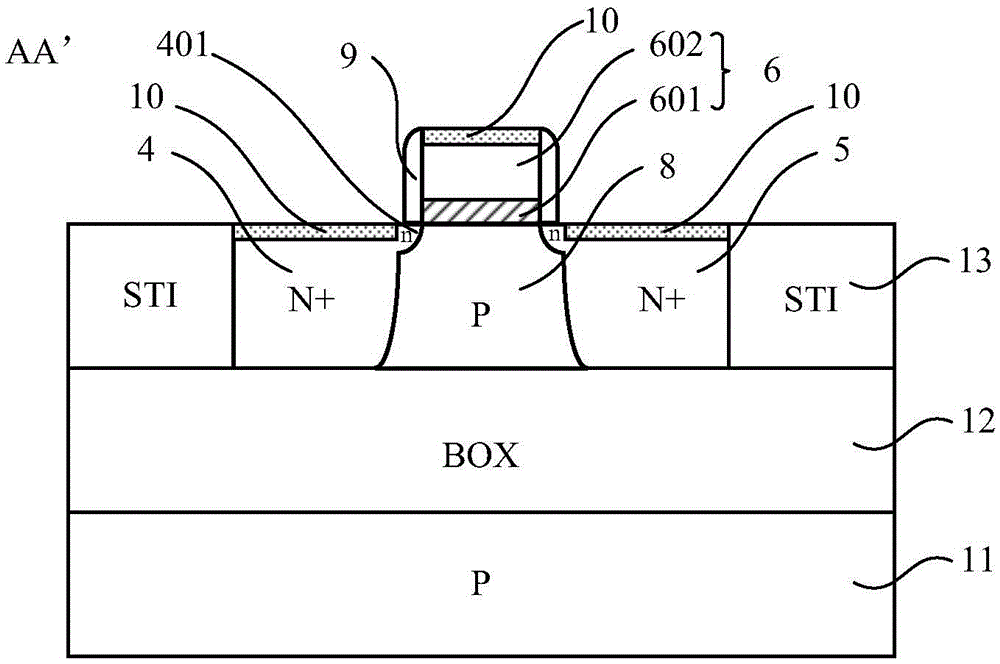

SOI single-port SRAM (Static Random Access Memory) unit and a preparation method thereof

ActiveCN105551518AImprove noise immunitySize matchSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectStatic random-access memory

The invention provides an SOI single-port SRAM unit and a preparation method thereof. The unit comprises a first phase inverter composed of a first PMOS transistor and a first NMOS transistor; a second phase inverter composed of a second PMOS transistor and a second NMOS transistor; an obtaining transistor composed of a third NMOS transistor and a fourth NMOS transistor. In the SRAM unit, the four transistors forming the first phase inverter and the second phase inverter are L-type gates; heavy dopant contact regions are arranged in the regions at the outer sides of the bending angles of the L-type gates. According to the unit and the method of the invention, leakage power consumption and transistor threshold voltage drift resulted from the floating body effect and parasitic triode effect in the PD SOI instrument can be effectively inhibited under the condition of sacrificing a relatively small unit area; the anti-noise capability of the unit is improved; the preparation technique of the invention introduces no extra mask plate and is fully compatible with the exiting logic technique; the inner part of the unit is a center symmetrical structure which is beneficial for matching the size and the threshold voltage of the MOS tube and for matching an array and is convenient for a full-custom SRAM chip.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

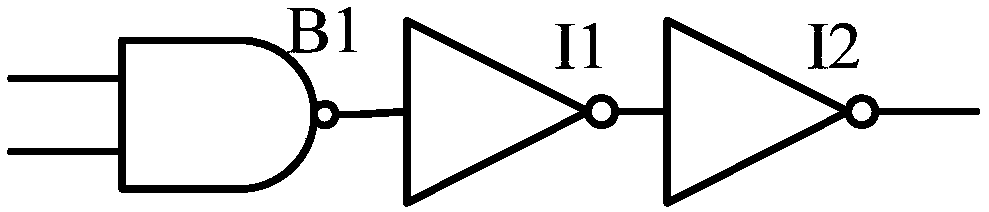

Full-custom AES SubByte circuit resisting differential power analysis attack

InactiveCN101527628AEncryption apparatus with shift registers/memoriesLogic circuitsFull customEngineering

The invention belongs to the technical field of the design of information security chips, in particular to a full-custom AES (advanced encryption standard) SubByte circuit resisting differential power analysis attack. The AES SubByte circuit is realized by the following basic units: a reactor INV, two input sensitive amplifier AND gates (AND2D1), three input sensitive amplifier AND gates (AND3D1), two input sensitive amplifier XOR gates (XOR2D1), and three input sensitive amplifier XOR gates (XOR3D1). The circuit uses a streamline structure to substitute the direct connection, and obtains higher speed with smaller area, and an adopted latch is a sense amplifier flip-flop. The circuit can realize the independency of power consumption of the circuit, operational data and operating sequence, thereby effectively preventing the differential power analysis attack. The circuit adopts an SMIC 0.18mu m CMOS process, the working frequency of the circuit achieves 83.3MHz, and the chip area of the circuit is about 0.85mm<2>. The circuit can be widely applied to symmetrical encryption operation equipment with high security.

Owner:FUDAN UNIV

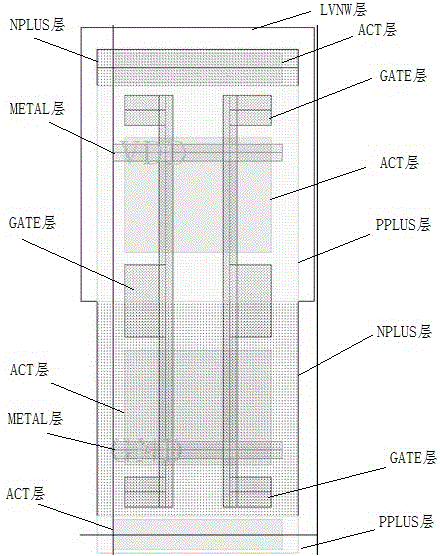

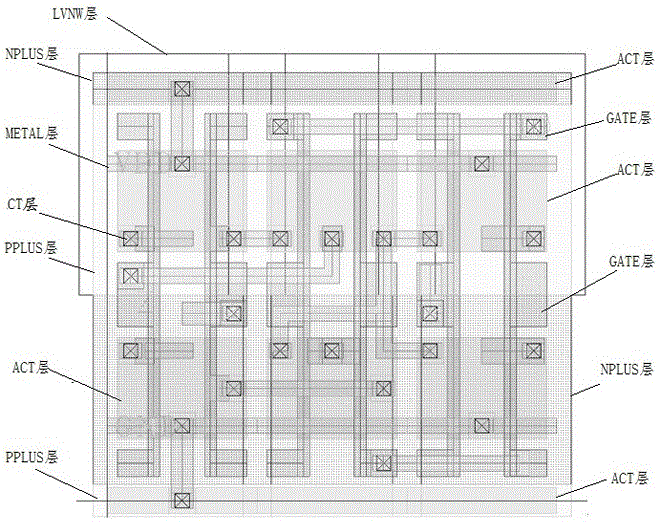

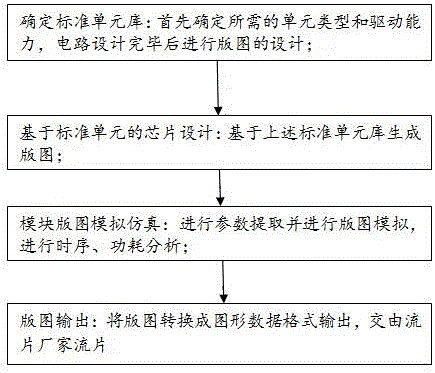

Basic cell, standard cell, standard cell library, back-end full-custom design method and chip

ActiveCN106339532AImprove placement and routing efficiencyImprove design efficiencyCAD circuit designSpecial data processing applicationsTime to marketComputer architecture

The invention discloses a basic cell, standard cell, standard cell library and back-end full-custom design method and a chip manufactured based on the method, and belongs to the technical field of integrated circuit layout designs. The basic cell disclosed by the invention at least comprises GATE layers, ACT layers, an LVNW layer, NPULS layers and PPLUS layers as well as a CT layer and a METAL layer which are all in regular shapes; the regular shapes of the GATE layers, the ACT layers, the LVNW layer, the NPULS layers and the PPLUS layers all need to meet process design rules. The layout of the standard cell comprises M basic cells in different Metal wiring manners, and M is a nonzero integer. The standard cell library comprises a plurality of the standard cells with different functions. The back-end full-custom design method of the invention comprises the following steps: determining the standard cell library, designing the chip based on the standard cell, carrying out analog simulation on a module layout and outputting the layout. The chip realized by adopting the back-end full-custom layout design method is more regular and standard in design to greatly optimize the layout design and improve the layout and processing efficiency so as to shorten the product time to market.

Owner:HANGZHOU CHIPJET TECH

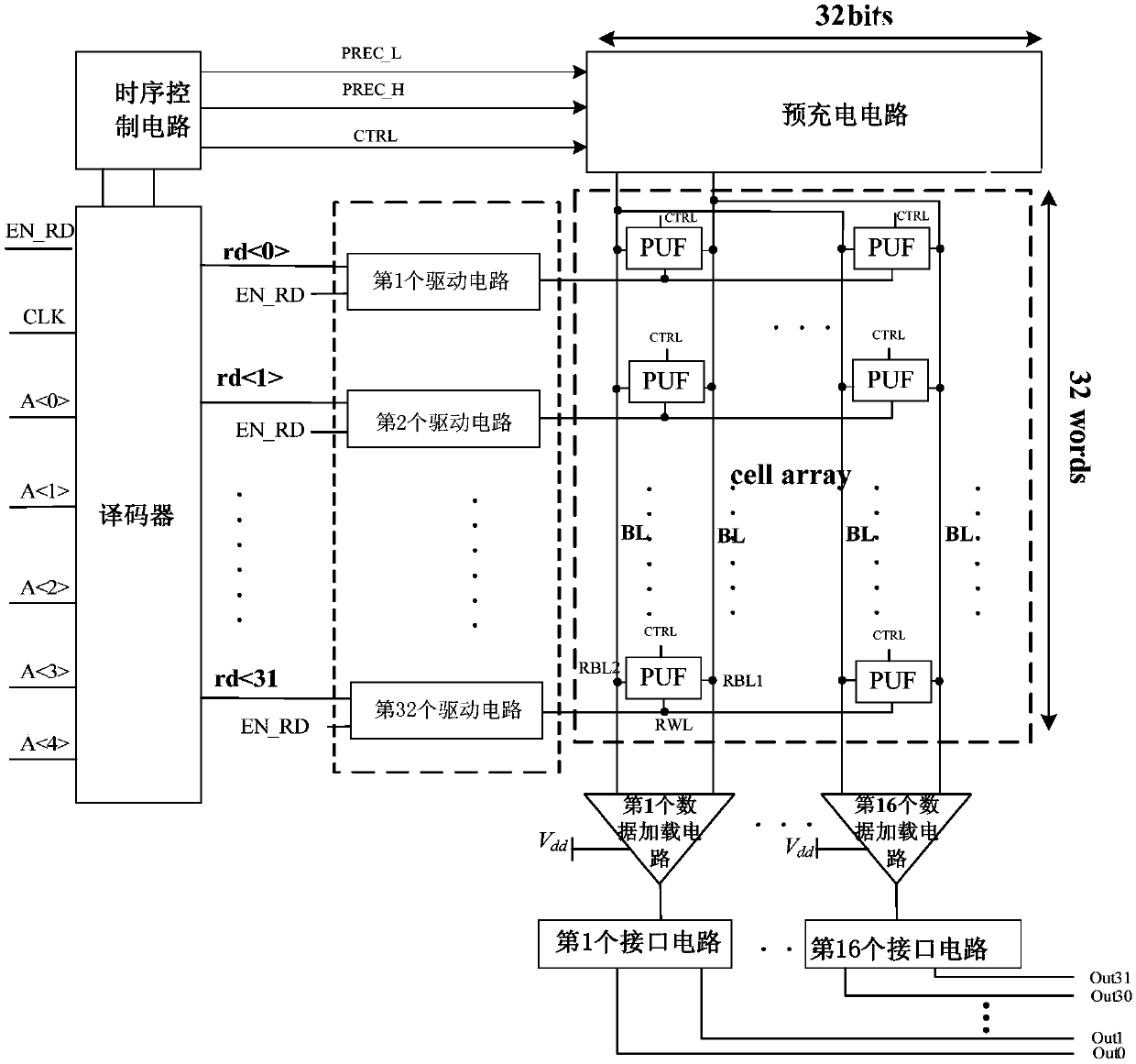

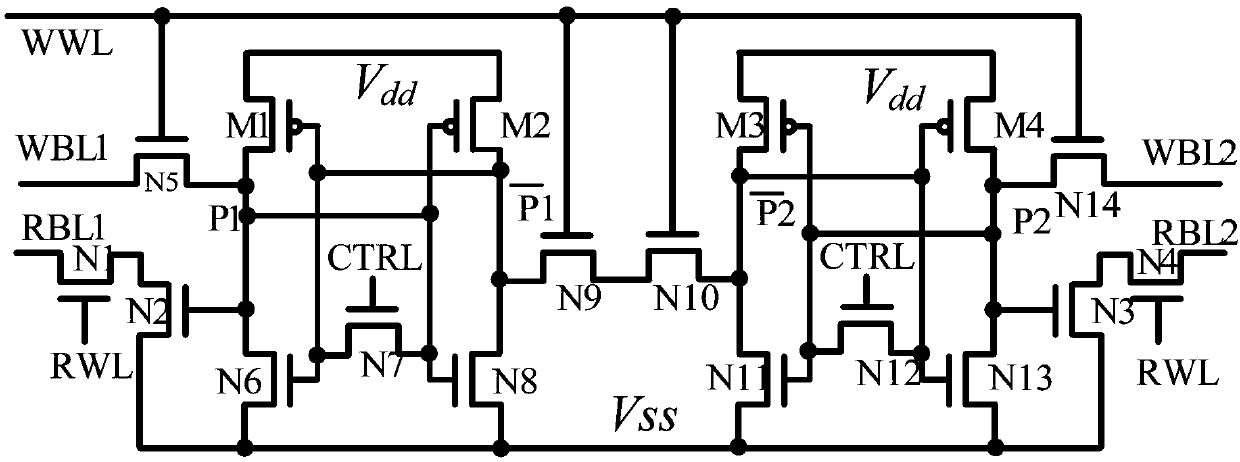

Twin-storage type multi-valued physically unclonable function circuit

ActiveCN107688755AIncrease profitReduce energy consumptionInternal/peripheral component protectionFull customPre-charge

The invention discloses a twin-storage type multi-valued physically unclonable functional circuit which comprises a time sequence control circuit, a decoder, a driver, a pre-charge circuit, a PUF (physically unclonable function) array, 16 data loading circuits and 16 interface circuits. The driver comprises 32 driving circuits with identical structures, and 512 PUF circuits are arranged accordingto a 32 row*16 column mode to form the PUF array. The twin-storage type multi-valued physically unclonable functional circuit has the advantages that 2-bit random source data can be generated by the PUF circuits which are of twin structures, four-valued data can be outputted by multi-valued logic circuits formed by the data loading circuits and the interface circuits, and accordingly the quantities of bit lines can be reduced by 50%; the twin-storage type multi-valued physically unclonable functional circuit is designed in full-custom modes by the aid of TSMC_LP65nm processes, and the area ofthe twin-storage type multi-valued physically unclonable functional circuit is 0.019 mm<2>; as shown by test results, the lowermost work voltages of the twin-storage type multi-valued physically unclonable functional circuit are 320 mV, corresponding work frequencies are 110 kHz, the hardware utilization rate is increased by 15% at least, and energy consumption is reduced by 30%.

Owner:NINGBO UNIV

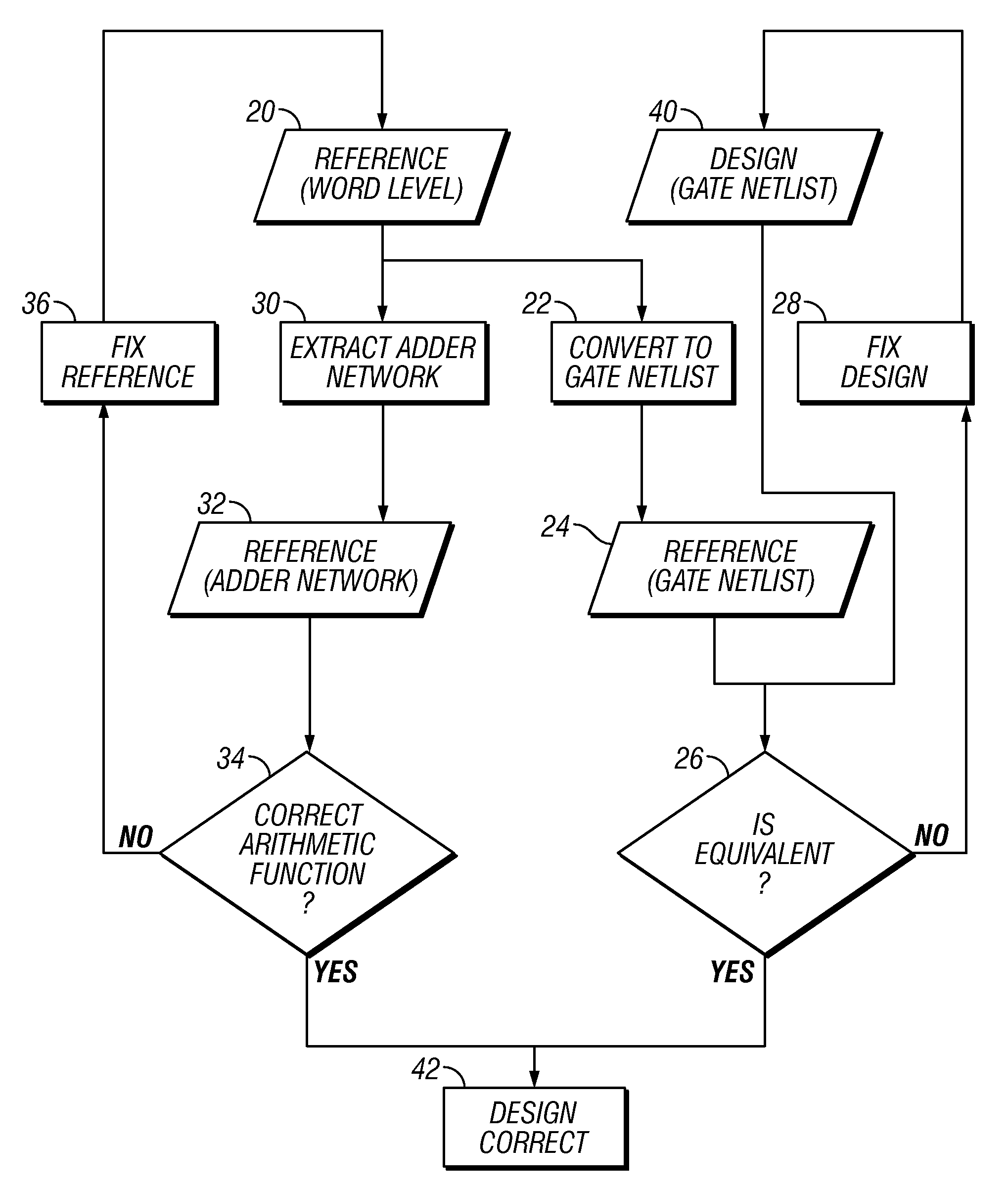

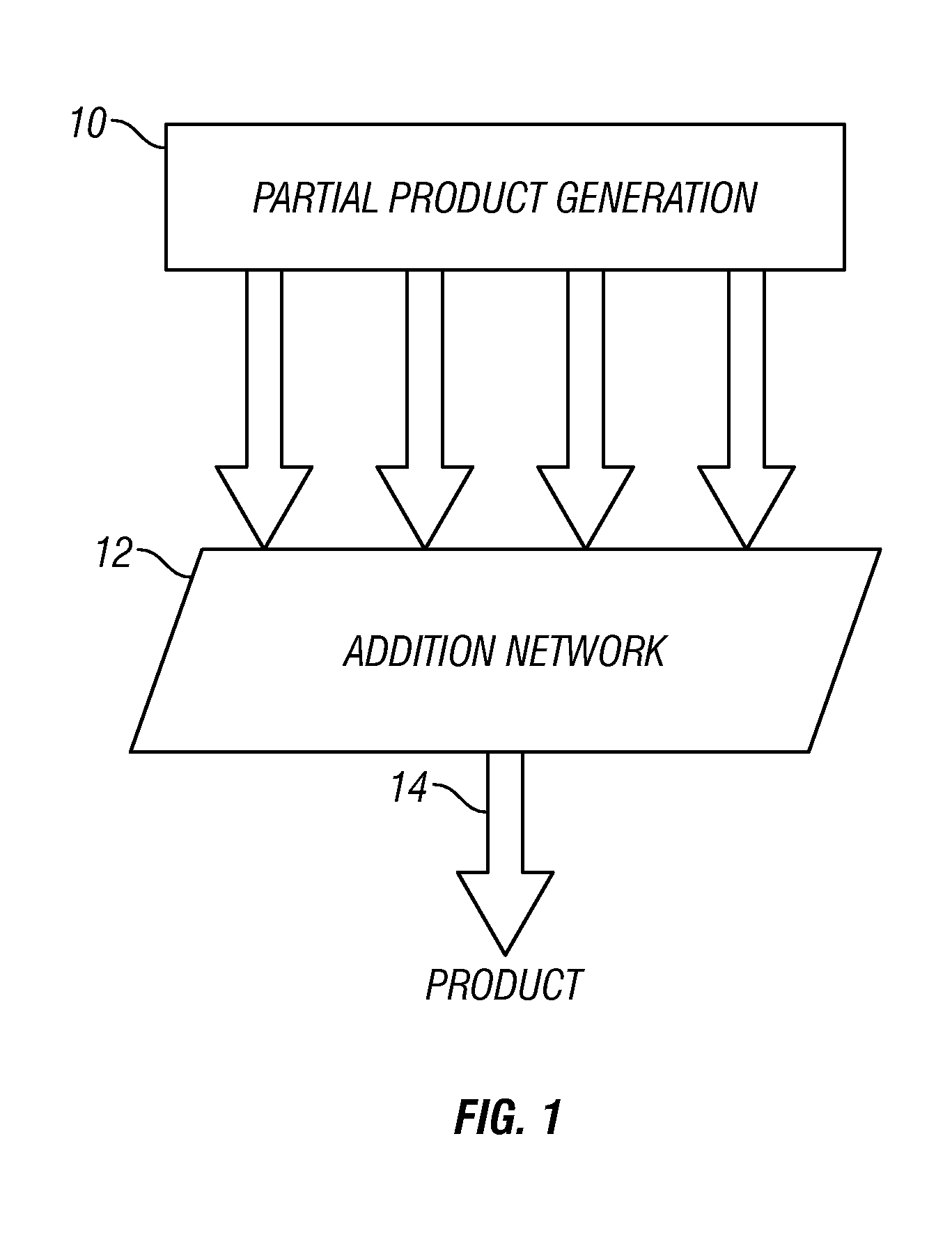

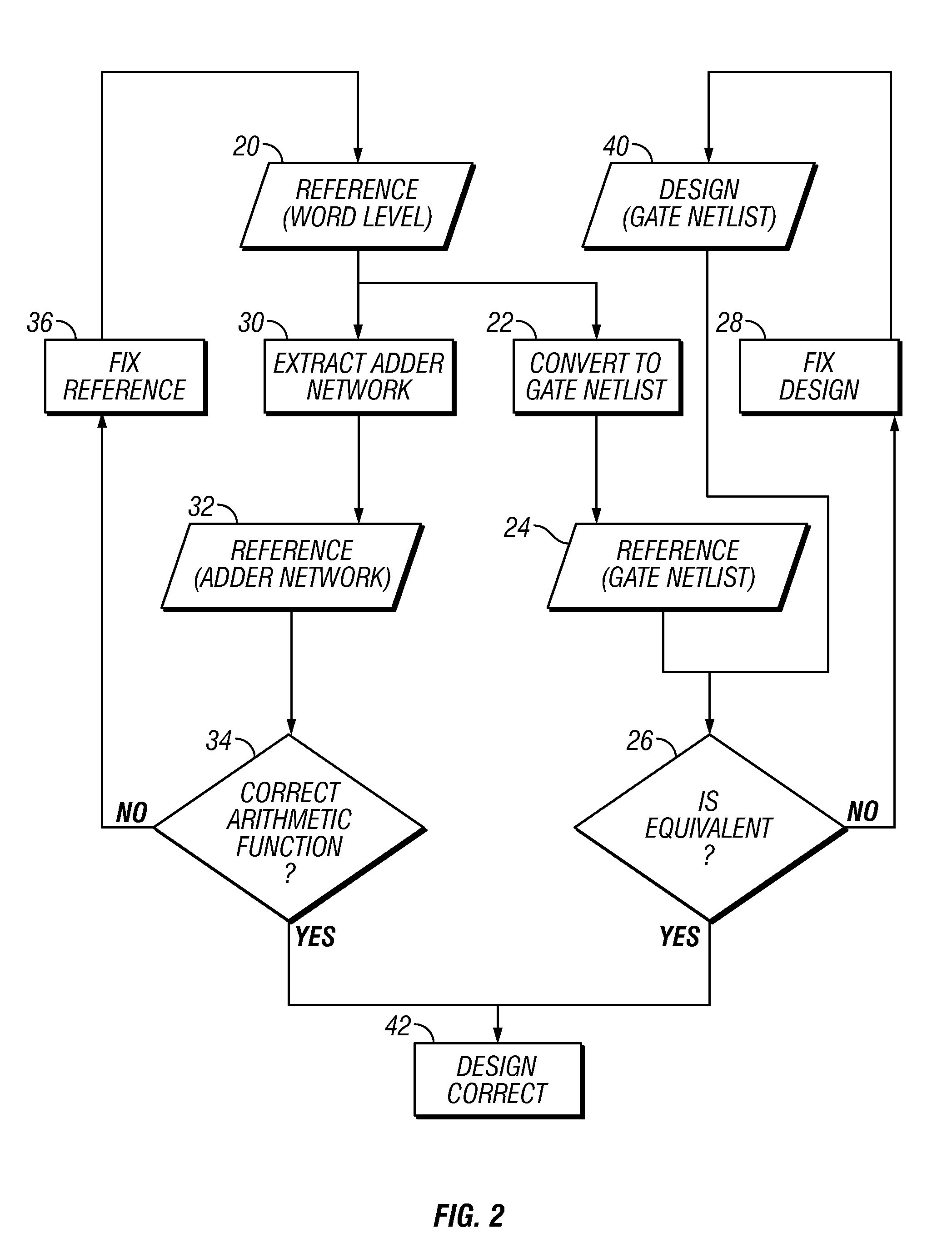

Method and system for formal verification of an electronic circuit design

ActiveUS20090300560A1Easy to carryComputer aided designSoftware simulation/interpretation/emulationComputer architectureFull custom

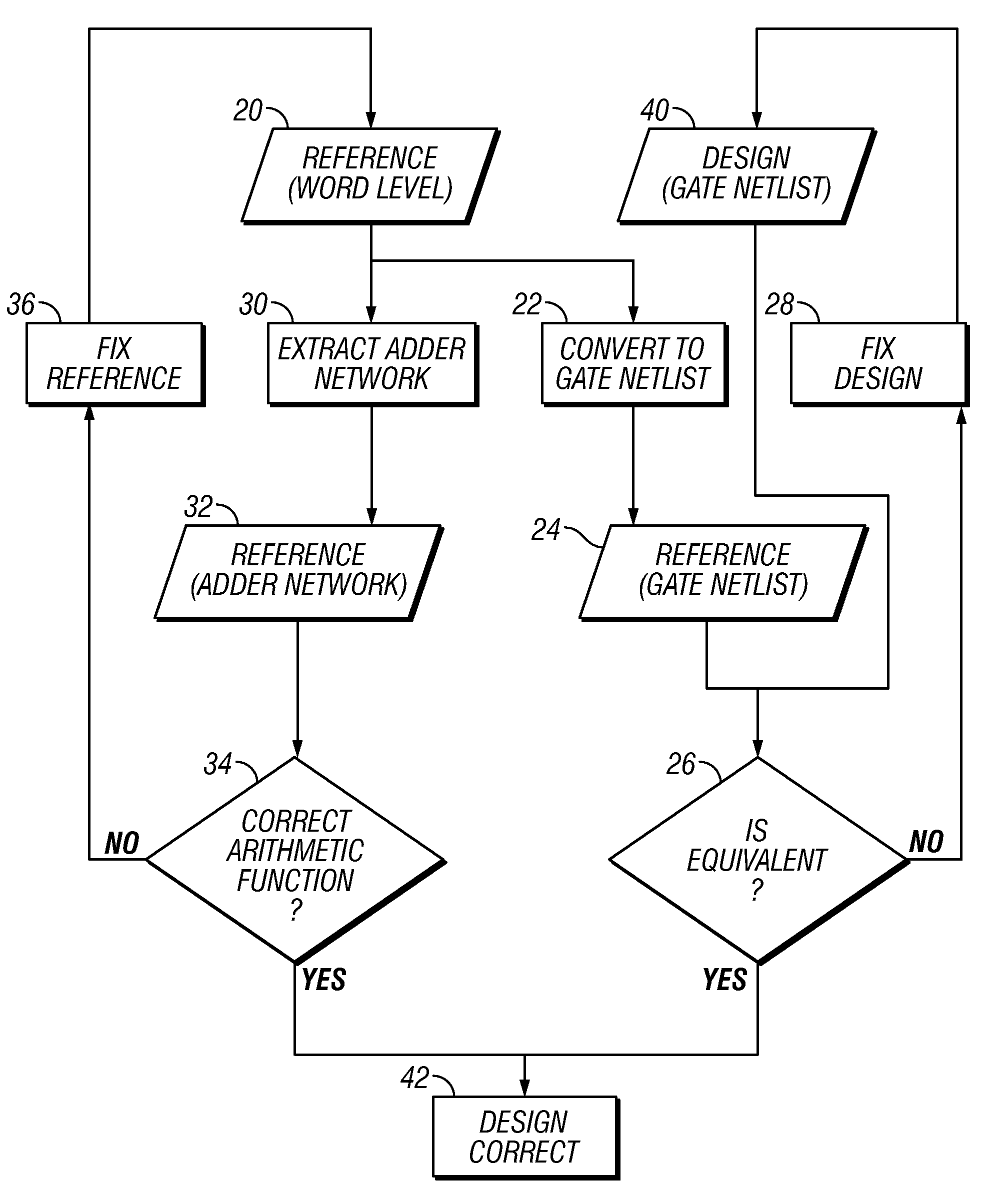

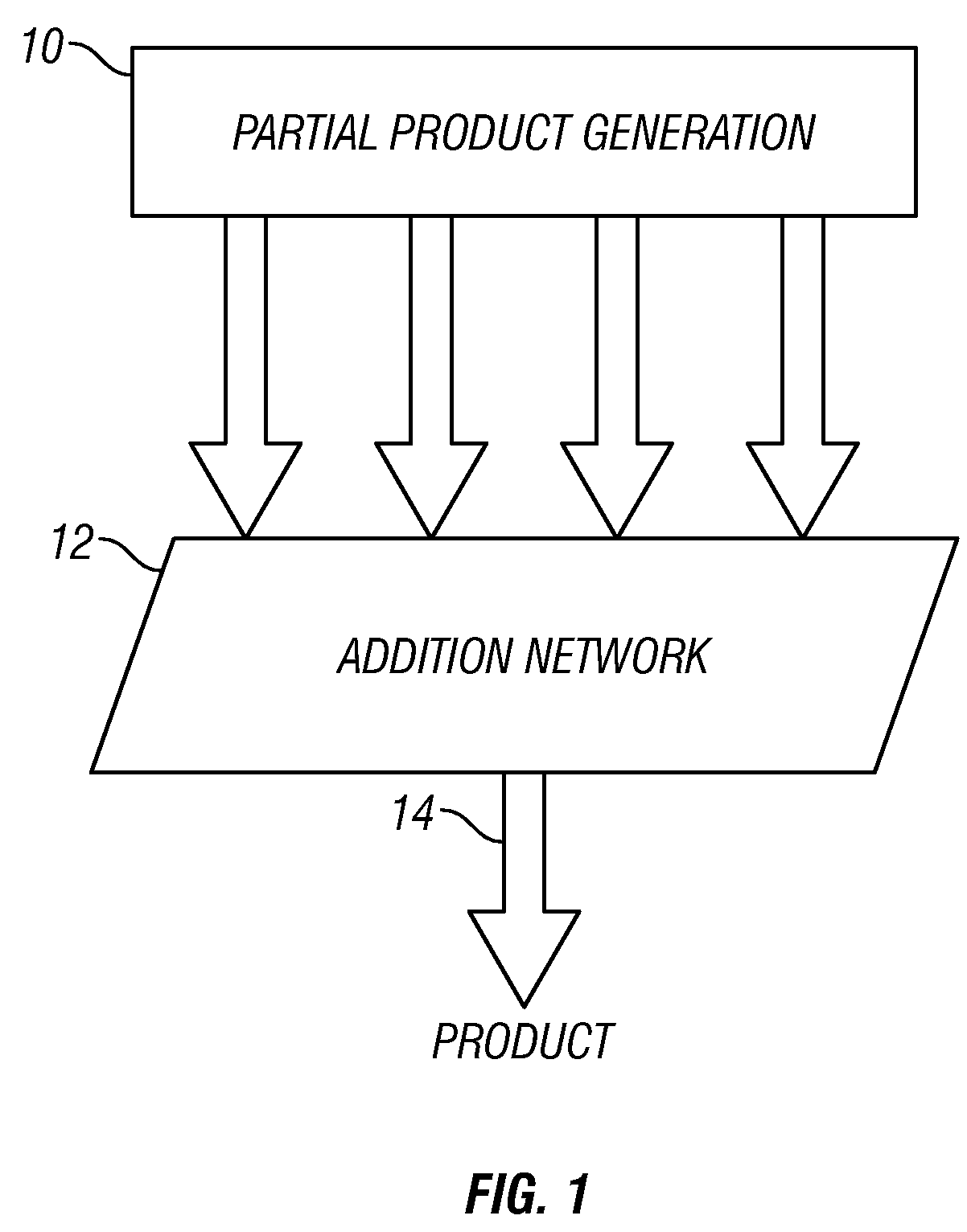

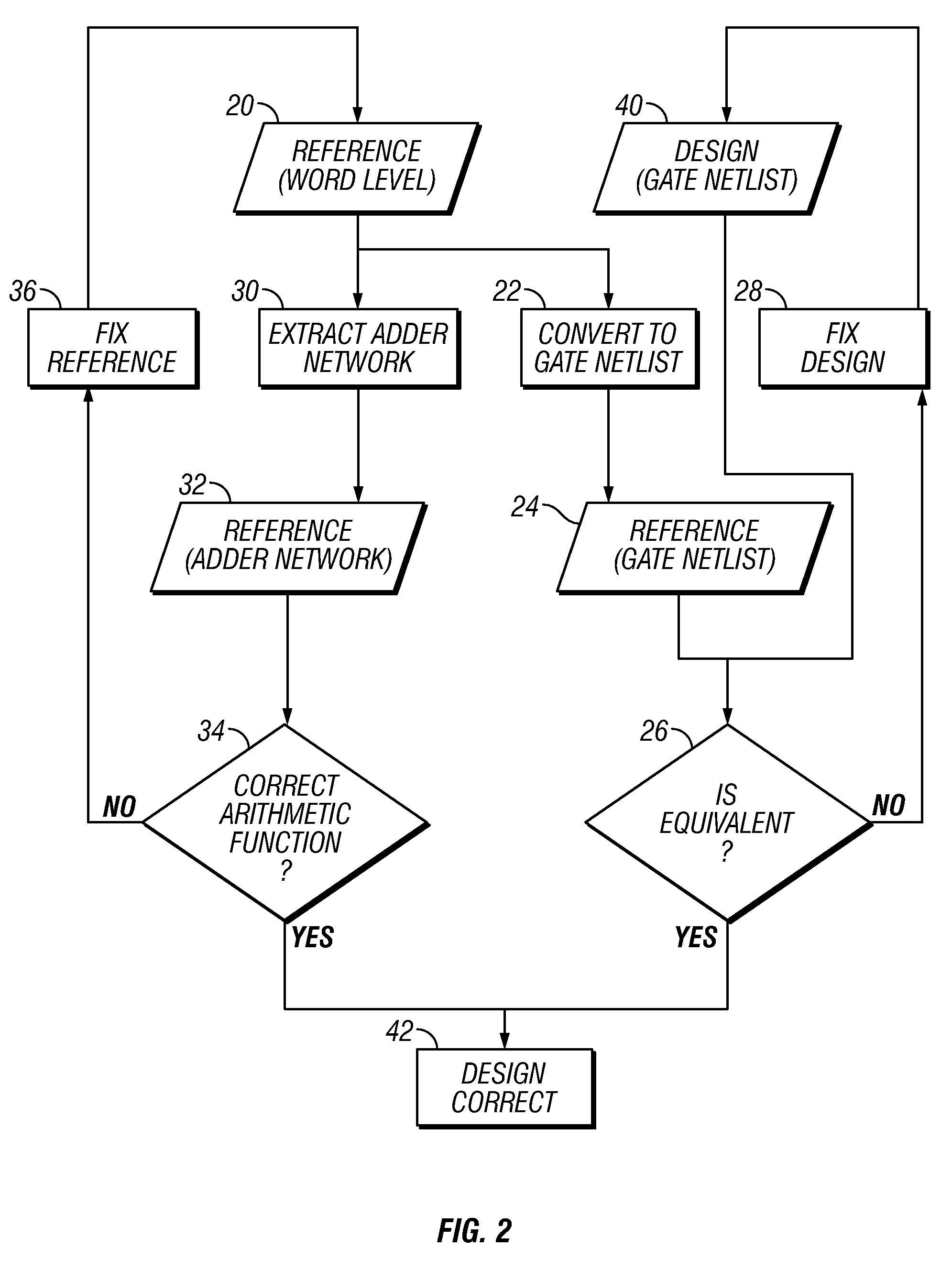

A new and convenient methodology for proving the correctness of multiplier and multiply-accumulate circuit designs in a full custom design flow. Such an approach utilizes a basic description of the implemented algorithm, which is created in early phases of the design flow and requires only little extra work for the designer who spends most of the time in full-custom optimizations. Such an approach also defines arithmetic circuit at the arithmetic bit level and allows for the generation of a gate level netlist. Given a structural similarity between the specification and design under verification, a large amount of structural similarity between the generated netlists is obtained so that a standard equivalence checker can be utilized to verify the design against the specification.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

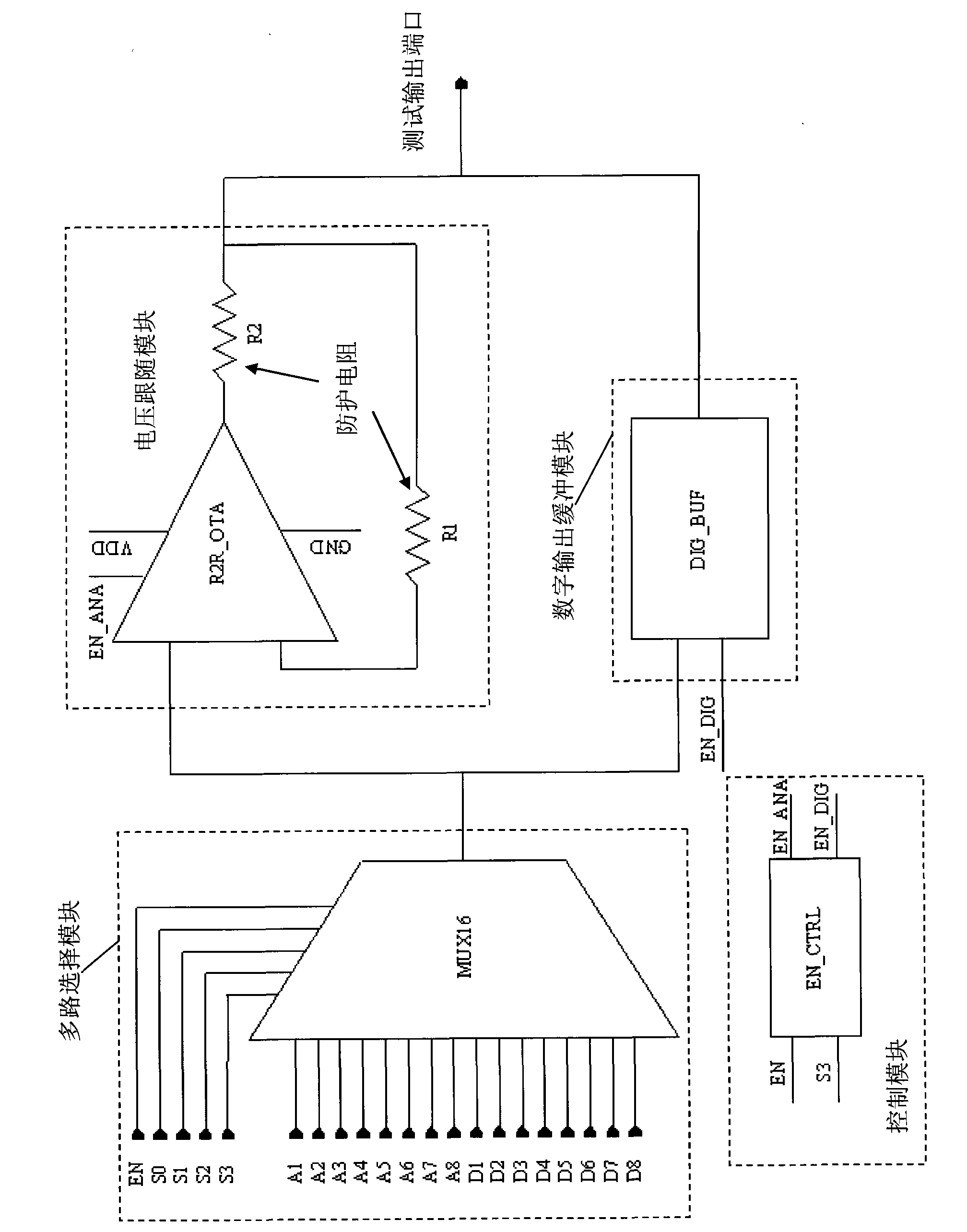

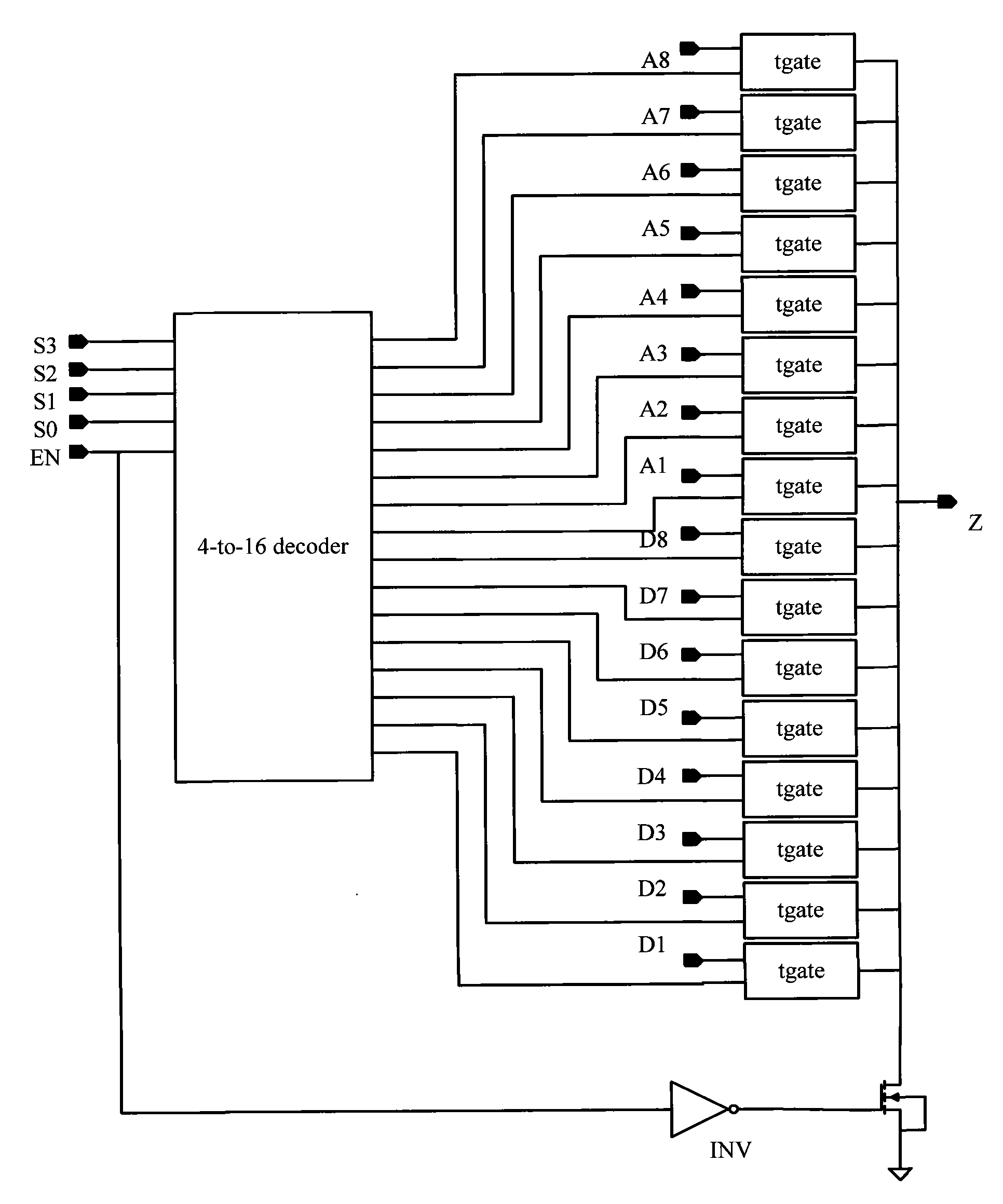

Testability circuit for digital/analog mixed signal chip

InactiveCN102117343AImprove ESD capabilitySpecial data processing applicationsFull customControl signal

The invention discloses a testability circuit for a digital / analog mixed signal chip. The testability circuit comprises a multi-path selection module, a control module, a voltage follower module and a digital output buffer module, wherein the multi-path selection module is used for selecting the signal to be observed and transmitting the signal to the voltage follower module or the digital output buffer module; the control module is used for generating a control signal to selectively open the voltage follower module or the digital output buffer module; and the selected signal is transmitted to the voltage follower module if the selected signal is an analog signal, or the selected signal is transmitted to the digital output buffer module if the selected signal is a digital signal. The testability circuit can observe the important digital signal and the analog signal in the chip through an output pin of the chip, which facilitates the chip fault analysis and debugging. The testability circuit is suitable for the digital / analog mixed signal chip and full-custom chip.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

Biological 3D printed full-custom skin and preparation method thereof

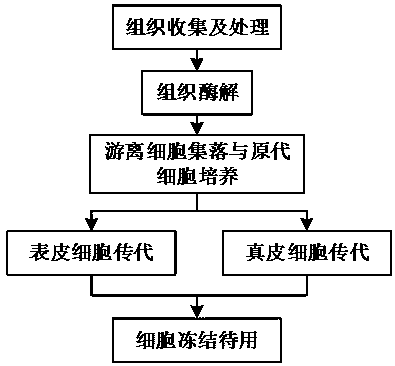

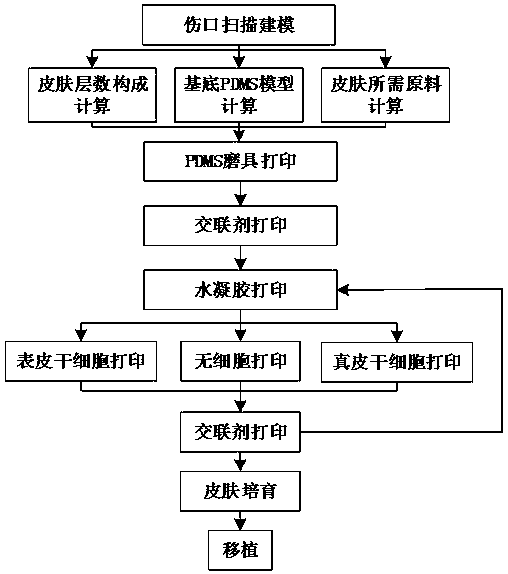

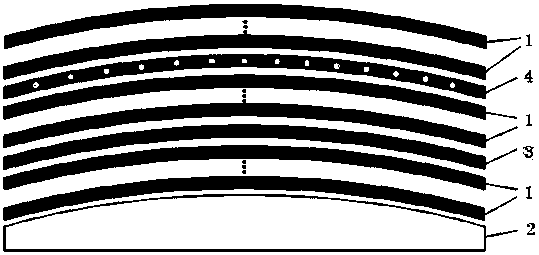

InactiveCN108392676AImprove the success rate of treatmentGood healing effectAdditive manufacturing apparatusProsthesisFull customPrimary cell

The invention relates to the technical field of tissue engineering skin and specifically relates to biological 3D printed full-custom skin and a preparation method thereof. The preparation method comprises two parts of a skin stem cell extraction technology and a skin biological 3D remodeling technology. The skin stem cell extraction comprises the steps: tissue obtaining and treatment, tissue enzymolysis, primary cell culture, subculture and the like. A biological 3D printer is utilized, a three-dimensional scanning modeling technology is utilized, a method of printing raw materials, calculating printing specifications, printing a substrate, printing layer by layer and stacking layer by layer is utilized, full-custom skin completely meeting a specific part and a specific three-dimensionalcharacteristic of the human body can be printed out, complete attachment between artificial skin and wound is ensured, and a transplanting success rate and a healing effect are improved. Meanwhile, the full-custom skin can be applied to research of in-vitro skin models and plays an important role in the aspects of tumor research, medicine, cosmetic testing and the like.

Owner:TAIYUAN UNIV OF TECH

Method and system for formal verification of an electronic circuit design

ActiveUS7890903B2Easy to carryComputer aided designSoftware simulation/interpretation/emulationComputer architectureFull custom

A new and convenient methodology for proving the correctness of multiplier and multiply-accumulate circuit designs in a full custom design flow. Such an approach utilizes a basic description of the implemented algorithm, which is created in early phases of the design flow and requires only little extra work for the designer who spends most of the time in full-custom optimizations. Such an approach also defines arithmetic circuit at the arithmetic bit level and allows for the generation of a gate level netlist. Given a structural similarity between the specification and design under verification, a large amount of structural similarity between the generated netlists is obtained so that a standard equivalence checker can be utilized to verify the design against the specification.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Asynchronous static random access memory based on internet protocol (IP) of synchronous static random access memory

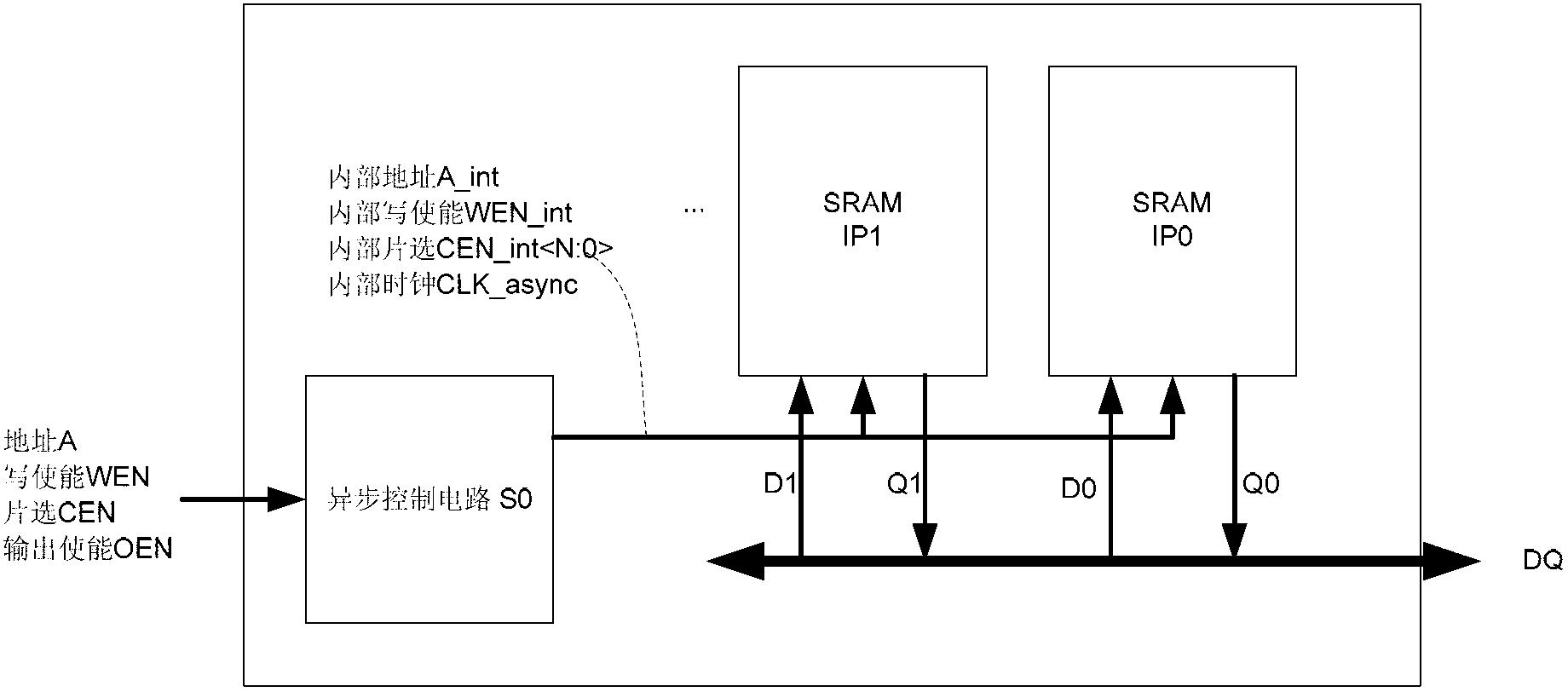

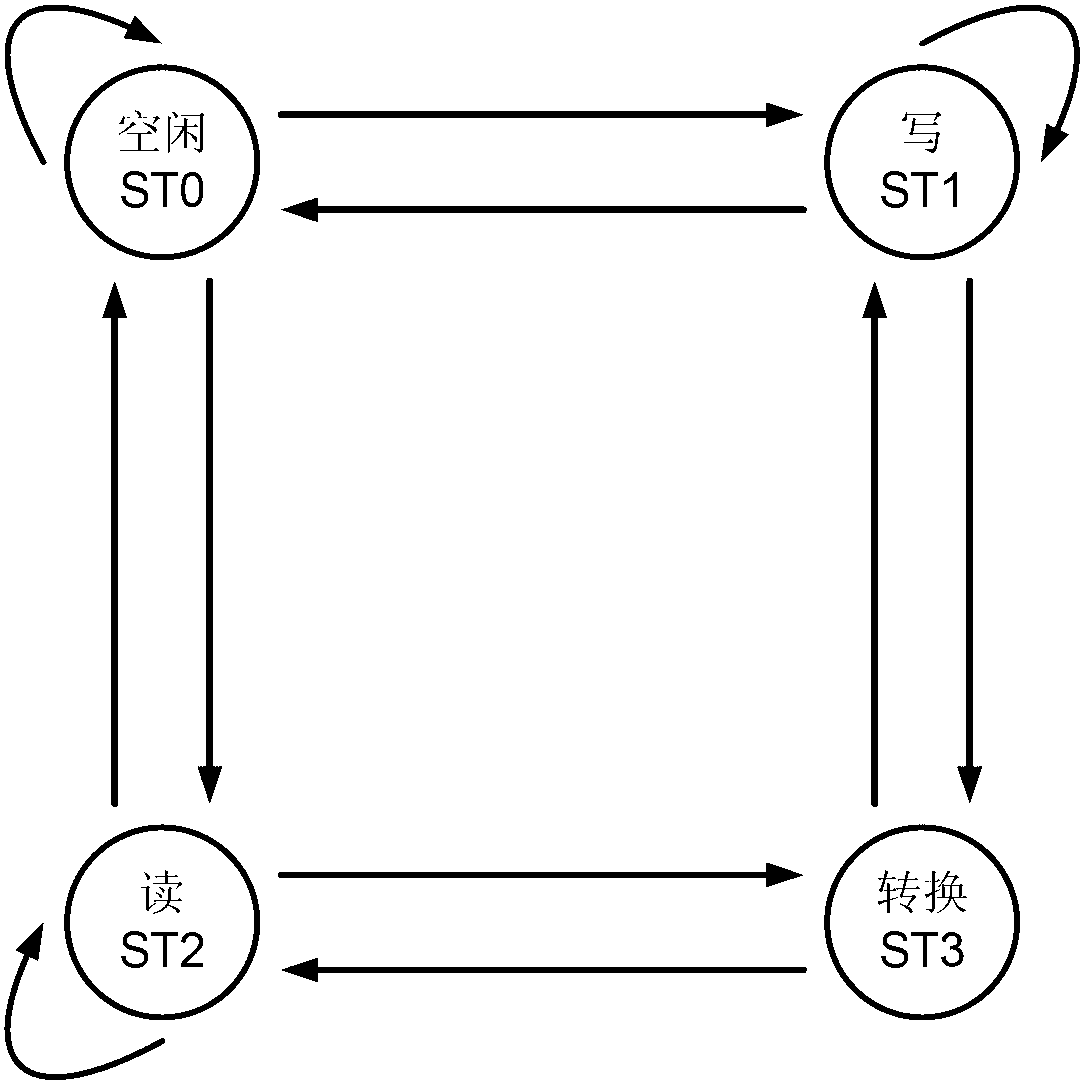

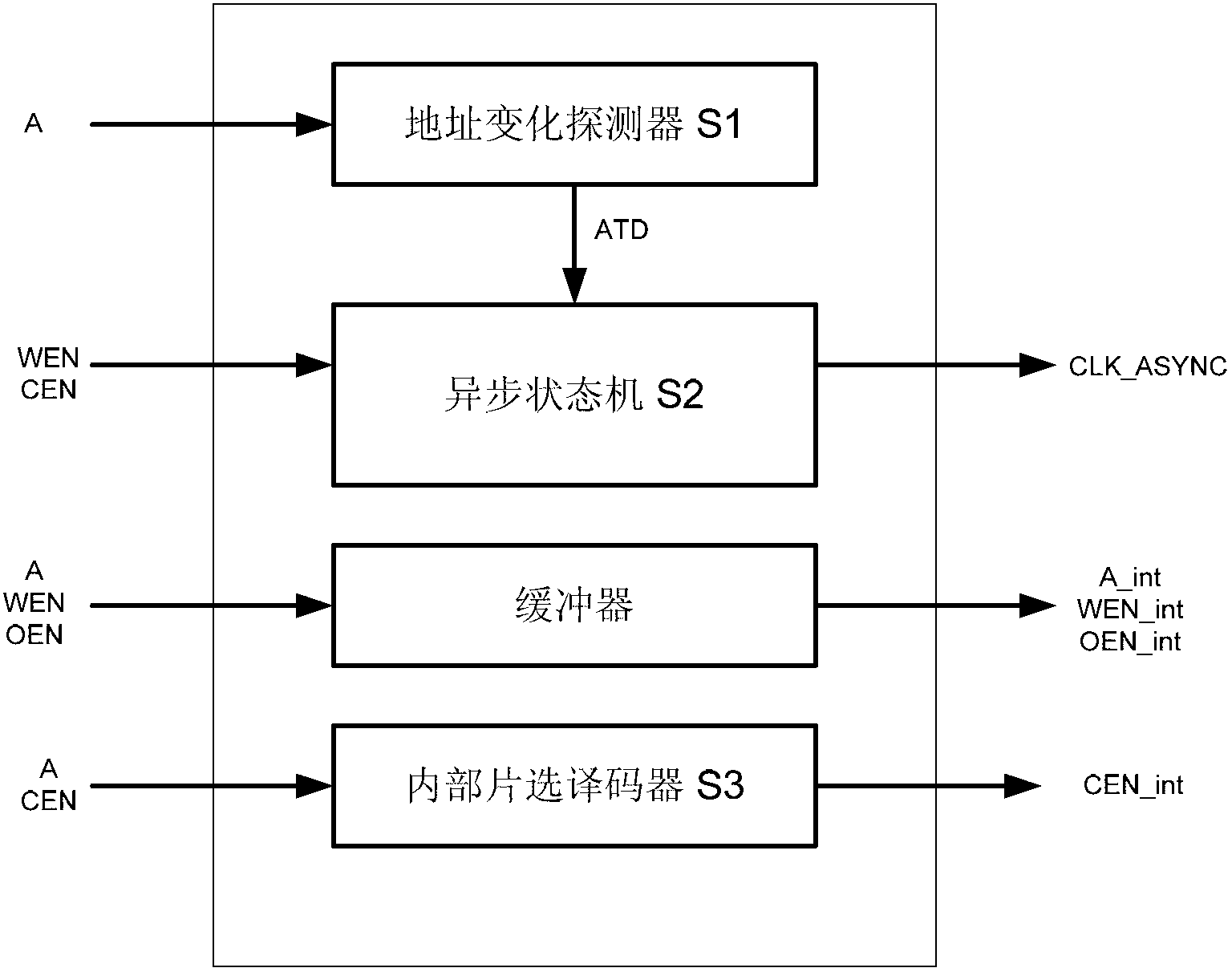

ActiveCN103065672AShorten the design cycleImprove reliabilityDigital storageInternet protocol suiteAsynchronous circuit

The invention provides an asynchronous static random access memory based on an internet protocol (IP) of a synchronous static random access memory, and the asynchronous static random access memory based on the IP of the synchronous static random access memory is formed by an asynchronous control circuit and a plurality of synchronous static random access memories. Internal clocking signals of the asynchronous control circuit are triggered for the plurality of synchronous static random access memories. The asynchronous control circuit is also responsible for buffering an address and other signals and sending the address and other signals to the selected synchronous static random access memory. Due to the fact that the IP of the synchronous static random access memory is one of the most basic IPs of an integrated circuit process line, the asynchronous static random access memory based on the IP of the synchronous static random access memory just needs to add an asynchronous control circuit to the complete an asynchronous static random access memory based on the IP of the mature synchronous static random access memory, and has the advantage of being short in design cycle, compared with a traditional full custom design process and method.

Owner:XI AN UNIIC SEMICON CO LTD

Interactive patient education system

Interactive patient education system for use in operatory or office settings, provides interactive 3-D animations, graphics and other media, enabling real-time markup and customization to better illustrate and communicate not only generic information, but the individual patient's physiology, treatment options, and anticipated outcomes. Preferred embodiments are portable, computer-implemented, interactive multimedia educational tools. Import of patient-specific graphics, video and audio contributes to full-custom educational content to optimize patient understanding.

Owner:REALITY ENG

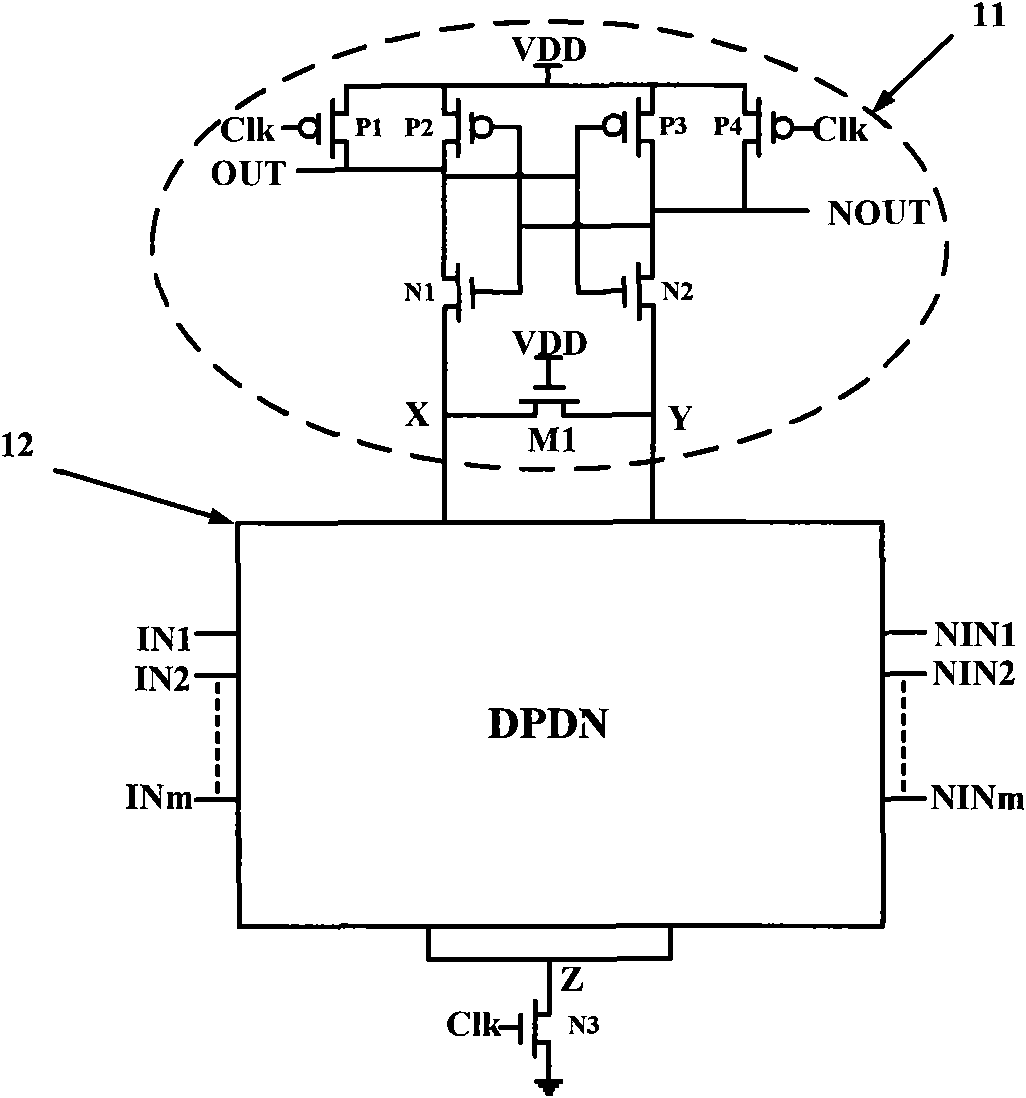

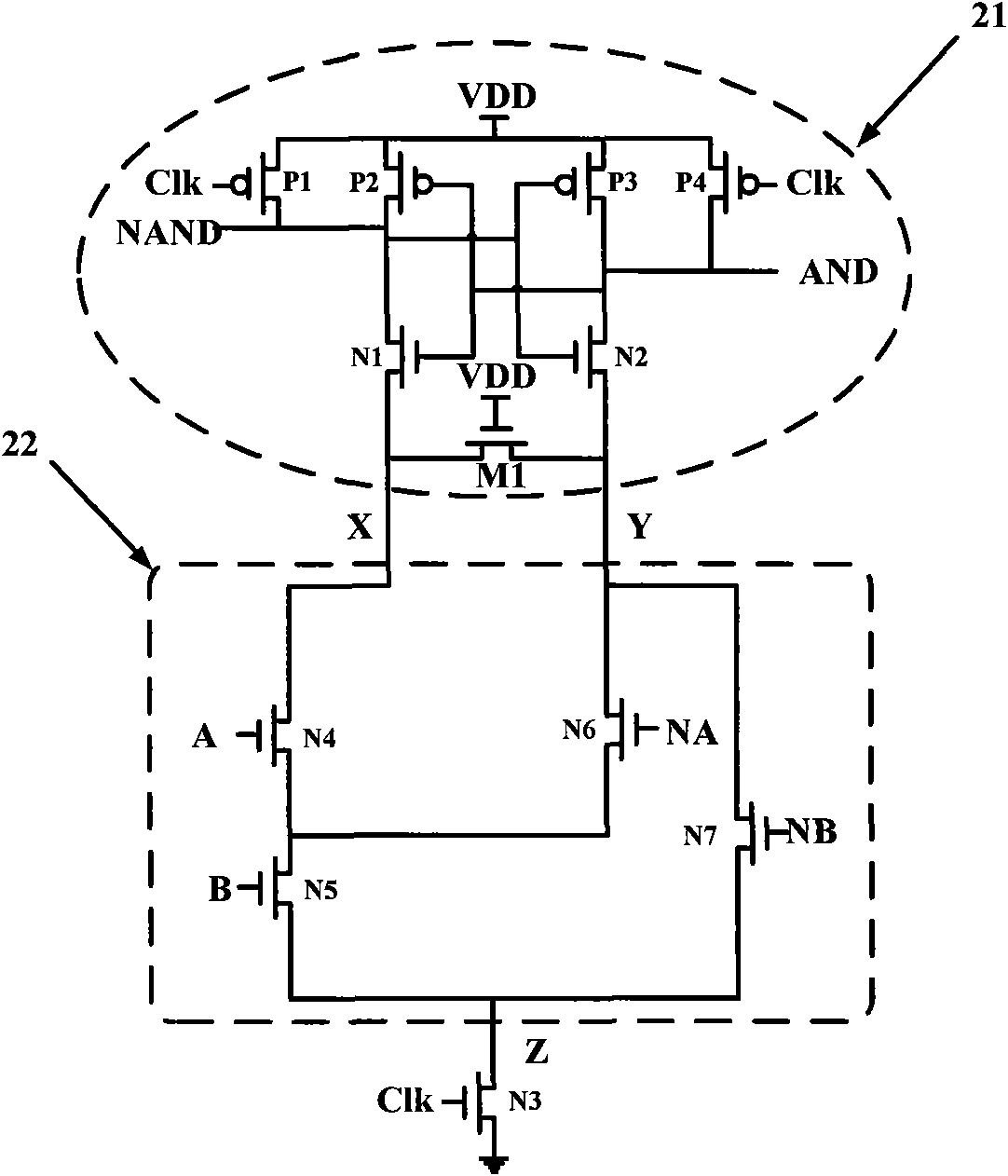

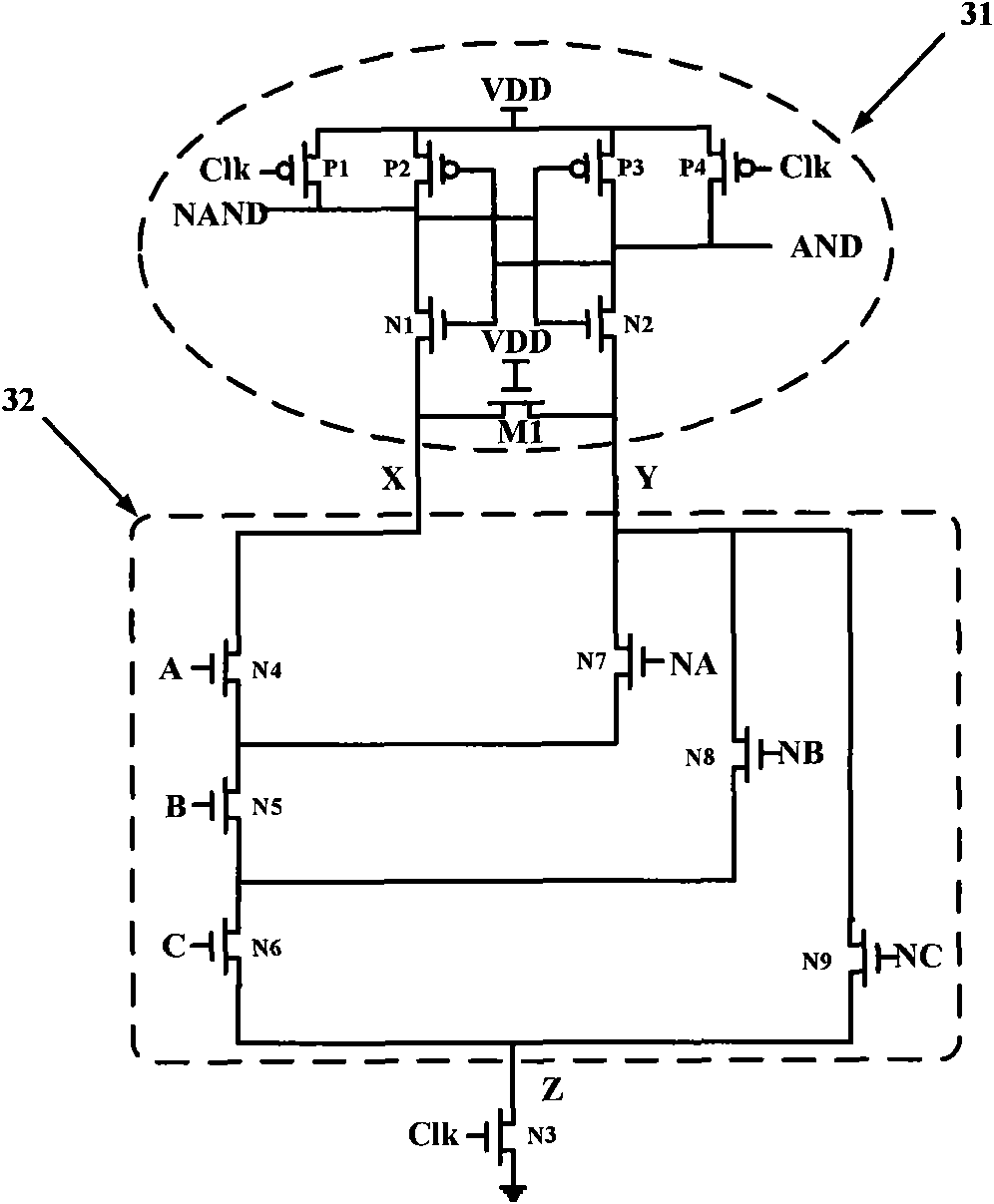

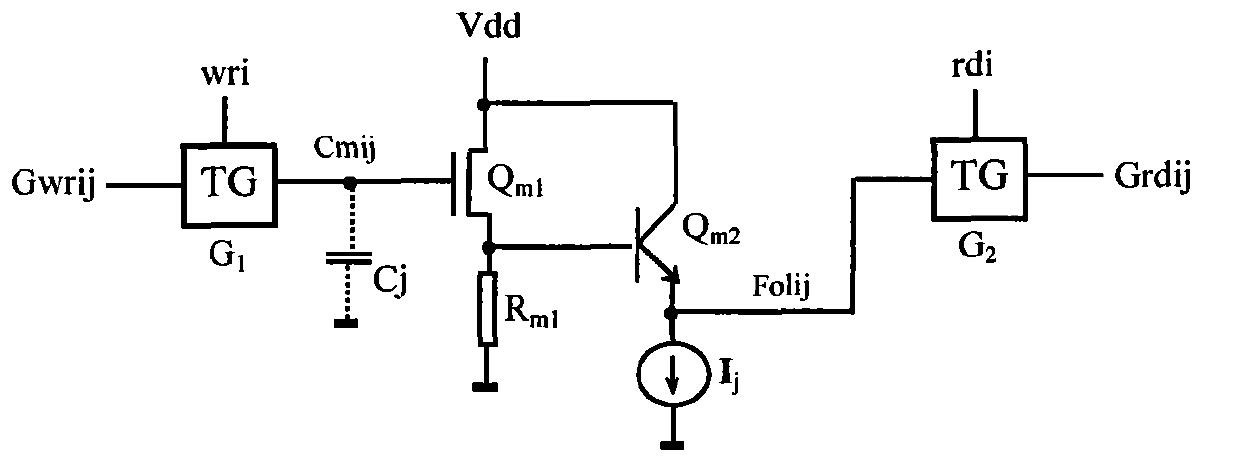

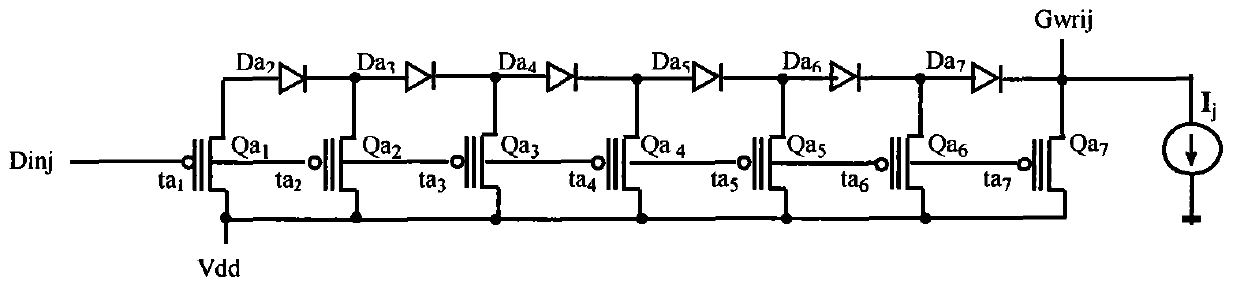

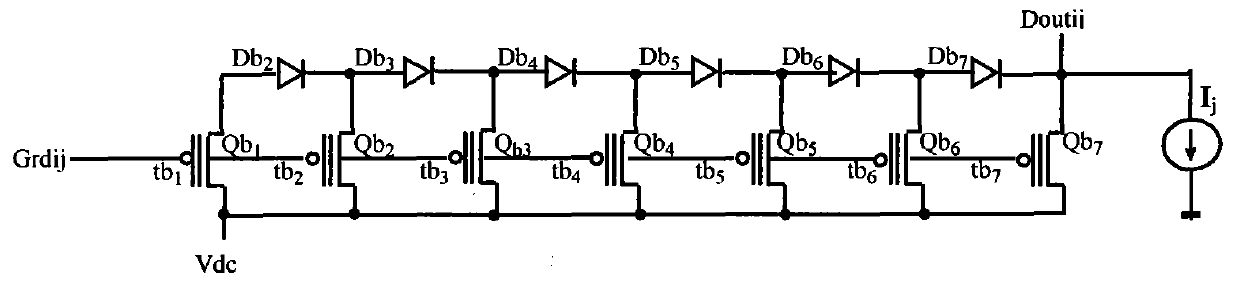

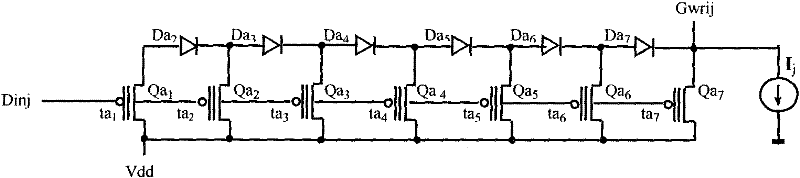

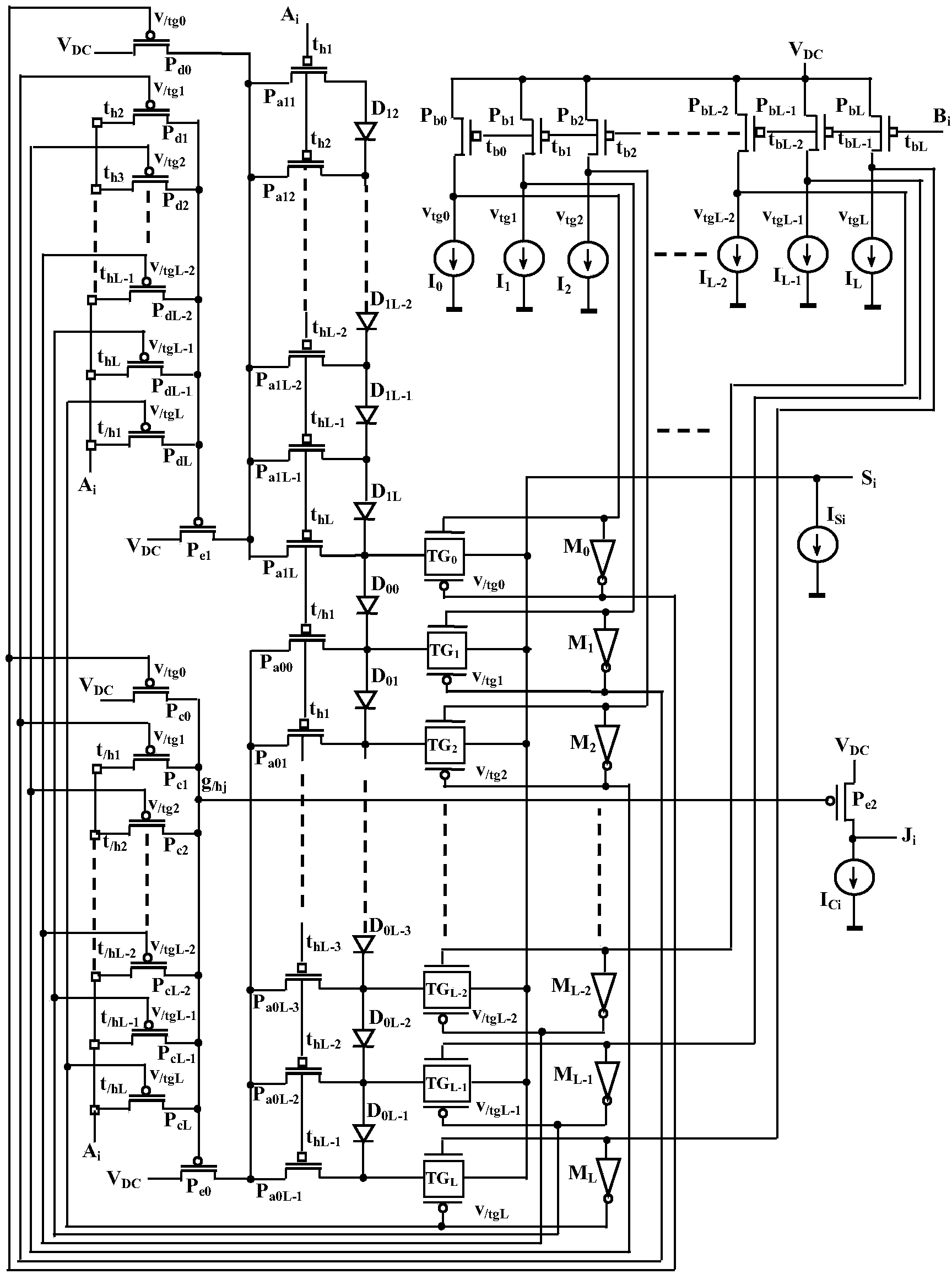

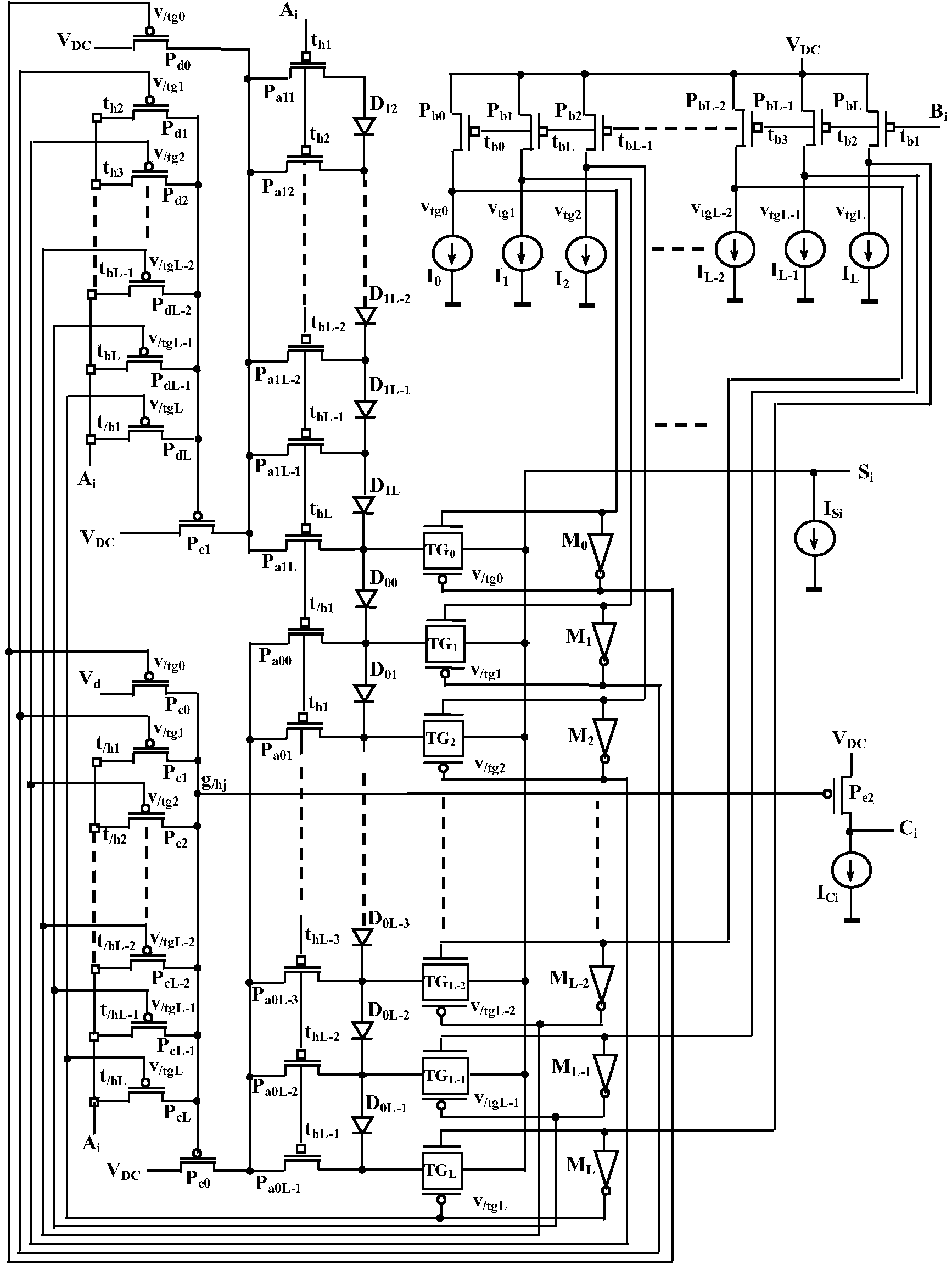

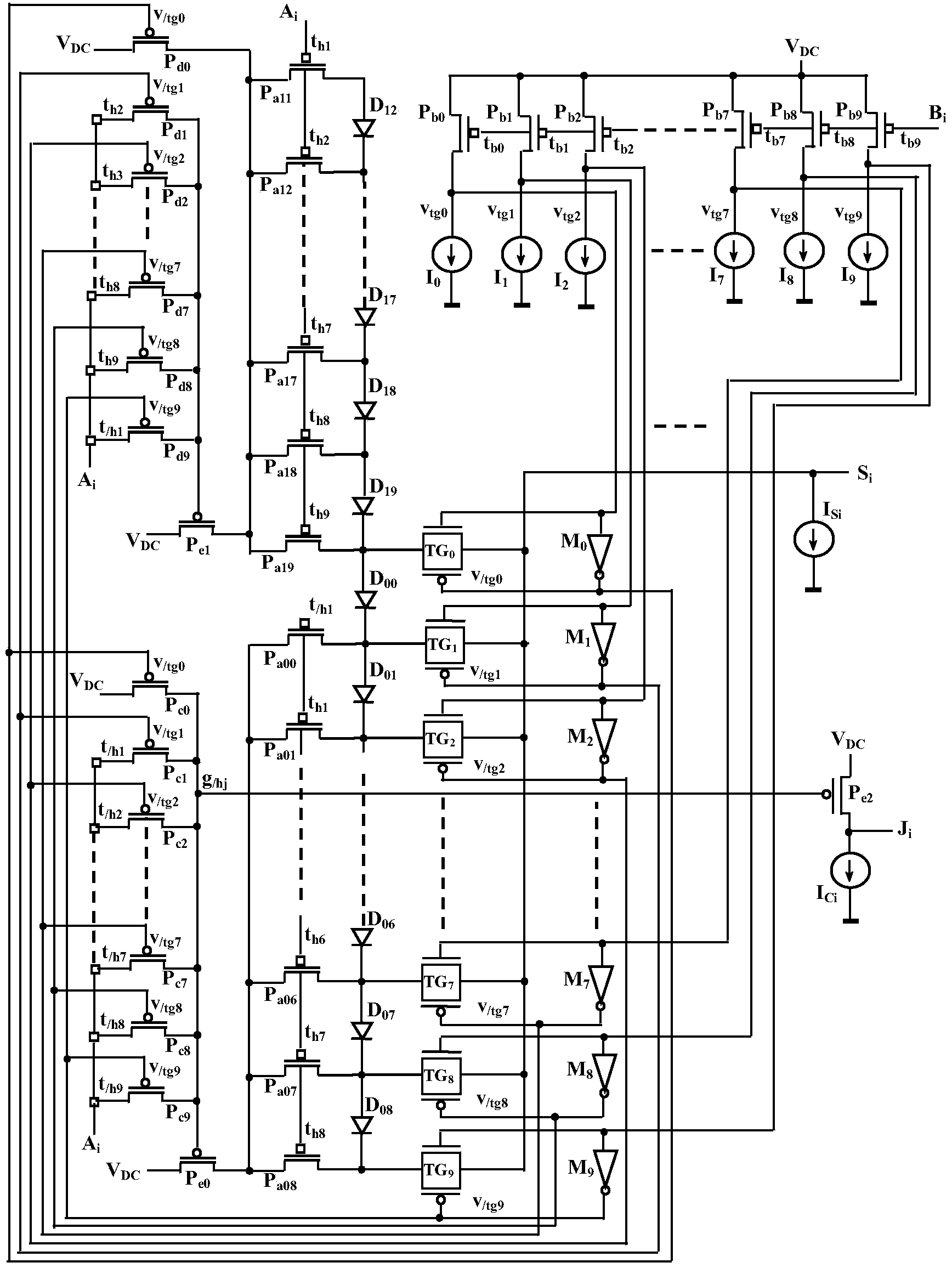

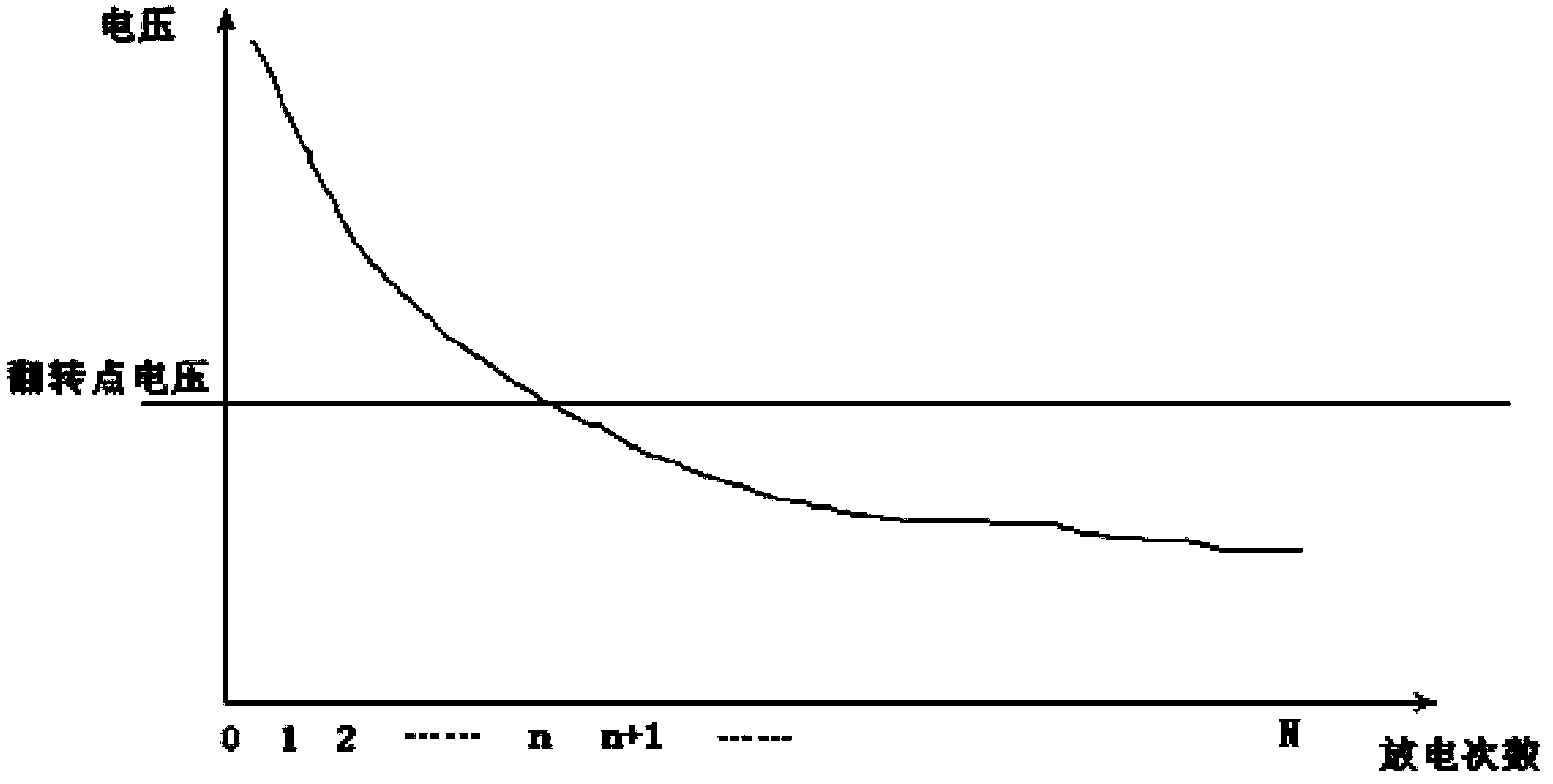

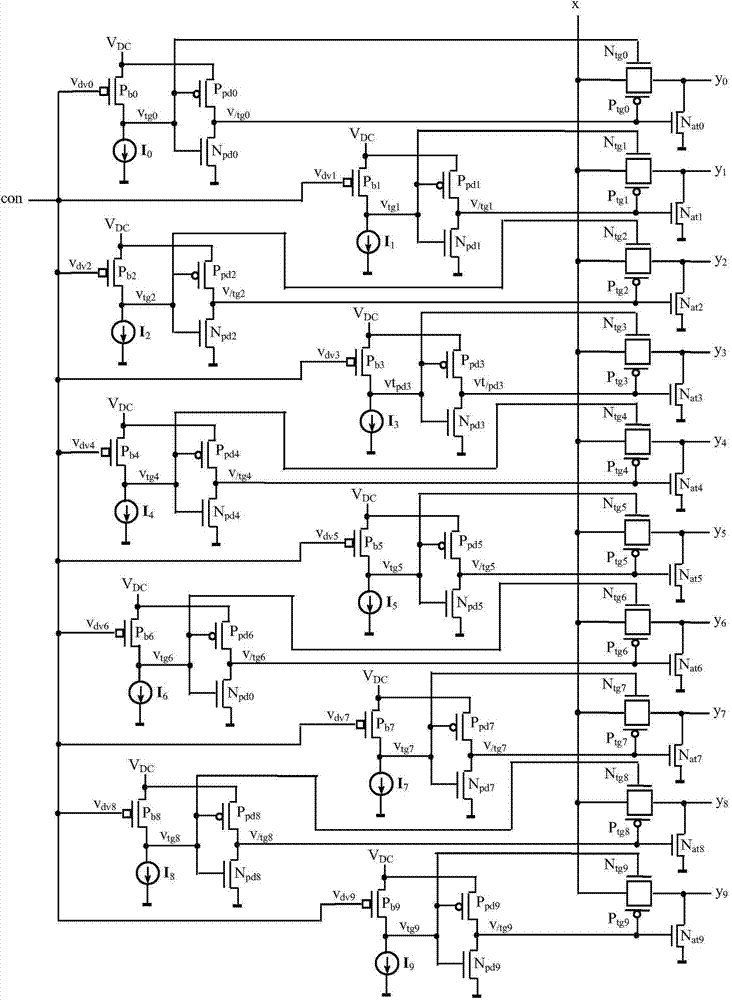

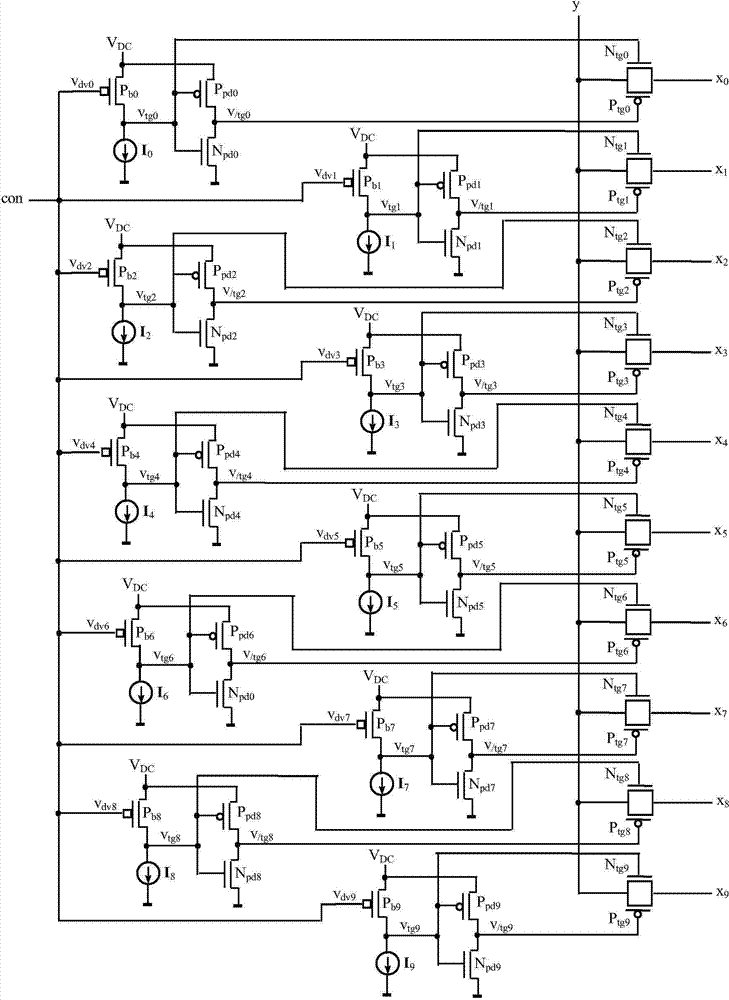

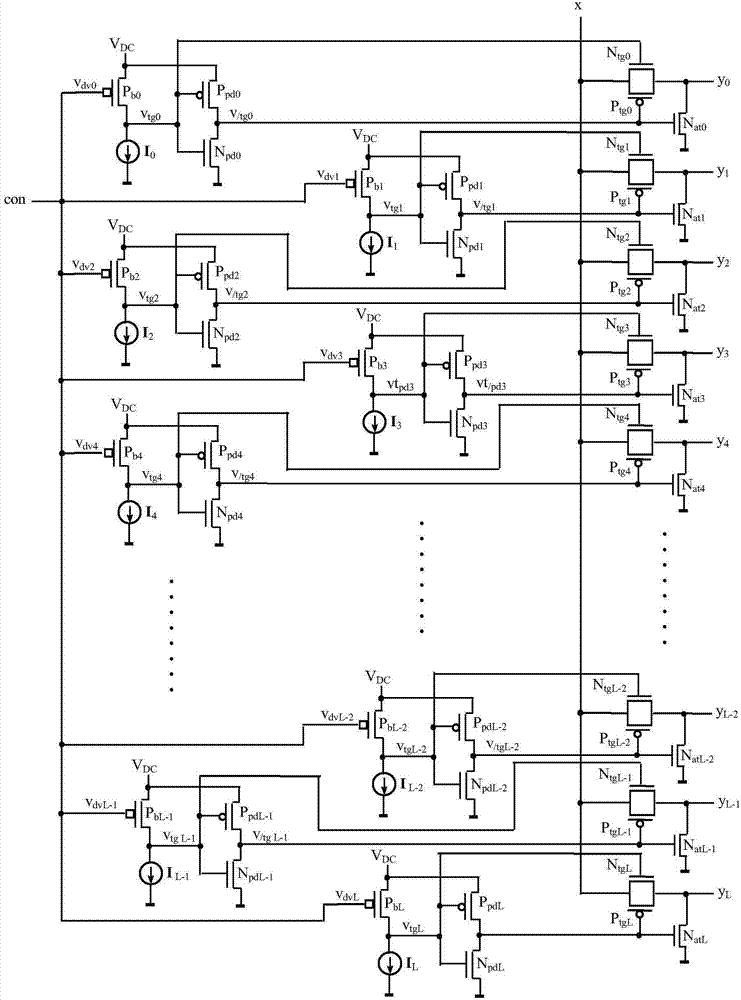

Write-in circuits and read-out circuits of arbitrary-K-value DRAM and eight-value DRAM

The invention relates to write-in circuits and read-out circuits of an arbitrary-K-value DRAM and an eight-value DRAM. The write-in circuits and the read-out circuits have same structure characteristics, and the write-in circuits are each designed to provide a multi-value signal increased by delta than write-in circuit input; an output waveform of a memory cell is considered to be smaller than an input waveform or be of an unequal step shape, the read-out circuits are each designed for correction, and an irregular multi-value signal is converted into a regular (equal step) multi-value signal. The write-in circuits and the read-out circuits both have good quantified shaping effects; when a change of a Cj voltage is not greater than an upper new threshold or a lower new threshold, original multi-value information can be easily recovered, so the write-in circuits and the read-out circuits have anti-jamming capability and multi-value information recovery capability. The write-in circuits and the read-out circuits are mainly applied to the fields of VLSI and other digital IC technologies, such as an FPGA, a CPLD, a semi-custom or a full-custom ASIC, a memorizer and the like.

Owner:HEILONGJIANG UNIV

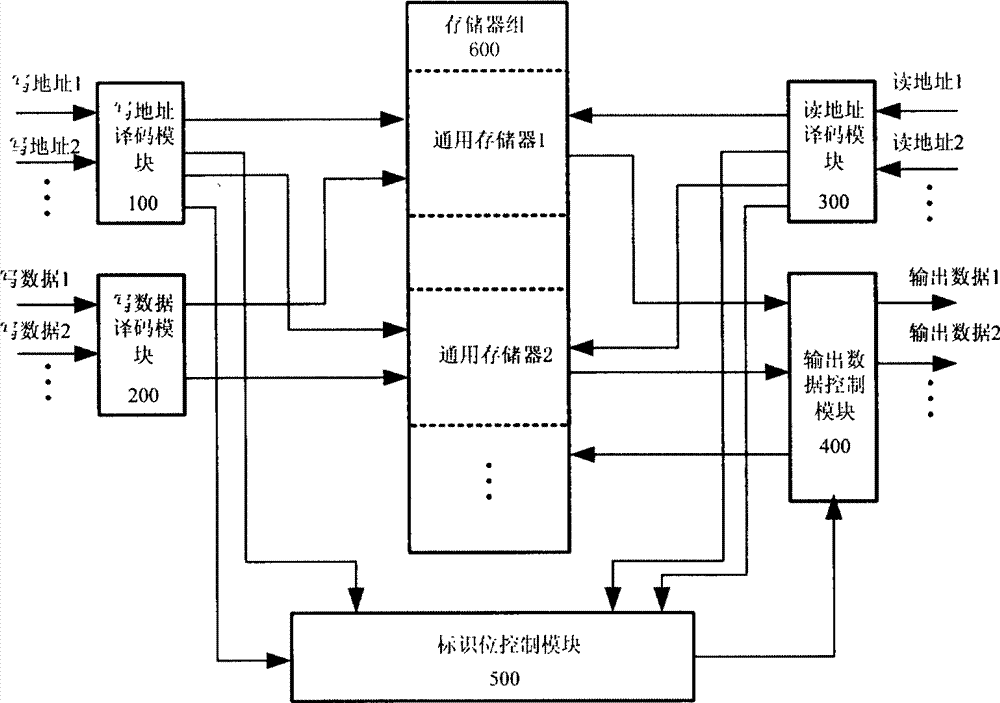

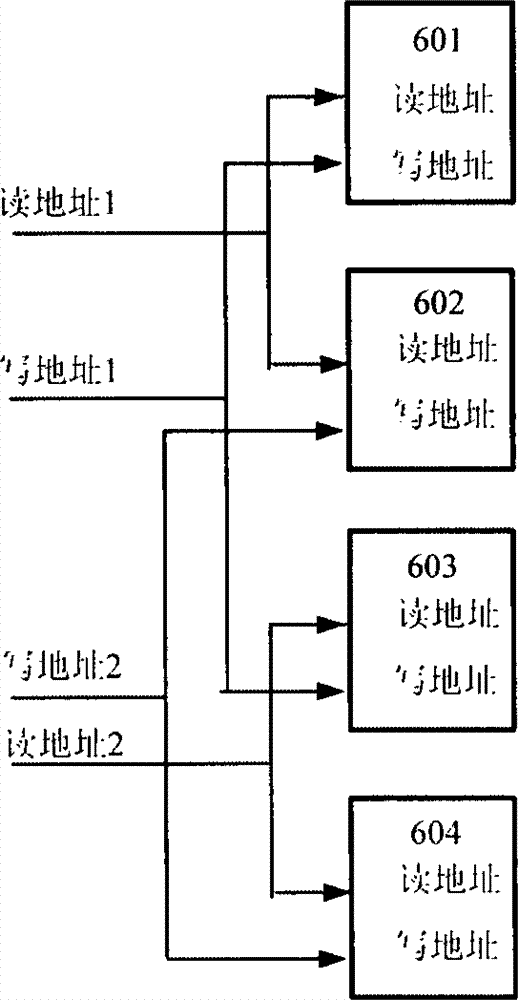

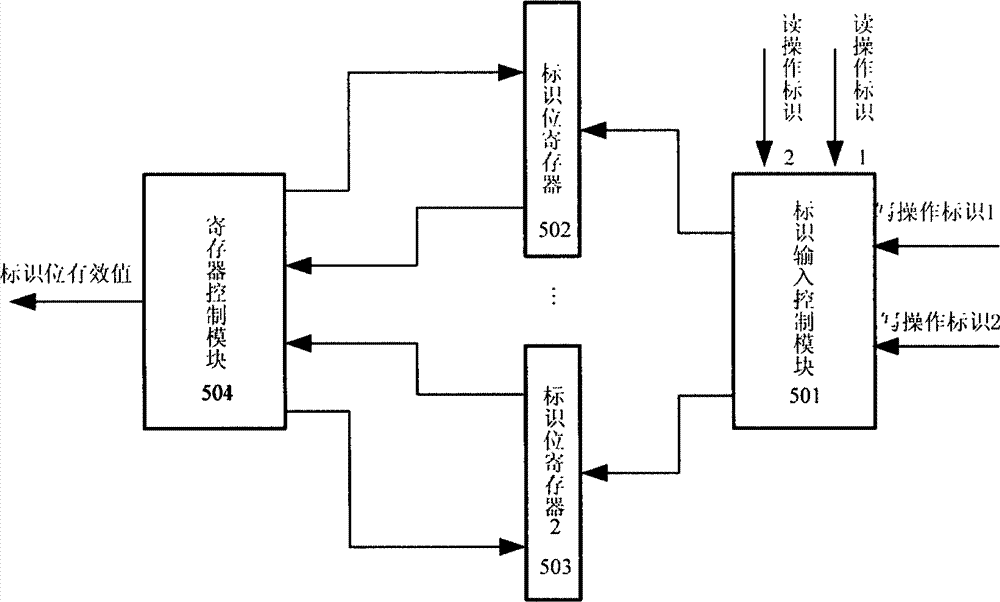

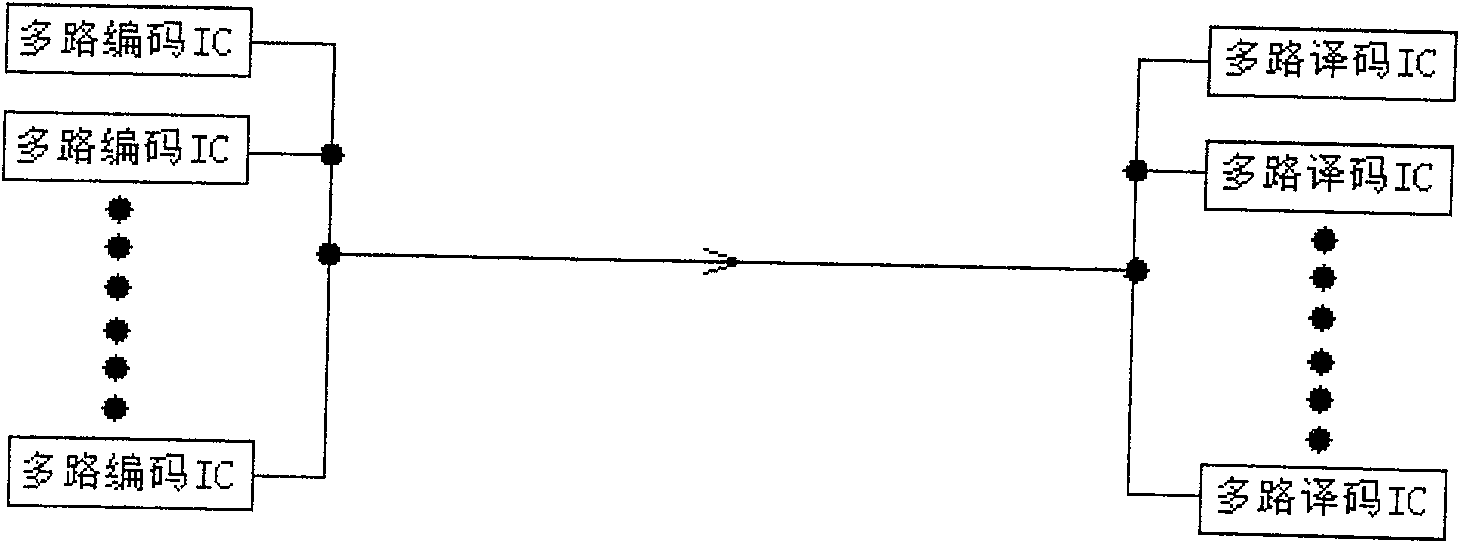

Method of structuring multiport asynchronous storage module

ActiveCN102930898AIncrease the number of portsIncrease storage capacityRead-only memoriesFull customComputer module

The invention discloses a method of structuring a multiport asynchronous storage module and relates to buffer storage and interchange of multichannel parallel data in the process of data interchange and processing. The method of structuring the multiport asynchronous storage module aims at solving the problem that in the process of design of a current semi-custom integrated circuit, a used storer of a technological library just has two types of single ports or double ports and can not meet certain situations of high data throughput rates. An addressing manner of address decoding control partitioning reading and writing is adopted by a plurality of double-port type storers in the technological library to structure the multiport asynchronous storage module, so that the aim that a simple port storage module is structured to the multiport storage module is achieved, and the requirement for the high data throughput rates is reached. The method of structuring the multiport asynchronous storage module has the advantages of flexibly expanding capacity and available access ports of the storer according to design requirements, reducing design difficulty, and shortening development time. Relative to a full-custom multiport storer, the method of structuring the multiport asynchronous storage module has the advantages of being good in flexible performance, high in reliability, small in design risk and the like.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

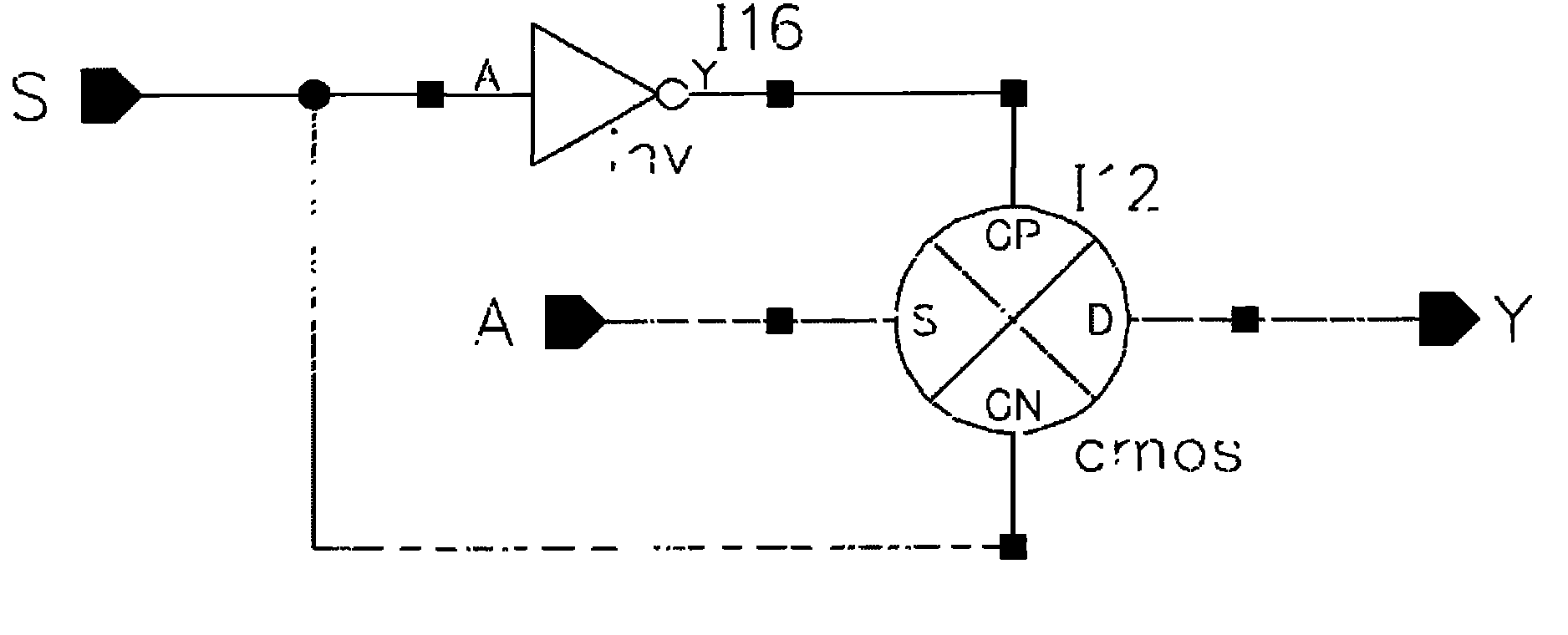

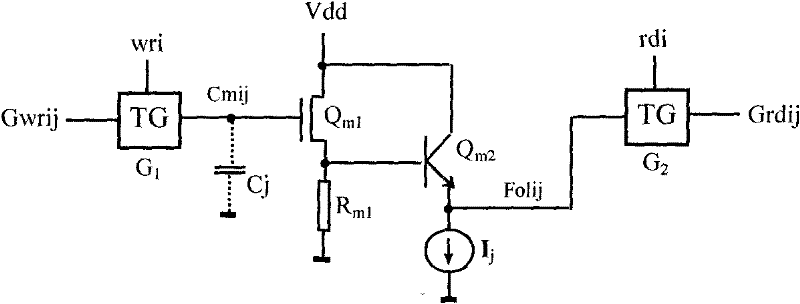

Any k-value and 8-value dram storage unit and writing and reading circuit

The invention discloses a storage unit circuit, a write circuit and a read circuit for any K-valued and 8-valued DRAM (dynamic random access memory). The storage unit circuit comprises a voltage follower (F), a storage capacitor (Cj) of the grid of the voltage follower (F), a CMOS (complementary metal oxide semiconductor) transmission gate (G1) and a CMOS transmission gate (G2); in consideration of the direct-current level offset (Delta) between the input and output of the voltage follower (F), the write circuit is so designed that a multi-valued signal which is direct-current level offset (Delta) higher than the input of the write circuit can be provided; and in addition, since the voltage amplification factor of the voltage follower (F) is less than 1, the output waveform of the voltage follower (F) is smaller than the input waveform or is unequi-stepped, and the read circuit is designed for correction, the non-regular multi-valued signal is converted into a regular (equi-stepped) multi-valued signal. Both the write circuit and the read circuit have a good quantitative shaping effect, the original multi-valued information can be easily recovered when the voltage change of the storage capacitor (Cj) does not exceed a maximum new threshold and a minimum new threshold, and therefore the invention has anti-interference capability and multi-valued information-recovering capability. The invention is mainly used in the technical fields of VLSIs (very large-scale integrated circuit), such as FPGAs (field programmable gate array), CPLDs (complex programmable logic device), semi-custom or full-custom ASICs (application specific integrated circuit) and memories, and other digital ICs (integrated circuit).

Owner:HEILONGJIANG UNIV

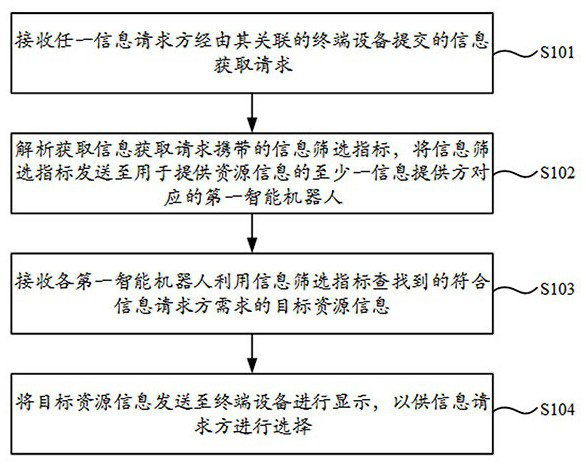

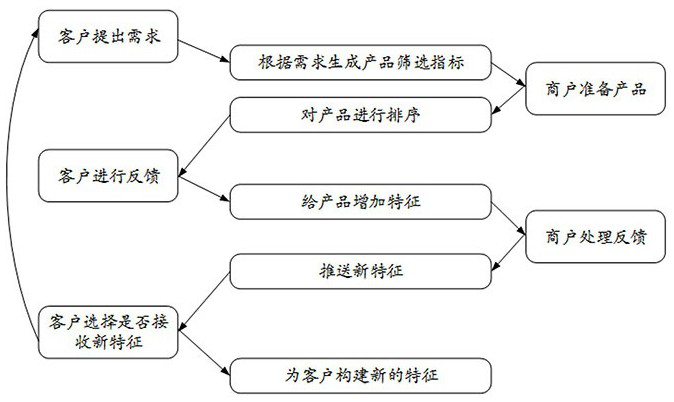

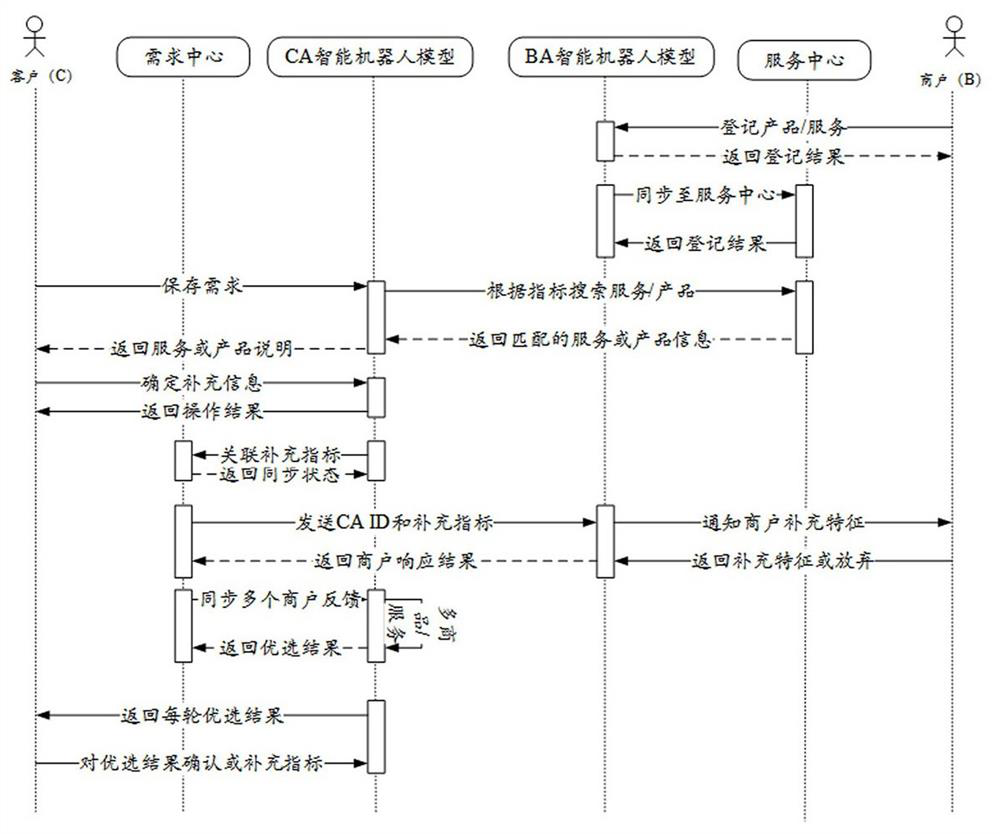

User service method and system based on digital twinning technology

ActiveCN113792134AIncrease awarenessHigh selectivityDigital data information retrievalBuying/selling/leasing transactionsFull customResource information

The invention provides a user service method and system based on a digital twinning technology, and the method comprises the steps: receiving an information obtaining request submitted by any information requester through an associated terminal device, analyzing and obtaining an information screening index carried by the information obtaining request, sending the information screening index to a first intelligent robot corresponding to at least one information provider used for providing resource information; receiving target resource information which is found by each first intelligent robot by using the information screening index and meets the requirement of the information requester; and sending the target resource information to the terminal equipment for display, so that the information requester can select the target resource information. According to the scheme provided by the invention, completely customized services and products can be recommended to the user, the user is supported to make more rational and better choices in commodity and service purchase, particularly business services and capability improvement and development which have important influences on the customer, and meanwhile, the cognition and selection capabilities of the customer on the products and the services and the like are effectively improved.

Owner:SHENZHEN SUNLINE TECH CO LTD

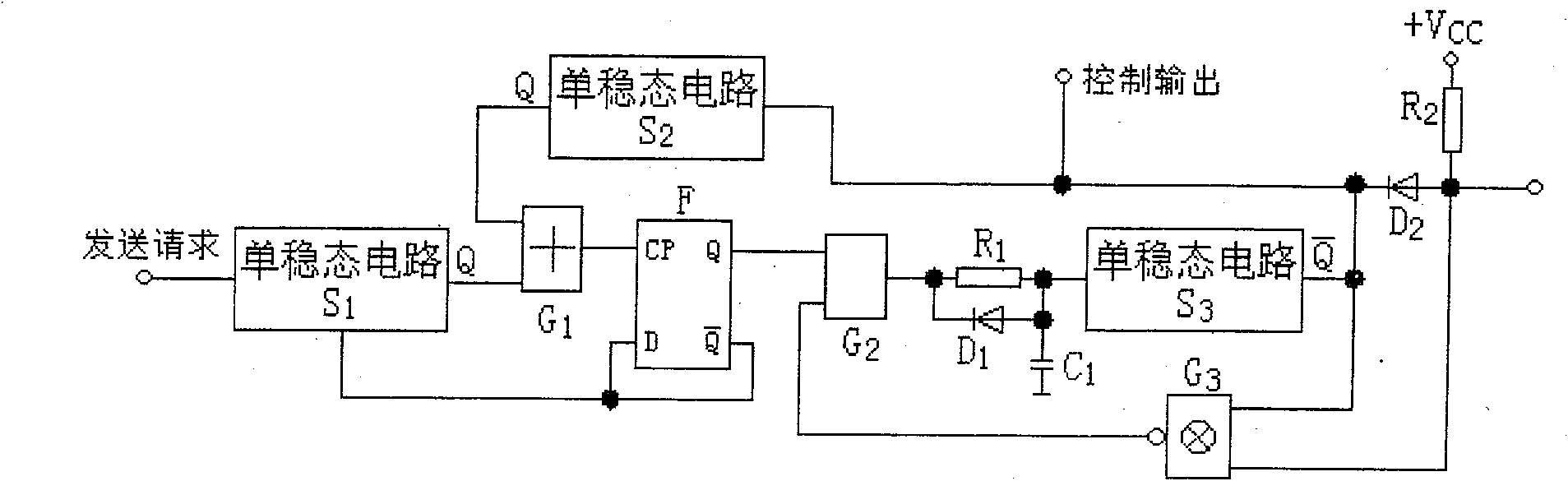

Master-slave follower type single-edge K value trigger constructing method utilizing circuit three-element theory and master-slave follower type single-edge K value trigger circuit

The invention discloses a master-slave follower type single-edge K value trigger constructing method utilizing the circuit three-element theory and a master-slave follower type single-edge K value trigger circuit. The master-slave follower type single-edge K value trigger composed of a digital follower and an analog follower is obtained by means of the circuit three-element theory, a distinctive three-beat work mode is adopted, clock falling edge triggering is adopted, an identical simplest element level circuit structure is obtained under eight optimum coding, due to the fact that a slave follower is an NMOS tube source electrode follower, only the structure scale of a main follower becomes large along with the increase of the K value which is equal to 4,5,6..., other circuit structures do not change, the main follower is the digital follower composed of a high-pass variable-threshold PMOS tube, the output logic level clamp function is realized, and the anti-jamming capability is high. The master-slave follower type single-edge K value trigger circuit is simple in structure, can serve as a K value static storage cell of a K value SSRAM, and can be used in the VLSI field such as FPGA, CPLD, semi-custom or full-custom ASIC and storer and other digital IC technical fields.

Owner:HEILONGJIANG UNIV

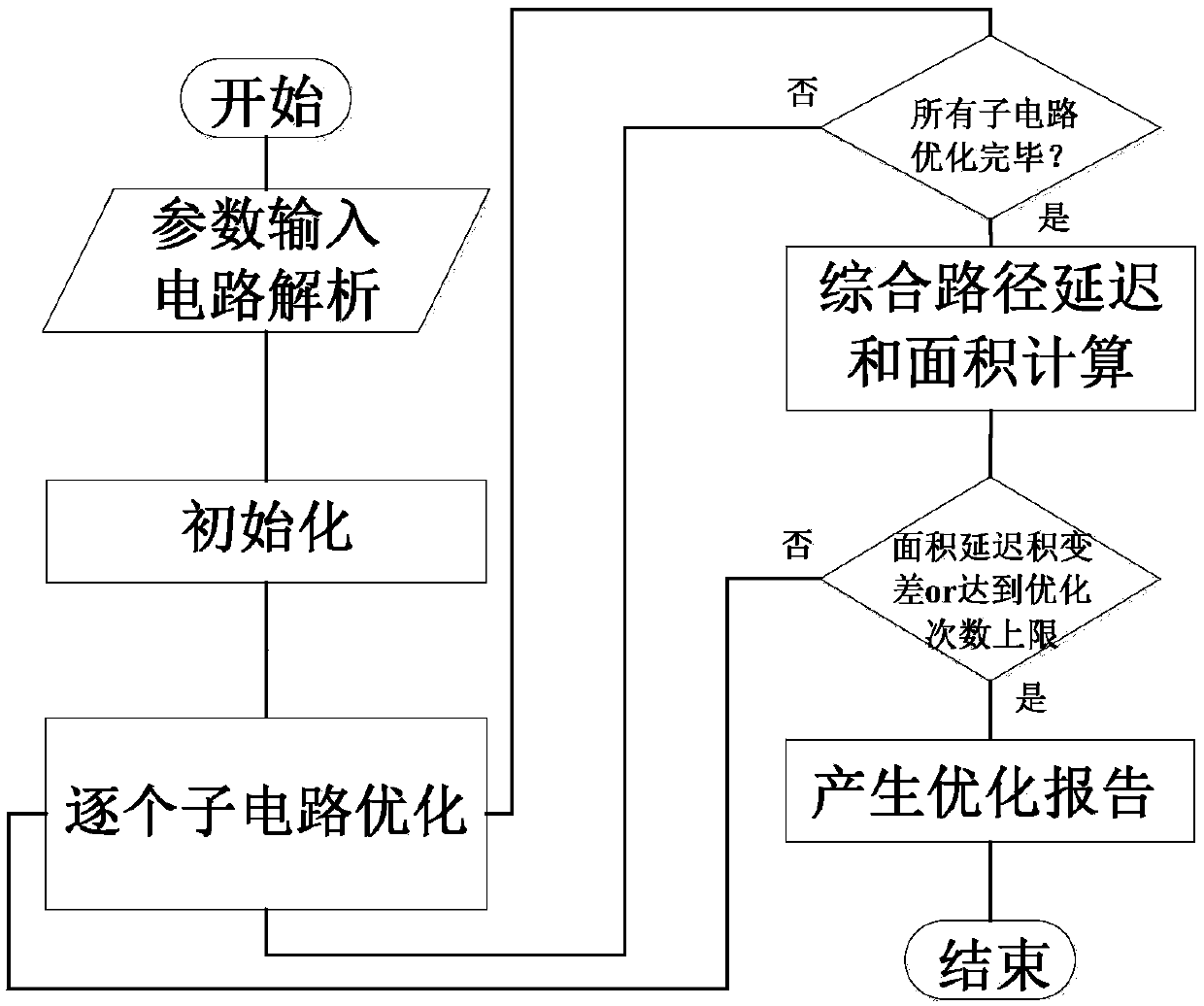

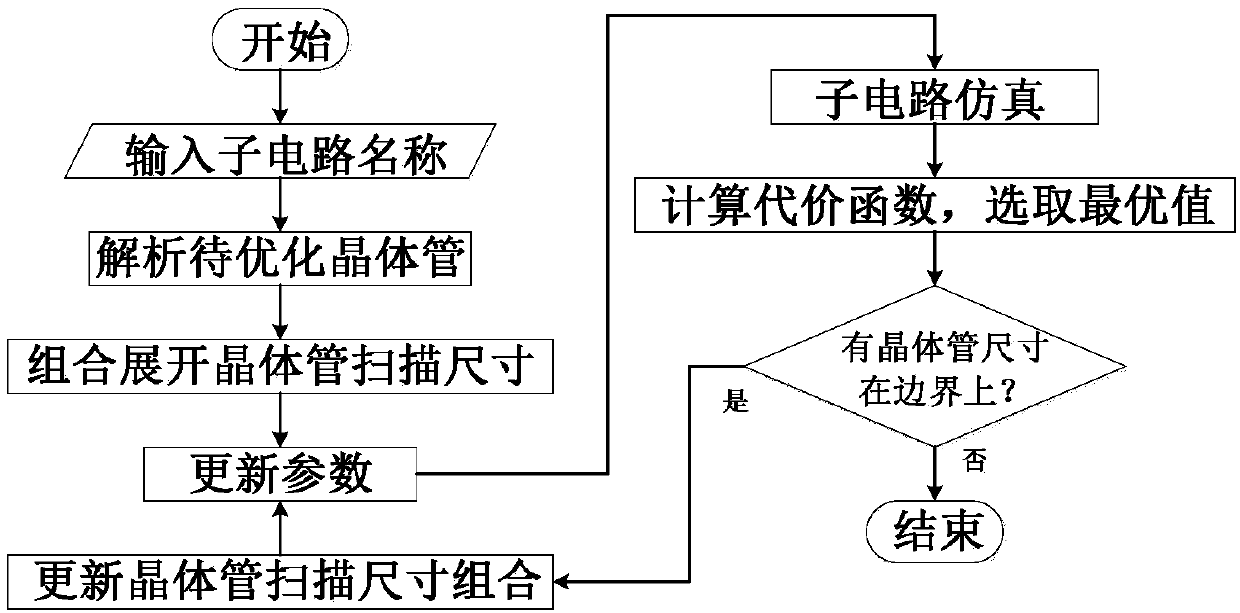

Rapid optimization method for size of FPGA circuit transistors

ActiveCN107742051AImprove design efficiencyReduce the number of combinationsDesign optimisation/simulationCAD circuit designFull customComputer science

The invention belongs to the technical field of integrated circuits, and particularly relates to an optimization method for the size of FPGA circuit transistors. The method mainly includes the steps of conducting related sub-circuit analysis based on FPGA parameters, initializing the parasitic parameters of a circuit combined with FPGA circuit implement features, then conducting one-by-one optimization on each sub-circuit, after all the sub-circuits are optimized, conducting comprehensive optimization of delay and areas, and outputting an optimization result report file. According to the optimization method, a related algorithm can be adopted to improve the optimization quality and increase the optimization speed; for example, the modes such as bundled circuit combination optimization areadopted to decrease the optimization number of the transistors and increase the optimization speed; multithreaded acceleration runs to conduct parallelization treatment on some circuits without mutualcoupling relationships so as to accelerate the optimization process. By the optimization method, the optimization time of the size of the FPGA circuit transistors can be greatly shortened, and compared with a traditional full custom circuit, the circuit has design efficiency which is improved by more than 10 times.

Owner:FUDAN UNIV

Method for establishing K-value and ten-value half adder and K-value and ten-value half subtracter based on band-pass threshold loading technology and circuit obtained based on method

The invention discloses a method for establishing a K-value and ten-value half adder and a K-value and ten-value half subtracter based on the band-pass threshold loading technology and a circuit obtained based on the method. According to the method for establishing the K-value and ten-value half adder and the K-value and ten-value half subtracter based on the band-pass threshold loading technology and the circuit obtained based on the method, the band-pass threshold loading technology is adopted, the demands in all stages are processed according to information, and band-pass thresholds required in different stages are loaded to a PMOS tube, so that the band-pass threshold of the PMOS tube can be changed at any time; the K-value half subtracter and the half adder are analyzed, the characteristic that a high-value area and a low-value area are unified is realized, based on the loading technology, two kinds of circuits can be replaced by one kind of circuits, the traditional method achieved based on a K-value logic gate is avoided, and the circuit structure is simplified greatly; the chaotic encryption method and the circuit can be popularized to K values from two values, K-value multiplication and division are replaced by K-value addition and subtraction, and the multiplication-and-division-free chaotic encryption method and circuit for K-value information are obtained. The method for establishing the K-value and ten-value half adder and the K-value and ten-value half subtracter based on the band-pass threshold loading technology and the circuit obtained based on the method are applied to the VLSIs such as the FPGAs, CPLDs, half-custom or full-custom ASICs and memorizers and the technical field of other digital ICs.

Owner:HEILONGJIANG UNIV

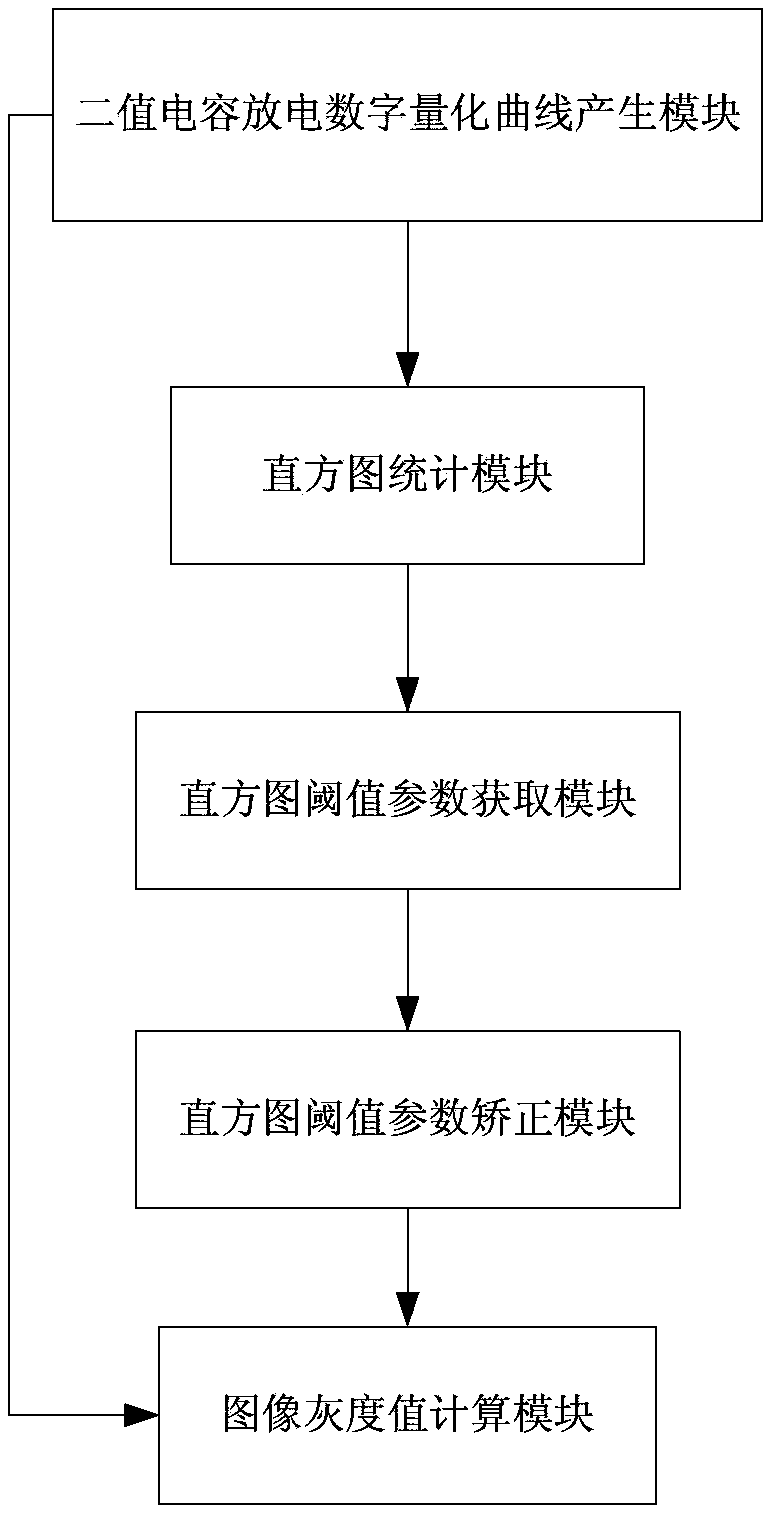

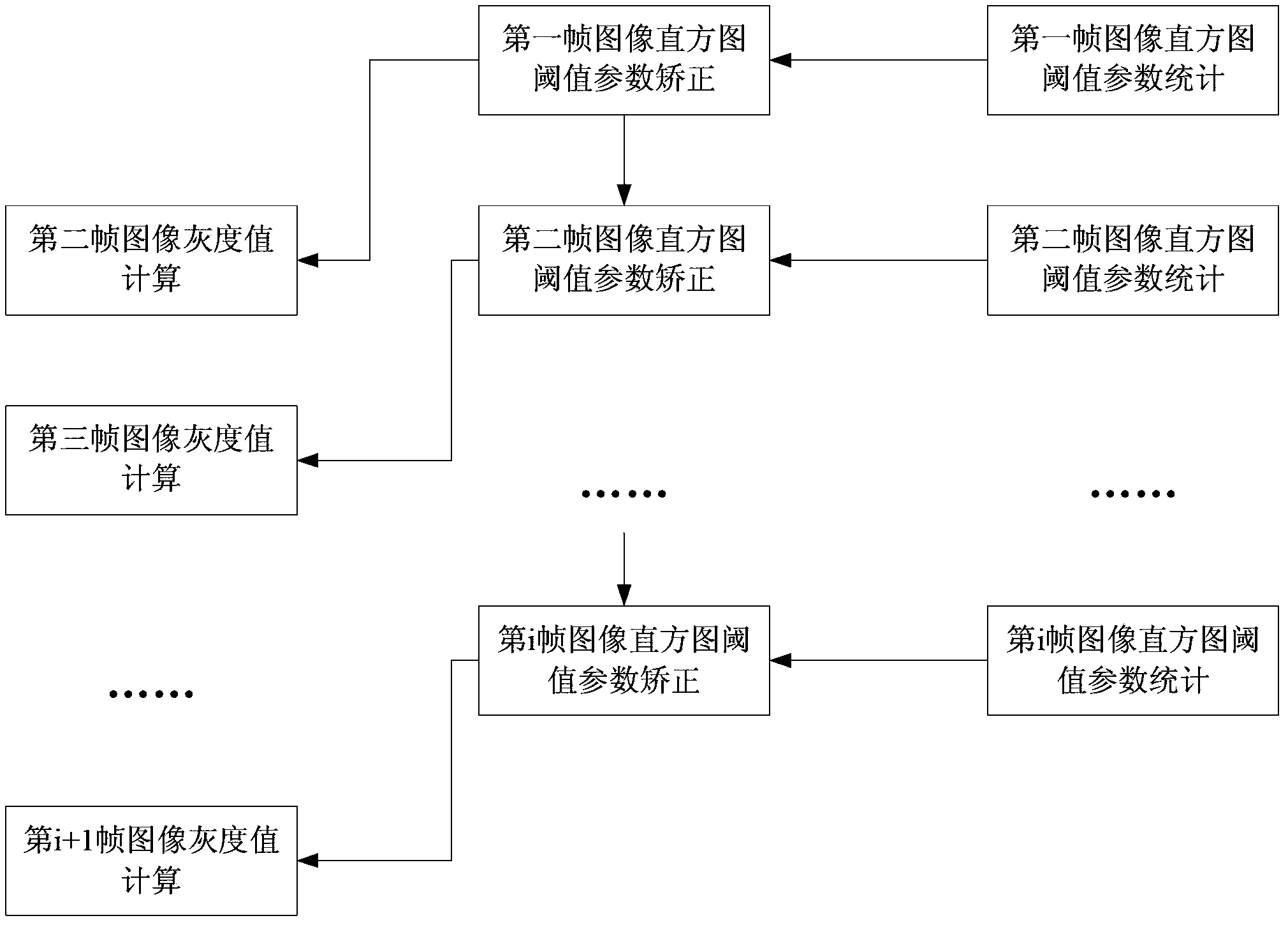

Image self-adaptive digital quantification method and structure

ActiveCN103679620AImprove unityProcessing Speed OptimizationImage data processing detailsCapacitanceFull custom

The invention provides an image self-adaptive digital quantification structure which comprises a two-value capacity discharge digital quantification curve generating module, a histogram statistic module, a histogram threshold value parameter acquiring module, a histogram threshold value parameter correcting module and a gray value calculating module. The image contrasts continuously acquired in real time are self-adaptively regulated on the basis of an ASIC (application specific integrated circuit) streamline structure, then images acquired through different dry, wet and shallow medium contact surfaces are excellent in contract uniformity, the processing speed is optimized, and the digital image which is regulated through same frame contrast is output while a frame image analog signal is acquired. According to the invention, full custom ASIC achieves image self-adaptive digital quantification, a streamline structure of processing the image while acquiring the image is conducted, the processing speed is high, the cost is low, and the power consumption is low.

Owner:合肥方程式电子科技有限公司

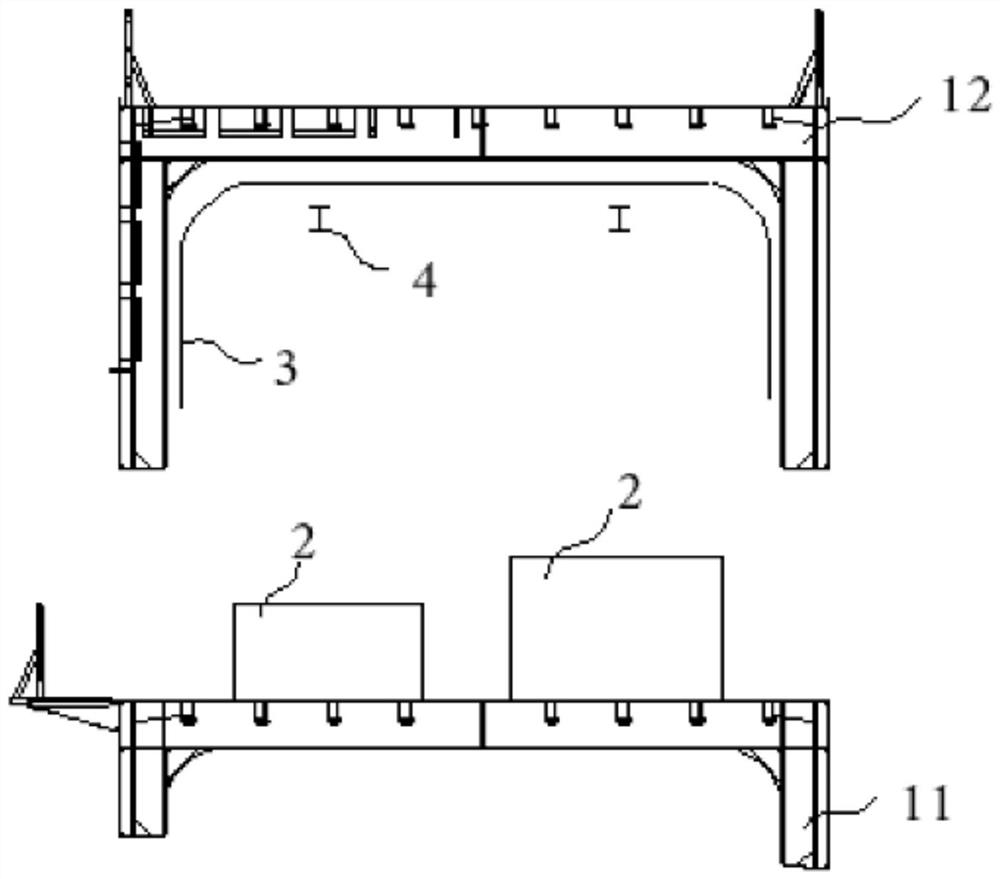

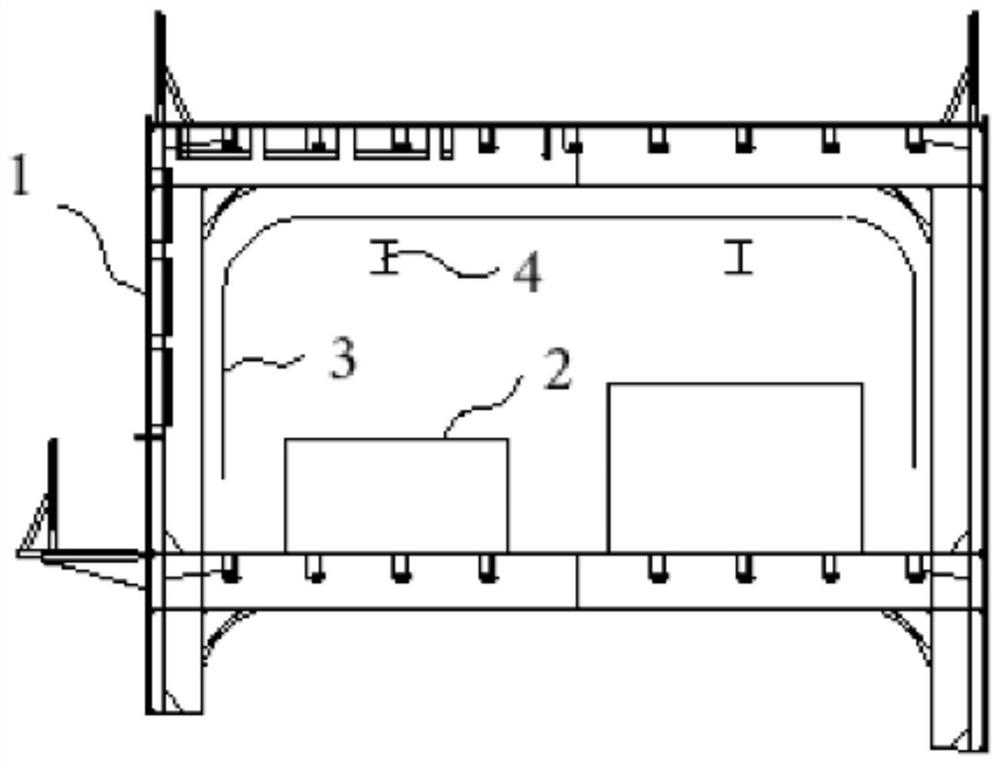

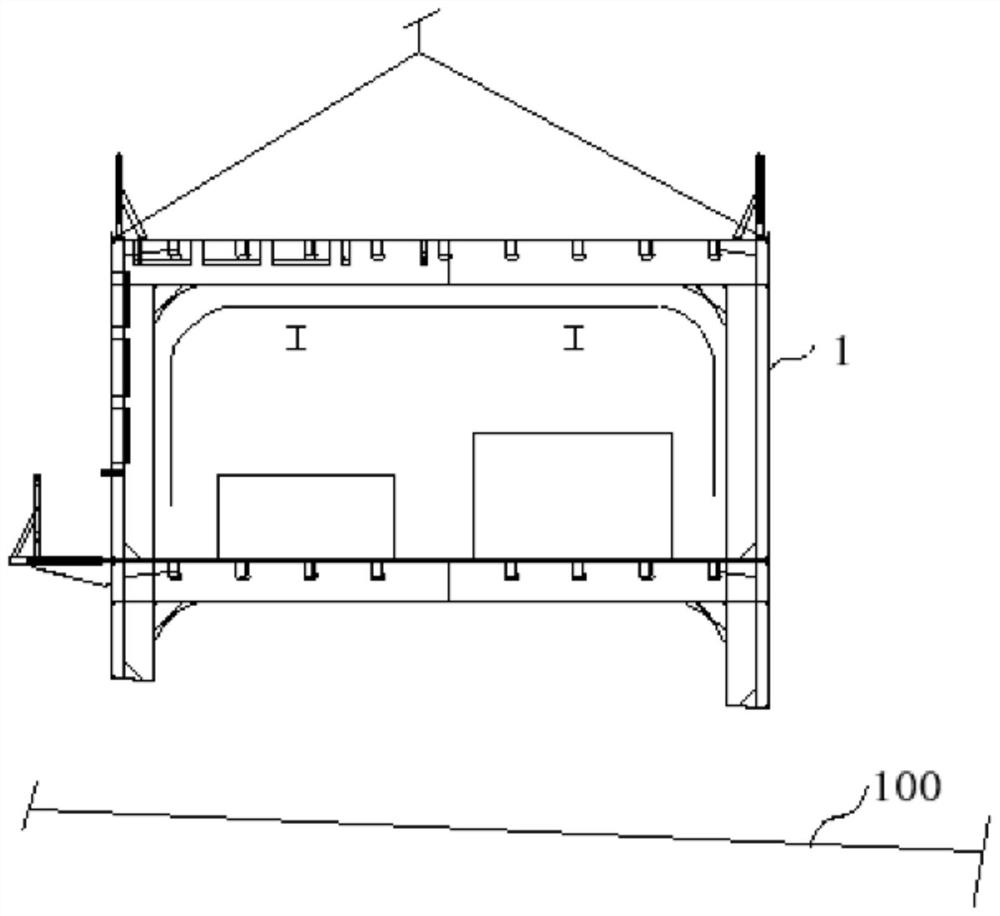

Arrangement method for FGSSROOM unit of dual-fuel ship

PendingCN113753176AWill not affect the construction periodSave installation timeVessel partsFull customStructural engineering

The invention belongs to the technical field of dual-fuel ships, and discloses an arrangement method for FGSSROOM unit of a dual-fuel ship. The method comprises the following steps: S1, according to an arrangement diagram of a standardized FGSSROOM unit, carrying out room structure design of the FGSSROOM unit; S2, according to the structural design, machining structural parts of the cabin, and completing FGSSROOM unit assembling; S3, fixedly installing the FGSSROOM unit on the ship body; and S4, conducting pipeline closing on the FGSSROOM unit and the ship body. According to the arrangement method for the FGSSROOM unit of the dual-fuel ship, the design process and the manufacturing and mounting process of the FGSSROOM unit are reconstructed, full-customized design is changed into standardized module design, flat assembly line type operation is changed into flat synchronous manufacturing, the design time is shortened, the design efficiency is improved, the mounting time on the ship is greatly saved, and the construction cost is reduced.

Owner:SHANGHAI WAIGAOQIAO SHIP BUILDING CO LTD

K-value and ten-value signal controlled data distributor and data selector

The invention discloses a K-value and ten-value signal controlled data distributor and data selector. The K-value data distributor is composed of K CMOS transmission gates, K CMOS NOT gates, K logic value discrimination gates and K NMOS tubes. The K NMOS tubes of the K-value data distributor are deleted, and then input is changed into output and output is changed into input so that the K-value data selector is obtained. The K-value data selector and the distributor are important devices for changing a K-value data transmission channel. In order to popularize a chaotic encryption method and an encryption circuit from 2-value information to K-value information, the K-value data selector and the distributor can be used so that a K-value shift data selector is realized, K-value multiplication and division operation is substituted by addition and subtraction operation, and thus a no-multiplication-and-division chaotic encryption circuit of K-value information is realized. The data distributor and the data selector are applied to the technical fields of VLSI like FPGA, CPLD, semi-custom or full-custom ASIC and memories and other digital IC.

Owner:HEILONGJIANG UNIV

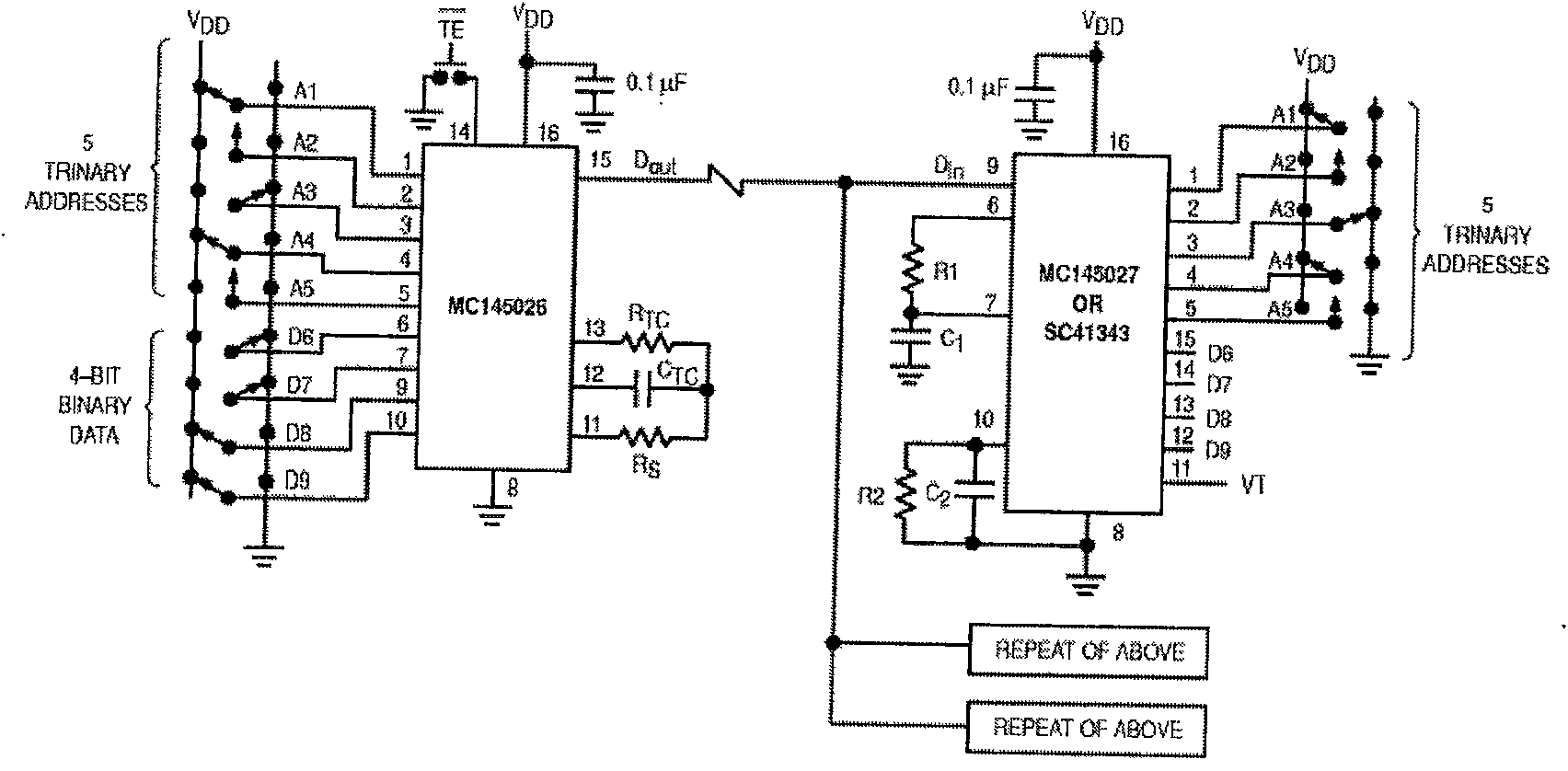

Method and circuit for controlling the parallel operation of multipath coding integrated circuit

InactiveCN100574113CAvoid Signal ConflictsSignal conflicts will not occurPulse automatic controlCode conversionCapacitanceFull custom

Owner:HUAQIAO UNIVERSITY