Rapid optimization method for size of FPGA circuit transistors

A size optimization and transistor technology, applied in CAD circuit design, design optimization/simulation, electrical digital data processing, etc., can solve problems such as difficult to obtain the global optimal solution and affect product performance, so as to shorten optimization time and improve circuit design The effect of improving efficiency and reducing the number of combinations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The specific implementation is as follows:

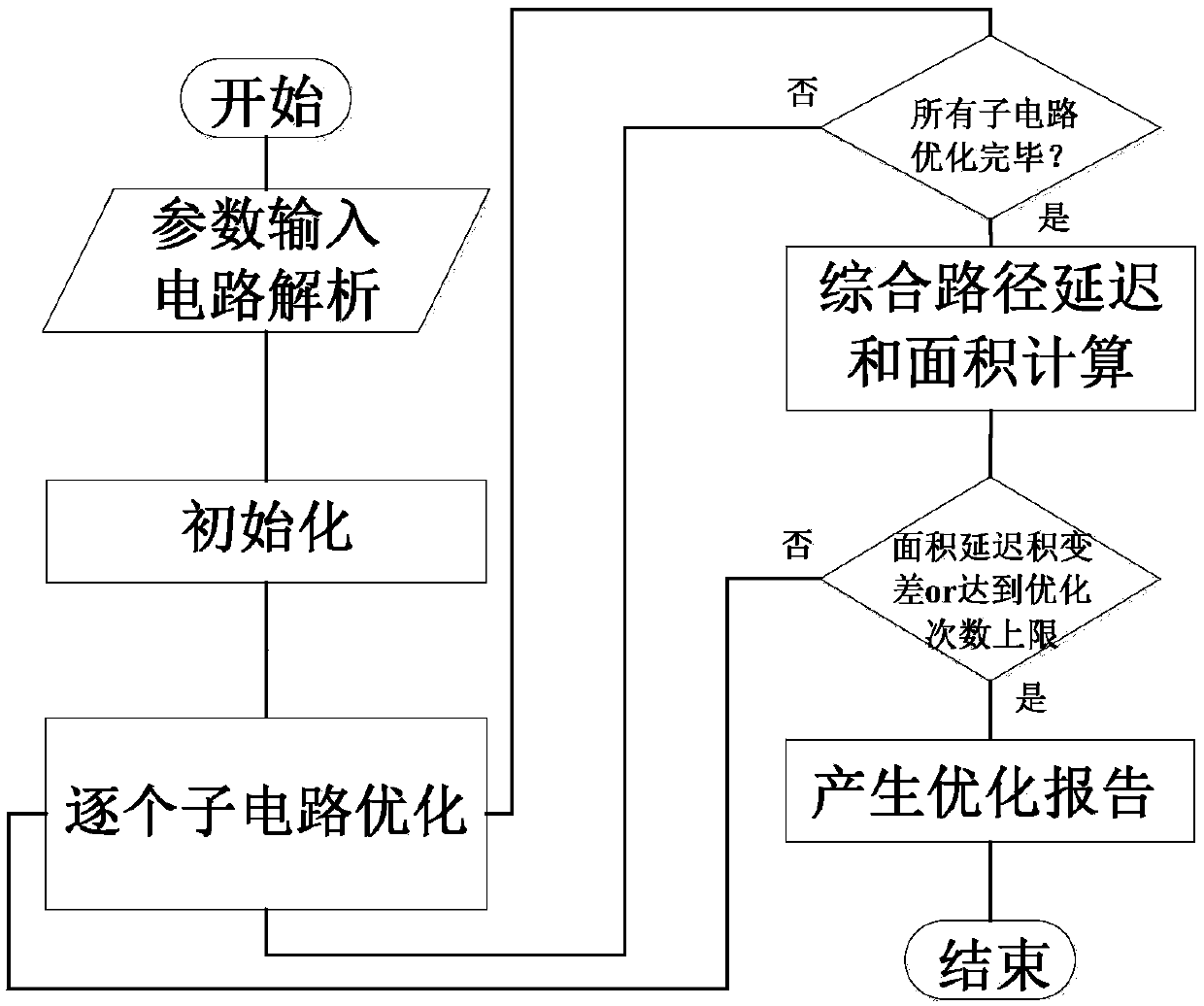

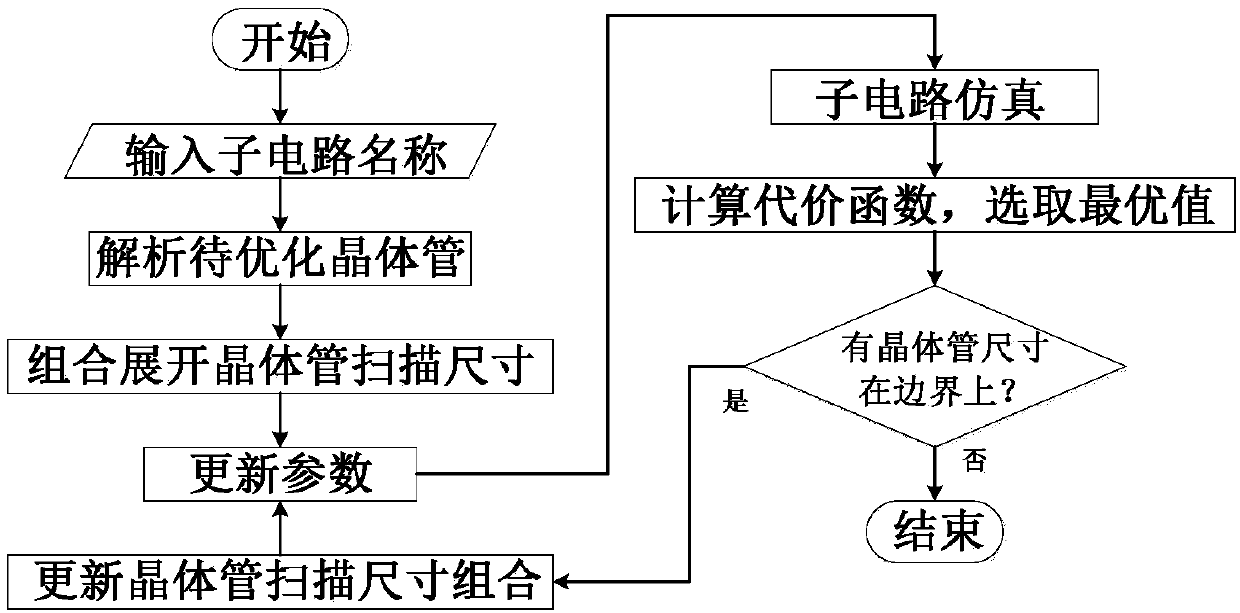

[0028] First, iterative optimization algorithms such as greedy algorithm, simulated fire algorithm, etc. are used. Here, the greedy algorithm is used as an example to perform traversal optimization on the transistors of each sub-circuit of the FPGA (such as figure 2 shown), here we take the double line sub-circuit as an example to illustrate, other circuits are similar. Such as image 3As shown in , the program first finds iso-optimized transistors in the subcircuit. Ptran_L1_nmos, Ptran_L2_nmos, inv_1_nmos, inv_1_pmos, inv_2_nmos, inv_2_pmos, rest_pmos a total of seven transistors. According to the greedy algorithm, it is necessary to expand the transistors to be optimized based on the existing values. For example, there are seven transistors in this example, and each transistor scans 5 values, then there are a total of 78125 (5 7 ) values, select the optimal value in this range, and check whether the optimal value is at...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More