Master-slave follower type single-edge K value trigger constructing method utilizing circuit three-element theory and master-slave follower type single-edge K value trigger circuit

A technology with three elements of a circuit and a construction method, which is applied in the construction field of a master-slave follower type single-edge K-value flip-flop, can solve the problems such as the reduced resolution of the K-value signal of the input gate, unfavorable multi-value circuits, and reduced high-frequency performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

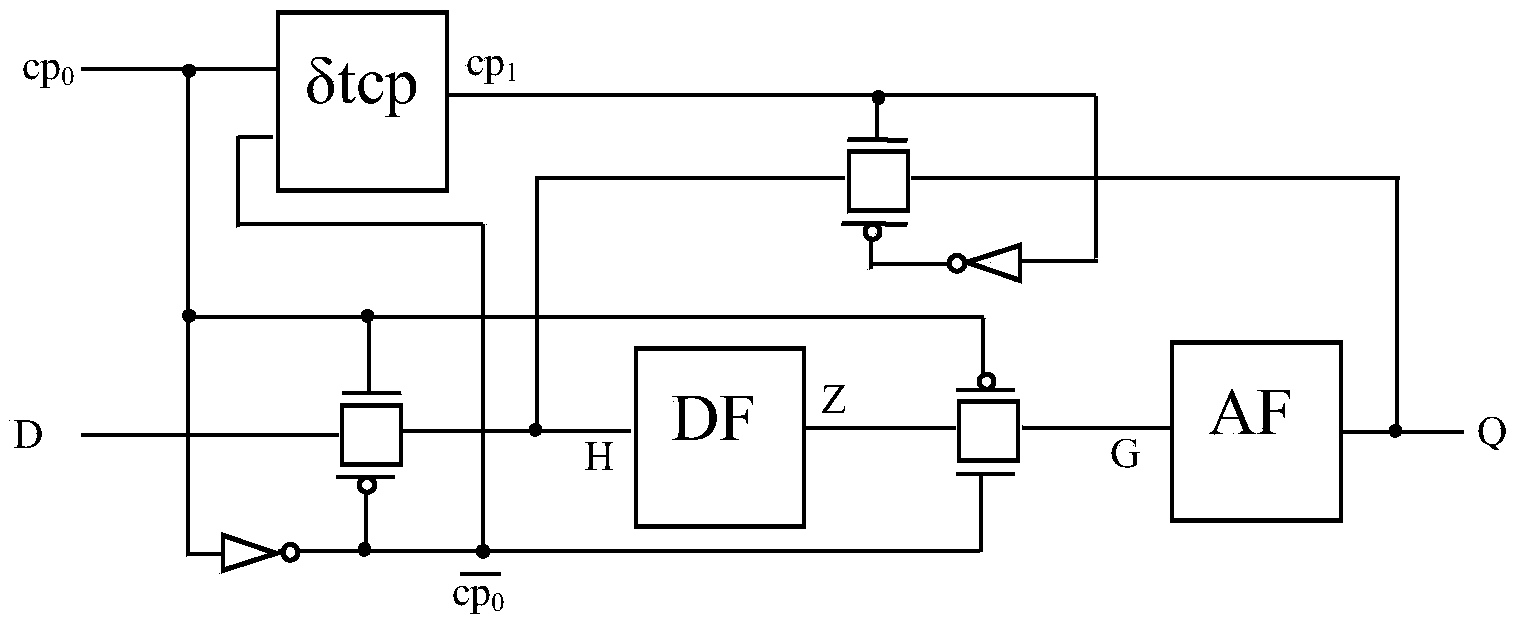

[0072] Embodiment 1: Utilize the circuit three-element theory The circuit three-element theory has formulas (5a) and (5b);

[0073] The binary value is similar to the multi-value circuit and the analog circuit. The main feature is the three elements of the circuit: signal, network and load; the multi-value signal is the rounding of the analog signal within a certain range. When the number of rounding is sufficiently large (equivalent to Since the number of scales is sufficiently large), the limit is the analog signal, and the focus of digital circuit research should be based on the "circuit behavior" of the three elements, rather than "logical realization"; it is customary to regard "logic circuit" as "logical thinking". "Logical realization", originally "circuit" and "logic" are not equivalent to each other, "circuit" is not the circuit realization of "logic", and "logic" is not the abstraction of "circuit", that is, the two are not equal If the problem is not fully descri...

Embodiment 2

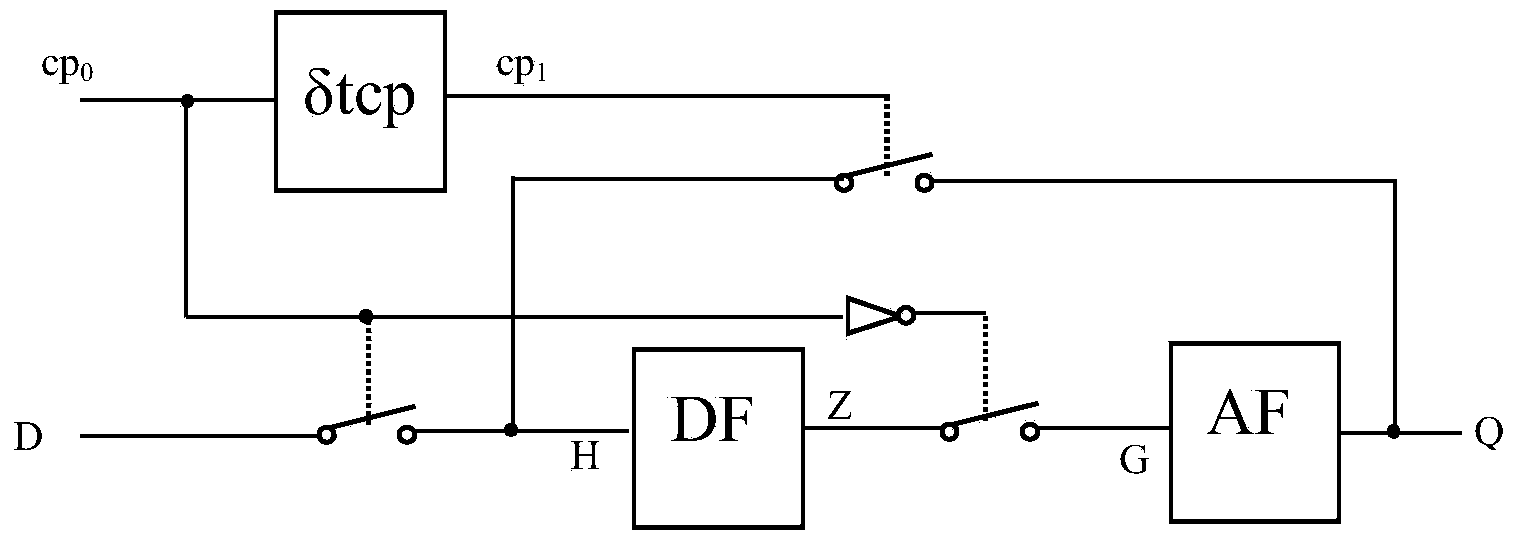

[0078] Embodiment 2: the working process of the clock falling edge delay circuit δtcp.

[0079] The clock falling edge delay circuit δtcp is shown as Figure 8 , the circuit works as follows: cp 0 Before the rising edge, the NMOS transistor N d1 cutoff, NOT gate UC d2 output cp 1 high level; when cp 0 When the rising edge comes, the tube N d1 Rapid turn-on (∵ tube N d1 gate to cp 0 ), tube N d1 Drain (i.e. Capacitance C d1 Potential and NOT gate UC d1 input) quickly drops to low level, the NOT gate UC d1 The output goes high and is sent to the NOT gate UC d2 enter, make cp 1 quickly by a high level V DC goes low, Quickly change from 0 to V DC , indicating that cp 1 falling edge (ie rising edge) and cp 0 The rising edge comes at the same time.

[0080] when cp 0 falling edge when the tube N d1 fast cut-off due to tube N d1 The drain is connected to a capacitor C d1 , so V DC Via resistor R d1 To capacitance C d1 char...

Embodiment 3

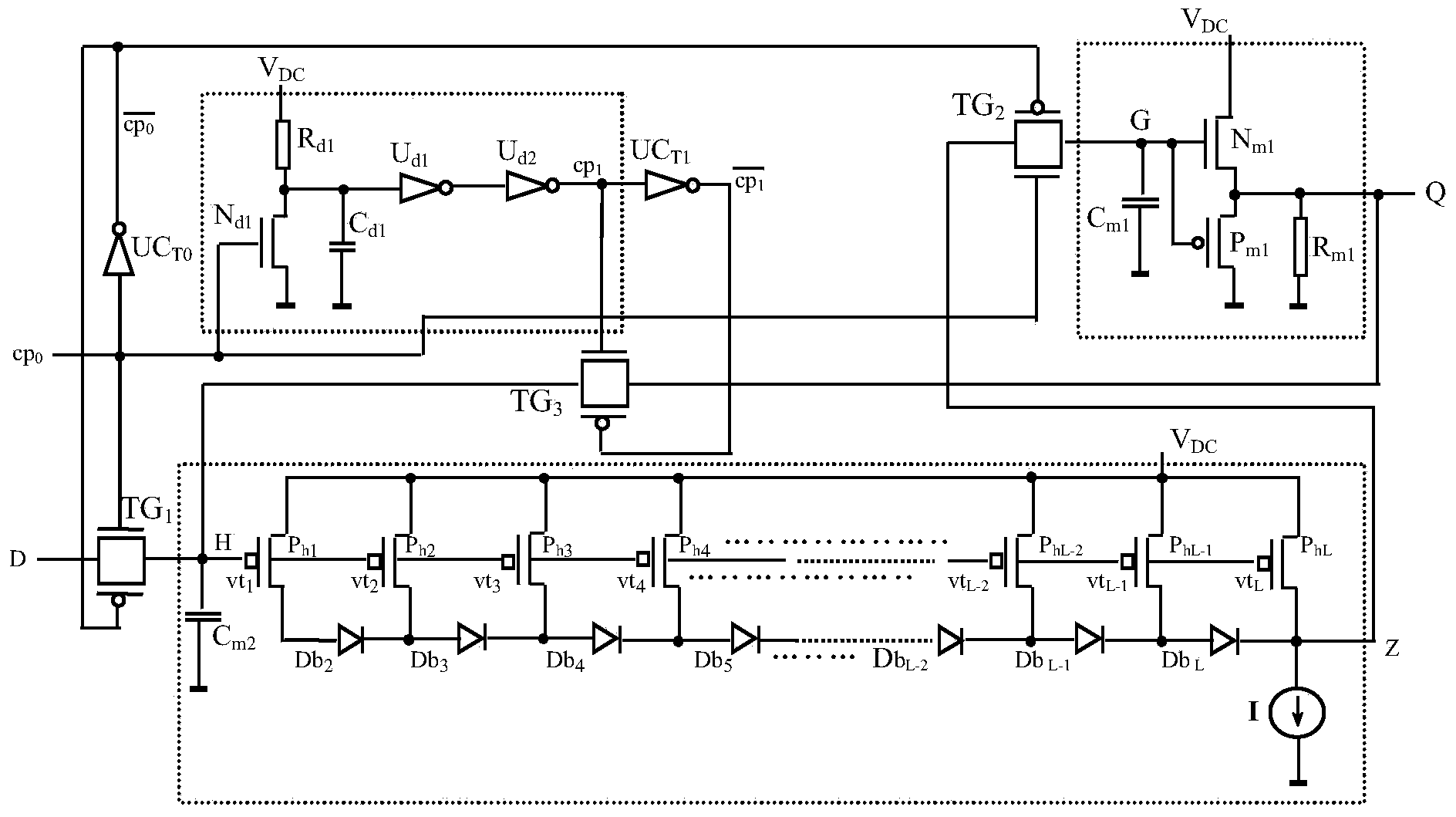

[0085] Example 3: Slave Follower AF.

[0086] The slave follower AF (analog follower) is shown as Figure 4 ,Will Figure 4 Middle PMOS tube P m1 delete, you get Figure 5 The common NMOS transistor source follower shown (by the NMOS transistor N m1 and source resistance R m1 composition), or the Figure 4 Middle source resistance R m1 delete, get Image 6 The CMOS transistor source follower shown (by the NMOS transistor N m1 and PMOS transistor P m1 composition). Because the output of the follower is connected to the gate of the next stage MOS transistor, the gate capacitance of the MOS transistor is a capacitive load to the AF output, so that Image 6 The shown CMOS transistor source follower has a hysteresis phenomenon similar to that of a Schmitt circuit. The output voltage rise and fall trajectories caused by the input voltage rise and fall are inconsistent, and the hysteresis voltage Δ=V TN +|V TP |(∵Capacitive load has a storage effect, with...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More