SOI single-port SRAM (Static Random Access Memory) unit and a preparation method thereof

A manufacturing method and single-port technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, static memory, etc., can solve the problems of large occupied area of SOI single-port SRAM unit, weak anti-noise ability, poor stability, etc., to achieve convenient and comprehensive Customized SRAM chip, improved anti-noise ability, and suppressed floating body effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

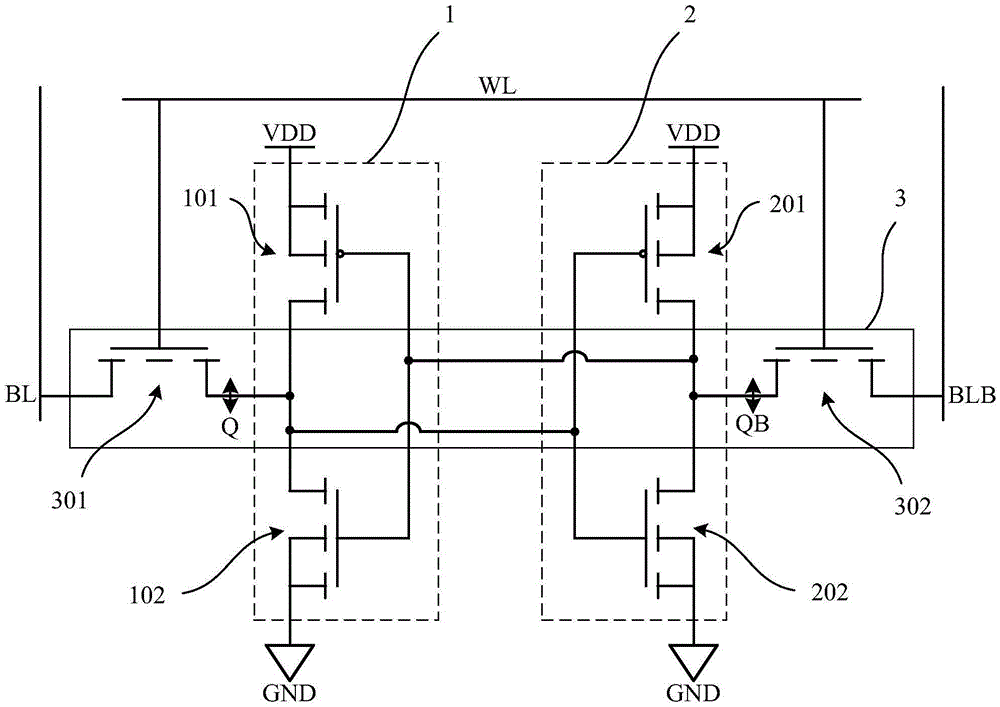

[0086] The present invention provides a SOI single-port SRAM unit, please refer to figure 1 , shown as a schematic diagram of the circuit principle of the SOI single-port SRAM cell, including:

[0087] The first inverter 1 is composed of a first PMOS transistor 101 and a first NMOS transistor 102;

[0088] The second inverter 2 is composed of a second PMOS transistor 201 and a second NMOS transistor 202;

[0089] The acquisition transistor 3 is composed of a third NMOS transistor 301 and a fourth NMOS transistor 302; the source of the third NMOS transistor 301 is connected to the output terminal of the first inverter and the input of the second inverter terminal, the gate is connected to the word line WL of the memory, and the drain is connected to the bit line BL of the memory; the source of the fourth NMOS transistor 302 is connected to the output end of the second inverter and the first inverter The gate is connected to the word line of the memory, and the drain is connec...

Embodiment 2

[0101] The present invention also provides a kind of manufacture method of SOI single-port SRAM unit, comprises the steps:

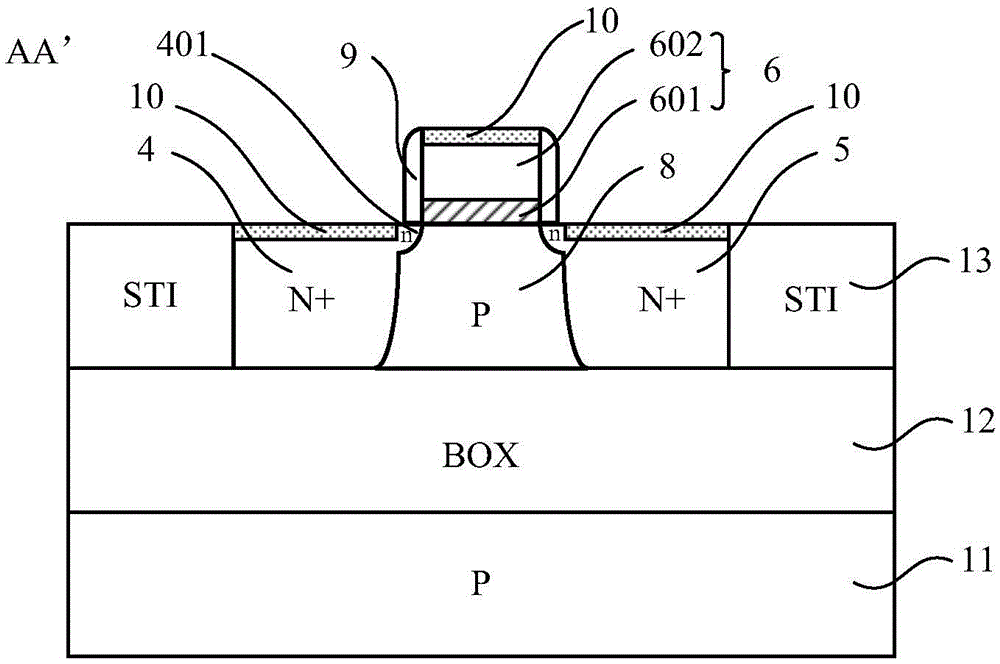

[0102] Step S1 is first performed: provide an SOI substrate including a back substrate, an insulating buried layer, and a top layer of silicon in sequence from bottom to top, and form a shallow trench isolation structure in the top layer of silicon to define an active region.

[0103] As an example, such as Figure 8 As shown, four active regions 20a, 20b, 20c, and 20d are defined. These four active regions are arranged in parallel in turn, and shallow trenches are formed around each active region, and the shallow trenches are filled with insulating materials to form shallow trenches. isolation structure. In this embodiment, the insulating material is silicon dioxide.

[0104] Then execute step S2: as Figure 9 As shown, an N well 30, a first P well 40 and a second P well 50 are fabricated in the top silicon according to the position of the active reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More