Patents

Literature

49results about How to "Avoid Threshold Voltage Drift" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

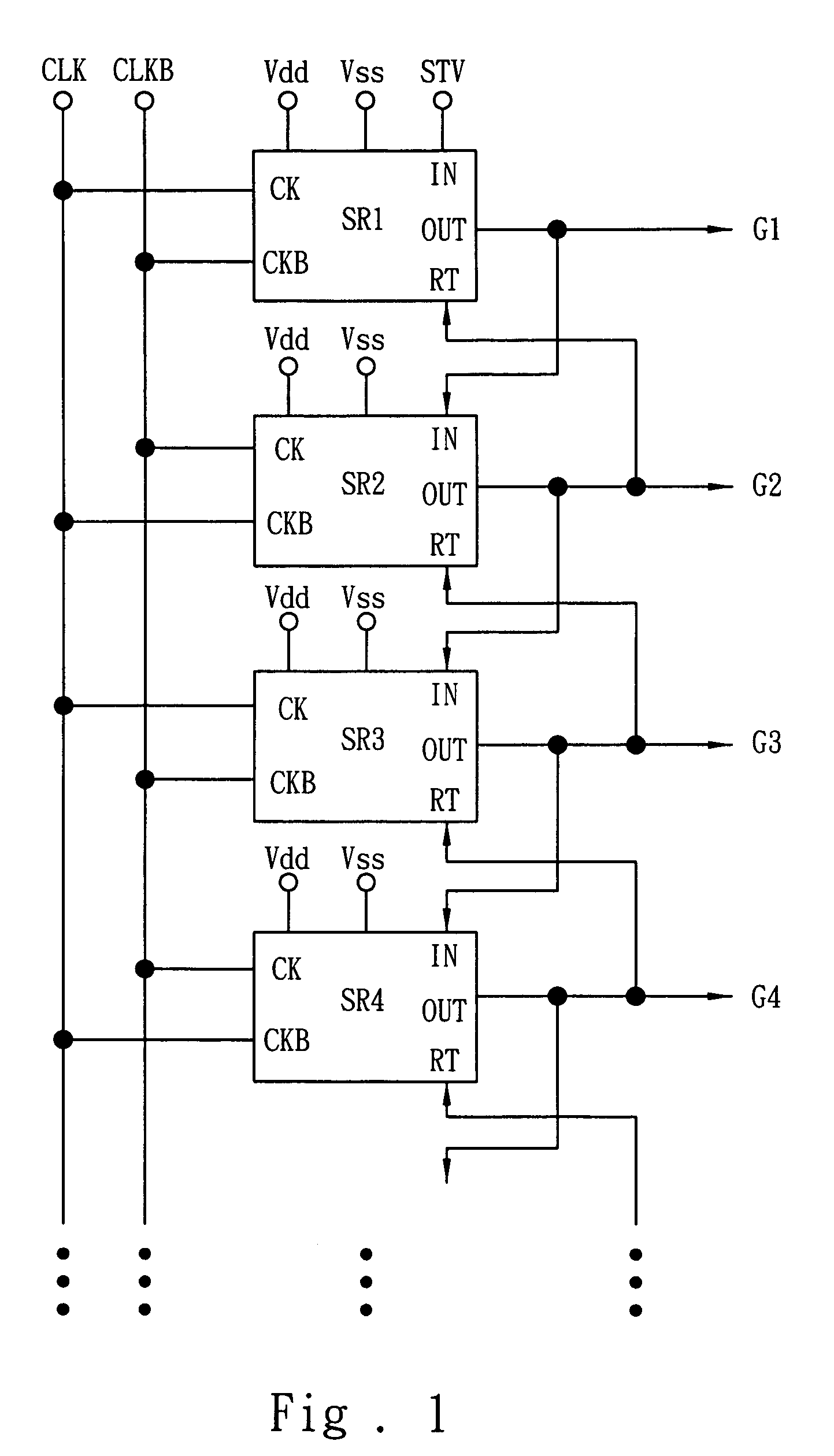

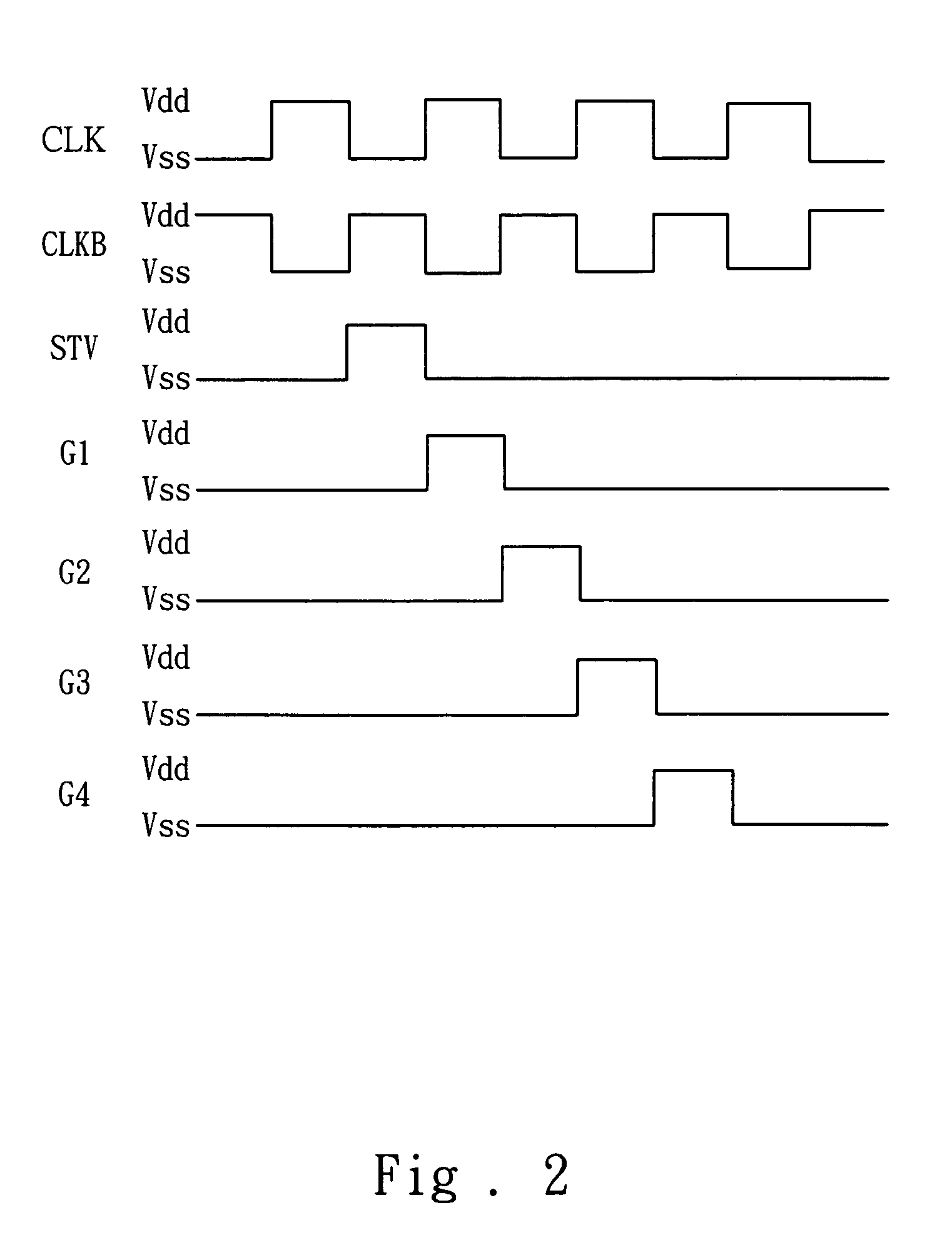

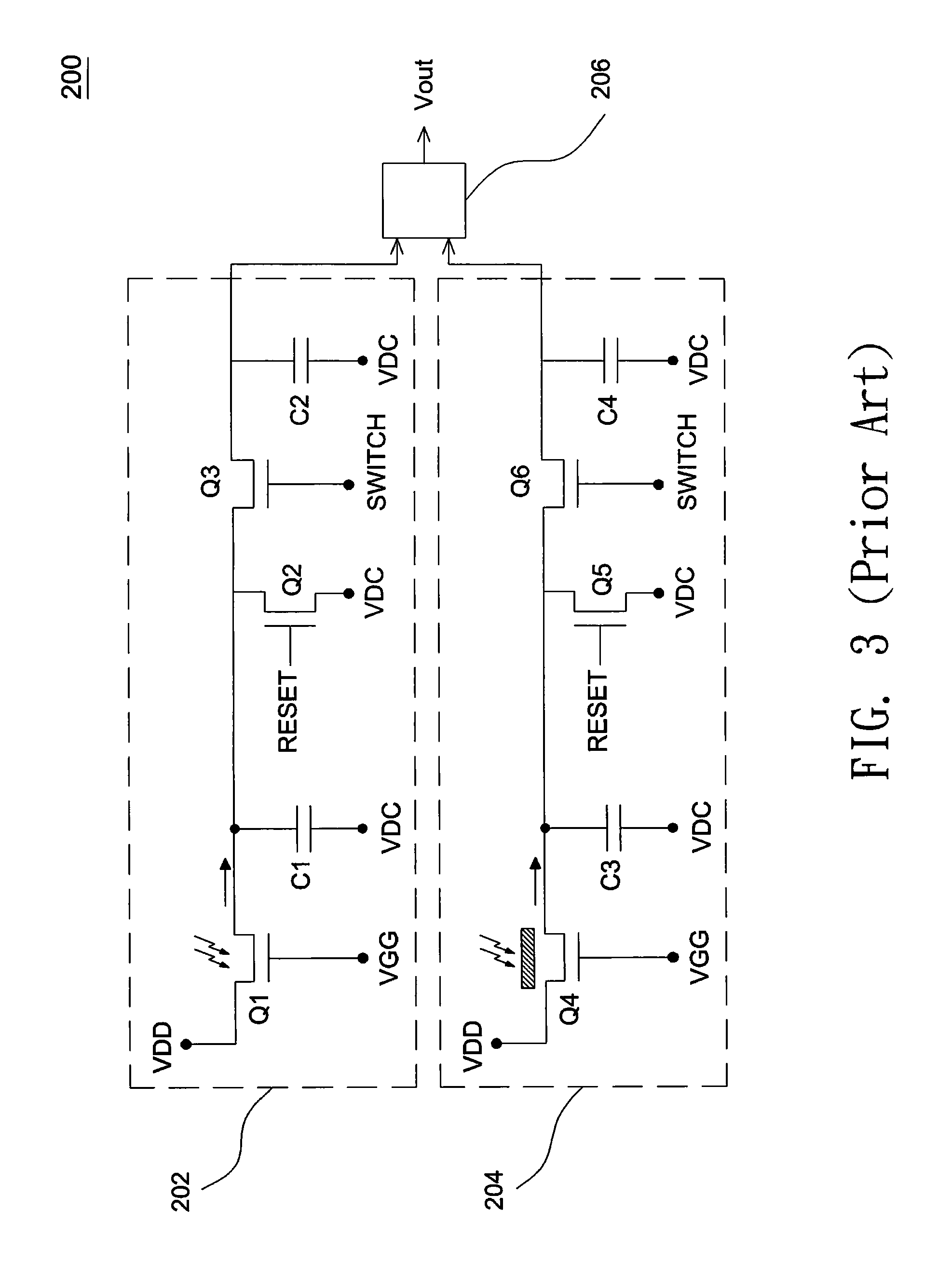

High-stability shift circuit using amorphous silicon thin film transistors

ActiveUS20060291610A1Prevent movementExtended operating timeStatic indicating devicesDigital storageWork periodAmorphous silicon

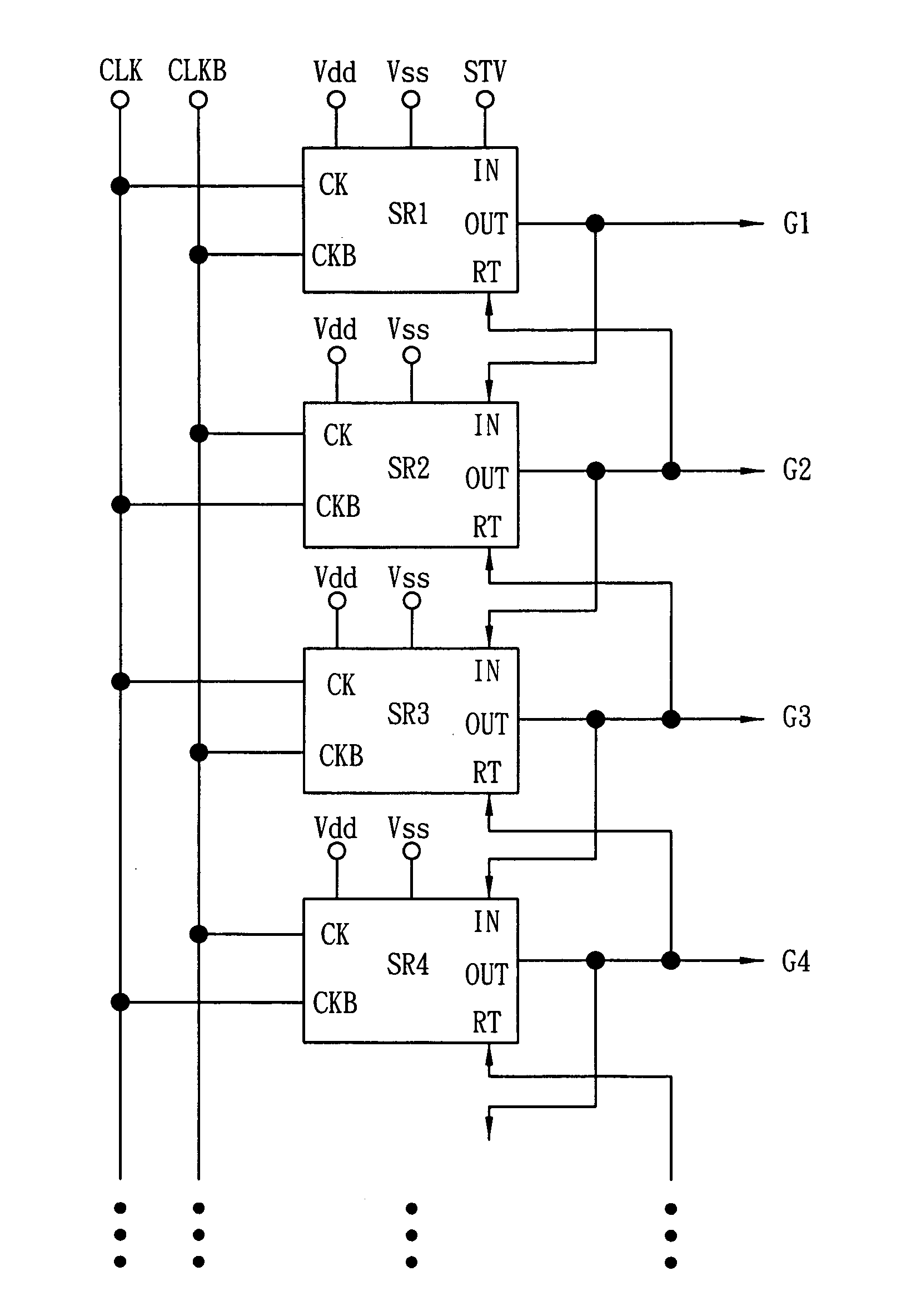

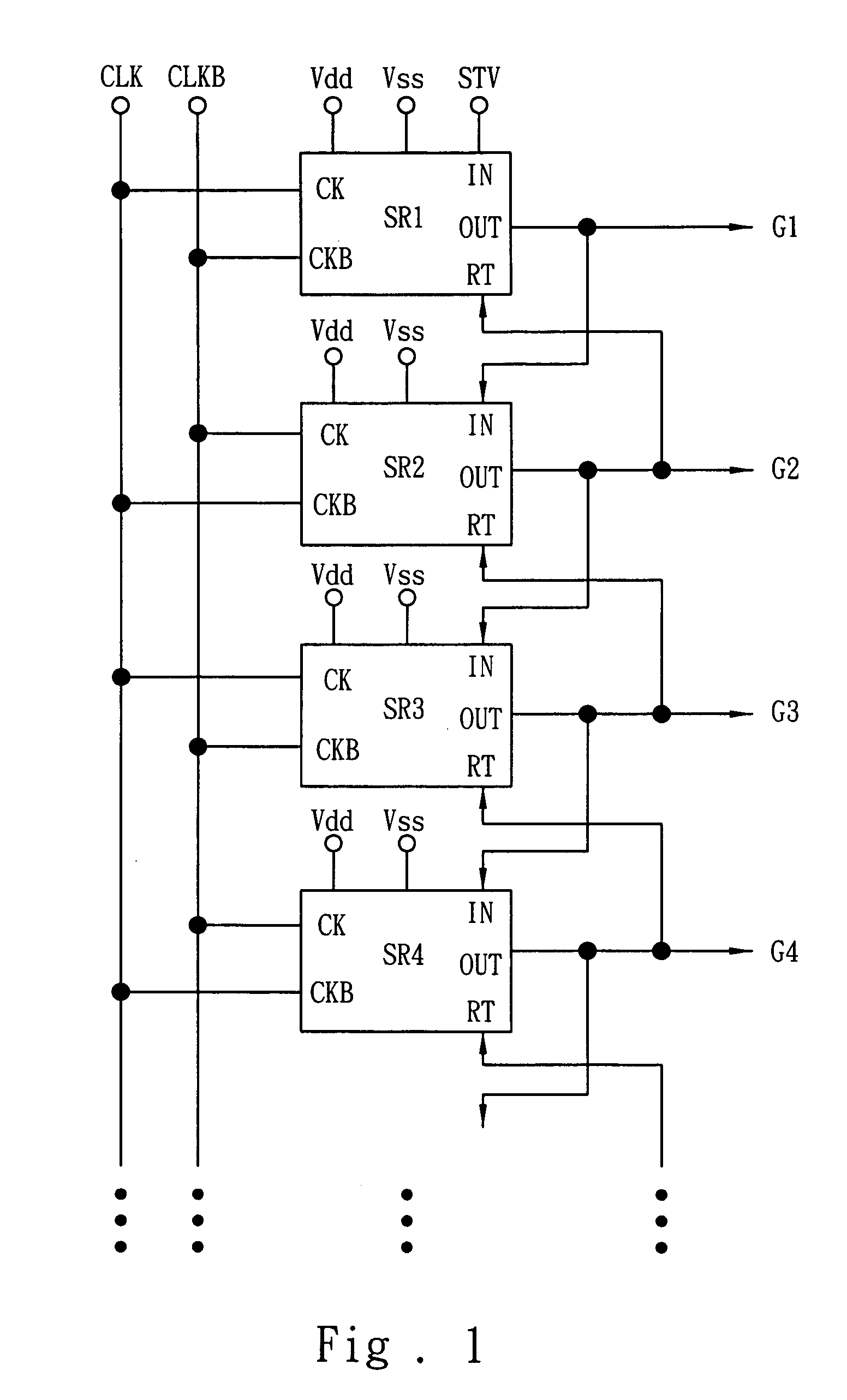

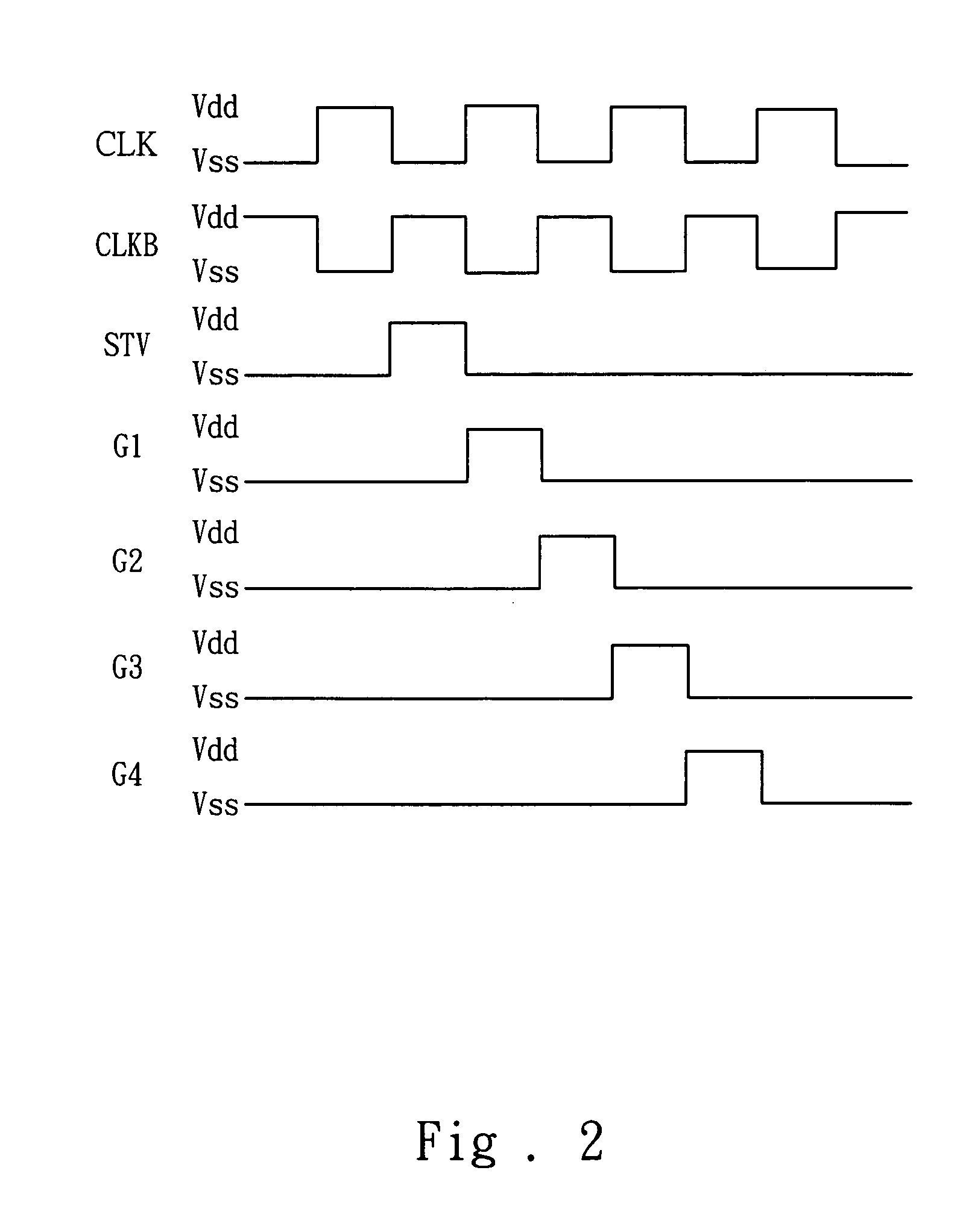

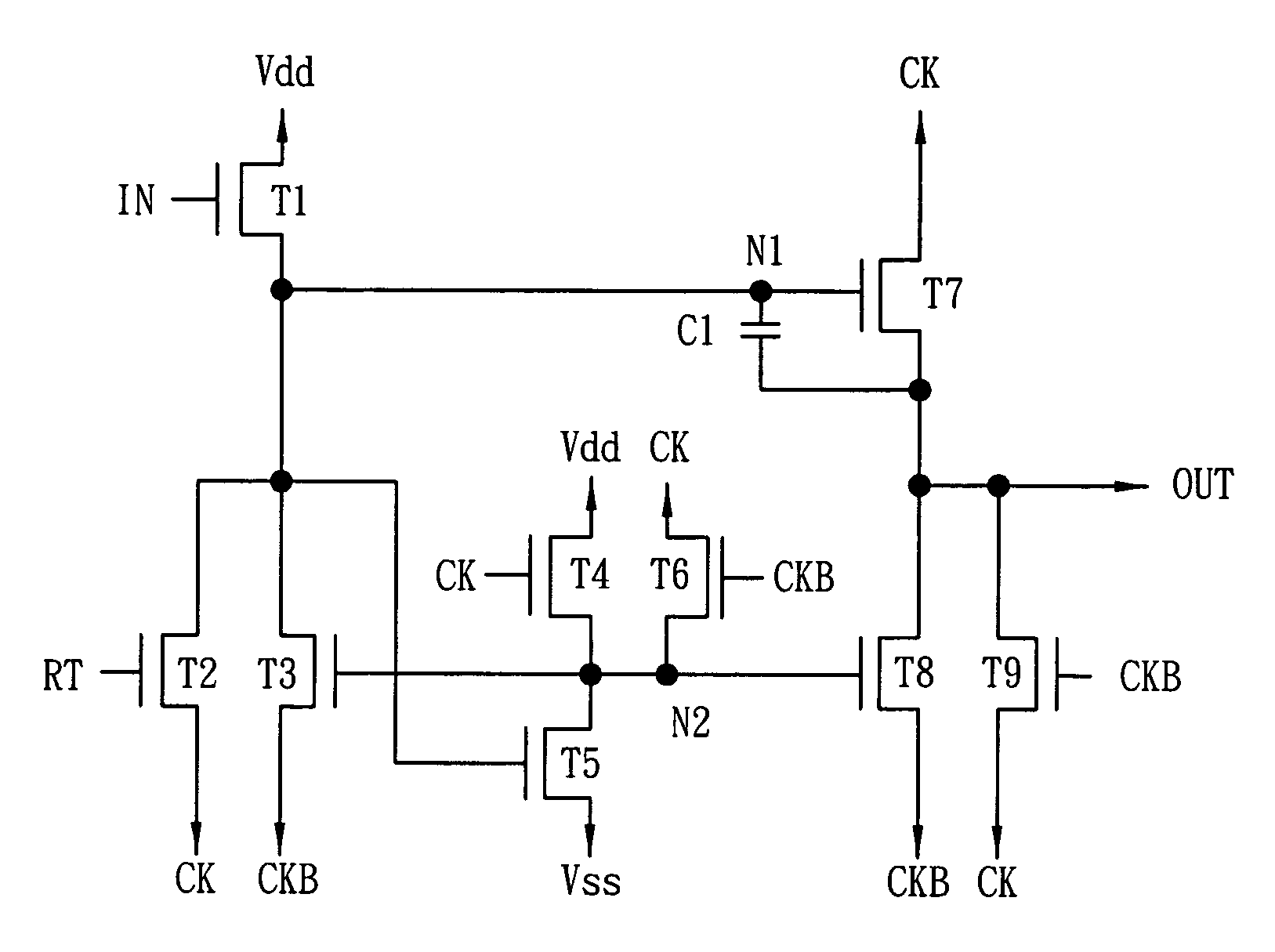

A high-stability shift circuit using amorphous silicon thin film transistors, which utilizes two out-of-phase pulses to control the operating mechanism and the bias-relations among transistors in the shift circuit. This makes the transistors under the driving conditions of positive / negative-alternating biases so as to restrain the voltage shift of the transistors such that the threshold voltage will not excessively increase along with the increasing operating time. This can not only increase the lifetime of the amorphous silicon thin film transistors but also extend the operating time of the shift circuit.

Owner:WINTEK CORP

High-stability shift circuit using amorphous silicon thin film transistors

ActiveUS7203264B2Avoid Threshold Voltage DriftImprove stabilityStatic indicating devicesDigital storageVoltage shiftHemt circuits

A high-stability shift circuit using amorphous silicon thin film transistors, which utilizes two out-of-phase pulses to control the operating mechanism and the bias-relations among transistors in the shift circuit. This makes the transistors under the driving conditions of positive / negative-alternating biases so as to restrain the voltage shift of the transistors such that the threshold voltage will not excessively increase along with the increasing operating time. This can not only increase the lifetime of the amorphous silicon thin film transistors but also extend the operating time of the shift circuit.

Owner:WINTEK CORP

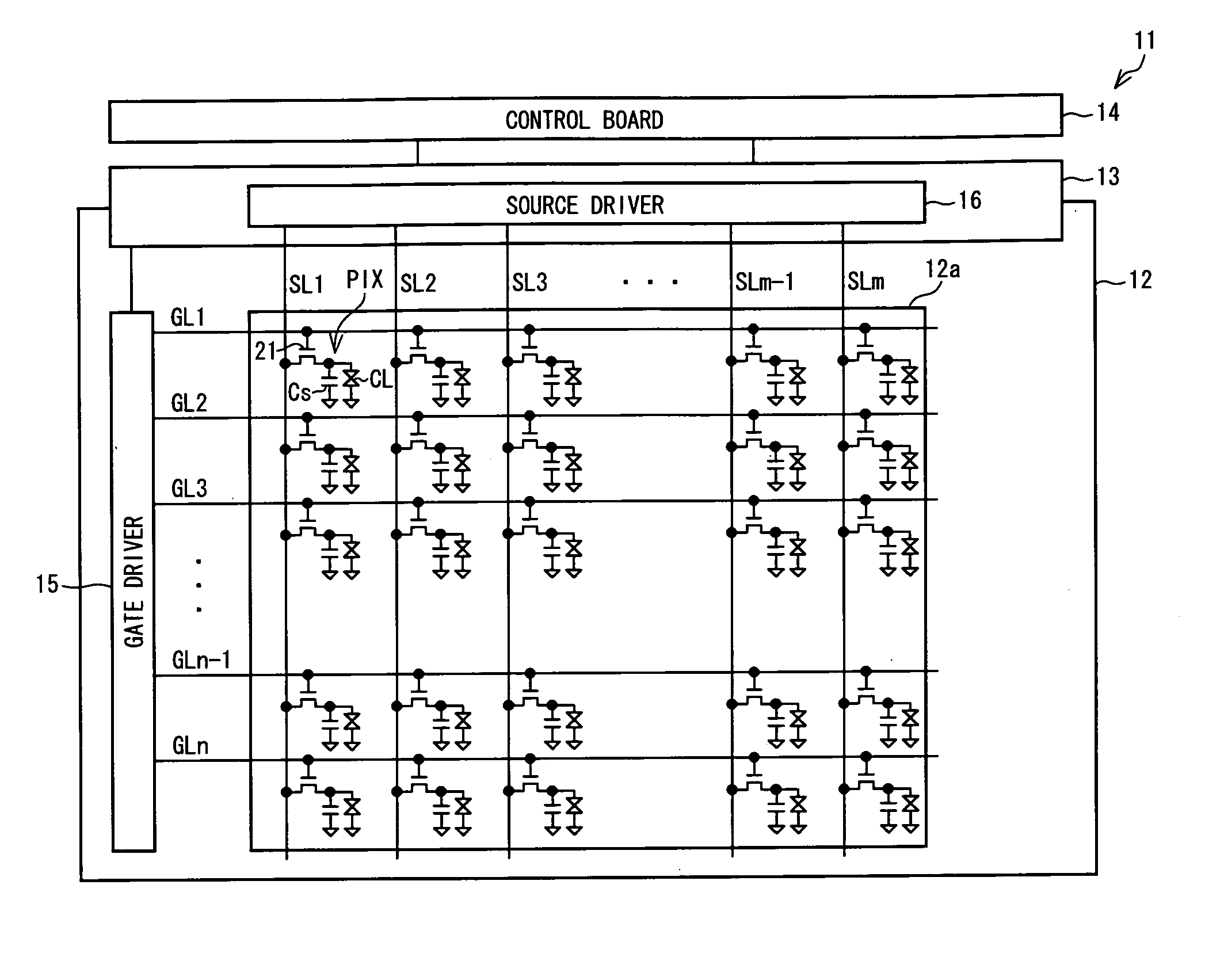

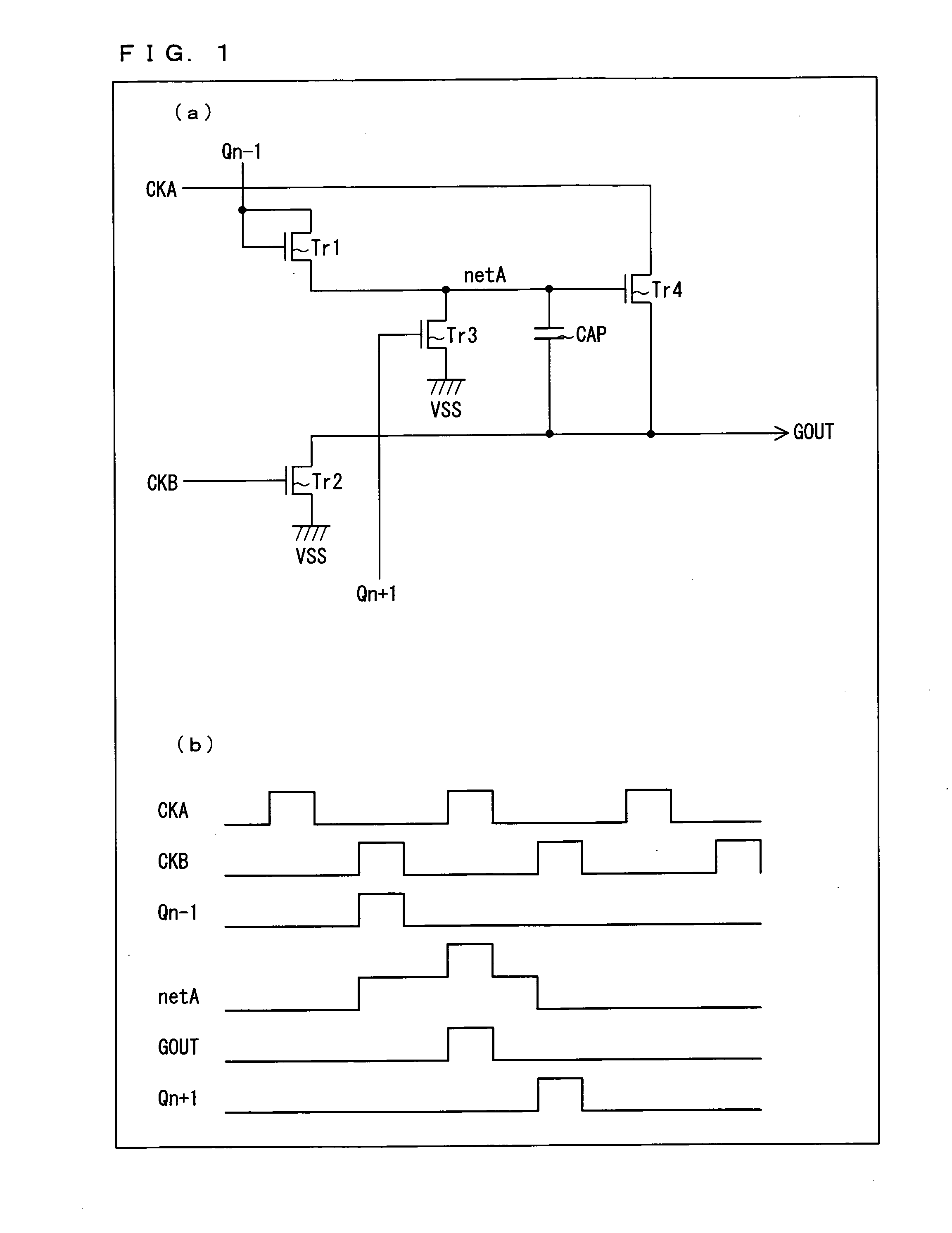

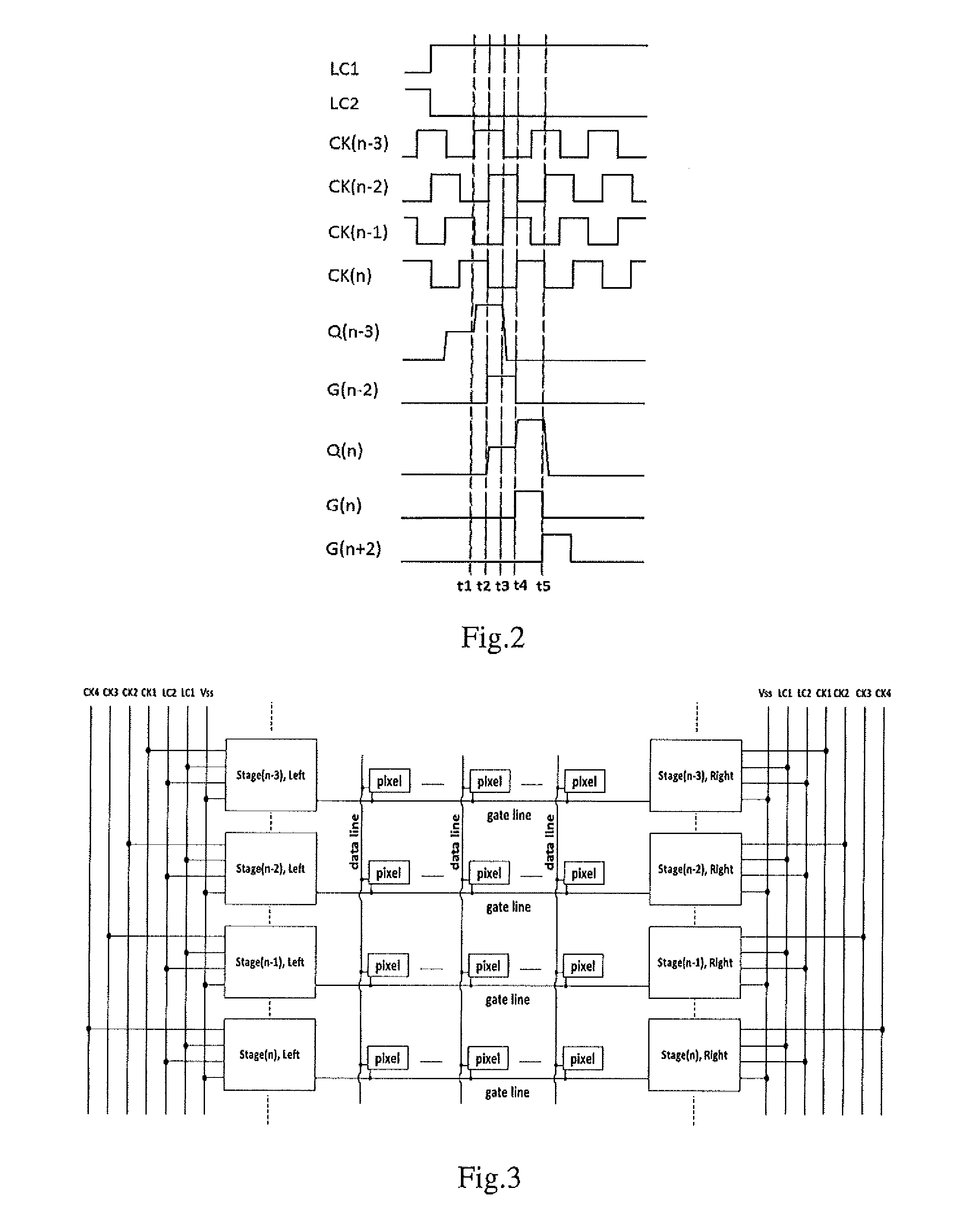

Display device and method for driving display

InactiveUS20100321372A1Reduce “ ON ” duty cycleAvoid Threshold Voltage DriftCathode-ray tube indicatorsDigital storageShift registerDisplay device

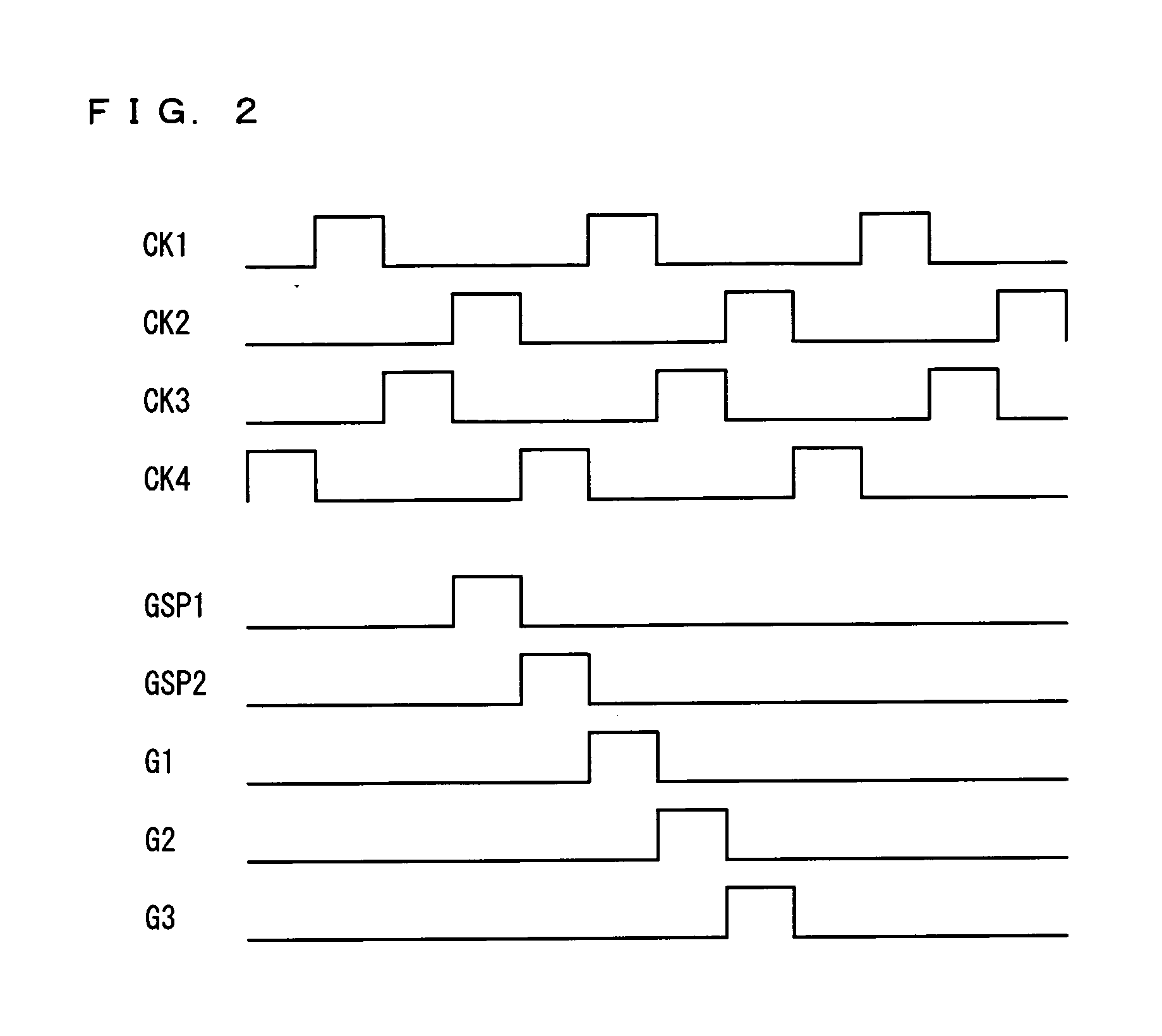

Each stage of first and second shift registers outputs a scan pulse by transferring a clock pulse of a clock signal supplied through a first clock input terminal. A first transistor is provided in at least one embodiment so as to connect and disconnect a scan signal line corresponding to the individual stage to and from a low-level power source of the scan pulse, and the first transistor has a gate that receives a clock signal supplied through a second clock input terminal. Two clock signals supplied to the first shift register and two clock signals supplied to the second shift register are different from each other in timings of their clock pulses. This realizes a display device capable of curbing the phenomenon in which a threshold voltage of a sink-down transistor is shifted, while sinking the gate line voltage down.

Owner:SHARP KK

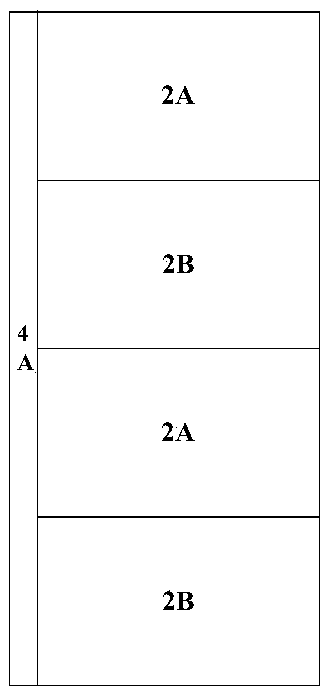

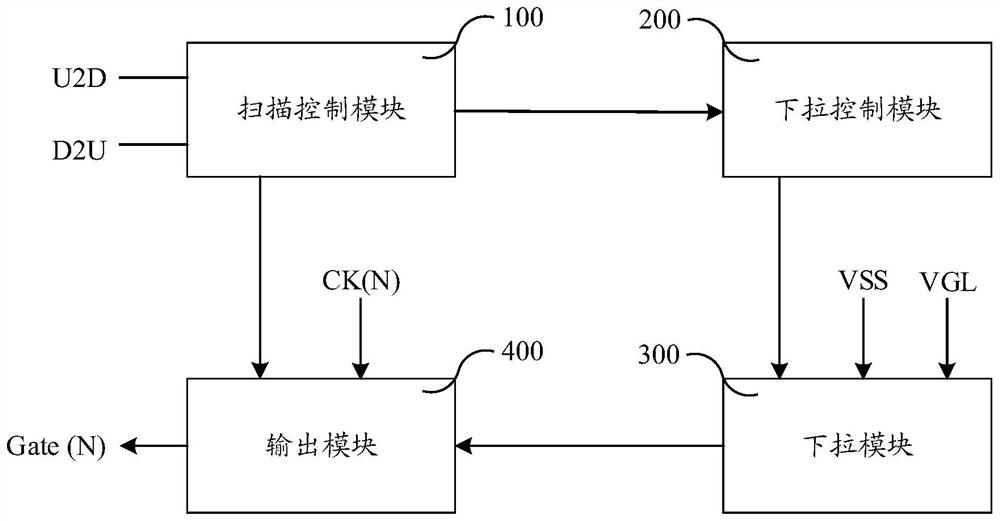

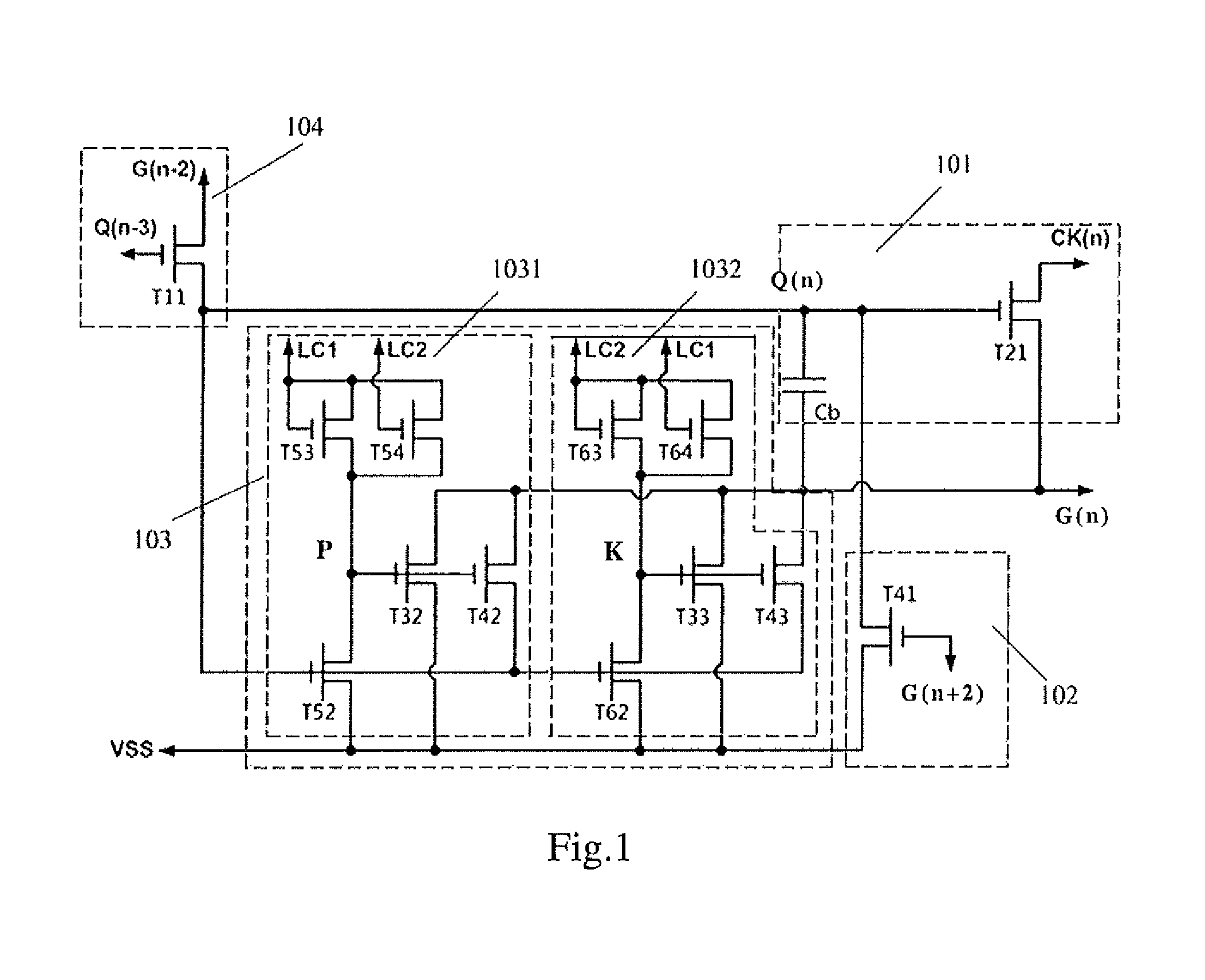

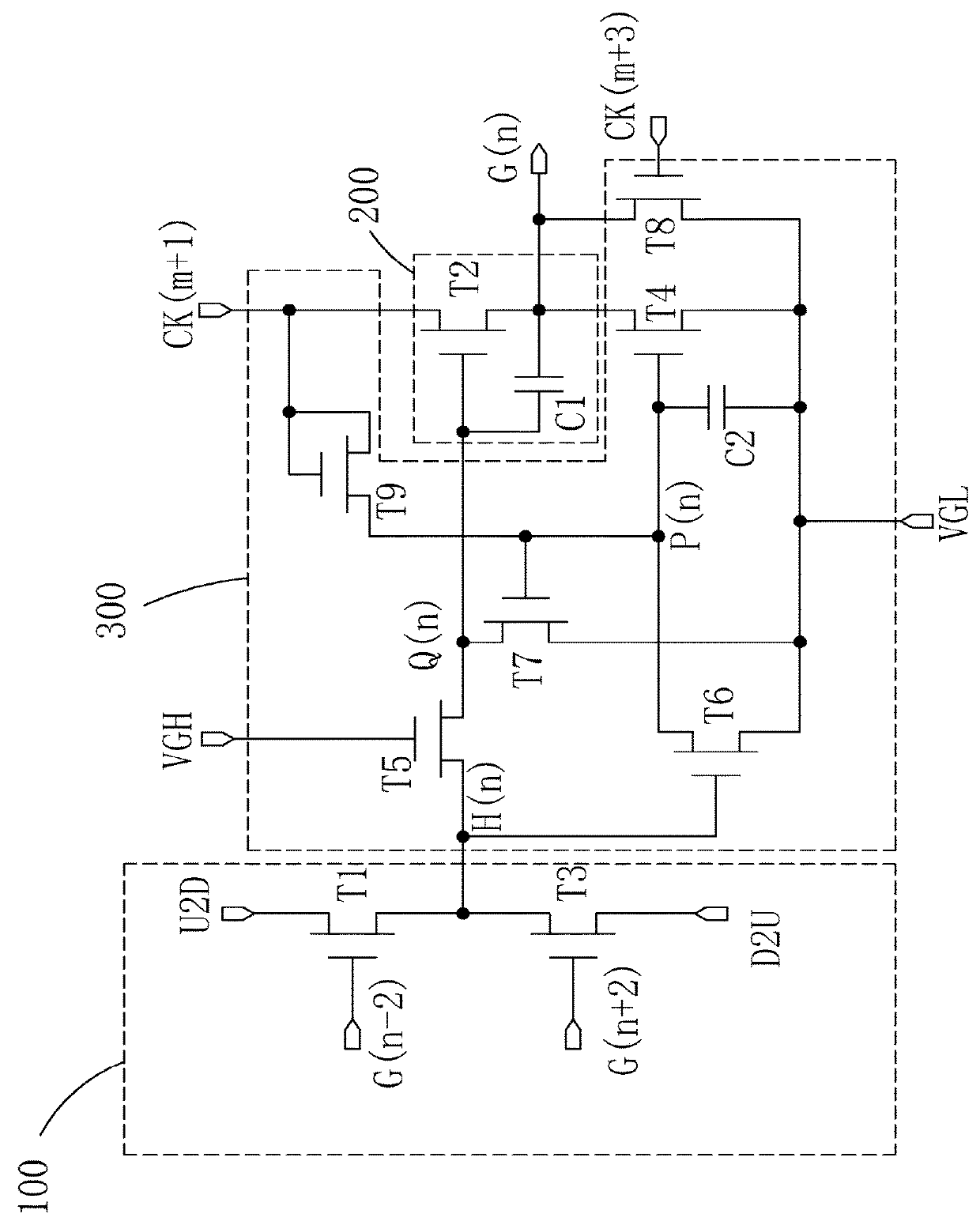

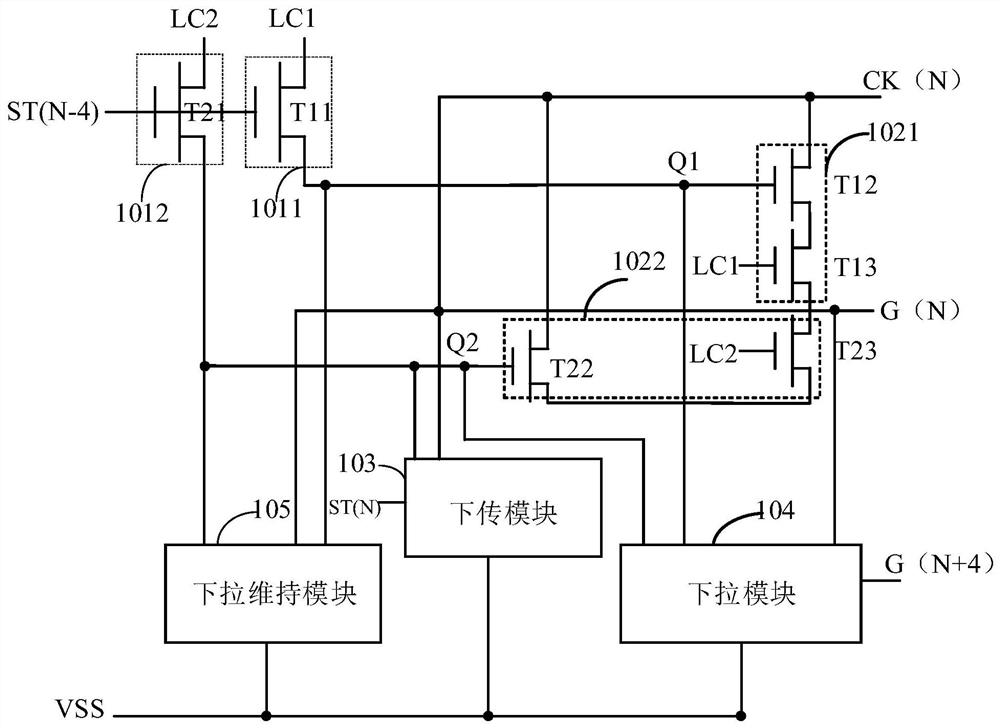

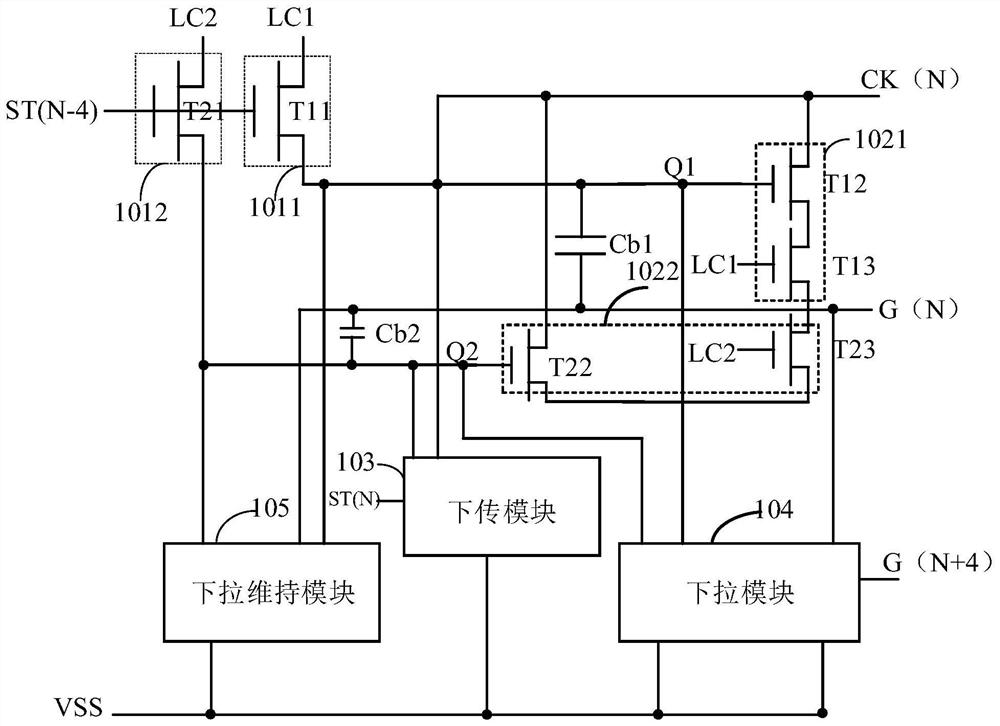

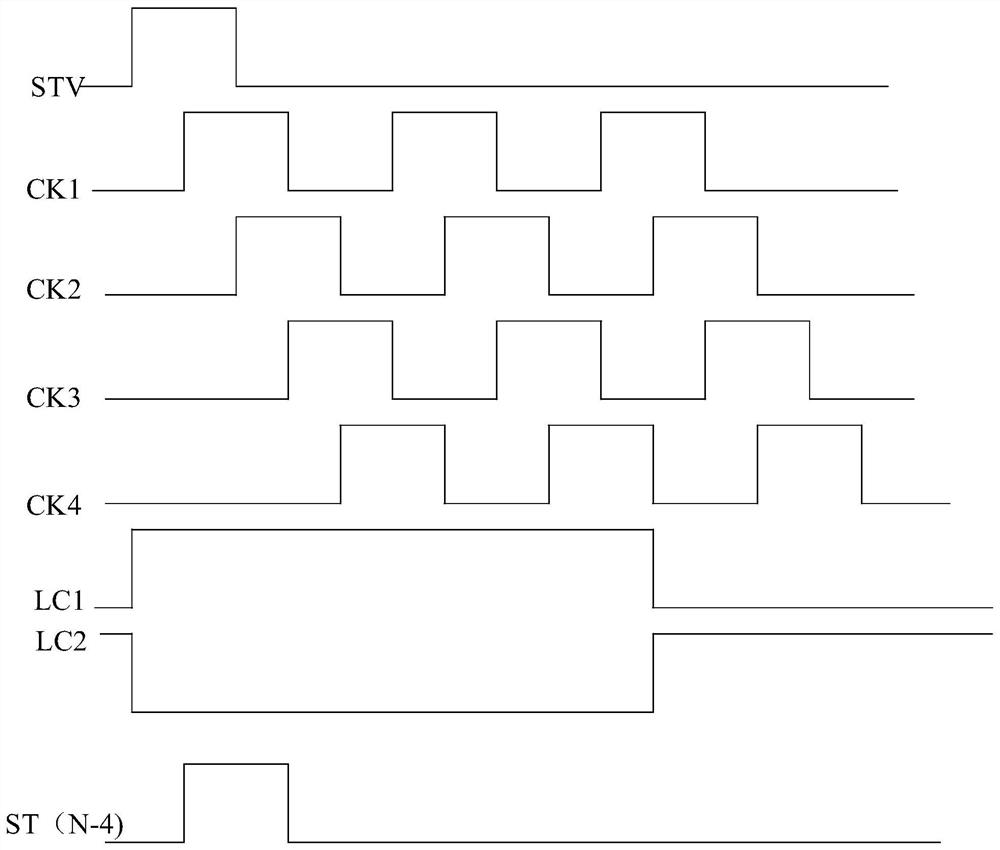

Shifting register unit, gate drive circuit and displayer

ActiveCN104332126AExtend your lifeReduce complexityStatic indicating devicesDigital storageShift registerCapacitance

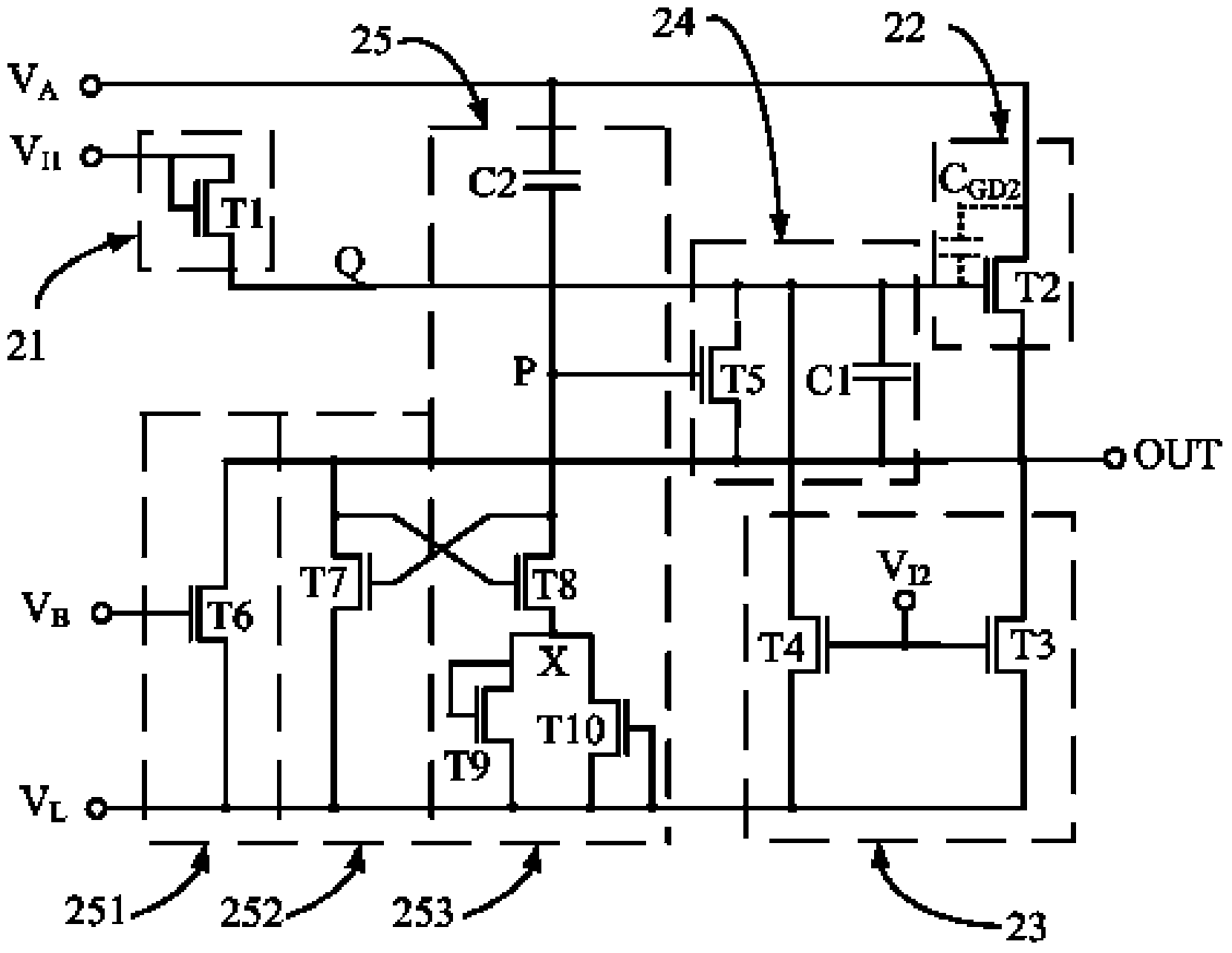

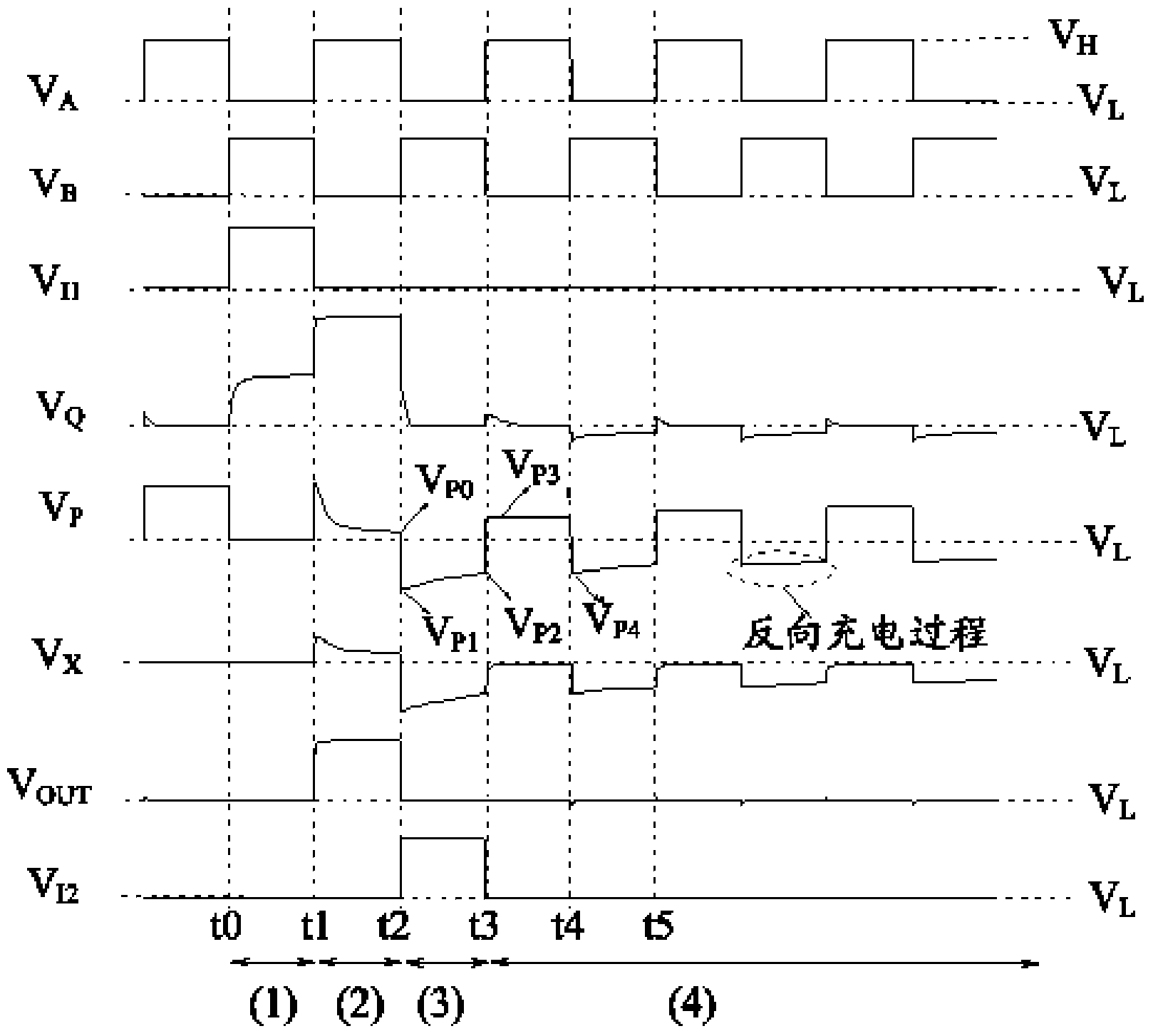

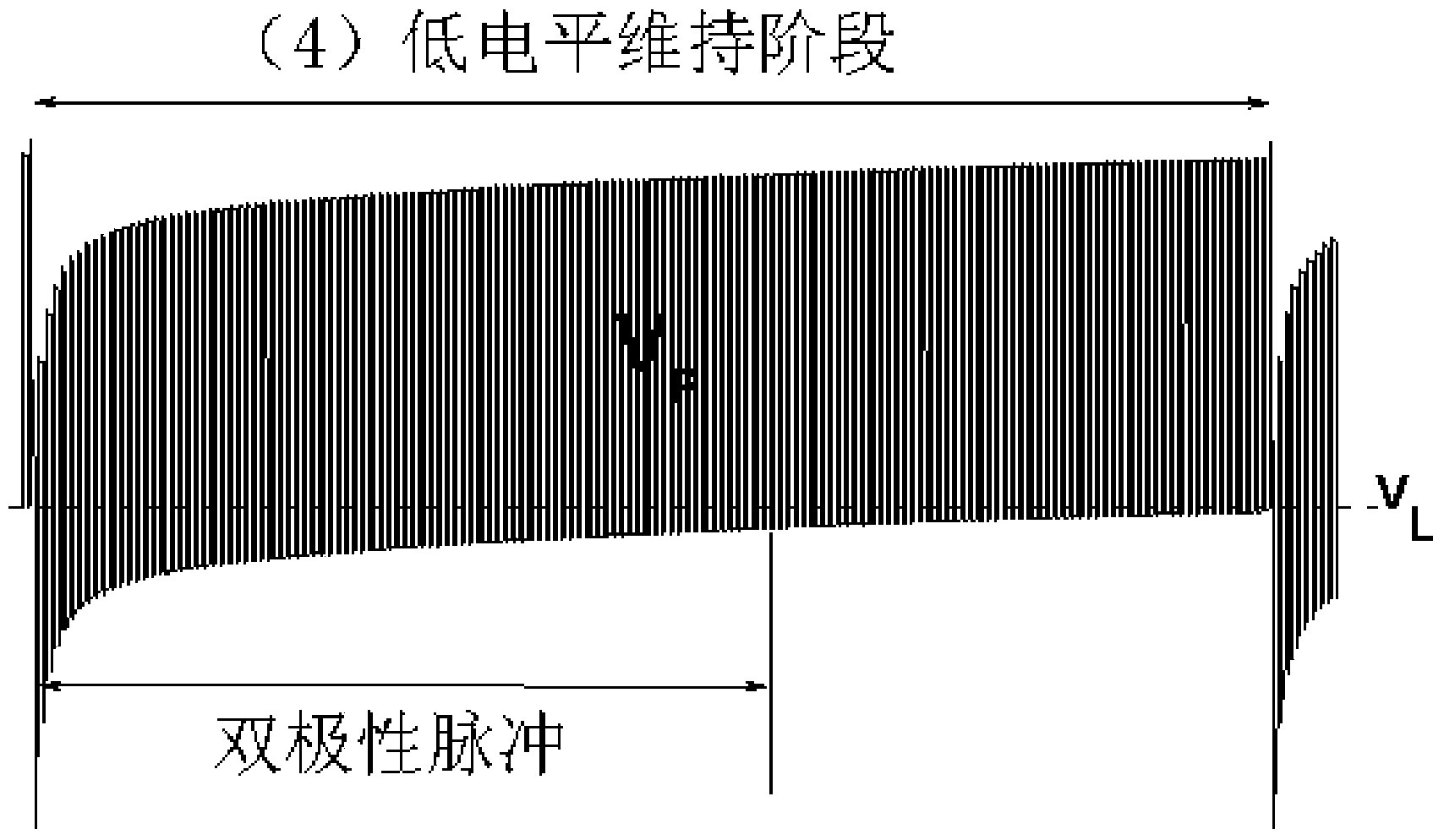

The invention relates to a shifting register unit, a gate drive circuit and a displayer. The shifting register unit comprises an input module, a drive module, a pull-down module and a low level maintaining module; the low level maintaining module comprises a first maintaining unit, a second maintaining unit and a positive and negative bothway polarity potential generation unit; and the positive and negative bothway polarity potential generation unit is used for generating positive and negative bothway polarity potentials in the non-gating stage of the shifting register unit and outputting the positive and negative bothway polarity potentials to the low level maintaining control end. All transistors in the shifting register unit are prevented from staying under direct-current stress; the key transistors will stay under positive and negative bipolar pulse stress polarization within a period of time; threshold voltage shifting of the key transistors is accordingly restrained; and the service life of the circuit is prolonged. In addition, positive and negative bipolar voltage polarization is achieved through fewer transistors and fewer capacitors; the circuit design complex rate is low; and the rate of finished products is high. The displayer is high in reliability and low in production cost.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

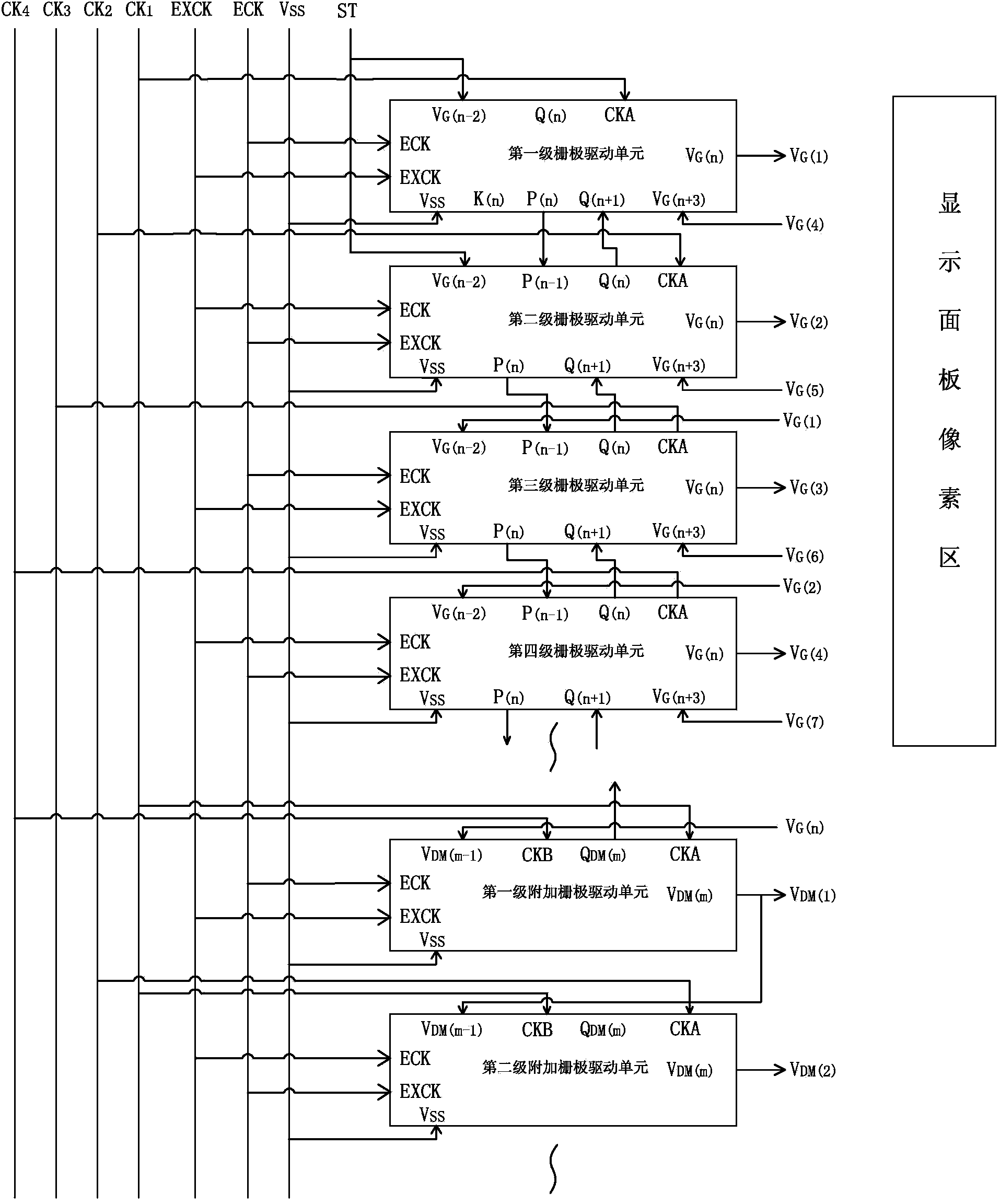

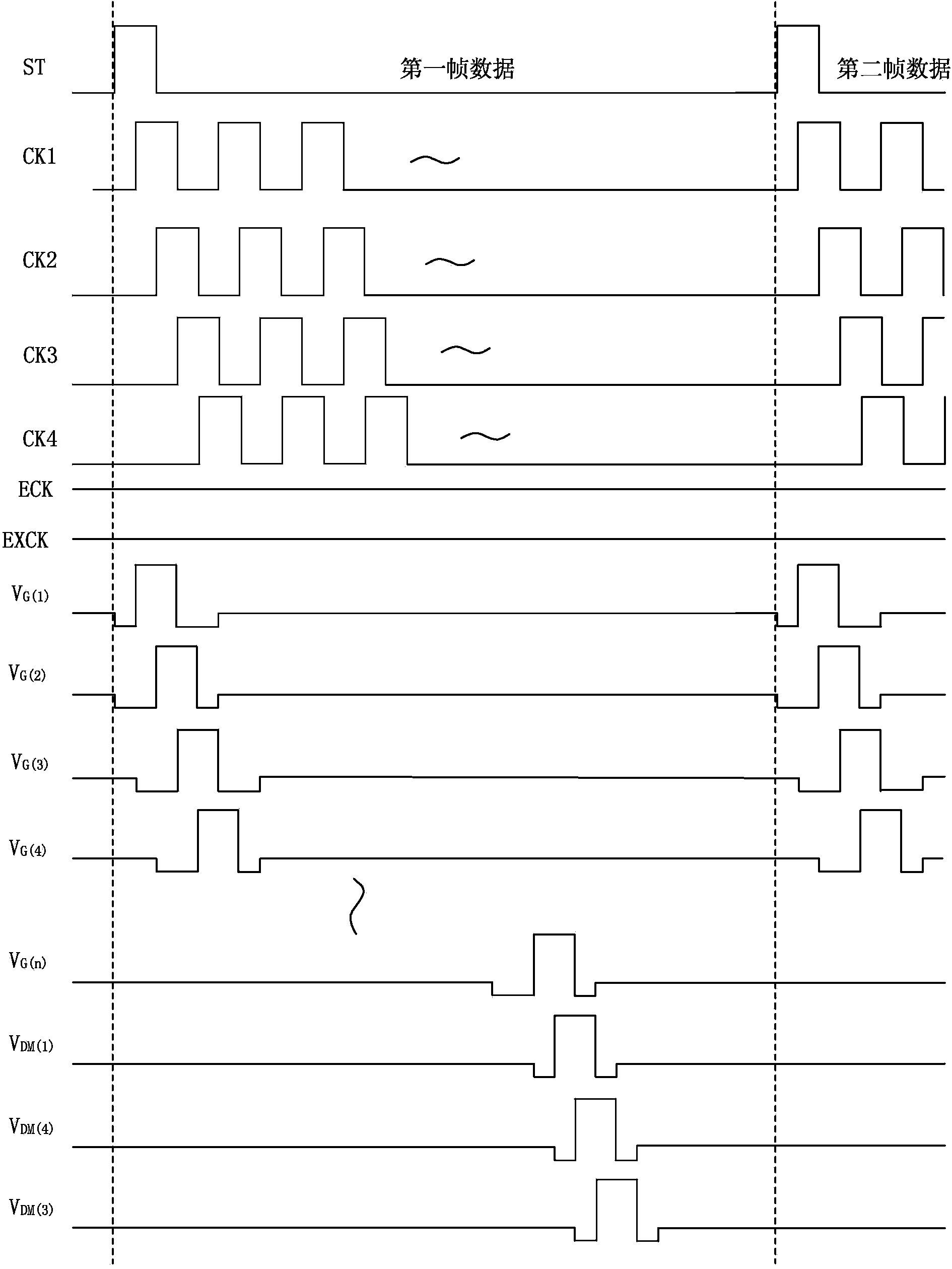

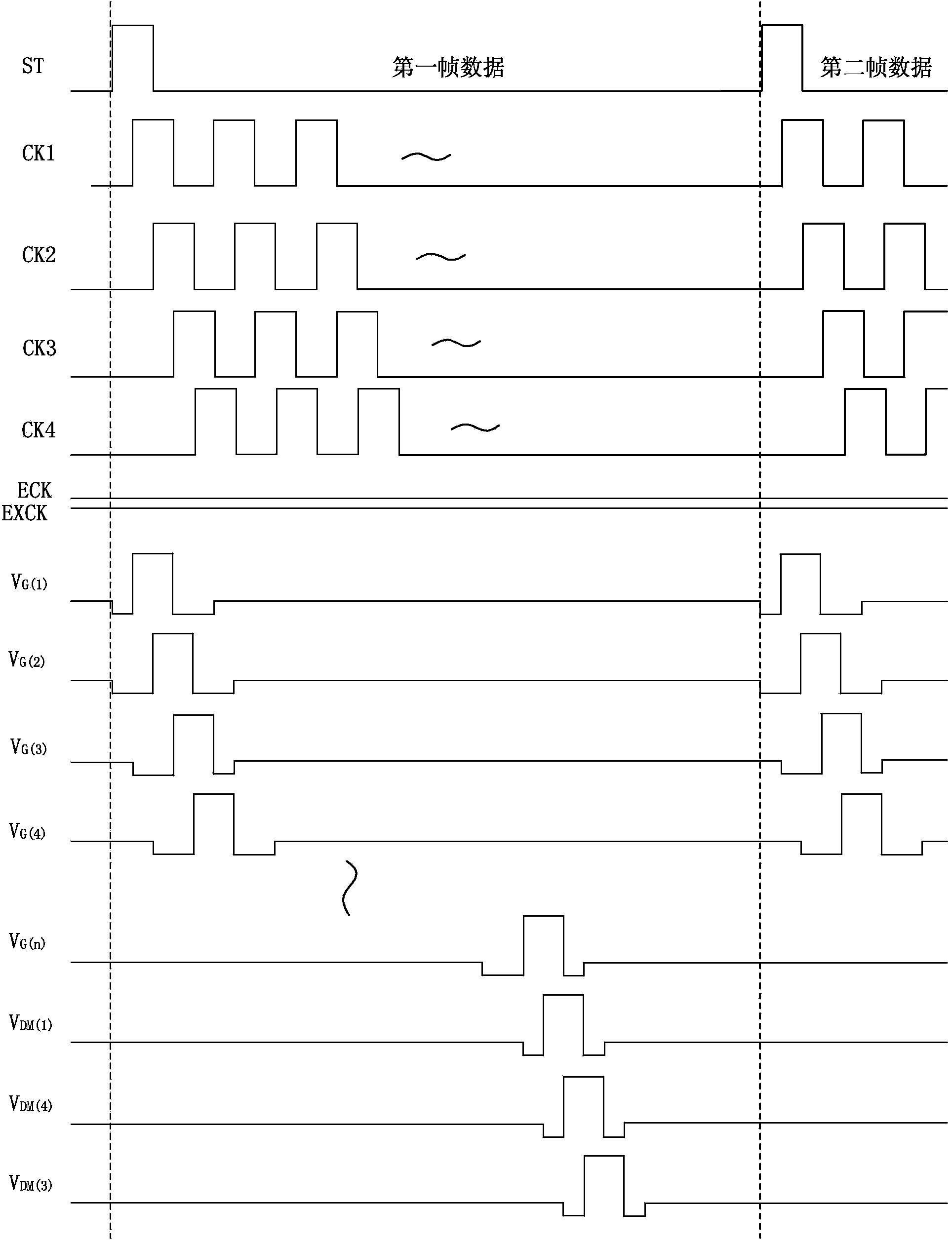

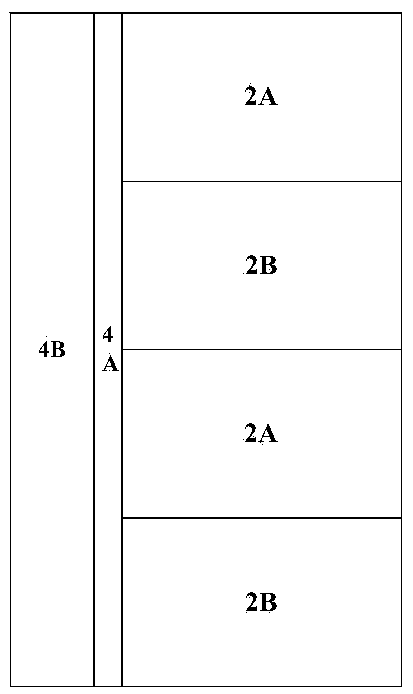

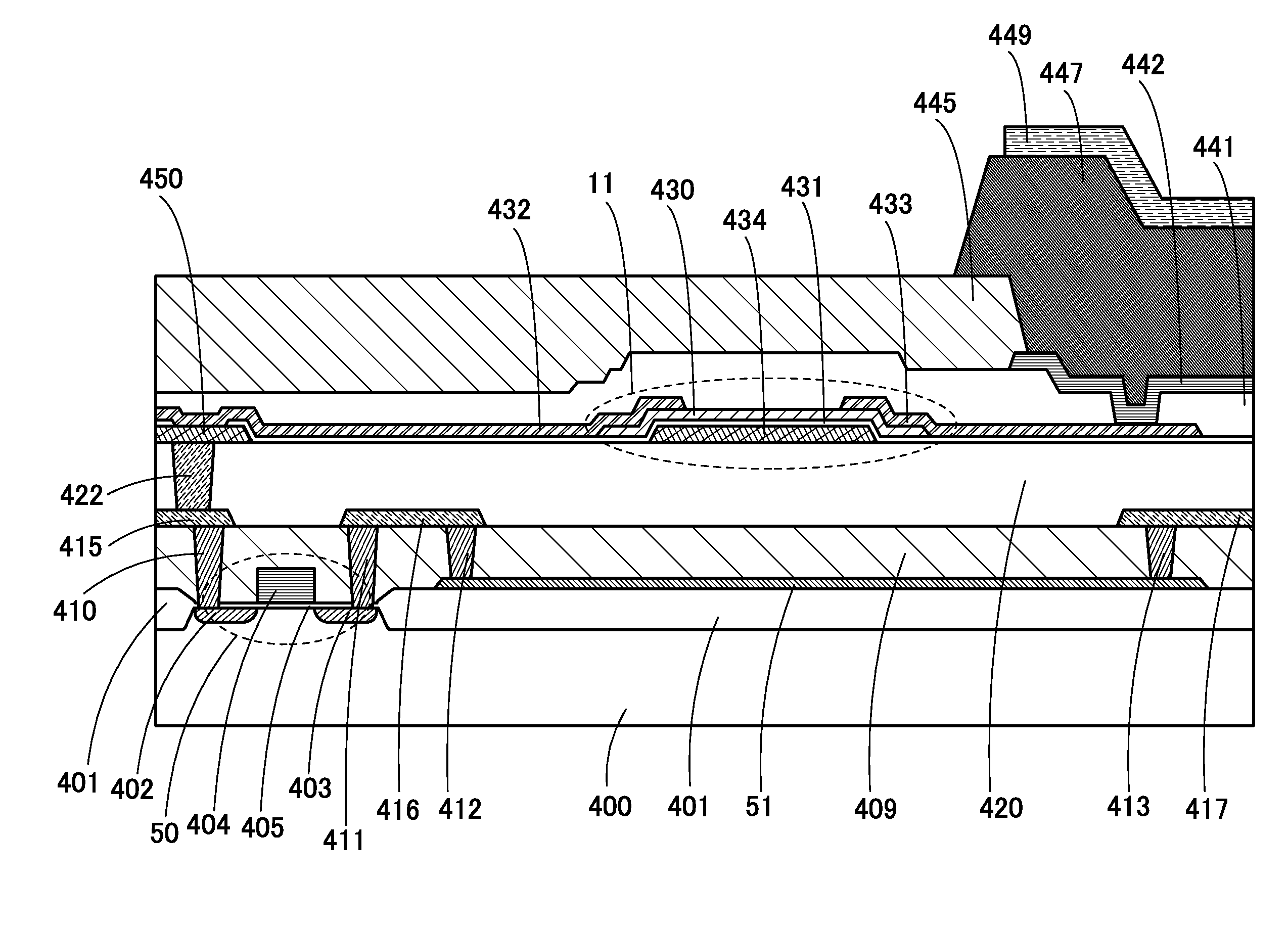

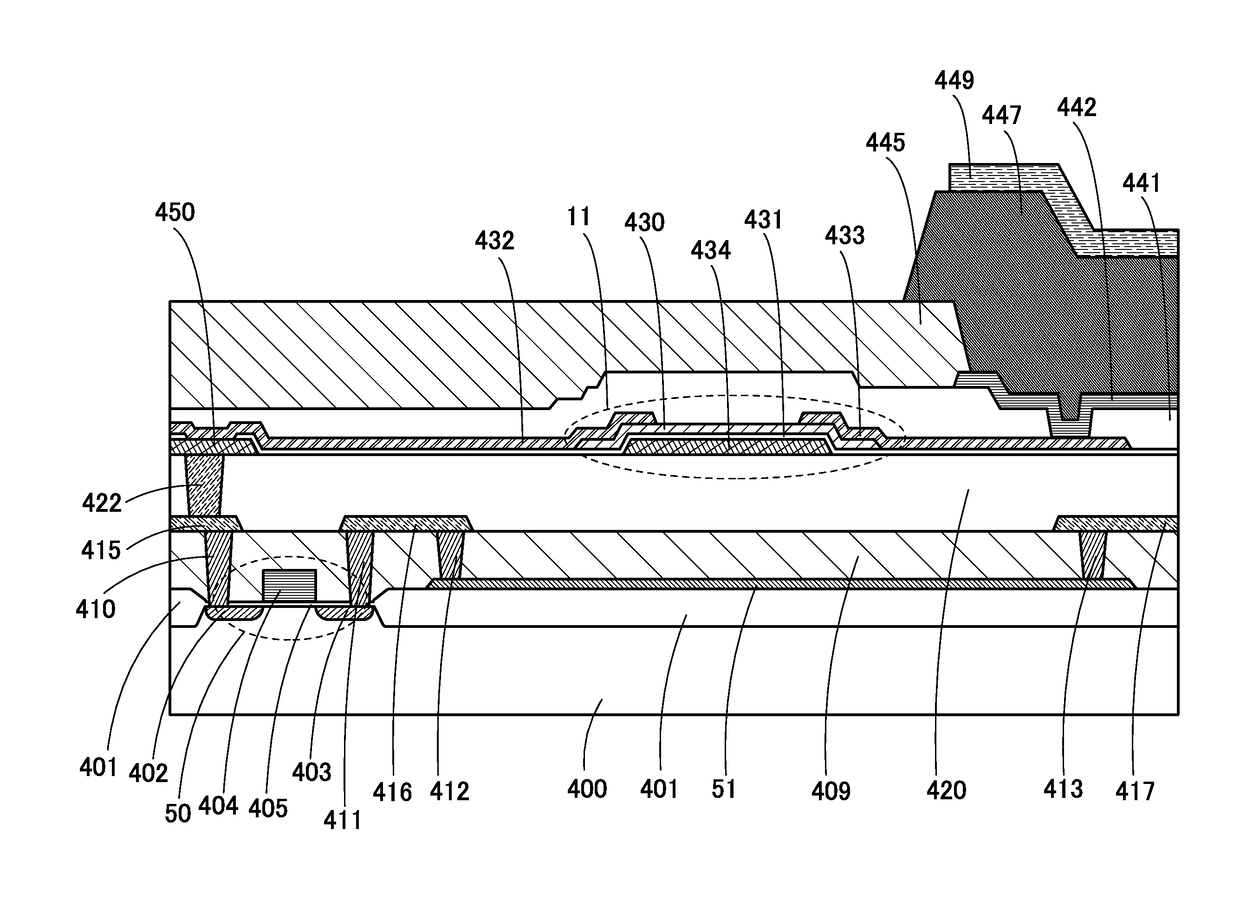

Integrated gate drive circuit and display panel with same

ActiveCN103778896ASimple structureExtend working lifeStatic indicating devicesBipolar voltageWorking environment

The invention provides an integrated gate drive circuit and a display panel with the same. The integrated gate drive circuit comprises cascaded multistage gate drive units and multistage additional gate drive units, wherein the nth-stage gate drive unit comprises a drive unit (42) and a drop-down unit (44), and the mth-stage additional gate drive unit comprises an additional drive unit (52) and an additional drop-down unit (54). A double-drop-down structure is adopted in the integrated gate drive circuit, a thin film transistor in the drop-down unit and a thin film transistor in the additional drop-down unit in the circuit can be in a bipolar voltage bias working environment, the drift of threshold voltages of the thin film transistor in the drop-down unit and the drift of threshold voltages of the thin film transistor in the additional drop-down unit are restrained effectively, the service life of the circuit is prolonged, and the circuit can meet the demands of large and medium size display panels better. Meanwhile, the circuit is simple in structure, low in power consumption and suitable for working at low temperature and high temperature.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Semiconductor device and manufacture method thereof

ActiveCN105374757AImprove reliabilityFacilitate horizontal diffusionSolid-state devicesSemiconductor/solid-state device manufacturingNitrideSemiconductor

Provided is a semiconductor device manufacture method which comprises steps of: forming a cushion layer mainly containing nitride on the side surface of a pseudo gate electrode; converting the cushion layer into a first barrier layer mainly containing oxide; successively forming a accumulation layer, a tunneling layer, and a channel layer on the first barrier layer; removing the pseudo gate electrode and forming a second barrier layer on the exposed first barrier layer; and forming a gate conductive layer on the second barrier layer. According to a semiconductor device and the manufacture method thereof, the nitride cushion layer is converted into the oxide barrier layers so that defect states can be effectively reduced, threshold voltage drift is inhibited, charge transverse diffusion in the accumulation layer is improved, and device reliability is enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

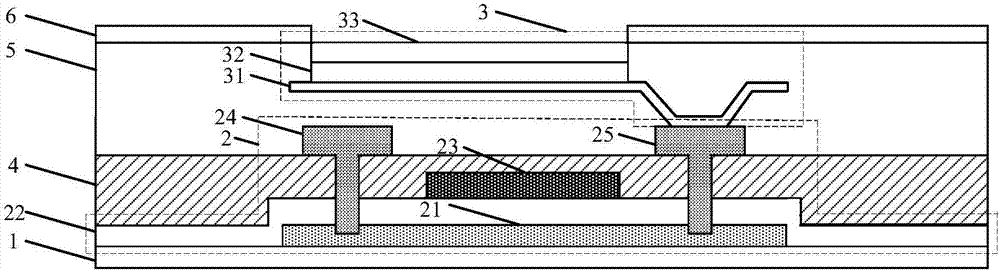

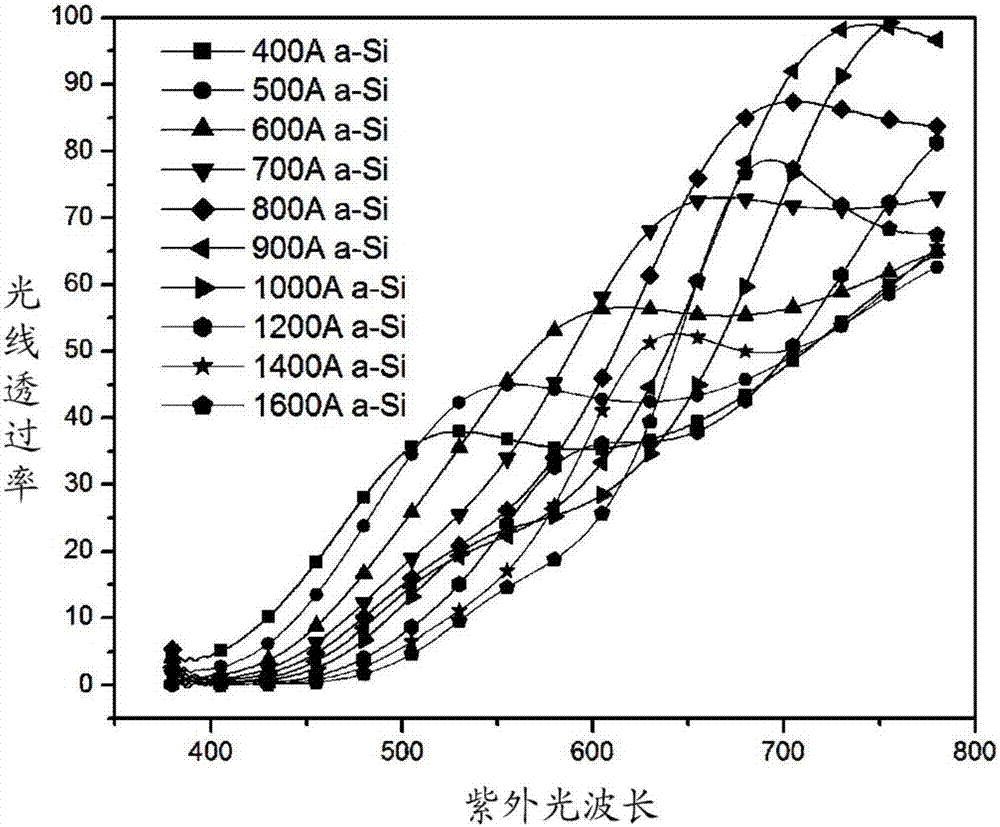

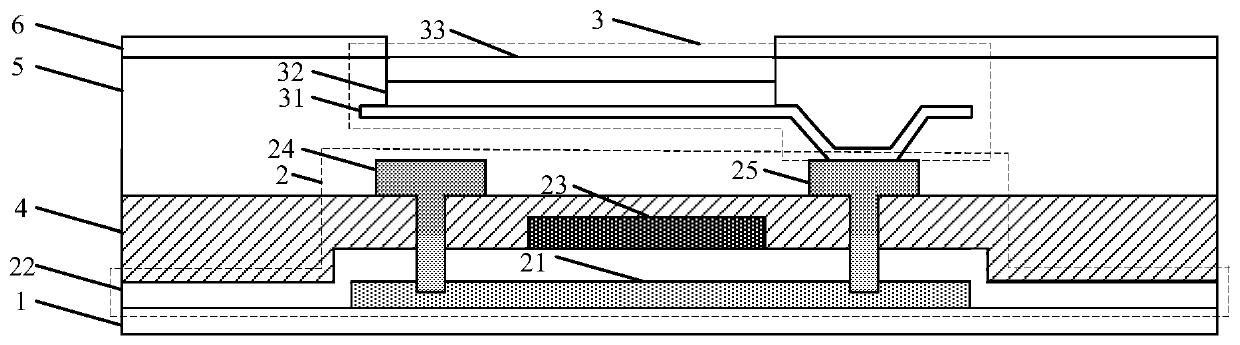

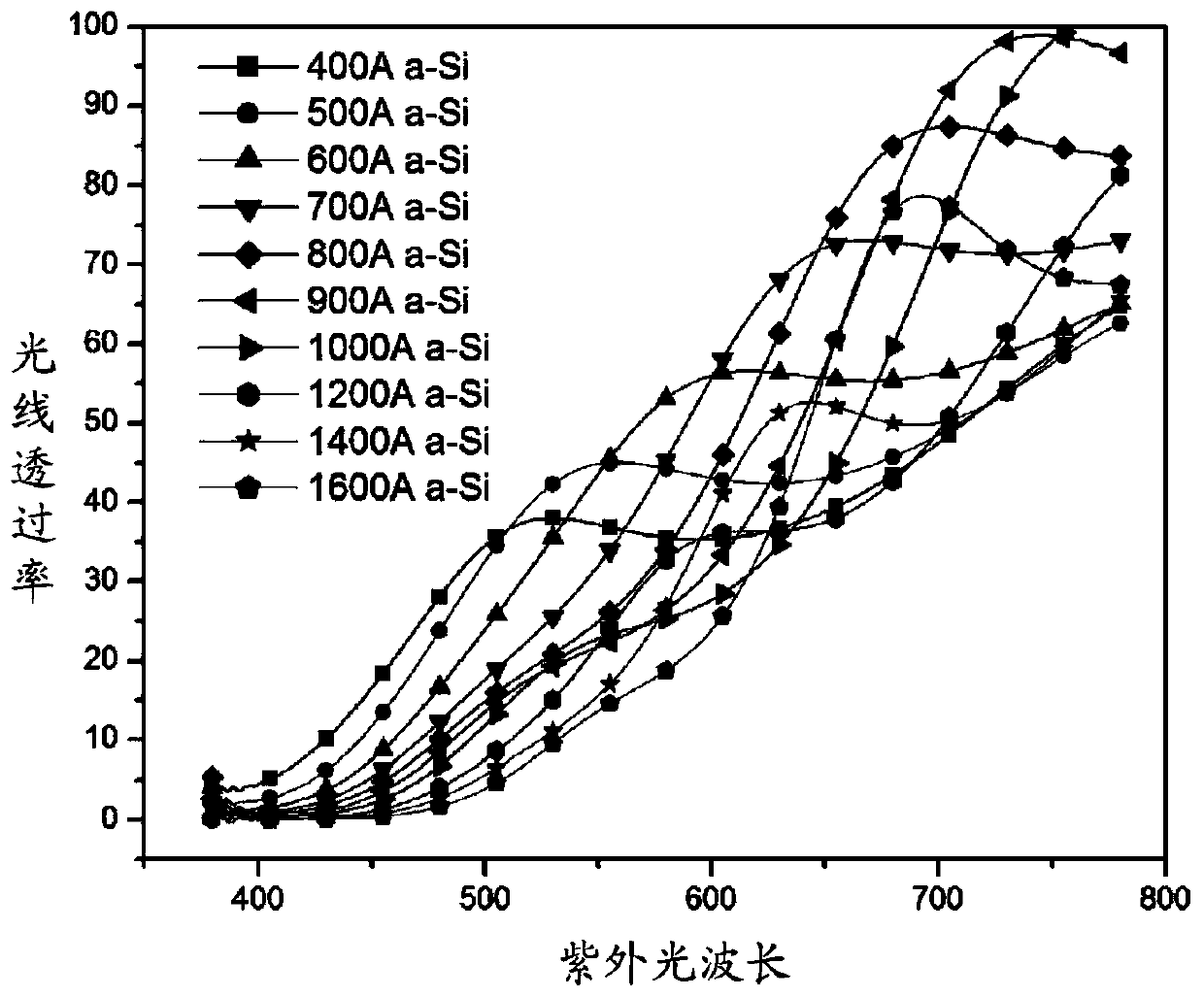

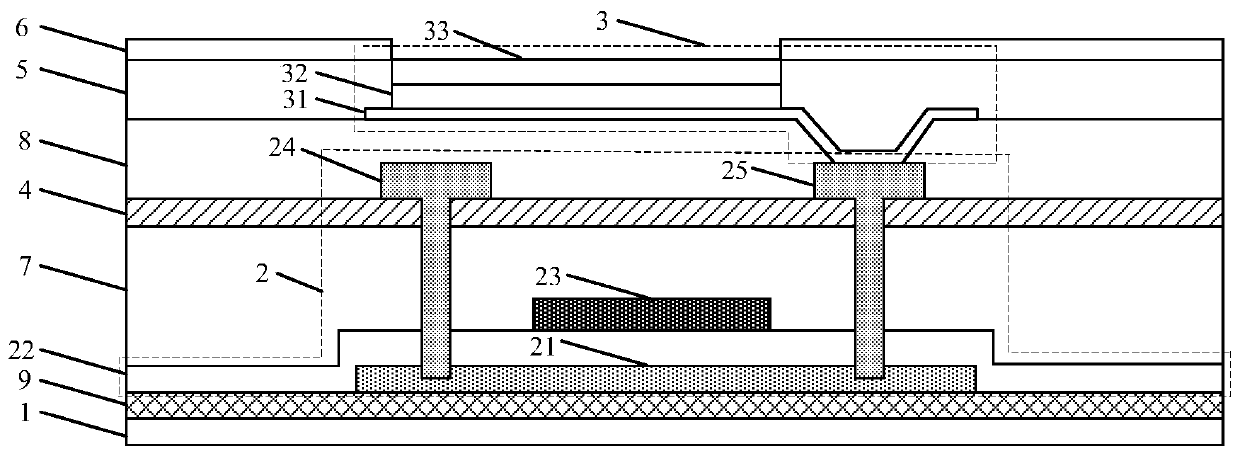

Display panel, making method and display device

ActiveCN107248373AShorten production timeAvoid Threshold Voltage DriftSolid-state devicesIdentification meansUltravioletDisplay device

The invention provides a display panel, a making method and a display device and relates to the technical field of display. The problem of threshold voltage drift of a thin film transistor caused by the fact that ultraviolet generates adverse influence on a polycrystalline silicon layer can be avoided. The display panel comprises a substrate baseplate, a thin film transistor formed on the substrate baseplate and a luminous structure formed on one side, back on to the substrate baseplate, of the thin film transistor, the thin film transistor comprises a polycrystalline silicone layer positioned between the luminous structure and the substrate baseplate, a light shielding layer for blocking ultraviolet is formed between the polycrystalline silicon layer and the luminous structure, and orthographic projection of the light shielding layer on the substrate baseplate covers that of the polycrystalline silicon layer on the substrate baseplate. The display panel is used for realizing picture display.

Owner:BOE TECH GRP CO LTD

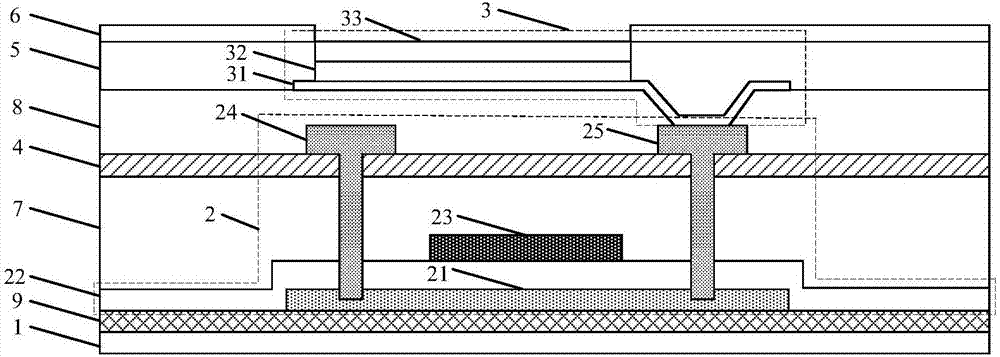

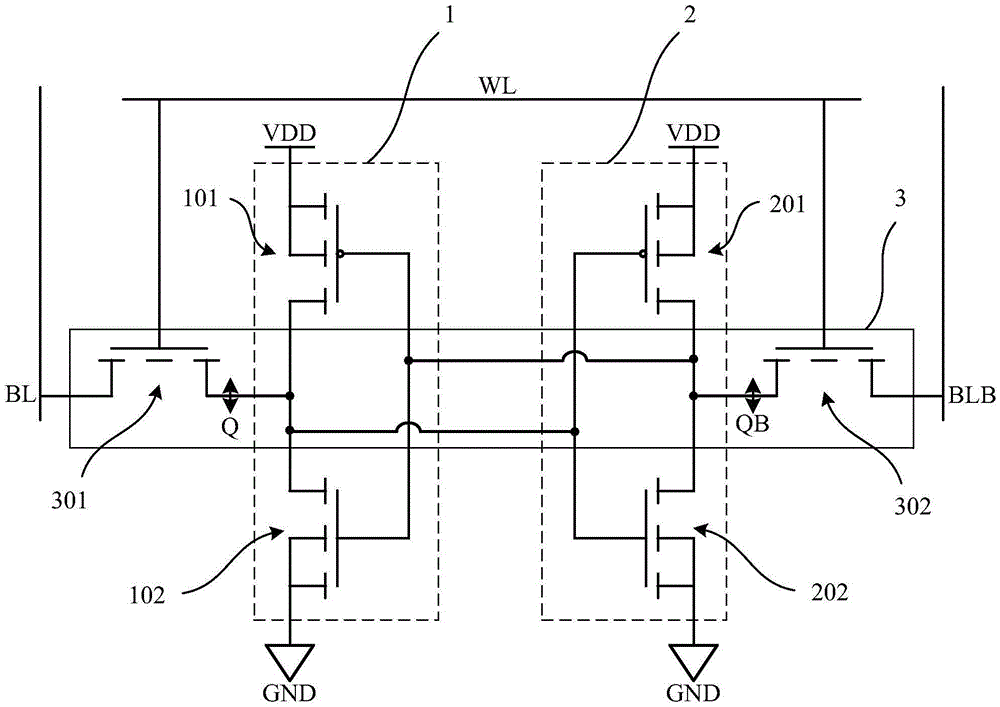

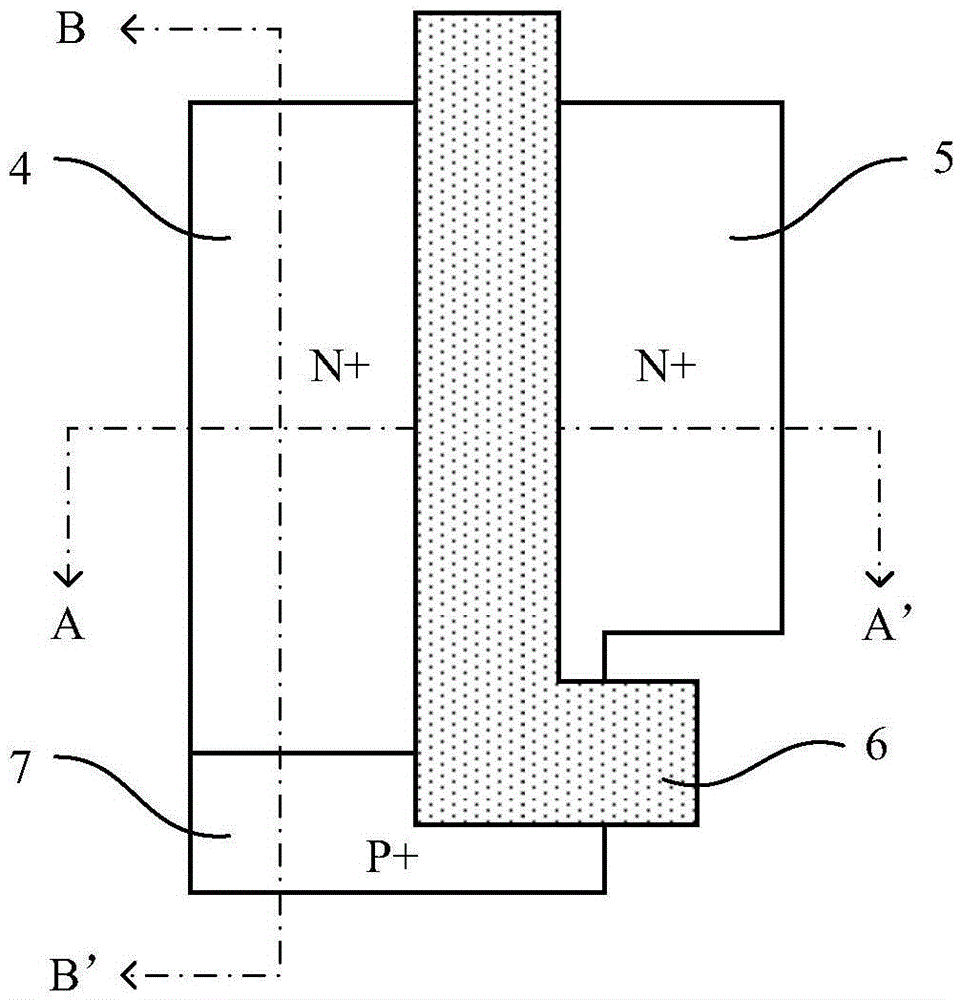

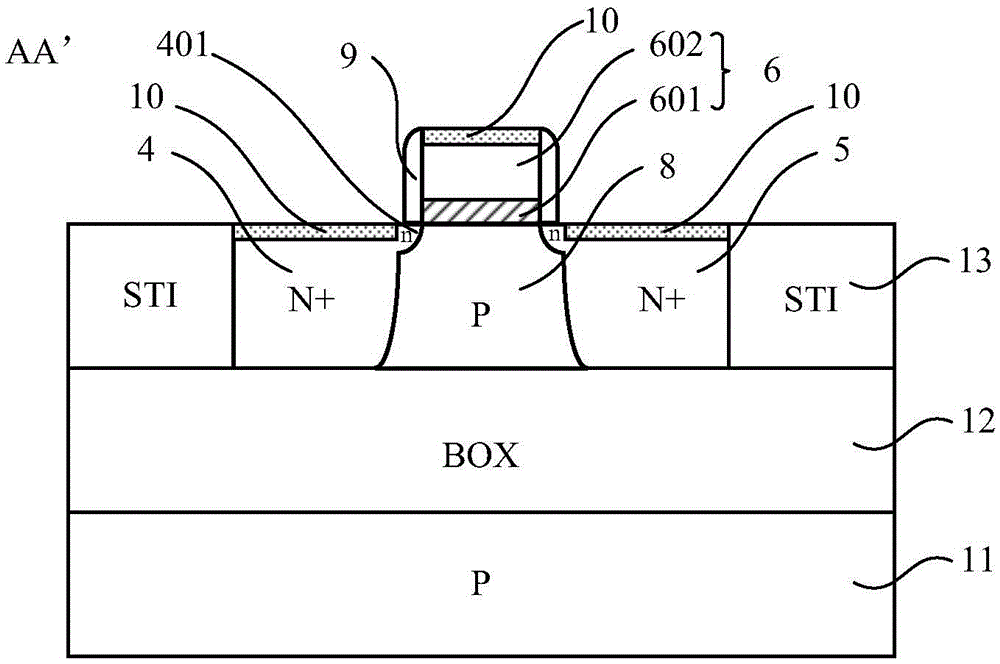

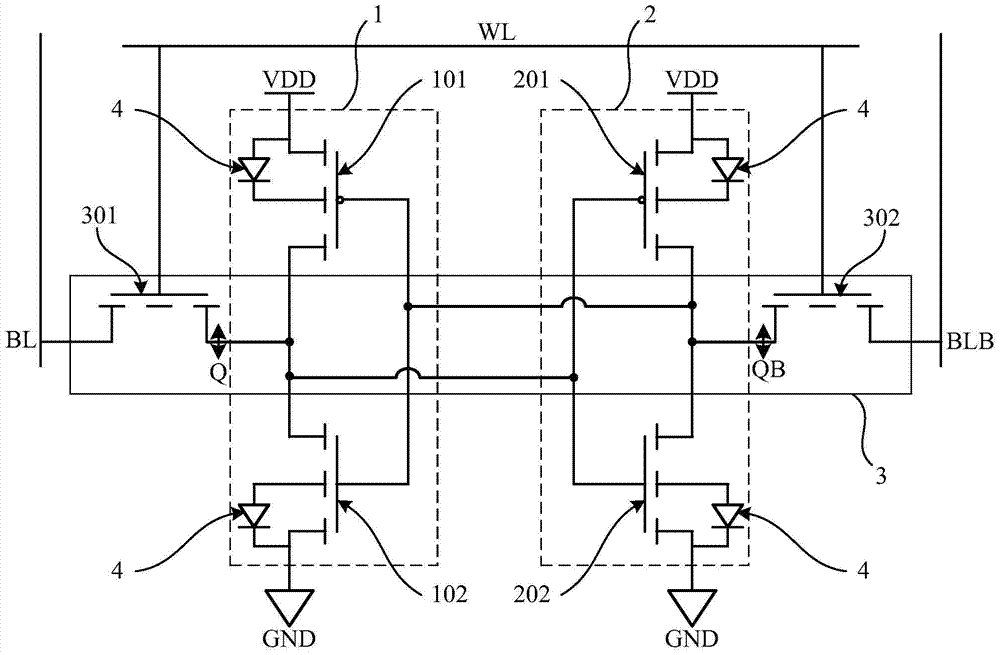

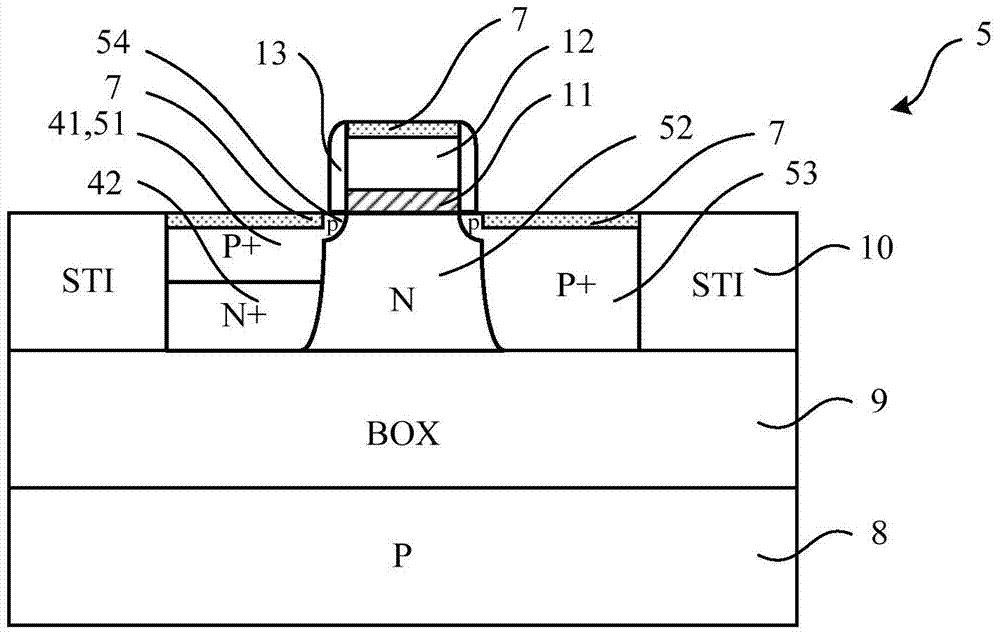

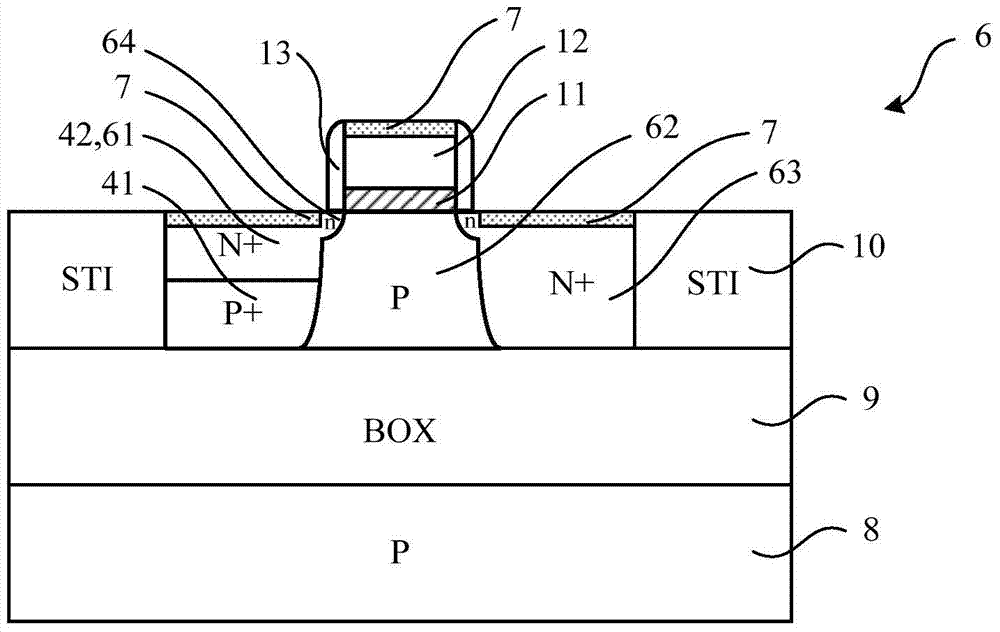

SOI single-port SRAM (Static Random Access Memory) unit and a preparation method thereof

ActiveCN105551518AImprove noise immunitySize matchSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectStatic random-access memory

The invention provides an SOI single-port SRAM unit and a preparation method thereof. The unit comprises a first phase inverter composed of a first PMOS transistor and a first NMOS transistor; a second phase inverter composed of a second PMOS transistor and a second NMOS transistor; an obtaining transistor composed of a third NMOS transistor and a fourth NMOS transistor. In the SRAM unit, the four transistors forming the first phase inverter and the second phase inverter are L-type gates; heavy dopant contact regions are arranged in the regions at the outer sides of the bending angles of the L-type gates. According to the unit and the method of the invention, leakage power consumption and transistor threshold voltage drift resulted from the floating body effect and parasitic triode effect in the PD SOI instrument can be effectively inhibited under the condition of sacrificing a relatively small unit area; the anti-noise capability of the unit is improved; the preparation technique of the invention introduces no extra mask plate and is fully compatible with the exiting logic technique; the inner part of the unit is a center symmetrical structure which is beneficial for matching the size and the threshold voltage of the MOS tube and for matching an array and is convenient for a full-custom SRAM chip.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

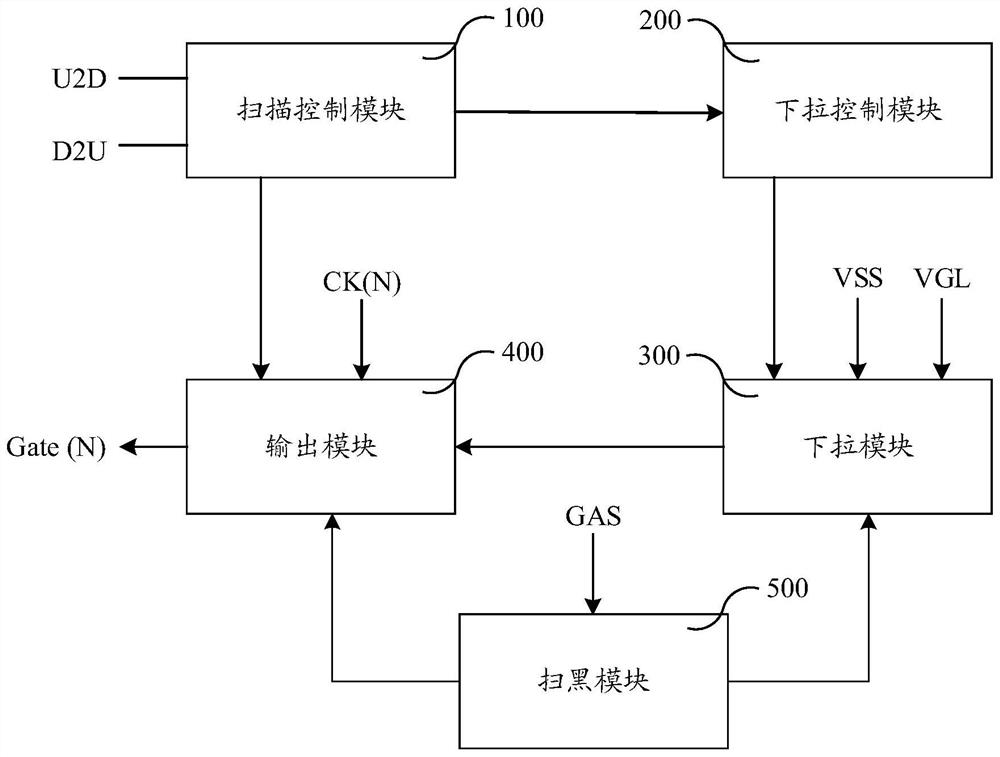

Display panel, gate driving circuit driving method and display device

InactiveCN111681624AImprove fault toleranceAvoid Threshold Voltage DriftStatic indicating devicesDisplay deviceHemt circuits

The invention discloses a display panel, a gate driving circuit driving method and a display device, the display panel comprises a display area and a non-display area, and the display panel comprisesa pixel driving circuit located in the display area and a gate driving circuit located in the non-display area; the gate drive circuit is connected with a first voltage end and a second voltage end; the first voltage end is used for switching off a driving transistor connected with the output end of the gate driving circuit in the pixel driving circuit; the second voltage end is used for turning off an output transistor in the gate drive circuit so as to restrain drifting of threshold voltage of the drive transistor in the pixel drive circuit, and reliability of the drive transistor and faulttolerance of the display panel are improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

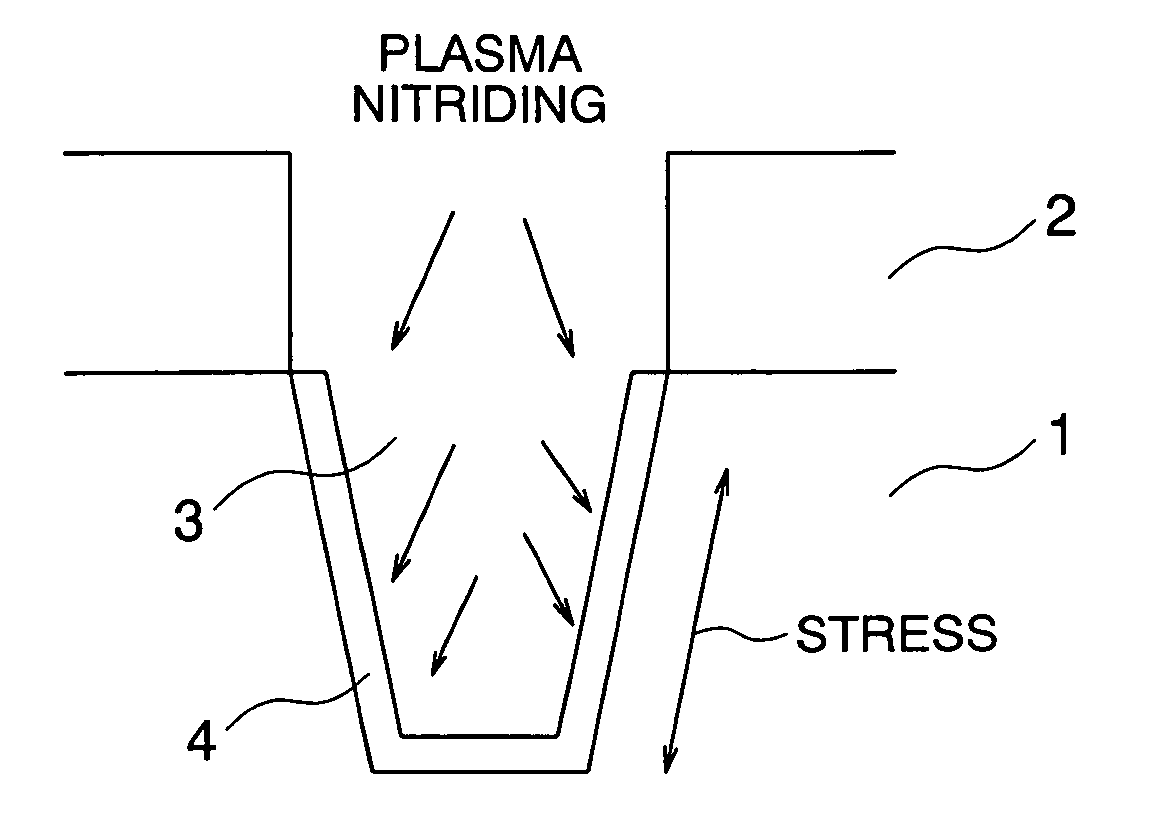

Method for producing semiconductor device

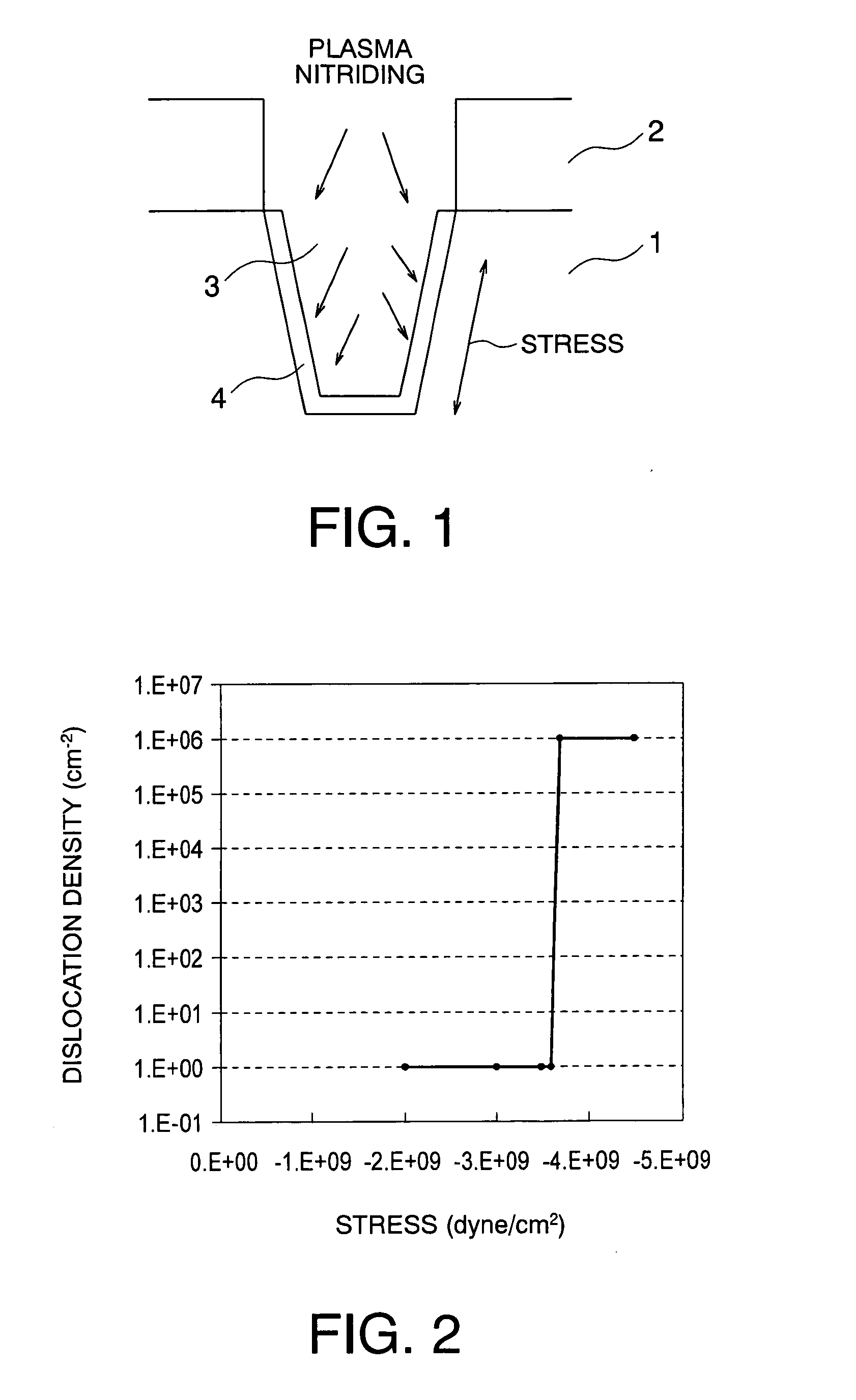

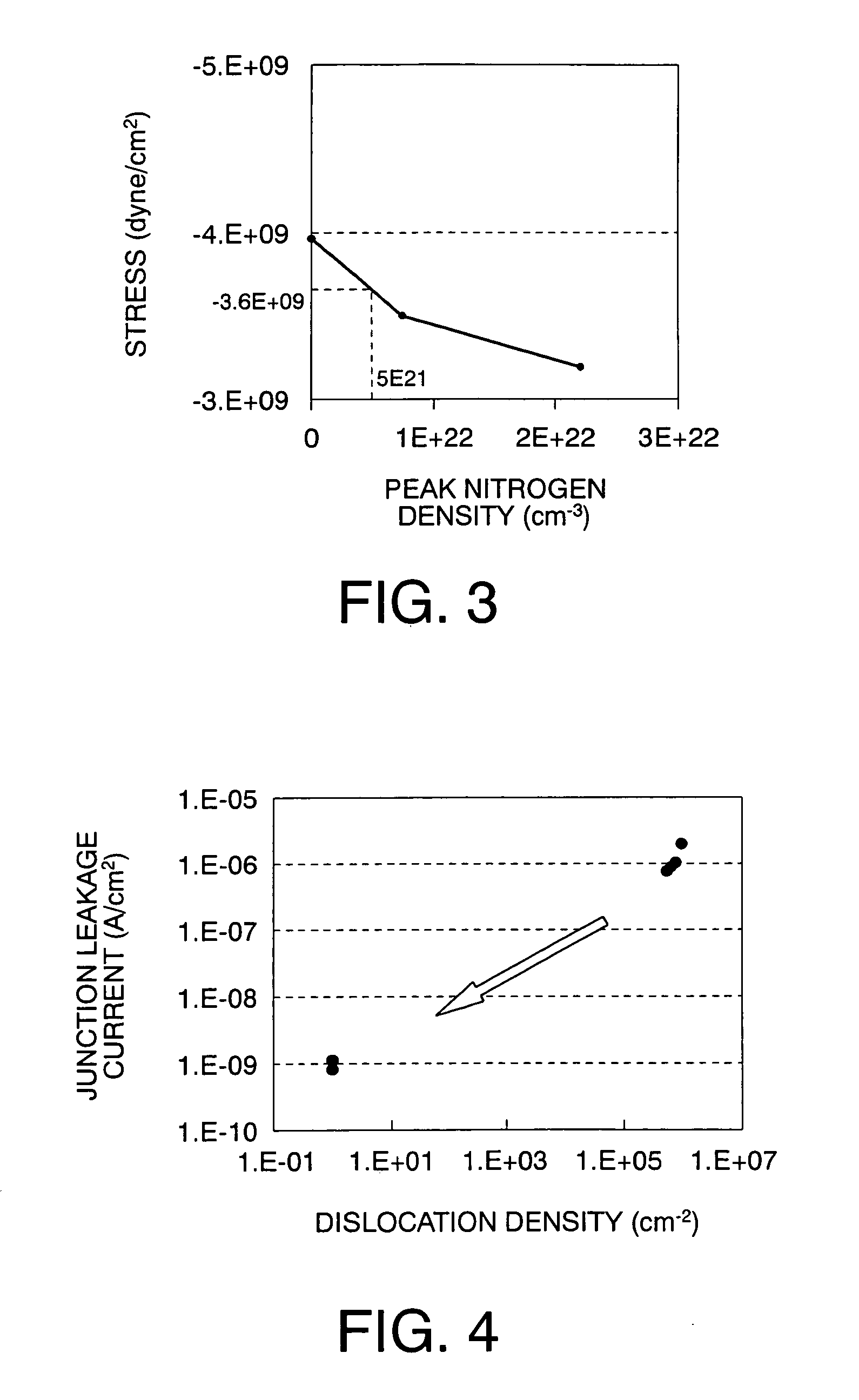

InactiveUS20050215026A1Relieve pressureLower threshold voltageTransistorSemiconductor/solid-state device manufacturingNitrogenPeak value

With respect to nitriding of an oxide film on an inner wall of a trench, a method for producing a semiconductor device is provided, the method preventing the characteristic deterioration of the semiconductor device by controlling and optimizing peak nitrogen concentration in an oxide film to reduce the stress and to suppress the threshold voltage shift due to the positive charge of nitrogen.

Owner:ELPIDA MEMORY INC

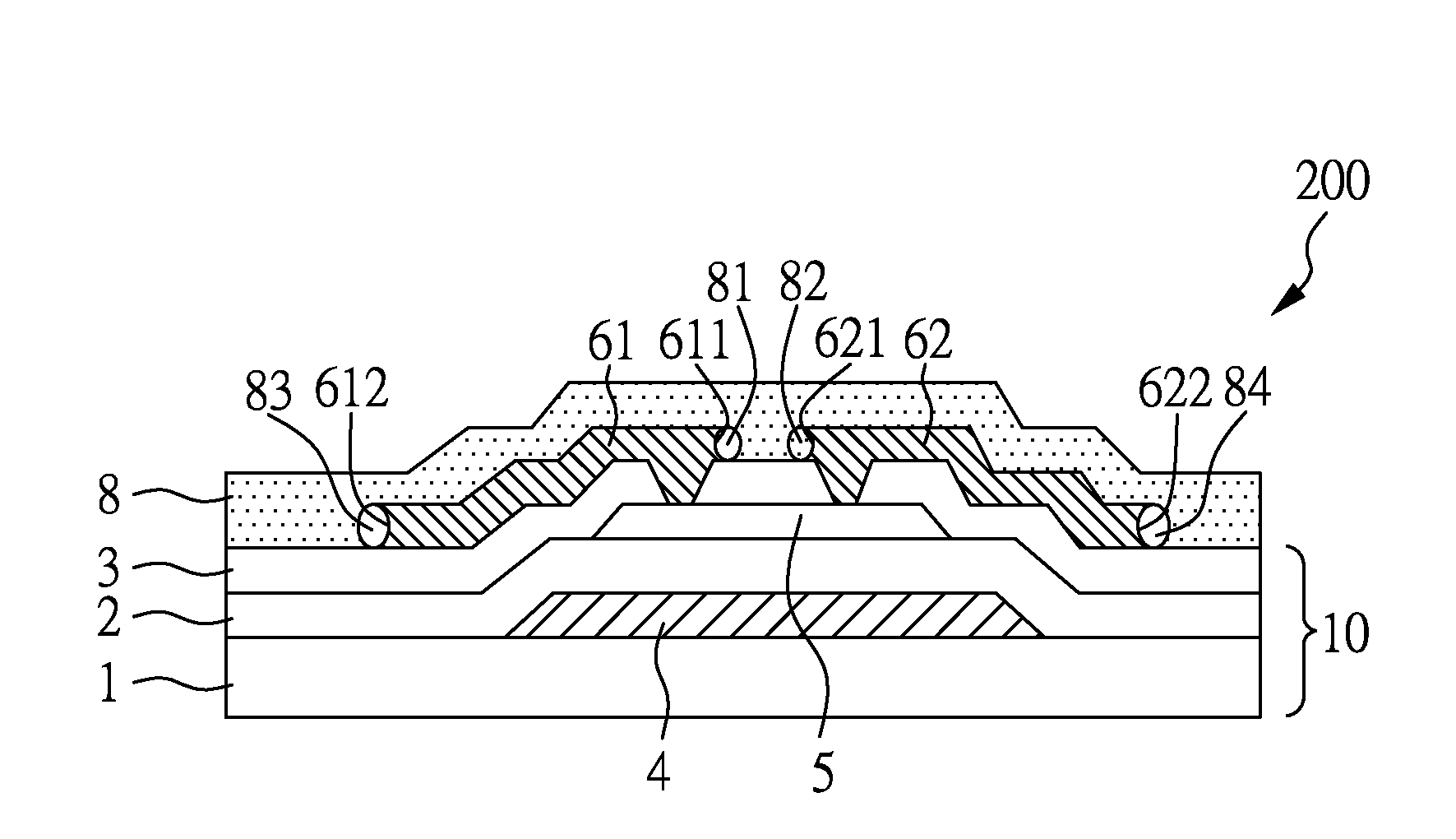

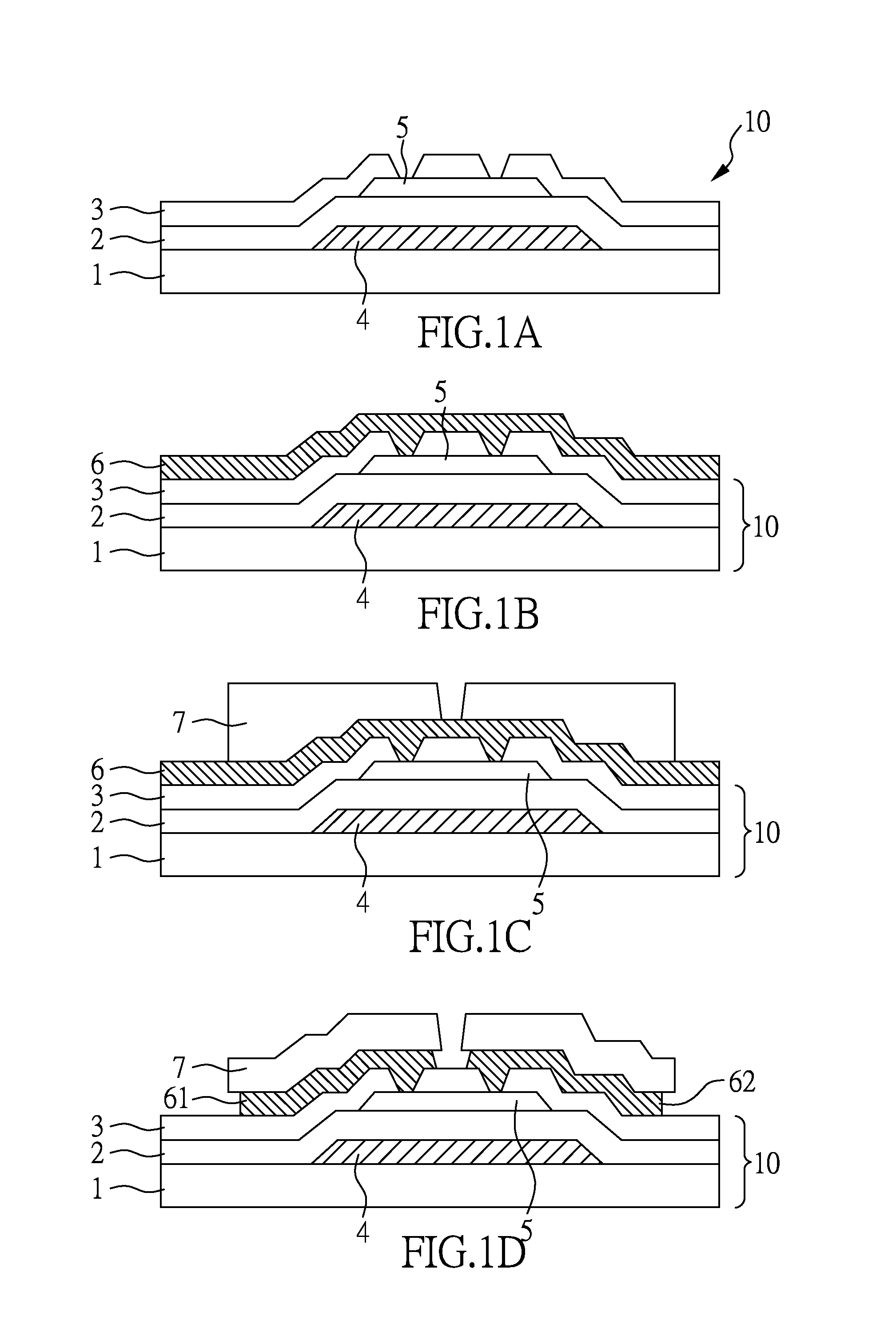

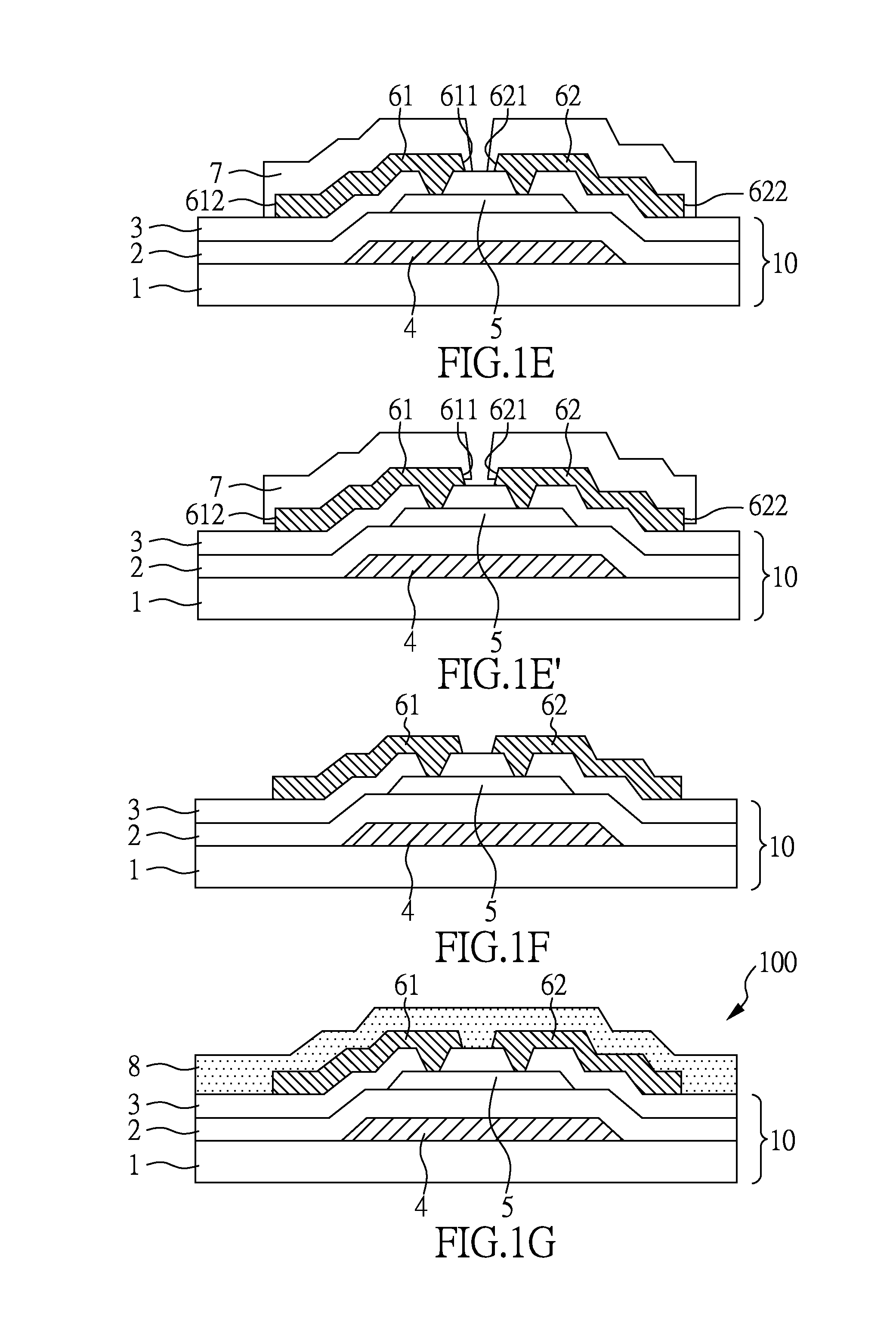

Method for manufacturing display panel

InactiveUS20160141390A1Improve reliabilityAvoid damageSolid-state devicesSemiconductor/solid-state device manufacturingResistPhotoresist

A method for manufacturing display panel is disclosed, which comprises: (A) providing a substrate, an oxide semiconductor layer disposed on the substrate, and a gate electrode disposed on the substrate and corresponding to the oxide semiconductor layer; (B) forming a metal layer on the oxide semiconductor layer; (C) forming a photoresist on the metal layer, and etching the metal layer to form a source electrode and a drain electrode; (D) heating the photoresist and the photoresist covers at least partial of side walls of the source electrode and the drain electrode; (E) applying an alkaline solution on the substrate; and (F) removing the photoresist to expose the source electrode and the drain electrode.

Owner:INNOLUX CORP

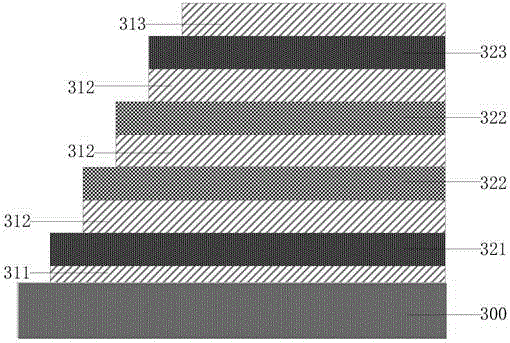

3D NAND flash memory structure and manufacturing method therefor

ActiveCN105810639AAvoid Threshold Voltage DriftPrevent leakageSolid-state devicesSemiconductor/solid-state device manufacturingEtchingElectron capture

The invention relates to the technical field of semiconductor manufacturing, and especially relates to a 3D NAND flash memory structure and a manufacturing method therefor. The method comprises the steps: providing a substrate, and sequentially forming a grid oxidation layer, a source selectron polycrystalline silicon layer, a plurality of stacked oxidation dielectric layers and sacrificial dielectric layers, a drain selectron polycrystalline silicon layer, and a protection oxidation layer; carrying out etching and forming a cylindrical trench exposing the substrate; forming a tunneling oxidation layer, polycrystalline silicon and a polycrystalline silicon isolation dielectric layer in the cylindrical trench; carrying out etching and forming a source trench exposing the substrate, and forming a public source electrode; carrying out wet etching, and removing the sacrificial dielectric layers; sequentially forming an electron capture layer and a blocking oxidation layer on a side wall of the source trench and an inner wall of the oxidation dielectric layer; and forming a grid electrode on the surface of the oxidation dielectric layer. A selectron prepared through the method does not contain electron capture layer silicon nitride, thereby avoiding the threshold voltage drift and electric leakage of the selectron, and improving the quality of a storage device.

Owner:GIGADEVICE SEMICON SHANGHAI INC +1

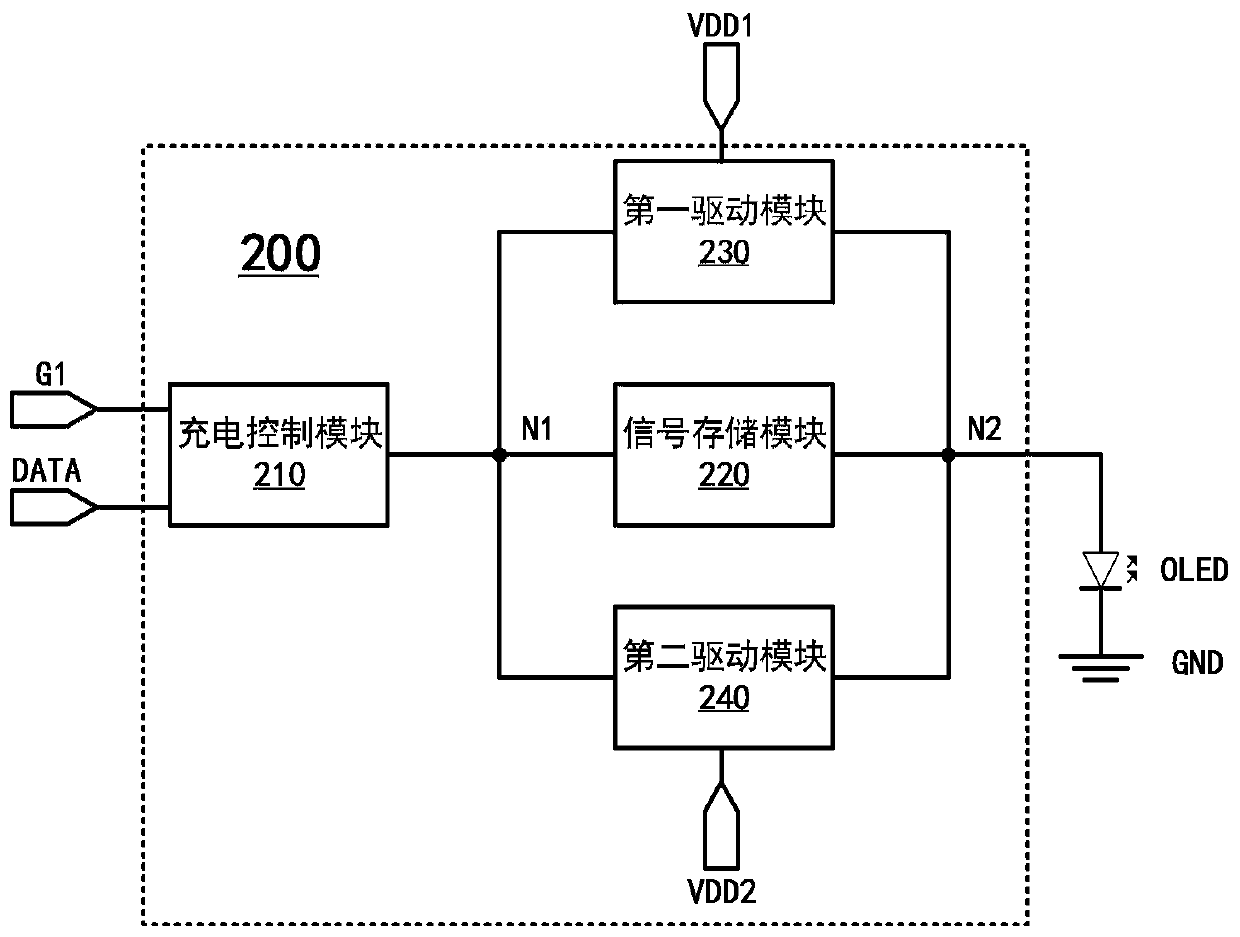

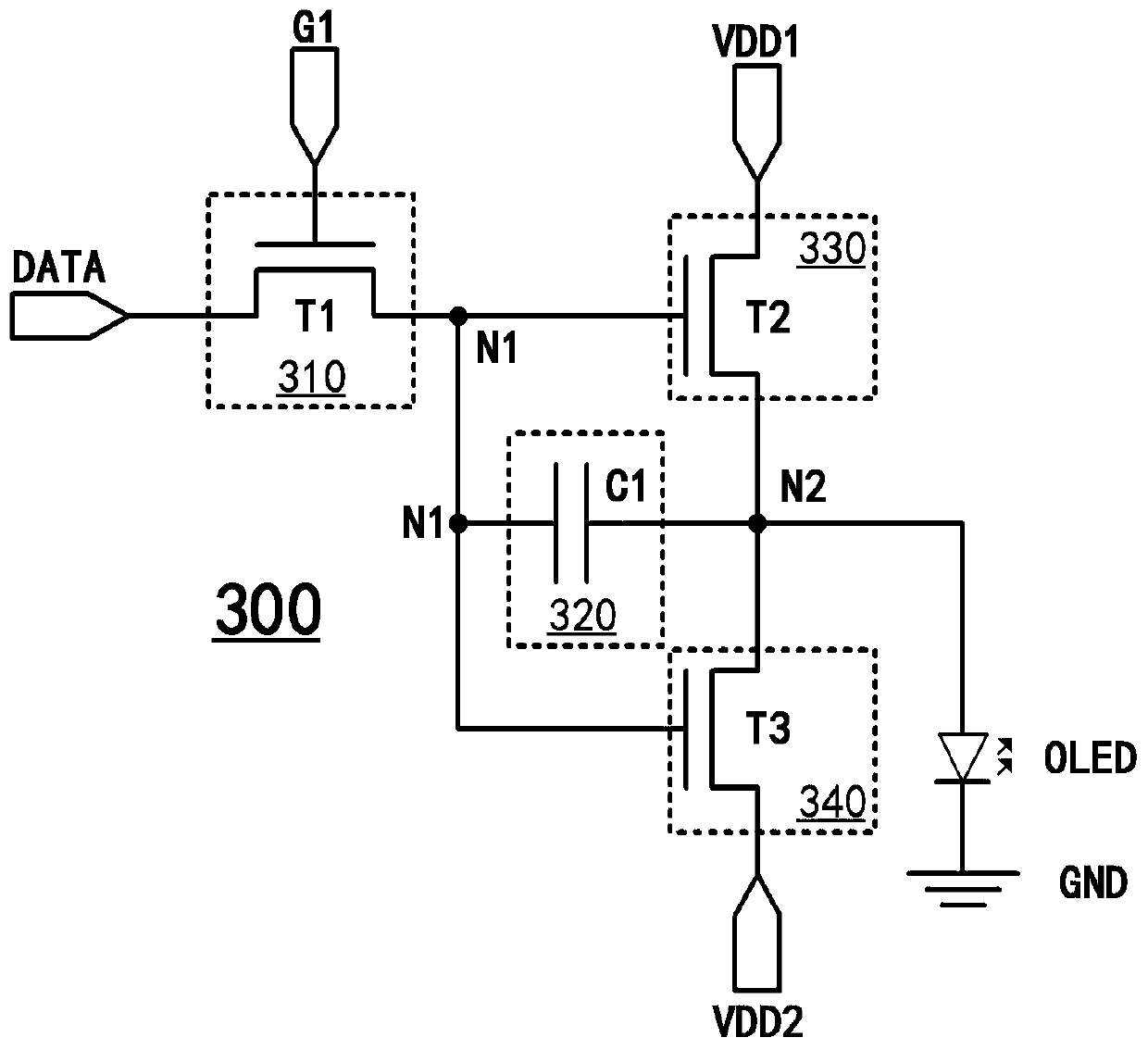

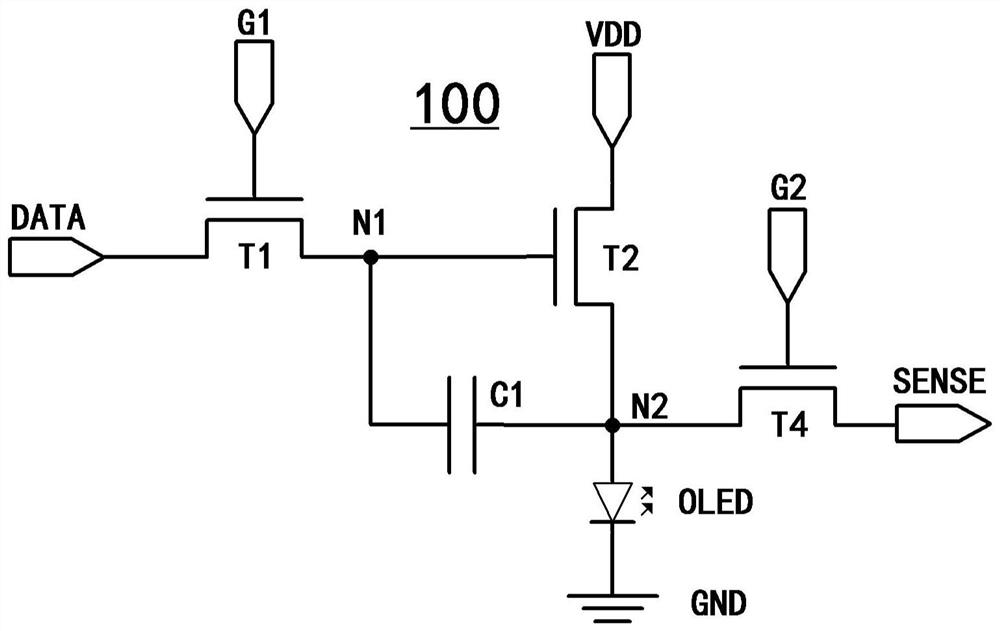

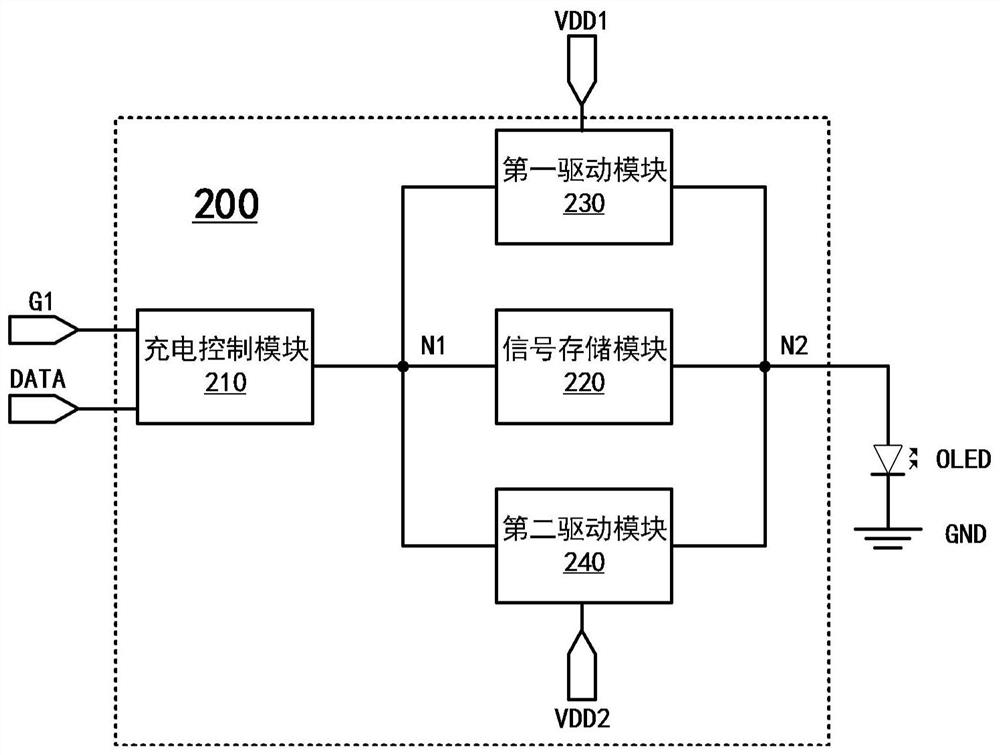

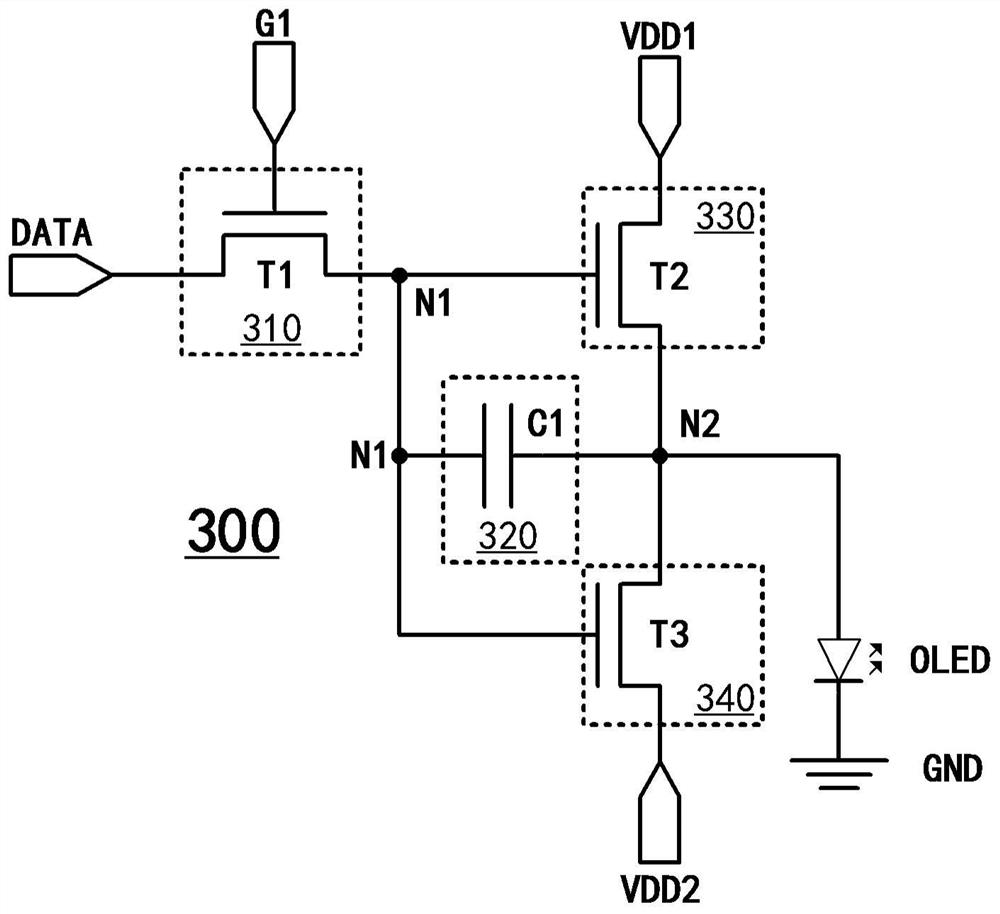

Pixel driving circuit and driving method thereof, display panel and display device

ActiveCN110047435AAvoid Threshold Voltage DriftReduce afterimageStatic indicating devicesComputer moduleDisplay device

The embodiment of the invention provides a pixel driving circuit and a driving method thereof, a display panel and a display device. The pixel driving circuit comprises a charging control module whichis configured to transmit a data signal from a data signal end to a first node under the control of a scanning signal from a scanning signal end; a signal storage module which is configured to be capable of storing signals from the first node or transmitting the stored signals to the first node; a first driving module which is configured to be capable of transmitting a first voltage signal from the first voltage signal end to the organic light emitting diode (OLED) element under the control of the level of the first node; and a second driving module which is configured to be capable of transmitting a second voltage signal from the second voltage signal end to the OLED element under the control of the level of the first node.

Owner:BOE TECH GRP CO LTD

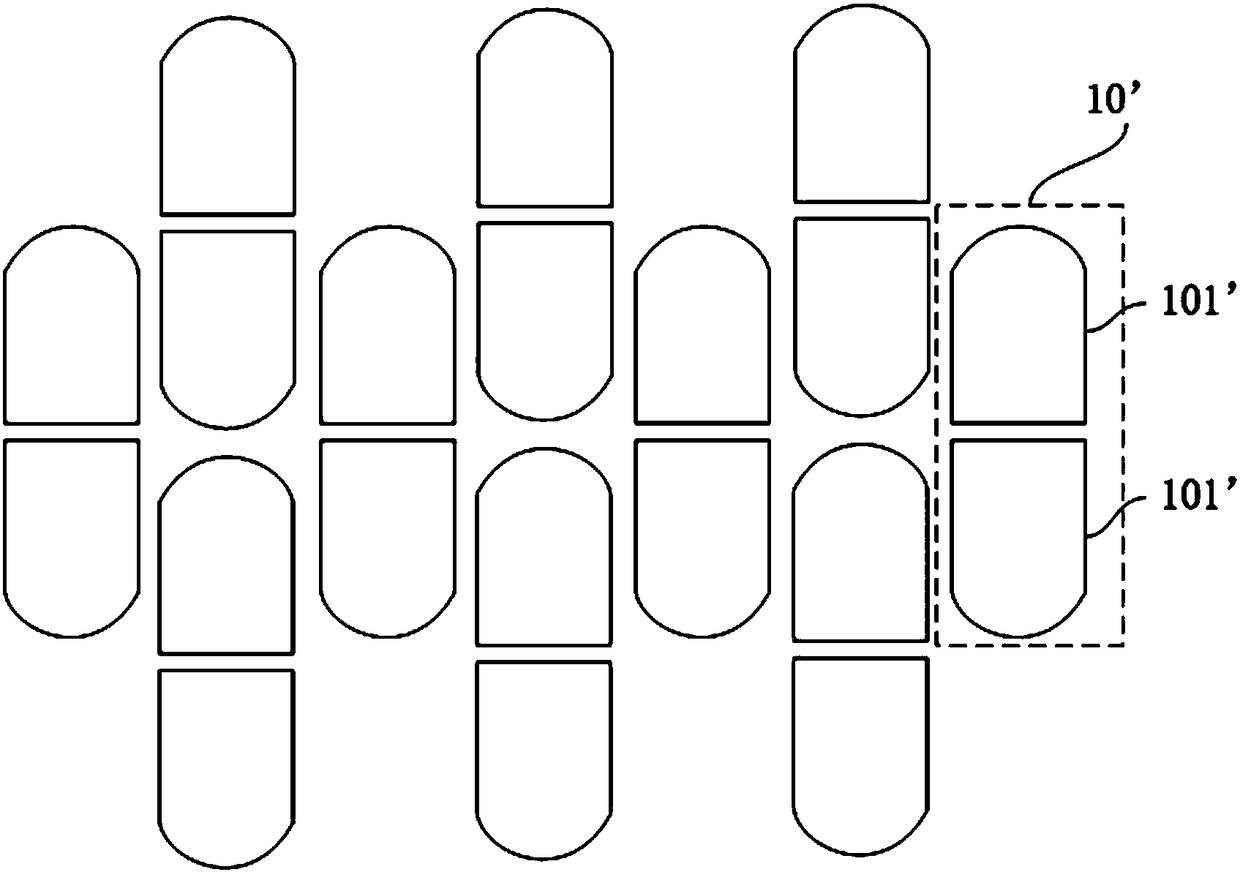

Inkjet printing OLED display panel and preparation method thereof

ActiveCN108565357ALower the altitudeSave manufacturing timeSolid-state devicesSemiconductor/solid-state device manufacturingGraphicsEngineering

The invention provides an inkjet printing OLED display panel and a preparation method thereof. The method comprises the steps that a passivation layer and a flat layer are successively formed on a glass substrate on which at least one pair of thin film transistors are prepared, and the passivation layer covers at least one pair of thin film transistors; at least one pair of via holes are formed onthe passivation layer and the flat layer; at least one pair of anodes are prepared on the flat layer, and the anodes are electrically connected with the thin film transistors through the via holes arranged on the flat layer and the passivation layer; a pixel defining layer is deposited on the flat layer to cover the anodes; the pattern of the pixel defining layer is defined by using a halftone photomask so that the region arranged on the anodes of the pixel defining layer is enabled to form a notch, and the height of the pixel defining layer between the anodes is reduced; and a light-emittinglayer is prepared in the notch by using the inkjet printing technology. A photomask can be saved, the performance of the thin film transistors in the inkjet printing OLED display panel can be improved without reducing the mobility of the thin film transistors, and threshold voltage drift can also be effectively suppressed.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

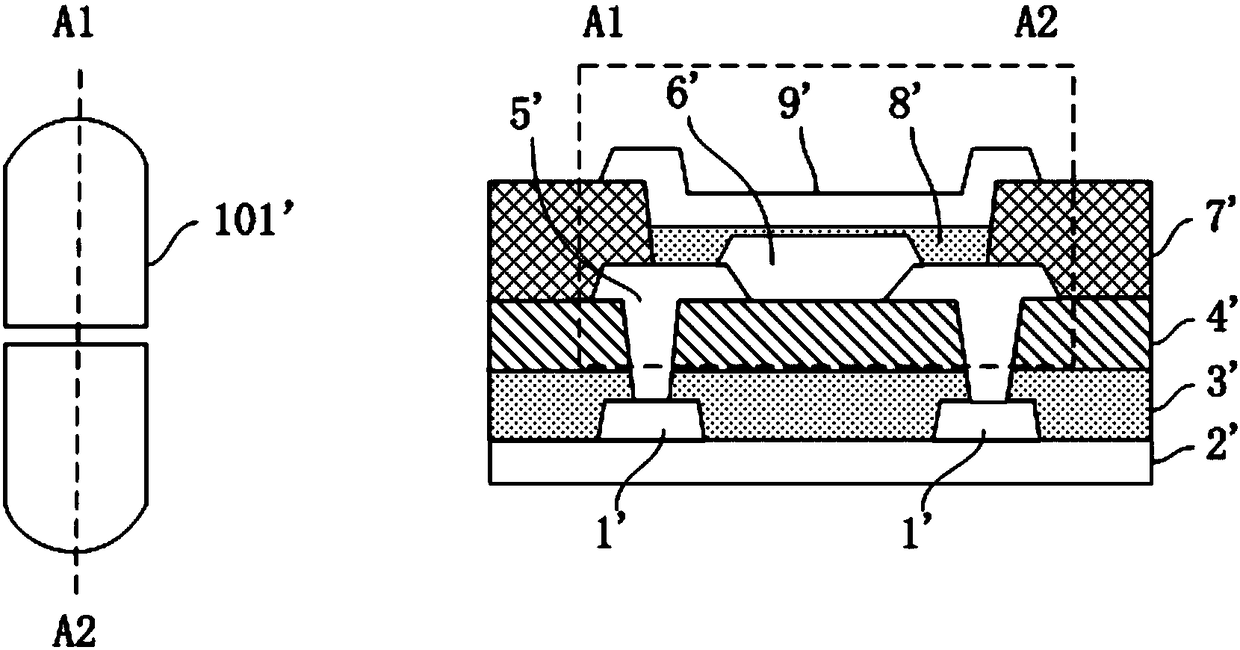

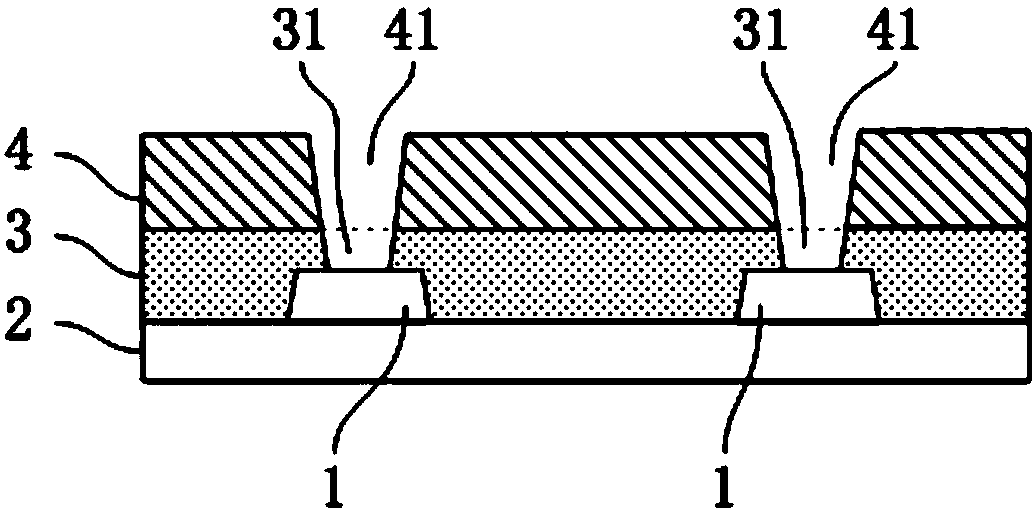

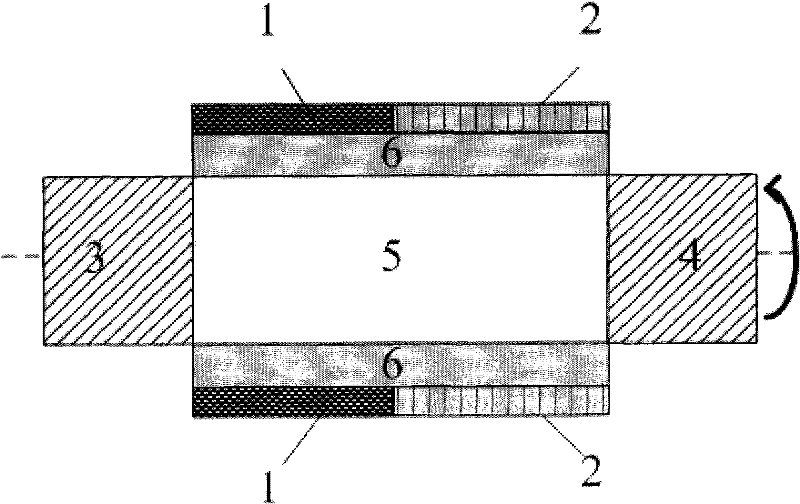

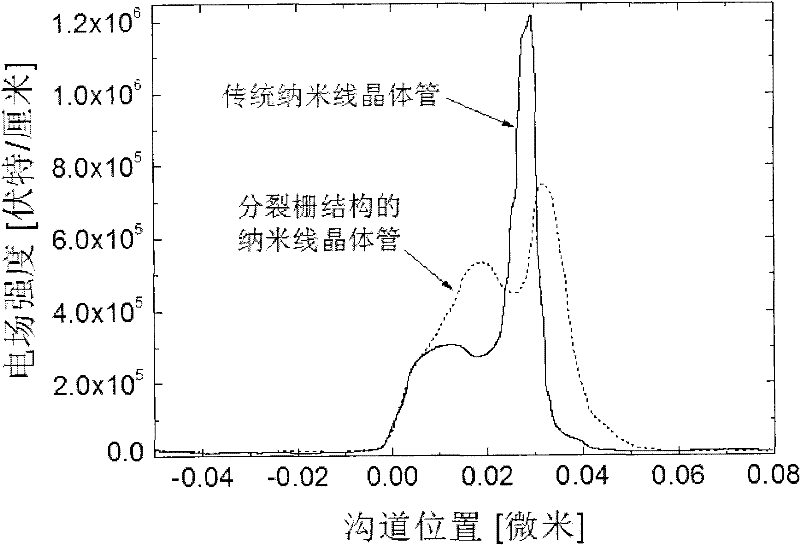

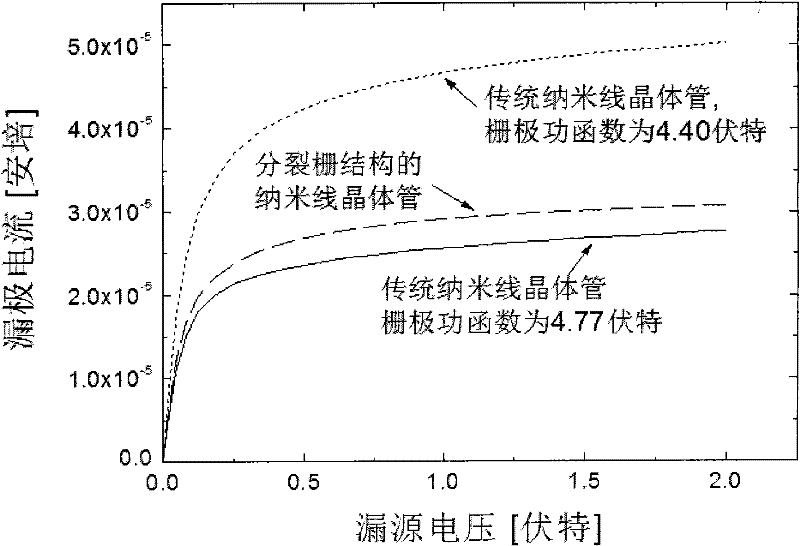

Nanowire field effect transistor with split-gate structure

InactiveCN102544094AIncrease the on-state currentReduce off-state currentSemiconductor devicesShort-channel effectElectricity

The invention discloses a nanowire field effect transistor with a split-gate structure. The transistor is formed by a split-gate electrode, a source region, a drain region, a channel region and a gate dielectric layer, wherein the channel region is columnar and is positioned in the center of the nanowire field effect transistor, and a material forming the channel region is a semiconductor material; the gate dielectric layer totally encircles the channel region coaxially; the split-gate electrode is positioned outside the gate dielectric layer and totally encircles the gate dielectric layer coaxially, and materials forming the split-gate electrode include two kinds of different materials; and the source region and the drain region are positioned at two sides of the channel region respectively. The introduction of the split-gate electrode structure can effectively improve the on-state current of nanowire transistors in prior arts and improve the current switch ratio and the working speed of devices. Simultaneously, the transistor is less affected by threshold voltage shift and drain induced barrier lowering effect resulted from short channel effect, and the performance of size reduction is more excellent.

Owner:PEKING UNIV

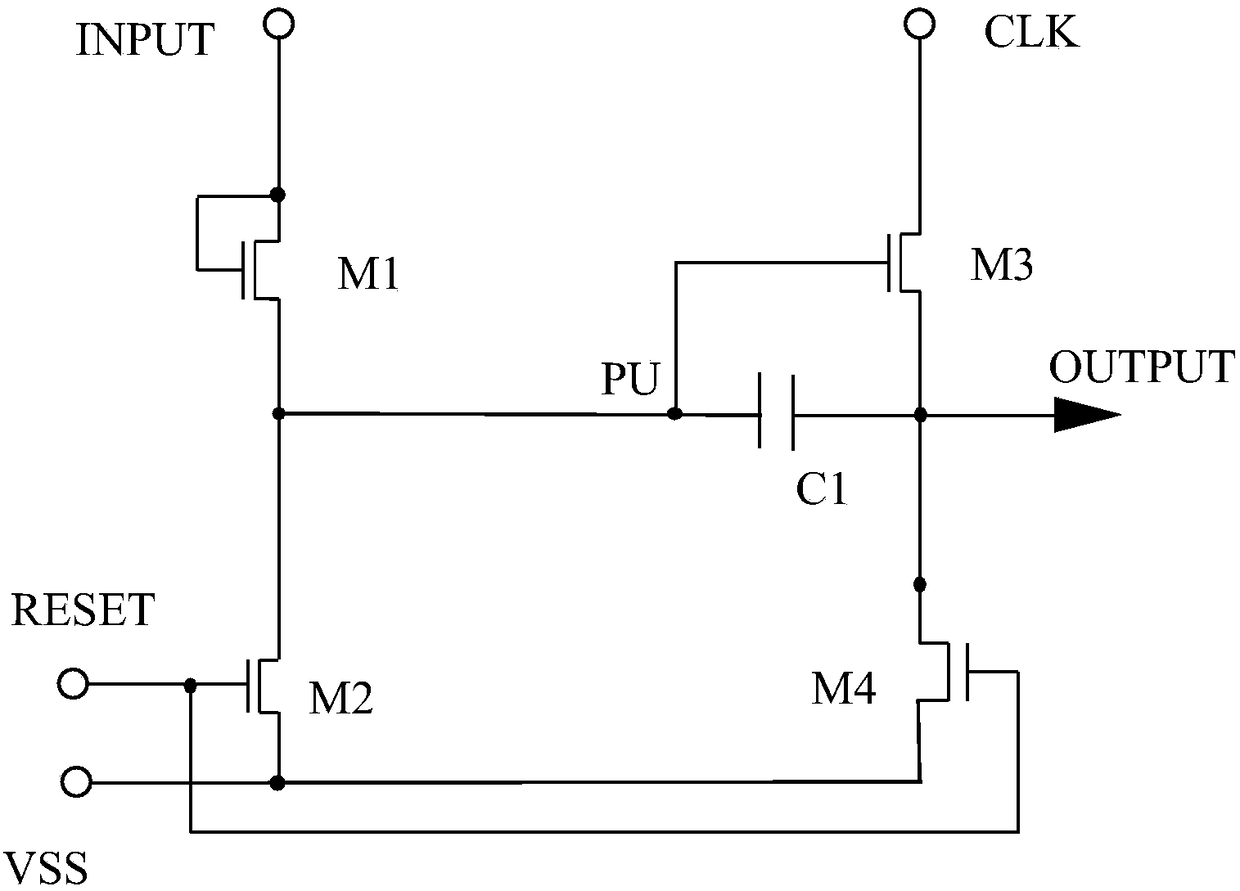

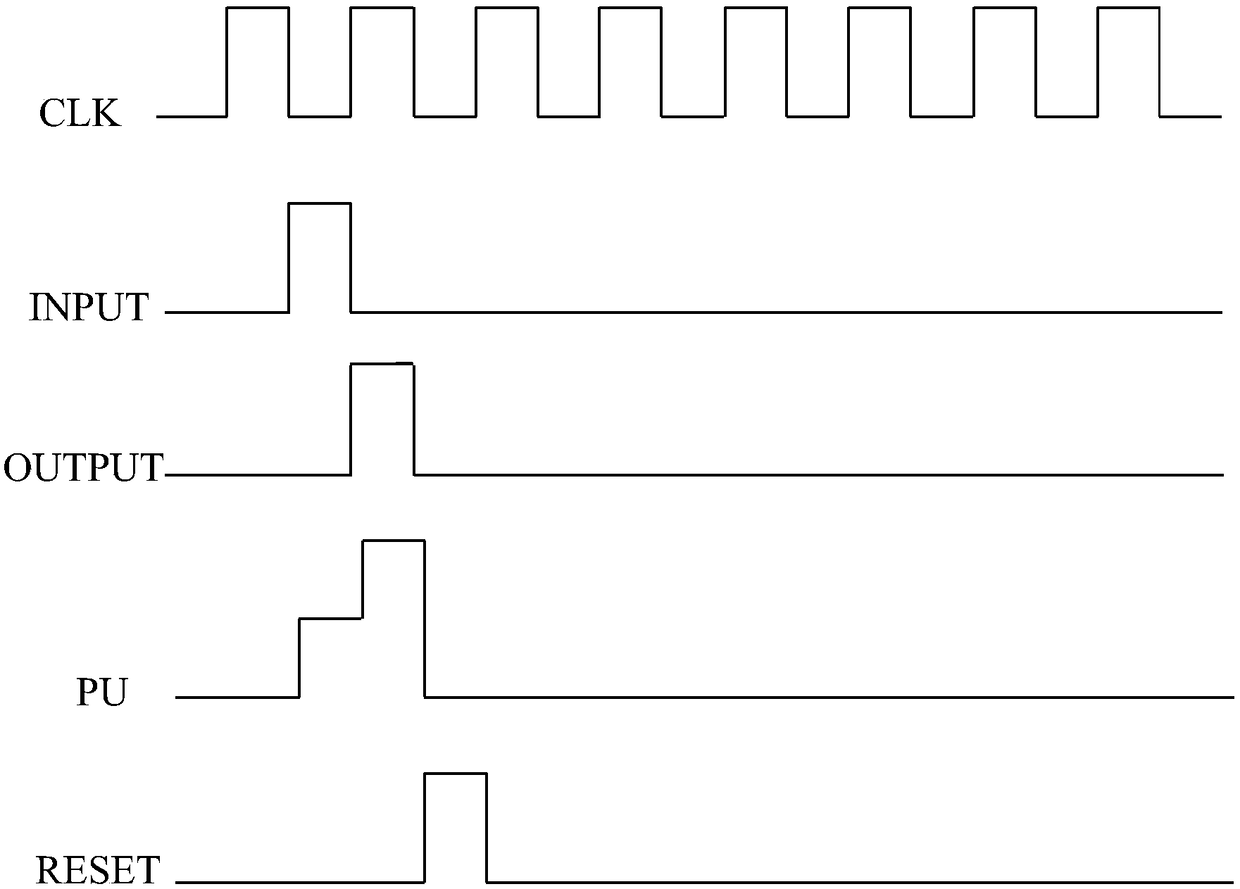

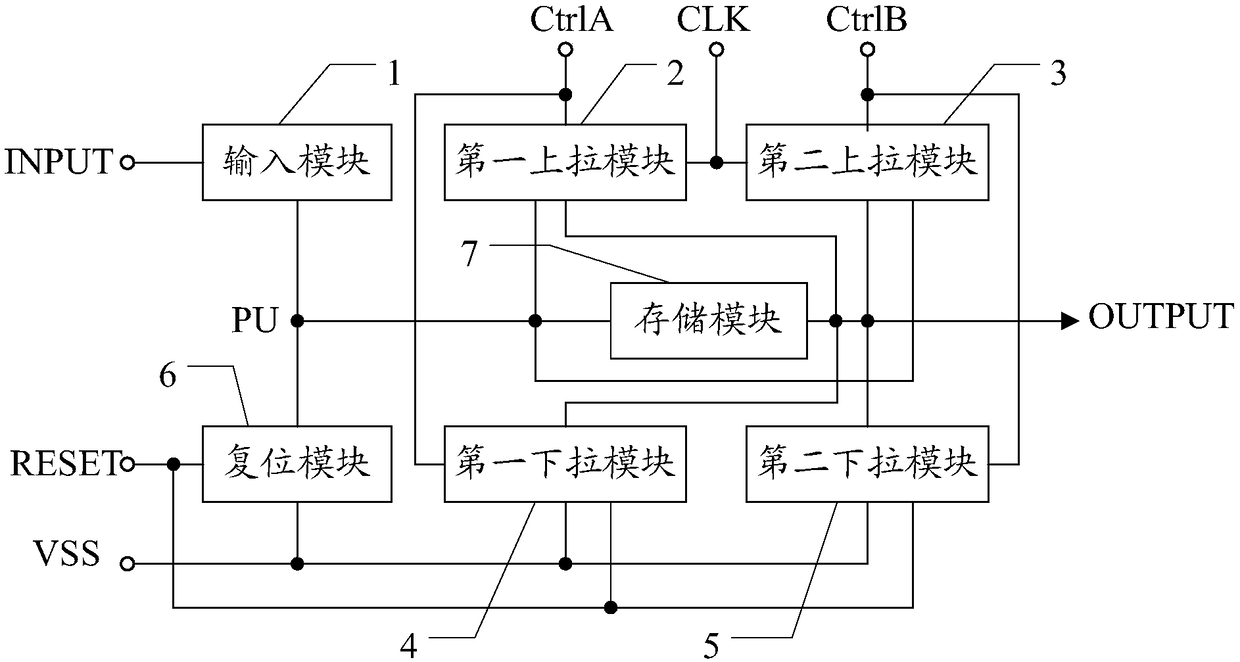

Grid electrode driving circuit and driving method thereof and display device

ActiveCN108231028AReduce the impact of the outputReduce the impactStatic indicating devicesDriver circuitControl signal

The invention provides a grid electrode driving circuit and a driving method thereof and a display device and relates to the technical field of display. A first control signal input through a first control signal end is adopted for controlling a first upward pulling module and a first downward pulling module to work, a second control signal input through a second control signal end is adopted forcontrolling a second upward pulling module and a second downward pulling module to work, and by controlling the electrical levels of the first control signal and second control signal, the first upward pulling module and the second upward pulling module are driven to alternatively work, and meanwhile the first downward pulling module and the second downward pulling module are driven to alternatively work, so that time for receiving signals of upward pulling nodes of each upward pulling module is shortened, time for receiving reset signals of each downward pulling module is also shortened, andthreshold voltage drift of a TFT is effectively suppressed. Therefore, stable electrical properties of the TFT is achieved, influences on the output of an output end are reduced, and the occurrence rate of various display failures caused by the properties of the TFT is decreased.

Owner:BOE TECH GRP CO LTD +1

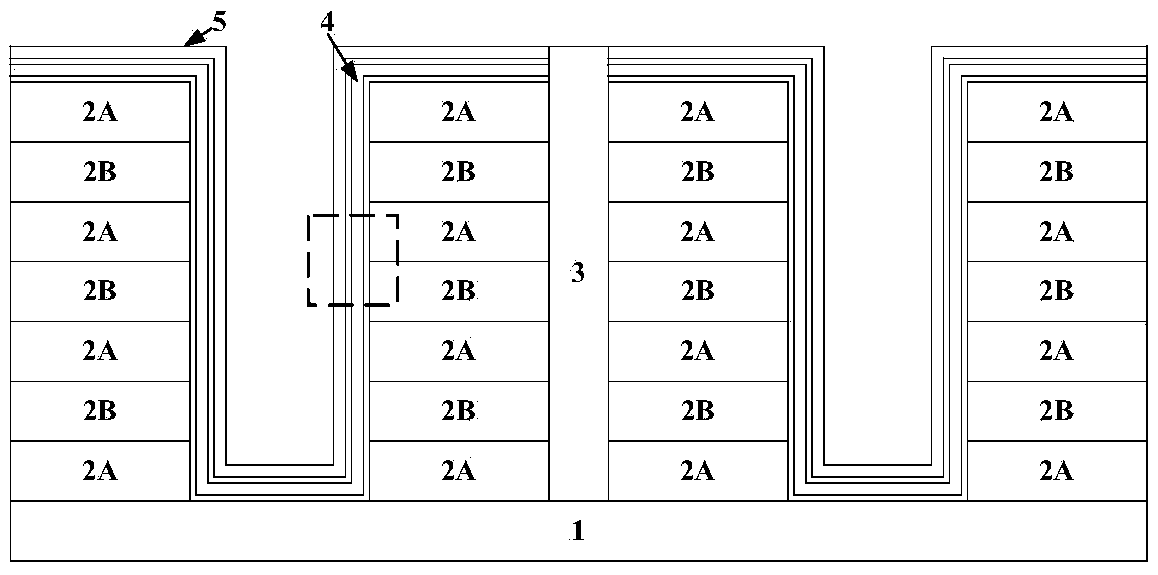

Row driving circuit for array substrate and liquid crystal display device

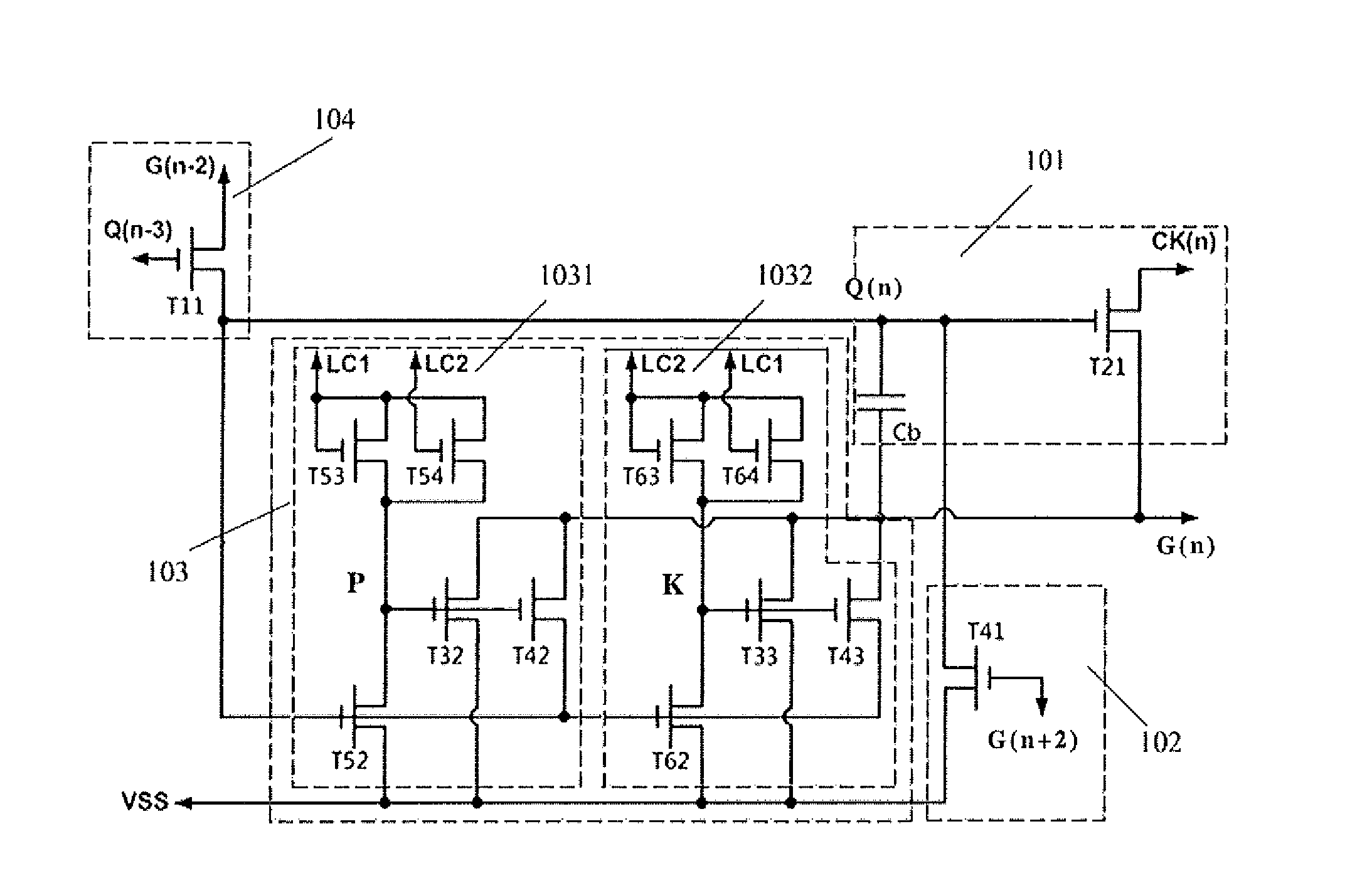

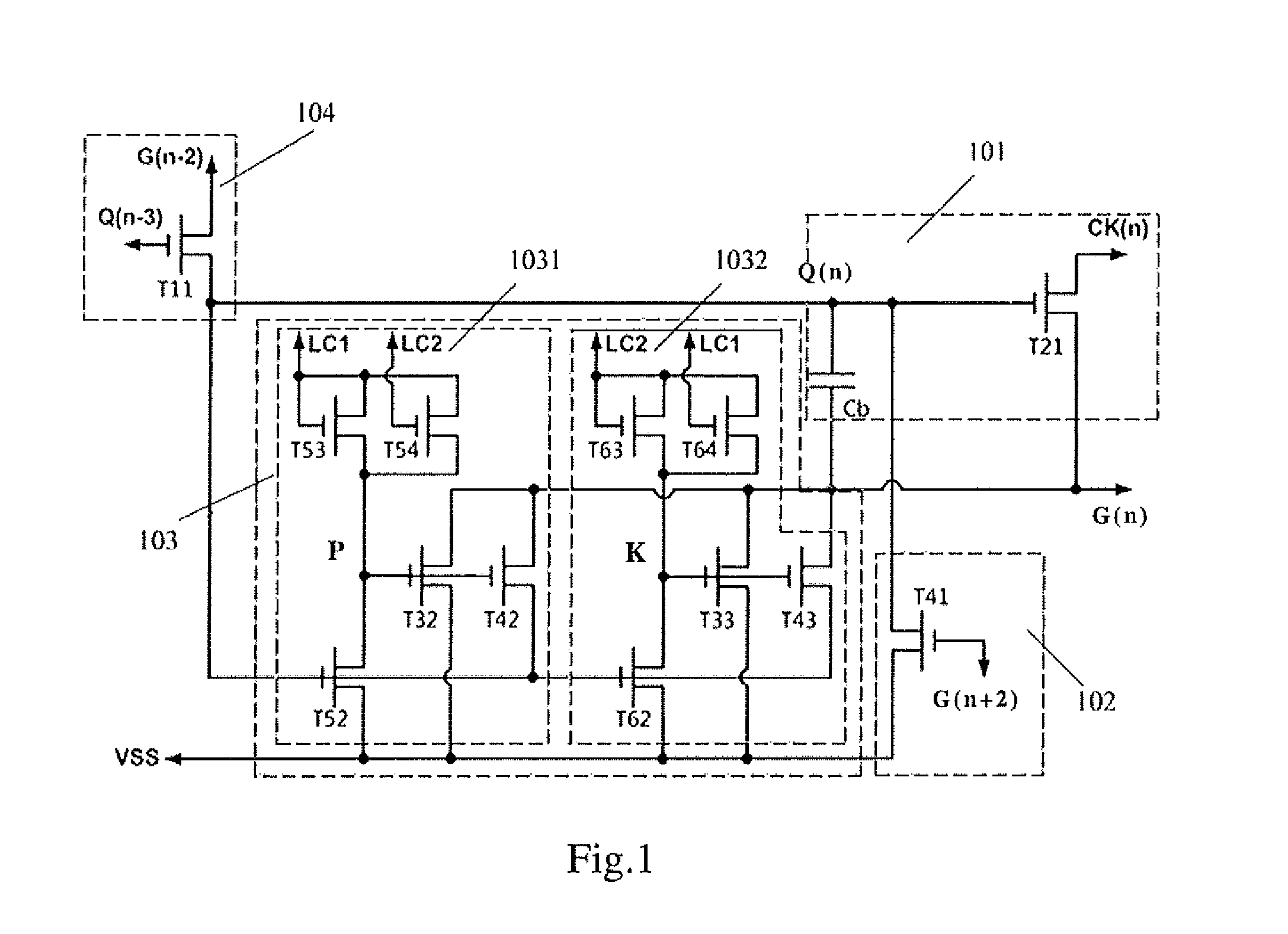

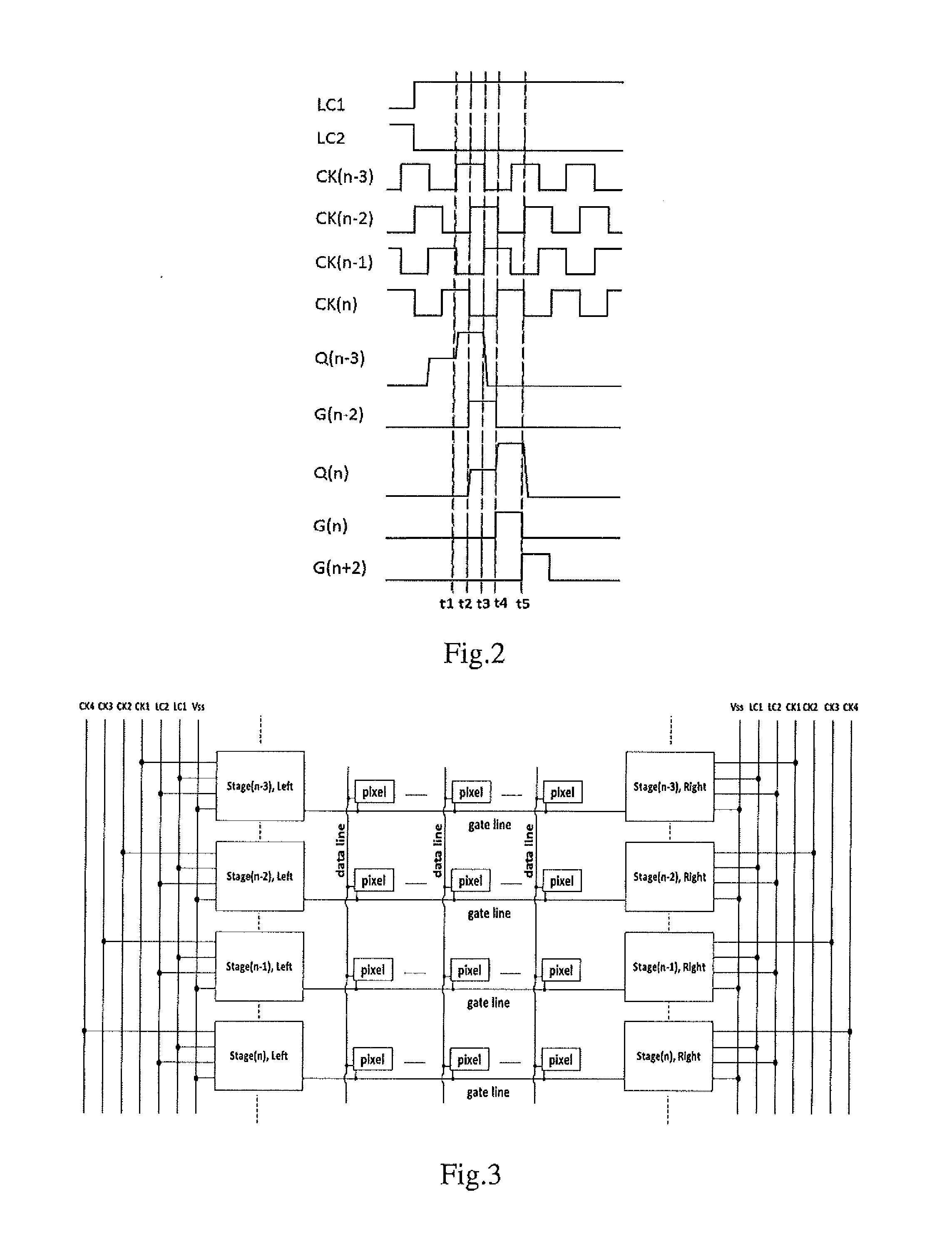

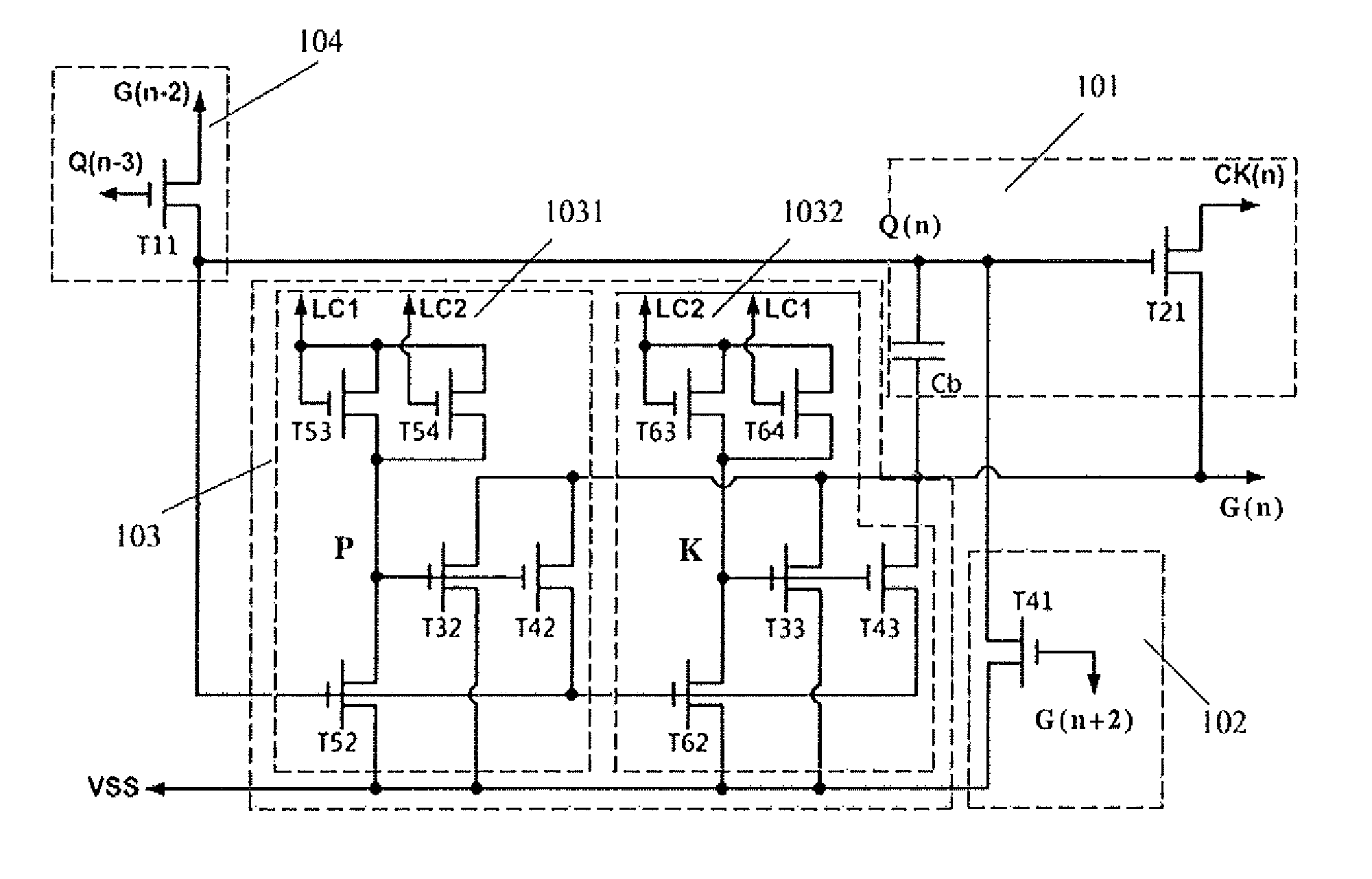

ActiveUS20150348484A1Improve stabilityAvoid Threshold Voltage DriftStatic indicating devicesLiquid-crystal displayThreshold voltage

An n-th stage array substrate row driving unit of a row driving circuit for an array substrate is provided. The n-th stage array substrate row driving unit comprises an (n−3)-th and an (n−2)-th stage signal input terminal and a pull-up controlling unit. The pull-up controlling unit is a first thin film transistor and is connected to the (n−2)-th and a (n−3)-th stage signal input terminal. A peak voltage of the (n−3)-th stage signal input terminal is twice a peak voltage of the (n−2)-th stage signal input terminal. Thus, the threshold voltage shift of the TFT elements can be avoided, and the stability of the output can be improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Row driving circuit for array substrate and liquid crystal display device

ActiveUS9214124B1Improve stabilityAvoid Threshold Voltage DriftStatic indicating devicesLiquid-crystal displayEngineering

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

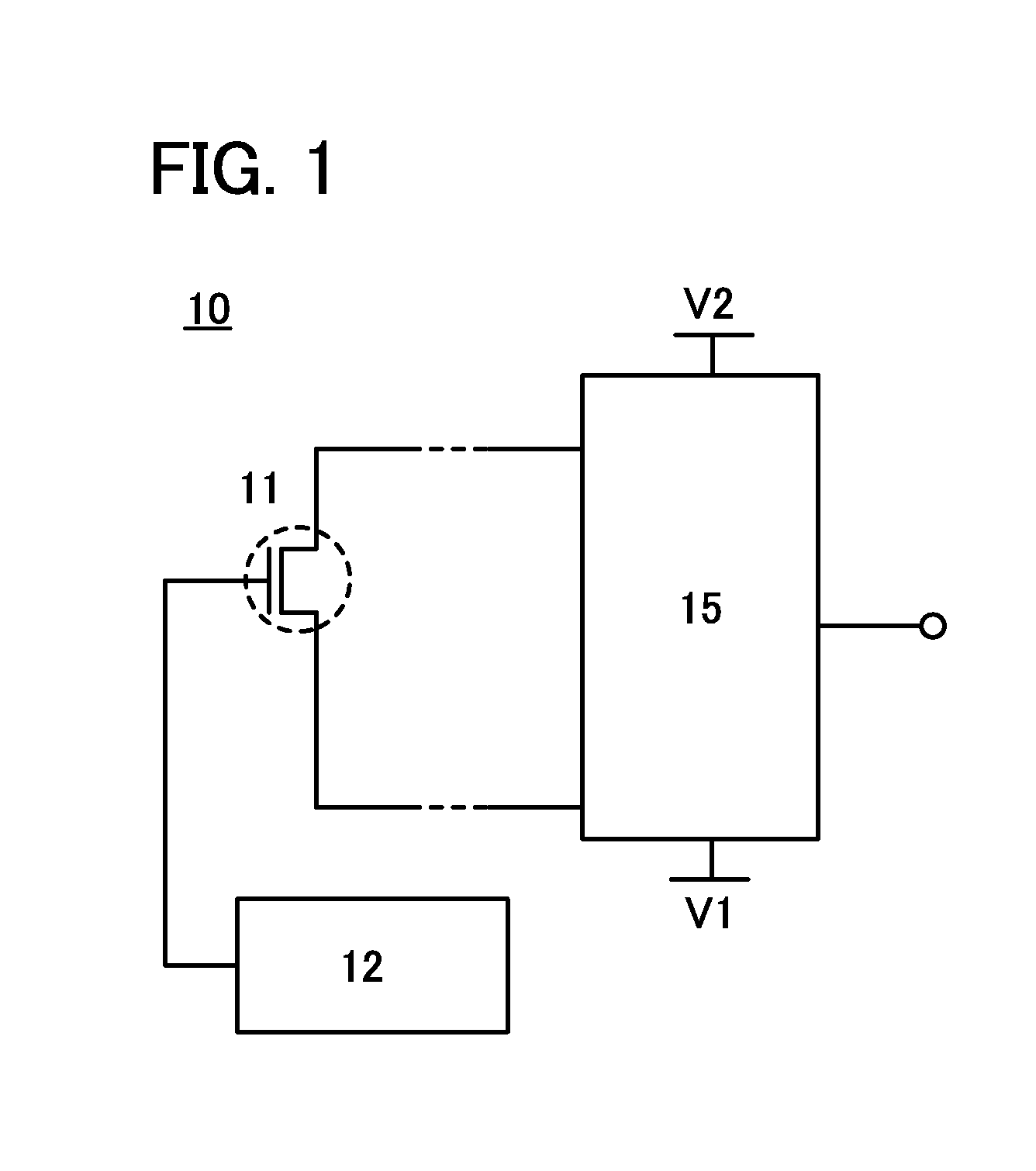

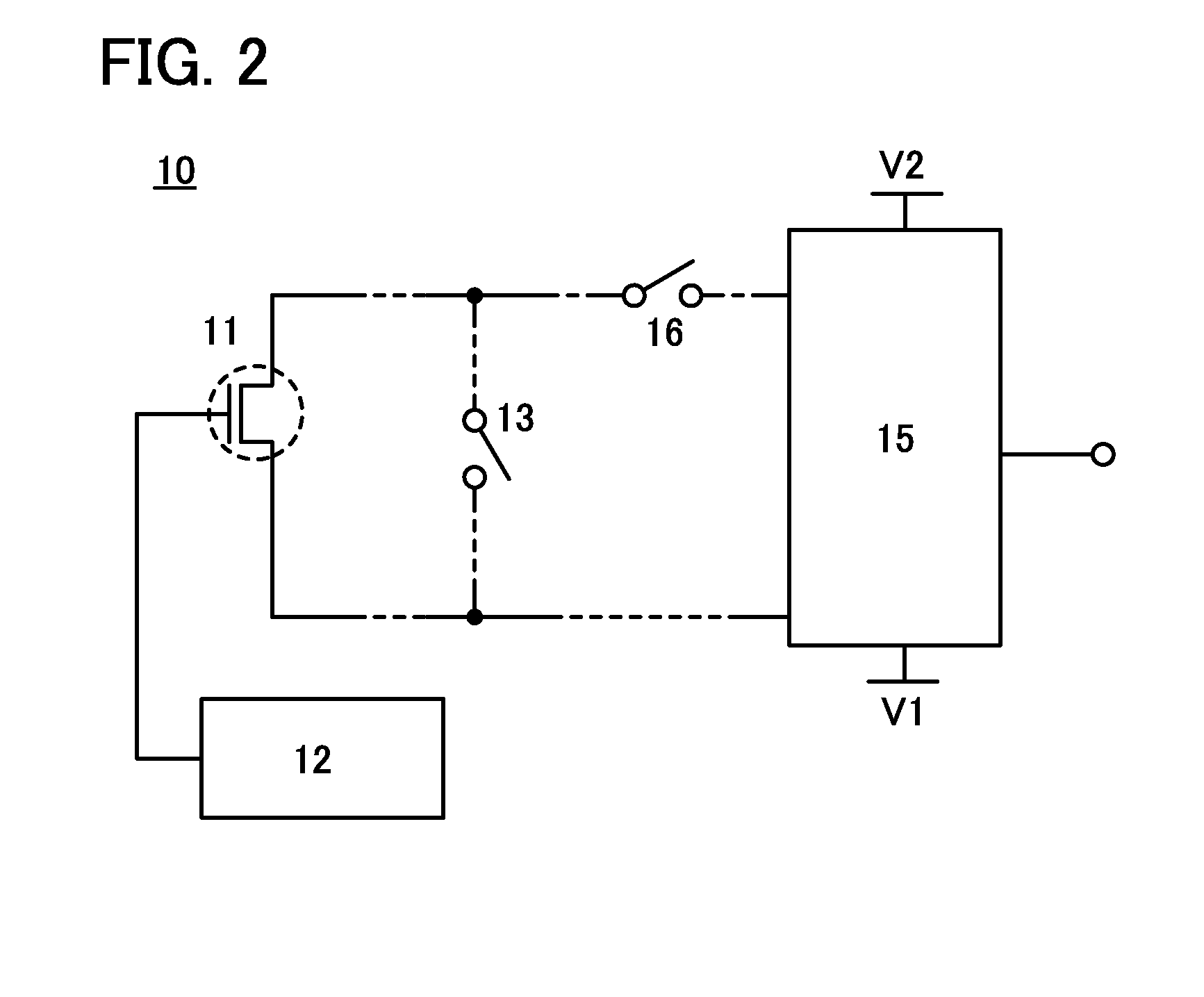

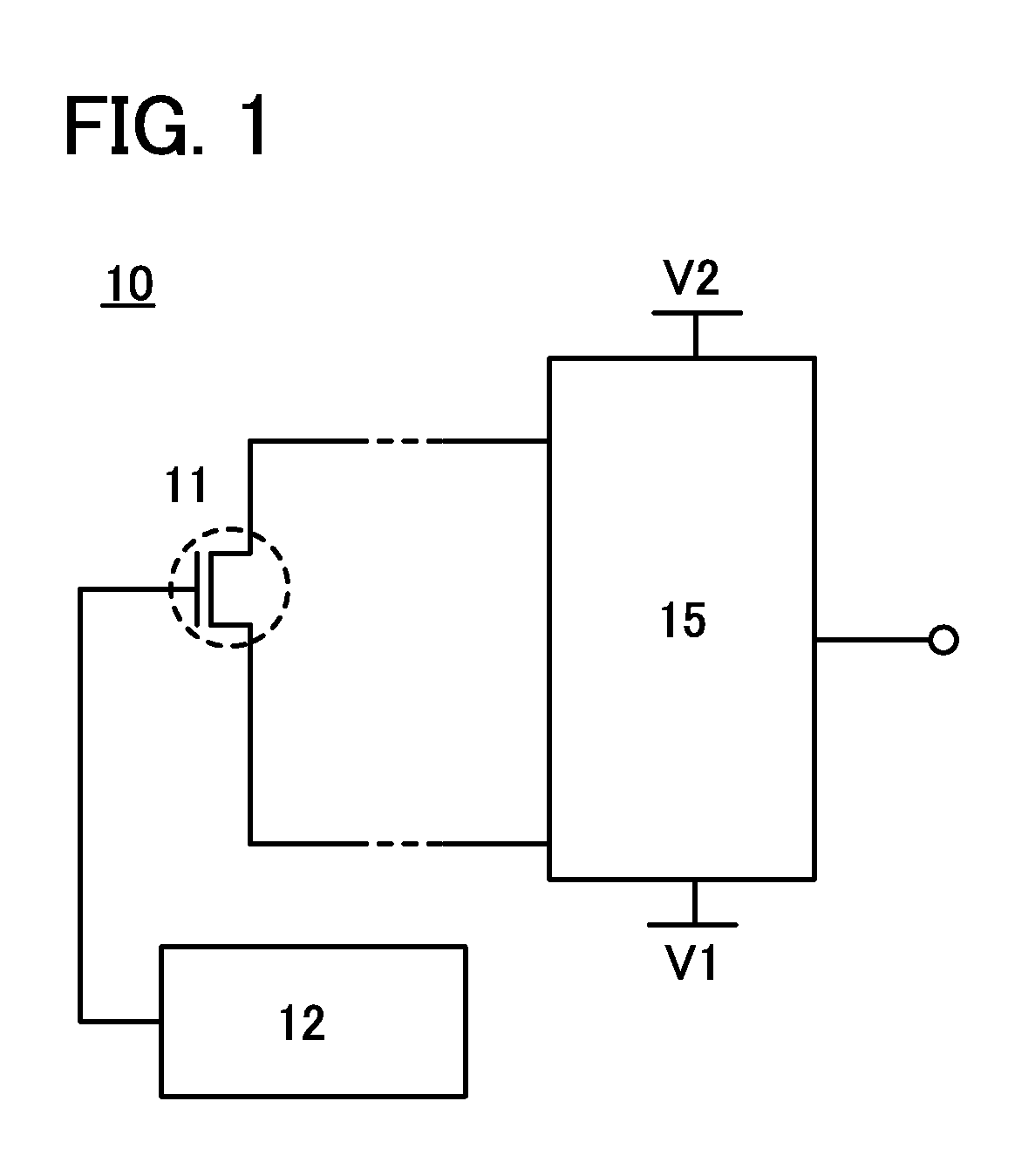

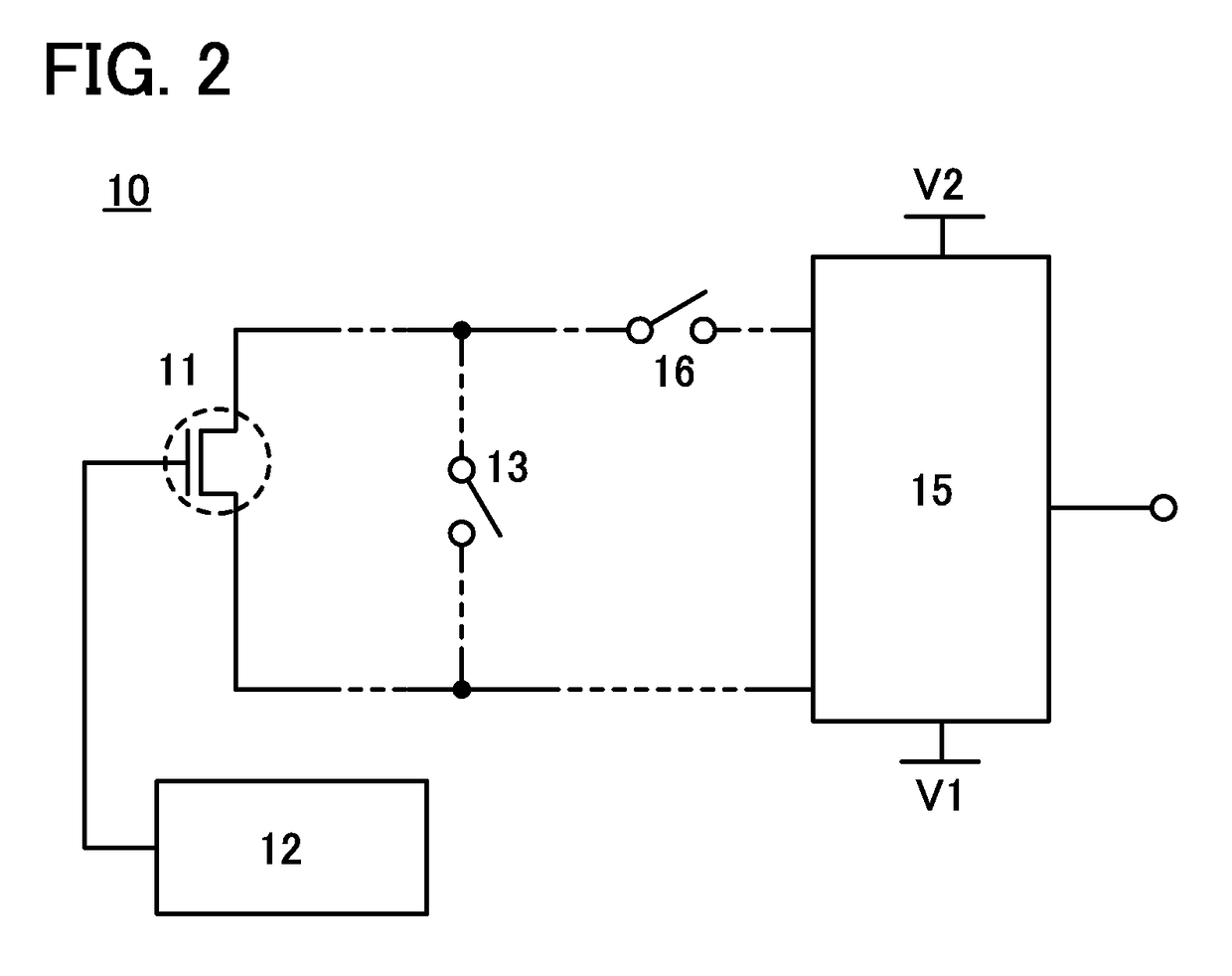

Sensor circuit and semiconductor device including sensor circuit

ActiveUS20140246667A1Improve reliabilityImprove performancePhotometry for measuring UV lightPhotometry electrical circuitsPower flowSemiconductor

A sensor circuit includes a transistor comprising an oxide semiconductor; a first circuit which supplies one of a first potential and a second potential; a first switch; a second switch; and a second circuit to which a current flowing between a source and a drain of the transistor is applied via the second switch when the first potential is applied to a gate of the transistor. The first potential is lower than a potential of the source or a potential of the drain of the transistor, and the second potential is higher than the potential of the source or the potential of the drain of the transistor. The first switch electrically connects the source and the drain of the transistor when the second potential is applied to the gate of the transistor, and electrically isolates them when the first potential is applied to the gate of the transistor.

Owner:SEMICON ENERGY LAB CO LTD

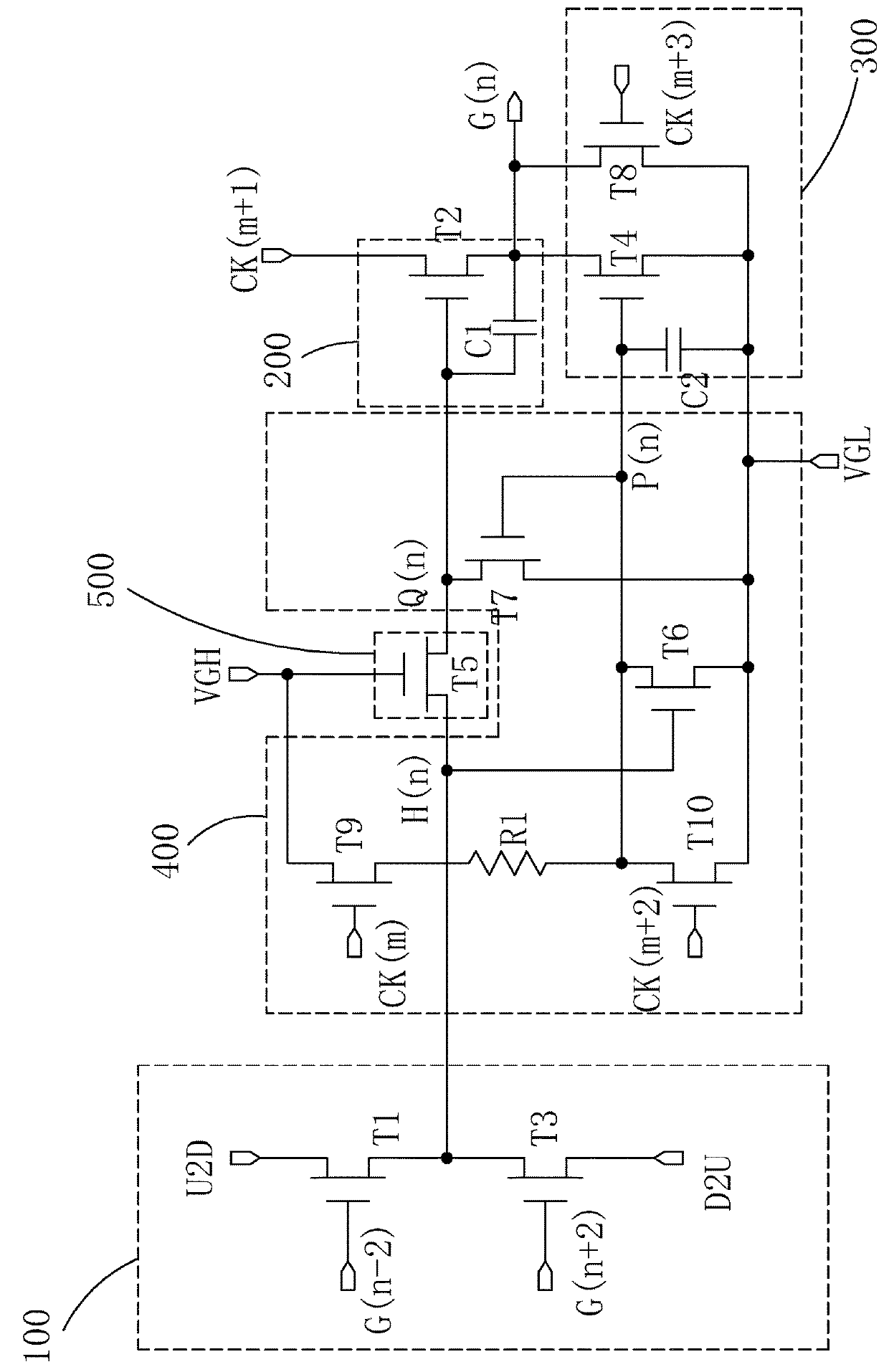

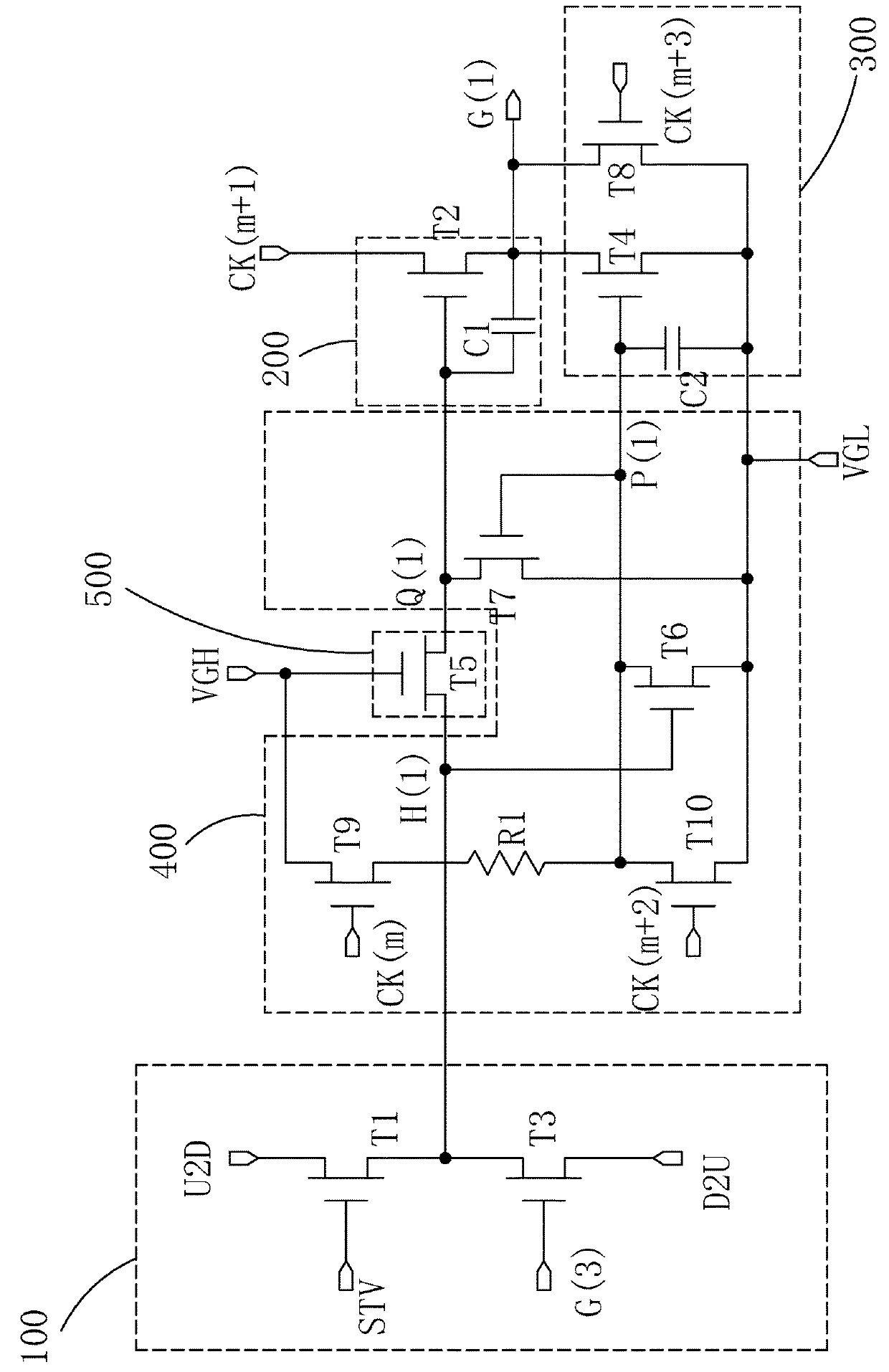

GOA circuit

ActiveUS10043477B2Guaranteed smooth progressAvoid Threshold Voltage DriftStatic indicating devicesDigital storageElectrical resistance and conductanceExtended time

The invention provides a GOA circuit, using the ninth and tenth TFTs and the resistor to control the voltage level of the third node, wherein ninth TFT having the gate connected to the m-th clock signal, the source connected to the first constant voltage, and the drain connected to one end of the resistor; the tenth TFT having the gate connected to the (m+2)-th clock signal, the source connected to the second constant voltage, and the drain connected to the other end of the resistor. Through the m-th and the (m+2)-th clock signal to control the ninth and the tenth TFTs to become conductive alternately, the present invention can charge and discharge the third node regularly to prevent the threshold voltage shift of the key TFT because the third node stays high for extended time, and ensure the stability of GOA circuit.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Method for manufacturing a semiconductor device

ActiveUS20060141690A1Avoid Threshold Voltage DriftDecrease in drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesDopantDevice material

Provided is a method for manufacturing a semiconductor device comprising forming a device isolation layer on a semiconductor substrate; forming gate insulating layers on the upper part of the semiconductor substrate having the device isolation layers formed thereon; forming an undoped layer for a gate electrode; implanting mixed dopant ions consisting of at least two dopant ions containing 11B ions into the undoped layer, utilizing an ion-implantation mask; and heat-treating the mixed dopant ion-implanted layer.

Owner:SK HYNIX INC

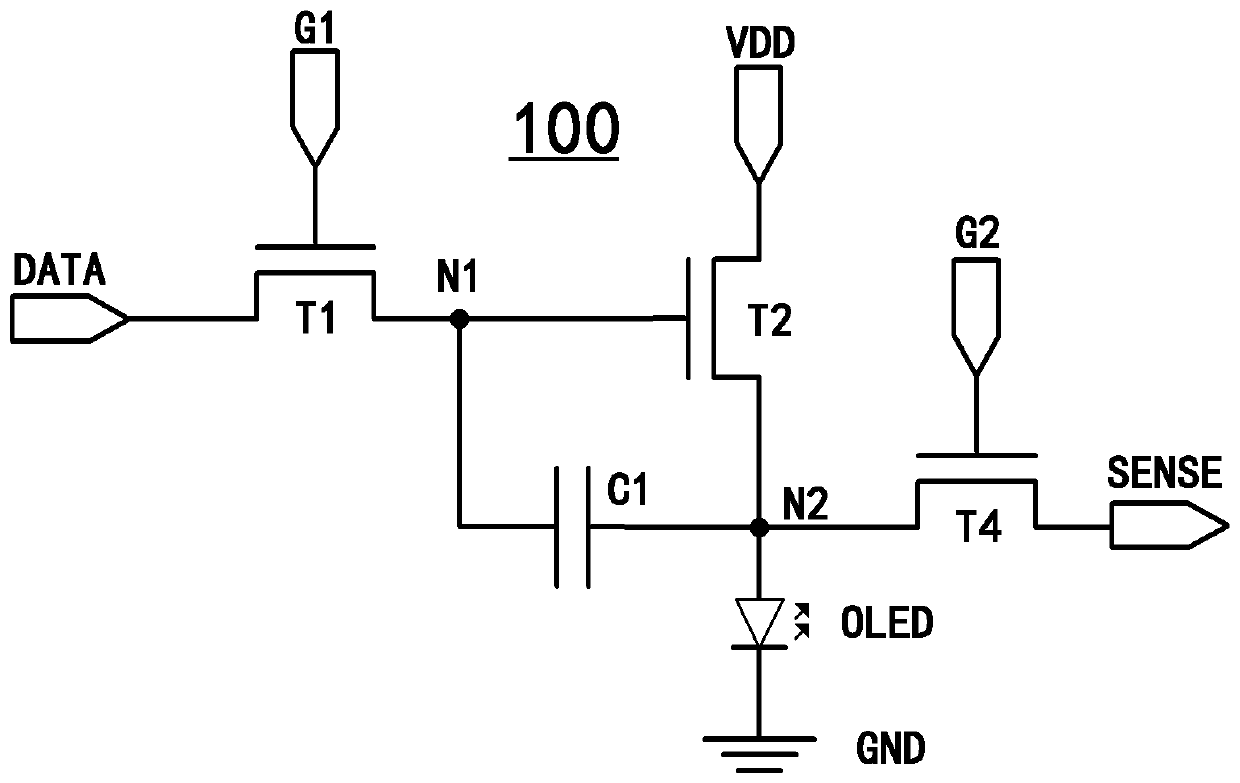

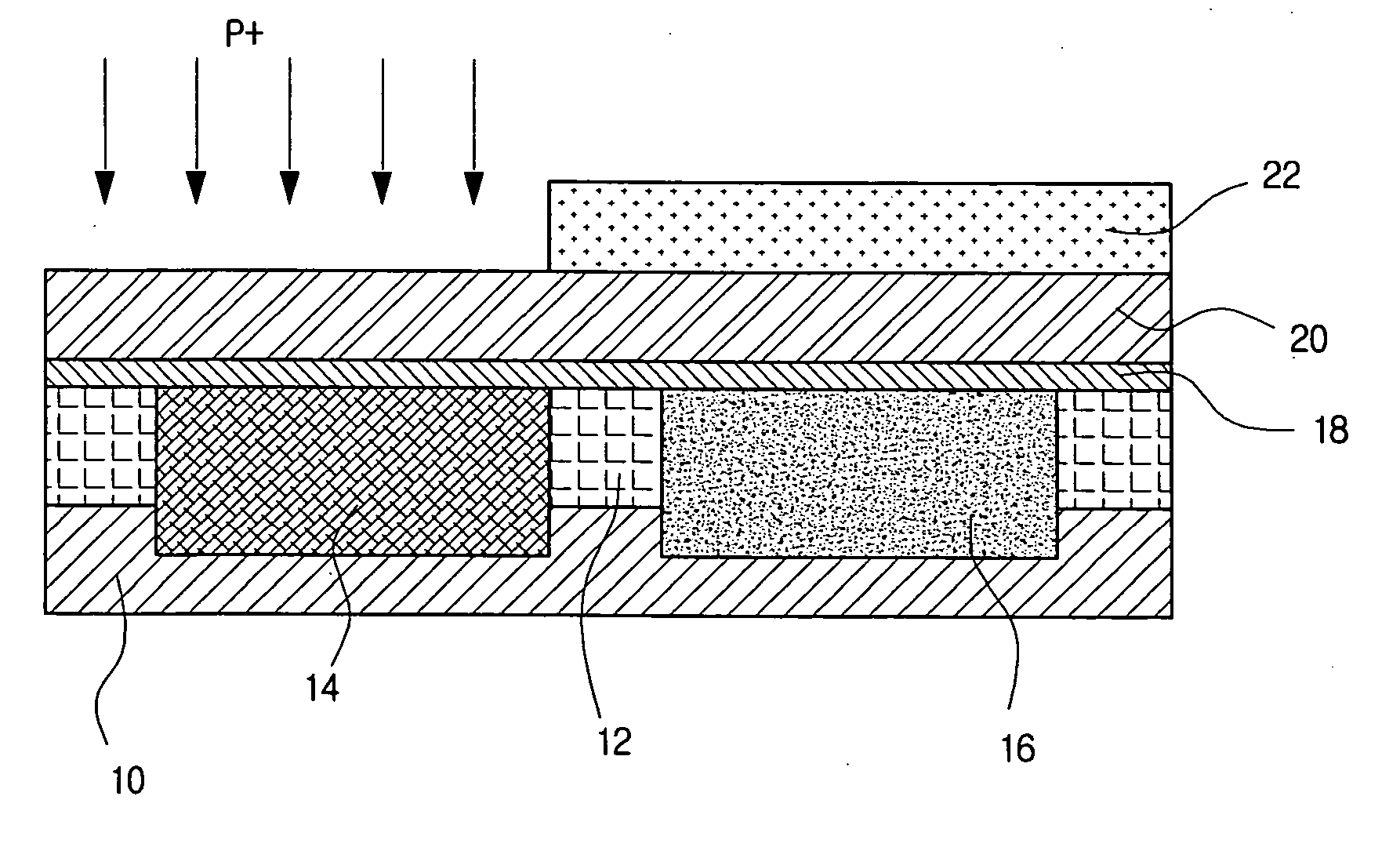

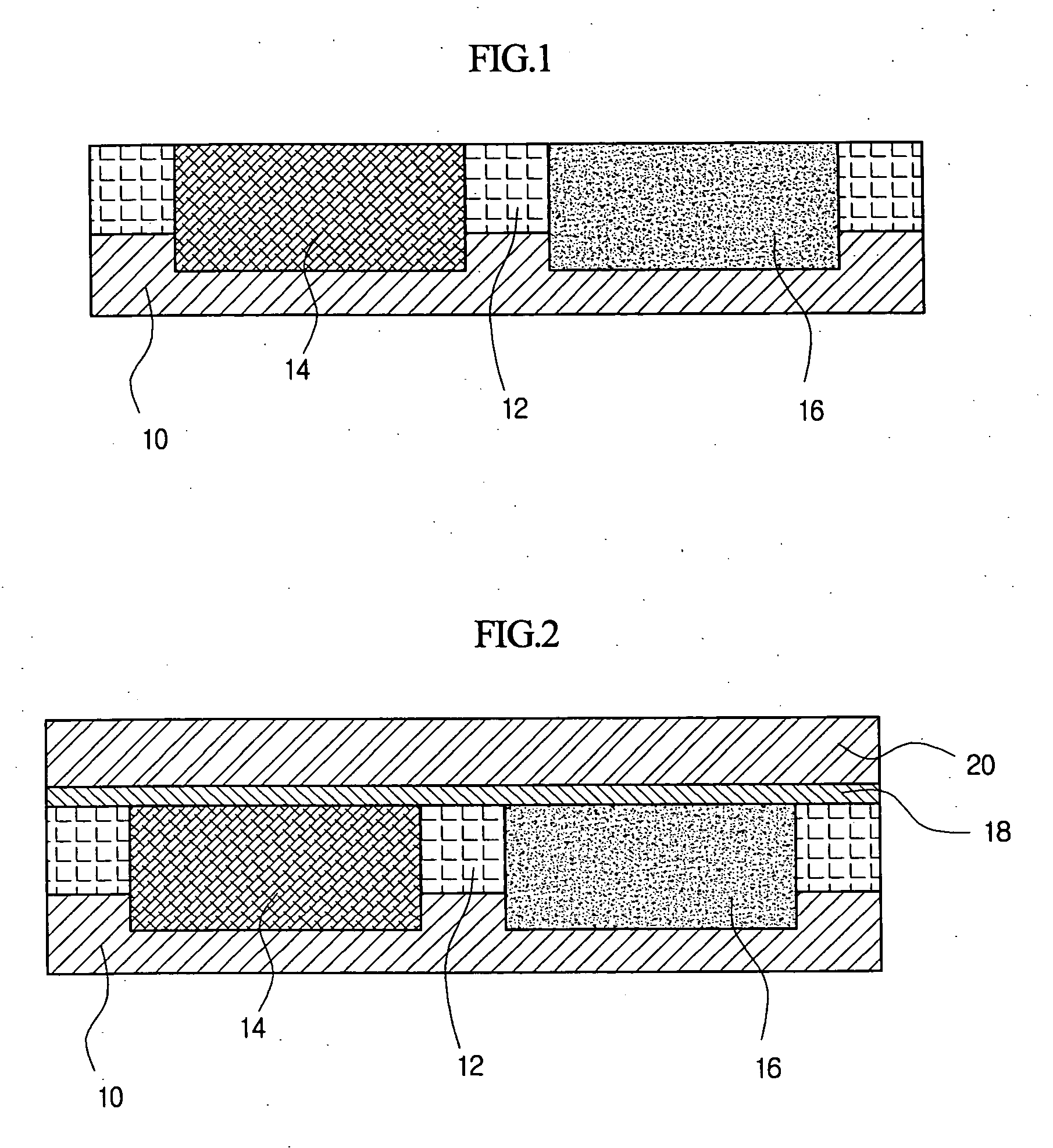

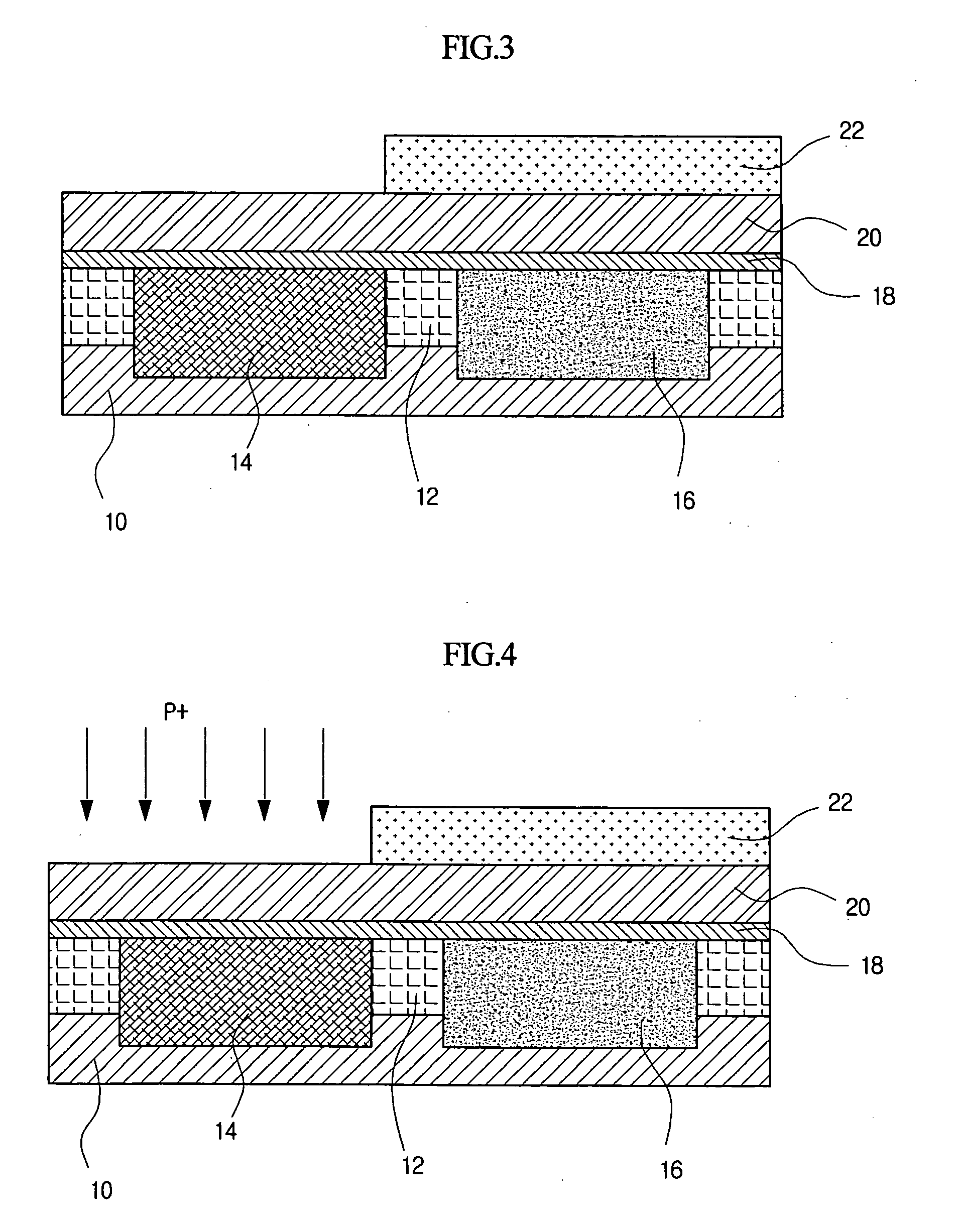

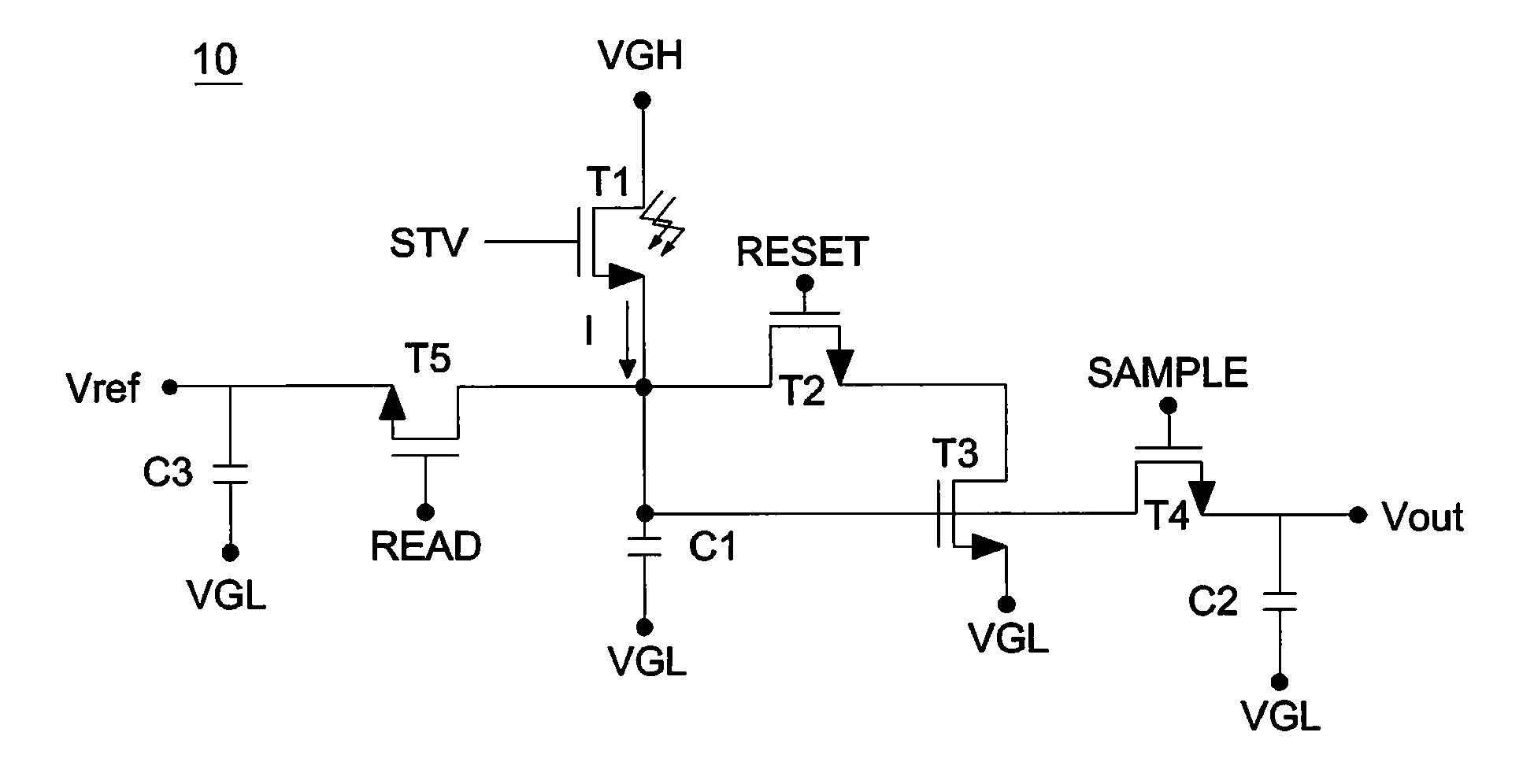

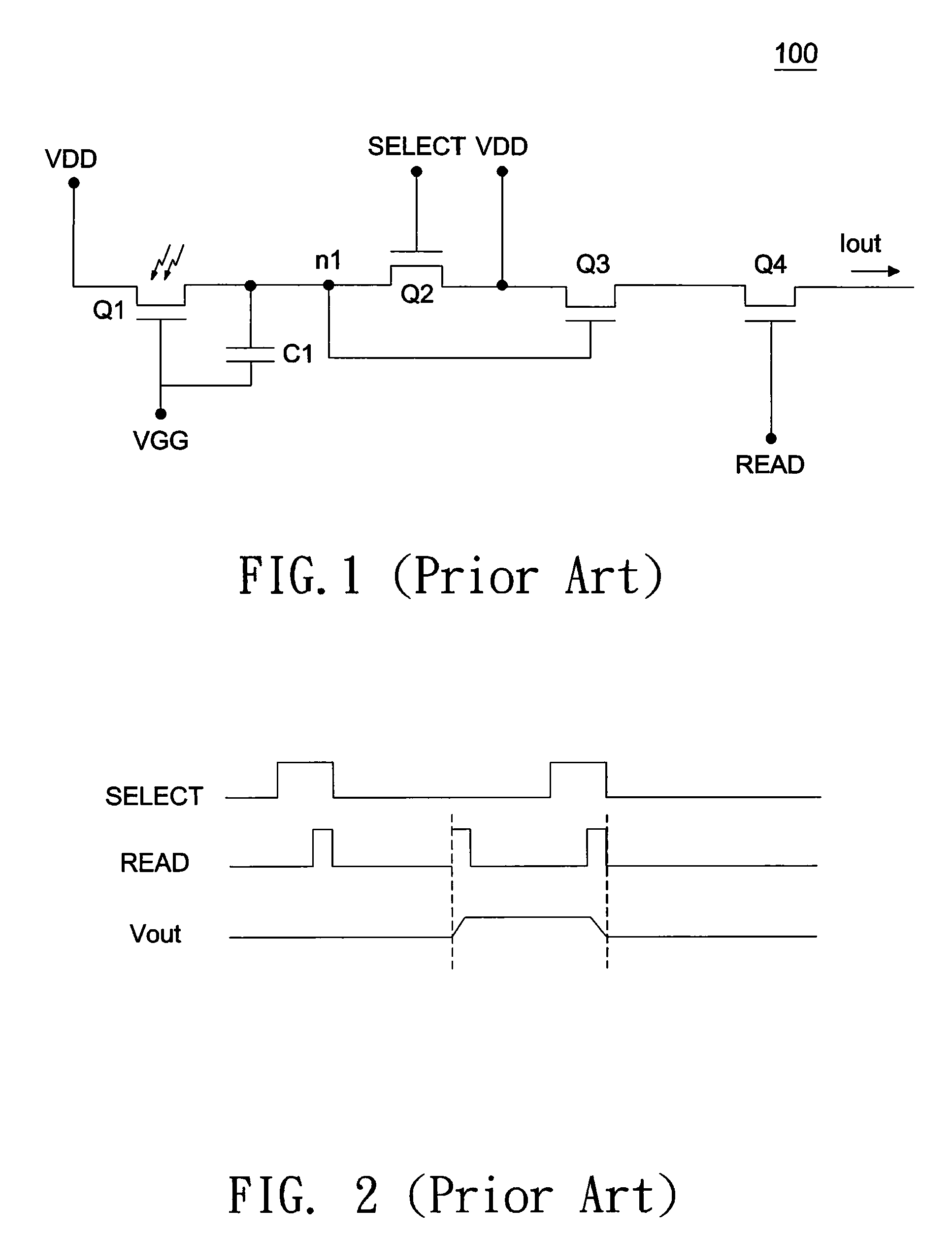

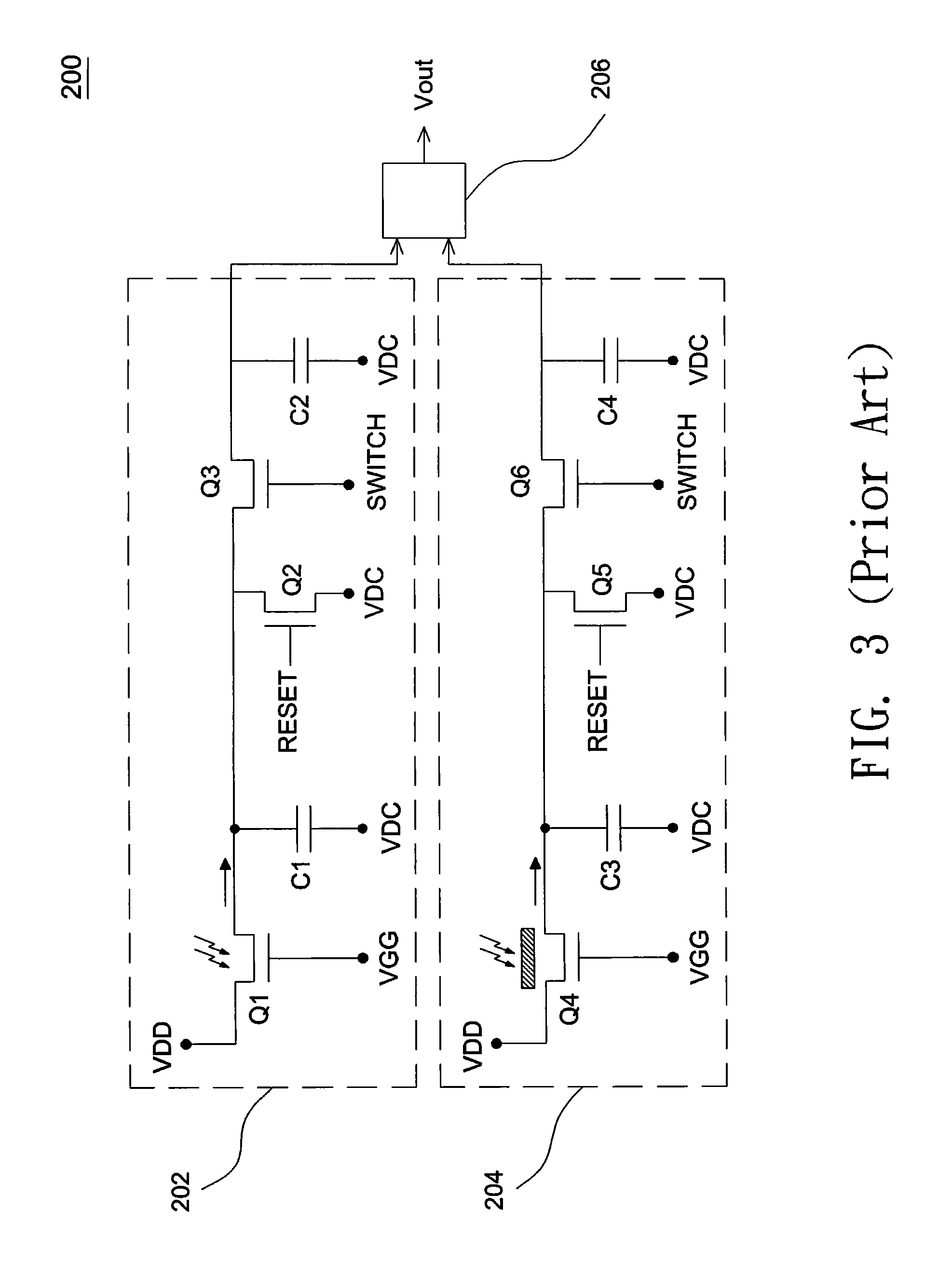

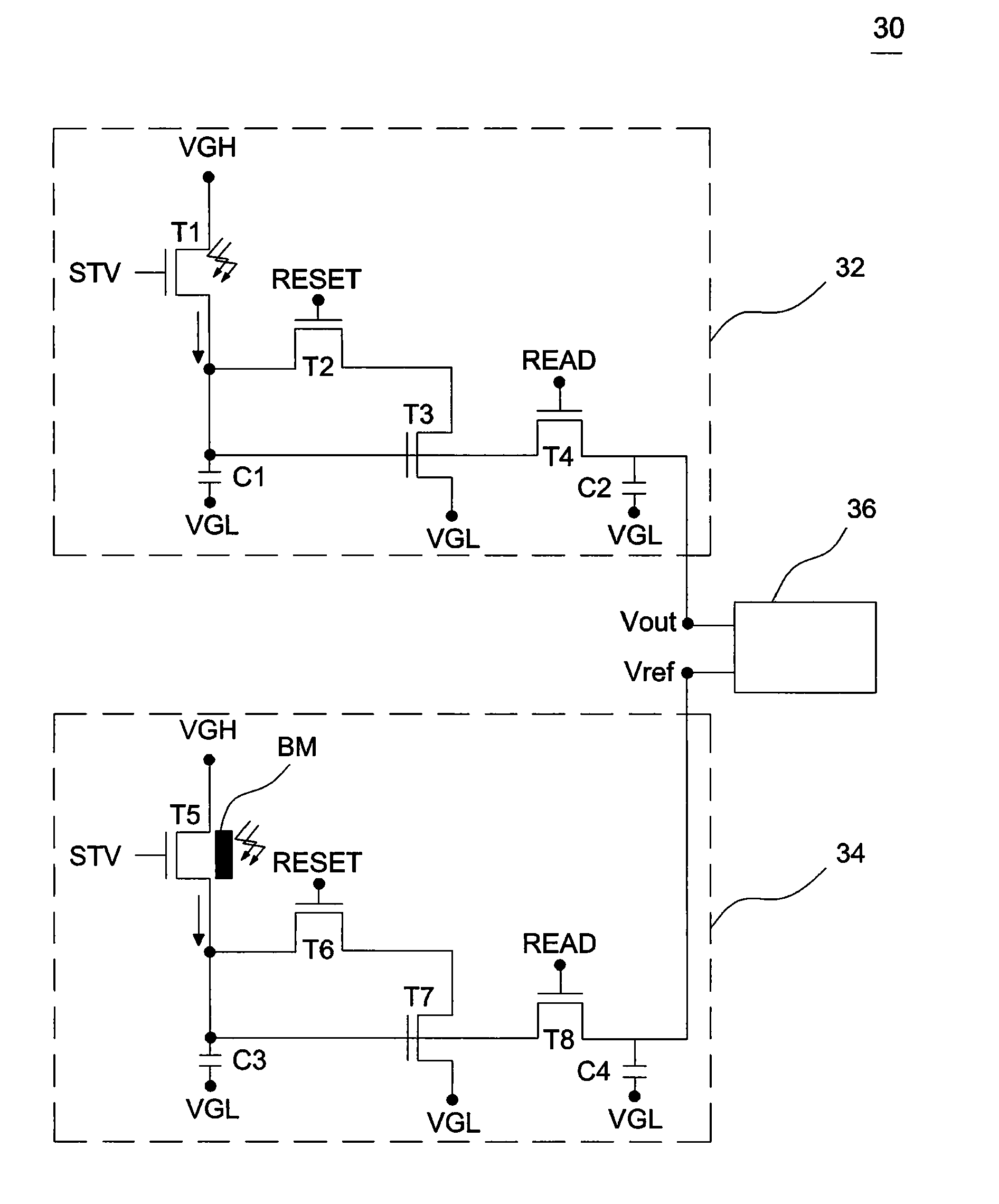

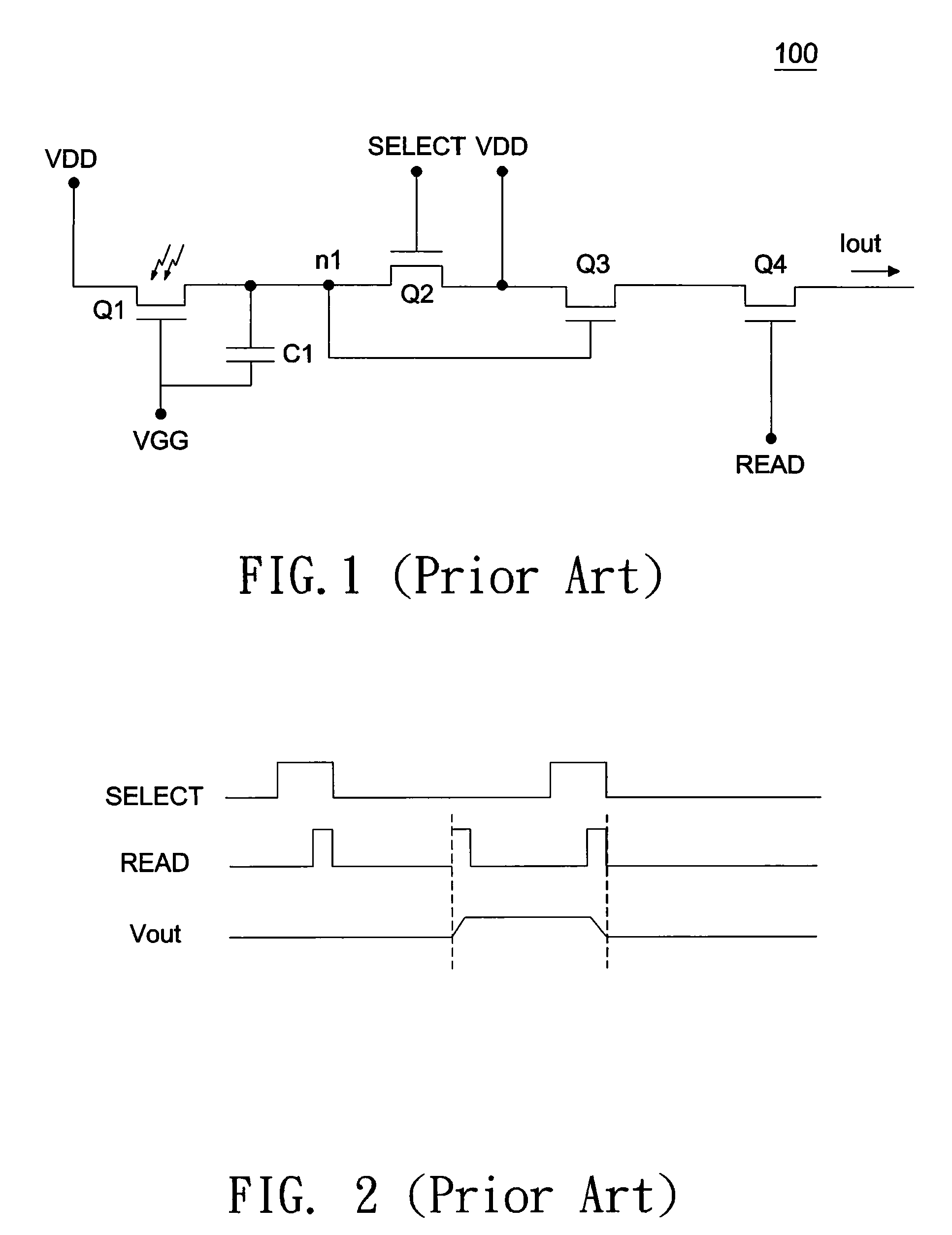

Photosensor for display device

ActiveUS20090207157A1Wide sensing rangeExtended service lifeCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceVoltage reference

A photosensor for a display device includes a light receiver, a reset unit, and a sample unit. The light receiver is used for receiving ambient light to generate a photovoltage. The light receiver includes a first transistor and a first conversion unit that transforms the output of the first transistor into the photovoltage. The reset unit is used for providing an initiated reference voltage in response to a reset signal and includes a second transistor and a third transistor that are connected with each other, where the first conversion unit is discharged through the third transistor to obtain the initiated reference voltage when the second transistor is turned on. The sample unit is used for outputting the photovoltage in respond to a sample signal, the sample unit comprising a fourth transistor in respond to the sample signal and a second conversion unit that transforms the output of the fourth transistor into the photovoltage.

Owner:WINTEK CORP

Photosensor for display device

ActiveUS8081176B2Wide sensing rangeExtended service lifeCathode-ray tube indicatorsInput/output processes for data processingDisplay deviceVoltage reference

A photosensor for a display device includes a light receiver, a reset unit, and a sample unit. The light receiver is used for receiving ambient light to generate a photovoltage. The light receiver includes a first transistor and a first conversion unit that transforms the output of the first transistor into the photovoltage. The reset unit is used for providing an initiated reference voltage in response to a reset signal and includes a second transistor and a third transistor that are connected with each other, where the first conversion unit is discharged through the third transistor to obtain the initiated reference voltage when the second transistor is turned on. The sample unit is used for outputting the photovoltage in respond to a sample signal, the sample unit comprising a fourth transistor in respond to the sample signal and a second conversion unit that transforms the output of the fourth transistor into the photovoltage.

Owner:WINTEK CORP

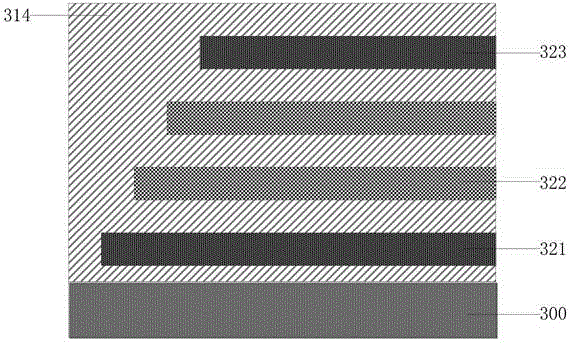

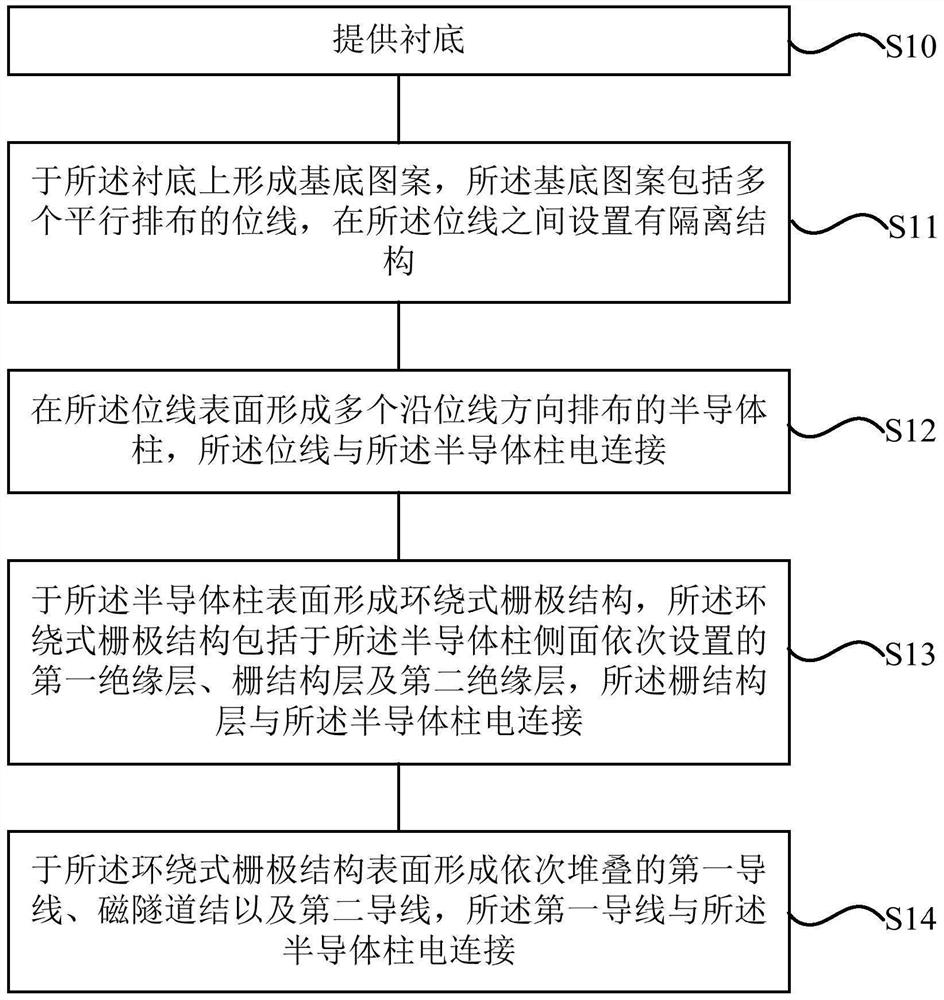

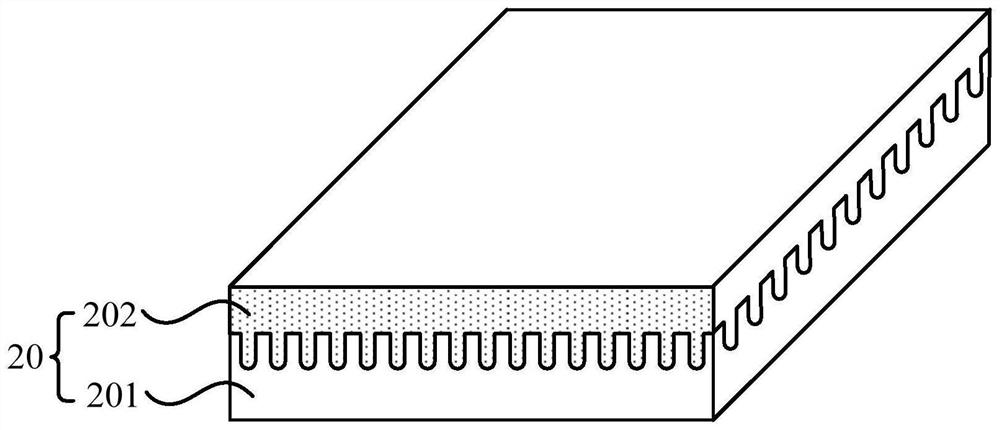

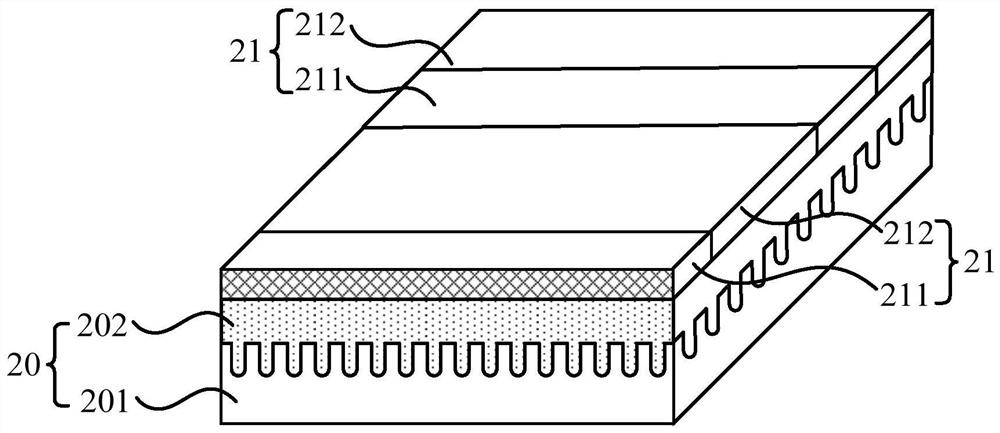

Semiconductor structure and preparation method thereof

PendingCN114709168AImprove performanceMinimization requirementsSemiconductor/solid-state device detailsMagnetic-field-controlled resistorsBit lineSemiconductor structure

The invention provides a semiconductor structure and a preparation method thereof. The preparation method of the semiconductor structure provided by the invention comprises the following steps: providing a substrate; a base pattern is formed on the substrate, the base pattern comprises a plurality of bit lines arranged in parallel, and isolation structures are arranged among the bit lines; forming a plurality of semiconductor columns arranged along the direction of the bit line on the surface of the bit line, wherein the bit line is electrically connected with the semiconductor columns; a surrounding gate structure is formed on the surface of the semiconductor column, the surrounding gate structure comprises a first insulating layer, a gate structure layer and a second insulating layer which are sequentially arranged on the side face of the semiconductor column, and the gate structure layer is electrically connected with the semiconductor column; and forming a first wire, a magnetic tunnel junction and a second wire which are stacked in sequence on the surface of the surrounding gate structure, wherein the first wire is electrically connected with the semiconductor column. The performance of the semiconductor structure is greatly improved, and the requirement for miniaturization is met.

Owner:CHANGXIN MEMORY TECH INC

GOA circuit and display panel

ActiveCN112634810AImprove the display effectAvoid Threshold Voltage DriftStatic indicating devicesControl engineeringHemt circuits

The invention provides a GOA circuit and a display panel, and the GOA circuit enables a first pull-up control module and a first pull-up module to work at the same time or enables a second pull-up control module and a second pull-up module to work at the same time under the control of a first low-frequency signal and a second low-frequency signal. Therefore, the first pull-up control module and the second pull-up control module can work alternately, and the first pull-up module and the second pull-up module can work alternately. Compared with a pull-up control module and a pull-up module of a GOA circuit in the prior art, the first pull-up control module and the first pull-up module in the GOA circuit, and the second pull-up control module and the second pull-up module in the GOA circuit only need to work for a part of time; therefore, the problem of threshold voltage drift caused by long-time work of the pull-up control module and the thin film transistor of the pull-up module can be suppressed, the GOA circuit failure caused by abnormal output of the scanning signal is avoided, the display effect of the display panel is improved, and the abnormal phenomenon of a picture is prevented.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Silicon-on-insulator (SOI) six-transistor static random access memory (SRAM) unit and fabrication method thereof

InactiveCN106952917AImprove noise immunityReduce the effective areaSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectTunnel diode

The invention provides a silicon-on-insulator (SOI) six-transistor static random access memory (SRAM) unit and a fabrication method thereof. The unit comprises a first phase inverter, a second phase inverter and an acquisition tube, wherein the first phase inverter comprises a first P-channel metal oxide semiconductor (PMOS) transistor and a first N-channel metal oxide semiconductor (NMOS) transistor, the second phase converter comprises a second PMOS transistor and a second NMOS transistor, and the acquisition tube comprises a third NMOS transistor and a fourth NMOS transistor. In the SOI six-transistor SRAM unit, tunneling diode structures are embedded into sources of the four transistors forming the first phase inverter and the second phase inverter, power consumption leakage and threshold voltage drift of the transistors caused by a floating body effect and a parasitic triode effect in a partially-depleted (PD) SOI device can be effectively suppressed on the condition of no increase on device area, and the noise resistant capability of the unit is improved; moreover, the fabrication method also has the advantages of simple manufacturing process and the like, and is completely compatible with an existing logic process; and a central symmetric structure and a sharing structure between units are employed in the unit, so that a storage array is convenient to form, and the design period of an SRAM chip is favorably shortened.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Pixel driving circuit and driving method thereof, display panel and display device

ActiveCN110047435BAvoid Threshold Voltage DriftImprove yieldStatic indicating devicesDisplay deviceData signal

Owner:BOE TECH GRP CO LTD

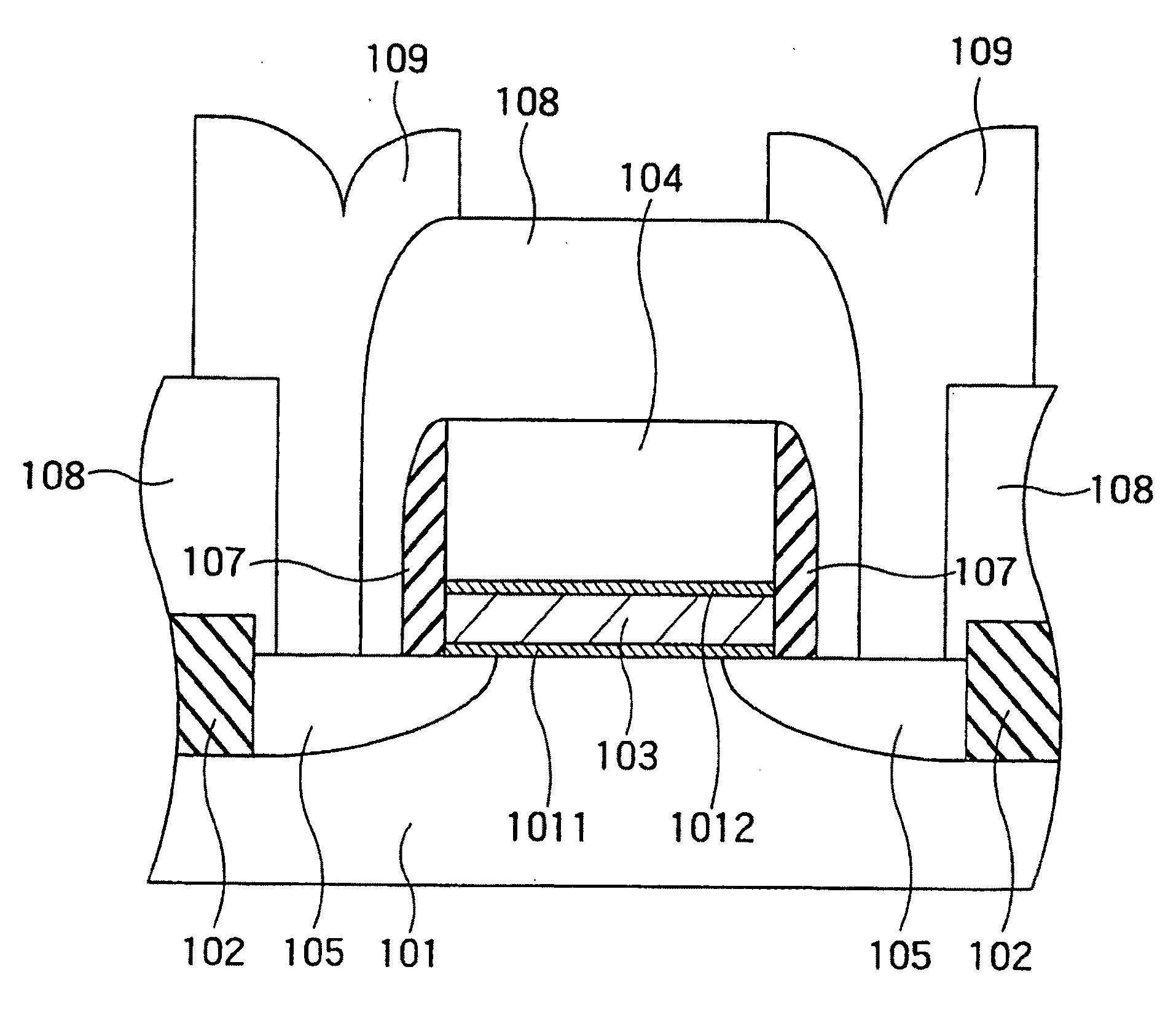

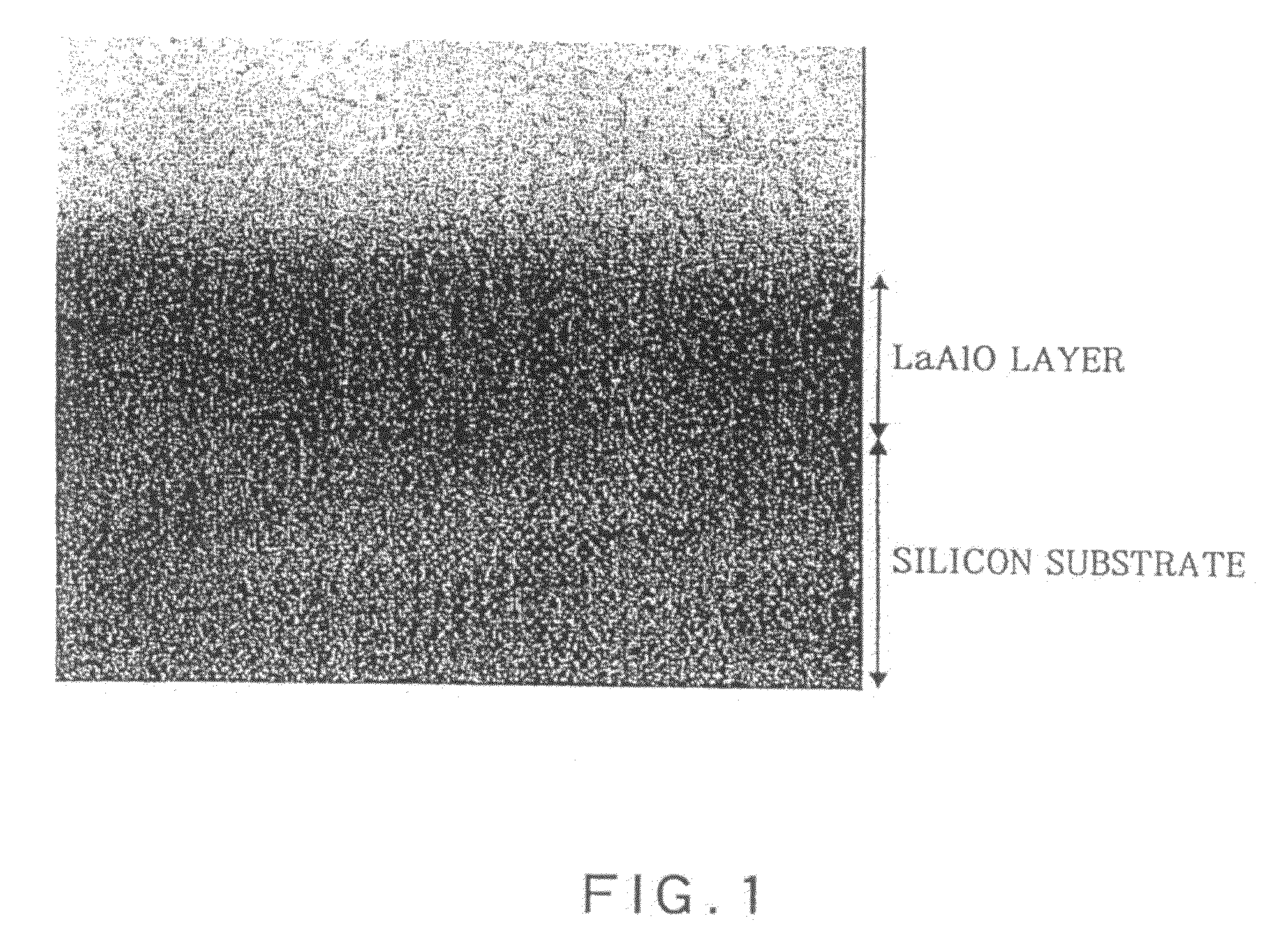

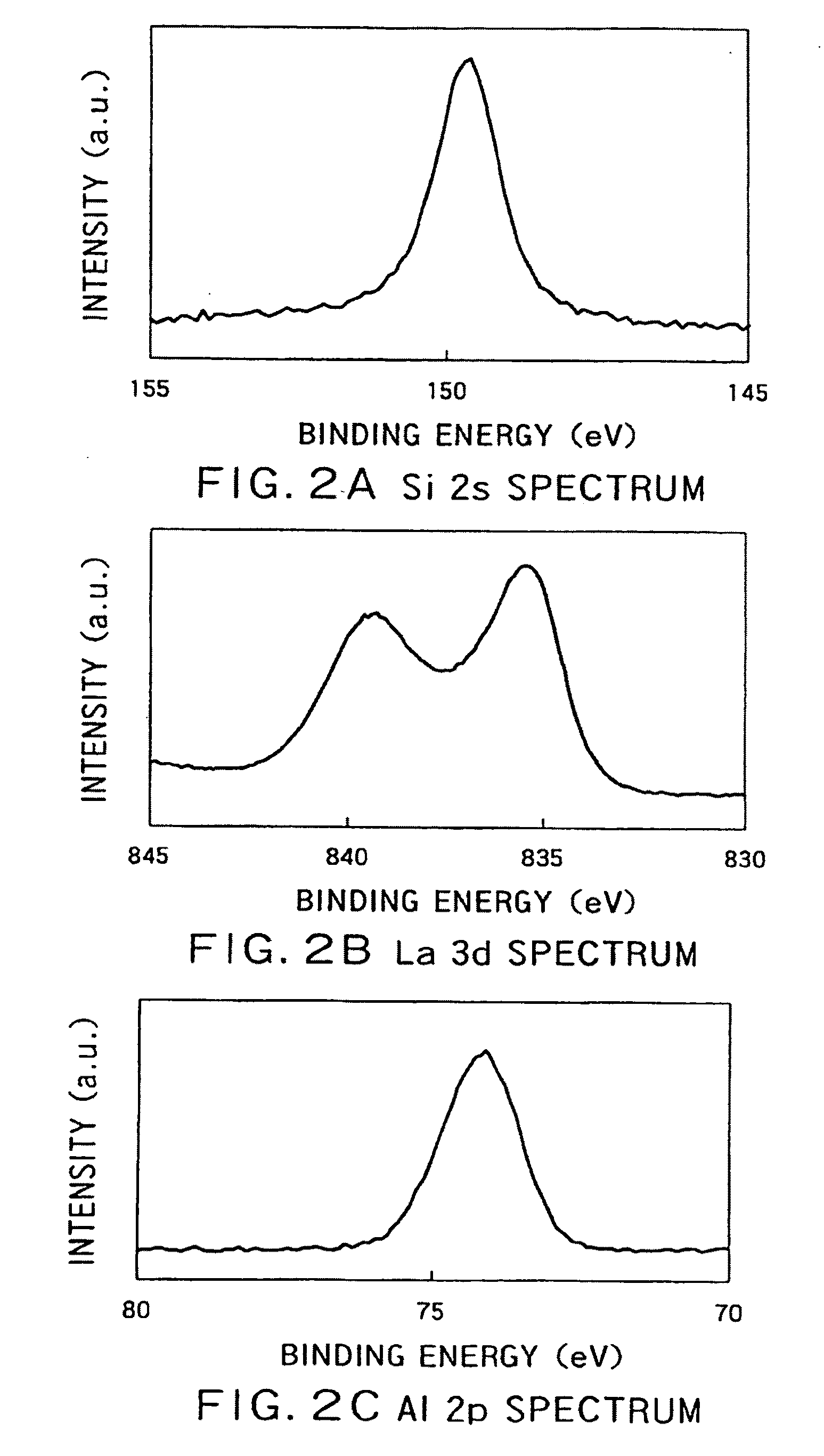

Semiconductor device and method for manufacturing the same

InactiveUS20080318404A1Inhibitory responseSuppressing formation of the low dielectric layerSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerSemiconductor

A semiconductor device includes a silicon substrate; an insulation layer formed on the silicon substrate, the insulation layer containing an oxide of an element of at least one kind selected from at least Hf, Zr, Ti and Ta; an electrode formed on the insulation layer; and a metal oxide layer containing La and Al, the metal oxide layer being provided at at least one of an interface between the silicon substrate and the insulation layer and an interface between the insulation layer and the electrode.

Owner:TOSHIBA MEMORY CORP

A display panel and its manufacturing method, and a display device

ActiveCN107248373BShorten production timeAvoid Threshold Voltage DriftSolid-state devicesIdentification meansUltraviolet lightsDisplay device

The invention provides a display panel, a manufacturing method, and a display device, which relate to the field of display technology, and can avoid adverse effects of ultraviolet light on polysilicon layers, thereby avoiding the problem of threshold voltage drift of thin film transistors. Among them, the display panel includes a base substrate, a thin film transistor formed on the base substrate, and a light emitting structure formed on the side of the thin film transistor facing away from the base substrate; wherein, the thin film transistor includes a light emitting structure located between the light emitting structure and the base substrate A polysilicon layer; a light-shielding layer for blocking ultraviolet light is formed between the polysilicon layer and the light-emitting structure, and the orthographic projection of the light-shielding layer on the base substrate covers the orthographic projection of the polysilicon layer on the base substrate. The above-mentioned display panel is used to realize screen display.

Owner:BOE TECH GRP CO LTD

Sensor circuit and semiconductor device including sensor circuit

ActiveUS9647152B2High sensitivityWide temperature rangePhotometry for measuring UV lightPhotometry electrical circuitsEngineeringSemiconductor

A sensor circuit includes a transistor comprising an oxide semiconductor; a first circuit which supplies one of a first potential and a second potential; a first switch; a second switch; and a second circuit to which a current flowing between a source and a drain of the transistor is applied via the second switch when the first potential is applied to a gate of the transistor. The first potential is lower than a potential of the source or a potential of the drain of the transistor, and the second potential is higher than the potential of the source or the potential of the drain of the transistor. The first switch electrically connects the source and the drain of the transistor when the second potential is applied to the gate of the transistor, and electrically isolates them when the first potential is applied to the gate of the transistor.

Owner:SEMICON ENERGY LAB CO LTD