3D NAND flash memory structure and manufacturing method therefor

A manufacturing method and technology of flash memory, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., to achieve the effect of avoiding threshold voltage drift and leakage and improving quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0039] Based on the above description, Embodiment 1 of the present invention provides the following solution.

[0040] figure 2 It is a schematic flow chart of the manufacturing method of the 3D NAND flash memory structure provided in the embodiment of the present invention, such as figure 2 As shown, the method may include the following steps:

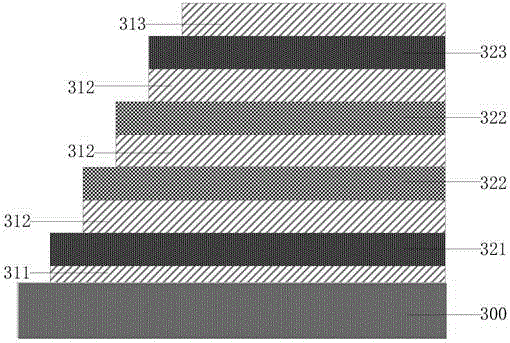

[0041] Step 21: Provide a substrate, and sequentially form a gate oxide layer, a GSL polysilicon layer, a plurality of stacked oxide dielectric layers and sacrificial dielectric layers, an SSL polysilicon layer, and a protective oxide layer on the substrate, wherein the sacrificial dielectric layer layers are formed between adjacent oxide dielectric layers;

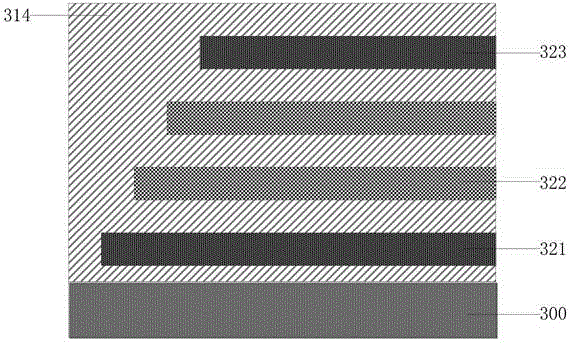

[0042] Step 22, etching to form a cylindrical channel exposing the substrate;

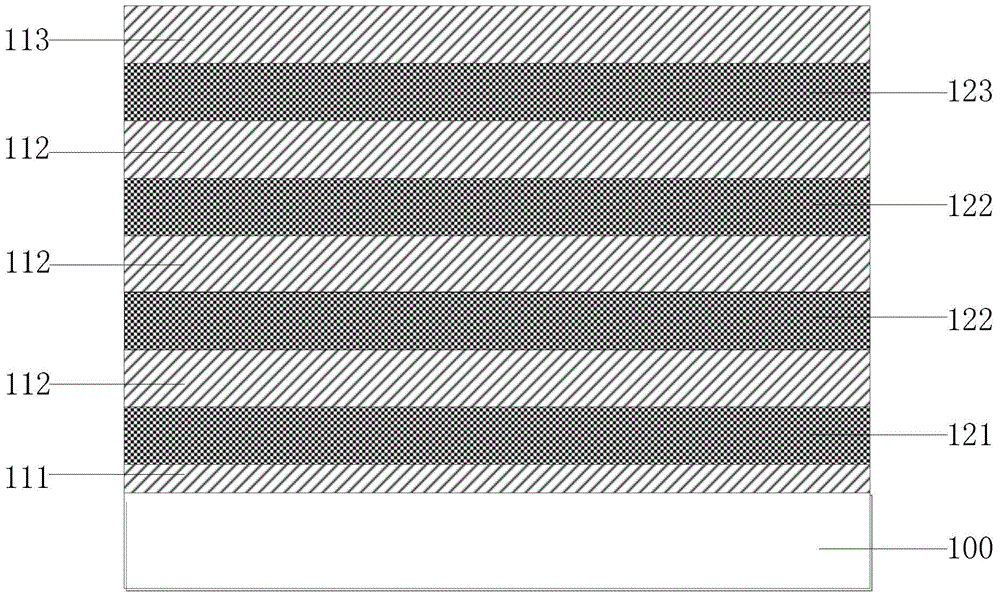

[0043] Step 23, sequentially forming a tunnel oxide layer, polysilicon and a polysilicon isolation dielectric layer in the cylindrical trench;

[0044] Step 24, etching to form a source trench e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More