Patents

Literature

169 results about "Electron trapping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

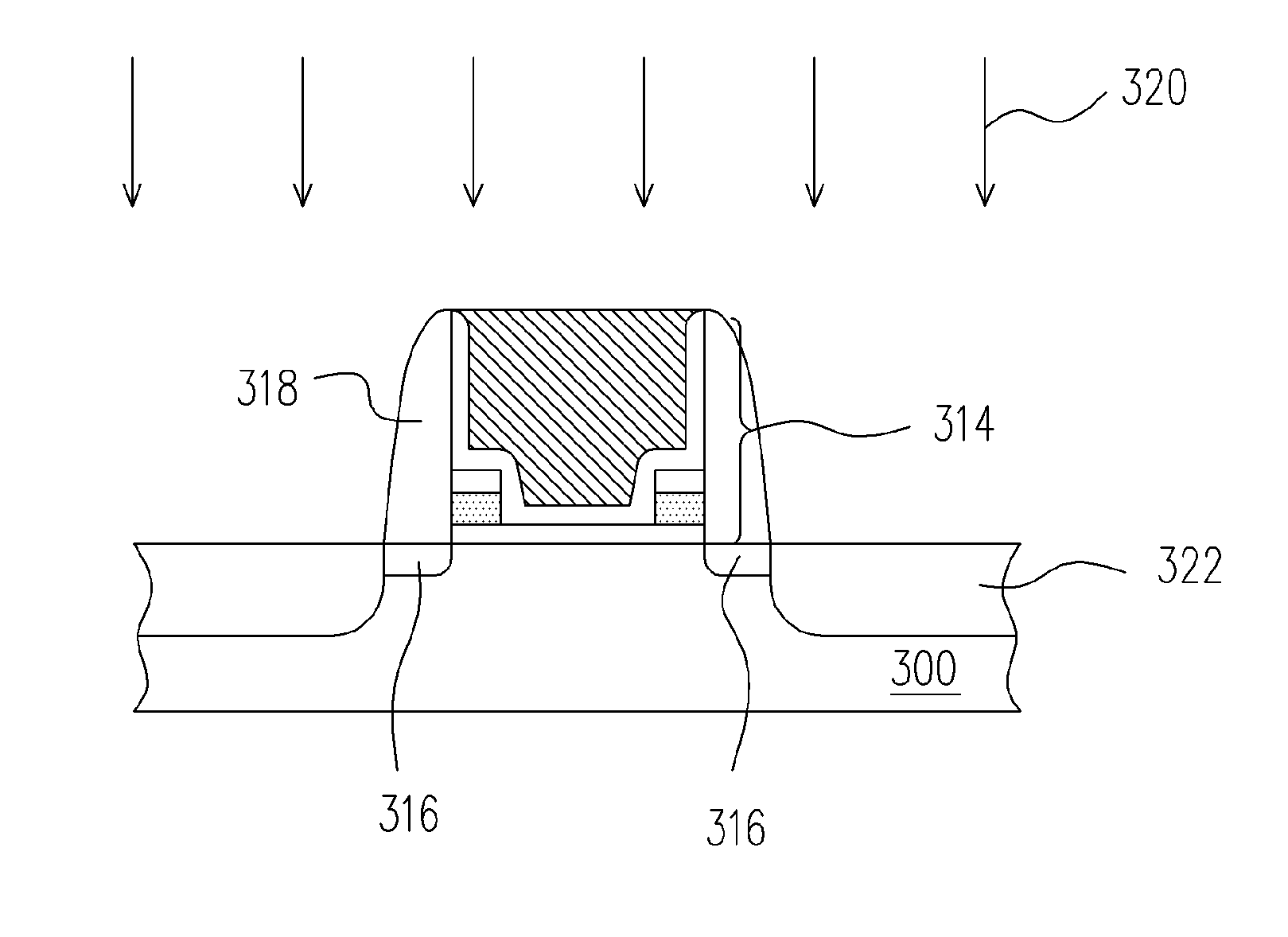

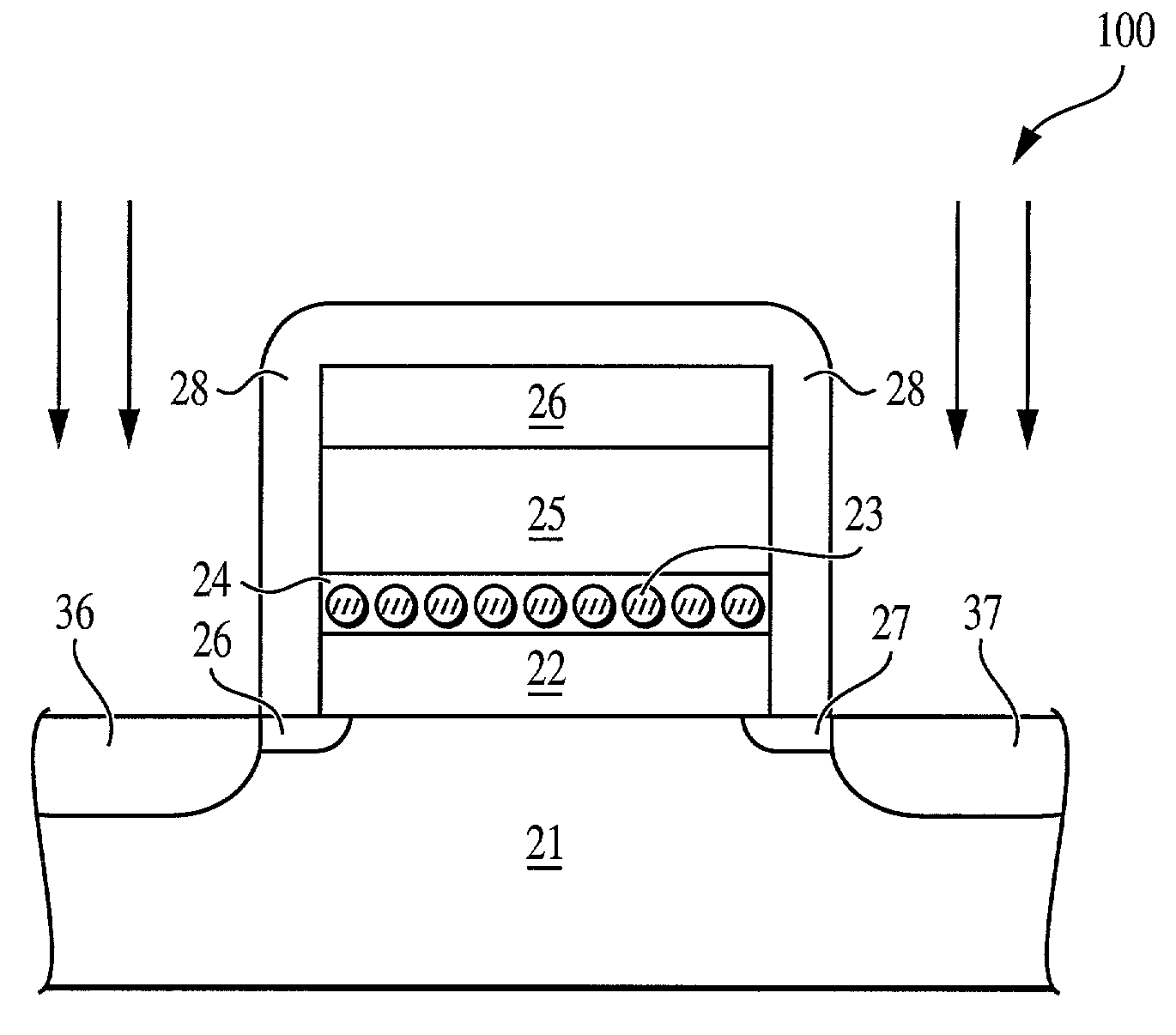

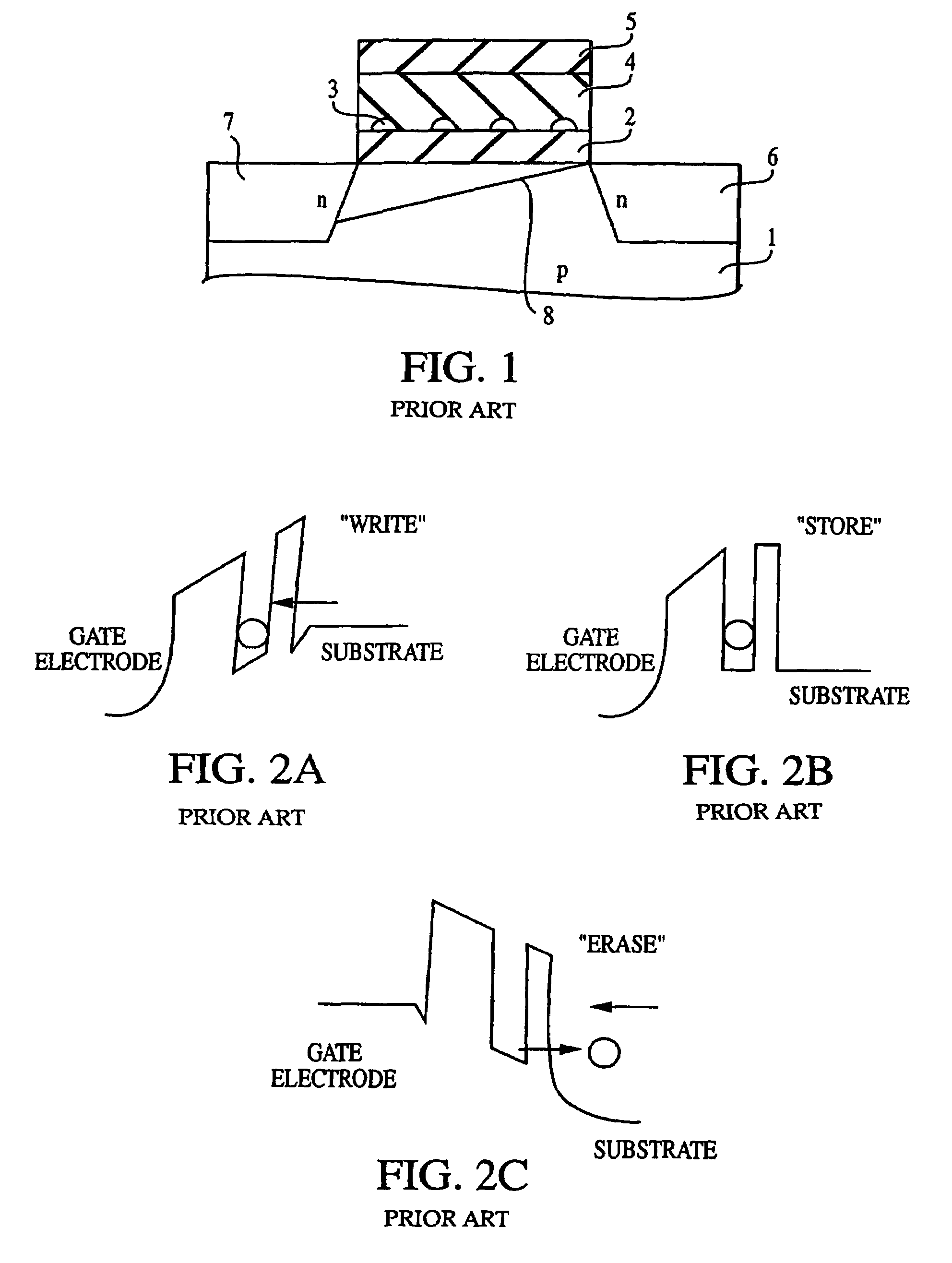

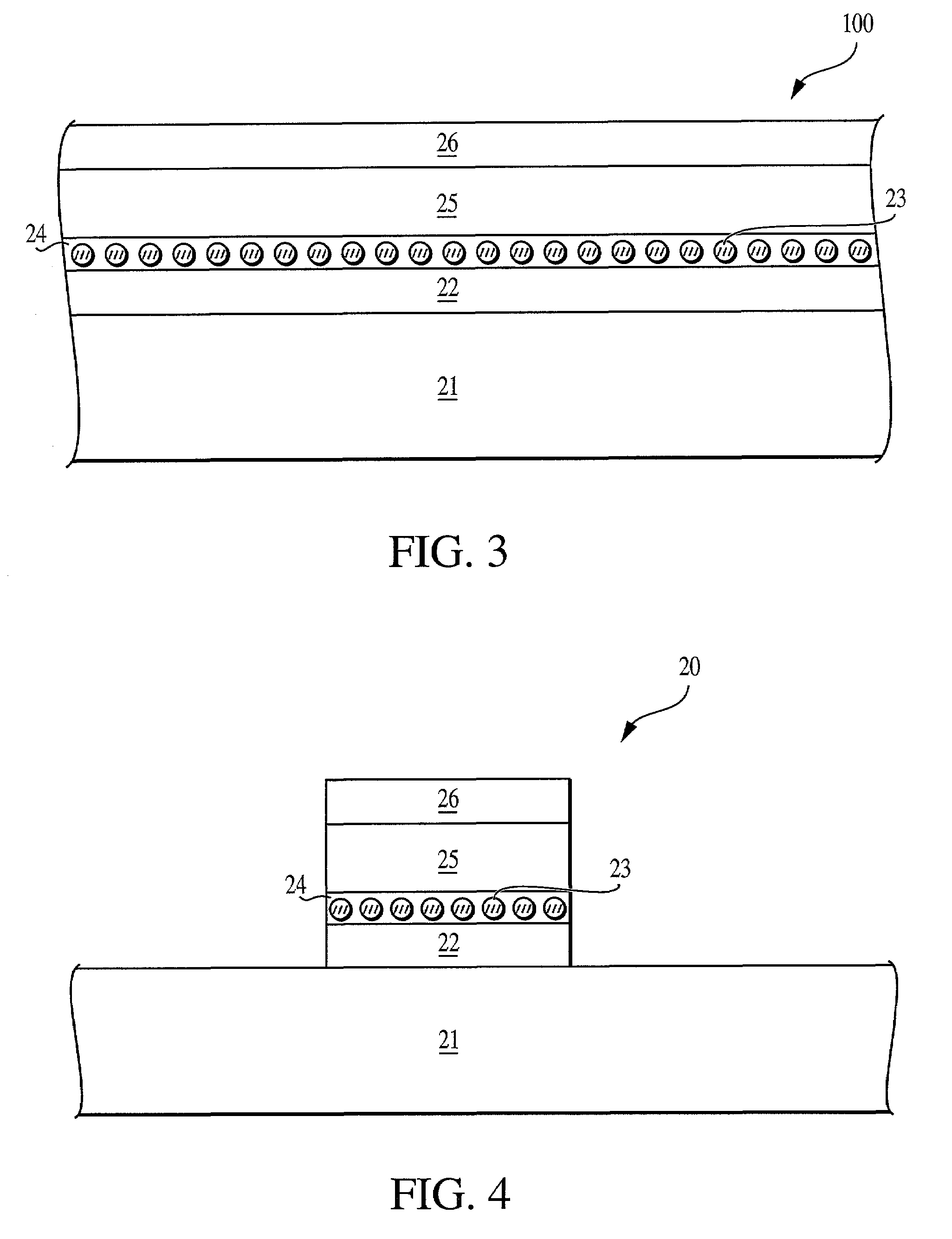

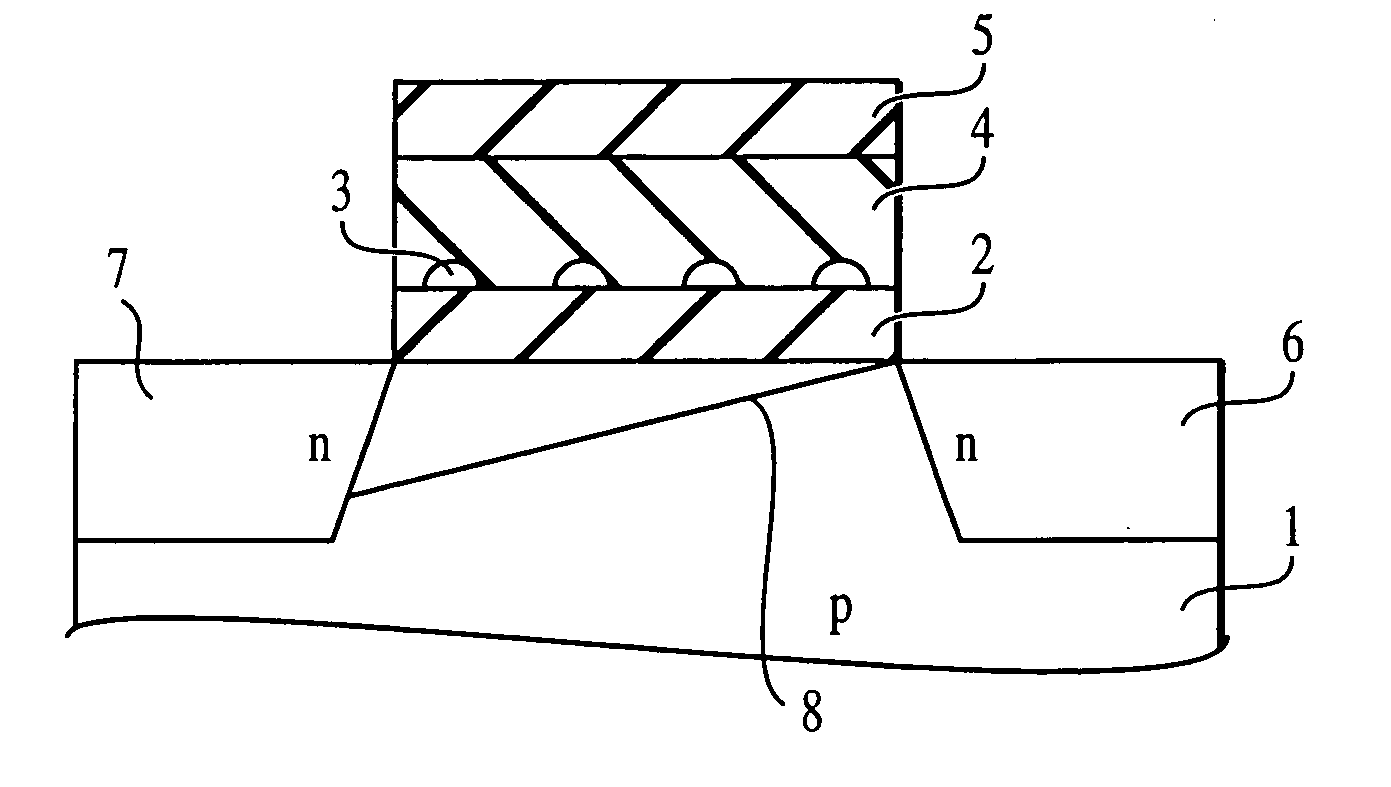

Method of forming a non-volatile electron storage memory and the resulting device

The invention provides a method of forming an electron memory storage device and the resulting device. The device comprises a gate structure which, in form, comprises a first gate insulating layer formed over a semiconductor substrate, a self-forming electron trapping layer of noble metal nano-crystals formed over the first gate insulating layer, a second gate insulating layer formed over the electron trapping layer, a gate electrode formed over the second gate insulating layer, and source and drain regions formed on opposite sides of the gate structure.

Owner:MICRON TECH INC

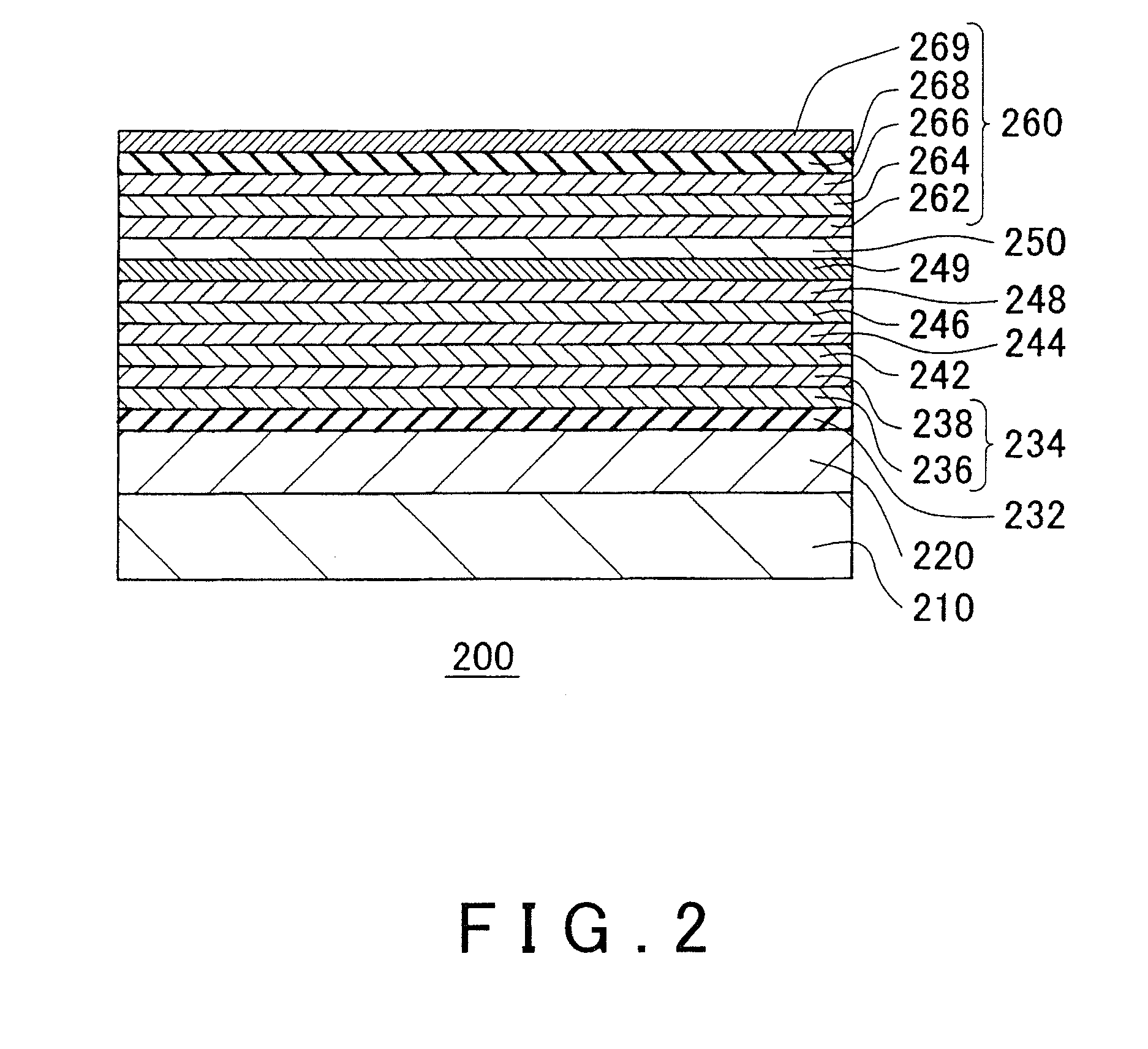

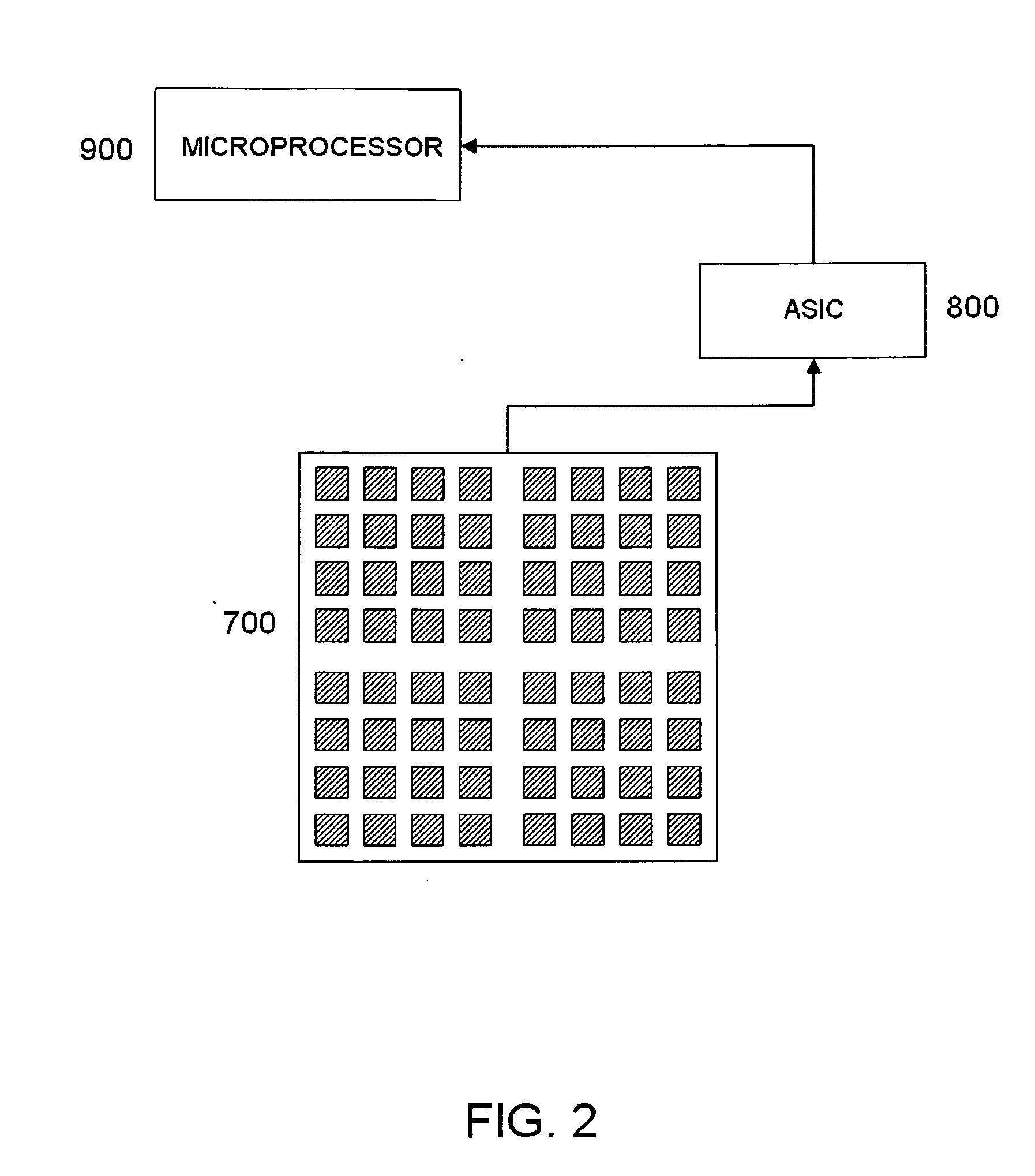

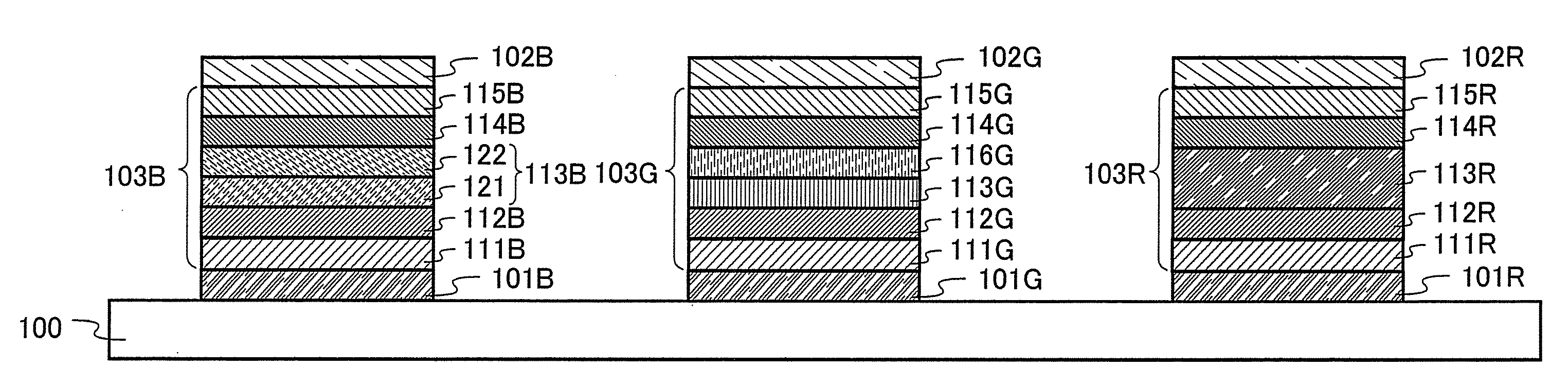

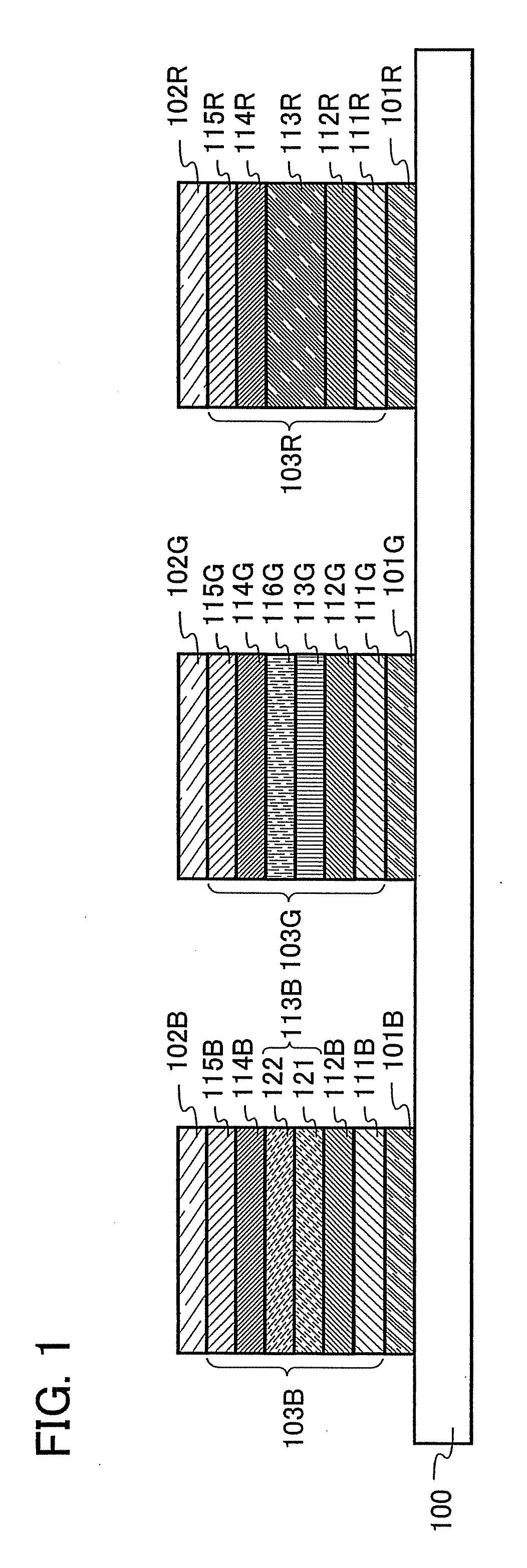

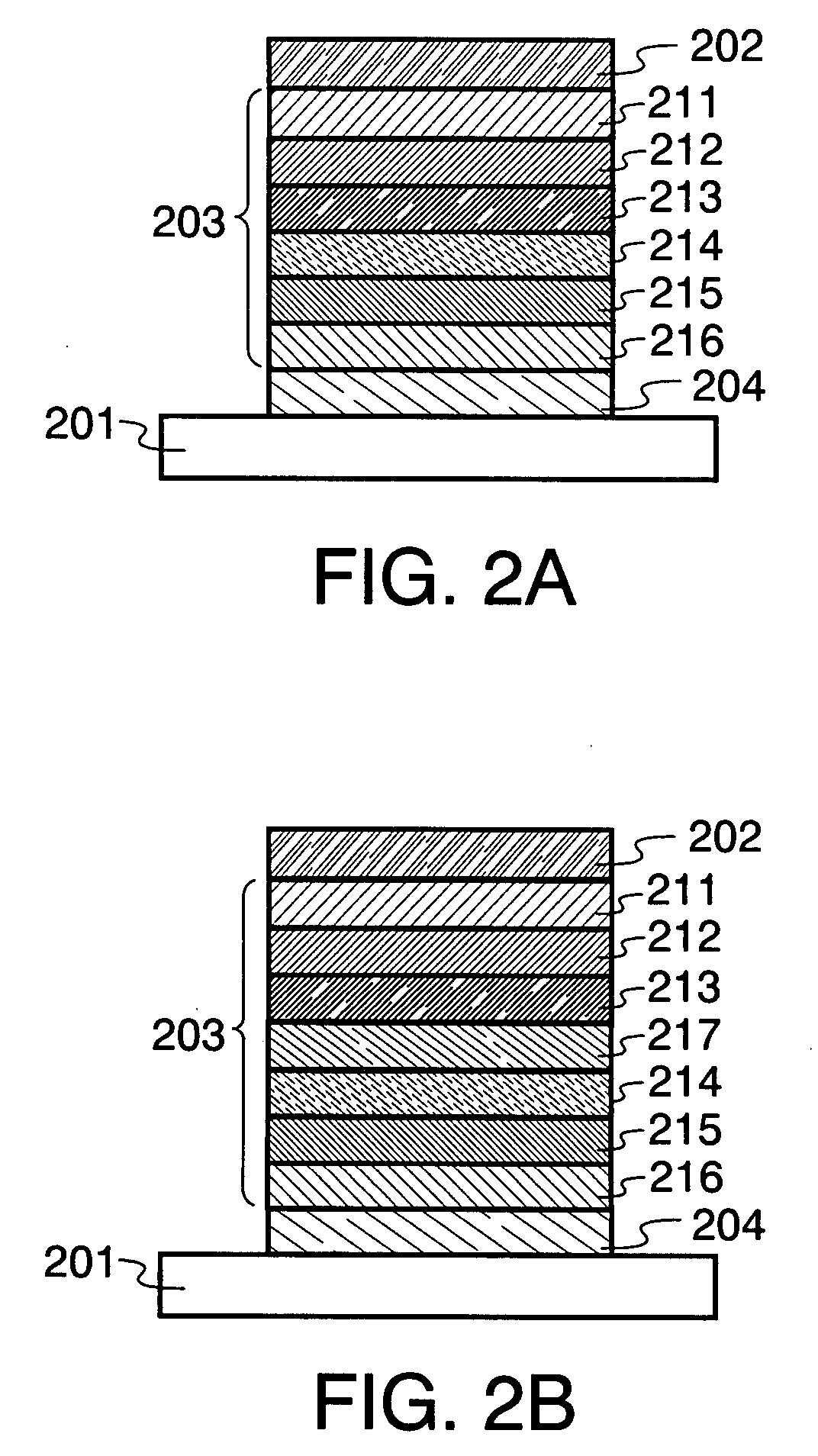

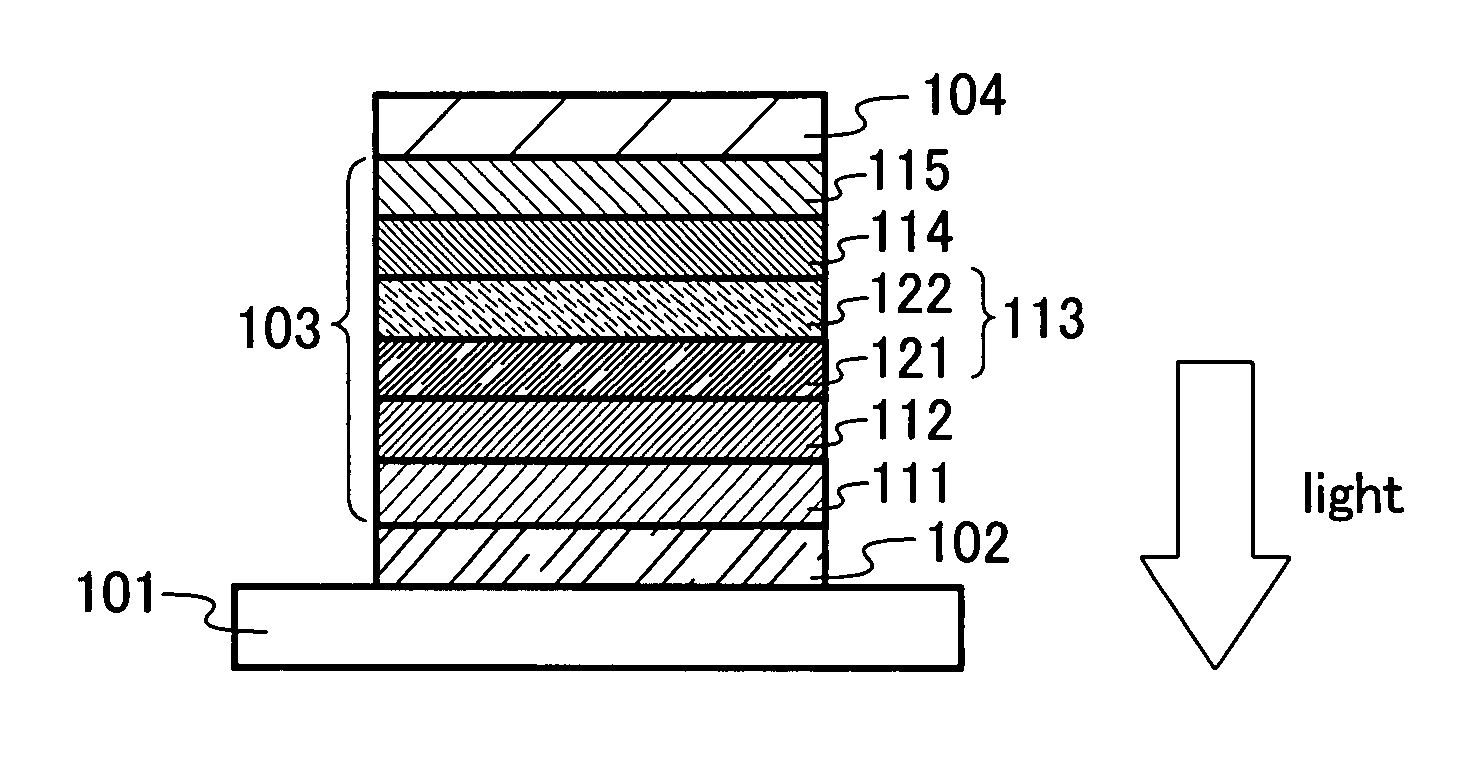

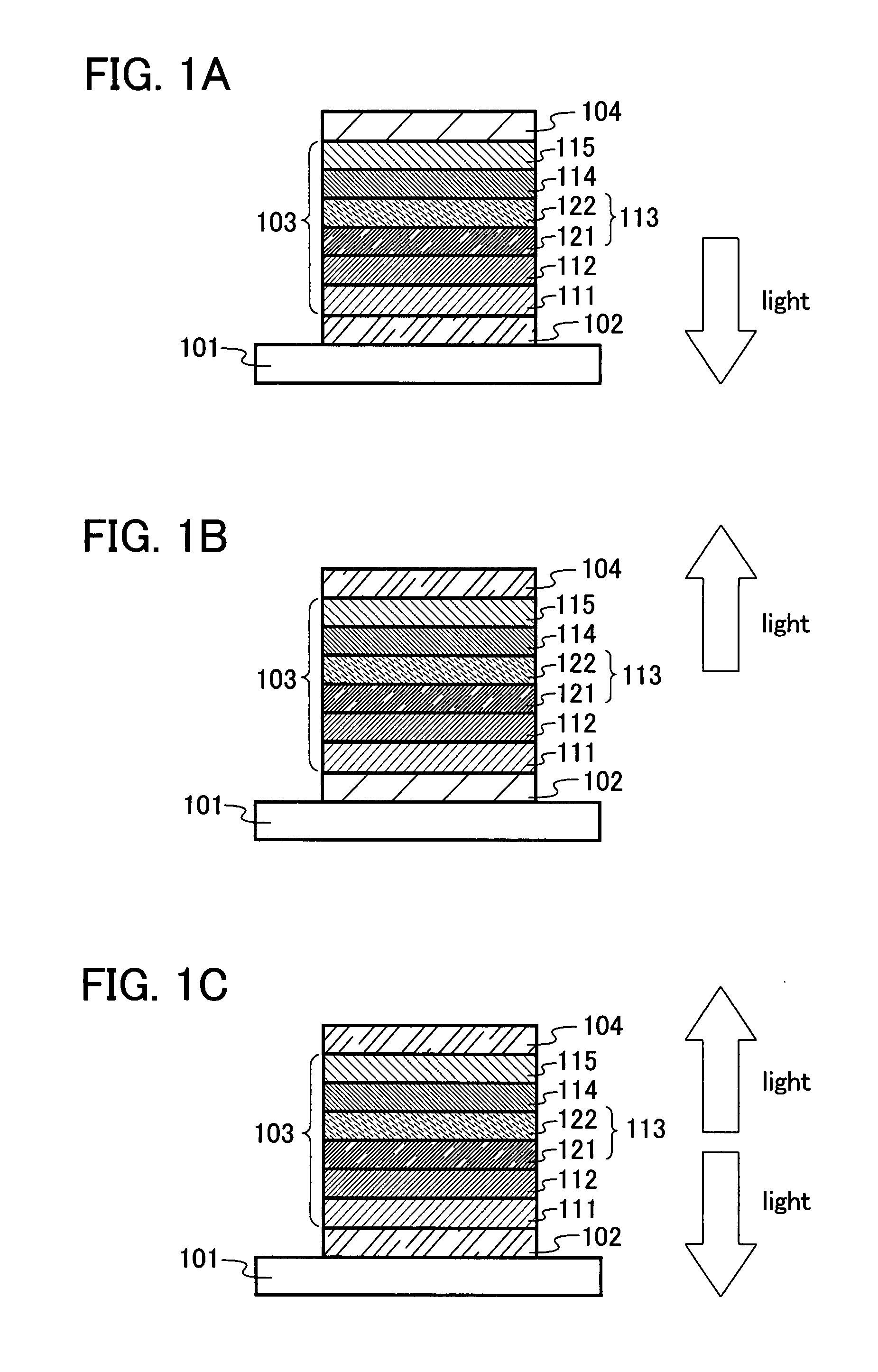

Light-Emitting Device and Electronic Device

InactiveUS20080231177A1Improve featuresSuitable structureDischarge tube luminescnet screensElectroluminescent light sourcesElectronic transmissionCharge carrier

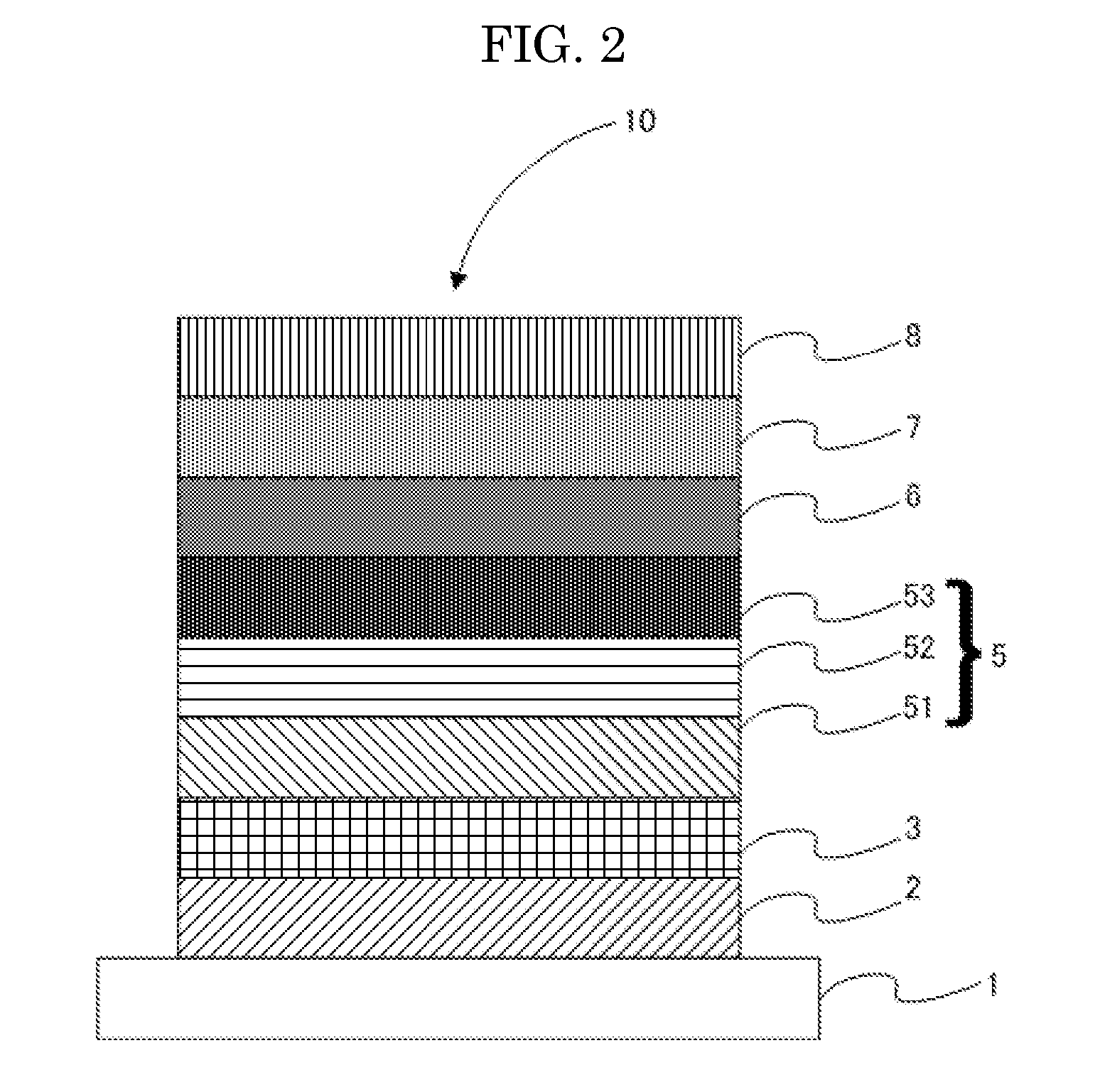

The present invention provides light-emitting devices having excellent characteristics and electronic devices having excellent characteristics, having such light-emitting devices. Specifically, the present invention provides a light-emitting device includes a first light-emitting element, a second light-emitting element, and a third light-emitting element which emit light having different color from each other. The first light-emitting element includes a first anode; a first cathode; and a first light-emitting layer and a second light-emitting layer between the first anode and the first cathode, wherein the first light-emitting layer includes a first high light-emitting substance and a first organic compound, and the second light-emitting layer includes the first high light-emitting substance and a second organic compound, wherein the first light-emitting layer is in contact with the first anode side of the second light-emitting layer, and wherein the first organic compound is an organic compound having a hole-transporting property and the second organic compound is an organic compound having an electron-transporting property. The second light-emitting element includes a second anode; a second cathode; and a third light-emitting layer and a layer for controlling carrier transfer between the second anode and the second cathode, wherein the third light-emitting layer includes a second high light-transmitting substance, wherein the layer for controlling carrier transfer includes a third organic compound and a fourth organic compound, and is provided between the third light-emitting layer and the second cathode, wherein the third organic compound is an organic compound having an electron-transporting property and the fourth organic compound is an organic compound having an electron-trapping property; and wherein the third organic compound is included more than the fourth organic compound in the layer for controlling carrier transfer. The third light-emitting element includes a third anode; a third cathode; and a fourth light-emitting layer, wherein the fourth light-emitting layer includes a fifth organic compound, a sixth organic compound, and a third high light-emitting substance, wherein the fifth organic compound is an organic compound having a hole-transporting property, and the sixth organic compound is an organic compound having an electron-transporting property, and wherein the third high light-emitting substance is a substance which emits phosphorescence.

Owner:SEMICON ENERGY LAB CO LTD

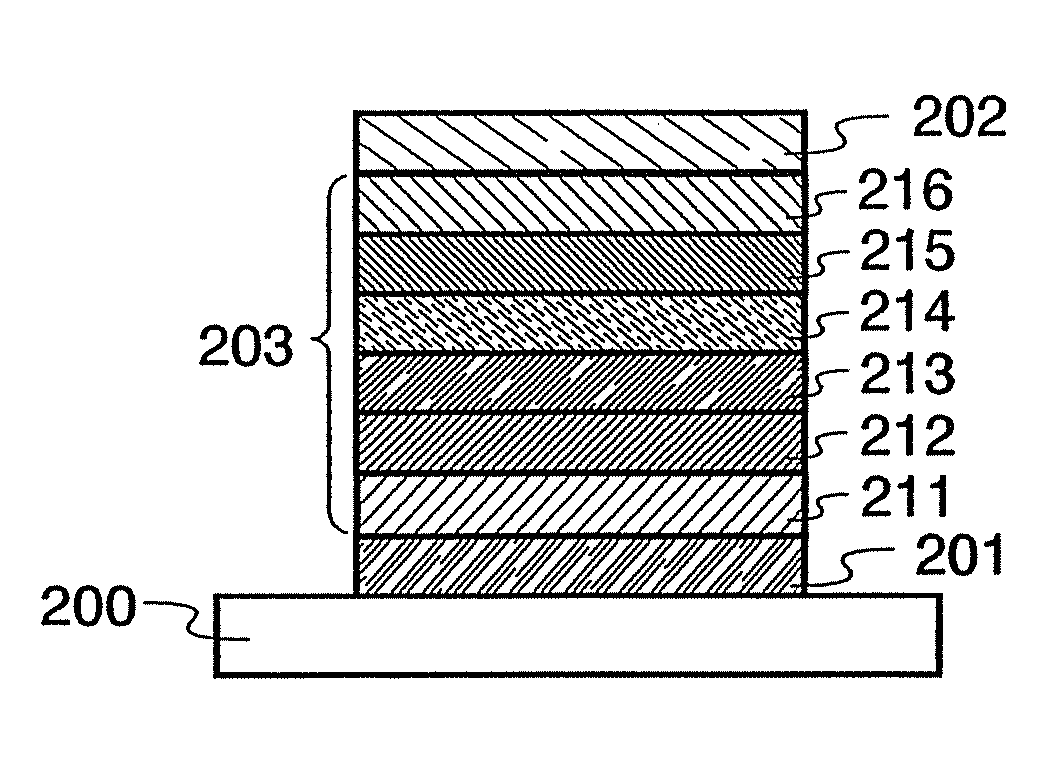

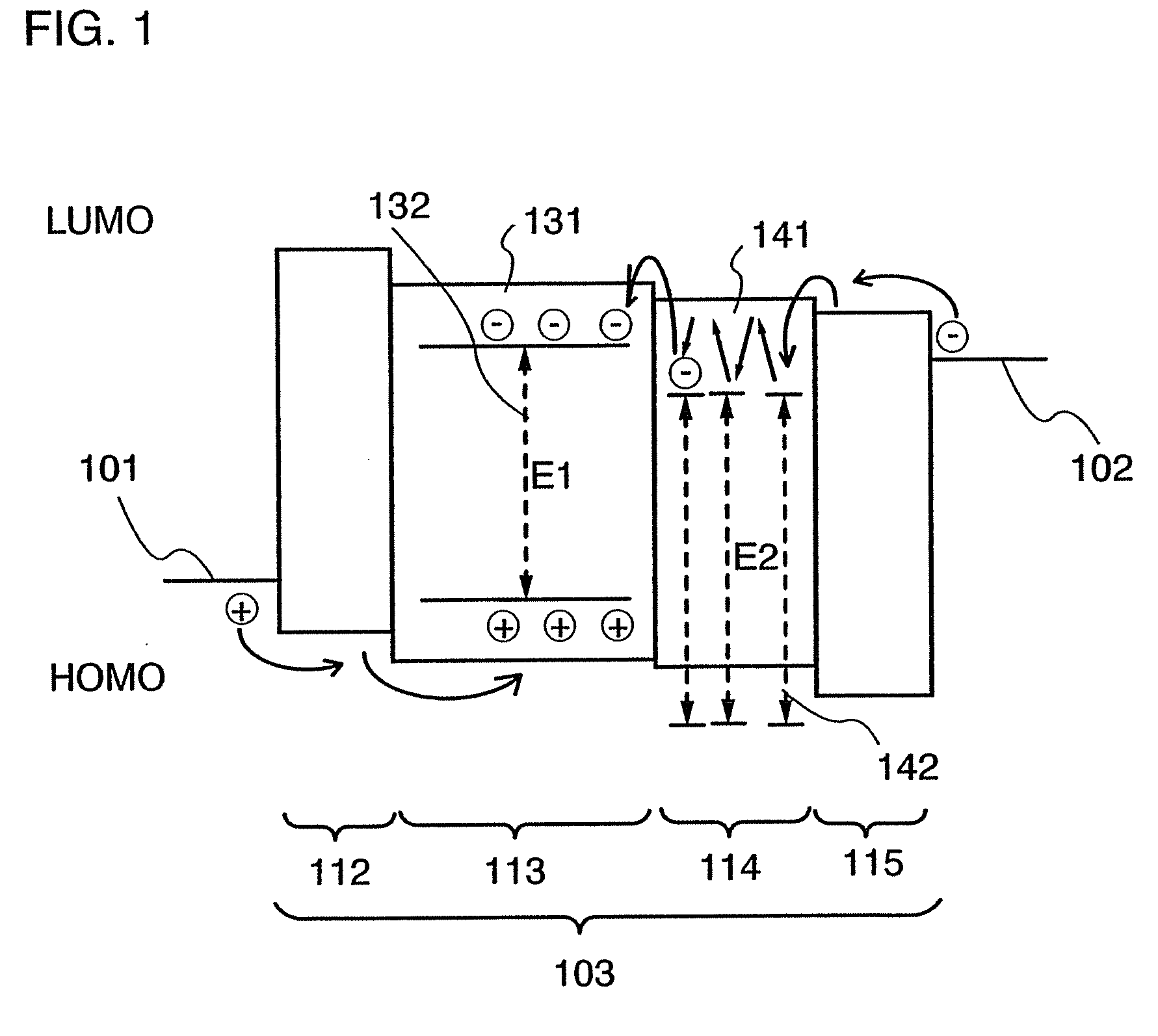

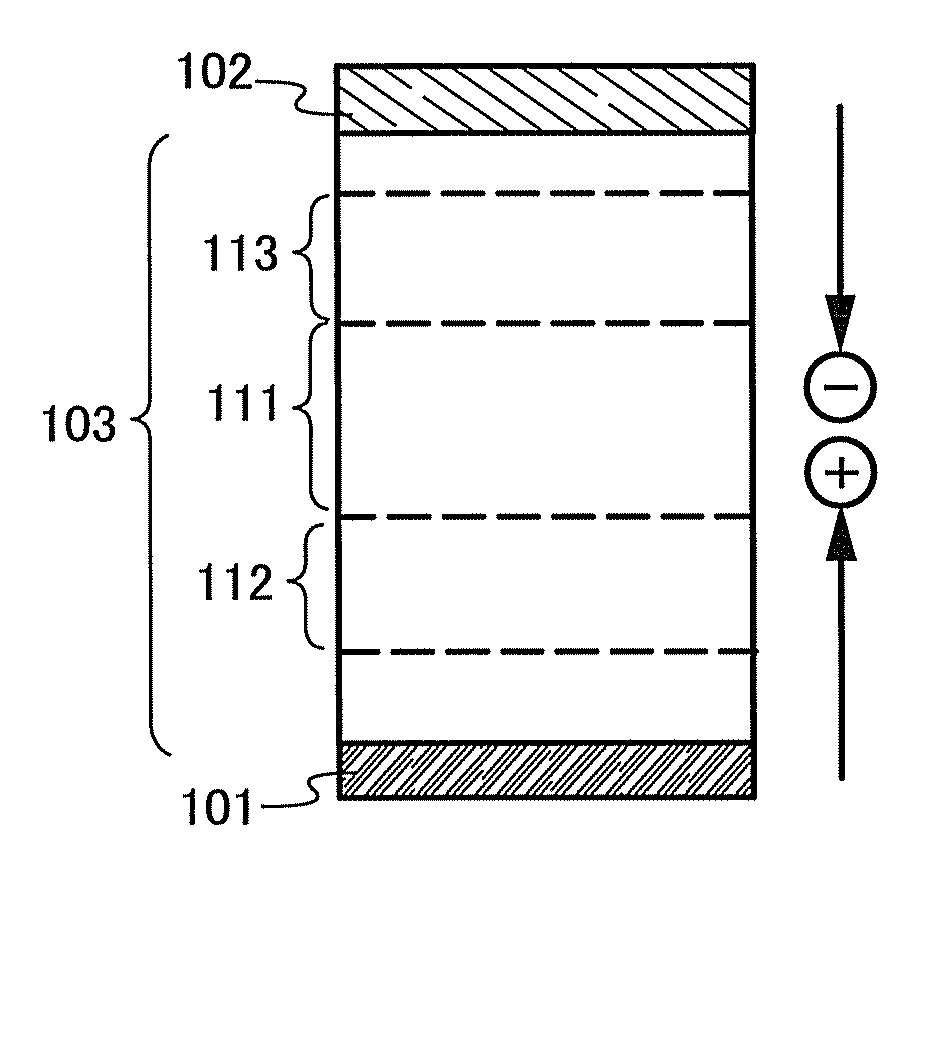

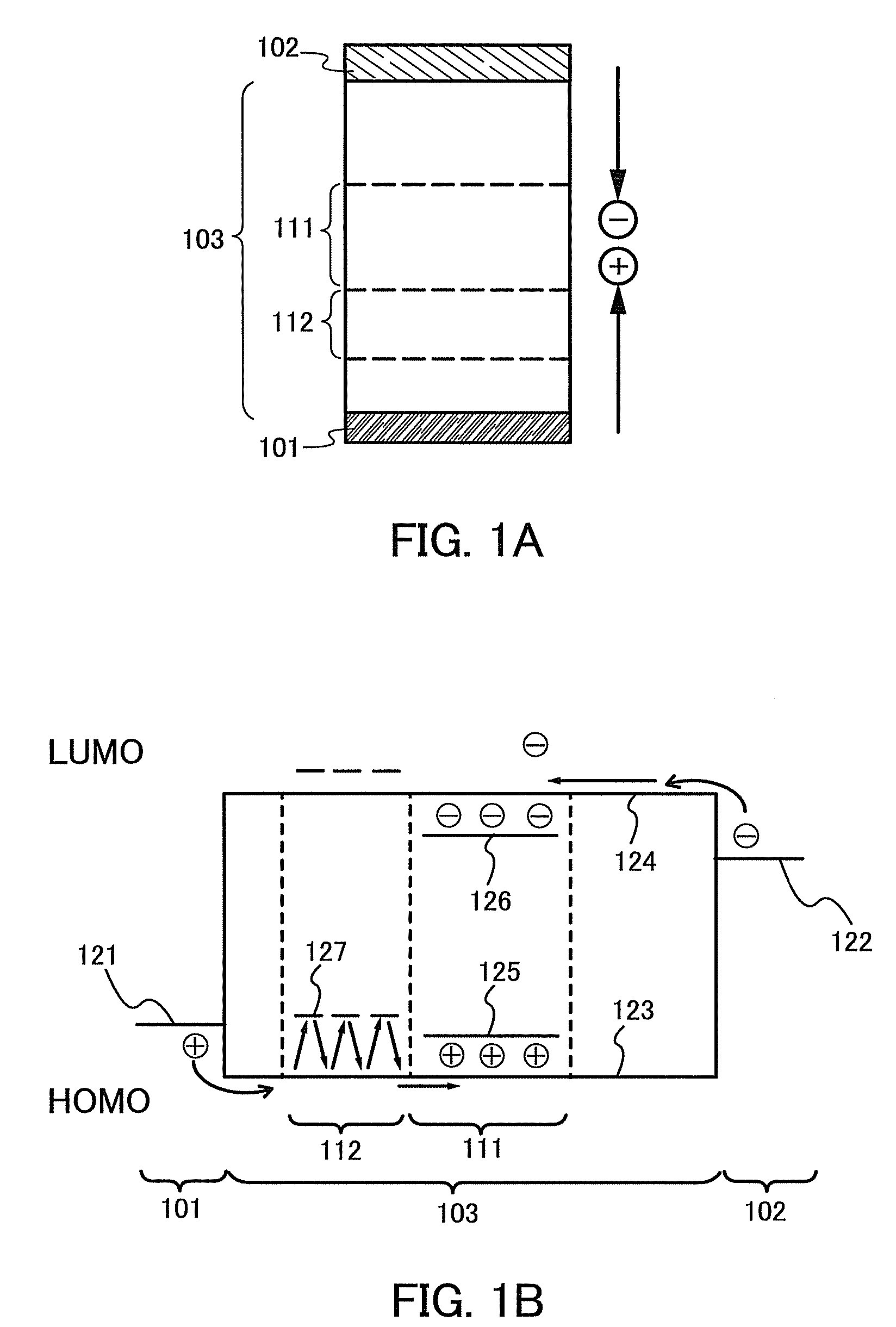

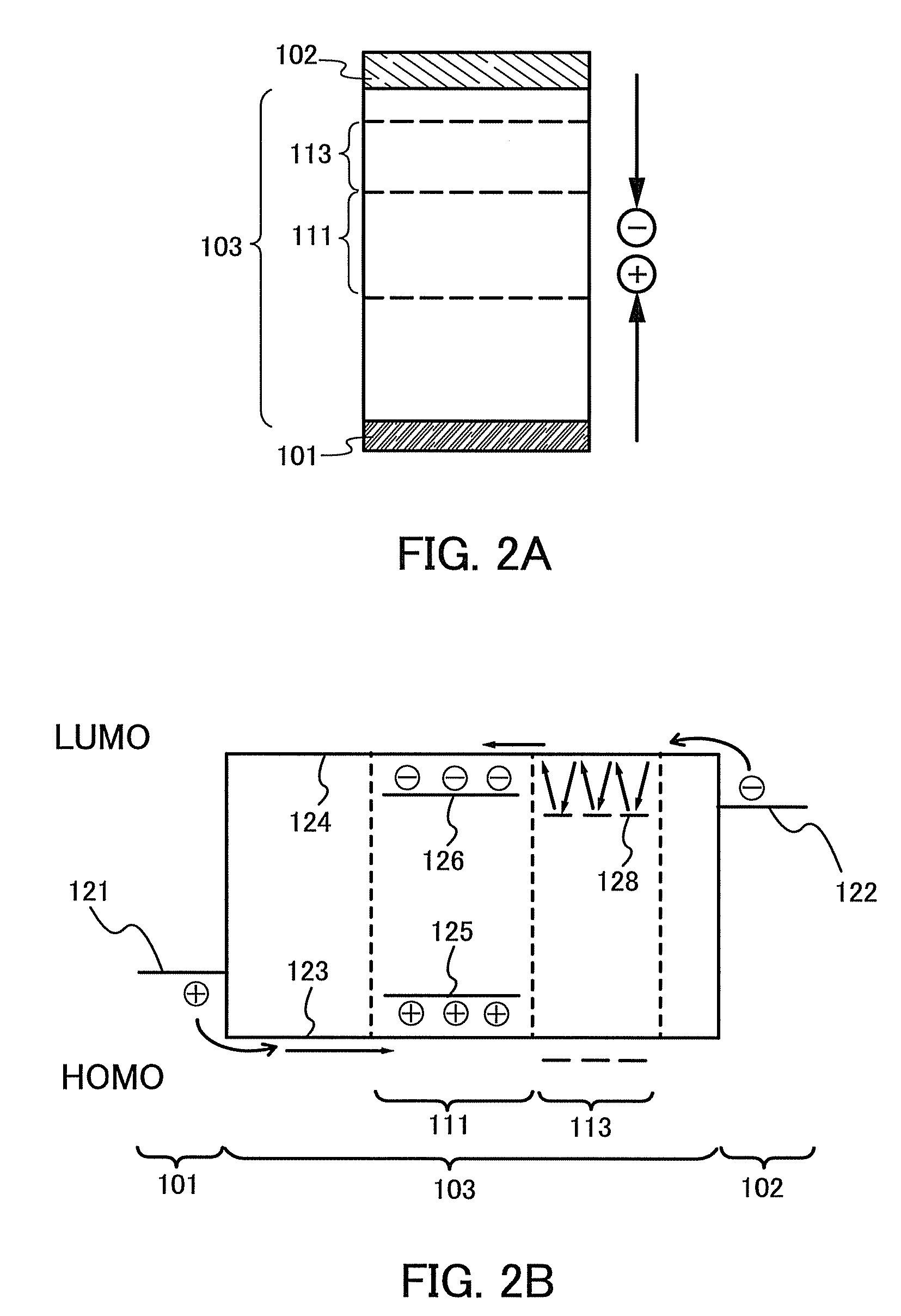

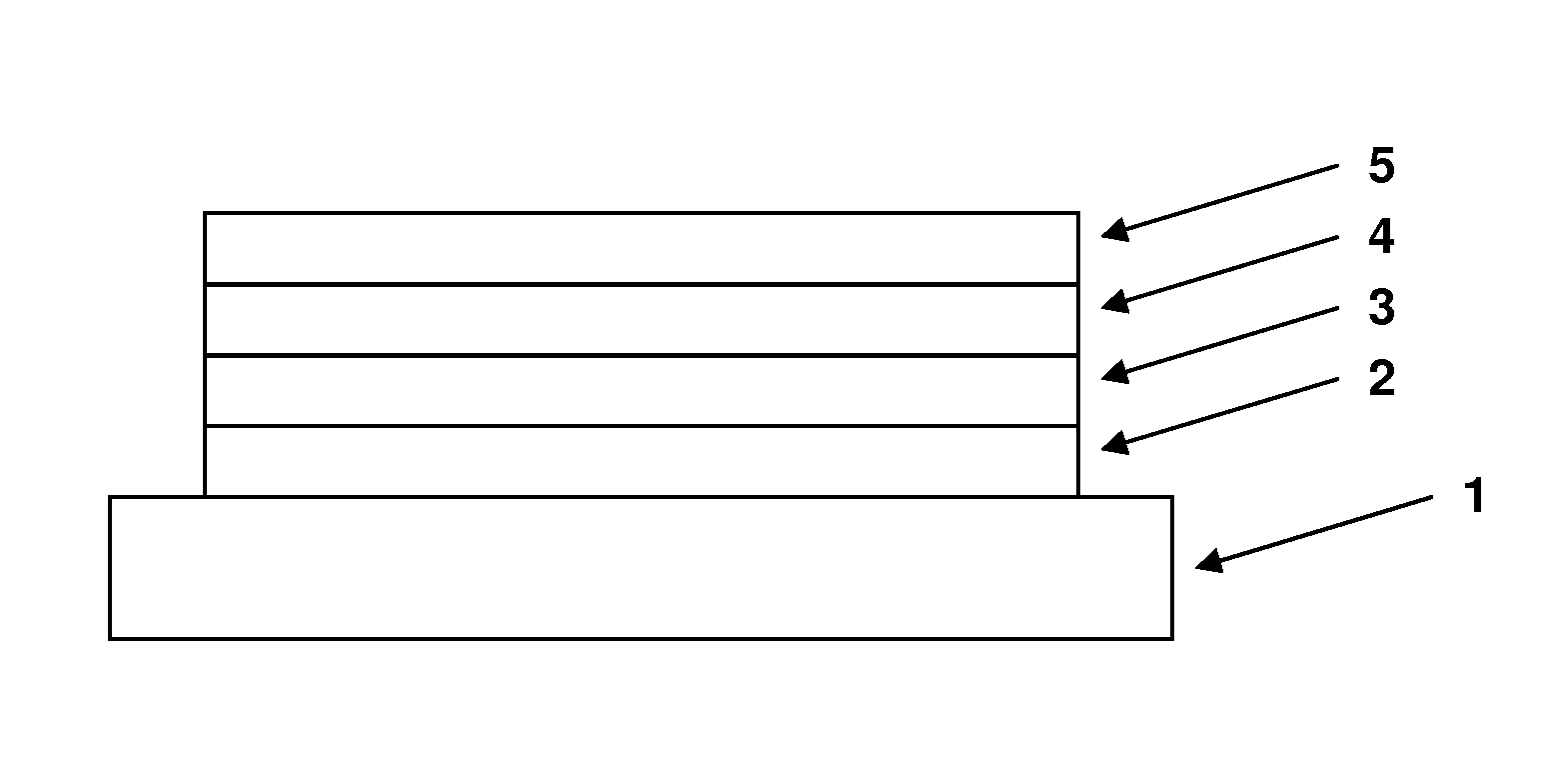

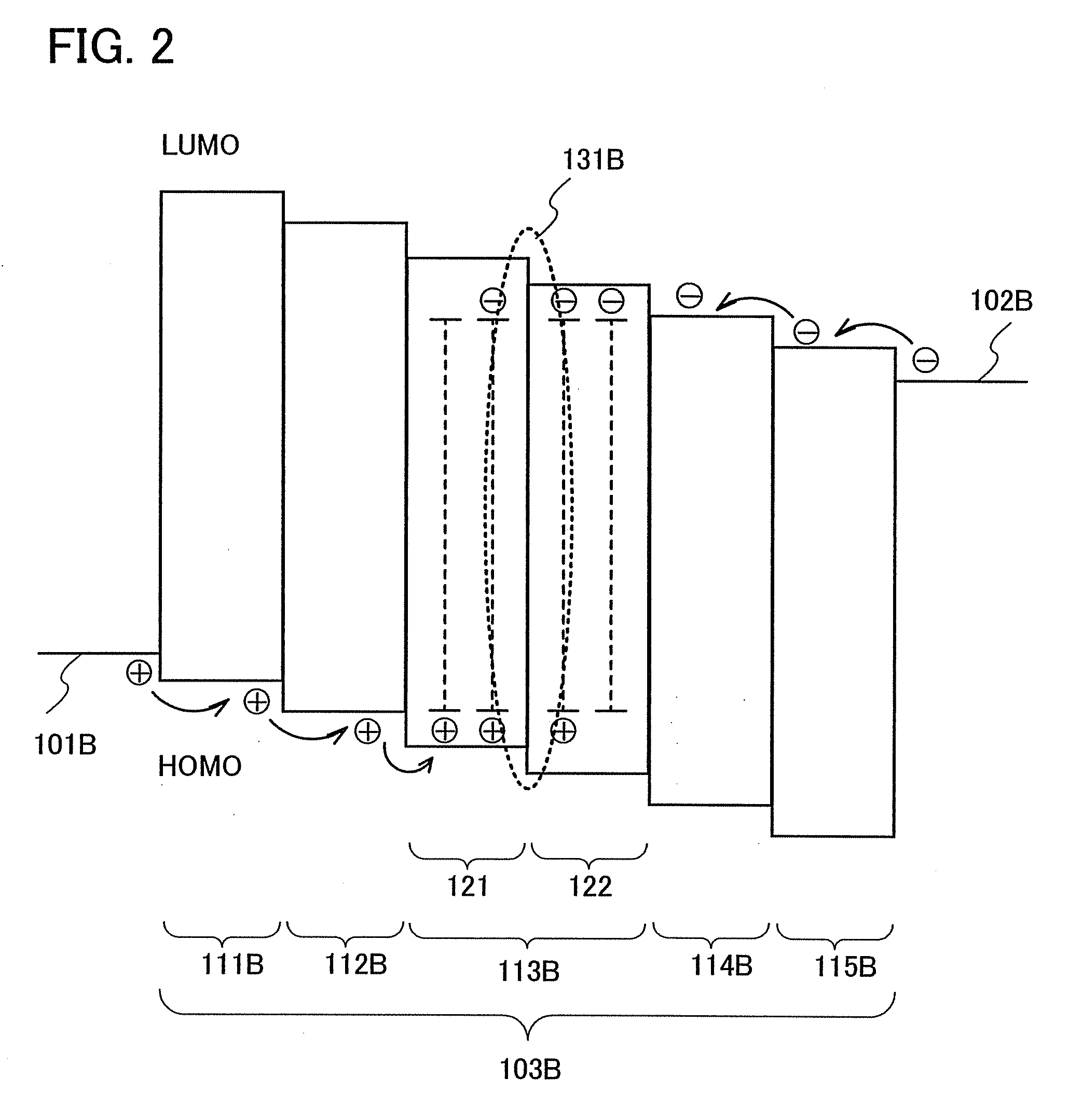

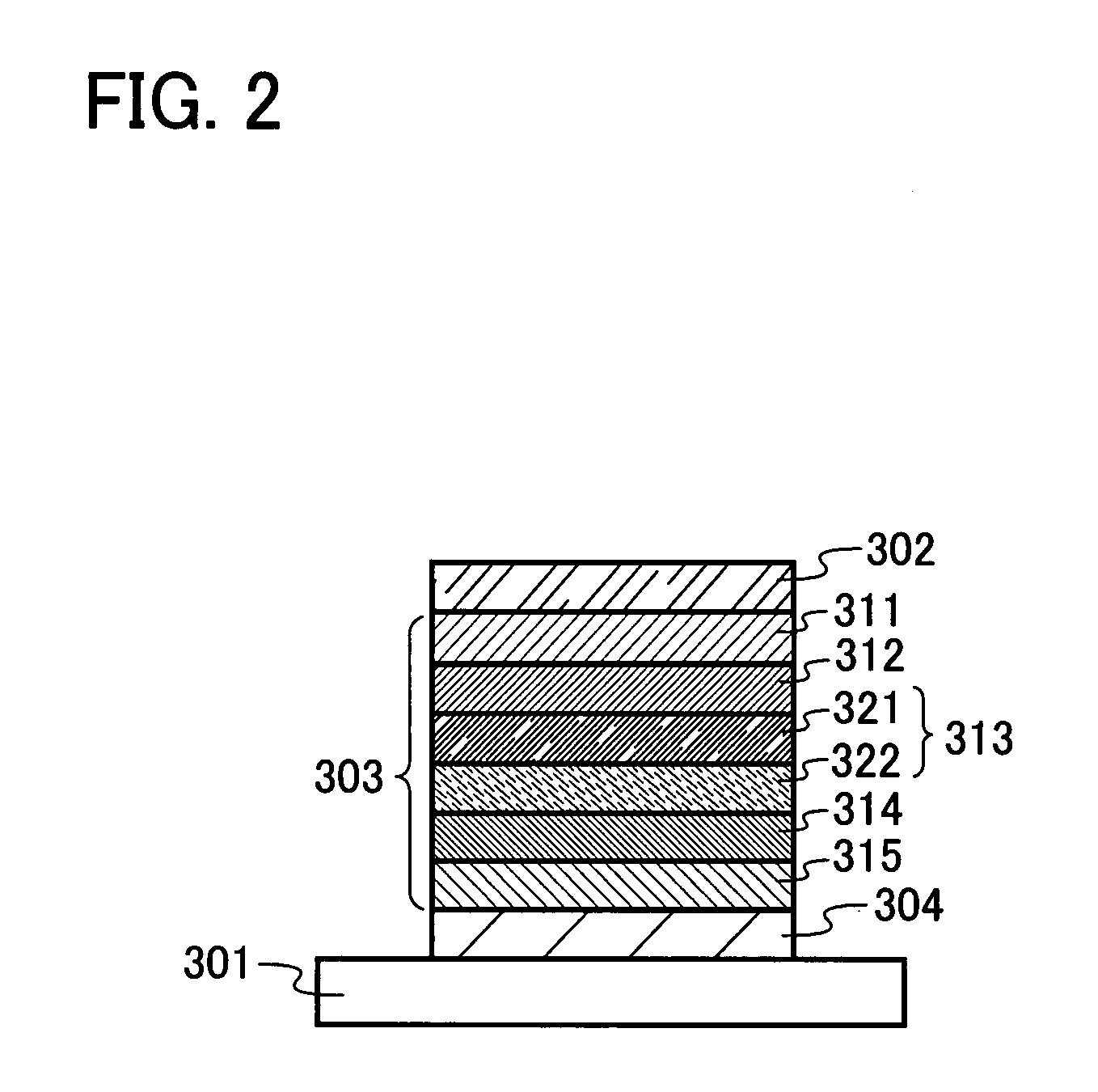

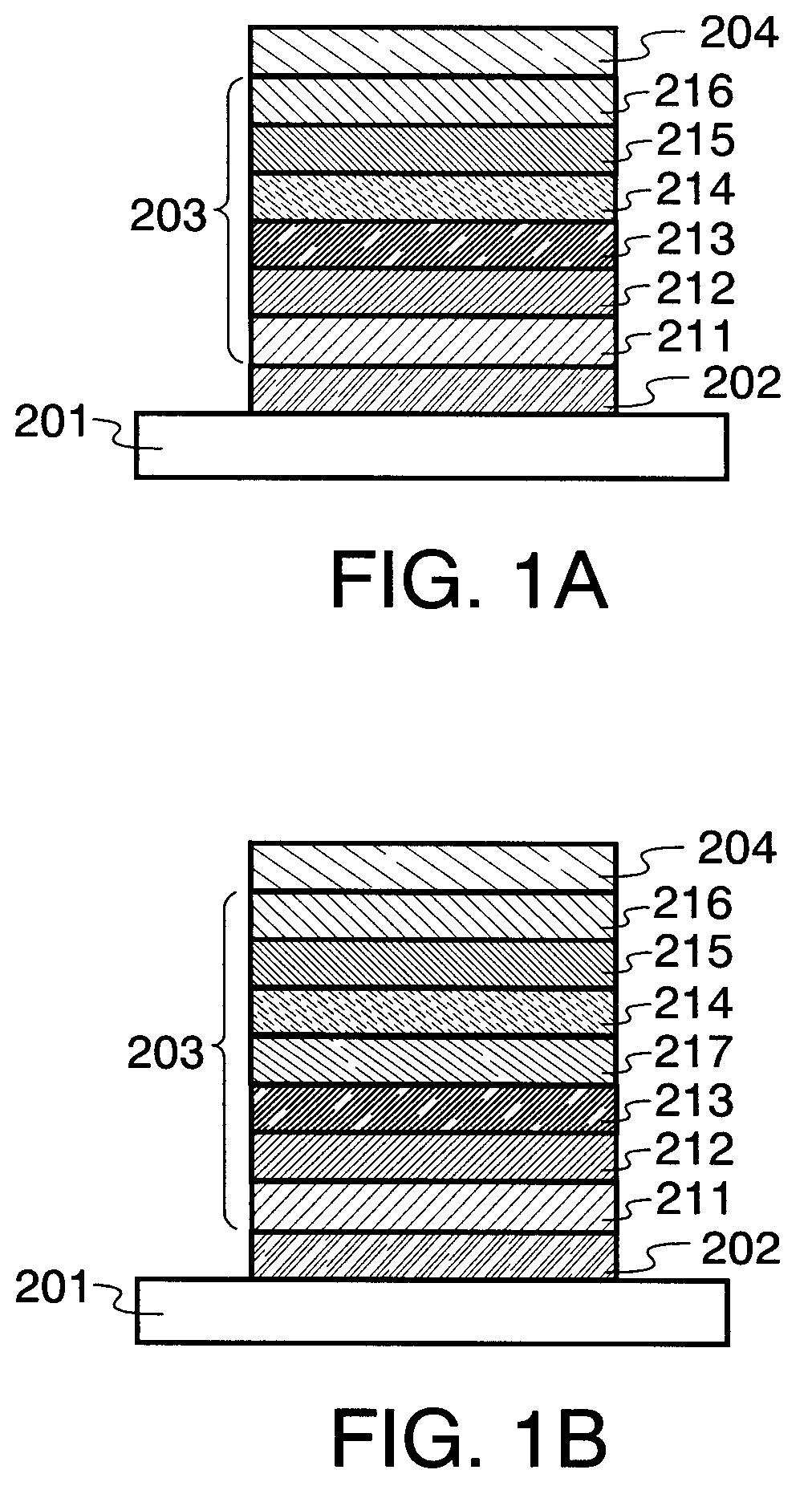

Ligth-emitting element, light-emitting device, and electronic device

ActiveUS20080007164A1Solve low luminous efficiencyReduce power consumptionDischarge tube luminescnet screensElectroluminescent light sourcesSimple Organic CompoundsMovement control

The light-emitting element includes: a light-emitting layer and a layer for controlling the movement of carriers between a first electrode and a second electrode. The layer for controlling the movement of carriers contains a first organic compound and a second organic compound, and is provided between the light-emitting layer and the second electrode. The first organic compound has an electron transporting property, and the second organic compound has an electron trapping property. The weight percent of the first organic compound is higher than that of the second organic compound. The light-emitting layer emits light when a voltage is applied such that the potential of the first electrode is higher than that of the second electrode. The first organic compound having the electron transporting property may be replaced with an organic compound having a hole transporting property, and the second organic compound having the electron trapping property may be replaced with an organic compound having a hole trapping property.

Owner:SEMICON ENERGY LAB CO LTD

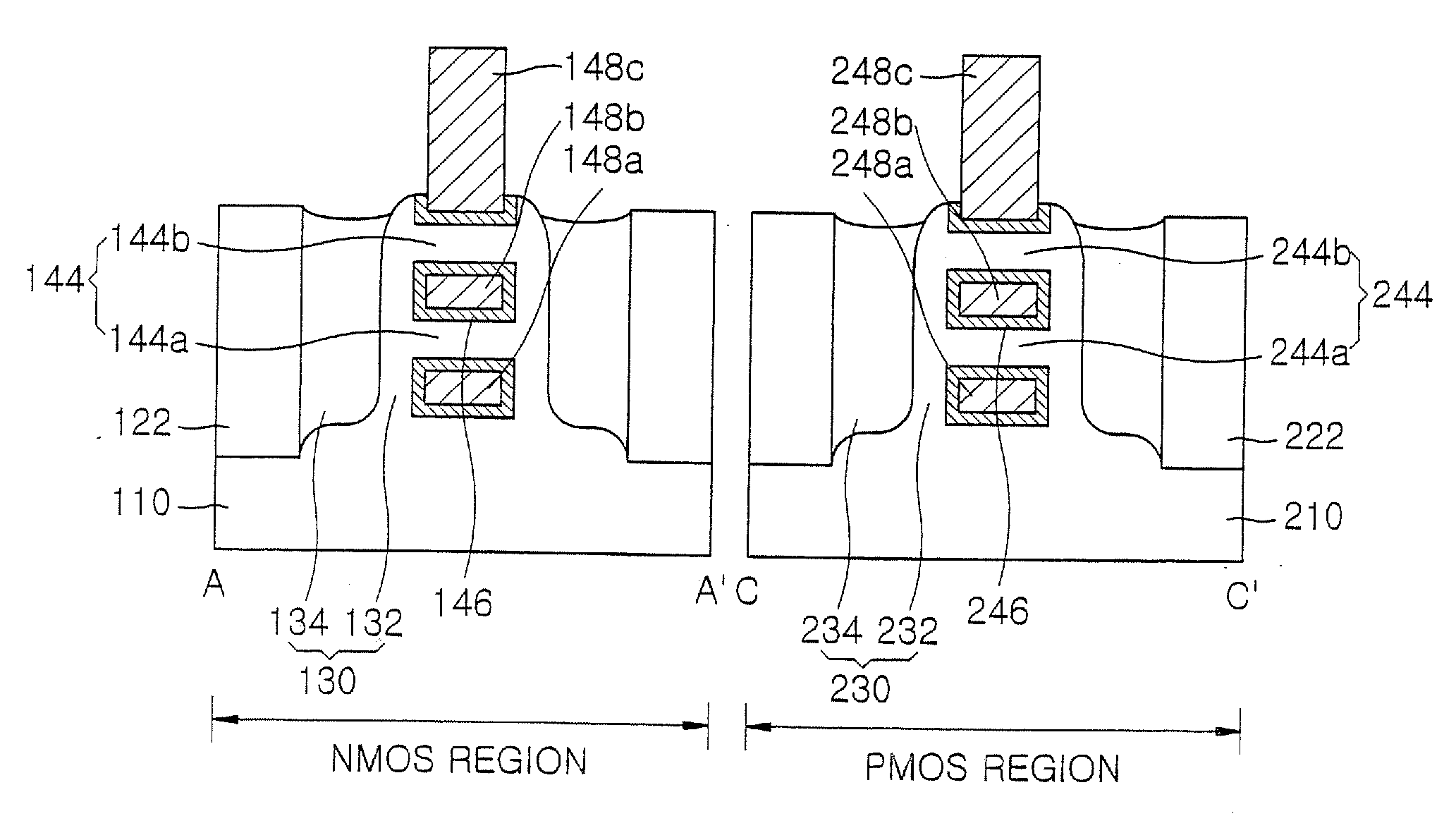

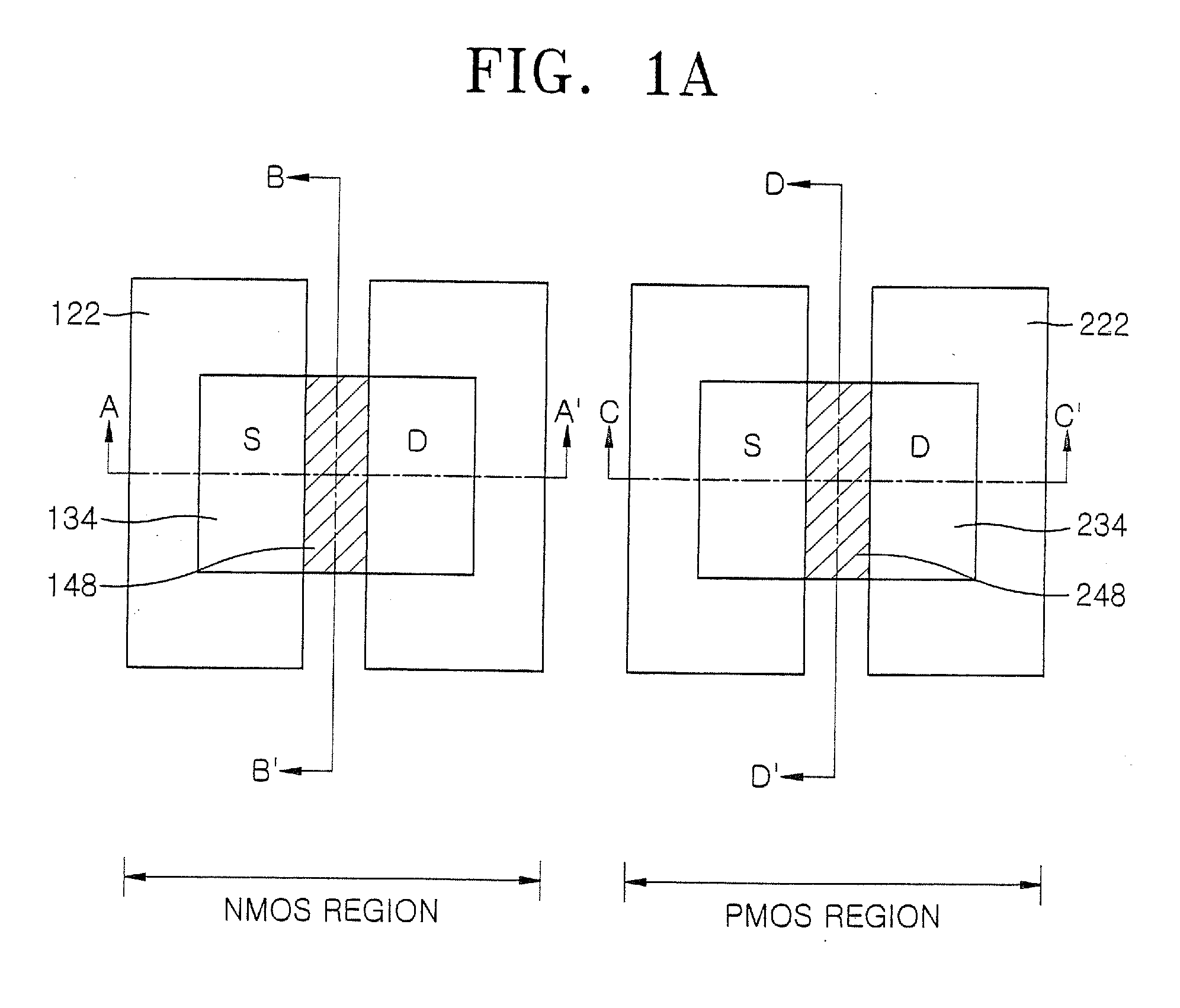

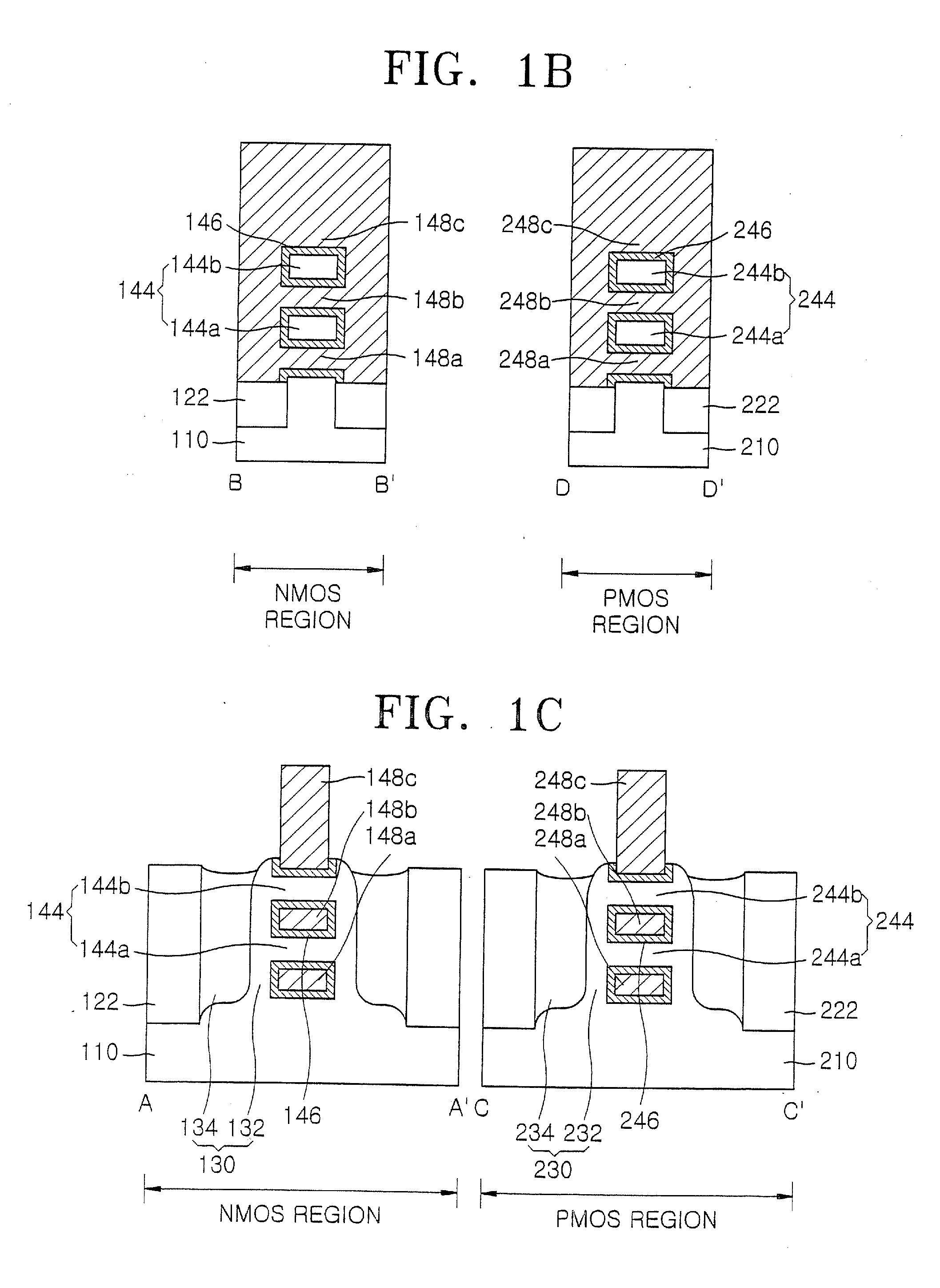

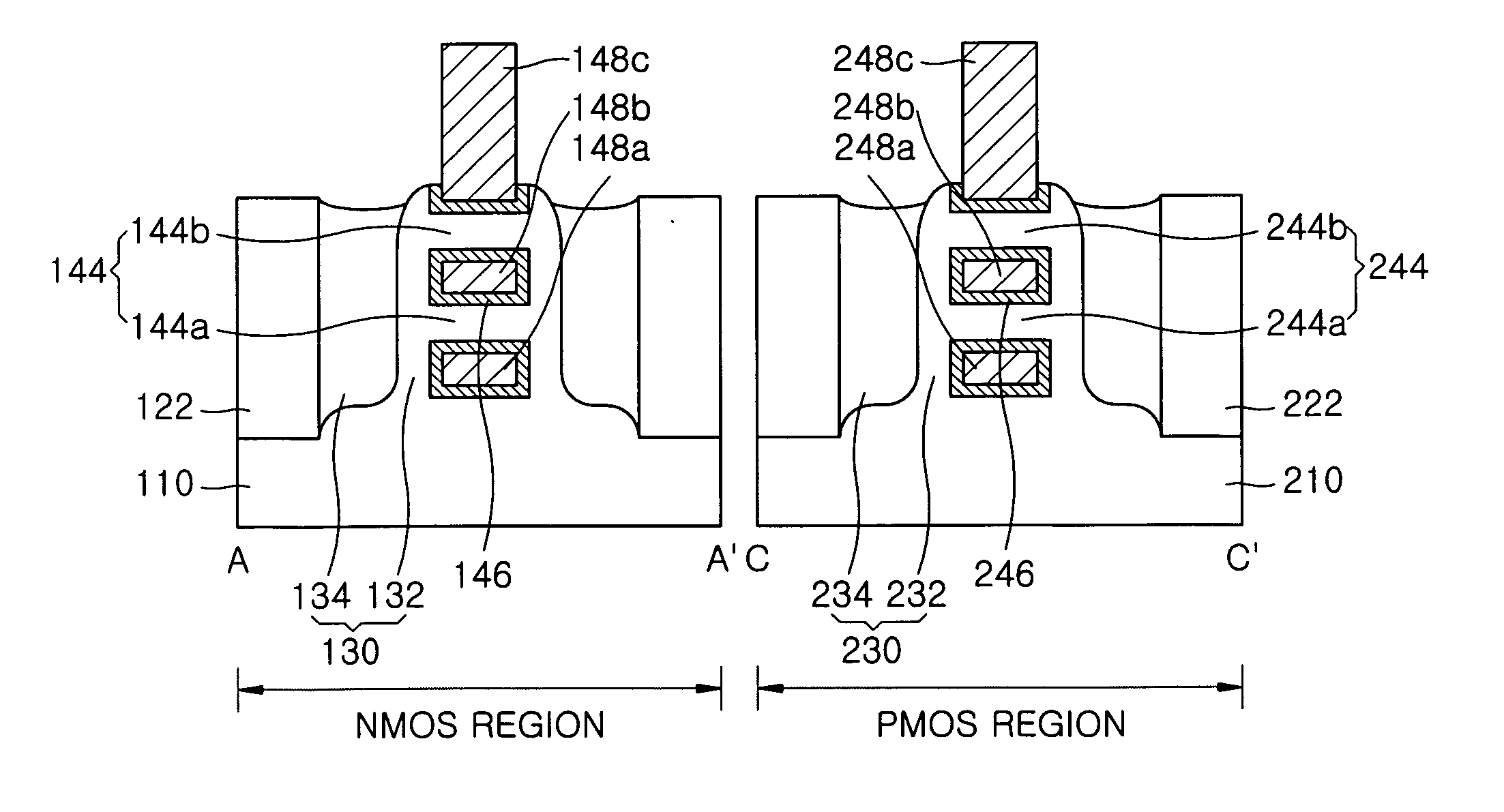

Complementary metal-oxide semiconductor (CMOS) devices including a thin-body channel and dual gate dielectric layers and methods of manufacturing the same

InactiveUS20060125018A1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSilicon oxide

A complementary metal-oxide semiconductor (CMOS) device includes an NMOS thin body channel including a silicon epitaxial layer. An NMOS insulating layer is formed on a surface of the NMOS thin body channel and surrounds the NMOS thin body channel. An NMOS metal gate is formed on the NMOS insulating layer. The CMOS device further includes a p-channel metal-oxide semiconductor (PMOS) transistor including a PMOS thin body channel including a silicon epitaxial layer. A PMOS insulating layer is formed on a surface of and surrounds the PMOS thin body channel. A PMOS metal gate is formed on the PMOS insulating layer. The NMOS insulating layer includes a silicon oxide layer and the PMOS insulating layer includes an electron-trapping layer, the NMOS insulating layer includes a hole trapping dielectric layer and the PMOS insulating layer includes a silicon oxide layer, or the NMOS insulating layer includes a hole-trapping dielectric layer and the PMOS insulating layer includes an electron-trapping dielectric layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of forming a non-volatile electron storage memory and the resulting device

The invention provides a method of forming an electron memory storage device and the resulting device. The device comprises a gate structure which, in form, comprises a first gate insulating layer formed over a semiconductor substrate, a self-forming electron trapping layer of noble metal nano-crystals formed over the first gate insulating layer, a second gate insulating layer formed over the electron trapping layer, a gate electrode formed over the second gate insulating layer, and source and drain regions formed on opposite sides of the gate structure.

Owner:MICRON TECH INC

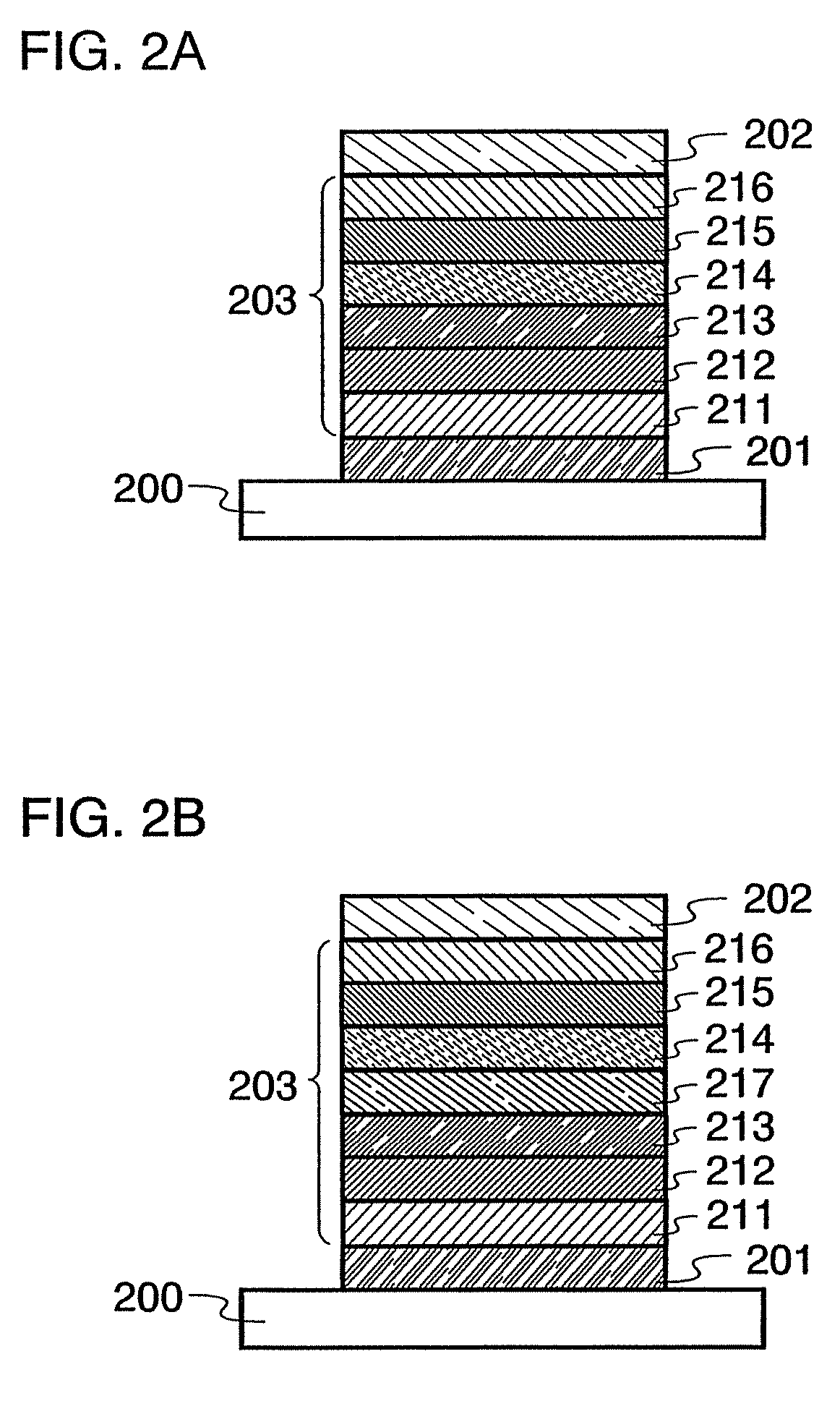

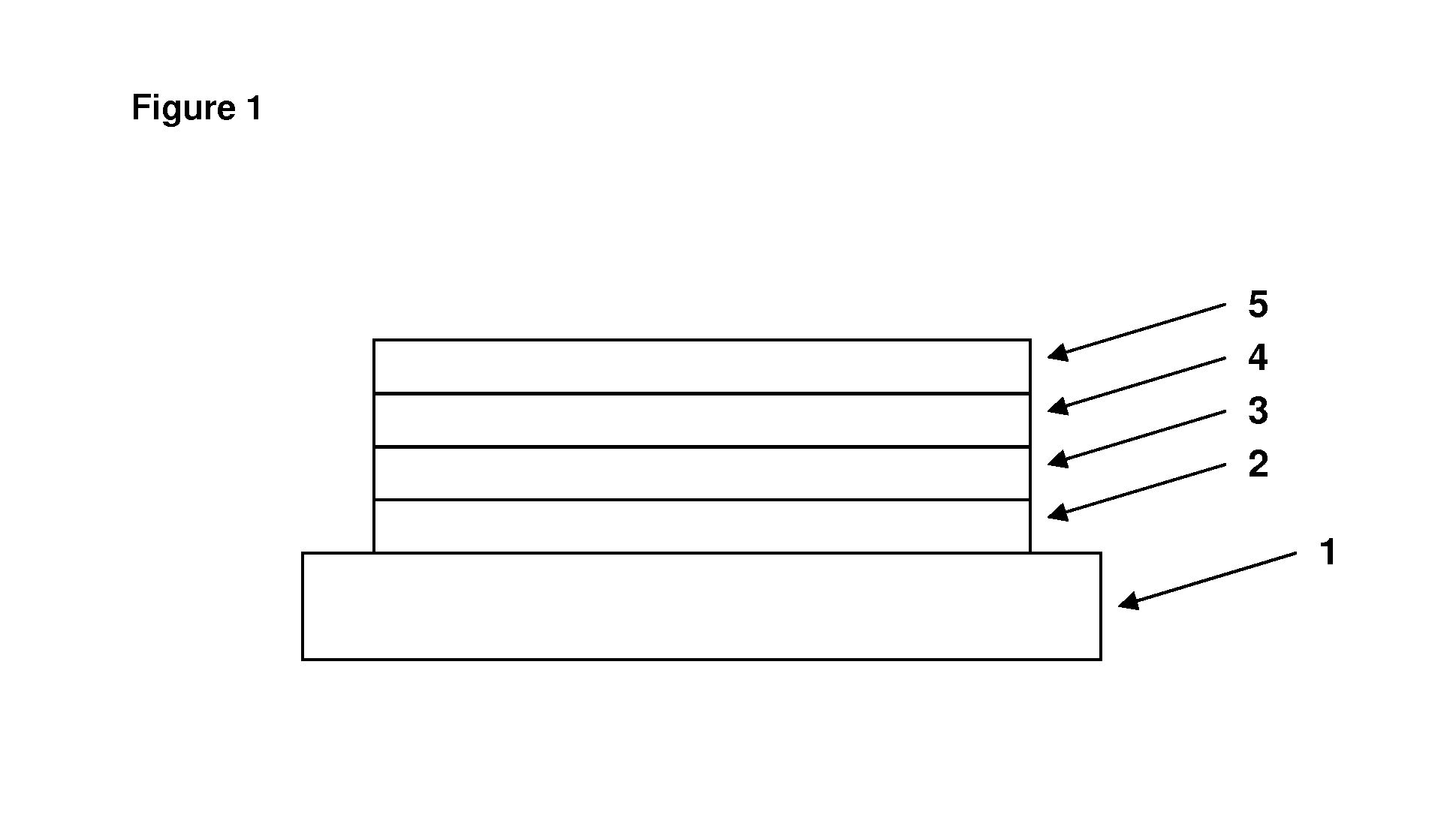

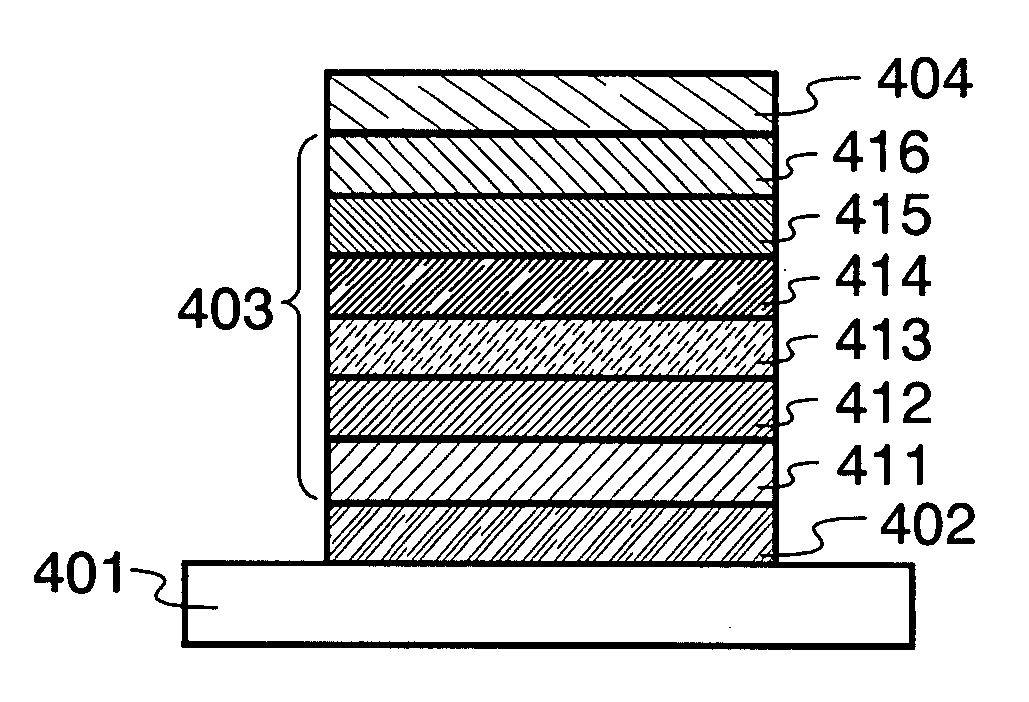

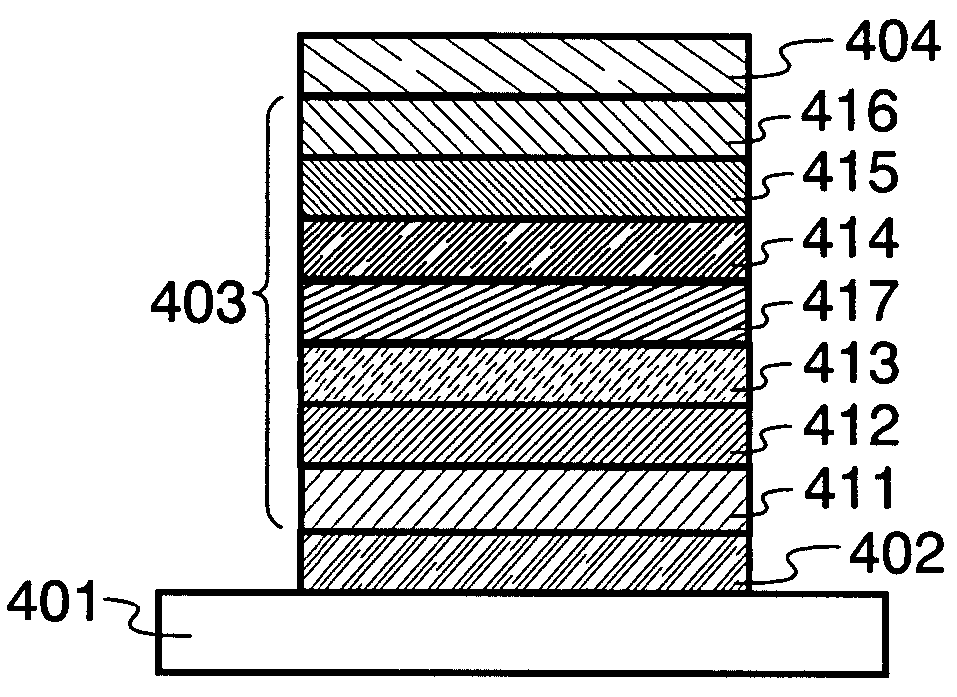

Light-emitting element, light emitting device, electronic appliance, and method of manufacturing the same

ActiveUS20080122350A1Short lifeHigh light emitting efficiencyDischarge tube luminescnet screensLamp detailsElectronic transmissionOrganic compound

A light-emitting element is provided which has a light-emitting layer between a first electrode and a second electrode, where the light-emitting layer has a first layer and a second layer; the first layer contains a first organic compound and a third organic compound; the second layer contains a second organic compound and the third organic compound; the first layer is provided to be in contact with the second layer on the first electrode side; the first organic compound is an organic compound with an electron transporting property; the second organic compound is an organic compound with a hole transporting property; the third organic compound has an electron trapping property; and light emission from the third organic compound can be obtained when voltage is applied to the first electrode and the second electrode so that the potential of the first electrode is higher than that of the second electrode.

Owner:SEMICON ENERGY LAB CO LTD

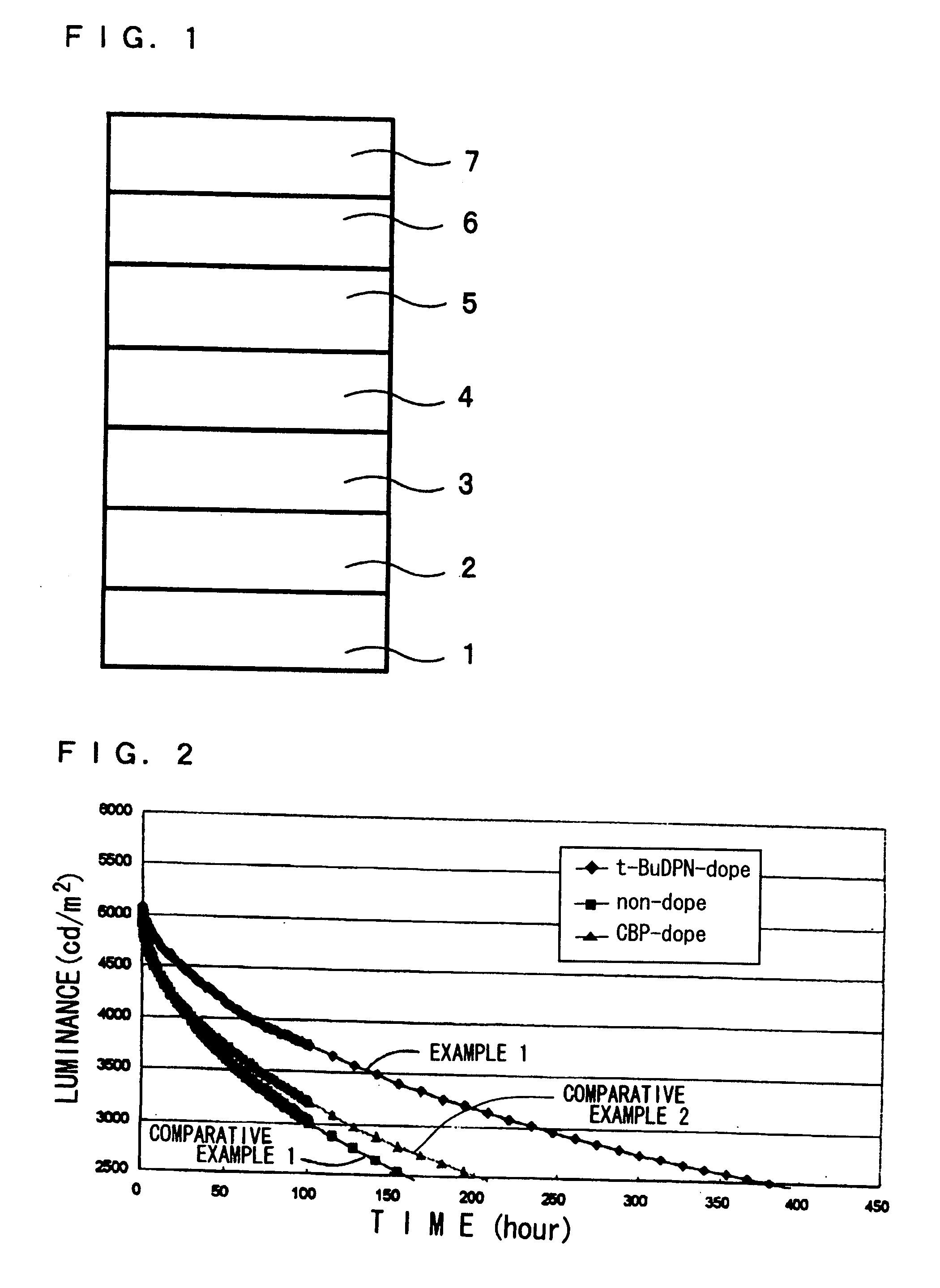

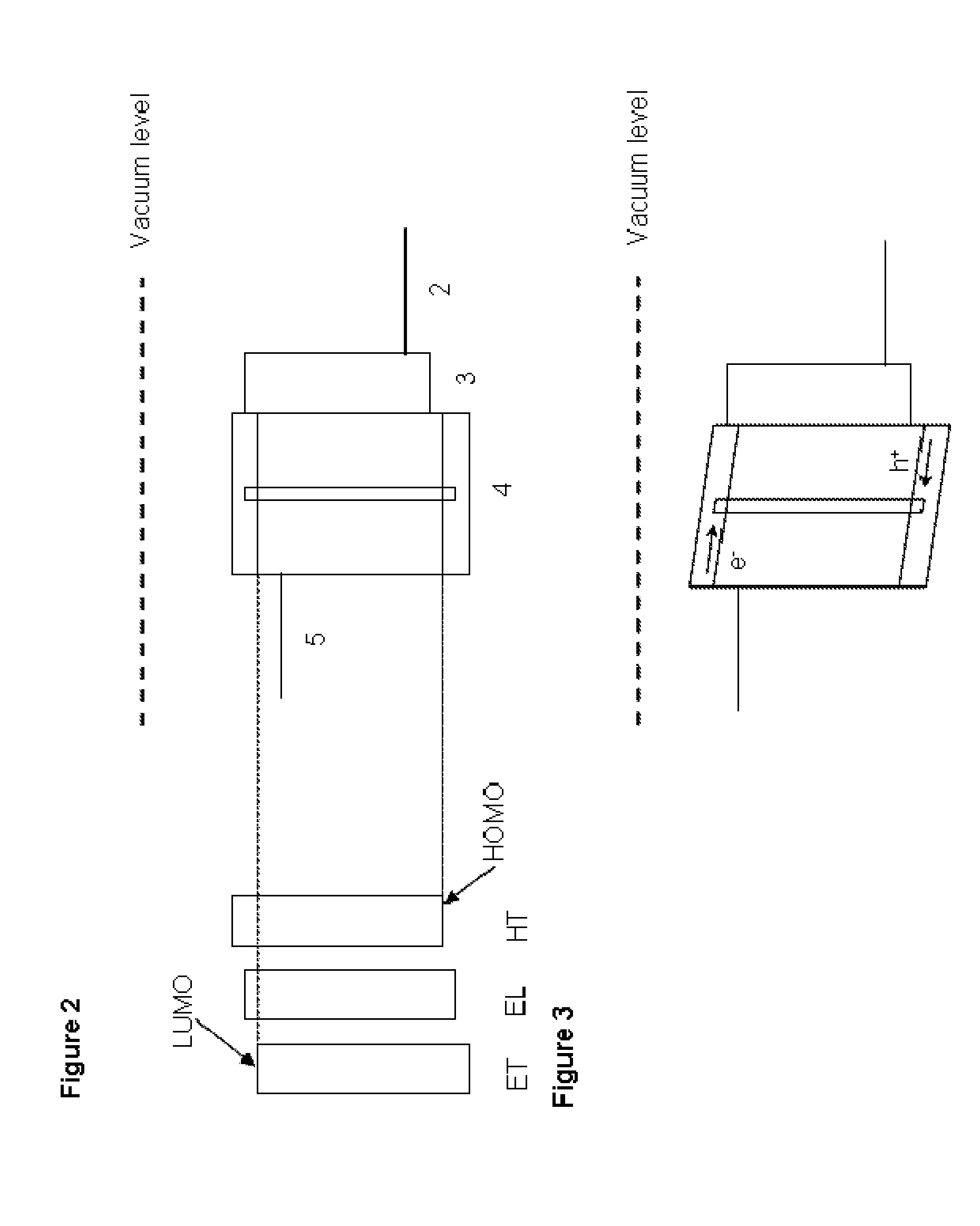

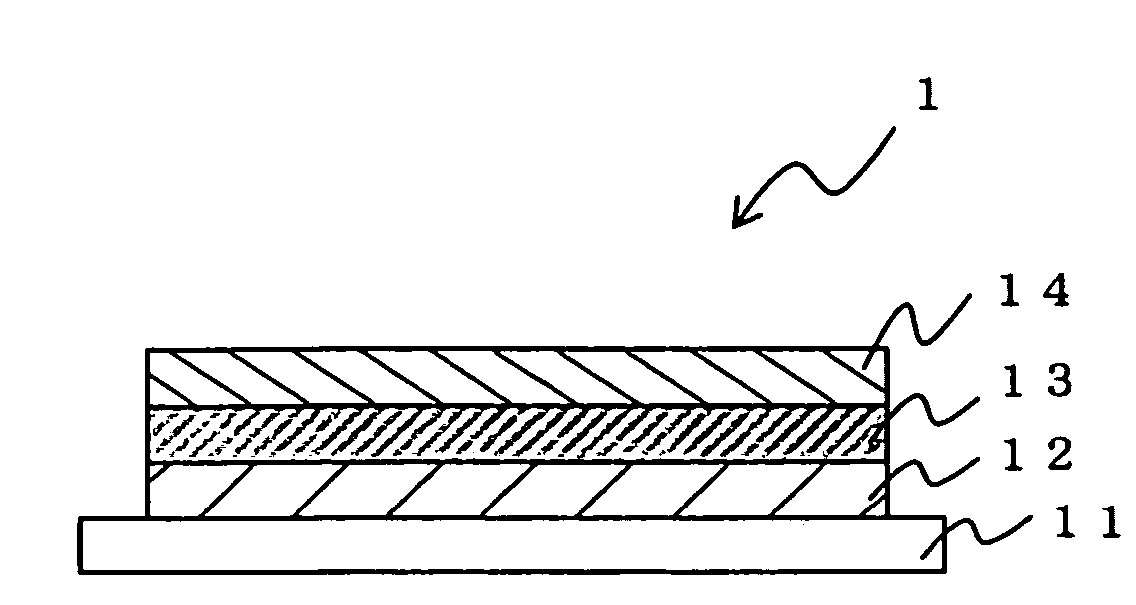

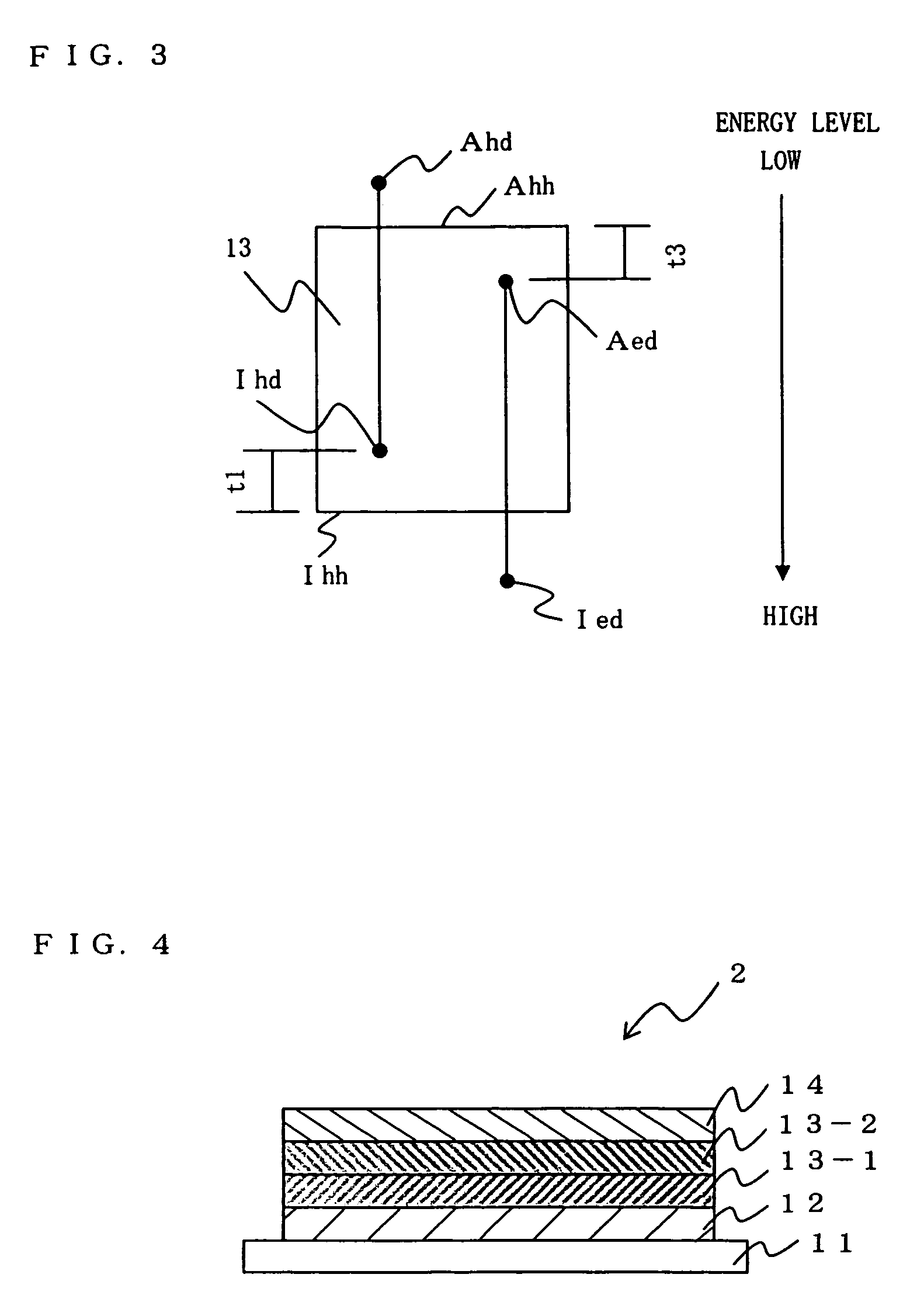

Organic electroluminescent device

ActiveUS7528542B2Reduced durabilityExtended service lifeDischarge tube luminescnet screensElectroluminescent light sourcesDopantHost material

An organic electroluminescent device 1 including: an anode 12, a cathode 14 and an organic emitting layer 13 held therebetween, the organic emitting layer 13 containing one or more host materials, a hole trapping dopant and an electron trapping dopant. The lifetime of an organic EL device 1 can be improved by causing a hole-trapping dopant and an electron-trapping dopant to be together present in its organic emitting layer.

Owner:IDEMITSU KOSAN CO LTD

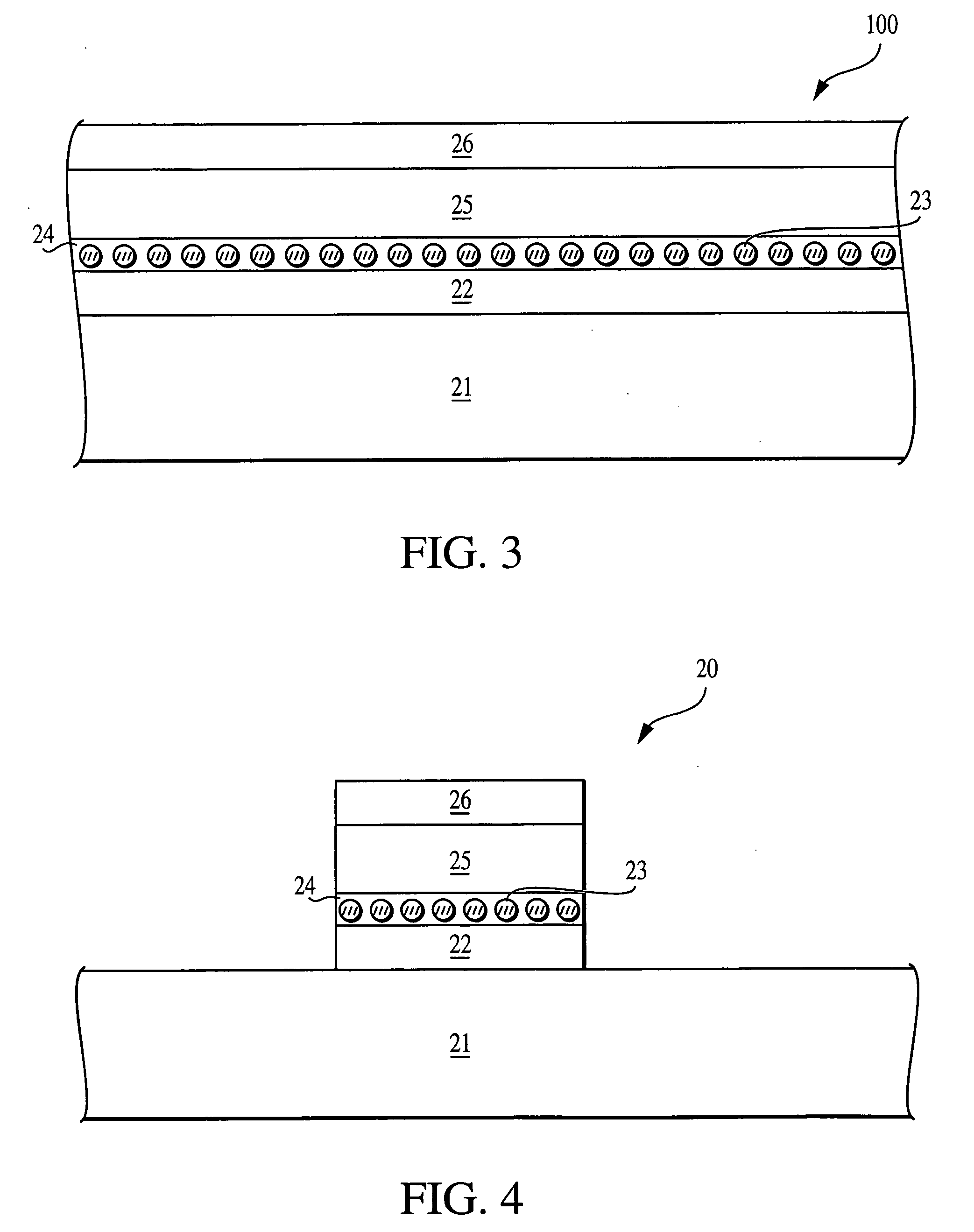

Method for fabricating non-volatile memory

ActiveUS7071061B1Improve efficiencySimple processSemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerNon-volatile memory

A method of fabricating a non-volatile memory is described. A substrate is provided and a first dielectric layer, an electron trapping layer and a second dielectric layer are sequentially formed thereon. Each of the stacked gate structures includes a first gate and a cap layer having a gap between every two stacked gate structures. An oxide layer is formed on the sidewalls of the first gate. A portion of the second dielectric layer not covered by the stacked gate structures is removed. A third dielectric layer is further formed on the substrate. A second conductive layer is formed over the substrate, and a portion thereof to form second gates. The second gates and the stacked gate structures form a column of memory cells. A source region and a drain region are formed in the substrate adjacent to two sides of the column of memory cells.

Owner:POWERCHIP SEMICON MFG CORP

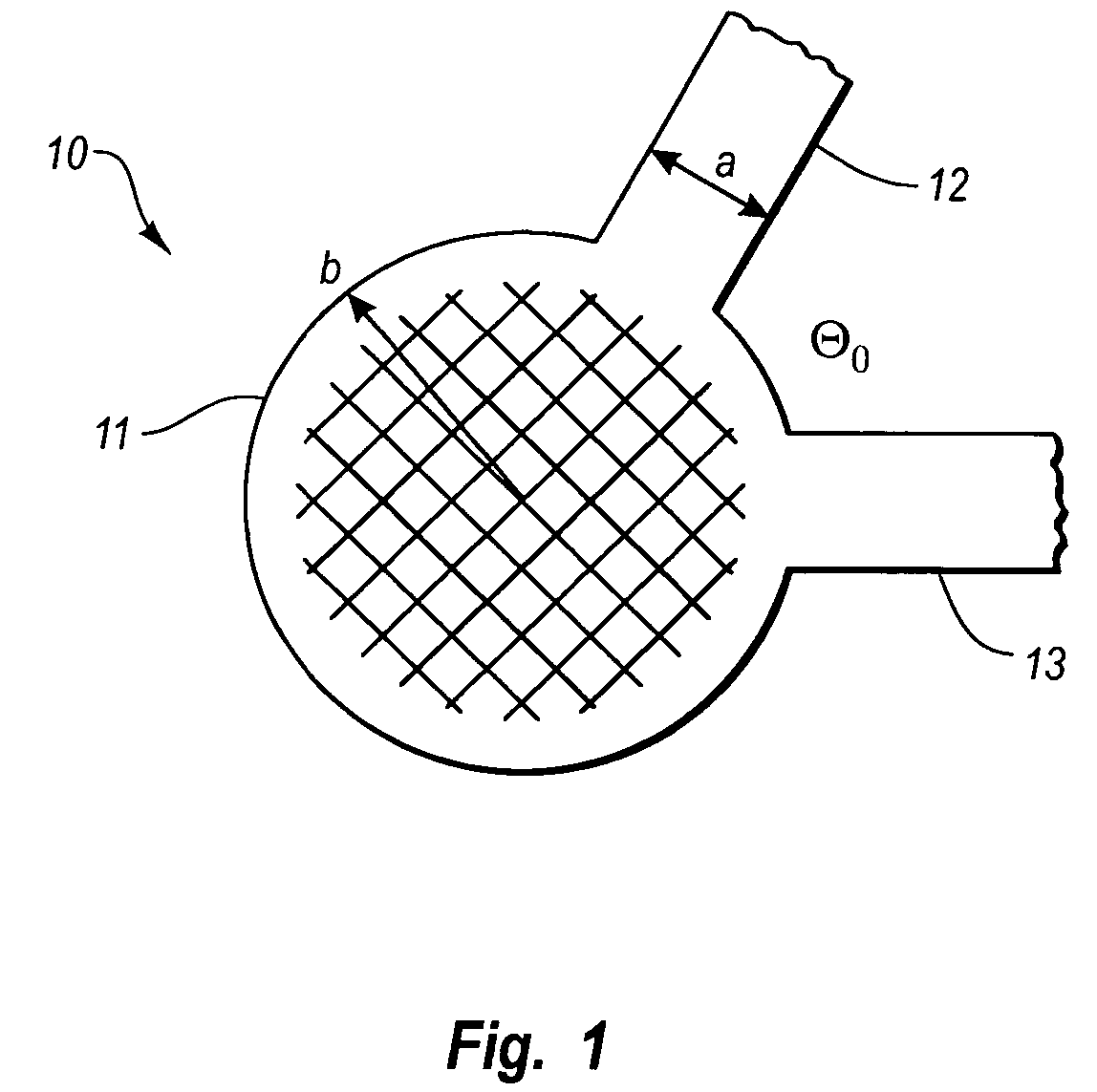

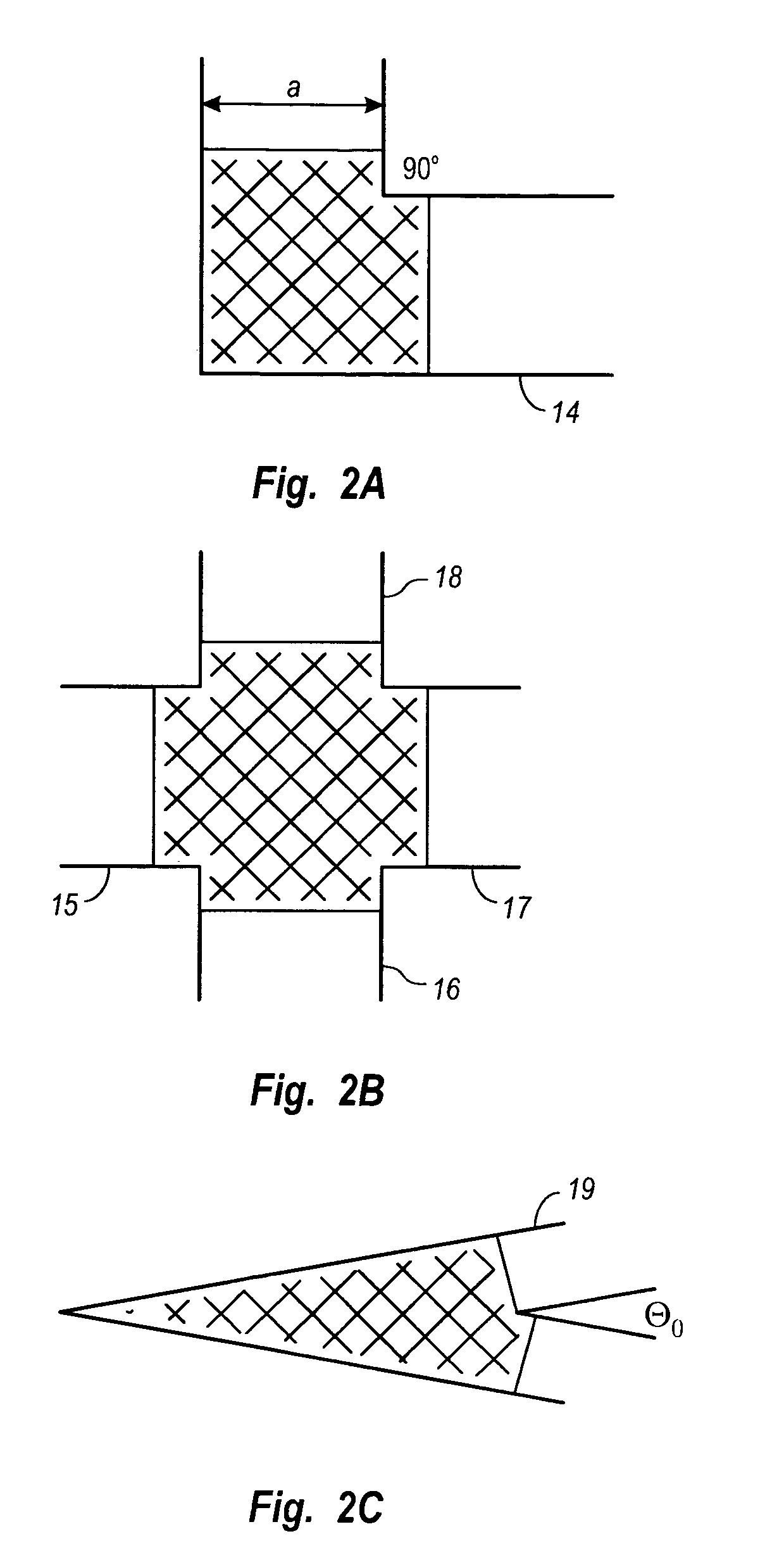

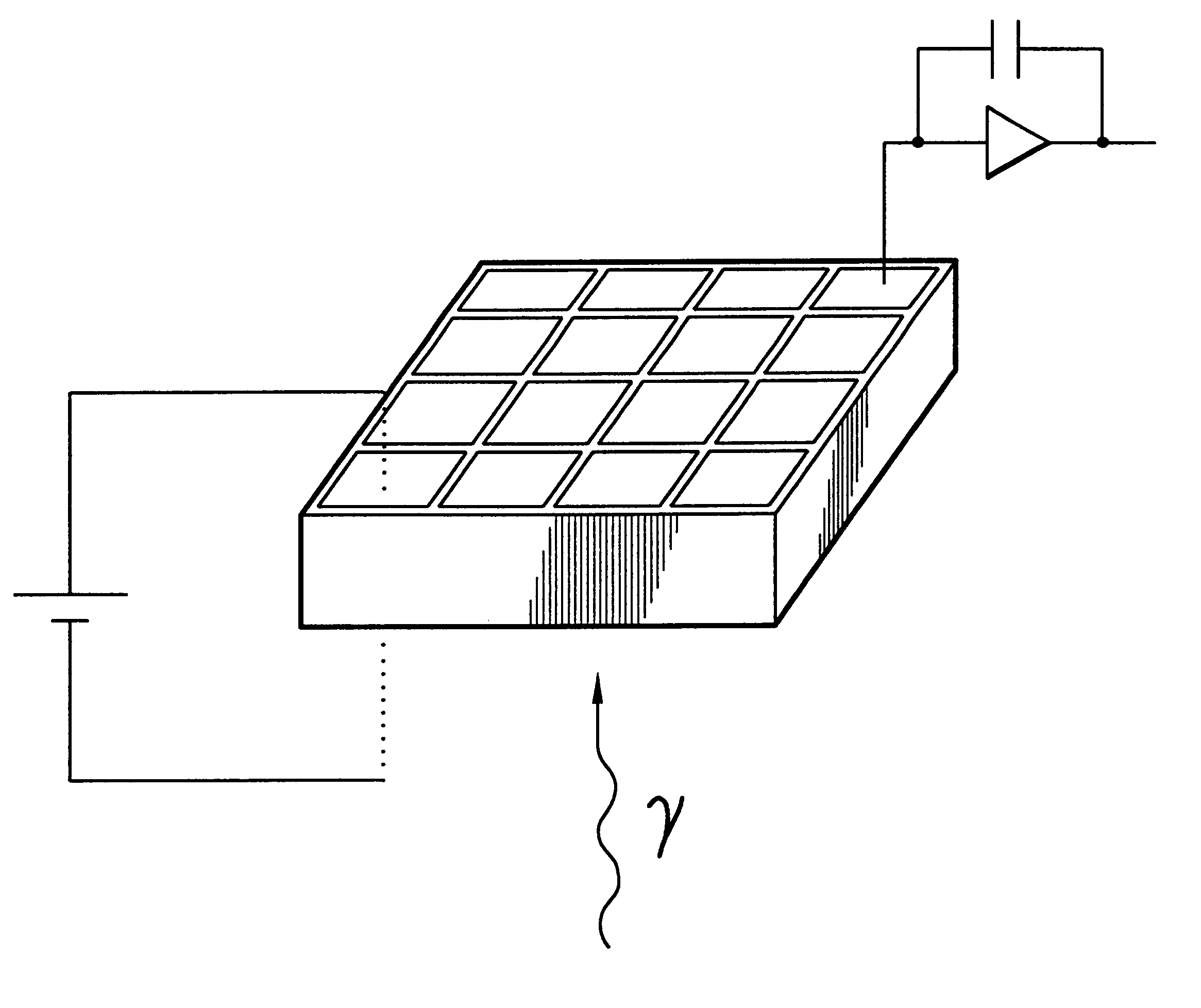

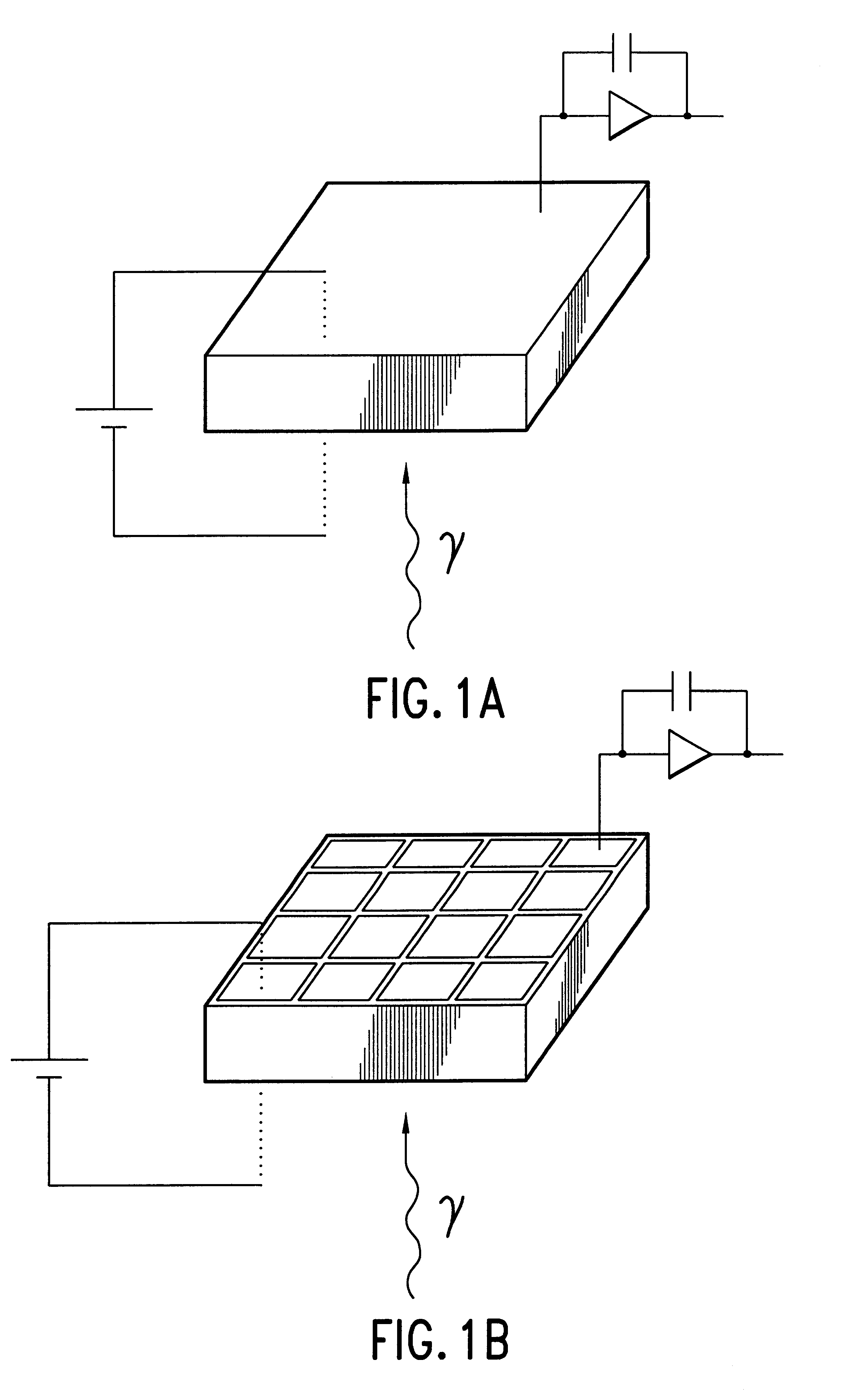

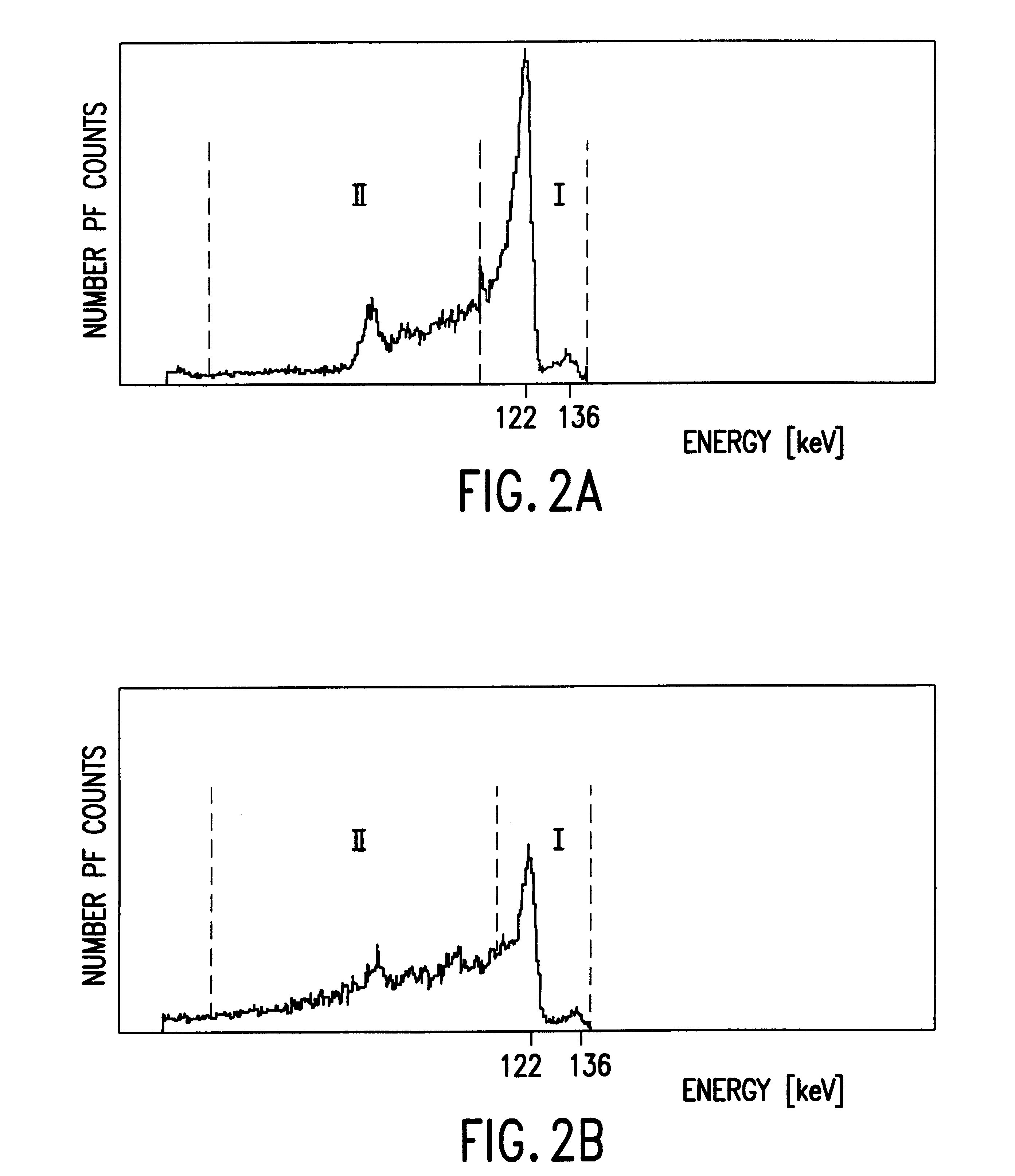

Room temperature solid state gamma or X-ray detectors

InactiveUS6331705B1Reduce in quantityWeaken energySolid-state devicesMaterial analysis by optical meansSolid state detectorX-ray

The invention provides a method for detecting gamma or X-ray radiation with a room temperature solid state detector, which comprises the selection of the detector's electron trapping parameter (muτ)e and / or the detector voltage V so as to tune the electron trapping to optimally compensate for the incomplete charge collection.

Owner:STATE OF ISRAEL ATOMIC ENERGY COMMISSION SOREQ NUCLEAR RES CENT THE

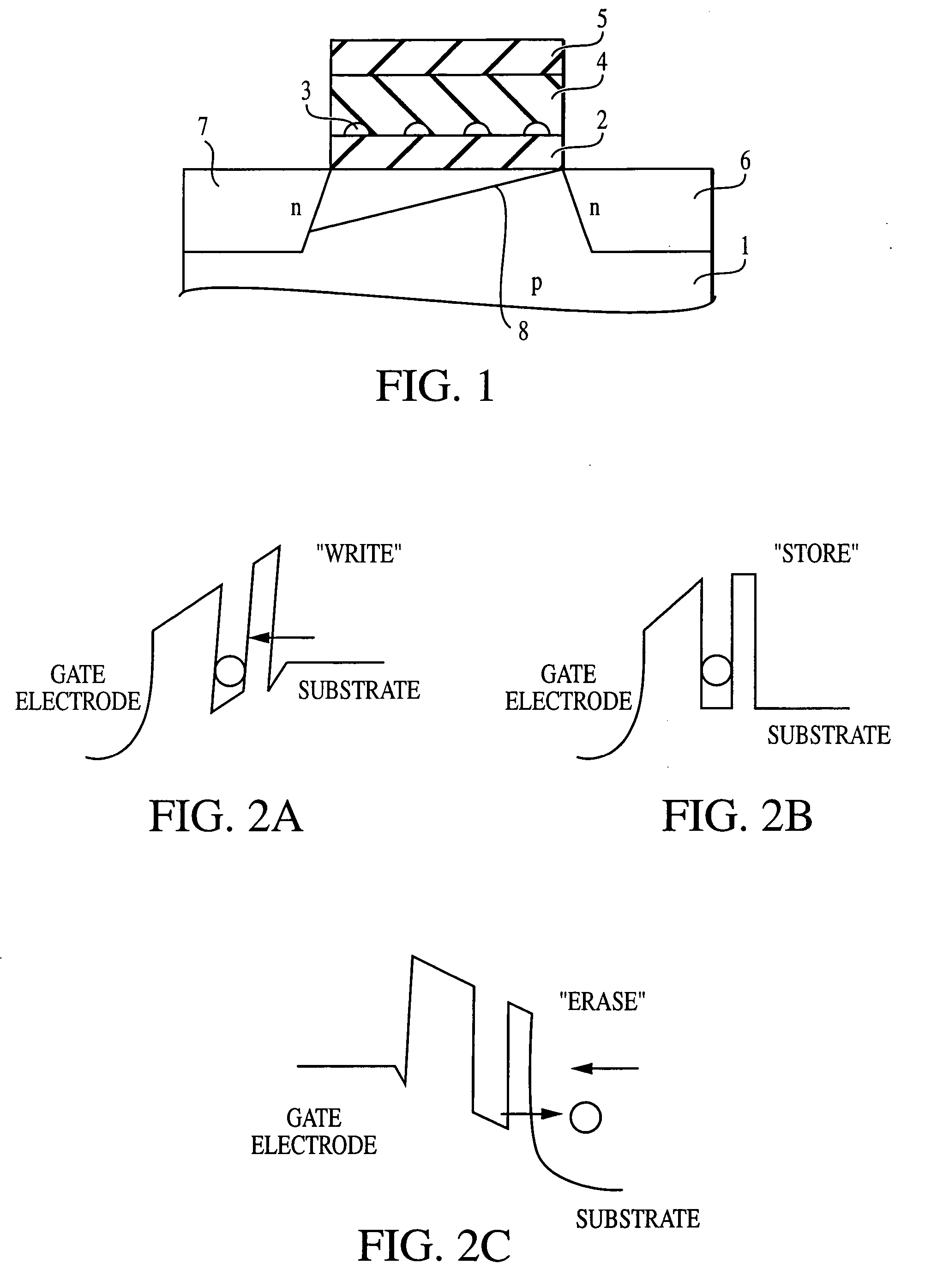

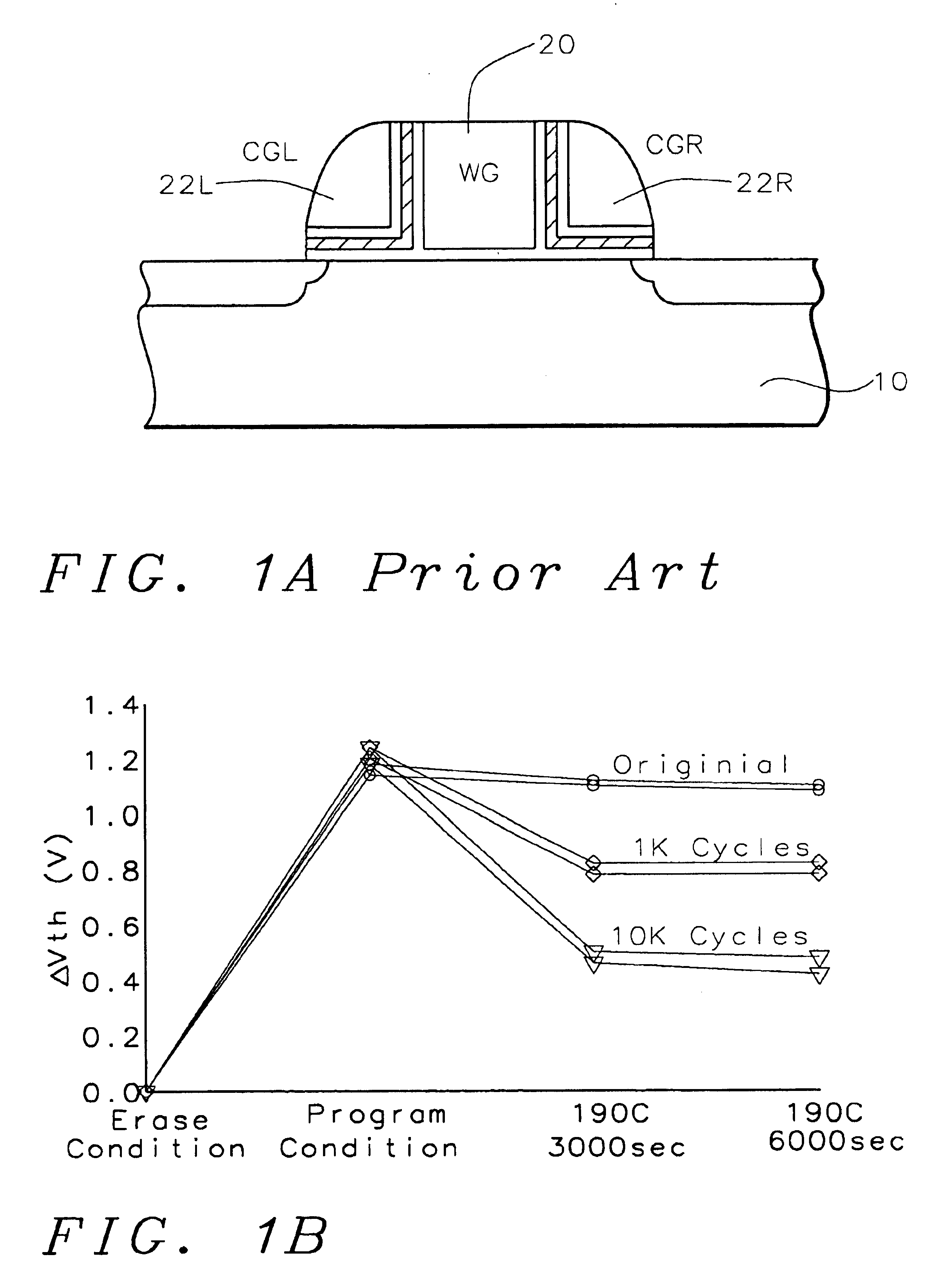

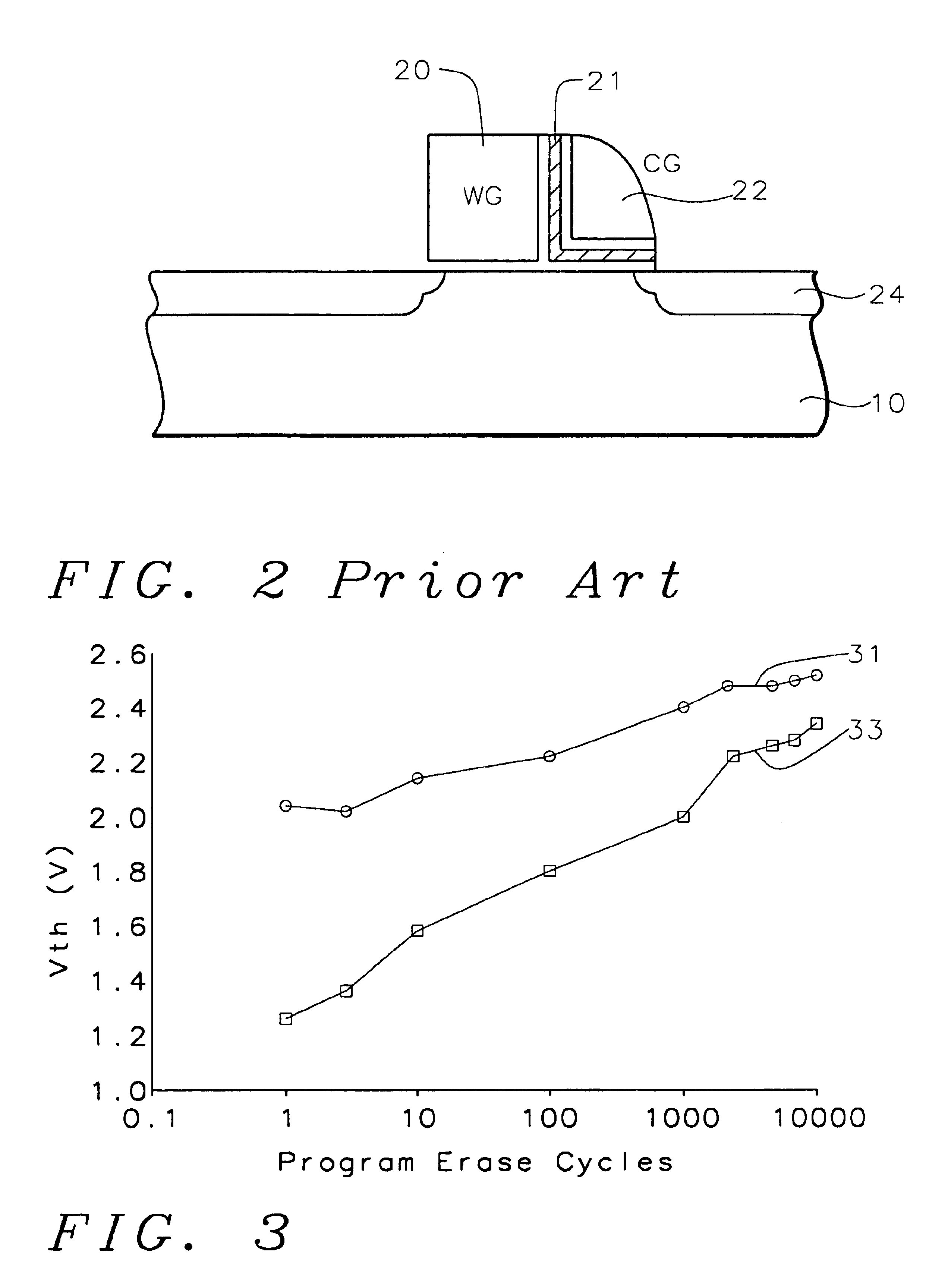

Twin insulator charge storage device operation and its fabrication method

ActiveUS6900098B1High densityEasily embedded into conventional CMOS platformSolid-state devicesRead-only memoriesCMOSEngineering

The invention proposes am improved twin MONOS memory device and its fabrication. The ONO layer is self-aligned to the control gate horizontally. The vertical insulator between the control gate and the word gate does not include a nitride layer. This prevents the problem of electron trapping. The device can be fabricated to pull the electrons out through either the top or the bottom oxide layer of the ONO insulator. The device also incorporates a raised memory bit diffusion between the control gates to reduce bit resistance. The twin MONOS memory array can be embedded into a standard CMOS circuit by the process of the present invention.

Owner:HALO LSI INC

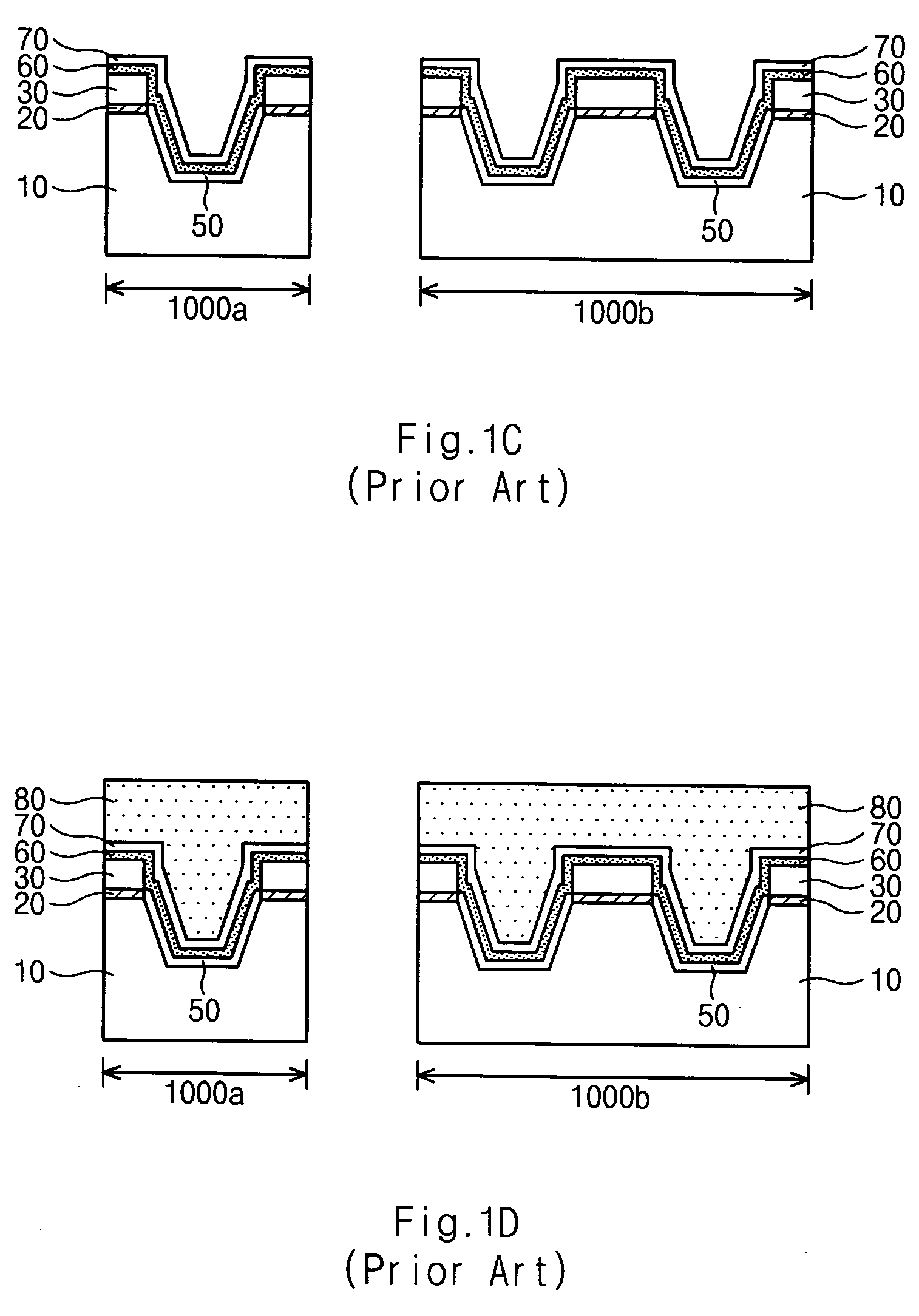

Method for manufacturing device isolation film of semiconductor device

ActiveUS20060024912A1Improving semiconductor device characteristicHEIP phenomenon is reduced or preventedSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialTrapping

A method for manufacturing device isolation film of semiconductor device is disclosed. The method utilizes a plasma oxidation of a liner nitride film exposed by etching a liner oxide the film in peripheral region prior to the formation of device isolation film to prevent the generation of a electron trap which causes trapping of electrons at the interface of the oxide film and the nitride film resulting in a HEIP phenomenon.

Owner:SK HYNIX INC

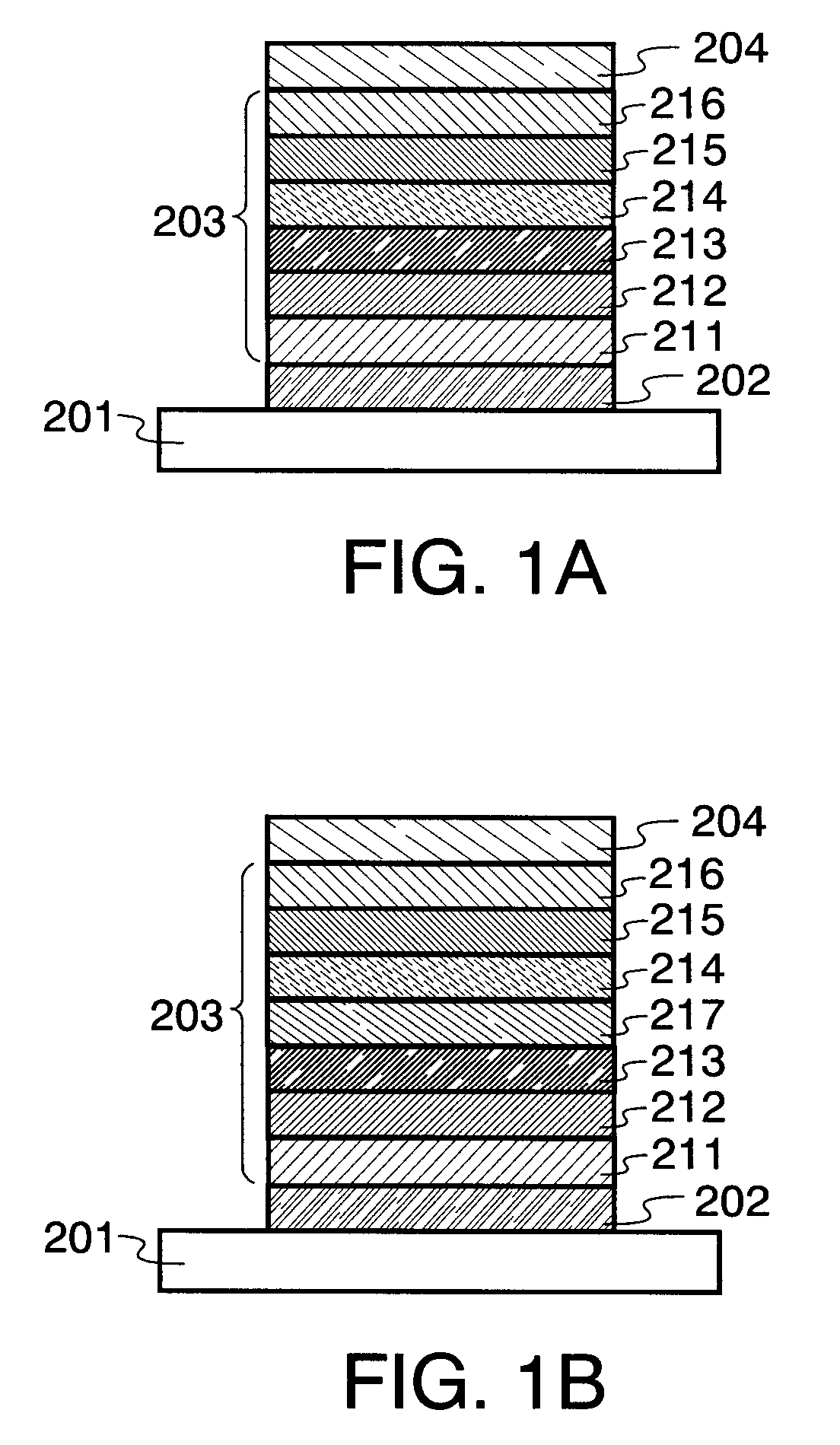

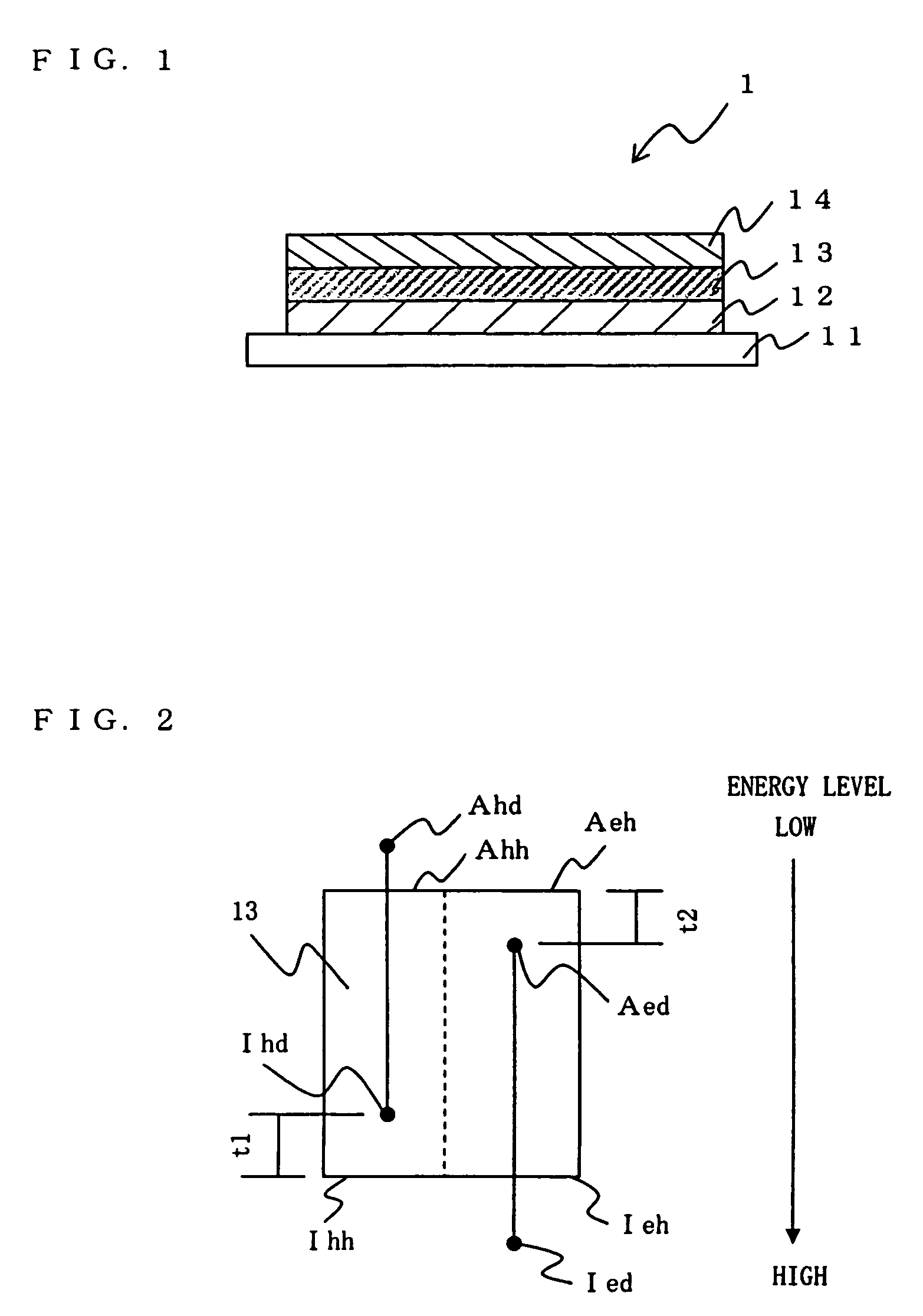

Light-emitting element, light-emitting device, and electronic device

ActiveUS7615925B2Avoid changeImprove suppression propertiesDischarge tube luminescnet screensLamp detailsElectronic transmissionCharge carrier

The light-emitting element includes: a light-emitting layer and a layer for controlling the movement of carriers between a first electrode and a second electrode. The layer for controlling the movement of carriers contains a first organic compound and a second organic compound, and is provided between the light-emitting layer and the second electrode. The first organic compound has an electron transporting property, and the second organic compound has an electron trapping property. The weight percent of the first organic compound is higher than that of the second organic compound. The light-emitting layer emits light when a voltage is applied such that the potential of the first electrode is higher than that of the second electrode. The first organic compound having the electron transporting property may be replaced with an organic compound having a hole transporting property, and the second organic compound having the electron trapping property may be replaced with an organic compound having a hole trapping property.

Owner:SEMICON ENERGY LAB CO LTD

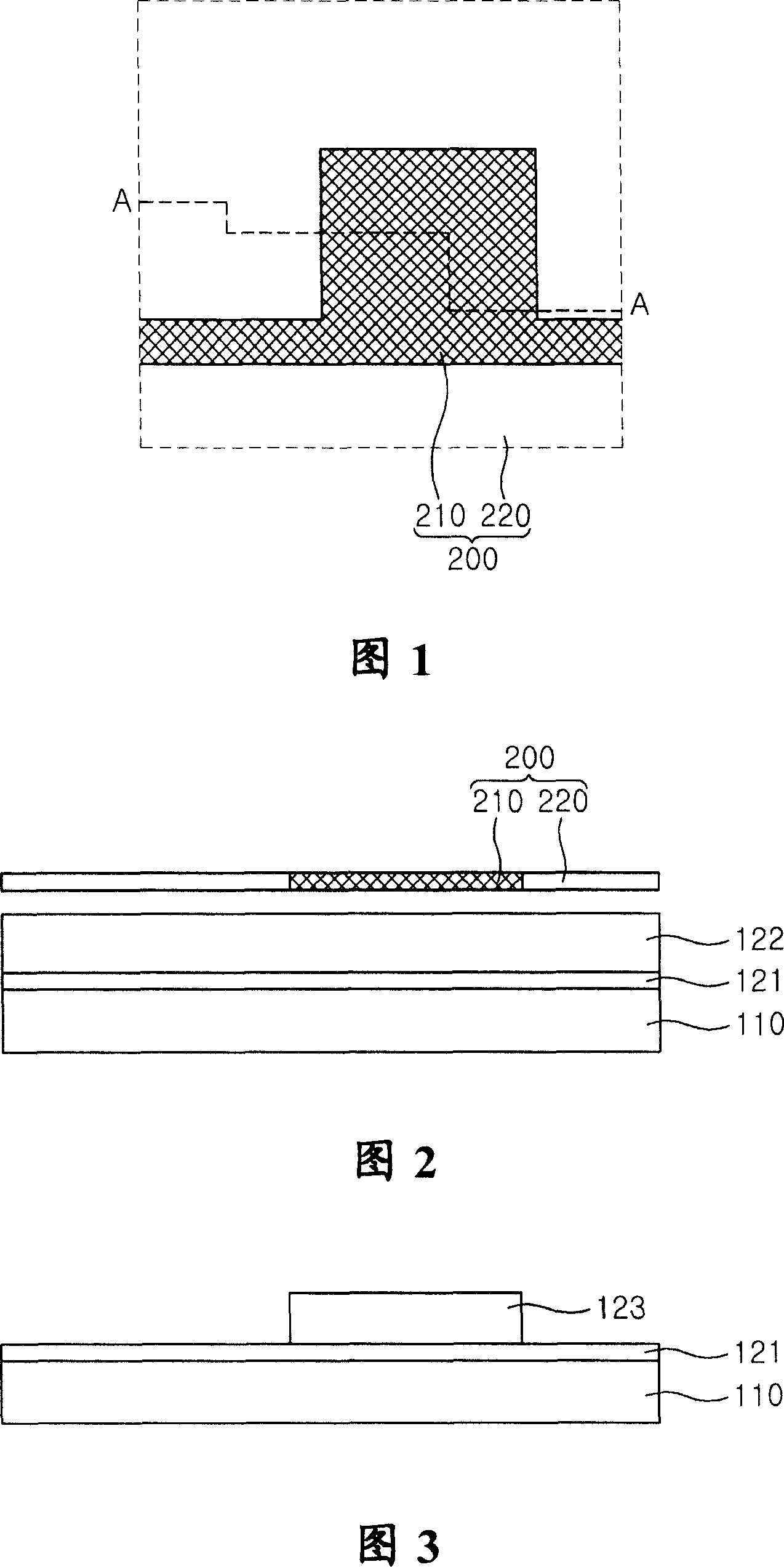

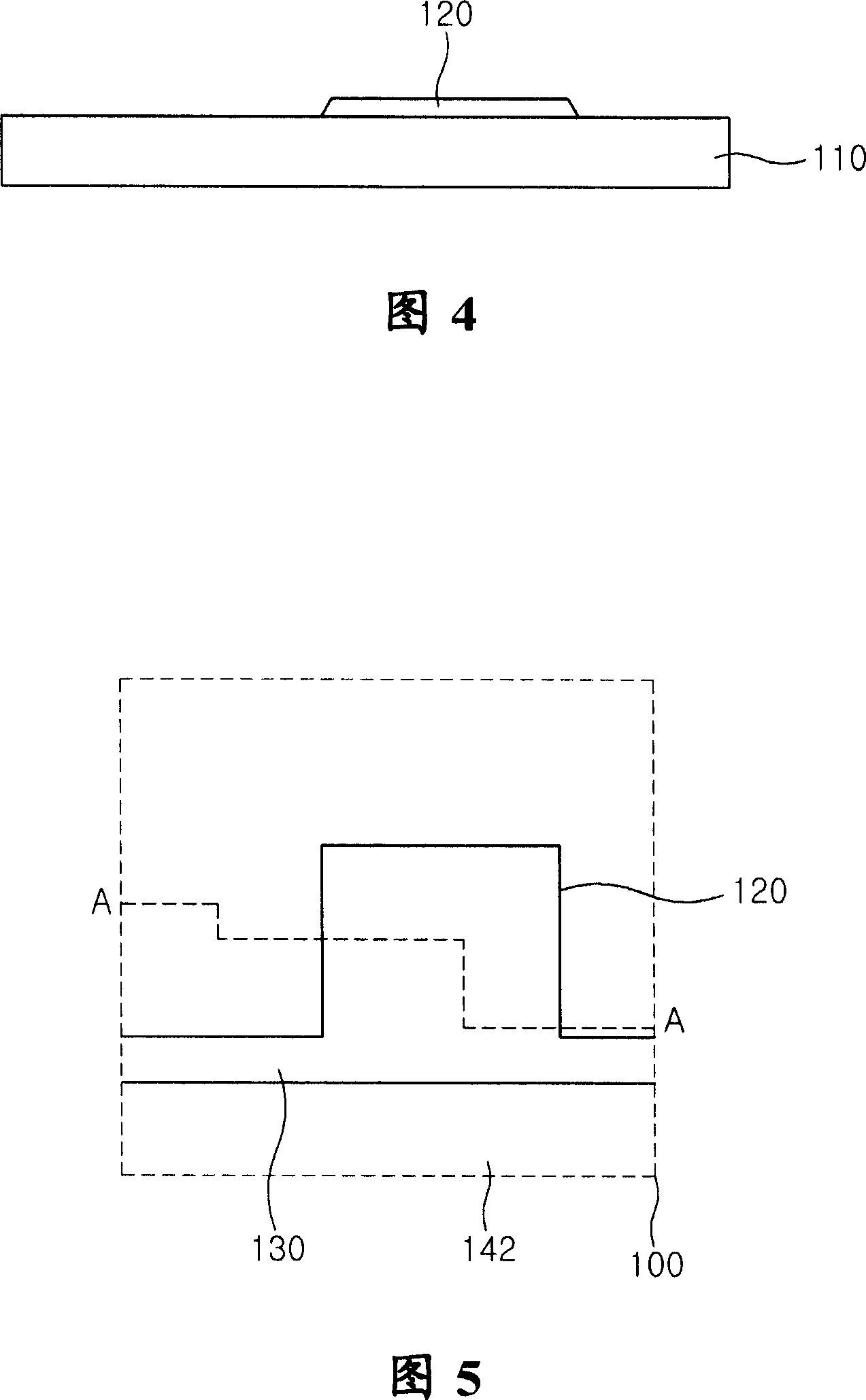

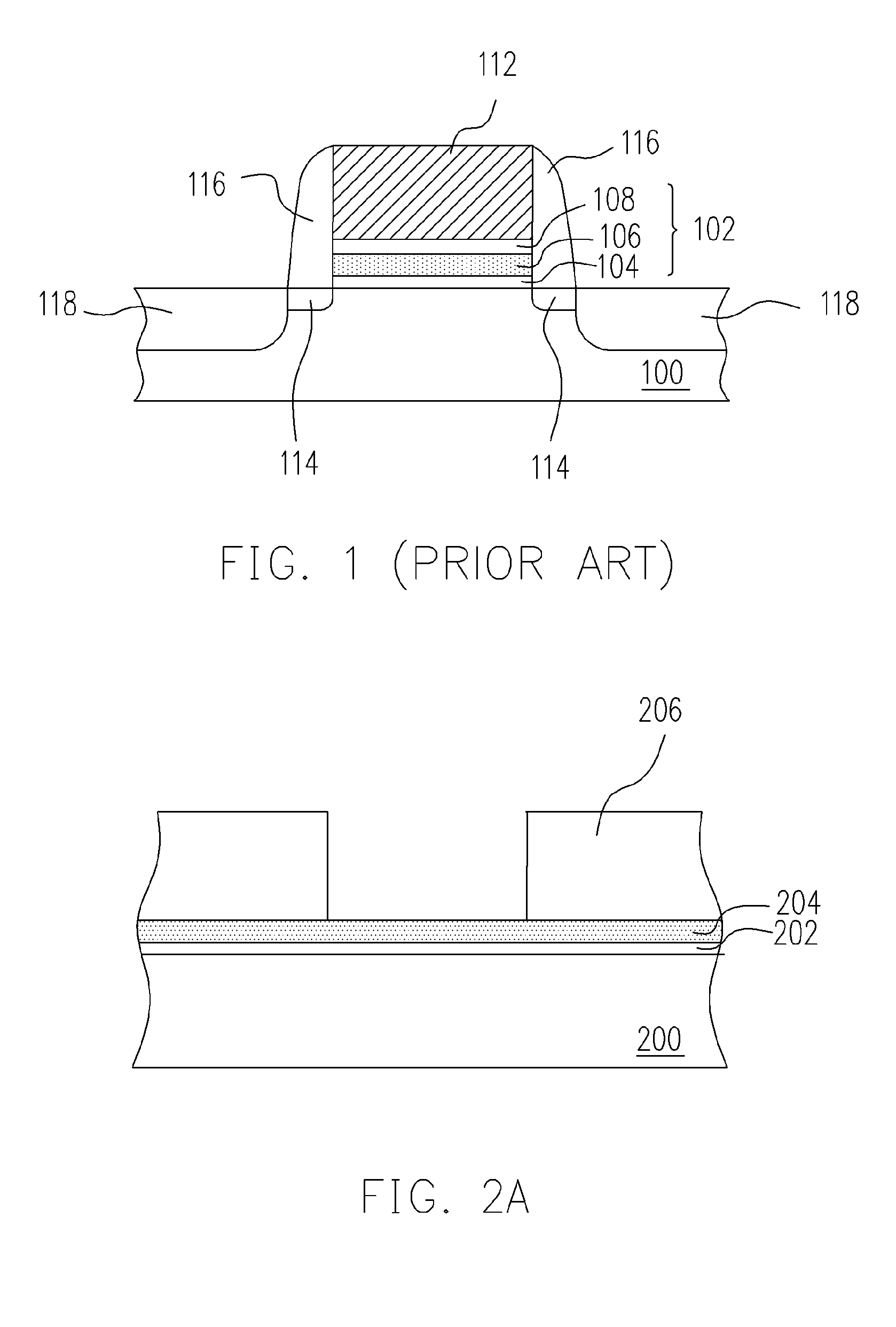

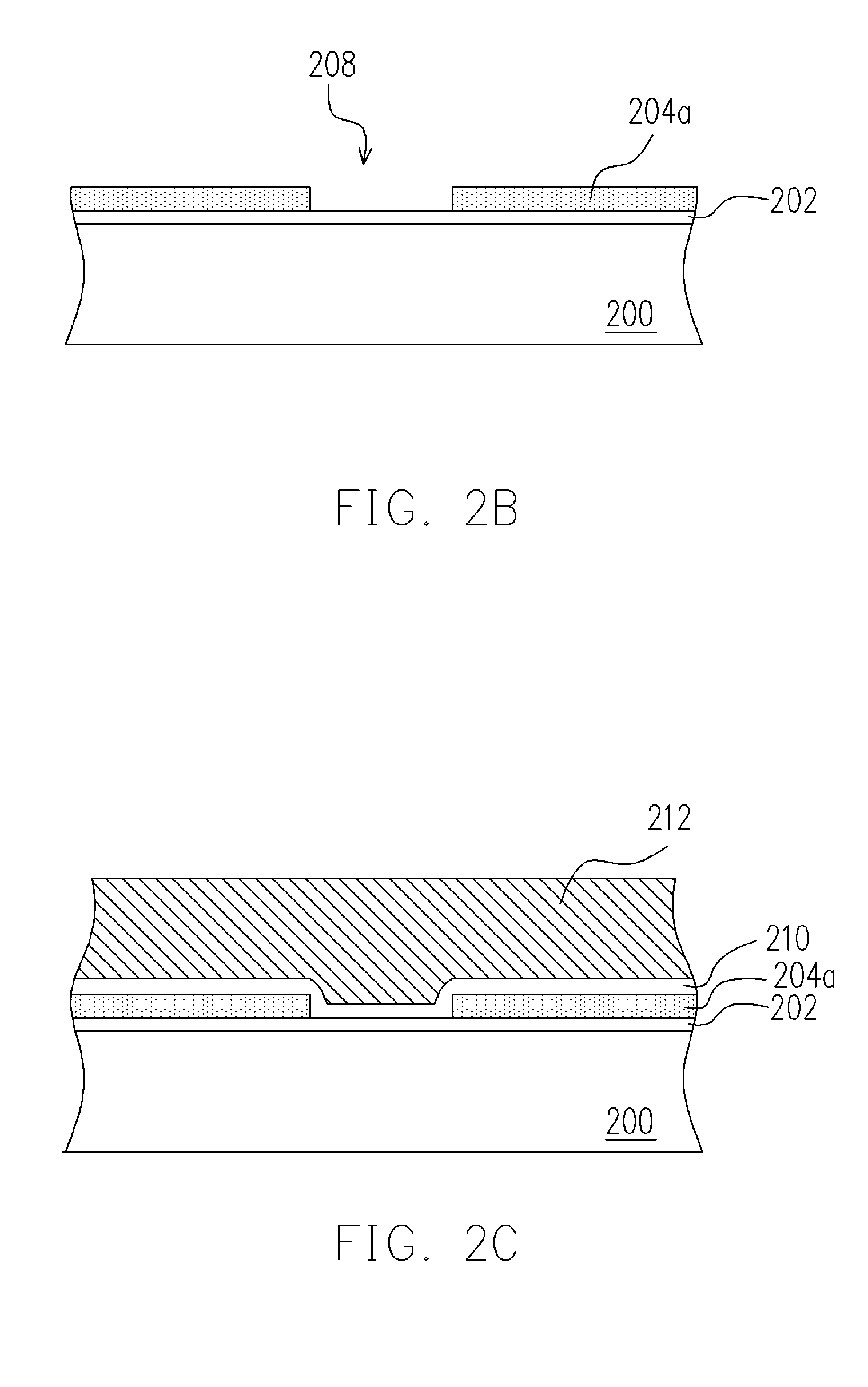

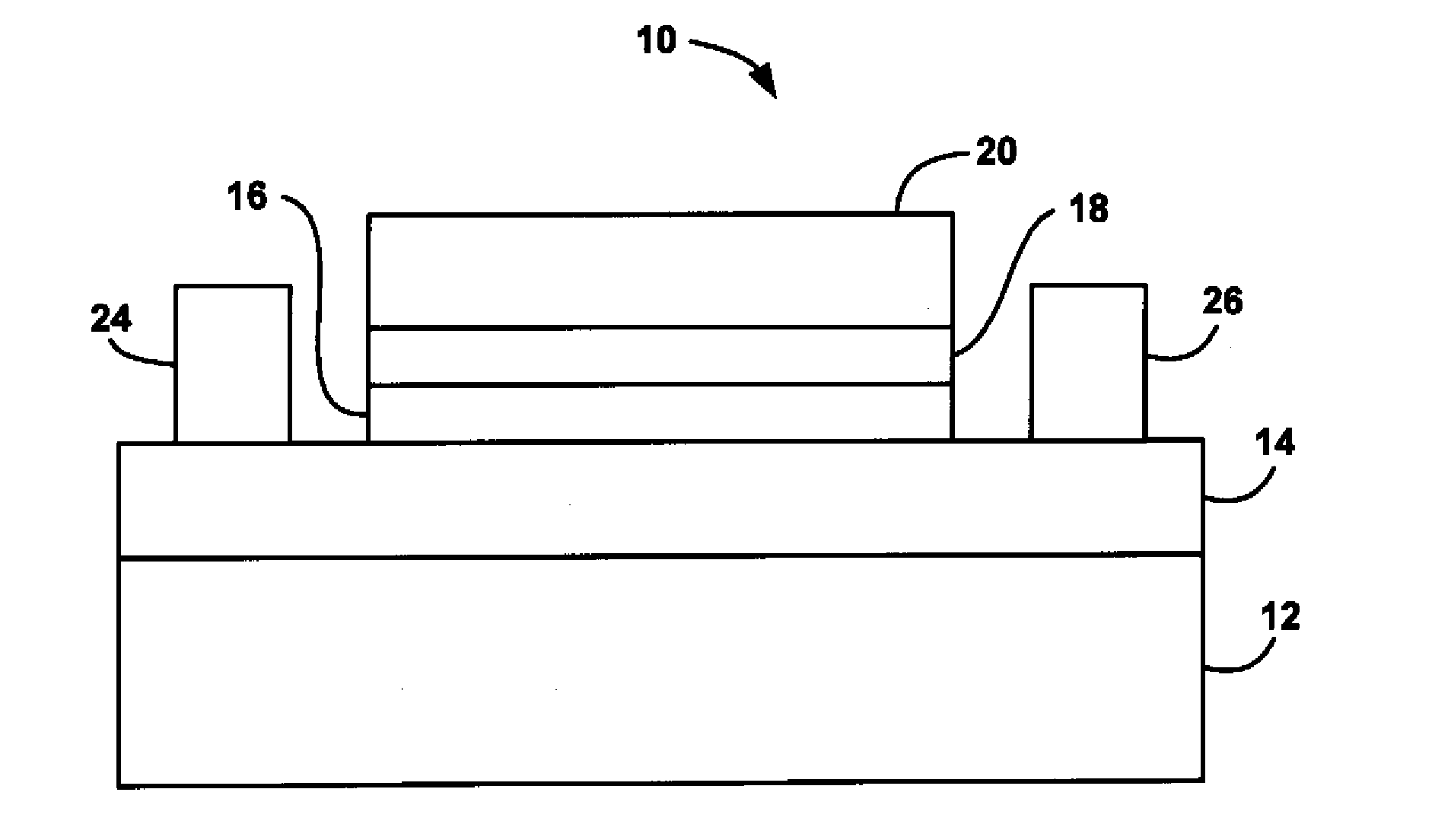

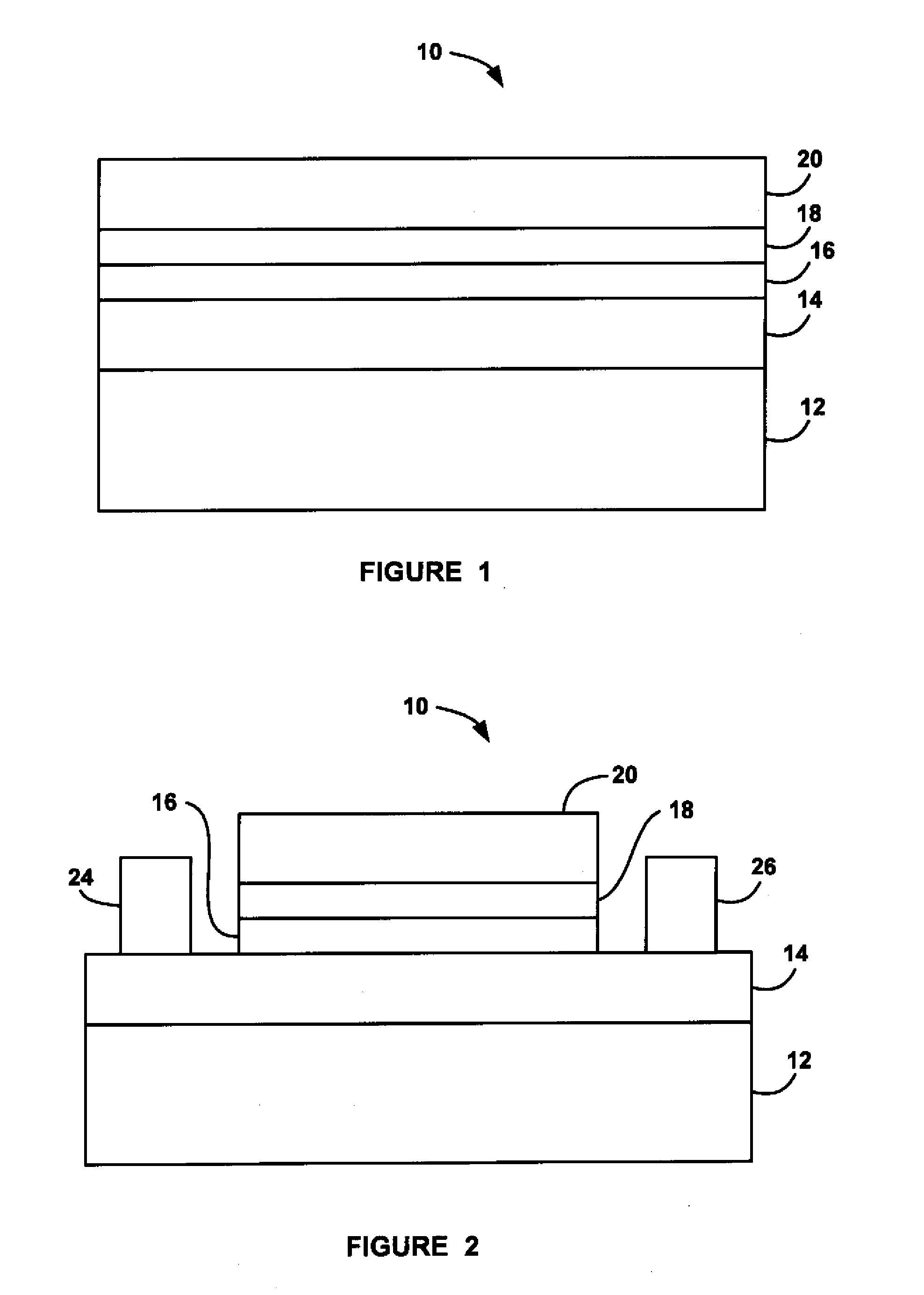

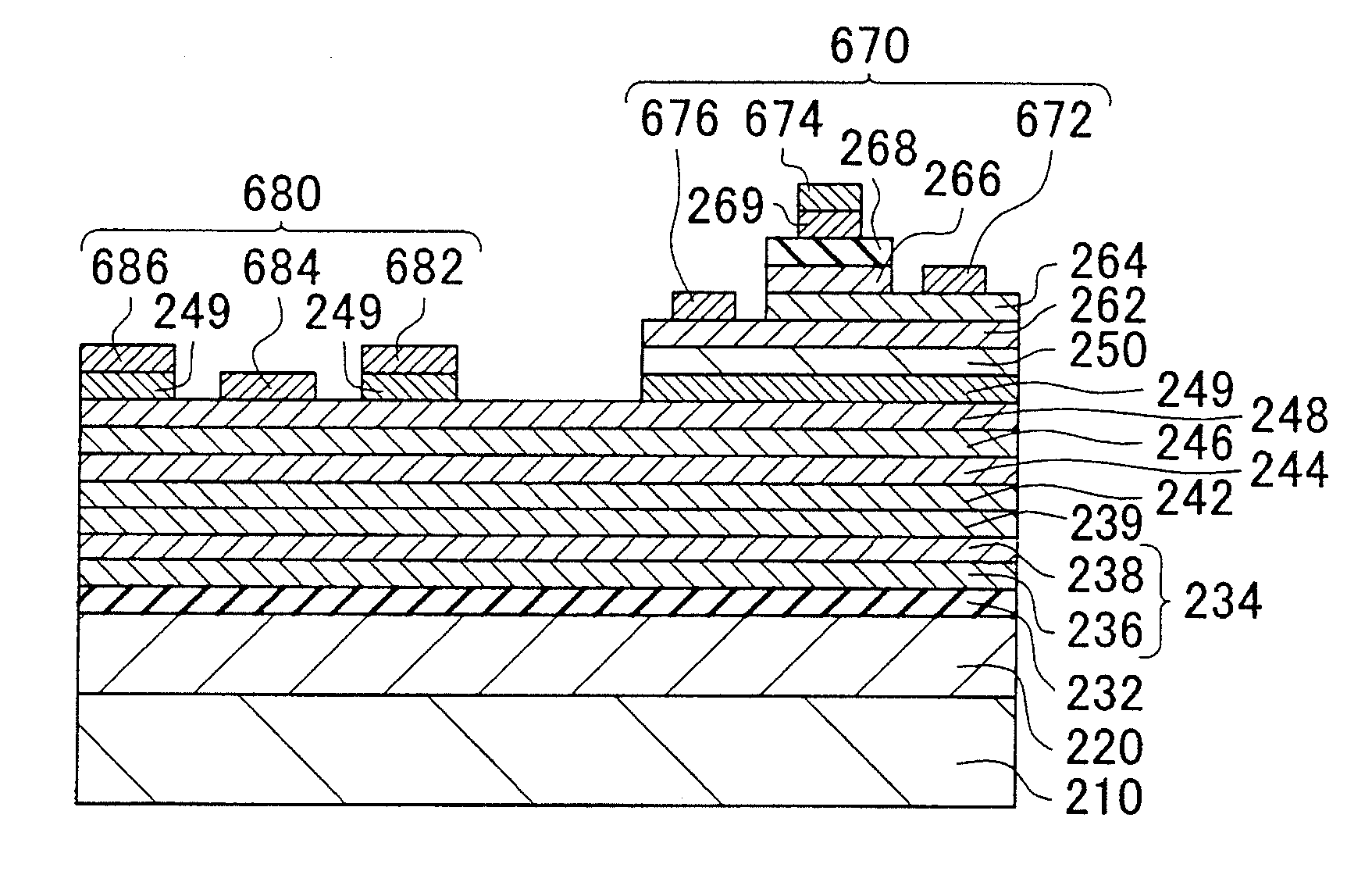

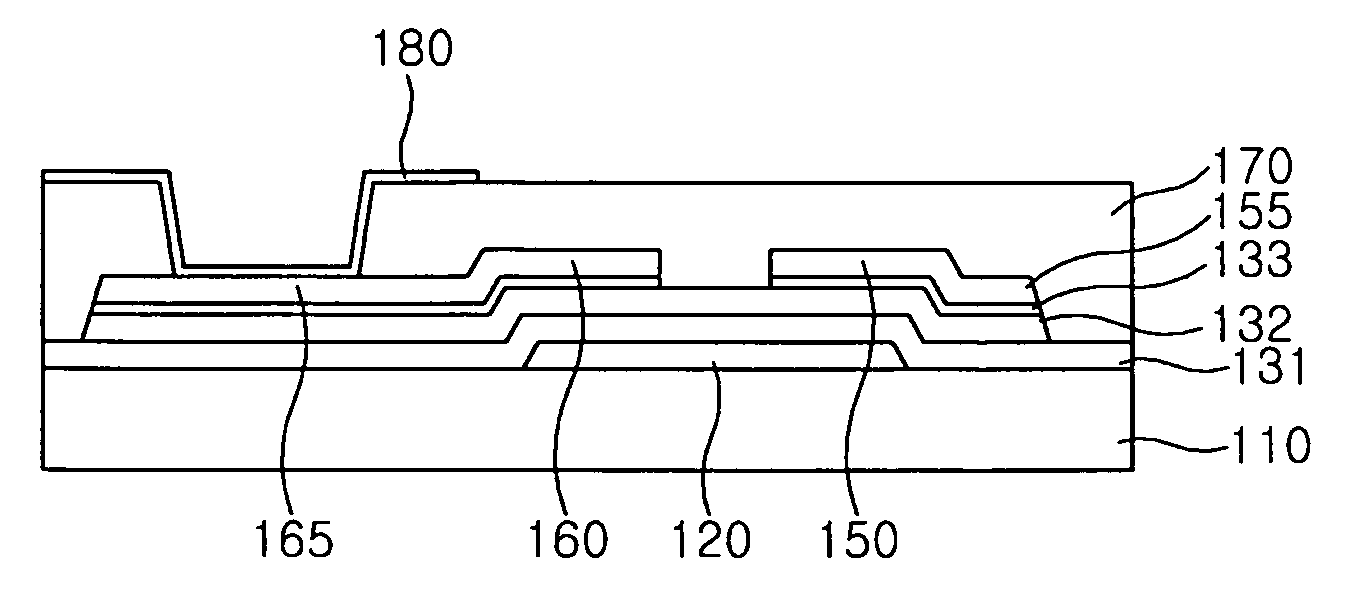

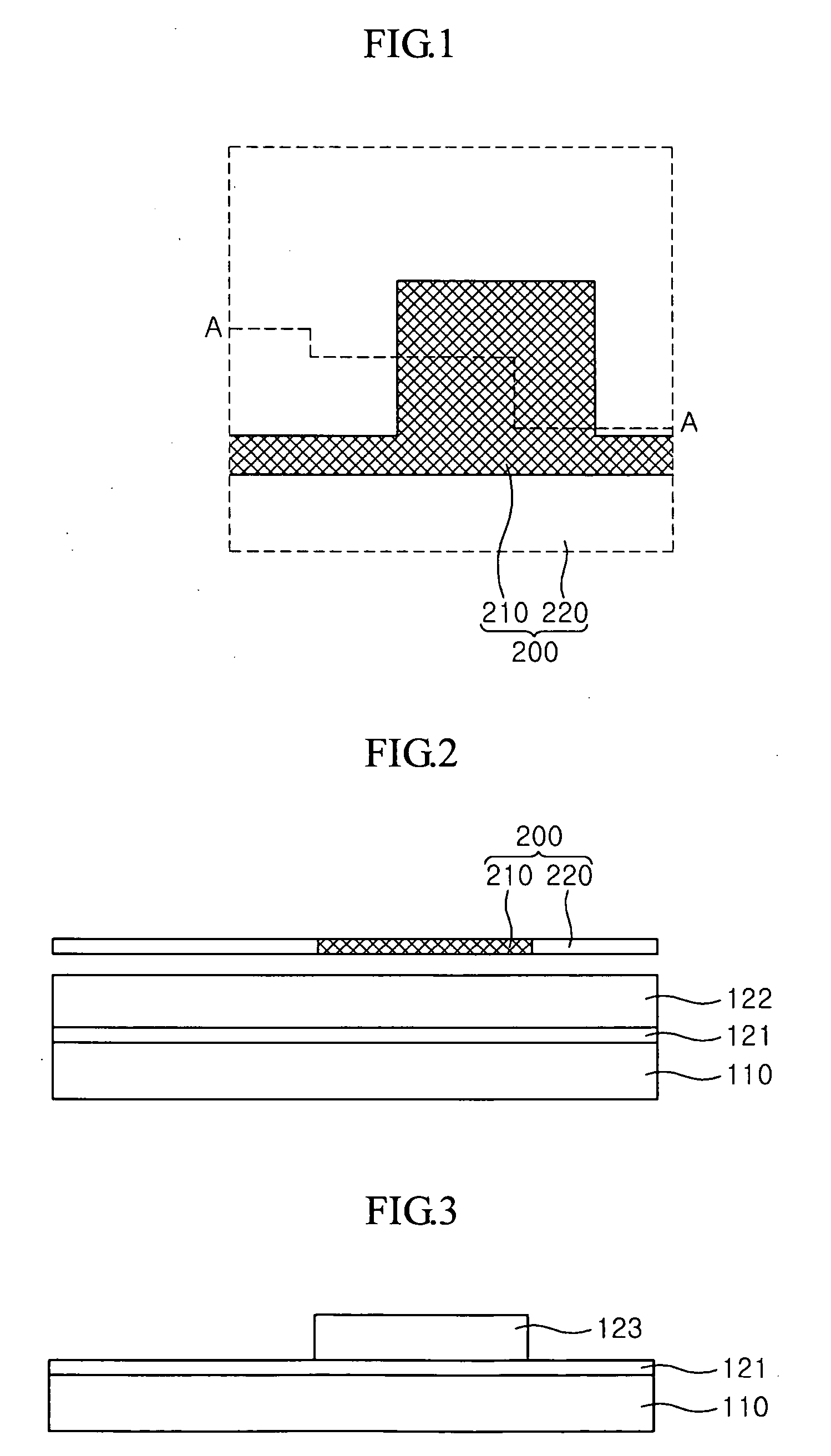

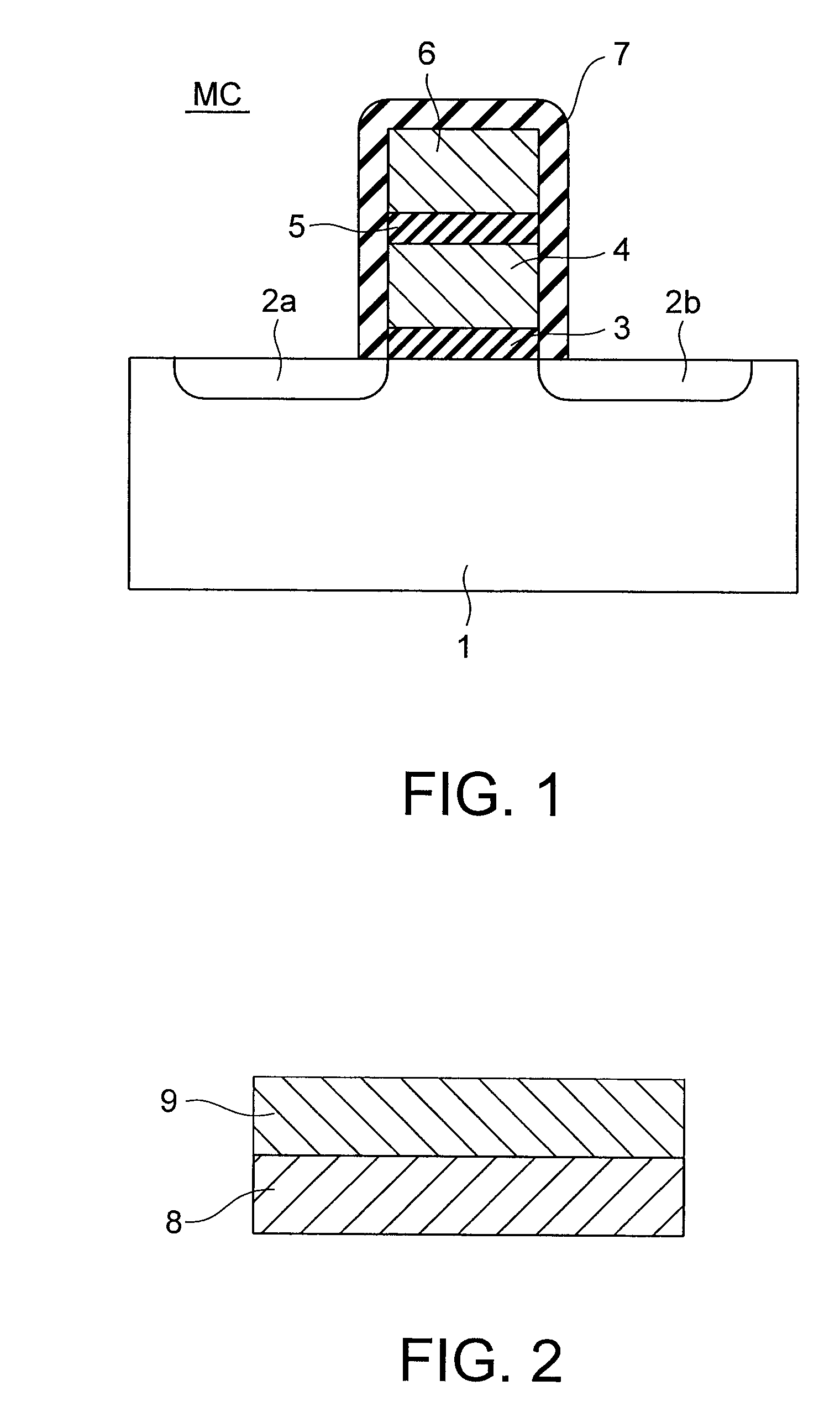

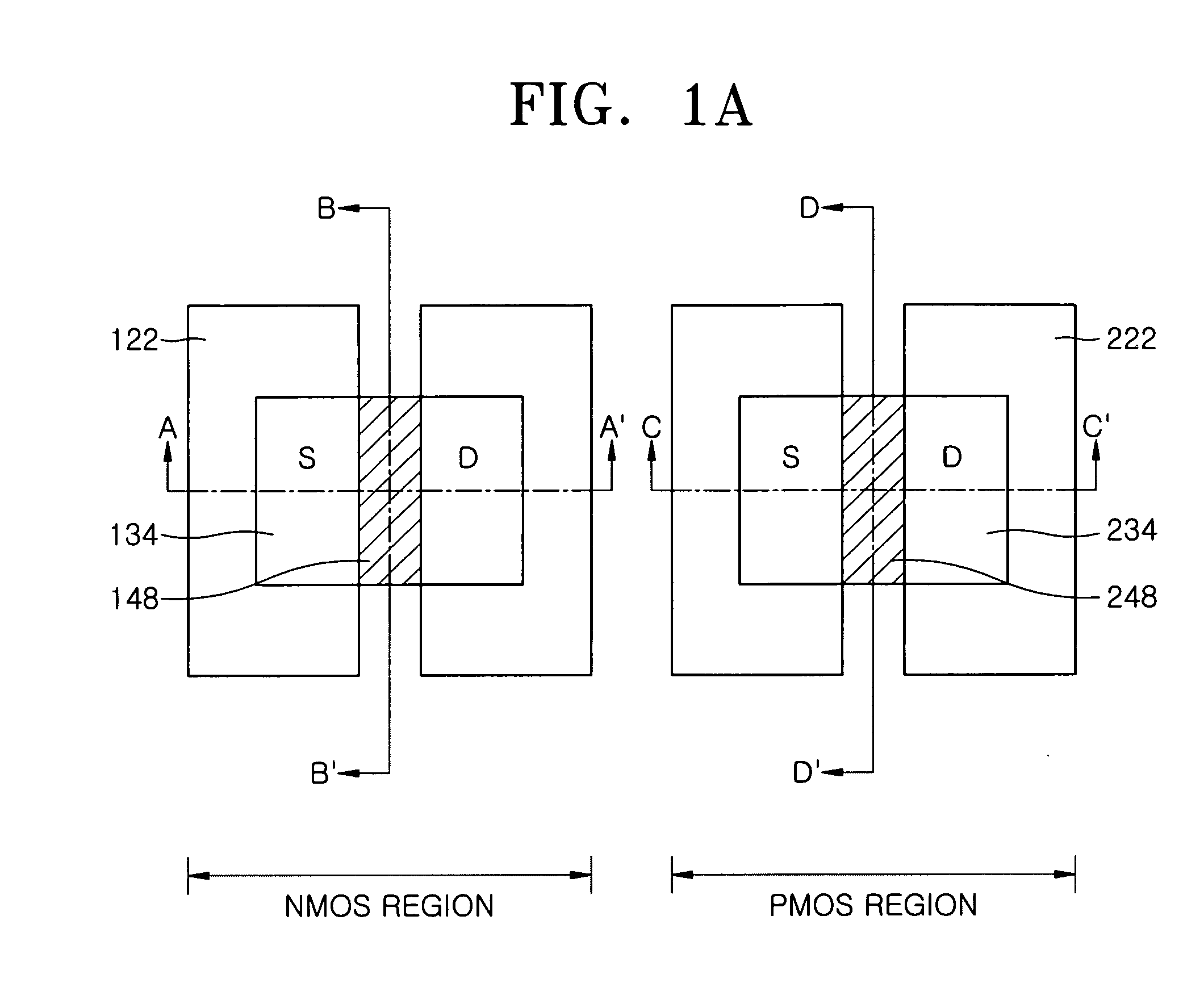

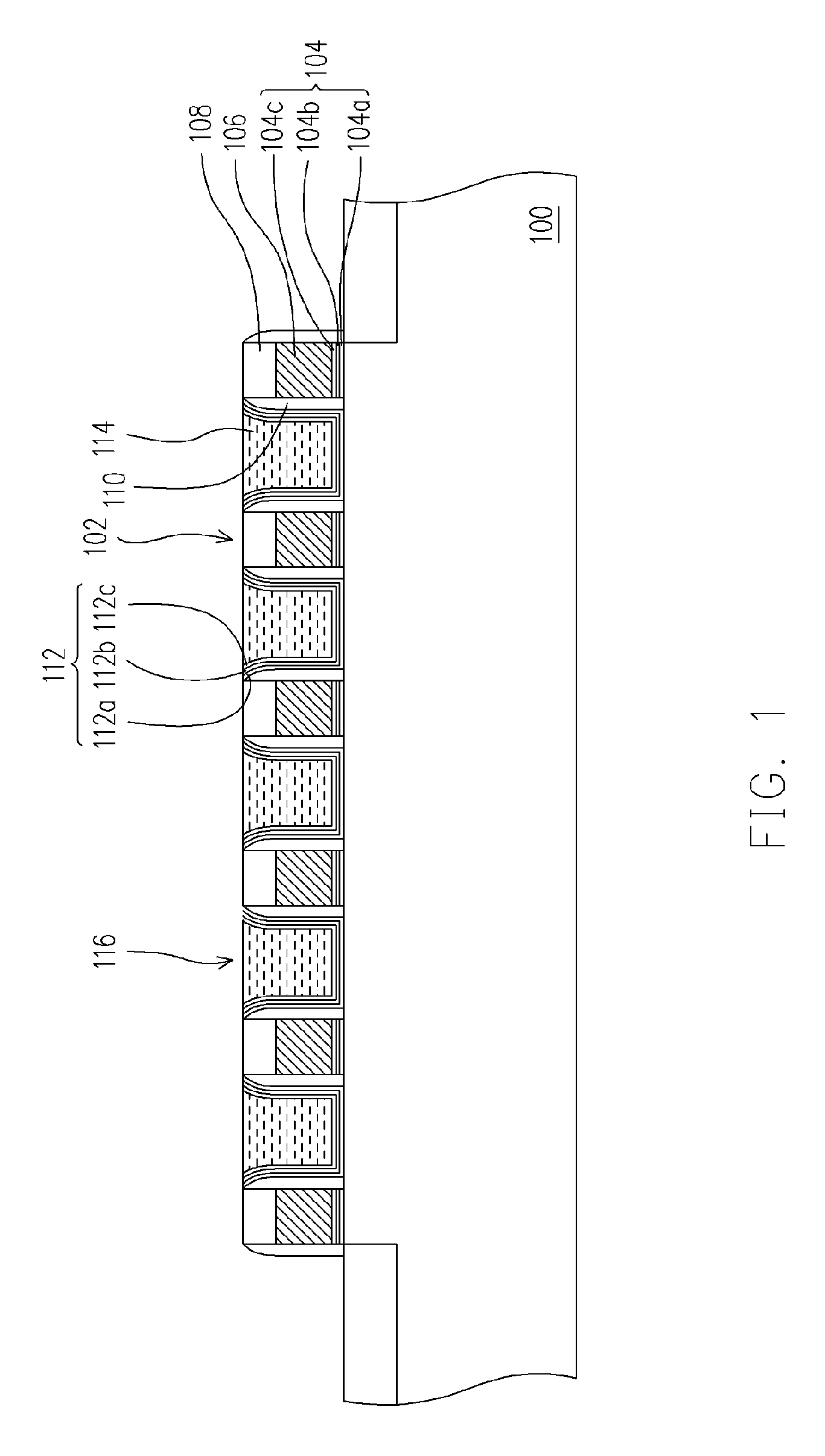

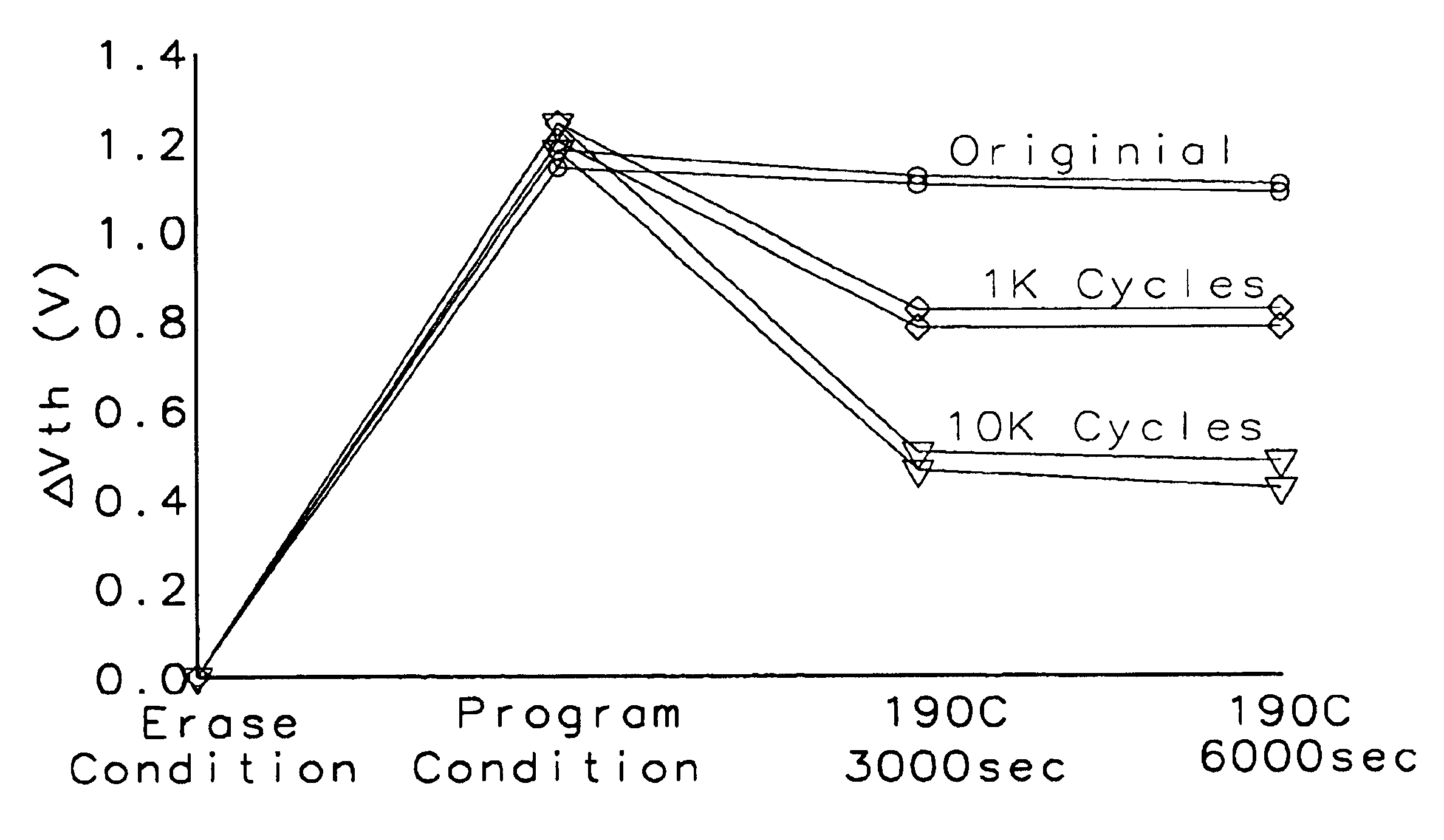

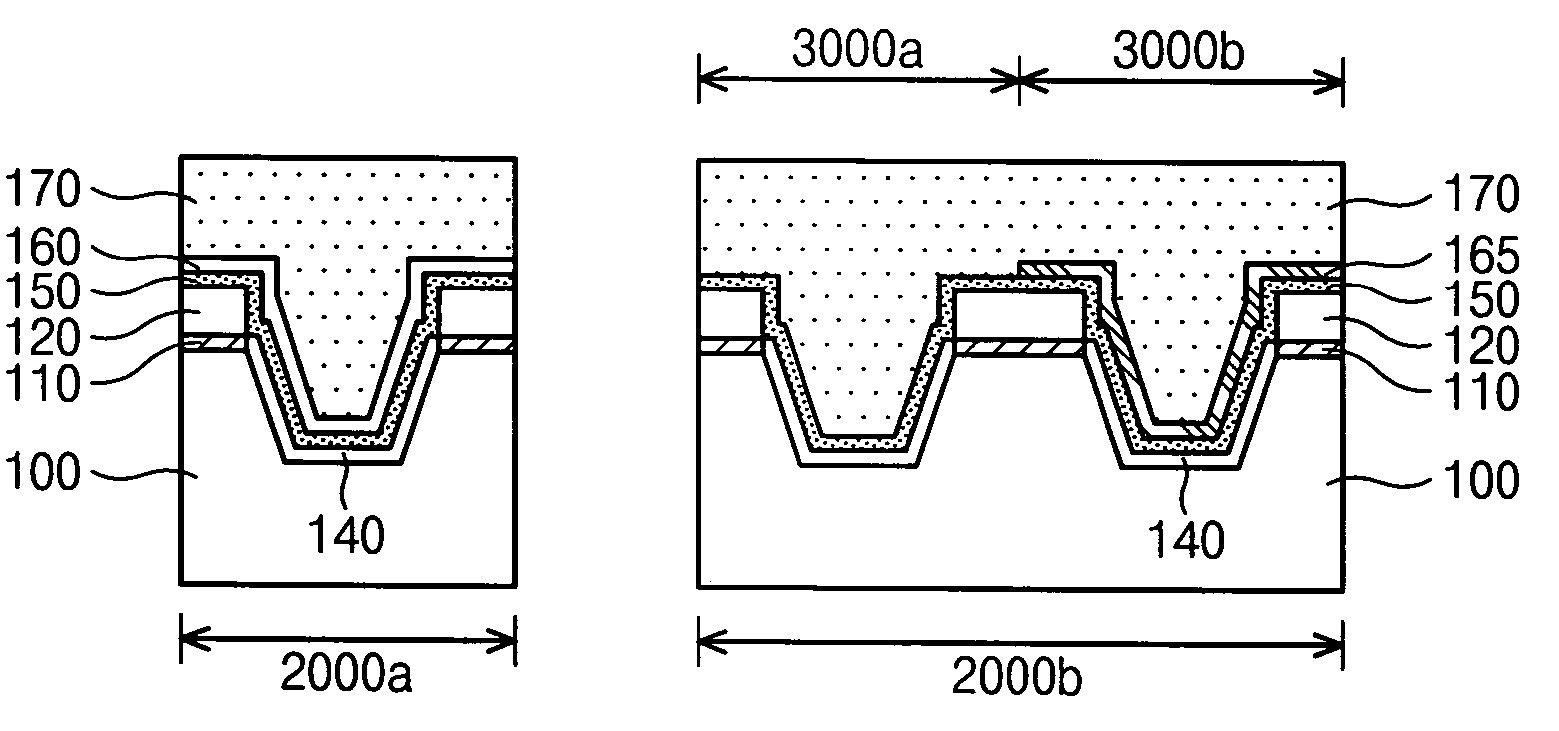

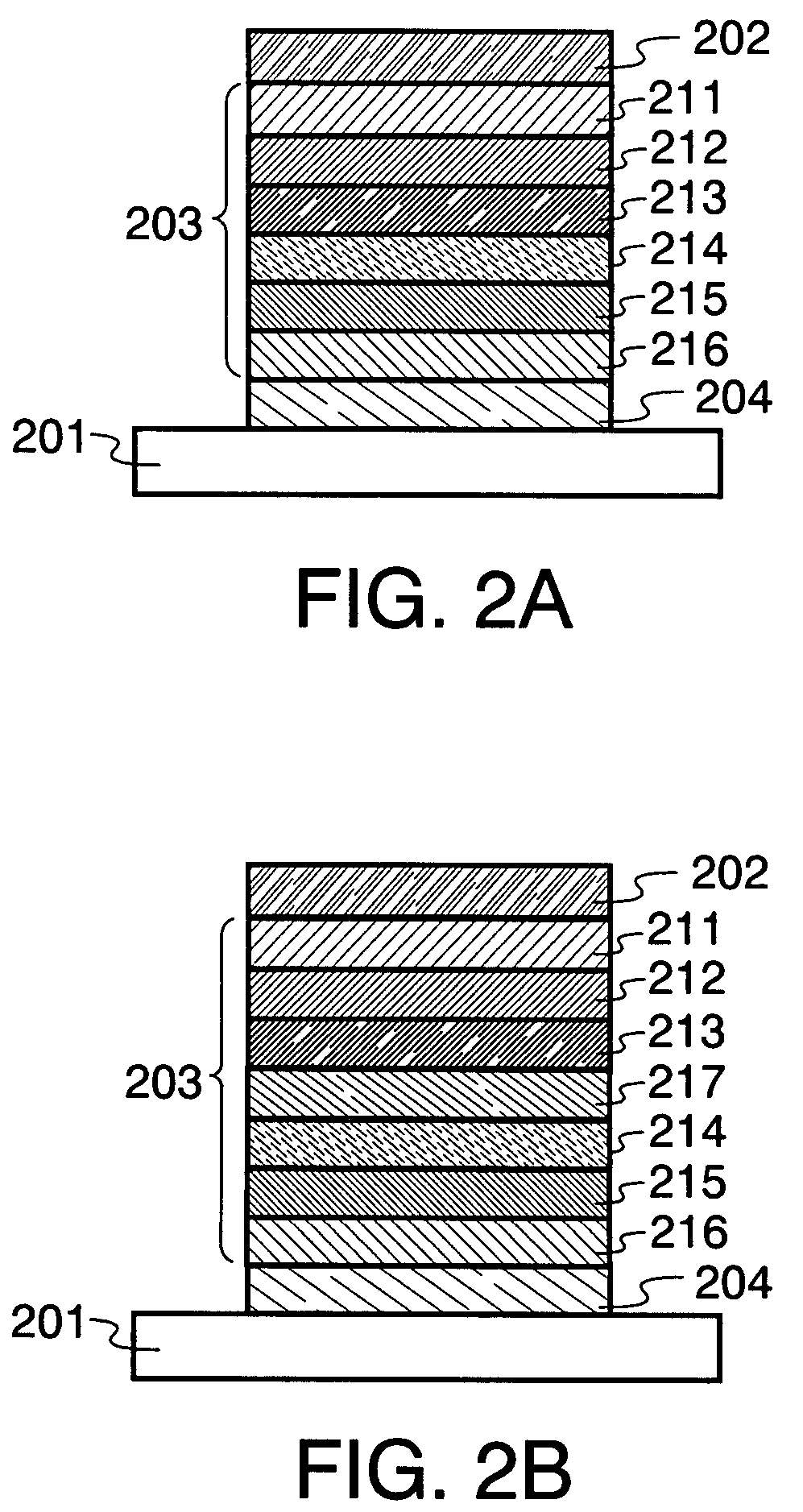

[method of fabricating non-volatile memory cell ]

ActiveUS20050176203A1Avoid failureAvoid misalignmentSemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerVolatile memory

A method of manufacturing a non-volatile memory cell includes forming a bottom dielectric layer and a charge trapping layer on a substrate sequentially. The electron trapping layer is patterned to form a trench exposing a portion of the bottom dielectric layer. A top dielectric layer is formed over the substrate and covers the electron trapping layer and the exposed bottom dielectric layer. A conductive layer is then formed on the top dielectric layer. The conductive layer, the top dielectric layer, the electron trapping layer and the bottom dielectric layer are patterned to form a stacked structure, wherein a width of the stacked structure is larger than a width of the trench. A source / drain region is formed in the substrate adjacent to the edges of the stacked structure. Because the electron trapping layer of the memory cell is divided into two isolation structures according to the invention, it is adapted for the integration of devices and for long-time operation.

Owner:POWERCHIP SEMICON MFG CORP

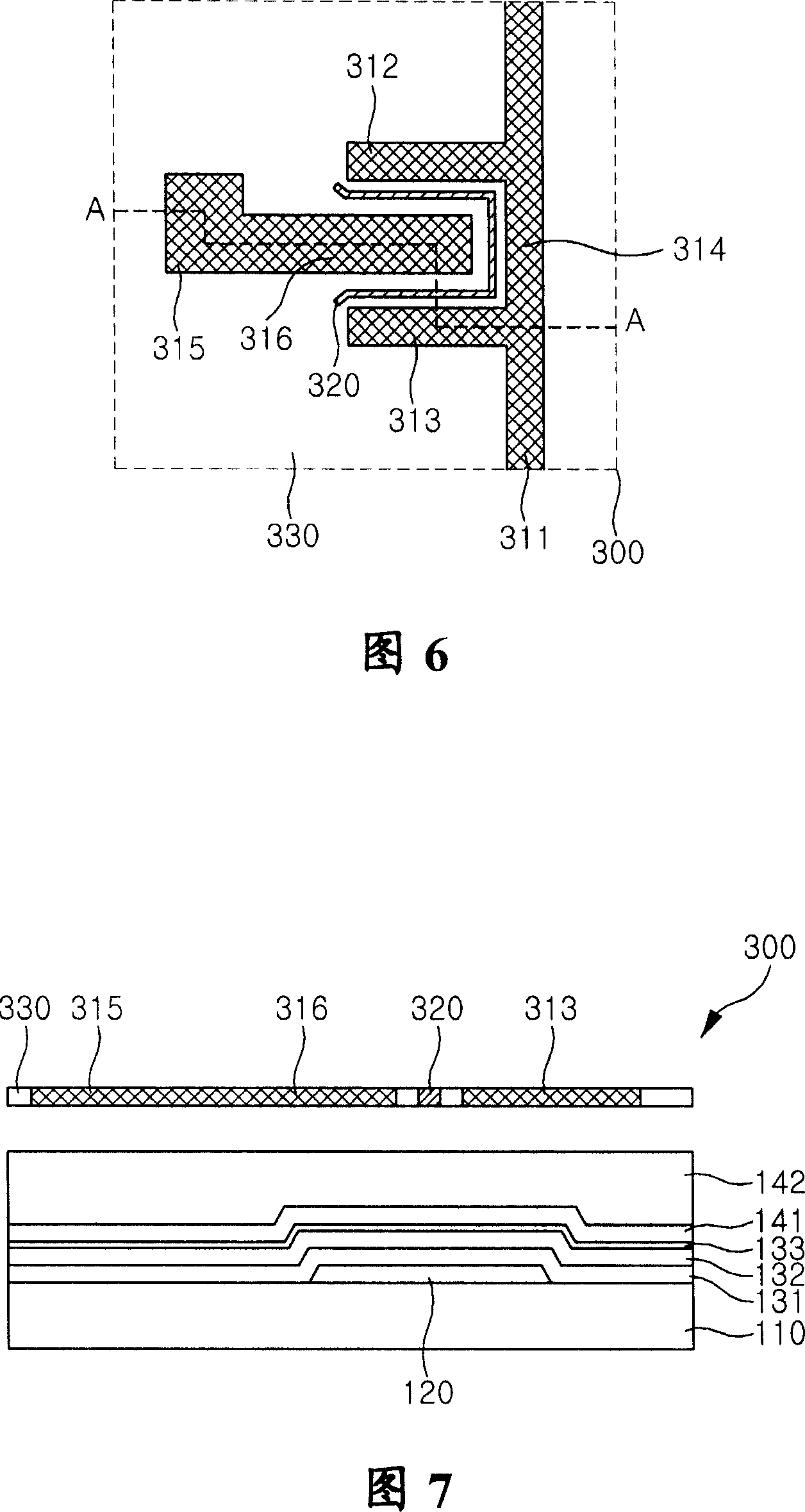

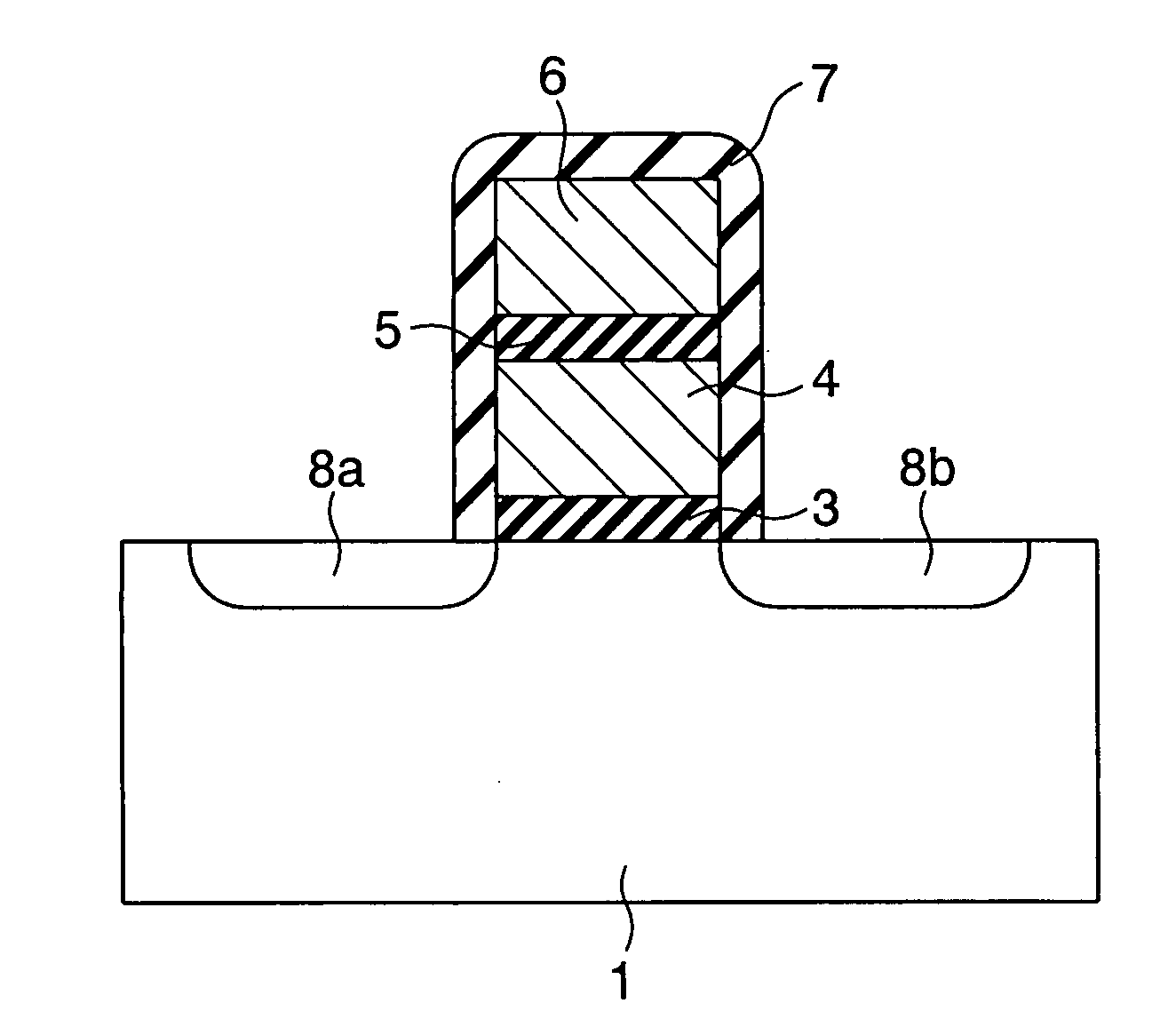

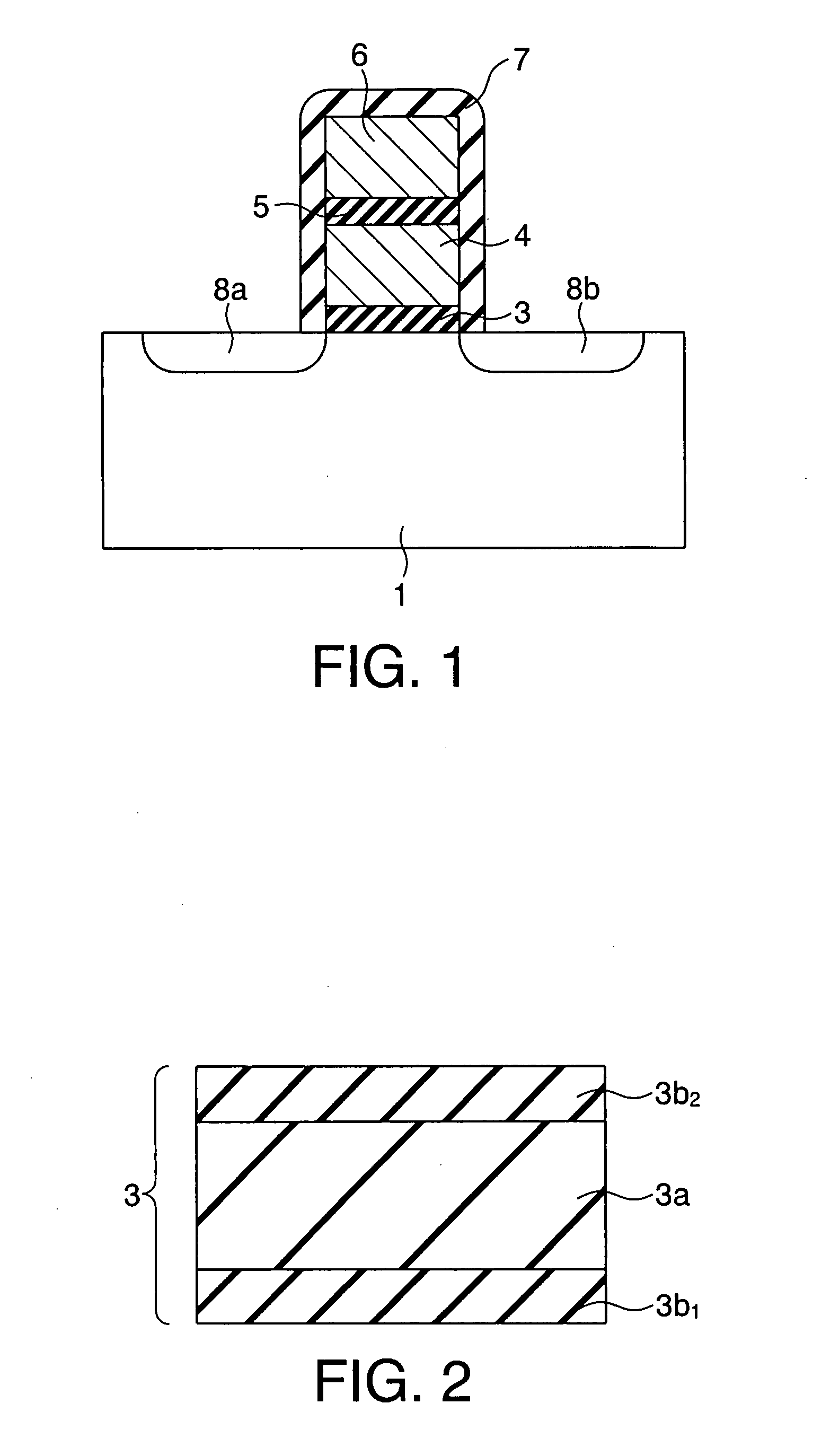

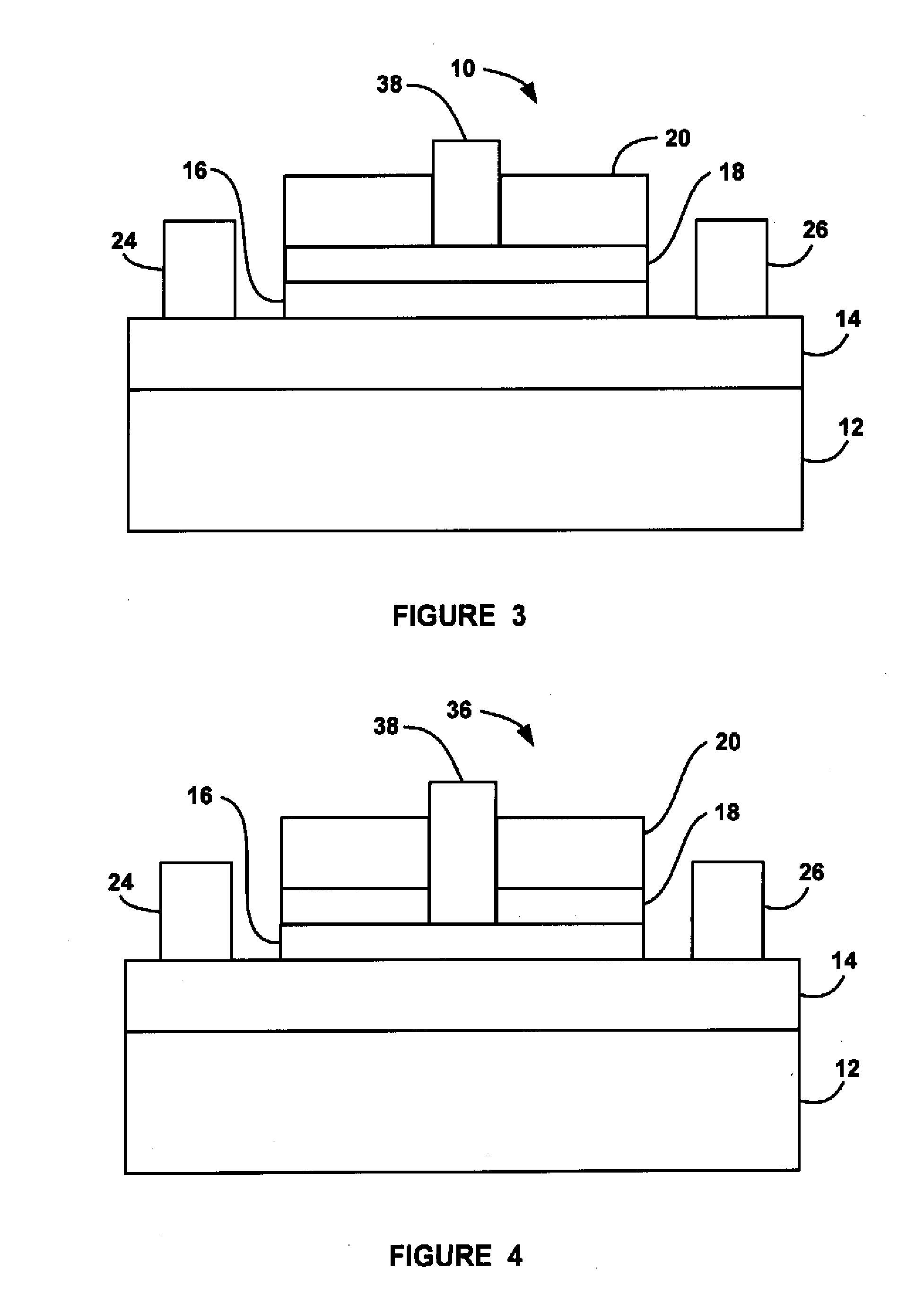

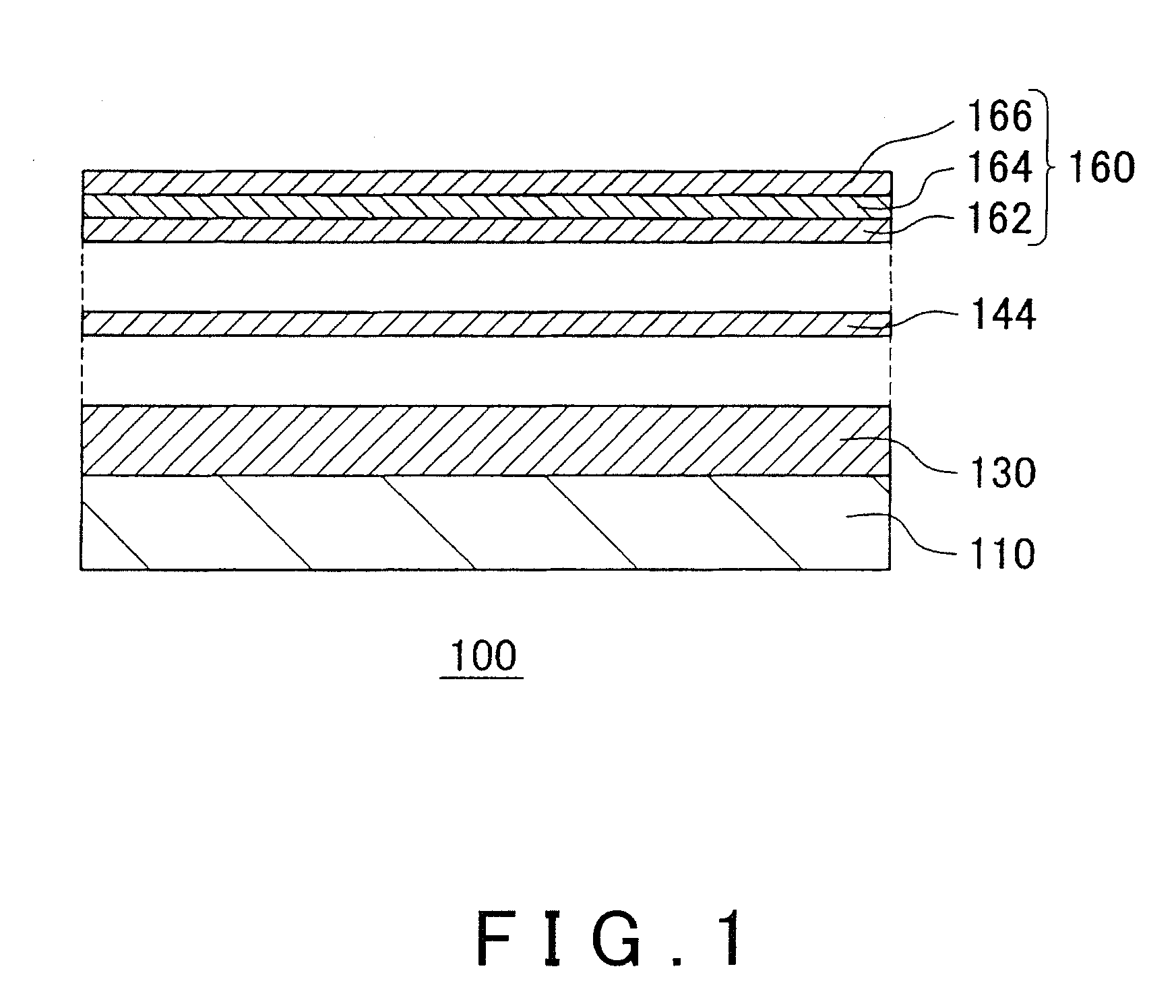

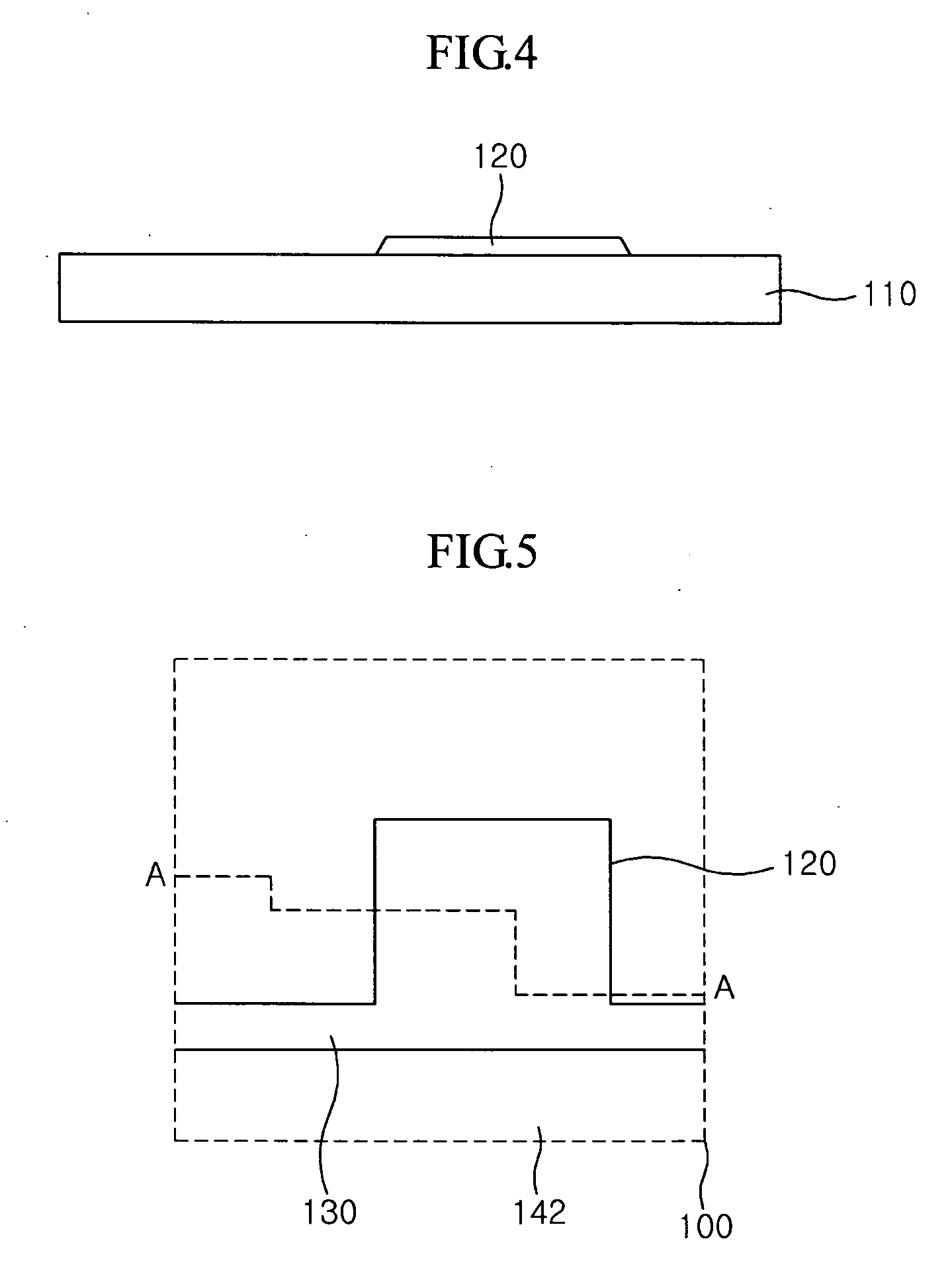

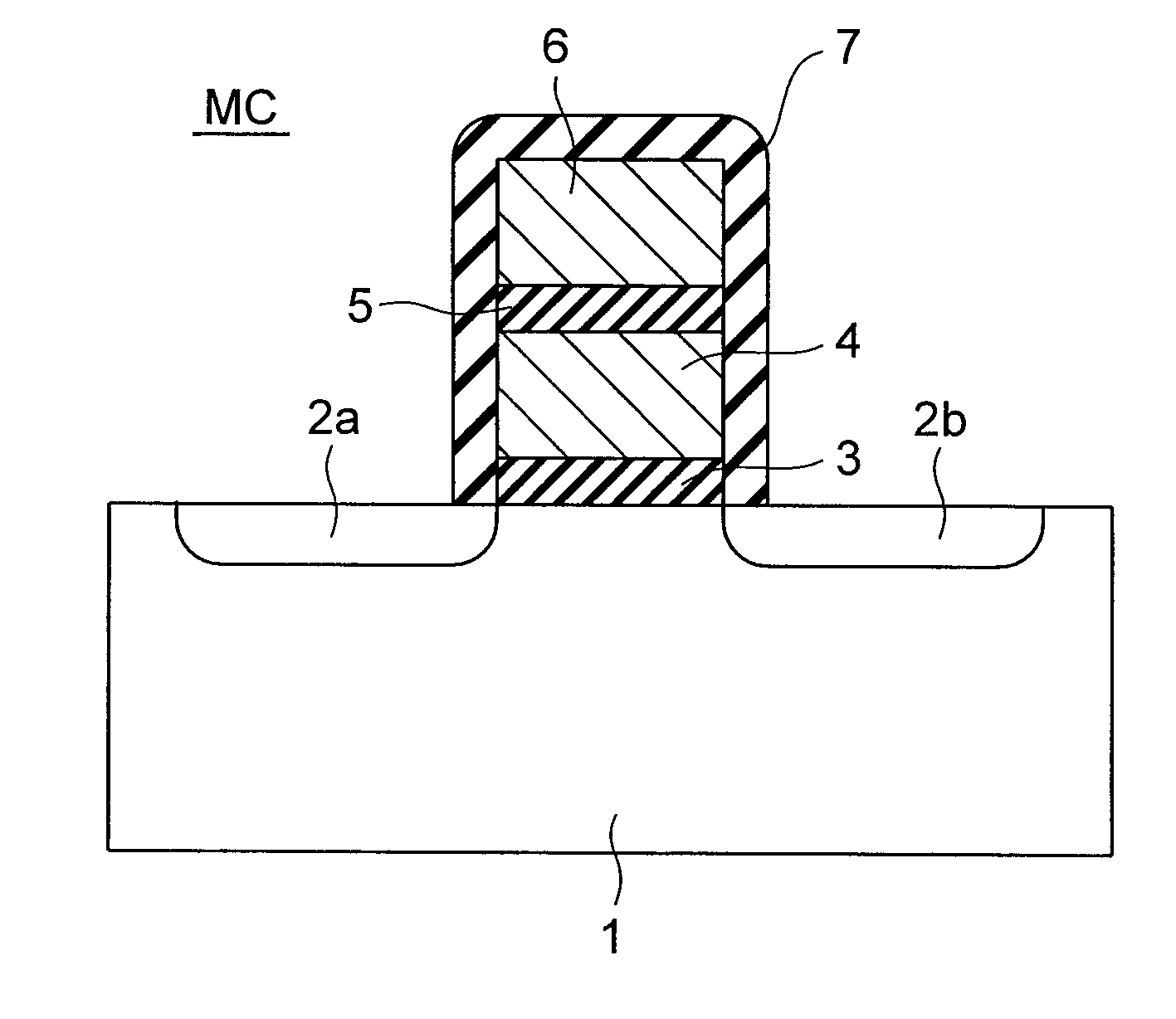

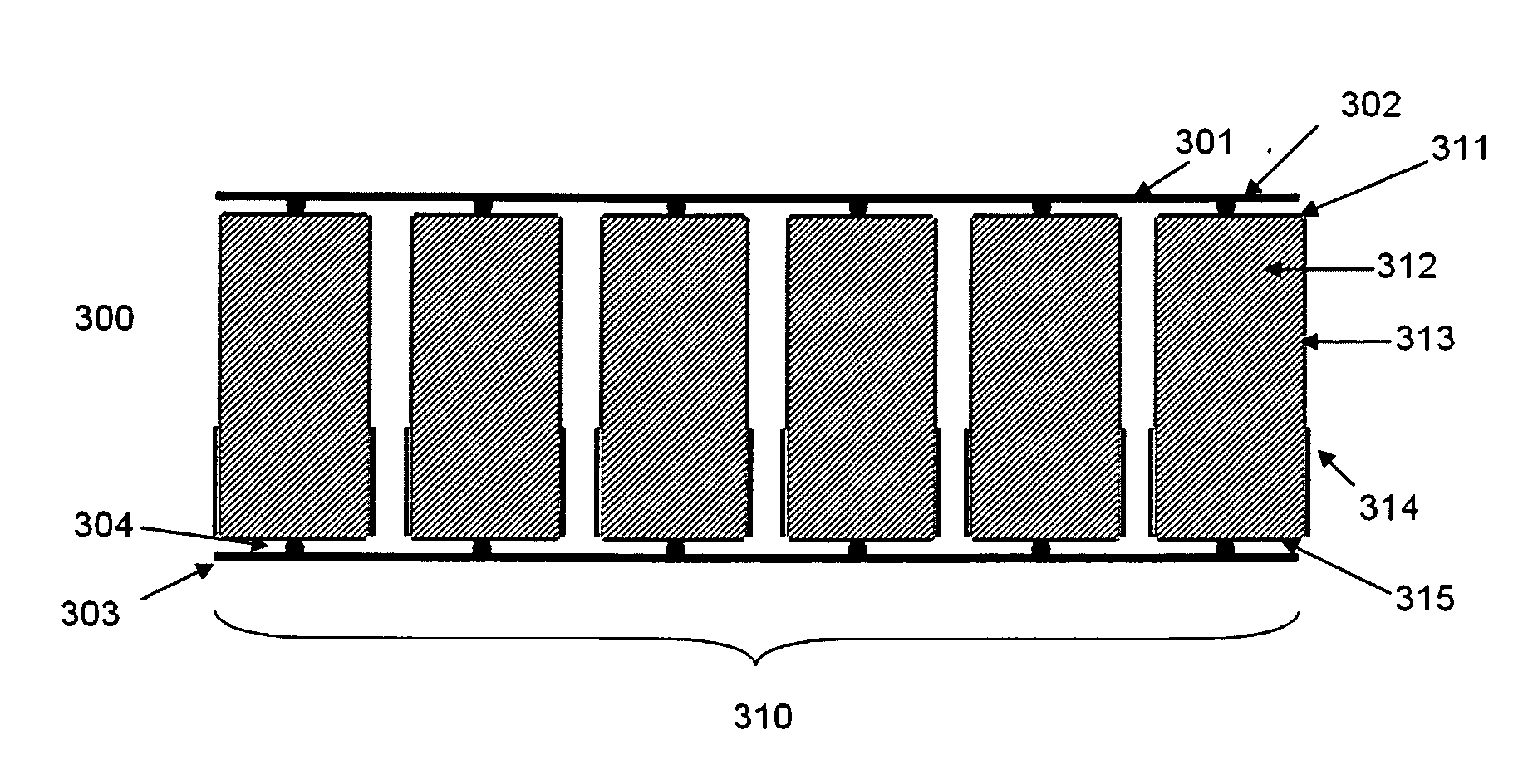

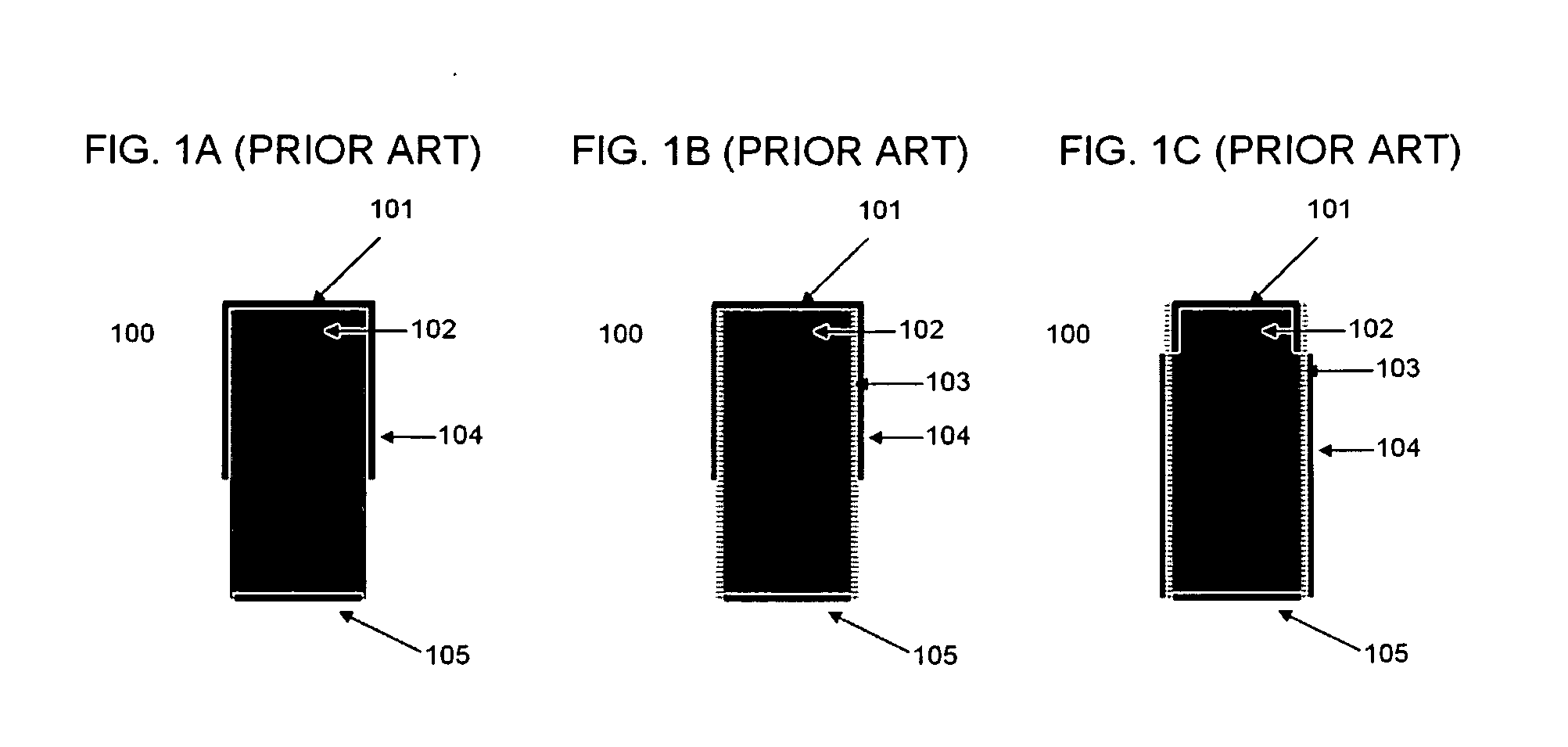

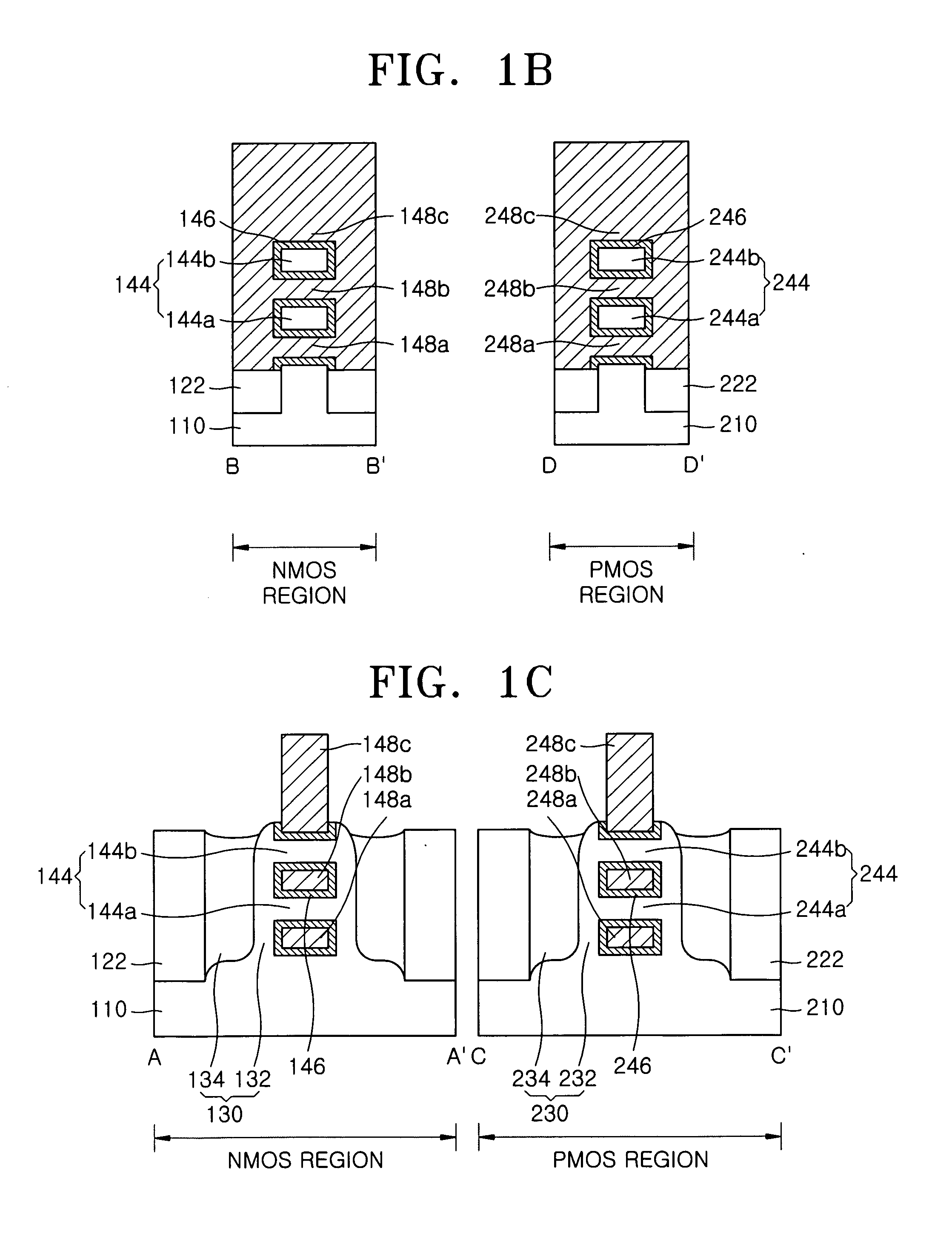

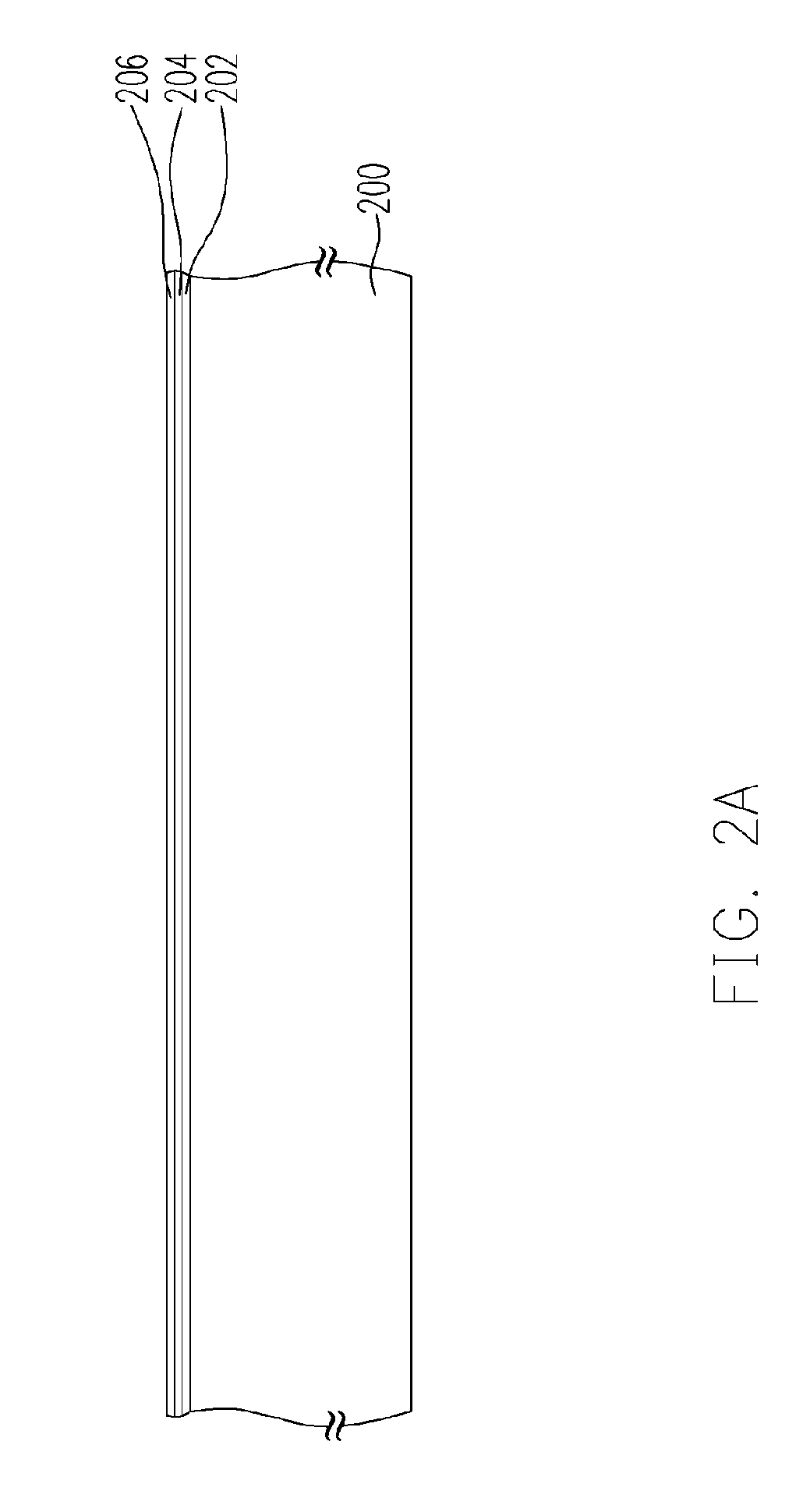

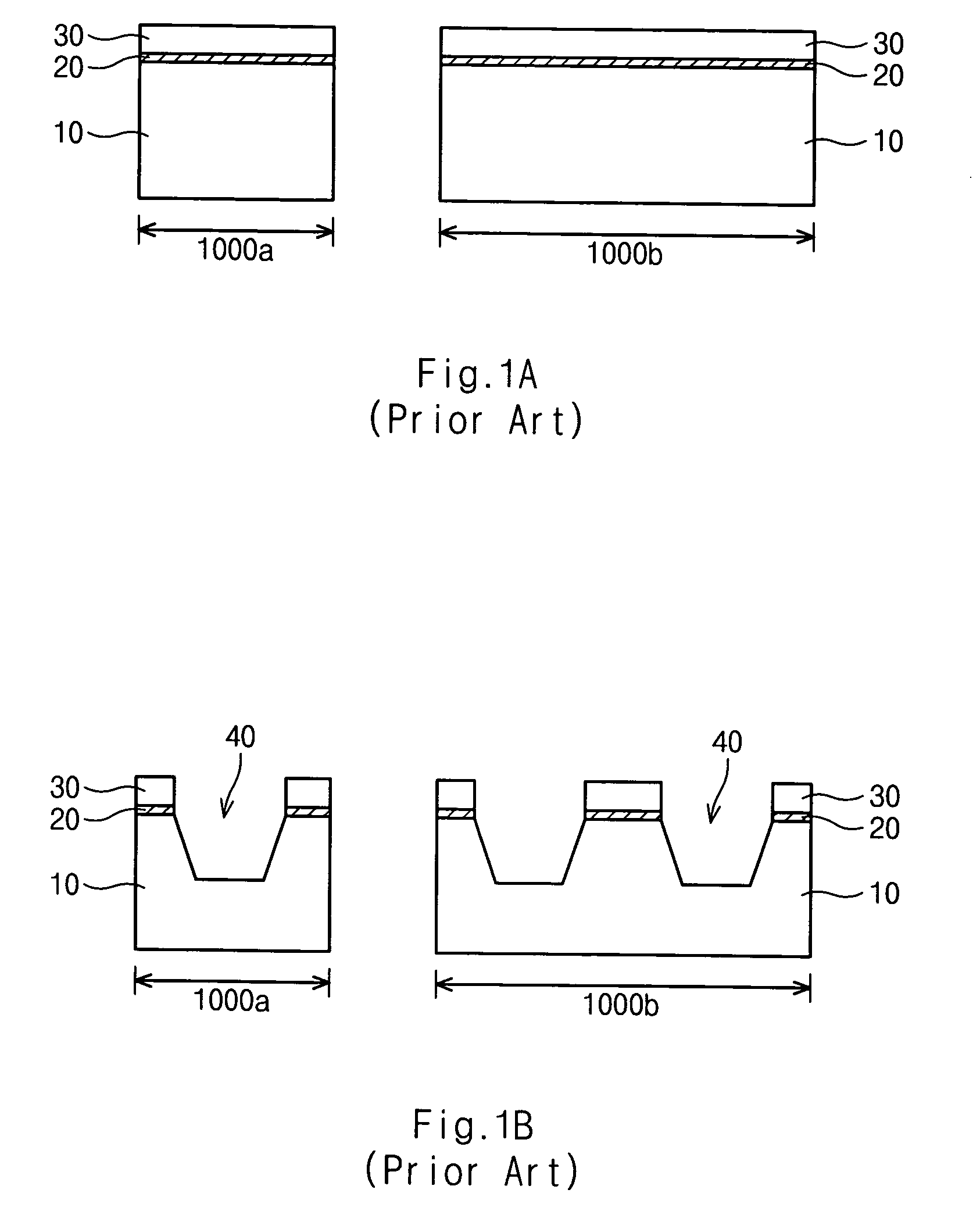

[non-volatile memory structure and manufacturing method thereof]

InactiveUS20050224858A1Easy to manufactureImprove programming speedSolid-state devicesRead-only memoriesGate dielectricDielectric layer

A non-volatile memory including a substrate, a plurality of gate structures, a plurality of select gate structures, spacers and source region / drain region is provided. Each gate structure on the substrate further includes a bottom dielectric layer, an electron trapping layer, an upper dielectric layer, a control gate and a cap layer. The select gate structures are disposed on one side of the respective each gate structure. Each select gate structure includes a select gate dielectric layer and a select gate. The select gate structures and the gate structures are connected in series to form a memory cell row. The spacers are disposed between the select gate structures and the gate structures. The source region and the drain region are disposed in the substrate on each side of the memory cell row.

Owner:POWERCHIP SEMICON CORP

Thin film transistor substrate and method of manufacturing the same and mask for manufacturing thin film transistor substrate

ActiveCN101013705ASolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsCapacitor

A thin film transistor substrate, wherein the moving area of electrons between source and drain electrodes of a thin film transistor (TFT) is minimized, the moving distance of electrons is increased, and the sizes of capacitors defined by a gate electrode together with the respective source and drain electrodes are identical to each other so that an off current generated when the TFT is off can be minimized; a method of manufacturing the thin film transistor substrate; and a mask for manufacturing the thin film transistor substrate. Accordingly, it is possible to minimize an off current induced due to a phenomenon of electron trapping by light.

Owner:SAMSUNG DISPLAY CO LTD

Light-Emitting Element, Light-Emitting Device, Electronic Device and Quinoxaline Derivative

ActiveUS20080217608A1Improve visibilityLong life-timeOrganic chemistryElectroluminescent light sourcesQuinoxalineOrganic compound

The present invention provides light-emitting element having long lifetime, and light-emitting devices and electronic devices having long lifetime. A light-emitting element comprises a first layer and a second layer including a light-emitting substance between a first electrode and a second electrode. The first layer includes a first organic compound and a second organic compound, the first layer is formed between the second layer and the second electrode, the first layer includes the first organic compound more than the second organic compound, the first organic compound is an organic compound having an electron-transporting property, the second organic compound is an organic compound having an electron-trapping property, an energy gap of the second organic compound is larger than that of the light-emitting substance; and a voltage is applied such that a potential of the first electrode is higher than that of the second electrode, so that the light-emitting layer emits light.

Owner:SEMICON ENERGY LAB CO LTD

Organic electric field light-emitting element

ActiveUS20110175071A1Improve emission efficiencyImprove permanenceSolid-state devicesSemiconductor/solid-state device manufacturingHost materialOrganic layer

An organic electric field light-emitting element, containing an anode; a cathode; and an organic layer provided therebetween and containing a first organic layer, a second organic layer and a third organic layer laminated in this order from the anode side, wherein the first organic layer contains a first host material in an amount of 10 to 90 mass % and a first hole-transporting phosphorescent material in an amount of 10 to 90 mass %; the second organic layer contains a second host material in an amount of 65 to 96.9 mass %, a second hole-transporting phosphorescent material in an amount of 3 to 30 mass %, and an electron-trapping material in an amount of 0.1 to 5 mass %; the third organic layer contain a hole-blocking material whose T1 is higher than that of the second hole-transporting phosphorescent material by at least 0.1 eV, wherein the second host material, the second hole-transporting phosphorescent material, and the electron-trapping material satisfy the following relationship:|HOMOt2|>|HOMOh2||HOMOt2|>|HOMOp2||LUMOh2|+0.25 eV<|LUMOt2||LUMOp2|+0.25 eV<|LUMOt2|and wherein the total average thickness of the first and second organic layers is at least 40 nm.

Owner:UDC IRELAND

Semiconductor light emitting device

InactiveUS20110272667A1Reduce overflowOverflow of the electrons can be reducedOptical wave guidanceNanoopticsQuantum wellElectron capture

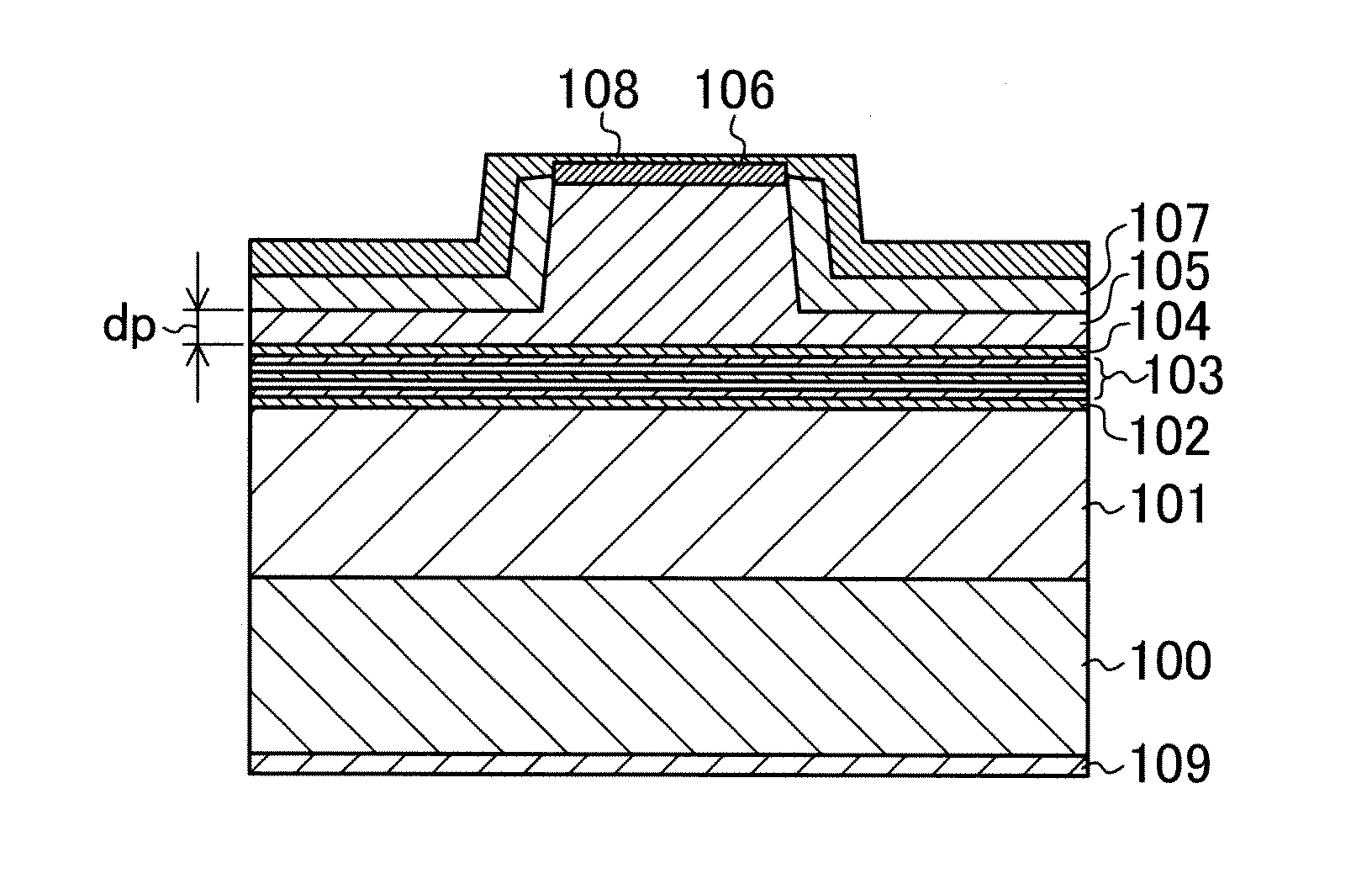

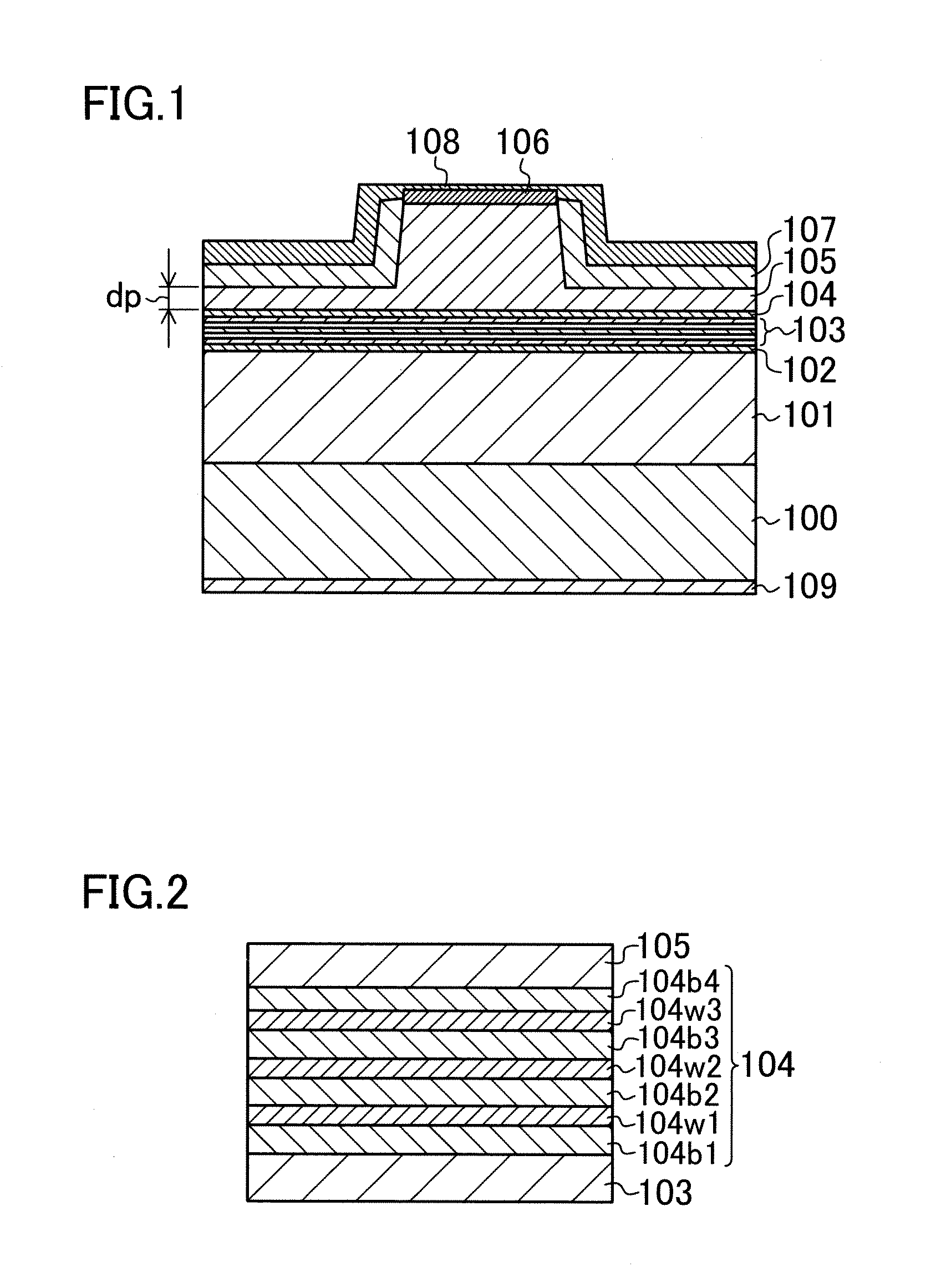

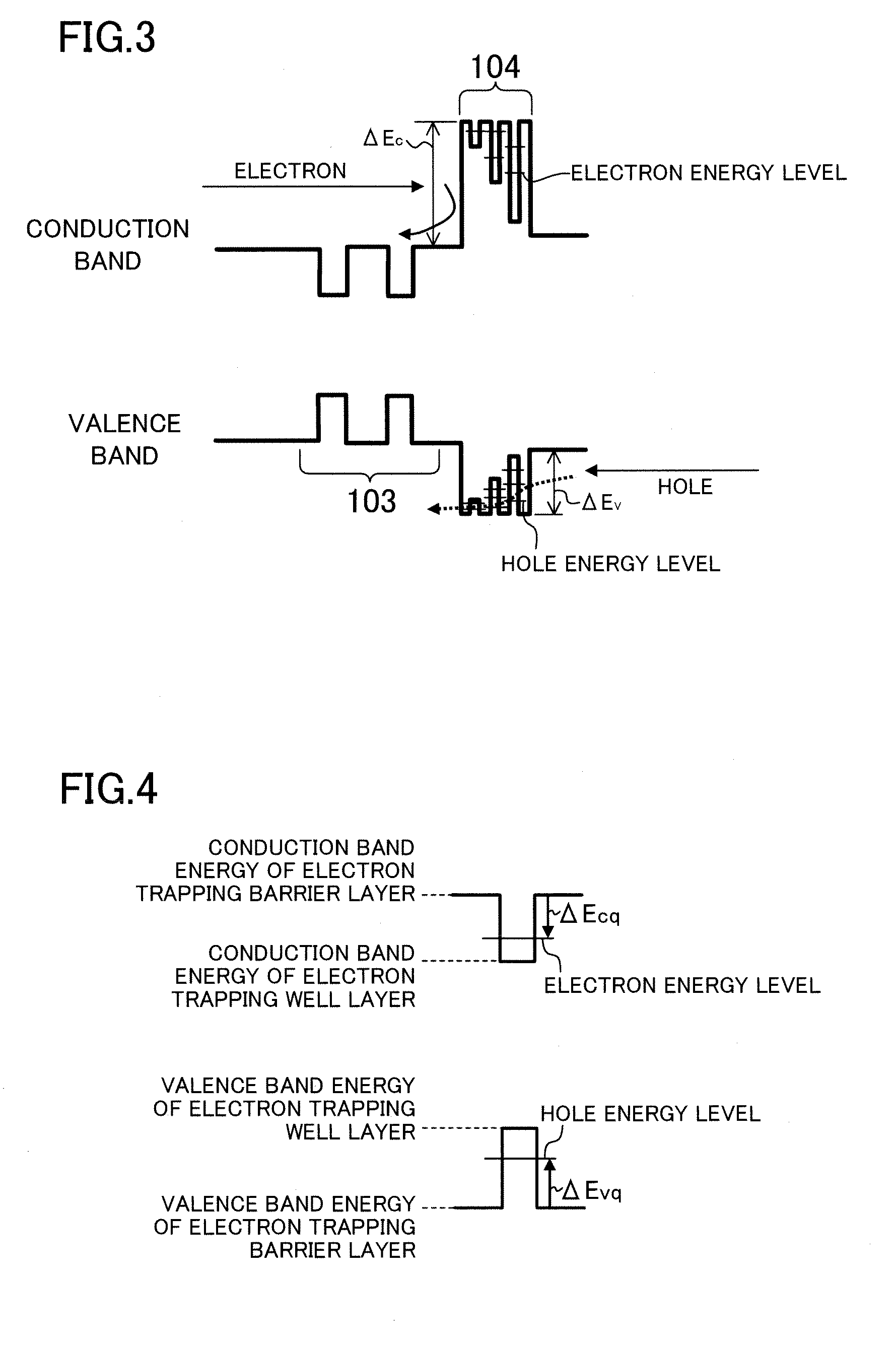

A semiconductor light emitting device includes: a first cladding layer made of a first conductivity type group III nitride semiconductor; an active layer formed on the first cladding layer; a quantum well electron barrier layer which is formed on the active layer, and includes electron trapping barrier layers made of AlxbGaybIn1-xb-ybN (0≦xb<1, 0<yb≦1, 0≦1-xb-yb<1), and two or more electron trapping well layers made of AlxwGaywIn1-xw-ywN (0≦xw<1, 0<yw≦1, 0≦1-xw-yw<1); and a second cladding layer which is formed on the quantum well electron barrier layer, and is made of a second conductive type group III nitride semiconductor. Each of the electron trapping well layers is formed between the electron trapping barrier layers, and band gap energies of the electron trapping well layers increase with decreasing distance from the active layer.

Owner:PANASONIC CORP

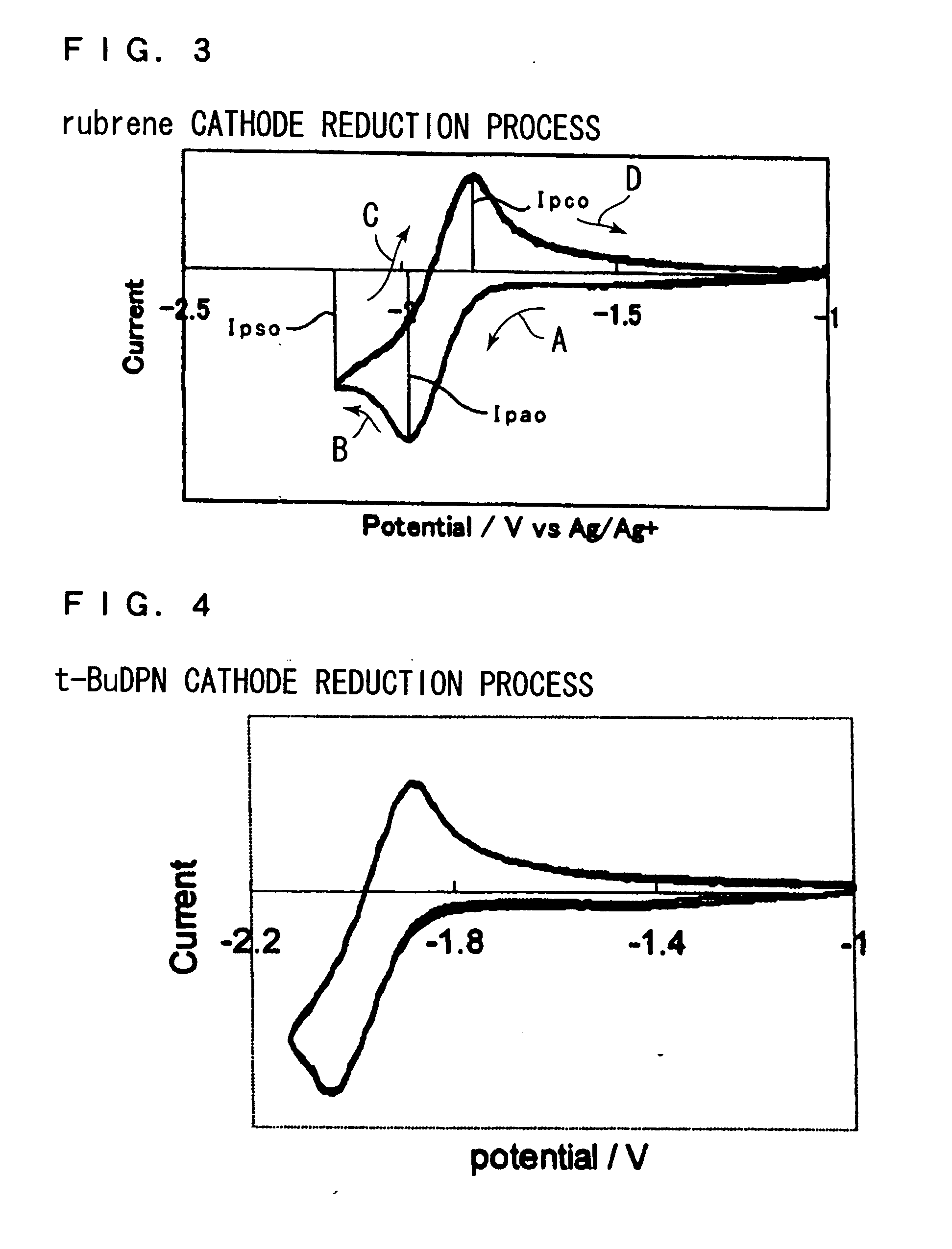

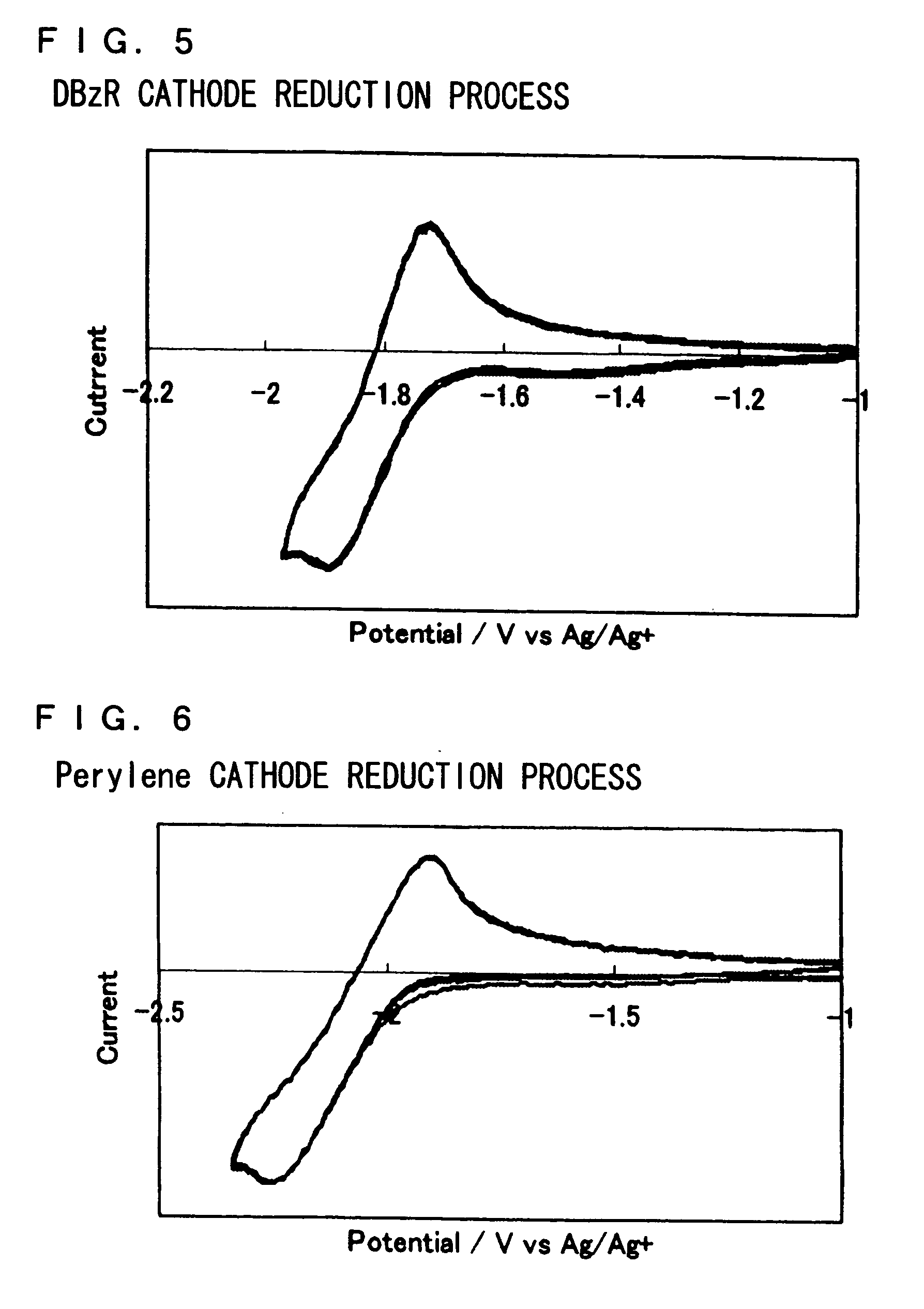

Organic electroluminescence device

InactiveUS20060051563A1Excellent in light emitting life propertyImprove propertiesDischarge tube luminescnet screensElectroluminescent light sourcesElectron holeElectron injection

An organic electroluminescent device in which a light emitting layer is disposed between a hole injection electrode and an electron injection electrode, and a hole transporting layer is disposed between a hole injection electrode and a light emitting layer, wherein the hole transporting layer contains an electron trapping material exhibiting a reversible cathode reduction process in cyclic voltammetry measurement and having a reduction potential smaller than that of a hole transporting material contained in the hole transporting layer, or wherein the electron transporting layer contains a hole trapping material exhibiting a reversible anode reduction process in cyclic voltammetry measurement and having an oxidation potential smaller than that of an electron transporting material contained in the electron transporting layer.

Owner:SANYO ELECTRIC CO LTD

Method of fabricating non-volatile memory cell adapted for integration of devices and for multiple read/write operations

ActiveUS7049189B2Avoid failureAvoid misalignmentSemiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerMolecular physics

A method of manufacturing a non-volatile memory cell includes forming a bottom dielectric layer and a charge trapping layer on a substrate sequentially. The electron trapping layer is patterned to form a trench exposing a portion of the bottom dielectric layer. A top dielectric layer is formed over the substrate and covers the electron trapping layer and the exposed bottom dielectric layer. A conductive layer is then formed on the top dielectric layer. The conductive layer, the top dielectric layer, the electron trapping layer and the bottom dielectric layer are patterned to form a stacked structure, wherein a width of the stacked structure is larger than a width of the trench. A source / drain region is formed in the substrate adjacent to the edges of the stacked structure. Because the electron trapping layer of the memory cell is divided into two isolation structures according to the invention, it is adapted for the integration of devices and for long-time operation.

Owner:POWERCHIP SEMICON MFG CORP

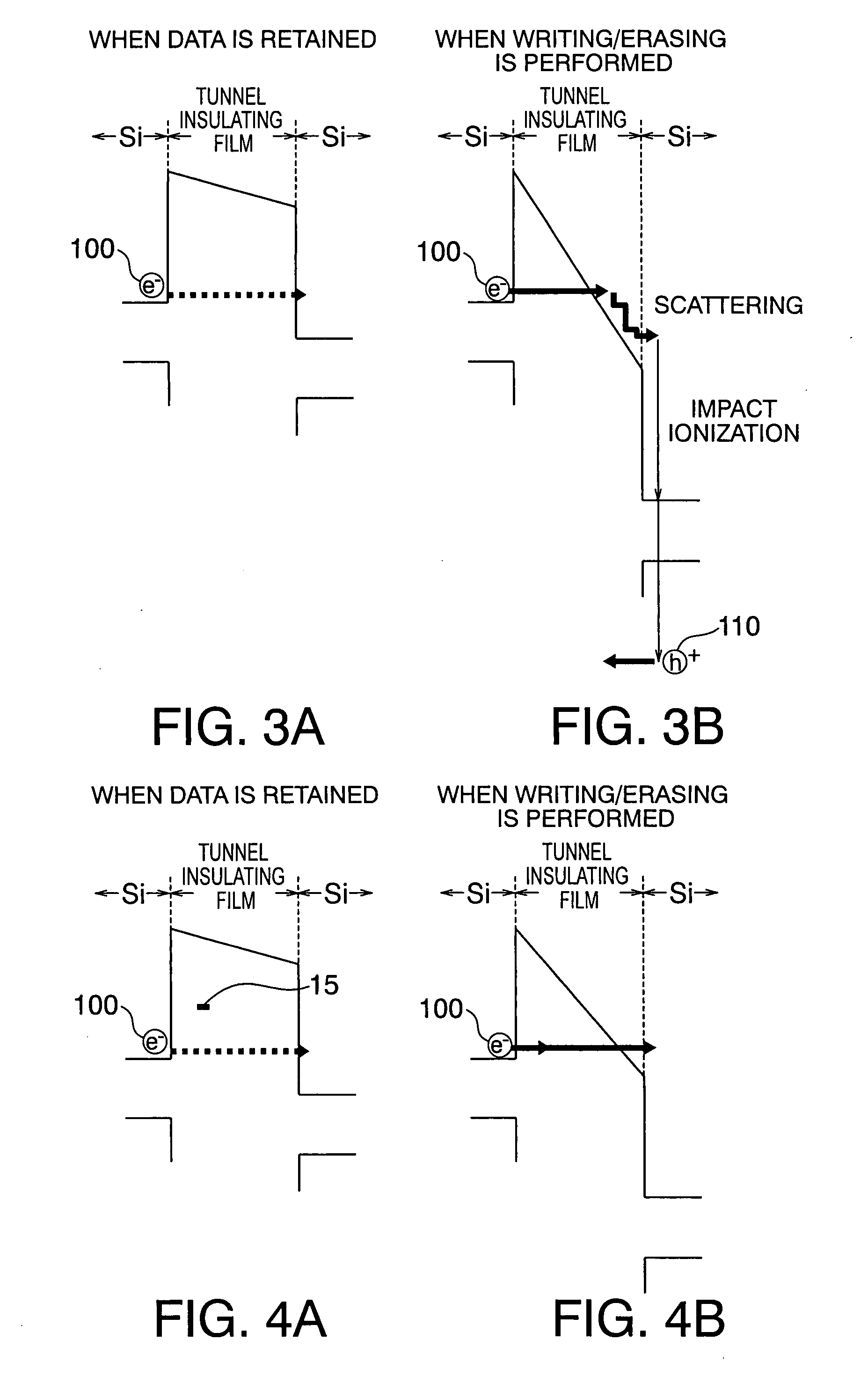

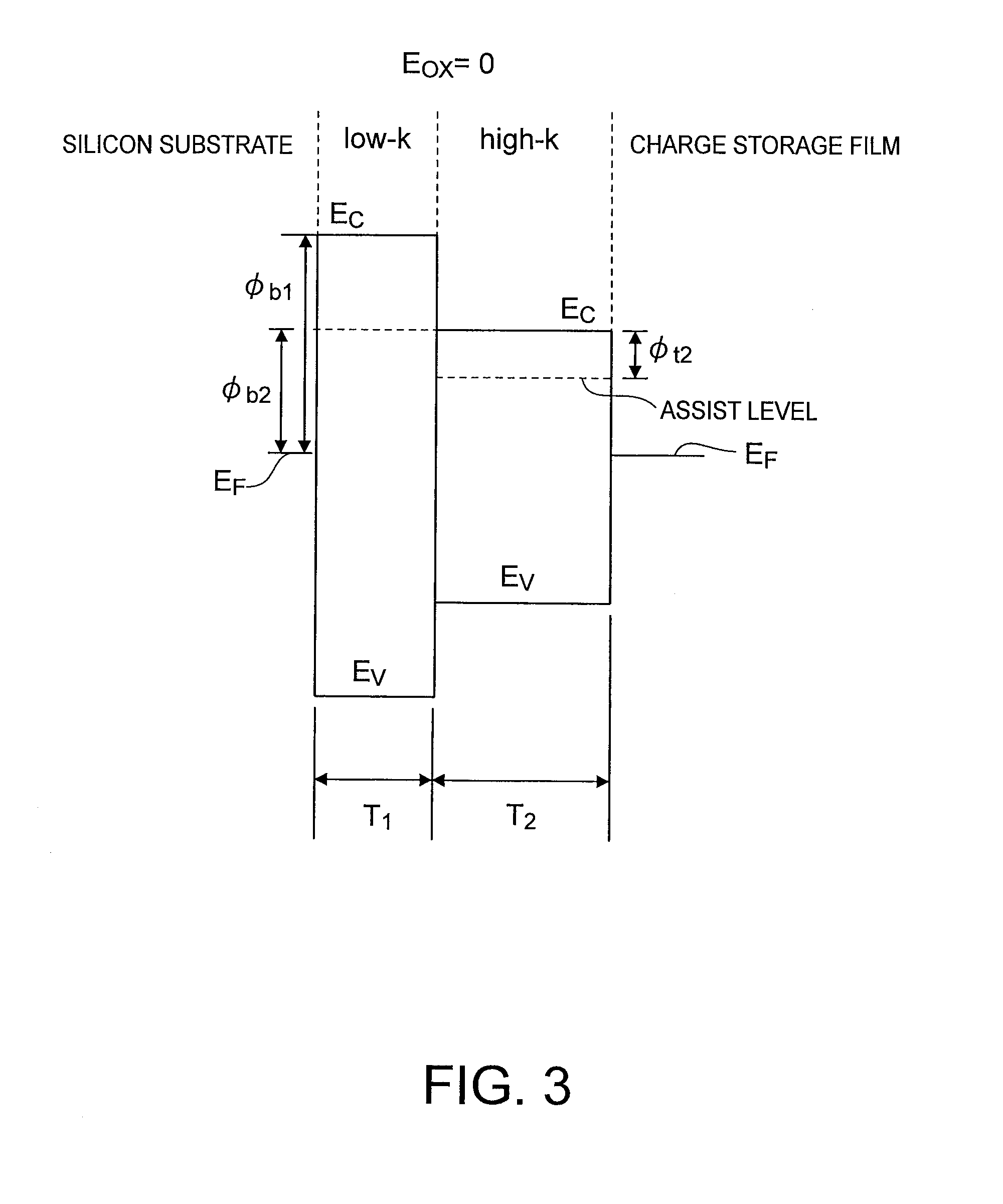

Nonvolatile semiconductor memory device and method for manufacturing the same

ActiveUS20080135922A1Lower programming voltageReducing stress-induced leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesConduction bandSemiconductor

A nonvolatile semiconductor memory device includes: a memory element, the memory element including: a semiconductor substrate; a first insulating film formed on a region in the semiconductor substrate located between a source region and a drain region, and having a stack structure formed with a first insulating layer, a second insulating layer, and a third insulating layer in this order, the first insulating layer including an electron trapping site, the second insulating layer not including the electron trapping site, and the third insulating layer including the electron trapping site, and the electron trapping site being located in a position lower than conduction band minimum of the first through third insulating layers while being located in a position higher than conduction band minimum of a material forming the semiconductor substrate; a charge storage film formed on the first insulating film; a second insulating film formed on the charge storage film; and a control gate electrode formed on the second insulating film.

Owner:KIOXIA CORP

Complementary metal-oxide semiconductor (CMOS) devices including a thin-body channel and dual gate dielectric layers and methods of manufacturing the same

ActiveUS20080233693A1Semiconductor/solid-state device manufacturingSemiconductor devicesCMOSSilicon oxide

A complementary metal-oxide semiconductor (CMOS) device includes an NMOS thin body channel including a silicon epitaxial layer. An NMOS insulating layer is formed on a surface of the NMOS thin body channel and surrounds the NMOS thin body channel. An NMOS metal gate is formed on the NMOS insulating layer. The CMOS device further includes a p-channel metal-oxide semiconductor (PMOS) transistor including a PMOS thin body channel including a silicon epitaxial layer. A PMOS insulating layer is formed on a surface of and surrounds the PMOS thin body channel. A PMOS metal gate is formed on the PMOS insulating layer. The NMOS insulating layer includes a silicon oxide layer and the PMOS insulating layer includes an electron-trapping layer, the NMOS insulating layer includes a hole trapping dielectric layer and the PMOS insulating layer includes a silicon oxide layer, or the NMOS insulating layer includes a hole-trapping dielectric layer and the PMOS insulating layer includes an electron-trapping dielectric layer.

Owner:SAMSUNG ELECTRONICS CO LTD

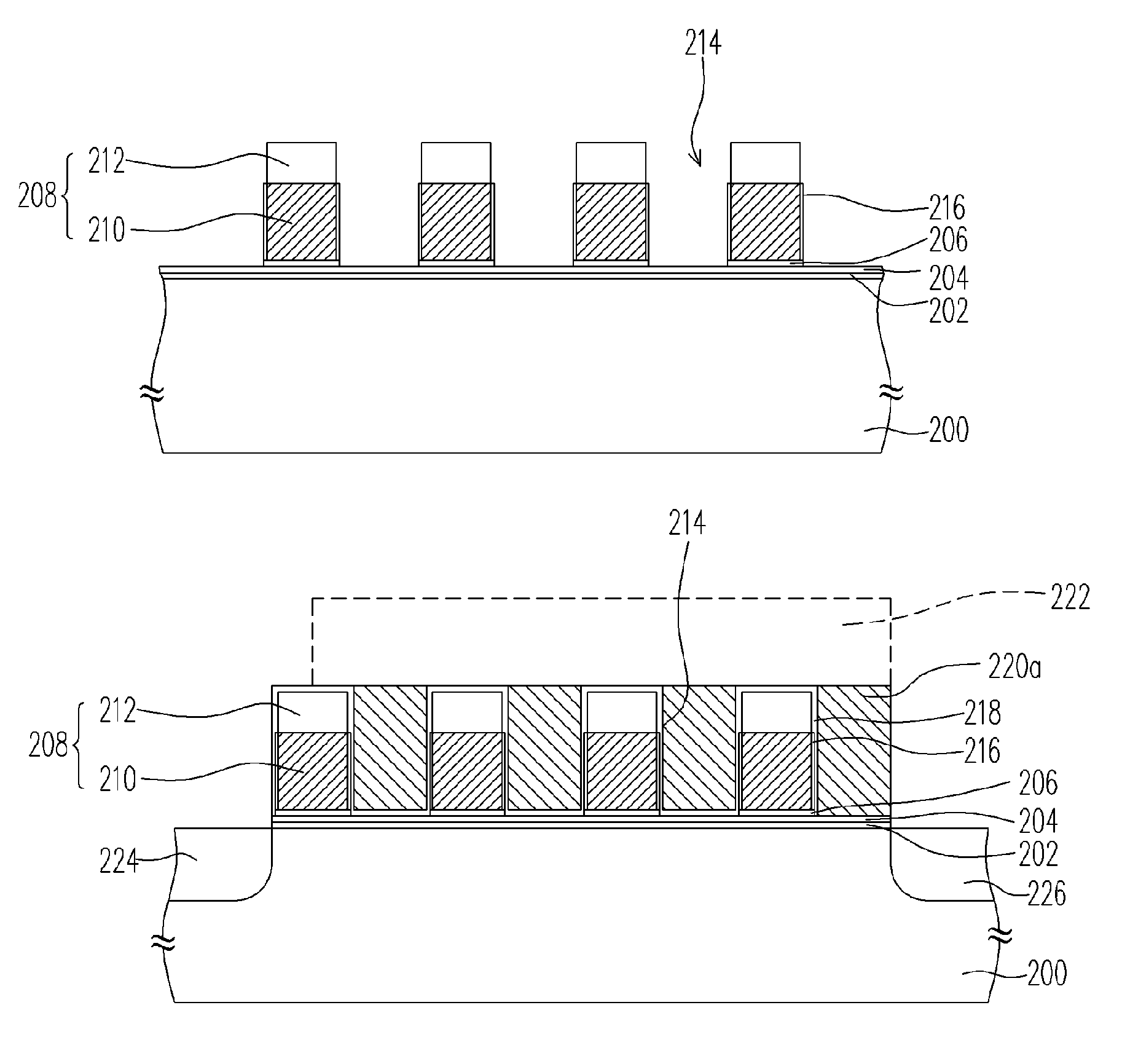

Method for Fabricating a Nitride FET Including Passivation Layers

ActiveUS20090148985A1Reduced electron trappingReduced gate current leakageSemiconductor/solid-state device detailsSolid-state devicesGate currentNitride

A method for fabricating a nitride-based FET device that provides reduced electron trapping and gate current leakage. The fabrication method provides a device that includes a relatively thick passivation layer to reduce traps caused by device processing and a thin passivation layer below the gate terminal to reduce gate current leakage. Semiconductor device layers are deposited on a substrate. A plurality of passivation layers are deposited on the semiconductor device layers, where at least two of the layers are made of a different dielectric material to provide an etch stop. One or more of the passivation layers can be removed using the interfaces between the layers as an etch stop so that the distance between the gate terminal and the semiconductor device layers can be tightly controlled, where the distance can be made very thin to increase device performance and reduce gate current leakage.

Owner:NORTHROP GRUMMAN SYST CORP

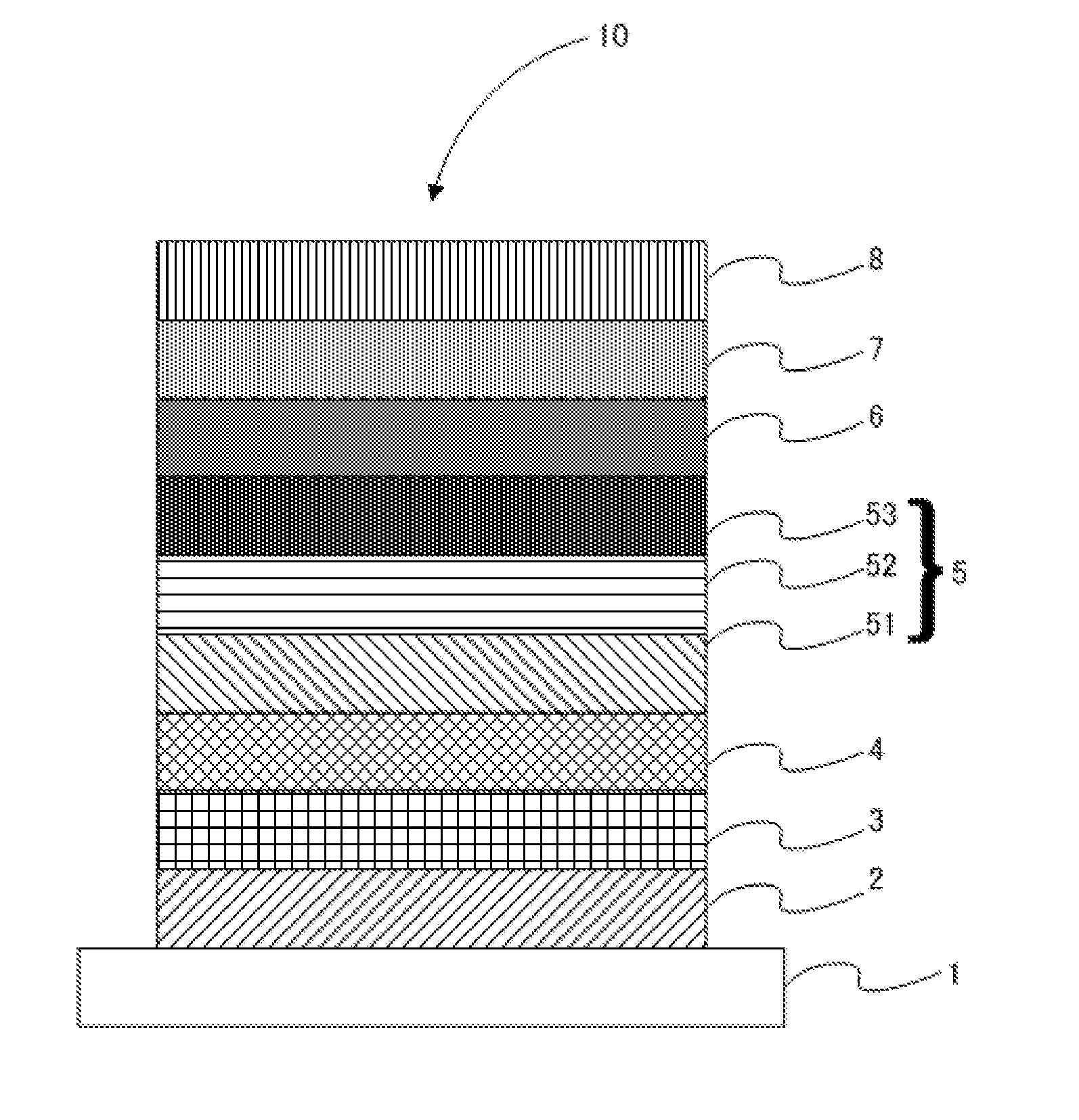

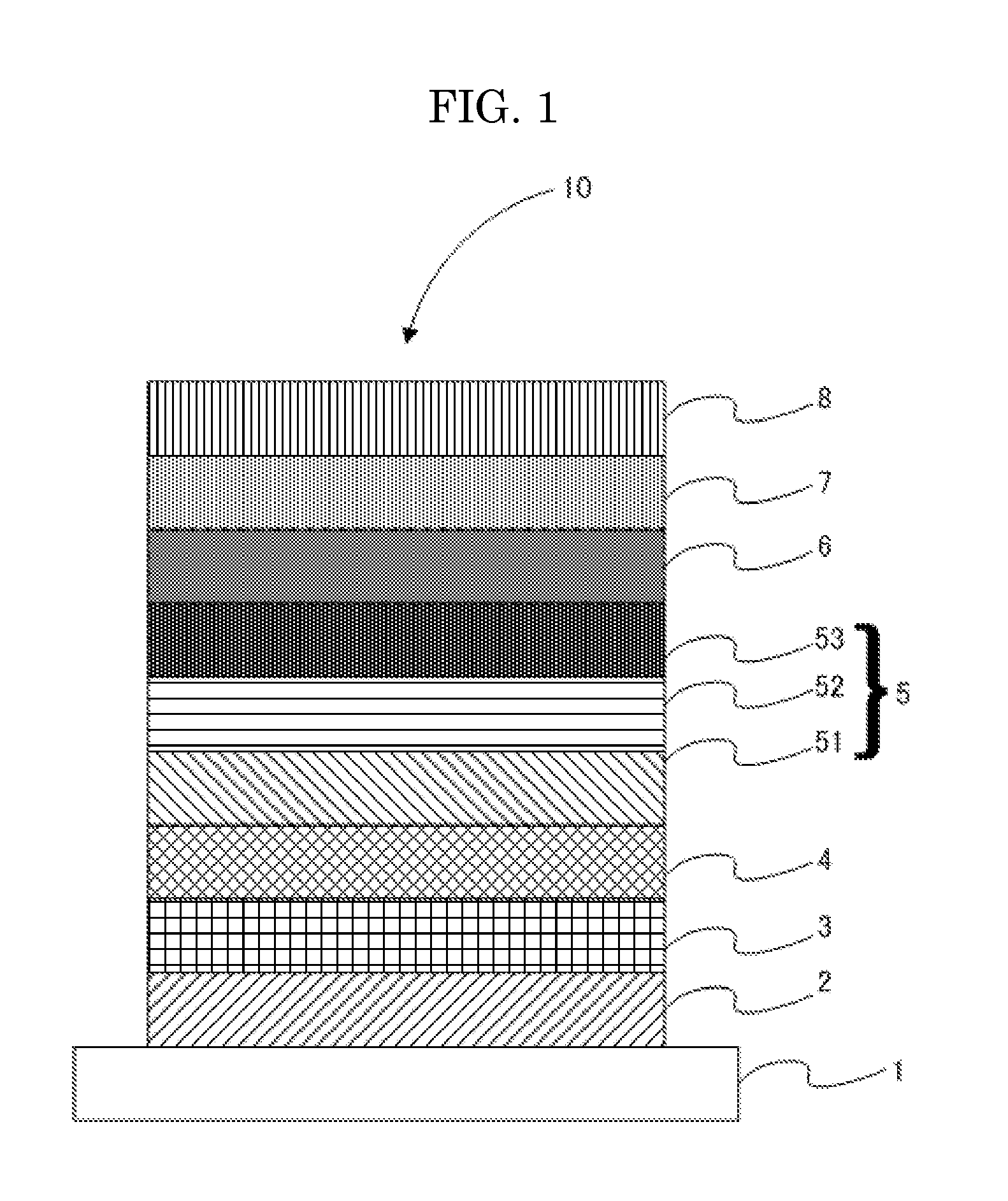

Light-emitting element, light-emitting device, and electronic device

ActiveUS8247804B2Improve carrier balanceEmit light moreSolid-state devicesSemiconductor/solid-state device manufacturingElectronic transmissionElectron capture

Disclosed is a light-emitting element with a good carrier balance and manufacturing method thereof which does not require the formation of the heterostructure. The light-emitting element includes an organic compound film containing a first organic compound as the main component (base material) between an anode and a cathode, wherein the organic compound film is provided in contact with the anode and with the cathode. The first organic compound further includes a light-emitting region to which a light-emitting substance is added and includes a hole-transport region to which a hole-trapping substance is added and / or an electron-transport region to which an electron-trapping substance is added. The hole-transport region is located between the light-emitting region and the anode, and the electron-transport region is located between the light-emitting region and the cathode.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor wafer, method of producing semiconductor wafer, and electronic device

There is provided a compound semiconductor wafer that is suitably used as a semiconductor wafer to form a plurality of different types of devices such as an HBT and an FET thereon. The semiconductor wafer includes a first semiconductor, a carrier-trapping layer that is formed on the first semiconductor and has an electron-trapping center or a hole-trapping center, a second semiconductor that is epitaxially grown on the carrier-trapping layer and serves as a channel in which a free electron or a free hole moves, and a third semiconductor including a stack represented by n-type semiconductor / p-type semiconductor / n-type semiconductor or represented by p-type semiconductor / n-type semiconductor / p-type semiconductor, where the stack epitaxially grown on the second semiconductor.

Owner:SUMITOMO CHEM CO LTD

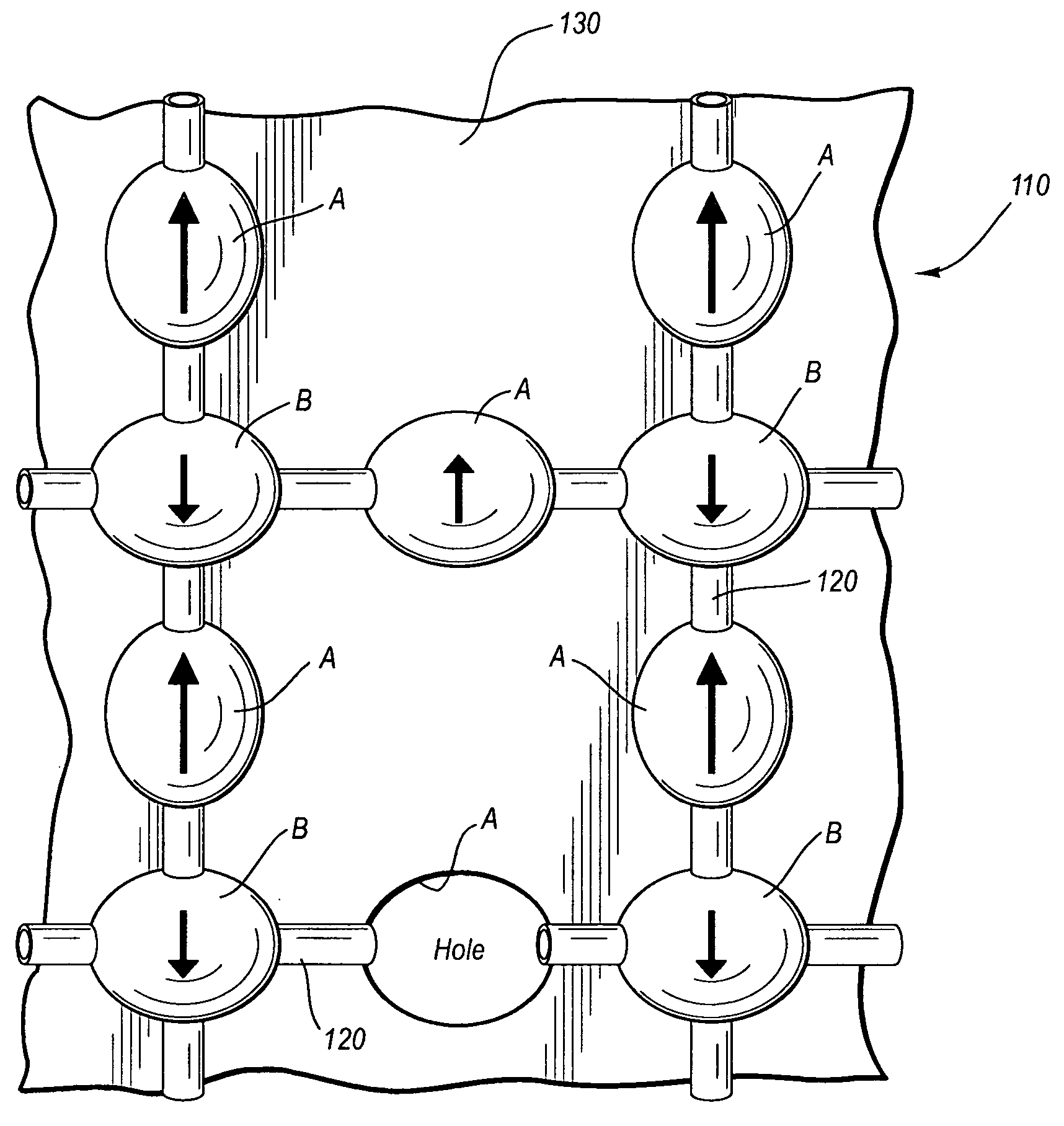

Manipulation of conductive and magnetic phases in an electron trapping semiconducting

InactiveUS20060138397A1Increase electron densitySolid-state devicesSuperconductor devicesMOSFETMagnetic phase

A semiconductor strip array that can be configured to exhibit distinct electrical and / or magnetic phase characteristics according to the many-body effects phenomenon in electron gases is disclosed. The strip array can be incorporated into a MOSFET architecture and utilized in amplifier and memory cell applications. Significantly, the strip array can exhibit superconductive characteristics under relatively high temperature conditions. In one embodiment, the strip array comprises a grounded substrate, a plurality of strips deposited on the substrate in an intersecting pattern to define the strip array, an insulating layer atop the array, a source, and a drain. The intersecting strip array defines primary electron trapping sites at the strip intersections and secondary electron trapping sites on the strips between the intersections. The strip array is further configured to exhibit distinct electrical and / or magnetic properties according to a selective concentration of electrons injected into the primary and secondary electron trapping sites.

Owner:UNIV OF UTAH RES FOUND

Thin film transistor substrate and method of manufacturing the same and mask for manufacturing thin film transistor substrate

A thin film transistor substrate, wherein the moving area of electrons between source and drain electrodes of a thin film transistor (TFT) is minimized, the moving distance of electrons is increased, and the sizes of capacitors defined by a gate electrode together with the respective source and drain electrodes are identical to each other so that an off current generated when the TFT is off can be minimized; a method of manufacturing the thin film transistor substrate; and a mask for manufacturing the thin film transistor substrate. Accordingly, it is possible to minimize an off current induced due to a phenomenon of electron trapping by light.

Owner:SAMSUNG DISPLAY CO LTD

Nonvolatile semiconductor memory apparatus

ActiveUS20090267134A1Restrict leakage currentImprove leakage currentSolid-state devicesSemiconductor devicesOptoelectronicsSemiconductor

A nonvolatile semiconductor memory apparatus includes: a memory element including: a semiconductor substrate; a source region and a drain region formed at a distance from each other in the semiconductor substrate; a first insulating film formed on a portion of the semiconductor substrate located between the source region and the drain region, having sites that perform electron trapping and releasing and are formed by adding an element different from a base material, and including insulating layers having different dielectric constants, the sites having a higher level than a Fermi level of a material forming the semiconductor substrate; a charge storage film formed on the first insulating film; a second insulating film formed on the charge storage film; and a control gate electrode formed on the second insulating film.

Owner:KIOXIA CORP

Array of virtual frisch-grid detectors with common cathode and reduced length of shielding electrodes

ActiveUS20130126746A1Enhance virtual shielding effectLow efficiencySolid-state devicesMaterial analysis by optical meansElectron captureAtomic physics

Owner:BROOKHAVEN SCI ASSOCS

Organic Electroluminescent Device and Method of Fabrication

ActiveUS20120062109A1Discharge tube luminescnet screensLamp detailsOrganic electroluminescenceMolecular physics

An organic electroluminescent device comprises an anode; a cathode; a first electroluminescent layer between the anode and the cathode comprising an electron transporting material; and a second electroluminescent layer between the first electroluminescent layer and the anode. The second electroluminescent layer comprises a hole transporting material and an electroluminescent electron trapping material. The first electroluminescent layer may comprises a polymer having an electron transporting material and an electroluminescent material, and may include an optionally electroluminescent hole-transporting material. The electron transporting material and one or both of the hole transporting material of the first electroluminescent layer and the electroluminescent material of the first electroluminescent layer are part of the same molecule or polymer. Preferably, the electron transporting material comprises a plurality of adjacent arylene repeat units.

Owner:CAMBRIDGE DISPLAY TECH LTD +1

![[method of fabricating non-volatile memory cell ] [method of fabricating non-volatile memory cell ]](https://images-eureka.patsnap.com/patent_img/1d1651da-bd2c-44c0-bf18-b495cf6273f0/US20050176203A1-20050811-D00000.png)

![[method of fabricating non-volatile memory cell ] [method of fabricating non-volatile memory cell ]](https://images-eureka.patsnap.com/patent_img/1d1651da-bd2c-44c0-bf18-b495cf6273f0/US20050176203A1-20050811-D00001.png)

![[method of fabricating non-volatile memory cell ] [method of fabricating non-volatile memory cell ]](https://images-eureka.patsnap.com/patent_img/1d1651da-bd2c-44c0-bf18-b495cf6273f0/US20050176203A1-20050811-D00002.png)

![[non-volatile memory structure and manufacturing method thereof] [non-volatile memory structure and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/754b3ed3-8dc8-4ae1-afef-ef843bfb71df/US20050224858A1-20051013-D00000.png)

![[non-volatile memory structure and manufacturing method thereof] [non-volatile memory structure and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/754b3ed3-8dc8-4ae1-afef-ef843bfb71df/US20050224858A1-20051013-D00001.png)

![[non-volatile memory structure and manufacturing method thereof] [non-volatile memory structure and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/754b3ed3-8dc8-4ae1-afef-ef843bfb71df/US20050224858A1-20051013-D00002.png)