Basic cell, standard cell, standard cell library, back-end full-custom design method and chip

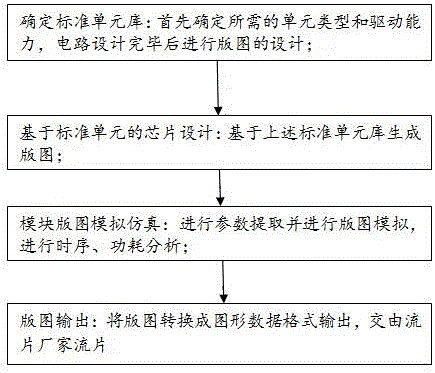

A standard cell library and basic cell technology, applied in computer-aided design, CAD circuit design, calculation, etc., can solve problems such as failure to meet market input demands in a timely manner, enterprise market competition losing opportunities to seize opportunities, and increasing the difficulty of single chip processing, etc. Achieve the effects of shortening the time to market, convenient layout design method, and optimized layout design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be described in further detail below in conjunction with the accompanying drawings.

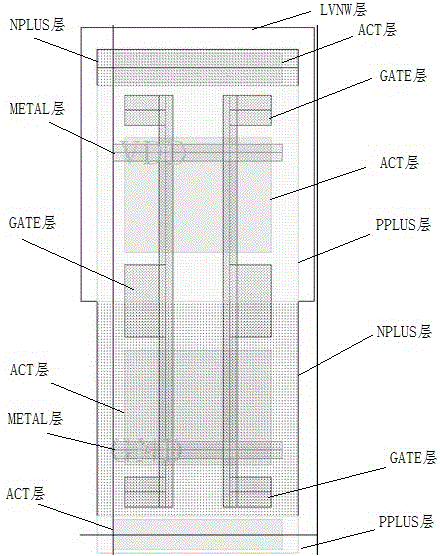

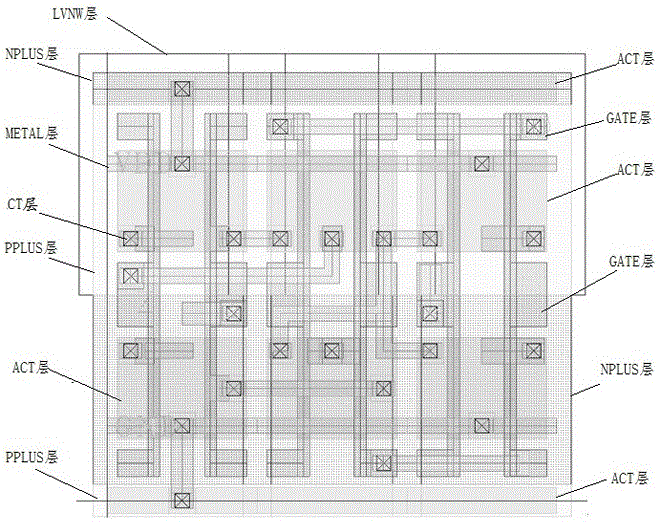

[0045] Such as figure 1 , the structure of the basic unit provided in the present invention. The basic unit of the present invention at least includes GATE layer, ACT layer, LVNW layer, NPULS layer and PPLUS layer, CT layer and METAL layer, all of which have regular shapes. The regular shapes of the GATE layer, the ACT layer, the LVNW layer, the NPULS layer and the PPLUS layer must conform to the process design rules. The process design rules include channel length, number of metal layers, layout size, metal wiring width, spacing and direction, power / ground bus width, and the like.

[0046]The specific regular shape design is: the GATE layer, ACT layer, LVNW layer, NPULS layer and PPLUS layer in the basic unit are symmetrically distributed with the center line in the height direction of the basic unit as the boundary, and / or the center line in the width dir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More