Two-stage time-to-digital converter

A time-to-digital converter technology, applied in the field of two-stage time-to-digital converters, can solve the problems of time quantization complexity and achieve the effect of easy matching, high resolution and linearity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0033] The TDC designed in this example is a TDC used in a 1.2G-2.5GHz all-digital phase-locked loop (ADPLL). Its reference frequency is 40MHz. (The highest sampling ratio) is 2.5G / 40M=62.5, the highest and lowest frequency ratio>2, which can be called broadband.

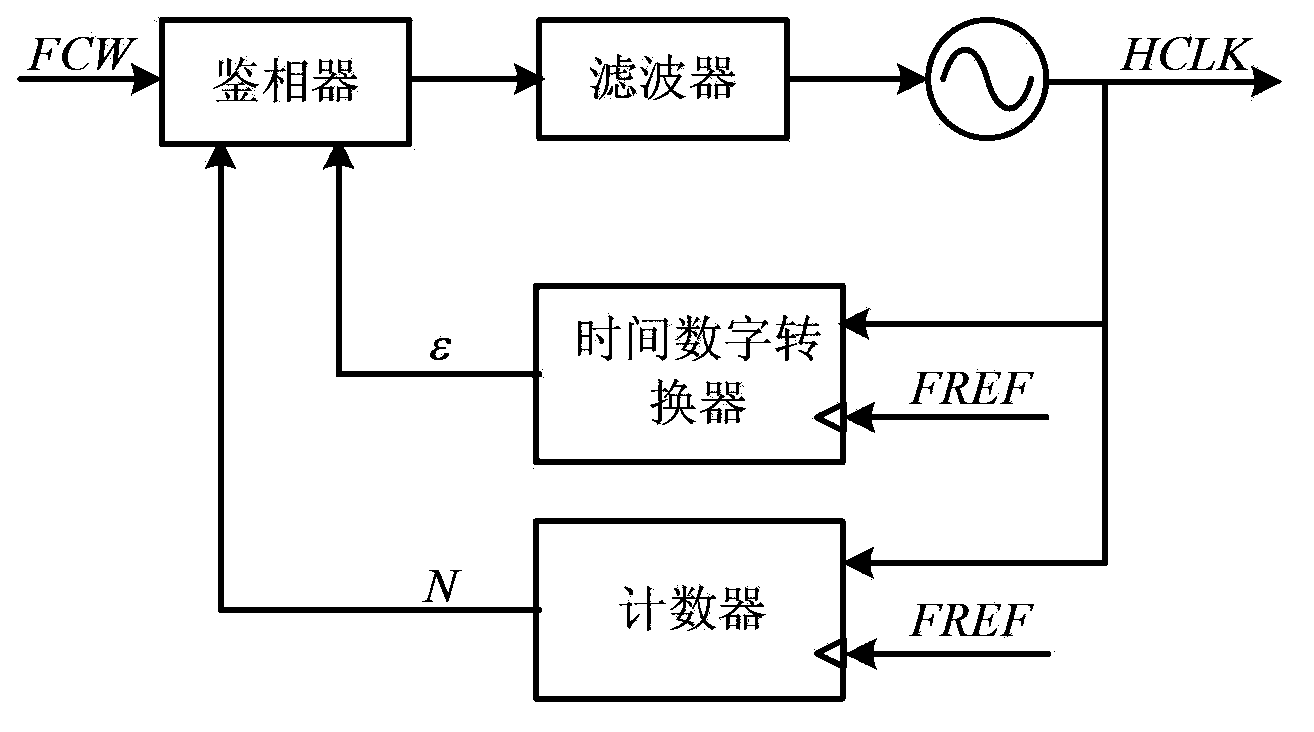

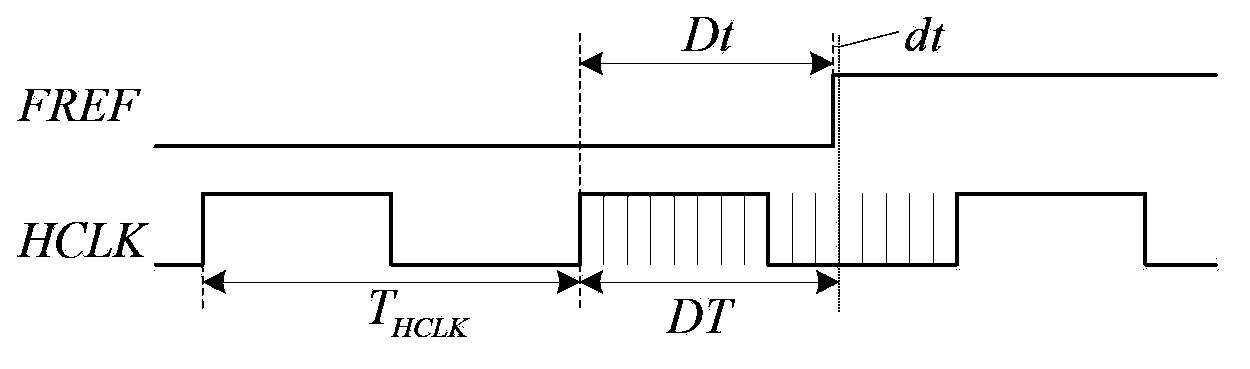

[0034] The structure of the all-digital phase-locked loop (ADPLL) applicable to the two-stage TDC proposed in this example is as follows: figure 1 As shown, the role of TDC in it is to quantify the time interval between HCLK and FREF, and at the same time normalize the period of HCLK, and finally obtain the fractional frequency division ratio and input it to the following circuit.

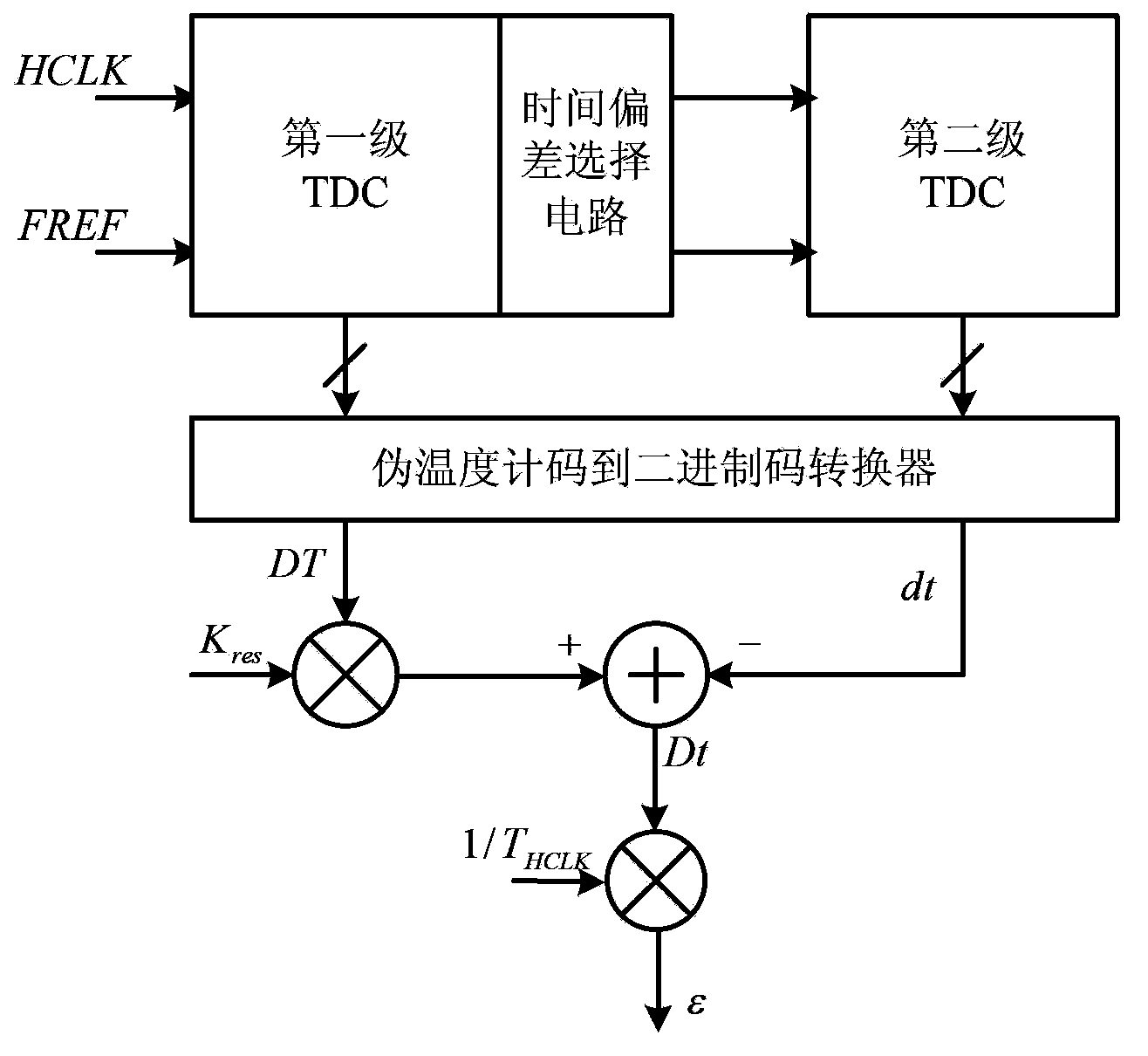

[0035] The TDC frame structure proposed in this example is as follows: figure 2 As shown, it includes a two-stage quantization circuit and a decoding circuit. The first-stage quantization is coarse quantization, the second-stage quantization is fine quantization, and the deviation selection circuit is between the two-stage quantization...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More