Patents

Literature

101 results about "Time to digital conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

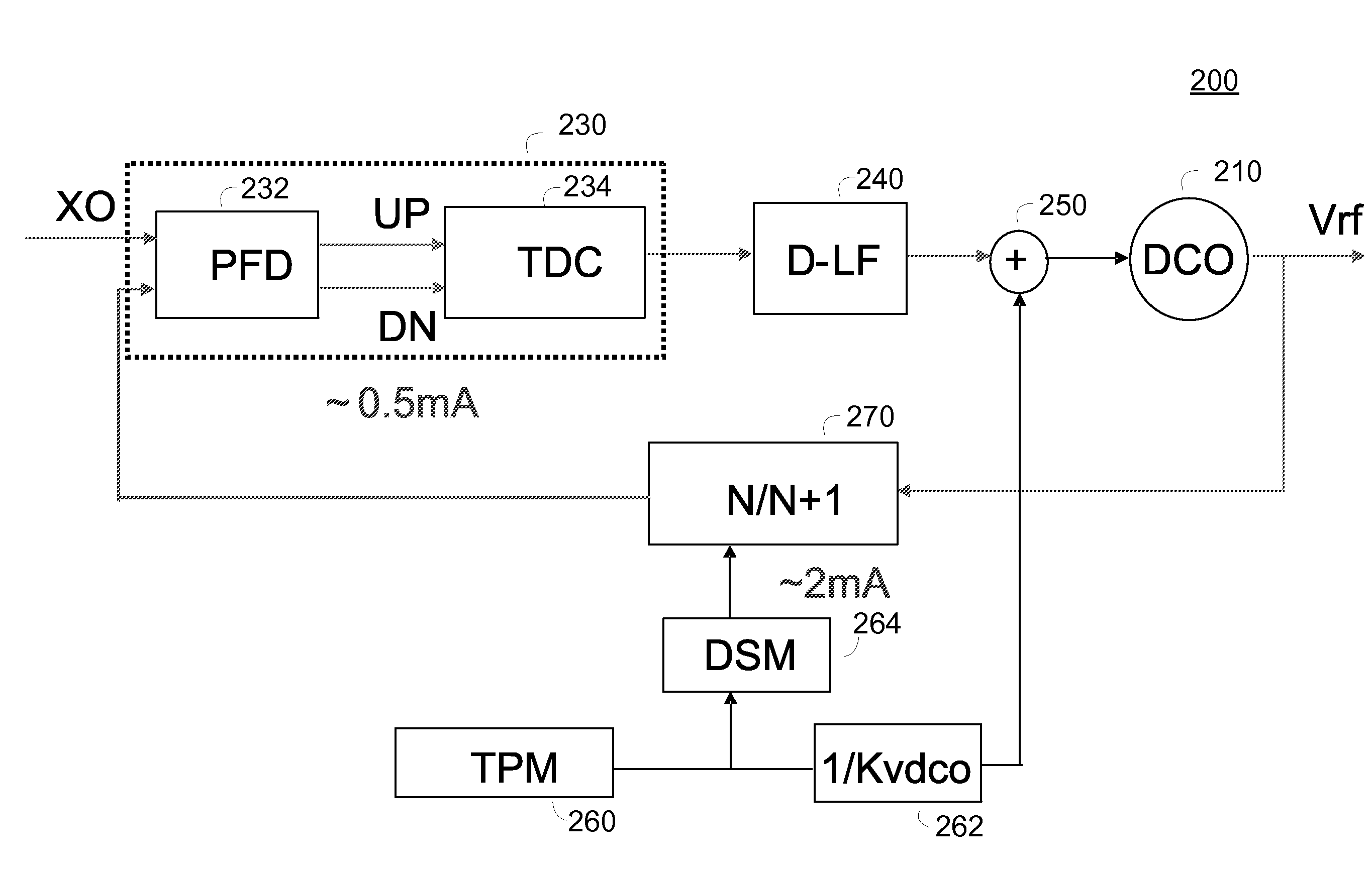

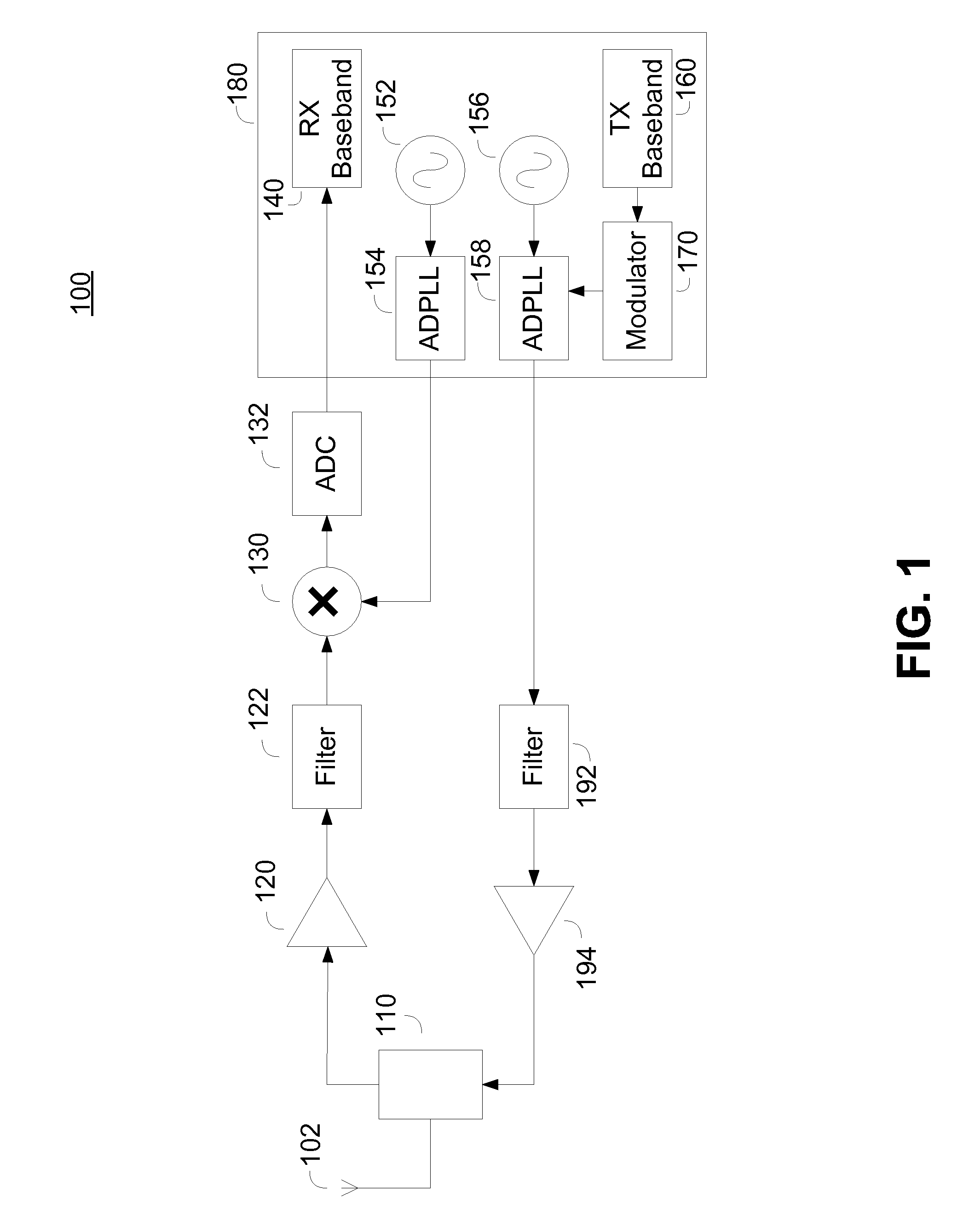

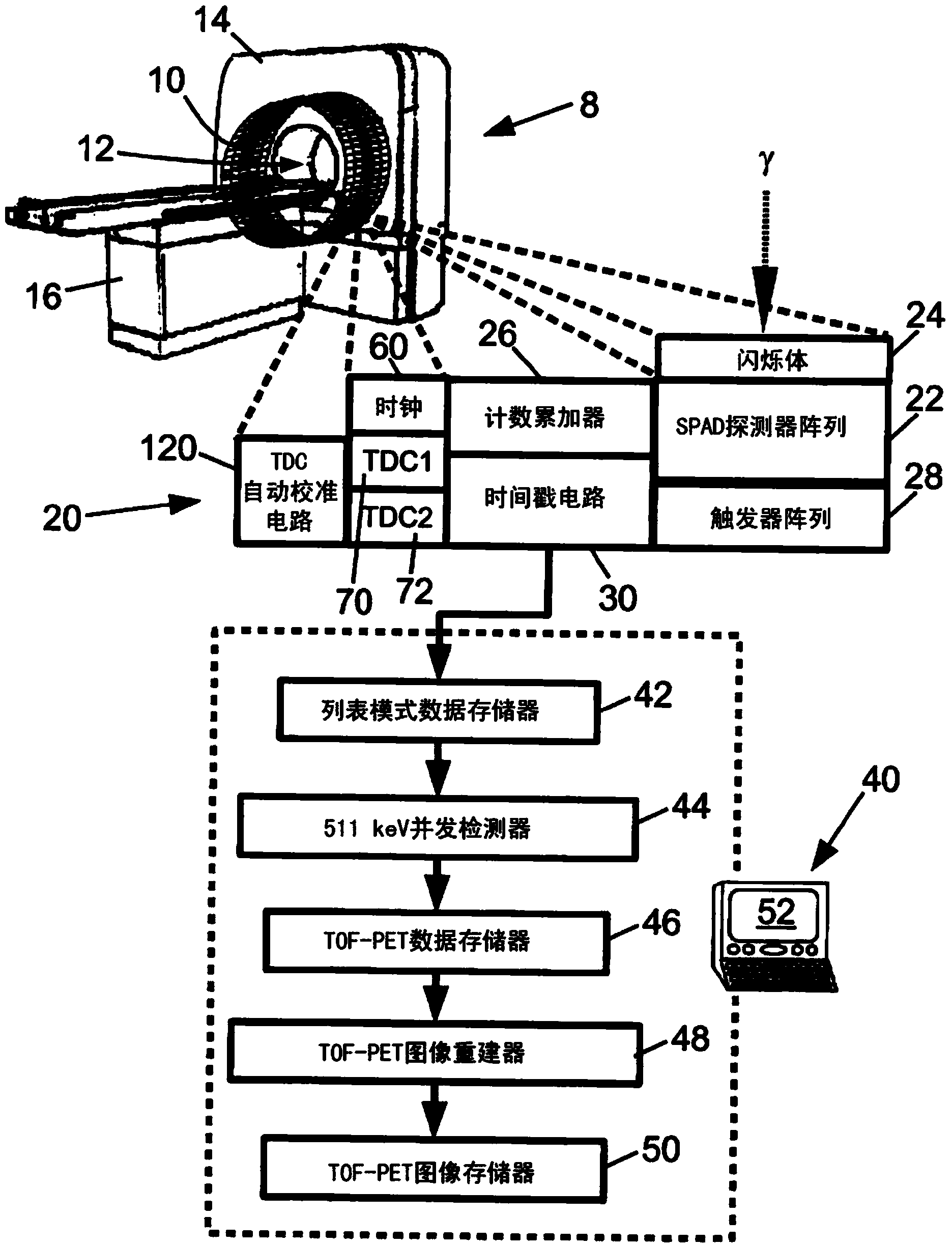

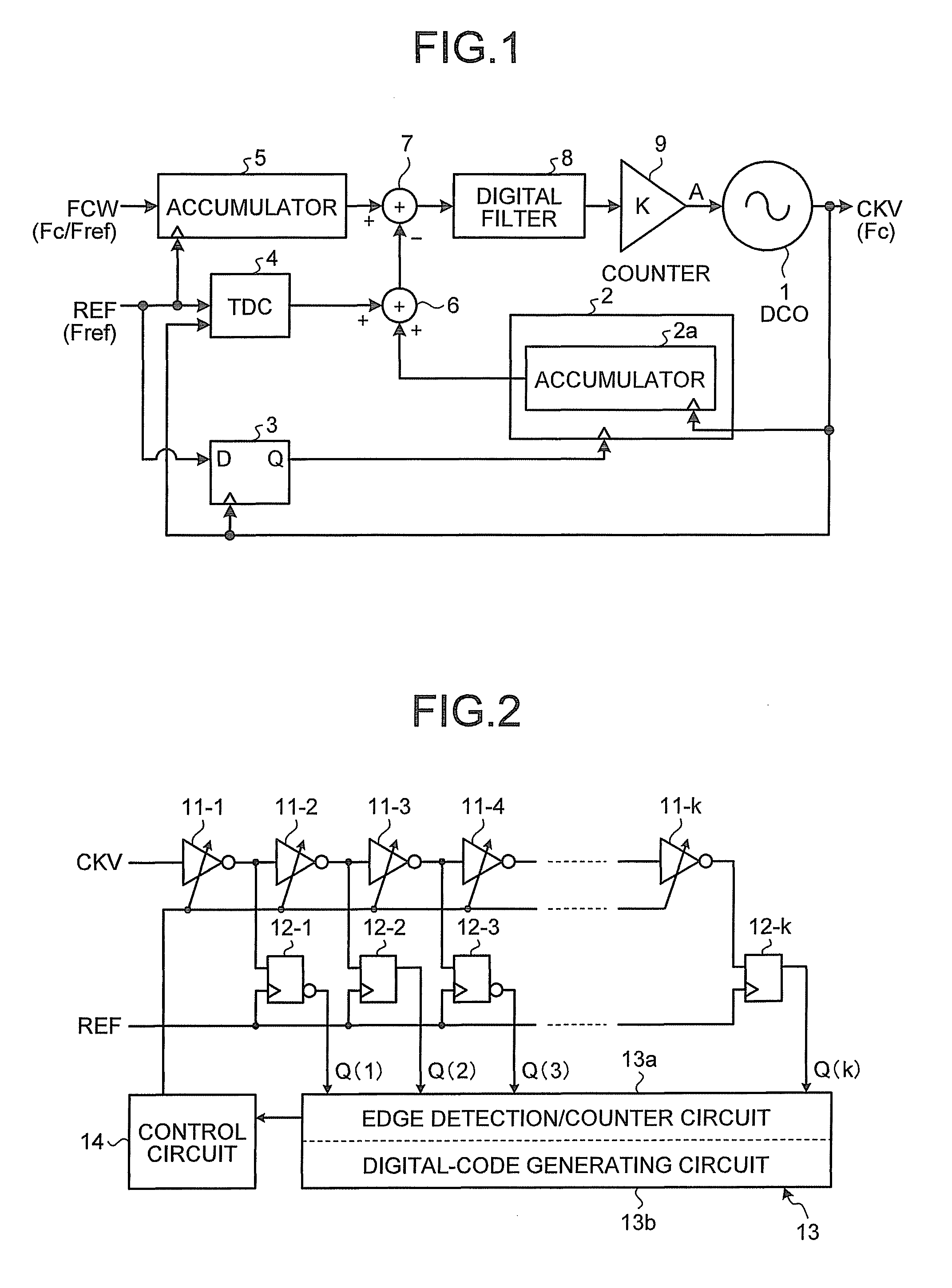

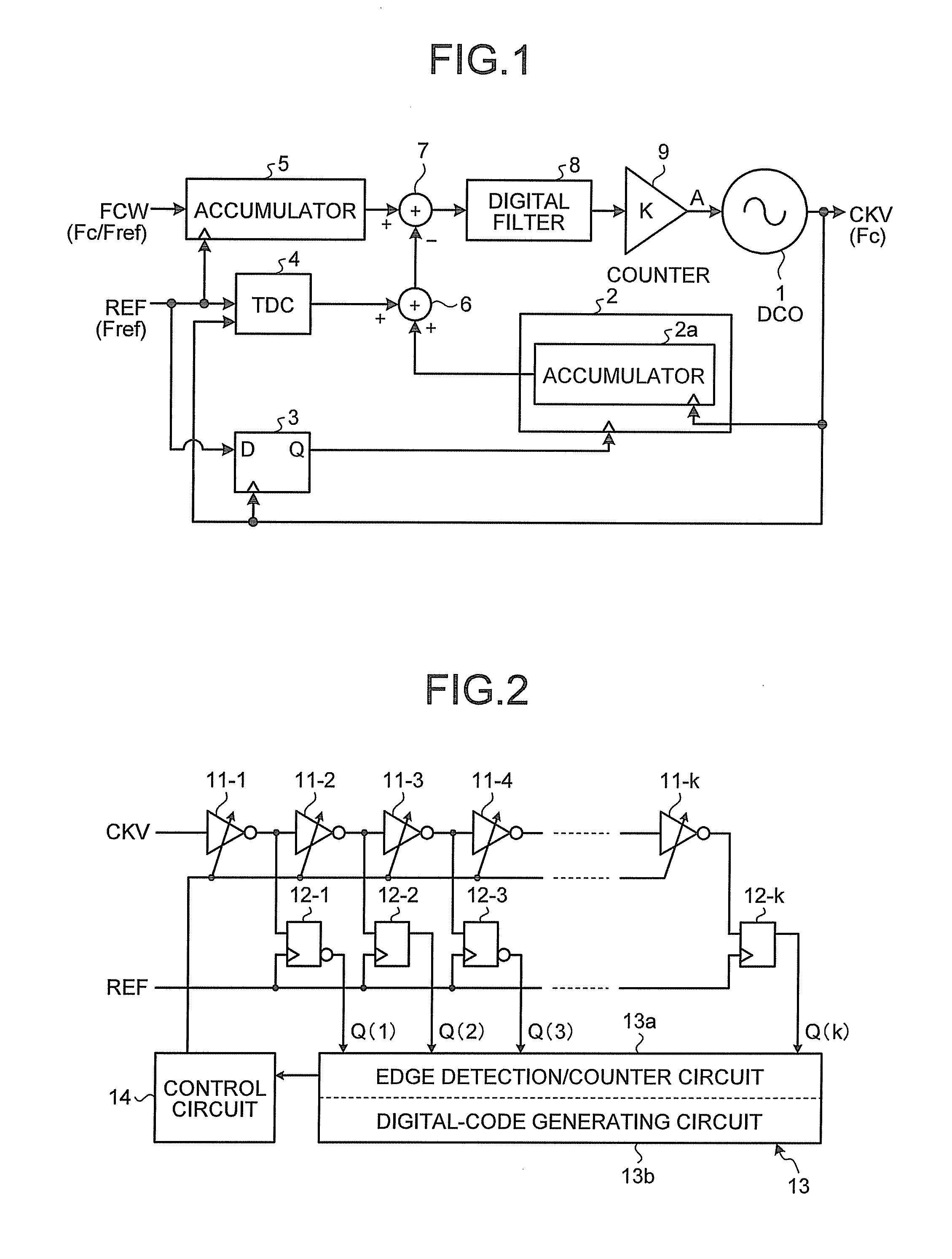

Phase to digital converter in all digital phase locked loop

ActiveUS20090256601A1Low power operationLower requirementElectric signal transmission systemsPulse automatic controlDigital down converterReference Period

A phase to digital converter, all digital phase locked loop, and apparatus having an all digital phase locked loop are described herein. The phase to digital converter includes a phase to frequency converter driving a time to digital converter. The time to digital converter determines a magnitude and sign of the phase differences output by the phase to frequency converter. The time to digital converter utilizes tapped delay lines and looped feedback counters to enable measurement of small timing differences typical of a loop tracking process and large timing differences typical of an loop acquisition process. The tapped delay lines permit the measurement of fractions of a reference period and enable lower power operation of the phase to digital converter by reducing requirements on the speed of the reference clock.

Owner:QUALCOMM INC

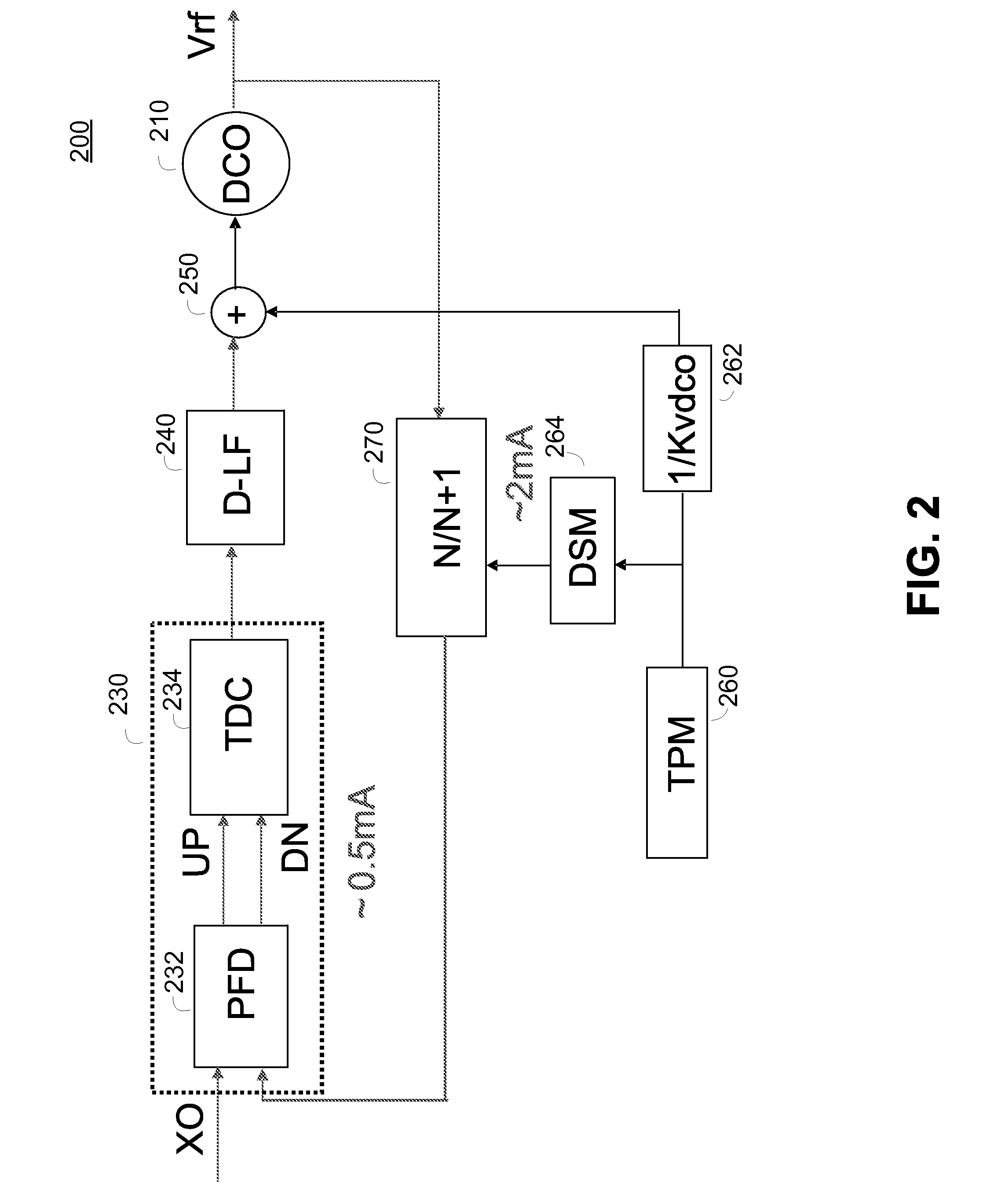

Detector array with time-to-digital conversion having improved temporal accuracy

ActiveCN103460072AImprove time resolutionAccurate time-of-flight PET imagingTomographyX/gamma/cosmic radiation measurmentDetector arrayDigital converter

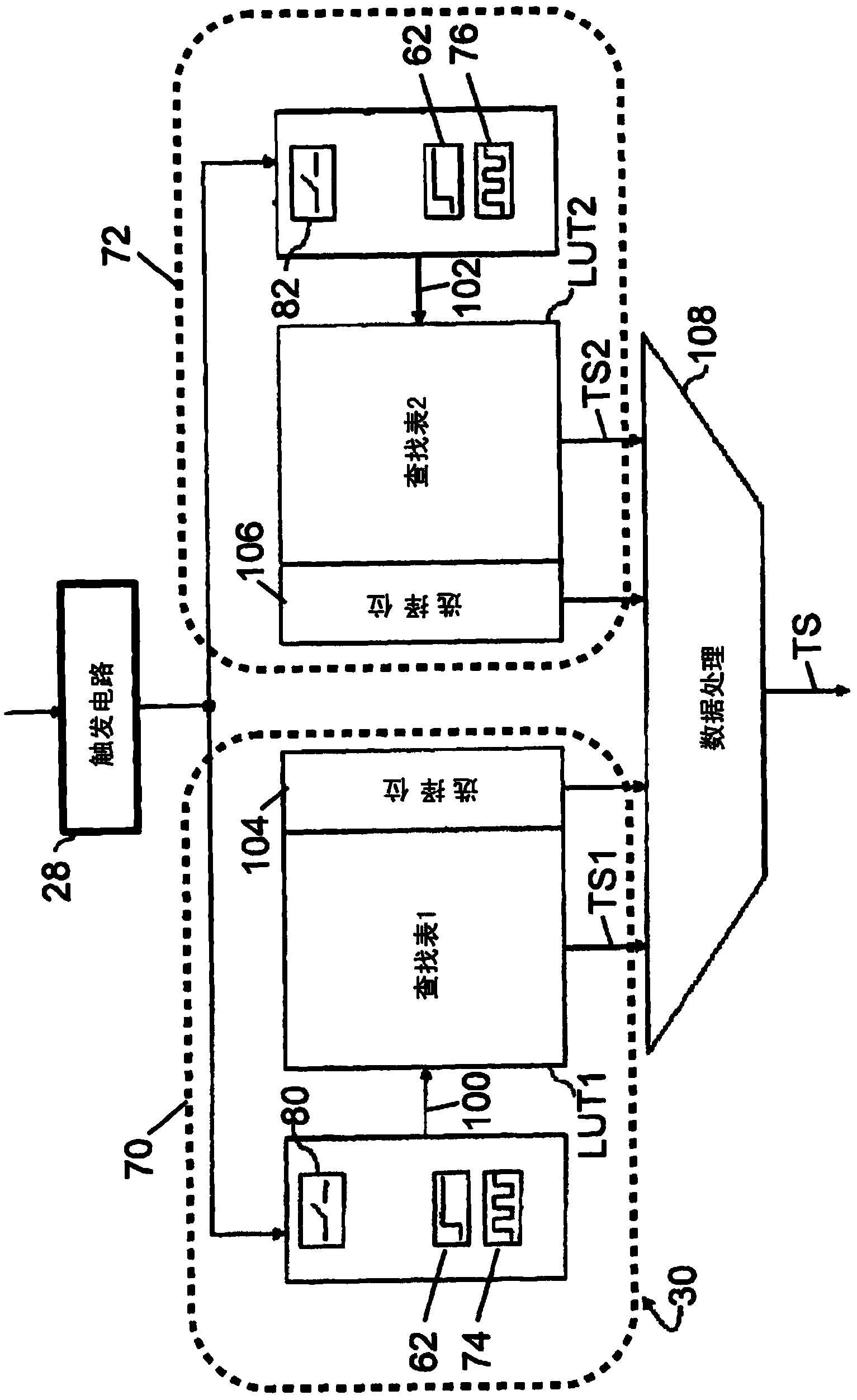

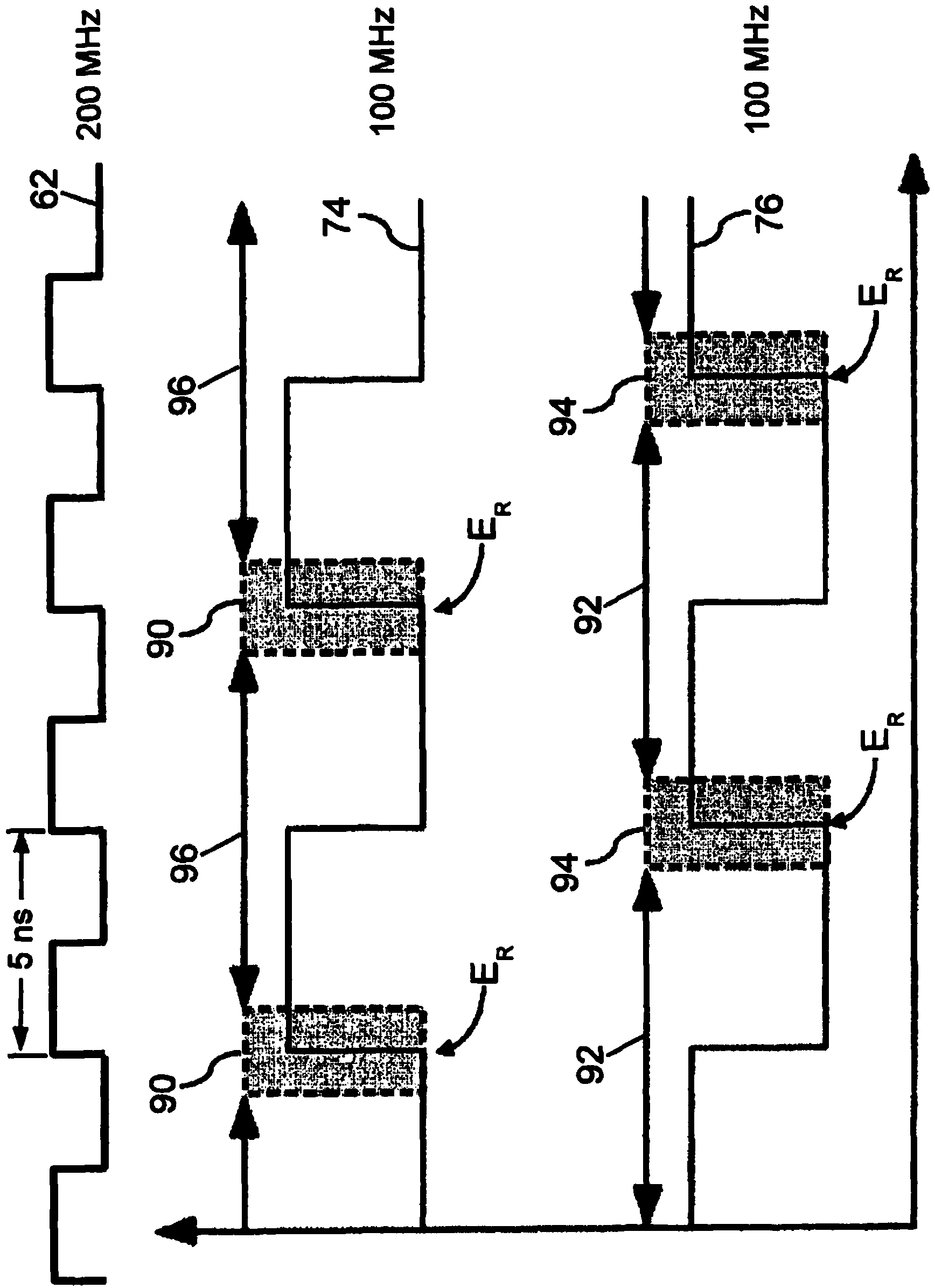

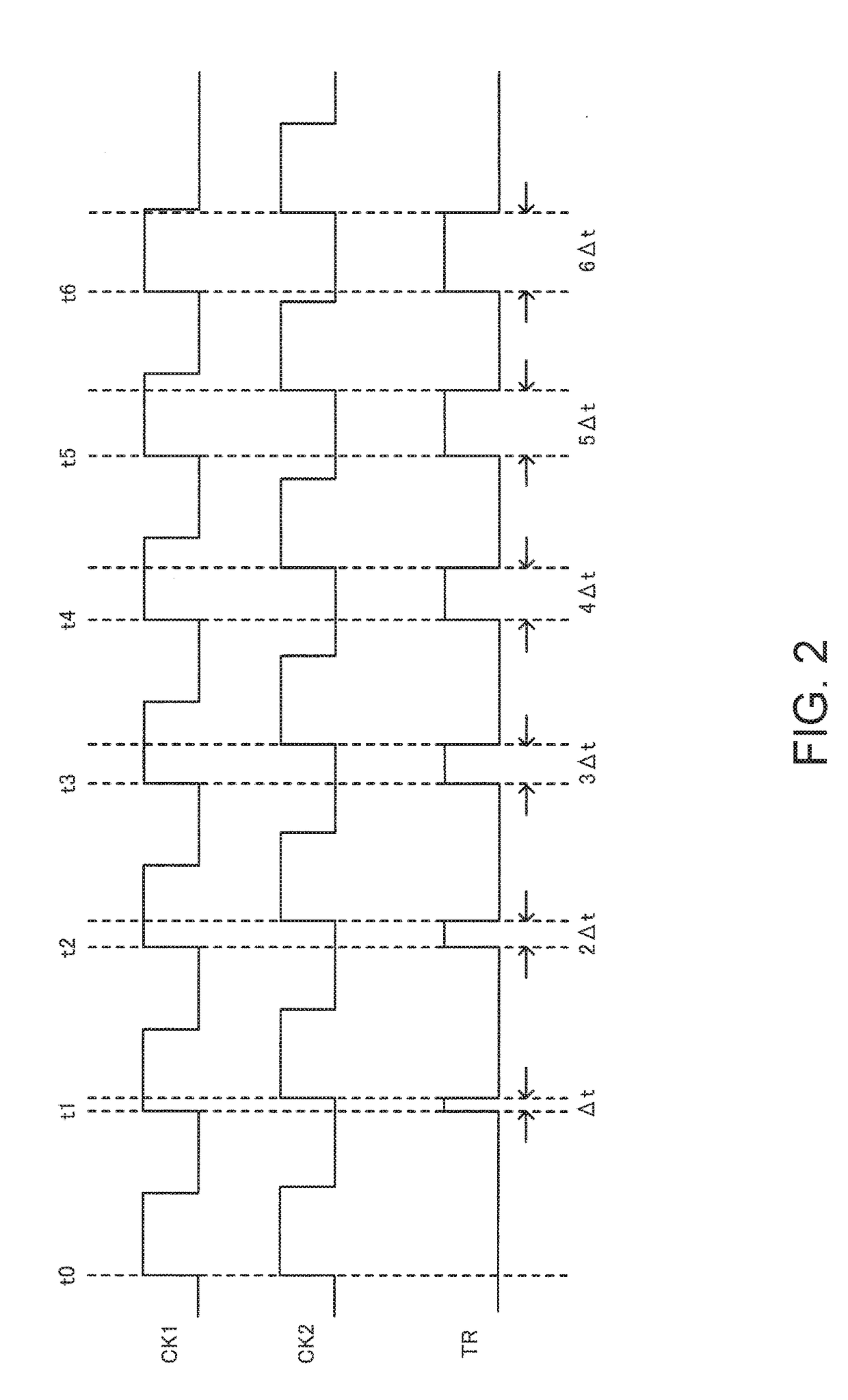

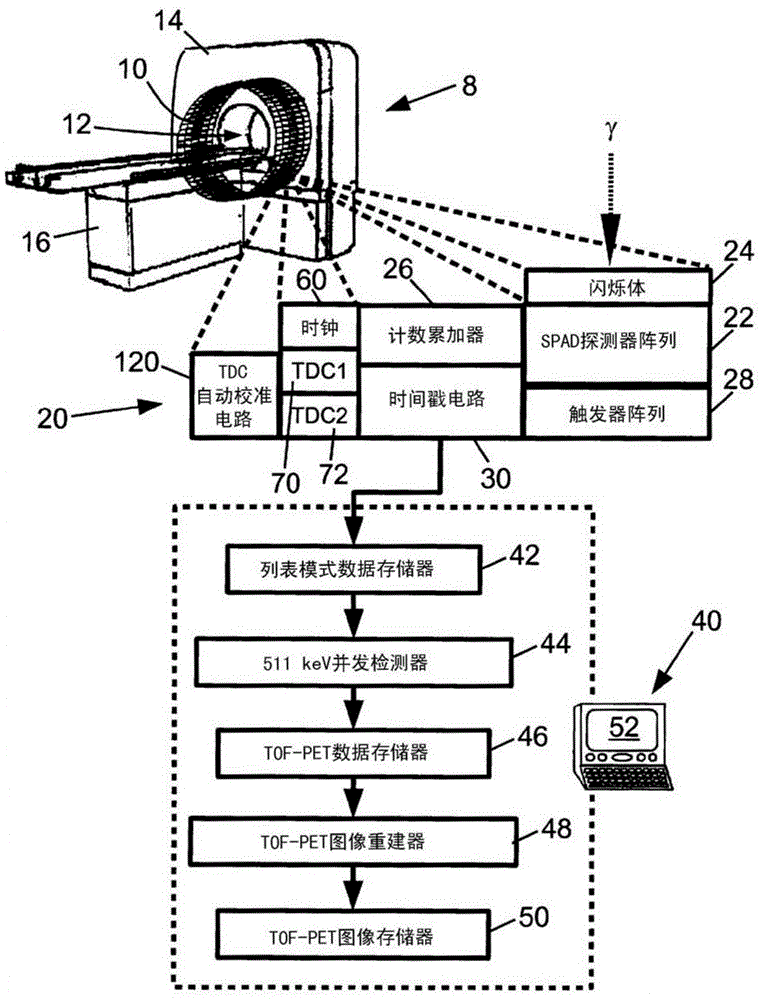

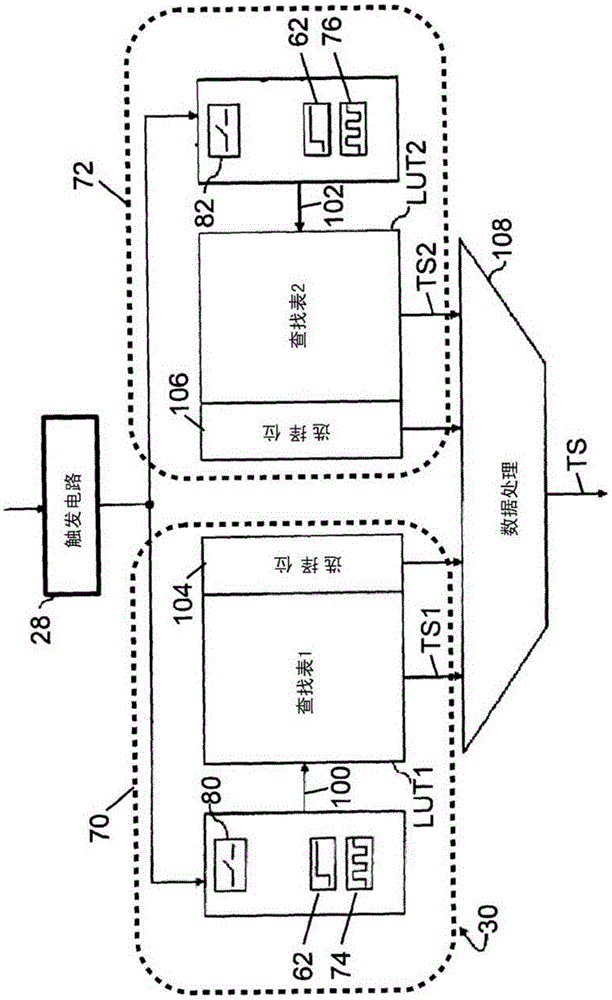

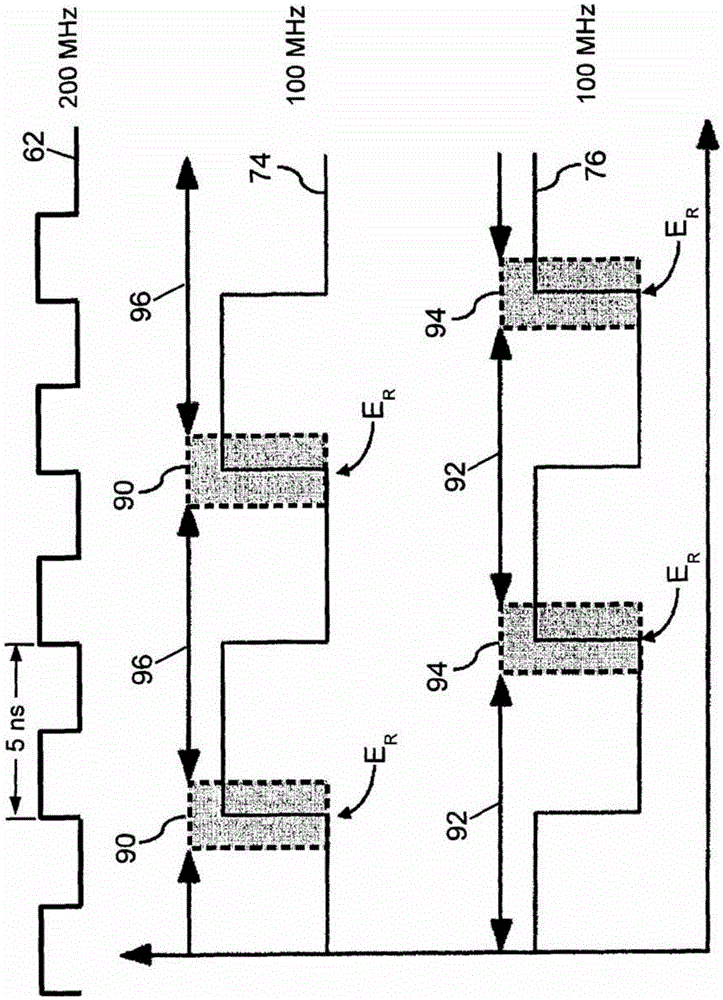

A detector (22) detects an event. First and second time-to-digital converters(TDCs) (70, 72) generate first and second time stamps (TS1, TS2) for the detection of the event. The first TDC and the second TDC are both synchronized with a common clock signal (62) that defines a fixed time offset between the second TDC and the first TDC. An autocalibration circuit (120) adjusts the first TDC and the second TDC to keep the time difference between the second time stamp and the first time stamp equal to the fixed time offset between the second TDC and the first TDC. The detector may be a detector array, and trigger circuitry (28) propagates a trigger signal from a triggering detector of the array of detectors to the first and second TDC's. Skew correction circuitry (132, 134, 136, 142, 60, 162) adjusts a timestamp (TS) based on which detector is the triggering detector.

Owner:KONINKLJIJKE PHILIPS NV

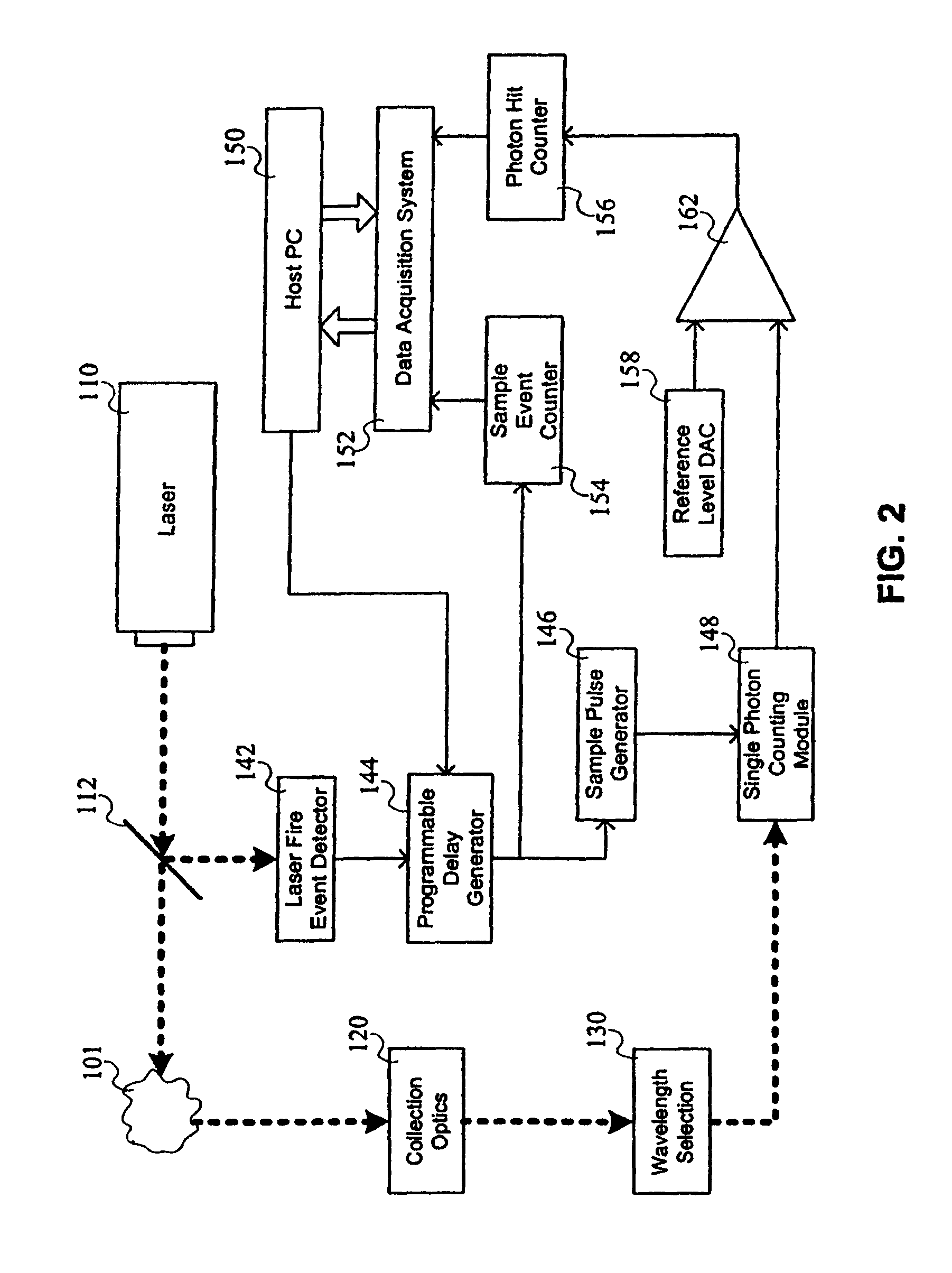

Time correlated single photon counting by time to digital conversion

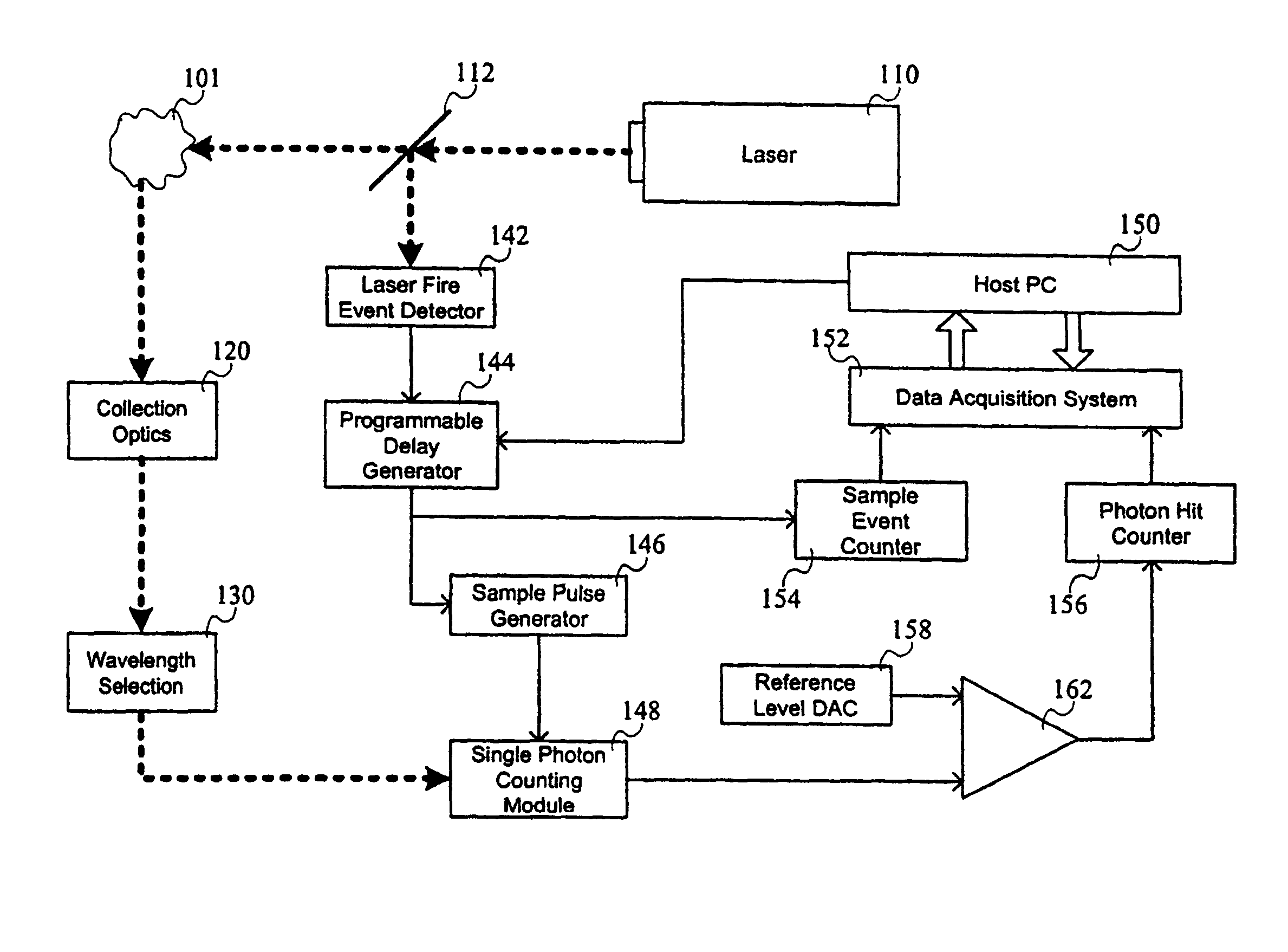

A time correlated single photon counting system having a time to digital converter triggered by a laser fire event detector and the reception of a single photon. The system may be used for chemical agent detection based on Rayleigh scattering using optical time domain reflectometry techniques. The system may also be used for Raman detection using frequency to time transformations.

Owner:OPTECH VENTURES

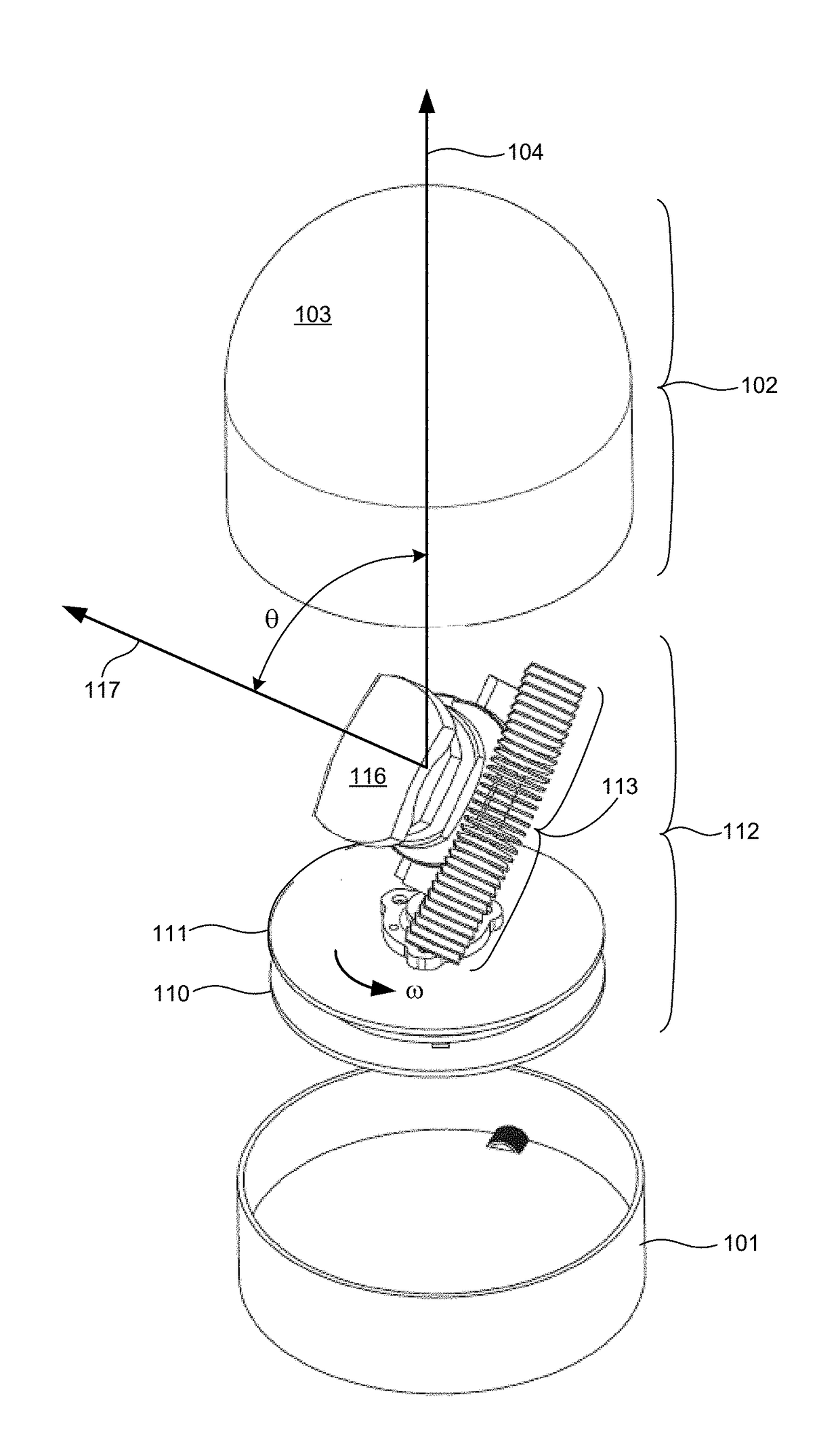

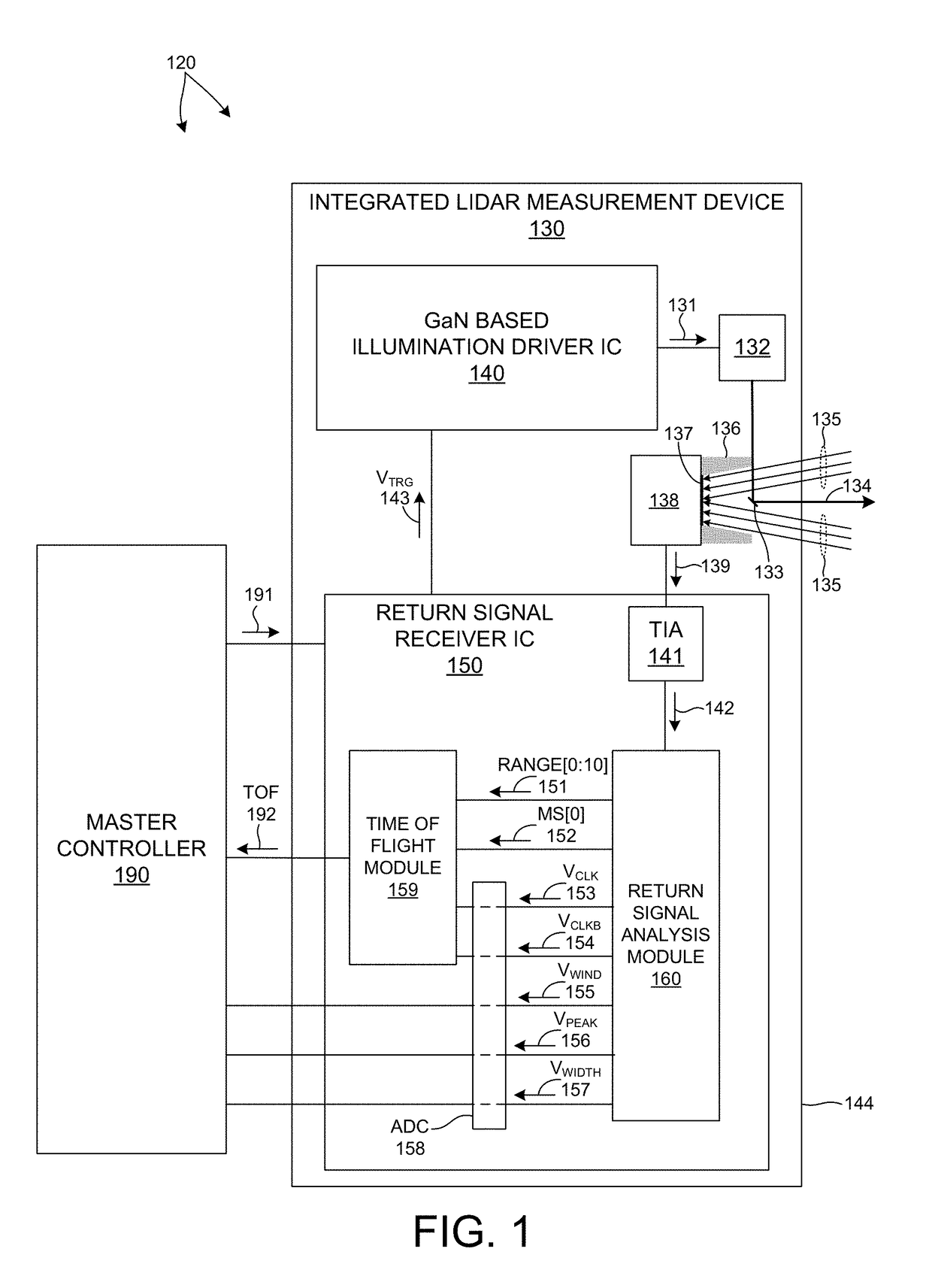

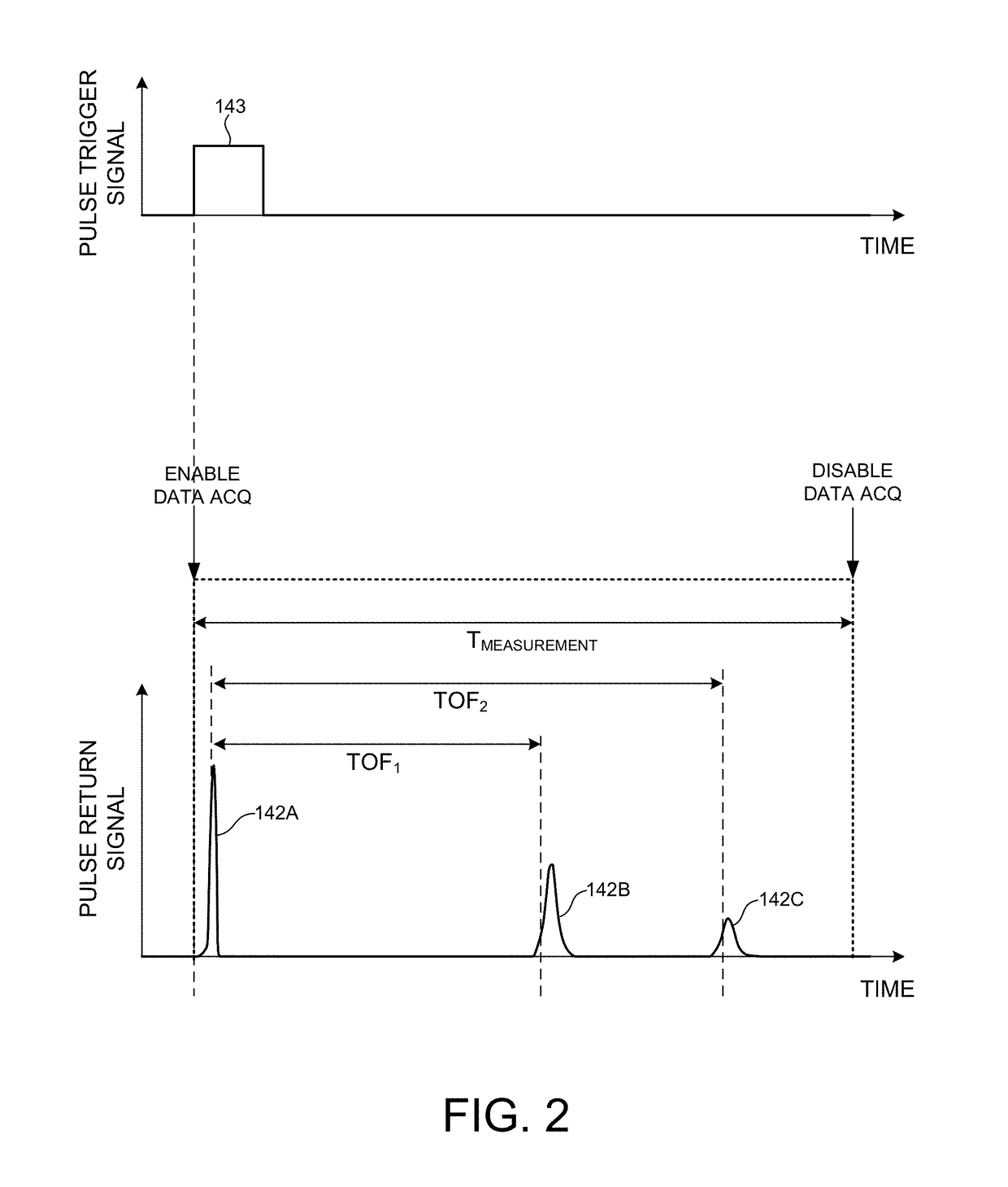

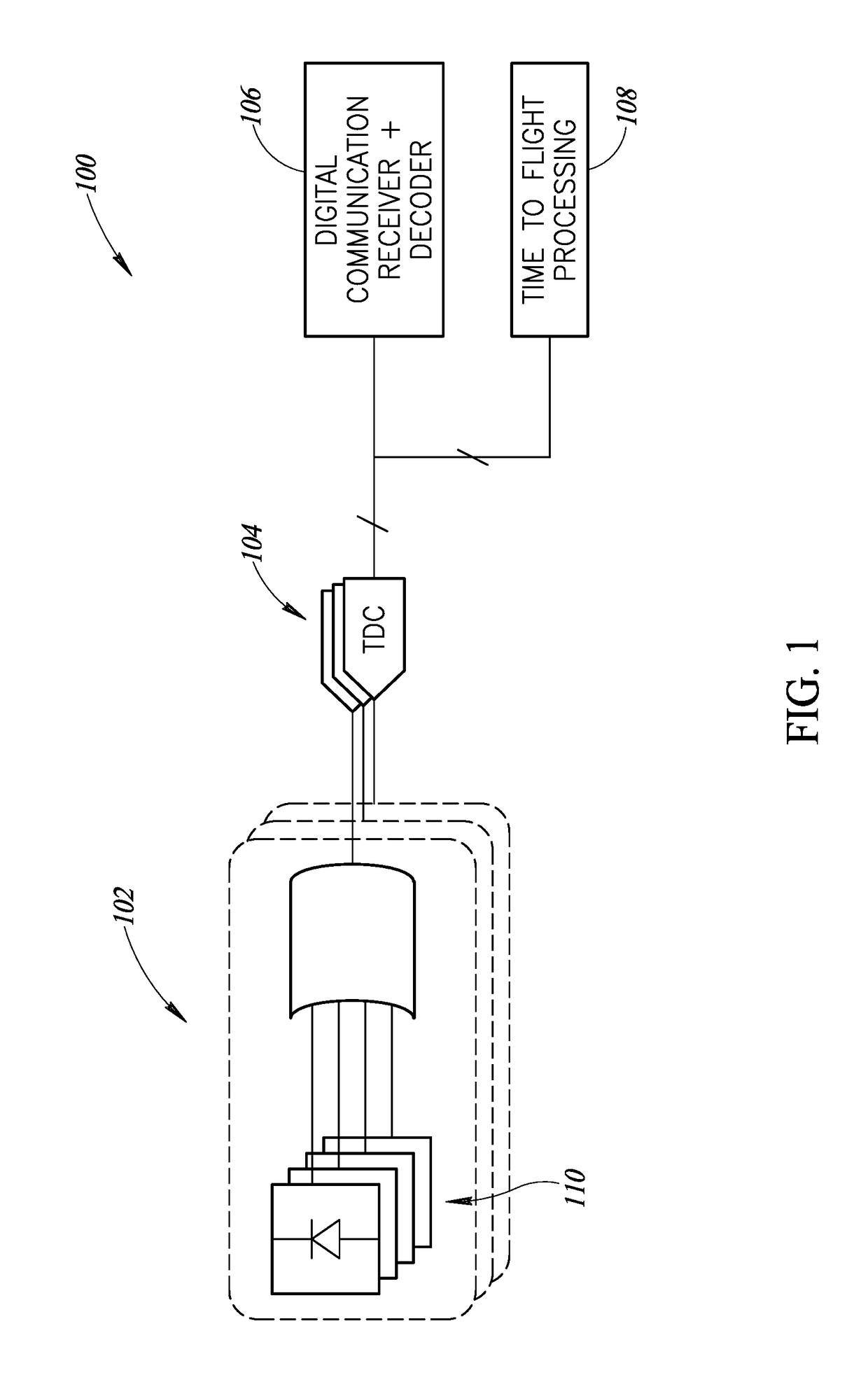

LIDAR Data Acquisition And Control

ActiveUS20180321360A1Accurate synchronizationAccurate timingElectromagnetic wave reradiationMeasurement deviceData acquisition

Methods and systems for performing three dimensional LIDAR measurements with an integrated LIDAR measurement device are described herein. In one aspect, a return signal receiver generates a pulse trigger signal that triggers the generation of a pulse of illumination light and data acquisition of a return signal, and also triggers the time of flight calculation by time to digital conversion. In addition, the return signal receiver also estimates the width and peak amplitude of each return pulse, and samples each return pulse waveform individually over a sampling window that includes the peak amplitude of each return pulse waveform. In a further aspect, the time of flight associated with each return pulse is estimated based on a coarse timing estimate and a fine timing estimate. In another aspect, the time of flight is measured from the measured pulse due to internal optical crosstalk and a valid return pulse.

Owner:VELODYNE LIDAR USA INC

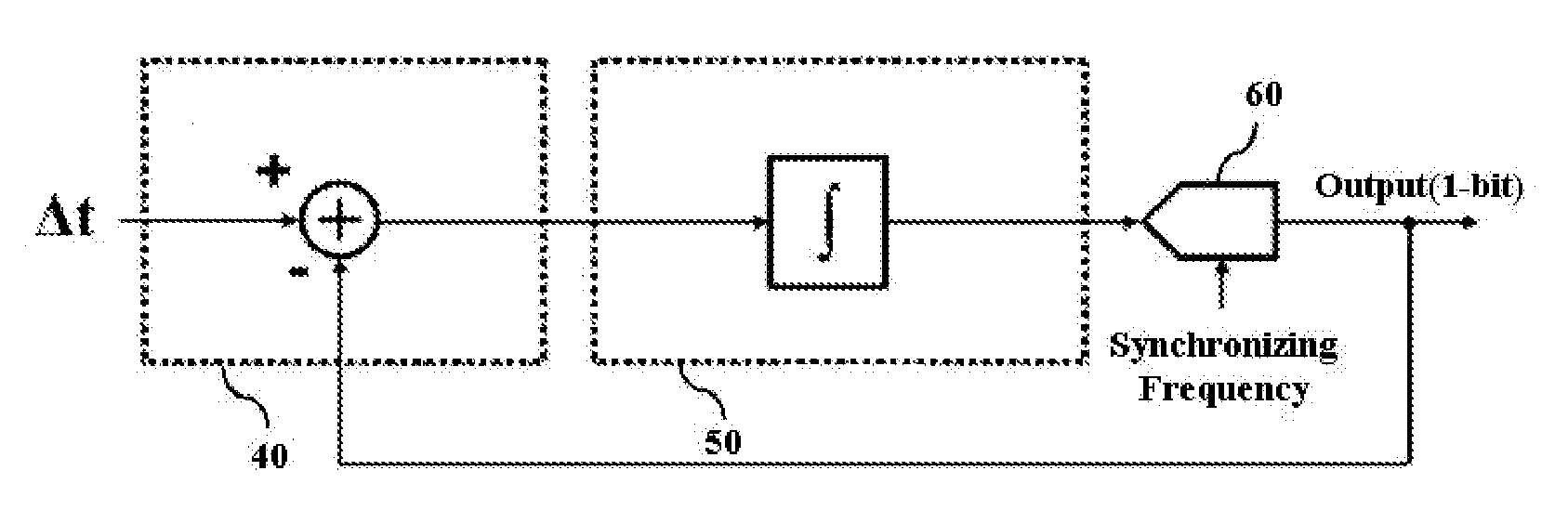

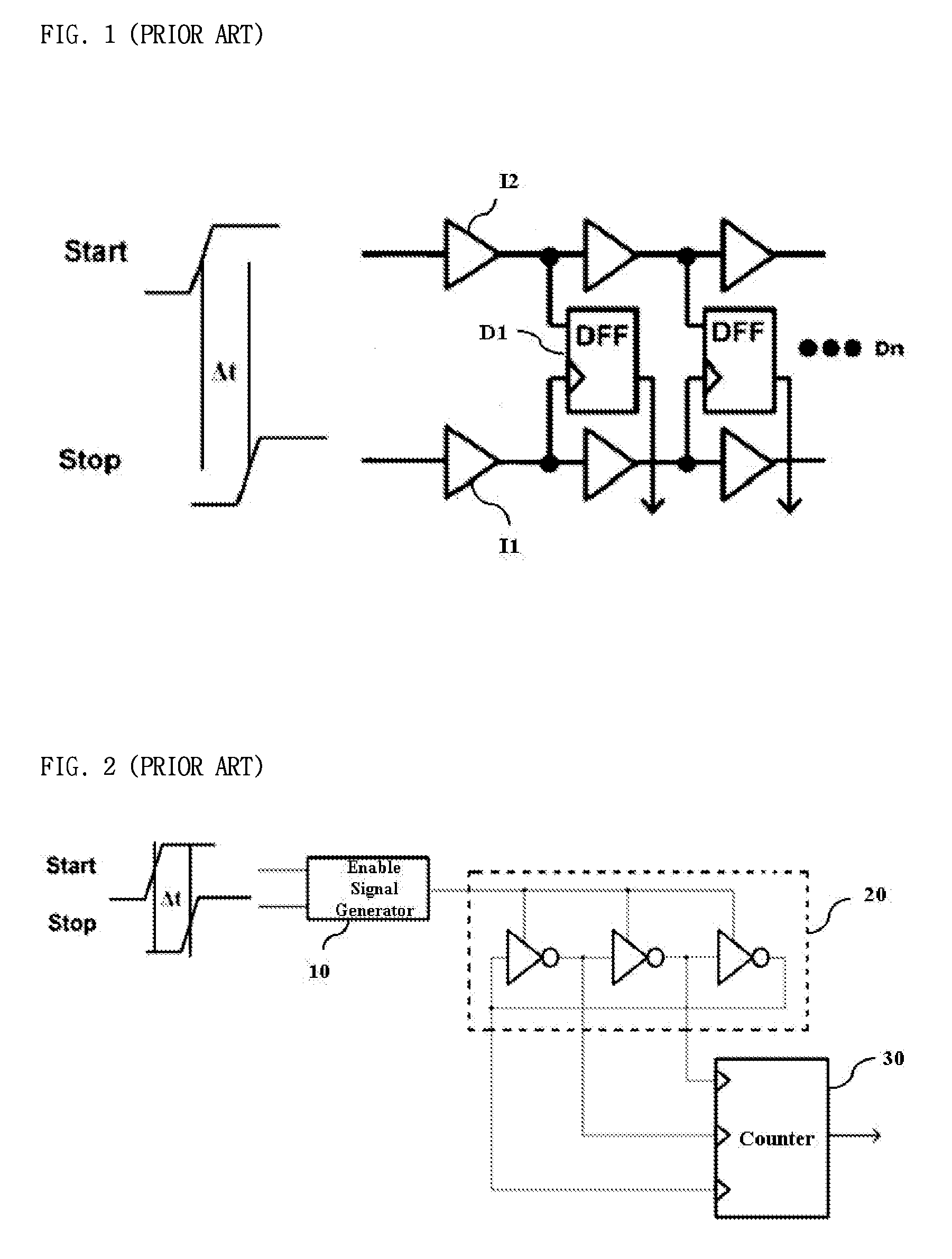

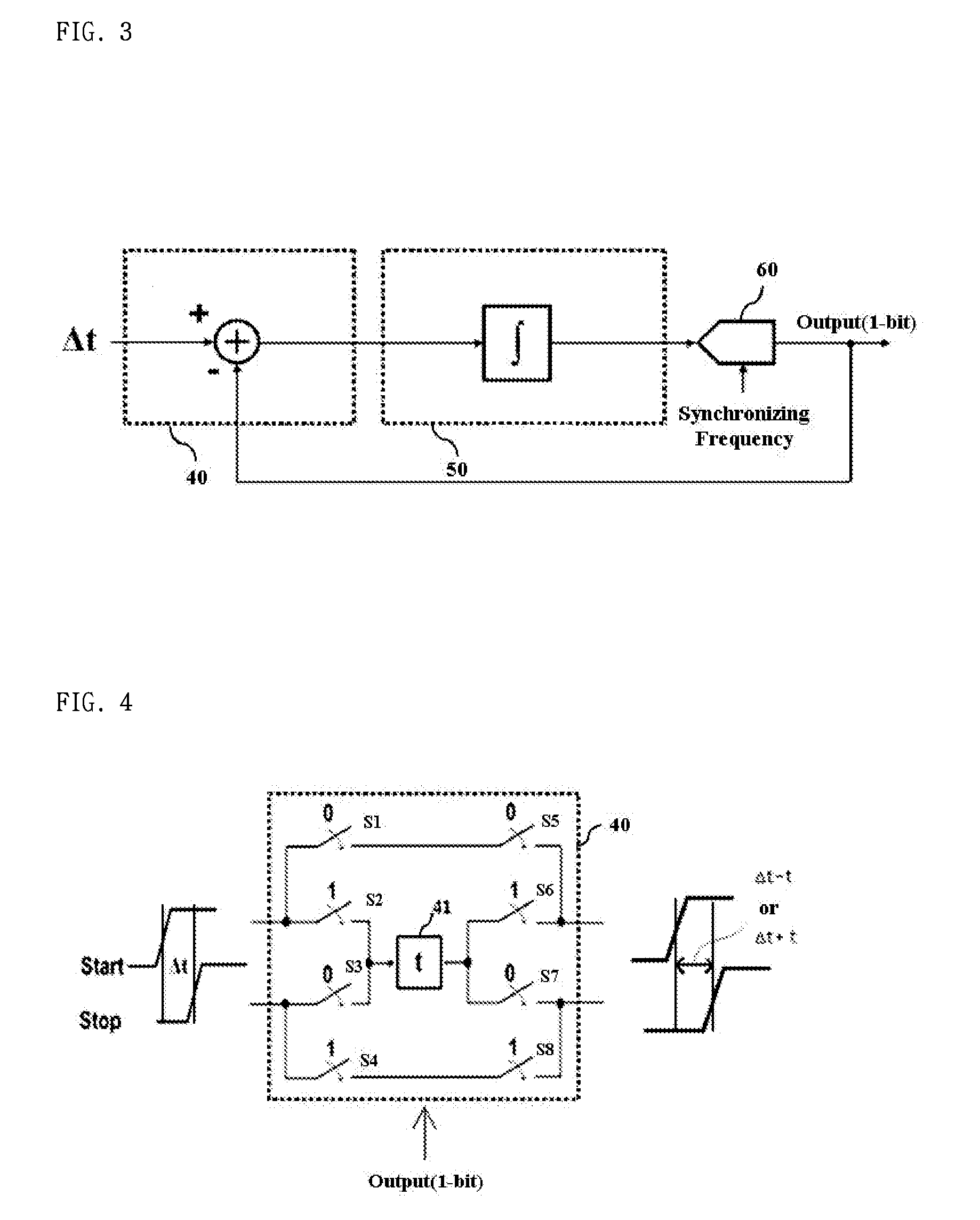

Noise-shaping time to digital converter (TDC) using delta-sigma modulation method

InactiveUS8421661B1Electric signal transmission systemsDelta modulationDigital down converterDelayed time

The present invention relates to a time digital converter, and more particularly, to a noise-shaping time to digital converter (TDC) that has a 1-bit output and uses a delta-sigma modulation method. The noise-shaping time to digital converter (TDC) that has the 1-bit output and uses the delta-sigma modulation method in accordance with the present invention eliminates the need for a large number of D flip-flops or counters and a plurality of delay units connected in series to one another because the time to digital converter is fabricated such that a delay element has a resolution of the effective delay time in a semiconductor process, unlike the conventional time to digital converter. Therefore, the time to digital converter of the present invention has an advantage in that an extremely high resolution and high linearity can be achieved with an efficient circuit configuration and low power consumption.

Owner:POSTECH ACAD IND FOUND

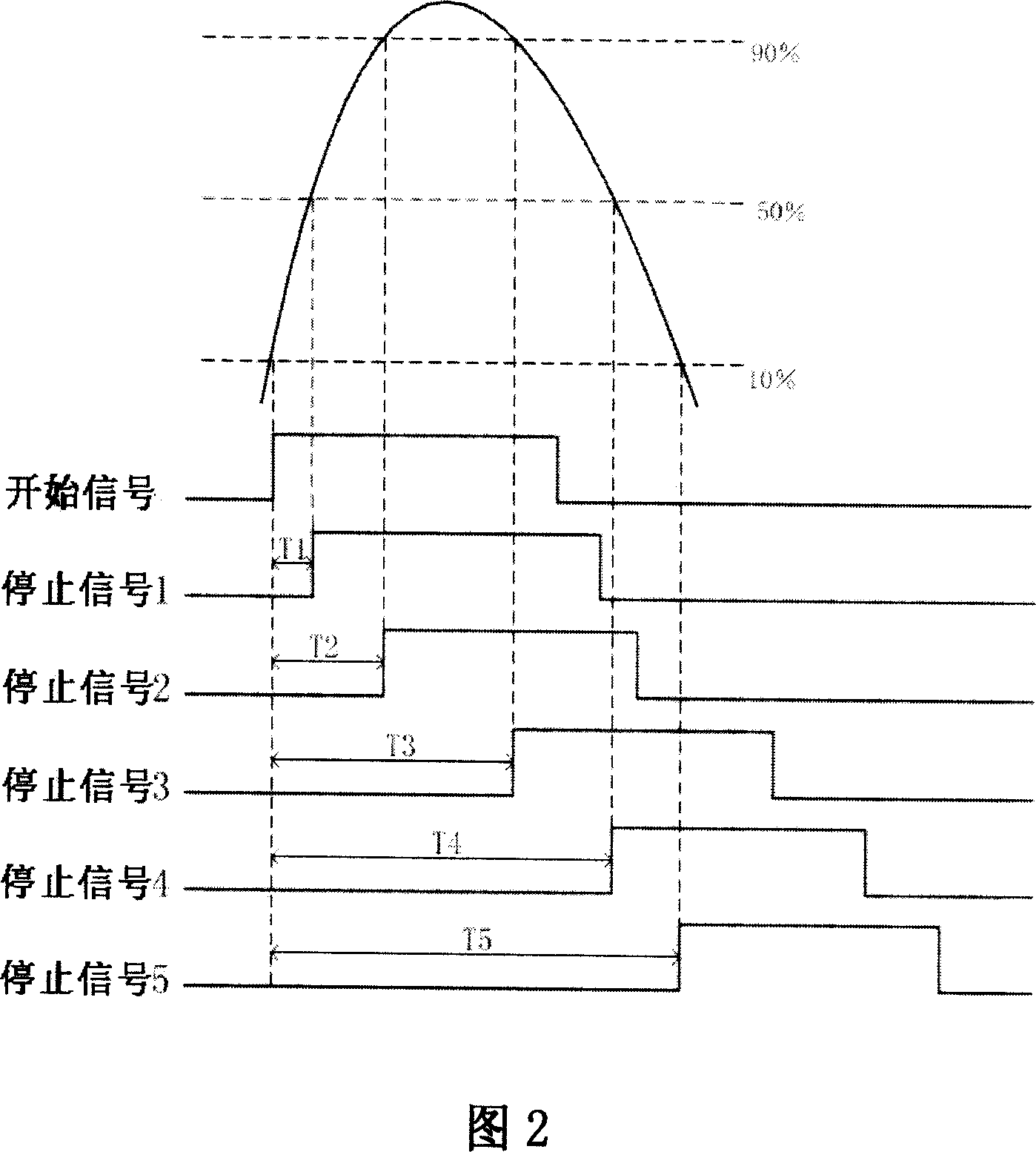

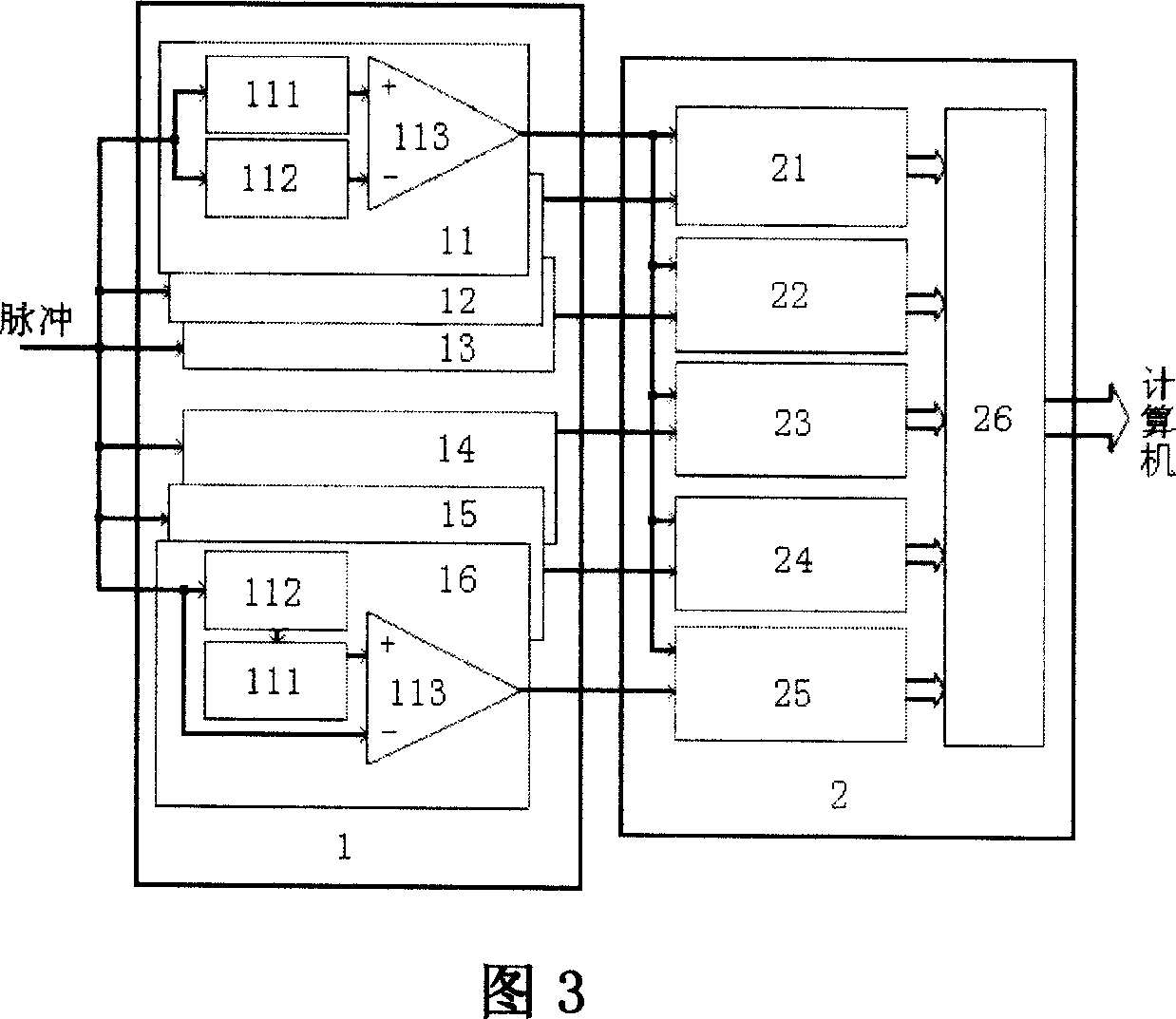

Pulse shape measuring device and measuring method thereof

InactiveCN101034120AHighly integratedGood value for moneyOptical rangefindersPulse characteristics measurementsDiscriminatorMeasurement device

This invention relates to a measuring method and device of impulse form. The invention includes one constant proportion timing discriminate module and one time-to-digital conversion module. Data of time-to-digital conversion modular enter calculator for handling. Constant proportion timing discriminate module has a group of leading edge discriminator and a group of back edge discriminator, which separately discriminate a series of points where the ratio of pulse front edge and back edge voltage and spike voltage are certain worth corresponding time. multipass time-to-digital conversion module convert time interval between first time and subsequently time to digital quantity, adopt digital counting method and combine digital delay line bracketing method, realize at a piece of field programmable logic array FPGA. sending obtained data into computer for calculation to gain time interval, base on voltage peak ratio of every time to indirectly reduce impulse form, and obtain pulsewidth. The invention has low cost, small bulk, and light weight, can apply to laser range finder.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

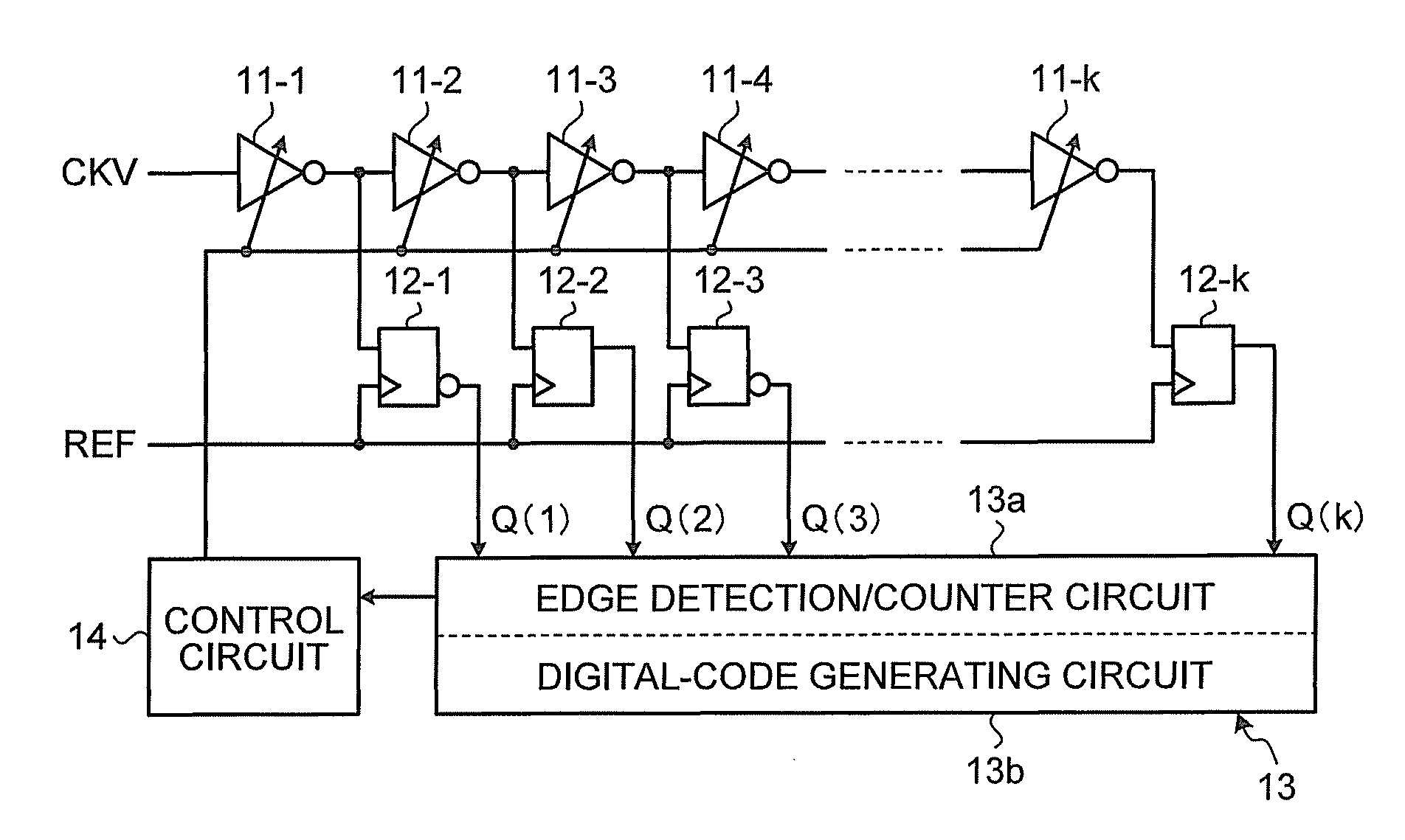

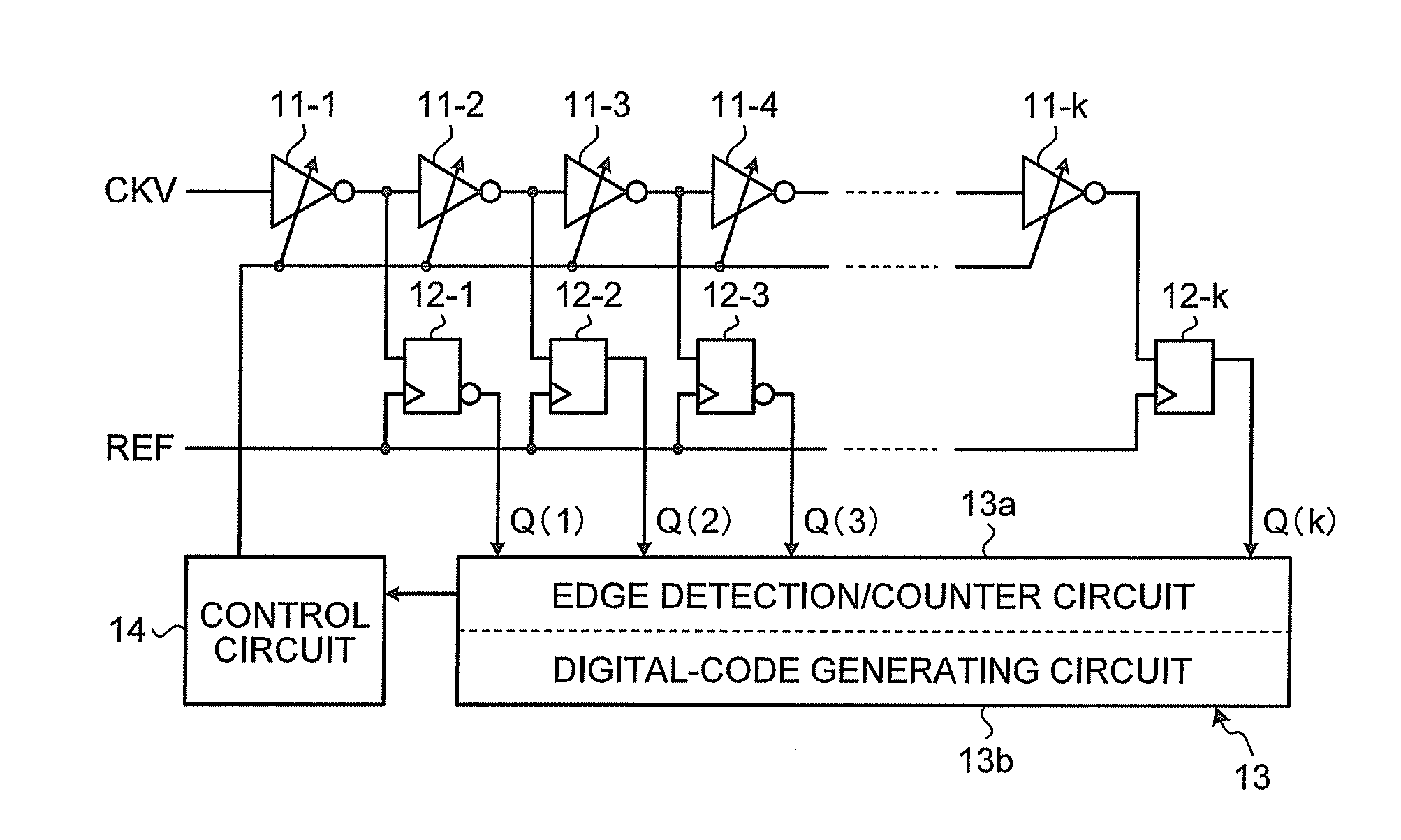

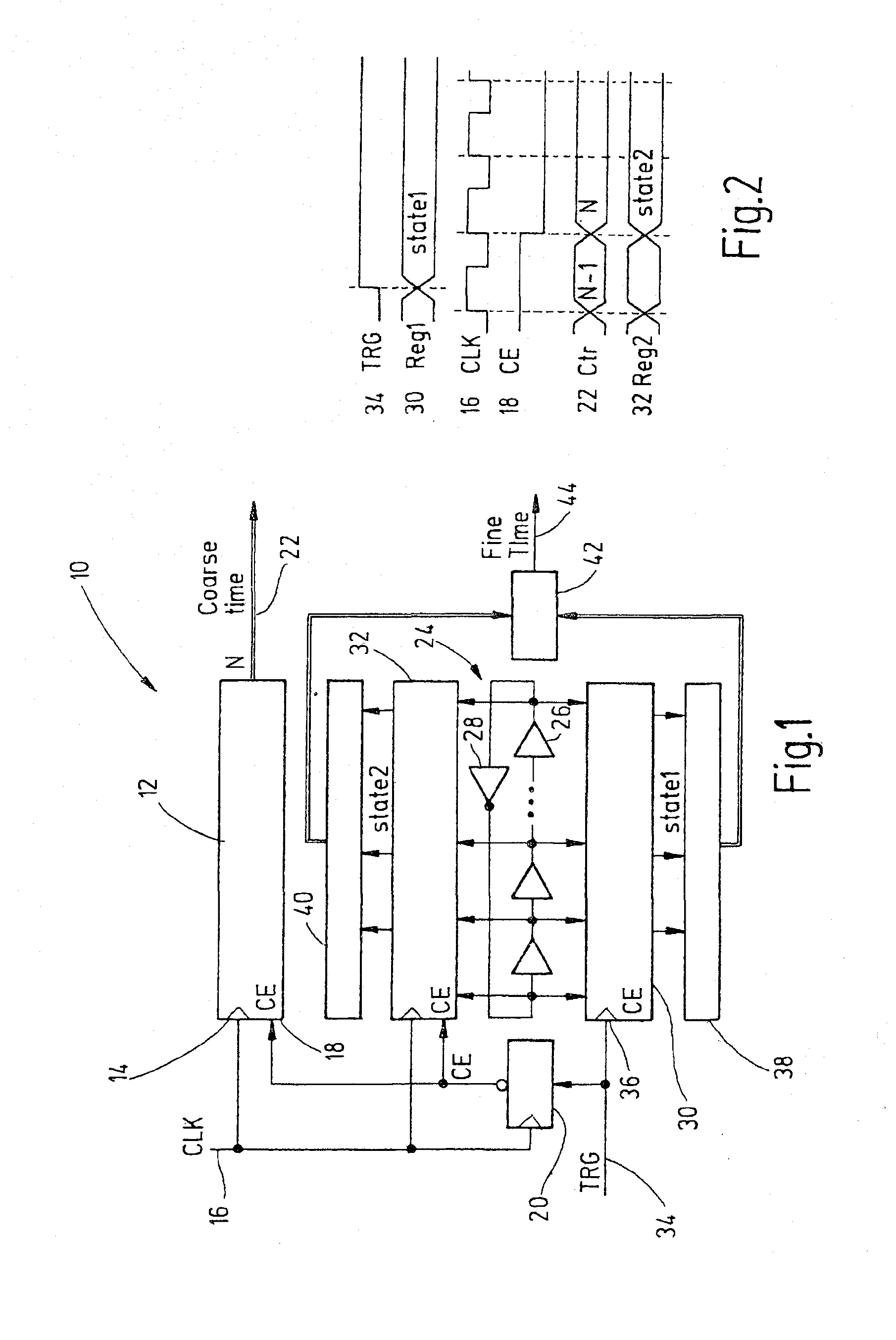

Time to digital converter

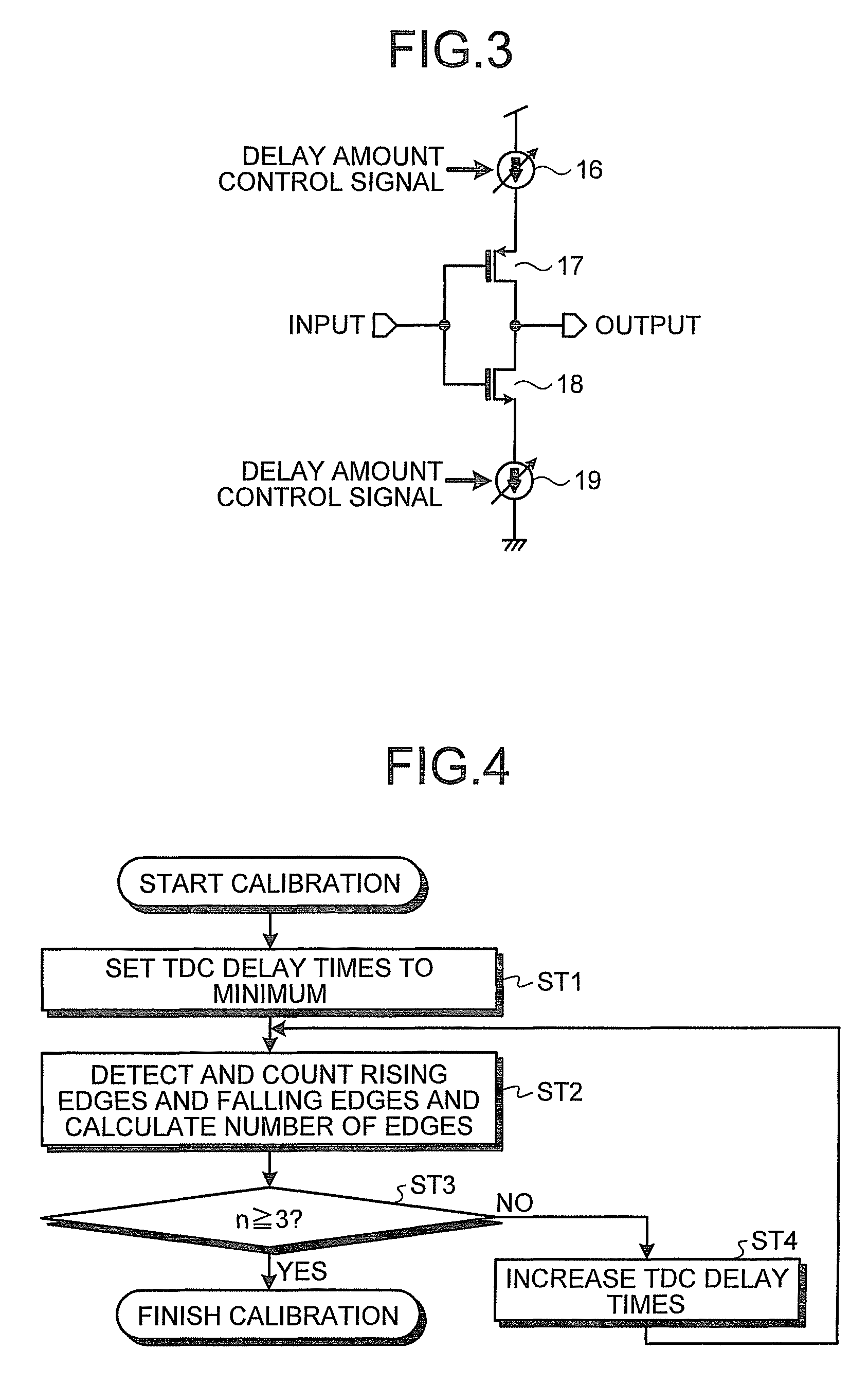

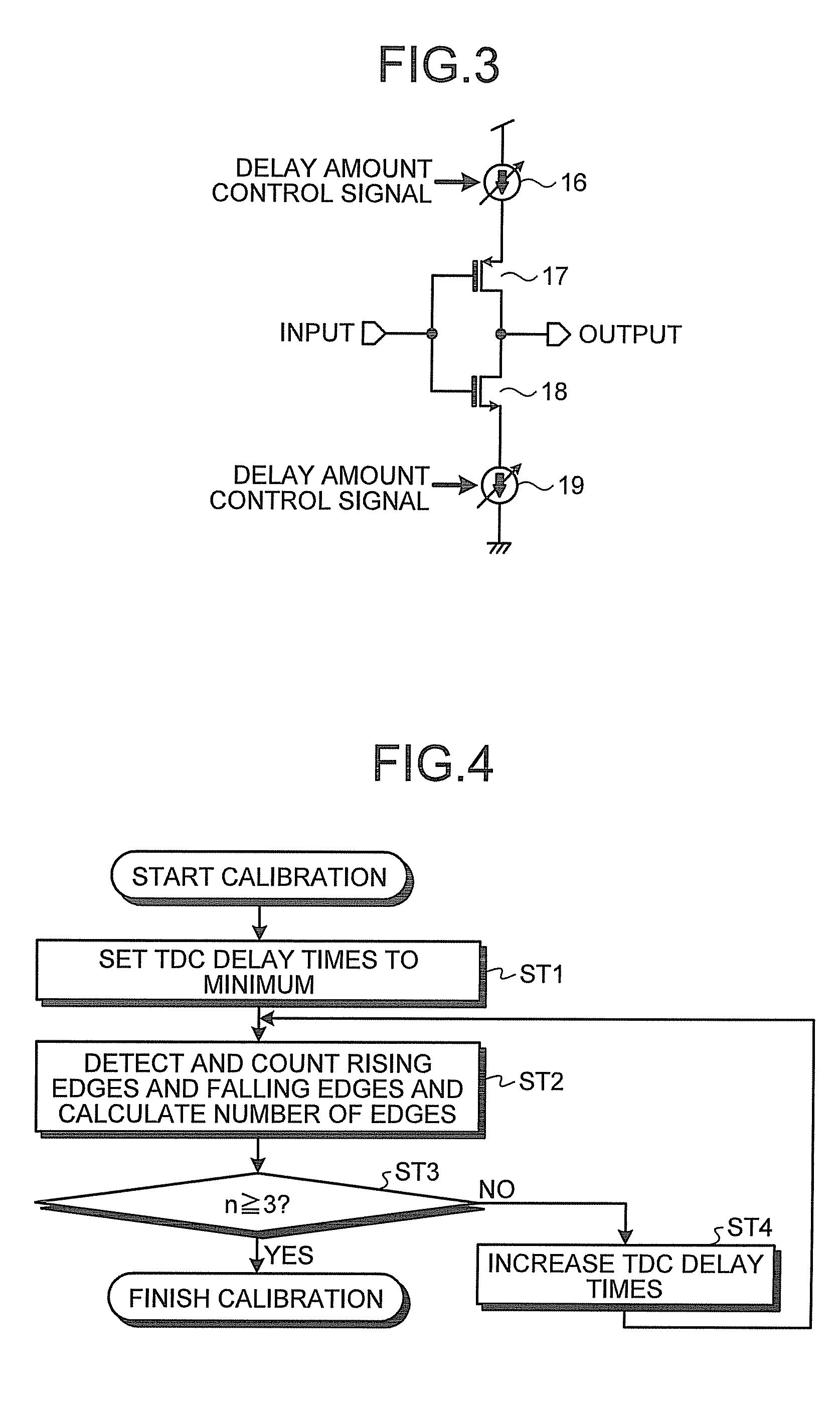

InactiveUS8174293B2Multiple input and output pulse circuitsPulse automatic controlDigital down converterEngineering

A time to digital converter includes: a delay circuit having a plurality of delay stages that delay an input clock signal in multiple stages, at least one of the delay stages being a variable delay stage; a plurality of flip flops that capture outputs of the delay stages corresponding thereto in a one-to-one relation in response to input of a reference signal; an edge detecting circuit that detects changing edges of respective outputs of the flip flops; a counter circuit that counts a number of edges detected by the edge detecting circuit; and a control circuit that controls a delay amount of the variable delay stage according to the number of edges counted by the counter circuit.

Owner:KK TOSHIBA

Phase to digital converter in all digital phase locked loop

ActiveUS8022849B2Low power operationLower requirementElectric signal transmission systemsPulse automatic controlDigital down converterReference Period

A phase to digital converter, all digital phase locked loop, and apparatus having an all digital phase locked loop are described herein. The phase to digital converter includes a phase to frequency converter driving a time to digital converter. The time to digital converter determines a magnitude and sign of the phase differences output by the phase to frequency converter. The time to digital converter utilizes tapped delay lines and looped feedback counters to enable measurement of small timing differences typical of a loop tracking process and large timing differences typical of an loop acquisition process. The tapped delay lines permit the measurement of fractions of a reference period and enable lower power operation of the phase to digital converter by reducing requirements on the speed of the reference clock.

Owner:QUALCOMM INC

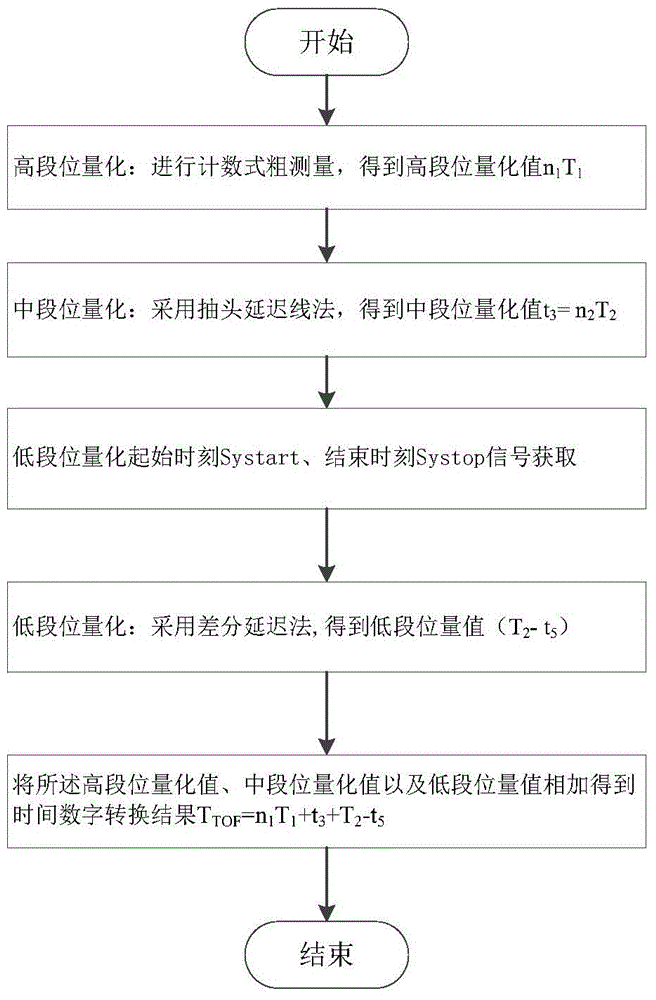

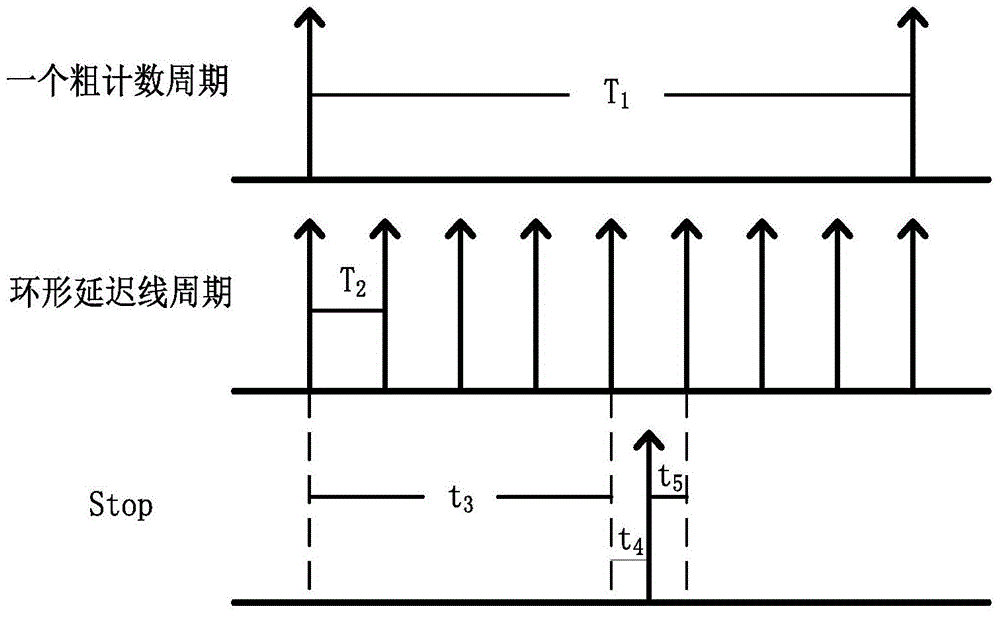

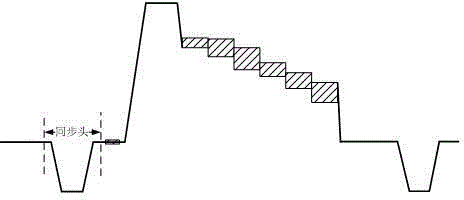

Dual-loop DLL-based three-segment type high-precision time-to-digital conversion method and circuit

InactiveCN104320130AHigh precision measurementImprove detection accuracyAnalogue/digital conversionElectric signal transmission systemsEngineeringVoltage control

The invention discloses a dual-loop DLL-based three-segment type high-precision time-to-digital conversion method and circuit. According to a measured time segment, a high-middle-low combined segmental type quantization method is adopted. A high-segment bit counting type quantizer in three-segment type TDC (time-to-digital conversion) is driven by a high-frequency stabilizing clock which is inputted from the outside, so that a wide-range stable distance measuring range can be realized; a middle-segment bit TDC is formed by a first DLL voltage controlled delay chain; high-segment bit subdivision can be realized through an asynchronous sampling mode, and repeatable uniform phase distinguishing can be accomplished in a stable clock period; a phase position at a termination time point is decoded, so that a middle-segment quantization function can be accomplished; and according to quantization errors generated by time-to-digital conversion in a middle-segment bit, error time is extracted, a low-segment bit accomplishes further quantization processing, and therefore, higher measurement precision can be realized.

Owner:SOUTHEAST UNIV

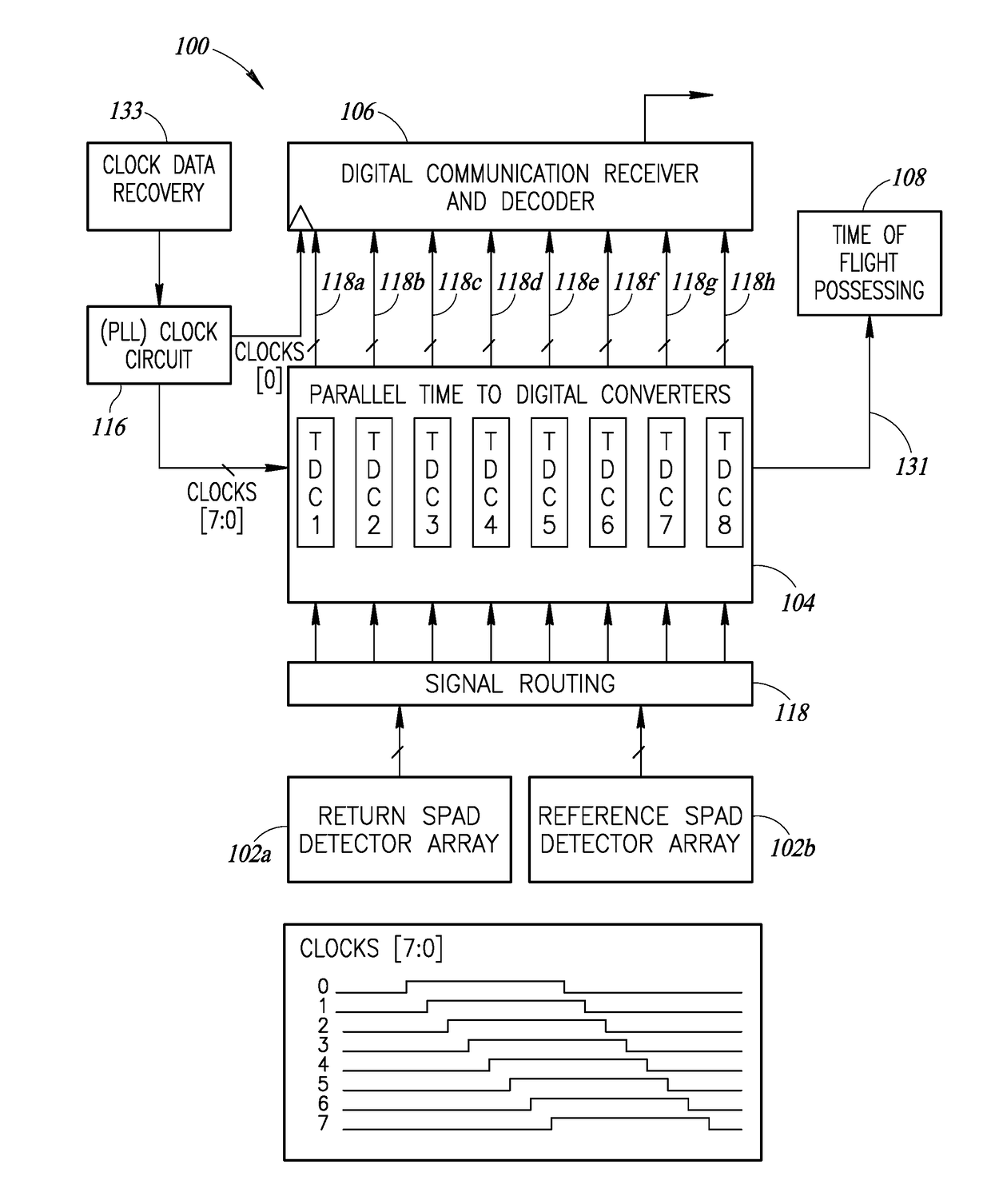

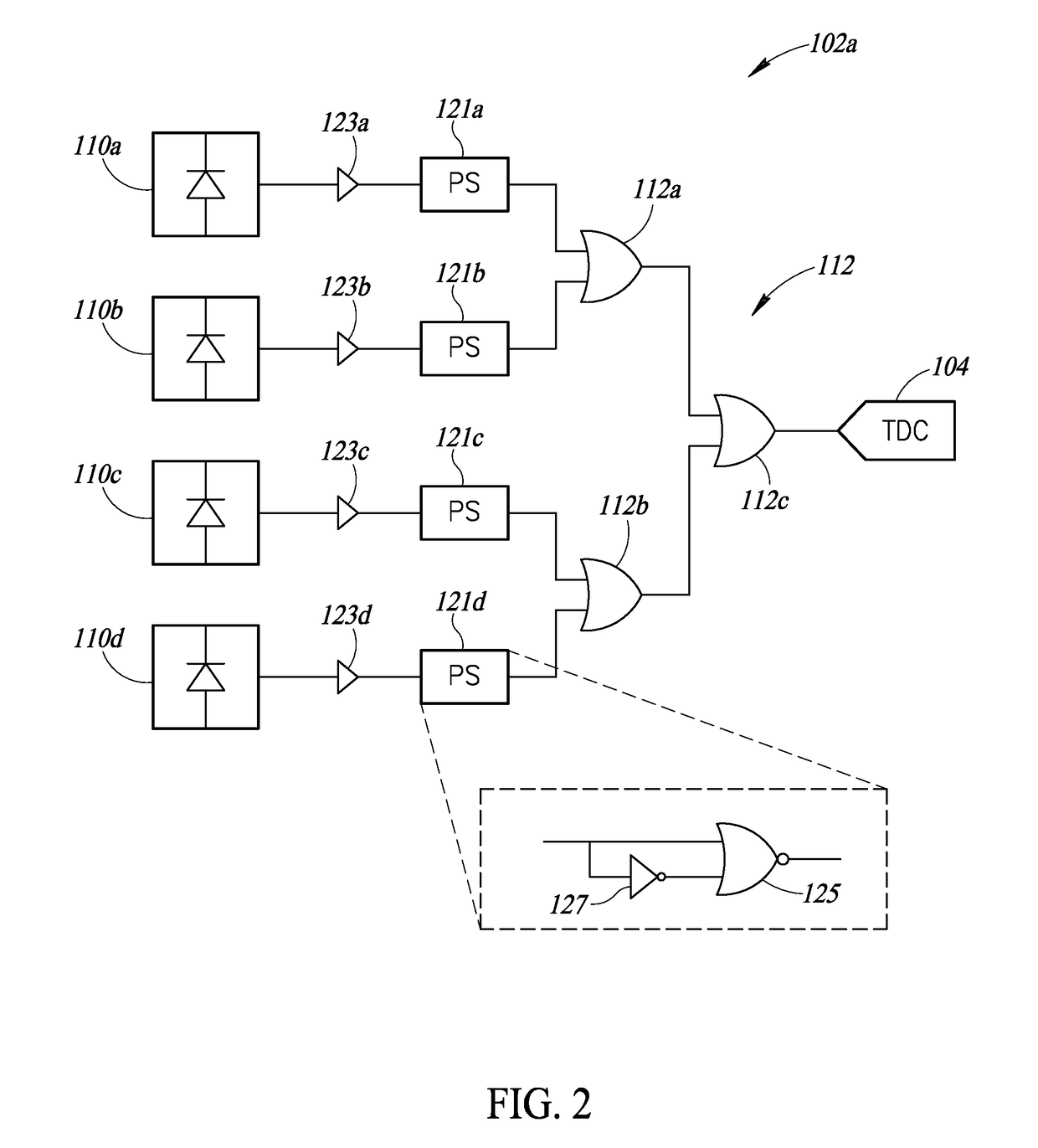

Light communications receiver and decoder with time to digital converters

ActiveUS20180123611A1Code conversionPhotometry electrical circuitsSingle-photon avalanche diodeDigital down converter

The present disclosure includes a method that includes generating a decoded output signal that corresponds to reflected light received by a plurality of single photon avalanche diodes (SPAD) by removing ambient light from a plurality of SPAD array output signals. The removing of ambient light including synchronizing the plurality of SPAD array output signals by using a plurality of parallel time to digital converters, each time to digital converter outputting a synchronized SPAD array output signal, determining a plurality of flexible thresholds for each one of the synchronized SPAD array output signals, comparing current data on the synchronized SPAD array output signals with the respective ones of the flexible threshold in a filter, and outputting the first output signal.

Owner:STMICROELECTRONICS (RES & DEV) LTD

Time to digital converter

InactiveUS20100295590A1Multiple input and output pulse circuitsPulse automatic controlDigital down converterEngineering

A time to digital converter includes: a delay circuit having a plurality of delay stages that delay an input clock signal in multiple stages, at least one of the delay stages being a variable delay stage; a plurality of flip flops that capture outputs of the delay stages corresponding thereto in a one-to-one relation in response to input of a reference signal; an edge detecting circuit that detects changing edges of respective outputs of the flip flops; a counter circuit that counts a number of edges detected by the edge detecting circuit; and a control circuit that controls a delay amount of the variable delay stage according to the number of edges counted by the counter circuit.

Owner:KK TOSHIBA

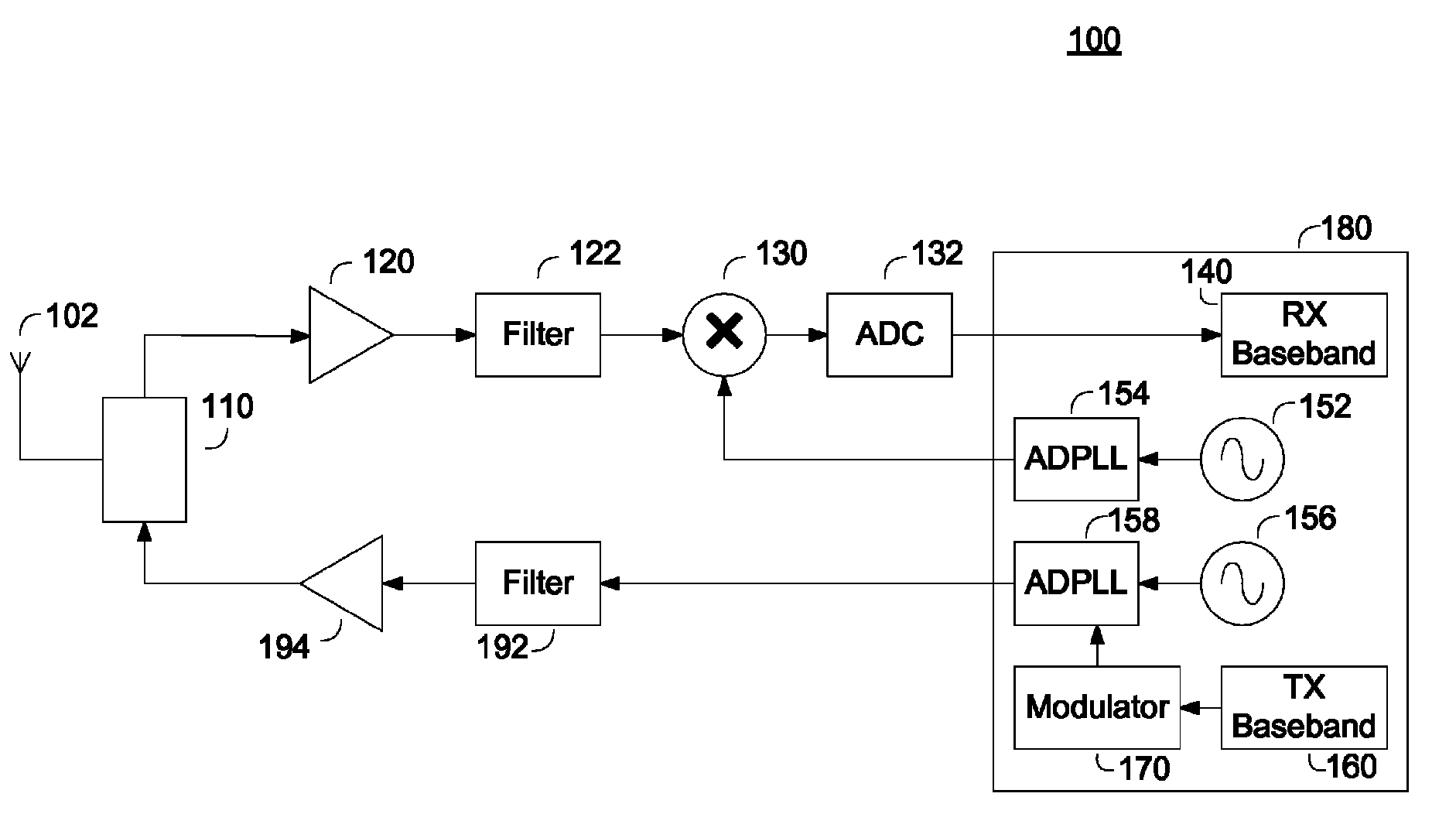

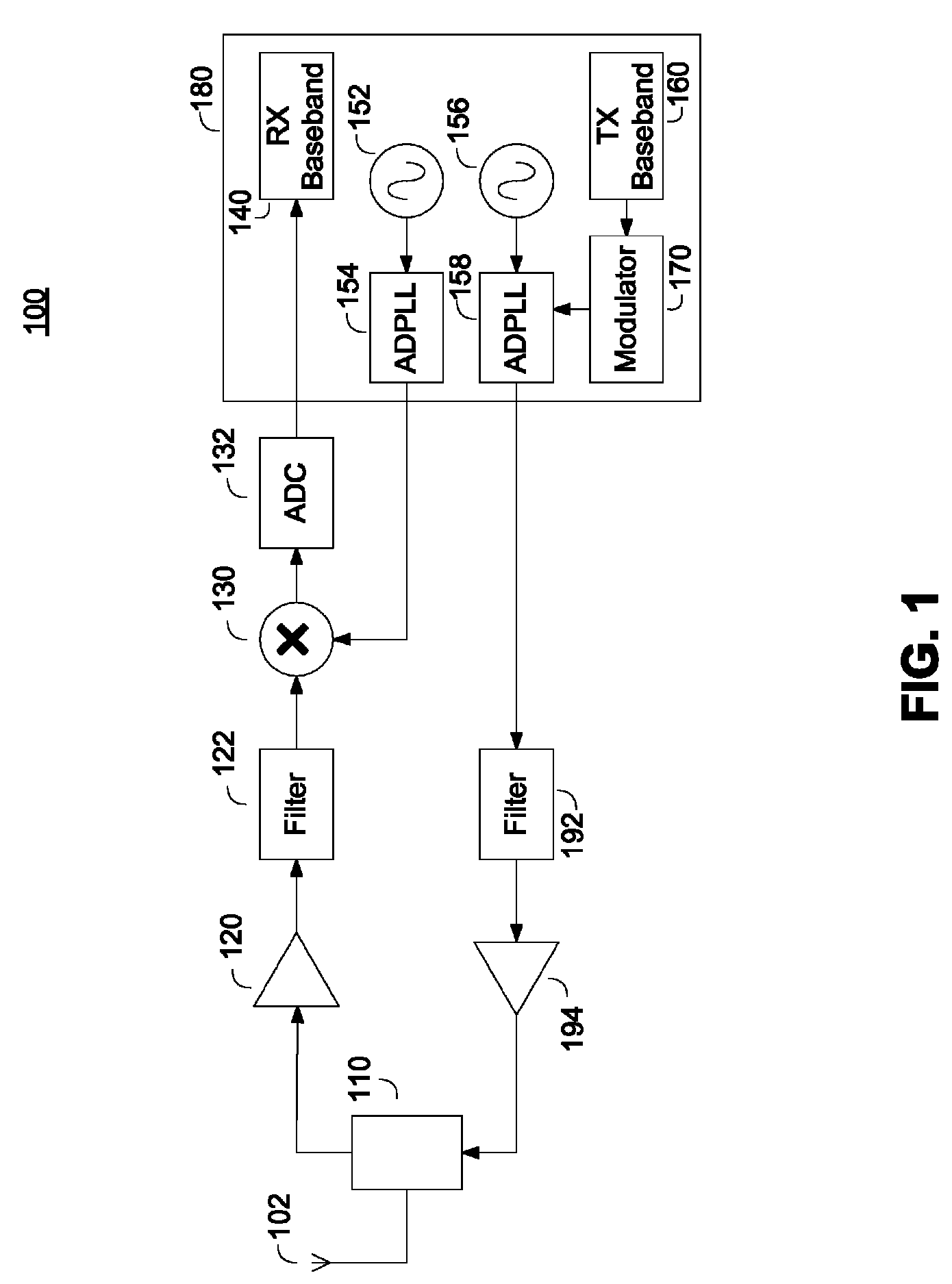

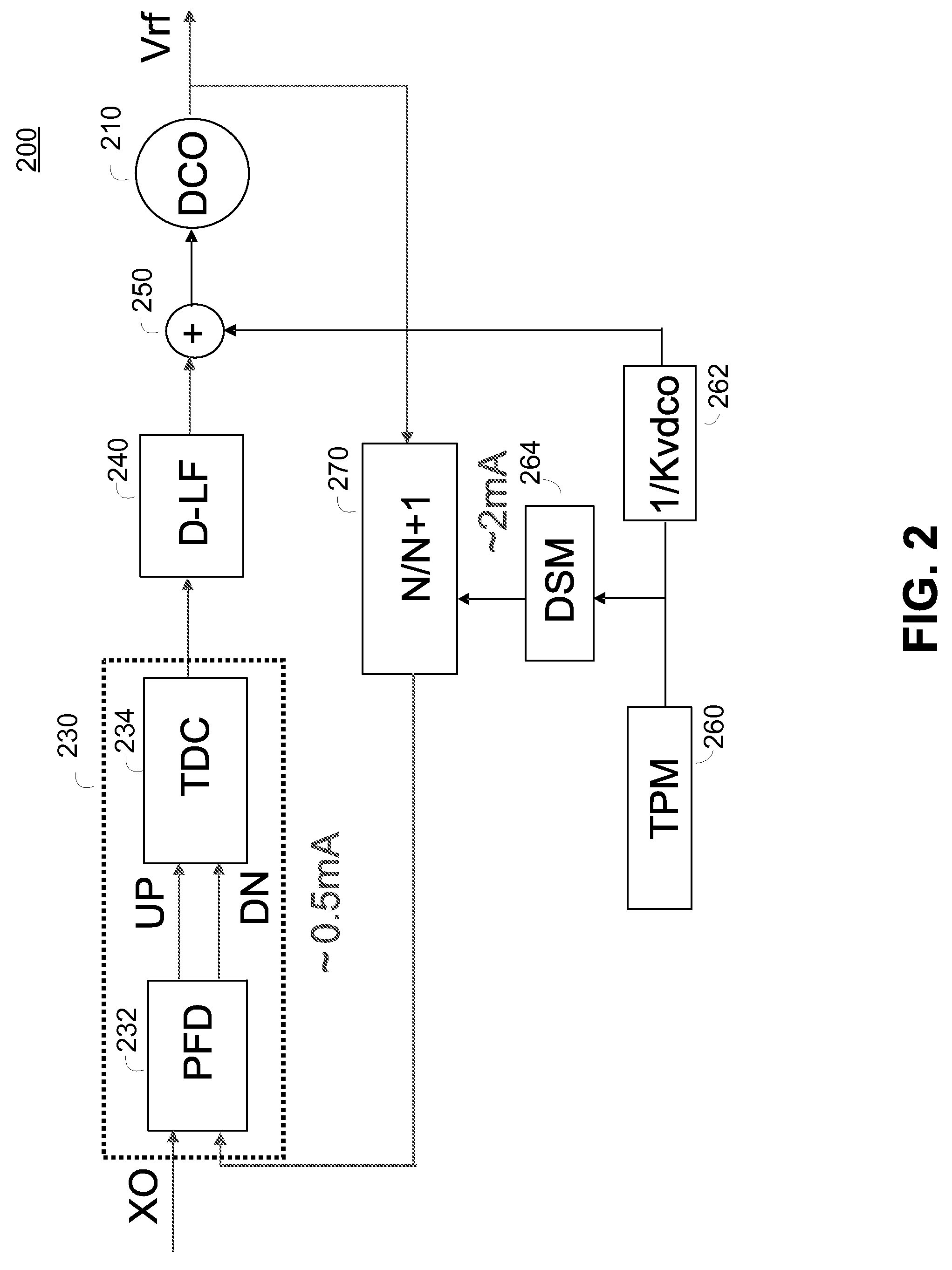

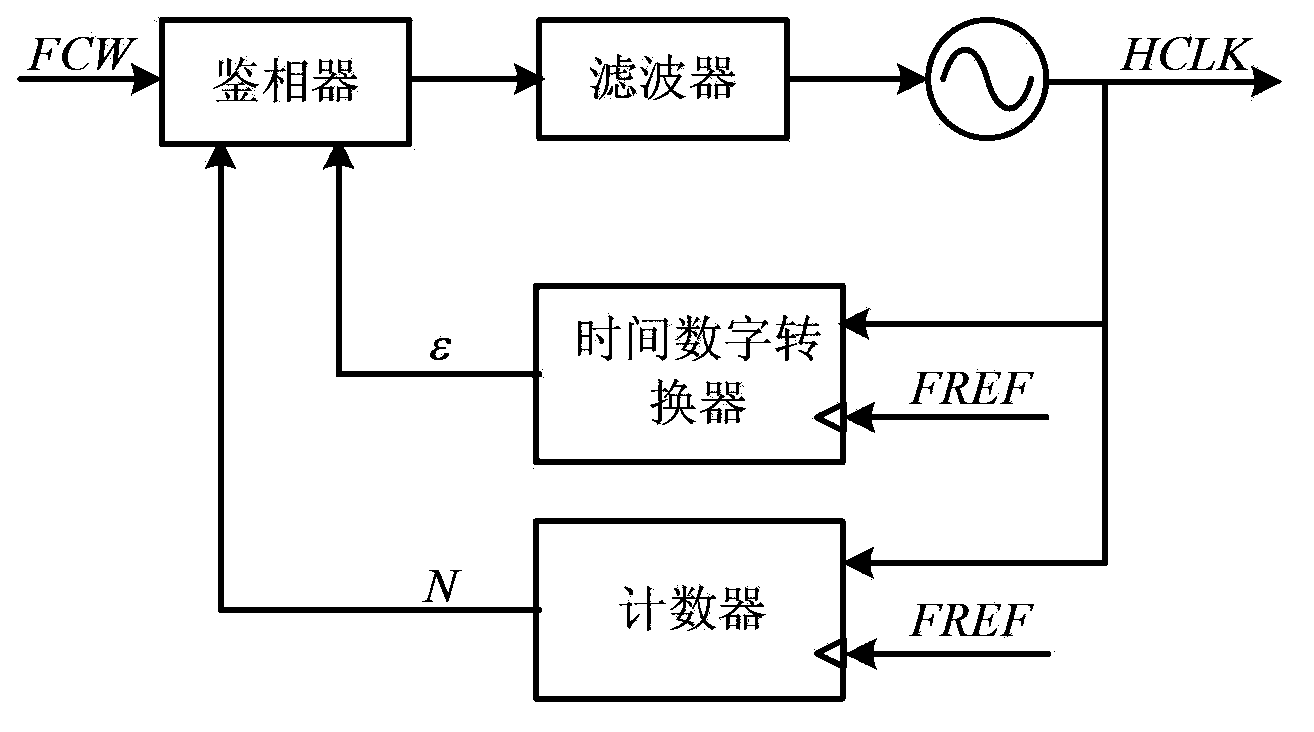

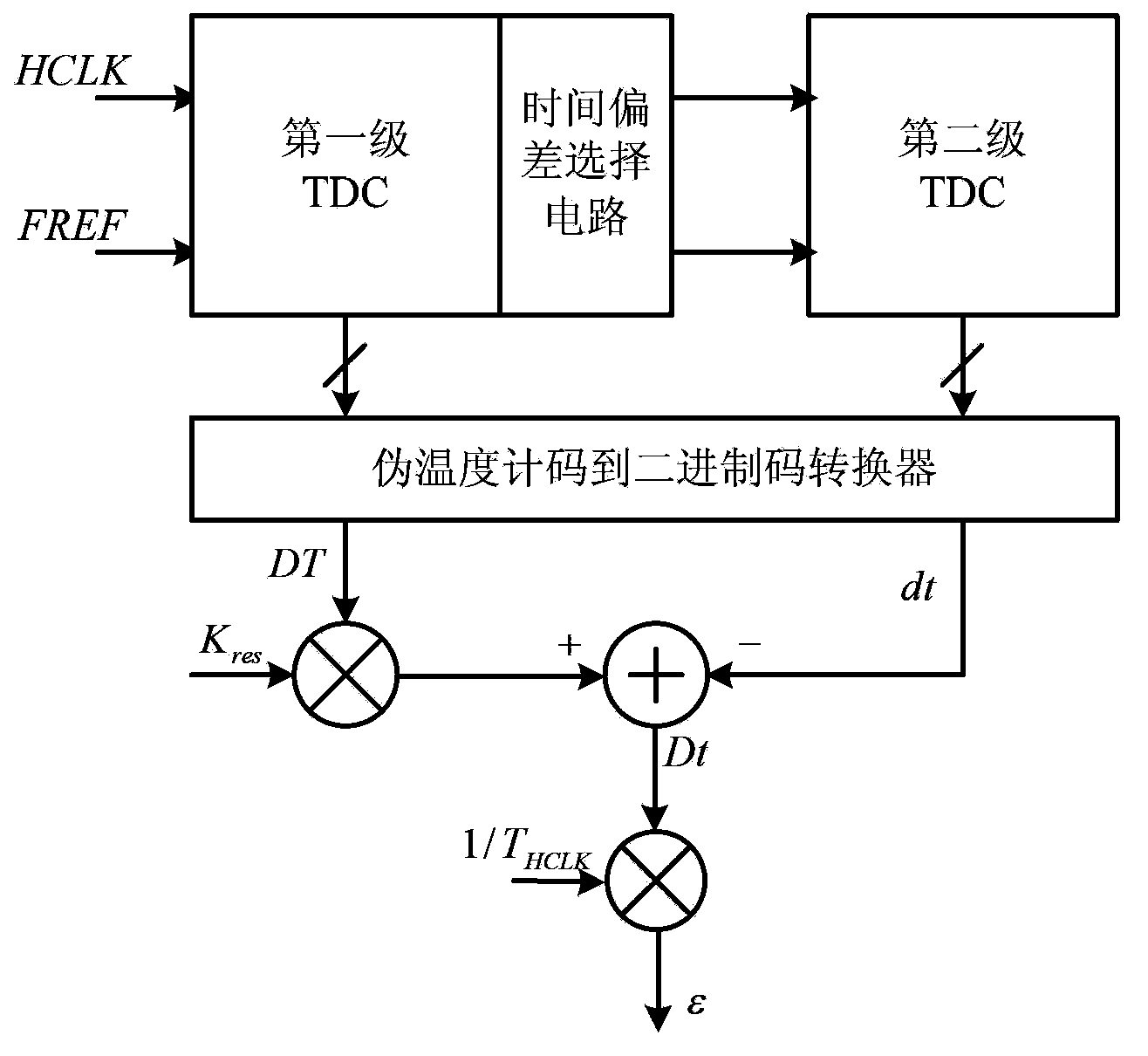

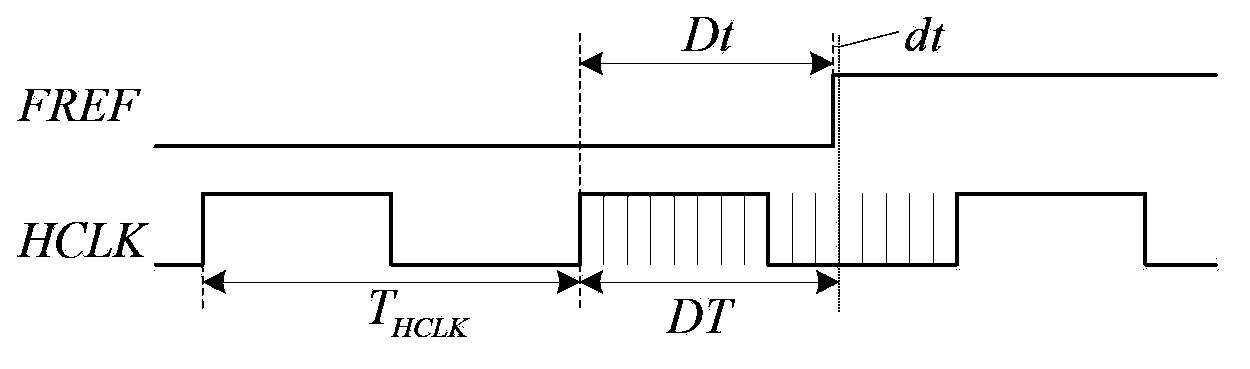

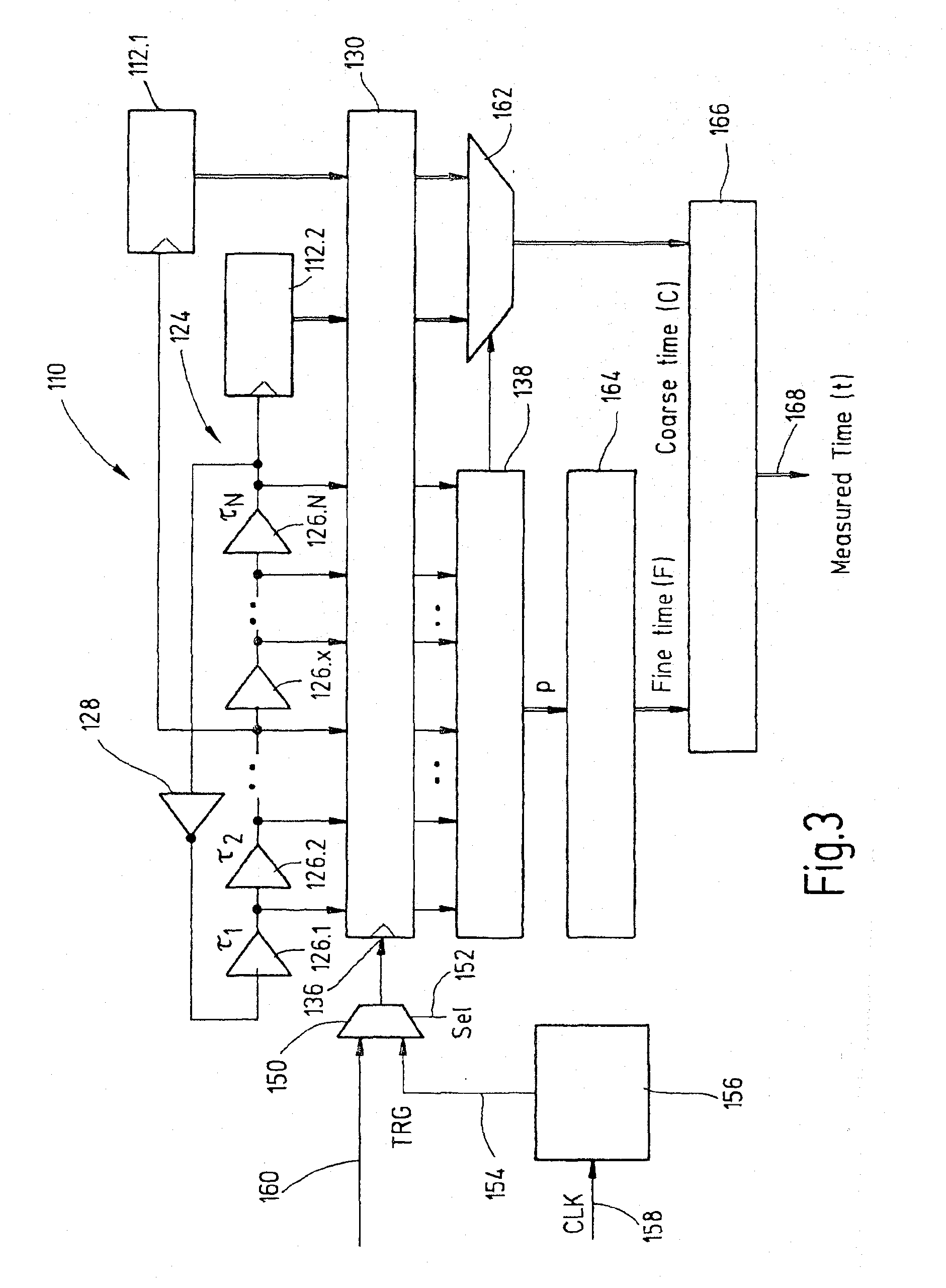

Two-stage time-to-digital converter

InactiveCN103684467AAdapt to needsHigh resolutionAnalogue/digital conversionElectric signal transmission systemsDigital down converterFull custom

The invention belongs to the field of microelectronics and time measurement, and particularly relates to a two-stage time-to-digital converter. The circuits of the converter can be applied to all digital phase-locked loops (ADPLL) with high frequency wide bands. According to the two-stage time-to-digital converter of the invention, the combination of semi custom and full custom is adopted, and two-stage time-to-digital converter comprises a first-stage quantizing structure, a time deviation selection circuit, a second-stage quantizing structure and a decoding circuit, wherein the first-stage quantizing structure adopts a buffer delay chain for coarse quantization; the time deviation selection circuit is composed of a selective signal generator, a delay chain and a multiplexer; the second-stage quantizing structure adopts a Vernier delay chain using a buffer as a basic unit to carry out fine quantization, and a duplication chain comprising a first-stage buffer chain simultaneously multiplexes the Vernier delay chain for measurement of a resolution ratio; the decoding circuit corresponds to a quantization scheme to realize transformation from pseudo thermometer codes to binary codes; the selective signal generator and the decoding circuit are realized by Verilog semi-custom, and the rest are realized by full-custom. The two-stage time-to-digital converter of the invention can be applied to ADPLL with the high frequency wide bands so as to realize time-to-digital conversion with high resolution and linearity.

Owner:FUDAN UNIV

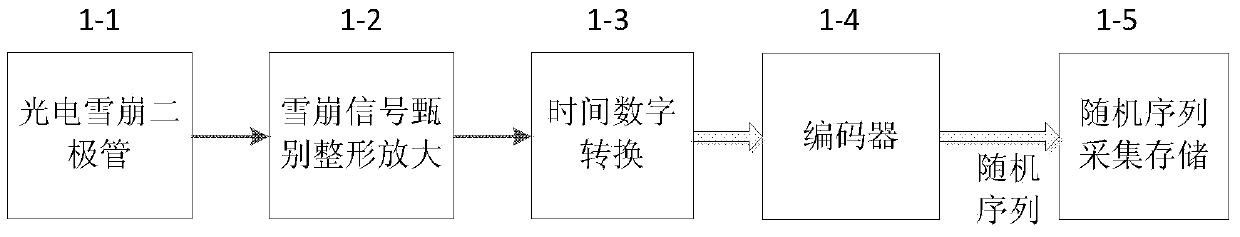

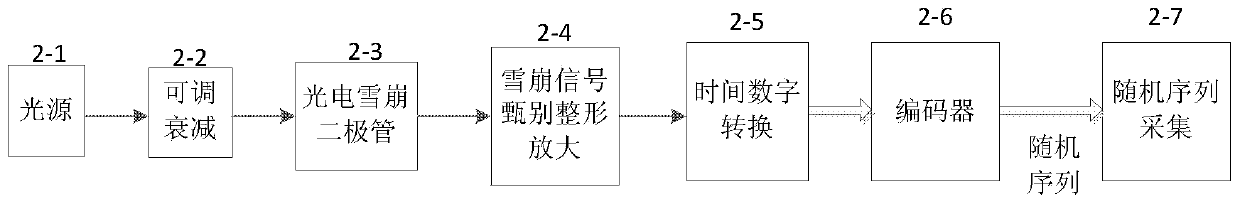

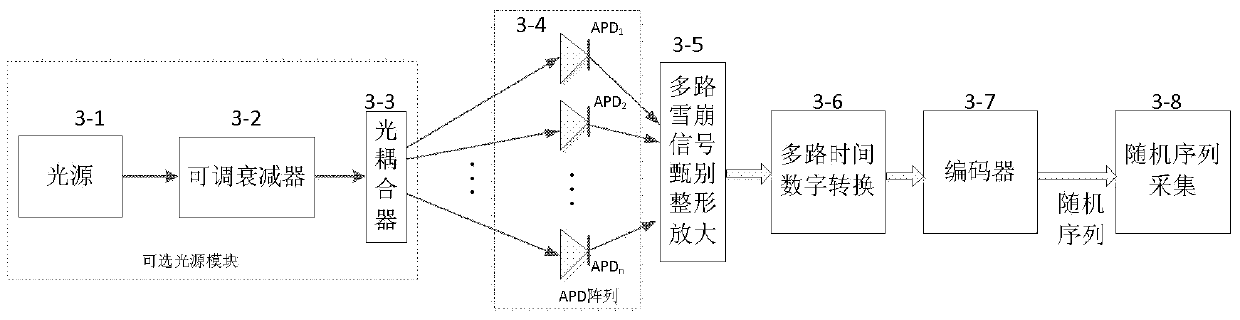

Unbiased random number generator and random number generation method

ActiveCN104216678AImprove production efficiencyDoes not affect random propertiesRandom number generatorsNumber generatorIntegrated circuit

The invention discloses an unbiased random number generator. The unbiased random number generator comprises an APD (Avalanche Photo Diode) module, an avalanche signal discriminating, shaping and amplifying module, a time-to-digital conversion module and an encoder module, wherein electronic pulse generated by the APD module is encoded to generate a random sequence. The invention discloses an unbiased random number generation method and an unbiased random number generator chip. The generated random number sequence can pass random statistical detection without complex post-processing processes. The device and the method have extremely high integration level, and the device can be packaged into a chip-level device by using an integrated circuit process. The device and the method can work without light source, and light quantum generated by an external light source can also be coupled though an optical fiber or free space to adjust the generation efficiency of the random number. Thus, the device and the method have good compatibility with the environment and can normally work without special working conditions such as low temperature and tight shading.

Owner:UNIV OF SCI & TECH OF CHINA

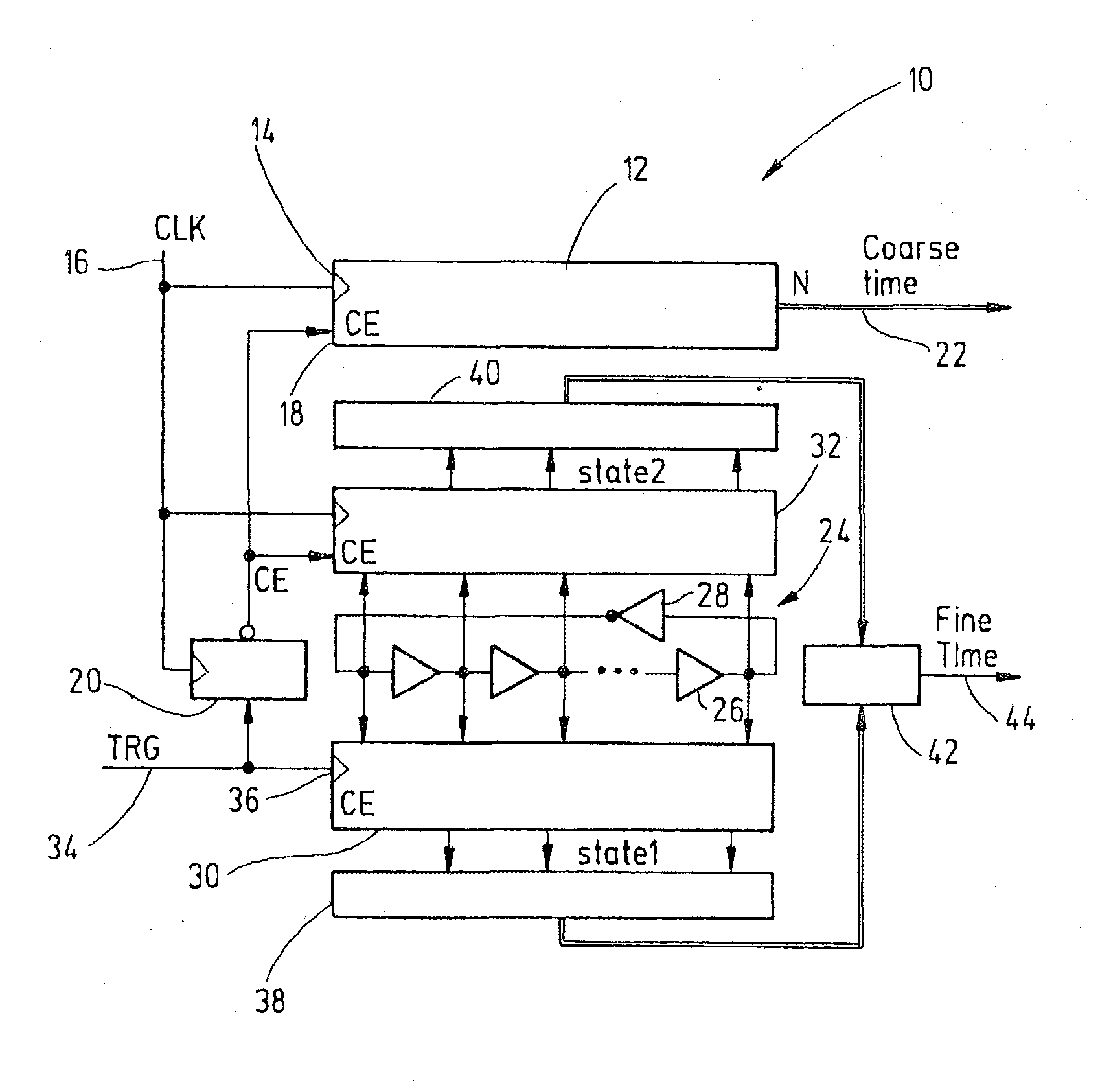

Time-to-digital conversion with delay contribution determination of delay elements

ActiveUS20090322574A1Good precisionShort delay timeElectric signal transmission systemsAnalogue-digital convertersDelayed timeDigital converter

A time-to-digital converter includes at least one chain of delay elements, a status of which represents a digital signal relating to a time interval to be converted. The converter includes a provider for providing trigger signals having statistically equally distributed variable positions relative to a pulse forwarded in the chain of delay elements, a capturer for capturing the status of the chain of delay elements in response to the calibration trigger signals, the status depending on delay times of the delay elements, a determiner for determining an actual contribution of at least some of the delay elements to an overall delay of the chain of delay elements on the basis of occurrences of pulse positions in response to the calibration trigger signals. The converter is configured to take into account the actual contribution of at least some of the delay elements when converting the time interval into said digital signal.

Owner:ADVANTEST CORP

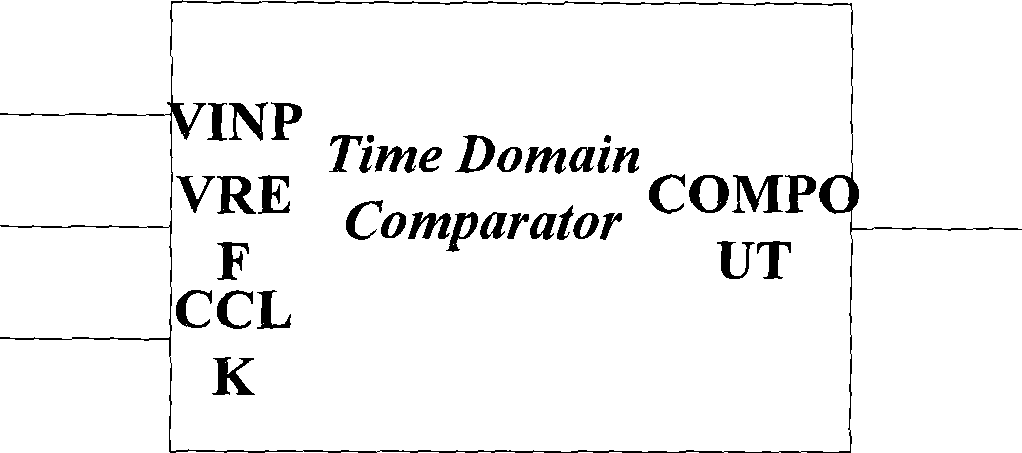

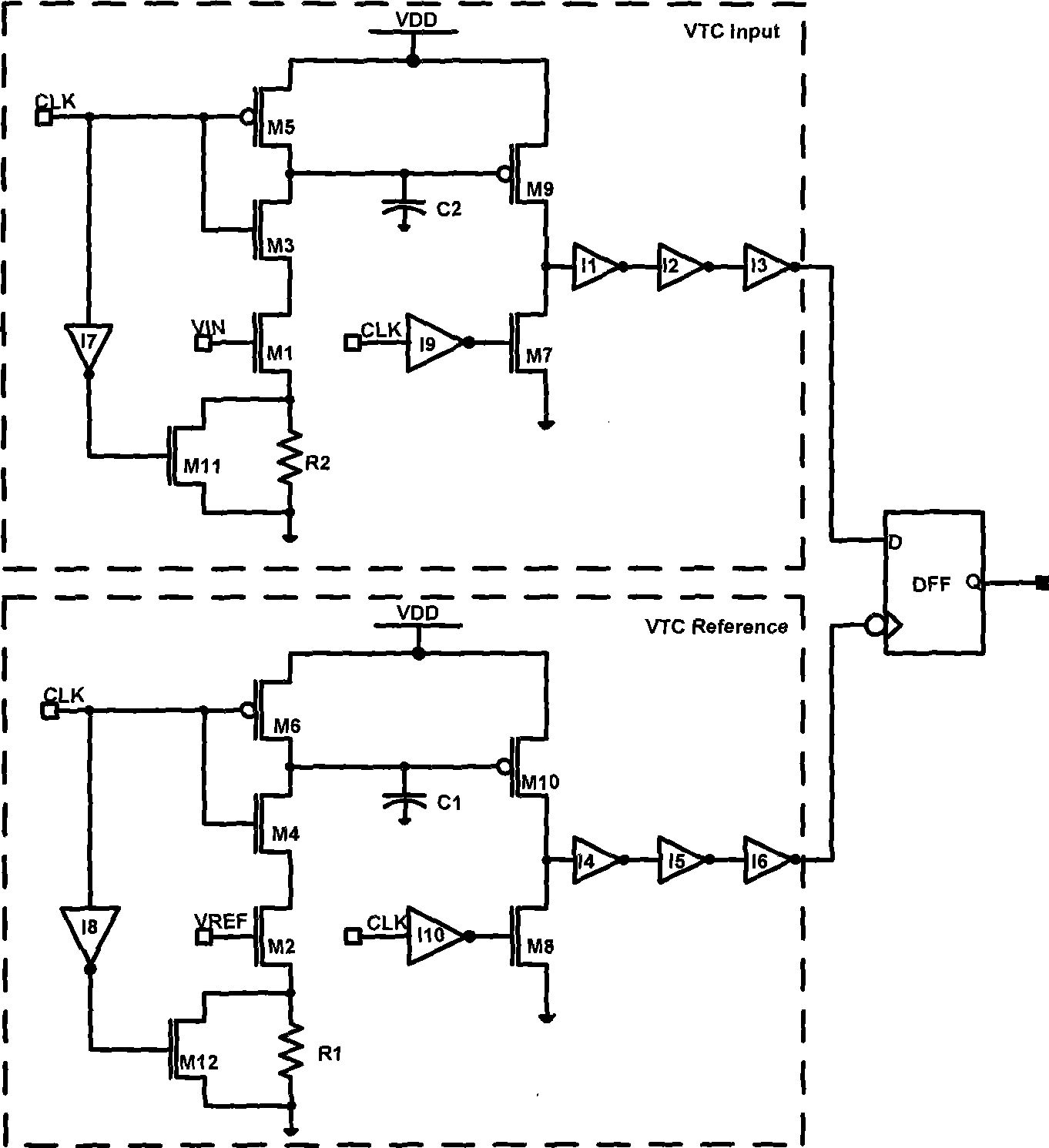

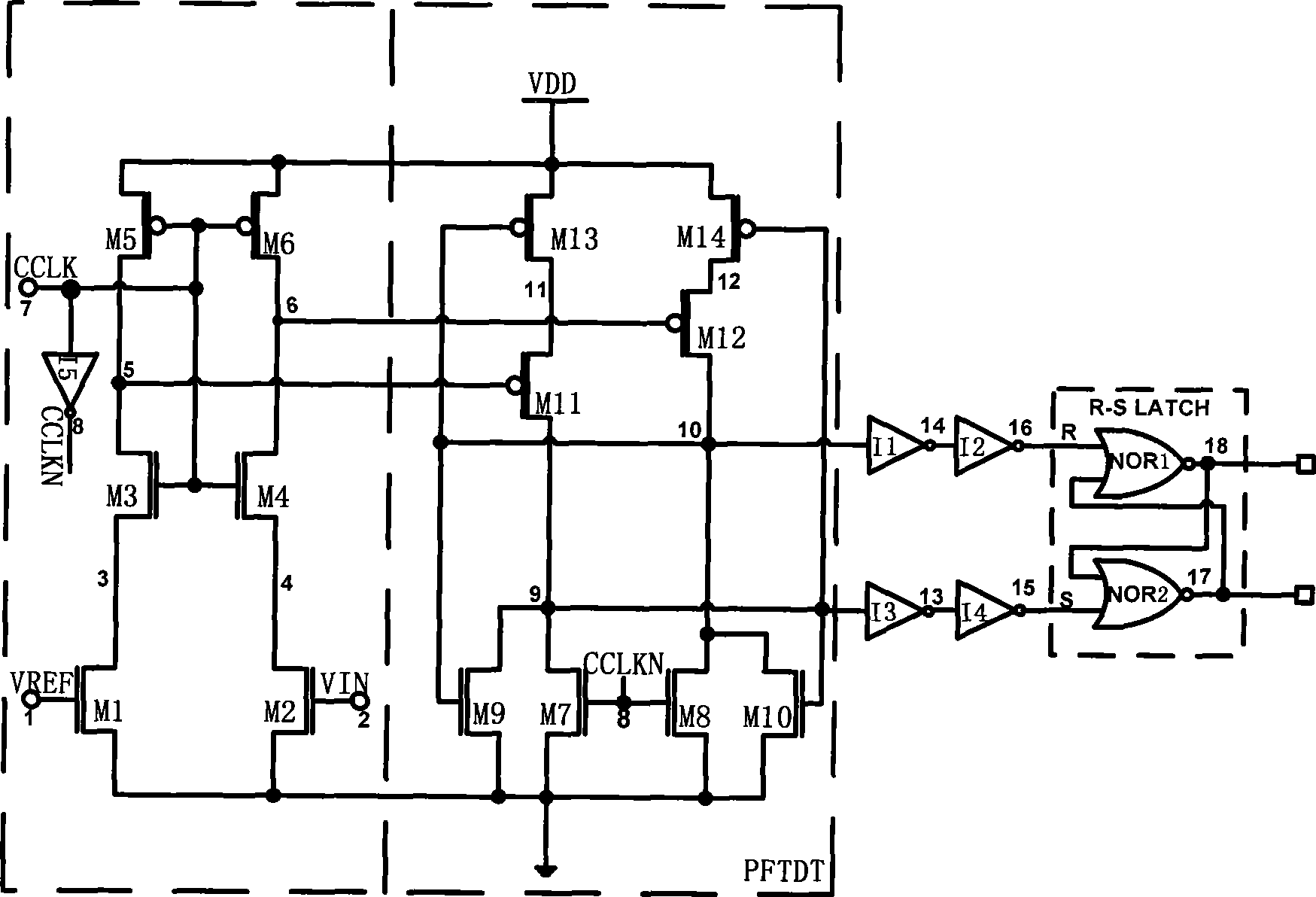

Successive approximation comparator for ADC based on time domain

ActiveCN101505153AReduce consumptionLow Toggle Dynamic PowerAnalogue/digital conversionElectric signal transmission systemsCapacitanceTime domain

The invention provides a successive approximation ADC comparator based on time domain, which belongs to the technical field of data converters. The comparator is characterized in that the comparator consists of a voltage time conversion circuit of voltage control delay, a positive feedback time-to-digital conversion circuit and a level RS latch in sequential series connection; as the comparator adopts a time-to-digital conversion technique and replaces a DFF trigger with the level RS latch, the comparator can distinguish input voltage difference lower than 10 mu V at a speed of 60 MHz; in addition, the comparator uses no resistor or capacitor elements, thereby having small area and low power consumption.

Owner:TSINGHUA UNIV

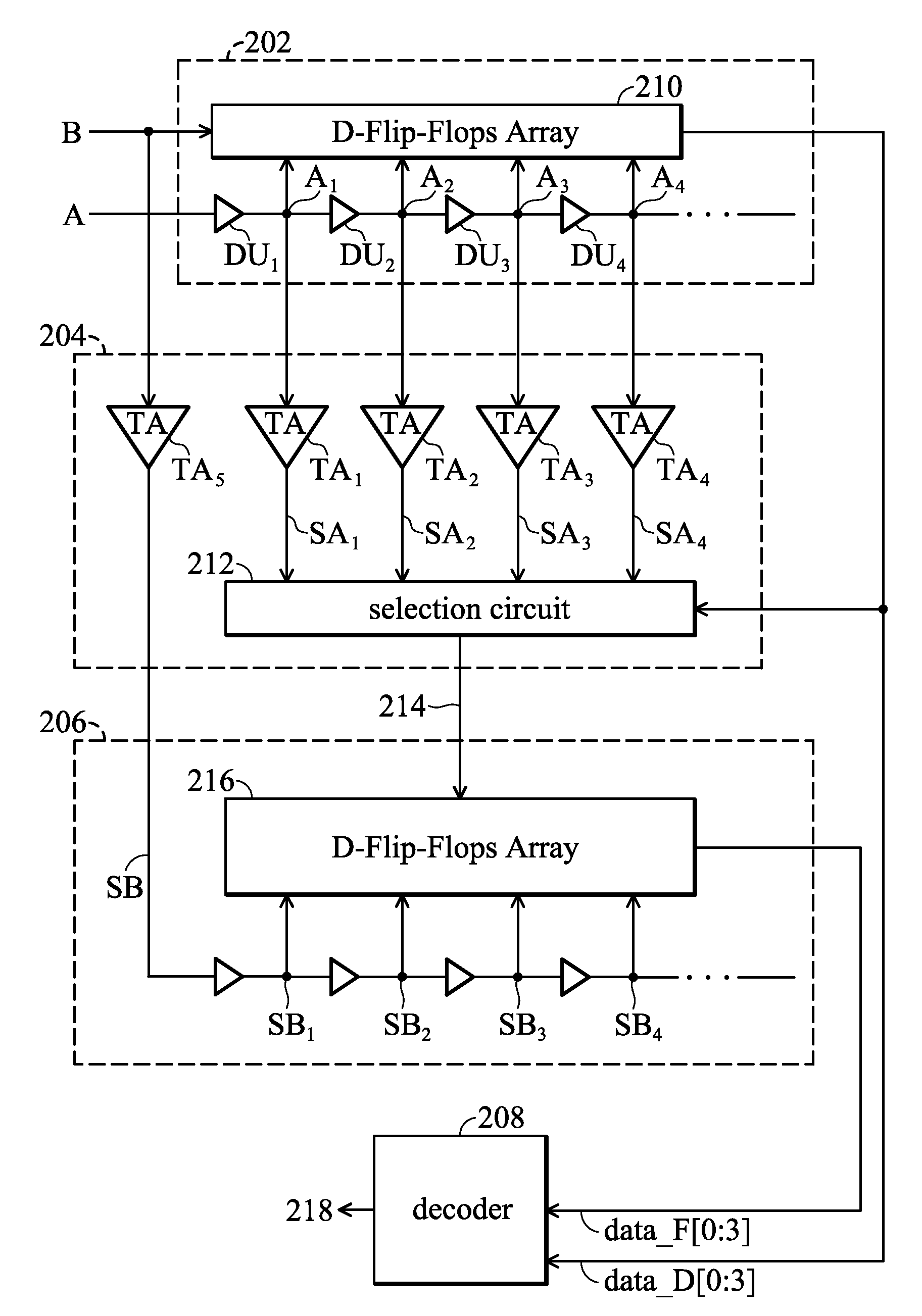

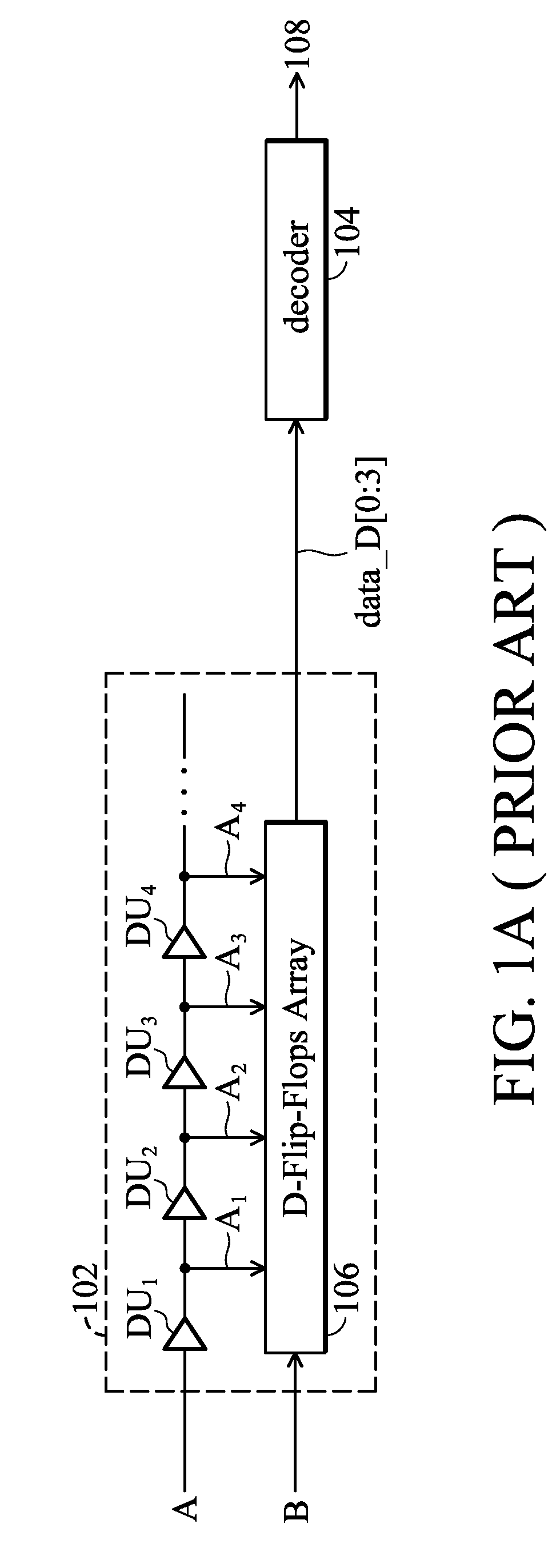

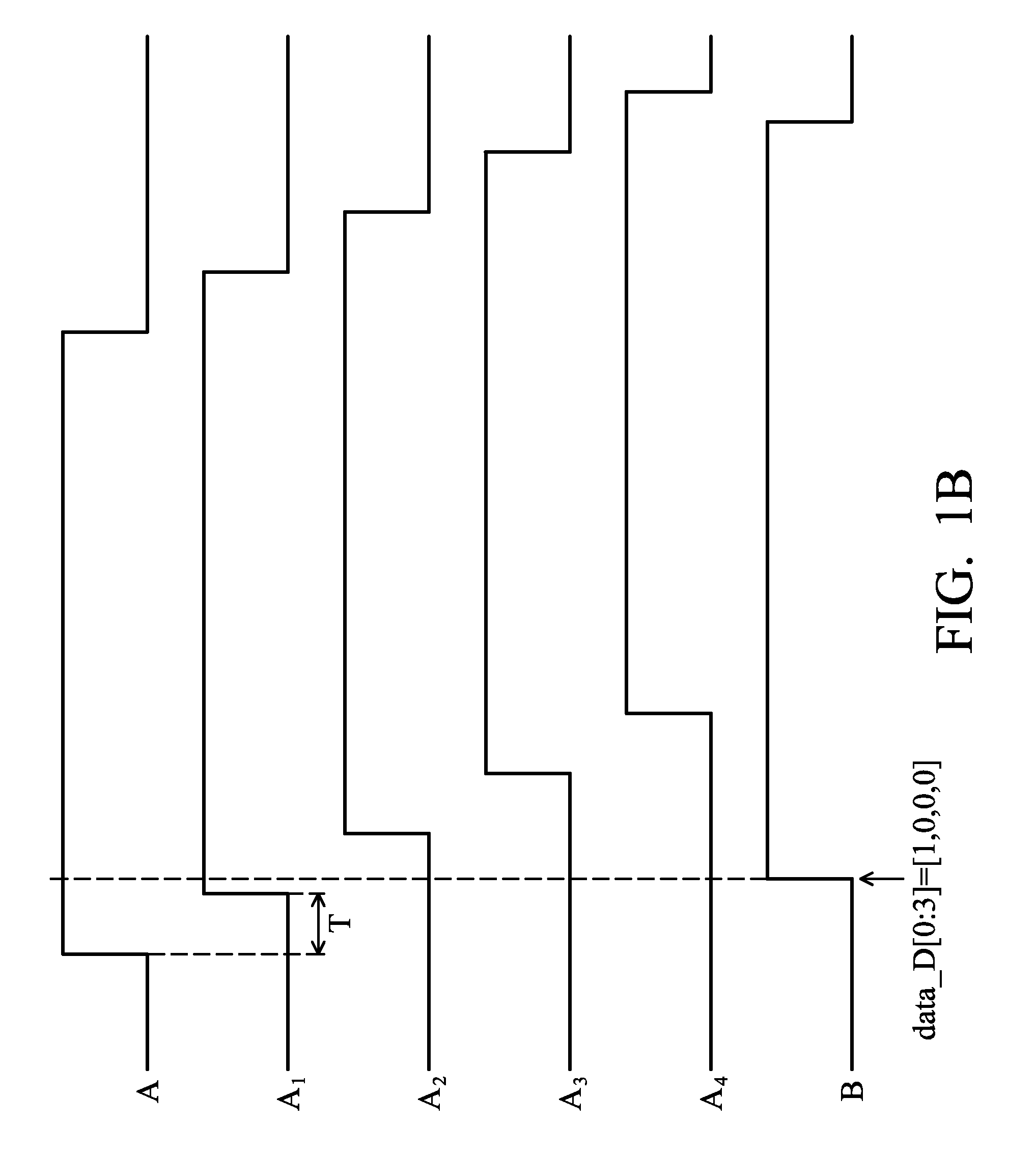

Time to digital converter with error protection

Time to digital converters (TDCs) with high resolution are disclosed. The TDC includes a first time to digital converting module, a selection and time amplifying module, a second time to digital converting module and a decoder, and is applied in estimating a time difference between a first signal and a second signal. As the delay time of the delay units of the time to digital converting modules is the unit of the time difference measurement, the first and second time to digital converting modules are responsible for the integral portion and the fractional portion of the estimated time difference, respectively. Moreover, by introducing the normalization process, the linearity of the converting characteristic of the TDC can be improved; by adding an error detection circuit to the TDC, the possible metastable problem can be prevented.

Owner:MEDIATEK INC

Time to digital converter

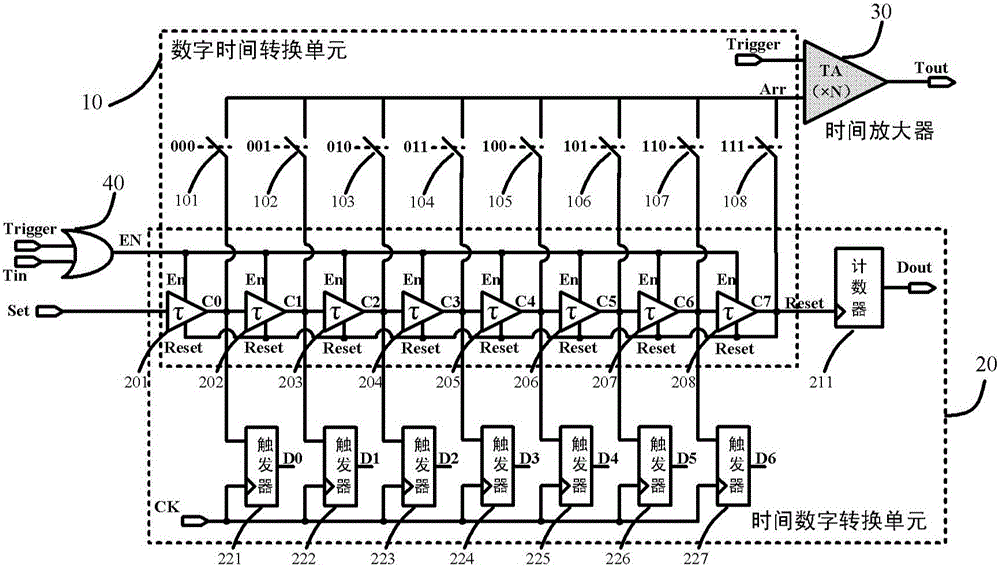

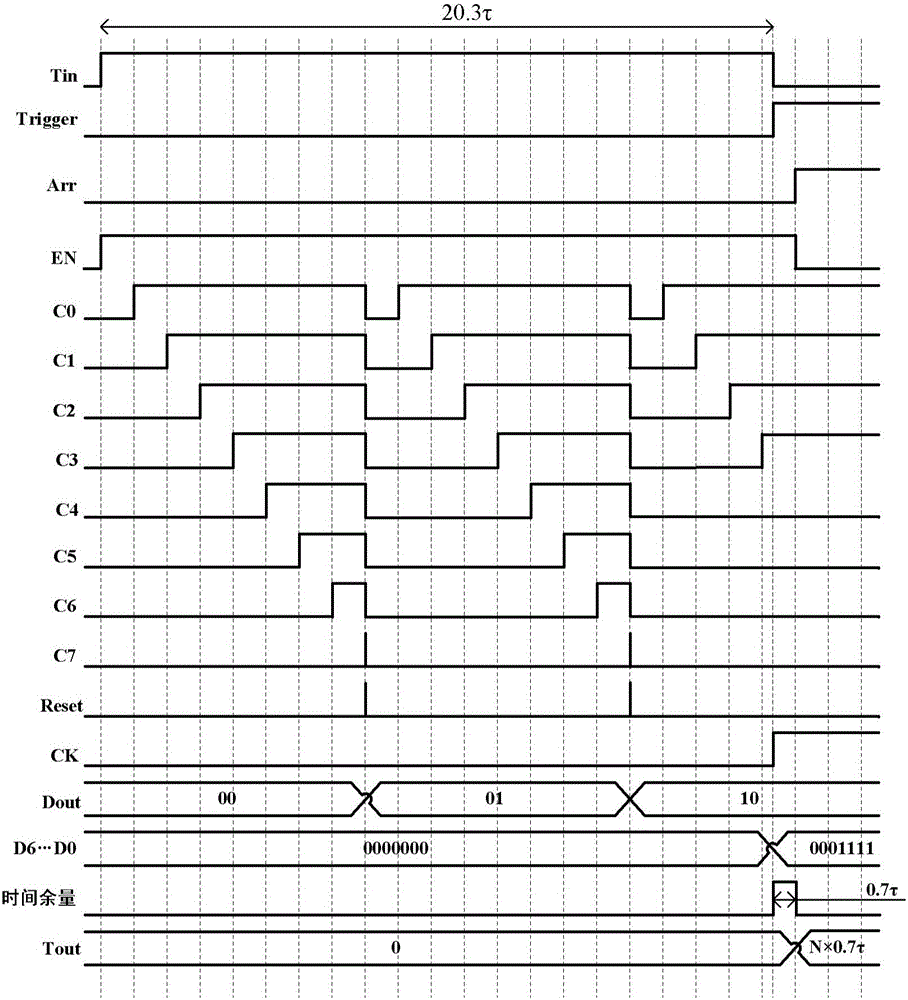

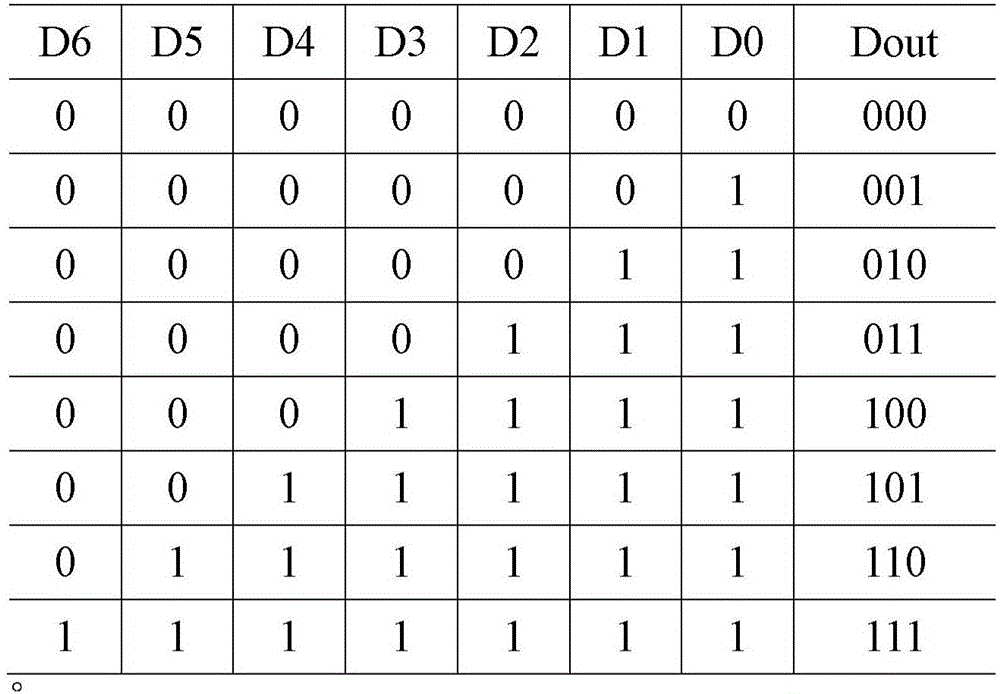

ActiveCN106168753AIncrease time scale rangeIncrease conversion rateTime-to-digital convertersTiming marginAudio power amplifier

The invention discloses a time to digital converter which comprises a time to digital converting unit, a digital to time converting unit and a time amplifier. The time to digital converting unit is used for digitally quantizing time so as to achieve a time digital quantization function. The digital to time converting unit is used for extracting the time margin part which is smaller than the quantization time unit and not be quantized. The time amplifier is used for linearly amplifying the time margin part extracted by the digital to time converting unit so as to further conduct digital quantization. By means of the time to digital converter, the performance requirements of high time precision, wide measuring range, high converting rate and the like can be met. The time to digital converter can improve the precision and speed of time to digital conversion when applied in the technical application field of time mode signal processing.

Owner:SOI MICRO CO LTD

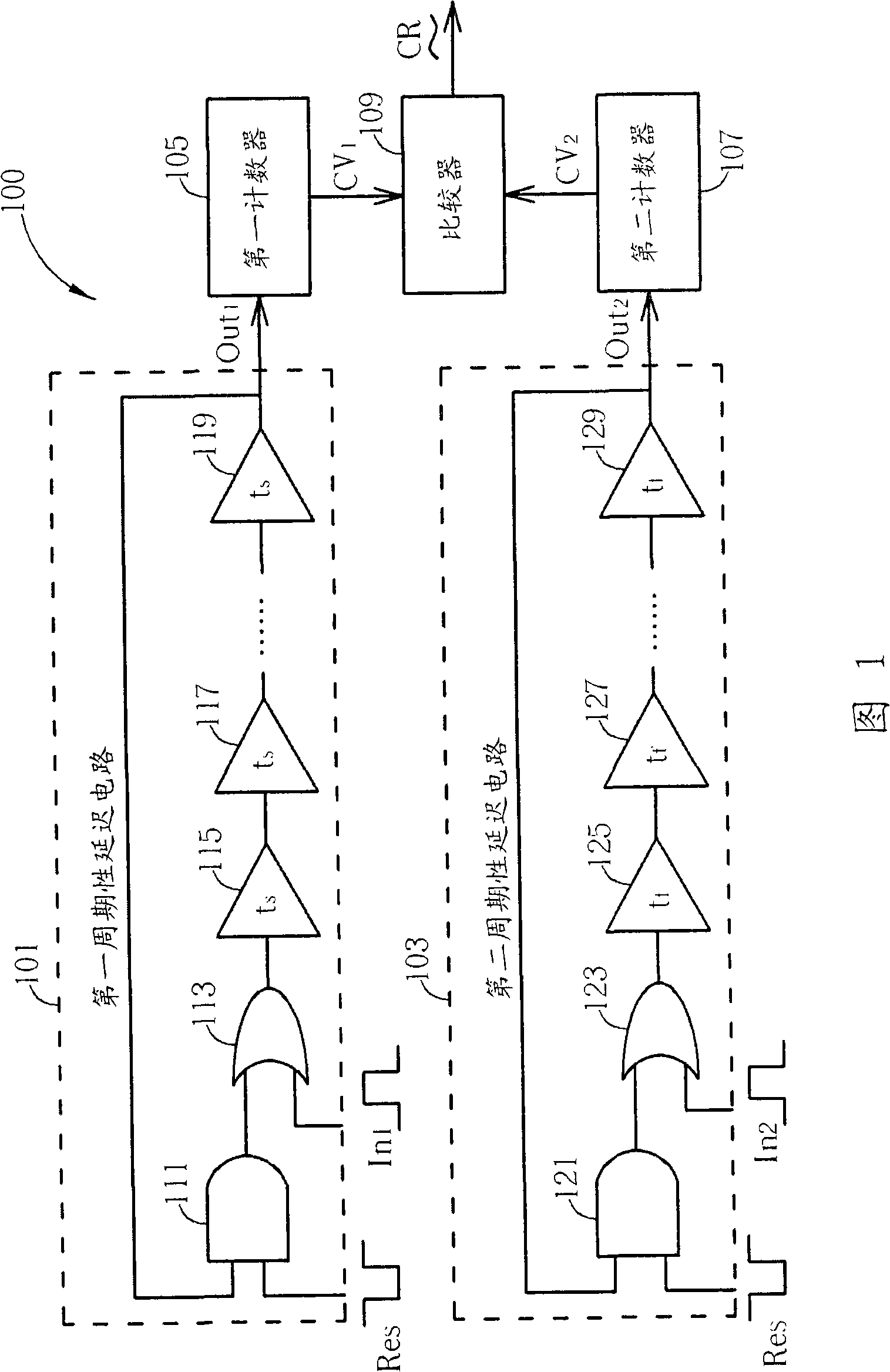

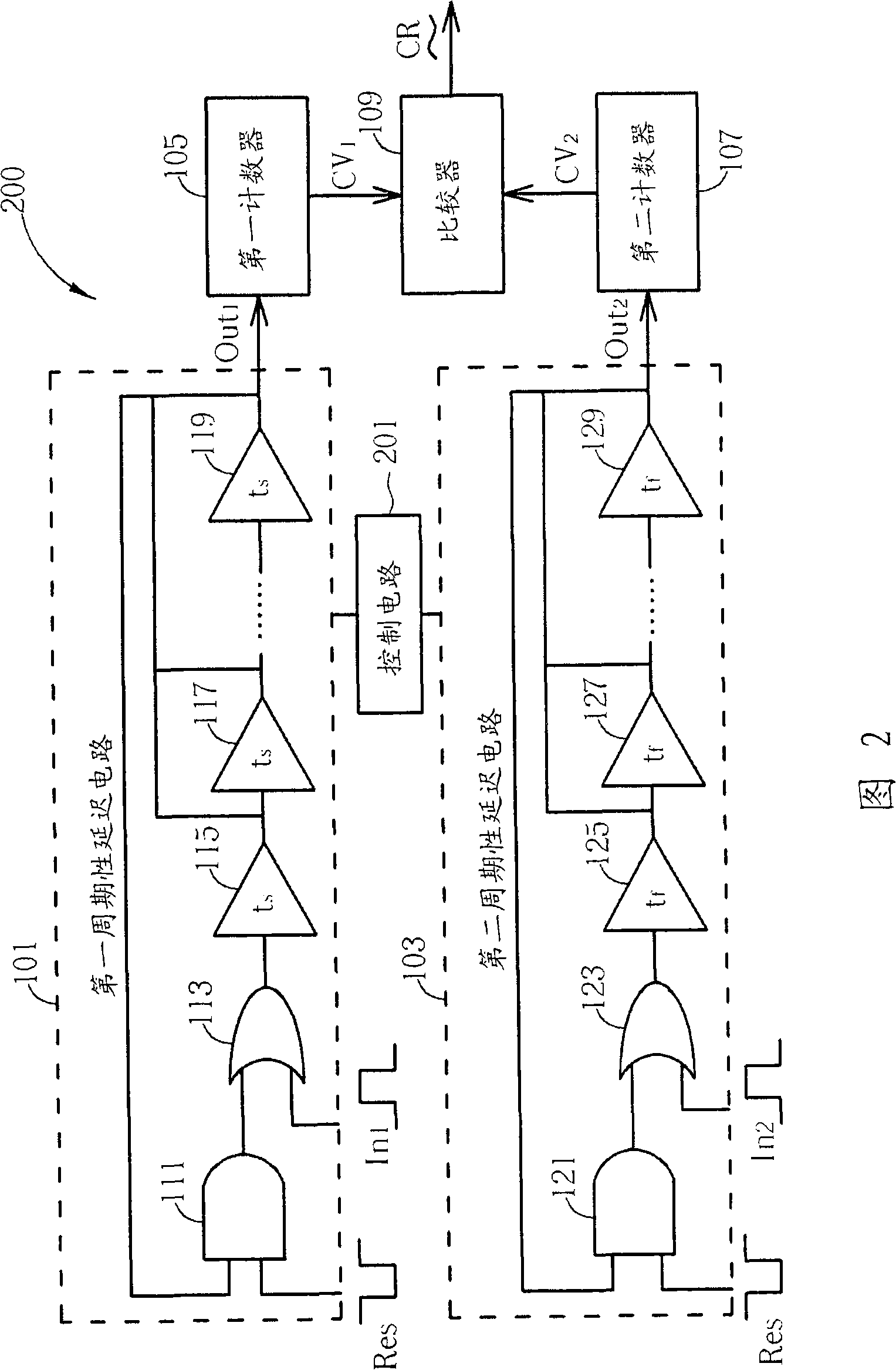

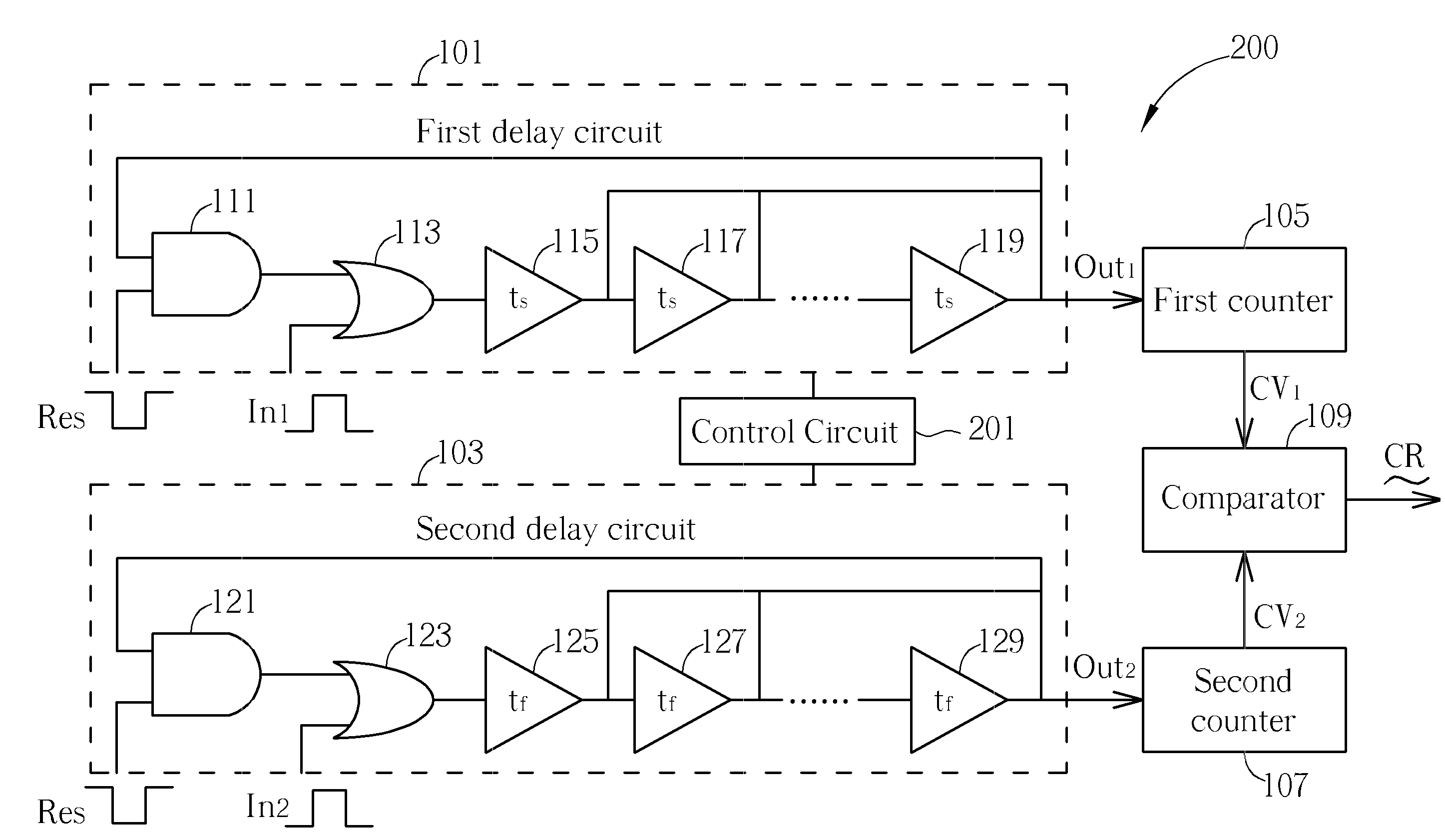

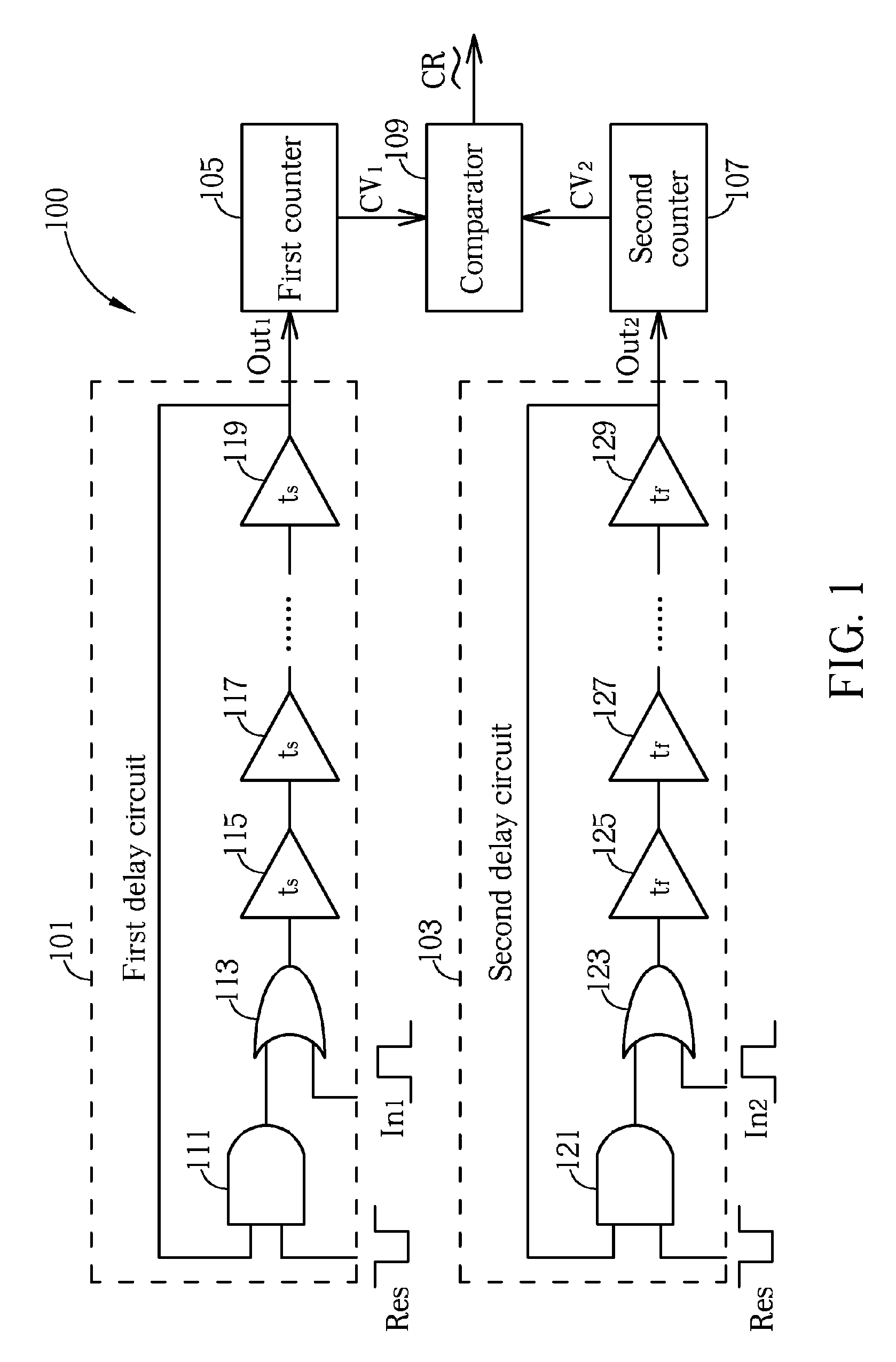

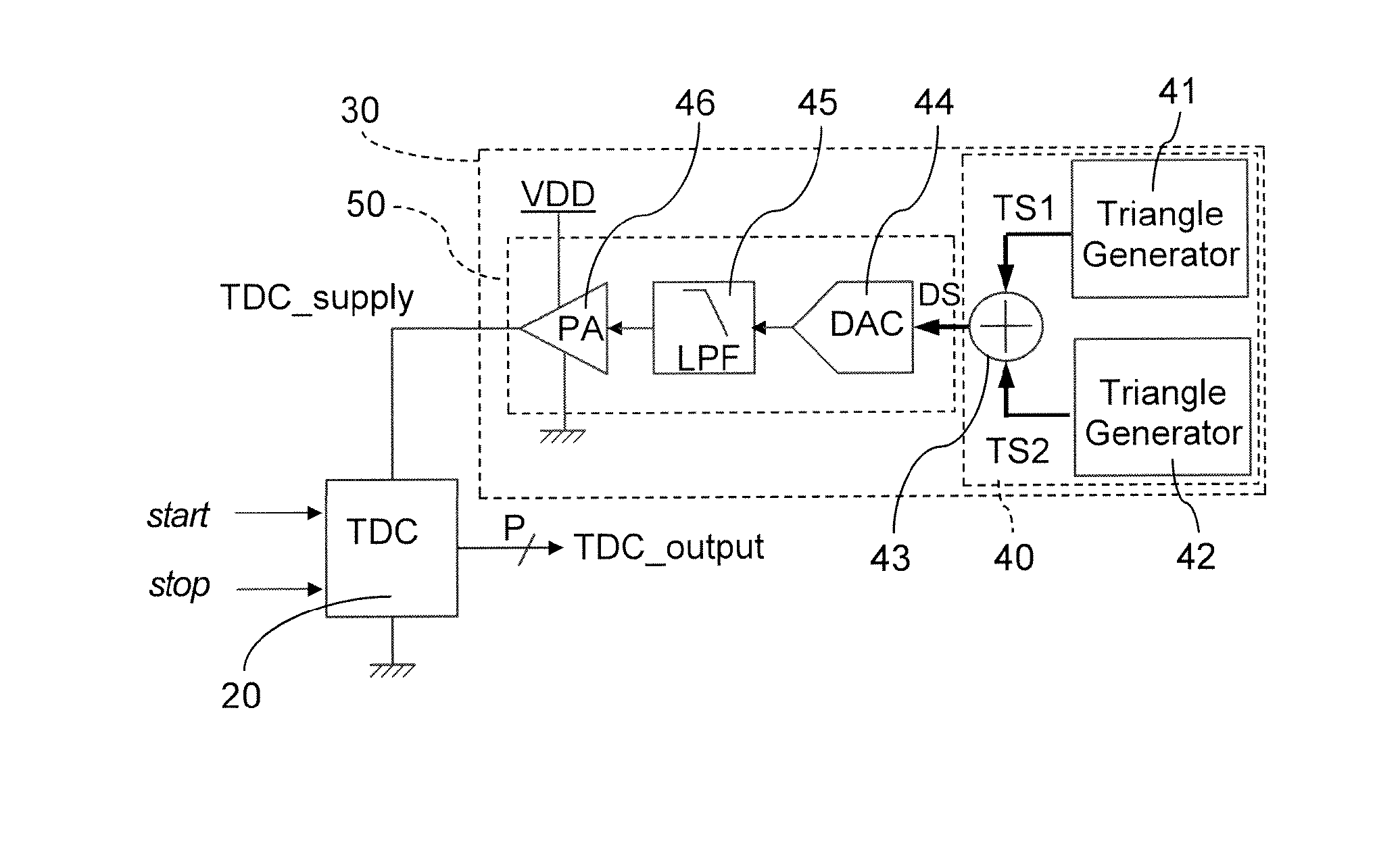

Time-to-digital conversion circuit and correlation method thereof

ActiveCN101515155AReduce areaElectric unknown time interval measurementComparatorTime to digital conversion

The invention provides a time-to-digital conversion circuit, which comprises a first delay circuit, a second delay circuit, a first counter, a second counter and a comparator, wherein the first delay circuit is provided with a first delay level and used for delaying a first input signal to generate a first output signal; the second delay circuit is provided with a second delay level and used for delaying a second input signal to generate a second output signal; the first counter is used for counting the first output signal to generate a first counting value; the second counter is used for counting the second output signal to generate a second counting value; the comparator is used for comparing the first counting value with the second counting value to generate a comparison result signal; the first delay level has larger delay quantity than the second delay level; the first counter begins to count earlier compared with the second counter; and when the second counting value is within a preset range comprising the first counting value, the comparator outputs the comparison result signal.

Owner:REALTEK SEMICON CORP

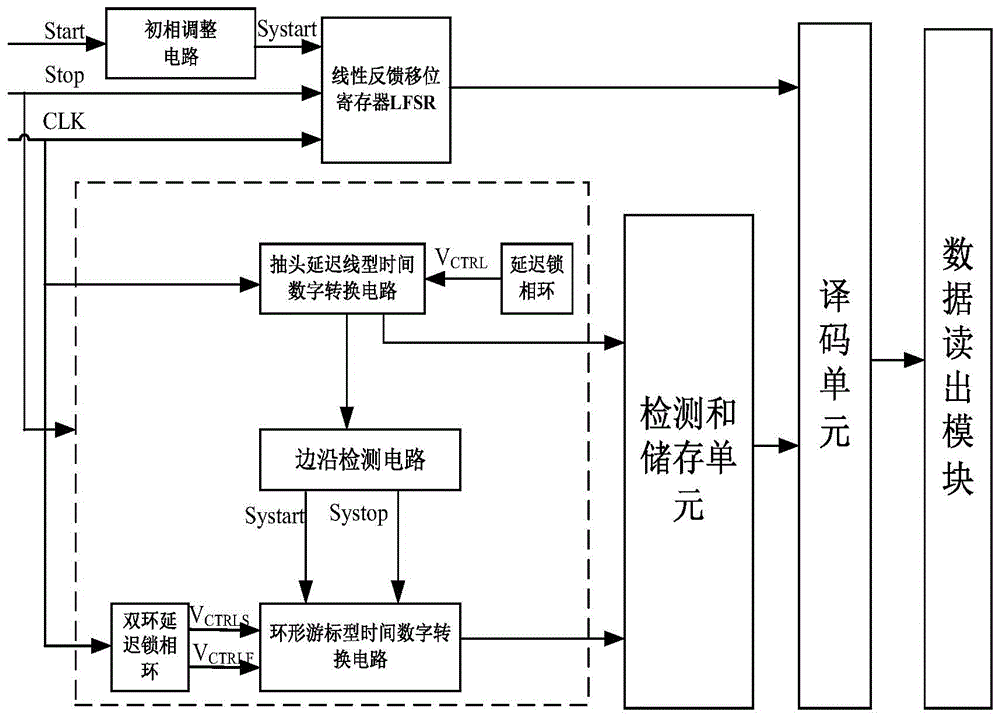

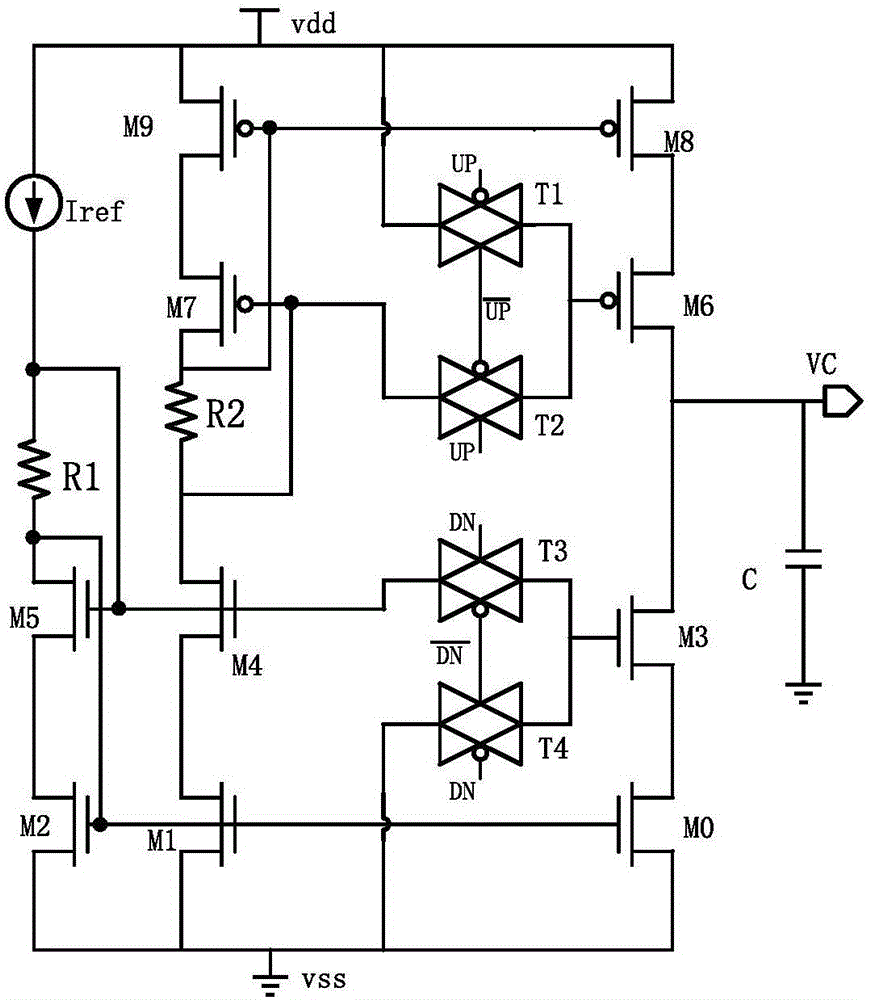

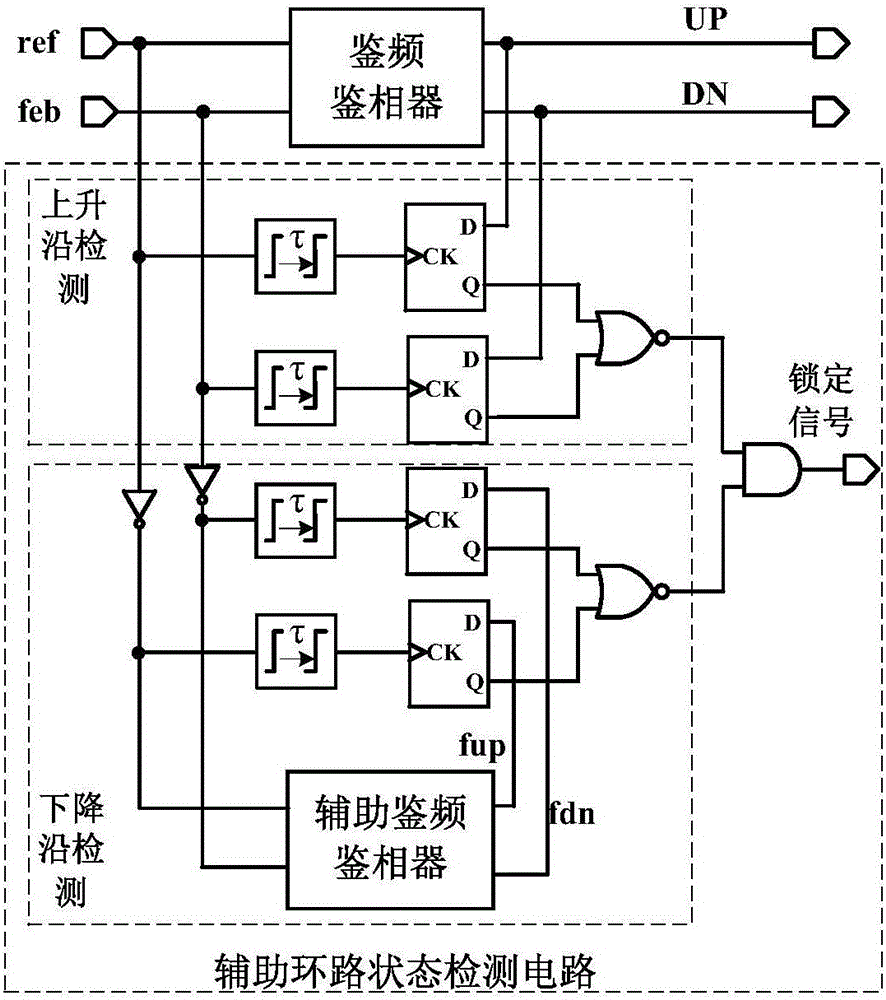

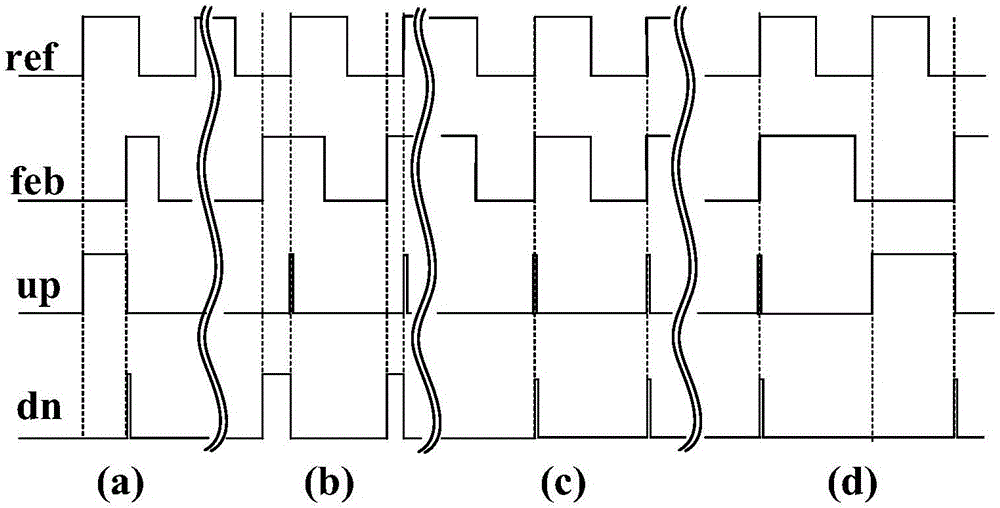

Three-segment time-to-digital conversion circuit based on phase-locked loop

ActiveCN105871371ADynamically adjust bandwidthQuick lockPulse automatic controlFrequency stabilizationShift register

The invention discloses a three-segment time-to-digital conversion circuit based on a phase-locked loop. Accurate counting clocks of a plurality of different frequencies and a plurality of uniform split phases are provided for a time-to-digital converter (TDC) through the phase-locked loop, so that accurate measurement of measured time by the TDC is ensured; the phase-locked loop is a three-order type-2 phase-locked loop, and comprises a phase frequency detector, a charge pump, a loop filter, a voltage-controlled oscillator, a frequency divider and an auxiliary state detection circuit; the TDC is a three-segment TDC including a high segment, a middle segment and a low segment; and the high segment of the TDC is provided with a 7-bit linear shift register. According to the three-segment time-to-digital conversion circuit, the phase-locked loop has the advantage of providing stable clocks of different frequencies and uniform phases, so that rough counting and fine quantitation and further fine quantitation of a measured time amount are finished; wide-range measurement is finished; and the measuring accuracy is ensured at the same time. Meanwhile, initial-phase time is measured at a same resolution, so that initial-phase time errors are eliminated, and the resolution and the measuring accuracy are kept constant at the same time.

Owner:SOUTHEAST UNIV

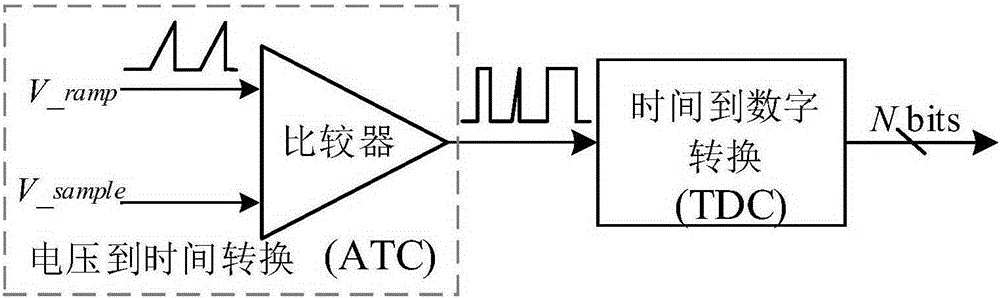

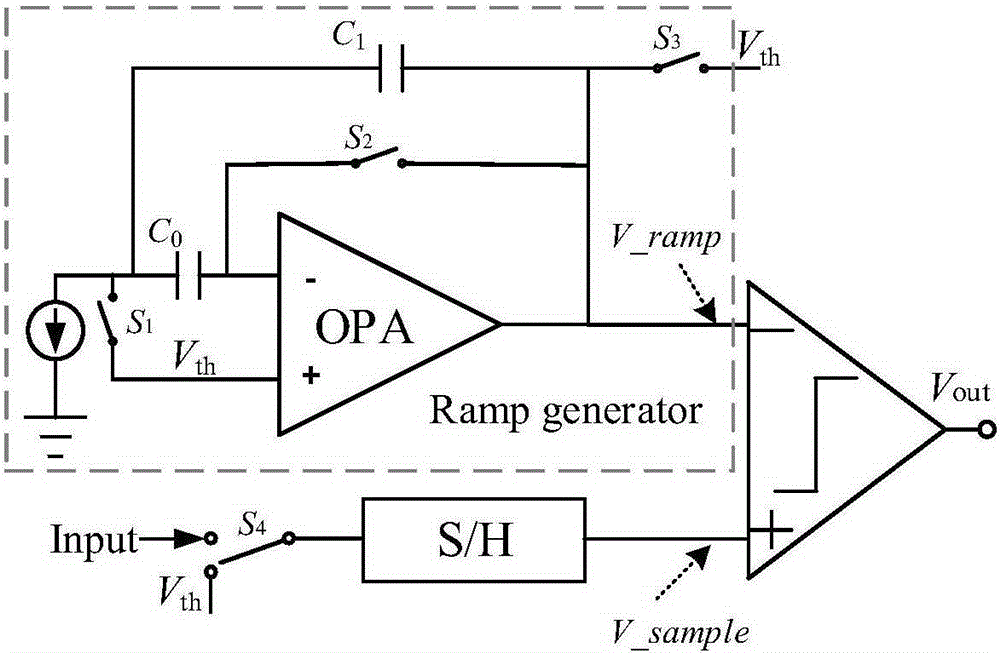

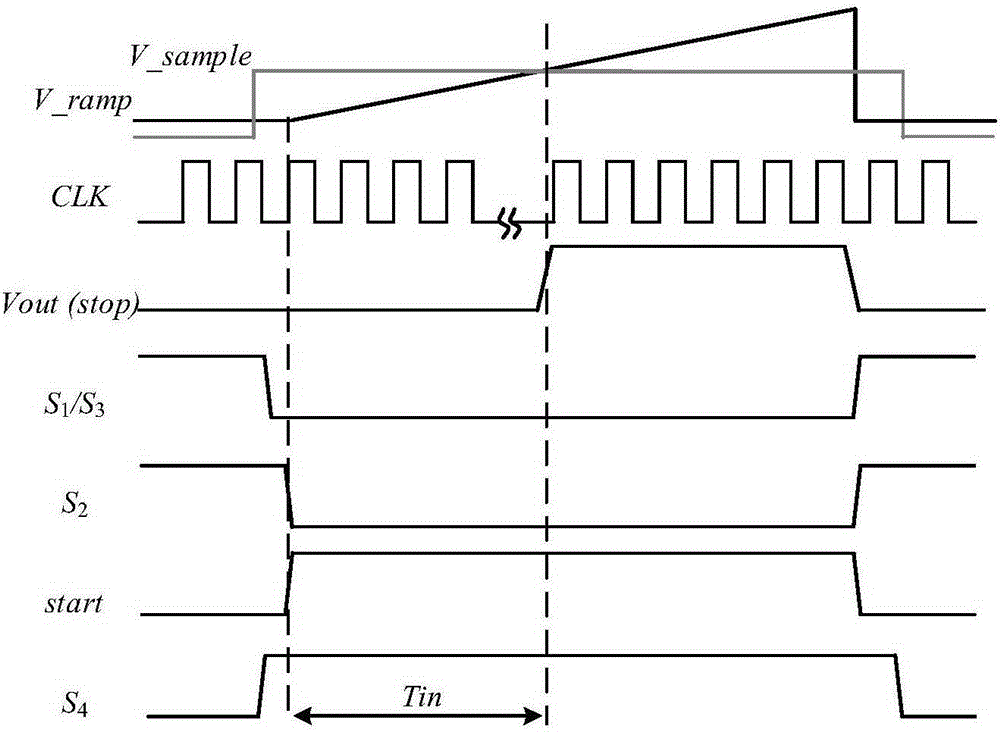

Column-level ADC for high-speed linear CMOS image sensor and implement method

The invention relates to the analog to digital conversion technology, and aims to reduce the conversion time of a column-level single-slope ADC for a high scanning speed linear CIS without a significant increase in the area and power consumption. To this end, the invention adopts a technical scheme of a column-level ADC for a high-speed linear CMOS image sensor, and the column-level ADC is formed by series connection of an analog voltage to time converter (ATC) and a time to digital converter. The analog voltage to time converter ATC is constructed as follows: an input signal is connected to a same-phase end through a switch S4 and an S / H; and a current source positive end is connected through a capacitor to an OPA amplifier anti-phase end and is further connected through a switch S1 to bias voltage and an OPA amplifier same-phase end, a current source negative end is grounded, an OPA amplifier output end is connected with an anti-phase end, a switch S2 is disposed between the OPA amplifier output end and the anti-phase end, and a C1 is disposed between the OPA amplifier output end and the current source positive end. The invention is mainly applied to analog to digital conversion.

Owner:TIANJIN UNIV

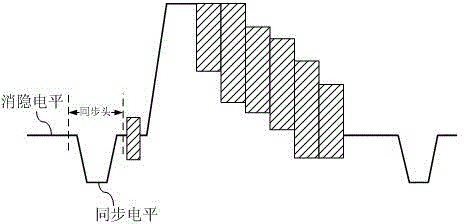

All-digital phase-locked ring applicable to video signal processing

The invention discloses an all-digital phase-locked ring applicable to video signal processing, comprising an analog-to-digital conversion circuit ADC, an automatic gain control circuit AGC, a digital low-pass filter DLPF, a synchronous header split circuit, a frequency detector FD, a time-to-digital conversion circuit TDC, a coarse tuning filter, a phase detector PD, a fine tuning filter, a summator, a digital-controlled oscillator and a pixel frequency divider circuit. The phase detector, the time-to-digital conversion circuit, the coarse tuning filter, the digital-controlled oscillator and the pixel frequency divider circuit constitute a frequency locking loop circuit, and the locking process of the all-digital phase-locked ring is accelerated. The analog-to-digital conversion circuit, the automatic gain control circuit, the digital low-pass filter, the frequency detector, the phase detector, the fine tuning filter, the digital-controlled oscillator and the pixel frequency divider circuit constitute a phase locking loop circuit, and the phase locking loop circuit is used for accurately locking the phase of a synchronous header in an analogue video signal.

Owner:CHANGSHA JINGJIA MICROELECTRONICS

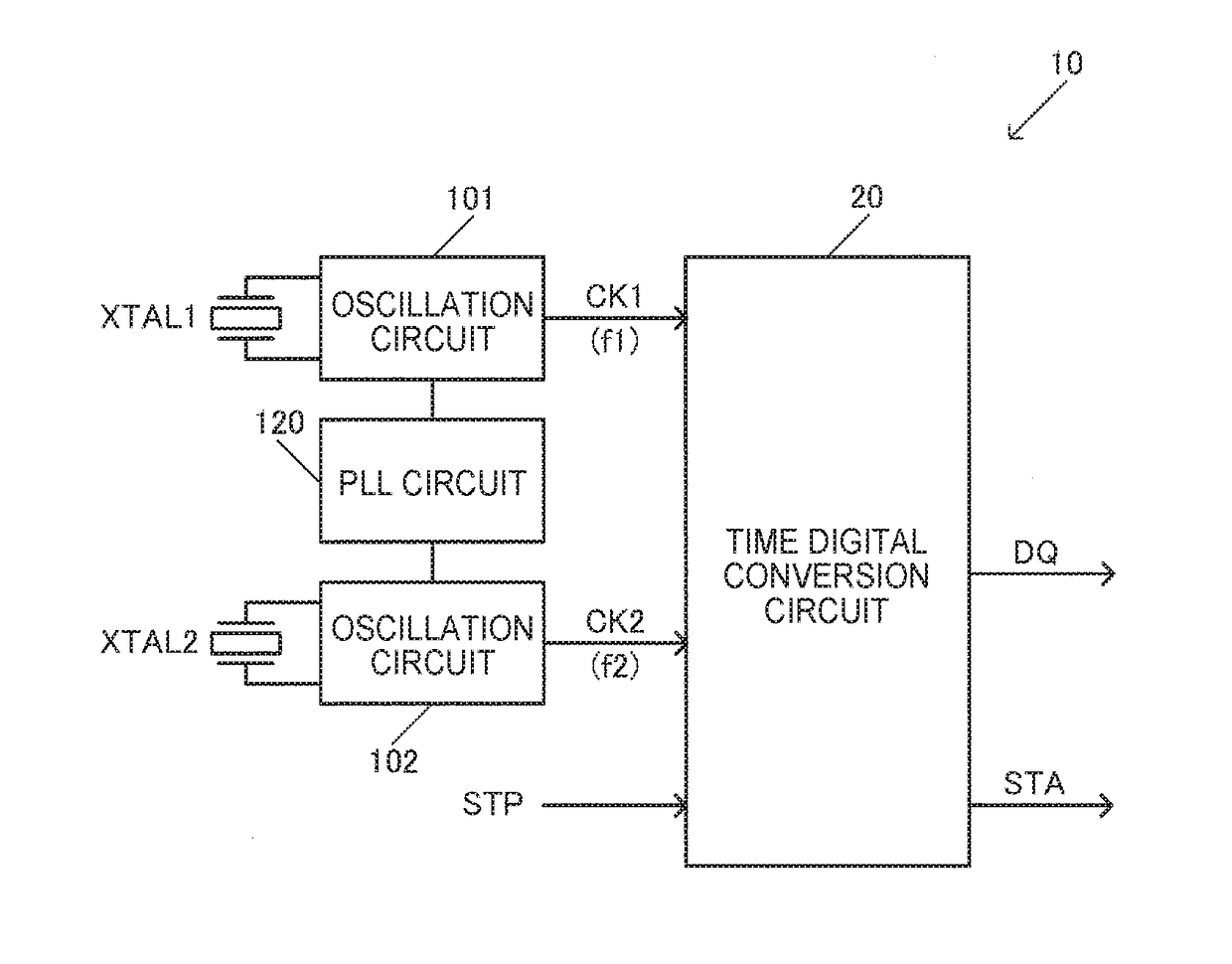

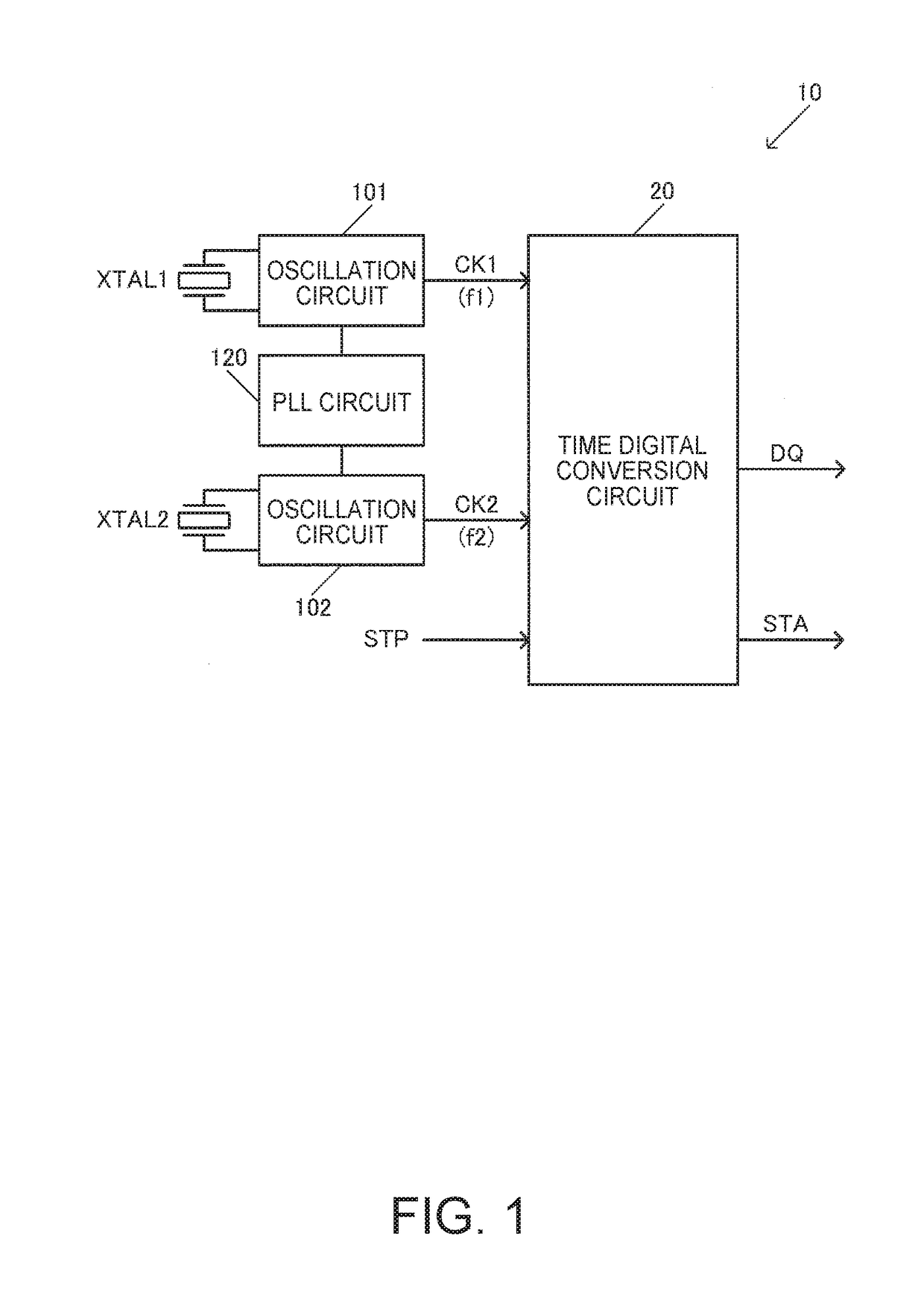

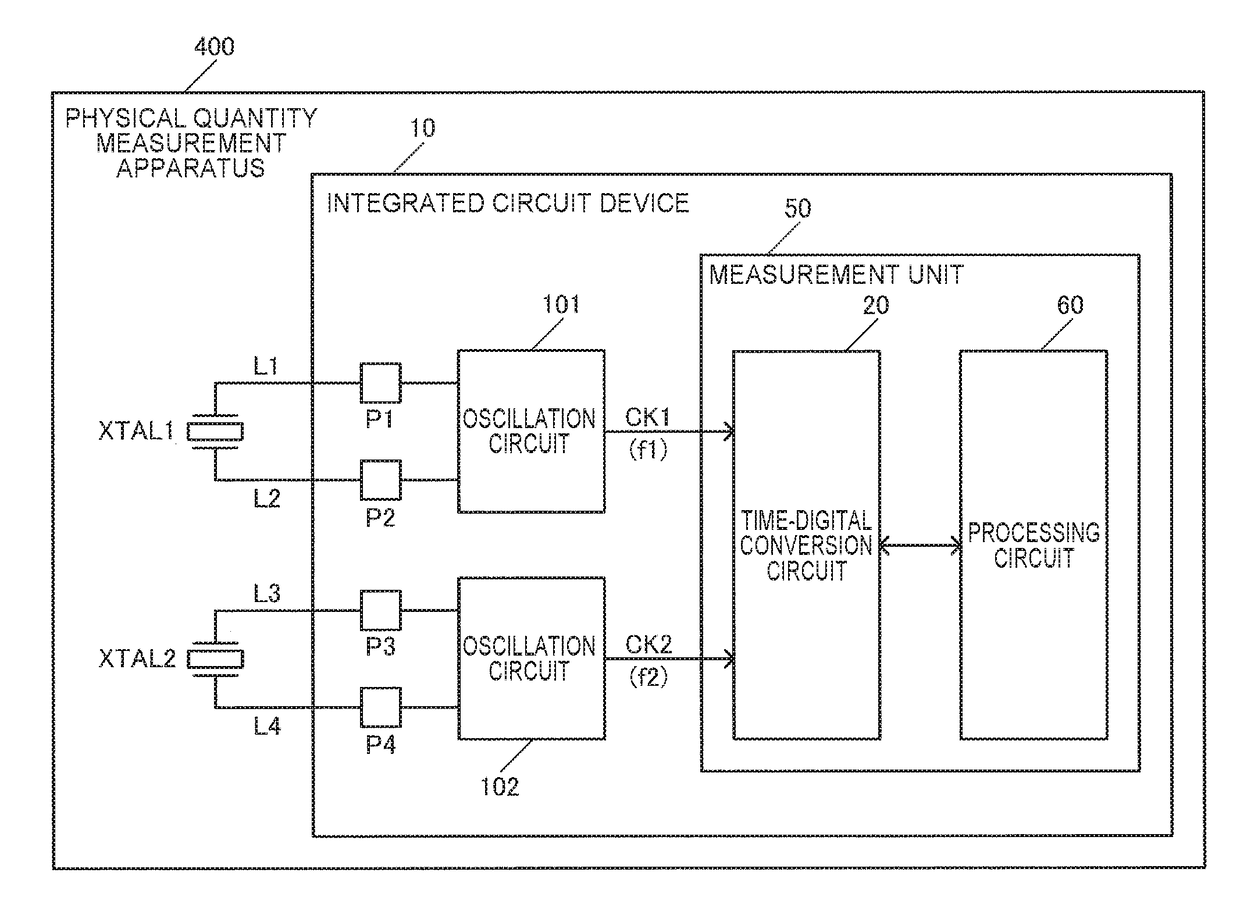

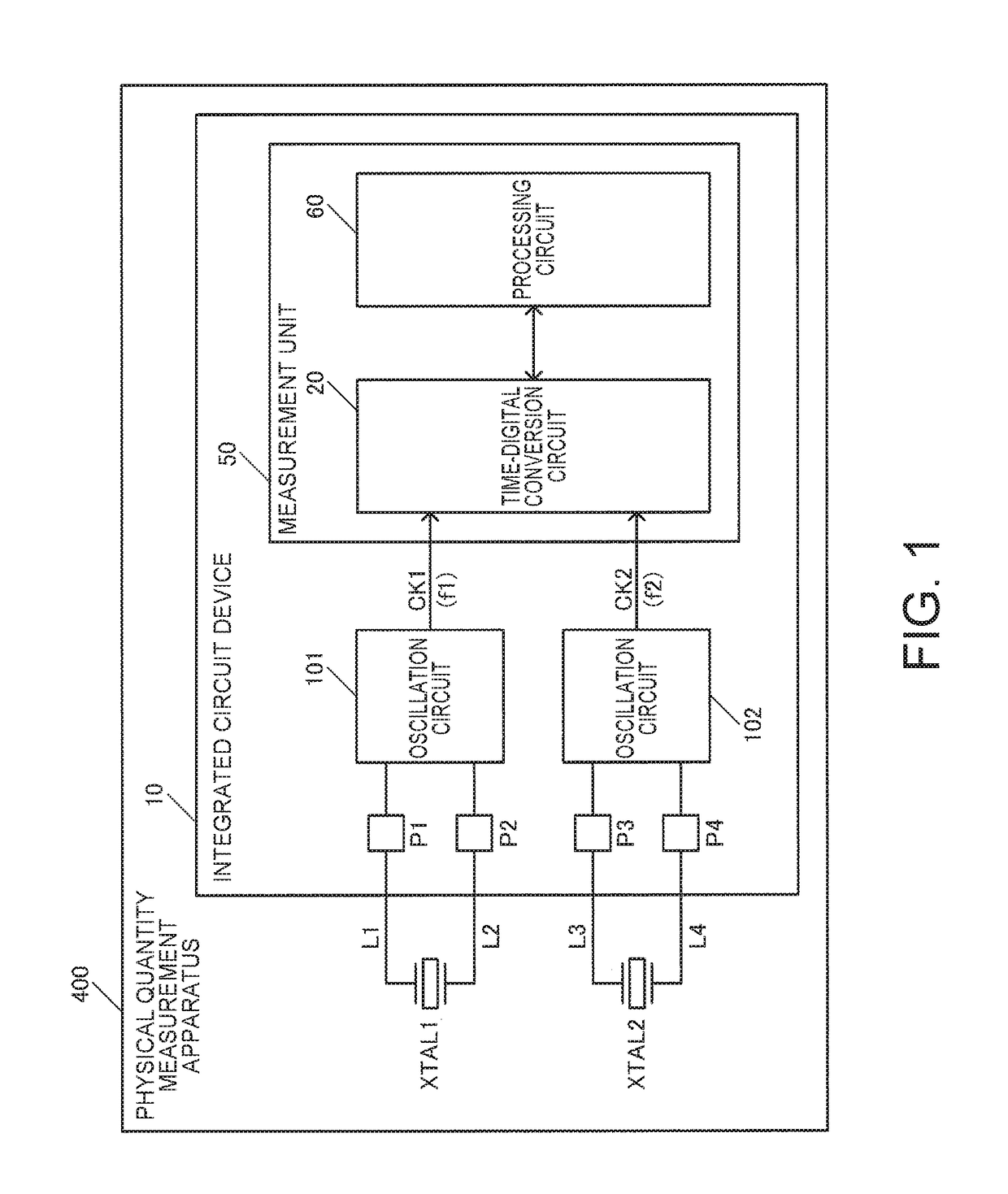

Circuit device, physical quantity measurement device, electronic apparatus, and vehicle

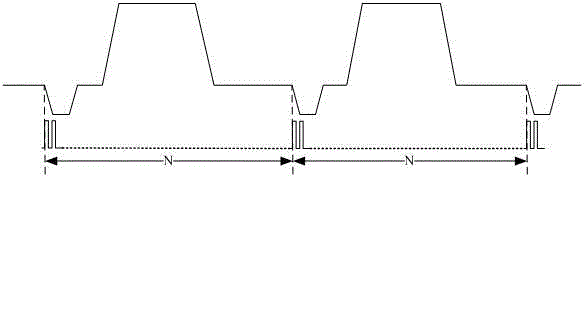

ActiveUS20180088536A1Improve performanceConducive to simplificationPulse automatic controlElectric vehiclesMeasurement deviceClock rate

A circuit device includes a time-to-digital conversion circuit, to which a first clock signal generated using a first resonator, and having a first clock frequency, and a second clock signal generated using a second resonator, and having a second clock frequency different from the first clock frequency are input, and which converts time into a digital value using the first and second clock signals, and a PLL circuit adapted to perform phase synchronization between the first and second clock signals.

Owner:SEIKO EPSON CORP

Detector array utilizing time-to-digital conversion with improved temporal precision

ActiveCN103460072BAccurate time-of-flight PET imagingAutomatic self-calibrationTomographyX/gamma/cosmic radiation measurmentDetector arrayEngineering

A detector (22) detects an event. First and second time-to-digital converters (TDCs) (70, 72) generate first and second time stamps (TS1, TS2) for the detection of the event. The first TDC and the second TDC are both synchronized with a common clock signal (62) that defines a fixed time offset between the second TDC and the first TDC. An autocalibration circuit (120) adjusts the first TDC and the second TDC to keep the time difference between the second time stamp and the first time stamp equal to the fixed time offset between the second TDC and the first TDC. The detector may be a detector array, and trigger circuitry (28) propogates a trigger signal from a trigger detector of the array of detectors to the first and second TDC's. Skew correction circuitry (132, 134, 136, 142, 60, 162) adjusts a timestamp (TS) based on which detector is the triggering detector.

Owner:KONINKLJIJKE PHILIPS NV

Physical quantity measurement apparatus, electronic apparatus, and vehicle

ActiveUS20180088160A1Improve performancePromote conversionPulse characteristics measurementsFrequency to pulse train conversionClock rateEngineering

A physical quantity measurement apparatus includes a first resonator, a second oscillator, and an integrated circuit device. The integrated circuit device includes a first oscillation circuit that causes the first resonator to oscillate, and thus generate a first clock signal having a first clock frequency, a second oscillation circuit that causes the second oscillator to oscillate, and thus generate a second clock signal having a second clock frequency which is different from the first clock frequency, and a measurement unit that is provided with a time-to-digital conversion circuit which converts time into a digital value by using the first clock signal and the second clock signal.

Owner:SEIKO EPSON CORP

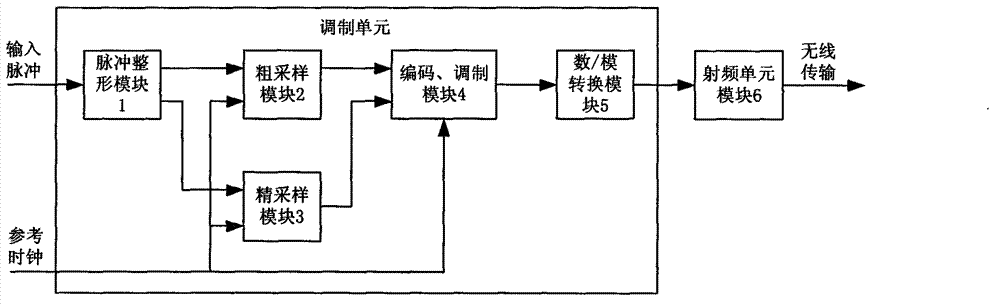

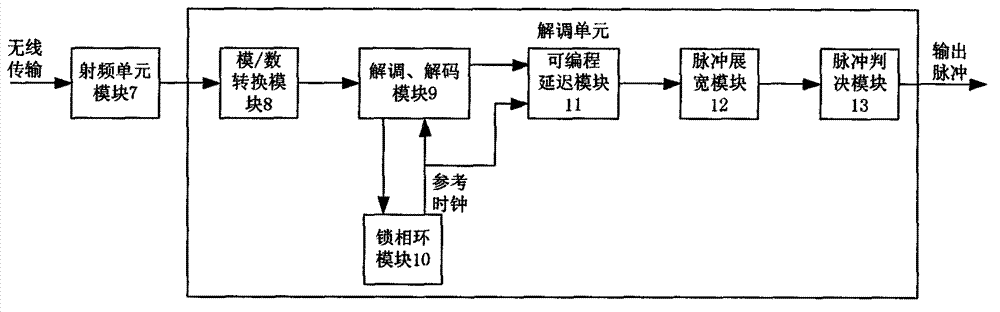

Wireless low-jitter transmission method for digital asynchronous pulse

InactiveCN102820872AGuaranteed for special applicationsReduce design difficultyPulse automatic controlPulse manipulationTime informationRadar

The invention discloses a wireless low-jitter transmission method for a digital asynchronous pulse, which belongs to the wireless pulse transmission and communication field. The wireless low-jitter transmission method for the digital asynchronous pulse is especially suitable for the wireless low-jitter transmission of radar pulse. Pulse shaping is carried out on a transmitting end; the pulse is subjected to rough sampling and fine sampling by utilizing a reference clock and a time-to-digital conversion circuit; the digitalized time information obtained by sampling is coded and modulated; on a receiving end, the steps of demodulating and decoding are finished by utilizing a synchronized reference clock; rough sampling information and fine sampling information are recovered; according to the rough sampling information and the fine sampling information, a clock period corresponding to a pulse signal to be recovered is determined; the rising edge of the corresponding clock period is delayed for a certain period of time by utilizing a programmable delay circuit to obtain a pulse rising edge to be recovered; the pulse rising edge is widened and judged; and finally, a low-jitter pulse signal is output. According to the wireless low-jitter transmission method for the digital asynchronous pulse, the transmitting end pulse can be favorable recovered, the wireless low-jitter transmission method has a low requirement on a clock in a system, and the main circuit component is realized by adopting an FPGA (field programmable gate array) or ASIC (application specific integrated circuit), thereby being low in designing and debugging difficulty.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

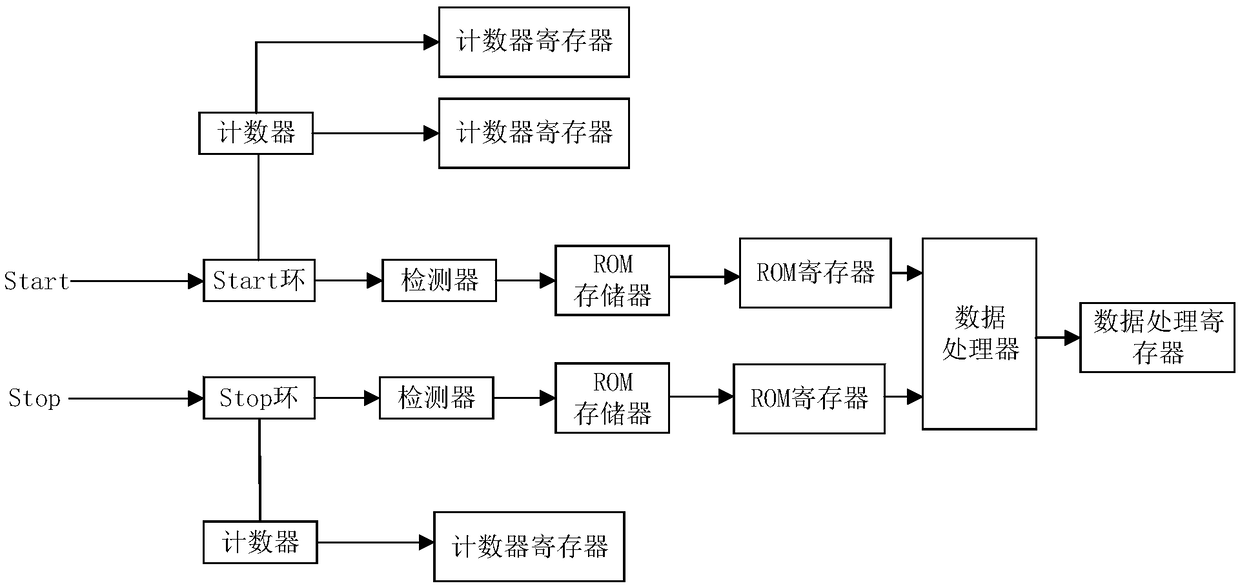

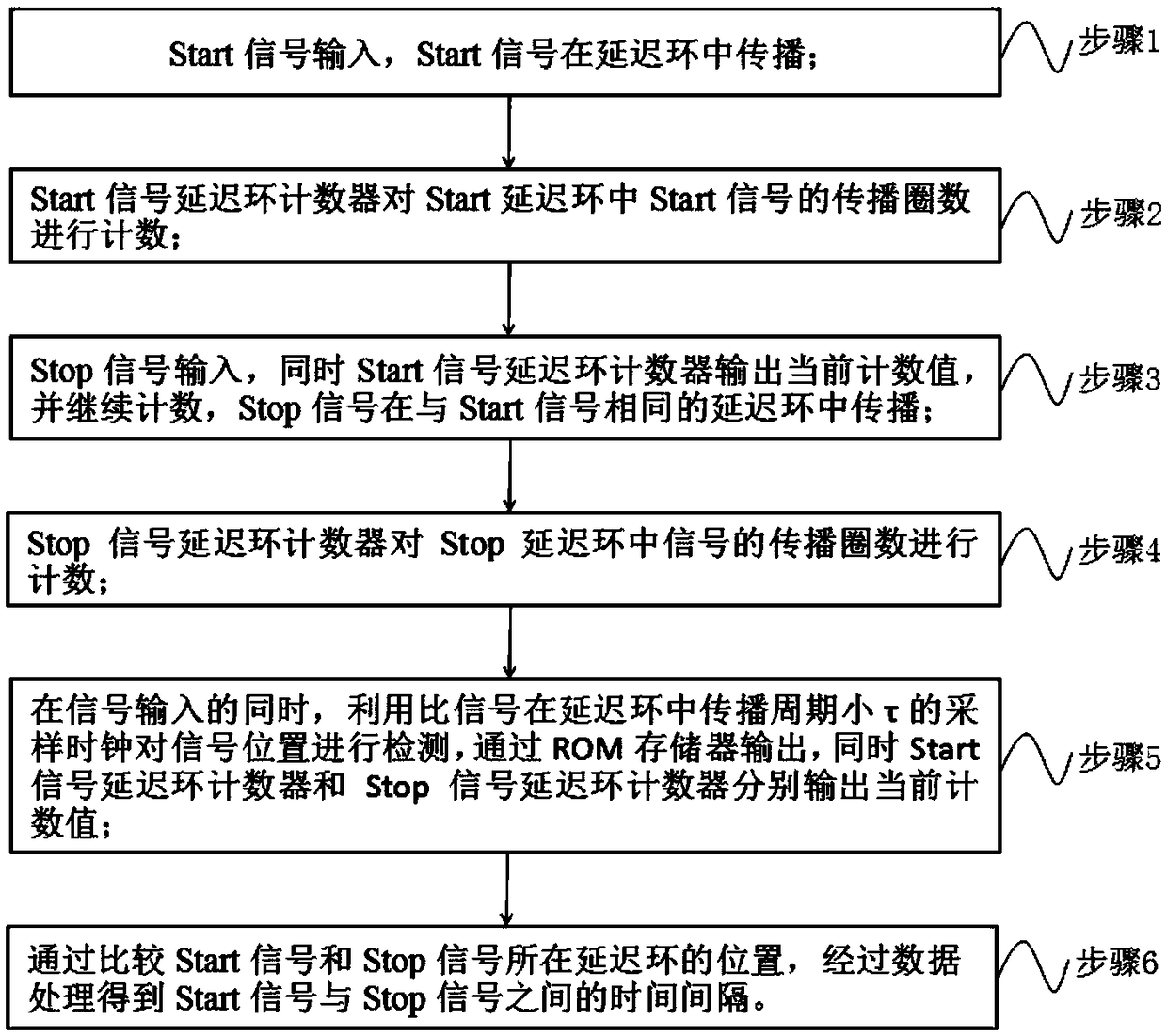

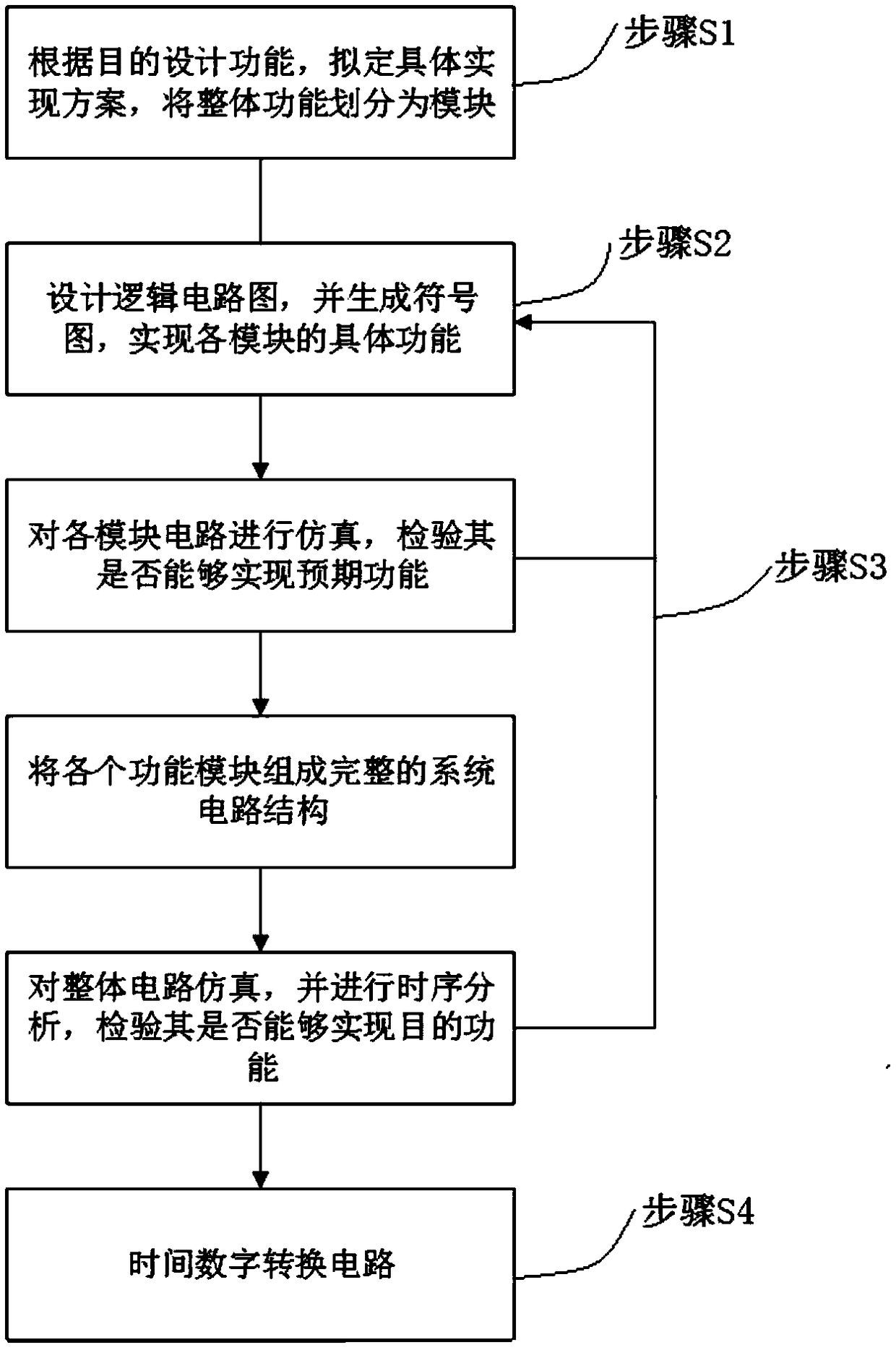

A time-to-digital conversion circuit based on multiple sampling

ActiveCN109104190ASimple structureEasy to detectAnalogue/digital conversion calibration/testingTime-to-digital convertersData treatmentDigital converter

The invention provides a time-to-digital conversion circuit based on multiple sampling, including enable reset signal generation module, Start delay loop, Stop delay loop, signal detector, Start delayloop and Stop delay loop counter, counter register, ROM memory, ROM memory register, data processor and data processor register. Start, At the input circuit of the stop signal, Propagate into the Start and Stop delay loops, respectively. The last delay cell of each delay loop is followed by a counter. Output connection register, the enable reset signal generation module is connected to the counter. At the same time, the output of each delay loop is connected with 16 signal detectors to sample the signals for many times. The sampling results are input into ROM memory, and the results of outputconnection register, counter register and ROM memory register are used as input and output connection register of data processor. The technical proposal of the invention solves the problem of low measurement accuracy of the existing time-to-digital converter and realizes higher measurement accuracy.

Owner:NORTHEASTERN UNIV

Time to digital converting circuit and related method

ActiveUS7872602B2Electric signal transmission systemsAnalogue-digital convertersComputer scienceComparator

A TDC circuit includes: a first delay circuit, including at least one first delay stage for delaying a first input signal to generate a first output signal; a second delay circuit, including at least one second delay stage for delaying a second input signal to generate a second output signal; a first counter, for computing the first output signal to generate a first counter value; a second counter, for computing the second output signal to generate a second counter value; and a comparator, for comparing the first counter value and the second counter value to generate a comparing result signal; wherein the first delay stage has a larger delay amount than the second delay stage, the first counter starts before the second counter, and the comparator outputs the comparing result signal when the second counter value falls within a predetermined range of the first counter value.

Owner:REALTEK SEMICON CORP

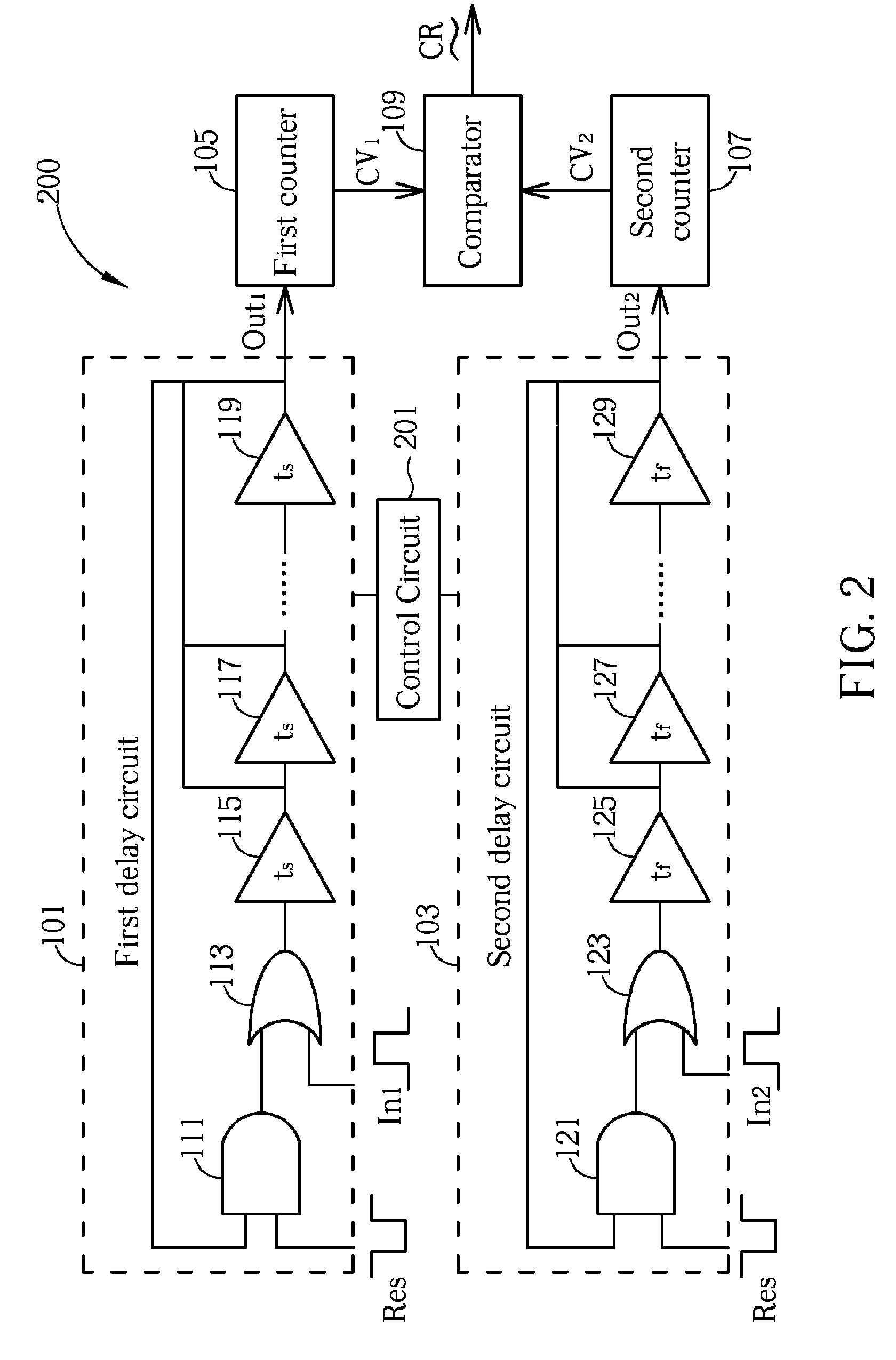

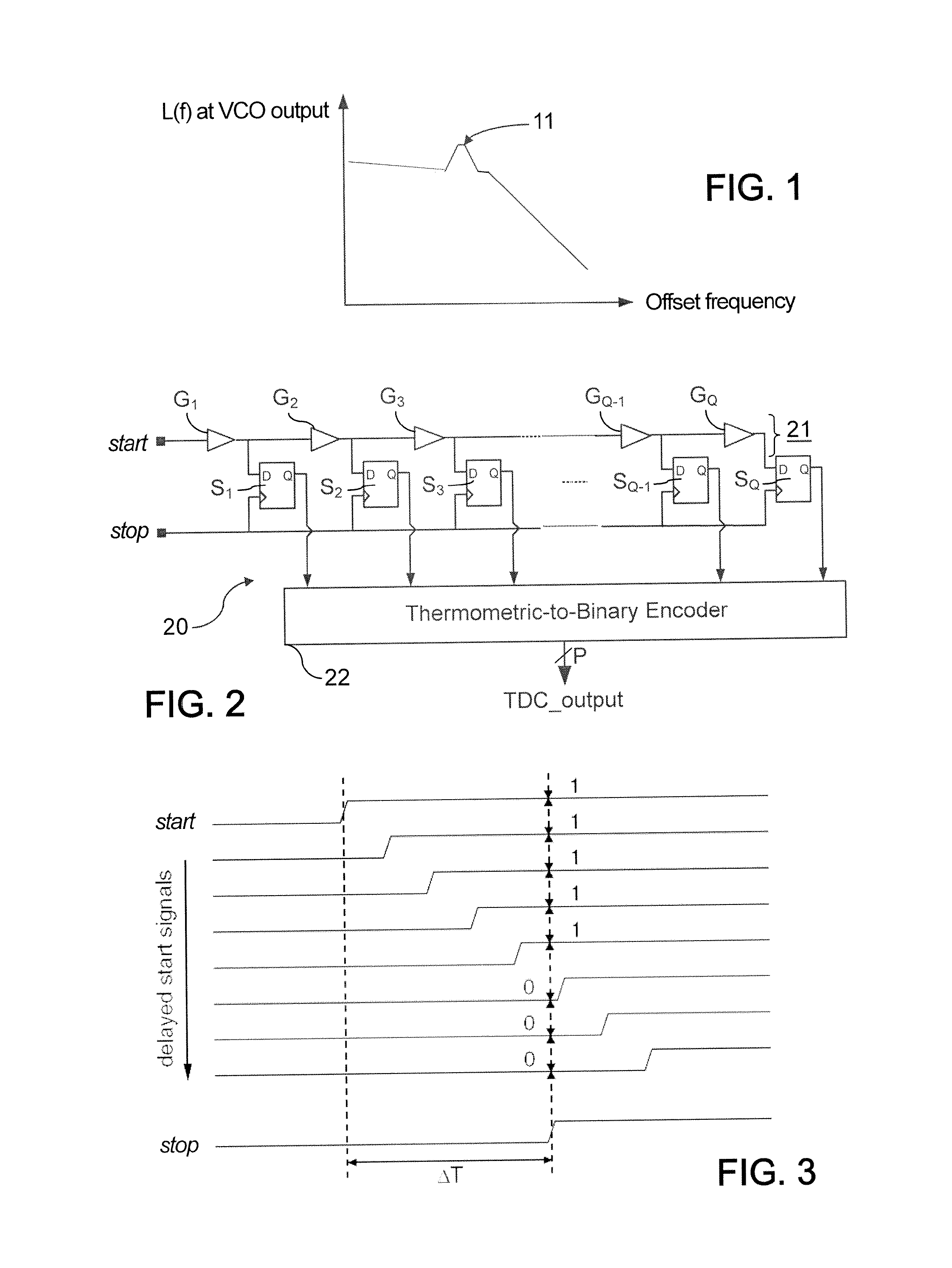

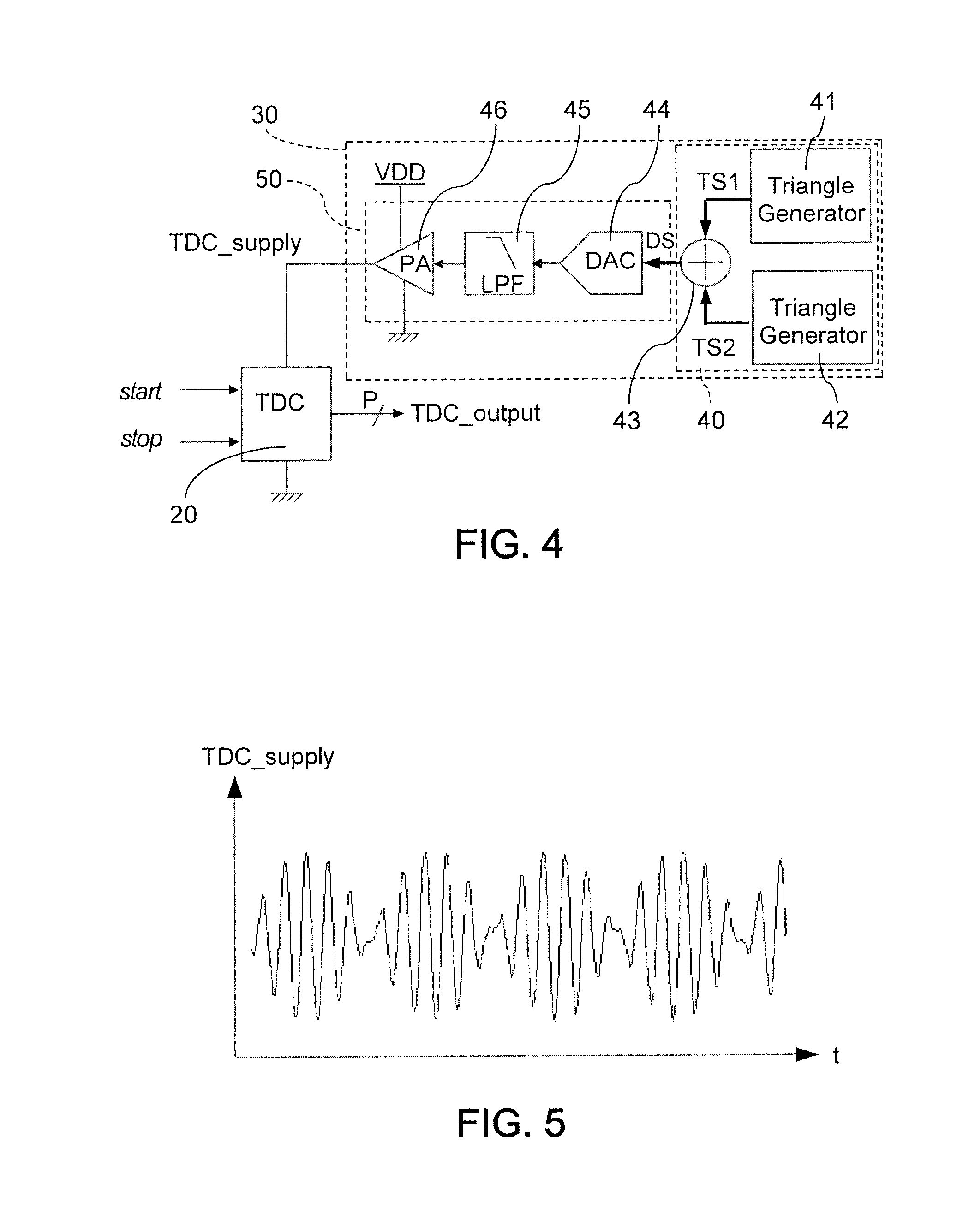

Time-to-digital conversion with analog dithering

ActiveUS20140320324A1Electric signal transmission systemsPulse automatic controlPropagation delayEngineering

There is described a time-to-digital conversion scheme using an arrangement of delay elements based Time-to-Digital Converter, TDC (20), wherein dithering is built in the digital domain and introduced in the analog domain as a modulation of a supply voltage (TDC-supply) supplying delay elements of the TDC, each having a propagation delay which exhibits a dependency to their supply voltage.

Owner:ASAHI KASEI ELECTRONICS CO LTD

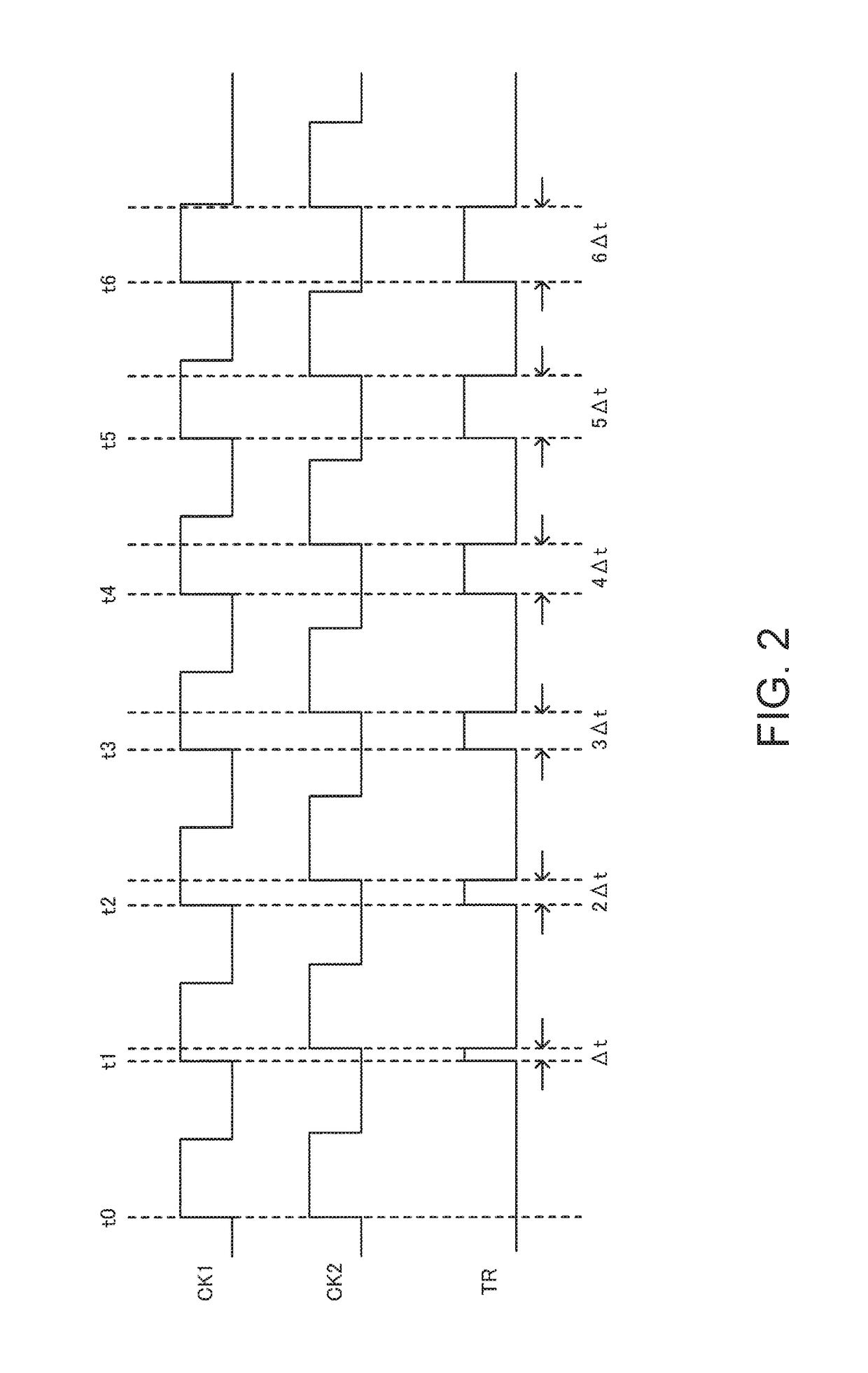

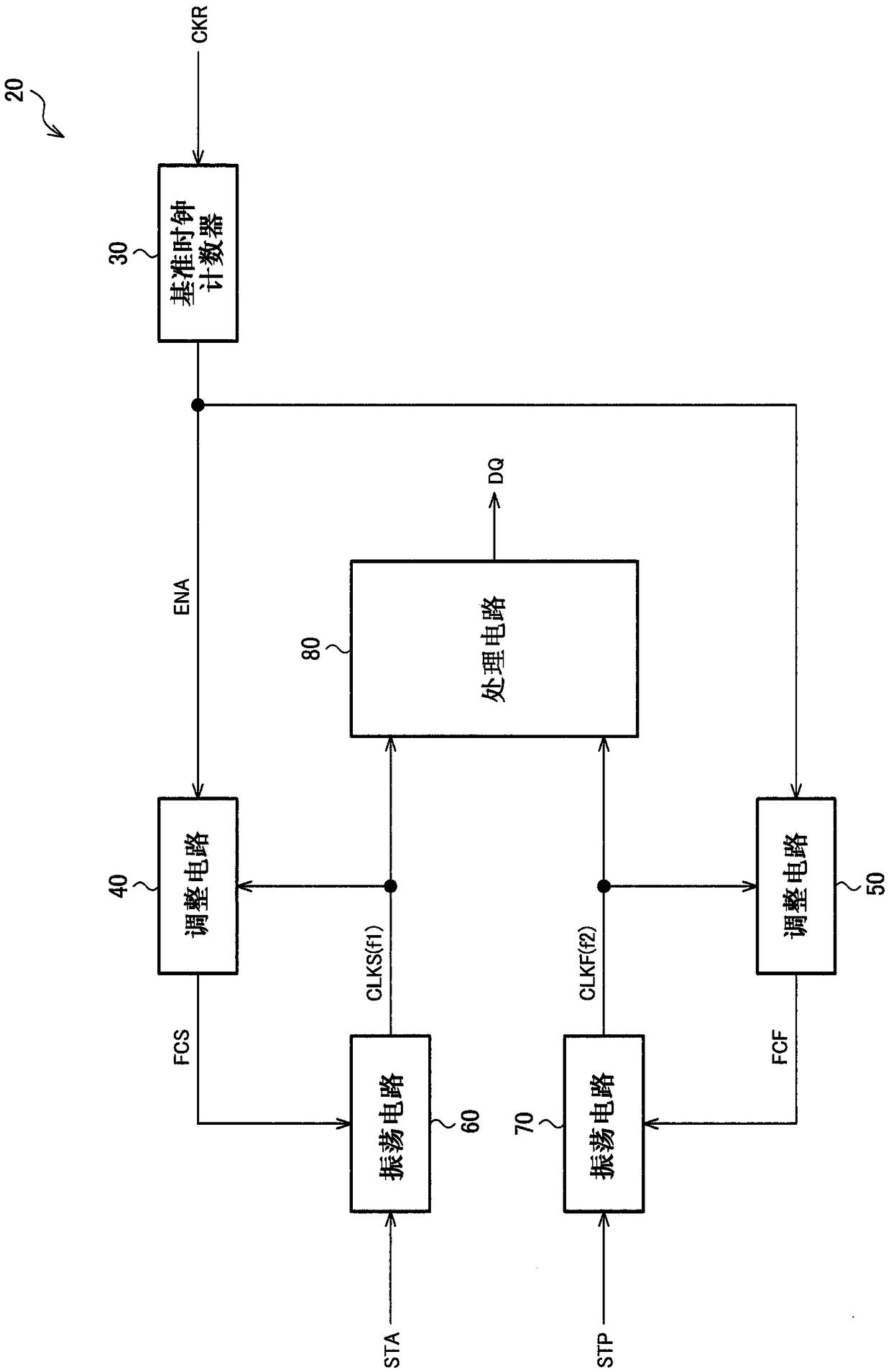

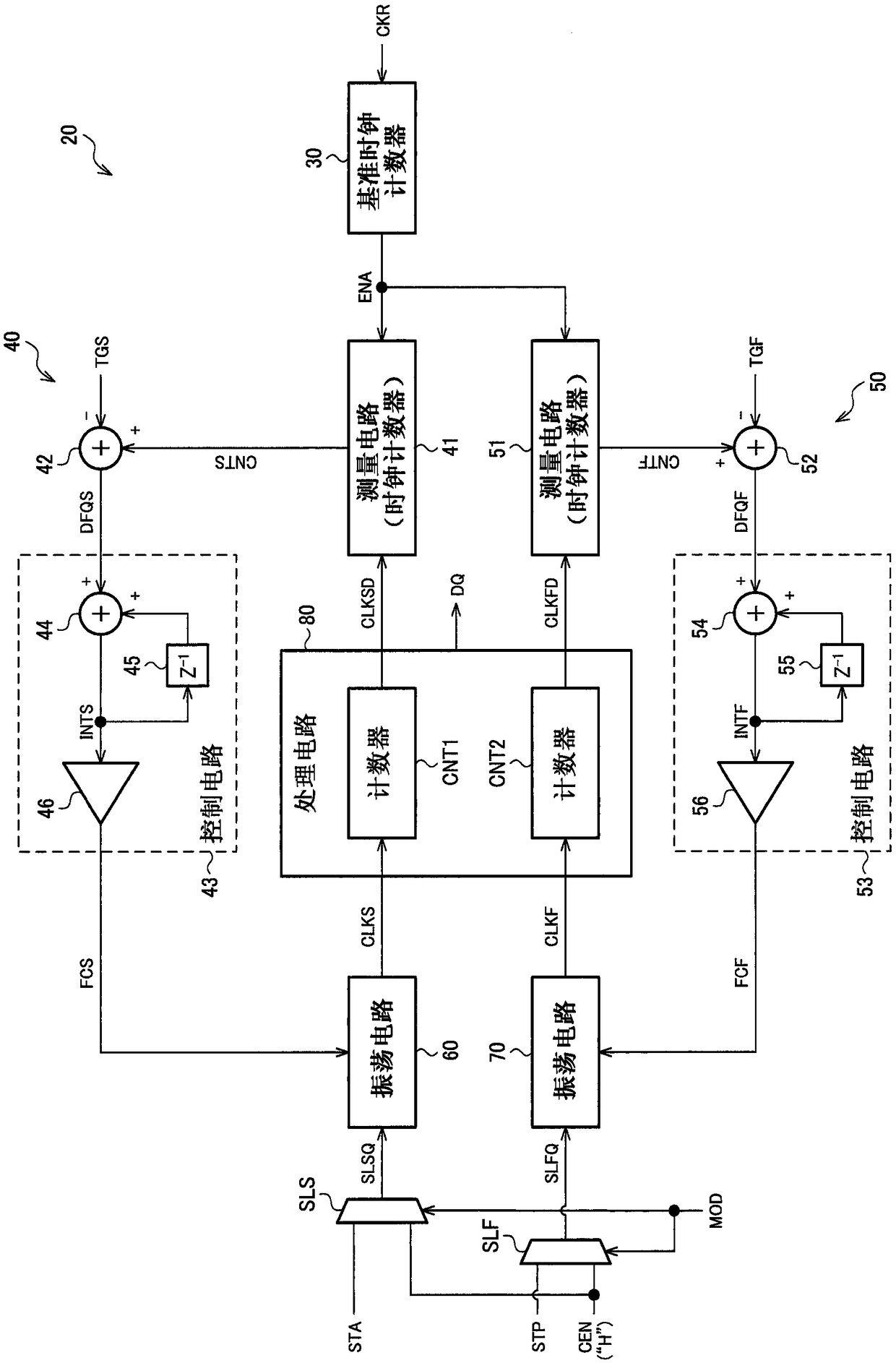

Time-To-Digital Conversion unit, Circuit Device, Physical Quantity Measurement Apparatus, Electronic Instrument, And Vehicle

The invention provides a time-to-digital conversion unit, a circuit device, a physical quantity measurement apparatus, an electronic instrument, and a vehicle, being able to realize high performance of the time-to-digital conversion circuit. The time-to-digital conversion circuit includes a first oscillation circuit that starts oscillating at the transition timing of a first signal and generates afirst clock signal having a first clock frequency, a second oscillation circuit that starts oscillating at the transition timing of a second signal and generates a second clock signal having a secondclock frequency, a first adjustment circuit that adjusts the oscillation frequency of the first oscillation circuit based on a reference clock signal, a second adjustment circuit that adjusts the oscillation frequency of the second oscillation circuit based on the reference clock signal, and a processing circuit that converts the time difference between the transition timing of the first signal and the transition timing of the second signal into a digital value based on the first and second clock signals.

Owner:SEIKO EPSON CORP