Dual-loop DLL-based three-segment type high-precision time-to-digital conversion method and circuit

A time-to-digital conversion, three-stage technology, applied in the direction of analog/digital conversion, code conversion, electrical components, etc., can solve the problems of TDC time resolution limitation, etc., to achieve extended measurement range, high measurement resolution, and high detection accuracy Effect

Inactive Publication Date: 2015-01-28

SOUTHEAST UNIV

View PDF5 Cites 27 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

For the traditional two-stage TDC structure, due to area and process limitations, the TDC time resolution is limited within a specific range

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment

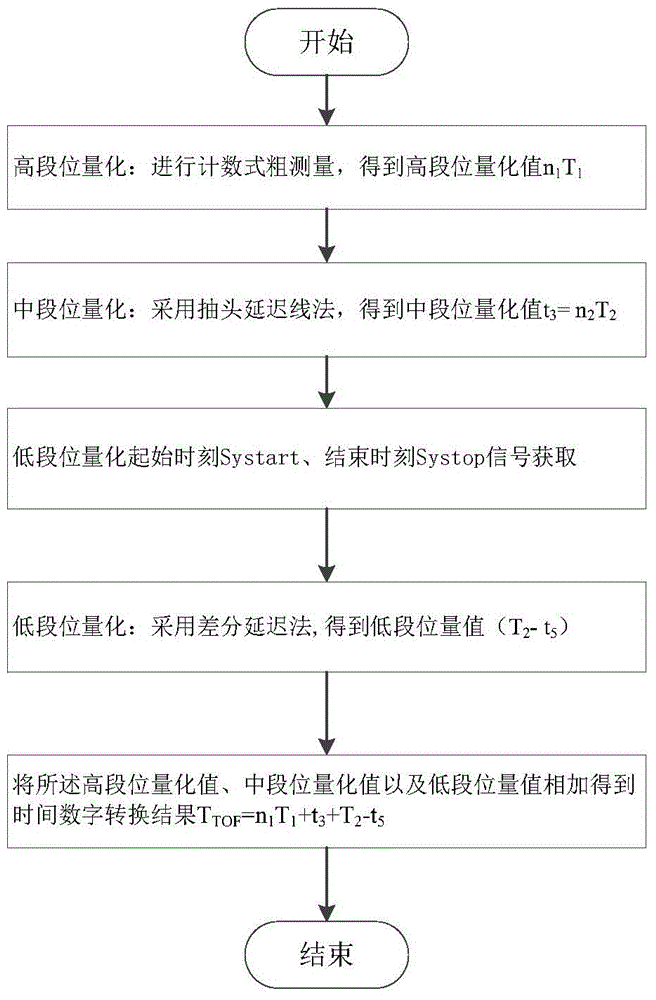

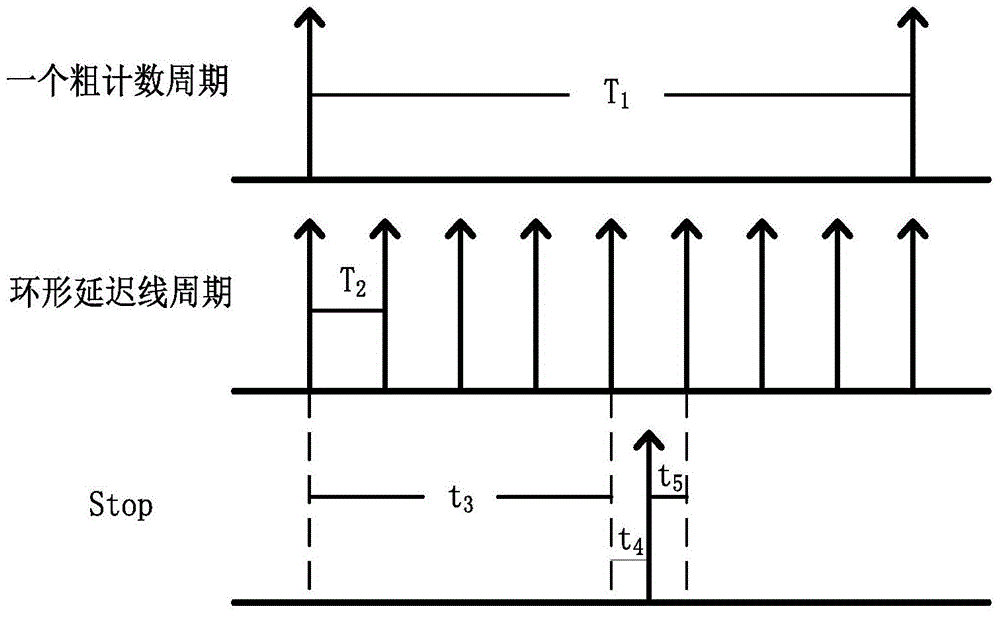

[0036] Embodiment: a kind of three-stage high-precision time-to-digital conversion method based on double-loop DLL, such as figure 1 , figure 2 shown, including the following steps:

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

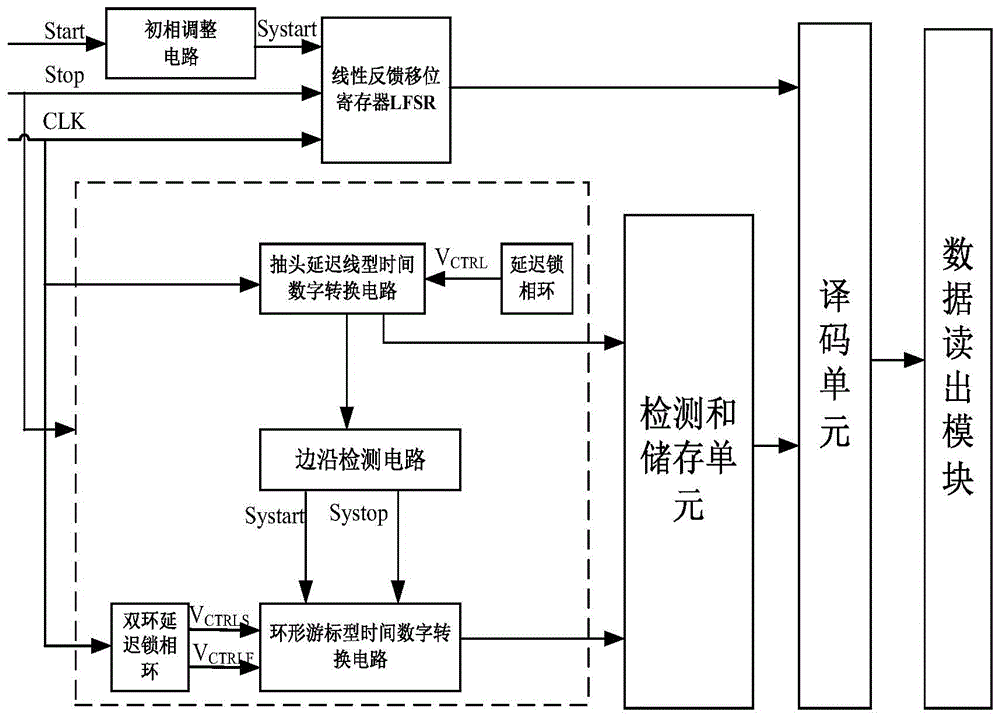

The invention discloses a dual-loop DLL-based three-segment type high-precision time-to-digital conversion method and circuit. According to a measured time segment, a high-middle-low combined segmental type quantization method is adopted. A high-segment bit counting type quantizer in three-segment type TDC (time-to-digital conversion) is driven by a high-frequency stabilizing clock which is inputted from the outside, so that a wide-range stable distance measuring range can be realized; a middle-segment bit TDC is formed by a first DLL voltage controlled delay chain; high-segment bit subdivision can be realized through an asynchronous sampling mode, and repeatable uniform phase distinguishing can be accomplished in a stable clock period; a phase position at a termination time point is decoded, so that a middle-segment quantization function can be accomplished; and according to quantization errors generated by time-to-digital conversion in a middle-segment bit, error time is extracted, a low-segment bit accomplishes further quantization processing, and therefore, higher measurement precision can be realized.

Description

technical field [0001] The invention relates to a time-to-digital conversion method and a circuit thereof, in particular to a three-stage wide dynamic range time-to-digital conversion method and a circuit thereof. Background technique [0002] The time-to-digital conversion (Time-to-Digital Converter, TDC) circuit is a circuit that converts a continuous period of time in the analog domain into a digital signal, and uses a digital integrated circuit to compare the signal between the Start signal at the start time and the Stop signal at the end time in the time domain. The processing of the time signal to be detected, and then realize the digital processing of the time signal, and finally obtain the digital output. The National Academy of Sciences of the United States has regarded TDC technology as one of the important symbols for evaluating national defense strength, and listed it as one of the science and technology that the country needs to vigorously develop. The precise ...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): H03L7/08H03M1/50

Inventor 吴金宋科孙东辰畅灵库郑丽霞李超孙伟峰

Owner SOUTHEAST UNIV