Column-level ADC for high-speed linear CMOS image sensor and implement method

A technology of image sensor and implementation method, applied in the electrical field, capable of solving the problems of limiting the readout rate of CMOS image sensors, column-level fixed pattern noise, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

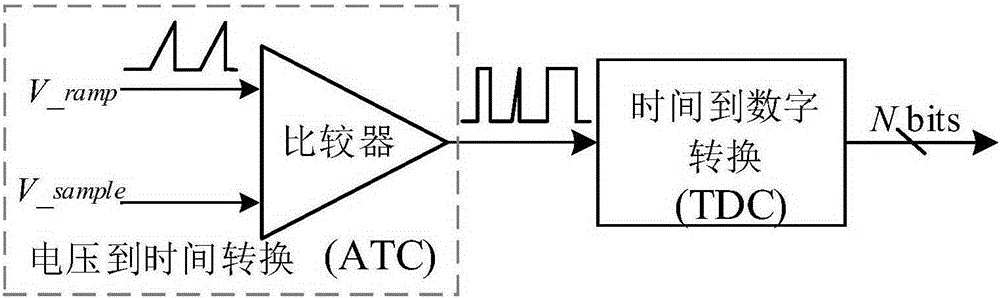

[0028] The basic idea of the present invention is to use time to digital conversion (TDC) technology to divide the conversion process from analog to digital into two parts, figure 1 It is an overall architecture diagram of the present invention. The first part is the analog-to-time conversion (ATC), which consists of a ramp generator and a comparator that converts the input analog voltage into a proportional amount of time. The second part uses TDC to quantify the time interval width to complete the conversion from time to digital.

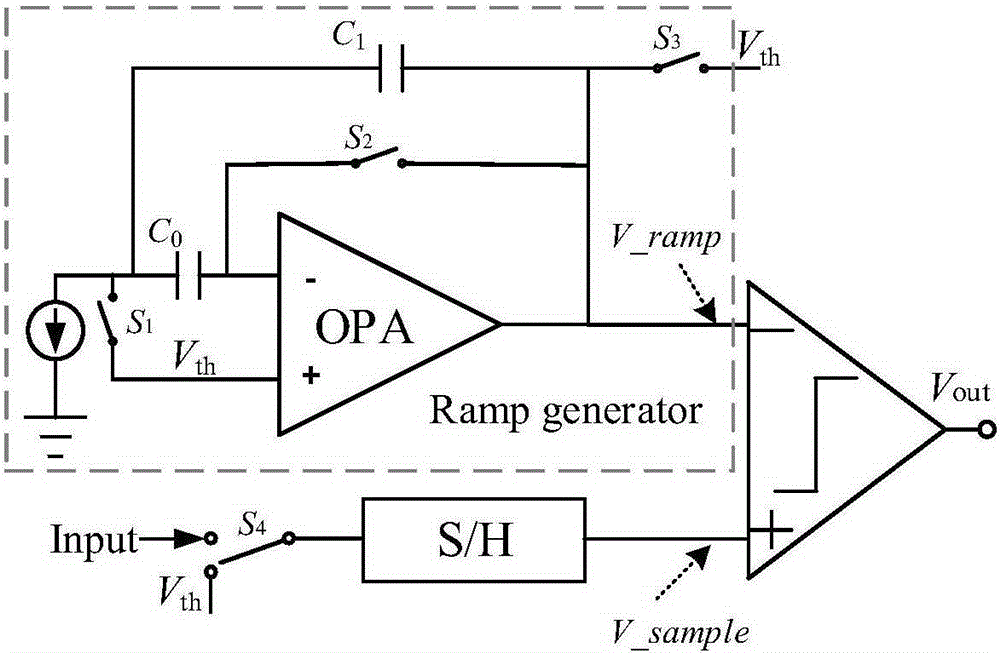

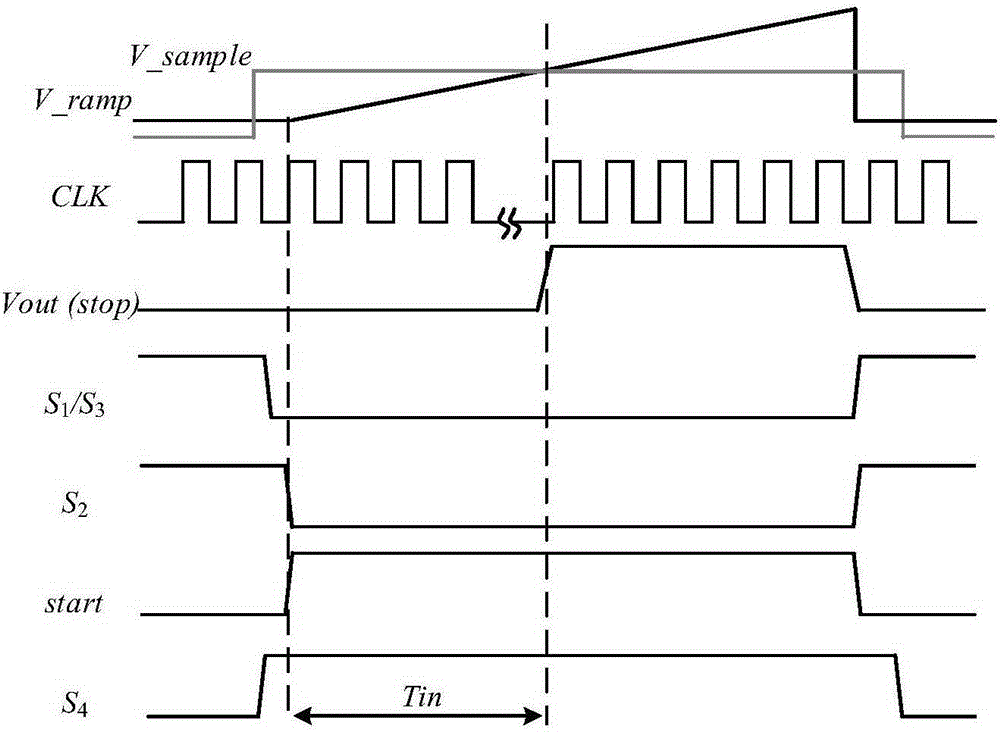

[0029] ATC consists of a ramp generator and a comparator, such as figure 2 As shown, it is used to generate a time signal proportional to the analog input voltage. As the front end of the entire ADC conversion, its linearity will directly affect the conversion accuracy of the entire ADC. In the present invention, in order to improve the linearity, the ramp generator adopts the integration of the current source and the cross-connected capacit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More