Patents

Literature

496results about "Pulse conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

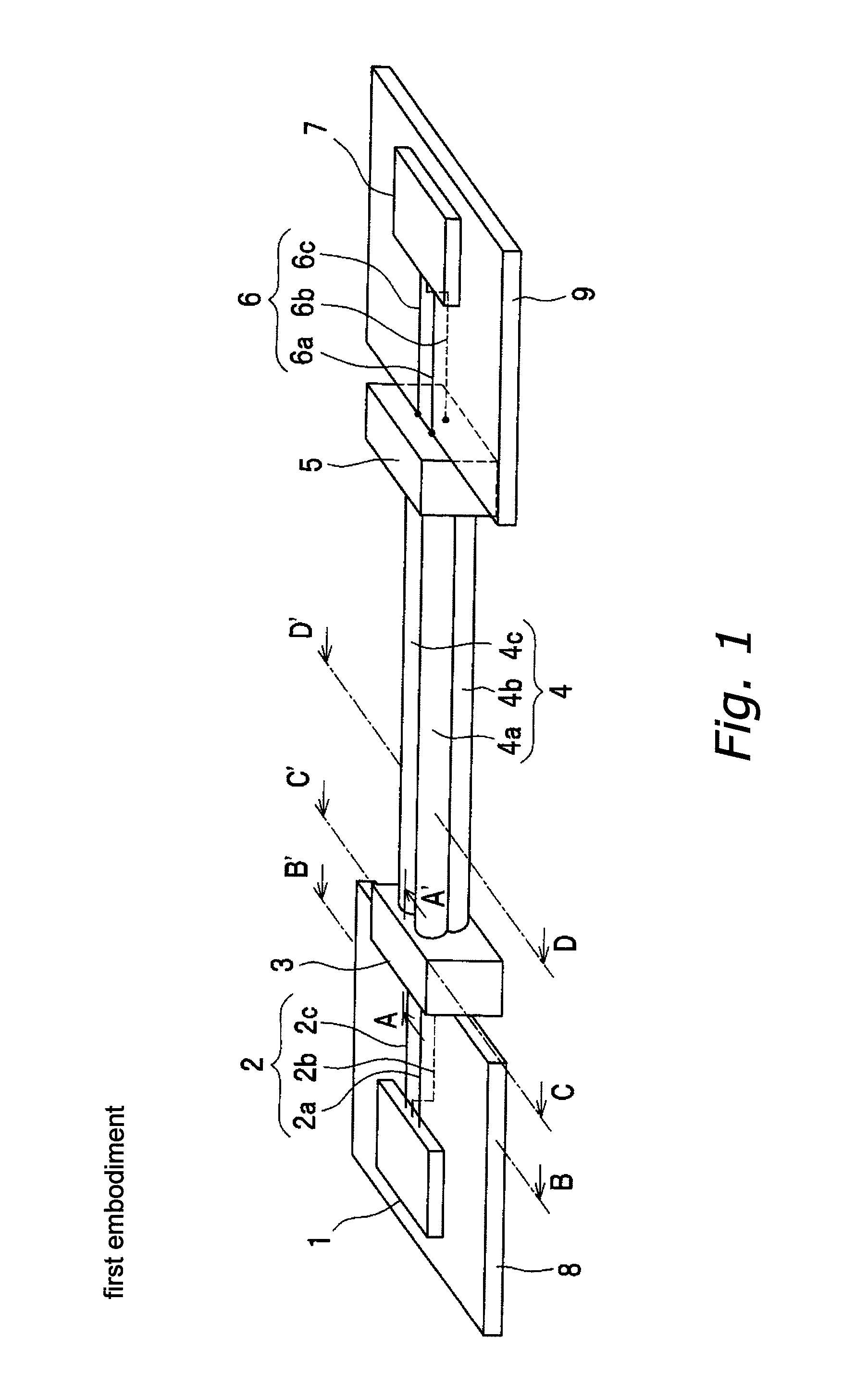

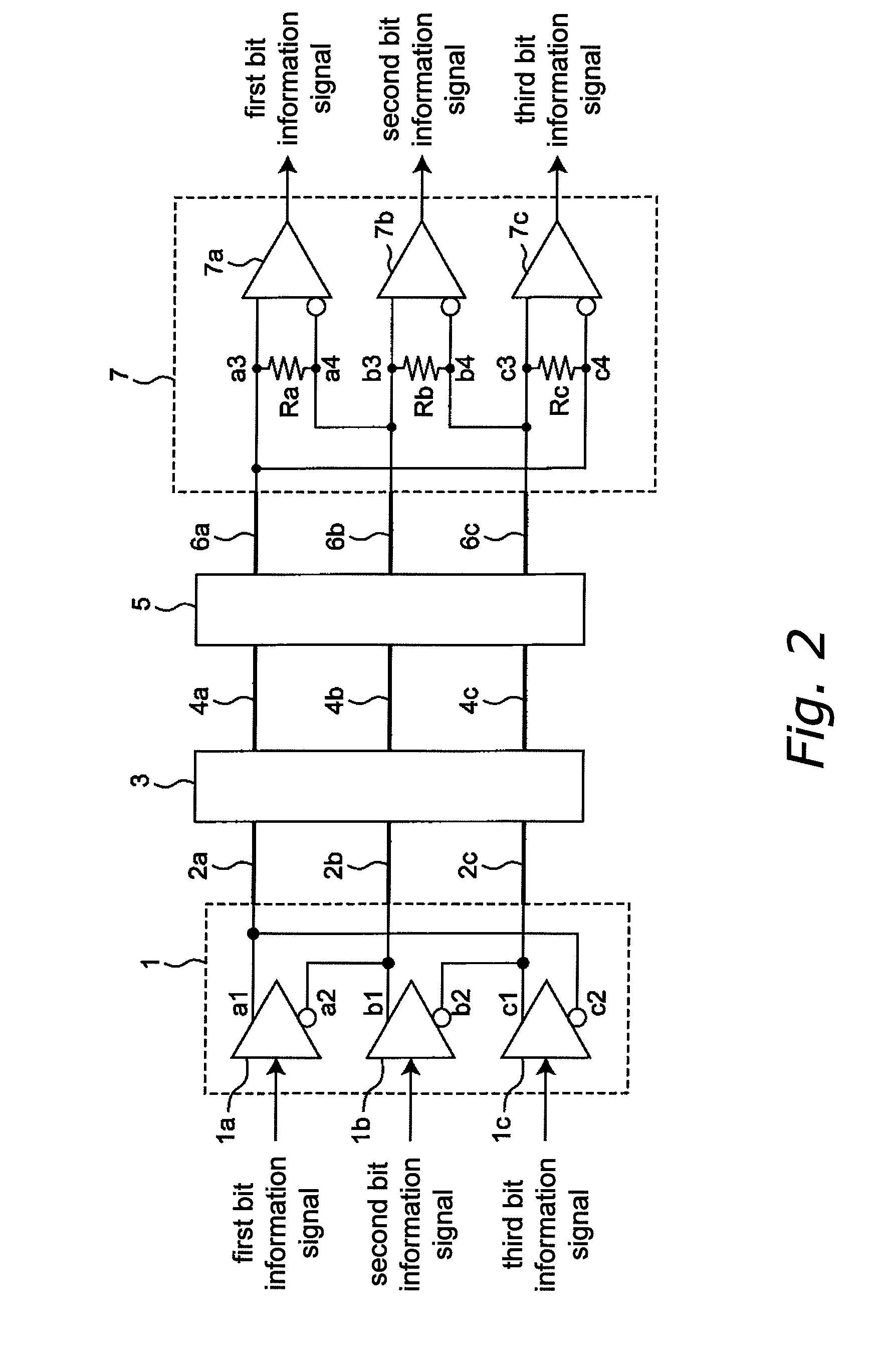

Differential transmission line connector

InactiveUS8027391B2Constant length of the signal linesLittle unwanted radiation noiseCurrent interference reductionCoupling device detailsIsoetes triquetraDifferential signaling

A differential transmission line connector with little unwanted radiation noise is provided. A connector connects a differential transmission pattern for multiple transmission of a group of three differential signals and a differential transmission cable. The differential transmission pattern is provided with three signal lines, and the differential transmission cable also is provided with three signal lines. In a plane that is perpendicular to the longitudinal direction of the differential transmission pattern and the differential transmission cable, the signal lines are positioned at the apexes of an equilateral triangle. The connector is provided with three signal lines that connect, at identical lengths, the signal lines of the differential transmission pattern and the signal lines of the differential transmission cable, between a predetermined first plane of the planes that perpendicularly intersect the longitudinal direction of the differential transmission pattern and a predetermined second plane of the planes that perpendicularly intersect the longitudinal direction of the differential transmission cable.

Owner:PANASONIC CORP

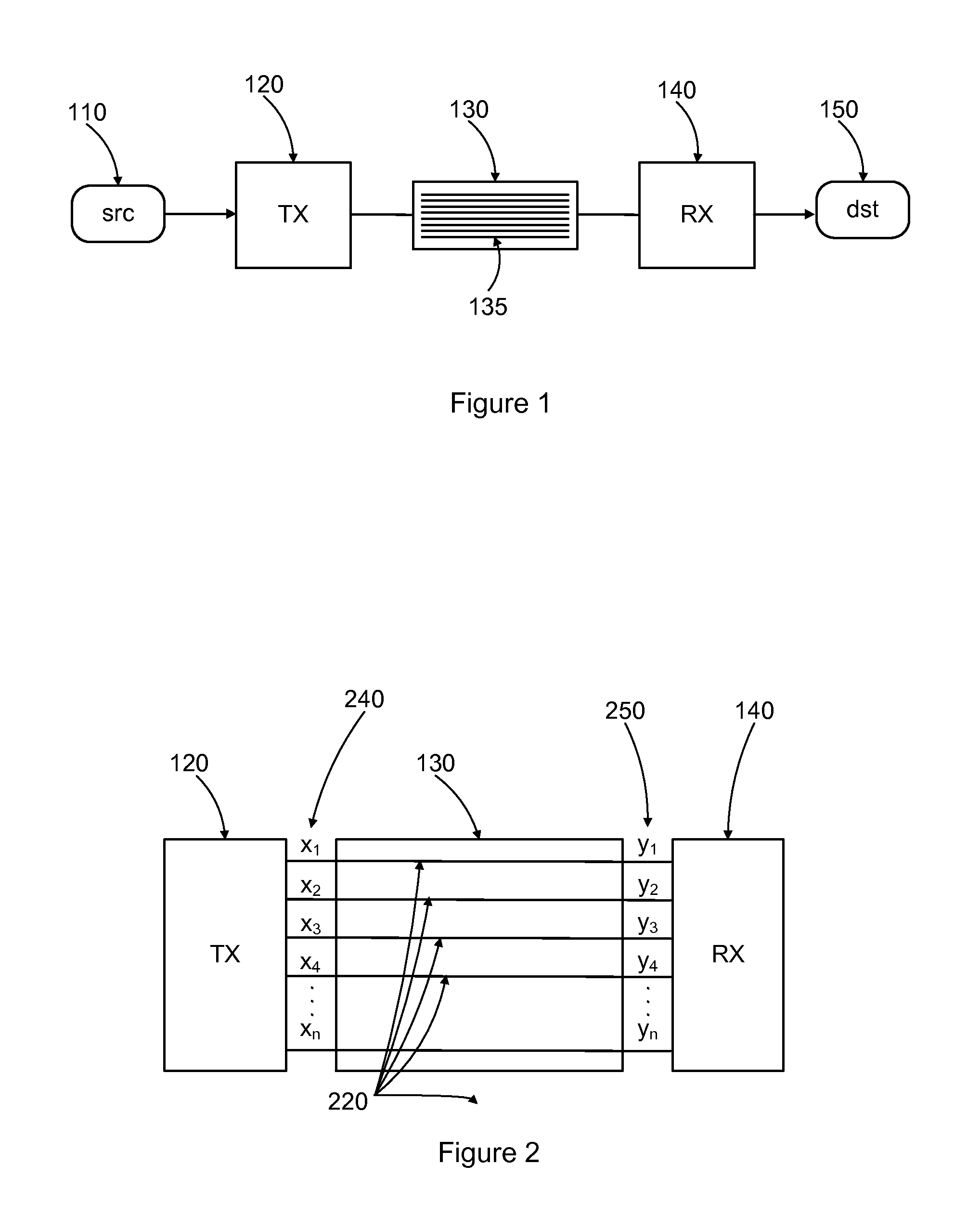

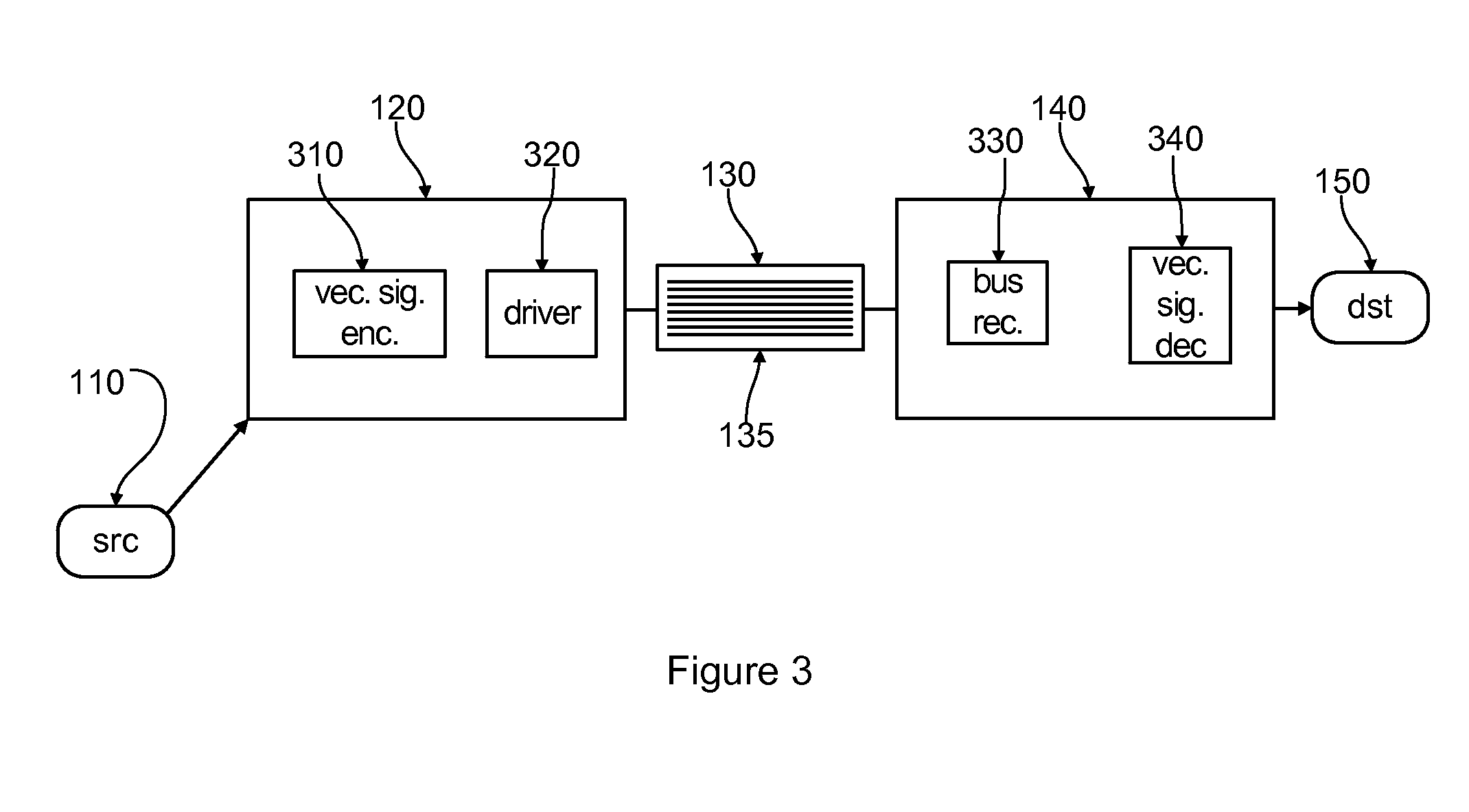

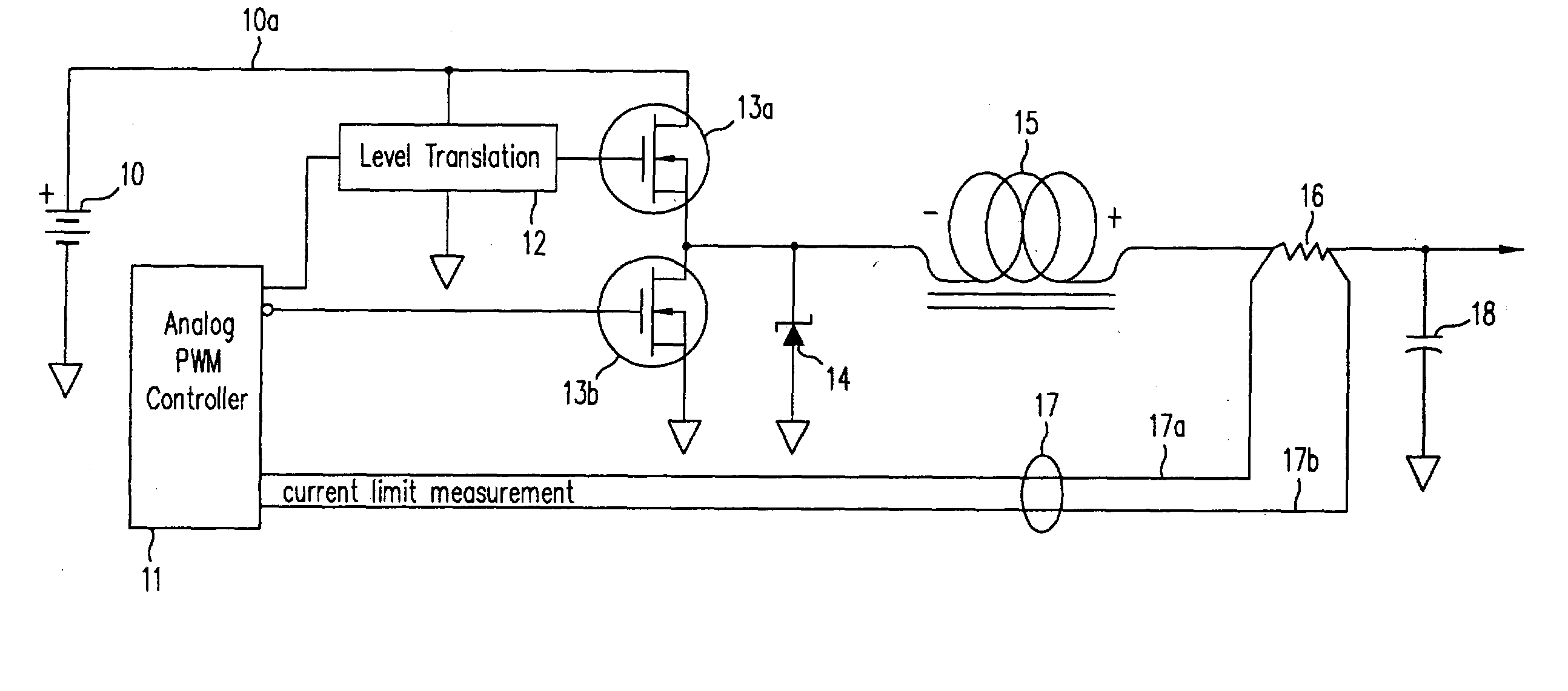

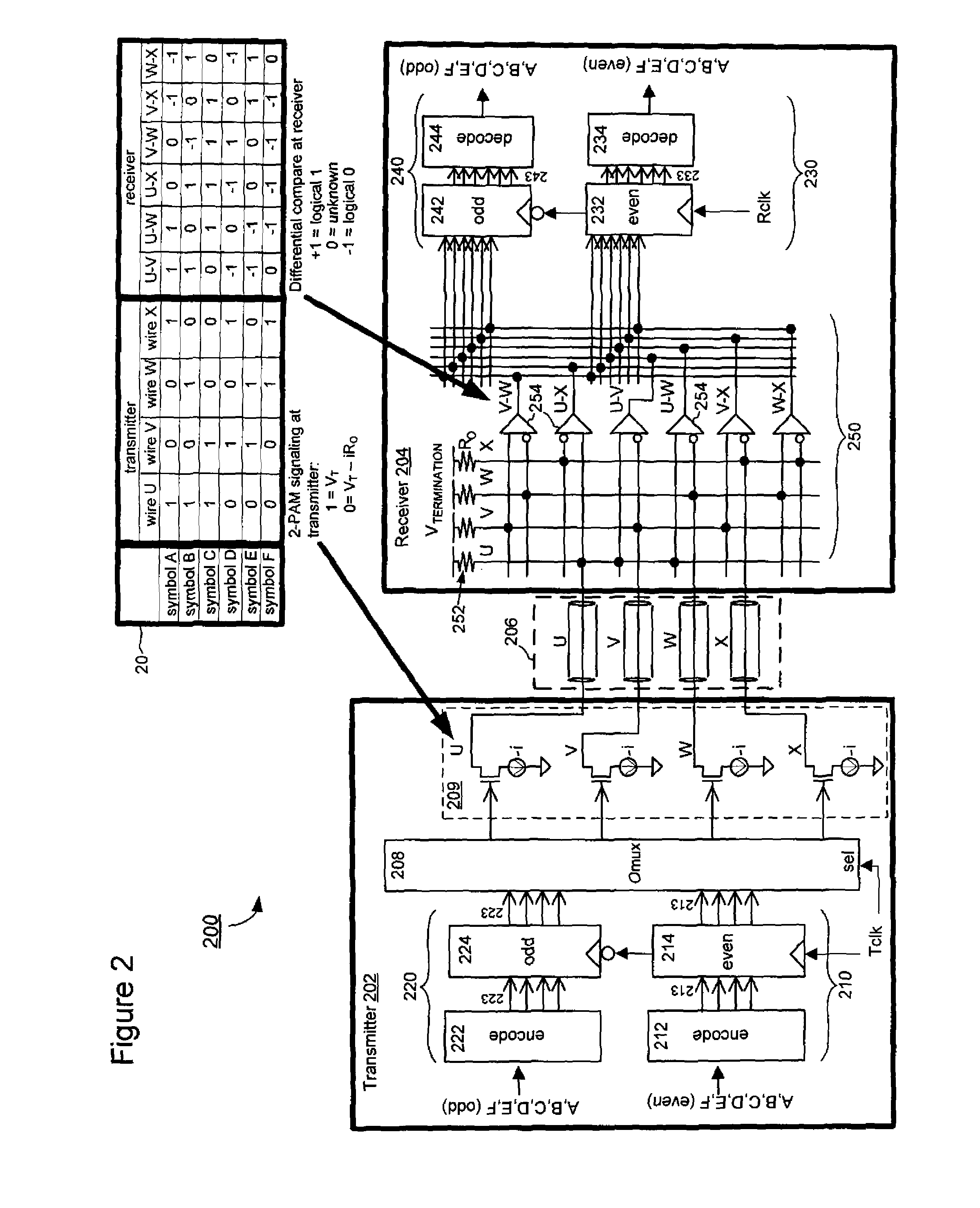

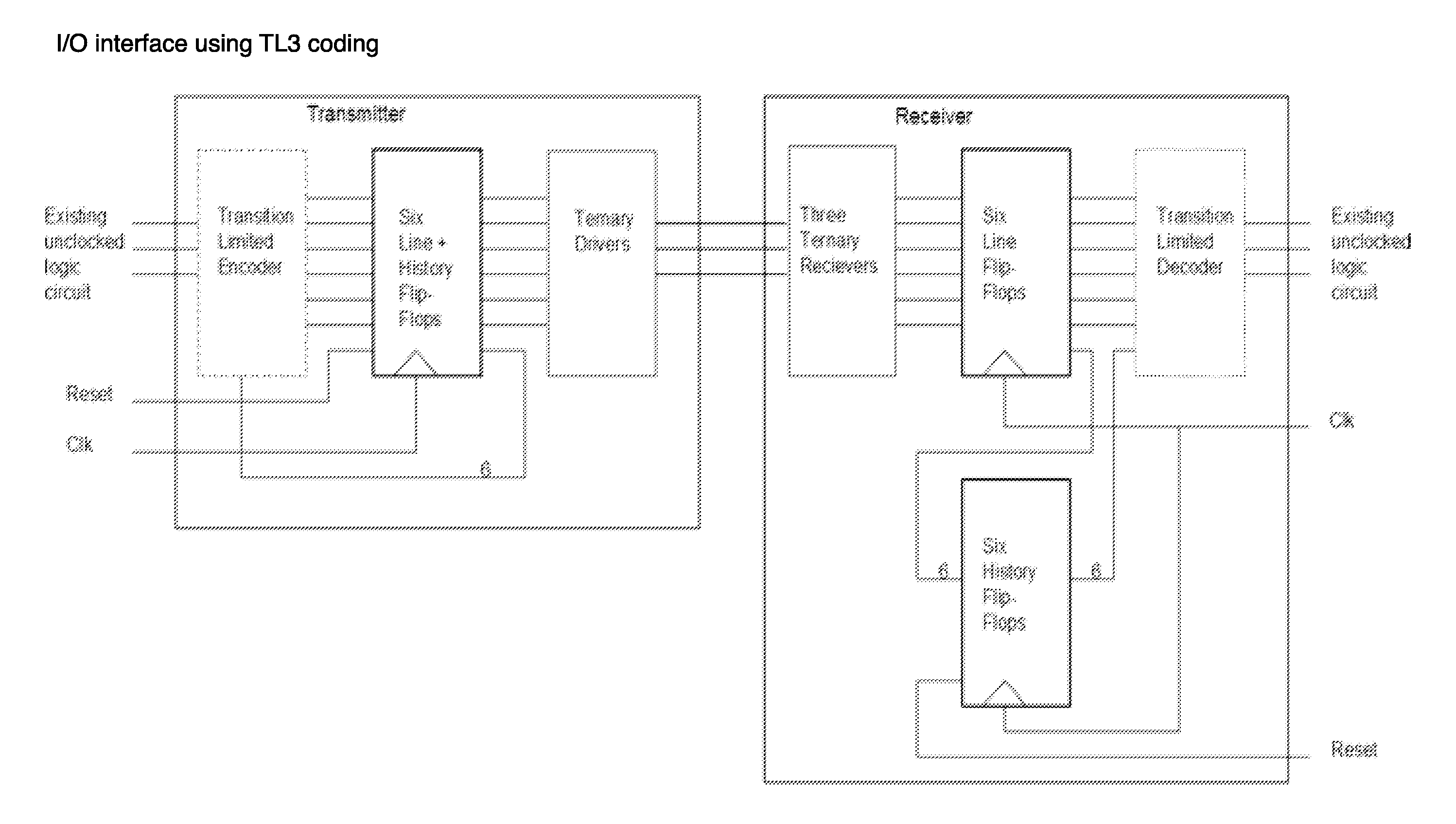

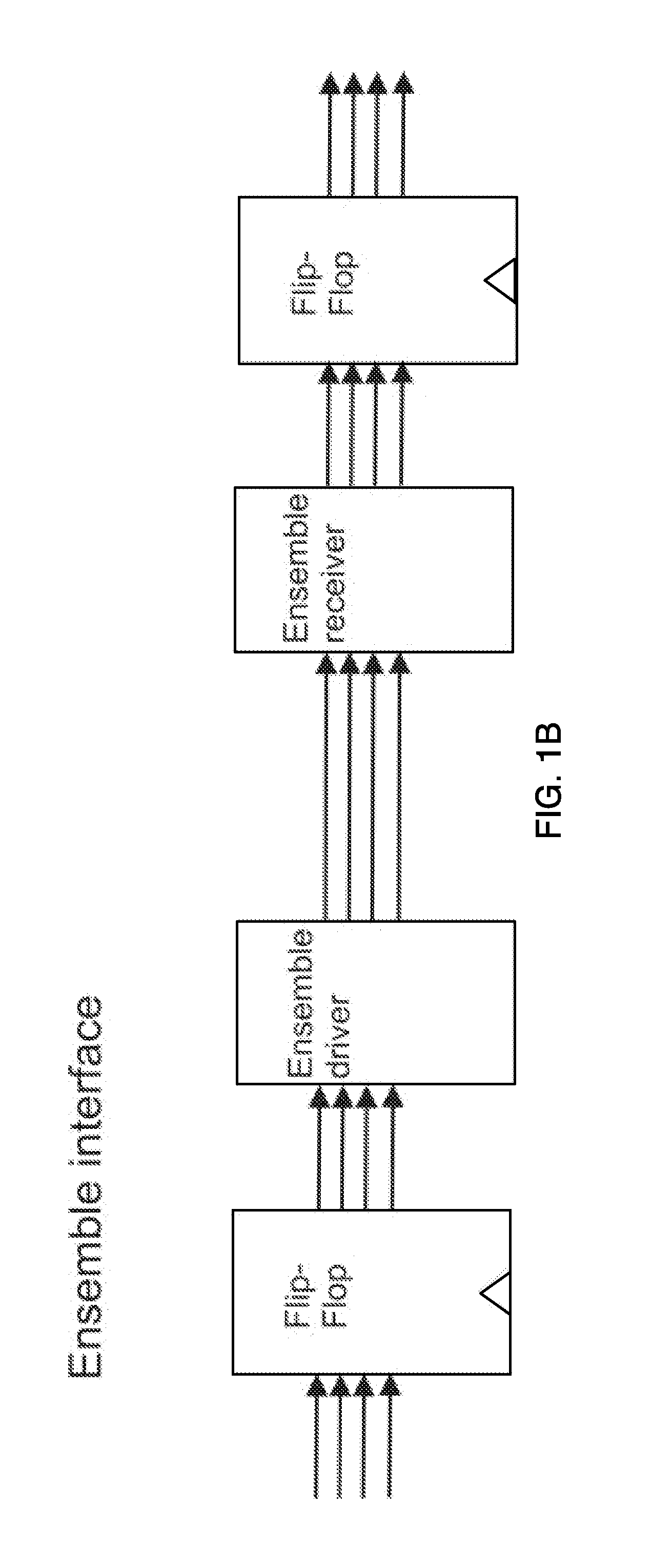

Power and pin efficient chip-to-chip communications with common-mode rejection and sso resilience

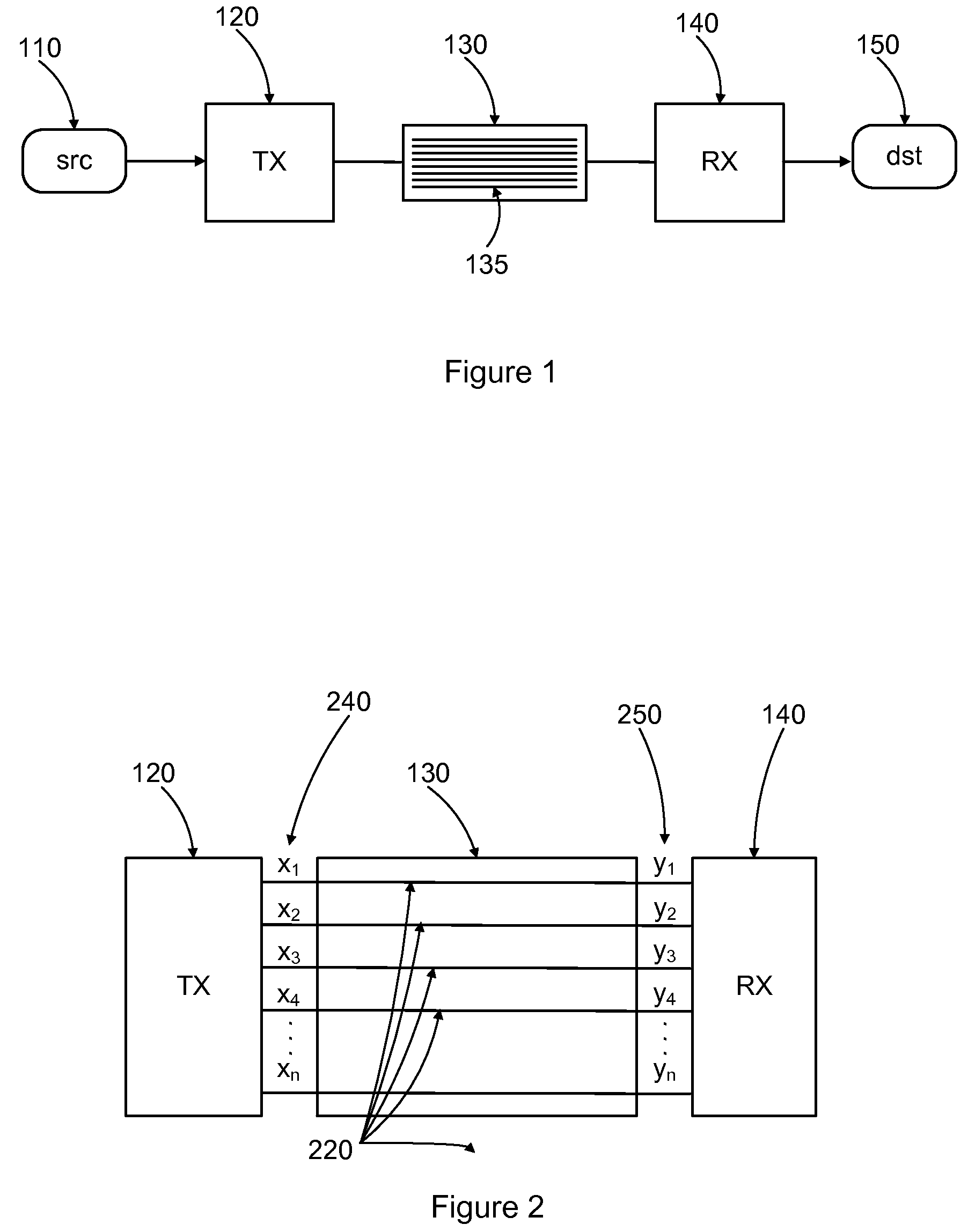

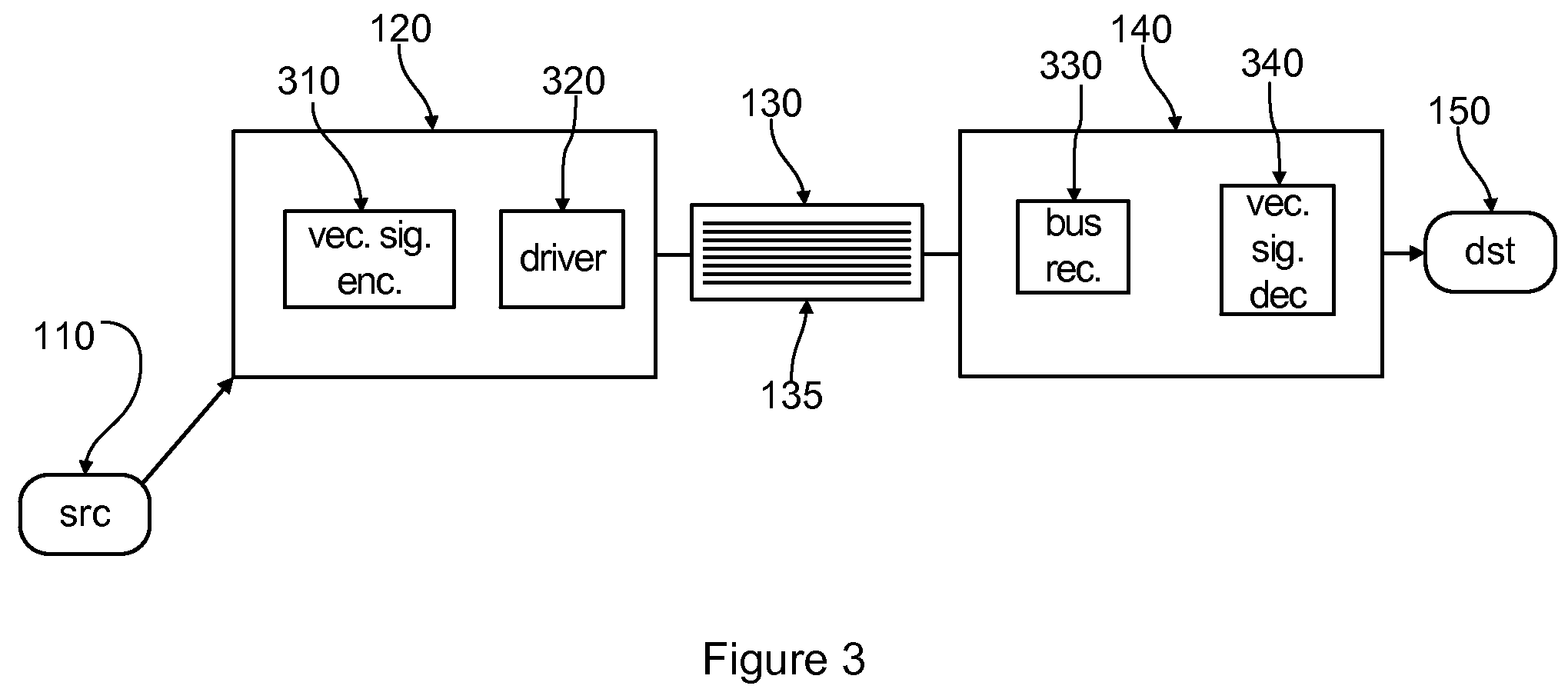

In bus communications methods and apparatus, a first set of physical signals representing the information to be conveyed over the bus is provided, and mapped to a codeword of a spherical code, wherein a codeword is representable as a vector of a plurality of components and the bus uses at least as many signal lines as components of the vector that are used, mapping the codeword to a second set of physical signals, wherein components of the second set of physical signals can have values from a set of component values having at least three distinct values for at least one component, and providing the second set of physical signals for transmission over the data bus in a physical form.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

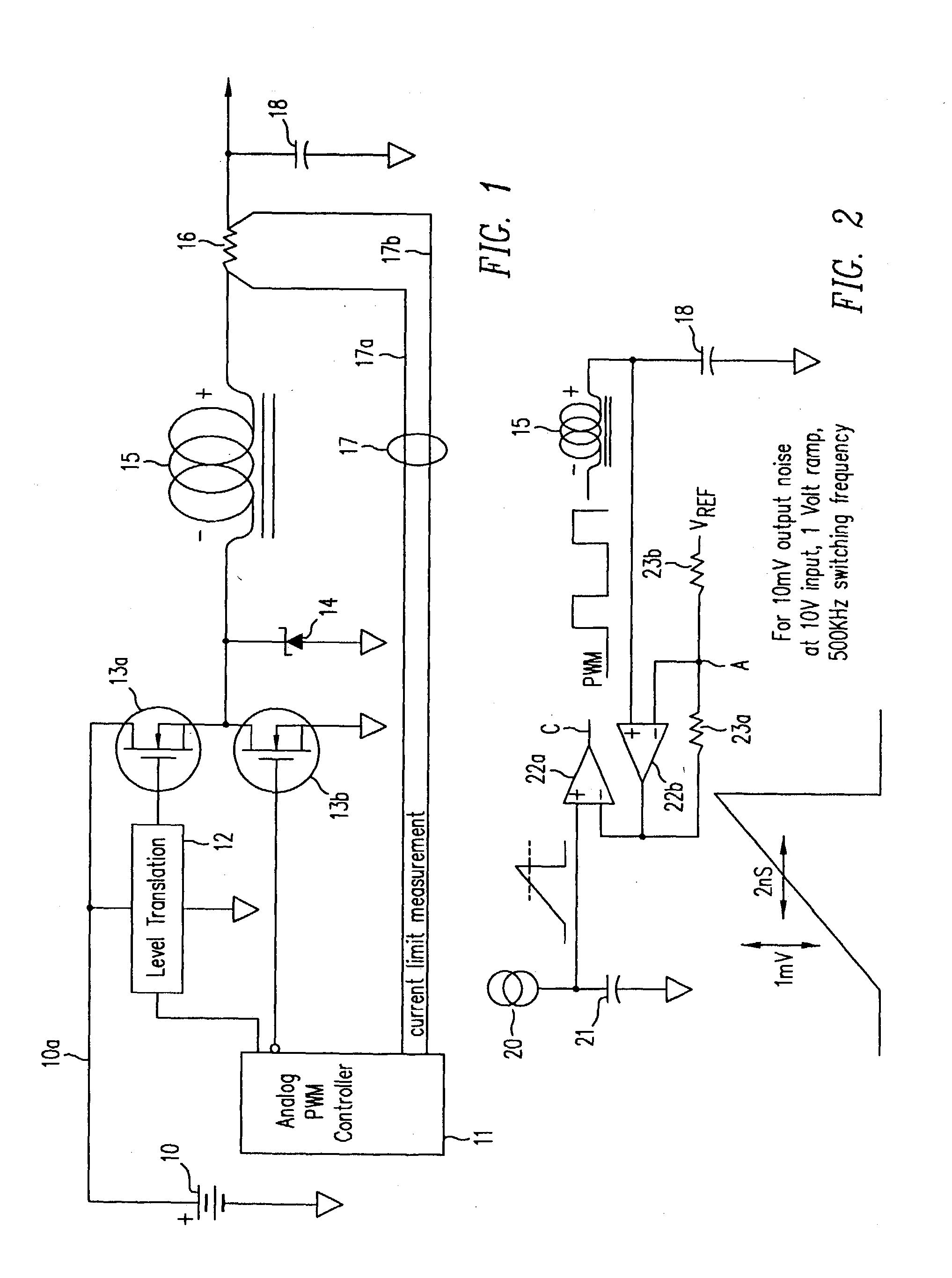

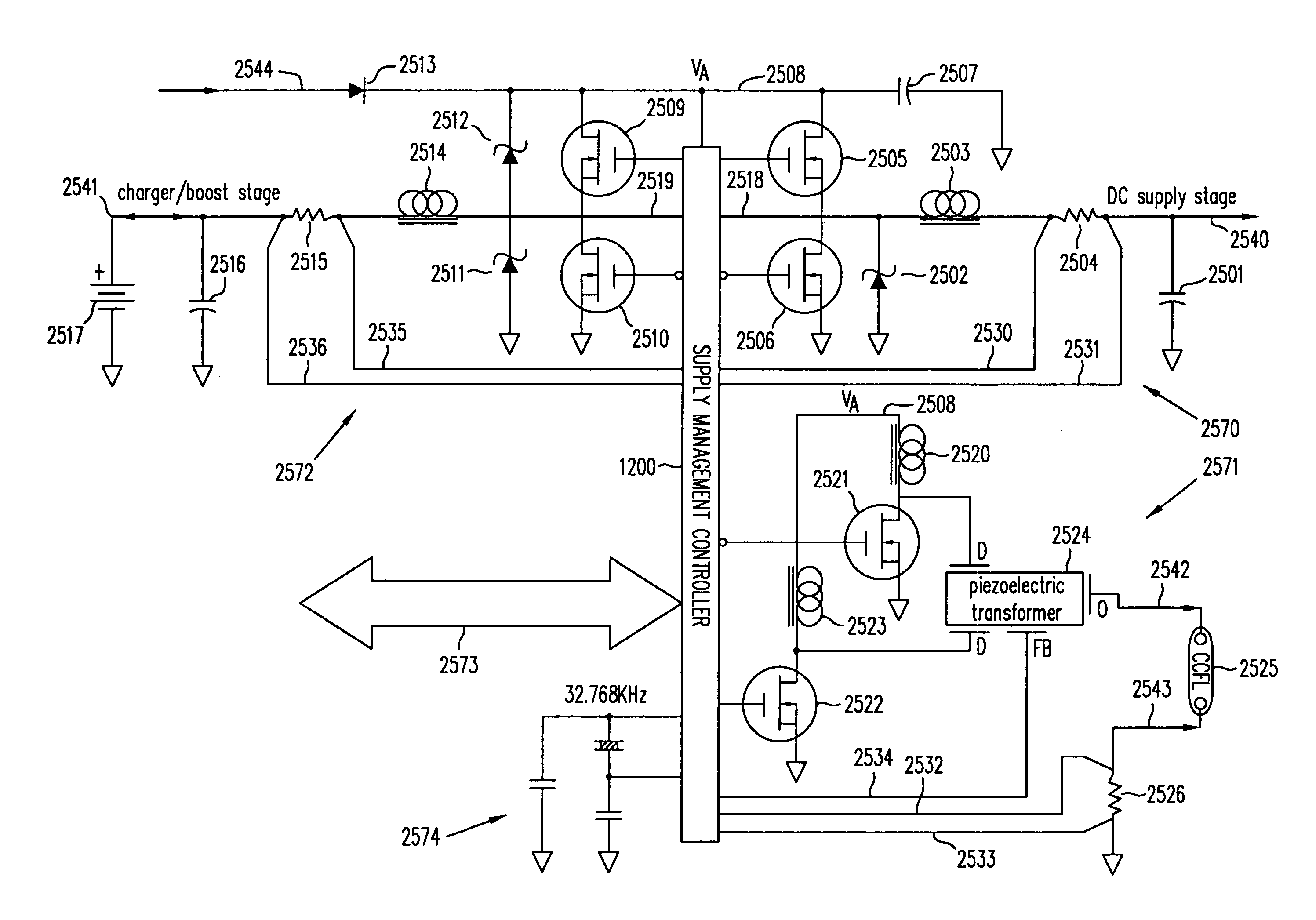

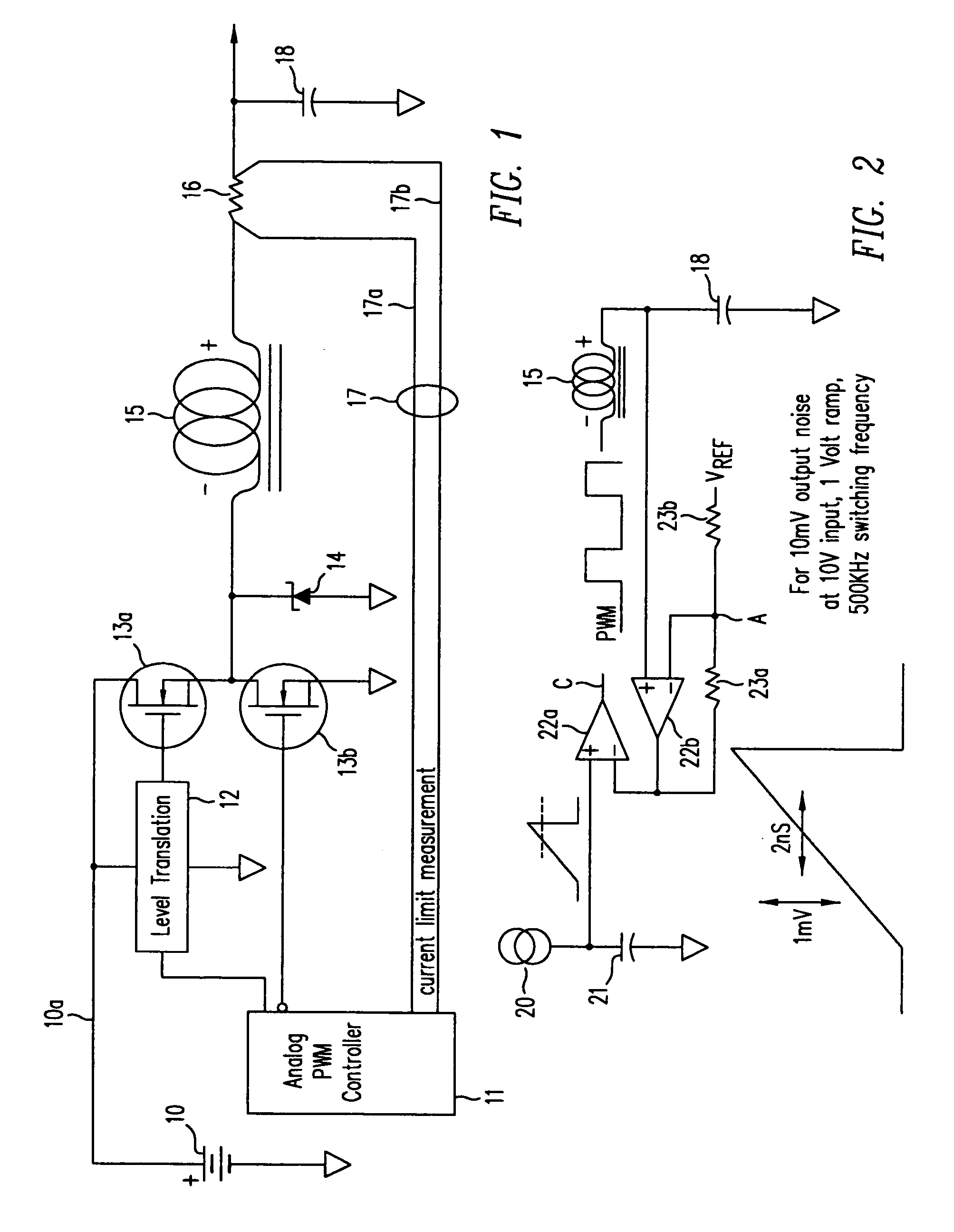

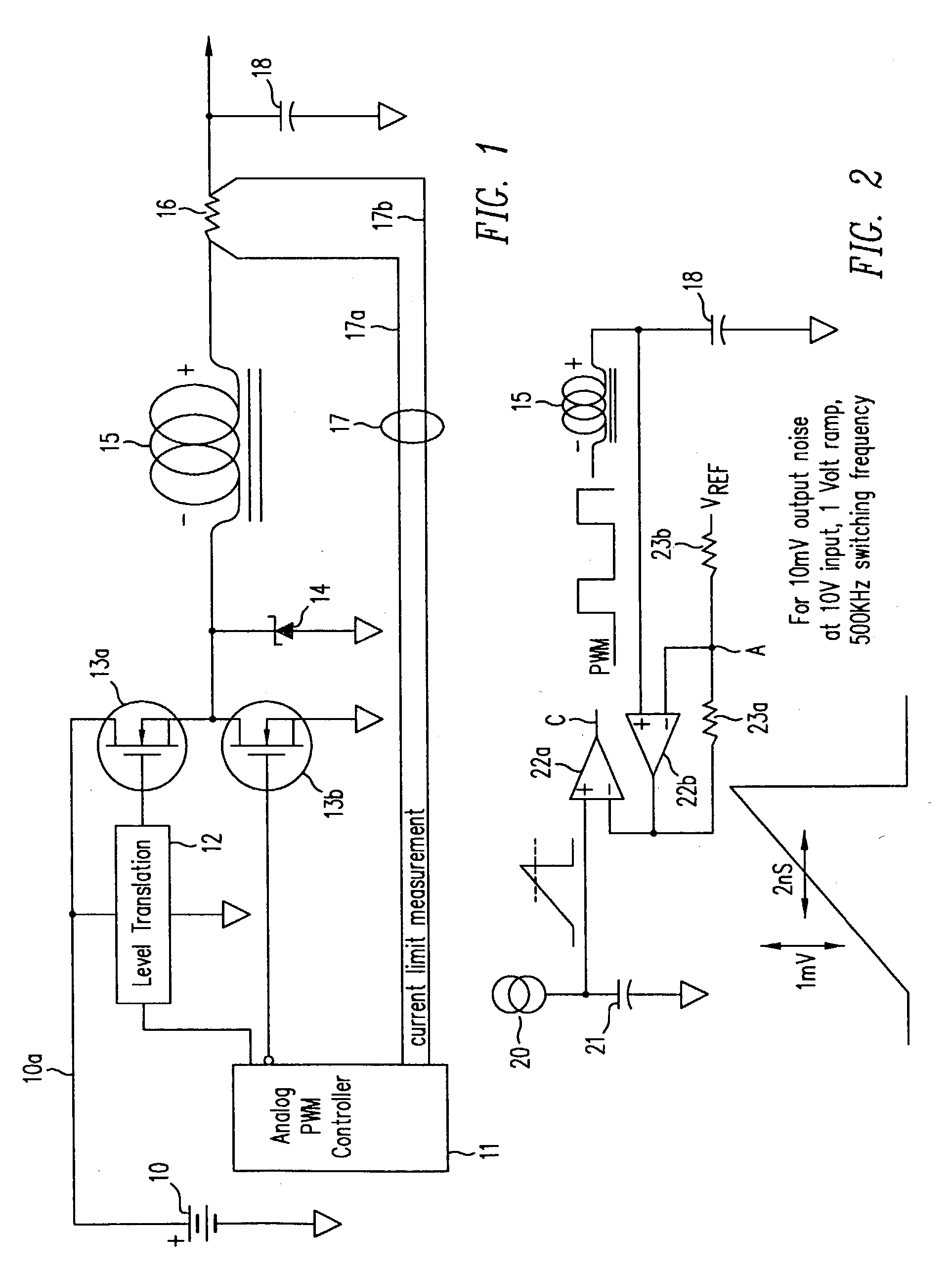

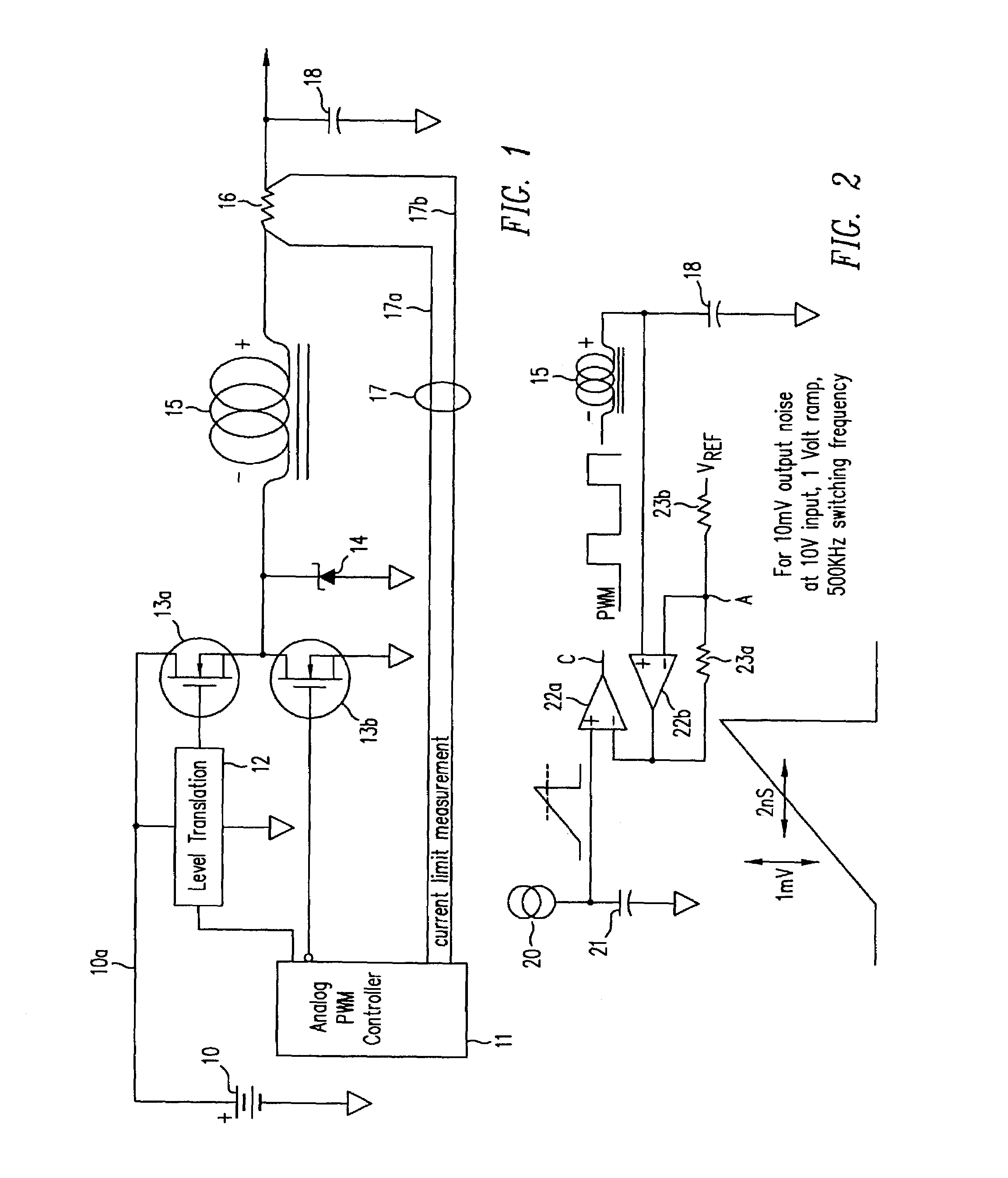

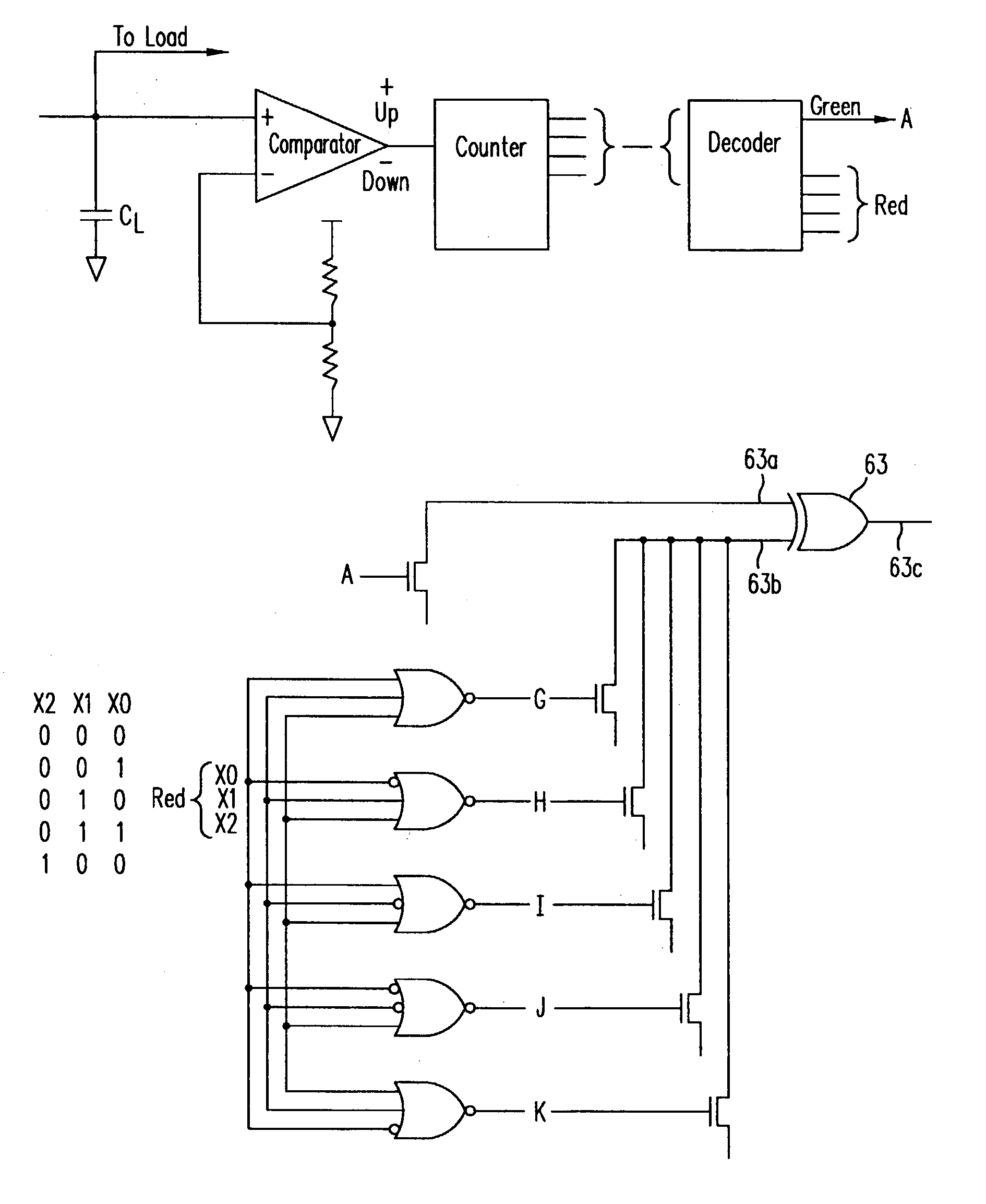

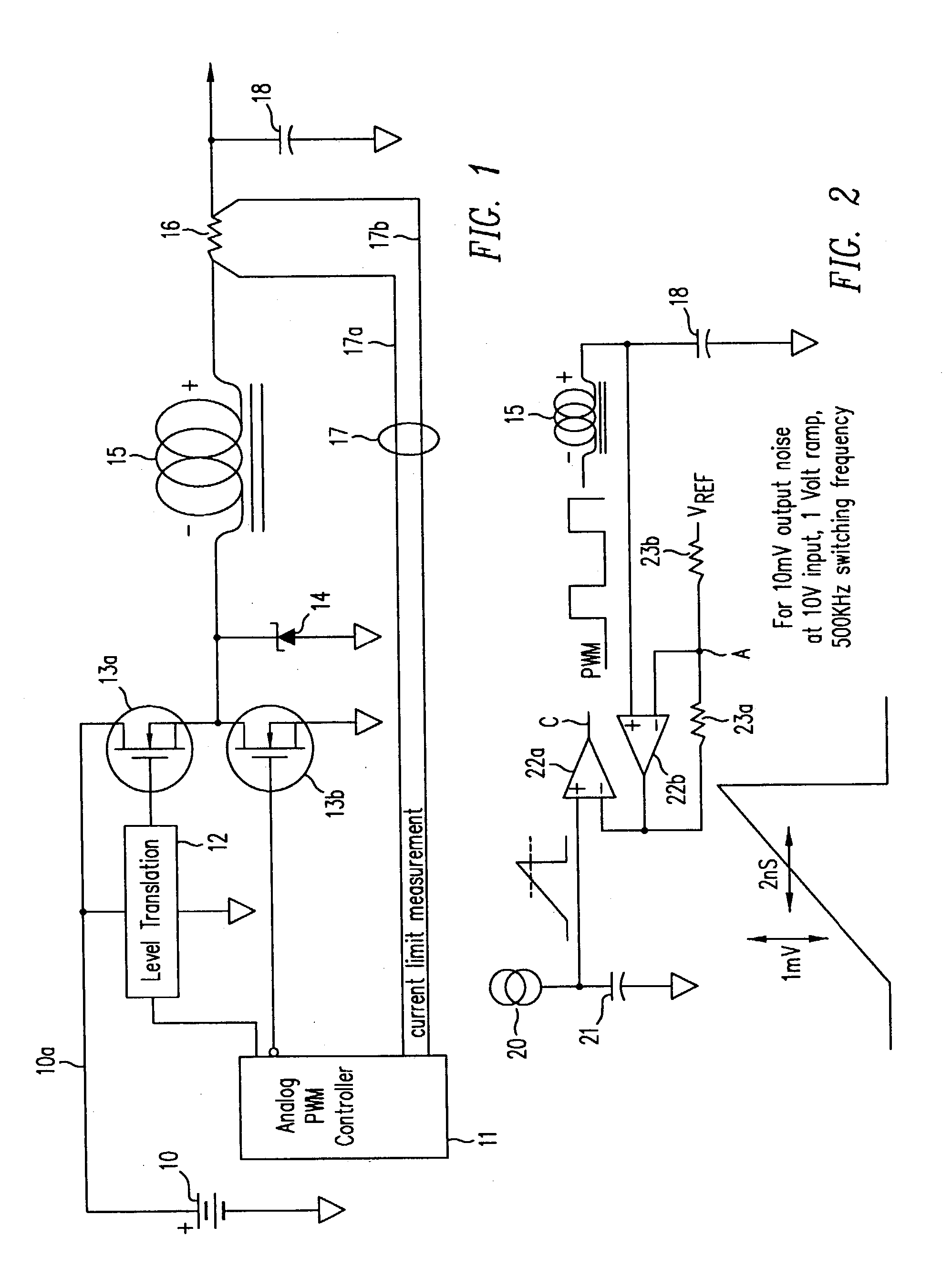

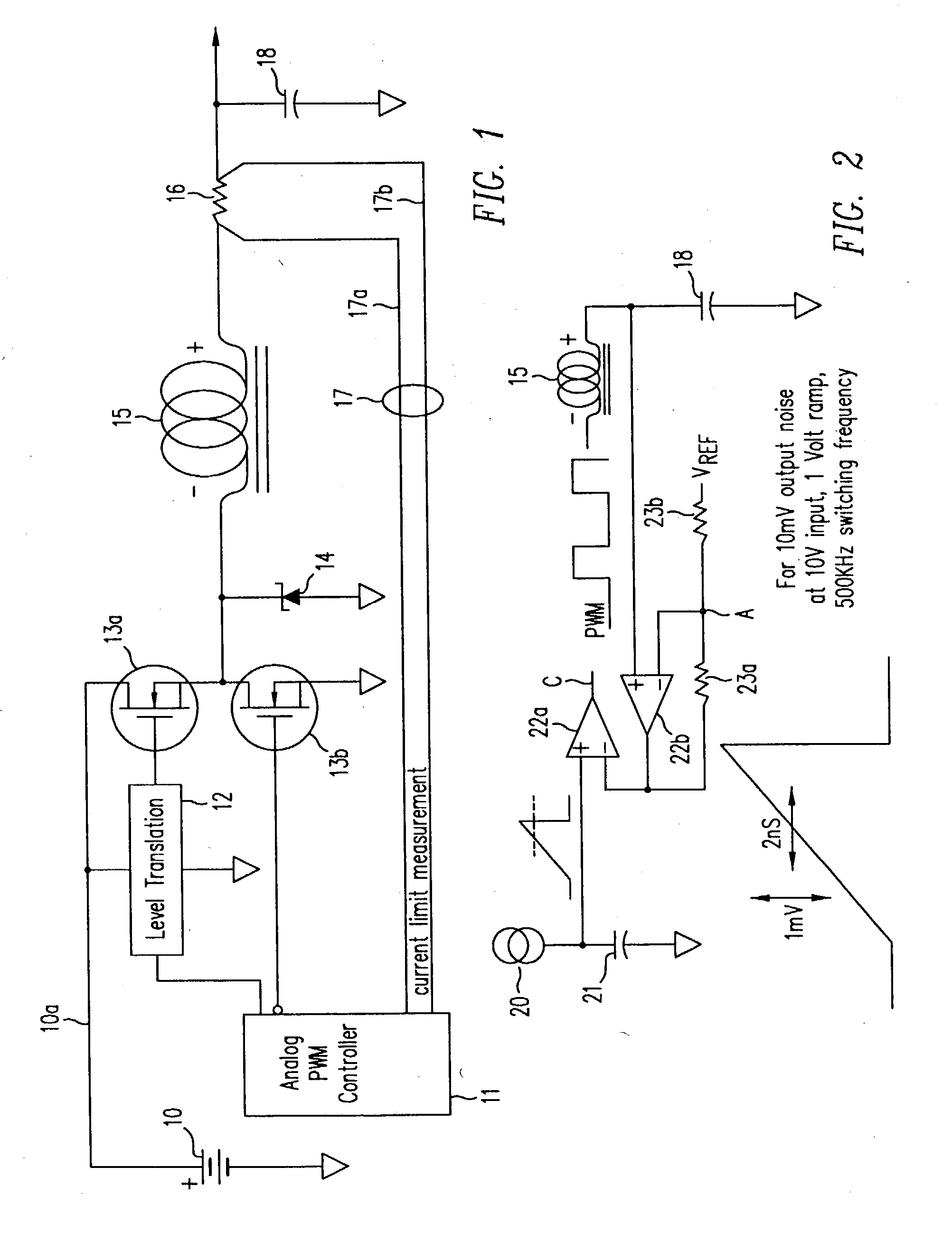

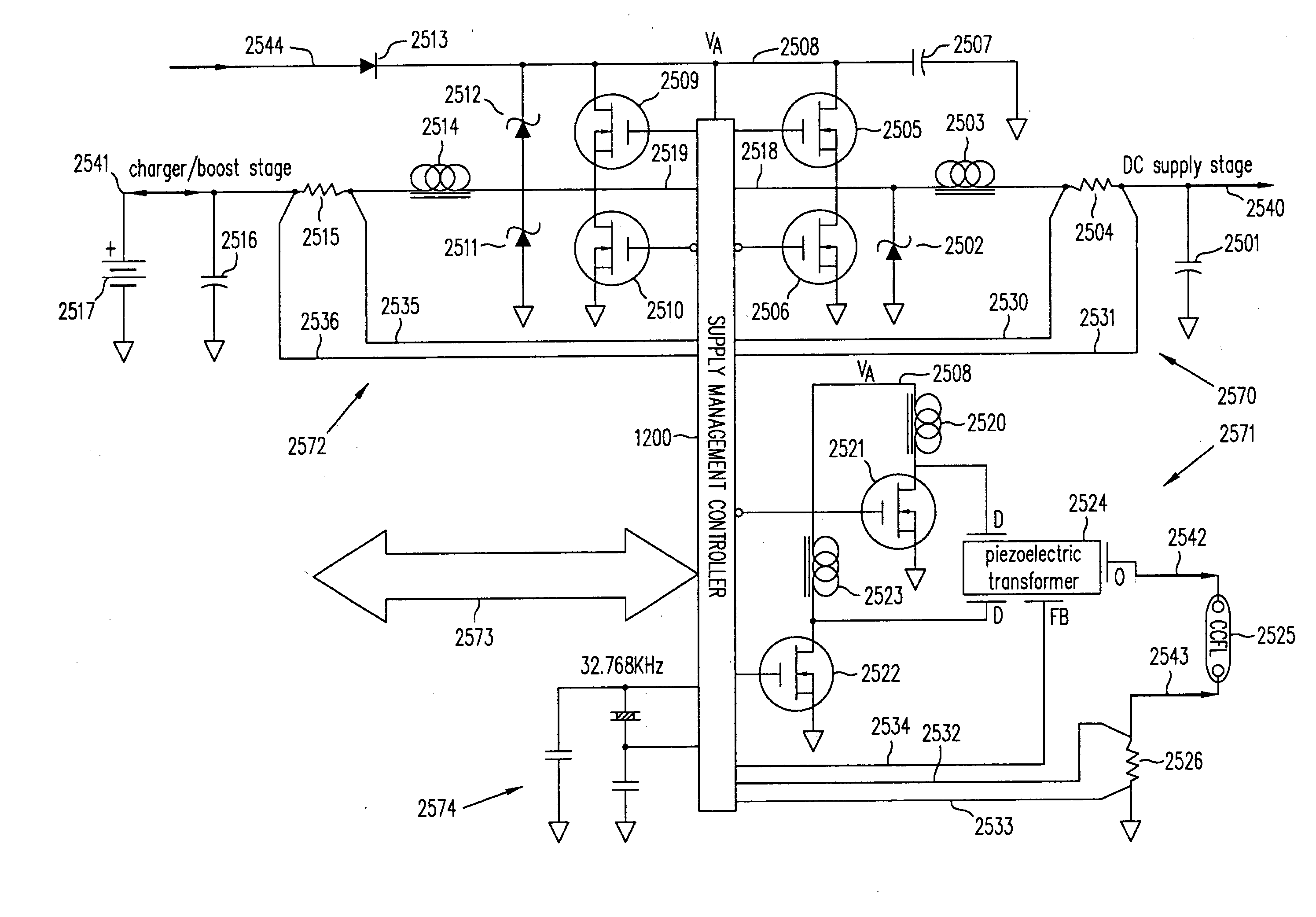

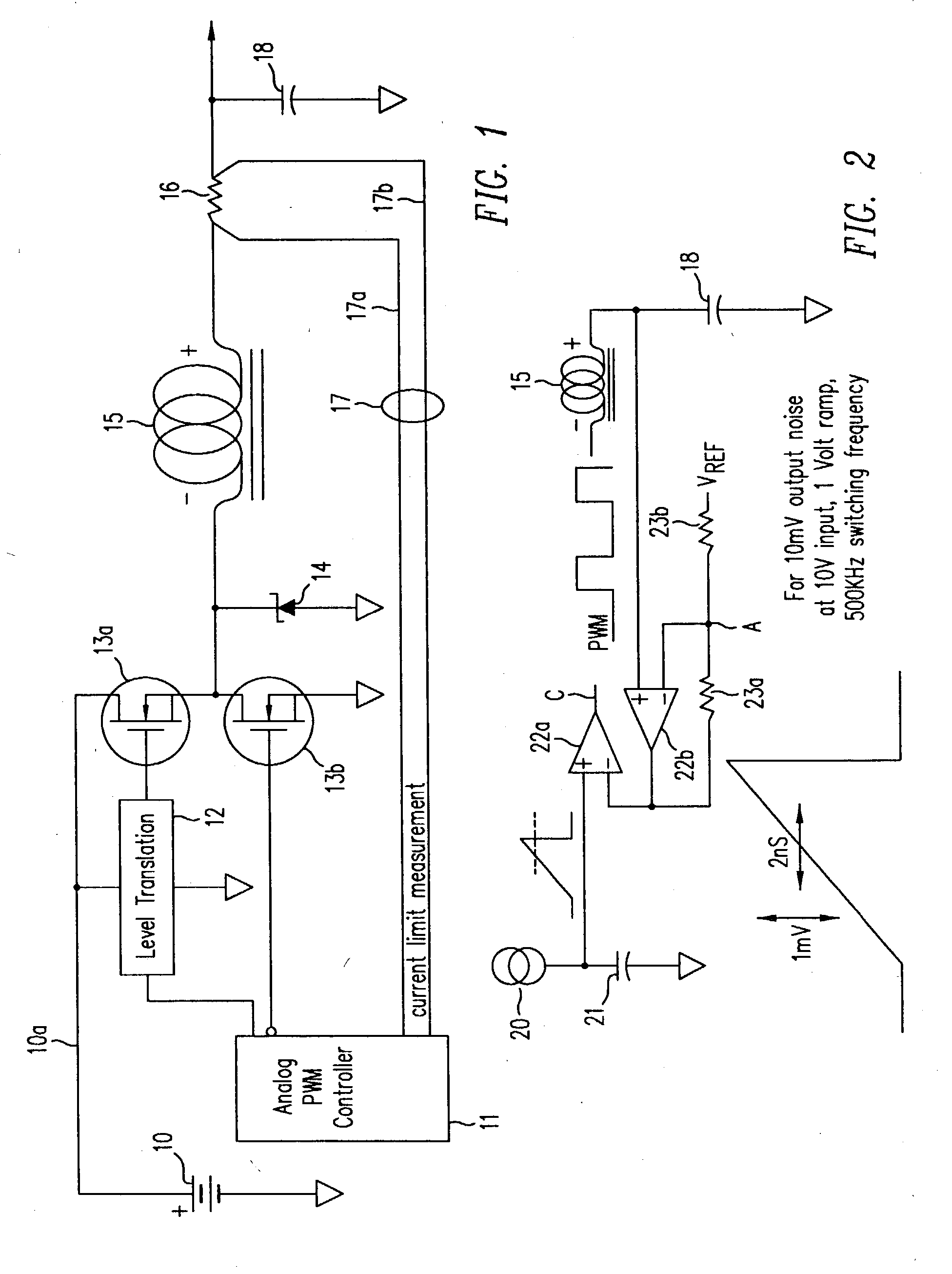

Power converter circuitry and method

InactiveUS20040135560A1Easy to makeBatteries circuit arrangementsEfficient power electronics conversionControl systemEngineering

A control system and method for simultaneously regulating the operation of a plurality of different types of switching power converters. The system utilizes in regulating the power converters sampled data and nonlinear feedback control loops.

Owner:EXAR CORP

Methods and systems for noise resilient, pin-efficient and low power communications with sparse signaling codes

ActiveUS8649445B2Weaken energyFrequency-division multiplex detailsModulated-carrier systemsComputer science

In bus communications methods and apparatus, a first set of physical signals representing the information to be conveyed over the bus is provided, and mapped to a codeword of a sparse signaling code, wherein a codeword is representable as a vector of a plurality of components, some of which are quiescent components and some of which are non-quiescent components, wherein the number of quiescent components and non-quiescent components meet a sparseness requirement.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

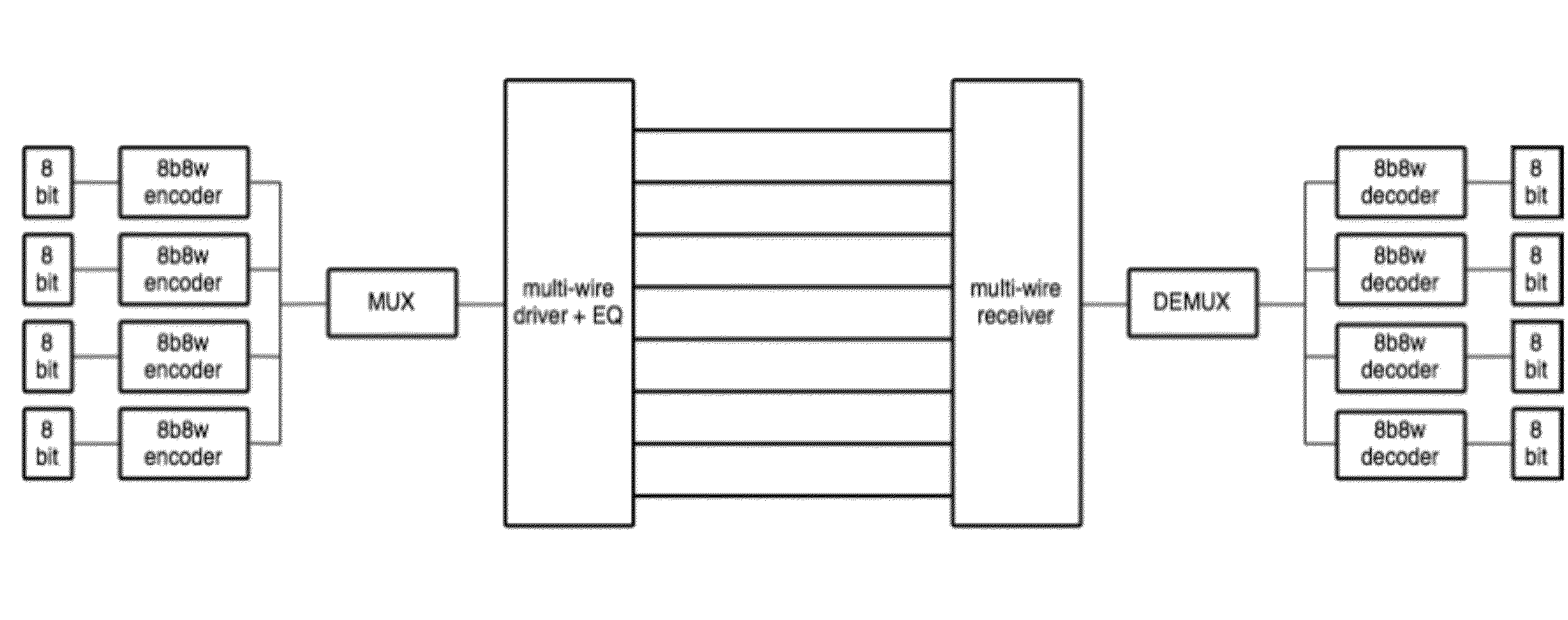

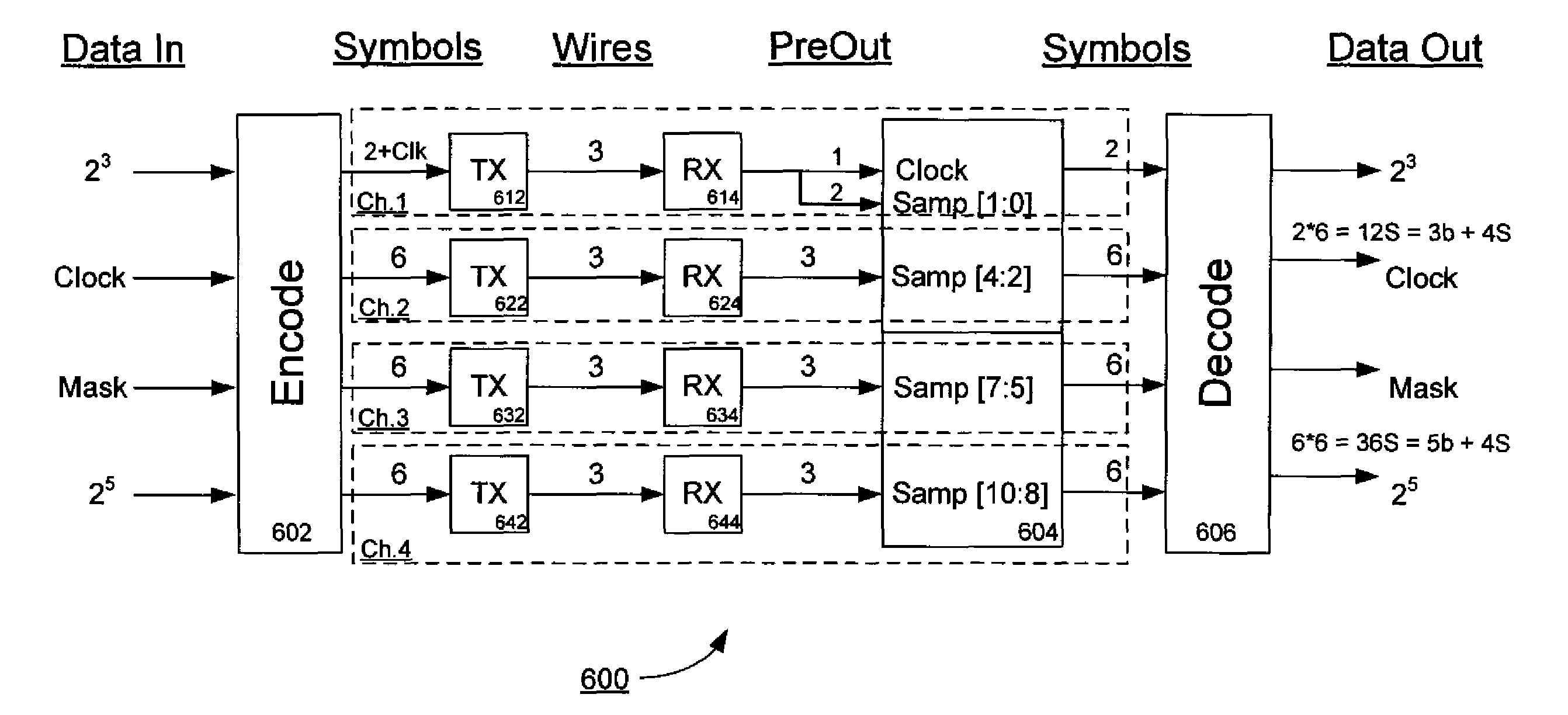

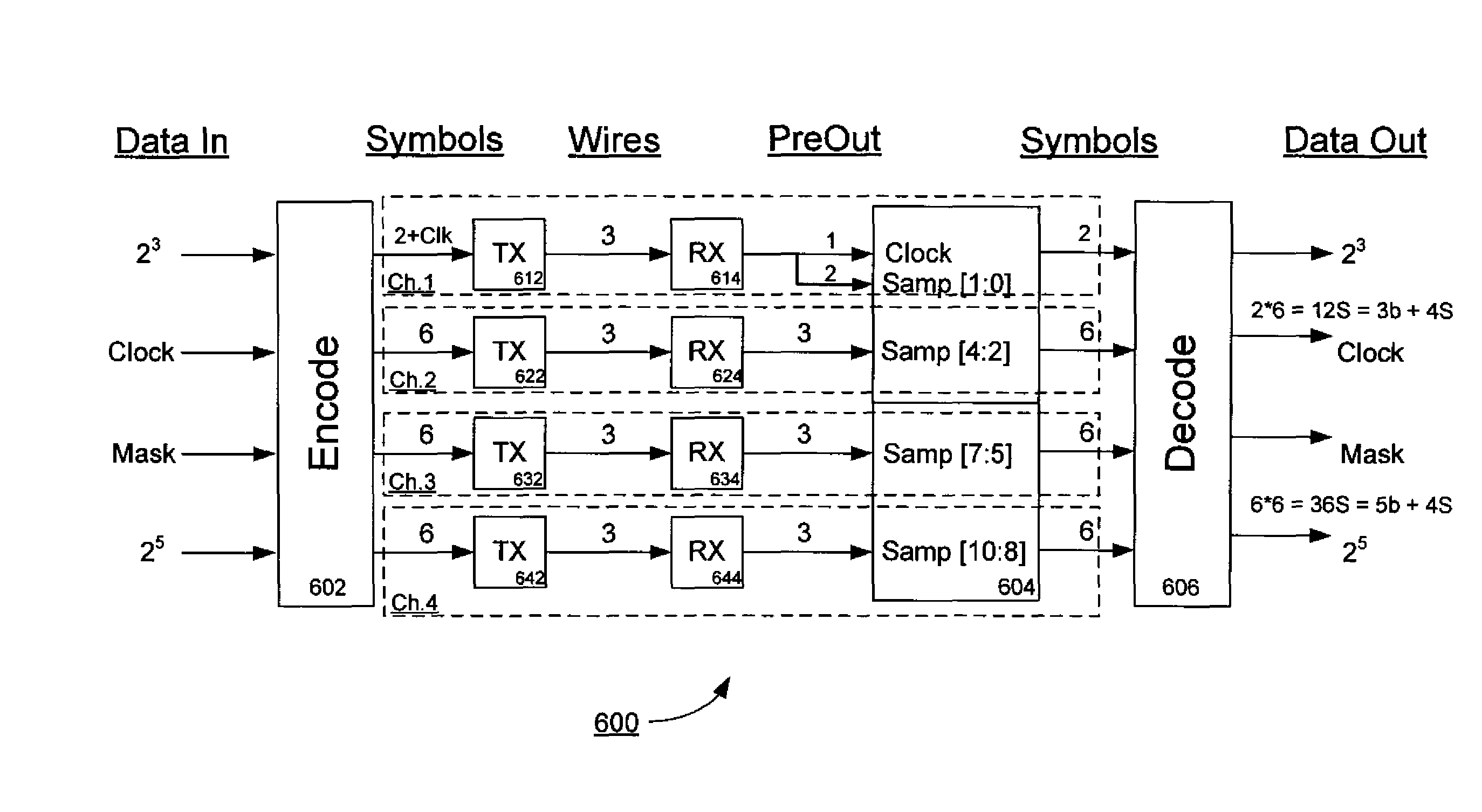

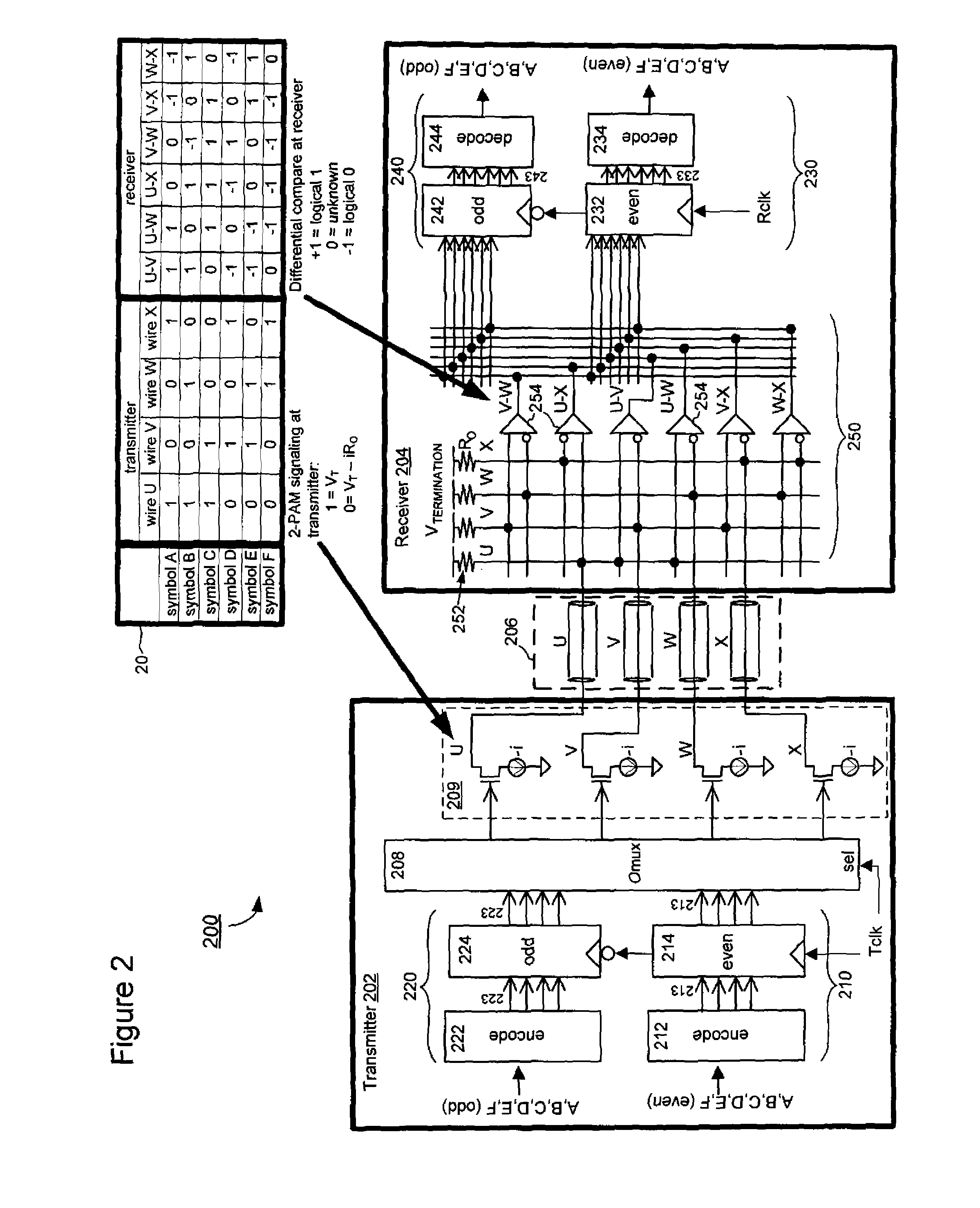

Techniques for multi-wire encoding with an embedded clock

ActiveUS8649460B2Simultaneous amplitude and angle modulationModulation with suppressed carrierComputer moduleComputer science

Techniques for multi-wire encoding with an embedded clock are disclosed. In one particular exemplary embodiment, the techniques may be realized as a transmitter component. The transmitter component may comprise at least one encoder module to generate a set of symbols, each symbol being represented by a combination of signal levels on a set of wires. The transmitter component may also comprise at least one signaling module to transmit one or more of the symbols over the set of wires according to a transmit clock. The transmitter component may additionally comprise control logic to restrict transmission of first and second subsets of the set of symbols to respective first and second portions of a clock cycle of the transmit clock, such that a signal differential among at least two of the set of wires exhibits a switching behavior that has a same frequency as the transmit clock.

Owner:RAMBUS INC

Power and pin efficient chip-to-chip communications with common-mode rejection and SSO resilience

ActiveUS8539318B2Modulated-carrier systemsError correction/detection using multiple codesPhysical formComputer science

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

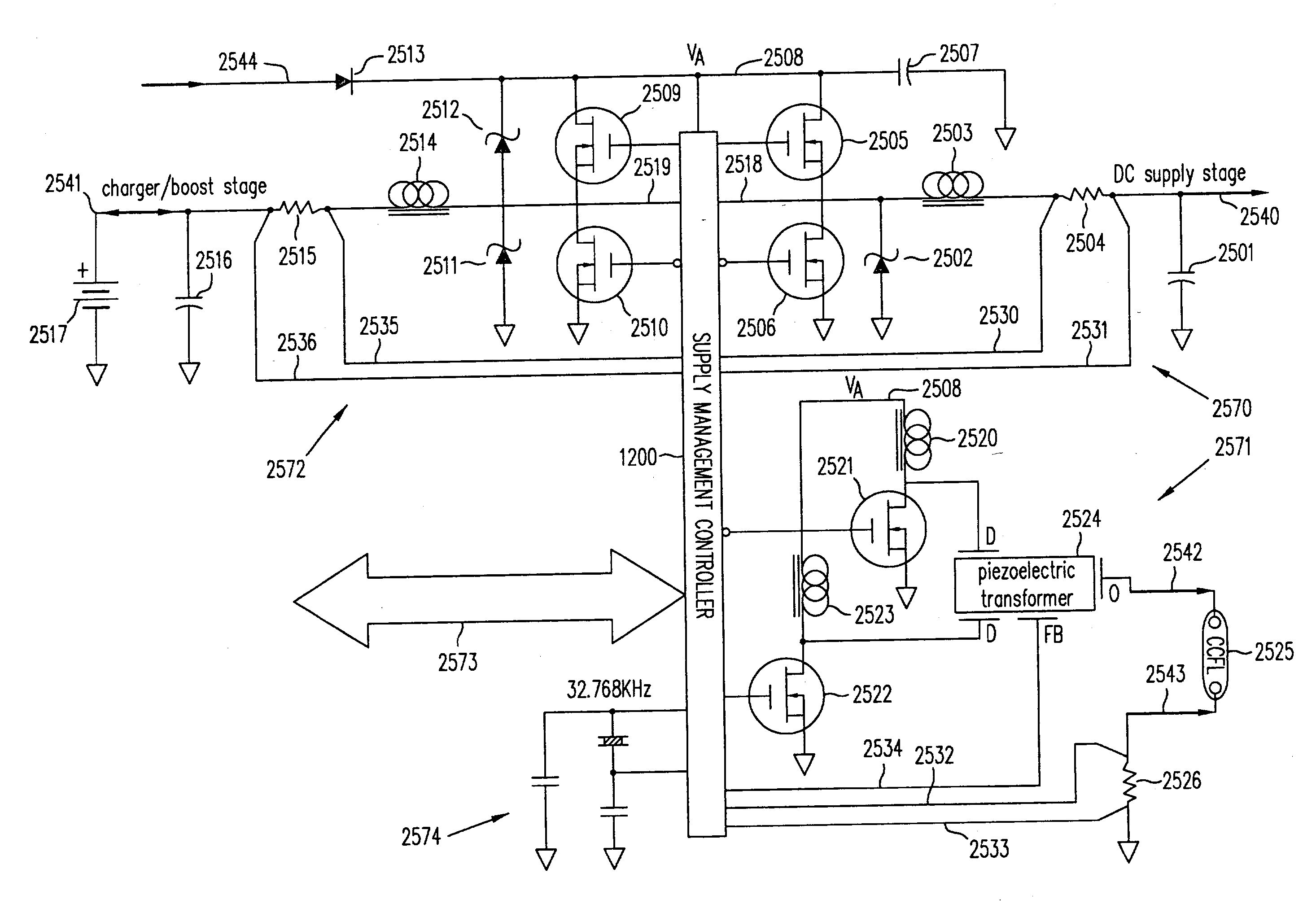

Power converter circuitry and method

InactiveUS20040095020A1Easy to makeBatteries circuit arrangementsEfficient power electronics conversionControl systemEngineering

A control system and method for simultaneously regulating the operation of a plurality of different types of switching power converters. The system utilizes in regulating the power converters sampled data and nonlinear feedback control loops.

Owner:EXAR CORP

Power converter circuitry and method

InactiveUS20040095118A1Easy to makeBatteries circuit arrangementsEfficient power electronics conversionControl systemEngineering

A control system and method for simultaneously regulating the operation of a plurality of different types of switching power converters. The system utilizes in regulating the power converters sampled data and nonlinear feedback control loops.

Owner:EXAR CORP

Single-ended balance-coded interface with embedded-timing

An interface includes an encoder to receive a stream of input symbols and, in response, to output a corresponding stream of output symbols of substantially equal weight via multiple signal lines, which can improve noise / speed performance. The encoder outputs the stream of output symbols so that no output symbol is consecutively repeated. A repeat symbol is used to indicate that the current symbol is identical to the immediately preceding symbol. This encoding allows an interface receiving the stream of output symbols can extract a clock signal from the stream.

Owner:APPLE INC

Techniques for multi-wire encoding with an embedded clock

Techniques for multi-wire encoding with an embedded clock are disclosed. In one particular exemplary embodiment, the techniques may be realized as a transmitter component. The transmitter component may comprise at least one encoder module to generate a set of symbols, each symbol being represented by a combination of signal levels on a set of wires. The transmitter component may also comprise at least one signaling module to transmit one or more of the symbols over the set of wires according to a transmit clock. The transmitter component may additionally comprise control logic to restrict transmission of first and second subsets of the set of symbols to respective first and second portions of a clock cycle of the transmit clock, such that a signal differential among at least two of the set of wires exhibits a switching behavior that has a same frequency as the transmit clock.

Owner:RAMBUS INC

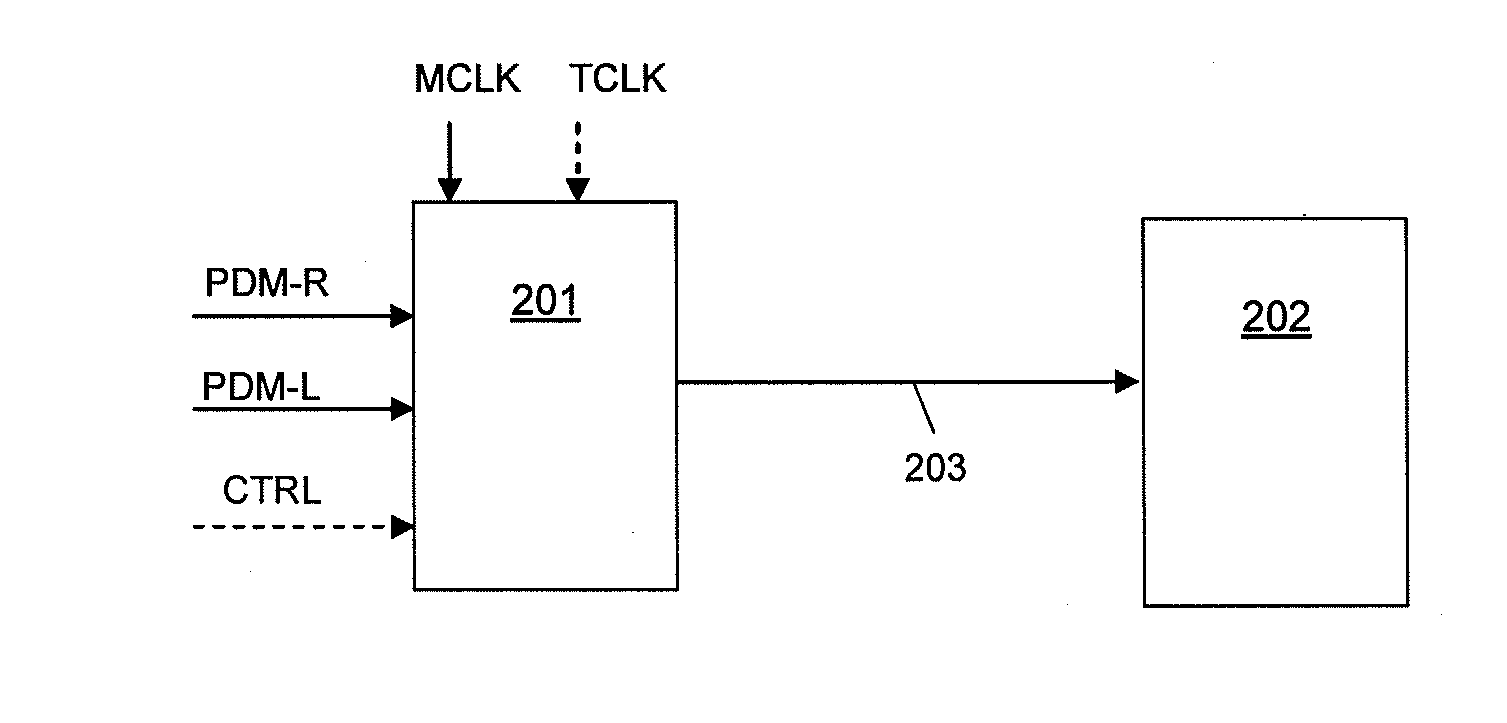

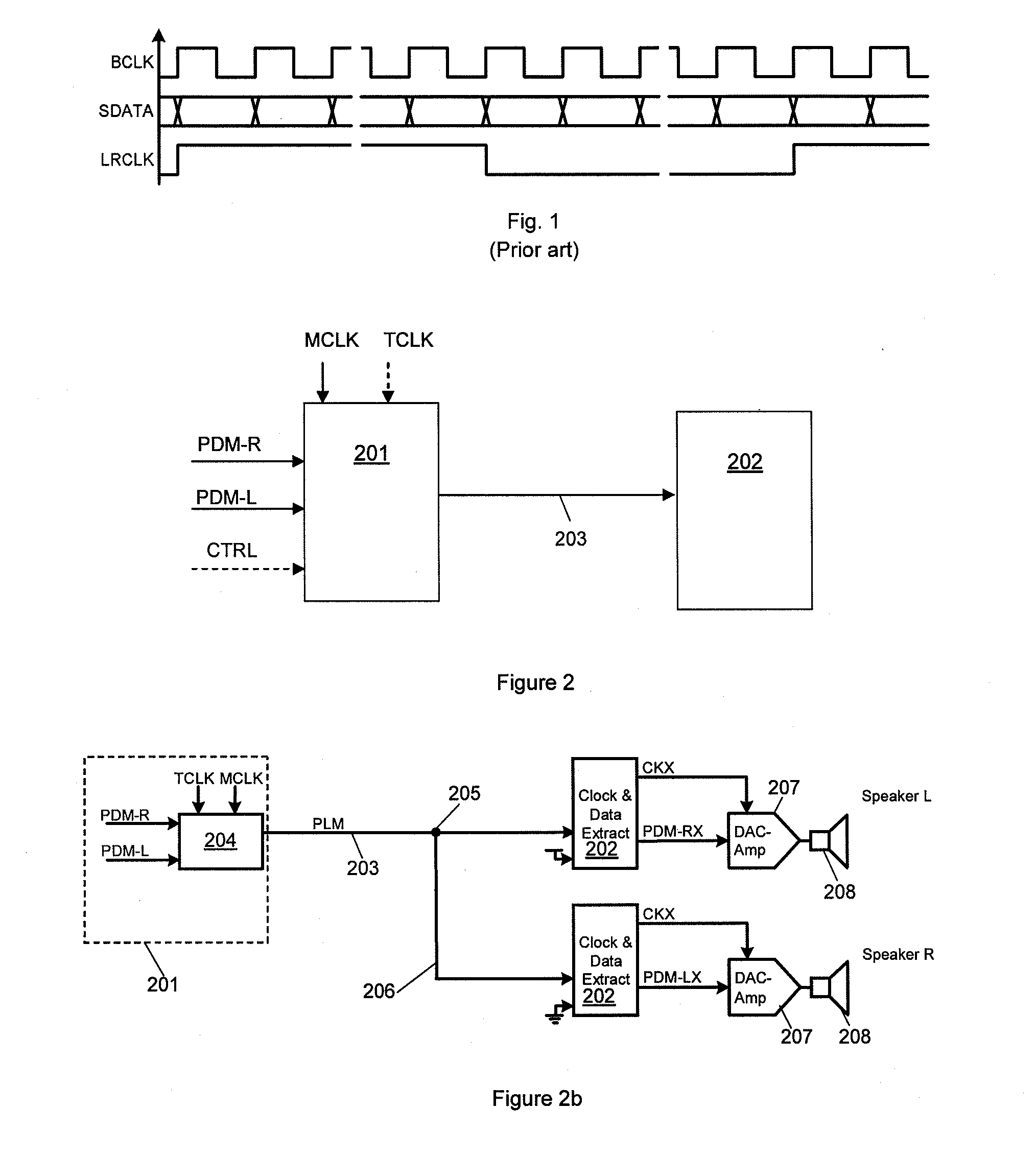

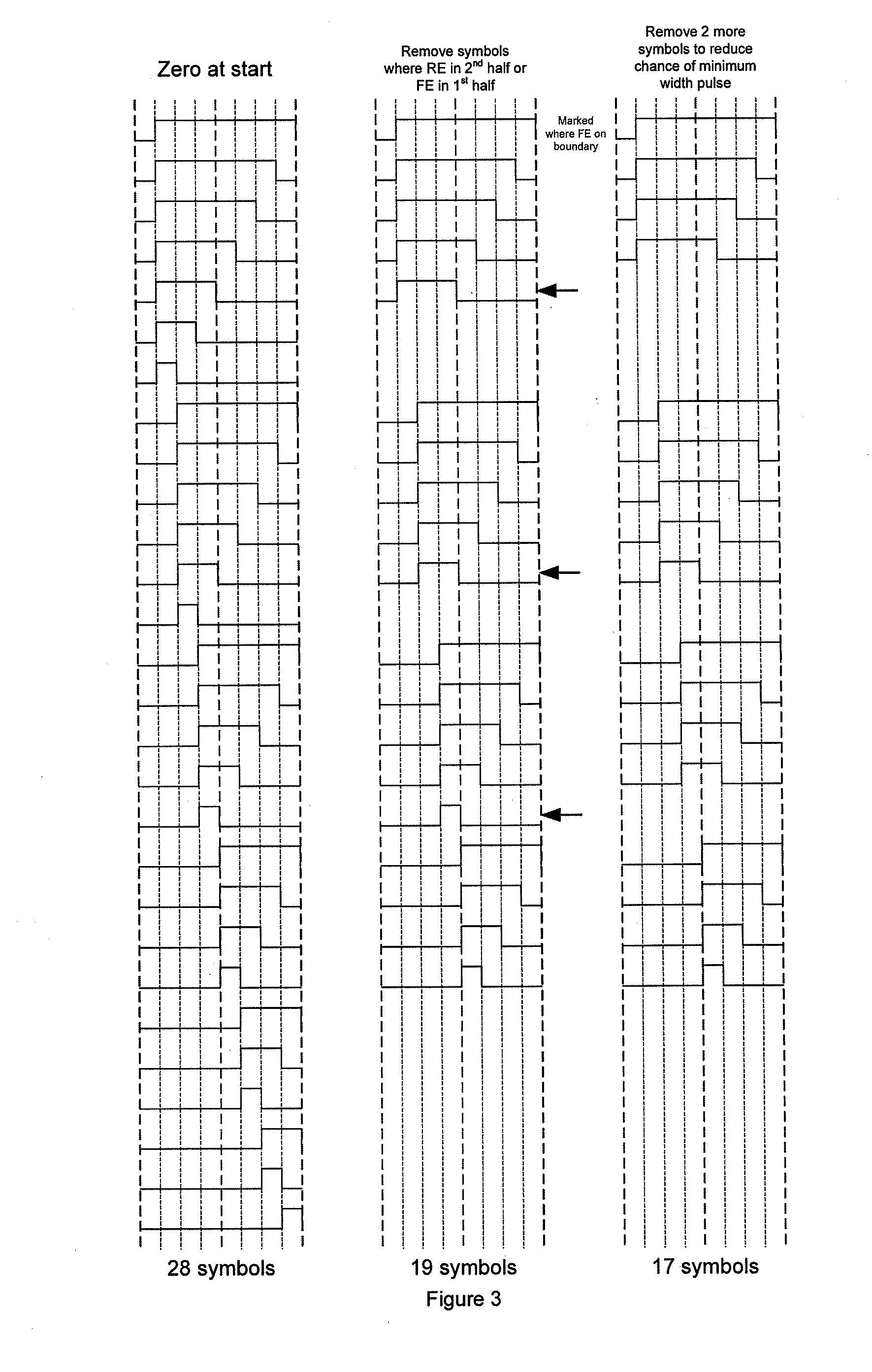

Data transfer

Circuitry for transferring multiple digital data streams, e.g. digital audio data, over a single communications link such as a single wire. A pulse-length-modulator is responsive to a plurality of data streams to generate a series of data pulses with a single data pulse having a rising and falling edge in each of a plurality of transfer periods defined by a first clock signal. The timing of the rising and falling edge of each data pulse is dependent on a combination of the then current data samples from the plurality of data streams. The duration and position of the data pulse in the transfer window in effect defines a data symbol encoding the data. An interface receives the stream of data pulses, and data extraction circuitry samples the data pulse to determine which of the possible data symbols the pulse represents and determines a data value for at least one received data stream.

Owner:CIRRUS LOGIC INC

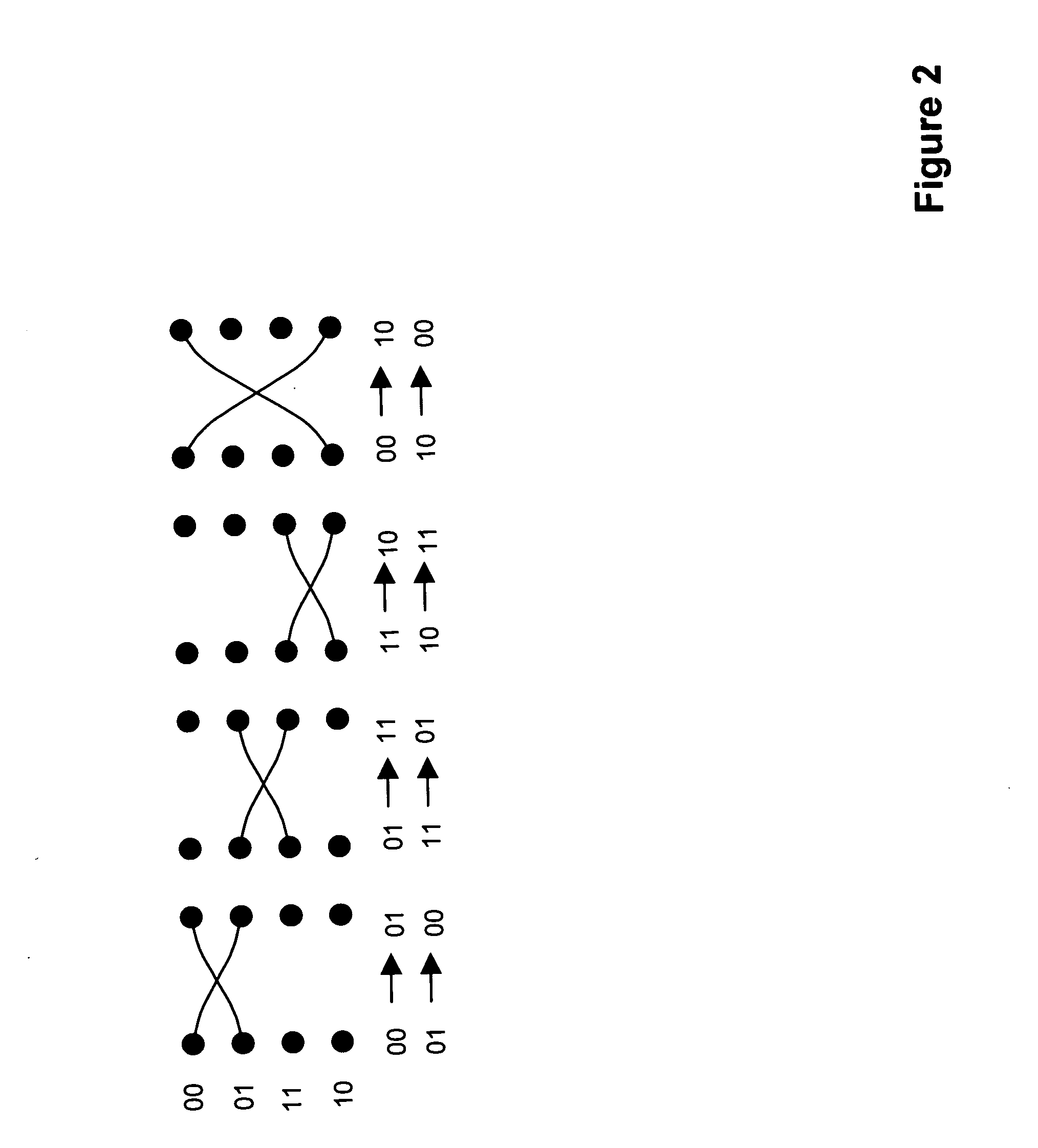

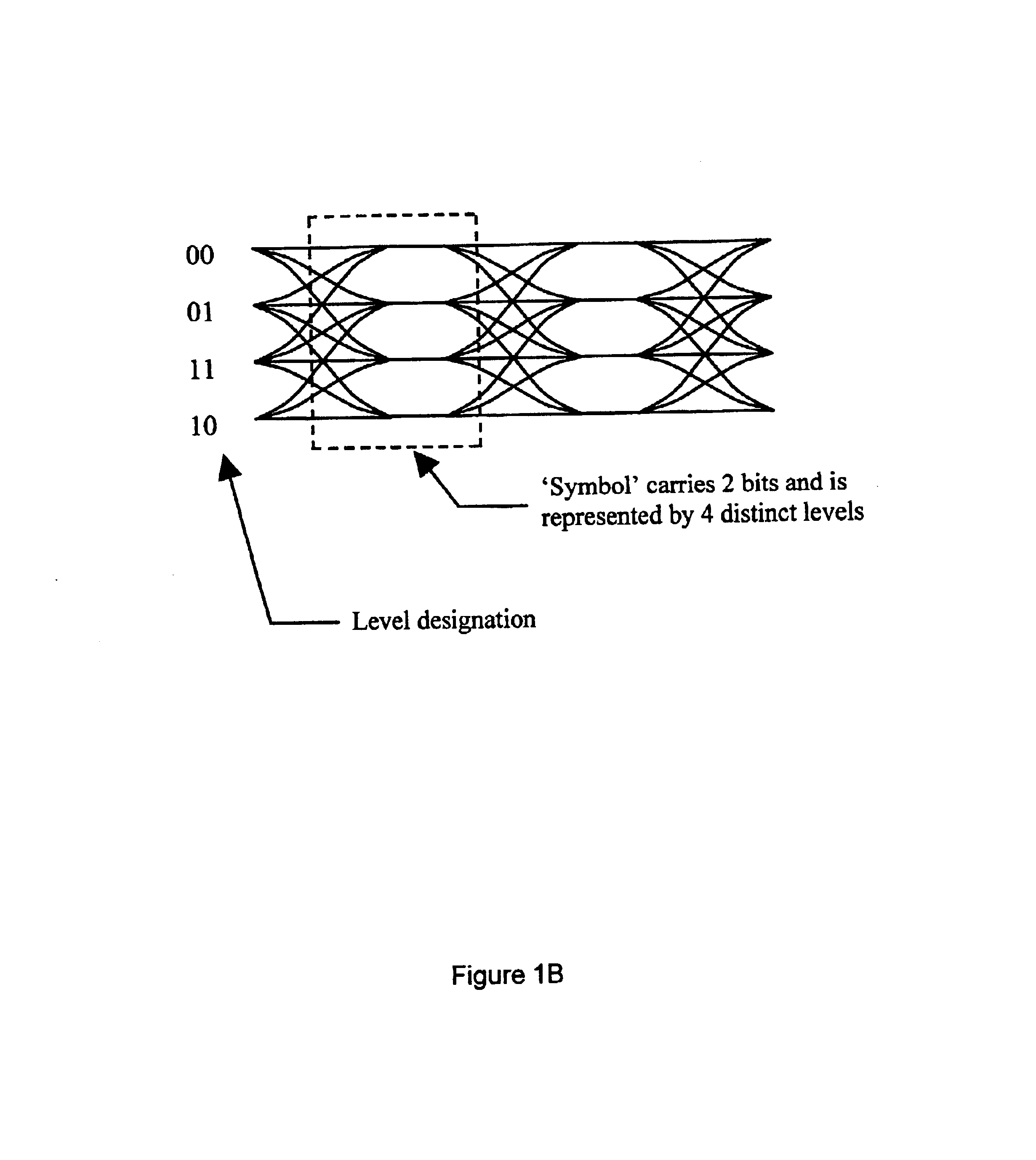

Technique for disparity bounding coding in a multi-level signaling system

A technique for coding information for transmission in a multi-level signaling system is disclosed. In one particular exemplary embodiment, the technique may be realized as a method for coding information for transmission in a multi-level signaling system. The method comprises receiving information organized into multiple information sets, mapping the received information according to the contents of each information set, and changing a current weight polarity of the mapped information based at least in part upon an accumulated weight polarity of previously encoded information so as to provide a substantially DC balanced codeword that is substantially DC balanced for transmission in a multi-level signaling system.

Owner:RAMBUS INC

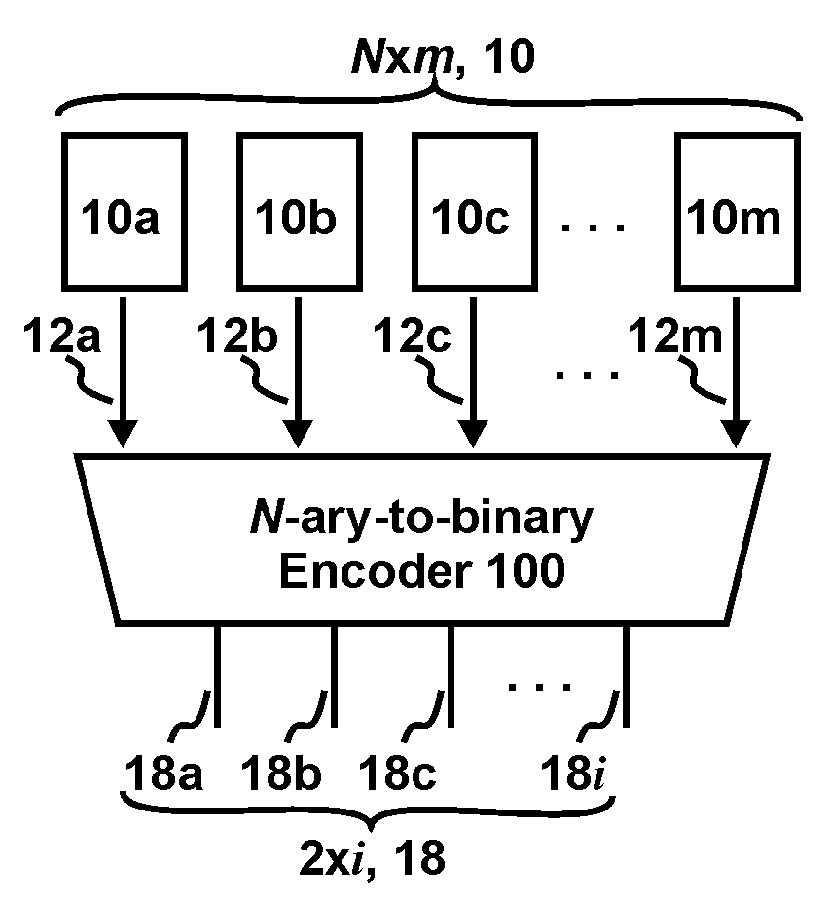

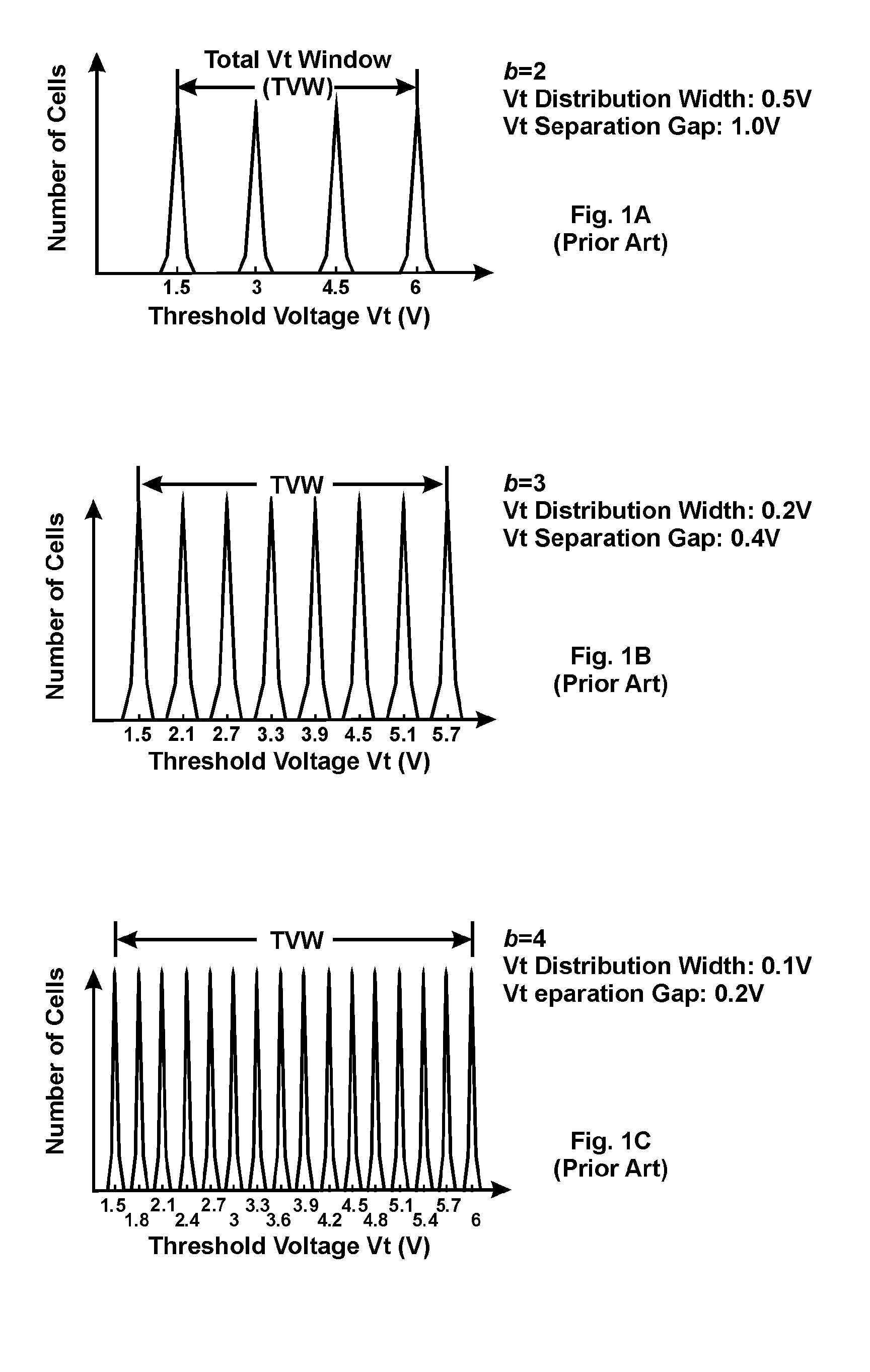

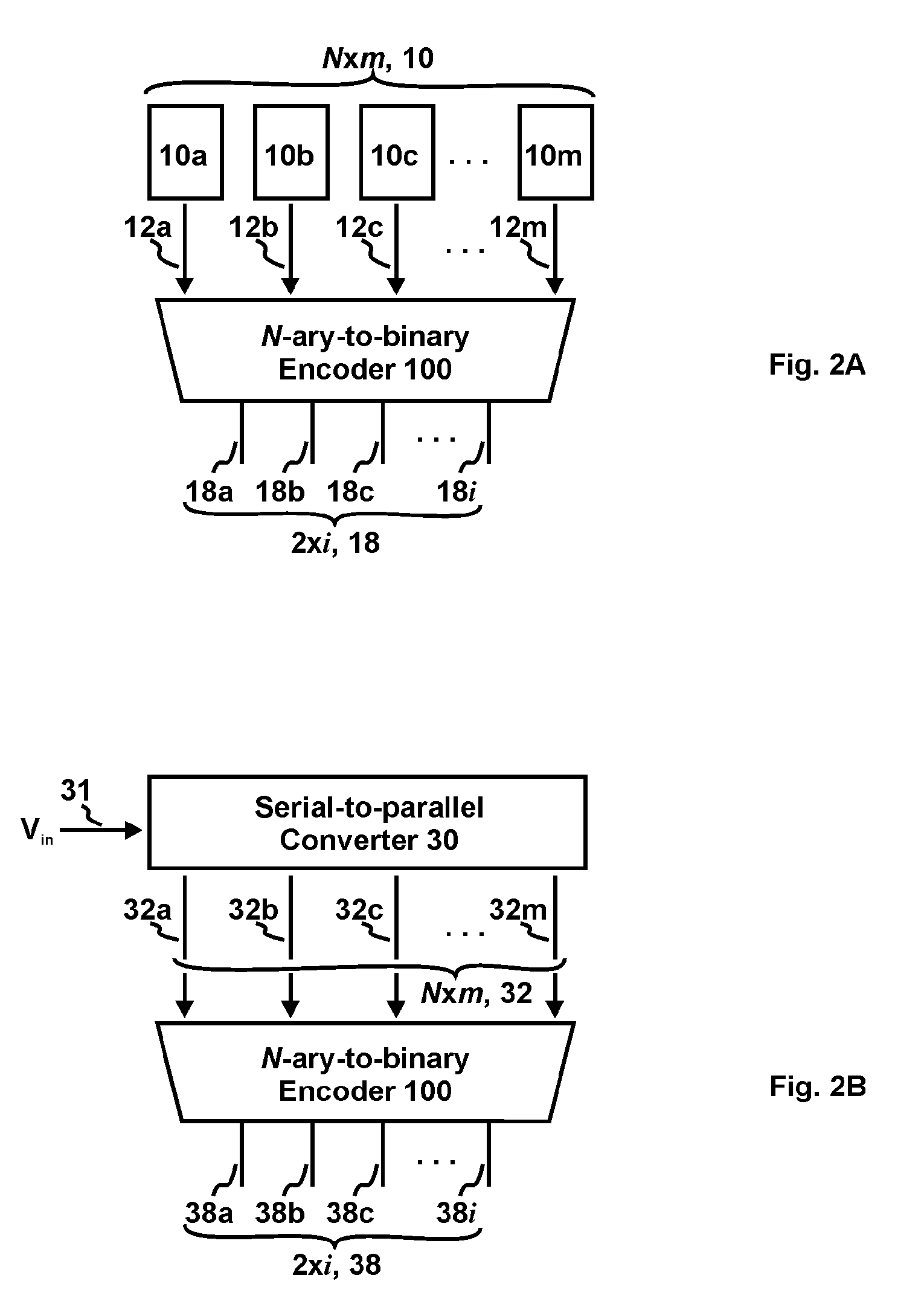

Fractional-Bit Systems

The present invention abandons the conventional approach of incrementing bits-per-cell b by 1, but allows increments of states-per-cell N by as little as 1 between product generations. Because N is no longer an integral power of 2, b takes a fractional value, resulting in a fractional-bit system. In a fractional-bit system, cells are decoded in unit of word. By adjusting the word-width, the system efficiency can be optimized.

Owner:ZHANG GUOBIAO

Power converter circuitry and method

InactiveUS7365661B2Different output voltageEasy to makeAnalogue/digital conversionElectric signal transmission systemsControl systemEngineering

A control system and method for simultaneously regulating the operation of a plurality of different types of switching power converters. The system utilizes in regulating the power converters sampled data and nonlinear feedback control loops.

Owner:EXAR CORP

Power converter circuitry and method

InactiveUS20040095264A1Analogue/digital conversionElectric signal transmission systemsControl systemEngineering

A control system and method for simultaneously regulating the operation of a plurality of different types of switching power converters. The system utilizes in regulating the power converters sampled data and nonlinear feedback control loops.

Owner:EXAR CORP

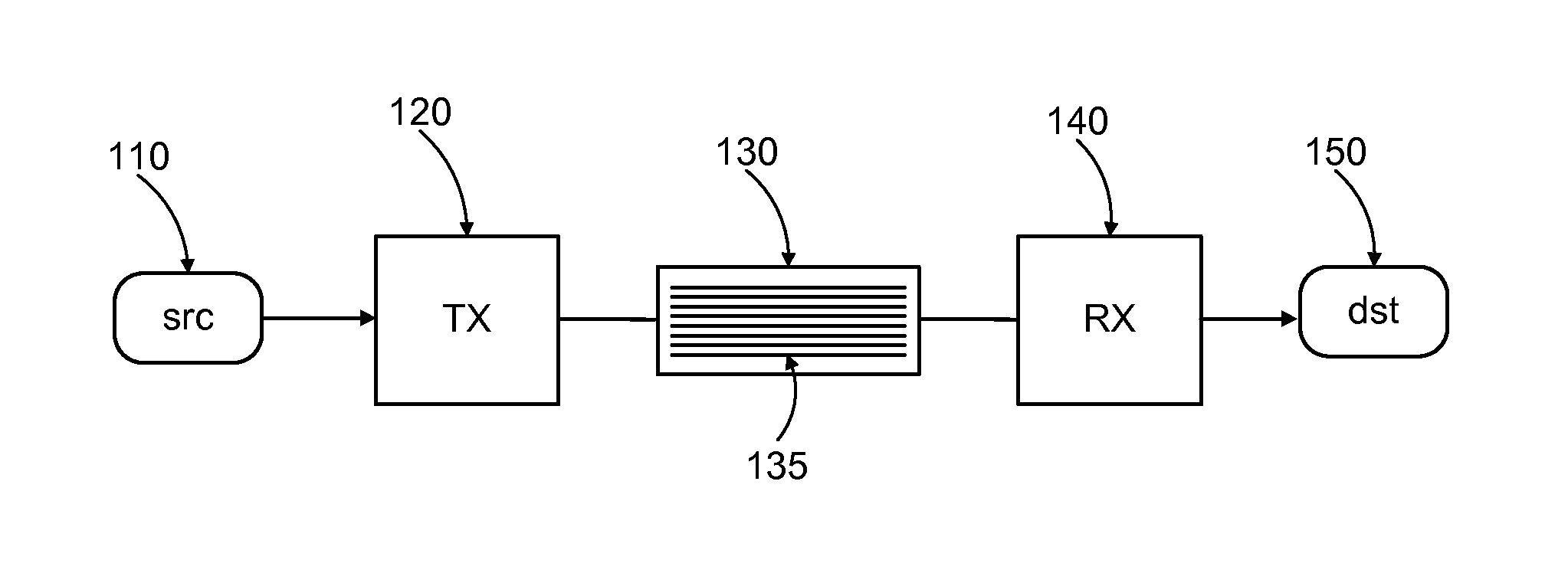

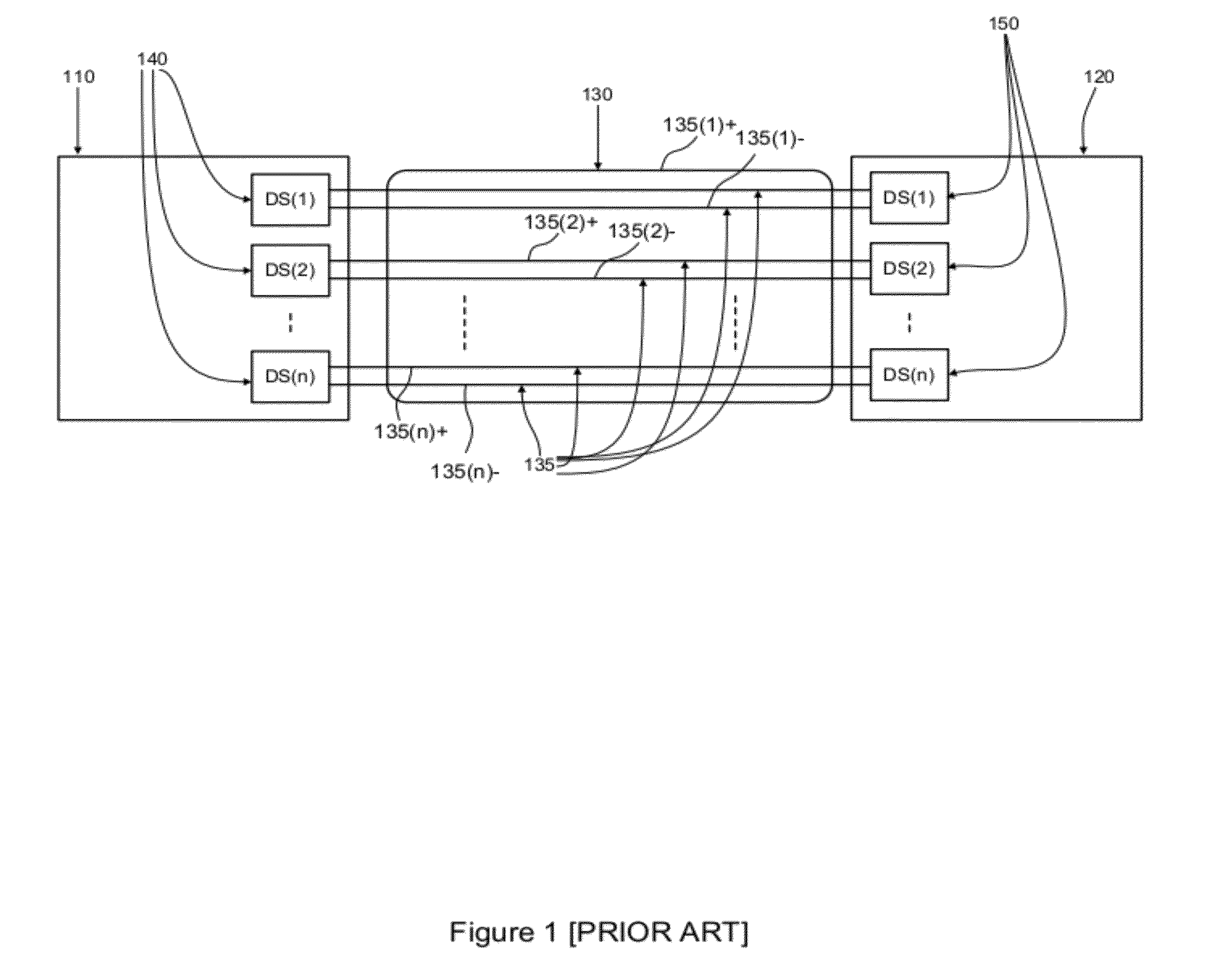

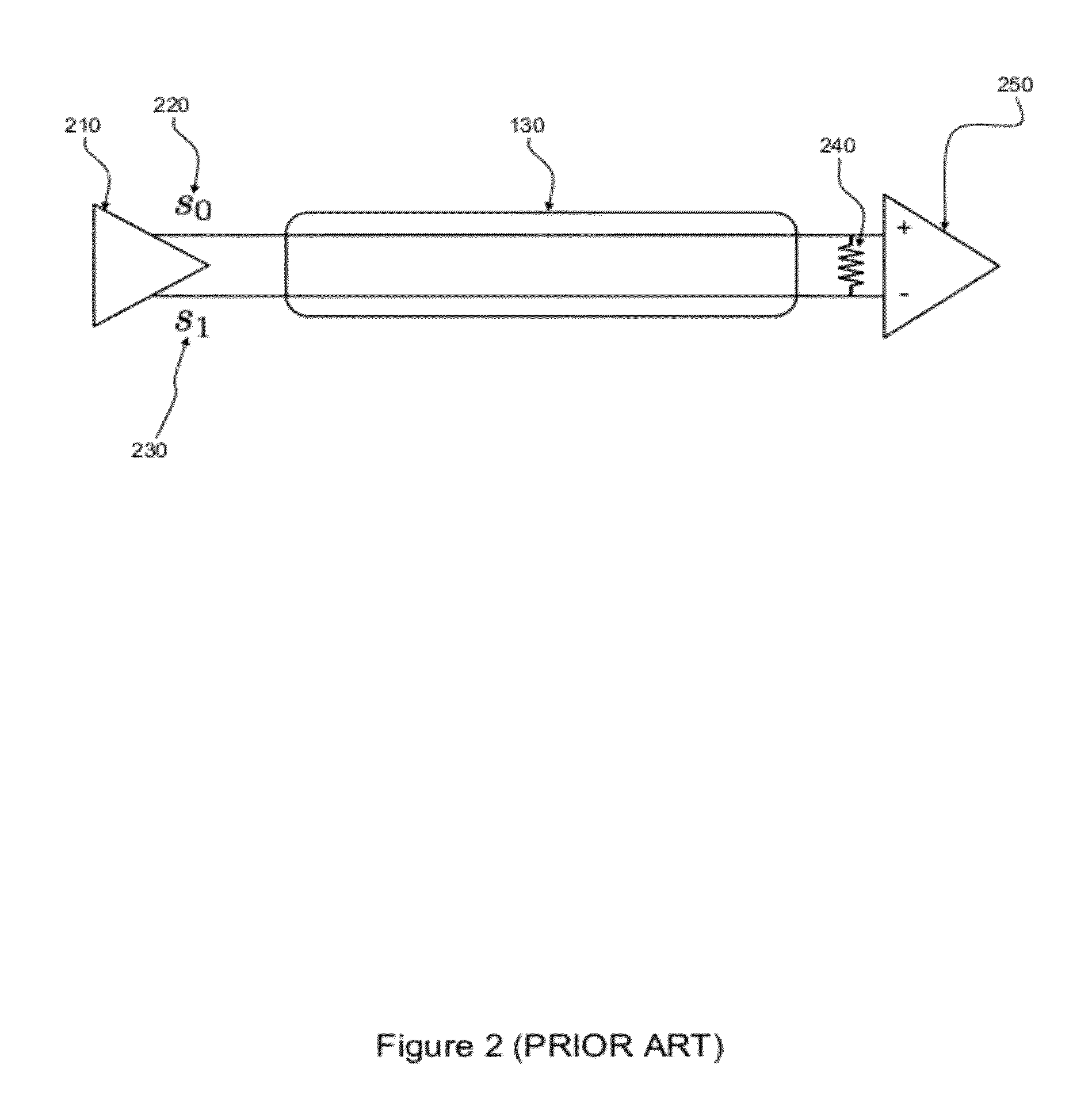

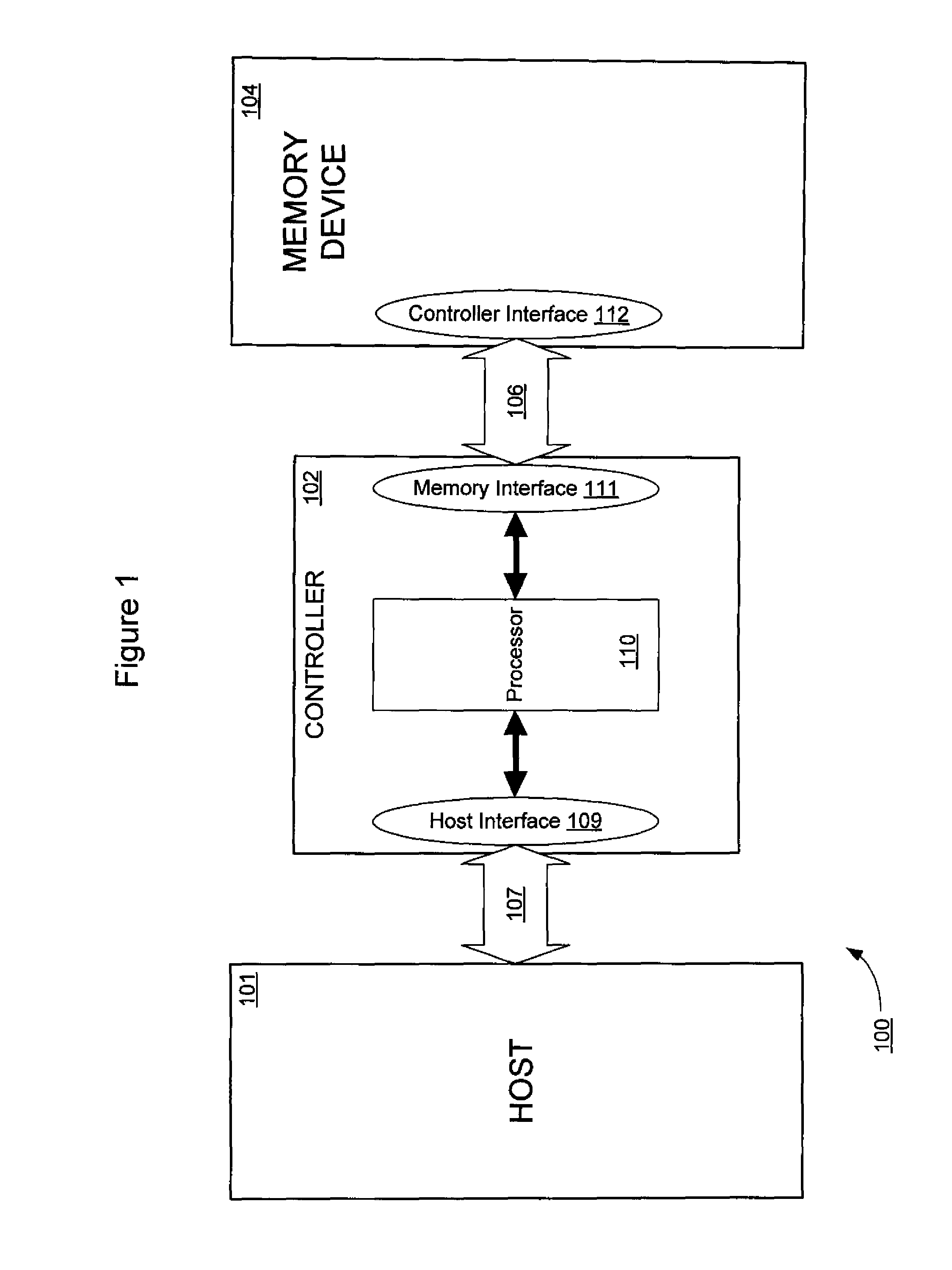

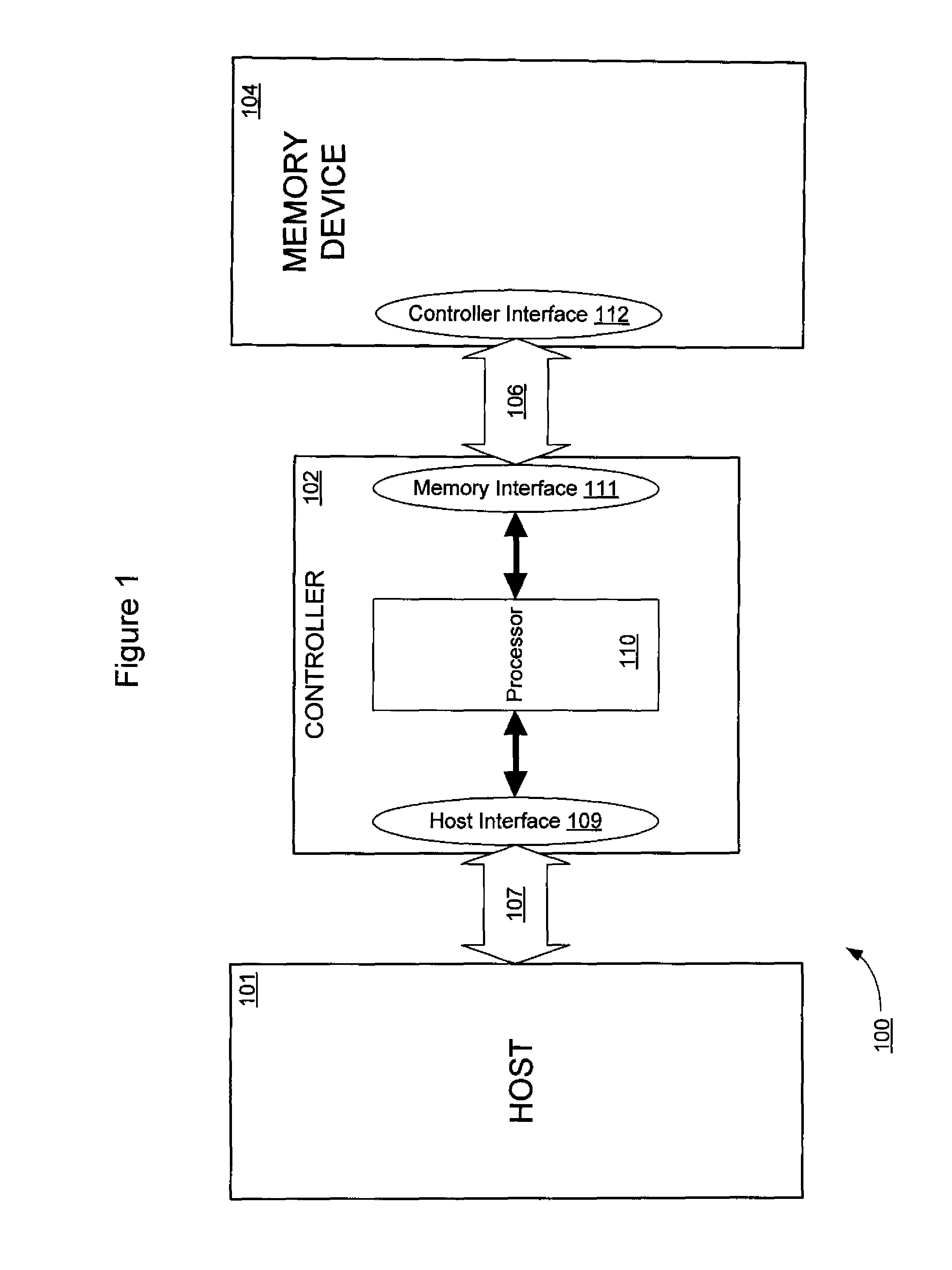

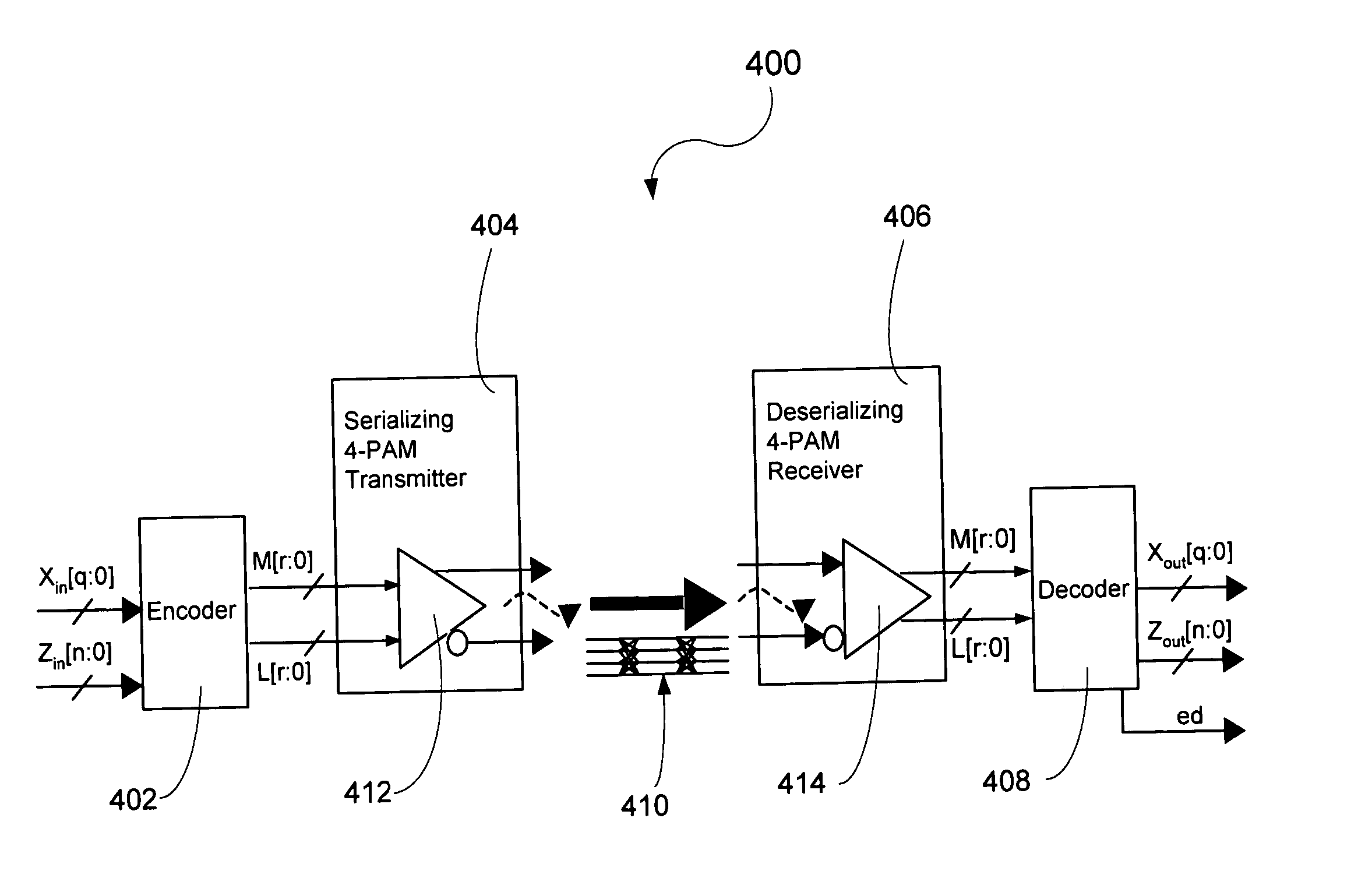

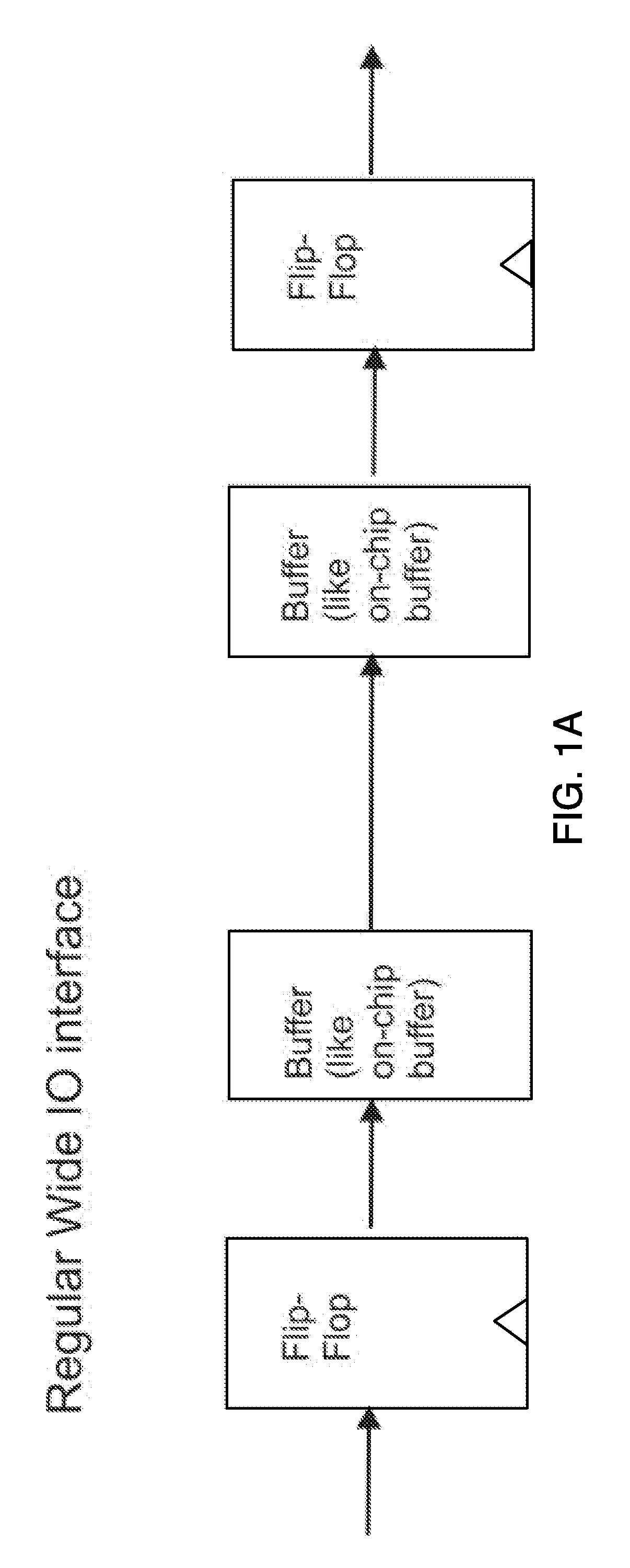

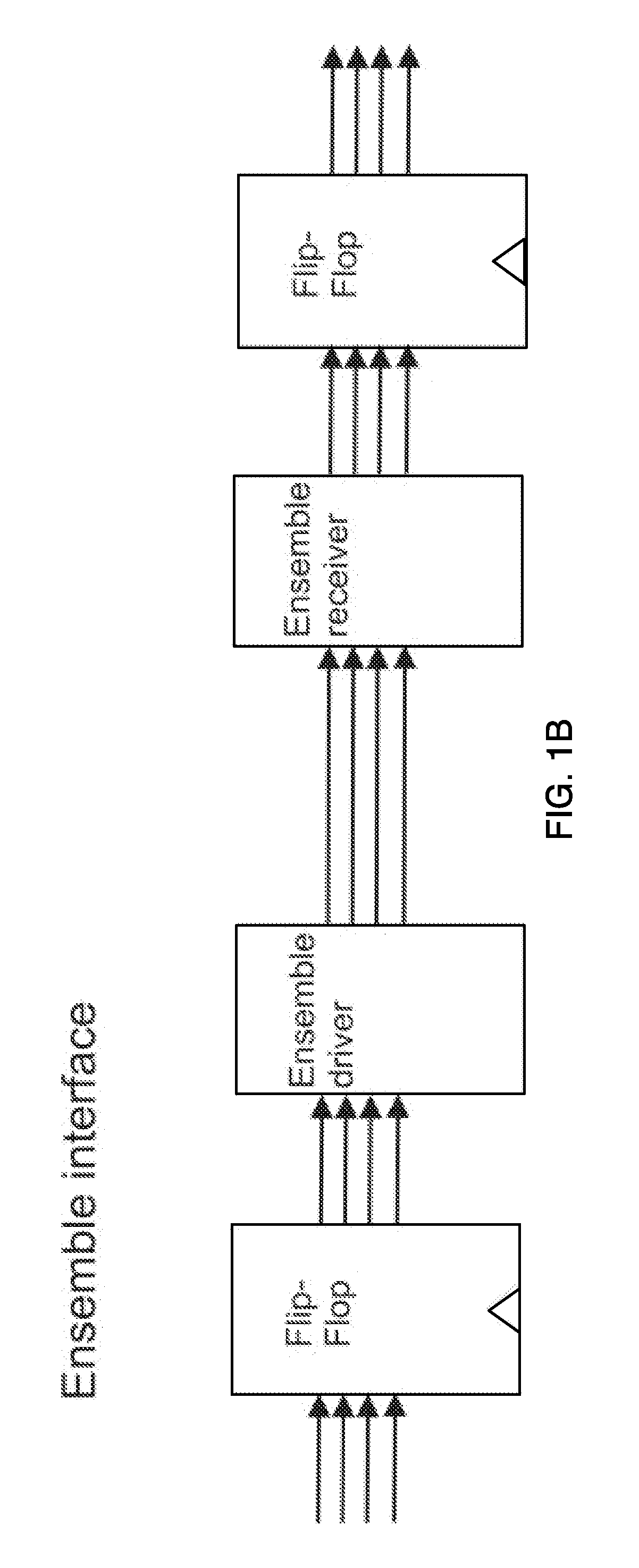

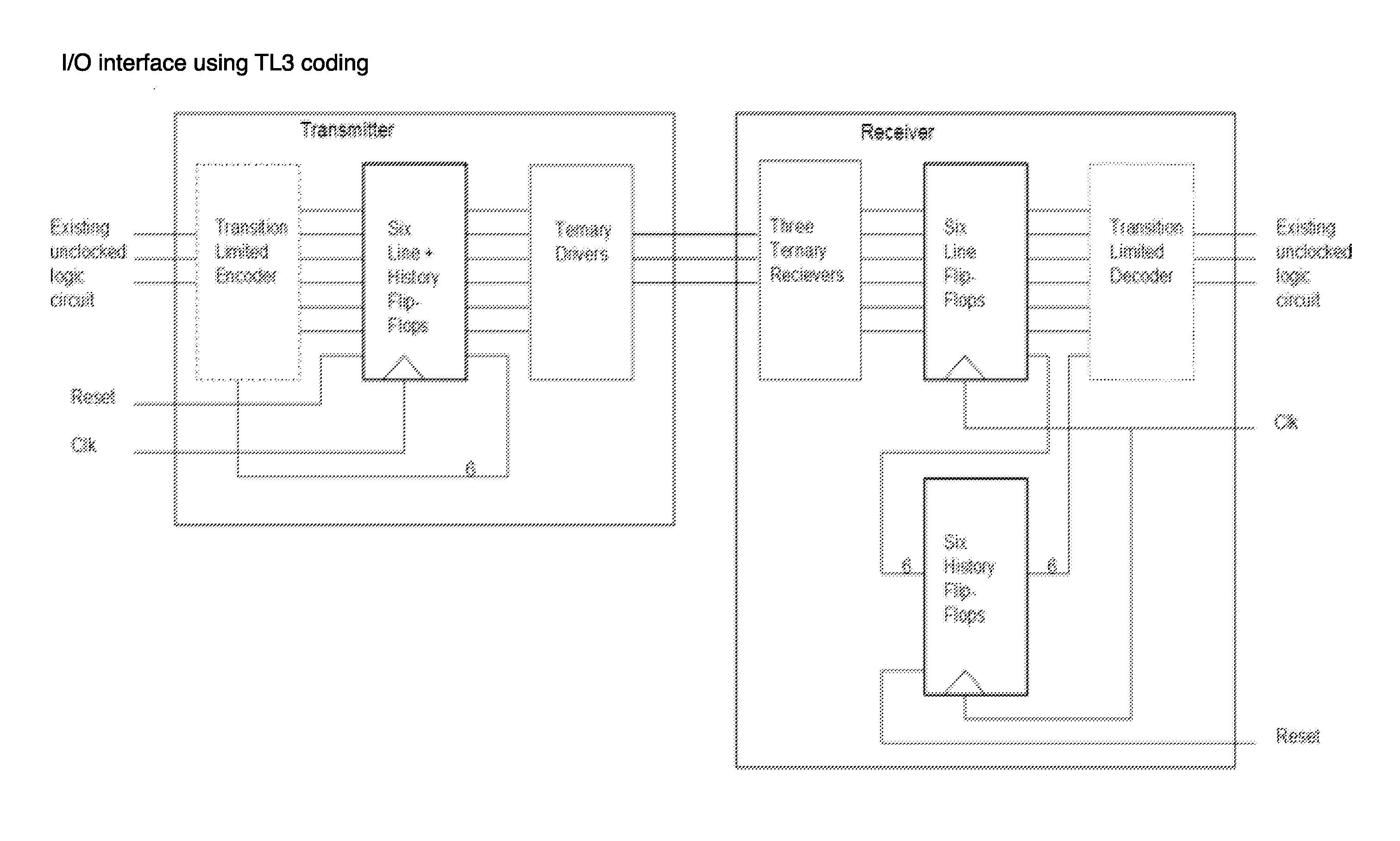

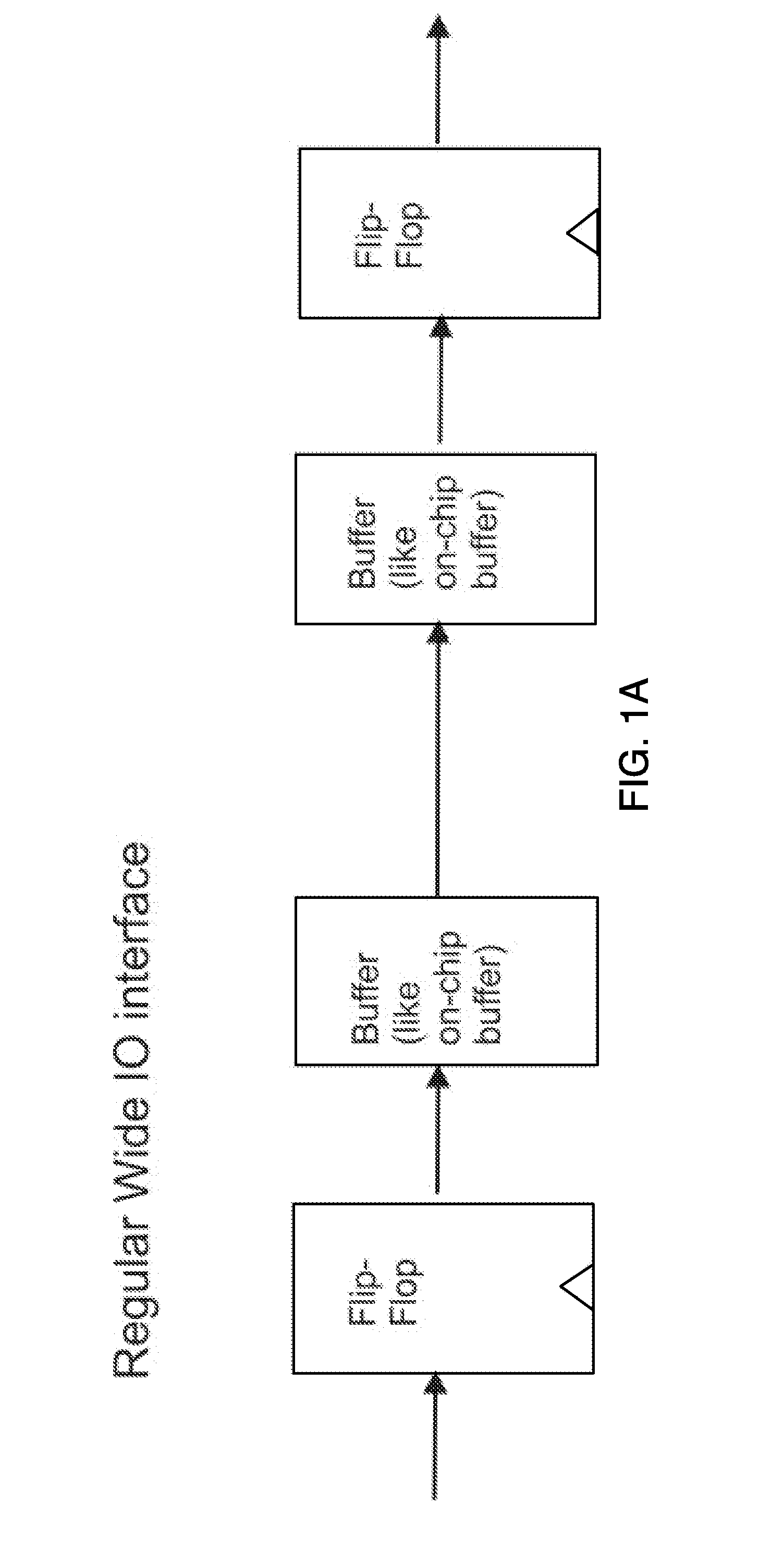

Methods and systems for chip-to-chip communication with reduced simultaneous switching noise

ActiveUS9124557B2Increase speedReduce interfaceEnergy efficient ICTPulse conversionLatency (engineering)Memory controller

Systems and methods are described for transmitting data over physical channels to provide a high speed, low latency interface such as between a memory controller and memory devices with significantly reduced or eliminated Simultaneous Switching Output noise. Controller-side and memory-side embodiments of such channel interfaces are disclosed which do not require additional pin count or data transfer cycles, have low power utilization, and introduce minimal additional latency. In some embodiments of the invention, three or more voltage levels are used for signaling.

Owner:KANDOU LABS

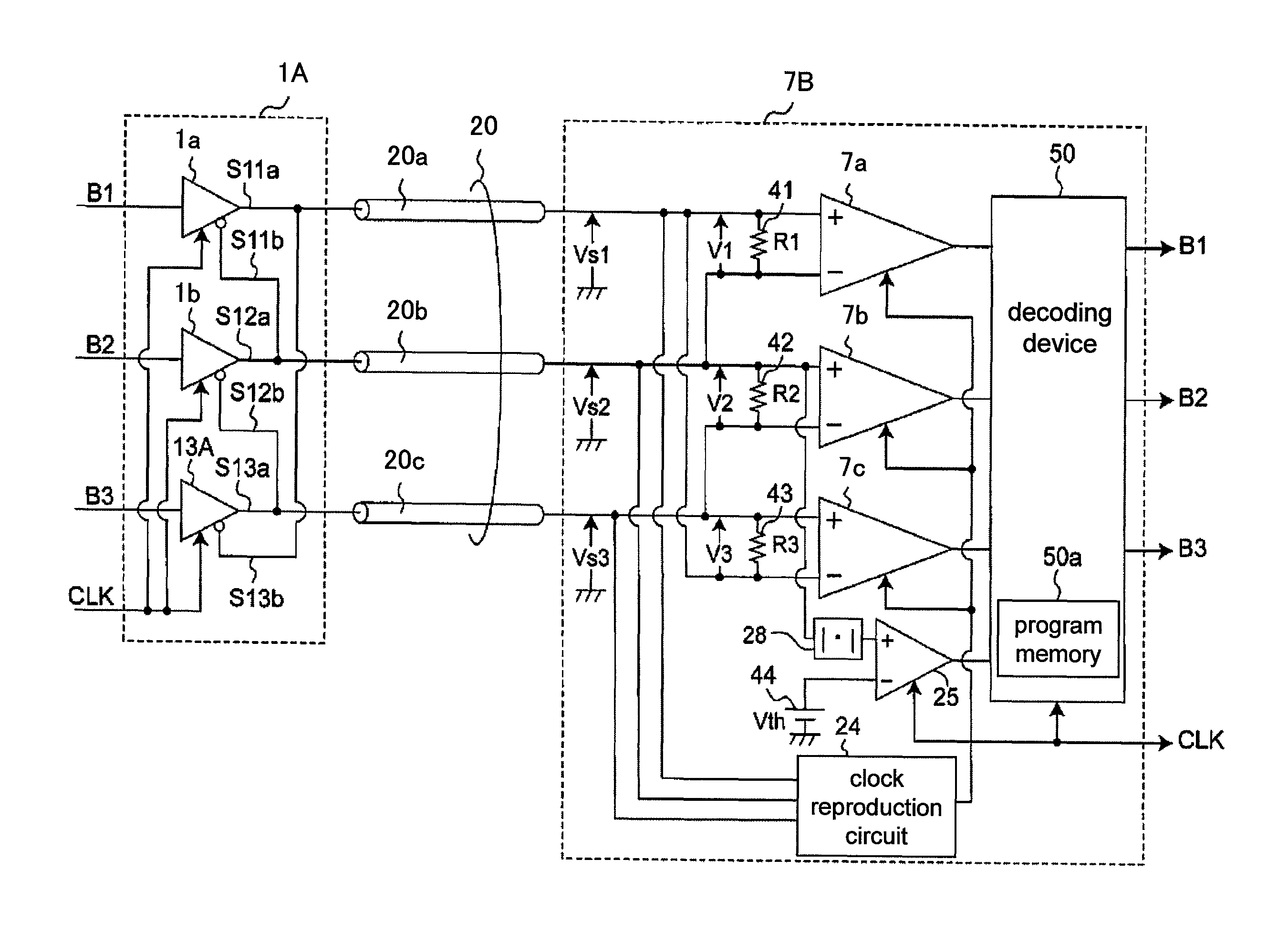

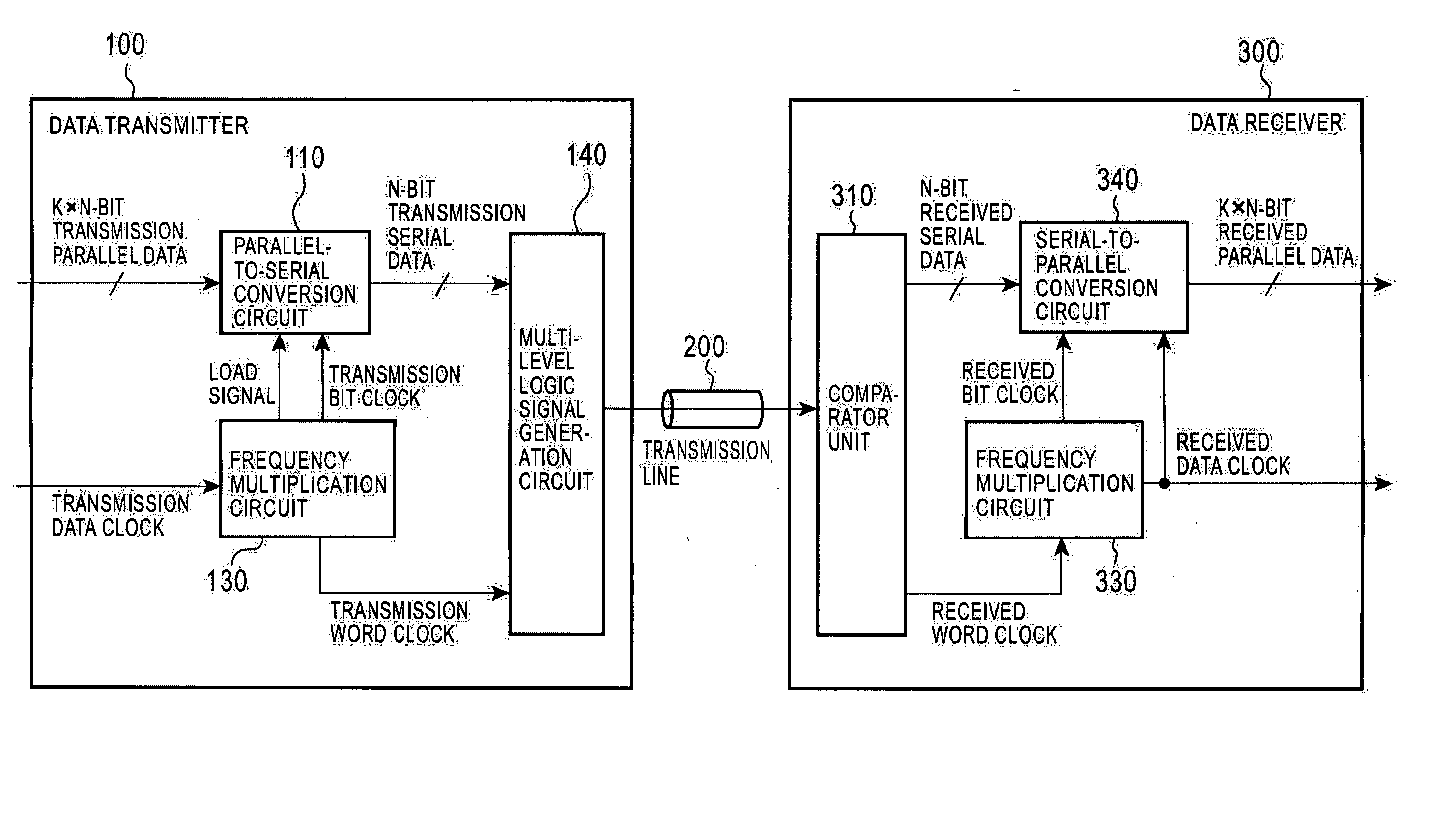

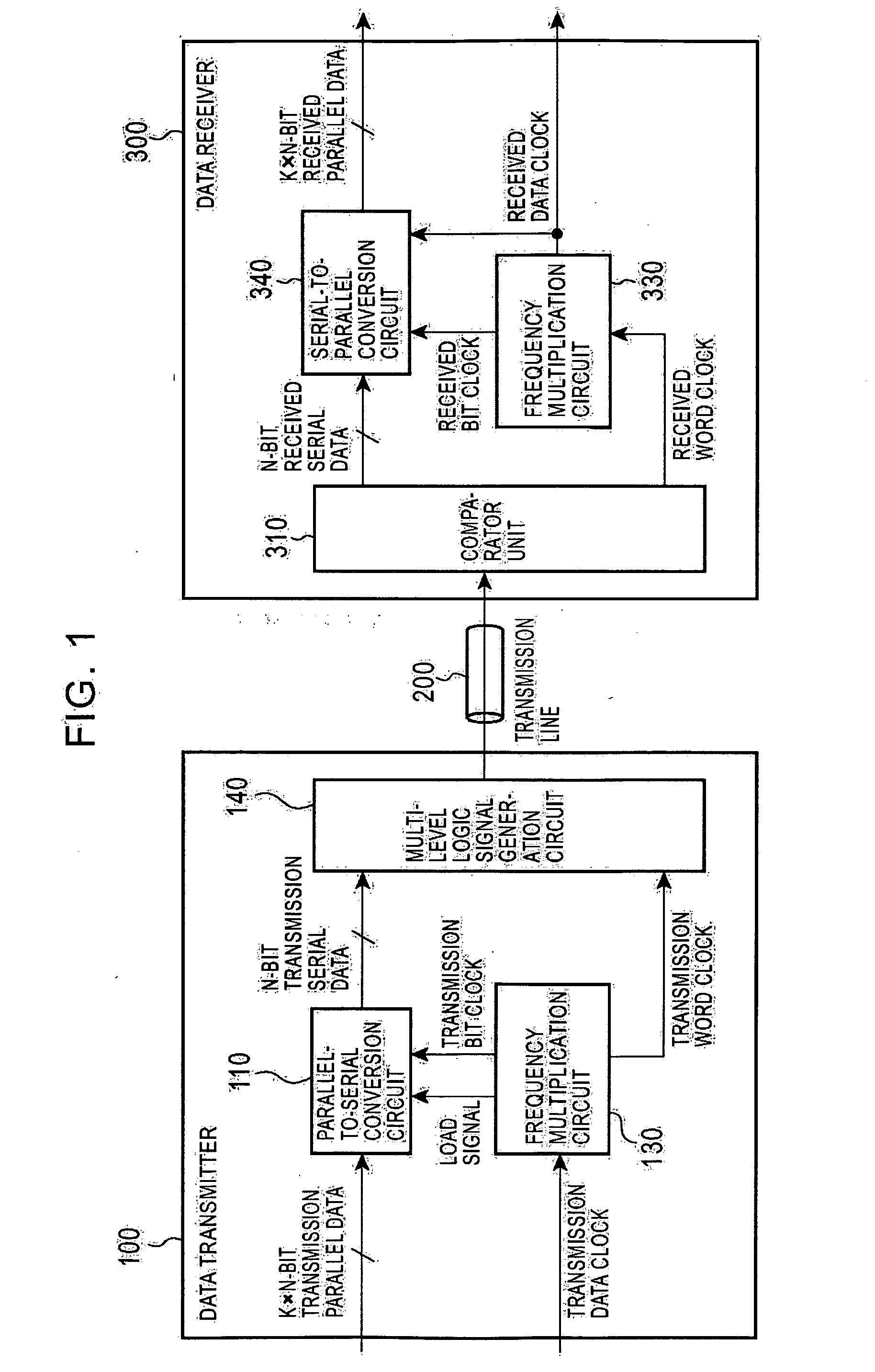

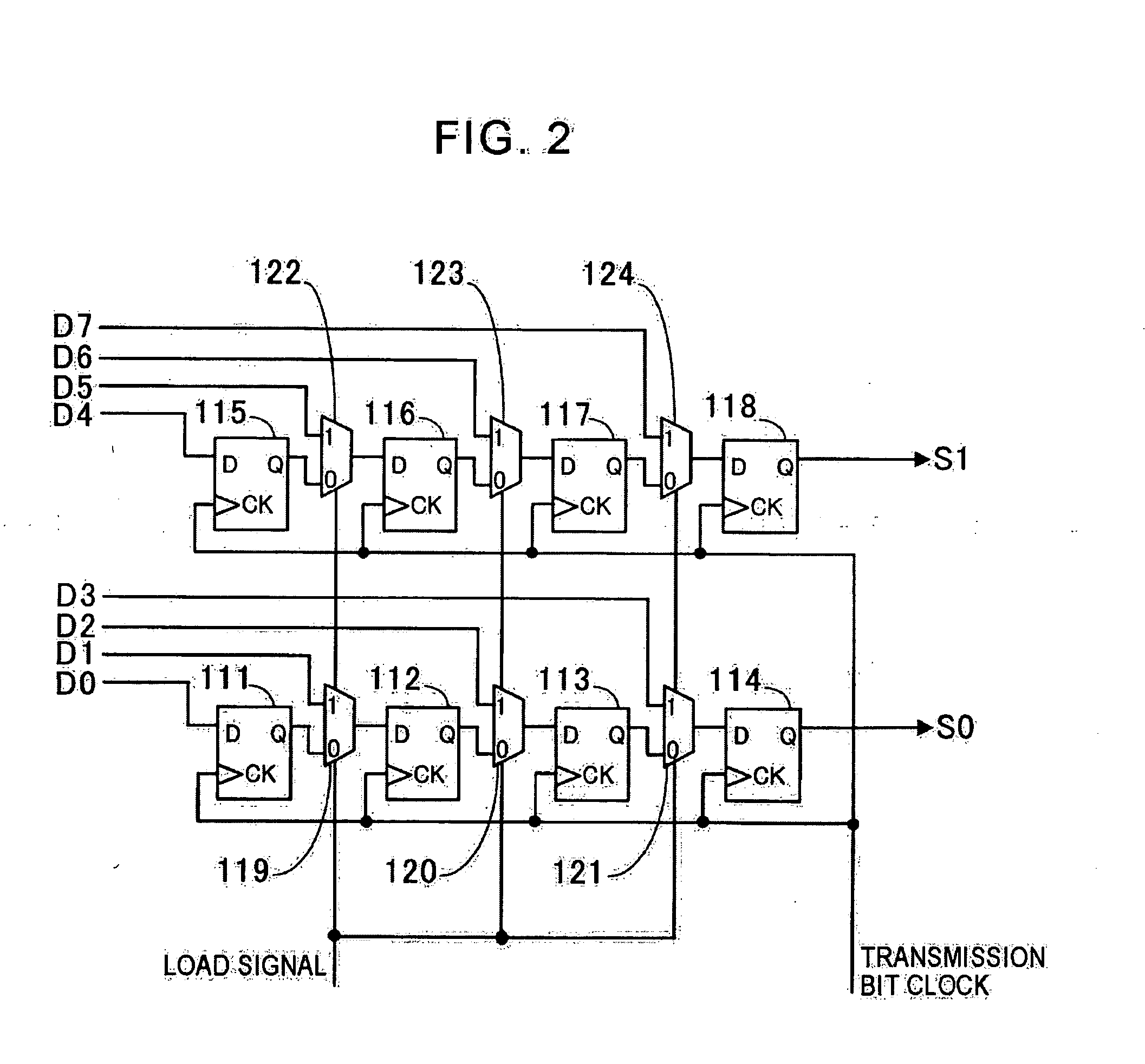

Data transfer system and method, data transmitter, data receiver, data transmission method, and data reception method

ActiveUS20050147178A1Simple structureReduce componentsParallel/series conversionLogic circuits characterised by logic functionTransfer systemWord clock

The present invention provides a data transfer system including a data transmitter and a data receiver. The data transmitter converts a plurality of bits of transmission parallel data into serial data and generates a multi-level logic signal representing a plurality of bits of information in one symbol, the information being obtained by combining the serial data with a word clock as one-bit information. The word clock indicates a word delimiter in the serial data. The data receiver receives the transmitted multi-level logic signal, extracts the serial data and the word clock from the signal, and reproduces the parallel data based on the extracted word clock. In the data transfer system, a multi-bit digital signal can be transmitted as one signal including a word clock. Thus, components and mounting space to be allocated to transfer can be reduced.

Owner:SONY CORP

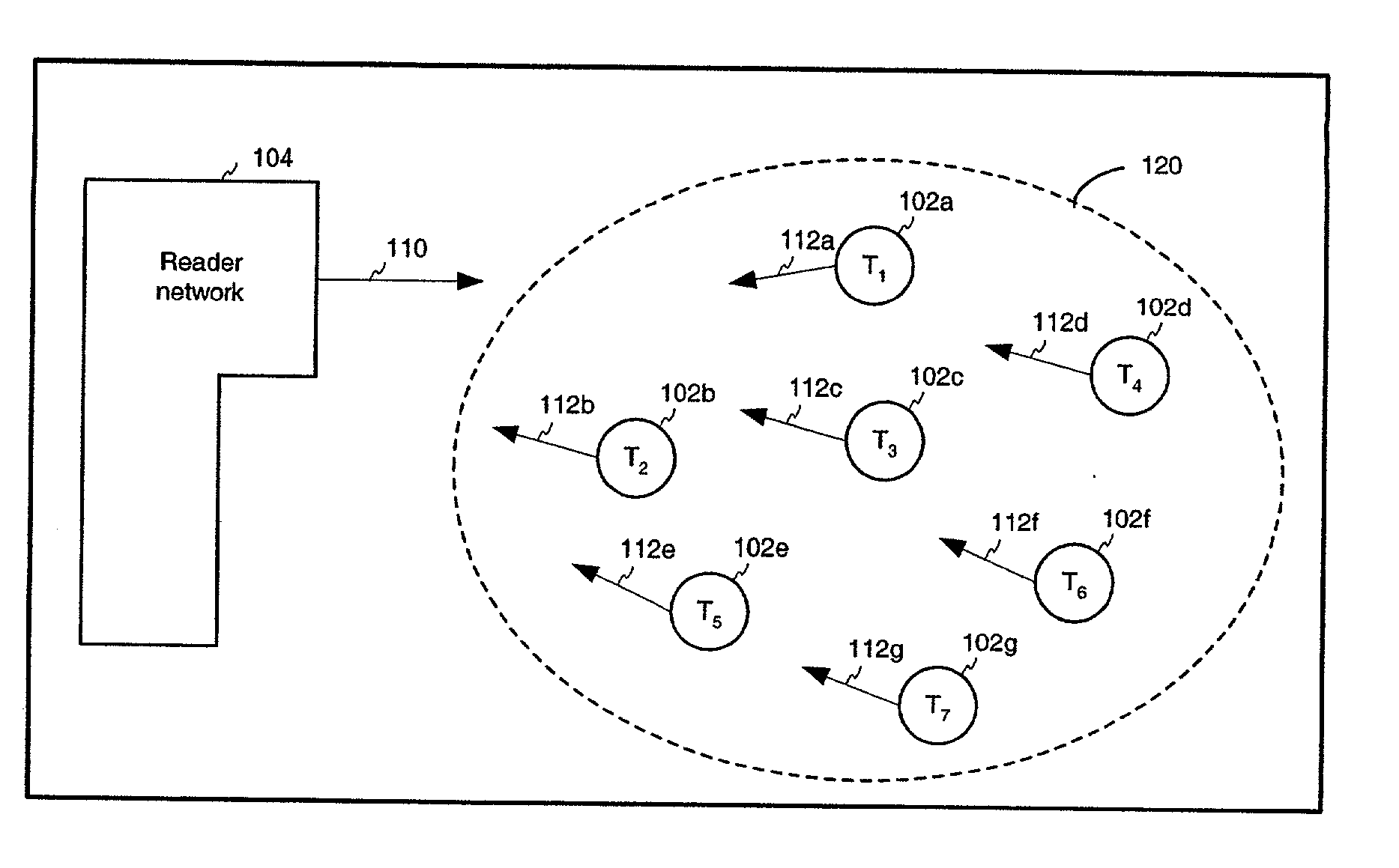

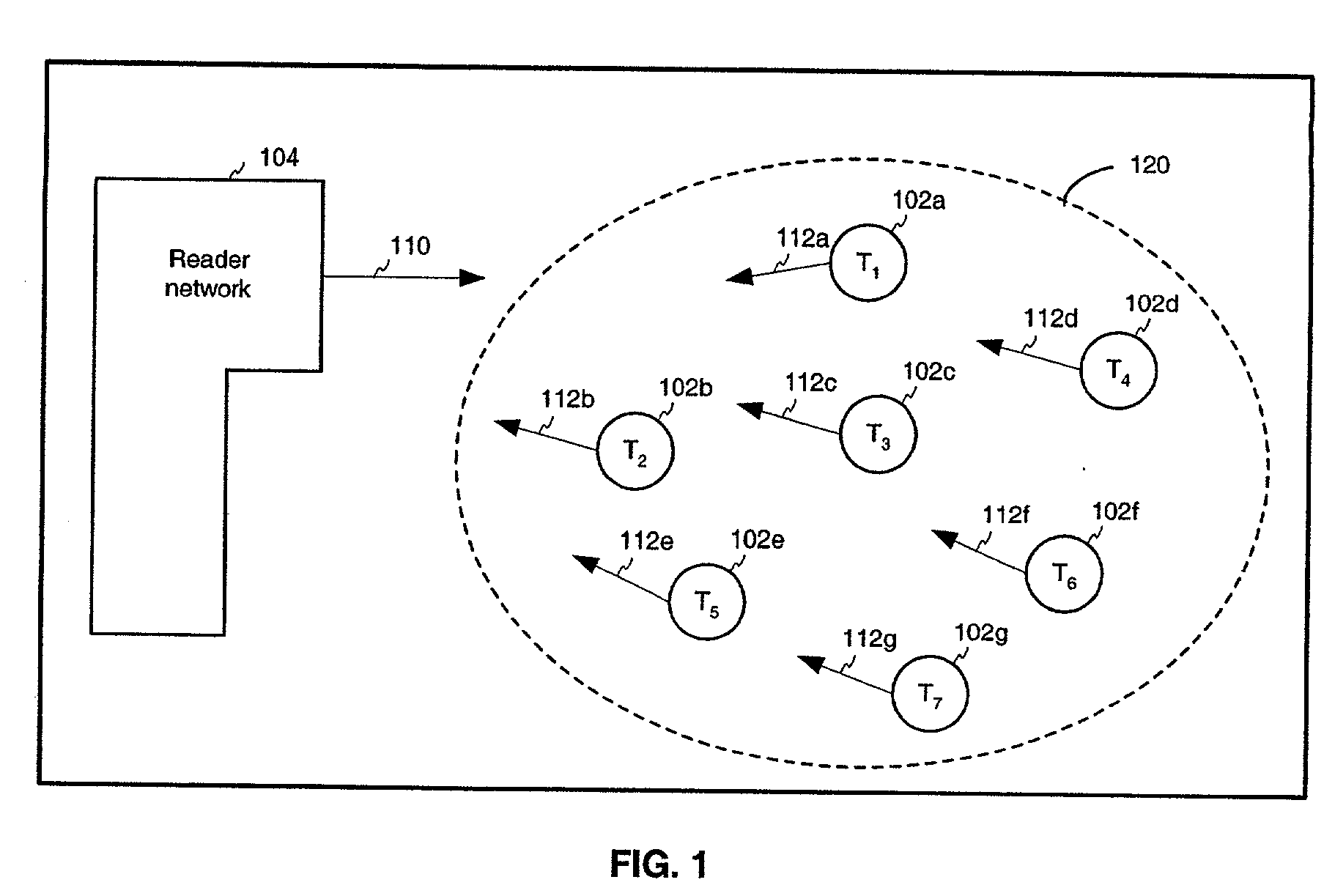

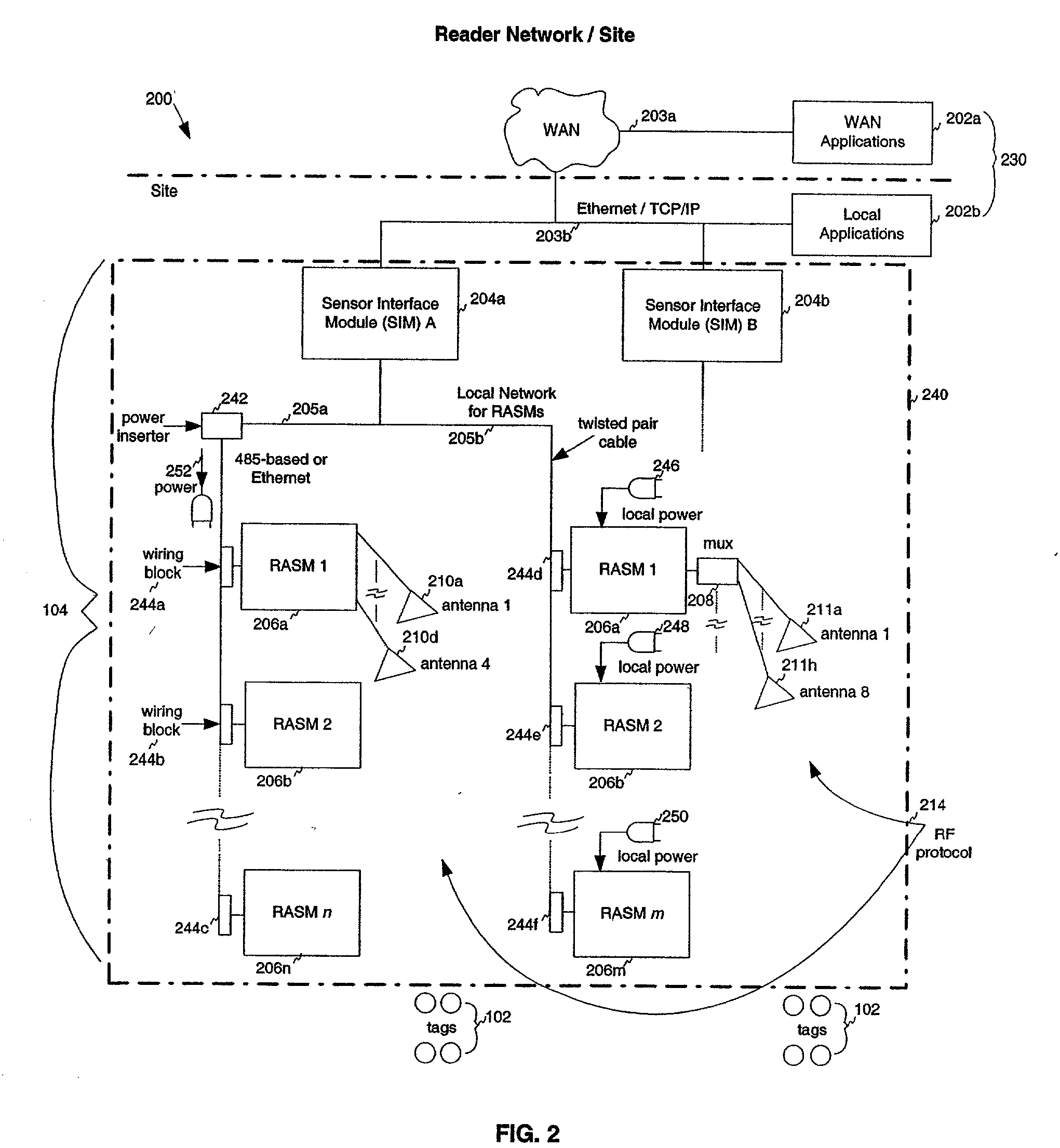

Method, system, and apparatus for remote data calibration of a RFID tag population

InactiveUS20020149480A1Processing intensiveHigh data rateMemory record carrier reading problemsCo-operative working arrangementsData calibrationComputer science

A method, system, and apparatus for remotely calibrating data symbols received by a radio frequency identification (RFID) tag population are described. Tags are interrogated by a reader, which may be located in a network of readers. The reader transmits data symbols to the tags. Tags respond to the interrogations with symbols that each represent one or more bits of data. To calibrate the tags, the reader transmits a plurality of pulses of different lengths to the tag population. The tags receive the plurality of pulses. A characteristic of each pulse, such as a pulse length, is stored by the tags. The stored pulse lengths are used to define different data symbols that are subsequently received by the tags from the reader.

Owner:SYMBOL TECH LLC

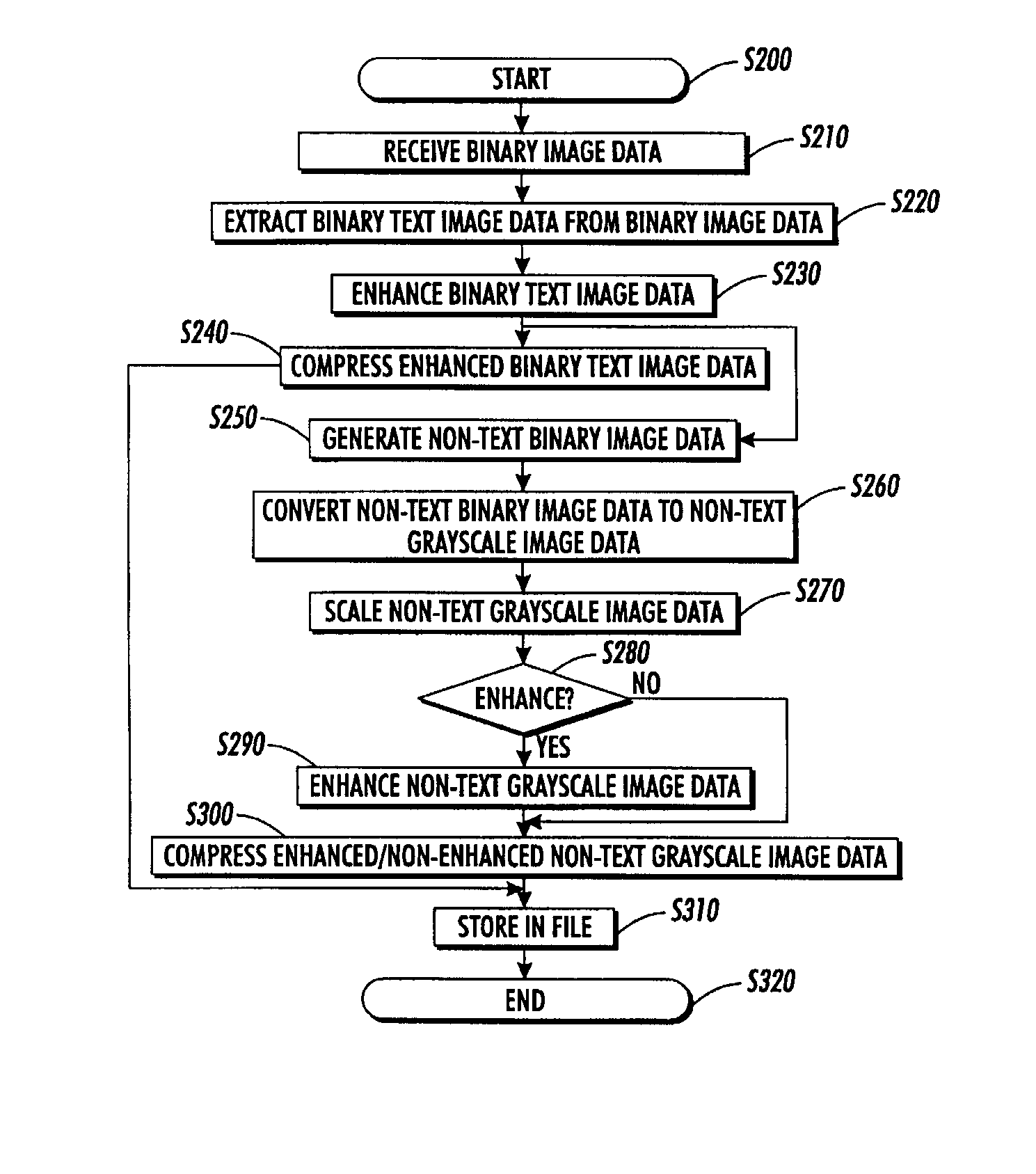

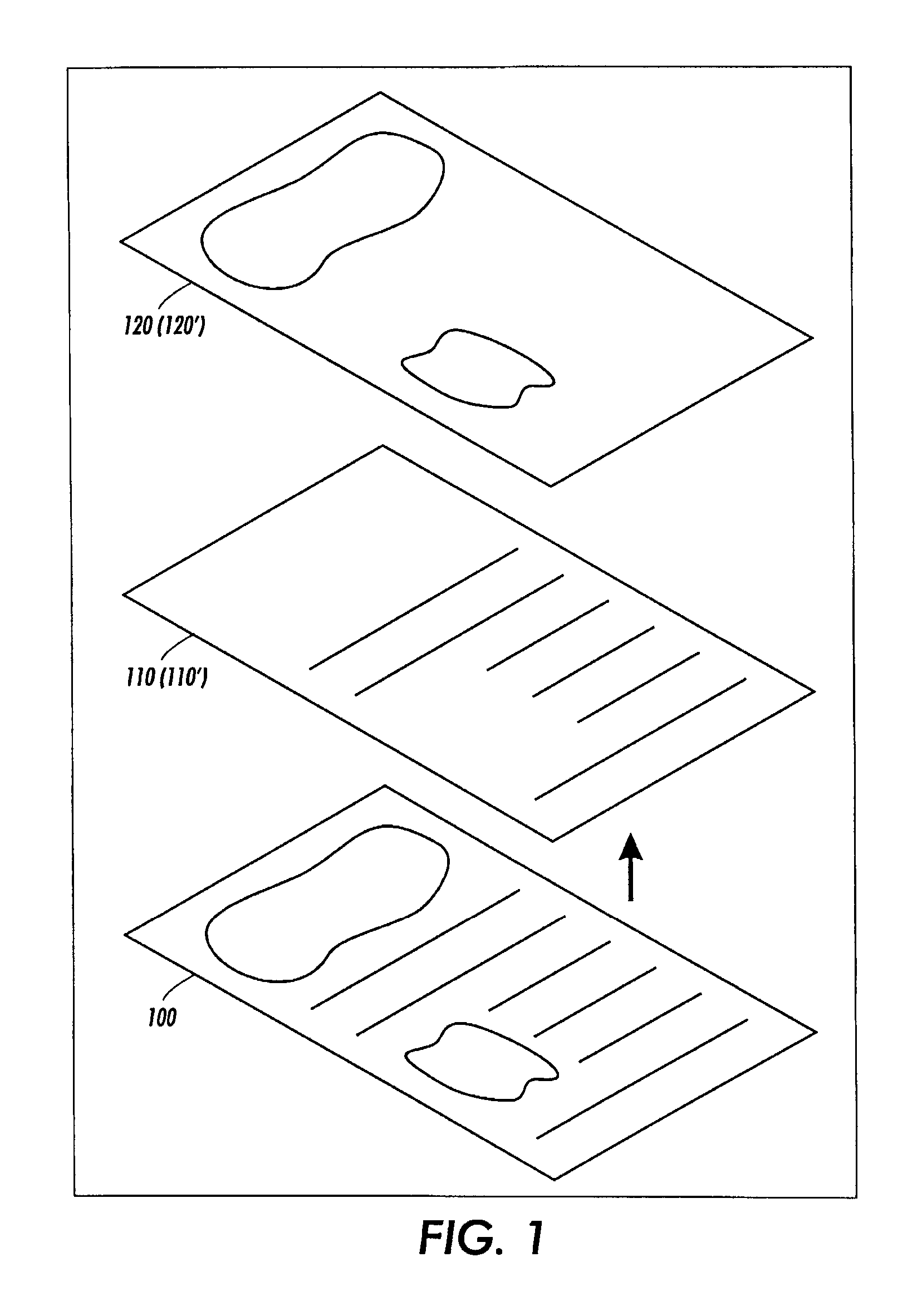

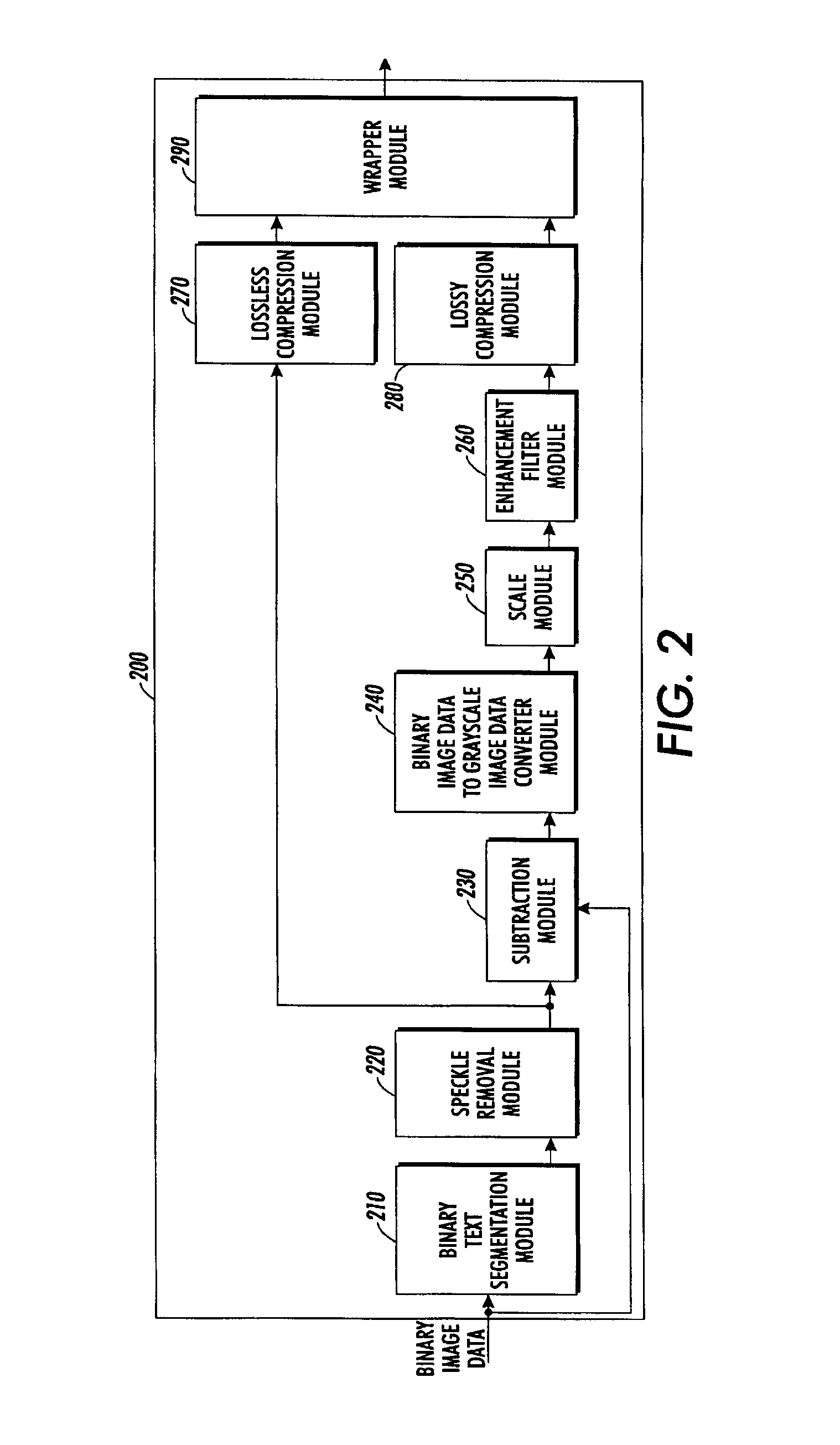

Reformatting binary image data to generate smaller compressed image data size

InactiveUS20050244060A1Stable changeEnhancing binary image data image dataCharacter and pattern recognitionPulse conversionComputer visionImaging data

In various exemplary embodiments, systems include a segmentor to segment text binary image data to a first plane. A subtractor subtracts text binary image from binary image data to generate a non-text binary image data in a second plane. A converter converts non-text binary image data in the second plane into non-text gray scale image data in the second plane. A first compressor compresses the text gray scale image data in the first plane. A second compressor compresses the non-text gray scale mage in the second plane.

Owner:XEROX CORP

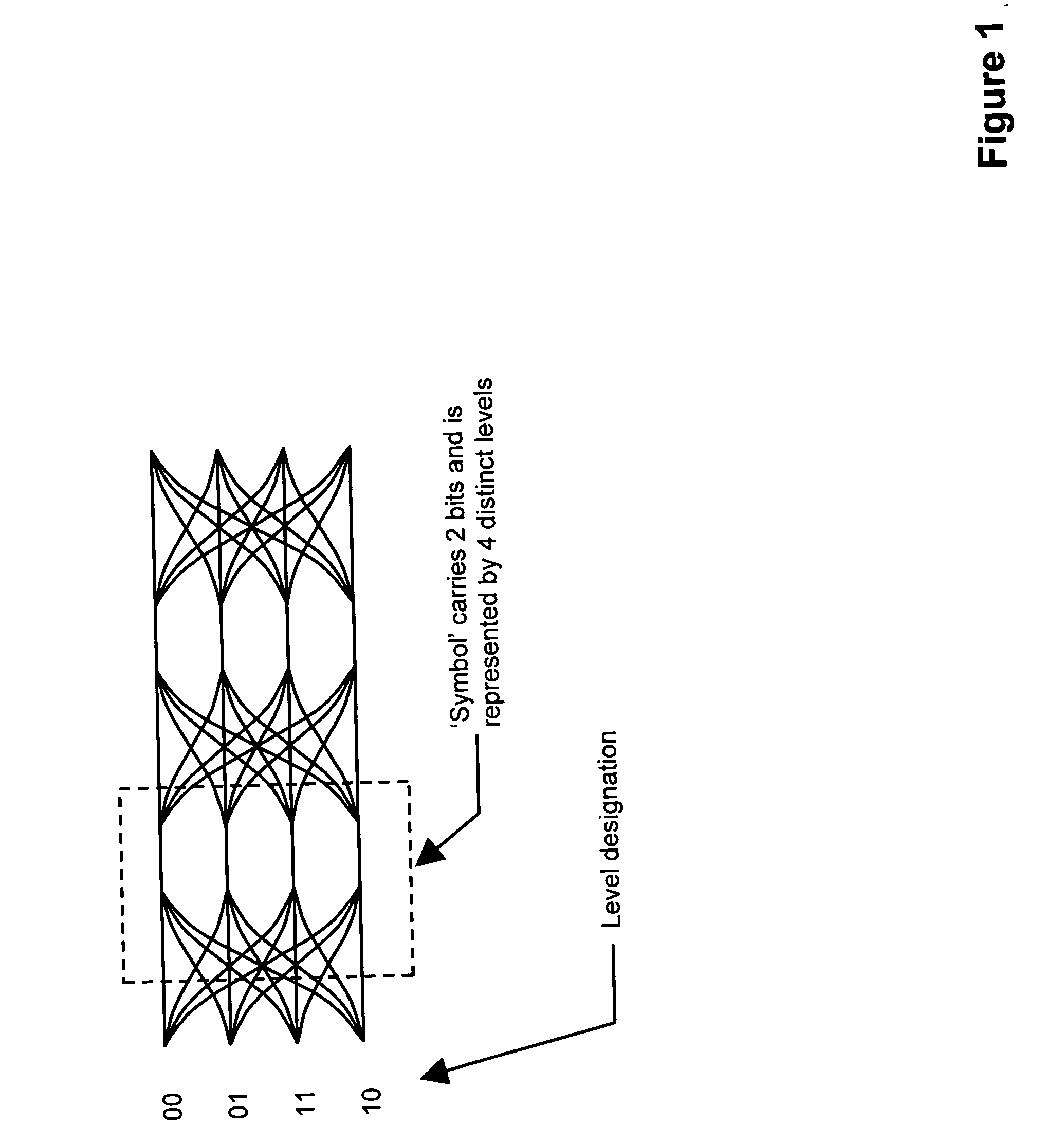

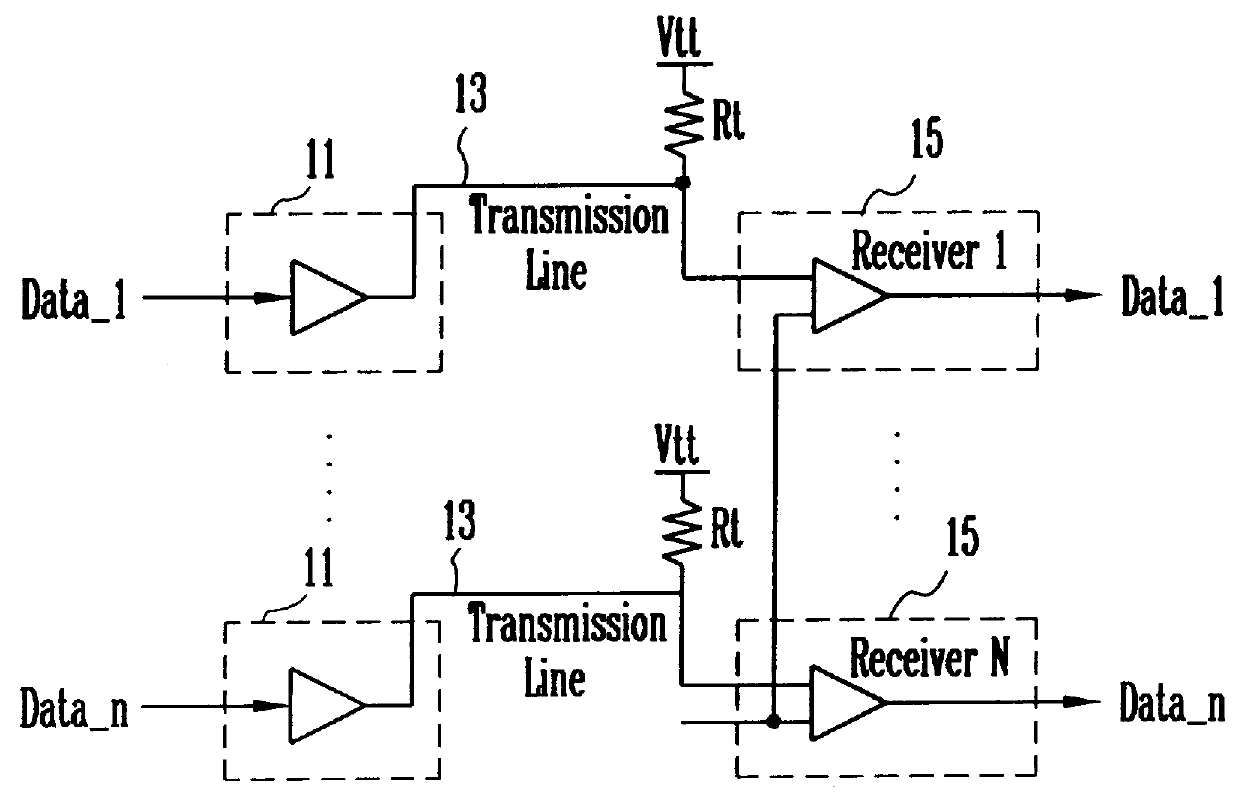

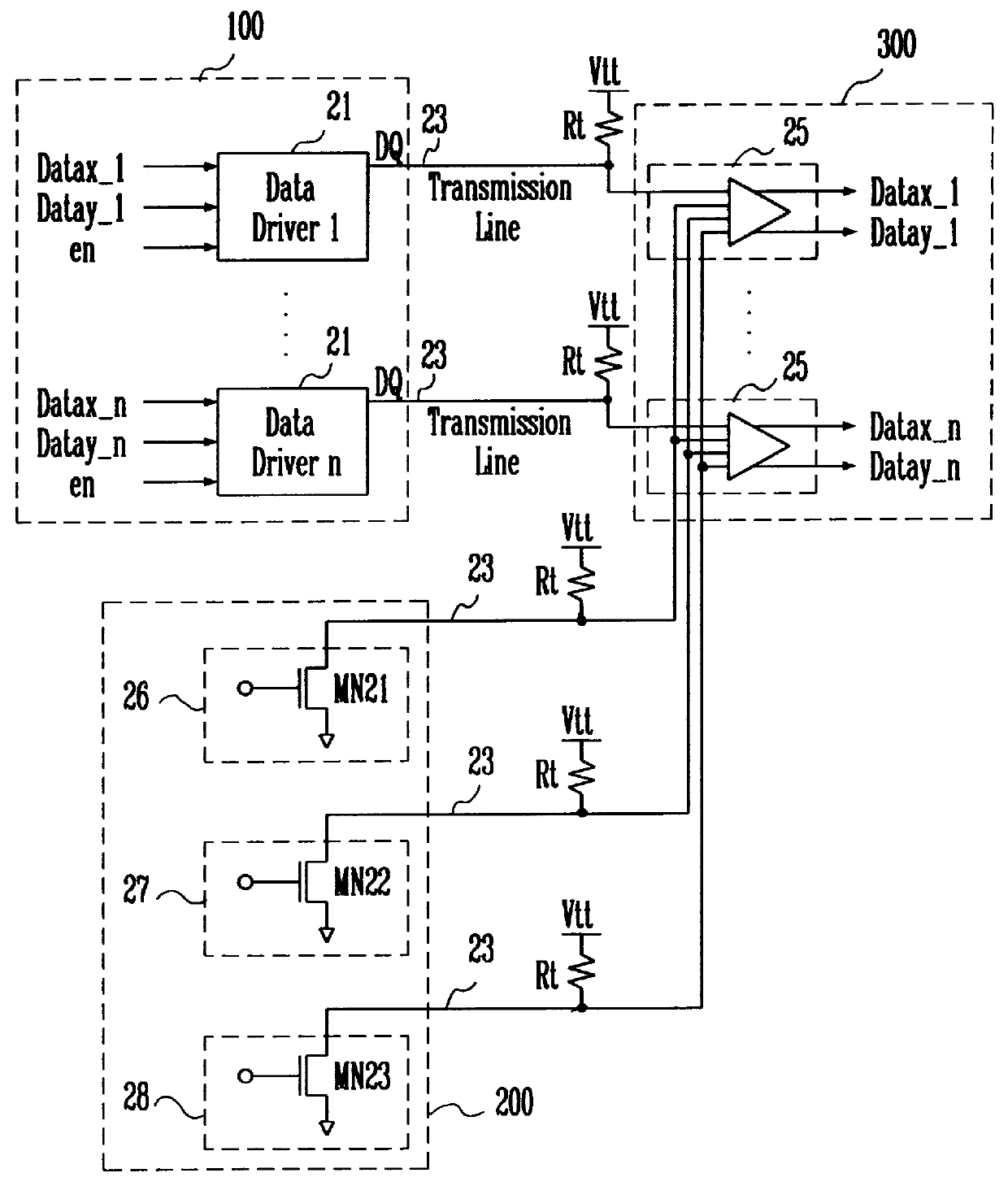

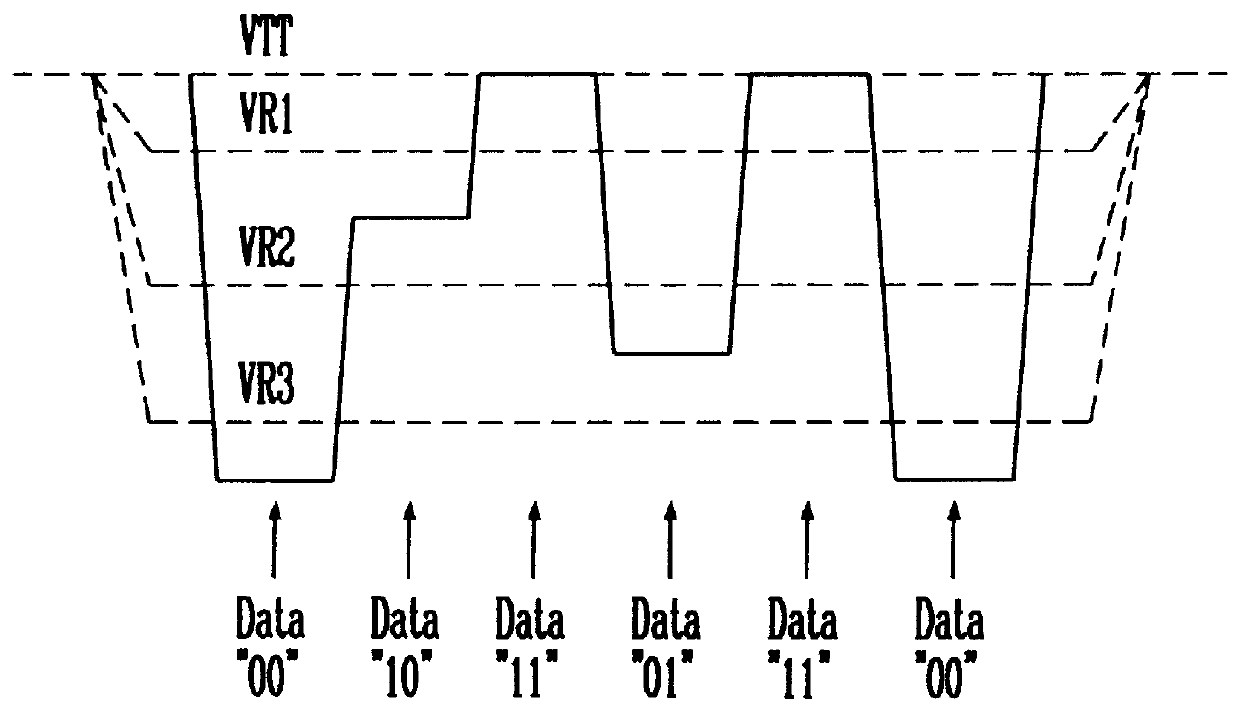

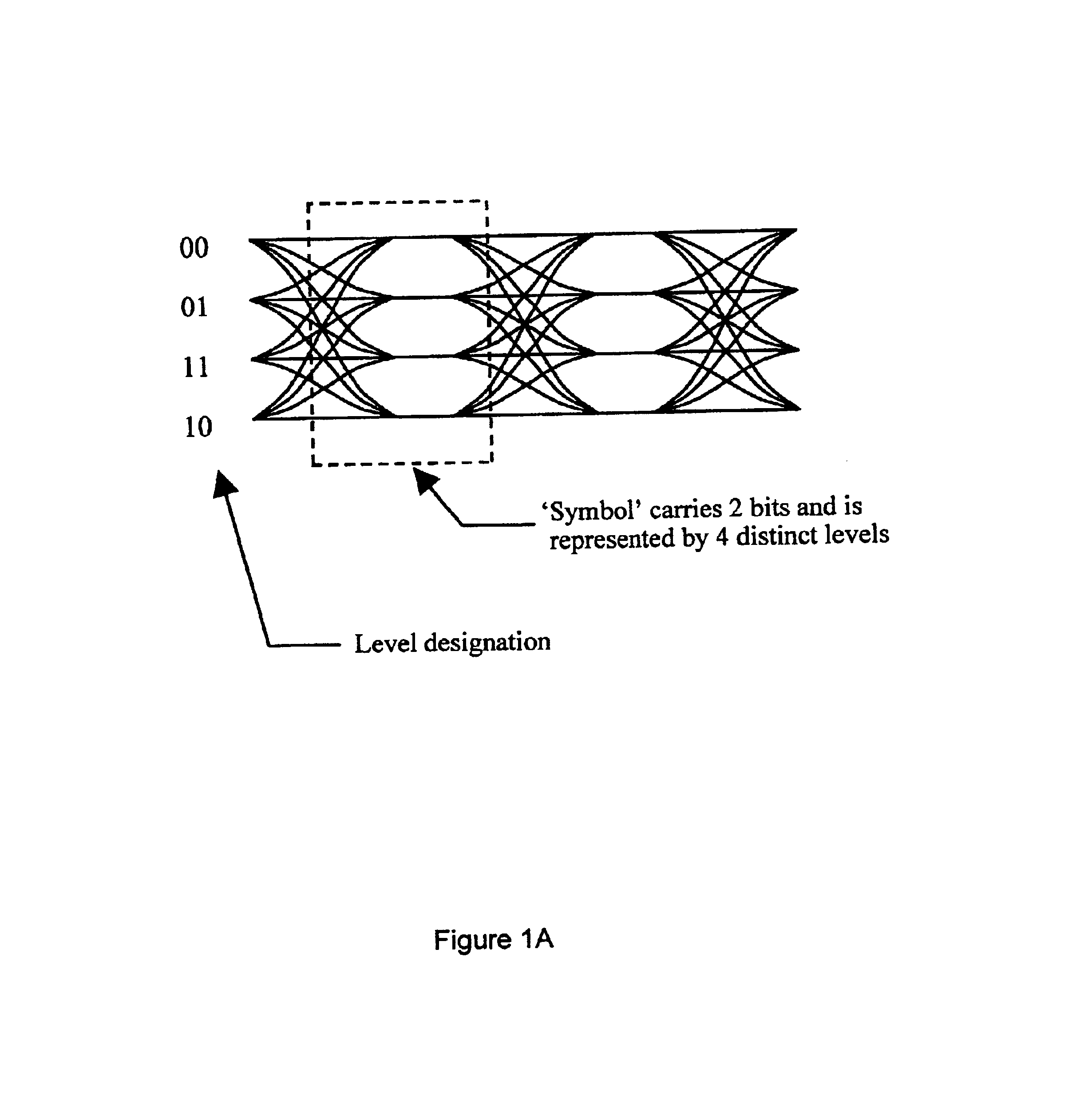

High speed interface apparatus

InactiveUS6140841AElectric signal transmission systemsElectric analogue storesThree levelData signal

The present invention discloses a much higher speed interface apparatus which comprises a data driving means for decoding two-bit data signals using them as inputs to output four-level data signals; a reference voltage generating means for generating three-level reference voltages to discriminate the voltage levels of the four-level data signals; and a receiver means for comparing the four-level data signals and the three-level reference voltage signals using them as inputs and for encoding the resulting signals to output two data signals.

Owner:HYUNDAI ELECTRONICS IND CO LTD

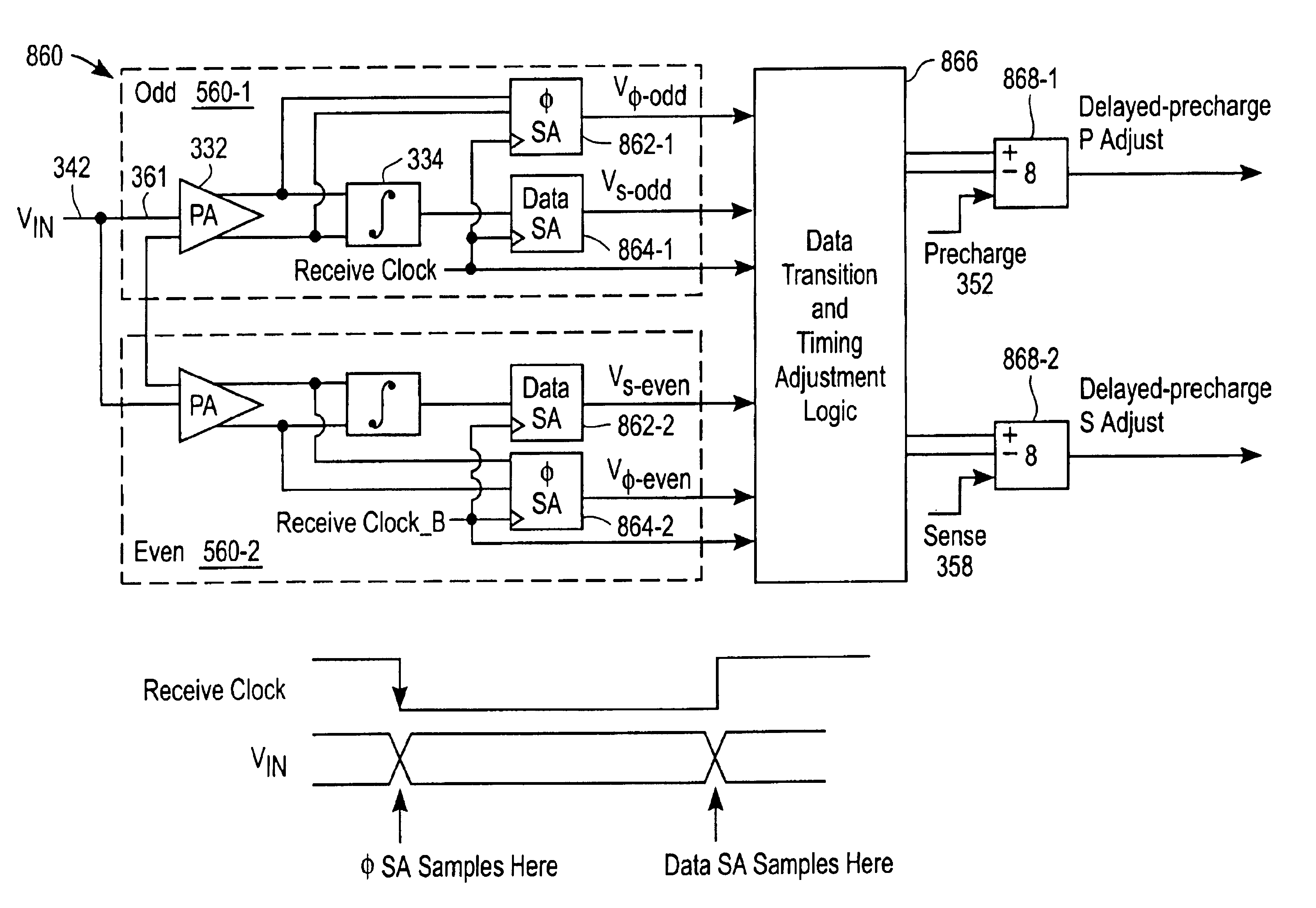

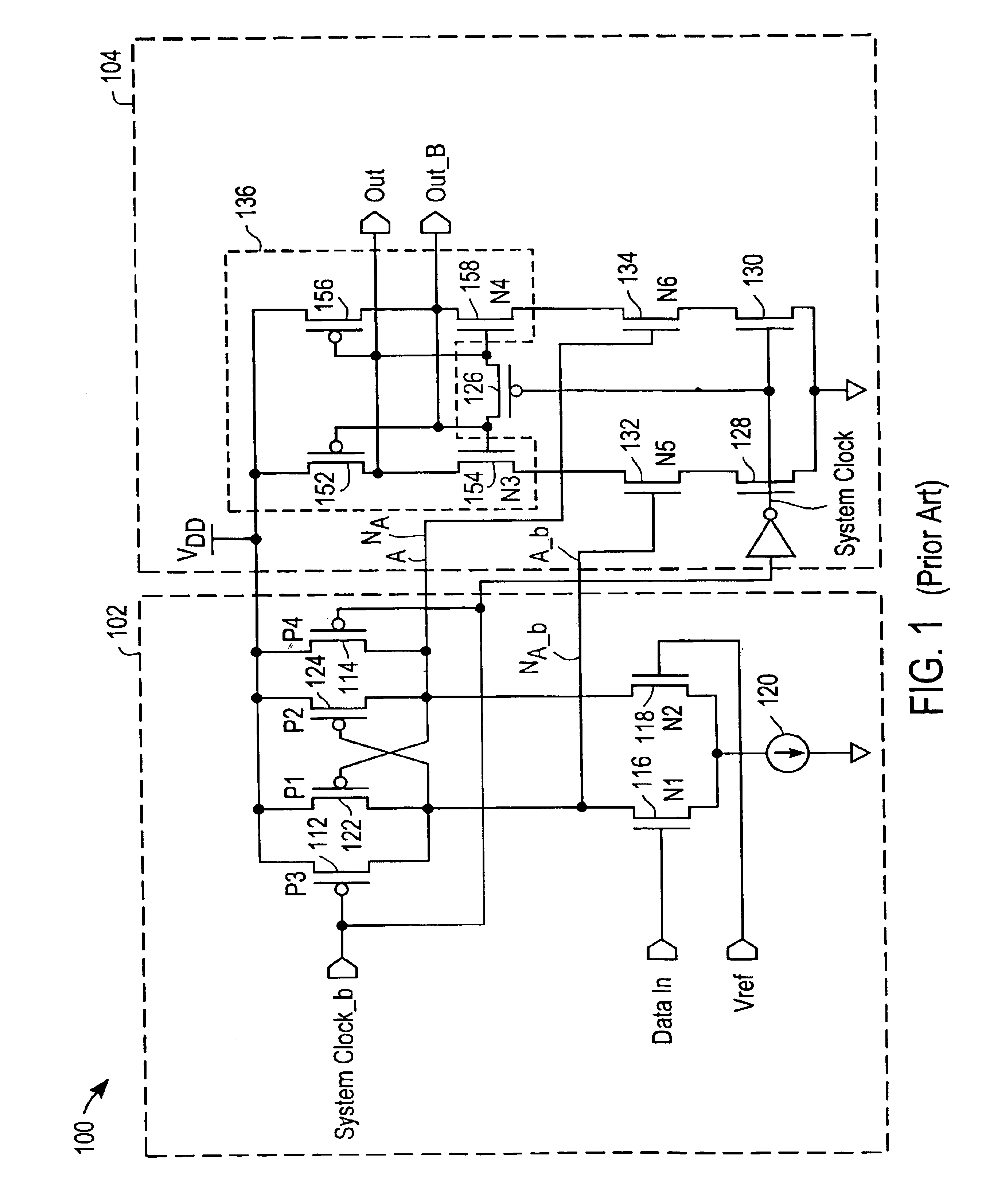

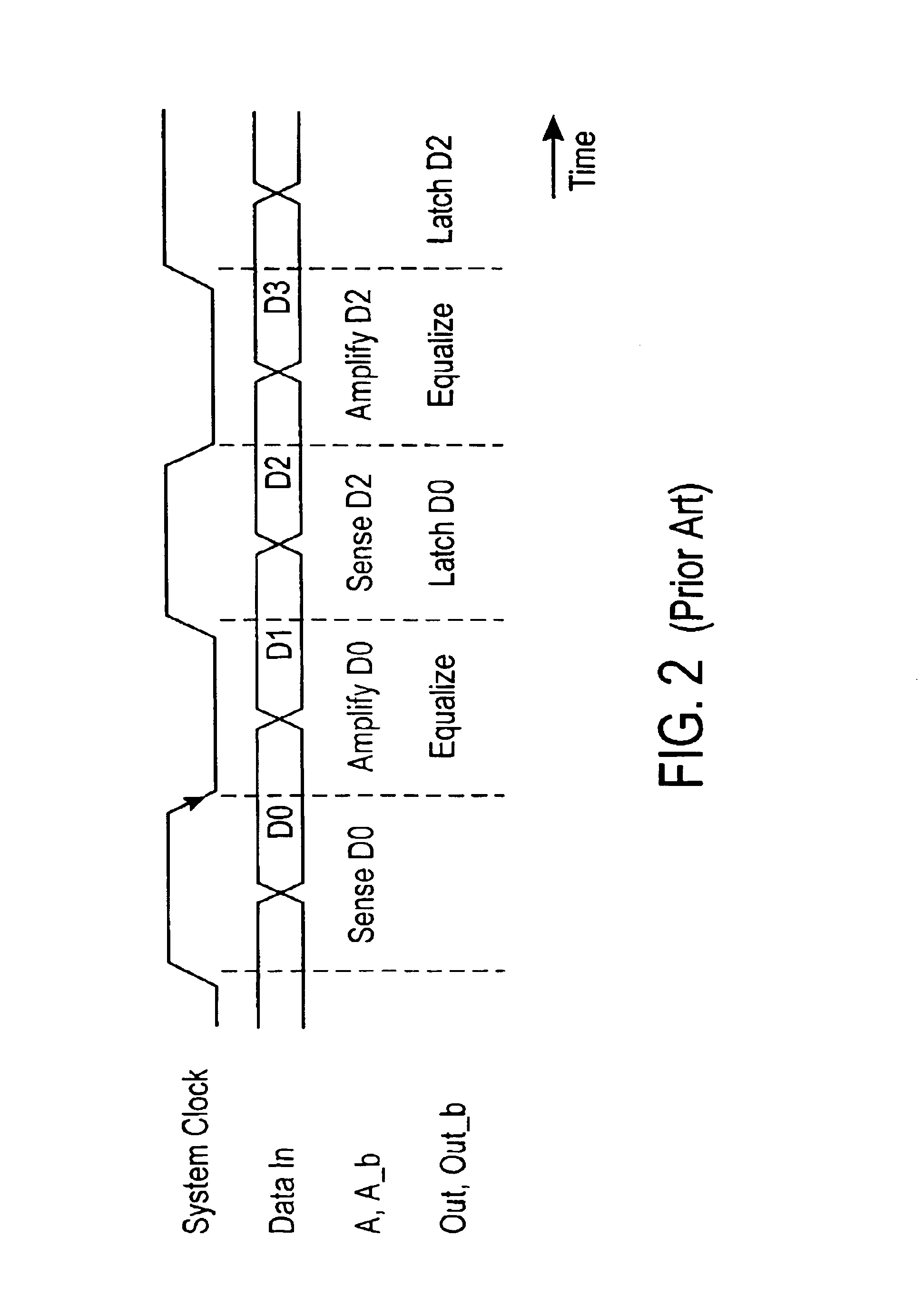

Method and apparatus for receiving high speed signals with low latency

InactiveUS6965262B2Reduces input-to-output latencyReduce static power consumptionDigital differential analysersDigital storageIntegratorAudio power amplifier

An apparatus and method for receiving high-speed signals having a wide common-mode range with low input-to-output latency. In one embodiment, the receiver includes an integrator to accumulate charge in accordance with an input signal during an integration time interval to produce an output voltage. A sense amplifier samples and converts the output voltage of the integrator to a logic signal; and a latch stores the logic signal. In an alternate embodiment, a preamplifier conditions the input signal prior to being integrated. In another embodiment using multiple receivers, circuitry is added to the receiver to compensate for timing errors associated with the distribution of the timing signals. In yet another embodiment, the integrator is coupled to an equalization circuit that compensates for intersymbol interference. In another embodiment, another circuit compensates for accumulated voltage offset errors in the integrator.

Owner:RAMBUS INC

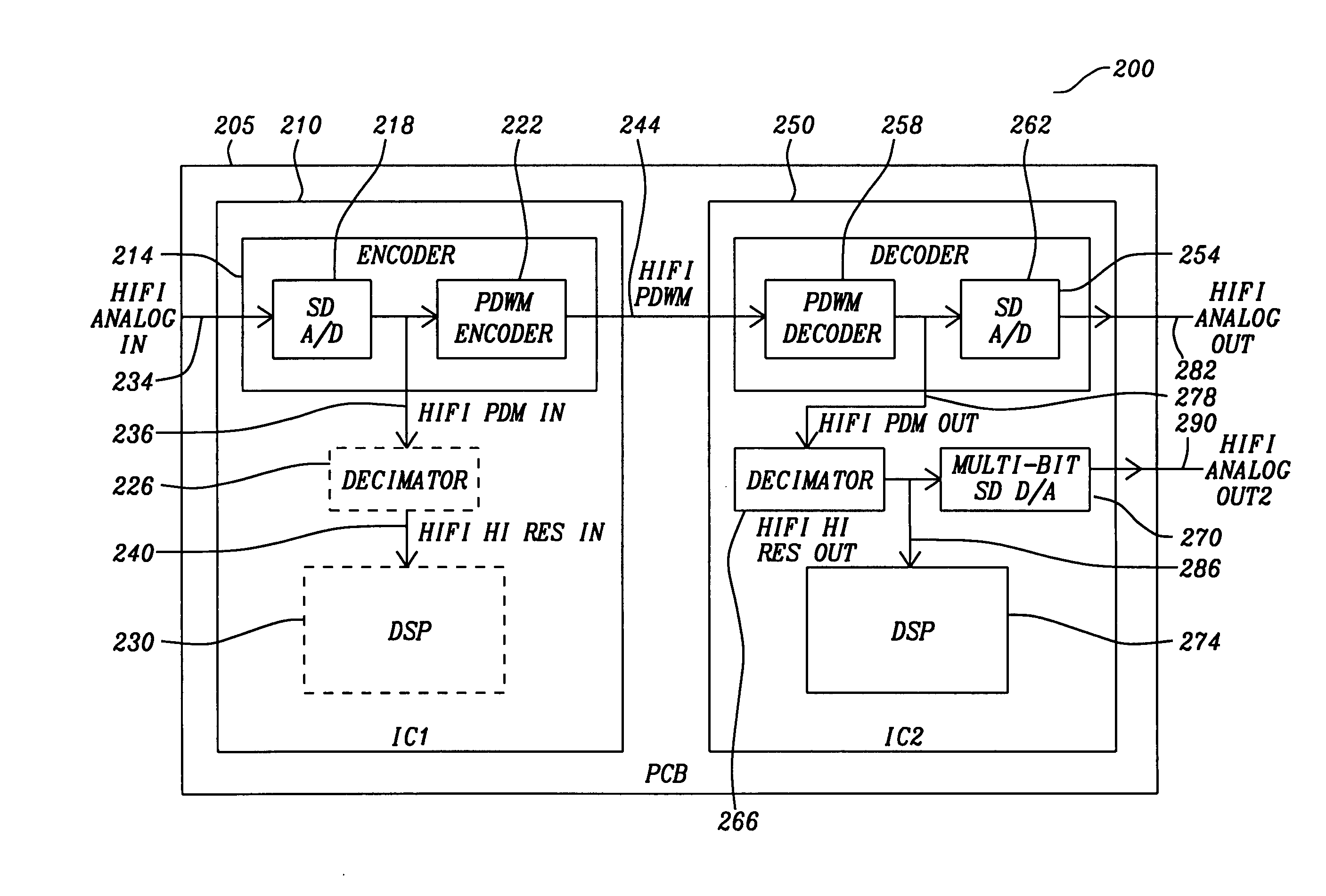

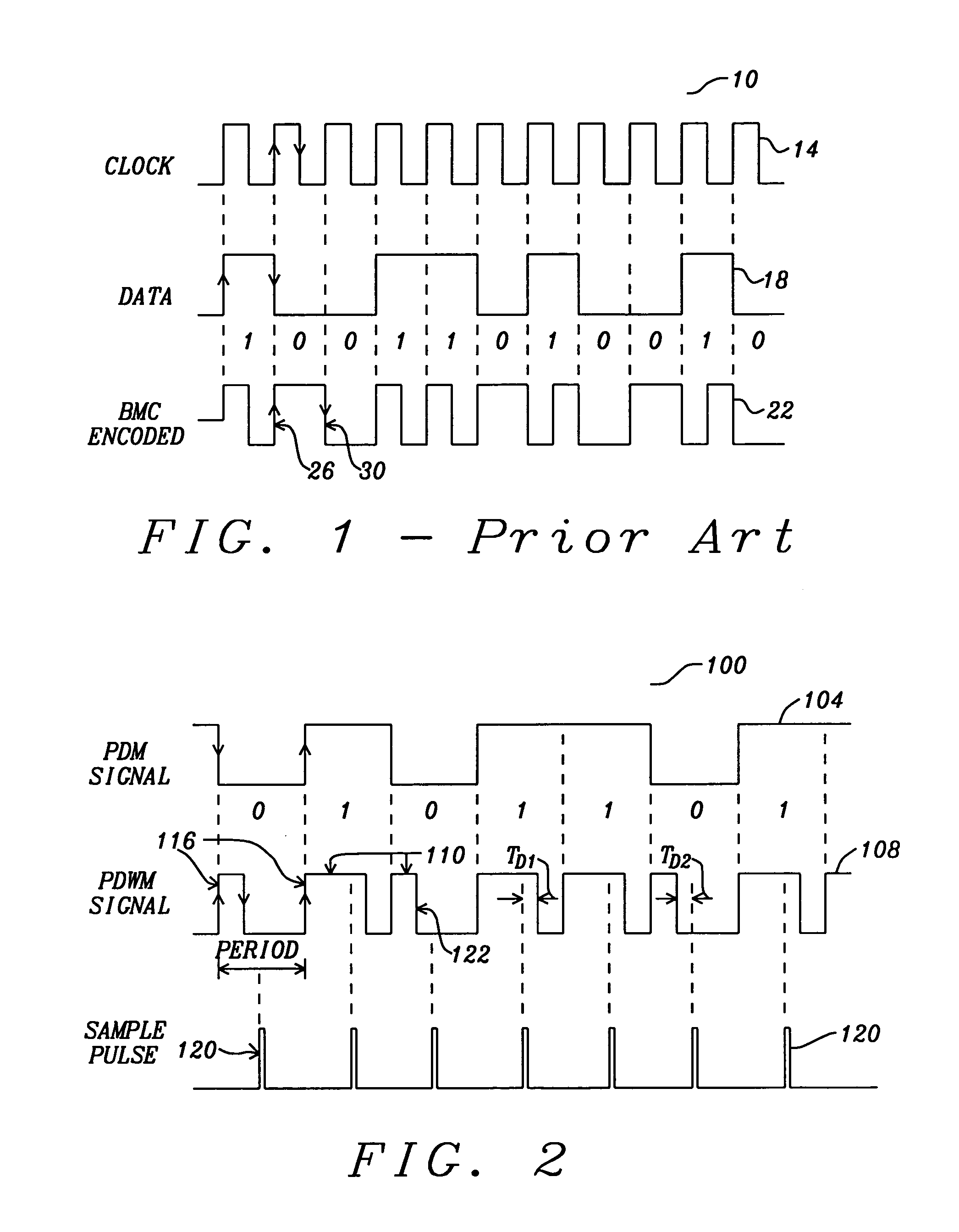

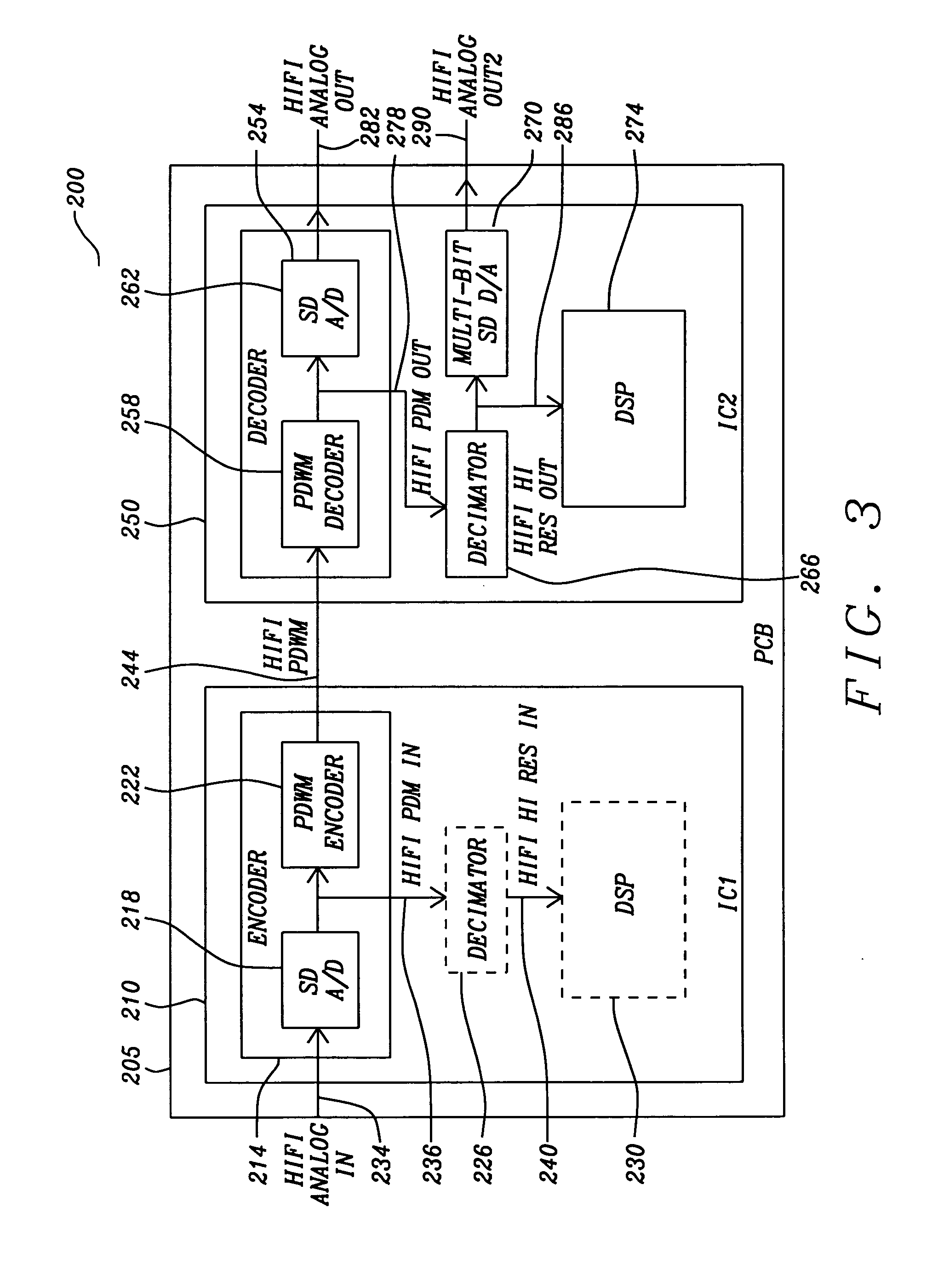

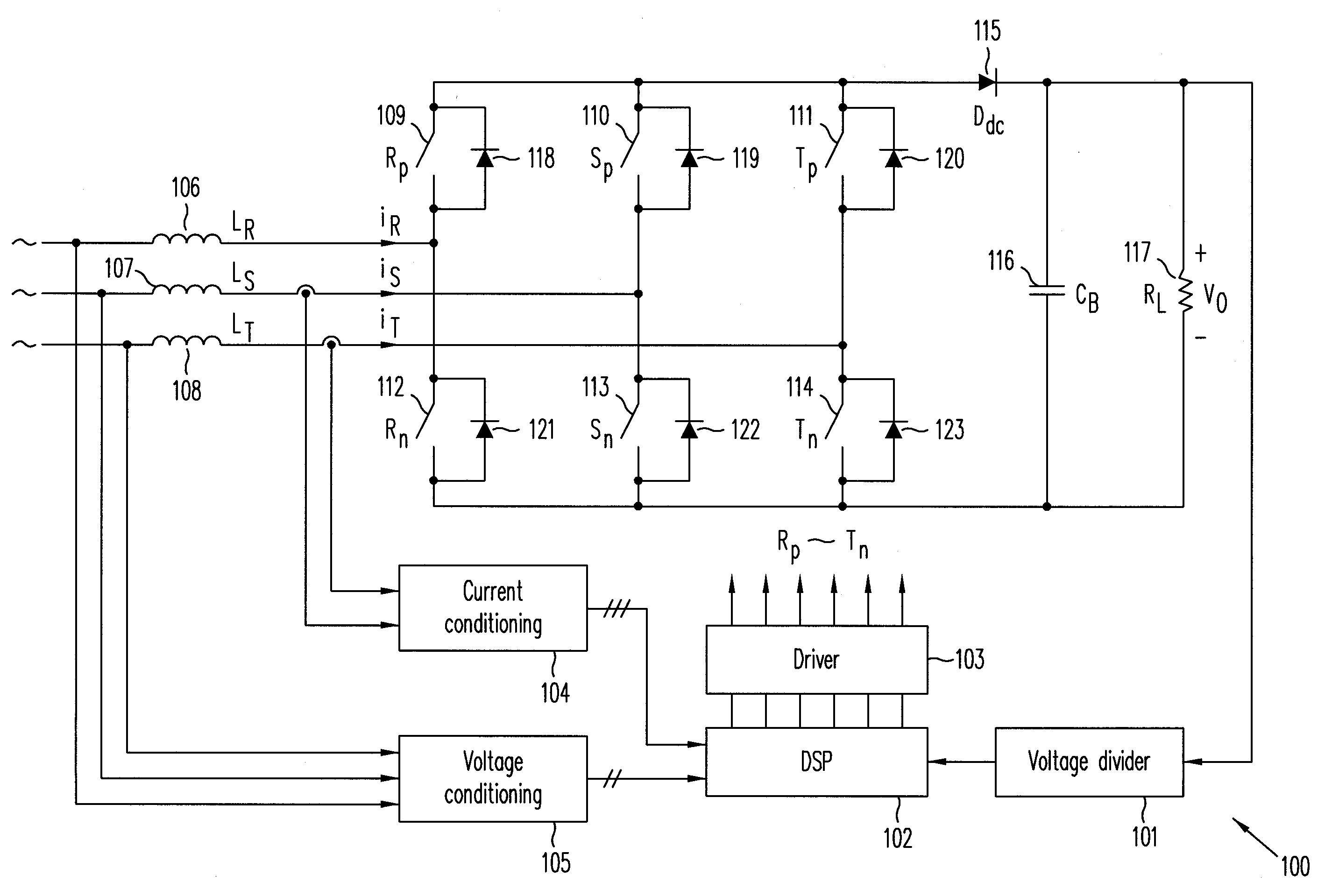

Device and method for the transmission and reception of high fidelity audio using a single wire

An audio device (200) includes a first and second ICs (210) and (250) and a substrate (205). The first IC includes a sigma-delta, A / D converter (218) operable to convert an analog signal (234) into a pulse density modulated signal (236). A pulse density width modulator encoder (222) is operable to encode the PDM signal into a PDWM signal (244). The PDWM has short and long pulse widths defining first and second bit levels. The leading edges of each pulse bounds each pulse period. The second IC (250) includes a means (254) to receive the PDWM signal, an edge detector (304) operable to detect the leading pulse edges of the PDWM signal, a time-averaging circuit (308) operable to calculate each pulse period from the leading pulse edges and to generate a sample pulse (120) at near the midpoint of each pulse period, and a latch (312) operable to sample and hold the PDWM signal at the sample pulse to decode a PDM signal (278). The substrate is operable to support the first and second ICs and to conduct the PDWM signal between the first and second ICs.

Owner:DIALOG SEMICONDUCTOR

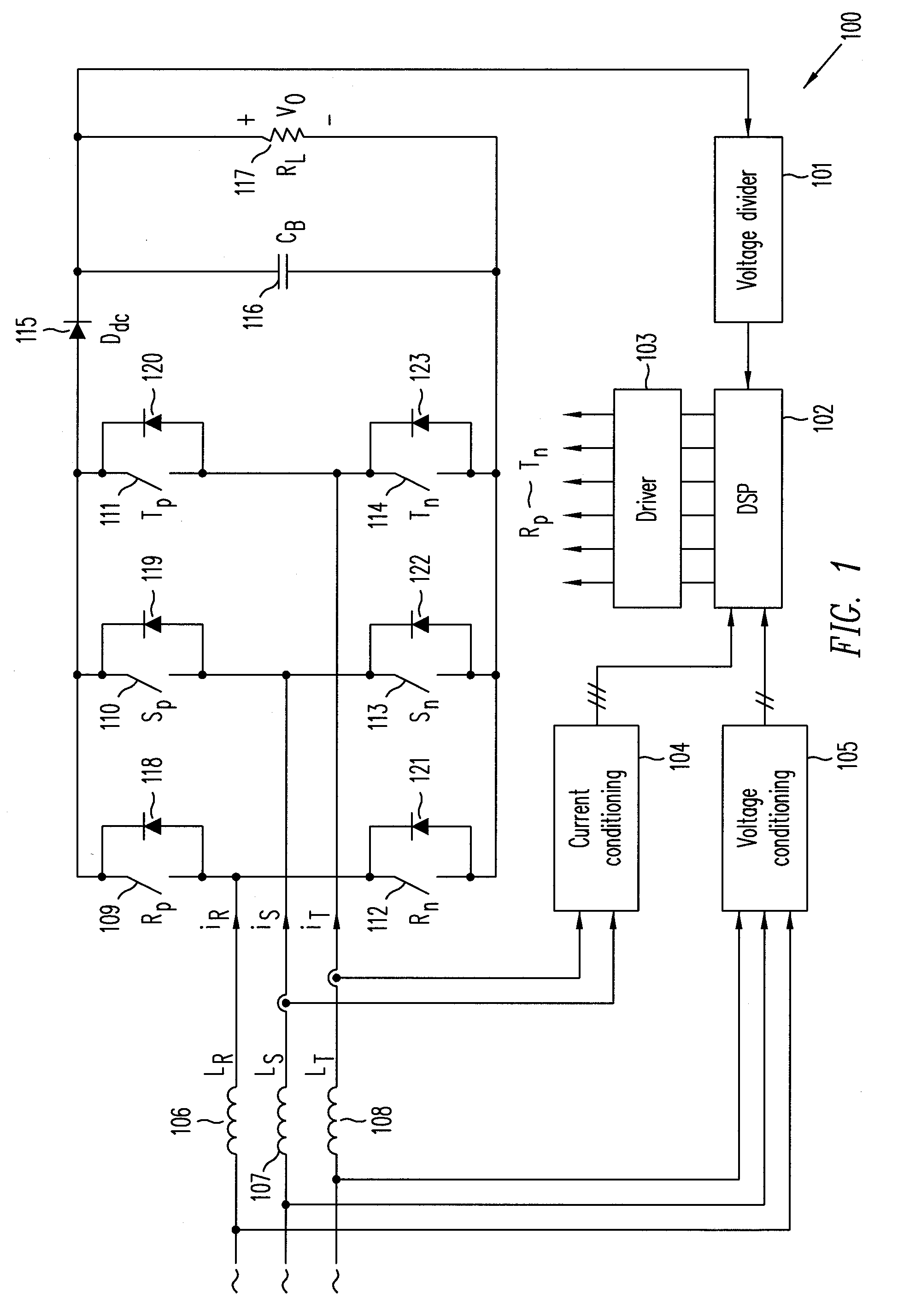

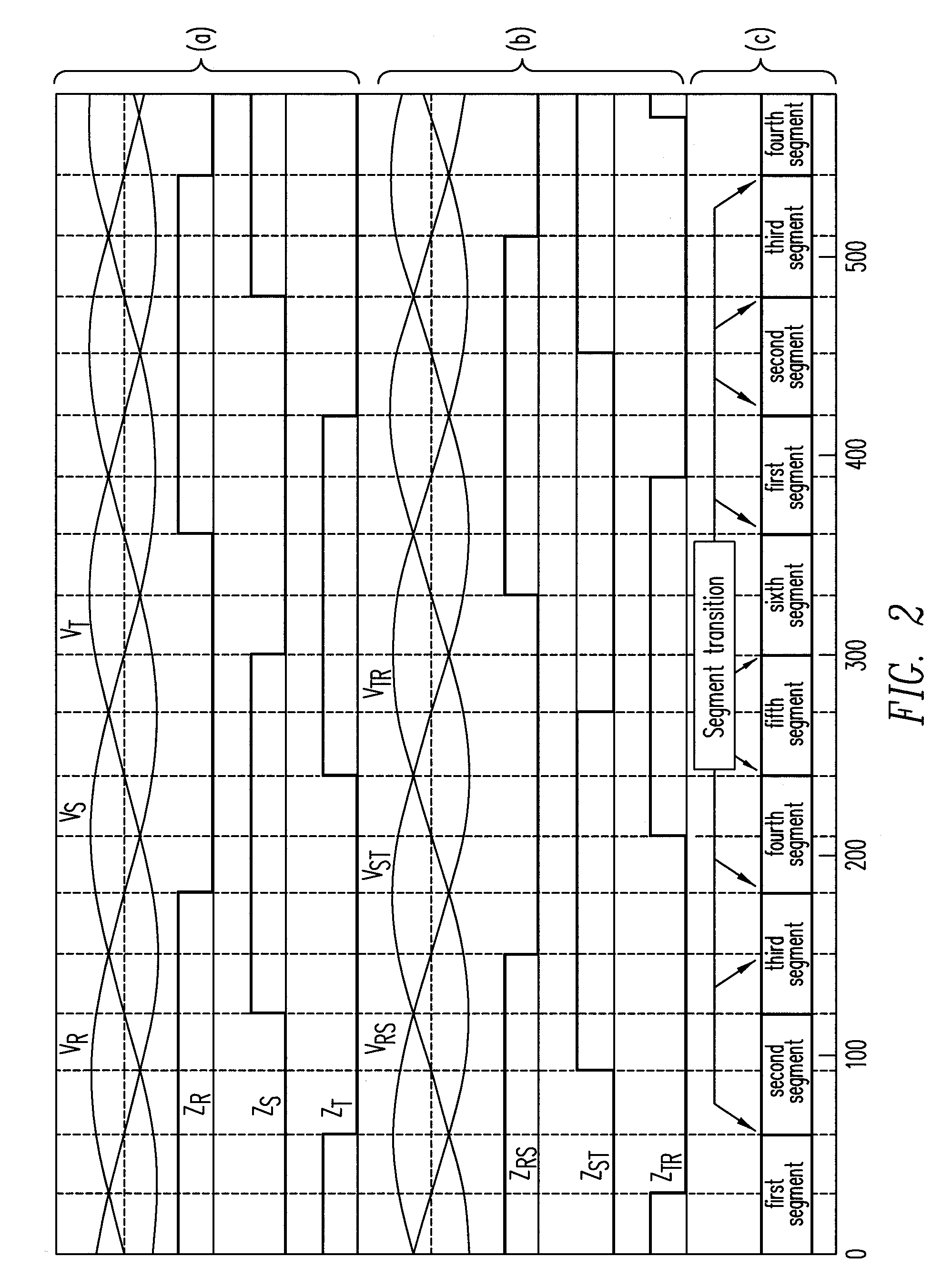

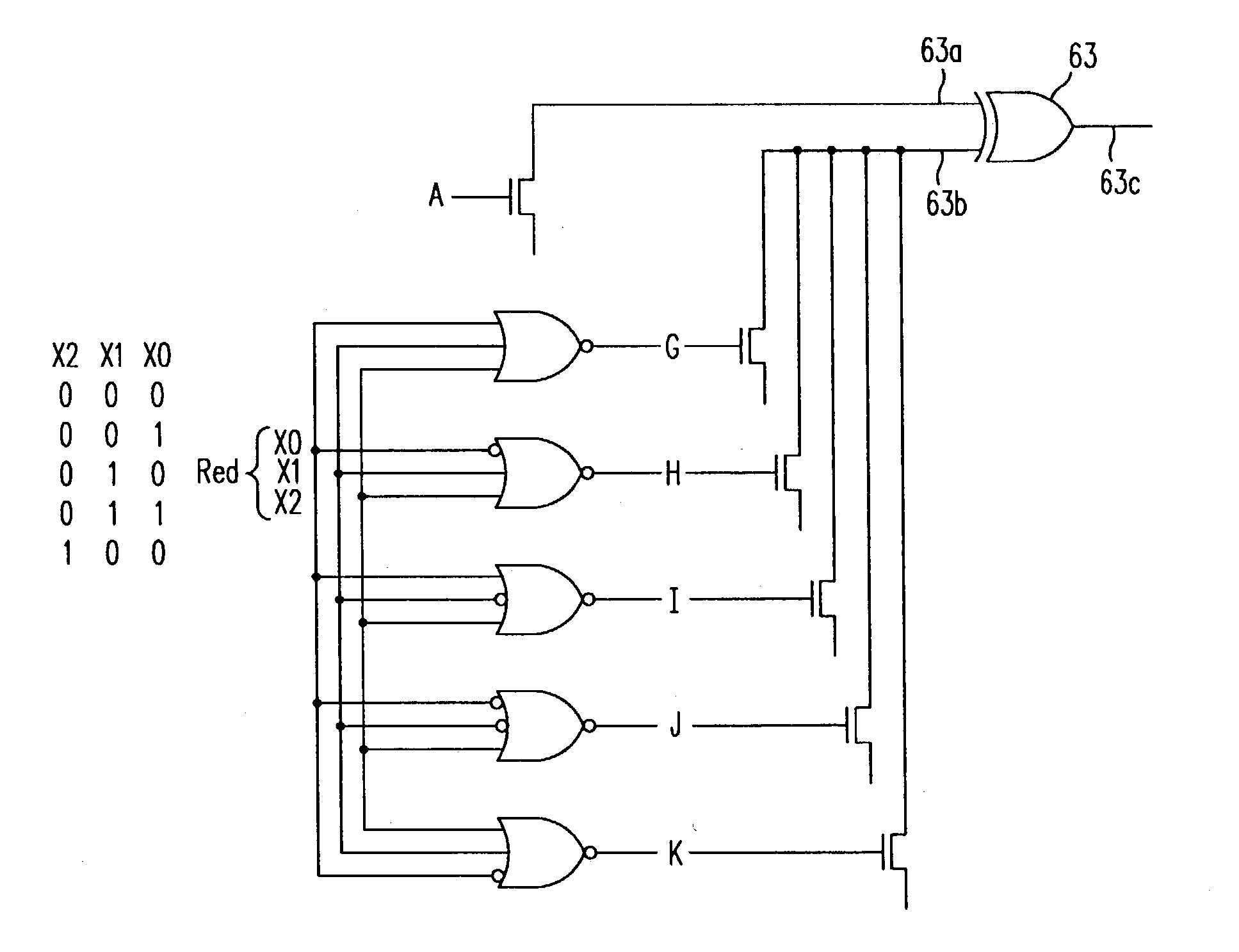

Digitally controlled three-phase pfc rectifier

ActiveUS20090122582A1Simple and practical methodPractical and convenientAc-dc conversion without reversalEfficient power electronics conversionThree-phaseInductor

A robust decoder generates an output state from input signals related to the line-voltage signals of a three-phase power system, using a segment identification method based on zero-crossings derived from line-voltage difference signals. The robust decoder includes a basic decoder that provides a current output state based on the input signals, a state table that provides a presumed previous state based on the current output state of the basic decoder, a binary feed back loop including a state element for storing a previous output state, and a selector for providing the output state based on the stored previous output state and the presumed previous state. The robust decoder may be implemented as hardware or software in a digital power converter. Such a digital power converter may include boost inductors each receiving an input line voltage signal from the three-phase power system to provide phase voltage signals, switches receiving the phase voltage signals to provide an intermediate voltage signal, the plurality of switches each being control by a driving signal, an output circuit coupled to the intermediate voltage signal to provide a rectified output voltage signal for digital power converter, and a digital control circuit receiving the input line voltages and the output voltage signal, the digital control circuit generating the driving signals to control the switches. The switches may be configured according to a state machine.

Owner:DELTA ELECTRONICS INC

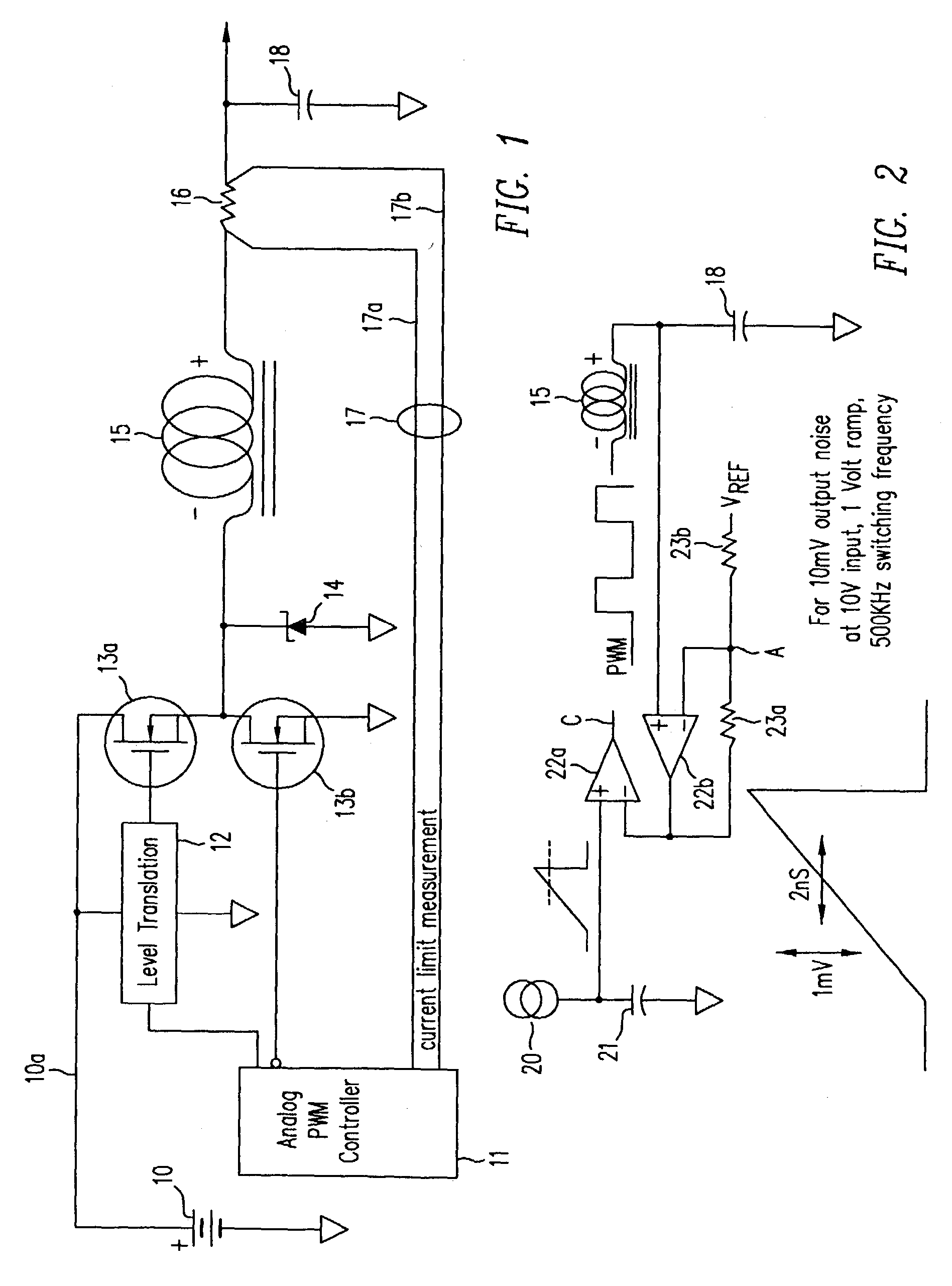

Power converter circuitry and method

InactiveUS20040095266A1Easy to makeAnalogue/digital conversionElectric signal transmission systemsControl systemEngineering

A control system and method for simultaneously regulating the operation of a plurality of different types of switching power converters. The system utilizes in regulating the power converters sampled data and nonlinear feedback control loops.

Owner:EXAR CORP

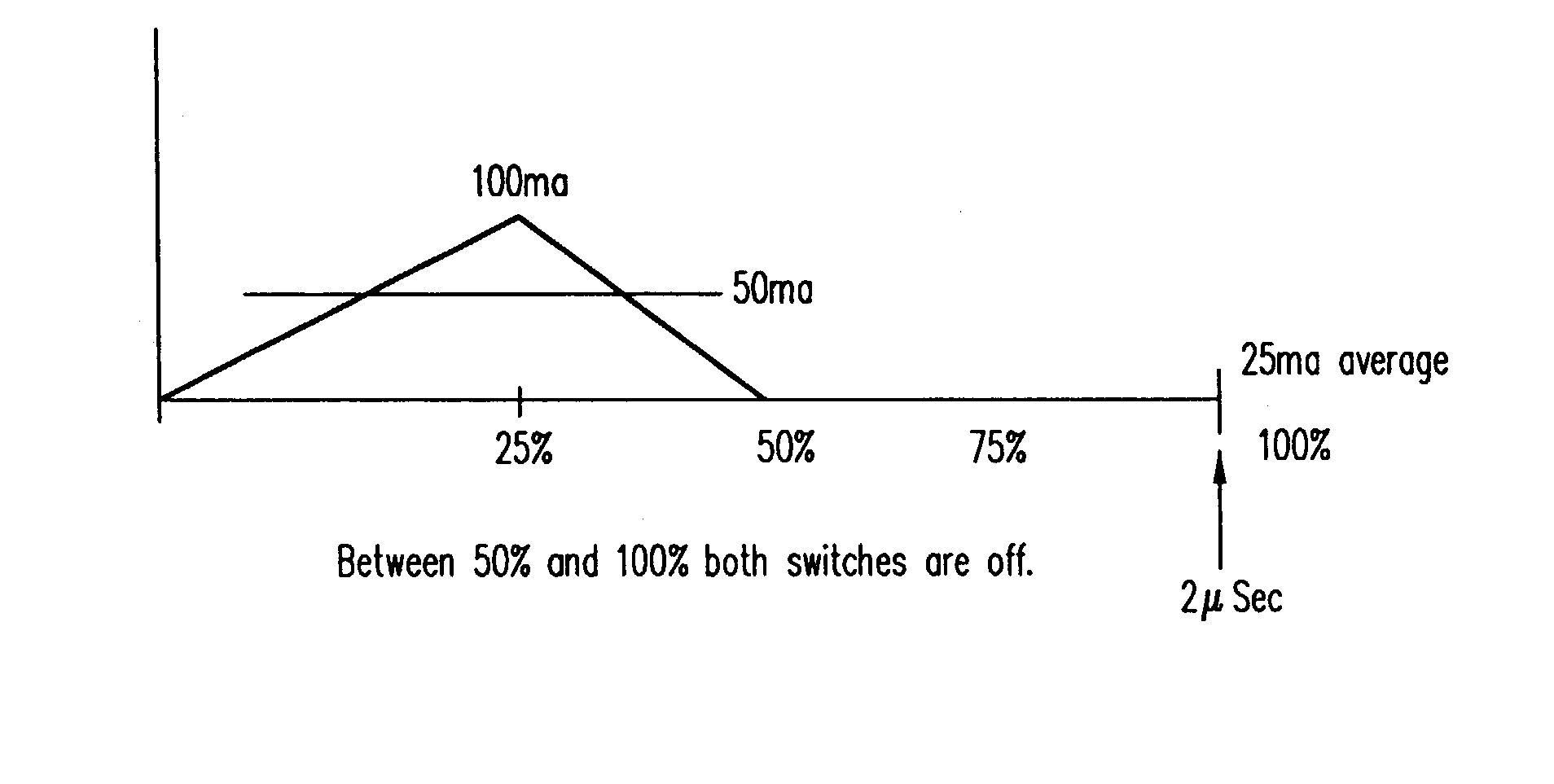

Switching power converter controller

InactiveUS20040095111A1Easy to makeBatteries circuit arrangementsEfficient power electronics conversionControl systemEngineering

A control system and method for simultaneously regulating the operation of a plurality of different types of switching power converters. The system utilizes in regulating the power converters sampled data and nonlinear feedback control loops.

Owner:EXAR CORP

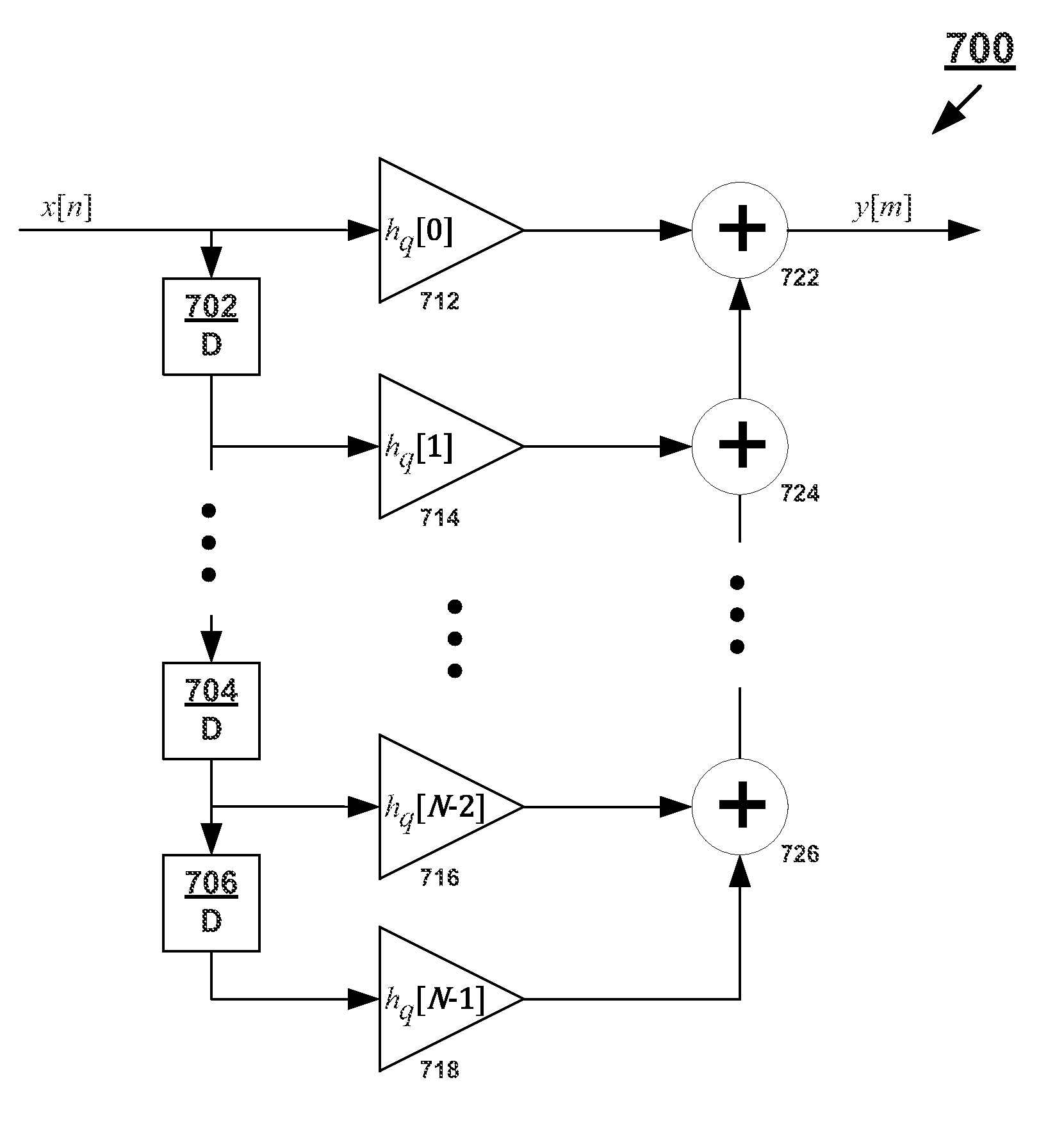

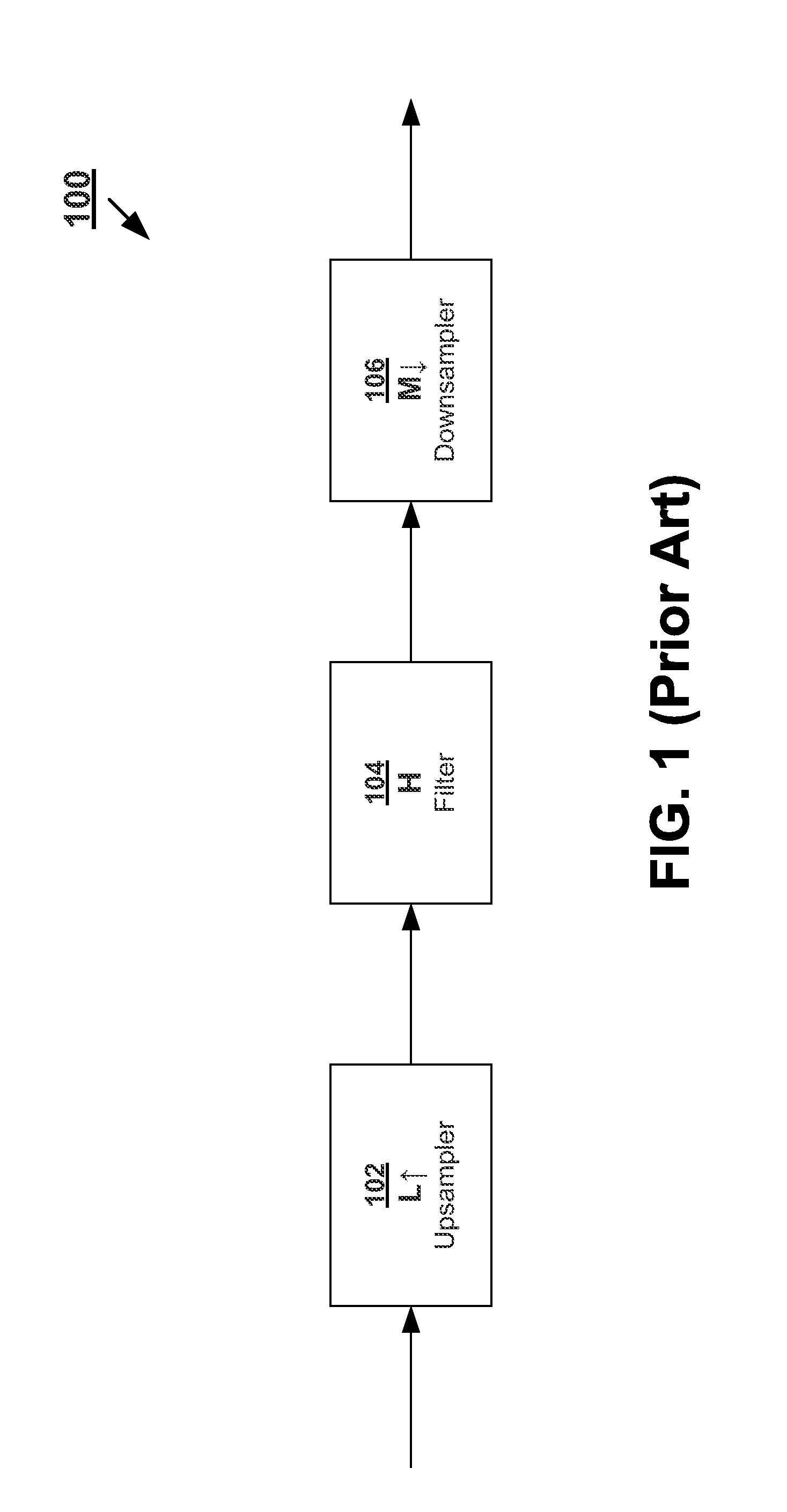

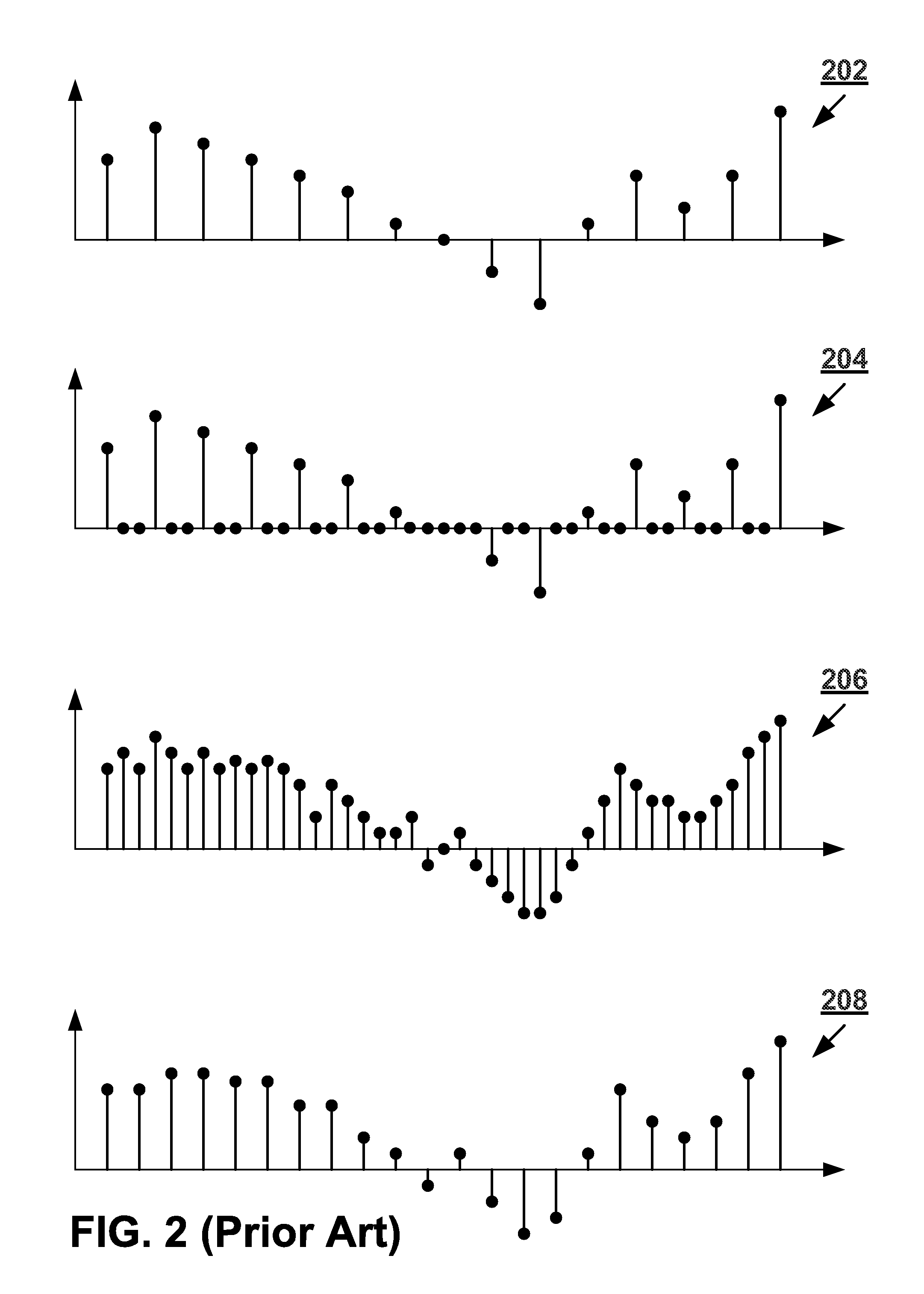

Systems and Methods for Variable Rate Conversion

Poly-phase filters are used to offer an efficient and low complexity solution to rate conversion. However, they suffer from inflexibility and are not easily reconfigured. A novel design for rate converters employ poly-phase filters but utilize interpolation between filter coefficients to add flexibility to rate conversion. This interpolation can be implemented as an interpolation of the poly-phase filter results. Additional approximations can be made to further reduce the amount of calculations required to implement a flexible rate converter.

Owner:SYNAPTICS INC

Technique for improving the quality of digital signals in a multi-level signaling system

InactiveUS7113550B2Quality improvementPulse conversionAmplitude-modulated pulse demodulationSignaling systemComputer science

A technique for improving the quality of digital signals in a multi-level signaling system is disclosed. In one particular exemplary embodiment, the technique may be realized as a method for improving the quality of transmitted digital signals in a multi-level signaling system wherein digital signals representing more than one bit of information may be transmitted at more than two signal levels on a single transmission medium. The method comprises encoding digital values represented by sets of N bits to provide corresponding sets of P symbols, wherein each set of P symbols is selected to eliminate full-swing transitions between successive digital signal transmissions. The method also comprises transmitting the sets of P symbols.

Owner:RAMBUS INC

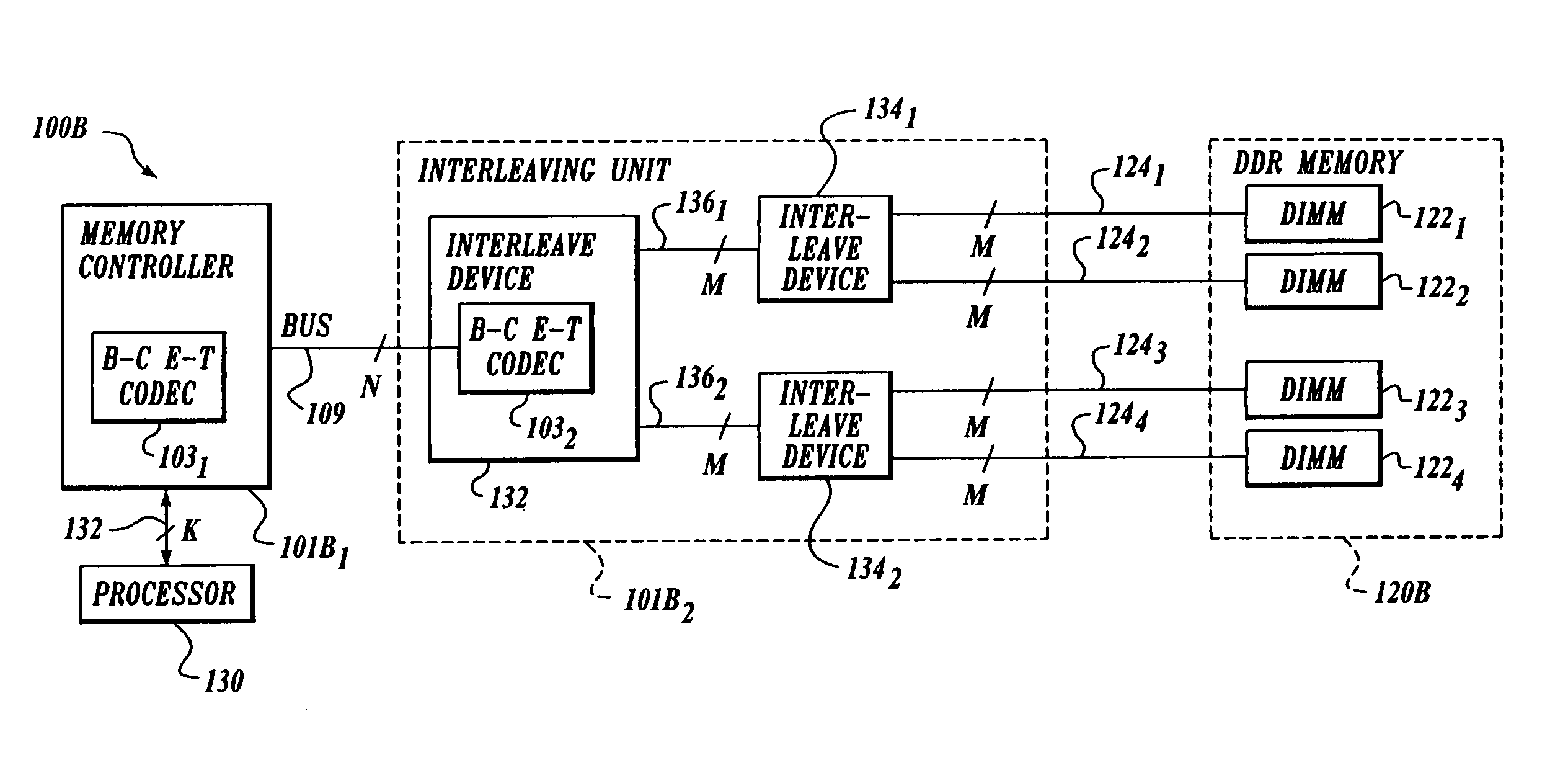

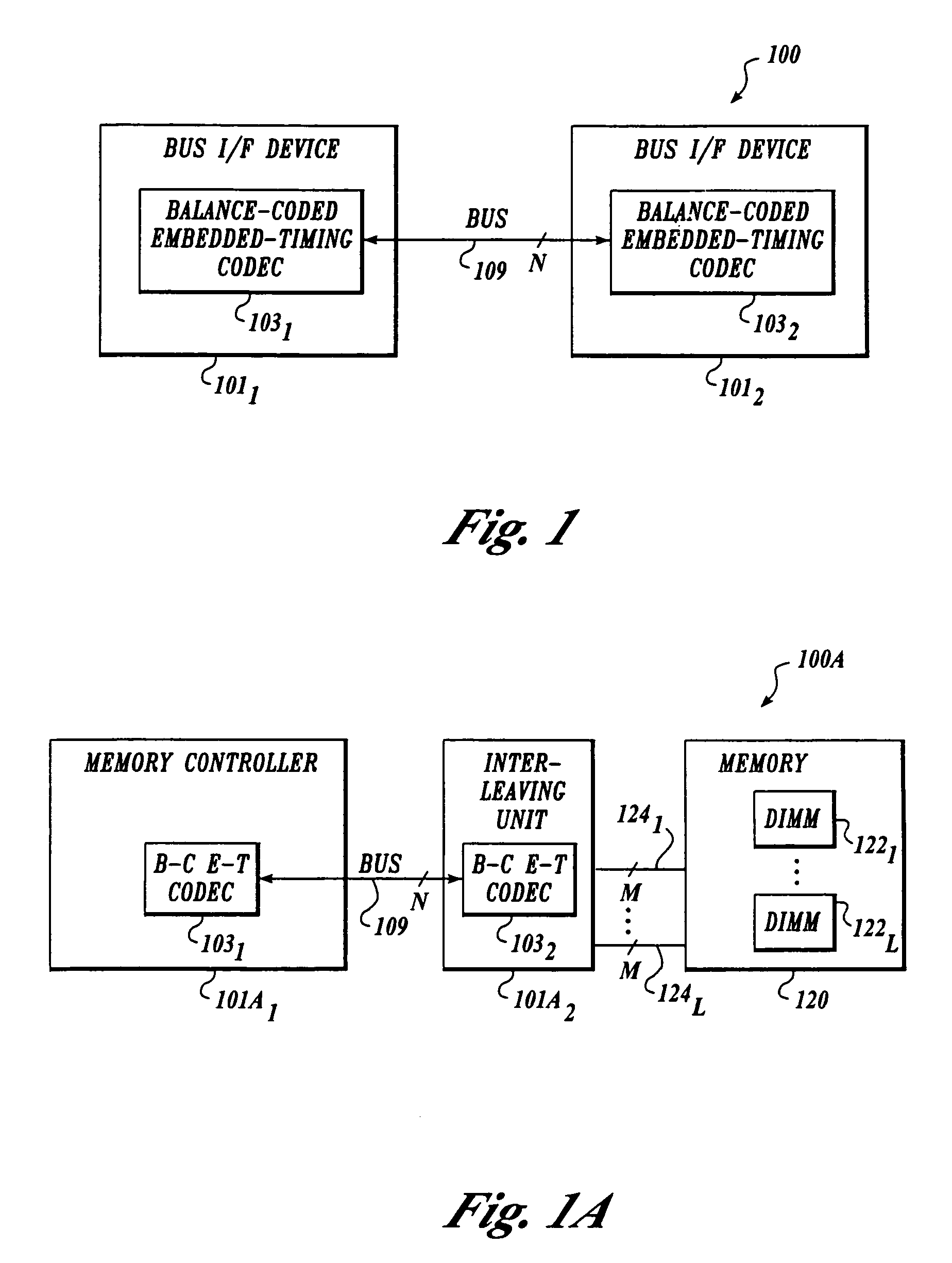

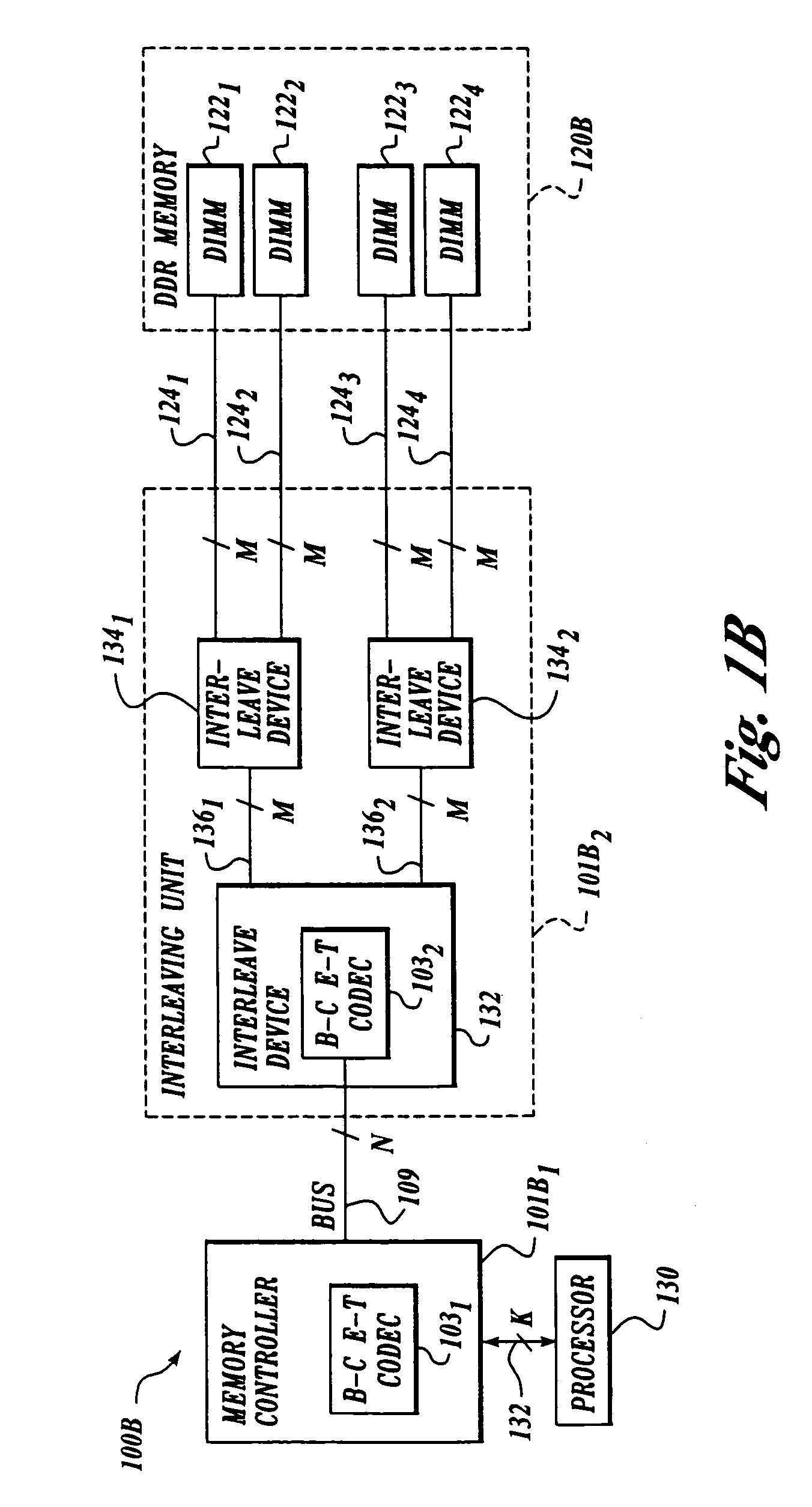

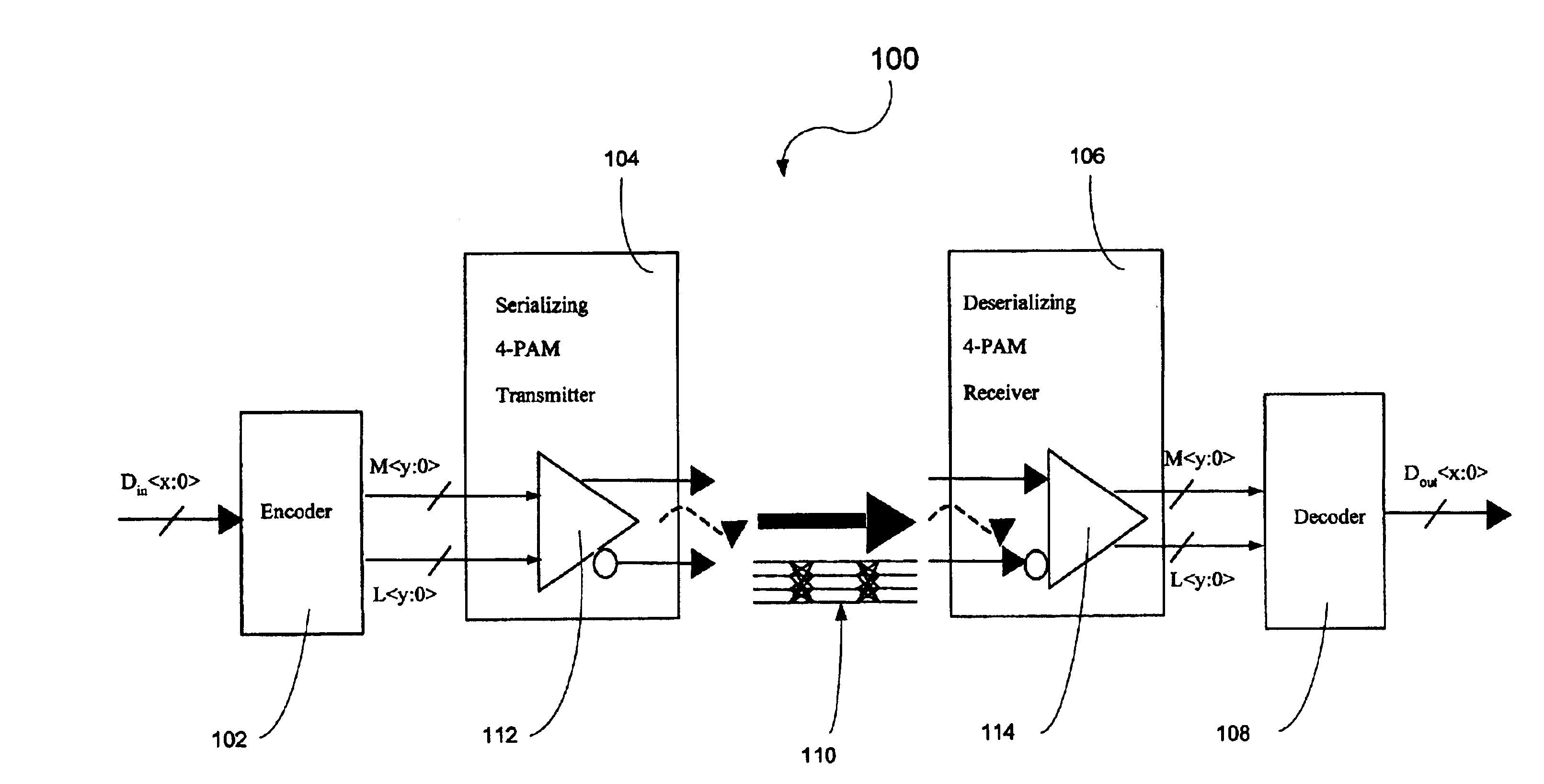

Methods and Systems for Chip-to-Chip Communication with Reduced Simultaneous Switching Noise

ActiveUS20140198837A1Increase speedLower latencyPulse conversionEnergy efficient computingLatency (engineering)Engineering

Systems and methods are described for transmitting data over physical channels to provide a high speed, low latency interface such as between a memory controller and memory devices with significantly reduced or eliminated Simultaneous Switching Output noise. Controller-side and memory-side embodiments of such channel interfaces are disclosed which do not require additional pin count or data transfer cycles, have low power utilization, and introduce minimal additional latency. In some embodiments of the invention, three or more voltage levels are used for signaling.

Owner:KANDOU LABS

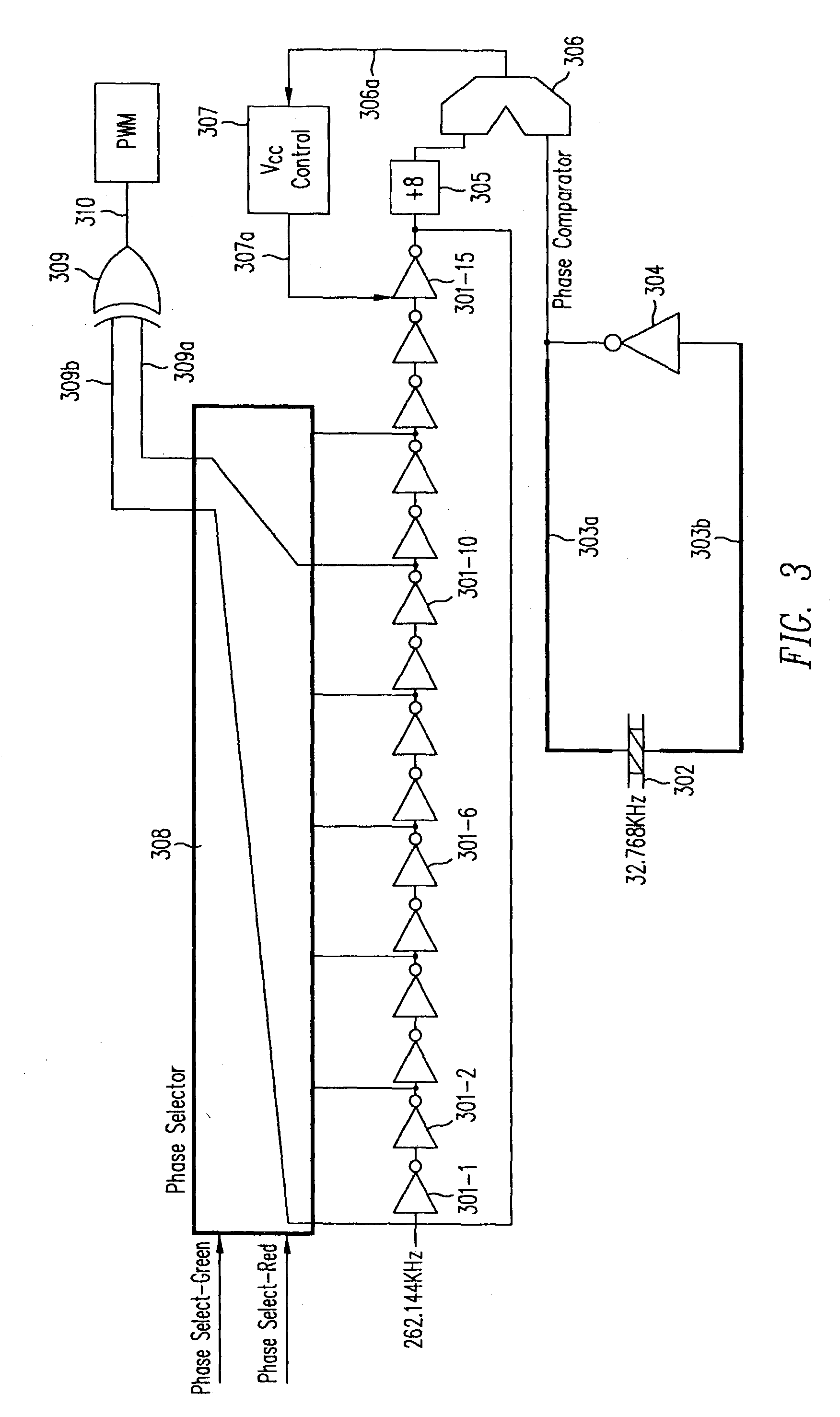

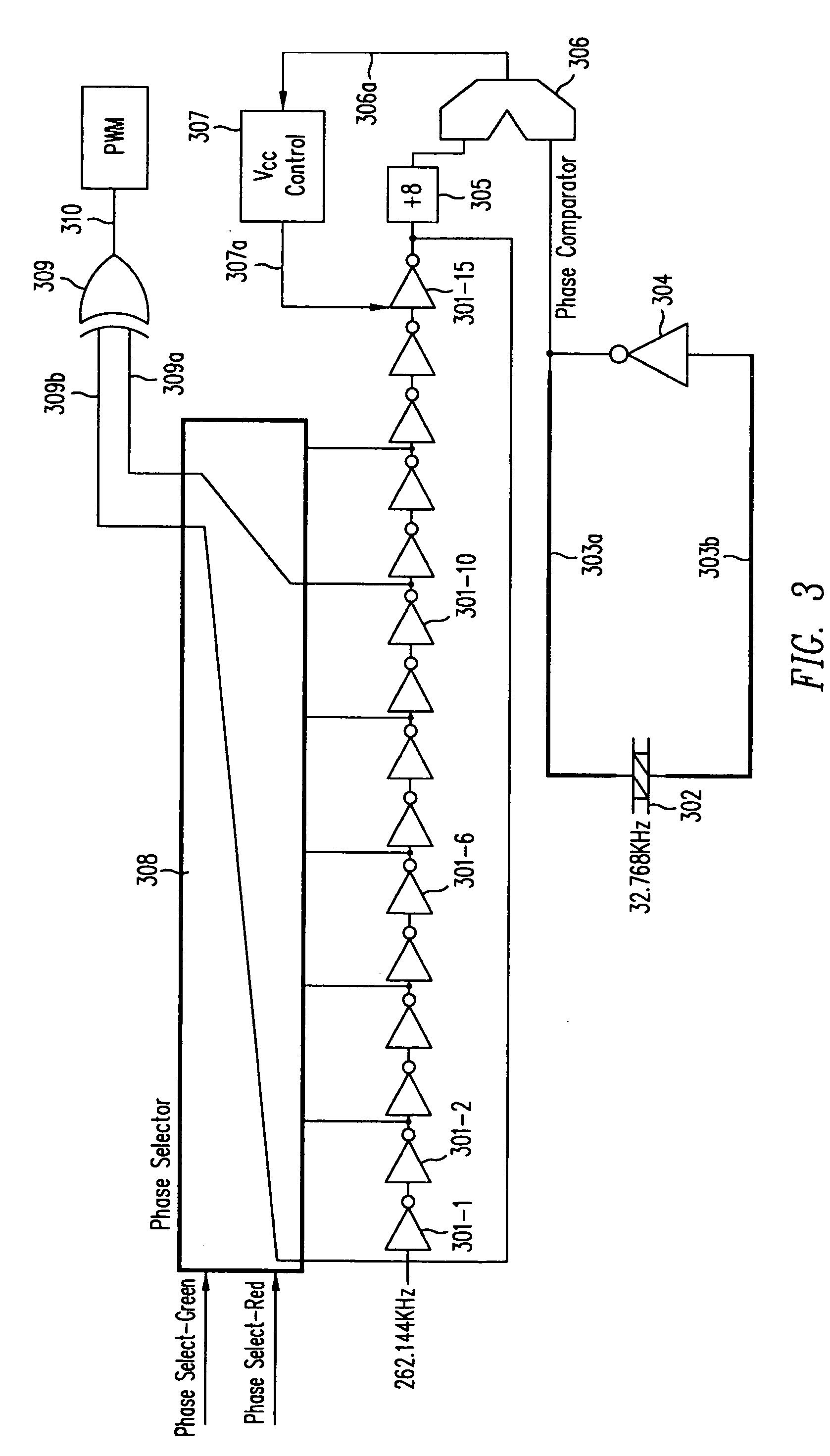

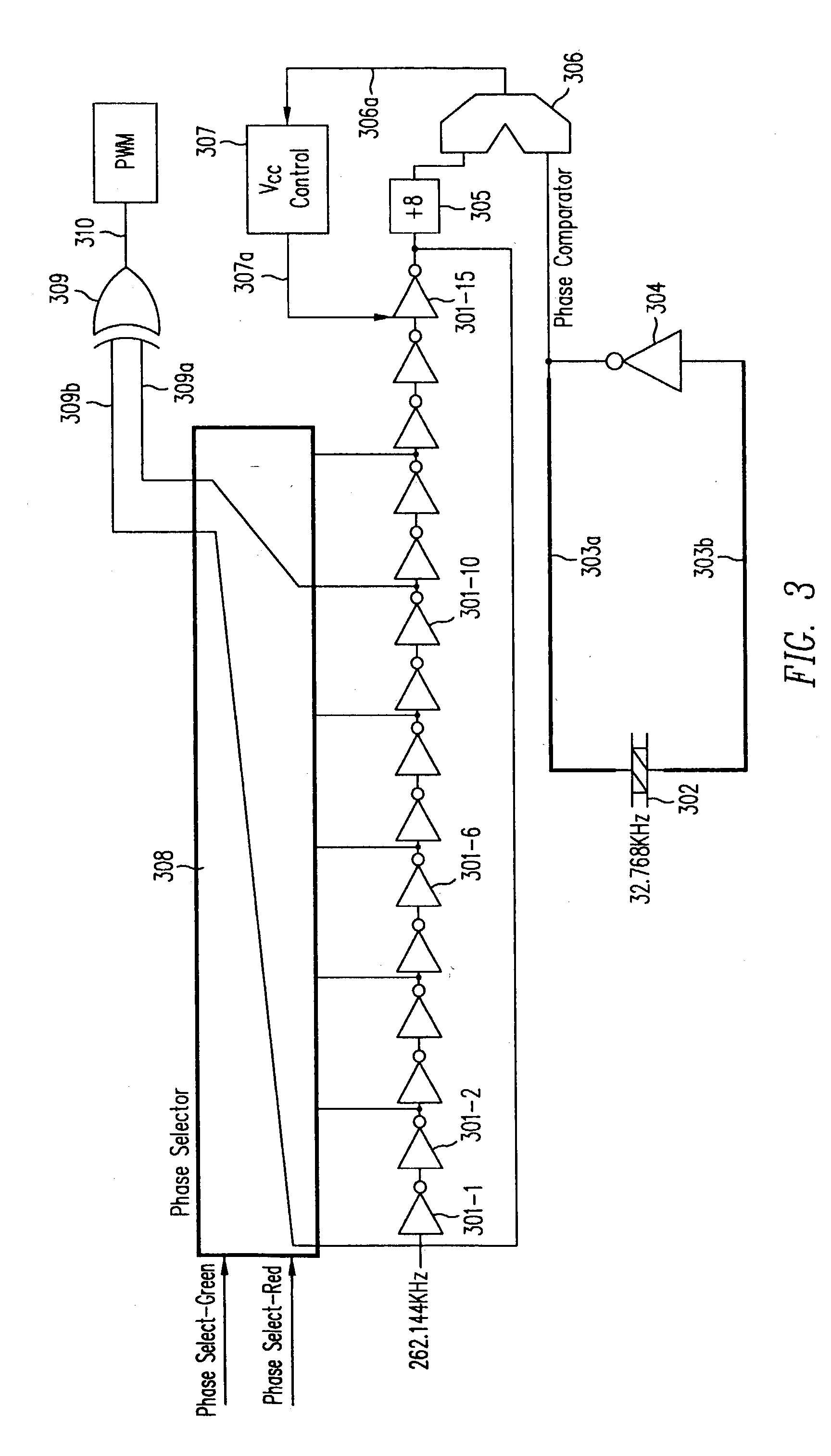

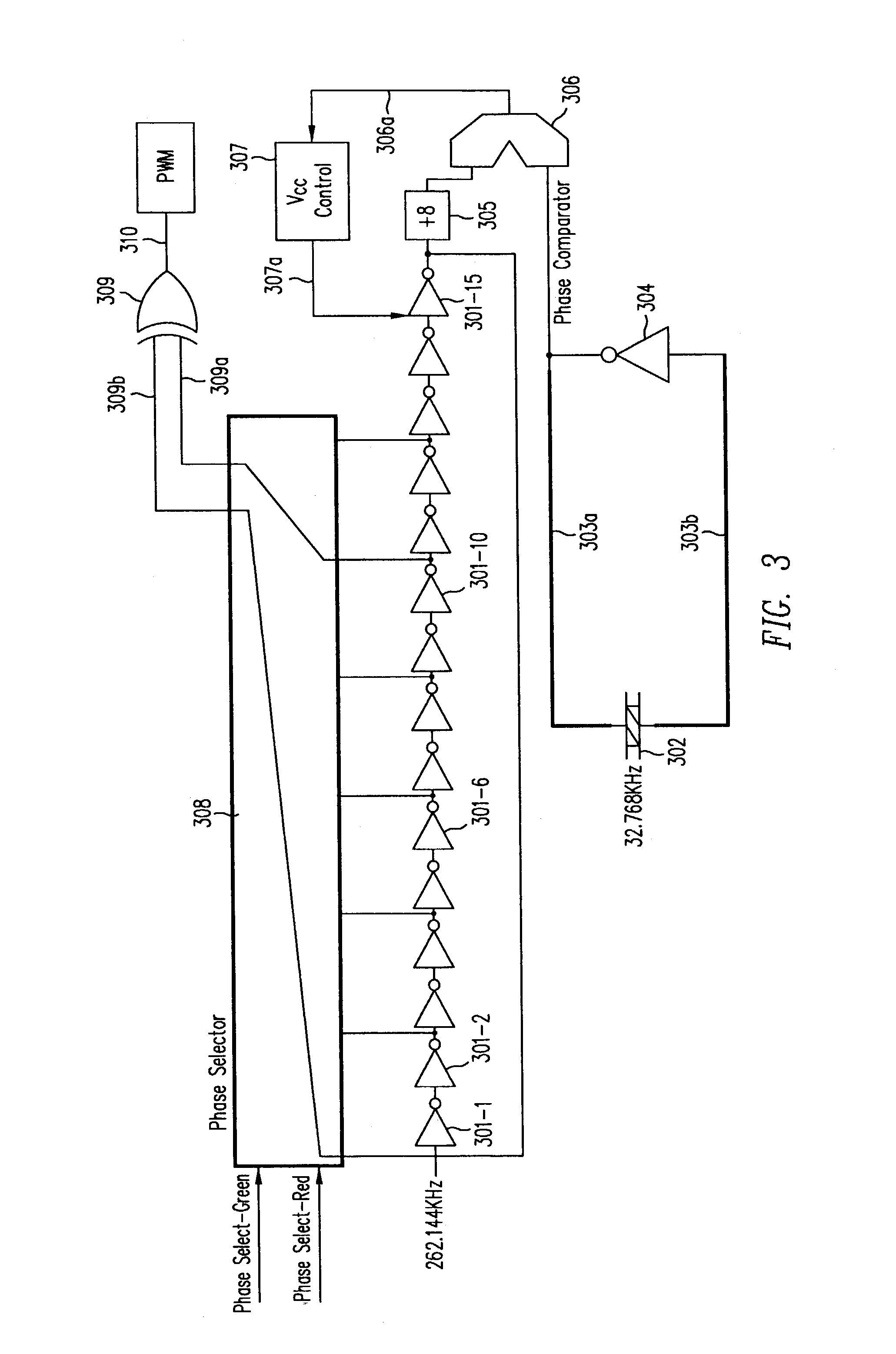

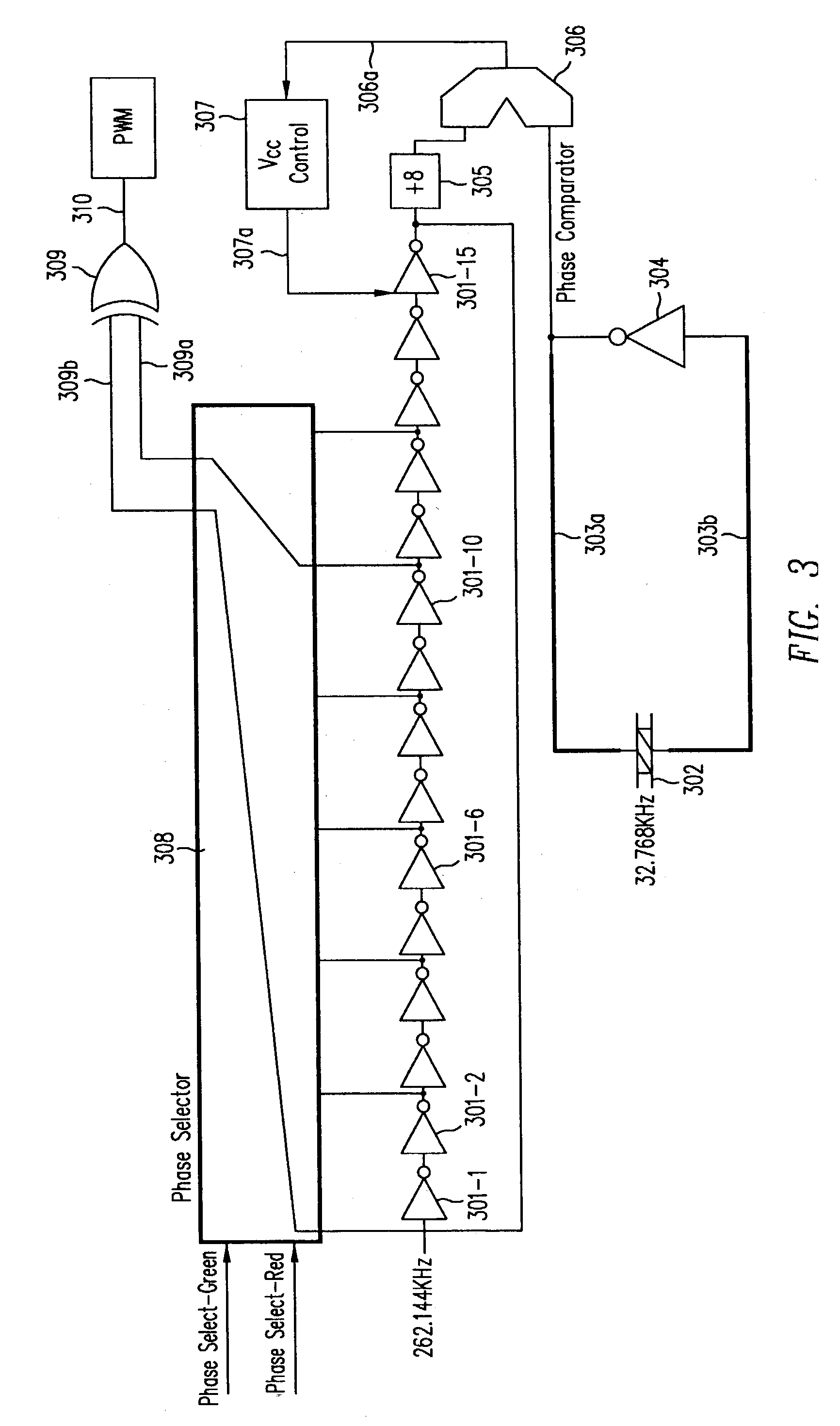

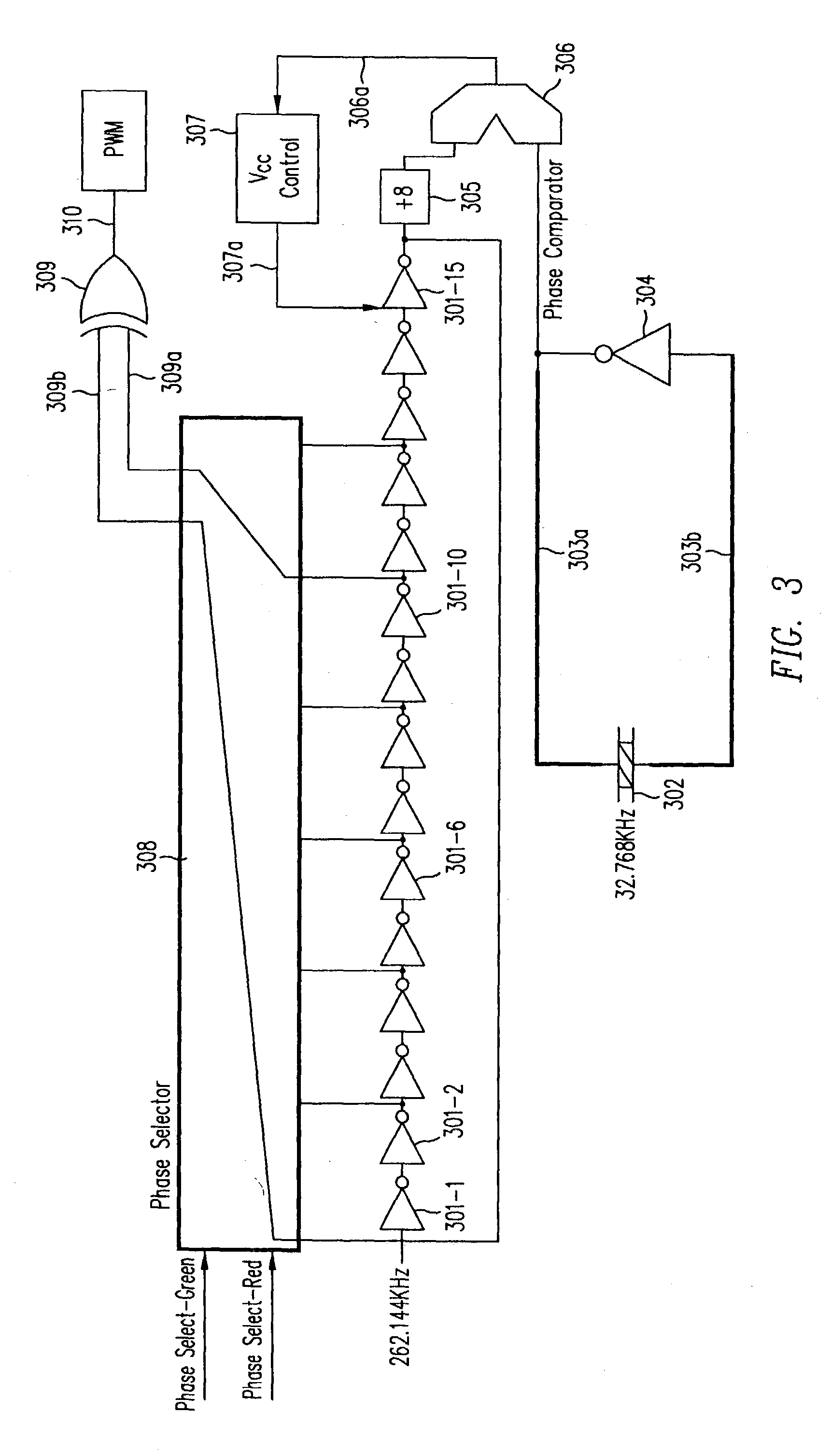

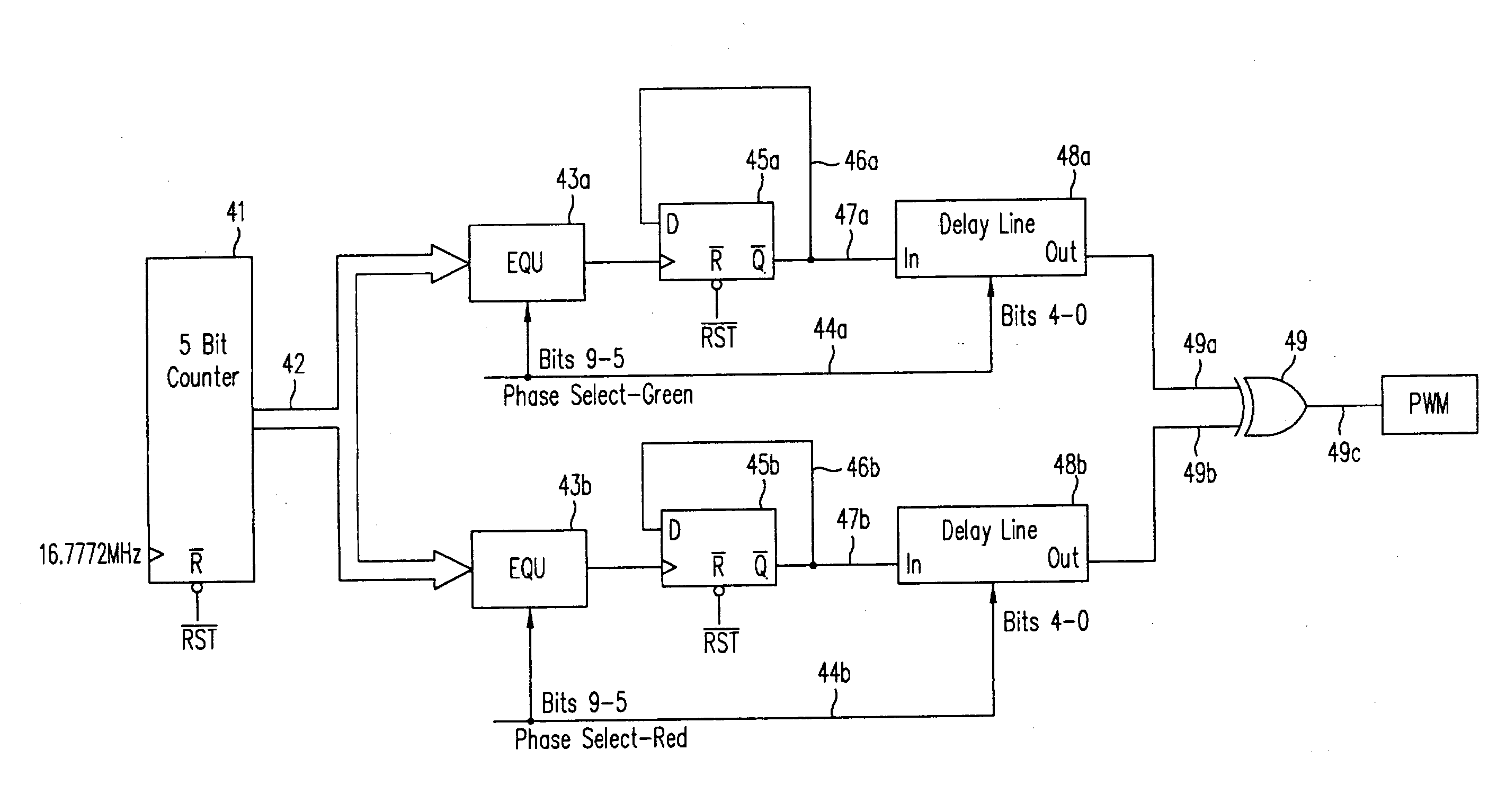

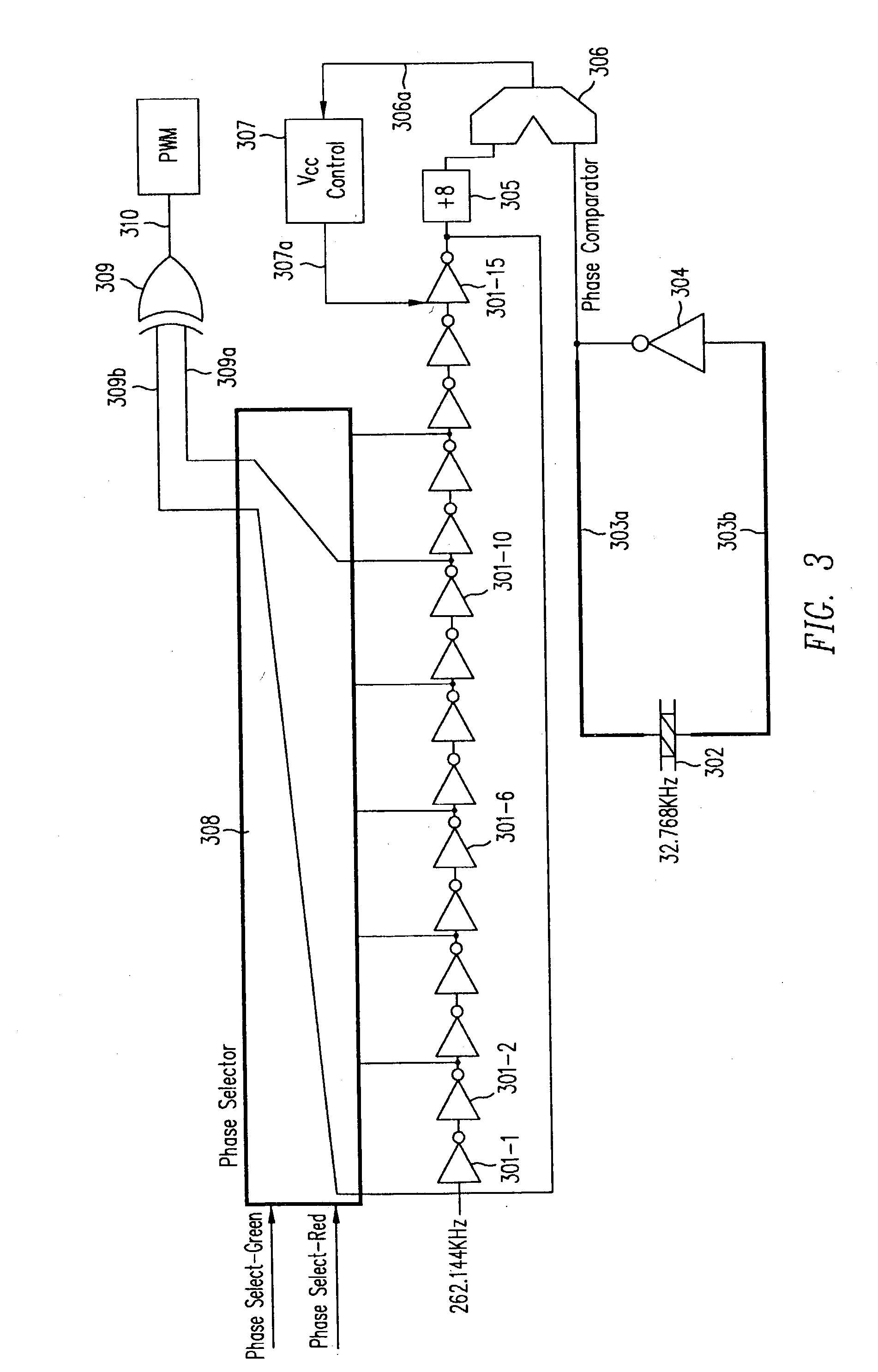

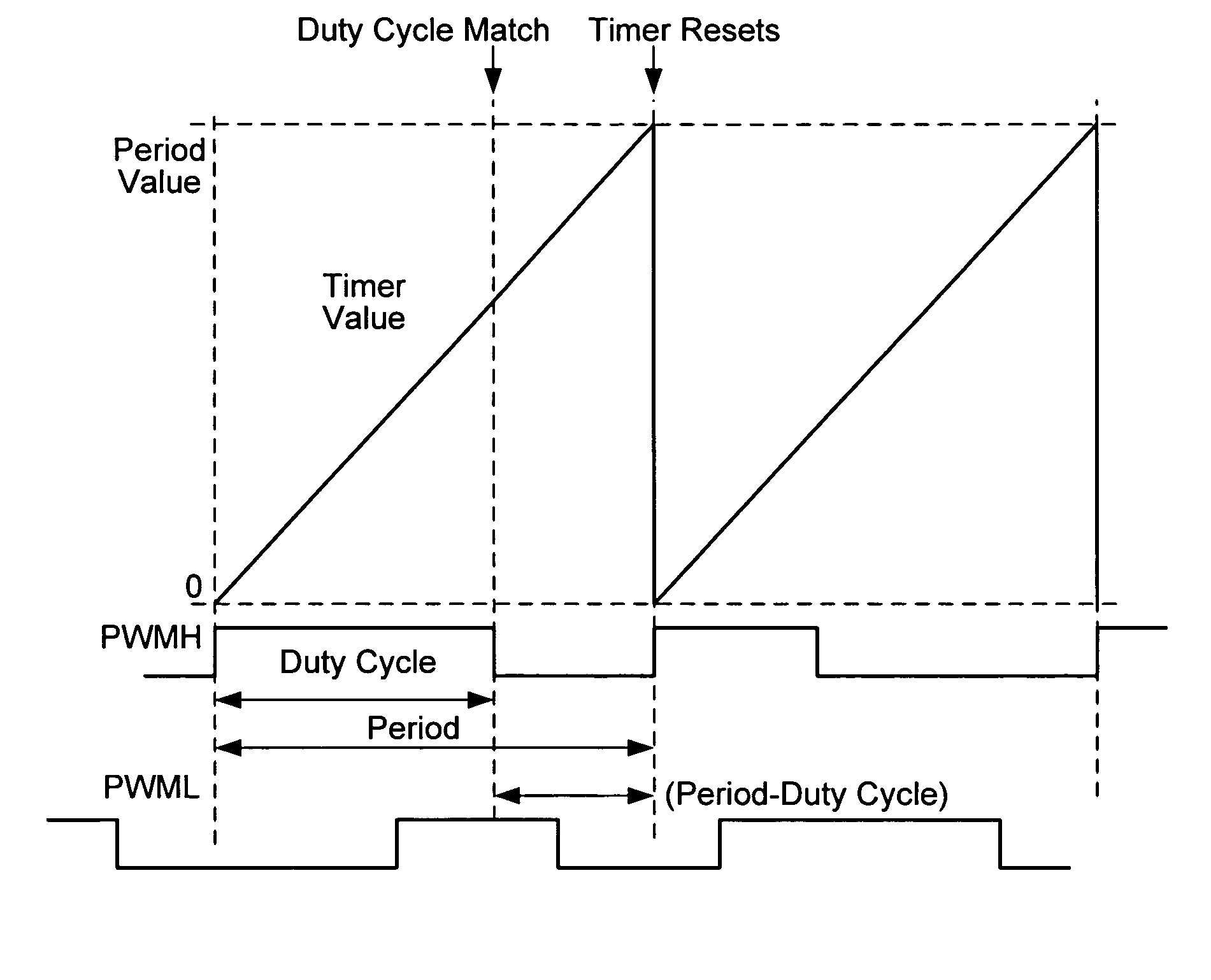

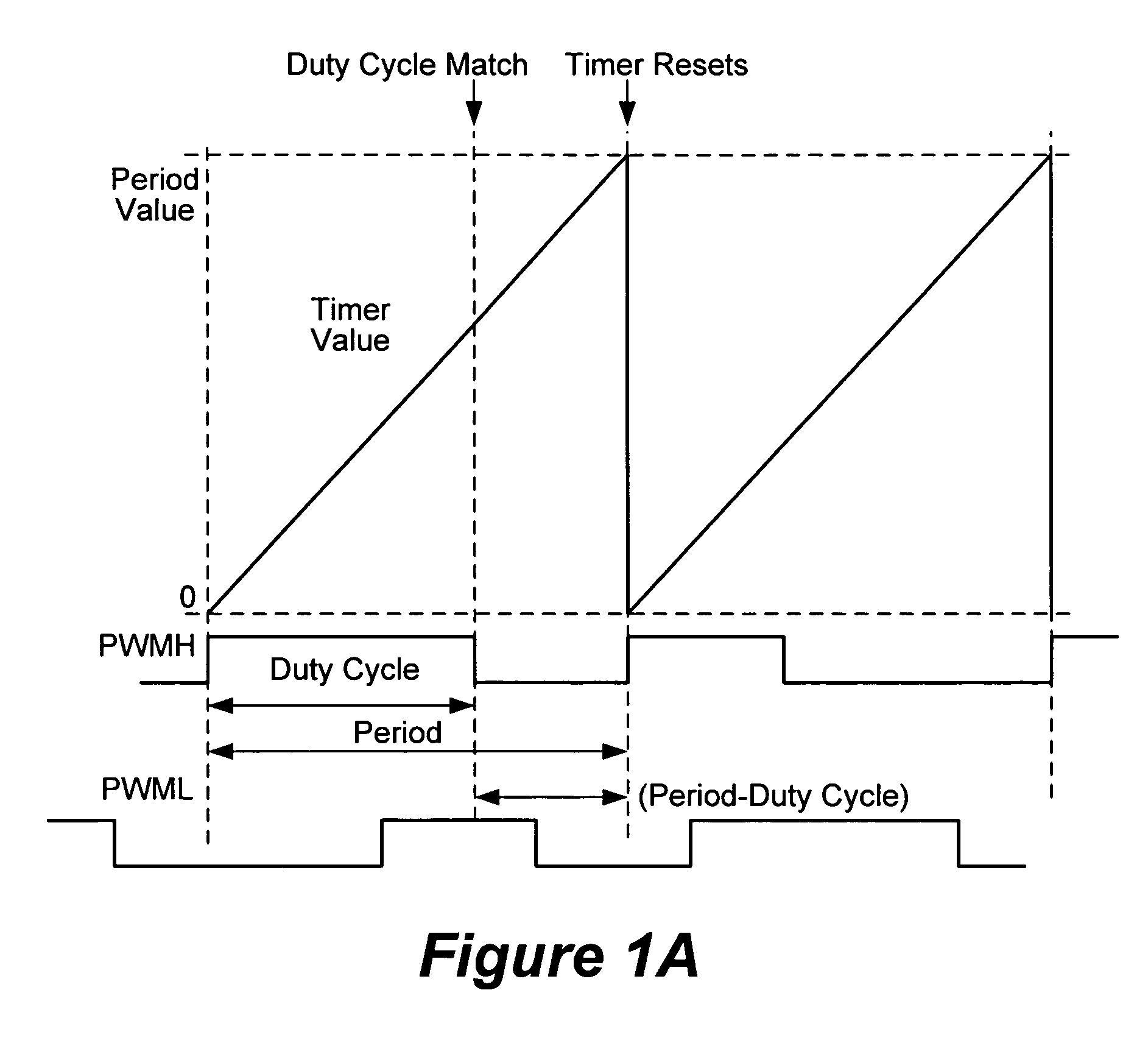

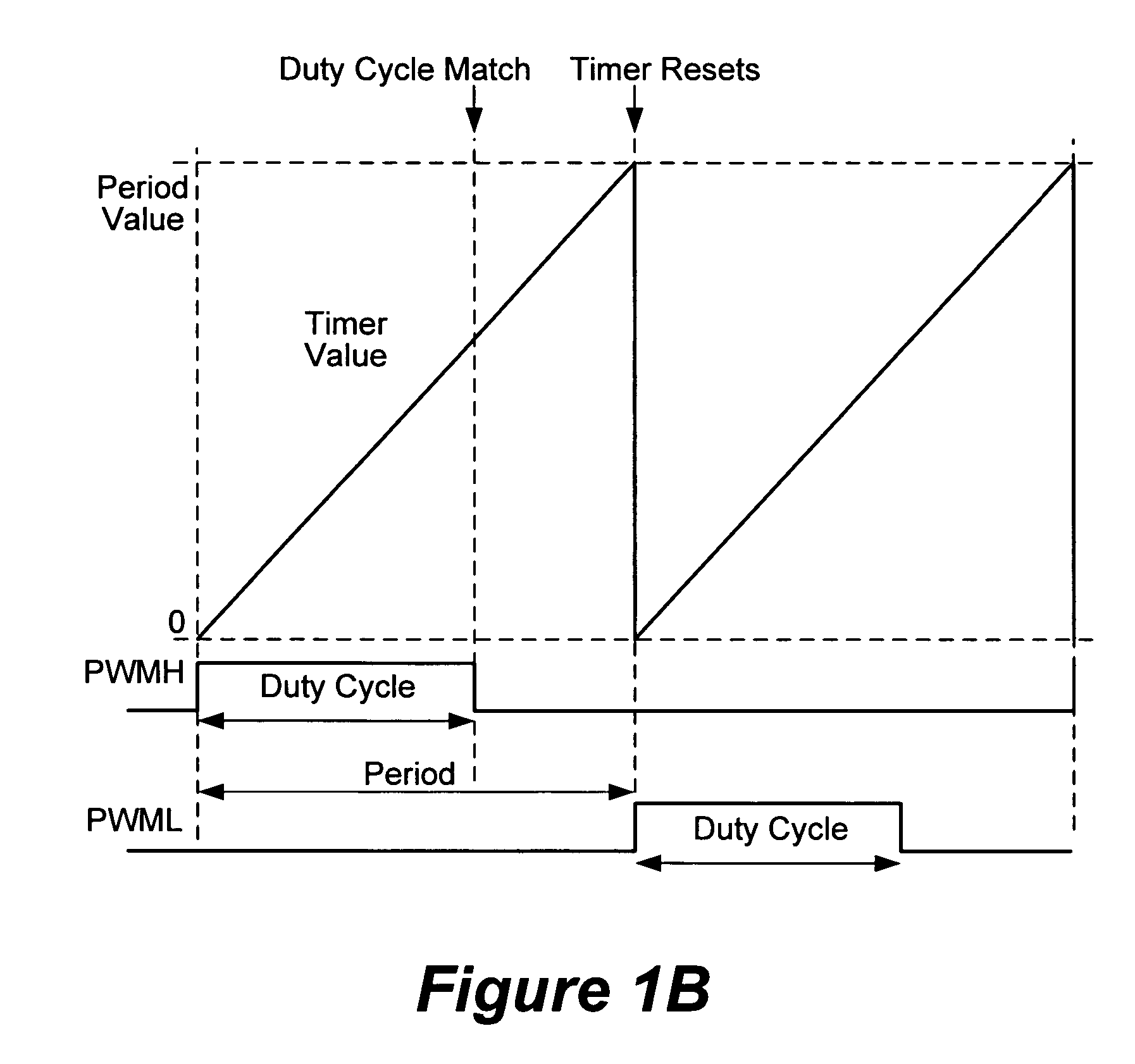

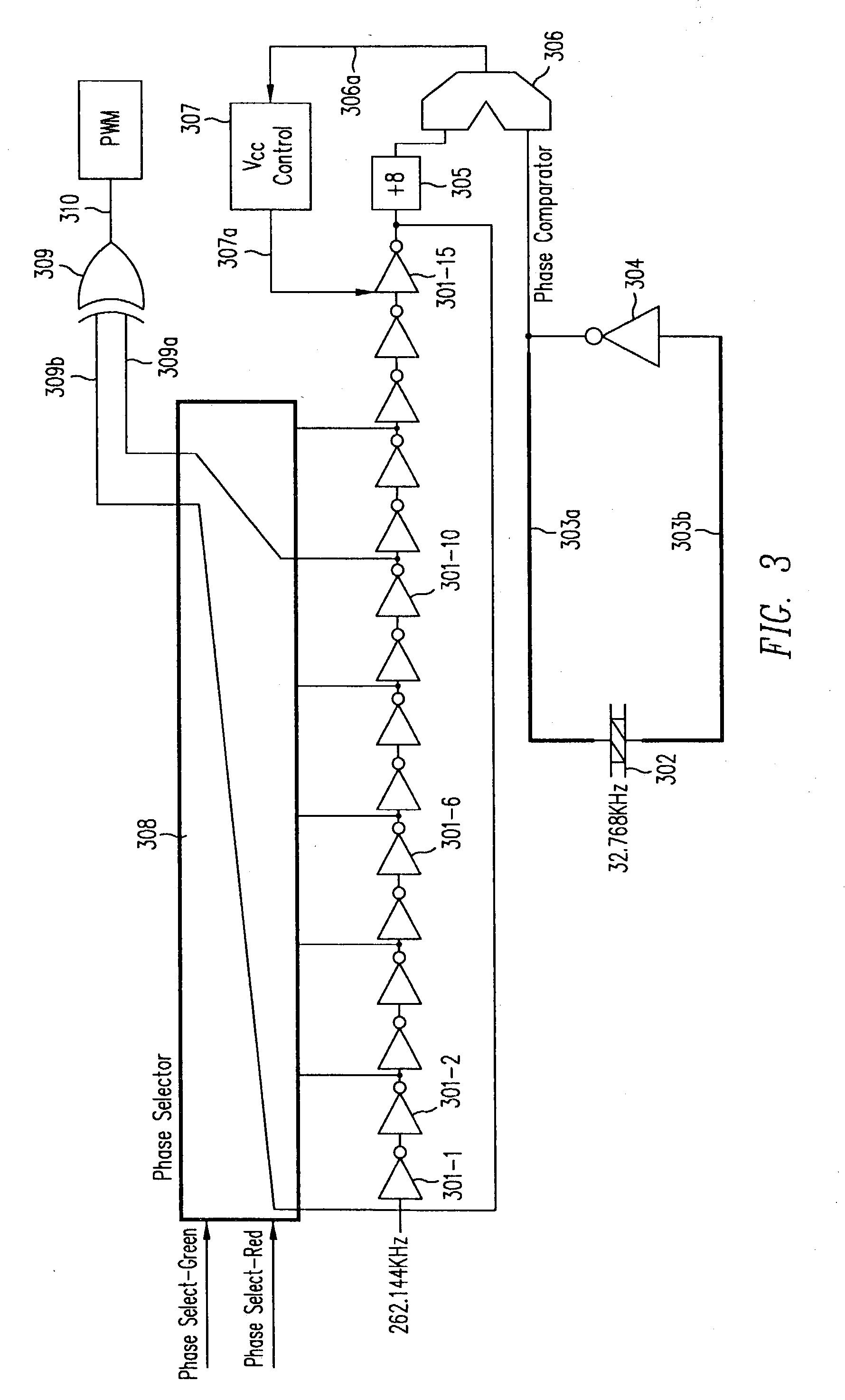

Digital processor with pulse width modulation module having dynamically adjustable phase offset capability, high speed operation and simultaneous update of multiple pulse width modulation duty cycle registers

ActiveUS20060064609A1Increase speedHigh resolution performanceRecord information storageDuration/width modulated pulse demodulationPush pullSwitching frequency

A pulse width modulation (PWM) generator featuring very high speed and high resolution capability and the ability to generate standard complementary PWM, push-pull PWM, variable offset PWM, multiphase PWM, current limit PWM, current reset PWM, and independent time base PWM while further providing automatic triggering for an analog-to-digital conversion (ADC) module that is precisely timed relative to the PWM signals. Applications include control of a switching power supply that requires very high speed operation to obtain high resolution at high switching frequencies, and the ability to vary the phase relationships among the PWM output signals driving the power supply power components. A single PWM duty cycle register may be used for updating any and / or all PWM generators at once to reduce the workload of a digital processor as compared to updating multiple duty cycle registers.

Owner:MICROCHIP TECH INC

Power converter circuitry and method

InactiveUS20040095119A1Easy to makeBatteries circuit arrangementsEfficient power electronics conversionControl systemEngineering

A control system and method for simultaneously regulating the operation of a plurality of different types of switching power converters. The system utilizes in regulating the power converters sampled data and nonlinear feedback control loops.

Owner:EXAR CORP