Patents

Literature

406 results about "Successive approximation ADC" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

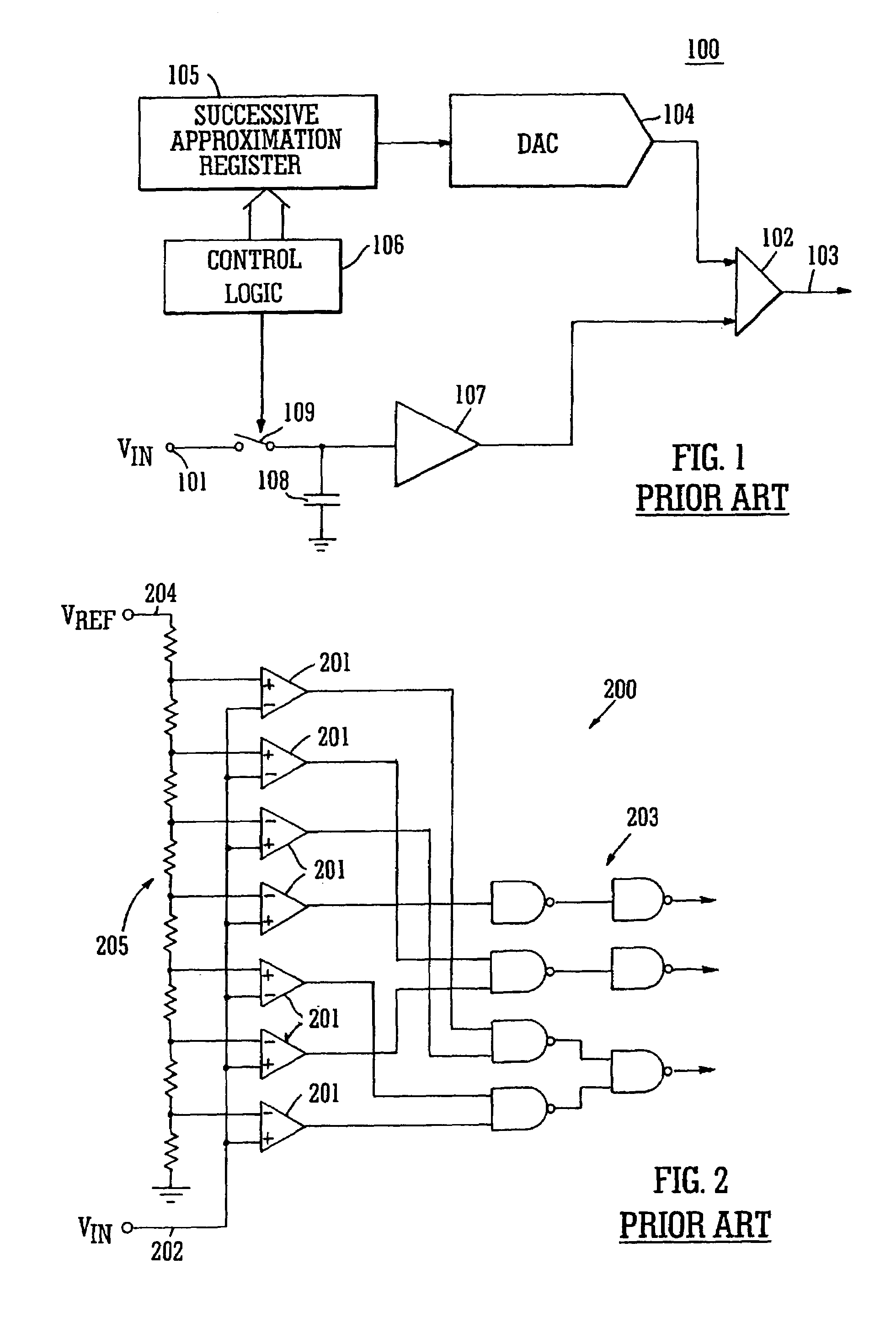

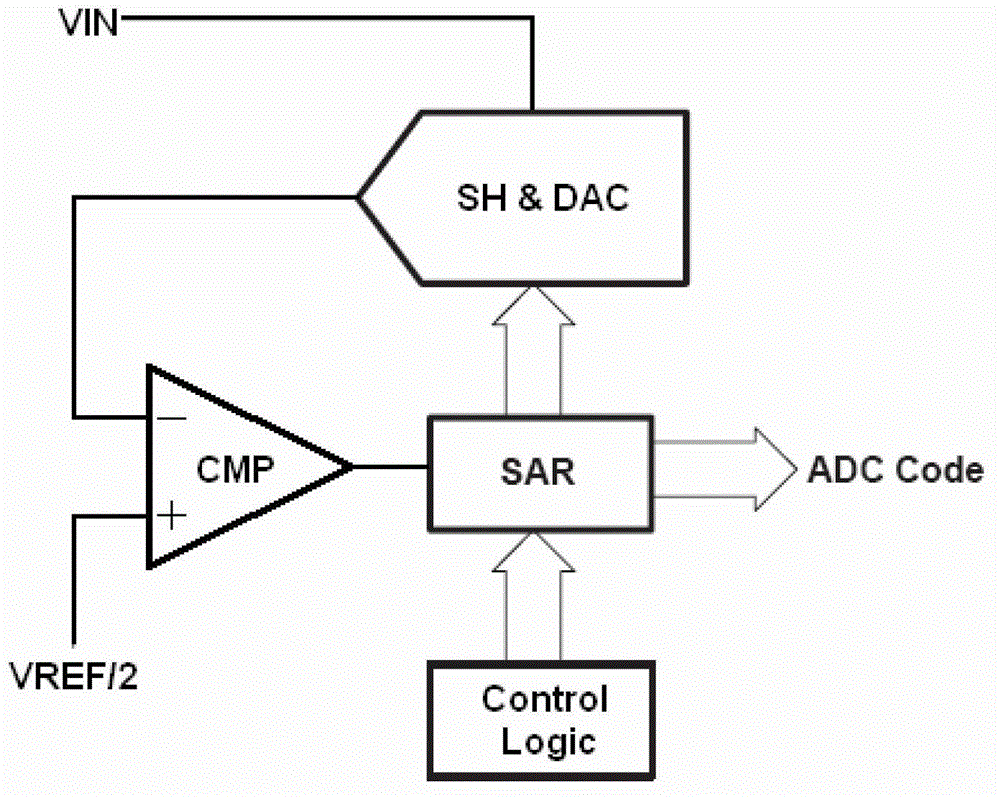

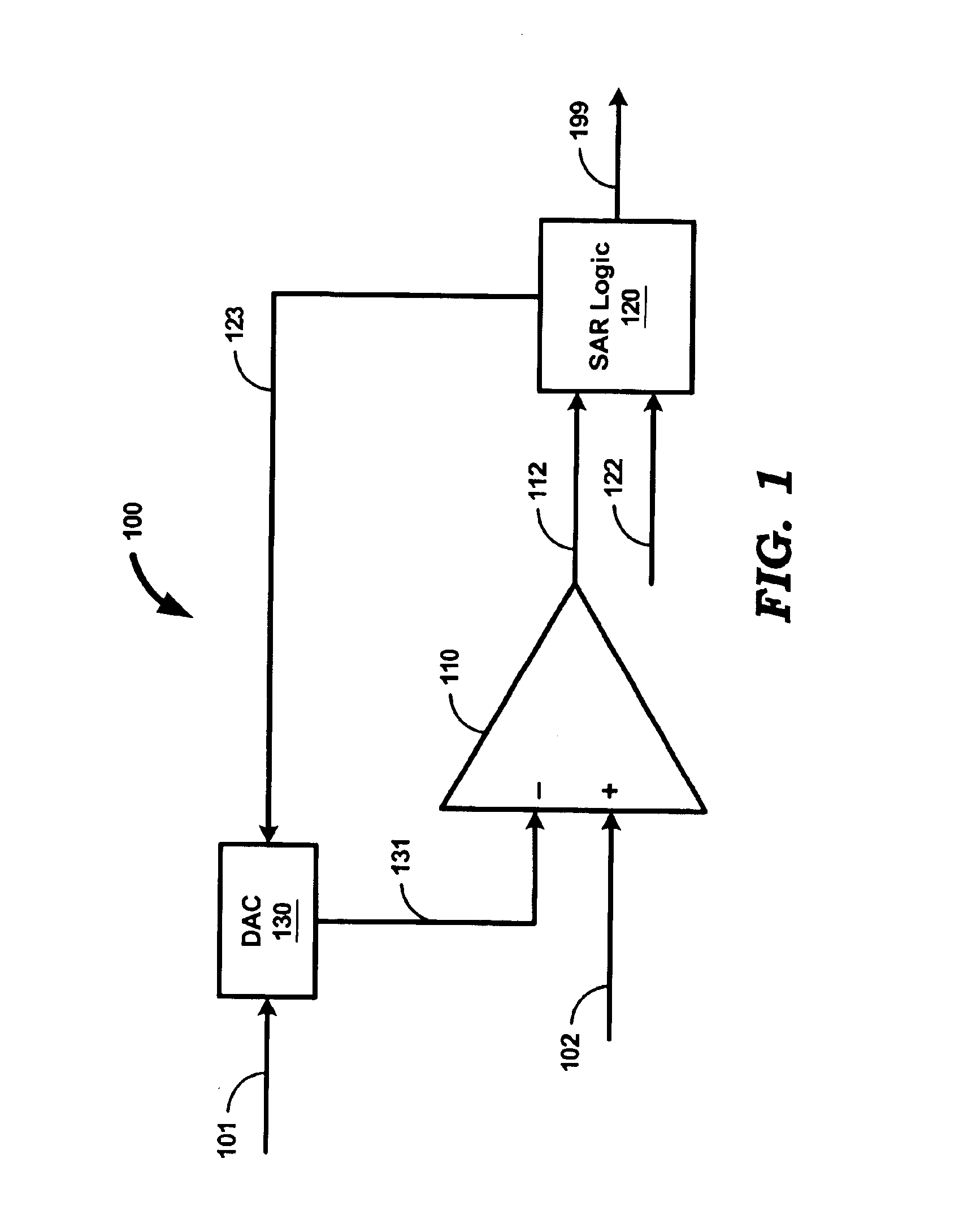

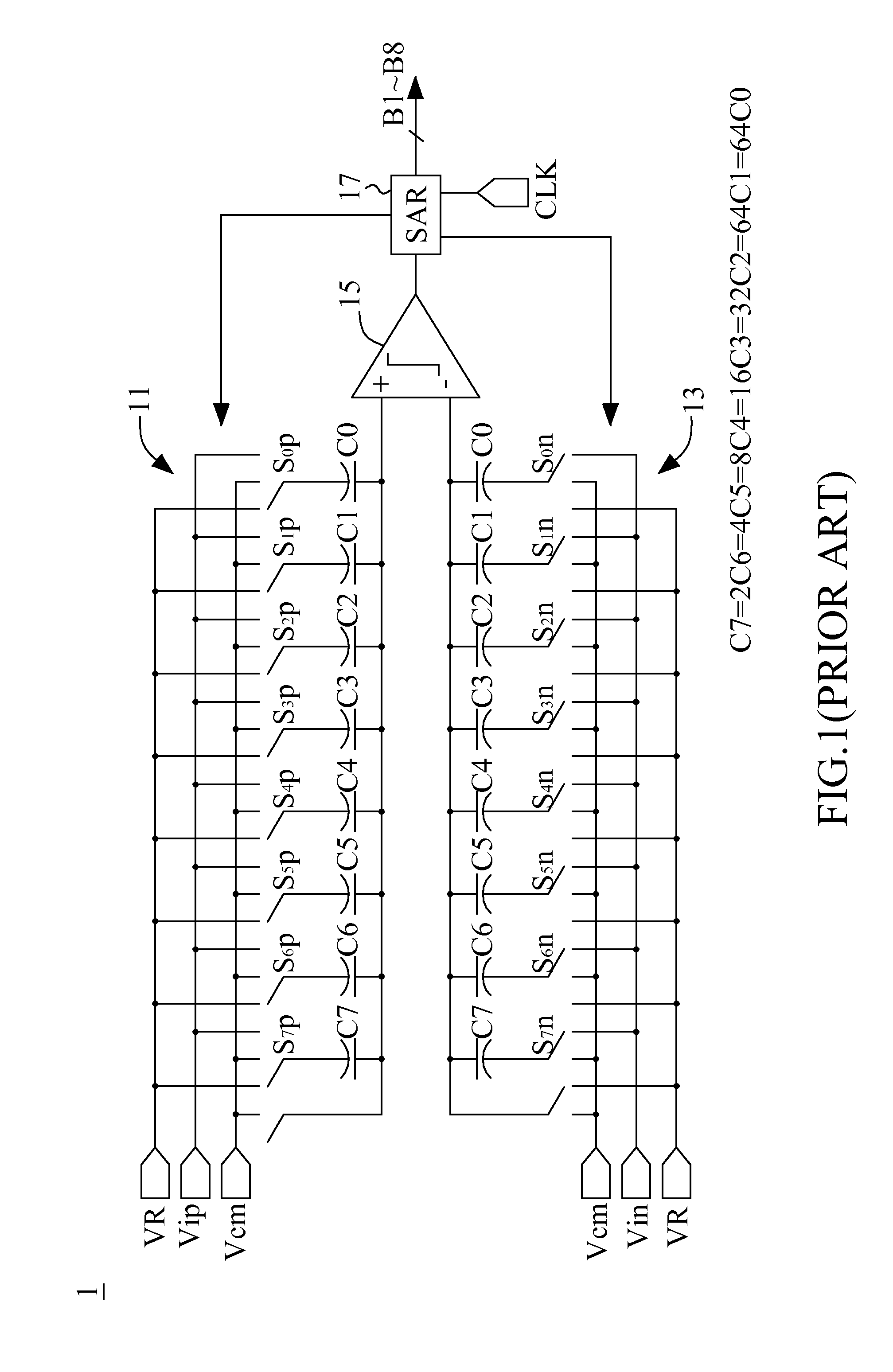

A successive approximation ADC is a type of analog-to-digital converter that converts a continuous analog waveform into a discrete digital representation via a binary search through all possible quantization levels before finally converging upon a digital output for each conversion.

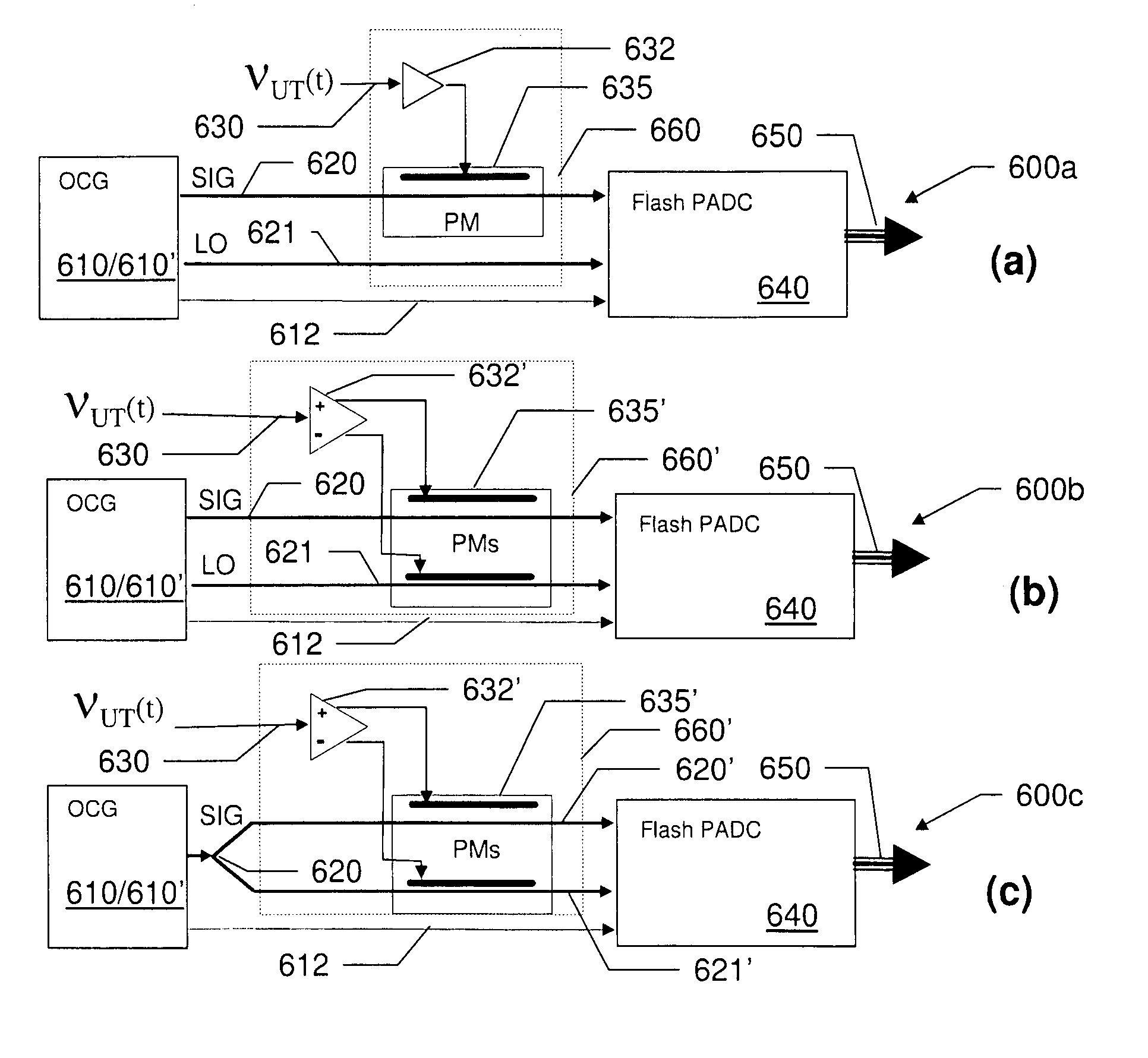

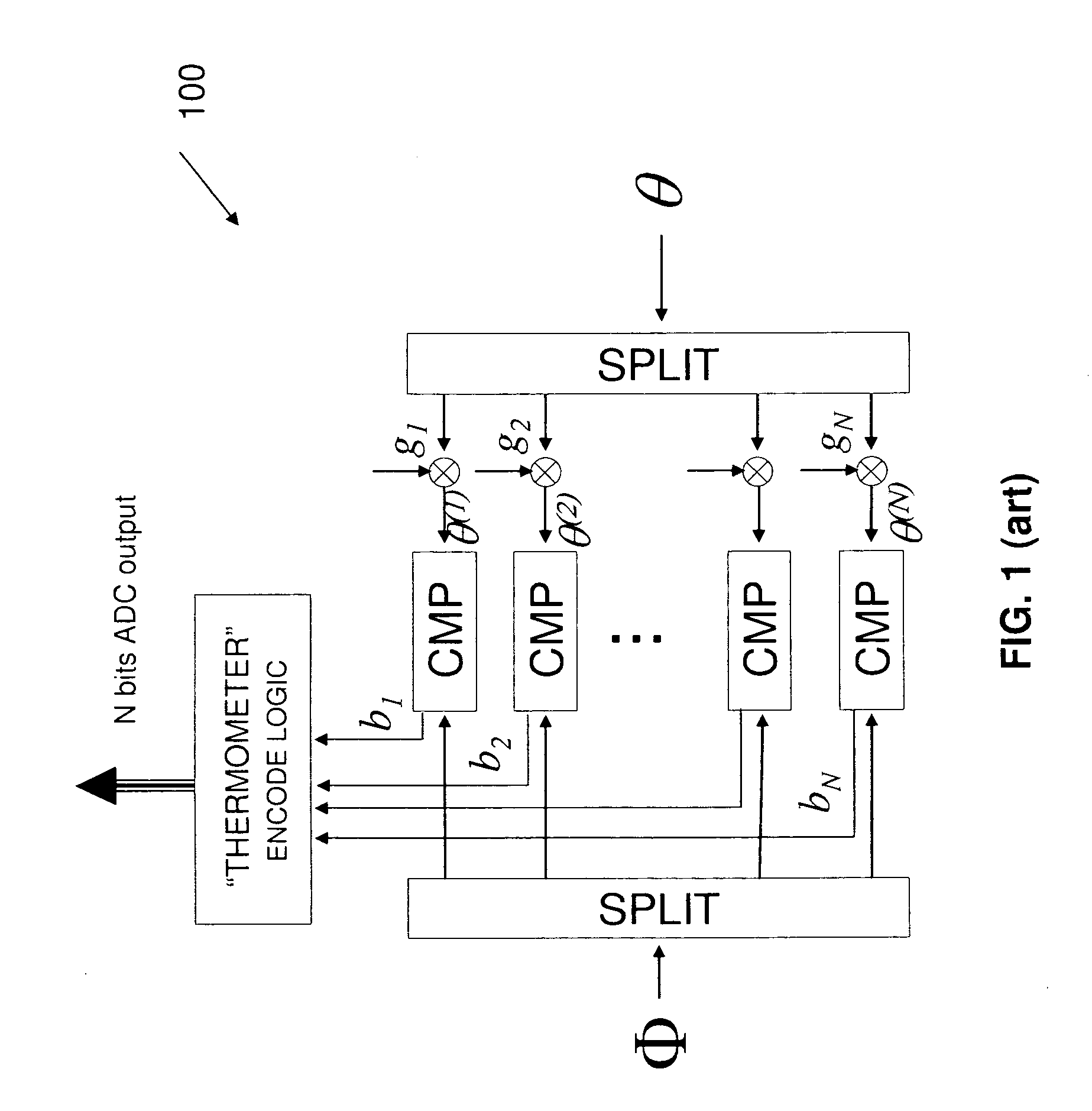

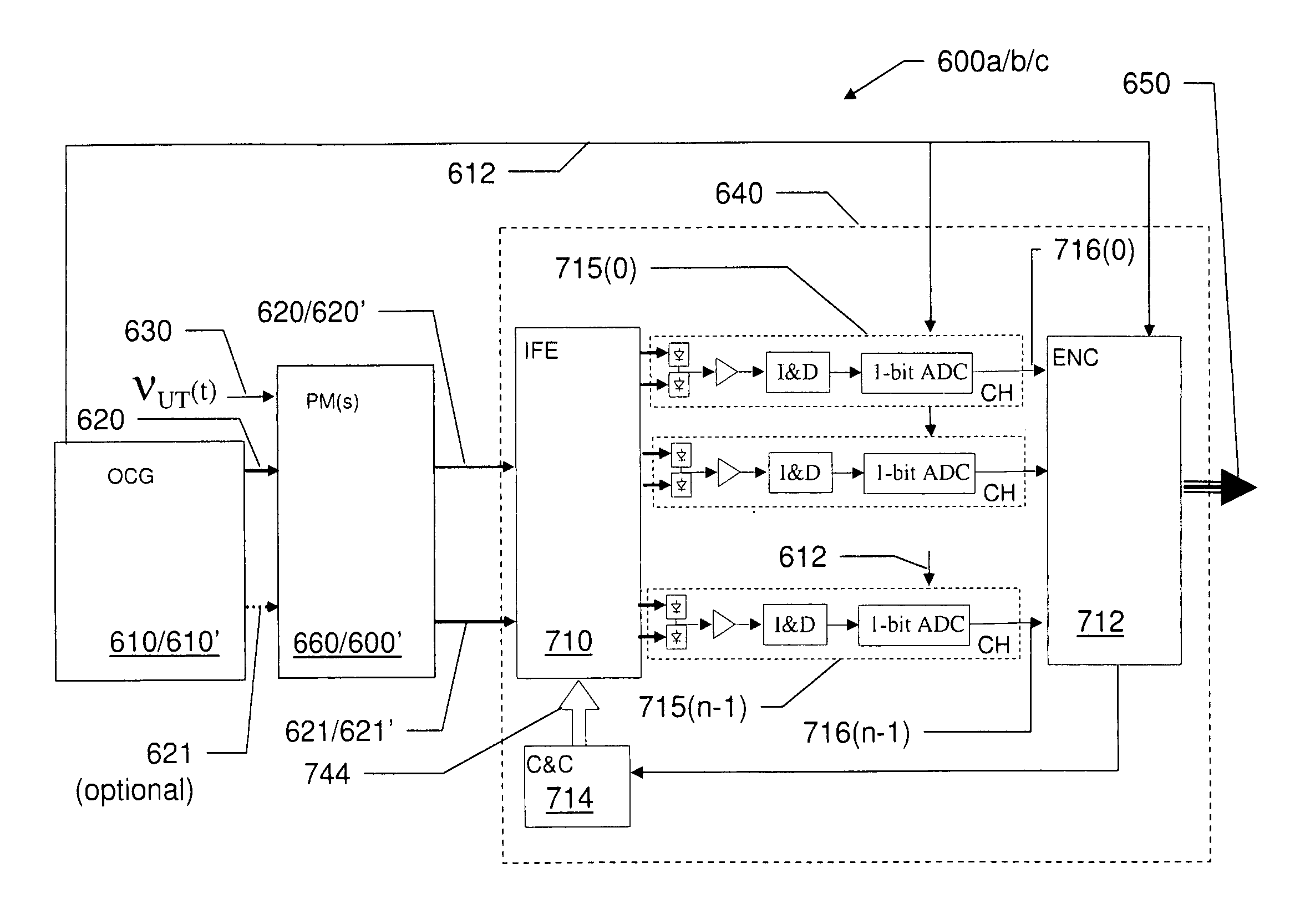

Ultra-high-speed photonic-enabled ADC based on multi-phase interferometry

InactiveUS20120213531A1Overcome disadvantagesAnalogue/digital conversionAnalogue conversionUltra high speedPhotonics

A ultra high speed photonic Analog to Digital Converted (ADC) for sampling and quantizing an electrical voltage signal, internally enabled by photonics uses coherent optical detection architectures for photonic quantization. Coherent light is phase modulated by the test signal. Using an interferometer, or an array of interferometers the phase of modulated light is compared with a reference light. Flash ADC, successive approximation ADC and delta-sigma ADC configurations are presented.

Owner:TECHNION RES & DEV FOUND LTD

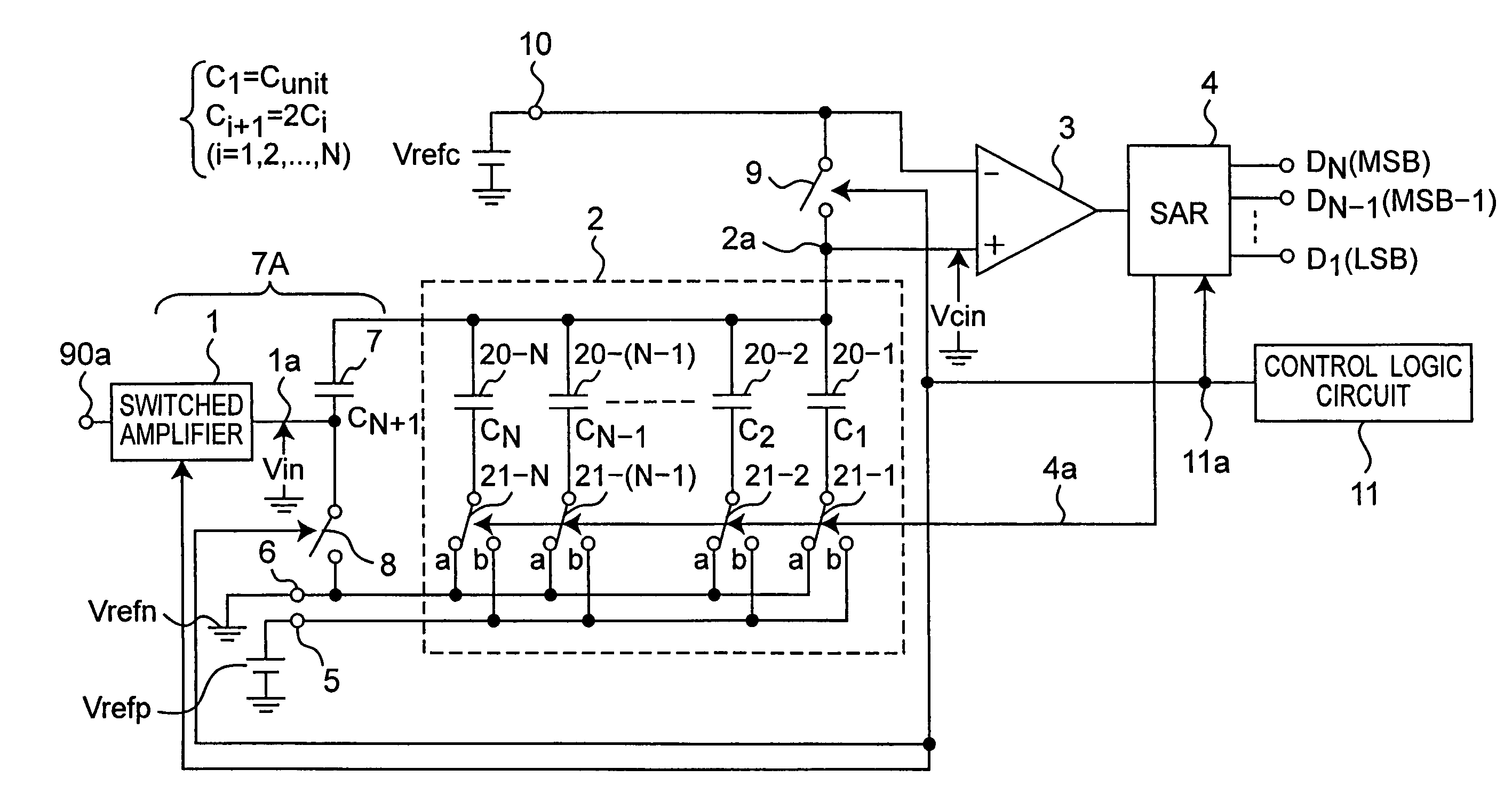

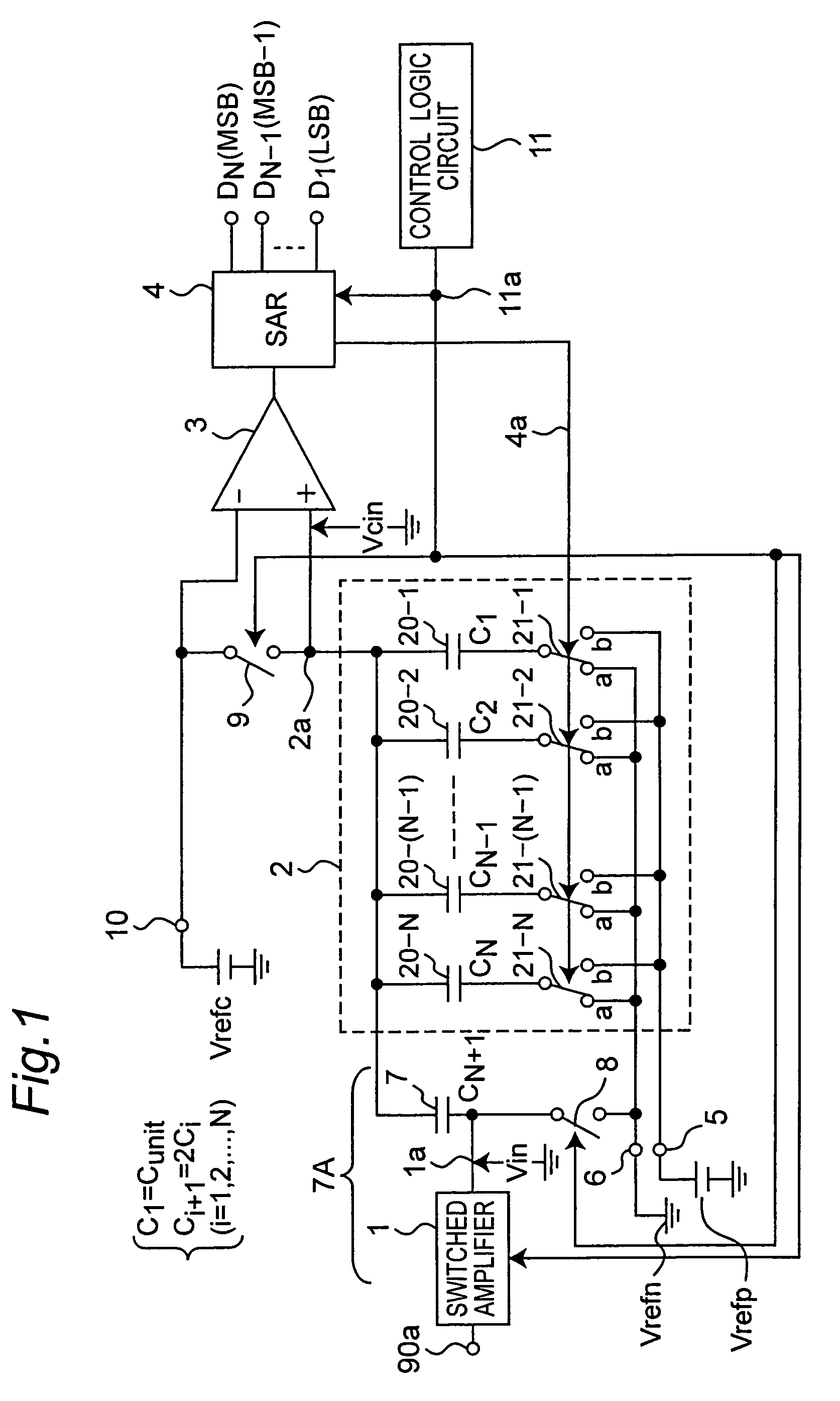

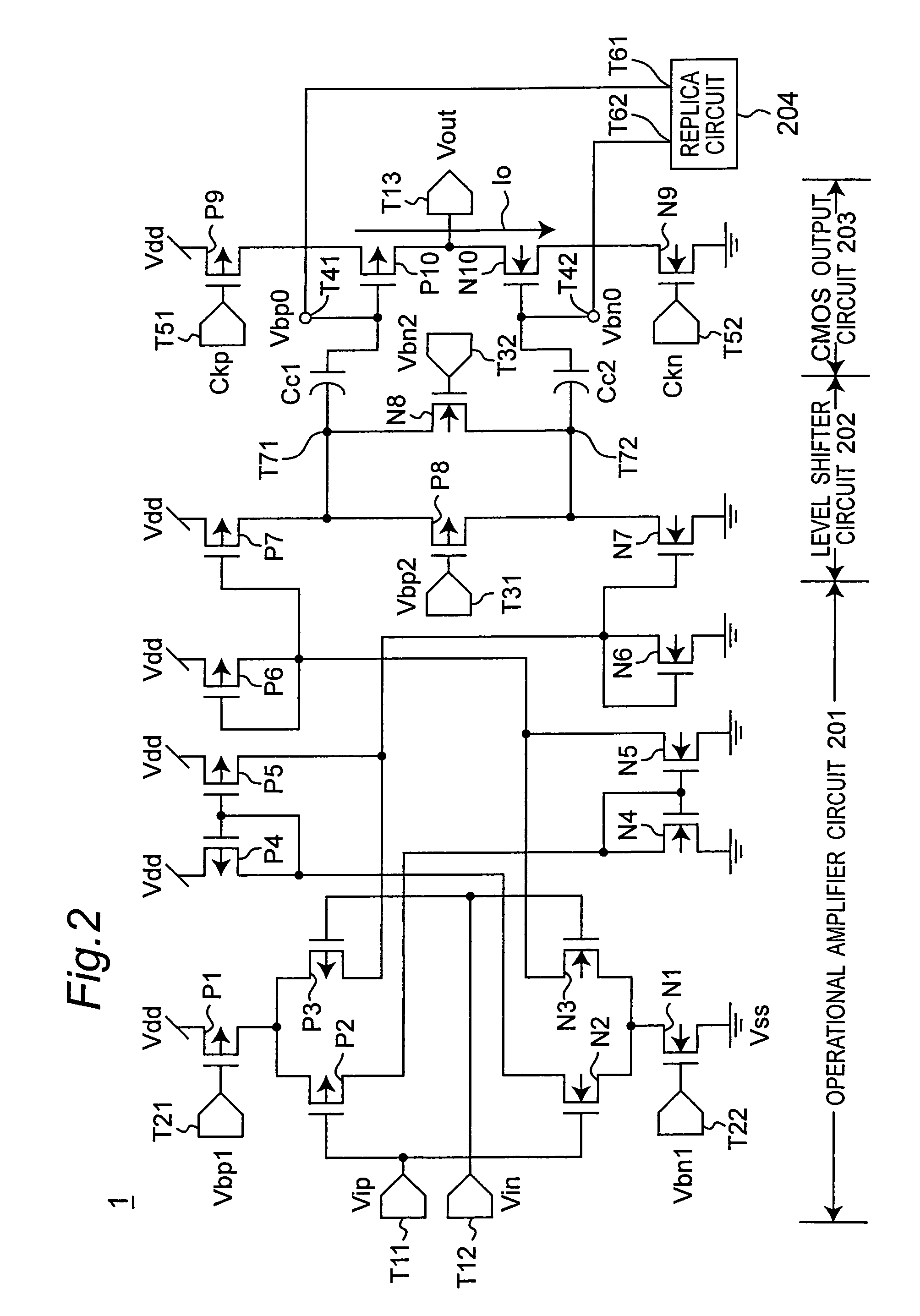

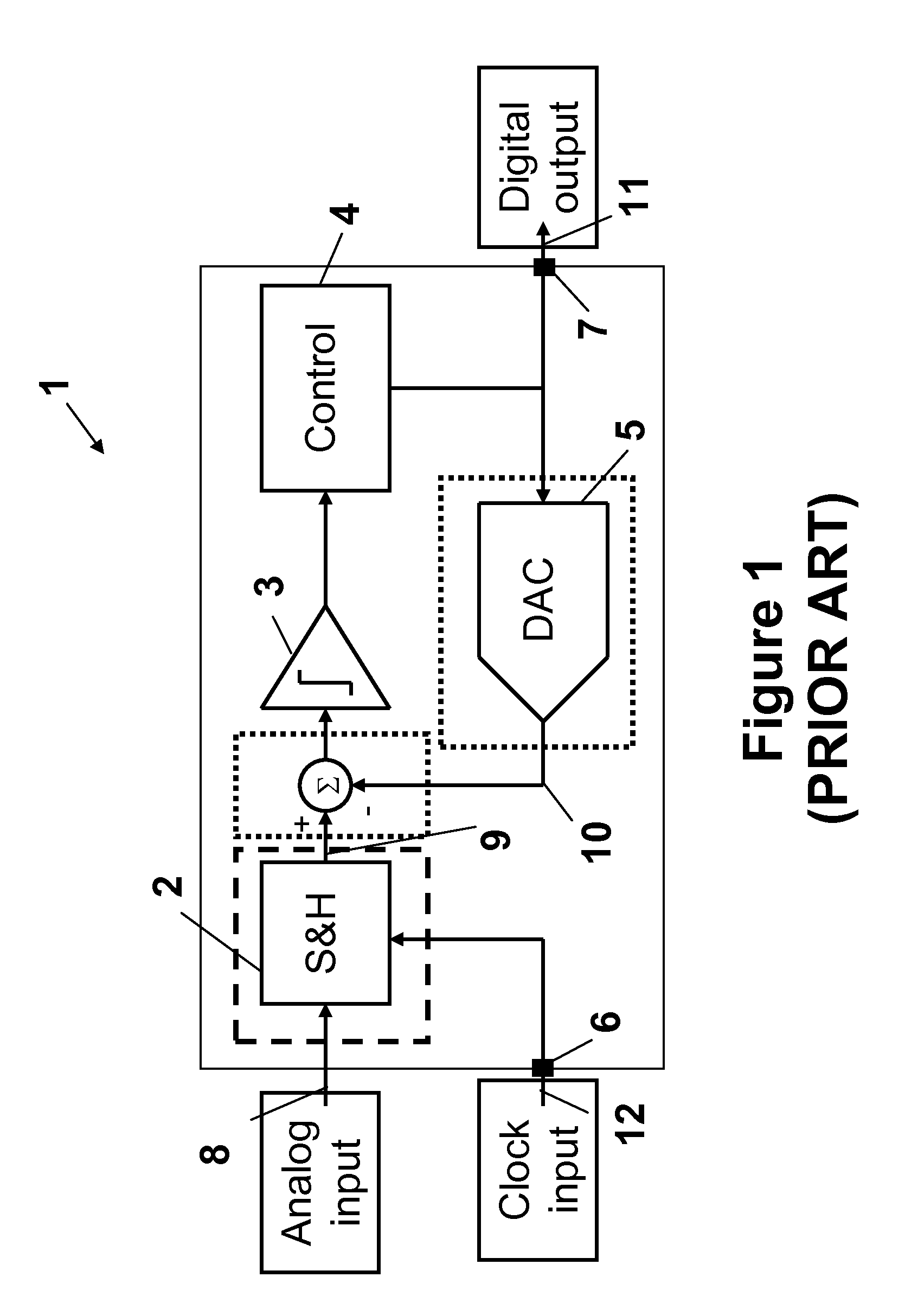

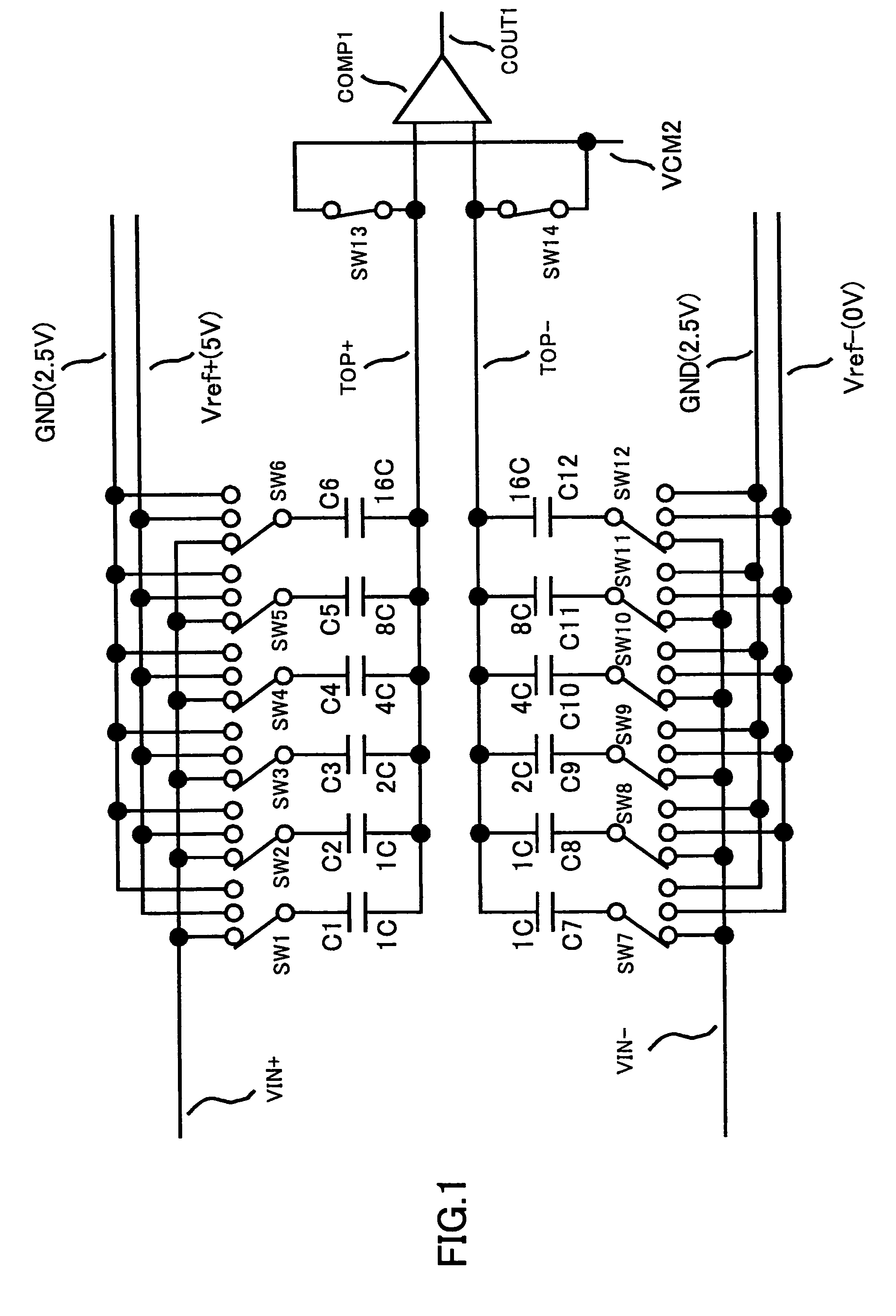

Analog to digital converter circuit of successive approximation type operating at low voltage

InactiveUS7015841B2Simple circuit configurationElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierLow voltage

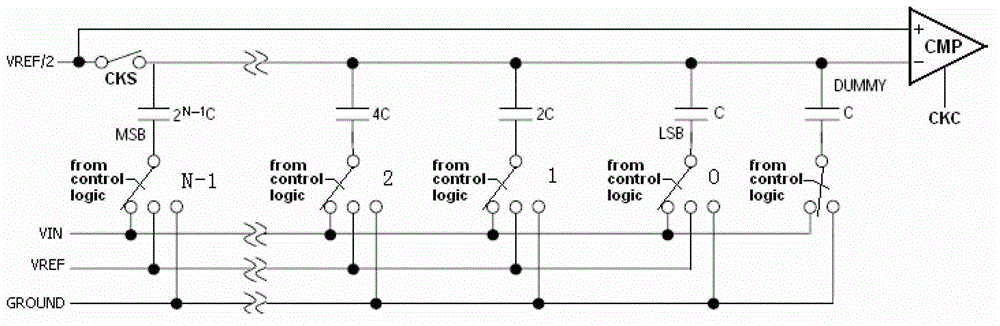

In a sampling and holding, a control logic circuit connects another end of each capacitor of a DA converter to a ground potential, and outputs a sampled input analog signal from a switched amplifier to one end of a hold capacitor to hold. In a successive approximation, it controls a switched amplifier to set an output terminal thereof to a high-impedance state and the hold capacitor to connect the one end thereof to the ground potential. Then, it switches over connection of another end of each capacitor from the ground potential to a power supply voltage based on a digital value held by a successive approximation register to output an output voltage from another end of the hold capacitor to a comparator, and compares the output voltage from another end thereof with an intermediate reference voltage to obtain a digital value from the successive approximation register.

Owner:SEMICON TECH ACADEMIC RES CENT

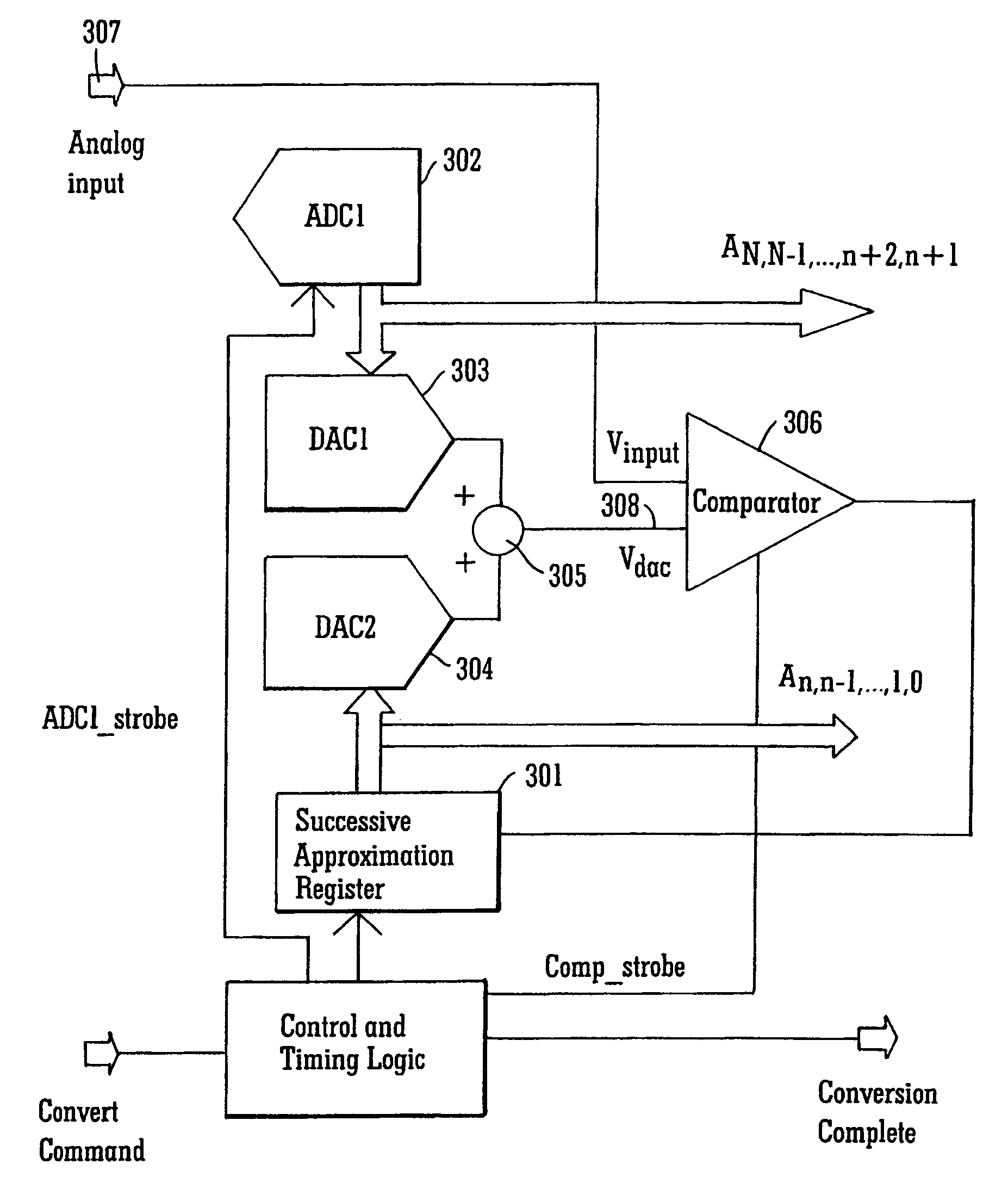

Successive approximation analog-to-digital converter with pre-loaded SAR registers

InactiveUS7038609B1Efficiently transitionEliminate effectiveElectric signal transmission systemsAnalogue-digital convertersDigital down converterFlash ADC

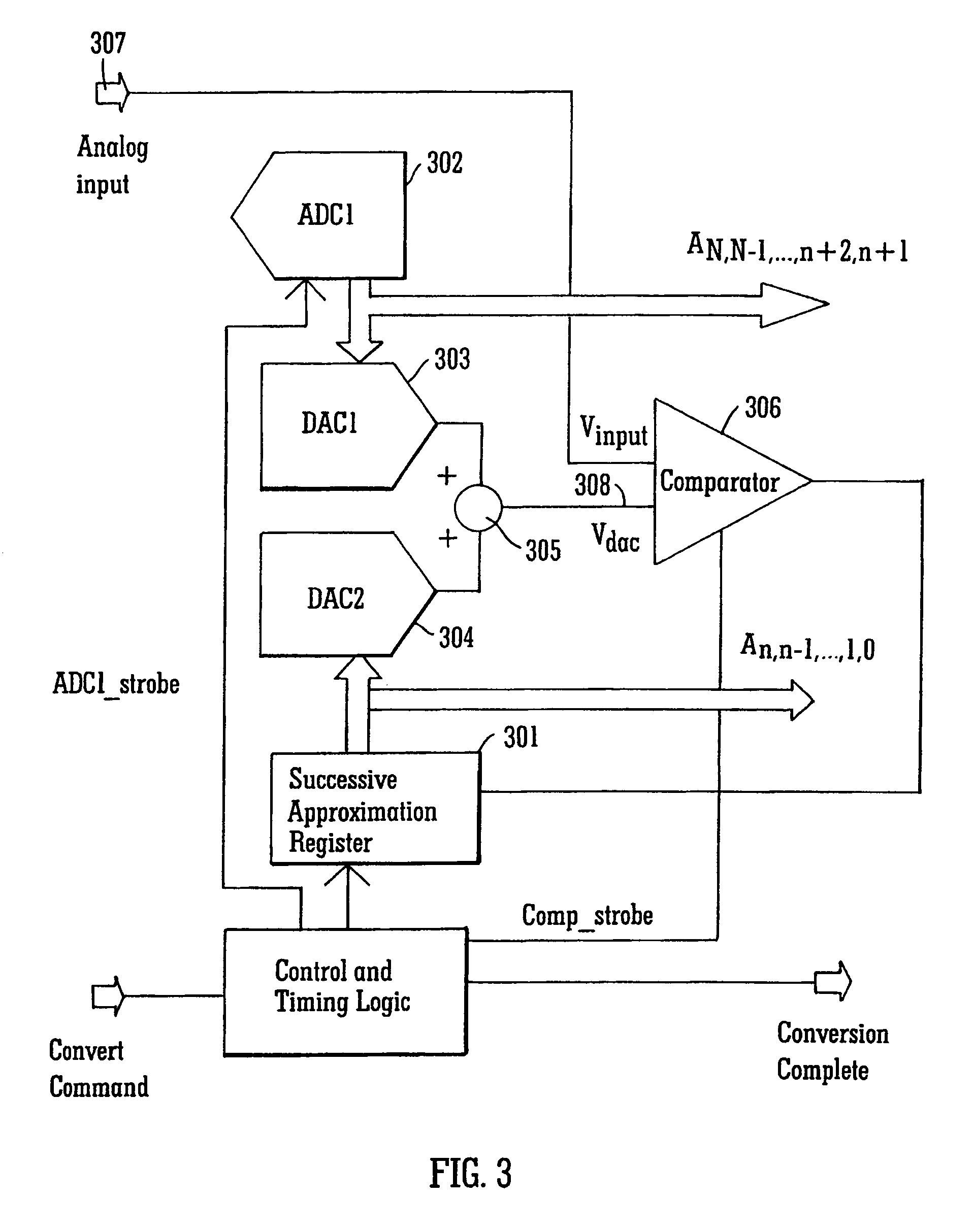

A SAR converter having enhanced performance by virtue of effectively pre-loading the SAR's most significant bits with a value that makes the associated DAC output almost equal to the signal to be converted. A normal SAR conversion is then completed with the SAR bits that have not been pre-loaded. The value used to pre-load the most significant bits of the SAR is preferably obtained from a low-resolution, high-speed converter, such as a flash. The range of DAC bits used in the normal SAR part of the conversion may be increased such that errors up to a certain magnitude in the high-speed converter can be corrected. Reducing power consumption of a SAR system can be readily accomplished by reducing comparator supply voltage. For a SAR converter architecture using a CAPDAC array or CAPDAC (capacitor array DAC), fairly large variations in comparator input voltage can be expected under these circumstances. If the input voltage variation becomes too large, damage to the comparator input devices can occur, or inaccuracies may develop. In one embodiment of the invention, the most significant bits are provided by sampling the input signal through a flash ADC that does not suffer from the input voltage restriction described above.

Owner:ANALOG DEVICES INC

Metastability error detection and correction system and method for successive approximation analog-to-digital converters

ActiveUS8957802B1Electric signal transmission systemsAnalogue-digital convertersDigital down converterNAND gate

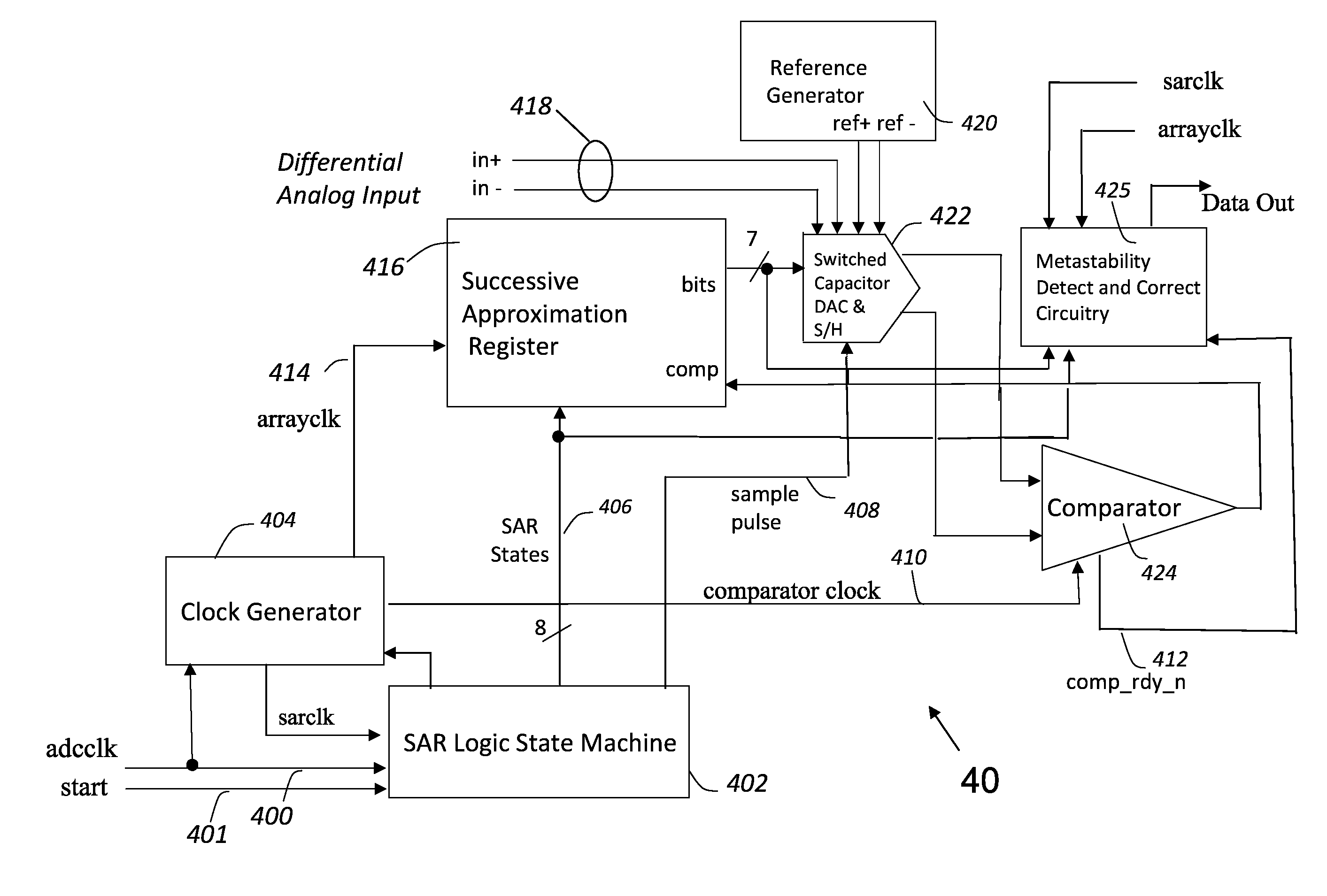

A system and method are provided for the detection and correction of metastability errors in a successive approximation analog to digital converter (ADC). The successive approximation ADC (40) includes a comparator unit (424) that includes a NAND gate circuit (550) that outputs a comp_rdy_n signal when the comparator (500) has latched a result. ADC (40) includes a metastability detection and correction circuit (425) that includes a first logic circuit (700) that monitors the comp_rdy_n signal and detects a metastable event if that signal is not received within a portion of a conversion time period of the ADC. Responsive to detection of a metastable event, a second logic circuit (750) generates a correct conversion code at the output of the ADC. If no metastable event is detected during a conversion cycle of the ADC, the second logic circuit (750) outputs the conversion codes determined by the comparator (500).

Owner:CADENCE DESIGN SYST INC

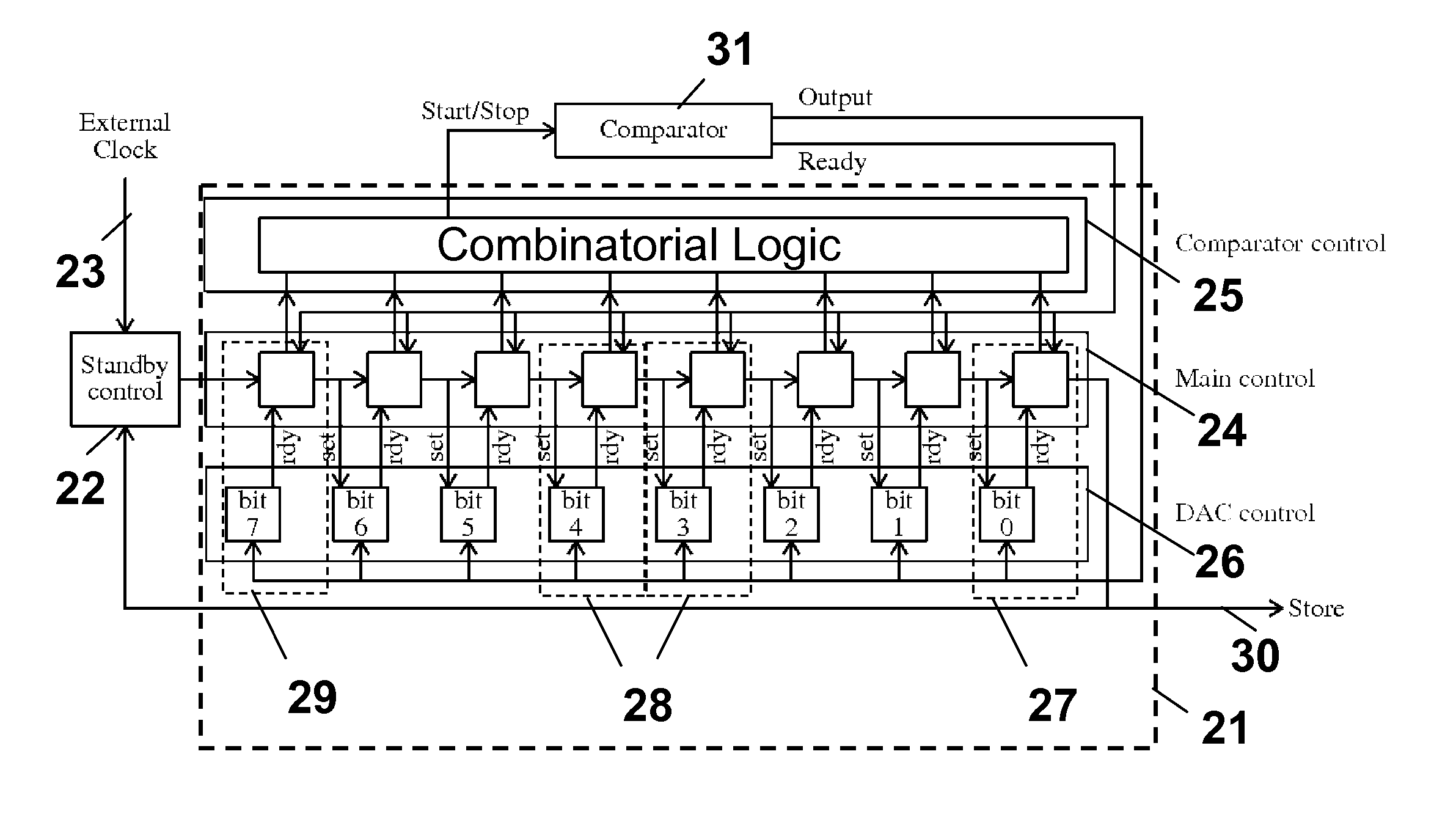

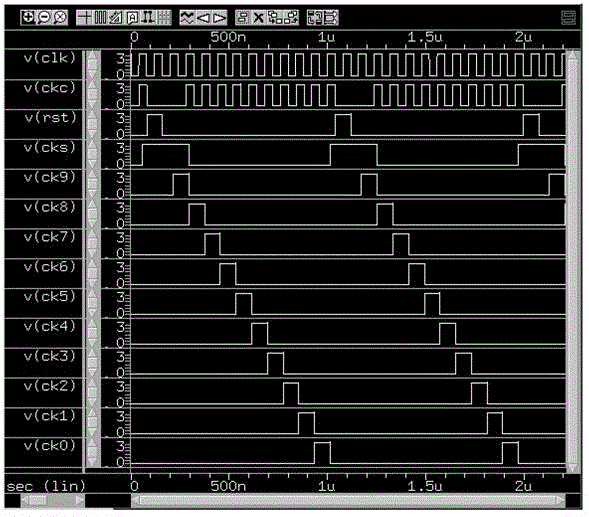

Asynchronous SAR ADC

ActiveUS20110057823A1Improve system robustnessMinimizes partElectric signal transmission systemsAnalogue-digital convertersControl signalProcessor register

An asynchronous analog to digital convertor for converting an analog input signal into a digital output is presented. According to an embodiment, the analog to digital convertor comprises a clock input operable to receive an external clock signal having a clock period, a comparator operable to compare the analog input signal to a reference signal, a digital to analog converter operable to generate the reference signal corresponding to a state of a successive approximation register, and a control block connected to the comparator and to the digital to analog converter. The control block is operable to generate and receive a sequence of control signals according to a successive approximation algorithm, to perform a plurality of comparisons, and to update the state of the successive approximation register thereby generating the digital output.

Owner:STICHTING IMEC NEDERLAND

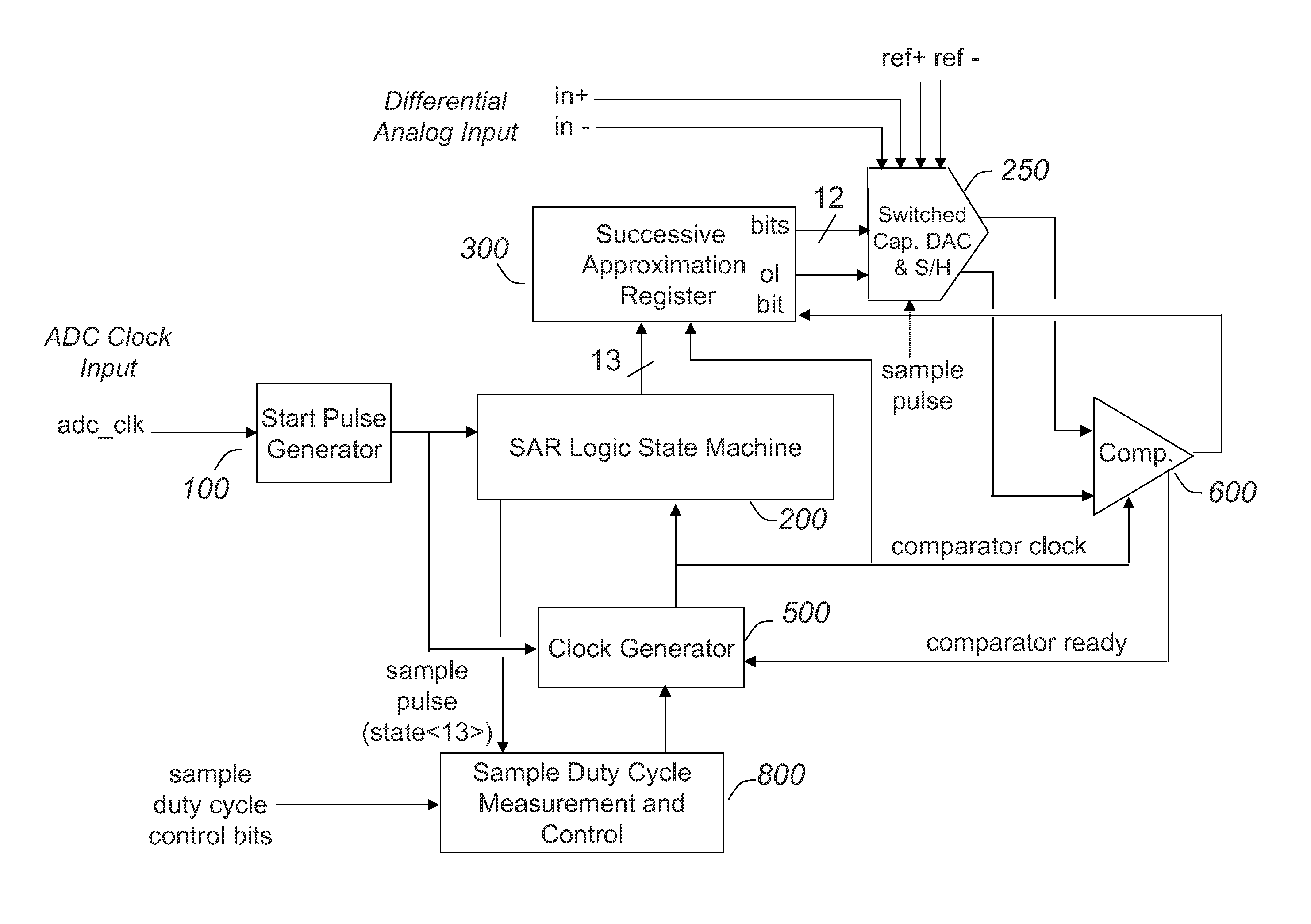

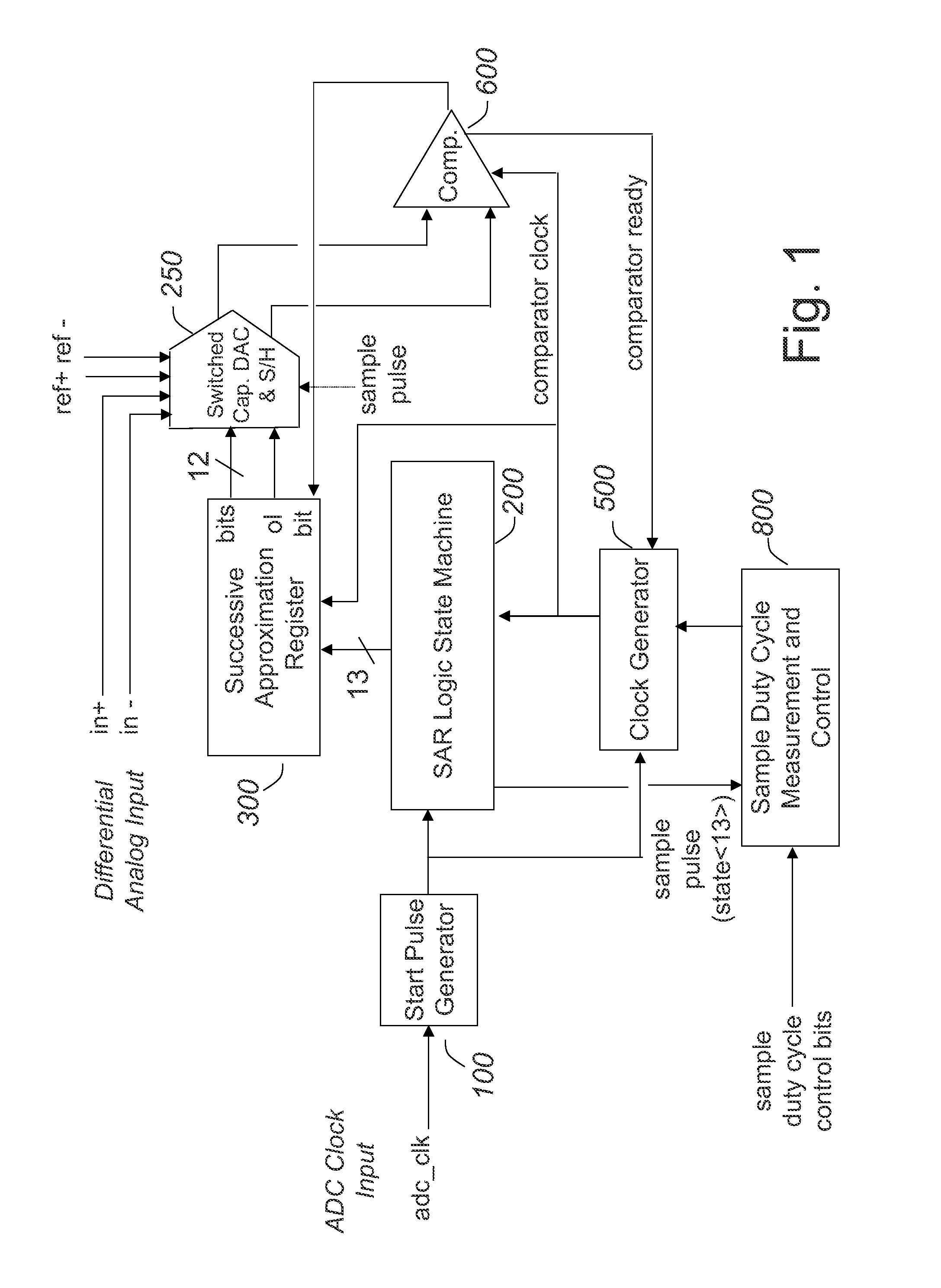

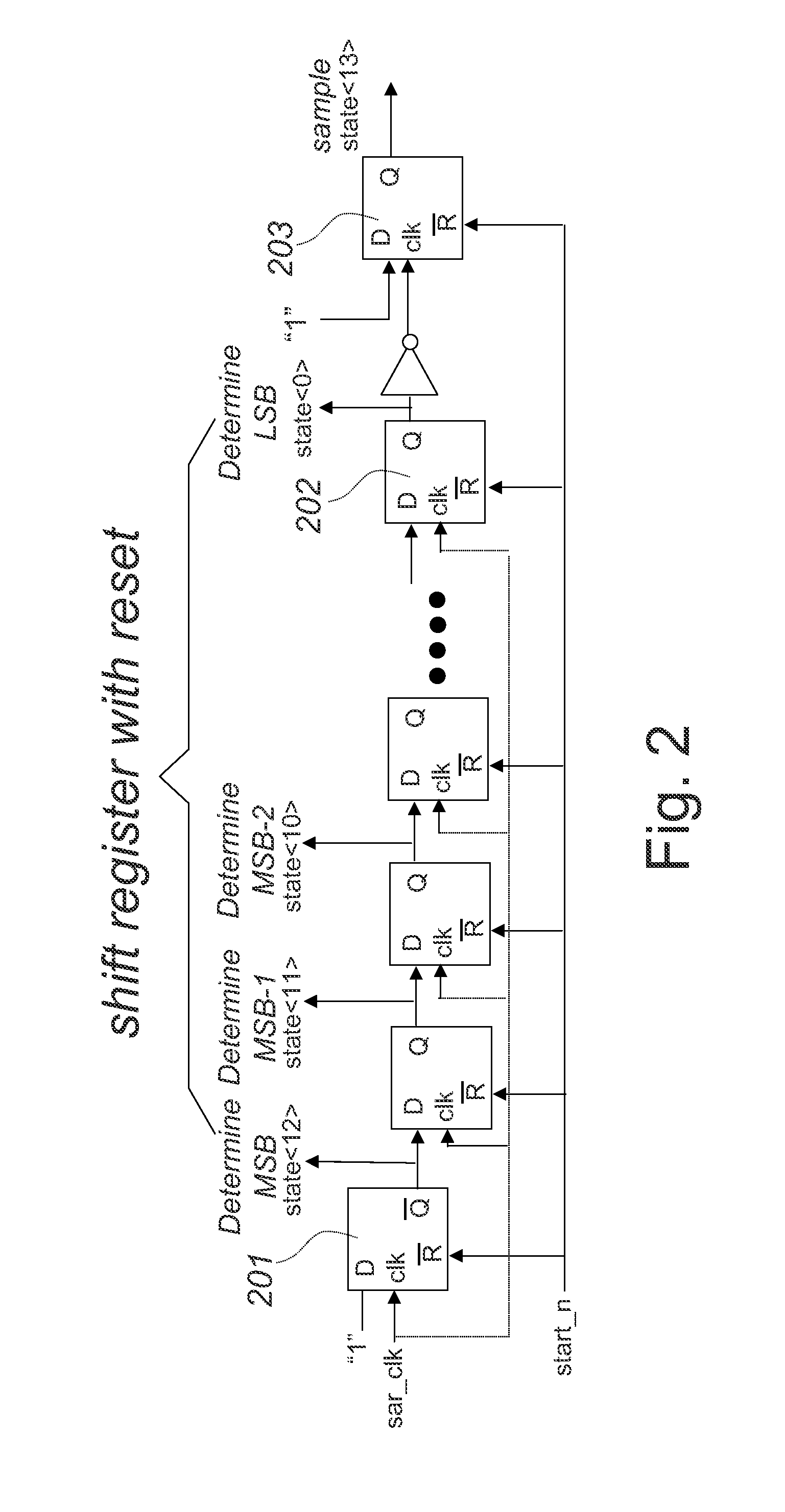

System and method for adaptive timing control of successive approximation analog-to-digital conversion

ActiveUS8344925B1Enough timeEnable selectivityElectric signal transmission systemsAnalogue-digital convertersPropagation timeAnalog signal

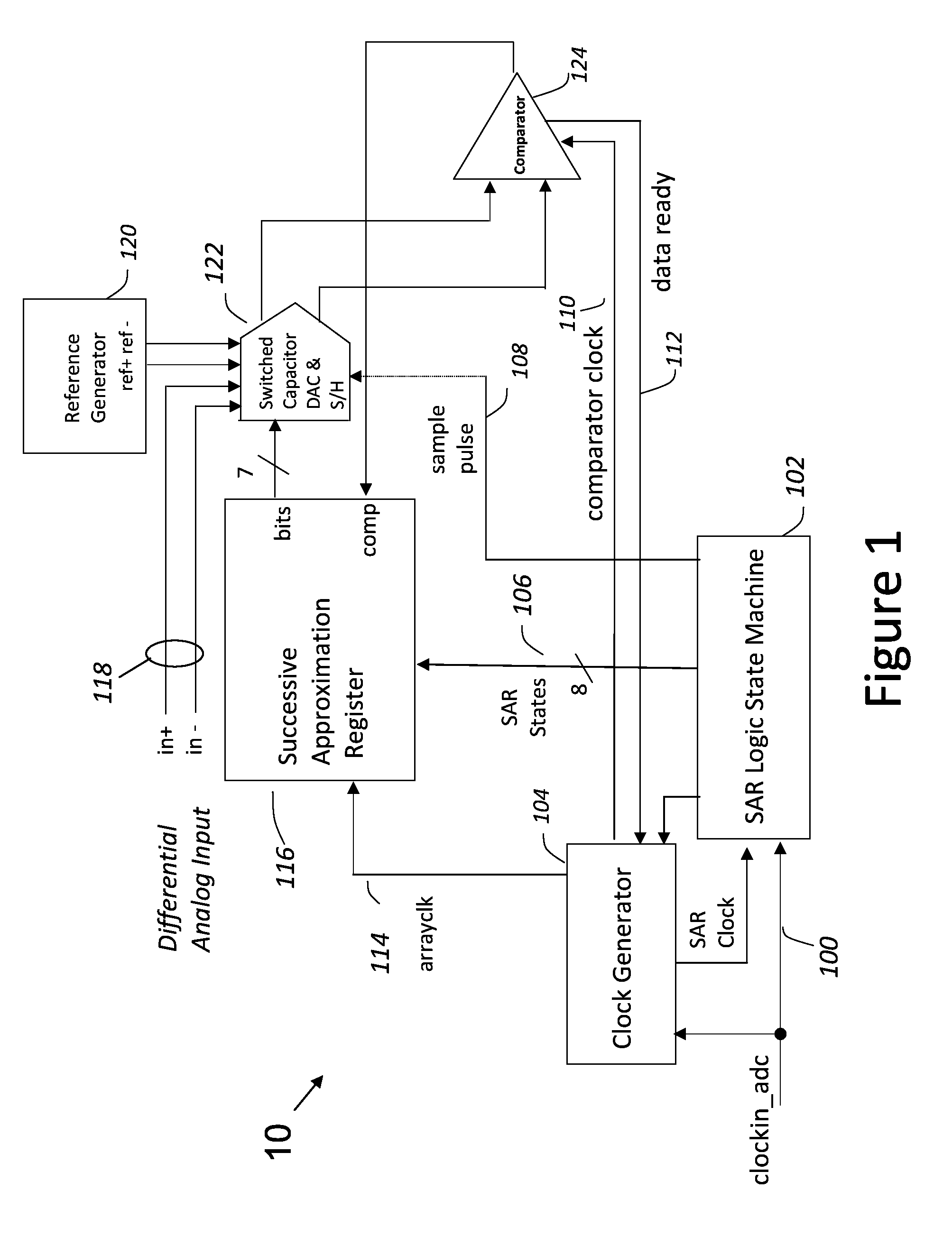

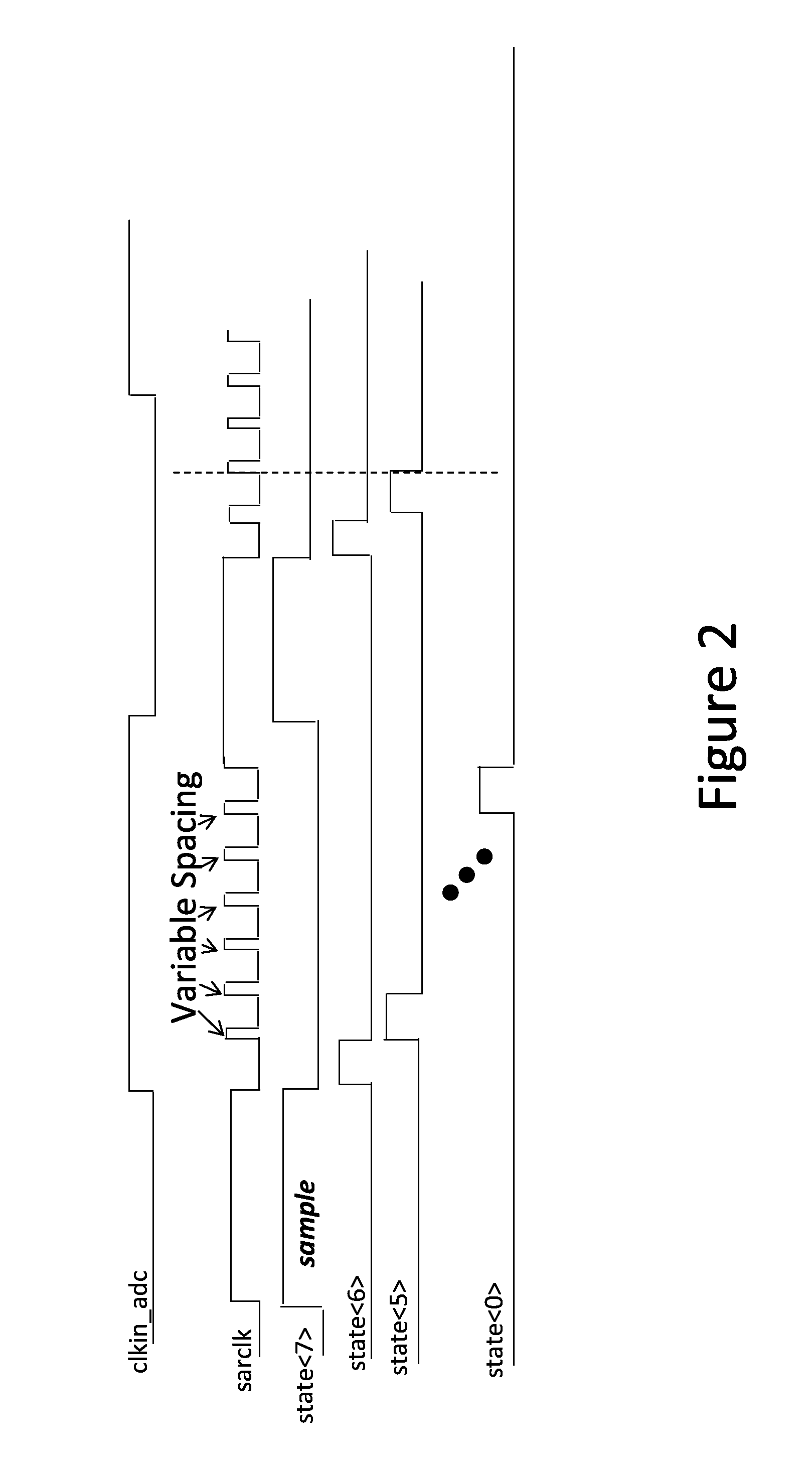

A system and method are provided for adaptively controlling timing in SAR ADC of a sampled analog signal within a conversion period. A state machine maintains a set of SAR states including a sampling state and a plurality of bit conversion states. A reference generator generates a quantization level reference for each of the bit conversion states within a parametric settling time thereof. A comparator compares the sampled analog signal with the quantization level reference over a parametric propagation time for determining a hit value for each hit conversion state. A clock generator adaptively defines signals for clocking the state machine and comparator for each SAR state, thereby adaptively delaying bit determination in each bit conversion state by an integration period not less than the settling time, while adaptively delaying quantization level reference generation for a next bit conversion state by a regeneration period not less than the propagation time.

Owner:CADENCE DESIGN SYST INC

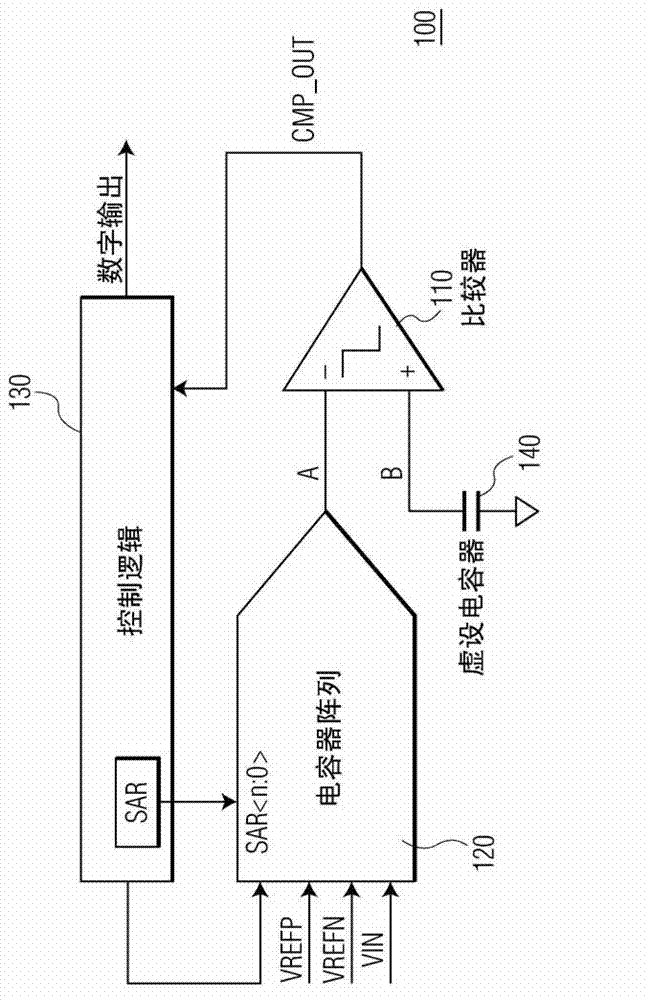

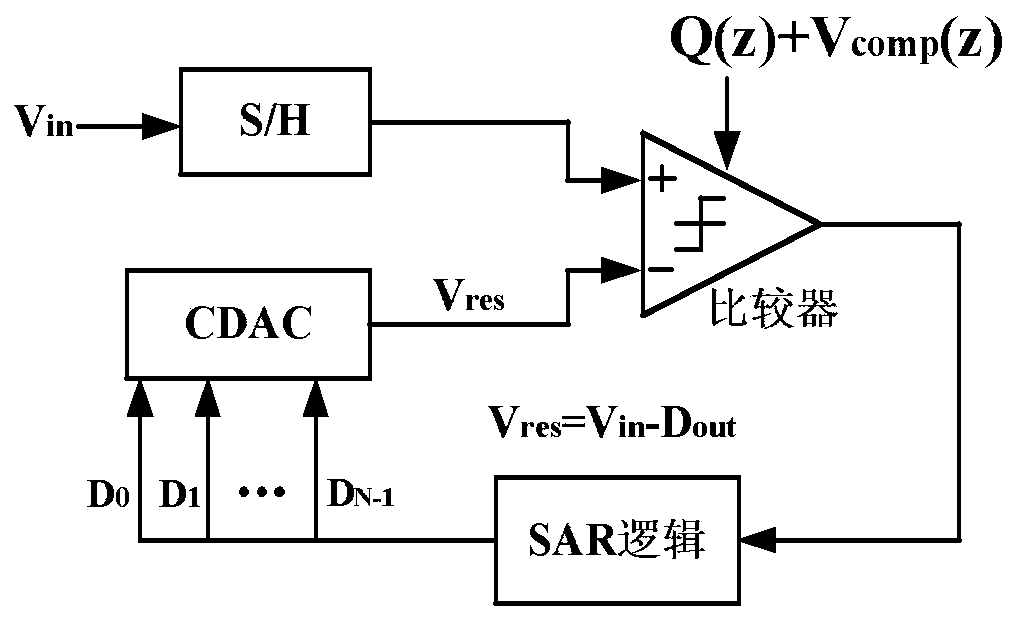

Input-independent self-calibration method and apparatus for successive approximation analog-to-digital converter with charge-redistribution digital to analog converter

ActiveCN103036564AAnalogue/digital conversion calibration/testingDigital down converterData acquisition

A method and apparatus for correcting the offset and linearity error of a data acquisition system. A charge redistribution digital to analog convertor (CDAC) is connected to one of the differential inputs of a comparator whose second input comes from a function CDAC. The calibration algorithm is built into a digital control unit. The digital control unit detects the offset and capacitor mismatch errors sequentially, stores the calibration codes for each error in calibration mode and provides the input-dependent error correction signals synchronized with the binary search timing to adjust the differential input of the comparator and compensate the input-dependent errors present at the output of the non-ideal function CDAC during normal conversions.

Owner:NXP BV

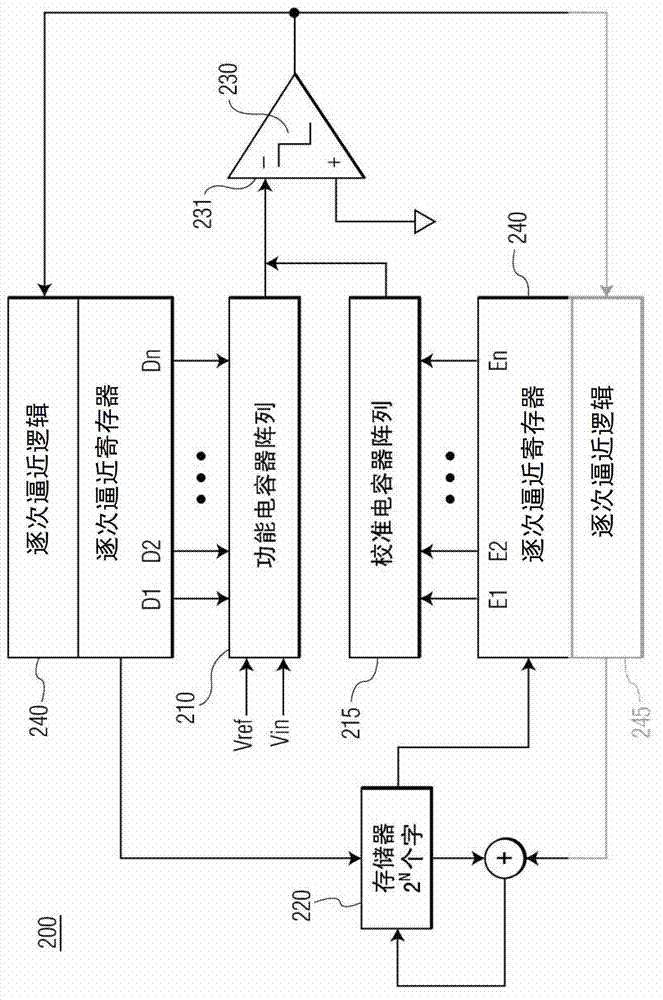

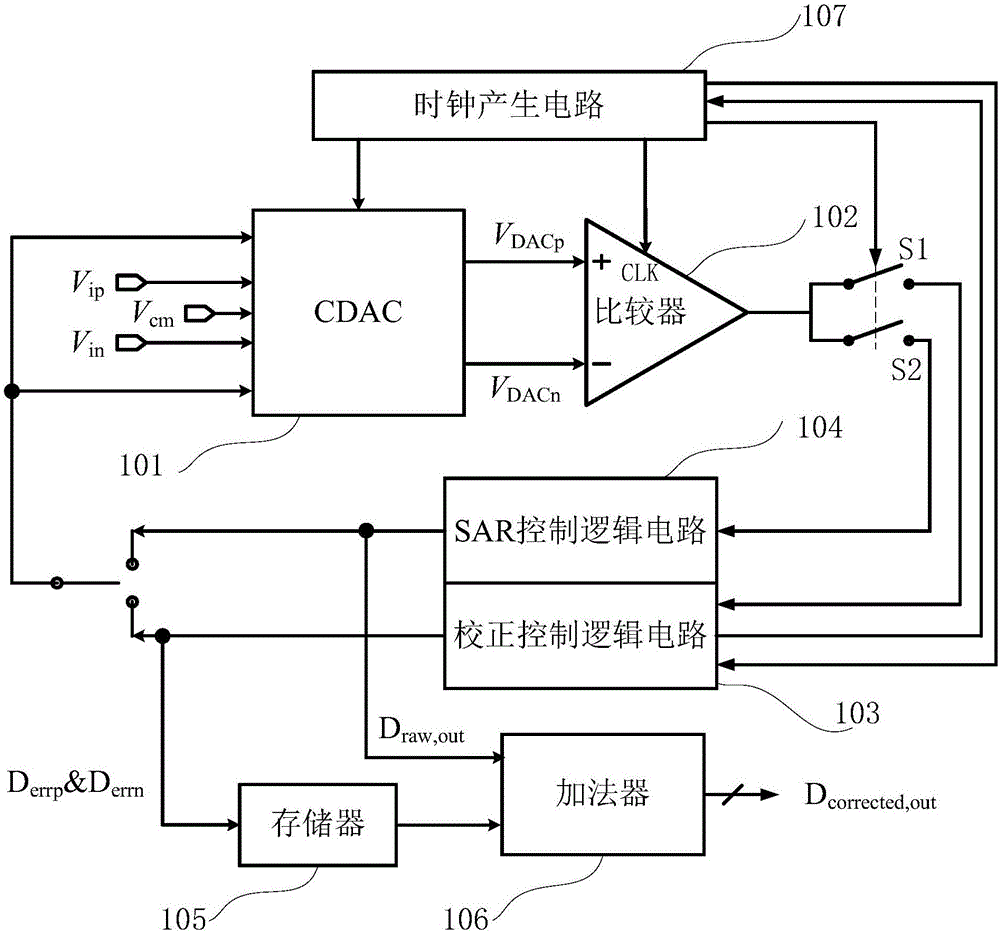

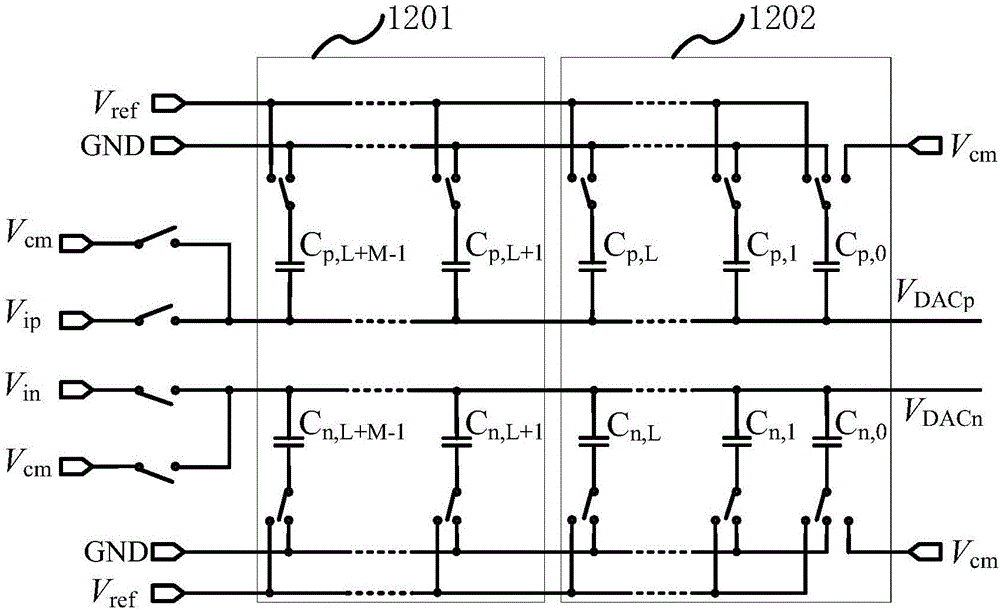

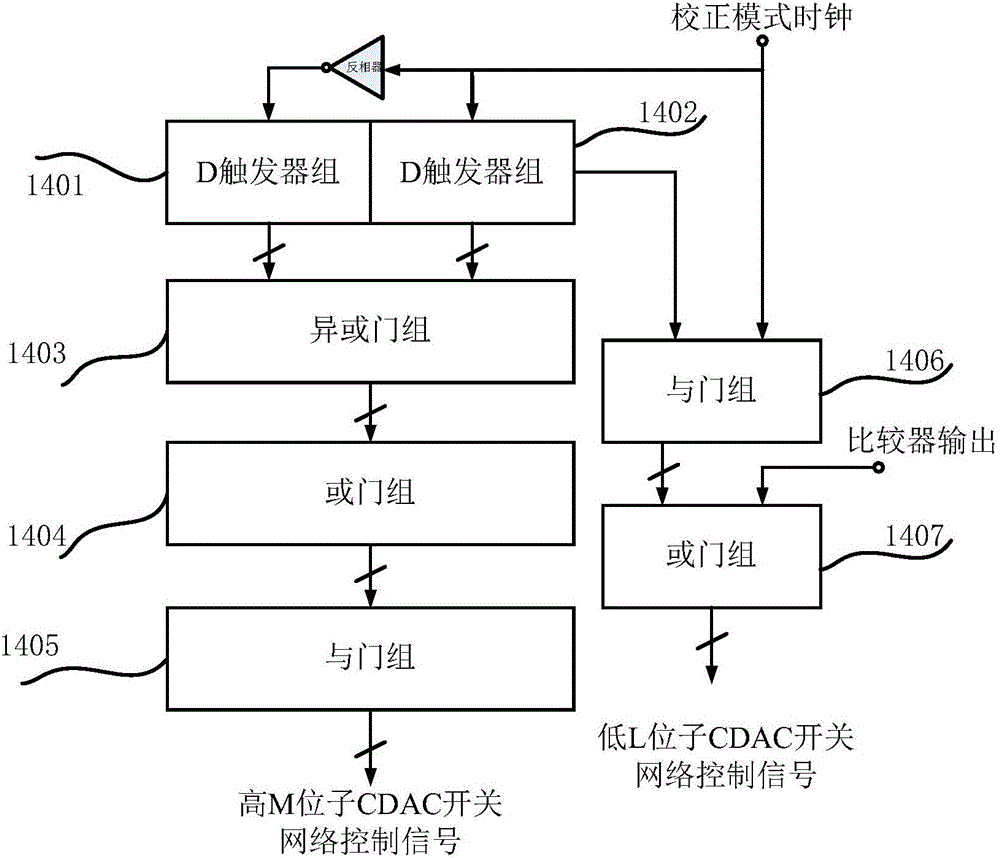

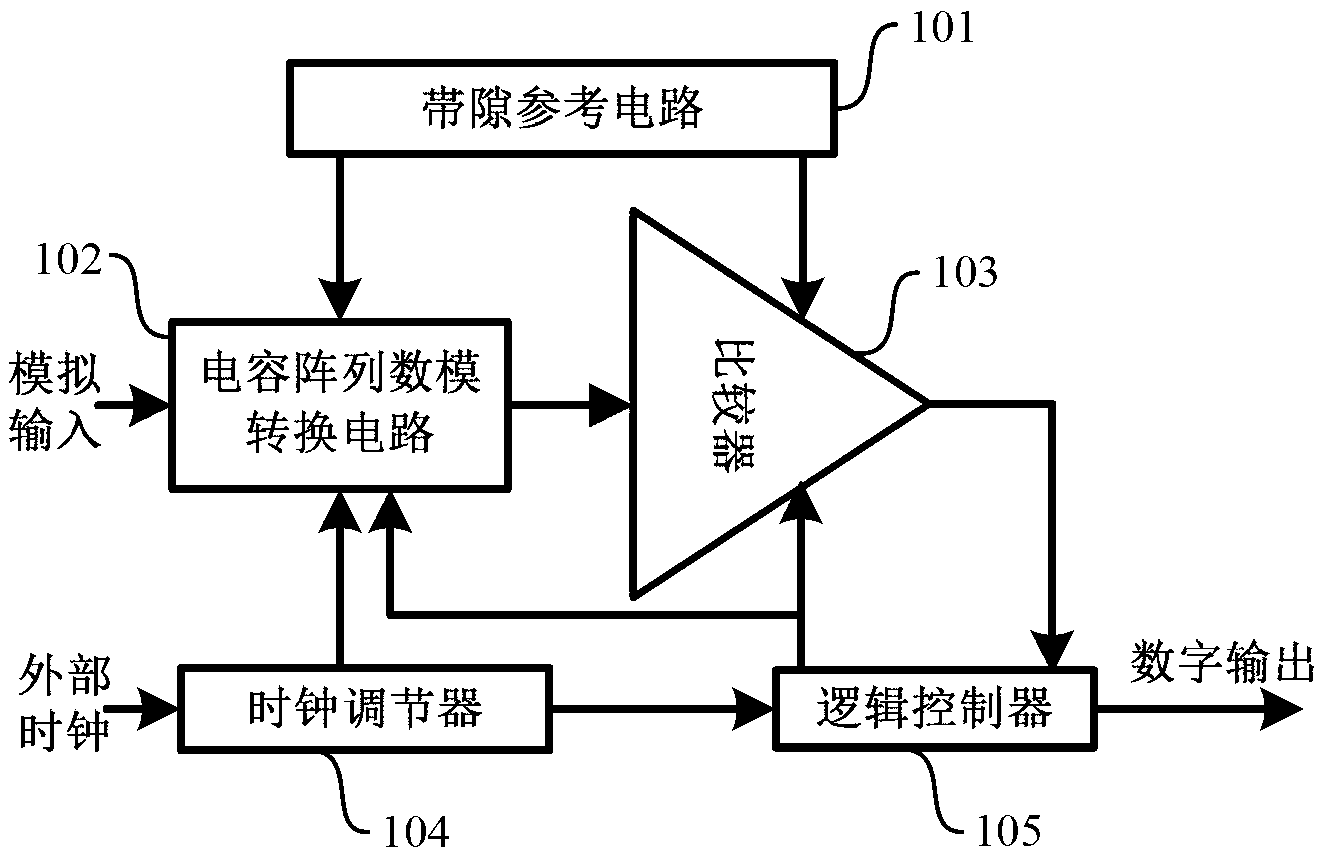

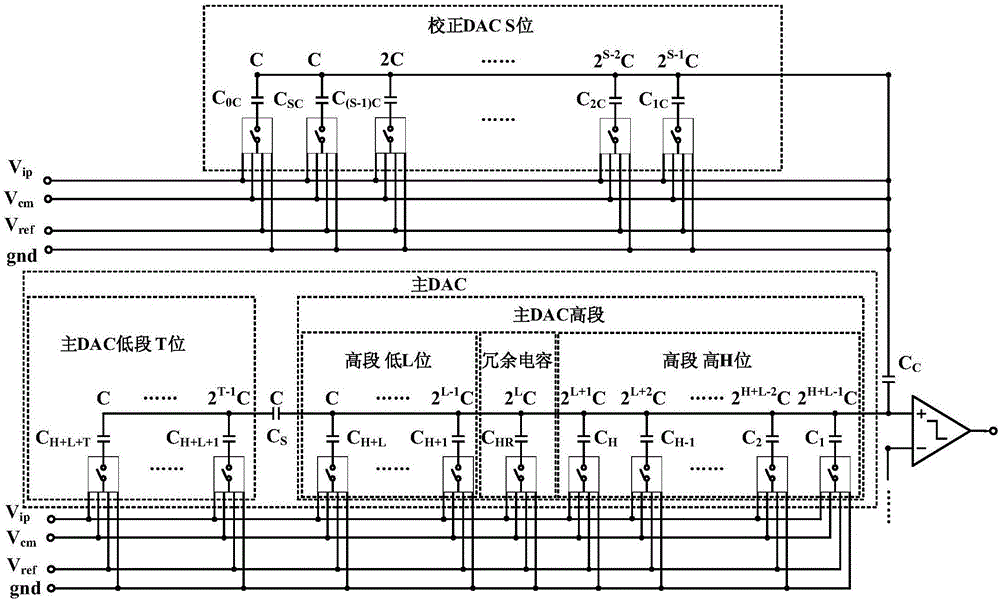

Successive approximation analog-digital converter and analog-digital conversion method based on digital domain self-correcting

ActiveCN106374930AReduce non-linearityHigh precisionElectric signal transmission systemsAnalogue/digital conversion calibration/testingCapacitanceDigital down converter

The invention provides a successive approximation analog-digital converter and an analog-digital conversion method based on digital domain self-correcting. The successive approximation analog-digital converter comprises a CDAC, a comparator, an SAR control logic circuit, a correction control logic circuit, a storage, an adder and a clock circuit; a differential structure is adopted in the CDAC; capacitor arrays of the CDAC respectively form a high-M-level CDAC and a low-L-level CDAC; on the basis of a capacitor array reusing thought, mismatching errors of various capacitors in the high-M-level CDAC capacitor array are detected by reusing the low-L-level CDAC in a self-correcting stage; detected error values are quantized; error voltage is converted into an error code to output; the output error code is output into the storage; after mismatching error detection and quantization are completed, digital conversion of an input analog signal begins to perform; an original code is output, and operated with the error code at the corresponding bit called from the storage; therefore, the final output codeword after being corrected is obtained; and thus, the linearity of the SAR ADC is increased.

Owner:SOUTHEAST UNIV

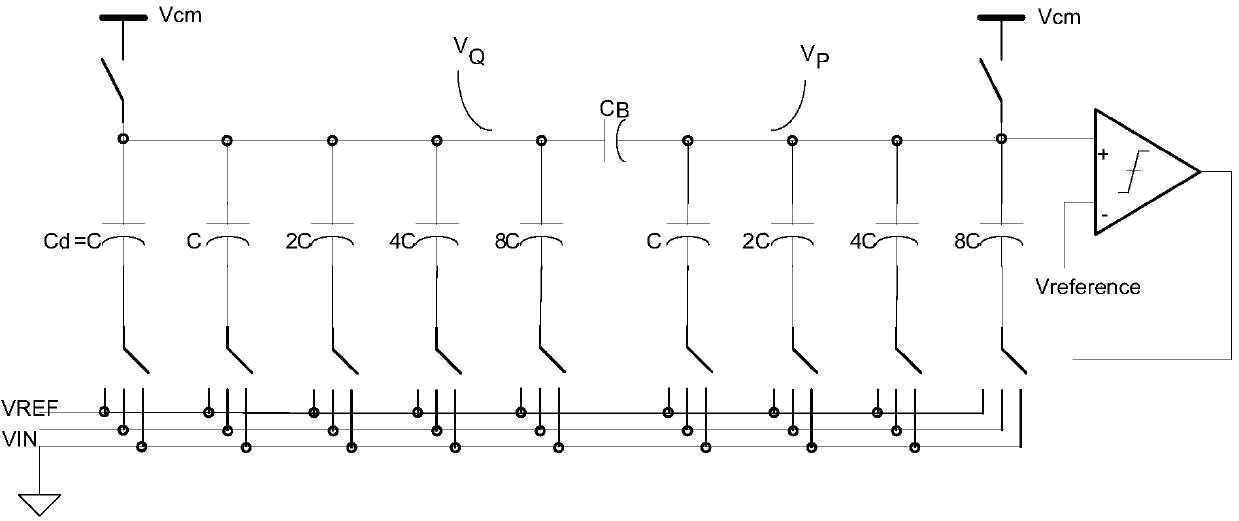

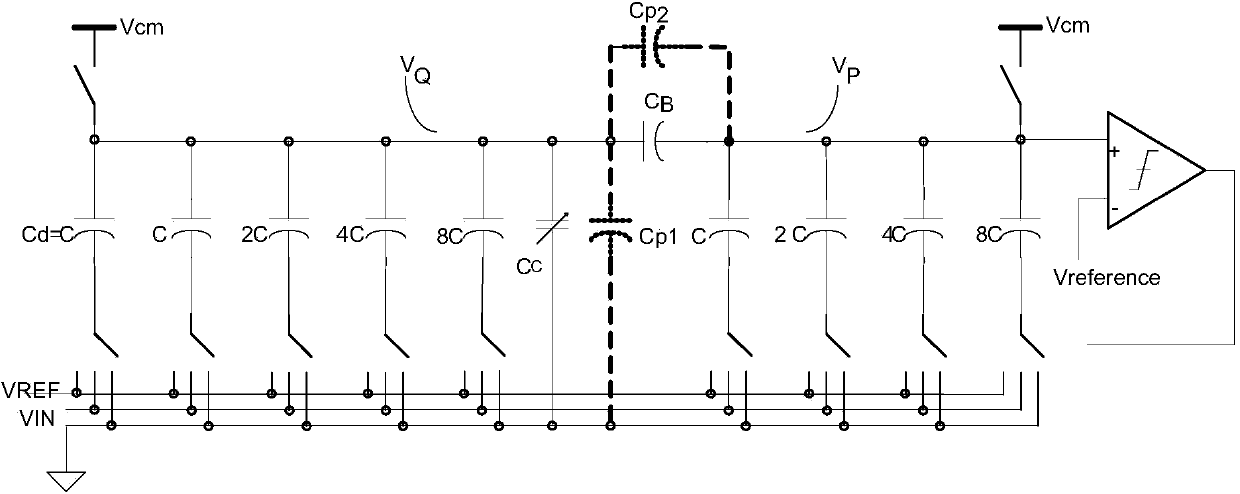

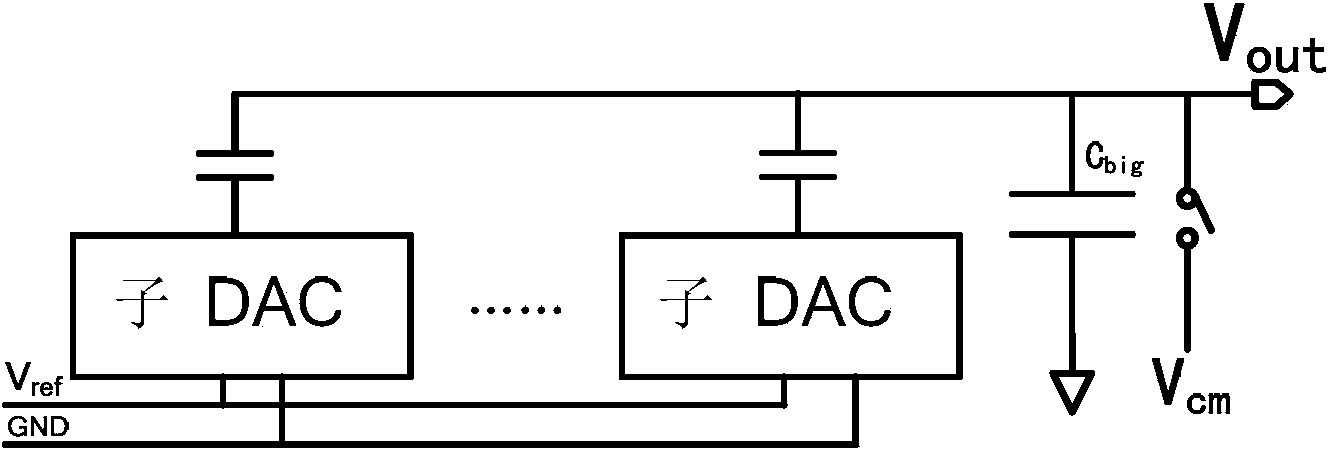

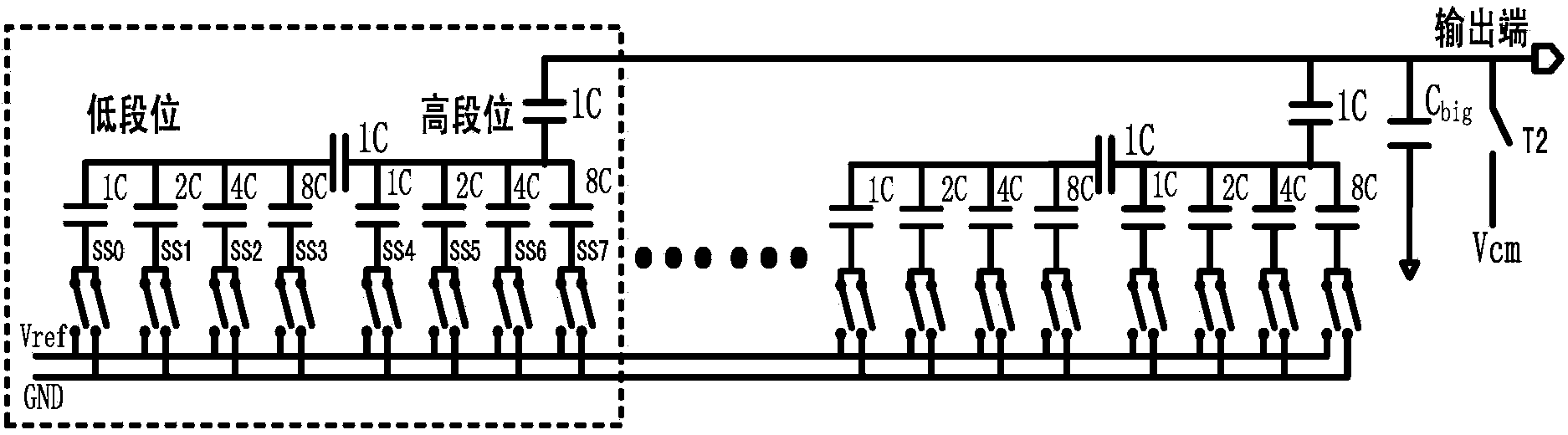

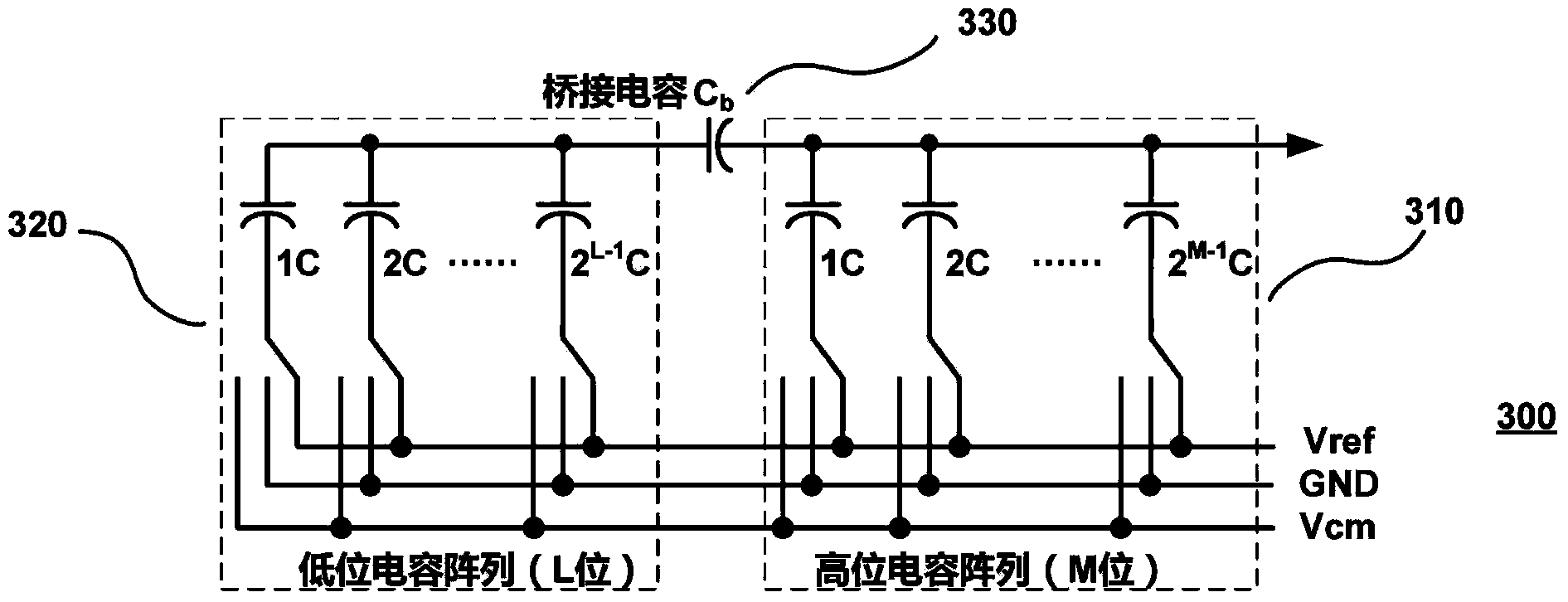

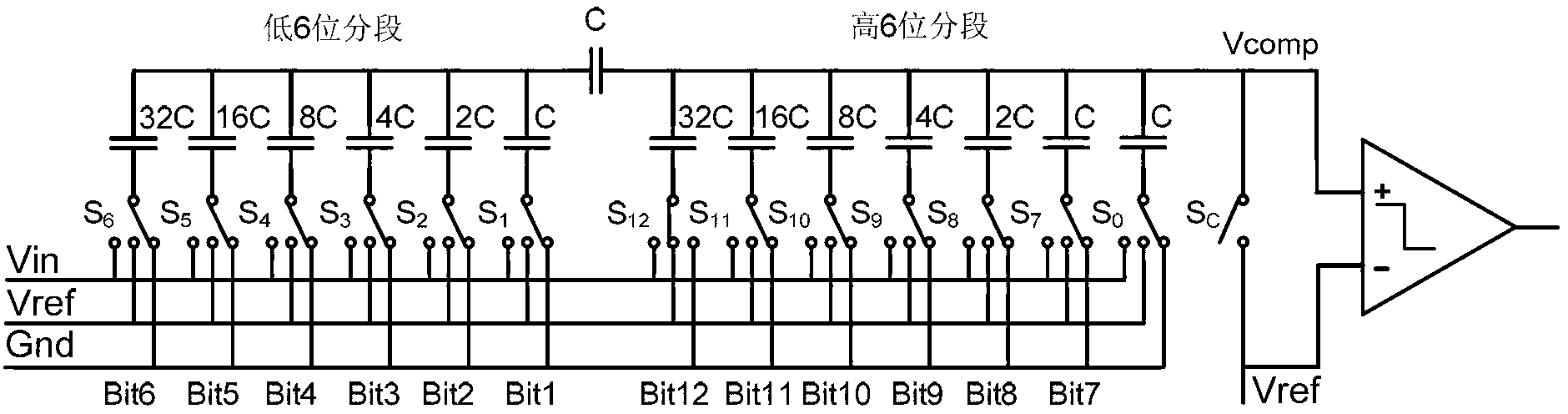

Digital-to-analog converter with sectional capacitor array structure

ActiveCN103475373AEliminate Capacitor MismatchEliminate Gain ErrorDigital-analogue convertorsParasitic capacitanceLinearity

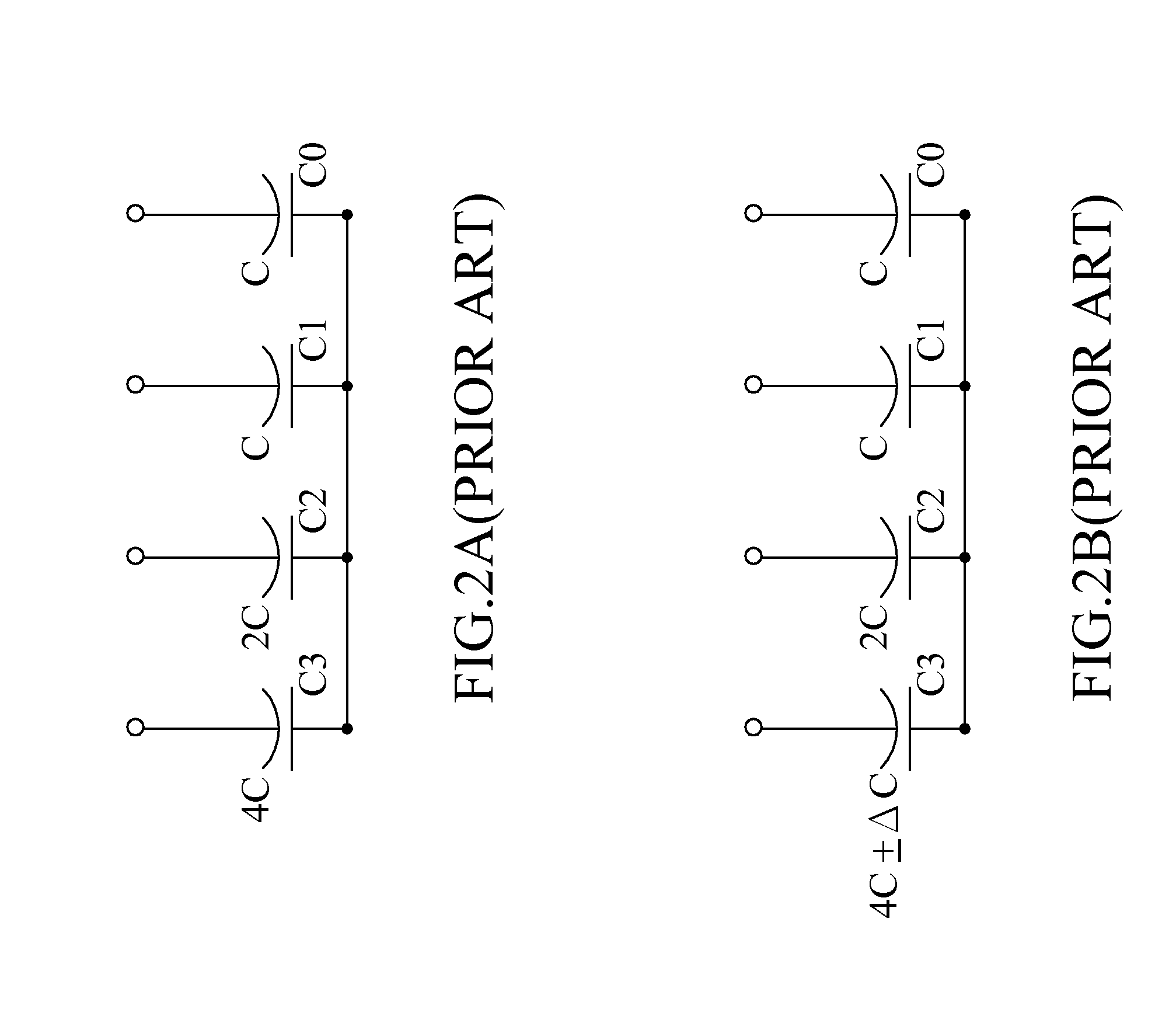

The invention discloses a digital-to-analog converter with a sectional capacitor array structure. The digital-to-analog converter comprises at least two capacitor subarrays and at least one bridging capacitor CB, wherein each bridging capacitor CB is connected with two qualification-bit capacitor subarrays with adjacent weights; the low-level capacitor subarray of each bridging capacitor CB is connected with a compensating capacitor CC with an adjustable capacitance value in parallel; the compensating capacitor CC enables the capacitance value of an equivalent capacitor in the compensated low-level capacitor subarray to be equal to that of the lowest-level capacitor in the high-level capacitor subarray connected with the bridging capacitor CB. The digital-to-analog converter disclosed by the invention has the advantages that by adoption of the embodiment, the compensating capacitor CC with the adjustable capacitance value is introduced, and the capacitance value of the compensating capacitor CC is set according to the bridging capacitor CB and parasitic capacitors at common nodes of the capacitor subarrays at the two ends, so that the capacitor mismatching among the capacitor subarrays is eliminated, the linearity is further improved while gain error is eliminated, and DNL (Differential Non Linearity) and INL (Integral Non Linearity) of a successive approximation ADC (Analog to Digital Converter) are finally improved.

Owner:SHENZHEN GOODIX TECH CO LTD

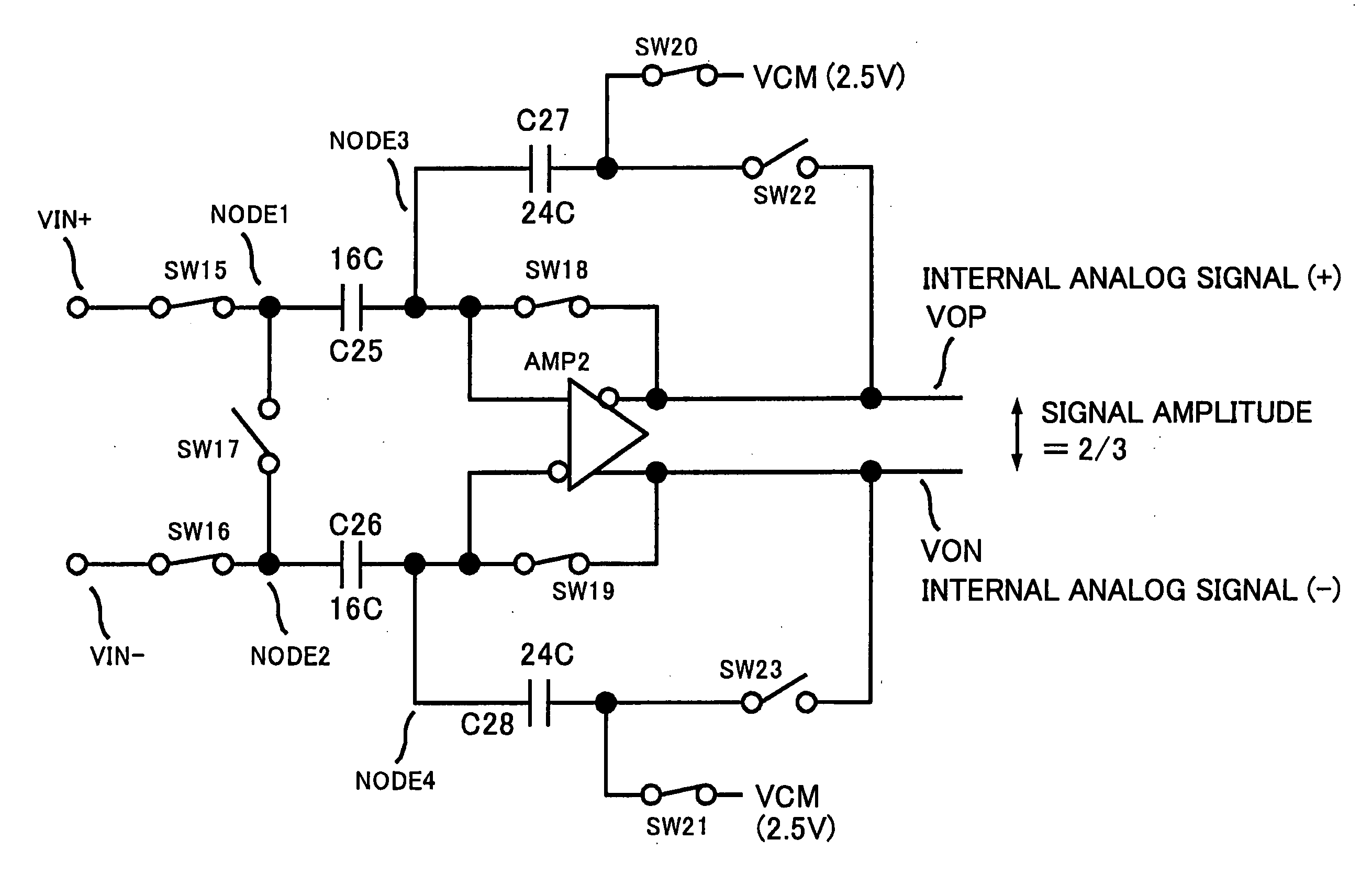

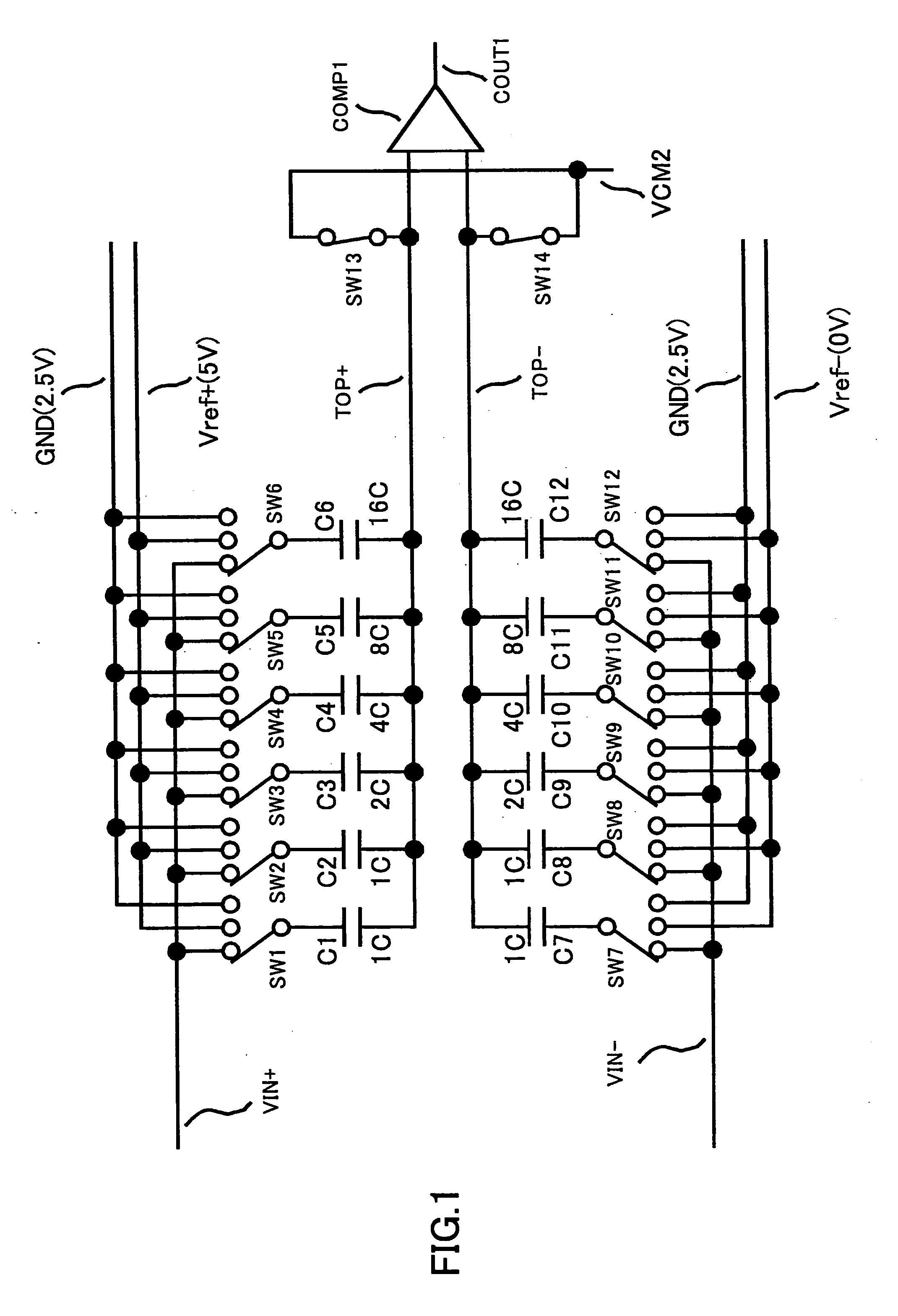

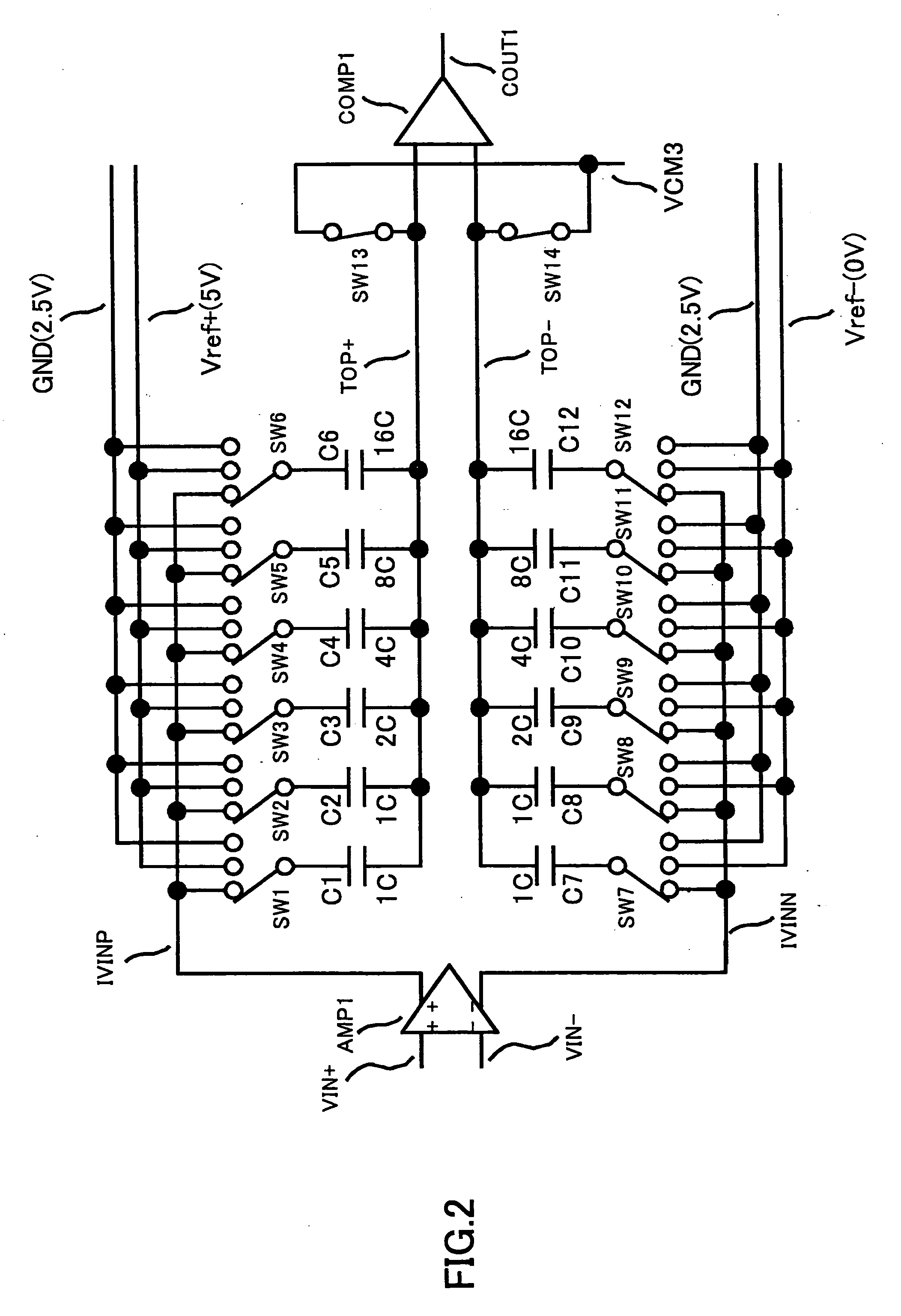

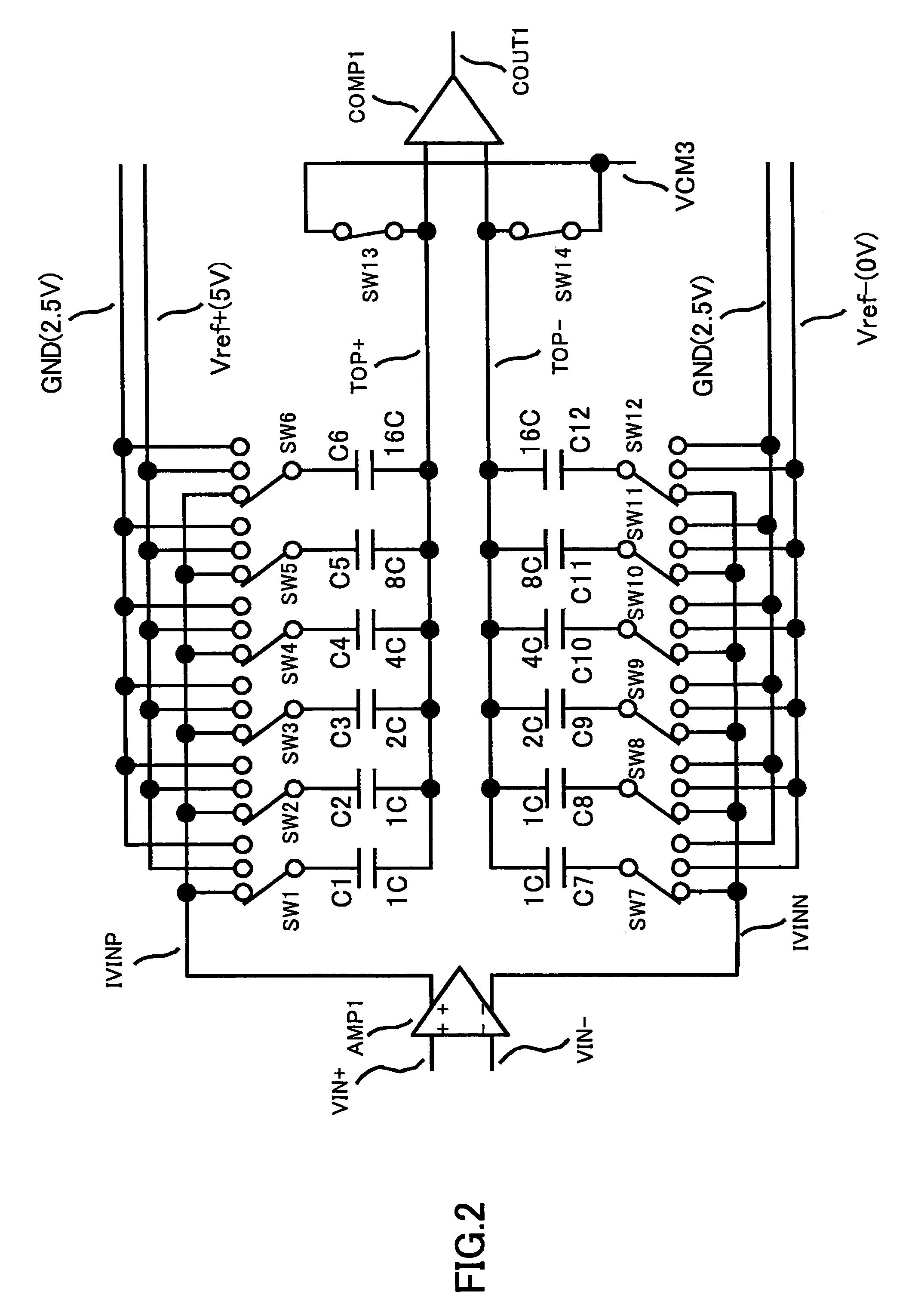

Successive approximation A/D converter

ActiveUS20070035434A1Increase speedElectric signal transmission systemsAnalogue-digital convertersControl signalĆuk converter

A successive approximation. A / D converter includes a sample-hold amplifier circuit configured to sample and hold an input analog voltage to produce an internal analog voltage proportional to the input analog voltage with a voltage gain being smaller than 1, a switched capacitor D / A converter coupled to the sample-hold amplifier circuit and including a plurality of capacitors for storing electric charge responsive to the internal analog voltage, the switched capacitor D / A converter configured to switch couplings of the capacitors in response to a control signal to produce a comparison analog voltage responsive to the internal analog voltage and the control signal, a comparator coupled to the switched capacitor D / A converter to produce a comparison result signal responsive to the comparison analog voltage, and a control circuit coupled to the comparator to supply the control signal responsive to the comparison result signal to the switched capacitor D / A converter.

Owner:CYPRESS SEMICON CORP

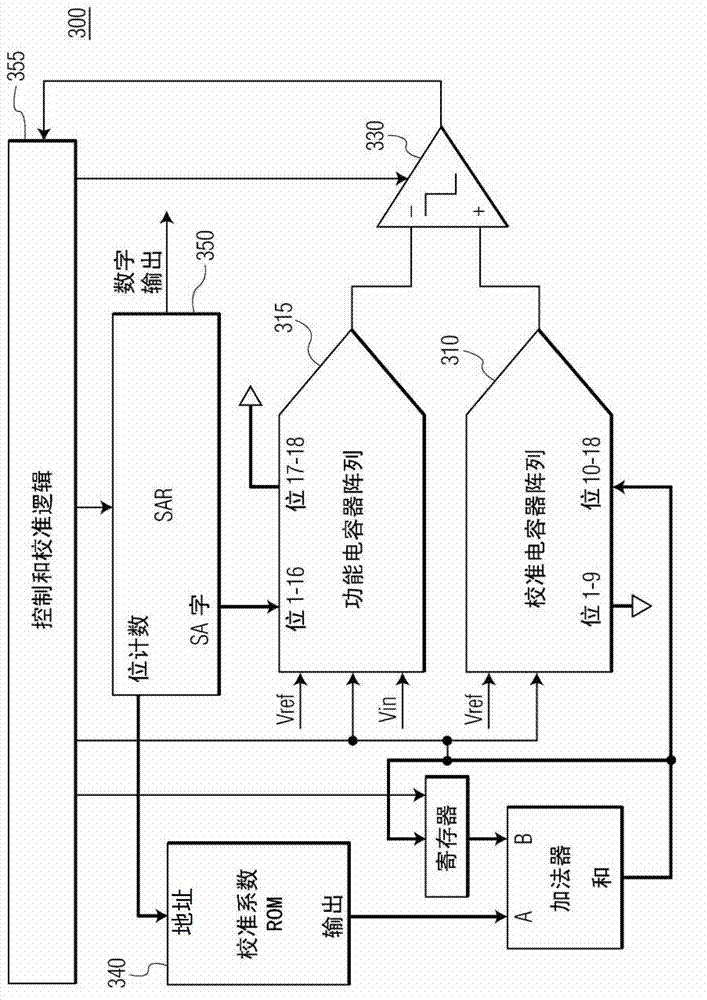

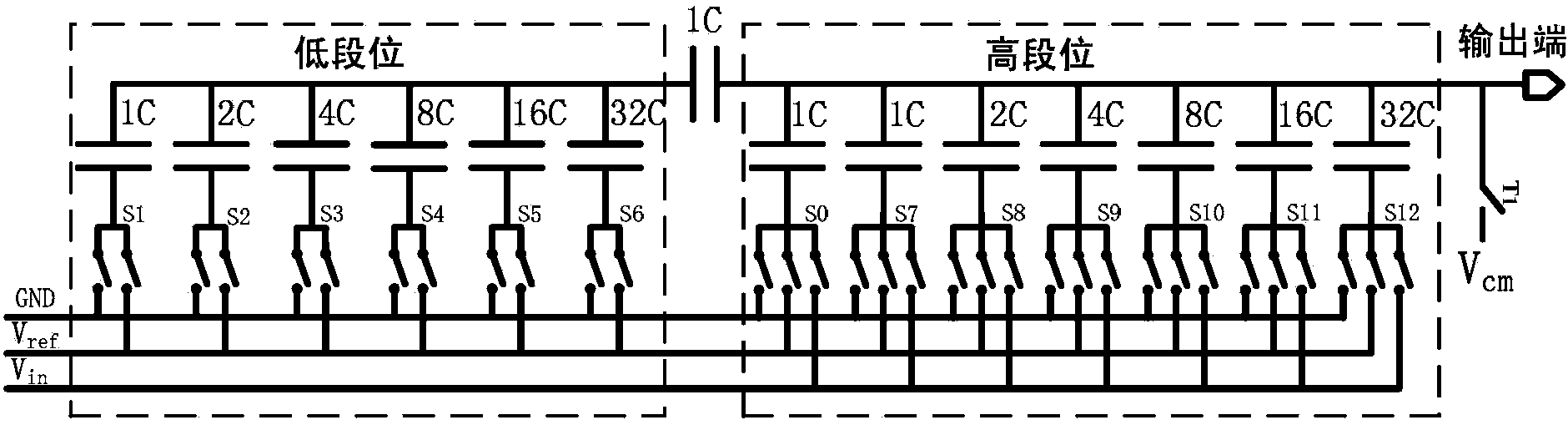

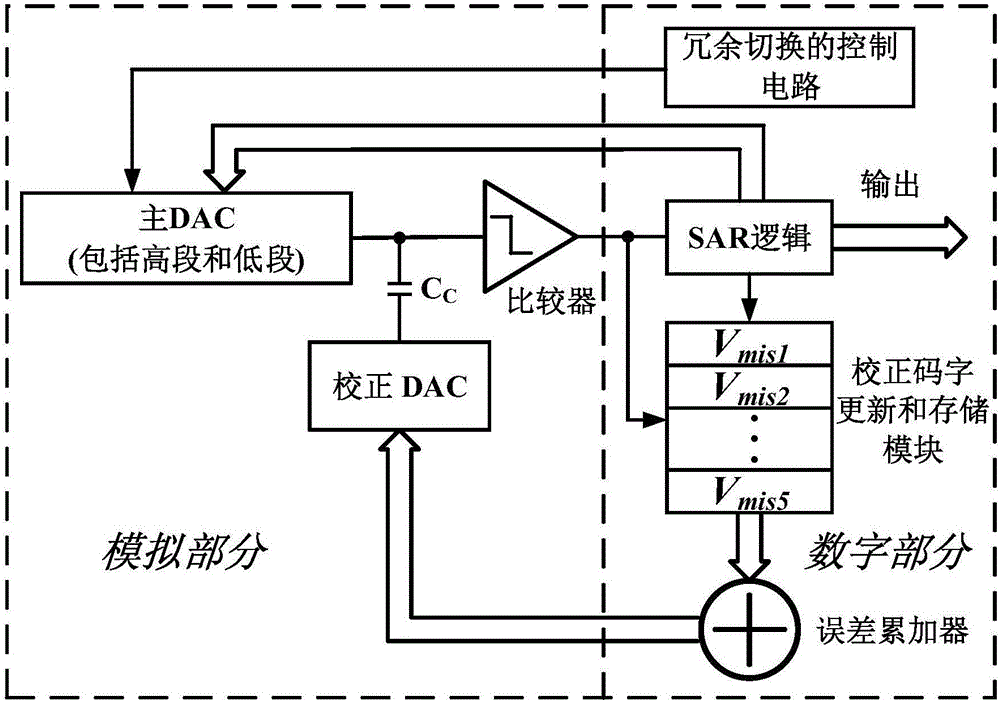

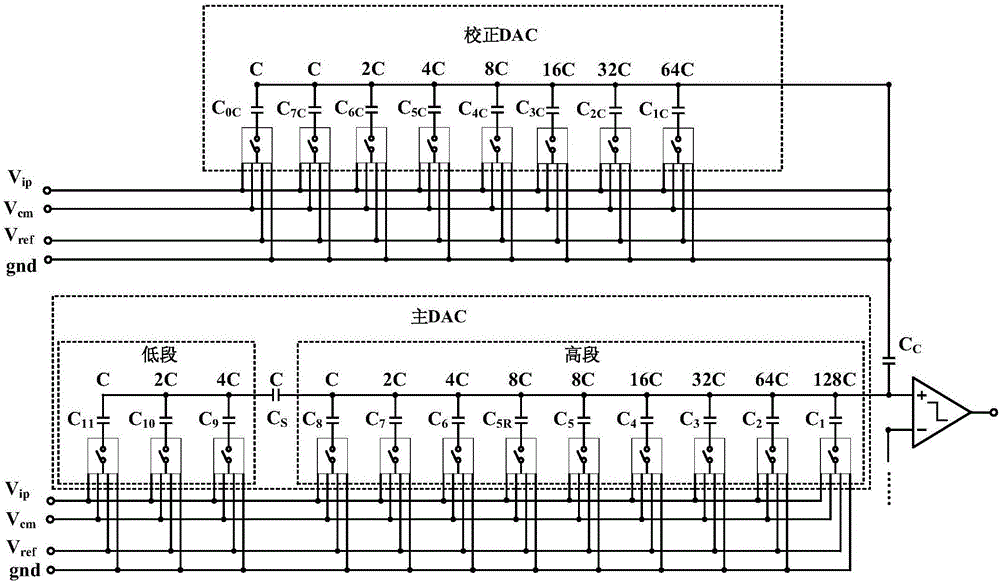

Digital calibration method for high-precision SAR ADC (successive approximation register analog to digital converter)

ActiveCN103873059AHigh precisionReduce areaAnalogue/digital conversion calibration/testingDigital down converterParasitic capacitance

The invention discloses a digital calibration method for a high-precision SAR ADC (successive approximation register analog to digital converter). The method comprises the following steps of (1) designing of a calibration DAC (digital to analog converter), digitalizing the error voltage of each capacitor in the high segment of a main DAC, and carrying out digital to analog conversion on the processed calibration codes; (2) designing of digital calibration time sequence, obtaining the calibration codes, maintaining sampling, and gradually converting. The method is applied to the high-precision SAR ADC, and a capacitor array of the high segment in the sectional main DAC is subjected to digital calibration, so the mismatch of the capacitors caused by parasitic capacitors and the process manufacturing error is reduced, the problem of unable realizing of precise double relationship due to the mismatch of the adjacent capacitors in the high segment is greatly corrected, and the precision of the SAR ADC is effectively improved.

Owner:TIANJIN UNIV

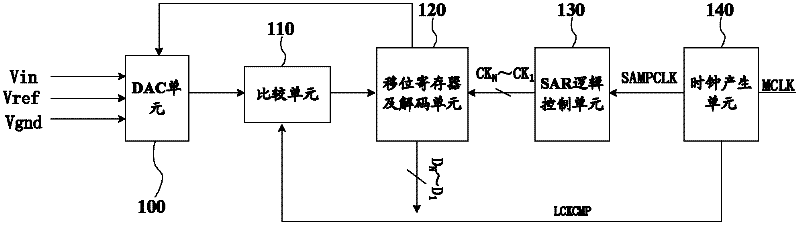

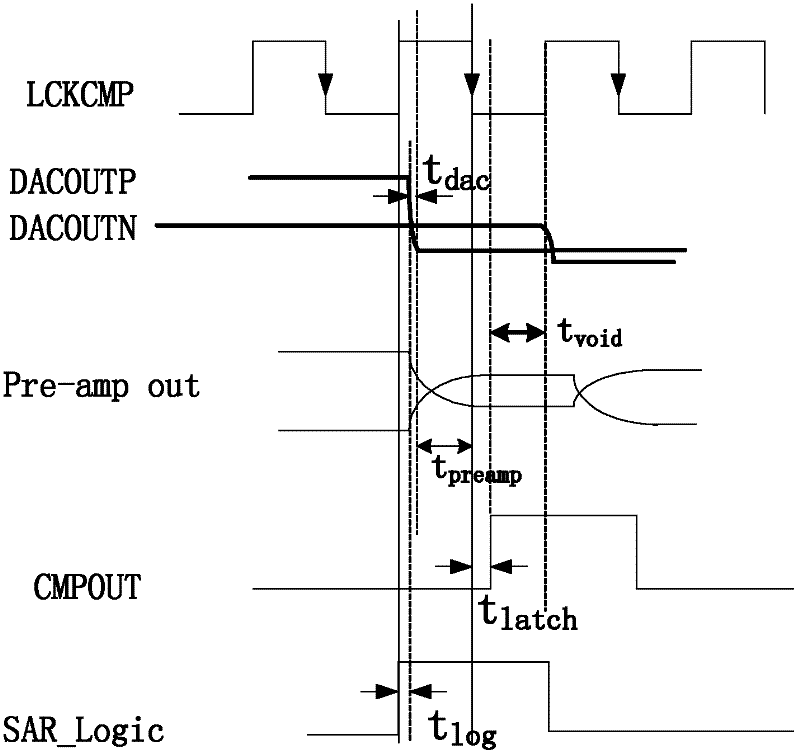

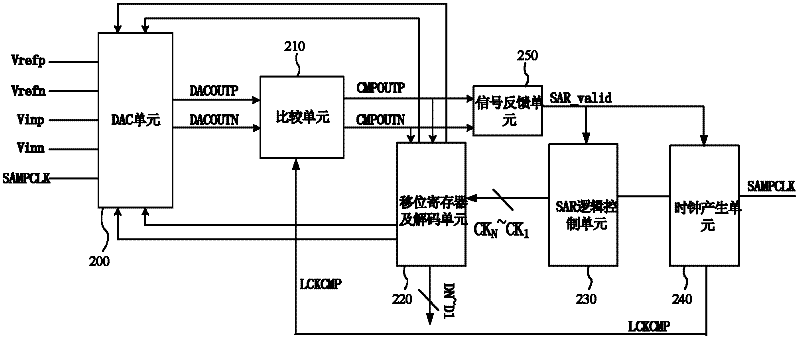

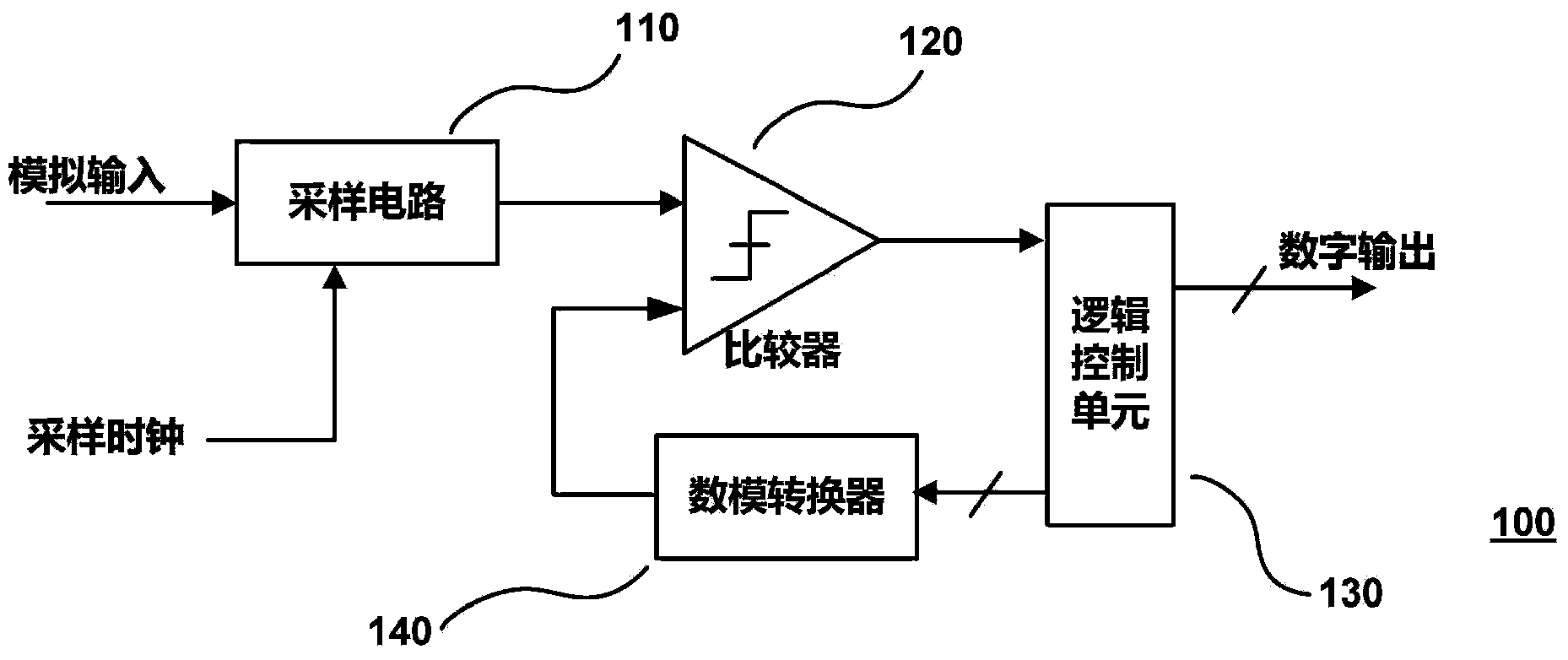

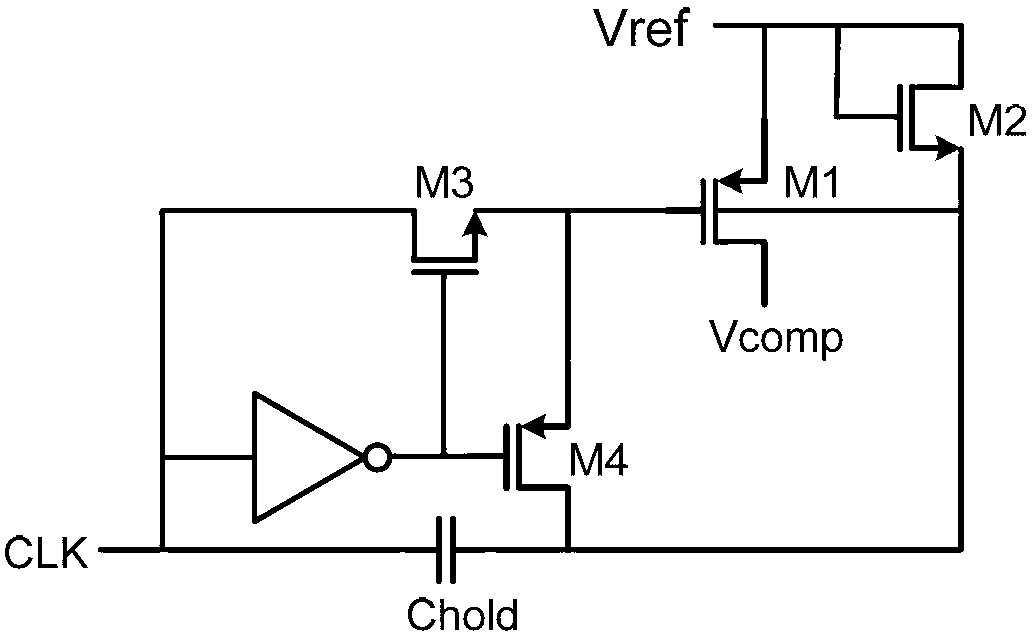

Successive approximation register analog-digital converter

ActiveCN102355266AWork fasterAnalogue/digital conversionElectric signal transmission systemsShift registerIdle time

The invention provides a successive approximation register analog-digital converter which comprises a digital-analog conversion unit, a comparison unit, a successive approximation logic control unit, a shift register and decoding unit and a clock generation unit. The successive approximation register analog-digital converter also comprises a signal feedback unit. An input terminal of the signal feedback unit connects with an output terminal of the comparison unit. An output terminal of the signal feedback unit connects with an input terminal of the successive approximation logic control unit. The signal feedback unit receives a comparison result outputted by the comparison unit, generates a feedback signal, outputs the feedback signal to the successive approximation logic control unit to trigger the successive approximation logic control unit to control the shift register and decoding unit to carry out shift motion, a problem that a whole analog-digital converter has a segment of idle time after a traditional successive approximation analog-digital converter compares unit latch difference signals is avoided, and a work speed of the successive approximation analog-digital converter is effective raised.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

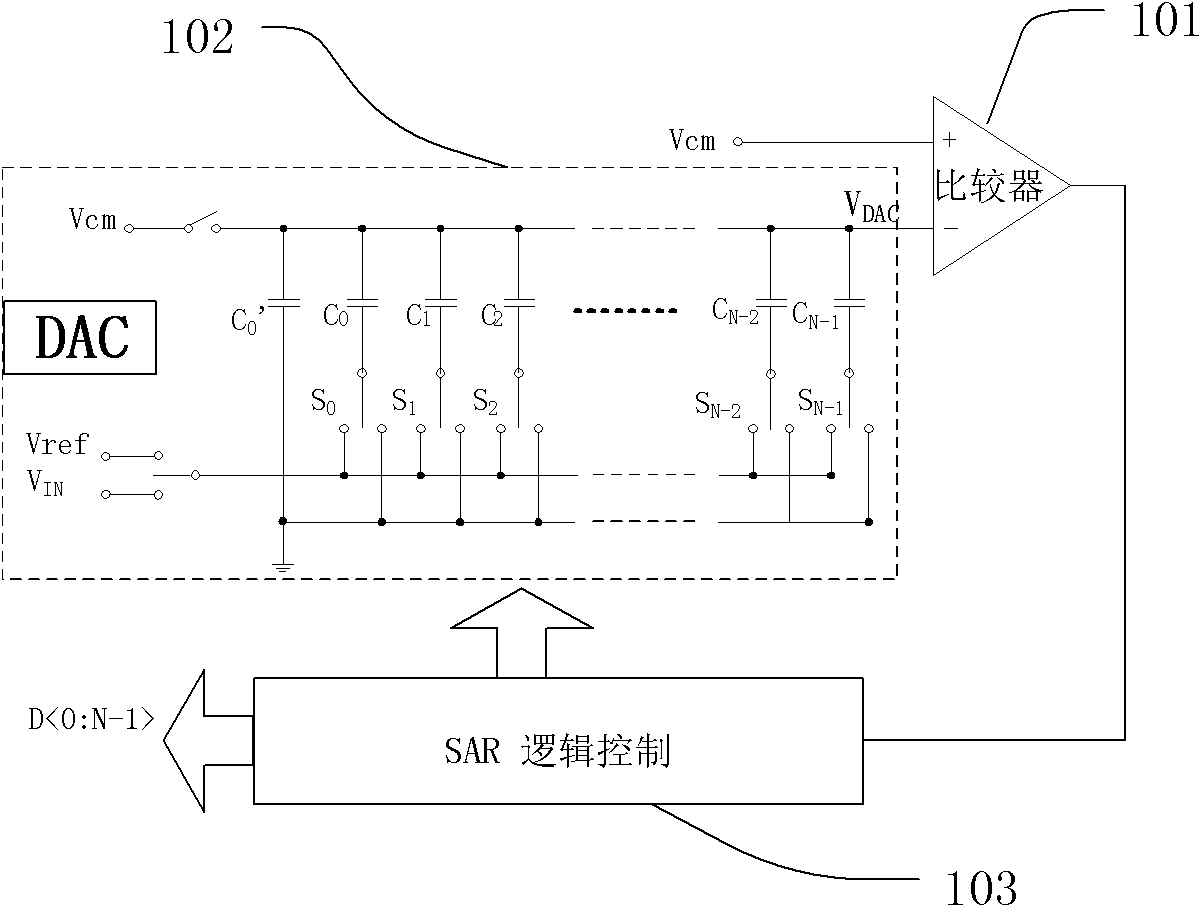

Successive approximation register type ADC (analog-digital converter)

InactiveCN103152049AIncrease conversion rateReduced drive capability requirementsAnalogue/digital conversionElectric signal transmission systemsCapacitanceDigital down converter

The invention discloses a successive approximation register type ADC (analog-digital converter) comprising a sample holding circuit, a N-bit digital-analog converter, a comparer, a successive approximation register and a control logic, wherein the sample holding circuit finishes and holds the sample of an input signal through a sampling capacitor smaller than 2NC and a switch, and outputs sample holding voltage to a first input end of the comparer; the N-bit digital-analog converter is used for converting a digital quantization result saved in the successive approximation register into an analog quantity, and the output end of the N-bit digital-analog converter is connected with a second input end of the comparer; the comparer is used for comparing the analog quantities through conversion of the N-bit digital-analog converter with the sample holding voltage, outputting an existing result of quantizing the input signal, and writing the result into the successive approximation register; the successive approximation register is used for saving the result of quantizing the input signal and outputting the final result of analog-digital conversion; and the control logic is used for generating a control signal of a whole circuit. According to the successive approximation register type ADC disclosed by the invention, the conversion speed of ADC can be increased and the requirement on the output resistance of a signal source is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

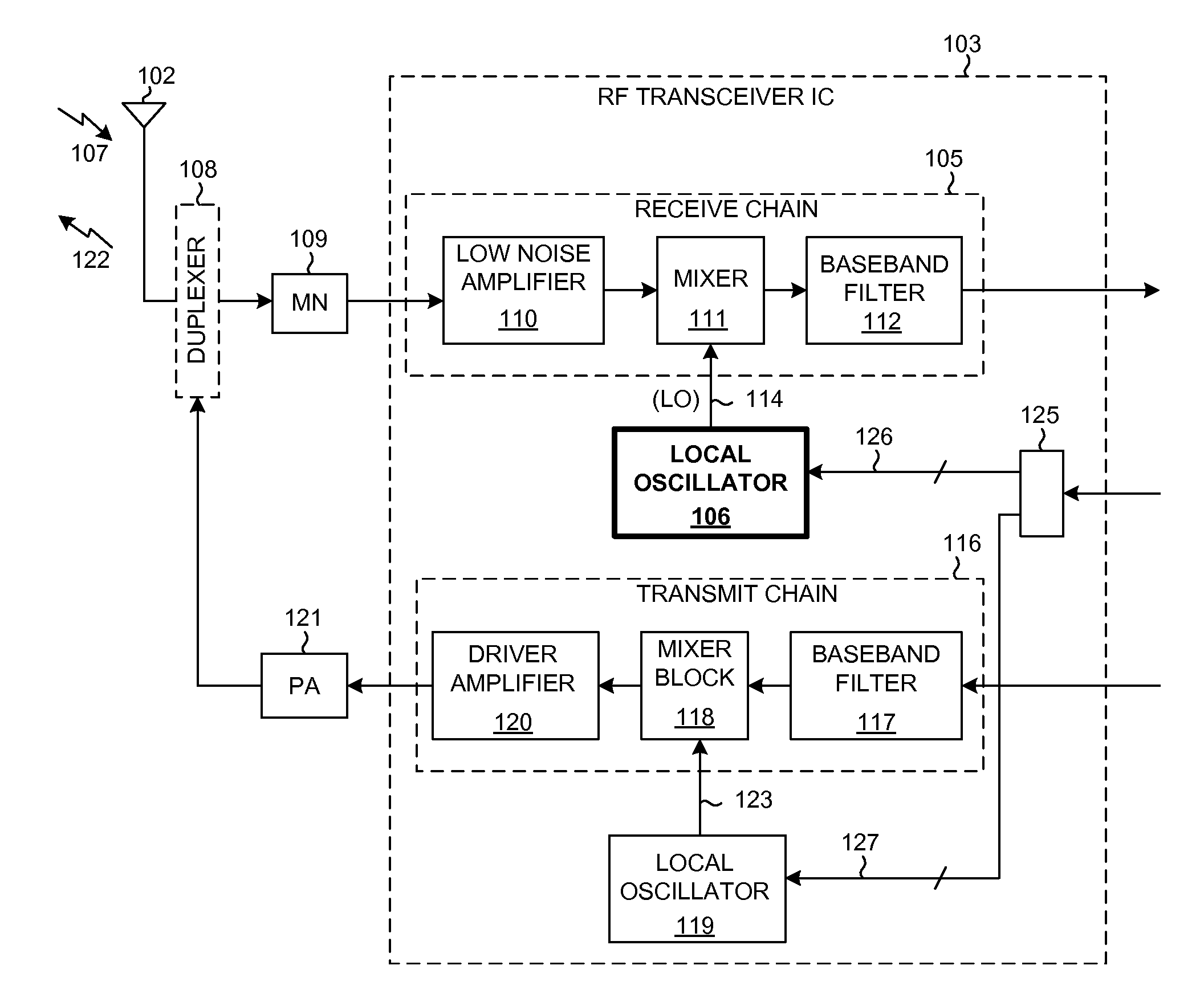

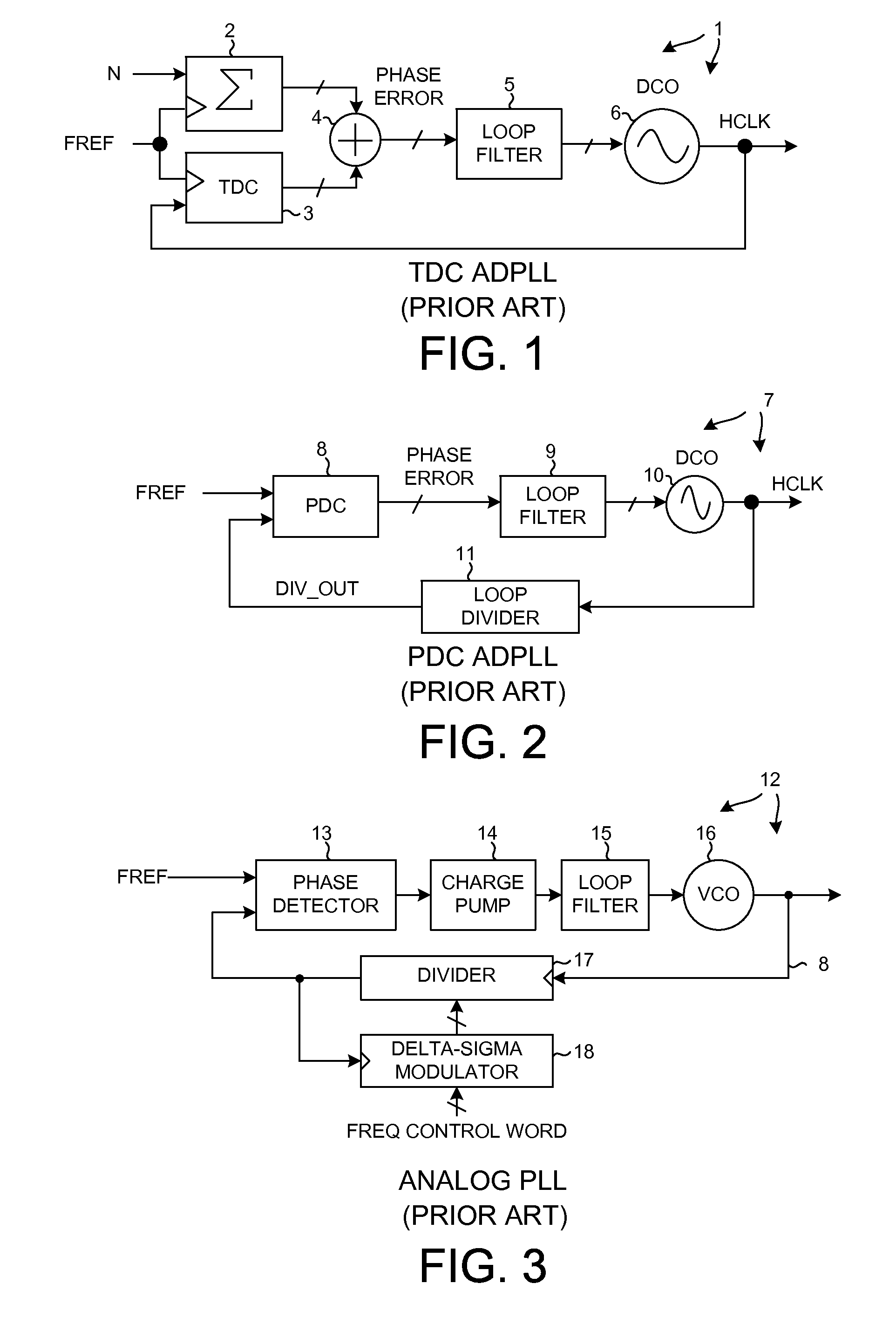

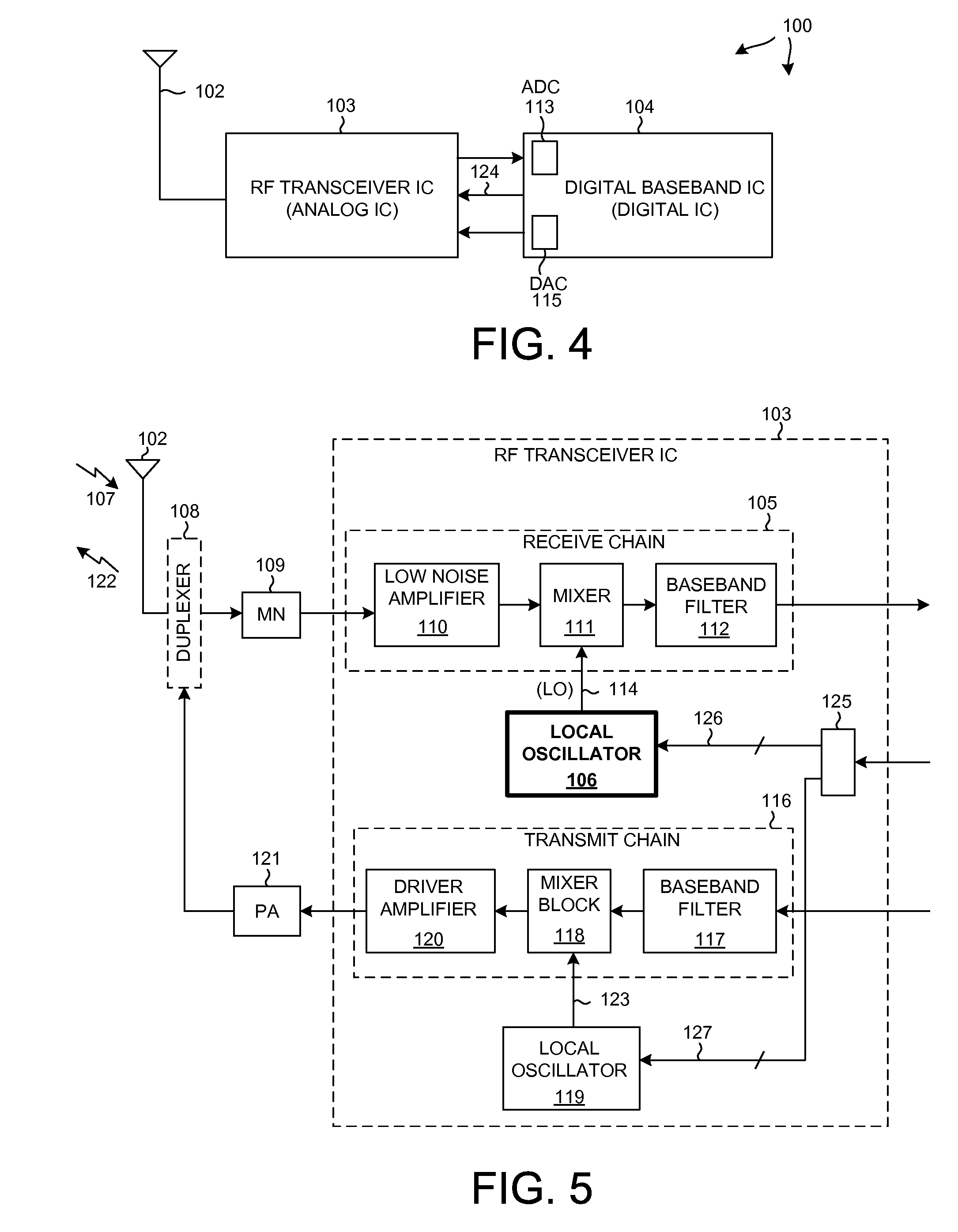

Adc-based mixed-mode digital phase-locked loop

InactiveUS20110090998A1Increase costReduce noisePulse automatic controlGenerator stabilizationDigital tuningVoltage amplitude

A Phase-Locked Loop (PLL) includes a Phase-to-Digital Converter (PDC), a programmable digital loop filter, a Digitally-Controlled Oscillator (DCO), and a loop divider. Within the PDC, phase information is converted into a stream of digital values by a charge pump and an Analog-to-Digital Converter (ADC). The stream of digital values is supplied to the digital loop filter which in turn supplies digital tuning words to the DCO. A number of types of ADCs can be used for the ADC including a continuous-time delta-sigma oversampling Digital ADC and a Successive Approximation ADC. The voltage signal on the charge pump output is a small amplitude midrange voltage signal. The small voltage amplitude of the signal leads to numerous advantages including improved charge pump linearity, reduced charge pump noise, and lower supply voltage operation of the overall PLL.

Owner:QUALCOMM INC

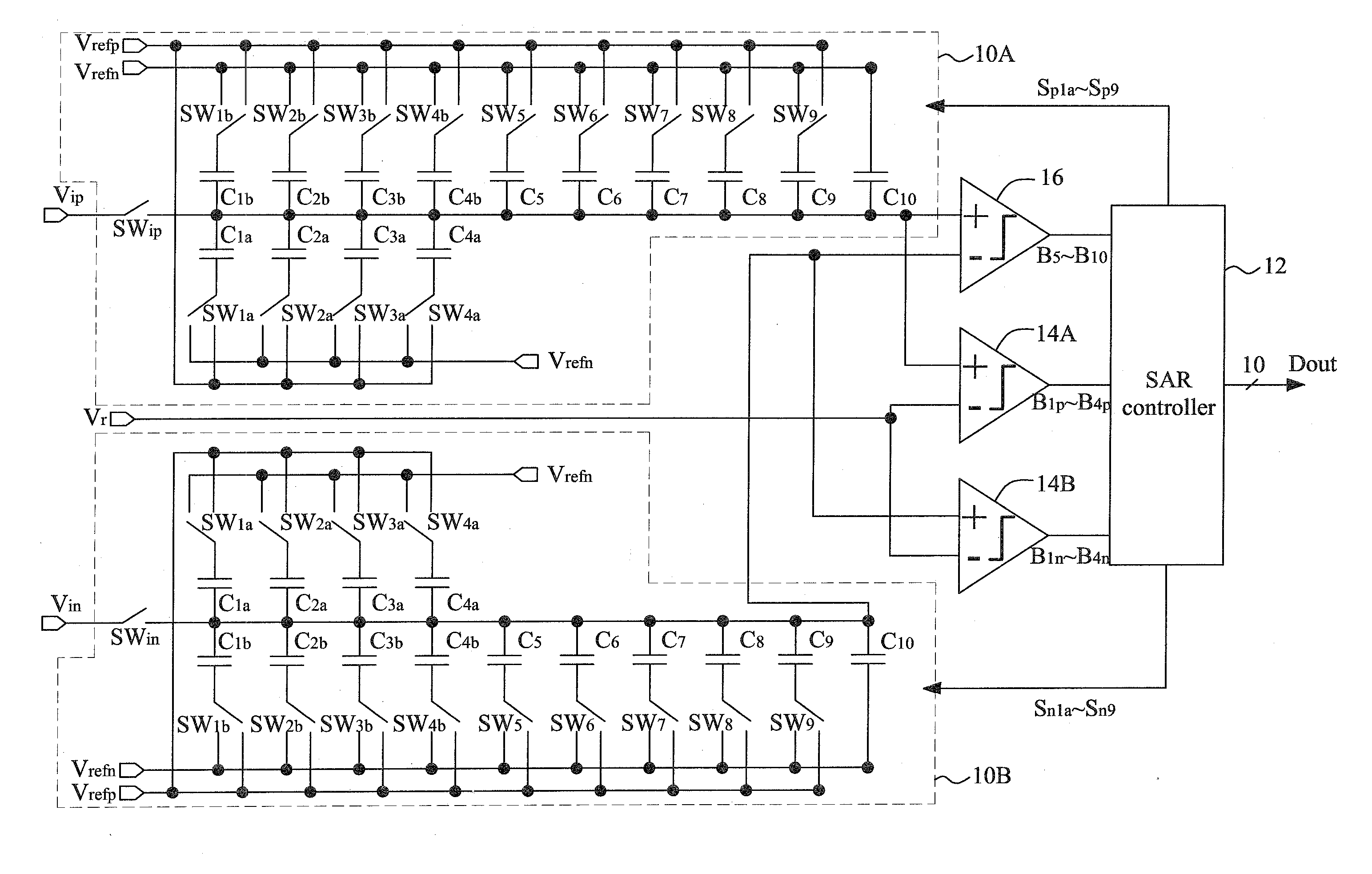

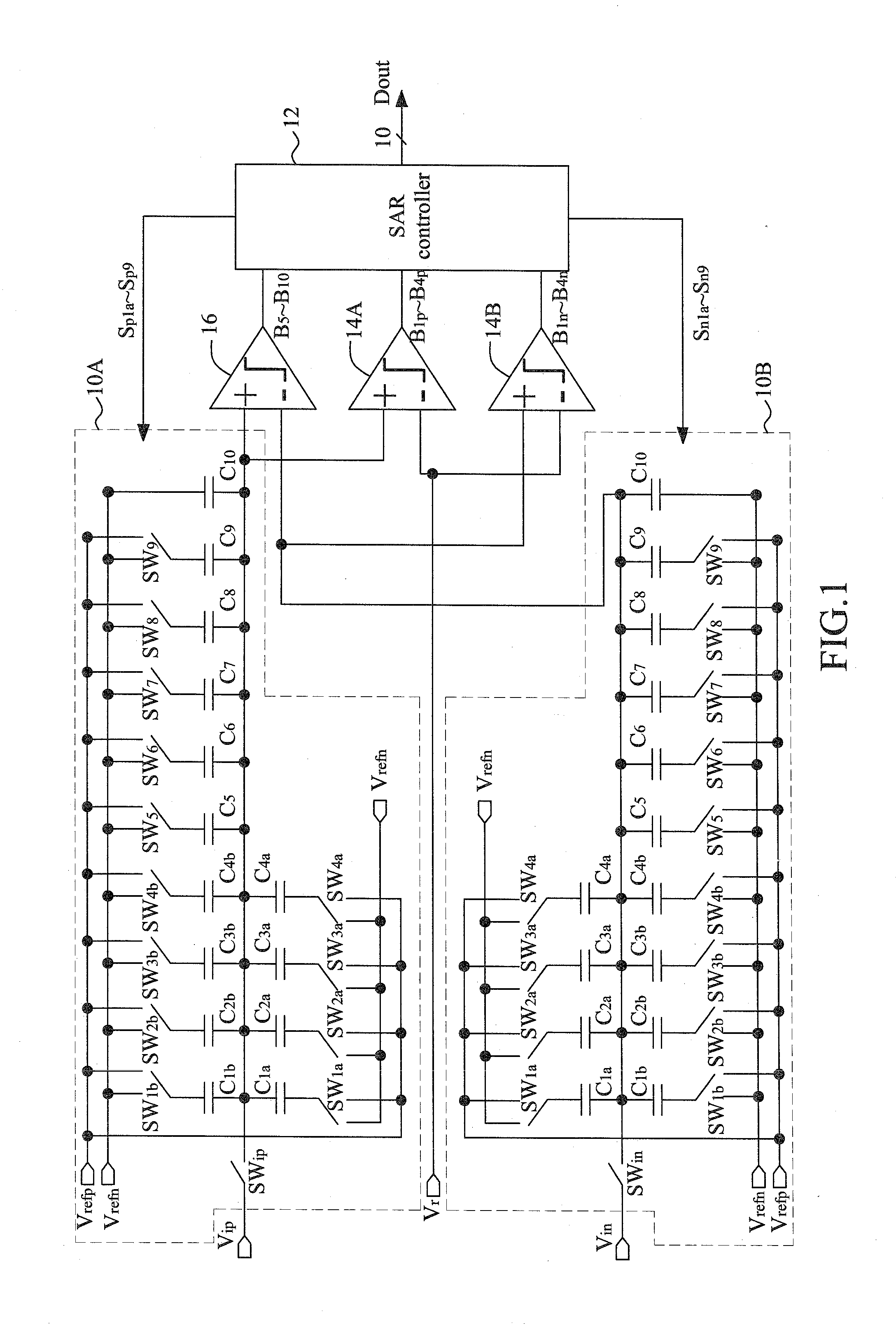

Successive approximation register ADC with a window predictive function

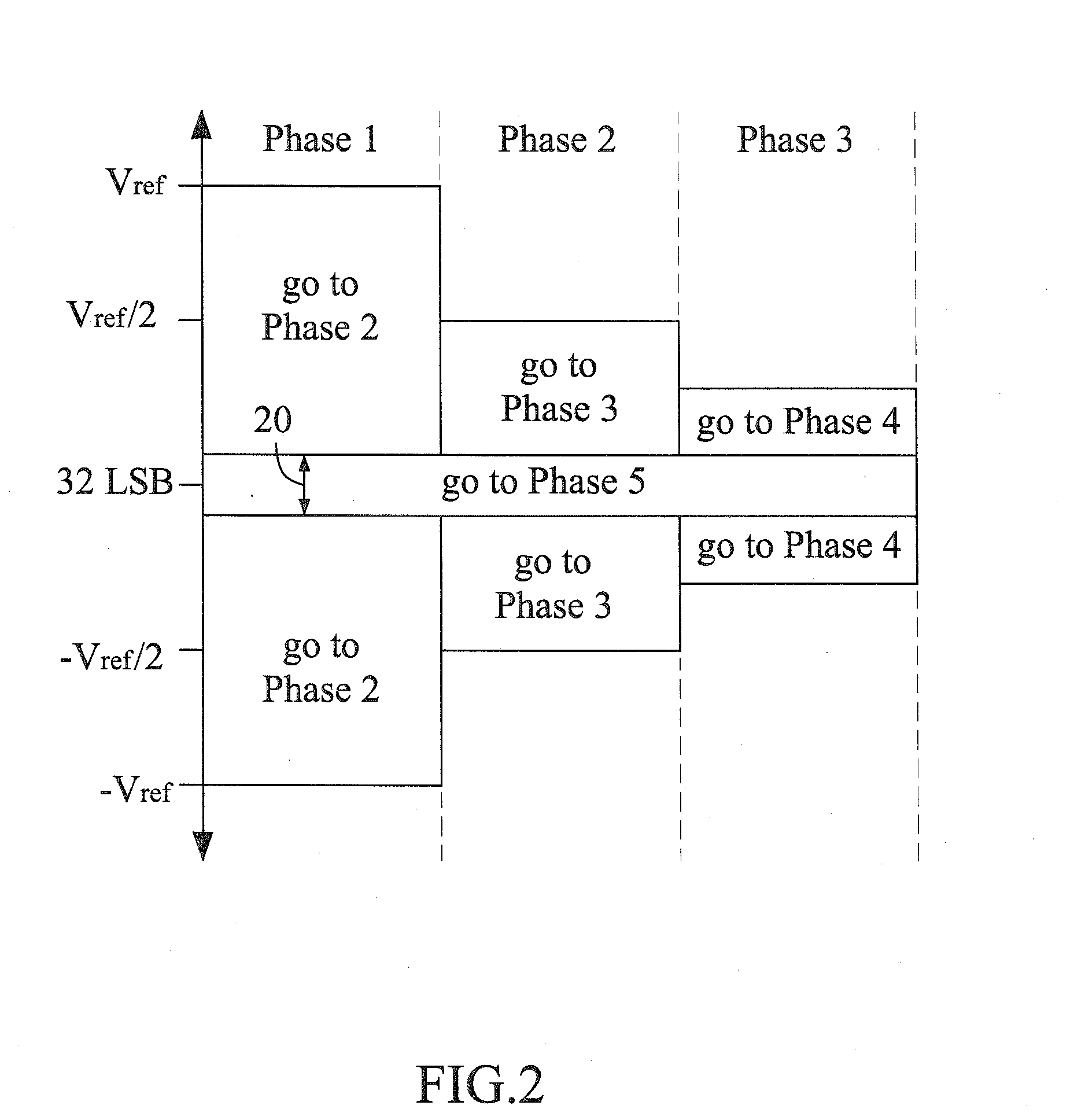

ActiveUS20120274489A1OperationReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersCapacitancePredictive function

A successive approximation register (SAR) analog-to-digital converter (ADC) is disclosed. A first and second capacitor DACs receive a first and second input signals respectively. A first coarse comparator compares an output of the first capacitor DAC with a window reference voltage, a second coarse comparator compares an output of the second capacitor DAC with the window reference voltage, and a fine comparator compares the output of the first capacitor DAC with the output of the second capacitor DAC. A SAR controller receives outputs of the first and second coarse comparators to determine whether the outputs of the first and second capacitor DACs are within a predictive window determined by the window reference voltage. The SAR controller bypasses at least one phase of analog-to-digital conversion of the SAR ADC when the outputs of the first capacitor DAC and the second capacitor DAC are determined to be within the predictive window. The SAR controller decodes the outputs of the first and second coarse comparators and the fine comparator to obtain a converted output of the SAR ADC.

Owner:NCKU RES & DEV FOUND +1

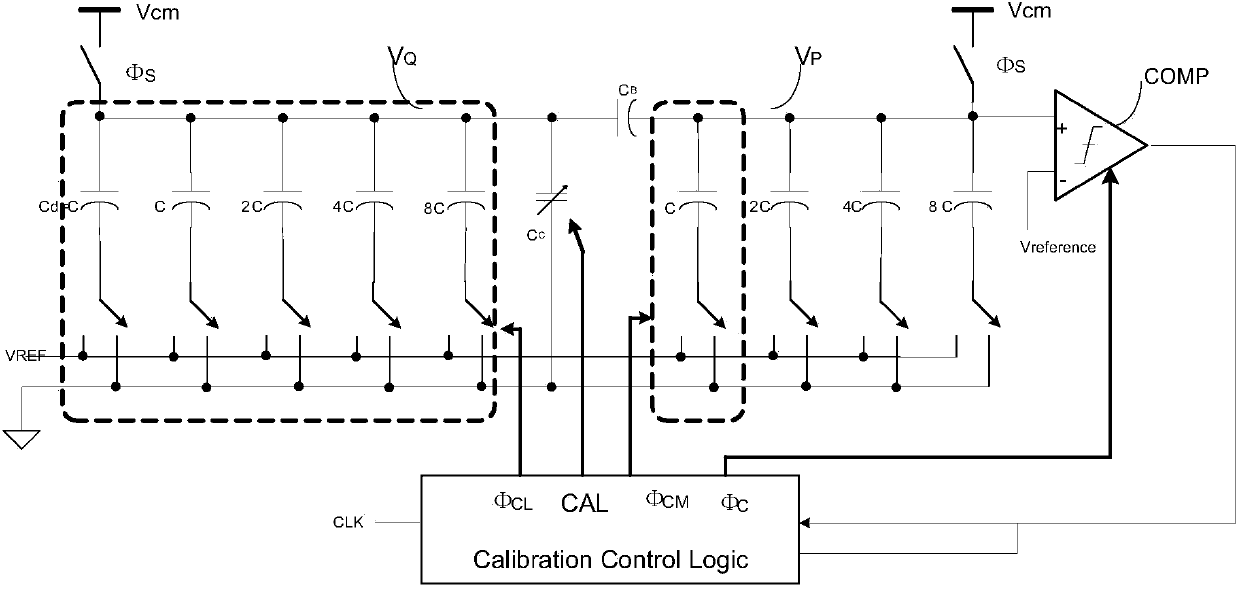

Successive approximation type analog-to-digital converter of self-calibration bridge-connection capacitor structure

InactiveCN104079298ASolving Bridging Nonlinear ProblemsAnalogue/digital conversion calibration/testingCapacitanceEngineering

The invention belongs to the technical field of analog-to-digital converters and particularly relates to a successive approximation type analog-to-digital converter of a self-calibration bridge-connection capacitor structure. The successive approximation type analog-to-digital converter of the self-calibration bridge-connection capacitor structure comprises a sample hold circuit, a comparer, a logic control circuit, a digital-to-analog converter and a calibrating circuit, wherein the capacitor-type digital-to-analog converter is of a redundant capacitor bridge-connection structure, and a redundant capacitor and an auxiliary capacitor are added in the bridge-connection structure; meanwhile, a calibrating algorithm is built in a calibration control unit and a calibration processing unit, and nonlinear characteristics caused by mismatch and parasitism of a manufacturing process in the bridge-connection capacitor structure are measured through the redundant capacitor bridge-connection structure in the calibration detection stage; in the normal analog-to-digital converting process, the calibration processing unit performs postprocessing on digital output of the analog-to-digital converter according to detected nonlinear information and outputs a calibrated digital signal.

Owner:FUDAN UNIV

Successive approximation type analog/digital converter

ActiveCN102801422AReduce application complexitySolve the problem of voltage overshootAnalogue/digital conversionElectric signal transmission systemsCapacitanceVoltage overshoot

The invention discloses a successive approximation type analog / digital converter, wherein a capacitor array digital / analog conversion circuit comprises a capacitor array, an auxiliary capacitor is connected between the capacitor array and the output end of a comparer, and the oscillation amplitude between the capacitor array and the output end of the comparer ranges from 0V to power voltage when the capacitance value of the auxiliary capacitor is selected in a range enabling the oscillation amplitude of the input voltage to be from 0V to the power voltage. A measure of carrying out limiting and compression on a quantification range or increasing complicated circuits, which is adopted for preventing voltage overshoot in the traditional scheme, is avoided. According to the circuit structure provided by the invention, the requirements on input offset of the comparer in the ADC (analog / digital converter) and performance of other internal circuits are reduced, so that higher resolution ratio can be achieved under the condition of not increasing power consumption of the ADC using the circuit structure.

Owner:SOI MICRO CO LTD

Successive approximation A/D converter provided with a sample-hold amplifier

ActiveUS7199745B2Increase speedElectric signal transmission systemsAnalogue-digital convertersControl signalĆuk converter

Owner:CYPRESS SEMICON CORP

Ultra-high-speed photonic-enabled ADC based on multi-phase interferometry

InactiveUS8953950B2Overcome disadvantagesElectric signal transmission systemsAnalogue conversionUltra high speedPhotonics

A ultra high speed photonic Analog to Digital Converted (ADC) for sampling and quantizing an electrical voltage signal, internally enabled by photonics uses coherent optical detection architectures for photonic quantization. Coherent light is phase modulated by the test signal. Using an interferometer, or an array of interferometers the phase of modulated light is compared with a reference light. Flash ADC, successive approximation ADC and delta-sigma ADC configurations are presented.

Owner:TECHNION RES & DEV FOUND LTD

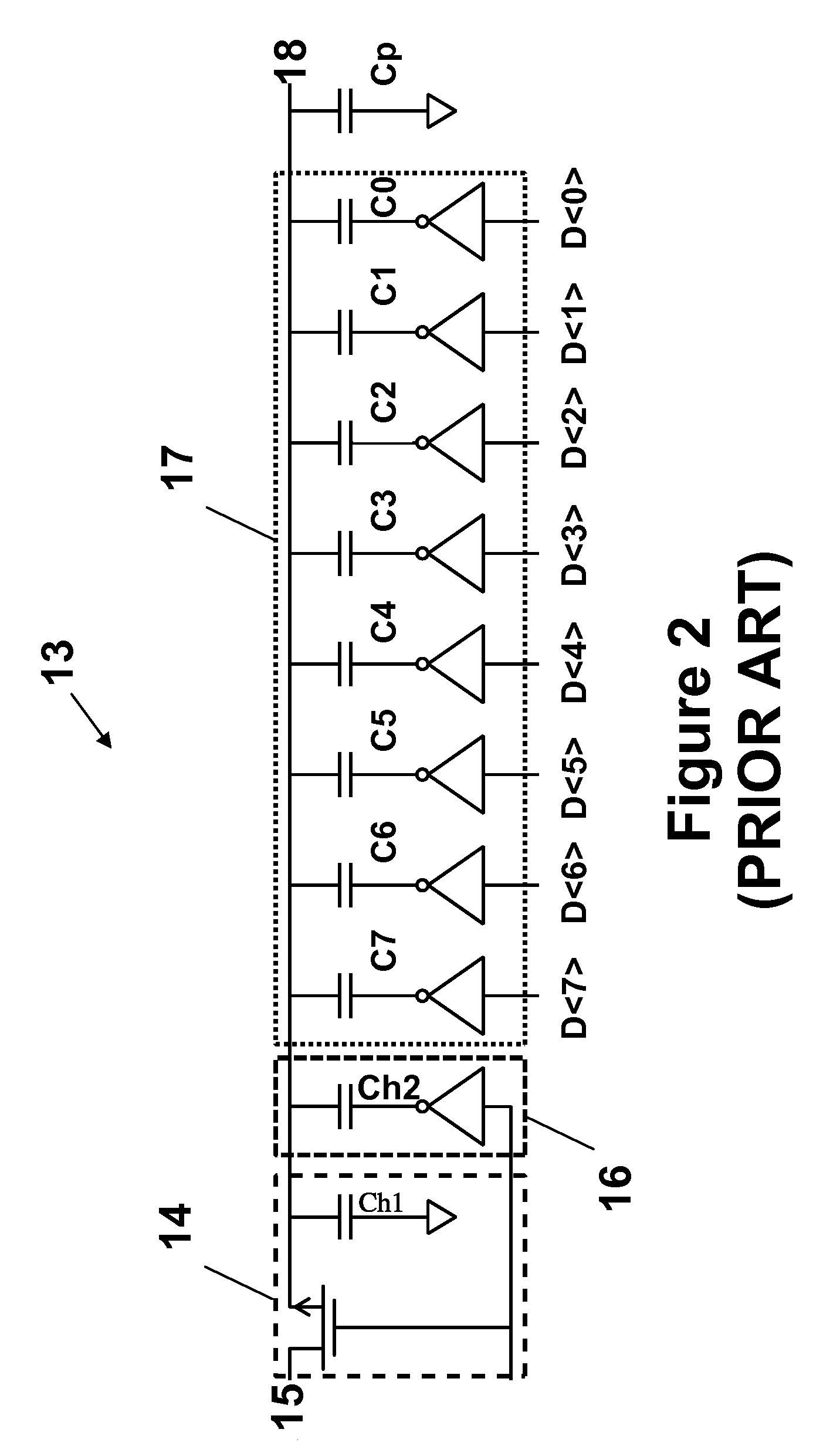

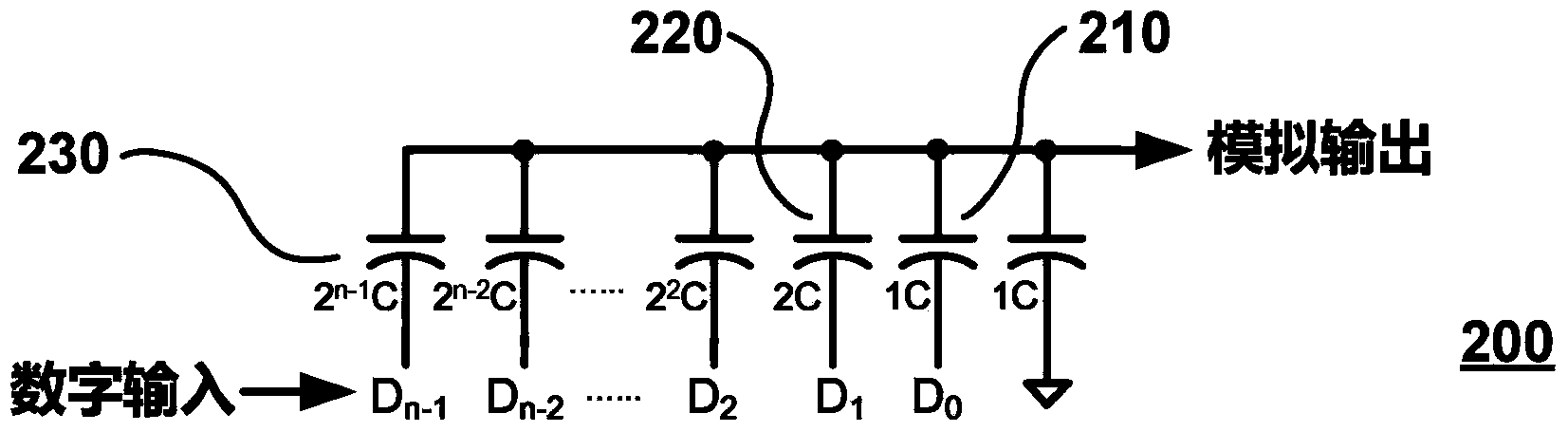

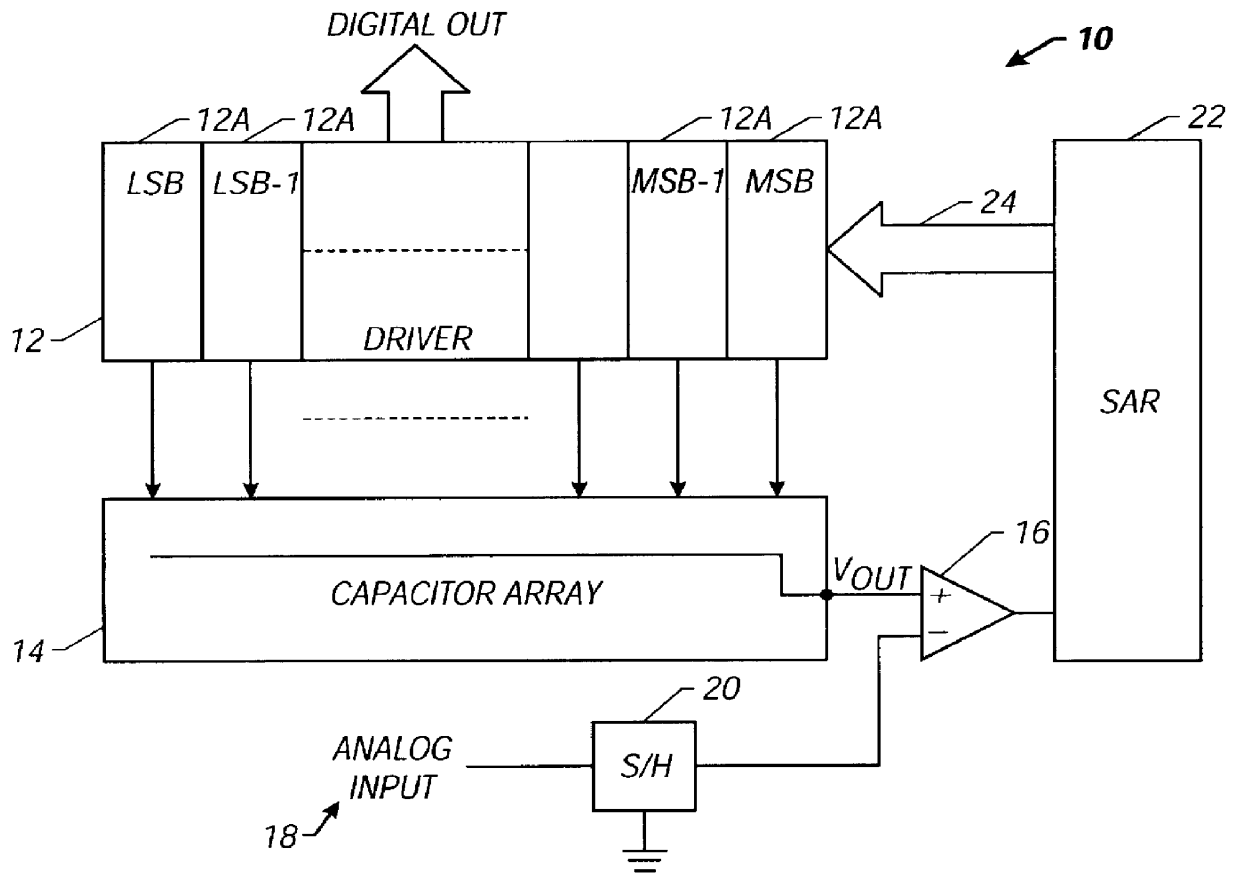

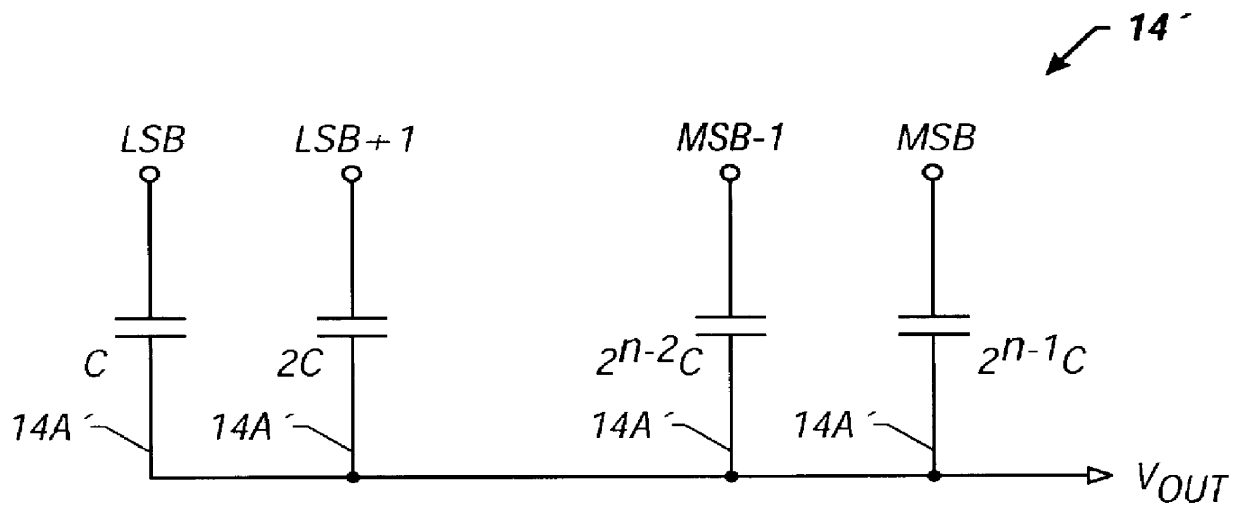

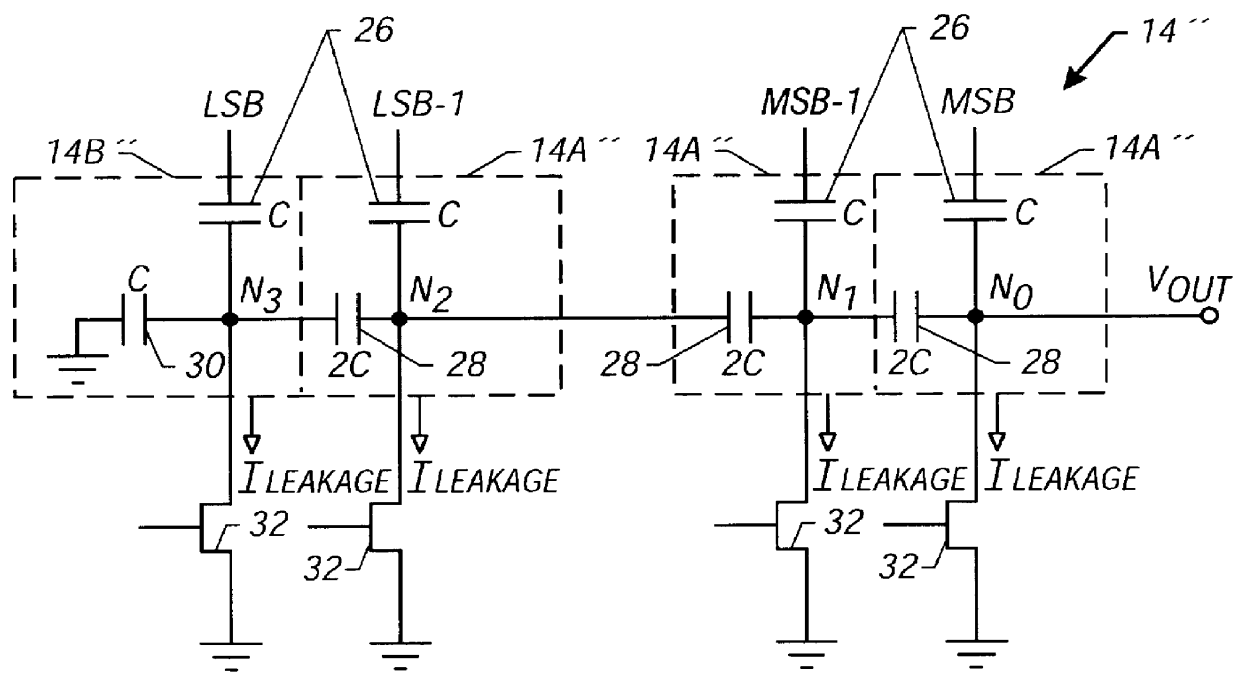

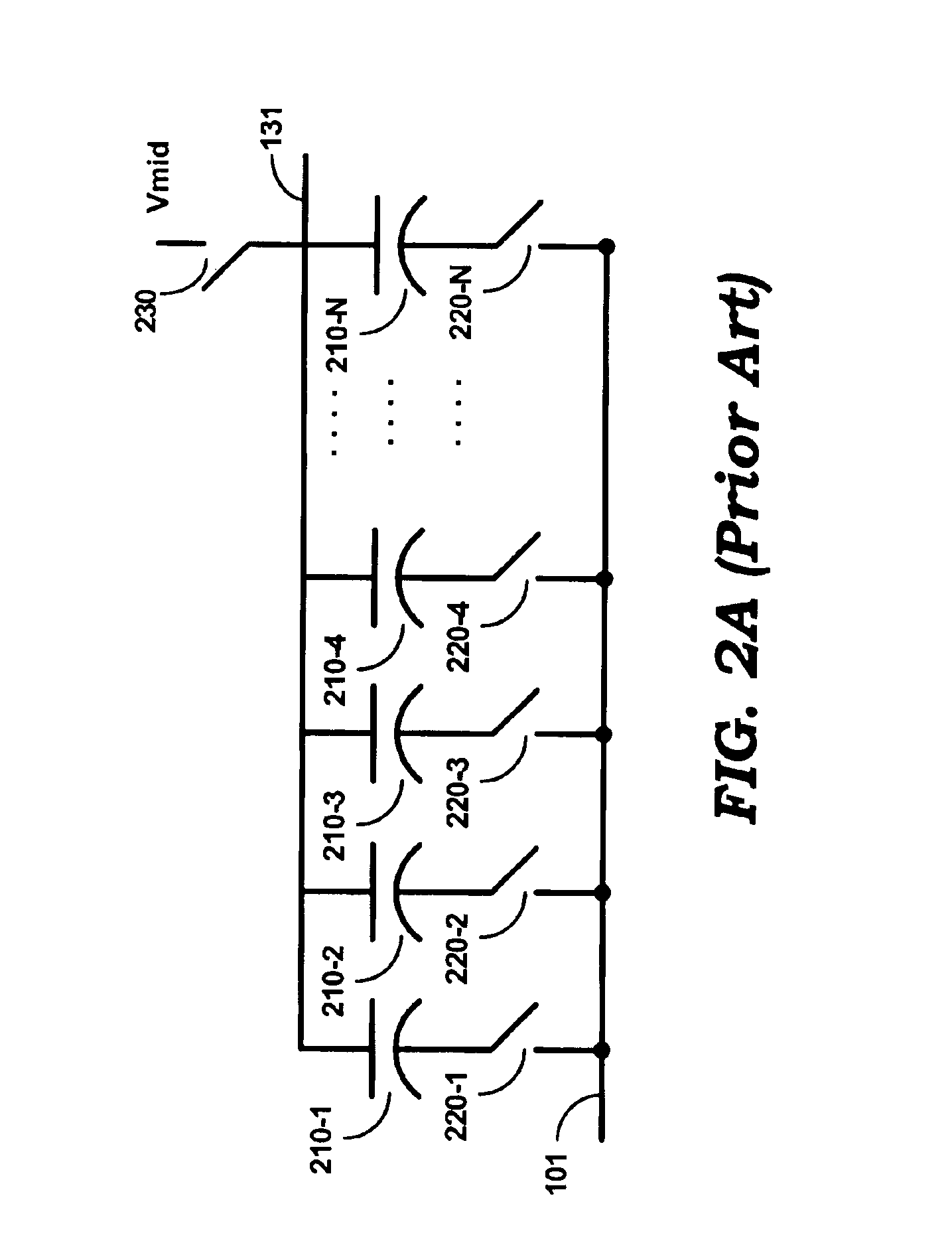

Capacitor array for a successive approximation register (SAR) based analog to digital (A/D) converter and method therefor

InactiveUS6118400AElectric signal transmission systemsAnalogue-digital convertersCapacitanceDriver circuit

Owner:MICROCHIP TECH INC

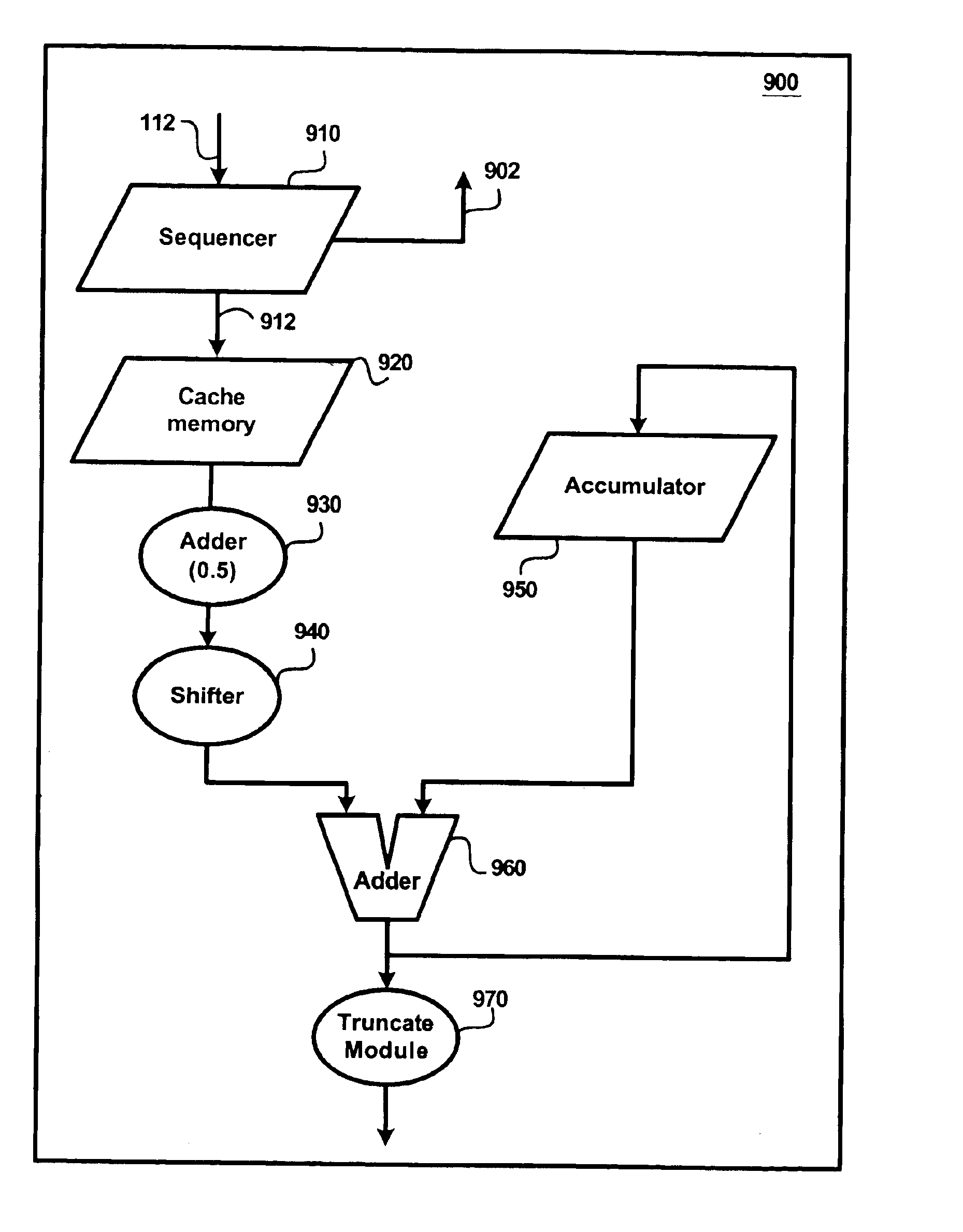

Increasing the SNR of successive approximation type ADCs without compromising throughput performance substantially

InactiveUS6894627B2Lower performance requirementsSignal-to-noise-ratio (SNR) is enhancedElectric signal transmission systemsAnalogue-digital convertersSignal-to-noise ratio (imaging)Analog signal

When converting an analog signal to N-bit digital codes, high SNR (signal to noise ratio) by generating multiple N-bit codes from the same analog sample and averaging the N-bit codes. However, the entire N-bit code is determined only a single time, and only P-bit (P less than N) codes are generated. The P-bit codes may be averaged, and the N-bit code is corrected based on the average value to generate an accurate N-bit digital code. As P can be much less than N, the correction can be implemented in a few iterations, thereby enabling the ADCs to be implemented with a high throughput performance. Due to the correction, a high SNR may be attained as well.

Owner:TEXAS INSTR INC

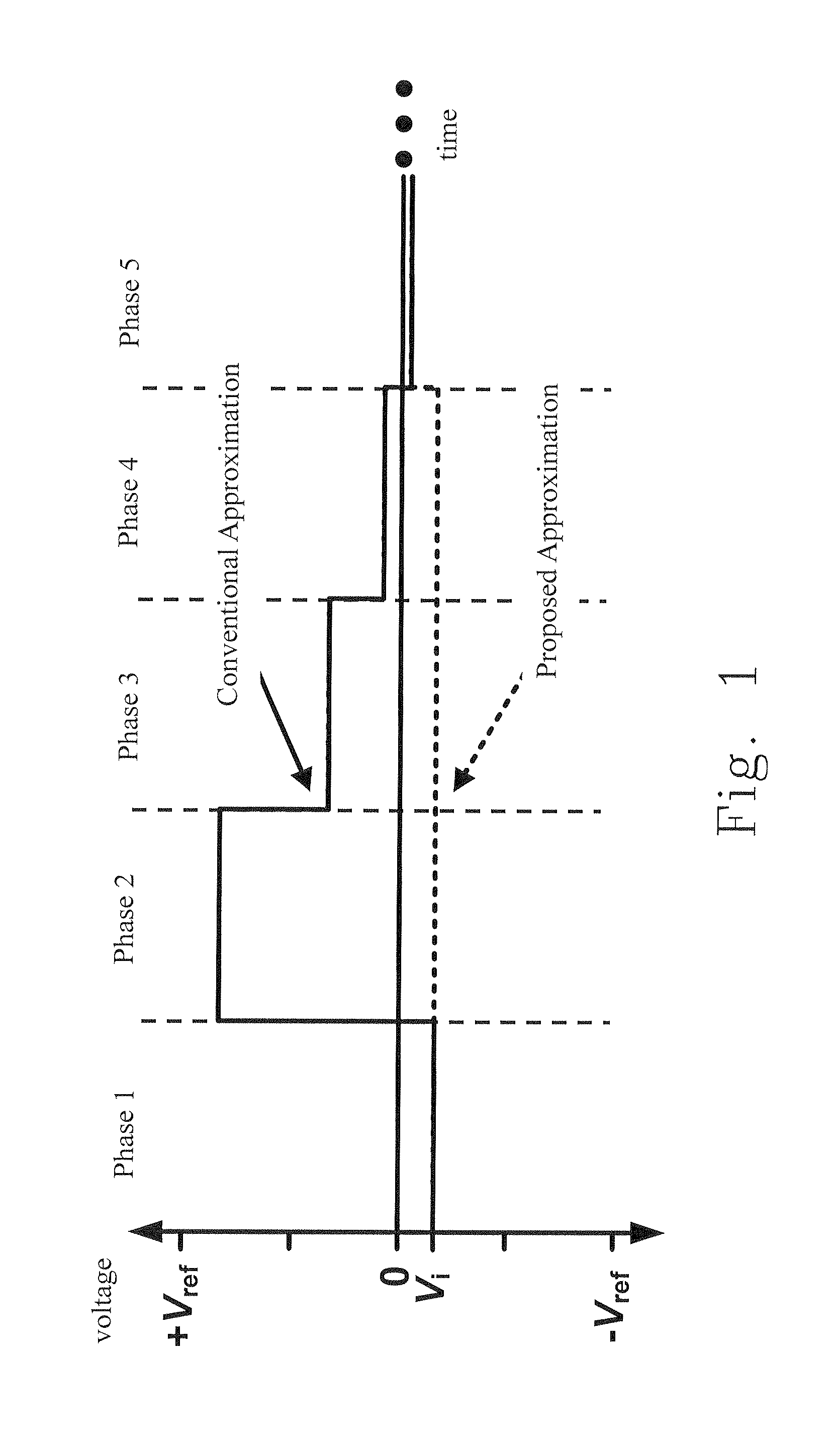

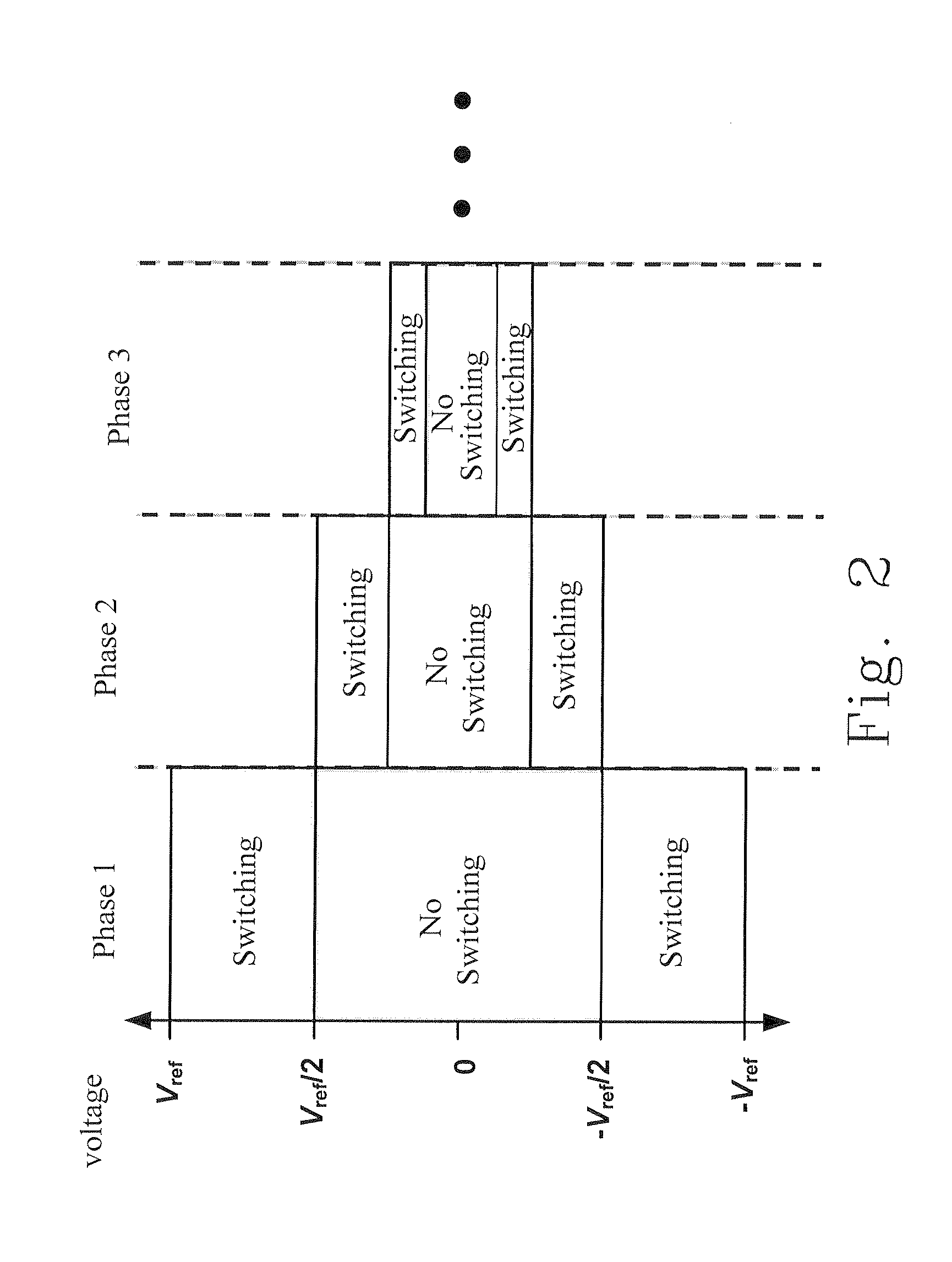

Successive approximation analog-to-digital converter having auxiliary prediction circuit and method thereof

ActiveUS20120154194A1Avoid unnecessary capacitor switchingSave energy consumptionPower saving provisionsElectric signal transmission systemsVoltage referenceEngineering

The configurations and adjusting method of a successive approximation analog-to-digital converter (SAR ADC) are provided. The provided SAR ADC includes at least one capacitor with a first and a second terminals, and a plurality of bits, each of which is connected to the at least one capacitor, wherein the first terminal receives an input signal, and the second terminal selectively receives one of a first and a second reference voltages, and a first comparator receiving an adjustable third reference voltage and a first voltage value generated by the input signal, wherein a connection of the second terminal of each the capacitor of the capacitor array is switched when the first voltage value is larger than the third reference voltage.

Owner:NAT CHENG KUNG UNIV

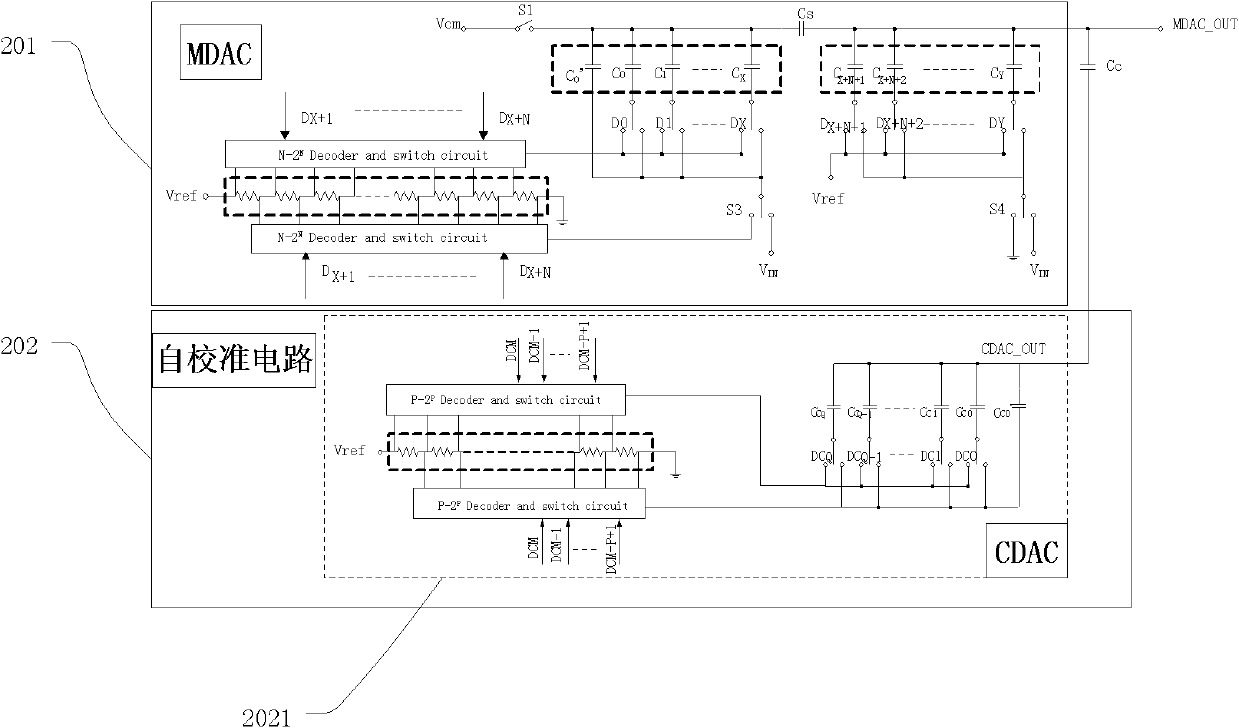

Resistance-string multiplexing circuit structure of SAR ADC (successive approximation analog to digital converter)

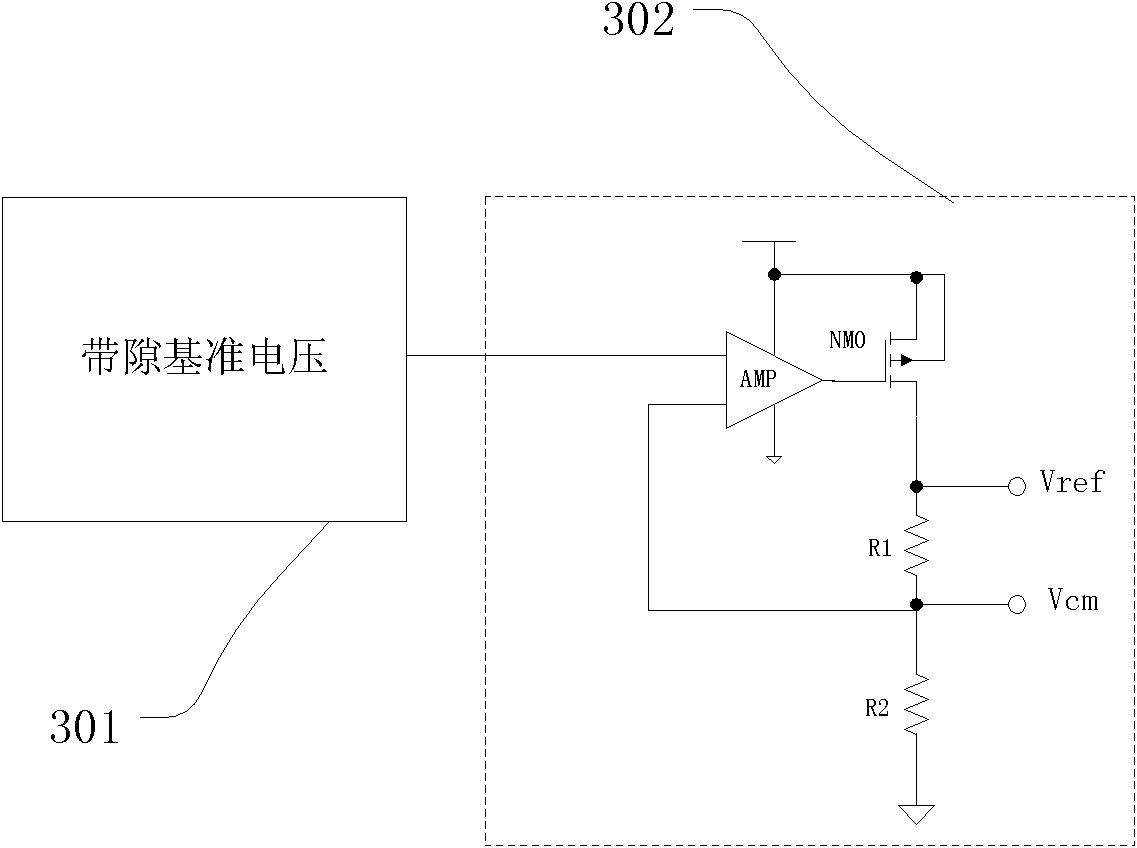

InactiveCN102324934ALow costReduce power consumptionElectric signal transmission systemsAnalogue/digital conversion calibration/testingCapacitanceElectrical resistance and conductance

The invention discloses a resistance-string multiplexing circuit structure of an SAR ADC (successive approximation analog to digital converter), and in particular relates to an SAR ADC circuit structure capable of reducing the cost and the power consumption, belonging to analog to digital conversion technologies. The structure comprises an MDAC (main digital to analog converter) (403), a CDAC (calibration digital to analog converter) (4041), a reference voltage generation circuit (401) and a resistance string (402), wherein the MDAC (403) is formed by mixing a capacitance DAC with a resistance DAC; the CDAC (4041) is formed by mixing a capacitance DAC with a resistance DAC; and an input stage of the reference voltage generation circuit (401) generates band-gap reference voltages in accordance with a band-gap voltage generation circuit, and an output stage of the reference voltage generation circuit (401) generates reference voltages (Vref) and reference voltages (Vcm) which are half of the reference voltages (Vref) based on a voltage regulator. The MDAC (403), the CDAC (4041) and the reference voltage generation circuit (401) in the SAR ADC structure multiplex the resistance string (402), so that the chip area can be reduced, and the power consumption can be decreased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Successive approximation type analog-to-digital converter of energy-saving capacitor array

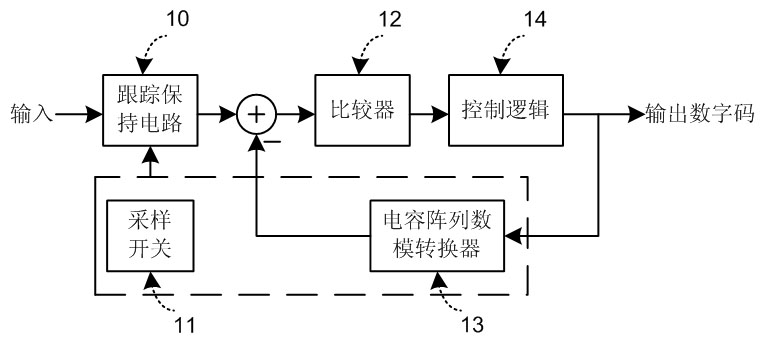

ActiveCN102006075AAnalogue/digital conversionElectric signal transmission systemsCapacitanceDigital analog converter

The invention belongs to the technical field of integrated circuits, in particular to a successive approximation type analog-to-digital converter of an energy-saving capacitor array. The analog-to-digital converter comprises a sampling switch, a track and hold circuit, a comparator, control logic and a capacitor array digital-to-analog converter, wherein the capacitor array digital-to-analog converter adopts a switch mode of the novel capacitor array digital-to-analog converter provided by the invention. By using the mode, the average switch consumption of the capacitor can be reduced.

Owner:FUDAN UNIV

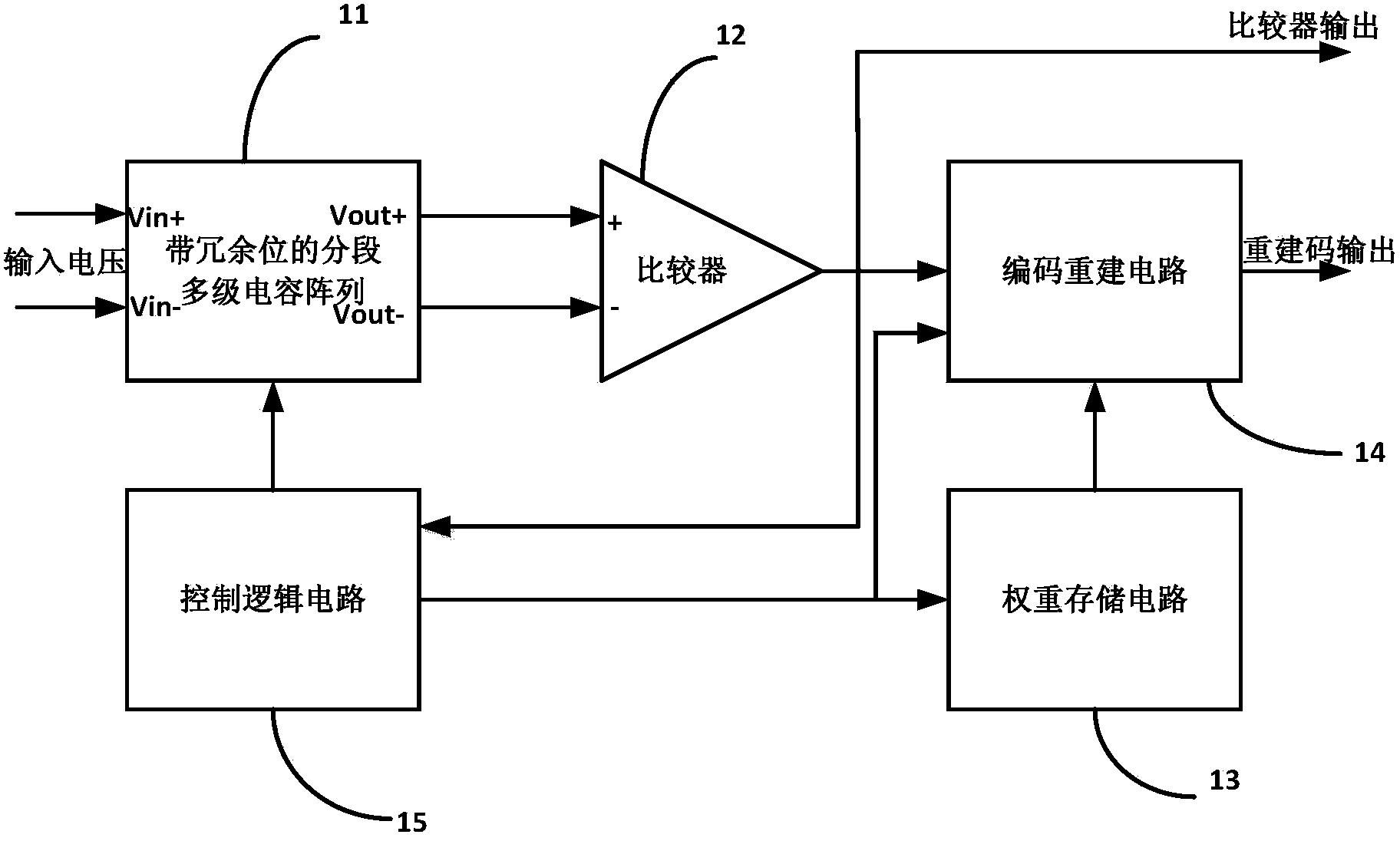

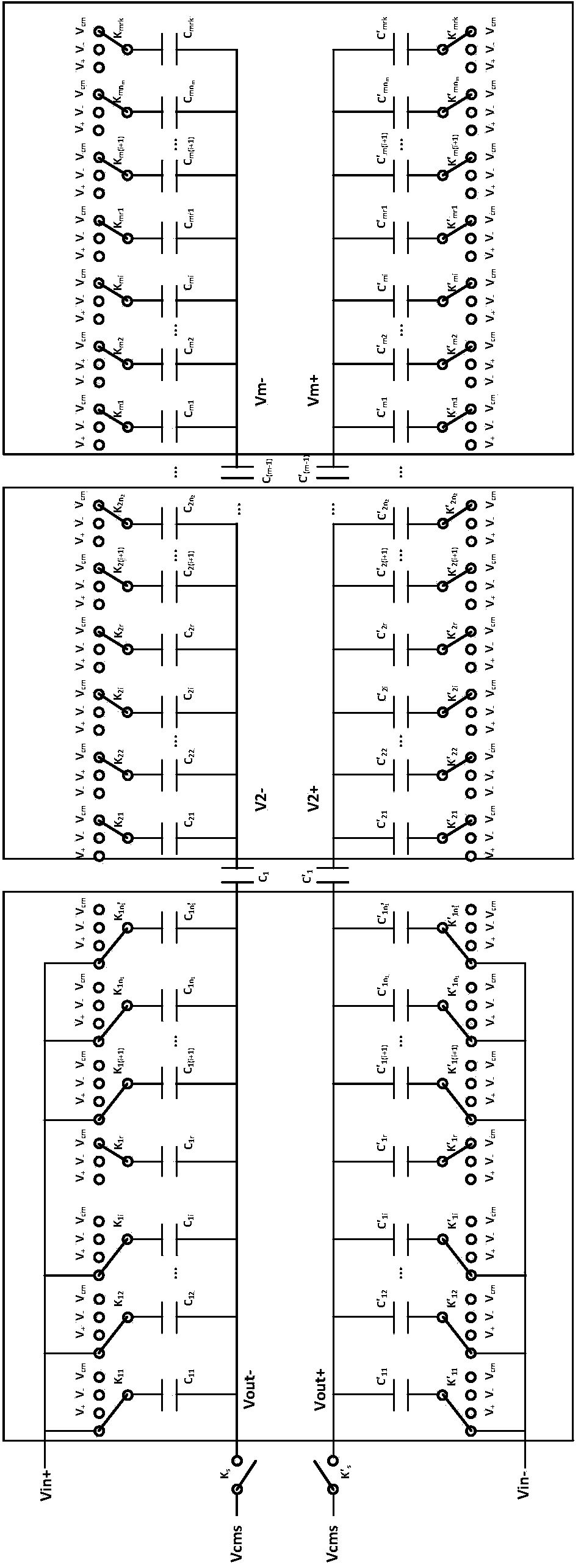

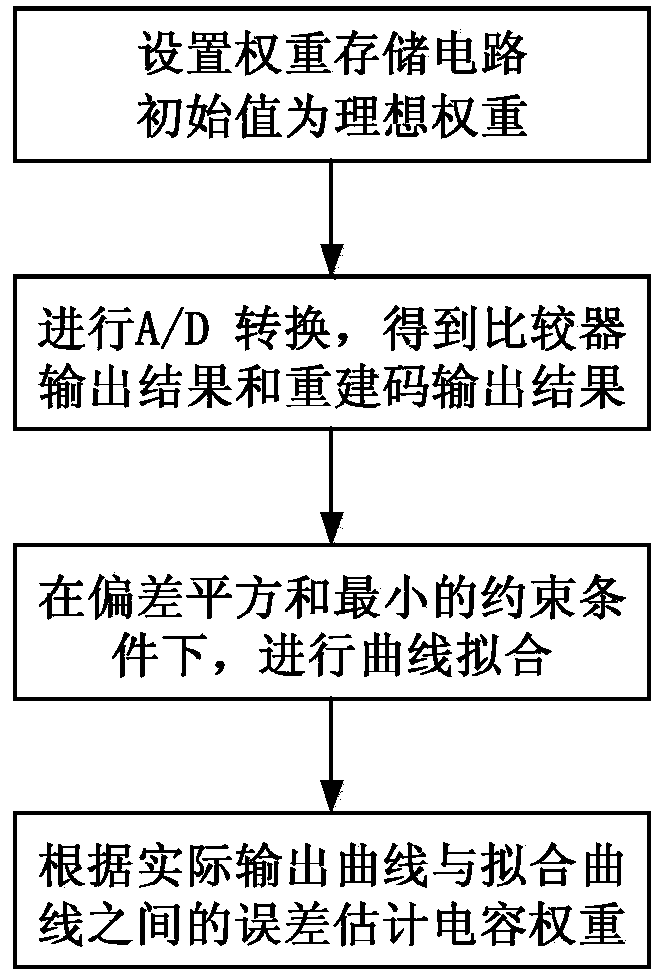

Successive approximation analog-digital converter and conversion method thereof

ActiveCN103929178AReduce the number of unit capacitorsSave the number of unit capacitorsAnalogue/digital conversionElectric signal transmission systemsA d converterEngineering

The invention discloses a successive approximation analog-digital converter and a conversion method thereof. The successive approximation analog-digital converter comprises a subsection multi-level capacitor array with a redundancy bit, a comparator, a weight storage circuit, a coding rebuilding circuit and a control logic circuit. The successive approximation analog-digital converter can reduce complexity of circuit design, save the layout area and power consumption, and accurately measure capacitor mismatch errors and conduct capacitor mismatch error correction without auxiliary capacitor arrays, auxiliary switches and control logics.

Owner:CHONGQING GIGACHIP TECH CO LTD

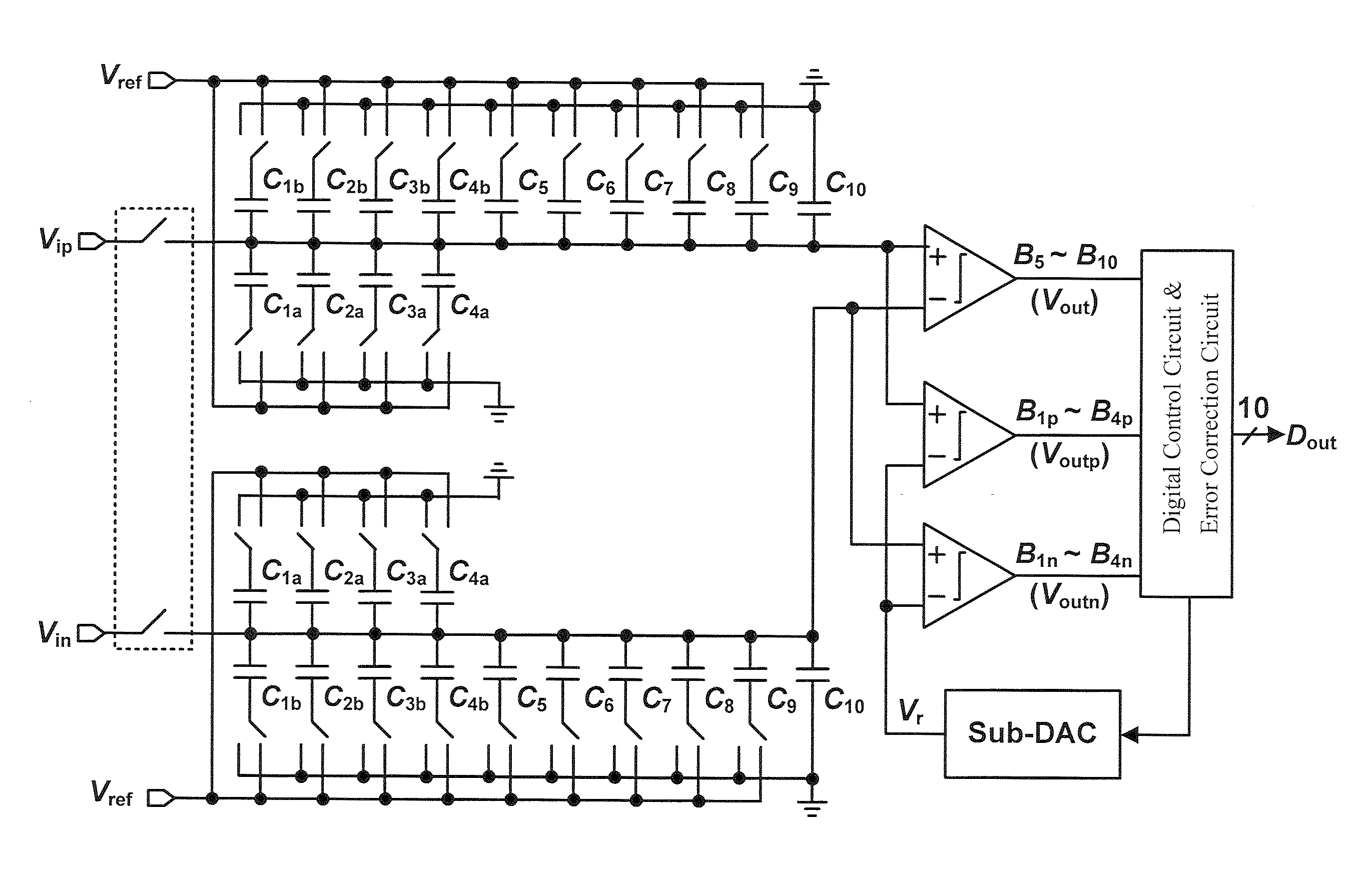

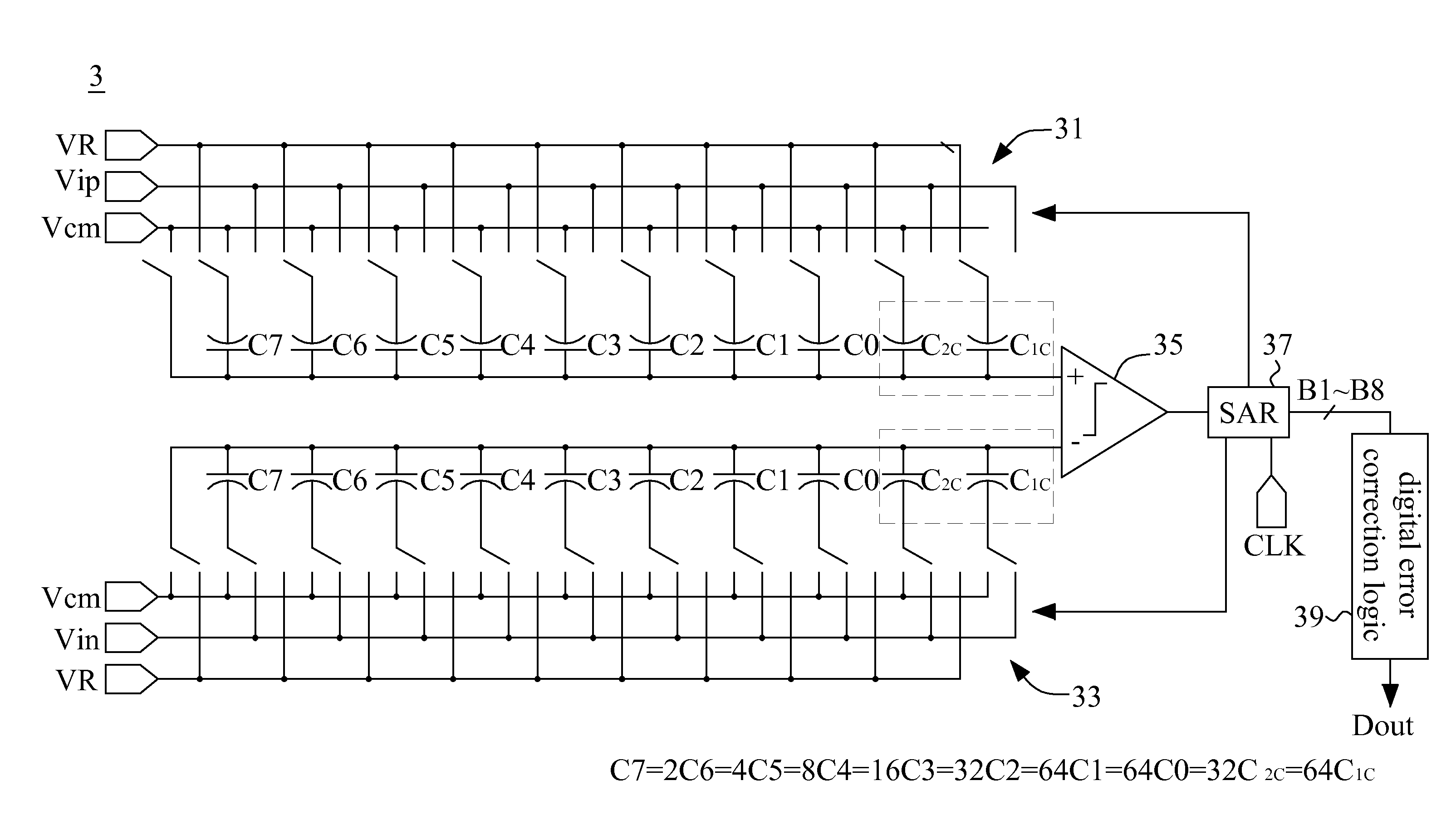

Successive approximation analog to digital converter with capacitor mismatch calibration and method thereof

ActiveUS20130044014A1Achieve original performanceAchieve precisionElectric signal transmission systemsAnalogue-digital convertersCapacitanceDigital down converter

A capacitance mismatch calibrating method for a successive approximation register ADC which includes at least one array of capacitors is provided. The method includes the following steps: firstly, at least two compensating capacitors are configured. A capacitor from the array of capacitors is selected as a capacitor-under-test. Then, the terminal voltages on the terminals of the array of capacitors and on the terminals of the compensating capacitors are determined. A first comparison voltage is outputted based on the determined terminal voltages. Afterwards, a sequence of comparisons is controlled based on the first comparison voltage and a second comparison voltage to output a sequence of corresponding digital bits. Finally, a calibration value is calculated to calibrate the value of a capacitor-under-test according to the digital bits.

Owner:HIMAX TECH LTD

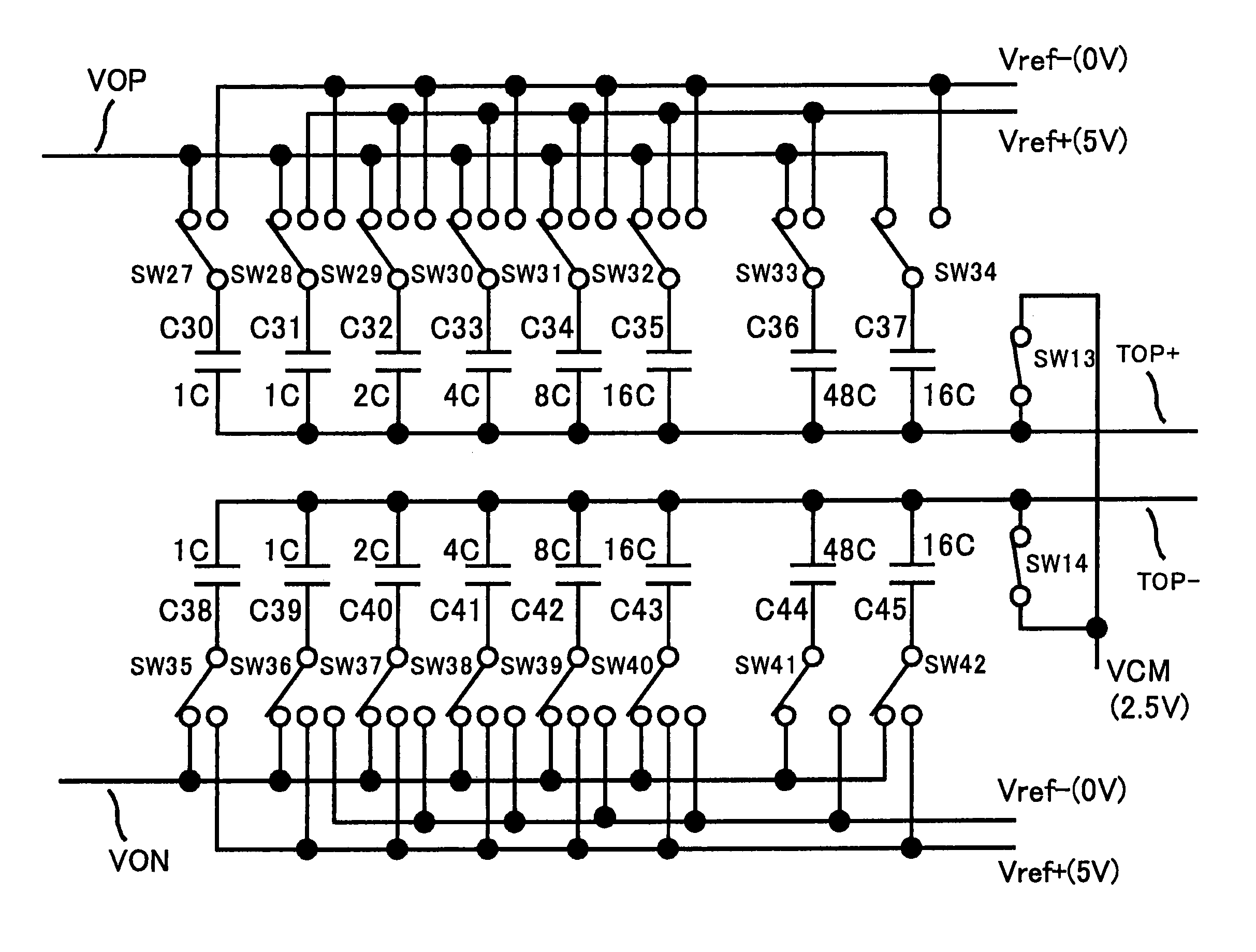

Successive approximation analog-to-digital converter and correction method

ActiveCN105811979AAchieve conversionMismatch Error CancellationAnalogue-digital convertersAnalogue/digital conversion calibration/testingCapacitanceDigital down converter

The invention discloses a successive approximation analog-to-digital converter and a correction method. The converter comprises a fully differential structured DAC based on common mode voltage restoration. The mismatch error of capacitance can be eliminated by background correction technologies. For an ideal binary capacitor array, the weight of one capacitor is equal to the sum of all weights of low position capacitors. However, mismatch of capacitance makes them different. According to the method of the invention, a redundancy switch is performed to compare the capacitance of a to-be-corrected to the sum of all weights of capacitances of the low position capacitors. Based on the two switching results of a redundancy switch of the to-be-corrected capacitor and a normal switch as well as the switching direction of the to-be-corrected capacitor, the correcting codes for each to-be-corrected capacitor are updated and stored at the background. And during ADC conversion, through a correcting DAC, the added value of the correcting codes is converted to analog quantity that is coupled to a main DAC. The system corrects all capacitances requiring correction successively and such process repeats itself.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

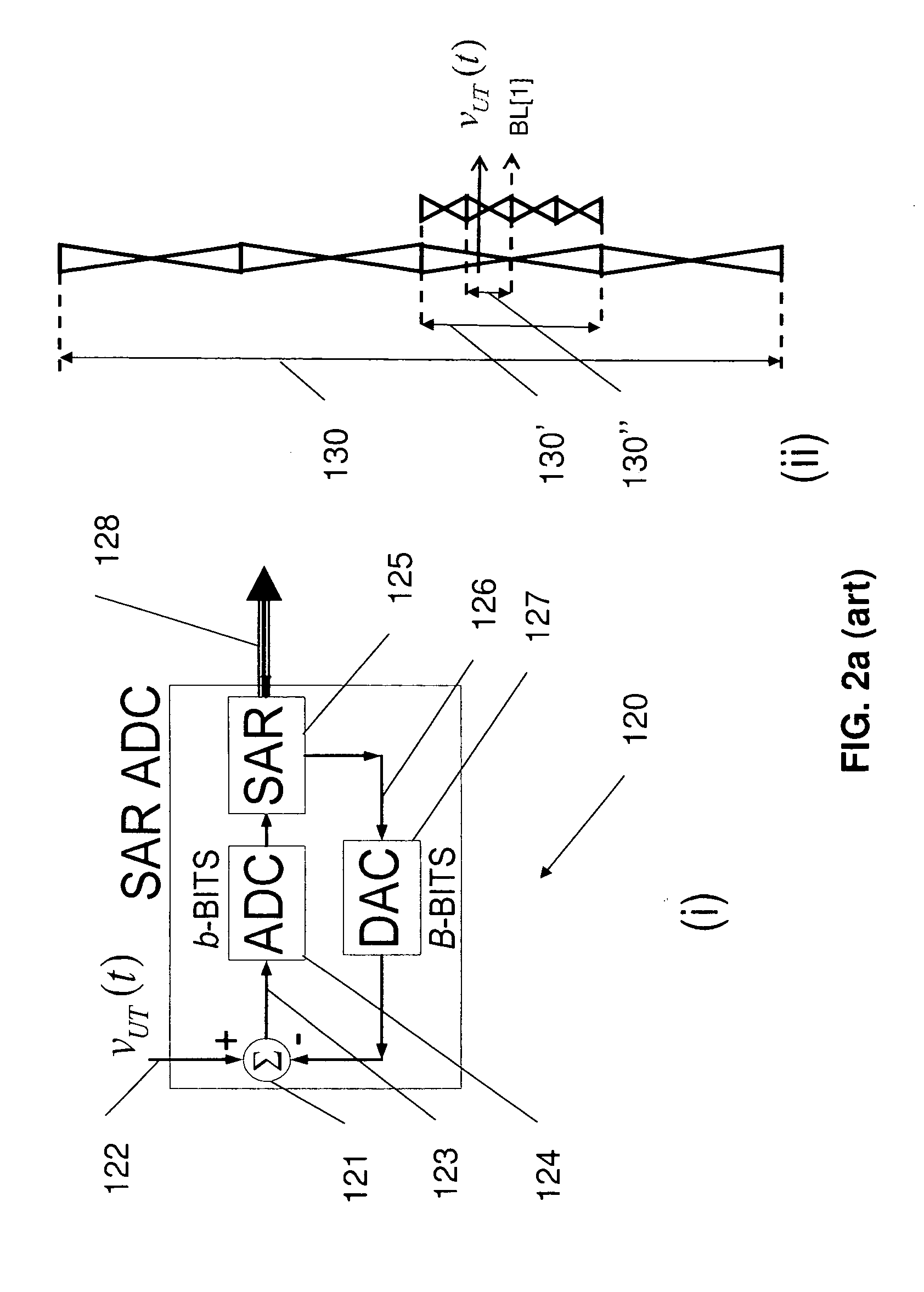

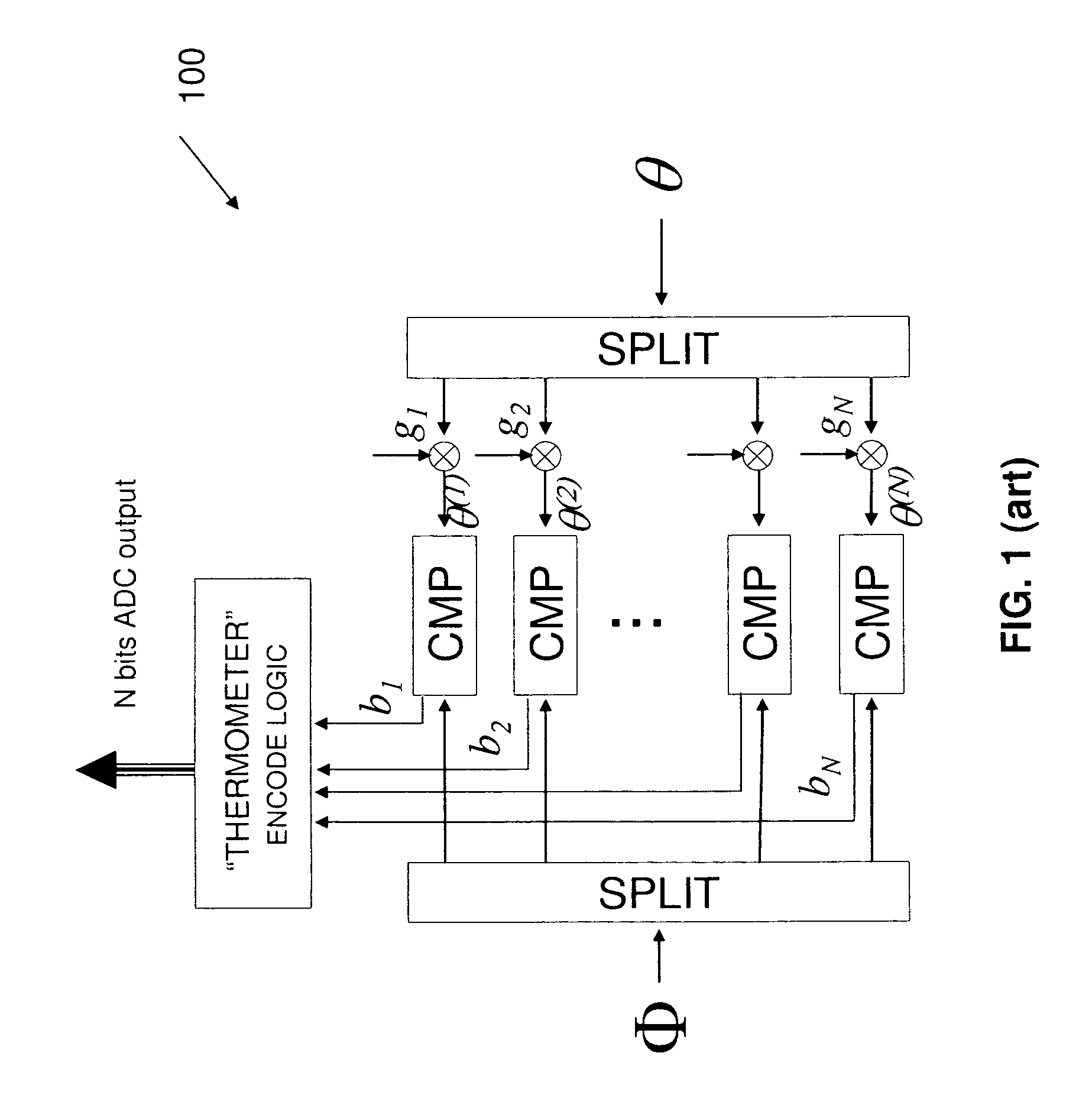

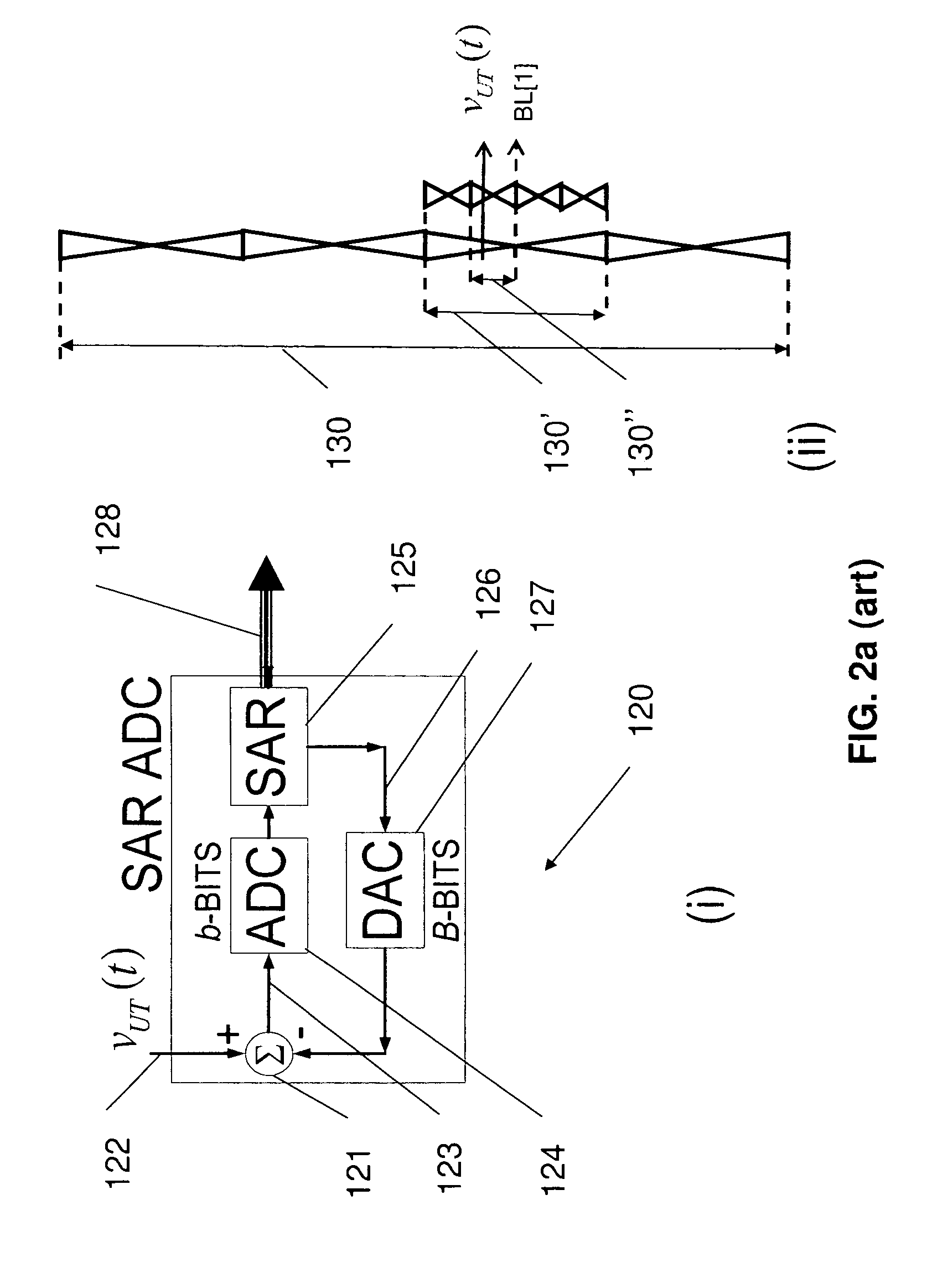

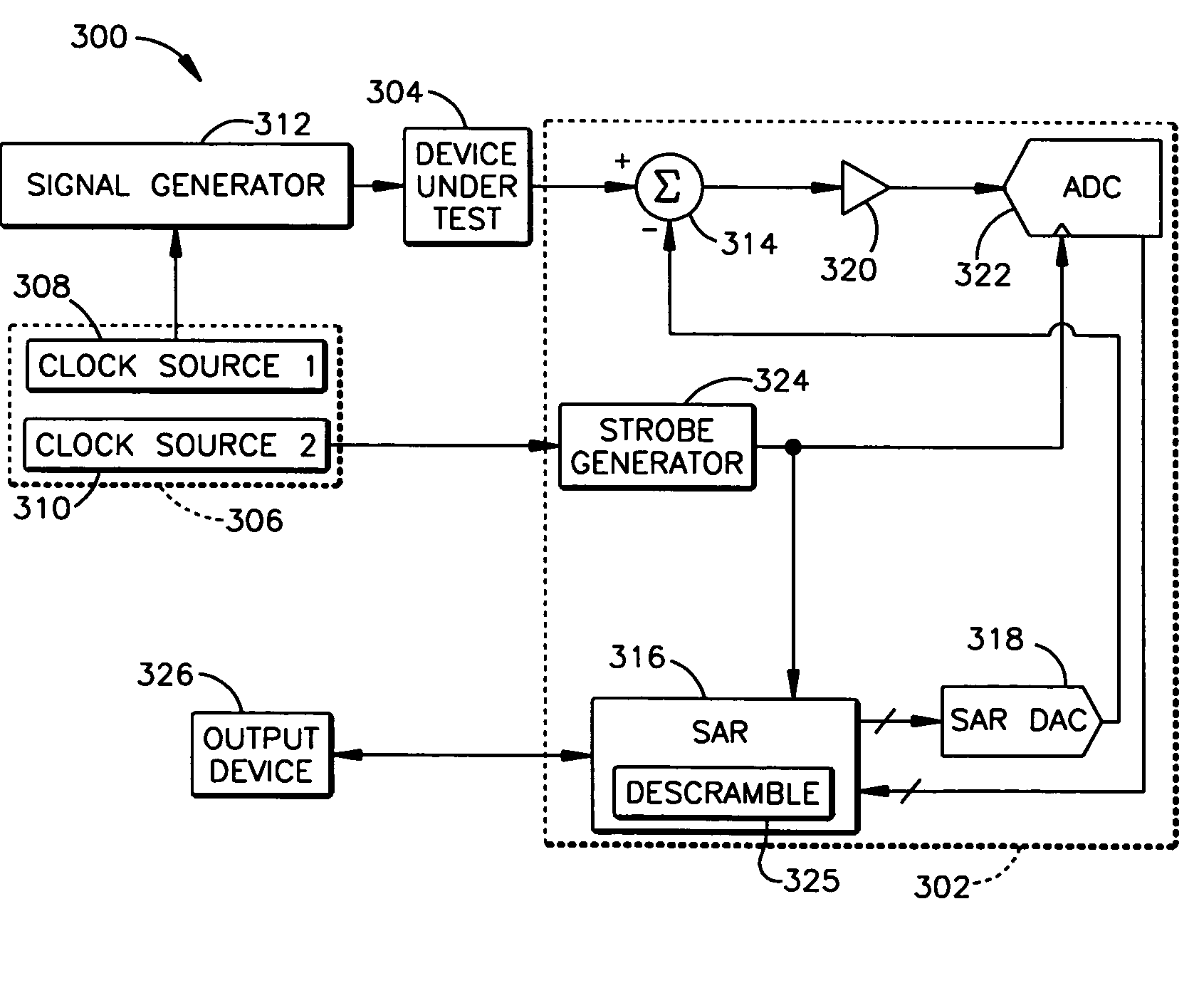

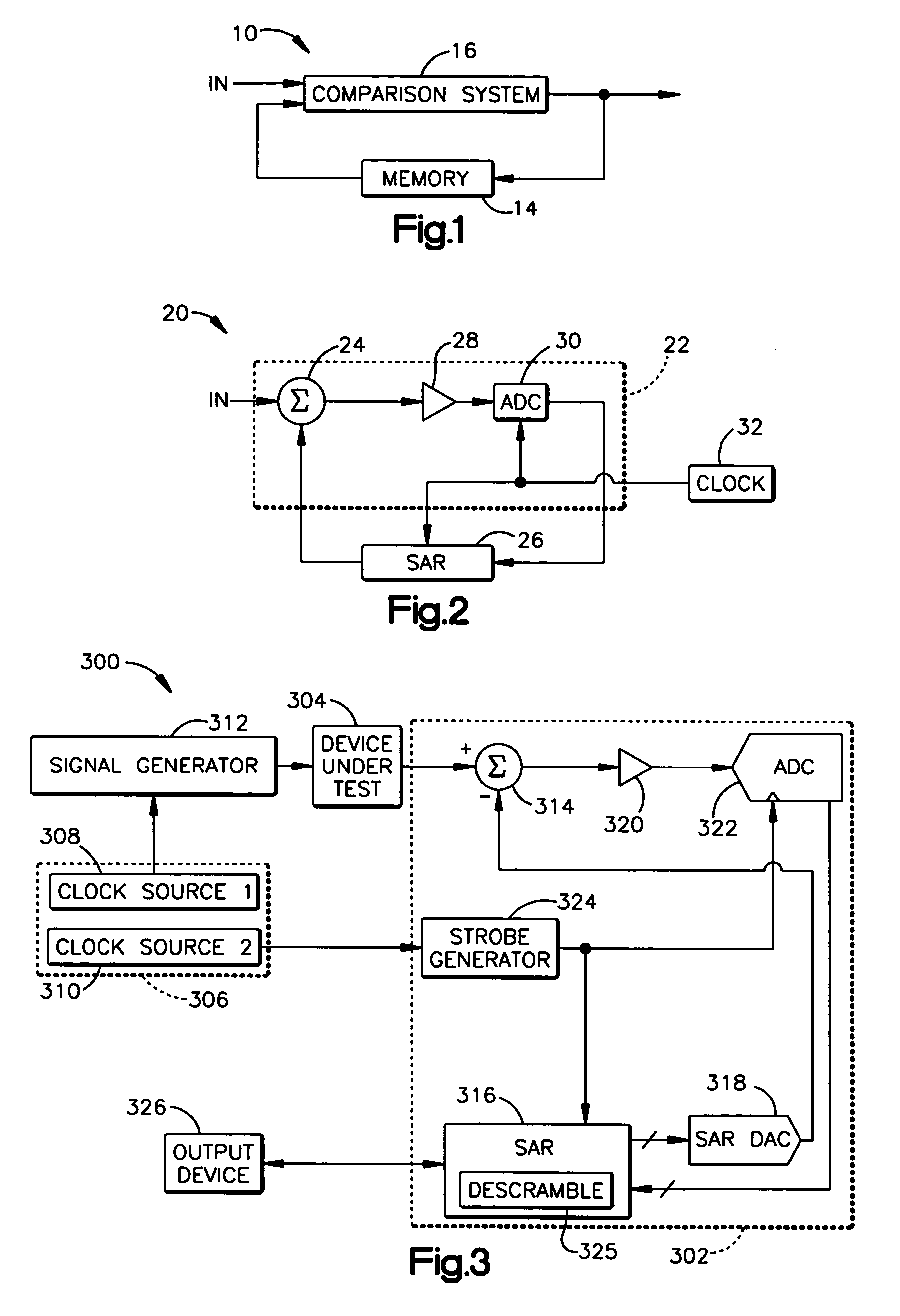

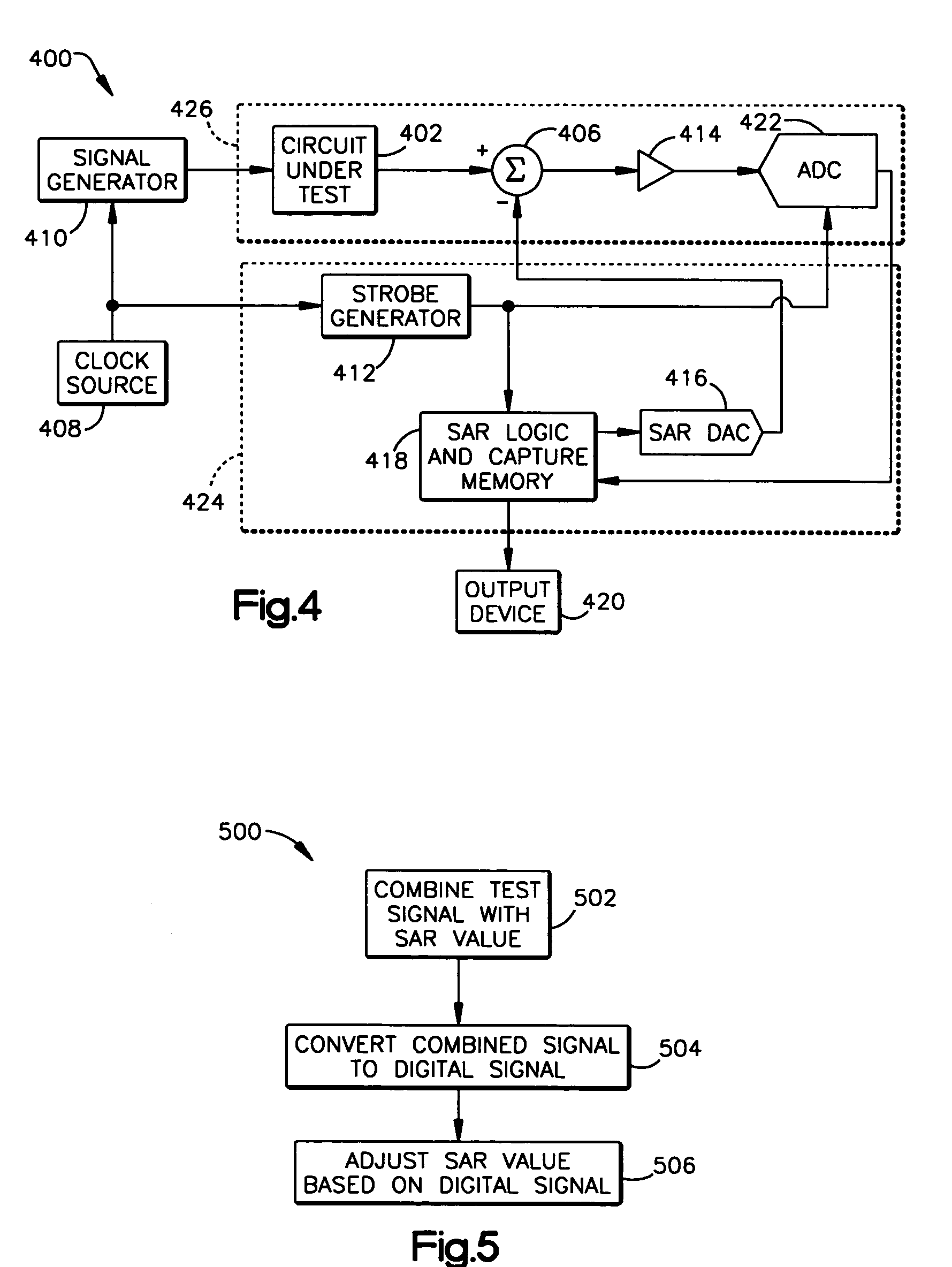

System and method for successive approximation

ActiveUS7265694B2Electric signal transmission systemsProduction of permanent recordsDigital converterDigital signal

A system and method for providing successive approximation, such as can be used by a successive approximation converter or by a coherent undersampling digitizer. The system comprising a memory having a successive approximation value and a comparison system configured to receive and amplify the difference between a test signal and the successive approximation value and to convert the amplified signal to a digital signal. A multi-bit analog to digital convert can be used to convert the amplified signal to a digital signal.

Owner:TEXAS INSTR INC

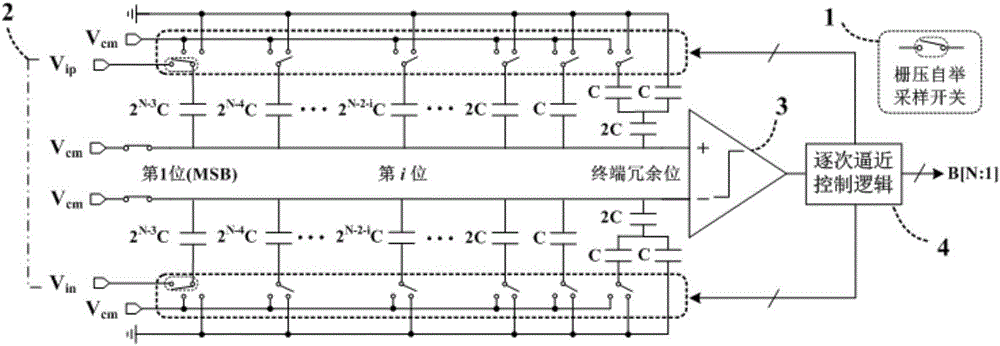

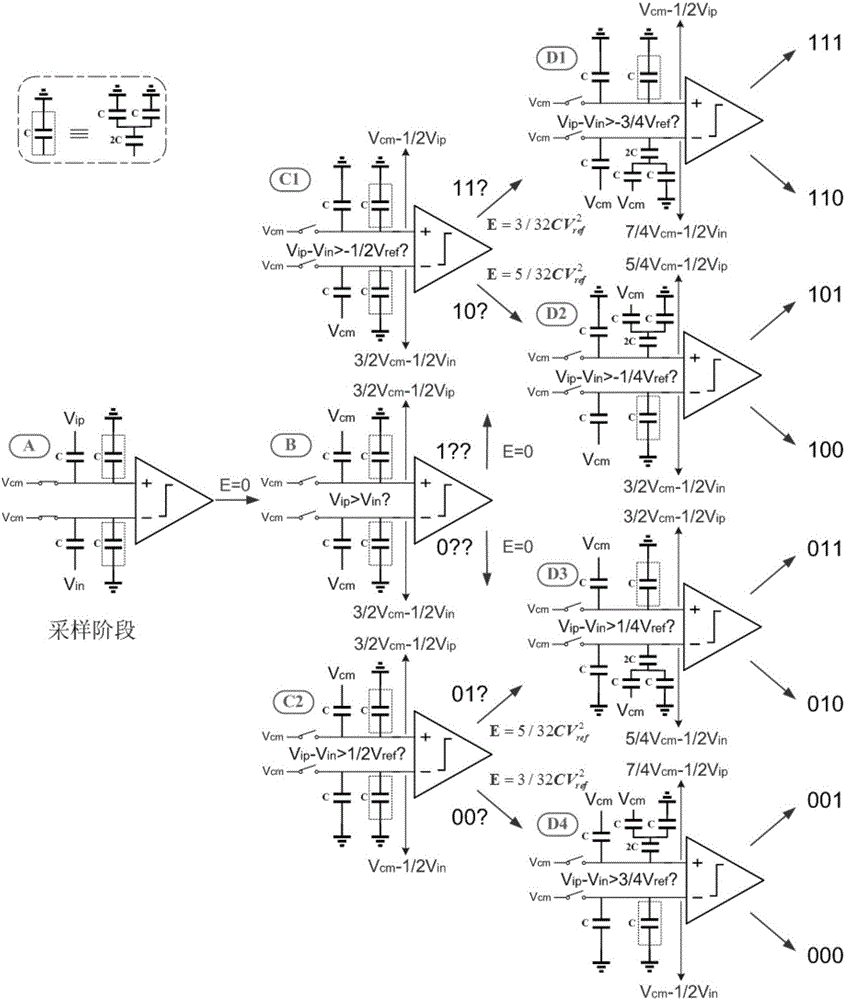

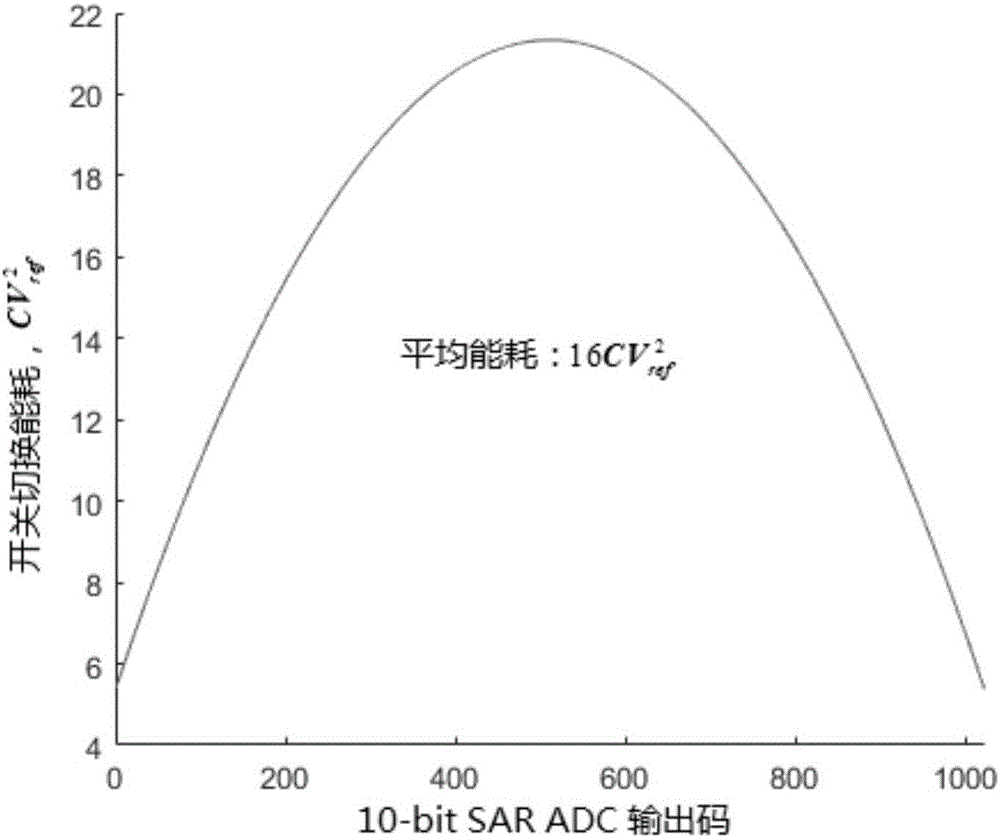

Successive approximation analog-digital converter structure and low-power-consumption switching method thereof

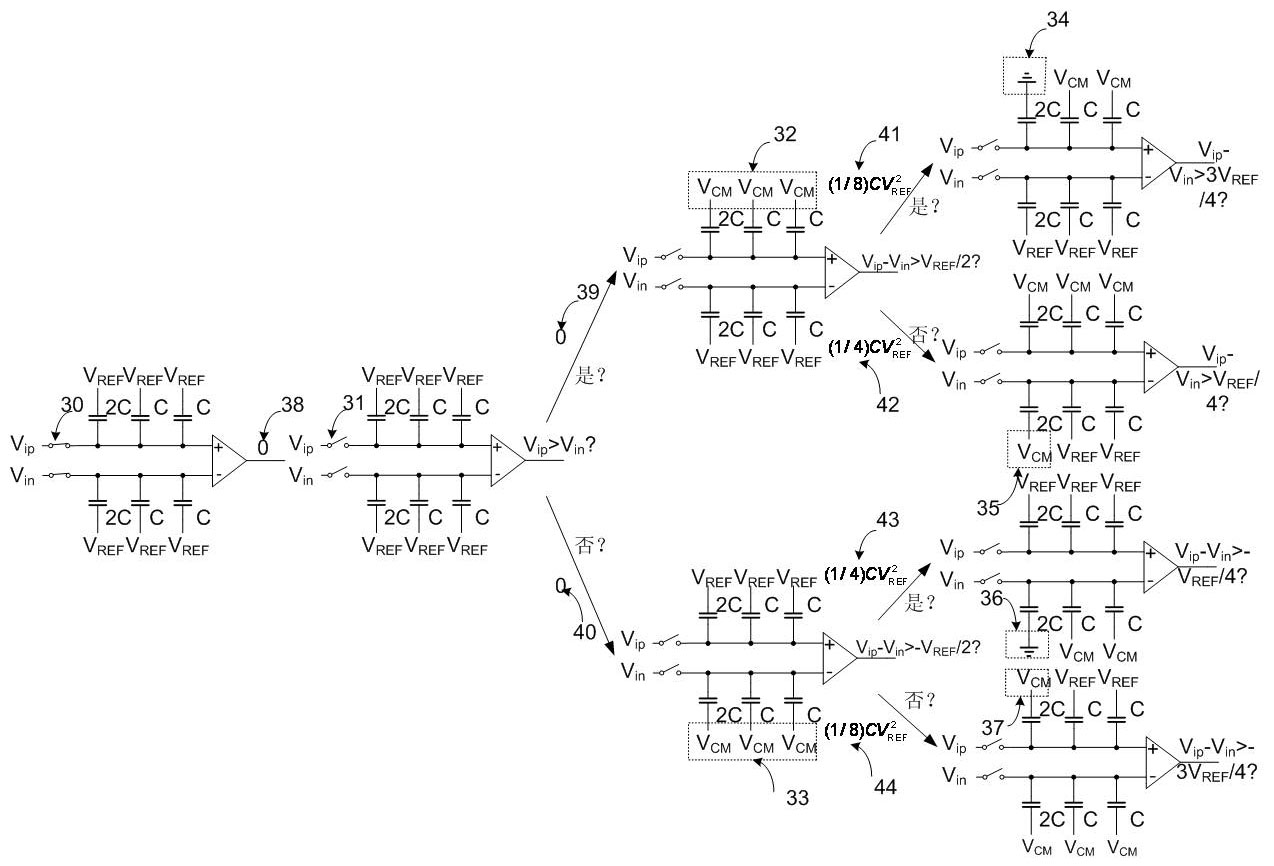

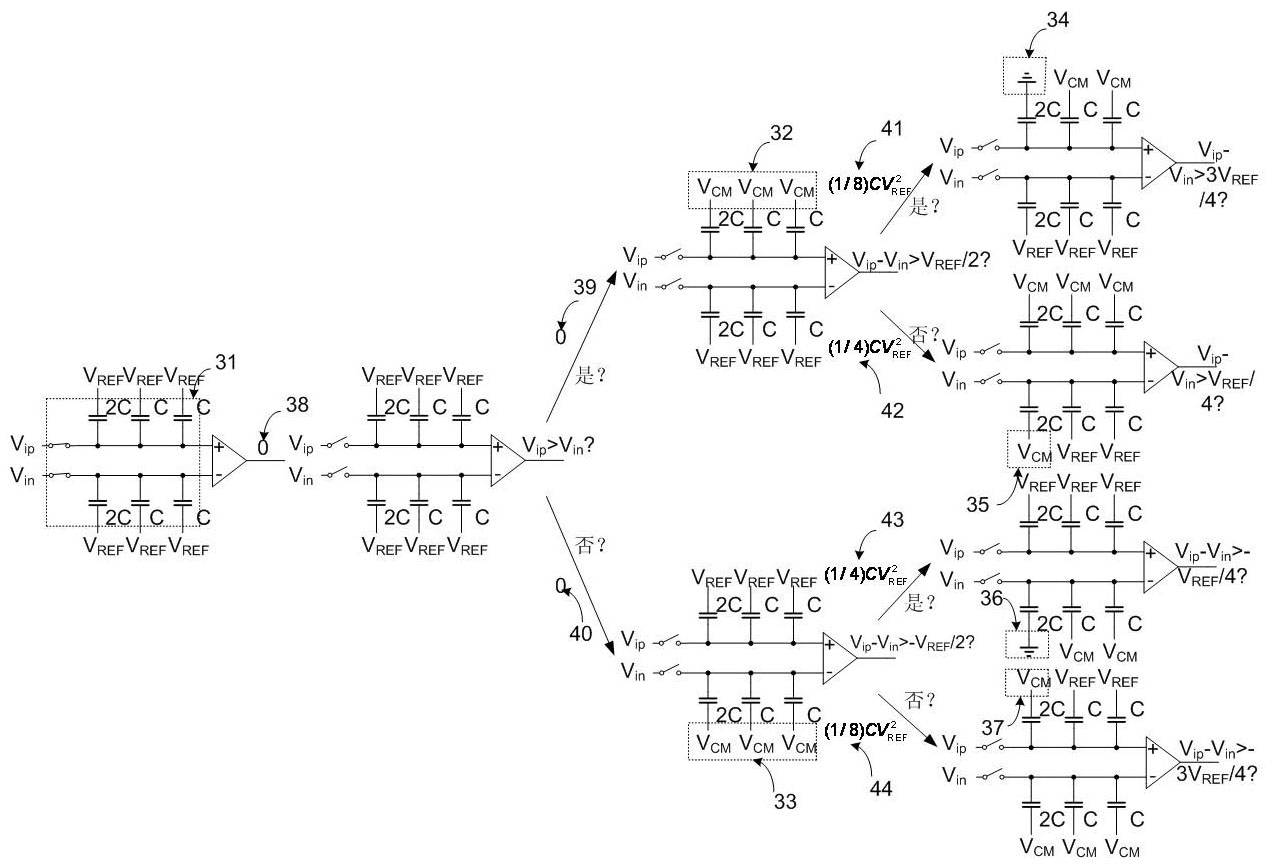

ActiveCN106301364AReduce areaHigh precisionPower saving provisionsElectric signal transmission systemsCapacitanceDigital analog converter

The invention discloses a successive approximation analog-digital converter structure and a low-power-consumption switch method thereof. Compared with a conventional full base plate sampling technology, the successive approximation analog-digital converter structure has the advantages that only one pair of bootstrapped sampling switches is needed by a highest-order capacitor bottom plate sampling technology, so that the accuracy of a successive approximation analog-digital converter is increased; the switching area is reduced; and the power consumption is lowered. Through adoption of the switching method provided by the invention, energy is not consumed during generation of first two orders in a switching process. Moreover, only a common-mode voltage V<cm>=(1 / 2)V<ref> is taken as a reference voltage, so that dynamic energy consumption in the switching process is lowered greatly. Redundant bit capacitors are introduced into conversion of a capacitor array digital-analog converter, so that the total area of the capacitors is reduced greatly, and the switching energy consumption is further lowered. The successive approximation analog-digital converter structure is suitable for a high-accuracy low-power-consumption successive approximation analog-digital converter, and has a very good economic benefit.

Owner:SOUTHEAST UNIV

Passive noise shaping successive approximation SAR analog-to-digital converter

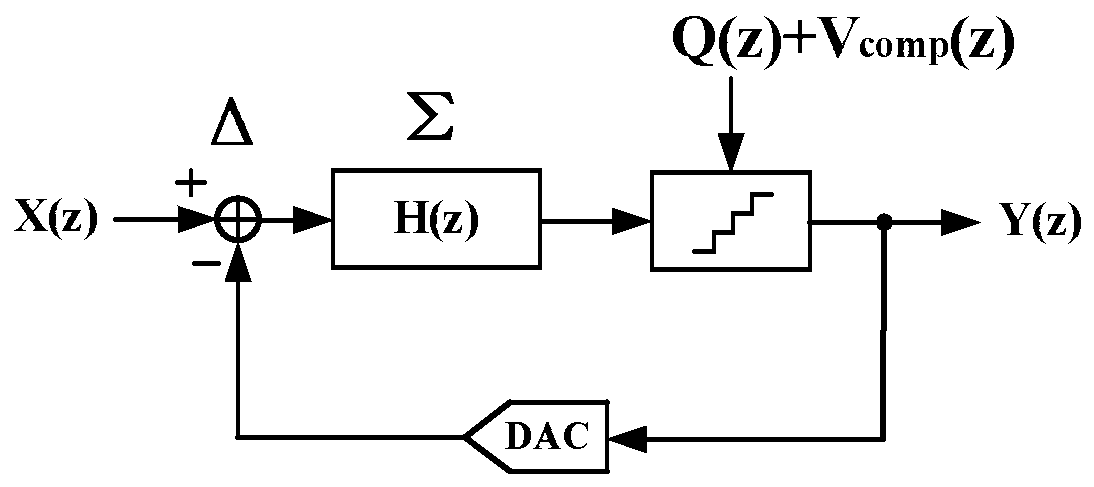

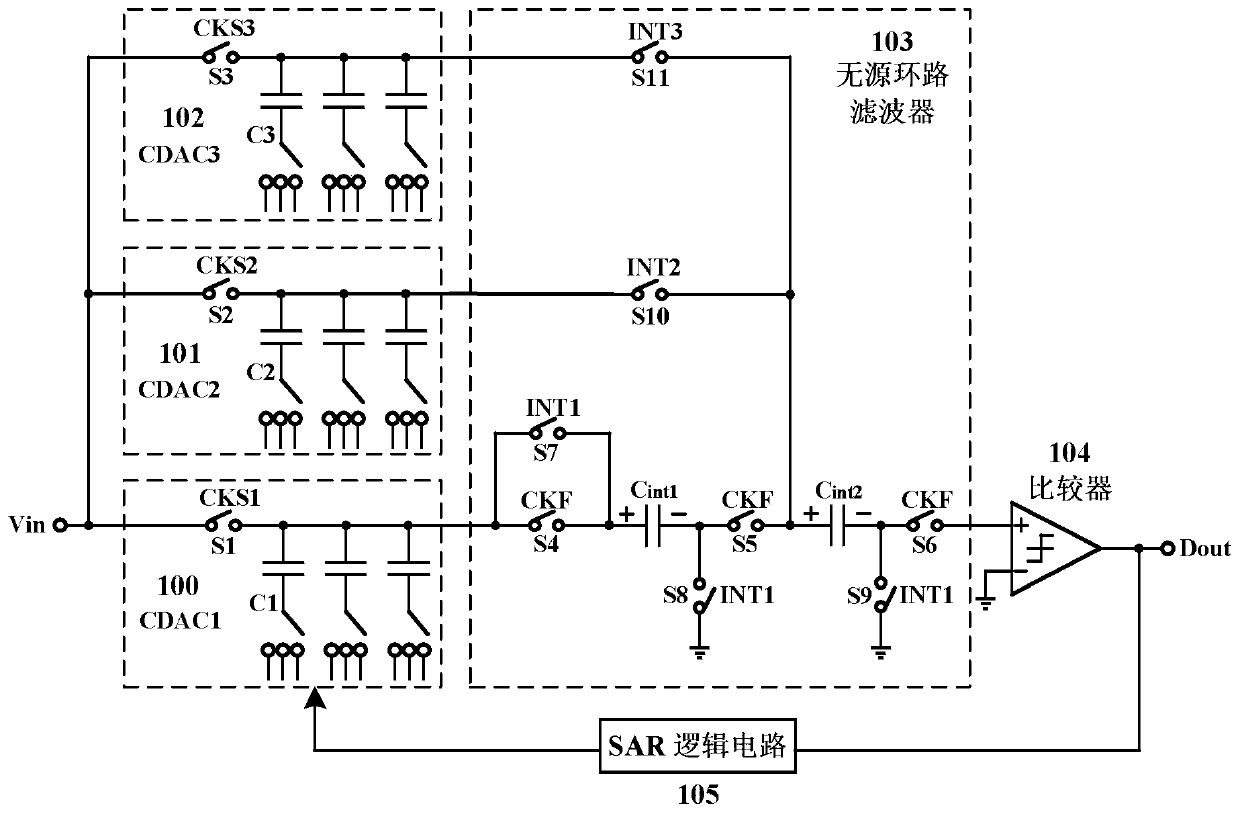

ActiveCN110492885AReduce capacitanceCancel noiseElectric signal transmission systemsPhysical parameters compensation/preventionCapacitanceLoop filter

The invention discloses a passive noise shaping successive approximation SAR analog-to-digital converter. The analog-to-digital converter comprises three capacitive digital-to-analog converters (CDACs), a passive loop filter, a comparator and an SAR logic circuit, wherein the three identical CDACs comprise a CDAC1 required by normal SAR conversion and two auxiliary CDAC2 and CDAC3 used for generating a margin voltage of a previous period. Two interlaced CDAC2 and CDAC3 are added, and KT / C noise and gain loss introduced by passive margin sampling are removed. Wherein the CDAC1 generates the margin voltage Vres (n) of the current period, and the CDAC2 and the CDAC3 alternately generate the margin voltage Vres (n-1) of the previous period. And the passive loop filter carries out noise shapingon the margin voltage and suppresses in-band noise of the signal. And the comparator quantizes the analog output of the passive loop filter into a digital code, the digital code toggles the next capacitor switch in the CDAC through the SAR logic circuit until the conversion is finished, and all the digital codes are sequentially spliced together to serve as the output code of the SAR ADC, which is the same as that of the common SAR ADC. According to the invention, the second-order noise shaping effect can be realized, the signal in-band quantization noise and the comparator noise are effectively suppressed, and the signal-to-noise ratio and the spurious-free dynamic range of the SAR ADC are obviously improved.

Owner:SOUTHEAST UNIV