Patents

Literature

70results about How to "Reduced drive capability requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

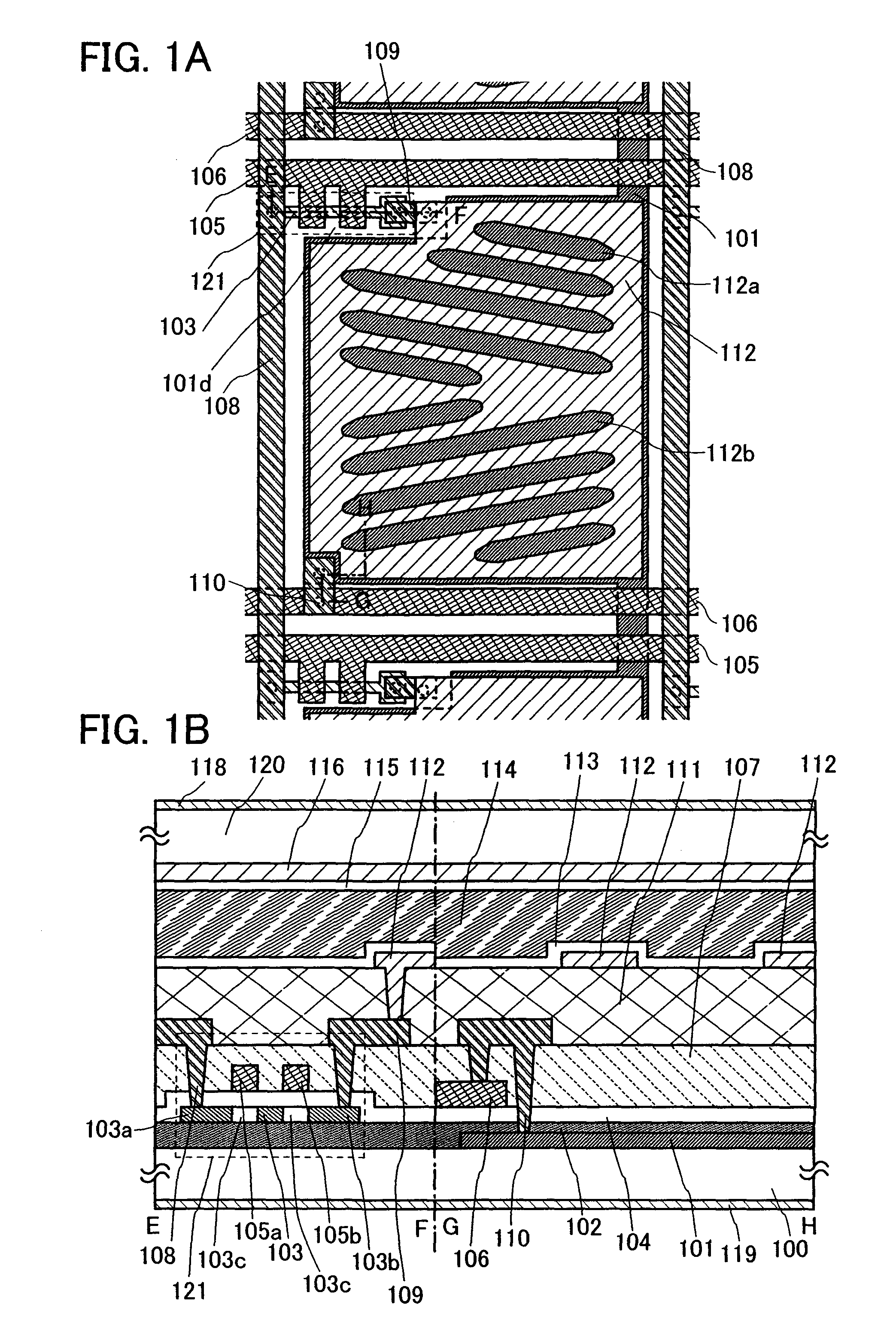

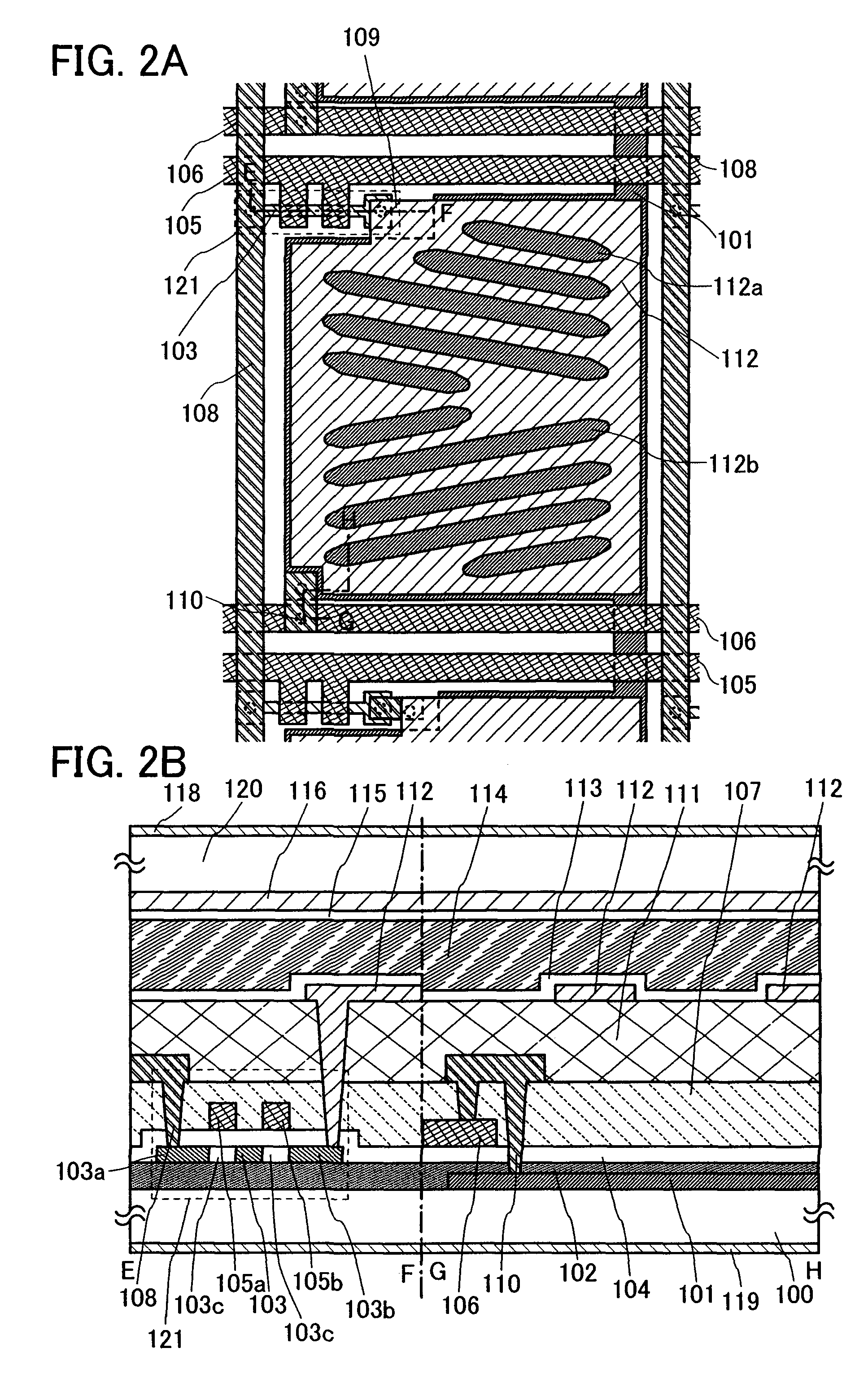

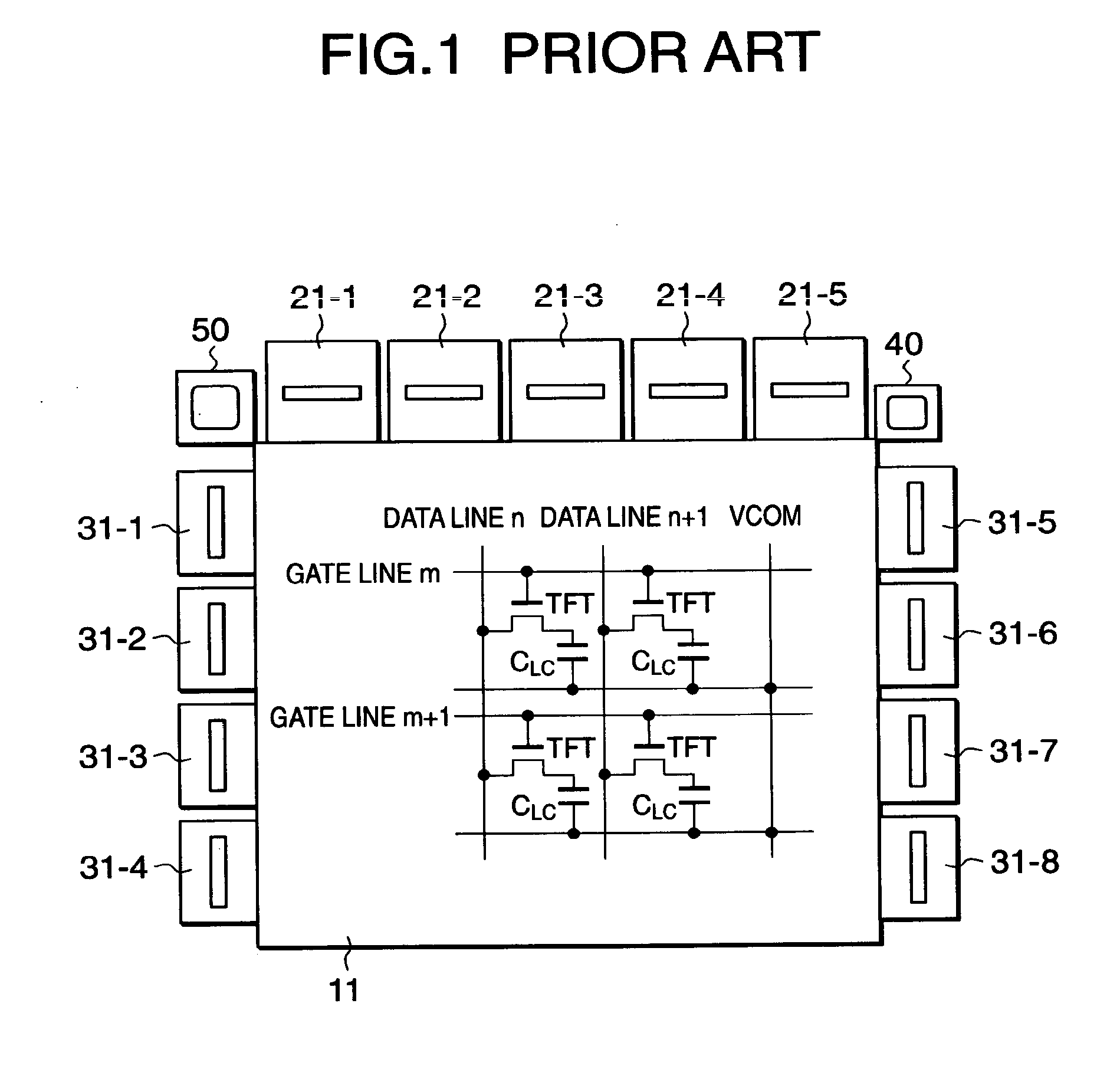

Liquid crystal display device and semiconductor device

InactiveUS20070284627A1Degree of freedomIncrease freedomTransistorNon-linear opticsLiquid-crystal displaySemiconductor

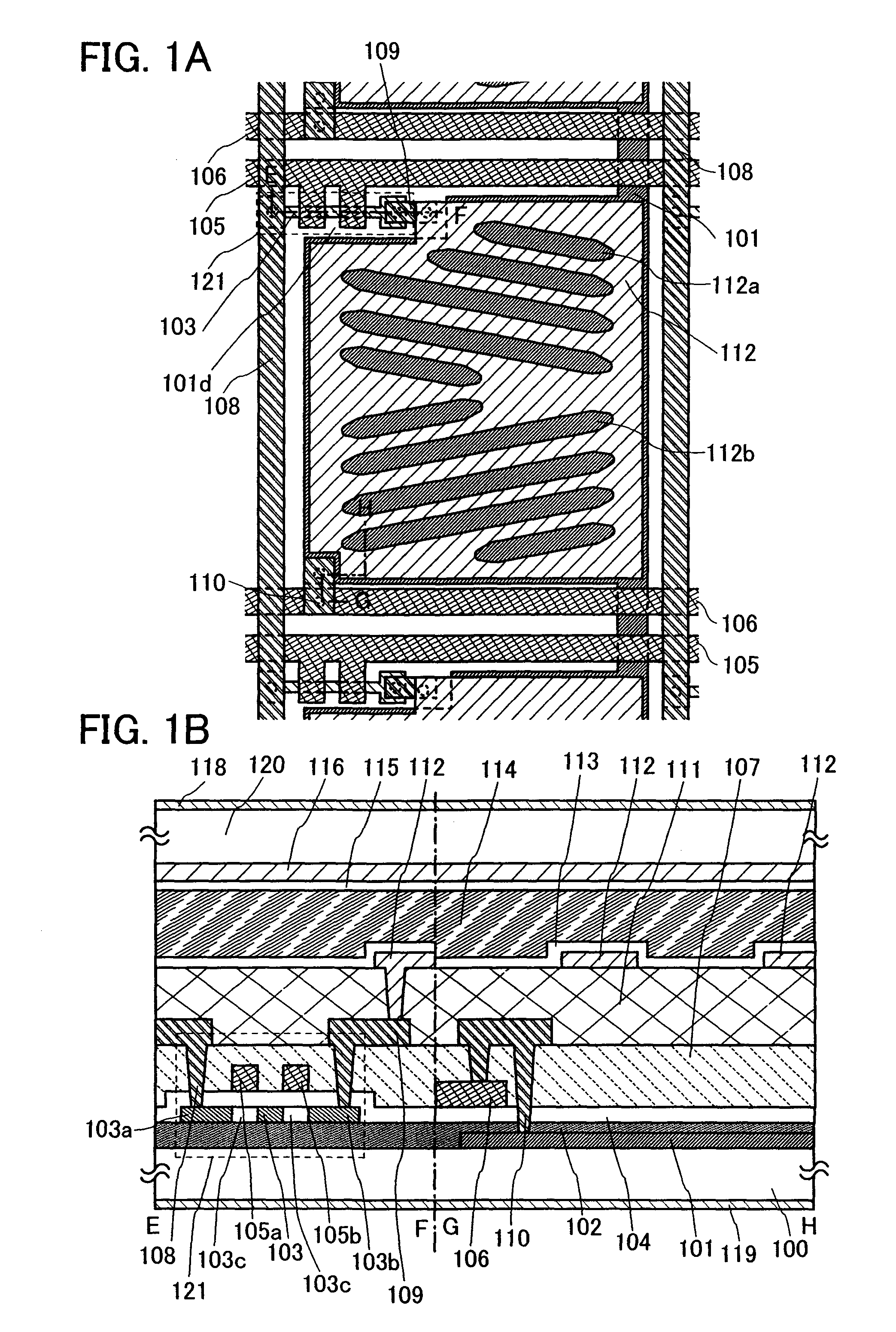

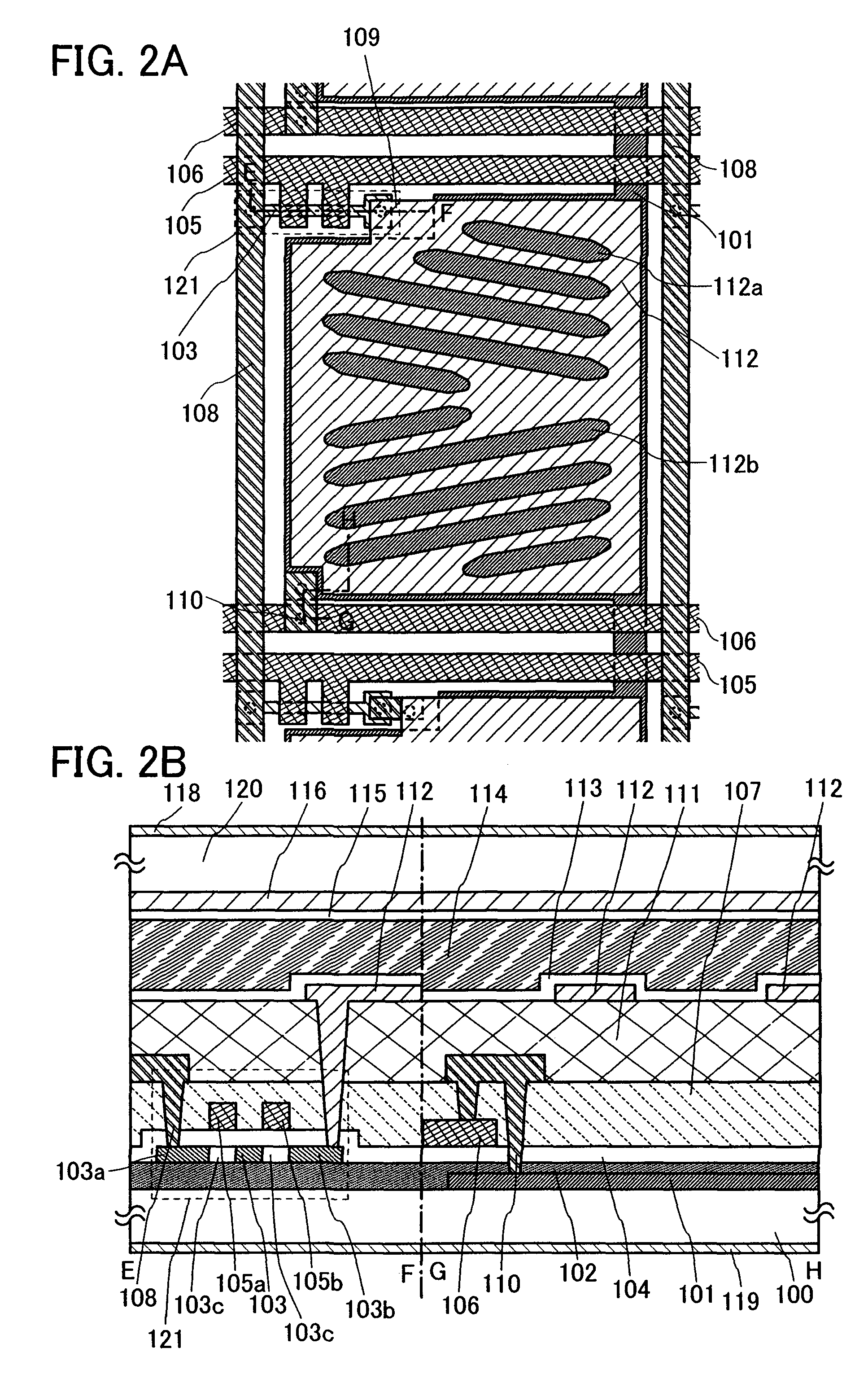

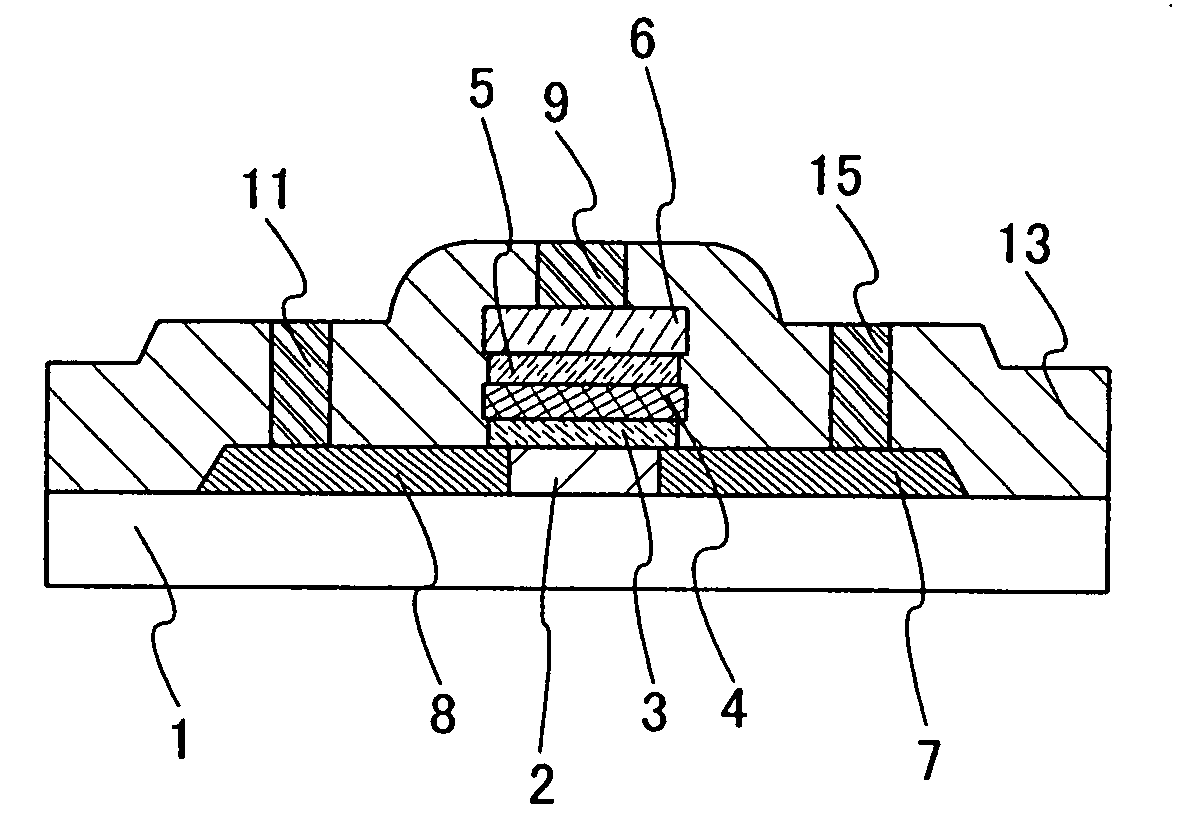

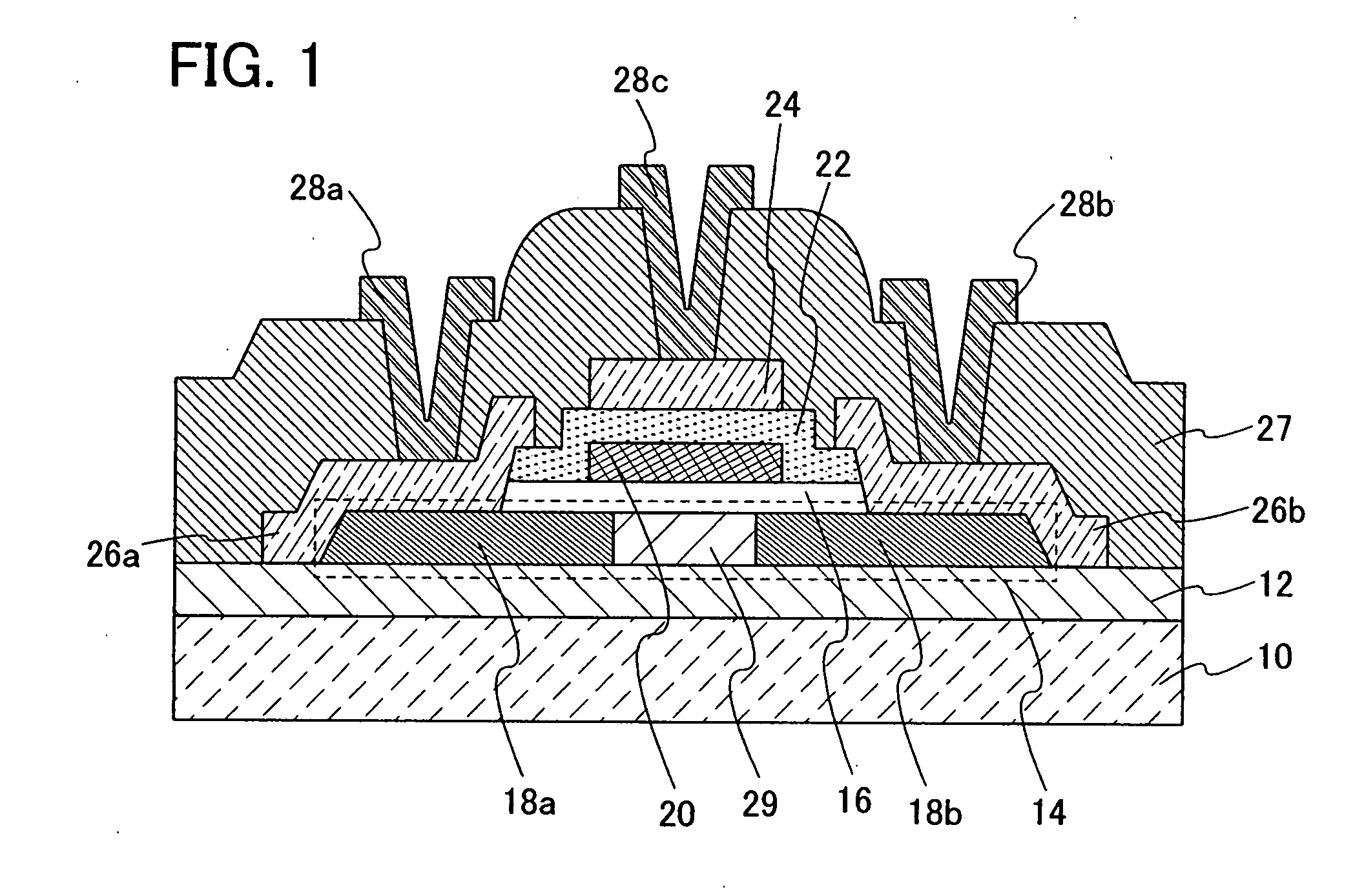

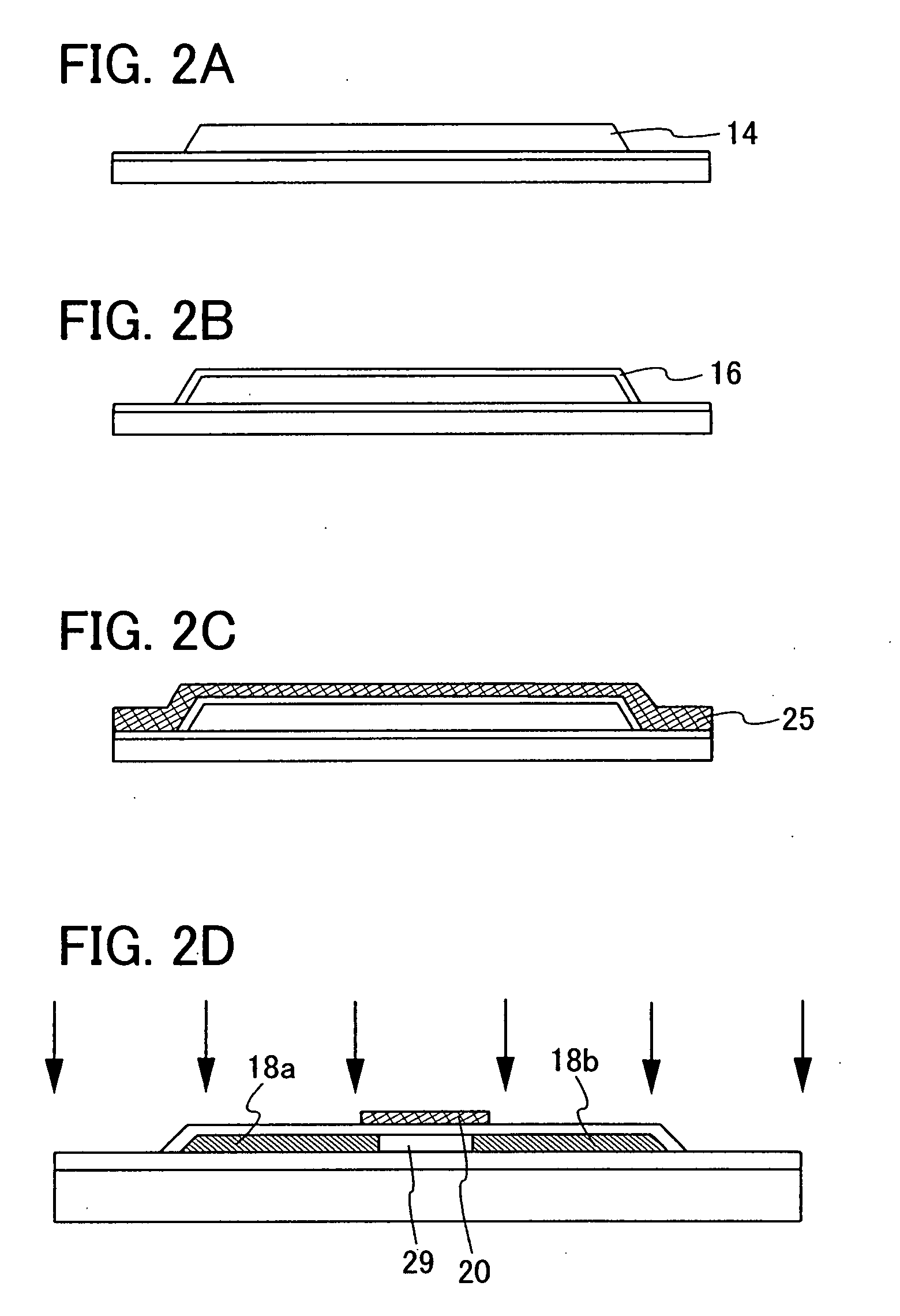

By increasing an interval between electrodes which drives liquid crystals, a gradient of an electric field applied between the electrodes can be controlled and an optimal electric field can be applied between the electrodes. The invention includes a first electrode formed over a substrate, an insulating film formed over the substrate and the first electrode, a thin film transistor including a semiconductor film in which a source, a channel region, and a drain are formed over the insulating film, a second electrode located over the semiconductor film and the first electrode and including first opening patterns, and liquid crystals provided over the second electrode.

Owner:SEMICON ENERGY LAB CO LTD

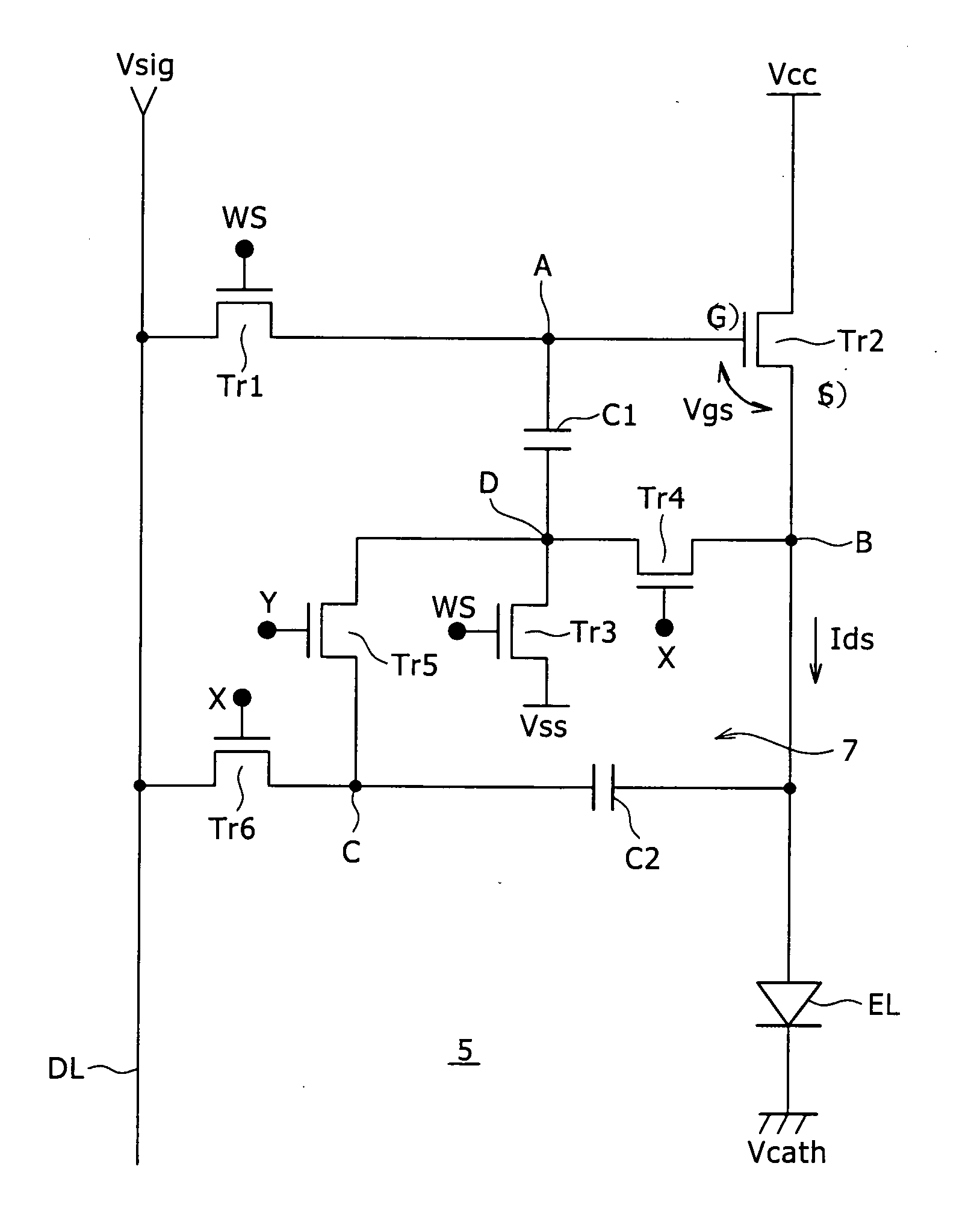

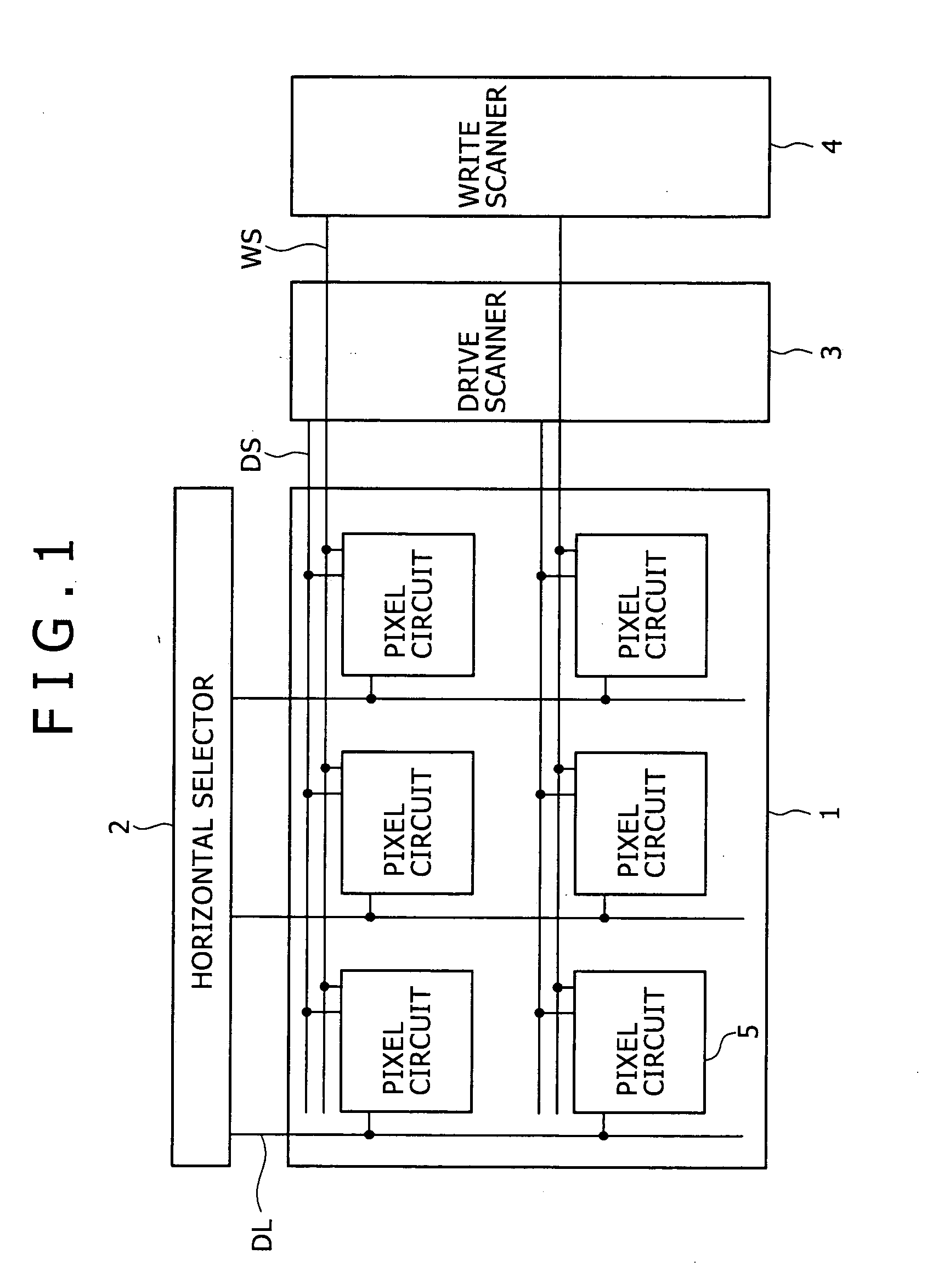

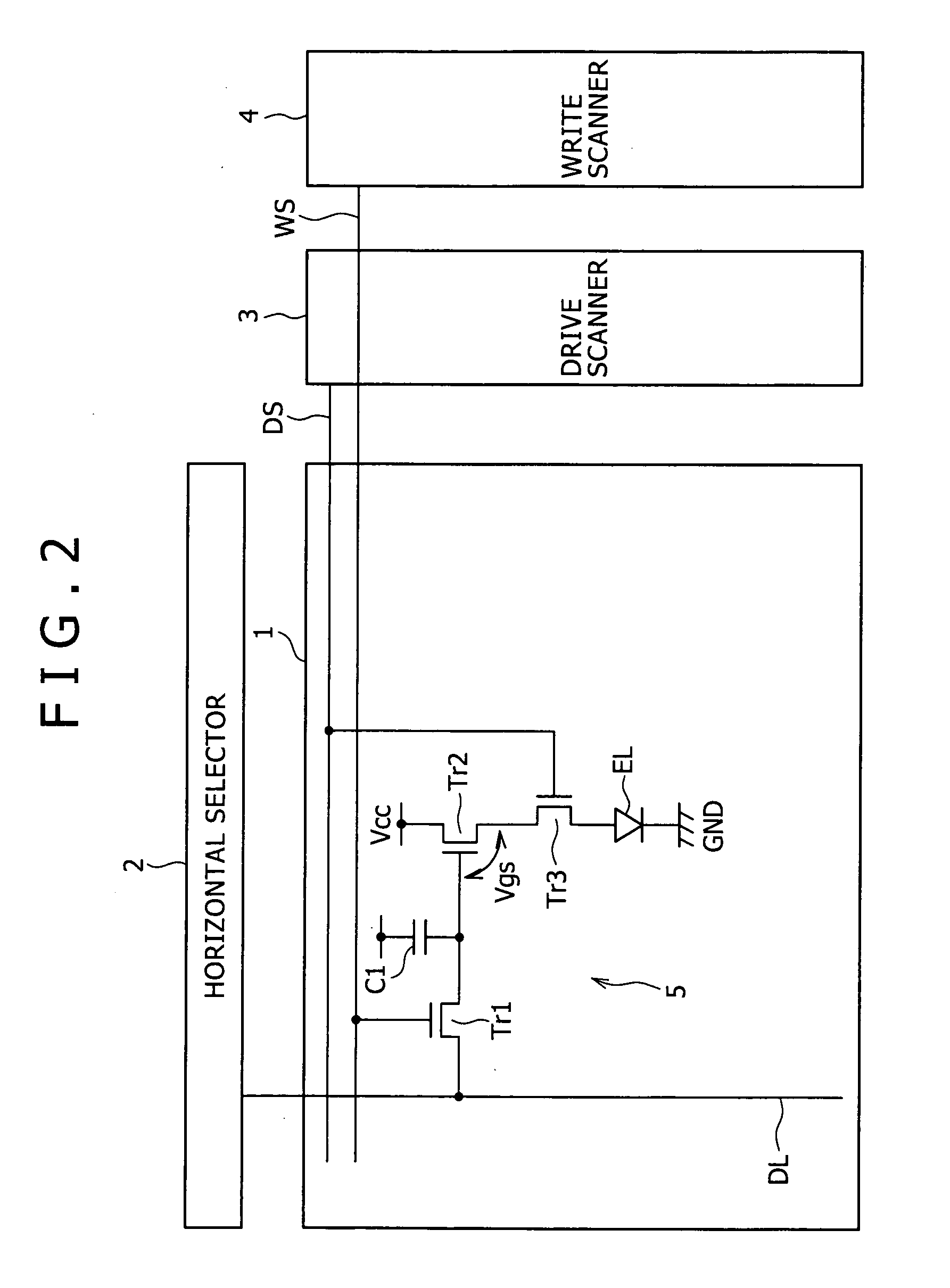

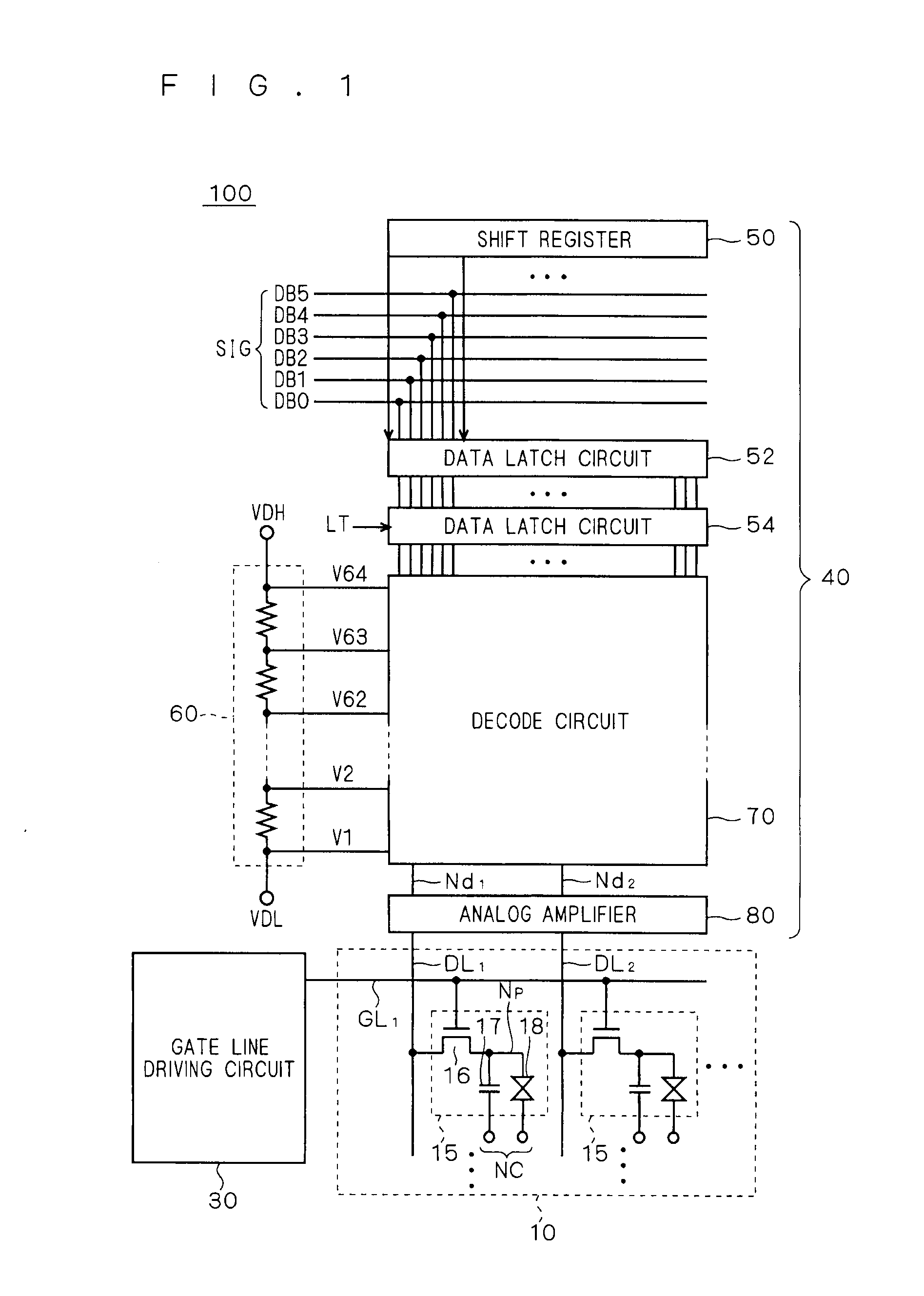

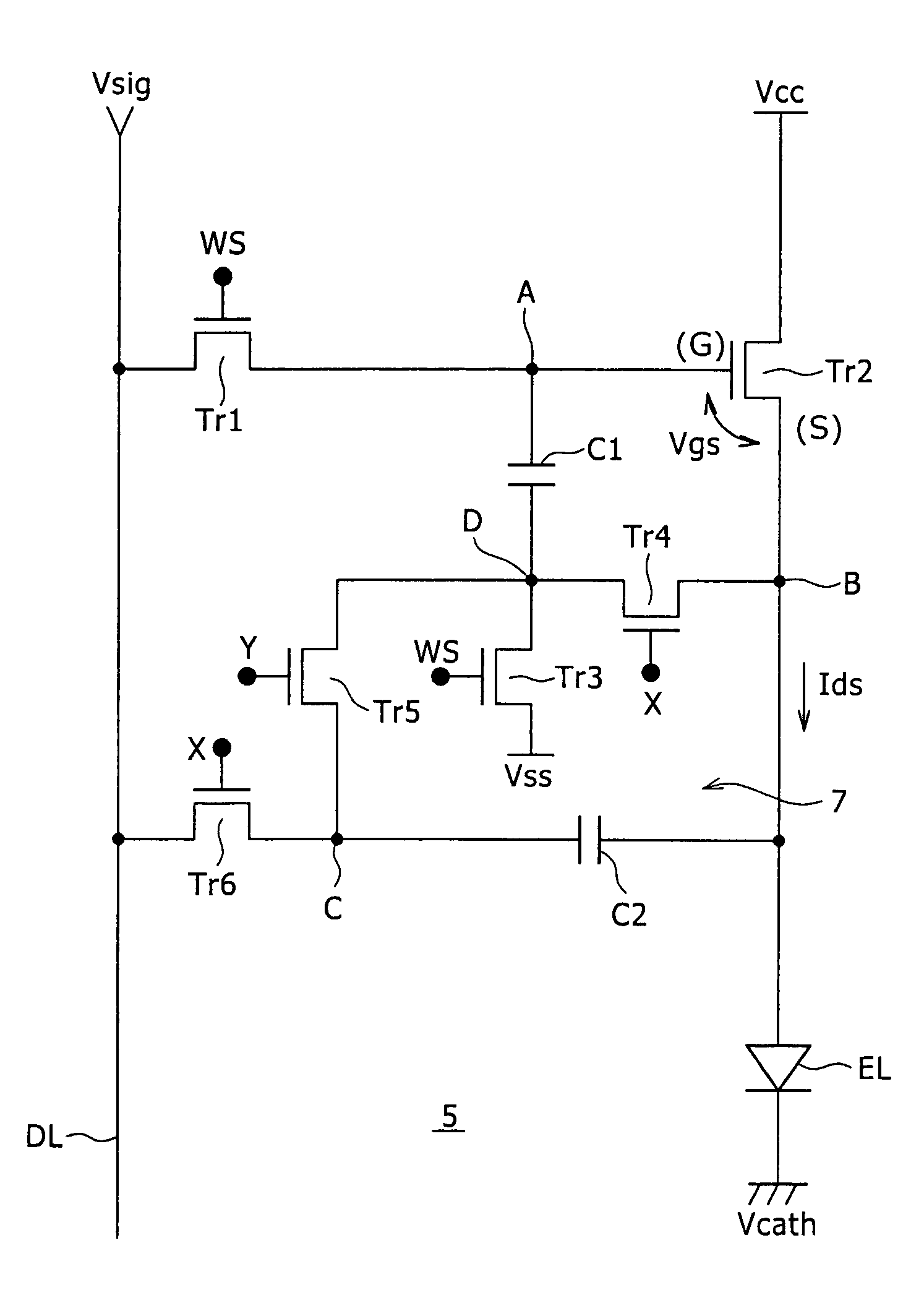

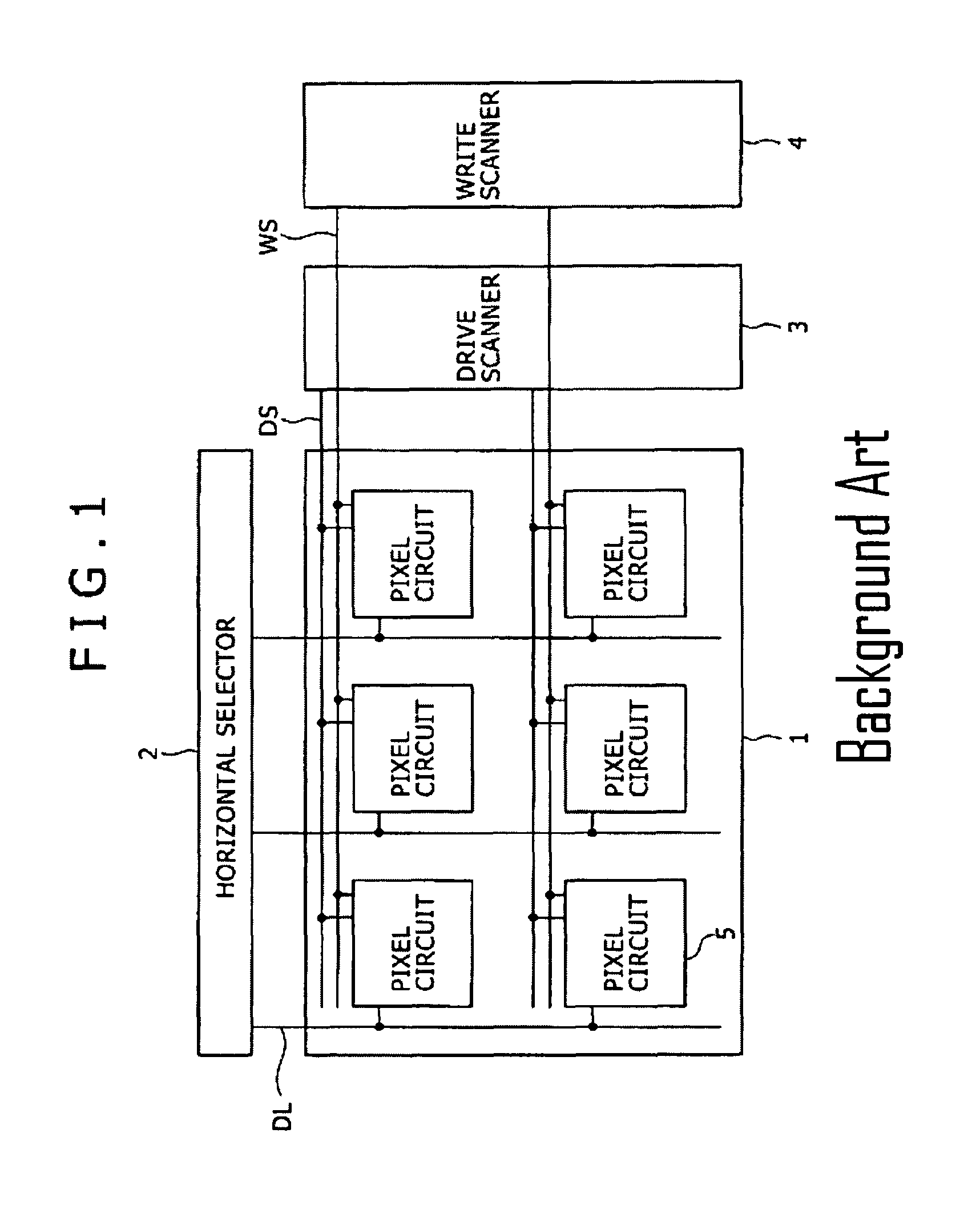

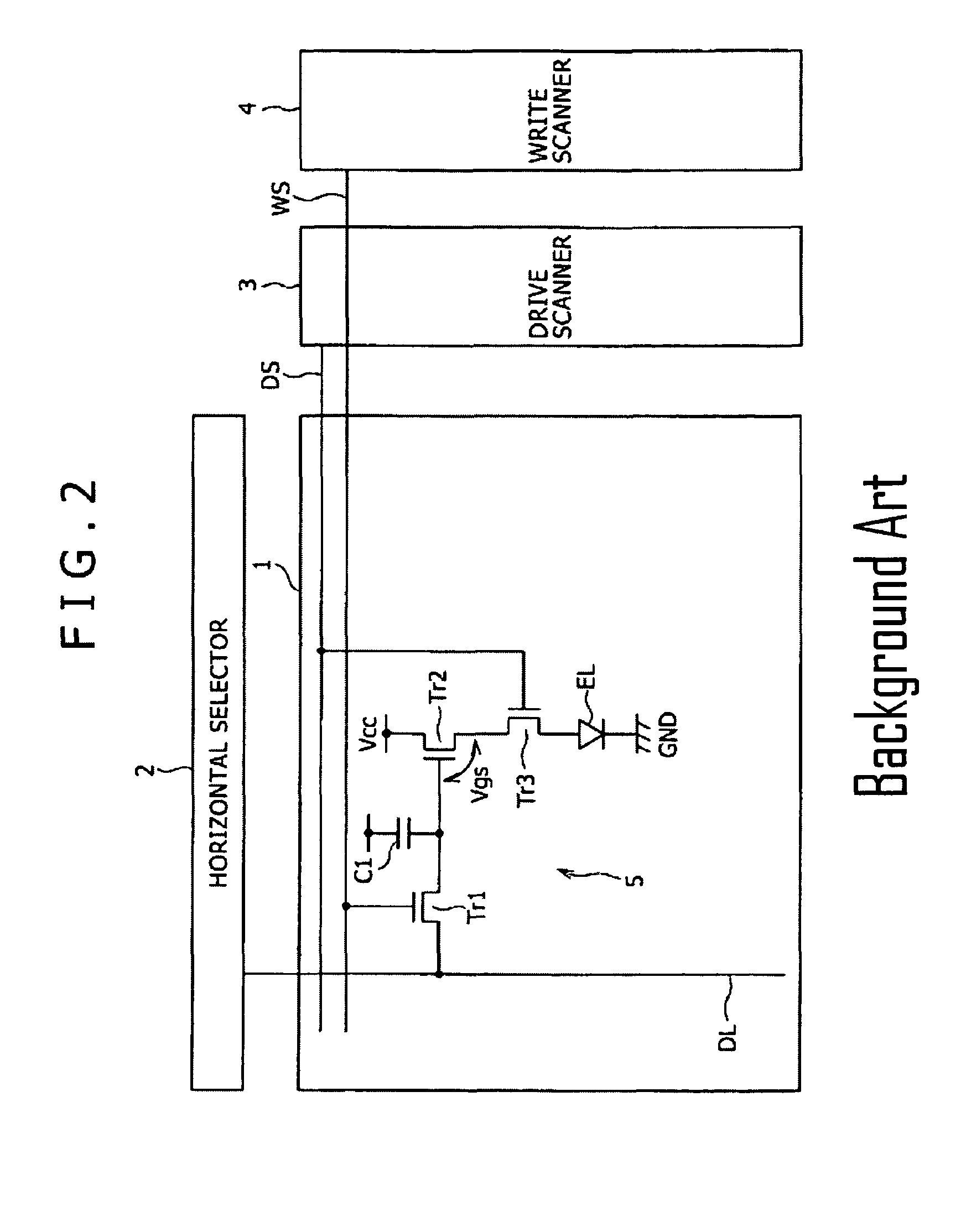

Pixel circuit, display device, driving method of pixel circuit, and driving method of display device

InactiveUS20060022907A1Increase brightnessLow mobilityStatic indicating devicesCapacitanceDriving current

A pixel circuit disposed at a part where a scanning line and a signal line intersect each other includes at least an electrooptic element, a drive transistor, a sampling transistor, and a retaining capacitance. The drive transistor has a gate connected to an input node, a source connected to an output node, and a drain connected to a predetermined power supply potential and supplies a driving current to the electrooptic element according to a signal potential retained in the retaining capacitance. The electrooptic element has one terminal connected to the output node and another terminal connected to a predetermined potential. The sampling transistor is connected between the input node and the signal line and operates when selected by the scanning line, samples an input signal from the signal line, and retains the input signal in the retaining capacitance. The retaining capacitance is connected to the input node. The pixel circuit further includes a compensating circuit which detects a decrease in the driving current from a side of the output node, and feeds back a result of detection to a side of the input node, for compensating for a decrease in the driving current which decrease is attendant on a secular change of the drive transistor.

Owner:SONY CORP

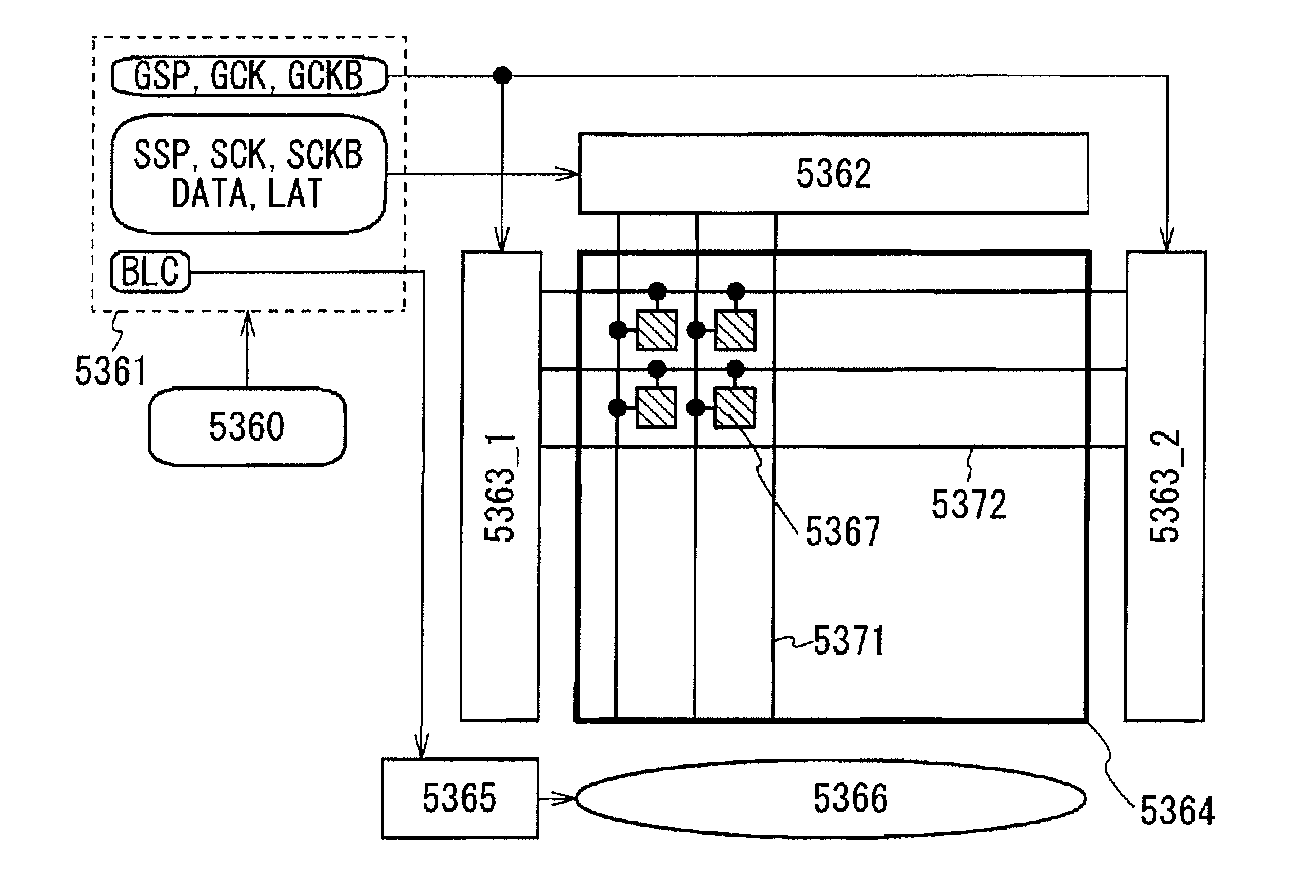

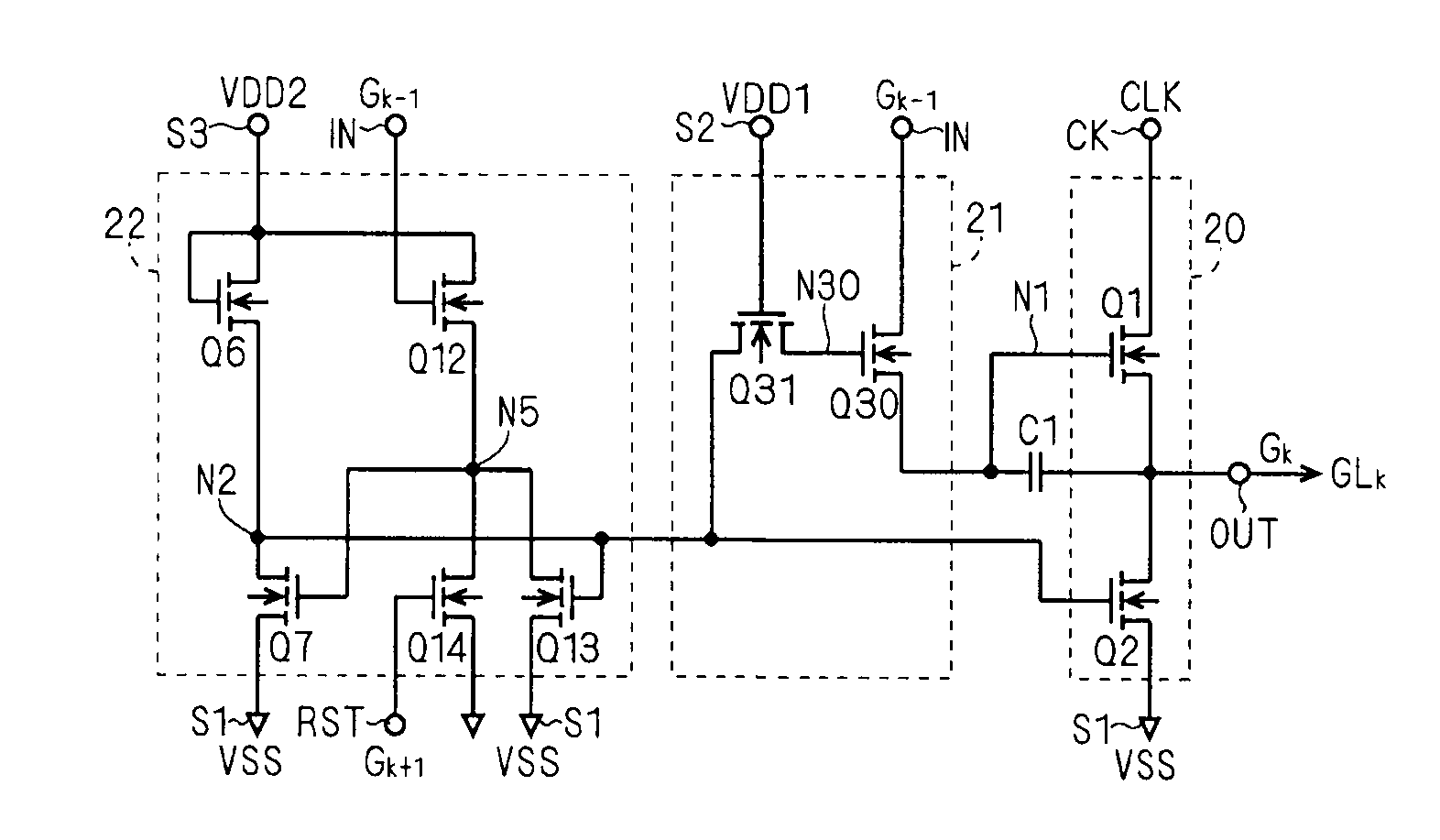

Display device and electronic device including the same

ActiveUS20100134396A1Reduce in quantityReduce parasitic capacitanceTransistorStatic indicating devicesDisplay deviceCapacitor

It is an object to decrease the number of transistors connected to a capacitor. In a structure, a capacitor and one transistor are included, one electrode of the capacitor is connected to a wiring, and the other electrode of the capacitor is connected to a gate of the transistor. Since a clock signal is input to the wiring, the clock signal is input to the gate of the transistor through the capacitor. Then, on / off of the transistor is controlled by a signal which synchronizes with the clock signal, so that a period when the transistor is on and a period when the transistor is off are repeated. In this manner, deterioration of the transistor can be suppressed.

Owner:SEMICON ENERGY LAB CO LTD

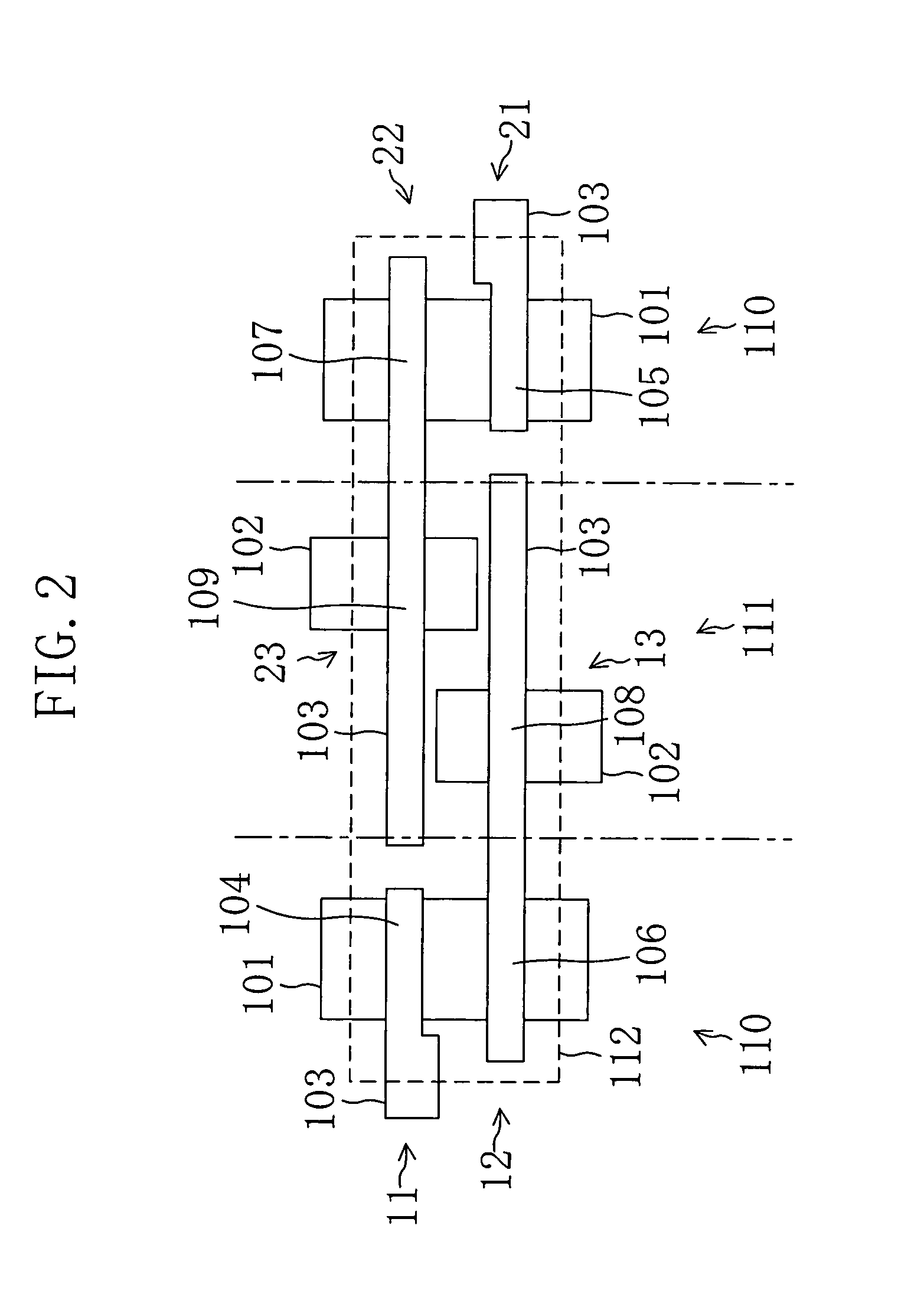

Nonvolatile semiconductor storage device and method for manufacturing the same

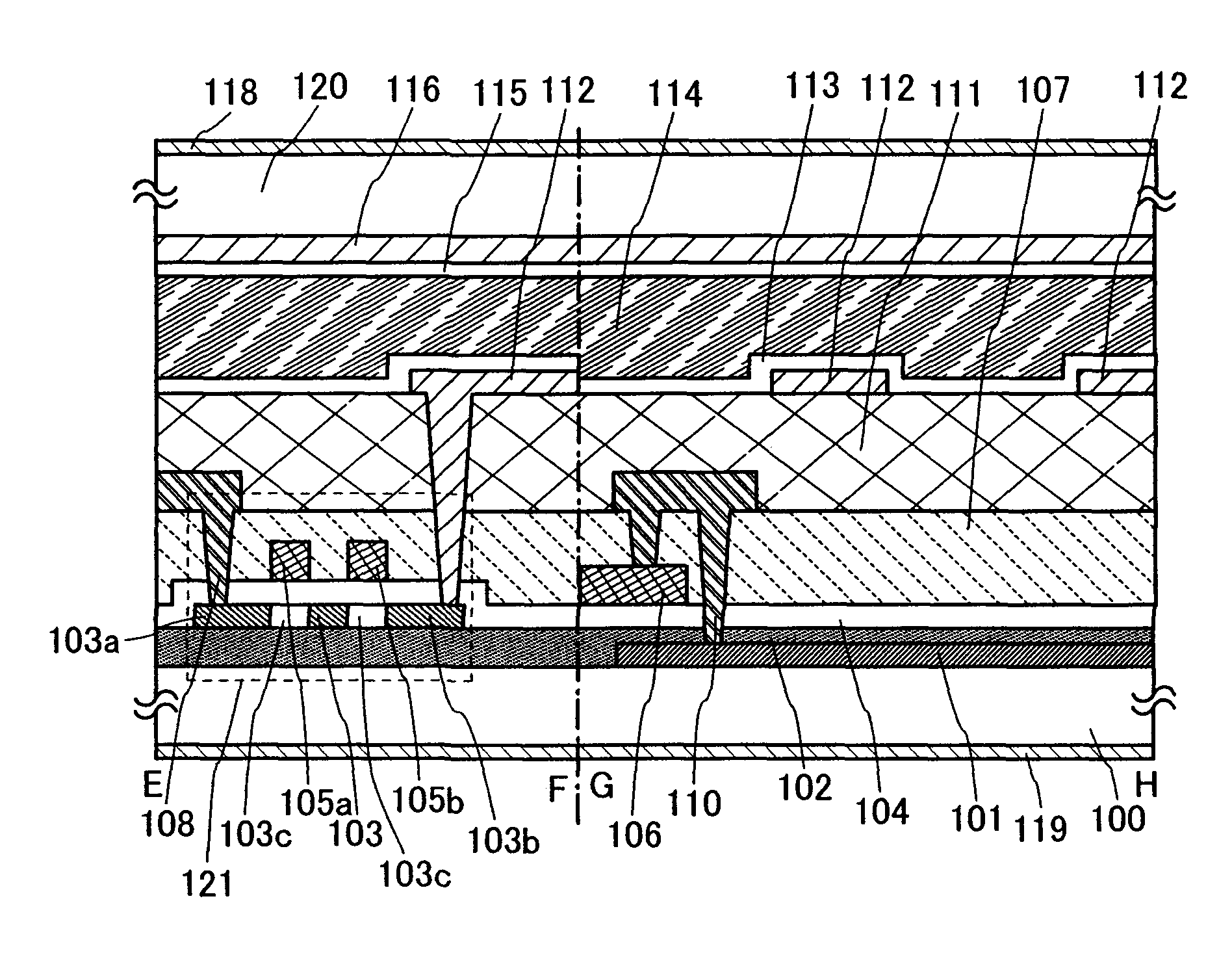

InactiveUS20070228452A1Reduce etch timeEtching of the semiconductor layer is suppressedTransistorSolid-state devicesElectrical resistance and conductanceCharge retention

It is an object to provide a nonvolatile semiconductor storage device that prevents increase in a contact resistance value due to etching of a semiconductor layer when etching an interlayer insulating film and that has superiority in a writing characteristic and an electric charge-holding characteristic, and a manufacturing method thereof. A conductive layer is provided between a source or drain region and a source or drain wiring. The conductive layer is made of the same conductive layer that forms a control gate electrode. An insulating film is provided so as to cover the conductive layer, and the insulating film has a contact hole for exposing part of the conductive layer. The source or drain wiring is formed so that the contact hole is filled.

Owner:SEMICON ENERGY LAB CO LTD

Liquid crystal display device and semiconductor device

InactiveUS7816682B2Total current dropReduced drive capability requirementsNon-linear opticsSemiconductor devicesLiquid-crystal displaySemiconductor

By increasing an interval between electrodes which drives liquid crystals, a gradient of an electric field applied between the electrodes can be controlled and an optimal electric field can be applied between the electrodes. The invention includes a first electrode formed over a substrate, an insulating film formed over the substrate and the first electrode, a thin film transistor including a semiconductor film in which a source, a channel region, and a drain are formed over the insulating film, a second electrode located over the semiconductor film and the first electrode and including first opening patterns, and liquid crystals provided over the second electrode.

Owner:SEMICON ENERGY LAB CO LTD

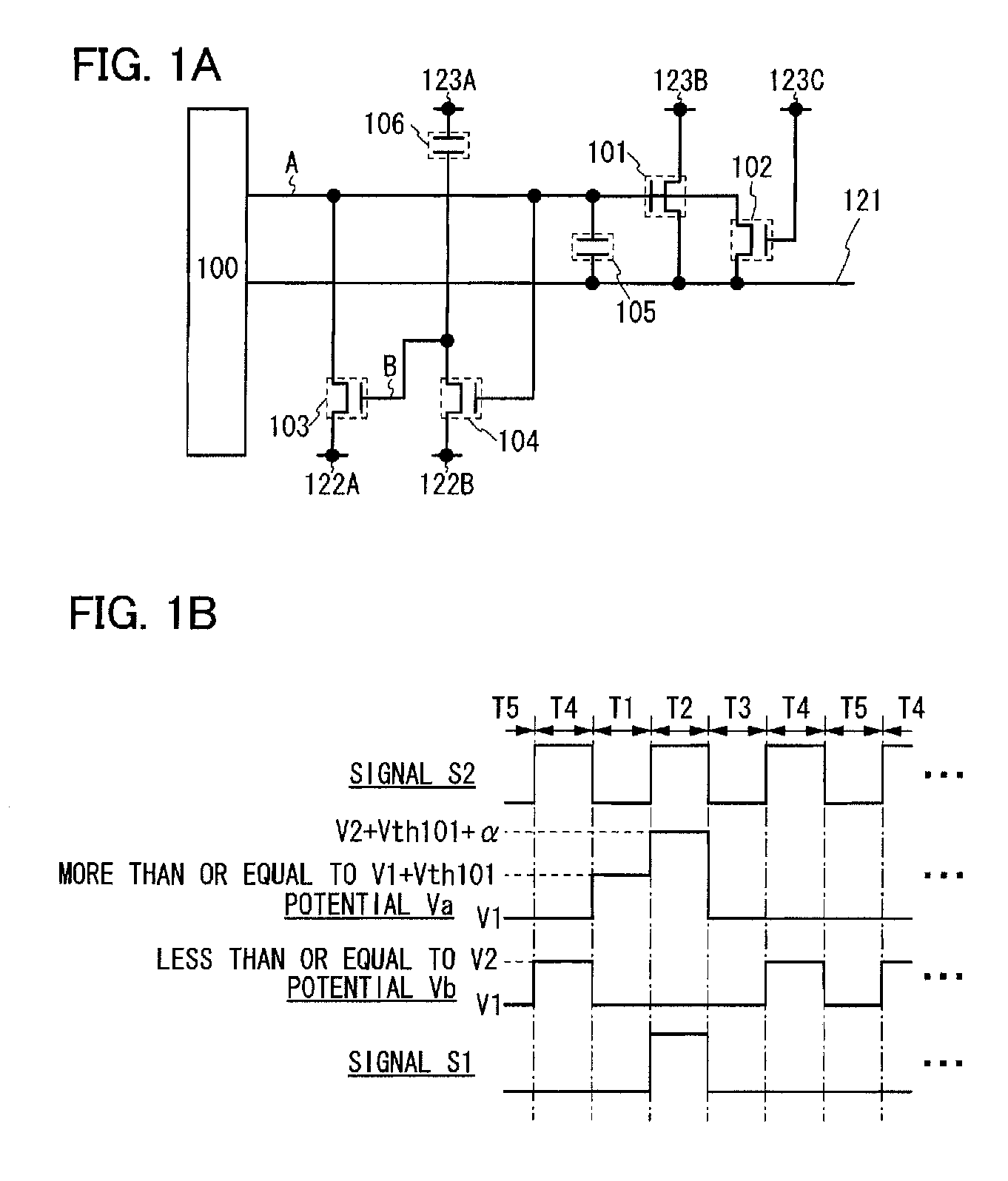

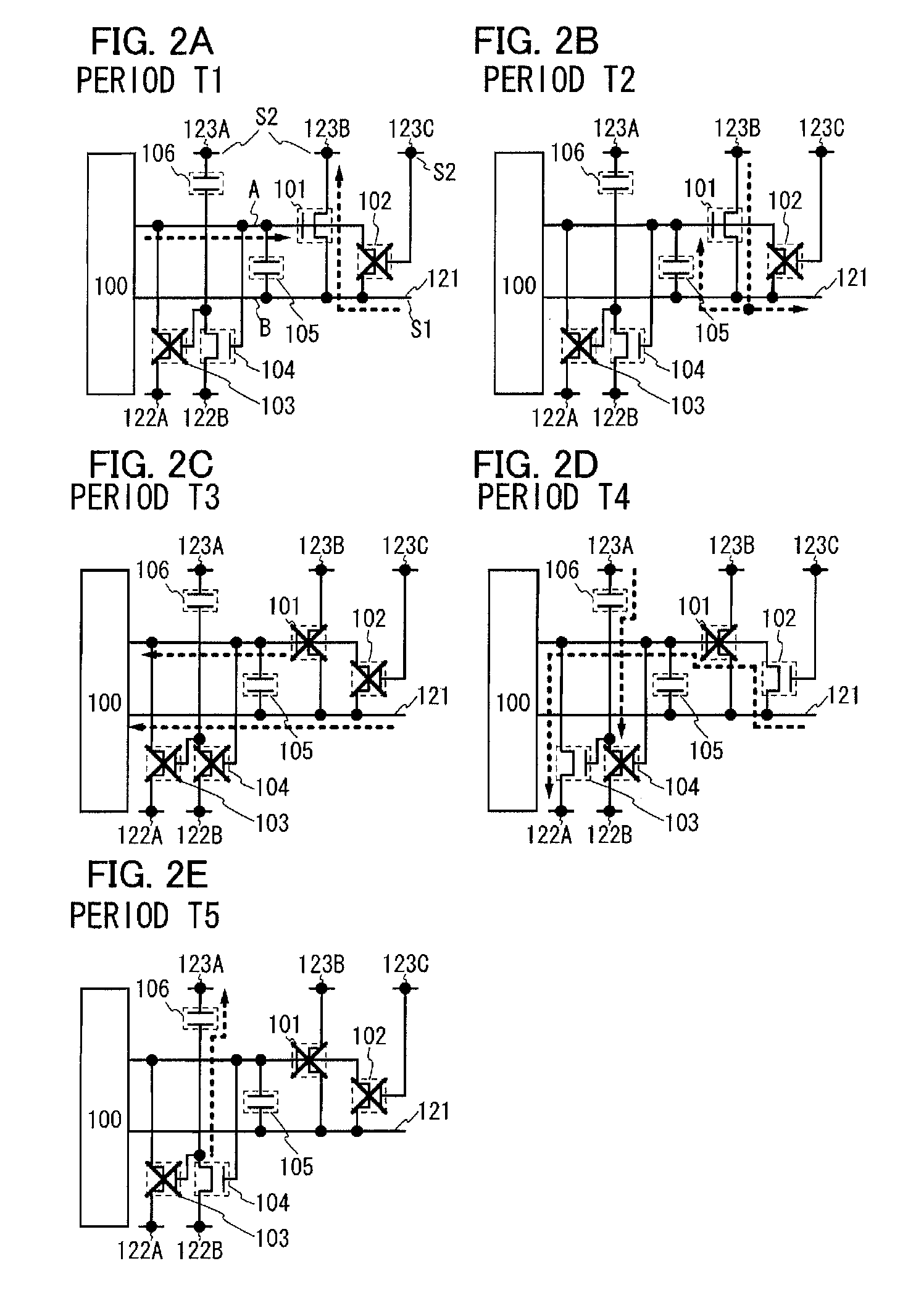

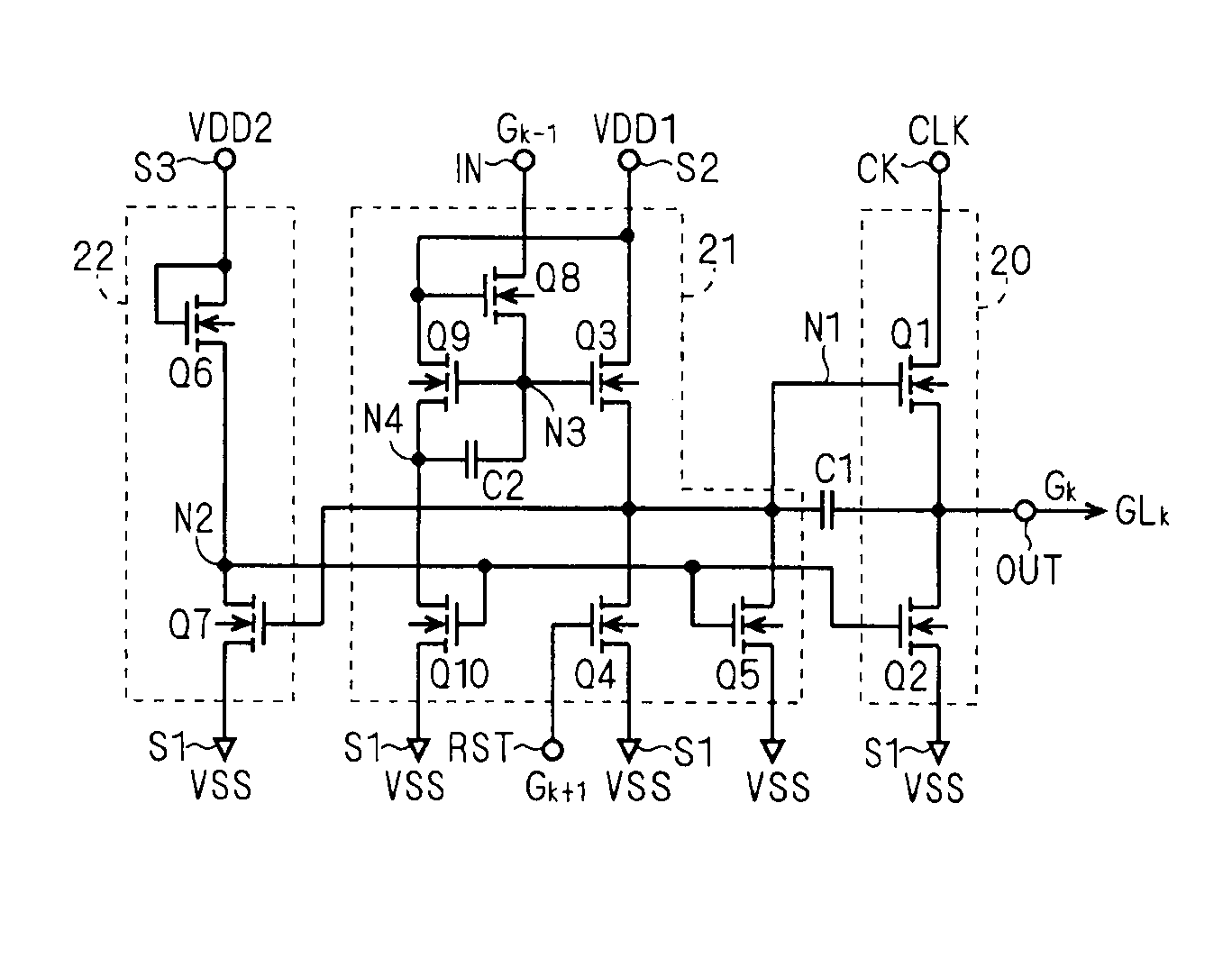

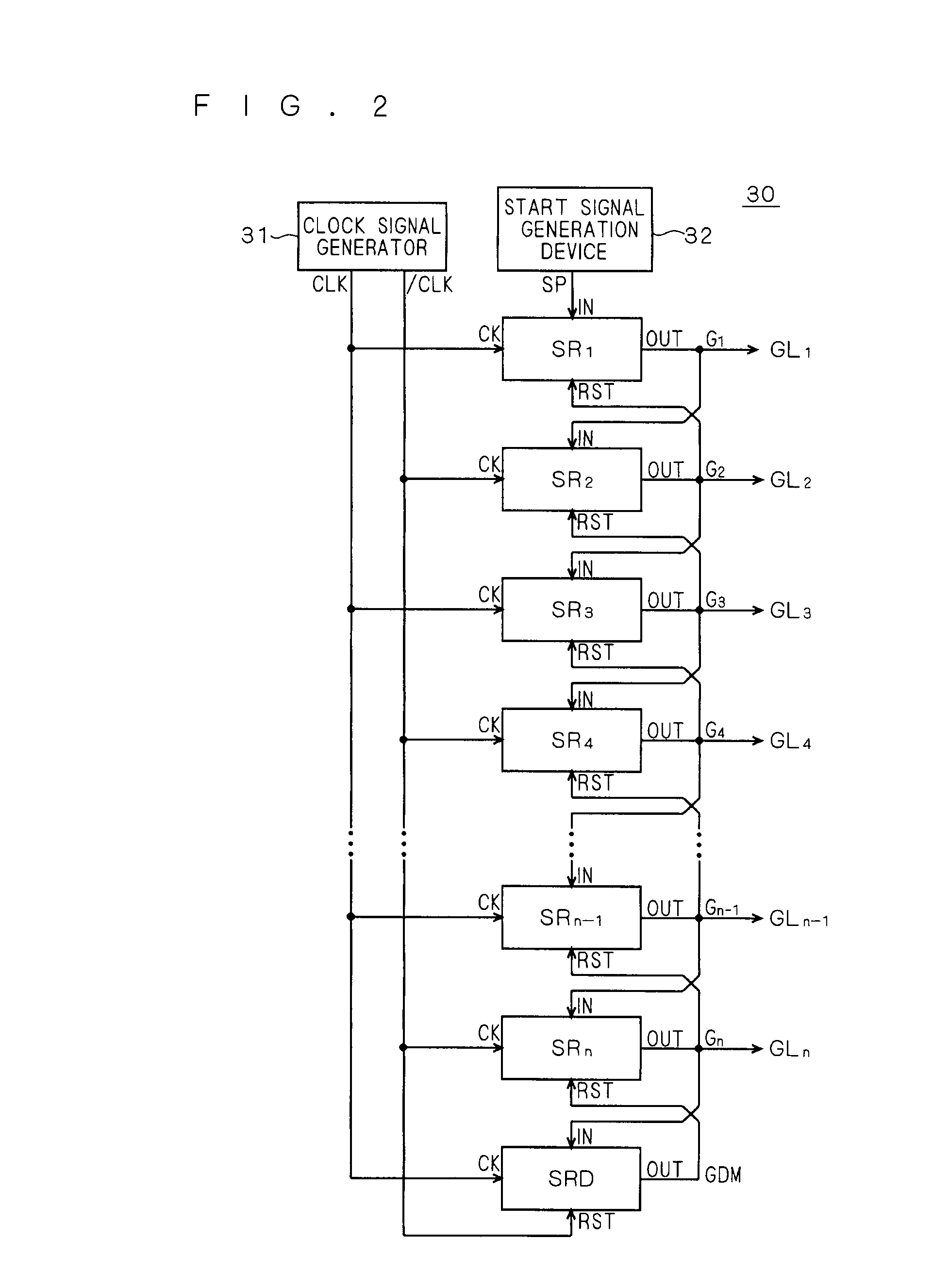

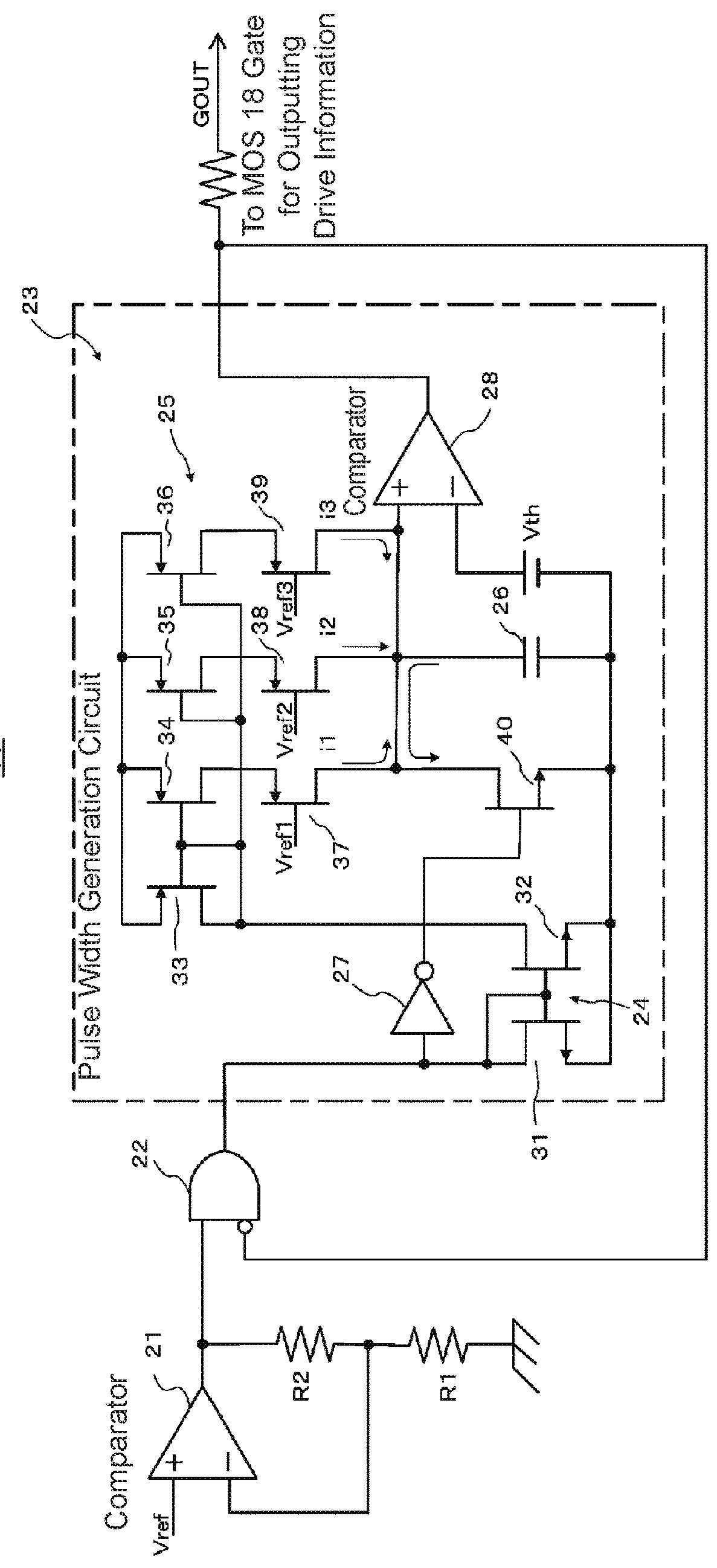

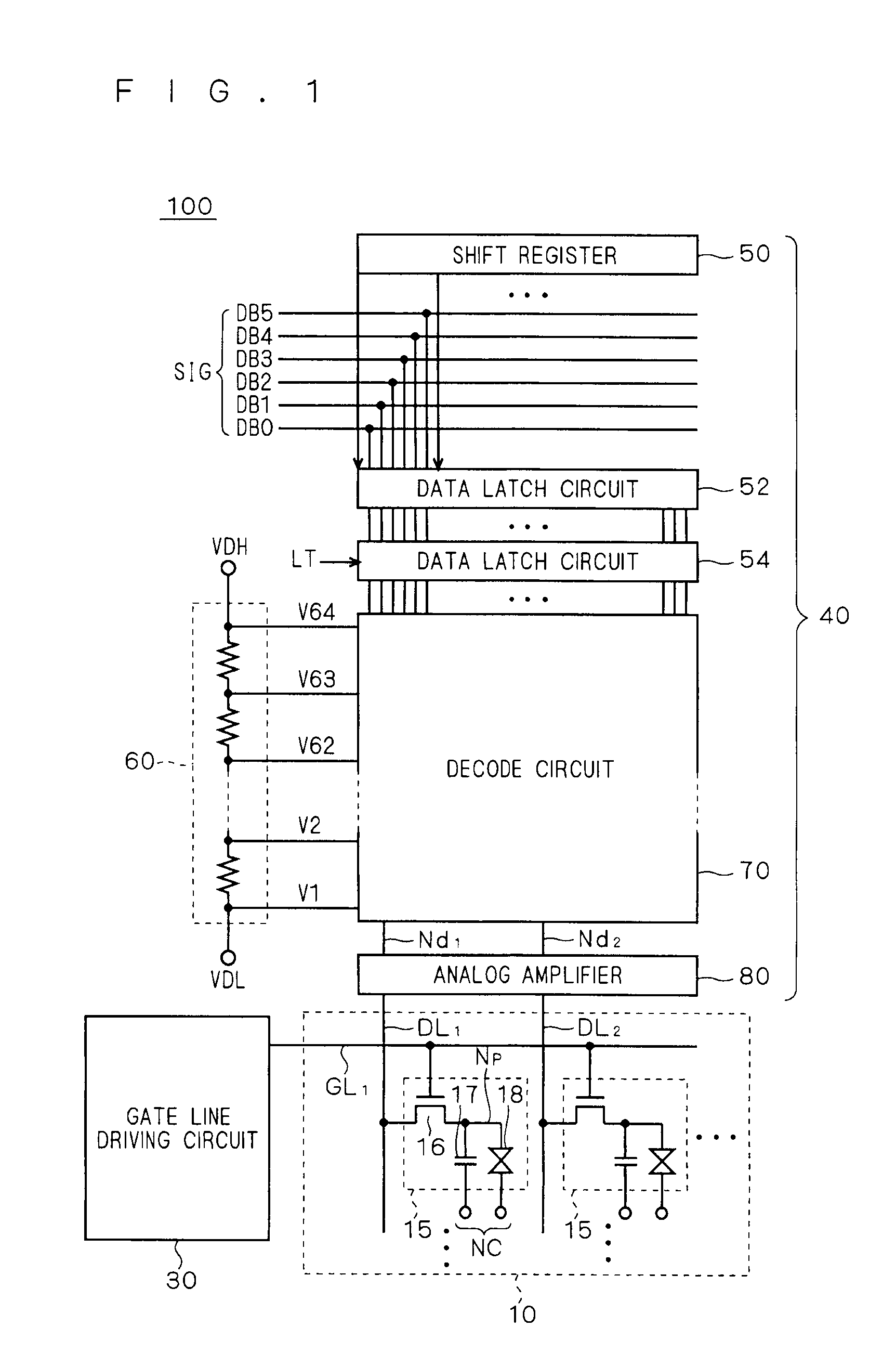

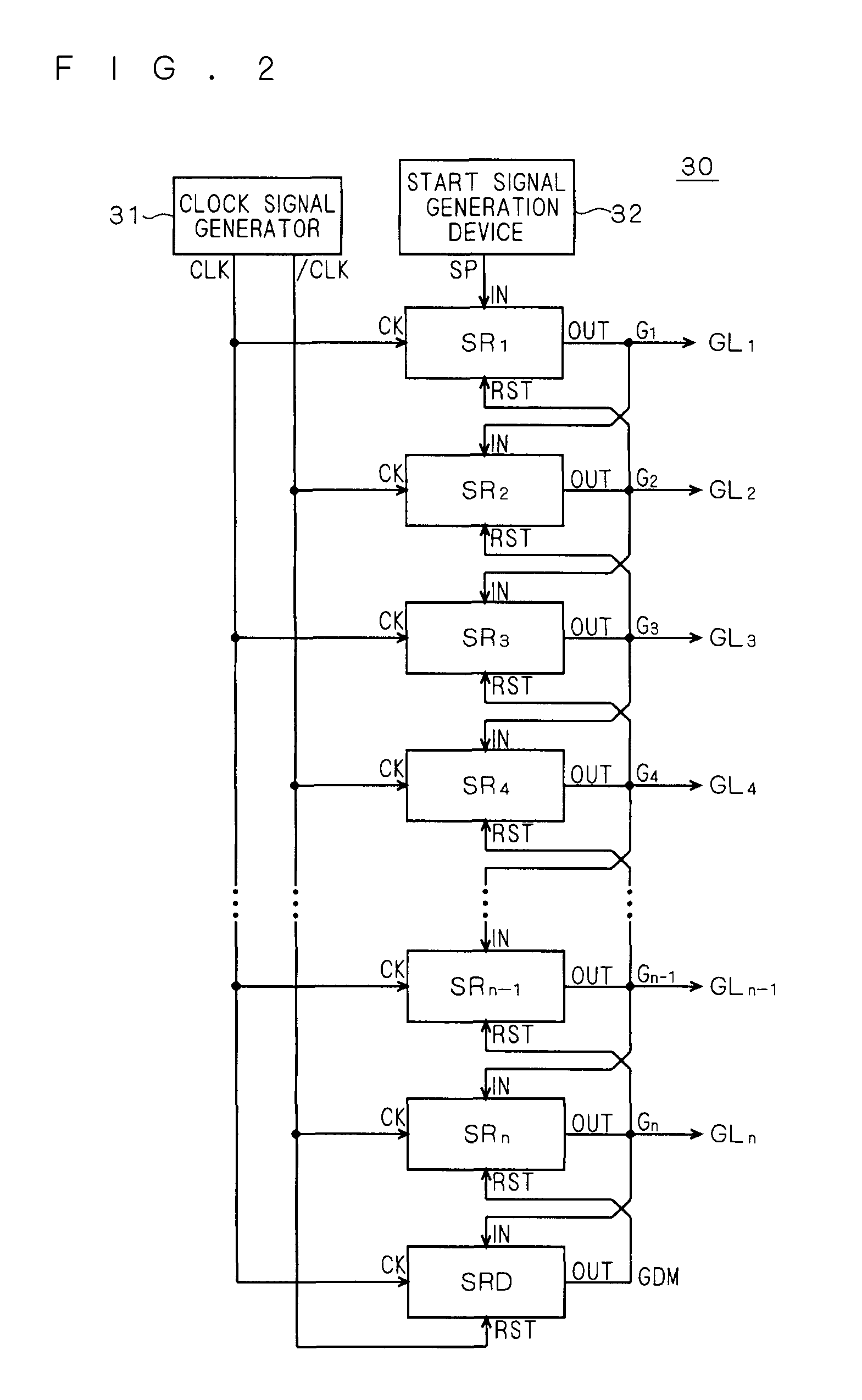

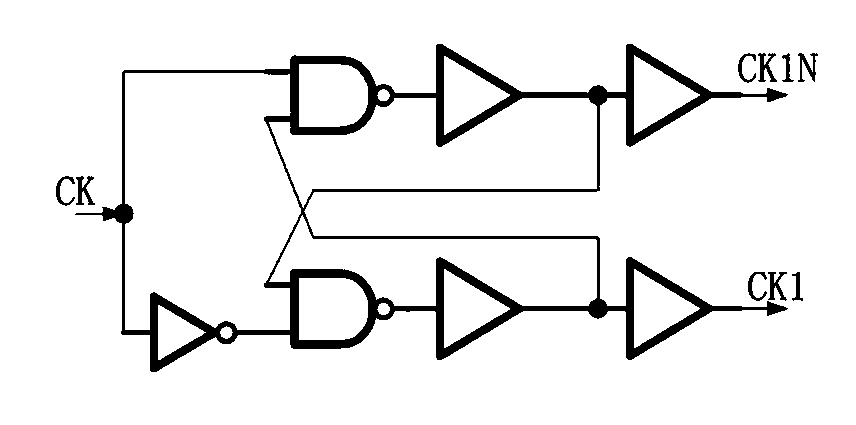

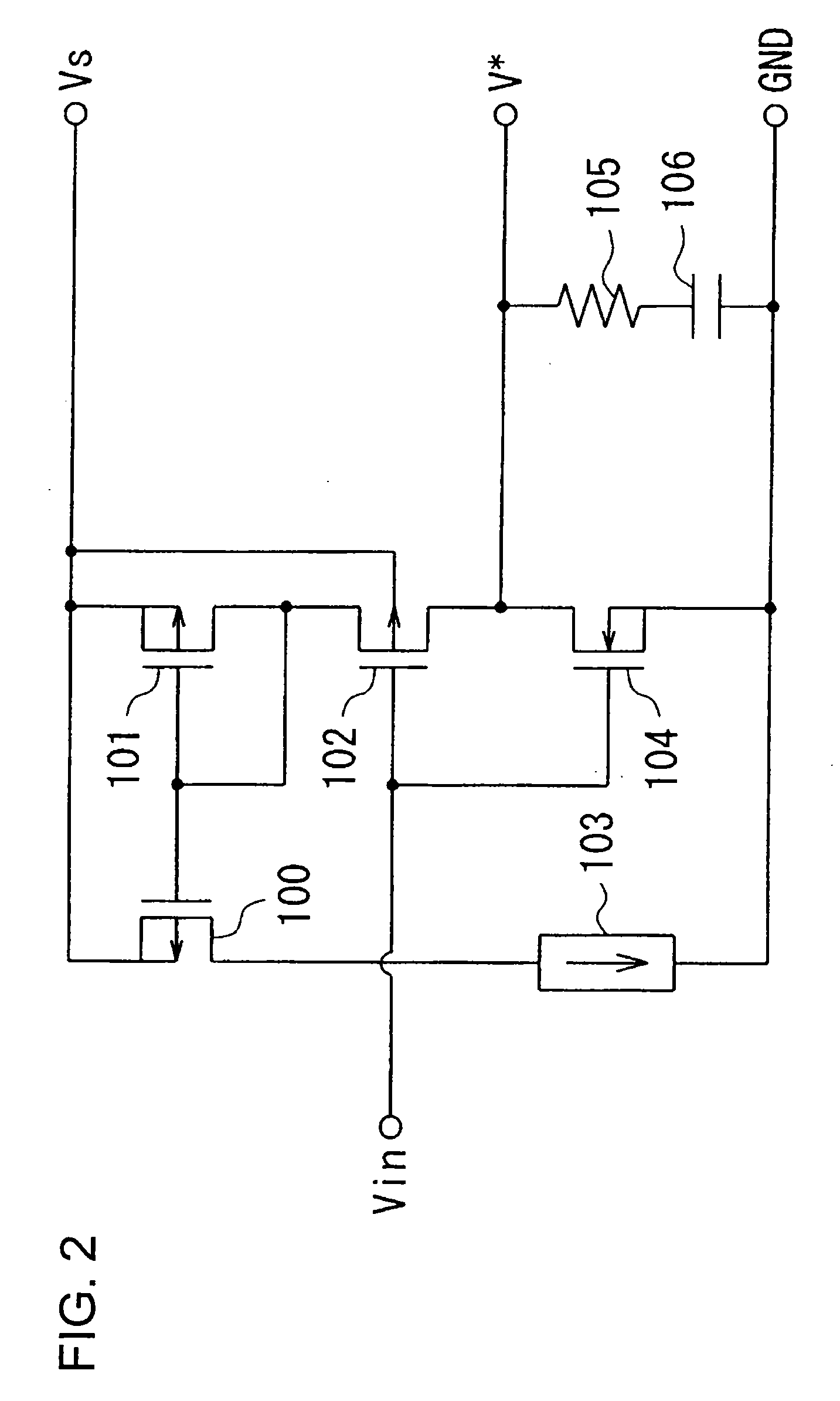

Shift register circuit

ActiveUS20100111245A1Reduced drive capability requirementsLower capability requirementsDigital storageDriver circuitCapacitance

A shift register circuit is provided that can suppress a decrease in a drive capability when a frequency of a clock signal increases. A unit shift register includes a first transistor for supplying a clock signal to an output terminal, a pull-up driving circuit for driving the first transistor, a second transistor for discharging the output terminal, and a pull-down driving circuit for driving the second transistor. In the pull-up driving circuit, the gate of a third transistor charging the gate of the first transistor is charged in accordance with activation of an output signal of preceding stage, and the potential at the gate of the third transistor is increased with a capacitive element. As a result, the third transistor operates in the non-saturated region.

Owner:TRIVALE TECH

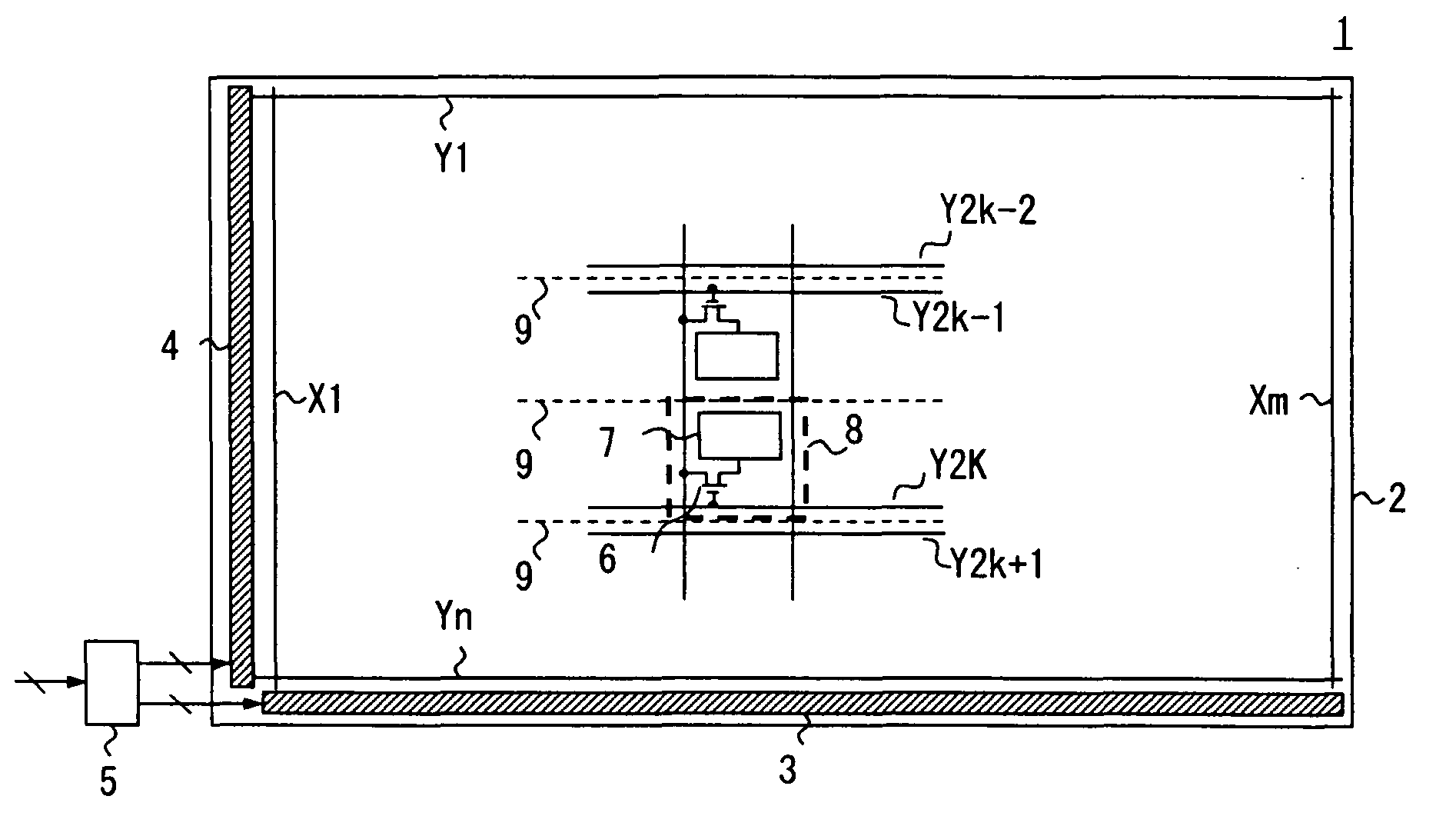

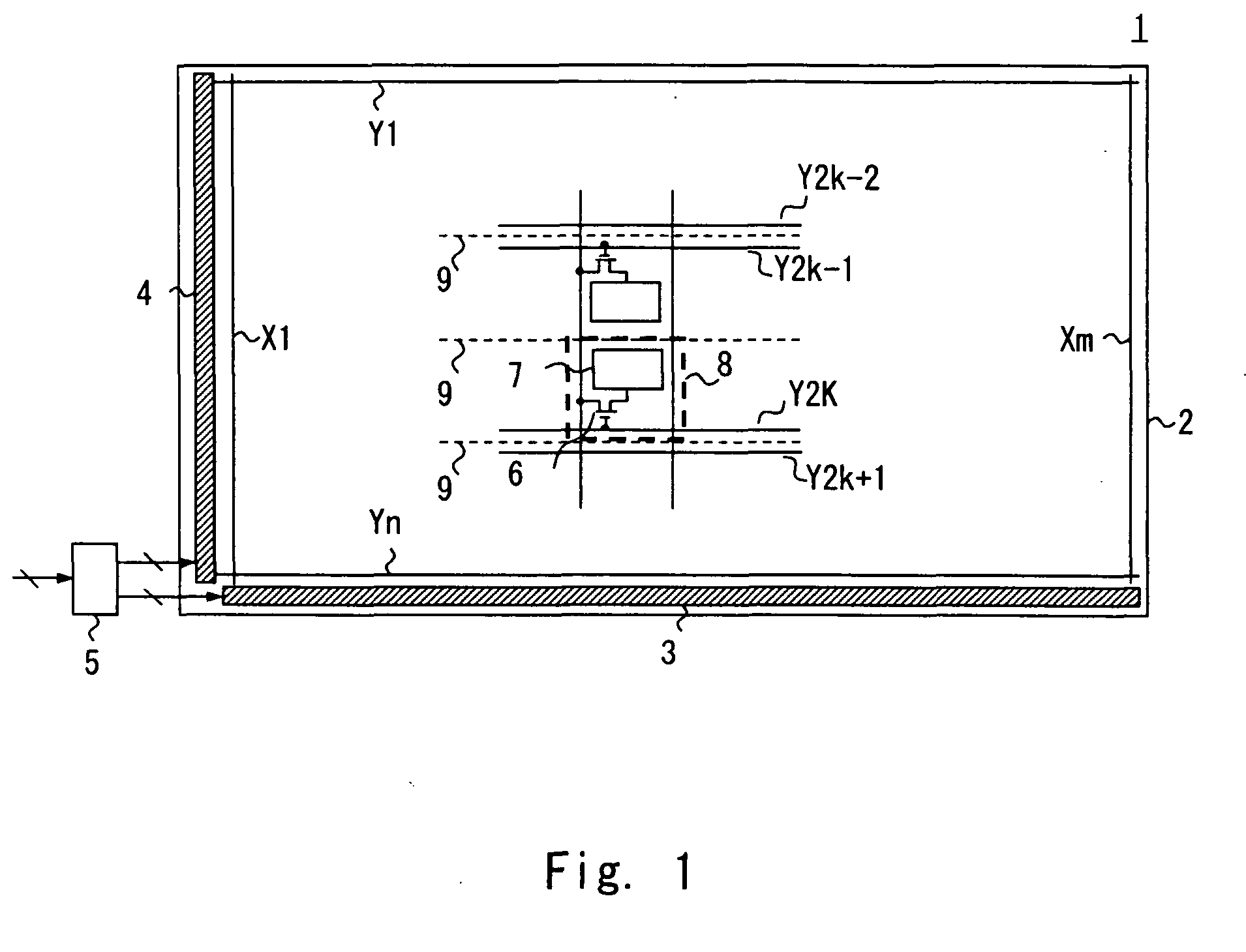

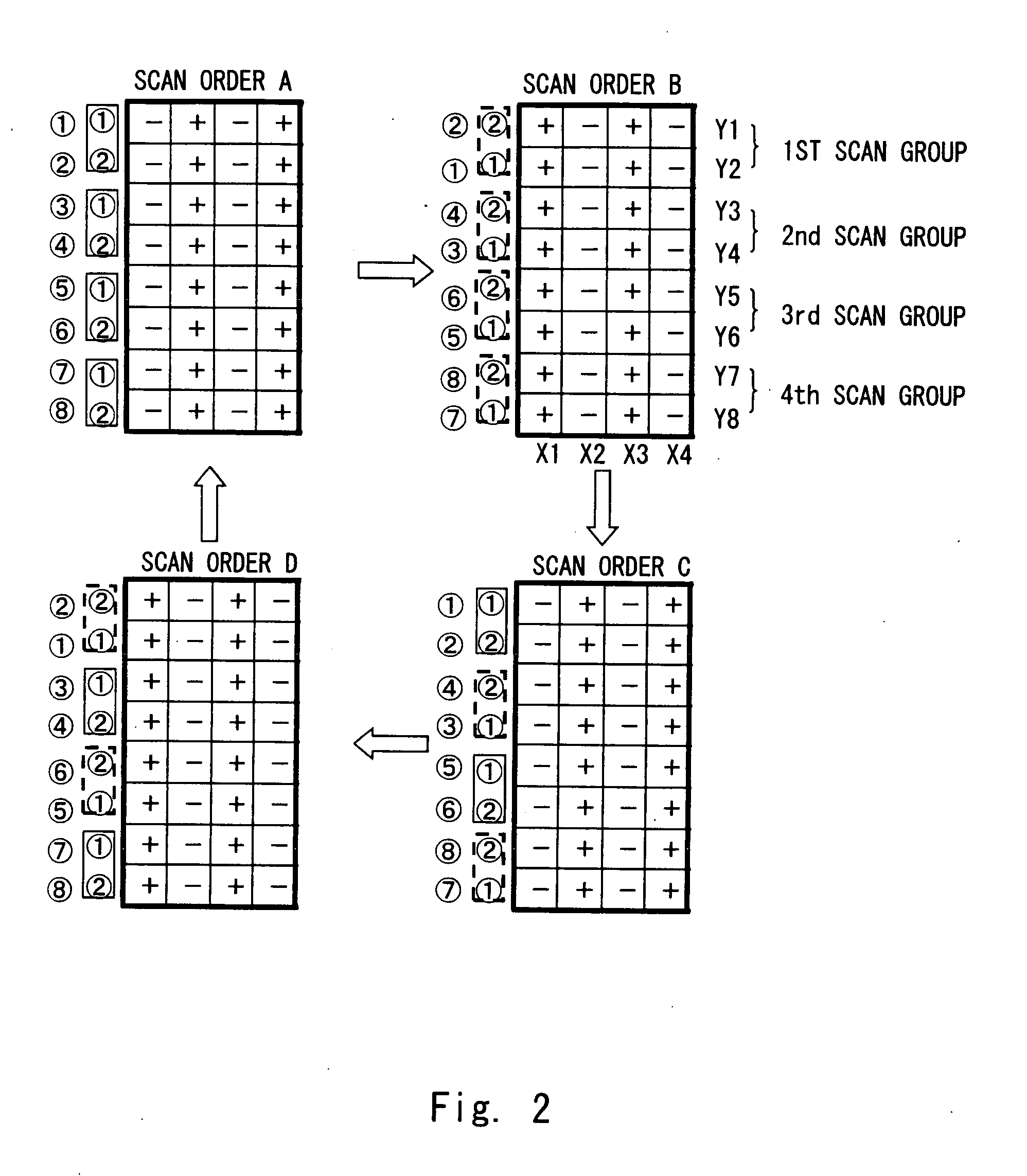

Display panel driving method, gate driver, and display apparatus

InactiveUS20100315402A1Reduce image qualityReduced drive capability requirementsCathode-ray tube indicatorsNon-linear opticsScan lineElectrical polarity

A method of driving a display panel in which a voltage polarity reverse cycle of a data signal is three or more scan periods, and multiple scan lines are driven by switching between a first and a second scan orders by a predetermined period. The method includes setting a display pattern as a first maximum current pattern, the display pattern in which the multiple scan lines are driven in the first scan order and a number of charge and discharge of the data signal becomes a maximum number, and specifying that the number of charge and discharge of the data signal when displaying the first maximum current pattern in the second scan order is to be ½ of that of the data signal when displaying the first maximum current pattern in the first scan order. Further, the voltage polarity reverse cycle for specifying the first and the second scan orders is one frame period.

Owner:RENESAS ELECTRONICS CORP

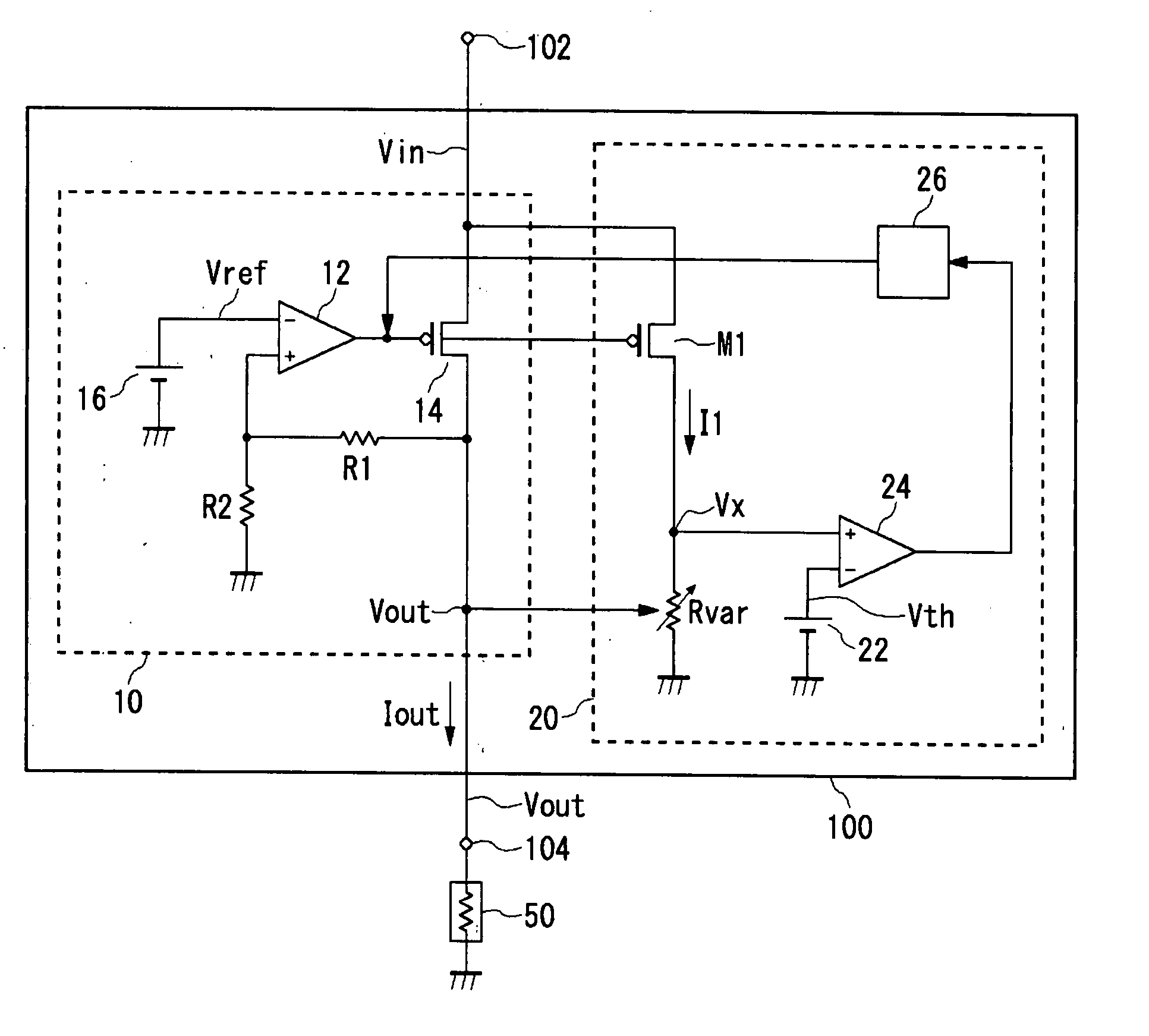

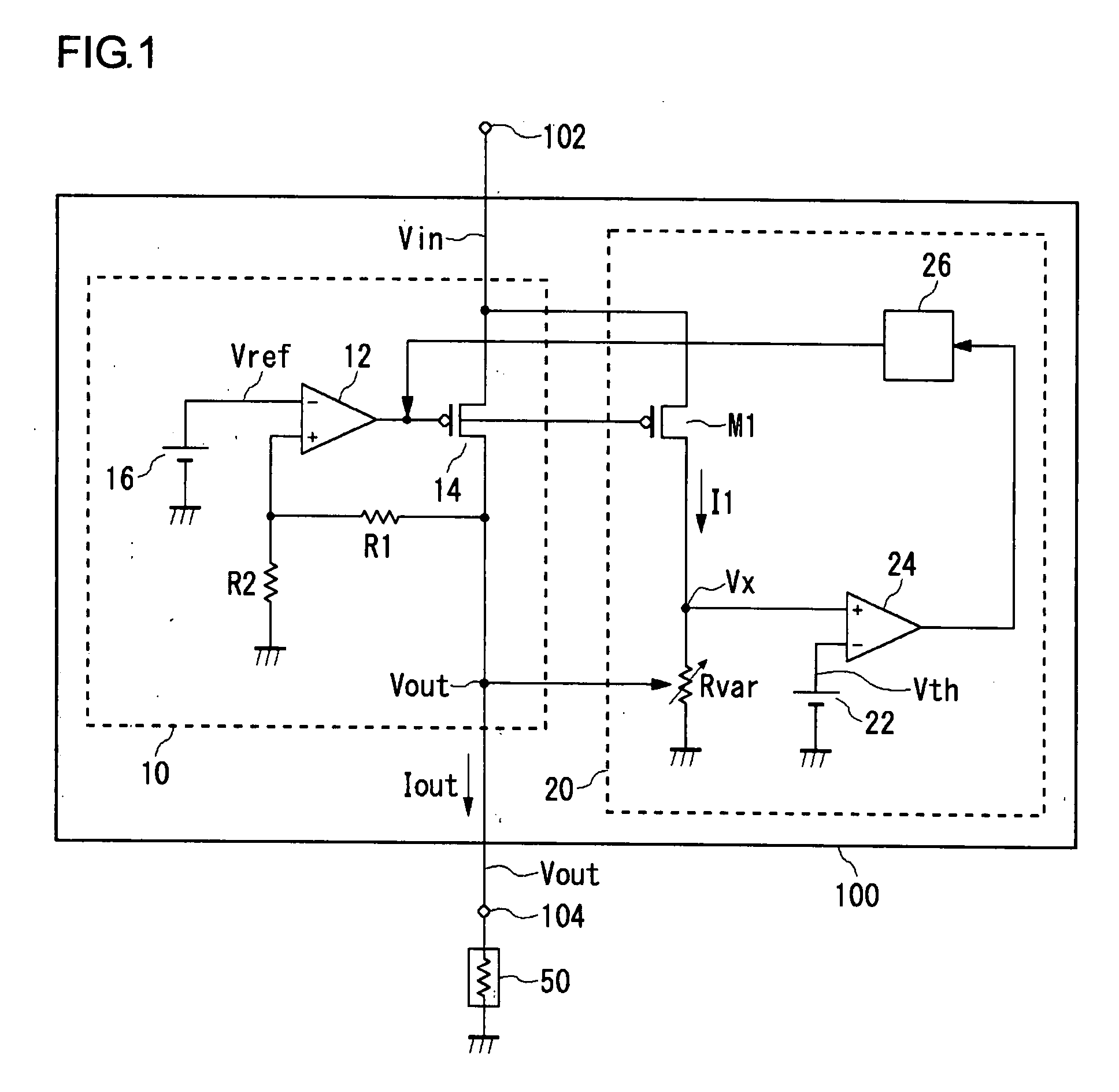

Circuit Protection Method, Protection Circuit and Power Supply Device Using The Protection Circuit

InactiveUS20070206338A1Simple structureReduced drive capability requirementsEmergency protective arrangements for limiting excess voltage/currentElectric variable regulationAudio power amplifierVoltage regulation

An excess current protection circuit which can change a limited current corresponding to an output voltage by simple constitution. A power supply device (100) is provided with a regulator (10), which regulates the output voltage to be constant based on a reference voltage, and an excess current protection circuit (20). The regulator (10) is a general three-terminal regulator which includes an output transistor (14), an error amplifier (12) and resistors (R1, R2). The excess current protection circuit (20) detects an output current (lout) by a first transistor (M1), and converts it into a voltage by a variable resistor (Rvar). A voltage comparator (24) compares the voltage with a threshold voltage (Vth) corresponding to a limited current and detects an excess current status. A current adjusting circuit (26) drops driving performance of the regulator (10) when the excess current status is detected, and protects the circuit. The resistance value of the variable resistor (Rvar) is set based on an output voltage (Vout), and a value of the limited current is changed corresponding to the output voltage.

Owner:ROHM CO LTD

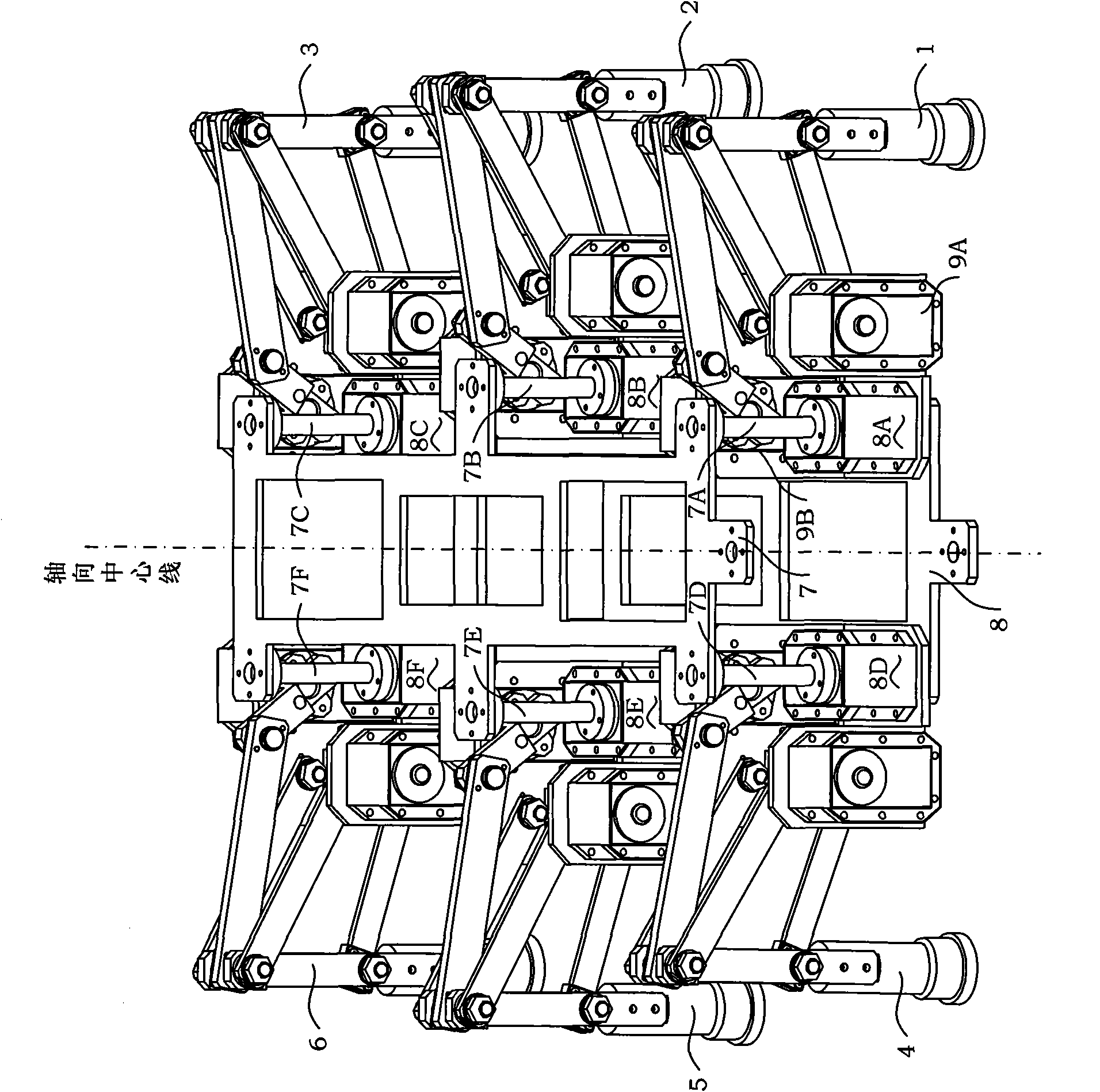

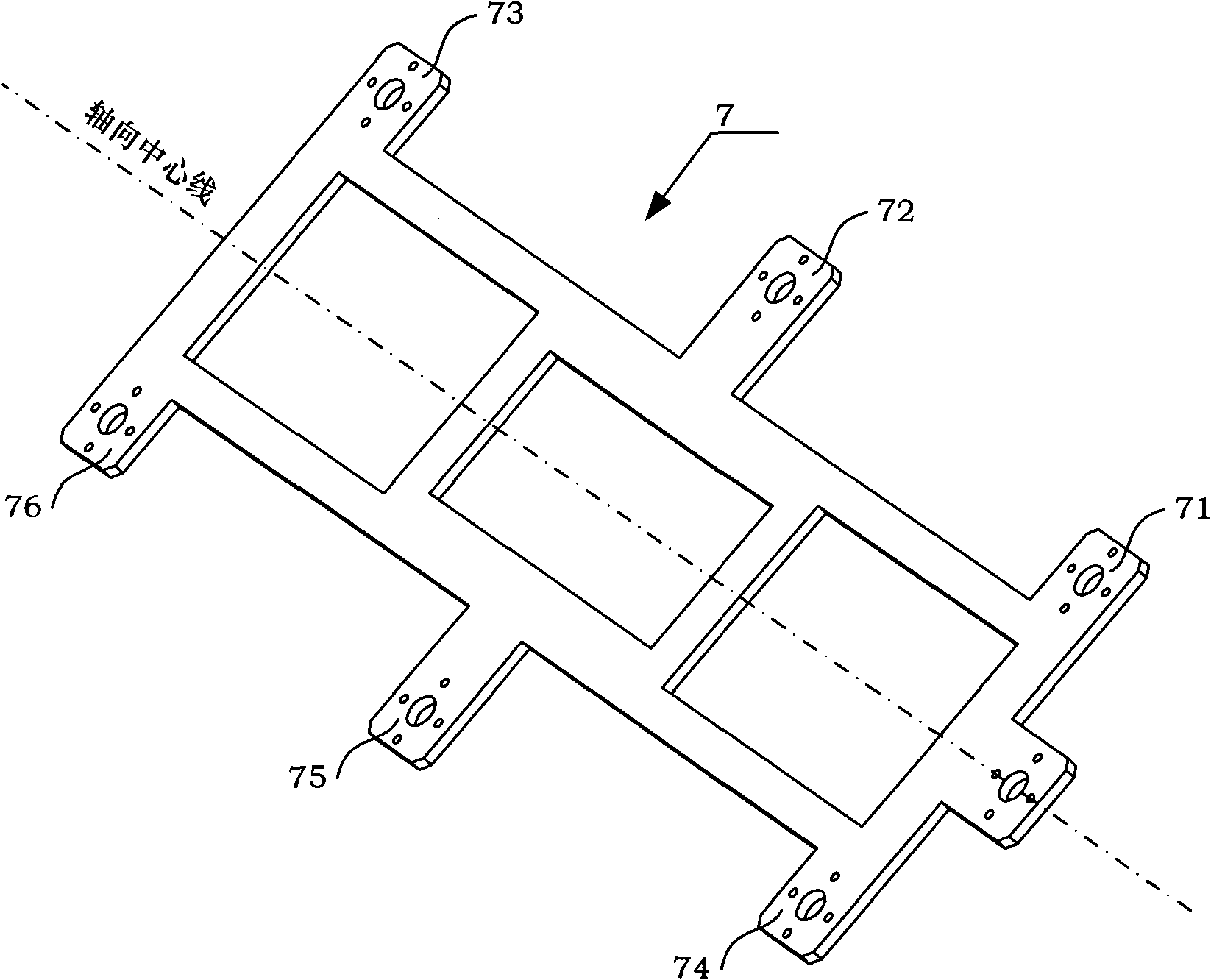

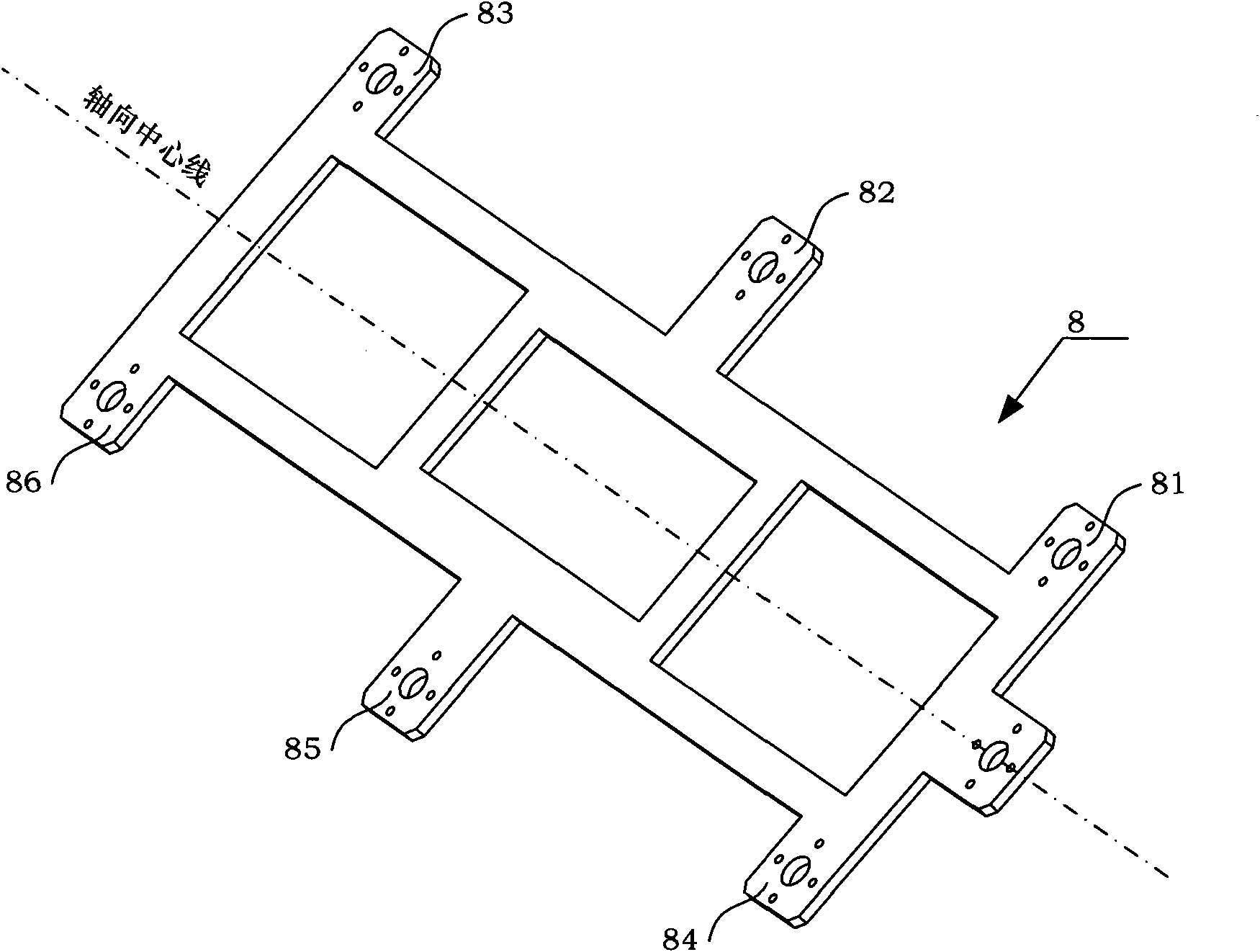

Bionic cockroach robot based on double-four link mechanism

InactiveCN101850798AReduced drive capability requirementsIncrease load capacityVehiclesTripod gaitGear drive

The invention discloses a bionic cockroach robot based on a double-four link mechanism; the robot comprises six groups of the same feet, and upper connecting plates and lower connecting plates used for connecting the feet together. The configuration of the feet adopts the double-four link mechanism, and three steering gears drive the double-four link mechanism to respectively simulate the motion of the hip, thigh and calf joints of a cockroach. The bionic cockroach robot advances in a tripod gait way so as to realize the tripod gait motion. In order to improve the bearing capability of the robot and simultaneously put the three steering gears on the feet so as to improve the rigidity and the stability of the whole robot, the invention uses the plane four-link mechanism in the design of the configuration of the feet, can achieve the amplification of force and motion, reduce the requirements on the driving capability of the steering gears, and improves the load capability of the robot. From the perspective of bionics, the bionic cockroach robot which adopts the multi-link structural design is reasonable.

Owner:BEIHANG UNIV

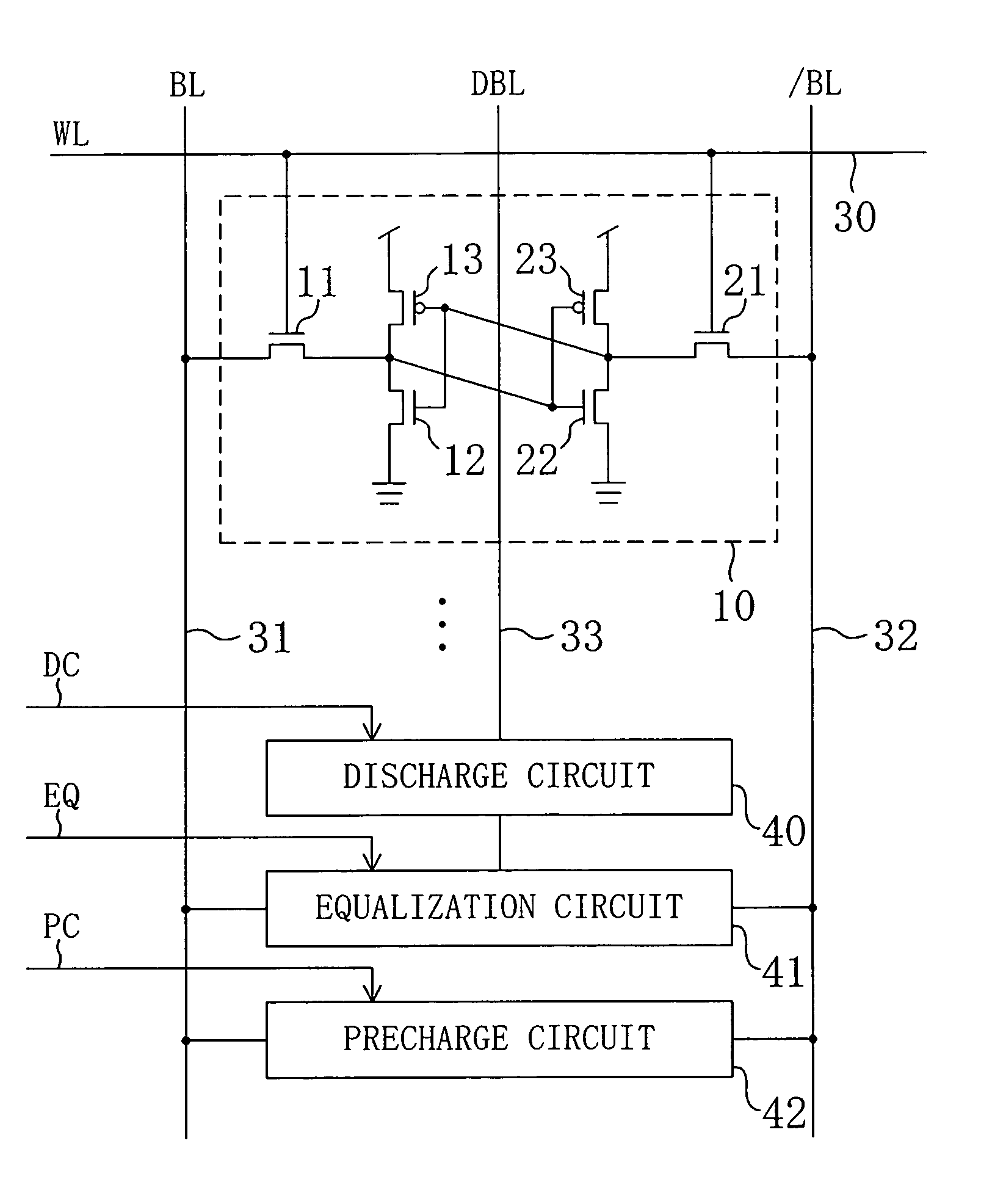

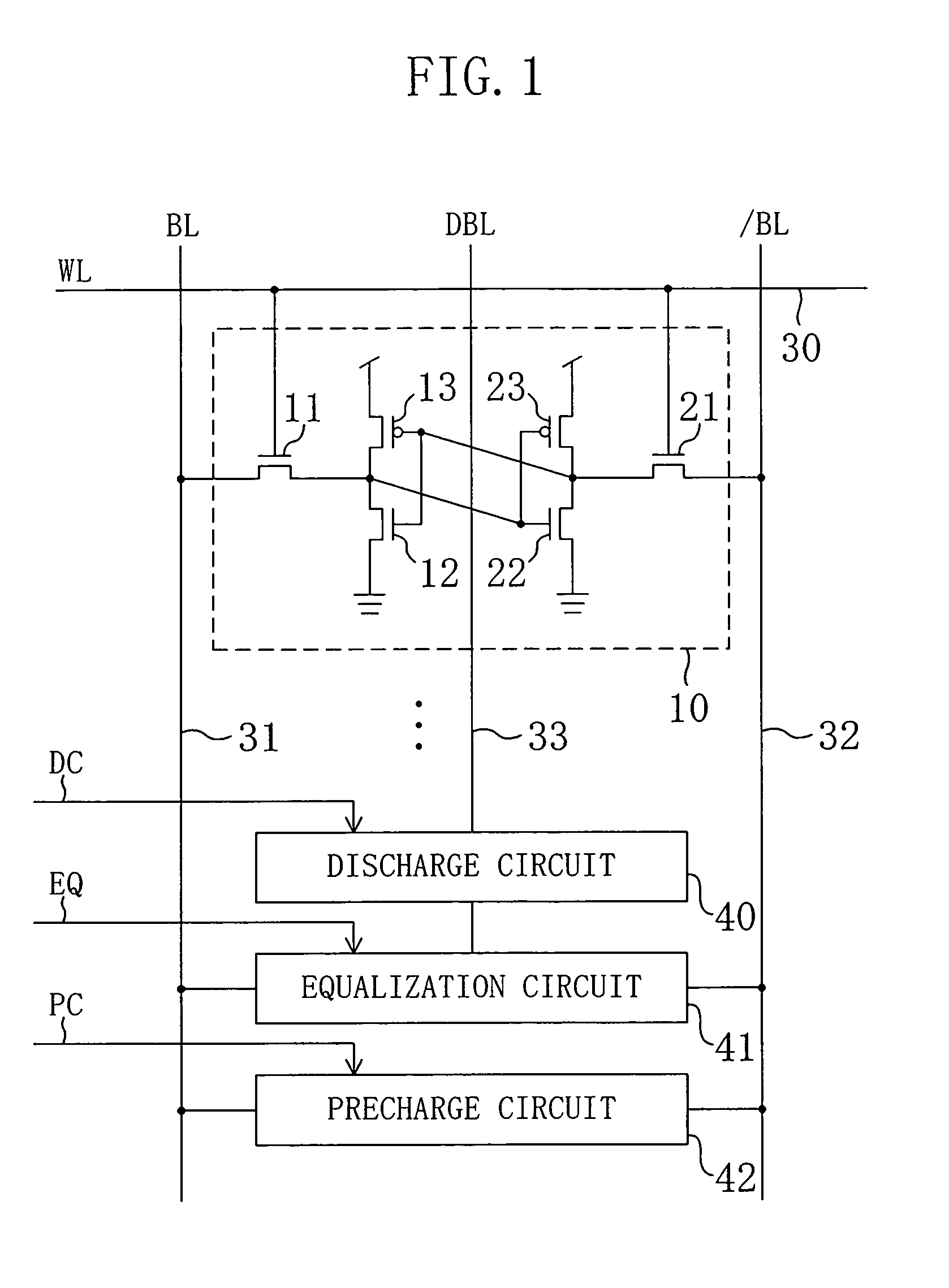

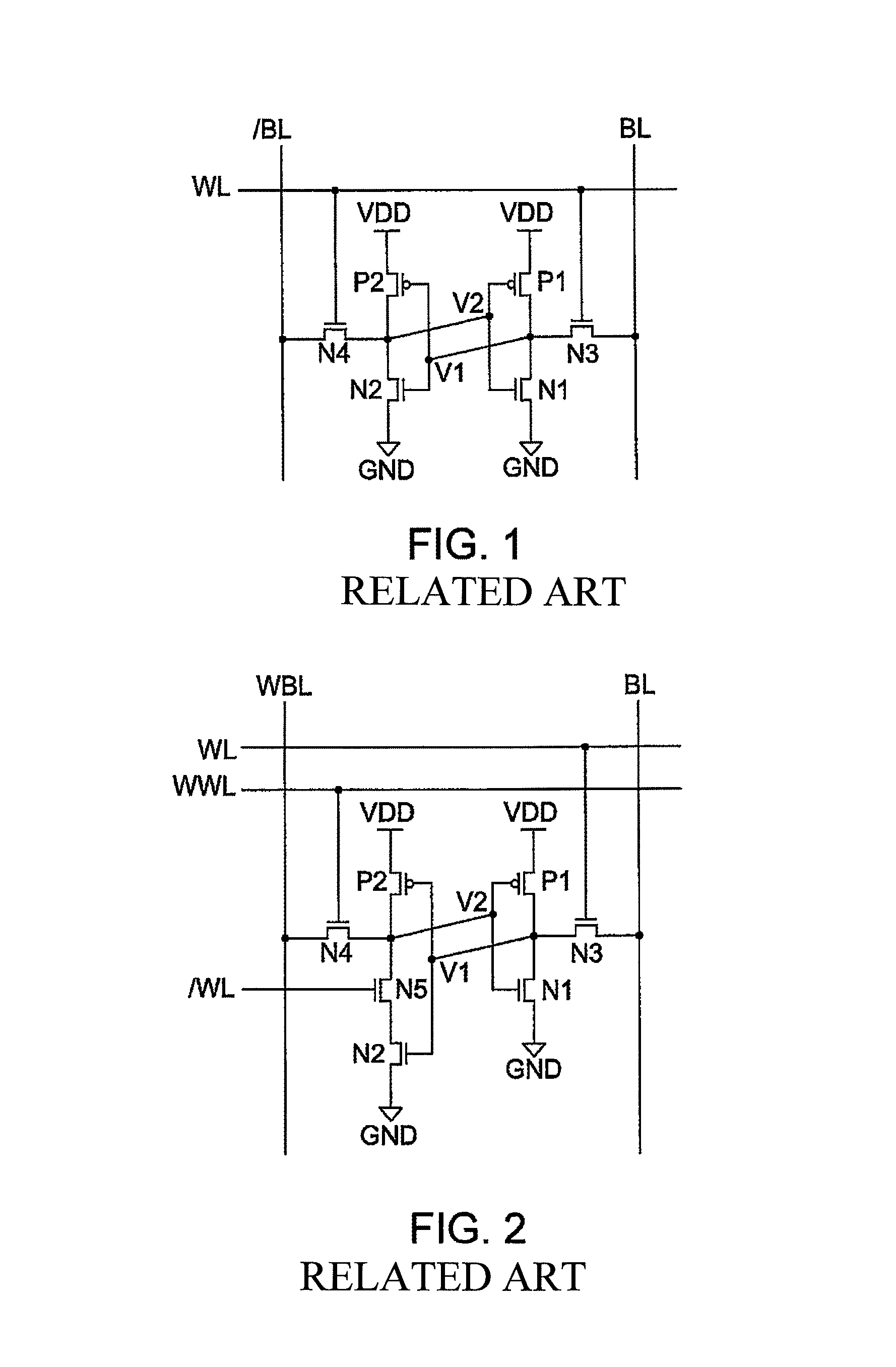

Semiconductor memory device

InactiveUS6982899B2Reduce voltageAvoid failureSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringStatic noise margin

A dummy bit line is provided between a pair of bit lines. The pair of bit lines is set at a power supply voltage and the dummy bit line is set at a ground voltage, and then the pair of bit lines and the dummy bit line are equalized. When a word line is activated in subsequent read operation, the pair of bit lines is at an intermediate potential lower than the power supply voltage, so that an apparent current drive capability of an access transistor decreases, and the static noise margin of a memory cell increases.

Owner:PANASONIC CORP

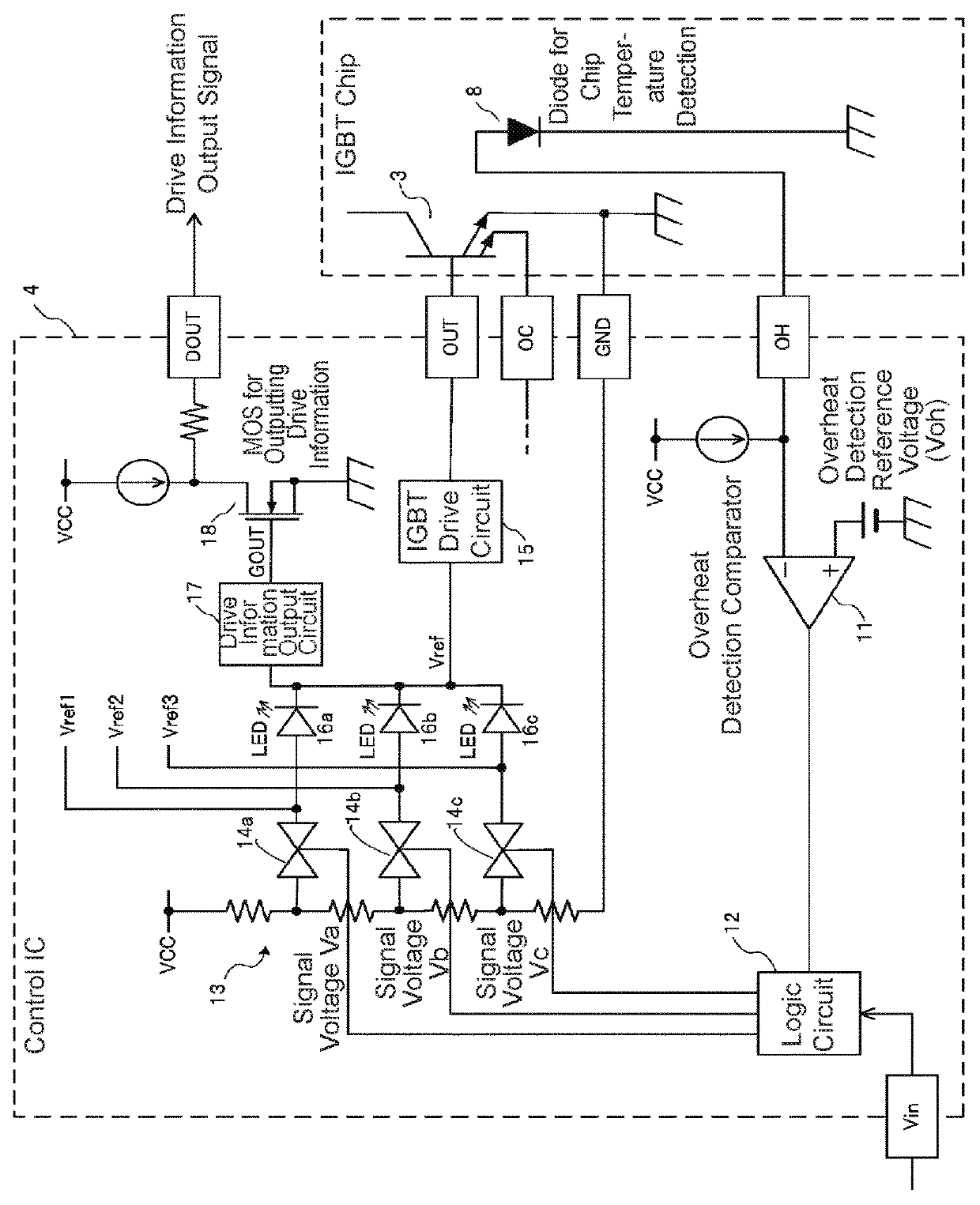

Drive device for semiconductor element

ActiveUS20180269867A1Curb risePrevent increase in switching lossElectronic switchingPower conversion systemsSemiconductor componentsThreshold temperature

A drive device for a semiconductor element includes a drive circuit receiving from outside a pulsed drive signal for driving ON / OFF of the semiconductor element; and a protection circuit receiving a signal representing a chip temperature of the semiconductor element and, when the detected chip temperature exceeds an overheating threshold temperature, controlling operation of the drive circuit so as to adjust a drive control voltage that is provided to the semiconductor element; and a drive information output circuit externally outputting drive information corresponding to the adjusted drive control voltage that is provided to the semiconductor element by the drive circuit.

Owner:FUJI ELECTRIC CO LTD

Shift register circuit

ActiveUS8040999B2Reduced drive capability requirementsLower capability requirementsDigital storageDriver circuitCapacitance

Owner:TRIVALE TECH

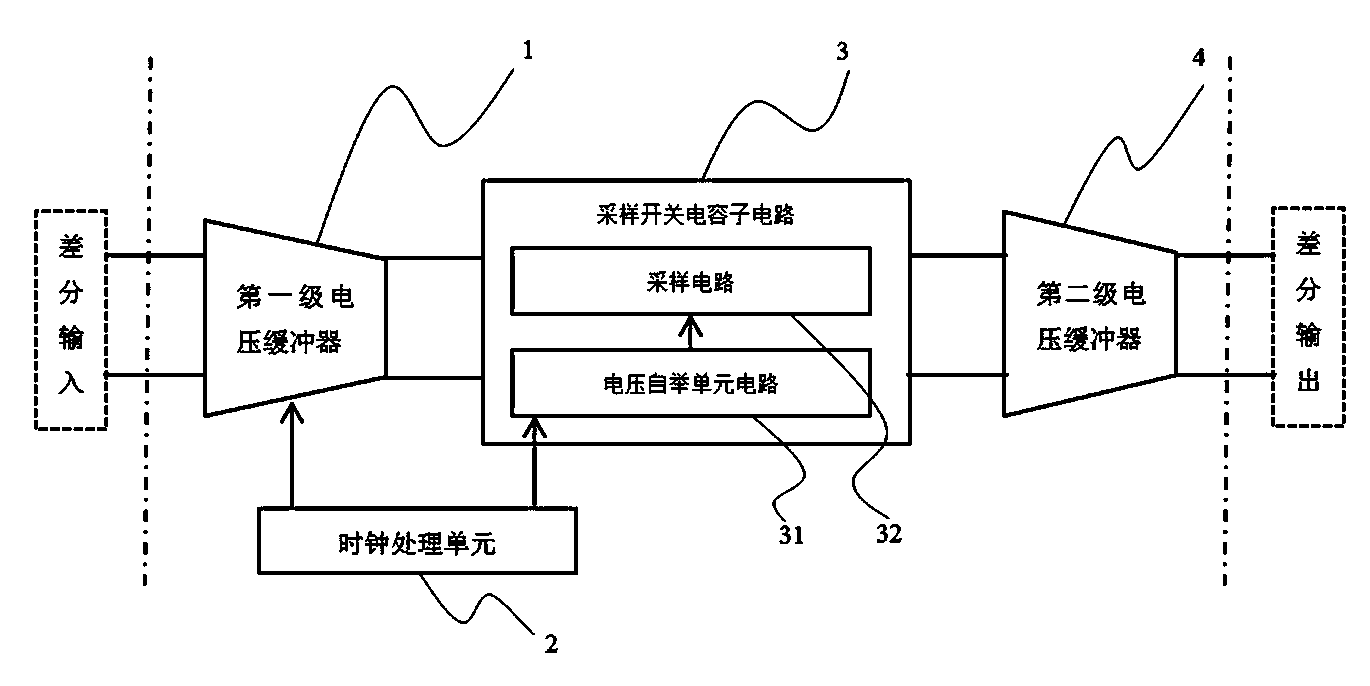

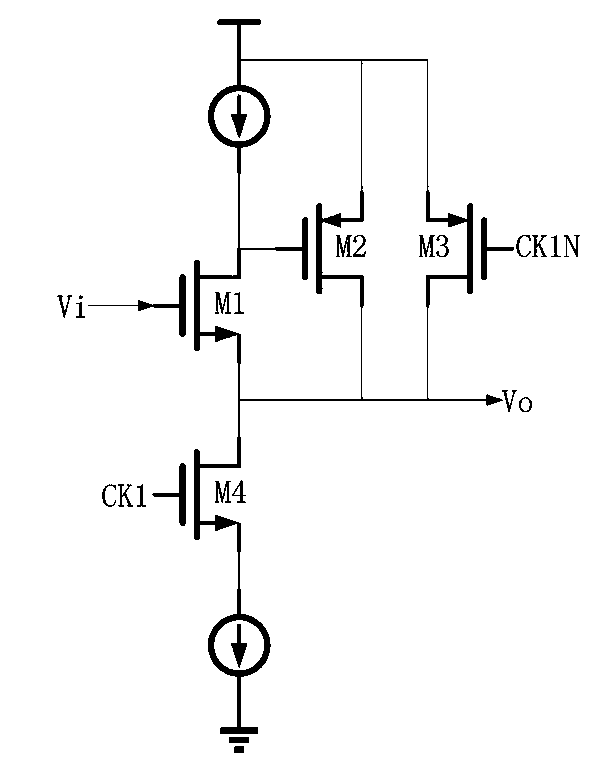

Broadband sampling holding circuit used for successive approximation type analog-to-digital converter front-end

ActiveCN103716054AHigh bandwidthReduced drive capability requirementsAnalogue/digital conversionElectric signal transmission systemsCapacitanceTelecommunications

The invention provides a broadband sampling holding circuit used for a successive approximation type analog-to-digital converter front end. The objective of the invention is to eliminate the defects of an existing sampling holding circuit. The broadband sampling holding circuit is composed of a first-stage voltage buffer, a clock processing unit, a sampling switched capacitor sub circuit and a second-stage voltage buffer; the output end of the first-stage voltage buffer is connected with the input end of the sampling switched capacitor sub circuit controlled by a voltage bootstrapping unit circuit; a signal output end of the sampling switched capacitor sub circuit is connected with a signal input end of the second-stage voltage buffer; and the clock processing unit provides clock signals for the first-stage voltage buffer and the sampling switched capacitor sub circuit respectively. According to the broadband sampling holding circuit of the invention, the broadband-reinforced and clock-controlled first-stage voltage buffer and the second-stage voltage buffer of a PMOS source follower which is used for performing replication unit biasing on N wells are adopted, and therefore, the bandwidth of input sampling signals can be improved, and at the same time, a requirement for signal linearity can be satisfied with extremely low power consumption.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

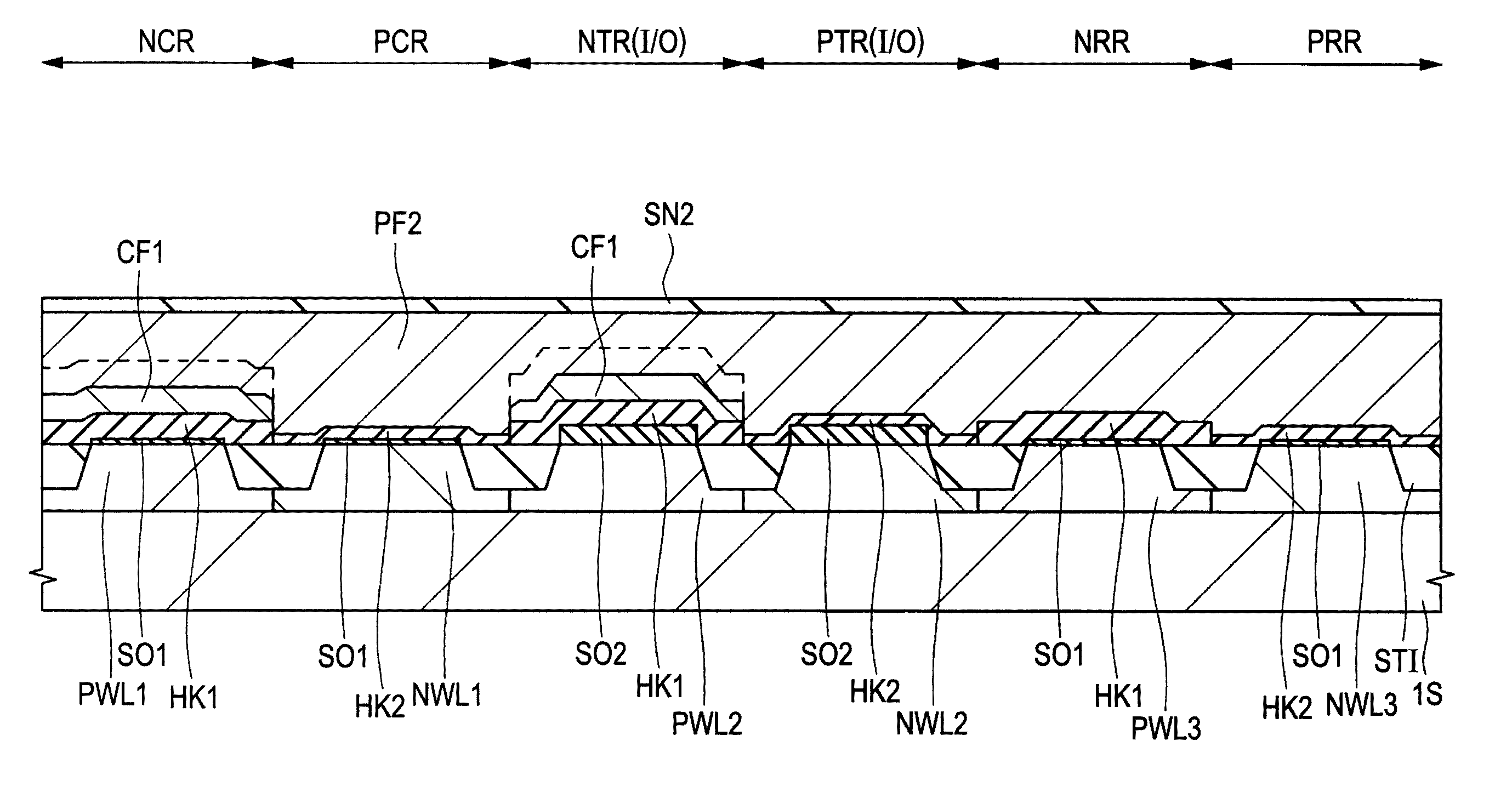

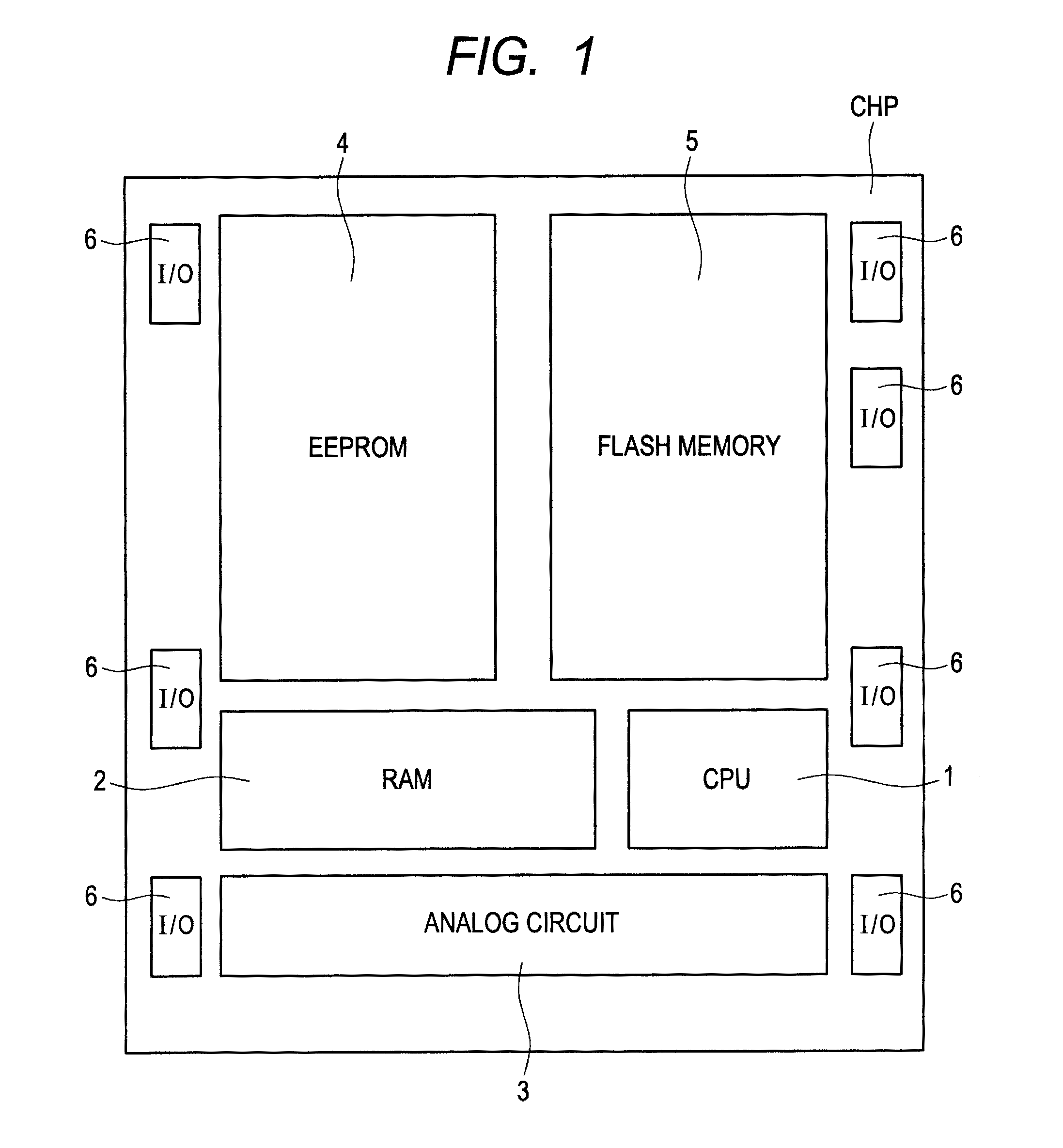

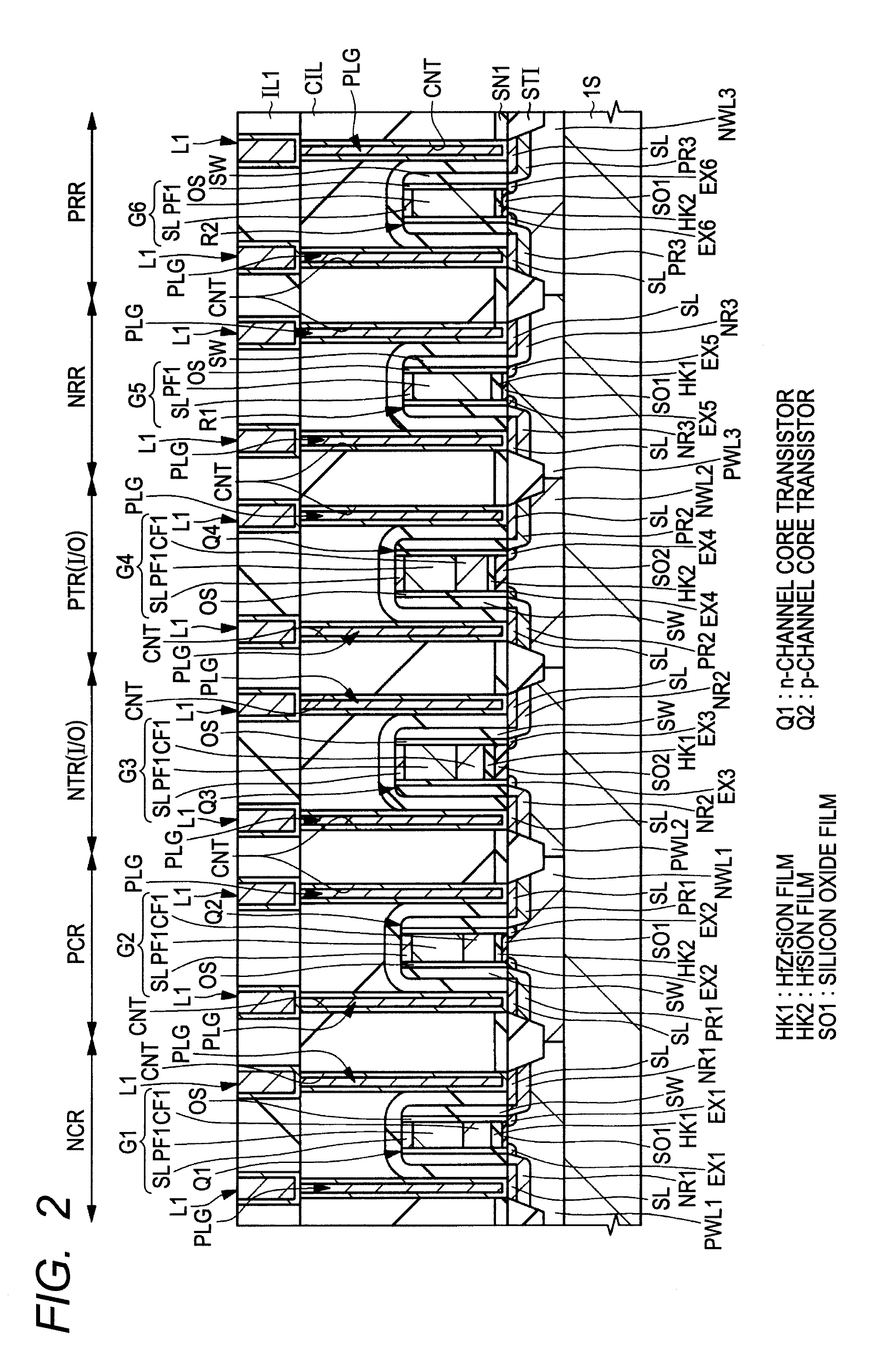

Semiconductor device and manufacturing method thereof

InactiveUS20120056268A1Improve reliabilityReduce thicknessTransistorSolid-state devicesPower semiconductor deviceHafnium

There is provided a technology capable of achieving, in a semiconductor device having a MISFET using an insulating film containing hafnium as a gate insulating film, an improvement in the reliability of a MISFET. In the present invention, the gate insulating film of an n-channel core transistor is provided with a structure different from that of the gate insulating film of a p-channel core transistor. Specifically, in the n-channel core transistor, as the gate insulating film thereof, a laminate film of a silicon oxide film and a HfZrSiON film is used. On the other hand, in the p-channel core transistor, as the gate insulating film thereof, a laminate film of a silicon oxide film and a HfSiON film is used.

Owner:RENESAS ELECTRONICS CORP

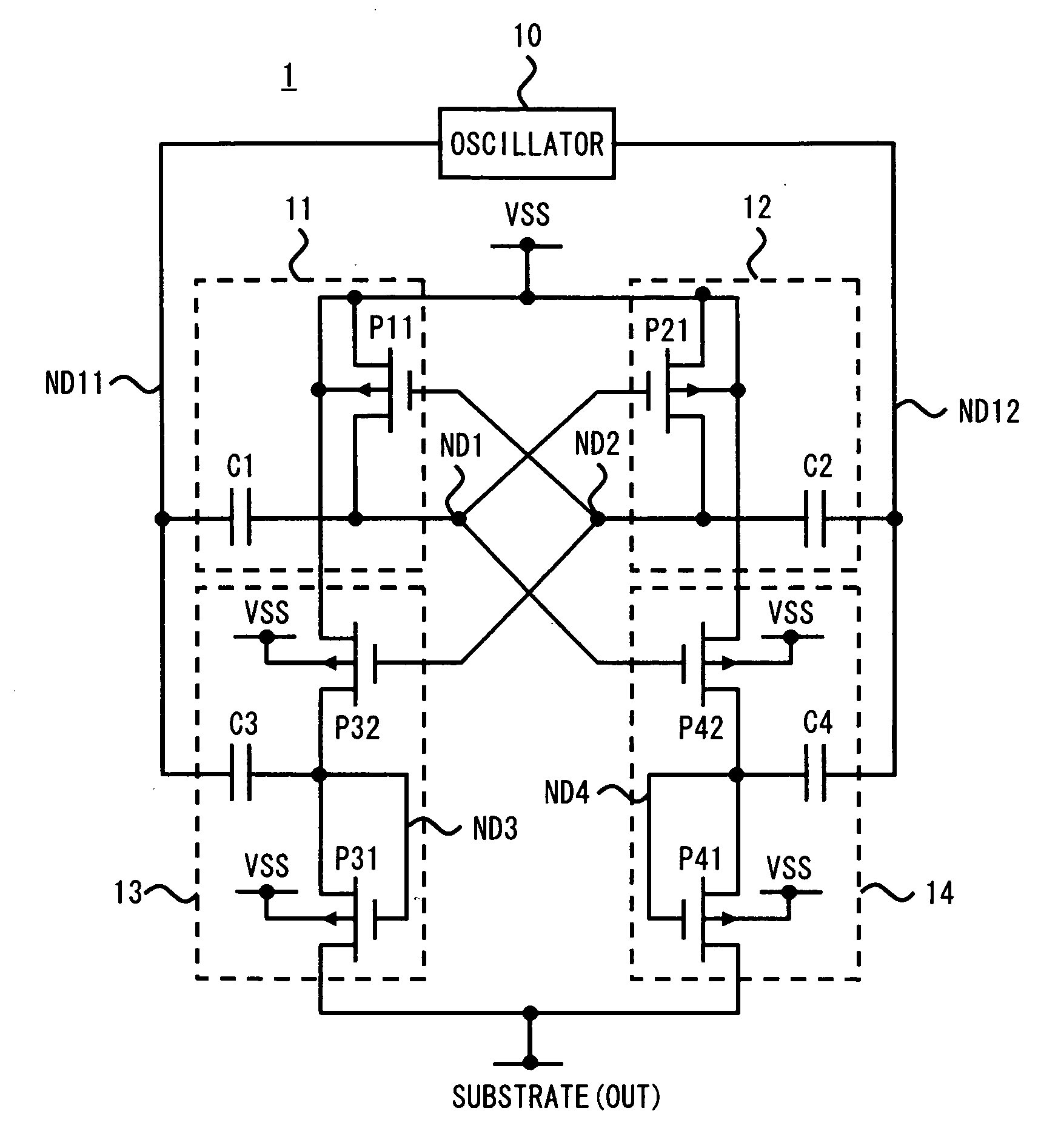

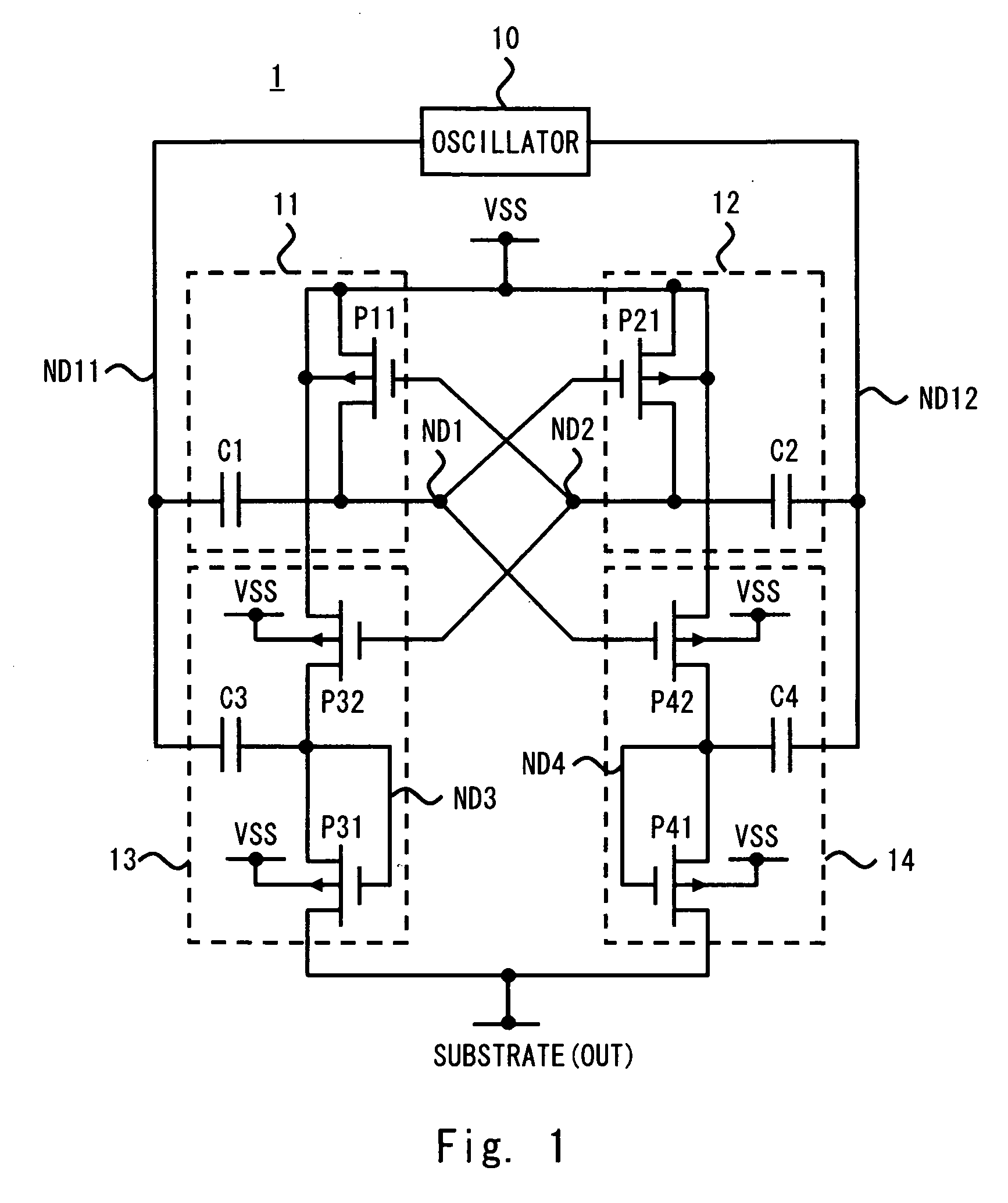

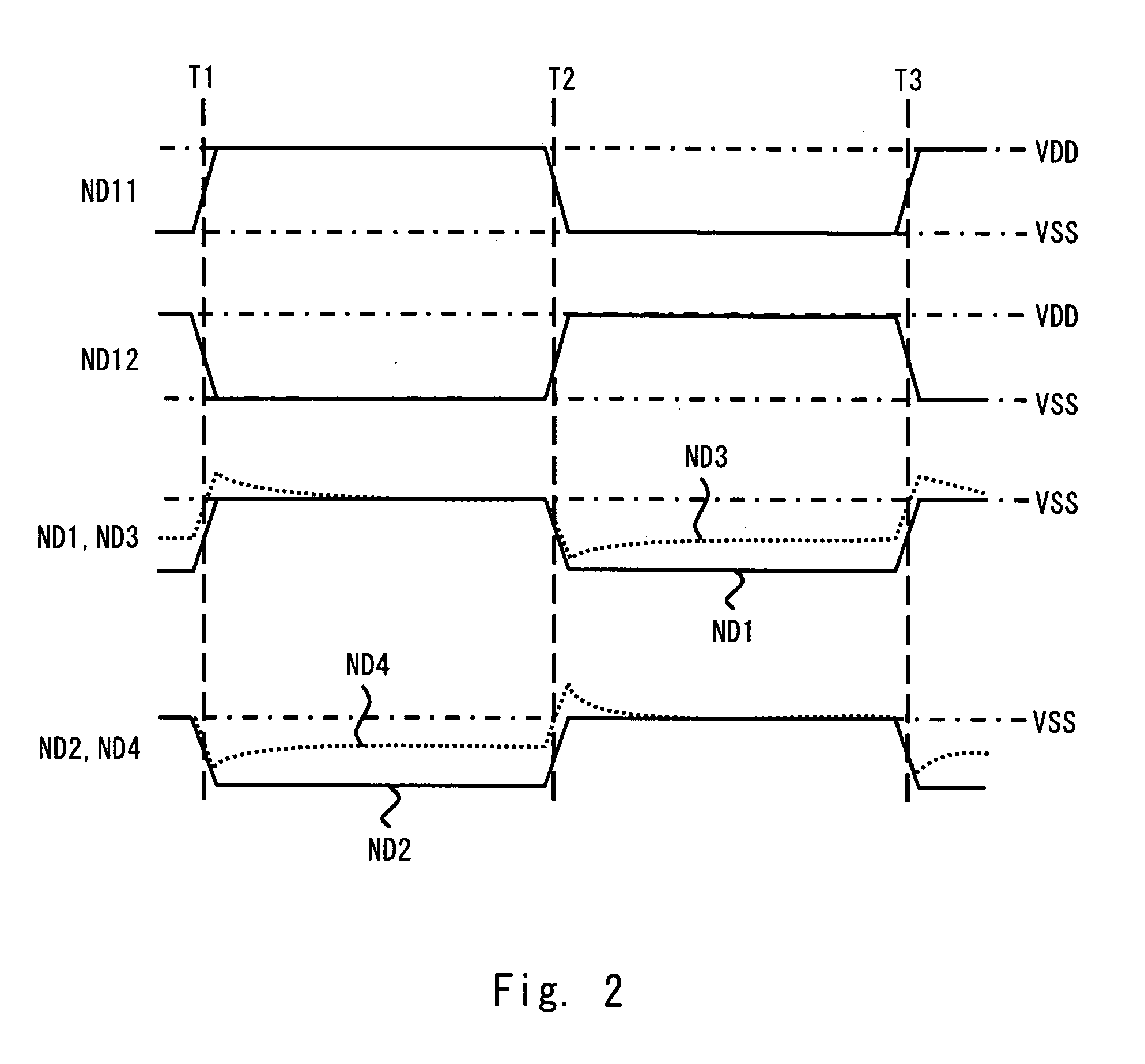

Semiconductor device

InactiveUS20110050327A1Reduction in current driving capability can be preventedReduced drive capability requirementsApparatus without intermediate ac conversionElectric variable regulationPower semiconductor deviceControl signal

Provided is a semiconductor device including: a first charge pump circuit that generates a first control signal based on electric charge of a first pumping capacitor accumulated through a first drive transistor; a second charge pump circuit that generates a second control signal based on electric charge of a second pumping capacitor accumulated through a second drive transistor; a third charge pump circuit that transfers electric charge between an output terminal and a reference voltage terminal through a third drive transistor; and a fourth charge pump circuit that transfers electric charge between the output terminal and the reference voltage terminal through a fourth drive transistor. Conductive states of the first and third drive transistors are controlled based on the second control signal, and conductive states of the second and fourth drive transistors are controlled based on the first control signal.

Owner:RENESAS ELECTRONICS CORP

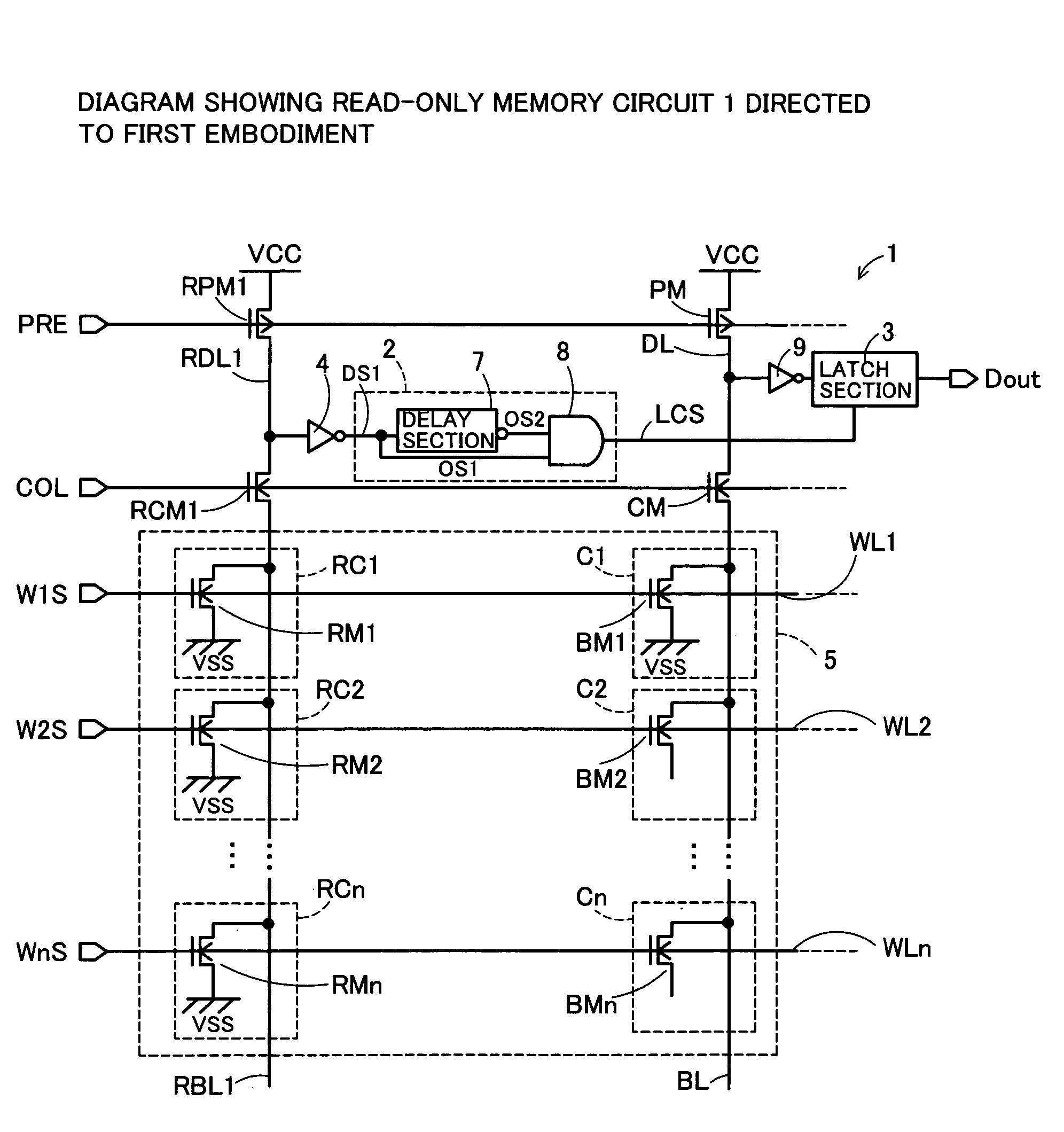

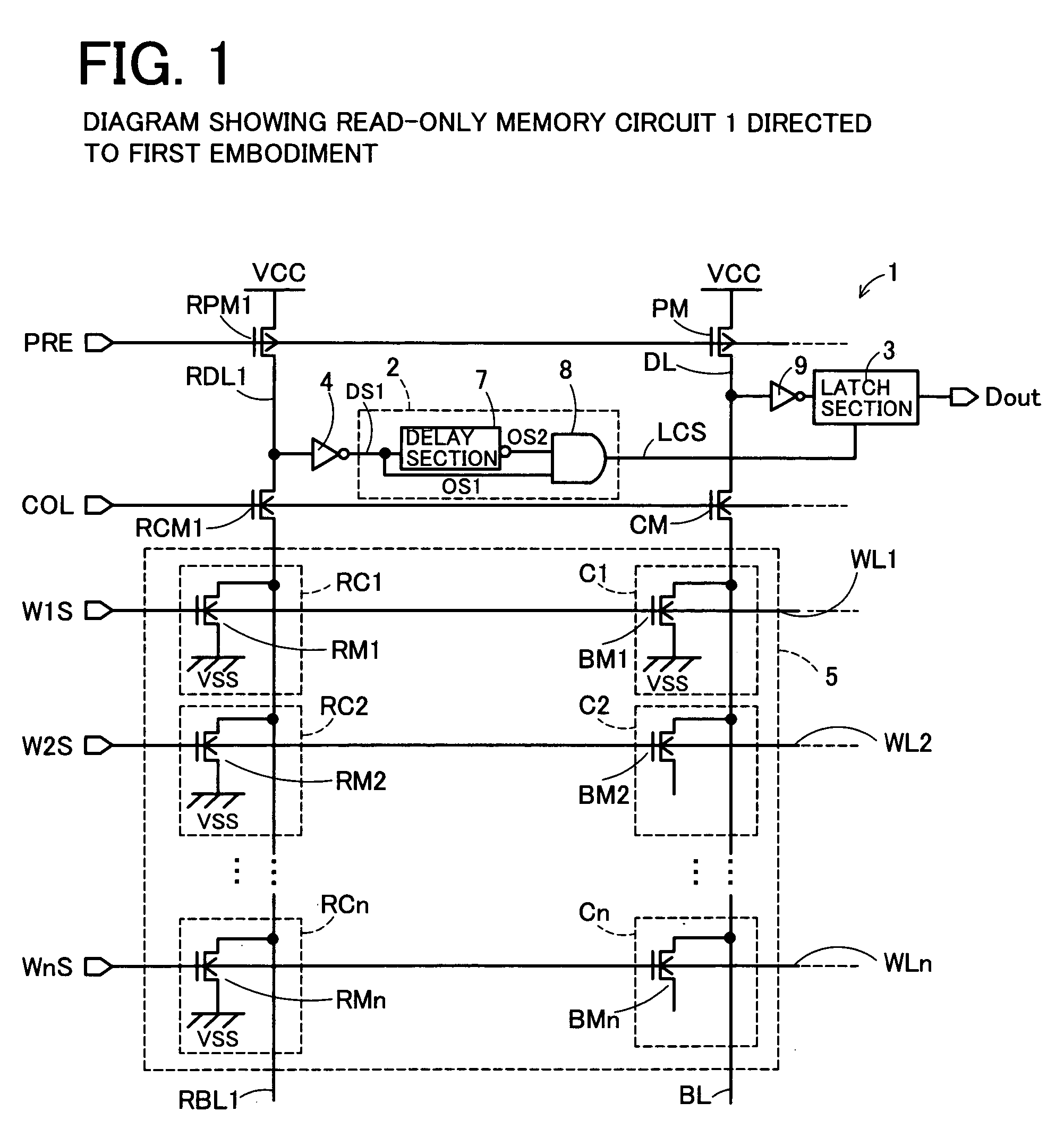

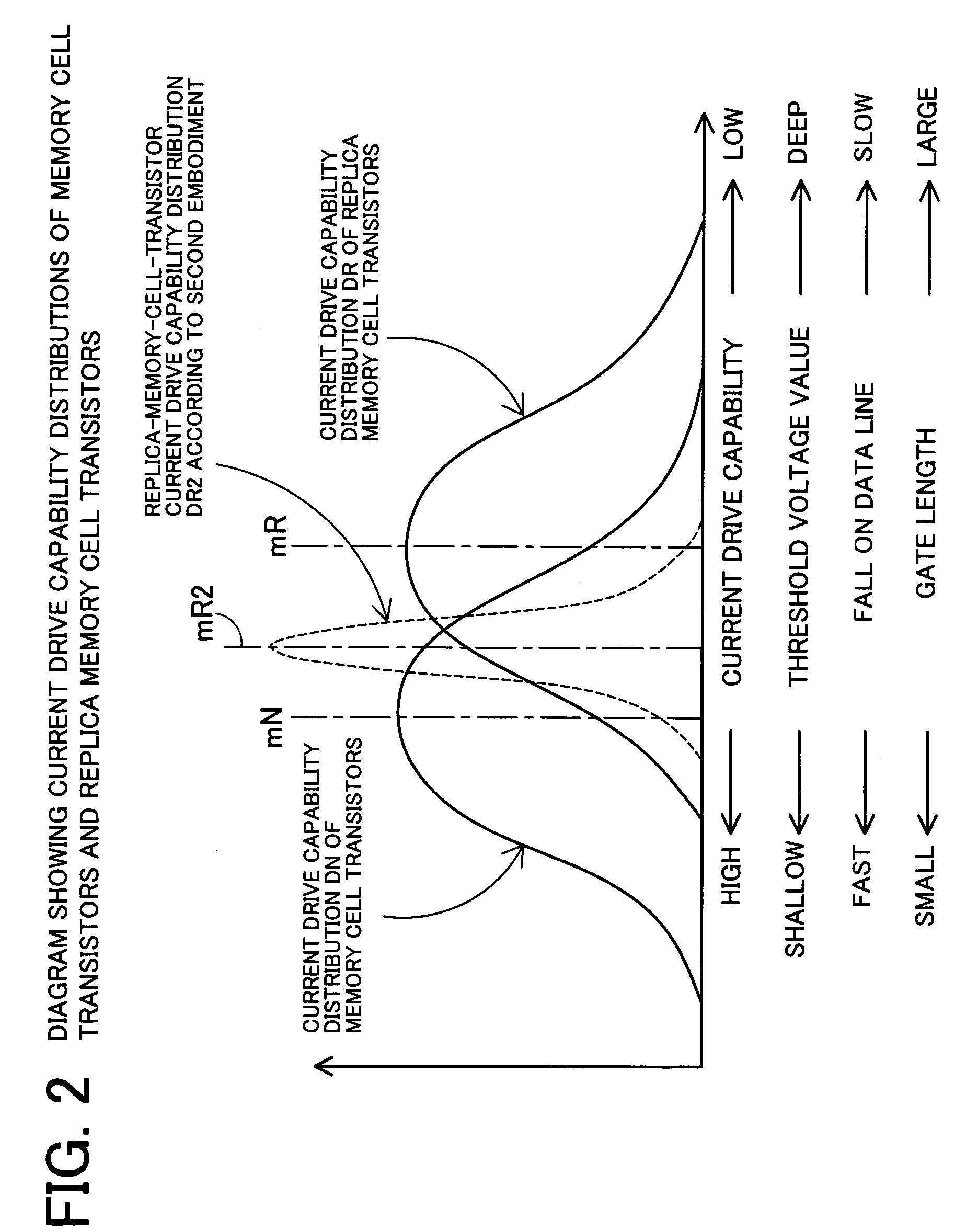

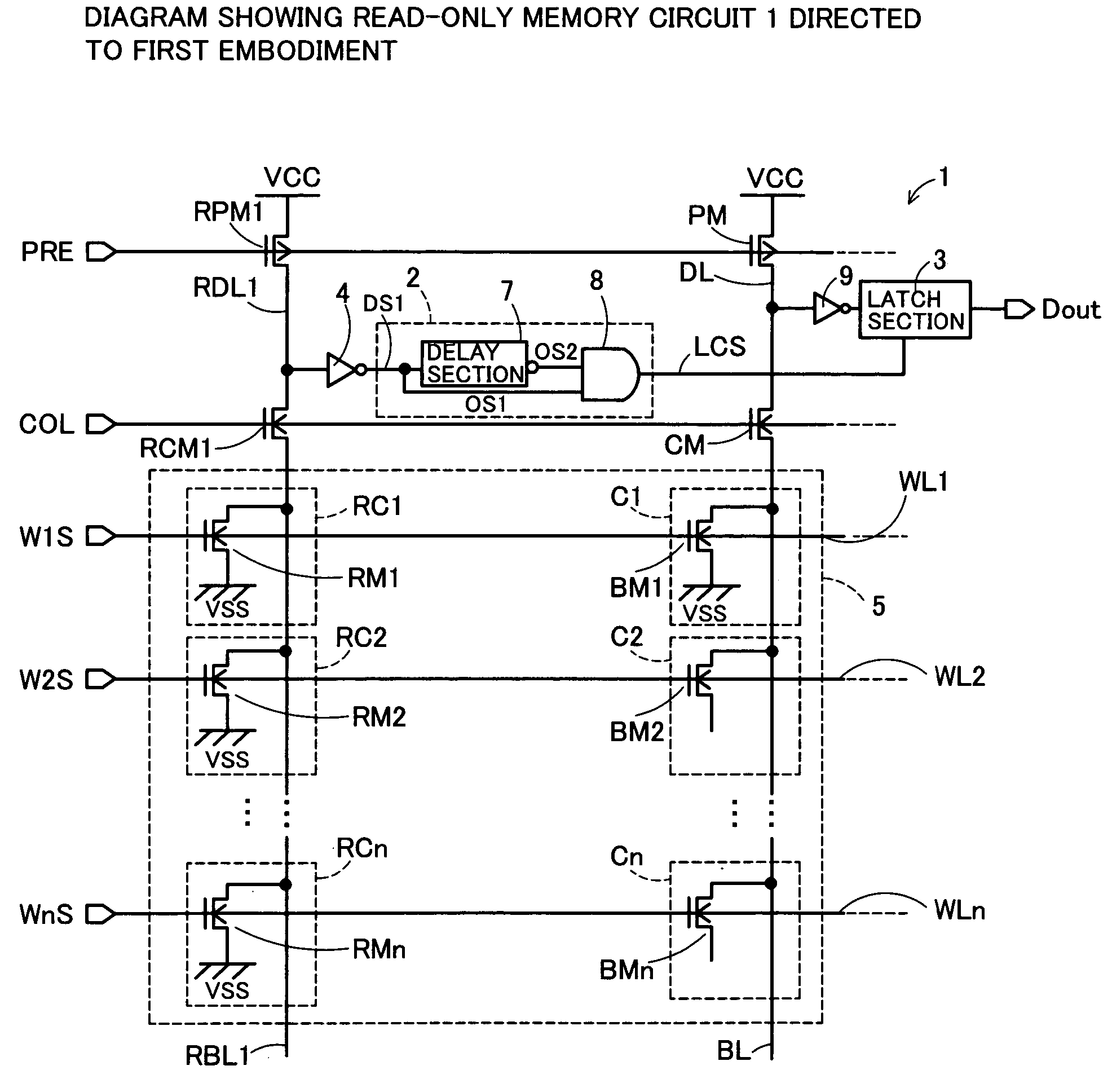

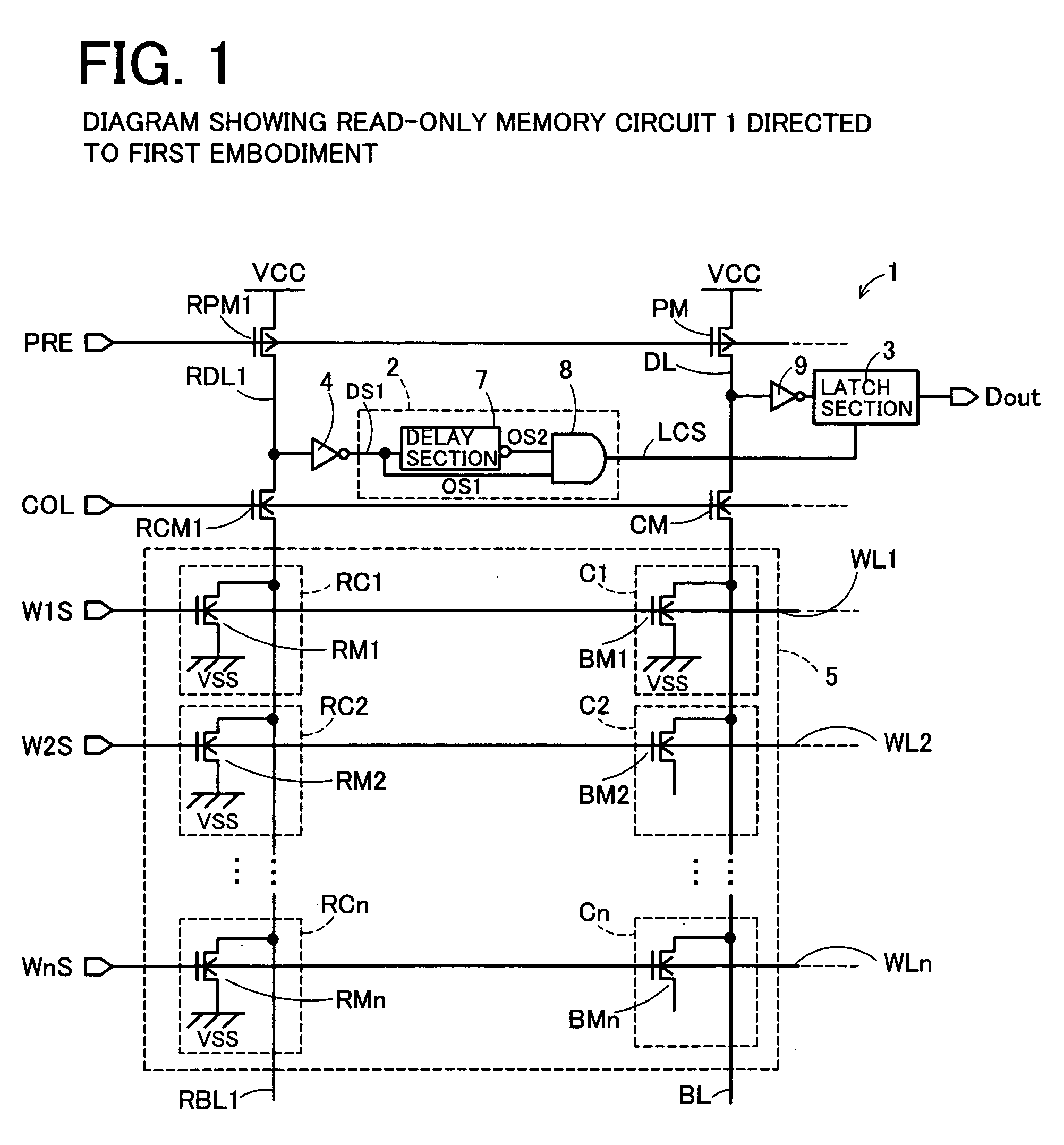

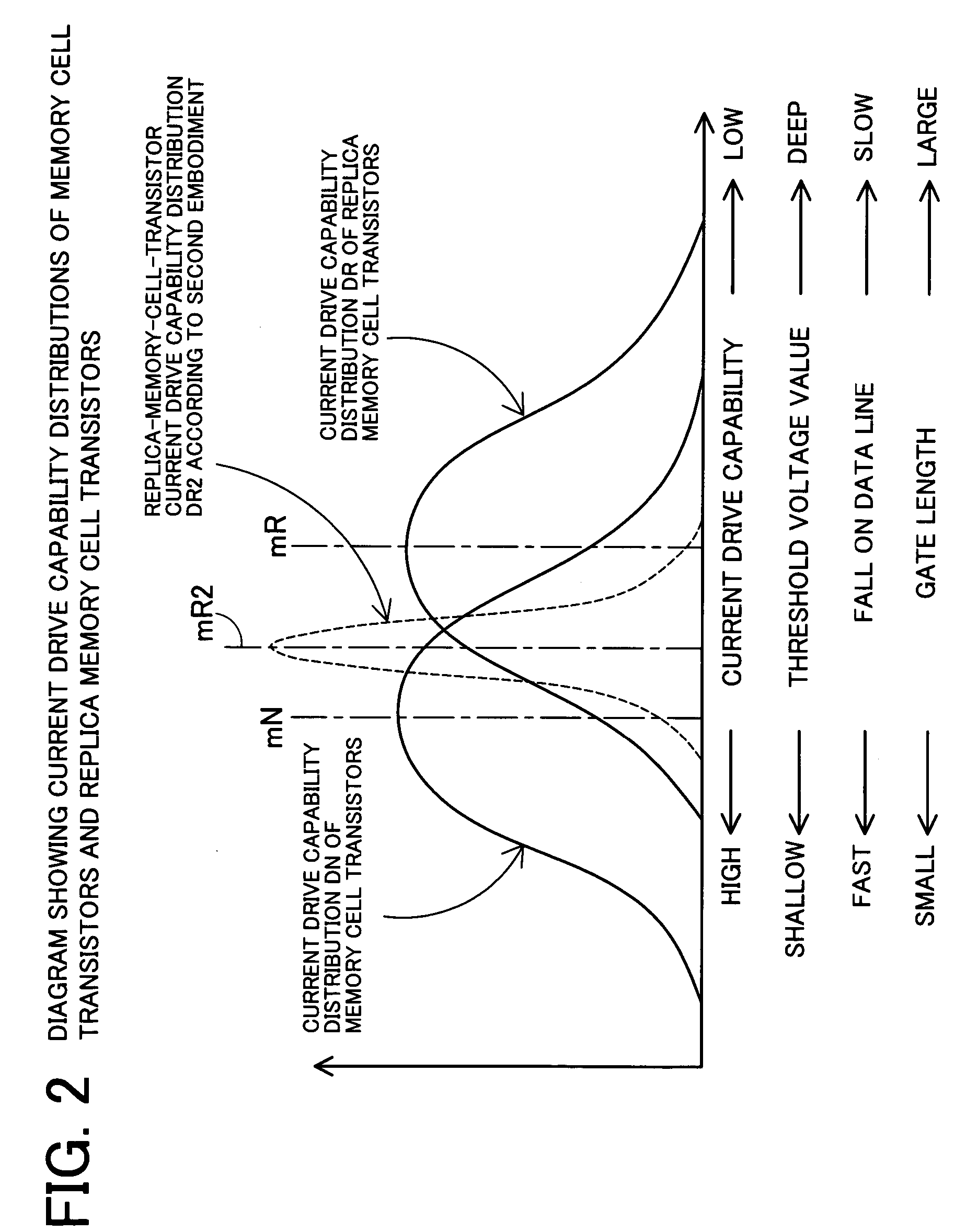

Semiconductor memory device and control method for semiconductor memory device

InactiveUS7149102B2Reduce incidenceReduced drive capability requirementsRead-only memoriesDigital storageStart timeControl signal

Provided is a semiconductor memory device using a single-bit line method that determines read operation timing in accordance with operation of a replica bit line. Further provided is a control method for the semiconductor memory device. Even when a transistor property fluctuation has occurred, the semiconductor memory device and the control method are capable of preventing, for example, increases in access time and circuit size and concurrently capable of reducing the occurrence probability of data readout error. The gate lengths of replica memory cell transistors are set as being values greater than the gate length of memory cell transistors. Thereby, a distribution center of a current drive capability distribution of the replica memory cell transistors is set lower than a distribution center of a current drive capability distribution of the memory cell transistors. Consequently, an occurrence probability of a delay in a voltage-fall start time on a regular data line can be reduced to be lower in comparison to a transmission timing of a latch control signal.

Owner:SOCIONEXT INC

Pixel circuit, display device, driving method of pixel circuit, and driving method of display device

InactiveUS7893895B2Increase brightnessLow mobilityStatic indicating devicesDriving currentCapacitance

A pixel circuit, disposed at a part where a scanning line and a signal line intersect each other, includes at least an electrooptic element, a drive transistor, a sampling transistor, and a retaining capacitance. The drive transistor has a gate connected to an input node, a source connected to an output node, and a drain connected to a predetermined power supply potential and supplies a driving current to the electrooptic element according to a signal potential retained in the retaining capacitance. The electrooptic element has one terminal connected to the output node and another terminal connected to a predetermined potential. The sampling transistor is connected between the input node and the signal line and operates when selected by the scanning line, samples an input signal from the signal line, and retains the input signal in the retaining capacitance. The retaining capacitance is connected to the input node. The pixel circuit further includes a compensating circuit which detects a decrease in the driving current from a side of the output node and feeds back a result of detection to a side of the input node to compensate for a decrease in the driving current, which decrease is attendant on a secular change of the drive transistor.

Owner:SONY CORP

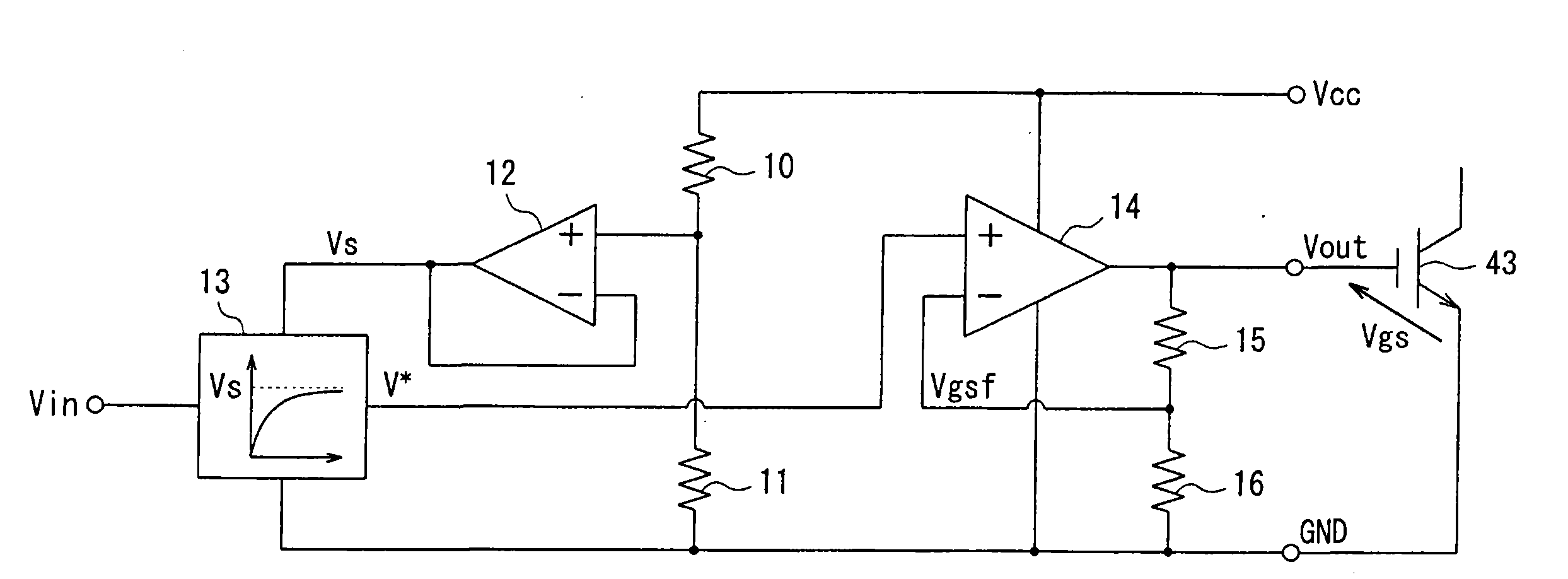

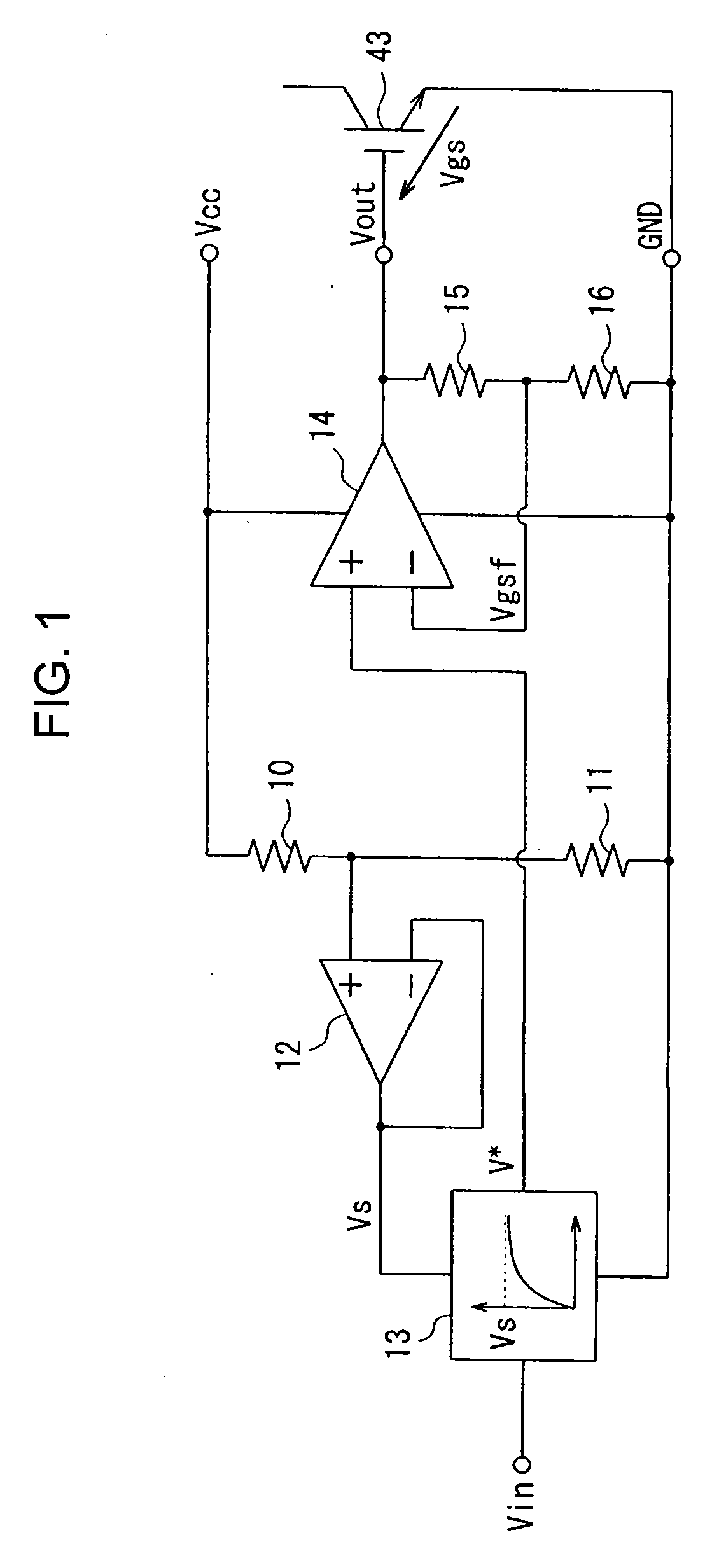

Driver circuit

ActiveUS20090146714A1Improve driving abilityReduced drive capability requirementsElectronic switchingElectric pulse generatorDriver circuitAudio power amplifier

A driver circuit facilitates reducing noises and losses and improving the driving performances thereof without connecting a series circuit of capacitor and a resistor to the gate of IGBT. The driver circuit includes a slope setting circuit that sets the gate voltage waveform of IGBT; and an operational amplifier that includes a non-inverting input terminal, to which an output voltage V* from slope setting circuit is inputted, and an inverting input terminal, to which a divided voltage Vgsf divided by resistors is inputted; and the operational amplifier outputs an output voltage Vout, proportional to the difference between the output voltage V* and the divided voltage Vgsf, to the gate of IGBT.

Owner:FUJI ELECTRIC CO LTD

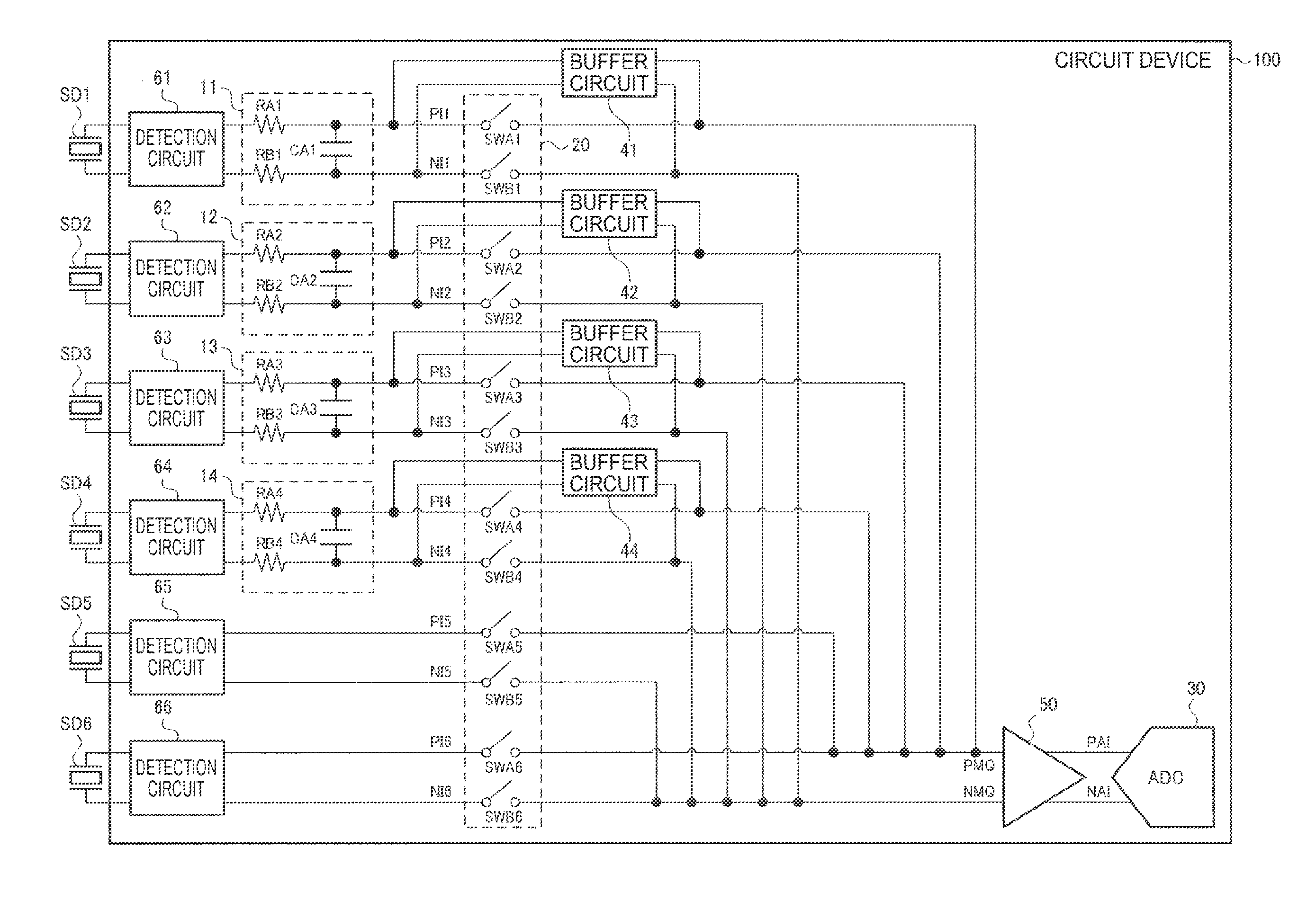

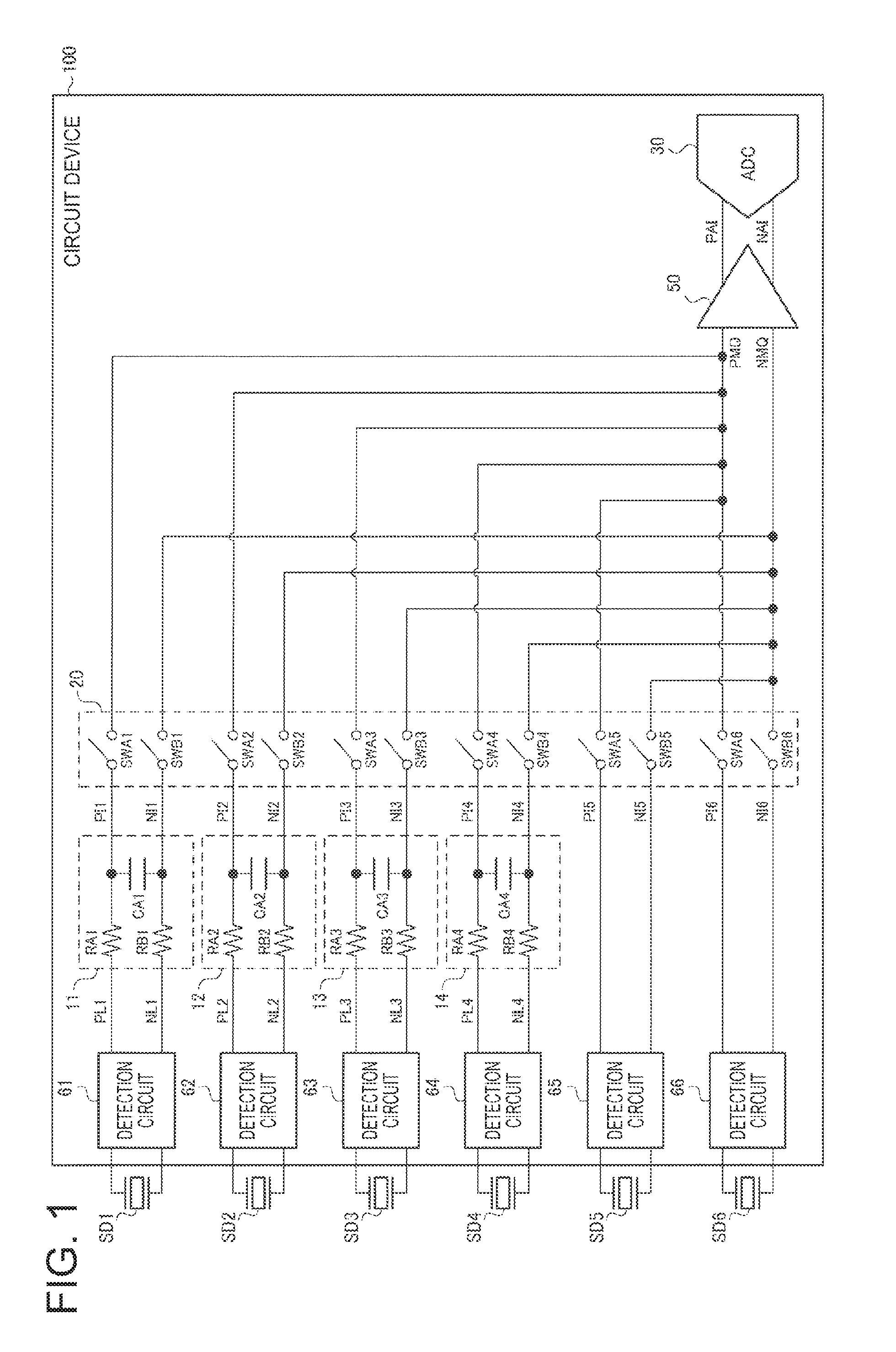

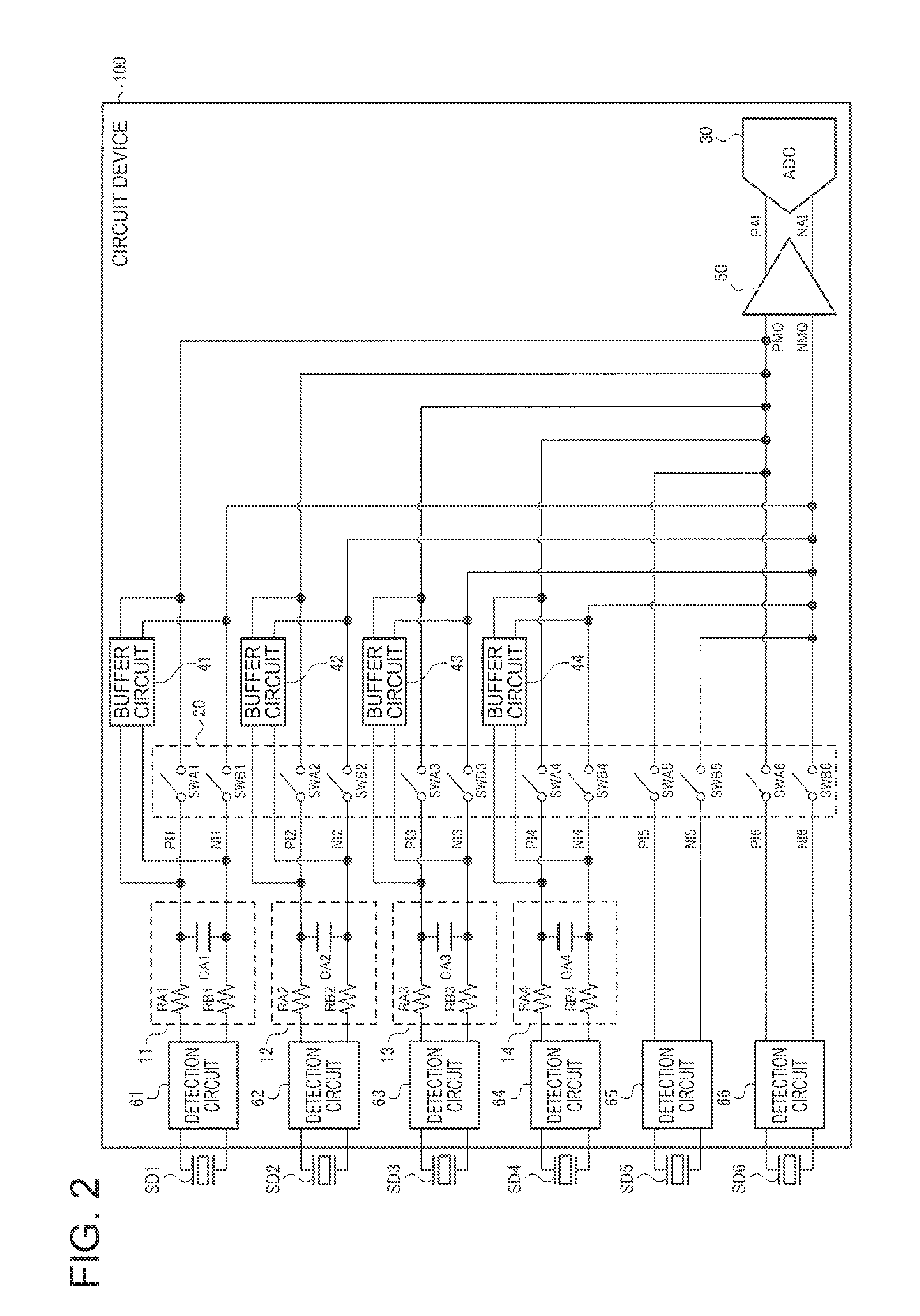

Circuit device, electronic apparatus, and moving object

InactiveUS20160269011A1Reduced drive capability requirementsAnalogue/digital conversionAcceleration measurement using interia forcesMultiplexerElectronic equipment

A circuit device includes a multiplexer that selects an input signal from first to n-th input signals in a time division manner and outputs the selected input signal to an output node, an A / D conversion circuit that receives the first to n-th input signals outputted from the multiplexer to the output node in a time division manner and A / D-converts the received first to n-th input signals in a time division manner, and a buffer circuit provided between an i-th input node and the output node of the multiplexer. The buffer circuit buffers the i-th input signal and outputs the buffered signal to the output node of the multiplexer in a first period. The multiplexer selects the i-th input signal and outputs the selected signal to the output node in a second period. End timing of the second period comes after end timing of the first period.

Owner:SEIKO EPSON CORP

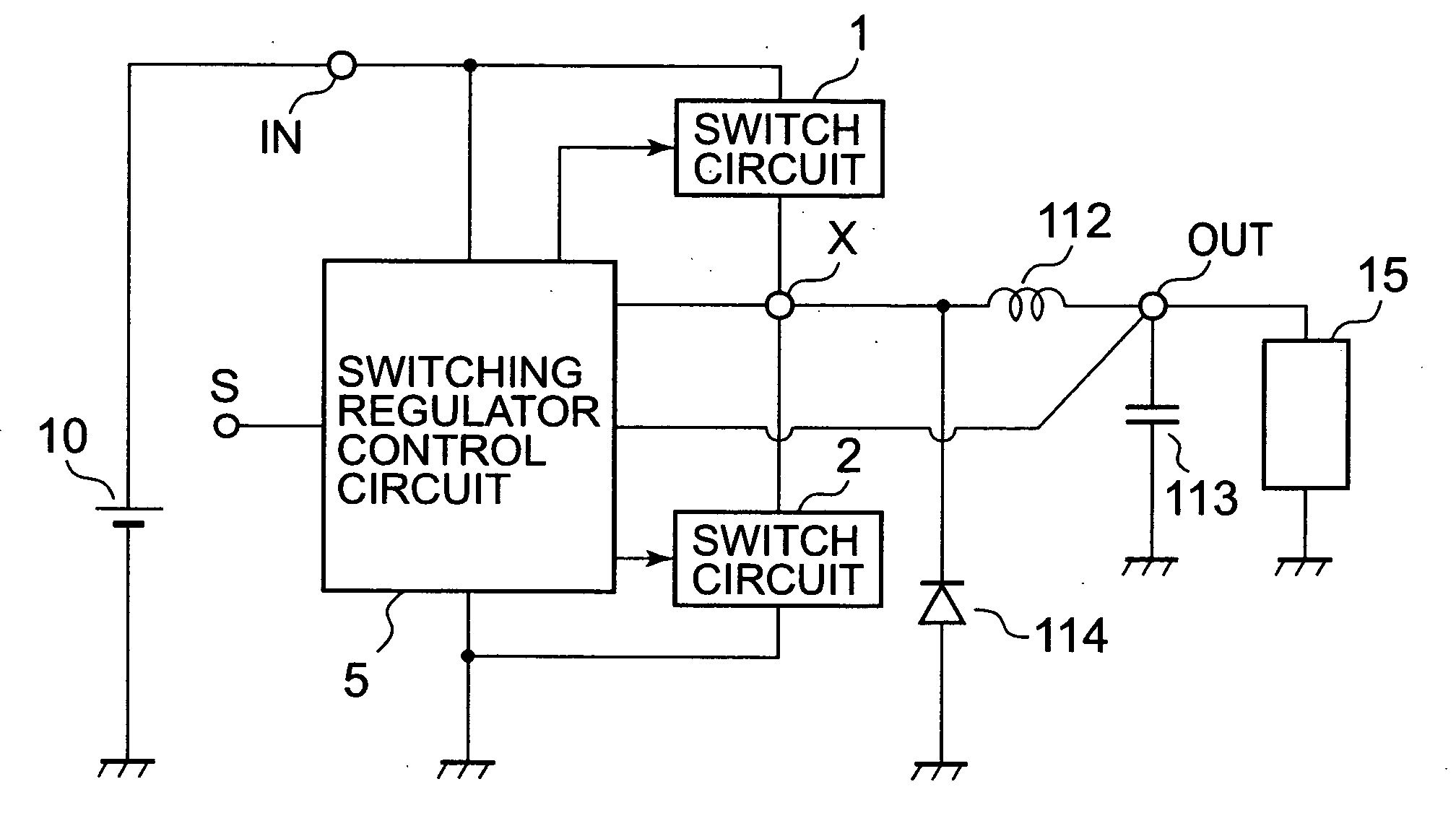

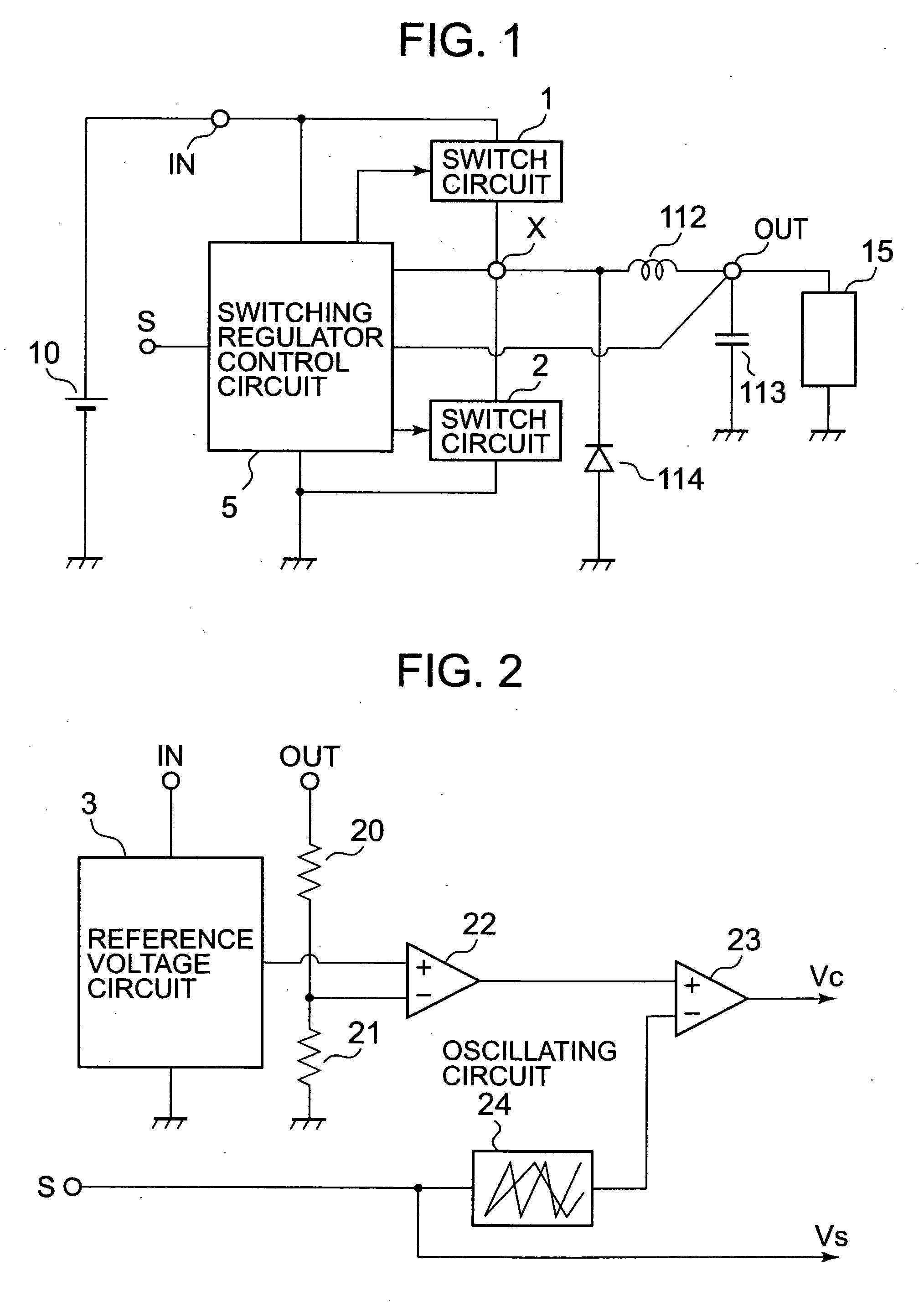

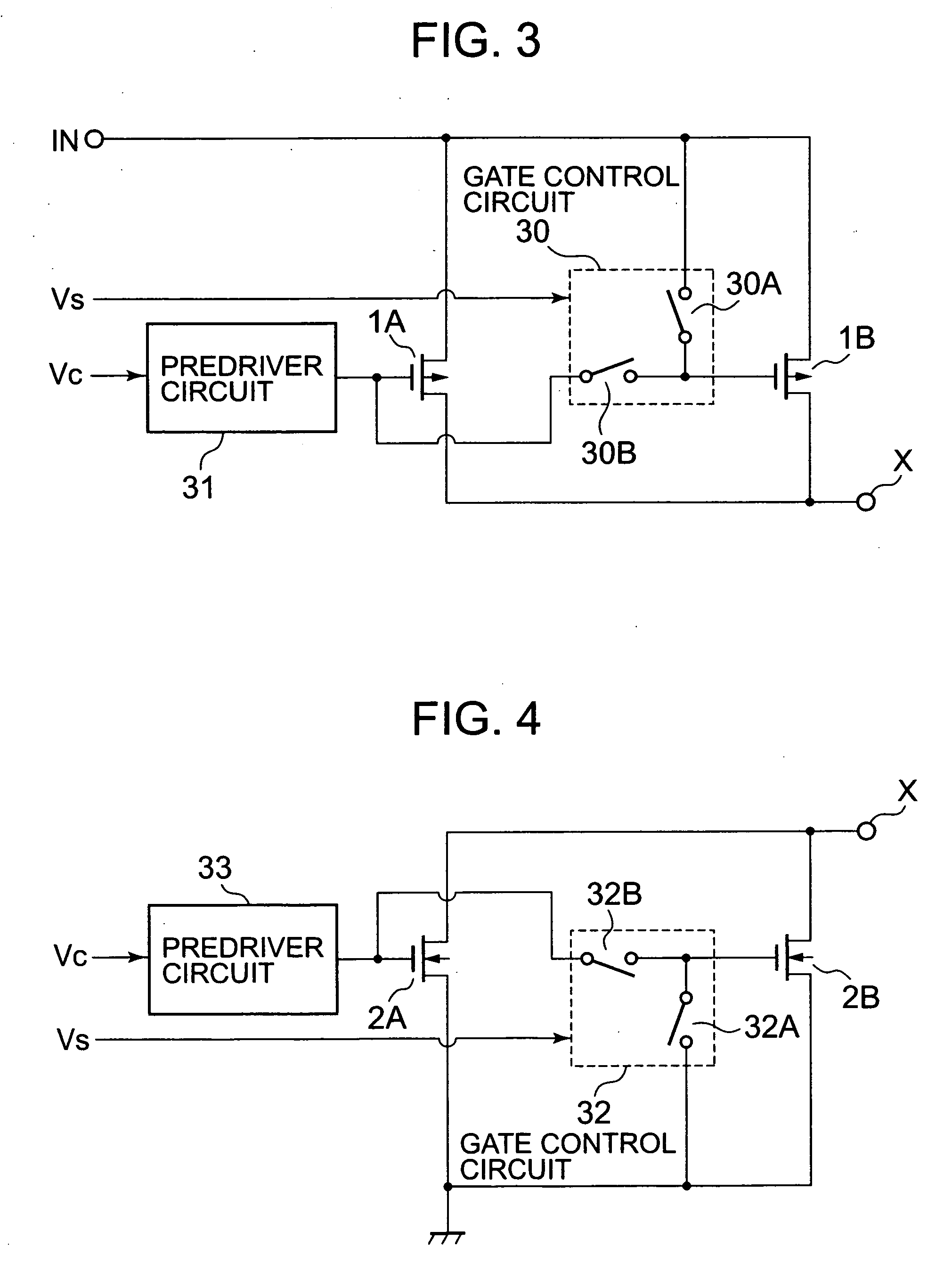

Switching regulator circuit

InactiveUS20060158915A1Improved power conversion efficiencyImprove conversion efficiencyEfficient power electronics conversionSelf-acting watering devicesEnergy conversion efficiencyControl theory

Provided is a switching regulator having satisfactory energy conversion efficiency during light load conditions. Such a structure is employed that an oscillating frequency for the switching regulator and a drive capability of a switch element are variable and such a control is taken that during the light load, the oscillating frequency for the switching regulator or the drive capability of the switch element is reduced.

Owner:SEIKO INSTR INC

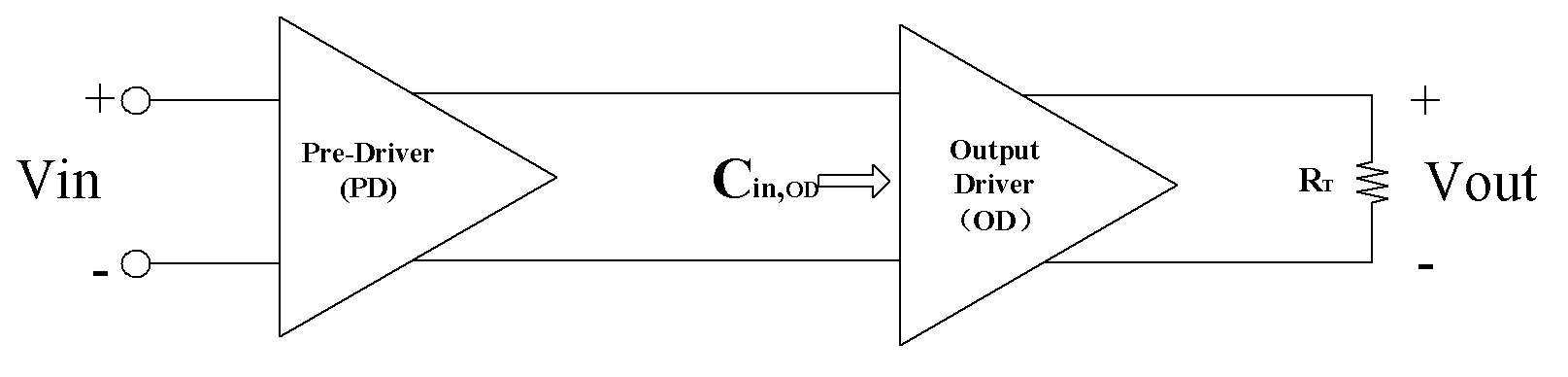

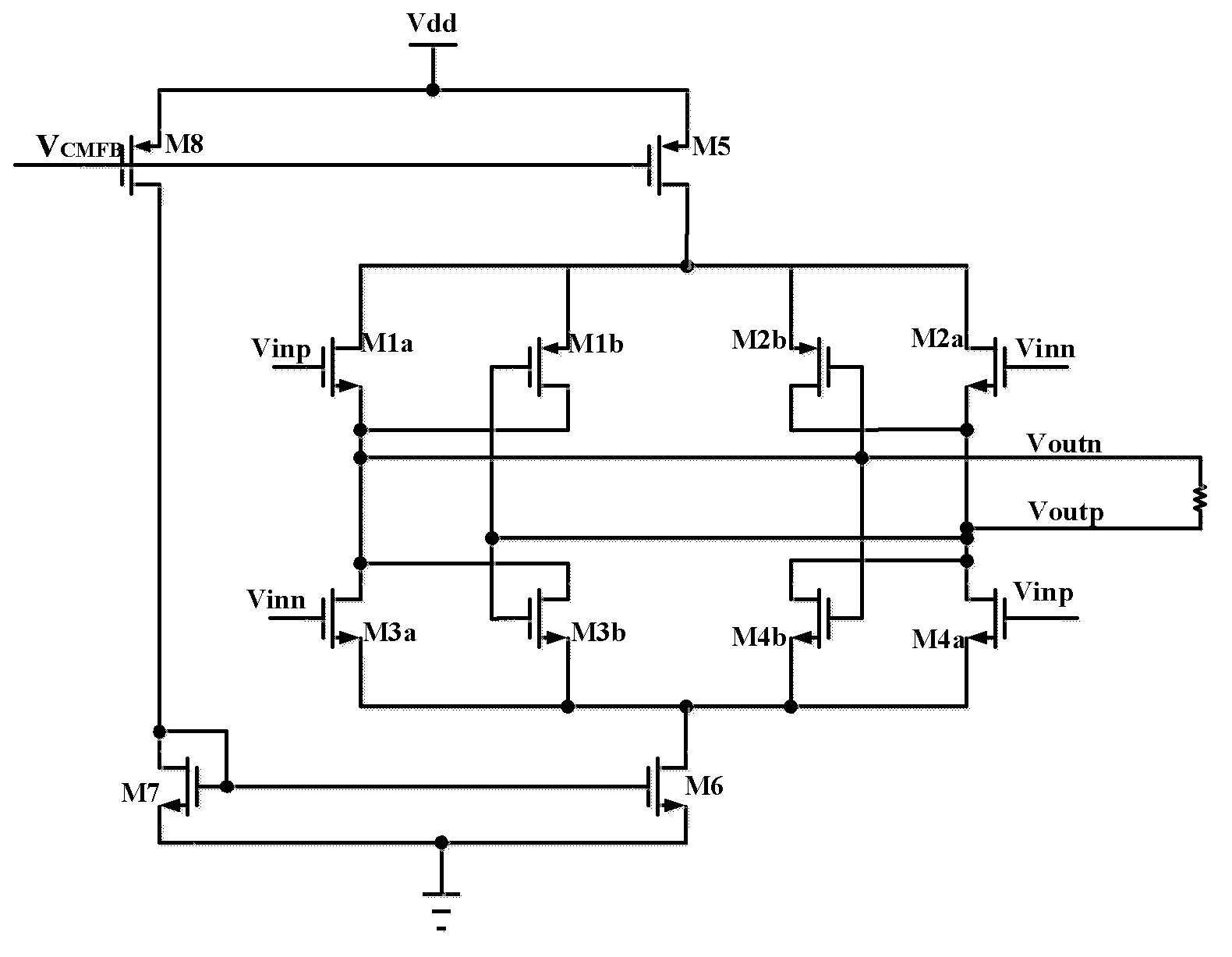

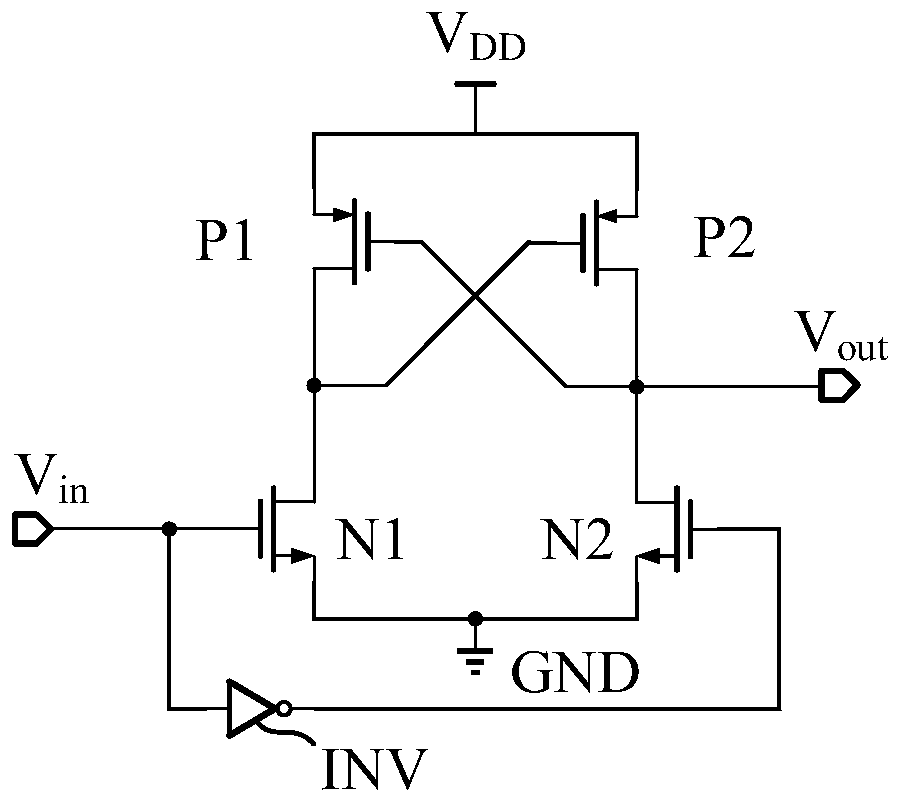

Circuit structure for reducing input load of output driving module of LVDS (low voltage differential signaling) driver

The invention discloses a circuit structure for reducing the input load of an output driving module of a LVDS (low voltage differential signaling) driver. Vinn and Vinp are outputs of a pre-driving module of the LVDS driver and used for controlling four switching MOS (metal oxide semiconductor) transistors of the output driving module of the LVDS driver. Compared with a conventional LVDS driver circuit, the circuit structure has the advantages that the input load capacitance of the output driving module of the LVDS driver can be effectively reduced only by adding four switching MOS transistors without increasing any power consumption by a positive feedback shunt mechanism, namely, the output load capacitance of the pre-driving module is reduced, power consumption of a pre-driving portion of the LVDS driver is reduced, and accordingly, the performance of the whole driver is improved.

Owner:SOI MICRO CO LTD

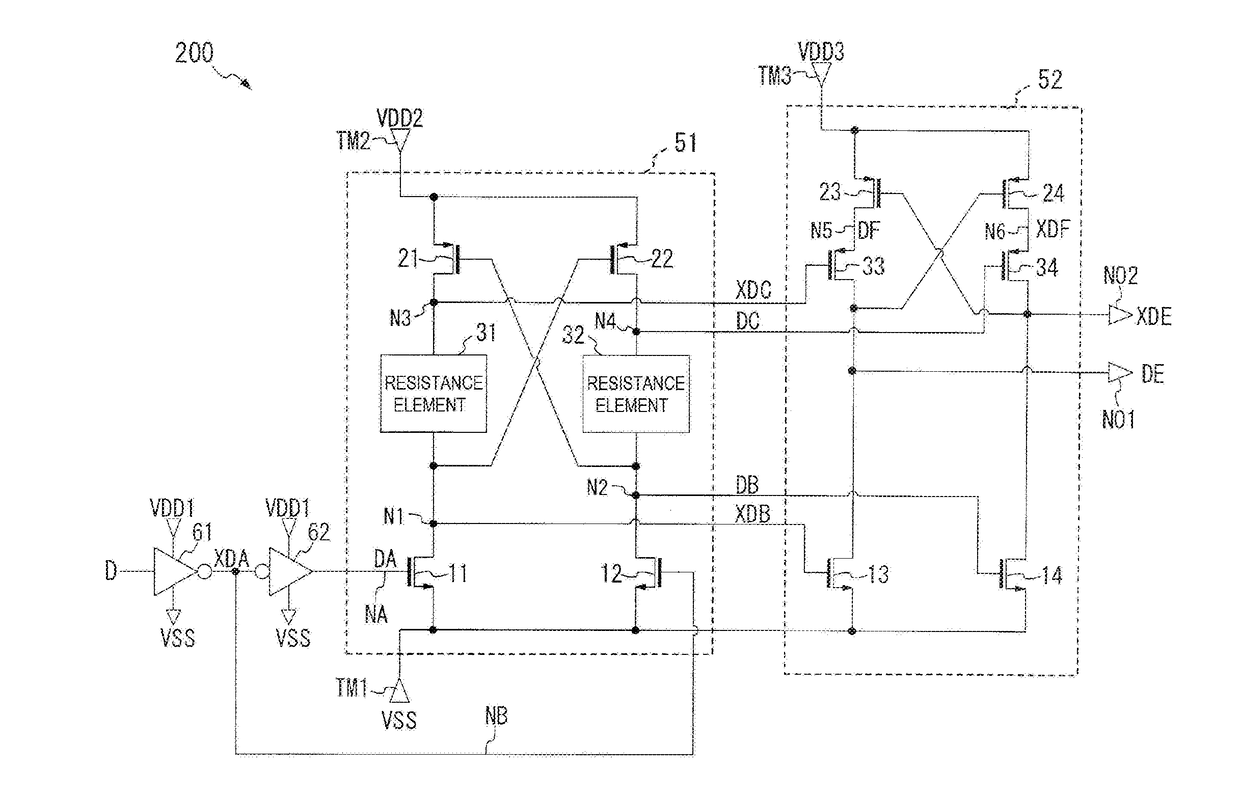

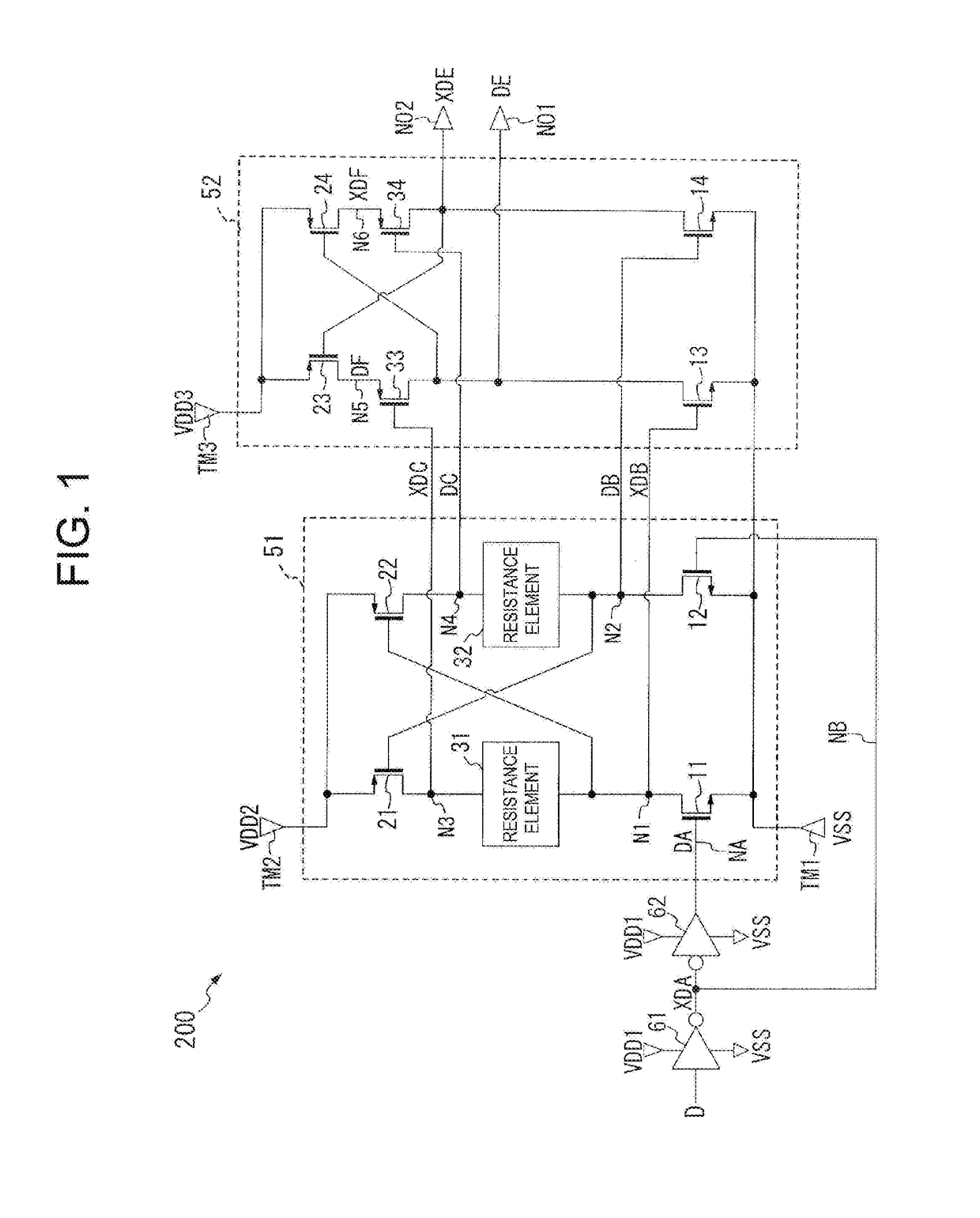

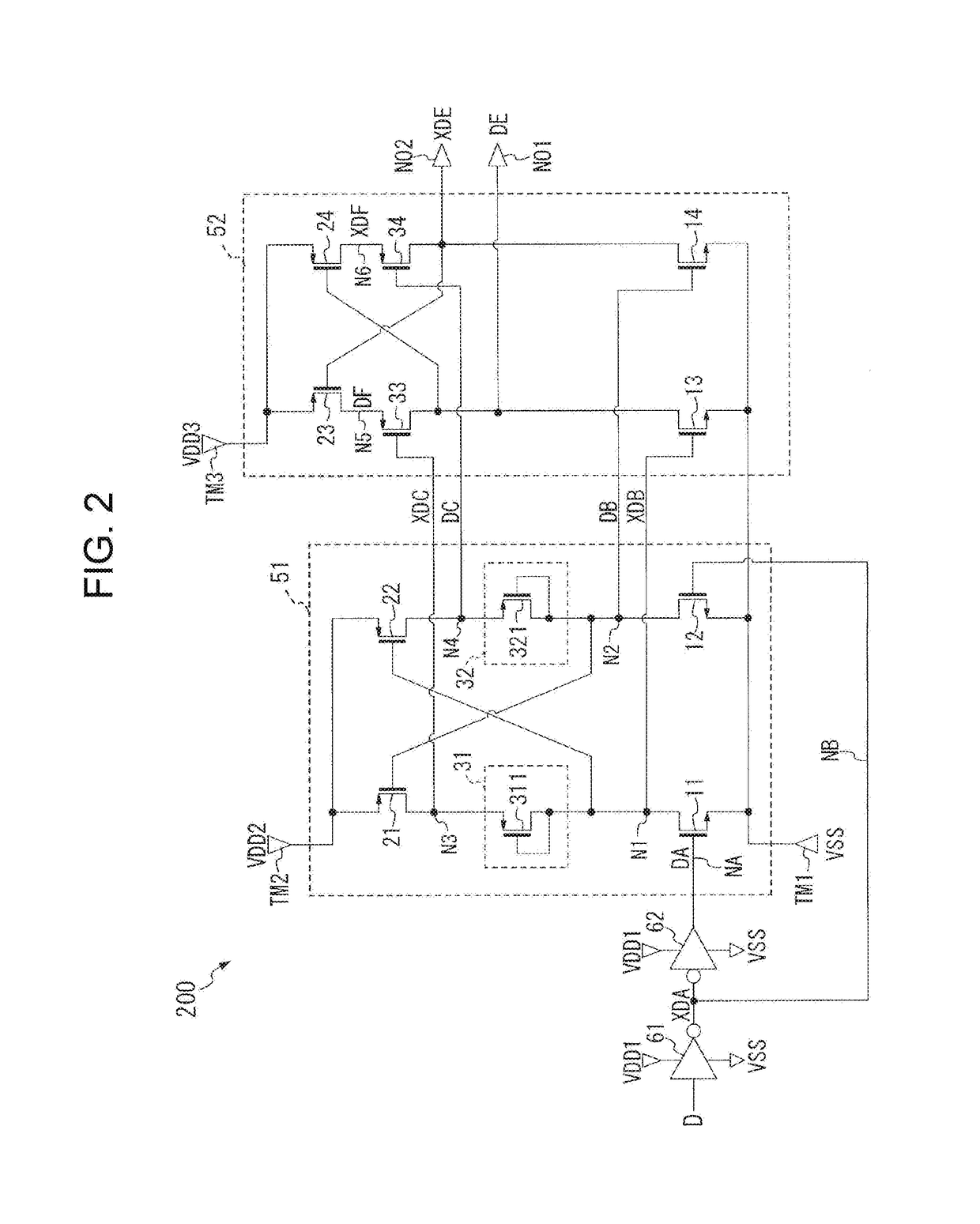

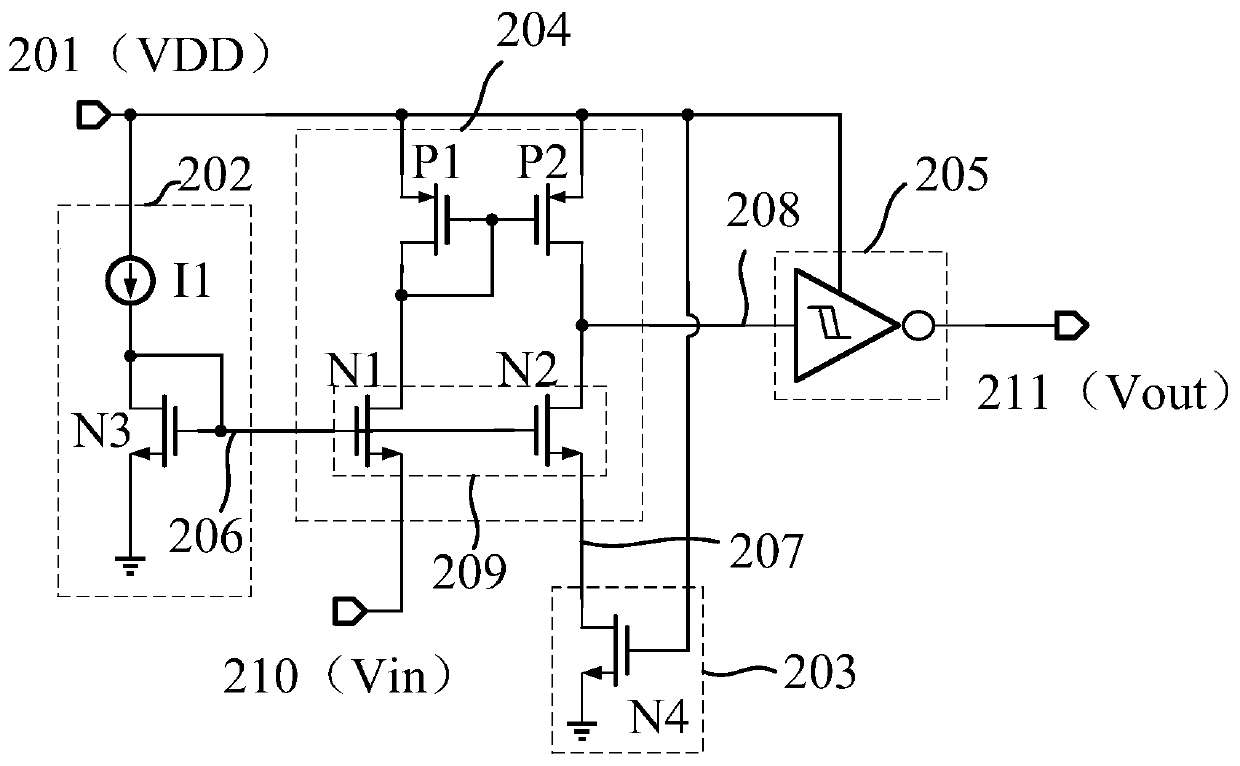

Level shift circuit and display driver

ActiveUS20170154568A1Reduce areaReduced drive capability requirementsStatic indicating devicesLogic circuits coupling/interface using field-effect transistorsPotential differenceEngineering

A level shift circuit configured to generate an output signal having higher amplitude than that of an input signal. The level shift circuit includes serially-connected first and second level shift circuit for two-step amplitude increase of the input signal. The first level shift circuit includes first to fourth transistors, each of which has a control terminal and first and second current terminals, and first and second resistance elements respectively connected between the first and third transistors, and between the second and fourth transistors. A potential difference between two ends of each resistance element is respectively smaller than, or no smaller than, a respective predetermined potential difference when a current does not flow, or flows, therethrough. The second level shift circuit has fifth to tenth transistors, each of which has a control terminal and first and second current terminals. The output signal is outputted through a connection between the second current terminals of the fifth and ninth transistors.

Owner:LAPIS SEMICON CO LTD

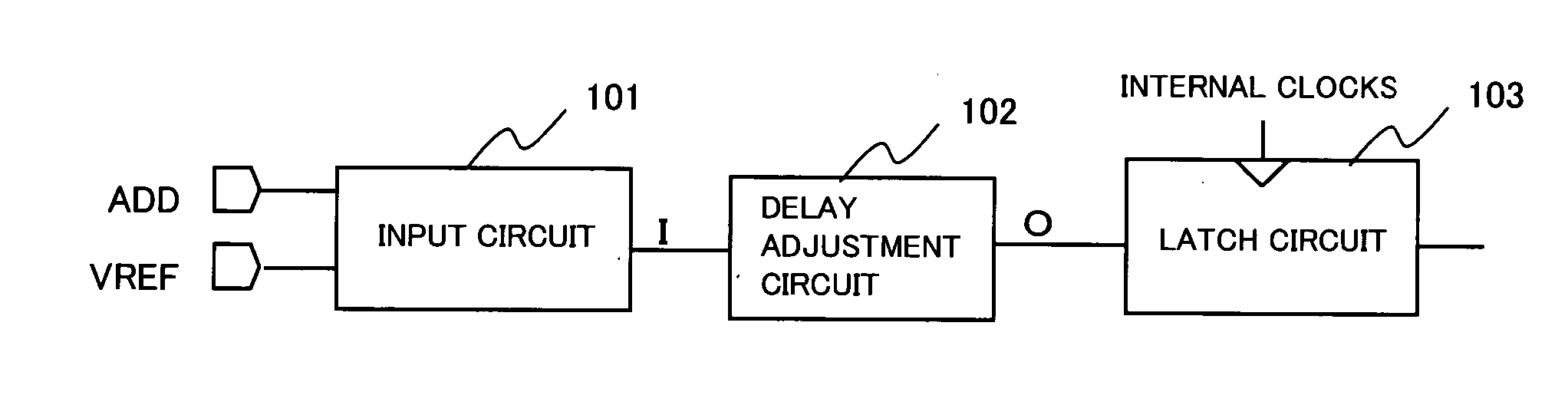

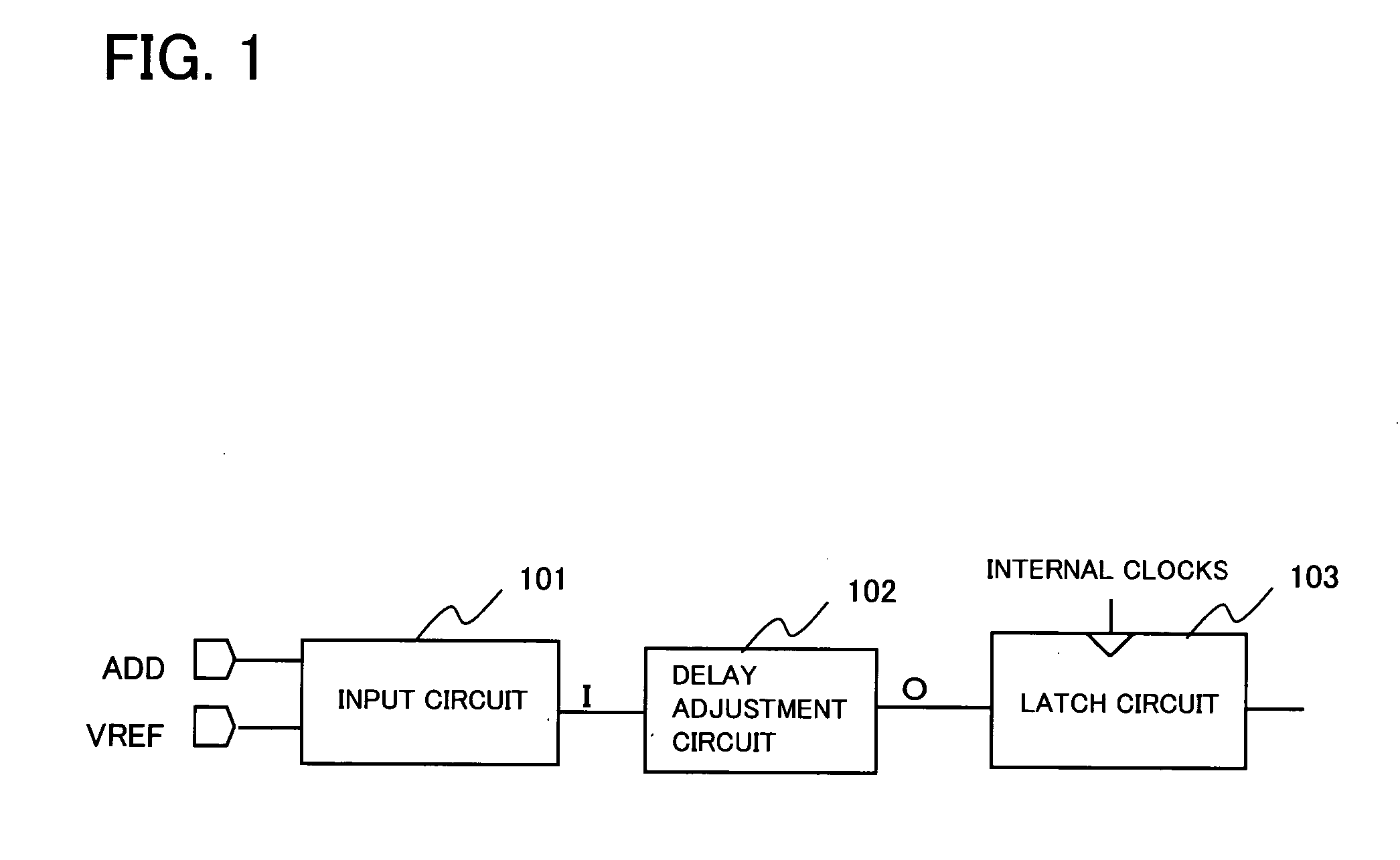

Delay adjustment circuit and synchronous semiconductor device having the delay adjustment circuit

InactiveUS20070046354A1Suppression capacitanceReduce capacitanceSingle output arrangementsTime-delay networksEngineeringSemiconductor

Disclosed is a delay adjustment circuit including a first set of transistors, which are connected between a PMOS transistor forming an inverter and a power supply in parallel and have gates supplied with control signals, respectively, a second set of transistors which are connected between an NMOS transistor forming the inverter, and the ground GND, in parallel and have gates supplied with control signals, respectively, and another inverter receiving an output of the inverter as an input. At least one of the transistors of the first set of transistors and at least one of the transistors of the second set of transistors are set in an on-state.

Owner:ELPIDA MEMORY INC

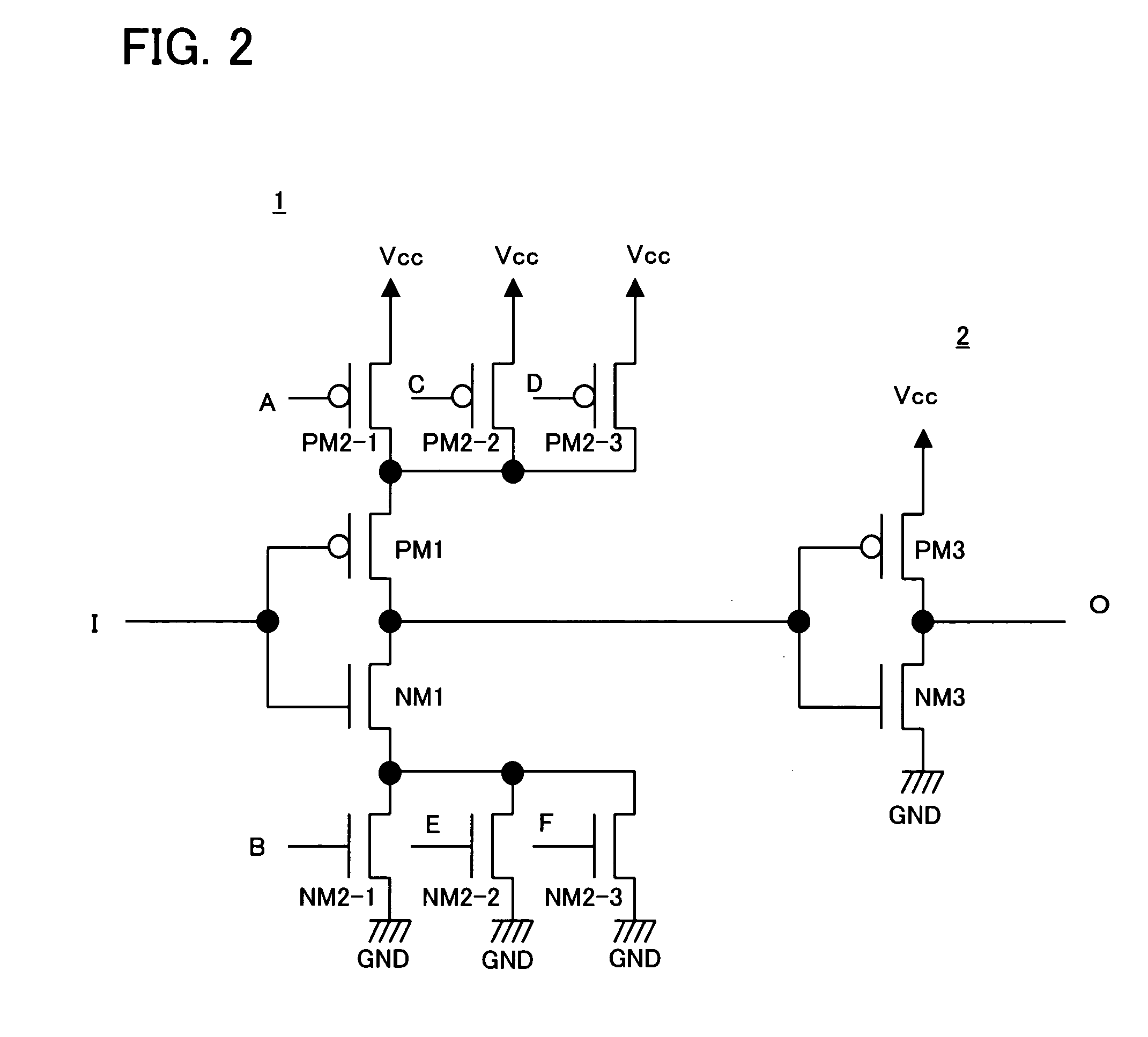

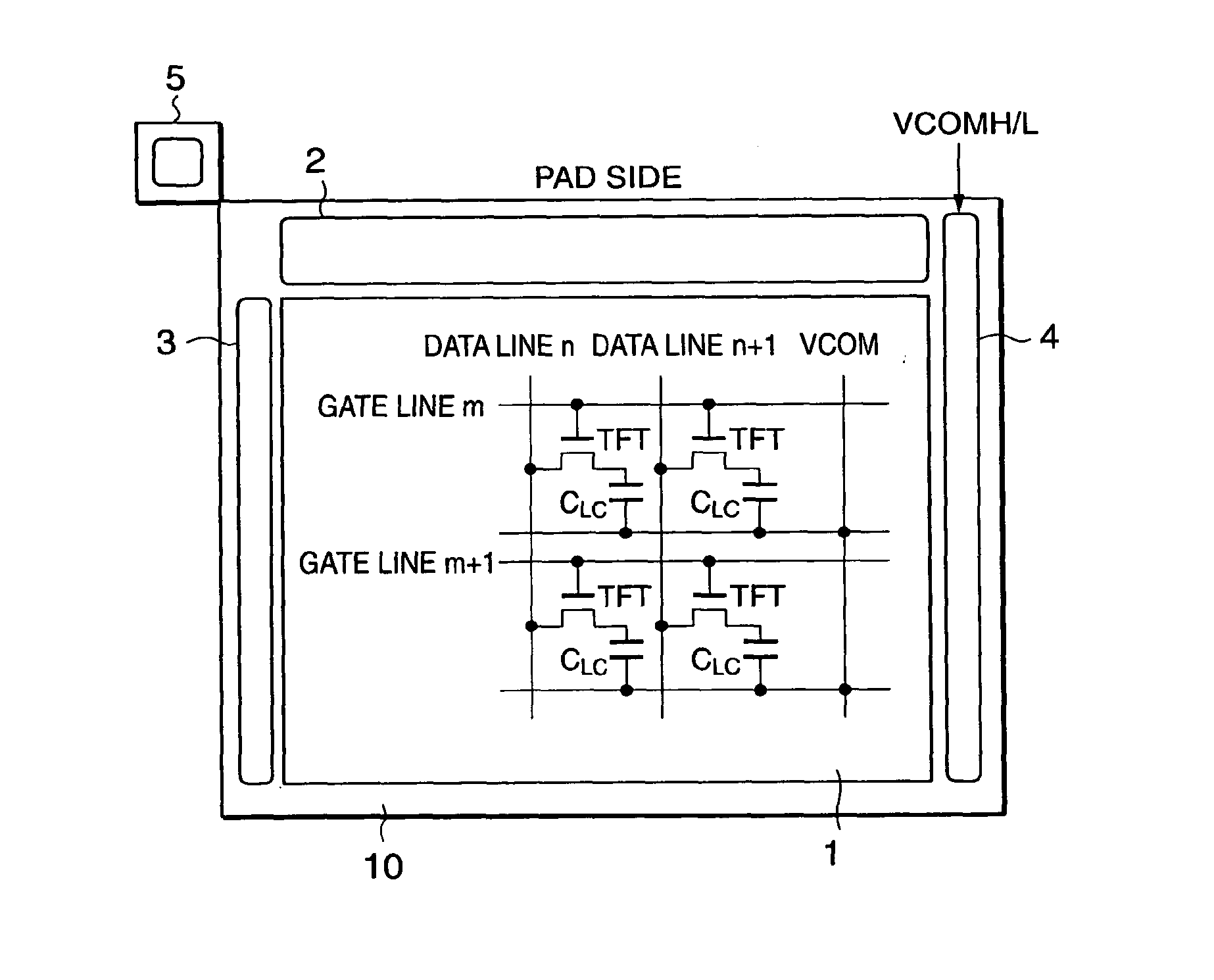

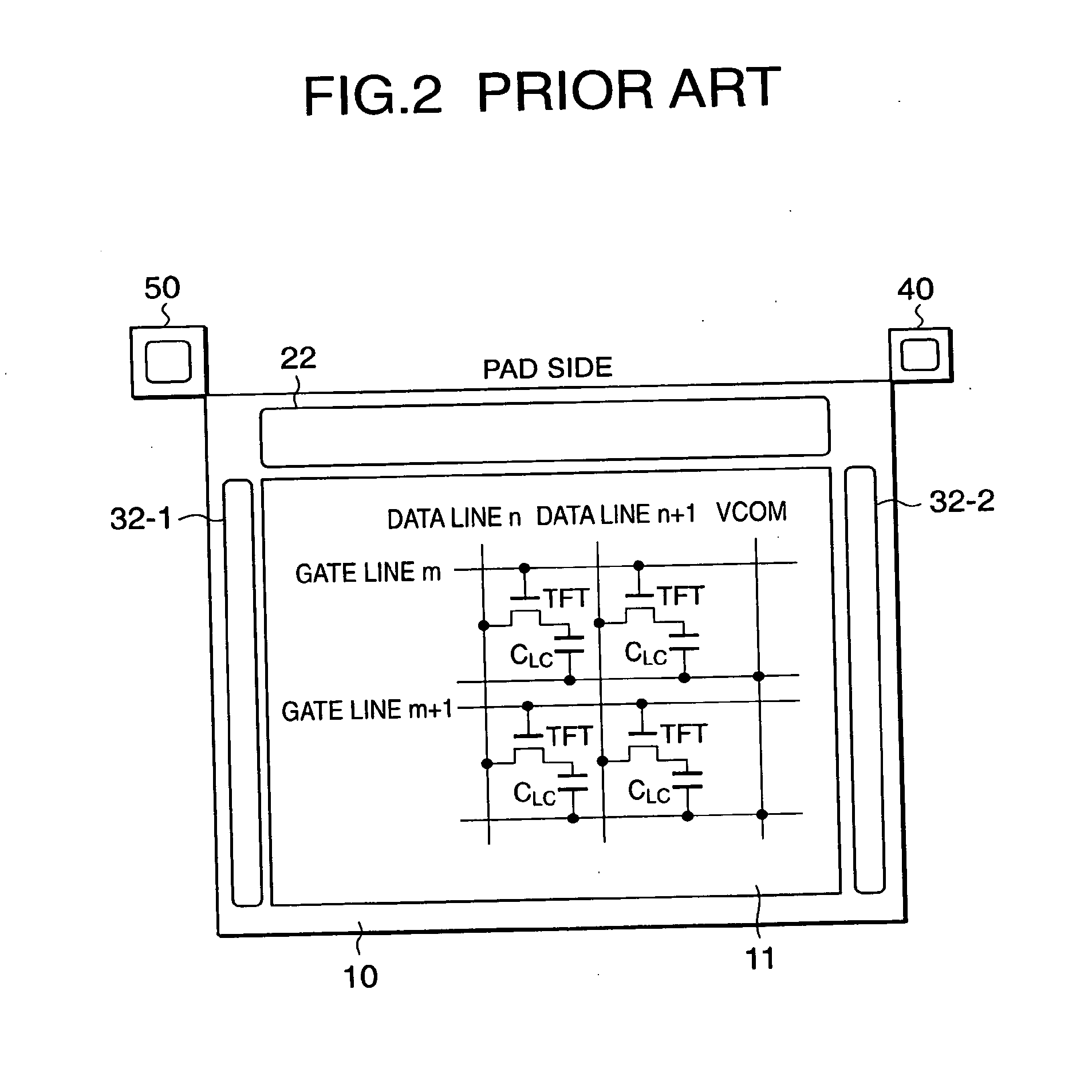

Driving circuit and voltage generating circuit and display unit using the same

ActiveUS20120212471A1Reduced drive capability requirementsLower on-resistanceCathode-ray tube indicatorsInput/output processes for data processingDriver circuitLiquid-crystal display

To provide a liquid crystal display capable of implementing a symmetrical frame and a narrower frame without lowering drive capability of a common drive circuit.[Solution]A liquid crystal display substrate 10 has a data driver circuit 2 and a gate driver circuit 3 for driving the liquid crystal display integrated thereon together with a common drive circuit 4, where common voltages VCOMH and VCOML are applied from the outside through a pad. The gate driver circuit 3 is placed to be adjacent to one of the four terminals of the liquid crystal display. The common drive circuit 4 is placed to be adjacent to the terminal opposite to where the gate driver circuit 3 is placed and as close to the pad as possible while having almost the same width as the area of the gate driver circuit 3. The pad close to where the common drive circuit 4 is placed is used as the pad for applying the common voltages VCOMH and VCOML.

Owner:GOLD CHARM LTD

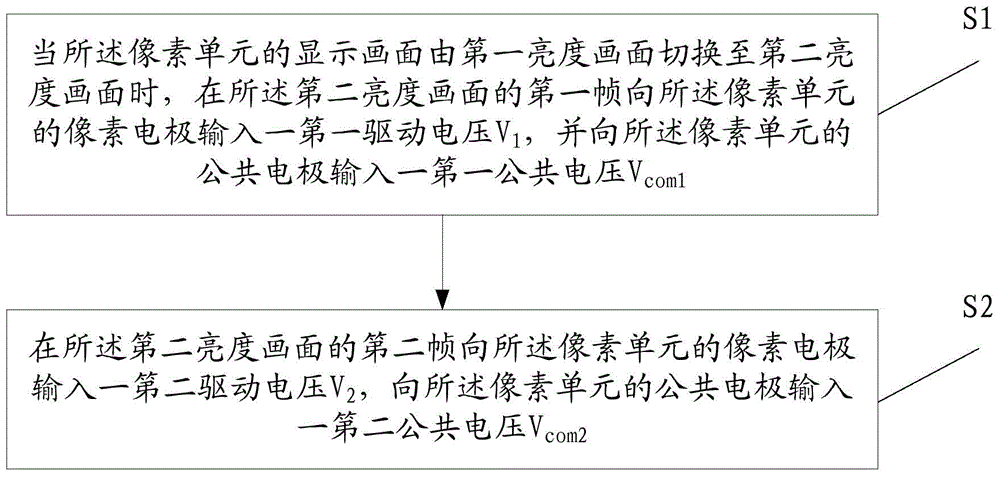

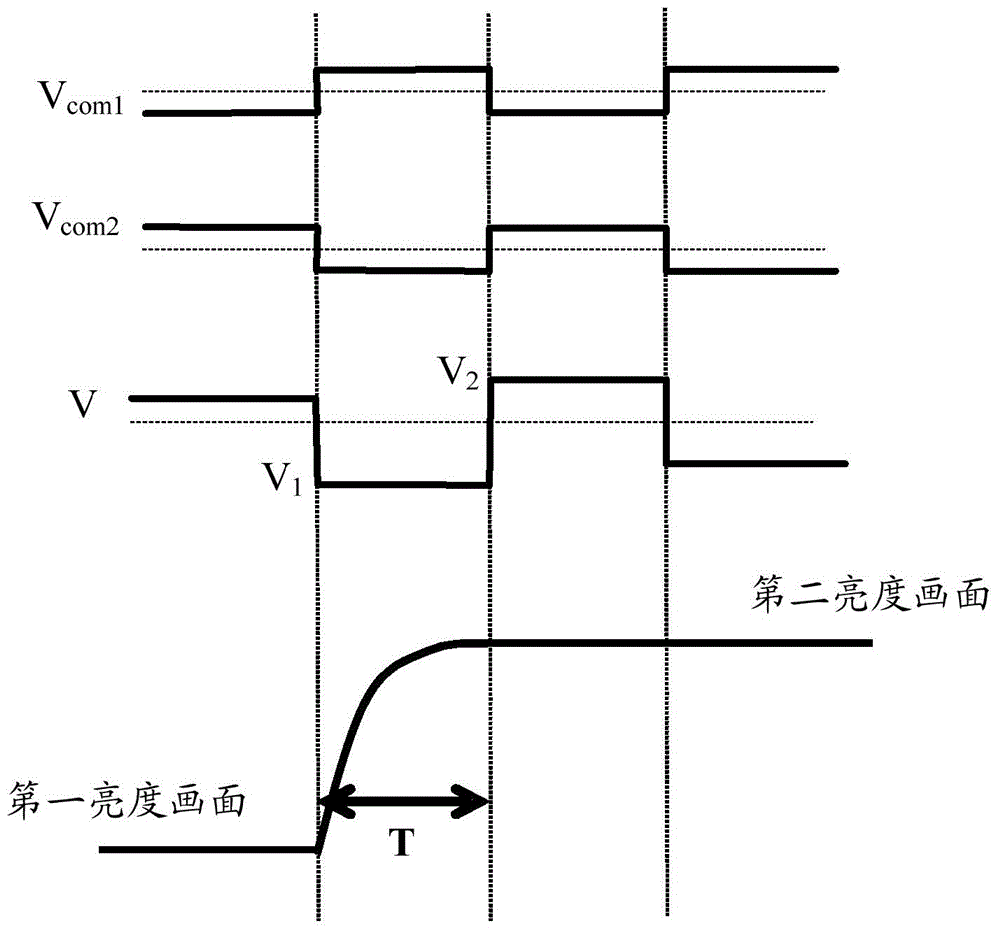

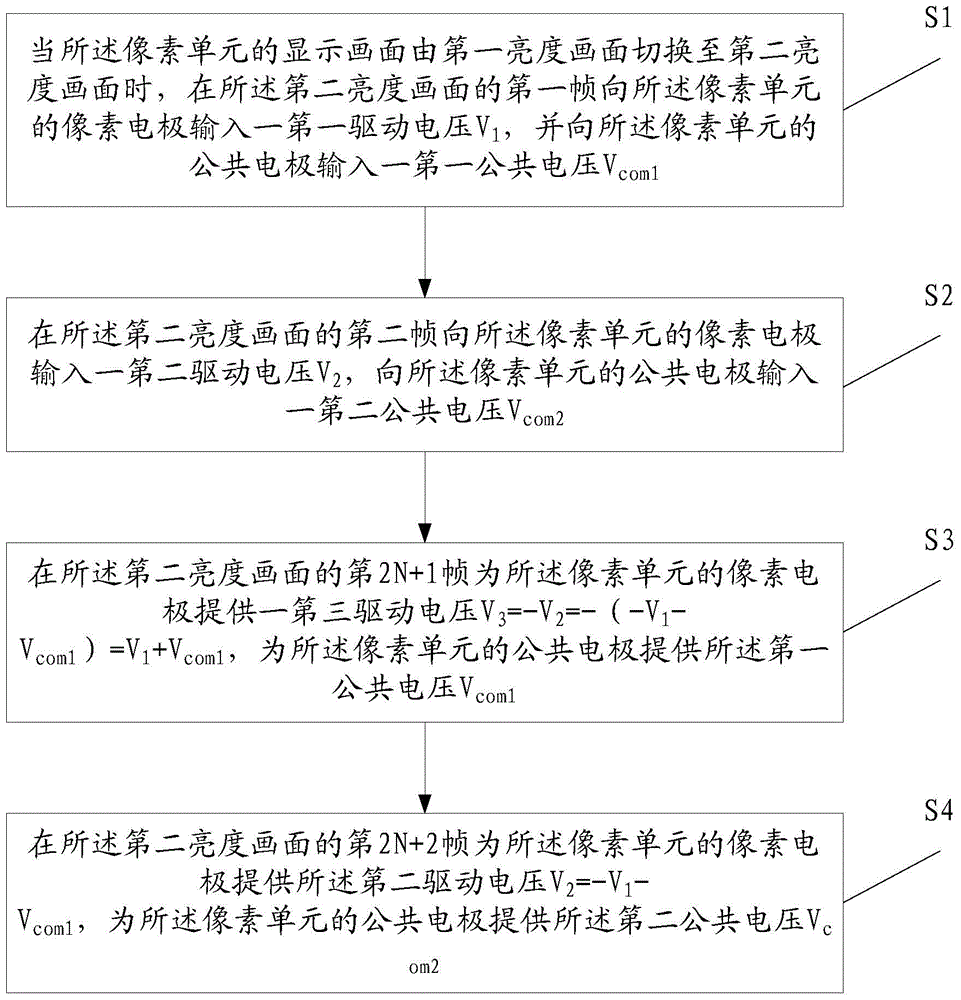

Liquid crystal display panel and driving method thereof

ActiveCN104882112ASolve the smear phenomenonImprove display qualityStatic indicating devicesLiquid-crystal displayComputer science

The invention discloses a liquid crystal display panel and a driving method thereof. The method comprises the steps that: when the display image of a pixel unit is switched from a first brightness image to a second brightness image, a first driving voltage V1 is input to a pixel electrode of the pixel unit at a first frame of the second brightness image, and a first common voltage Vcom1 is input to a common electrode of the pixel unit, wherein the phase of the first driving voltage V1 is opposite to the phase of the first common voltage Vcom1, and the absolute value of the voltage difference between the first driving voltage V1 and the first common voltage Vcom1 is an over-driving voltage value needed by finishing the switching from the first brightness image to the second brightness image in the responding time of one frame, so that each pixel unit in the liquid crystal display panel is enabled to finish the switching from the first brightness image to the second brightness image in the responding time of one frame. Thus, a streaking phenomenon of the liquid crystal display panel in the prior art is prevented, and the display quality of the liquid crystal display panel is improved.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

Semiconductor memory device and control method for semiconductor memory device

InactiveUS20060007756A1Extended access timeOccurrence probabilityRead-only memoriesDigital storageStart timeControl signal

Provided is a semiconductor memory device using a single-bit line method that determines read operation timing in accordance with operation of a replica bit line. Further provided is a control method for the semiconductor memory device. Even when a transistor property fluctuation has occurred, the semiconductor memory device and the control method are capable of preventing, for example, increases in access time and circuit size and concurrently capable of reducing the occurrence probability of data readout error. The gate lengths of replica memory cell transistors are set as being values greater than the gate length of memory cell transistors. Thereby, a distribution center of a current drive capability distribution of the replica memory cell transistors is set lower than a distribution center of a current drive capability distribution of the memory cell transistors. Consequently, an occurrence probability of a delay in a voltage-fall start time on a regular data line can be reduced to be lower in comparison to a transmission timing of a latch control signal.

Owner:SOCIONEXT INC

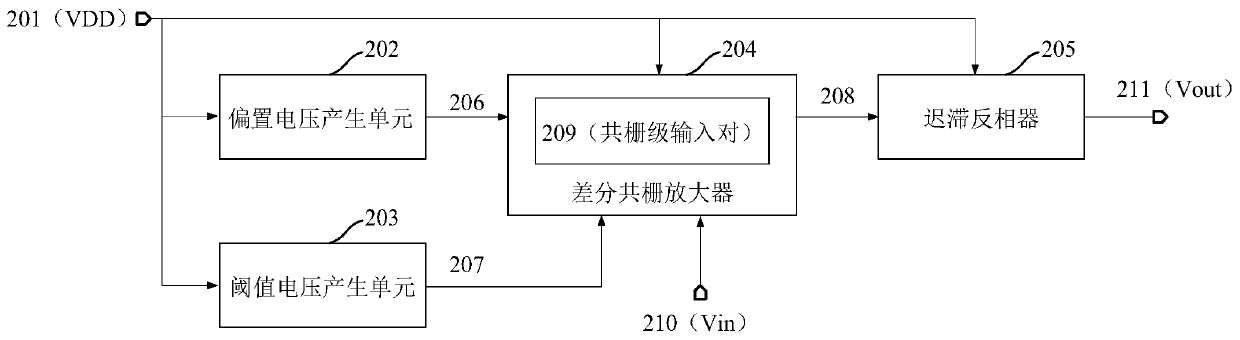

Level conversion circuit and level conversion method

InactiveCN110729995AFlexible designLower requirementLogic circuits coupling/interface using field-effect transistorsLevel shiftingHemt circuits

The invention discloses a level conversion circuit and a level conversion method. The level conversion circuit comprises a current mirror, a first NMOS transistor and a second NMOS transistor, gates of the first NMOS transistor and the second NMOS transistor are connected to the same bias voltage. A drain electrode of the first NMOS tube is connected with one side of the current mirror, and the drain electrode of the second NMOS tube is connected with the other side of the current mirror. The source electrode of the first NMOS transistor is connected with an input voltage, and the source electrode of the second NMOS transistor is connected with a threshold voltage; the first NMOS transistor and the second NMOS transistor convert the input voltage and the threshold voltage into corresponding currents respectively and input the currents to the two sides of the current mirror; the current mirror compares two currents input from the first NMOS tube and the second NMOS tube, converts the two currents into corresponding voltages and outputs the voltages from the other side of the current mirror; the first input end of the hysteresis inverter is connected with voltage output by the current mirror, and the second input end is connected with power supply voltage; and when the input voltage is greater than the threshold voltage, the voltage output by the current mirror is zero, and the output voltage of the hysteresis inverter is the power supply voltage. According to the invention, the requirement on an input signal is reduced, and level conversion is realized.

Owner:HUAZHONG UNIV OF SCI & TECH

Semiconductor memory device and method of controlling power source

InactiveUS7872927B2Reduced drive capability requirementsTimely controlRead-only memoriesDigital storageVoltage generatorControl power

A voltage generator that monitors a writing margin as a control amount in order to carry out an optimum power source control when control of a SRAM cell power source is carried out at writing operation, and always keeps the writing margin constant; and a power source selector are included to switch power source voltage at writing. By switching the power source voltage at writing, a semiconductor memory device in which a stable writing operation is achieved without largely deteriorating writing time in the SRAM cell and an ultrahigh speed operation or ultralow power operation can be carried out is obtained.

Owner:NEC CORP

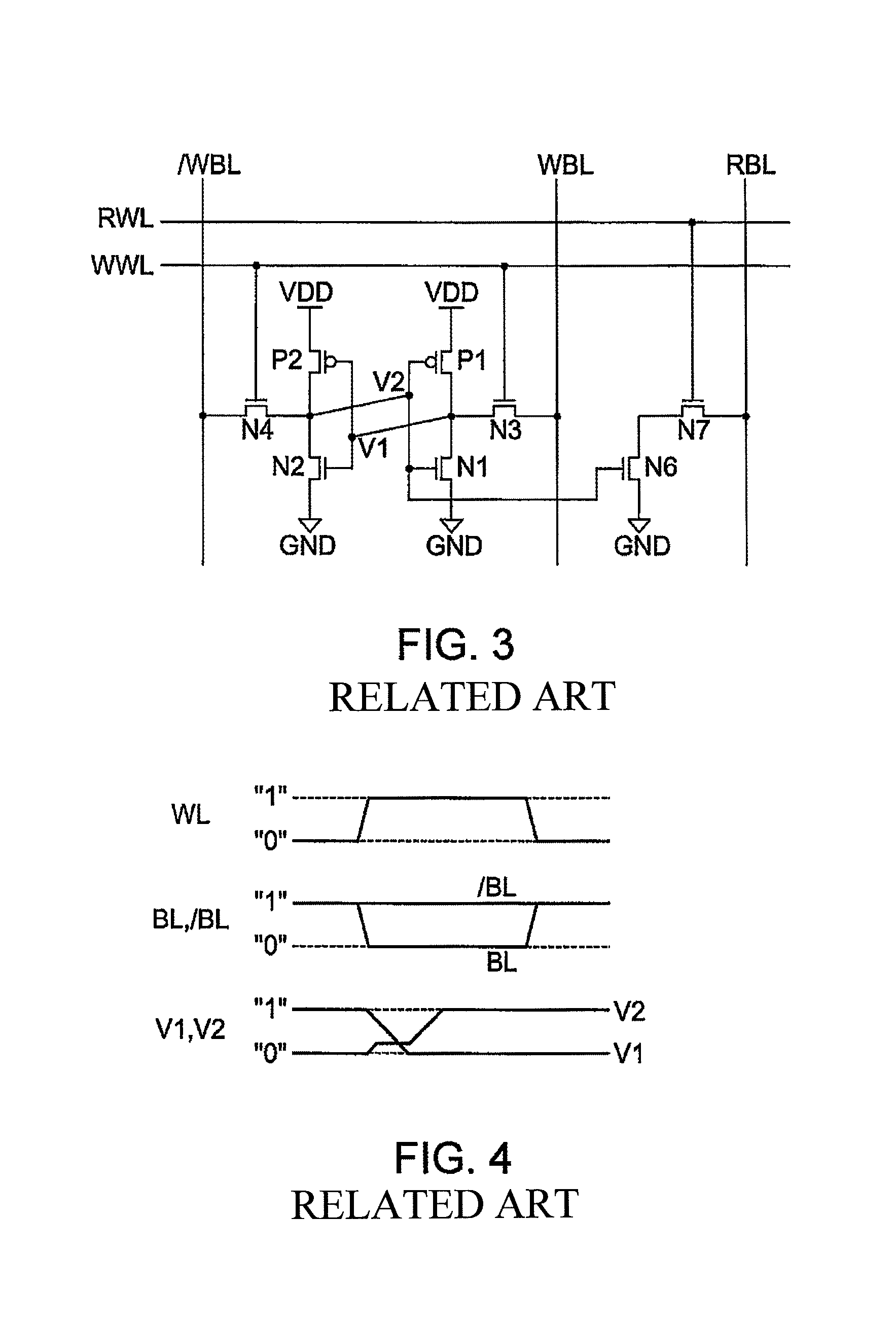

Power battery pre-charging switch device based on IGBT module

ActiveCN110406381AImprove execution speedQuick response to control signalsCharging stationsElectric devicesMicrocontrollerPower battery

The invention discloses a power battery pre-charging switch device based on an IGBT module. The power battery pre-charging switch device is used for controlling the on / off of a pre-charging branch circuit of a power battery. The power battery pre-charging switch device comprises a low-voltage auxiliary power supply, a microcontroller, a low-voltage control circuit, a disconnector power supply, a gate drive circuit and the IGBT module, wherein the IGBT module is connected in the pre-charging branch circuit; the low-voltage auxiliary power supply is connected to the disconnector power supply through the low-voltage control circuit, and suitable for providing a low-voltage power supply to the disconnector power supply; the microcontroller is connected to the low-voltage control circuit, and suitable for controlling the on / off of the low-voltage control circuit; the disconnector power supply is connected to the gate drive circuit; and the gate drive circuit is connected to the IGBT module.The power battery pre-charging switch device based on the IGBT module uses the IGBT module as an execution switch so as to not only enhance the real-time performance of the pre-charging switch operation but also reduce the requirement on the driving capability of the microcontroller. In addition, the power battery pre-charging switch device has good electromagnetic compatibility, and also has thedevelopment advantages of miniaturization, low cost and the like.

Owner:常州是为电子有限公司

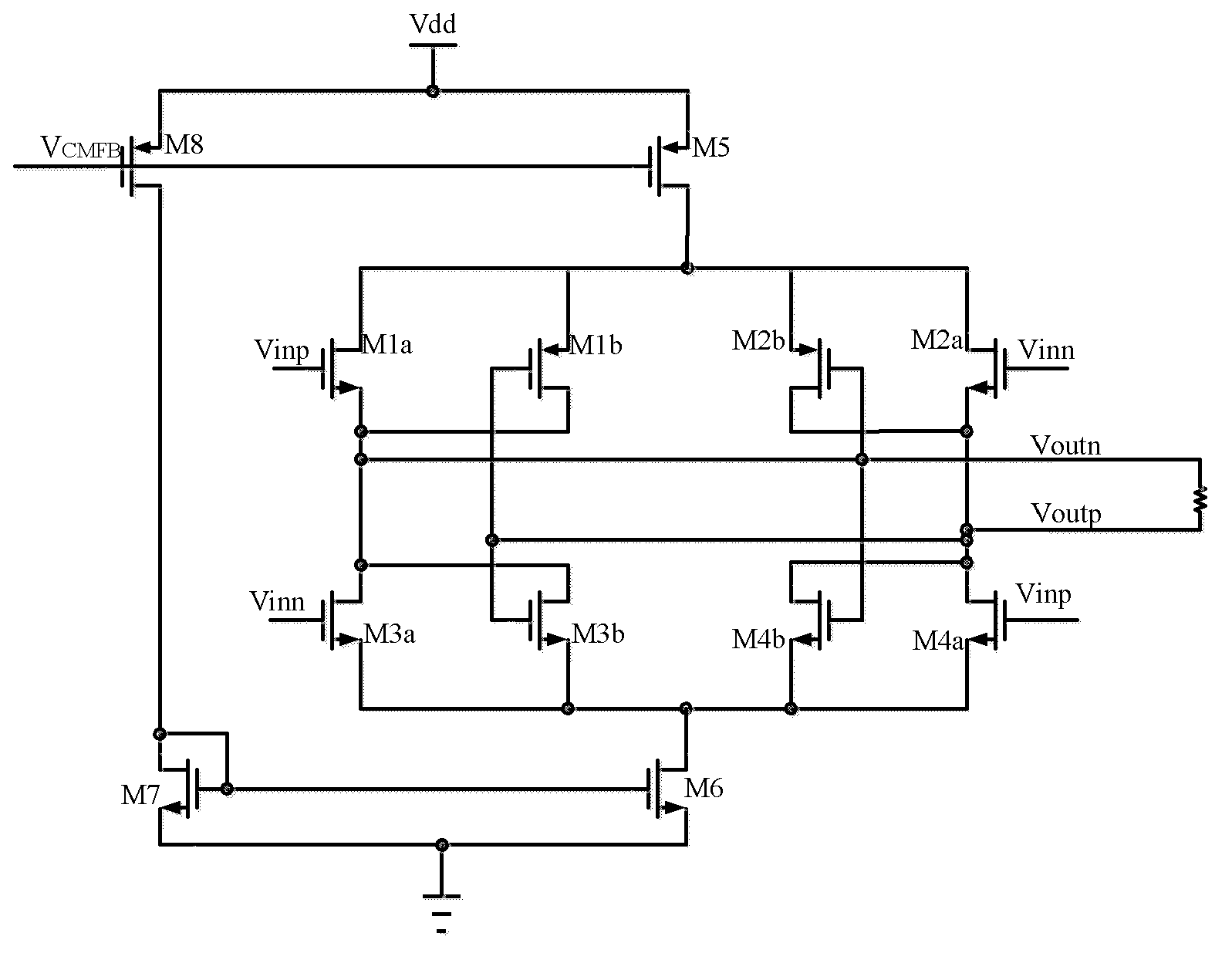

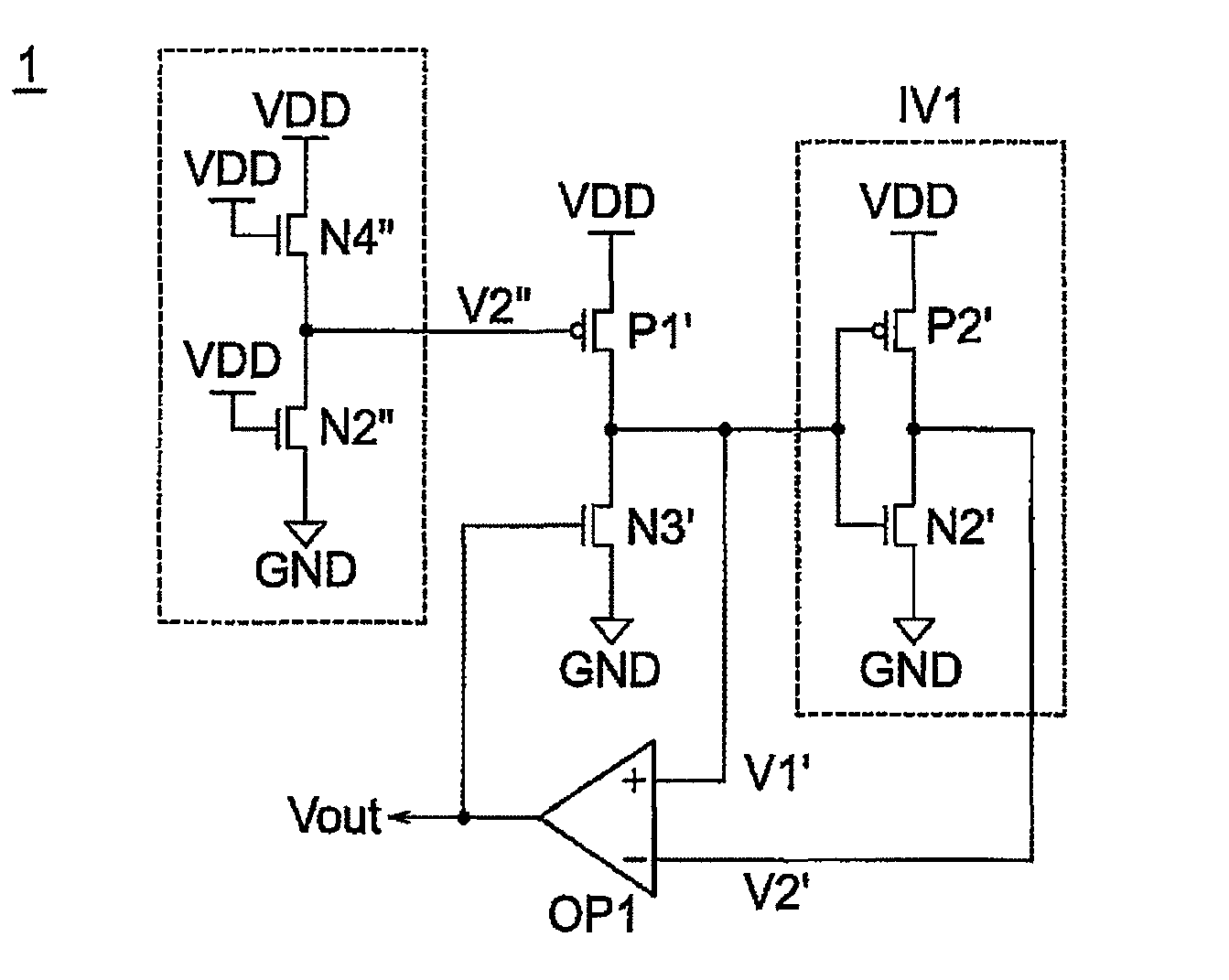

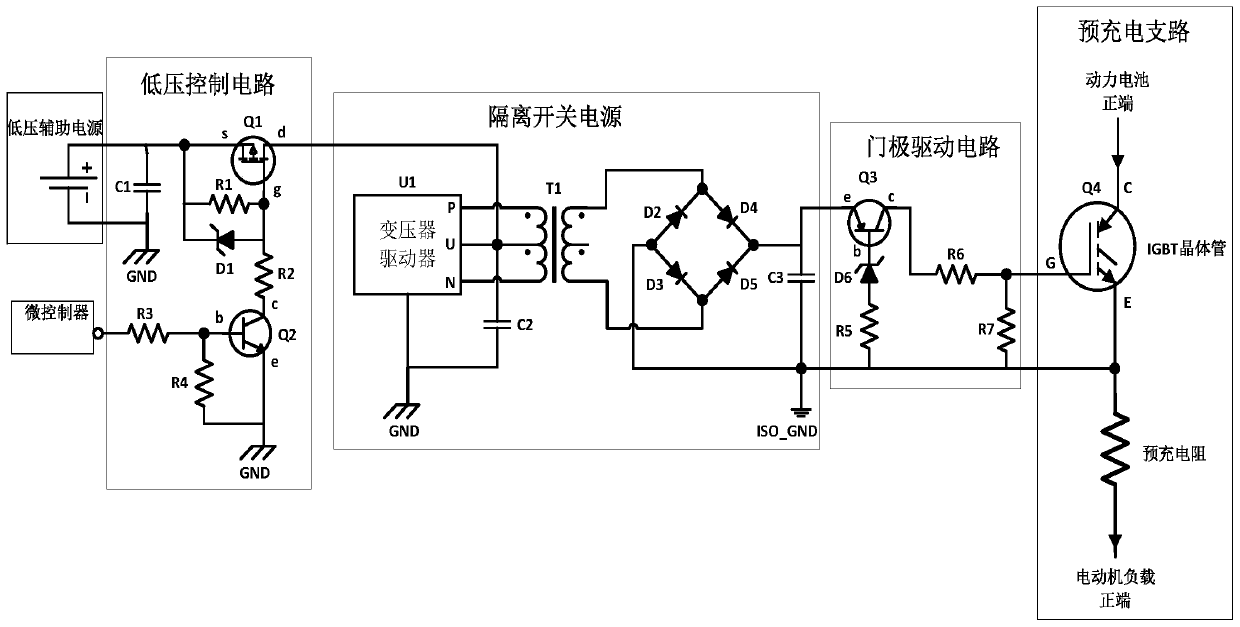

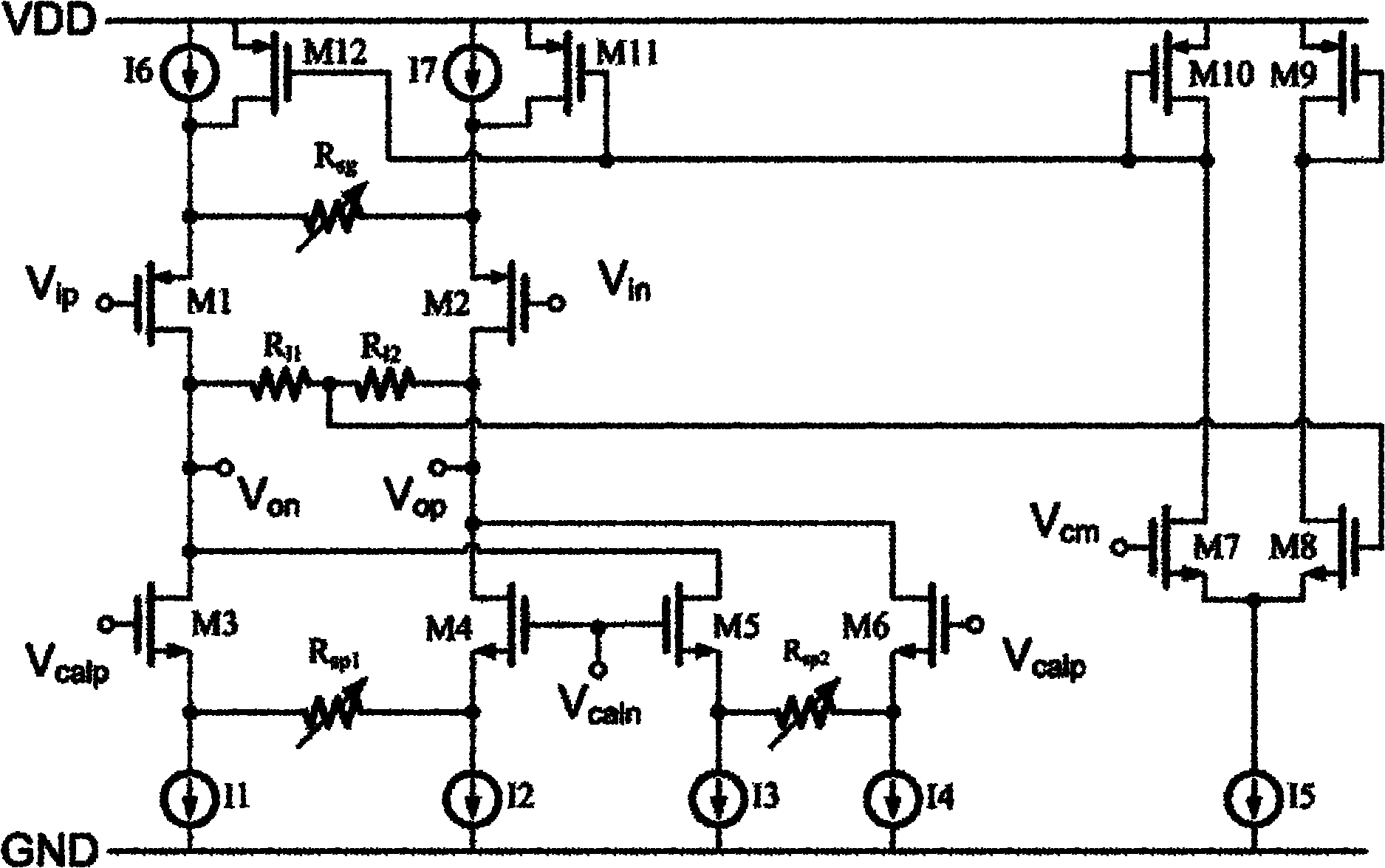

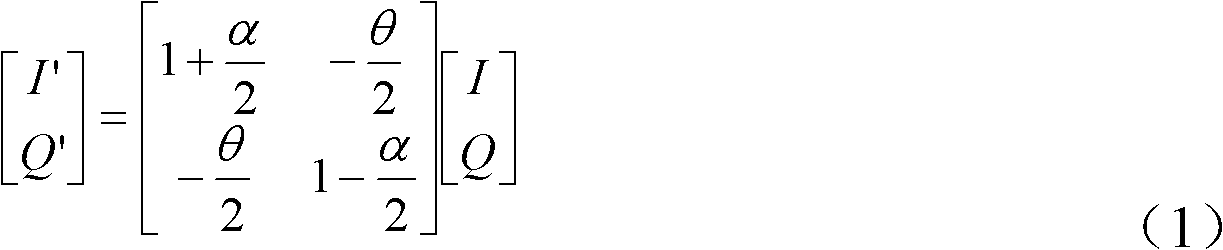

Mismatch calibrating device for I and Q channel signals of orthogonal down-conversion receiver

ActiveCN102185622AReduced drive capability requirementsGood mismatch calibration performanceTransmissionElectrical resistance and conductanceFrequency conversion

The invention discloses a mismatch calibrating device for I and Q channel signals of an orthogonal down-conversion receiver, which belongs to the technical field of frequency conversion receiver calibration. The device comprises two calibrating modules with same structures of an I channel and a Q channel, wherein each calibrating module comprises twelve MOS (Metal Oxide Semiconductor) transistors M1-M12, two load resistors R11 and R12, three adjustable resistors Rsp1, Rsp2 and Rsg and seven bias current sources I1-I7. The phase mismatch of I and Q channel signals of the orthogonal down-conversion receiver can be calibrated by adjusting resistance values of the first adjustable resistor Rsp1 and the second adjustable resistor Rsp2; and the amplitude mismatch of the I and Q channel signals of the orthogonal down-conversion receiver can be calibrated by adjusting a resistance value of the third adjustable resistor Rsg. The calibrating device improves the capability for inhibiting an image signal of the frequency conversion receiver and reduces the error rate of the receiver. A calibrating method is simple.

Owner:TSINGHUA UNIV