Patents

Literature

188results about How to "Reduce etch time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

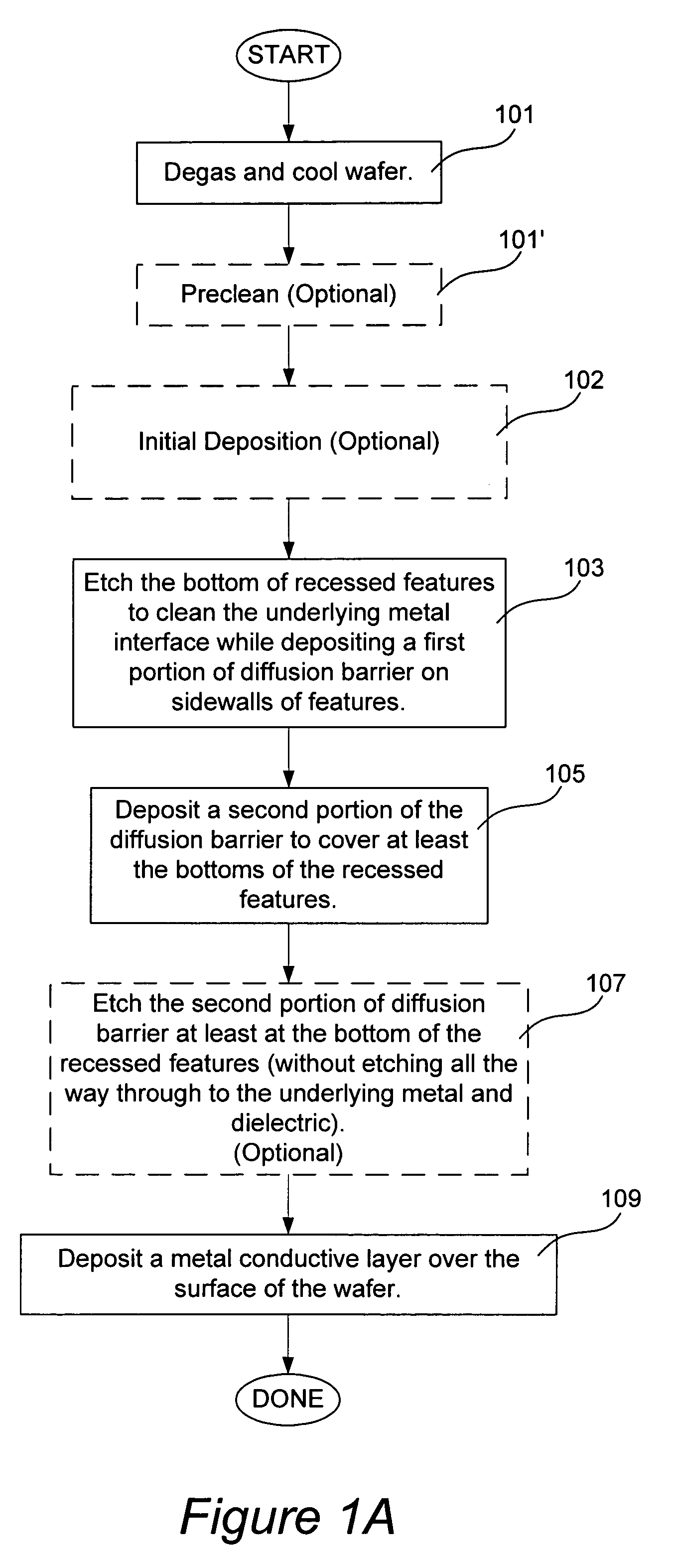

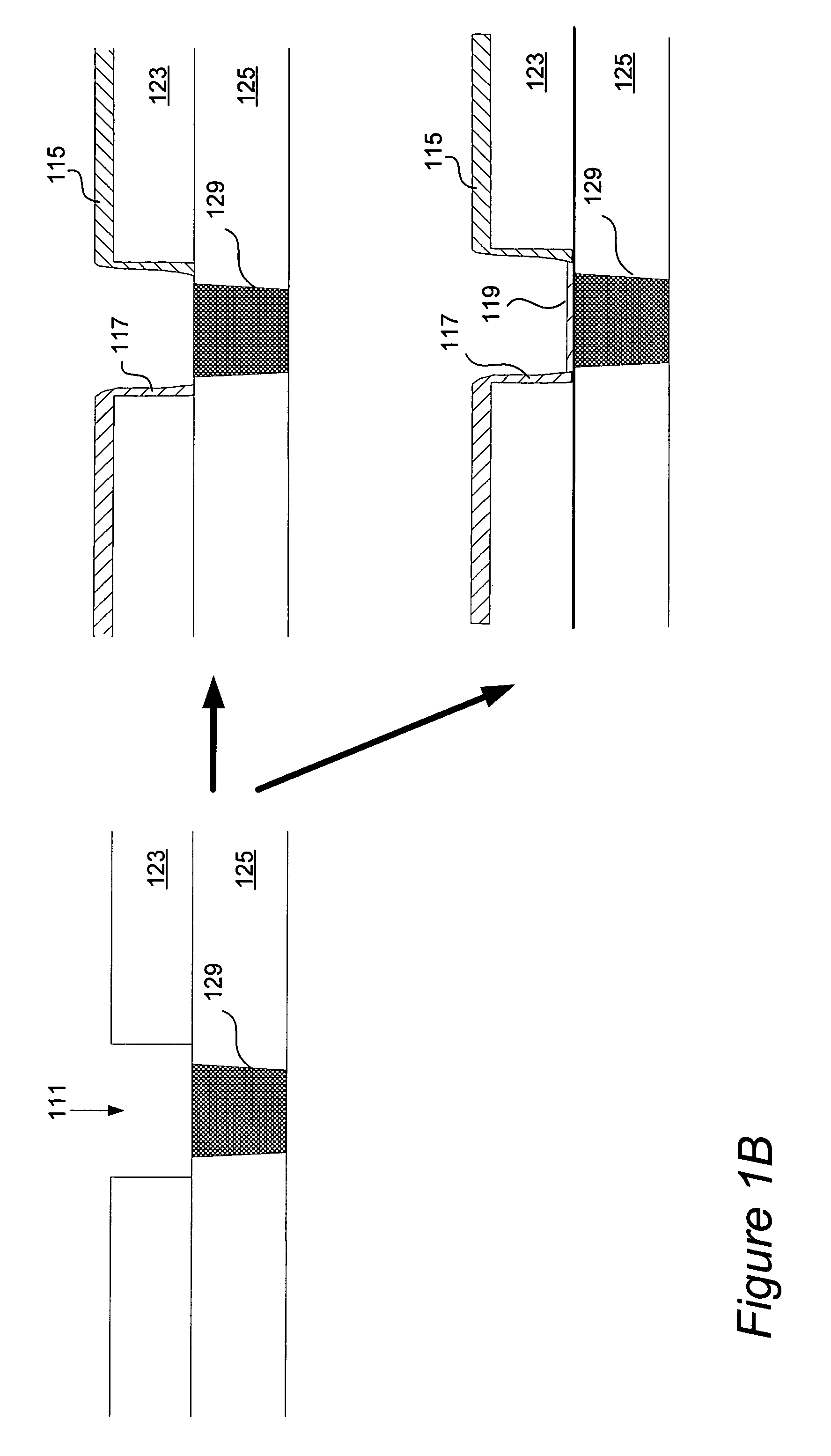

Barrier first method for single damascene trench applications

InactiveUS7186648B1Increase throughputHigh throughputSemiconductor/solid-state device manufacturingMetal interconnectEtching

Methods for forming a diffusion barrier on low aspect features of an integrated circuit include at least three operations. The first operation deposits a barrier material and simultaneously etches a portion of an underlying metal at the bottoms of recessed features of the integrated circuit. The second operation deposits barrier material to provide some minimal coverage over the bottoms of the recessed features. The third operation deposits a metal conductive layer. Controlled etching is used to selectively remove barrier material from the bottom of the recessed features, either completely or partially, thus reducing the resistance of subsequently formed metal interconnects.

Owner:NOVELLUS SYSTEMS

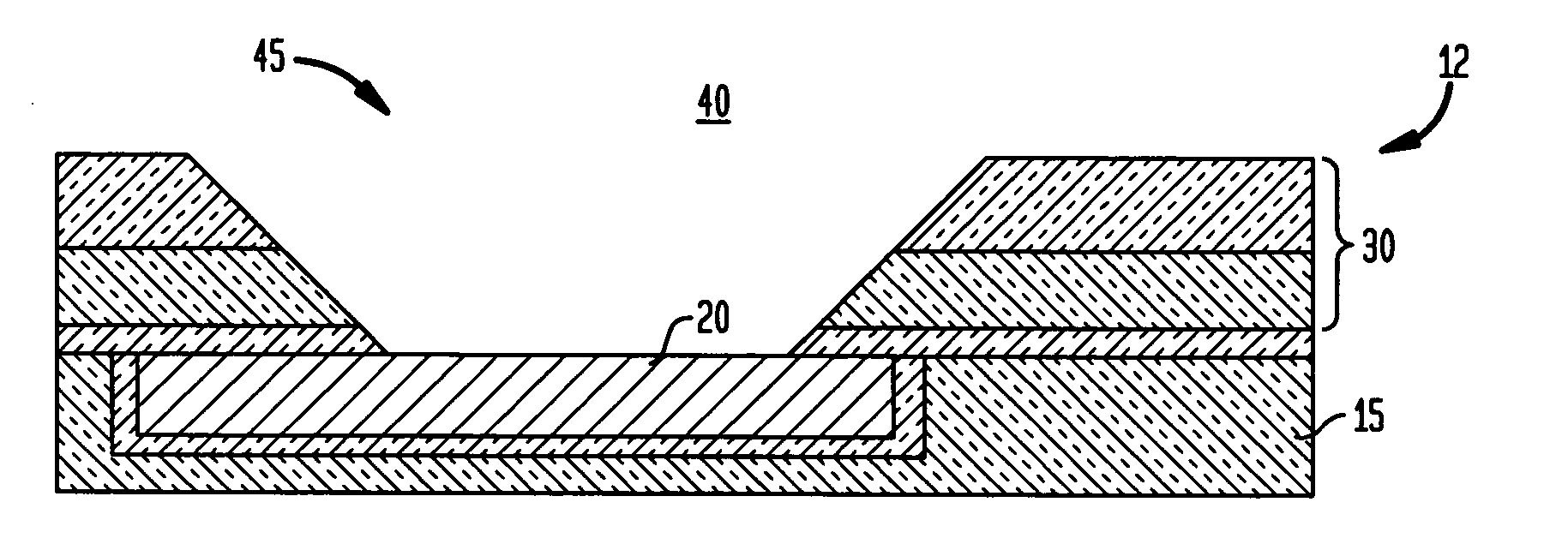

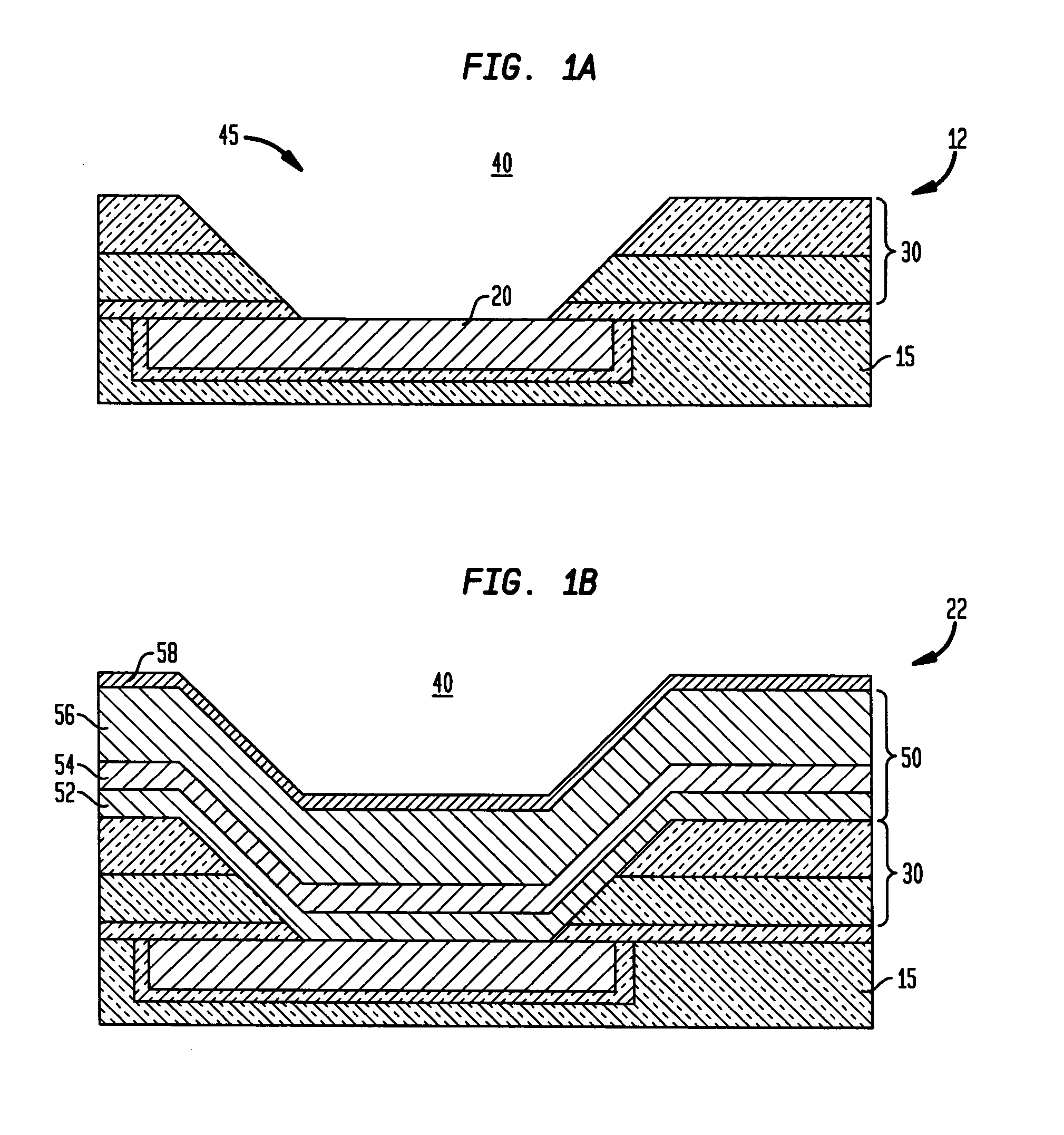

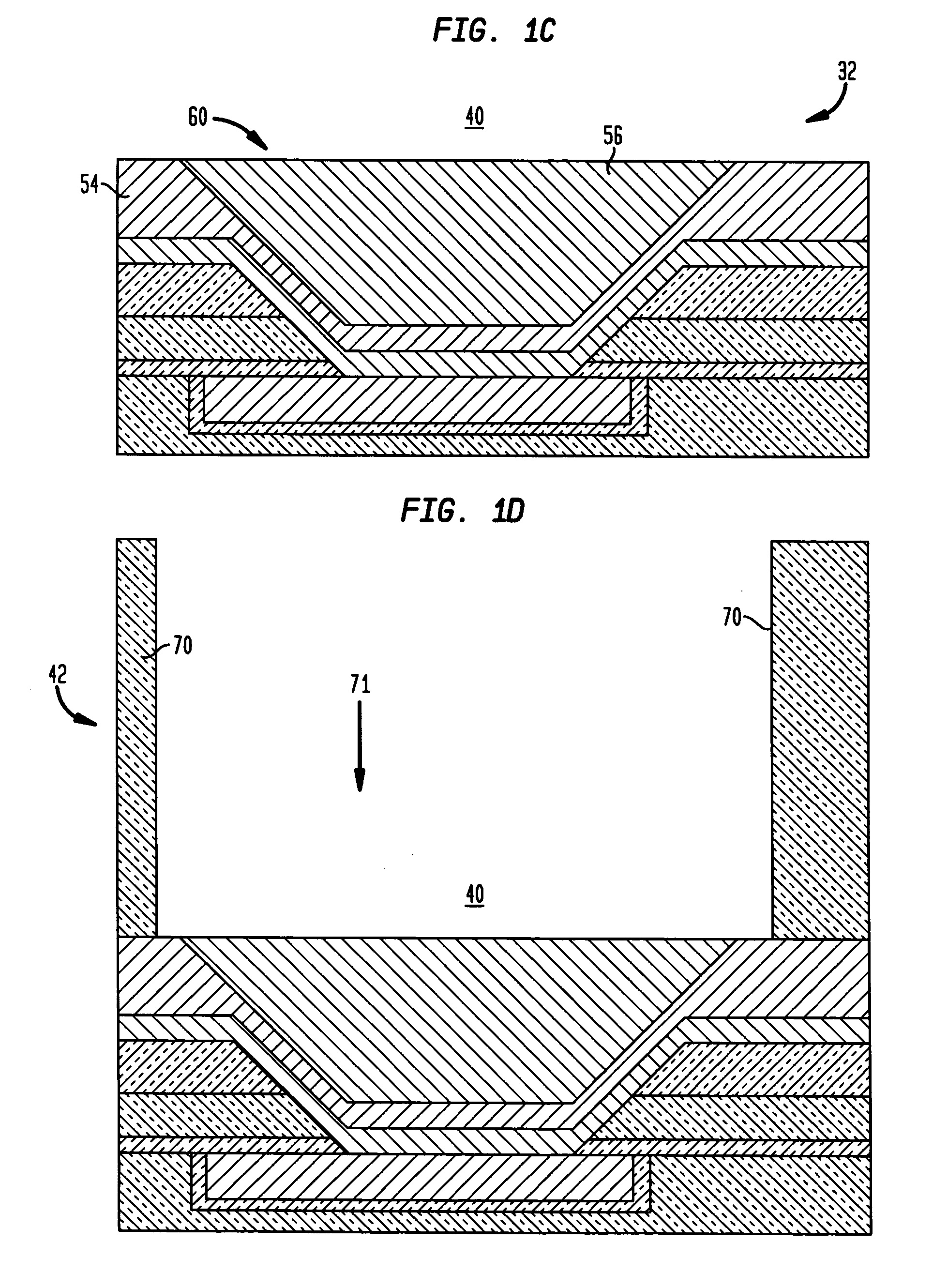

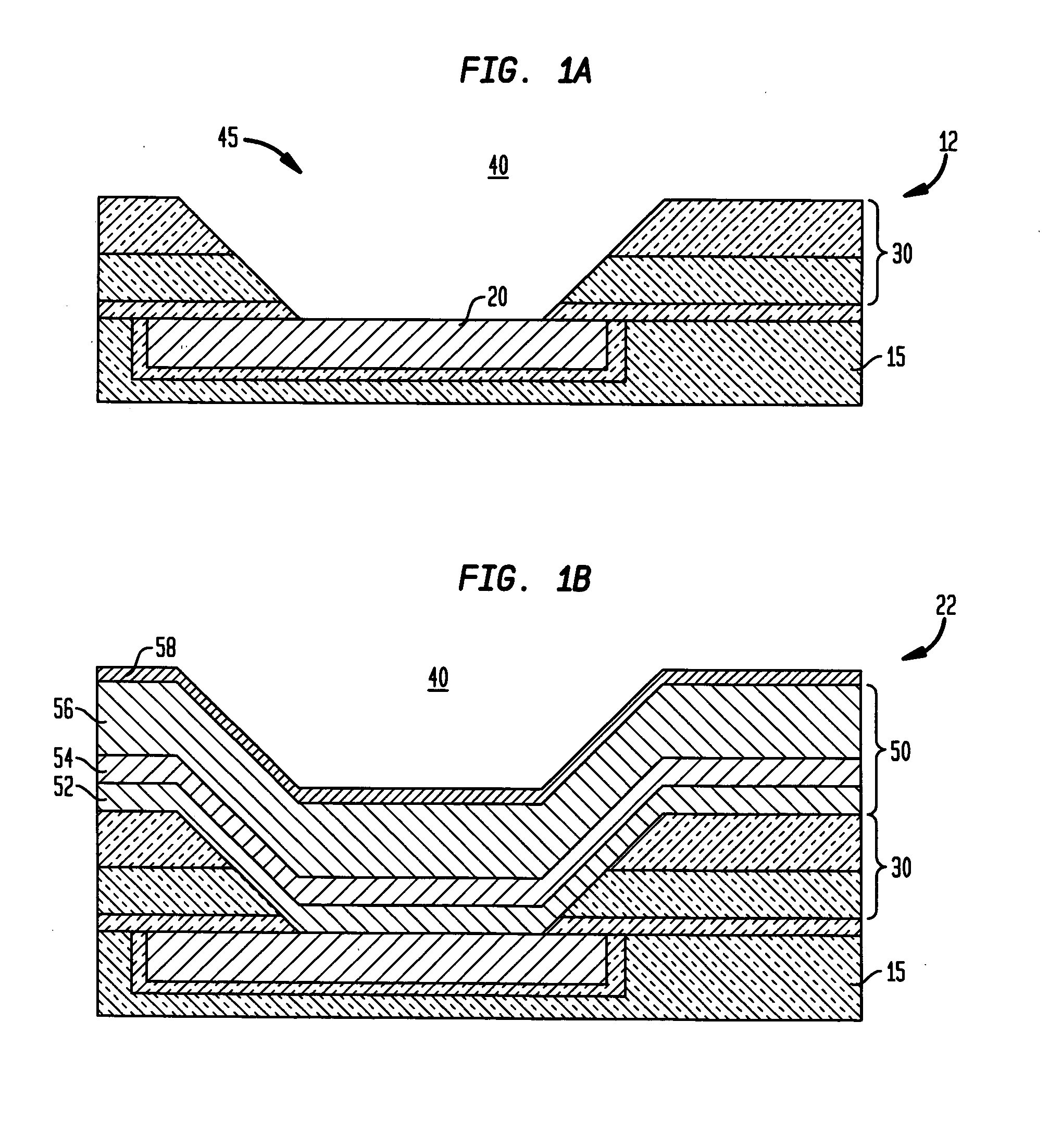

Damascene patterning of barrier layer metal for C4 solder bumps

InactiveUS20060016861A1Reduce the amount presentReduce spacingPrinted circuit assemblingSemiconductor/solid-state device detailsEtchingCopper

A system and method for forming a novel C4 solder bump for BLM (Ball Limiting Metallurgy) includes a novel damascene technique is implemented to eliminate the Cu undercut problem and improve the C4 pitch. In the process, a barrier layer metal stack is deposited above a metal pad layer. A top layer of the barrier layer metals (e.g., Cu) is patterned by CMP. Only bottom layers of the barrier metal stack are patterned by a wet etching. The wet etch time for the Cu-based metals is greatly reduced resulting in a reduced undercut. This allows the pitch of the C4 solder bumps to be reduced. An alternate method includes use of multiple vias at the solder bump terminal.

Owner:GLOBALFOUNDRIES INC

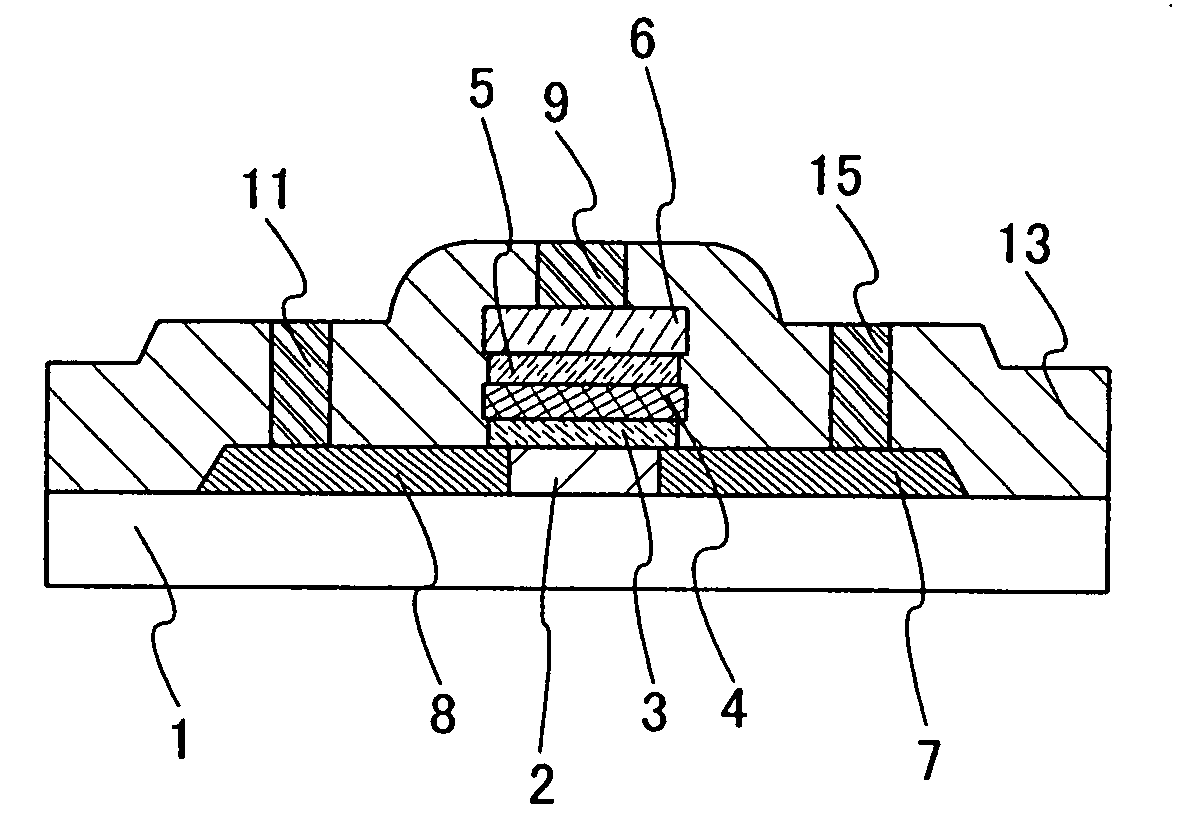

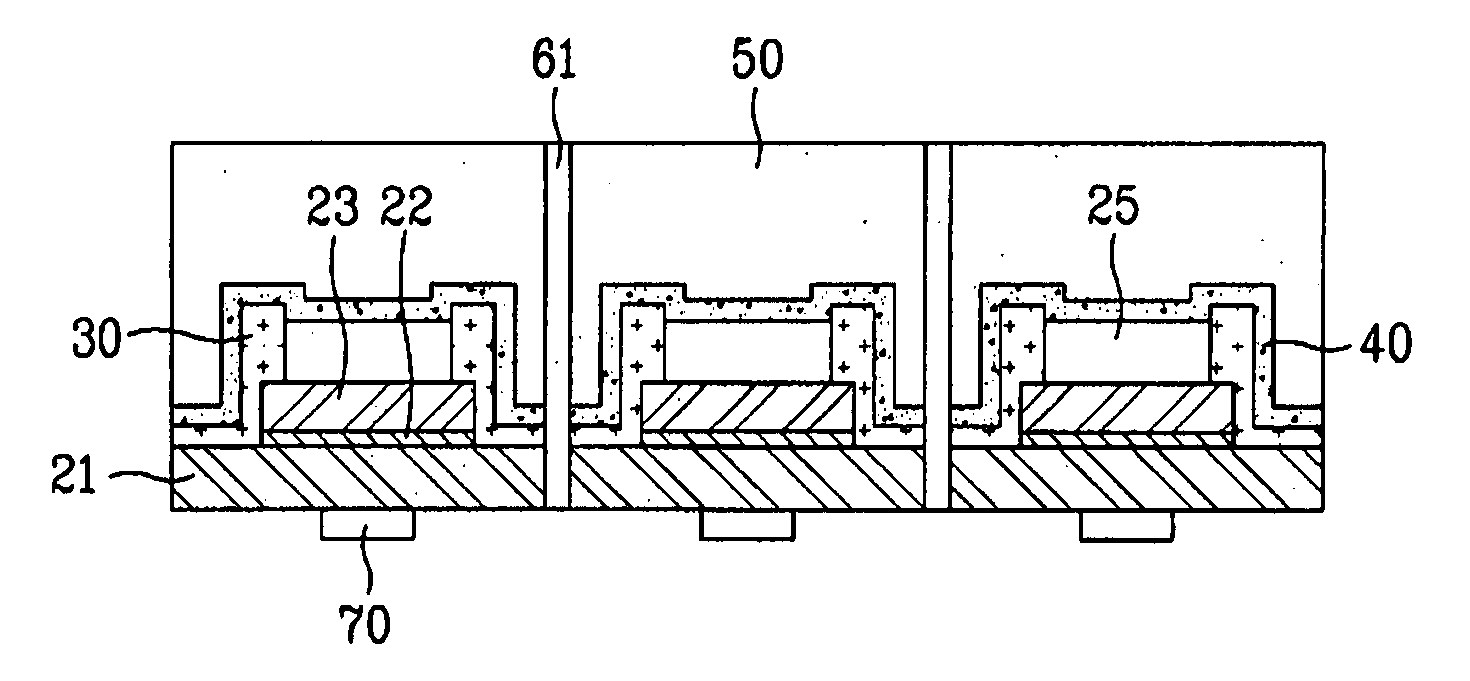

Nonvolatile semiconductor storage device and method for manufacturing the same

InactiveUS20070228452A1Reduce etch timeEtching of the semiconductor layer is suppressedTransistorSolid-state devicesElectrical resistance and conductanceCharge retention

It is an object to provide a nonvolatile semiconductor storage device that prevents increase in a contact resistance value due to etching of a semiconductor layer when etching an interlayer insulating film and that has superiority in a writing characteristic and an electric charge-holding characteristic, and a manufacturing method thereof. A conductive layer is provided between a source or drain region and a source or drain wiring. The conductive layer is made of the same conductive layer that forms a control gate electrode. An insulating film is provided so as to cover the conductive layer, and the insulating film has a contact hole for exposing part of the conductive layer. The source or drain wiring is formed so that the contact hole is filled.

Owner:SEMICON ENERGY LAB CO LTD

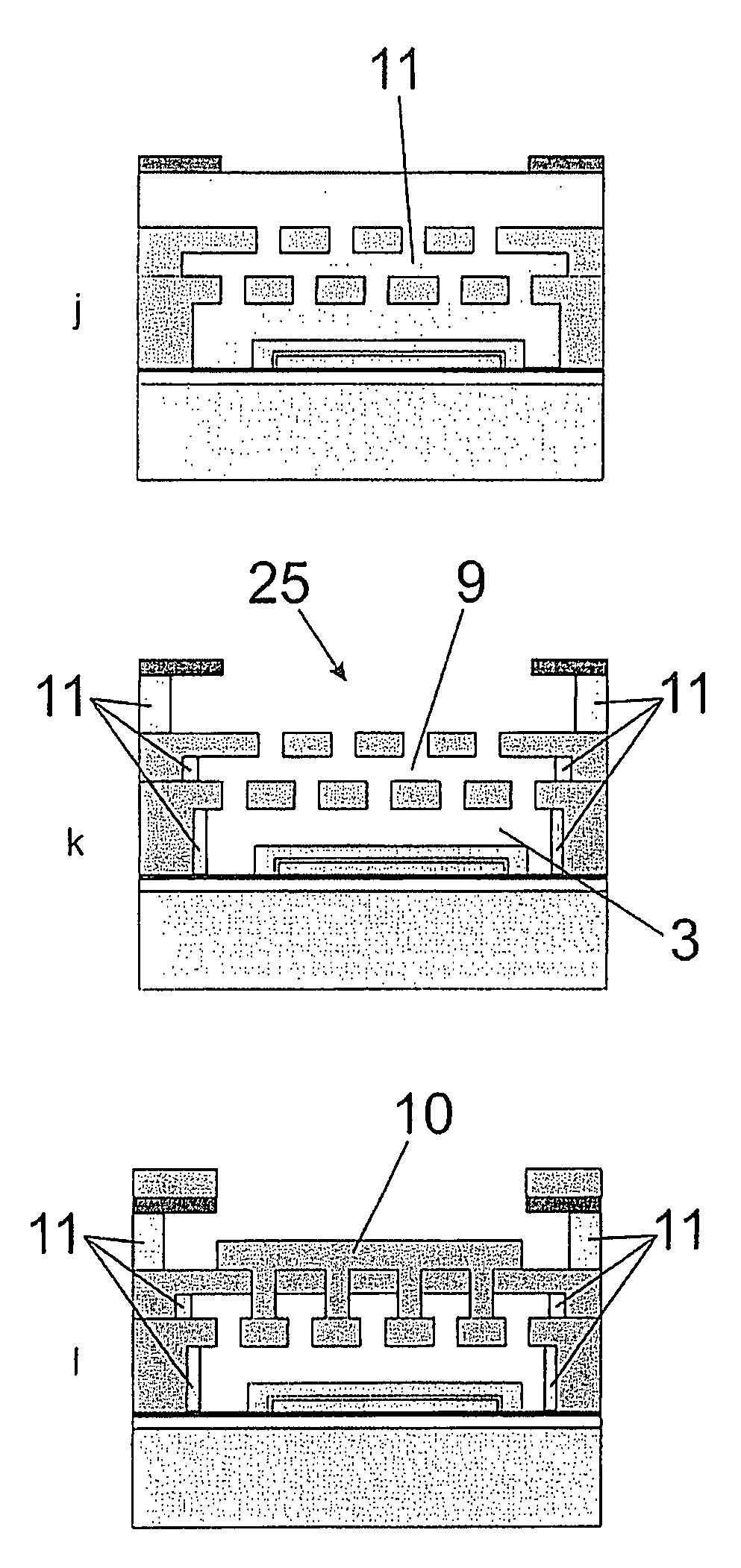

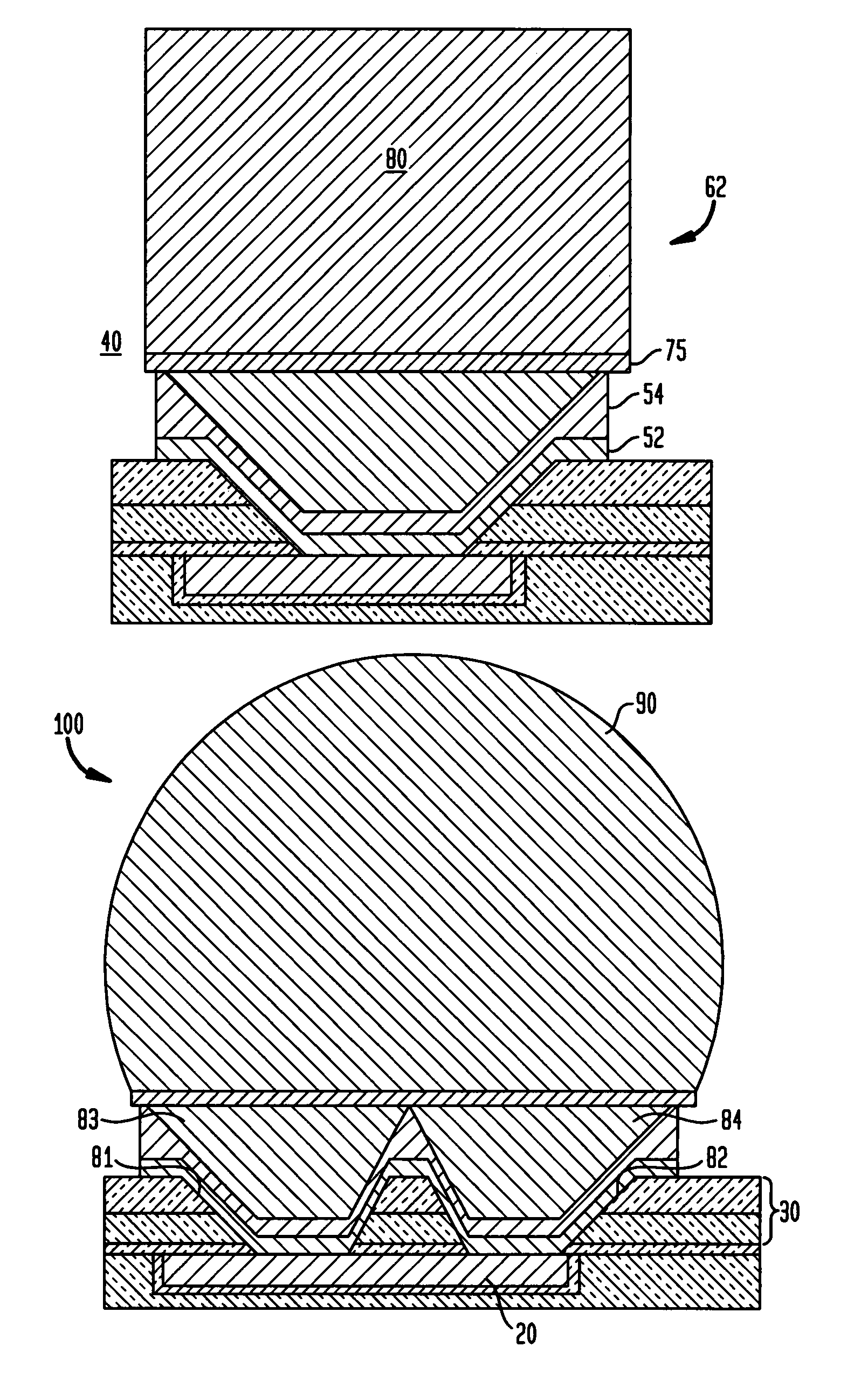

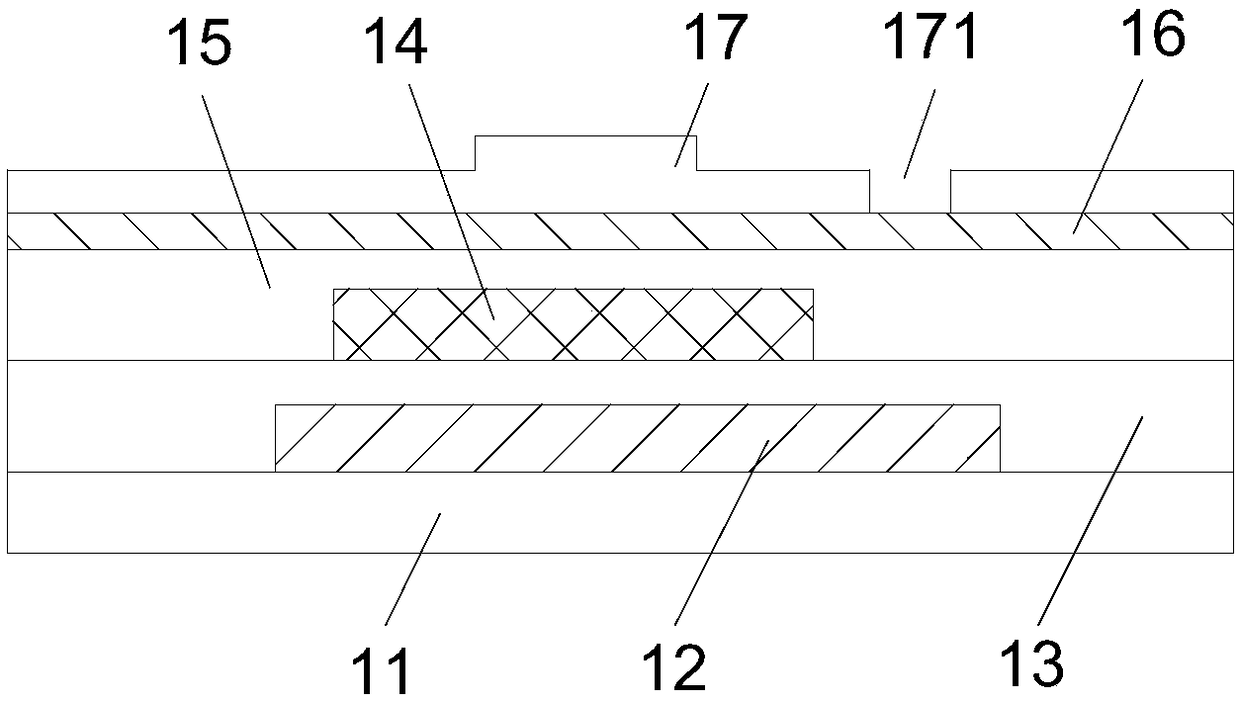

Wafer-level MEMS package and manufacturing method thereof

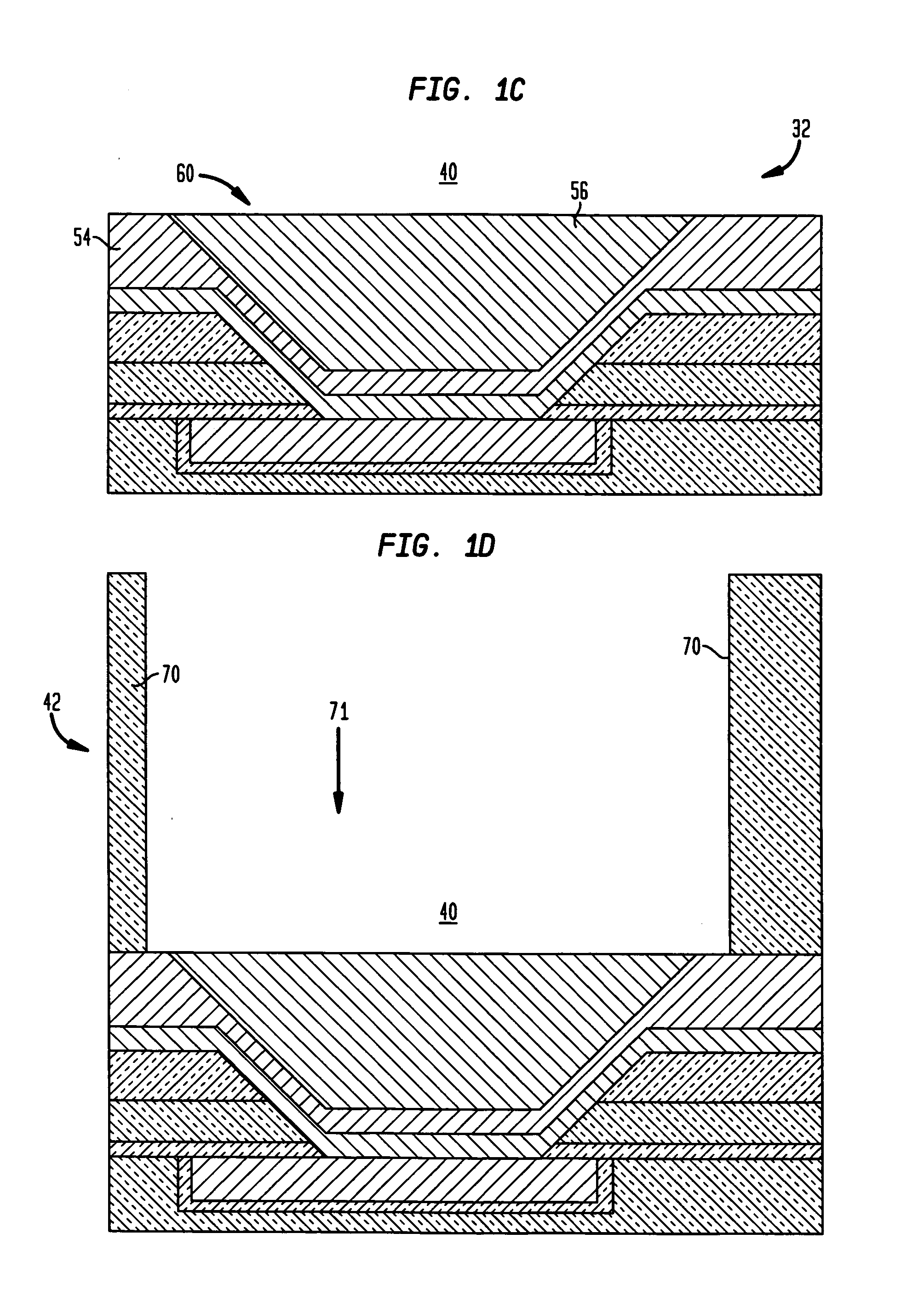

InactiveUS20080079142A1Low costReduce etch timeSemiconductor/solid-state device detailsSolid-state devicesEngineeringTotal etch

The present invention is related in general to a wafer-level packaging technique for micro-electro-mechanical systems (MEMS). A cap structure is provided encapsulating a MEMS element formed on a base substrate. A channel communicates etching holes provided on said cap structure, for the passage of an etching fluid to a chamber in which the MEMS element is housed. The holes are arranged in such a manner that they do not overlap, which allows the provision of a large number of etching holes above the MEMS element, but prevents a sealing material from reaching the MEMS element. The invention provides a low cost wafer-level packaging technique for MEMS devices, that reduces the total etching time of the sacrificial material and provides a reinforced protective cap structure for the MEMS package.

Owner:SEIKO EPSON CORP

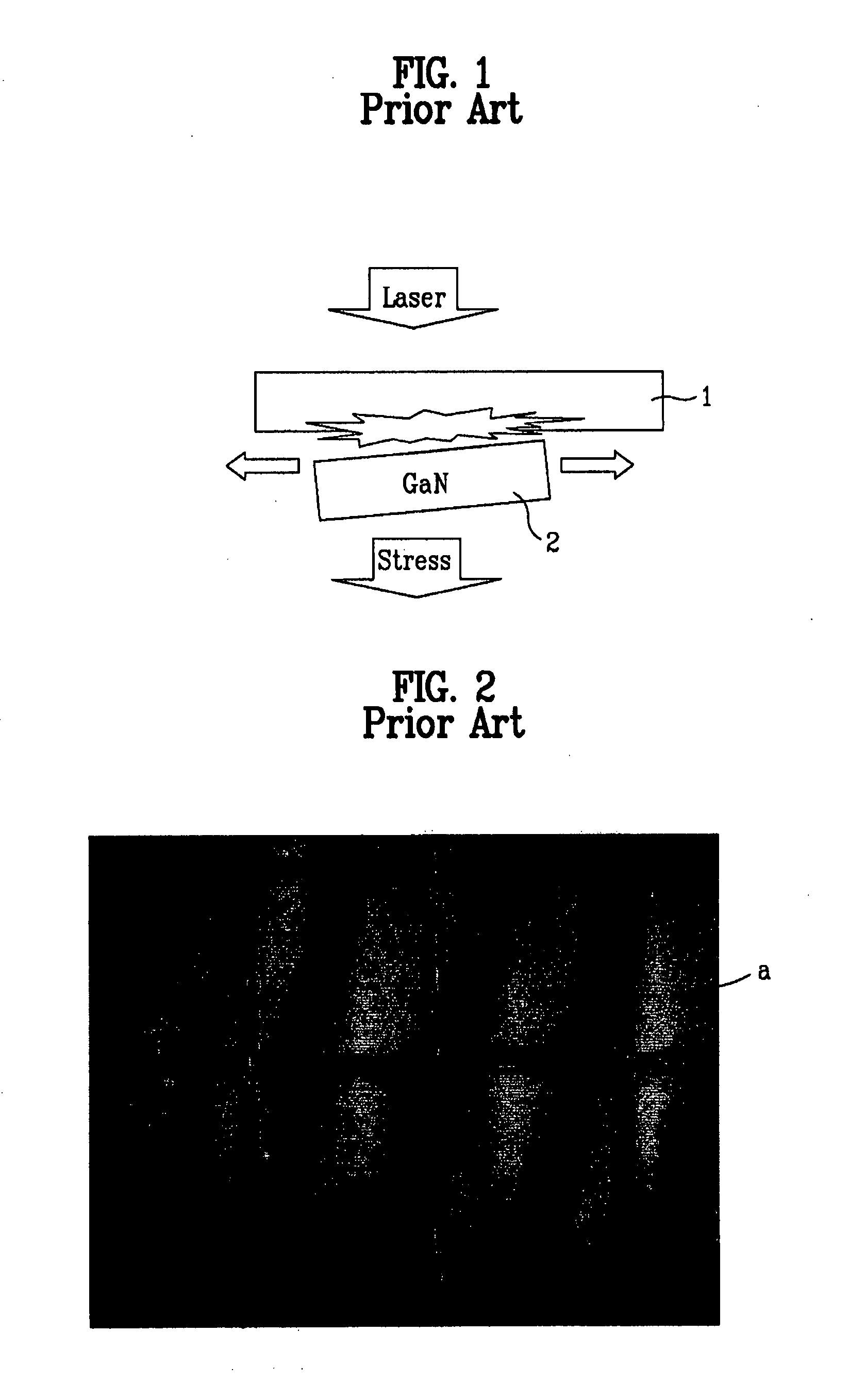

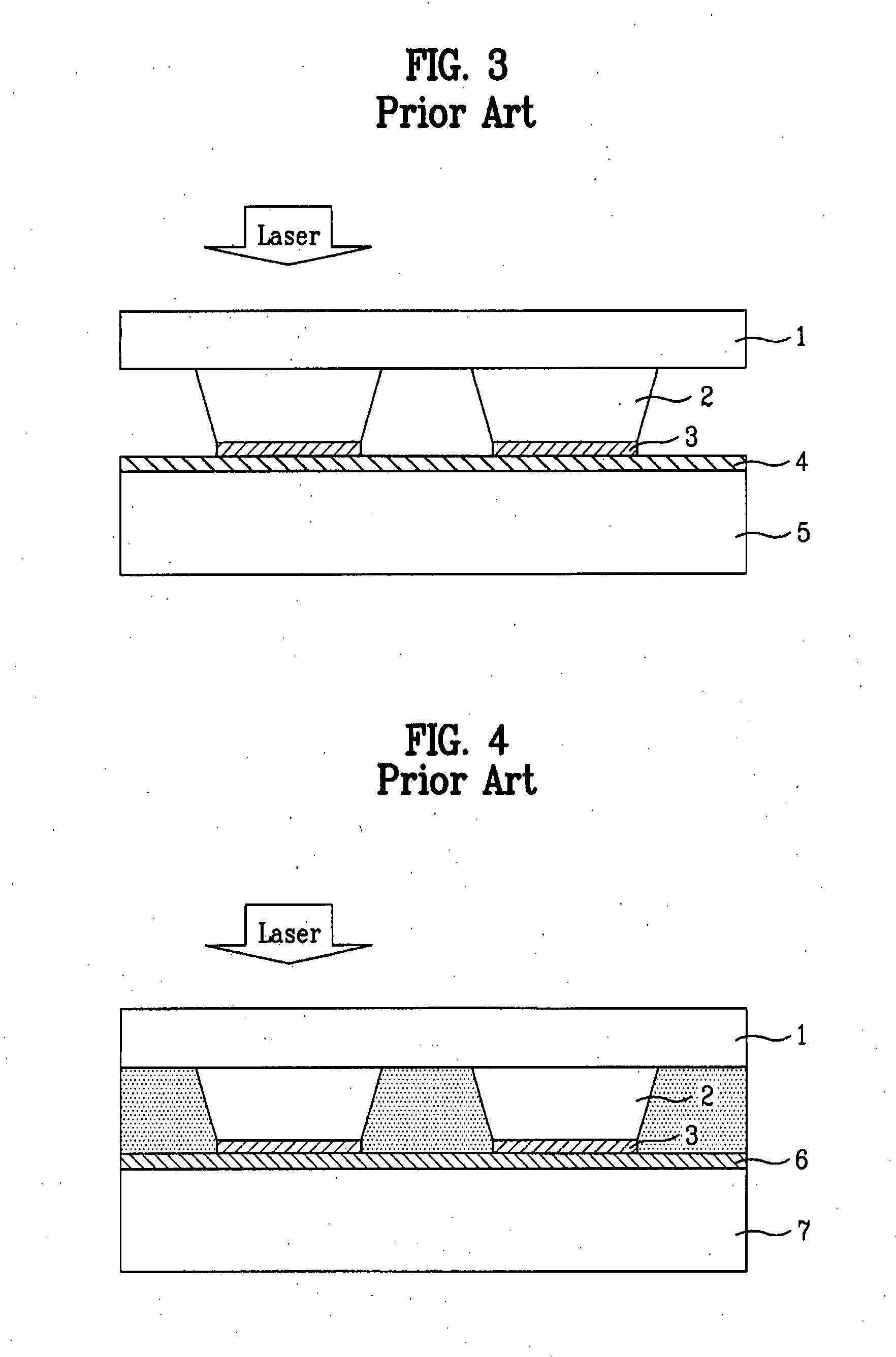

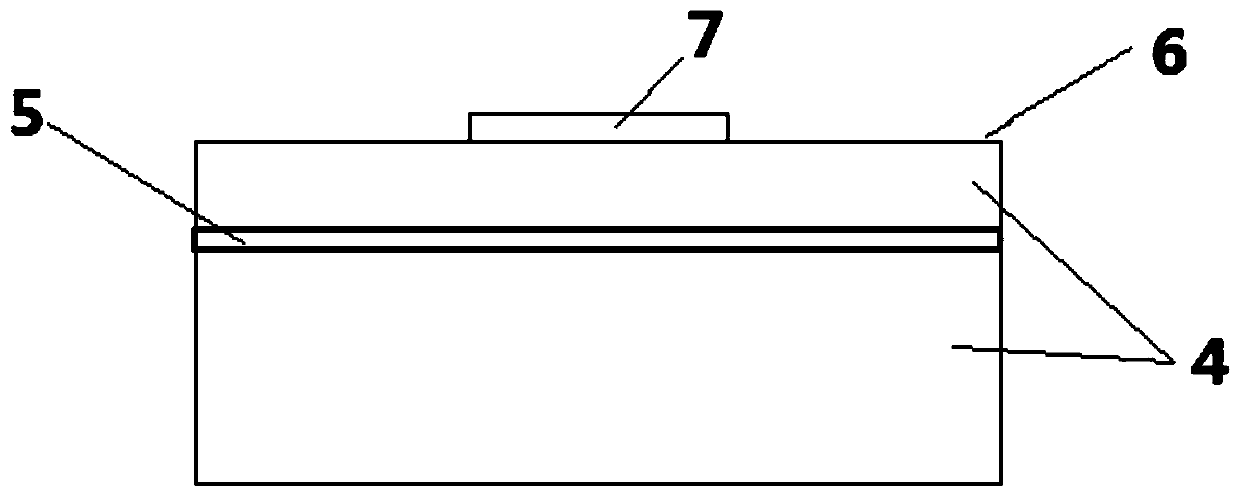

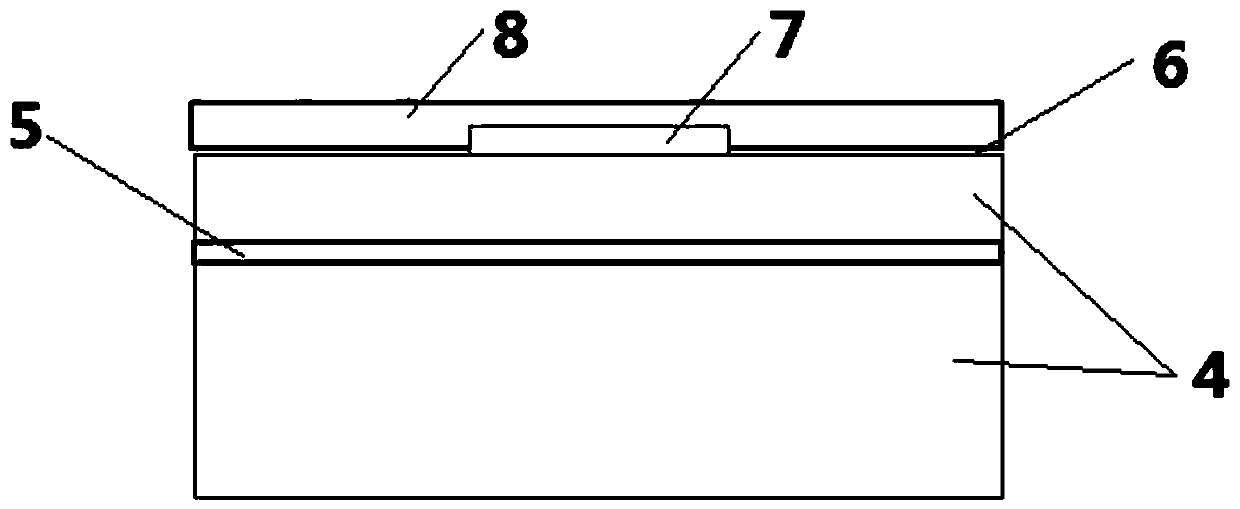

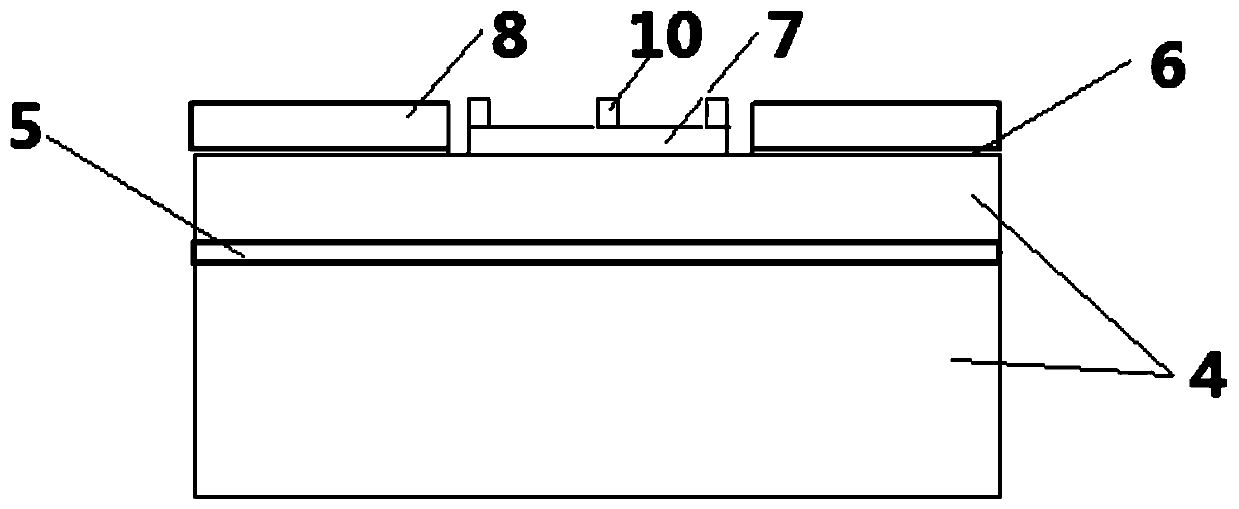

Light emitting device having vertical structure and method for manufacturing the same

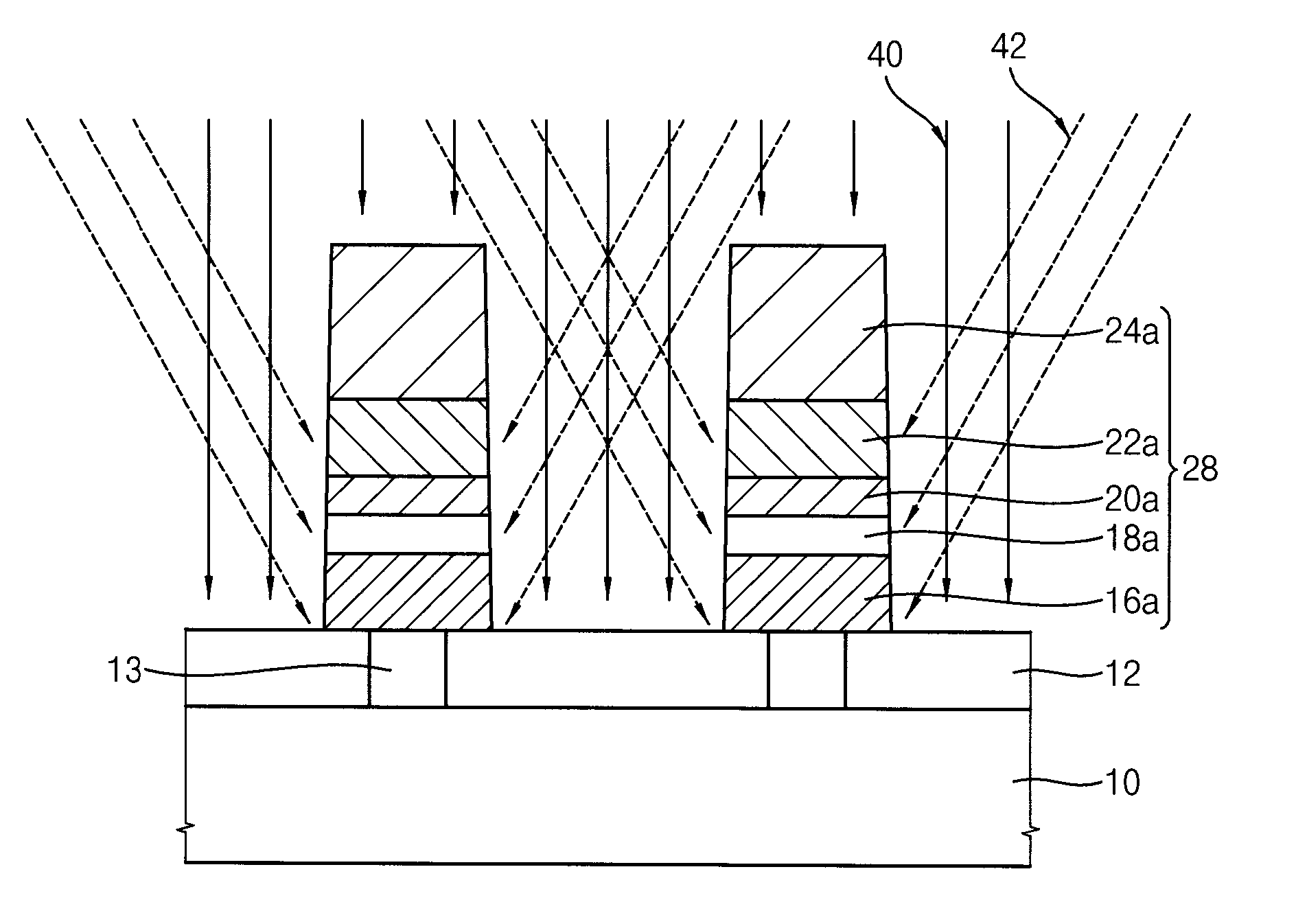

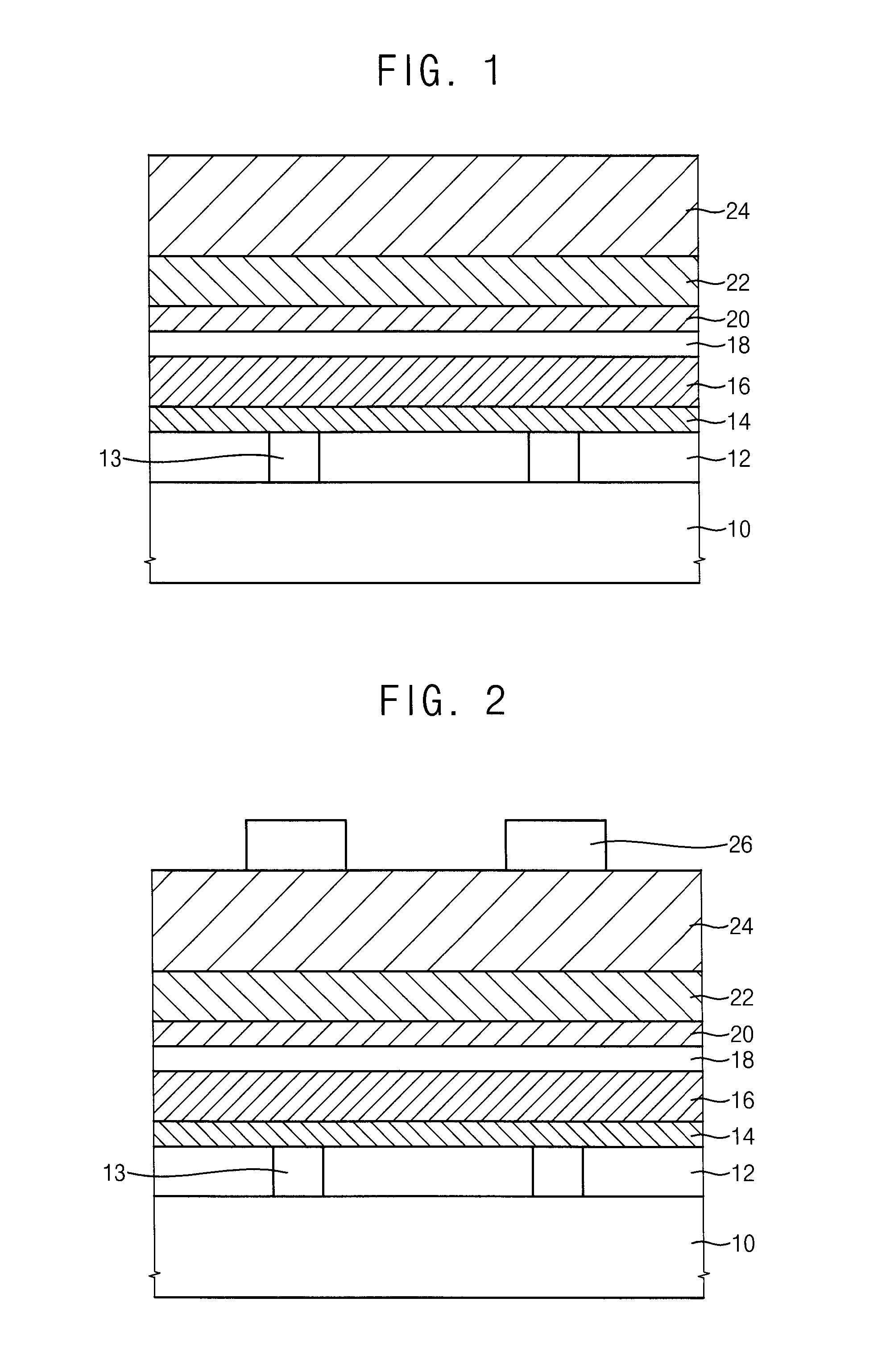

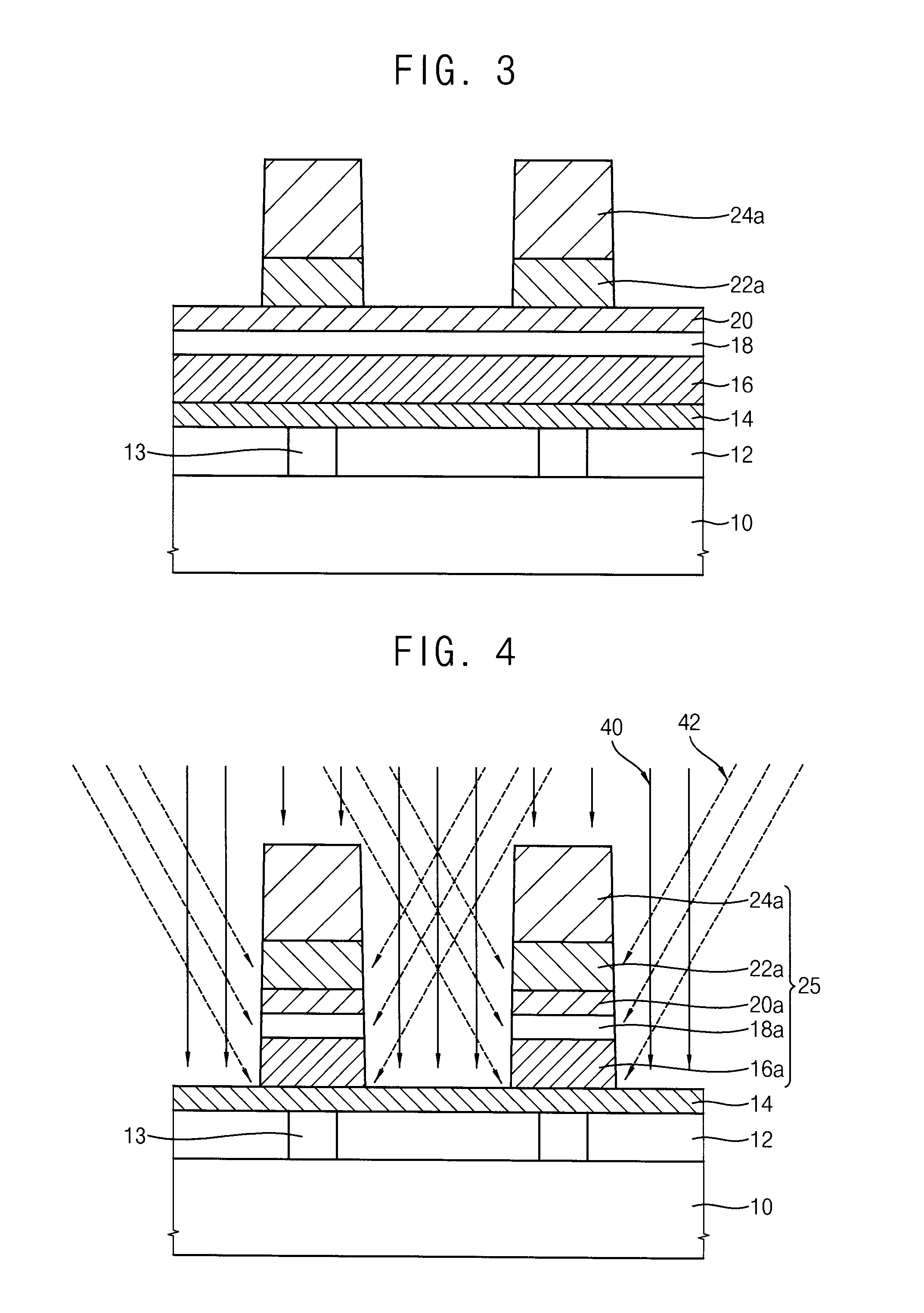

ActiveUS20080142809A1Avoid damageReduce etch timeSolid-state devicesSemiconductor/solid-state device manufacturingProduction rateLight emitting device

A light emitting device having a vertical structure and a method for manufacturing the same, which are capable of damping impact generated during a substrate separation process and achieving an improvement in mass productivity, are disclosed. The light emitting device includes a semiconductor layer having a multilayer structure, a first electrode arranged at one surface of the semiconductor layer, a metal support arranged on the first electrode, and an impact damping layer arranged between the first electrode and the metal support, and made of a metal having a ductility higher than a ductility of a metal for the metal support.

Owner:SUZHOU LEKIN SEMICON CO LTD

Damascene patterning of barrier layer metal for C4 solder bumps

InactiveUS7176583B2Improve the C<b>4</b> pitchWell formedPrinted circuit assemblingSemiconductor/solid-state device detailsEtchingMetal

A system and method for forming a novel C4 solder bump for BLM (Ball Limiting Metallurgy) includes a novel damascene technique is implemented to eliminate the Cu undercut problem and improve the C4 pitch. In the process, a barrier layer metal stack is deposited above a metal pad layer. A top layer of the barrier layer metals (e.g., Cu) is patterned by CMP. Only bottom layers of the barrier metal stack are patterned by a wet etching. The wet etch time for the Cu-based metals is greatly reduced resulting in a reduced undercut. This allows the pitch of the C4 solder bumps to be reduced. An alternate method includes use of multiple vias at the solder bump terminal.

Owner:GLOBALFOUNDRIES INC

Methods of manufacturing a magnetoresistive random access memory device

ActiveUS20150287911A1Reduce processing timeExcellent electrical propertiesSolid-state devicesSemiconductor/solid-state device manufacturingMagnetic reluctanceAtomic physics

In a method of manufacturing a MRAM device, a lower electrode is formed on a substrate. A first magnetic layer, a tunnel barrier layer, and a second magnetic layer are sequentially formed on the lower electrode layer. An etching mask is formed on the second magnetic layer. An ion beam etching process in which a first ion beam and a second ion beam are simultaneously emitted onto the substrate is performed to form a MTJ structure including a first magnetic layer pattern, a tunnel layer pattern, and a second magnetic layer pattern from the first magnetic layer, the tunnel barrier layer, and the second magnetic layer, respectively, the MTJ structure has no by-products remaining after the ion beam etching process is performed.

Owner:SAMSUNG ELECTRONICS CO LTD

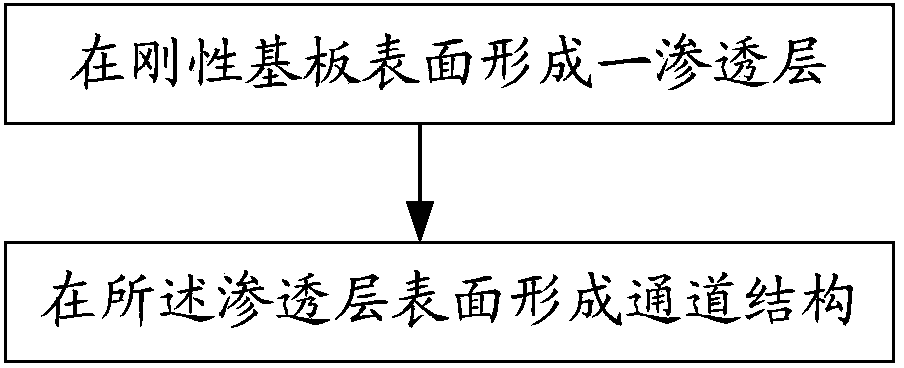

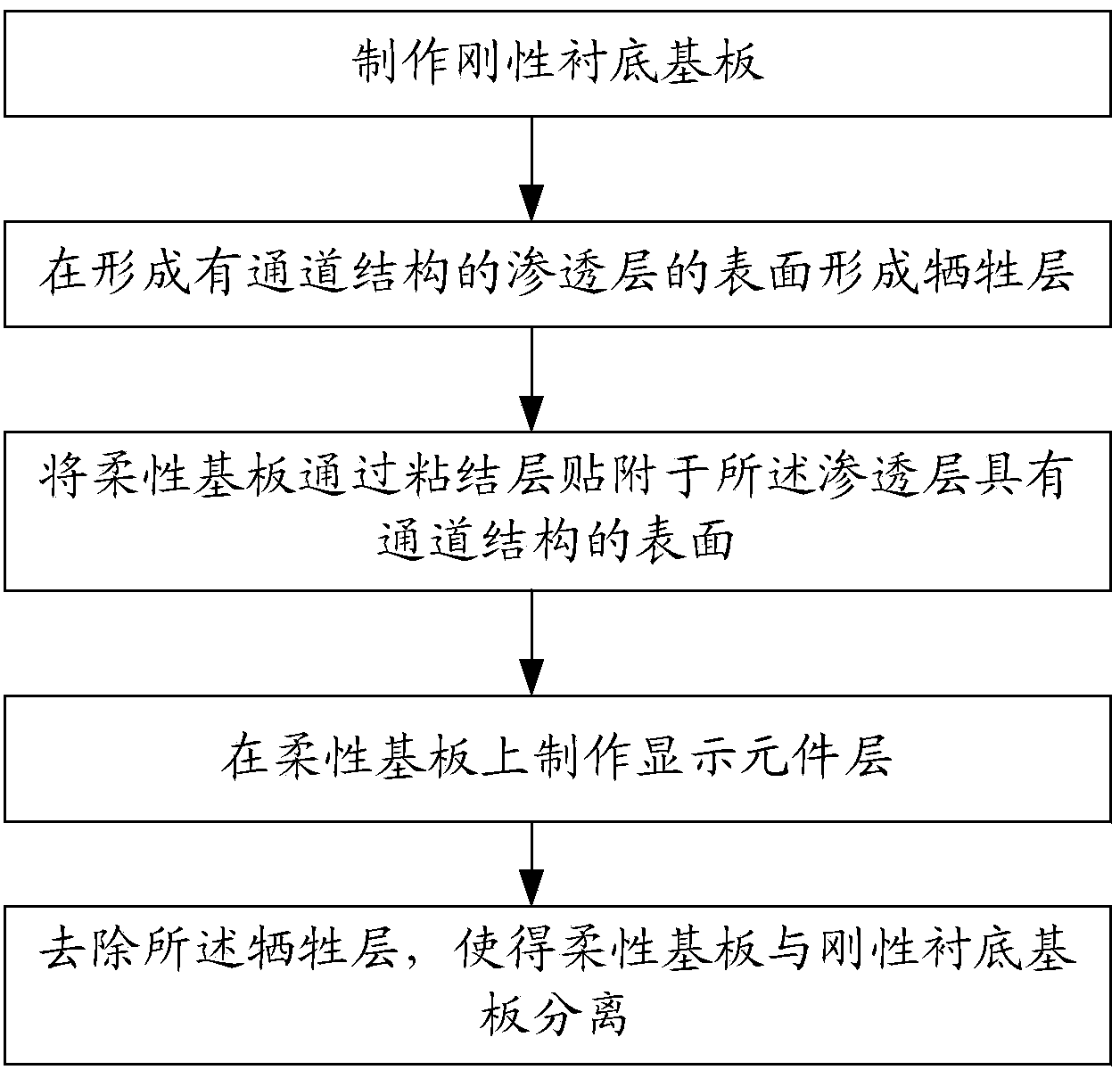

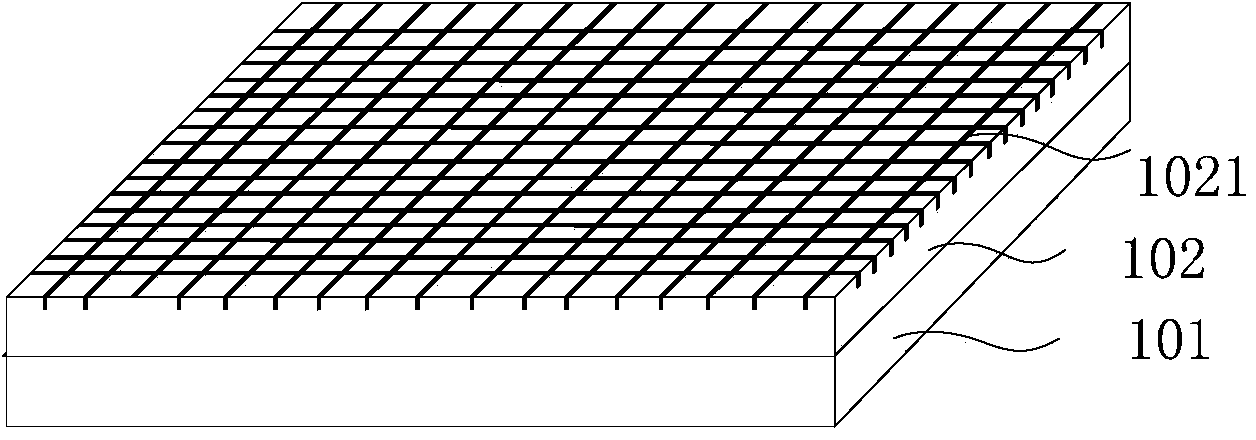

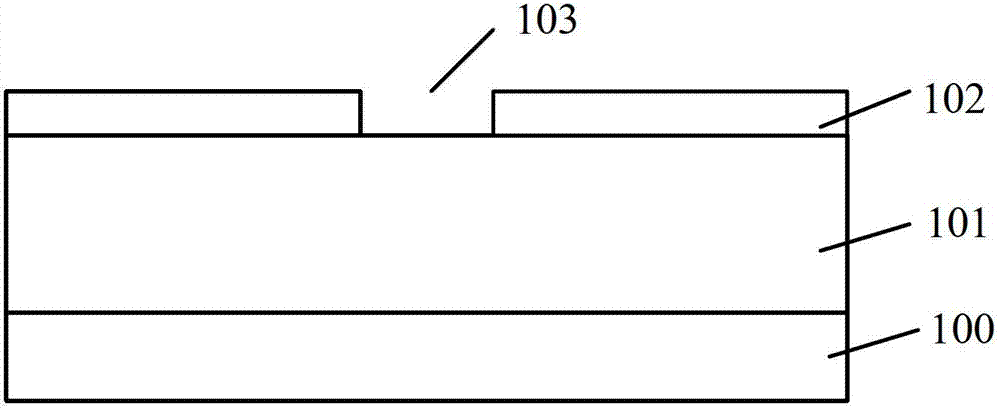

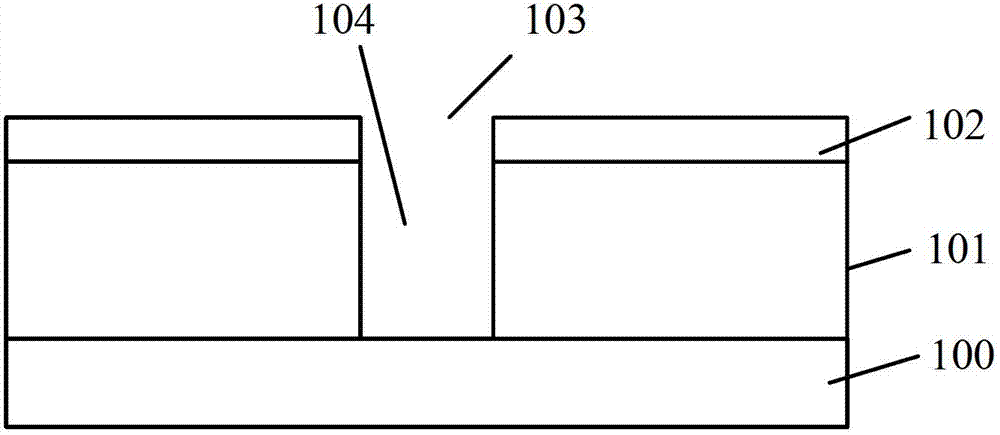

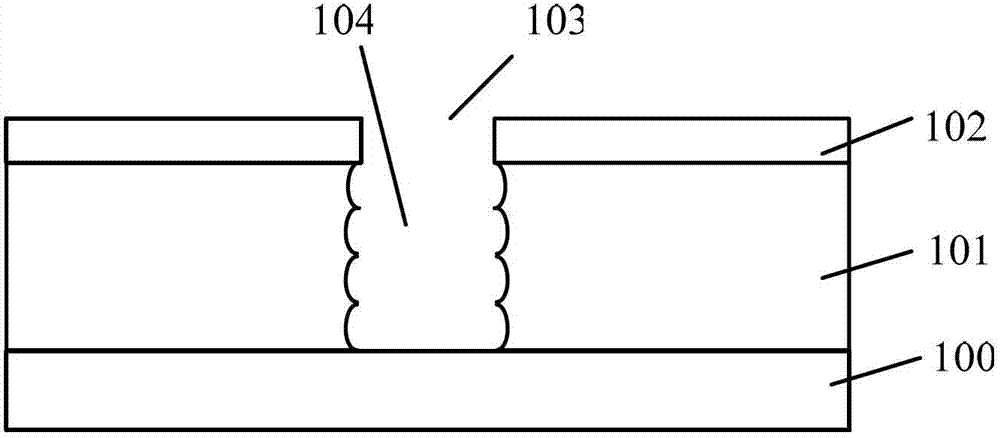

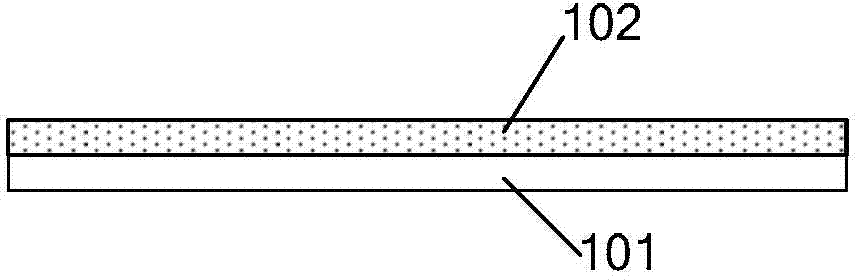

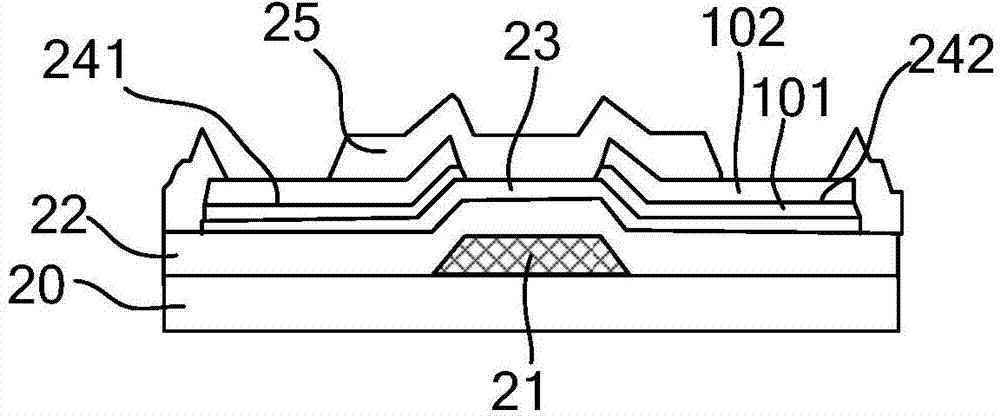

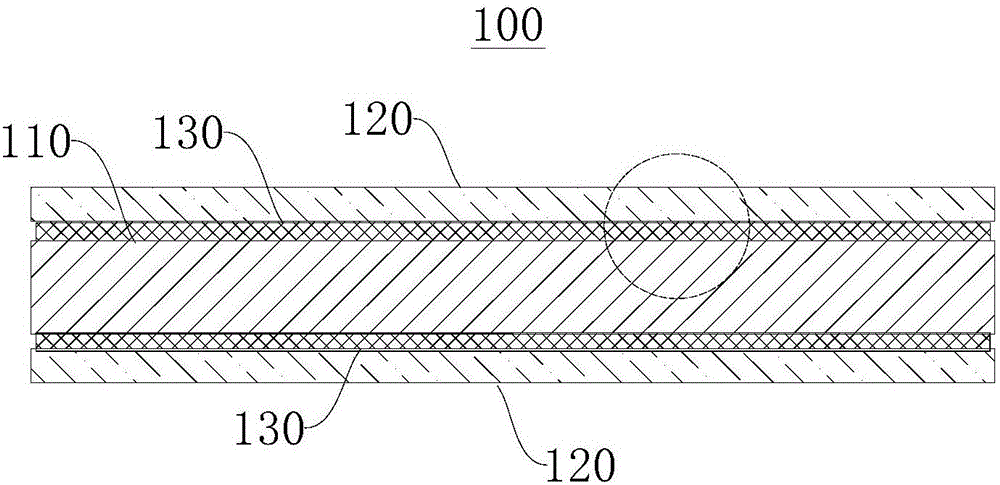

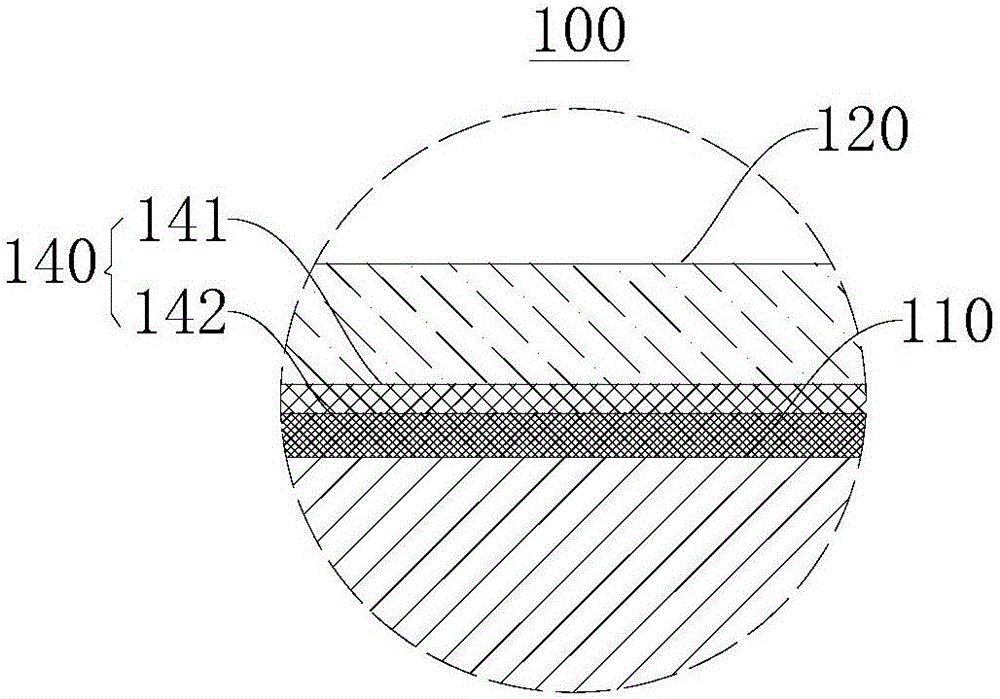

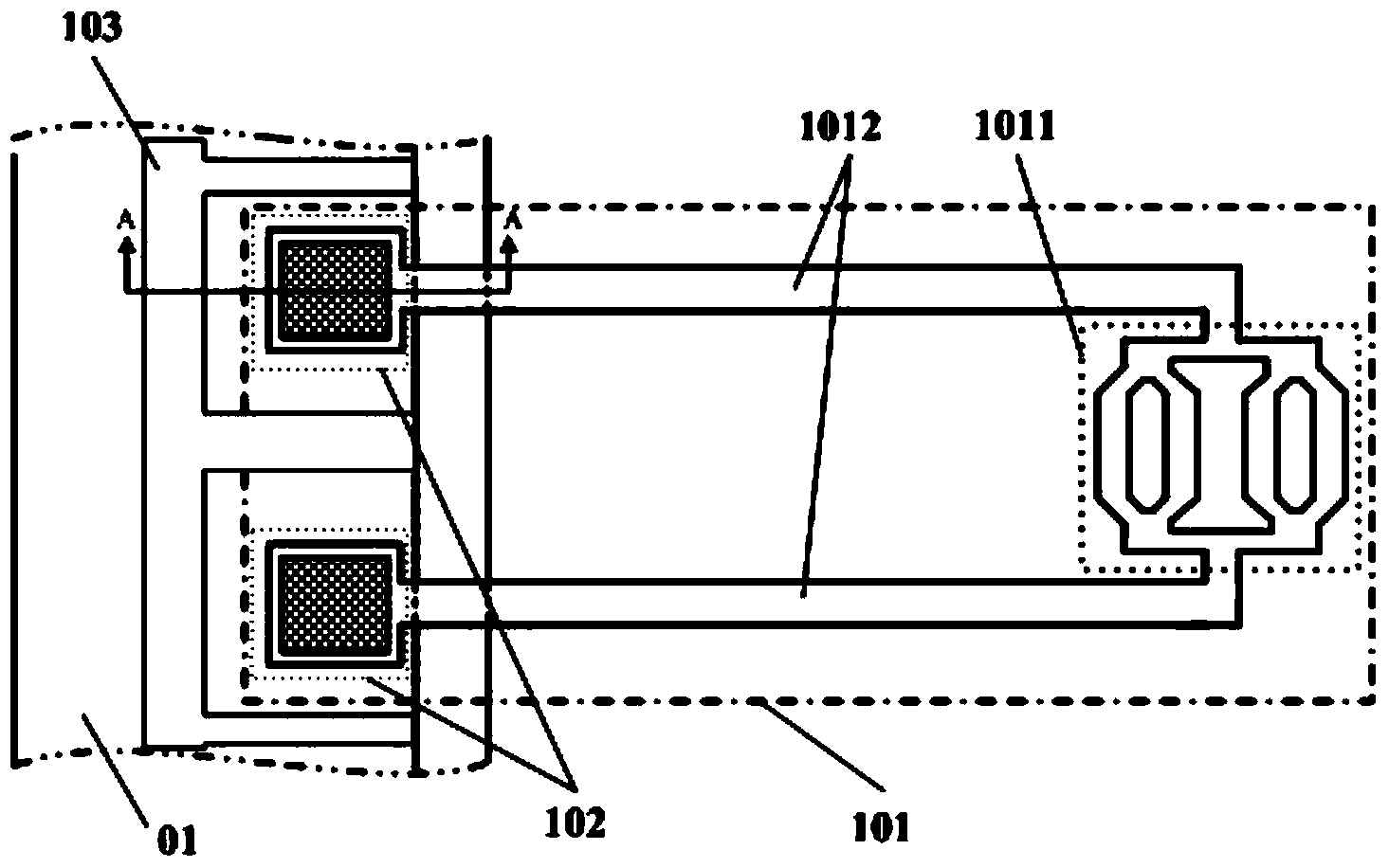

Manufacturing method for rigid substrate and flexible display device and rigid substrate

ActiveCN103682176AReduce etch timeGood peeling effectFinal product manufactureSolid-state devicesEngineeringFlexible display

The invention relates to a manufacturing method for a rigid substrate and a flexible display device and the rigid substrate. The manufacturing method for the rigid substrate used for manufacturing the flexible display device includes the following steps that a permeable layer is formed on the surface of the rigid substrate, and channel structures are formed in the surface of the permeable layer. The manufacturing method for the rigid substrate and the flexible display device has the advantages of shortening the etching time of a sacrificial layer and improving the stripping effect of a flexible substrate.

Owner:BOE TECH GRP CO LTD

Method for forming semiconductor structure

ActiveCN102738074AAdd depthShorten the timeSemiconductor/solid-state device manufacturingSemiconductor structurePulsed mode

The invention discloses a method for forming a semiconductor structure, which comprises the following steps: providing a substrate, forming a multi-layer stack structure in which a silicon nitride layer and a silicon oxide layer are alternately distributed on the substrate; carrying out a plasma etching on the stack structure, wherein outputting a bias power in pulse mode by a bias power source, when the bias power source is turned on, etching part of the stack structure to form an etch-hole, when the bias power source is turned off, forming a polymer on the side wall and the bottom of the formed etching hole, repeating the process of turning on the bias power resource and turning off the bias power resource till a through hole is formed. The etching step and the polymer forming step are carried out alternately, after the etch-hole with a depth is etched, correspondingly, the polymer is formed on the side of the etch-hole, subsequently, the formed etch-hole is protected from being over-etched when continuing to etch the stack structure along the etch-hole, so that the finally formed through hole keeps a vertical side wall morphology.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

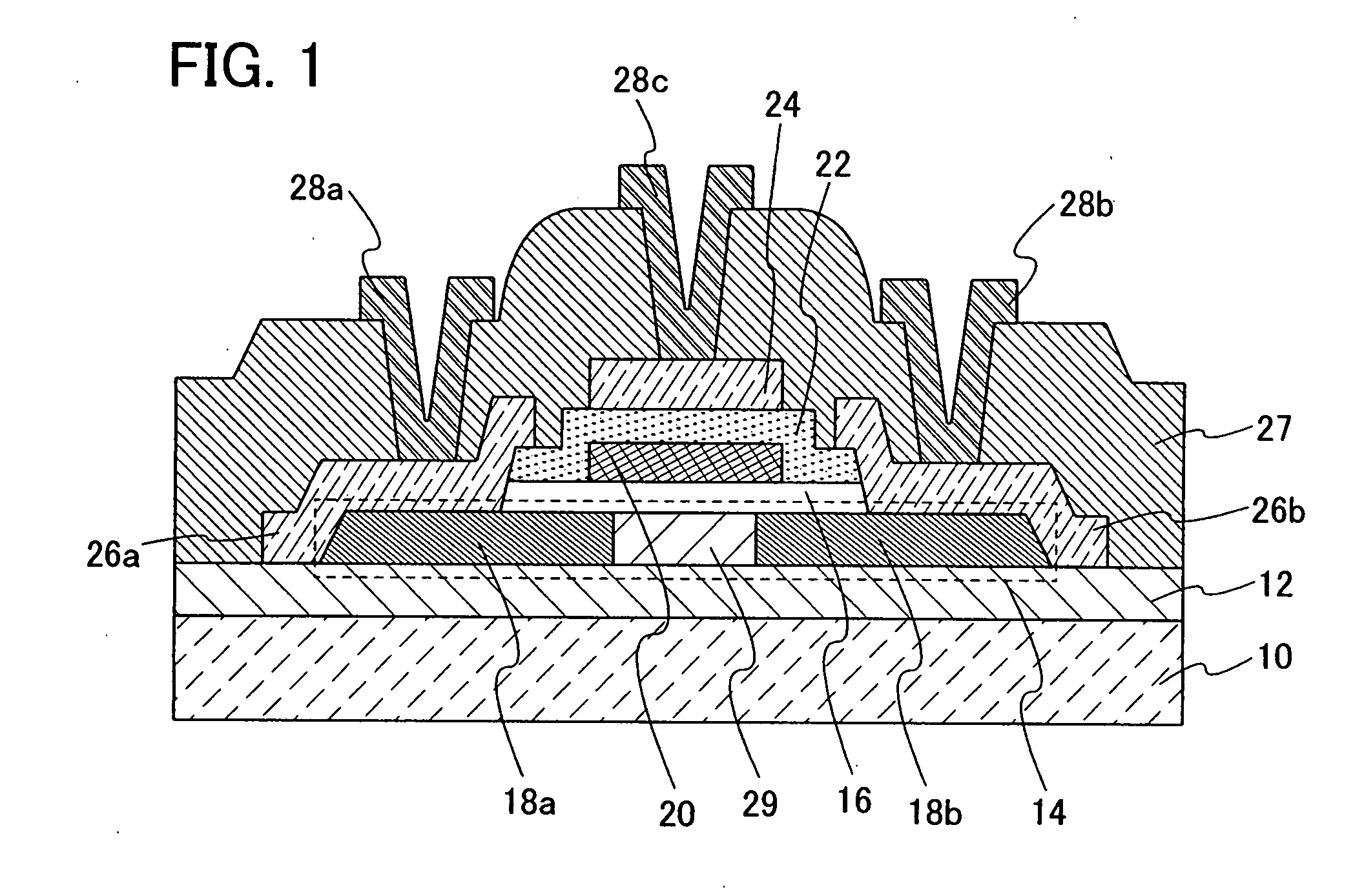

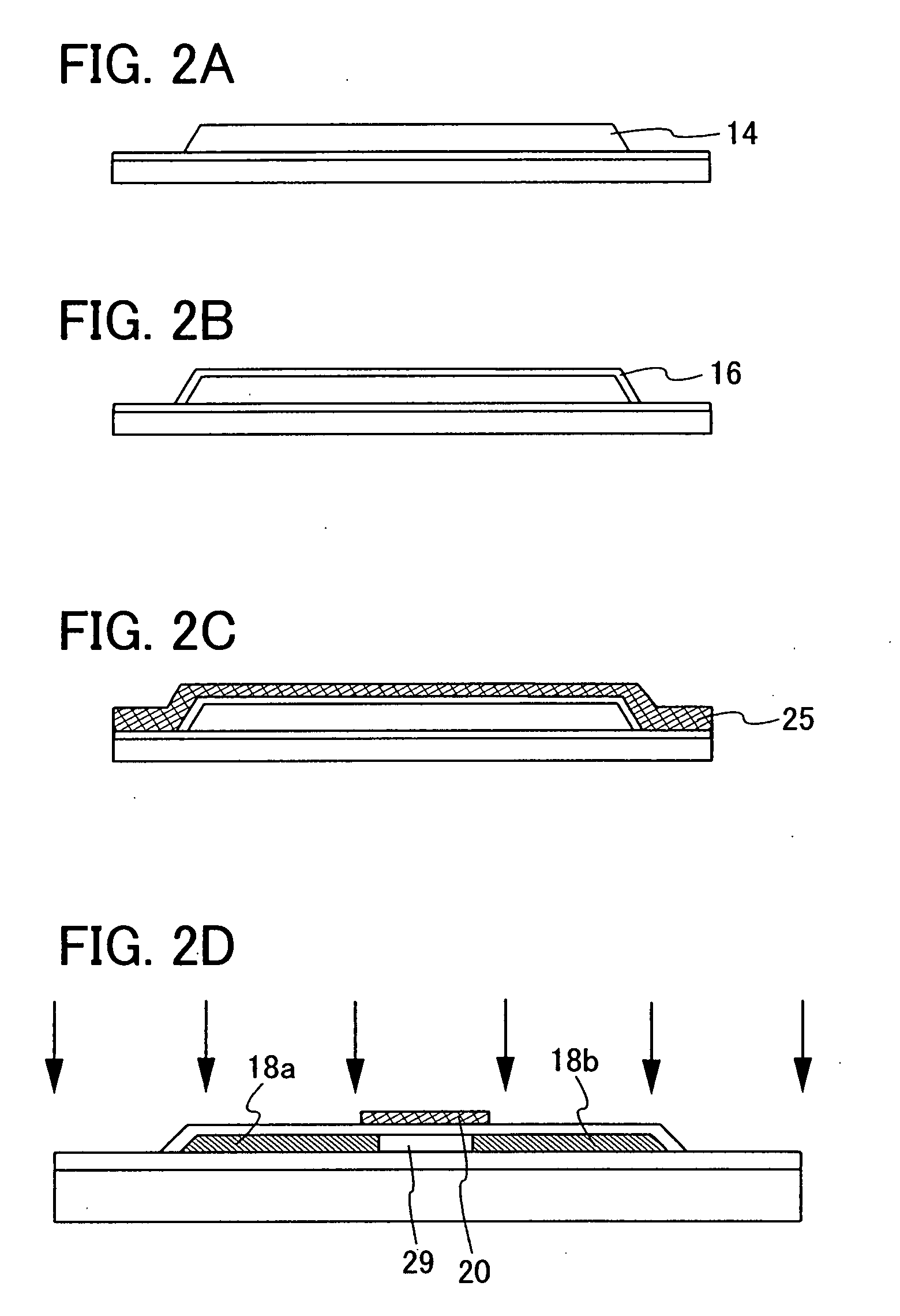

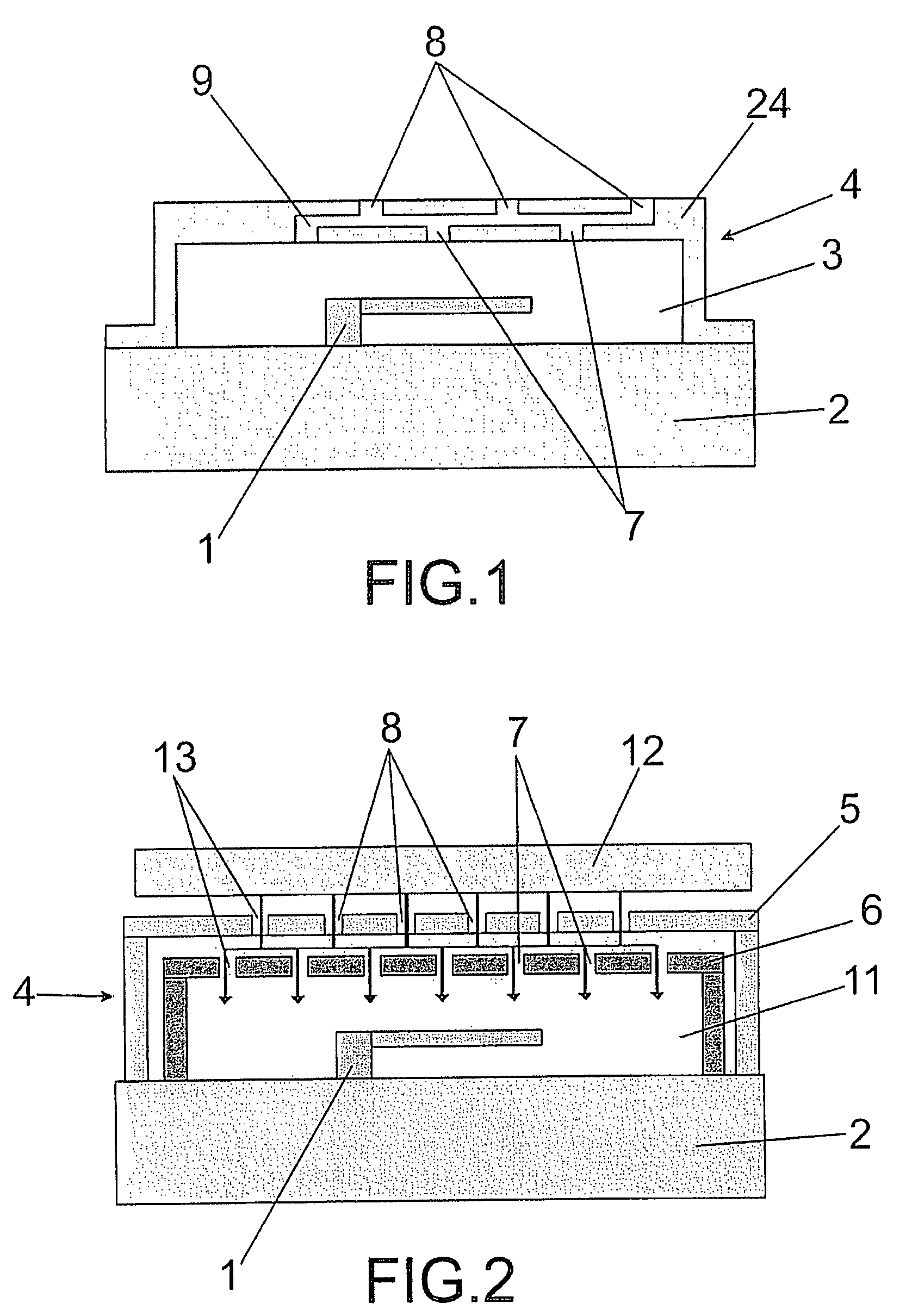

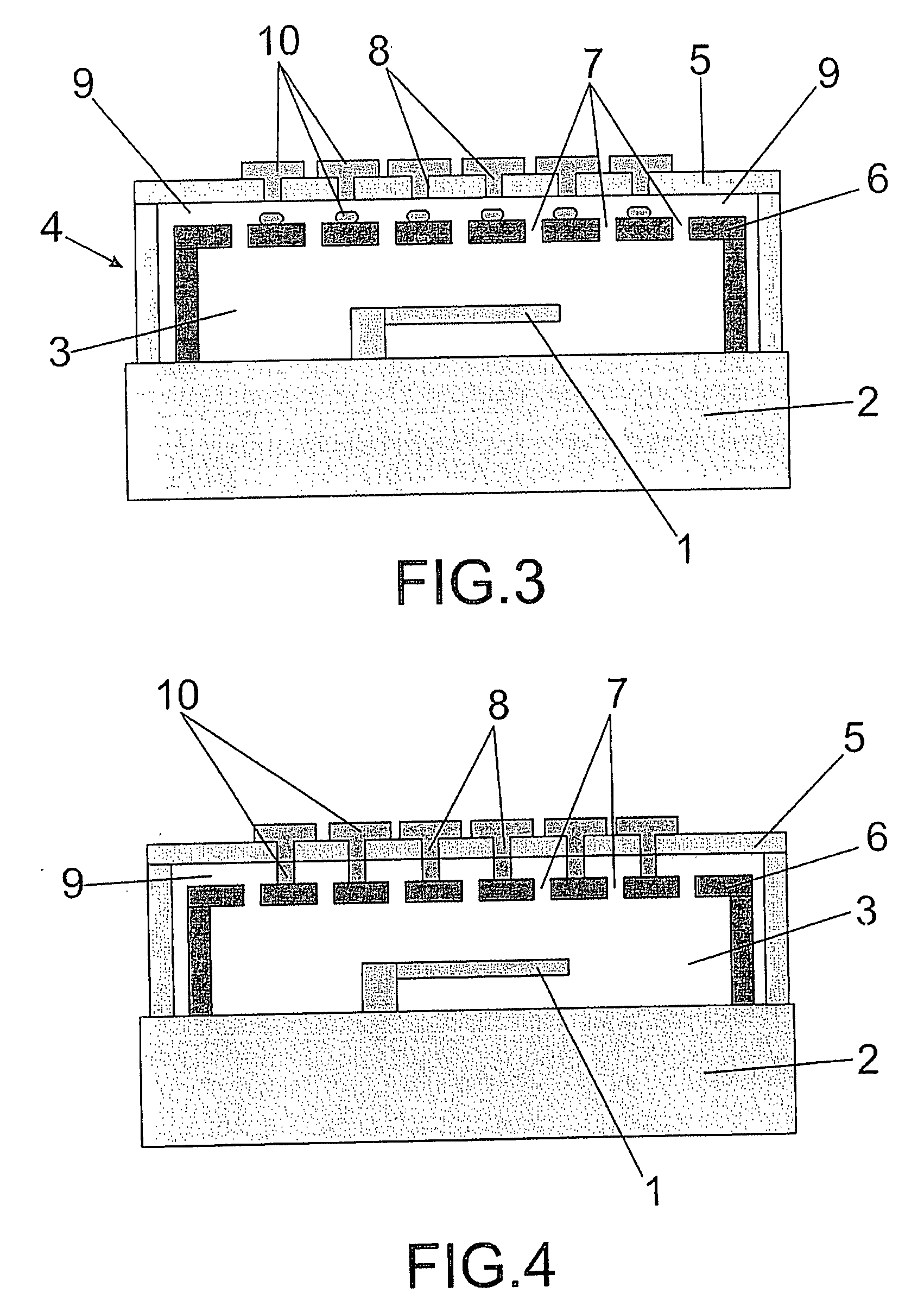

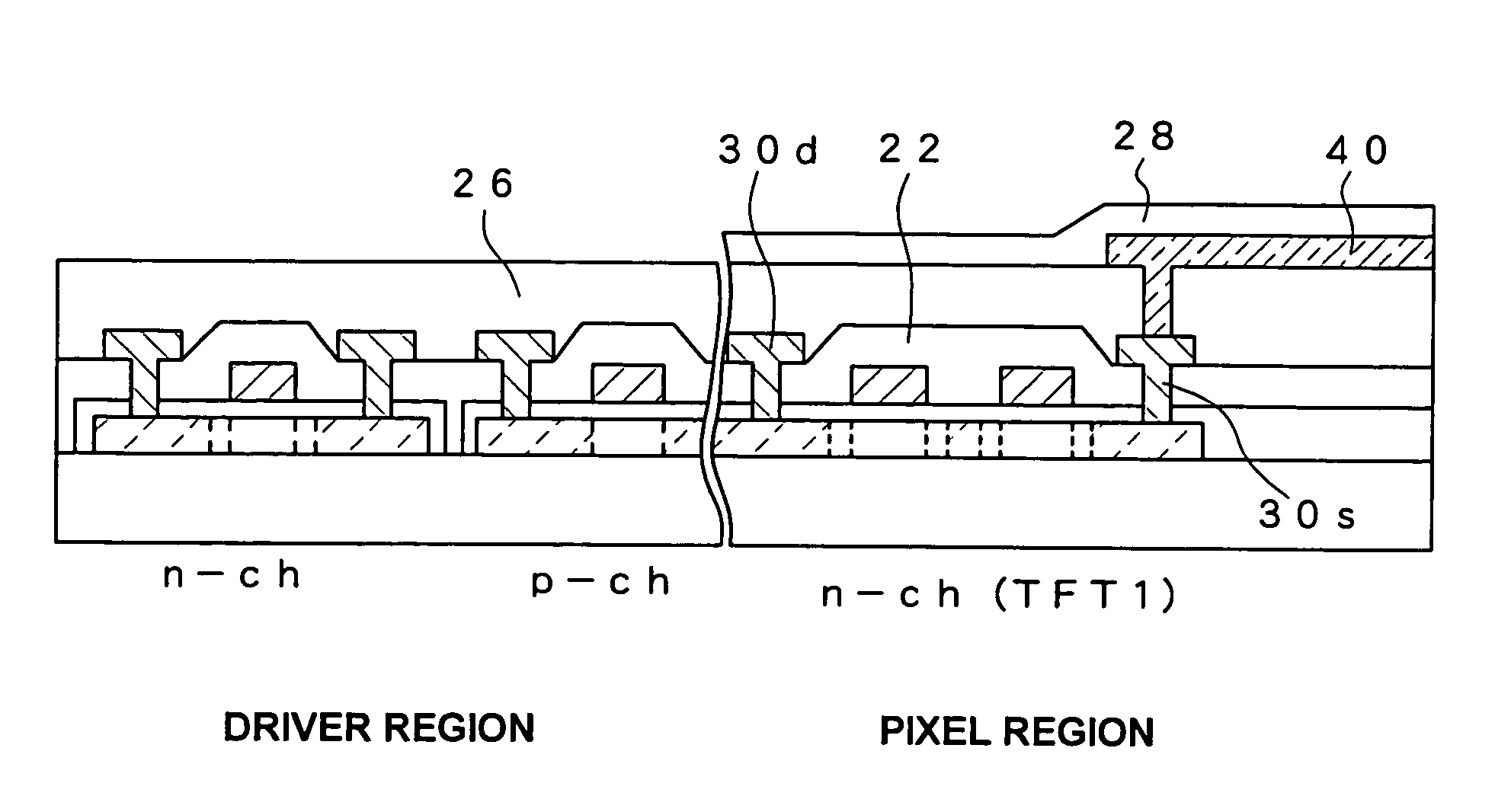

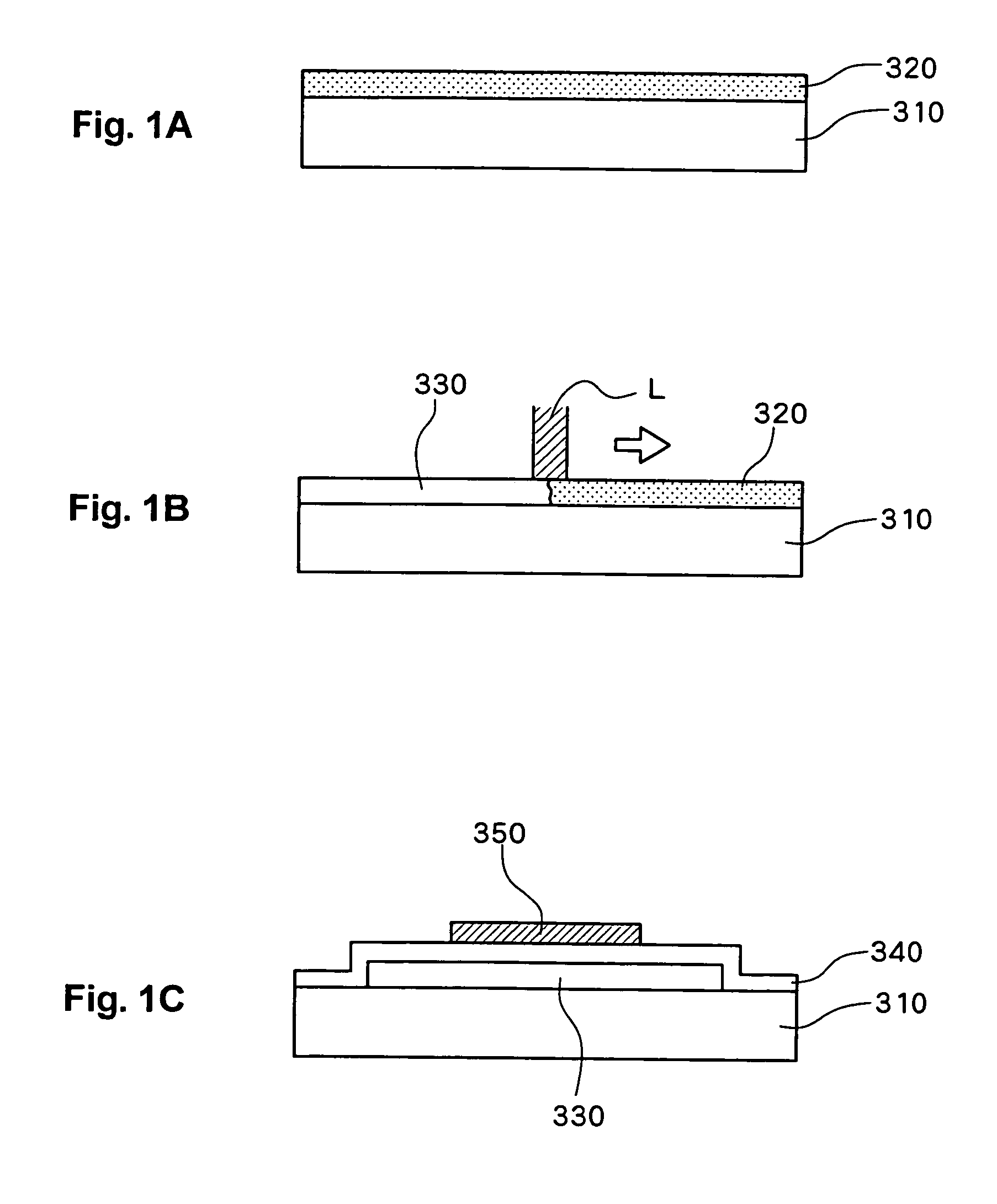

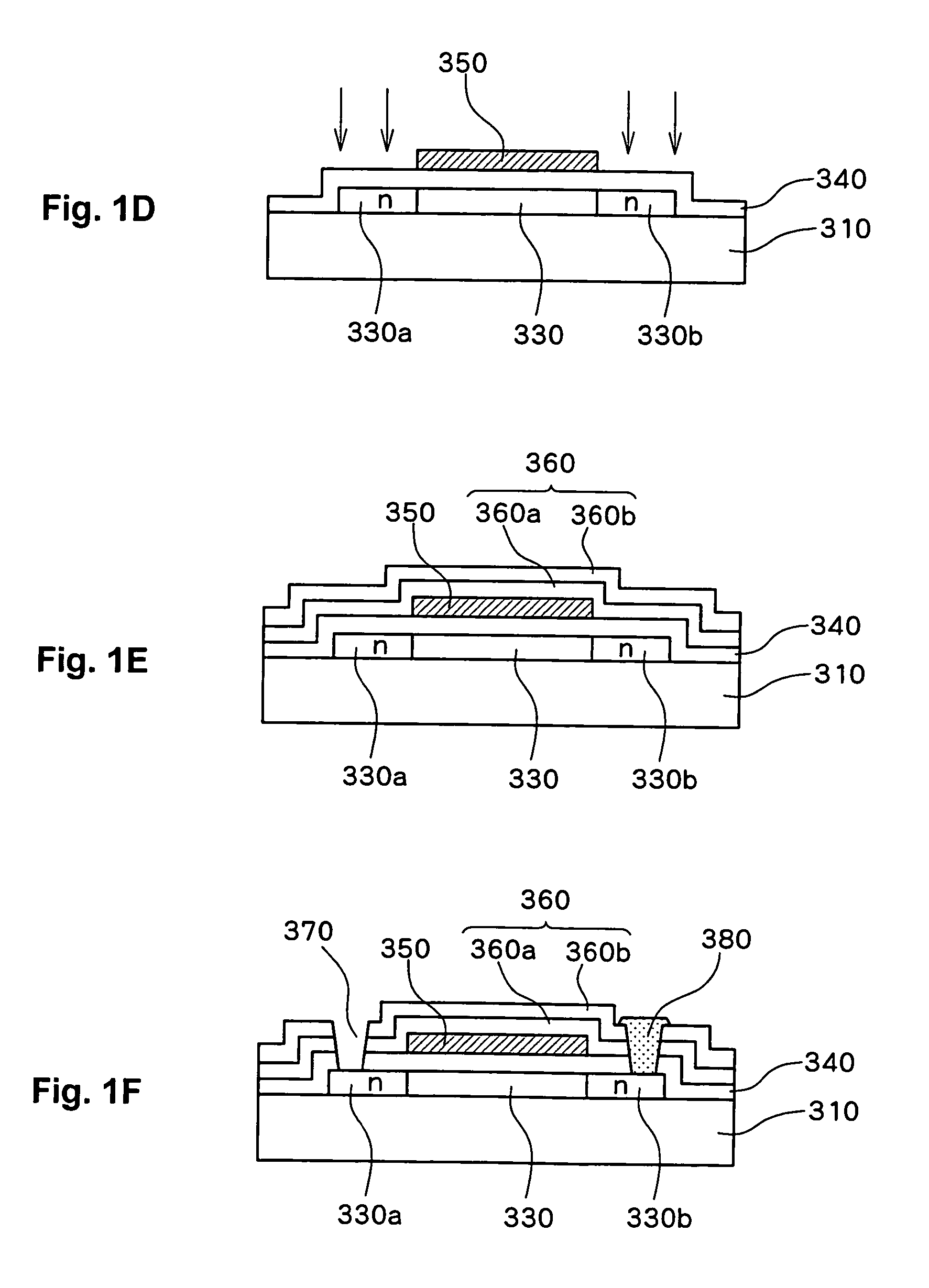

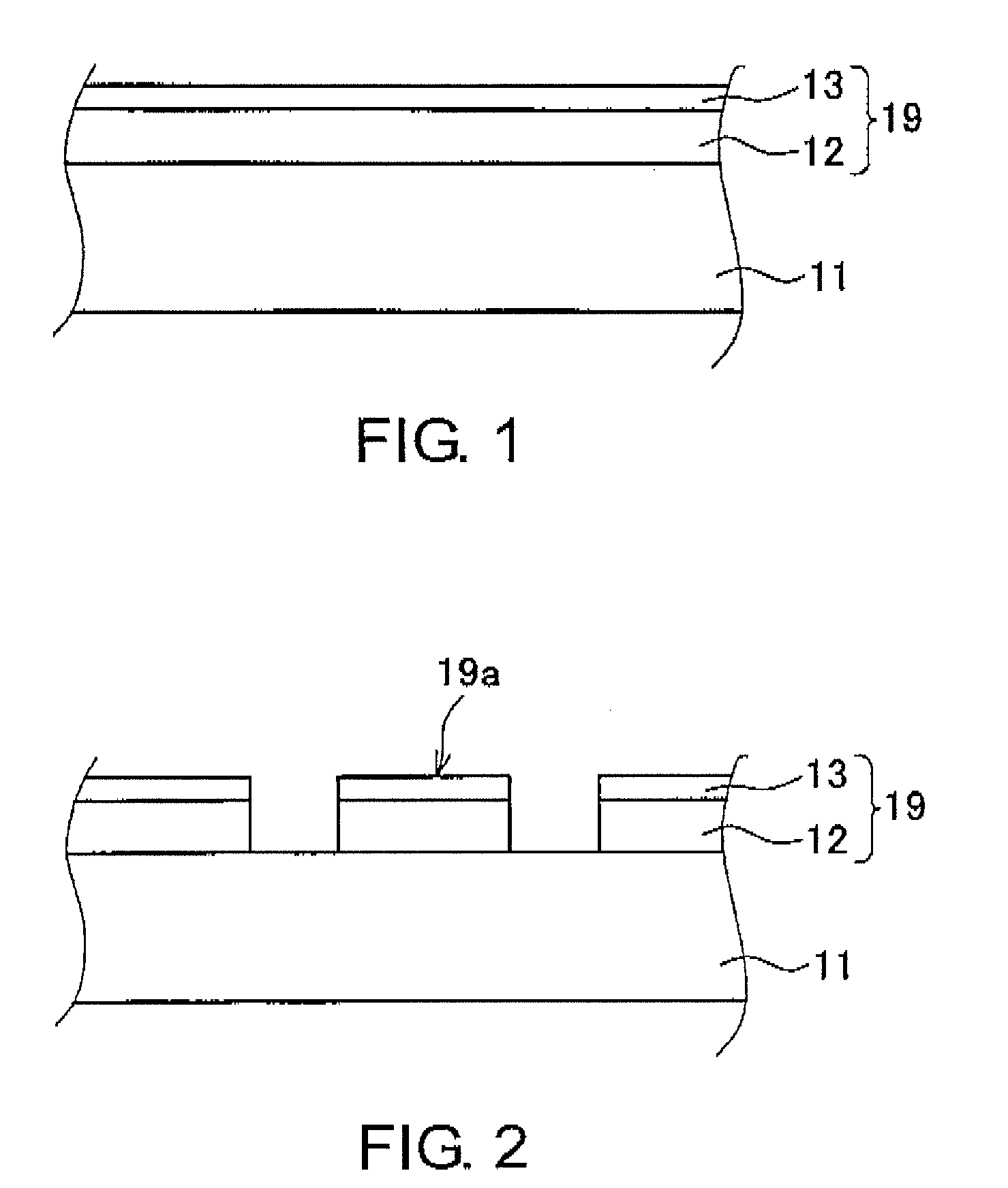

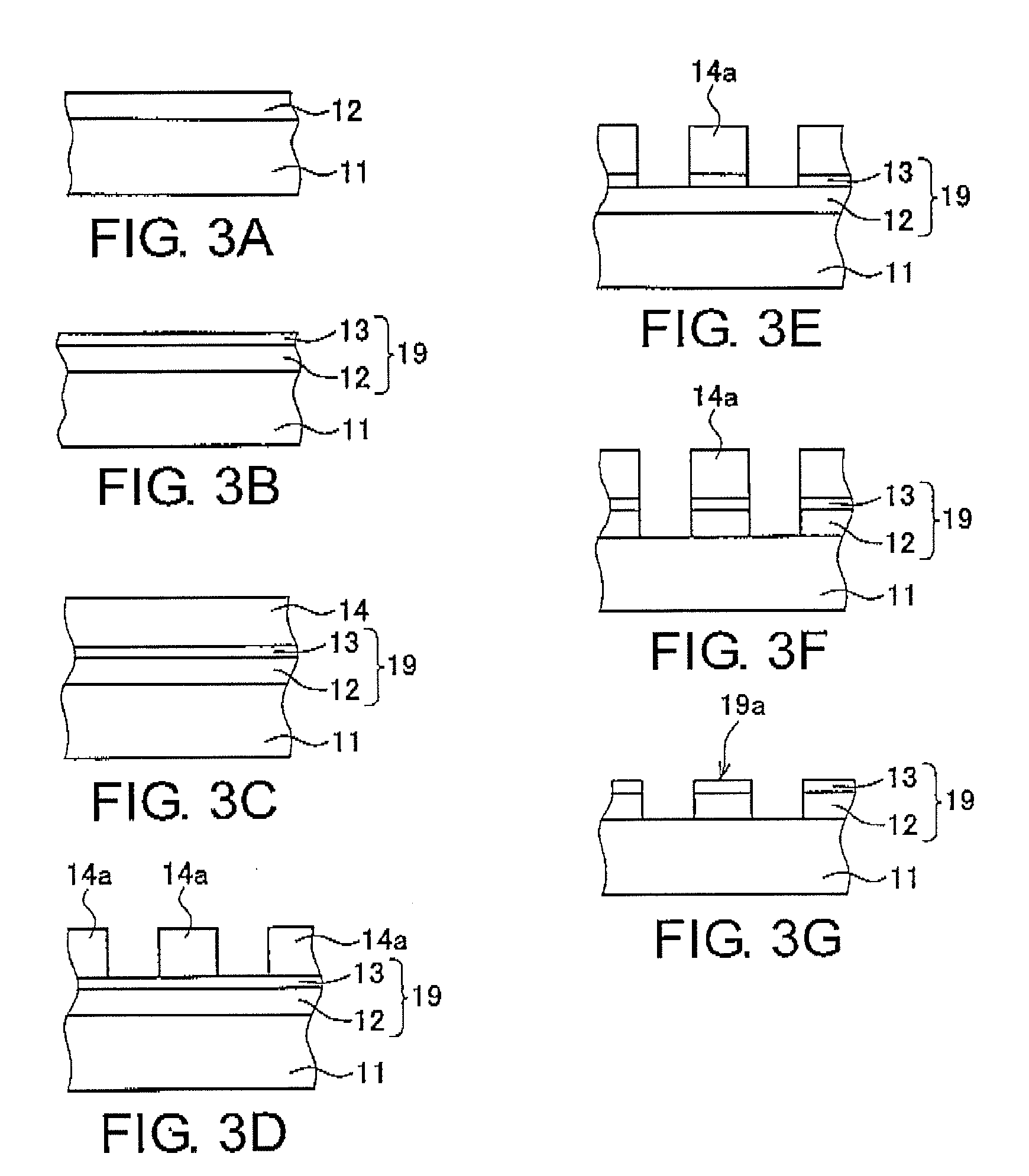

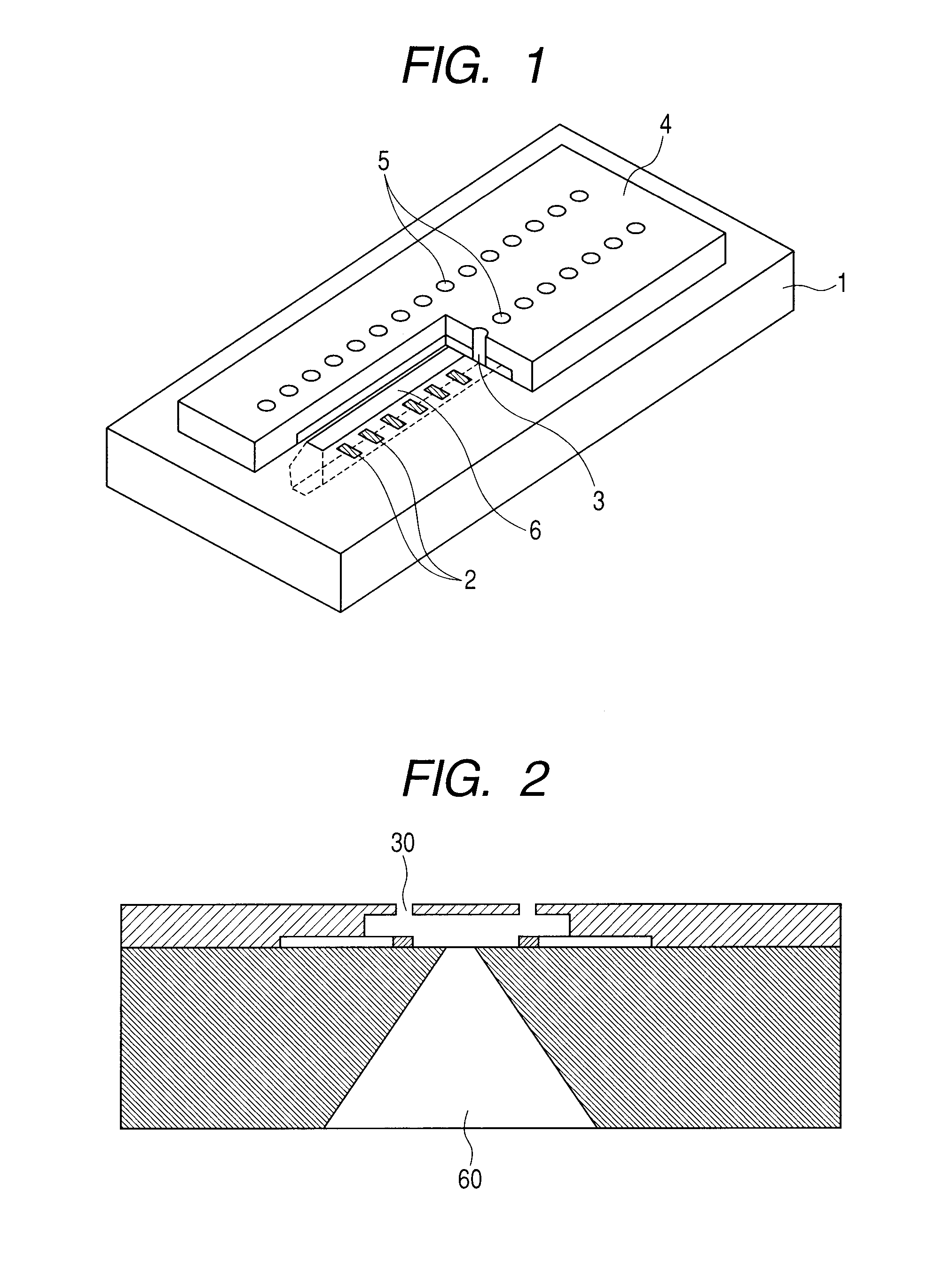

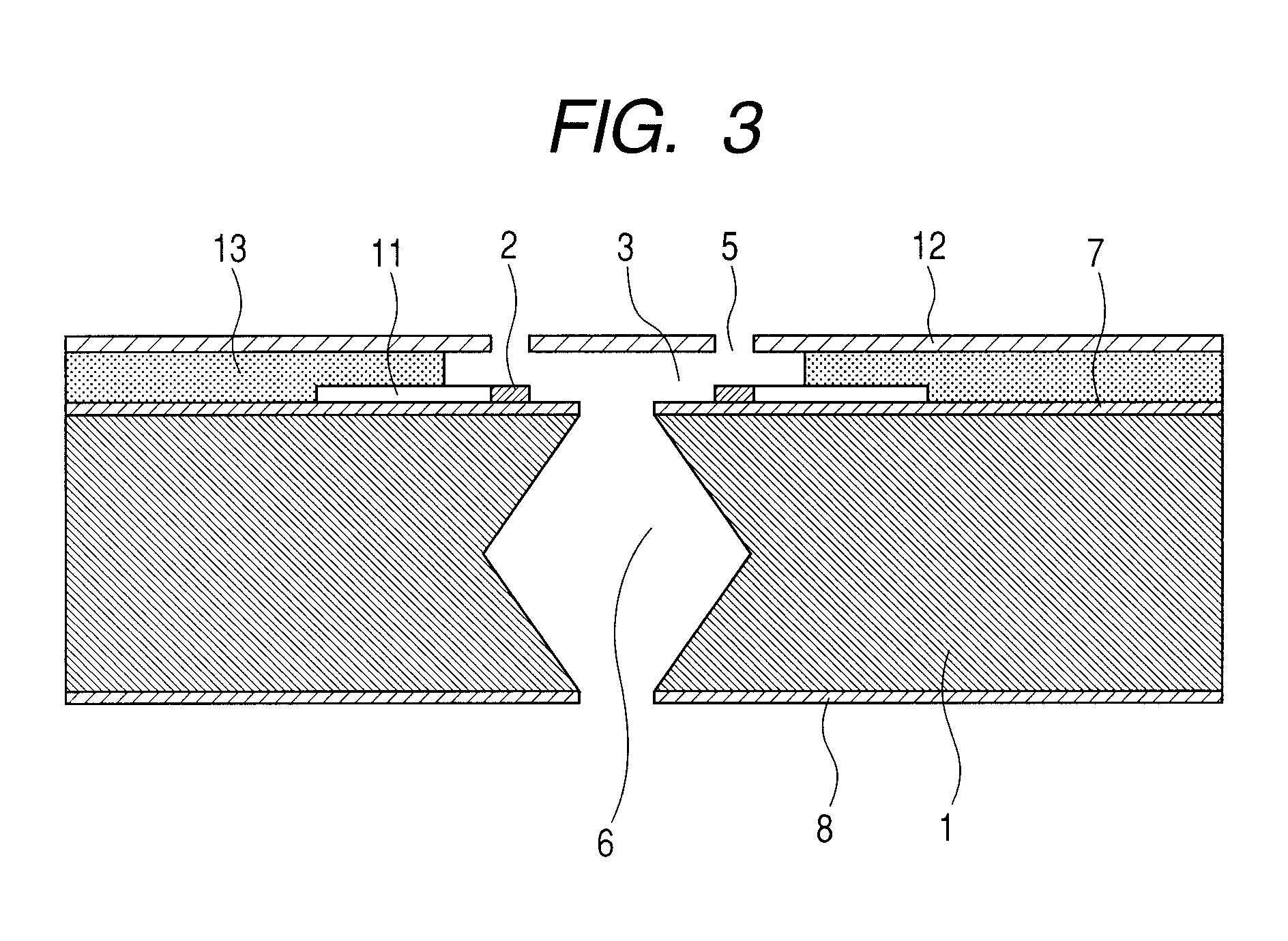

Thin film transistor and active matrix type display unit production methods therefor

A first contact hole is formed penetrating a gate insulating film, on which a gate electrode is formed and simultaneously a first contact is formed in the first contact hole. A second contact hole penetrating an interlayer insulating film is formed, and a second contact is formed in the second contact hole. A third contact hole is formed penetrating a planarization film, and an electrode is formed in the third contact hole. By using a plurality of contact holes for electrically connecting the electrode and a semiconductor film, the aspect ratio of each contact hole can be reduced, thereby achieving improvement in yield, high-level integration due to a reduction in difference in area between upper and bottom surfaces of the contact, and other advantageous improvements.

Owner:SANYO ELECTRIC CO LTD

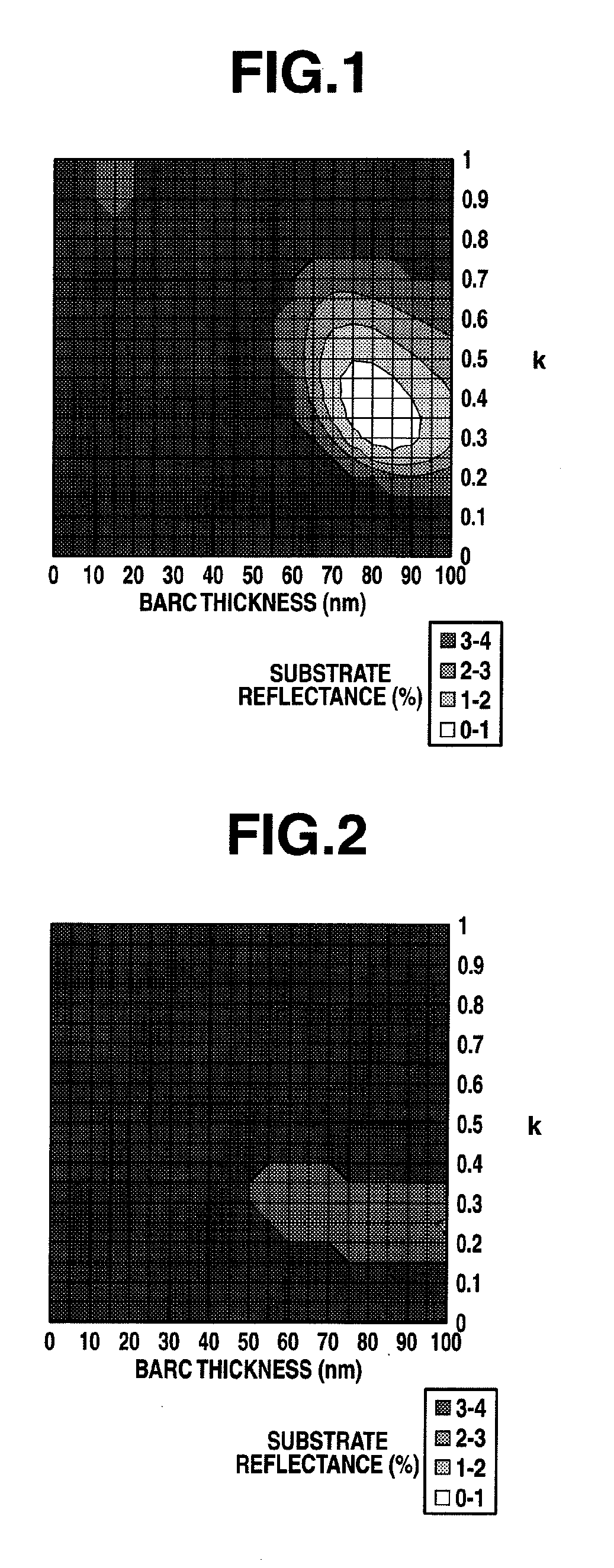

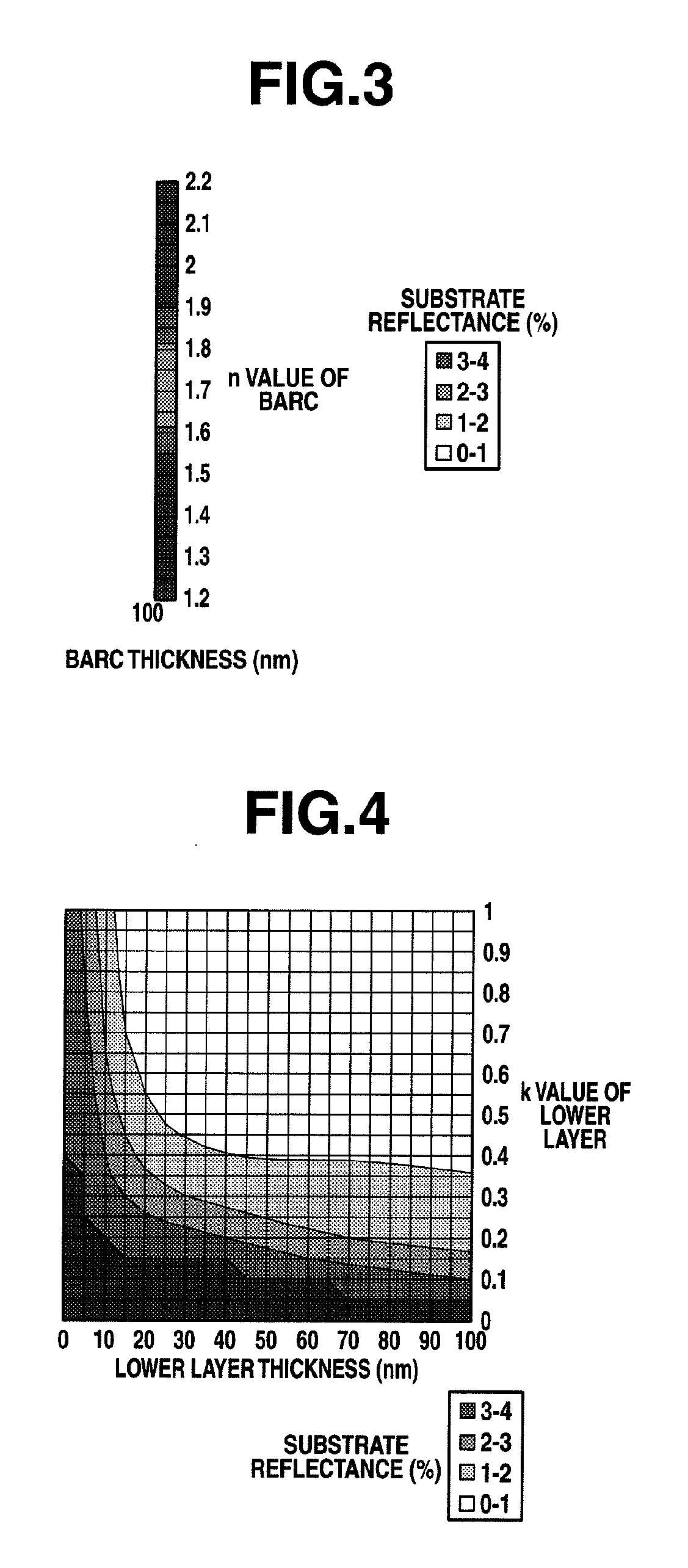

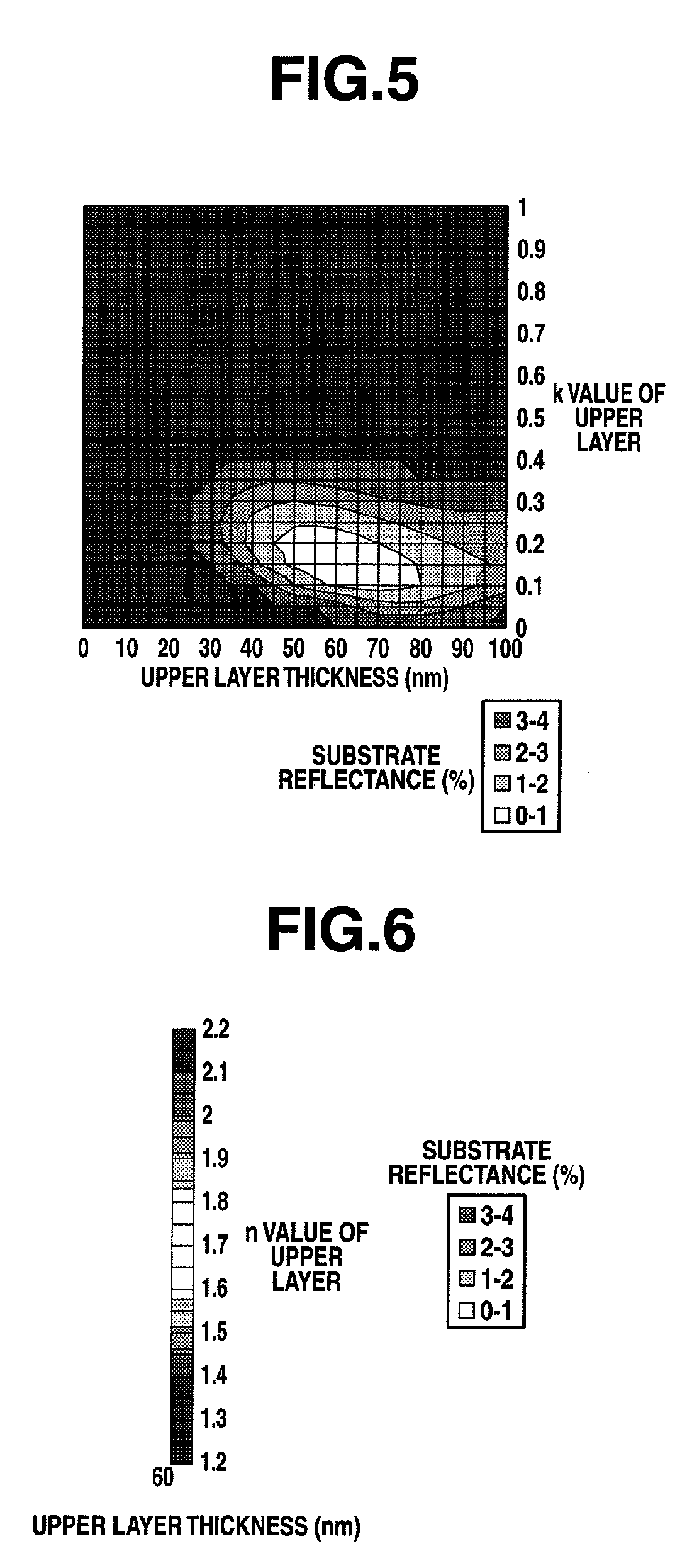

Antireflective coating composition, antireflective coating , and patterning process

ActiveUS20100151381A1Reduce etch timeAvoid contactPhotosensitive materialsSemiconductor/solid-state device manufacturingDry etchingFluorinated polymer

A composition comprising (A) a fluorinated polymer having k=0.01-0.4 and n=1.4-2.1 and (B) an aromatic ring-bearing polymer having k=0.3-1.2 is used to form an antireflective coating. The ARC-forming composition can be deposited by the same process as prior art ARCs. The resulting ARC is effective in preventing reflection of exposure light in photolithography and has an acceptable dry etching rate.

Owner:SHIN ETSU CHEM IND CO LTD

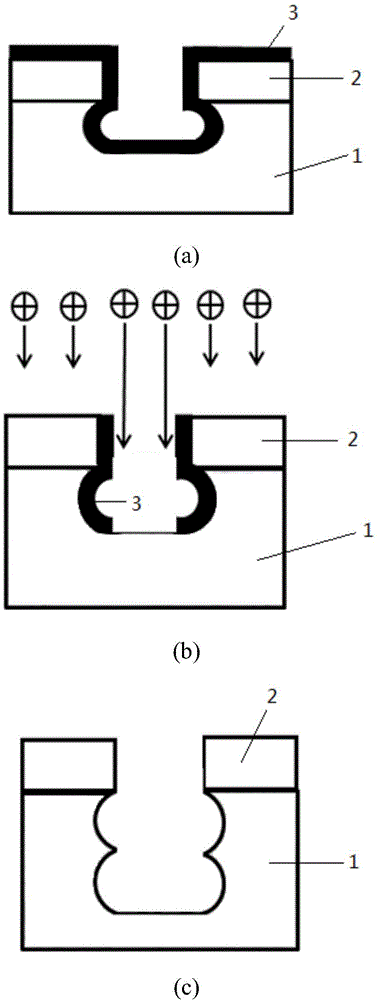

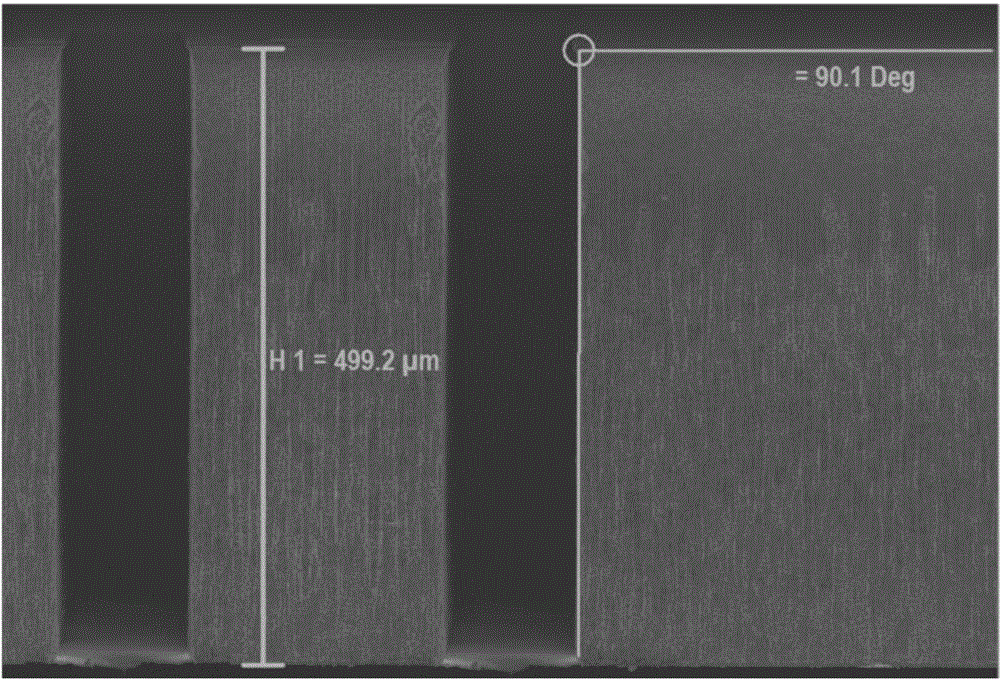

Deep silicon etching method

ActiveCN103950887AAchieve physical bombardmentReduce physical bombardmentDecorative surface effectsChemical vapor deposition coatingInductively coupled plasmaSilicon etching

The invention discloses a deep silicon etching method which comprises the following steps: (1) preparing a graphic photoresist mask on a silicon chip surface; (2) performing deep inductively coupled plasma dry etching of the silicon chip, wherein the etching is divided into several phases, each etching phase is completed in a inductively coupled plasma machine, and is completed through alternate circular processing of three steps of passivation, bombardment, and etching, and with the increase of the etching depth, the bombardment intensity in the bombardment step of each etching phase increases gradually. The method of the invention effectively solves the problems of difficult control of sidewall verticality and roughness, and difficult realization of large etching depth in the prior art, both improves the etching efficiency and increases the selection ratio or photoresist, and is high in etching groove sidewall verticality, low in roughness, and large in etching depth.

Owner:HUAZHONG UNIV OF SCI & TECH

Thin film transistor and manufacturing method thereof as well as display device

ActiveCN104716198AEtching speed is fastSolve the problem of easy corrosionTransistorSemiconductor/solid-state device manufacturingEtchingDisplay device

Owner:BOE TECH GRP CO LTD

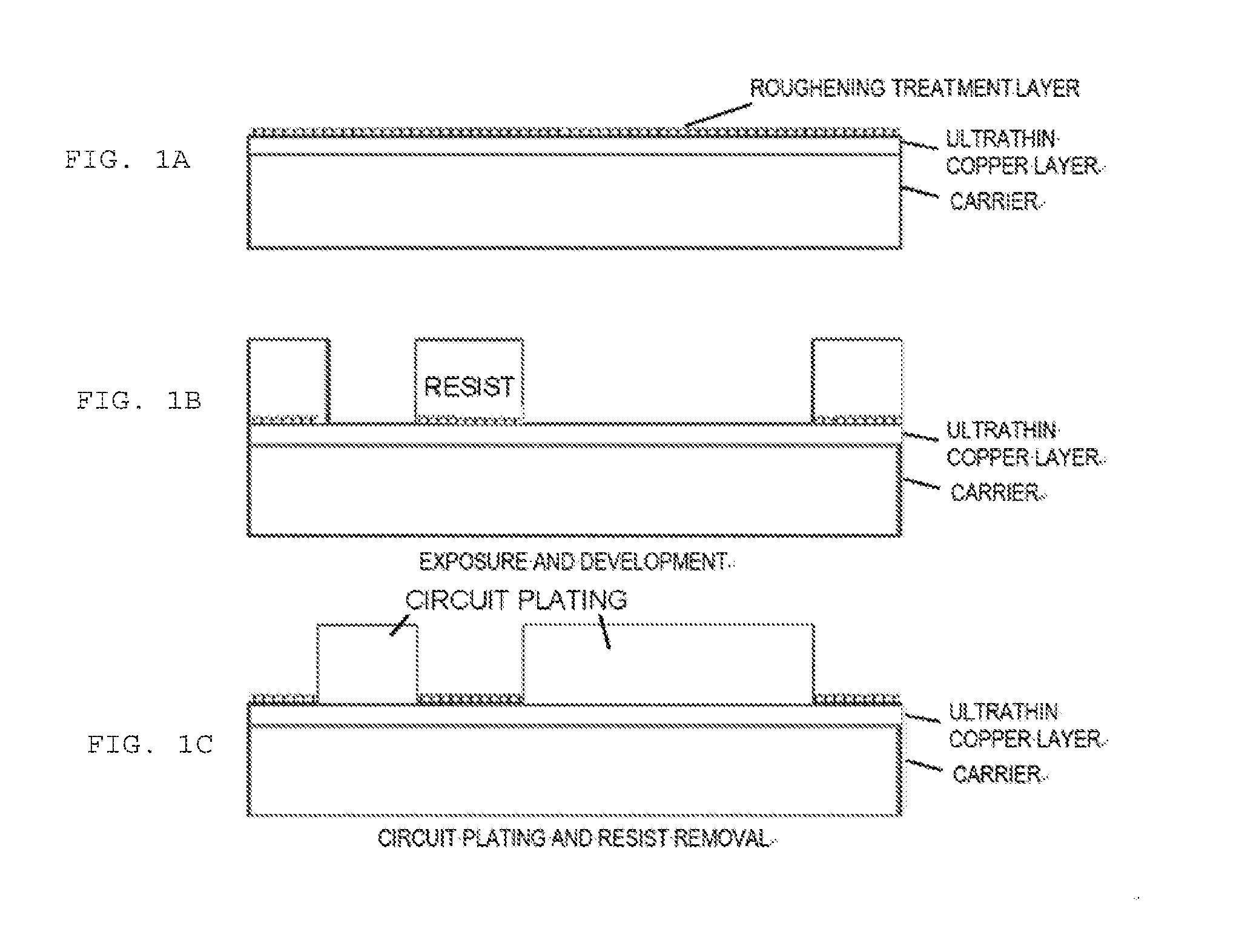

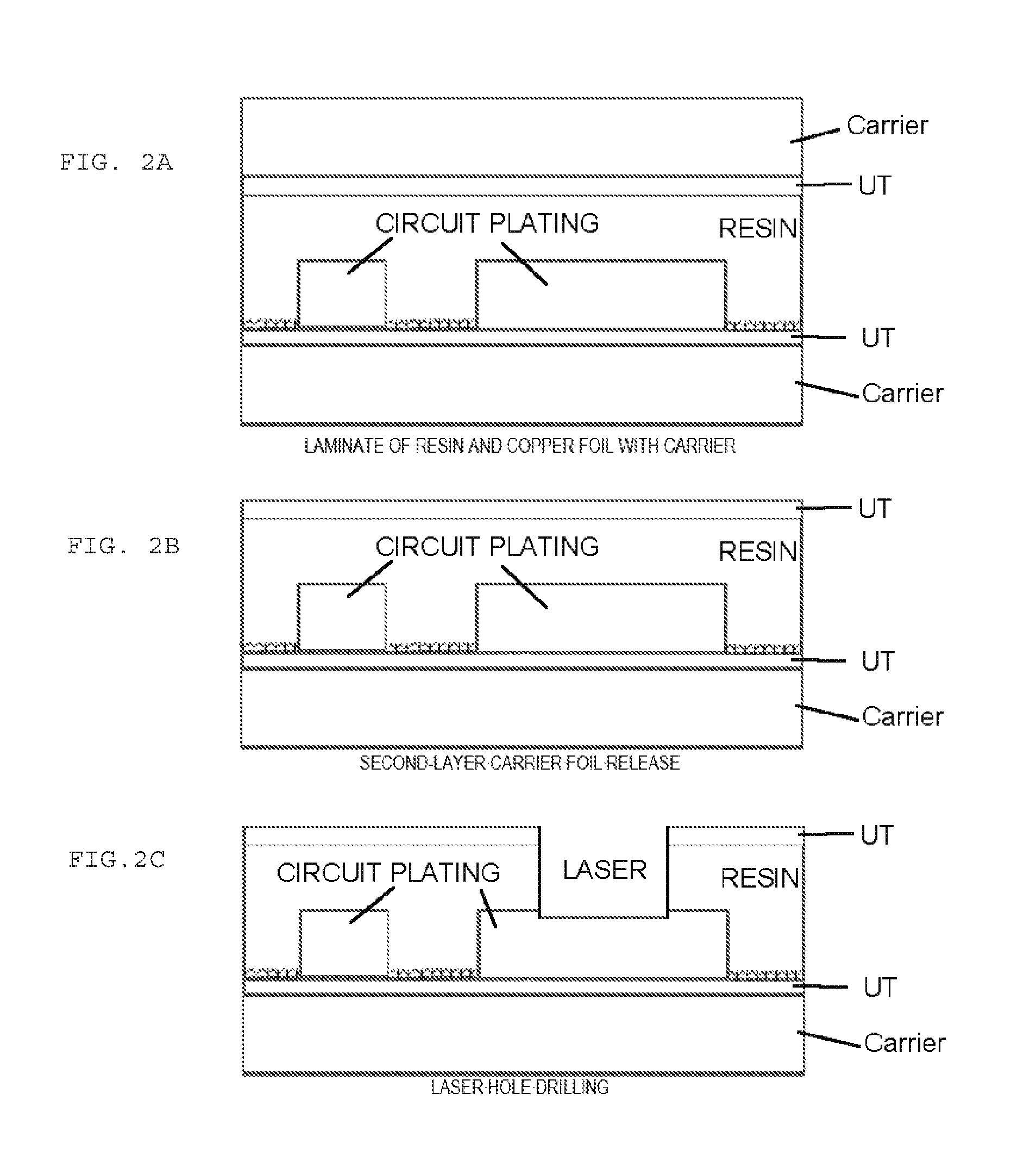

Carrier-Attached Copper Foil, Laminate, Method For Producing Printed Wiring Board, And Method For Producing Electronic Device

ActiveUS20170042036A1Improve surface smoothnessReduce etch timeElectrical connection printed elementsCircuit susbtrate materialsISO 25178Inter layer

Provided herein is a carrier-attached copper foil having desirable fine circuit formability. The carrier-attached copper foil includes a carrier, an interlayer, and an ultrathin copper layer in this order. The maximum trough depth Sv as measured with a laser microscope according to ISO 25178 on a surface of a bismaleimide-triazine resin substrate exposed by detaching the carrier and etching and removing the ultrathin copper layer after the carrier-attached copper foil is heat pressed against the resin substrate from the ultrathin copper layer side under the pressure of 20 kgf / cm2 at 220° C. for 2 hours is 0.181 to 2.922 μm.

Owner:JX NIPPON MINING & METALS CORP

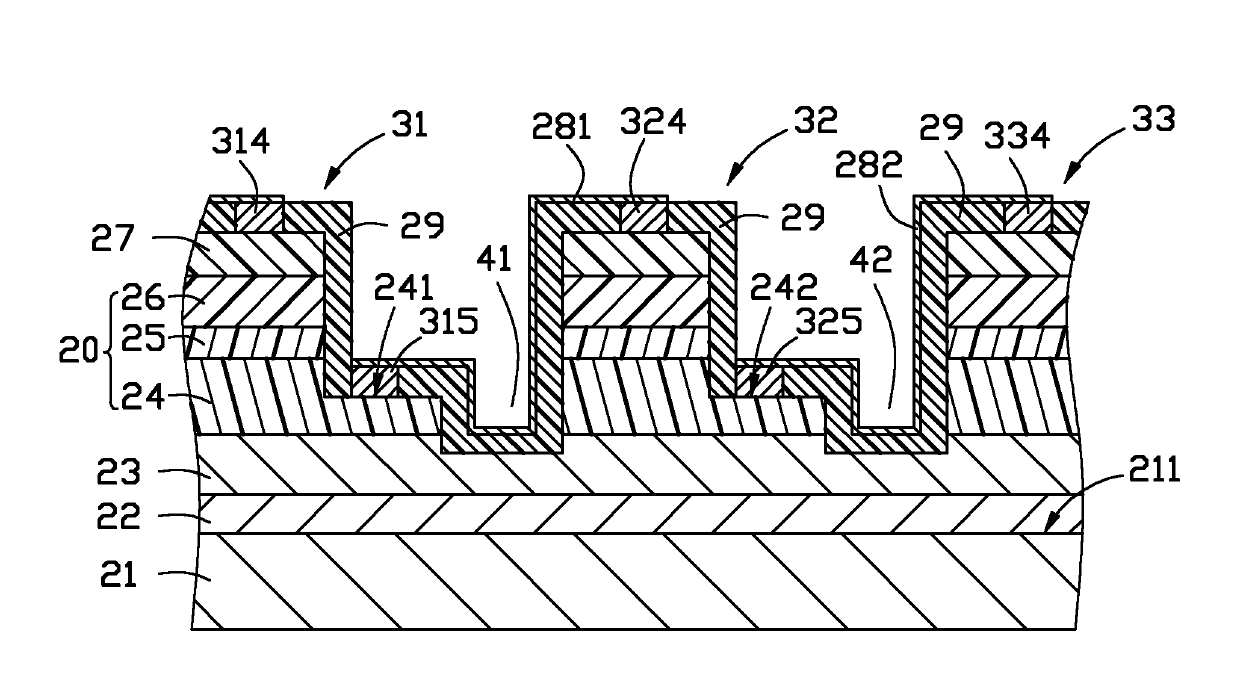

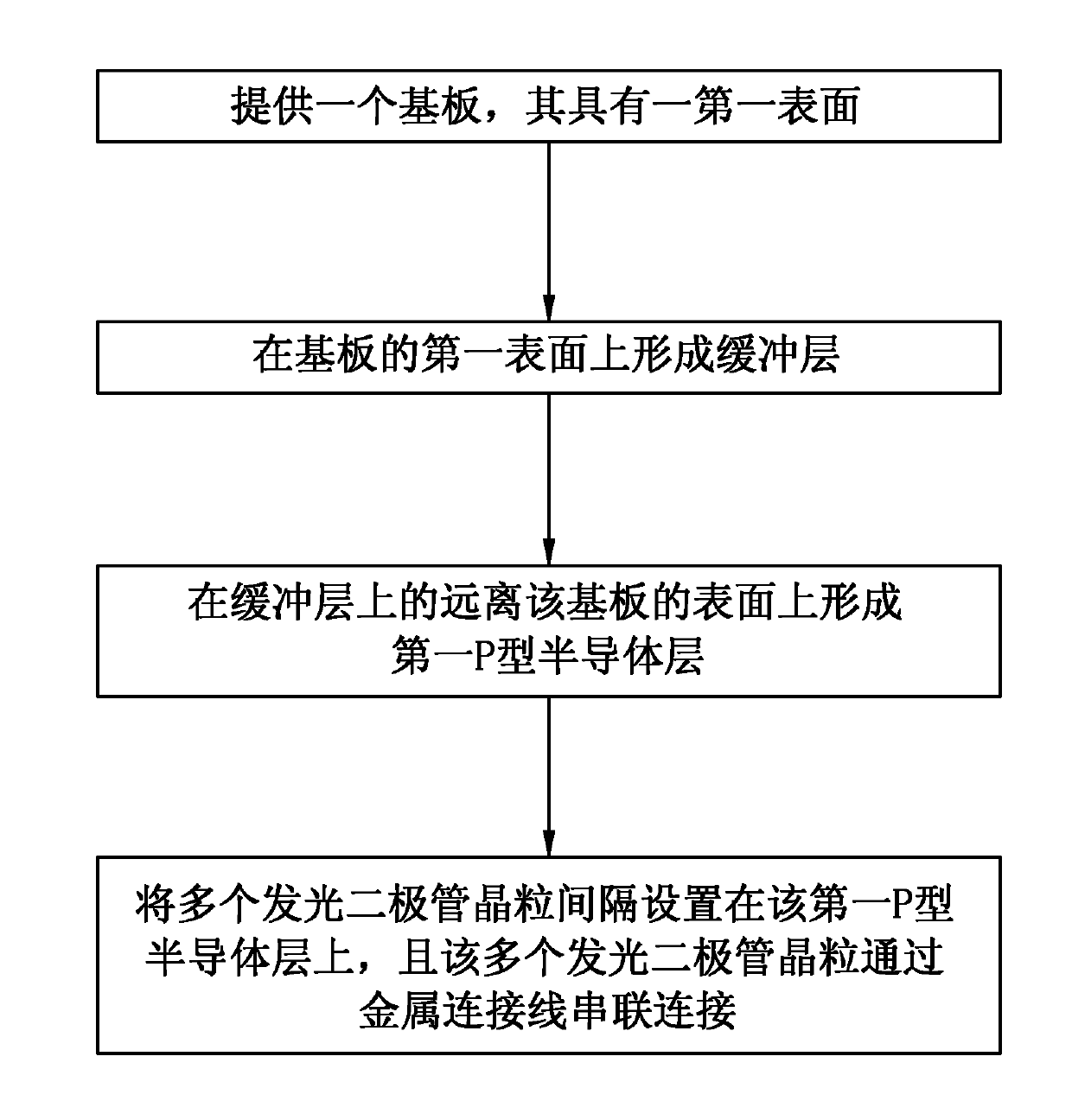

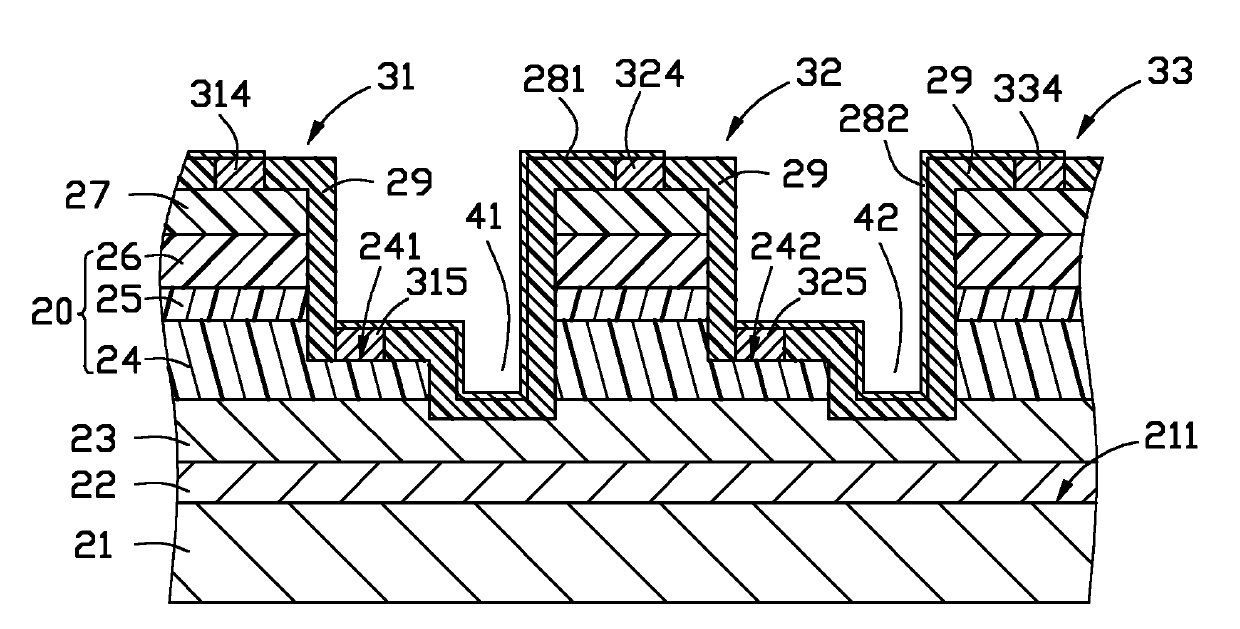

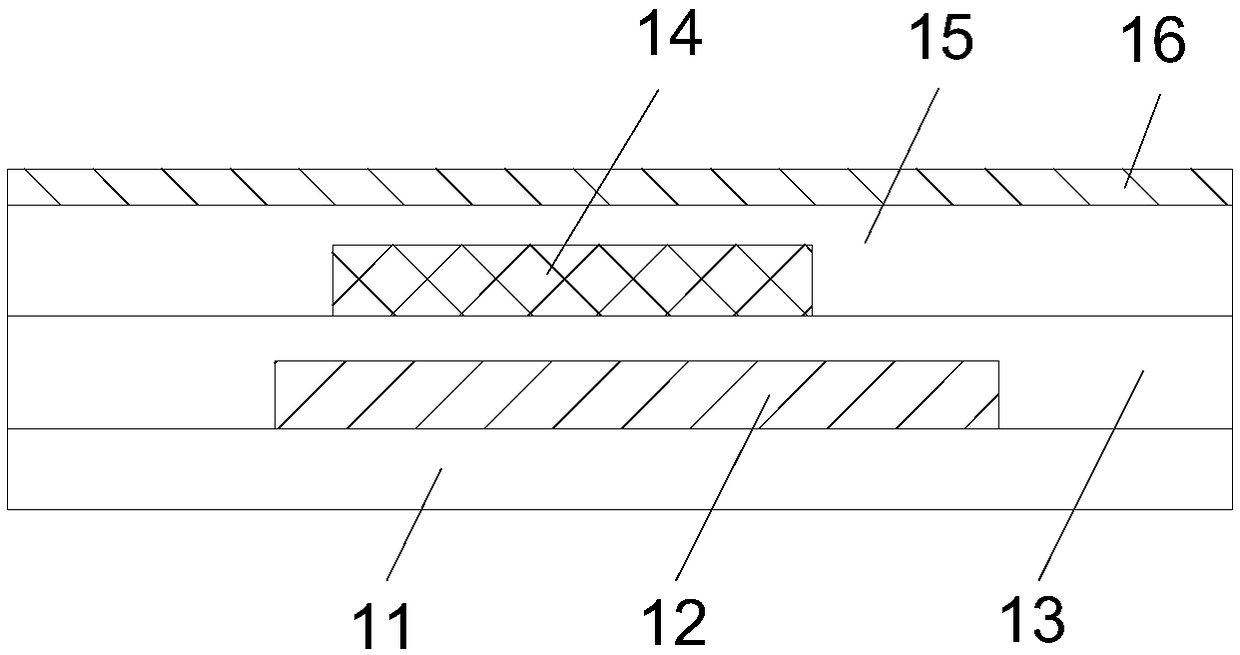

Light-emitting diode and formation method thereof

InactiveCN102446908AAvoid short circuitReduce etch timeSolid-state devicesSemiconductor devicesLight-emitting diodeSemiconductor

The invention relates to a light-emitting diode which comprises a baseplate, a buffer layer, a first P-type semiconductor layer and a second P-type semiconductor layer, wherein the baseplate is provided with a first surface, and the buffer layer is formed on the first surface of the baseplate; and the first P-type semiconductor layer is arranged on the surface, far from the baseplate, of the buffer layer; and multiple light-emitting diode grains are arranged on the first P-type semiconductor layer at intervals and are connected in series through metal connecting lines. The invention also relates to a formation method of the light-emitting diode.

Owner:ZHANJING TECH SHENZHEN +1

Mask blank, transfer mask, and methods of manufacturing the same

ActiveUS20110053057A1Excellent etch resistanceSuppress damage to antireflectionVacuum evaporation coatingPhotomechanical apparatusNitrogenOptoelectronics

Provided is a mask blank for producing a transfer mask adapted to ArF excimer laser exposure light. The mask blank has a light-shielding film on a transparent substrate. The light-shielding film has a structure in which a light-shielding layer and a front-surface antireflection layer are laminated in this order from the transparent substrate side. The light-shielding layer is made of a material containing tantalum and nitrogen. The front-surface antireflection layer is made of a material containing tantalum and silicon and further containing one or more elements selected from oxygen and nitrogen.

Owner:HOYA CORP

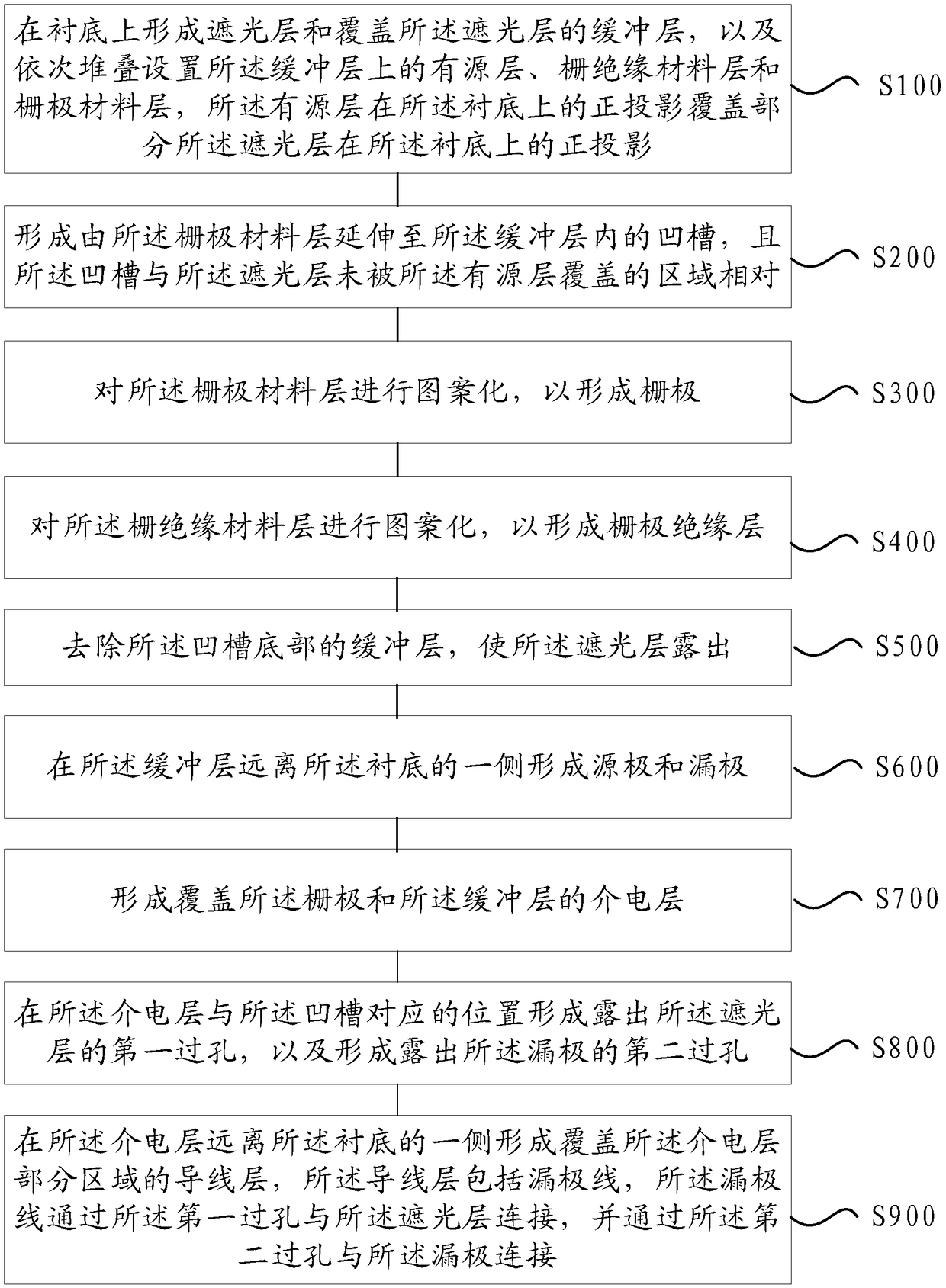

Display panel, array substrate, thin film transistor and manufacturing method of thin film transistor

ActiveCN109509707APrevent hardeningReduce etch timeTransistorSolid-state devicesEngineeringActive layer

The present invention relates to a manufacturing method of a thin film transistor, a thin film transistor, an array substrate, and a display panel. The manufacturing method includes the following steps that: a light shielding layer and a buffer layer covering the light shielding layer are formed on a substrate, and an active layer, a gate insulating material layer, and a gate material layer sequentially stacked on the buffer layer are also formed, the orthographic projection of the active layer on the substrate covers the orthographic projection of a portion of the light shielding layer on thesubstrate; a groove extending from the gate material layer into the buffer layer is formed, and the groove is opposite to a region of the light shielding layer which is not covered with the active layer; patterning is performed on the gate material layer, so that a gate is formed; patterning is performed on the gate insulating material layer, so that a gate insulating layer is formed; the bufferlayer at the bottom of the groove is removed, so that the light shielding layer can be exposed; a source and a drain are formed on a surface of the buffer layer, wherein the surface of the buffer layer is away from the substrate; a dielectric layer covering the gate and the buffer layer is formed; a first via hole exposing the light shielding layer is formed at a position of the dielectric layer which is corresponding to the groove, and a second via hole exposing the drain is also formed in the dielectric layer.

Owner:HEFEI XINSHENG OPTOELECTRONICS TECH CO LTD +1

Cavity type bulk acoustic wave resonator with pillar and preparation method thereof

The invention provides a cavity type bulk acoustic wave resonator with a support column and a preparation method of the cavity type bulk acoustic wave resonator. The method comprises the following steps of: taking a piezoelectric single crystal wafer which is subjected to ion implantation and is provided with a bottom electrode; forming a plurality of supporting columns on one side, with the bottom electrode, of the piezoelectric single crystal wafer; forming a cavity at the gap of supporting columns, taking the substrate, bonding the substrate with one side of the piezoelectric single crystalwafer with the cavity, carrying out heat treatment on the substrate after bonding, stripping a film of the piezoelectric single crystal wafer, and producing a top electrode on the stripped side of the piezoelectric single crystal wafer to obtain the piezoelectric single crystal wafer. According to the technical scheme provided by the invention, a sacrificial layer does not need to be grown, etching and trepanning are not carried out on the thin film, the mechanical strength of the device is improved, and the thin film is not easily damaged; the cavity structure is formed before film formation, the rate of finished products is high, residues left by etching after film formation do not exist, and the influence of incomplete release on the device does not need to be considered.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method of plating a metal or metal or metal compound on a semiconductor substrate that includes using the same main component in both plating and etching solutions

InactiveUS20050064700A1Suppress coarseningFew stepsSemiconductor/solid-state device manufacturingMetallic material coating processesCopper oxideAmmonia

A method of forming a copper oxide film including forming a copper oxide film including an ammonia complex by causing a mixed solution of aqueous ammonia and aqueous hydrogen peroxide, which has been adjusted to have pH of 8 to 10 or pH of 9 to 10, to contact a surface of a copper film. A method of fabricating a semiconductor device including burying a copper film to be a wiring or a contact wiring in a wiring groove or a contact hole formed in a surface of an insulating film formed on a semiconductor substrate, or in both the wiring groove and the contact hole, forming a copper oxide film including an ammonia complex on a surface of the copper film by using the copper oxide film forming method, and removing the copper oxide film from the copper film using acid or alkali.

Owner:KK TOSHIBA

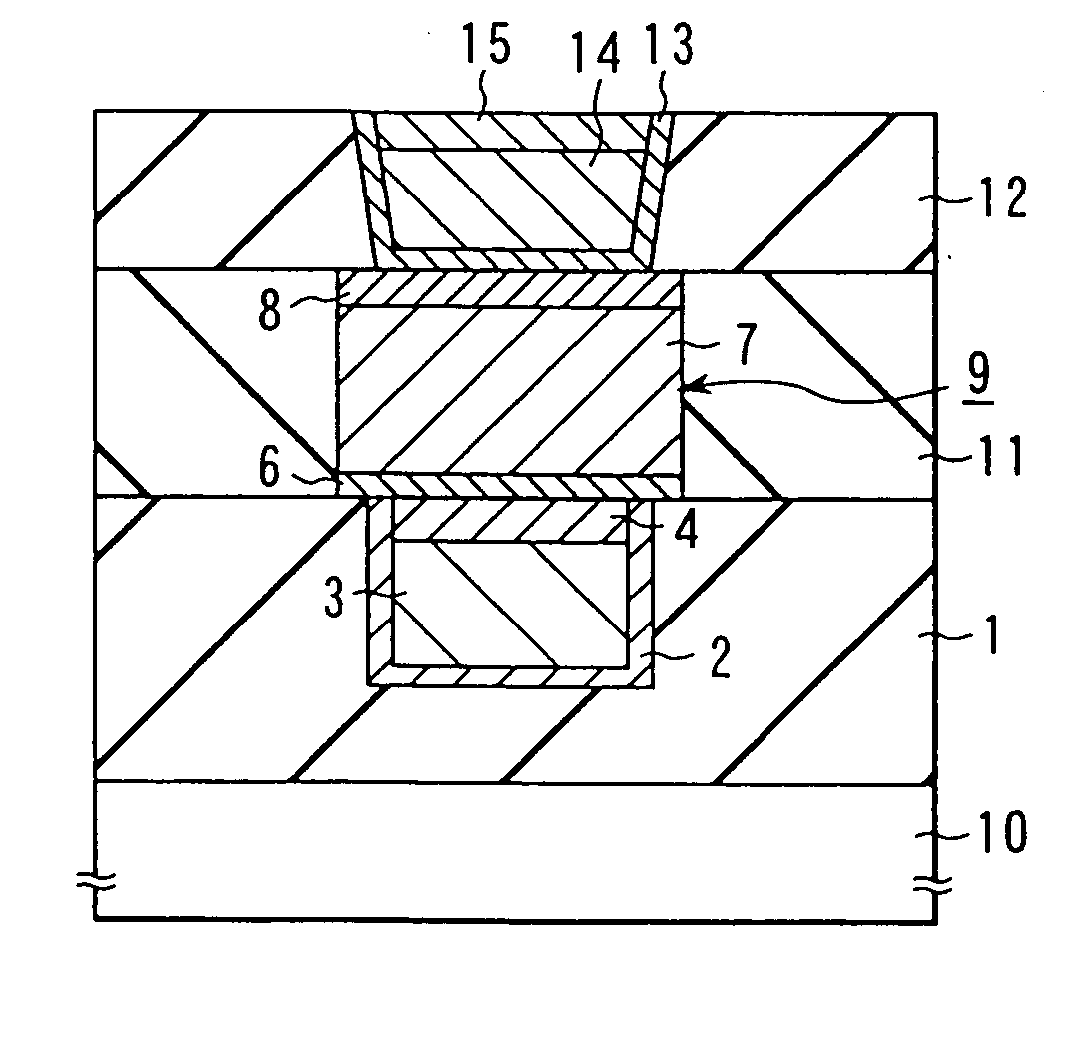

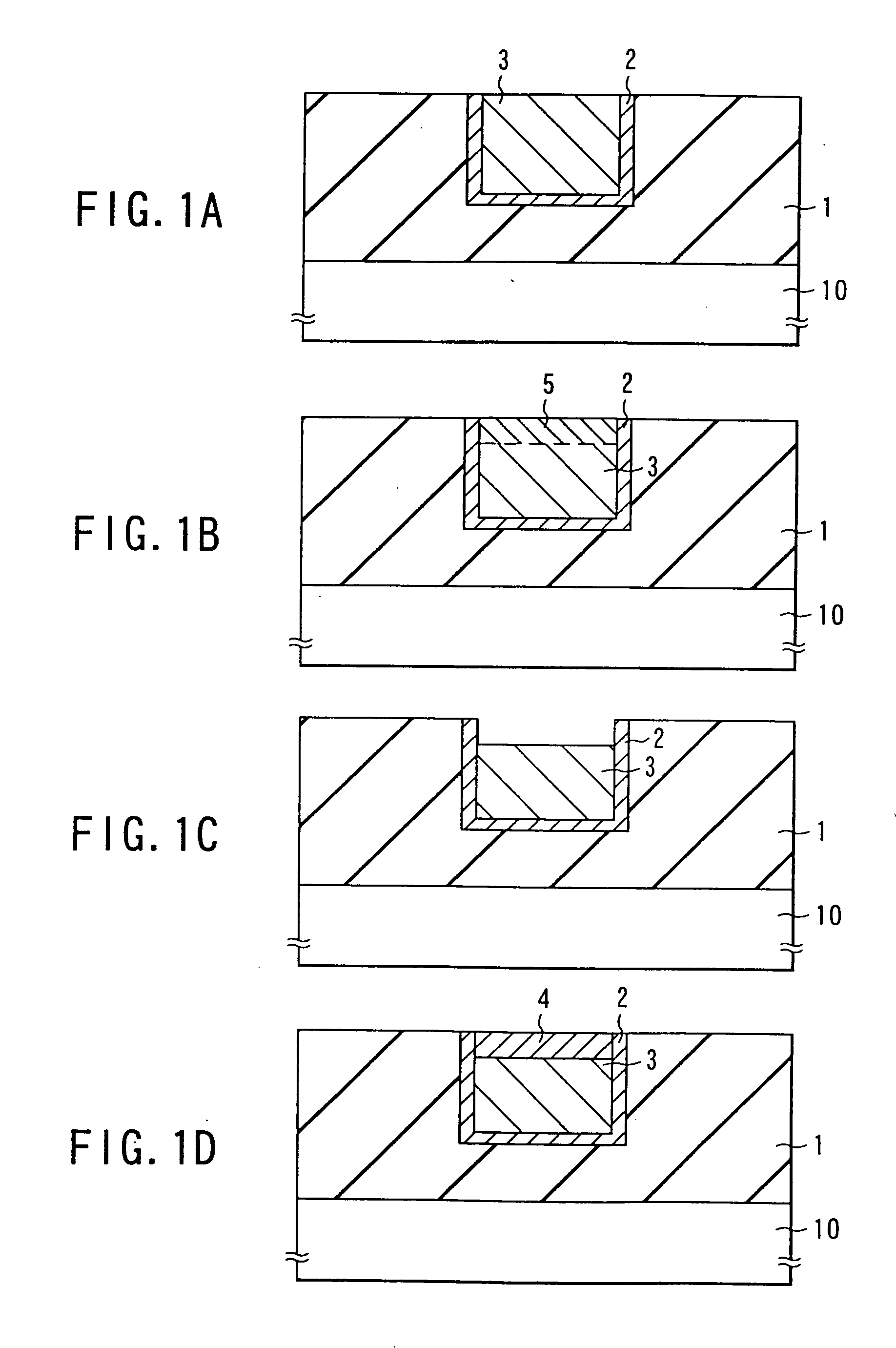

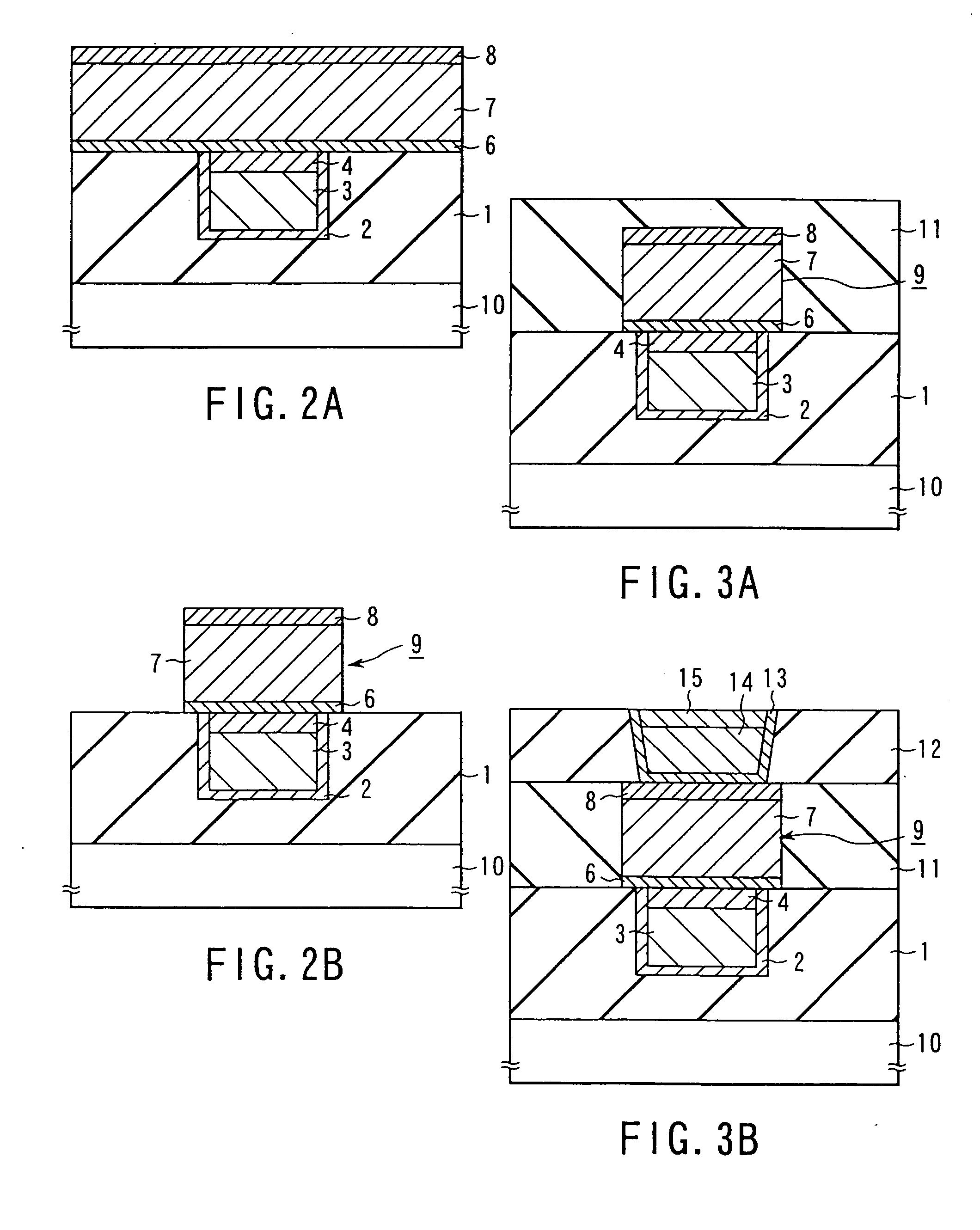

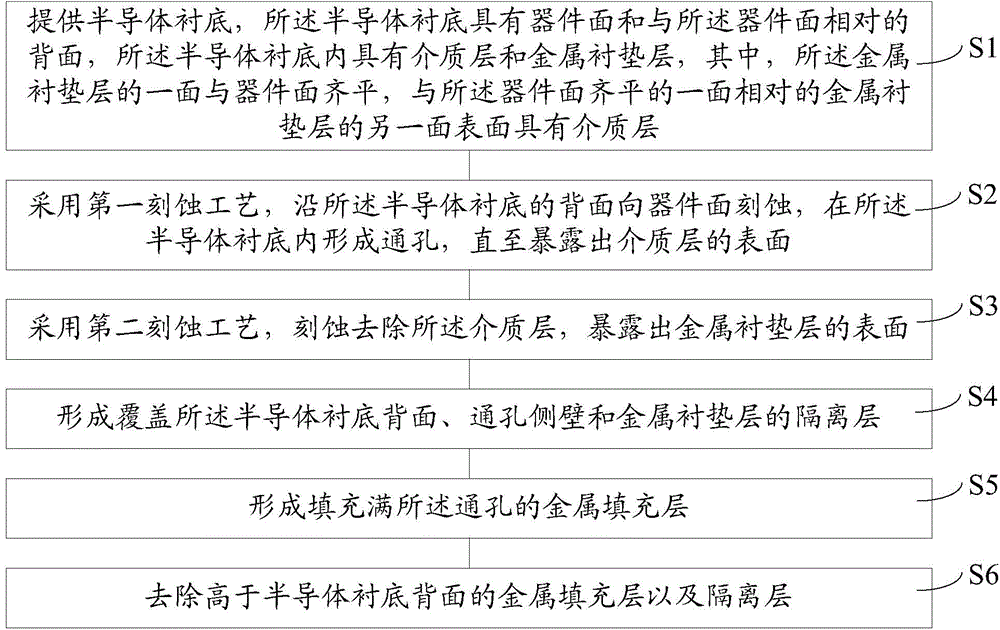

Forming method of semiconductor device

InactiveCN104617035AImprove reliabilityImprove electrical performanceSemiconductor/solid-state device manufacturingAnisotropic etchingDielectric layer

The invention provides a forming method of a semiconductor device. The forming method comprises the steps of providing a semiconductor substrate which is provided with a device surface and a back opposite to the device surface, etching the semiconductor substrate in a direction from the back of the semiconductor substrate to the device surface of the semiconductor substrate, forming a through hole in the semiconductor substrate to expose the surface of a dielectric layer, forming an insulating layer for covering the back of the semiconductor substrate, the sidewall of the through hole and the insulating layer of the dielectric layer, and etching off the insulating layer and the dielectric layer located at the bottom of the through hole by use of an anisotropic etching process to expose the surface of a metal liner layer, wherein the dielectric layer and the metal liner layer are formed in the semiconductor substrate; the insulating layer thinnest on the surface of the dielectric layer. The forming method has the advantages that the process of etching off the dielectric layer is prevented from damaging the sidewall of the through hole, the roughness of the sidewall of the through hole is improved, and therefore, the reliability of the semiconductor device can be improved, and the electric leakage problem can be avoided.

Owner:SEMICON MFG INT (SHANGHAI) CORP

High-temperature-resistant lithium battery diaphragm and production method thereof

InactiveCN103928648AImprove heat resistanceSolving Etching ProblemsCell seperators/membranes/diaphragms/spacersHeat resistanceEngineering

The invention belongs to the technical field of battery diaphragms, and discloses a high-temperature-resistant lithium battery diaphragm and a production method thereof. A base material of the high-temperature-resistant diaphragm is a polyimide thin film, and micropores are uniformly formed in the base material. The production method comprises the steps of irradiating the polyimide thin film by heavy ions, and etching the irradiated polyimide thin film through a sodium hypochlorite solution. The high-temperature-resistant lithium battery diaphragm and the production method thereof have the advantages that the heat resistance is high, the tensile strength is high, environment pollution is avoided, the micropores are uniformly distributed, and high-current quick charging and discharging requirements for a lithium battery are met.

Owner:CHINA INSTITUTE OF ATOMIC ENERGY

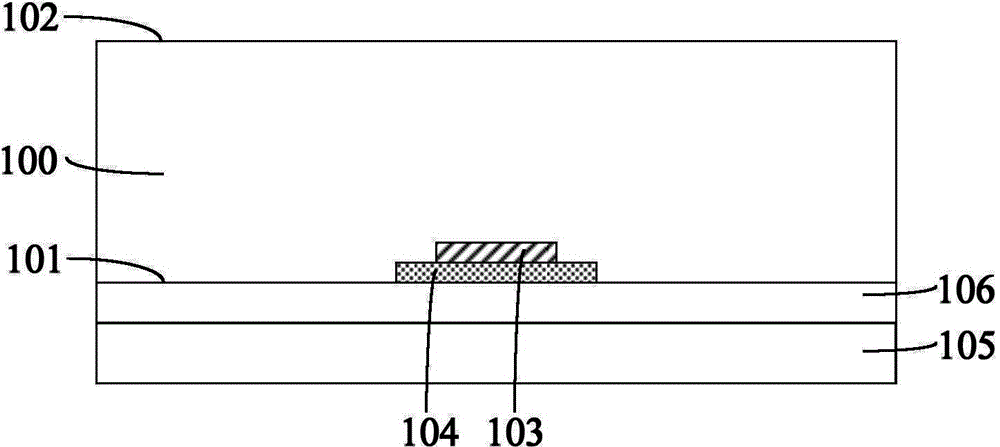

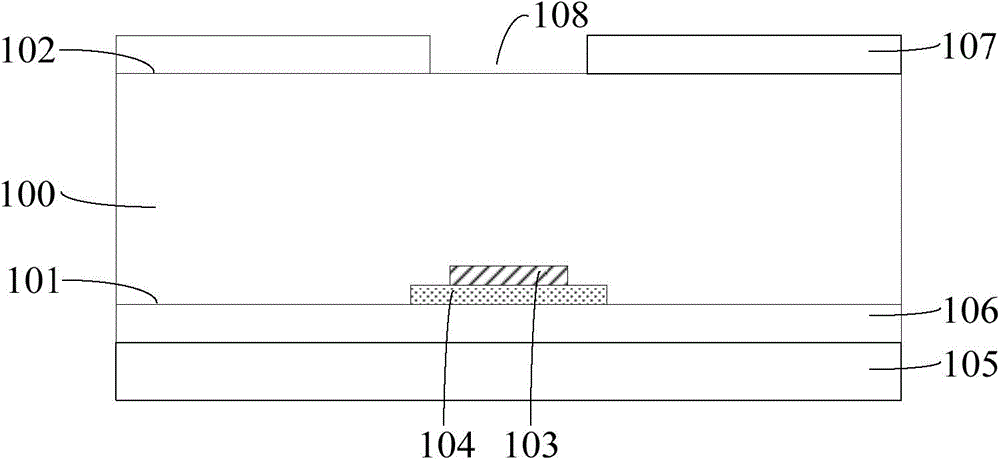

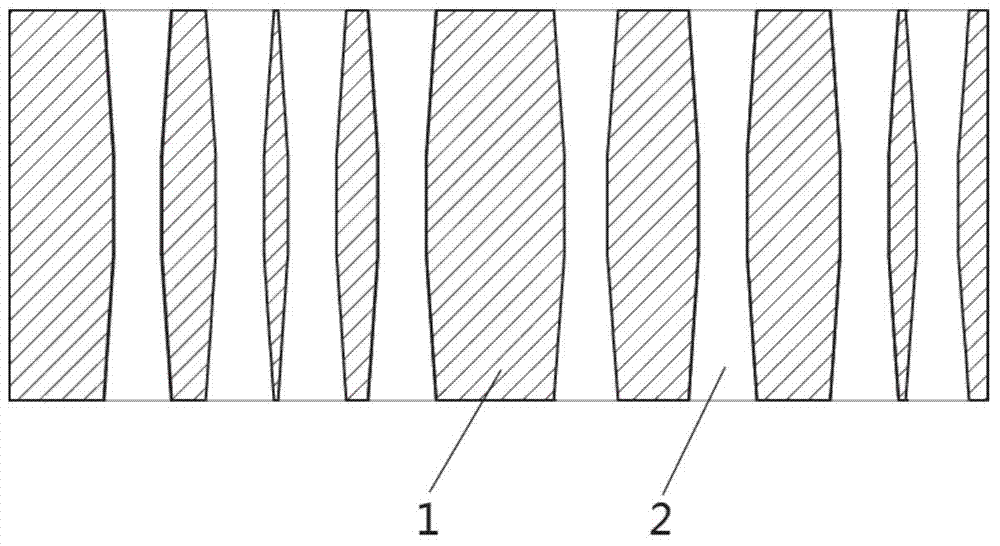

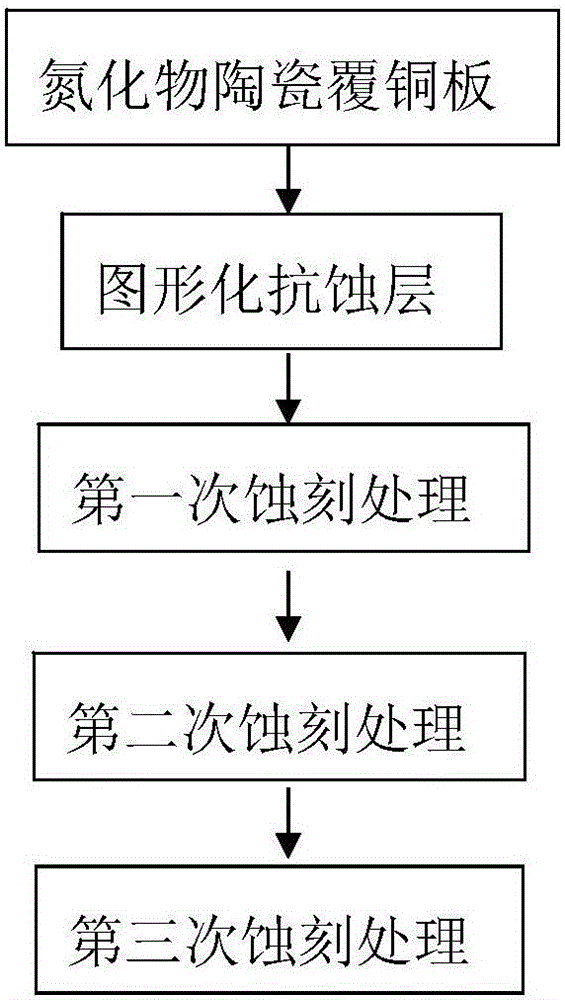

Patterning method of nitride ceramic copper-clad plate and nitride ceramic copper-clad plate

InactiveCN106328544AReduce etch timeImprove efficiencySemiconductor/solid-state device detailsSolid-state devicesEtchingCopper

The invention discloses a patterning method of a nitride ceramic copper-clad plate and a nitride ceramic copper-clad plate. The patterning method comprises the following steps: arranging a patterned anti-corrosion layer on the surface of the nitride ceramic copper-clad plate, wherein the nitride ceramic copper-clad plate is formed by an active brazing method; performing first etching treatment on the nitride ceramic copper-clad plate by using a first etching solution, wherein the first etching solution comprises a CuCl<2> solution or a FeCl<3> solution; performing second etching treatment on the nitride ceramic copper-clad plate being subjected to the first etching treatment by using a second etching solution; and performing third etching treatment on the nitride ceramic copper-clad plate being subjected to the second etching treatment by using a third etching solution. The patterning method has the advantages of high etching efficiency, uniform etching and freeness from residues; the etching quality is improved; and a metal layer has a good plate surface state.

Owner:ZHEJIANG TC CERAMIC ELECTRONICS

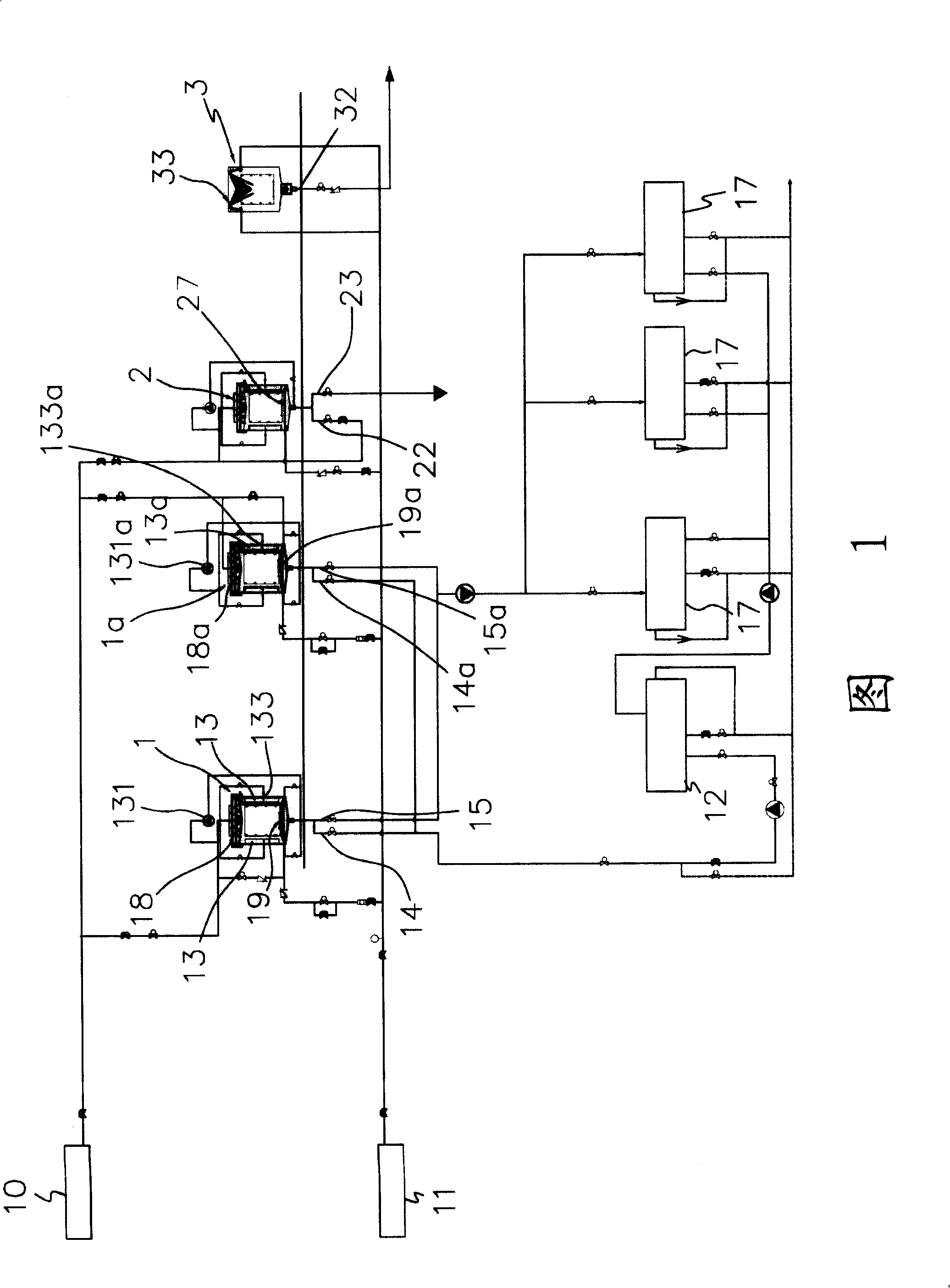

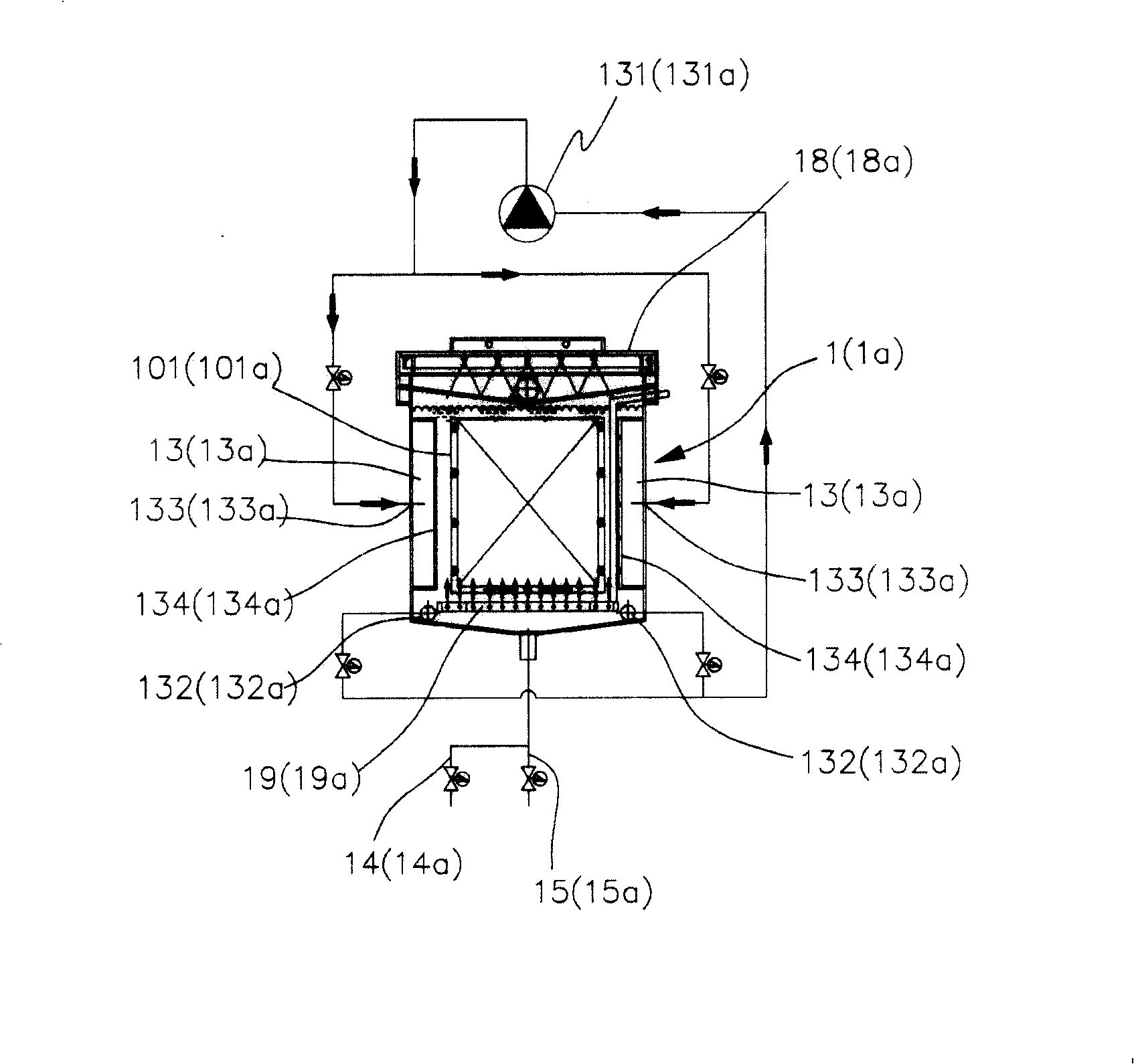

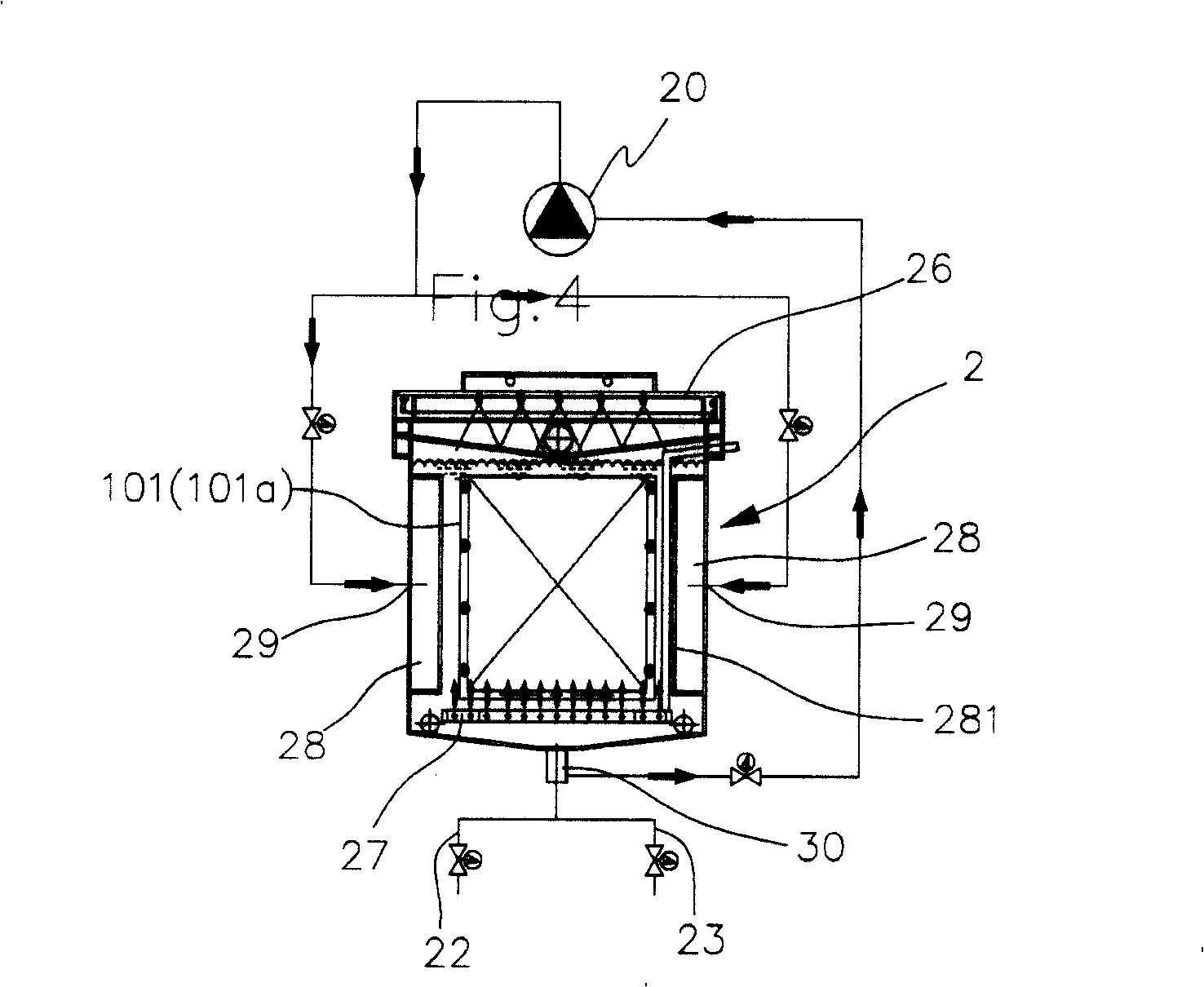

Device for etching TFT LCD glass substrate and etching method thereof

ActiveCN101255012AReduce etch timeSimplify the etch processSemiconductor/solid-state device manufacturingEtchingEngineering

The invention discloses an etching device for a TFT LCD glass substrate and etching method thereof, wherein, the device comprises two bearing boxes, two etching washing grooves, a washing groove and a drying groove; the method is that one of the bearing boxes with a plurality of TFT LCD glass substrates are etched and first-step washed in the etching washing groove; then the bearing box is transferred to the washing groove to be second-step washed; meanwhile, the other bearing box with a plurality of TFT LCD glass substrates are arranged in the other etching washing groove to be etched and first-step washed; the washed TFT LCD glass substrates in the first bearing box are placed in the drying groove to be dried, meanwhile, the other bearing box is transferred to the washing groove to have a plurality of TFT LCD glass substrates second-step washed; then the washed TFT LCD glass substrates in the second bearing box are dried in the drying groove; therefore, the etching of a plurality of TFT LCD glass substrates in the two bearing boxes can be simultaneously finished in one processing, thereby achieving the effect of shortening the etching time and simplifying the etching process.

Owner:DALUX TECH

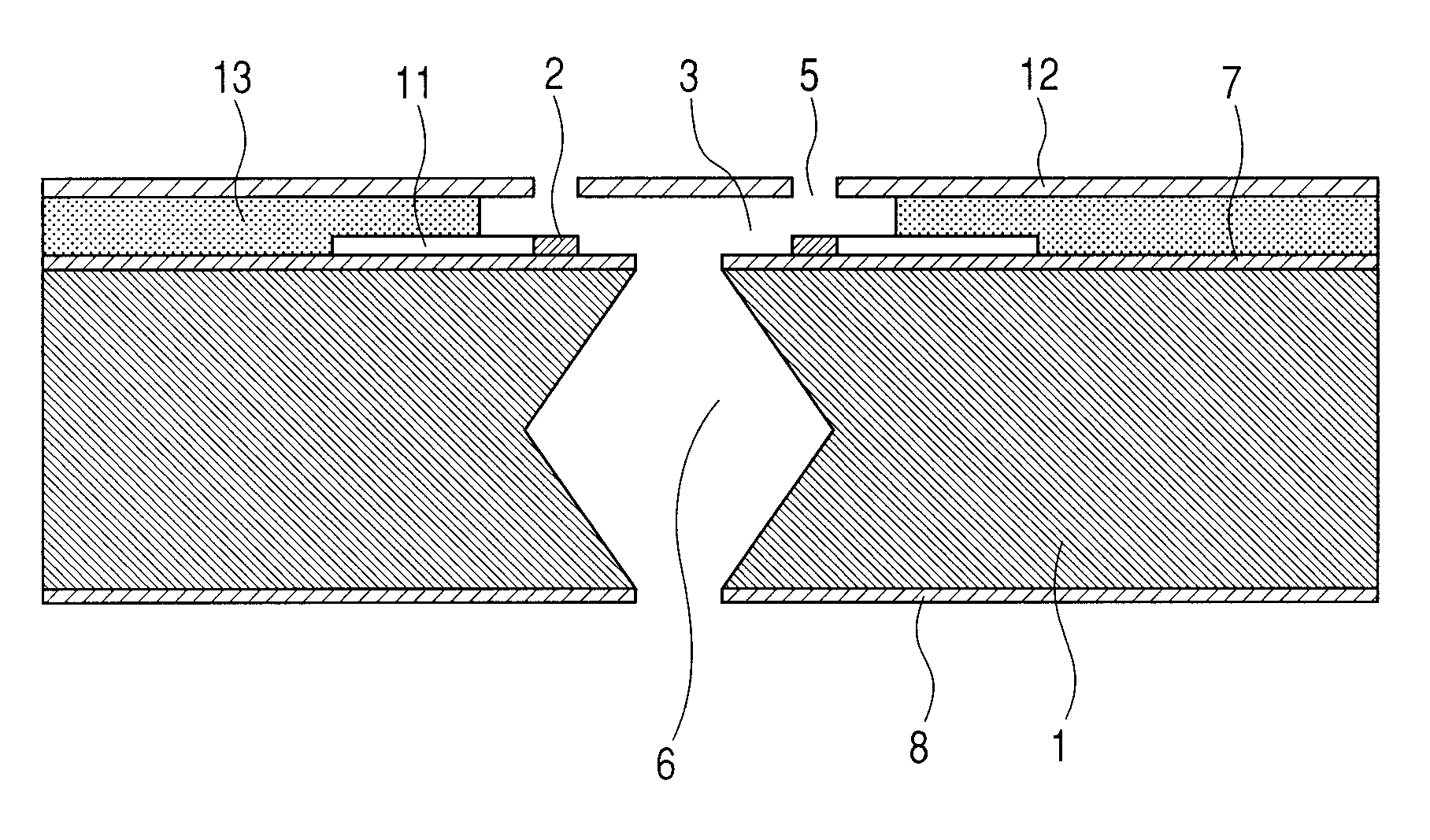

Method of manufacturing substrate for liquid discharge head

InactiveUS20100255616A1Shorten production timeSmall sizeSemiconductor/solid-state device manufacturingPrintingEngineeringAnisotropic etching

A method of manufacturing a substrate for a liquid discharge head having a supply port passing through a silicon substrate provided with an energy-generating element generating the energy used to discharge a liquid and allowing liquid to be supplied to the energy-generating element, includes preparing a silicon substrate in which a first etching mask having a first opening is provided on a first face, and a second etching mask having a second opening is provided on a second face that is the rear face of the first face; forming a first recess towards the second face from the first face within the first opening, and forming a second recess towards the first face from the second face within in the second opening; and performing crystalline anisotropic etching using the first and second etching masks as masks from both of the first and second faces, to form the supply port.

Owner:CANON KK

Photomask blank, method for manufacturing photomask, and method for manufacturing phase shift mask

ActiveUS20130309601A1Increase etch rateImprove accuracySemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentOptoelectronicsOxygen

A light-shielding film 2 formed on a transparent substrate 1 has a monolayer structure or a multilayer structure. At least one layer is formed by film-formation with a chromium-containing material including tin. The light-shielding film 2 has an optical density of 2 or higher and 4 or lower and has a reflection-preventing function. The layer made of a chromium-containing material including tin, which constitutes the light-shielding film 2, can cause a significant increase in the etching rate at the time of chlorine-containing dry etching including oxygen. Thus, burden on the resist pattern or hard mask pattern at the time of transferring a pattern on the light-shielding film is reduced, and therefore it is possible to carry out pattern transfer with high precision.

Owner:SHIN ETSU CHEM IND CO LTD

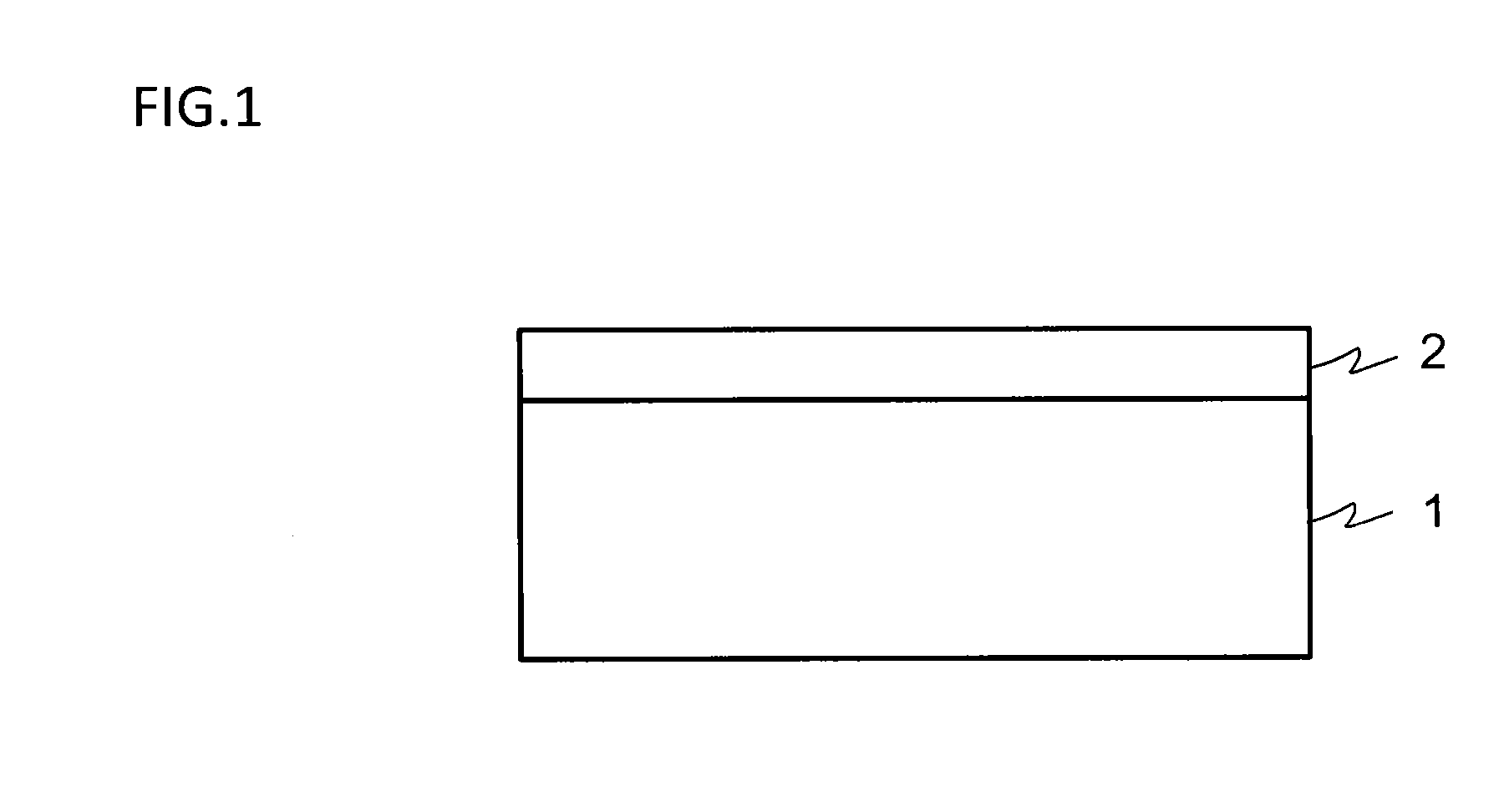

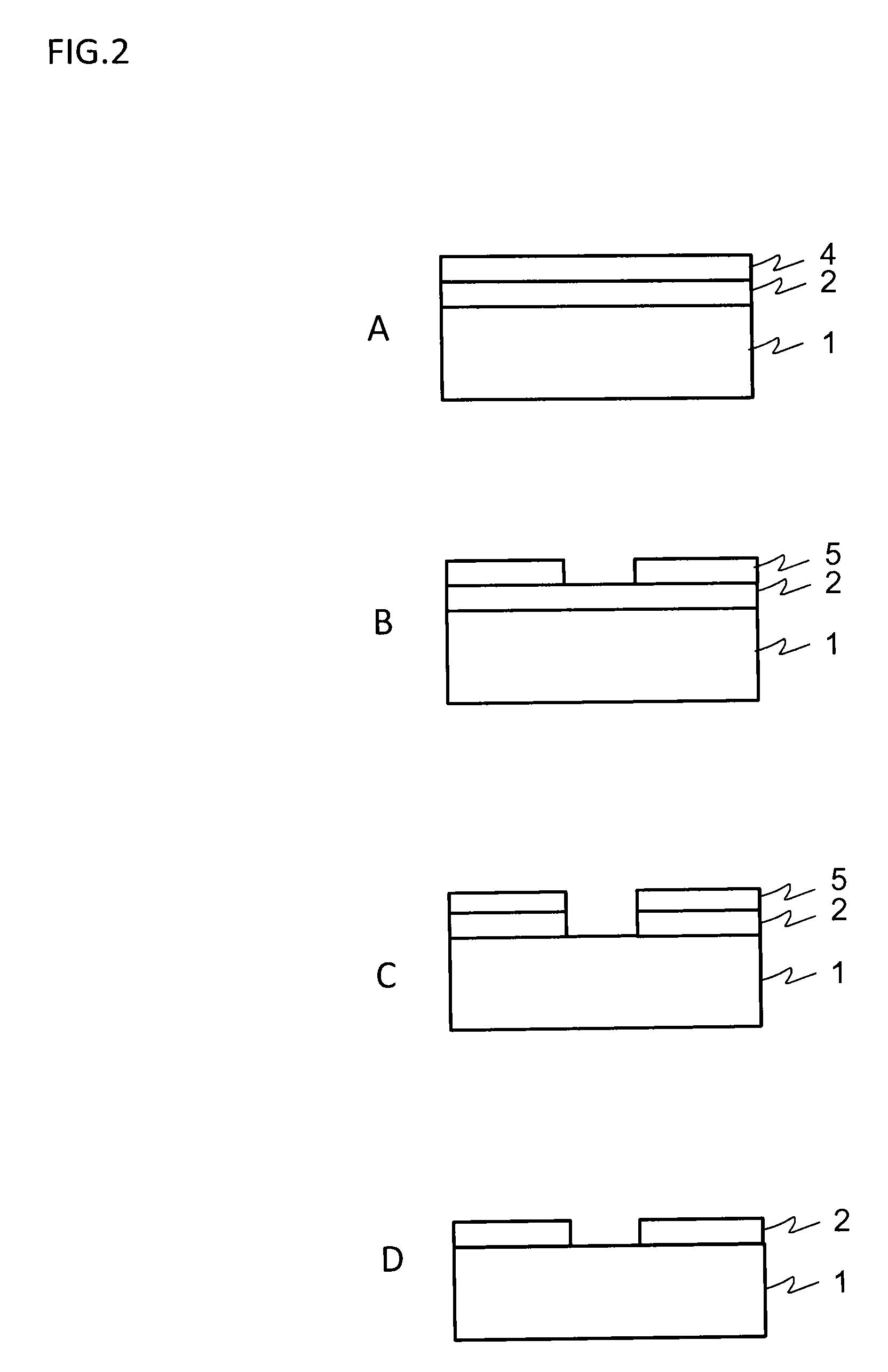

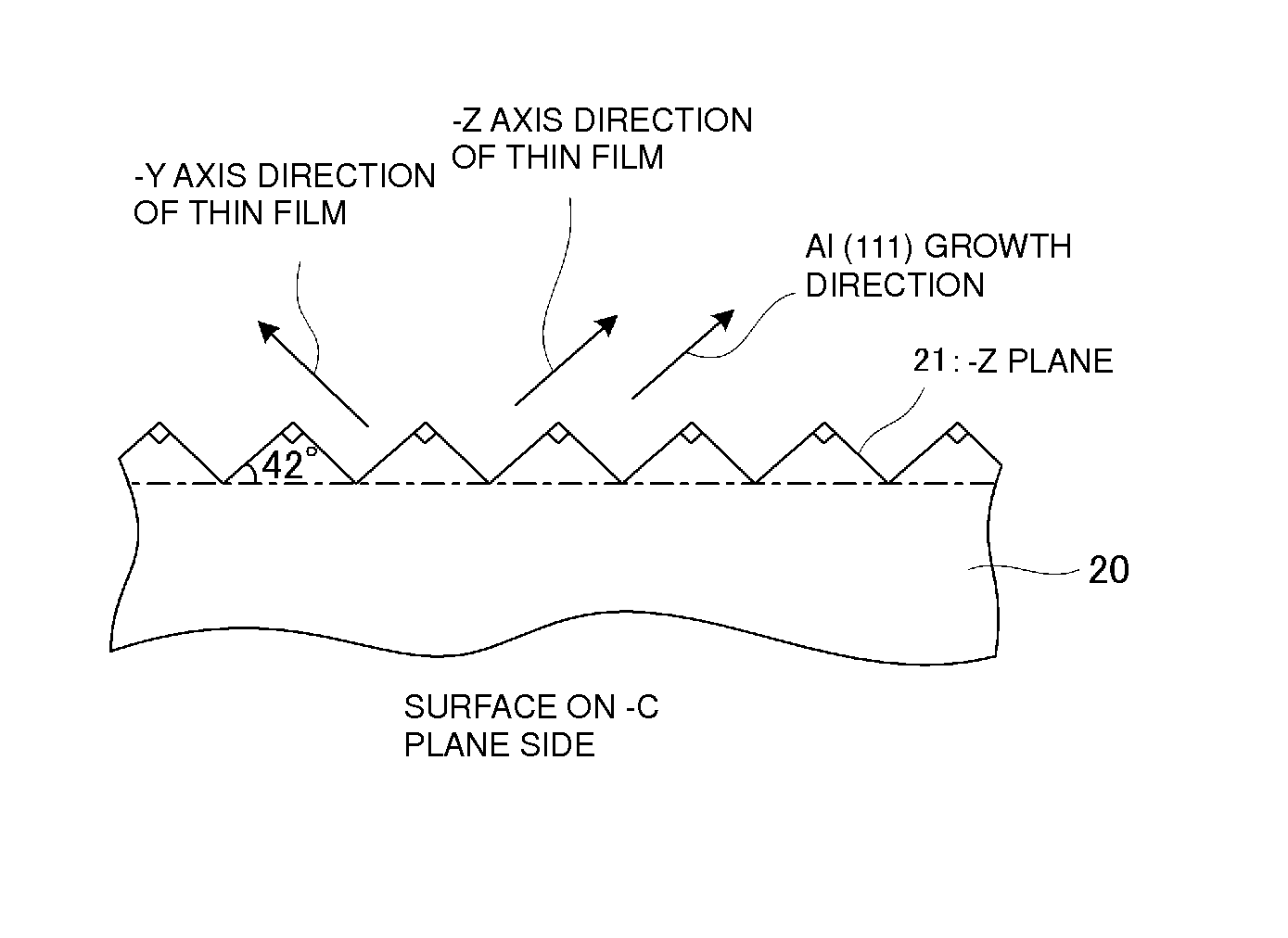

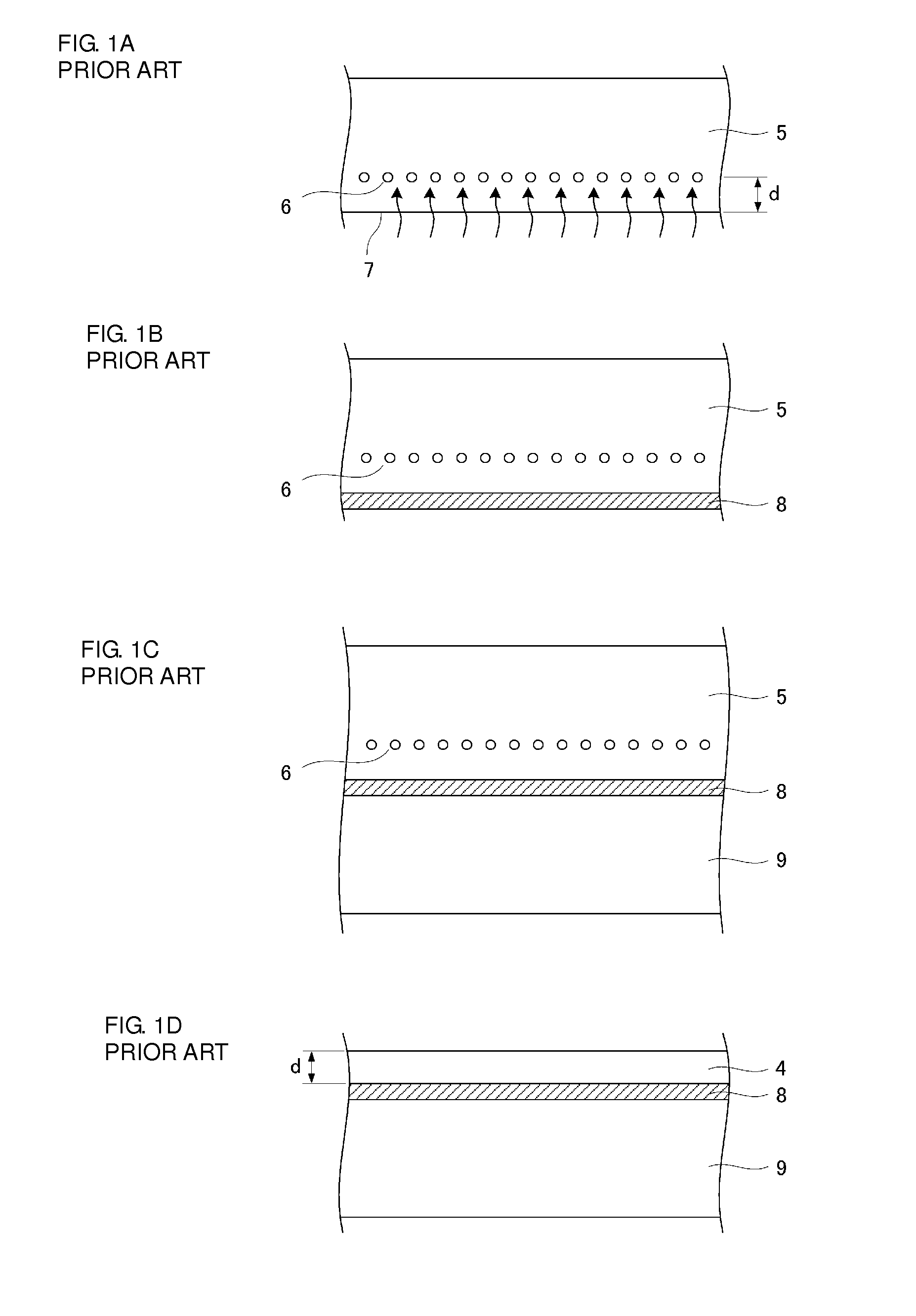

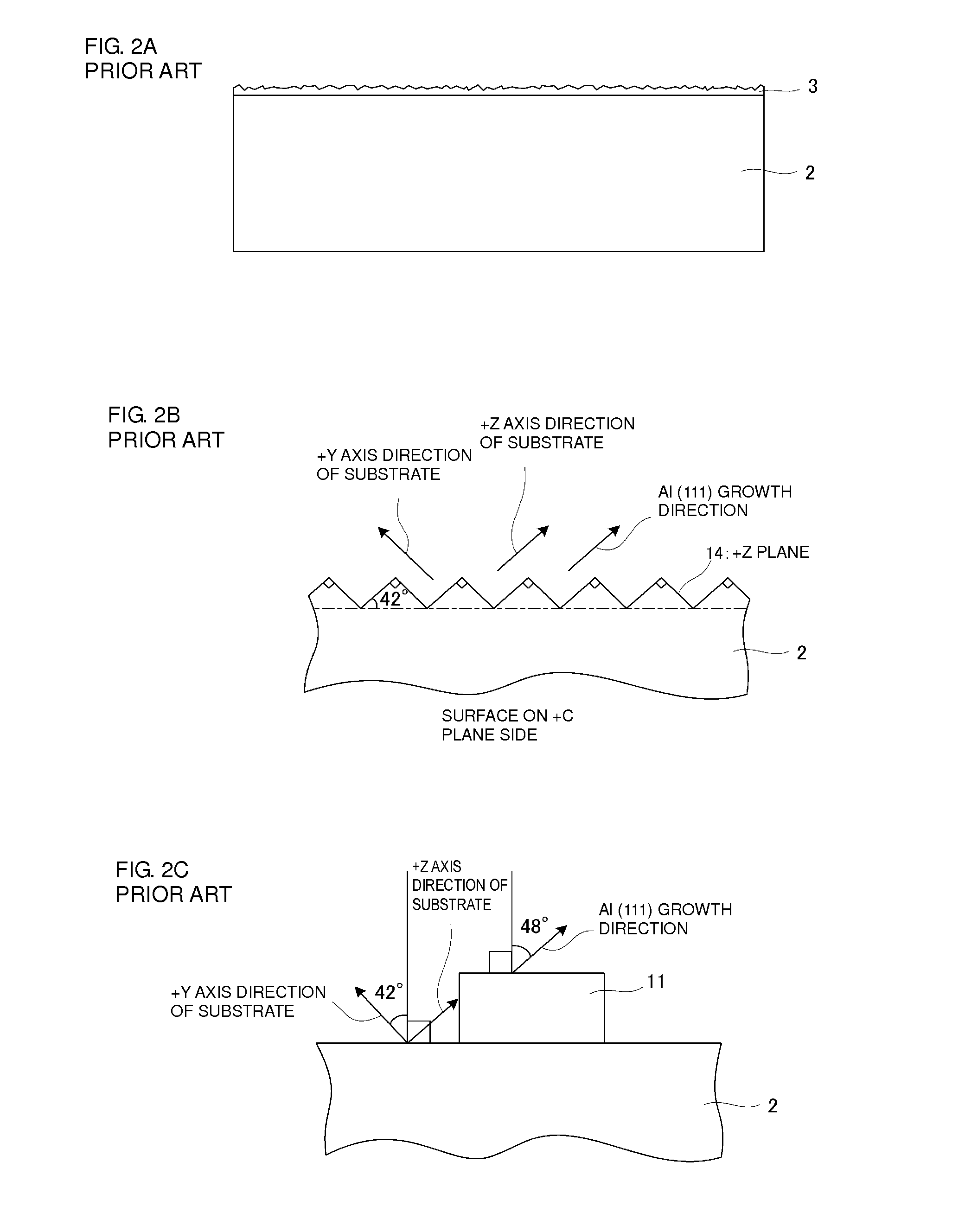

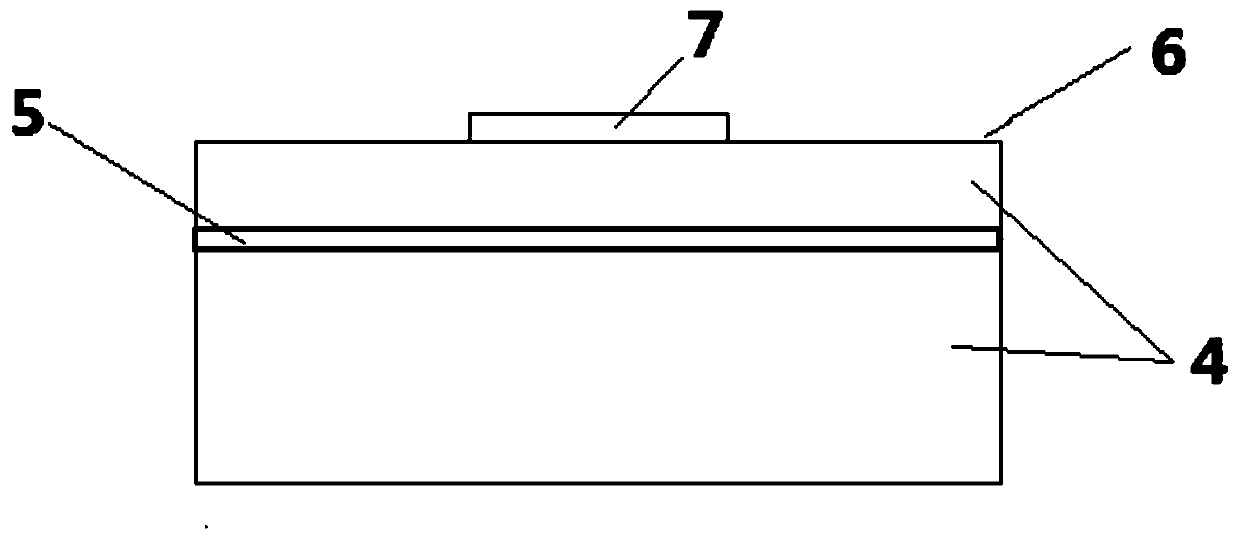

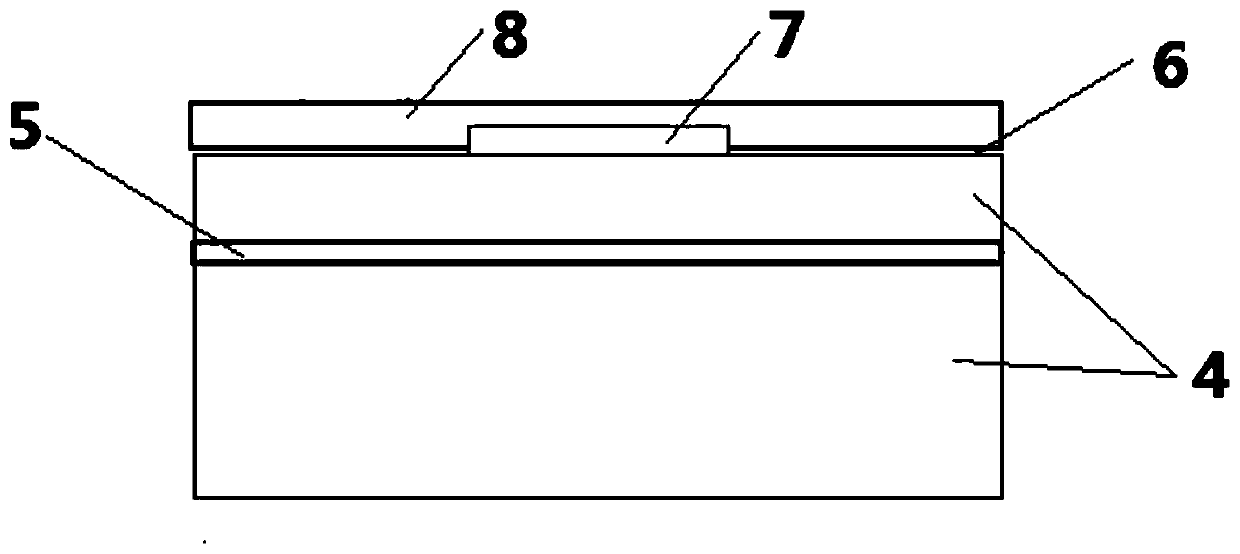

Piezoelectric device and method for manufacturing piezoelectric device

ActiveUS20140191619A1Improved power durabilityReduction in etchant concentrationPiezoelectric/electrostriction/magnetostriction machinesImpedence networksOptoelectronicsCrystal growth

In a method of manufacturing a piezoelectric device, among a +C plane on a +Z axis side of a piezoelectric thin film and a −C plane on a −Z axis side of the piezoelectric thin film, the −C plane on the −Z axis side of the piezoelectric thin film is etched. Thus, −Z planes of the piezoelectric thin film on which epitaxial growth is possible are exposed. Ti is epitaxially grown on the −Z planes of the piezoelectric thin film in the −Z axis direction such that the crystal growth plane thereof is parallel to the −Z planes of the piezoelectric thin film. Al is then epitaxially grown on the surface of the Ti electrode in the −Z axis direction such that the crystal growth plane thereof is parallel to the −Z planes of the piezoelectric thin film.

Owner:MURATA MFG CO LTD

Cavity type bulk acoustic wave resonator without preparing sacrificial layer and preparation method of cavity type bulk acoustic wave resonator

The invention provides a cavity type bulk acoustic wave resonator without preparing a sacrificial layer and a preparation method of the cavity type bulk acoustic wave resonator. The method comprises the following steps that a piezoelectric single crystal wafer which is subjected to ion implantation and provided with a bottom electrode is taken, a cavity is formed in the side, provided with the bottom electrode, of the piezoelectric single crystal wafer, then a substrate is taken, and the substrate and the side, provided with the cavity, of the piezoelectric single crystal wafer are bonded; andheat treatment is carried out on the bonded intermediate product to strip the film of the piezoelectric single crystal wafer, and then a top electrode is produced on one stripped side of the piezoelectric single crystal wafer to obtain the cavity type bulk acoustic wave resonator. According to the preparation method of the cavity type bulk acoustic resonator without the need of preparing the sacrificial layer, the sacrificial layer does not need to be grown, etching and trepanning are not carried out on the thin film, the mechanical strength of the device is improved, and damage to the thin film is not likely to be generated; the cavity structure is formed before film formation, the rate of finished products is high, residues left by etching after film formation do not exist, and the influence of incomplete release on the device does not need to be considered.

Owner:CHIMEMS MICROELECTRONICS CO LTD

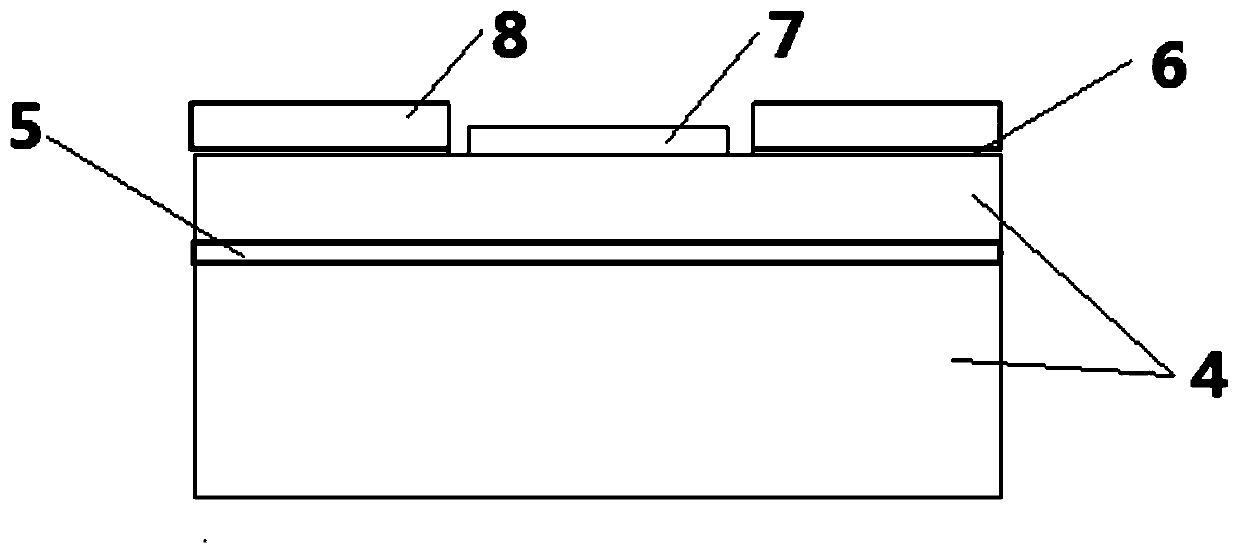

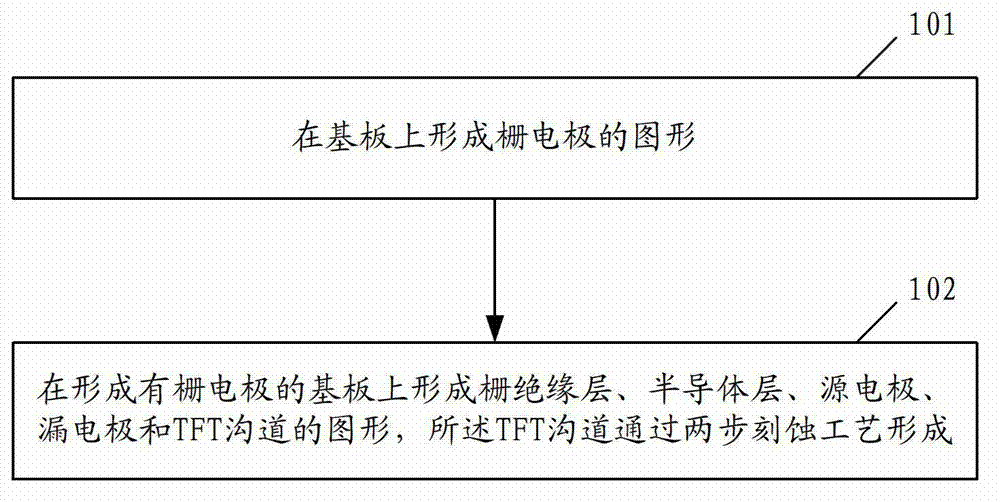

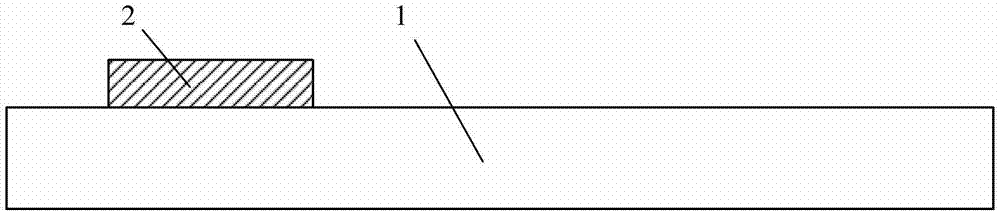

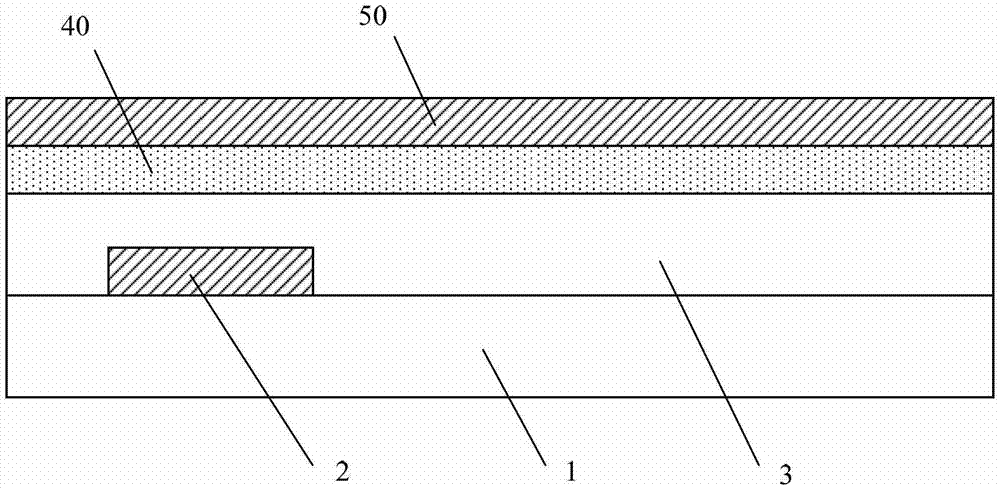

Method for manufacturing thin film transistor, method for manufacturing array substrate and display device

ActiveCN102881598AReduce etch timeOverscaling reductionSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorOxide

The invention provides a method for manufacturing a thin film transistor (TFT), another method for manufacturing an array substrate and a display device, which belongs to the technical field of manufacturing of semiconductors. The semiconductor layer of the thin film transistor is formed by metal oxide. According to the method for manufacturing the thin film transistor, a TFT channel is formed by etching in two steps, first step, a part of a source drain metal layer in a channel area above the semiconductor layer is removed by dry etching; and second step, the rest source drain metal layer in the channel area above the semiconductor layer is removed by wet etching to form the TFT channel. According to the invention, the metal oxide semiconductor layer below the TFT channel can be protected without forming an etching barrier layer.

Owner:BOE TECH GRP CO LTD

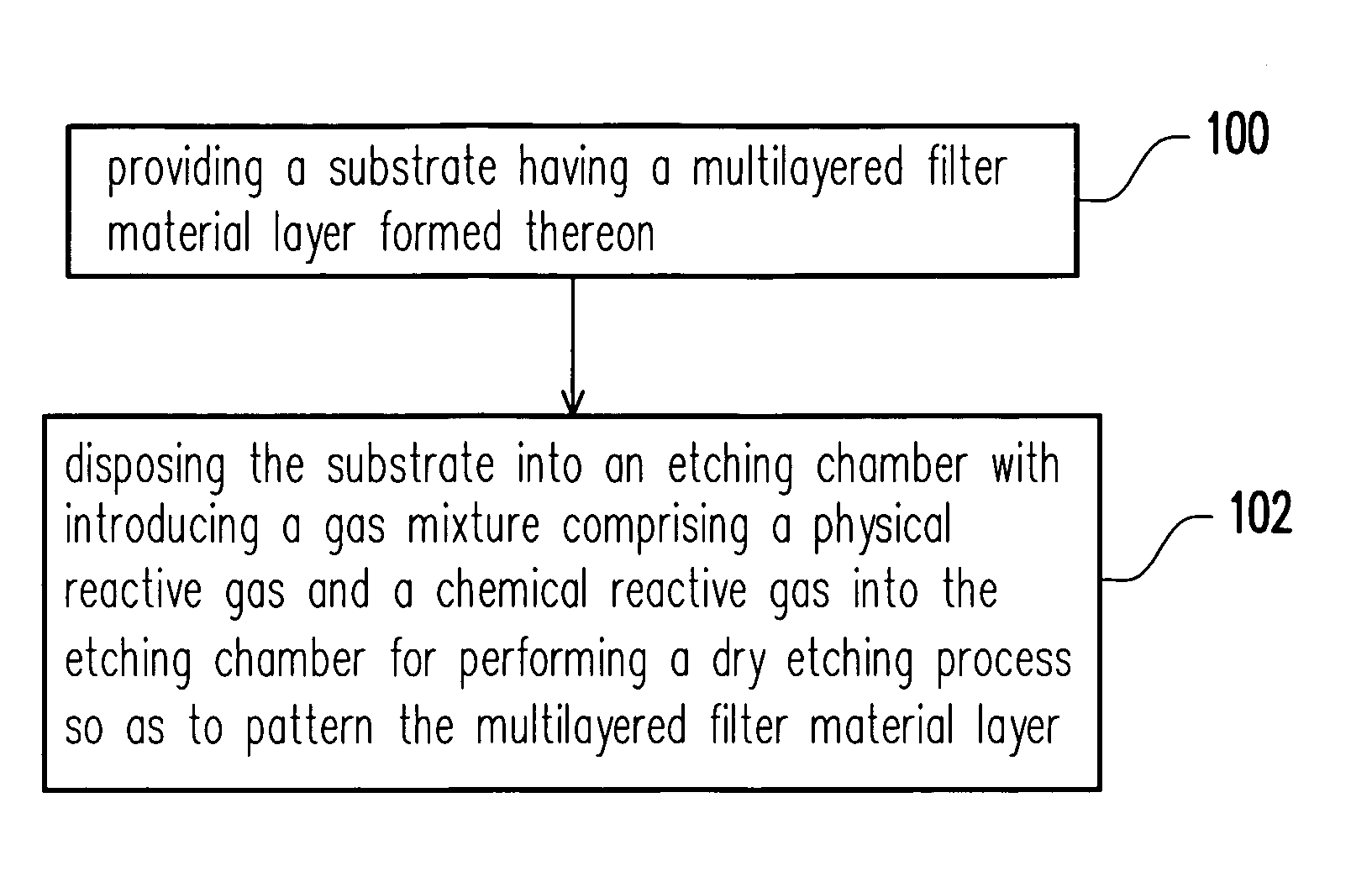

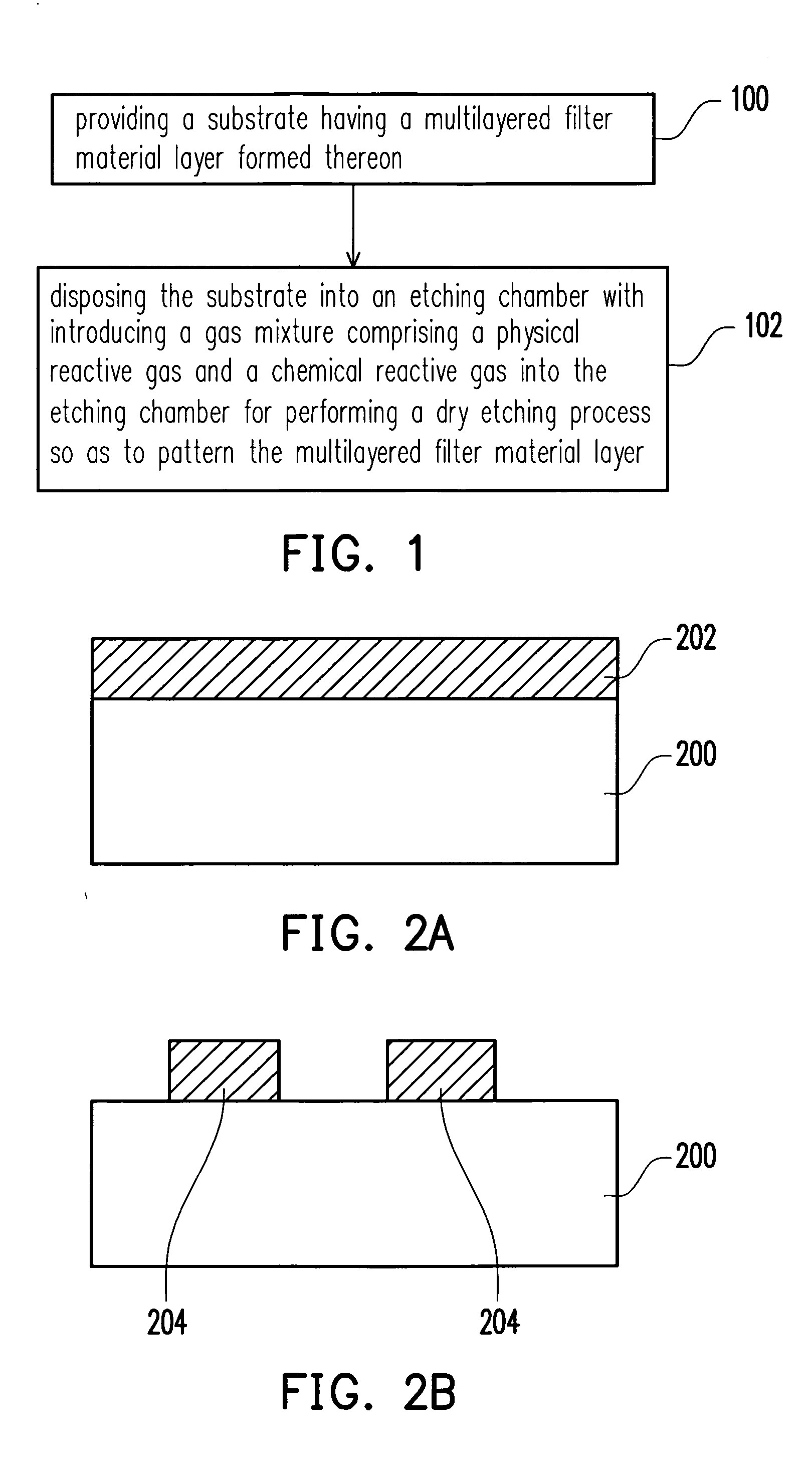

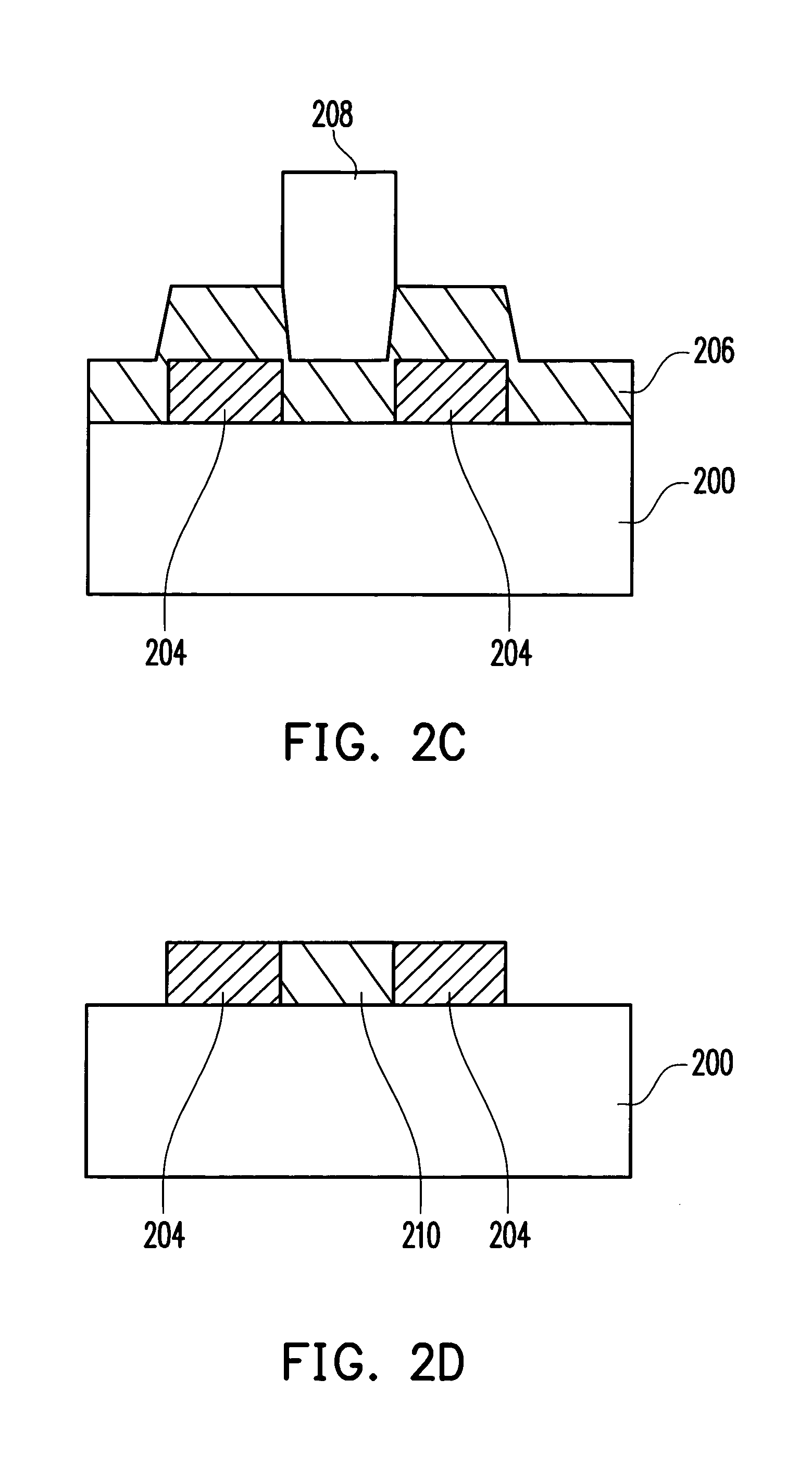

Etching method

InactiveUS20070221616A1Increase etch rateReduce etch timeDecorative surface effectsNon-linear opticsChemical reactionReactive gas

The invention is directed to a method for etching a color filter. The method comprises steps of providing a substrate having a multilayered filter material layer formed thereon and then disposing the substrate into an etching chamber with introducing a gas mixture into the etching chamber for performing a dry etching process so as to pattern the multilayered filter material layer, wherein the gas mixture comprises a physical reactive gas and a chemical reactive gas.

Owner:UNITED MICROELECTRONICS CORP

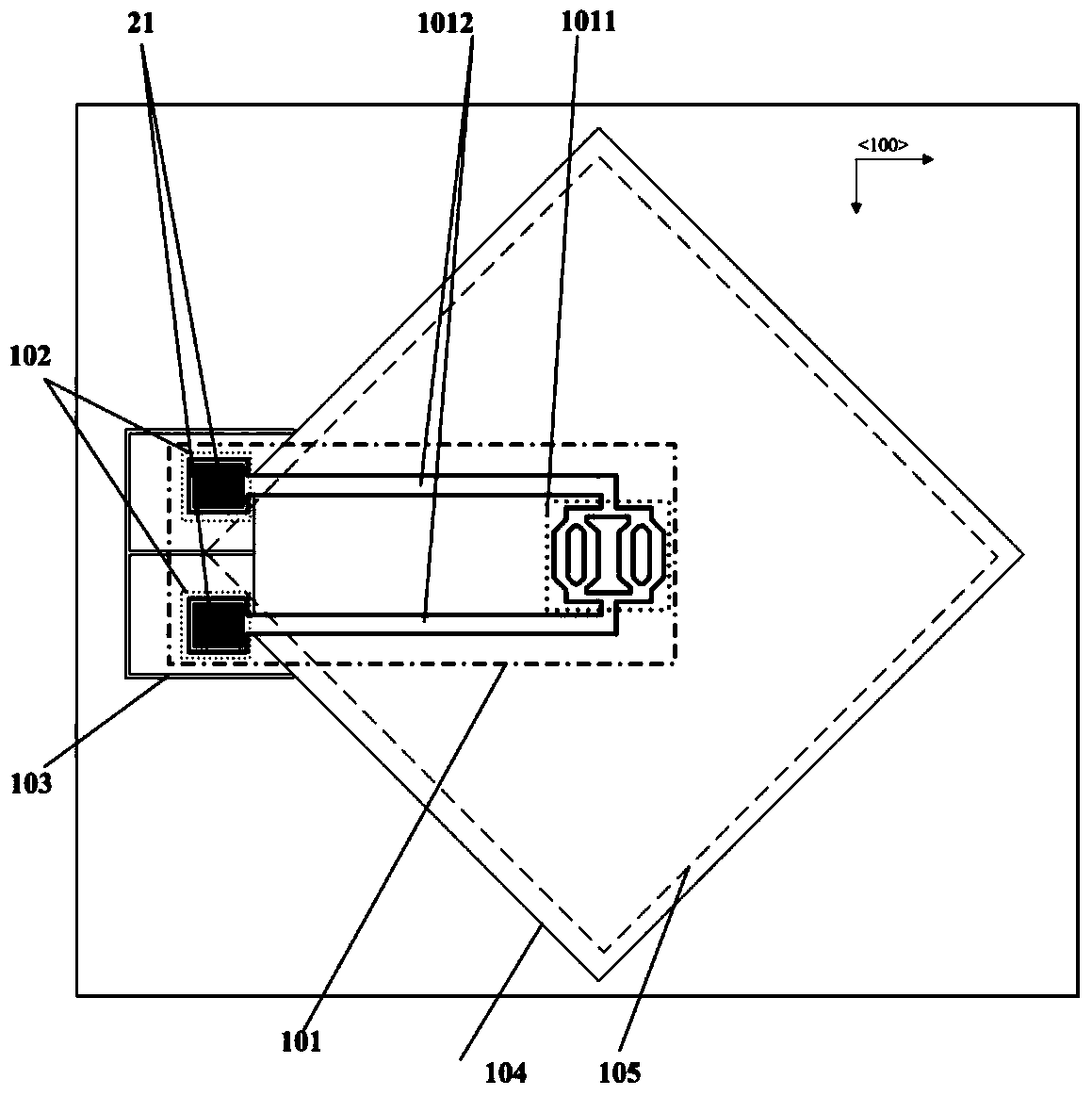

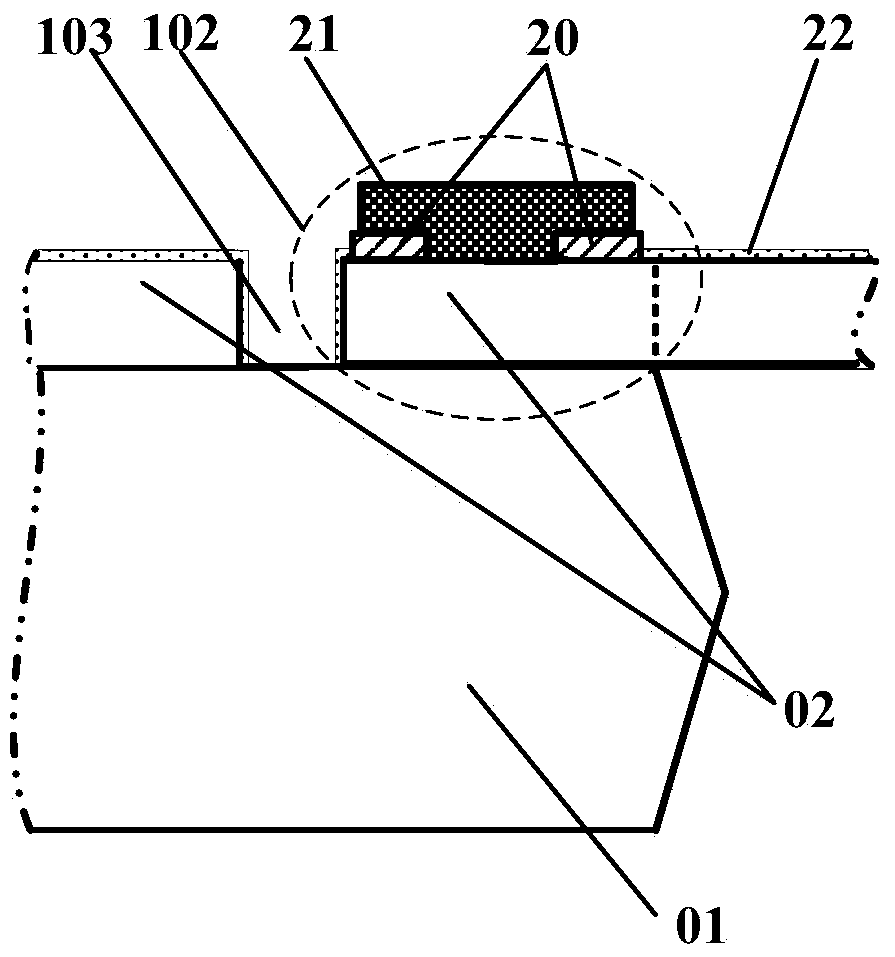

MEMS (micro-electromechanical system) methane sensor as well as application and preparation method thereof

InactiveCN104316578ALarge high temperature surface areaHigh sensitivityMaterial resistanceOxide semiconductorCMOS

The invention discloses an MEMS (micro-electromechanical system) methane sensor as well as application and a preparation method thereof. The MEMS methane sensor is suitable for coal mine detection. The invention particularly belongs to a methane sensor adopting an MEMS processing technology and a methane detection method thereof. According to the sensor, common monocrystalline silicon is used as a material of a heating element; the heating element is also used as a sensitive element, and no catalyst carrier and no catalyst material are needed; a processing technology is compatible with a CMOS (complementary metal oxide semiconductor) technology; the heating element is released by adopting a wet silicon etching technology which can realize synchronous etching in two directions. The sensor has the advantages of low cost, high sensitivity and low power consumption, and the measurement cannot be influenced by the oxygen concentration and cannot be influenced by carbon deposition and poisoning.

Owner:CHINA UNIV OF MINING & TECH