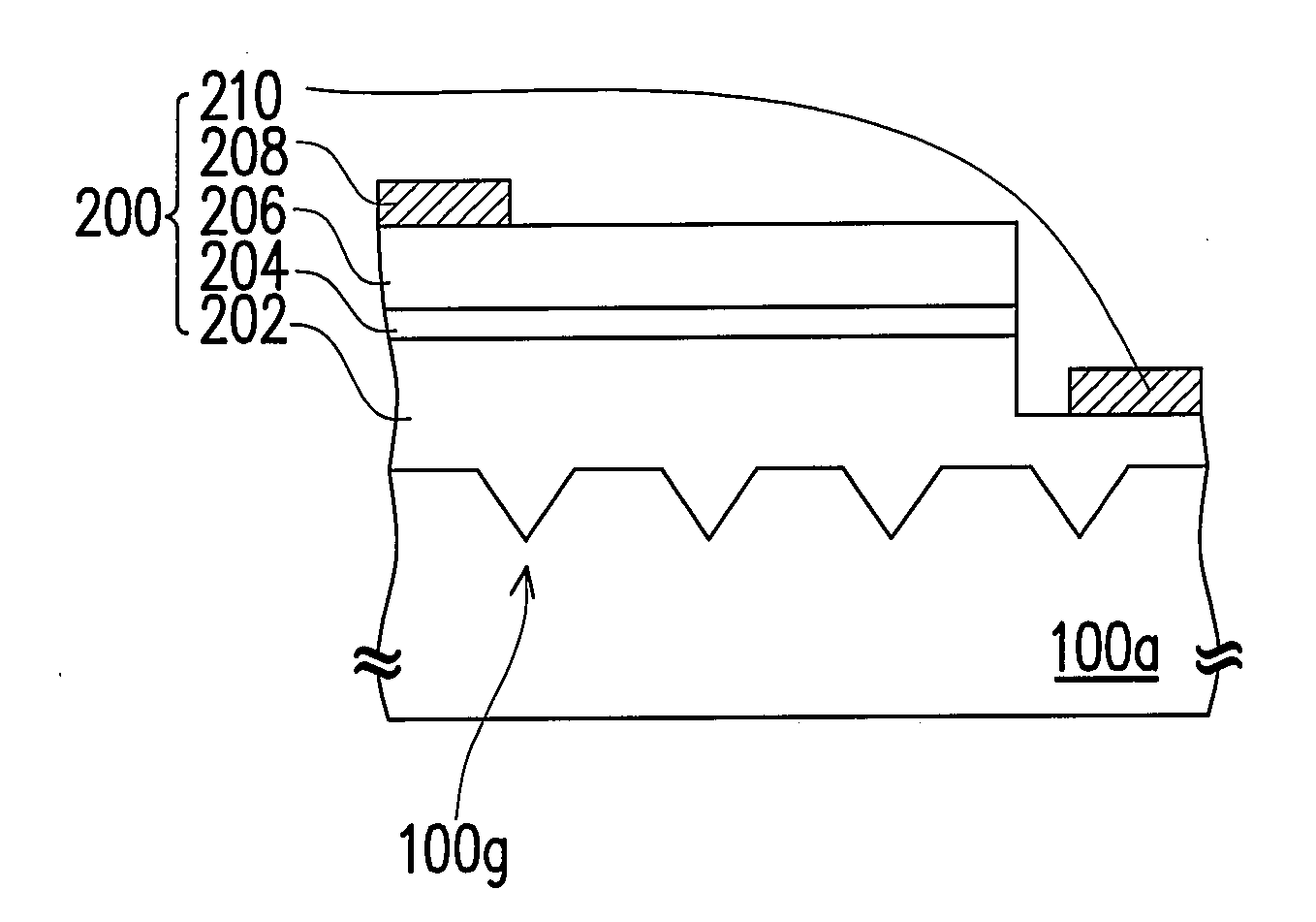

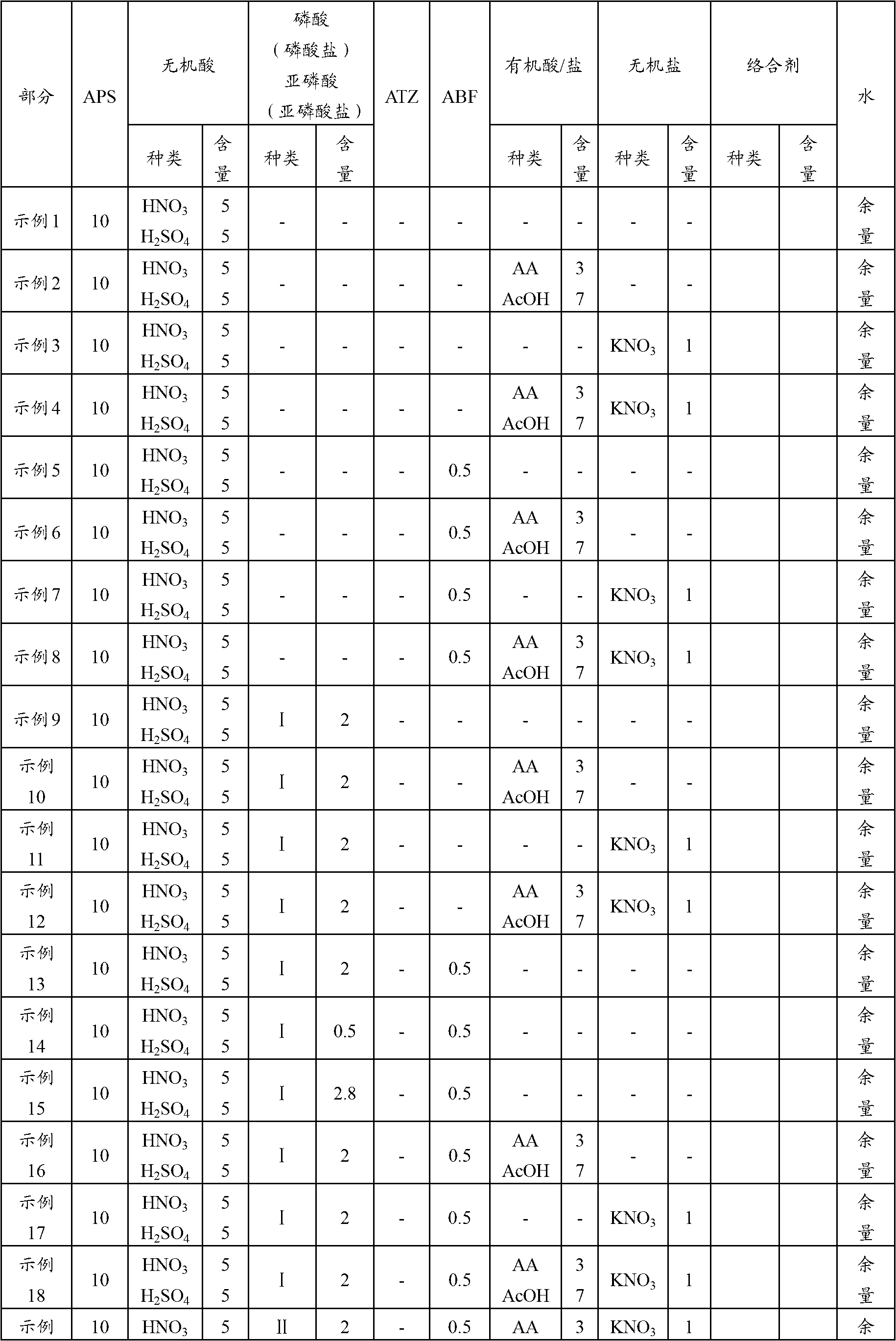

Patents

Literature

97results about How to "Simplify the etch process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

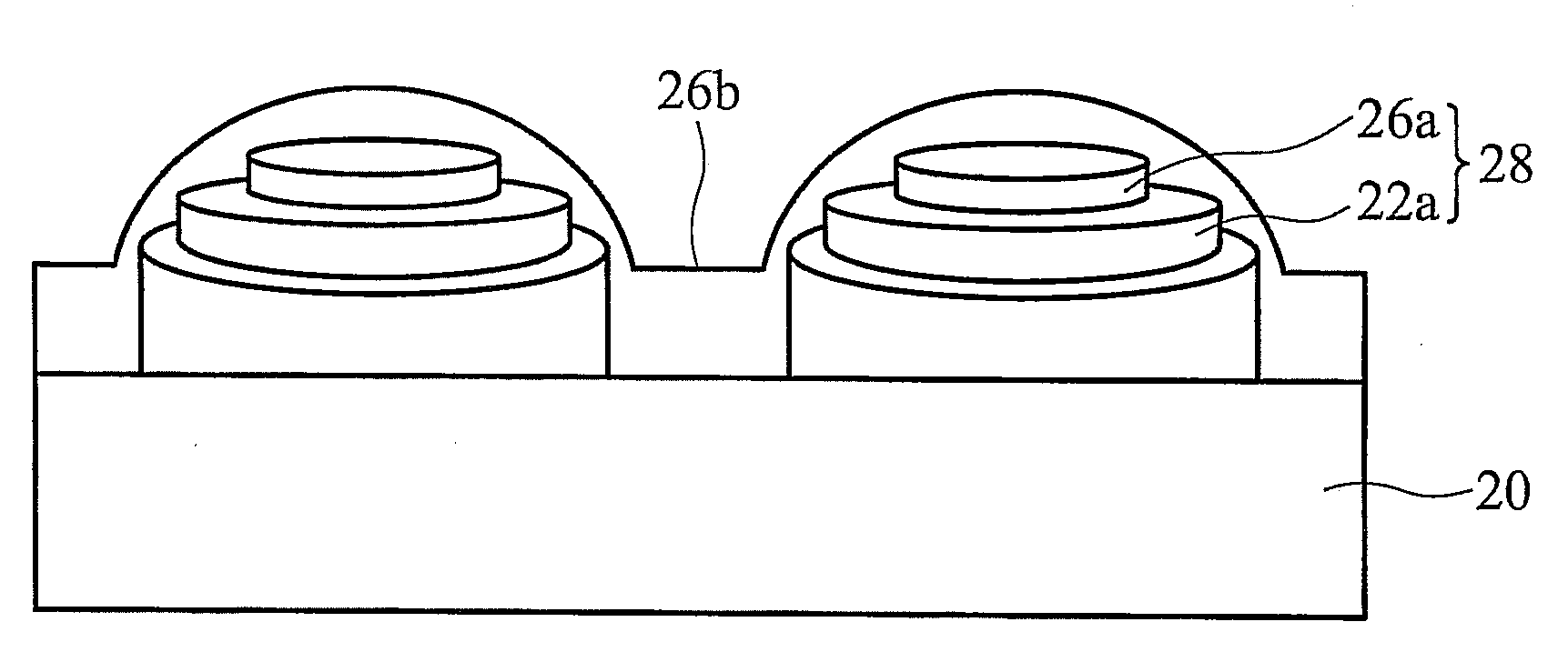

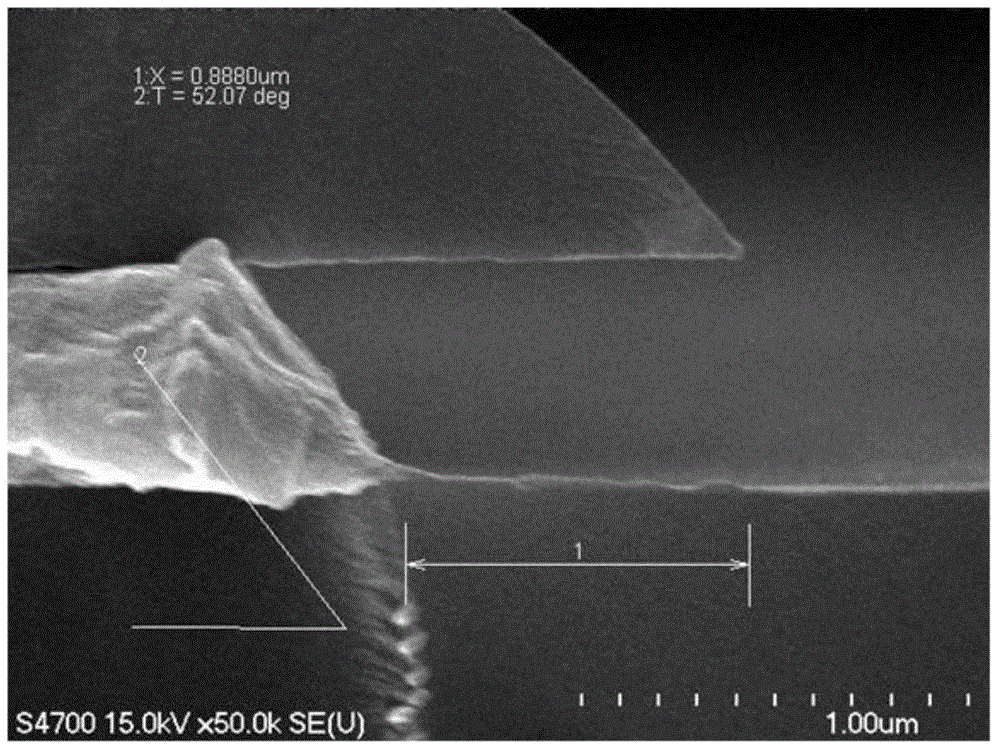

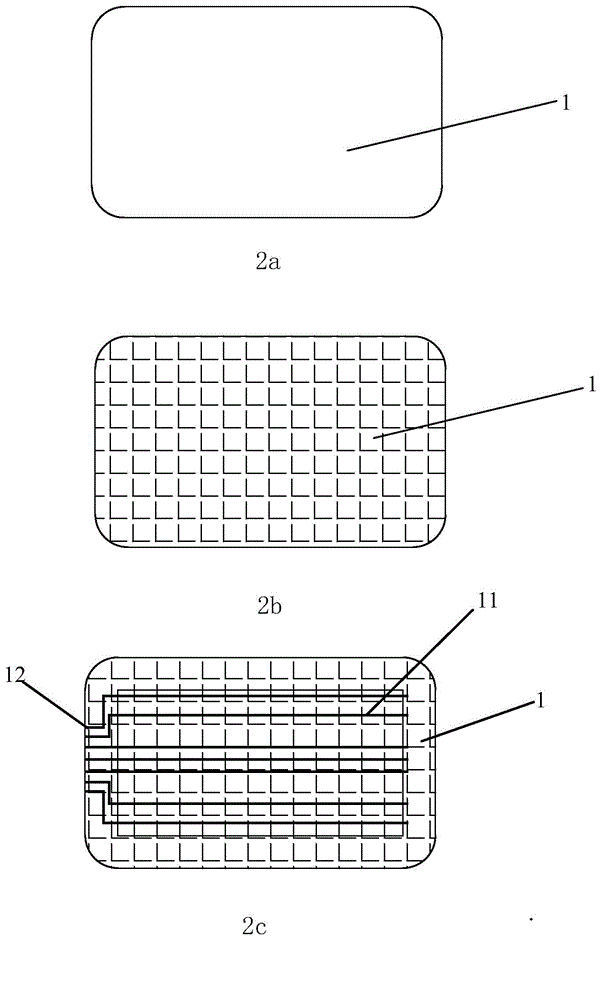

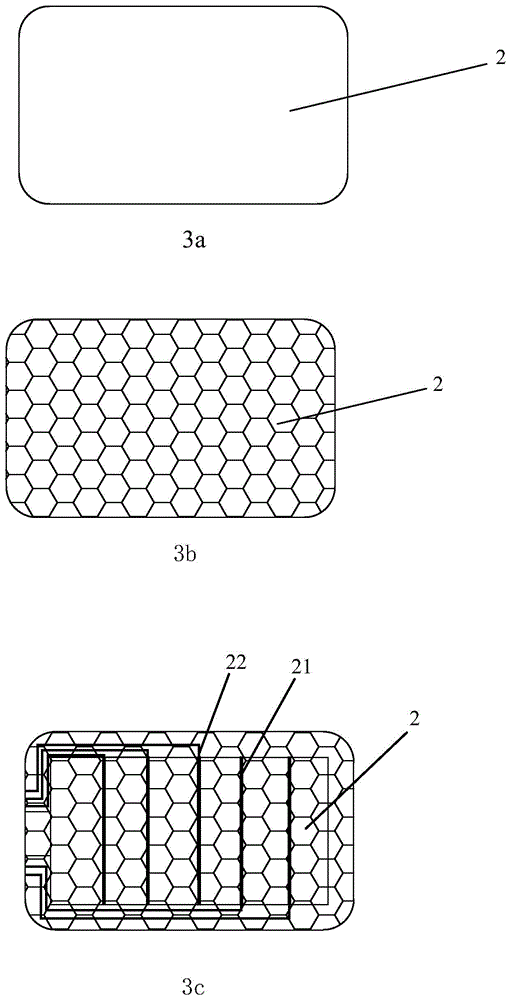

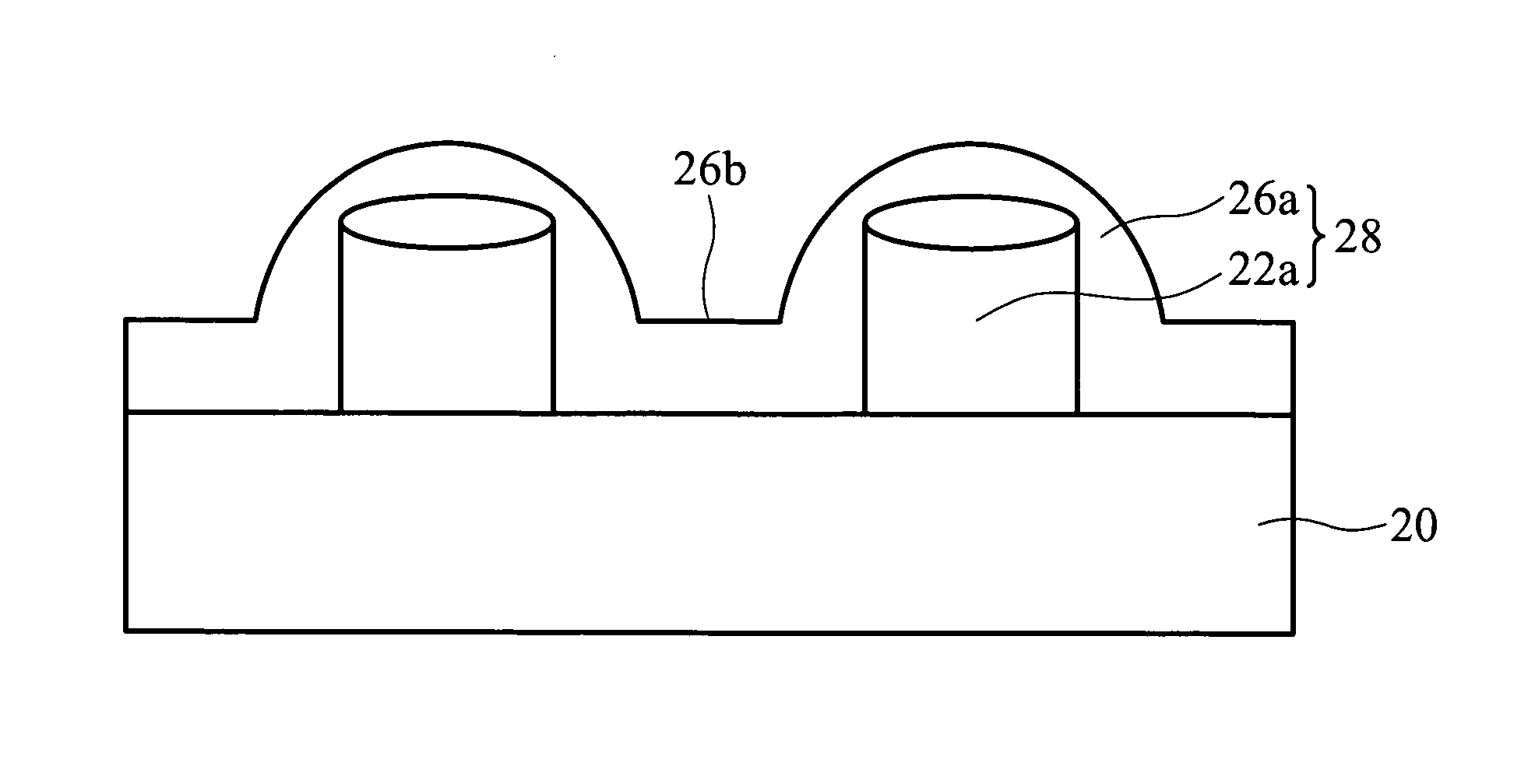

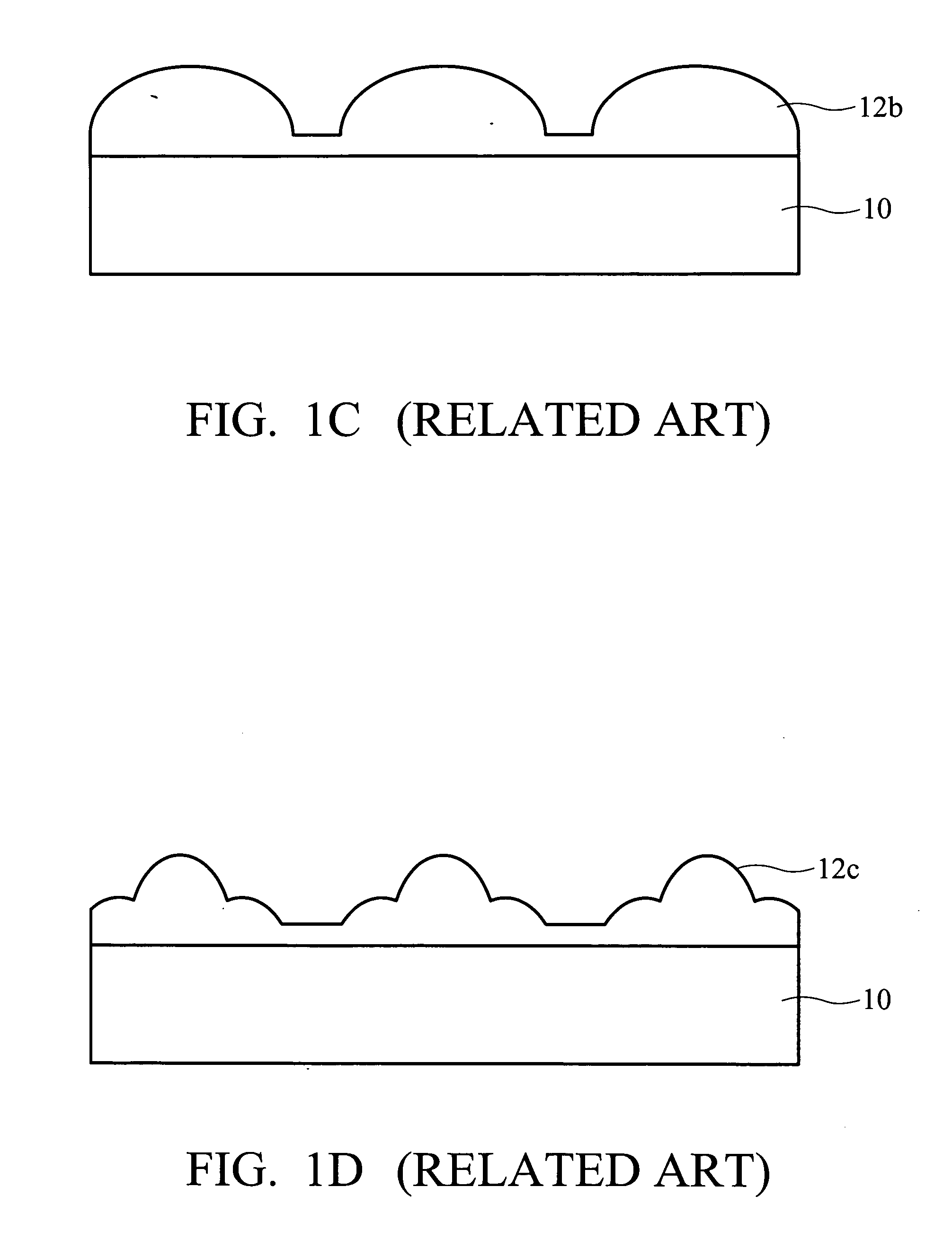

Hemi-spherical structure and method for fabricating the same

InactiveUS20080166883A1Simplify the etch processOptical articlesSemiconductor/solid-state device manufacturingEngineeringSpherical form

Owner:TAIWAN SEMICON MFG CO LTD

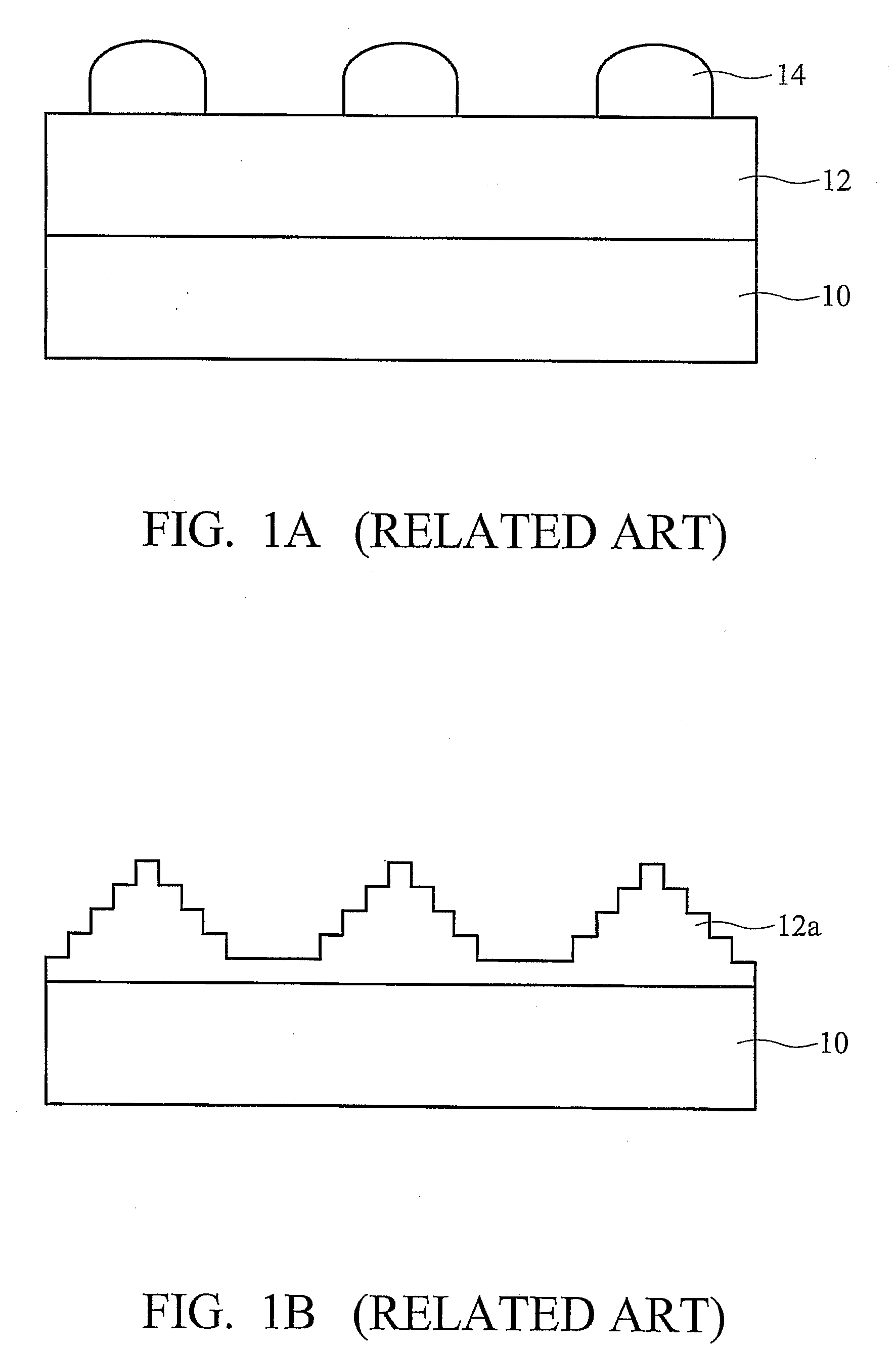

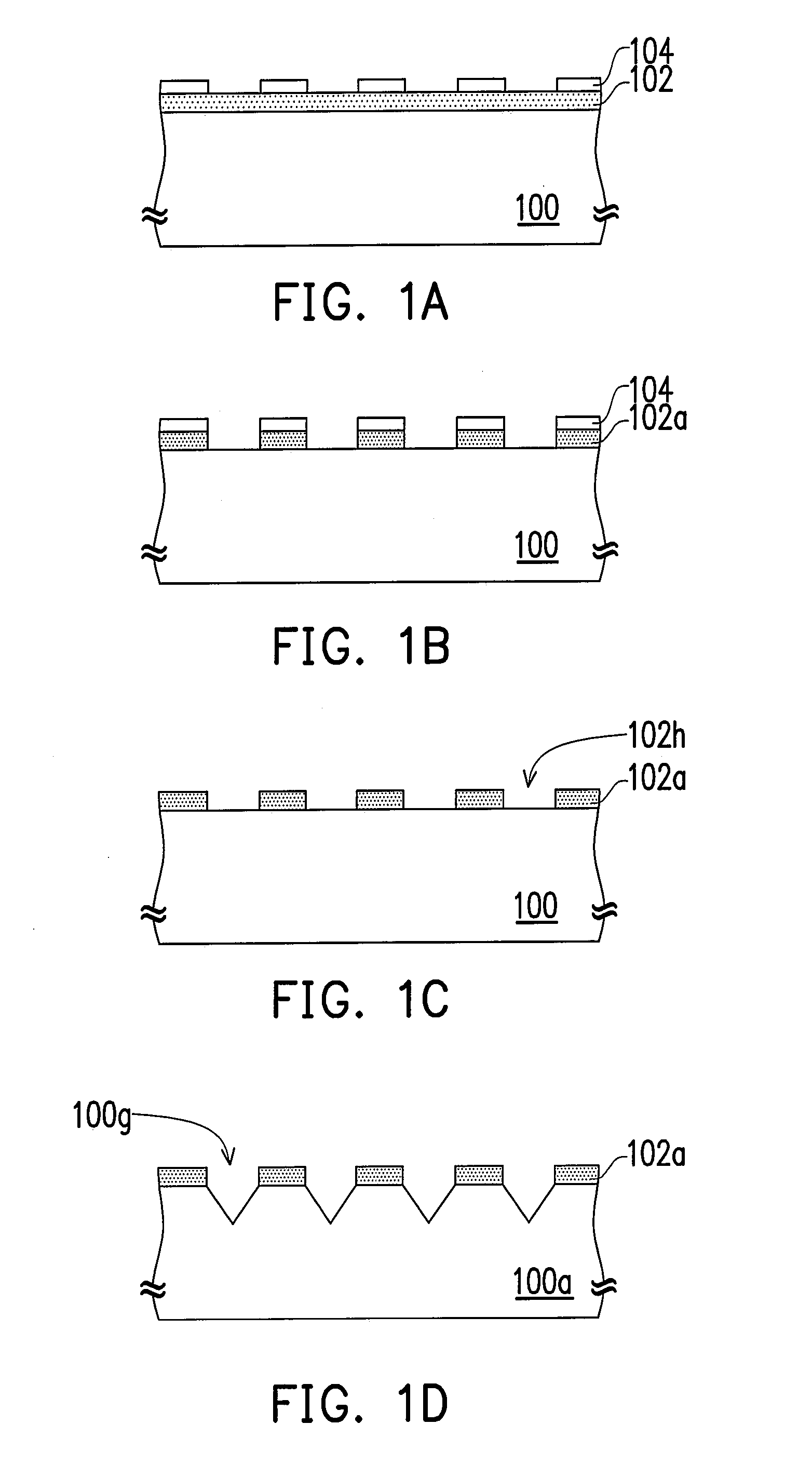

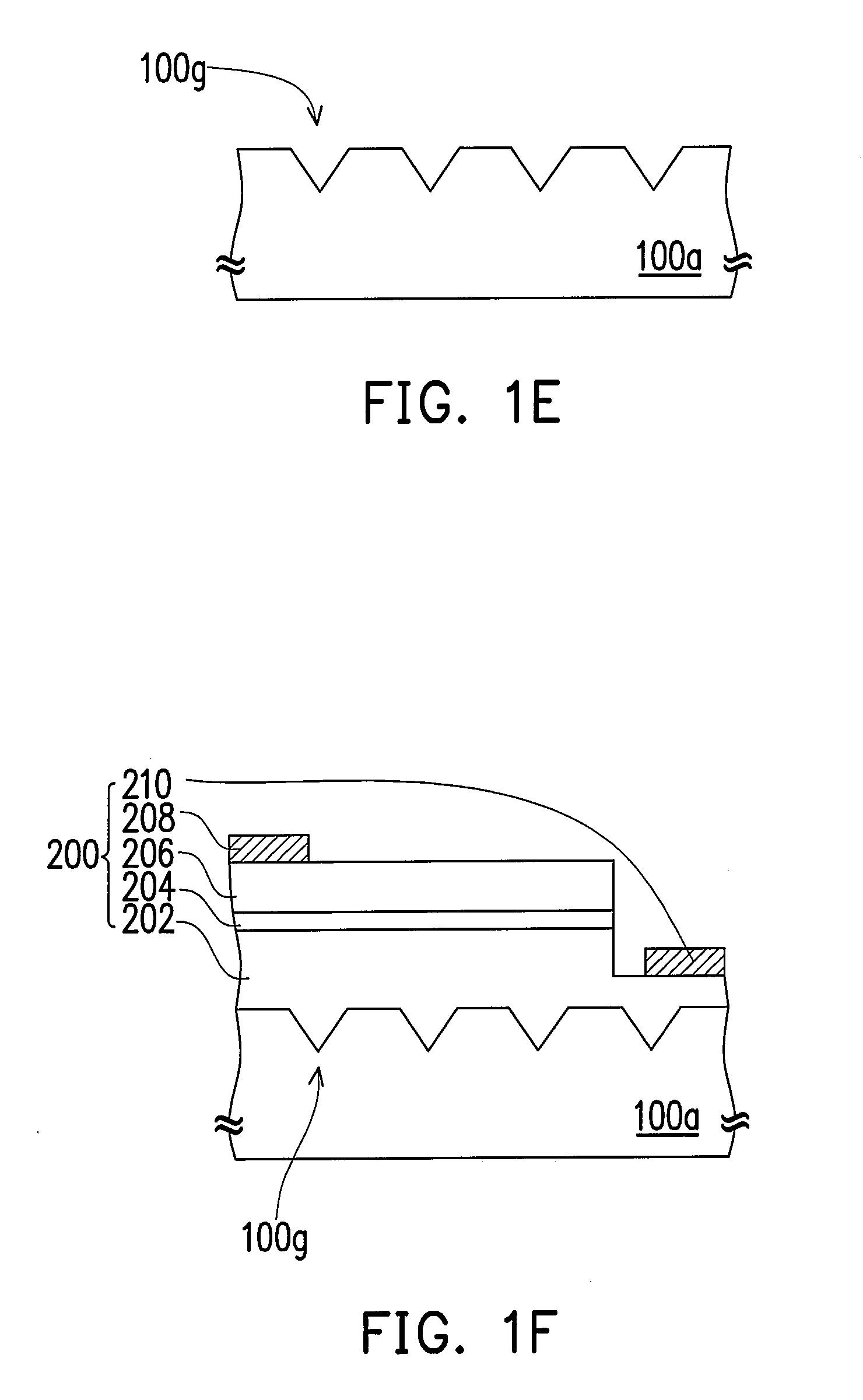

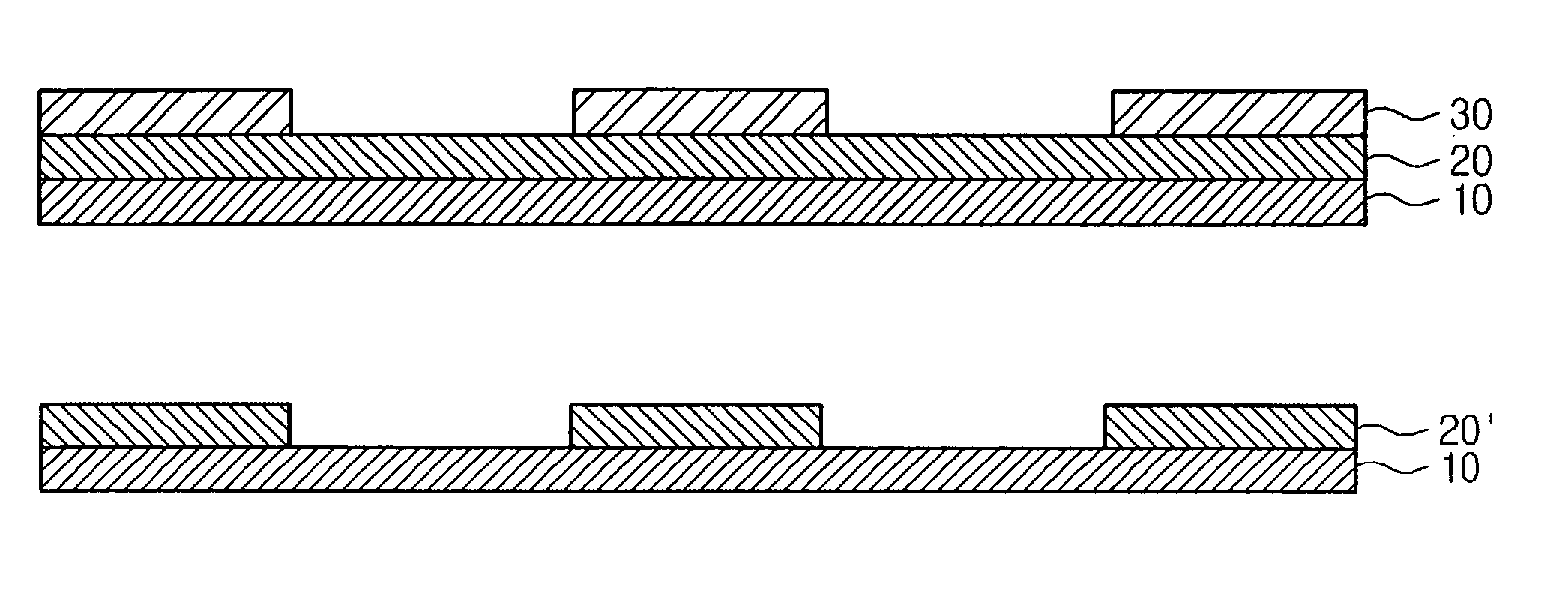

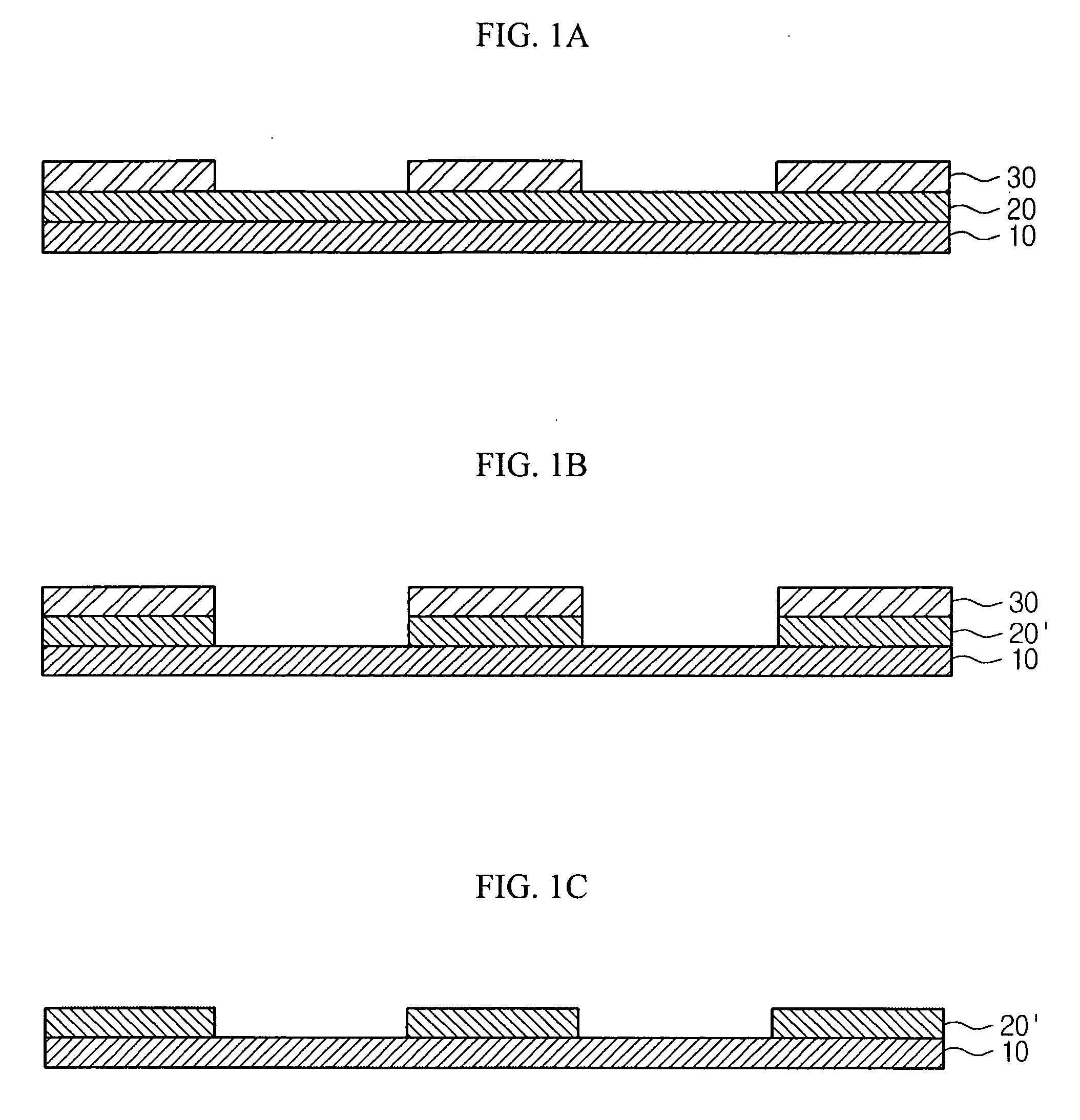

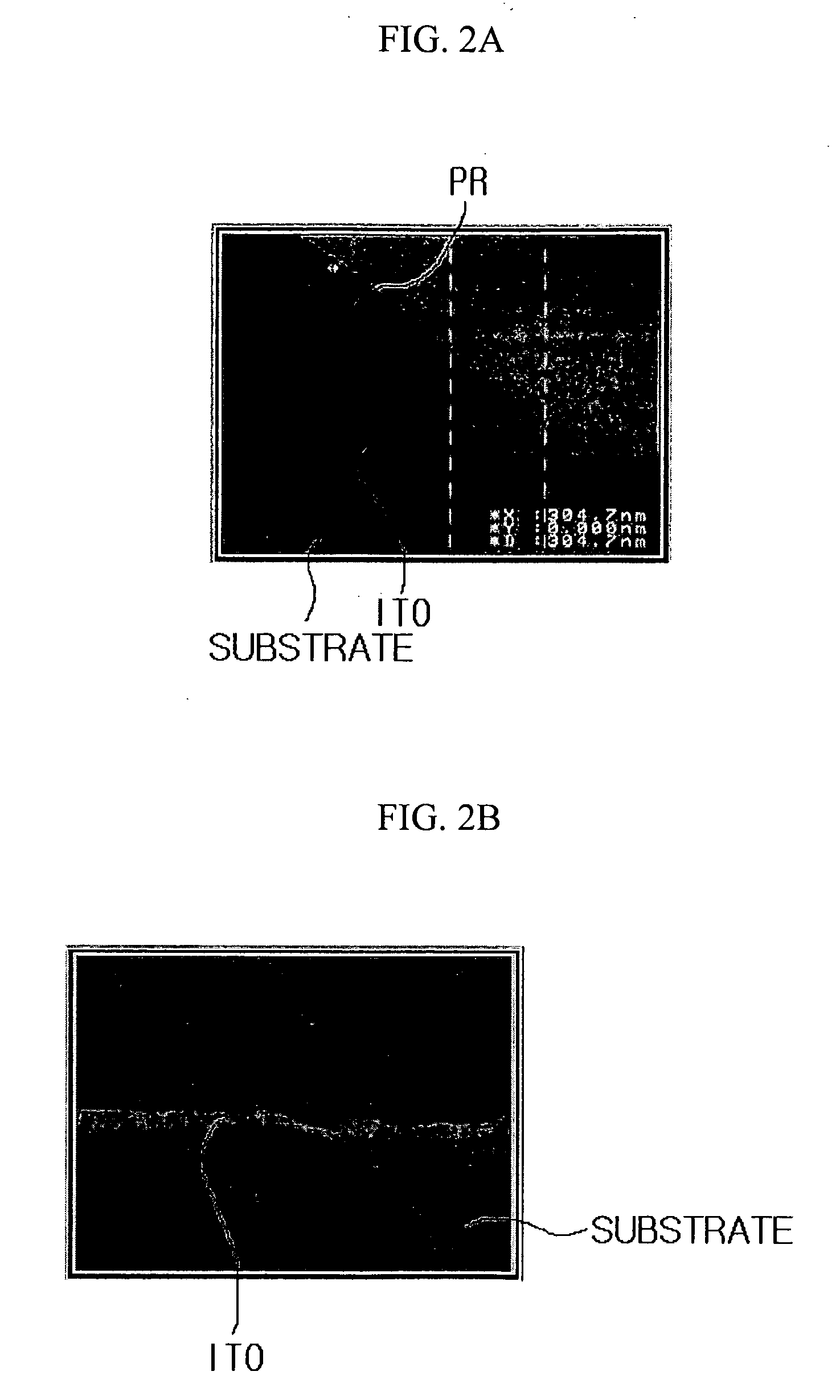

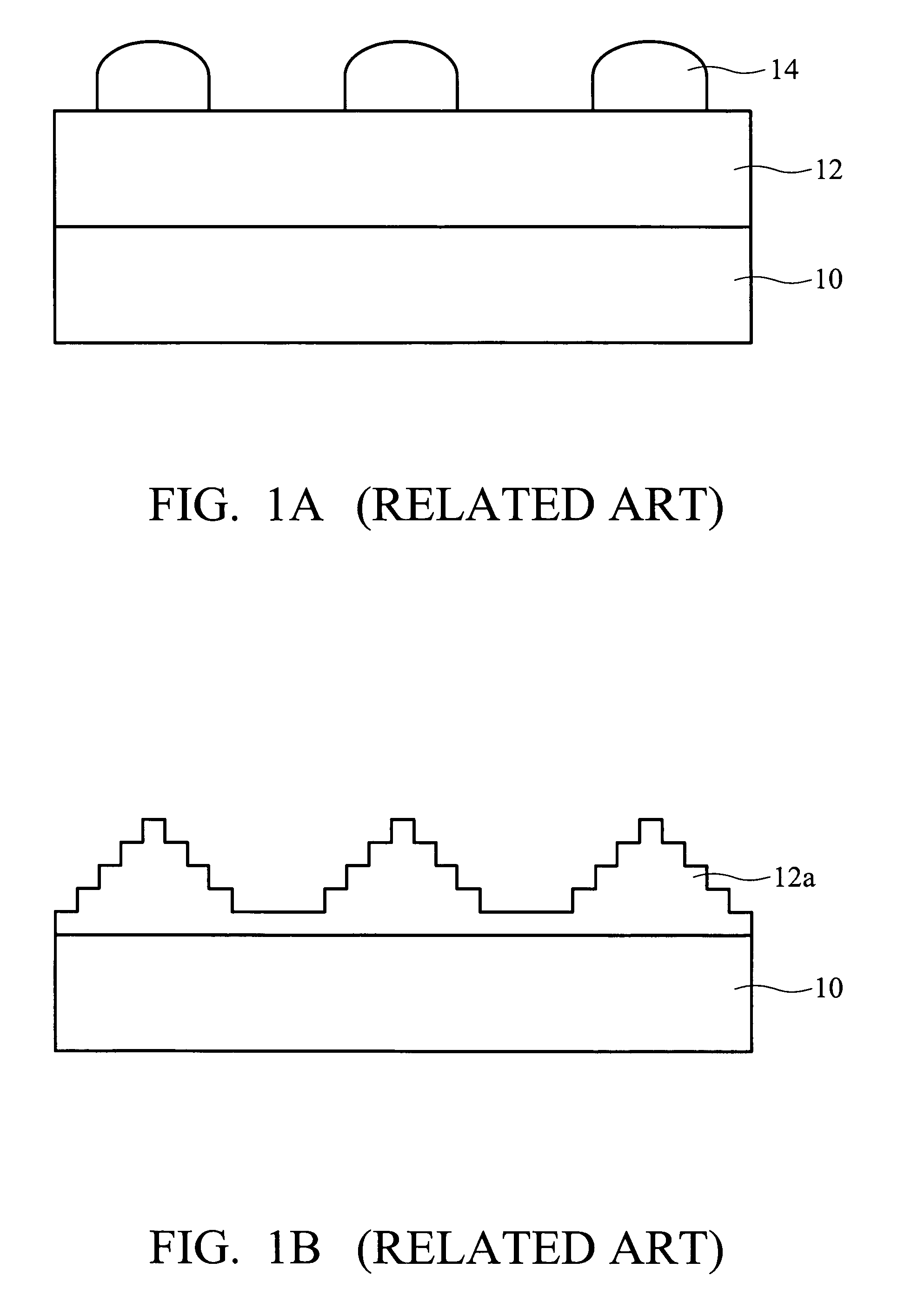

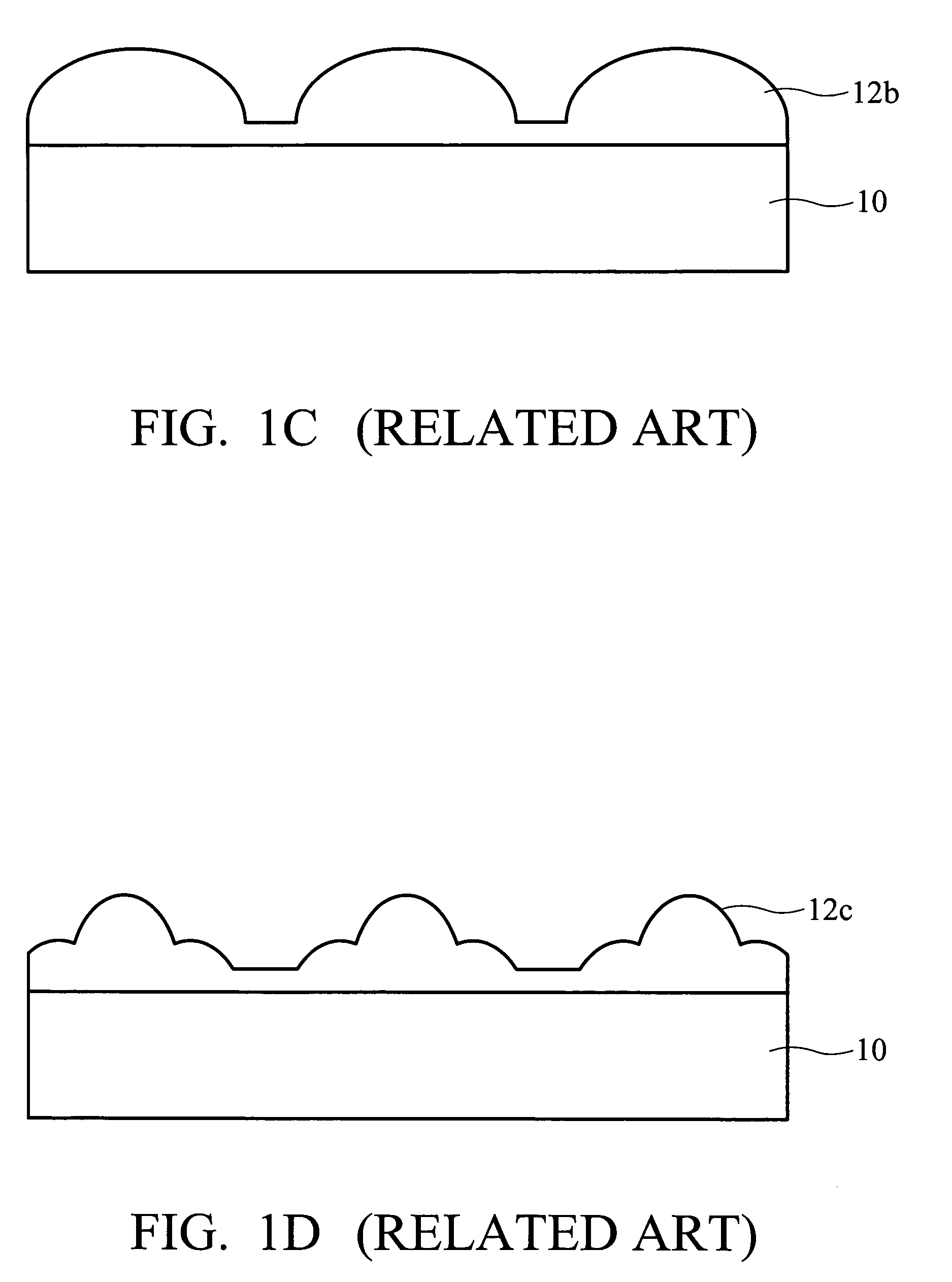

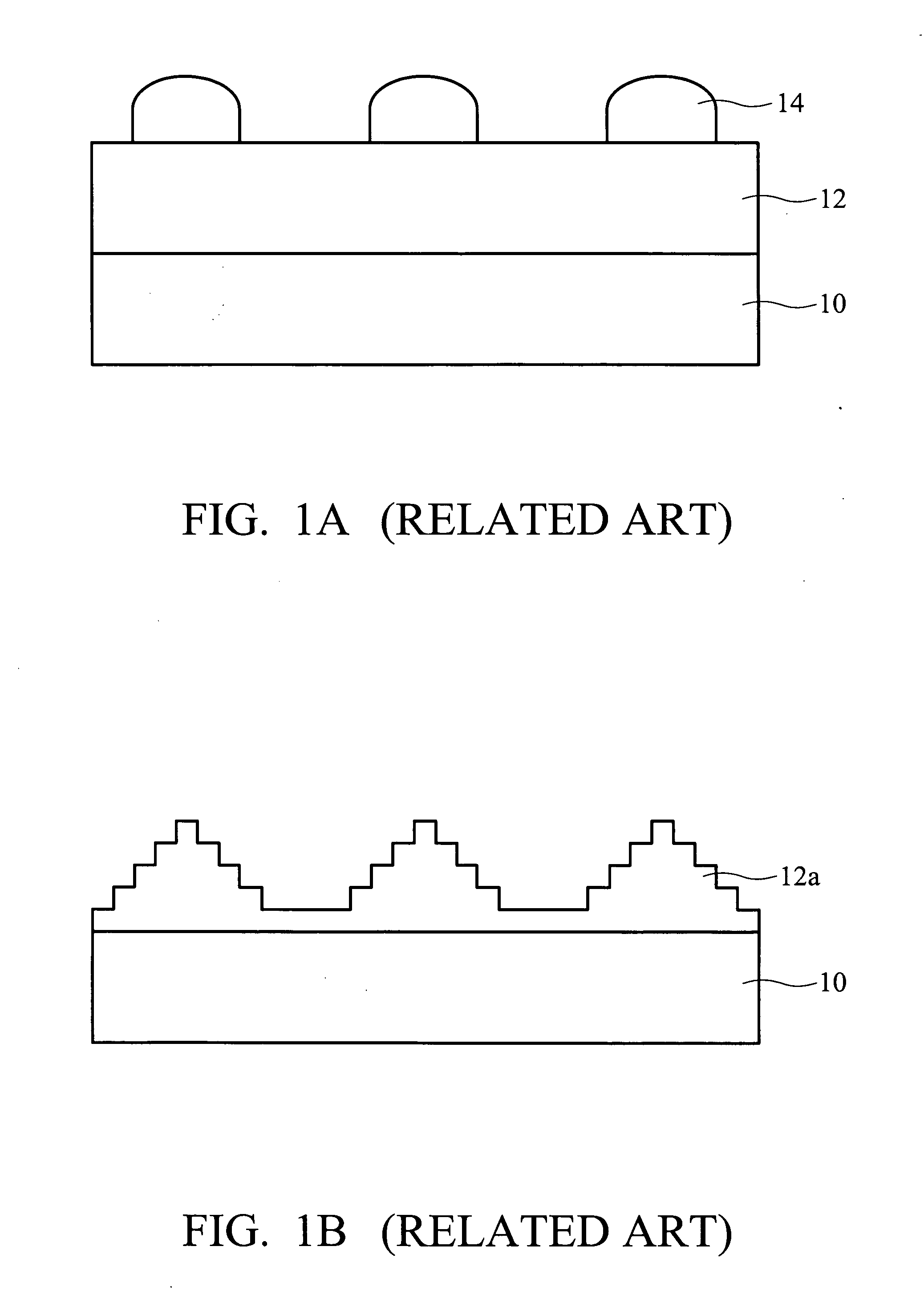

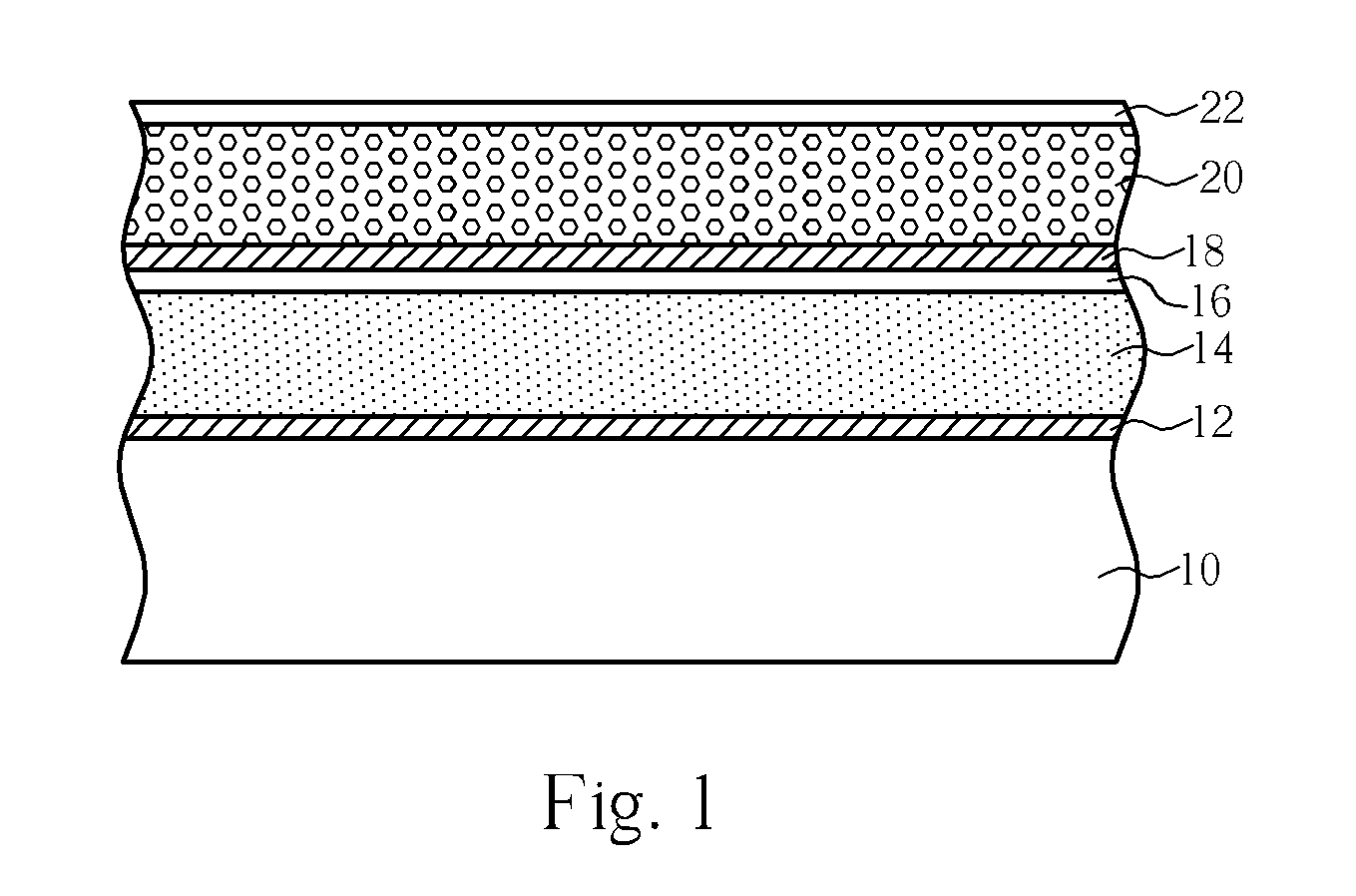

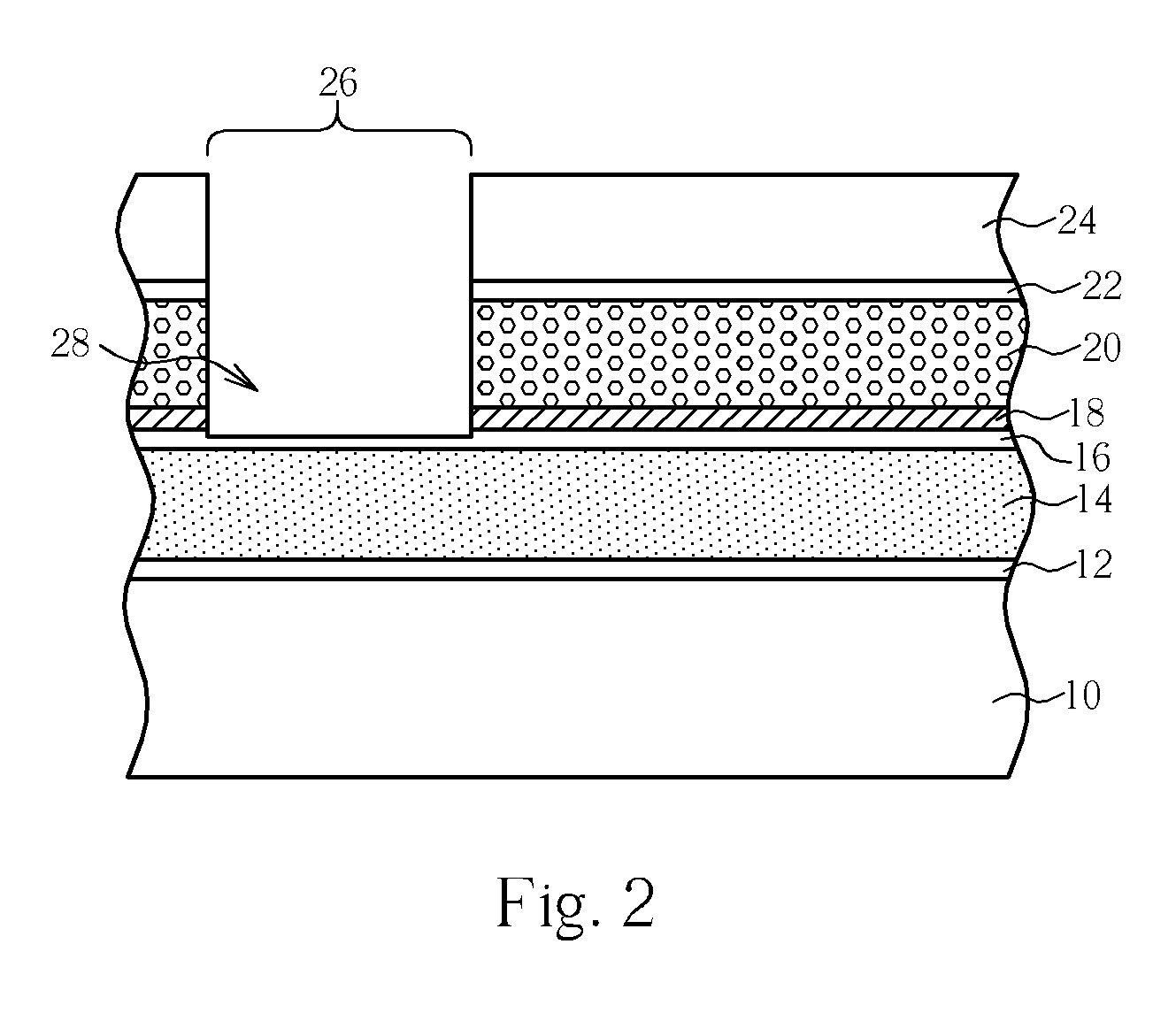

Fabrication methods of a patterned sapphire substrate and a light-emitting diode

InactiveUS20080070413A1Simple processLow costSemiconductor/solid-state device manufacturingSemiconductor devicesPhosphoric acidLight-emitting diode

A fabricating method for patterned sapphire substrate is provided. The fabricating method includes the following processes. First, a sapphire substrate is provided, and a mask layer is formed on the sapphire substrate, wherein the mask layer with appropriate pattern exposes a part of the sapphire substrate. Then, a wet etching process is performed to remove the exposed part of the sapphire substrate, wherein an etchant in the wet etching process includes sulfuric acid and the mixture of the sulfuric acid and the phosphoric acid. Next, the mask layer is removed to form the patterned sapphire substrate. Further, a fabricating method for light-emitting diode is provided.

Owner:NAT CENT UNIV

Method for preparing array substrate for liquid crystal display device

ActiveCN103052907AEnvironmental friendlyPrevent poor wiringSolid-state devicesNon-linear opticsCrystallographyOrganic acid

The present invention relates to preparation method for an array substrate for the use in a liquid crystal display device, using an etchant composition comprising: a) 5-25 wt% of hydrogen peroxide (H2O2); b) 0.1-5 wt% of an organic acid; c) 0.1-5 wt% of a phosphate compound; d) 0.1-5 wt% of a water-soluble cyclic amine compound; e) 0.1-5 wt% of a water-soluble compound having a nitrogen atom and a carboxyl group in a molecule; f) 0.01-1.0 wt% of a fluorine-containing compound; g) 0.001-5 wt% of a polyhydric alcohol-based surfactant; and h) the balance of water based on the total weight of the composition.

Owner:DONGWOO FINE CHEM CO LTD

Etchant composition, methods of patterning conductive layer and manufacturing flat panel display device using the same

ActiveUS20070029280A1Simplify the etch processReduce manufacturing costAfter-treatment detailsDecorative surface effectsManufacturing cost reductionAcetic acid

An etchant composition, and methods of patterning a conductive layer and manufacturing a flat panel display device using the same are provided. The etchant composition may include phosphoric acid, nitric acid, acetic acid, water and an additive, wherein the additive includes a chlorine-based compound, a nitrate-based compound, and an oxidation regulator. In addition, the flat panel display device may be manufactured by patterning a gate electrode, source / drain electrodes and a pixel electrode using the same etchant composition. The gate electrode, source / drain electrodes and the pixel electrode may be formed of different conductive materials. Accordingly, processes are simplified so that manufacturing costs may be reduced and productivity may be improved.

Owner:LG DISPLAY CO LTD

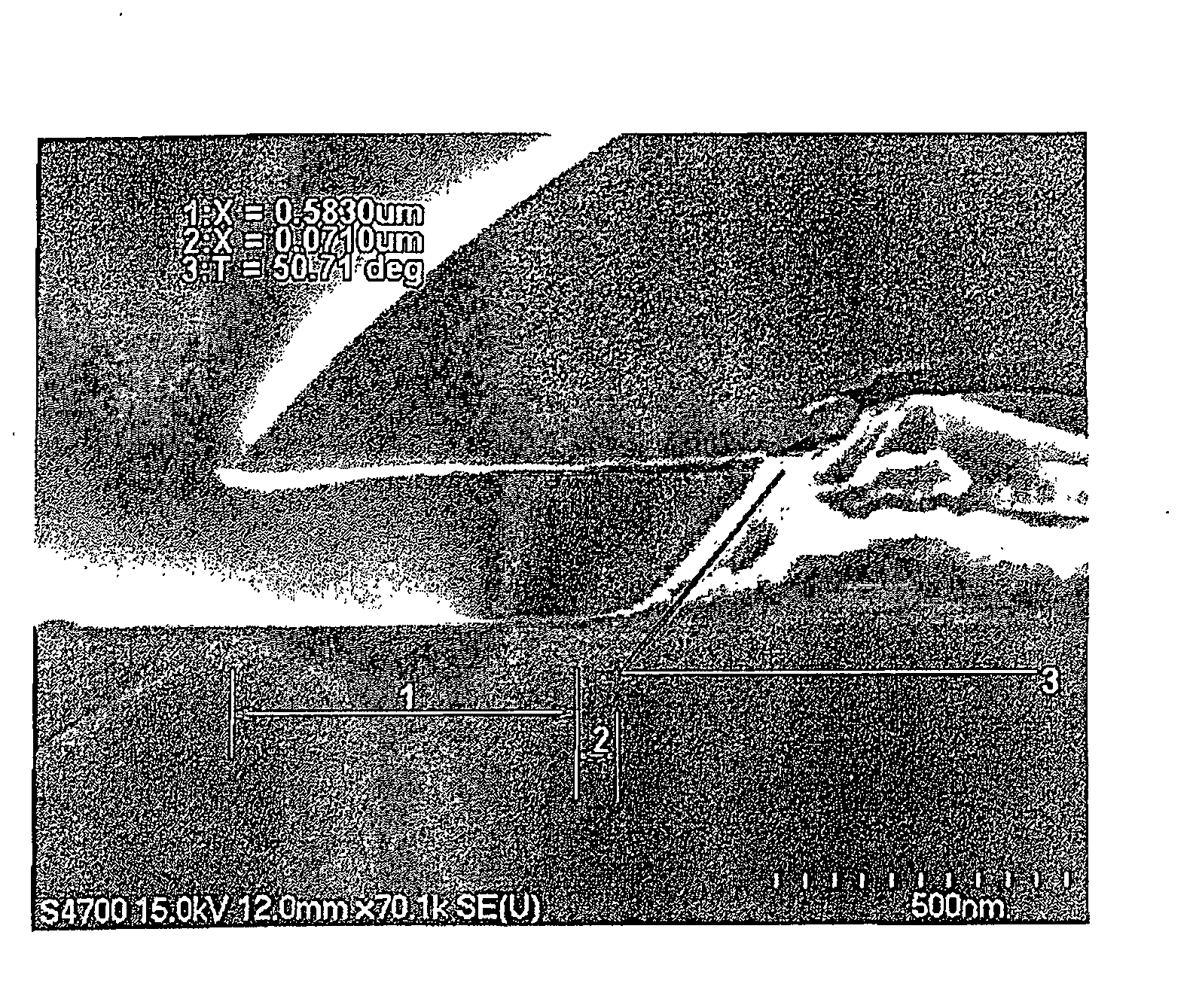

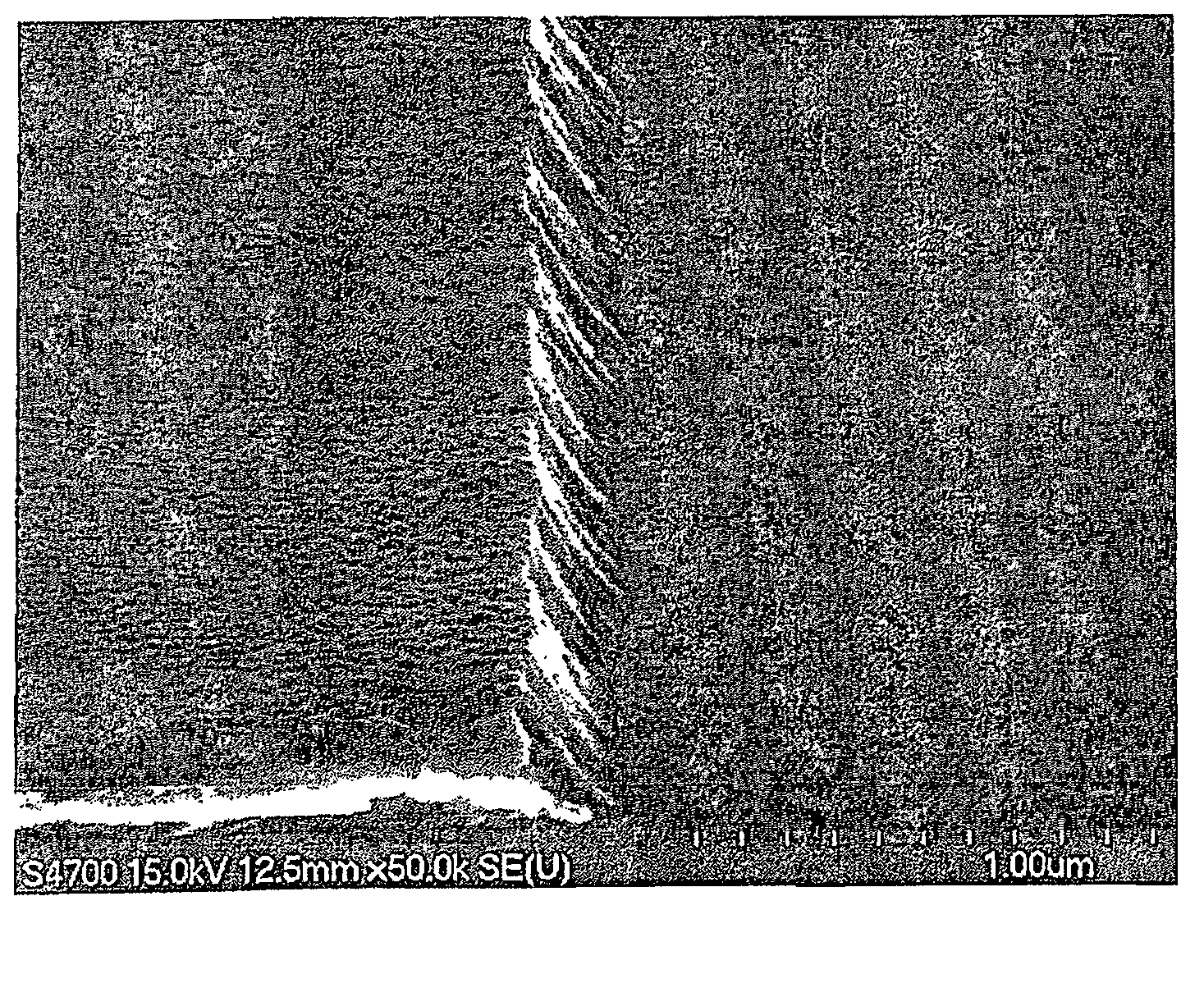

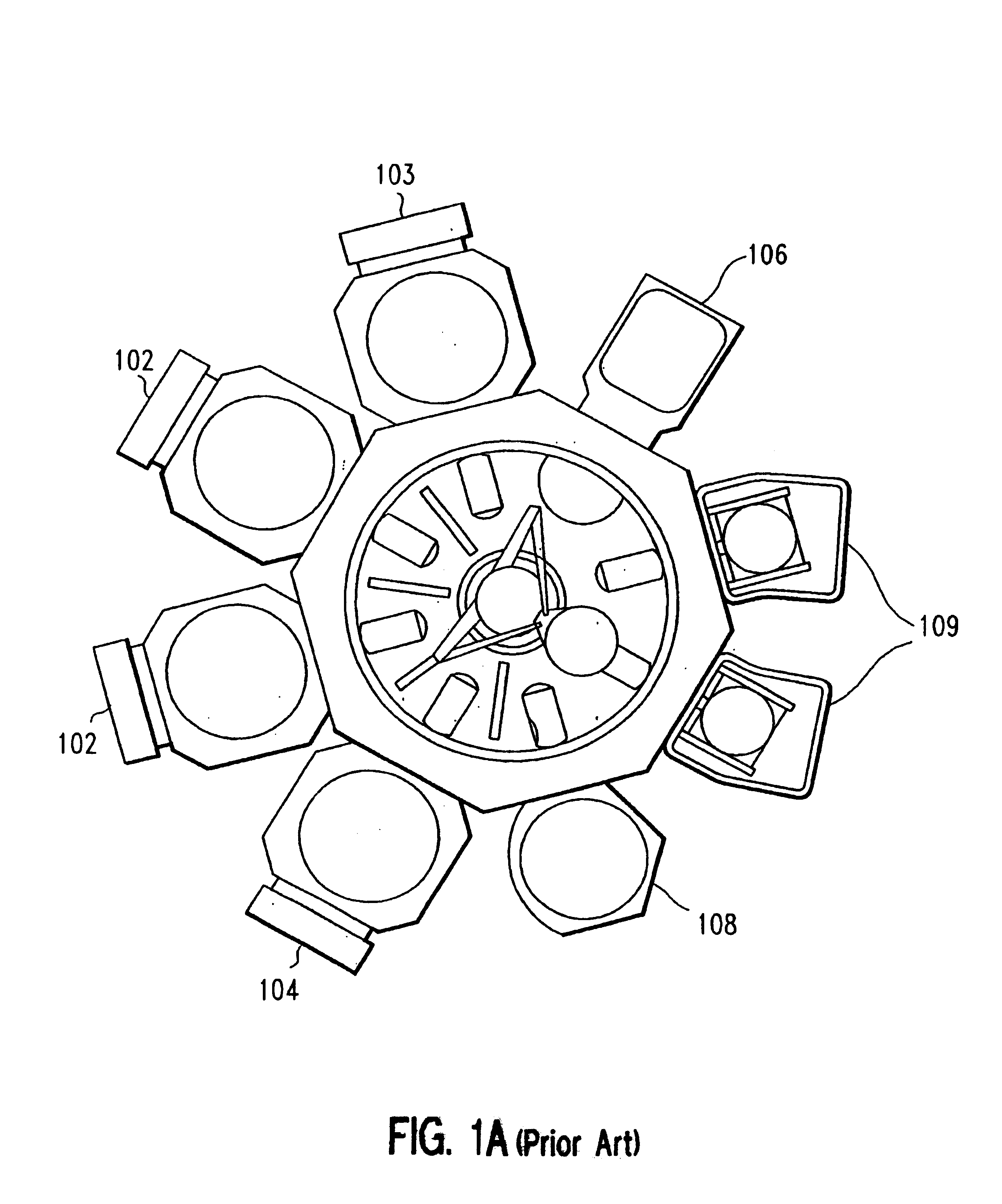

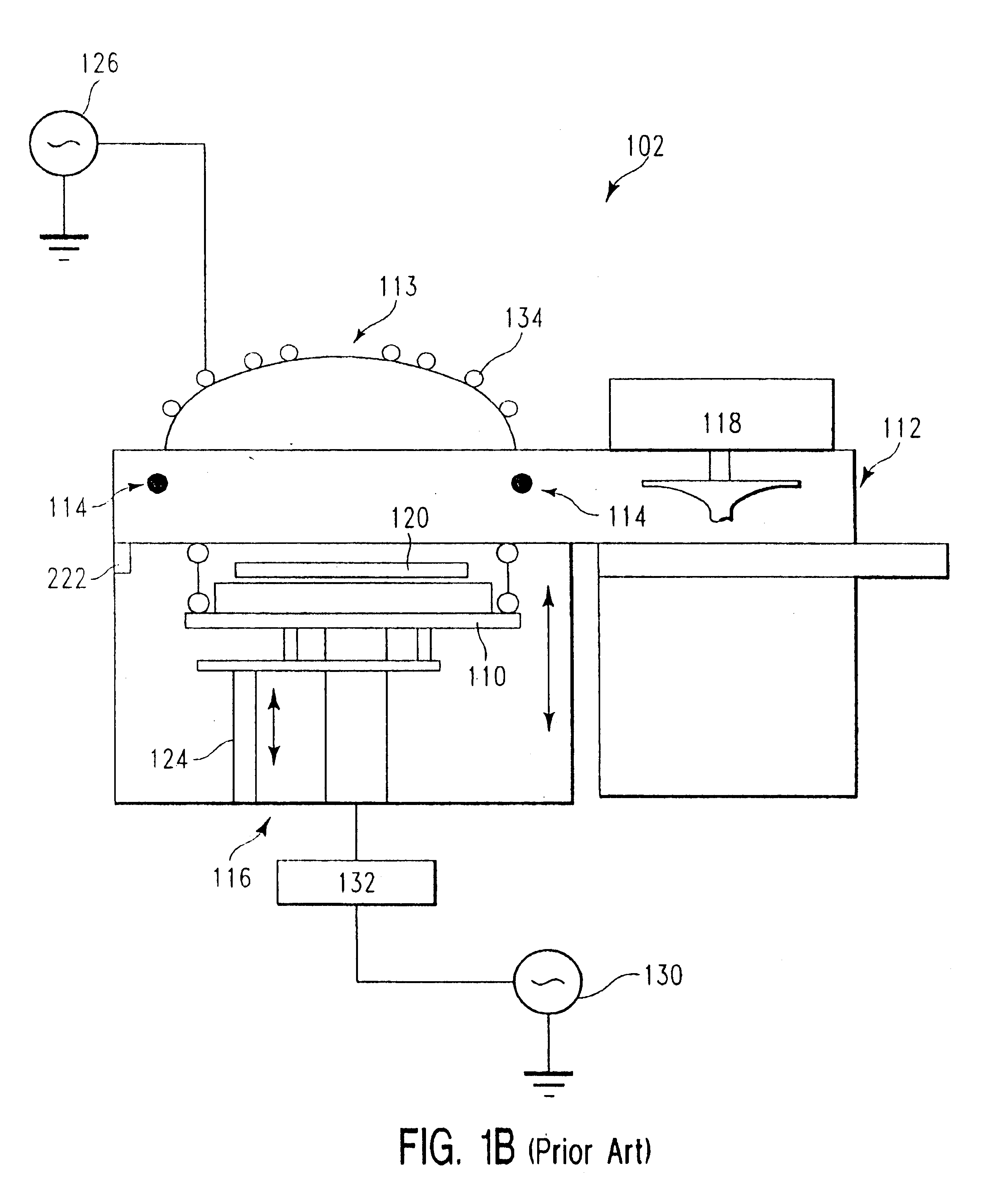

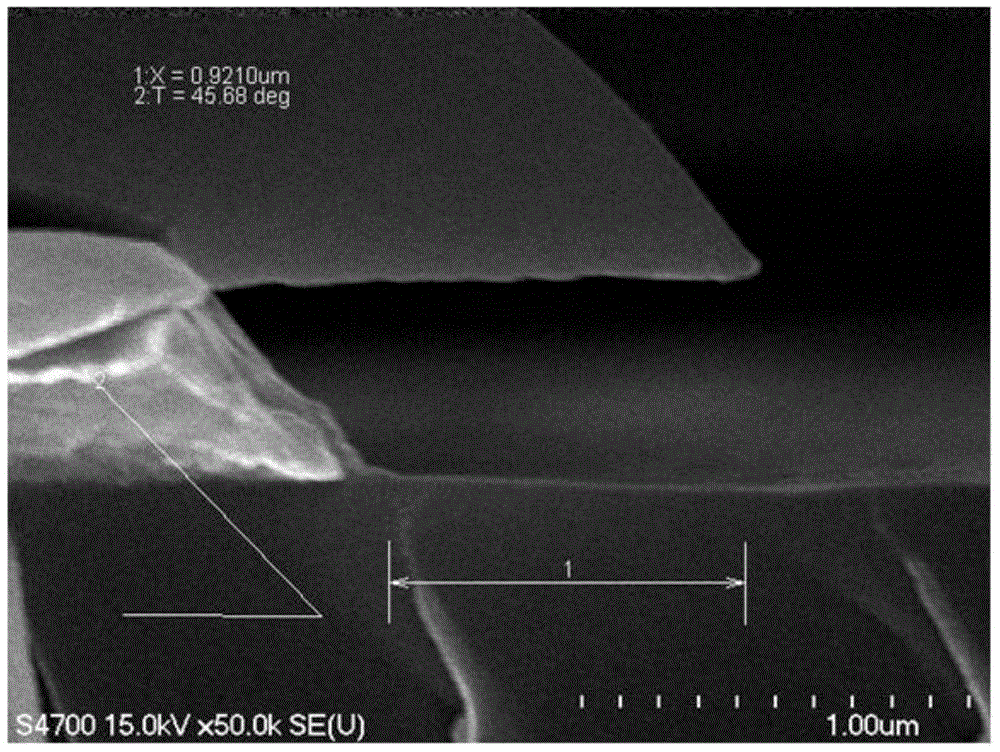

Method of plasma etching a deeply recessed feature in a substrate using a plasma source gas modulated etchant system

InactiveUS7074723B2Reduce the amount requiredSimplify the etch processSemiconductor/solid-state device manufacturingSiliconPolymer

We have developed an uncomplicated method of plasma etching deeply recessed features such as deep trenches, of at least 5 μm in depth, in a silicon-containing substrate, in a manner which generates smooth sidewalls, having a roughness of less than about 1 μm, typically less than about 500 nm, and even more typically between about 100 nm and 20 nm. Features having a sidewall taper angle, relative to an underlying substrate, typically ranges from about 85° to about 92° and exhibiting the smooth sidewalls are produced by the method. In one embodiment, a stabilizing etchant species is used constantly during the plasma etch process, while at least one other etchant species and at least one polymer depositing species are applied intermittently, typically periodically, relative to each other. In another embodiment, the stabilizing etchant species is used constantly and a mixture of the other etchant species and polymer depositing species is used intermittently.

Owner:APPLIED MATERIALS INC

Etchant composition, method for forming metal wire patterns and method for manufacturing array substrate

InactiveCN106148961AExtend the lifespanSimplify the etch processNon-linear opticsOrganic acidLiquid-crystal display

The invention discloses an etchant composition used for copper layers and titanium layers and a method for manufacturing an array substrate of a liquid crystal display using the etchant composition. The etchant composition comprises 0.5 wt.% to 20 wt.% of persulfate, 0.01 wt.% to 2 wt.% of a fluorine compound, 1 wt.% to 10 wt.% of inorganic acid (salt), 5 wt.% to 20 wt.% of organic acid (salt), 0.1 wt.% to 5 wt.% of a cyclamine compound containing alkyl (containing 1 to 5 carbon atoms) tetrazole, 0.1 wt.% to 10 wt.% of a sulfonic acid compound and the balance of water. Thus, the copper layers and the titanium layers can be evenly etched in batches at a high etching speed, and even when the number of treated sheets is increased, the inclination angles of etched patterns are reduced.

Owner:DONGWOO FINE CHEM CO LTD

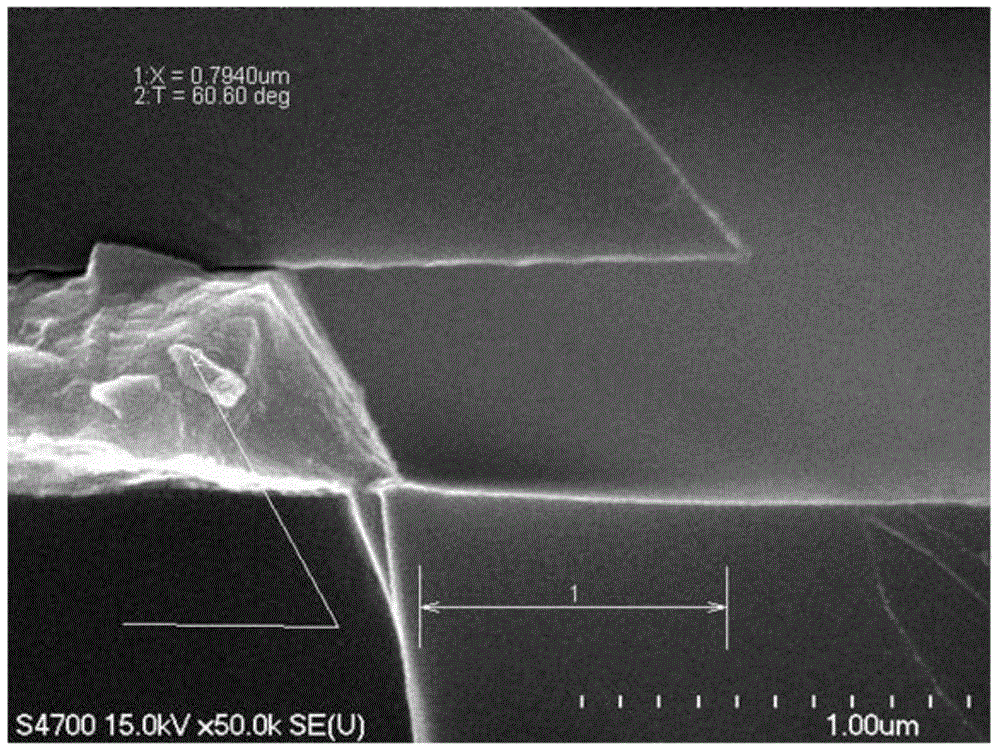

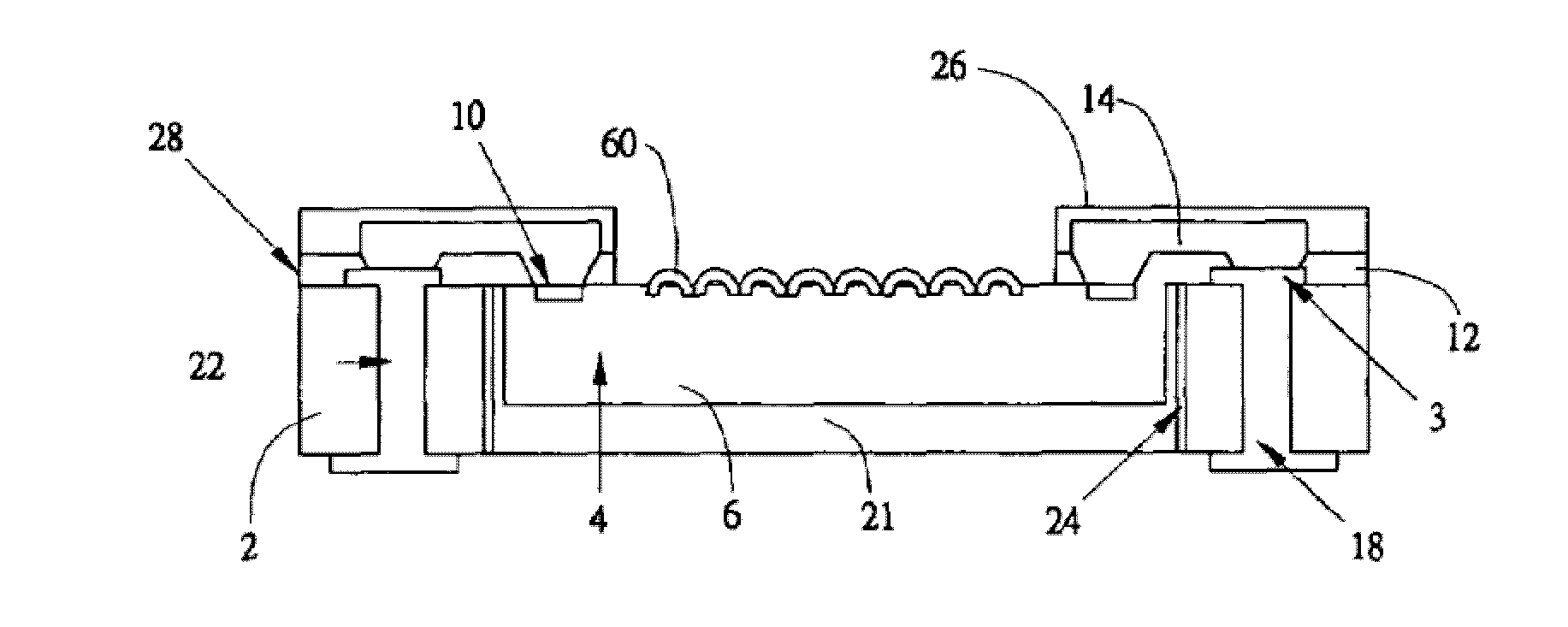

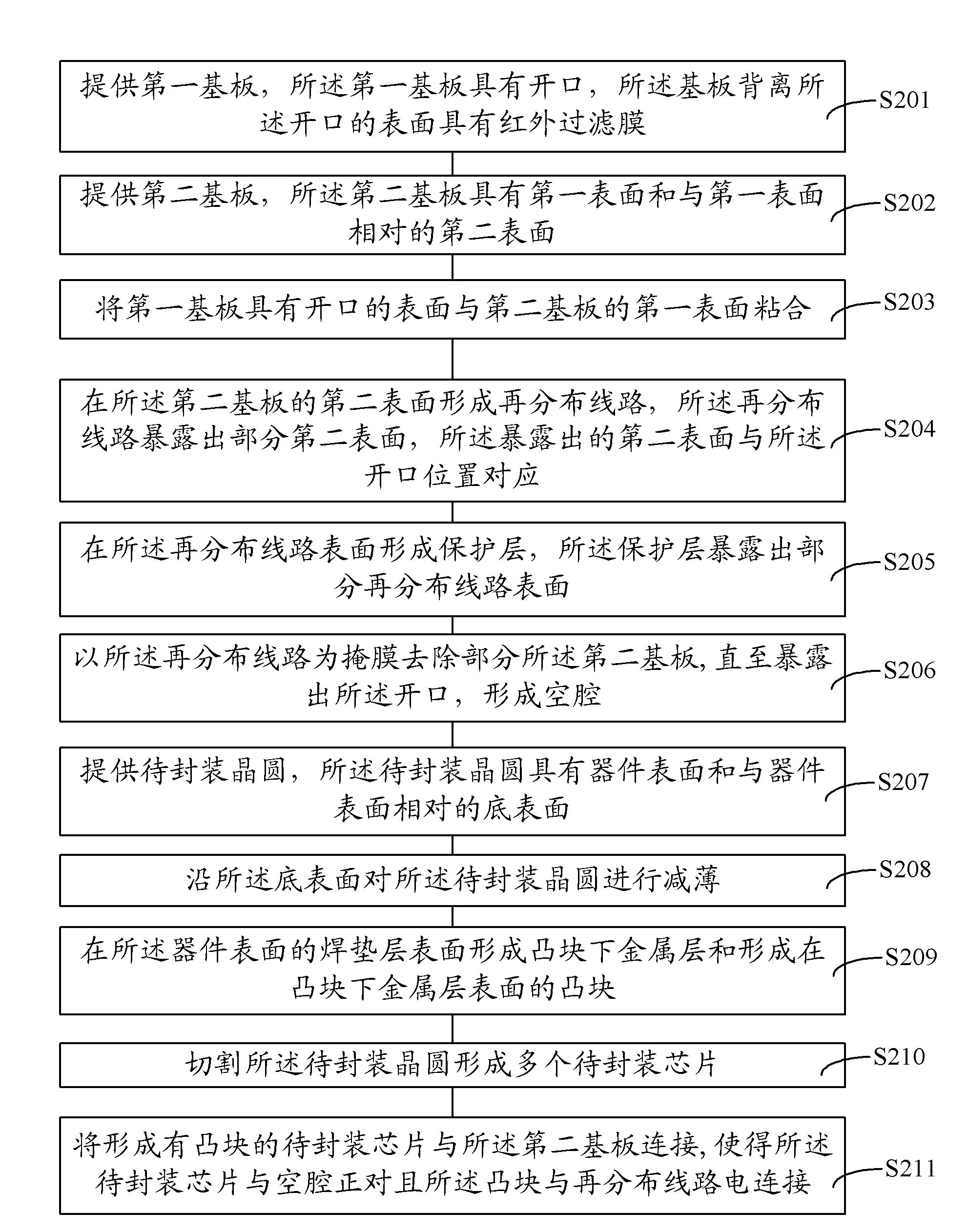

Wafer-level packaging structure and method of forming the same

ActiveCN102280391ASimple structureSimple processSemiconductor/solid-state device detailsSolid-state devicesStructure formationElectrical and Electronics engineering

The invention provides a wafer level package structure and a formation method thereof. The method comprises the following steps: providing a substrate; forming a cavity in the substrate; forming a redistribution line in the substrate and on part surface of the cavity; providing a chip to be packaged, wherein the chip has a device surface and a basal surface opposite to the device surface; formingan Under Bump Metal on a soldering pad layer surface of the device surface and forming a bump on a surface of the Under Bump Metal; connecting the chip to be packaged with the substrate such that thechip to be packaged faces the cavity and the bump is electrically connected with the redistribution line. The wafer level package structure in the invention has the advantages of a simple structure, high packaging quality, and high compatibility in subsequent combination with PCB plate process. The wafer level package structure formation method in the invention has the advantages of simple process sequence and low cost.

Owner:CHINA WAFER LEVEL CSP

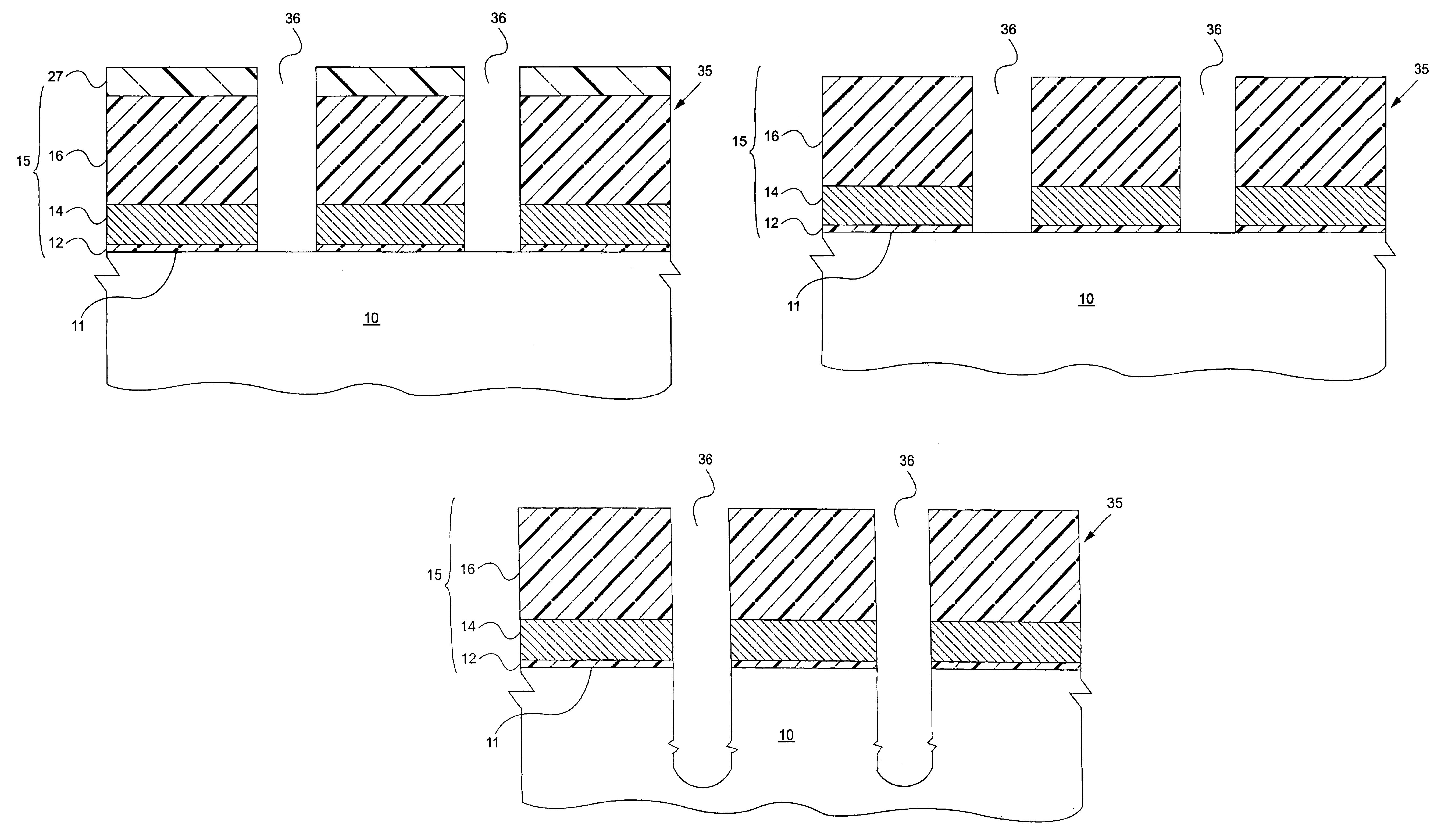

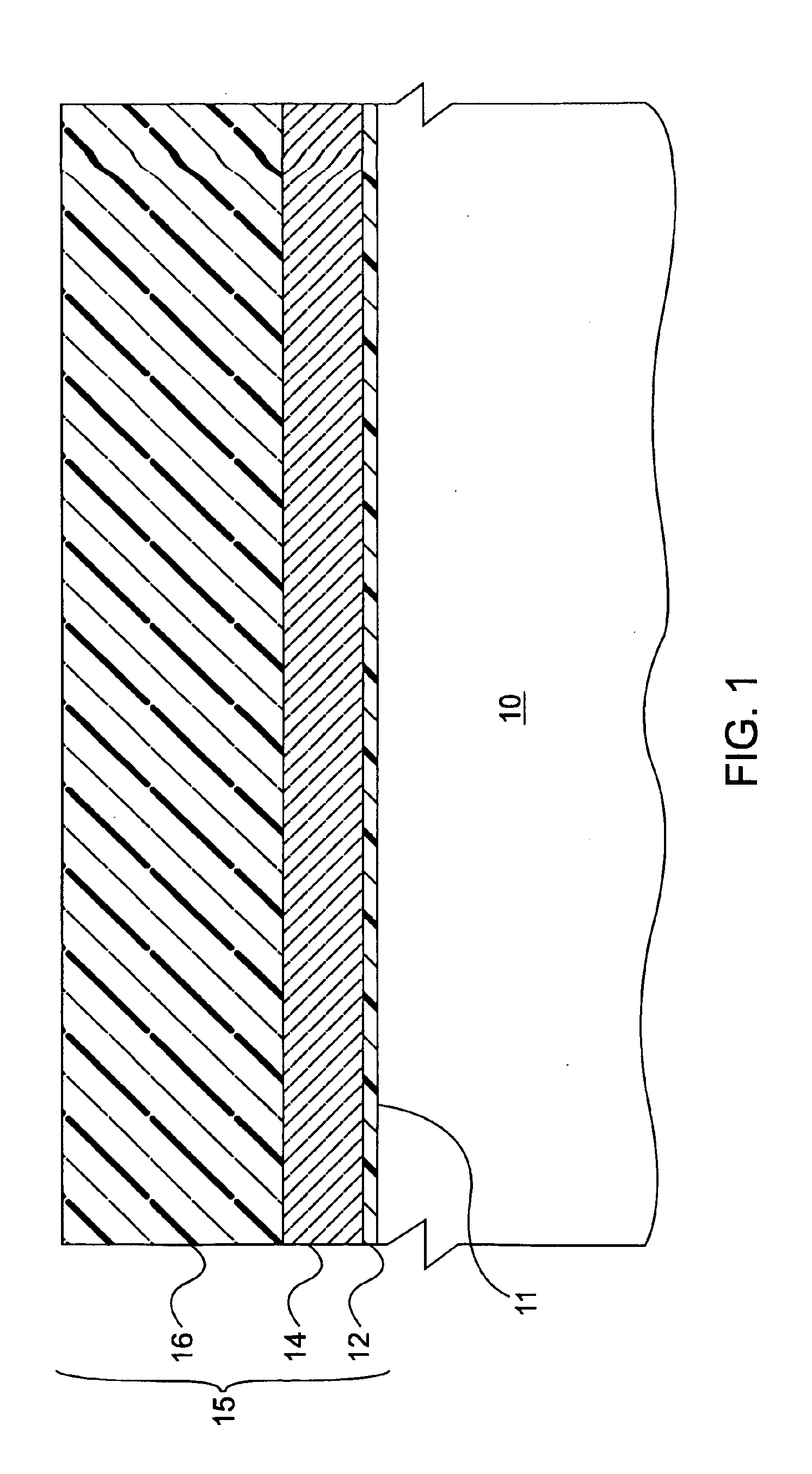

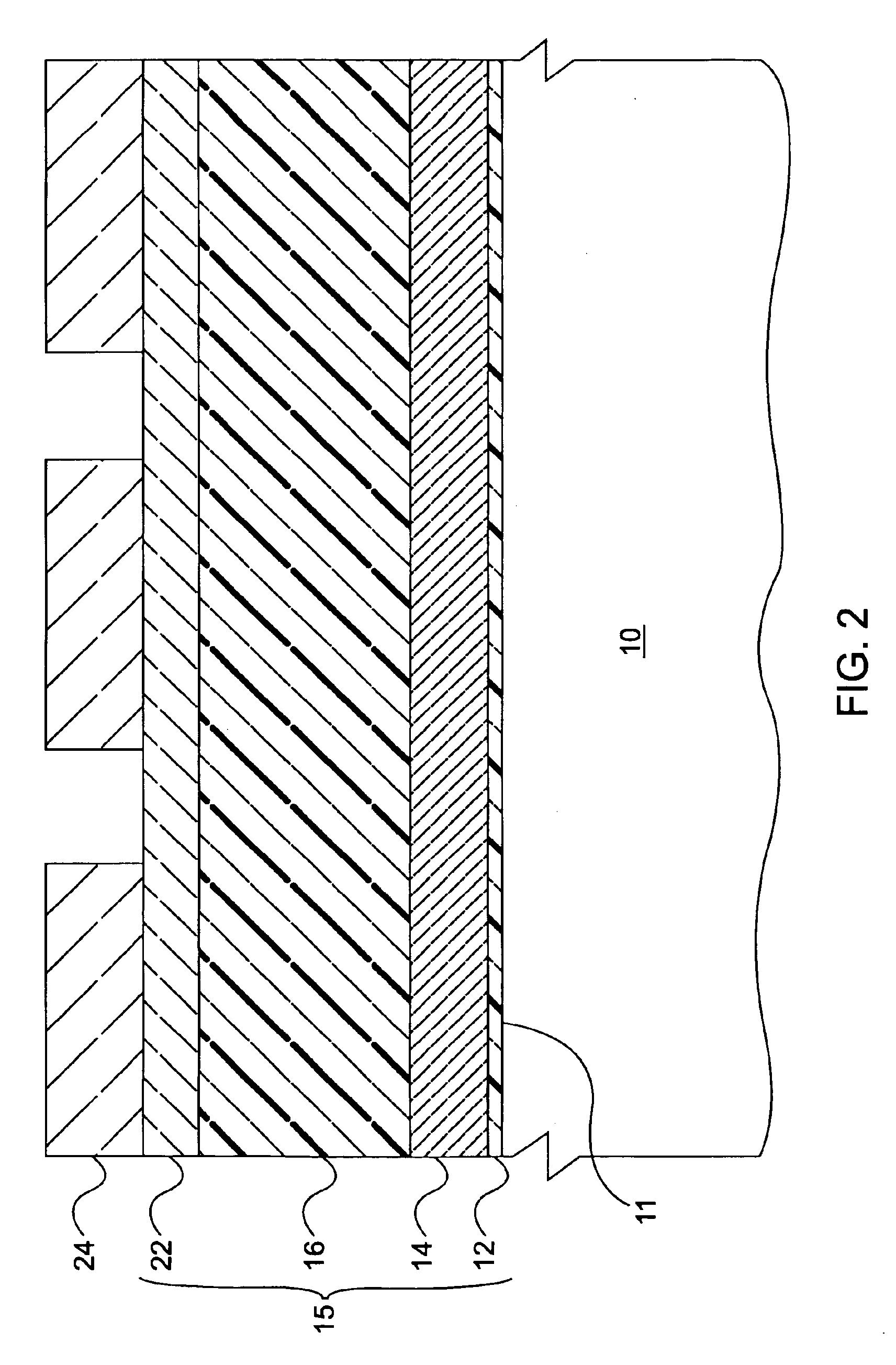

Method for etching a semiconductor substrate using germanium hard mask

InactiveUS6867143B1High densityHigh performanceSemiconductor/solid-state device manufacturingResistSemiconductor

An etching process using germanium hard mask (25) includes forming a dielectric layer (15) over a major surface (11) of a semiconductor substrate (10) and depositing a metallic germanium layer (22) over the dielectric layer (15). The metallic germanium layer (22) is patterned through a photo resist (24) to form the germanium hard mask (25). The dielectric layer (15) is selectively etched through the germanium hard mask (25) to form a dielectric hard mask (35), through which the semiconductor substrate (10) is subsequently etched. After forming the dielectric hard mask (35), the germanium hard mask (25) is stripped away by oxidizing the metallic germanium hard mask (25) to transform it into a layer (27) of germanium oxide and rinsing the semiconductor substrate (10) in water to remove the germanium oxide layer (27). Preferably, the germanium hard mask (25) is removed before etching the semiconductor substrate (10).

Owner:IBM CORP

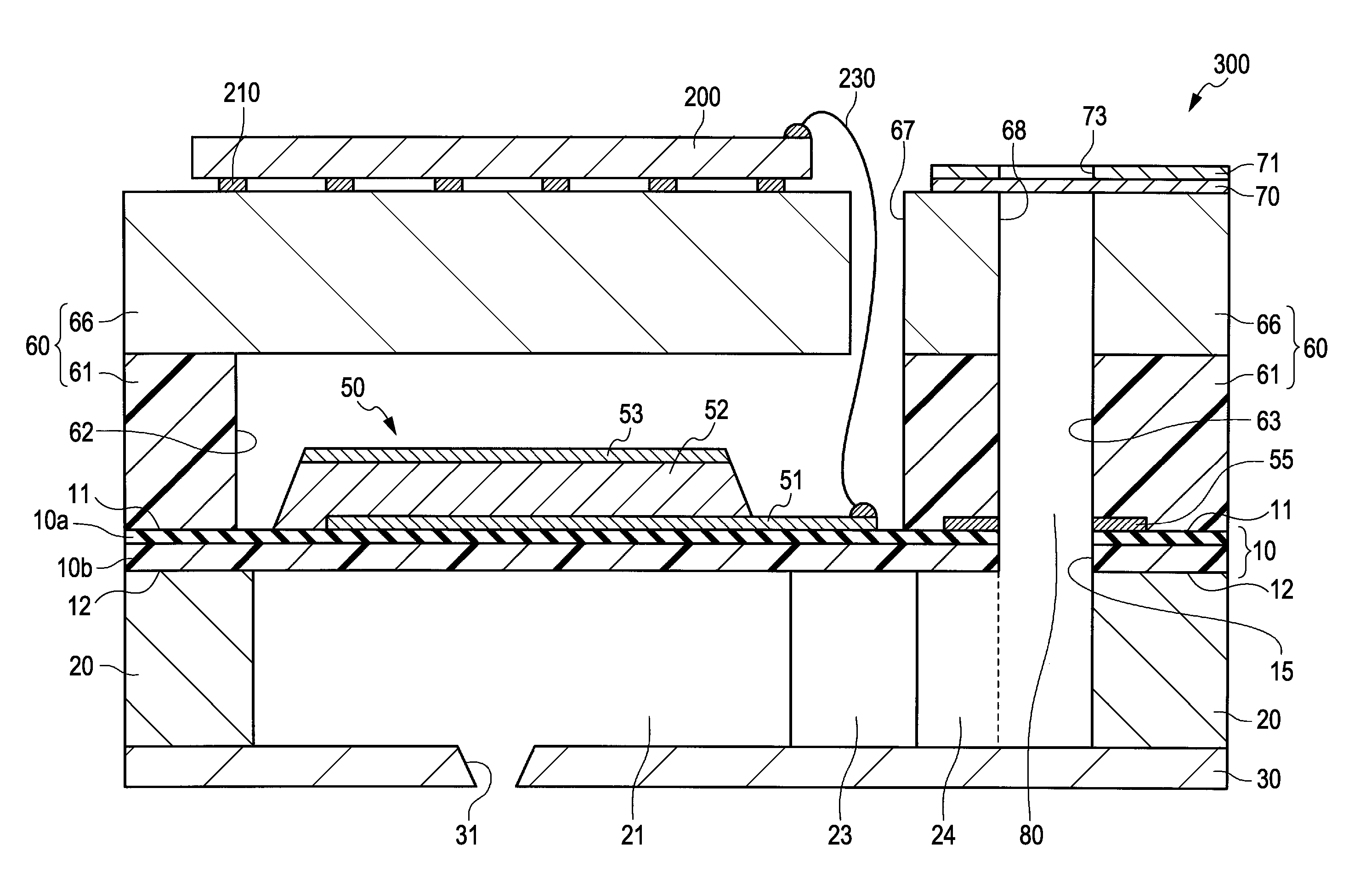

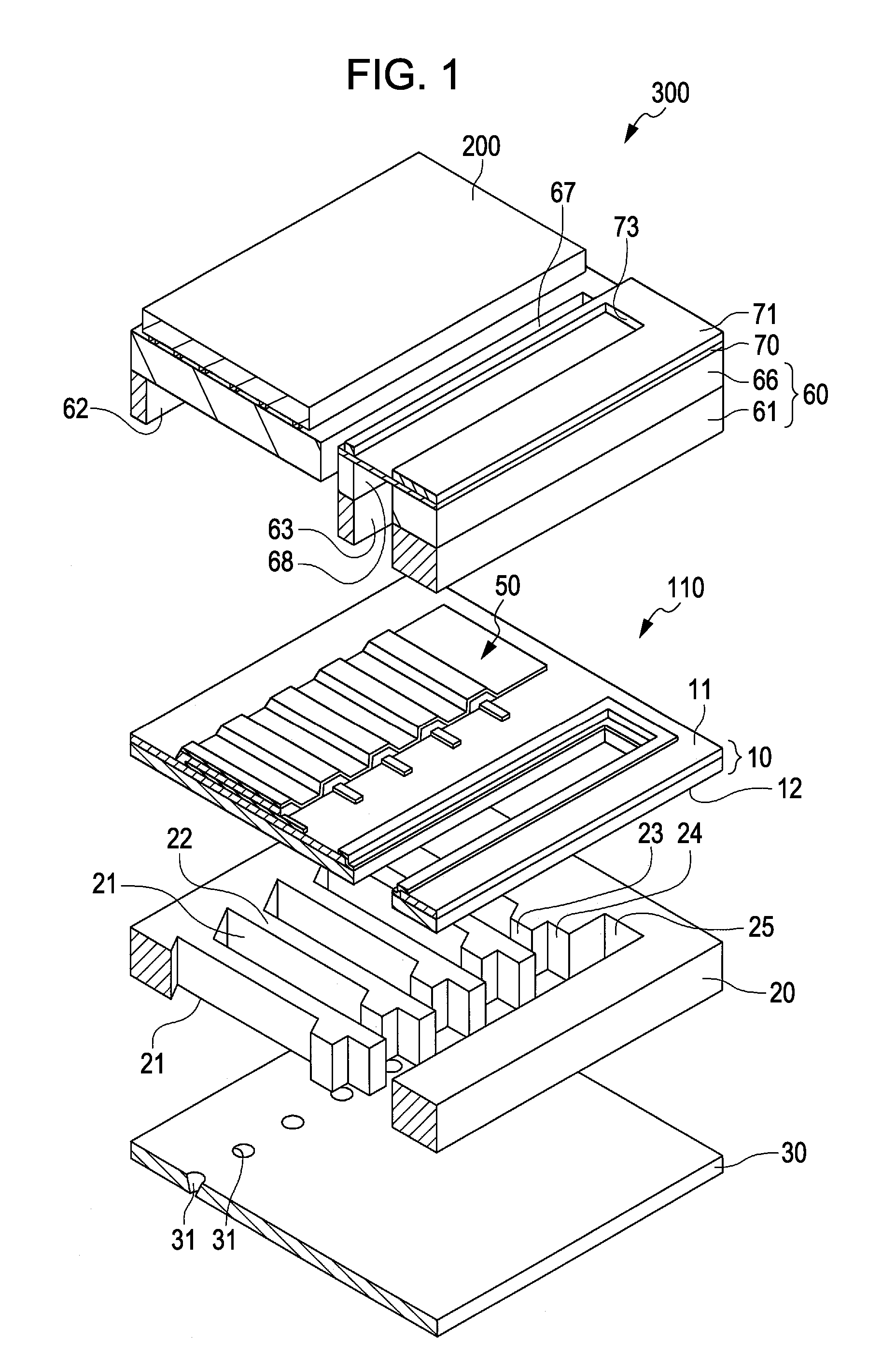

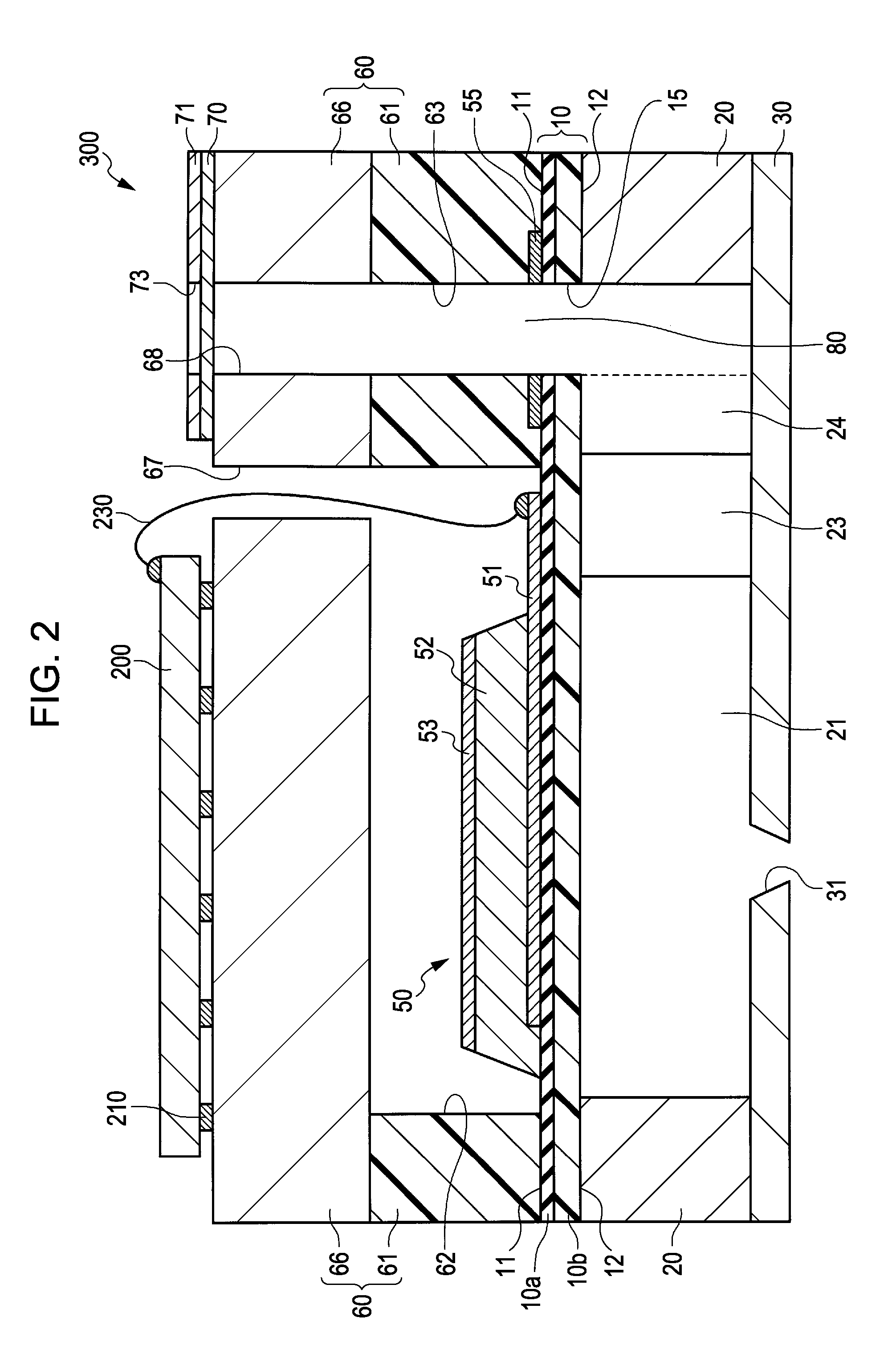

Liquid droplet ejecting head, method for manufacturing the same, and liquid droplet ejecting apparatus

ActiveUS20110109704A1Improve reliabilityImprove productivityPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostrictive transducersEngineeringElectrode

A liquid droplet ejecting head includes a fluid path forming substrate having a fluid path communicating with nozzle holes and a diaphragm on the fluid path forming substrate. The diaphragm has a first surface facing a second surface. A piezoelectric element on the first surface of the diaphragm has a piezoelectric body layer interposed between a first electrode and a second electrode. A support substrate on the first surface of the diaphragm has a space for containing the piezoelectric element. The support substrate includes a first member formed on the first surface of the diaphragm, and a second member formed on the first member. The first member has a first opening for containing the piezoelectric element. The space of the support substrate is defined by the first opening of the first member and the second member. The main material of the first member is resin.

Owner:SEIKO EPSON CORP

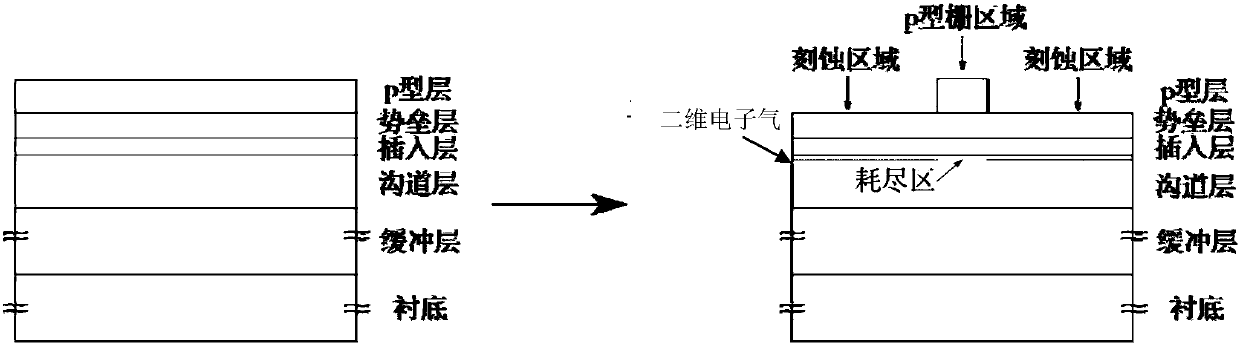

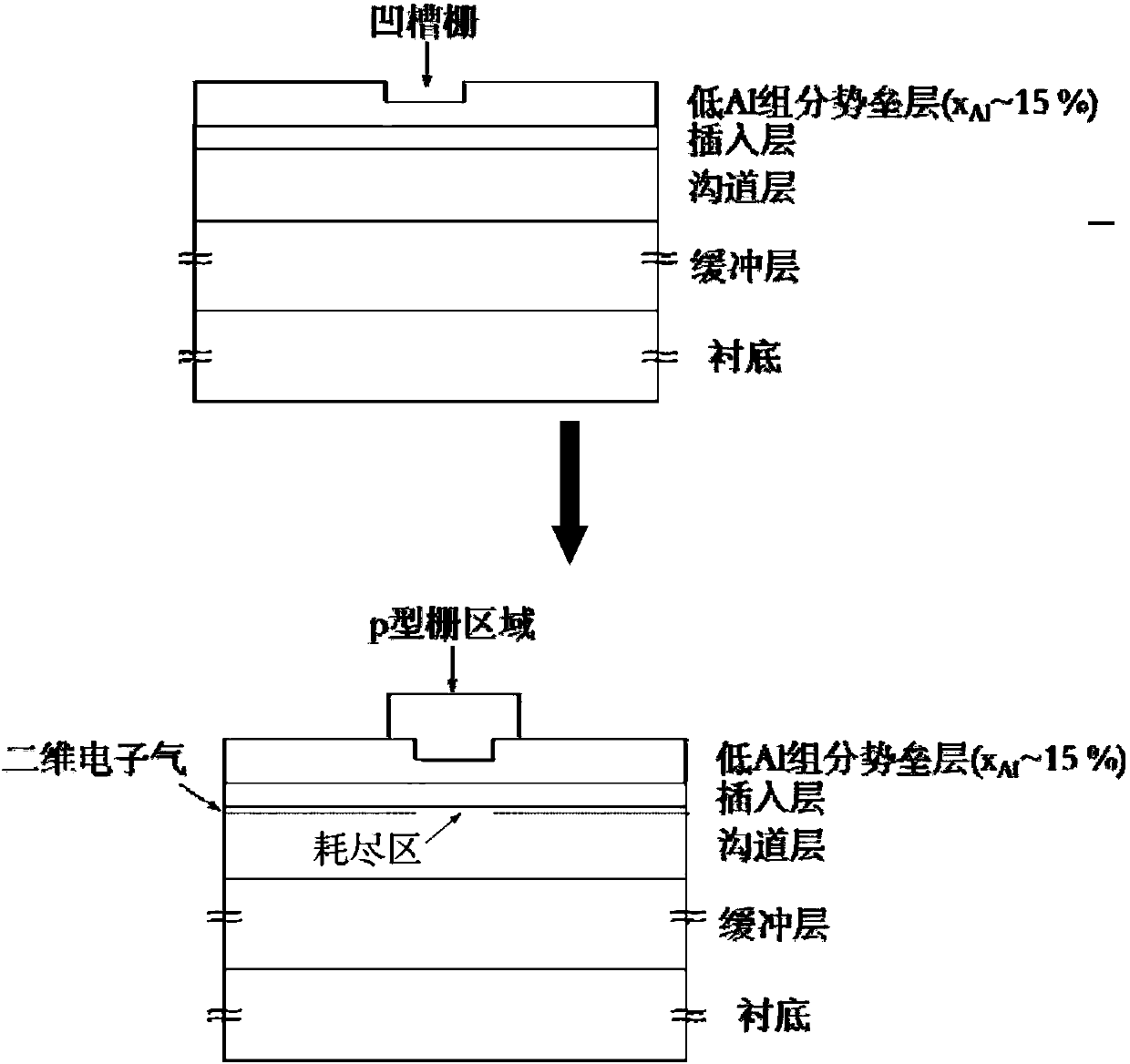

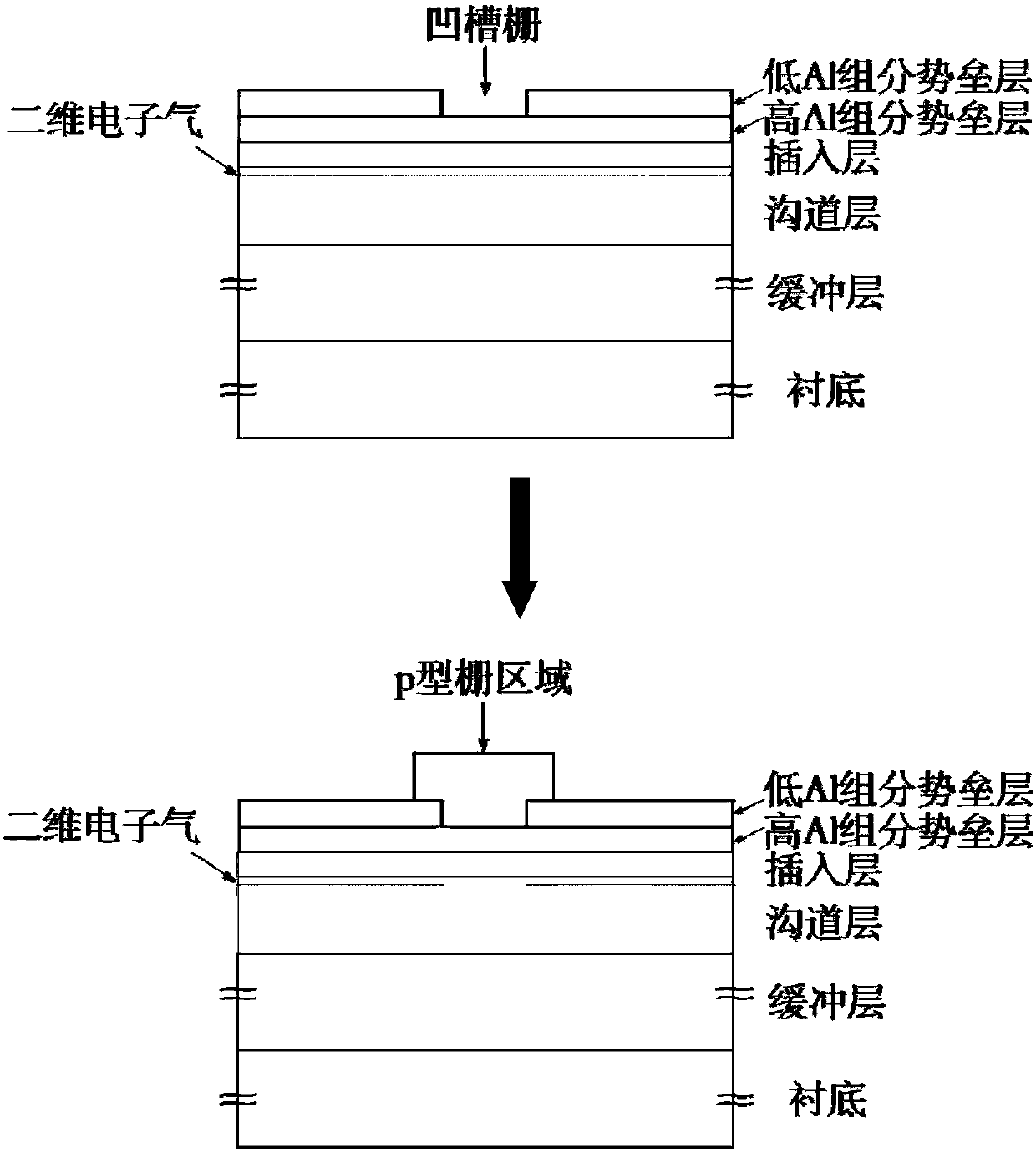

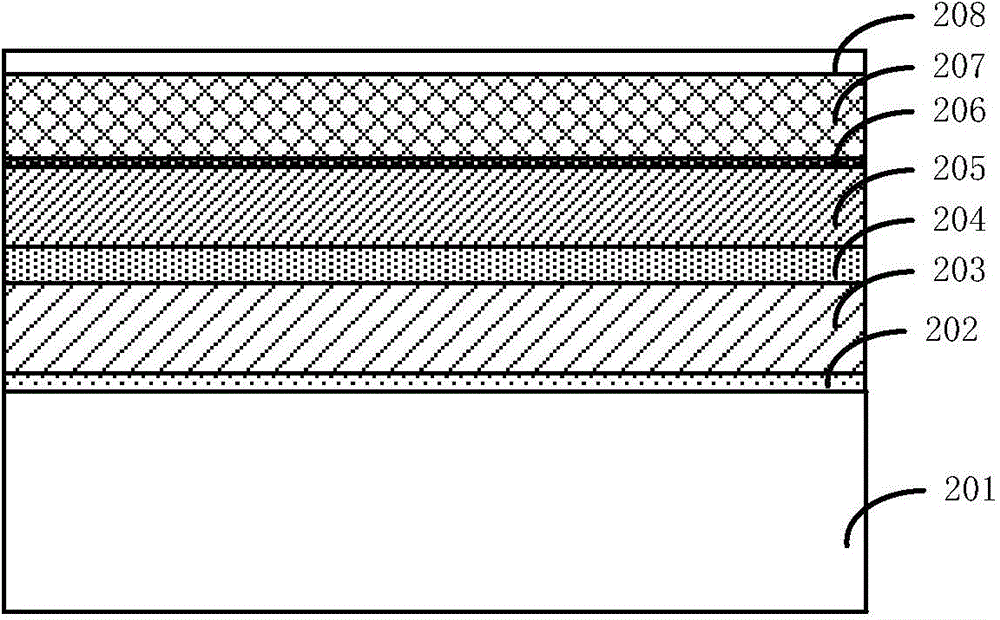

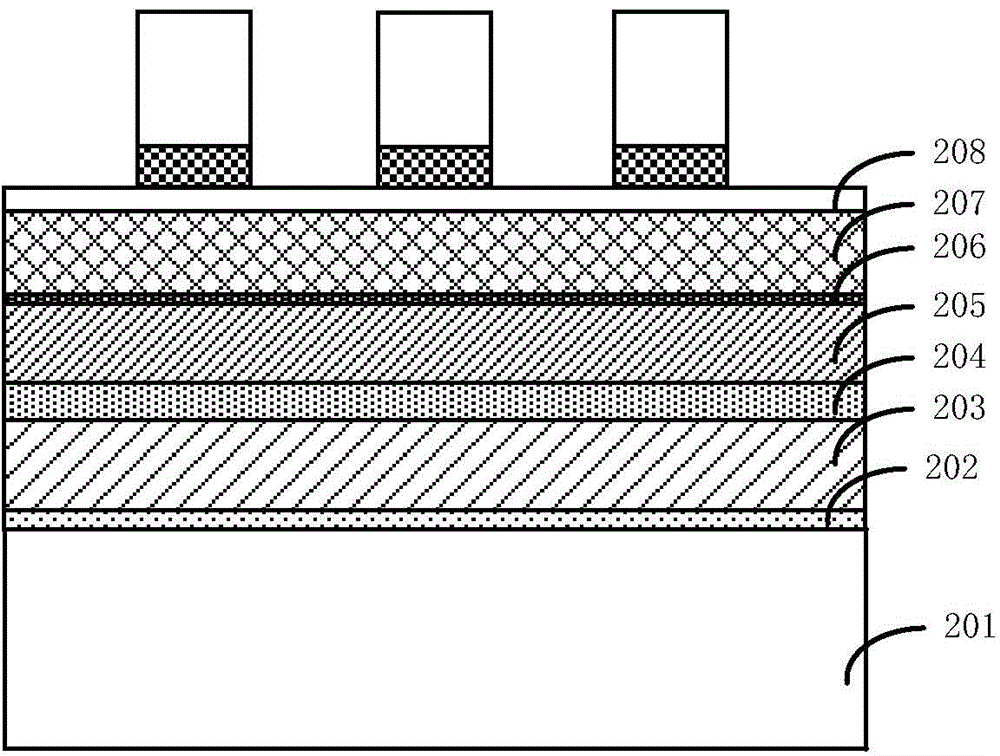

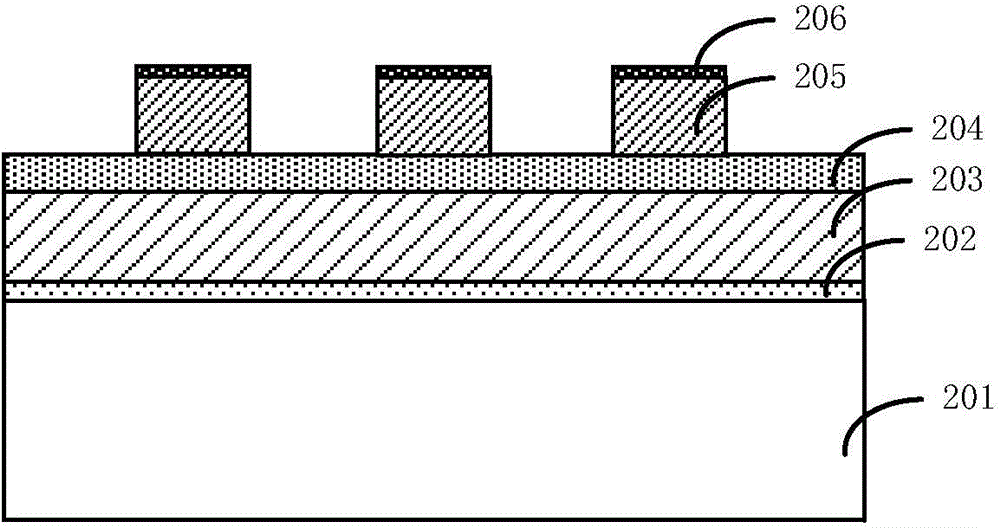

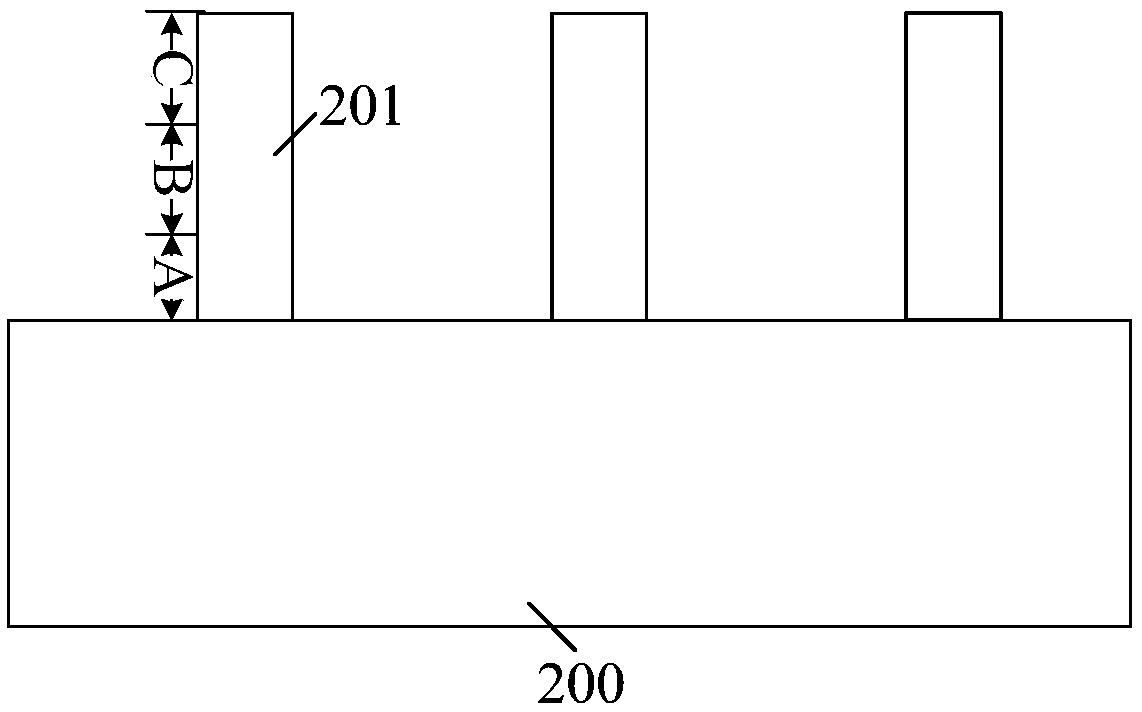

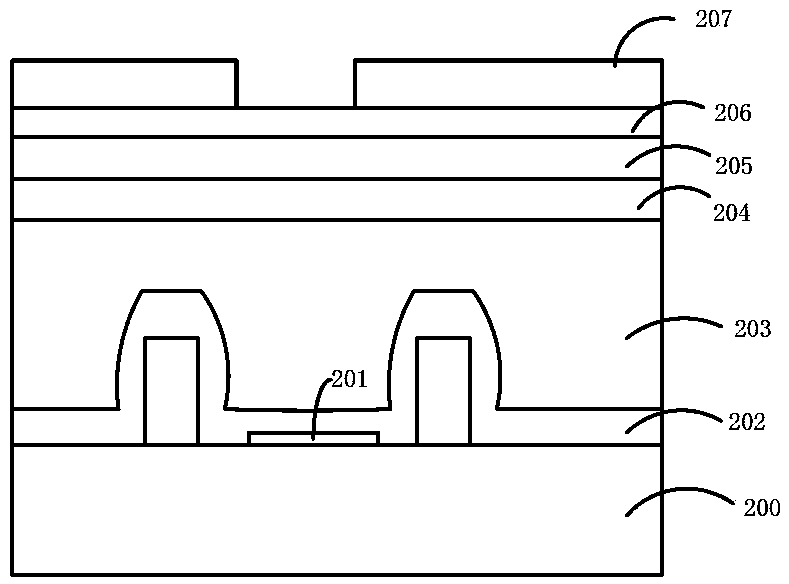

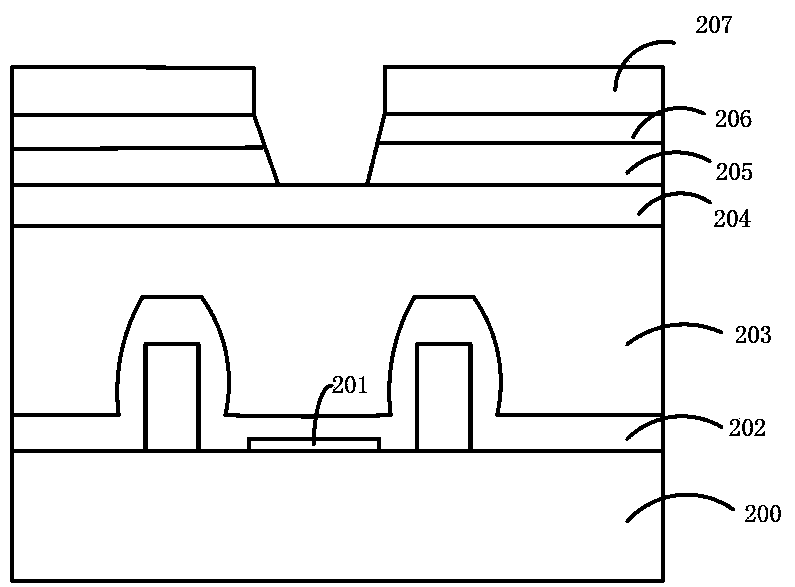

III-nitride enhanced HEMT based on composite barrier layer structure and manufacturing method of III-nitride enhanced HEMT

ActiveCN110034186ASuppress leakageSimplify the etch processSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringNitride

The invention discloses a III-nitride enhanced HEMT based on a composite barrier layer structure and a manufacturing method of the III-nitride enhanced HEMT. The HEMT comprises a first semiconductor,a second semiconductor, a third semiconductor serving as a p-type layer, a source electrode, a drain electrode, a grid electrode and the like, wherein the first semiconductor and the second semiconductor respectively serve as a channel layer and a barrier layer, a groove structure is formed in the area, corresponding to the grid electrode, of the barrier layer, the groove structure cooperates withthe third semiconductor and the grid electrode to form a p-type grid, and the second semiconductor comprises a first structure layer and a second structure layer which are sequentially arranged on the first semiconductor. Compared with a mode of determining an etching reagent, the first structure layer has higher etching resistance than the second structure layer. The HEMT structure can be more accurately regulated and controlled, meanwhile, the HEMT has the better device performance. For example, the forward gate leakage and gate threshold voltage swing amplitude are remarkably improved, thein-chip uniformity of threshold voltage of the device can be guaranteed, and meanwhile, the HEMT structure is easier to manufacture and suitable for large-scale production.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

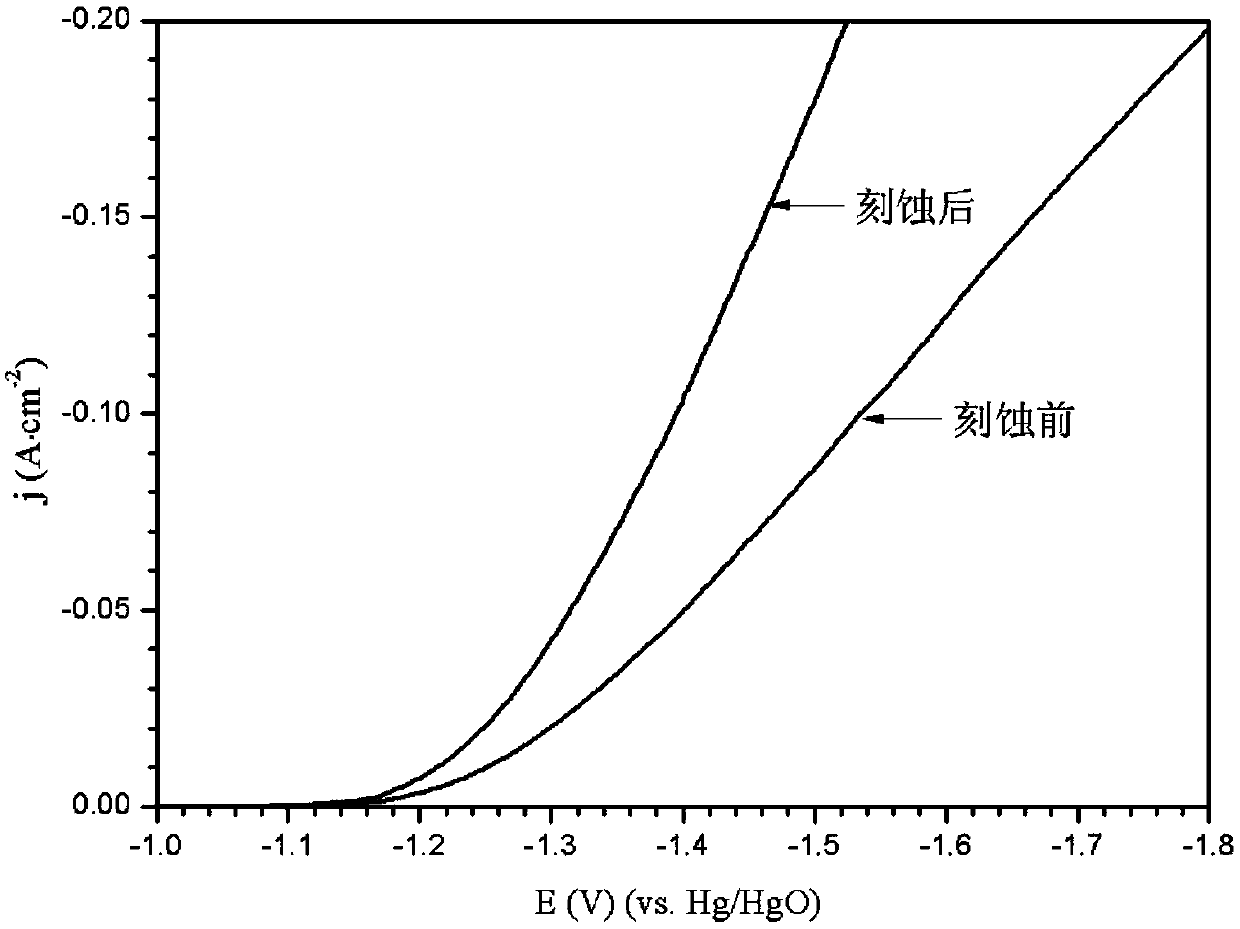

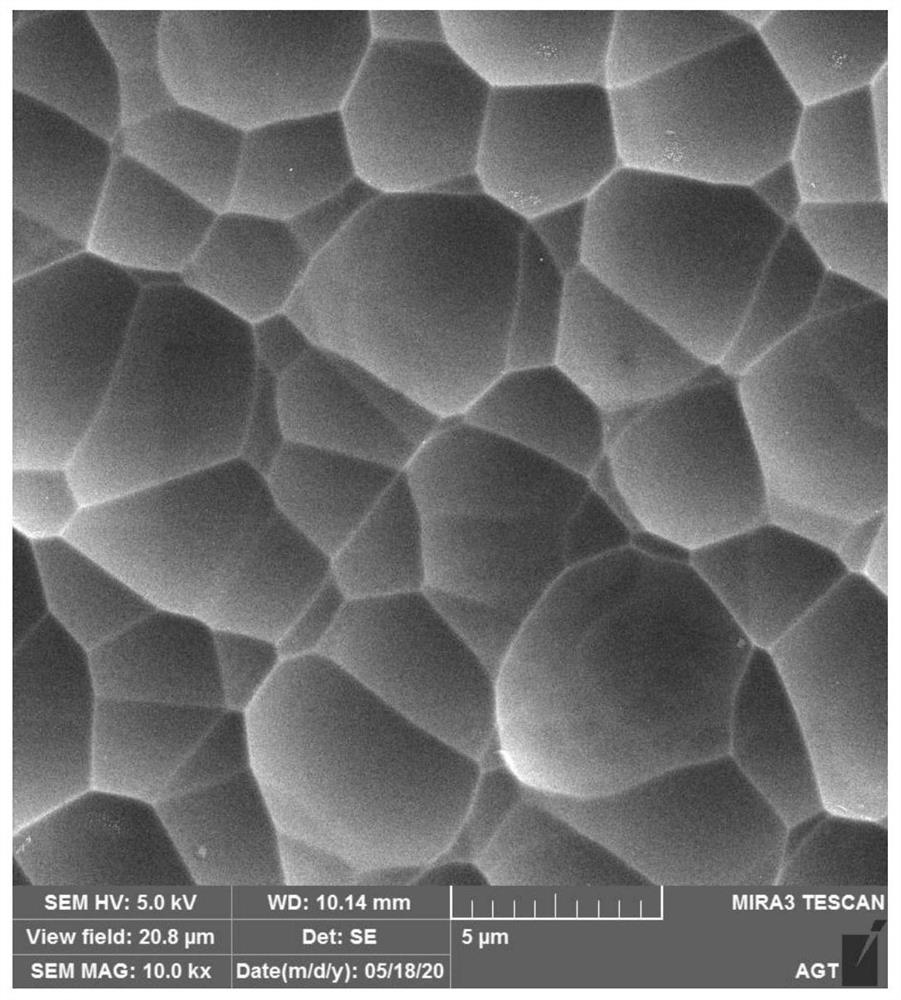

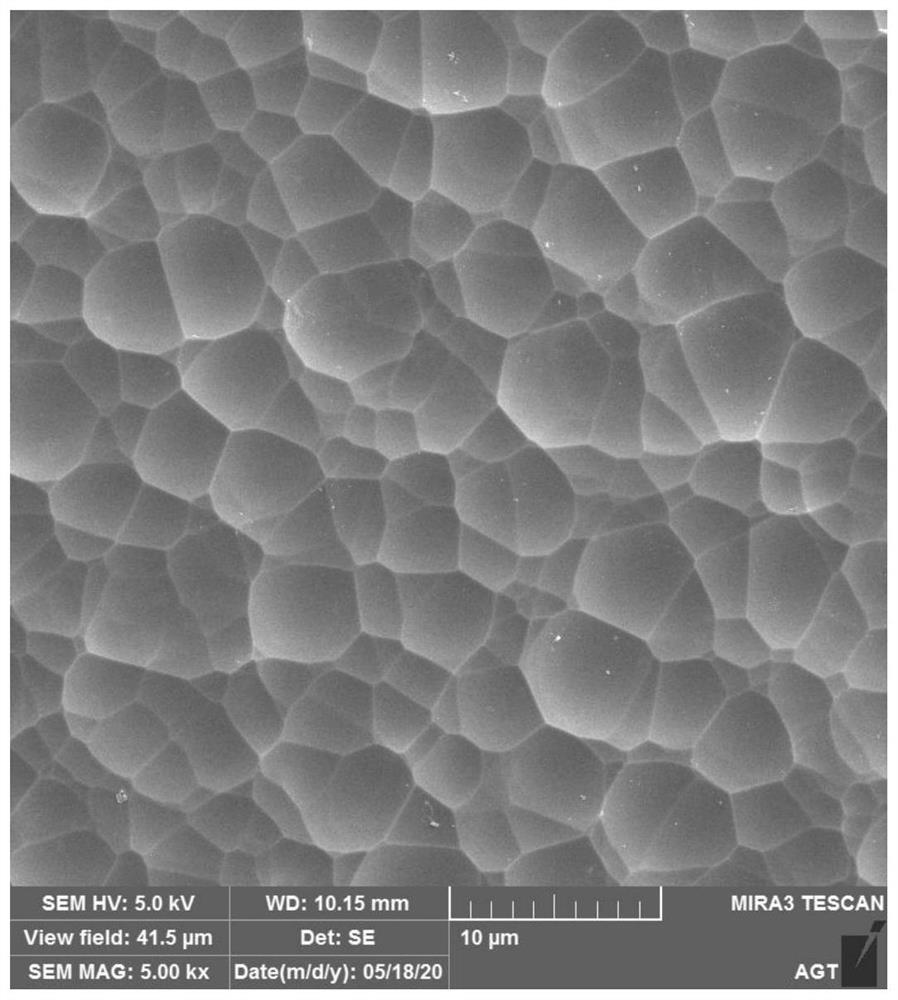

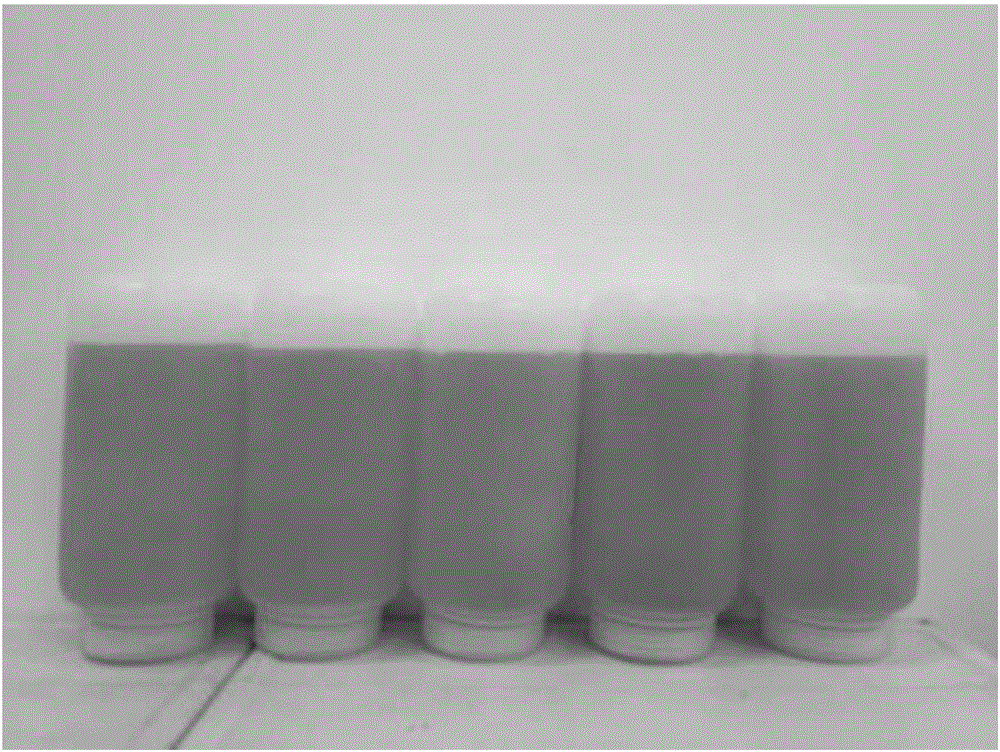

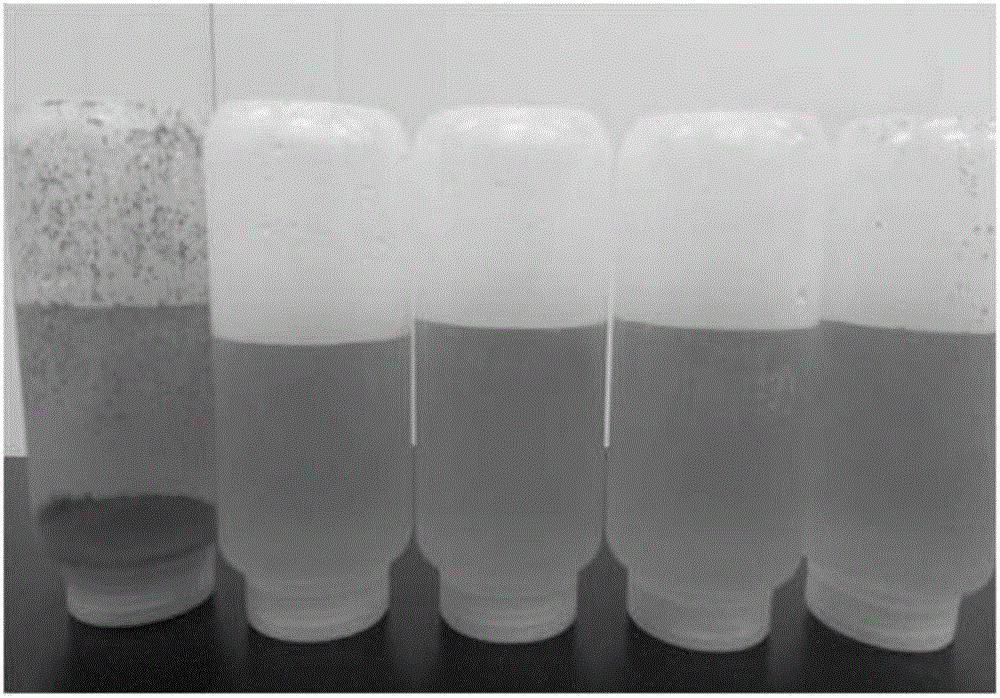

Etching method capable of increasing electrochemical active area of nickel foam electrode

The invention relates to an etching method capable of increasing the electrochemical active area of a nickel foam electrode, belonging to the fields of surface treatment technology for materials and electrocatalysis. According to the invention, a chemical etching solution with hydrochloric acid and an oxidizing agent as main components is used for soaking and etching of the nickel foam electrode,and the nickel foam electrode with a large active area and high stability is prepared by controlling etching time and the concentration of the etching solution. The prepared nickel foam electrode canprovide more active sites for hydrogen evolution and oxygen evolution of electrolysed water and reduce energy consumption in electrolysis. The etching method is simple in process and suitable for large-scale industrial production.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

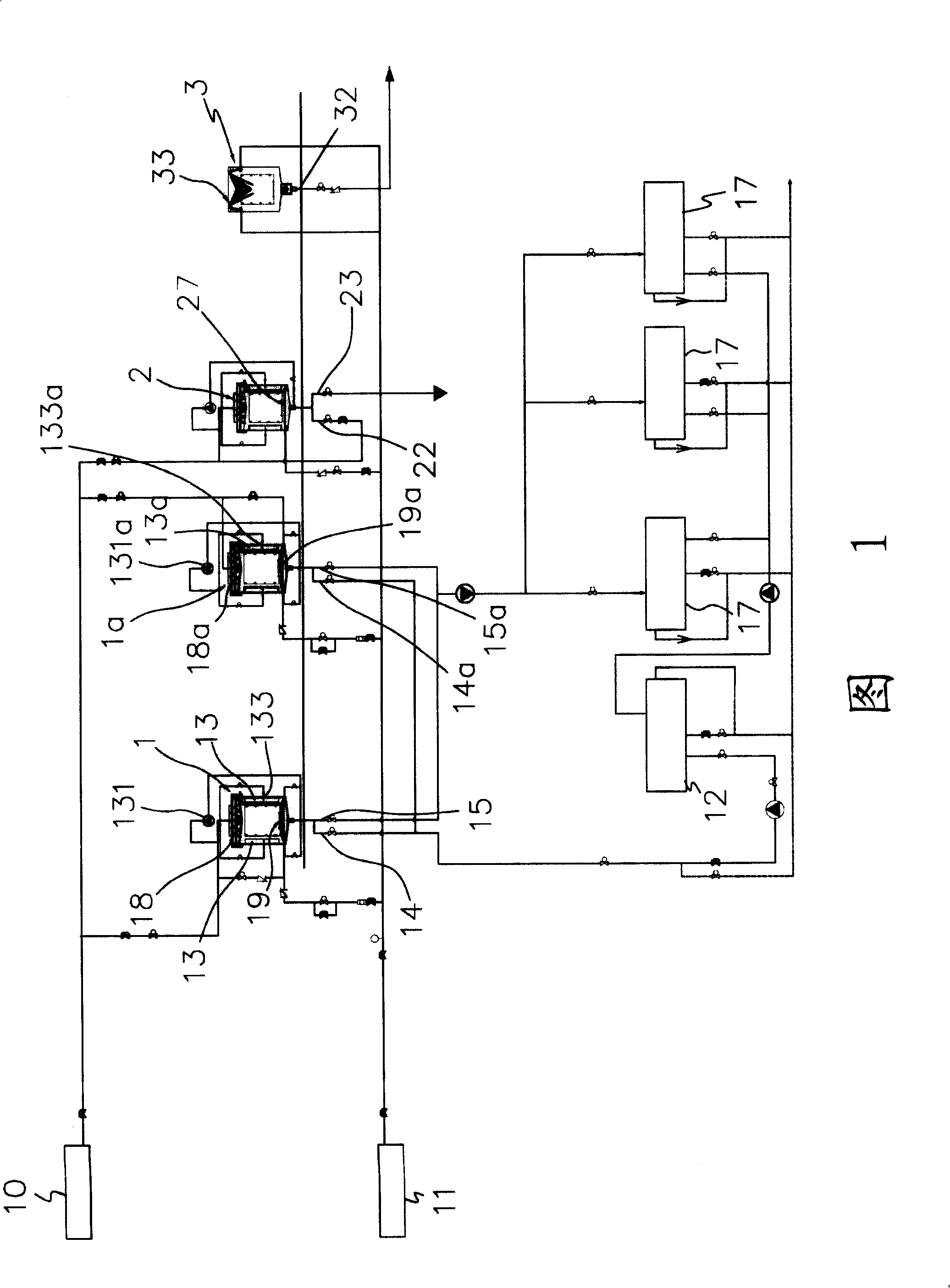

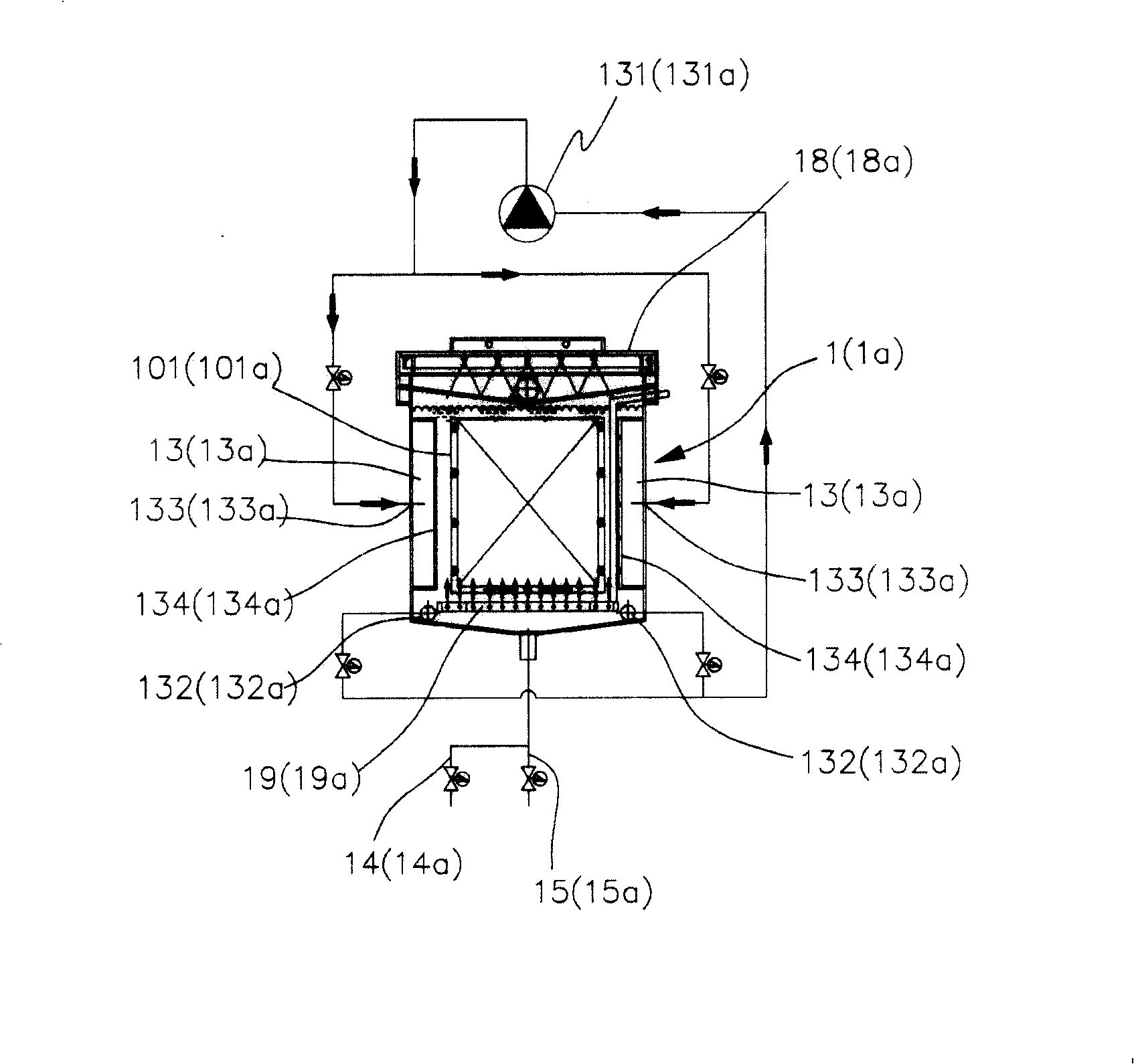

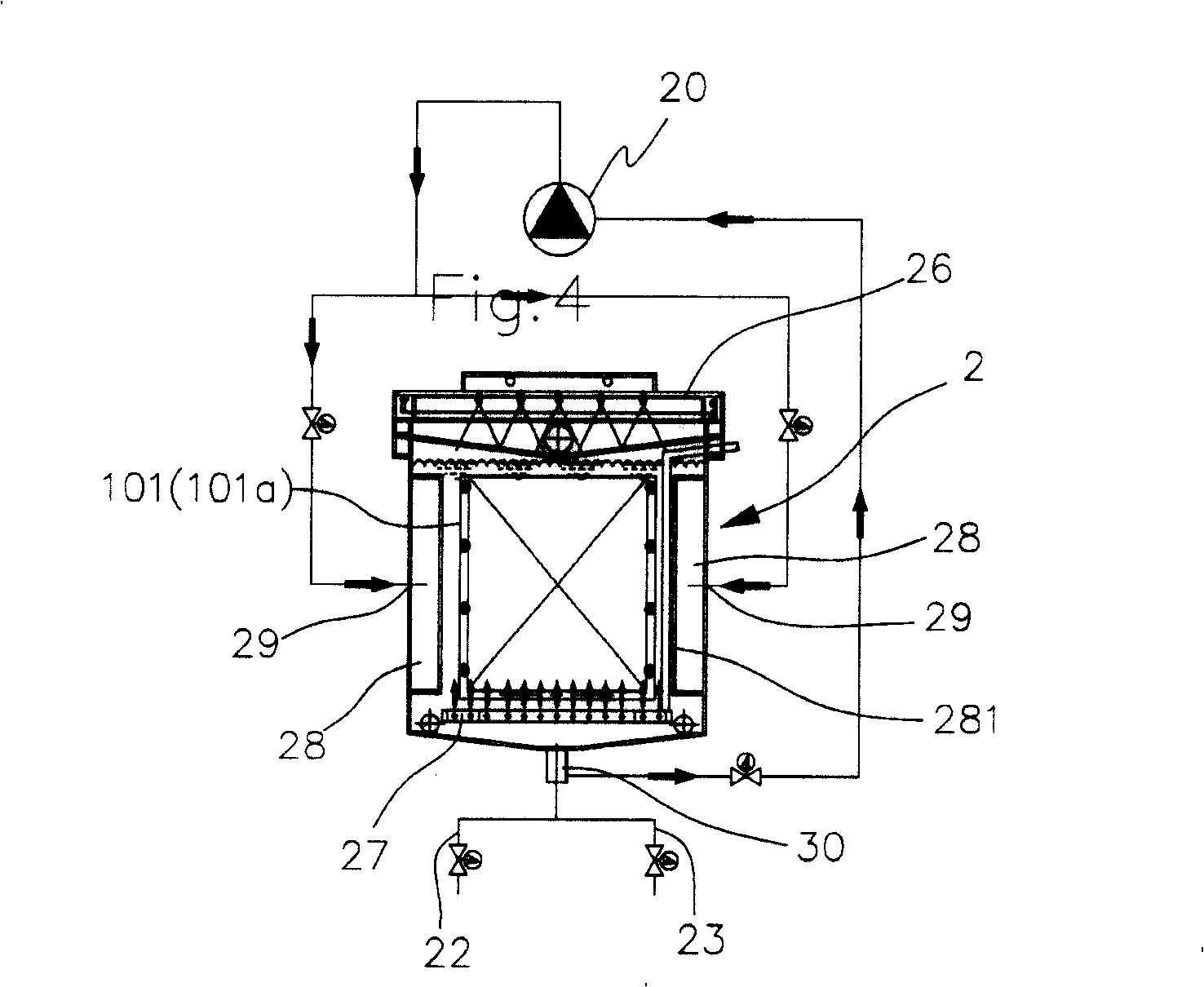

Device for etching TFT LCD glass substrate and etching method thereof

ActiveCN101255012AReduce etch timeSimplify the etch processSemiconductor/solid-state device manufacturingEtchingEngineering

The invention discloses an etching device for a TFT LCD glass substrate and etching method thereof, wherein, the device comprises two bearing boxes, two etching washing grooves, a washing groove and a drying groove; the method is that one of the bearing boxes with a plurality of TFT LCD glass substrates are etched and first-step washed in the etching washing groove; then the bearing box is transferred to the washing groove to be second-step washed; meanwhile, the other bearing box with a plurality of TFT LCD glass substrates are arranged in the other etching washing groove to be etched and first-step washed; the washed TFT LCD glass substrates in the first bearing box are placed in the drying groove to be dried, meanwhile, the other bearing box is transferred to the washing groove to have a plurality of TFT LCD glass substrates second-step washed; then the washed TFT LCD glass substrates in the second bearing box are dried in the drying groove; therefore, the etching of a plurality of TFT LCD glass substrates in the two bearing boxes can be simultaneously finished in one processing, thereby achieving the effect of shortening the etching time and simplifying the etching process.

Owner:DALUX TECH

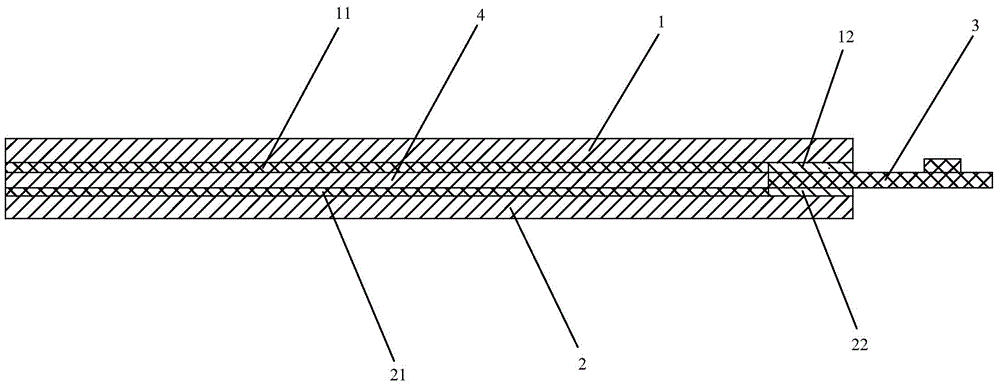

Capacitive touch screen and preparation method

InactiveCN104808871AReduce thicknessGood etchingInput/output processes for data processingLaser etchingFlexible circuits

The invention discloses a capacitive touch screen and a preparation method. The capacitive touch screen comprises a glass panel layer, a film layer and a flexible circuit board, wherein the glass panel layer and the film layer are sequentially laminated from top to bottom, the lower surface of the glass panel layer is provided with an induction electrode layer and an induction electrode outgoing line layer, and the induction electrode outgoing line layer is an ITO (Indium Tin Oxide) induction electrode layer; the upper surface of the film layer is provided with a drive electrode layer and a drive electrode outgoing line layer, the surface of glass panel layer provided with the induction electrode layer and the surface of the film layer provided with the drive electrode layer are mutually glued through a transparent insulating glue layer, and the induction electrode outgoing line layer and the drive electrode outgoing line layer are connected in such a way that the front sides and reverse sides are bonded through the flexible circuit board. According to the capacitive touch screen provided by the invention, the induction electrode layer and the drive electrode layer can be etched by a laser etching technology, and the relevant parameters can be regulated to etch a conducting film and relevant leads better, therefore the etching process can be simplified, the process yield can be greatly improved, and the production cost can be reduced.

Owner:FUJIAN HUIRUI TOUCH TECH

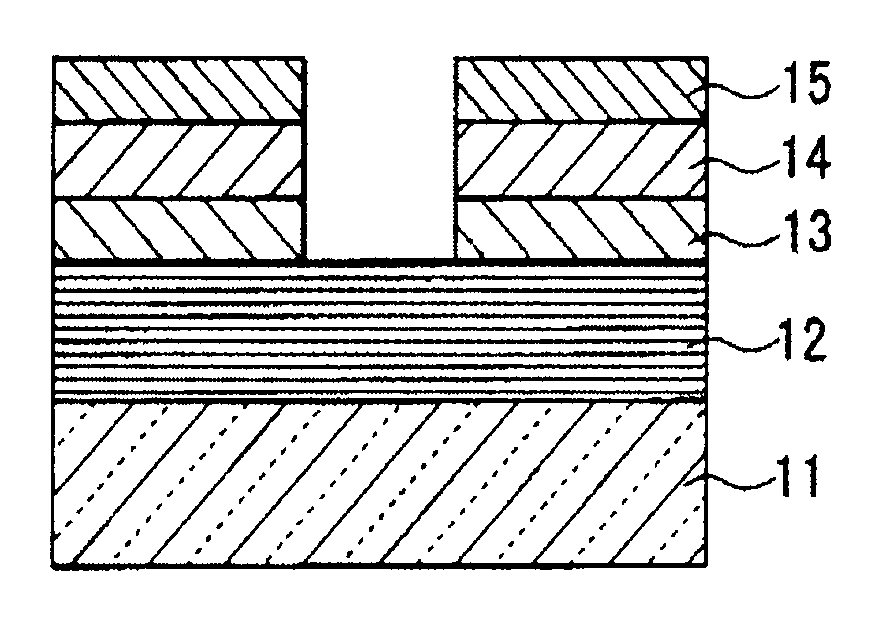

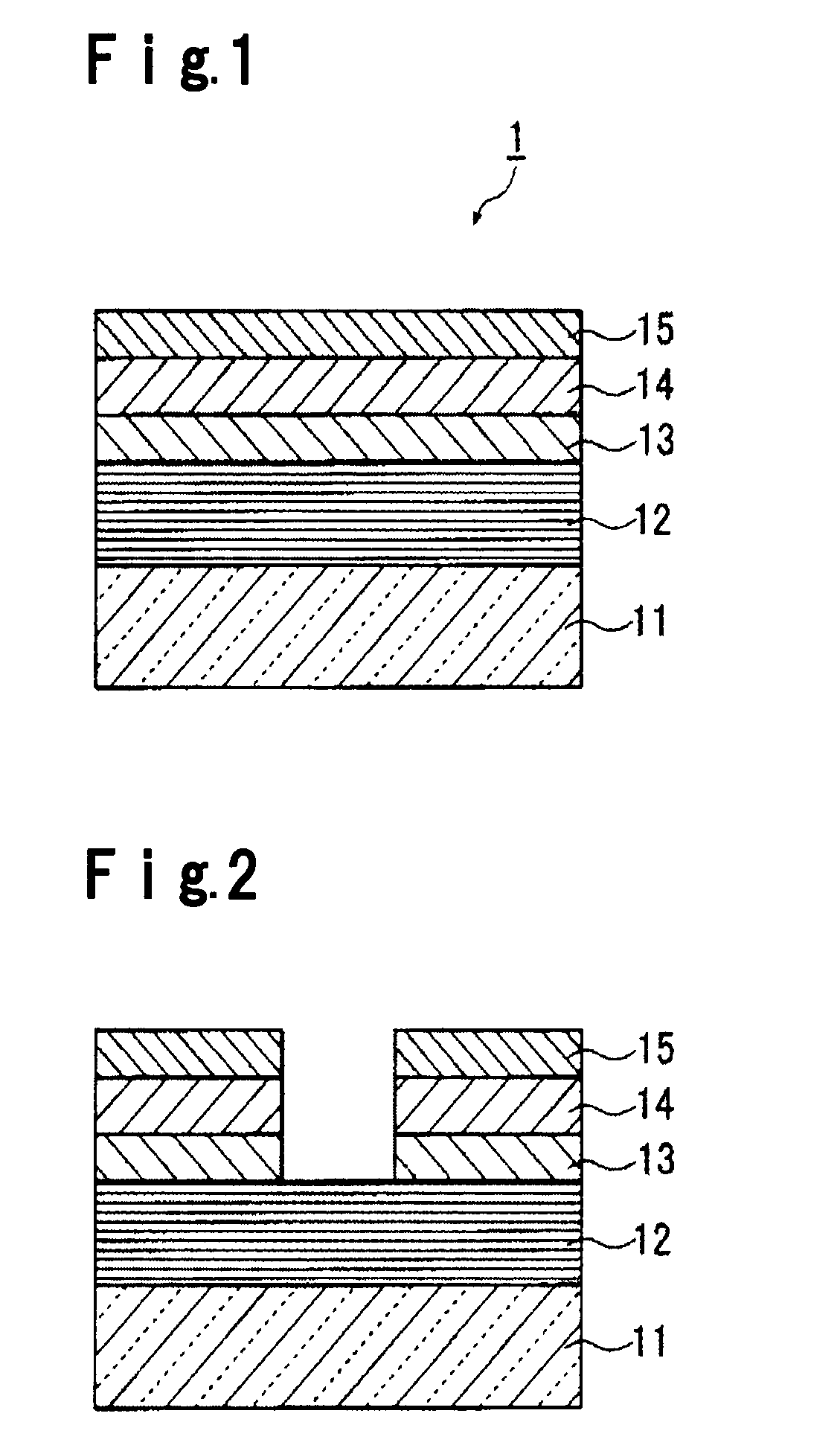

Reflective mask blank for EUV lithography

InactiveUS8137872B2Increase etch rateSimplify the etch processNanoinformaticsPhotomechanical apparatusLithographic artistNitrogen

To provide a reflective mask blank for EUV lithography having a low reflective layer having a low reflectance in the wavelength region of EUV light and an inspection light for a mask pattern, particularly having low reflection properties in the entire wavelength region (190 to 260 nm) of an inspection light for a mask pattern, and having a high etching rate in chlorine type gas etching. A reflective mask blank for EUV lithography, comprising a substrate, and a reflective layer to reflect EUV light, an absorber layer to absorb EUV light and a low reflective layer to an inspection light (wavelength:190 nm to 260 nm) for a mask pattern, formed in this order over the substrate, wherein the low reflective layer contains silicon (Si) and nitrogen (N) in a total content of at least 95 at %, has a Si content of from 5 to 80 at %, and a N content of from 15 to 90 at %.

Owner:ASAHI GLASS CO LTD

Etching solution composition for metal oxide layer containing gallium

InactiveCN102977889AFast and Uniform Wet EtchingSimplify the etch processSemiconductor/solid-state device manufacturingSurface treatment compositionsIndiumEtching

The invention discloses an etching solution composition for metal oxide layer containing gallium. The composition comprises: 5%-20% of persulfate in weight percentage, 1%-15% of mineral acid or mineral acid salt in weight percentage, and residual water to form the composition, wet etching to the metal oxide layer is uniformly carried out in a high etching speed, the metal oxide layer comprises indium oxide, zinc oxide or mixture and gallium or gallium oxide, thereby simplifying etching process and improving production efficiency.

Owner:DONGWOO FINE CHEM CO LTD

Water-soluble solid etching reagent for anti-dazzle high-aluminum glass, and etching process for high-aluminum glass

PendingCN111908800AReduce usageGood etchingSurface treatment compositionsHydrogen fluorideOrganic solvent

The invention provides a water-soluble solid etching reagent for anti-dazzle high-aluminum glass, and an etching process for the high-aluminum glass. The solid etching reagent comprises the followingraw materials by weight: 15-45 parts of ammonium bifluoride, 20-60 parts of citric acid, 6-15 parts of ammonium sulfate, 2-14 parts of potassium bifluoride or potassium sulfate, 1-10 parts of titaniumdioxide, and 5-50 parts of a thickener. The solid etching reagent disclosed by the invention can be dissolved in water, so strong acid and toxic organic solvents are not used; the high-alumina glasscan be well etched under the condition of normal temperature; and the prepared finished anti-dazzle high-alumina glass product can generate a good anti-dazzle effect.

Owner:海南海控特玻科技有限公司

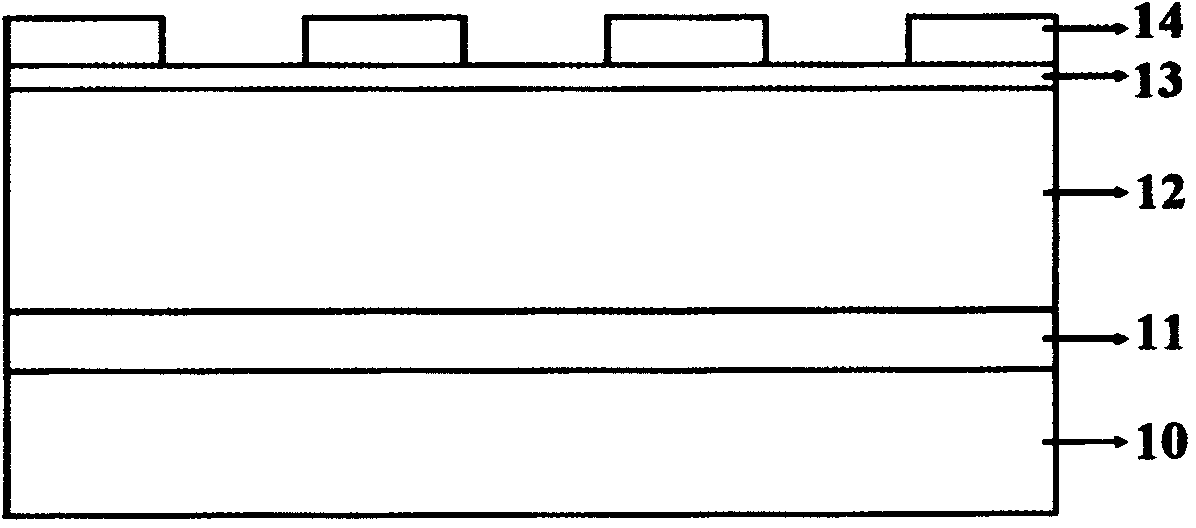

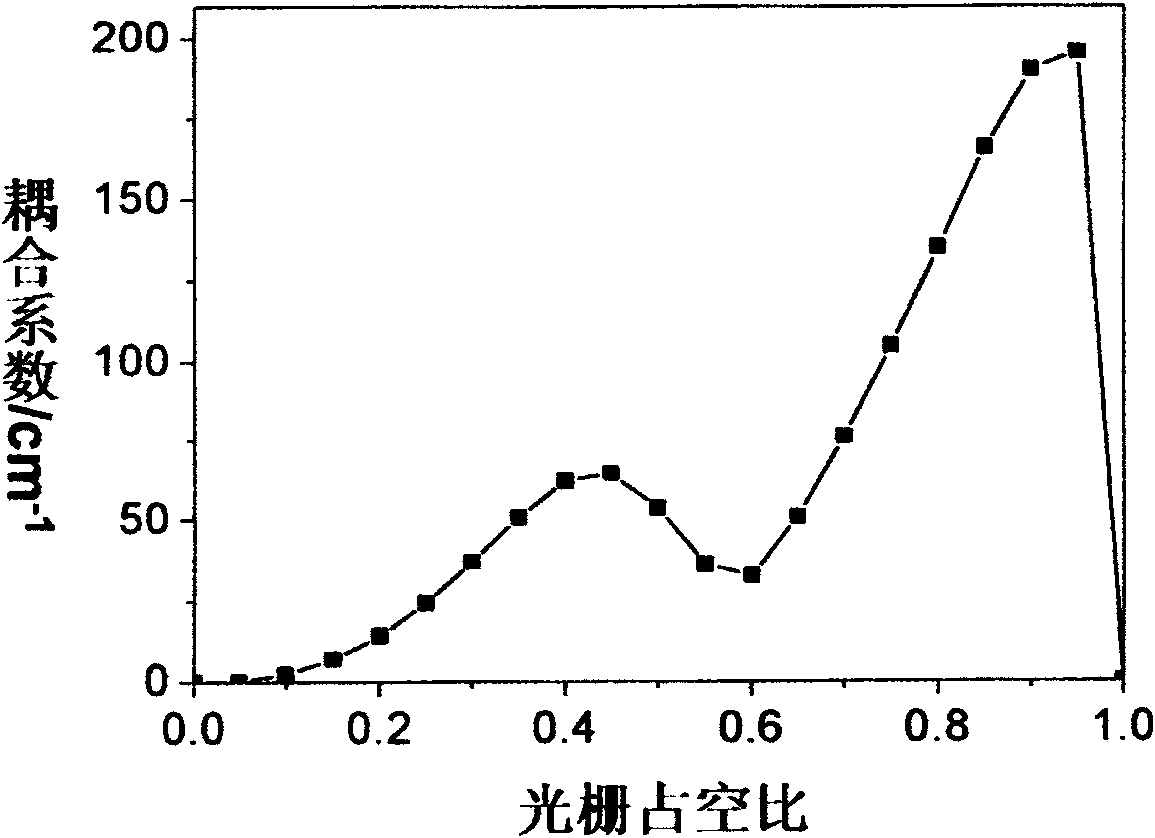

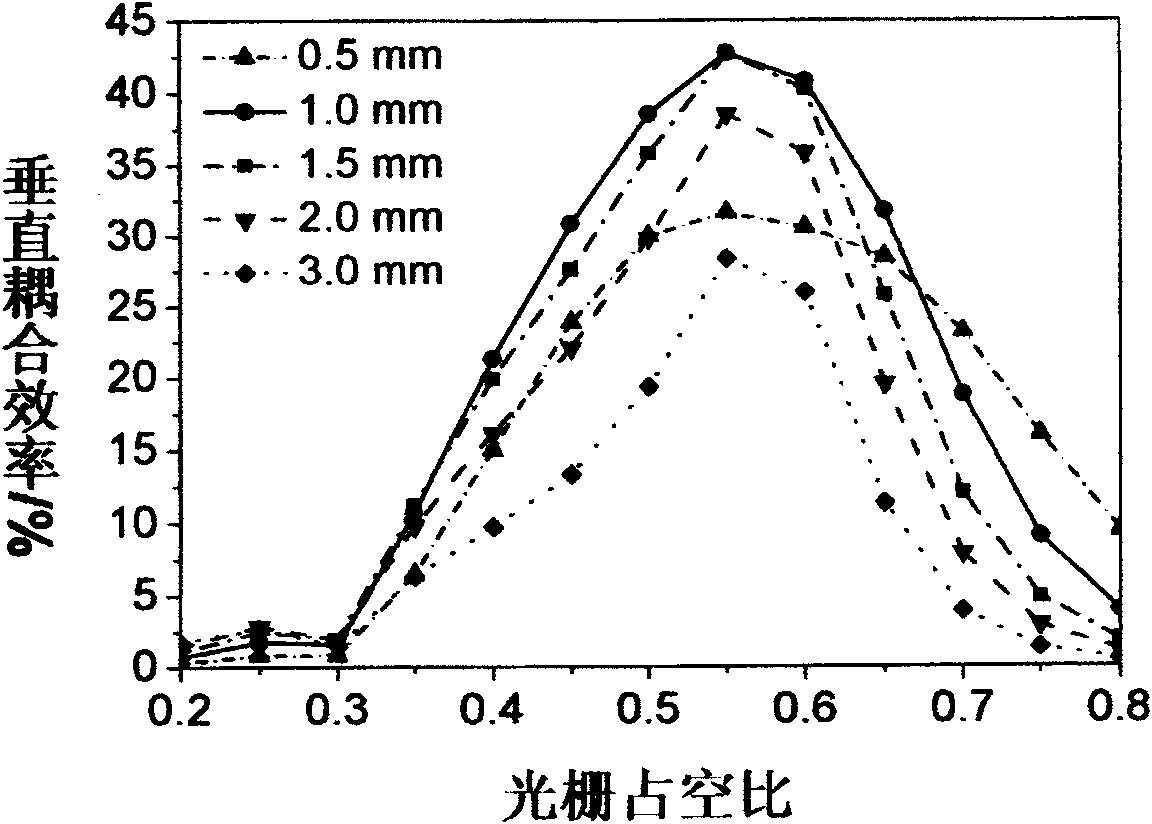

Vertical launching quantum cascade laser structure

InactiveCN101847828APromote growthIncrease overlapLaser detailsSemiconductor lasersContact layerQuantum cascade laser

The invention provides a vertical launching quantum cascade laser structure comprising a substrate and a metal grating layer, wherein a waveguide layer, an active layer and a contact layer sequentially grow on the substrate; and the metal grating layer is positioned on the contact layer and has a secondary Bragg period.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

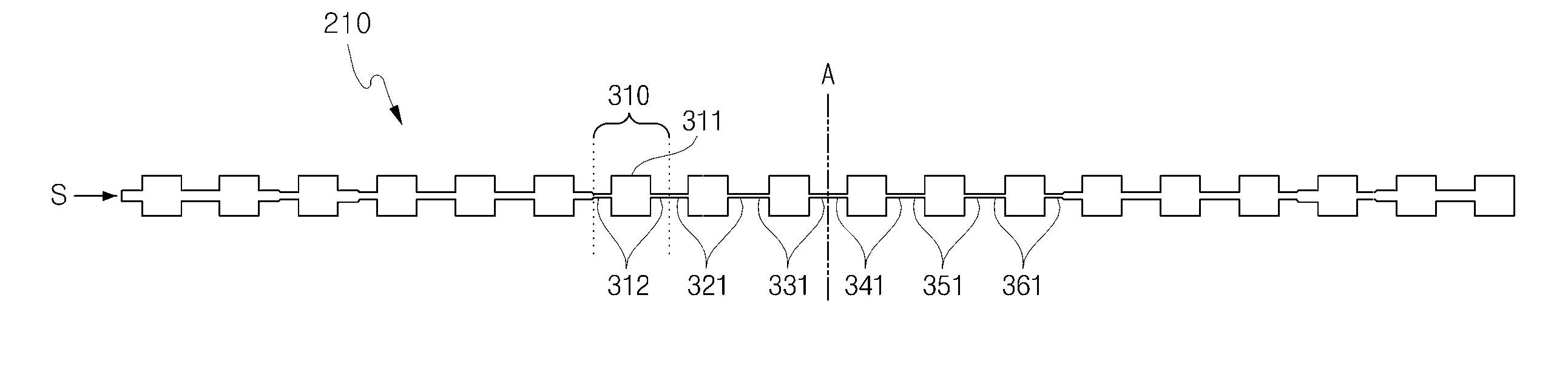

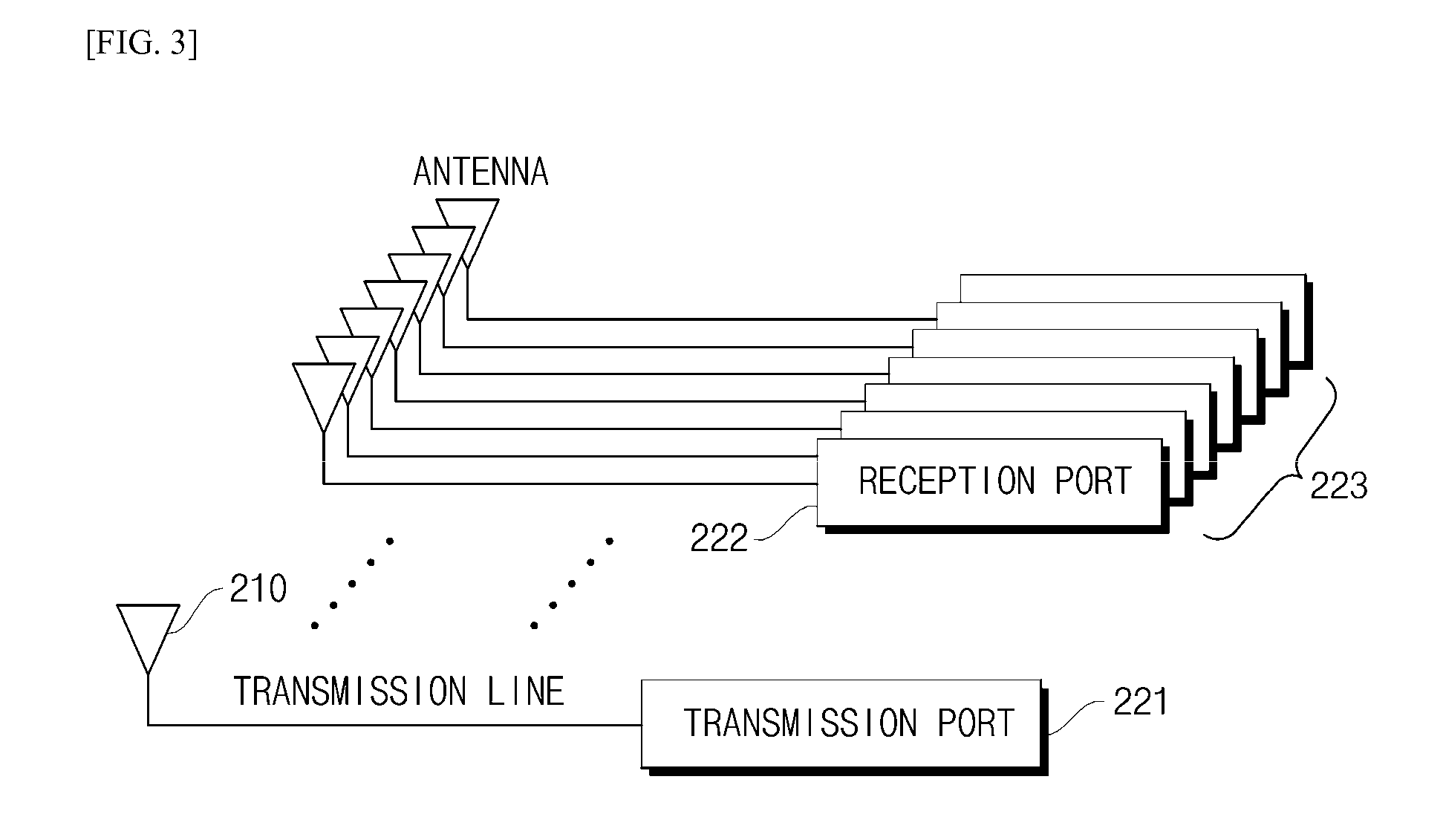

Patch array antenna and apparatus for transmitting and receiving radar signal including the same

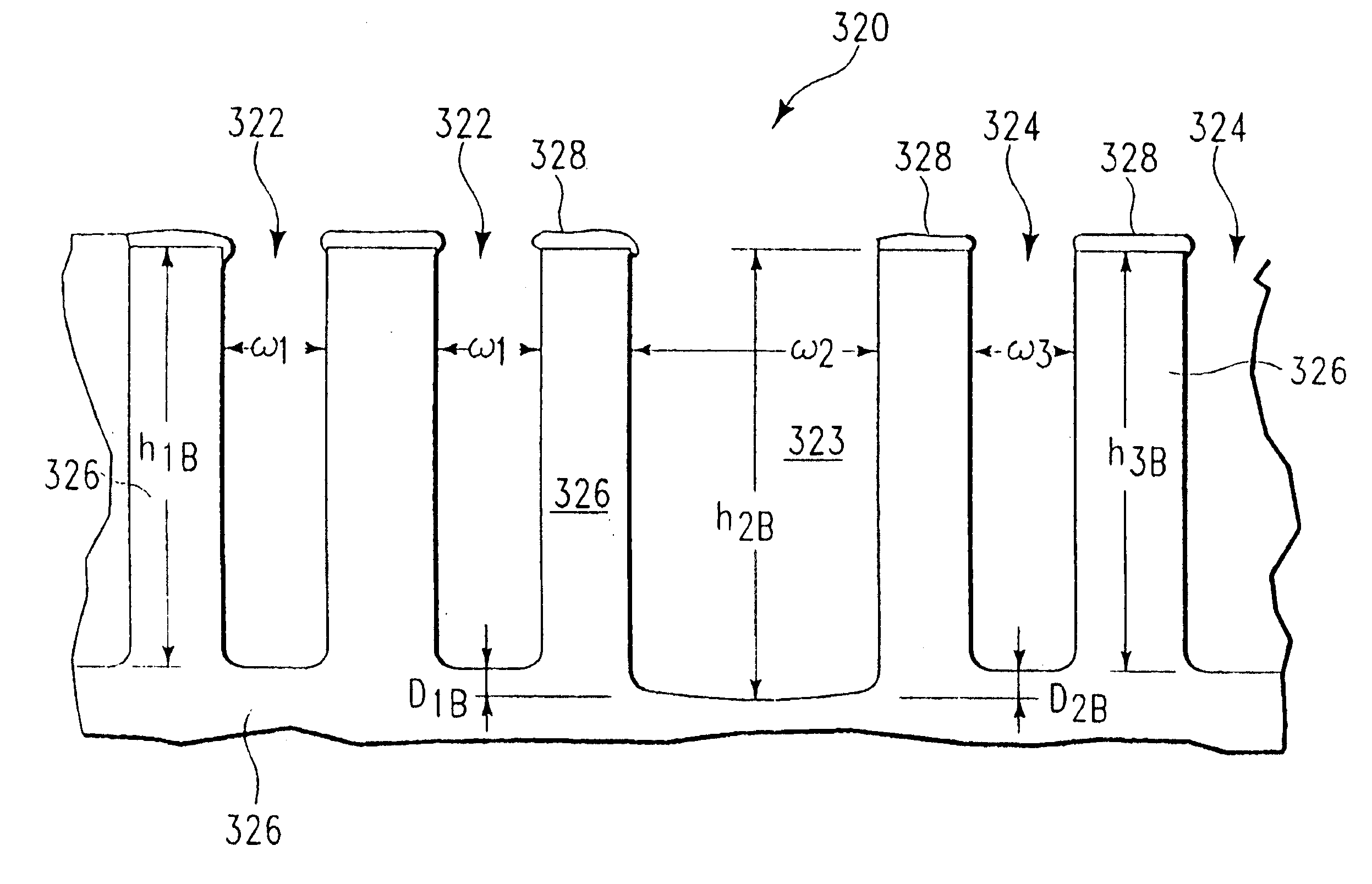

InactiveUS20150349412A1Simplify the etch processReduce component countParticular array feeding systemsAntenna adaptation in movable bodiesVIT signalsFeed line

The present invention suggest a patch array antenna which secures a side lobe level by changing a width of a feeder without changing a radiator and a radar signal transmitting and receiving apparatus including the same. The present invention provides a patch array antenna, including: a first unit element which includes a first patch which creates a predetermined radiation pattern and first feeders which are formed at both sides of the first patch and have the same width; and a second unit element is adjacent to the first unit element and includes a second patch which creates a radiation pattern and second feeders which are formed at both sides of the second patch and have the same width in which the width of the second feeders is different from the width of the first feeders.

Owner:HYUNDAI MOBIS CO LTD

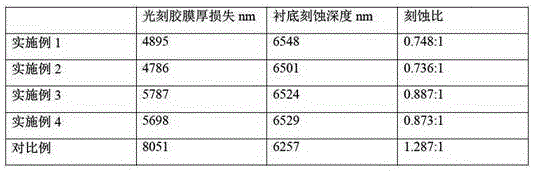

Method for preparing semiconductor device

ActiveCN104952706AGood etchingImprove process marginSemiconductor/solid-state device manufacturingPower semiconductor deviceSemiconductor

The invention relates to a method for preparing a semiconductor device. The method comprises the steps of providing a semiconductor substrate on which a self-aligning double-pattern mask laminate is formed, wherein the self-aligning double-pattern mask laminate comprises a hard mask layer, a stopping layer and a virtual core material layer which are successively formed; patterning the virtual core material layer for forming a plurality of insulated virtual cores; forming a gap wall on the sidewall of the virtual core; eliminating the virtual cores and reserving the gap wall; etching the stopping layer and the hard mask layer in a manner that the gap wall is used as the mask, thereby transferring the pattern to the hard mask layer; and etching partial of the semiconductor substrate in a manner that the hard mask layer is used as the mask, thereby forming a plurality of fins in the semiconductor substrate. The method of the invention is advantageous in that a state-of-the-art fin structure is prepared through the simple self-aligning mask laminate and a simple technological process.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Phenolic positive photoresist with etching resistance

ActiveCN106502052AIncreased etch resistanceAct as a hindrance to etchingPhotomechanical apparatusChemical reactionOxygen

The invention discloses a phenolic positive photoresist with etching resistance. The phenolic positive photoresist comprises the following main components: phenolic resin, a photosensitive compound and a solvent. The phenolic positive photoresist is characterized by also containing 0.5-30wt% of metal compound capable of being dissolved into the solvent. According to the photoresist disclosed by the invention, in a dry etching process after photoetching, physical bombardment and chemical reaction double etching is carried out on adhesive film patterns by plasma, volatile reactants formed by carbon and oxygen components in an adhesive layer are removed while the metal components are slowly deposited, and a new metal protection layer is formed on the surface of an adhesive film, thereby achieving the target of improving the etching resistance of the photoresist. The photoresist disclosed by the invention can be widely used for the field of production of microelectronic components requiring dry etching.

Owner:SUNTIFIC MATERIALS WEIFANG LTD

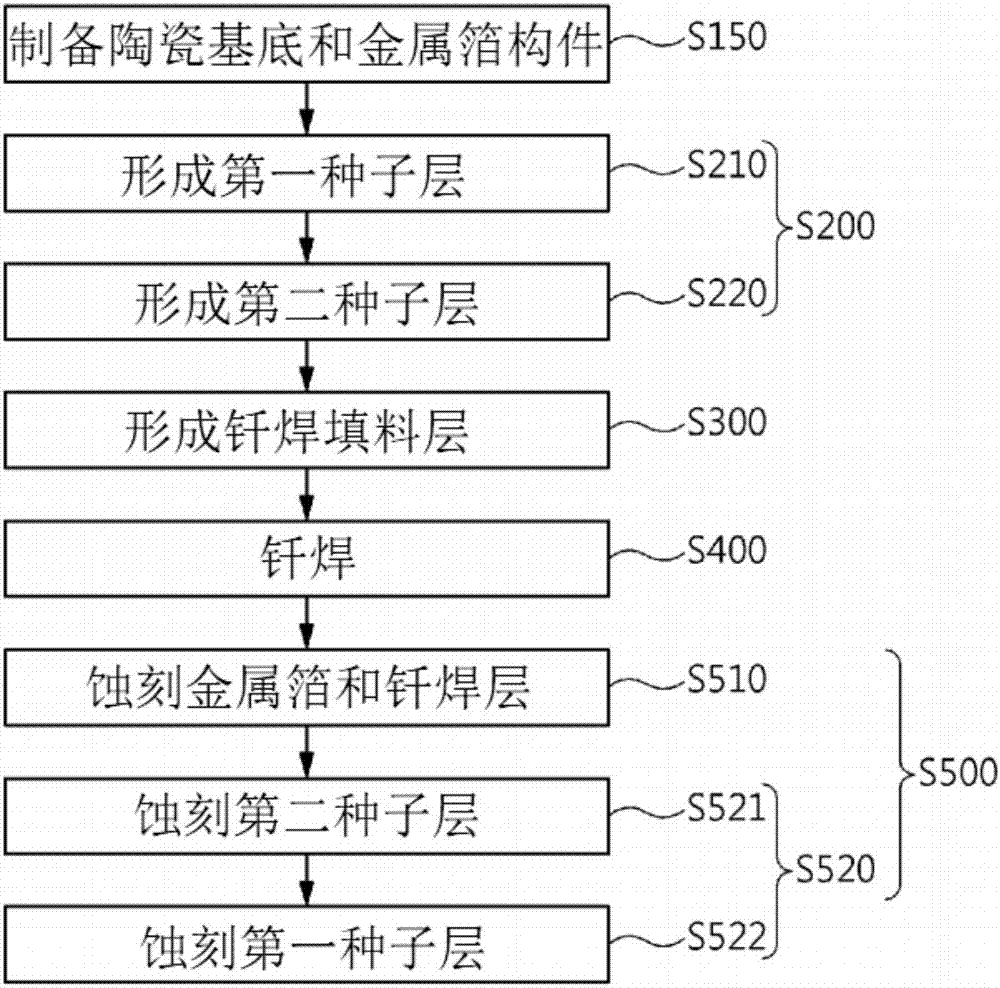

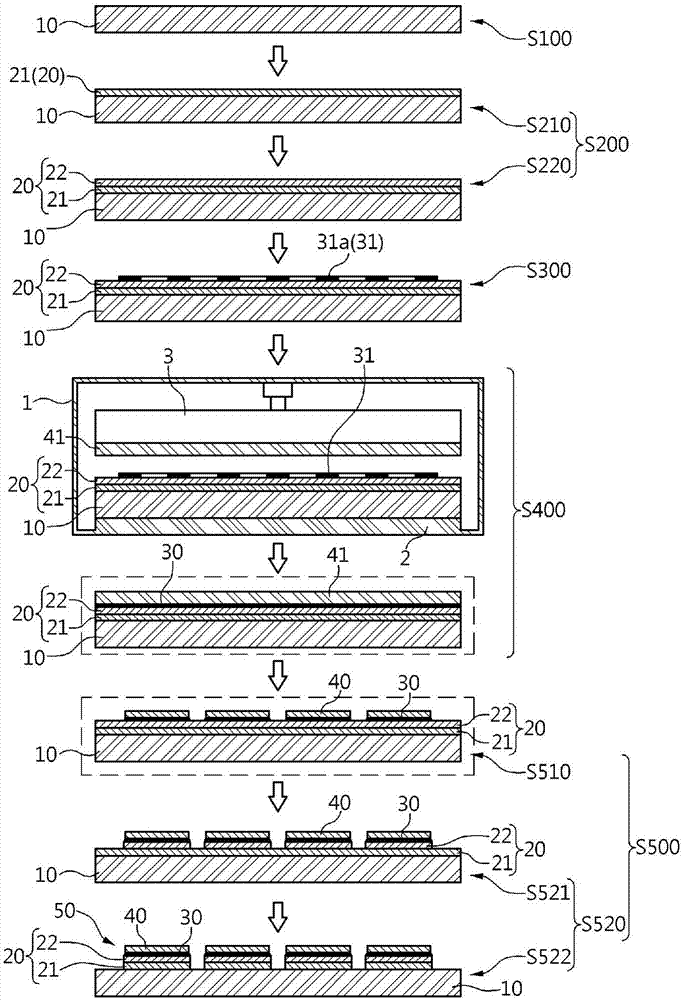

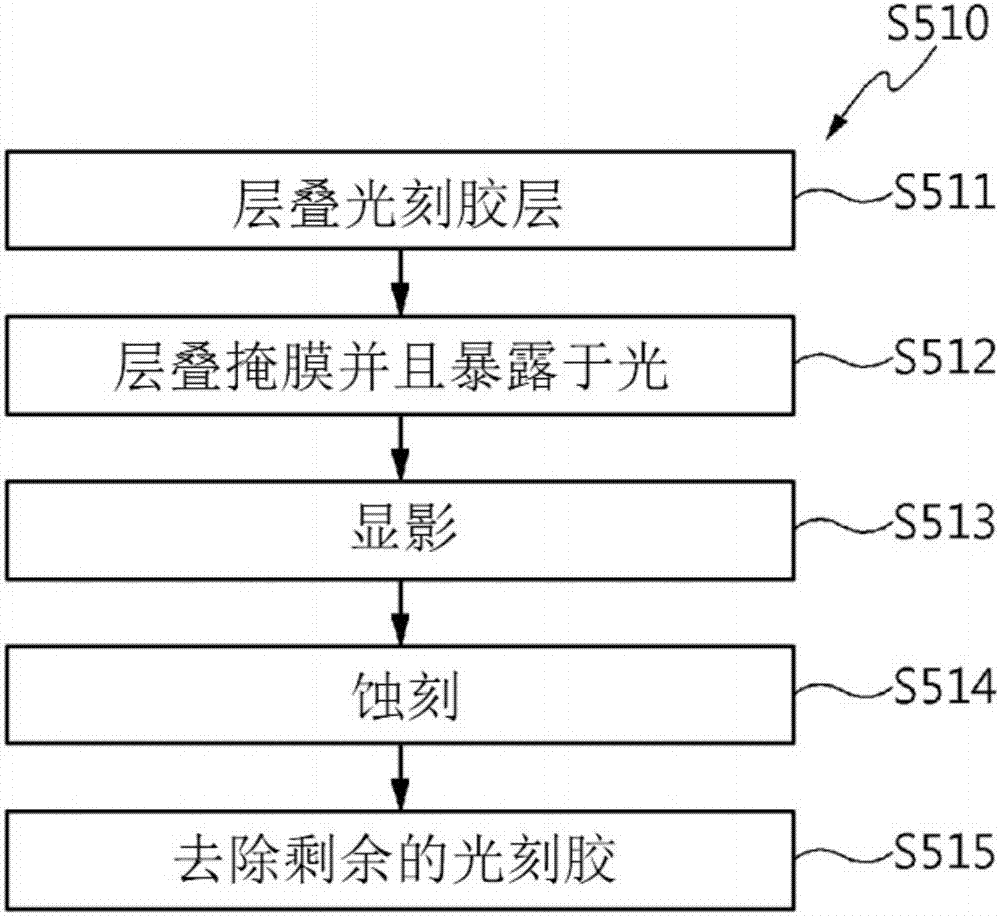

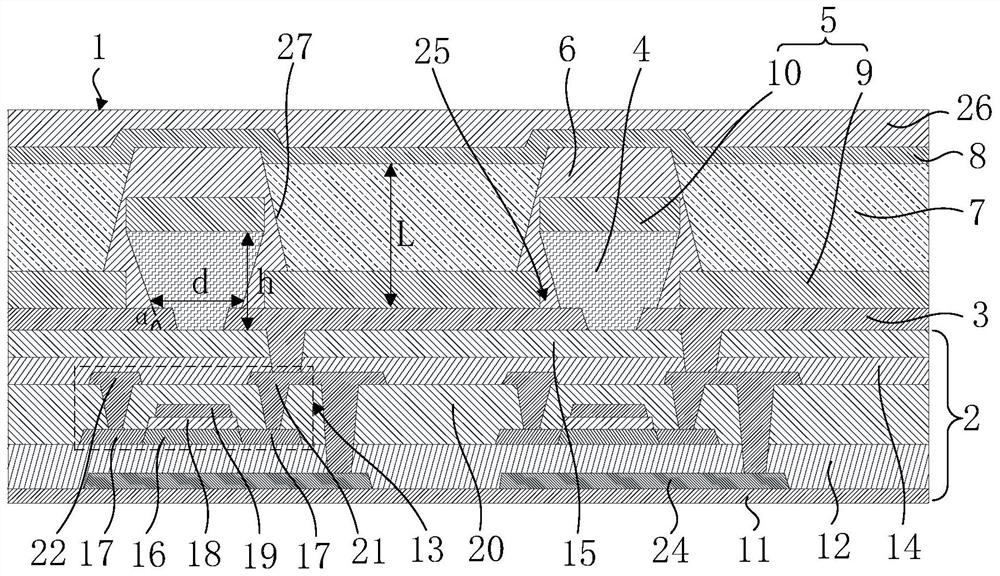

Ceramic substrate manufacturing method and ceramic substrate manufactured thereby

ActiveCN107889559AImprove adhesionReduce manufacturing costSemiconductor/solid-state device detailsPrinted circuit aspectsMetal foilMetallurgy

Owner:AMOSENSE

Display panel and manufacturing method thereof

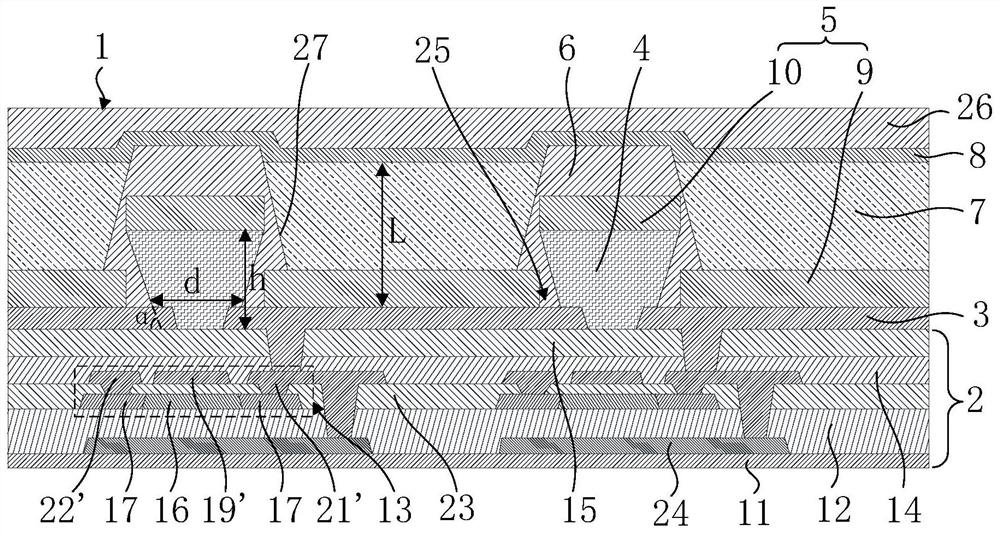

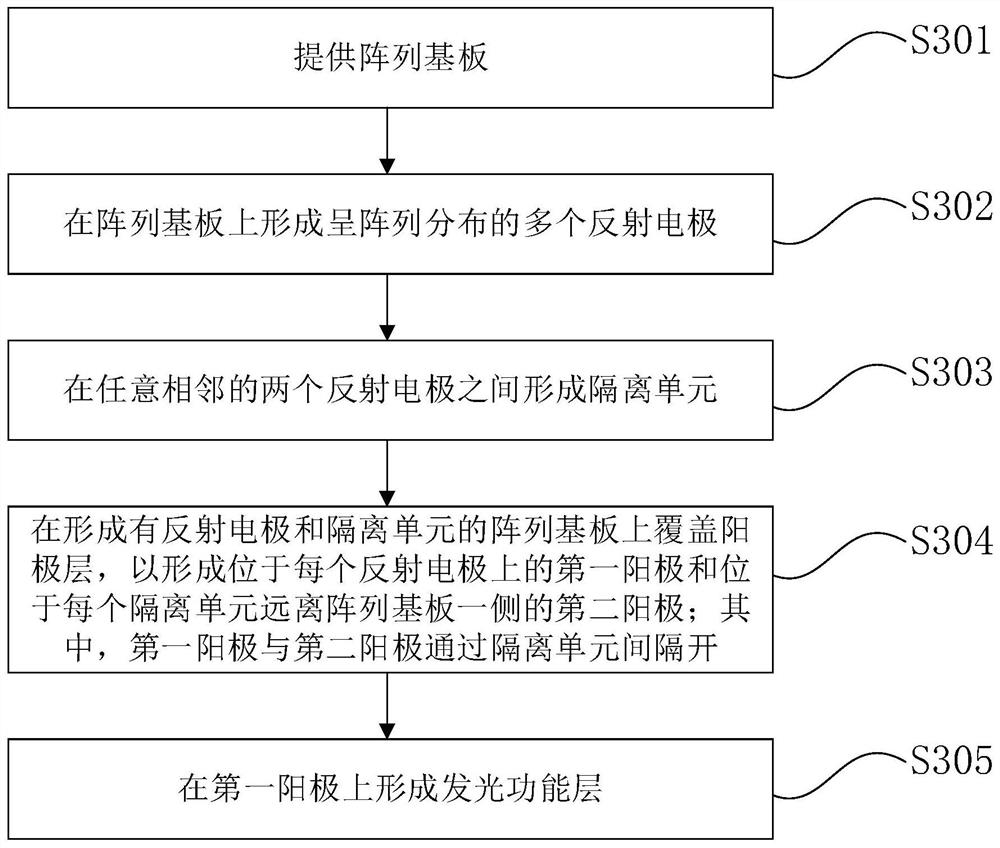

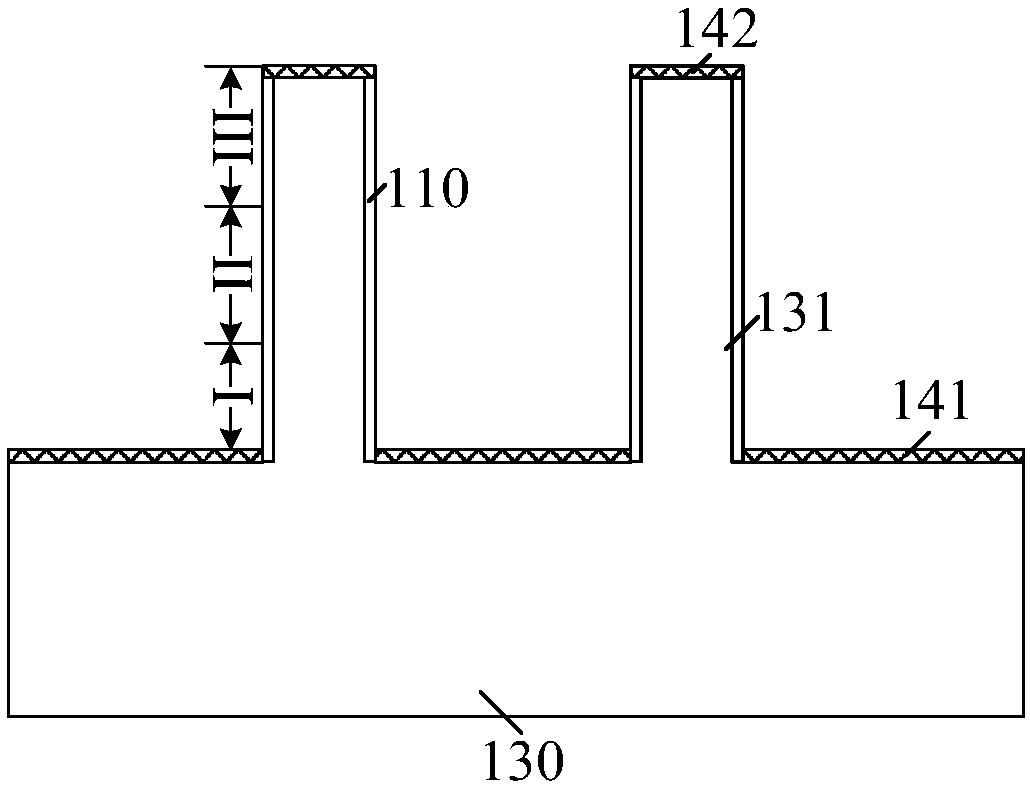

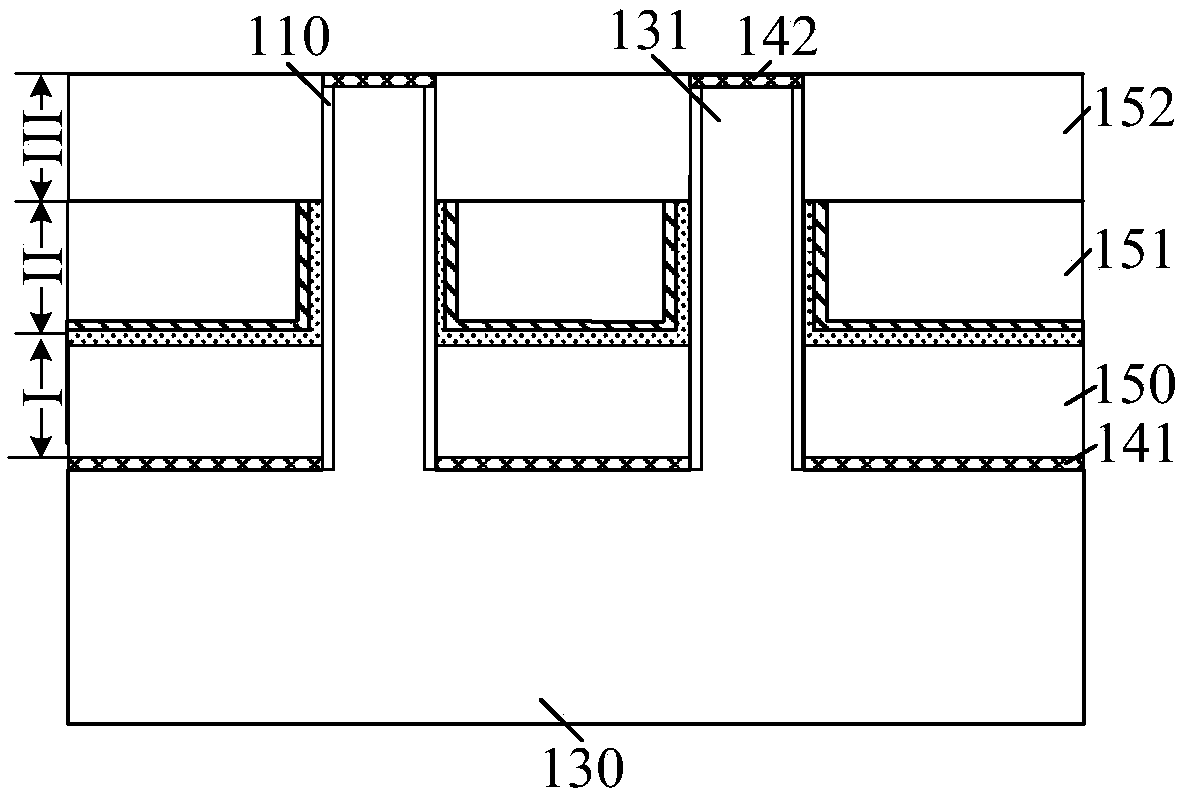

InactiveCN111900194AImprove overall lifespanGood for mass productionSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringMaterials science

The invention discloses a display panel and a manufacturing method thereof. The display panel comprises an array substrate, a plurality of reflecting electrodes, a plurality of isolation units, an anode layer and a light-emitting function layer. The plurality of reflecting electrodes are positioned on the array substrate and are distributed in an array manner; one isolation unit is arranged between any two adjacent reflecting electrodes; the anode layer comprises a first anode located on each reflecting electrode and a second anode located on the side, away from the array substrate, of each isolation unit, and each first anode and the adjacent second anode are spaced through the corresponding isolation unit; and the light-emitting function layer is located on the first anodes. According tothe invention, two adjacent first anodes can be naturally disconnected through the isolation unit, and the cavity length of the device can be adjusted through the thickness of the first anodes.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Semiconductor structure and formation method thereof

ActiveCN109979880AHighly integratedIt is not easy to increase the threshold voltageTransistorSolid-state devicesEngineeringSemiconductor structure

The present invention provides a semiconductor structure and a formation method thereof. The formation method of the semiconductor structure comprises the steps of: providing a substrate, wherein thesubstrate comprises fin columns, and each fin column comprises a bottom portion region, a channel region located on the bottom portion region and a top portion region located on the channel region; forming first isolation layers on the substrate, wherein the first isolation layers cover the bottom portion regions of the fin columns; forming first gate oxide layers and second gate oxide layers at the surfaces of the side walls of the channel regions of the fin columns, wherein the second gate oxide layers are located at the surfaces of the top portions of the first gate oxide layers, and the thicknesses of the first gate oxide layers and the second gate oxide layers are different; forming gate structures at the surfaces of the top portions of the first isolation layers, wherein the gate structures cover the first gate oxide layers and the second gate oxide layers; and forming second isolation layers at the surfaces of the top portions of the gate structures, wherein the second isolationlayers cover the side walls of the top portion regions of the fin columns. The formation method provided by the invention can improve the performances of the semiconductor structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

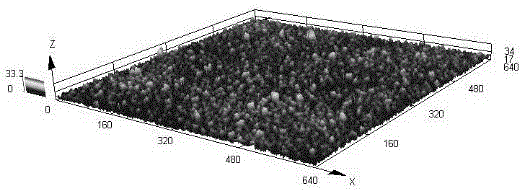

Metal-modified superhydrophobic material and preparation method thereof

ActiveCN106835083AImprove hydrophobicityHas hydrophobic propertiesLiquid/solution decomposition chemical coatingMetalNanotechnology

The invention discloses a metal-modified superhydrophobic material and a preparation method thereof, belongs to the field of preparation of superhydrophobic materials, and aims to solve the technical problems in environmentally-friendly, energy-saving and efficient preparation of the superhydrophobic material. The preparation method comprises the following steps: S1, preparing conical nano nickel by using a polylactic acid template; S2, impregnating the conical nano nickel in a gold ion-containing gold plating solution for replacement reaction; S3, carrying out cleaning and drying; S4, then impregnating the conical nano nickel in a hexadecyl mercaptan solution for complex reaction; S5, carrying out cleaning and drying, thus obtaining the metal-modified superhydrophobic material, wherein the metal-modified superhydrophobic material is sulfydryl-carried metal gold, and hill-shaped bulges are formed on the surface of the metal-modified superhydrophobic material. The metal-modified superhydrophobic material is prepared according to the preparation method; the metal-modified superhydrophobic material is the sulfydryl-carried metal gold, and the hill-shaped bulges are formed on the surface of the metal-modified superhydrophobic material.

Owner:QILU UNIV OF TECH

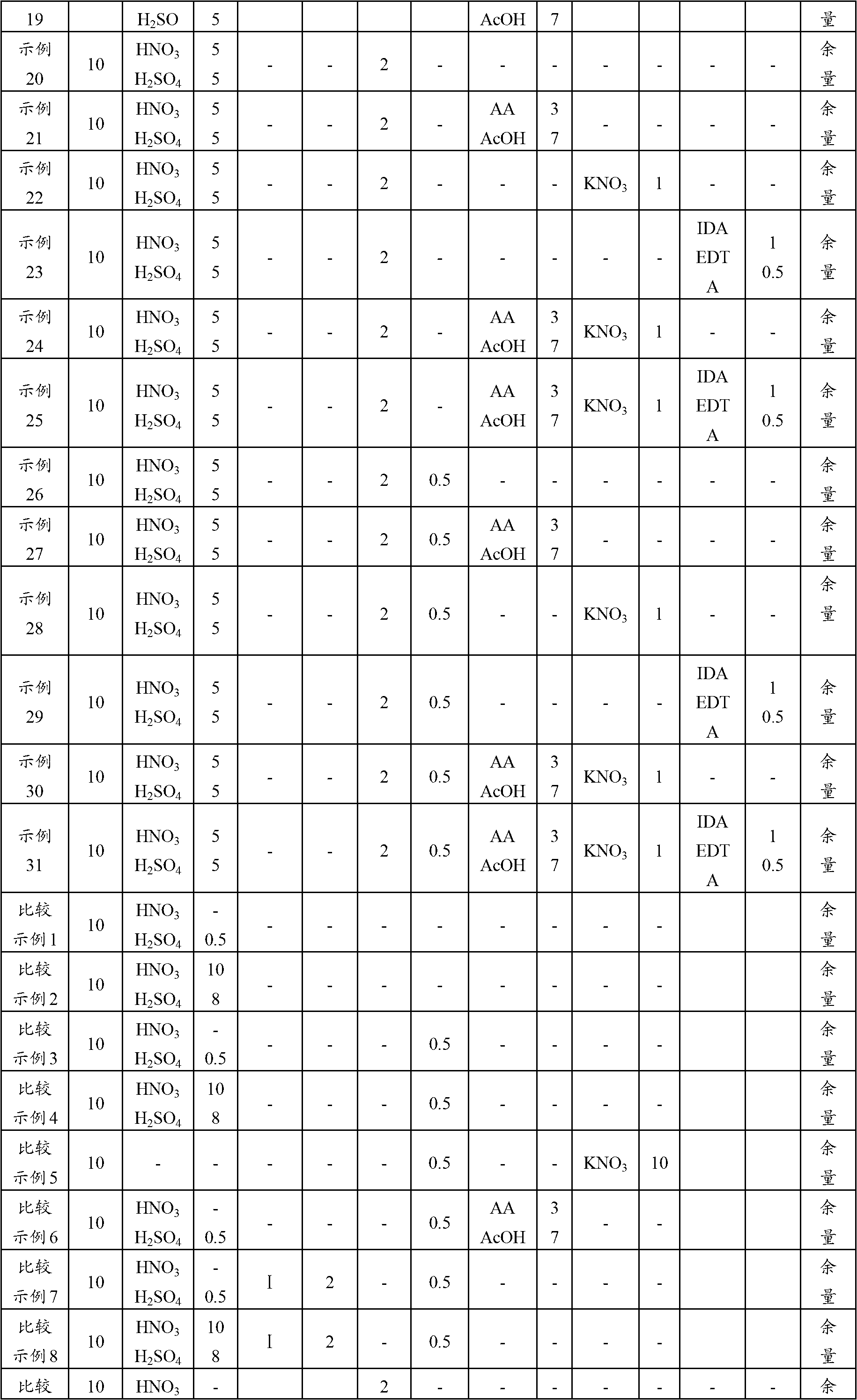

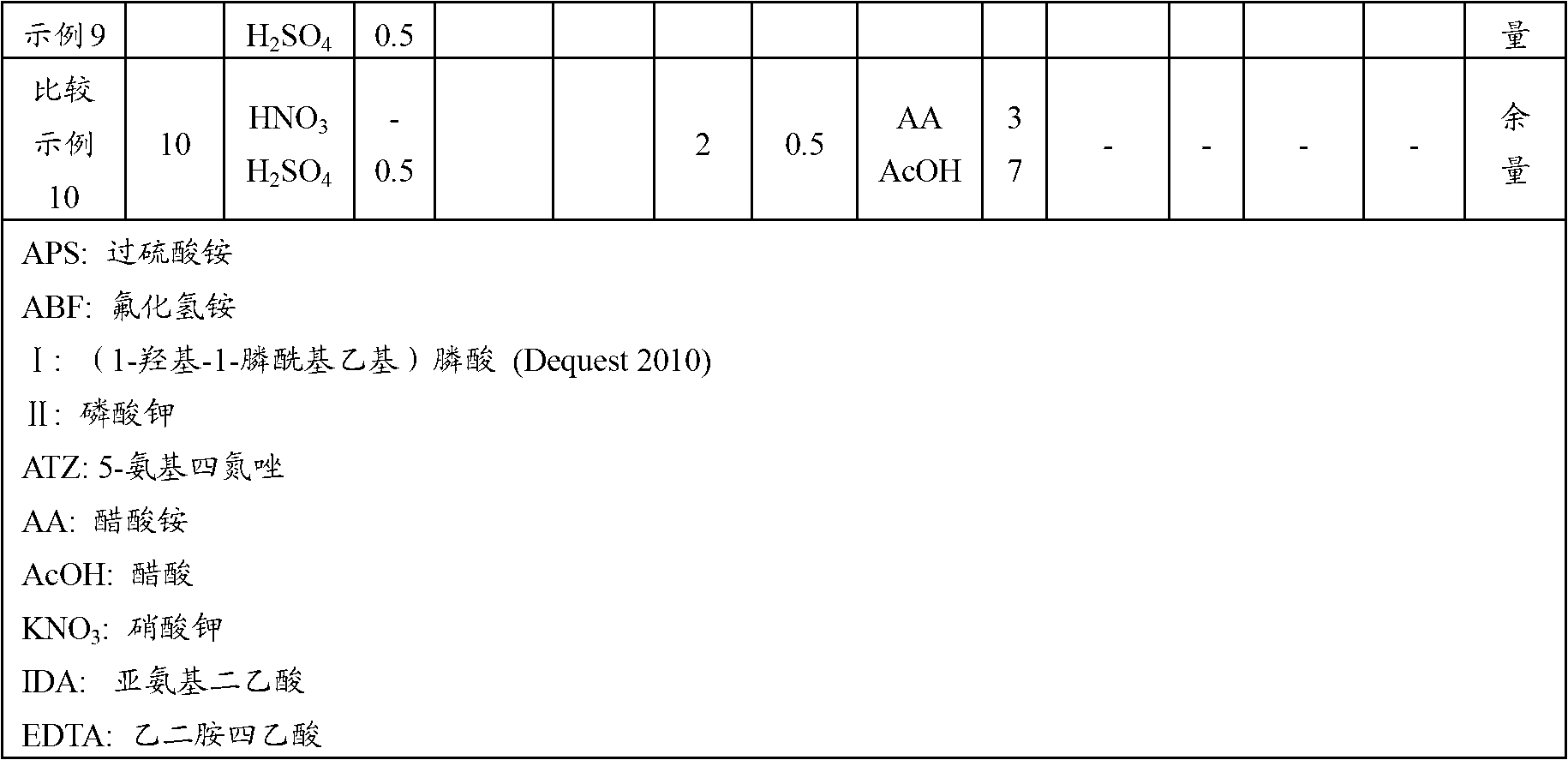

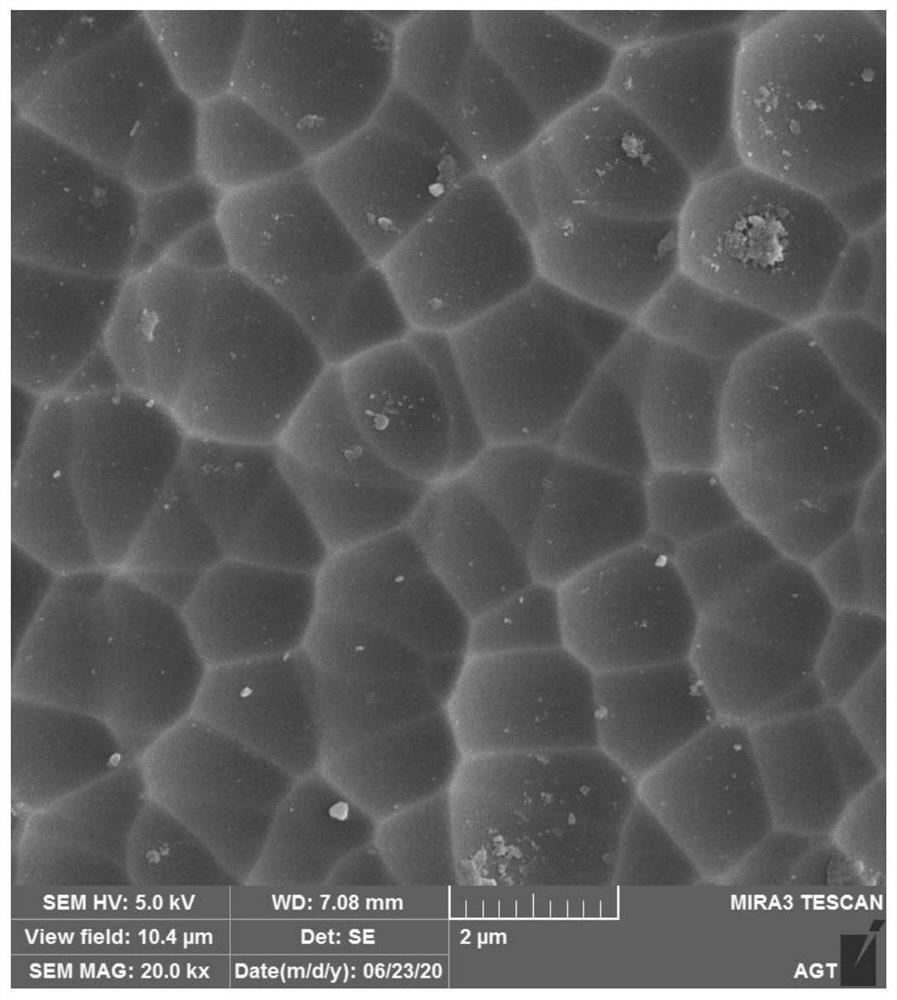

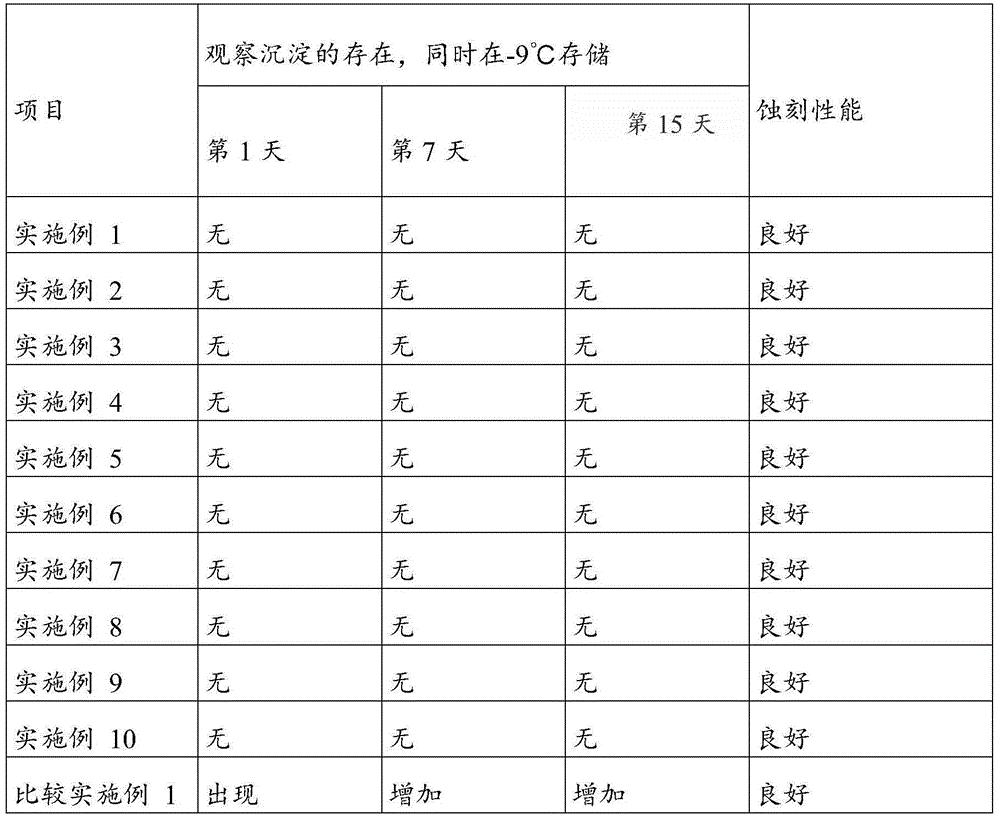

Etching solution composition for copper layer and titanium layer and method of preparing array substrate for liquid crystal display using same

InactiveCN105316679ASimplify the etch processHigh yieldSemiconductor/solid-state device manufacturingSurface treatment compositionsLiquid-crystal displayElectron donor

The invention provides an etching solution composition for a copper layer and a titanium layer and a method of preparing an array substrate for a liquid crystal display using the same. The etching solution composition for etching the copper layer and the titanium layer comprises sulfate, chlorine compounds, nantokite, cyclammonium compounds and electron donor compounds, so that the copper layer and the titanium layer are uniformly etched in batches at a high etching speed, and simultaneously precipitates difficult to dissolve are prevented.

Owner:DONGWOO FINE CHEM CO LTD

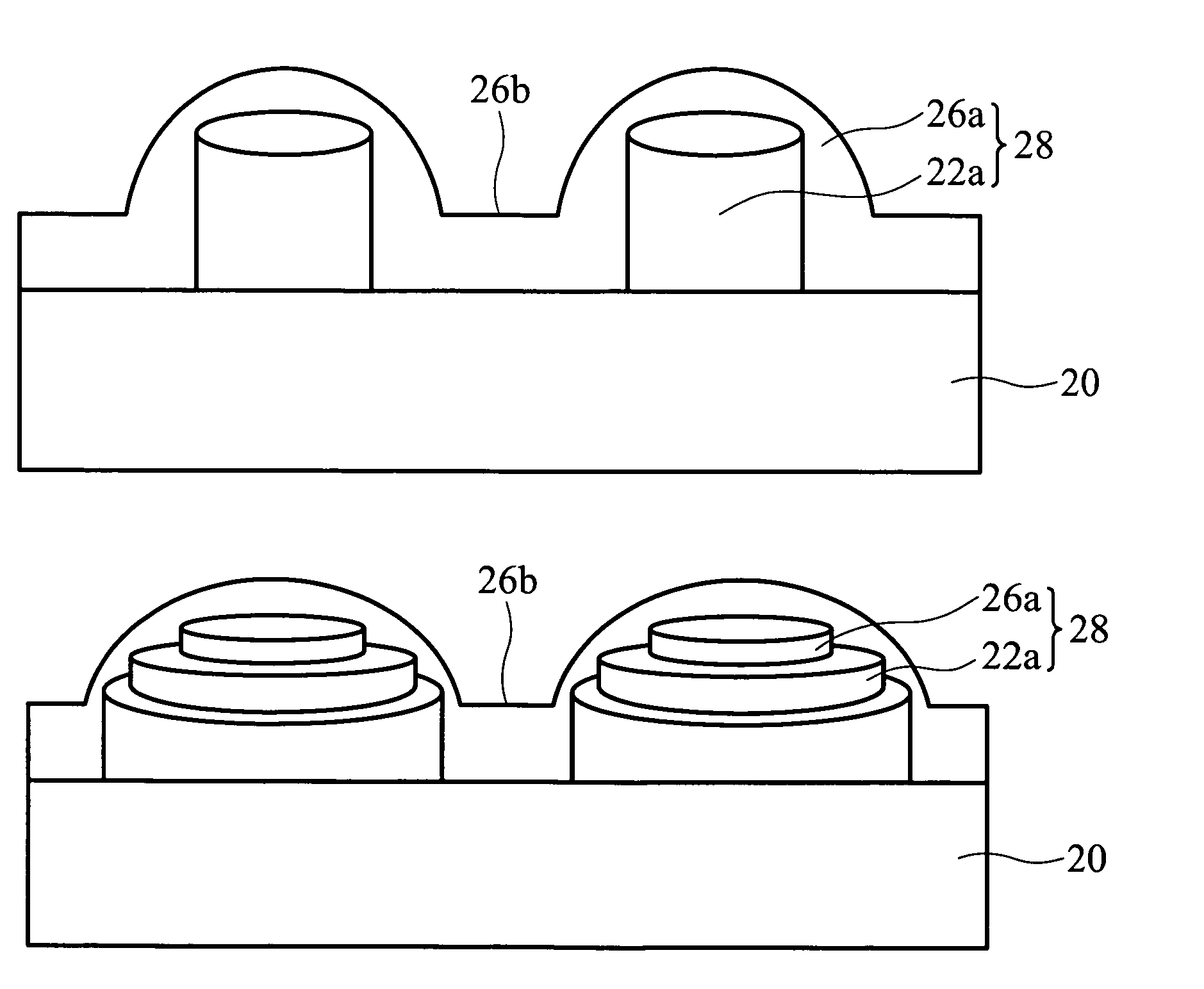

Hemi-spherical structure and method for fabricating the same

InactiveUS7368779B2Simplify the etch processTransistorSemiconductor/solid-state device detailsEngineeringSpherical form

Owner:TAIWAN SEMICON MFG CO LTD

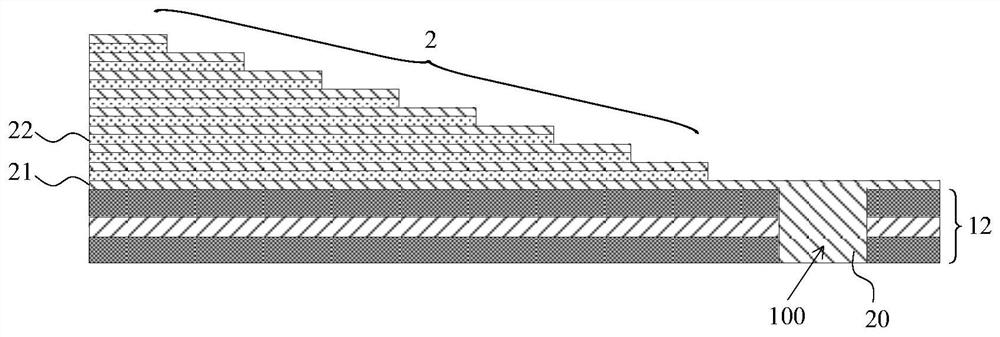

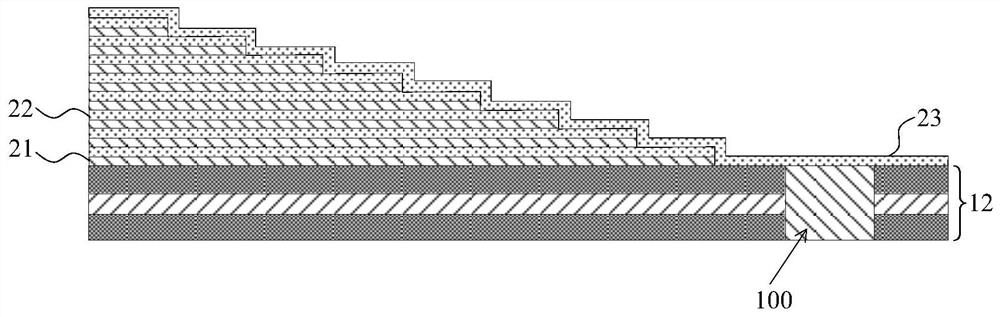

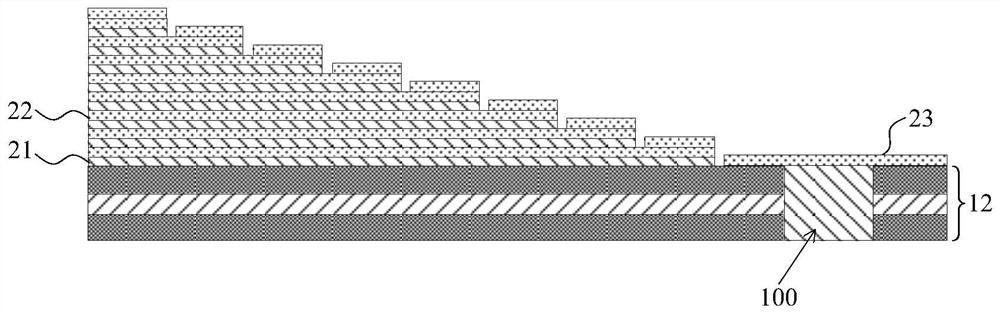

Manufacturing method of three-dimensional memory and three-dimensional memory

ActiveCN112185978ASimplify the etch processMask savingSolid-state devicesSemiconductor devicesEtchingEngineering

The invention provides a manufacturing method of a three-dimensional memory and the three-dimensional memory, in the manufacturing method of the three-dimensional memory provided by the invention, after an additional pseudo gate covering layer is deposited on a step structure, only the pseudo gate covering layer on the side wall of the step is removed, and the residual pseudo gate covering layer on a semiconductor layer is not removed, instead, the dielectric layer is directly formed on the residual dummy gate covering layer and is etched and filled to form the metal plug, so that the etchingprocess is simplified, the mask is saved, the production efficiency is improved, and the production cost is reduced; meanwhile, when the contact hole is formed by etching, the etching which originallypasses through the contact hole of the semiconductor layer is changed to stay on the dummy gate covering layer, so that a corresponding etching window is reduced, and the design flexibility of the three-dimensional memory is enhanced.

Owner:YANGTZE MEMORY TECH CO LTD

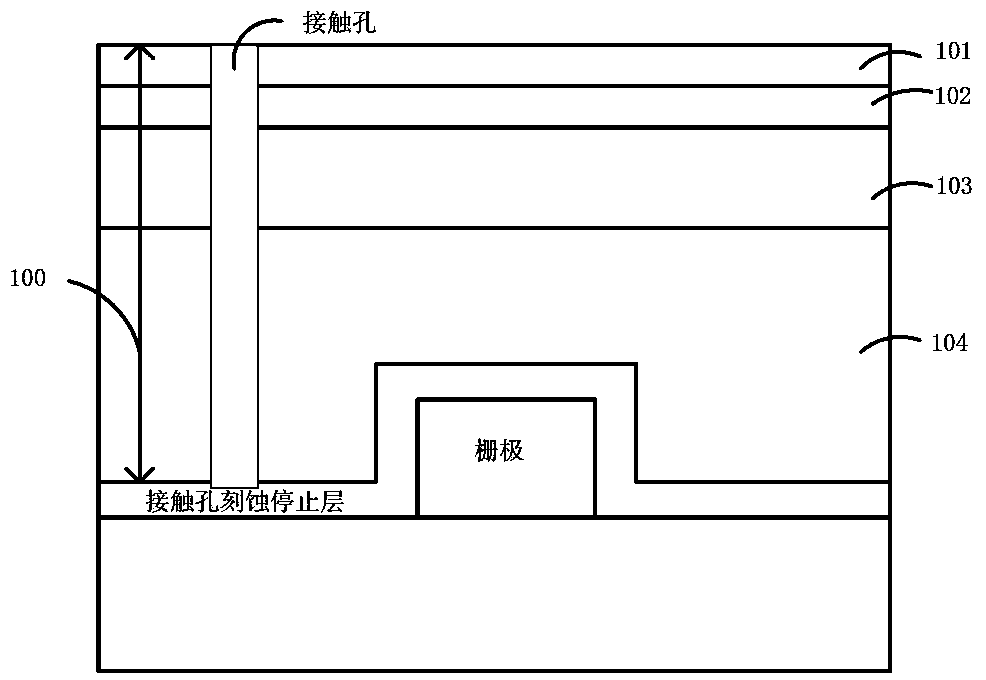

Manufacturing method of semiconductor device

ActiveCN104347485AAvoid lossAvoid etch stopSolid-state devicesSemiconductor/solid-state device manufacturingMetal silicideEngineering

The invention provides a manufacturing method of a semiconductor device. The manufacturing method comprises the following steps: providing a semiconductor substrate, wherein a gate electrode and a side wall structure are formed on the semiconductor substrate, and a self-aligned metal silicide is formed on a source / drain region on the two sides of the gate electrode and the side wall structure; forming a first interlayer dielectric layer, a covering layer and a patterned photoresist layer on the semiconductor substrate in sequence; etching the covering layer and the first interlayer dielectric layer in sequence according to the patterned photoresist layer to expose a contact hole of the self-aligned metal silicide; filling metal in the contact hole; removing excess metal by using a chemical mechanical polishing process, wherein the loss of the first interlayer dielectric layer is not caused in the process of forming the contact hole through etching and in the metal chemical mechanical polishing process. According to the manufacturing process, the etching process can be simplified, the contact hole of a good structure is formed, and the formed contact hole meets the requirements of an integrated circuit.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Hemi-spherical structure and method for fabricating the same

InactiveUS20070155066A1Simplify the etch processTransistorSemiconductor/solid-state device detailsEngineering

Owner:TAIWAN SEMICON MFG CO LTD

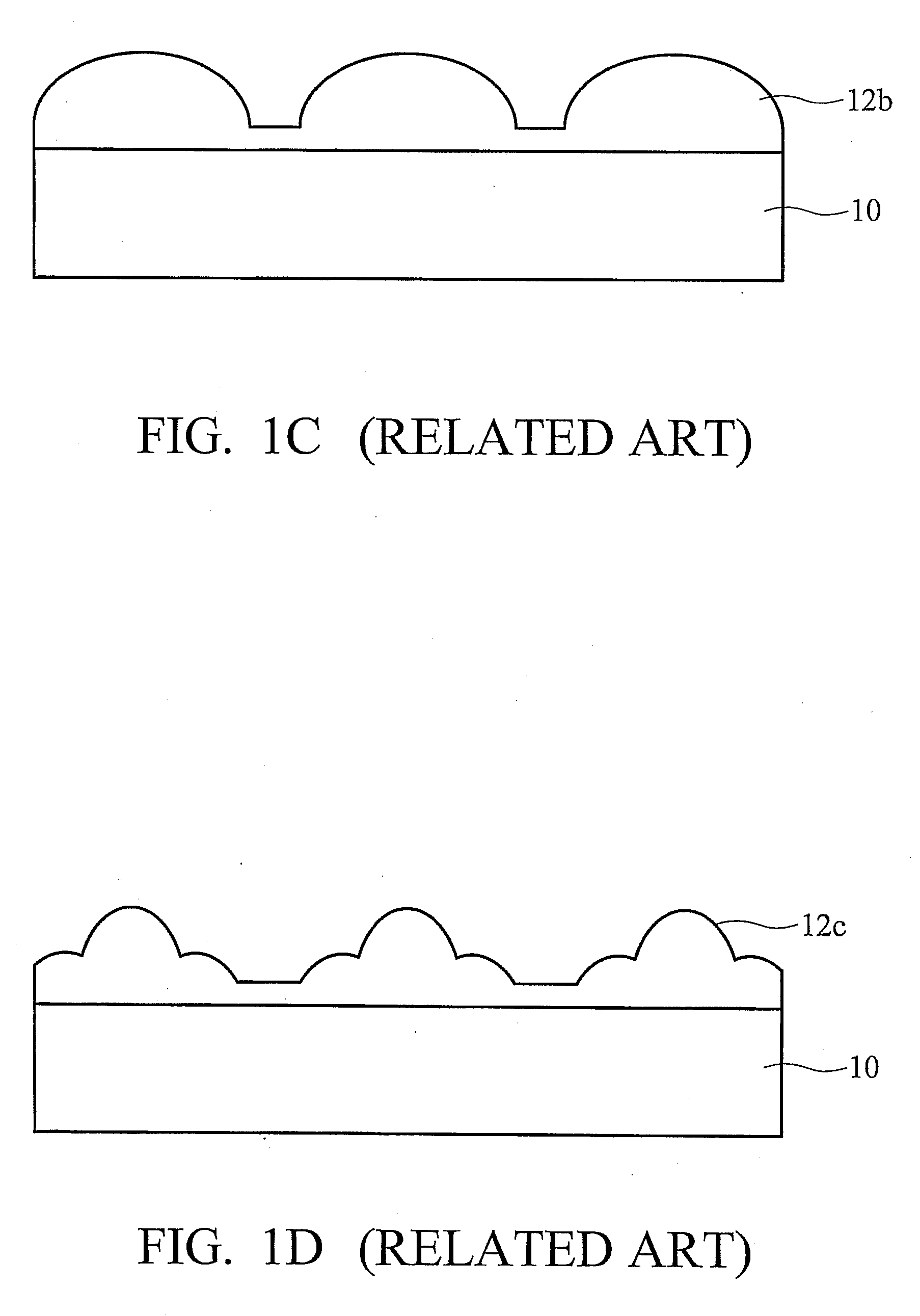

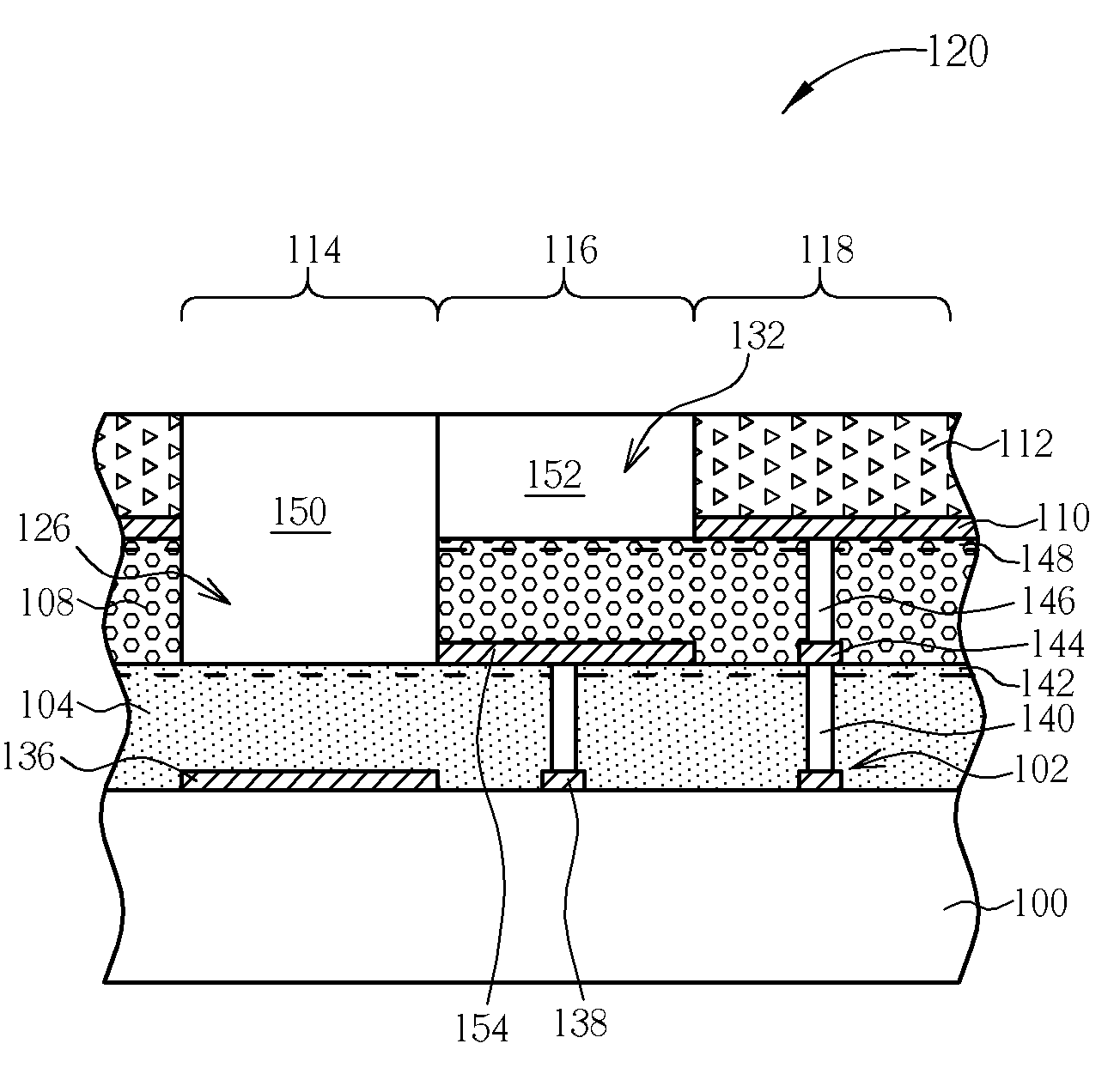

LCoS DISPLAY WITH A COLOR PIXEL ARRAY AND FABRICATION METHOD THEREOF

ActiveUS20080291373A1Simplify the manufacturing processSimplify the etch processNon-linear opticsComputer visionReflective layer

A method of fabricating an LCOS display with a color pixel array contains disposing reflective layers between various color filter layers. The reflective layers are used as etching stop layers between color filter layers so that etching processes are capable of carrying out to define the patterns of the color filter layers in different sub-pixels for forming the color pixel array.

Owner:UNITED MICROELECTRONICS CORP