Patents

Literature

150 results about "Structure formation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In physical cosmology, structure formation is the formation of galaxies, galaxy clusters and larger structures from small early density fluctuations. The universe, as is now known from observations of the cosmic microwave background radiation, began in a hot, dense, nearly uniform state approximately 13.8 billion years ago. However, looking in the sky today, we see structures on all scales, from stars and planets to galaxies and, on still larger scales, galaxy clusters and sheet-like structures of galaxies separated by enormous voids containing few galaxies. Structure formation attempts to model how these structures formed by gravitational instability of small early density ripples.

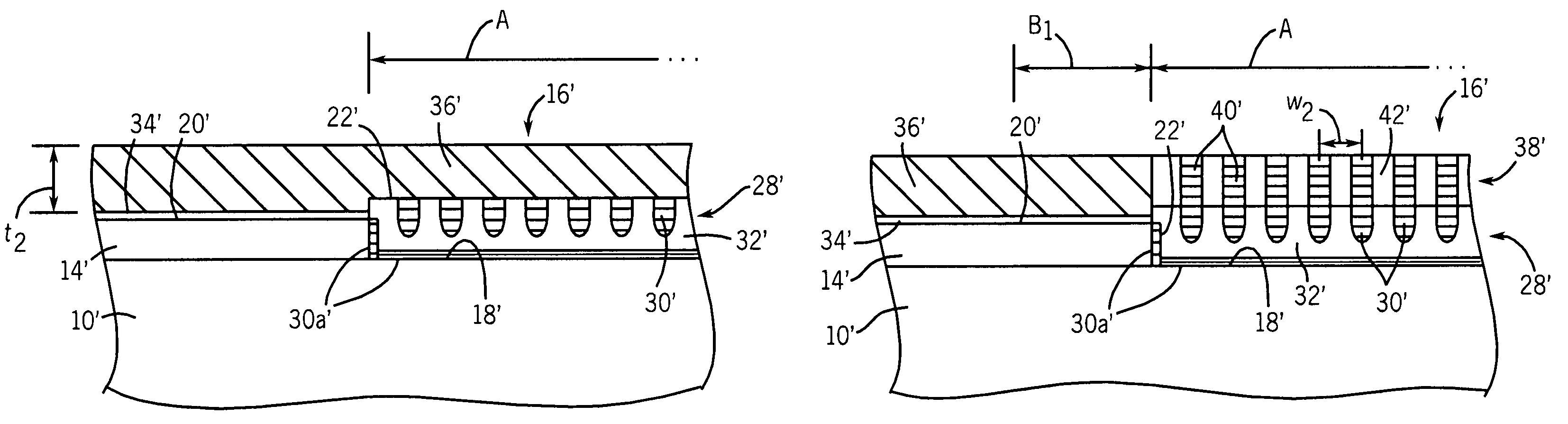

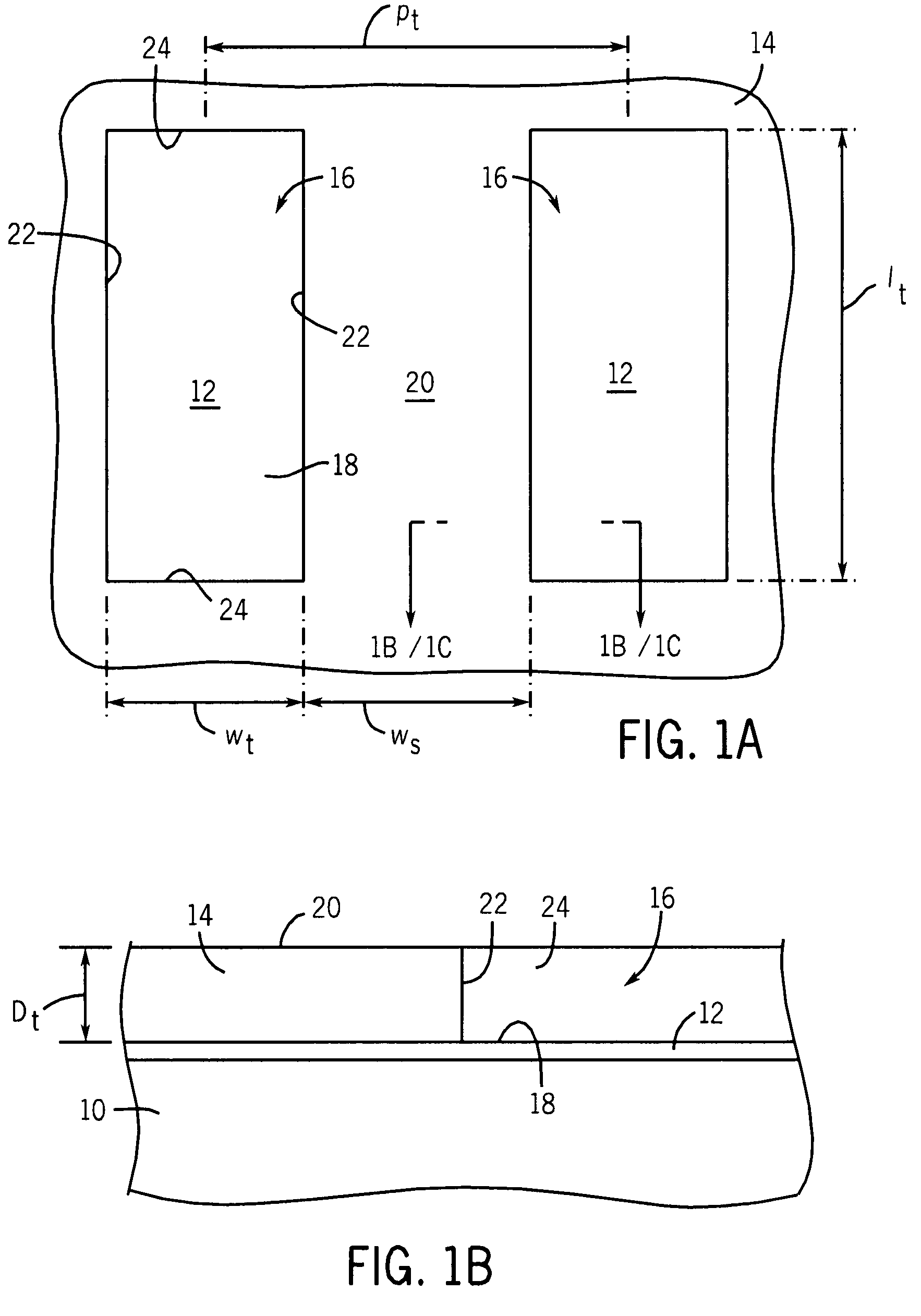

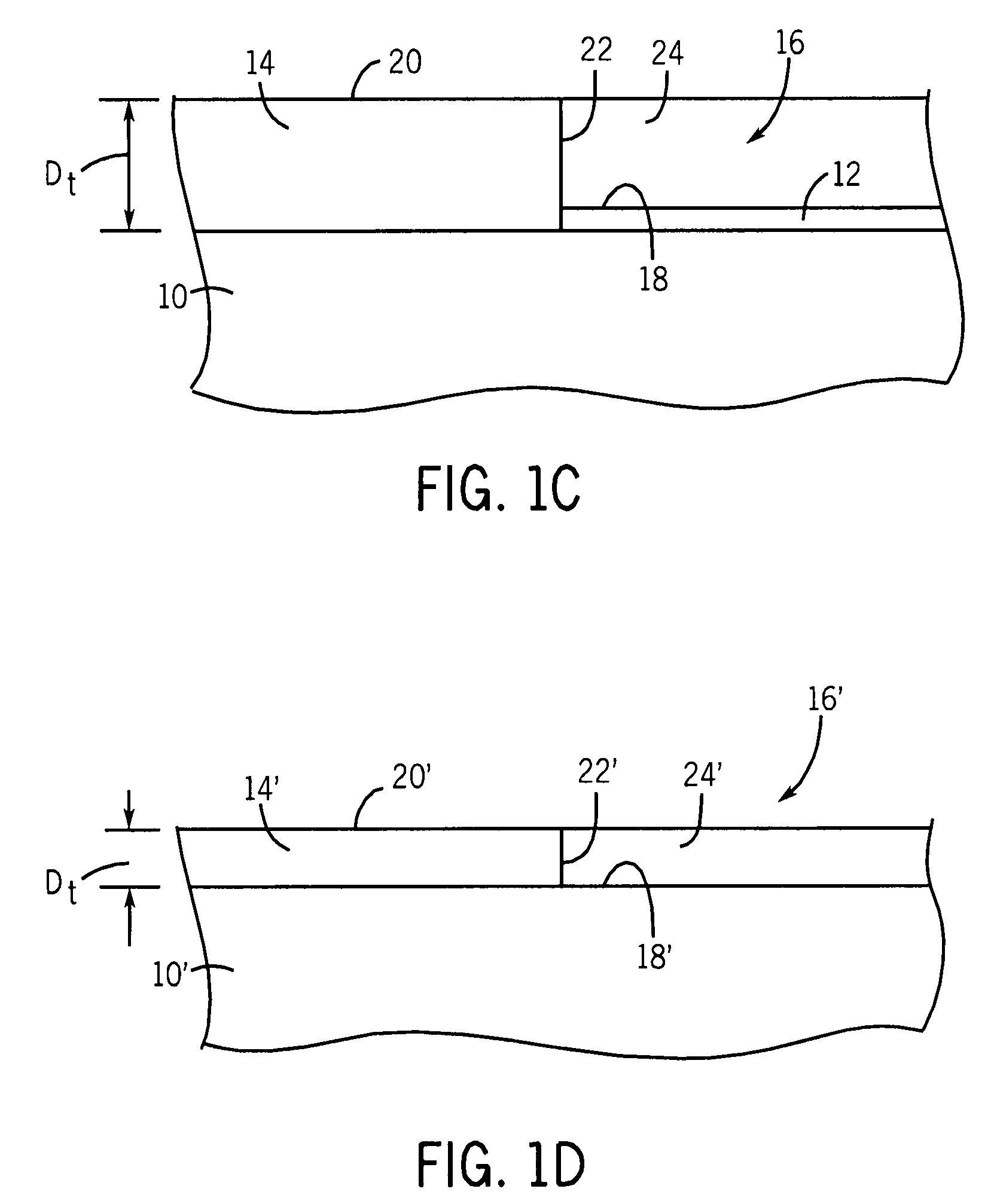

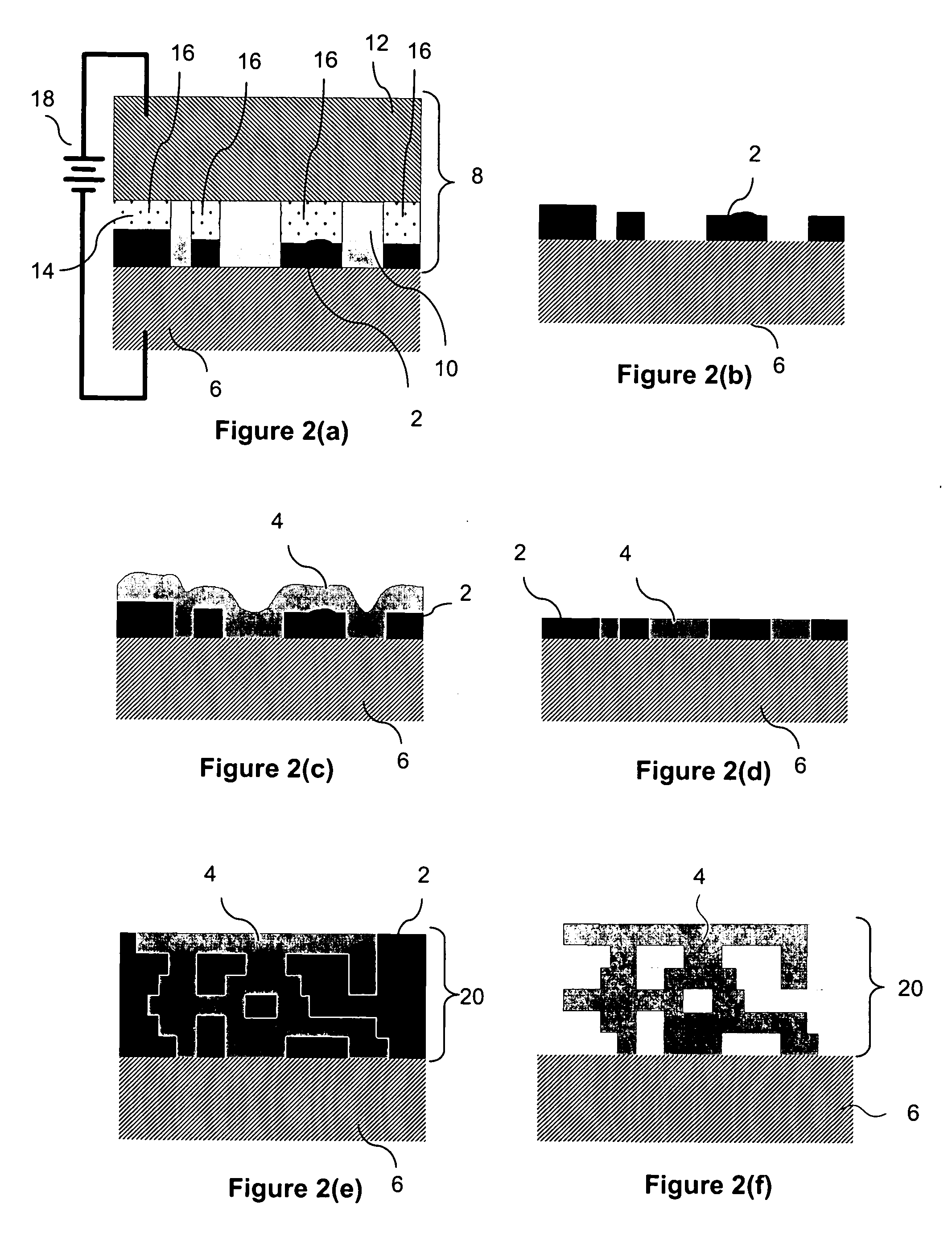

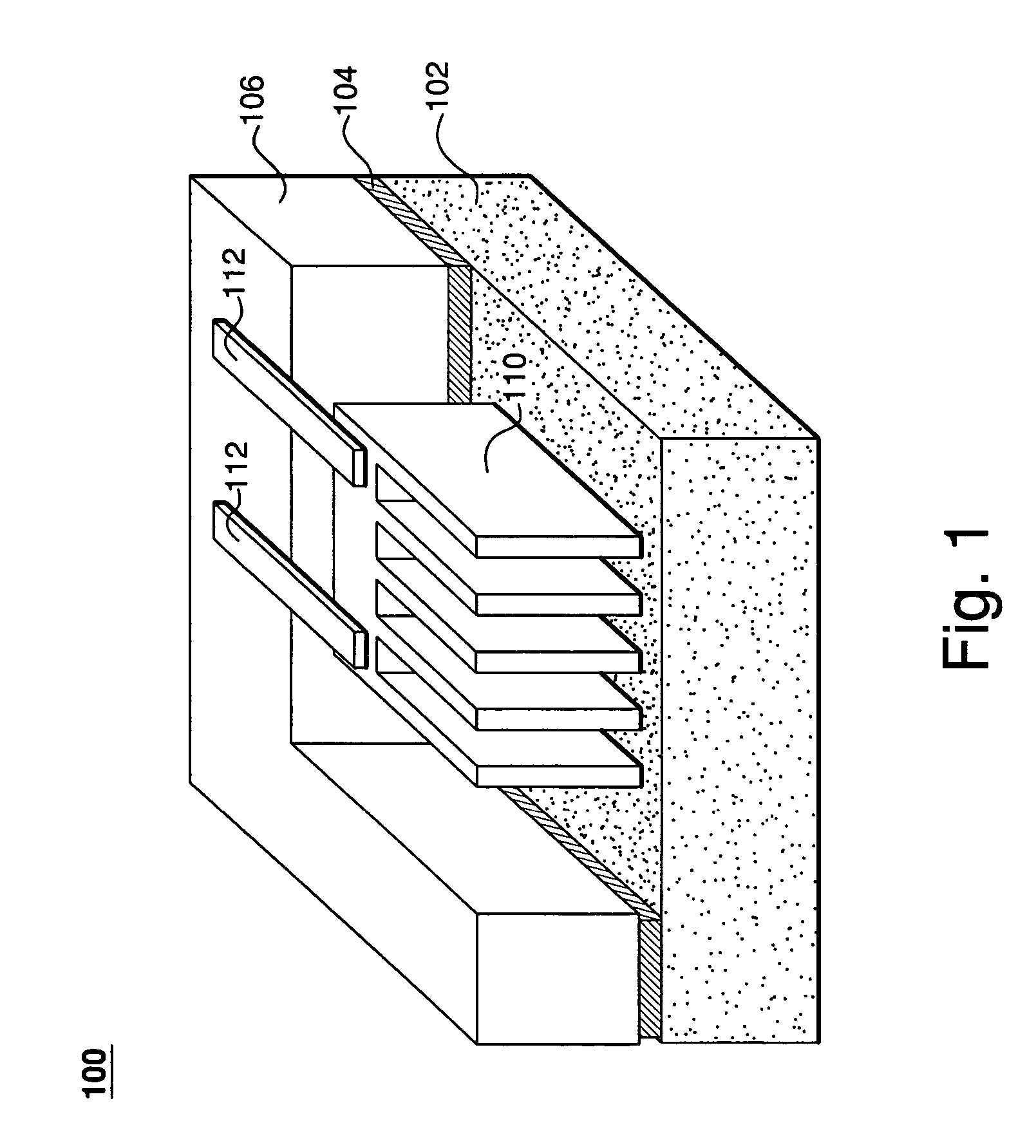

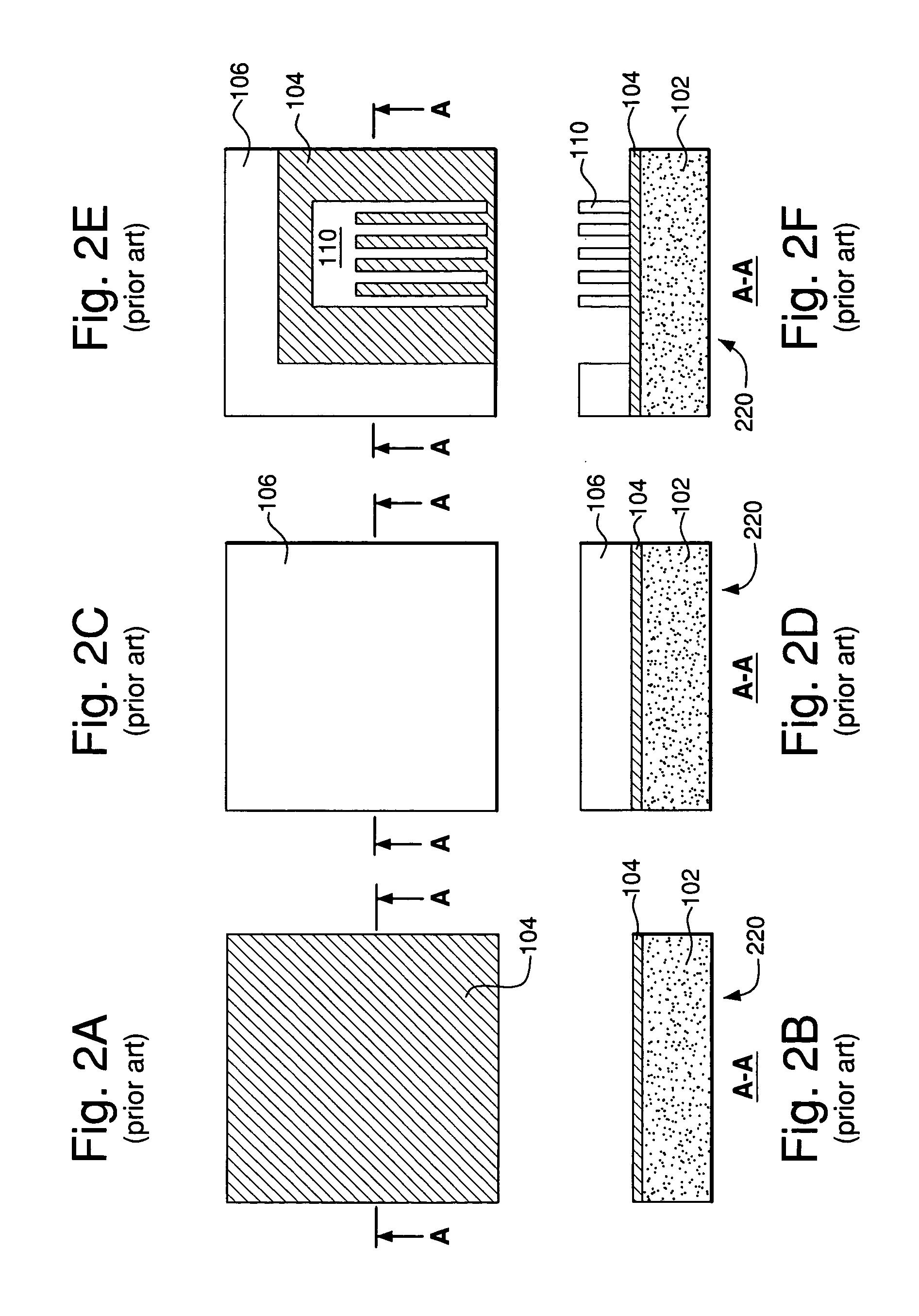

Registered structure formation via the application of directed thermal energy to diblock copolymer films

Owner:MICRON TECH INC

Method of fabricating an integrated circuit channel region

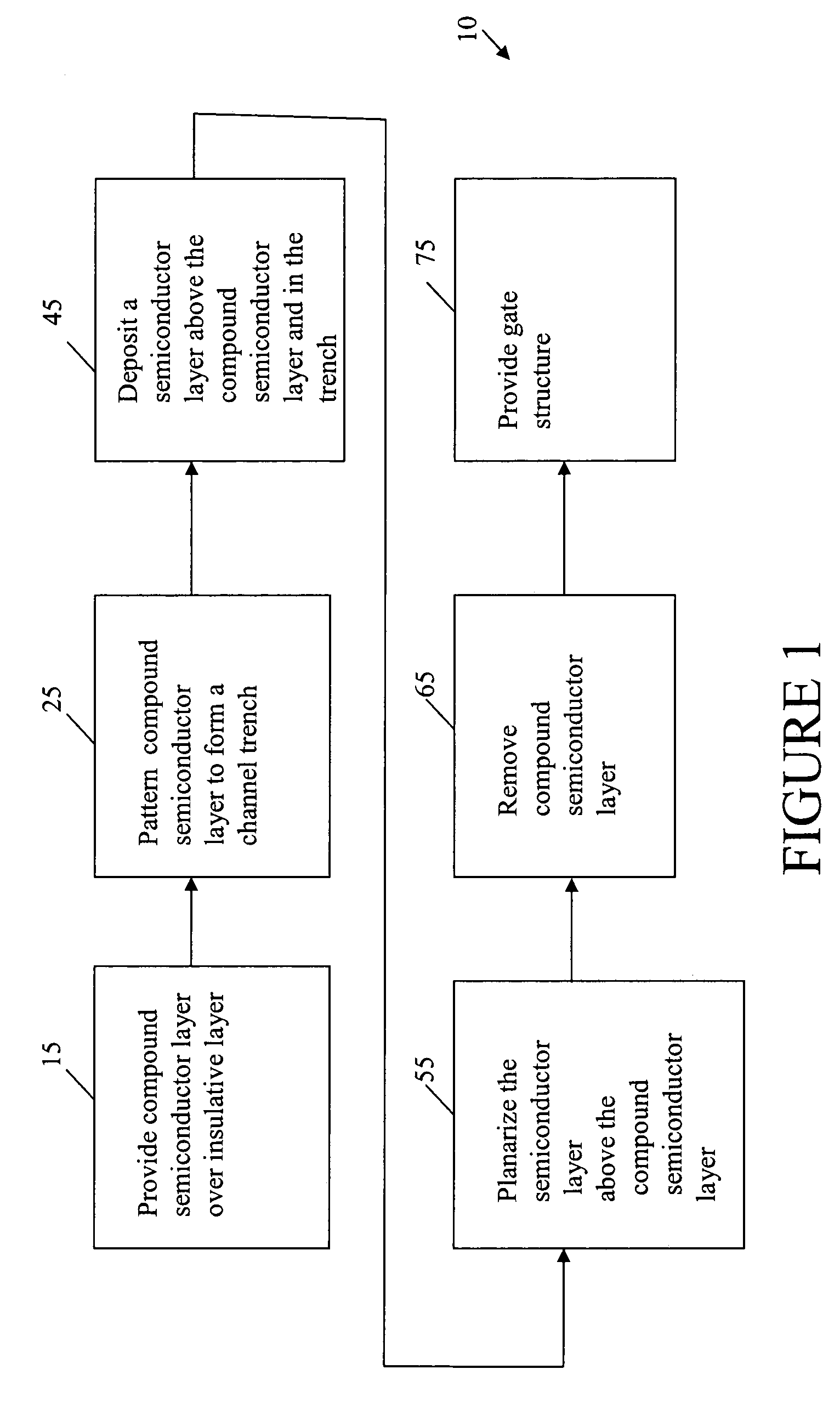

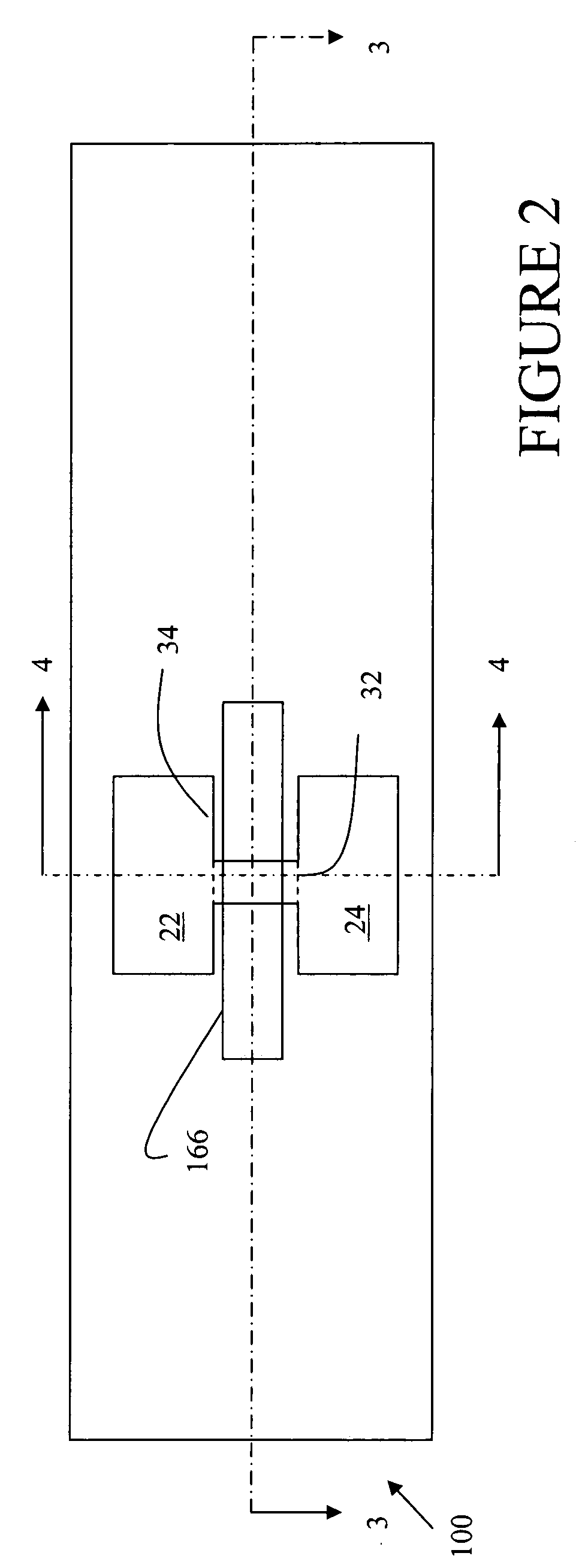

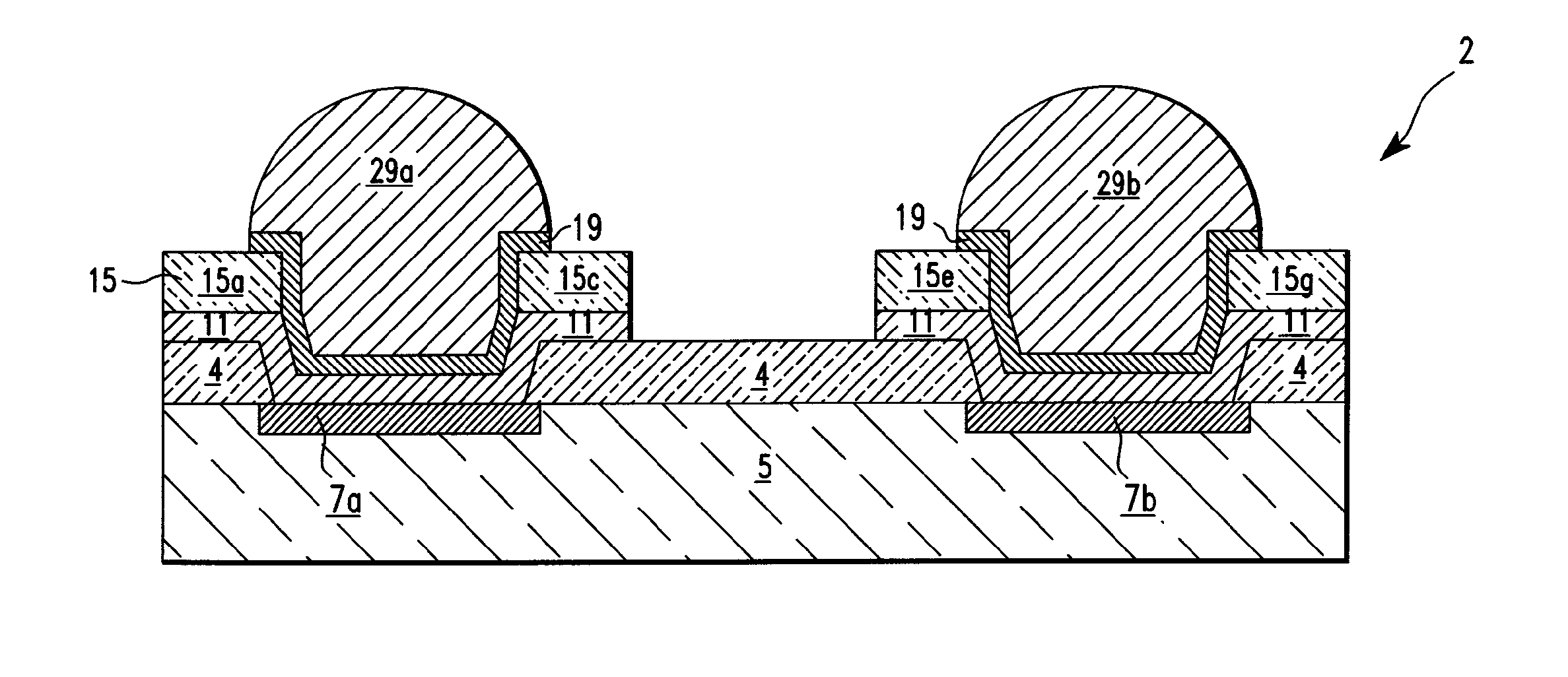

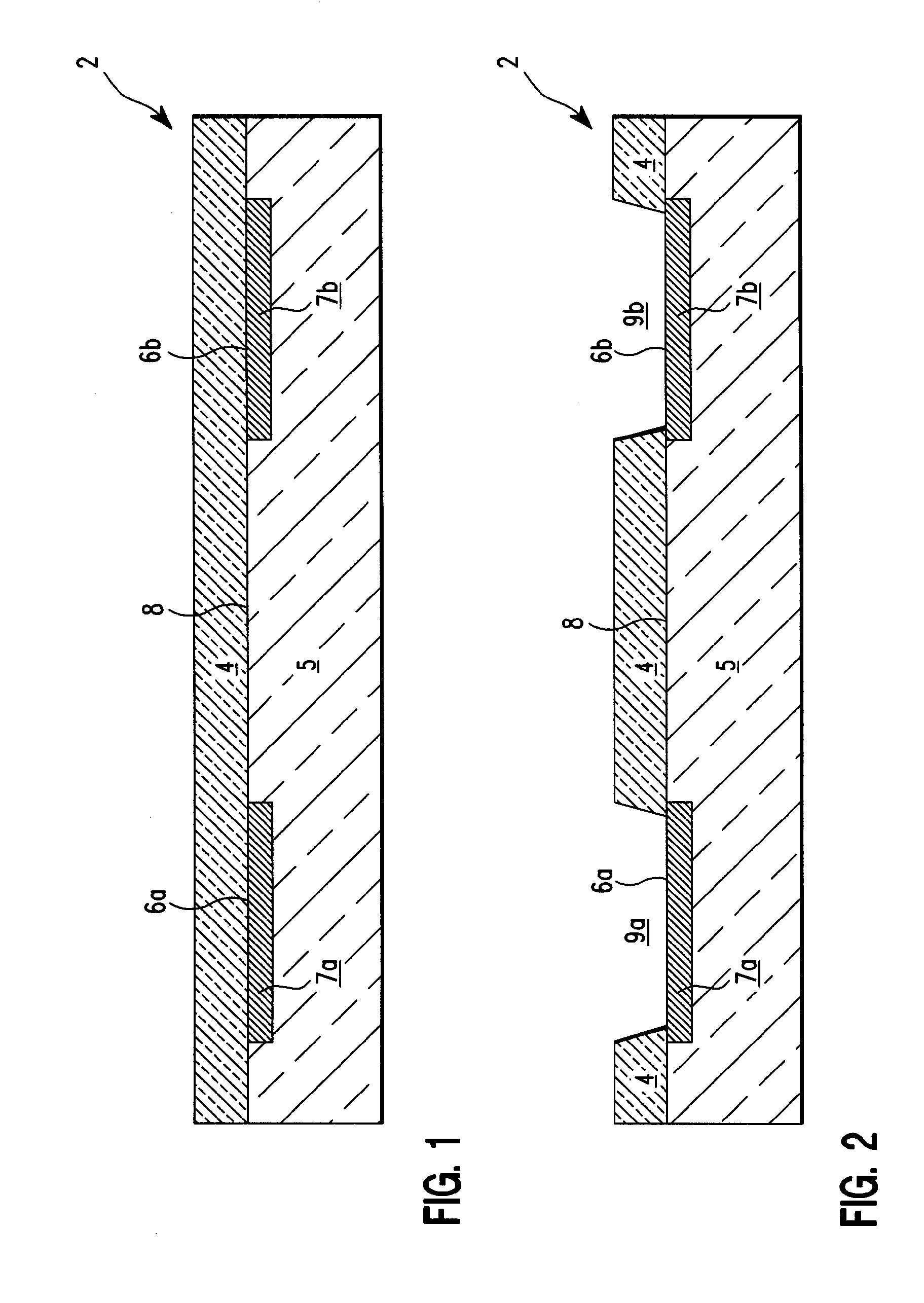

An exemplary embodiment relates to a method of FinFET channel structure formation. The method can include providing a compound semiconductor layer above an insulating layer, providing a trench in the compound semiconductor layer, and providing a strained semiconductor layer above the compound semiconductor layer and within the trench. The method can also include removing the strained semiconductor layer from above the compound semiconductor layer, thereby leaving the strained semiconductor layer within the trench and removing the compound semiconductor layer to leave the strained semiconductor layer and form the fin-shaped channel region.

Owner:GLOBALFOUNDRIES U S INC

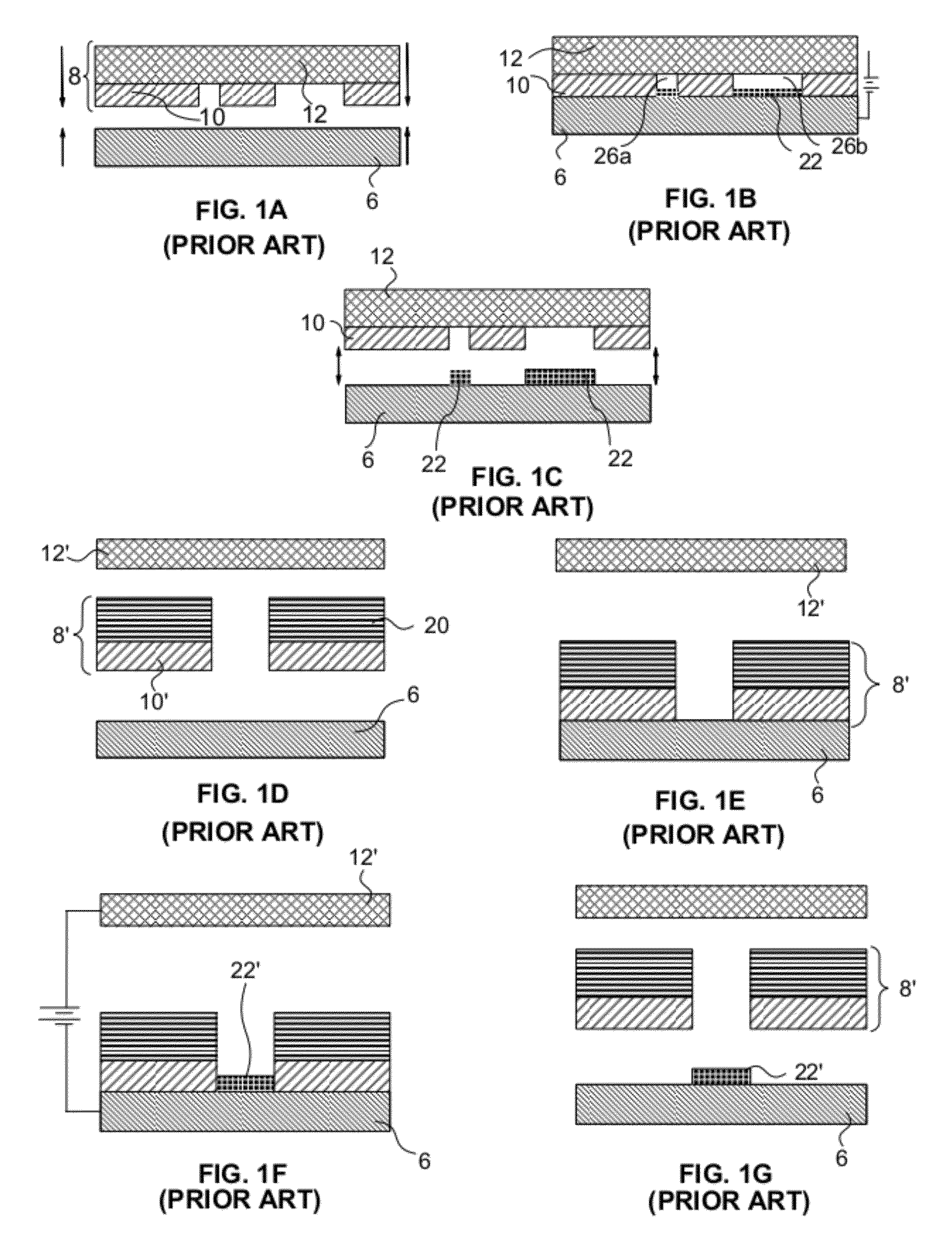

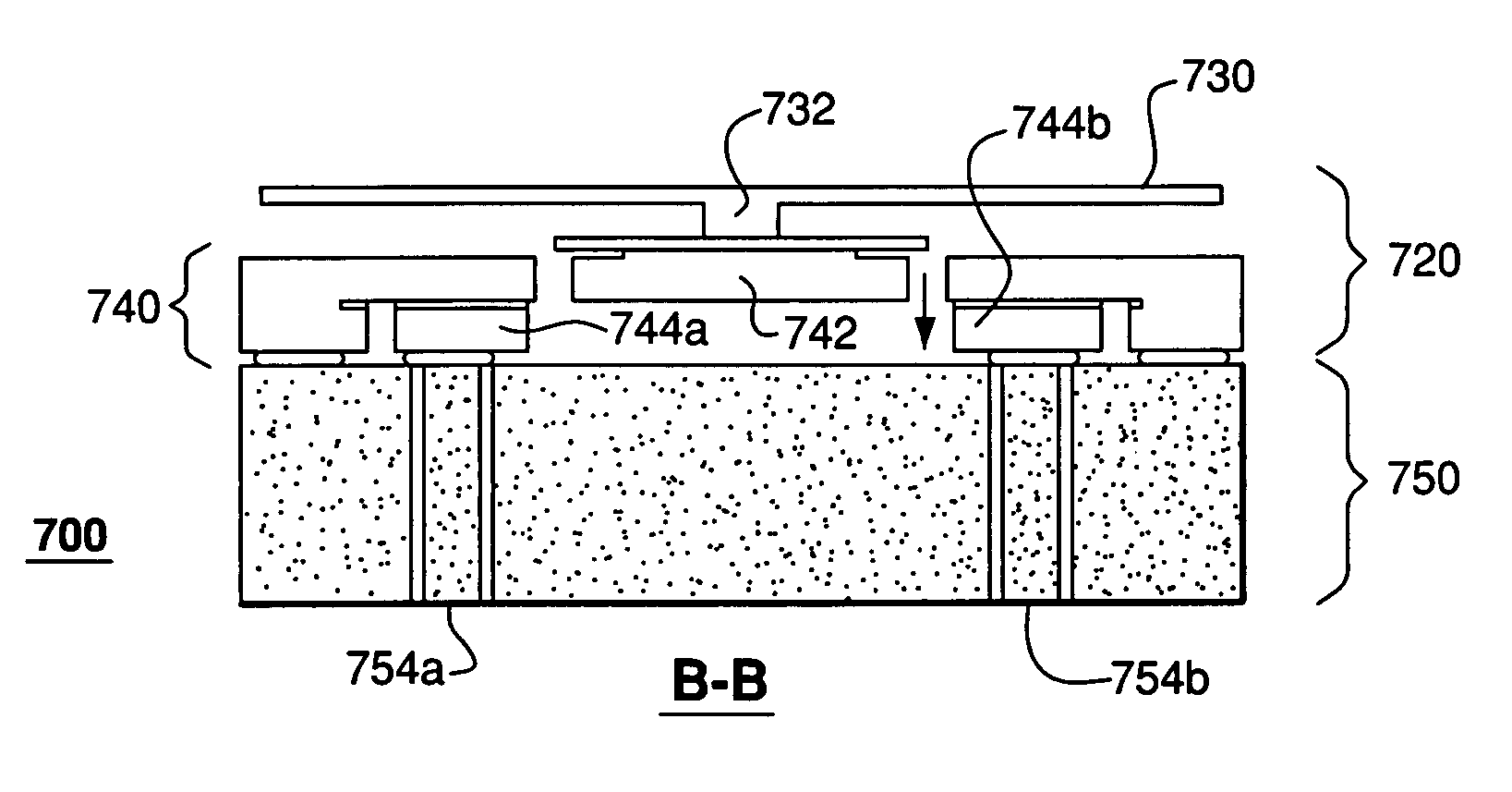

Electrical interconnection structure formation

ActiveUS7323780B2Semiconductor/solid-state device detailsSolid-state devicesSolder ballInterconnection

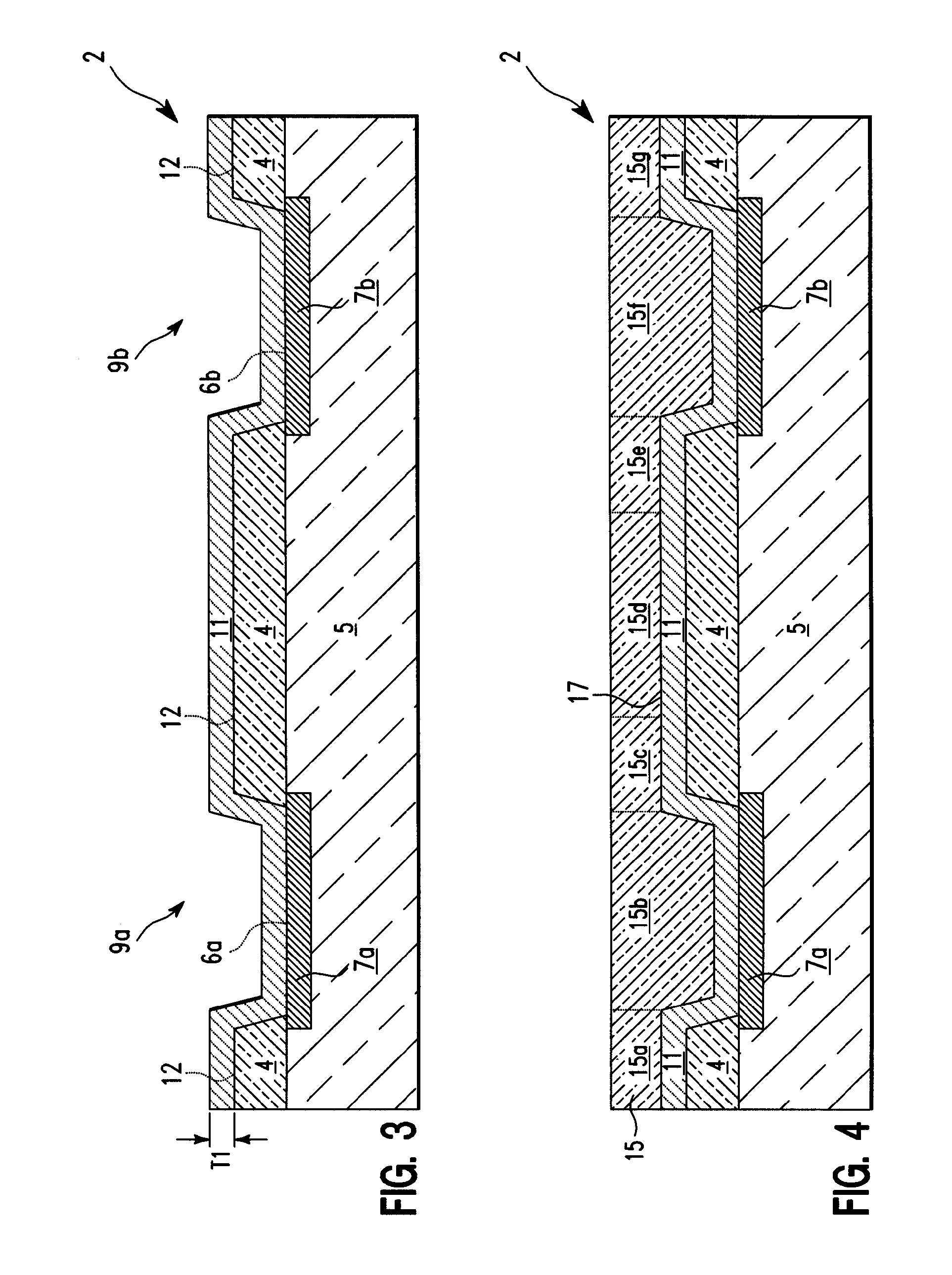

An electrical interconnection structure and method for forming. The electrical structure comprises a substrate comprising electrically conductive pads and a first dielectric layer over the substrate and the electrically conductive pads. The first dielectric layer comprises vias. A metallic layer is formed over the first dielectric layer and within the vias. A second dielectric layer is formed over the metallic layer. A ball limiting metallization layer is formed within the vias. A photoresist layer is formed over a surface of the ball limiting metallization layer. A first solder ball is formed within a first opening in the photoresist layer and a second solder ball is formed within a second opening in the photoresist layer.

Owner:AURIGA INNOVATIONS INC

Optical device and method of manufacturing the same

InactiveUS20120064303A1High positioning accuracyStably form a reflective layerLayered productsSpecial surfacesRefractive indexEngineering

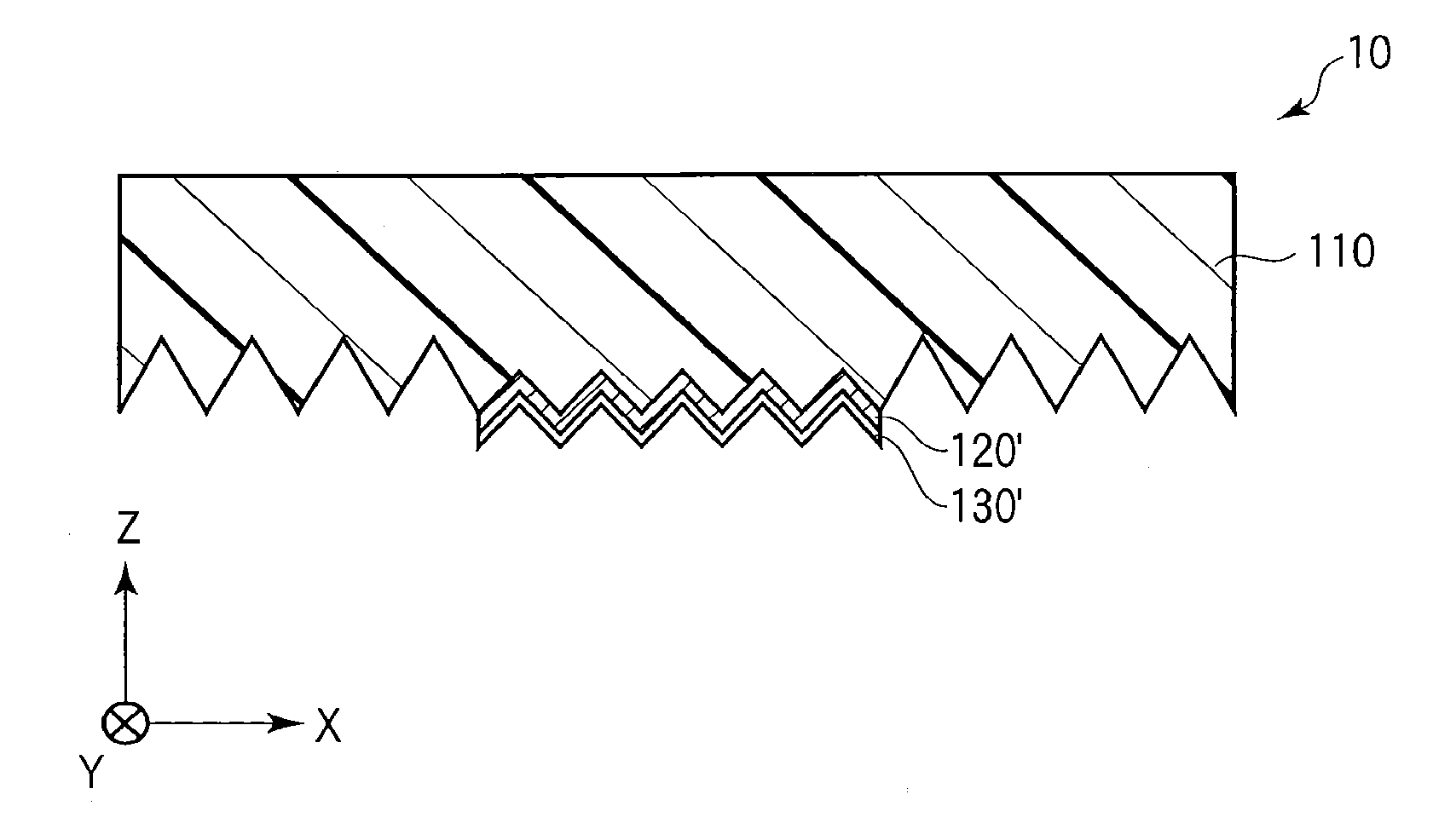

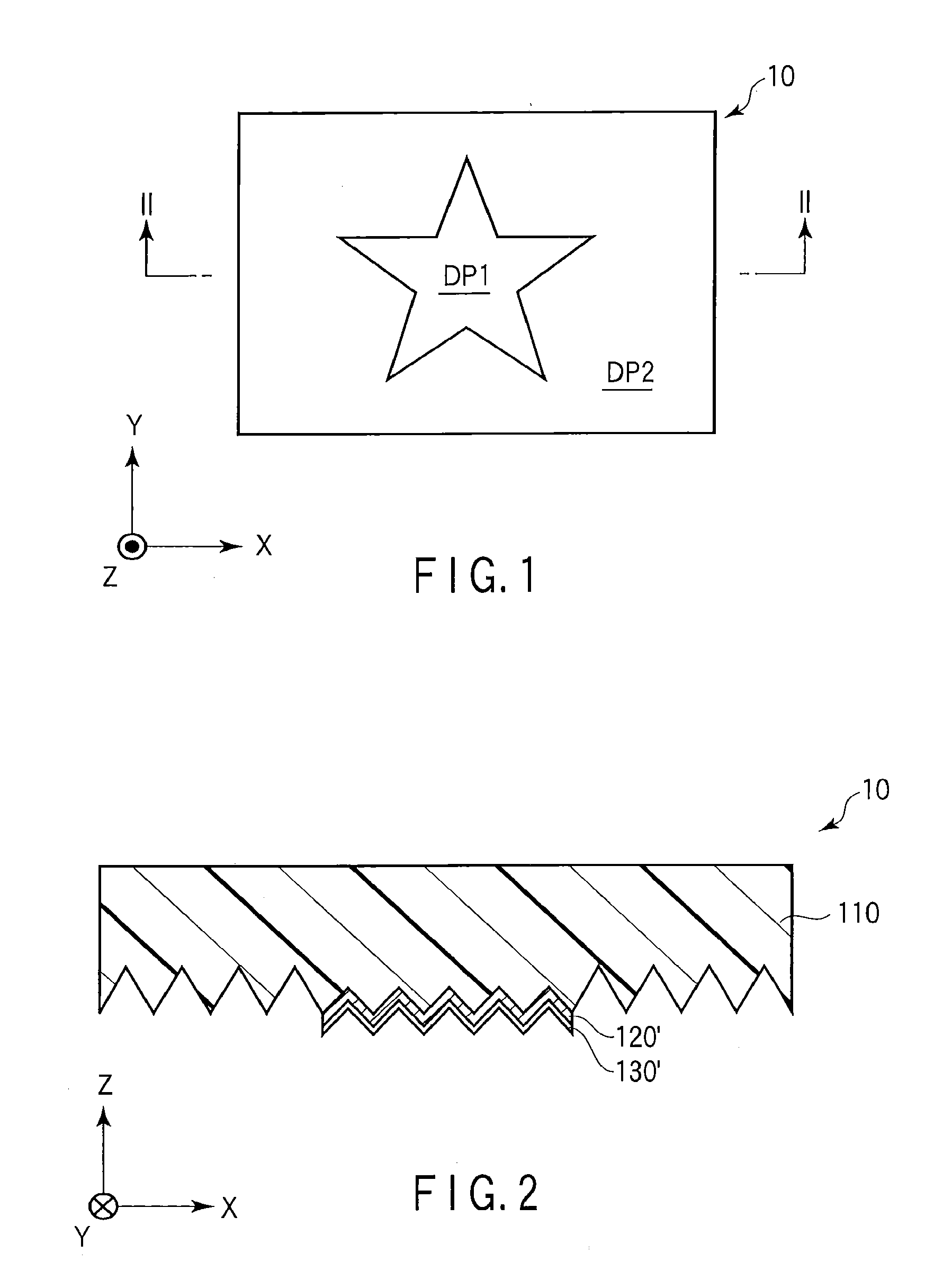

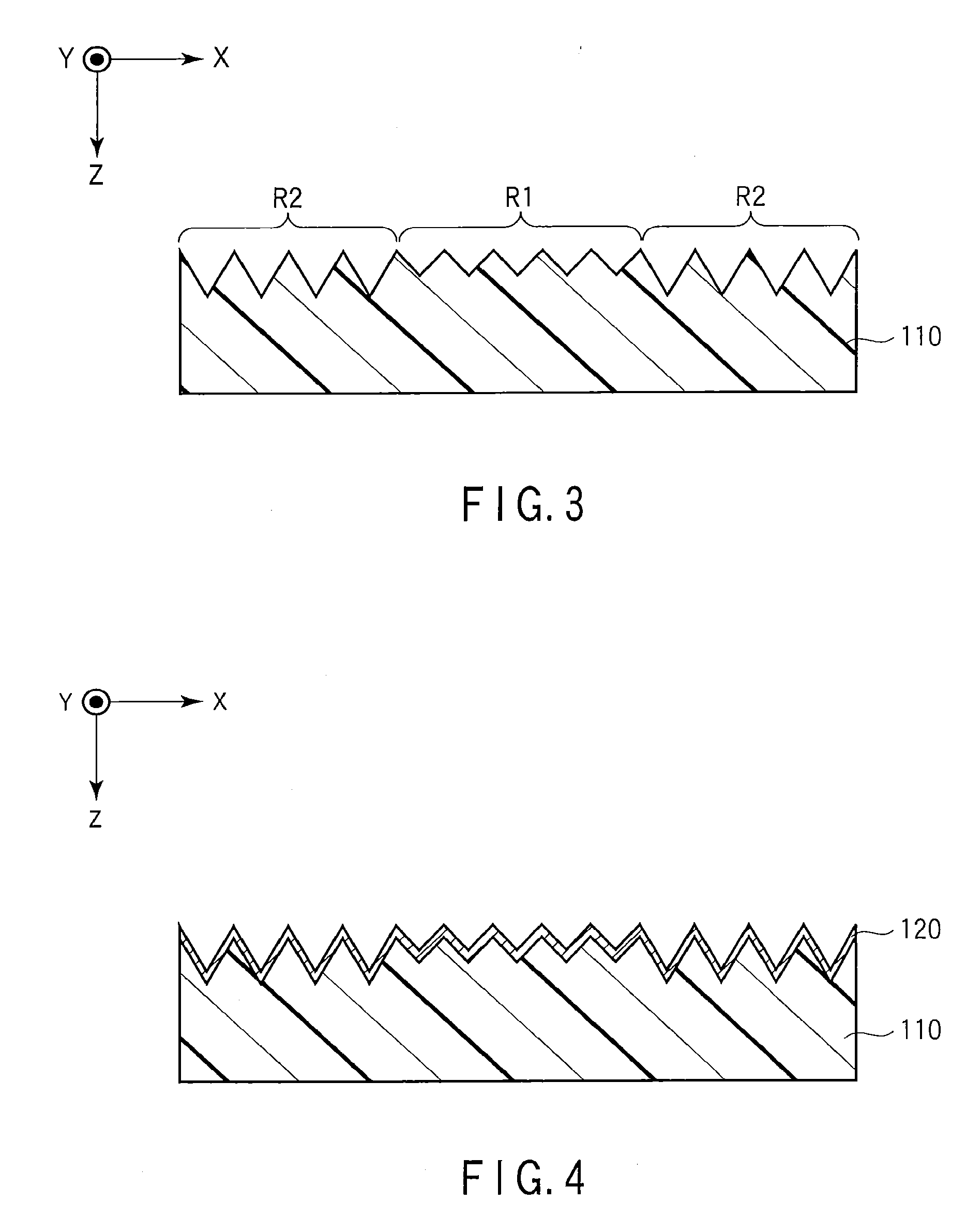

An optical device includes a relief structure formation layer, a first layer made of a first material having a refractive index different from that of a material of the relief structure formation layer, and a second layer made of a second material different from the first material and covering the first layer. A ratio of an amount of the second material at a position of the second region to an apparatus area of the second region is zero or smaller than a ratio of an amount of the second material at the position of the second sub-region to an apparatus area of the second sub-region.

Owner:TOPPAN PRINTING CO LTD

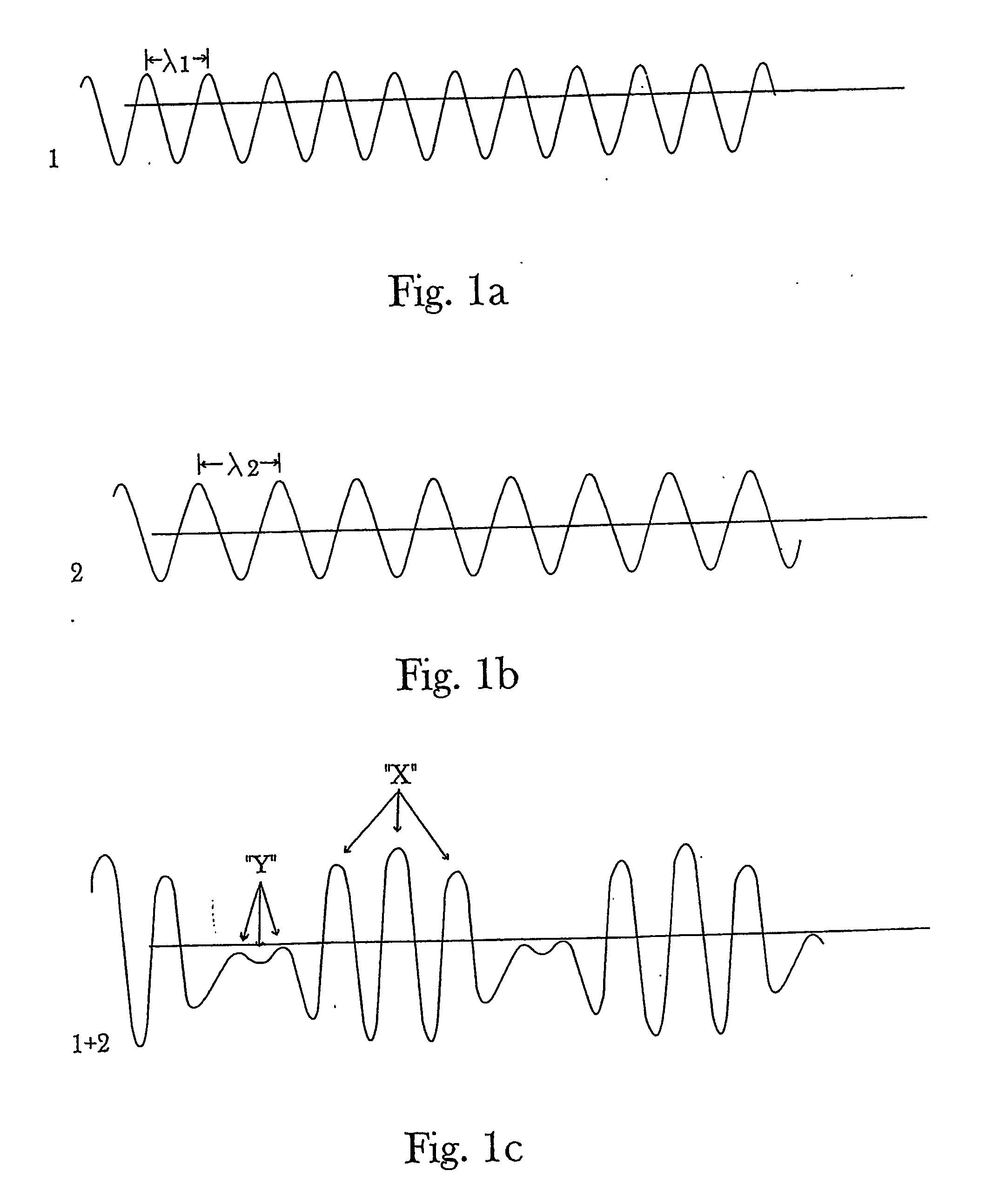

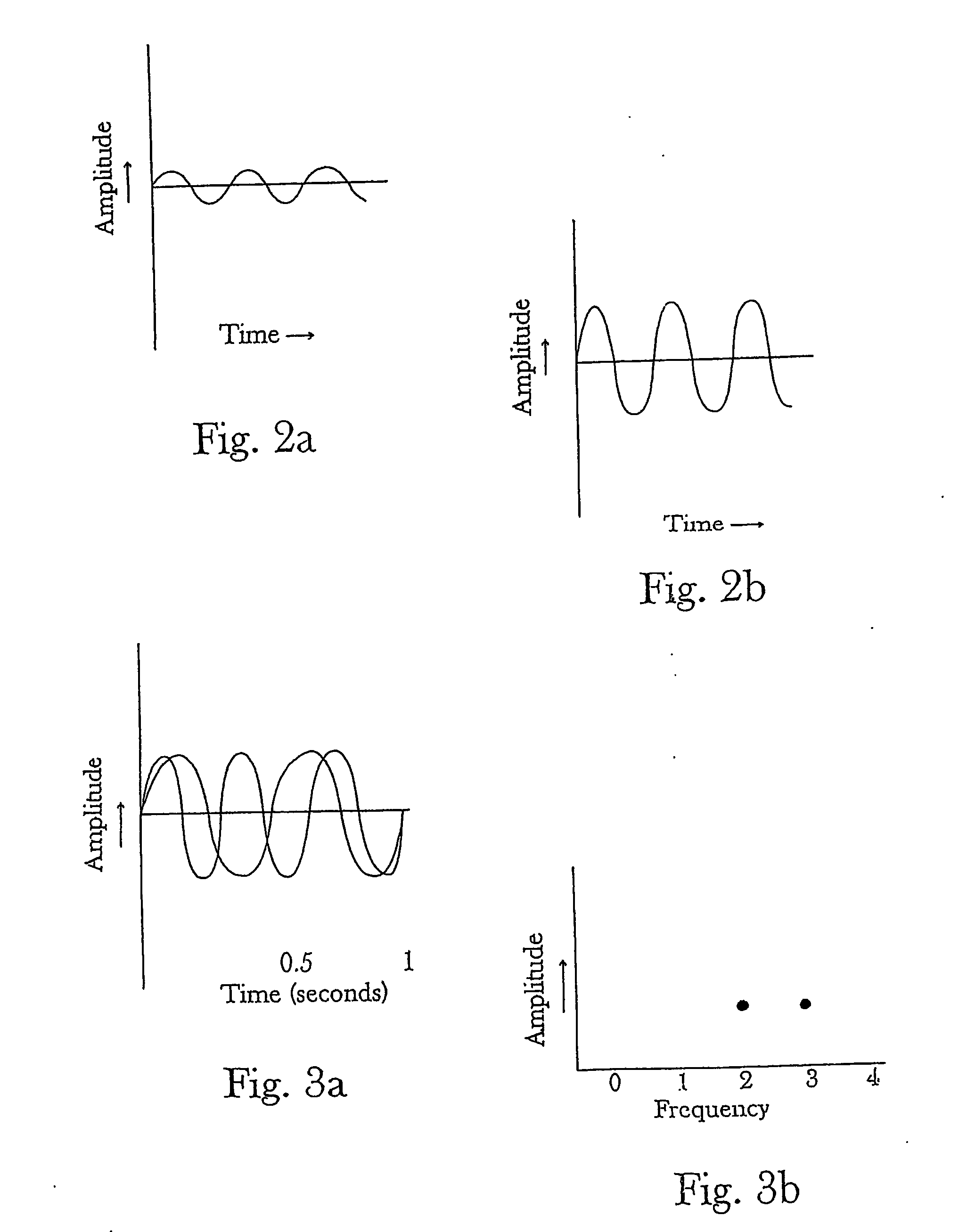

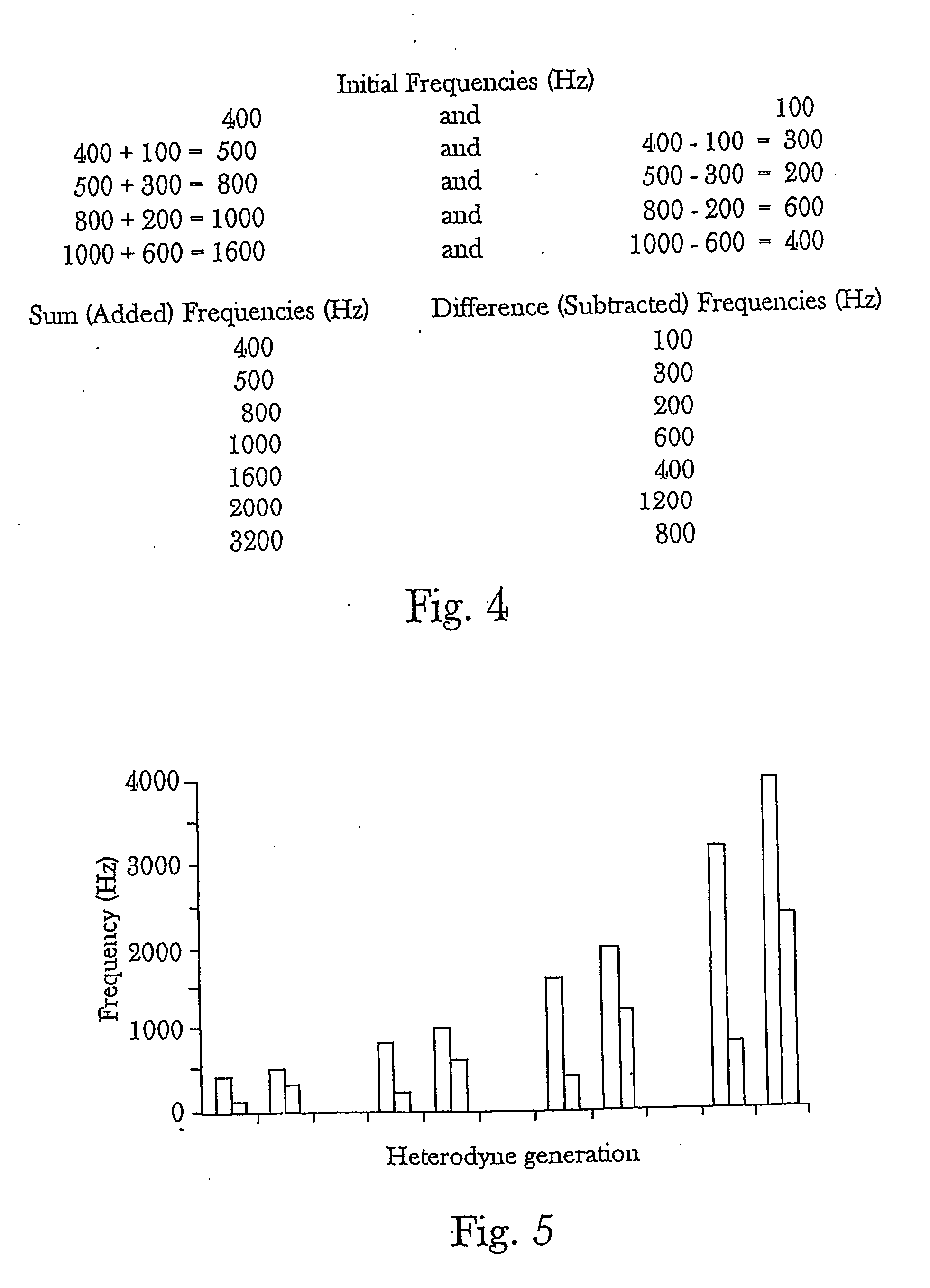

Methods for controlling crystal growth, crystallization, structures and phases in materials and systems

InactiveUS20060037177A1Growth inhibitionExisting techniquePolycrystalline material growthOxygen/ozone/oxide/hydroxidePhase formationEnergy regulation

This invention relates to novel methods for affecting, controlling and / or directing various crystal formation, structure formation or phase formation / phase change reaction pathways or systems by exposing one or more components in a holoreaction system to at least one spectral energy pattern. In a first aspect of the invention, at least one spectral energy pattern can be applied to a crystallization reaction system. In a second aspect of the invention, at lest one spectral energy conditioning pattern can be applied to a conditioning reaction system. The spectral energy conditioning pattern can, for example, be applied at a separate location from the reaction vessel (e.g., in a conditioning reaction vessel) or can be applied in (or to) the reaction vessel, but prior to other (or all) crystallization reaction system participants being introduced into the reaction vessel.

Owner:GR INTELLECTUAL RESERVE LLC

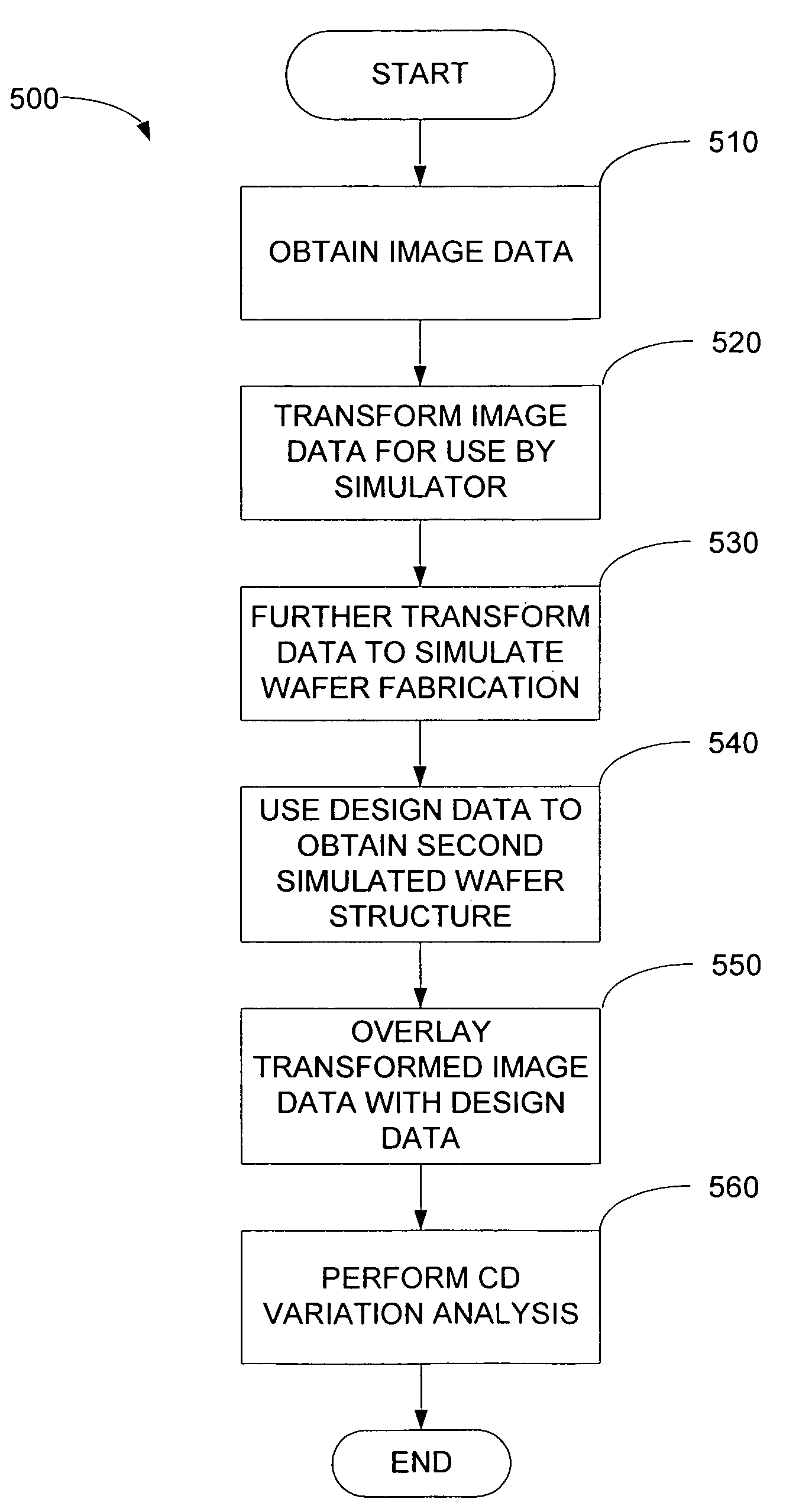

Method for evaluation of reticle image using aerial image simulator

InactiveUS7120285B1Semiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingScanning electron microscopeComputer science

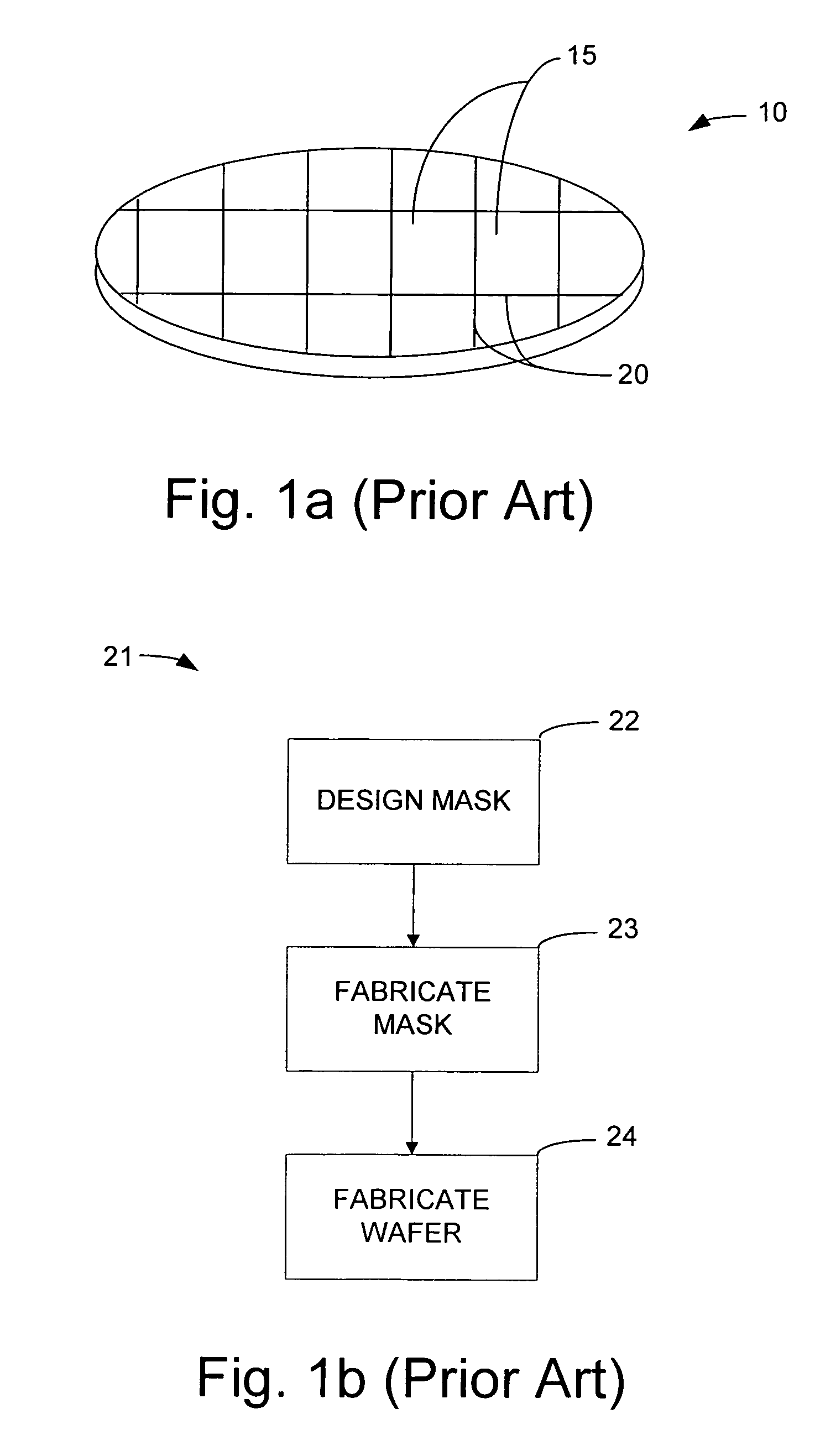

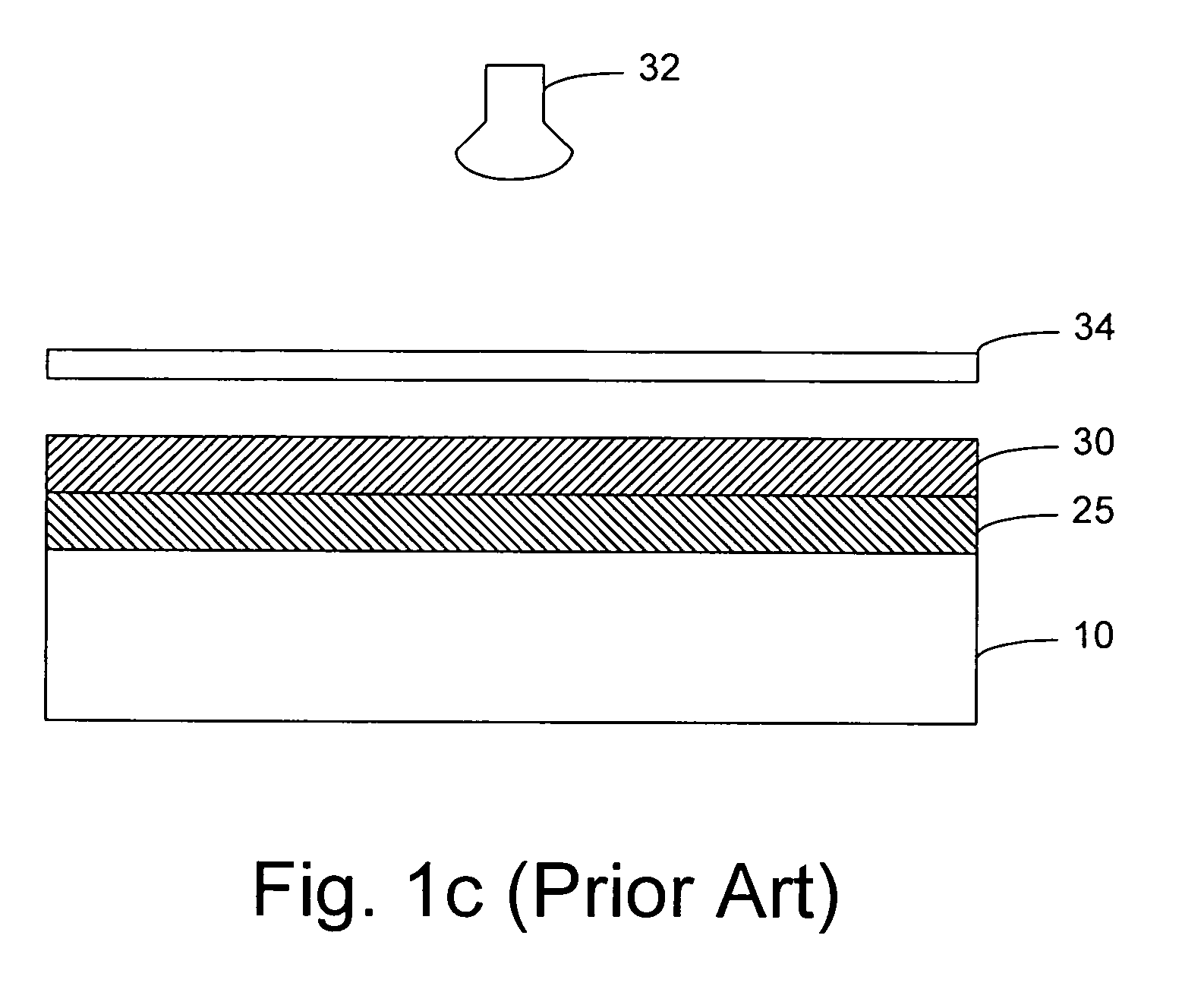

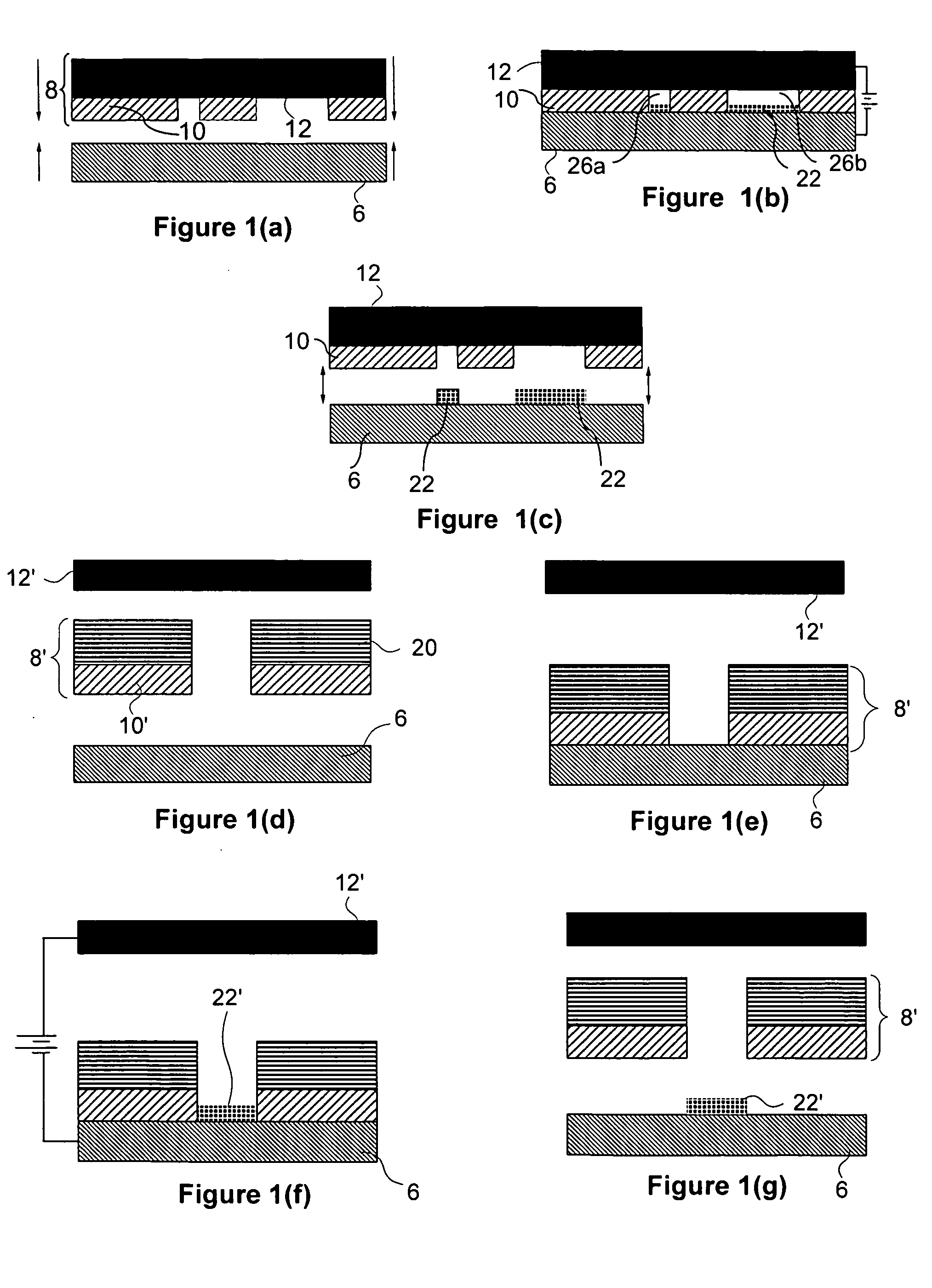

A method of evaluating a wafer structure formation process includes extracting the outline of an actual mask pattern, and simulating a lithographic process using the actual mask pattern to obtain a simulated wafer structure. The extracting the outline of the actual mask pattern may include, for example, imaging the actual mask using a scanning electron microscope (SEM). A second simulated wafer structure may also be obtained, by simulating the lithographic process using the ideal mask pattern design that was used in producing the actual mask pattern. Thus the relative contribution of mask pattern effects to overall wafer proximity effects may be evaluated by comparing the two simulated wafer structures, either with each other or against a benchmark such as a desired, ideal structure. This information may then be used to generate optical proximity correction (OPC) mask designs which compensate for mask patterning errors and give better wafer performance. The simulated wafer structures may be overlaid upon one another to allow for a direct comparison and full analysis of CD variations.

Owner:GLOBALFOUNDRIES INC

Multi-step release method for electrochemically fabricated structures

InactiveUS20050072681A1Improve electrochemical fabrication production reliabilityImprove product reliabilityAcceleration measurement using interia forcesLiquid/solution decomposition chemical coatingMaterial removalEngineering

Multi-layer structures are electrochemically fabricated from at least one structural material (e.g. nickel), that is configured to define a desired structure and which may be attached to a substrate, and from at least one sacrificial material (e.g. copper) that surrounds the desired structure. After structure formation, the sacrificial material is removed by a multi-stage etching operation. In some embodiments sacrificial material to be removed may be located within passages or the like on a substrate or within an add-on component. The multi-stage etching operations may be separated by intermediate post processing activities, they may be separated by cleaning operations, or barrier material removal operations, or the like. Barriers may be fixed in position by contact with structural material or with a substrate or they may be solely fixed in position by sacrificial material and are thus free to be removed after all retaining sacrificial material is etched.

Owner:MICROFAB

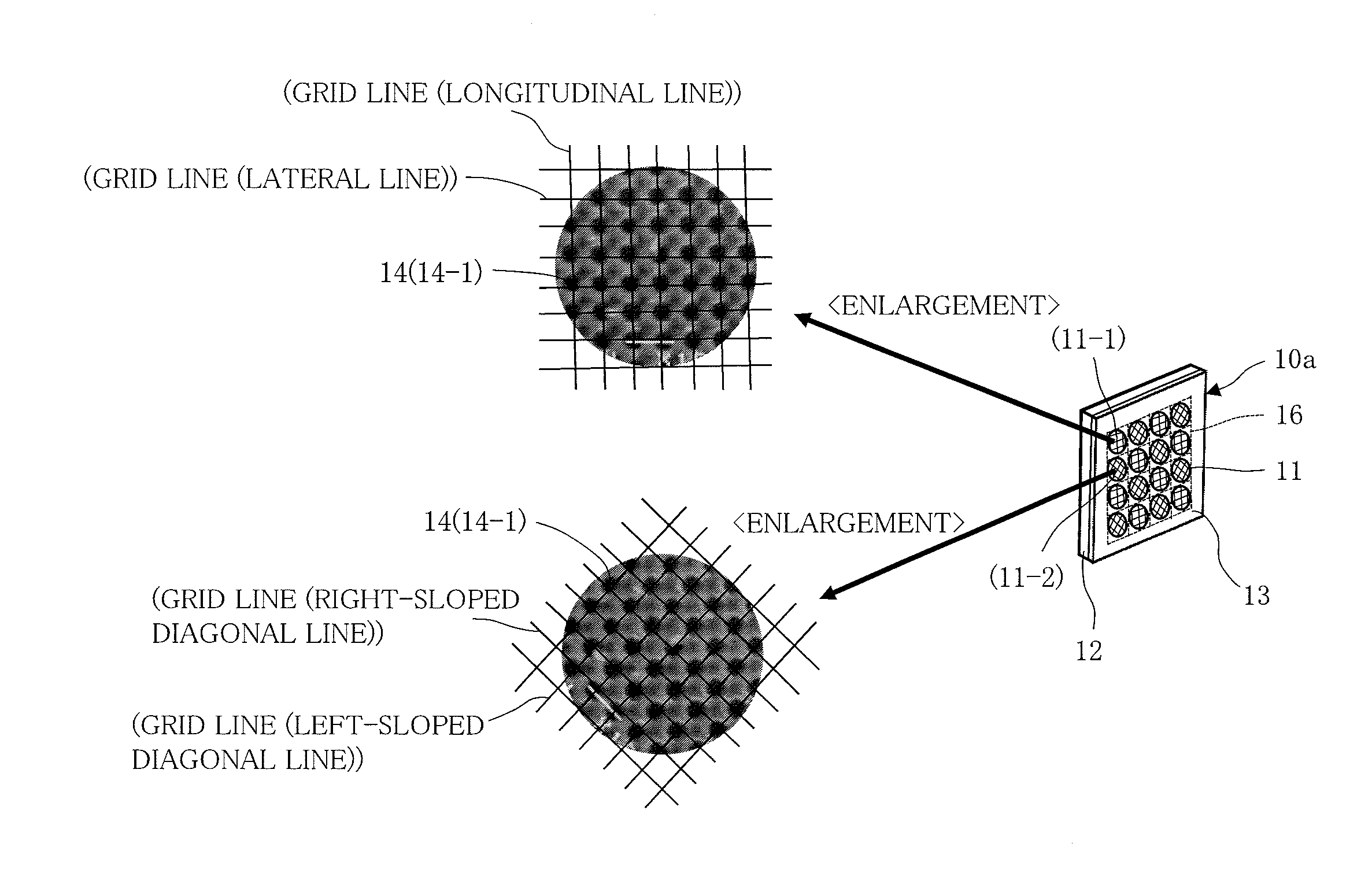

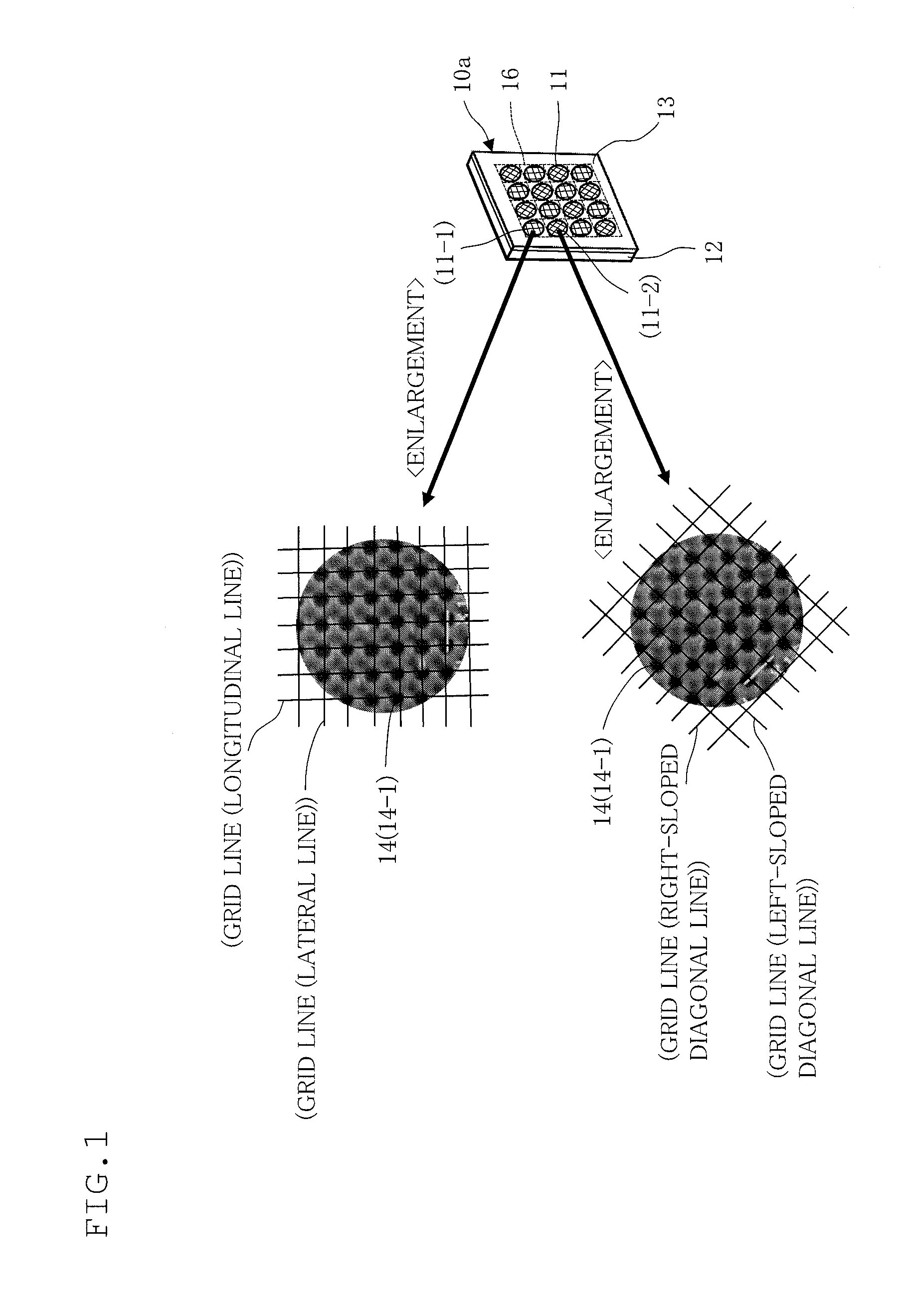

Structure, structure-forming method, and structure-forming device

InactiveUS20140104686A1Improve the decorative effectGood effectDecorative surface effectsOptical articlesPhotodisintegrationEngineering

A structure has a processed part formed by the occurrence of photodisintegration attributed to the application of pulsed laser light. A fine periodic composition in which a plurality of processed parts are arranged in the form of grid cross points is formed in one region of the structure. A large number of regions are arranged in the structure. Each of a plurality of ranges obtained by the division of a surface in which the regions are arranged is a region-forming range. One or more regions are arranged in one region-forming range, and the arrangement directions of the processed parts formed in each of the large number of regions vary according to the region-forming ranges.

Owner:TOYO SEIKAN GRP HLDG LTD

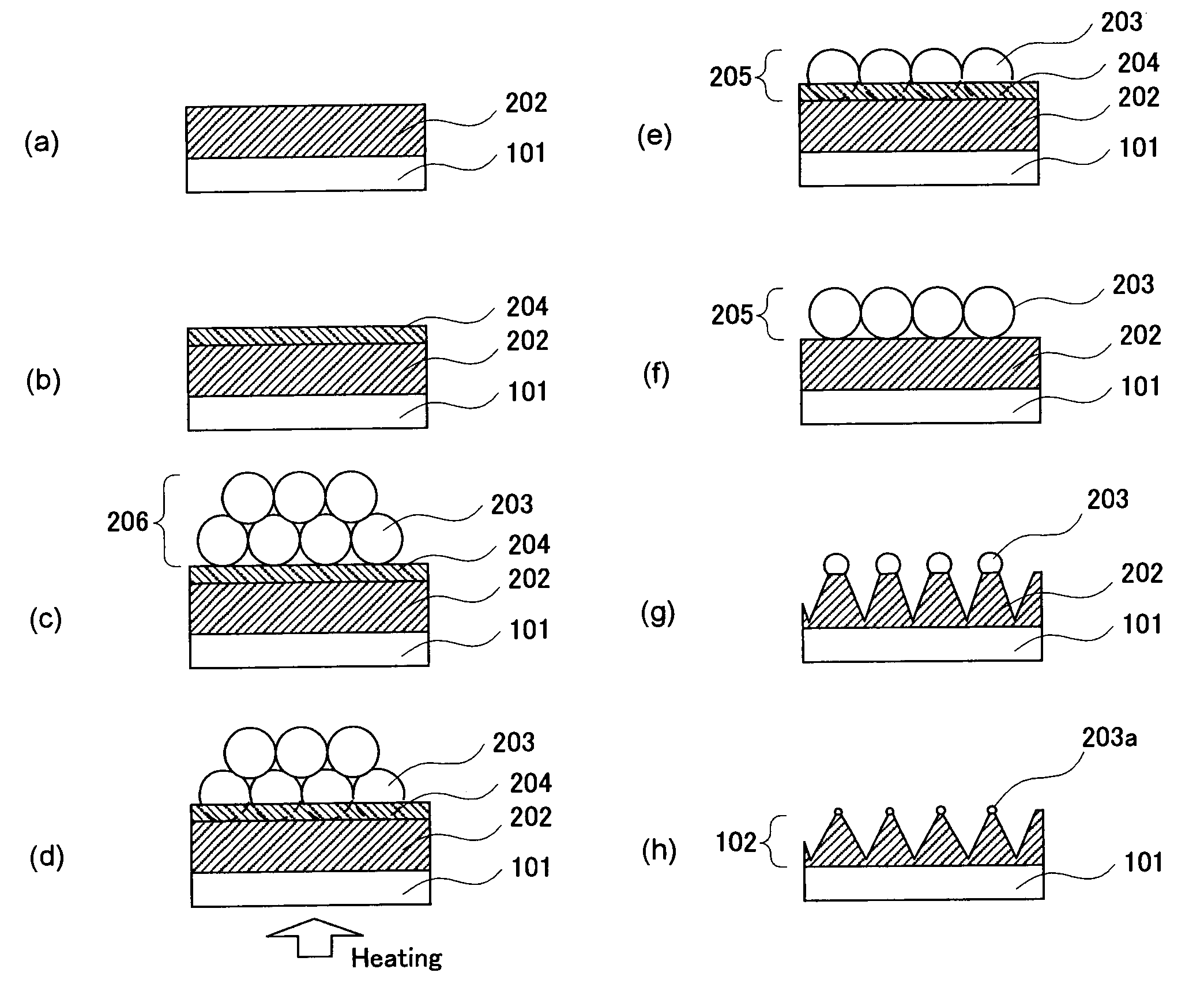

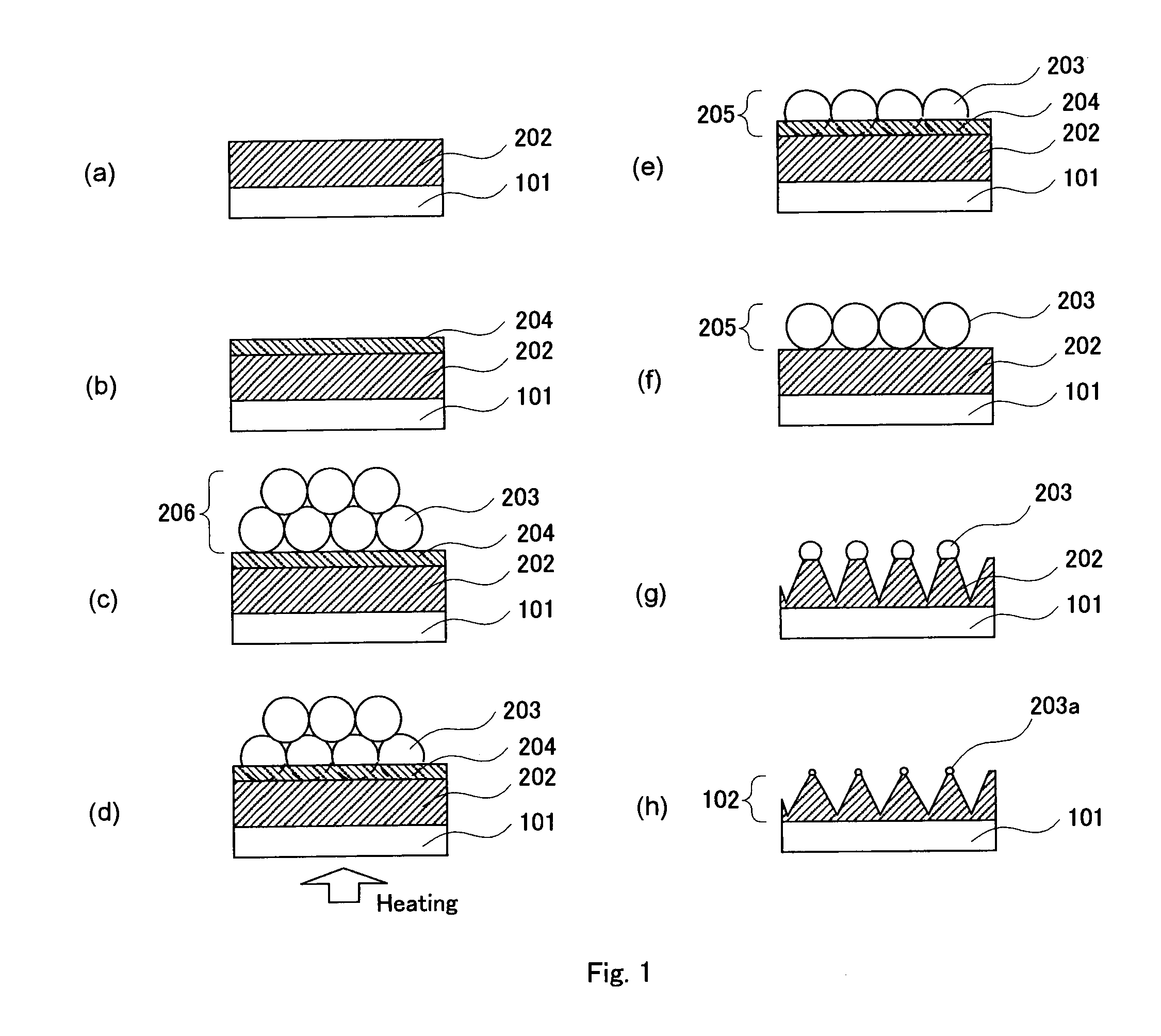

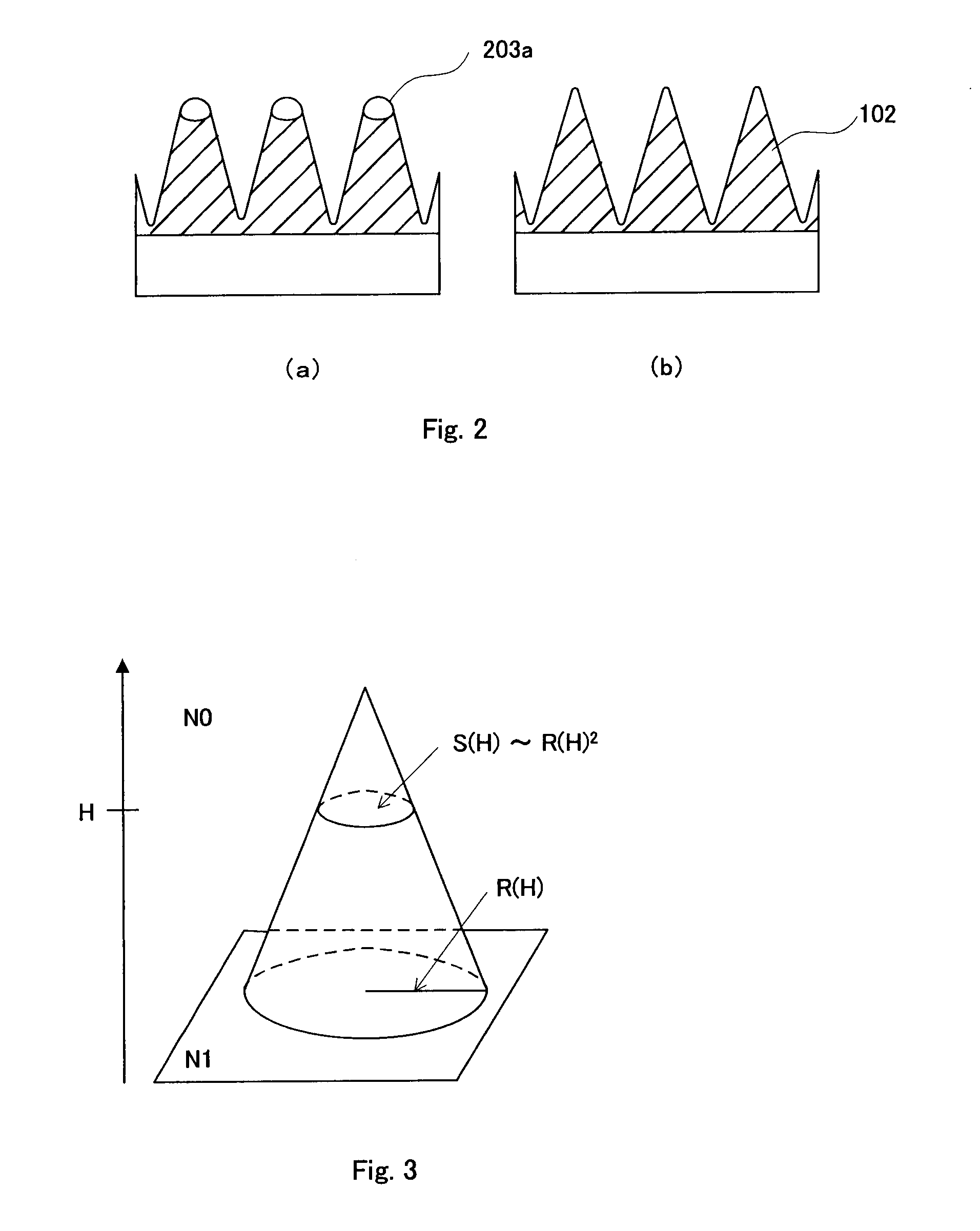

Antireflection structure formation method and antireflection structure

InactiveUS20090176015A1Excellent anti-reflection functionLow costDecorative surface effectsLayered productsNanometreReflection function

The present invention provides such a formation method that an antireflection structure having excellent antireflection functions can be formed in a large area and at small cost. Further, the present invention also provides an antireflection structure formed by that method. In the formation method, a base layer and particles placed thereon are subjected to an etching process. The particles on the base layer serve as an etching mask in the process, and hence they are more durable against etching than the base layer. The etching rate ratio of the base layer to the particles is more than 1 but not more than 5. The etching process is stopped before the particles disappear. It is also possible to produce an antireflection structure by nanoimprinting method employing a stamper. The stamper is formed by use of a master plate produced according to the above formation method.

Owner:KK TOSHIBA

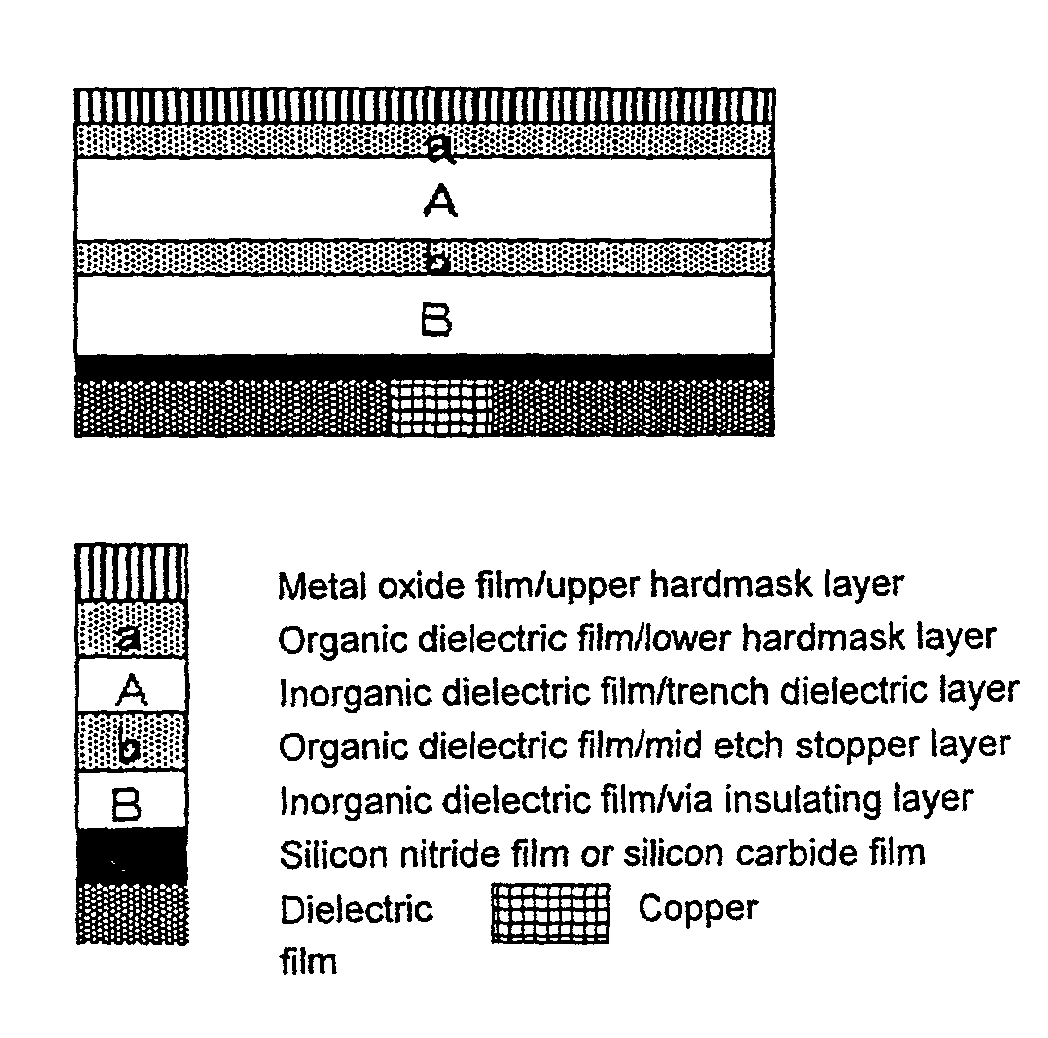

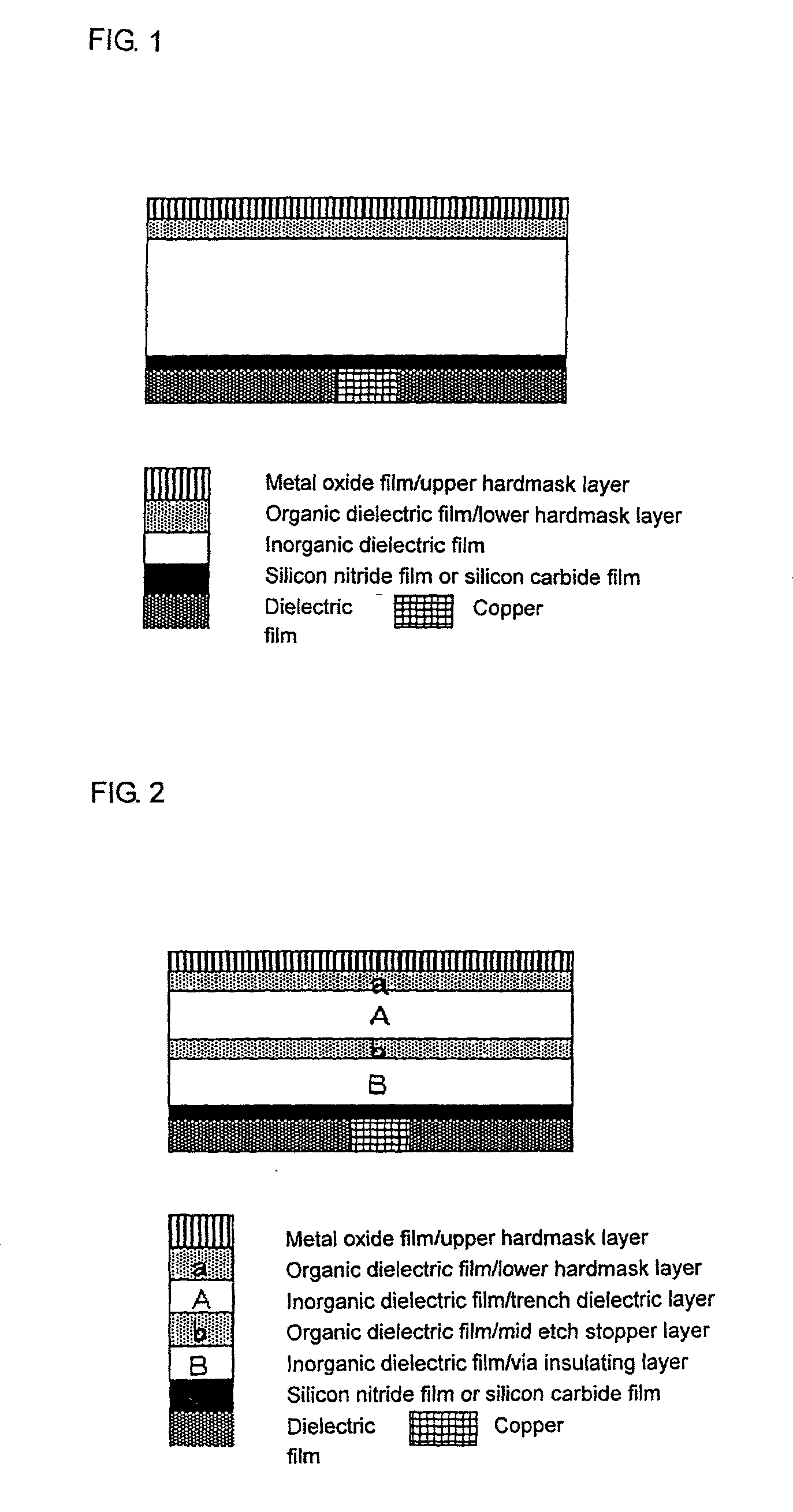

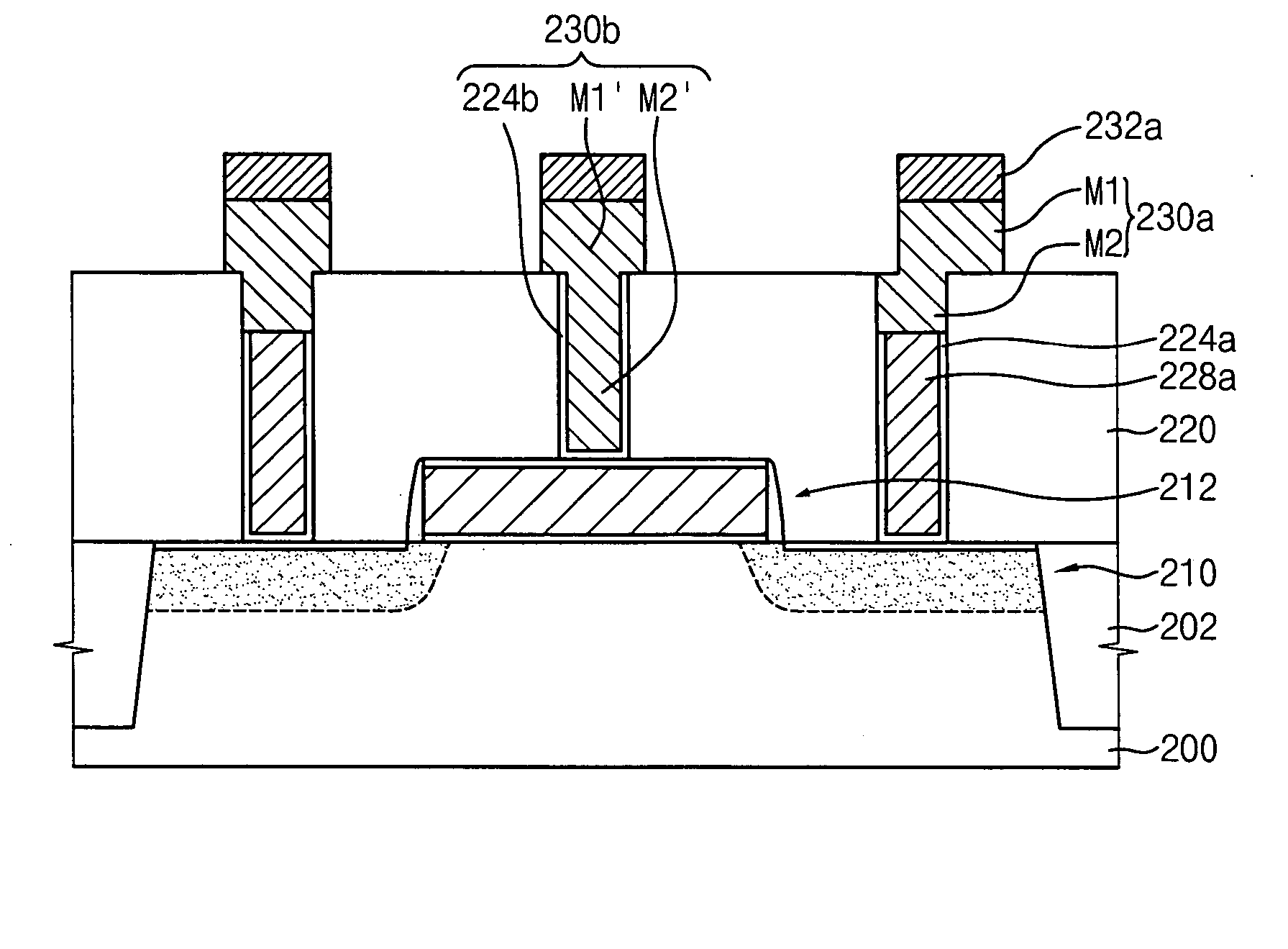

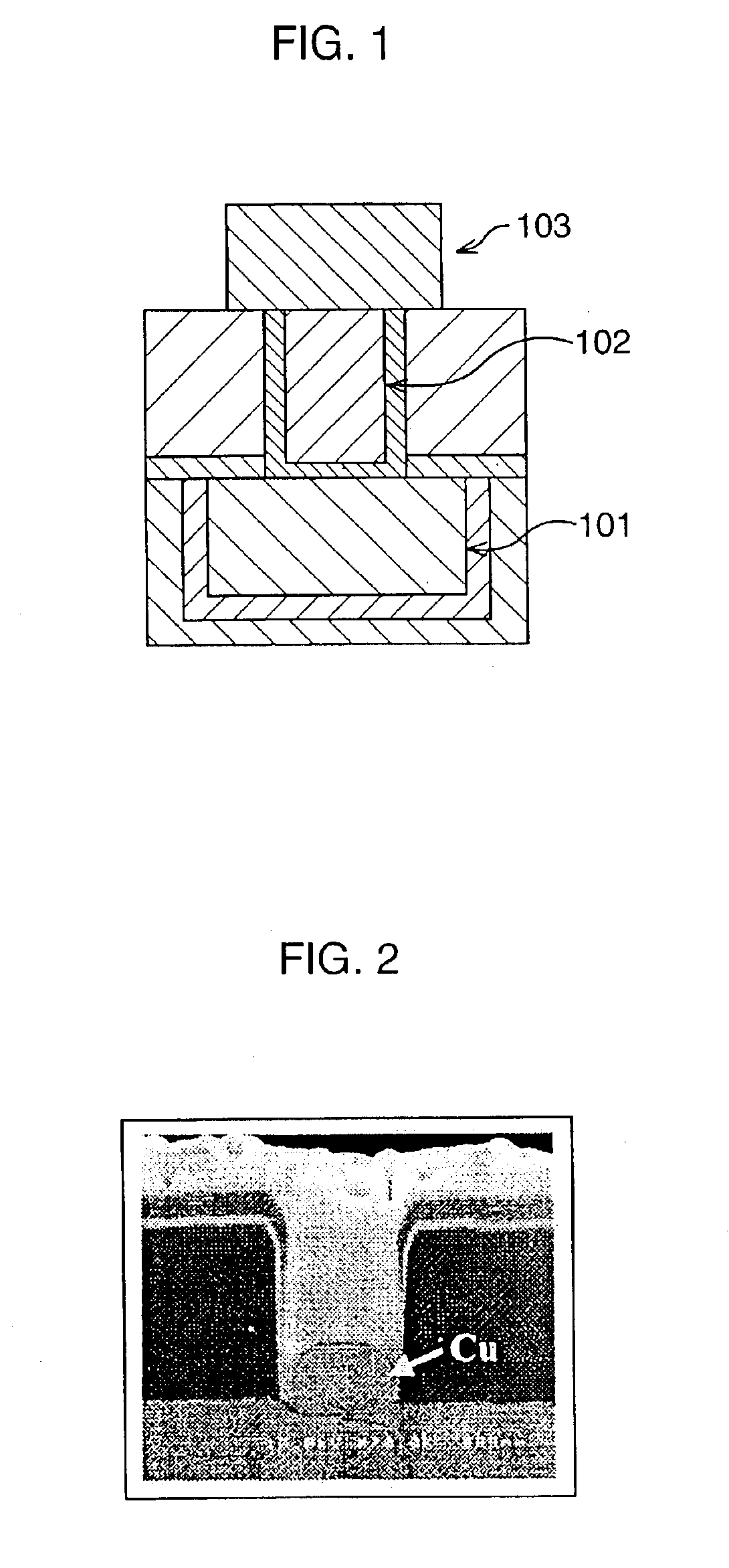

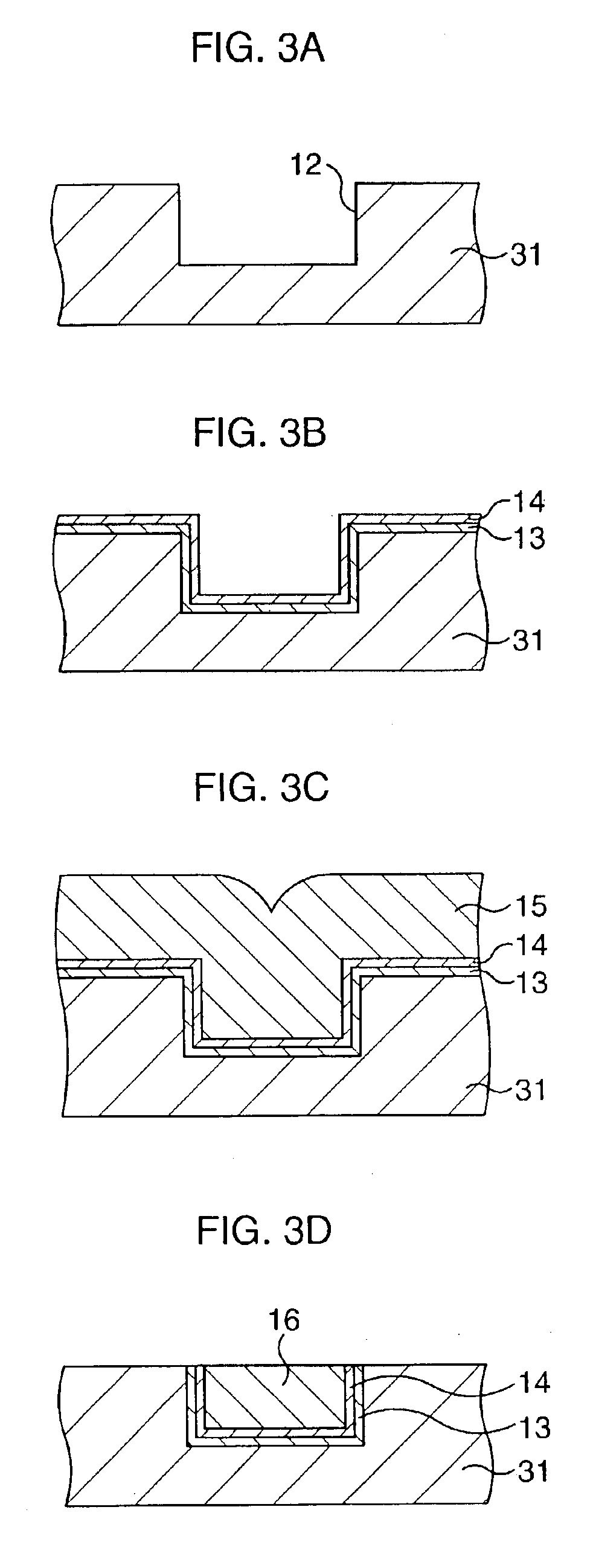

Method of forming dual damascene structure

InactiveUS20020142586A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductorMetal

A method of dual damascene structure formation suitable for wiring on semiconductors. The method of forming a dual damascene structure includes the steps of forming an organic dielectric film and a metal oxide film on an inorganic dielectric film, forming a pattern on the resulting multilayer structure, and then etching the structure.

Owner:JSR CORPORATIOON

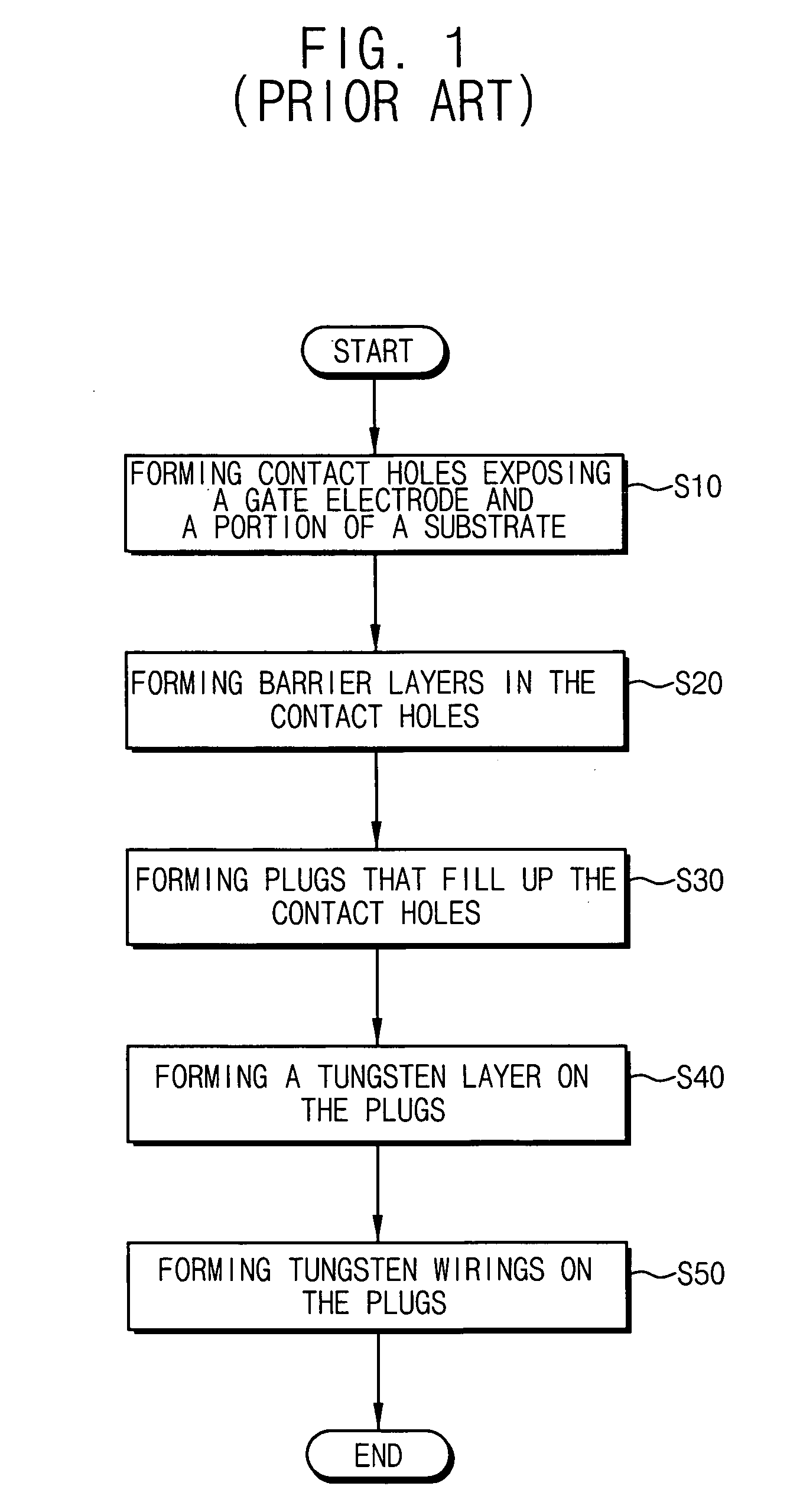

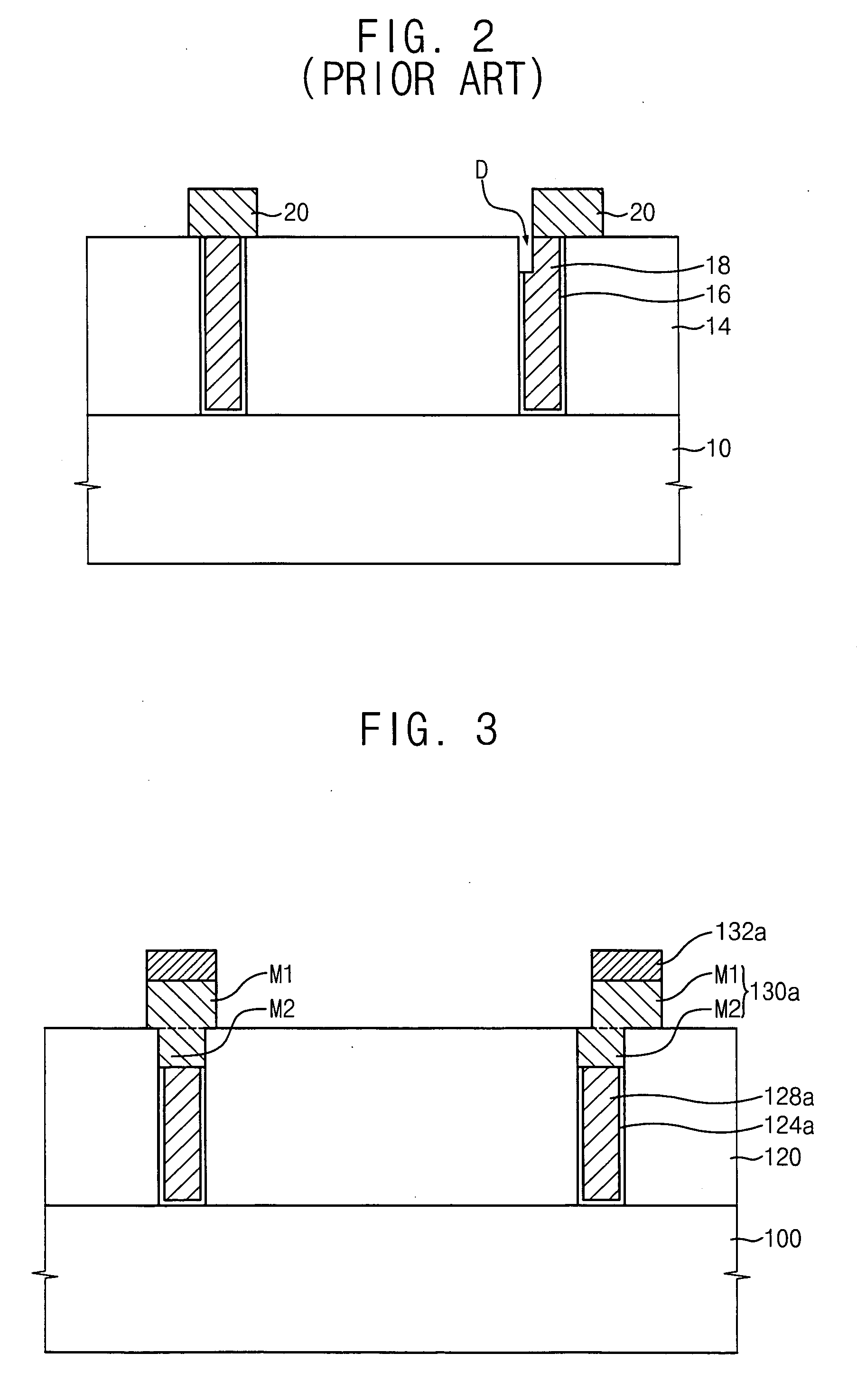

Semiconductor device having a metal wiring structure and method of manufacturing the same

ActiveUS20050287803A1Avoid damageAvoid contact failureSemiconductor/solid-state device detailsSolid-state devicesInsulation layerDevice material

After an insulation layer is formed on a substrate, a contact hole is formed through the insulation layer. A recessed plug is formed to partially fill up the contact hole. The recessed plug has a height substantially smaller than a depth of the contact hole. A metal wiring structure is formed on the recessed plug and on the insulation layer. A lower portion of the metal wiring structure, formed within the contact hole, prevents damage to the recessed plug during an etching process for forming the metal wiring structure. Therefore, the recessed plug may be formed without damage thereof even if an alignment error occurs between an etching mask and the recessed plug during metal wiring structure formation.

Owner:SAMSUNG ELECTRONICS CO LTD

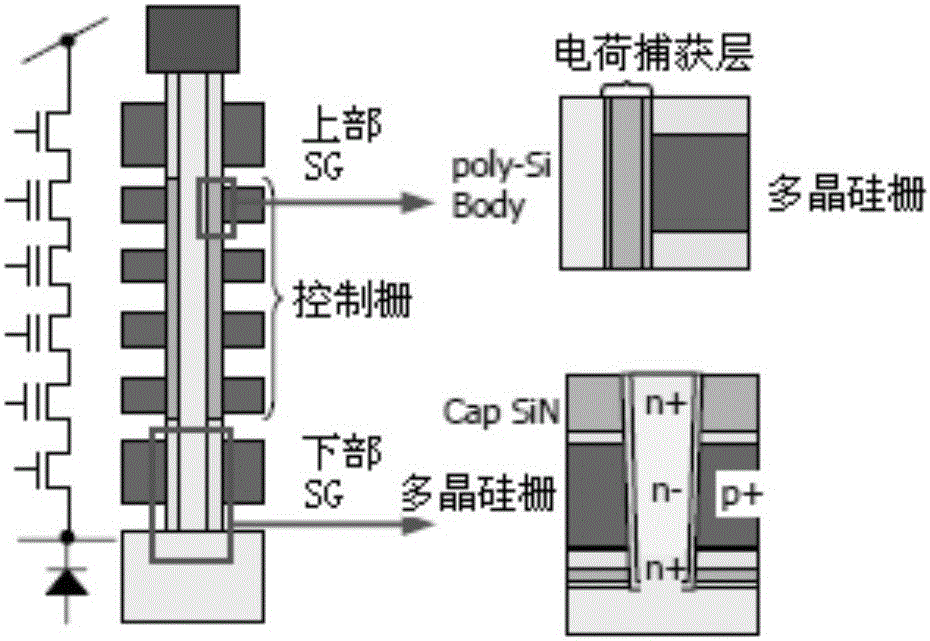

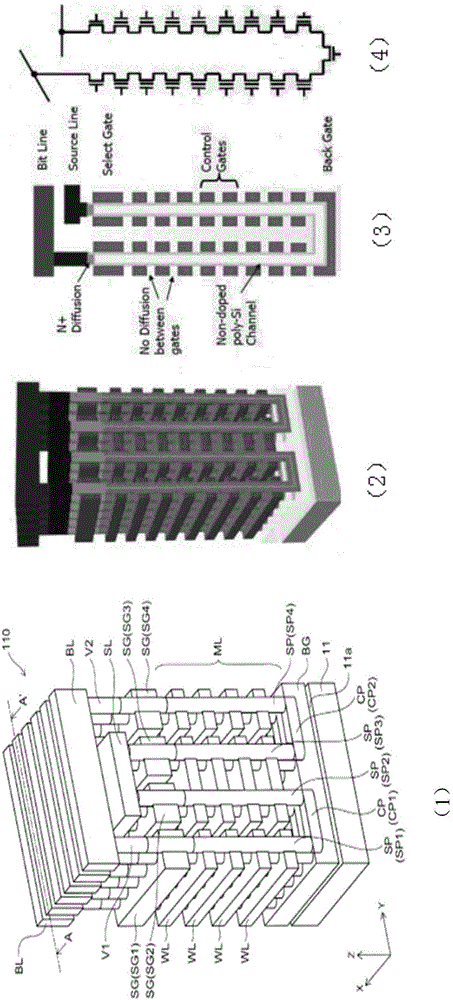

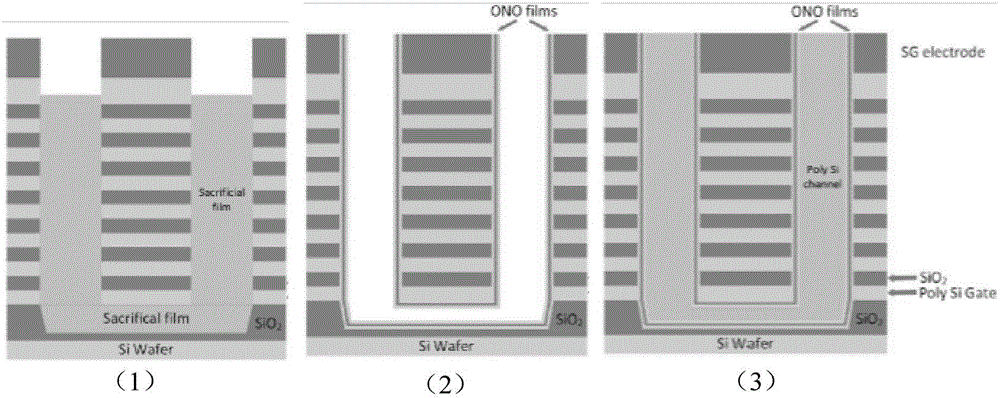

NAND memory structure, NAND memory structure formation method and three dimensional memory array

ActiveCN106409768AReduce process complexityLow costSolid-state devicesSemiconductor/solid-state device manufacturingBit lineEngineering

The invention discloses an NAND memory structure formation method. The formation method comprises the following steps of providing a semiconductor substrate, and forming multiple groups of source electrode selection transistors in the substrate; forming a storage unit of a vertical laminated structure on the source electrode selection transistors, wherein the storage unit of the vertical laminated structure comprises a vertical channel, a multi-layer storage gate medium, and a bit line selection tube grid and a laminated word line formed outside the vertical channel, and drain electrodes of the source electrode selection transistors are contacted with the multi-layer storage gate medium on the bottom of the vertical channel; and forming a bit line on the storage unit of the vertical laminated structure; and applying breakdown voltage to the multi-layer storage gate medium between the drain electrodes of the source electrode selection transistors and the vertical channel through the bit line and the laminated word line. The NAND memory structure formation method can reduce the process difficulty and the cost and improve the integration density. The invention also discloses an NAND memory structure and a formation method thereof and a three dimensional memory array.

Owner:TSINGHUA UNIV

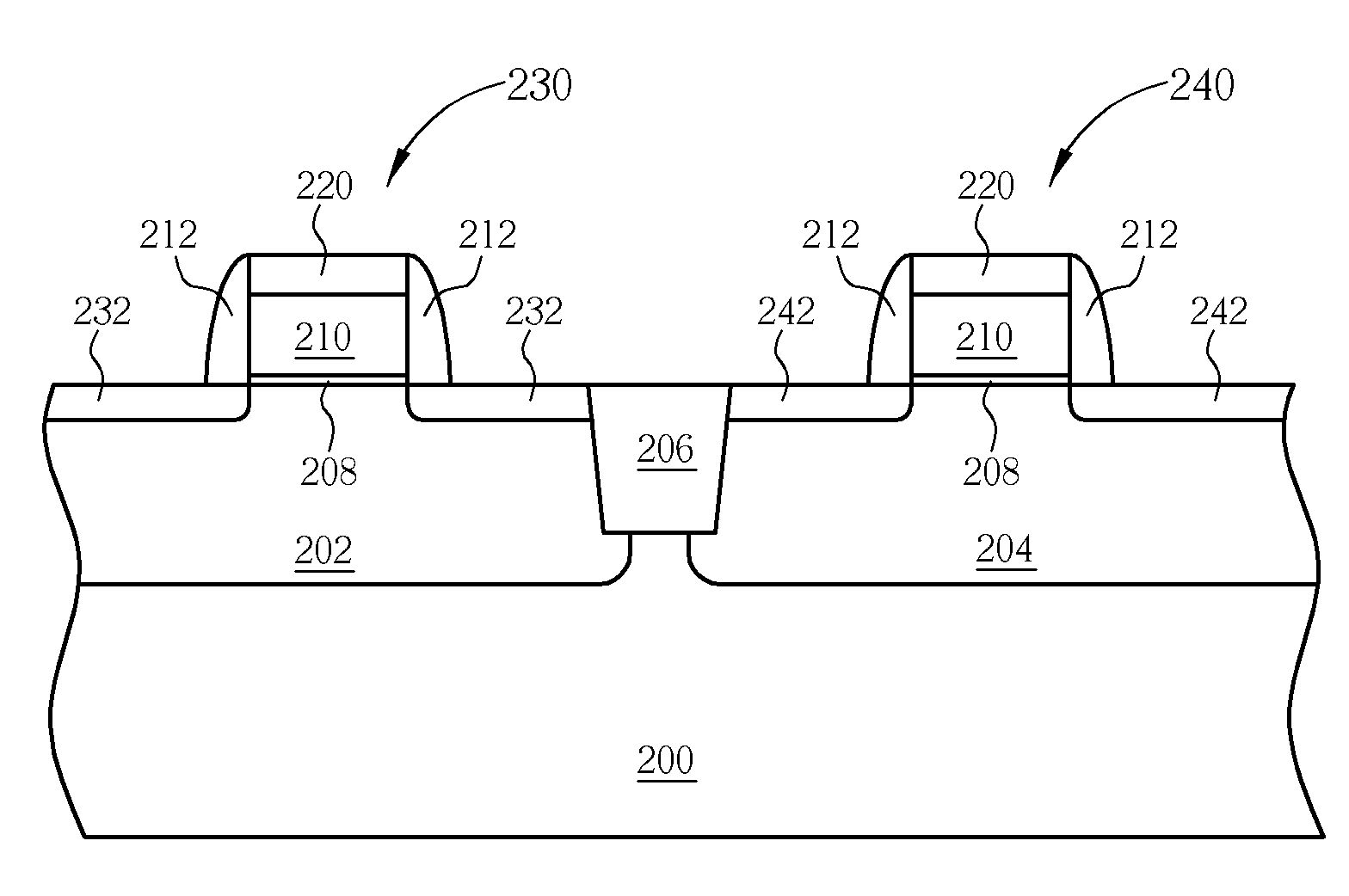

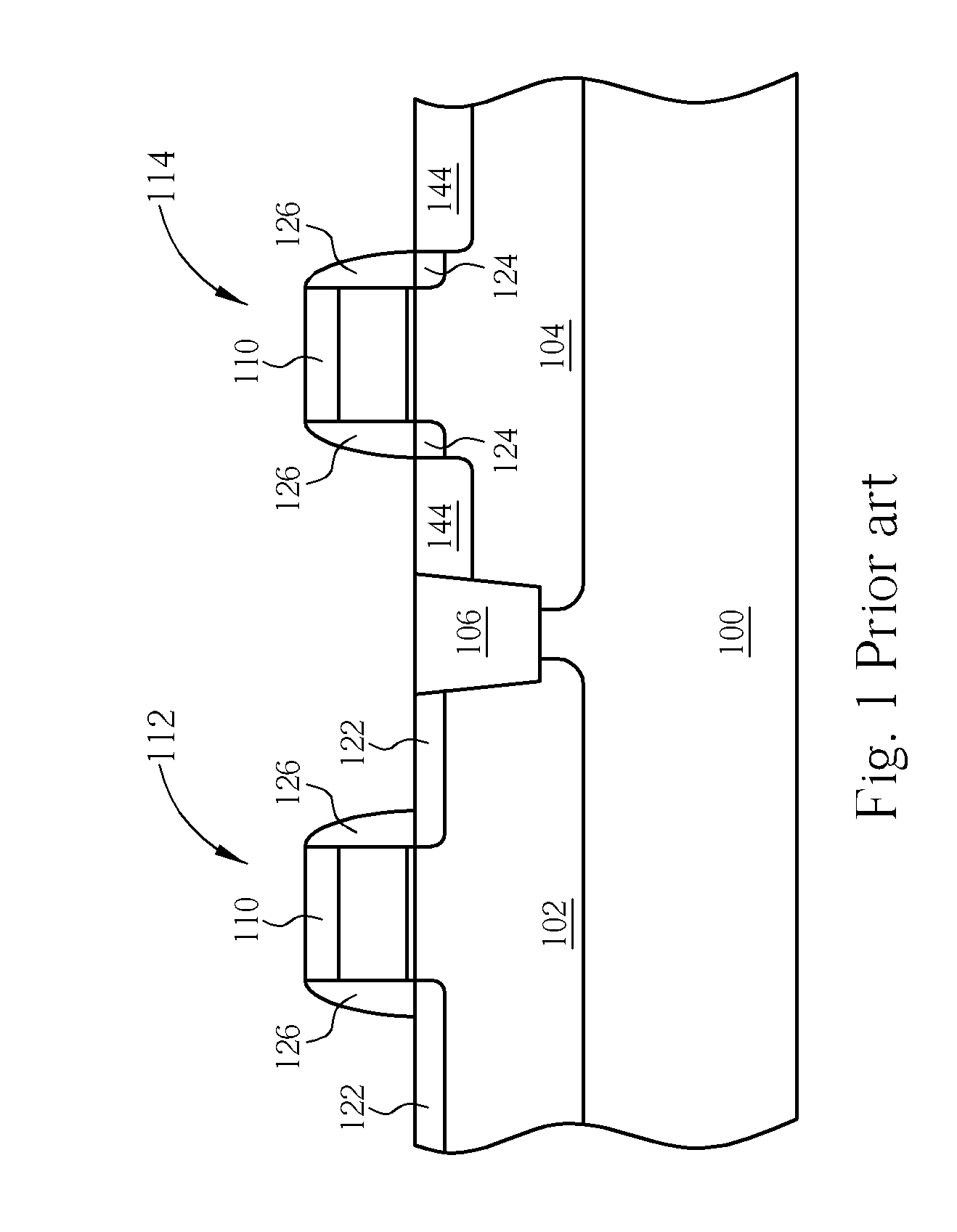

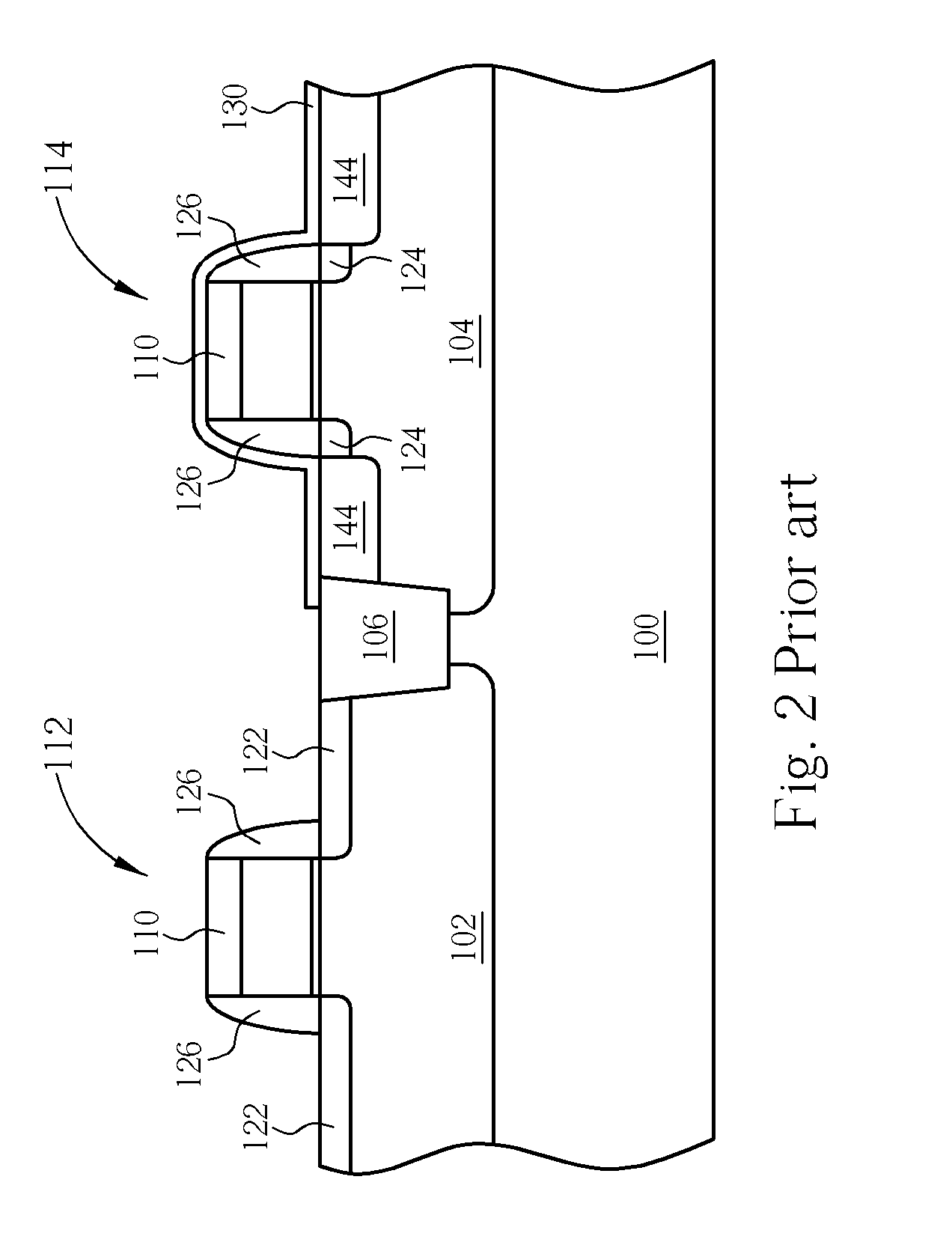

Method of manufacturing complementary metal oxide semiconductor transistors

ActiveUS20090023258A1Prevent deviationReduce thickness variationSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSEngineering

A method for manufacturing CMOS transistors includes an etching back process alternatively performed after the gate structure formation, the lightly doped drain formation, source / drain implantation, or SEG process to etch a hard mask layer covering and protecting a first type gate structure, and to reduce thickness deviation between the hard masks covering the first type gate structure and a second type gate structure. Therefore the damage to spacers, STIs, and the profile of the gate structures due to the thickness deviation is prevented.

Owner:MARLIN SEMICON LTD

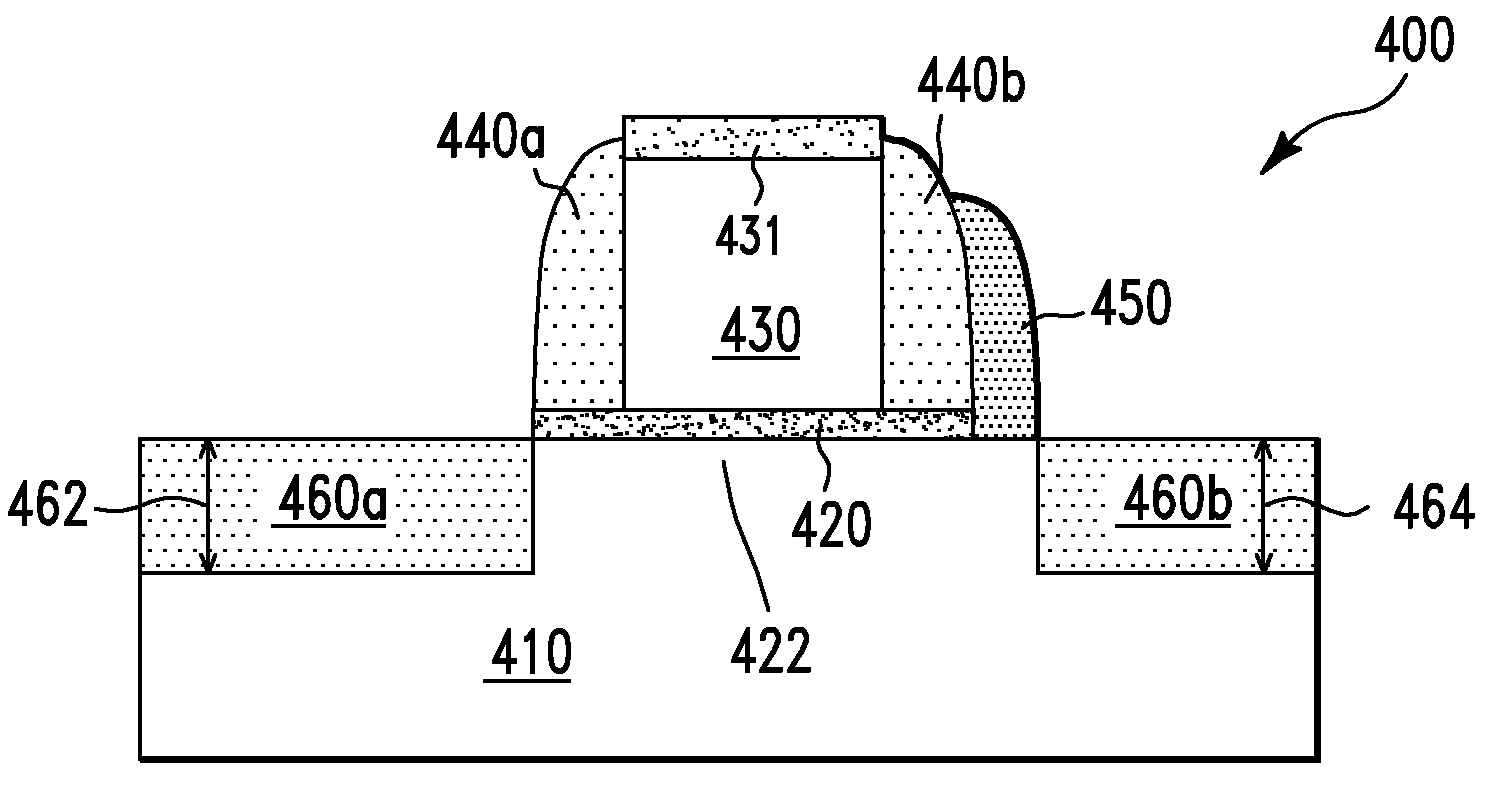

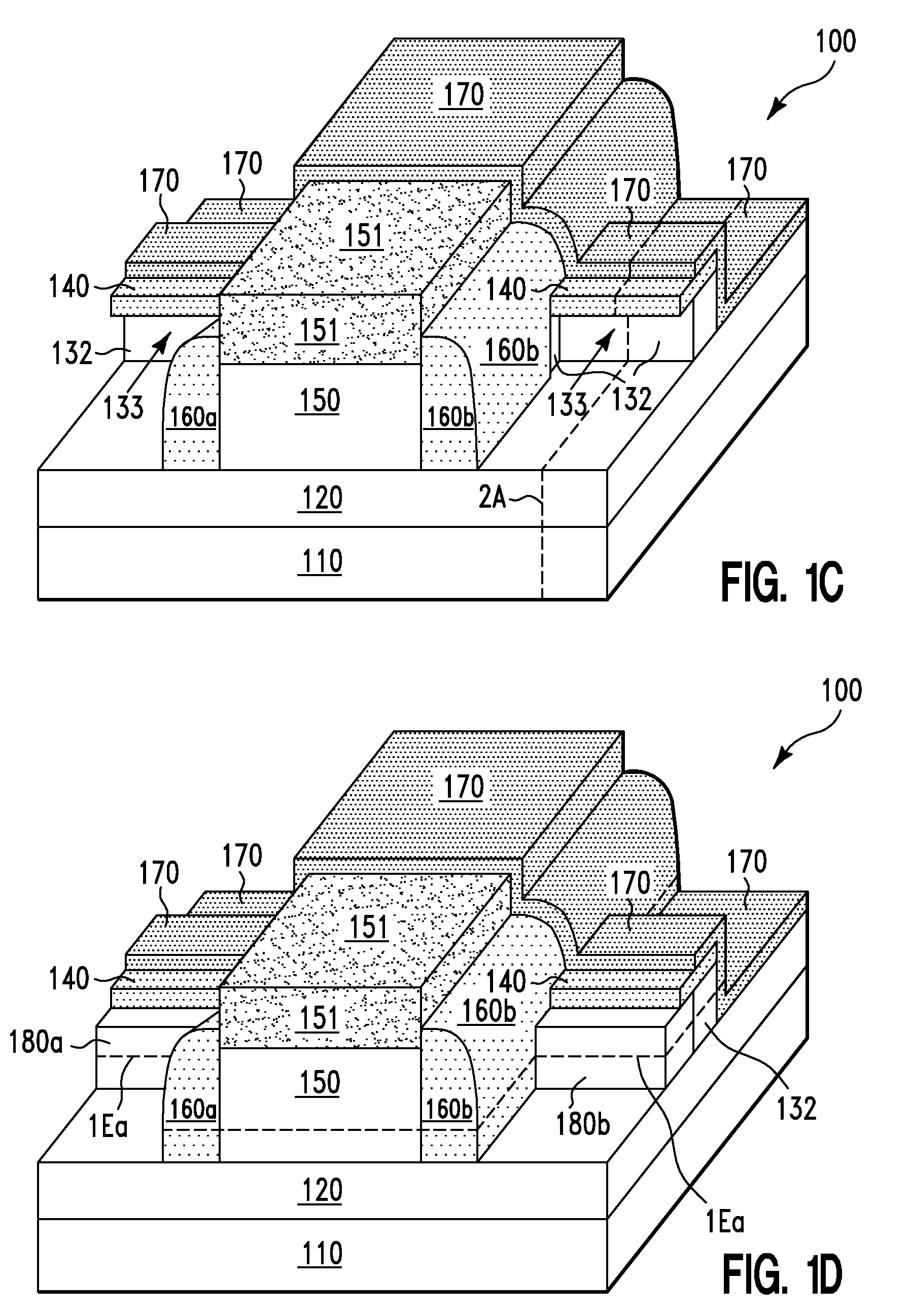

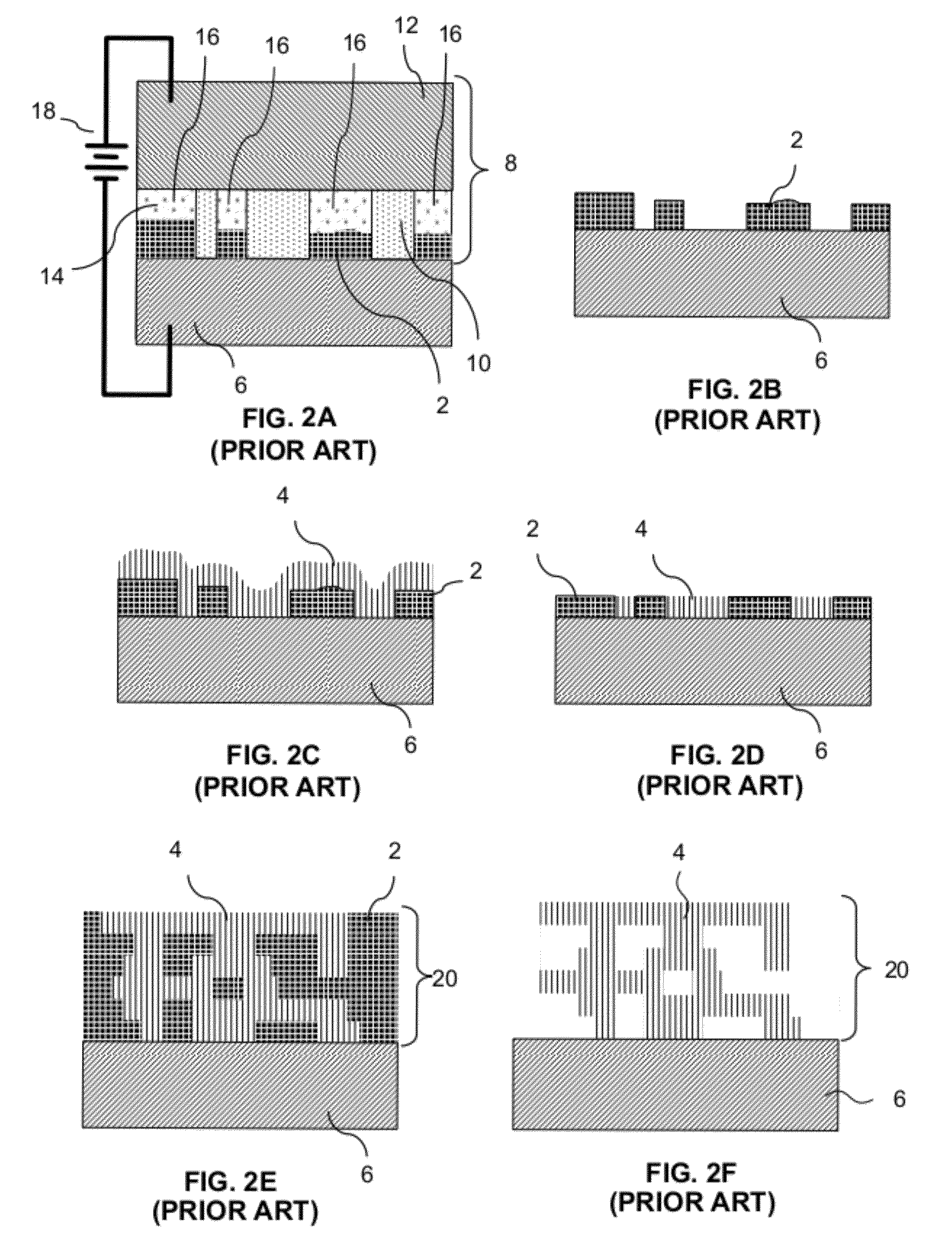

Transistors having asymmetric strained source/drain portions

InactiveUS20090263949A1Increase strainSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricStructure formation

A structure formation method. First, a structure is provided including (a) a fin region comprising (i) a first source / drain portion having a first surface and a third surface parallel to each other, not coplanar, and both exposed to a surrounding ambient, (ii) a second source / drain portion having a second surface and a fourth surface parallel to each other, not coplanar, and both exposed to the surrounding ambient, and (iii) a channel region disposed between the first and second source / drain portions, (b) a gate dielectric layer, and (c) a gate electrode region, wherein the gate dielectric layer (i) is sandwiched between, and (ii) electrically insulates the gate electrode region and the channel region. Next, a patterned covering layer is used to cover the first and second surfaces but not the third and fourth surfaces. Then, the first and second source / drain portions are etched at the third and fourth surfaces, respectively.

Owner:GLOBALFOUNDRIES INC

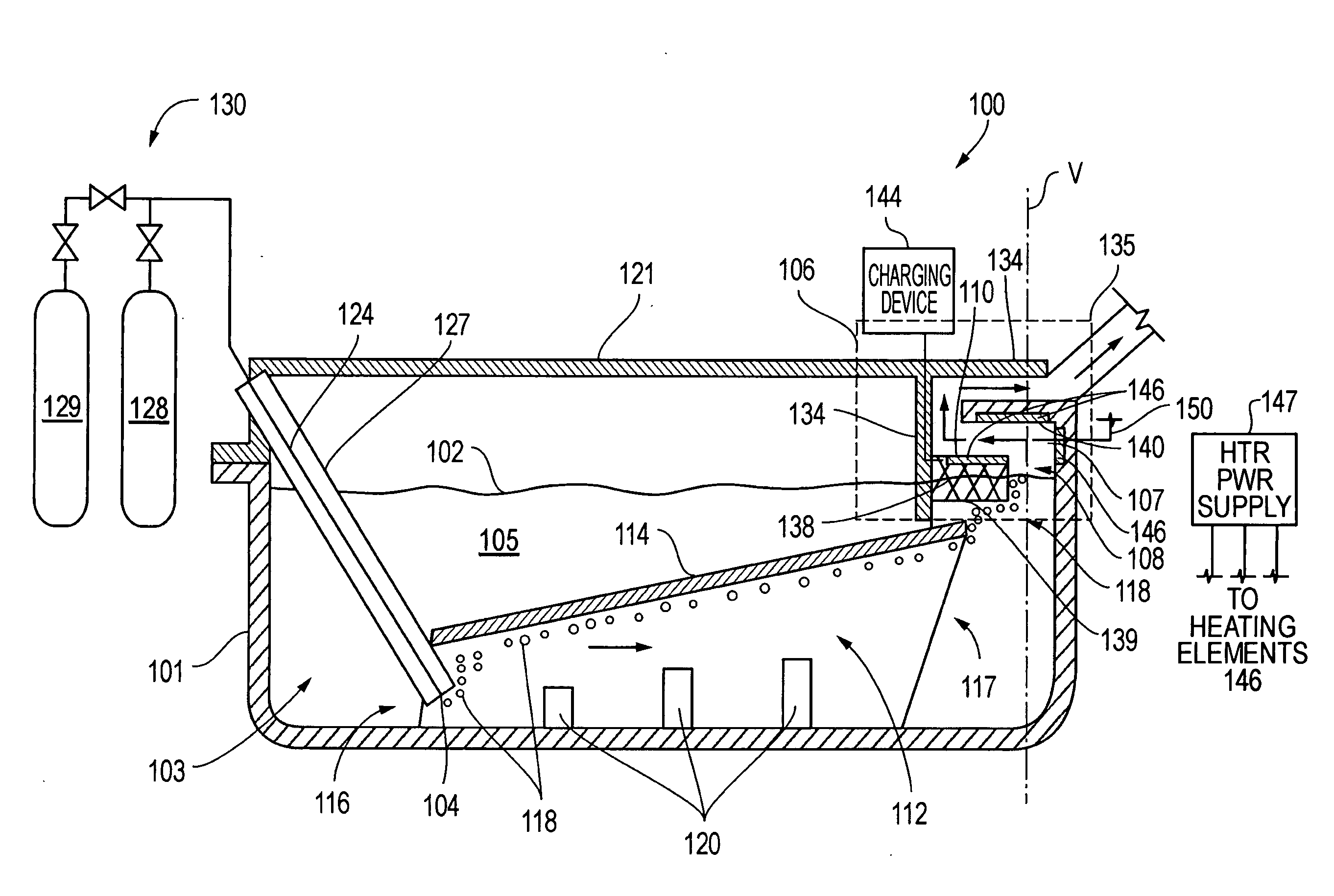

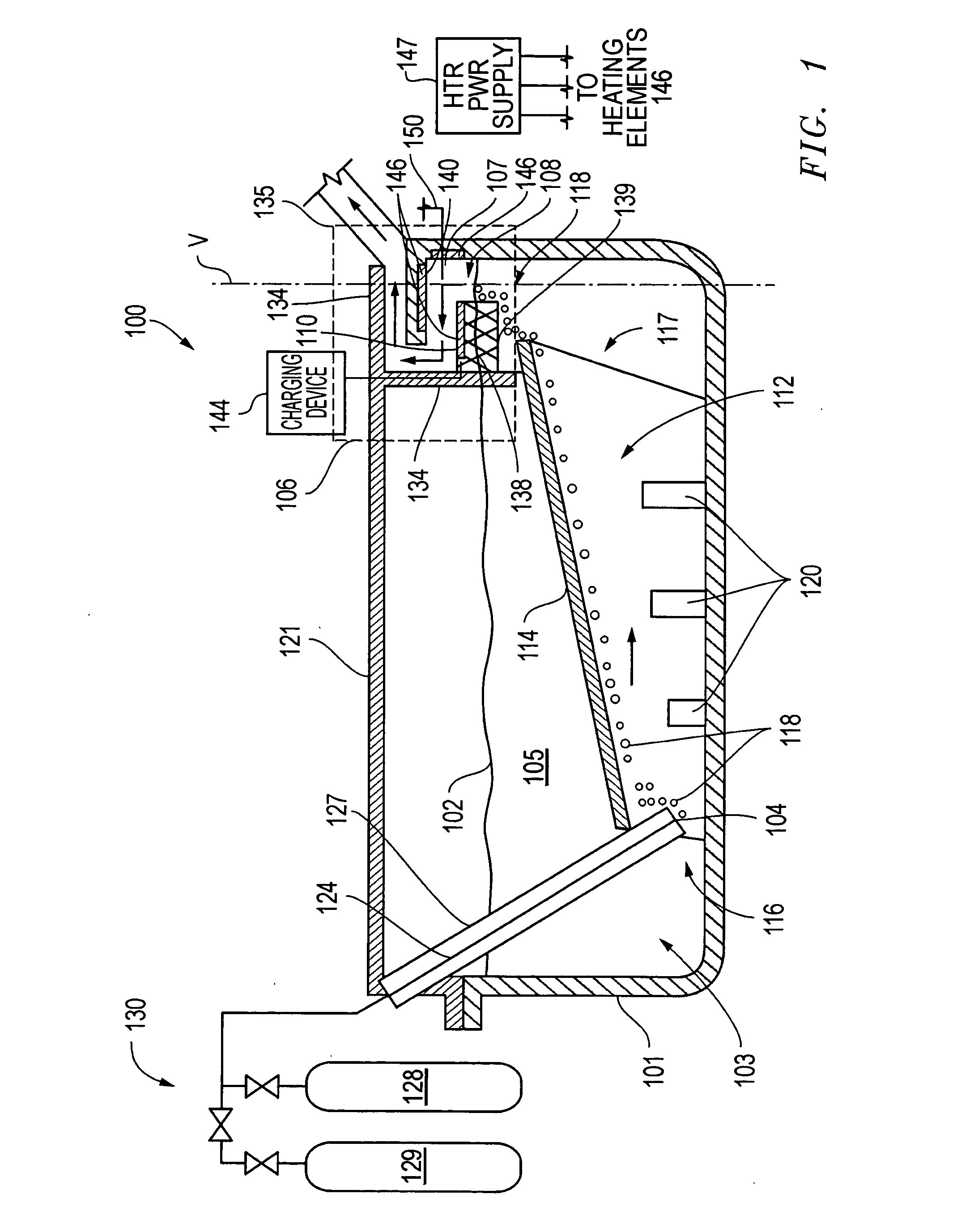

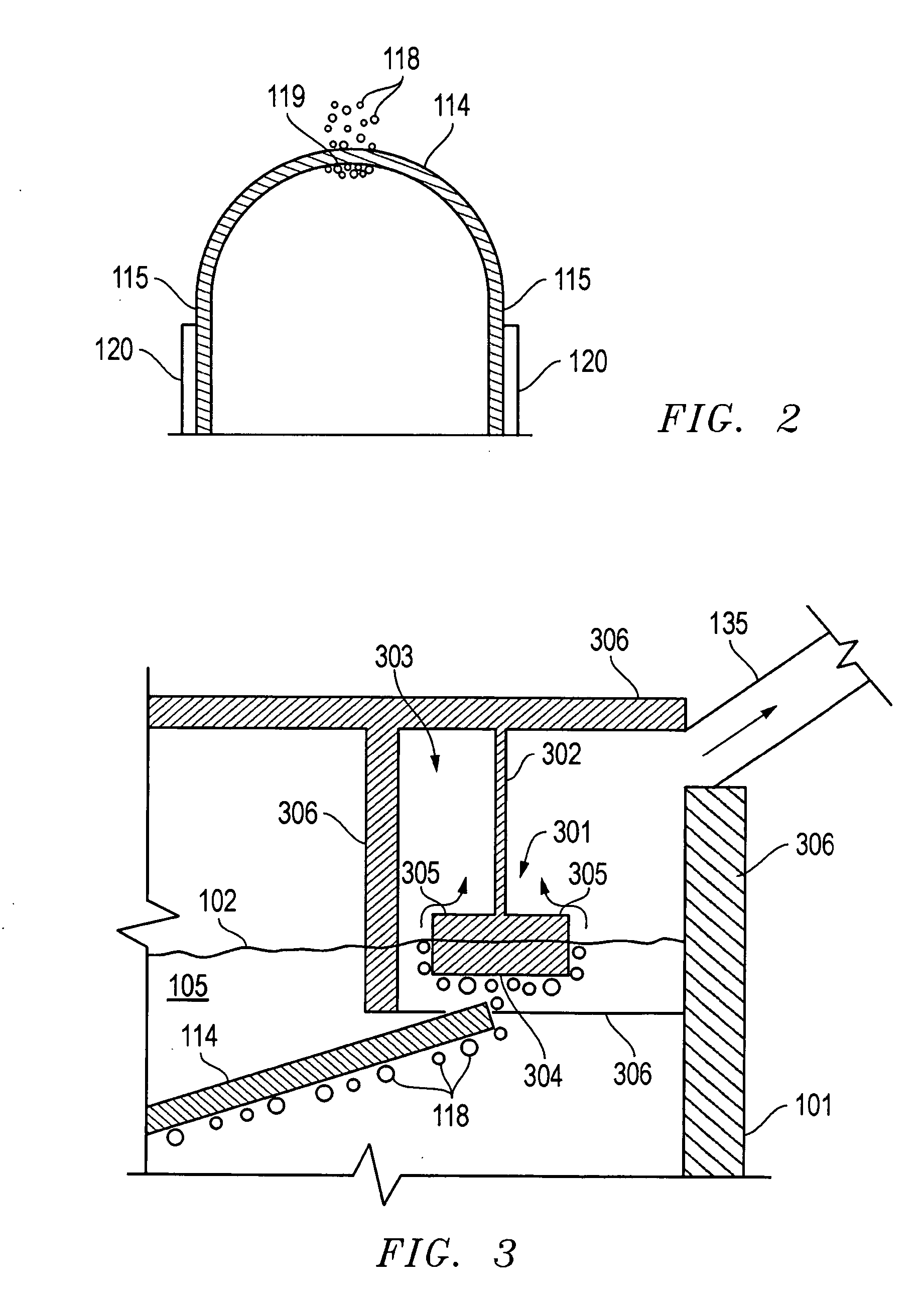

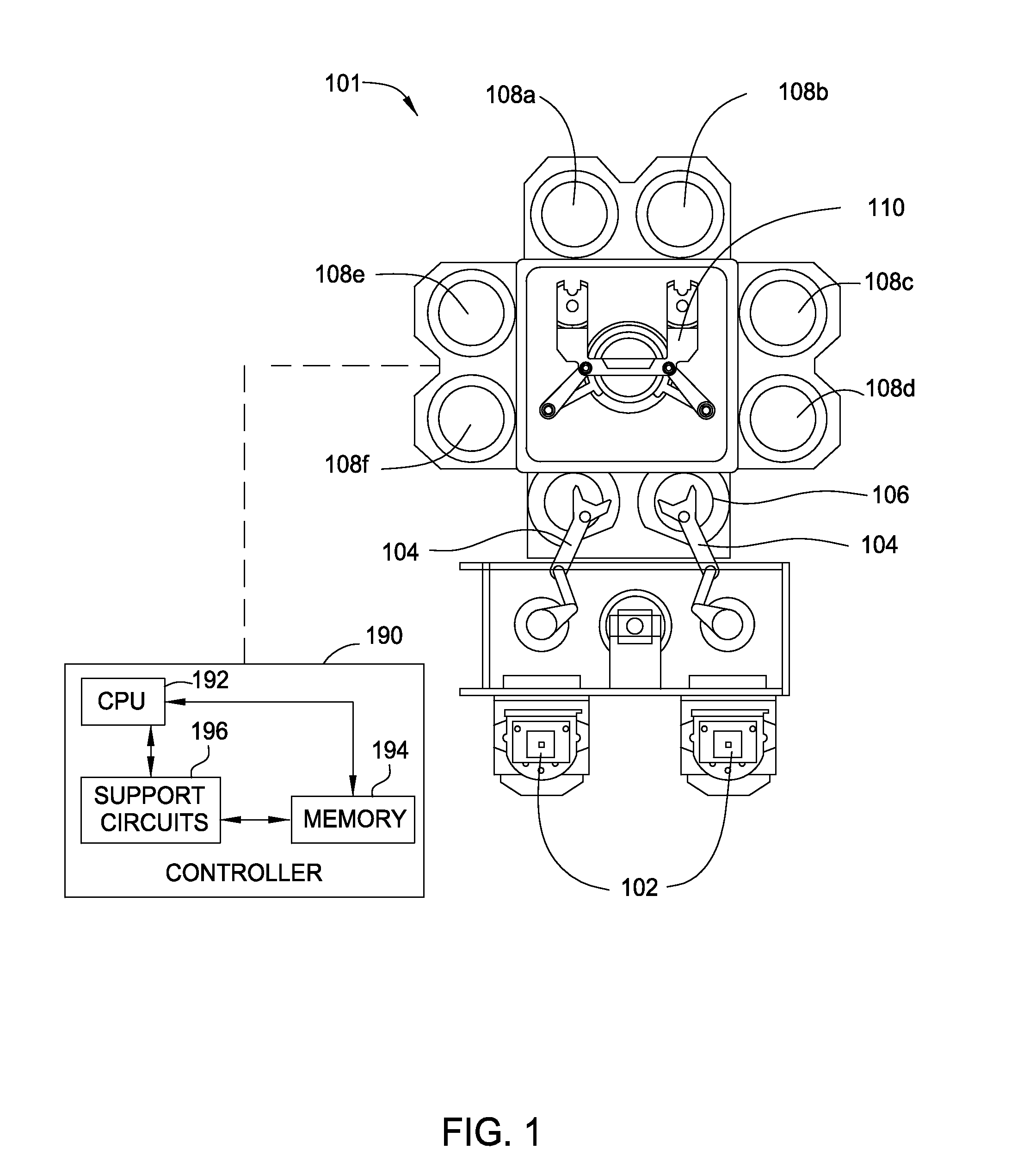

Method and apparatus for preparing a collection surface for use in producing carbon nanostructures

A method includes producing deposition conditions in a collection area above a reactant liquid containing one or more catalyst metals. The reactant liquid is maintained under conditions in which atoms of the catalyst metal may escape from the reactant liquid into the collection area. A suitable carrier gas is directed to traverse a surface of the reactant liquid and flow along a collection path that passes over a collection surface in the collection area. This flow of carrier gas is maintained so that escaped atoms of catalyst metal are entrained in the gas traversing the surface of the reactant liquid and are deposited on the prior to or concurrently with nanocarbon structure formation at the collection surface.

Owner:CLEAN TECH INT

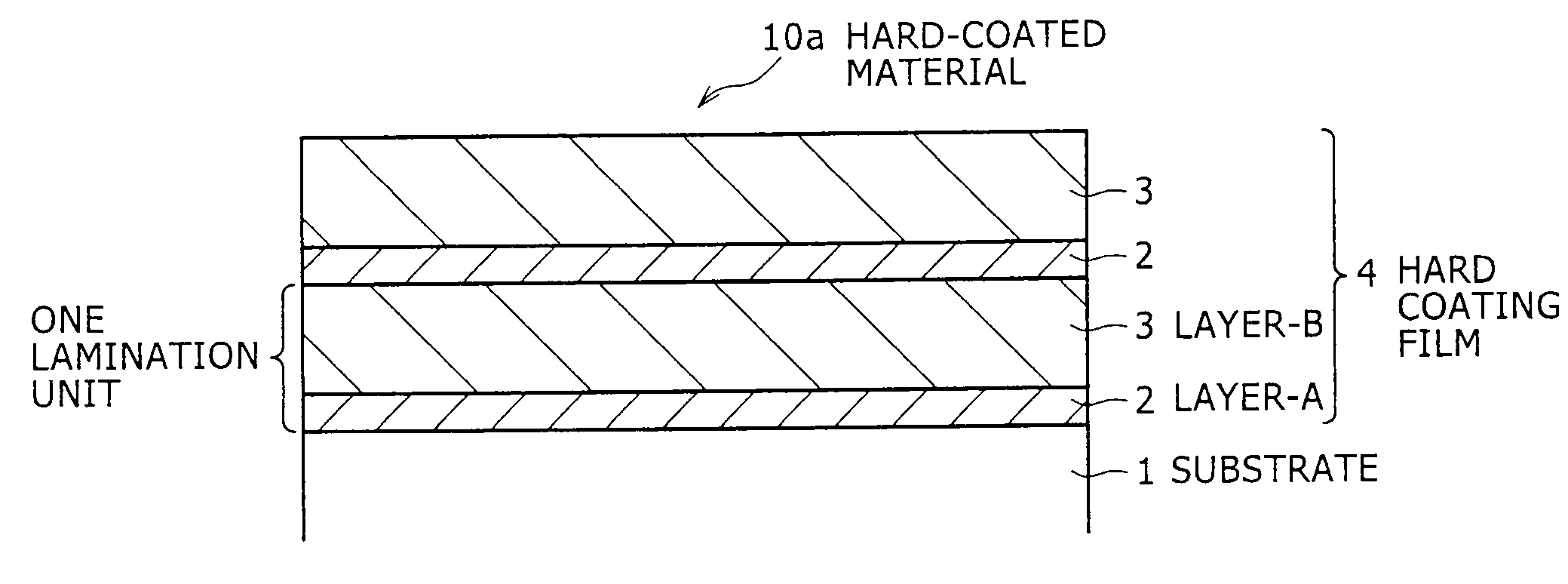

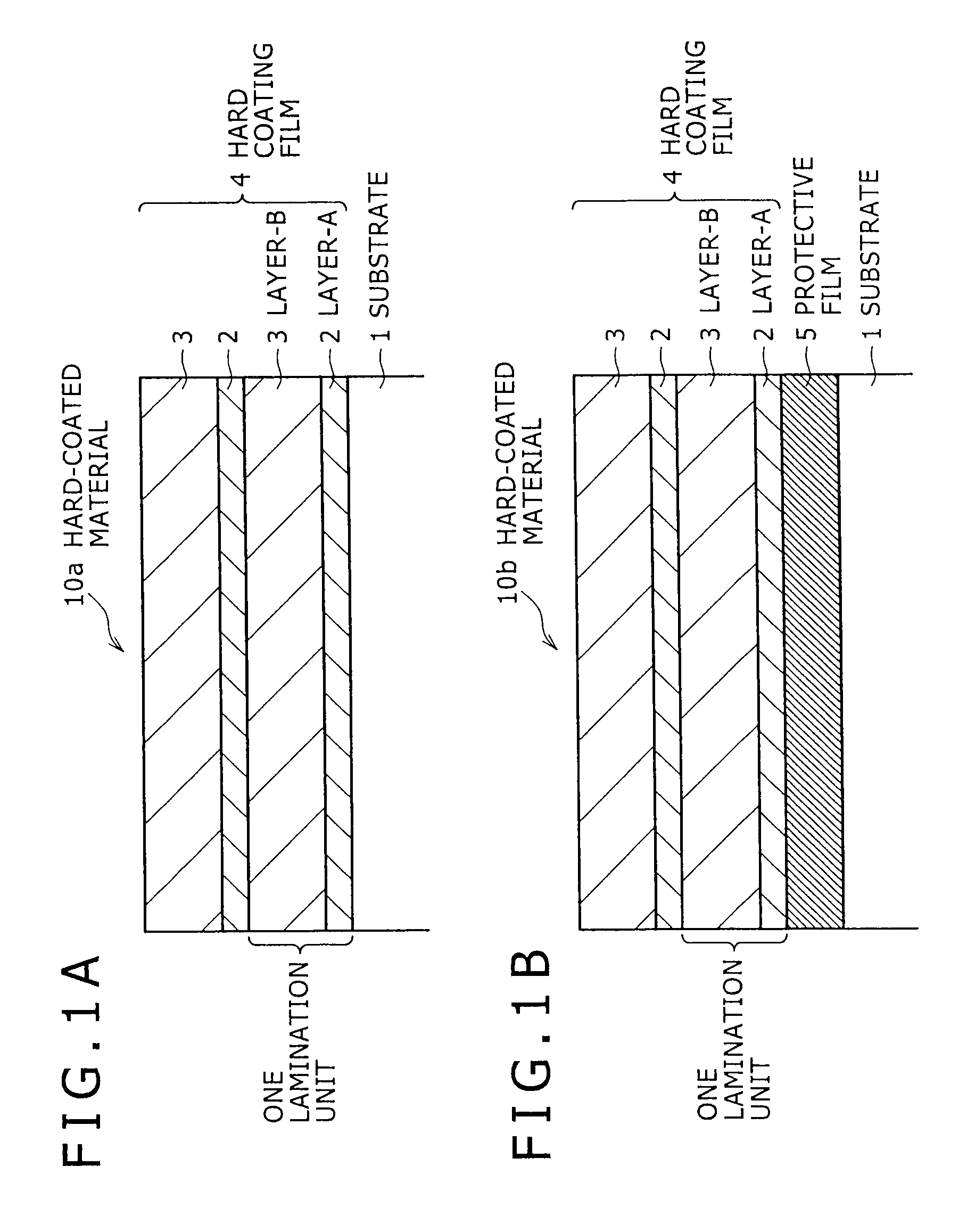

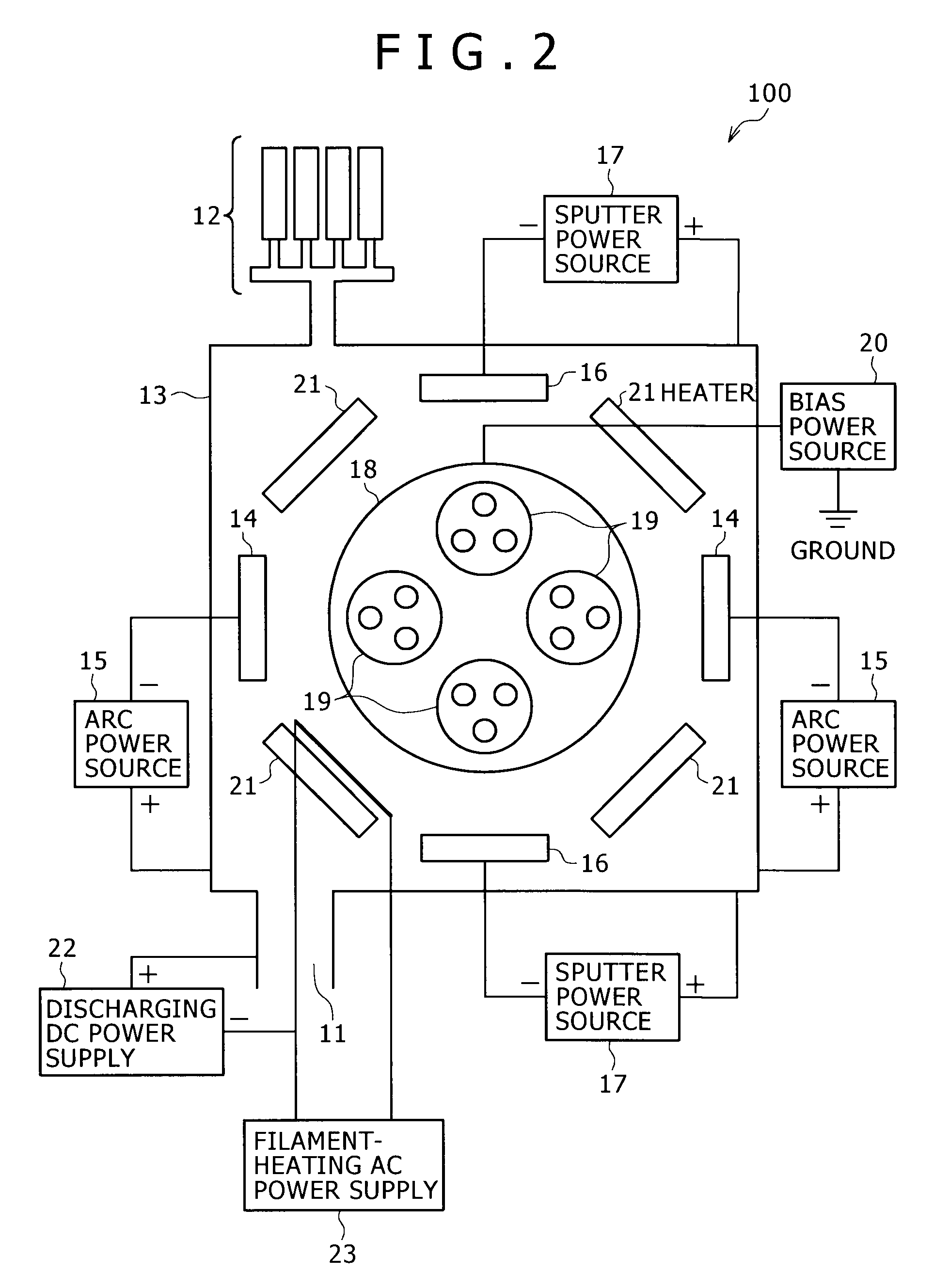

Material with hard coating film formed on substrate surface thereof

ActiveUS20100047545A1Improve wear resistanceImprove removabilitySynthetic resin layered productsVacuum evaporation coatingTotal thicknessWear resistance

There is provided a hard-coated material in which a substrate thereof is coated with a hard coating film that is excellent in wear resistance and also excellent in film removability to allow easy removal thereof once damaged or worn for the purpose of recycled use of the substrate. The hard coating film formed on the substrate comprises a layer-A and a layer-B; wherein the layer-A has a component composition represented by the formula TivM1-v(CxNyOz) (where M denotes at least one species selected from predetermined elements, and the variables v, x, y, and z indicate predetermined ratios of the respective elements); and wherein the layer-B has a component composition represented by the formula TivCrwM1-v-w(CxNyOz) (where M denotes at least one species selected from predetermined elements, and the variables v, w, x, y, and z indicate predetermined ratios of the respective elements). The layer-A and the layer-B are laminated alternately in succession. In terms of lamination units each corresponding to a combination of a singularity of the layer-A disposed at the lower level and a singularity of the layer-B disposed at the upper level, at least two lamination units are provided in laminated structure formation. The ratio in thickness of a singularity of the layer-B to a singularity of the layer-A is at least 2. The thickness of a singularity of the layer-A is within the range of 0.1 to 3 μm both inclusive, the thickness of a singularity of the layer-B is within the range of 1 to 10 μm both inclusive, and the total thickness of a plurality of the layers-B is at least 5 μm.

Owner:KOBE STEEL LTD

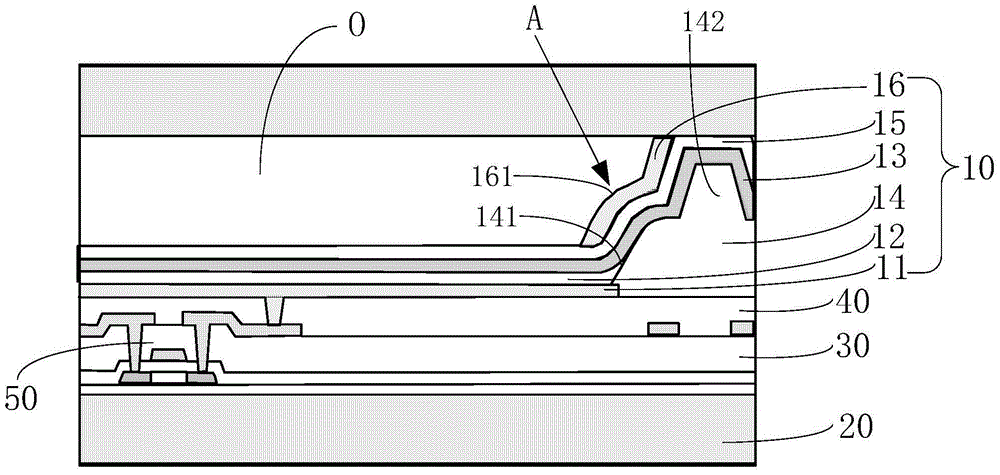

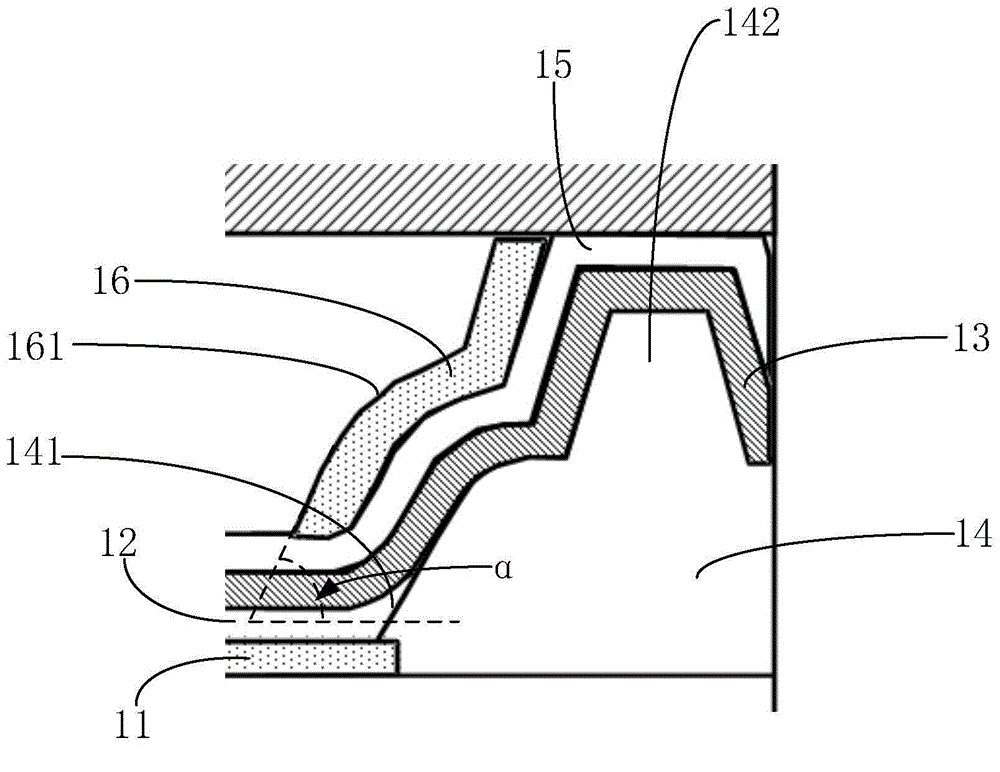

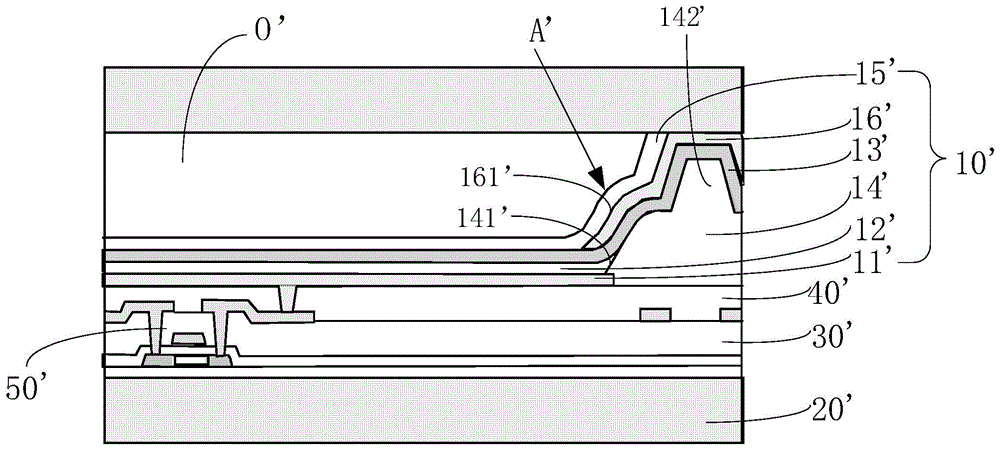

Organic light emitting structure, organic light emitting device possessing the structure and panel

InactiveCN106033800AIncrease lossAvoid breakingSolid-state devicesSemiconductor/solid-state device manufacturingOrganic light emitting deviceOptoelectronics

The present invention relates to an organic light-emitting structure and an organic light-emitting device and a panel with the structure. In the organic light-emitting structure of the present invention, an inclined portion is formed on a pixel definition layer, and a reflective layer is provided in the inclined portion. The reflective layer has a relatively The inclined light reflecting surface of the organic light-emitting layer can improve the loss of light in the lateral direction, change the light output path in the lateral direction, and improve the light output efficiency; on the other hand, the reflective layer is located above the second electrode layer, which can prevent The fracture phenomenon that may occur in the second electrode layer due to the formation of an inclined structure.

Owner:EVERDISPLAY OPTRONICS (SHANGHAI) CO LTD

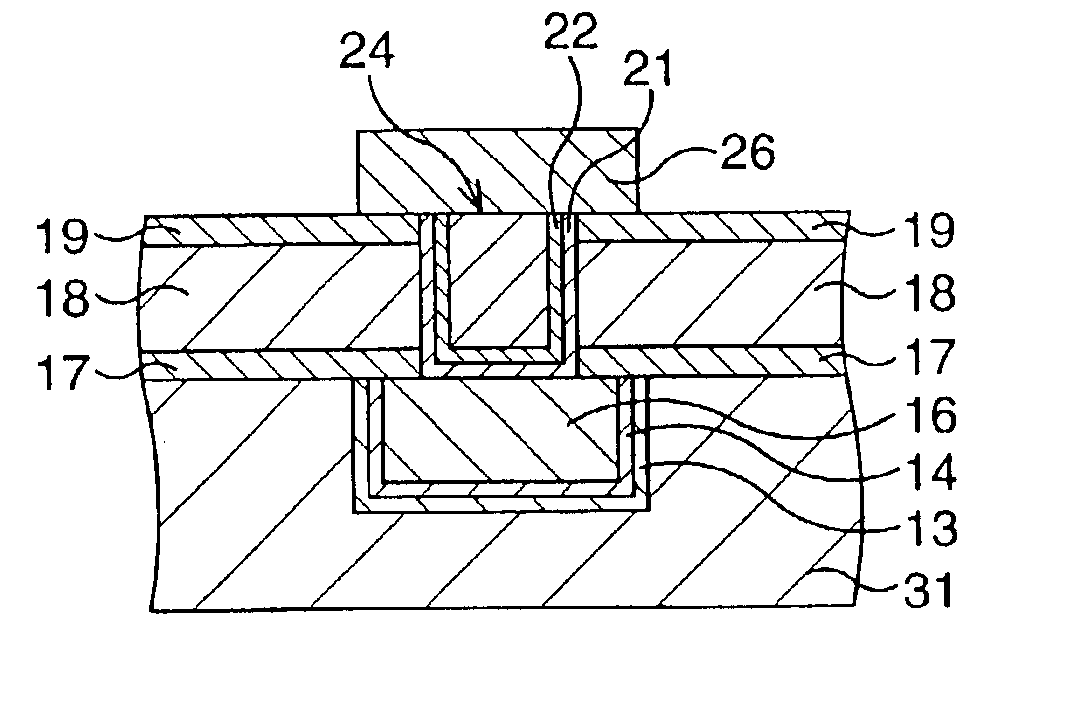

Interconnection structure and interconnection structure formation method

InactiveUS6933609B2Preventing wiring delayImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesElutionEngineering

An insulating film covering a Cu interconnection is formed. A contact hole which partially exposes the surface of the Cu interconnection is formed in the insulating film. A series of steps (steps (a) to (d)) including (a) a step of continuously supplying WF6 gas for a predetermined time, (b) a step of continuously exhausting the WF6 gas atmosphere for a predetermined time, (c) a step of continuously supplying SiH4 gas for a predetermined time, and (d) a step of continuously exhausting the SiH4 gas atmosphere for a predetermined time, is repeatedly executed to form W nuclei in the contact hole. Then, a W film is buried into the contact hole. This interconnection structure formation method can reliably bury the W film into the contact hole while preventing Cu elution from the Cu interconnection to the W plug.

Owner:FUJITSU SEMICON LTD

Enhanced methods for at least partial in situ release of sacrificial material from cavities or channels and/or sealing of etching holes during fabrication of multi-layer microscale or millimeter-scale complex three-dimensional structures

ActiveUS8262916B1Improve sealingDecorative surface effects3D structure electroformingMulti materialEngineering

Embodiments of the invention are directed to multi-layer, multi-material fabrication methods (e.g. electrochemical fabrication methods) which provide improved versatility in producing complex microdevices and in particular in removing sacrificial material from passages, channels, or cavities that are complex or that include etching access ports in their final configurations that are small relative to passage, channel, or cavity lengths. Embodiments of the present invention provide for removal of sacrificial material from these passages, channels or cavities using one or more initial or preliminary removal steps that occur prior to completion of the such passages that results from the completion of the layer forming steps. In some embodiments, first sacrificial material is replaced after a secondary solid sacrificial material after the initial removal step or steps. In other embodiments, the first sacrificial material is replaced after a liquid material after the initial removal step or steps. In some embodiments, desired structure formation may occur along or separately from one or more etchant directing manifolds that can force etchant into the passages, channels, and cavities.

Owner:MICROFAB

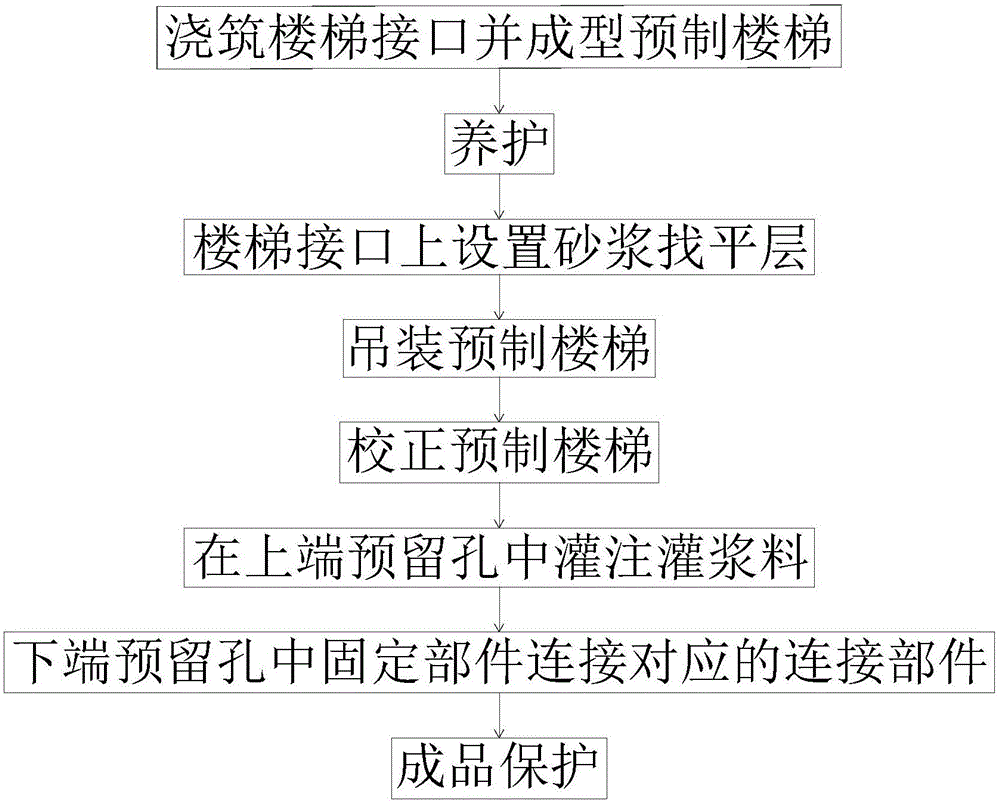

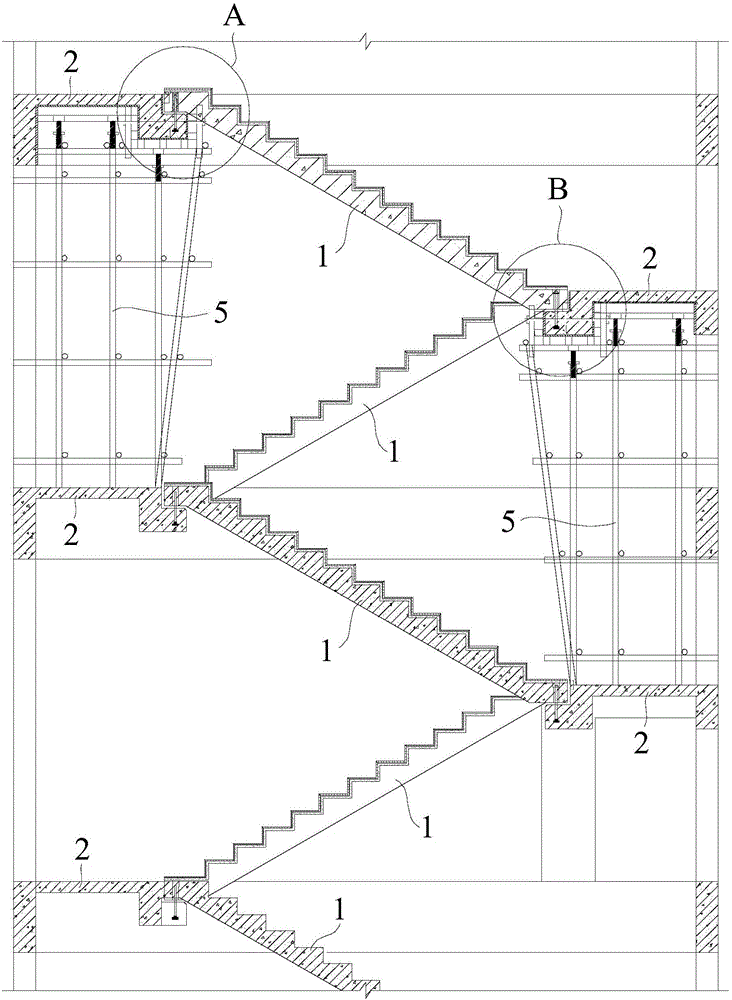

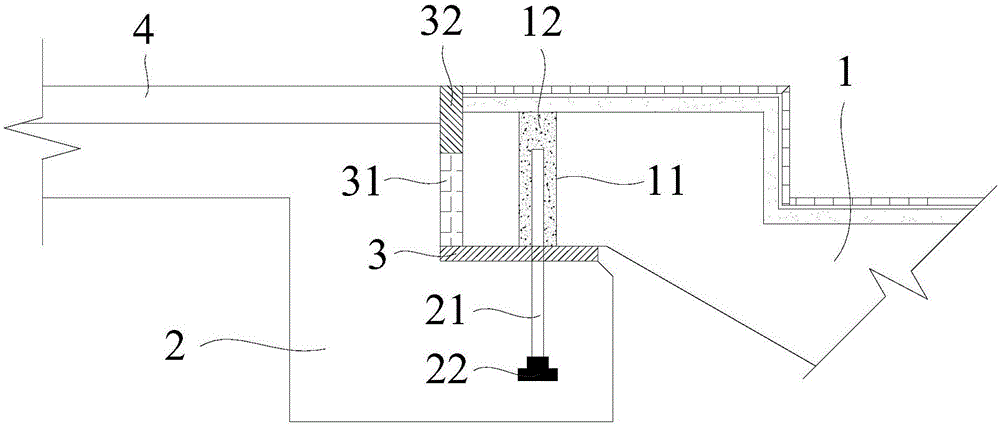

Assembling type stair and mounting method thereof

InactiveCN106284877AImprove assembly efficiencyTime-consuming and laborious to solveStairwaysSupporting systemReinforced concrete

The invention discloses an assembling type stair and a mounting method thereof. The mounting method comprises the following steps: A, building a supporting system and a mold pouring stair interface; B, maintaining; C, setting a mortar leveling layer on the stair interface; D, hoisting a precast stair; E, correcting a precast stair; F, pouring a grouting material in a preformed hole in the upper end and sealing with mortar; G, connecting a fixed part in a preformed hole in the lower end with a corresponding part and sealing with mortar; H, protecting a finished product. By the assembling type stair and the mounting method thereof, the problems that the conventional building structure system, comprising the stair, adopts cast-in-place reinforced concrete, a large amount of brackets need to be built on the construction site and a large amount of pouring molds and mold plates need to be paved on the construction site, and time and labor are consumed can be effectively solved by splicing the precast stair on the construction site. The method is simple in construction process and good in structure formation, the construction period is greatly shortened, and manpower and material resources are saved.

Owner:CHENGDU NO 4 CONSTR ENG

Ecological soil conditioner capable of improving acid soil and preparation method

InactiveCN105950166AReduce acidityRaise the pHAgriculture tools and machinesOther chemical processesChemical structureEcological environment

The invention belongs to the technical field of soil improvement and particularly relates to an ecological soil conditioner capable of improving acid soil and a preparation method. The ecological soil conditioner comprises raw materials in parts by weight as follows: 30-60 parts of carbonized distillers' grains, 10-20 parts of industrial and agricultural waste, 10-15 parts of sargassum, 10-15 parts of water hyacinth, 5-10 parts of plant ash, 5-15 parts of nano-modified clay, 5-10 parts of sodium alginate, 1-10 parts of tamarind polysaccharide gum, 1-5 parts of chelated secondary elements and trace elements and 0.1-3 parts of graphene oxide. The ecological soil conditioner can regulate the pH value of the soil, promote granular structure formation of the soil, improve the physical and chemical structures of the acid soil, increase organic matter content of the soil, improve the moisture and fertilizer retention capacity, improve physical characteristics of the soil, creates a good ecological environment for plant growth, is excellent, meets the organic and pollution-free agricultural development trend and has larger popularization and application value.

Owner:SICHUAN SHILIWANG AGRI SCI & TECH DEV CO LTD

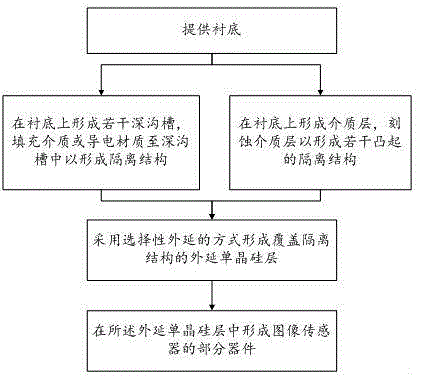

Image sensor adopting deep groove isolation and manufacturing method thereof

ActiveCN104637968AGuaranteed performanceWithout regard to damageSemiconductor/solid-state device manufacturingRadiation controlled devicesEngineeringEpitaxy

The invention provides an image sensor adopting deep groove isolation and a manufacturing method thereof. The method at least comprises the following steps that a substrate is provided; an isolation structure of an isolation pixel unit is formed on the substrate; an epitaxial monocrystalline silicon layer covering the isolation structure is formed in a selective epitaxy mode; partial devices of the image sensor are formed in the epitaxial monocrystalline silicon layer. The deep groove isolation structure is formed before an image sensor device is formed, the isolation structure has better surface shape and fewer defects, in addition, the restoration can be carried out through the epitaxy high-temperature process, and the influence of defects is further eliminated, so that the interface of the isolation structure is more excellent, and the deep groove isolation structure is formed before the device is made, so the selectivity of process means and environment is wider, the damage to the device does not need to be considered, the epitaxial monocrystalline silicon layer is used for forming the device grows after the isolation structure formation, the condition that no stress is conducted into a silicon device is ensured through a high-temperature manufacture procedure, and the performance of the image sensor device is ensured.

Owner:GALAXYCORE SHANGHAI

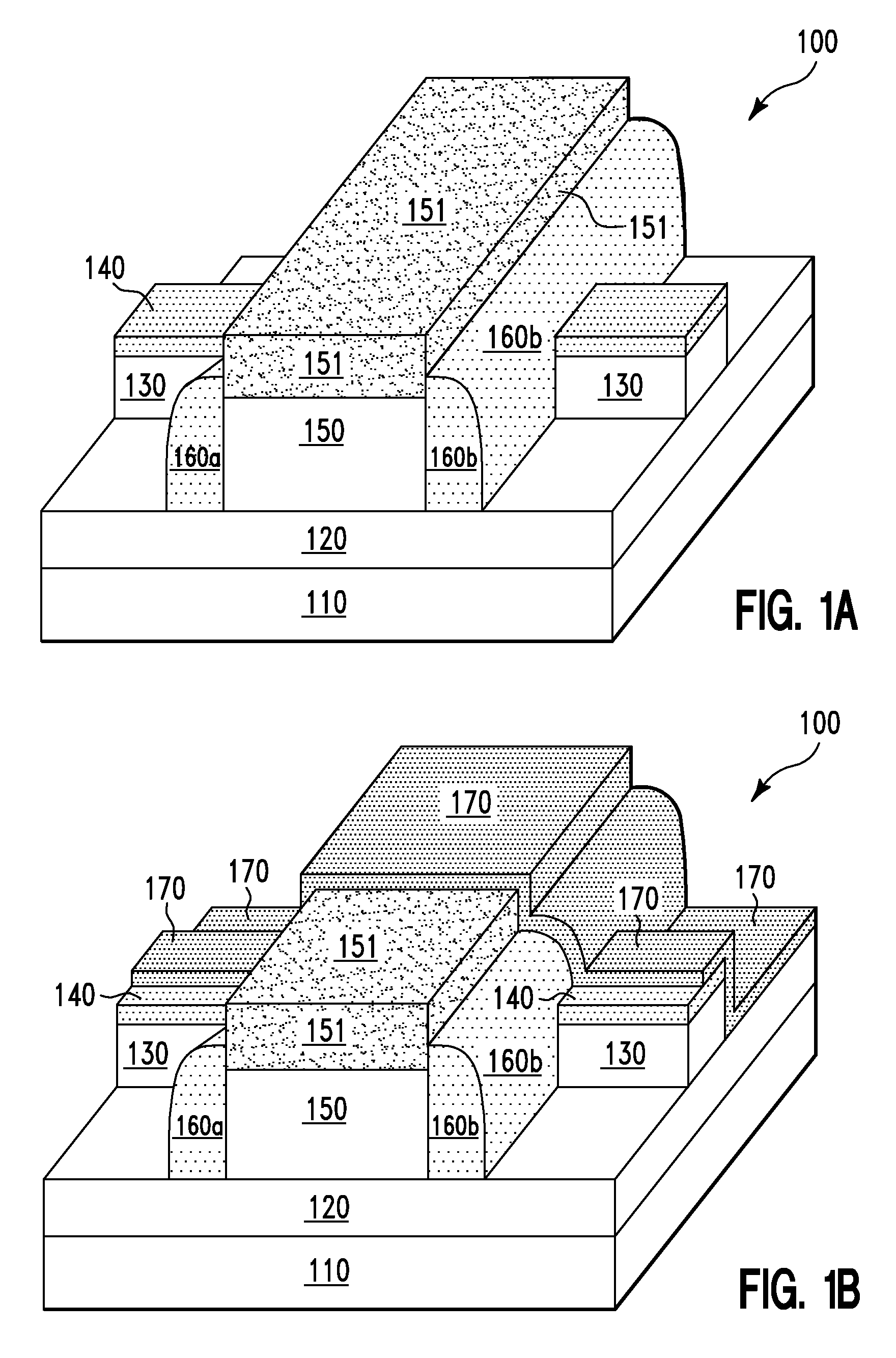

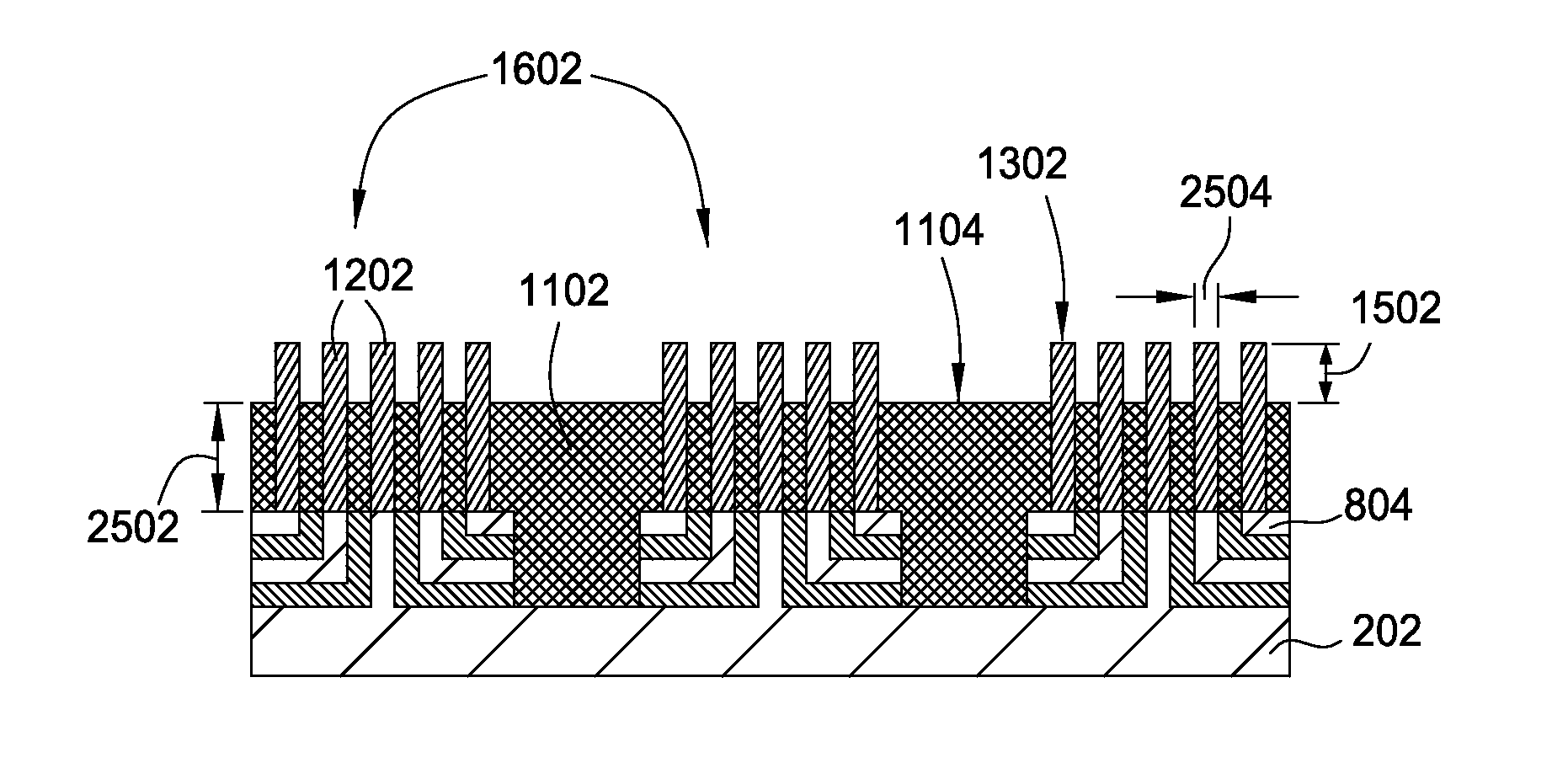

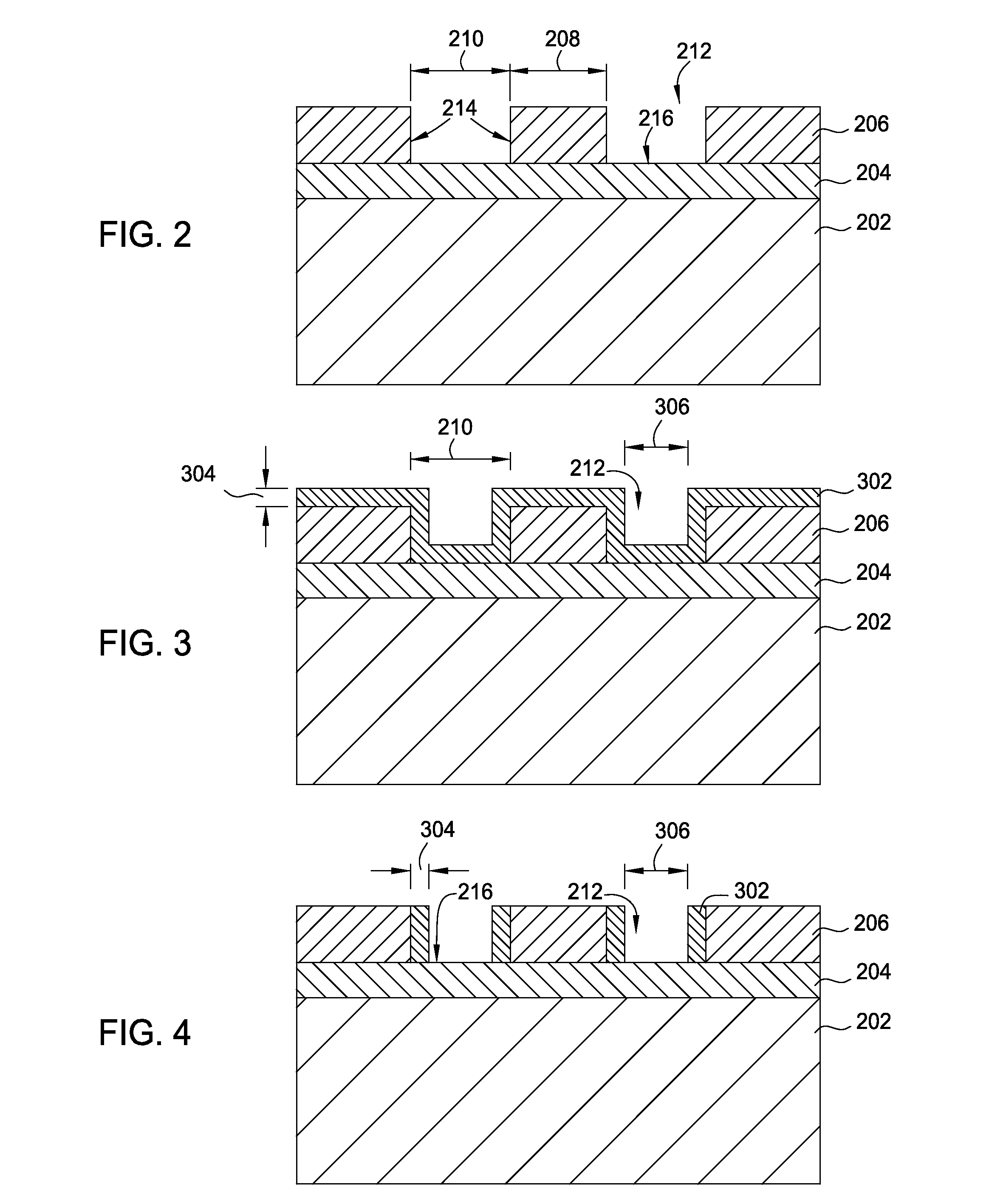

Fin structure formation by selective etching

ActiveUS20160099178A1Semiconductor/solid-state device manufacturingSemiconductor devicesEtchingDeposition process

Methods and apparatus for forming FinFET structures are provided. Selective etching and deposition processes described herein may provide for FinFET manufacturing without the utilization of multiple patterning processes. Embodiments described herein also provide for fin material manufacturing methods for transitioning from silicon to III-V materials while maintaining acceptable crystal lattice orientations of the various materials utilized. Further embodiments provide etching apparatus which may be utilized to perform the methods described herein.

Owner:APPLIED MATERIALS INC

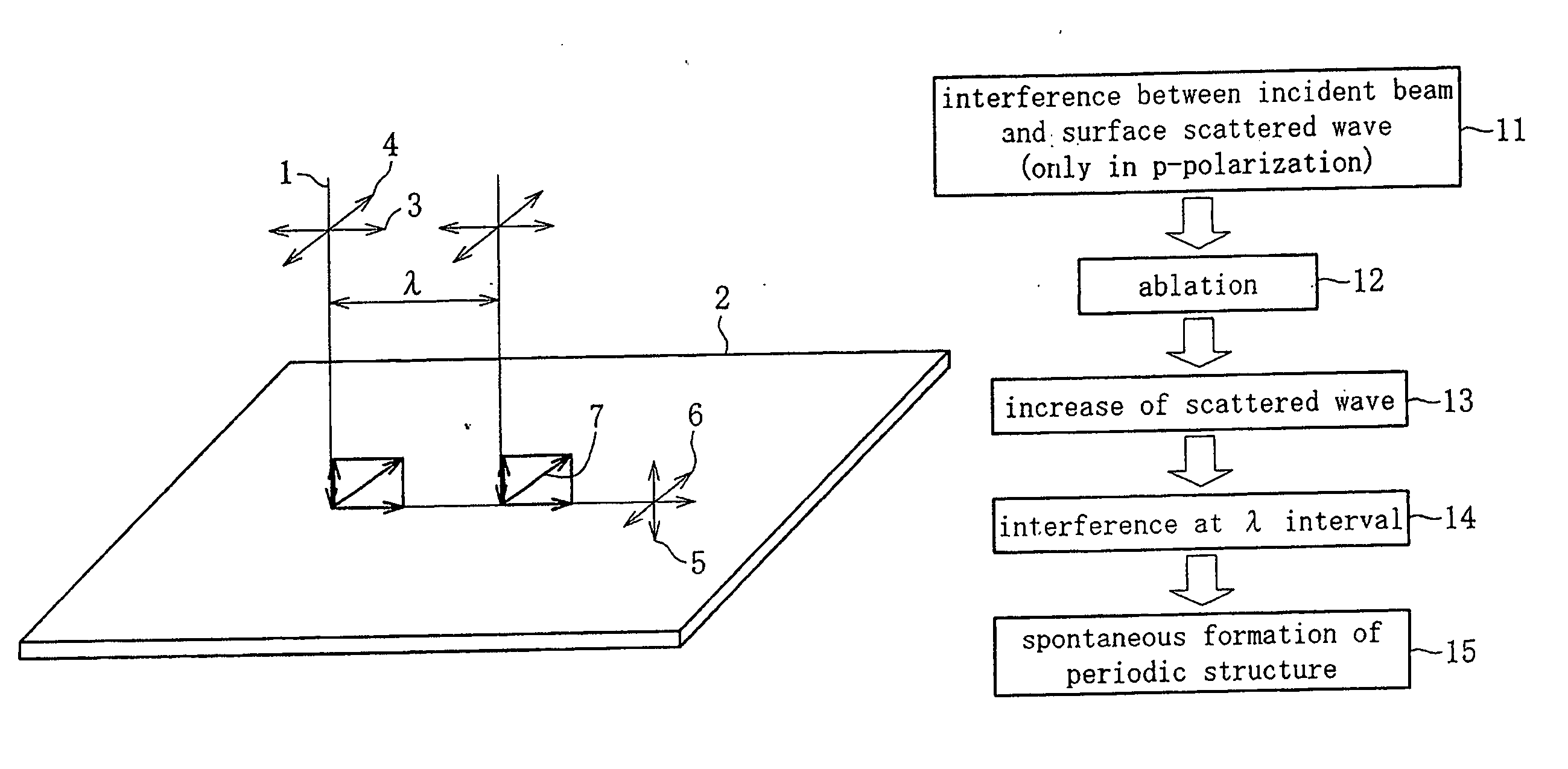

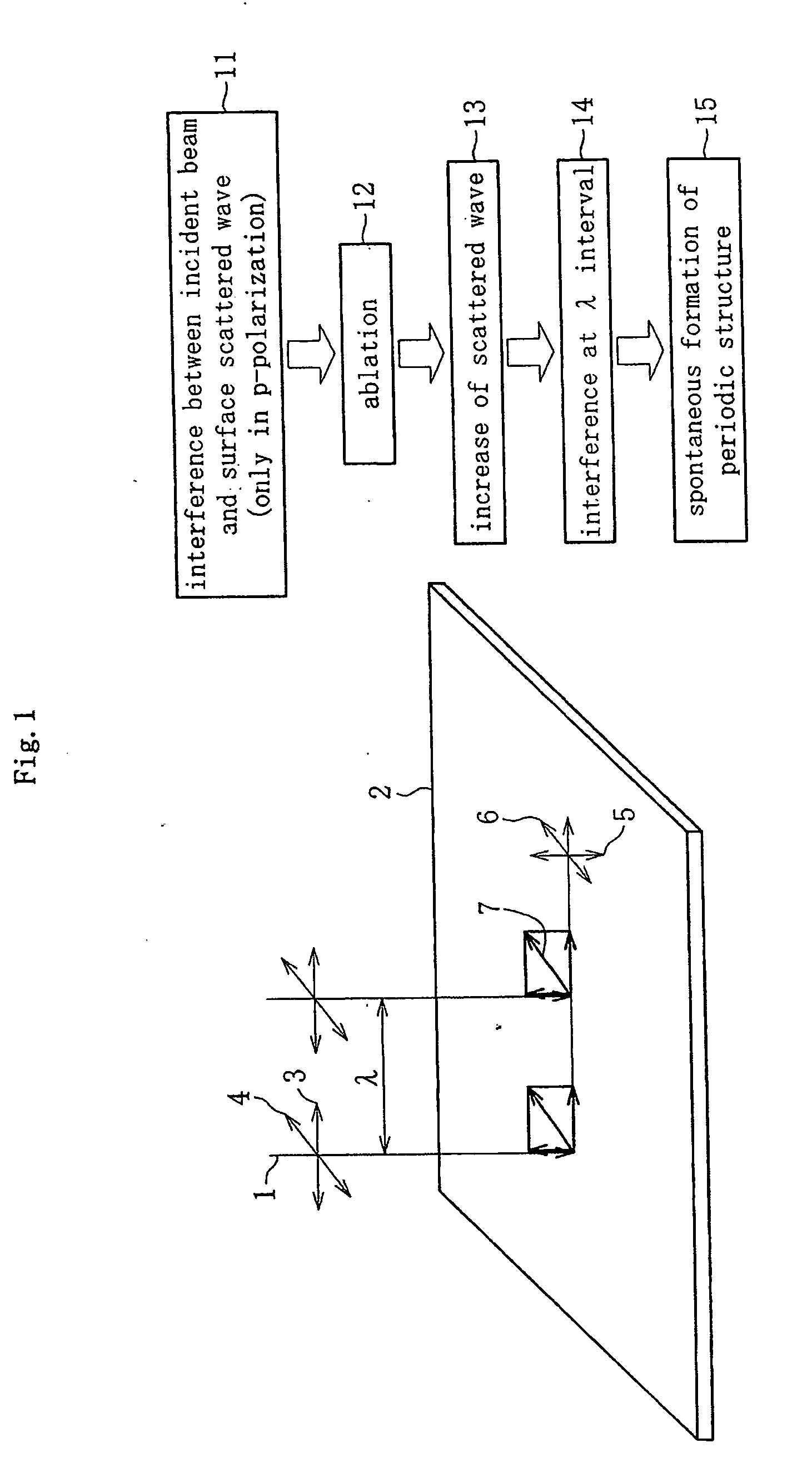

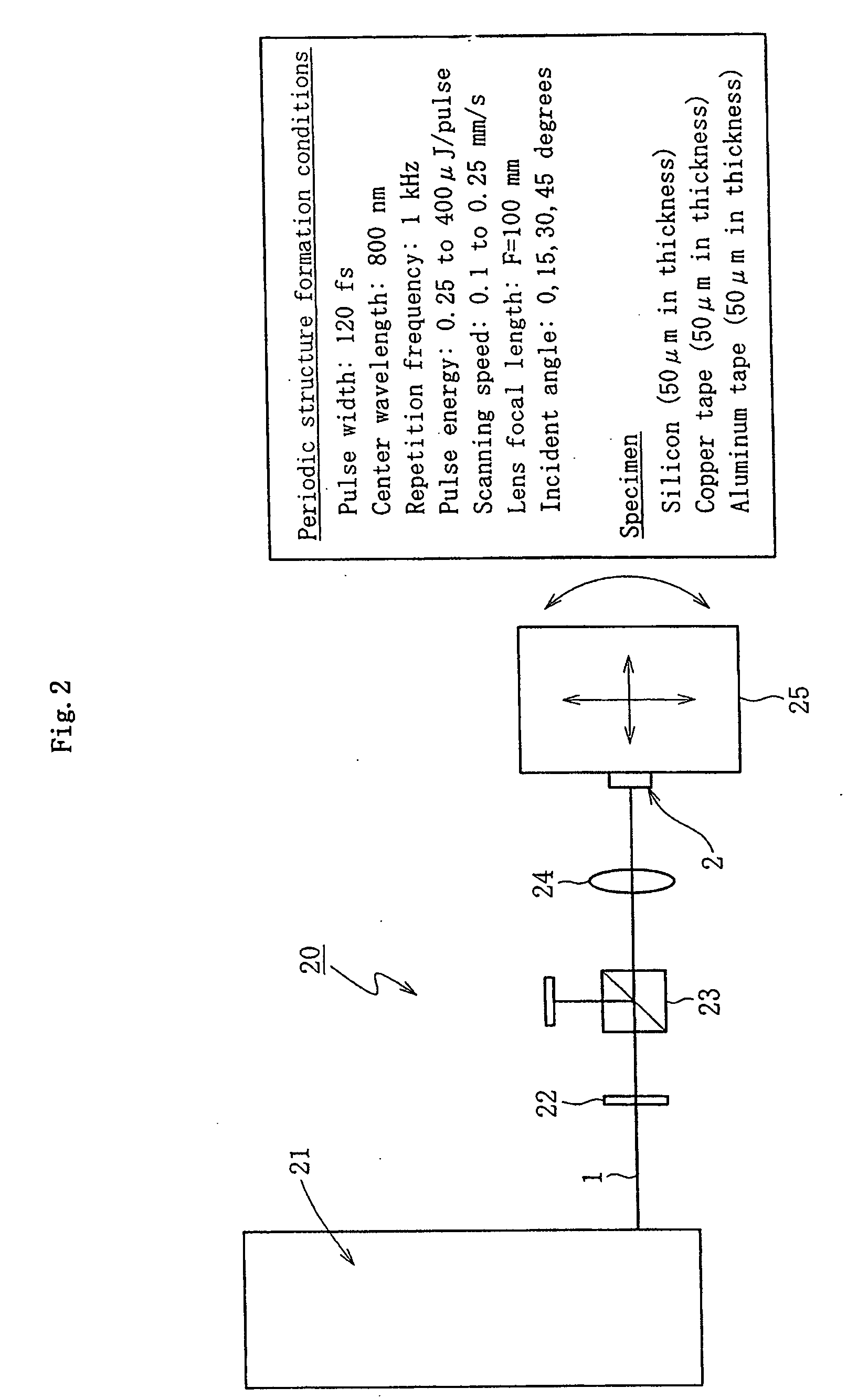

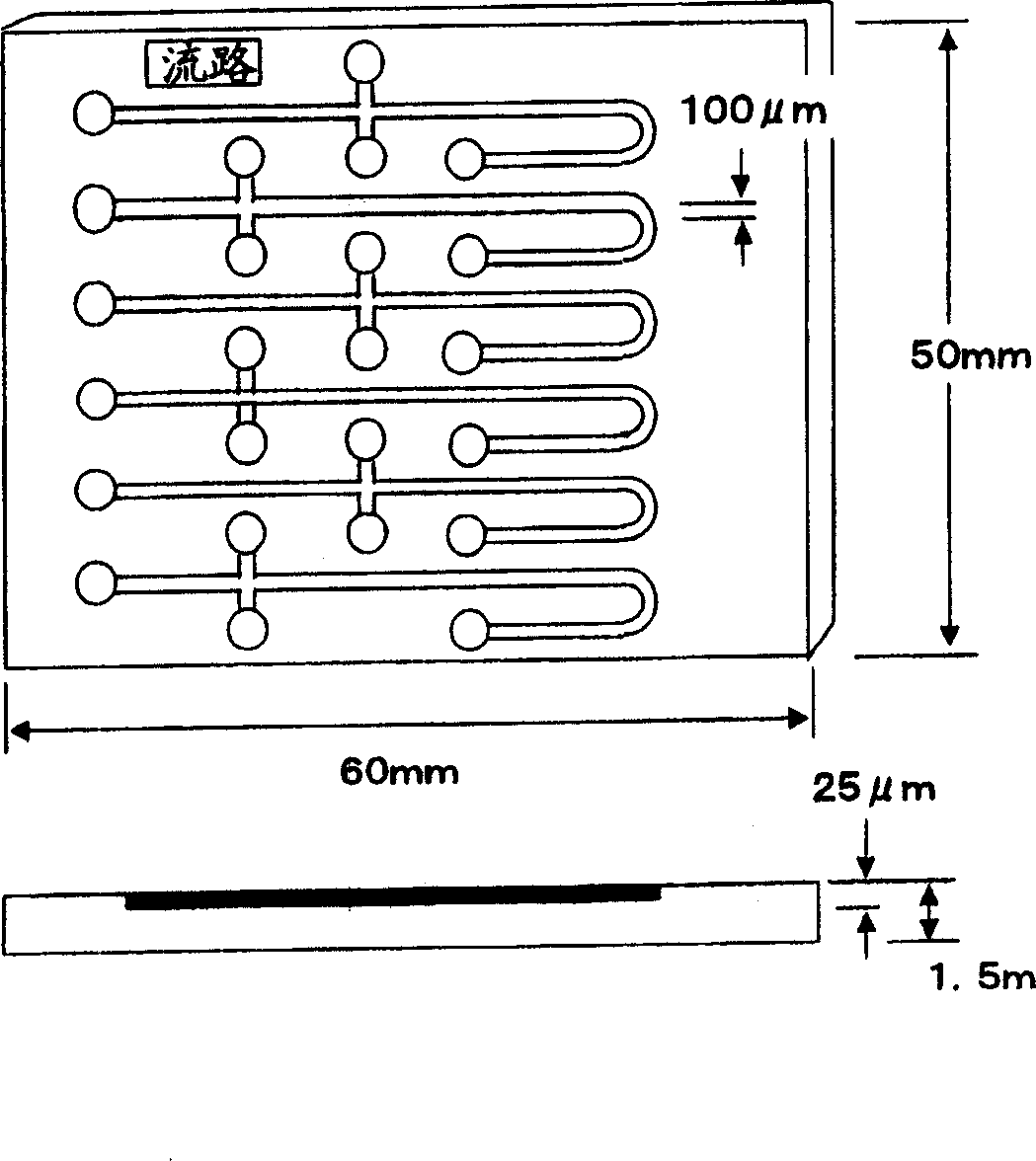

Cyclic structure formation method and surface treatment method

InactiveUS20060138102A1Short timeConvenient spacingPhotomechanical apparatusOptical articlesClassical mechanicsLight beam

A periodic structure is to be successively formed over an extensive area with a uniaxial laser beam. Such method includes irradiating a uniaxial laser beam near an ablation threshold to a surface of a material; and executing an overlapped scanning on the irradiated region, so as to cause an ablation by interference between an incident beam and a surface scattered wave along the material surface; increasing the scattered wave; causing an interference at an interval equal to a wavelength of the laser beam, to thereby cause spontaneous formation of a periodic structure. The periodic structure can be made to have a different ripple spacing by changing an incident angle of the laser beam to the material surface. When the laser incident beam has an angle, the ripple spacing can be changed by changing a scanning direction.

Owner:CANON MACHINERY

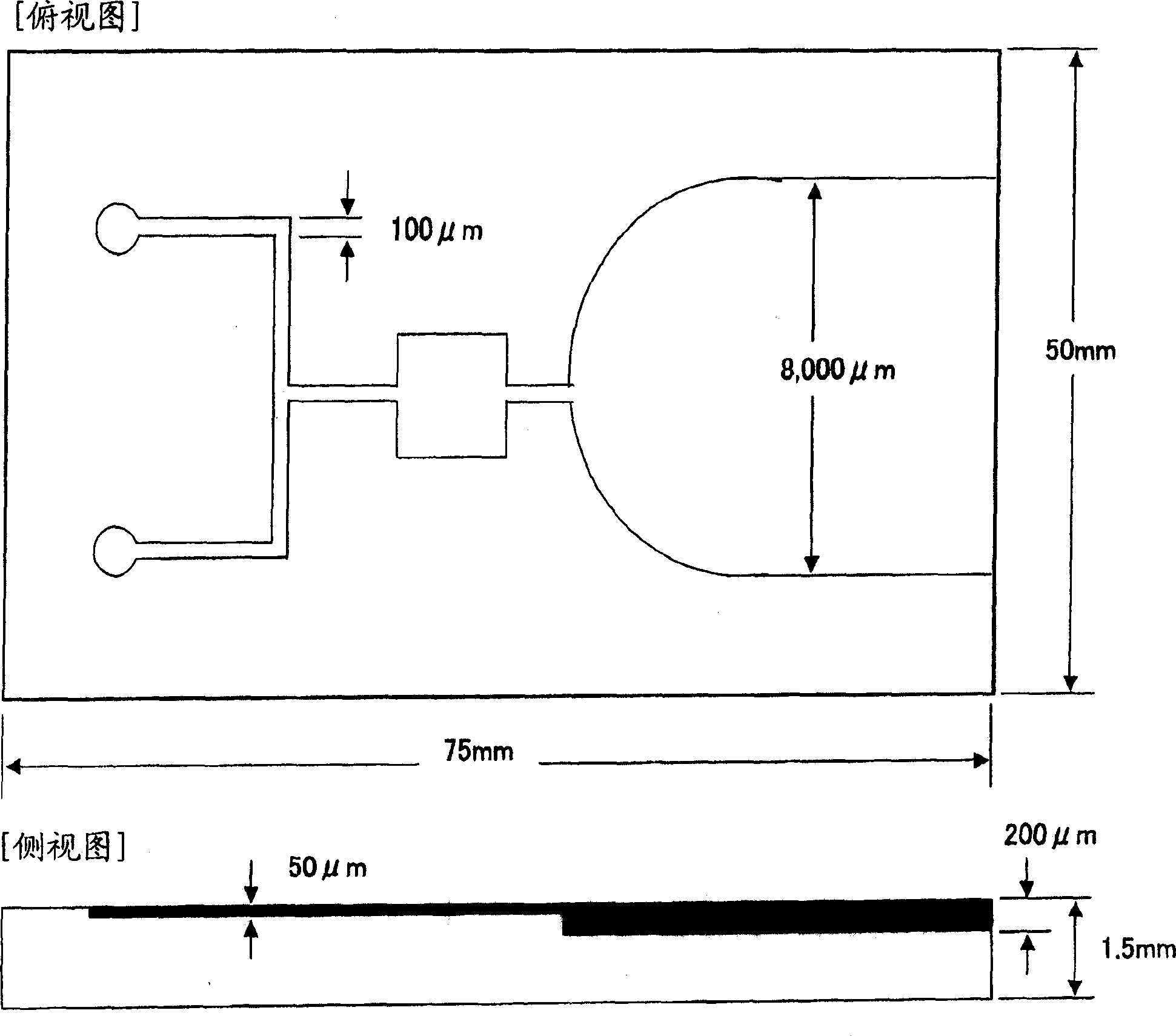

Method for producing resin formed product, method for producing metal structure budy and resin forming product

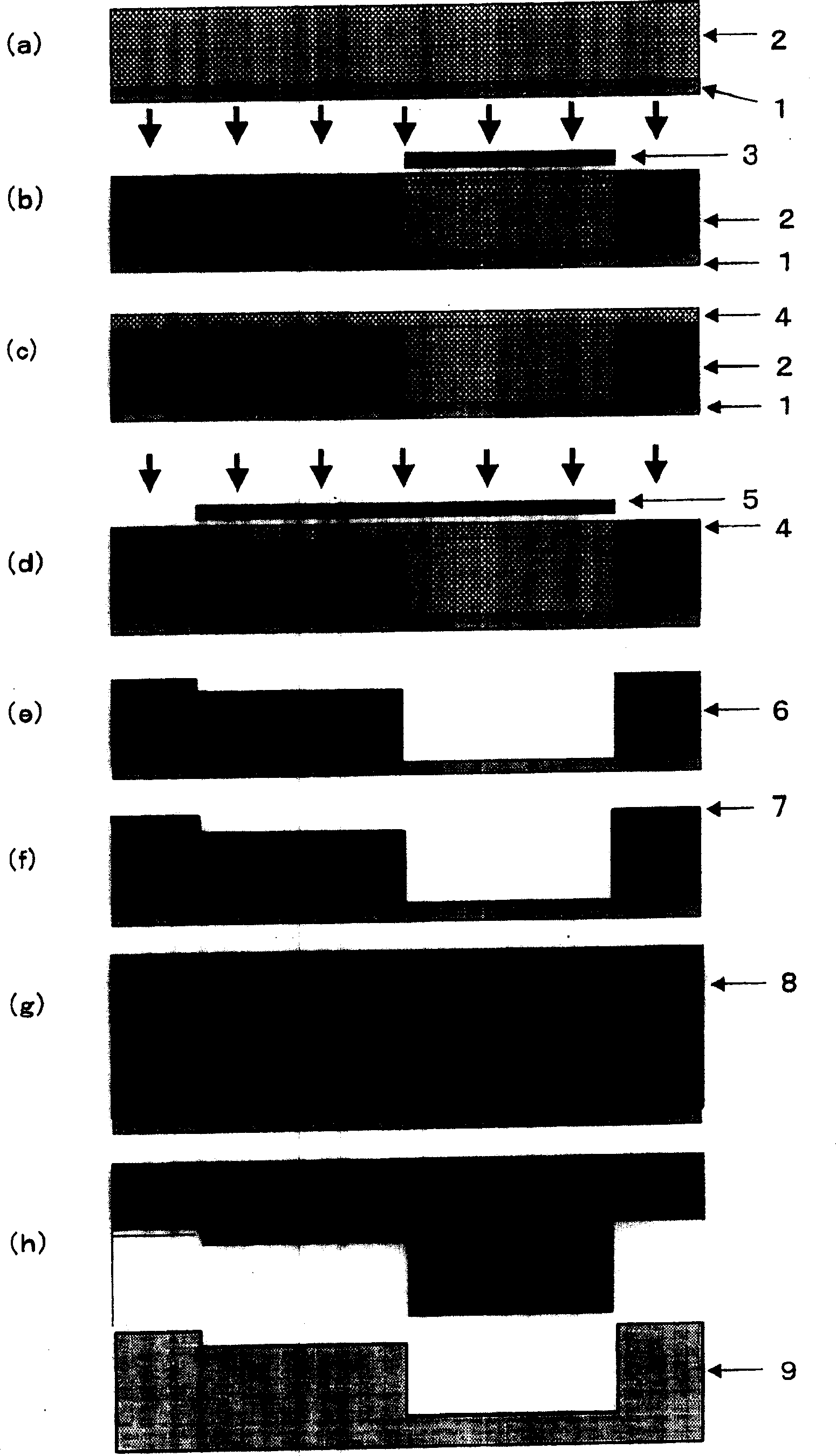

ActiveCN1532036AIncrease productivityLow costSemiconductor/solid-state device manufacturingPhotosensitive material processingResistProduct formation

A resin molded product production process has a resist pattern formation step including formation of the first resist layer on s substrate, positioning of the substrate and a mask A, exposure of the first resist layer using the mask A, heat-treatment of the first resist layer, formation of the second resist layer on the first resist layer, positioning of the substrate and a mask B, exposure of the second resist layer using the mask B, heat-treatment of the second resist layer, and development of the resist layers, thereby creating a given resist pattern. The production process further has a metal structure formation step of depositing a metal on the substrate in accordance with the resist pattern by plating, and a molded product formation step of forming a resin molded product by using the metal structure as a mold. A resin molded product is thereby produced.

Owner:KURARAY CO LTD

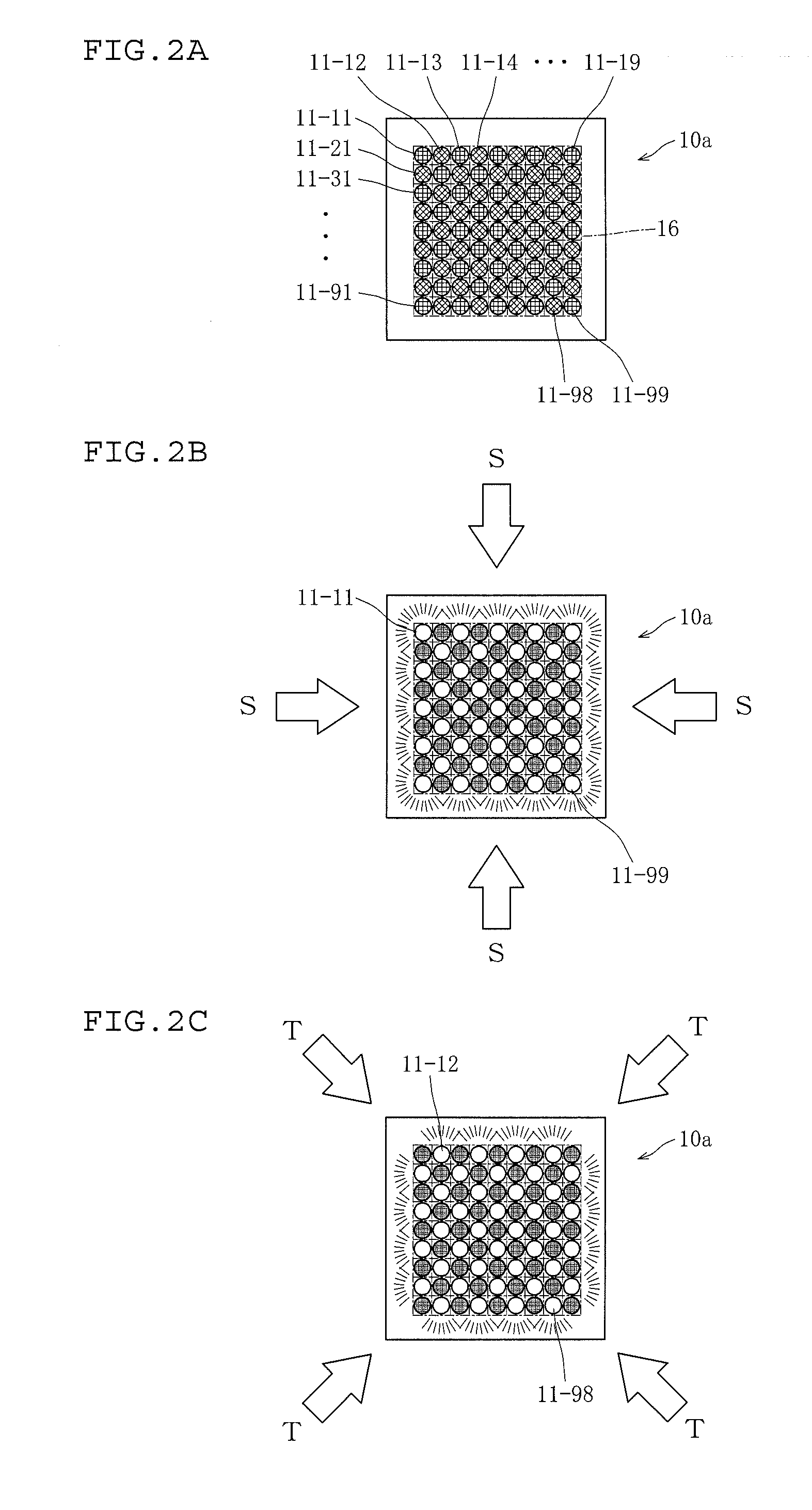

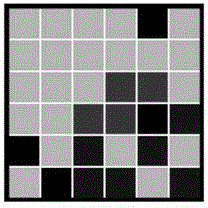

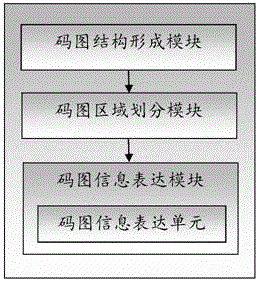

Colorful three-dimensional code structure and colorful three-dimensional code reading method

ActiveCN104657768AGuaranteed information capacityRapid positioningRecord carriers used with machinesSensing by electromagnetic radiationProgramming languageInside information

The invention provides a colorful three-dimensional code structure which at least comprises a code symbol structure formation module, a code symbol area division module and a code symbol information expression module, wherein the code symbol structure formation module is used for arranging three-dimensional codes into a square according to the capacity of to-be-stored data and displaying; the code symbol area division module is connected with the code symbol structure formation module, and is used for dividing the square three-dimensional codes, generated by the code symbol structure formation module, into a boundary positioning area and an internal information storage area; and the code symbol information expression module is connected with the code symbol area division module, and comprises a plurality of code symbol information expression units, and the code symbol information expression module is used for expressing the to-be-stored data by using the code symbol information expression units, and presenting the to-be-stored data into the three-dimensional codes.

Owner:HUAZHONG UNIV OF SCI & TECH

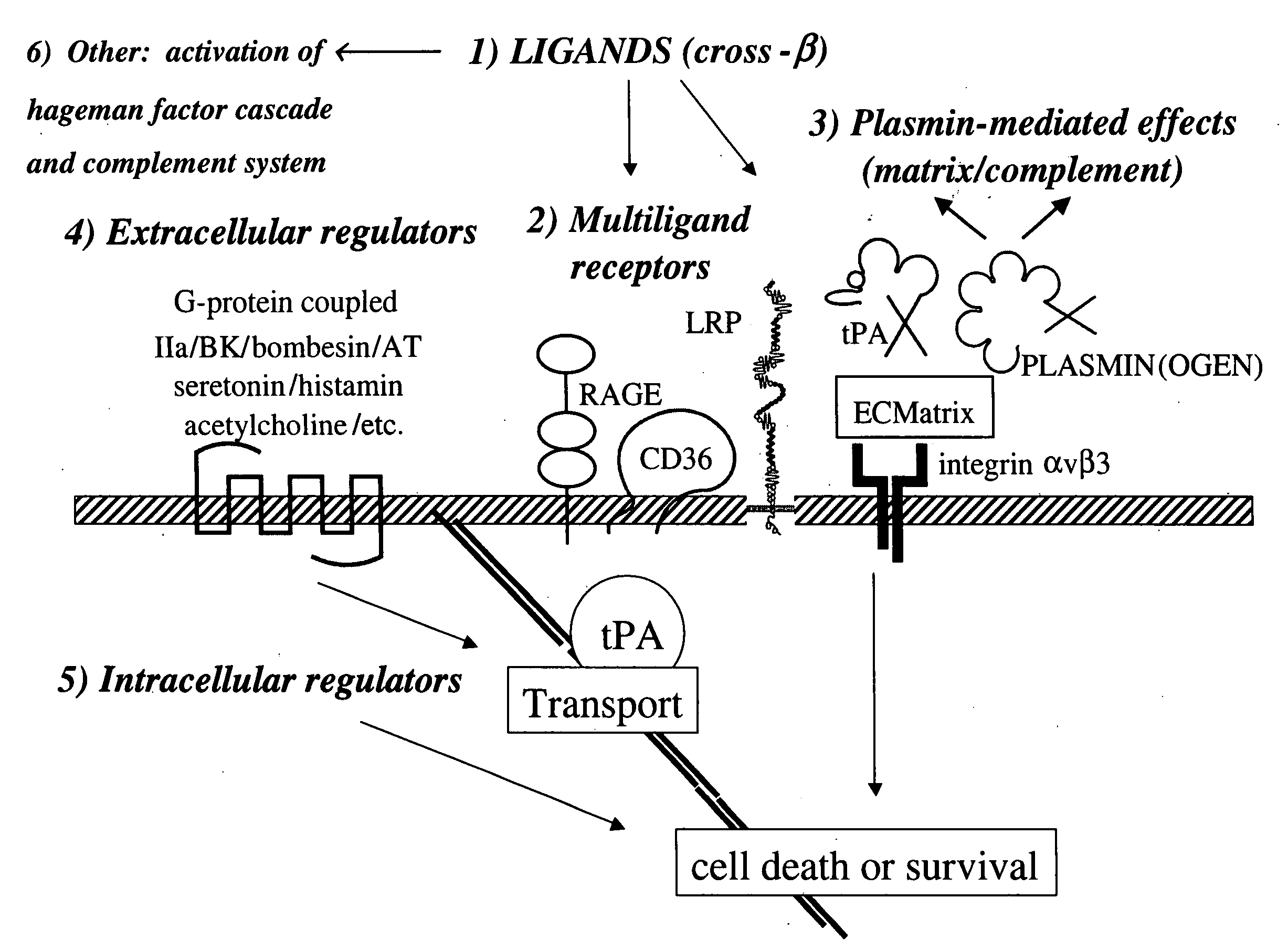

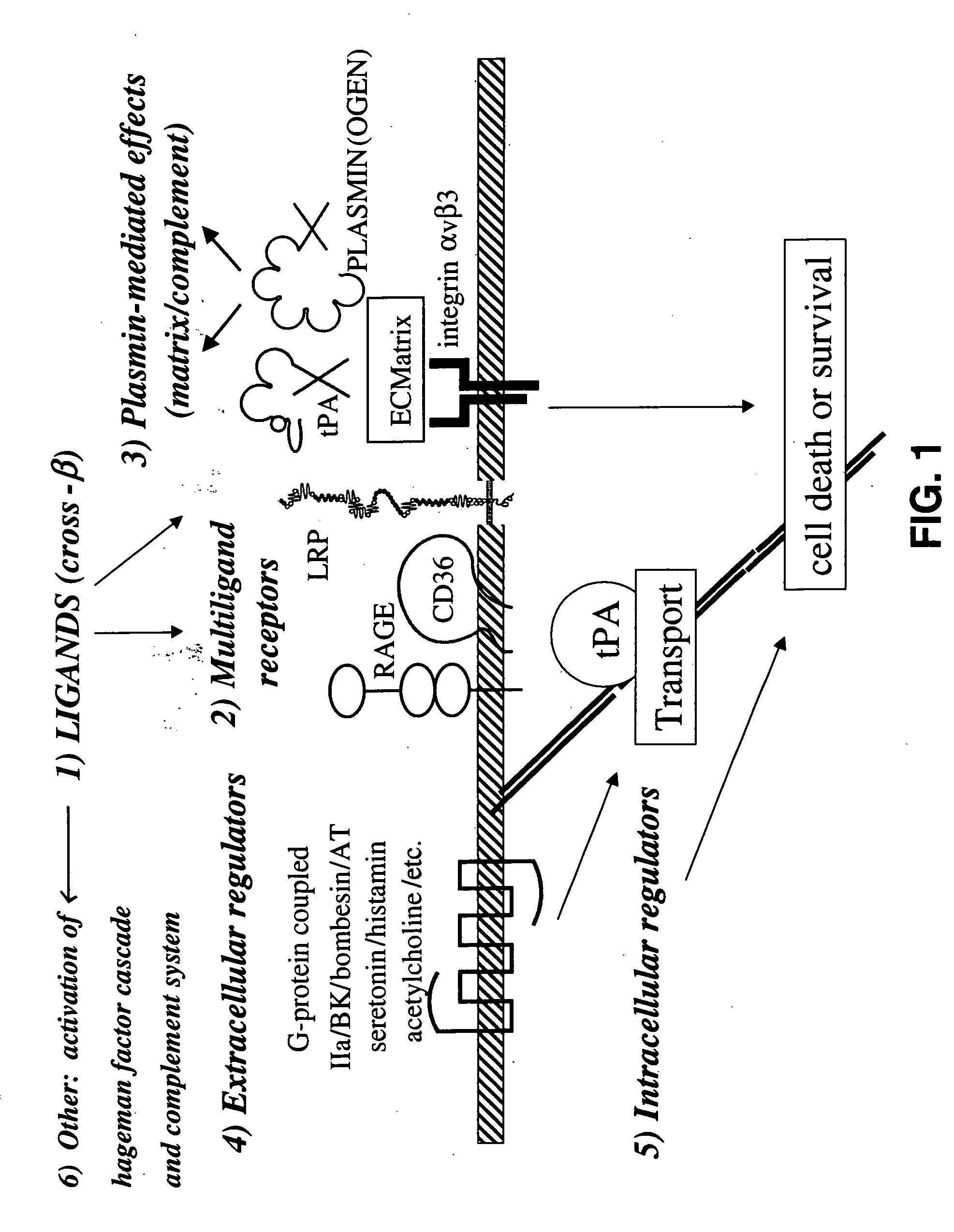

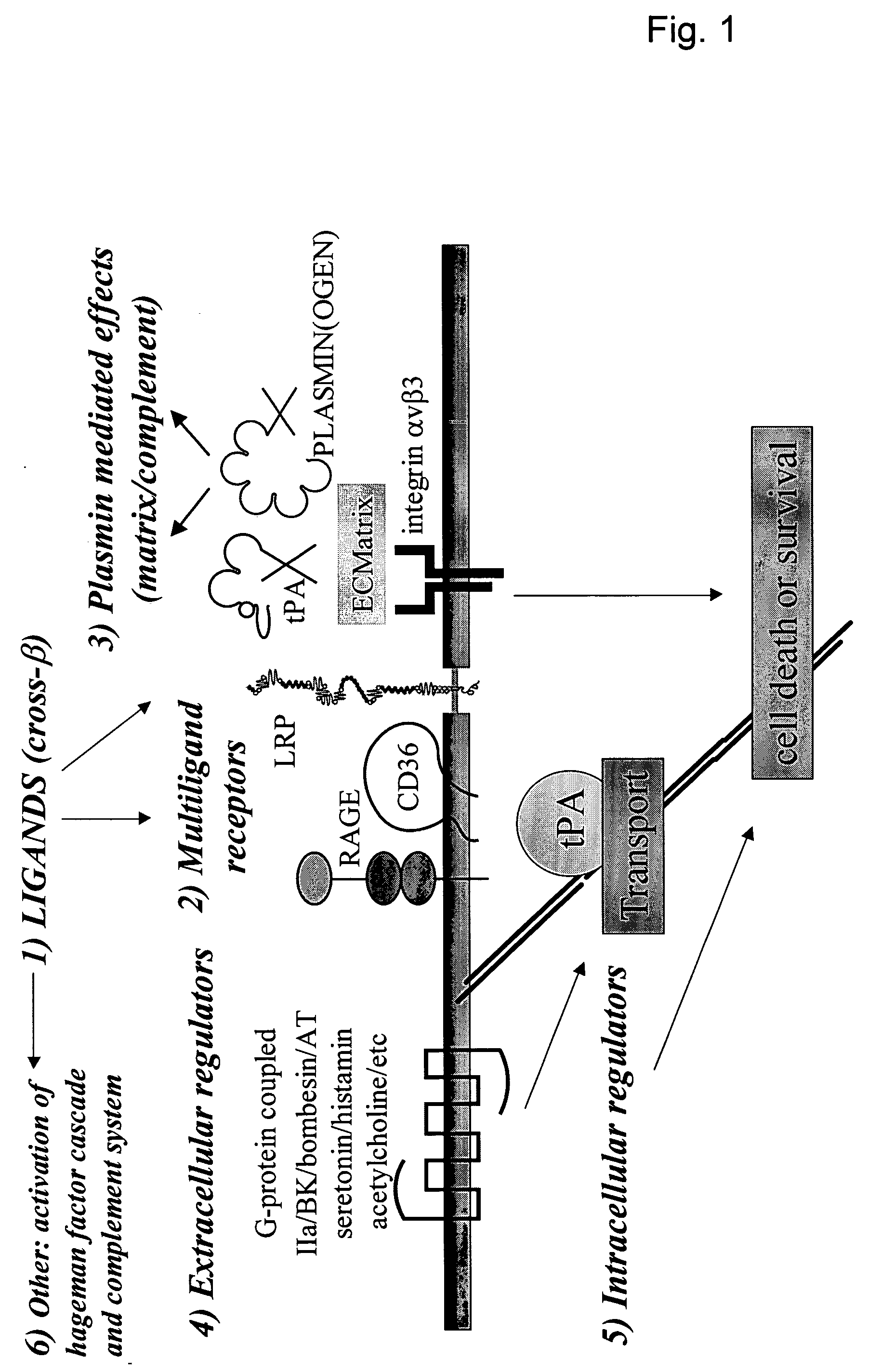

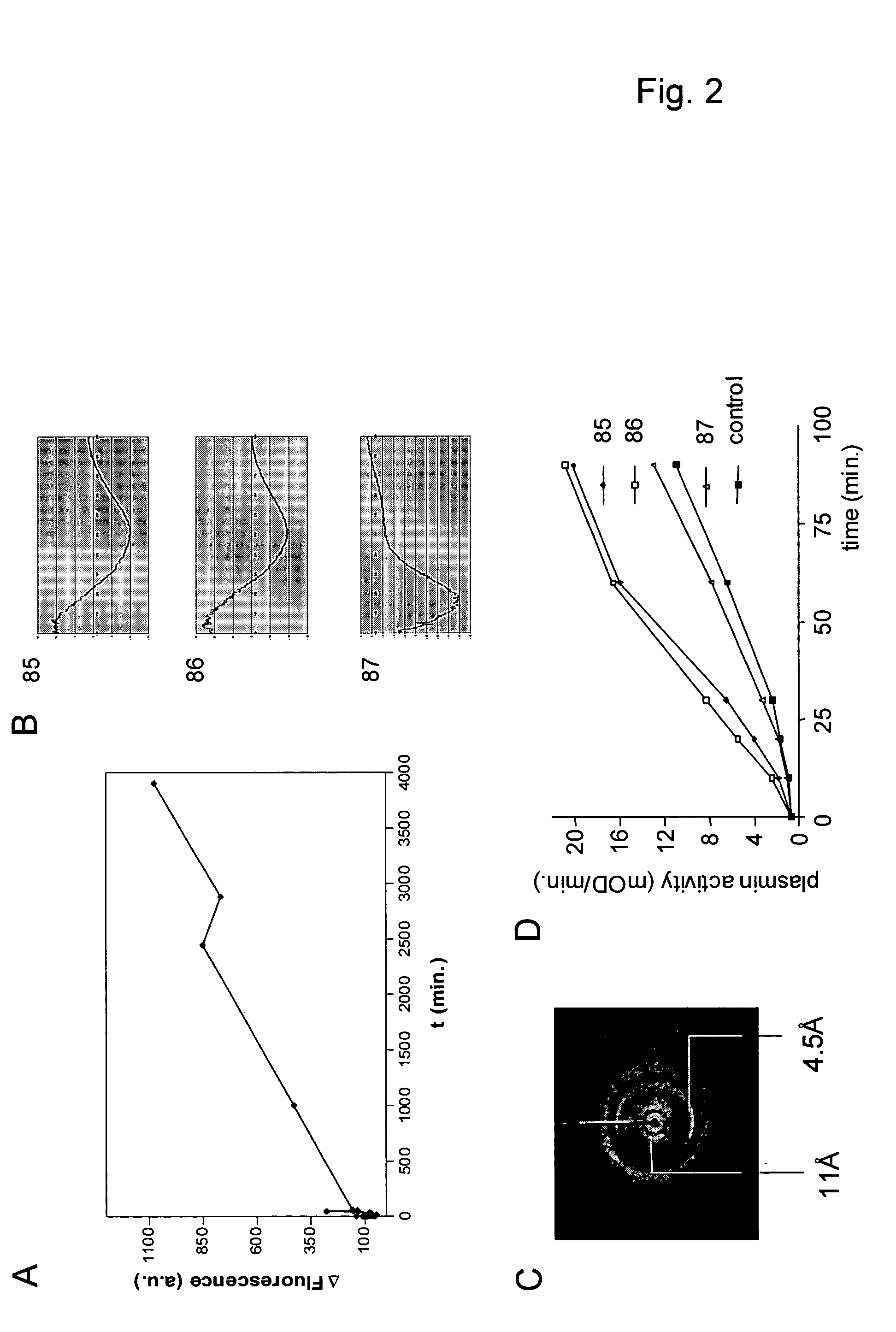

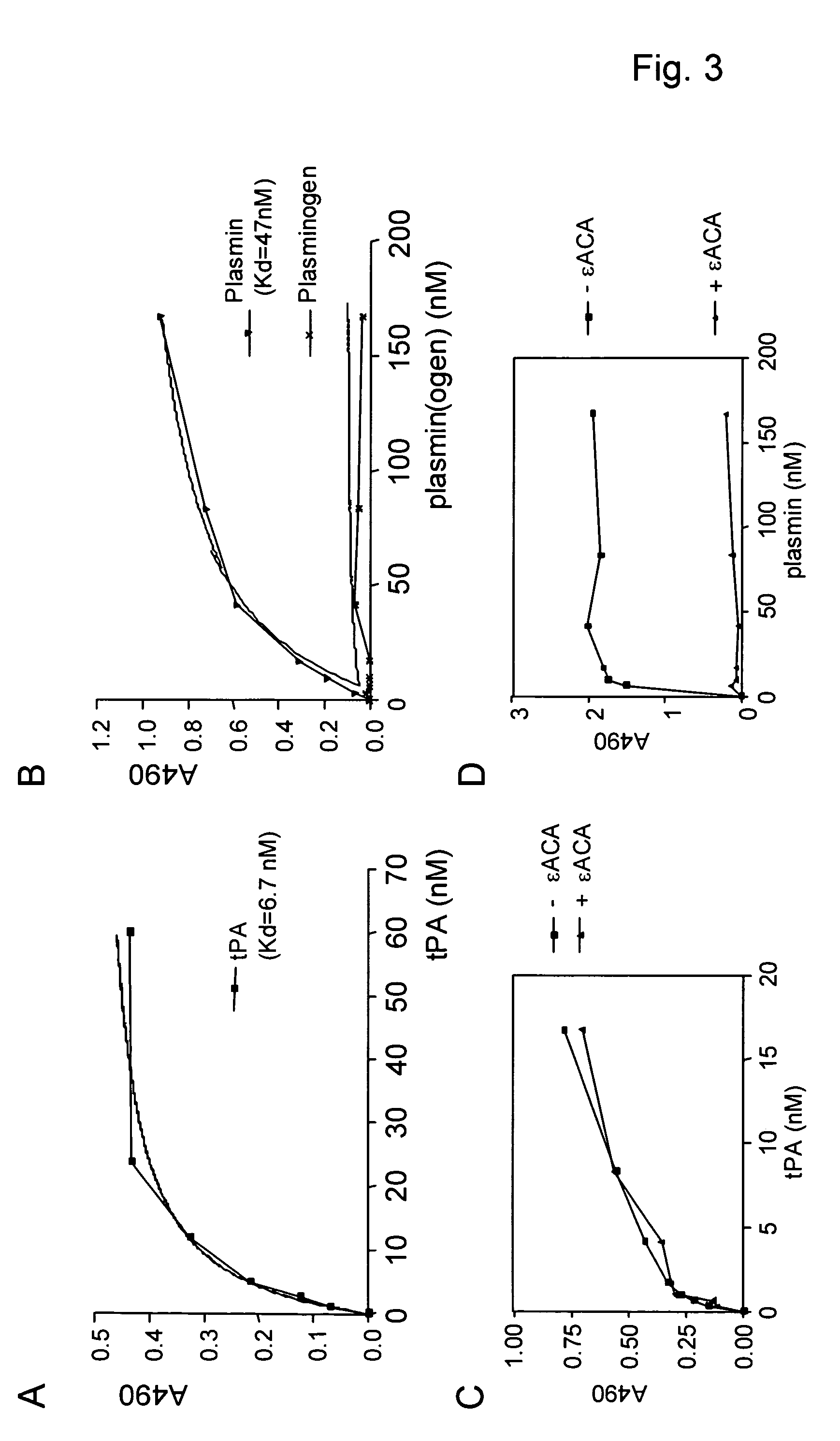

Cross-beta structure comprising amyloid-binding proteins and methods for detection of the cross-beta structure, for modulating cross-beta structures fiber formation and modulating cross-beta structure-mediated toxicity

The invention relates to the field of biochemistry, molecular biology, structural biology and medicine. More in particular, the invention relates to cross-β structures and the biological role of these cross-β structures. In one embodiment, the invention discloses a method for modulating extracellular protein degradation and / or protein clearance comprising modulating cross-β(beta) structure formation (and / or cross-β structure-mediated activity) of the protein present in the circulation.

Owner:CROSSBETA BIOSCIENCES BV

Cross-beta structure comprising amyloid-binding proteins and methods for detection of the cross-beta structure, for modulating cross-beta structures fibril formation and for modulating cross-beta structure-mediated toxicity

The invention relates to the field of biochemistry, molecular biology, structural biology and medicine. More in particular, the invention relates to cross-β structures and the biological role of these cross-β structures. In one embodiment, the invention discloses a method for modulating extracellular protein degradation and / or protein clearance comprising modulating cross-β(beta) structure formation (and / or cross-β structure-mediated activity) of the protein present in the circulation.

Owner:CROSSBETA BIOSCIENCES BV

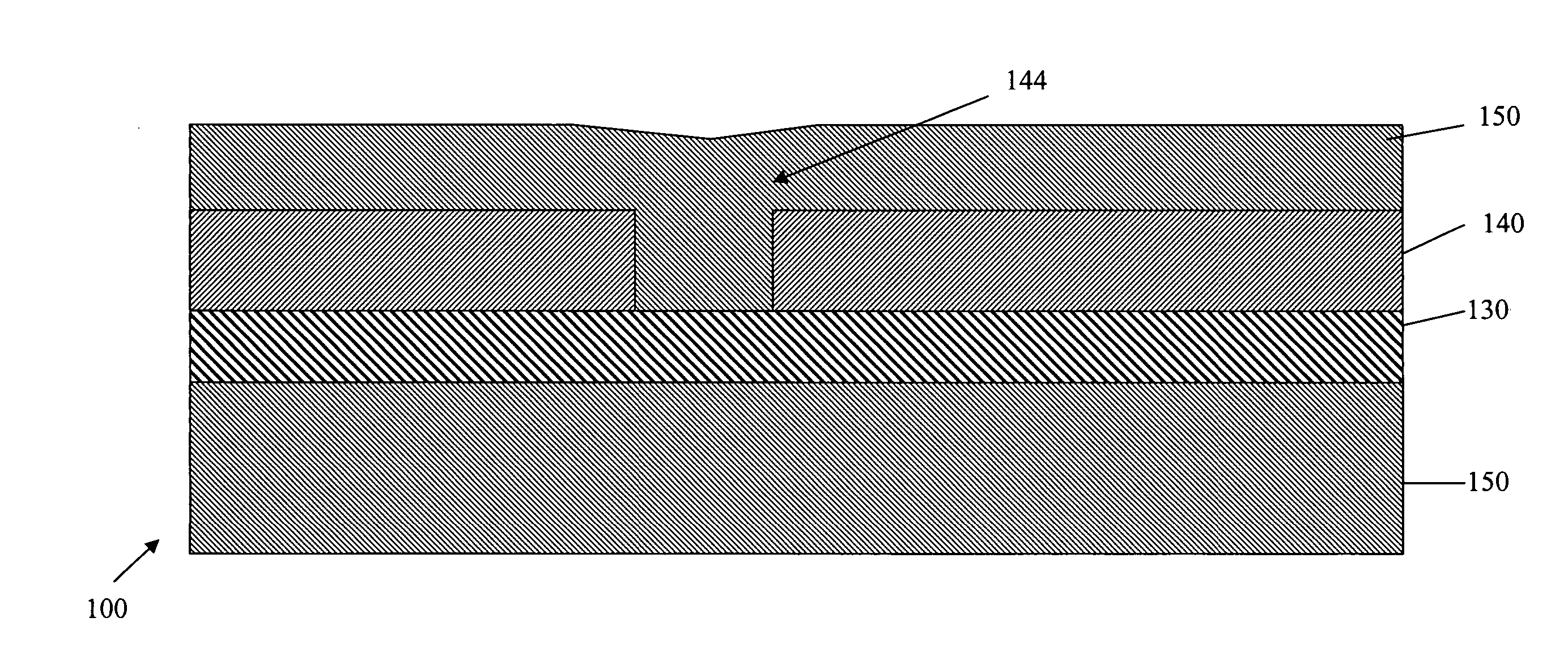

Fabricating integrated devices using embedded masks

ActiveUS20060228896A1Improve flatnessEliminate needSemiconductor/solid-state device manufacturingMicrostructural device manufactureEtchingEngineering

A method of fabricating a device using a multi-layered wafer that has an embedded etch mask adapted to map a desired device structure onto an adjacent (poly)silicon layer. Due to the presence of the embedded mask, it becomes possible to delay the etching that forms the mapped structure in the (poly)silicon layer until a relatively late fabrication stage. As a result, flatness of the (poly)silicon layer is preserved for the deposition of any necessary over-layers, which substantially obviates the need for filling the voids created by the structure formation with silicon oxide.

Owner:LUCENT TECH INC

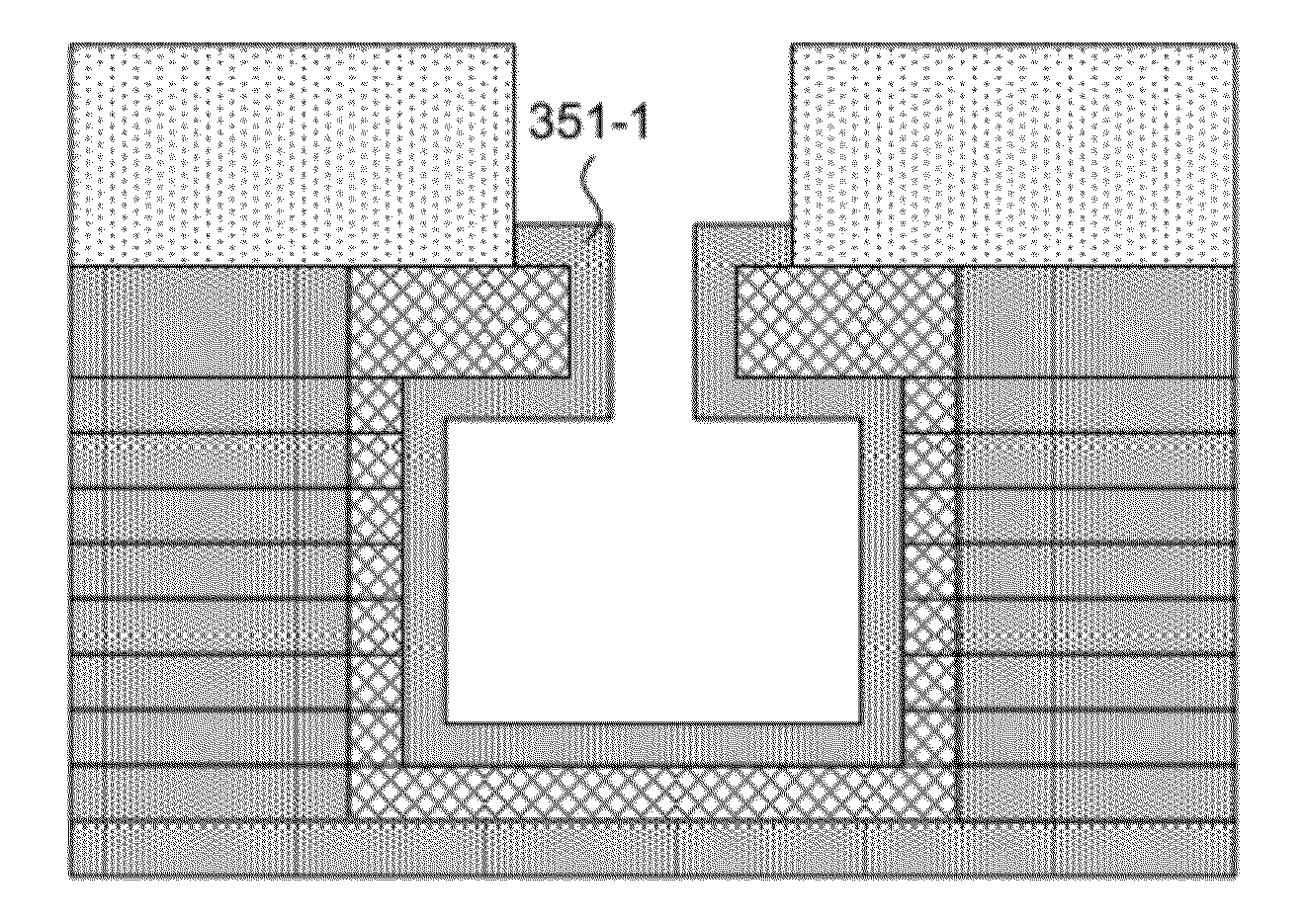

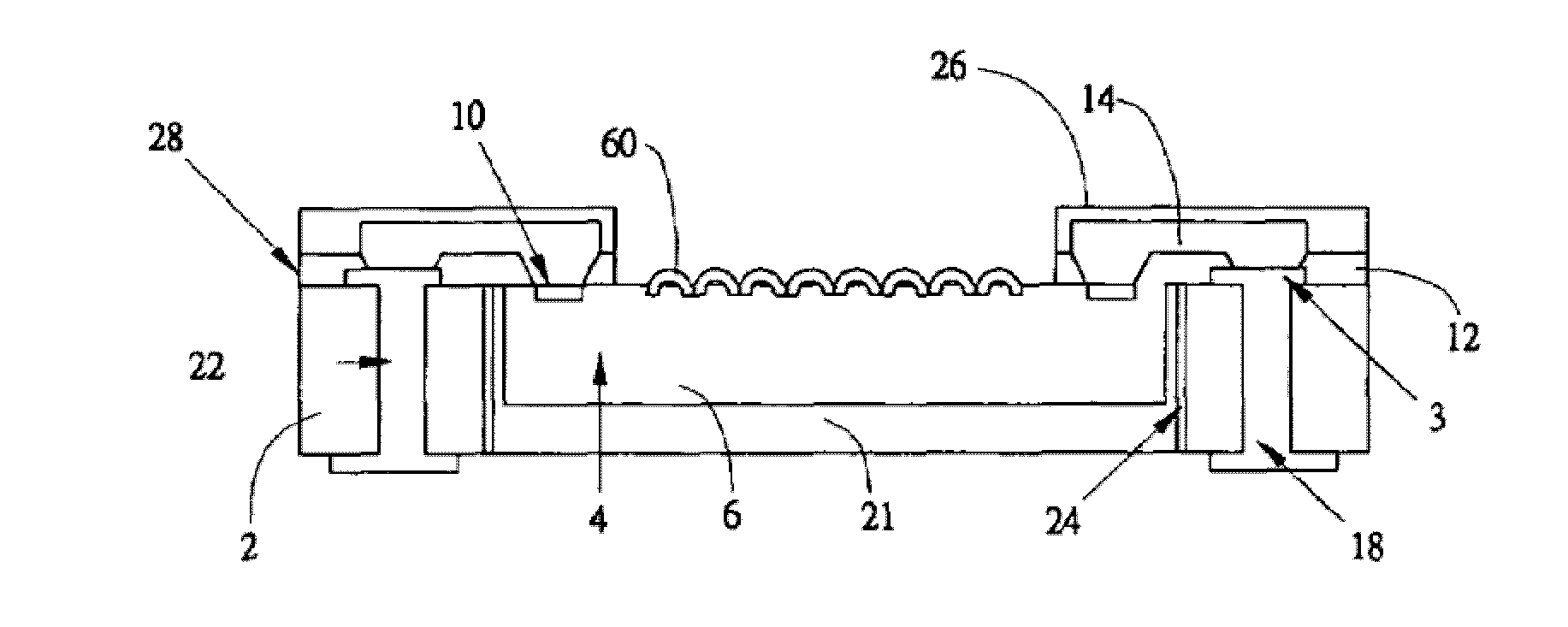

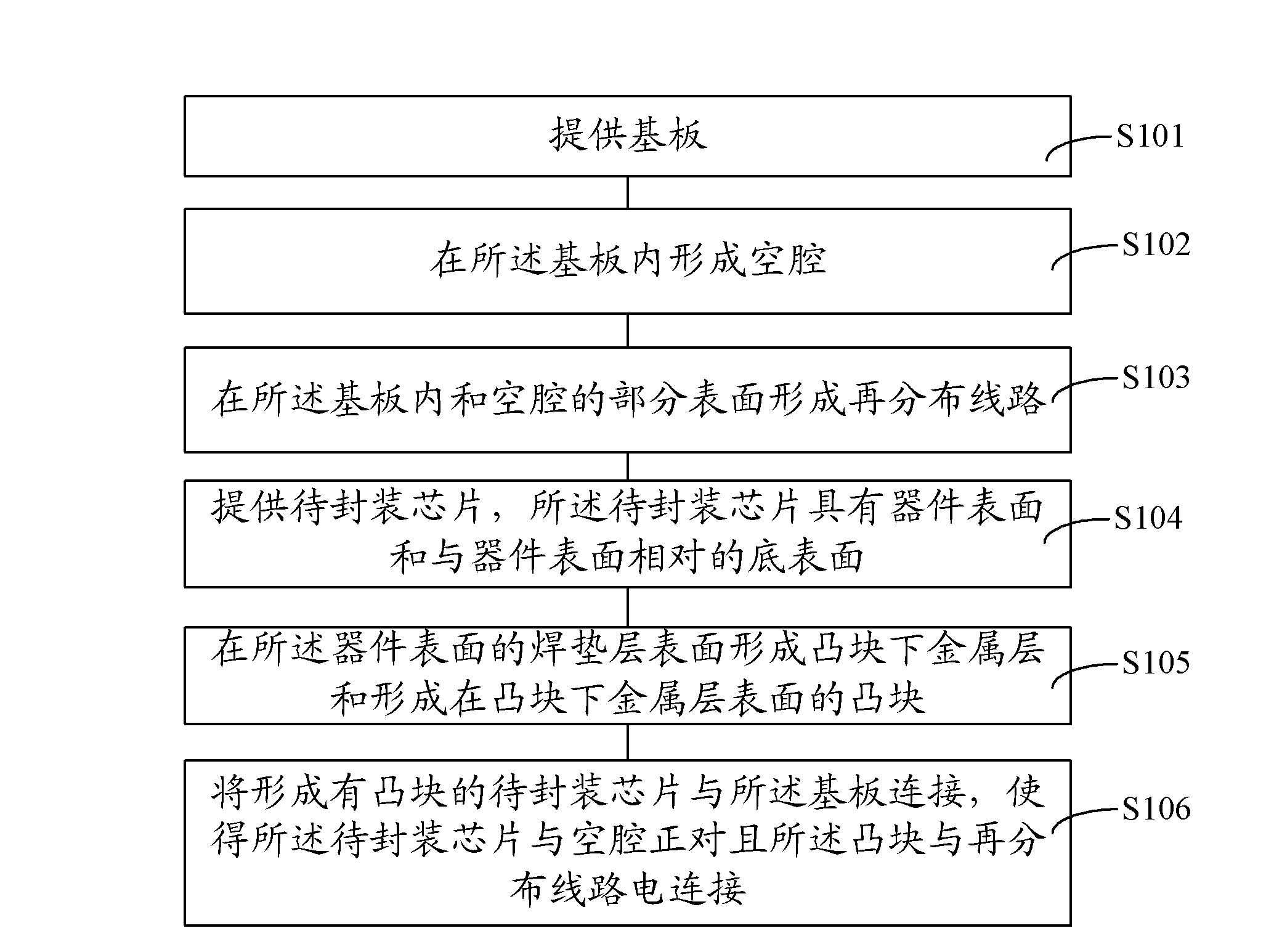

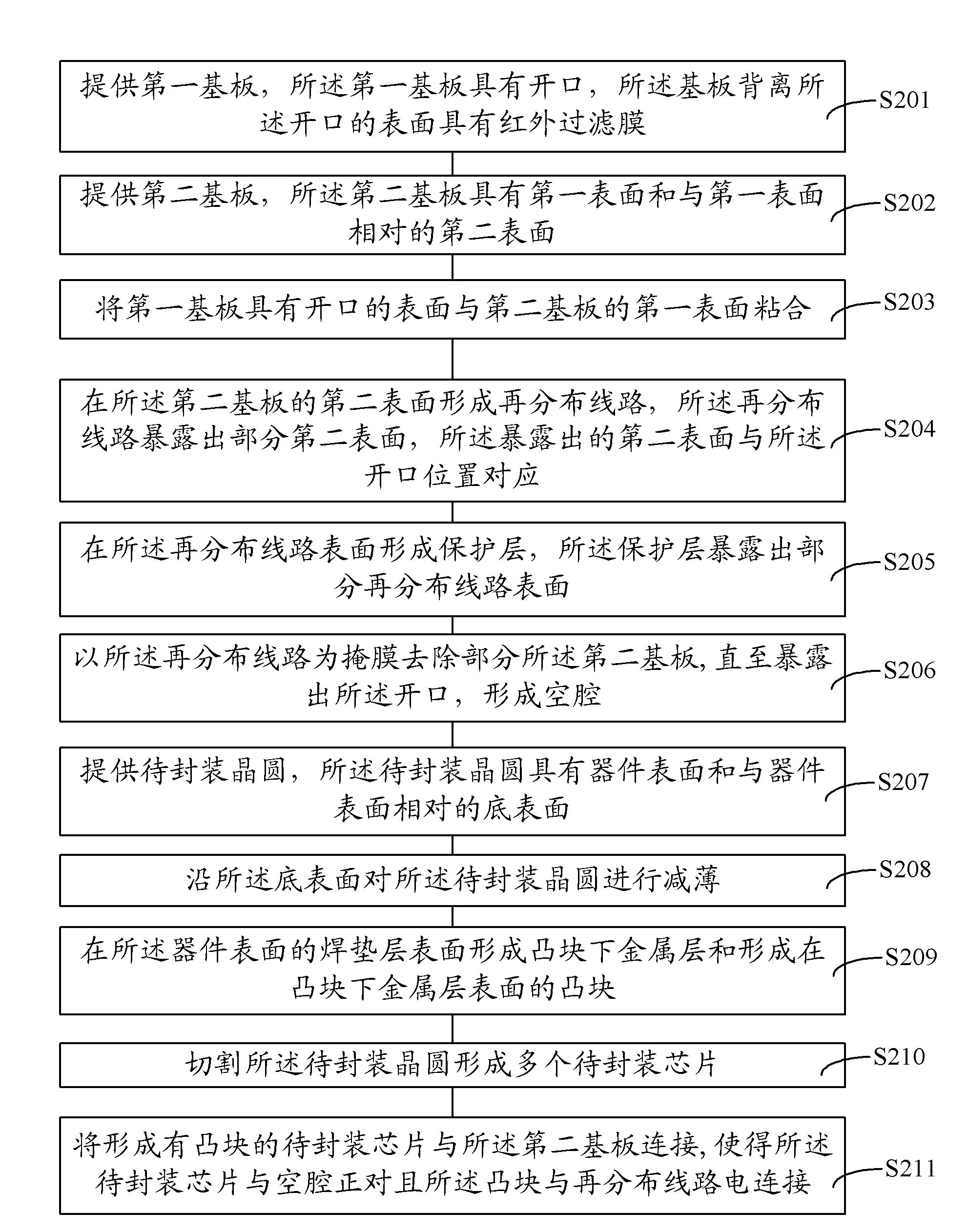

Wafer-level packaging structure and method of forming the same

ActiveCN102280391ASimple structureSimple processSemiconductor/solid-state device detailsSolid-state devicesStructure formationElectrical and Electronics engineering

The invention provides a wafer level package structure and a formation method thereof. The method comprises the following steps: providing a substrate; forming a cavity in the substrate; forming a redistribution line in the substrate and on part surface of the cavity; providing a chip to be packaged, wherein the chip has a device surface and a basal surface opposite to the device surface; formingan Under Bump Metal on a soldering pad layer surface of the device surface and forming a bump on a surface of the Under Bump Metal; connecting the chip to be packaged with the substrate such that thechip to be packaged faces the cavity and the bump is electrically connected with the redistribution line. The wafer level package structure in the invention has the advantages of a simple structure, high packaging quality, and high compatibility in subsequent combination with PCB plate process. The wafer level package structure formation method in the invention has the advantages of simple process sequence and low cost.

Owner:CHINA WAFER LEVEL CSP