Patents

Literature

1497results about How to "Reduce process complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

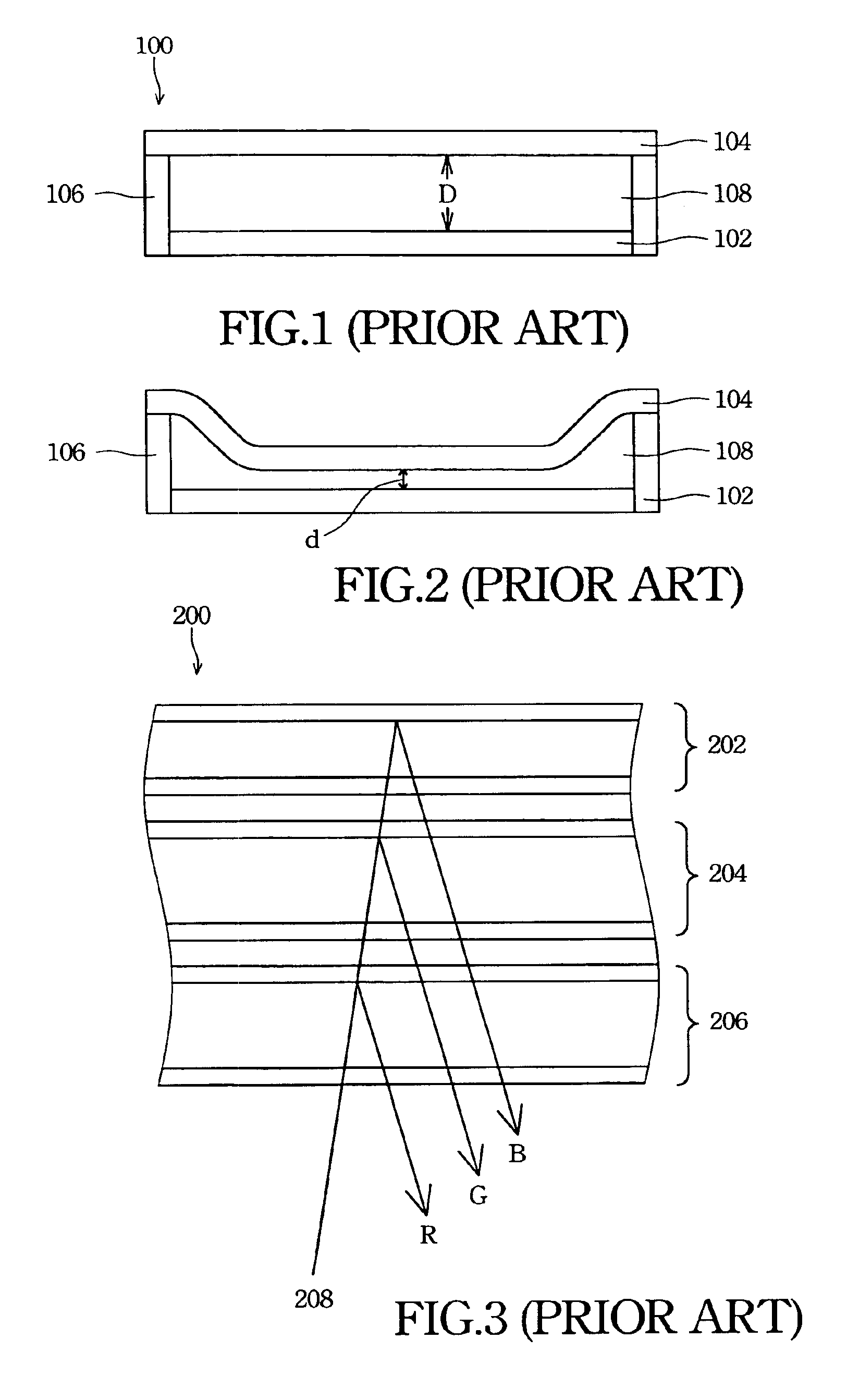

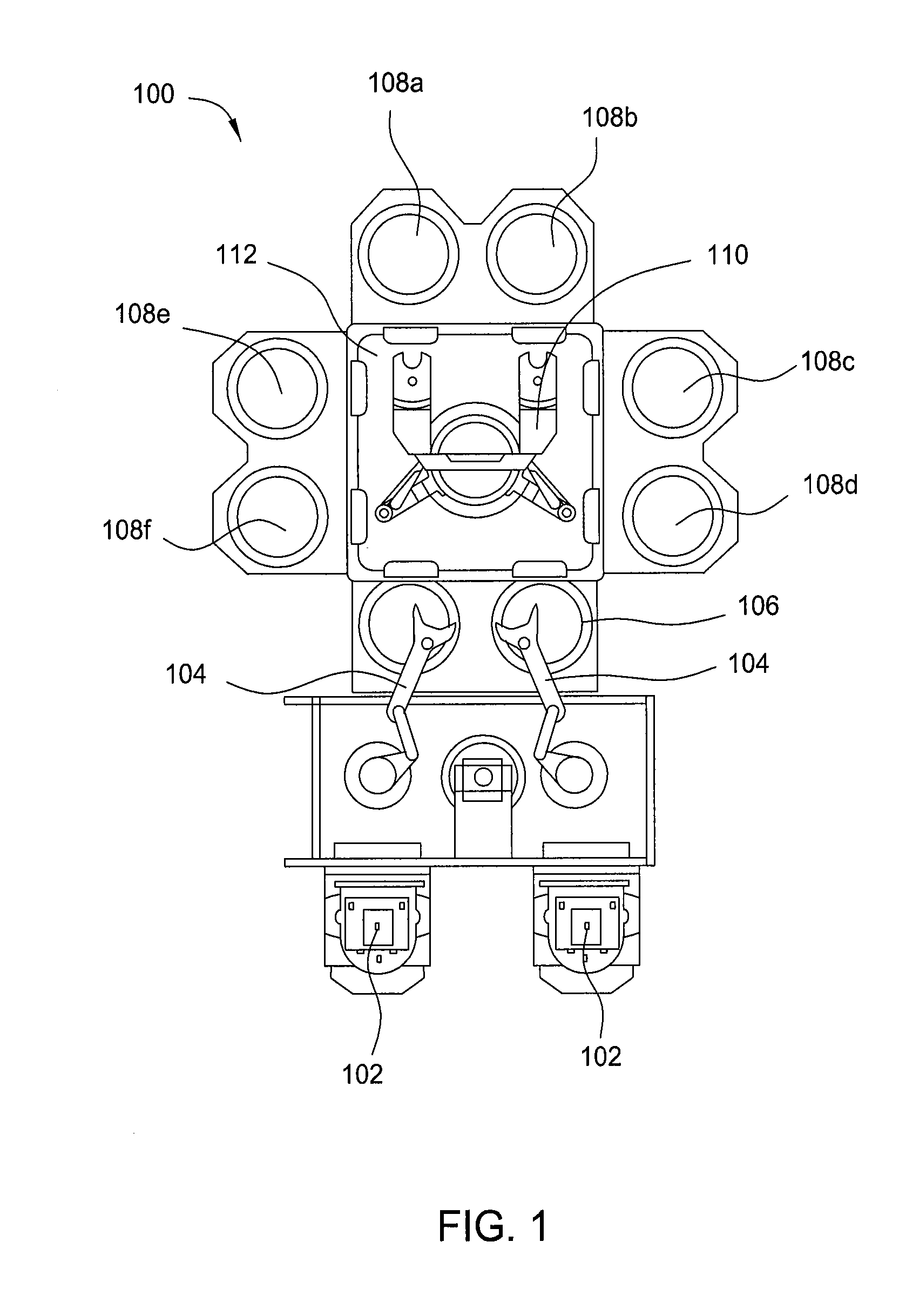

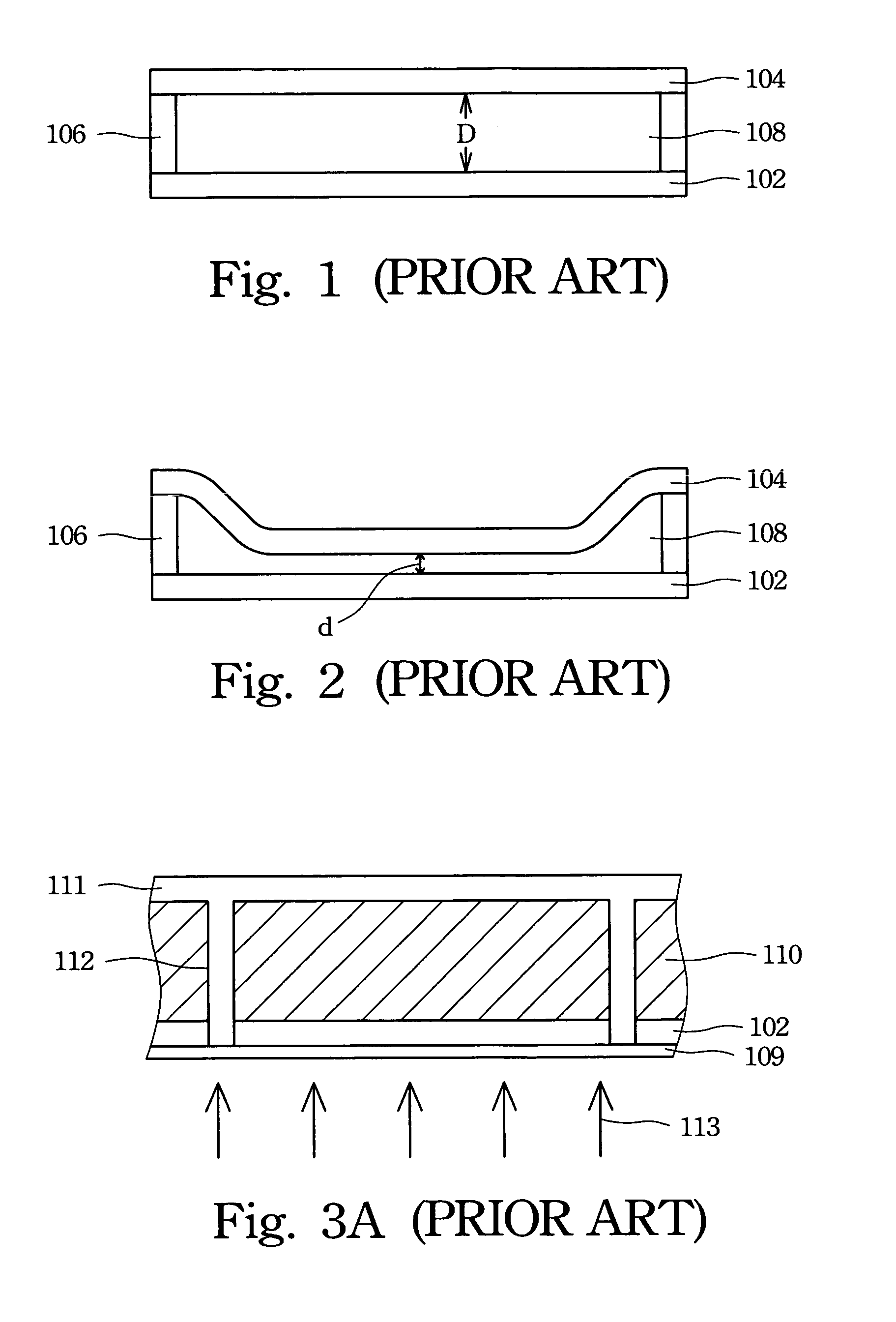

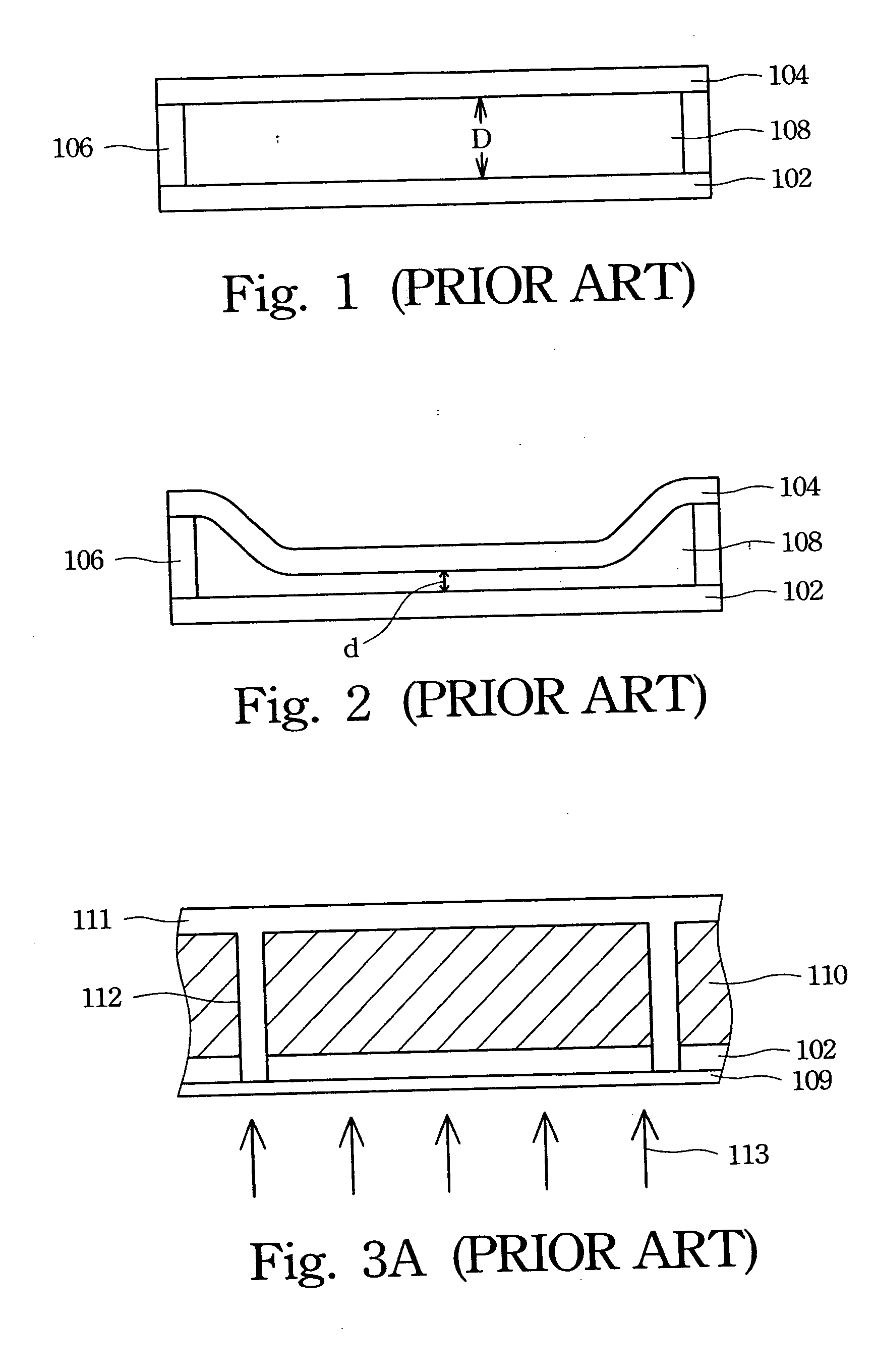

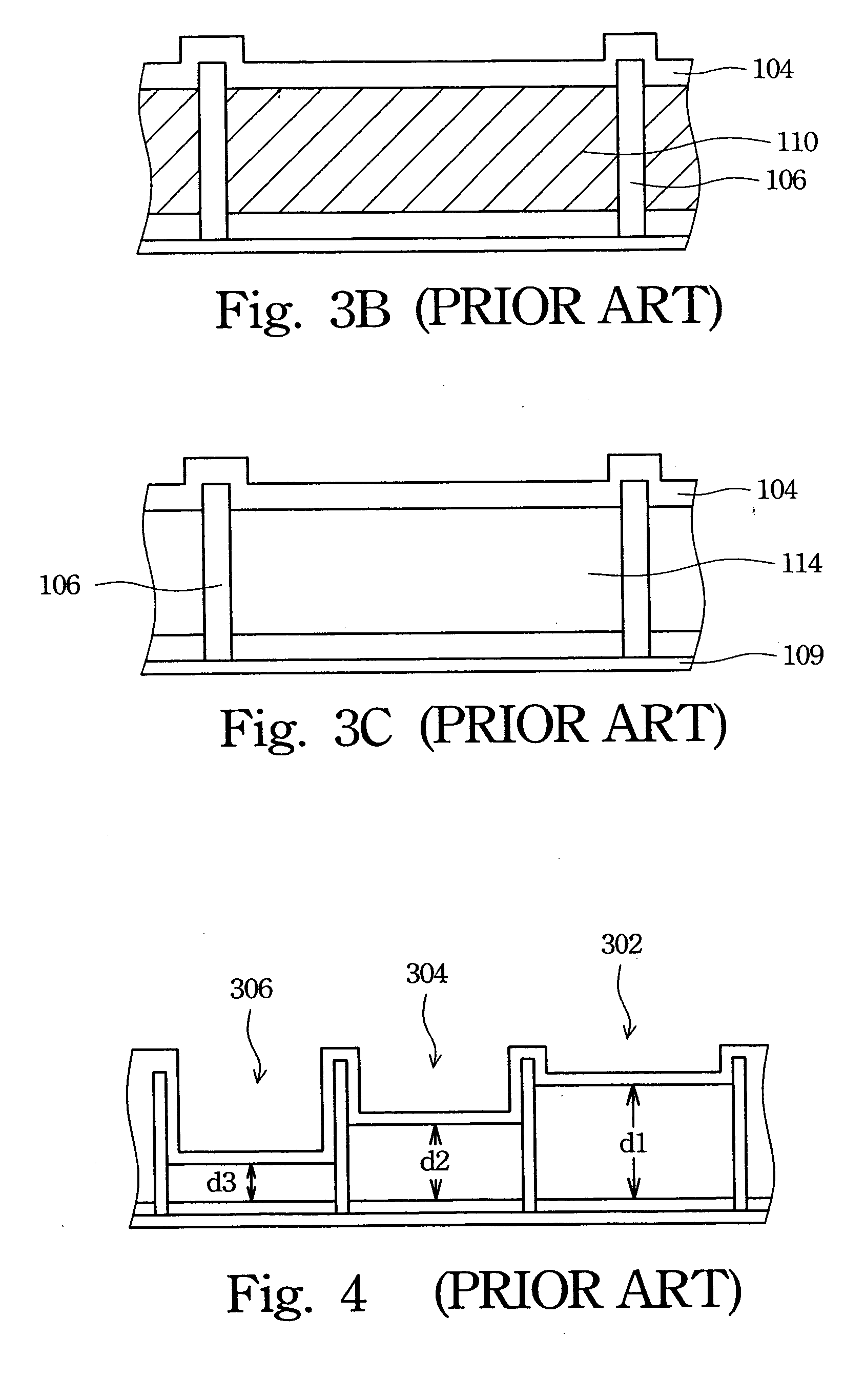

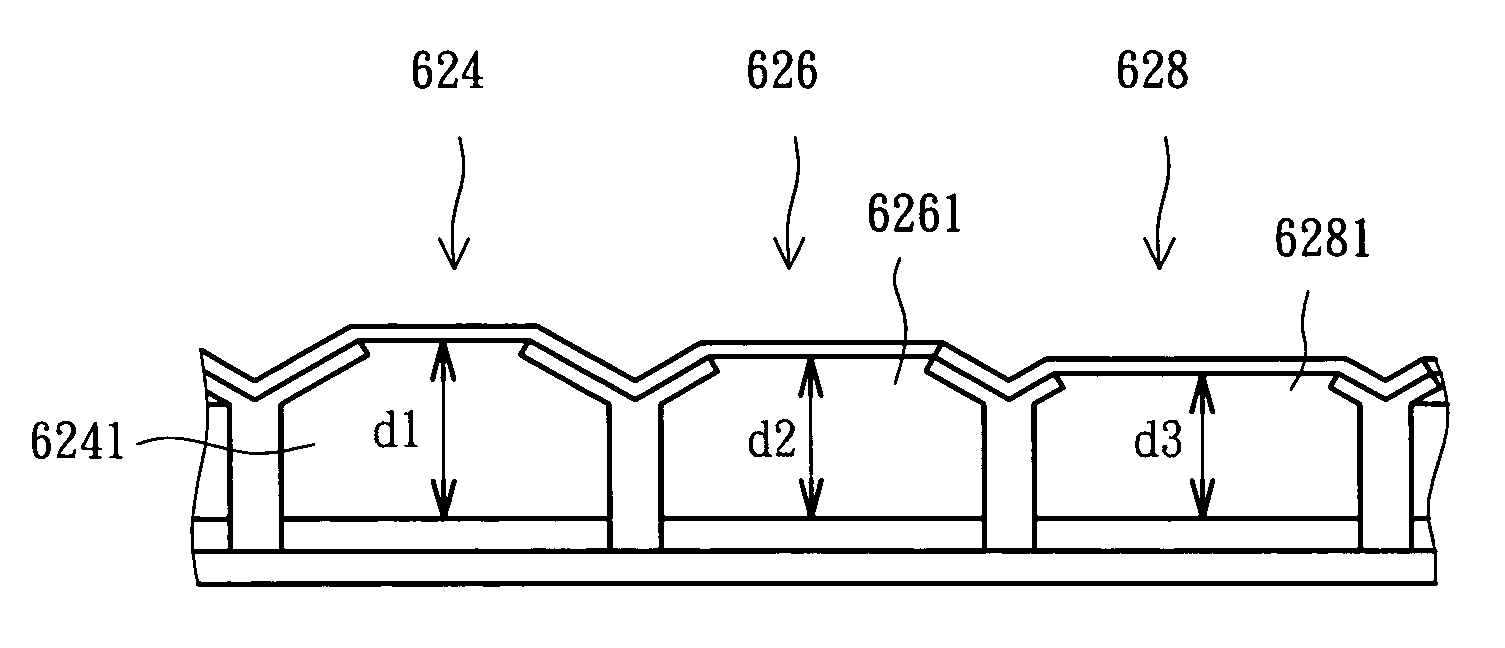

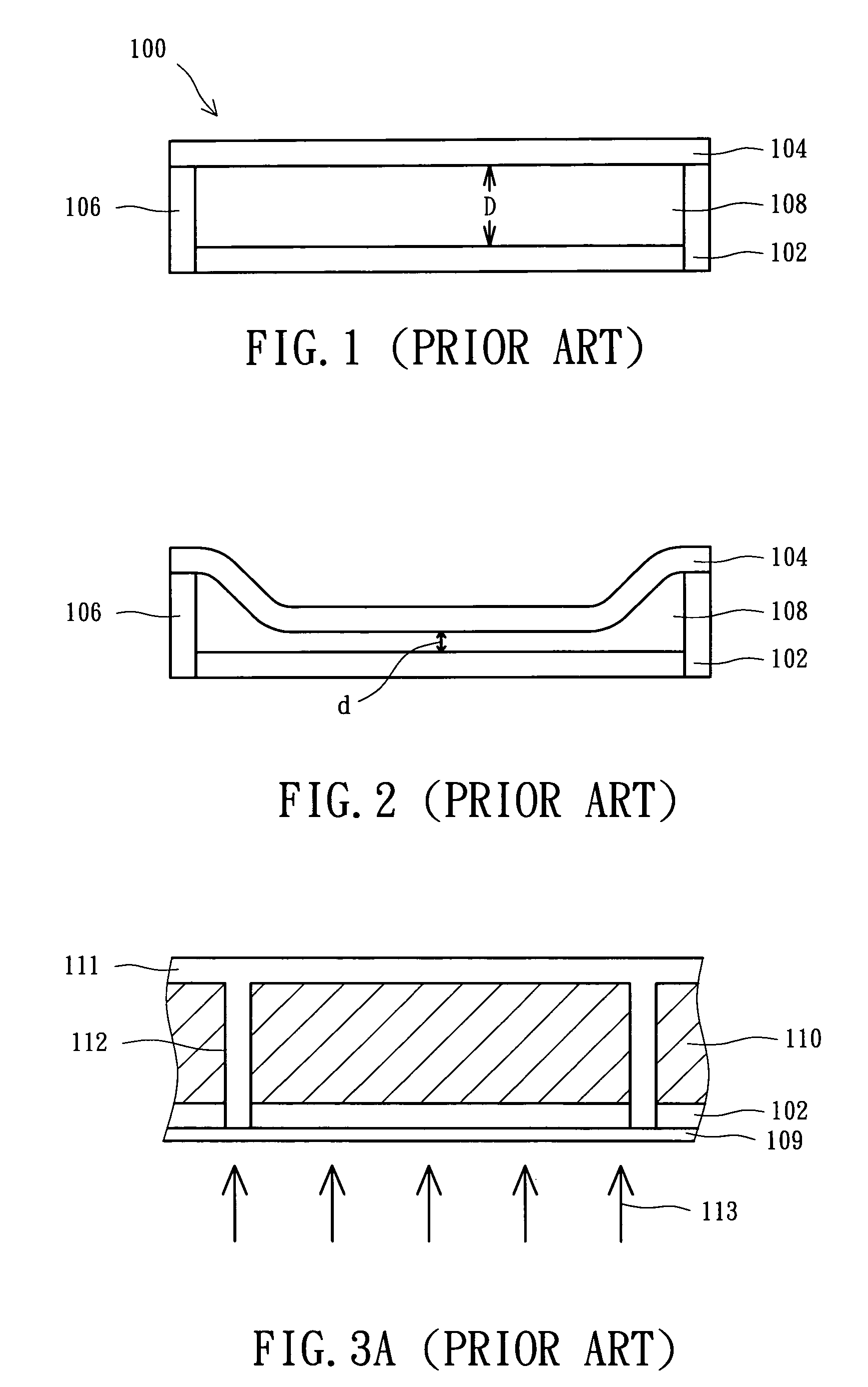

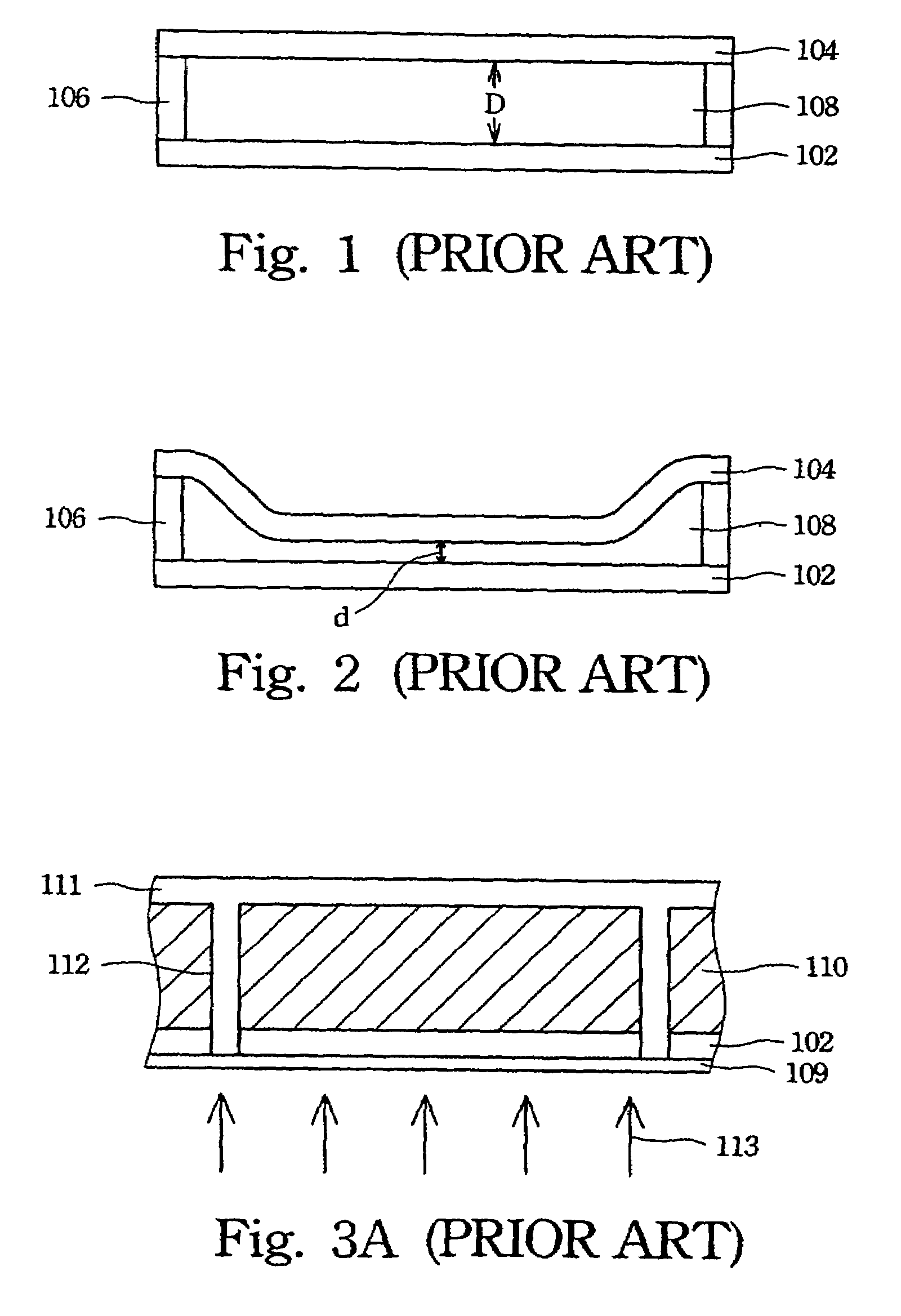

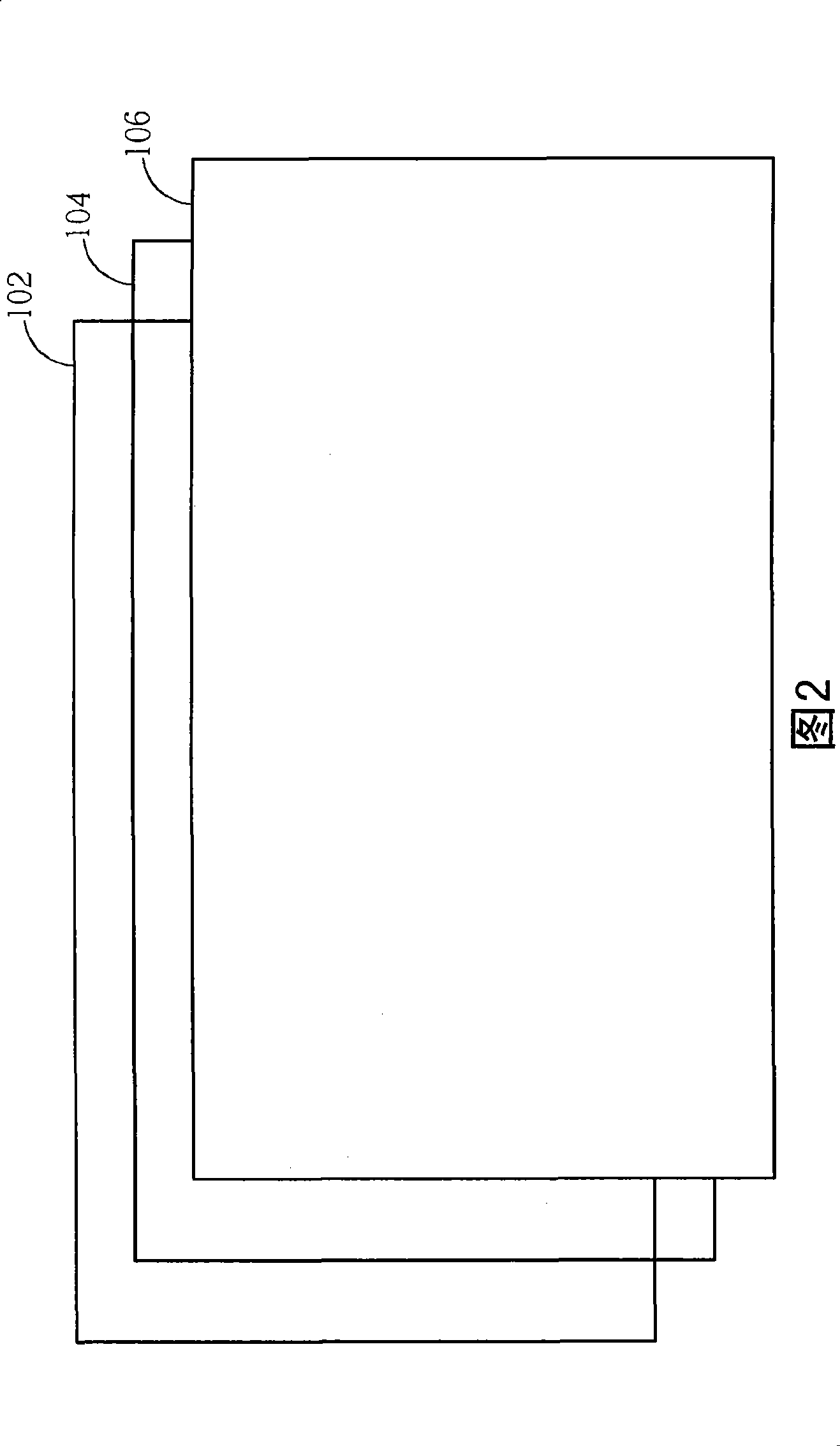

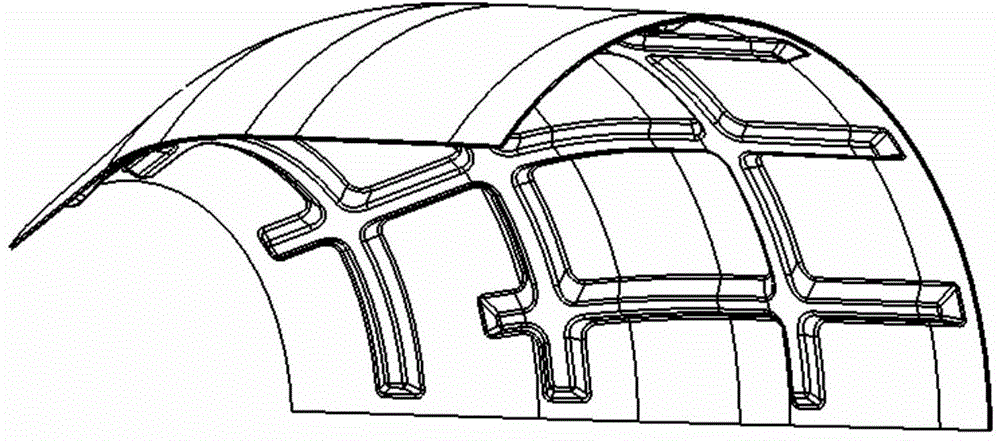

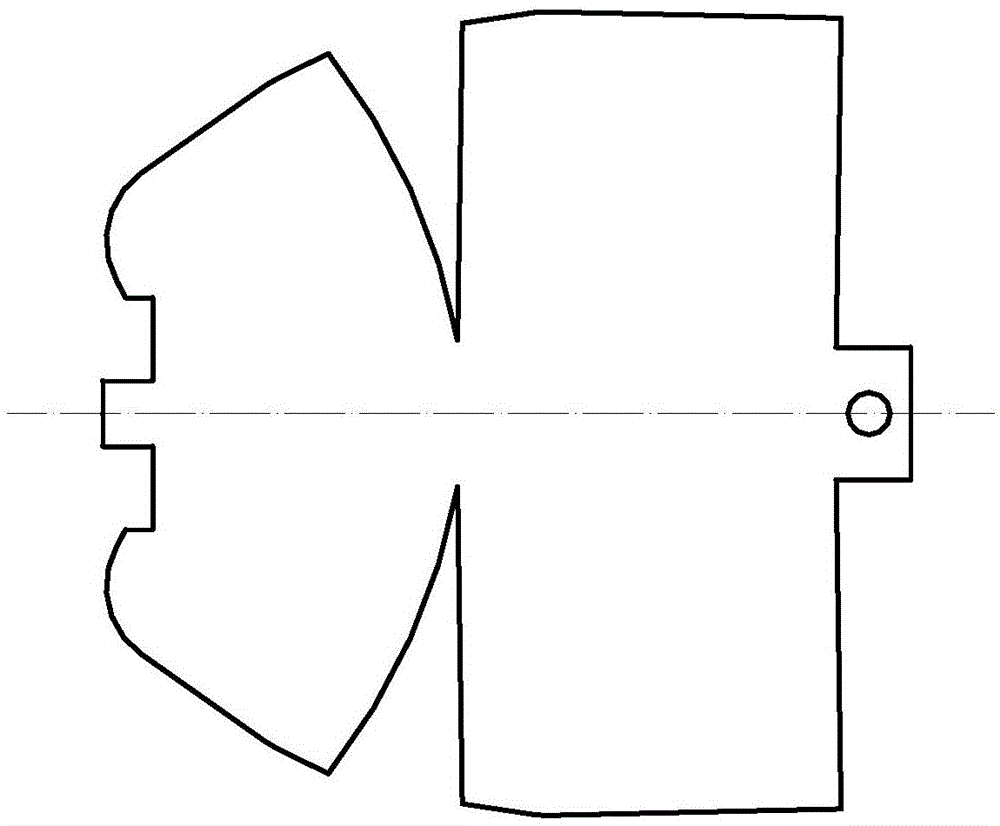

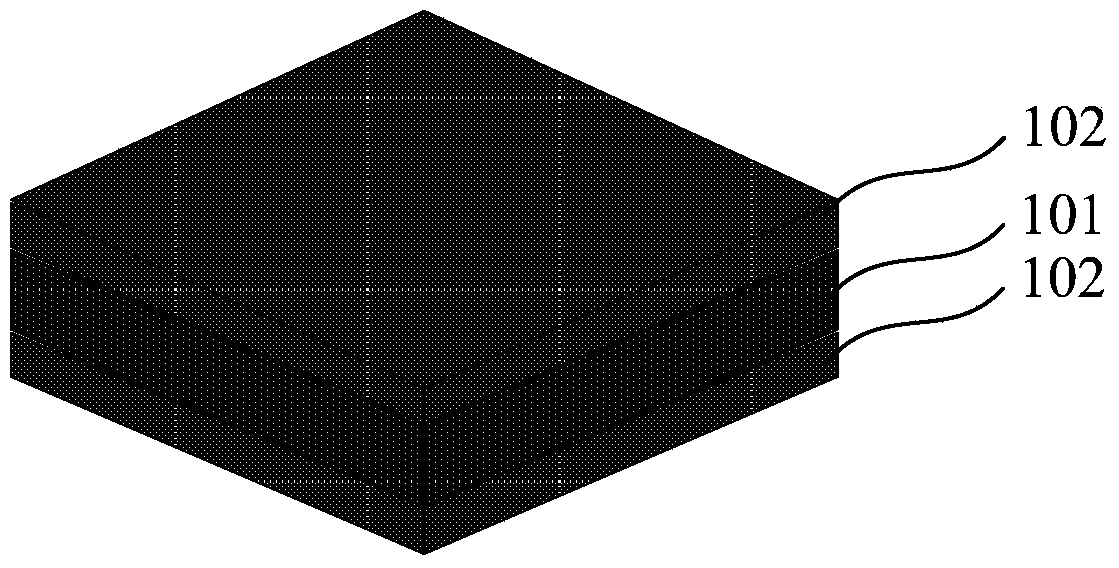

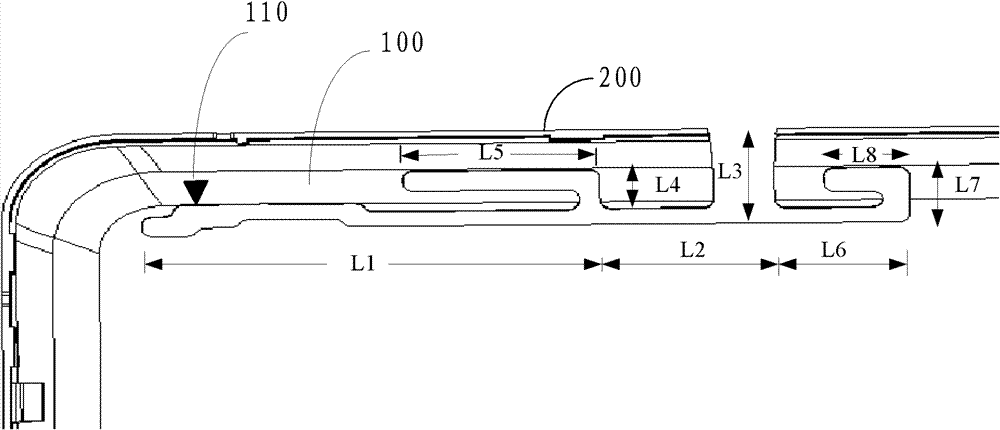

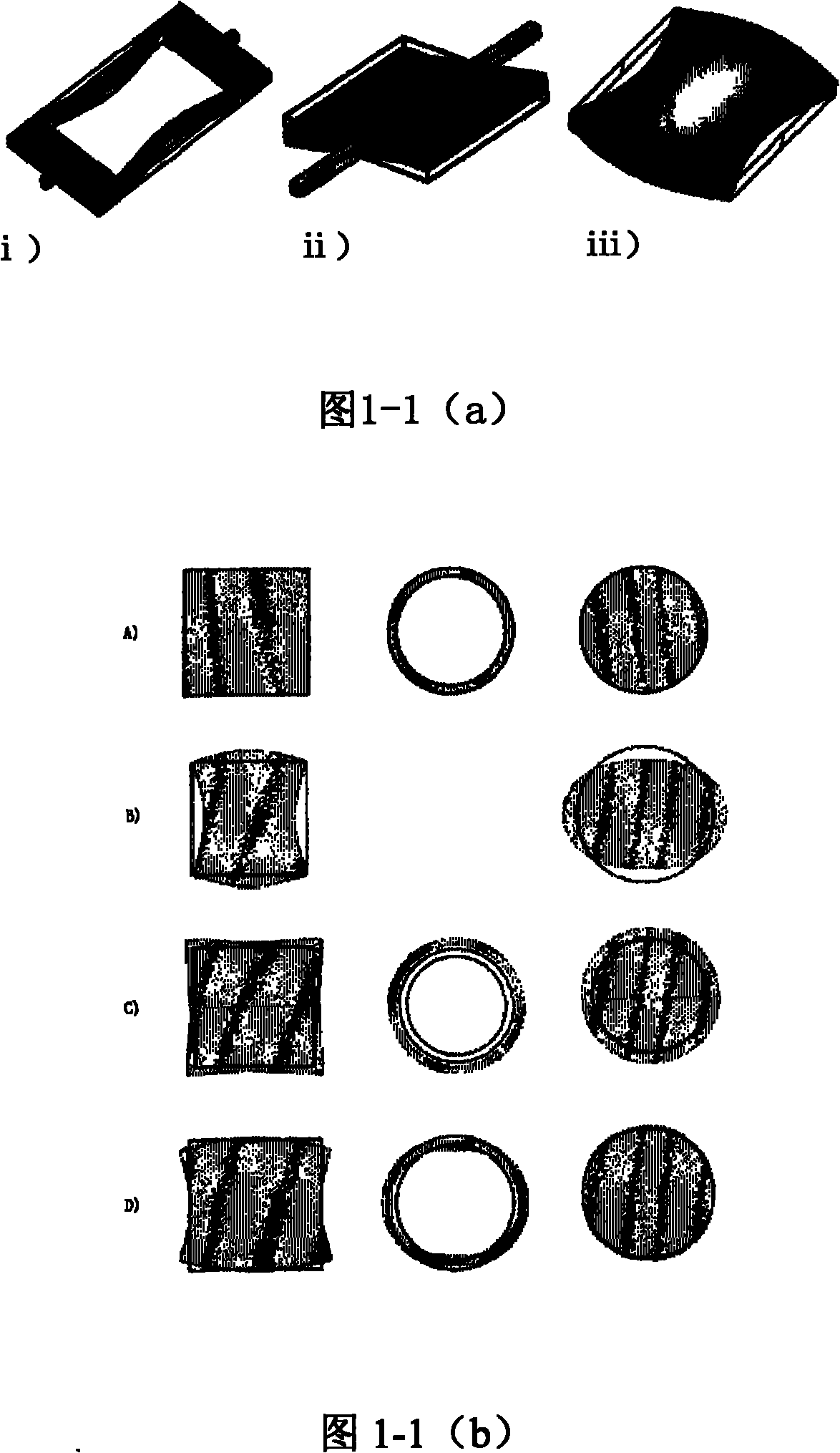

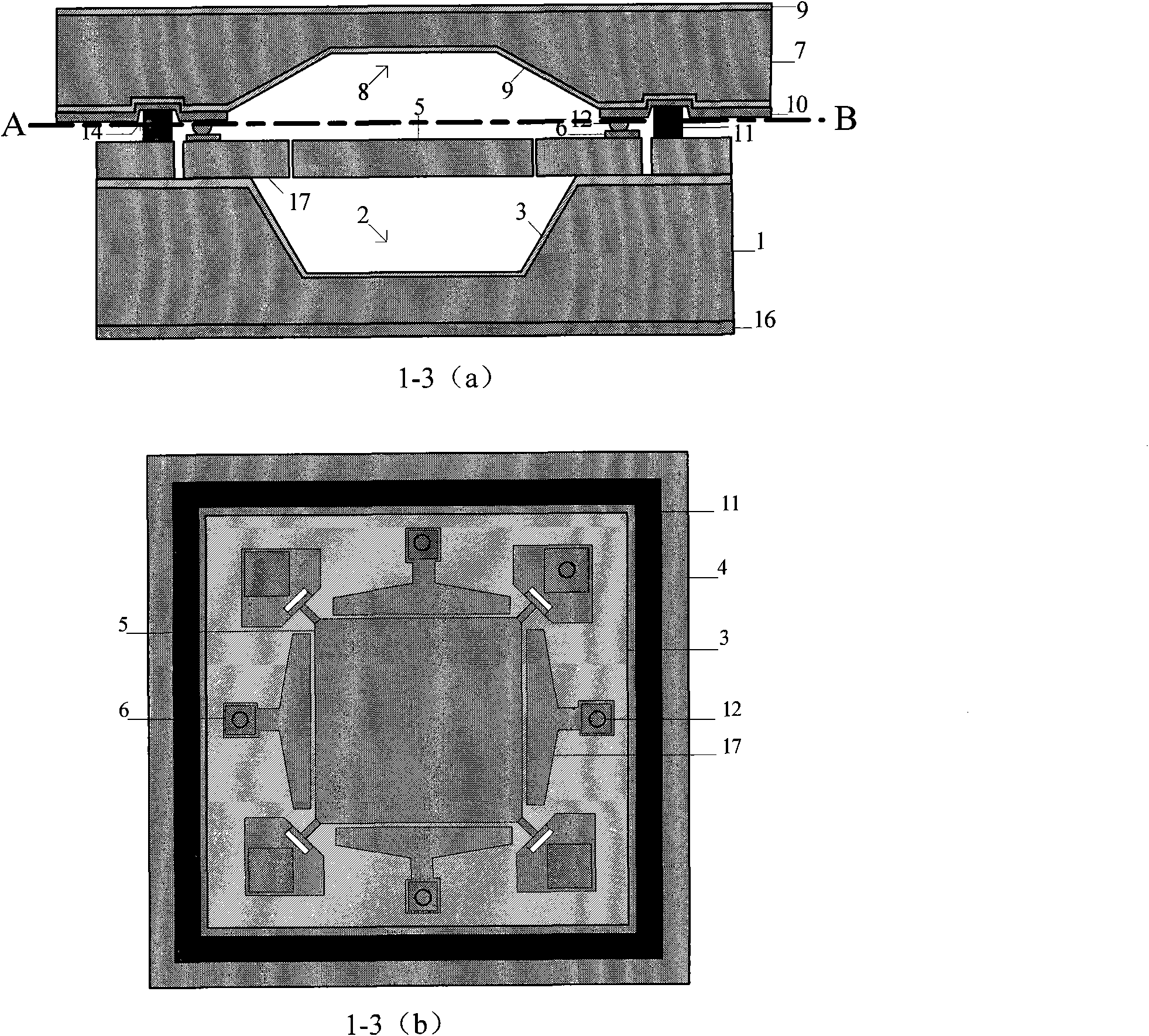

Structure of an optical interference display cell

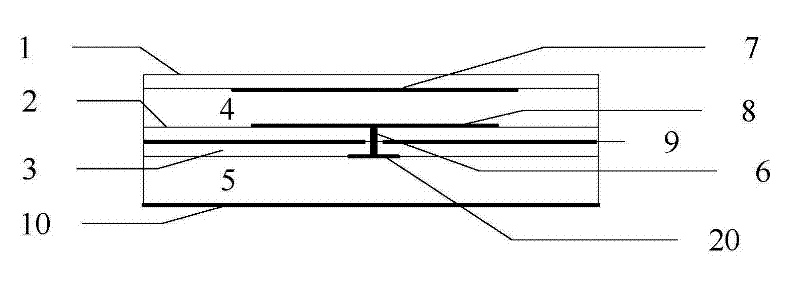

A structure of an interference display cell is provided. The cell comprises a first plate and a second plate, wherein a support is located between the first plate and the second plate. The second plate is a deformable and reflective plate. An incident light from one side of the first plate is modulated and only specific frequency light reflects by the second plate. The frequency of the reflected light is related to the distance between the first plate and the second plate. The support has at least one arm. The arm's stress makes the arm hiking upward or downward. The distance between the first plate and the second plate is also changed. Therefore, the frequency of the reflected light is altered.

Owner:SNAPTRACK

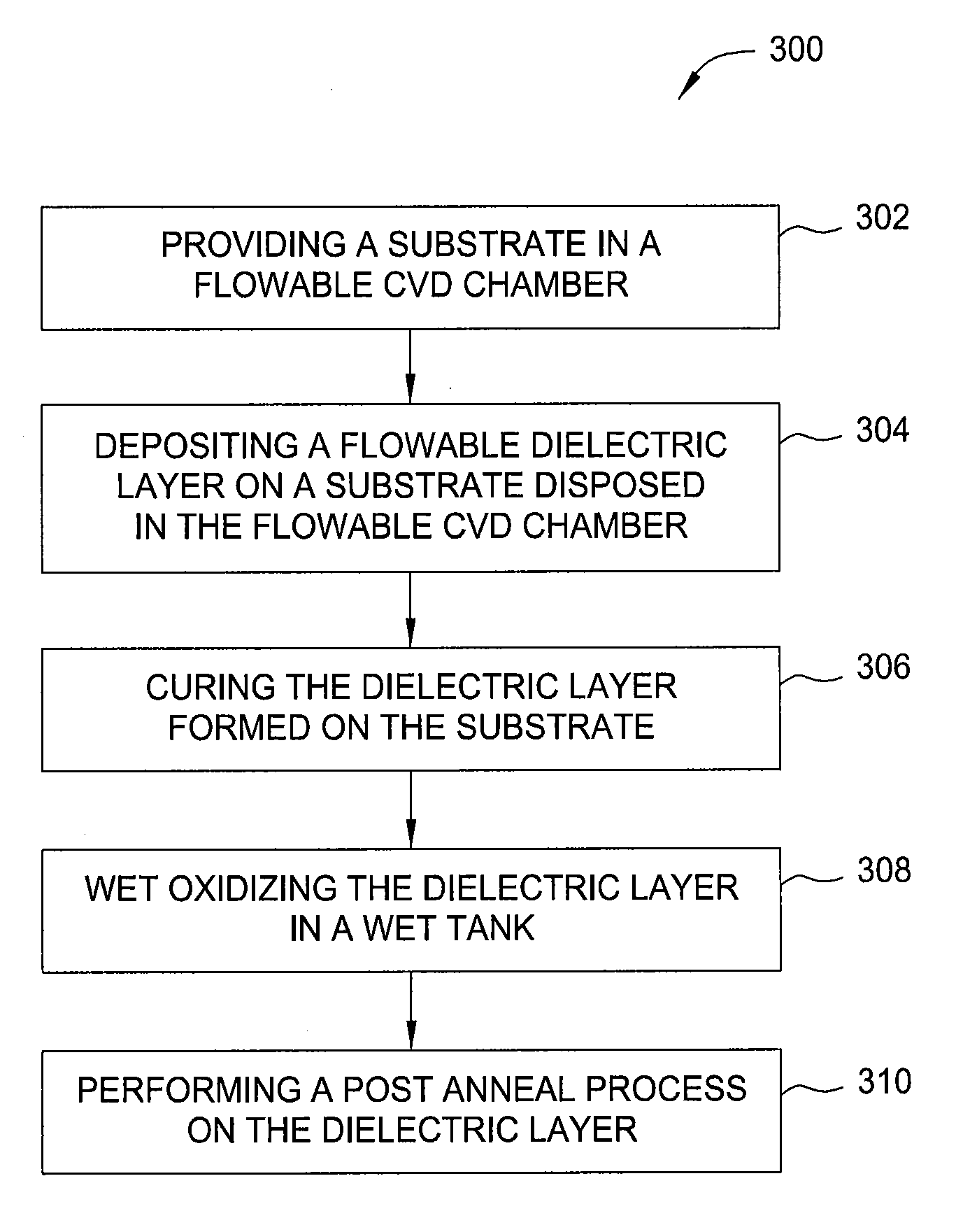

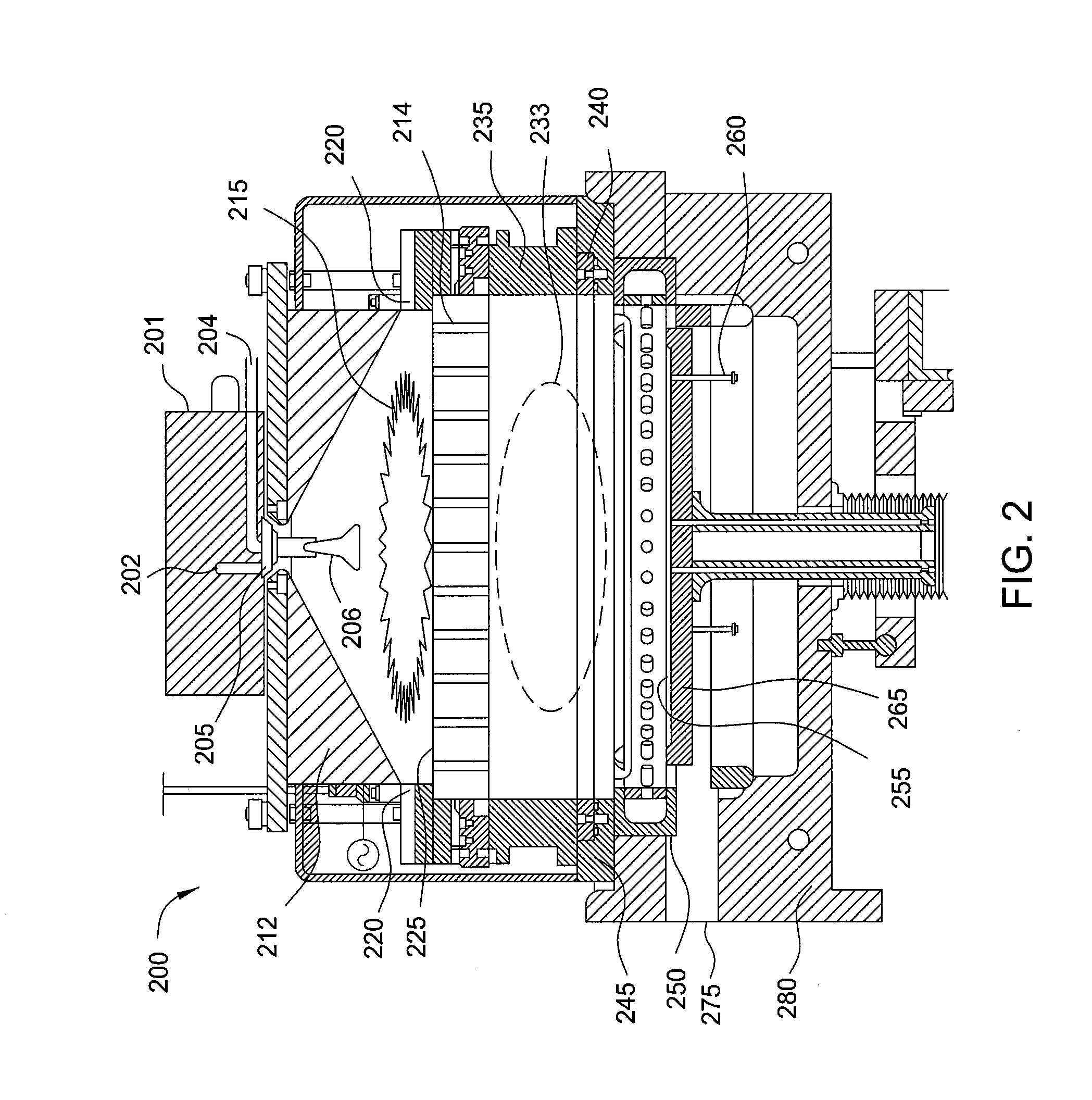

Wet oxidation process performed on a dielectric material formed from a flowable CVD process

InactiveUS20110151677A1Low costReduce process complexitySemiconductor/solid-state device manufacturingSiliconWet oxidation

Methods of performing a wet oxidation process on a silicon containing dielectric material filling within trenches or vias defined within a substrate are provided. In one embodiment, a method of forming a dielectric material on a substrate includes forming a dielectric material on a substrate by a flowable CVD process, curing the dielectric material disposed on the substrate, performing a wet oxidation process on the dielectric material disposed on the substrate, and forming an oxidized dielectric material on the substrate.

Owner:APPLIED MATERIALS INC

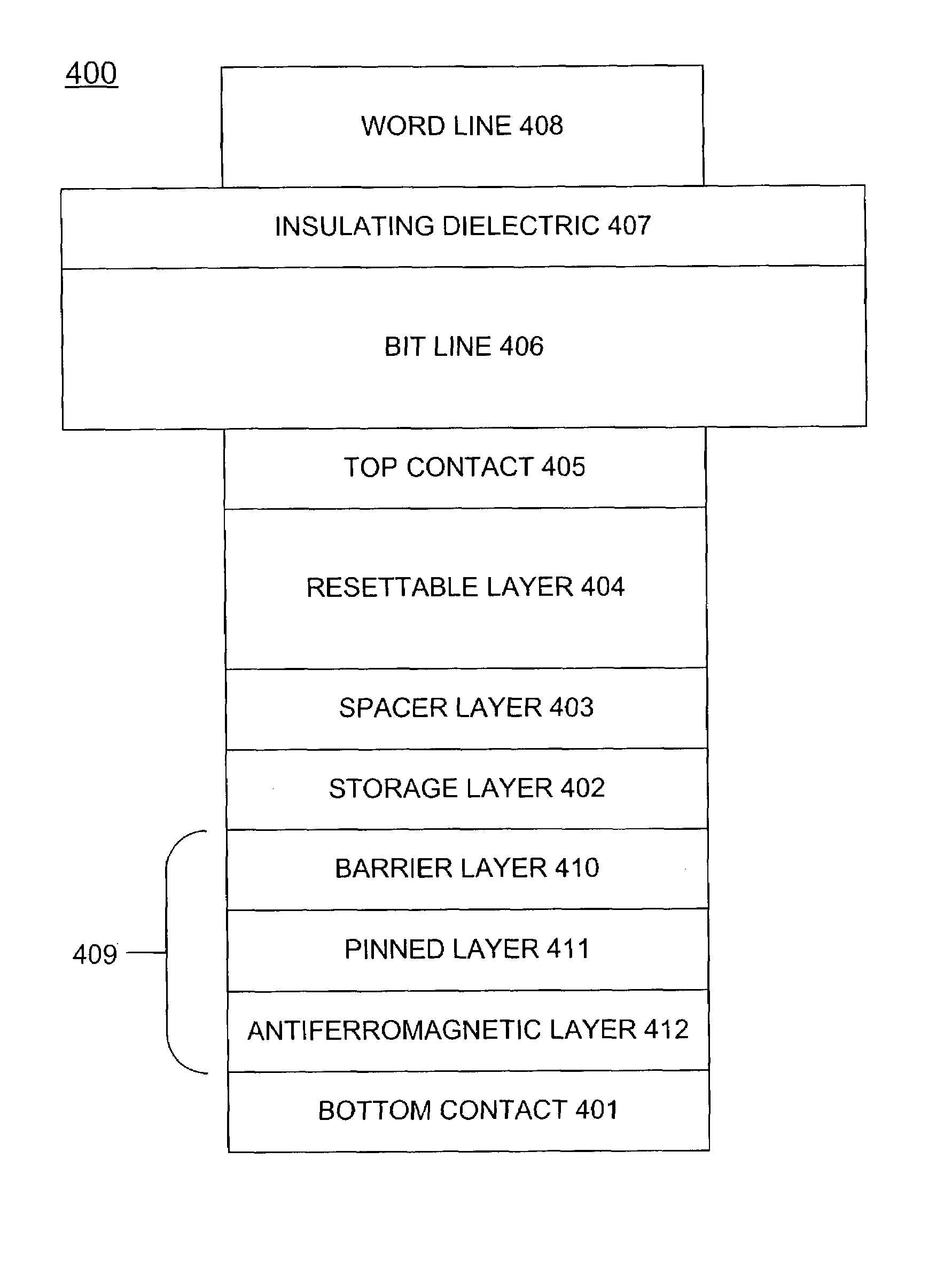

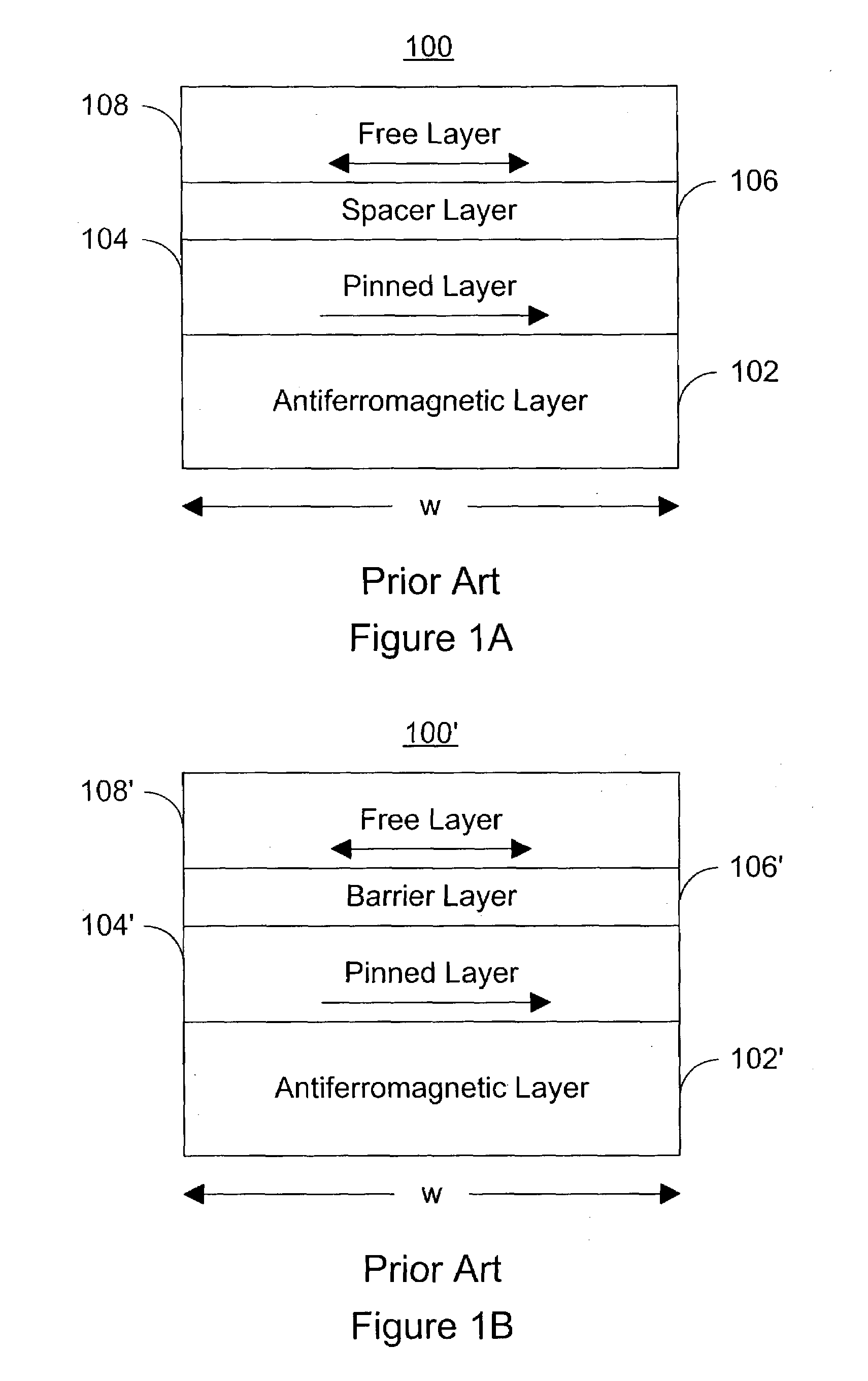

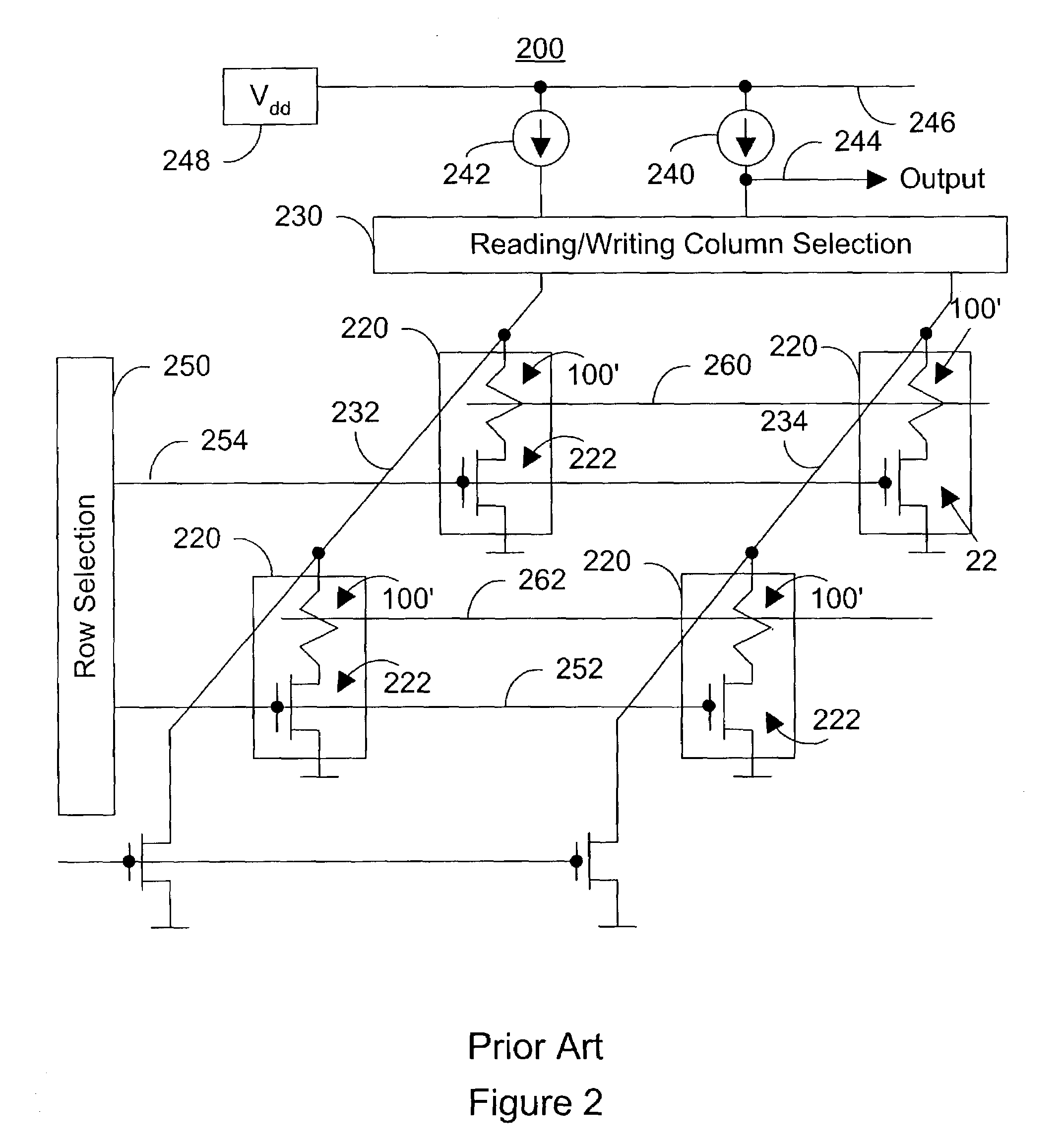

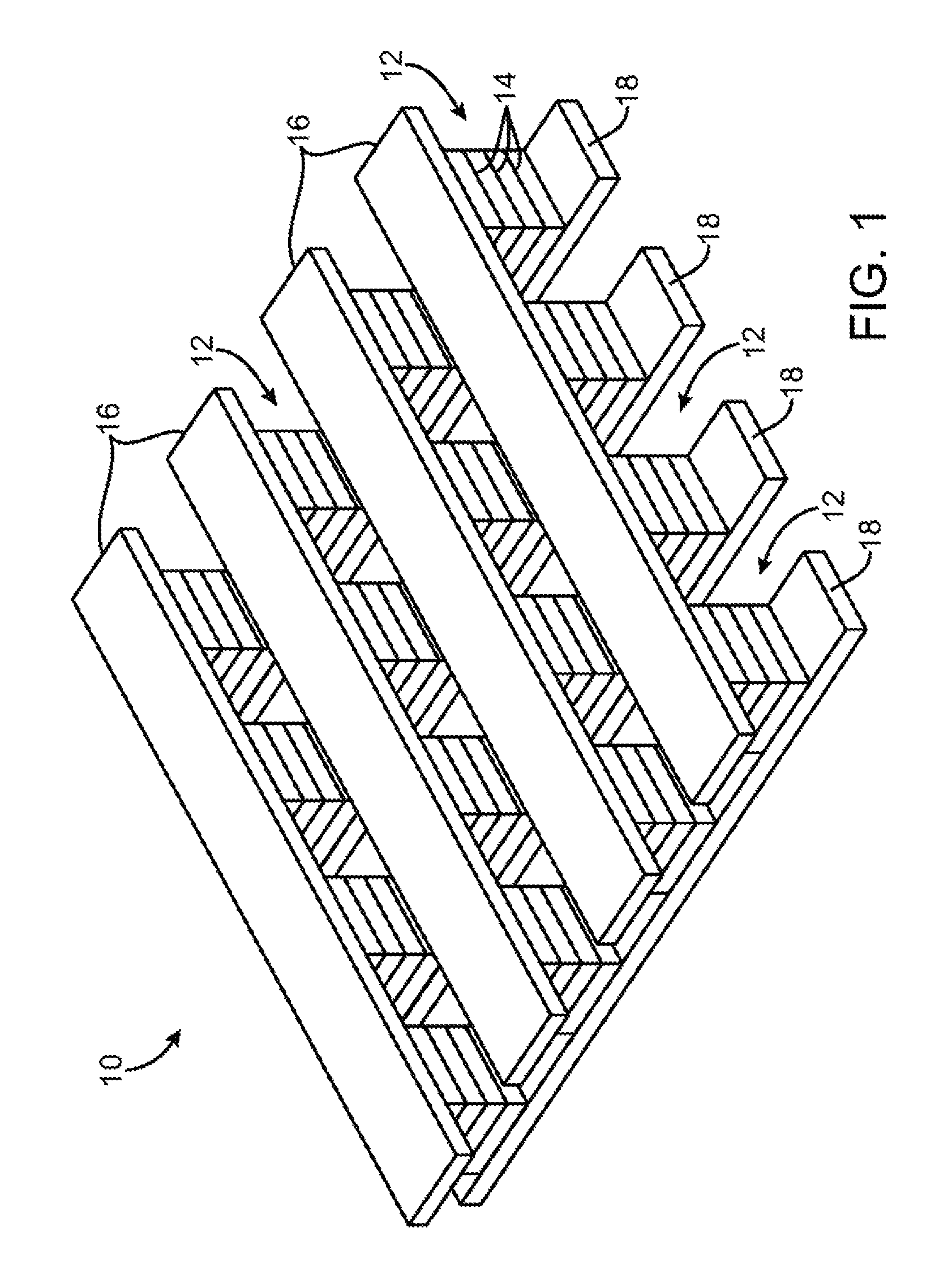

Spin-transfer multilayer stack containing magnetic layers with resettable magnetization

InactiveUS7190611B2Minimizing densityReduce process complexityGalvano-magnetic devicesSolid-state devicesHigh densitySpin transfer

A magnetic element for a high-density memory array includes a resettable layer and a storage layer. The resettable layer has a magnetization that is set in a selected direction by at least one externally generated magnetic field. The storage layer has at least one magnetic easy axis and a magnetization that changes direction based on the spin-transfer effect when a write current passes through the magnetic element. An alternative embodiment of the magnetic element includes an additional multilayer structure formed from a tunneling barrier layer, a pinned magnetic layer and an antiferromagnetic layer that pins the magnetization of the pinned layer in a predetermined direction. Another alternative embodiment of the magnetic element includes an additional multilayer structure that is formed from a tunneling barrier layer and a second resettable layer having a magnetic moment that is different from the magnetic moment of the resettable layer of the basic embodiment.

Owner:SAMSUNG SEMICON

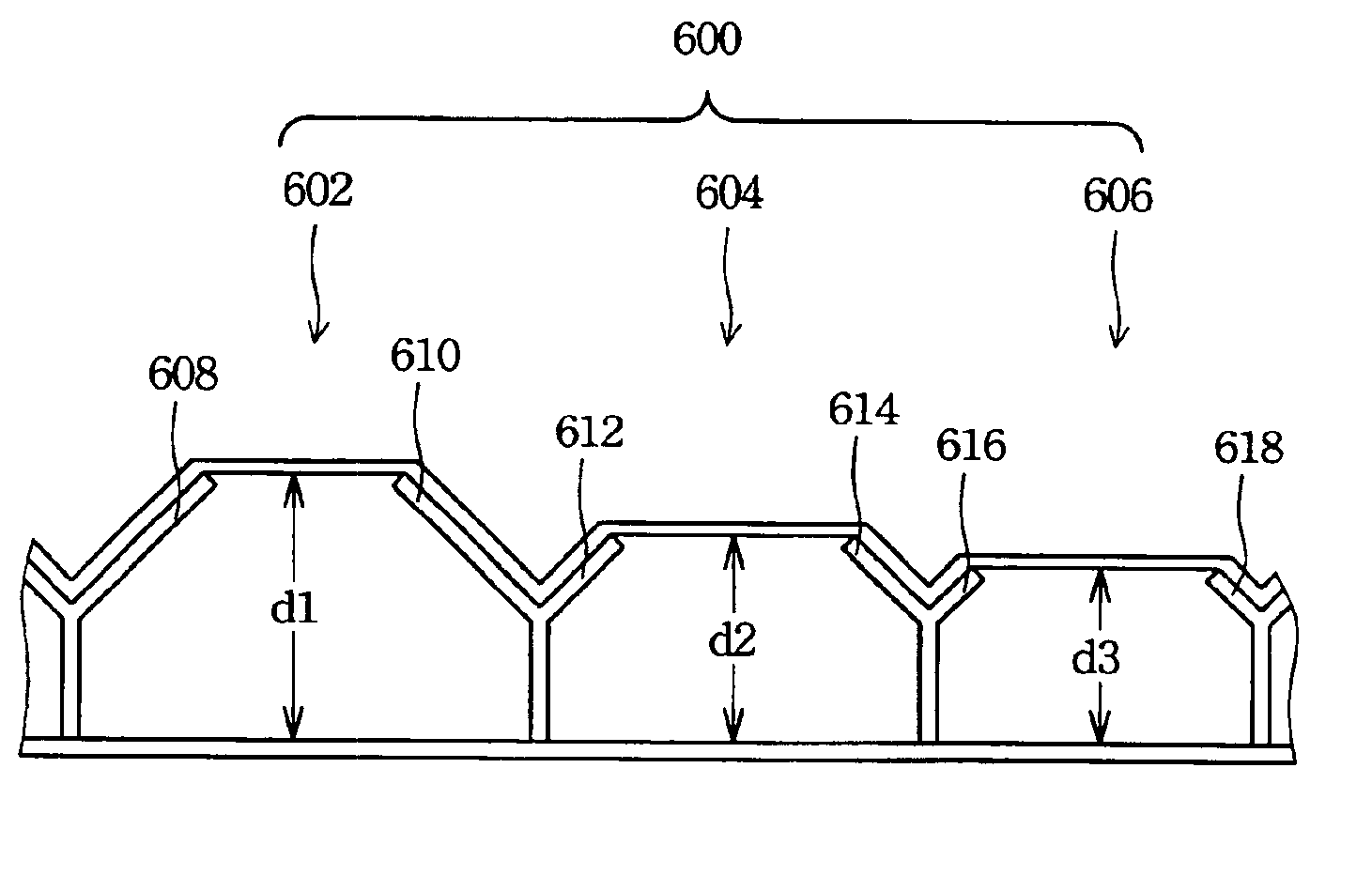

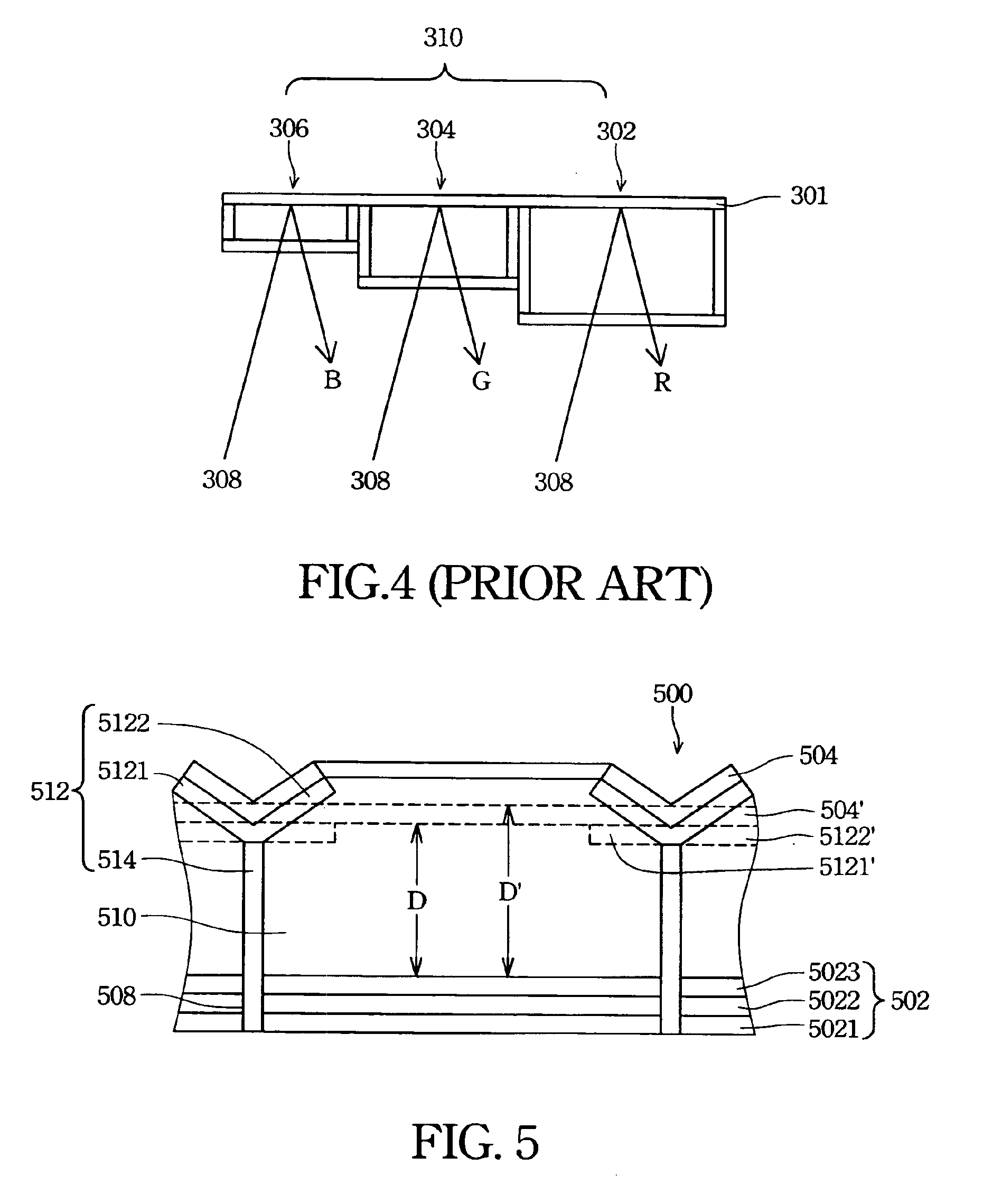

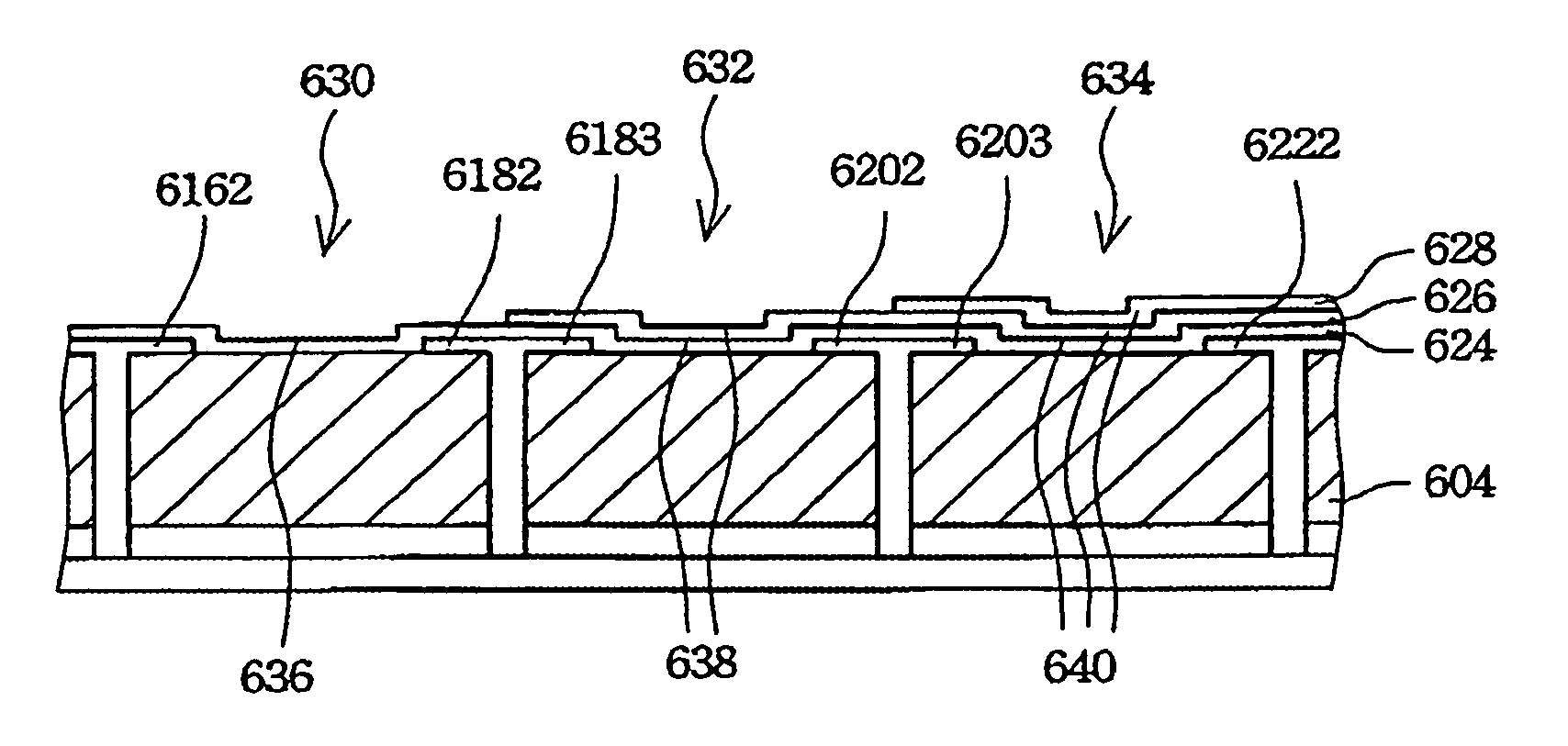

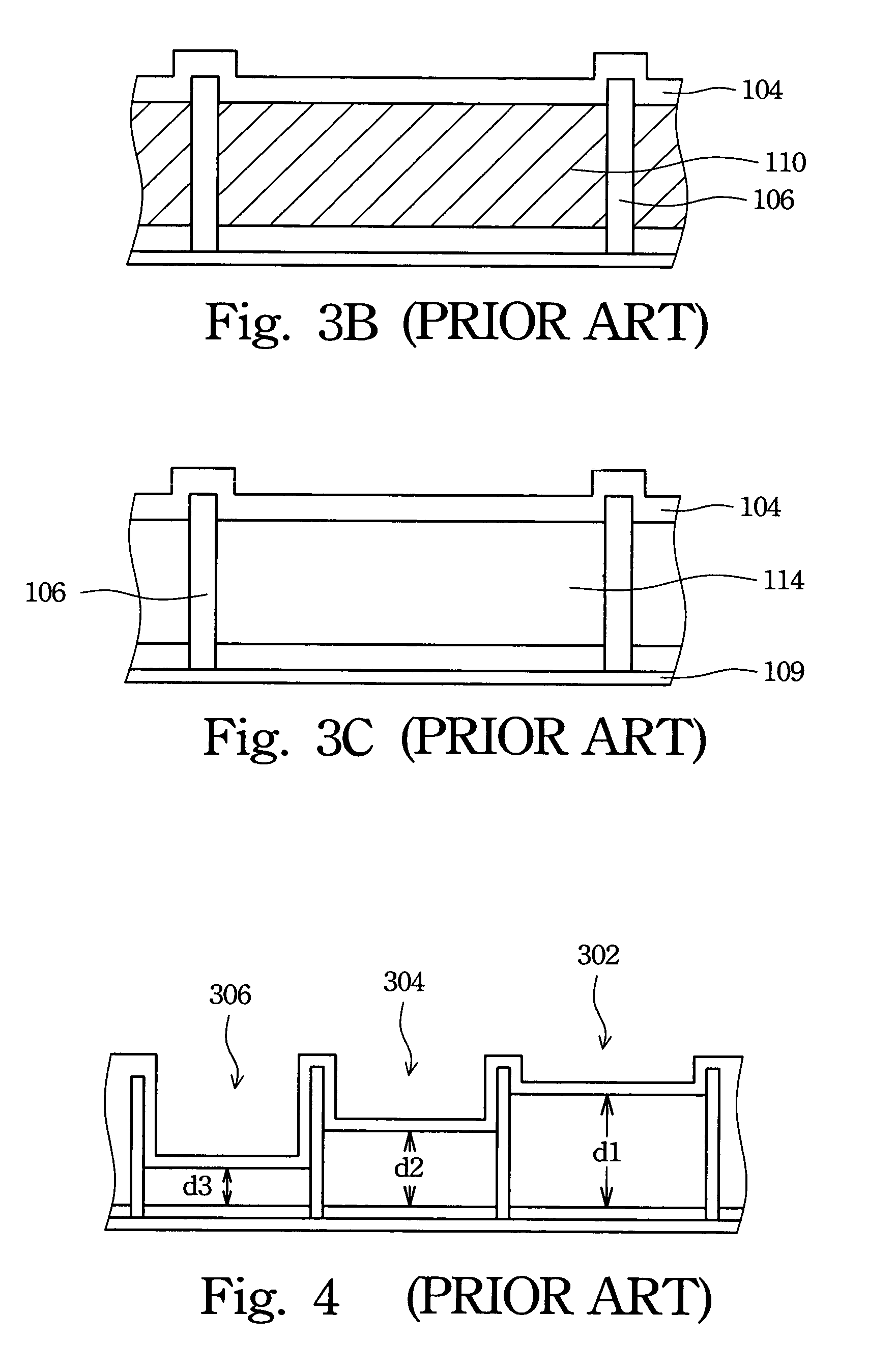

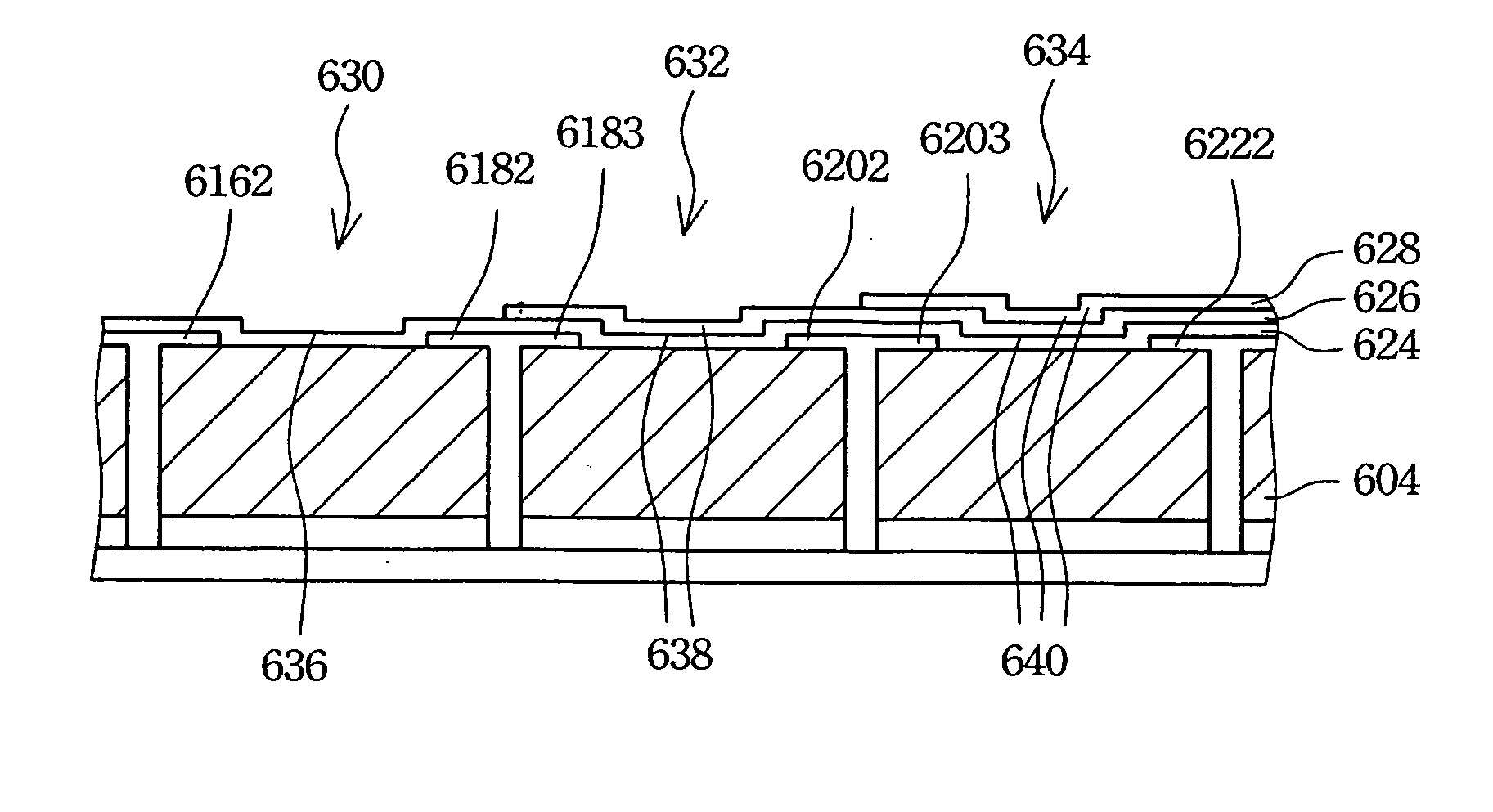

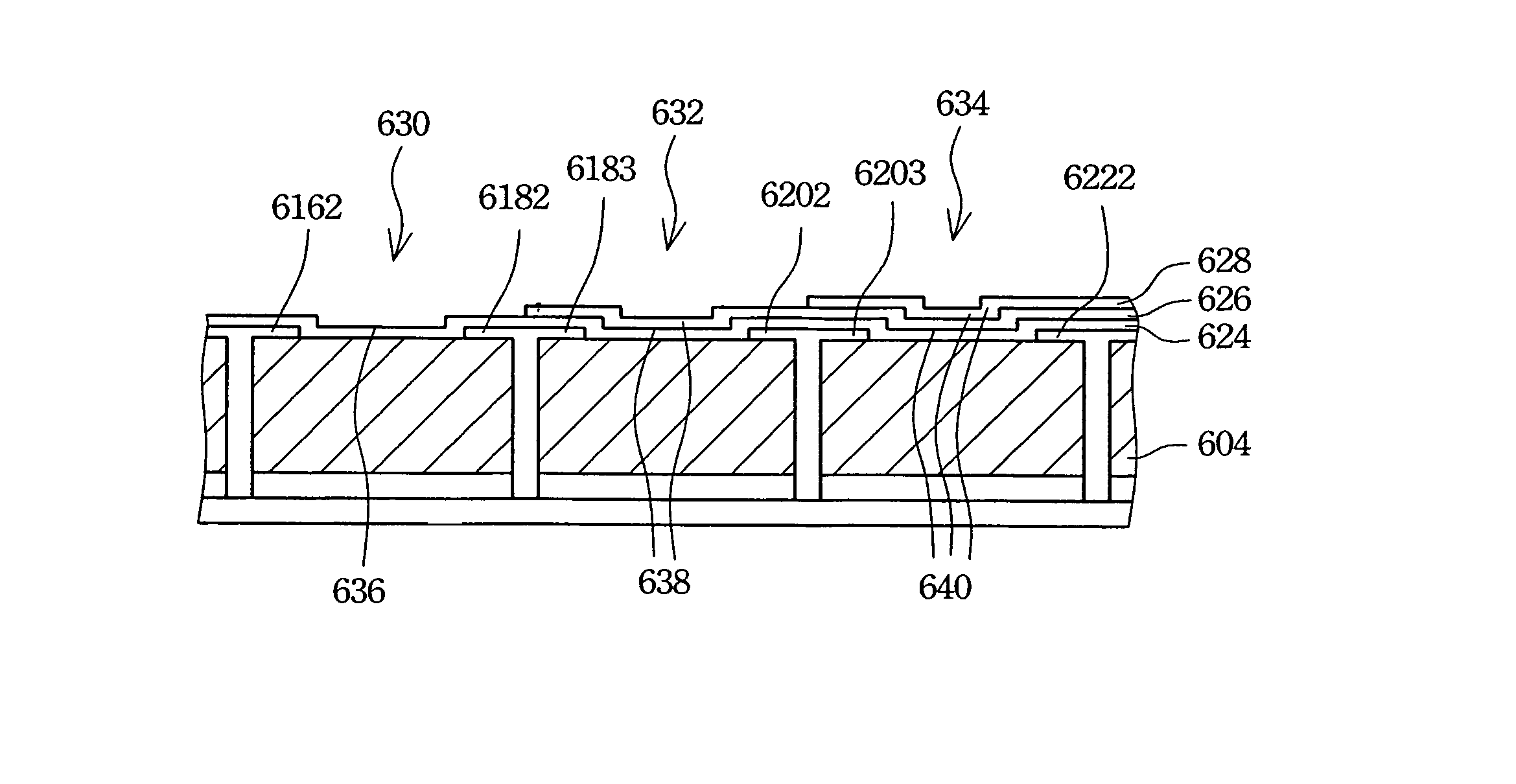

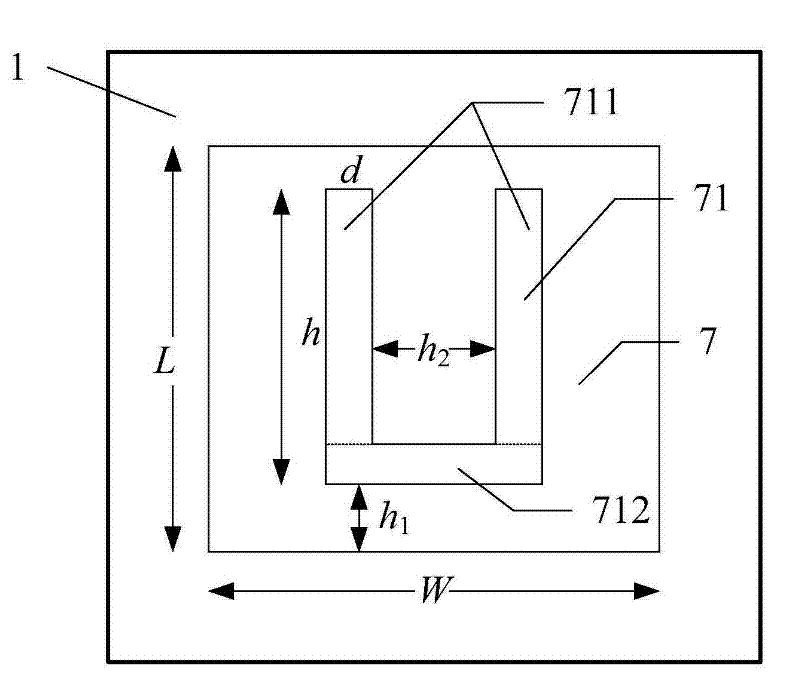

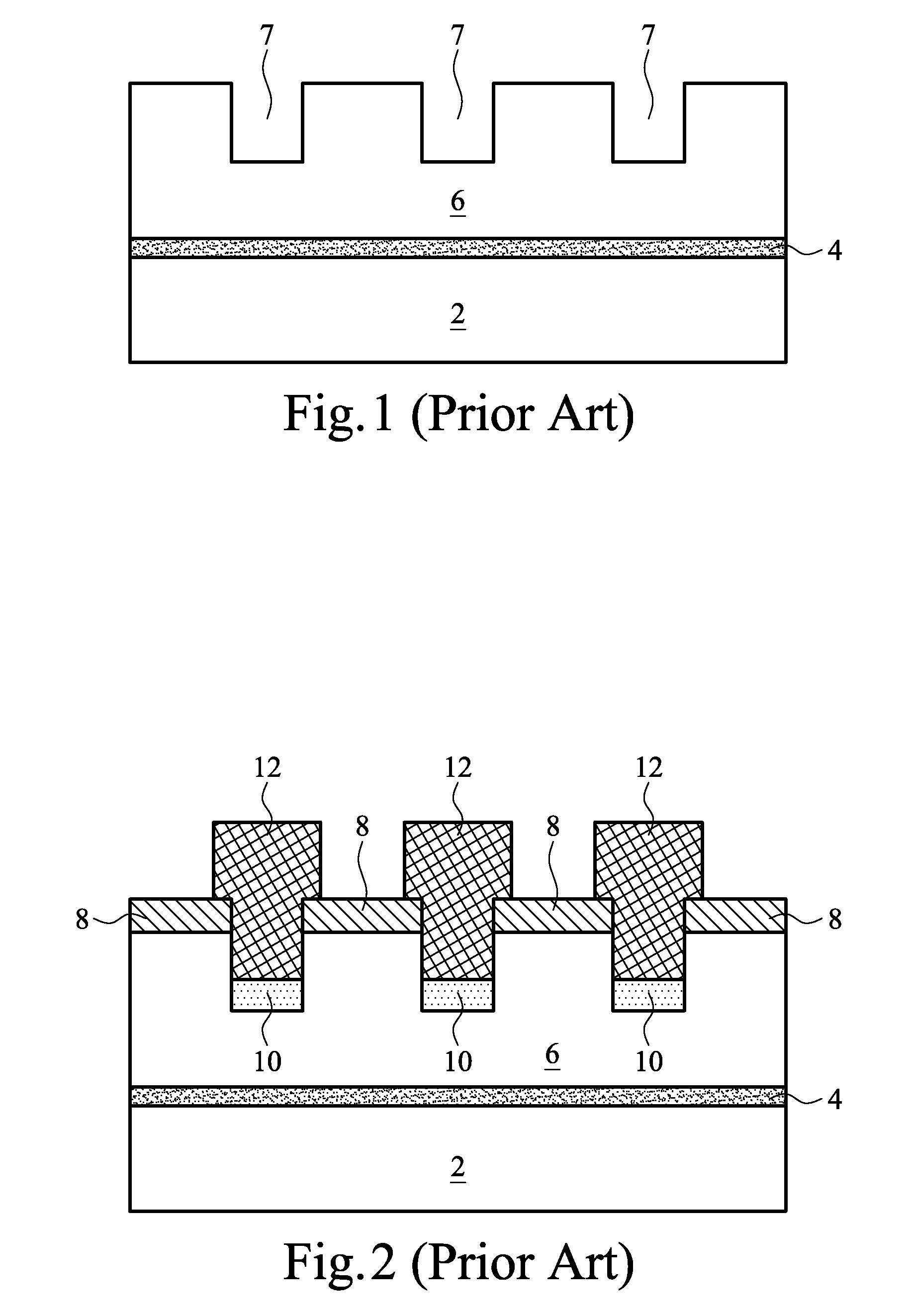

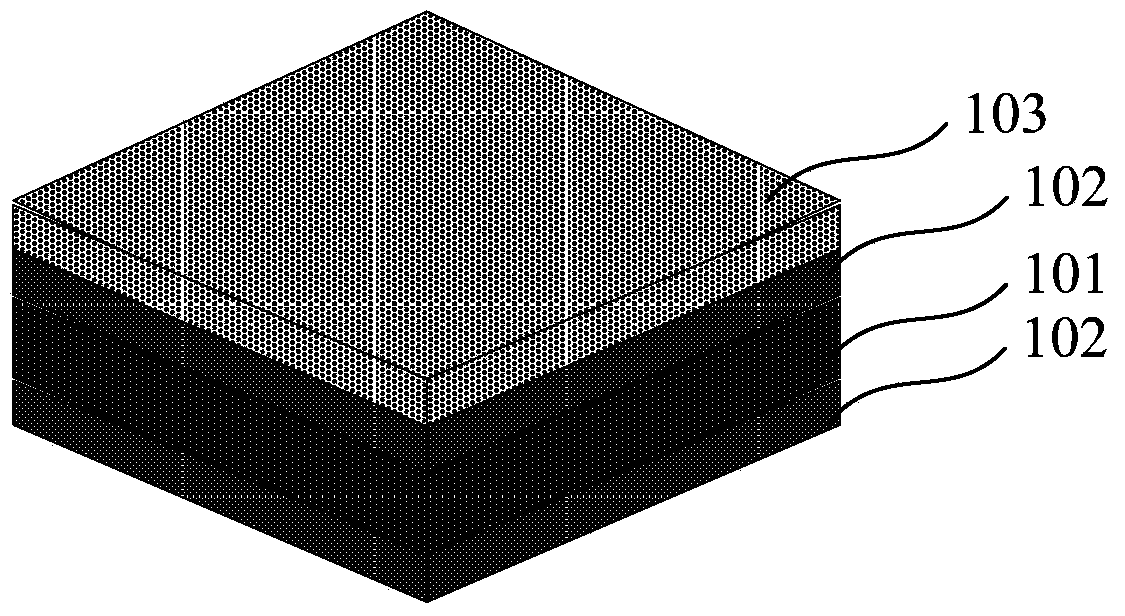

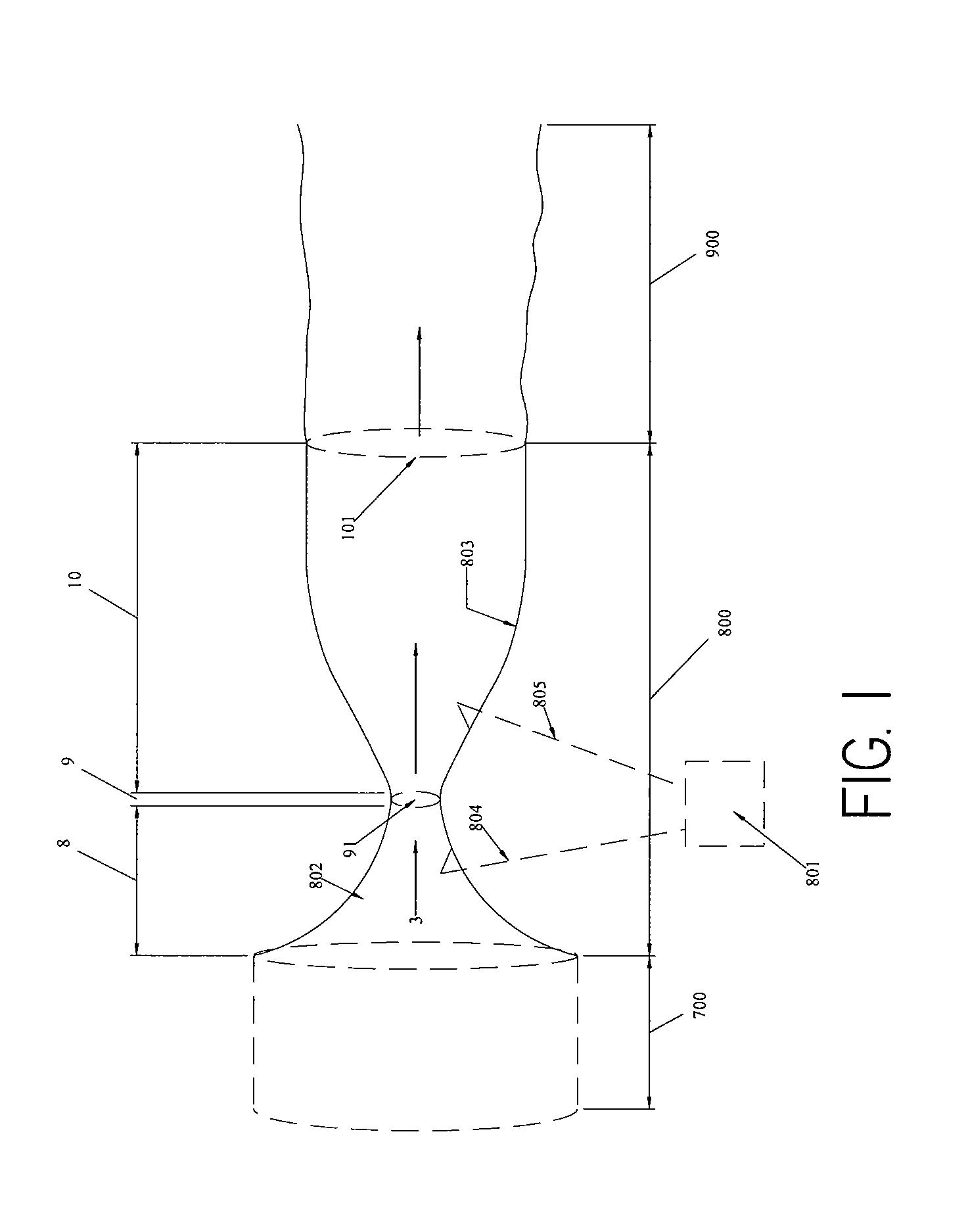

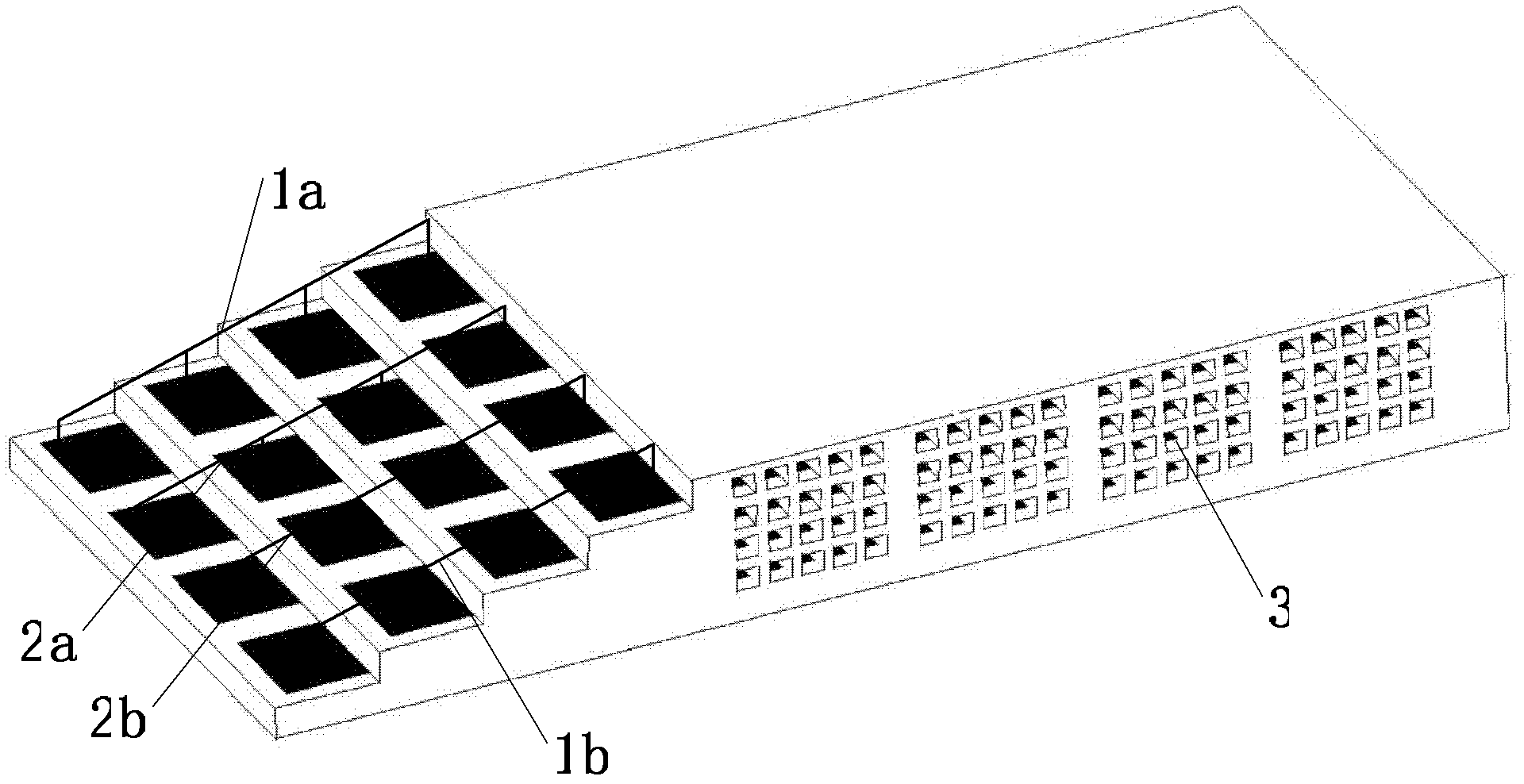

Interference display unit

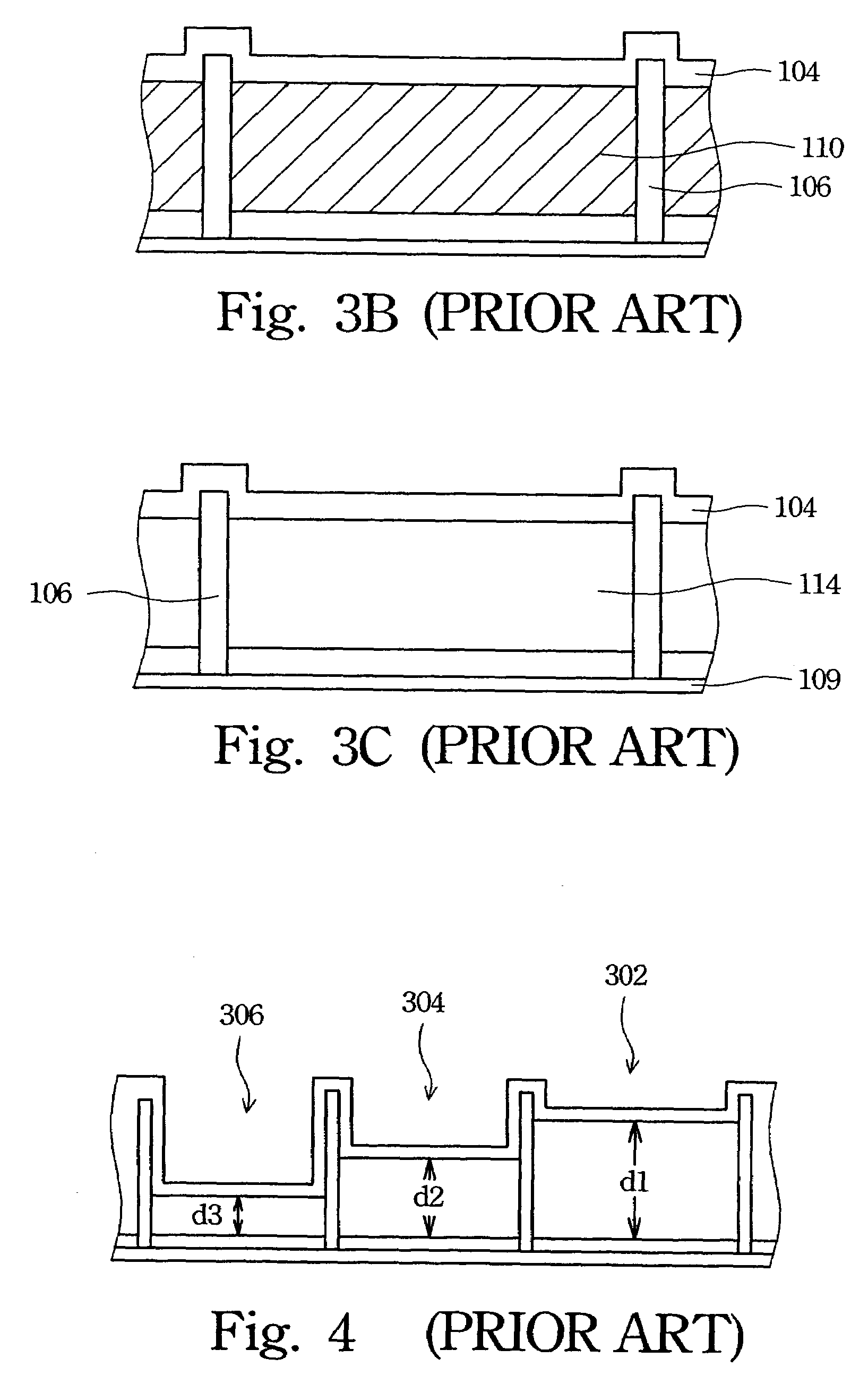

InactiveUS6995890B2Increase brightnessSimple and easy manufacturing processDecorative surface effectsOptical filtersEngineeringHeat treated

An interference display unit with a first electrode, a second electrode and posts located between the two electrodes is provided. The characteristic of the interference display unit is that the second electrode's stress is released through a thermal process. The position of the second electrode is shifted and the distance between the first electrode and the second electrode is therefore defined. A method for fabricating the structure described as follow. A first electrode and a sacrificial layer are sequentially formed on a substrate and at least two openings are formed in the first electrode and the sacrificial layer. A supporter is formed in the opening and the supporter may have at least one arm on the top portion of the supporter. A second electrode is formed on the sacrificial layer and the supporter and a thermal process is performed. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

Method for fabricating an interference display unit

InactiveUS20050168849A1Increase brightnessSimple and easy manufacturing processMirrorsDecorative surface effectsEngineeringHeat treated

An interference display unit with a first electrode, a second electrode and posts located between the two electrodes is provided. The characteristic of the interference display unit is that the second electrode's stress is released through a thermal process. The position of the second electrode is shifted and the distance between the first electrode and the second electrode is therefore defined. A method for fabricating the structure described as follow. A first electrode and a sacrificial layer are sequentially formed on a substrate and at least two openings are formed in the first electrode and the sacrificial layer. A supporter is formed in the opening and the supporter may have at least one arm on the top portion of the supporter. A second electrode is formed on the sacrificial layer and the supporter and a thermal process is performed. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

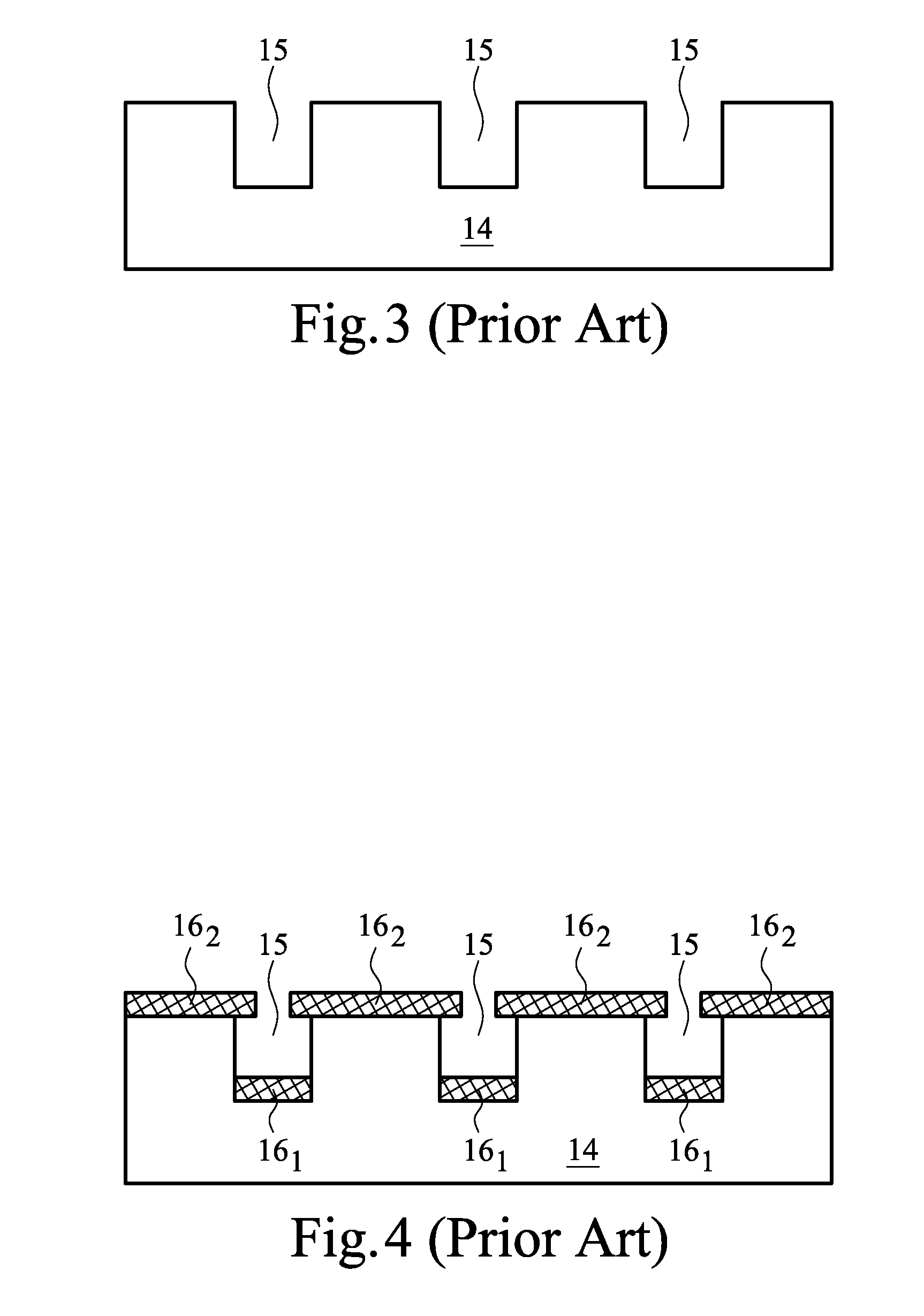

Method for fabricating an interference display unit

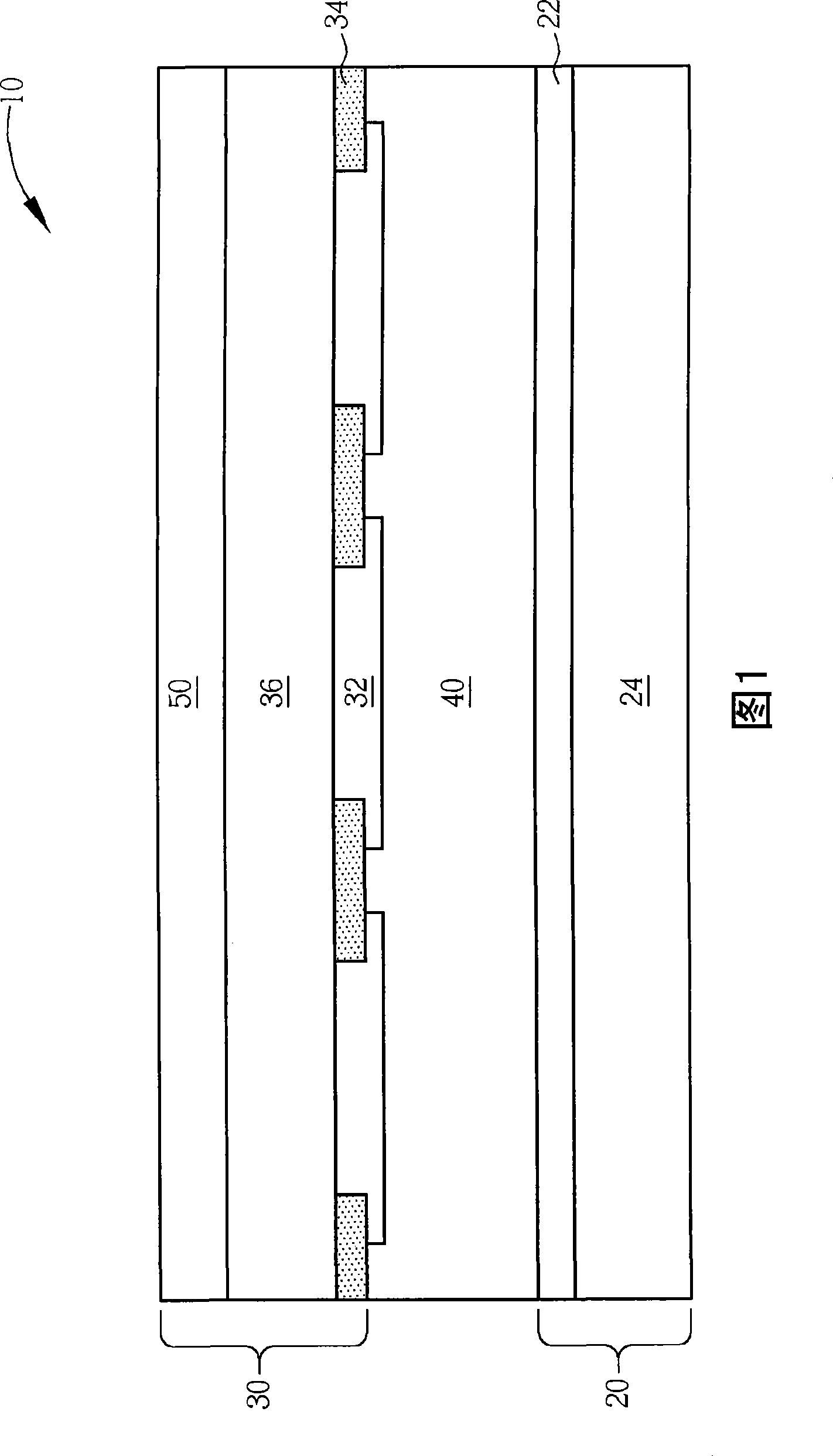

InactiveUS7198973B2Increase brightnessSimple and easy manufacturing processPhotomechanical apparatusSemiconductor/solid-state device manufacturingProcess patternsEngineering

A method for fabricating an interference display unit is provided. A first plate and a sacrificial layer are formed in order on a substrate and at least two openings are formed in the first plate and the sacrificial layer. A photoresist layer is spin-coated on the sacrificial layer and fills the openings. A photolithographic process patterns the photoresist layer to define a support with an arm. A second plate is formed on the sacrificial layer and posts. The arm's stress is released through a thermal process. The position of the arm is shifted and the distance between the first plate and the second plate is therefore defined. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

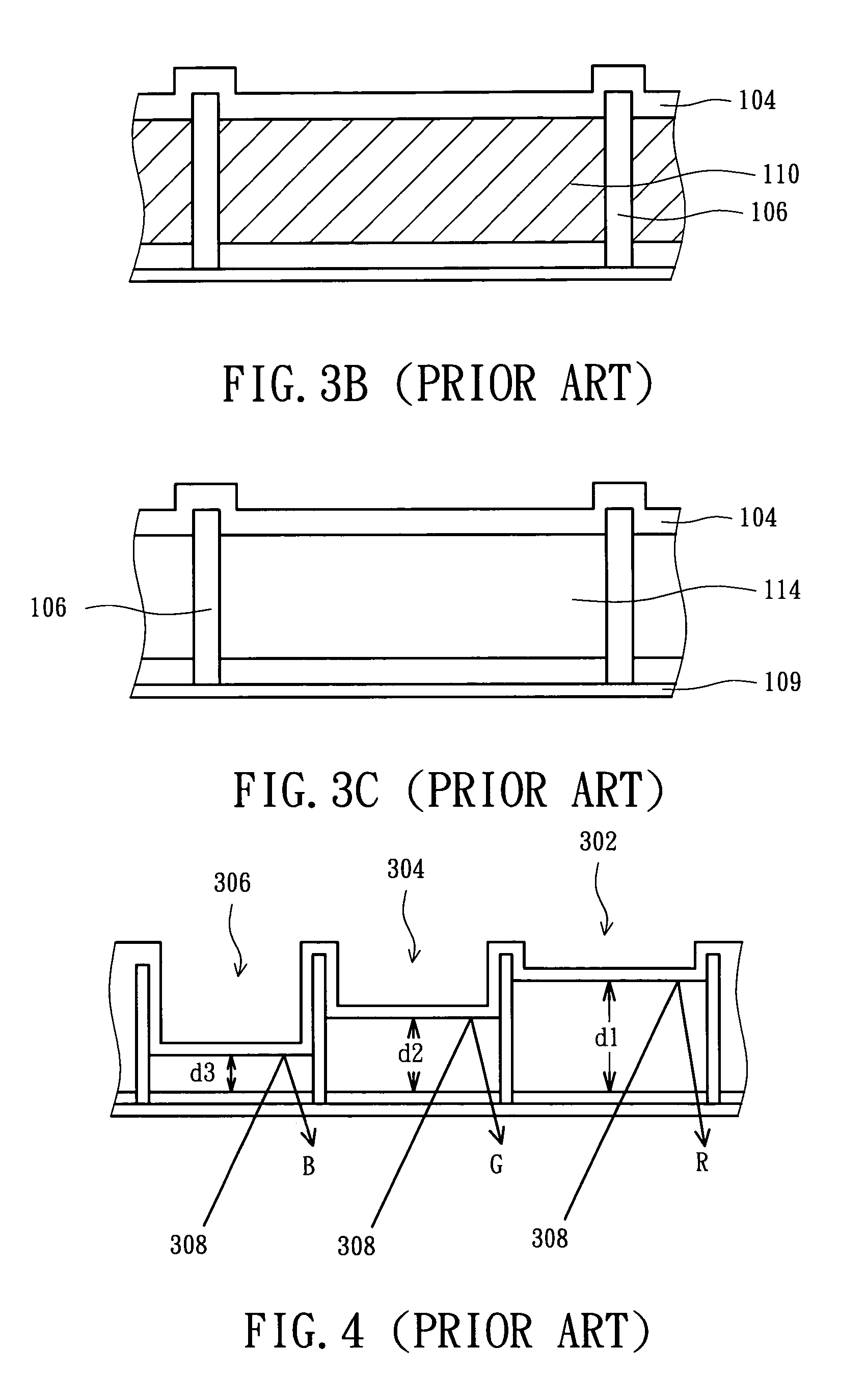

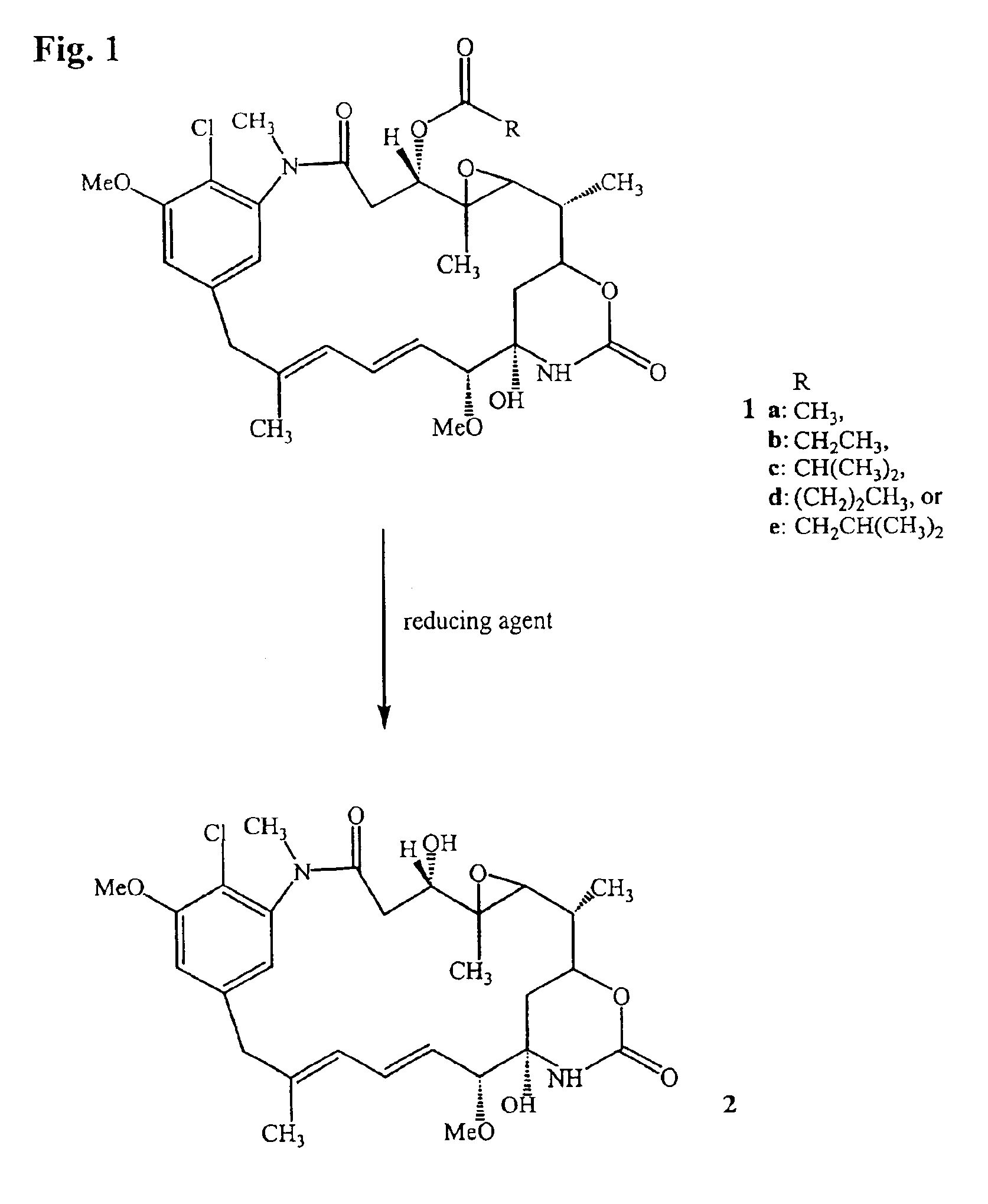

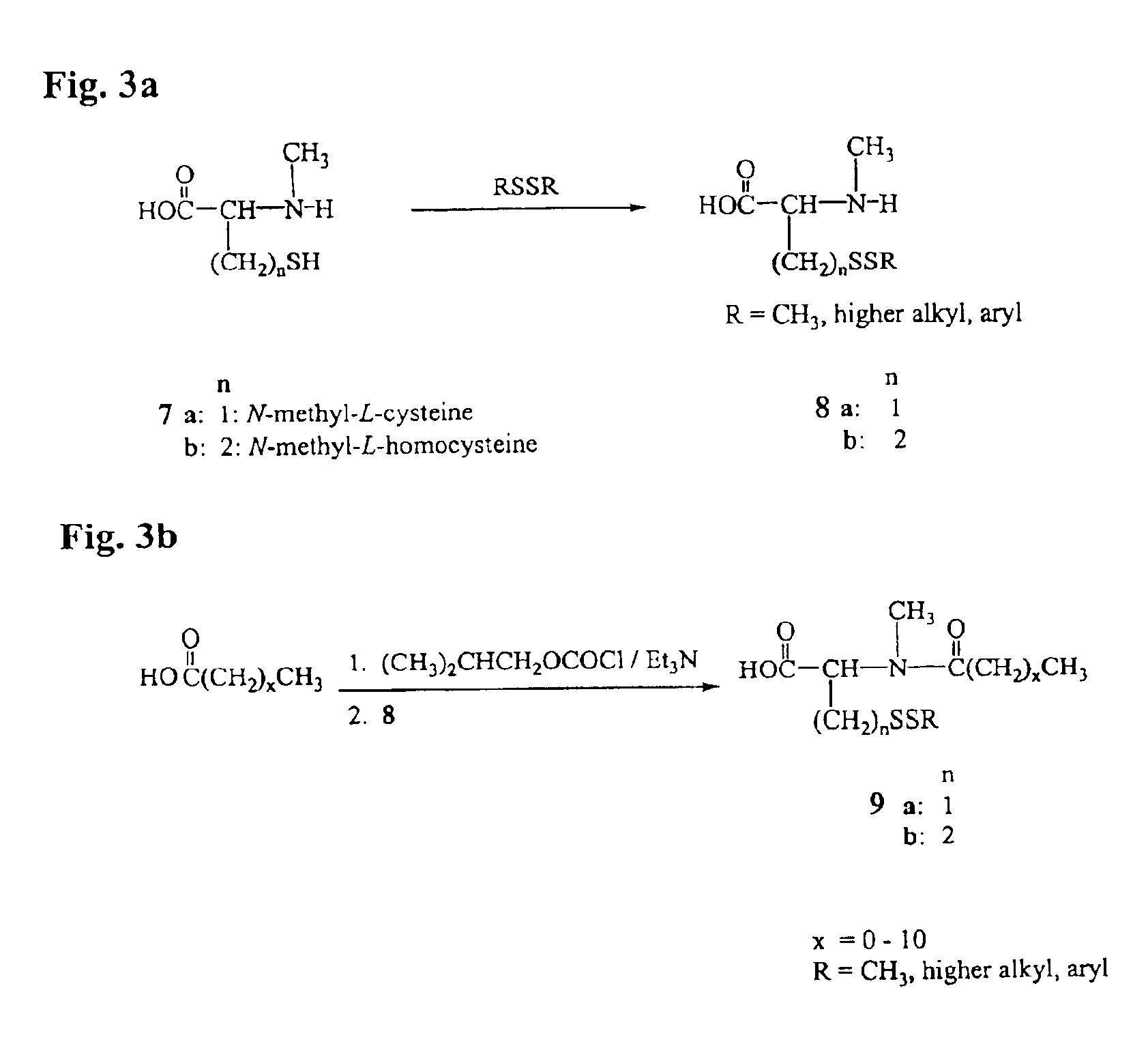

Process for the preparation and purification of thiol-containing maytansinoids

InactiveUSRE39151E1Reduce process complexityAllows scalabilityOrganic active ingredientsOrganic chemistryLithiumThiol

The present invention provides a process for the preparation and purification of thiol-containing maytansinoids comprising the steps of: (1) reductive hydrolysis of a maytansinoid C-3 ester with a reducing agent selected from the group consisting lithium trimethoxyaluminum hydride (LiAl (OMe)3H), lithium triethoxyaluminum hydride (LiAl(OEt)3H), lithium tripropoxyaluminum hydride (LiAl (OPr)3H), sodium trimethoxyaluminum hydride (NaAl (OMe)3H), sodium triethoxyaluminum hydride (NaAl(OEt)3H) and sodium tripropoxyaluminum hydride (NaAl(OPr)3H) to yield a maytansinol; (2) purifying the maytansinol to remove side products when present; (3) esterifying the purified maytansinol with a carboxylic acid to yield a mixture of an L- and a D-aminoacyl ester of maytansinol; (4) separating the L-aminoacyl ester of maytansinol from the reaction mixture in (3); (5) reducing the L-aminoacyl ester of maytansinol to yield a thiol-containing maytansinoid; and (5) purifying the thiol-containing maytansinoid.

Owner:IMMUNOGEN INC

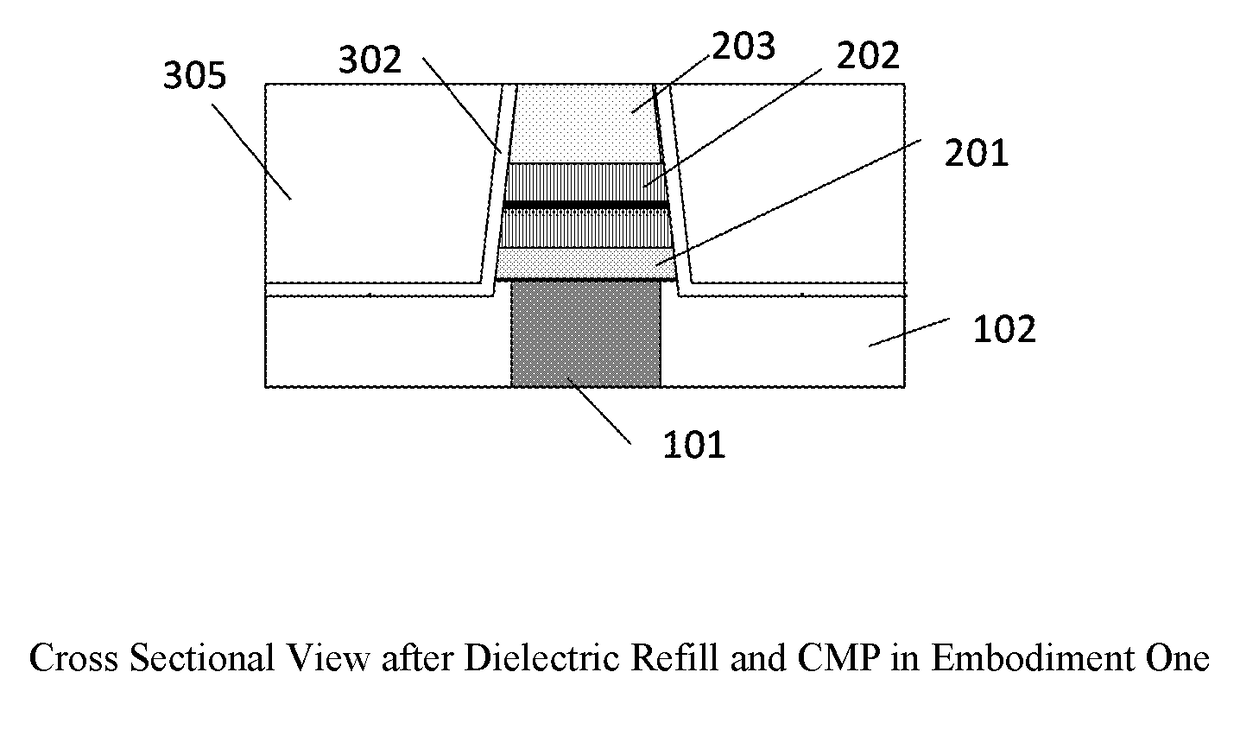

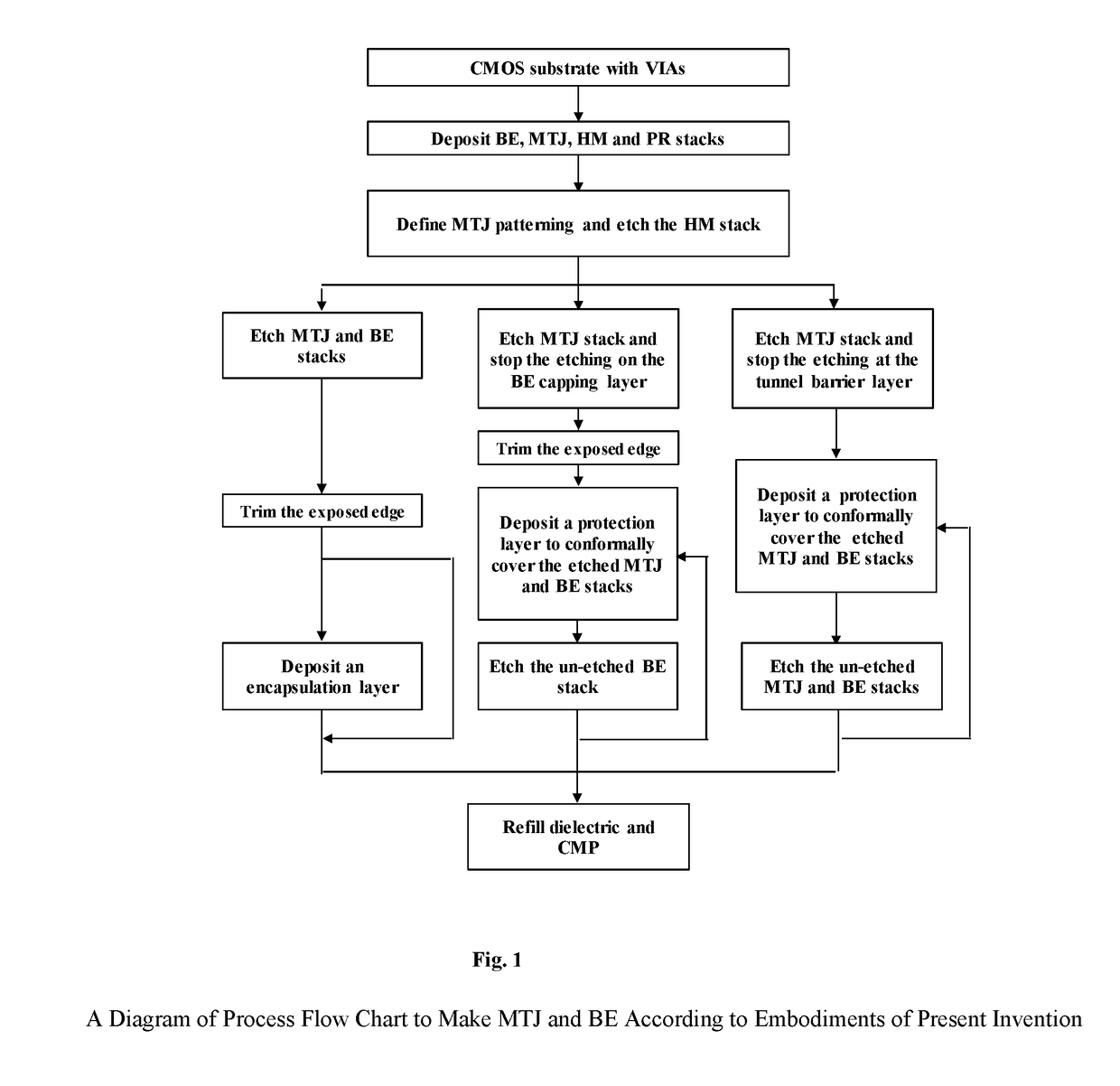

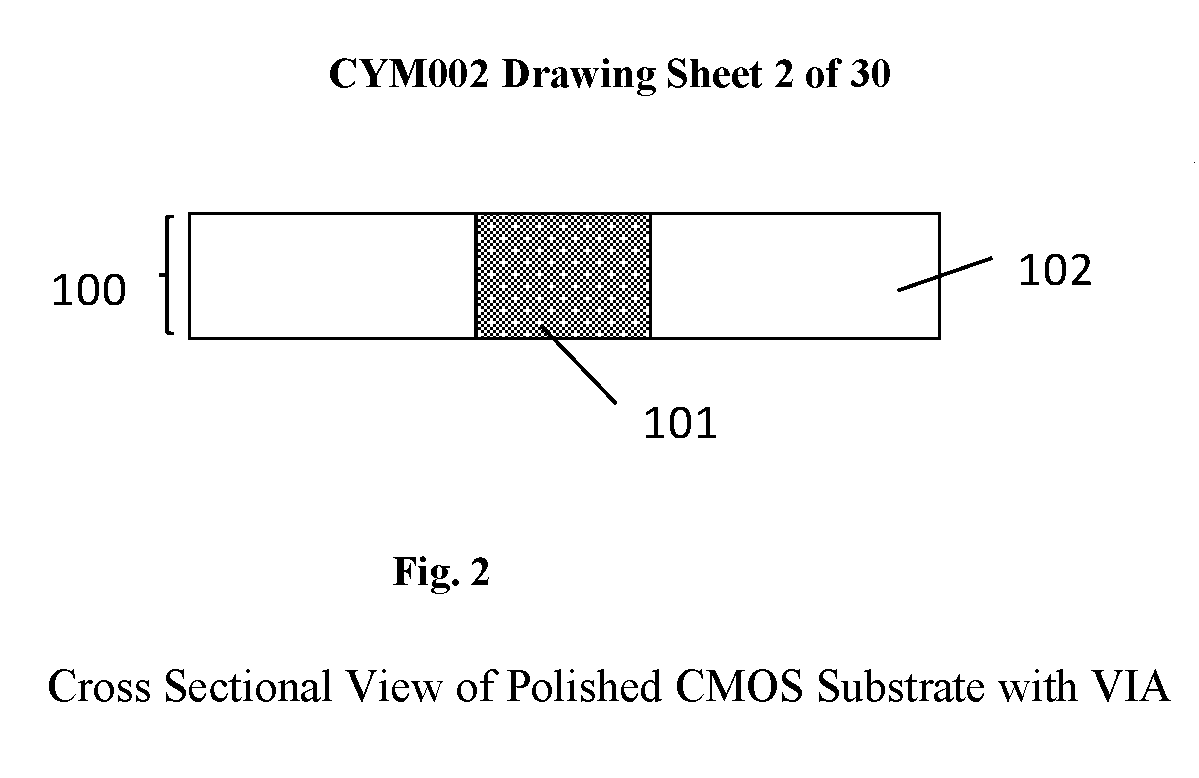

Method to make magnetic ramdom accesss memroy array with small footprint

InactiveUS20180033957A1Increase productionImprove propertiesMagnetic-field-controlled resistorsSolid-state devicesCMOSRandom access memory

This invention is about a method to make magnetic random access memory with small footprint directly on CMOS VIA with a self-aligned etching process. The process schemes of the method proceeds as: (1) Etch MTJ and BE using one or more of RIE and / or IBE processes with Ta as hard mask; (2) Etch BE using one or more of RIE and / or IBE processes with Ta & sidewall protection layer on MTJ as hard mask; and (3) Etch a part of MTJ and BE using one or more of RIE and / or IBE processes with Ta & sidewall protection layer on top portion of MTJ as hard mask. All the three schemes lead the BE to be self-aligned to MTJ cells, the photo overlay margin is not necessary and circuits could be made extremely small with lower manufacturing cost; The invention also provides schemes to prevent the electrical shorting across the tunnel barrier layer. Through trimming and sidewall protection deposition process, device performance and electrical / magnetic properties could be greatly improved.

Owner:SHANGHAI CIYU INFORMATION TECH

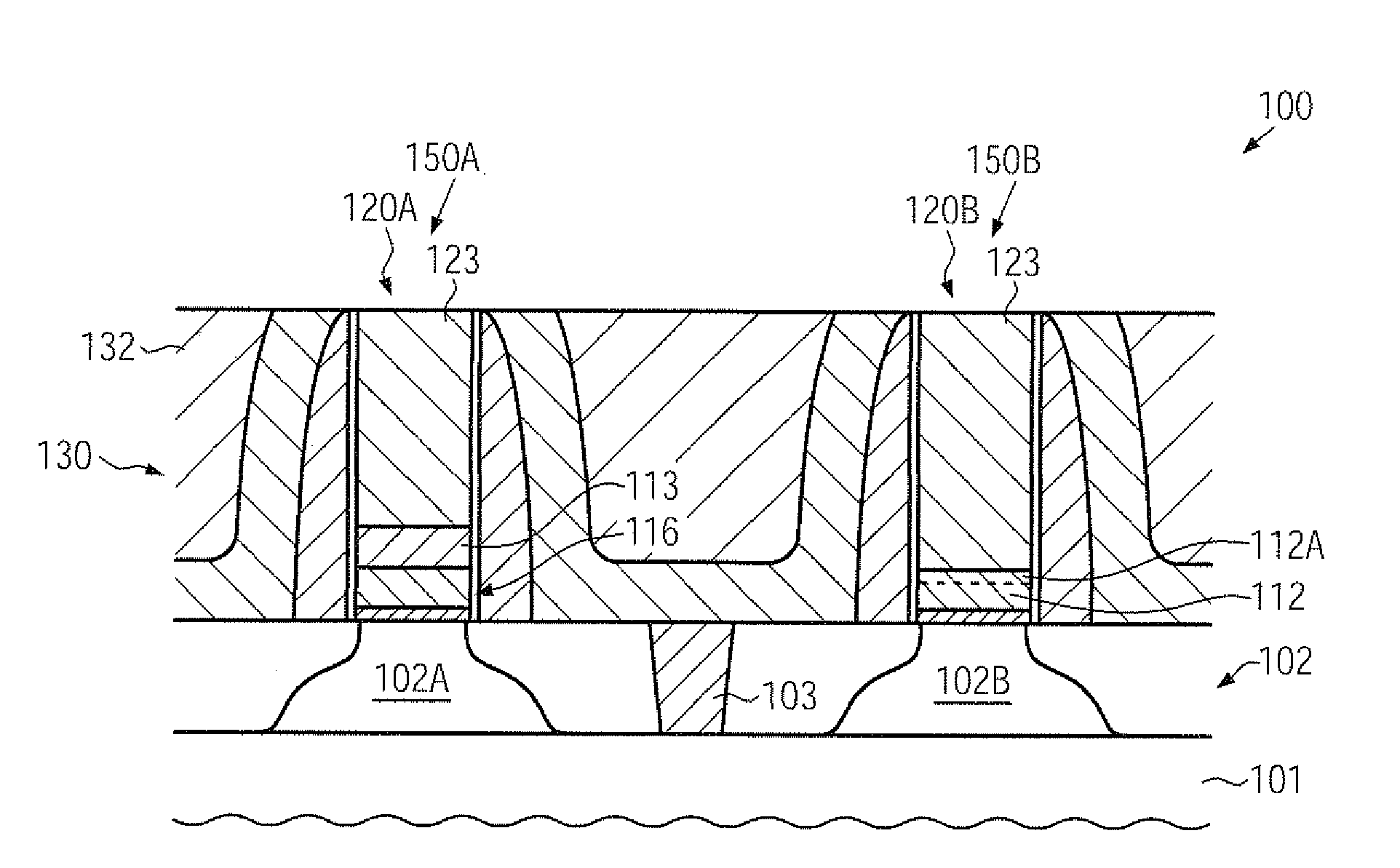

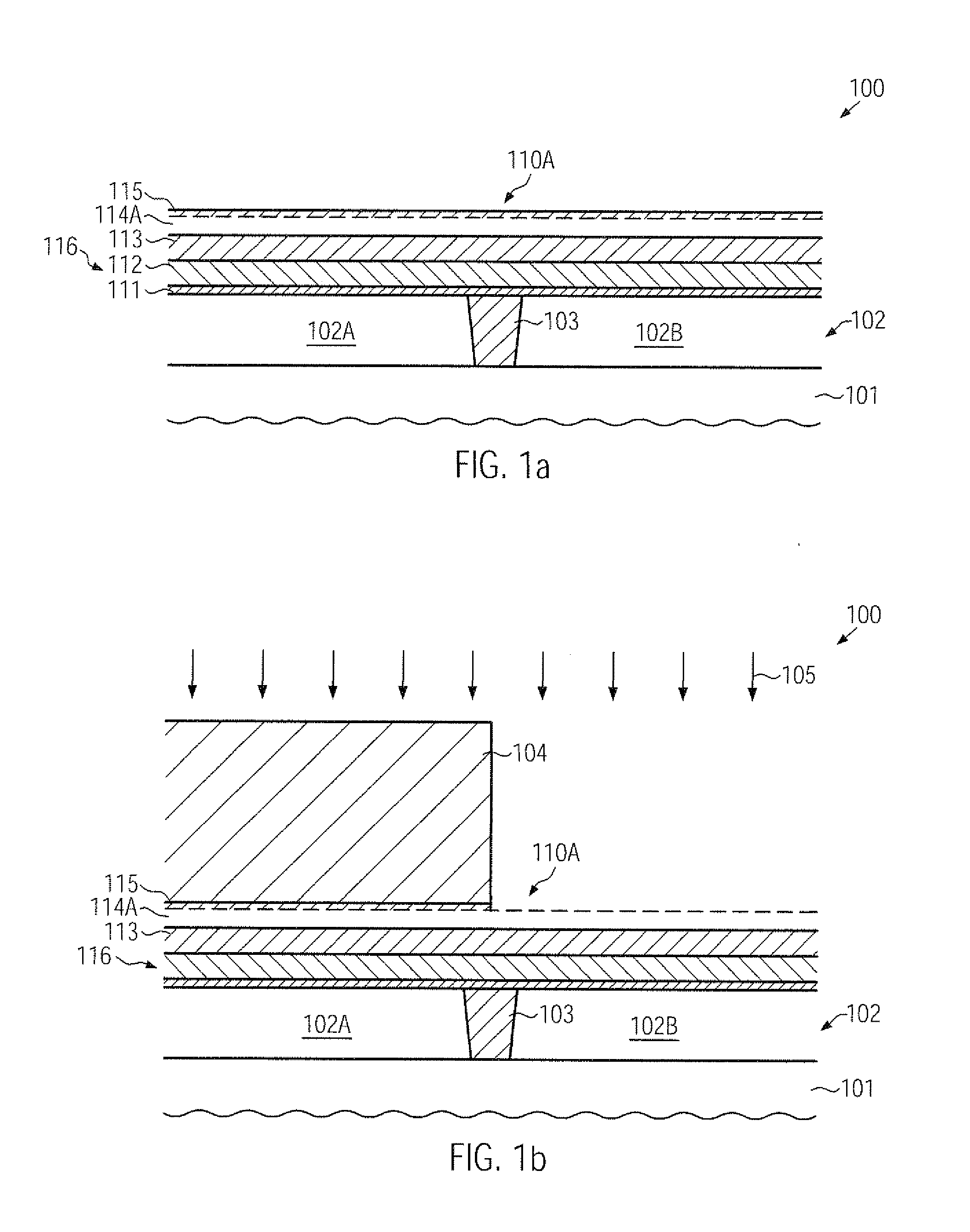

Threshold adjustment of transistors including high-k metal gate electrode structures comprising an intermediate etch stop layer

ActiveUS20100244141A1Reduce probabilitySimple process conditionsTransistorSemiconductor/solid-state device manufacturingPattern sequenceWork function

During the formation of sophisticated gate electrode structures, a replacement gate approach may be applied in which plasma assisted etch processes may be avoided. To this end, one of the gate electrode structures may receive an intermediate etch stop liner, which may allow the replacement of the placeholder material and the adjustment of the work function in a later manufacturing stage. The intermediate etch stop liner may not negatively affect the gate patterning sequence.

Owner:GLOBALFOUNDRIES US INC

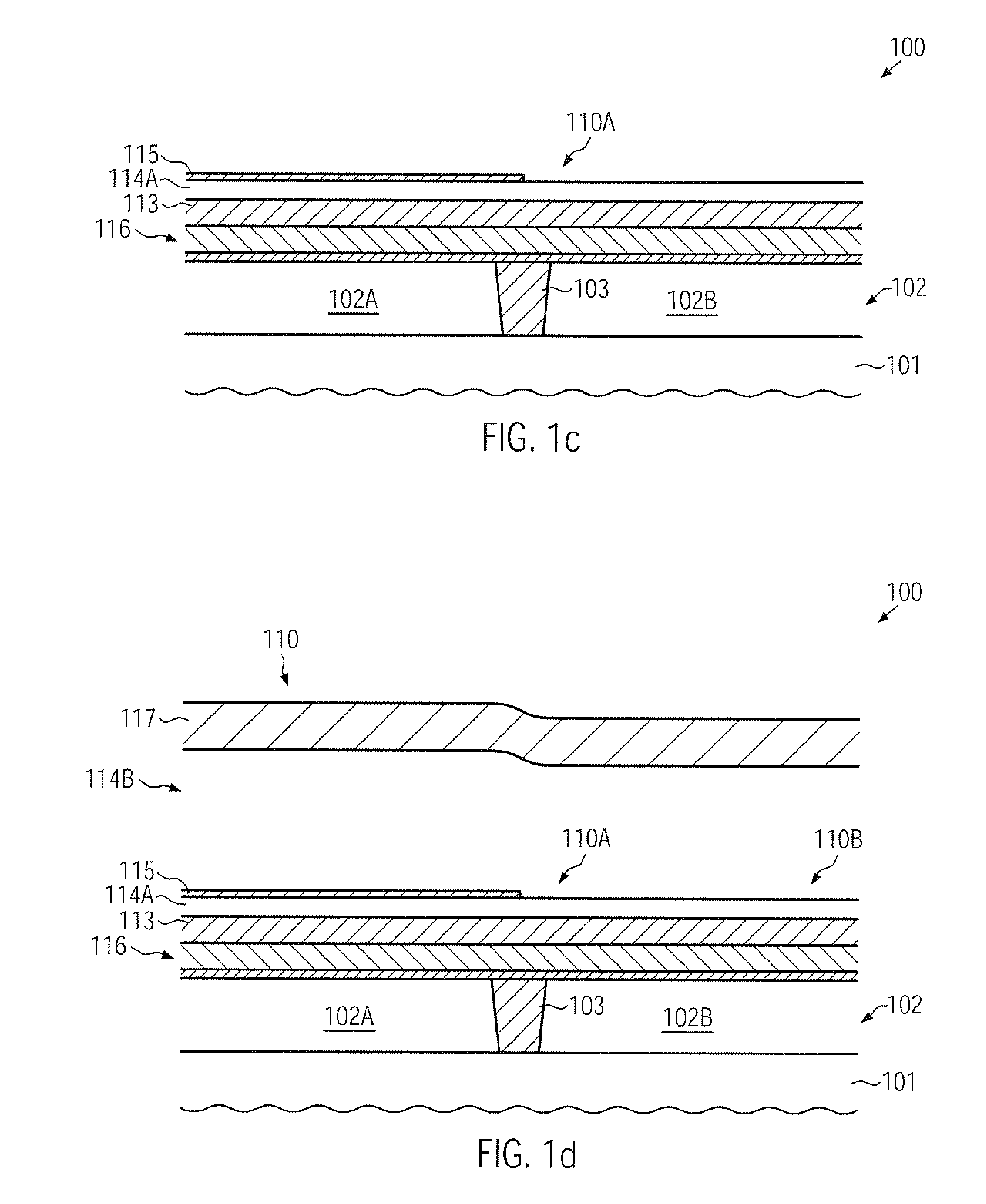

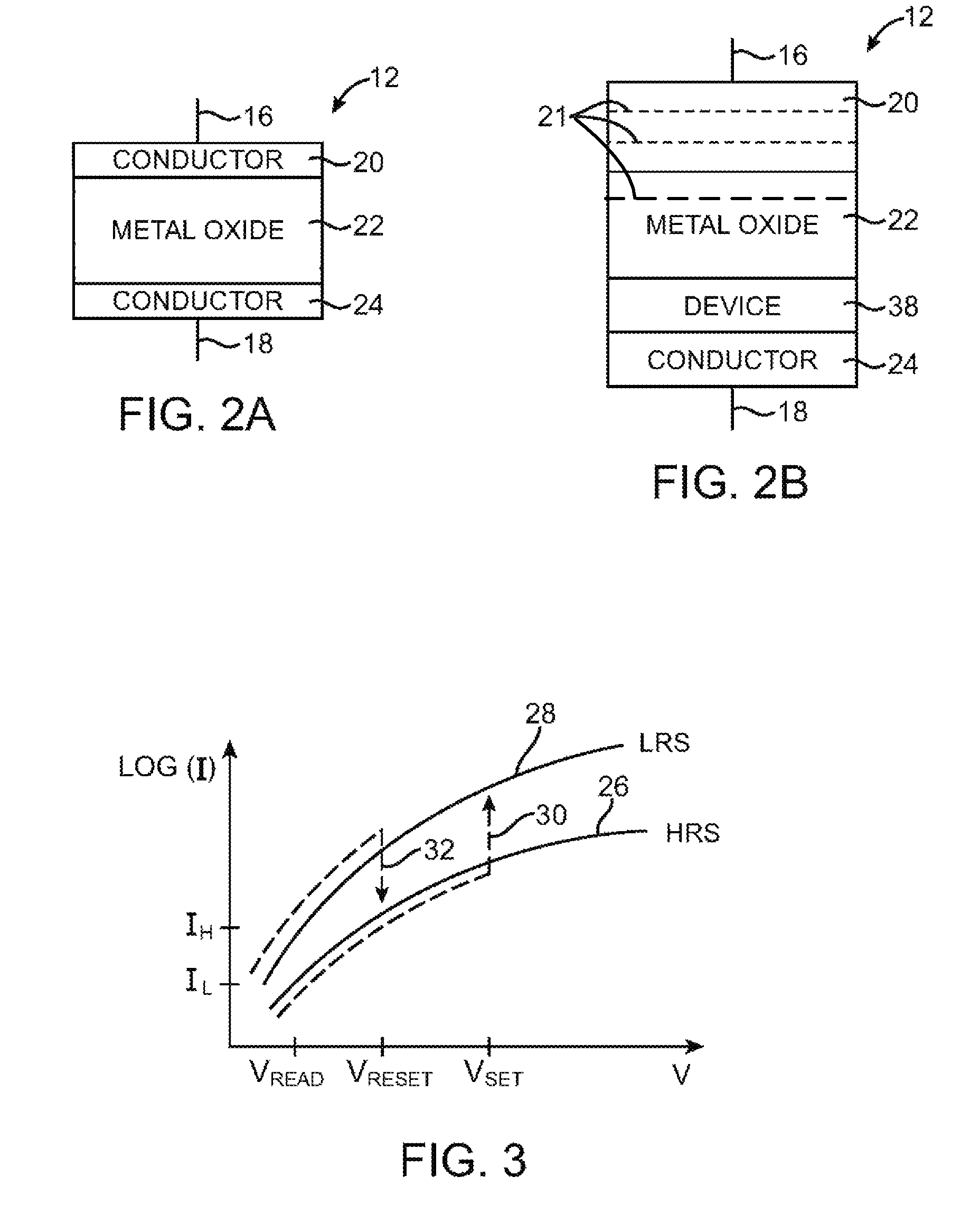

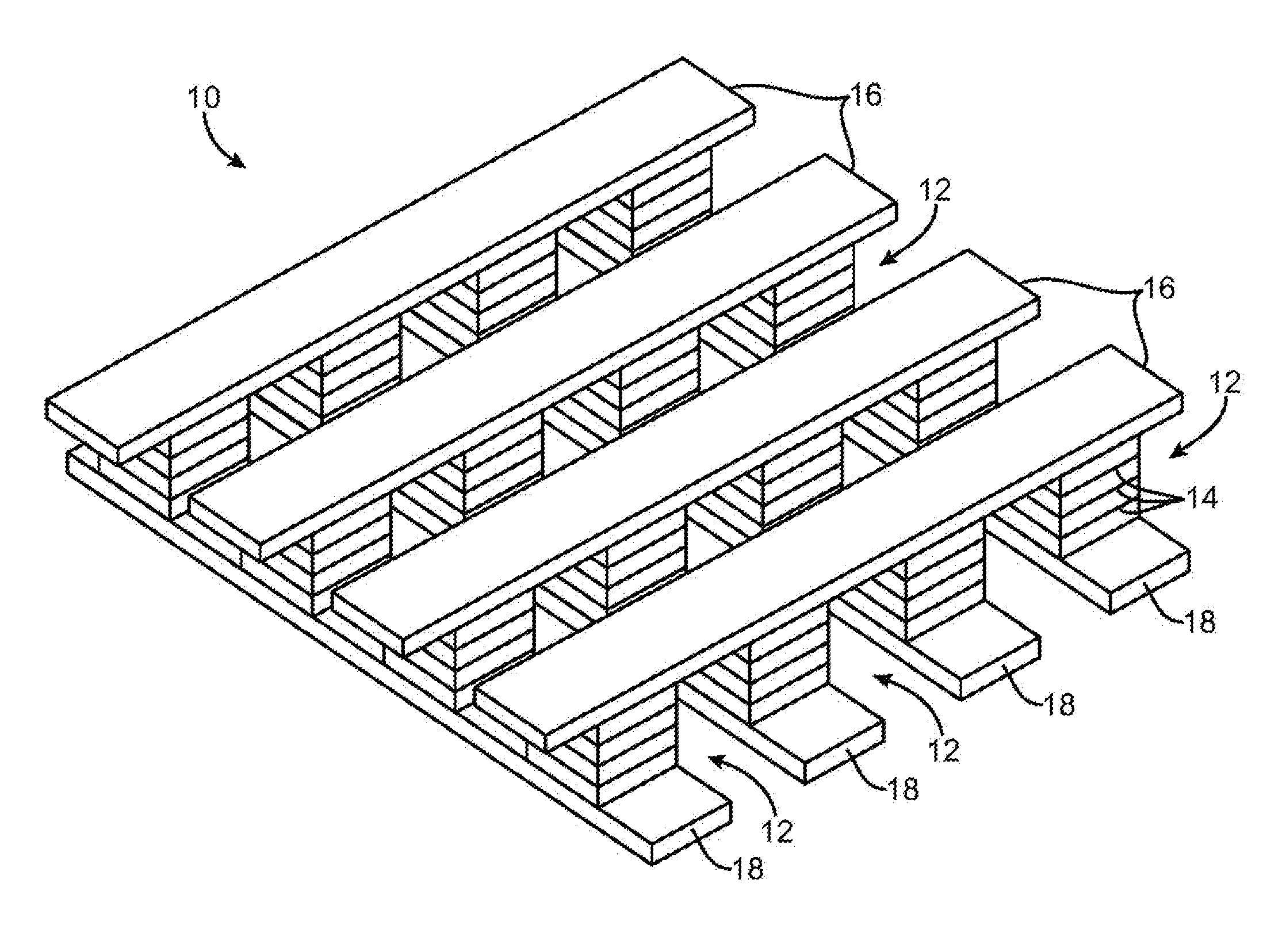

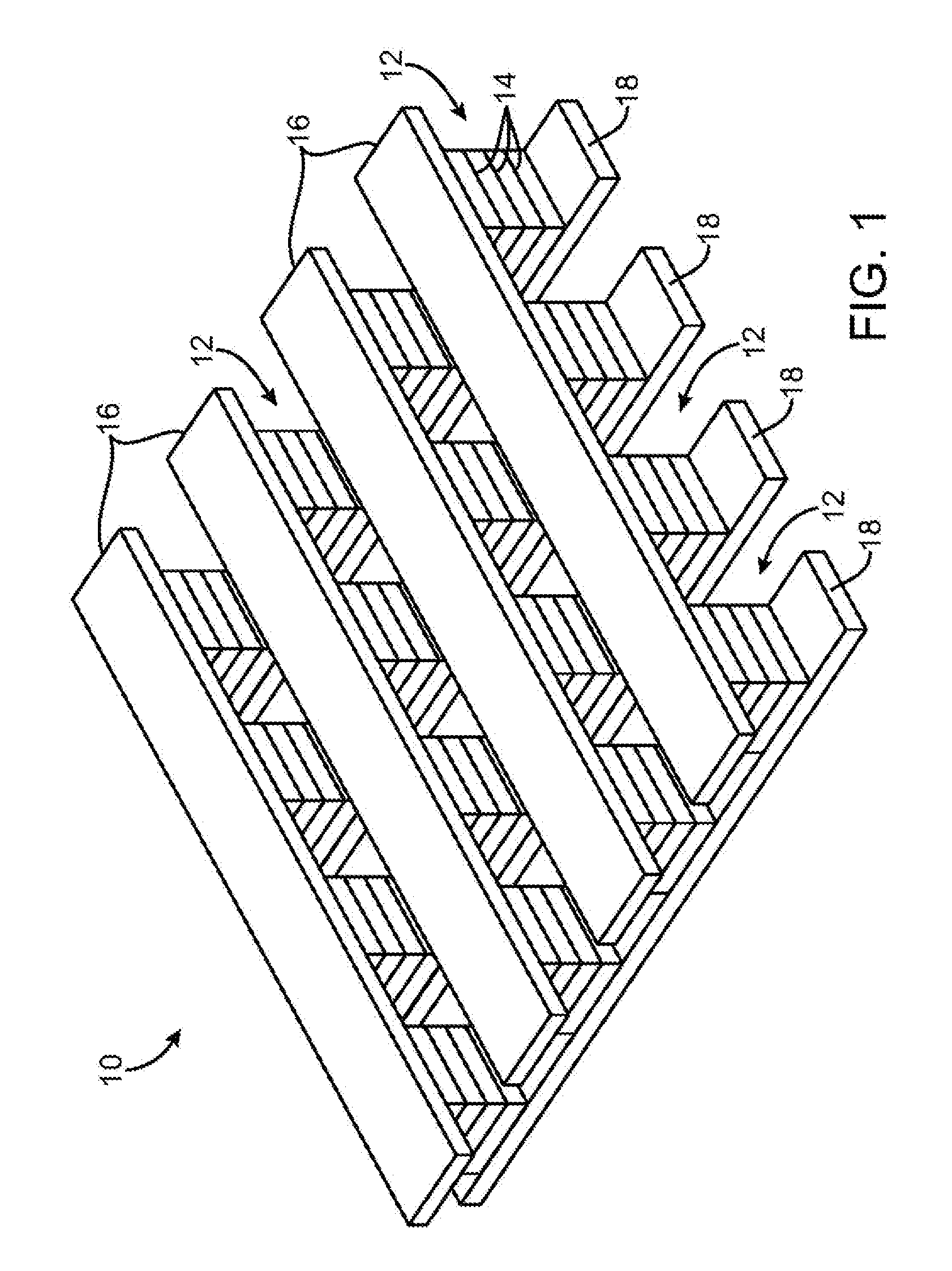

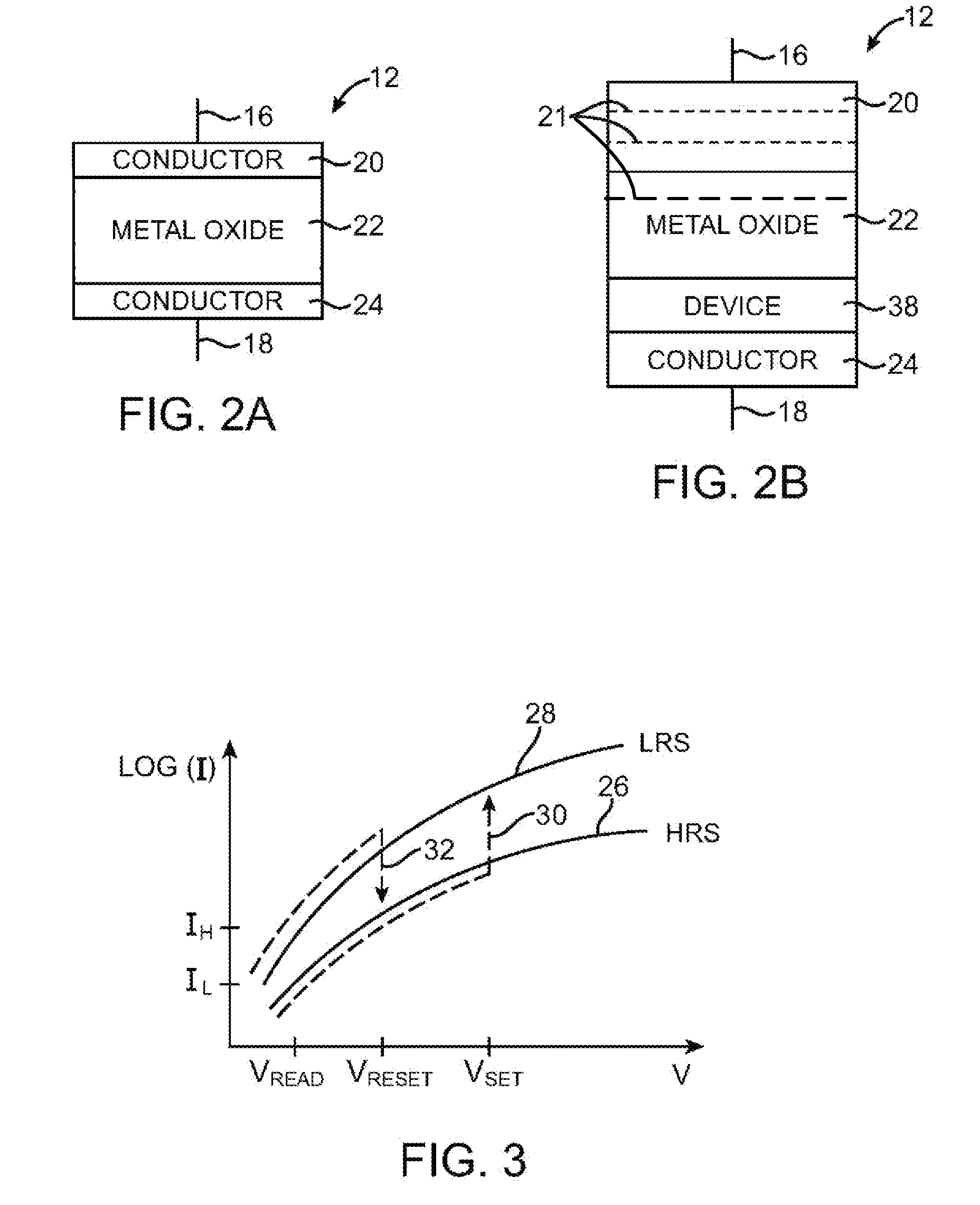

Methods for forming resistive switching memory elements by heating deposited layers

ActiveUS8143092B2Reduce process complexitySolid-state devicesSemiconductor/solid-state device manufacturingOxygenRapid thermal annealing

Resistive switching nonvolatile memory elements are provided. A metal-containing layer and an oxide layer for a memory element can be heated using rapid thermal annealing techniques. During heating, the oxide layer may decompose and react with the metal-containing layer. Oxygen from the decomposing oxide layer may form a metal oxide with metal from the metal-containing layer. The resulting metal oxide may exhibit resistive switching for the resistive switching memory elements.

Owner:INTERMOLECULAR

Method for fabricating an interference display unit

InactiveUS7016095B2Increase brightnessSimple and easy manufacturing processMirrorsDecorative surface effectsEngineeringPosition shift

An interference display unit with a first electrode, a second electrode and posts located between the two electrodes is provided. The characteristic of the interference display unit is that the second electrode's stress is released through a thermal process. The position of the second electrode is shifted and the distance between the first electrode and the second electrode is therefore defined. A method for fabricating the structure described as follow. A first electrode and a sacrificial layer are sequentially formed on a substrate and at least two openings are formed in the first electrode and the sacrificial layer. A supporter is formed in the opening and the supporter may have at least one arm on the top portion of the supporter. A second electrode is formed on the sacrificial layer and the supporter and a thermal process is performed. Finally, The sacrificial layer is removed.

Owner:SNAPTRACK

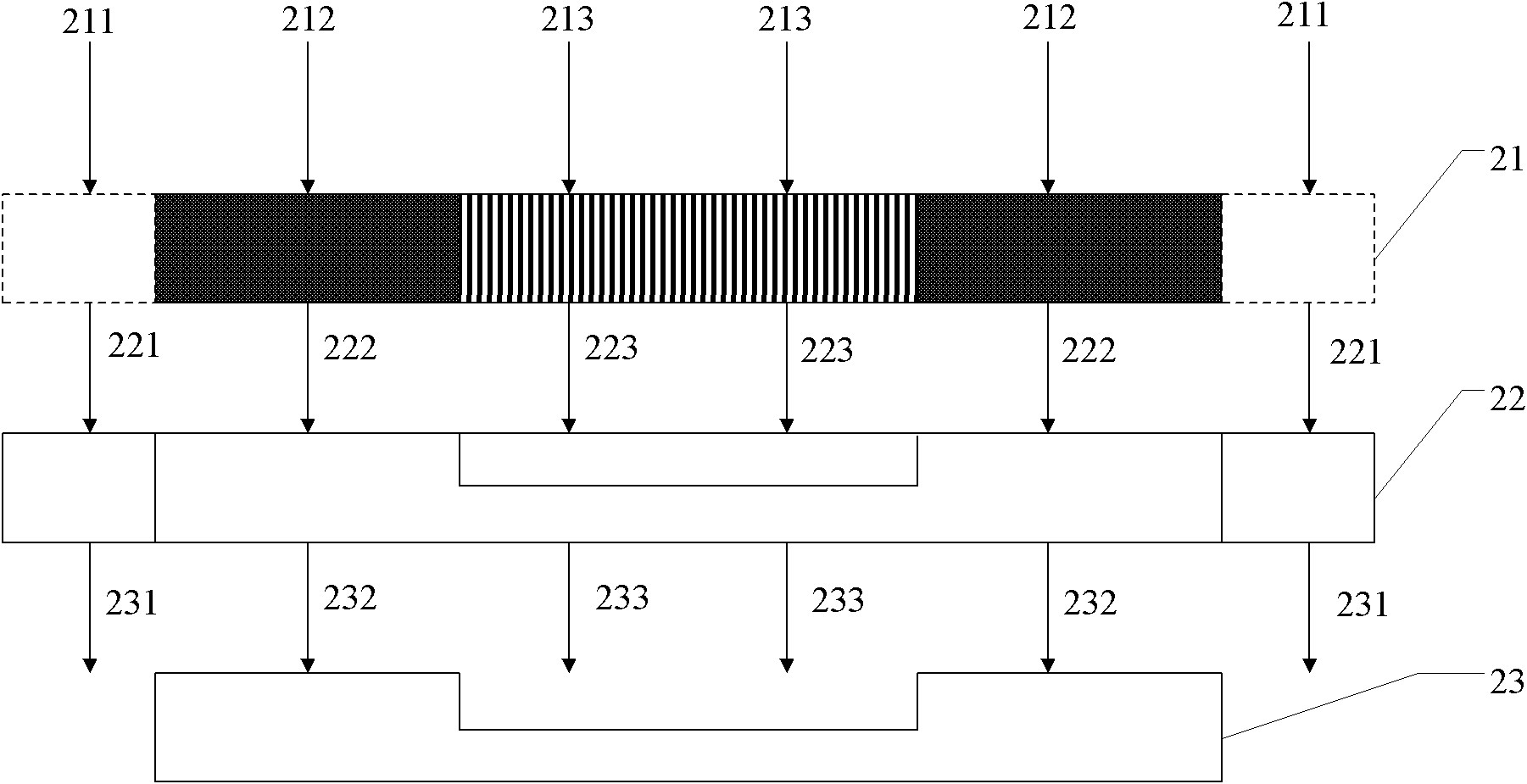

Method for making colourful filtering touch control substrate

ActiveCN101424817AReduce diversityReduce process complexityStatic indicating devicesNon-linear opticsElectrical connectionEngineering

The invention provides a method for manufacturing a chromatic filter touch control base plate, in particular that a touch control sensing structure (element) in a touch control panel is integrated to one side where the chromatic filter touch control base plate faces to a thin film transistor base plate, and the surfaces of transparent sensing pads form patterned assistant electrodes to reduce the equivalent resistance value of the touch control sensing structure (element). Besides, because the invention utilizes a transparent conductive layer and an assistant electrode layer which are adjacent to form the transparent sensing pads and the patterned assistant electrodes, a simplified pattern transfer process can be utilized to manufacture the transparent sensing pads and the patterned assistant electrodes, or part of the assistant electrode layer is utilized to form a joint bridging structure which is arranged between parts of the transparent sensing pads to be used as electrical connection, and the goal of process simplification is reduced.

Owner:AU OPTRONICS CORP

Methods for Forming Resistive Switching Memory Elements by Heating Deposited Layers

ActiveUS20090227067A1Reduce process complexitySolid-state devicesSemiconductor/solid-state device manufacturingOxideResistive switching memory

Resistive switching nonvolatile memory elements are provided. A metal-containing layer and an oxide layer for a memory element can be heated using rapid thermal annealing techniques. During heating, the oxide layer may decompose and react with the metal-containing layer. Oxygen from the decomposing oxide layer may form a metal oxide with metal from the metal-containing layer. The resulting metal oxide may exhibit resistive switching for the resistive switching memory elements.

Owner:INTERMOLECULAR

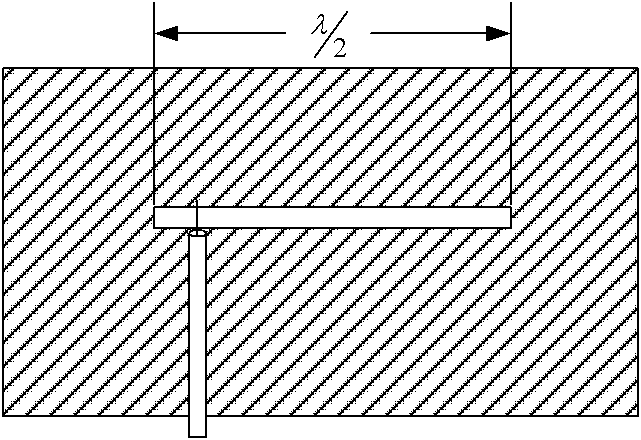

Multilayer Broadband Microstrip Antenna

InactiveCN102299418ADirectionalHigh bandwidthRadiating elements structural formsBroadband microstrip antennaAntenna gain

The invention discloses a multilayer broadband microstrip antenna, comprising an upper dielectric baseplate, a middle dielectric baseplate, a lower dielectric baseplate, an upper low dielectric constant insulating dielectric layer, a lower low dielectric constant insulating dielectric layer, a reflection plate and a feed probe, wherein rectangle radiators of metallic copper pasters are arranged on the lower surface of the upper dielectric baseplate and the upper surface of the middle dielectric baseplate and provided with U-shaped slot structures with different sizes respectively. Due to a special double-layer inverted U-shaped slot coupling feed way, the symmetry of directional diagrams on an E surface or H surface of the antenna is good, thus ensuring that the antenna has more consistent performances in more directions, and having more actual meanings as an exploration antenna and a communication antenna. The reflection plate with an EBG (electromagnetic band gap) structure can preferably restrain backward radiation in the specified frequency relative to a traditional metal reflection plate, thus improving the directivity of the antenna, thereby further improving the gain of theantenna.

Owner:JIMEI UNIV

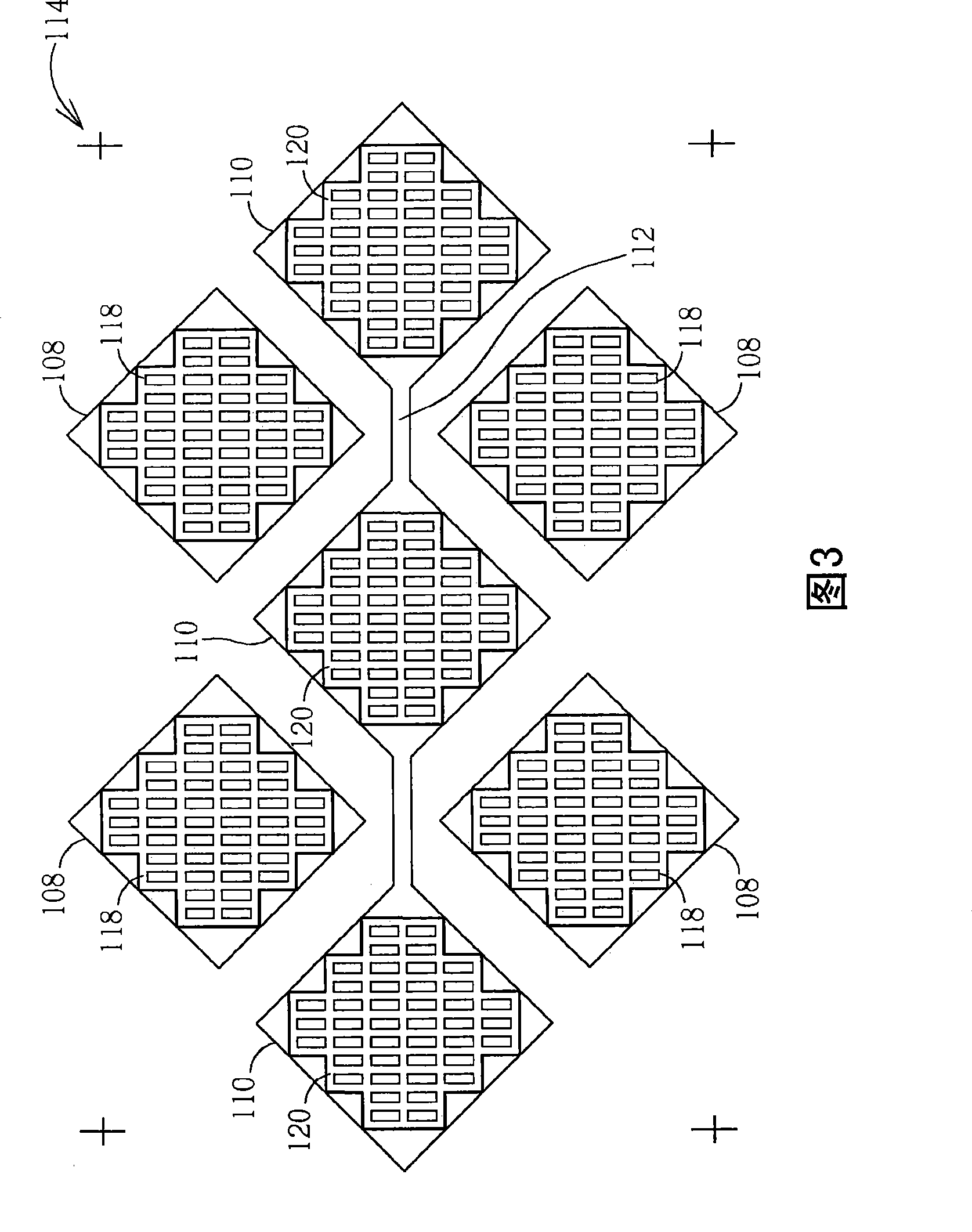

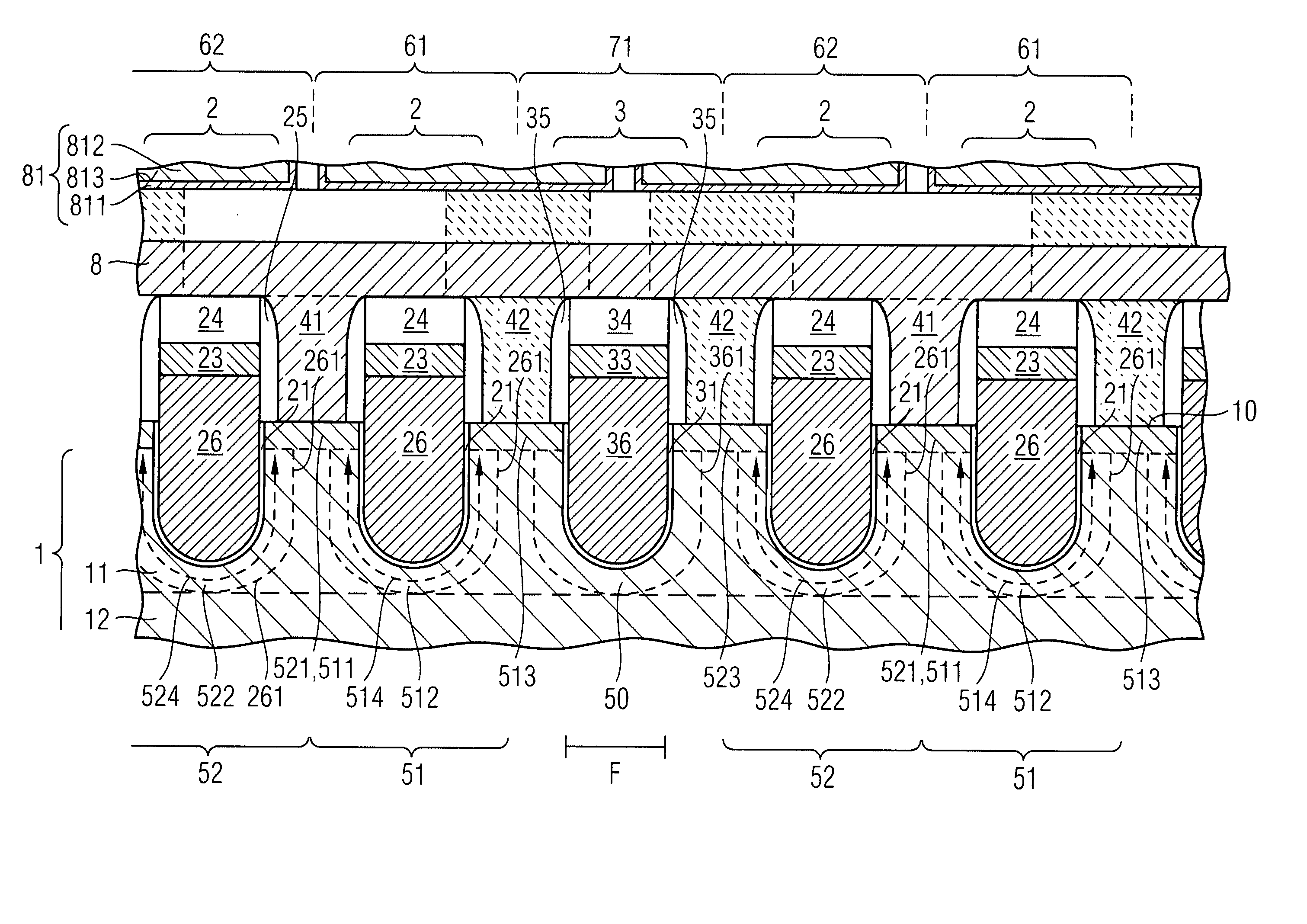

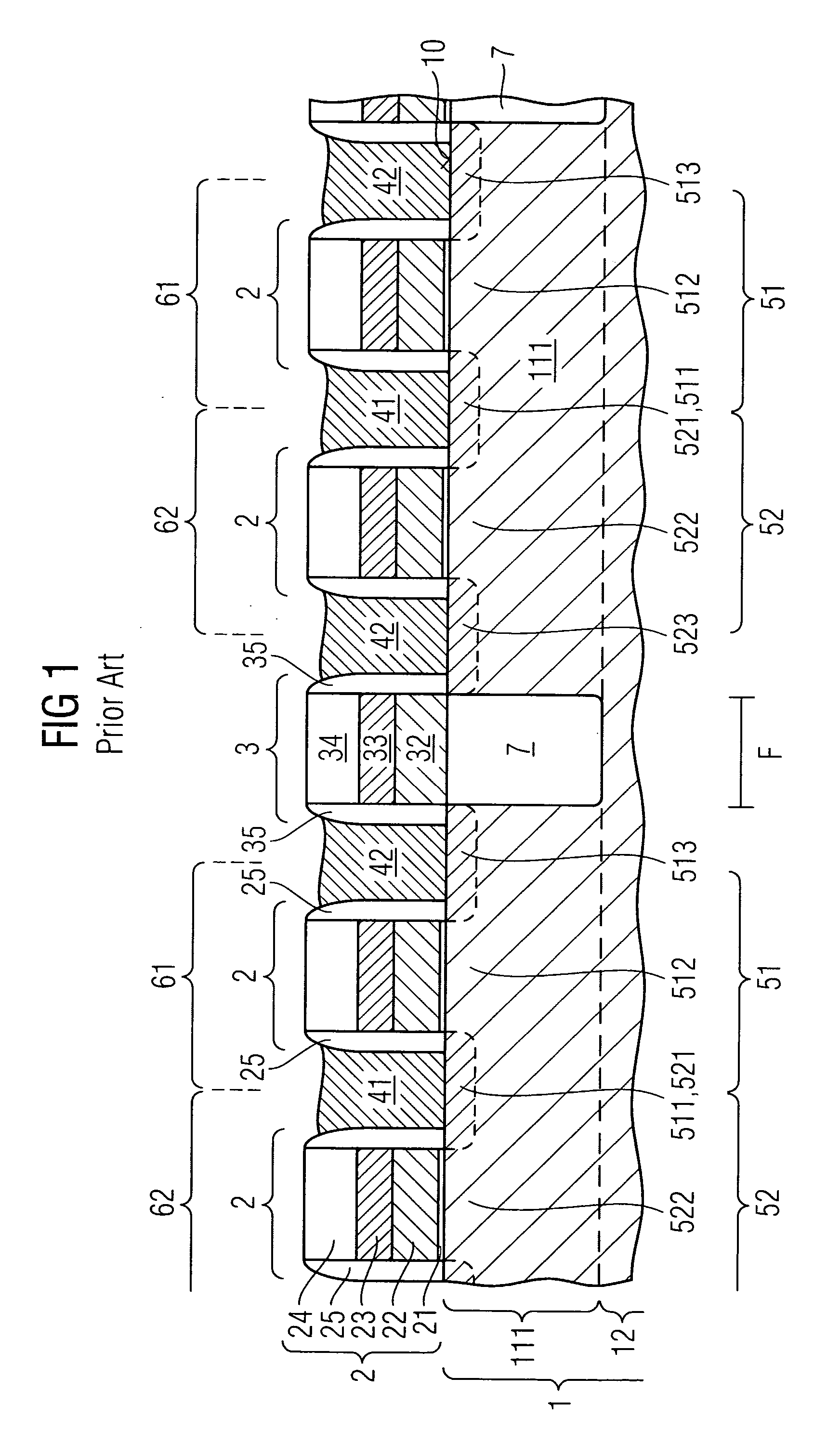

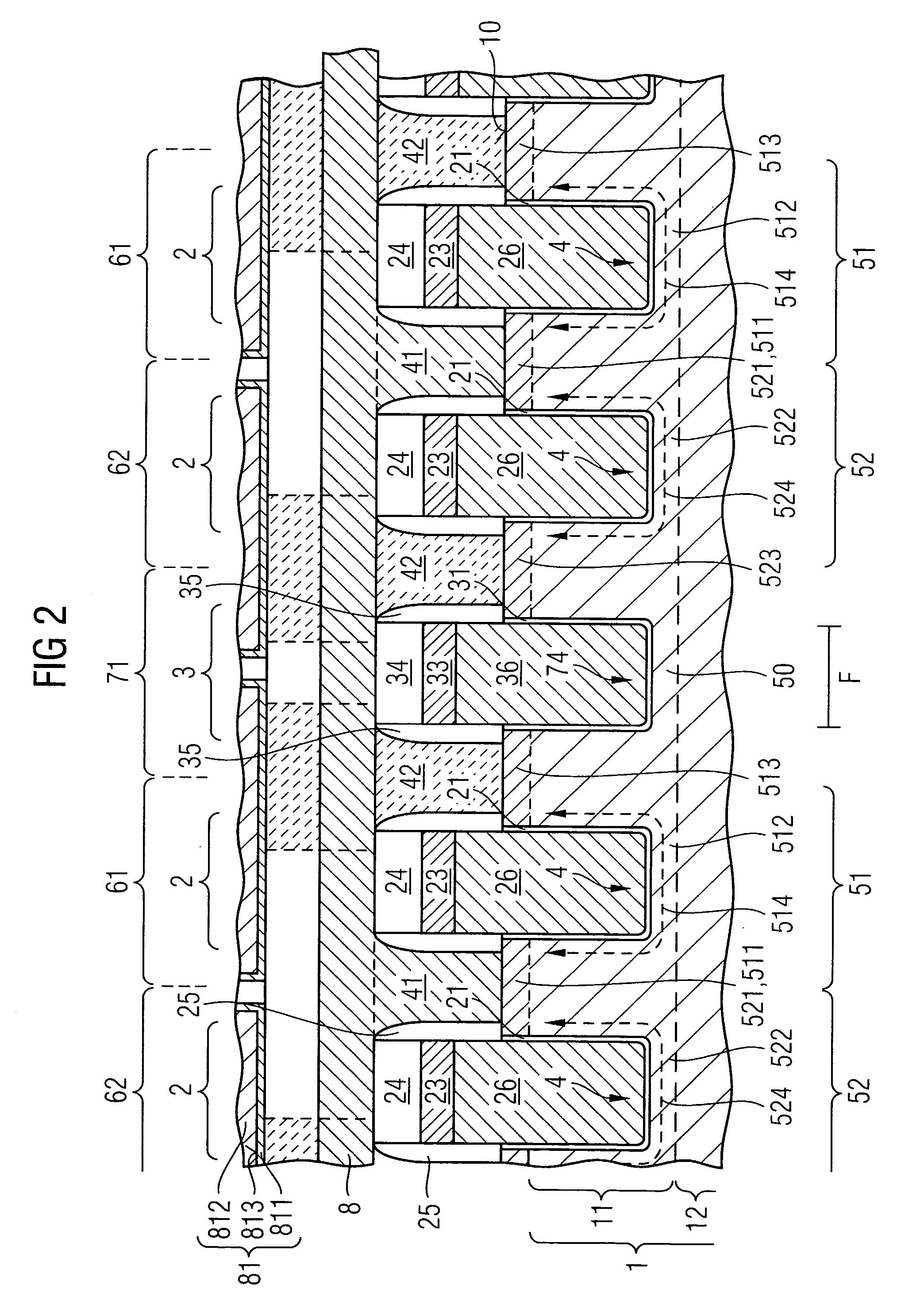

6F2 access transistor arrangement and semiconductor memory device

InactiveUS20060281250A1Improve insulation performanceImprove isolationTransistorSolid-state devicesDopantBit line

An access transistor arrangement is provided for a 6F2 stacked capacitor DRAM memory cell layout with shared bit line contacts. The access transistors are arranged in pairs along semiconductor lines. The two transistors of each pair of transistors are arranged laterally reversed opposing the respective common bit line section. Each pair of access transistors is separated from the adjacent pair of access transistors by an isolation transistor which is permanently turned off. The access transistors and the isolation transistors are formed as identical recessed channel transistors with elongated channel and enhanced isolation properties. The same dopant concentration may be provided for both junctions of the access transistors. As identical devices are provided both as access transistor and as isolation transistors, the complexity of lithographic patterning processes is reduced.

Owner:POLARIS INNOVATIONS LTD

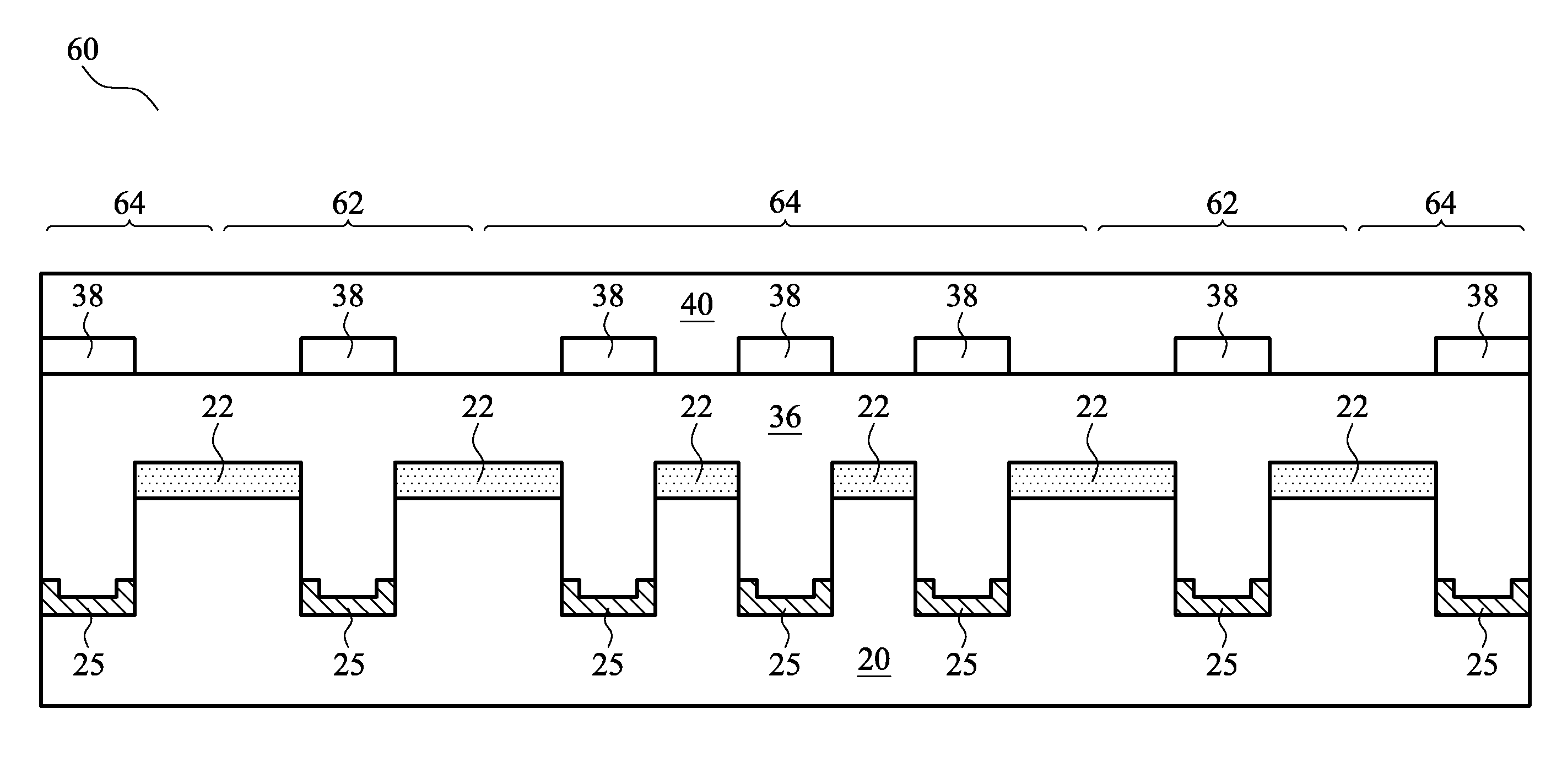

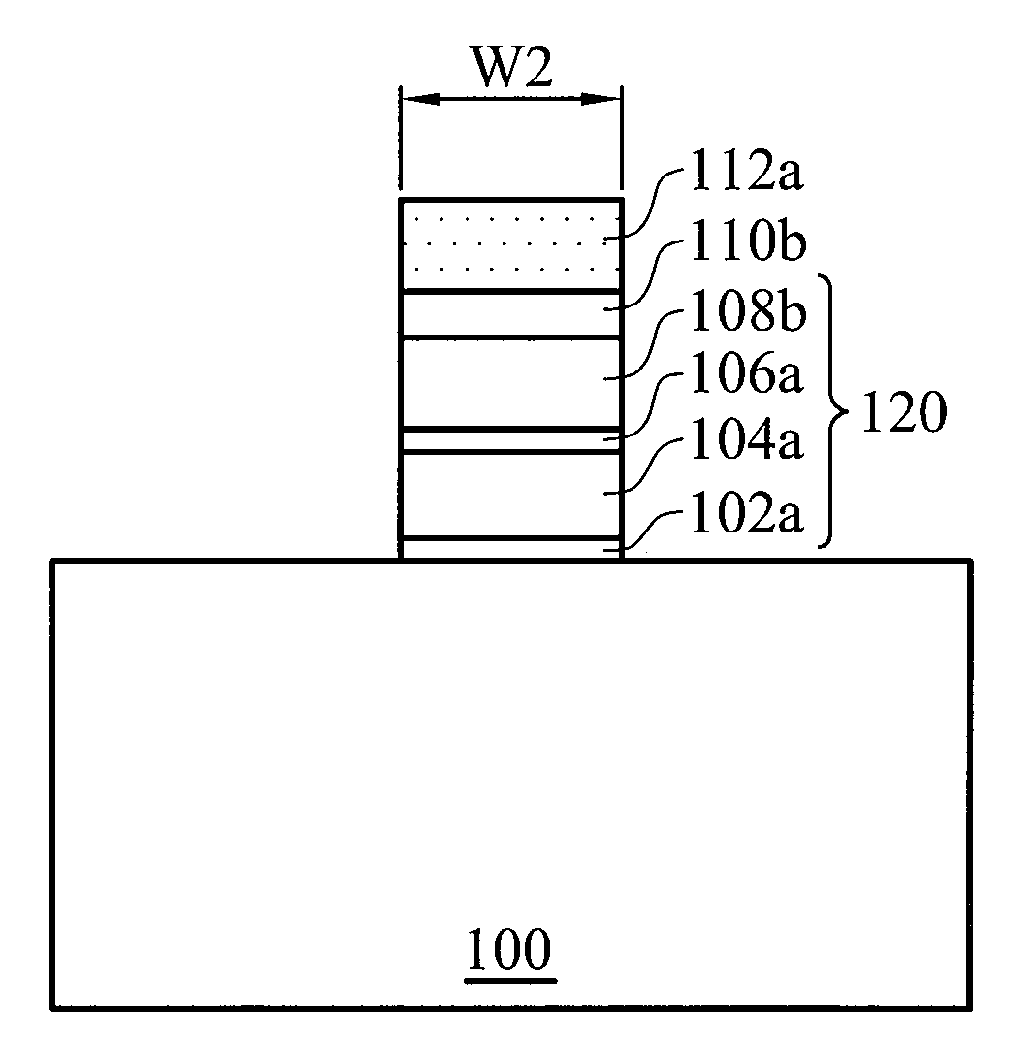

III-V Compound Semiconductor Epitaxy From a Non-III-V Substrate

ActiveUS20100068866A1Increased lateral growth effectReduced process complexitySemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsMask layer

A method of forming a circuit structure includes providing a substrate; forming recesses in the substrate; forming a mask layer over the substrate, wherein the mask layer covers non-recessed portions of the substrate, with the recesses exposed through openings in the mask layer; forming a buffer / nucleation layer on exposed portions of the substrate in the recesses; and growing a group-III group-V (III-V) compound semiconductor material from the recesses until portions of the III-V compound semiconductor material grown from the recesses join each other to form a continuous III-V compound semiconductor layer.

Owner:TAIWAN SEMICON MFG CO LTD

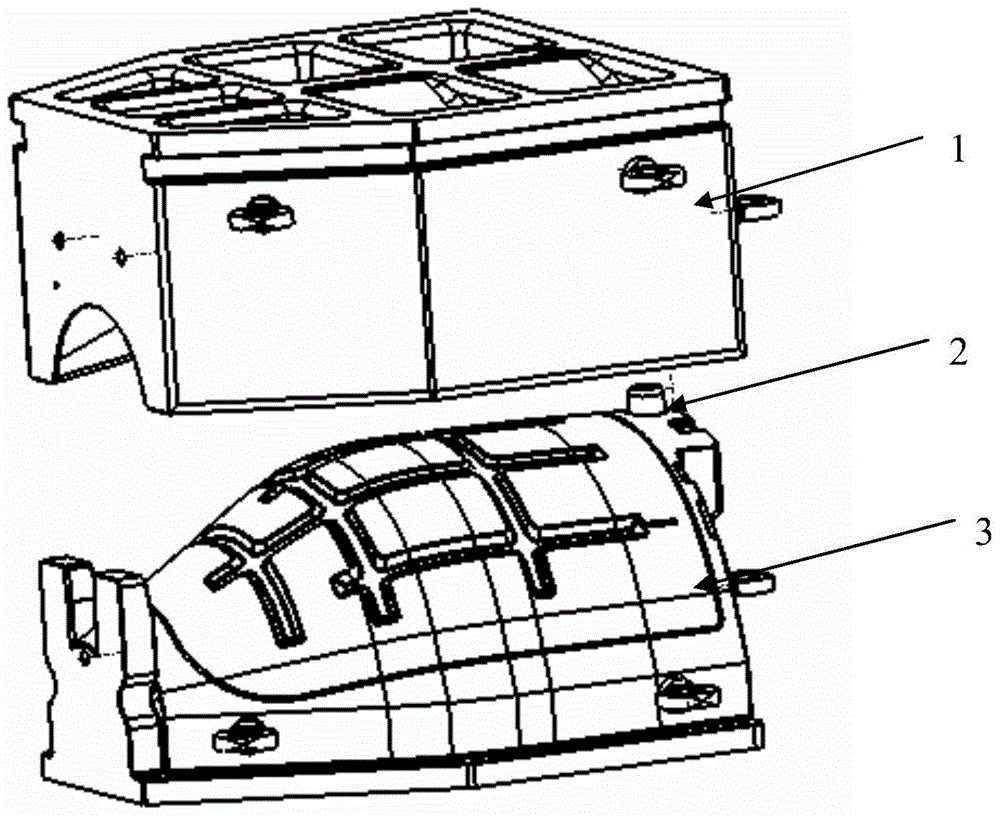

Super-plastic forming/diffusion bonding forming method for large-curvature complex surface titanium alloy part

ActiveCN104588982AThe overall structure is light in weightHigh strengthShaping toolsNon-electric welding apparatusHot workingTitanium alloy

The invention relates to a super-plastic forming / diffusion bonding forming method for a large-curvature complex surface titanium alloy part and belongs to the field of metal plates and hot working. Through reasonably and accurately calculating the unfold size of a part, residual materials on the wrinkled region of the part are removed through cutting in advance, after pre-forming is completed, overall welding and hot shape correction are performed, and the pre-formed and welded part is placed in the same tool so that super-plastic forming / diffusion bonding forming can be performed on the part. Without the help of blank holder force, pre-forming and super-plastic forming / diffusion bonding forming are completed through the same tool, one-time hot forming of the large-curvature complex surface part is completed, the defect that the part is wrinkled and loses stability is overcome, and technology difficulty and tool structure complexity are lowered. The part formed through the method has advantages.

Owner:BEIJING HANGXING MACHINERY MFG CO LTD

Colorful transparent polished-glazed brick and production method thereof

The invention discloses a colorful transparent polished-glazed brick and a production method thereof. The production method for the colorful transparent polished-glazed brick comprises the following steps: enameling a dried ceramic blank, spreading one or more glazes in different colors and with different burning temperature and different refractive indexes on the brick blank, and performing calcining and profiling soft polishing treatment to obtain the brick. According to the colorful transparent polished-glazed brick and the production method thereof, the layering effects and transition of the surface of the colorful transparent polished-glazed brick are closer to those of a natural stone, and the grade of the product is improved to a certain extent; original color effects can be achieved without adding a coloring material, so that process complexity is reduced, the labor intensity of a worker is reduced, and the production efficiency is favorably improved, and the colorful transparent polished-glazed brick and the production method thereof are suitable for popularization and application.

Owner:GUANGDONG JIA MEI CERAMIC

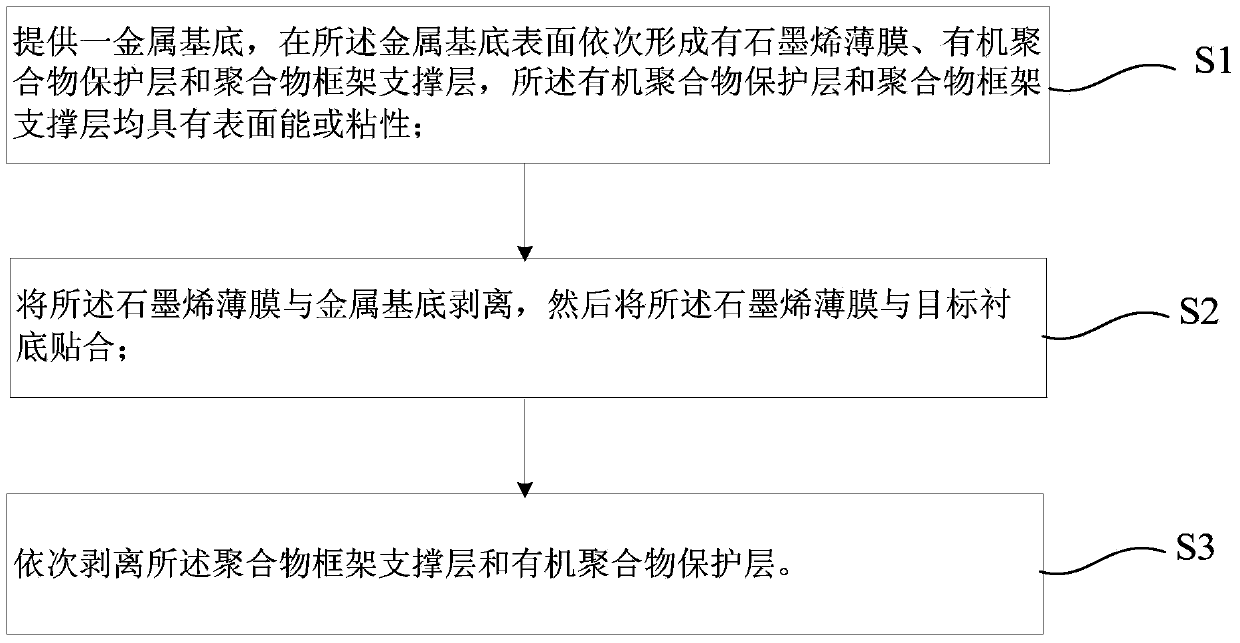

Transfer method of graphene film

The invention provides a transfer method of a graphene film, which at least comprises the following steps: providing a metal substrate, and sequentially forming a graphene film, an organic polymer protective layer and a polymer frame support layer on the metal substrate surface, wherein the organic polymer protective layer and polymer frame support layer respectively have surface energy or viscosity; peeling the graphene film from the metal substrate, and attaching the graphene film to a target substrate; and finally, sequentially peeling the polymer frame support layer and organic polymer protective layer. By utilizing the proper surface energy or proper viscosity of the organic polymer protective layer and polymer frame support layer, the organic polymer protective layer and polymer frame support layer can be directly attached without any adhesive, and can be peeled without damage after transfer, thereby simplifying and stabilizing the technique and ensuring the complete transfer of the graphene film and the reutilization of the metal substrate.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

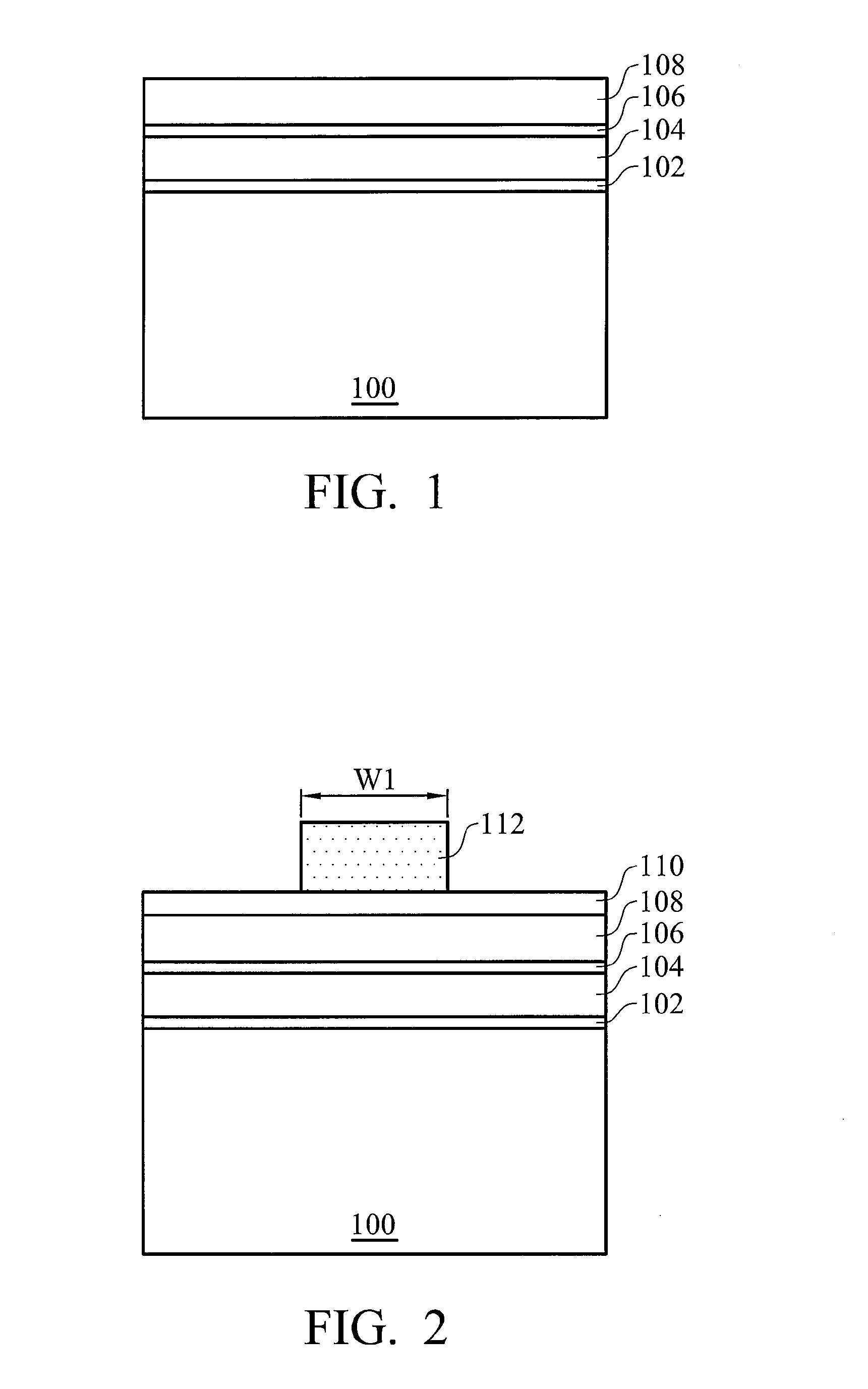

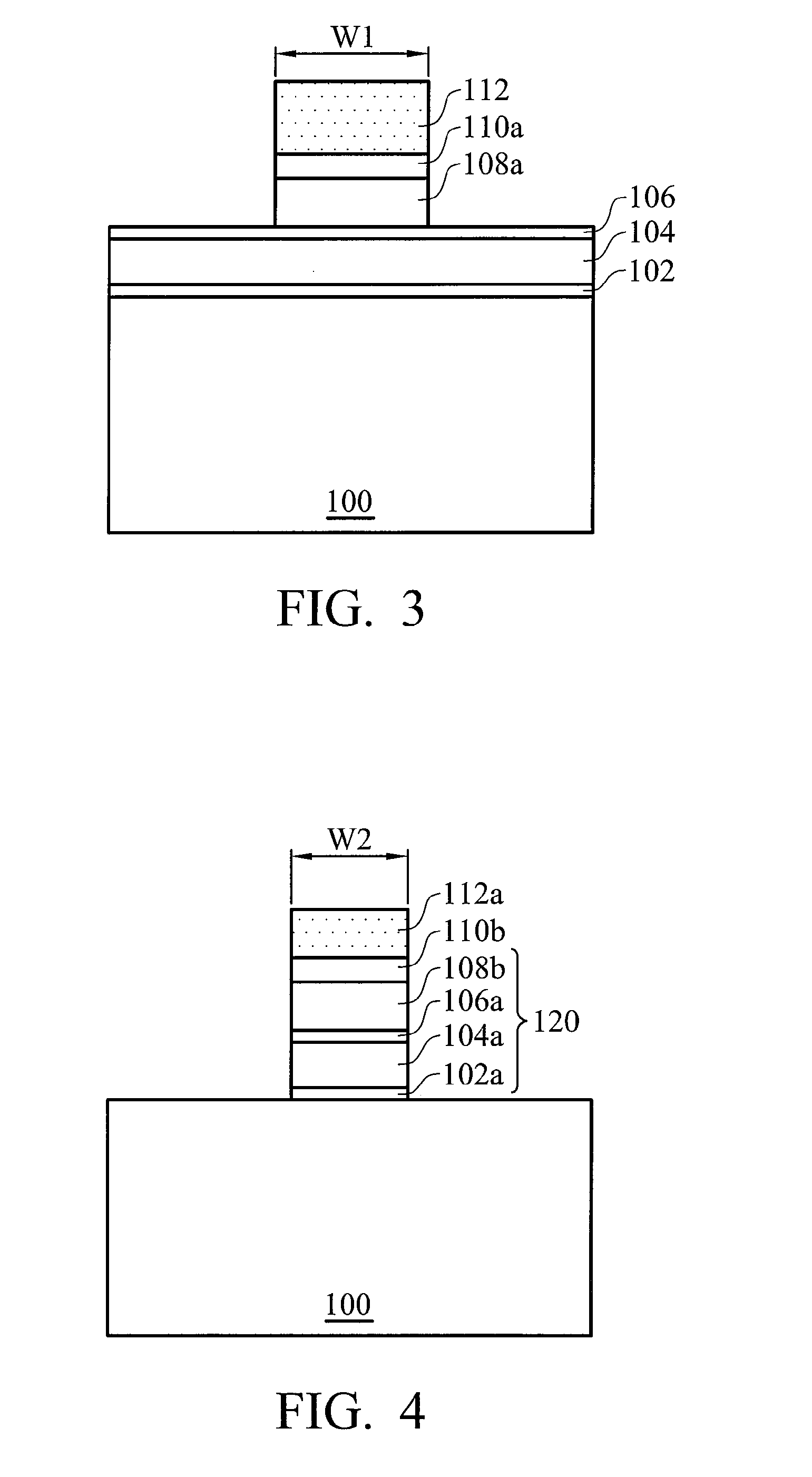

Fin filled effect transistor and method of forming the same

ActiveUS20080277745A1Improve electrical performanceHigh process complexityTransistorSolid-state devicesGate dielectricEngineering

A fin field effect transistor and method of forming the same. The fin field effect transistor comprises a semiconductor substrate having a fin structure and between two trenches with top portions and bottom portions. The fin field effect transistor further comprises shallow trench isolations formed in the bottom portions of the trenches and a gate electrode over the fin structure and the shallow trench isolation, wherein the gate electrode is substantially perpendicular to the fin structure. The fin field effect transistor further comprises a gate dielectric layer along sidewalls of the fin structure and source / drain electrode formed in the fin structure.

Owner:TAIWAN SEMICON MFG CO LTD

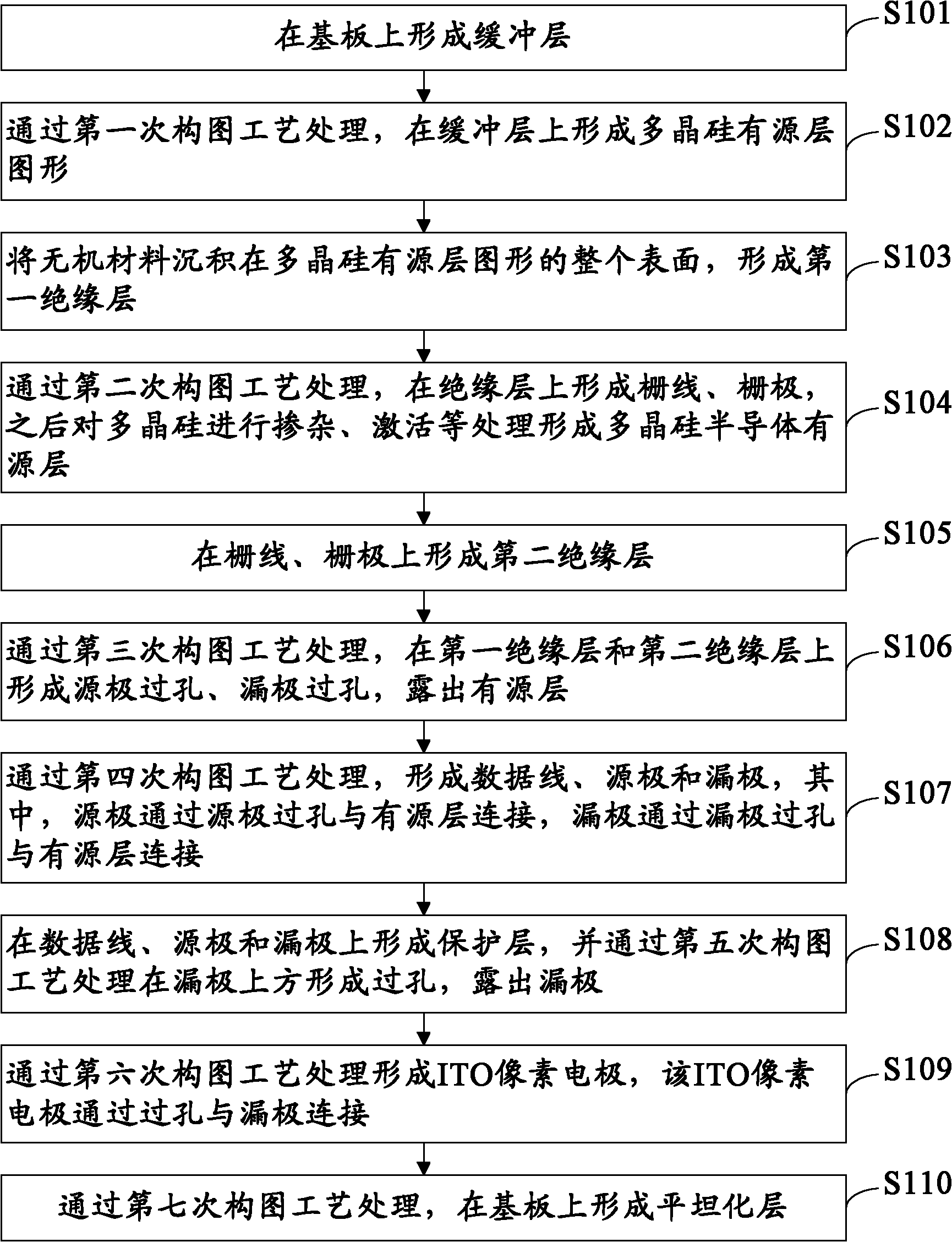

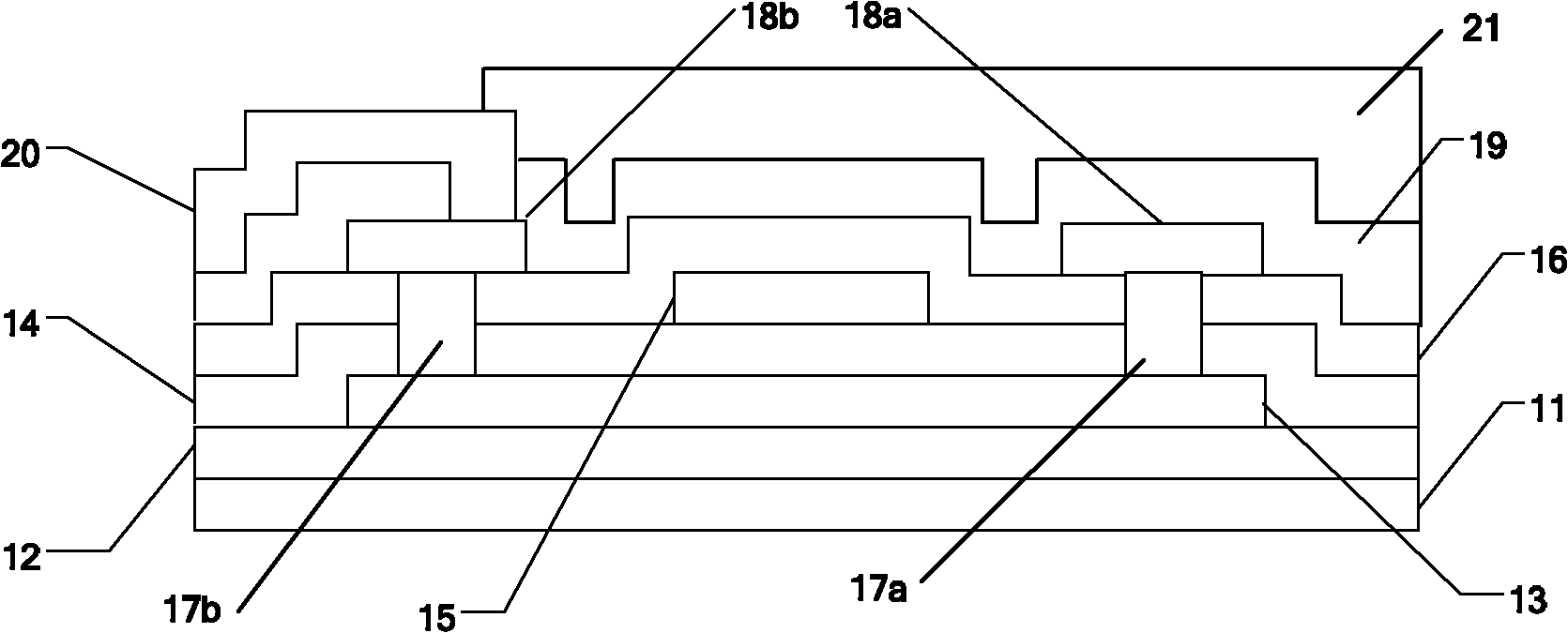

Low-temperature polycrystalline silicon TFT (Thin Film Transistor) array substrate and manufacturing method thereof

ActiveCN102683338AReduce operational processingReduce process complexitySolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayActive matrix

The embodiment of the invention provides a low-temperature polycrystalline silicon TFT (Thin Film Transistor) array substrate and a manufacturing method thereof, and relates to the field of manufacturing of liquid crystal displays and AMOLED (Active Matrix / Organic Light Emitting Diode) displays. The treatment frequency of a composition technology is reduced, so that the manufacturing flow is simplified and the manufacturing cost is reduced. The method provided by the invention comprises the following steps of: forming a buffer layer on a substrate; forming a polycrystalline silicon layer on the buffer layer; forming a first metal layer on the polycrystalline silicon layer; performing composition process treatment on the first metal layer and the polycrystalline silicon layer by using a gray tone mask plate or semitransparent mask plate; and obtaining patterns of a data line, a source electrode, a drain electrode and a polycrystalline silicon semiconductor part through one-time composition process. The embodiment of the invention is used for manufacturing the low-temperature polycrystalline silicon TFT array substrate.

Owner:BOE TECH GRP CO LTD

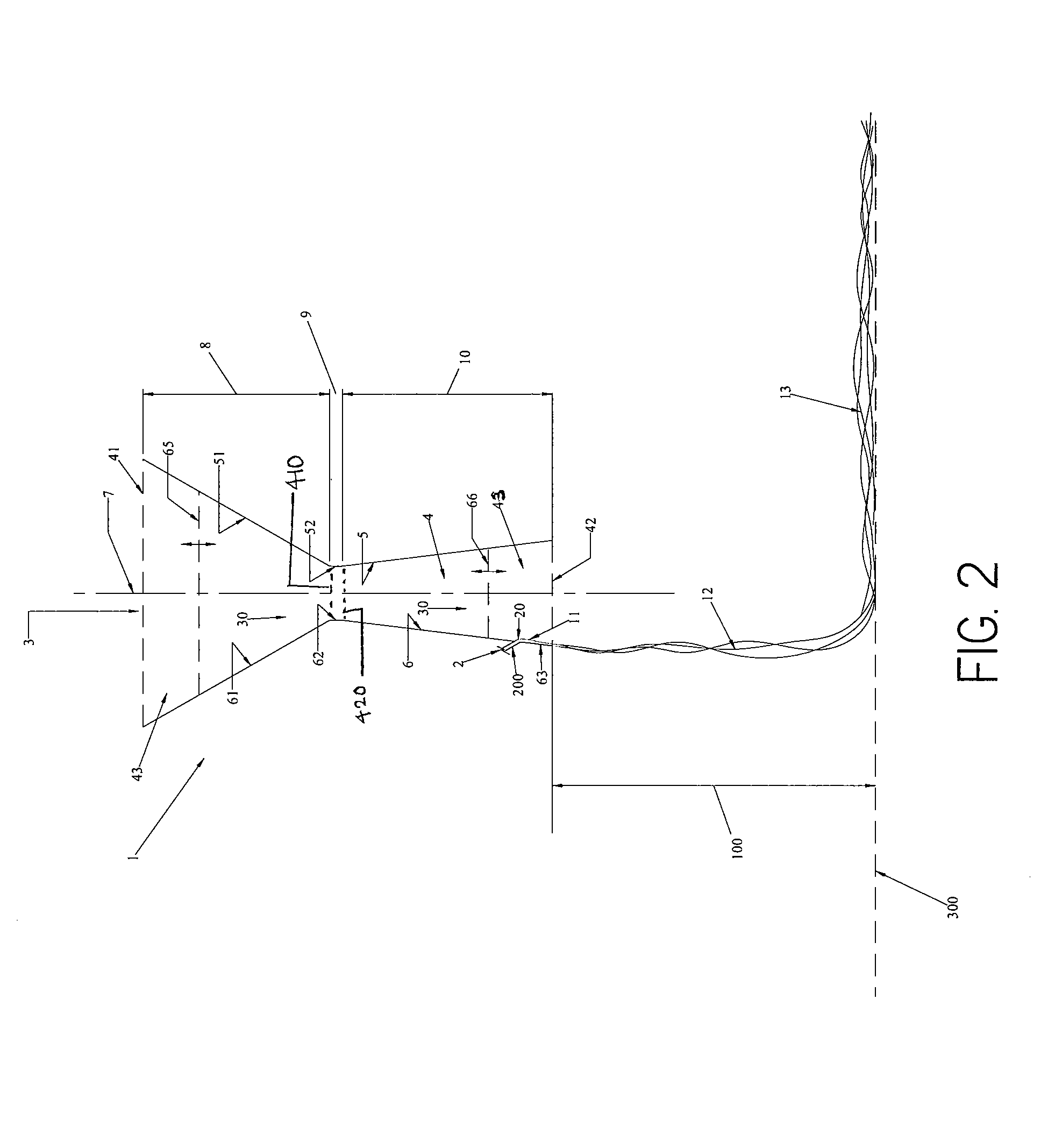

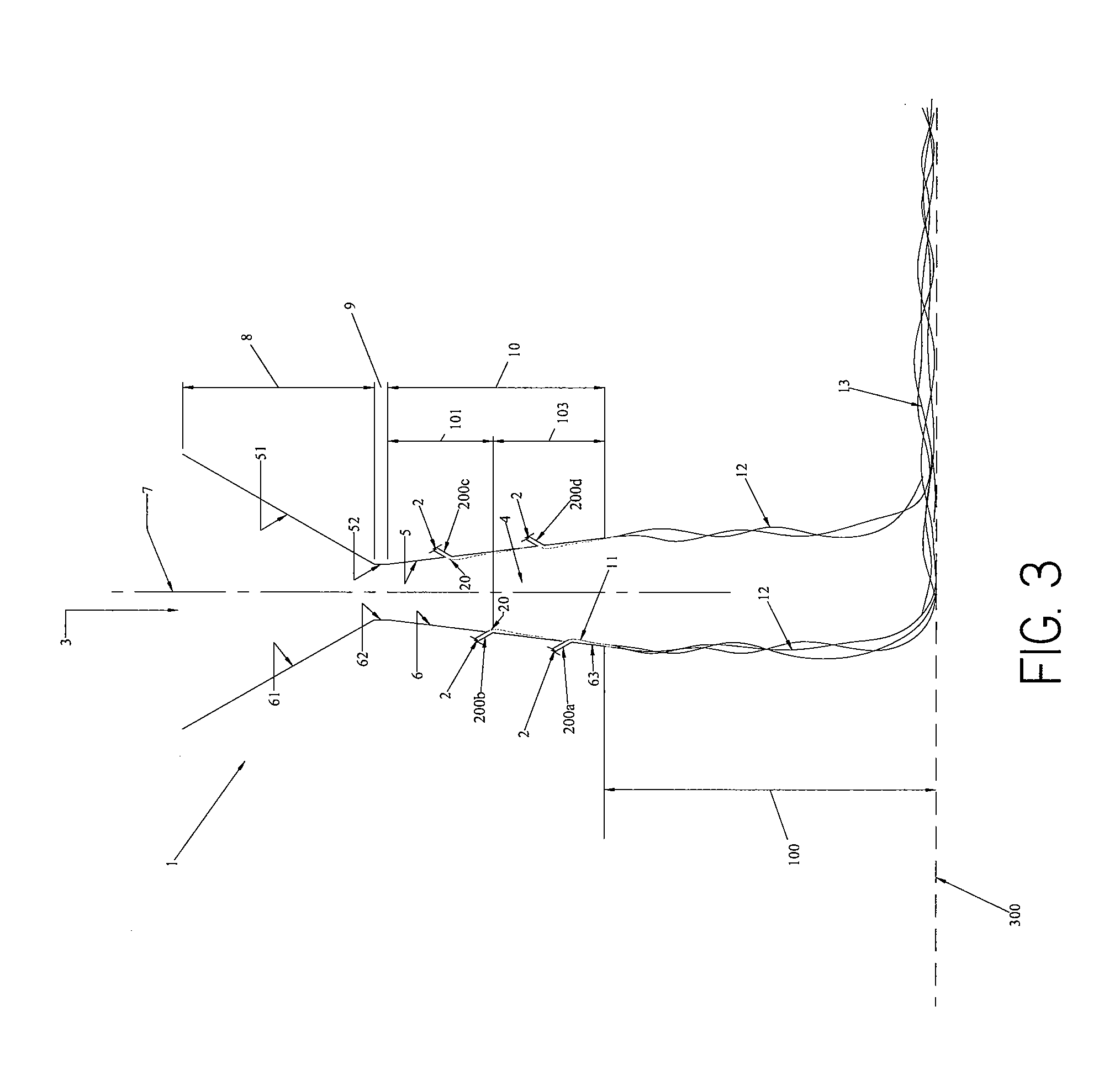

Process and apparatus for producing sub-micron fibers, and nonwovens and articles containing same

InactiveUS20080093778A1Increased sub-micron fiber outputGas demandSpinnerette packsFilament/thread formingFiberPolymer science

A process and apparatus for producing sub-micron fibers, and more specifically a process and apparatus for effecting formation of sub-micron fibers by fibrillation of polymer films, and nonwoven materials and articles incorporating them.

Owner:AVINTIV SPECIALTY MATERIALS INC

Mobile electronic equipment

ActiveCN102736686AReduce areaHigh strengthDigital data processing detailsAntenna supports/mountingsMetallic enclosureCoaxial cable

The invention provides mobile electronic equipment, which comprises a shell, a slot antenna and a communication module, wherein the shell at least comprises a first part of a metal material; the first part at least comprises a first metal surface and a second metal surface which are connected with each other; the slot antenna is engraved on the first part and used for radiating a signal and comprises a first resonance branch provided with a feedback point; the first resonance branch comprises a main body and a tail; the main body is engraved on the first metal surface; the tail extends to the second metal surface from the main body and hollows out of the second metal surface; the first resonance branch forms a 1 / 4-wavelength slot antenna and corresponds to a first resonance point; and the communication module is connected with the slot antenna through coaxial cables at the feedback point and used for supplying the signal. According to the mobile electronic equipment, the problem about implementation of the antenna of the mobile equipment with the full metal shell is solved; and the size of a 3G antenna can be effectively reduced.

Owner:LENOVO (BEIJING) LTD

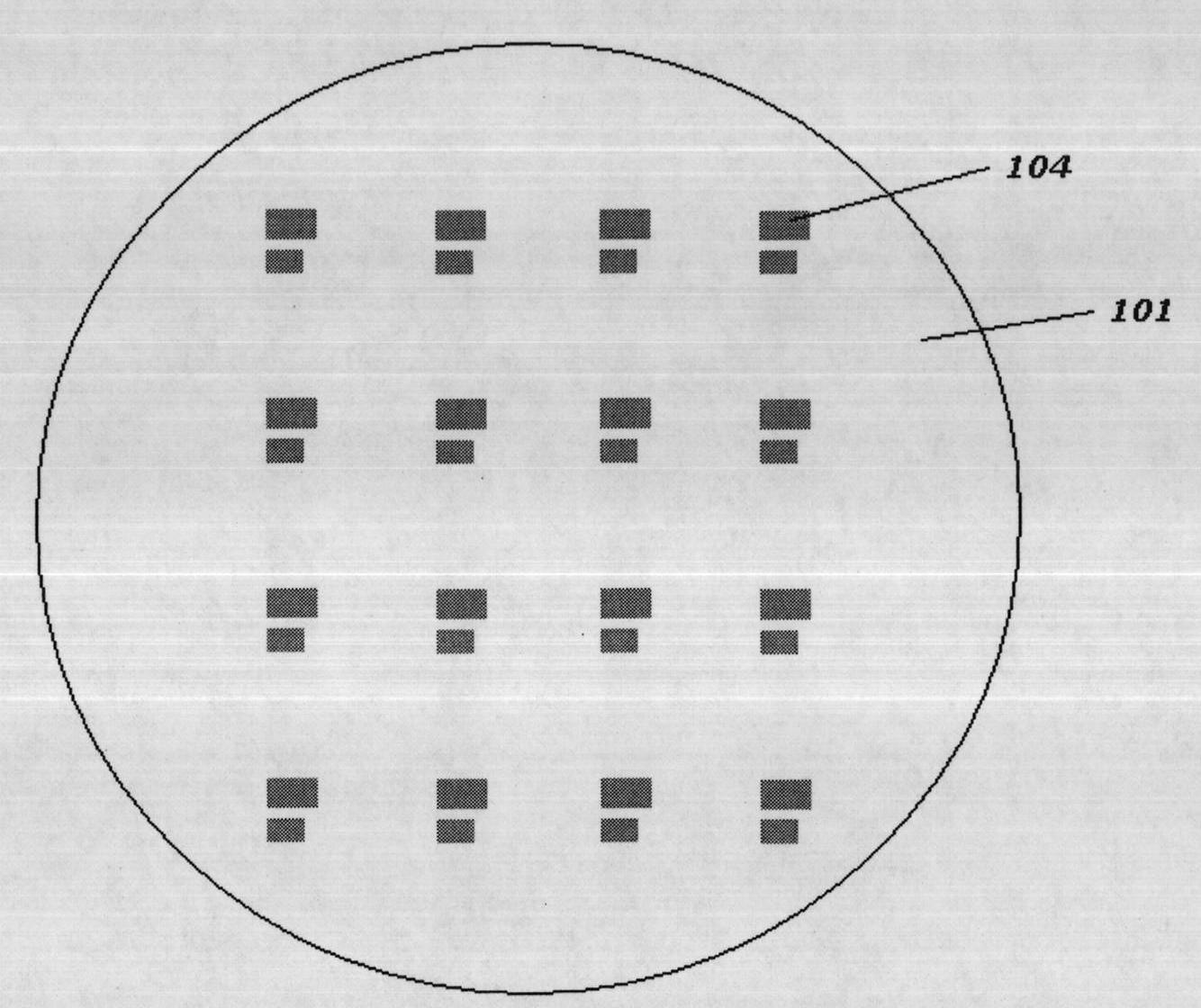

Bulk silicon micro mechanic resonator and manufacturing method thereof

ActiveCN101867080AReduce process complexityReduce manufacturing costDecorative surface effectsResonatorsSilicon chipResonator

The invention relates to a bulk silicon micro mechanic resonator and a manufacturing method thereof. The invention is characterized in that: the resonator is formed by bonding a substrate silicon chip, a structural silicon chip and a cover plate silicon chip, the front side of the substrate silicon chip bonded together with the back side of the structural silicon chip, and the front side of the structural silicon chip is bonded with the back side of the cover plate silicon chip; when the resonator is manufactured, a suspended structure, namely a cavity under a resonant vibration generator, ismanufactured first, then an element structural layer is formed above the cavity by bonding, next the element structure of the resonator is released during the manufacturing of the element structure of the resonator by a dry-method erosion, and finally the cover plate silicon chip is fixed above the structural silicon chip by using a vacuum wafer for alignment and bonding. Before the element structure is manufactured, the cavity under the resonator is corroded by a wet method and the wafer package is used for the vacuum sealing of the element.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

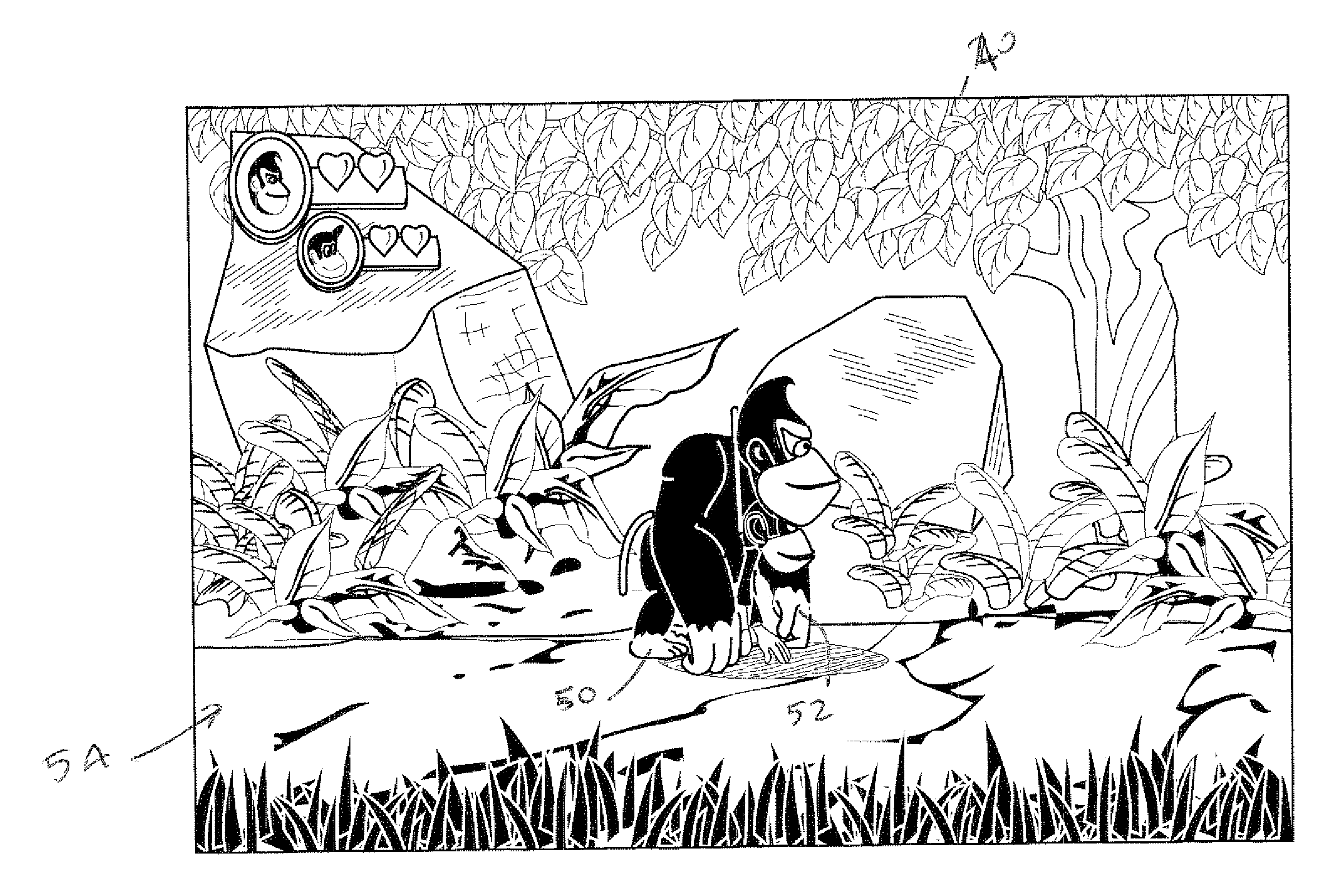

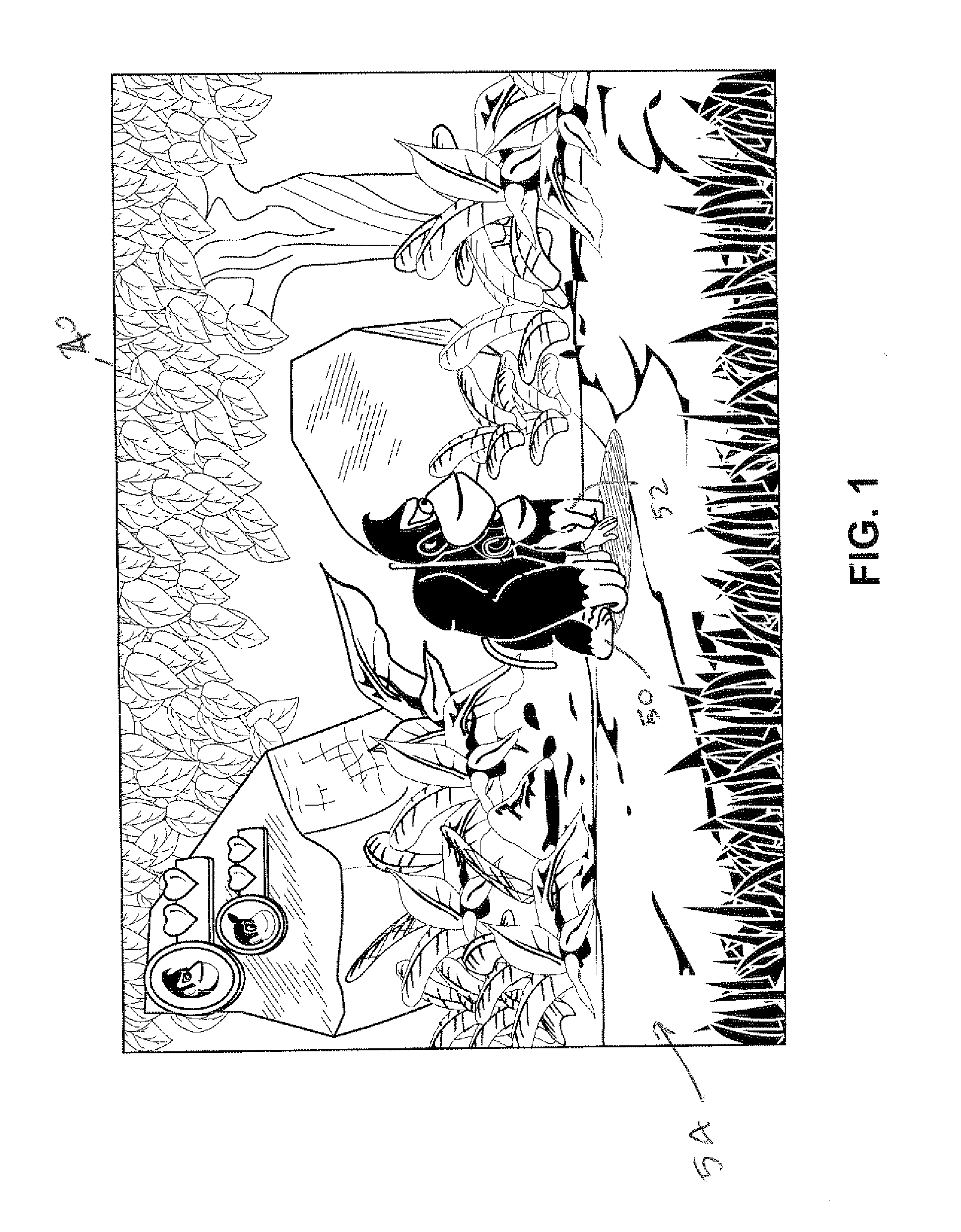

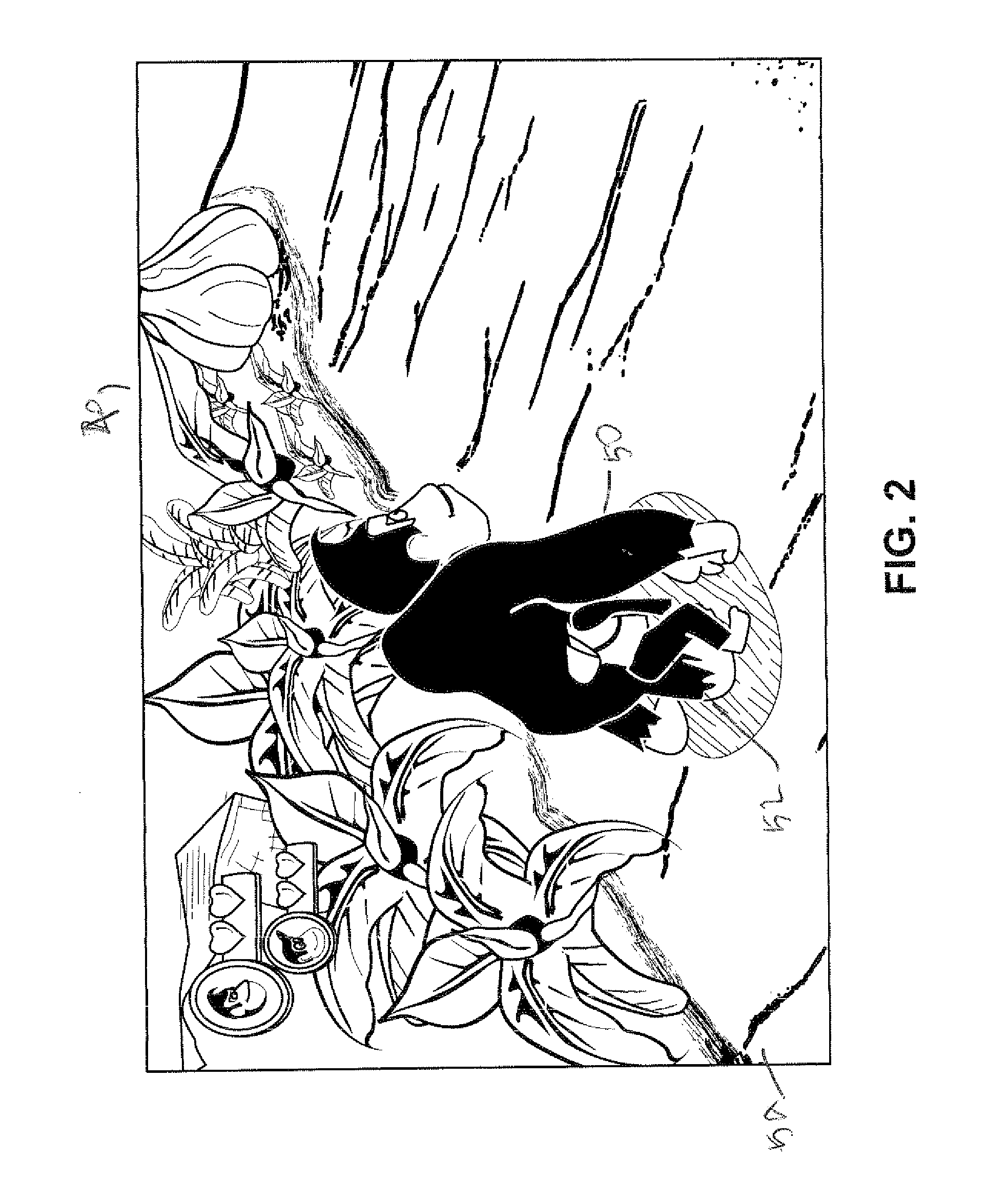

2d imposters for simplifying processing of plural animation objects in computer graphics generation

ActiveUS20110306417A1Reduce process complexityReduce memory loadAnimationVideo gamesGraphicsViewpoints

The technology herein involves use of 2D imposters to achieve seemingly 3D effects with high efficiency where plural objects such as animated characters move together such as when one character follows or carries another character. A common 2D imposter or animated sprite is used to image and animate the plural objects in 2D. When the plural objects are separated in space, each object can be represented using its respective 3D model. However, when the plural objects contact one another, occupy at least part of the same space, or are very close to one other (e.g., as would arise in a situation when the plural objects are moving together in tandem), the animation system switches from using plural respective 3D models to using a common 2D model to represent the plural objects. Such use of a common 2D model can be restricted in some implementations to situations where the user's viewpoint can be restricted to be at least approximately perpendicular to the plane of 2D model, or the 2D surface on which the combined image is texture mapped can be oriented in response to the current virtual camera position.

Owner:NINTENDO CO LTD

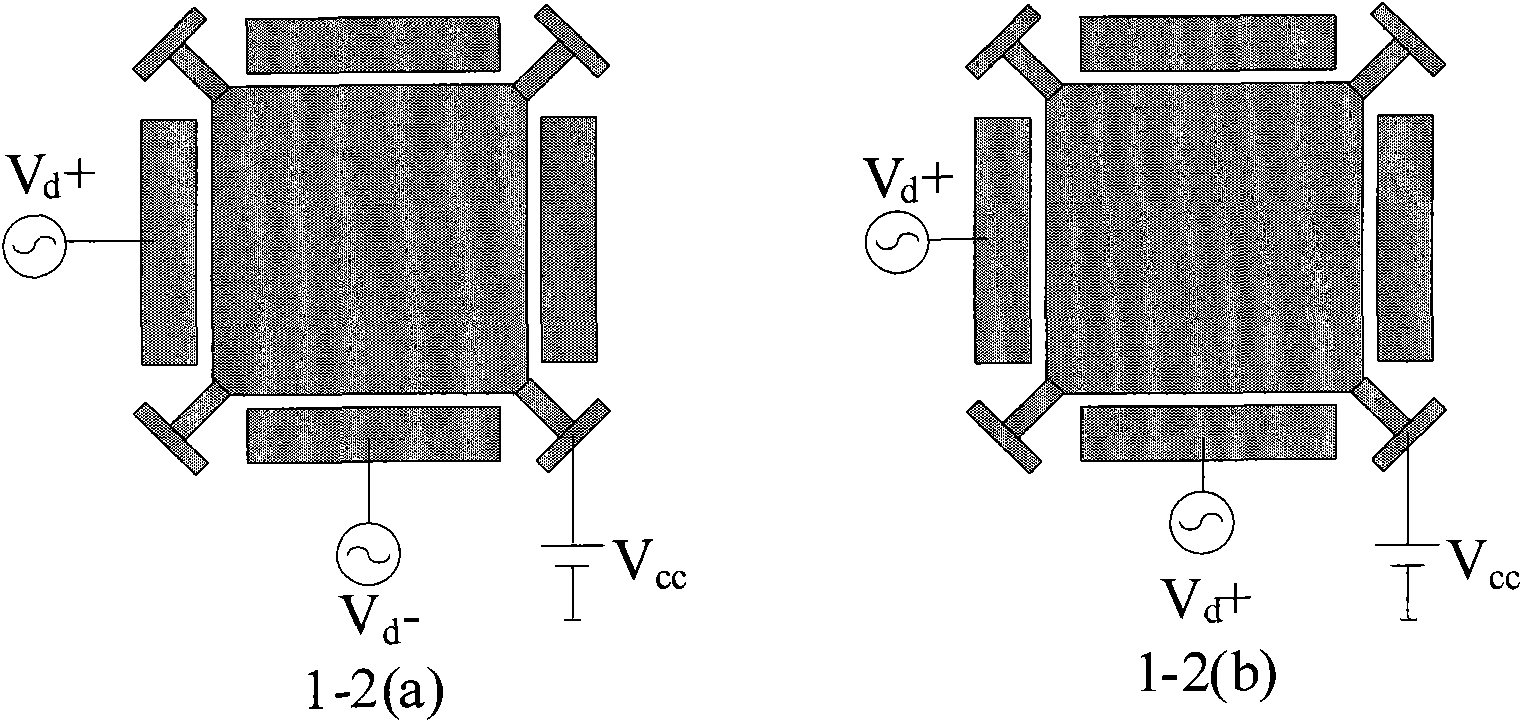

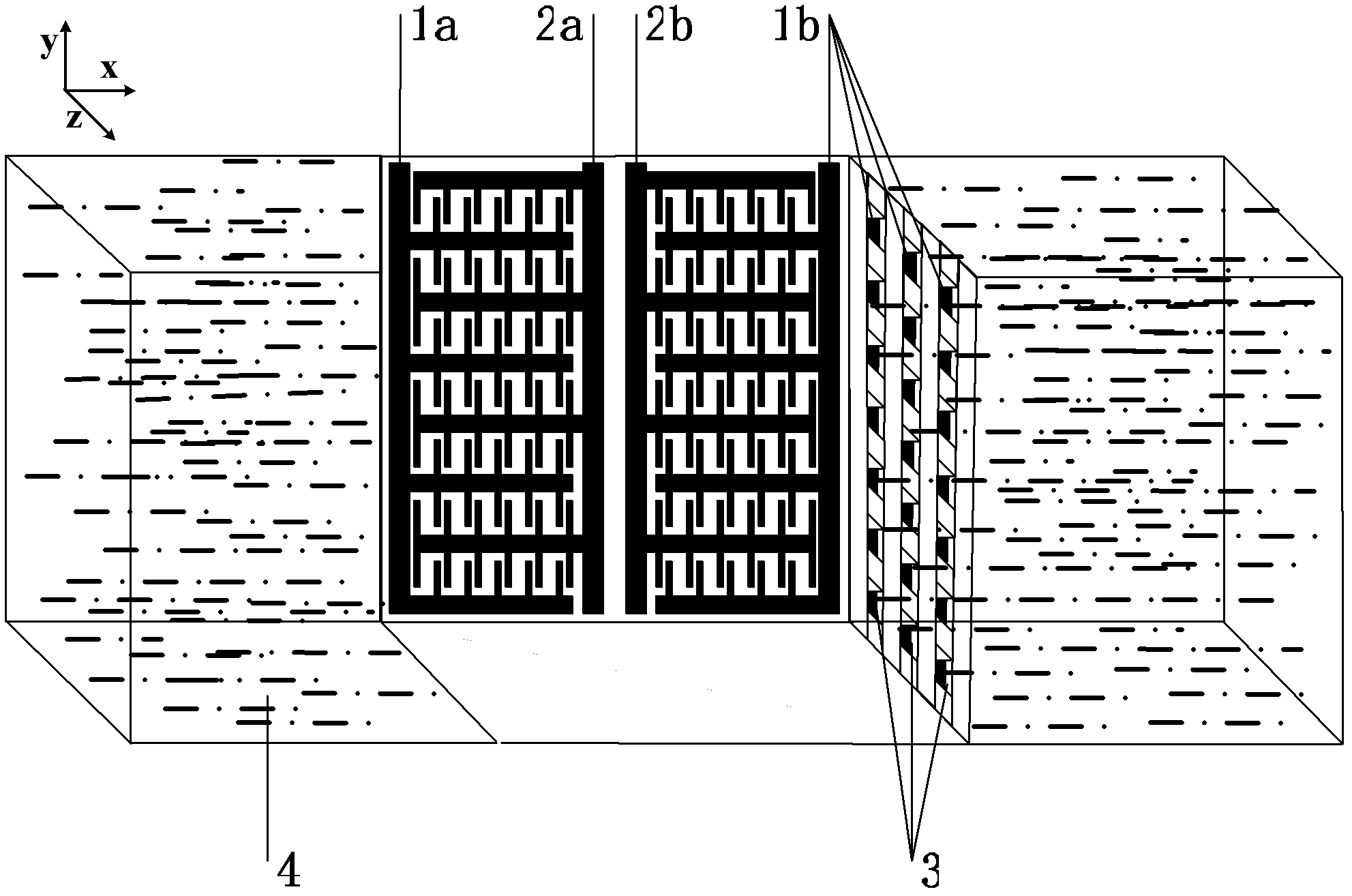

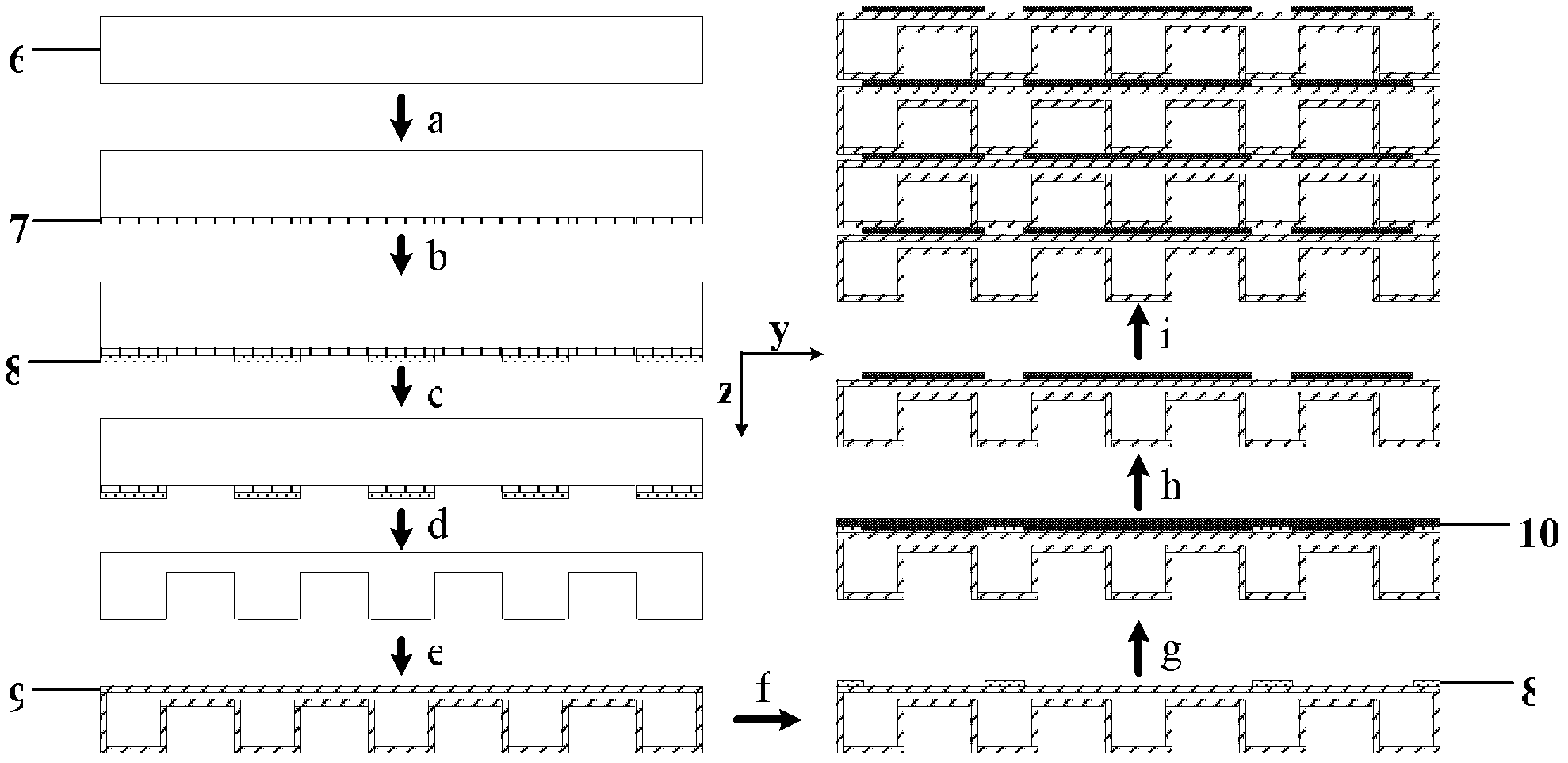

Electrochemical seism radiodetector based on MEMS (Micro-electromechanical Systems) technology

ActiveCN103048680AImprove consistencyEasy to adjust the widthSolid-state devicesSeismic signal receiversGeophoneElectrochemical response

The invention discloses an electrochemical seism radiodetector based on MEMS (Micro-electromechanical Systems) technology and relates to the technology of seism detection. The electrochemical seism radiodetector can detect weak seismic wave. A sensitive unit with a laminar laminated structure is sealed in a cavity fully filled with electrolyte solution, wherein each layer of the sensitive unit comprises two pairs of electrodes and a channel insulating runner; the electrodes of each layer share the same plane, are arranged in an interdigital shape and are arranged on the front surface of the layer; and each channel insulating runner is arranged on the back surface of the related layer. When the seism radiodetector is vibrated by seismic wave, equivalently the seism radiodetector is acted by an accelerated speed, pressure gradient is generated in the solution, the ion concentration distribution and the velocity field of the solution are changed, and the electrochemical reaction speed at the electrodes is affected, so that electrode current is changed. The seismic wave is detected by measuring the change of the electrode current. Due to the adoption of the laminated and plane-shared interdigital electrodes in the sensor, the sensitivity of the radiodetector is improved, the consistency of the electrodes is high, and the width of the electrode and the distance between the electrodes are convenient to adjust.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

Wafer level MMCM (microwave multichip module) packaging structure using photosensitive BCB (benzocyclobutene) as dielectric layer and method

ActiveCN102110673ASolve the defect of large lossImprove performanceSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSurface-mount technology

The invention relates to a wafer level MMCM (microwave multichip module) packaging structure using photosensitive BCB (benzocyclobutene) as a dielectric layer and a method. The packaging structure is characterized by 1) manufacturing metal ground (GND) shielding layers on a silicon substrate with cavities for embedding; 2) using the photosensitive BCB as the dielectric layers and forming an interconnected through hole structure on the BCB by utilizing photoetching and developing processes; and 3) forming a multi-layer interconnection packaging structure through alternate occurrence of metal layers and the dielectric layers. The method is characterized by eroding or etching the cavities for embedding on the silicon substrate, sputtering a metal seed layer and carrying out electroplating to form the GND, embedding MMIC (monolithic microwave integrated circuit) chips, using conductive adhesives to bond the chips and the substrate, coating the photosensitive BCB and carrying out photoetching and developing to form the interconnected through hole patterns and carrying out curing to realize multi-layer MMCM package. The thickness of the dielectric layers is 20-35mu m. Capacitors, resistors, inductors, power dividers and antenna passive devices can be integrated in the multi-layer interconnection structure or discrete components are integrated through surface mount technology, thus realizing the functionalization of the module.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

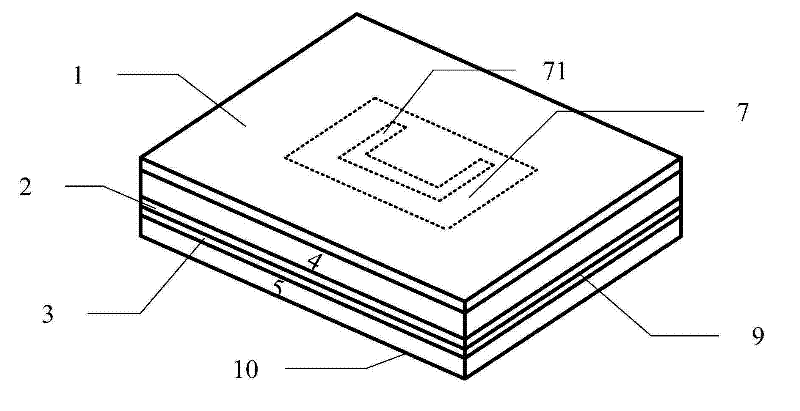

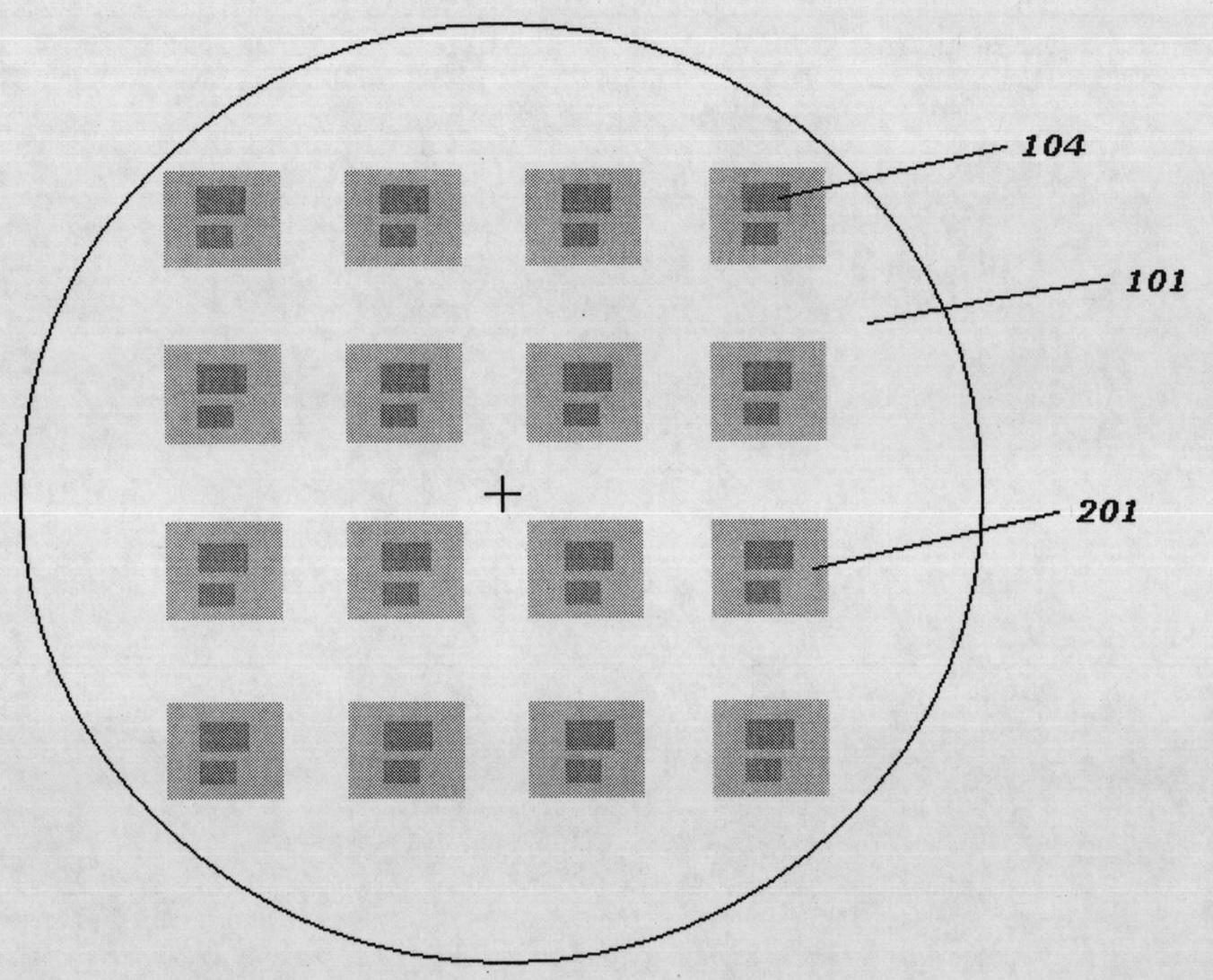

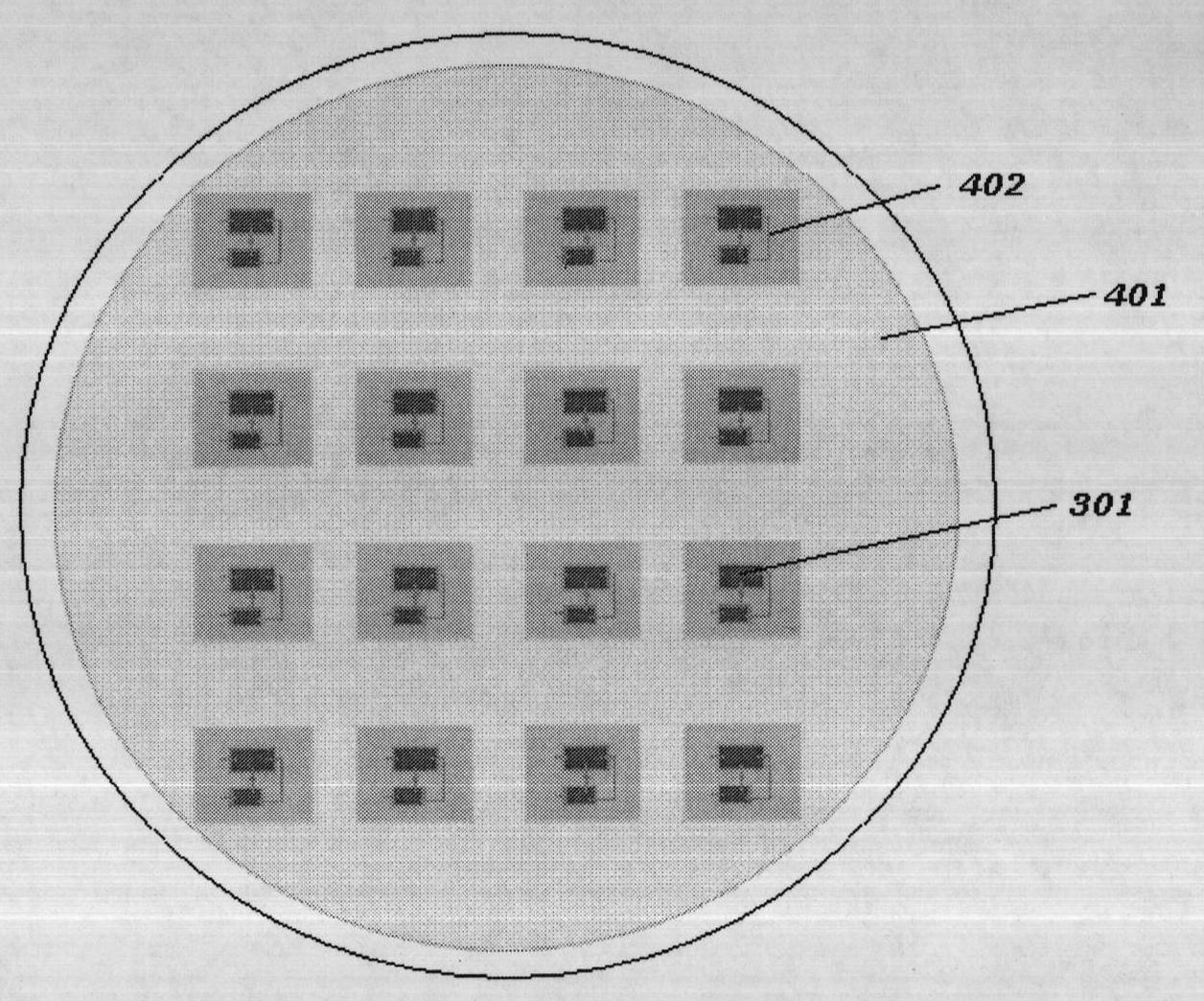

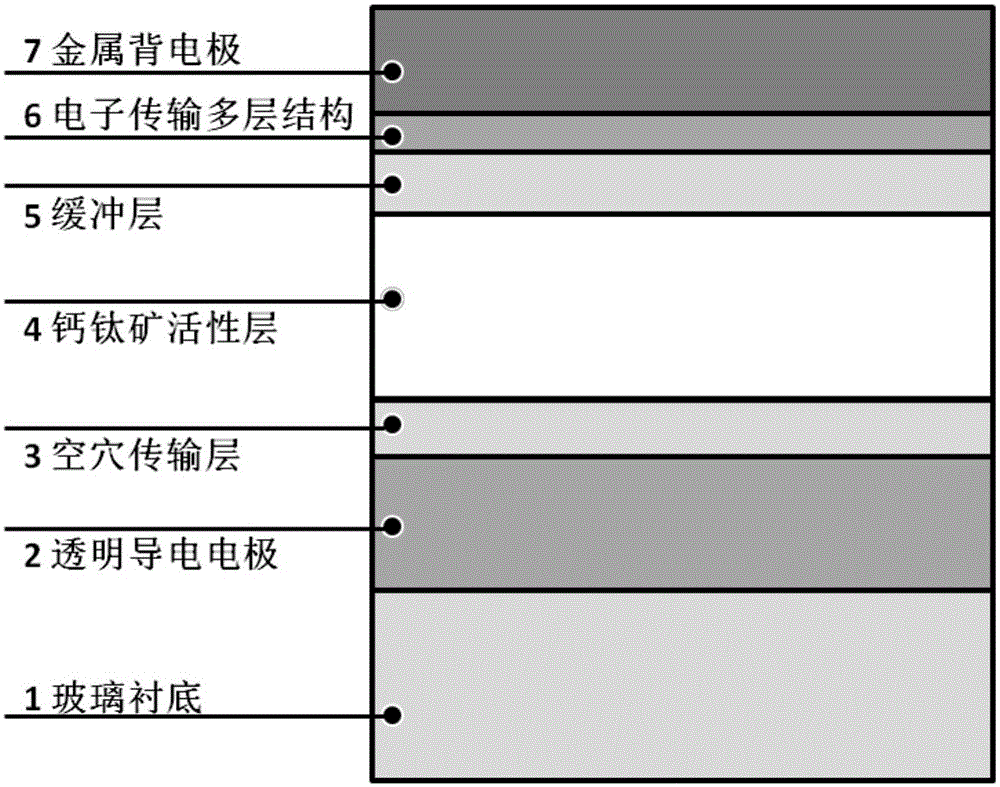

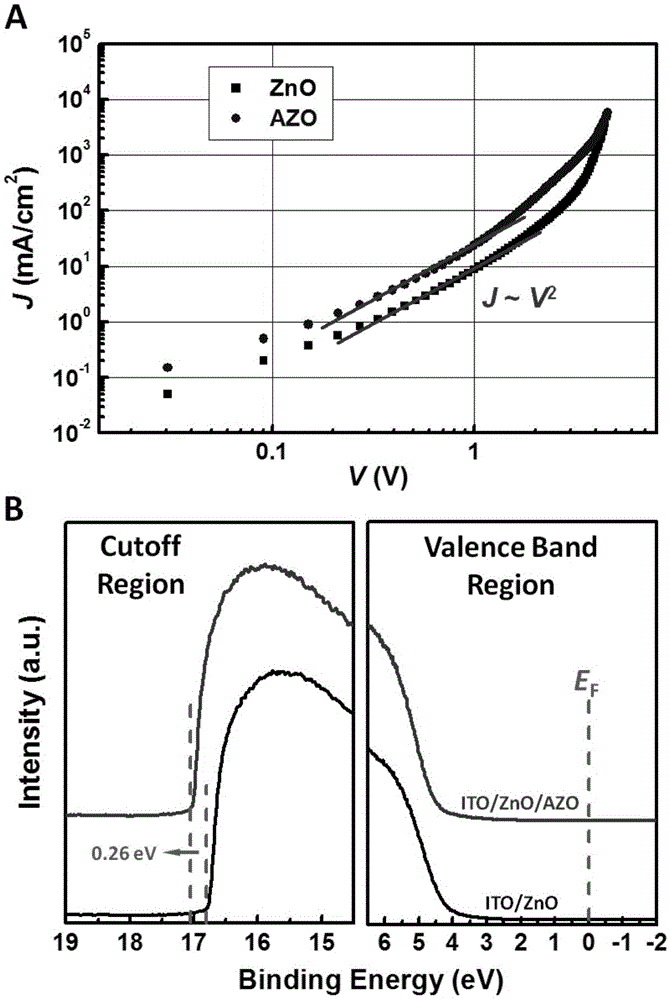

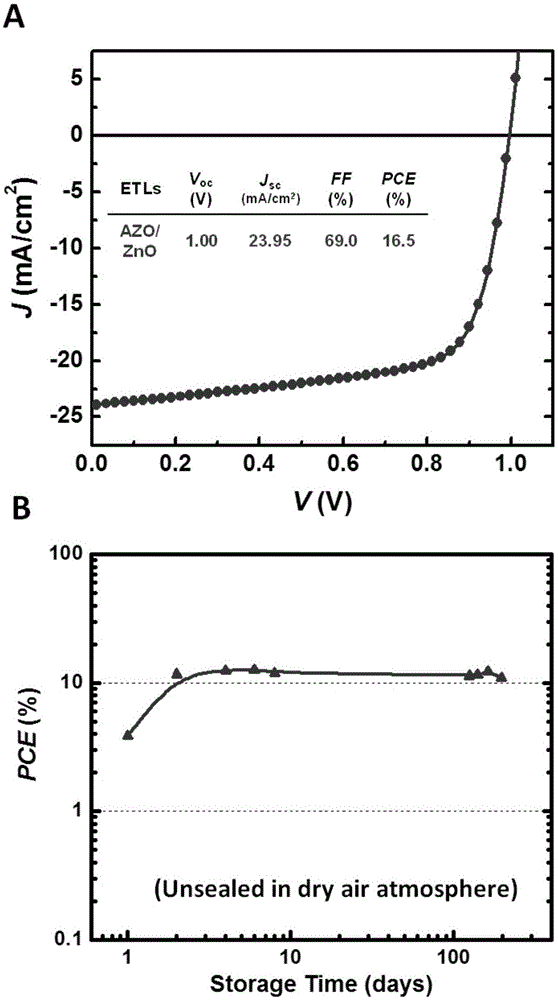

Novel planar heterojunction perovskite solar cell with high efficiency and long life manufactured by adopting low-temperature solution method

InactiveCN105024013AImprove conversion efficiencyExtend working lifeFinal product manufactureSolid-state devicesHeterojunctionPerovskite solar cell

The invention discloses a novel planar heterojunction perovskite solar cell with high efficiency and long life manufactured by adopting a low-temperature solution method. The novel planar heterojunction perovskite solar cell is mainly characterized in that an ingenious design of an electron transmission multi-layer structure and a buffer layer structure is introduced into the cell, the electron conduction and extraction efficiency are increased, the stability of the cell is effectively improved, the conversion efficiency of the novel perovskite solar cell is significantly increased and the operating life of the cell is substantially prolonged. According to the novel planar heterojunction perovskite solar cell, the short-circuit current density is up to 23.95mA / cm<2>, and the cell conversion efficiency reaches 16.5%; and attenuation of the cell conversion efficiency in 6 months is less than 10% when the unencapsulated cell is stored in a dry atmosphere. In addition, the whole manufacturing procedure of the novel planar heterojunction perovskite solar cell is obtained through low-temperature processing by adopting the solution method, the process complexity and production cost can be significantly reduced, and the novel planar heterojunction perovskite solar cell is matched with large-area flexible substrates.

Owner:SUZHOU RUISHENG SOLAR ENERGY TECH

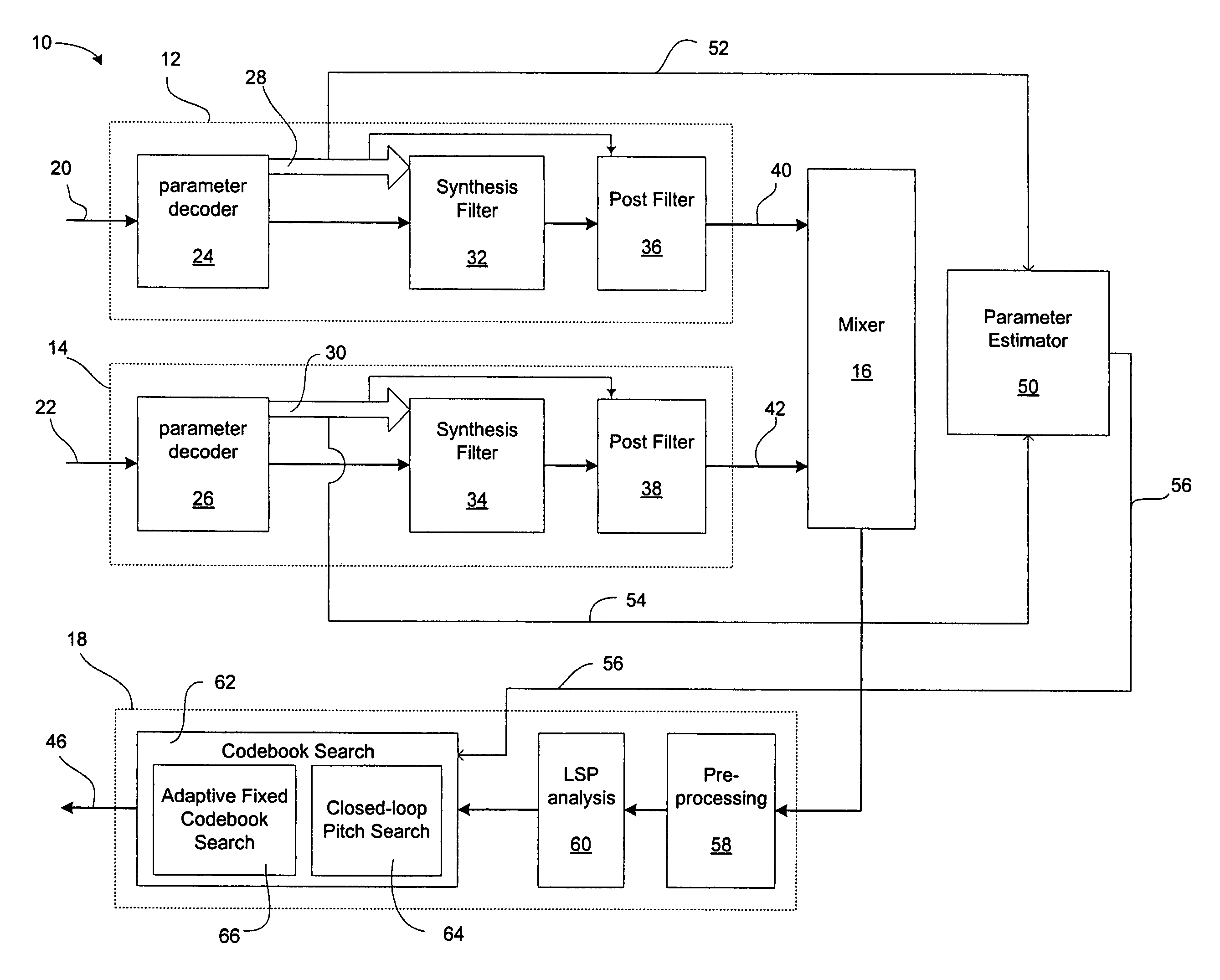

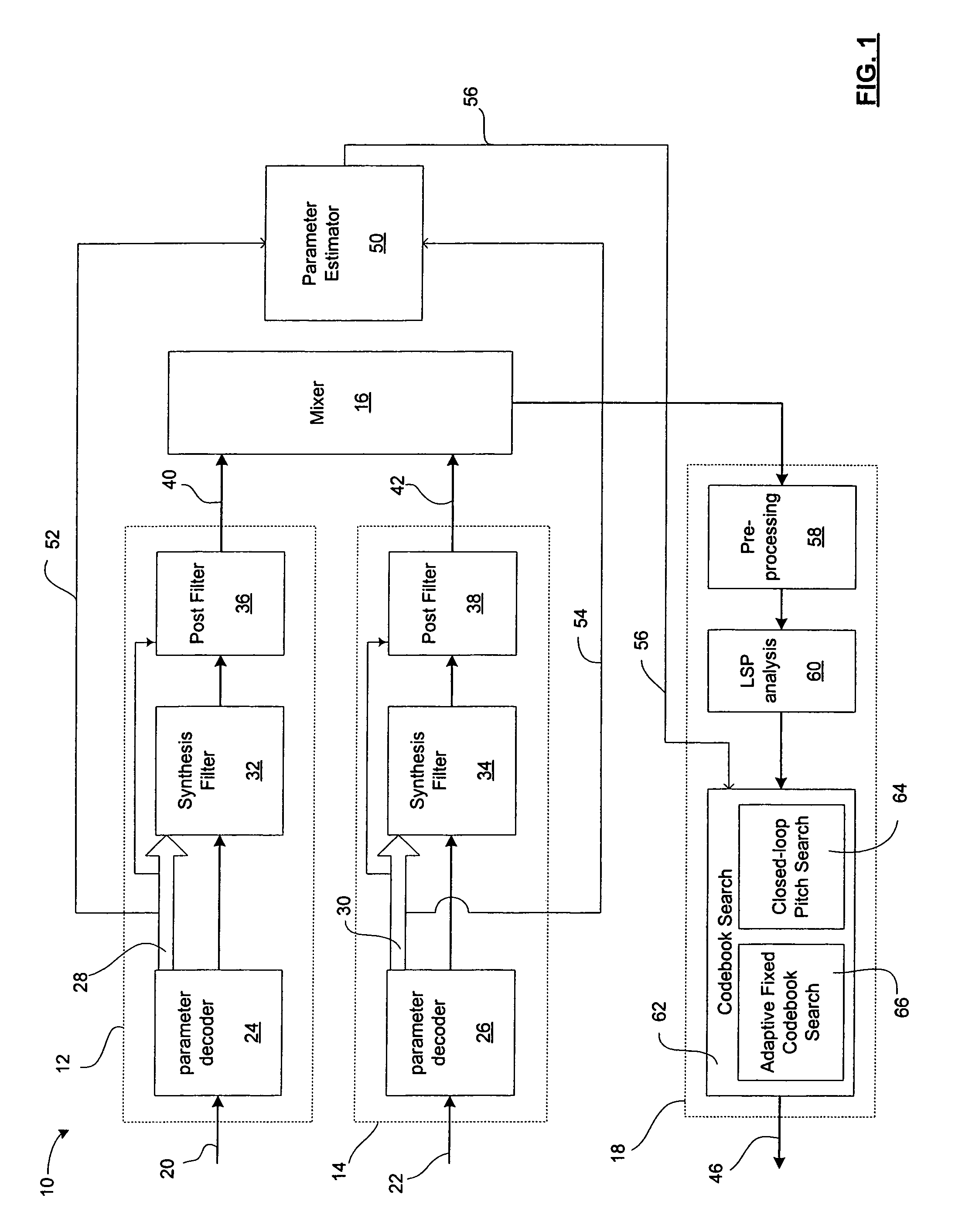

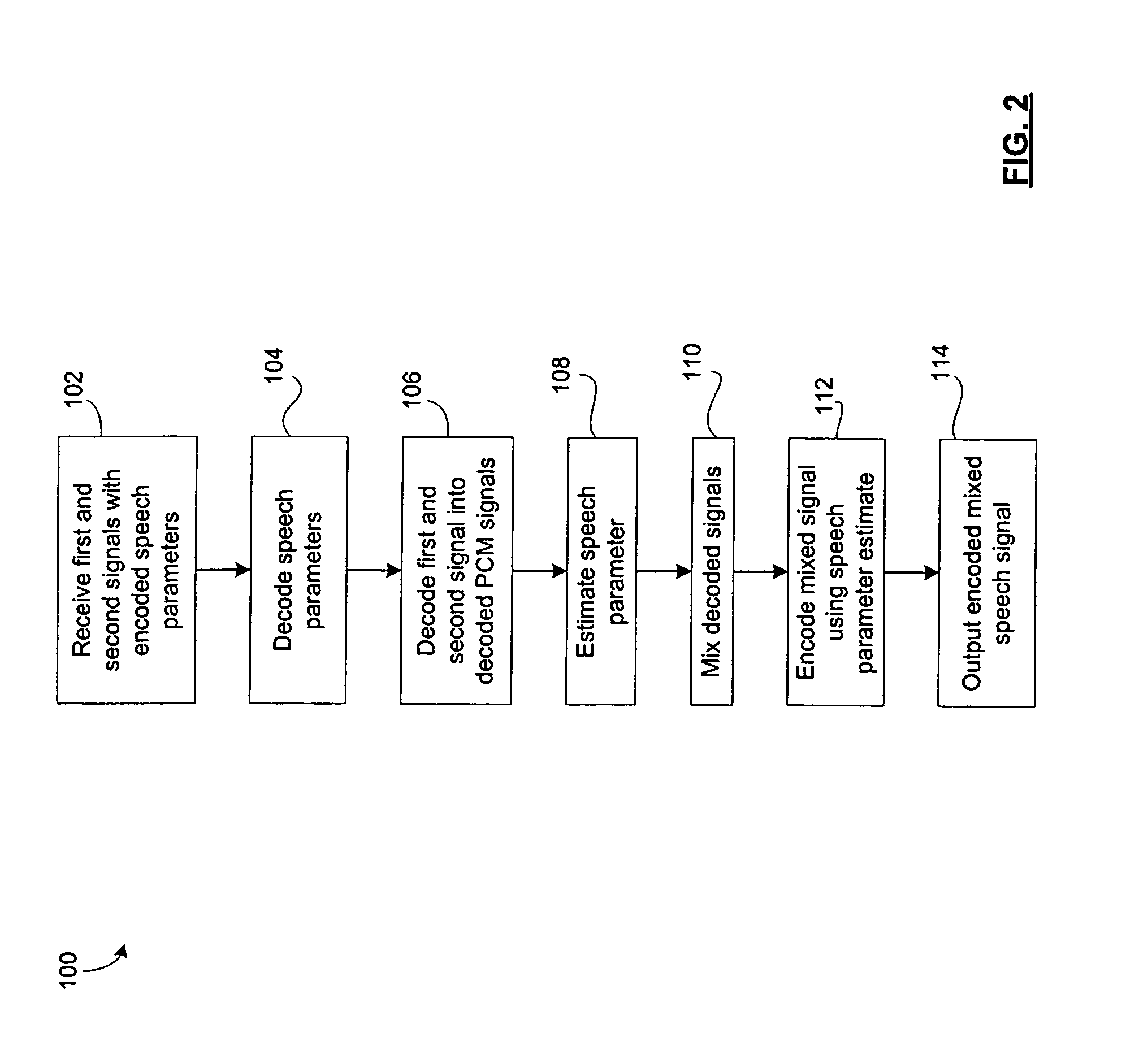

Transcoders and mixers for voice-over-IP conferencing

InactiveUS7619995B1Improved VoIP technologyReduced algorithmicSpecial service provision for substationMultiplex system selection arrangementsFrequency mixerBroadband

Transcoders and mixers having reduced algorithmic delay and processing complexity. An improved mixer for signals having encoded speech parameters wherein the parameters obtained through decoding are used by a parameter estimator to improve the encoding by providing a parameter estimate for the mixed signal. In the case of pitch parameters, the mixer uses the principle of strong-pitch-domination. The mixing of wideband signals is simplified by performing mixing of individual lower and upper sub-bands. A transcoder and a mixer that converts a wideband signal into a narrowband signal relies upon high frequency suppression. A transcoder and a mixer that converts a narrowband signal into a wideband signal relies upon filter combination.

Owner:CARLETON UNIV +1

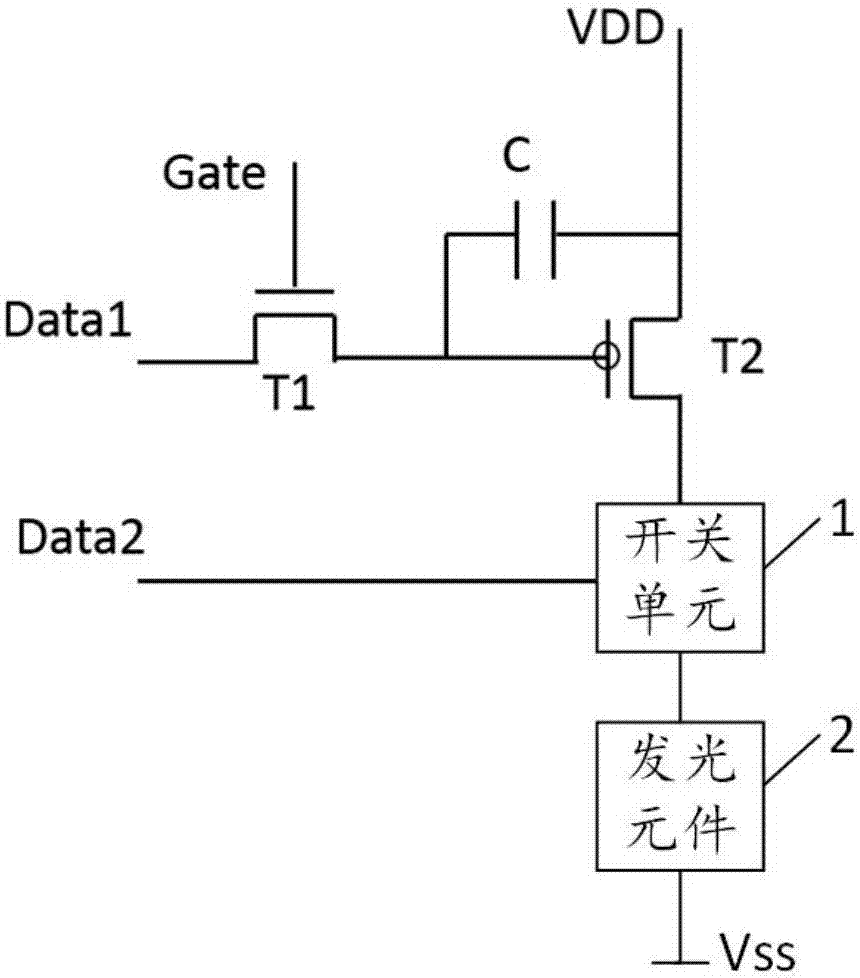

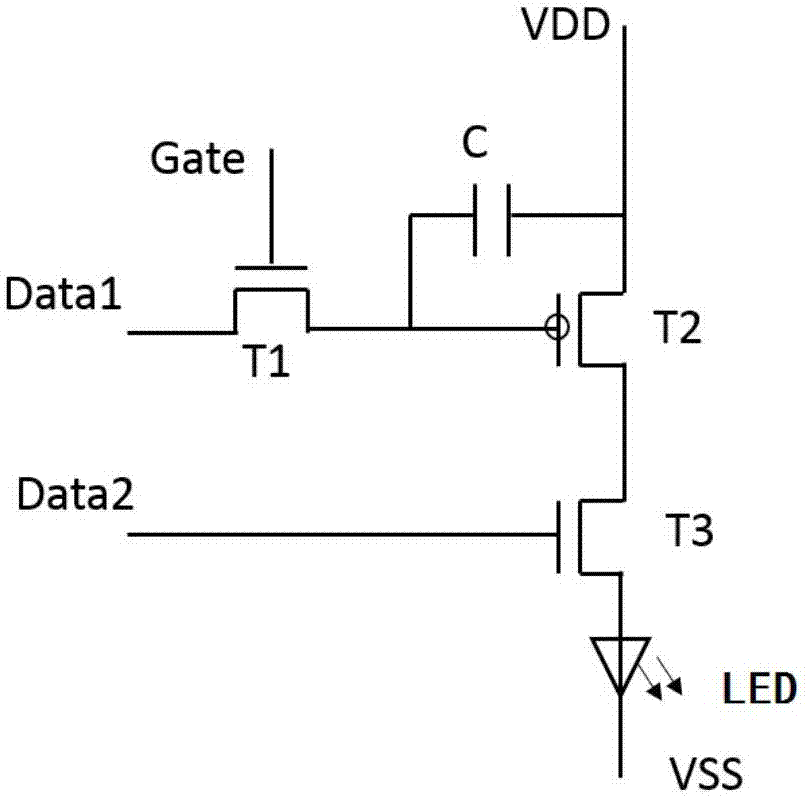

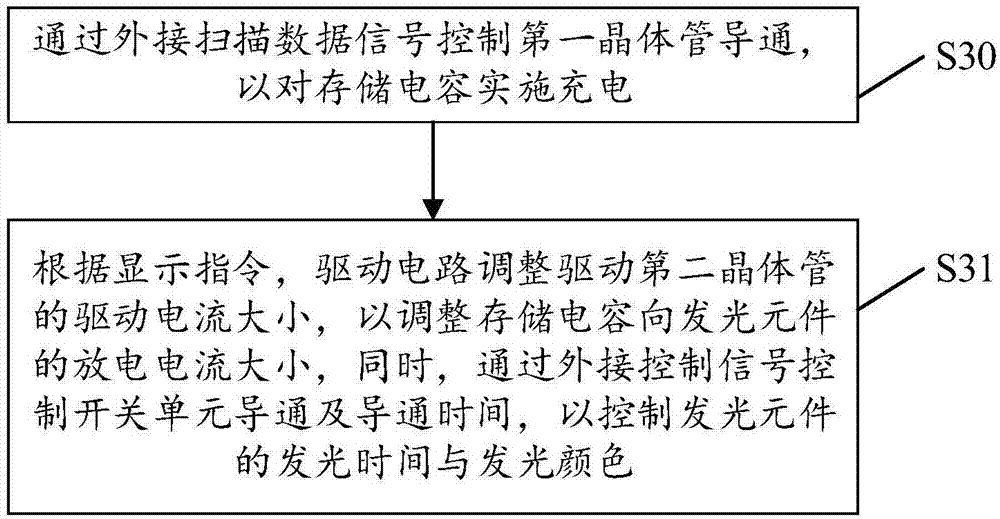

Display panel, driving method of display panel and display device

InactiveCN107481664AReduced emission wavelengthReduce process complexityTransistorStatic indicating devicesDriving currentPower flow

The invention relates to the technical field of display, in particular to a display panel, a driving method of the display panel and a display device. The display panel comprises a pixel circuit and a driving circuit, the pixel circuit comprises at least one light-emitting element, and the light-emitting element comprises a multi-layer quantum well structure; the driving circuit is used for adjusting the driving current input into the light-emitting element, so that the light-emitting element emits light in corresponding colors according to the driving current. The display panel can control the light-emitting element to display different colors and display brightness through a simple pixel circuit, and the display performance of the display panel and the display device is improved.

Owner:BOE TECH GRP CO LTD