NAND memory structure, NAND memory structure formation method and three dimensional memory array

A memory and multi-layer storage technology, which is applied in the field of information storage, can solve the problems of high process complexity and achieve the effects of low process complexity, reduction of channel aperture, and increase of integration density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

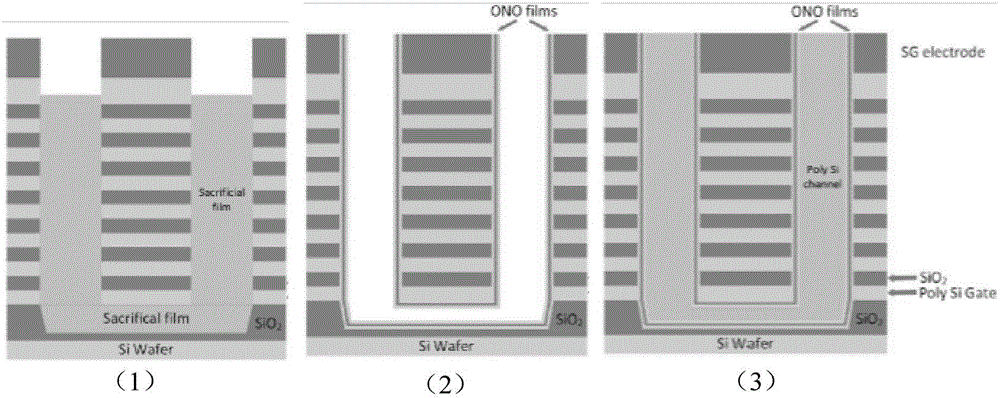

[0053] Embodiments of the present invention are described in detail below, examples of which are shown in the drawings, wherein the same or similar reference numerals designate the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary and are intended to explain the present invention and should not be construed as limiting the present invention.

[0054] A method for forming a NAND memory, a structure of a NAND memory and a method for forming the structure according to an embodiment of the present invention will be described below with reference to the accompanying drawings.

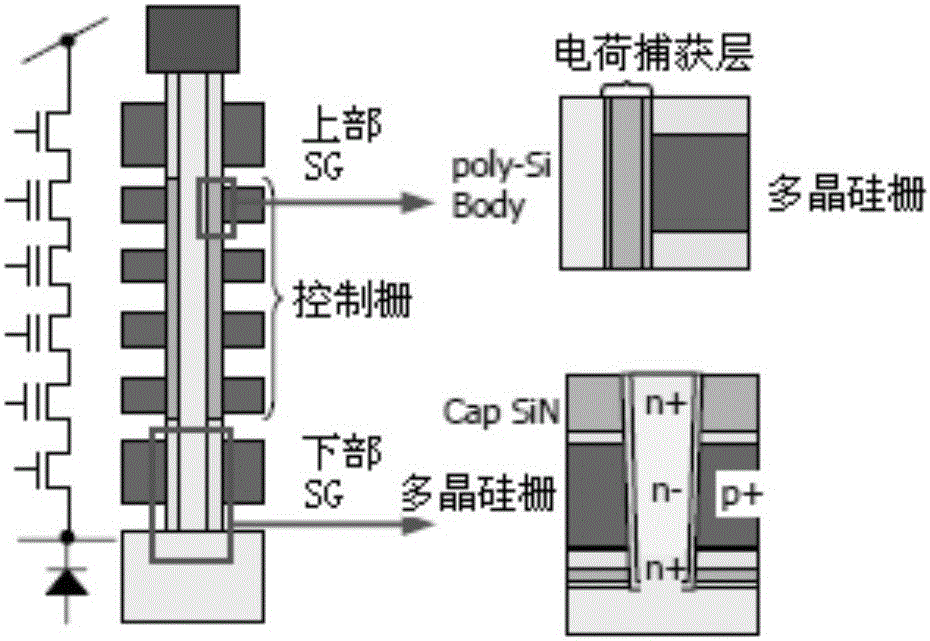

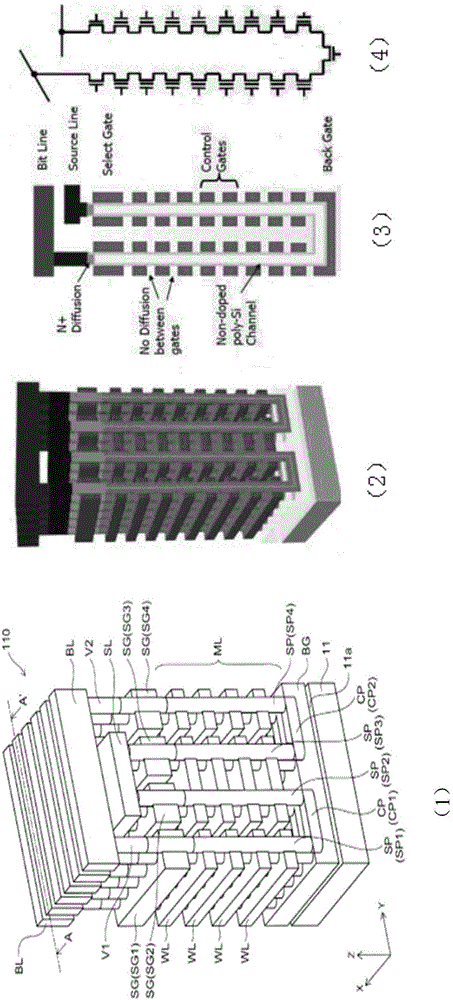

[0055] Figure 6 is a schematic diagram of the NAND memory structure according to an embodiment of the present invention, such as Figure 6 As shown, the NAND memory structure 100 includes a vertically stacked memory cell, a source select transistor and a bit line layer 400 (BL).

[0056] Among the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More