Patents

Literature

81results about How to "Prevent electrical short circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

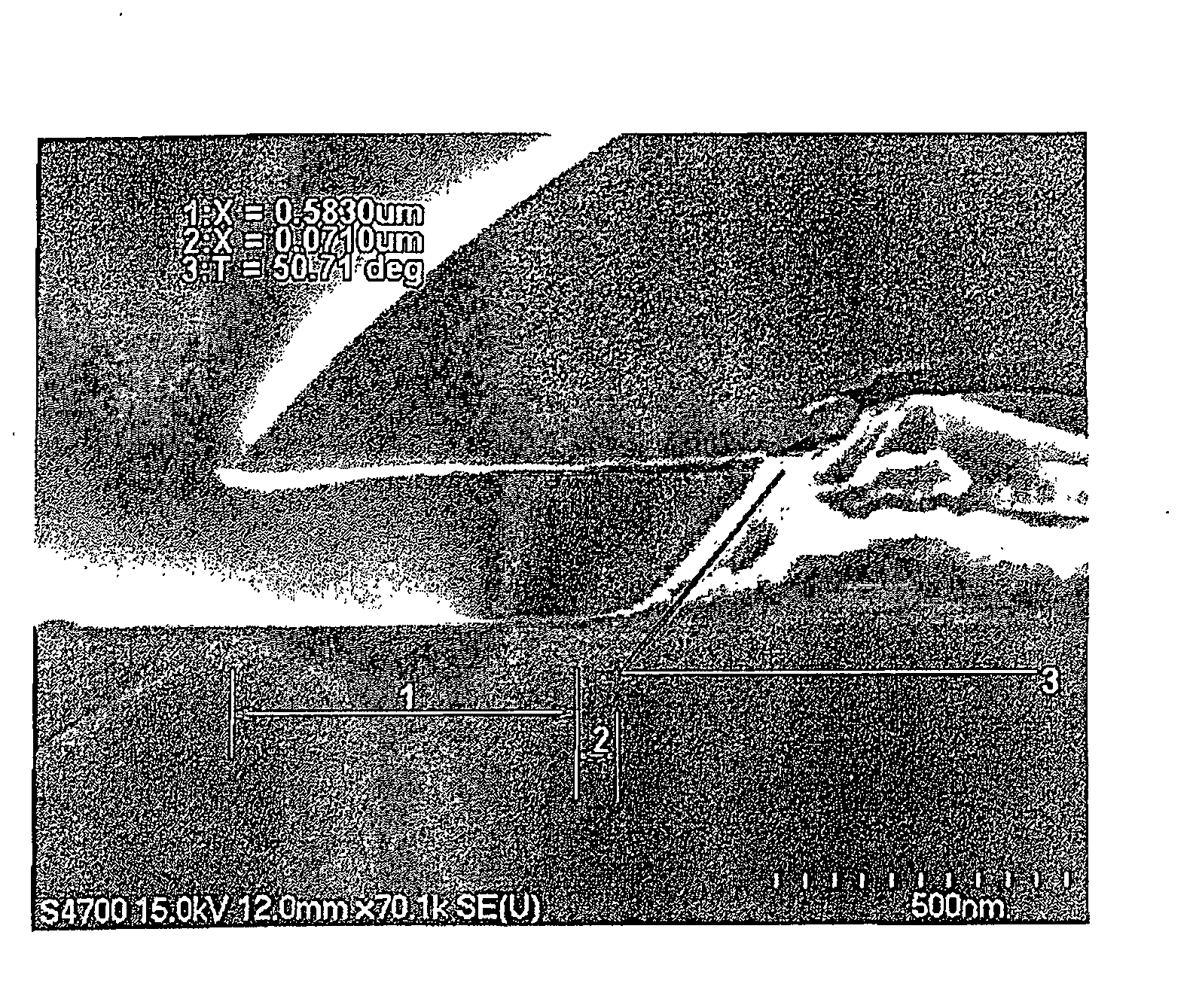

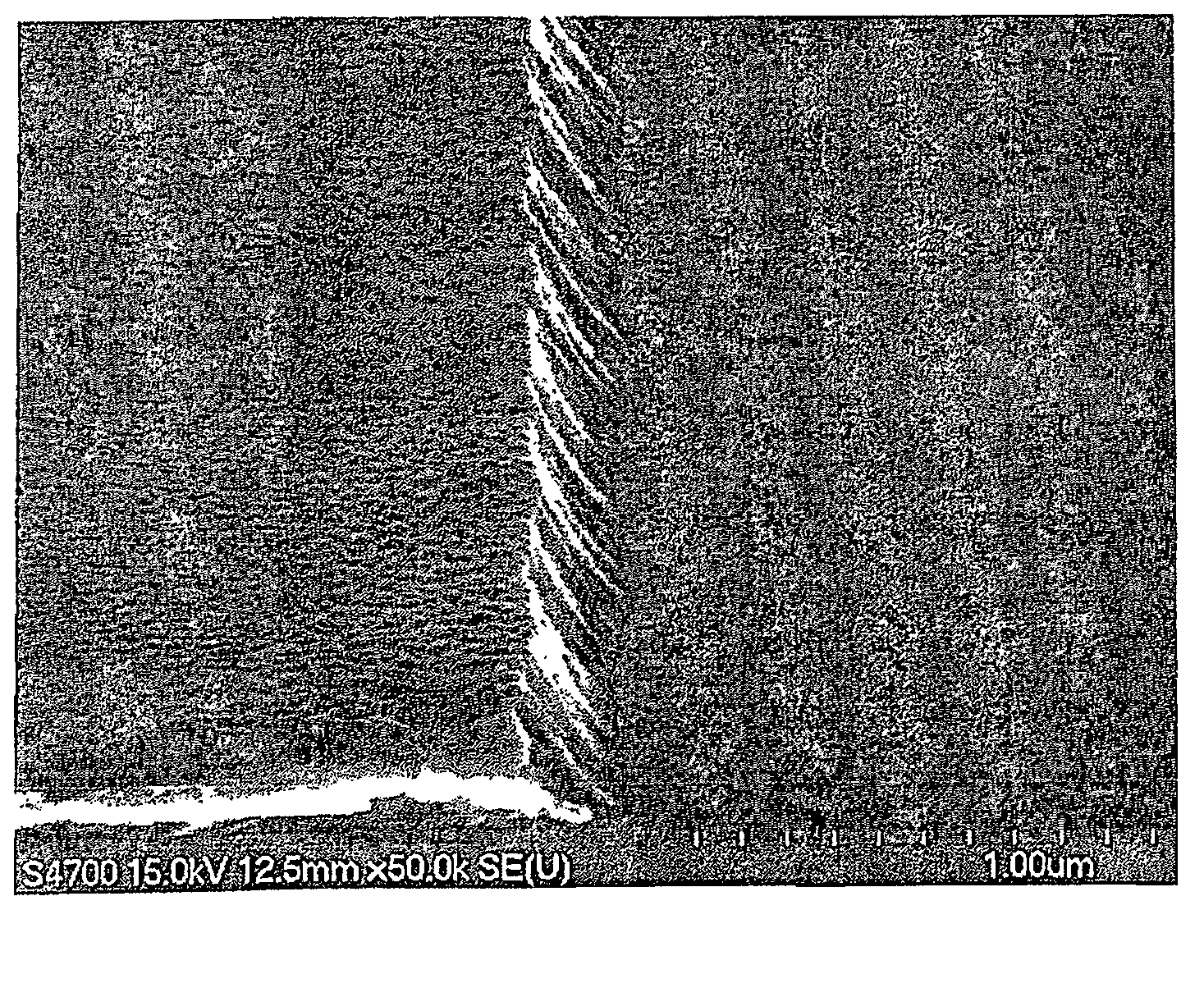

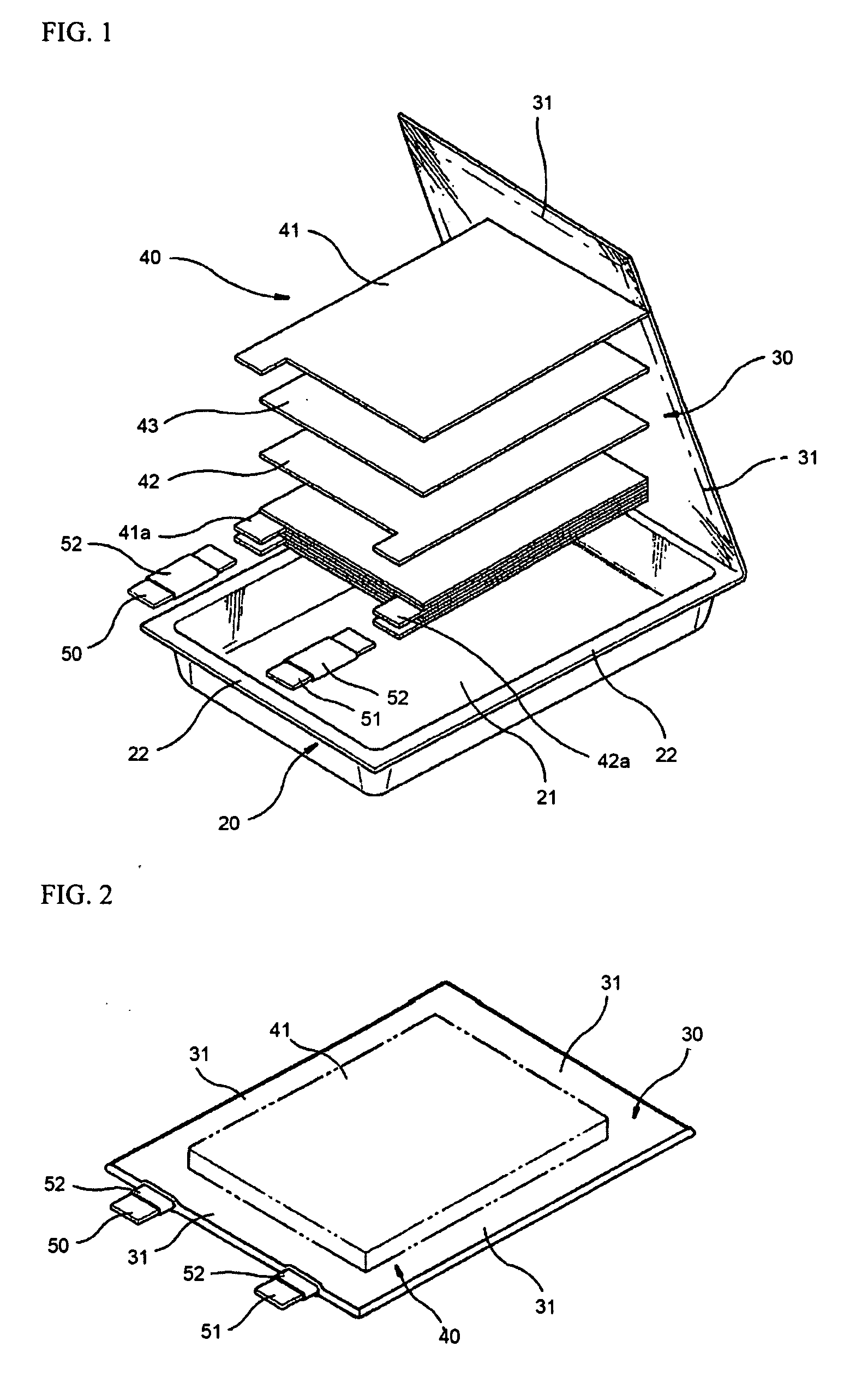

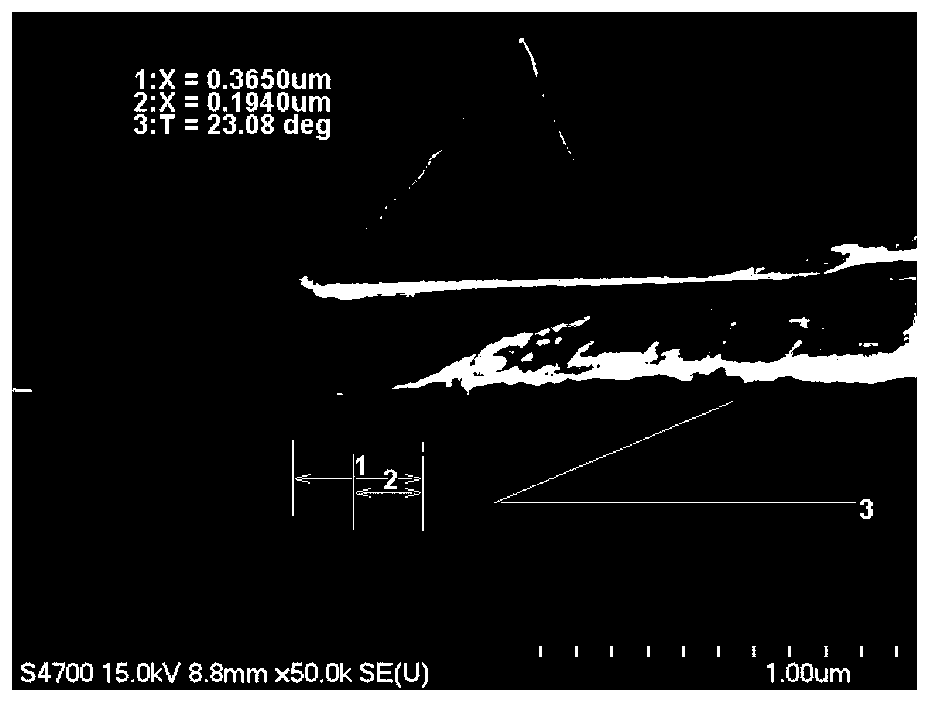

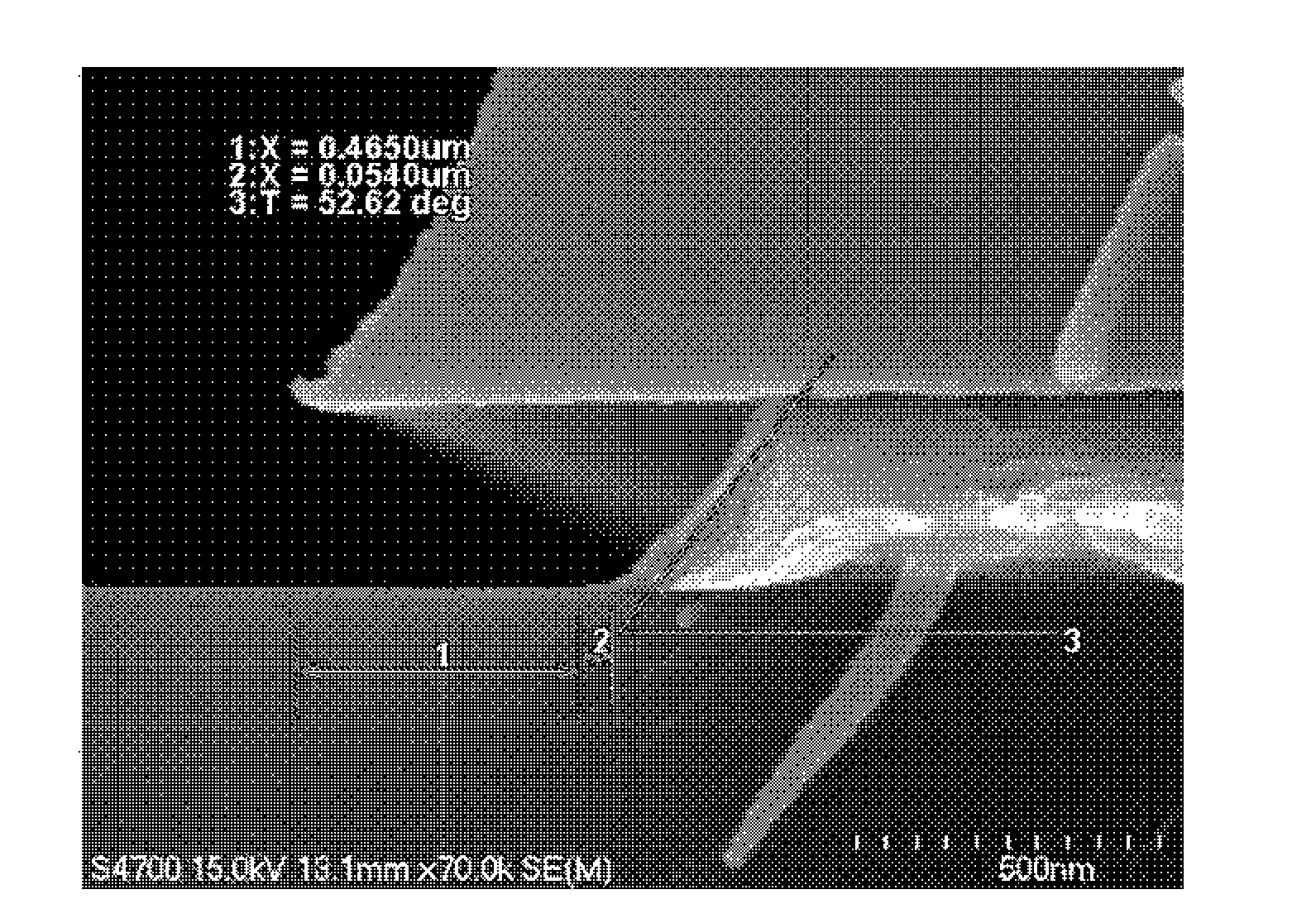

Organic/inorganic composite separator having porous active coating layer and electrochemical device containing the same

ActiveCN101542777AAvoid separationPrevent electrical short circuitSolid electrolytesLi-accumulatorsPorous substratePolyolefin

Owner:LG ENERGY SOLUTION LTD +1

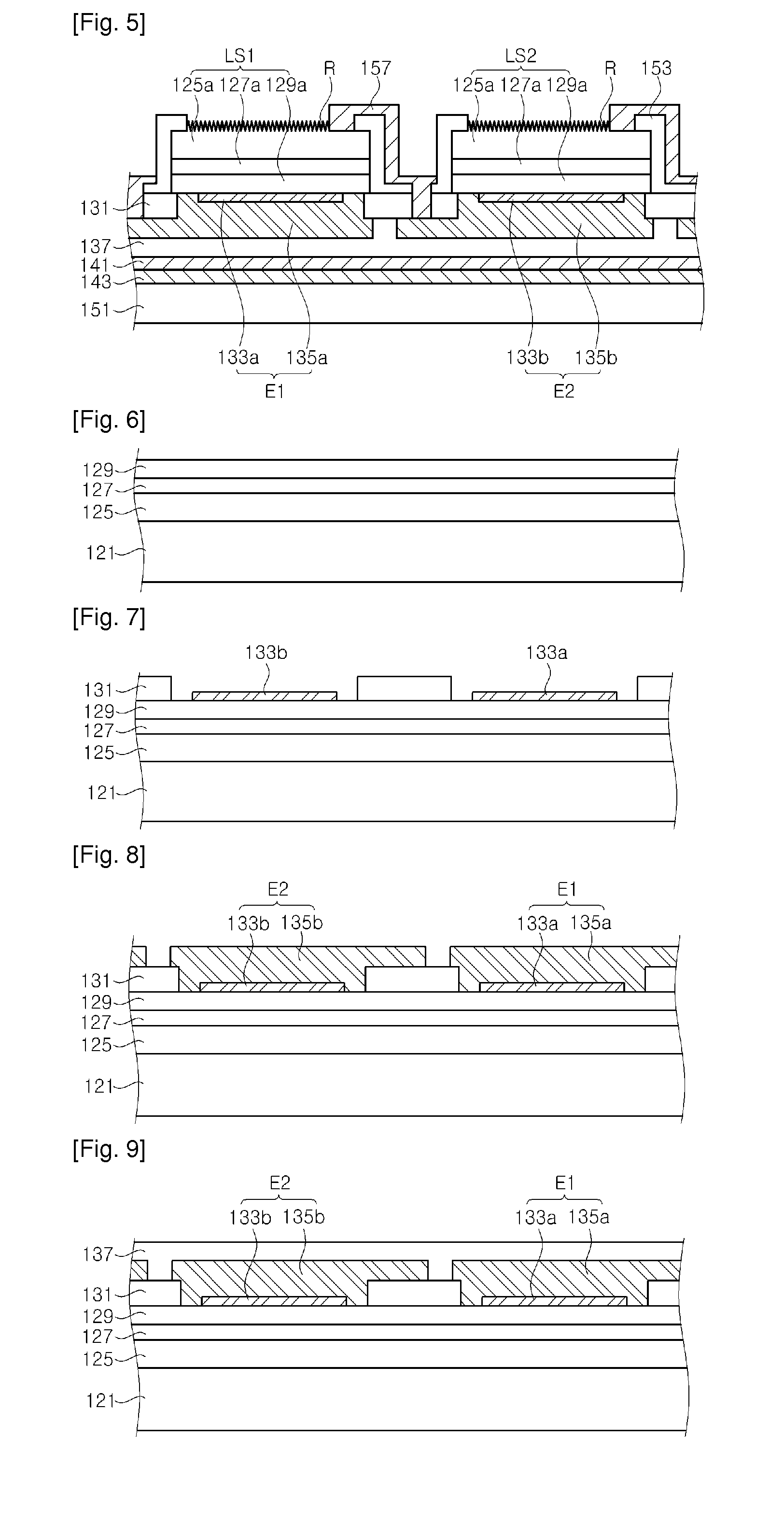

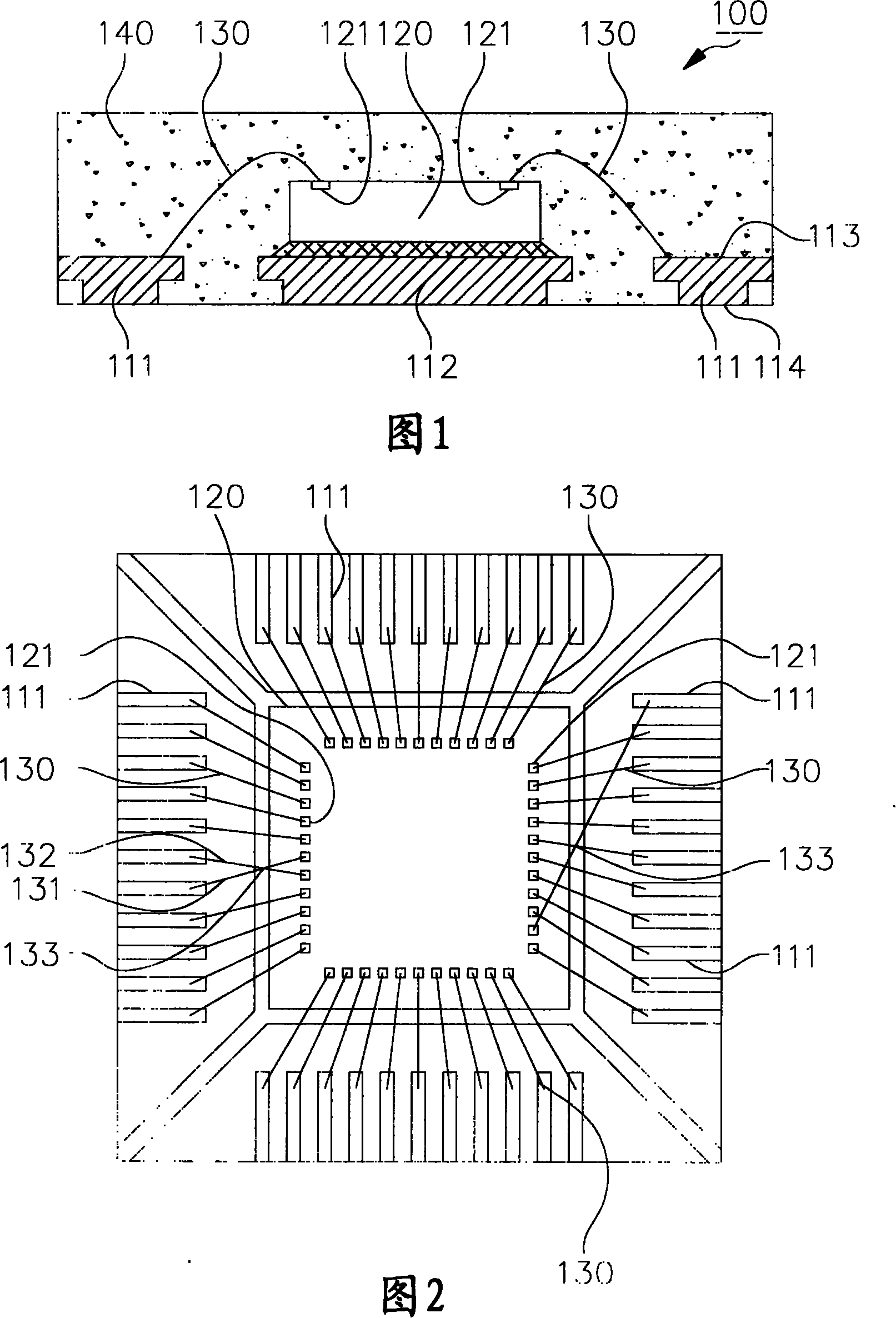

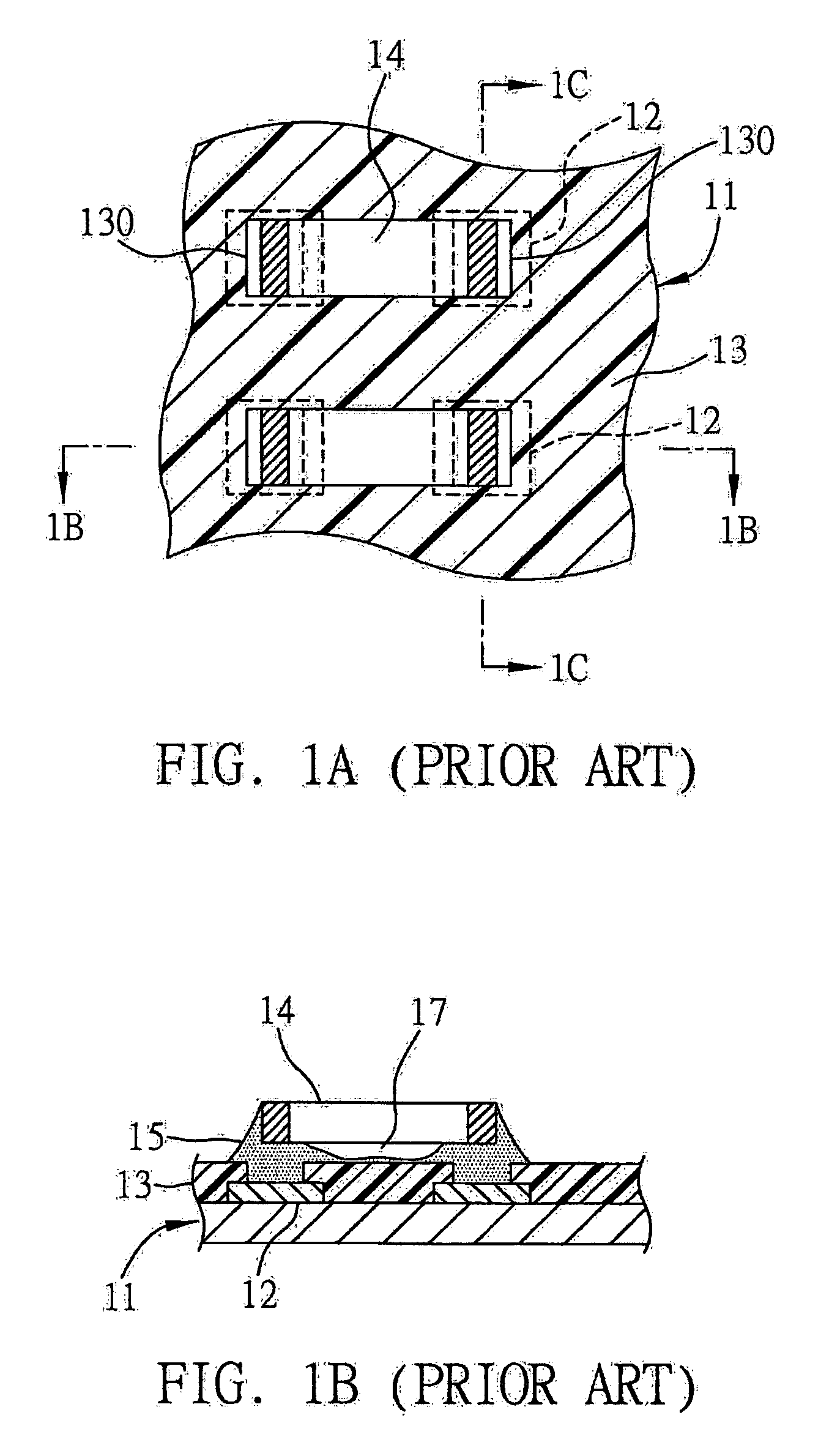

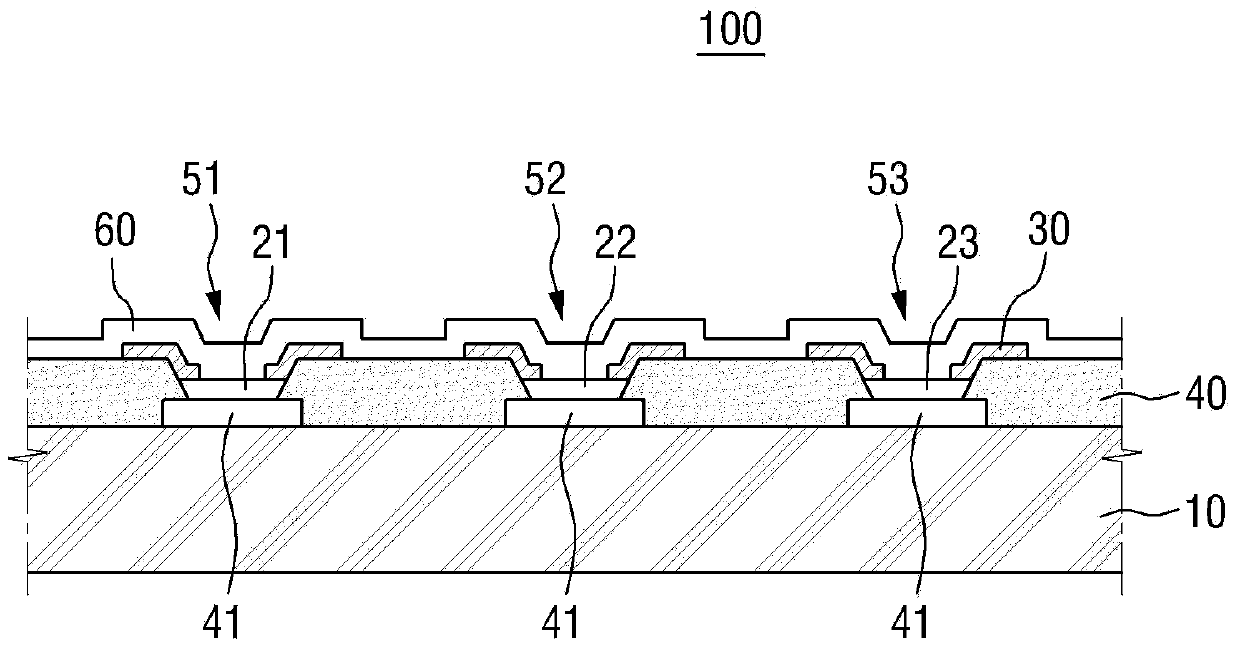

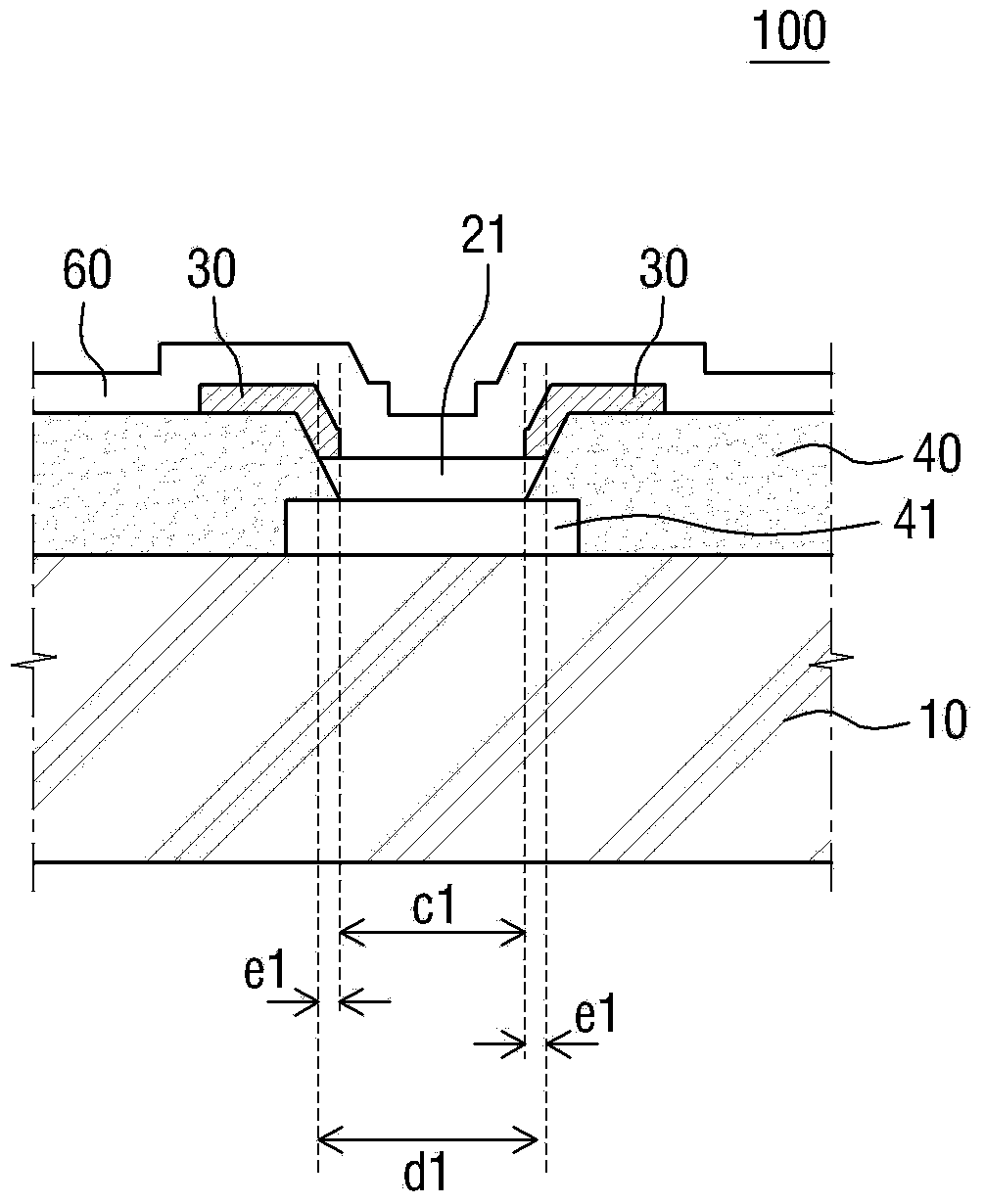

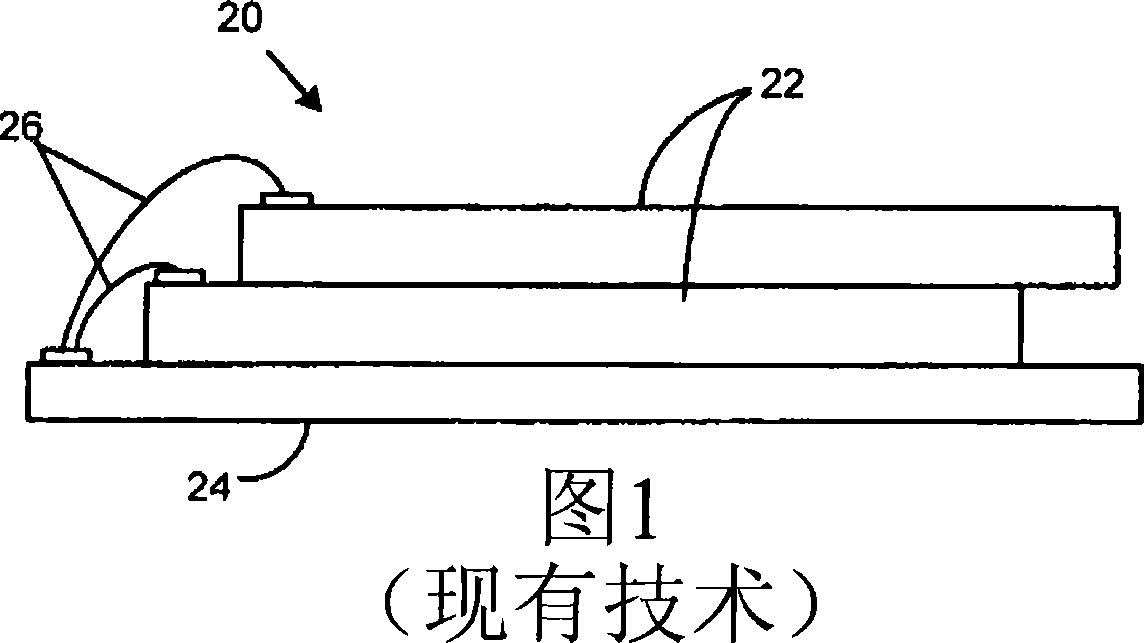

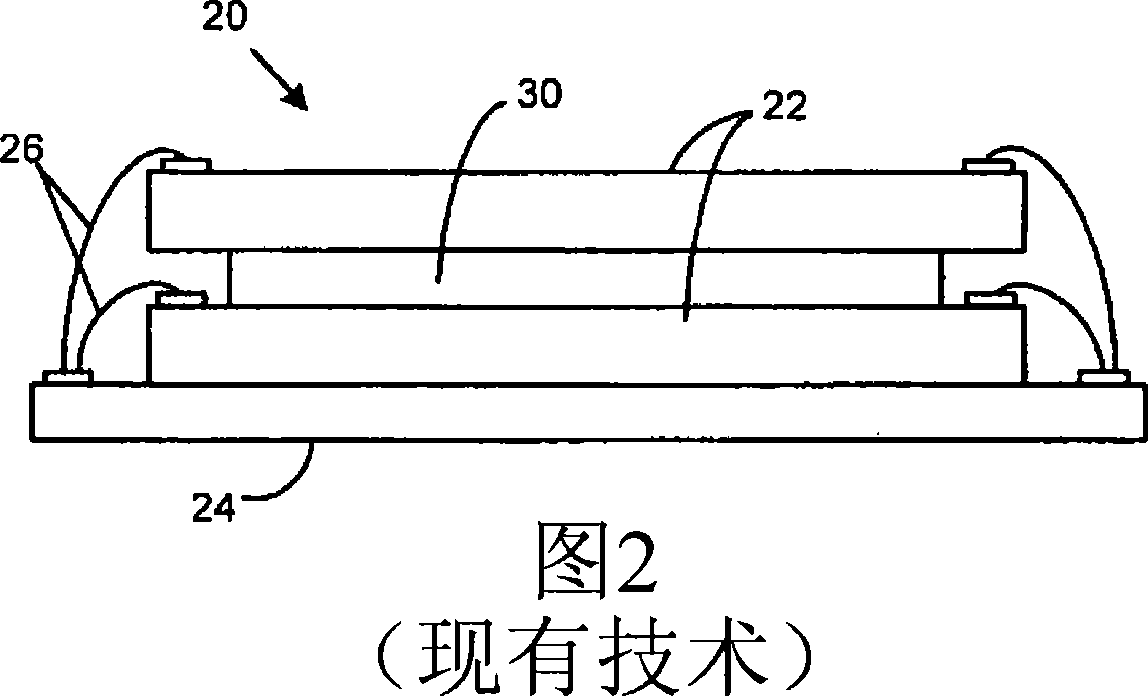

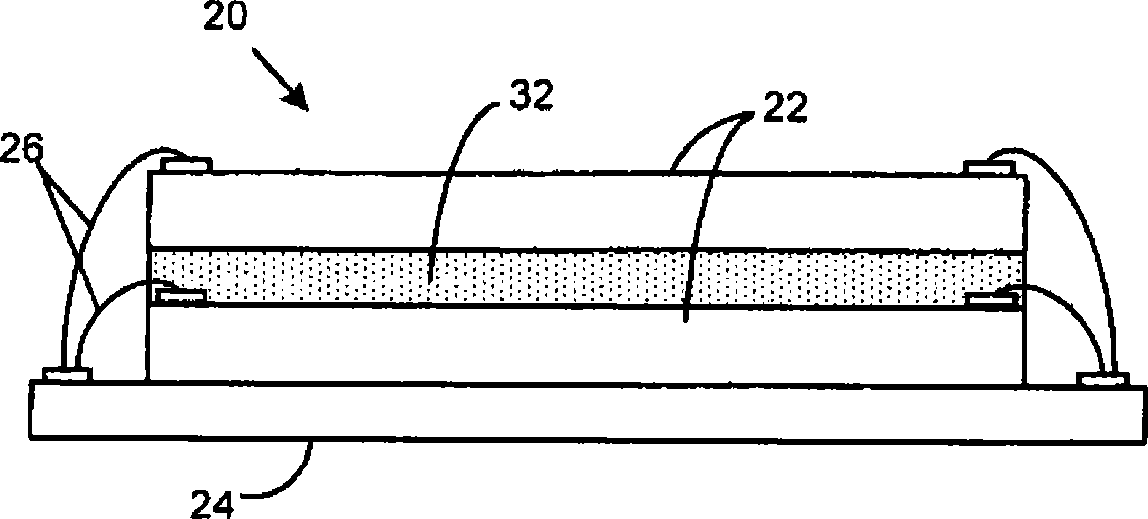

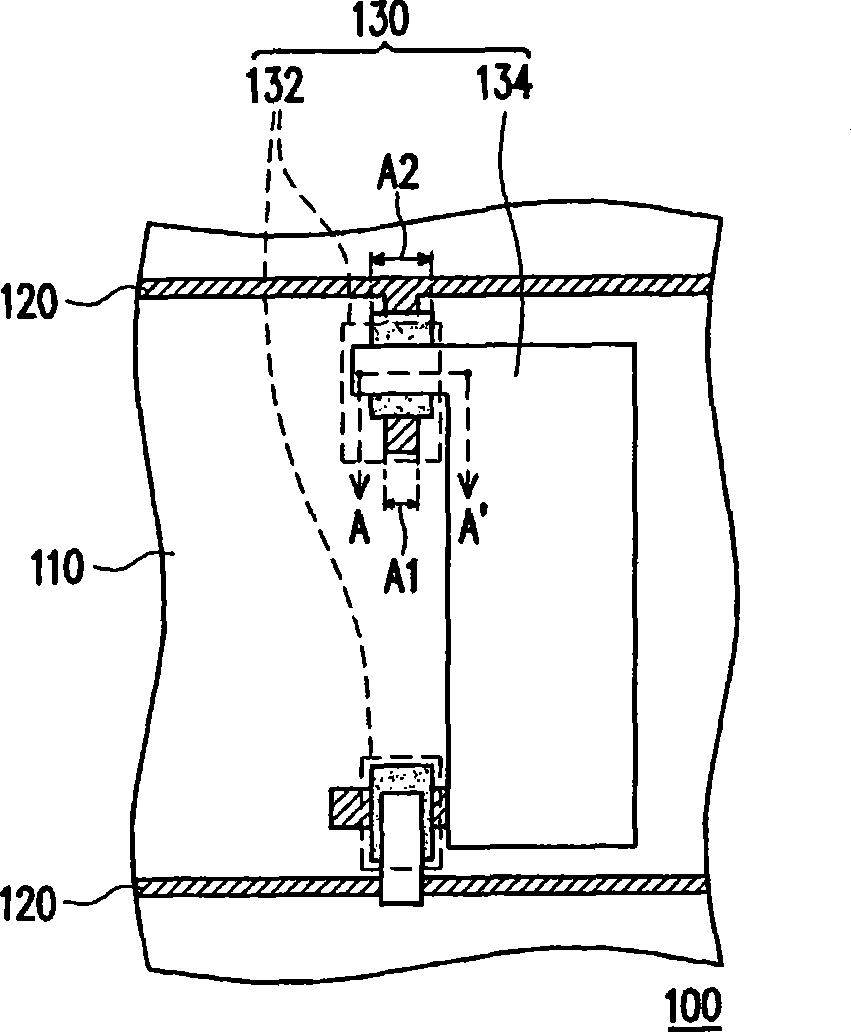

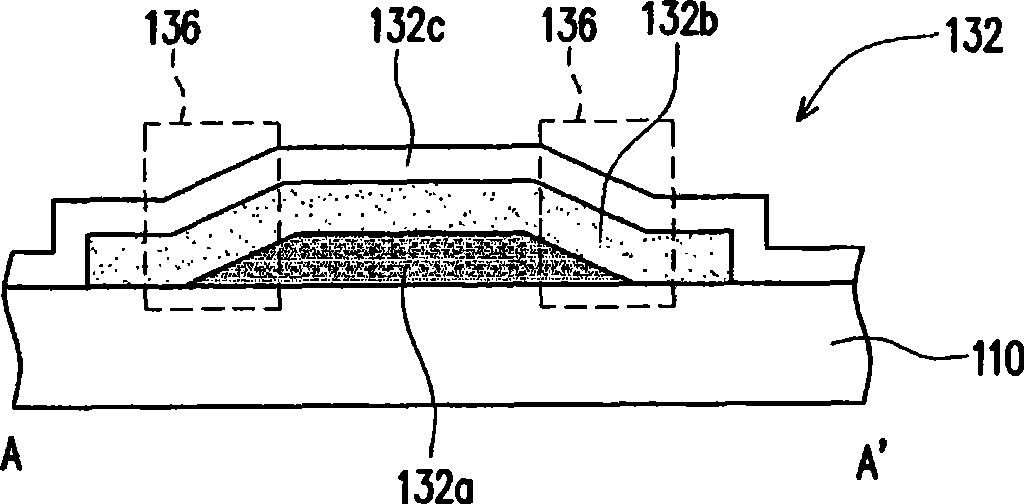

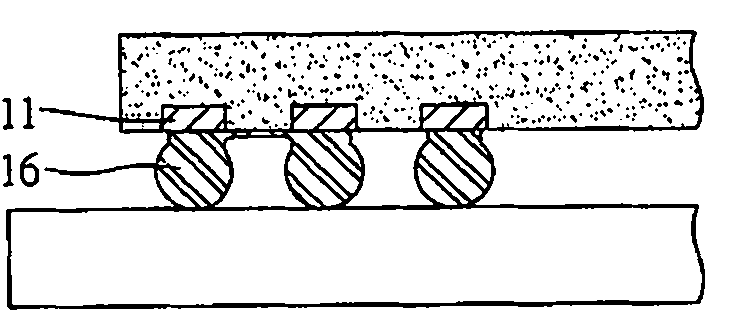

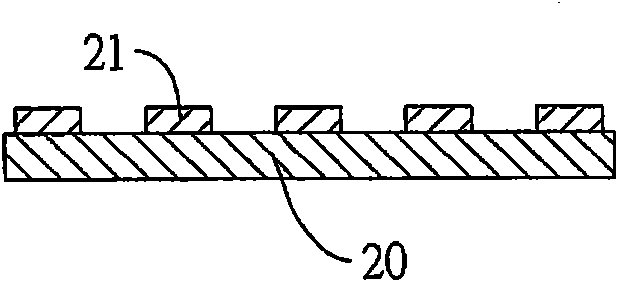

Light emitting device having plurality of light emitting cells and method of fabricating the same

ActiveUS20110297972A1Prevent electrical short circuitEvenly distributedSolid-state devicesSemiconductor devicesLight CellLight-emitting diode

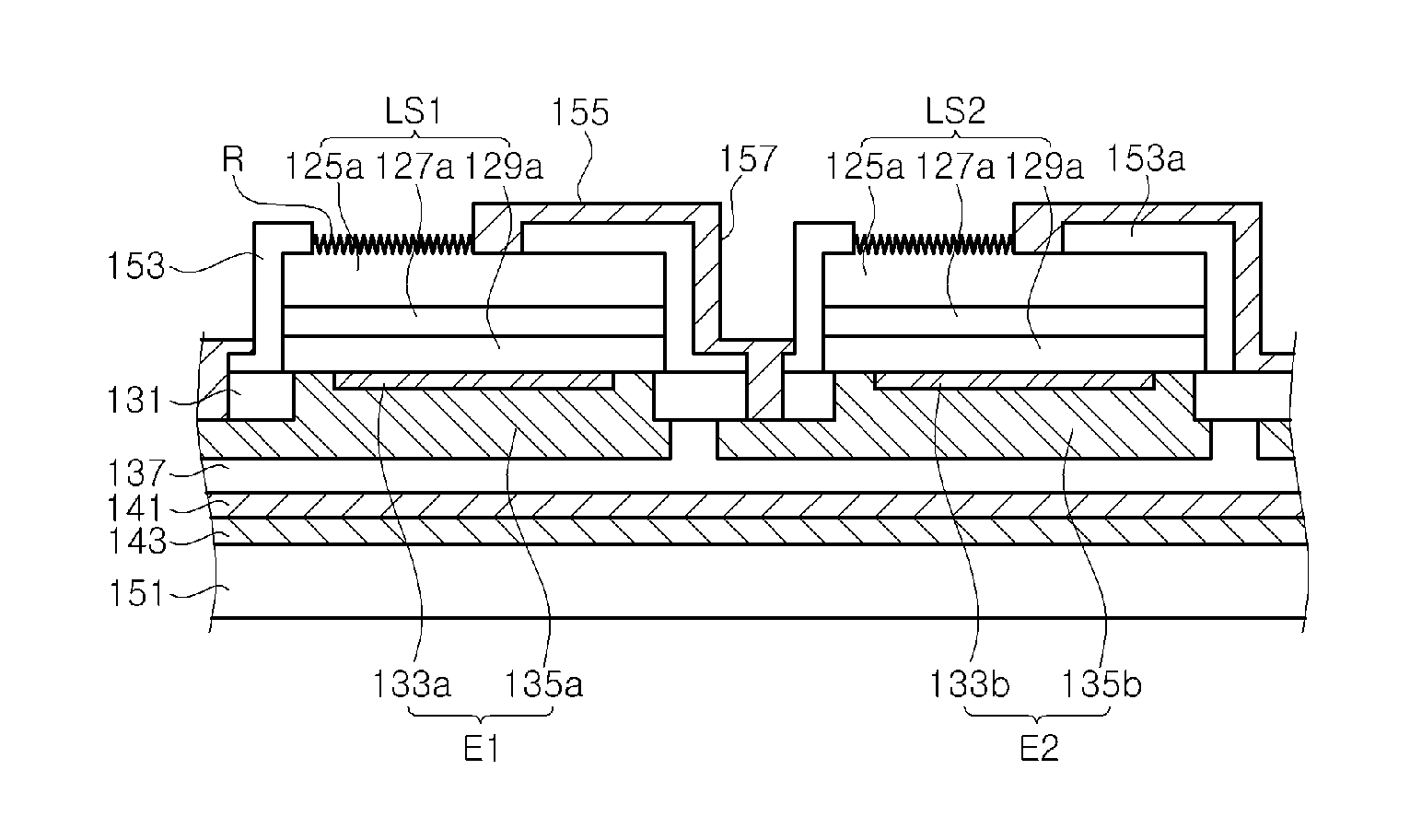

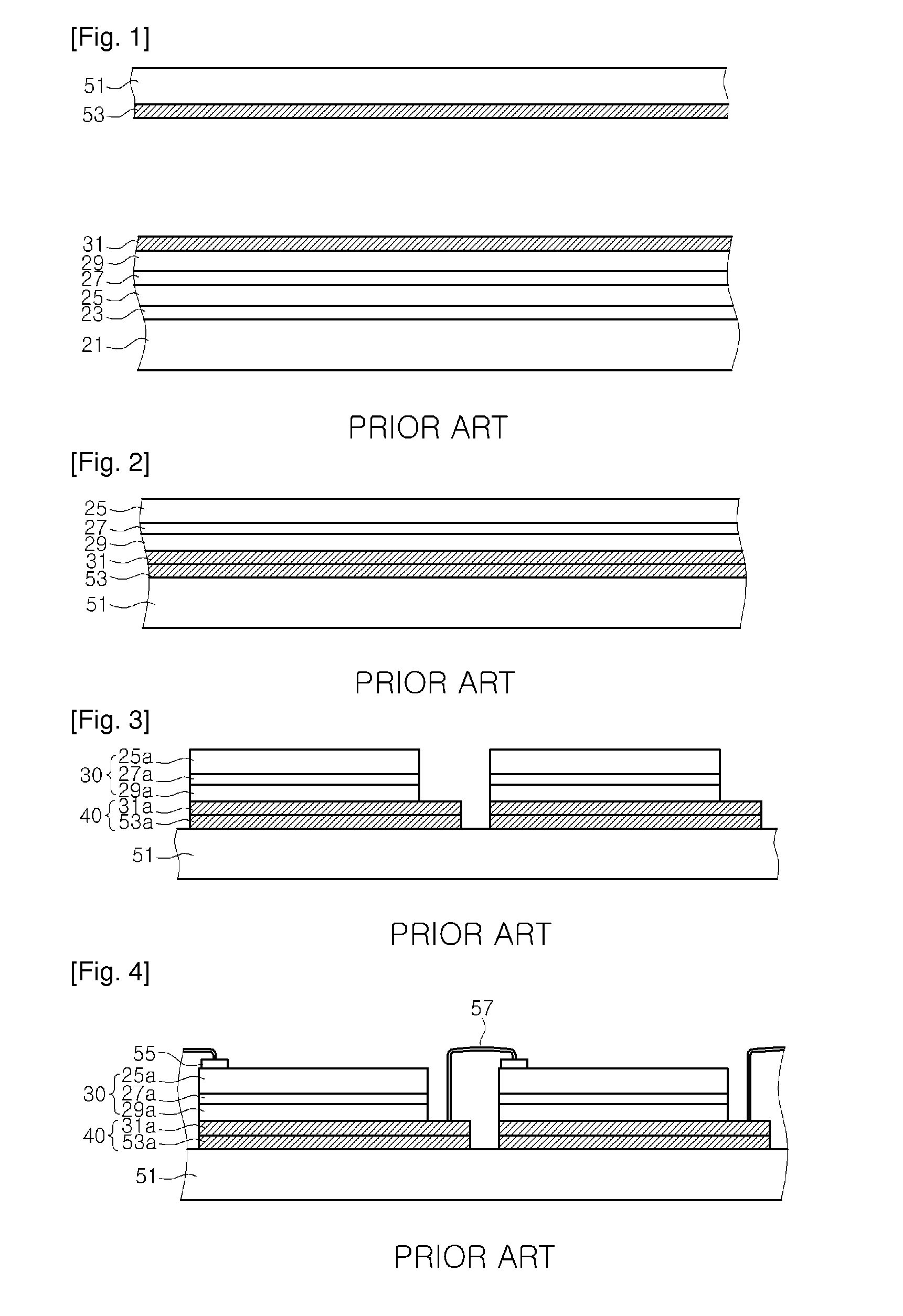

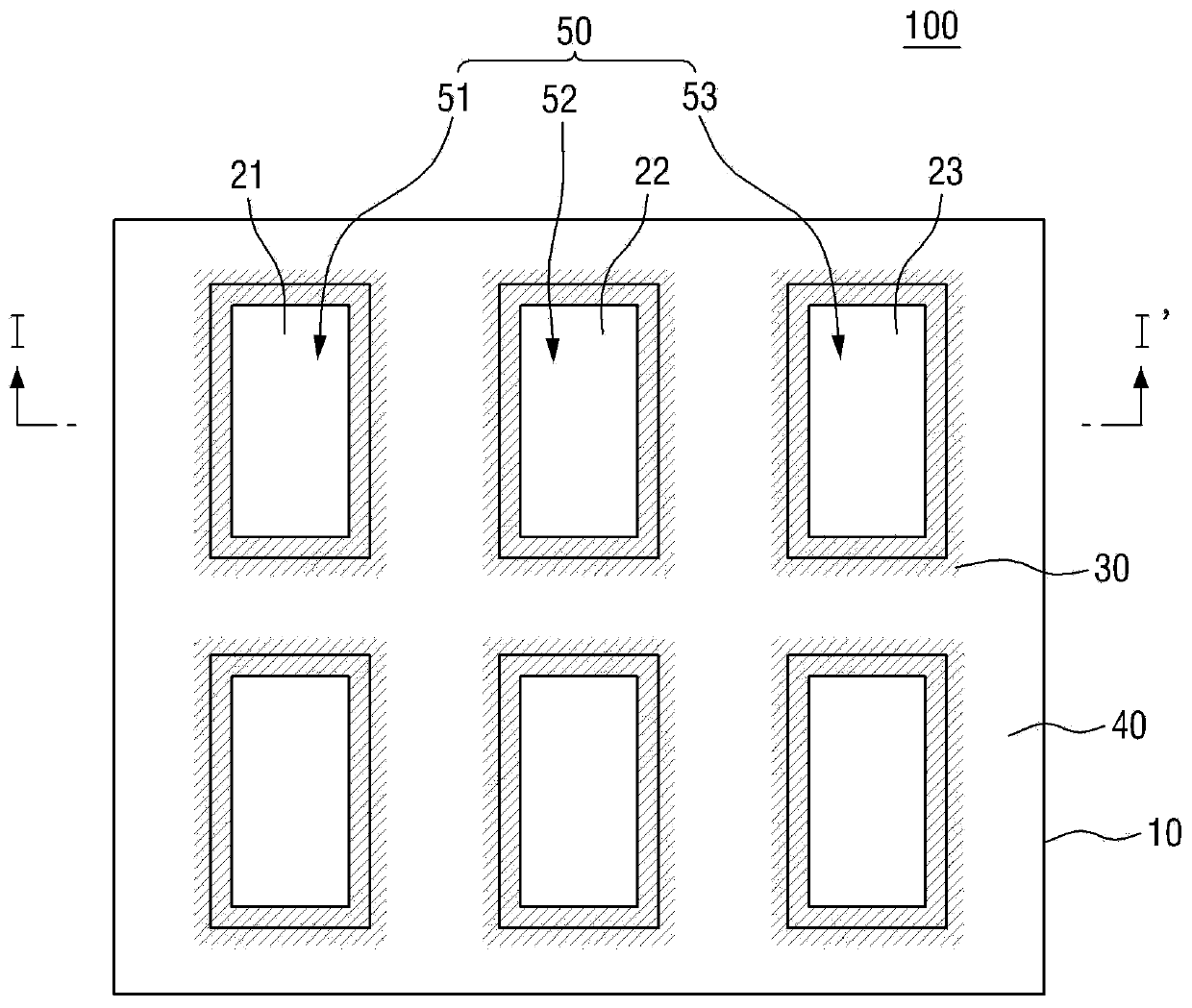

A light emitting device having a plurality of light emitting cells is disclosed. The light emitting device comprises a substrate; a plurality of light emitting cells positioned on the substrate to be spaced apart from one another, each of the light emitting cells comprising a p-type lower semiconductor layer, an active layer and an n-type upper semiconductor layer; p-electrodes positioned to be spaced apart from one another between the substrate and the light emitting cells, the respective p-electrodes being electrically connected to the corresponding lower semiconductor layers, each of the p-electrodes having an extension extending toward adjacent one of the light emitting cells; n-electrodes disposed on upper surfaces of the respective light emitting cells, wherein a contact surface of each of the n-electrodes electrically contacting with each light emitting cell exists both sides of any straight line that bisects the light emitting cell across the center of the upper surface of the light emitting cell; a side insulating layer for covering sides of the light emitting cells; and wires for connecting the p-electrodes and the n-electrodes, the wires being spaced apart from the sides of the light emitting cells by the side insulating layer.

Owner:SEOUL SEMICONDUCTOR

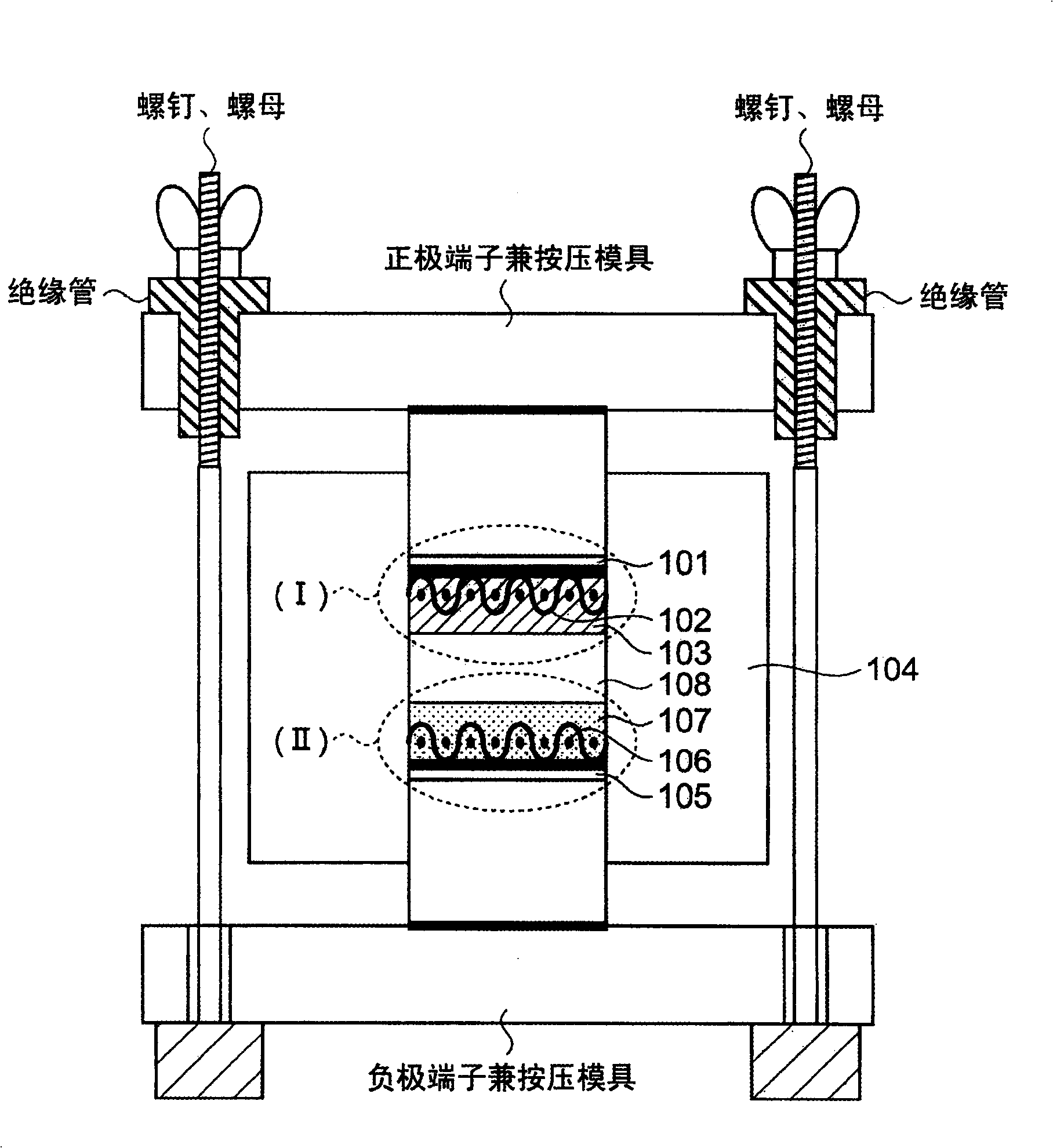

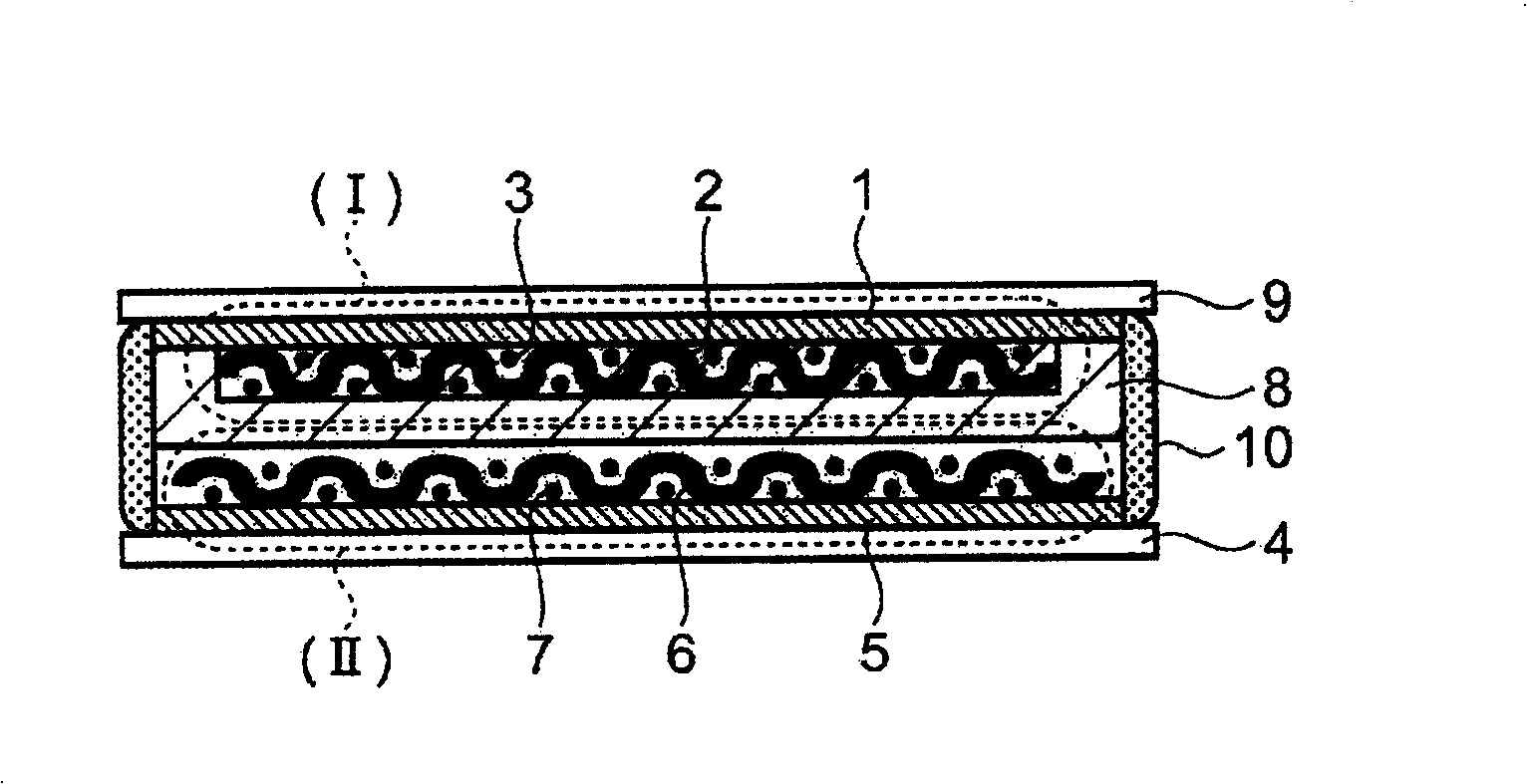

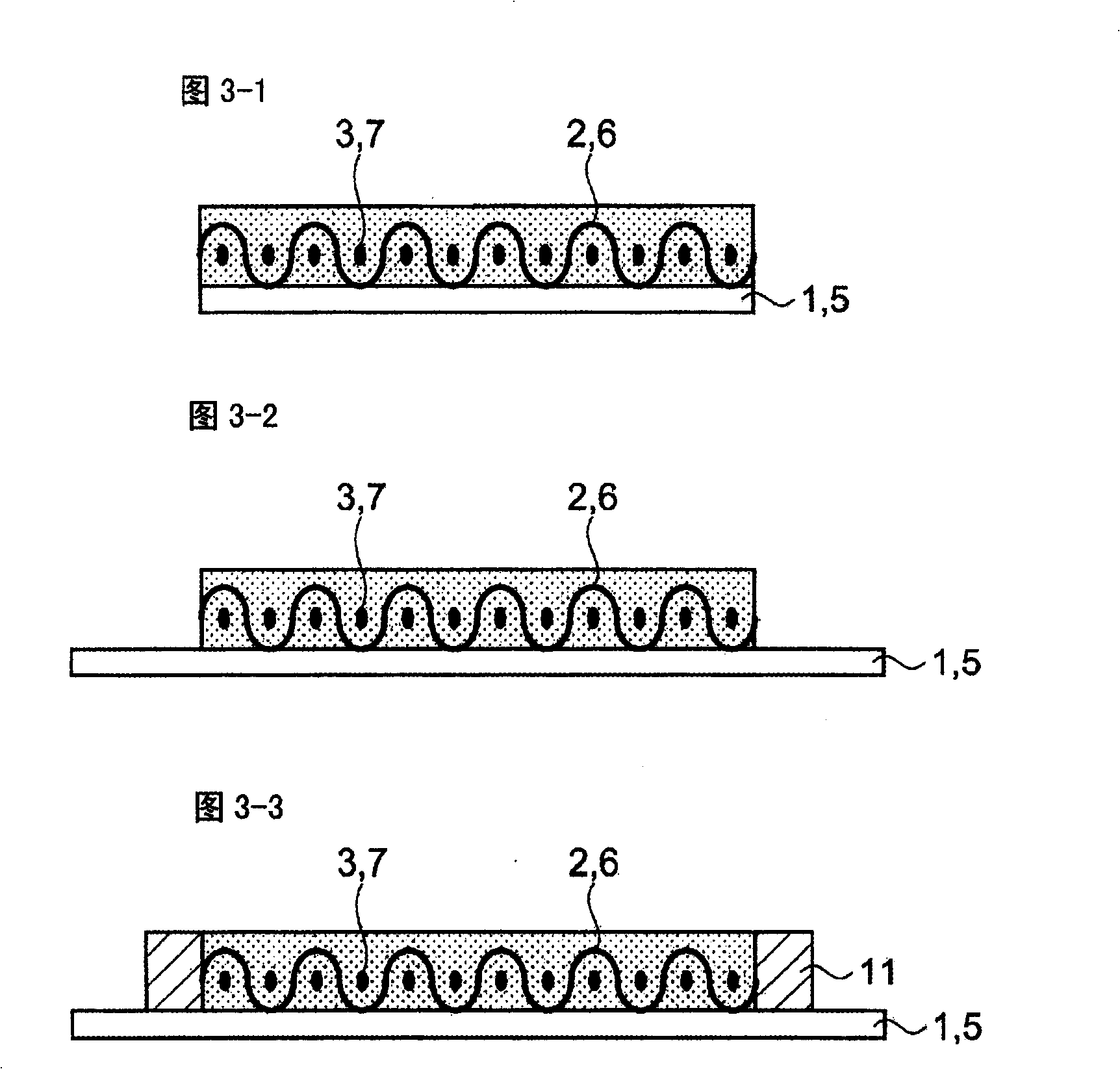

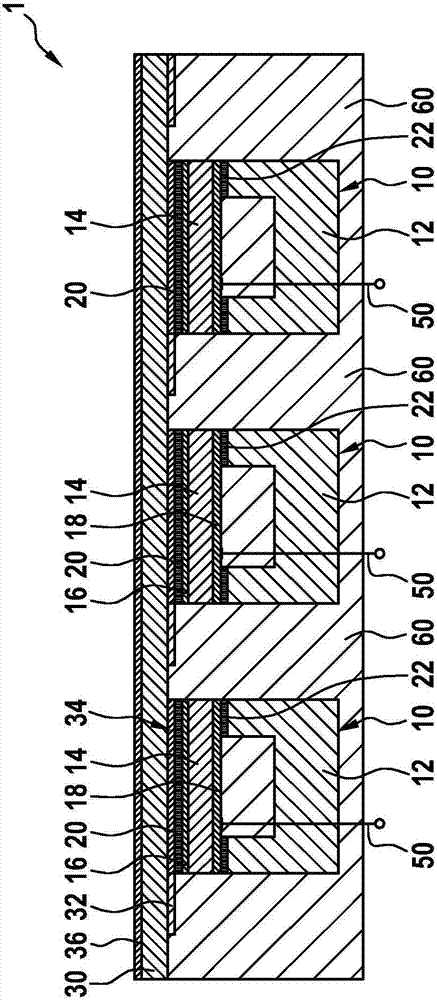

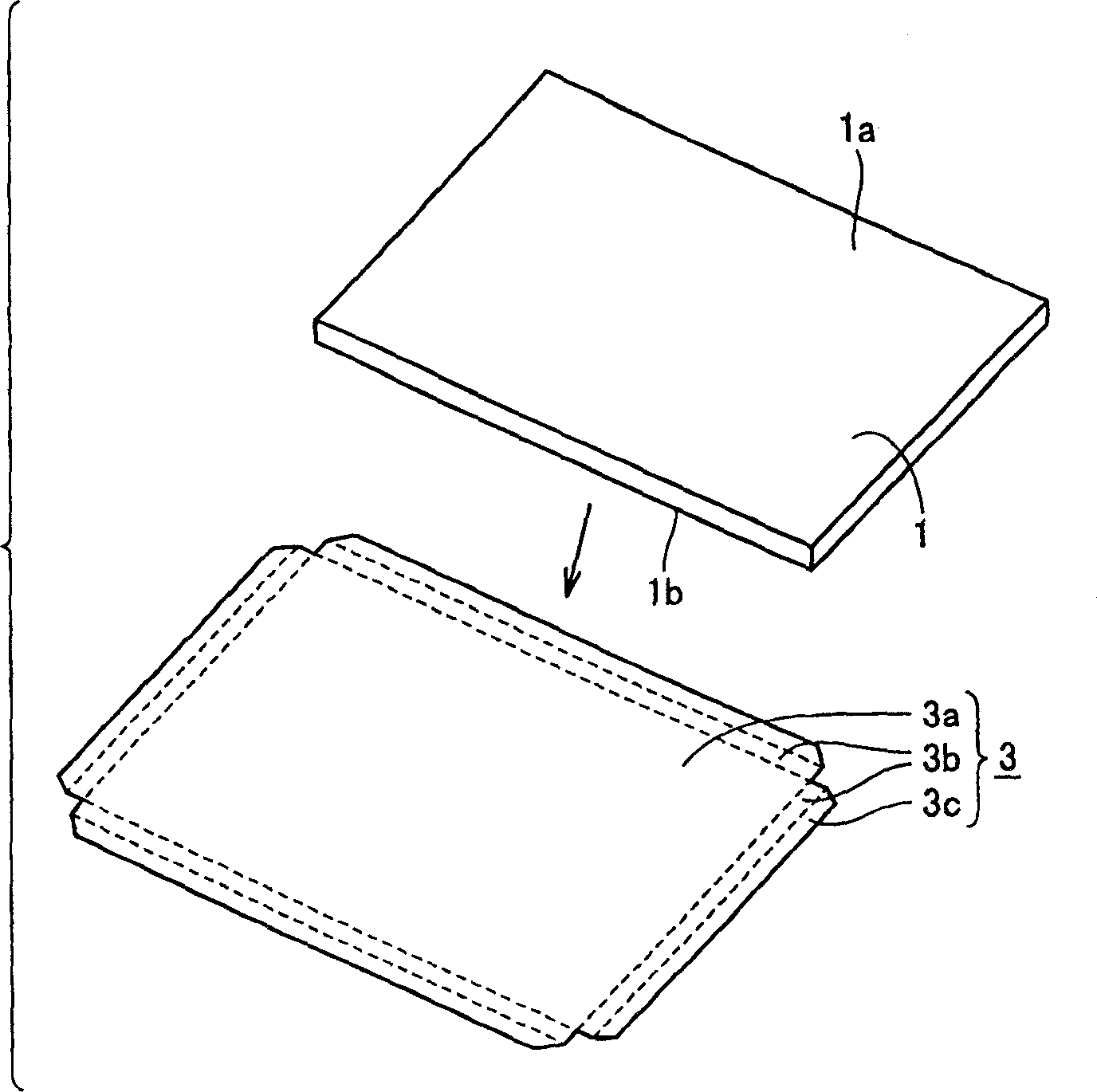

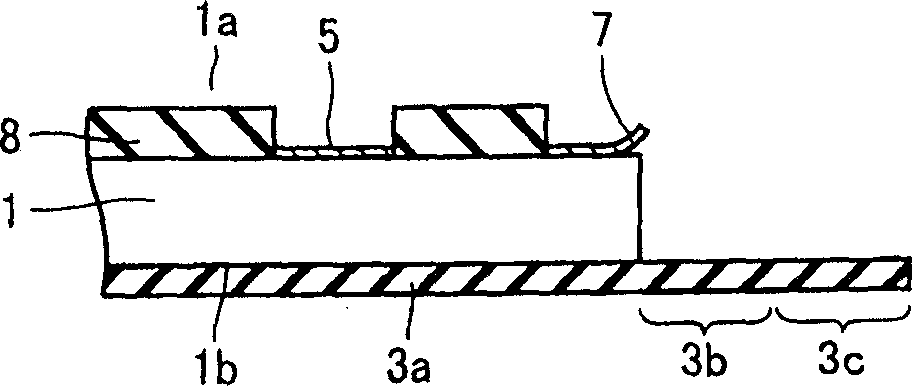

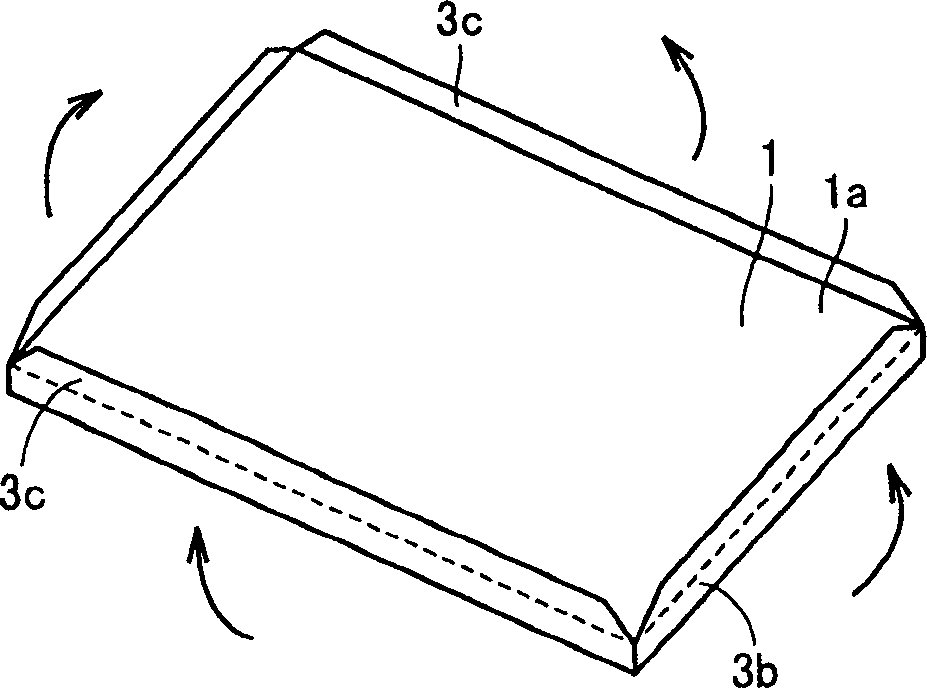

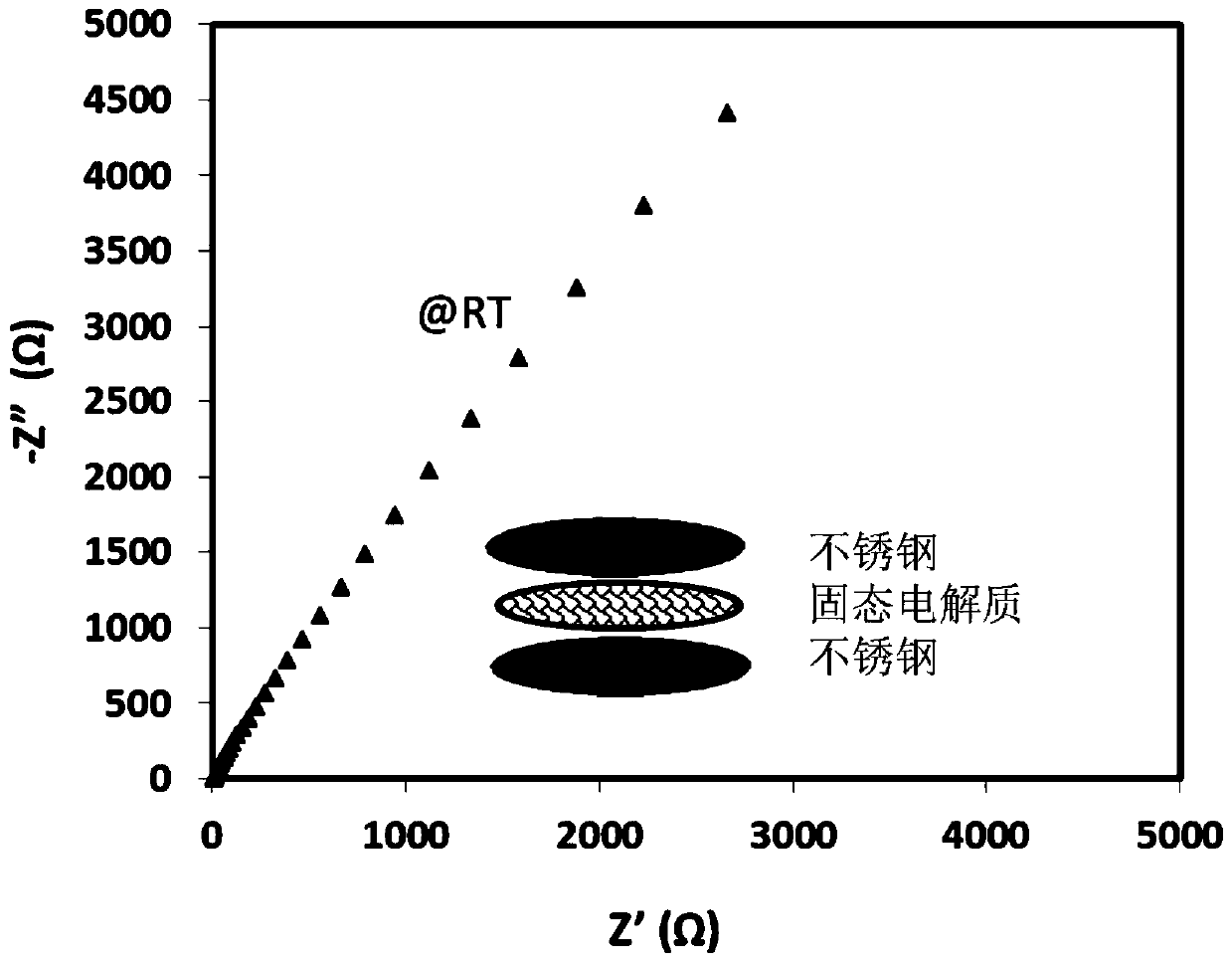

Sulfide-based lithium-ion-conducting solid electrolyte glass, all-solid lithium secondary battery, and method for manufacturing all-solid lithium secondary battery

InactiveCN101494299APrevent precipitationPromote precipitationNon-metal conductorsCell electrodesVitrificationLithium

The present invention discloses a all-solid lithium secondary battery that has large chare and discharge output current denseness and excellent charge and discharge cycle life which can be easily manufactured at low cost. In the manufacturing process of the all-solid lithium secondary battery, a new lithium ion conductor with ionic conduction improved can be obtained through vitrification to mixed electrolytes by mixing Alpha-oxide of alumina in various sulfide system lithium ion conductivity solid electrolyte. The electrolytes layer 8 used the lithium ion conductor, and positive and negative electrode (I), (II) are formed by positive and negative electrode material 3, 7 are constituted. Subsequently, cascading at least 1 layer in positive and negative electrode (I), (II) with electrolytes layer, and producing battery while electrolytes not crystallizes by heating and compressing as a whole.

Owner:SEIKO EPSON CORP

Method for preparing array substrate for liquid crystal display device

ActiveCN103052907AEnvironmental friendlyPrevent poor wiringSolid-state devicesNon-linear opticsCrystallographyOrganic acid

The present invention relates to preparation method for an array substrate for the use in a liquid crystal display device, using an etchant composition comprising: a) 5-25 wt% of hydrogen peroxide (H2O2); b) 0.1-5 wt% of an organic acid; c) 0.1-5 wt% of a phosphate compound; d) 0.1-5 wt% of a water-soluble cyclic amine compound; e) 0.1-5 wt% of a water-soluble compound having a nitrogen atom and a carboxyl group in a molecule; f) 0.01-1.0 wt% of a fluorine-containing compound; g) 0.001-5 wt% of a polyhydric alcohol-based surfactant; and h) the balance of water based on the total weight of the composition.

Owner:DONGWOO FINE CHEM CO LTD

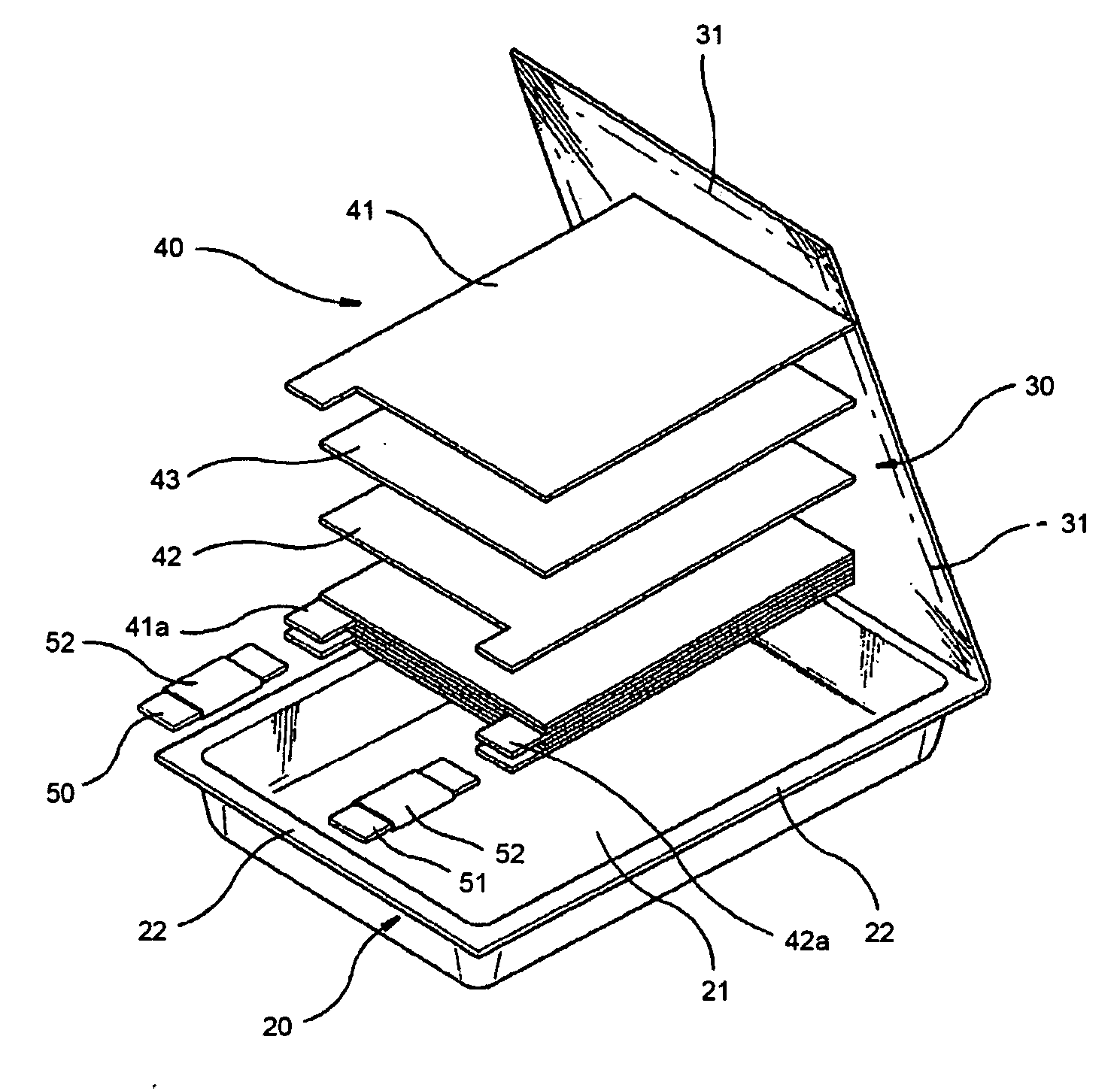

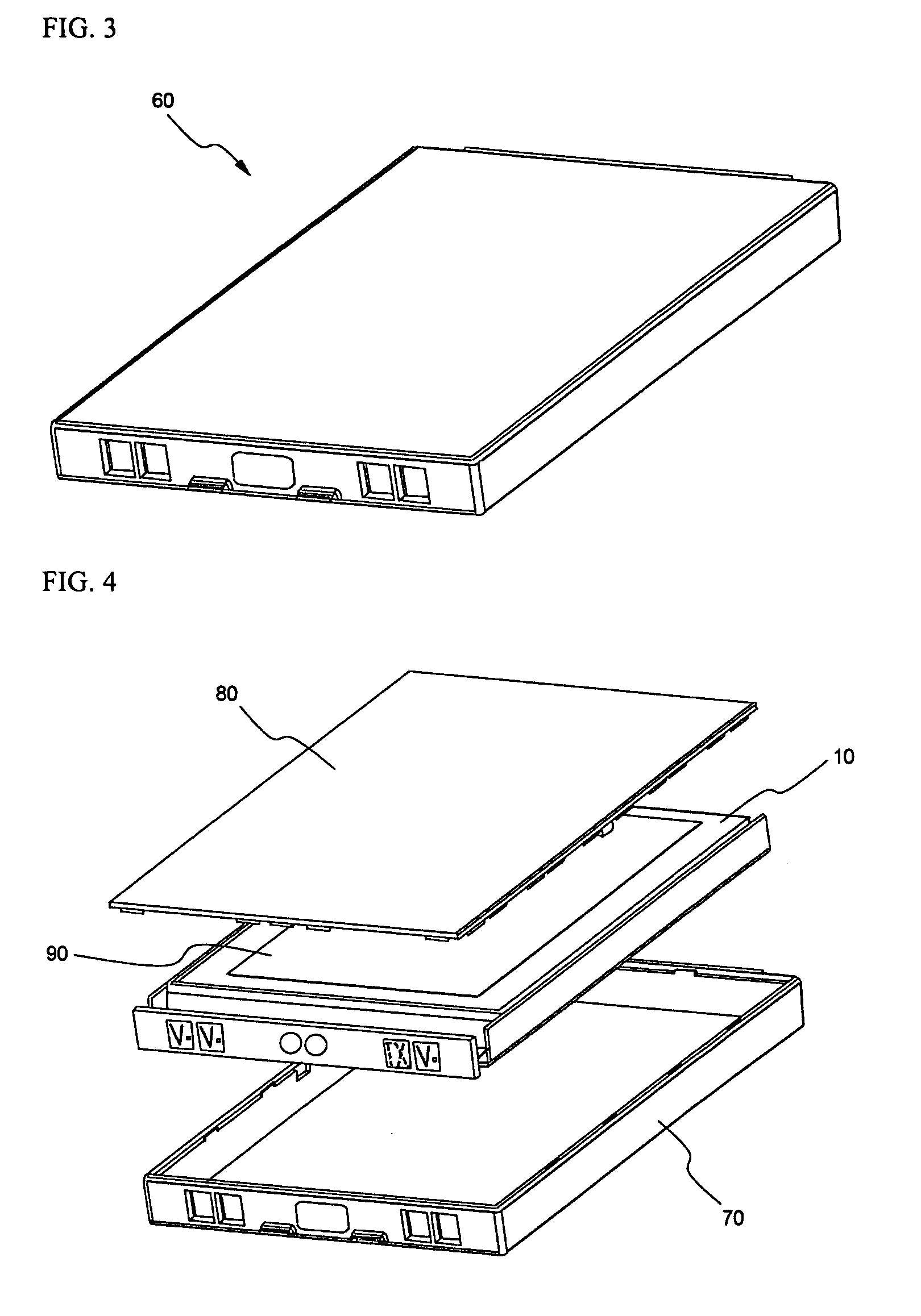

Battery pack of improved stability

ActiveUS20060199075A1Simplify the assembly processLower battery costsFinal product manufactureBattery isolationBattery packElectrolyte

Disclosed herein is a battery pack wherein a rectangular battery having an electrode assembly and an electrolyte contained therein in a sealed state is received in a pack case, and an insulating material is filled in a space defined between the inner surface of the upper end of the pack case and the upper end of the battery, whereby the battery pack is manufactured with a reduced thickness, the assembly process of the battery pack is very simple, and short circuit of the battery pack or suspension of power supply from the battery pack, which may occur as the battery is moved, is effectively prevented even when the battery pack falls down or external impacts are applied to the battery pack.

Owner:LG ENERGY SOLUTION LTD

Manufacturing method of array substrate for liquid crystal display

ActiveCN102983101AImprove straightnessAchieving Etch UniformitySemiconductor/solid-state device manufacturingNon-linear opticsLiquid-crystal displayInsulation layer

The invention relates to a manufacturing method of an array substrate for a liquid crystal display, and the method comprises steps of: a) forming a grid on the substrate; b) forming a gate insulation layer on the substrate comprising the grid; c) forming a semiconductor layer on the gate insulation layer; d) forming a source electrode / drain electrode on the semiconductor layer; and e) forming a pixel electrode connected with the drain electrode; the step a) comprises steps of: forming a copper based metal film on the substrate, a multi-layer of a copper based metal layer and a metal oxide film, or a multi-layer of a copper based metal layer and a molybdo-based metal layer; and etching the film to form the grid through etching agent composition; the step d) comprises steps of: forming a copper based metal layer on the semiconductor, a multi-layer of a copper based metal layer and a metal oxide film, or a multi-layer of a copper based metal layer and a molybdo-based metal layer; and etching the film to from the source electrode / drain electrode through the etching agent composition.

Owner:DONGWOO FINE CHEM CO LTD

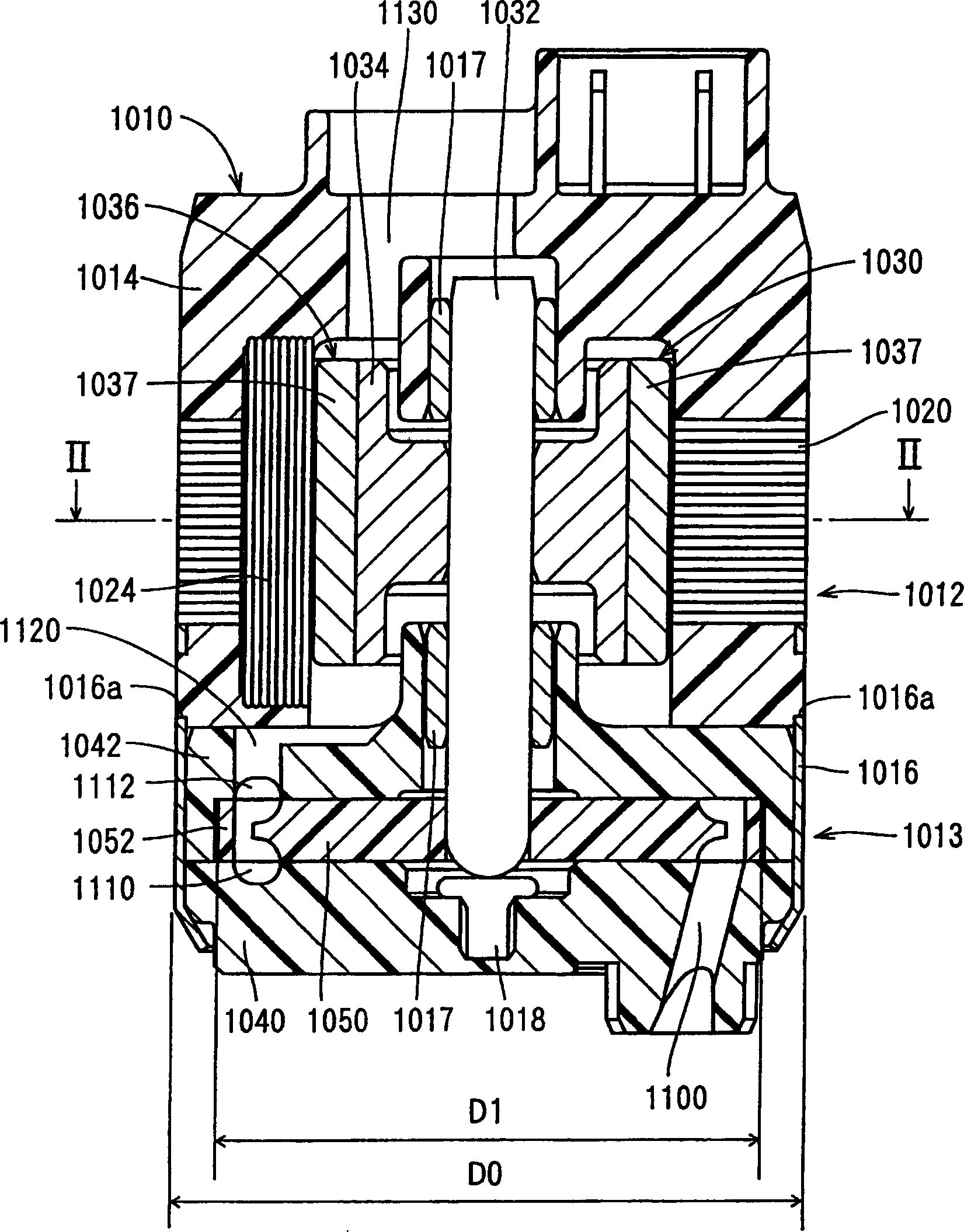

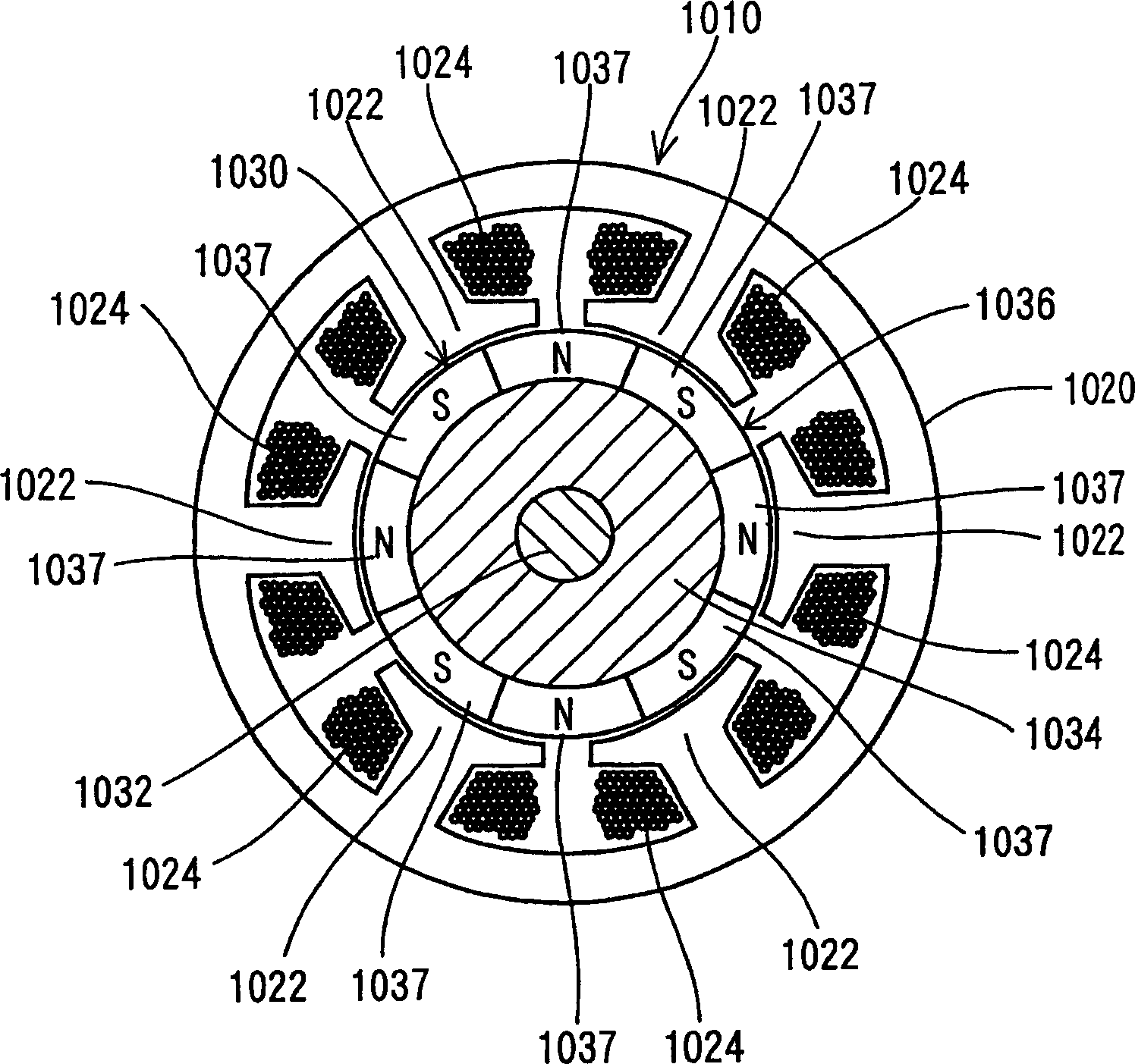

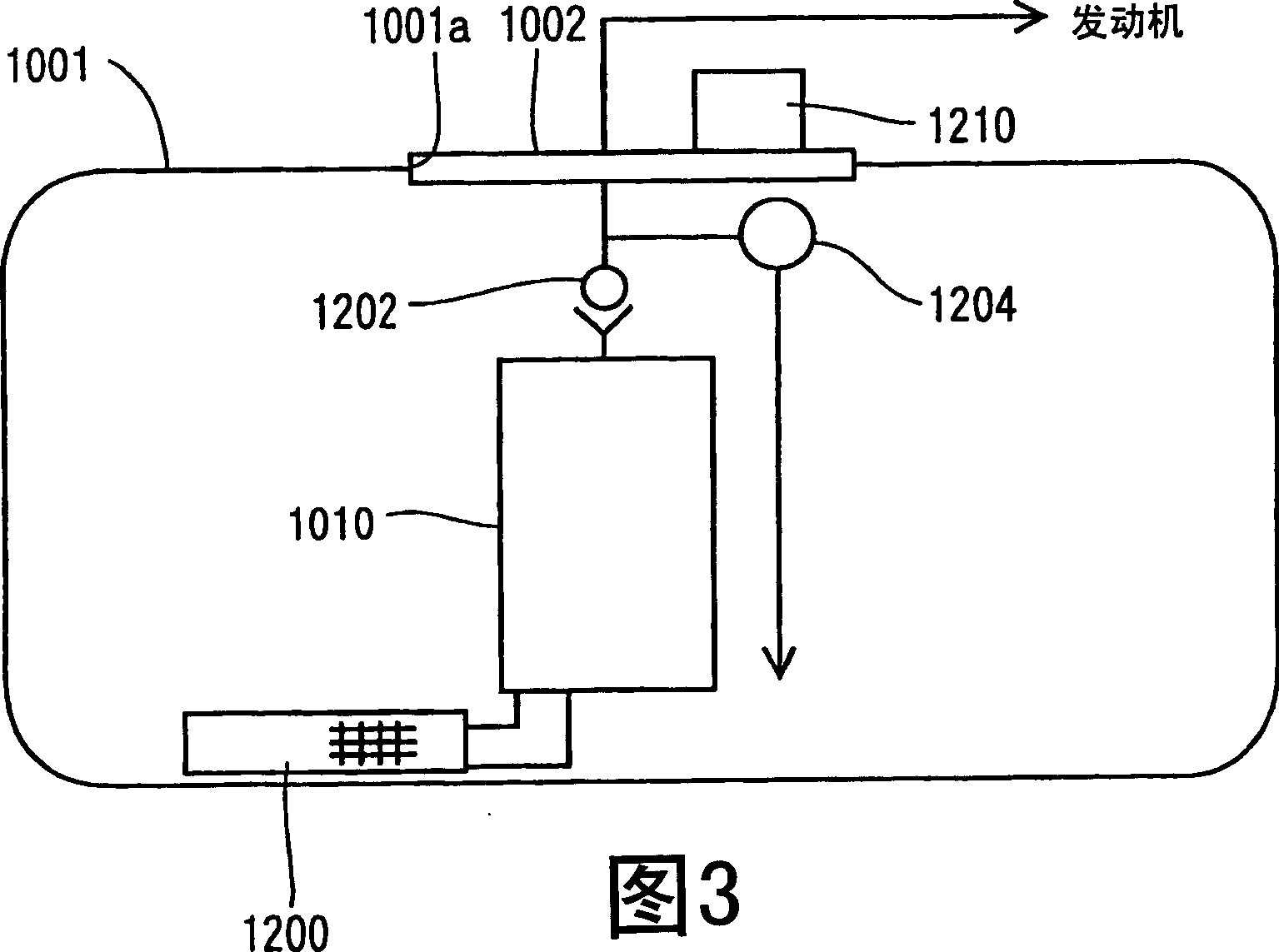

Fuel pump, fuel supply equipment using fuel pump and method for manufacturing fuel pump

ActiveCN1676915AEasy to wrapStop sheddingCircumferential flow pumpsTransverse flow pumpsElectricityBrushless motors

The fuel pump 1010 is installed in a fuel tank for a motorcycle. The fuel pump 1010 comprises a motor 1012 and a pump 1013 driven by the motor 1012 for pressurizing sucked fuel. The motor 1012 is a brushless motor, and has a stator 1020, coils 1024 and a rotor 1030. Current-passage to the coils 1024 wound around the stator core 1020 is controlled on the basis of a rotational position of the rotor, and thereby the rotor 1030 is rotated. The rotor 1030 has a shaft 1032, a rotary core 1034, and a permanent magnet 1036. The rotor 1030 is rotatably mounted on the inner circumstance of the stator core 1020. The permanent magnet 1036 is mounted on the outer circumference of the rotary core 1034, and magnetized so as to form magnetic poles different alternately in the rotation direction on the side of the outer circumferential surface facing to the stator core 1020.

Owner:DENSO CORP

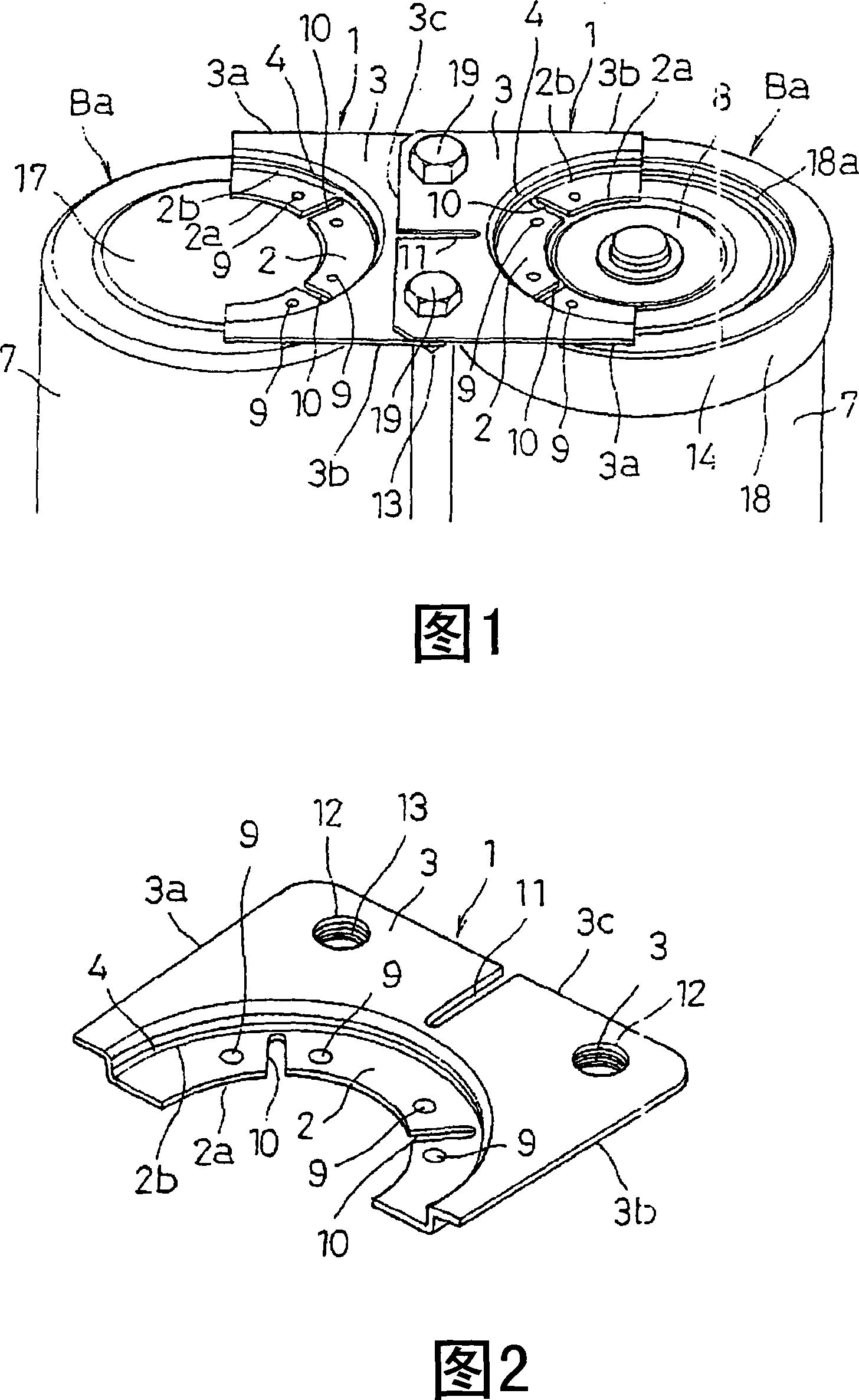

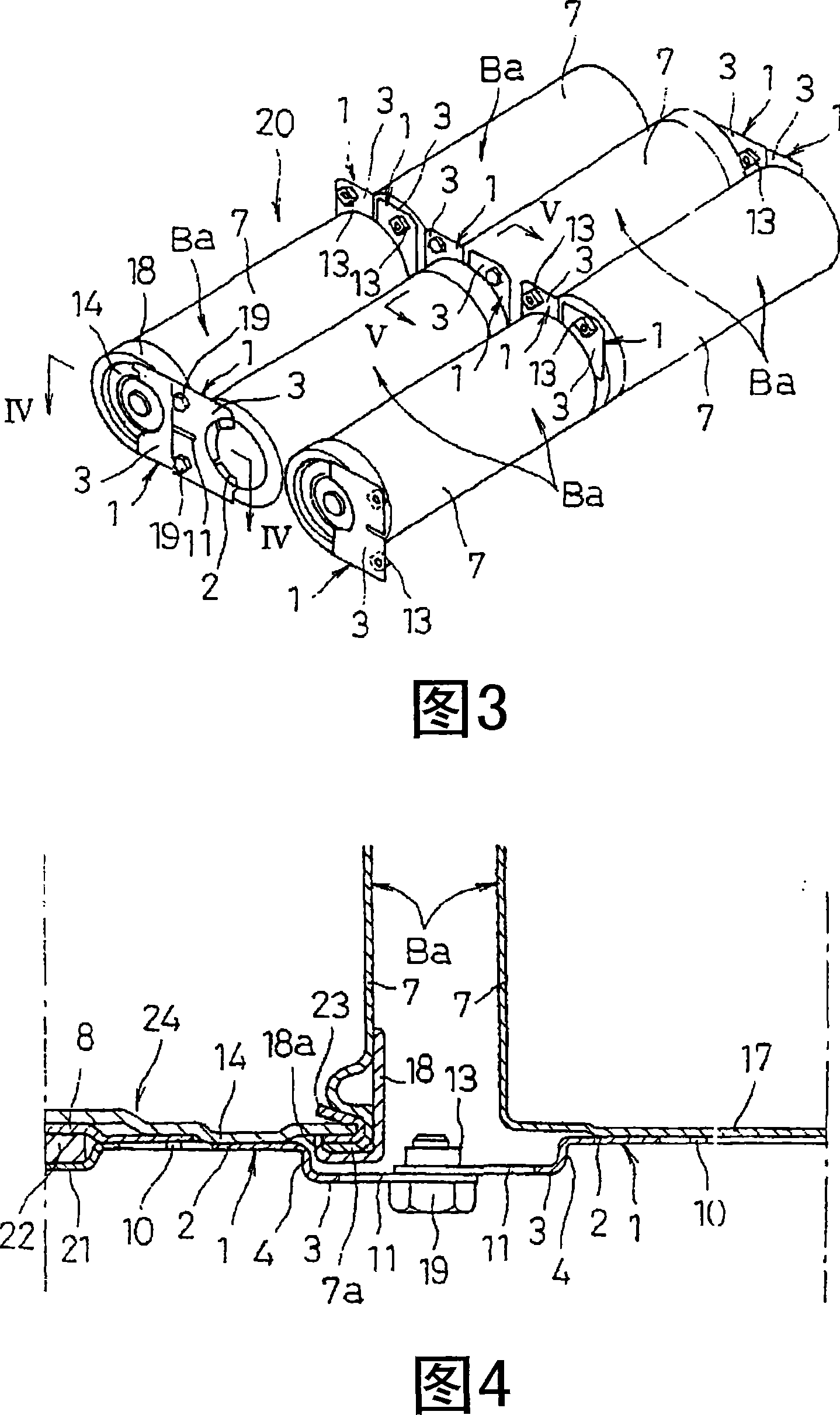

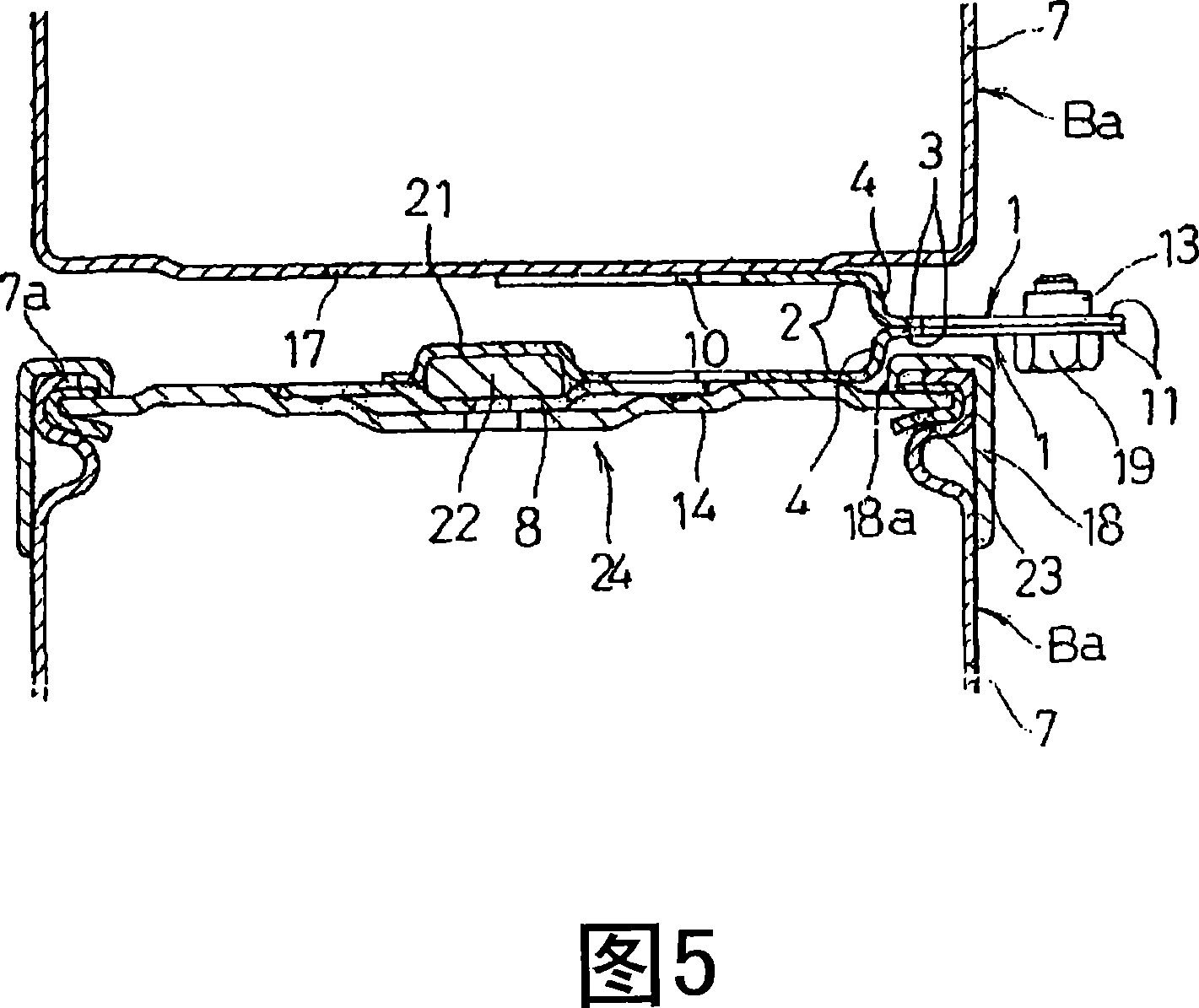

Production method for electric device assembly and electric device assembly

InactiveCN101160676ASimplify the manufacturing processSimple structurePrimary cell to battery groupingCurrent conducting connectionsEngineeringAssembly cells

Cell-to-cell connection plates (1) each integrally having a welding part (2) shaped to fall within a circular end of a battery case (7) and a connecting part (2) extending from this welding part (2) are provided. The cell-to-cell connection plates (1) are attached to one electrode terminal and the other electrode terminal of the battery case (7) by welding the welding parts (2), respectively. The connecting parts (3) of the respective cell-to-cell connection plates (1) attached to each adjoining pair of cylindrical batteries (Ba) are overlapped with each other and coupled into electric connection. Consequently, regardless of whether a plurality of cylindrical batteries (Ba) are axially arranged in series or radially juxtaposed, each adjoining two can be connected to each other by using the identical cell-to-cell connection plates (1) for cost reduction. It is also possible to provide a sufficient heat dissipation effect and achieve sufficient robustness and weight saving even when connecting large-sized cylindrical batteries.

Owner:PANASONIC CORP

Method for fabricating an array substrate for a liquid crystal display device

ActiveCN102472938APrevent electrical short circuitSimplify etch procedureNon-linear opticsChemistryLiquid-crystal display

The present invention relates to a method for fabricating an array substrate for a liquid crystal display device, using an etchant composition for a copper-based metal film, wherein the etchant composition comprises, based on the total weight of the etchant composition: a) 2 to 30 wt % of hydrogen peroxide (H2O2); b) 0.1 to 5 wt % of nitric acid (HNO3); c) 0.01 to 1.0 wt % of a fluorine compound; d) 0.1 to 5 wt % of an azole compound; e) 0.1 to 8.0 wt % of an imidazole compound; and f) the remainder being water.

Owner:DONGWOO FINE CHEM CO LTD

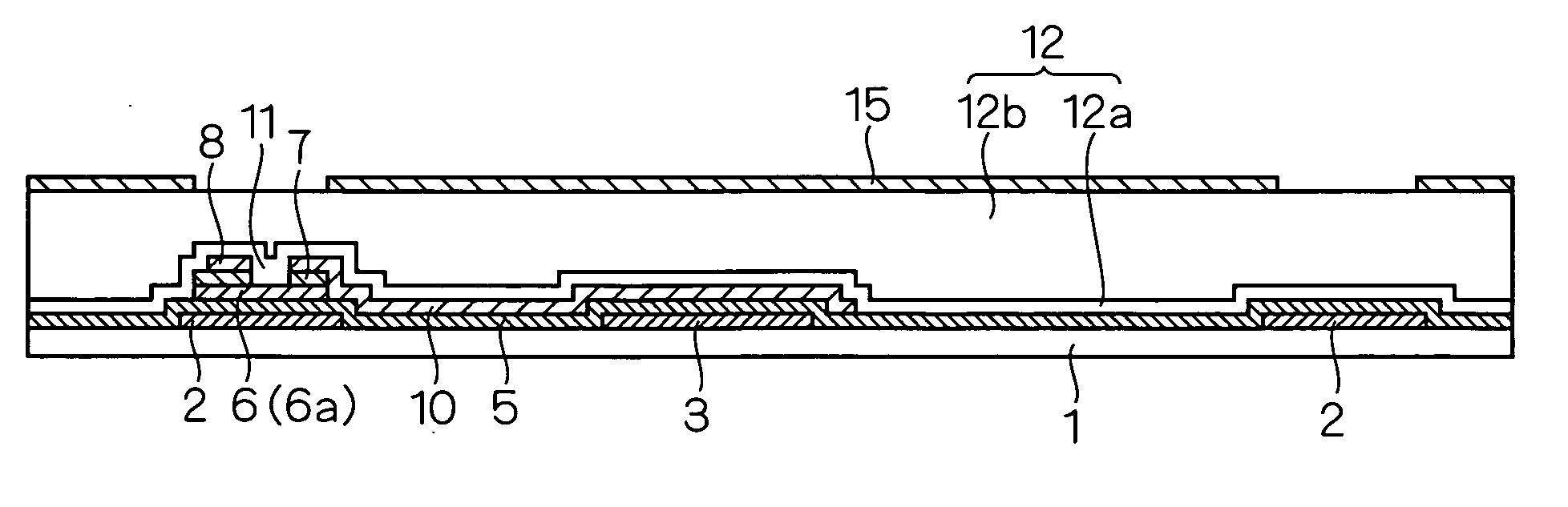

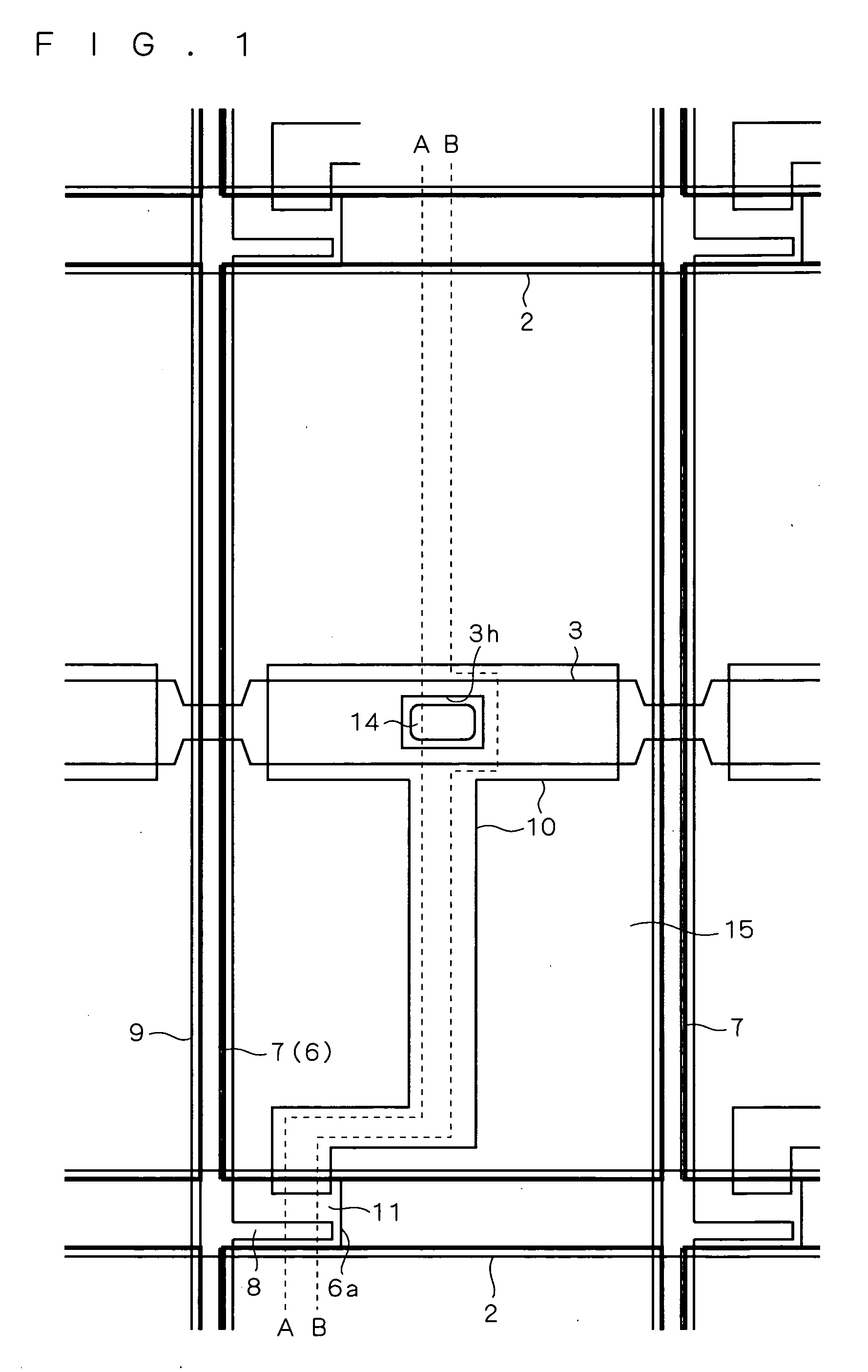

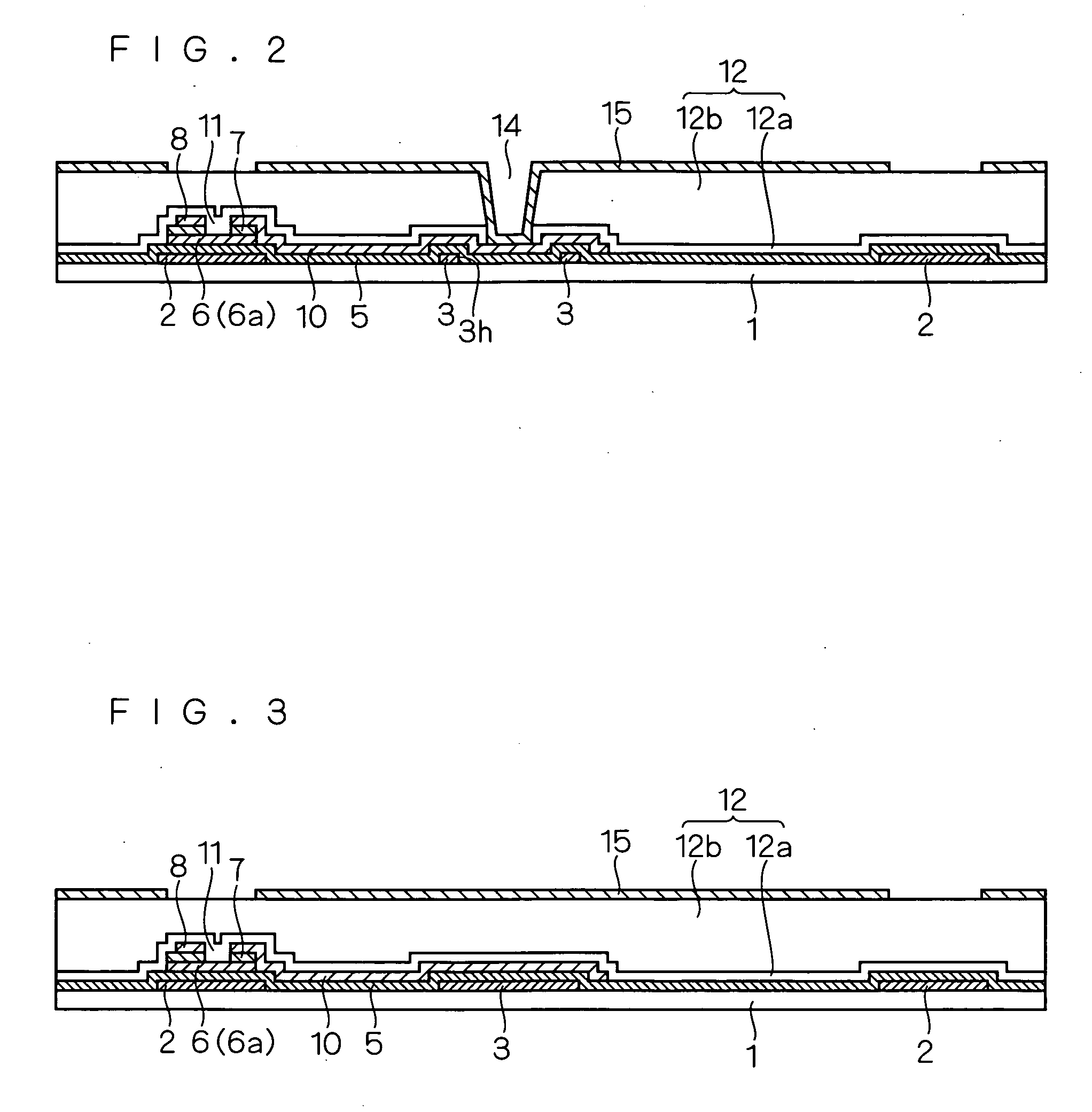

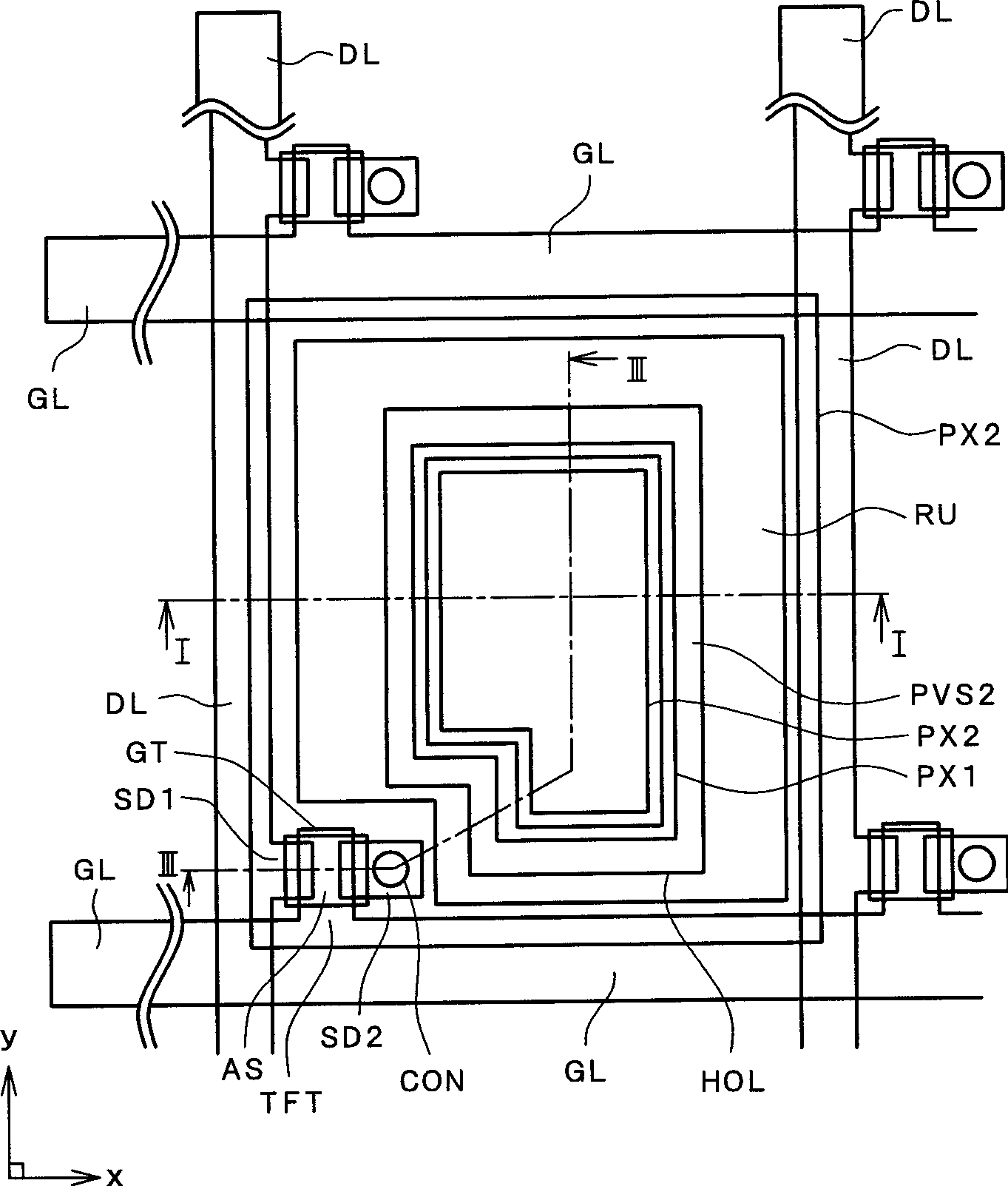

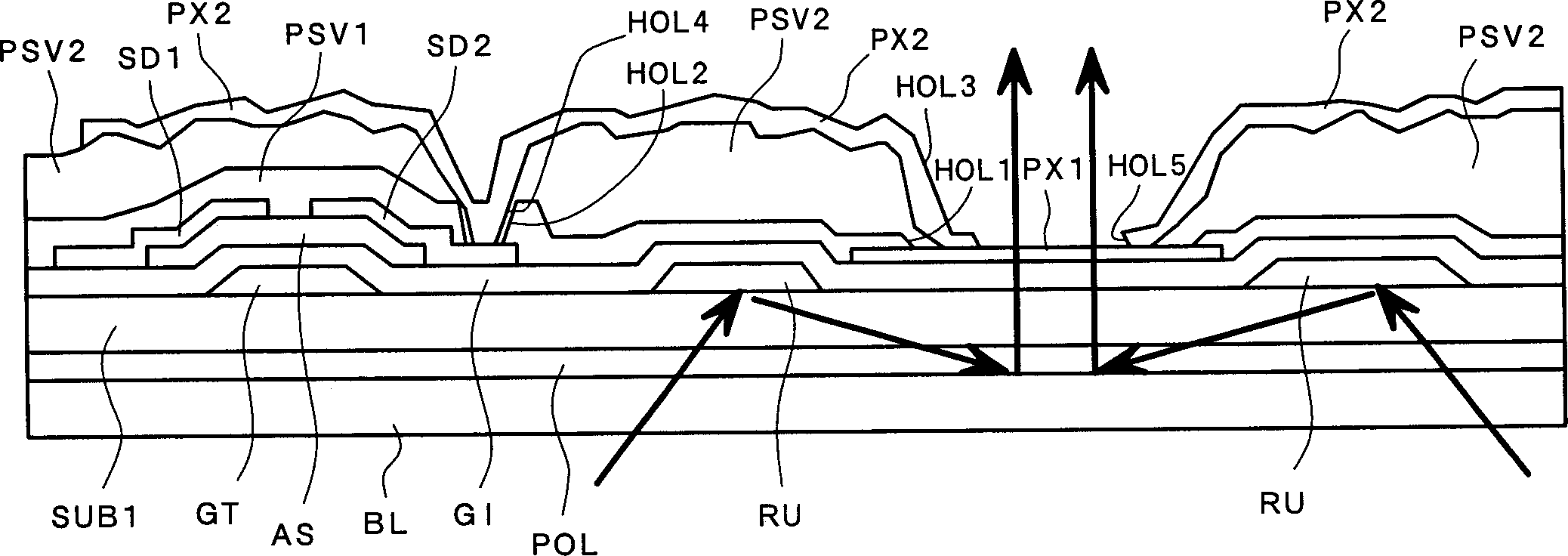

Active matrix substrate and its manufacturing method

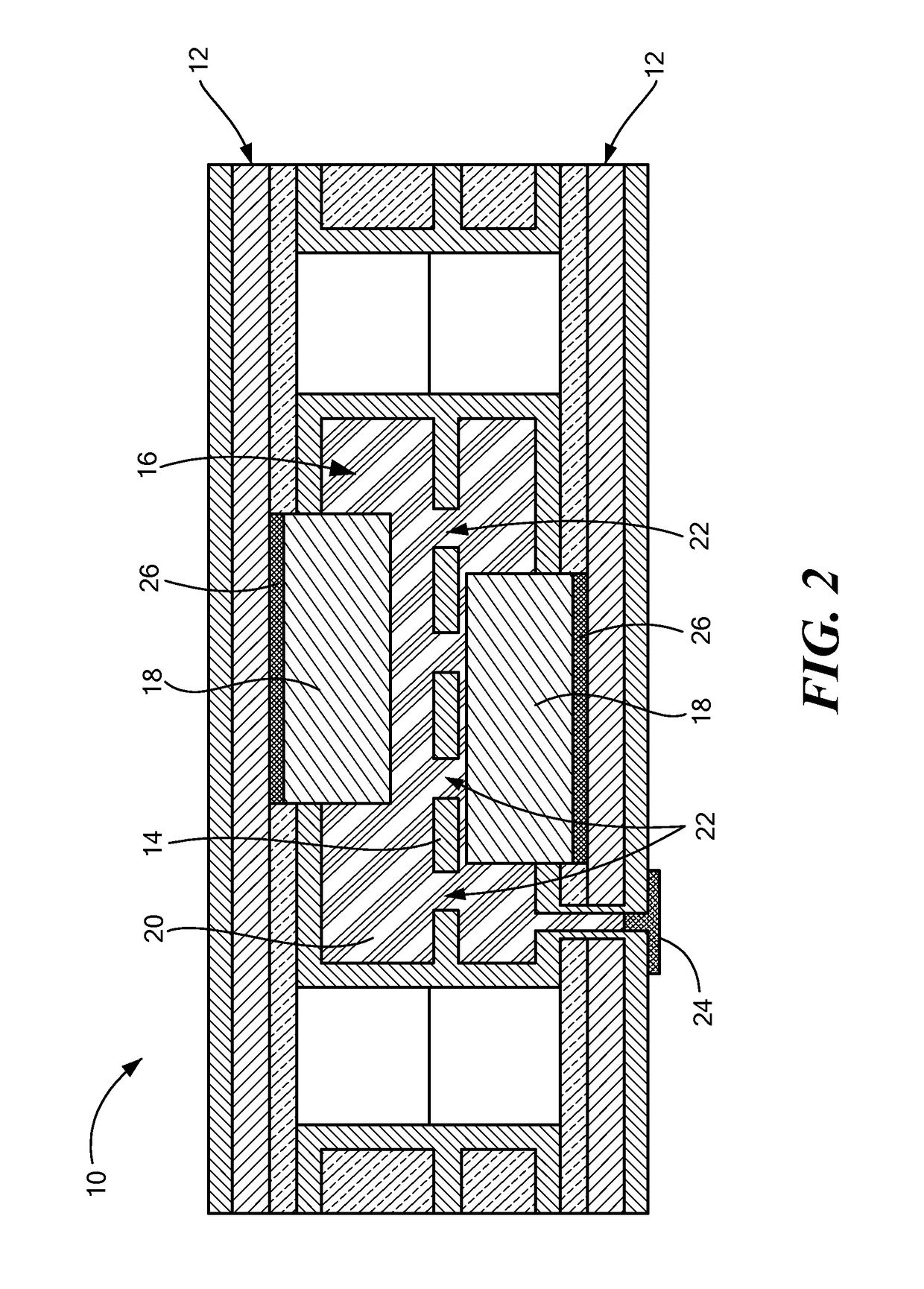

ActiveUS20060169983A1Prevent electrical short circuitHigh aperture ratioTransistorSolid-state devicesCapacitanceEngineering

An active matrix substrate with a high aperture ratio is provided, which is capable of preventing electrical short circuits between pixel electrodes and auxiliary capacitive electrodes. Gate lines and auxiliary capacitive electrodes are formed on an insulated substrate. The auxiliary capacitive electrodes have holes formed therethrough. To cover the gate lines and the auxiliary capacitive electrodes, a first interlayer insulating film is formed, on which source lines, a semiconductor layer, and drain electrodes are formed. Then, a second interlayer insulating film is formed to cover all those layers. In the second interlayer insulating film, contact holes are formed to reach the drain electrodes in areas corresponding to the areas of the holes. Pixel electrodes formed on the second interlayer insulating film are connected to the drain electrodes through the contact holes.

Owner:TRIVALE TECH

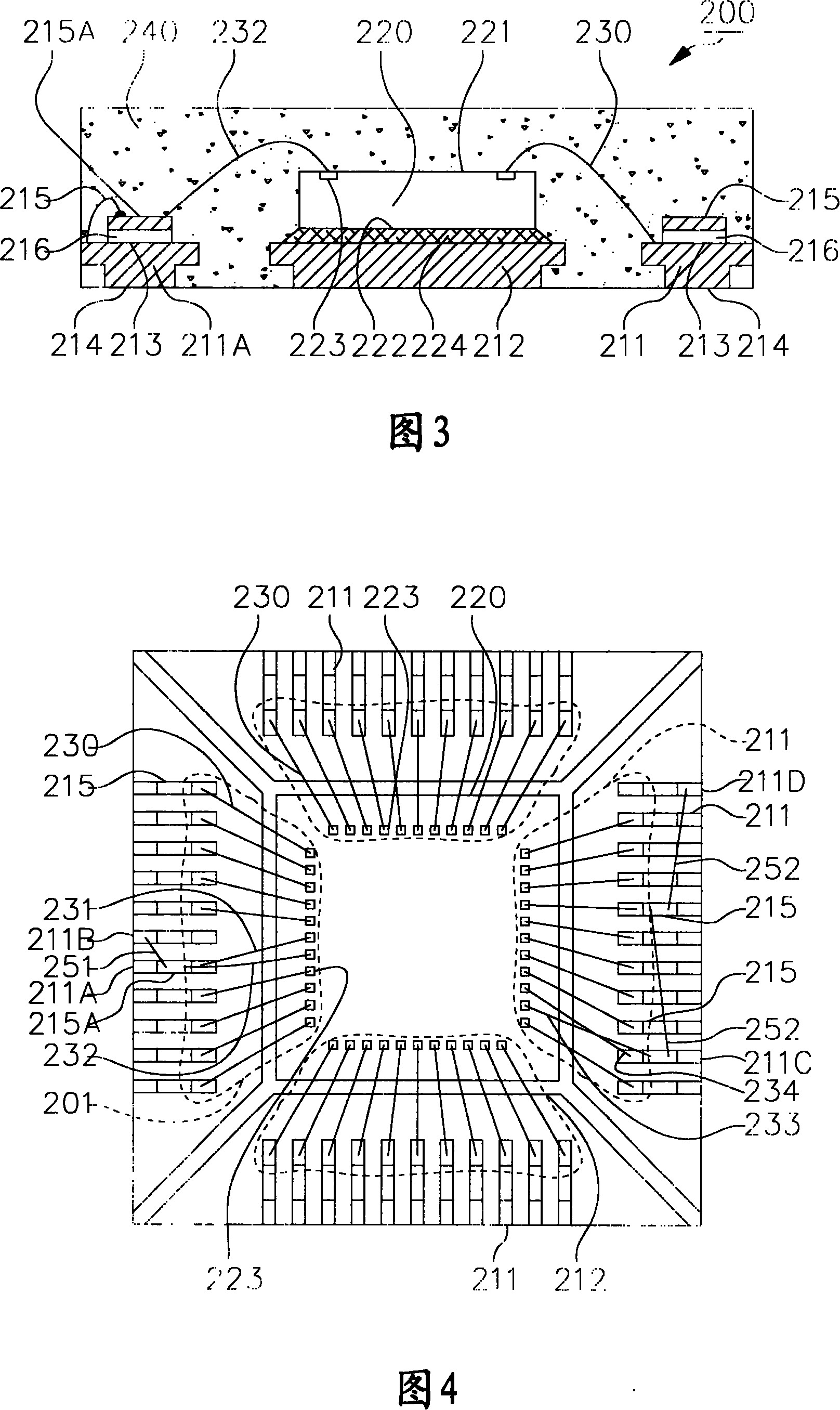

Integrated circuit packaging construction and multi-layer conducting wire holder used for it

InactiveCN101131978APrevent electrical short circuitIncrease the scope of application of the packageSemiconductor/solid-state device detailsSolid-state devicesShortest distanceColloid

The present invention relates to an IC packaging and its multi-layer conductor frame. The IC packaging has been defined with a wire-bonded region which mainly includes a multi-layer conductor frame with pins, a wafer, even numbers of welding lines in this region and at least an electric-transferred component. At least one of these pins carries a transferred finger which is insulating to the corresponding pin and does not cover inner terminal of the pin. The electric-transferred component has at least one part which is formed outside the wire-bonded region, and the transferred finger is connected to one pin which is not under the transferred finger. The shortest distance between staggered welding lines can be added, or staggered points of these welding lines can be reduced, thus staggered short circuit of welding lines can be avoided during colloid sealing.

Owner:CHIPMOS TECH INC

Wiring structure of semiconductor device and method of forming a wiring structure

InactiveCN101740545AAvoid damagePrevent electrical short circuitTransistorSemiconductor/solid-state device detailsContact padEngineering

In a wiring structure of a semiconductor device and a method of manufacturing the same, a wiring structure includes a contact pad, a contact plug, a spacer and an insulation interlayer pattern. The contact pad is electrically connected to a contact region of a substrate. The contact plug is provided on the contact pad and is electrically connected to the contact pad. The spacer faces an upper side surface of the contact pad and sidewalls of the contact plug. The insulation interlayer pattern has an opening, the contact plug and the spacer being provided in the opening. The spacer of the wiring structure may prevent the contact pad from being damaged by a cleaning solution while forming a contact plug to be connected to a capacitor.

Owner:SAMSUNG ELECTRONICS CO LTD

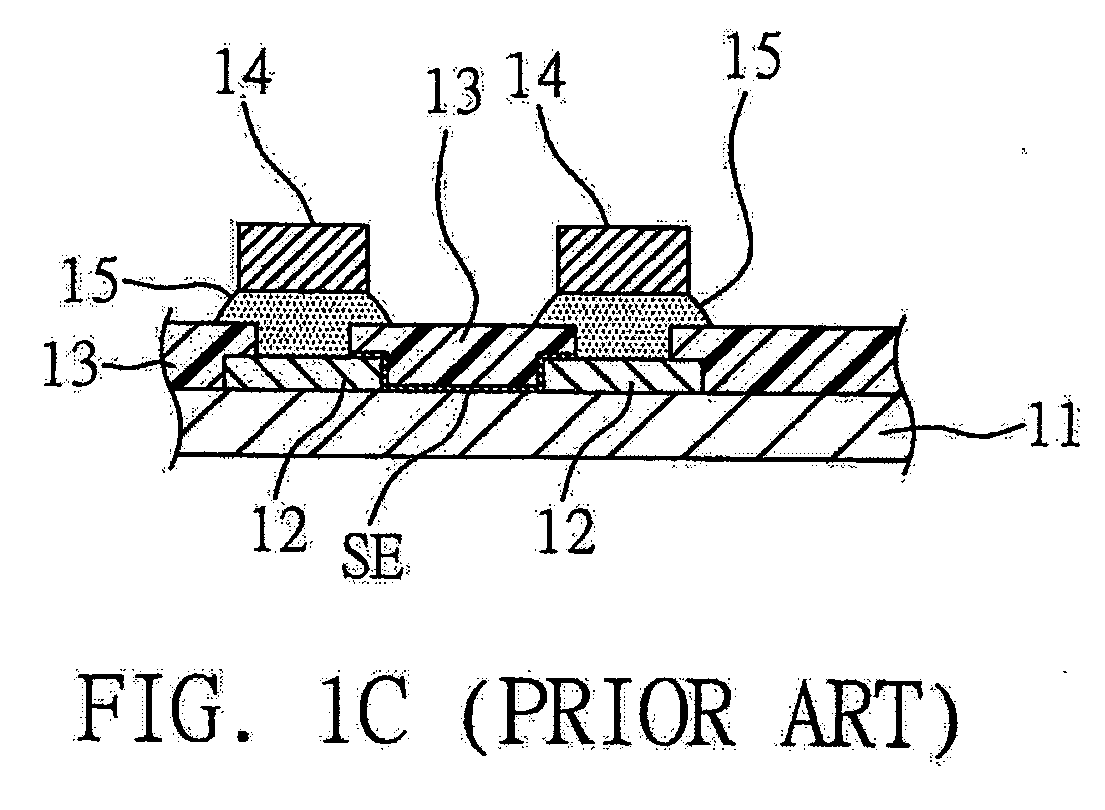

Electronic carrier board and package structure thereof

InactiveUS20070138632A1Efficient fillingPrevent electrical short circuitFinal product manufactureSemiconductor/solid-state device detailsEngineeringElectronic component

An electronic carrier board and a package structure thereof are provided. The electronic carrier board includes a carrier, at least one pair of bond pads formed on the carrier, and a protective layer covering the carrier. An opening is formed in the protective layer to expose at least three sides of each of the paired bond pads. The protective layer includes at least one independent residual portion located in the opening and between the paired bond pads, such that an electronic component is mounted on the independent residual portion and electrically connected to the bond pads. A groove without a dead space is formed between the electronic component and the carrier, such that a molding compound for encapsulating the electronic component can flow through the groove to fill the opening and a space under the electronic component and encapsulate the at least three sides of each of the bond pads.

Owner:SILICONWARE PRECISION IND CO LTD

Super-capacitor with separator and method of producing the same

ActiveUS9601278B2Prevent electrical short circuitAvoid electrical contactHybrid capacitor separatorsHybrid capacitor electrolytesSupercapacitorEngineering

A method of producing a super-capacitor provides a first substrate having a first base, forms a first electrode on the first substrate, and forms a separator so that the electrode is between the first base and the first separator. The method also micromachines holes through the separator, forms a chamber, and adds electrolyte, having ions, to the chamber. The electrolyte is in contact with the first electrode within the chamber. In addition, the holes are sized to permit transmission of the ions of the electrolyte through the holes.

Owner:ANALOG DEVICES INC

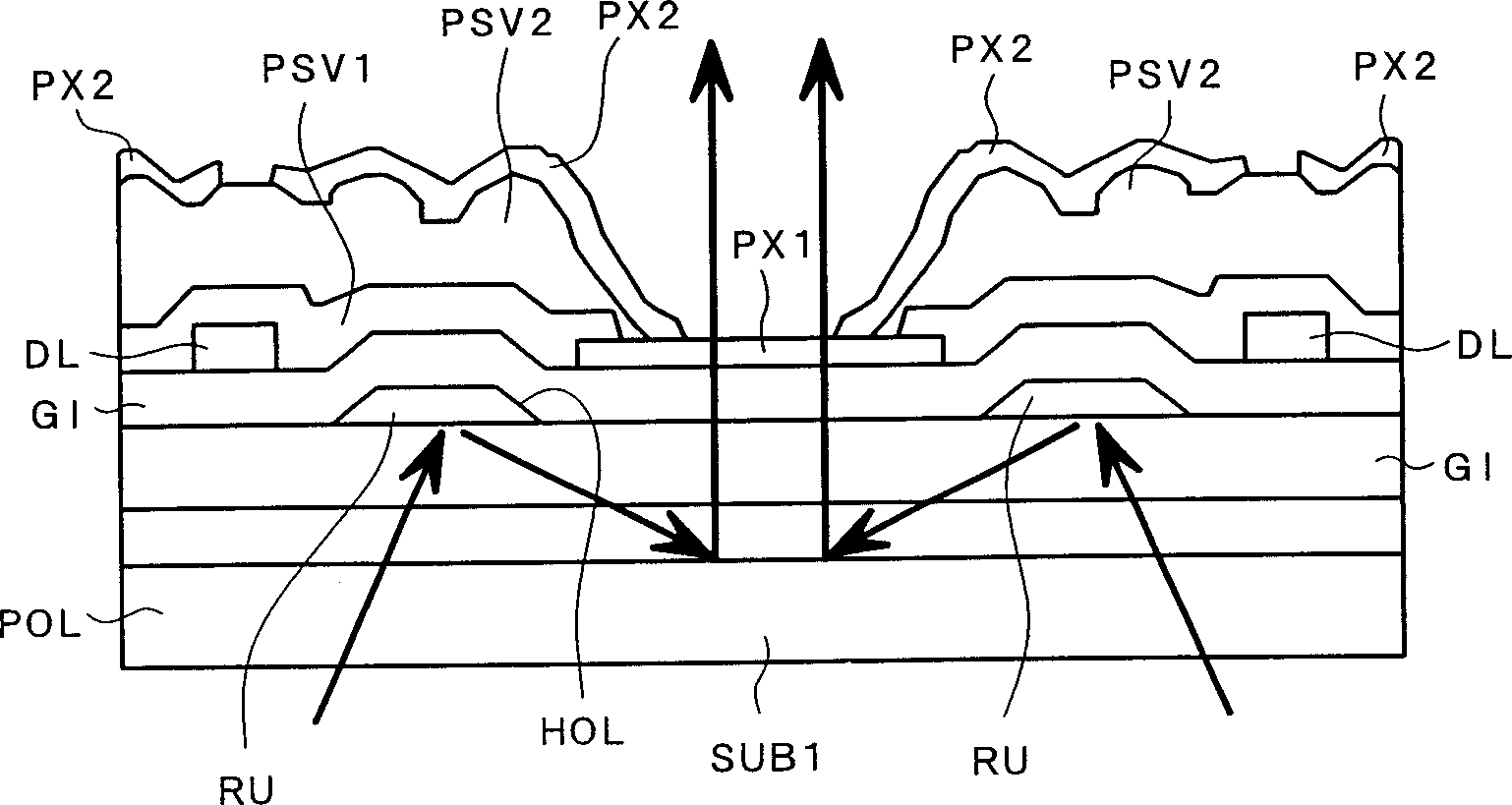

Liquid crystal display device

InactiveCN1354381ACapacitive coupling will no longer occurPrevent electrical short circuitNon-linear opticsIdentification meansElectricityOptical reflection

To improve optical transmission efficiency without reducing optical reflection efficiency. While rays of light coming from a backlight are irradiated from the side of one substrate of respective substrates disposed to oppose each other with a layer of liquid crystal material interposed therebetween, a certain region on a liquid crystal side surface of the one substrate which is surrounded by neighboring gate signal lines being disposed adjacent to each other and drain signal lines being disposed adjacent to each other is adapted for use as a pixel region, in which a pixel electrode is formed for receiving an image signal as supplied from one drain signal line via a thin-film transistor rendered operative by supplement of a scan signal from one gate signal line, wherein this pixel electrode is generally made up from a conductive reflection film and a transparent conductive film that are electrically connected together with a light reclamation or ''reuse'' film being formed beneath the conductive reflection film through the conductive reflection film and a dielectric film, this light reuse film being electrically insulated from either the gate signal lines or the drain signal lines.

Owner:JAPAN DISPLAY INC

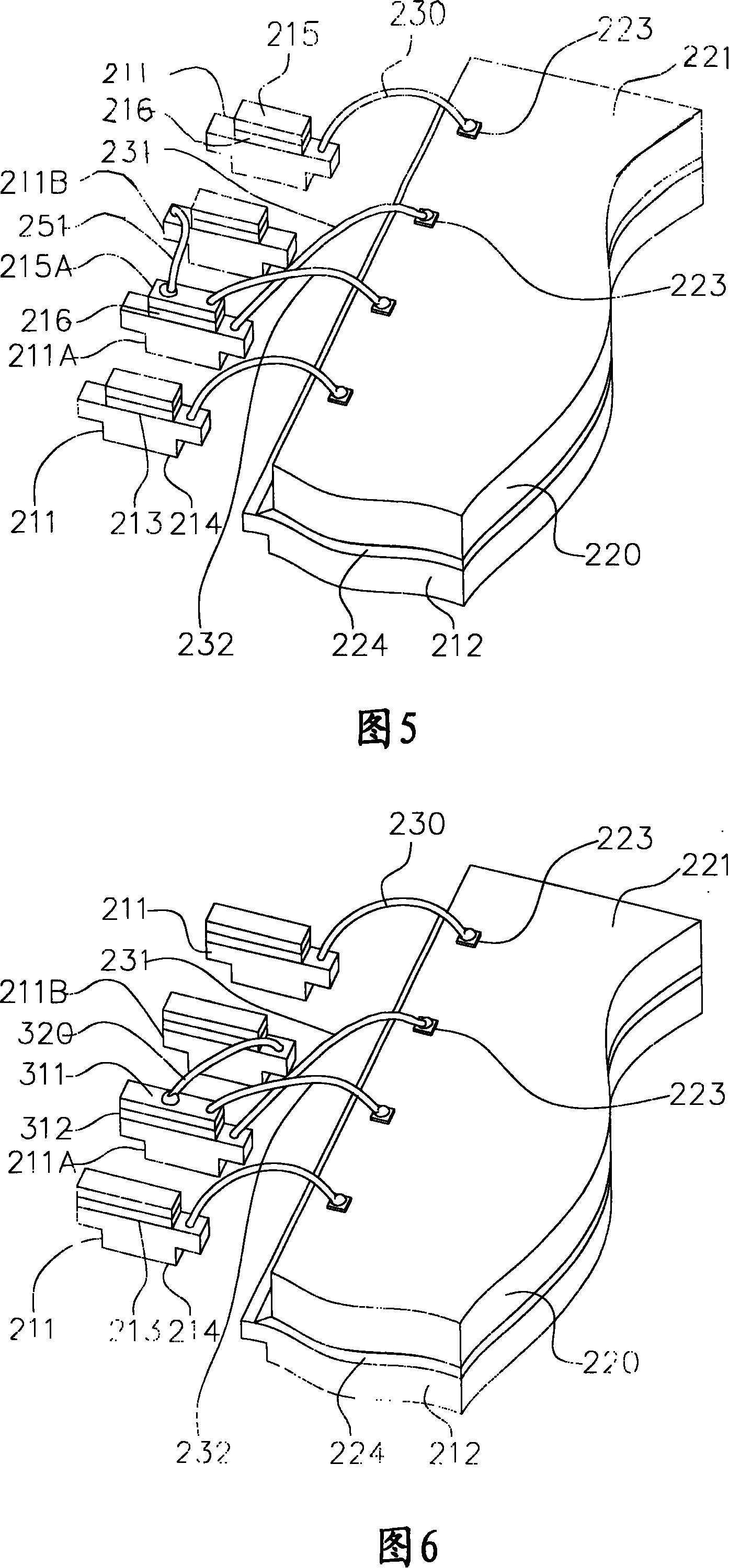

Semiconductor device and wire bonding method used for the same

InactiveCN101127340AAvoid contactPrevent electrical short circuitSemiconductor/solid-state device detailsSolid-state devicesWire bondingSemiconductor chip

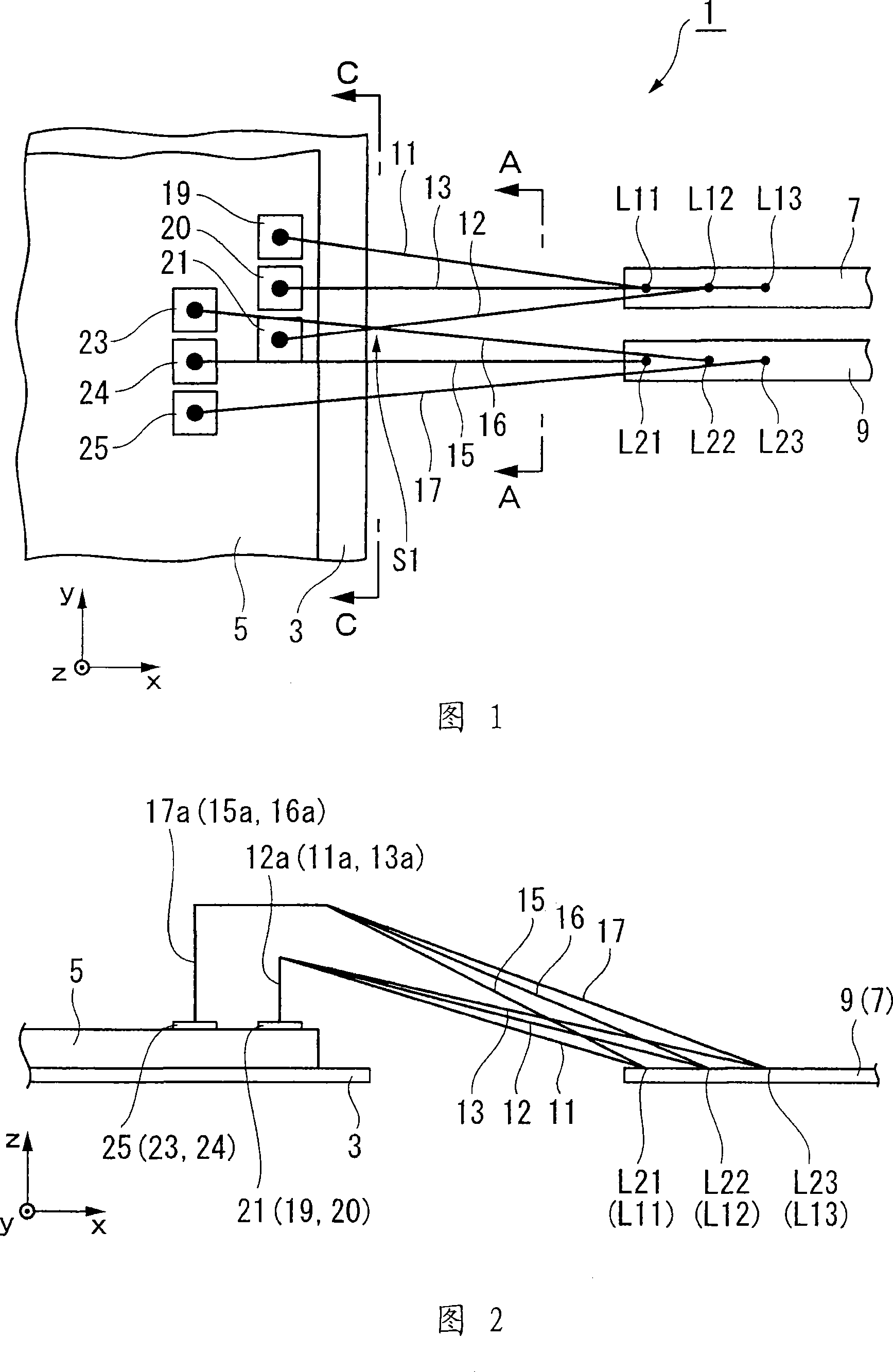

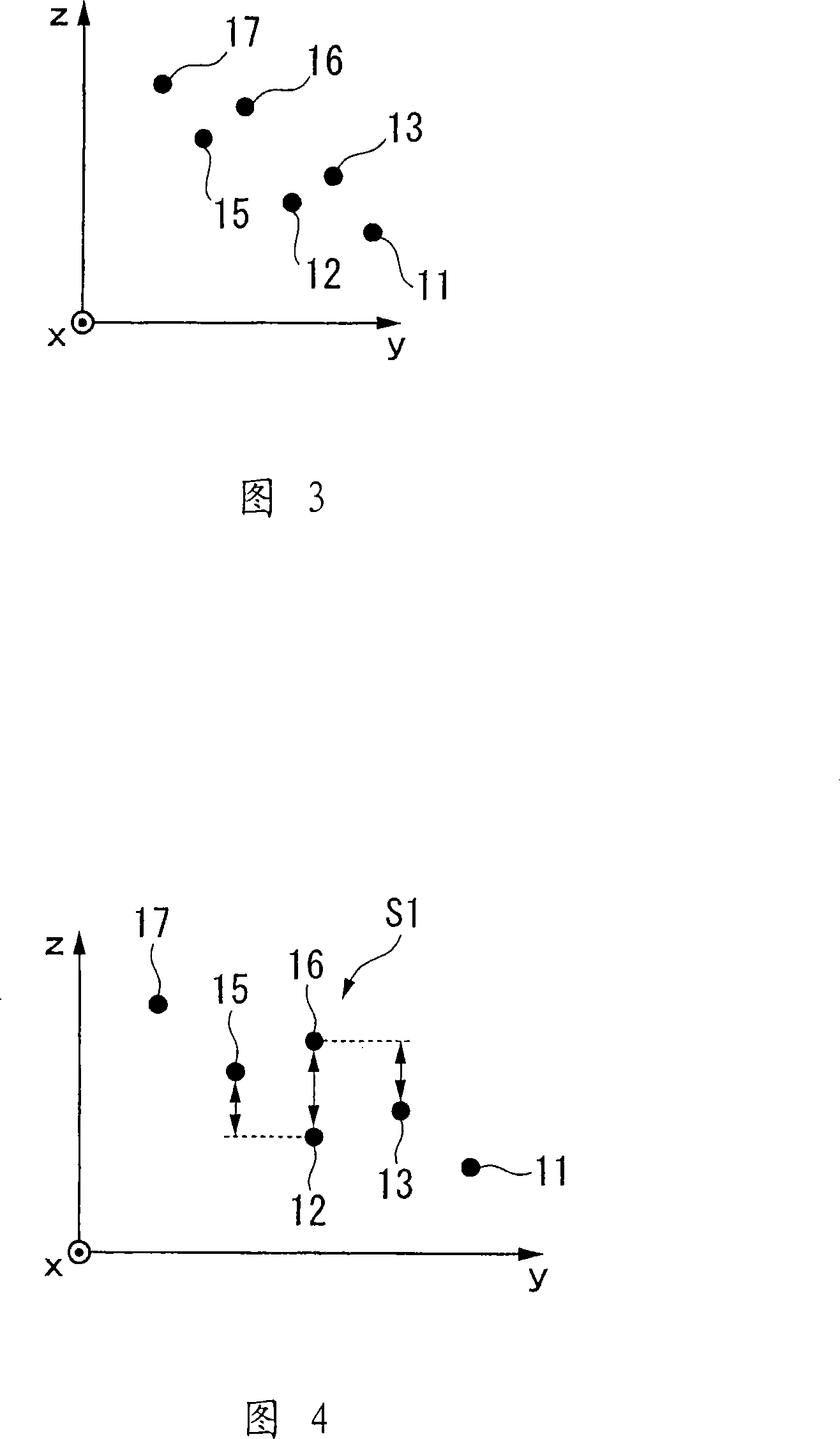

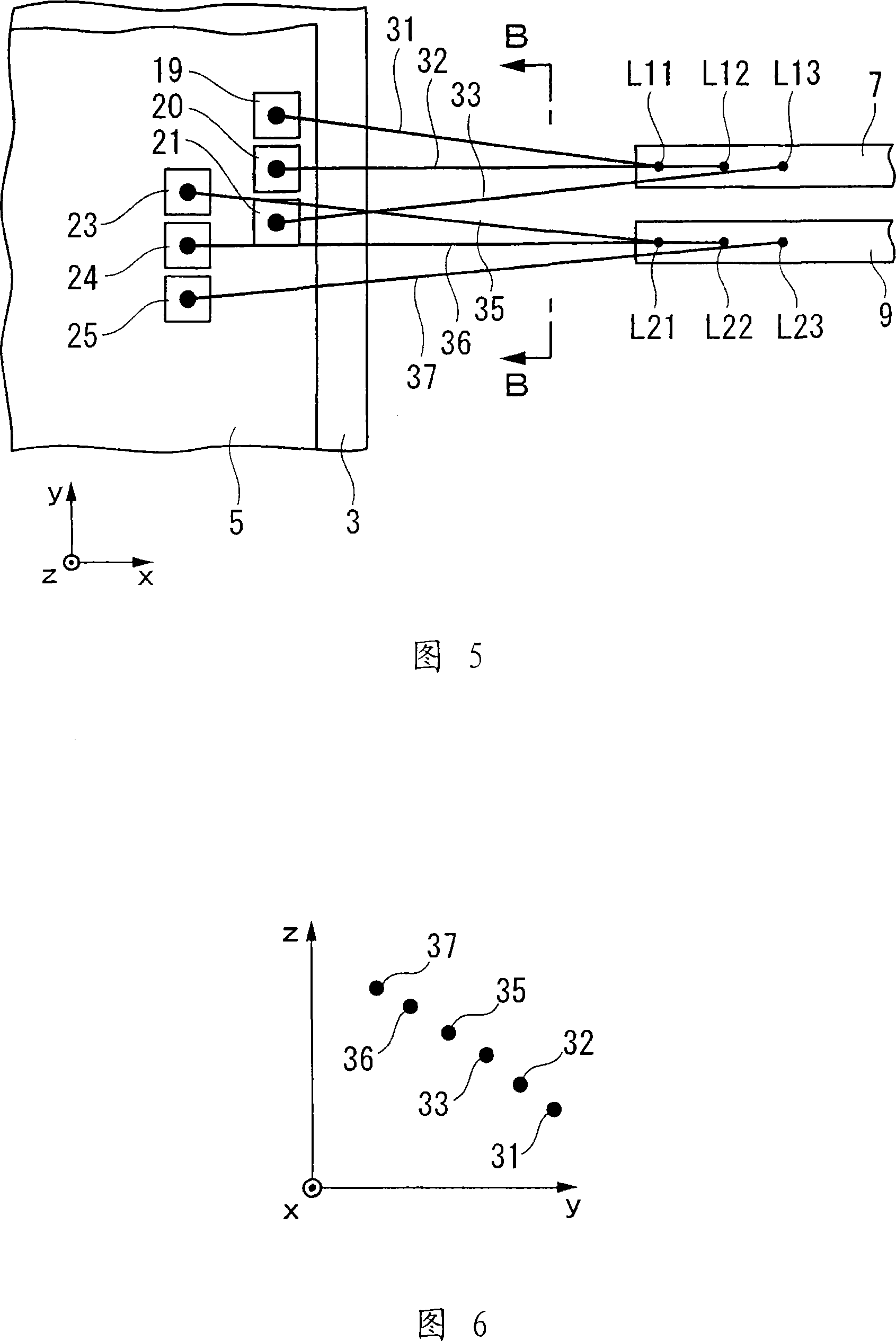

PROBLEM TO BE SOLVED: To prevent the occurrence of electric short circuits between the most closely arranged wires out of a plurality of wires for connecting individual groups of electrode pads of a semiconductor chip and two leads arranged adjacent to each other around the semiconductor chip, respectively.SOLUTION: In the semiconductor device 1, second bonds of each three wires 11-13 and 15-17 of each lead 7 and 9 are arranged in the longitudinal direction of the leads 7 and 9. The three first wires 11-13 connected to one lead 7 are connected to the electrode pads 19-21 in a first row arranged in the arranging direction of the leads 7 and 9, while the three second wires 15-17 connected to the other lead 9 are connected to the electrode pads 23-25 in a second row arranged further away from the leads 7 and 9 than those in the first row. The first wire 13 connected to the most posteriorly located second bond of the lead 7 is connected to other electrode pad 20 in the first row than the electrode pad 21 in the first row which is closest to the electrode pads 23-25 in the second row.

Owner:YAMAHA CORP

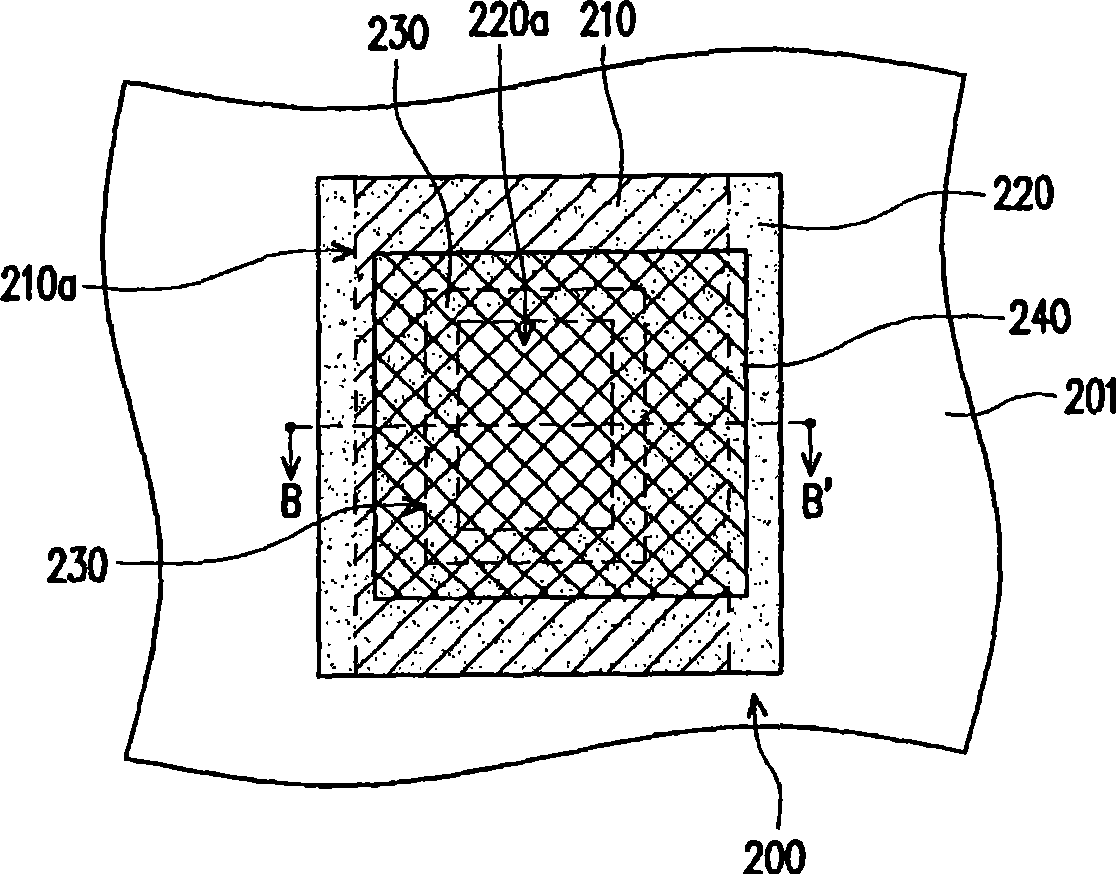

Organic light emitting display device and method for manufacturing the same

InactiveCN104183617APrevent electrical short circuitNon-uniform emissionSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceMaterials science

Provided are an organic light emitting display device and a method for manufacturing the same. The organic light emitting display device includes a substrate, first electrode positioned on the substrate, a pixel defining film positioned on the substrate and at least partially exposing the first electrode, an organic layer positioned on the first electrode and having a central portion and an edge portion, and a cover film at least partially overlapping the edge portion of the organic layer.

Owner:SAMSUNG DISPLAY CO LTD

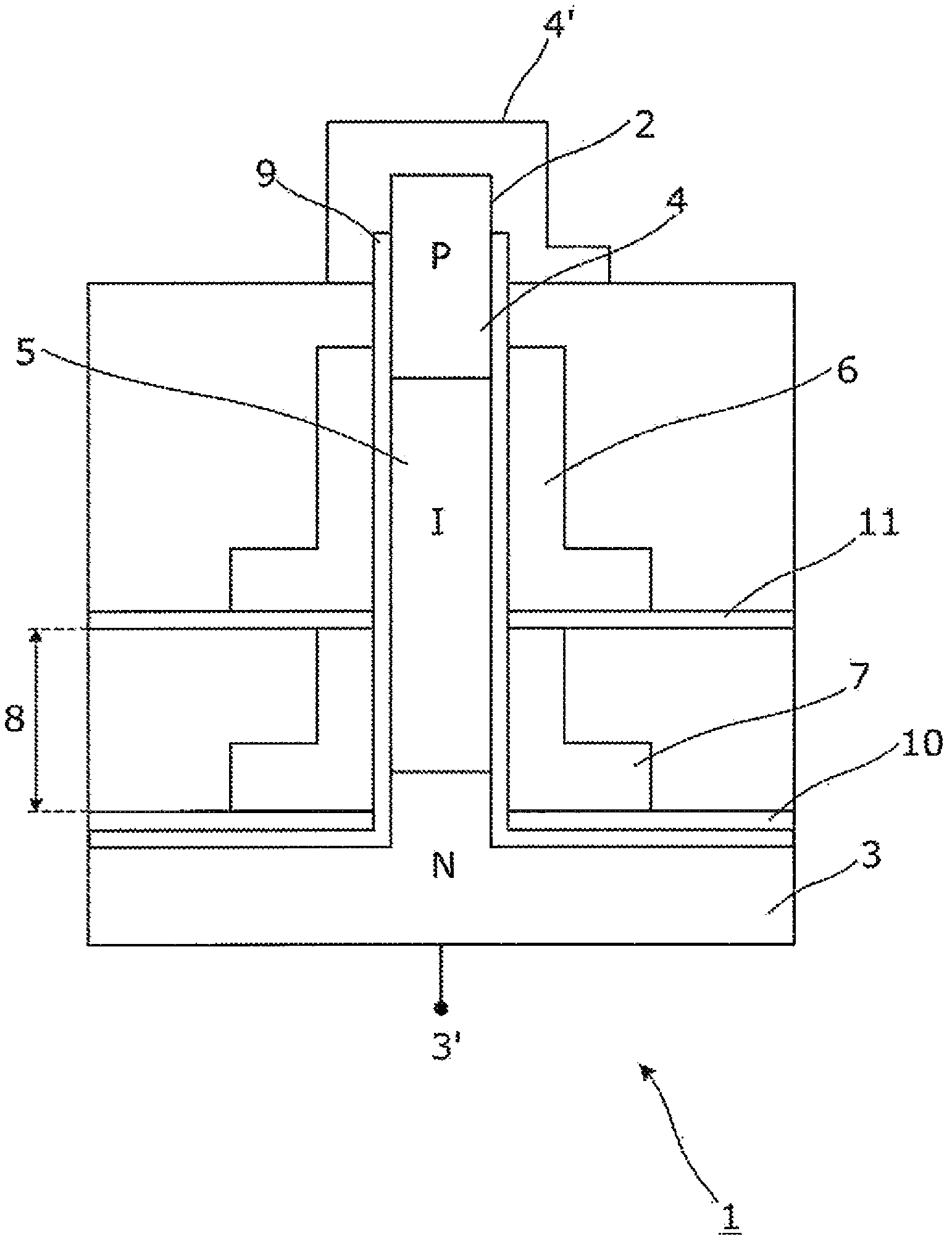

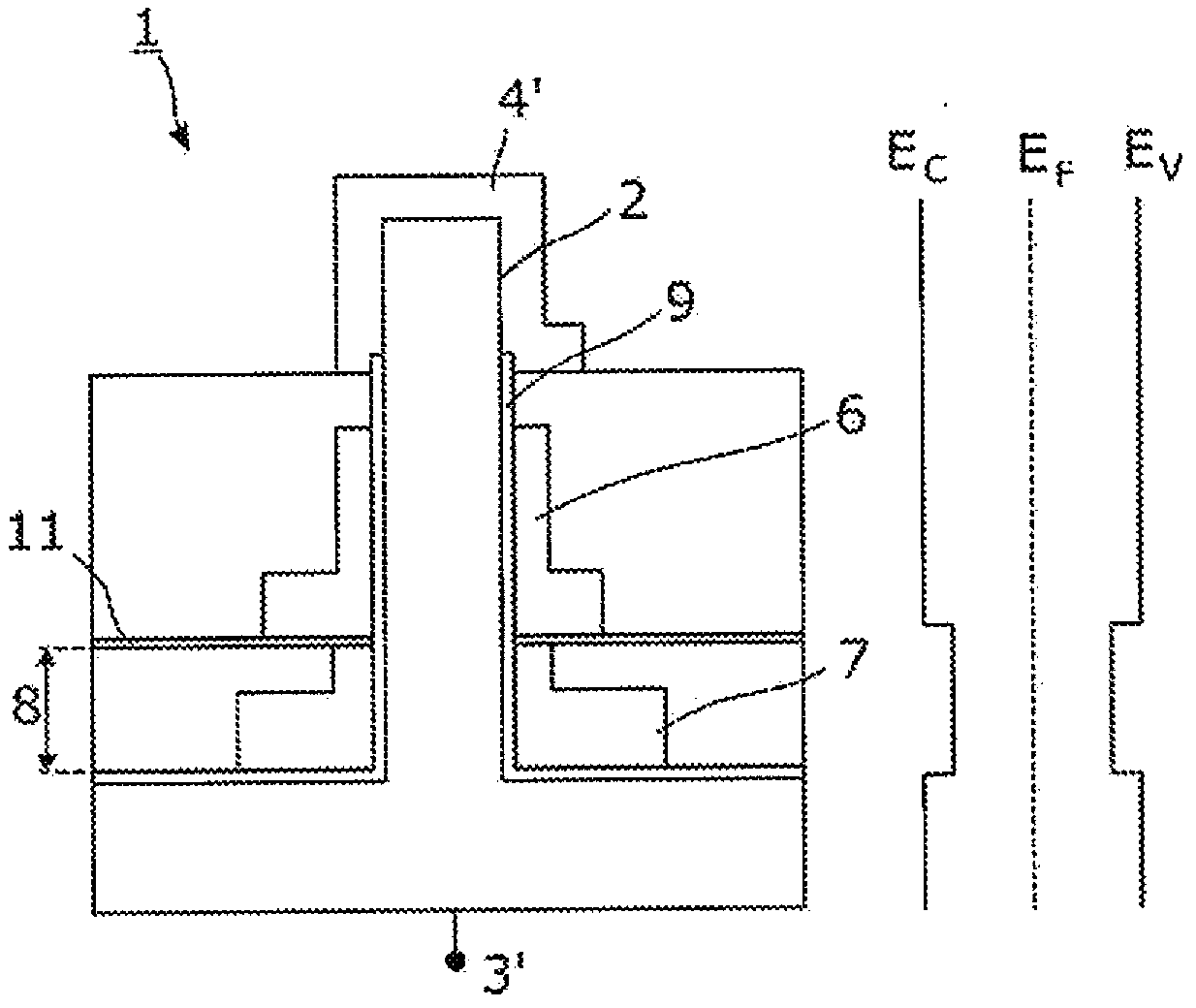

Nanowire field-effect device with multiple gates

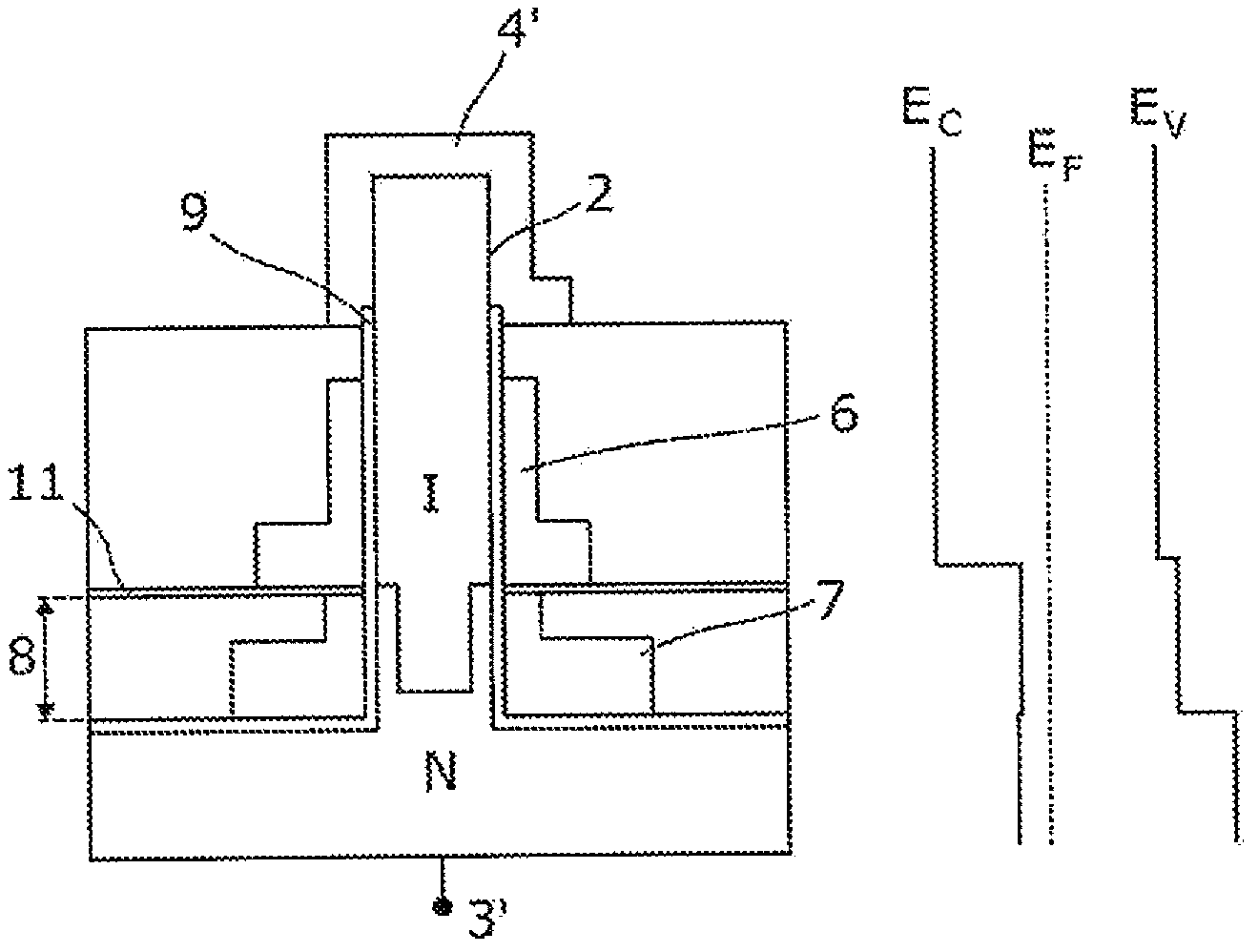

InactiveCN103262243AFacilitates electrostatic dopingAvoid dopingNanoinformaticsSemiconductor devicesNanowireSemiconductor materials

The present invention relates to a semiconductor device (1) comprising: at least a nanowire (2) configured to comprise: at least a source region (3) comprising a corresponding source semiconductor material, at least a drain region (4) comprising a corresponding drain semiconductor material and at least a channel region (5) comprising a corresponding channel semiconductor material, the channel region (5) being arranged between the source region (3) and the drain region (4), at least a gate electrode (6) that is arranged relative to the nanowire (2) to circumferentially surround at least a part of the channel region (5), and at least a strain gate (7) that is arranged relative to the nanowire (2) to circumferentially surround at least a part of a segment of the nanowire (2), the strain gate (7) being configured to apply a strain to the nanowire segment (8), thereby to facilitate at least an alteration of the energy bands corresponding to the source region (3) relative to the energy bands corresponding to the channel region (5).

Owner:IBM CORP

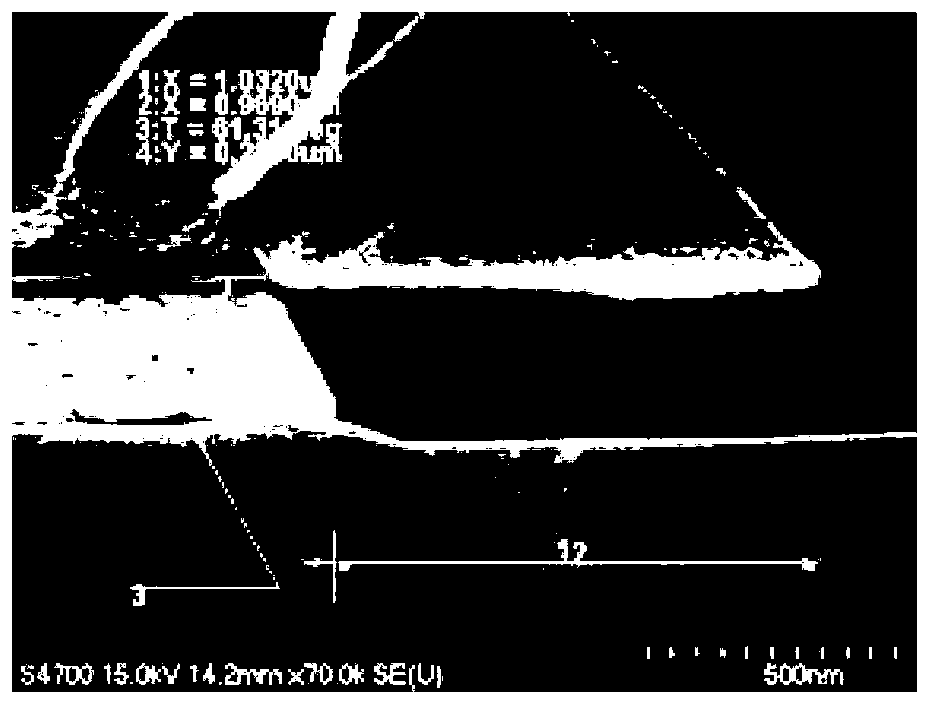

Method of forming a semiconductor die having a sloped edge for receiving an electrical connector

InactiveCN101393876AReduce the overall heightReduce areaSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectrical connection

Owner:SANDISK CORP

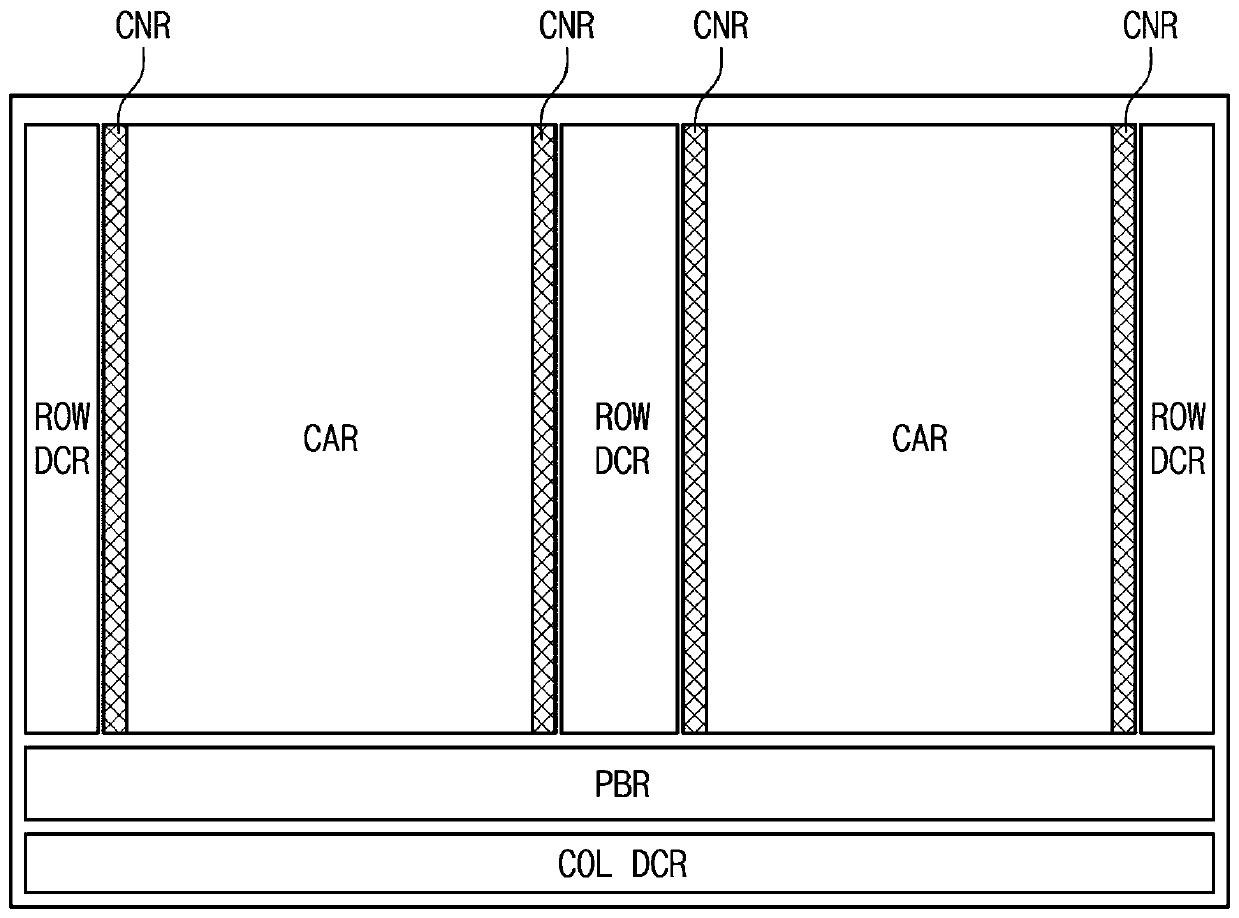

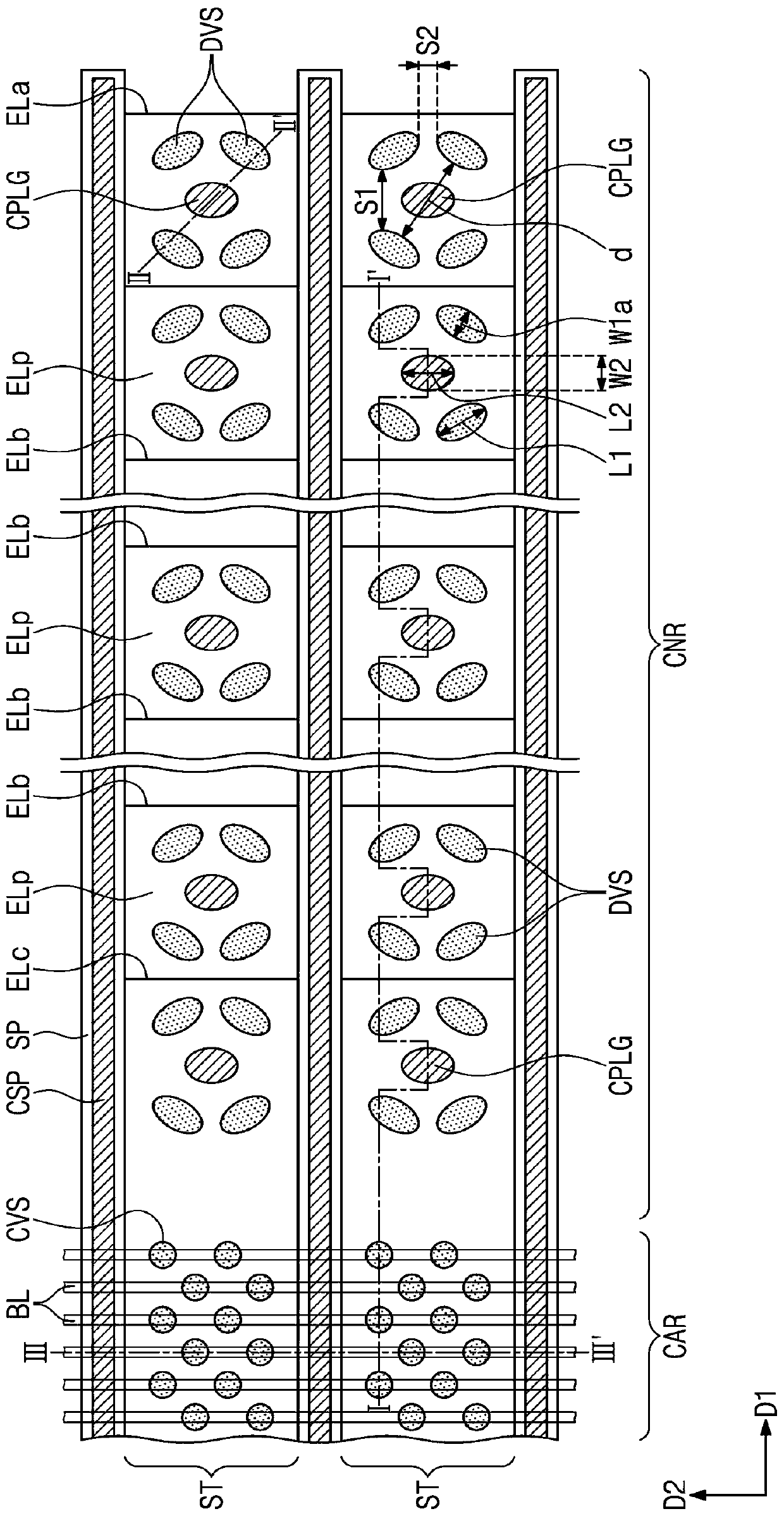

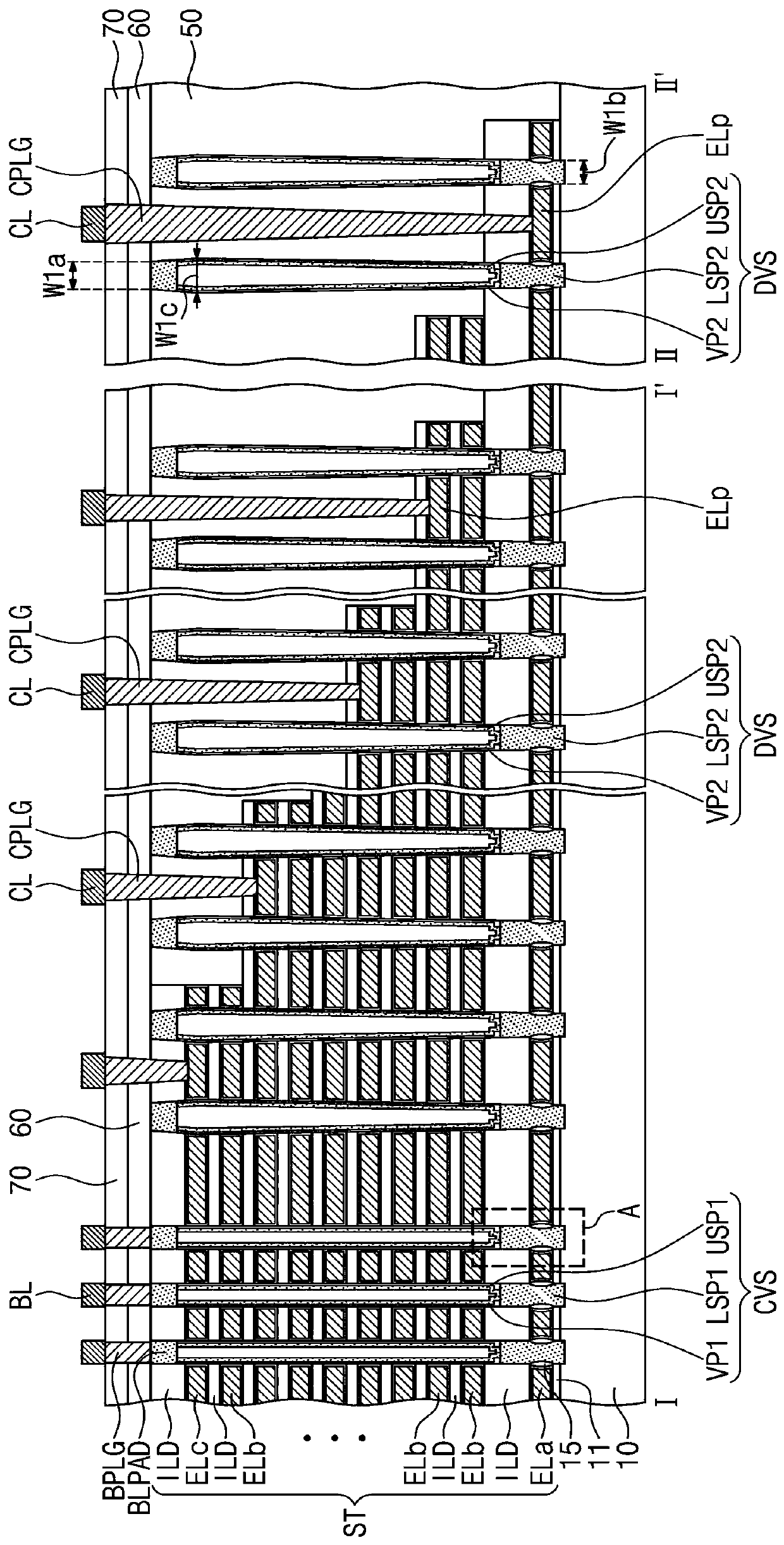

Three dimensional semiconductor memory device

PendingCN109817626AMeet the technical requirements for the minimum distancePrevent electrical short circuitSolid-state devicesRead-only memoriesCell contactSemiconductor

Provided is a three-dimensional semiconductor memory device. The device may include a substrate that includes a cell array region and a connection region; an electrode structure provided on the substrate to extend in a first direction and include electrodes that are vertically stacked on the substrate and include pad portions which are stacked on the connection region to have a staircase structure; cell vertical structures provided on the cell array region to penetrate the electrode structure; dummy vertical structures provided on the connection region to penetrate the pad portion of each electrode; and cell contact plugs coupled to the pad portions of the electrodes. Each cell contact plug may have a non-circular top surface, and the dummy vertical structures may be arranged to surround each cell contact plug, in a plan view.

Owner:SAMSUNG ELECTRONICS CO LTD

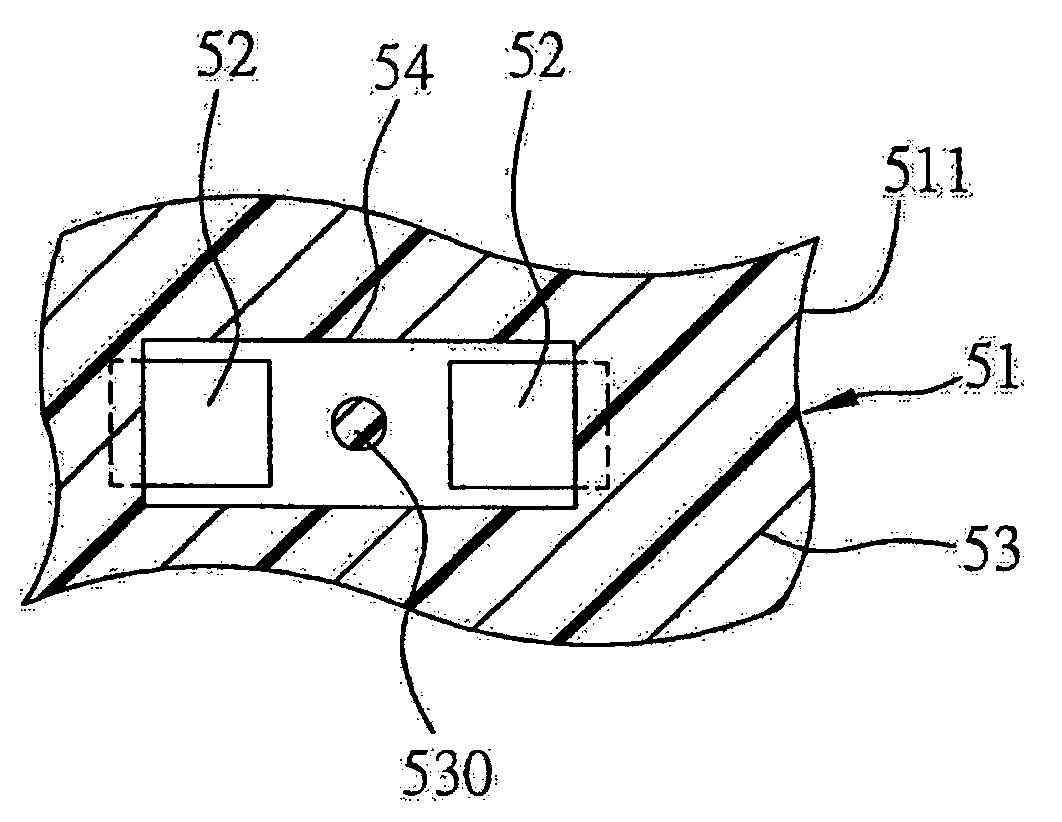

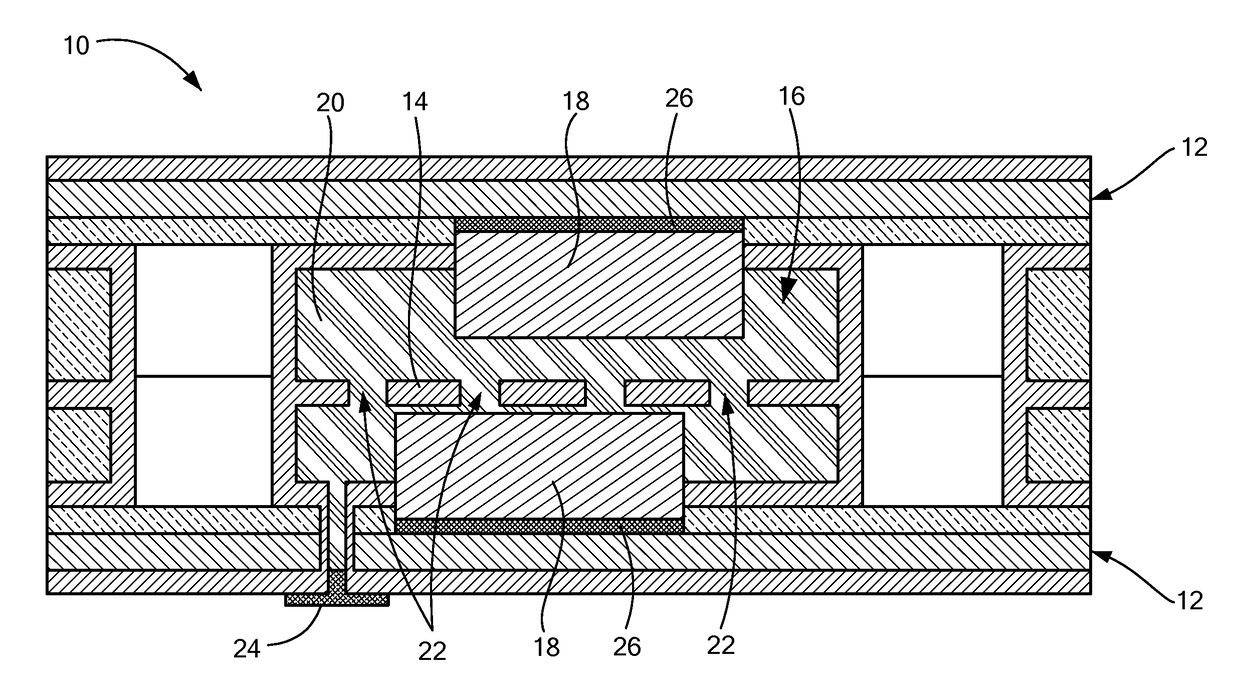

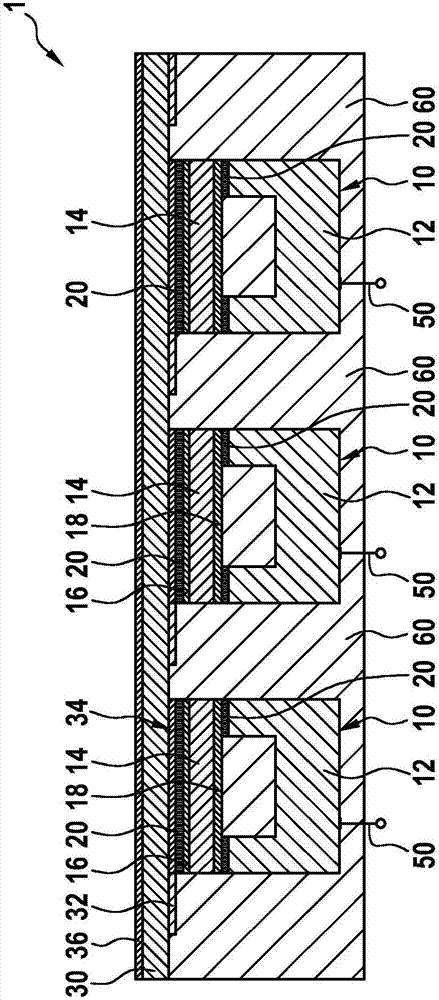

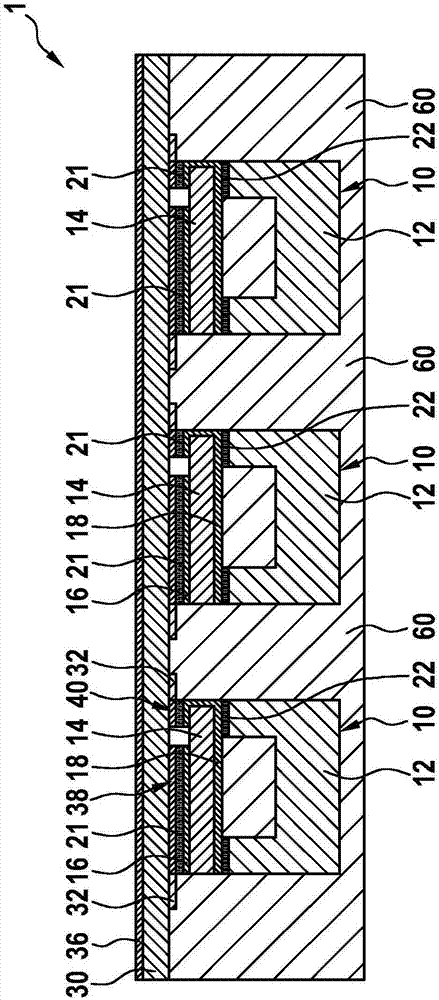

Sound transducer comprising a plurality of single transducers and method for the production thereof

ActiveCN107249763AConductivity disappears or is negligibleTo achieve a conductive connectionMechanical vibrations separationSound producing devicesTransducerElectrode

The invention relates to a sound transducer (1) comprising a plurality of single transducers (10), wherein the single transducers (10) have a carrier (12) and a piezoelectrical element (14) with a first electrode (16) and a second electrode (18). According to the invention, the single transducer (10) is adhered to a flexible film (30) in the form of an array, and the surfaces of the single transducers (10) that are not connected to the flexible film (30) are surrounded by an encapsulation material (60) having vibration damping properties. The invention also relates to a method for producing a sound transducer (1) of this type.

Owner:ROBERT BOSCH GMBH

Thin-film diode, double scanning diode array substrate and LCD board

InactiveCN101383380APrevent electrical short circuitAvoid damageSolid-state devicesNon-linear opticsThin-film diodeActive layer

The invention provides a thin-film diode, a dual scanning diode array substrate and a liquid crystal display panel, wherein the thin-film diode is suitable for being configured on a substrate. The thin-film diode comprises a first electrode, an insulating layer, an active layer and a second electrode, wherein the first electrode is configured on the substrate, the insulating layer is configured on the substrate so as to cover the first electrode, and the insulating layer is provided with an opening so as to expose the partial area of the first electrode; the active layer is configured on the first electrode, and extends to the insulating layer from the first electrode exposed through the opening; the second electrode is respectively configured on the insulating layer and the active layer; and the active layer is at least positioned in the coverage range of the second electrode. The invention also provides a liquid crystal display panel and a dual scanning diode array substrate with the thin-film diode.

Owner:AU OPTRONICS CORP

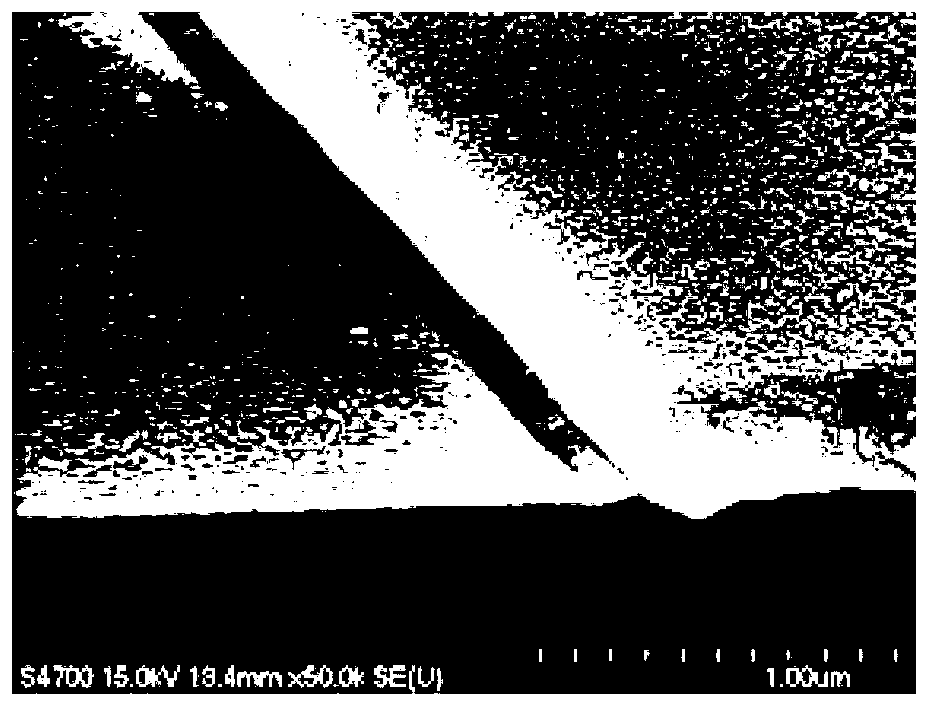

Semiconductor device

InactiveCN1523645APrevent electrical short circuitSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

A semiconductor chip is produced through dicing without removing a conductive film for forming an interconnection and the like from a dicing line region. A prescribed insulating sheet member is adhered to this semiconductor chip at its back face, and the back face and the side face of semiconductor chip, and part of a front face along the periphery of semiconductor chip are covered by insulating sheet member. Thus, even when the conductive film in the dicing line region is curled up by dicing and a burr is resulted at the periphery of semiconductor chip, burr is covered by insulating sheet member to prevent a wire and burr from directly contacting to each other. Thus, a semiconductor device in which an electrical short circuit is prevented without removing a conductive film from a dicing line can be obtained.

Owner:RENESAS TECH CORP

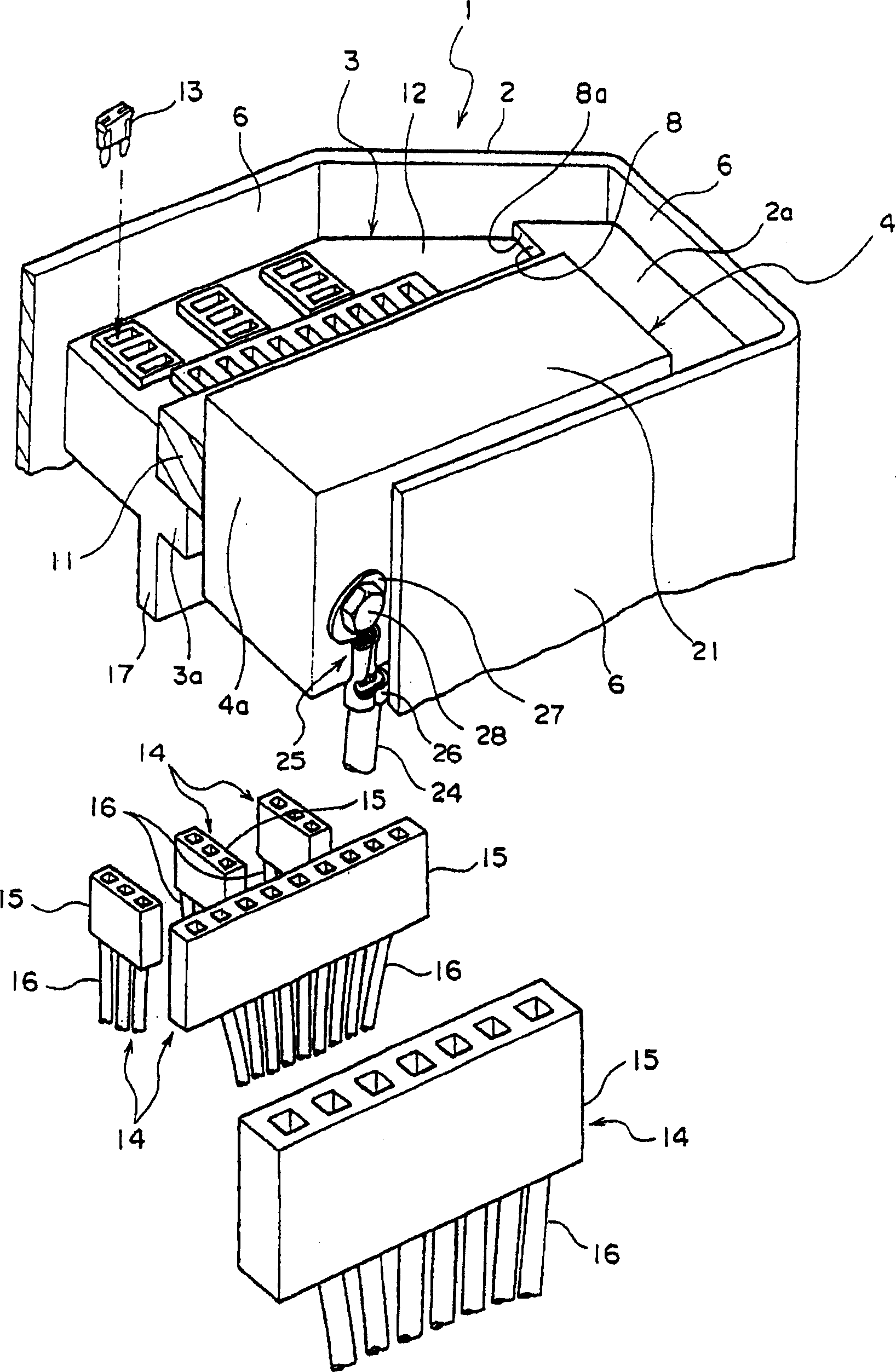

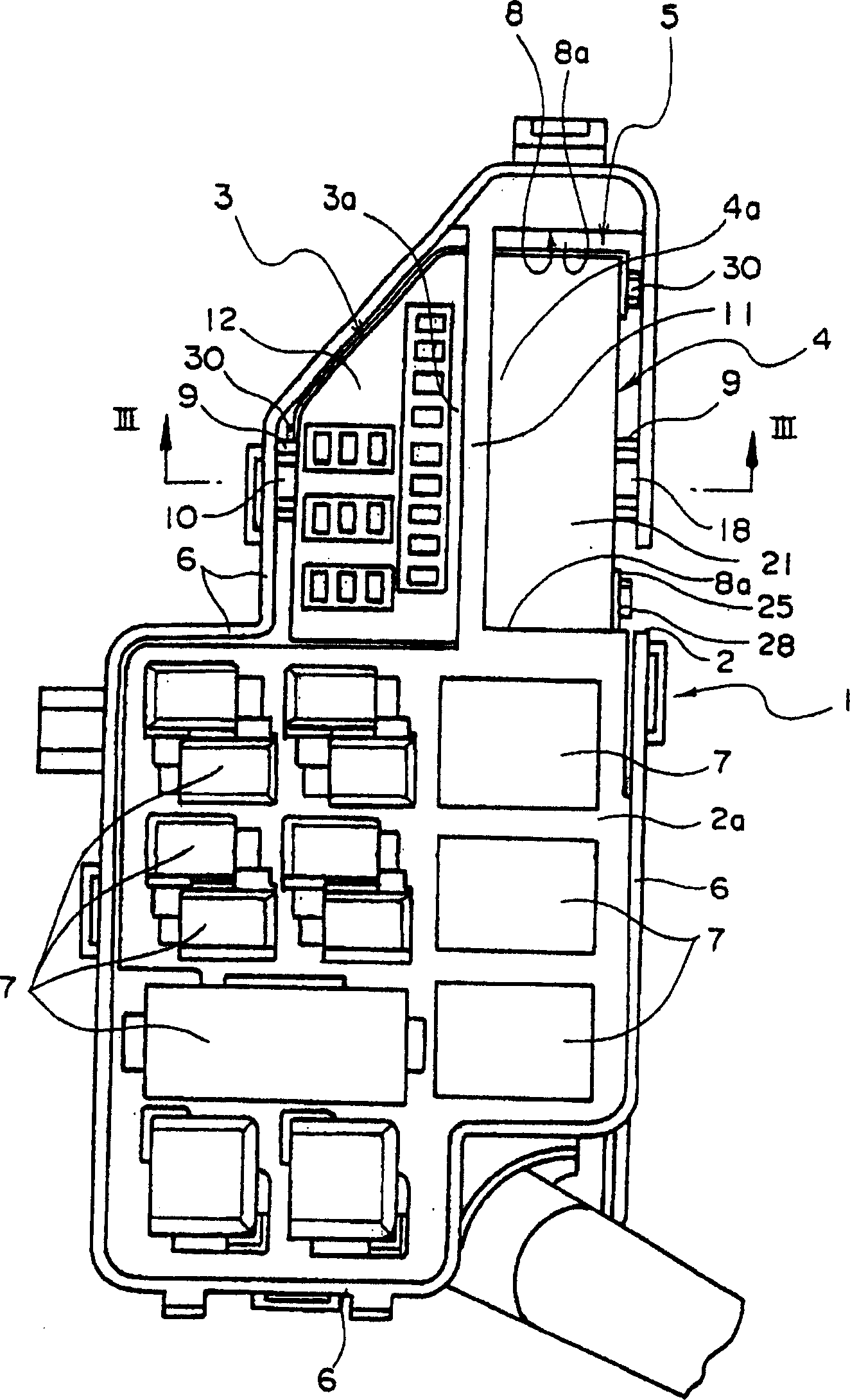

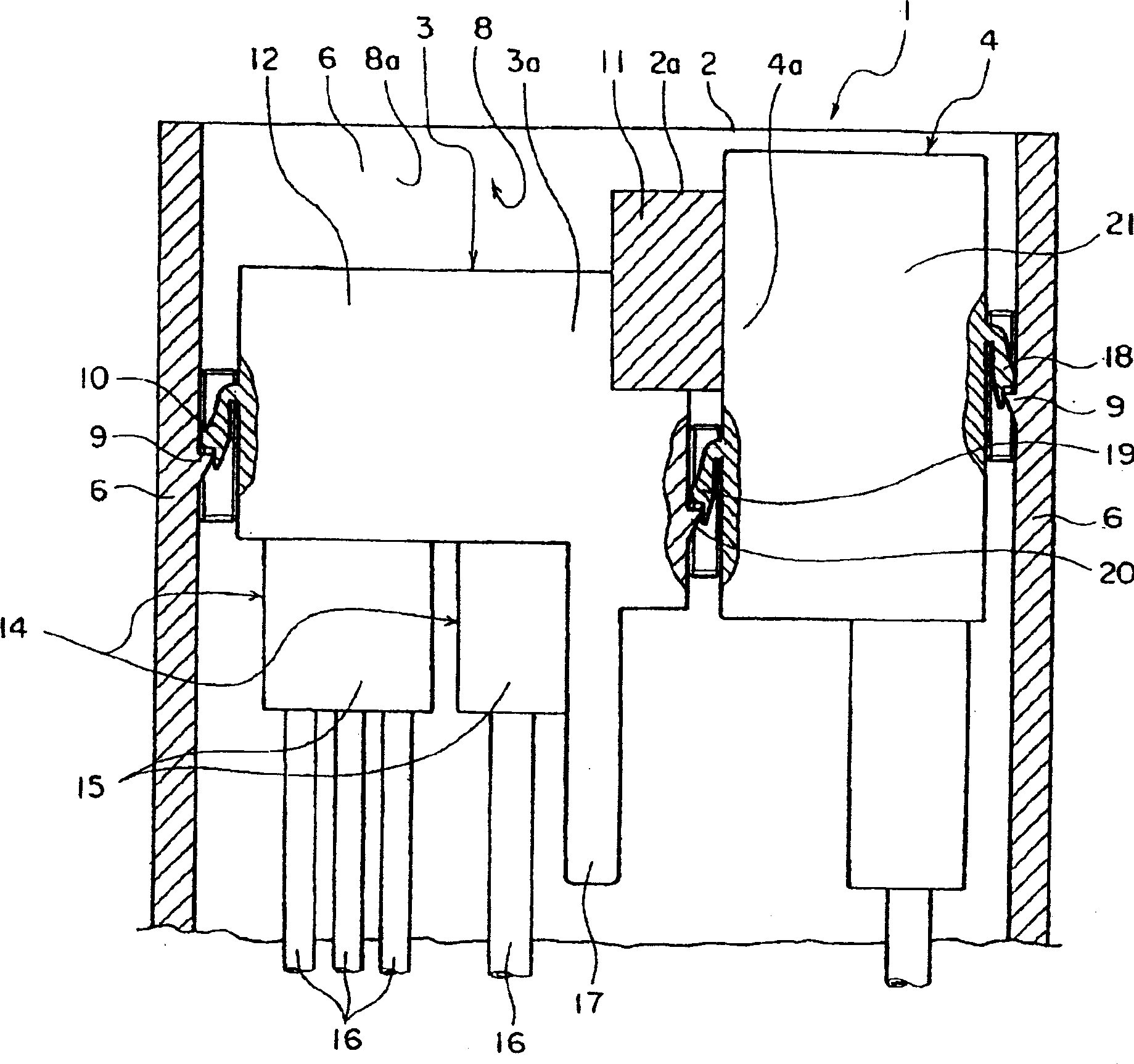

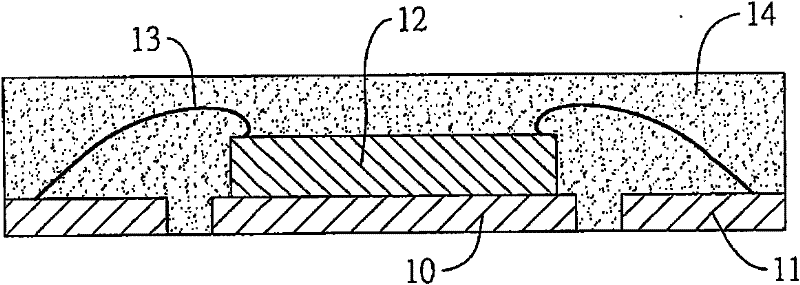

Electric distribution box

InactiveCN1866656AIncrease vertical lengthReduce stiffnessVehicle connectorsCoupling device detailsMechanical engineeringEngineering

An electric distribution box includes a first cassette block that includes a flat face having a first long side and a second short side, and provided with a first electric parts, a second cassette block that includes a flat face having a second long side and a second short side, and provided with a second electric parts, and a bus bar that connects a terminal of the first electric parts to a terminal of the second electric parts. The first cassette block is arranged with the second cassette block so that the first long side of the first cassette block and the second long side of the second cassette block are disposed in parallel and opposed to each other. The bus bar is disposed along outer surfaces of the first and second cassette blocks.

Owner:YAZAKI CORP

Semiconductor package with electrical connection structure and manufacturing method thereof

ActiveCN102130085AShorten the lengthImprove adhesion strengthSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionSemiconductor package

The invention provides a semiconductor package with an electrical connection structure and a manufacturing method thereof, and the semiconductor package comprises a conducting wire layer, a chip, a welding wire, a packaging colloid, an anti-welding layer and welding balls, wherein the conducting wire layer comprises a chip carrier and a plurality of conducting wires annularly arranged on the periphery of the chip carrier; the packaging colloid comprise a plurality of recesses which are used for embedding the chip carrier and the conducting wires, in the depth of greater than the thickness of the chip carrier and the conducting wires and further exposed on the surface of the conducting wires and the chip carrier; the anti-welding layer is formed in the recesses of the packaging colloid, and the anti-welding layer comprises a plurality of open holes of the anti-welding layer for exposing all conducting wire terminals and part of the chip carrier; and the welding balls are formed in all the open holes of the anti-welding layer to electrically connect with the corresponding conducting wire terminals. Therefore, the adhesion strength of the anti-welding layer is improved by mutual embedding and clamping between the anti-welding layer and the packaging colloid, a path for enabling wet gas to infiltrate into the package is prolonged, and the product reliability is enhanced.

Owner:SILICONWARE PRECISION IND CO LTD

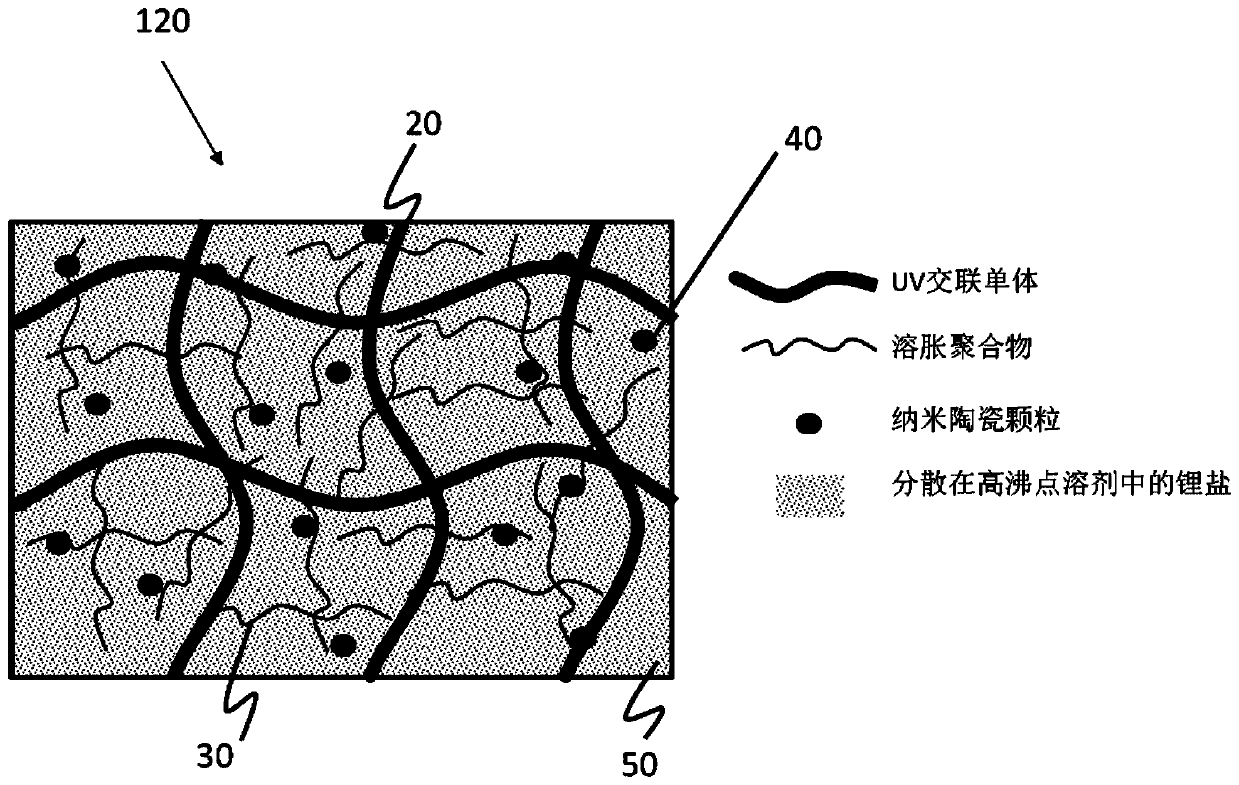

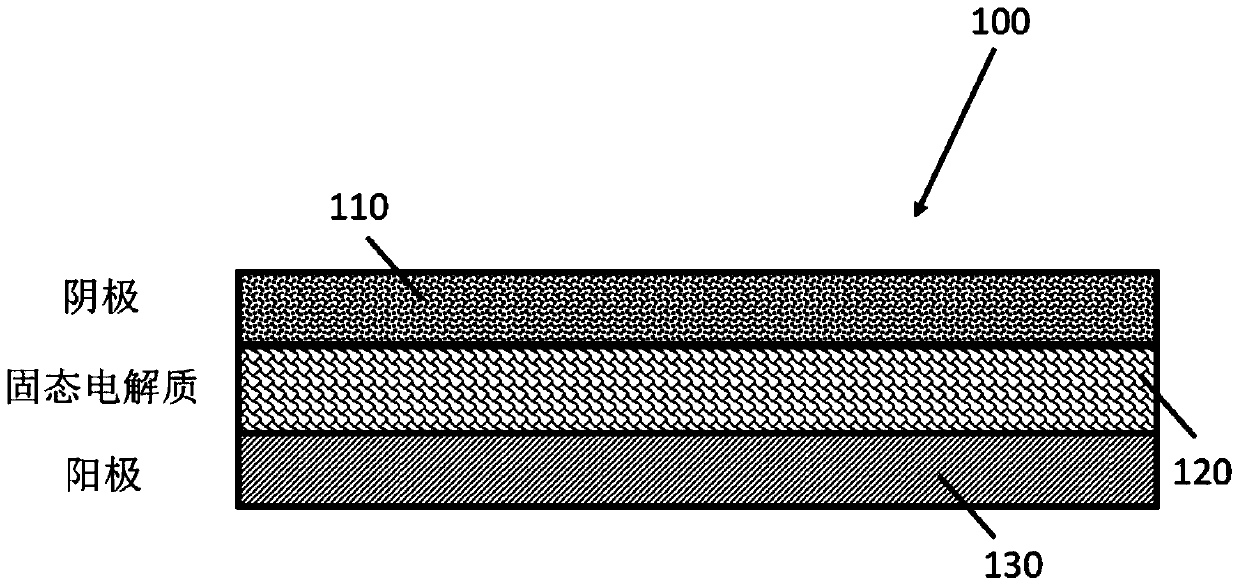

A precursor material for lithium ion batteries and a method for manufacturing lithium ion batteries

ActiveCN109994770AAct as an electrolyteHigh mechanical strengthFinal product manufactureCell component detailsSolid state electrolyteConductive polymer

A precursor material for lithium ion batteries and a method for manufacturing lithium ion batteries are provided. The precursor material is UV-curable and printable and can be used as a separator anda solid electrolyte. The precursor material includes a lithium salt dissolved in one or more organic solvents; UV-curable monomer in an amount from approximately 4 weight percent to approximately 10 weight percent, a UV-initiator; one or more host ion conductive polymers in an amount less than approximately 5 weight percent of the precursor material; and a ceramic powder. The precursor material, when cured, has sufficient mechanical rigidity to act as a separator preventing electrical shorting between a lithium ion battery cathode and a lithium ion battery anode, and also has sufficient electrical conductivity to function as an electrolyte for a lithium ion battery. The provided method enables the formation of batteries with complex shapes through printing.

Owner:NANO & ADVANCED MATERIALS INST

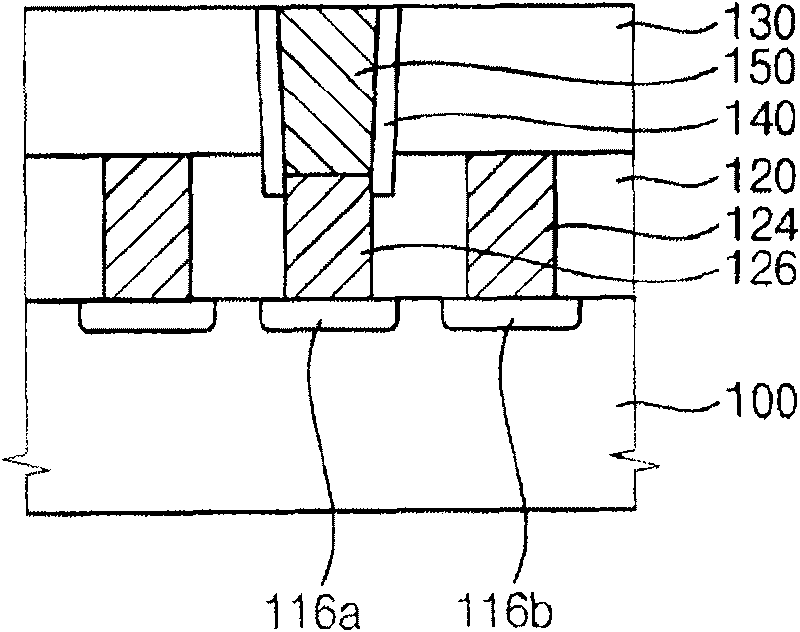

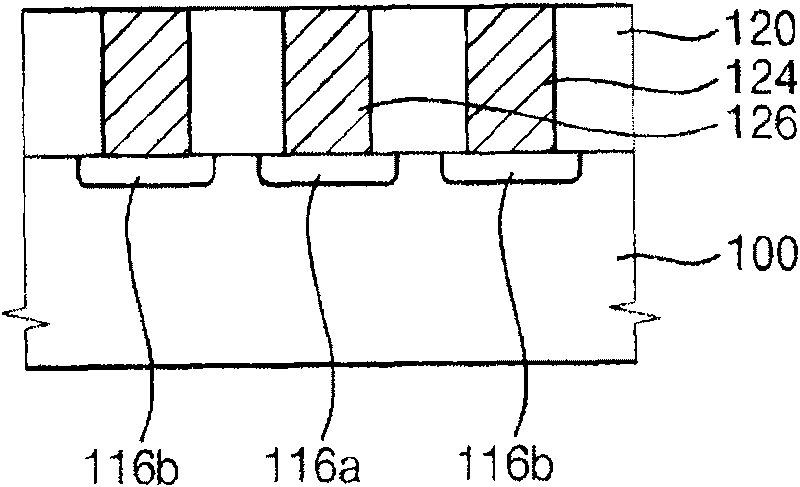

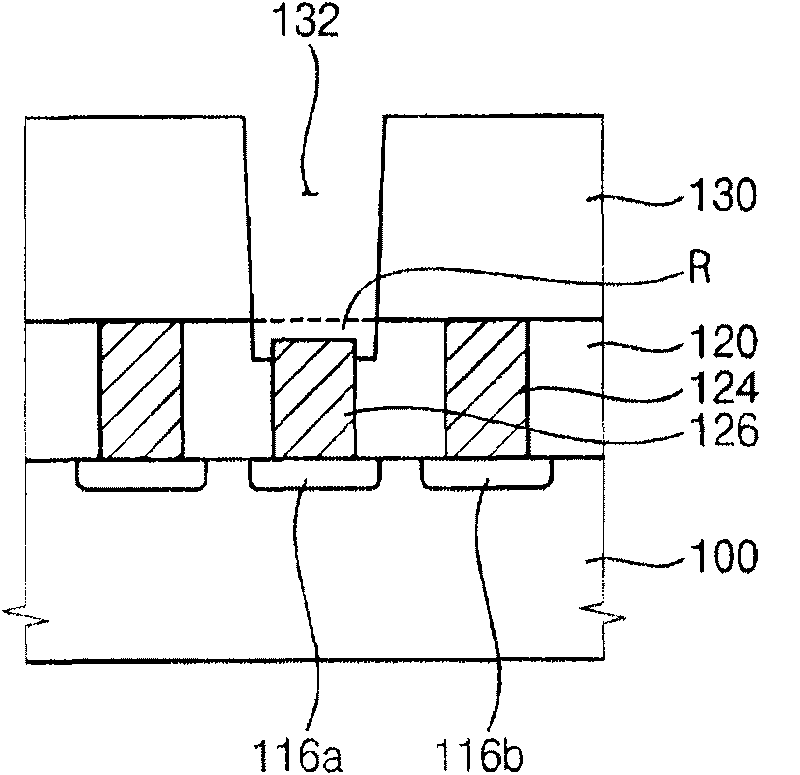

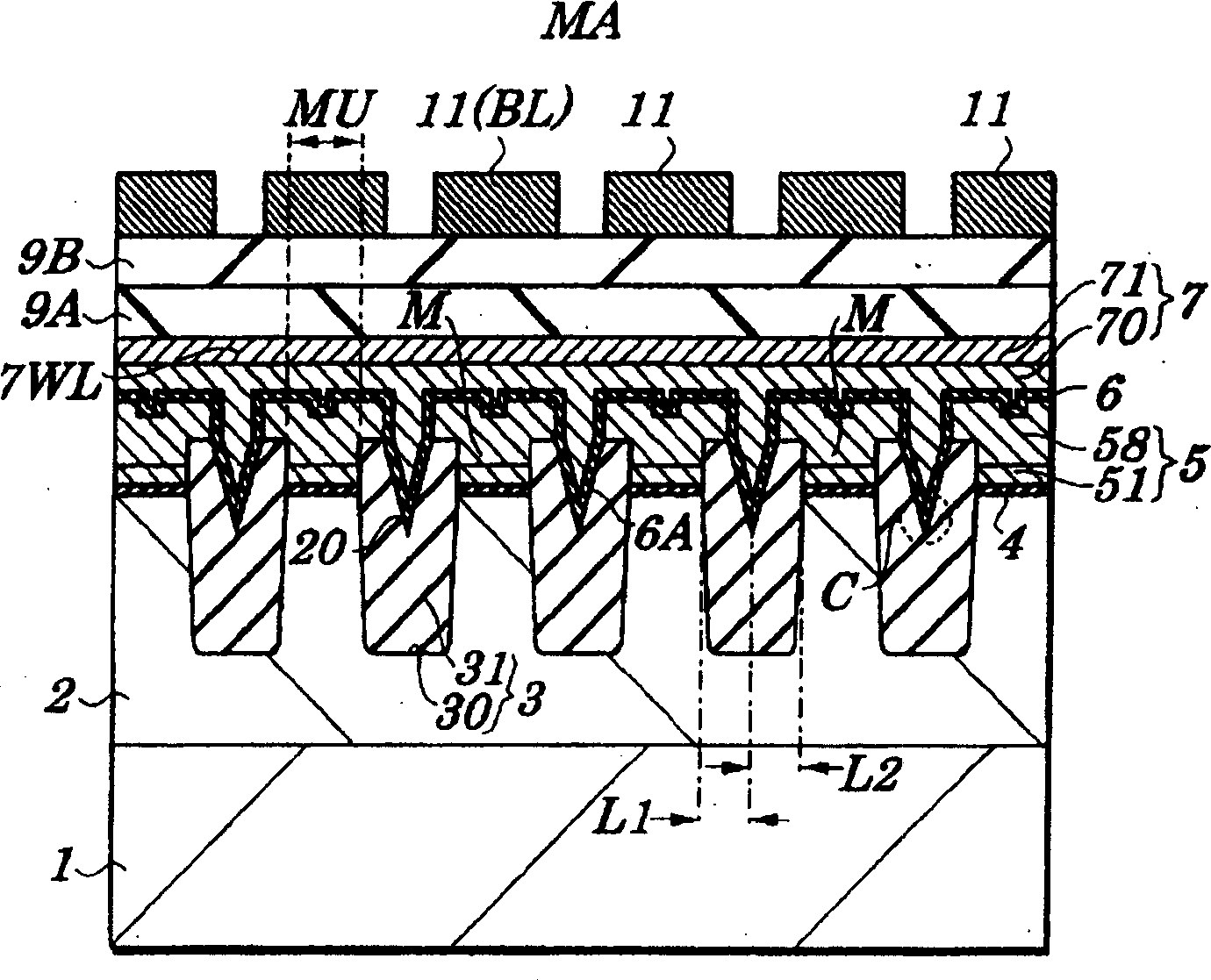

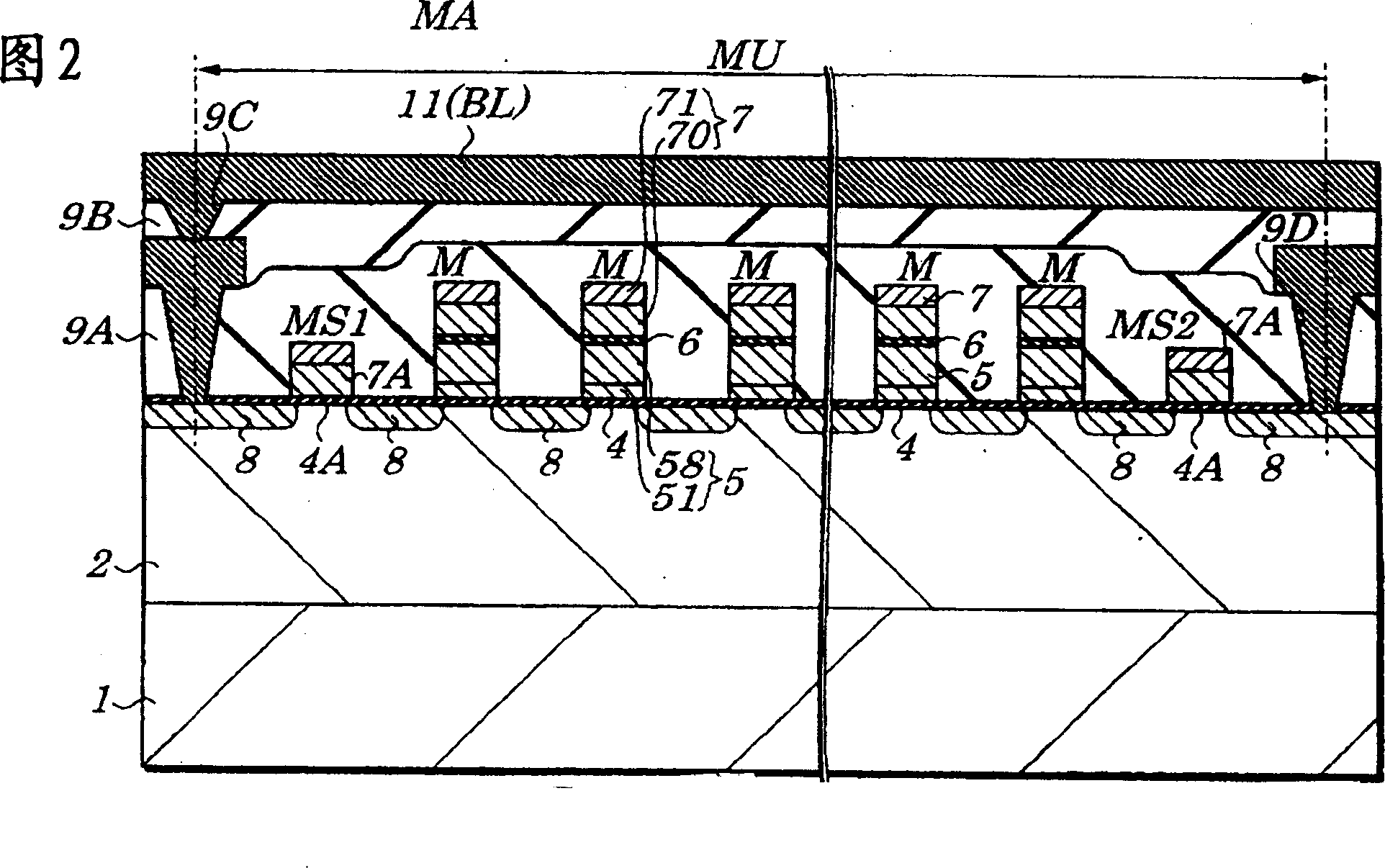

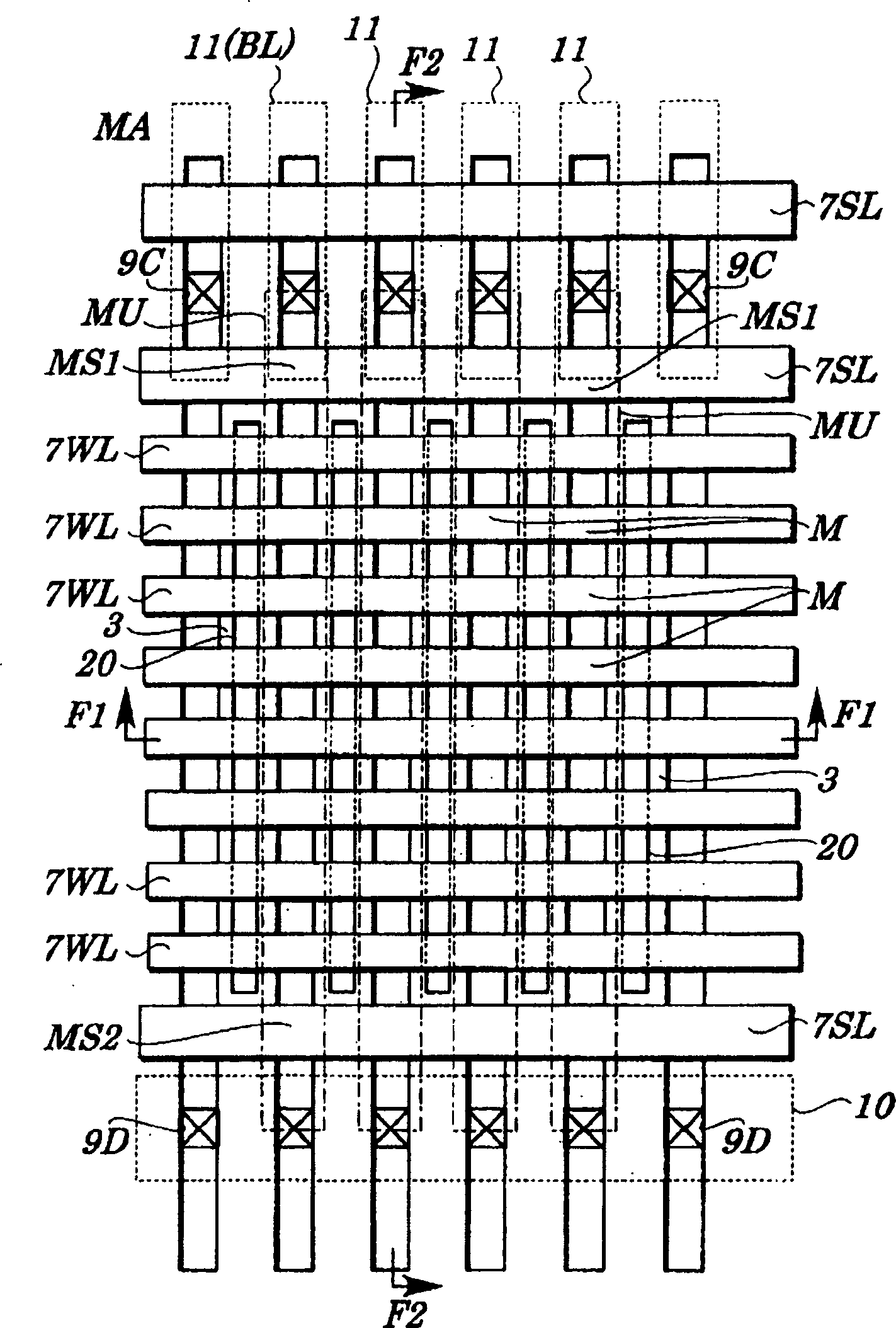

Semiconductor device and method of manufacturing the same

InactiveCN1503364APrevent electrical short circuitImprove electrical reliabilityTransistorSolid-state devicesEngineeringMemory circuits

A semiconductor device having a high reliability nonvolatile memory circuit that can avoid the word line to substrate short, and its manufacturing method are provided. The semiconductor device with a nonvolatile memory circuit consists of: a device isolation area 3 that has a first trench 30 and isolation filler 31 filled in the trench; a second trench 20 that is formed between the floating electrodes 5 of the memory cells M adjacent to each other along the gate width direction, and is narrow on the bottom thereof; and word line (WL) 7 that has a part buried in the second trench 20.

Owner:KK TOSHIBA

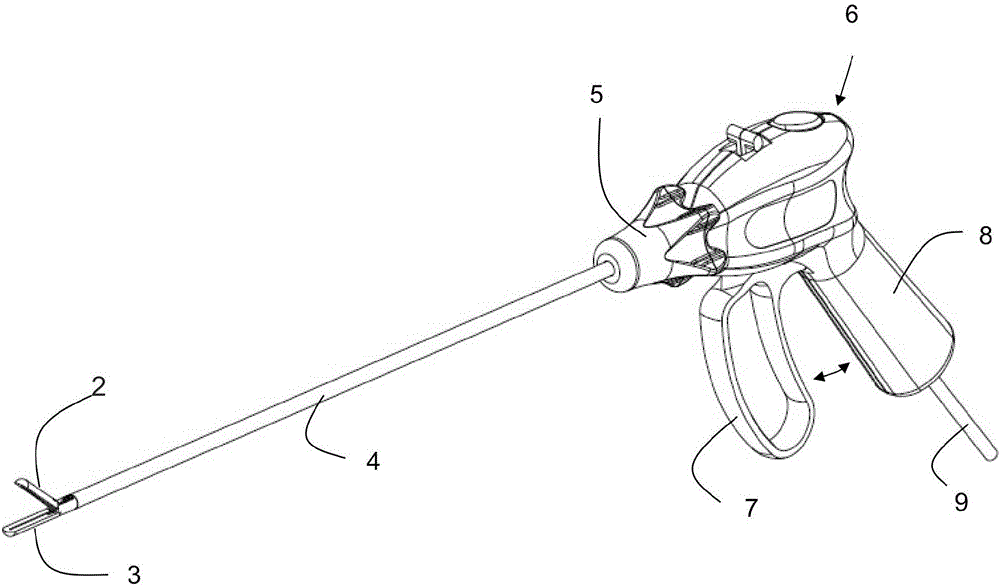

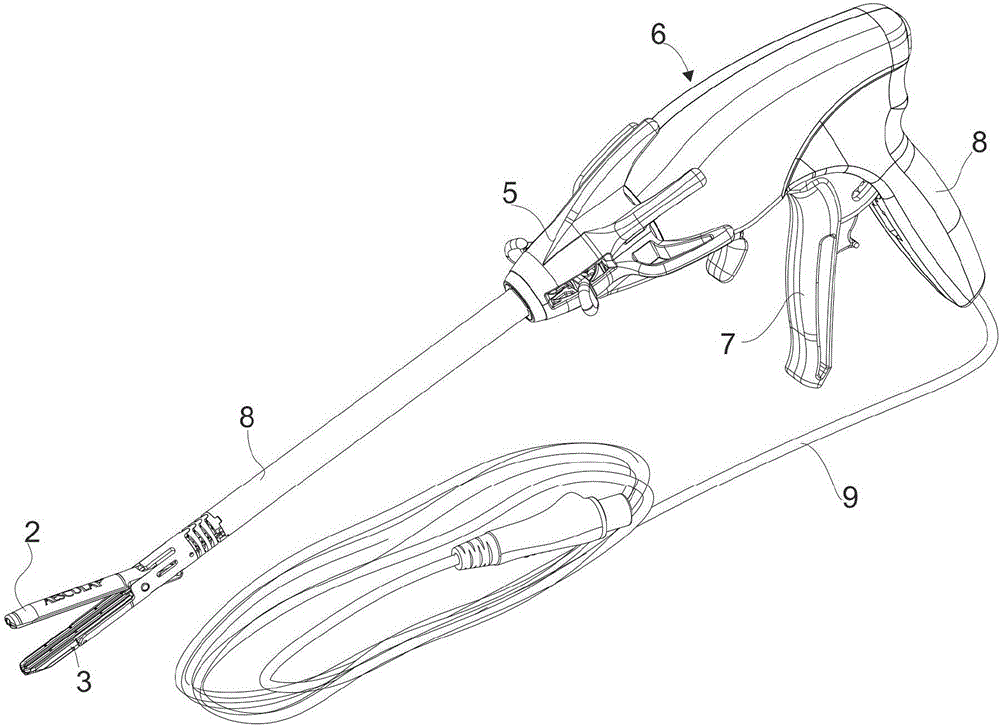

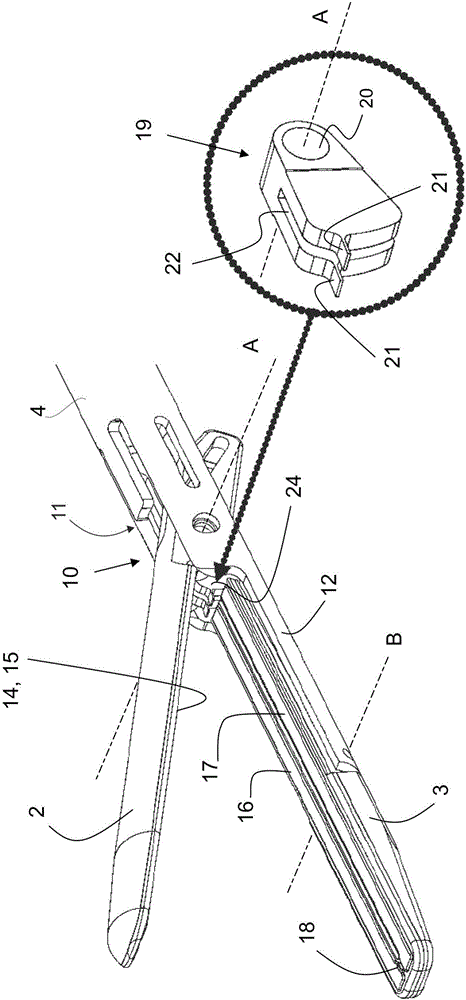

Electrosurgical instrument and jaw part for same

InactiveCN106456248AReduced risk of short circuitsUniform surface pressureDiagnosticsSurgical instruments for heatingConductive materialsBiomedical engineering

An electrosurgical instrument is disclosed having a jaw part composed of instrument branches which are movable towards each other and on each mutually facing side of which one or more electrode surfaces are arranged / formed, wherein the movement of the instrument branches relative to each other can be limited by at least one proximal spacer acting on proximal end portions of the instrument branches, at least one medial spacer acting on a medial portion, and at least one distal spacer acting on distal end portions of the instrument branches. According to the invention, the proximal and / or the distal spacer are made of electrically non-conductive material and the at least one medial spacer is composed of at least one electrode made of an electrically conductive material and connected electrically conductively to the electrode. Furthermore, the at least one medial spacer interacts with a local insulation component made of a non-conductive material, which insulation component is arranged in an electrically insulating manner on at least one opposite electrode.

Owner:AESCULAP AG

Method for producing an array substrate for a liquid crystal display device

ActiveCN103026293AEnvironmental friendlyPrevent poor wiringNon-linear opticsSurface treatment compositionsLiquid-crystal displayPhysical chemistry

The present invention relates to method for producing an array substrate for a liquid crystal display device, wherein an etching solution composition is used which comprises, with respect to the entire weight of the composition, a) from 5 to 25 percent by weight of hydrogen peroxide (H2O2); b) from 0.1 to 5 percent by weight of sulphuric acid; c) from 0.01 to 1.0 percent by weight of a fluorine-containing compound; d) from 0.1 to 5 percent by weight of an azole compound; e) from 0.1 to 5 percent by weight of an imidazole compound; and f) a balance of water.

Owner:DONGWOO FINE CHEM CO LTD

Hot melt adhesive for electric power equipment

InactiveCN102575136AStickiness disappearsImprove heat resistanceWax adhesivesPolymer scienceElectric power equipment

Disclosed is a hot melt adhesive with quick tack loss and superior heat resistance that is capable of contributing to improvements in the productivity and safety of electric power equipment. Additionally disclosed is electric power equipment that is produced using the hot melt adhesive. The hot melt adhesive for the electric power equipment comprises (A) a copolymer of an ethylene and a carboxylic acid derivative with an ethylene double bond, (B) a polypropylene wax, (C) a polyethylene wax, and (D) a Fischer-Tropsch wax. (A) An ethylene-vinyl acetate copolymer is preferable as the copolymer. The electronic power equipment can be excellently produced by using the abovementioned hot melt adhesive.

Owner:HENKEL KGAA