Patents

Literature

561results about How to "Reduced risk of short circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Metal lithium negative electrode piece, preparation method thereof and metal lithium secondary battery

InactiveCN107579204AIncrease surface areaReduce current densityCell electrodesLi-accumulatorsPolymer electrolytesSolvent

The invention discloses a metal lithium negative electrode piece, a preparation method thereof and a metal lithium secondary battery. The metal lithium negative electrode piece comprises a current collector, wherein a metal lithium layer is formed on the current collector; a composite conductive film is formed on the metal lithium layer. The preparation method of the metal lithium negative electrode piece comprises the following steps: laminating a metal lithium foil and the current collector together, or plating lithium metal on the surface of the current collector; dissolving a polymer electrolyte in a solvent to prepare a polymer electrolyte solution; adding a conductive agent into the polymer electrolyte solution; stirring uniformly and then coating a mixed solution on the metal lithium layer; after evaporating the solvent, forming the composite conductive film on the surface of the metal lithium layer to obtain the metal lithium negative electrode piece; or, coating the mixed solution on a substrate and evaporating the solvent to obtain the composite conductive film, laminating the composite conductive film on the surface of the metal lithium layer to form the composite conductive film and obtain the metal lithium negative electrode piece. The metal lithium negative electrode piece provided by the invention can inhibit lithium dendrites, prevent batteries from being short-circuited, and improve safety performance and cycling performance of lithium batteries.

Owner:ZHUHAI COSMX BATTERY CO LTD

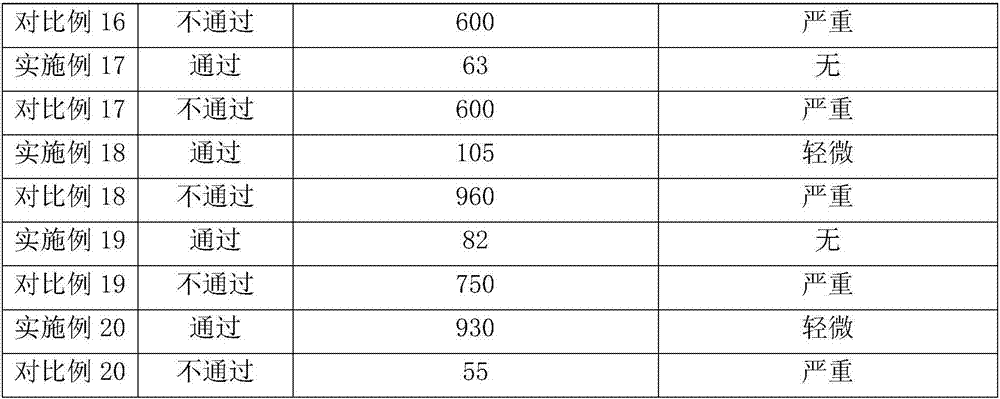

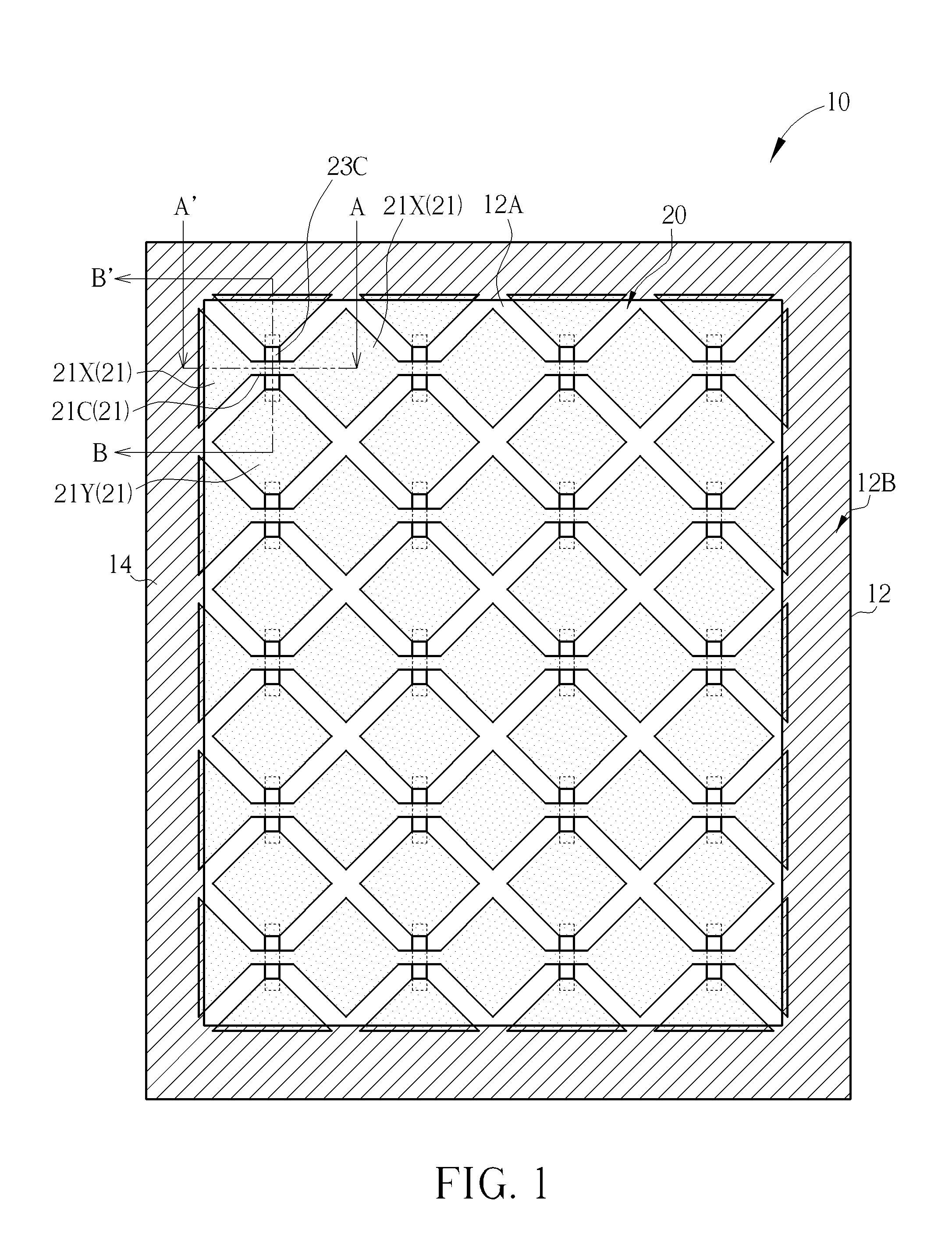

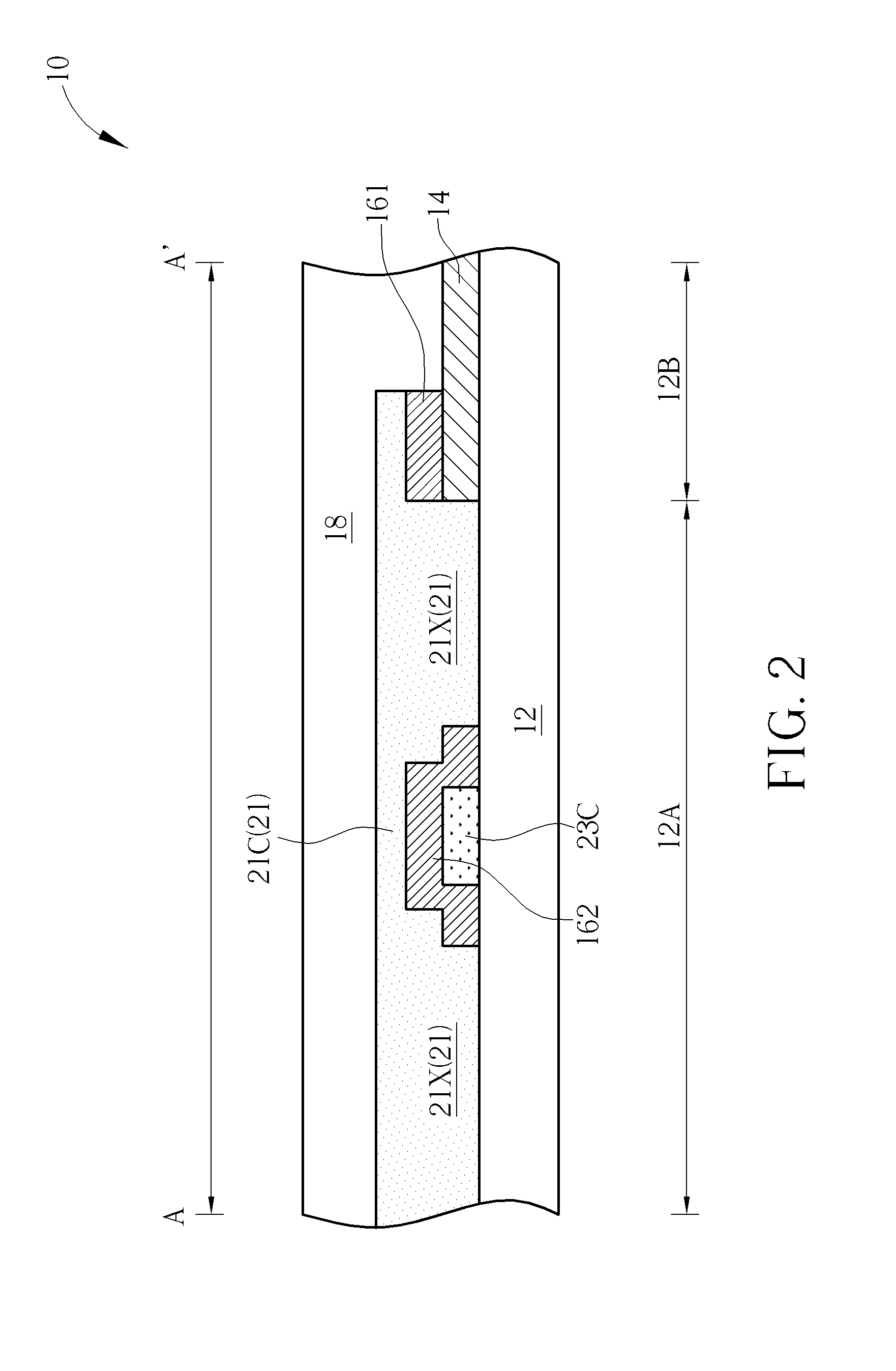

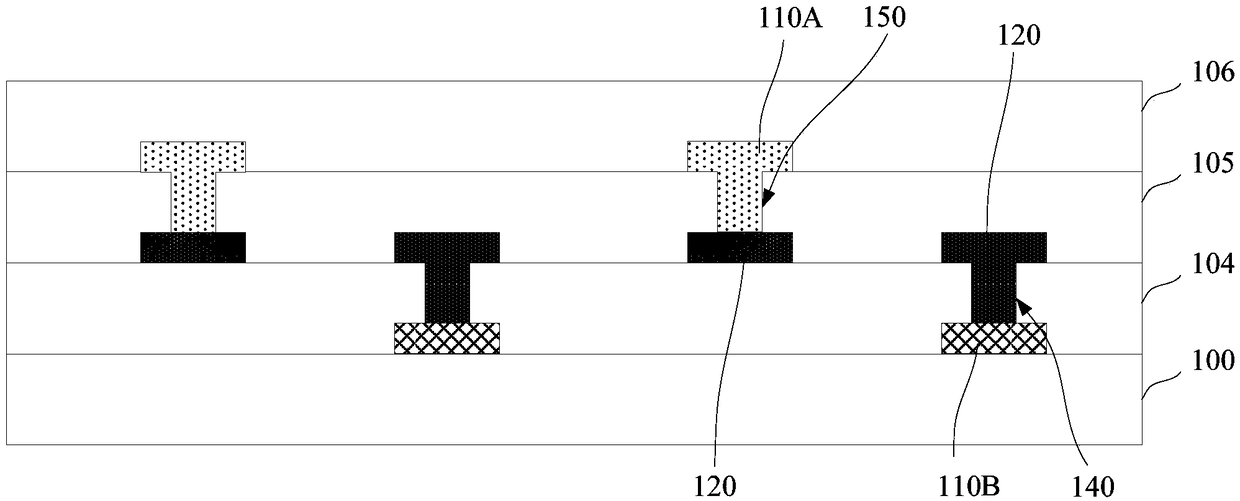

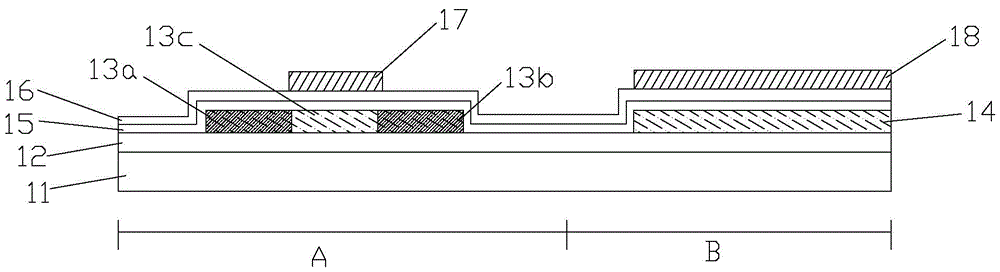

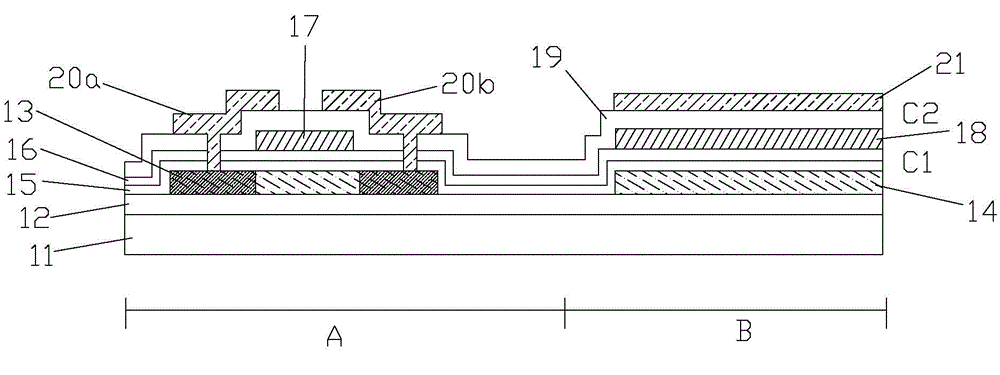

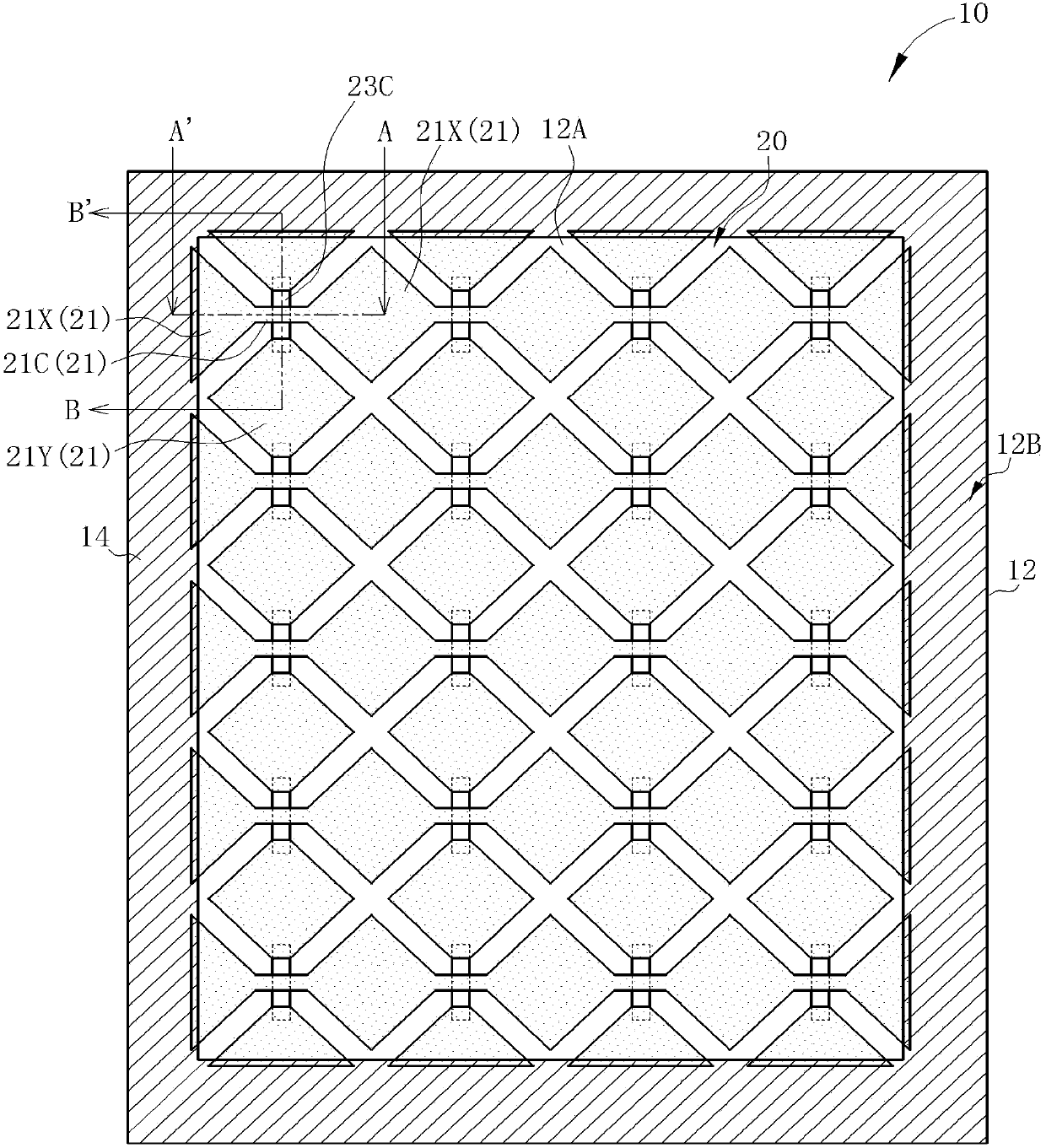

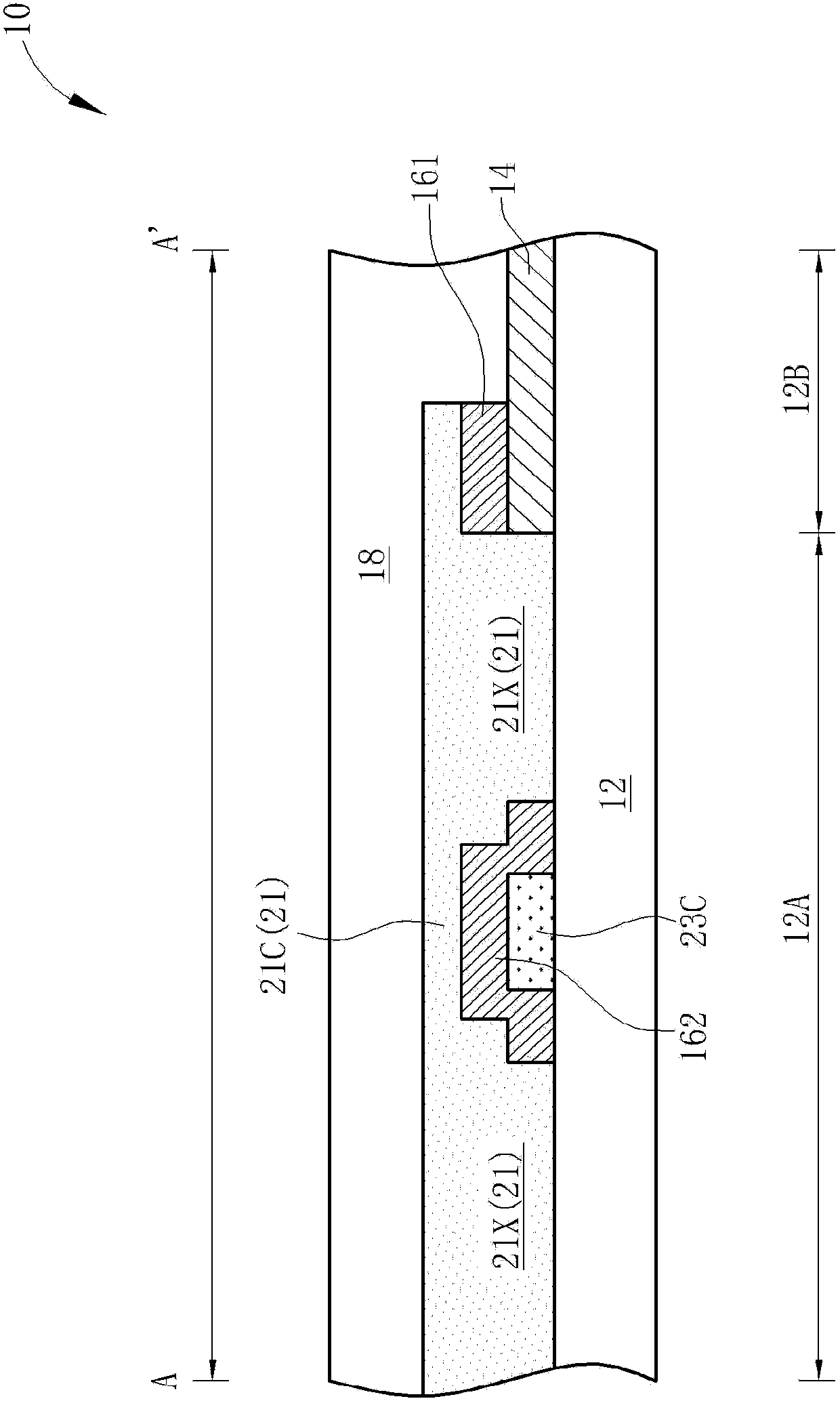

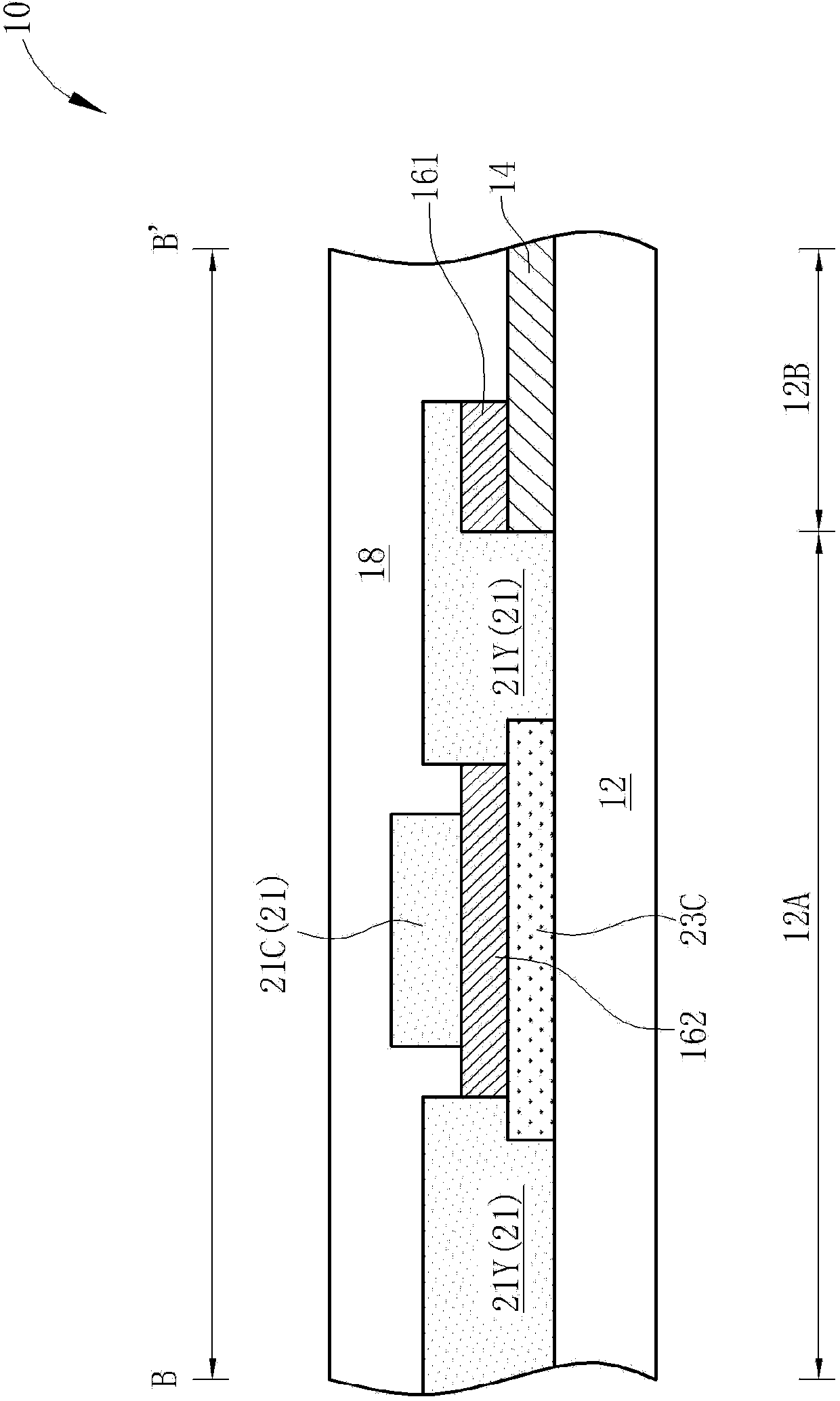

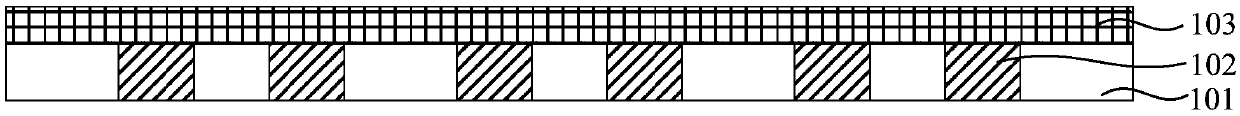

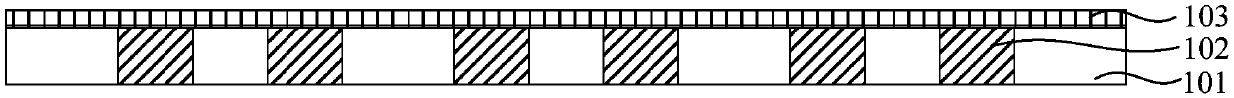

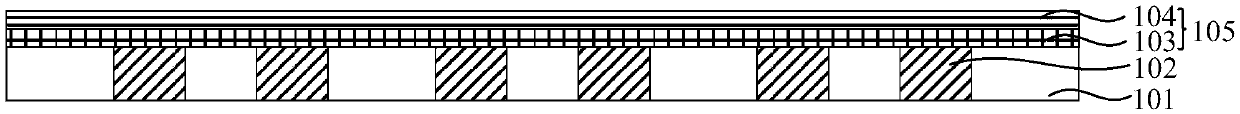

Touch panel and touch display panel and method of making the same

InactiveUS20130241857A1Reduced risk of short circuitsReduce riskCable/conductor manufactureInput/output processes for data processingTouch SensesComputer science

A touch panel includes a substrate, a decoration layer, a touch sensing device, and at least one first insulation pattern. The substrate has a light transmissible region and a peripheral region. The decoration layer is disposed in the peripheral region. The touch sensing device includes a first patterned transparent sensing layer disposed at least in the light transmissible region. The first patterned transparent sensing layer extends to the peripheral region, partially overlapping the decoration layer. The first insulation pattern is disposed in the peripheral region and located between the first patterned transparent sensing layer and the decoration layer, so that the first patterned transparent sensing layer and the decoration layer are not in contact with each other.

Owner:WINTEK CHINA TECH LTD +1

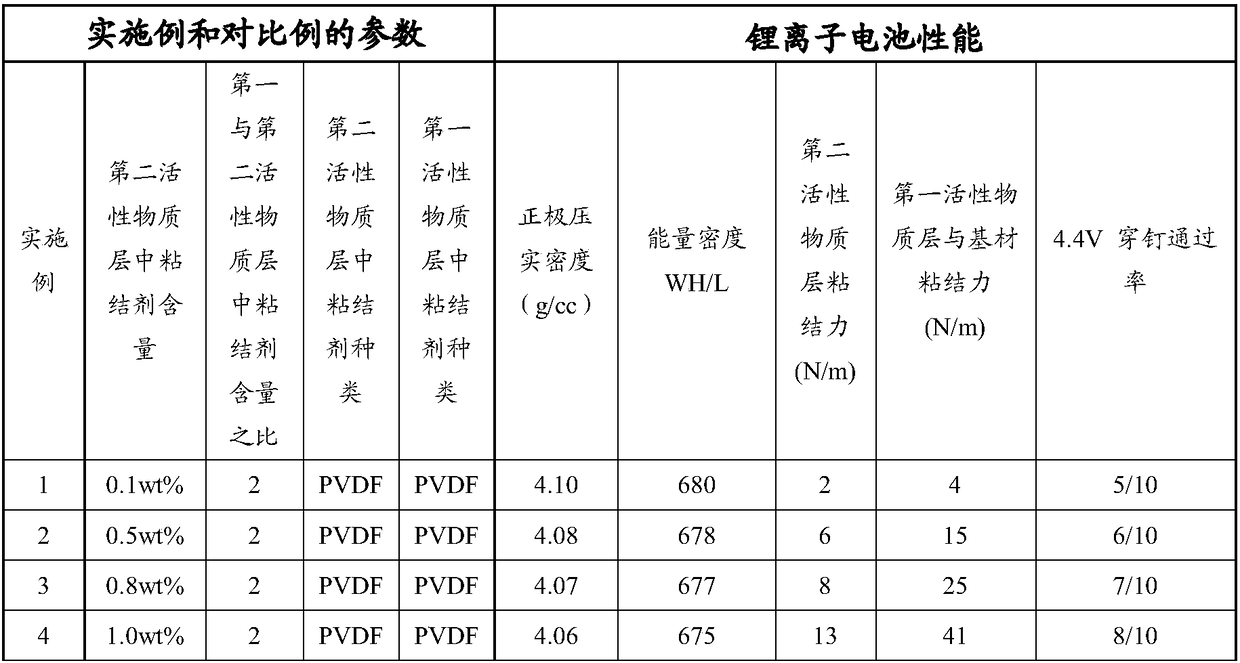

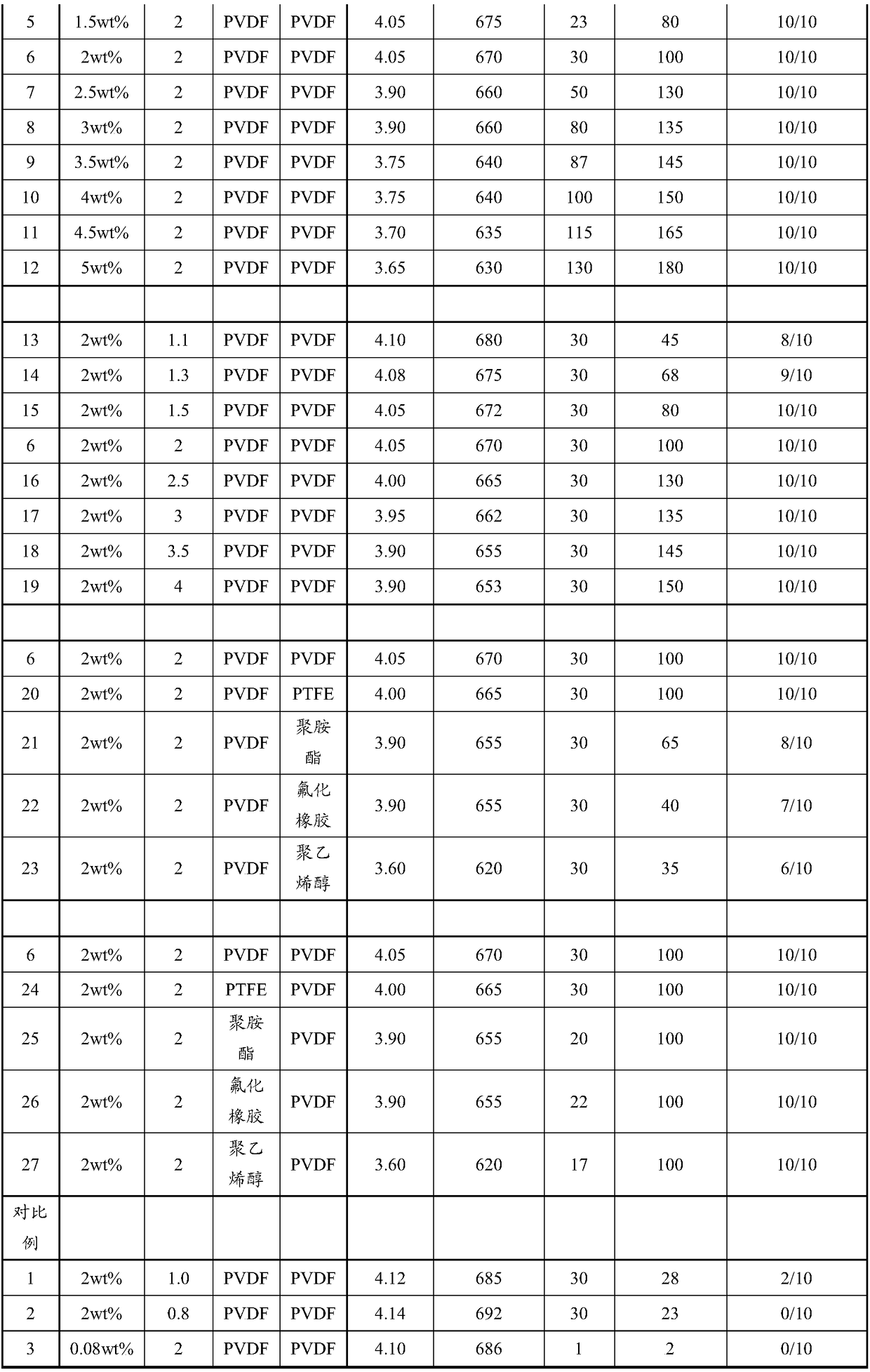

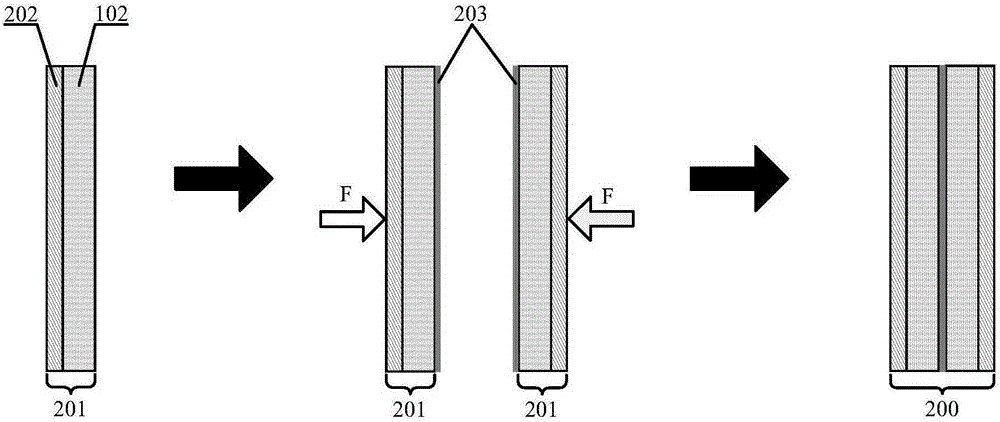

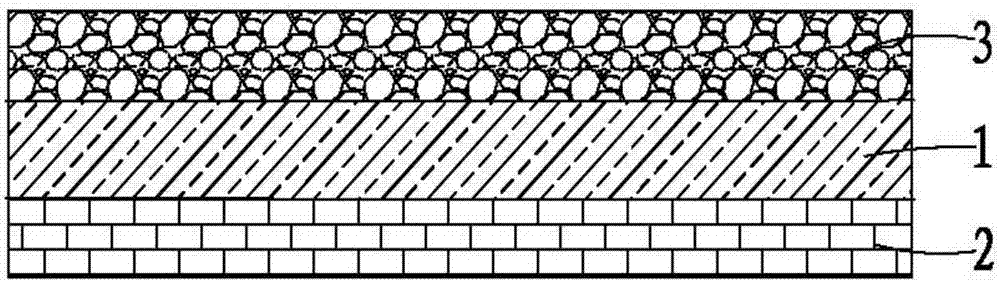

A positive electrode plate and a lithium ion battery

InactiveCN109004171AGuaranteed Energy DensityImprove nail penetration safety performanceFinal product manufactureNon-aqueous electrolyte accumulator electrodesElectrical batteryEngineering

A positive electrode sheet and a lithium ion battery are provided. A positive electrode sheet includes: a current collector; A first active material layer; And a second active material layer; Whereina first active material layer is disposed between the current collector and the second active material layer, the first active material layer and the second active material layer each comprising a binder, and the binder content in the first active material layer is greater than the binder content in the second active material layer. In the present application, the active material in the positive electrode sheet adopts a two-layer design, and the content of the binder in the first active material layer is higher than that in the second active material layer, so that the energy density of the lithium ion battery is ensured, and the purpose of improving the bonding force of the active material layer and the safety performance of the lithium ion battery is achieved.

Owner:NINGDE AMPEREX TECH

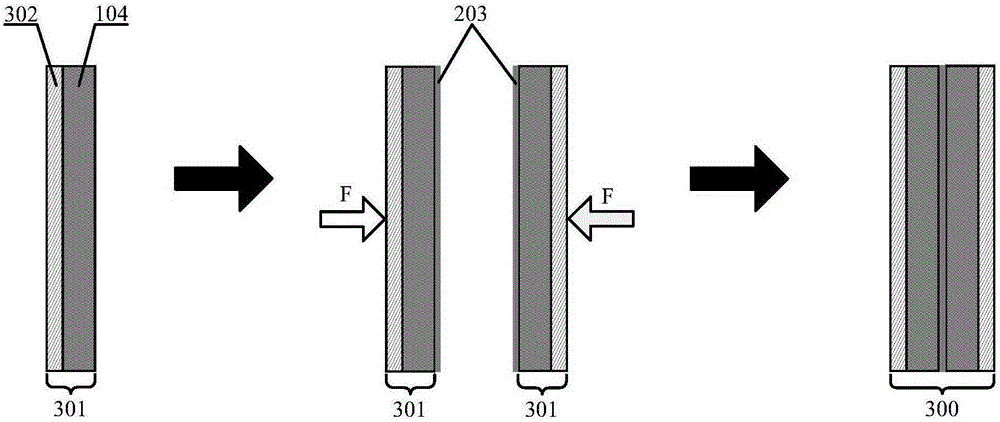

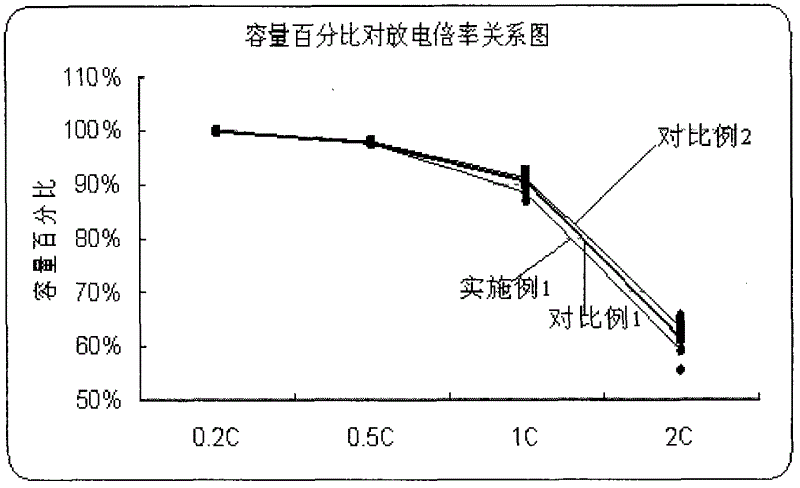

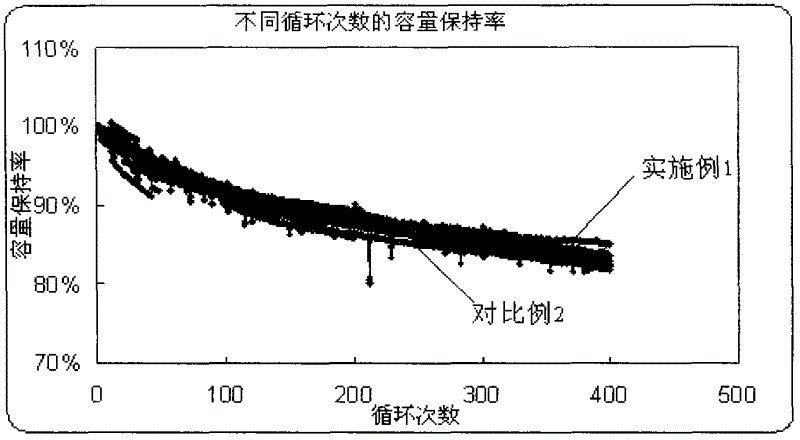

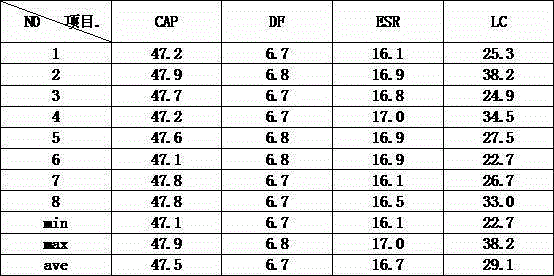

High-power high-capacity lithium ion battery and preparation method thereof

ActiveCN106469825AMeet the requirements of instantaneous high-power workMeet the requirements of large capacityFinal product manufactureElectrode carriers/collectorsInternal resistanceElectrical battery

Owner:BEIJING HAWAGA POWER STORAGE TECH

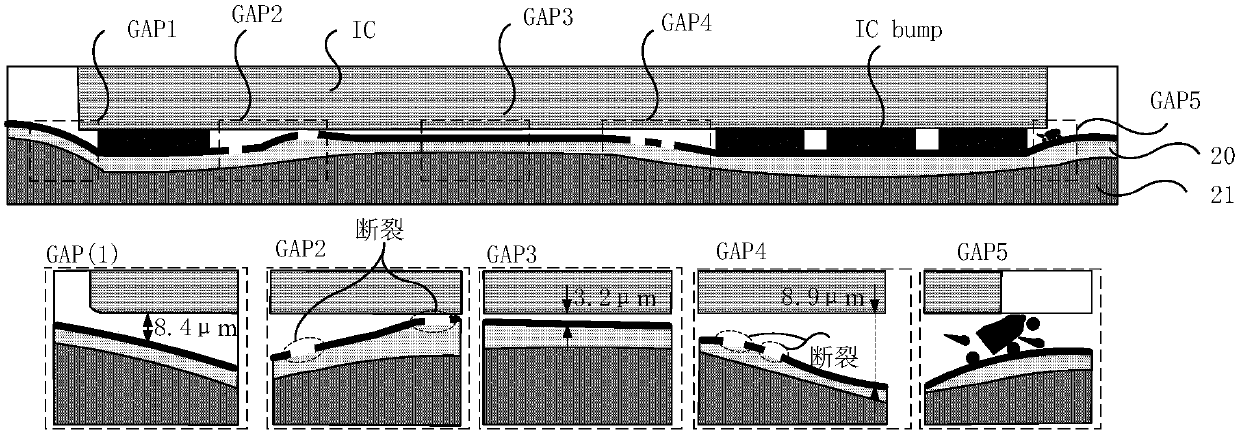

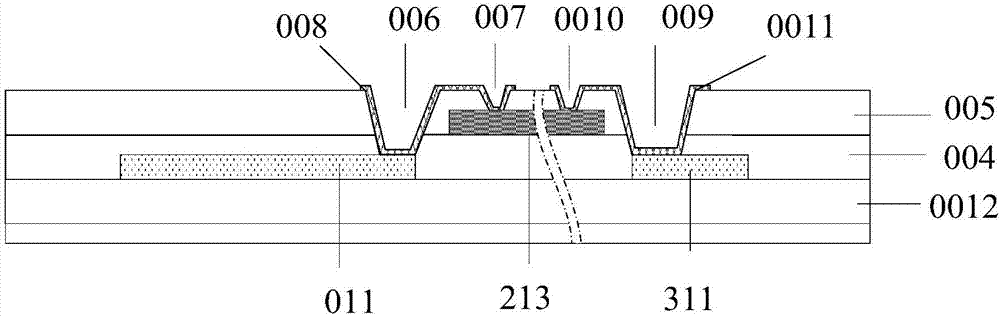

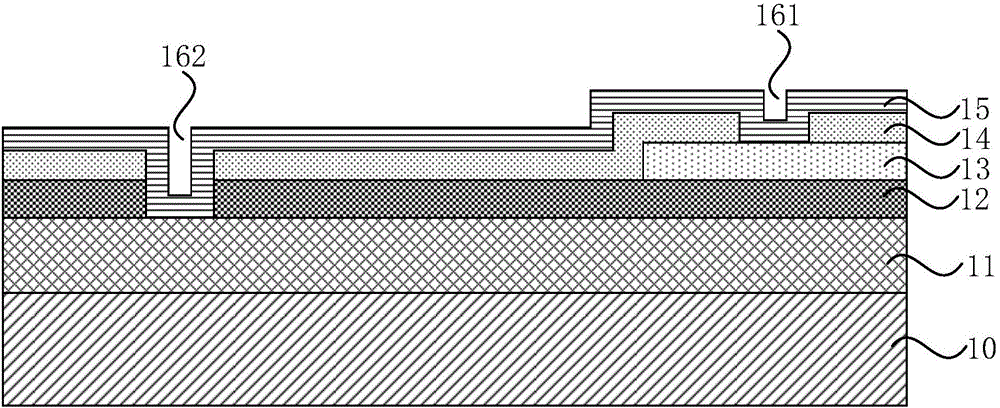

Array substrate and preparation method thereof, flexible display device

ActiveCN107564923APlay a supporting roleAvoid contactSemiconductor/solid-state device detailsSolid-state devicesEngineeringFlexible display

An embodiment of the invention provides an array substrate and a preparation method thereof, and a flexible display device, relates to the technical field of flexible display and is used for solving aproblem of proneness of circuit breakage and short circuit when an IC is bound to the flexible display panel directly. The array substrate including a binding area and a plurality of binding bondingpad arranged in the binding area of the flexible substrate. The array substrate also includes an insulation support part disposed in the binding area and in a position without the binding bonding pad.The upper surface of the insulation support part protrudes from the upper surface of the binding bonding pad. The array substrate is used for forming the flexible display device.

Owner:BOE TECH GRP CO LTD

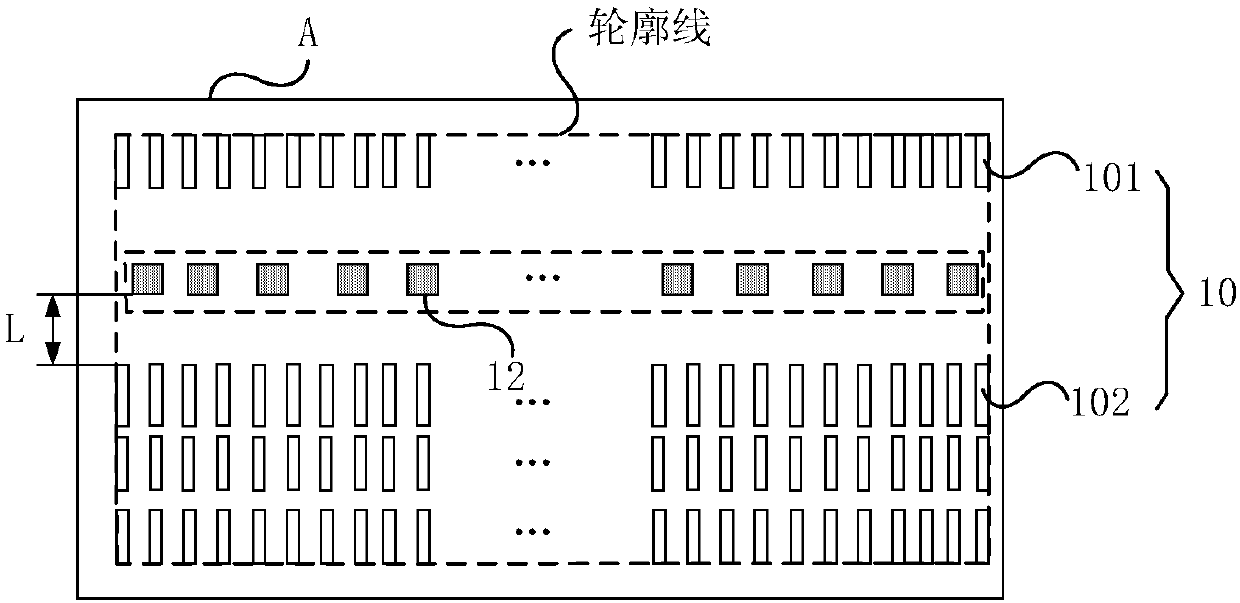

Display substrate and display device

PendingCN107037646AReduce the number of settingsReduce the setting densitySolid-state devicesNon-linear opticsDisplay deviceData signal

The embodiment of the invention discloses a display substrate and a display device. According to the technical scheme, data signal fan-out lines are arranged on a touch electrode layer, a grid layer and a source drain electrode layer, compared with the prior art that data signal fan-out lines are arranged on the grid layer and the source drain electrode layer, the number of the arranged data signal fan-out lines on the grid layer and the source drain electrode layer can be reduced, and thus the setting density of the data signal fan-out lines of the grid layer and / or the source drain electrode layer can be lowered; when a data signal is led out of a display area, the distance between the lines which are aslant arranged is increased, and a short-circuited risk between respective data signal fan-out lines of the grid layer and / or the source drain electrode layer is lowered.

Owner:BOE TECH GRP CO LTD +1

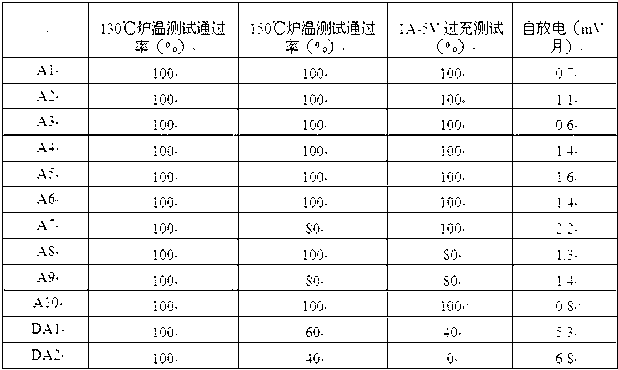

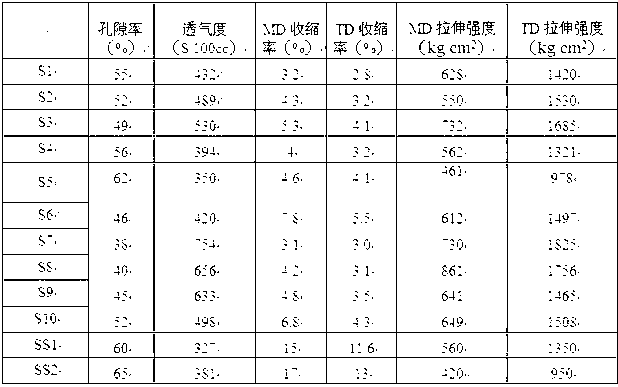

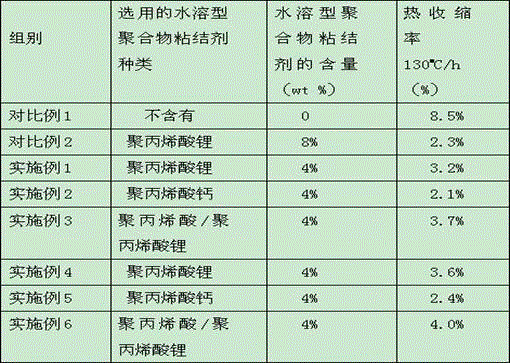

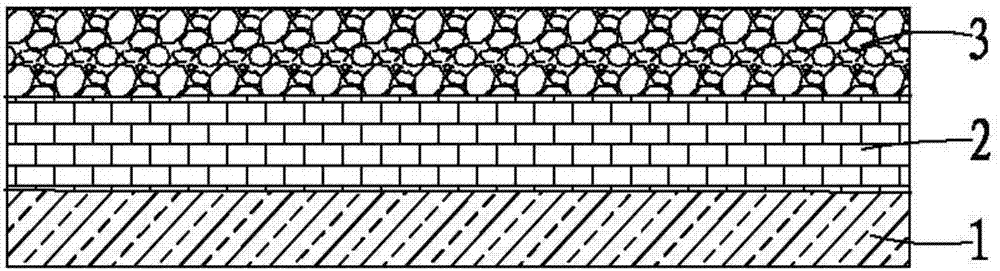

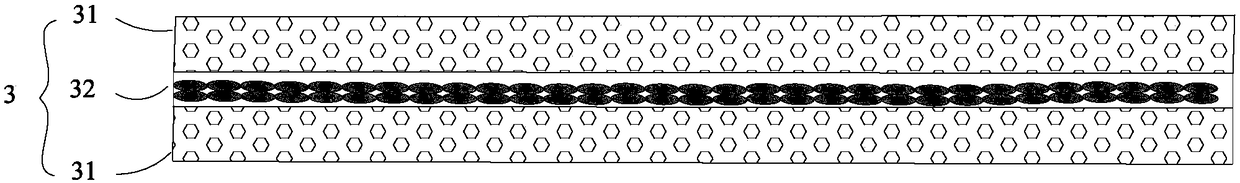

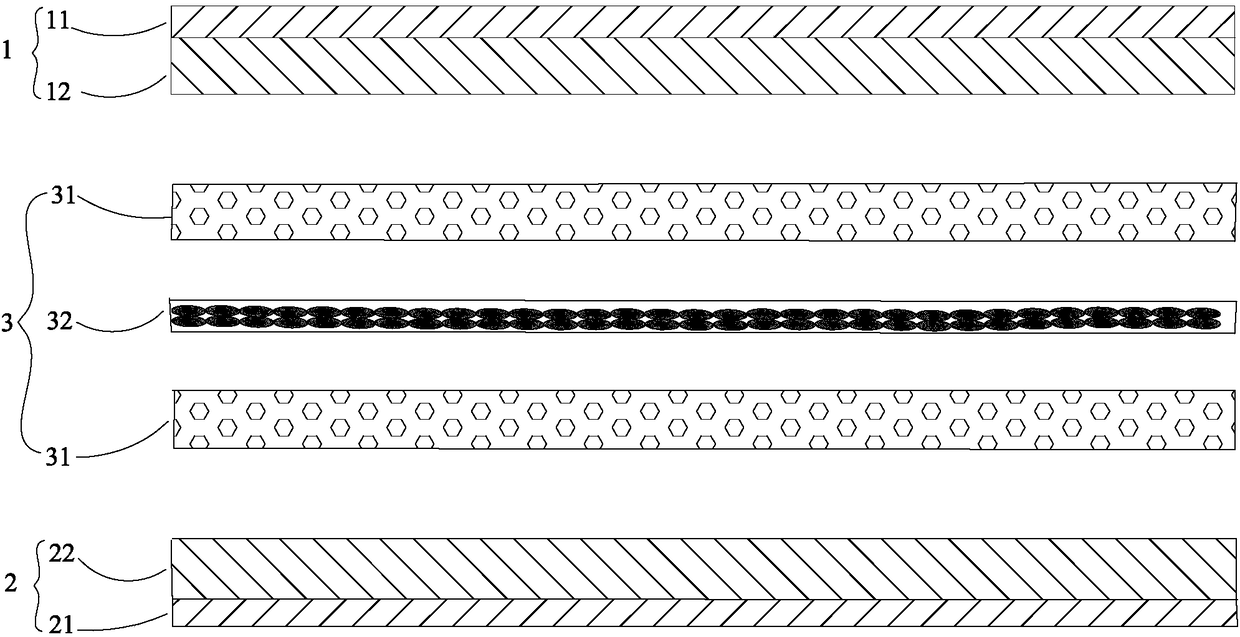

Diaphragm and preparation method thereof, and lithium ion battery

ActiveCN102623658AThe absolute value of the surface potential is largeEvenly distributedSecondary cellsCell component detailsHexafluoropropyleneLithium-ion battery

The invention belongs to the technical field of lithium ion batteries, and particularly relates to an inorganic and organic composite multihole diaphragm. The diaphragm comprises a multihole diaphragm base material and an active coating layer attached to at least one surface of the multihole diaphragm base material, wherein the active coating layer comprises inorganic particles, vinylidene fluoride and hexafluoropropylene copolymer, cellulose based polymer with the molecular weight of 100,000 to 1,000,000 and at least one of polyacrylic acid and polyacrylate. Compared with the prior art, the diaphragm keeps relatively high air permeability and lithium ion transmission capacity; the active coating layer and the multihole diaphragm base material are well bonded; and the overheating contraction performance and the puncture strength of a diaphragm base can be improved remarkably. Furthermore, the invention also discloses a preparation method for the diaphragm and a lithium ion battery with the diaphragm.

Owner:NINGDE AMPEREX TECH +1

Lithium ion battery diaphragm, preparation method of the lithium ion battery diaphragm, and lithium ion battery containing the lithium ion battery diaphragm

InactiveCN103137929AHigh lithium ion conductivityReduced risk of short circuitsSecondary cellsCell component detailsPhysicsLithium electrode

The invention provides a lithium ion battery diaphragm. The lithium ion battery diaphragm comprises a diaphragm base material and a solid electrolyte layer arranged on at least one surface of the diaphragm base material. The invention also provides a preparation method of the lithium ion battery diaphragm, a device adopted by the preparation method and a lithium ion battery containing the lithium ion battery diaphragm. A high rate of lithium ion transmission between positive and negative poles of the lithium ion battery containing the lithium ion battery diaphragm is kept, a risk of short circuit between the positive and negative poles is reduced, and a diaphragm heat shrinkage problem and battery safety are improved.

Owner:BYD CO LTD

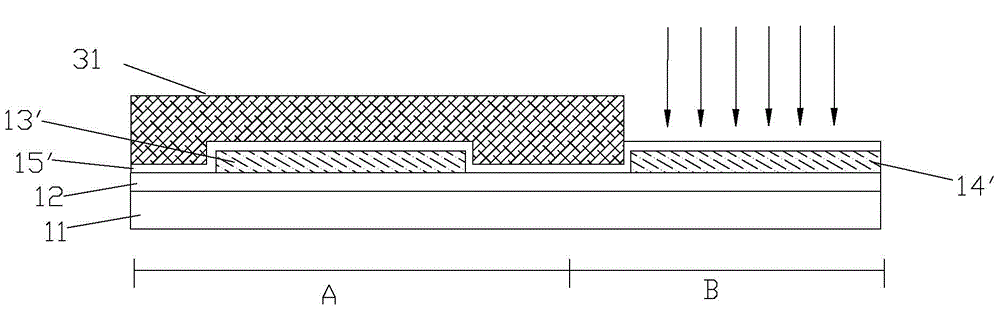

Dye sensitized solar cell and preparation method thereof

InactiveCN102005301ALose weightOperableLight-sensitive devicesFinal product manufactureElectronic transmissionSolar cell

The invention discloses a dye sensitized solar cell, which comprises an optical anode, a counter electrode, electrolyte and a packaging shell. The counter electrode is positioned above the optical anode and is arranged inside the packaging shell; the electrolyte is full of the packaging shell; the optical anode comprises a transparent conductive substrate, a transparent conductive film and a porous transition metal oxide film which adsorbs dye molecules; the porous transition metal oxide film is coated on the transparent conductive film; and the counter electrode comprises a diaphragm serving as a substrate of the counter electrode, and a catalytic material and a grid electrode which are deposited on the diaphragm in turn. The invention also discloses a method for preparing the dye sensitized solar cell. The invention reduces the manufacturing cost, lightens the cell weight, reduces the short circuit risk and shortens the electronic transmission distance, and the dye sensitized solar cell is high-efficiency.

Owner:EAST CHINA NORMAL UNIV +1

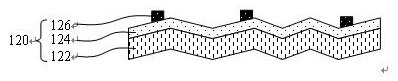

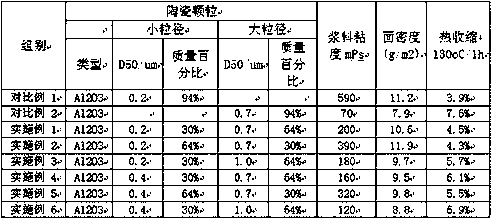

Inorganic/organic composite porous isolating membrane, preparation method and lithium-ion battery thereof

InactiveCN107895765AHigh mechanical strengthImprove reliabilityCell component detailsSecondary cells servicing/maintenancePolymer adhesiveSlurry

The invention discloses an inorganic / organic composite functional porous isolating membrane. The isolating membrane comprises porous base material and at least one inorganic functional coating adhering to the surface of the porous base material, and aqueous slurry prepared for the inorganic functional coatings is prepared from inorganic ceramic particles, water-soluble polymer thickener and aqueous polymer adhesive; the inorganic ceramic particles comprise the same substance in two types of particle sizes, wherein the average particle size (D50) of the smaller inorganic ceramic particles is 0.2-0.5 micrometer, and the average particle size (D50) of the larger inorganic ceramic particles is 0.6-1.0 micrometer; the aqueous polymer adhesive is a hydrophobic high-molecular polymer with the water drop contact angle of the dry adhesive of the aqueous polymer adhesive 110-140 degrees; the solid content of the aqueous slurry is 40-60%. According to the inorganic / organic composite functional porous isolating membrane, the high-temperature thermal stability of the isolating membrane can be effectively improved by means of the inorganic functional coatings, and the water content of the inorganic coatings is effectively reduced, so that the safe performance of a battery and the stability of long-term circulation are improved.

Owner:深圳市旭然电子有限公司

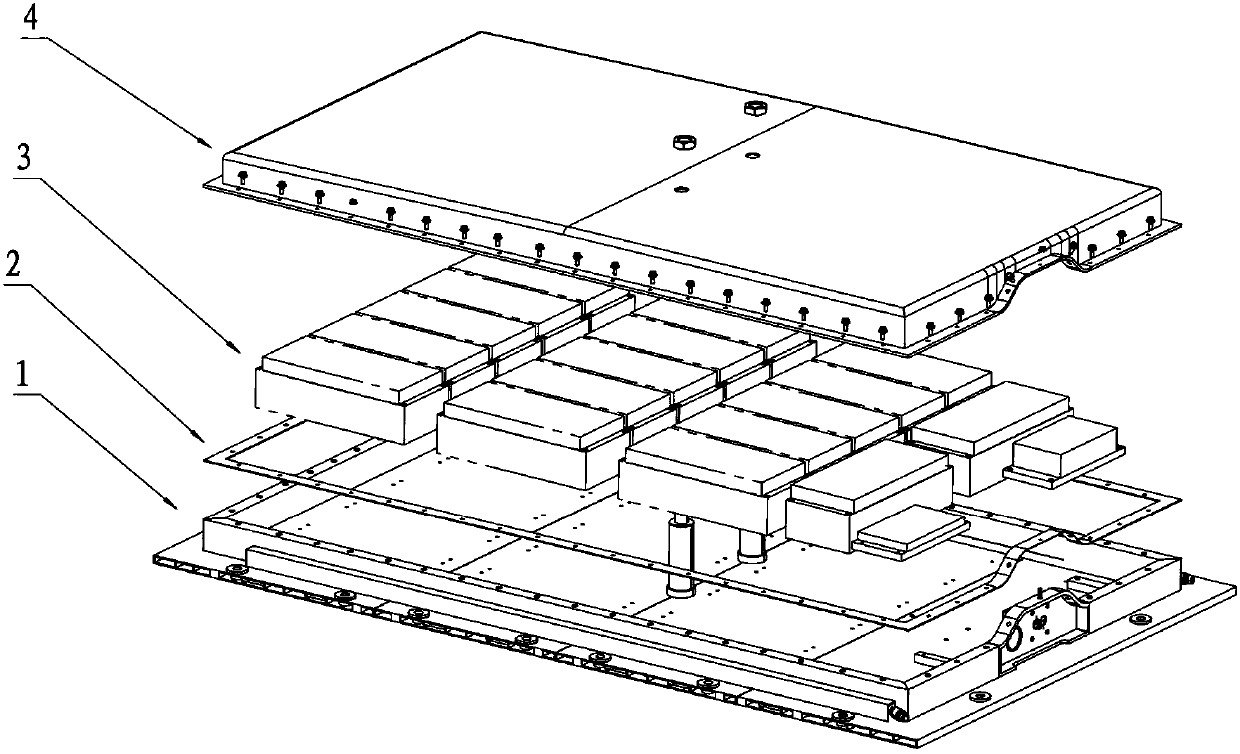

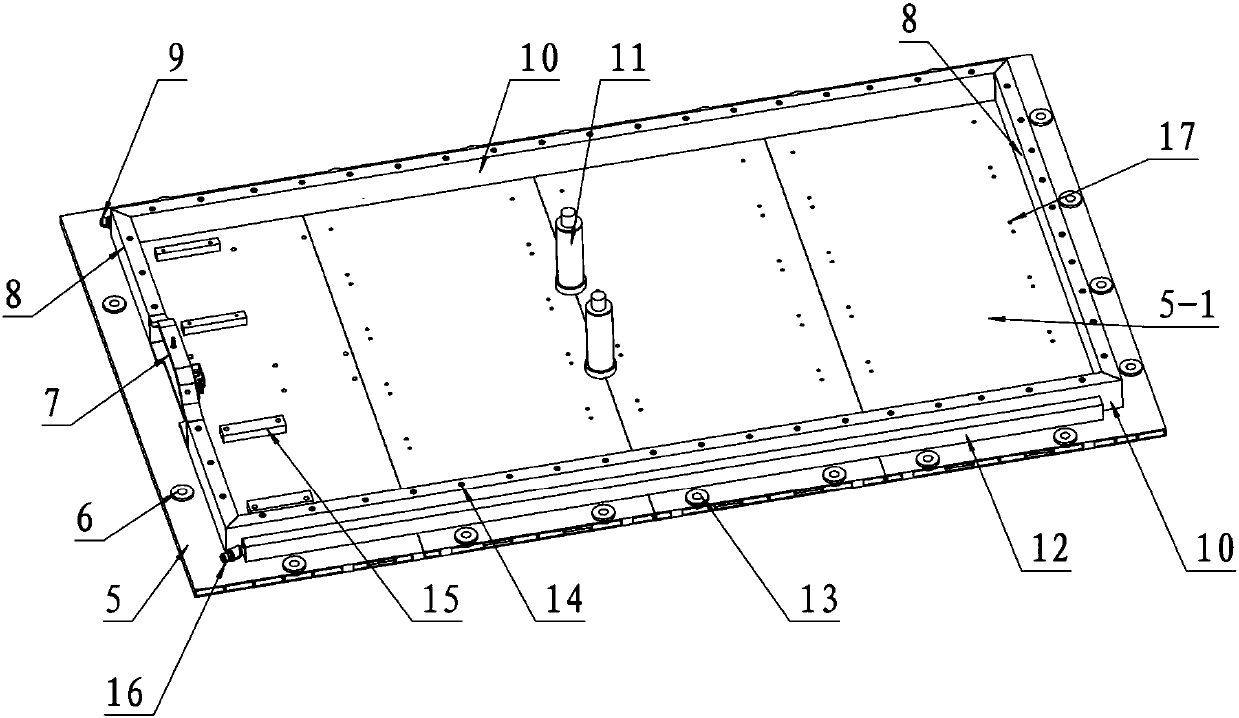

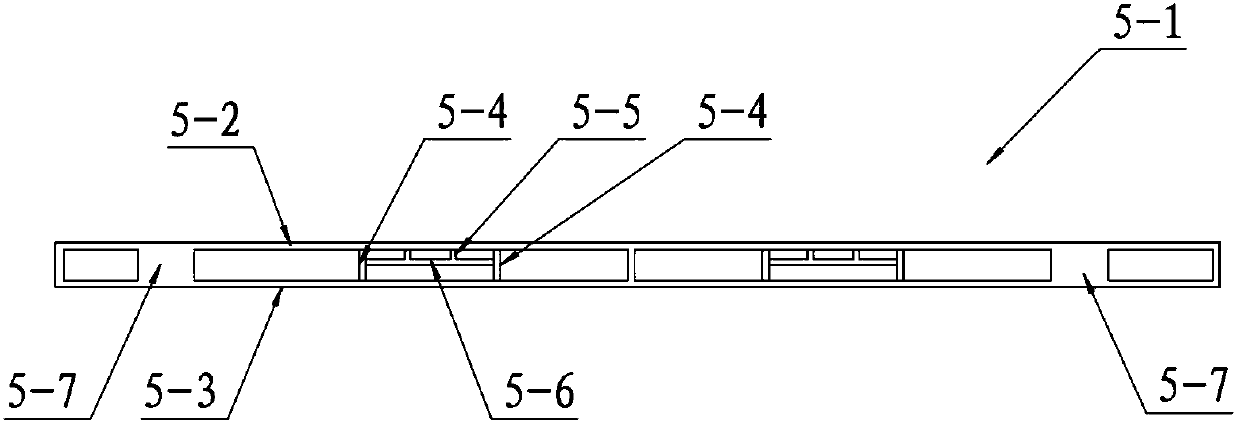

Integrated-form water-cooling power battery shell used for new energy automobiles

PendingCN107732061AHigh strengthEnhanced stone chip resistanceBattery isolationSecondary cellsRear quarterPower battery

The invention discloses an integrated-form water-cooling power battery shell used for new energy automobiles. The integrated-form water-cooling power battery shell used for new energy automobiles comprises an upper shell body and a lower shell body; the lower shell body is composed of a bottom plate and a side plate; the bottom plate is a cuboid, and is of a double layer structure composed of an upper layer bottom plate and a lower layer bottom plate; vertical ribs are uniformly arranged between the upper layer bottom plate and the lower layer bottom plate; a plurality of cooling water runnersare arranged between the upper layer bottom plate and the lower layer bottom plate; the cooling water runners are arranged to be parallel to the width direction of the bottom plate; the side plate isa rectangle frame composed of two long edge side plates and two short edge side plates; a water inlet channel and a water outlet channel are arranged on the external sides of the two long edge side plates respectively; one end of each cooling water runner is communicated with the water inlet channel, and the other end is communicated with the water outlet channel. According to the integrated-formwater-cooling power battery shell, a cooling device is arranged on the lower shell body via integration, so that the battery shell whole structure is simplified greatly, and the cost of the battery shell is reduced; the cooling water runners are arranged in the bottom plate of the lower shell body, so that the risk of module short circuit caused by water leakage of conventional cooling pipelinesis reduced; and the external walls of the cooling water runners are contacted with battery modules, so that cooling effect is improved.

Owner:LINGYUN INDAL CORP

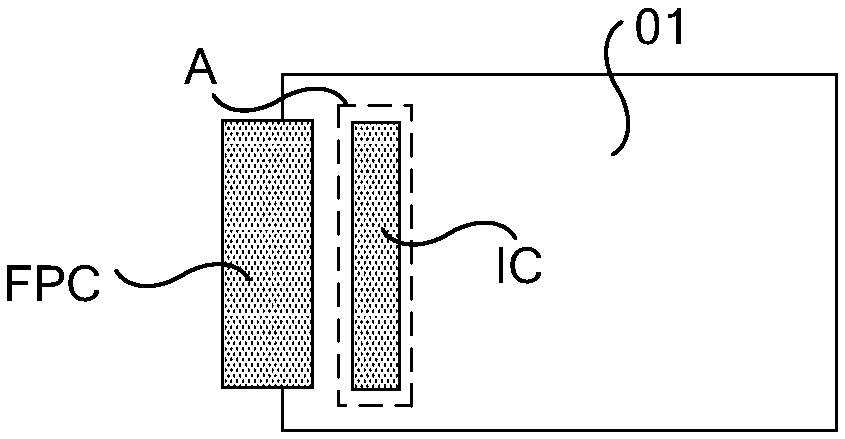

Narrow frame display panel and display

ActiveCN106873222AReduce spacingSimple designPrinted circuit aspectsPrinted circuit manufactureFlexible circuitsDisplay device

The embodiment of the invention discloses a narrow frame display panel. The narrow frame display panel includes an integrated circuit input pad which is positioned on a lower side of the display panel and includes a plurality of input terminals; a flexible printed circuit bonding pad which is position on a lower edge of the display panel and is positioned under the integrated circuit input pad, wherein the flexible printed circuit bonding pad includes a plurality of binding terminals, binding terminals at one end, of the flexible printed circuit bonding pad are first binding terminals, and each first binding terminal includes at least one three-side surrounded structure extending outward in the horizontal direction; and a wire which is electrically connected to the integrated circuit input pad and the flexible printed circuit bonding pad. The embodiment of the invention also discloses a display. The narrow frame display panel and the display are conductive to a narrow frame design.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Inorganic/organic compound functional porous isolating membrane and preparation method as well as lithium ion battery adopting inorganic/organic compound functional porous isolating membrane

ActiveCN105789523AGood dispersionImproved high temperature thermal stabilitySecondary cellsCell component detailsPorous substrateOrganic compound

The invention provides an inorganic / organic compound functional porous isolating membrane. The inorganic / organic compound functional porous isolating membrane comprises a porous substrate and an inorganic functional coating which is adhered to at least one surface of the porous substrate, wherein the inorganic functional coating is prepared from inorganic ceramic particles, a water-soluble macromolecular thickening agent, a water emulsion type polymer binding agent and a water soluble type polymer binding agent; the water emulsion type polymer binding agent is a macromolecular polymer with the surface tensile force of 40dyne / cm to 50dyne / cm, and a water drip contact angle of water emulsion type polymer binding agent dry glue is 100 degrees to 130 degrees; the water emulsion type polymer binding agent is a polar macromolecular polymer with the glass transition temperature of 100 DEG C to 150 DEG C. Therefore, the inorganic / organic compound functional porous isolating membrane has the advantages that the heat stability of the isolating membrane can be effectively improved, and the moisture content of the inorganic coating can also be reduced, so that the safety performance of a battery and the stability of long-period cycle are improved.

Owner:深圳市旭然电子有限公司

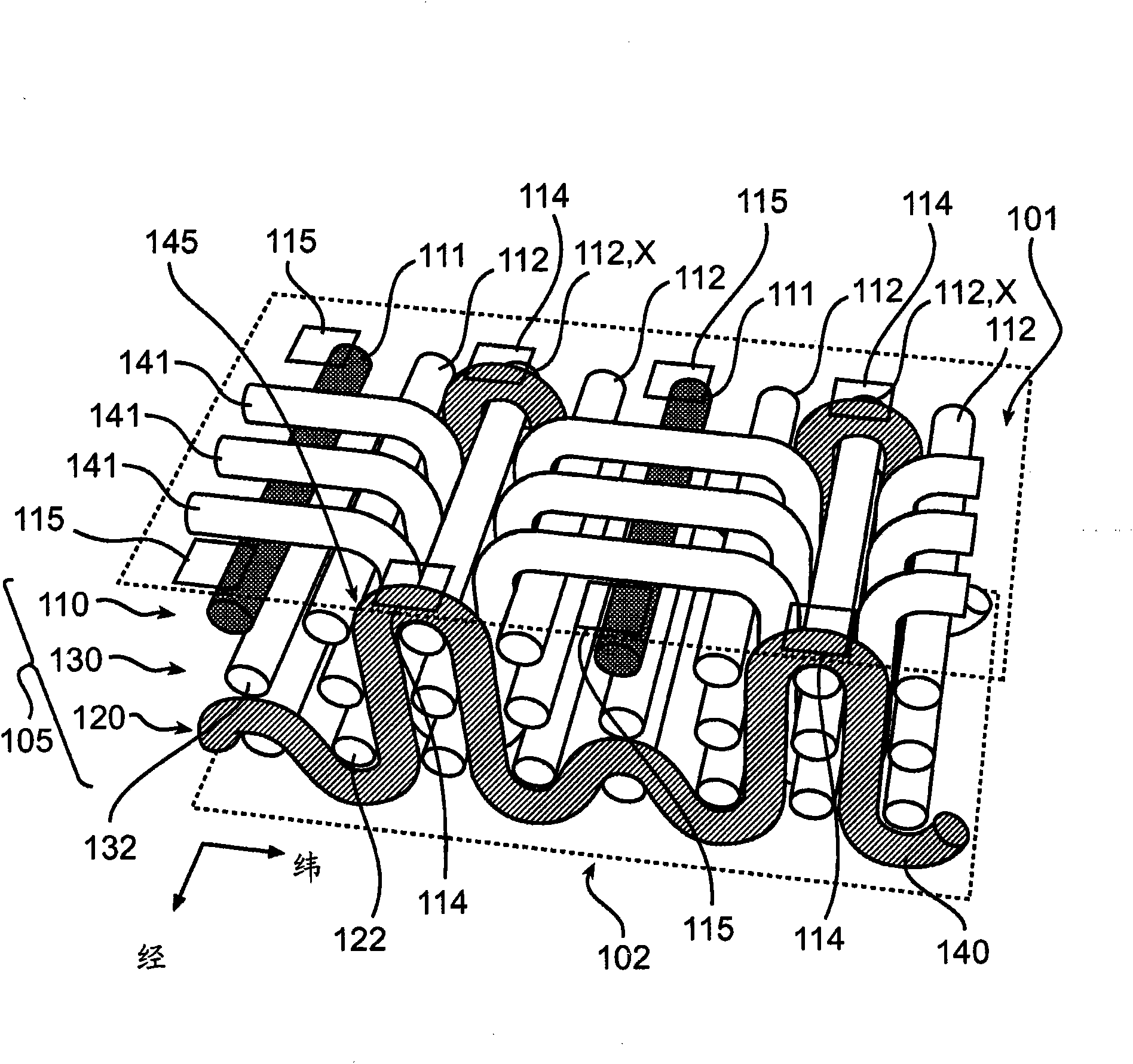

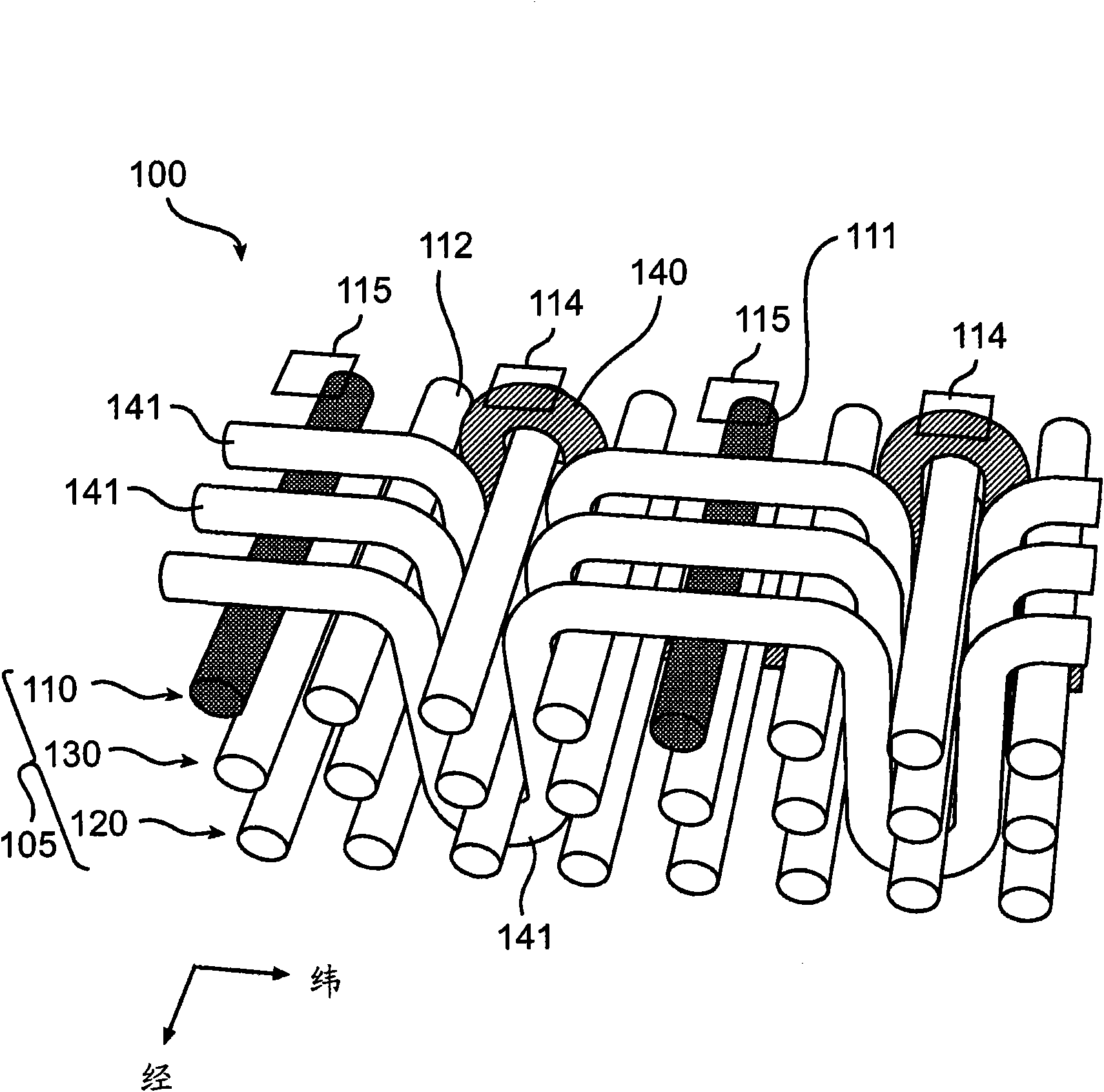

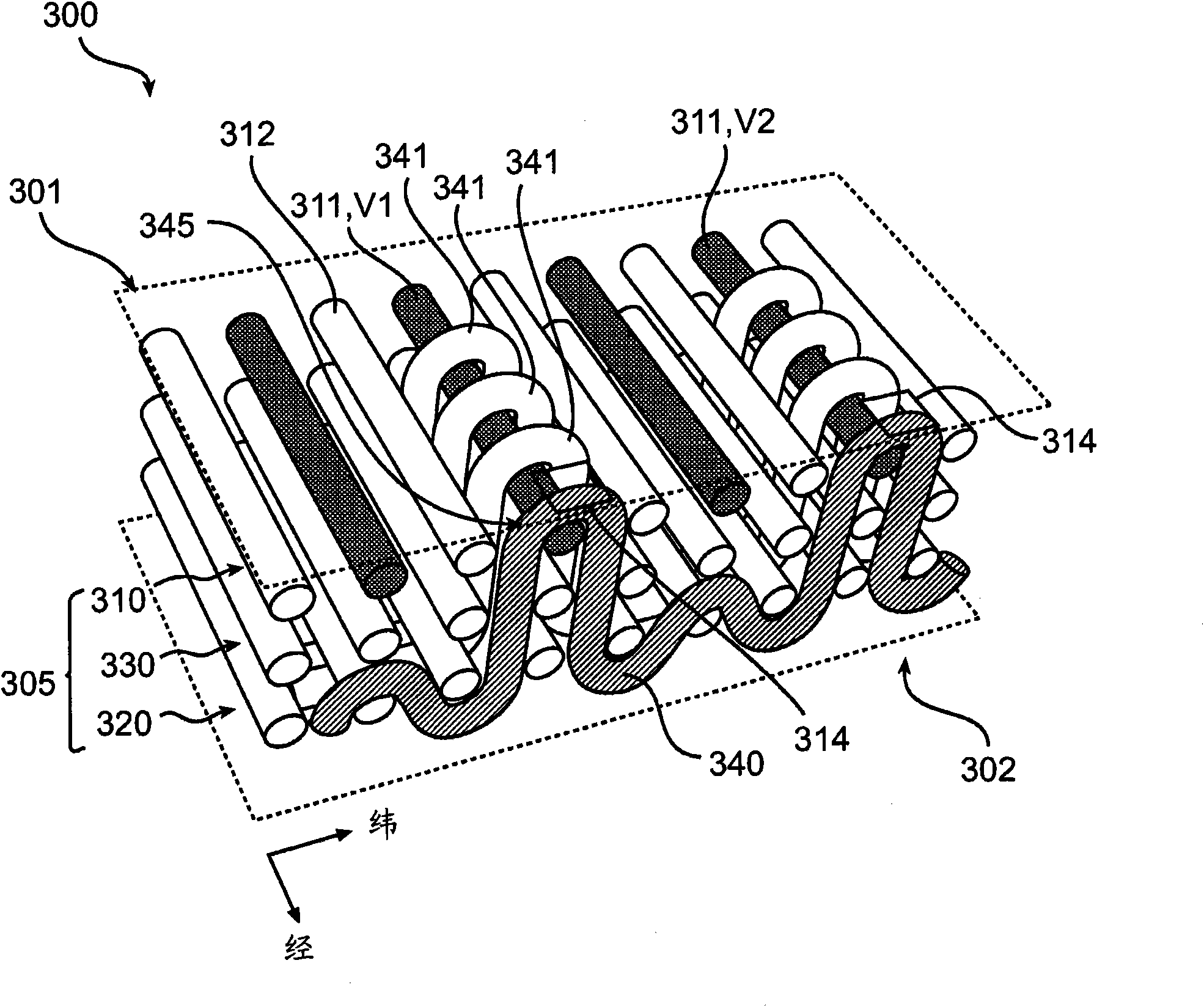

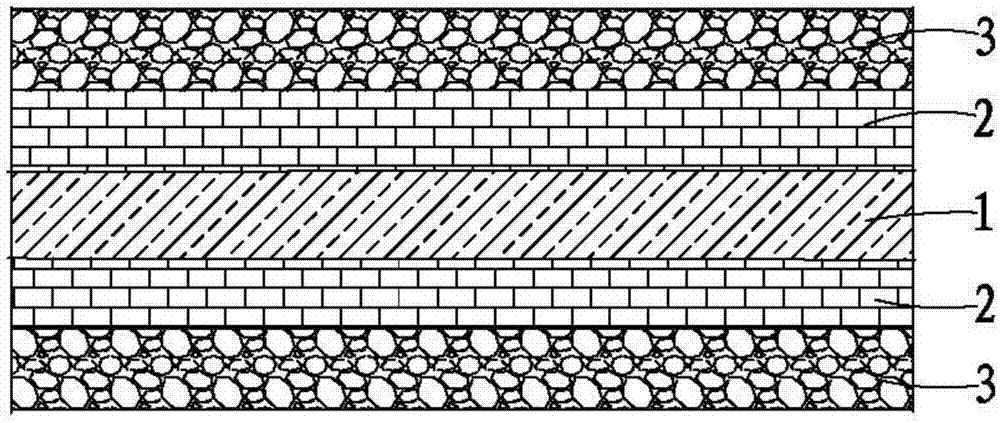

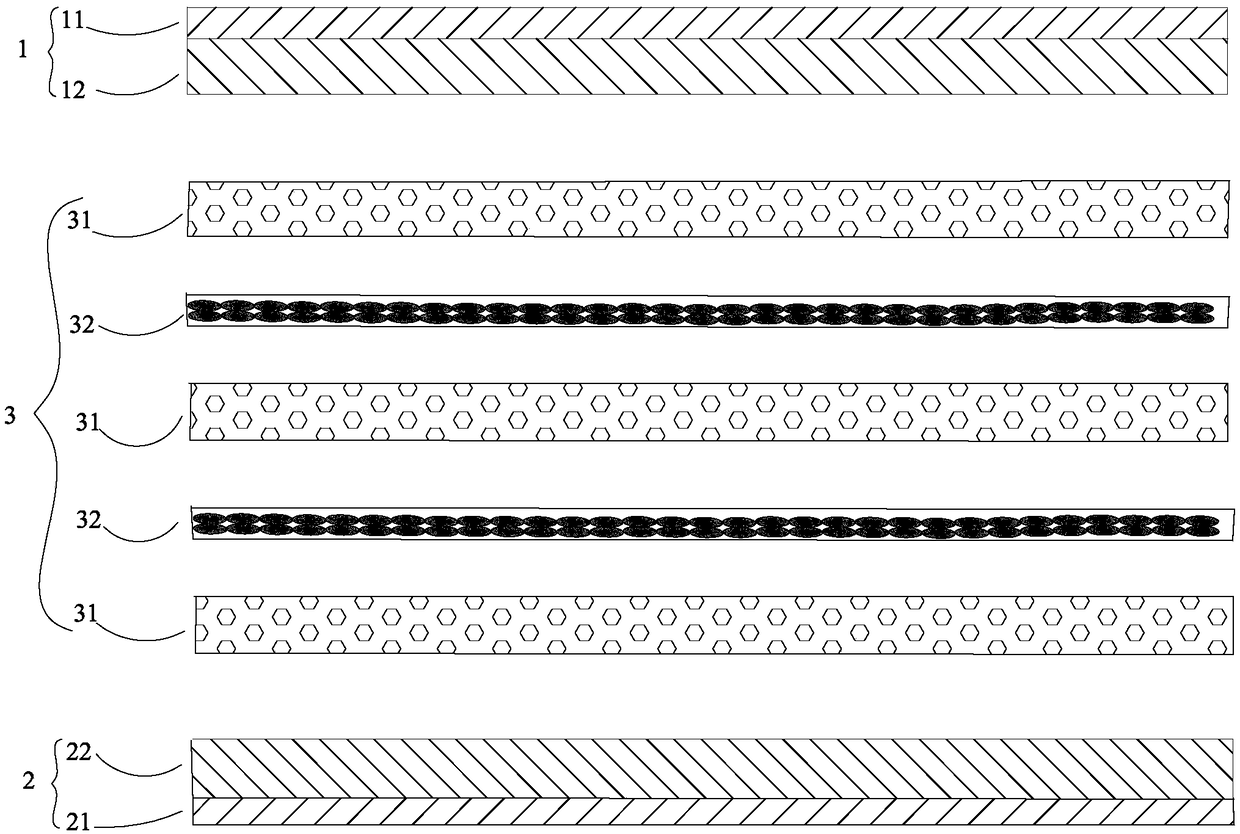

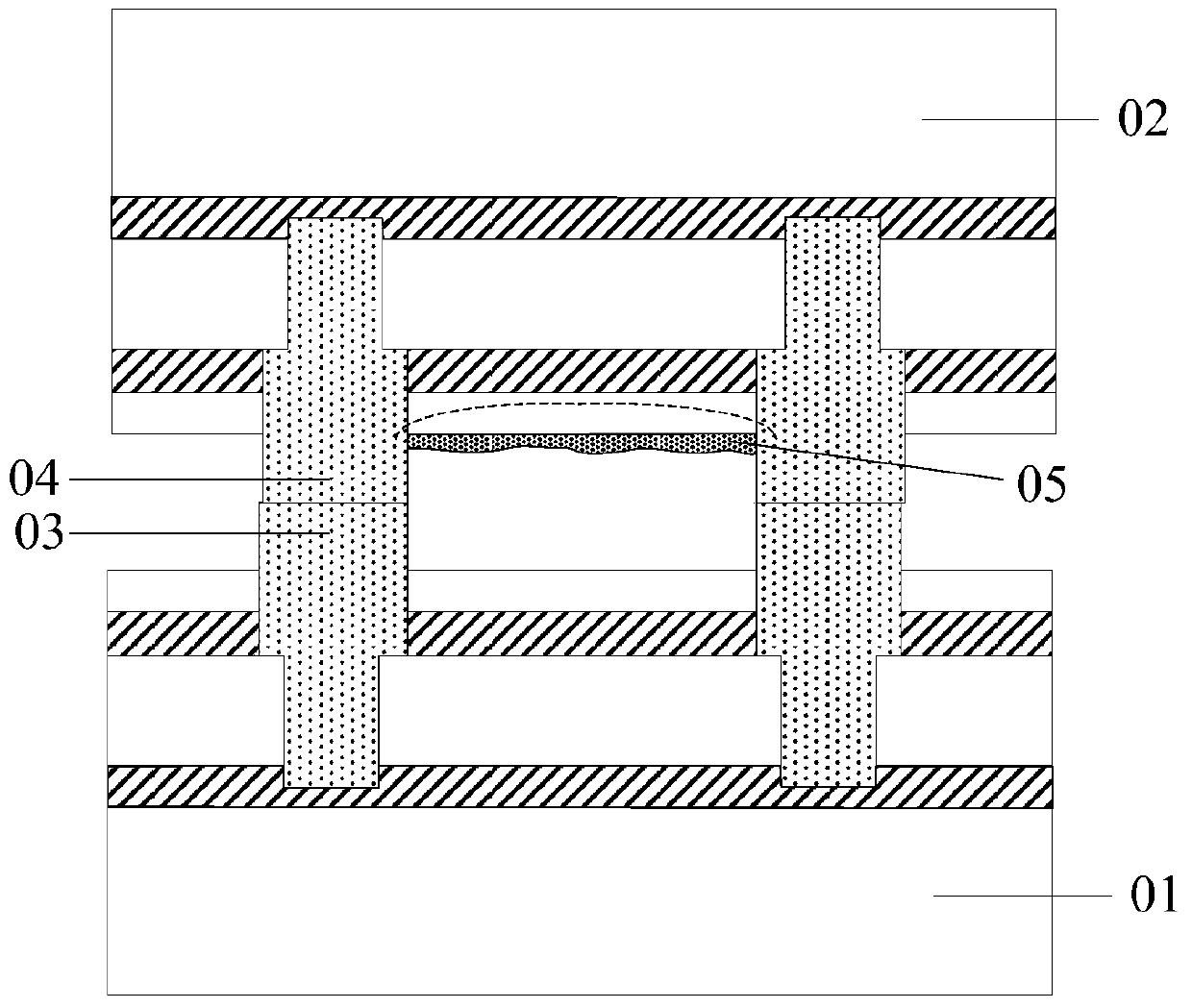

Multi-layer woven fabric display

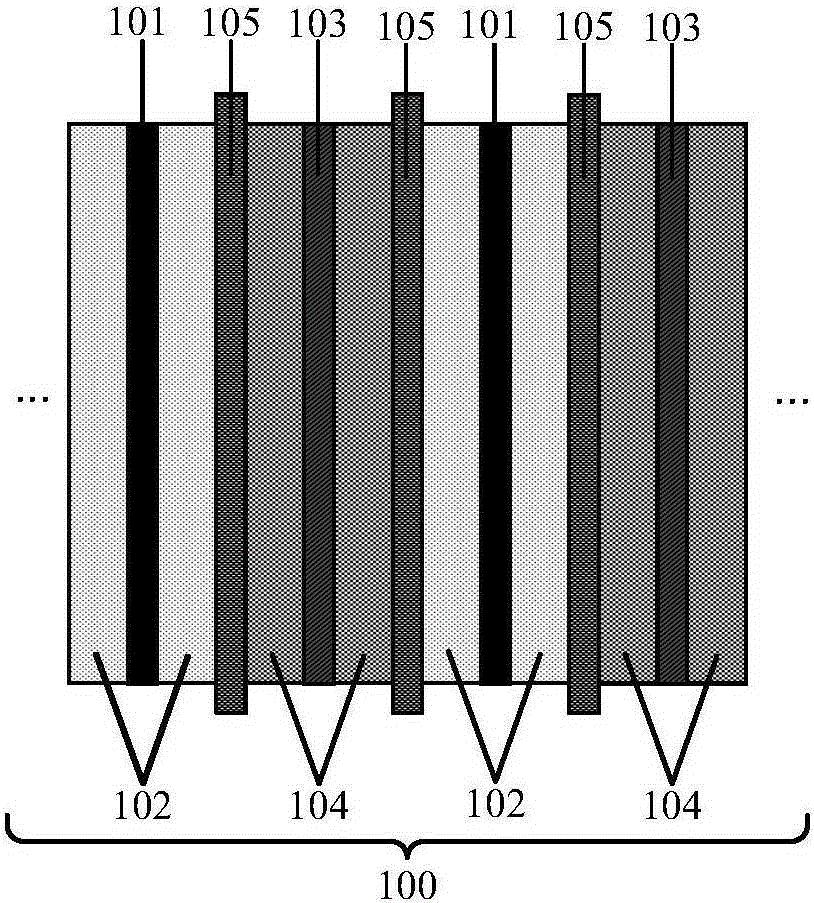

InactiveCN101827967AEasy to coverReduced risk of short circuitsPrinted circuit aspectsMulti-ply fabricsPhotonicsDisplay device

The present invention relates to textiles for photonic and electronic applications, particularly to multilayer textiles made of electrically conductive yarns for driving electrical components such as light emitting diodes connected to the textile. The light emitting diodes may be arranged in the form of an array in order to realize a flexible and foldable display. In the textile according to the present invention, insulating weft yarns are interwoven in a multilayer wrap (105) such that the electrically warp yarns (111) are partially covered by the insulating weft yarns (141), thereby preventing from short-circuit between electrically conductive yarns of the textile. In particular, the structure of the textile according to the present invention may be satin / sateen weave structure.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

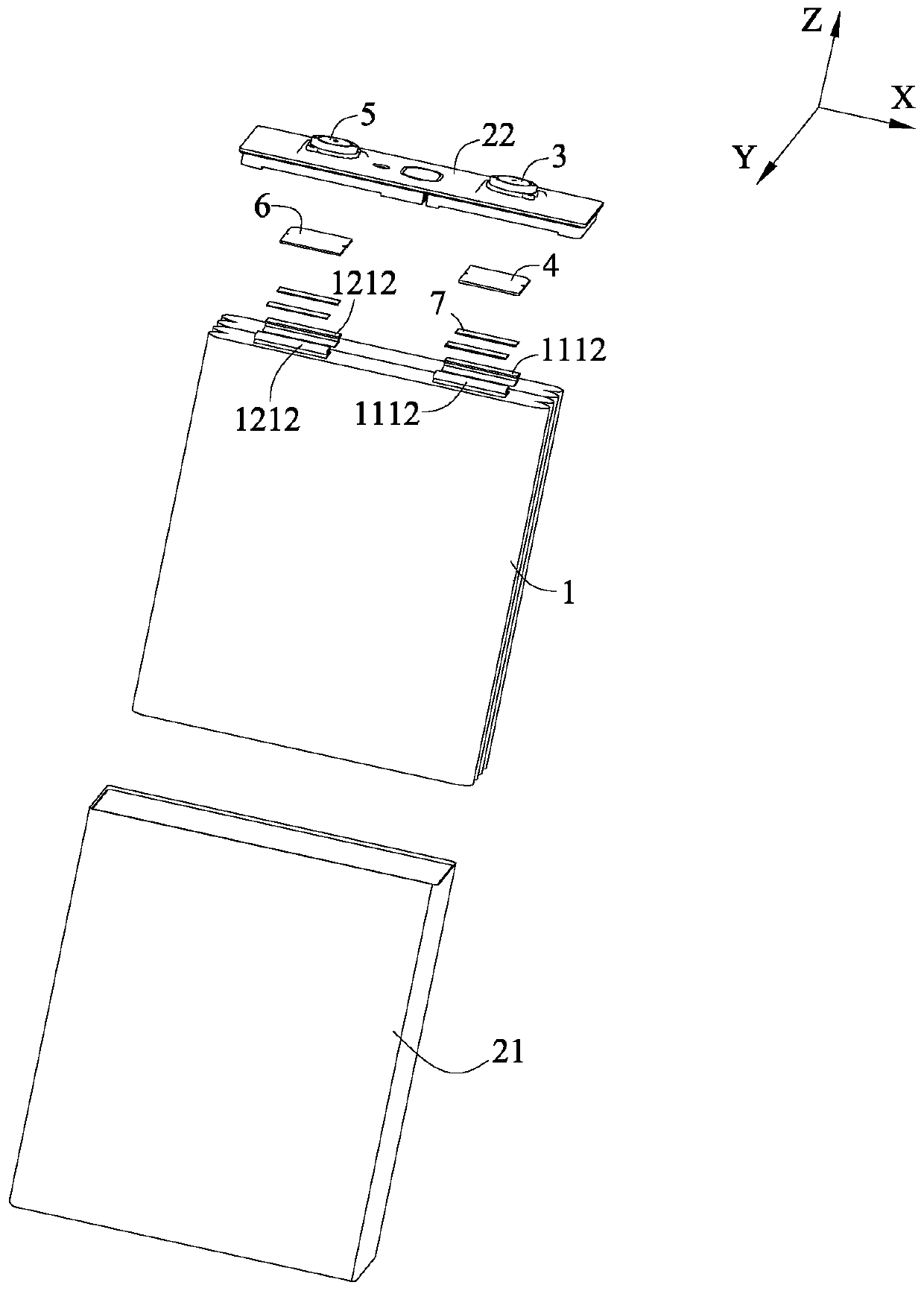

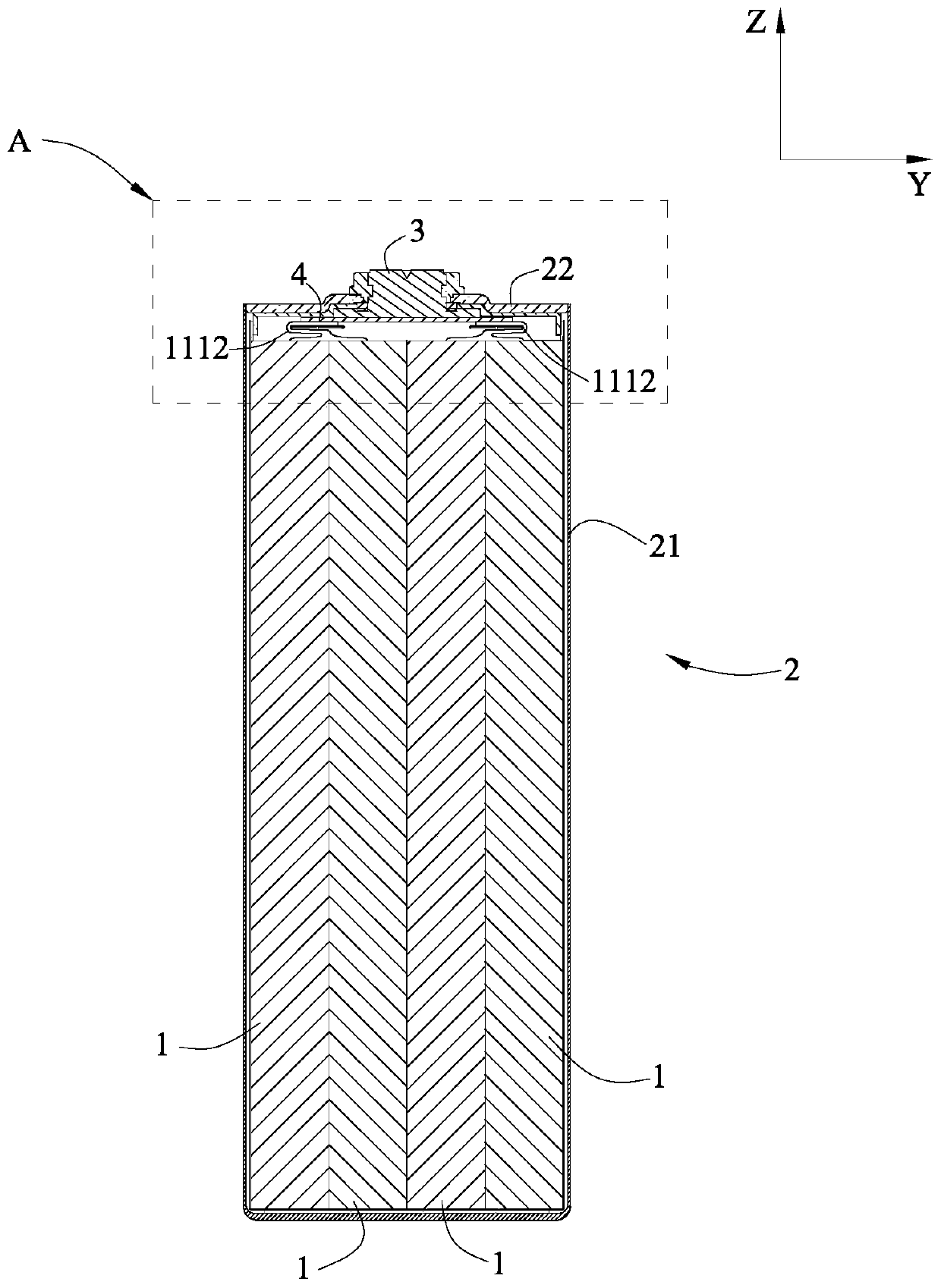

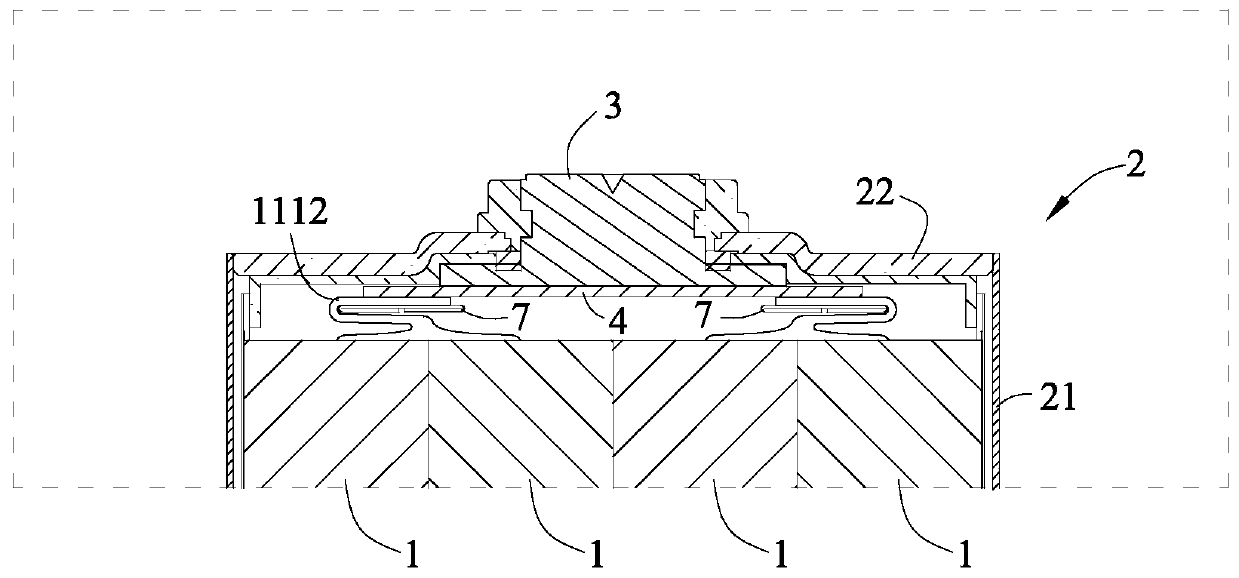

Secondary battery and automobile

PendingCN107968182AIncrease energy densityReduced risk of short circuitsFinal product manufactureWound/folded electrode electrodesElectrical and Electronics engineeringElectrode

The application relates to the technical field of energy-storing devices, in particular to a secondary battery and an automobile. The secondary battery comprises: a top cover; a pole arranged on the top cover; an electrode component including a body and a plurality of tabs extended out of the body and stacked, wherein the body is formed by jointly winding a first plate, a second plate and a diaphragm between the first plate and the second plate; a connector allowing the tabs to be electrically connected to the pole. The tabs are extended out of one side of the thickness direction of the body,are bent relative to the height direction and are connected to the connector. In assembly of the secondary battery, the electrode component is easy to connect with the connector; safety of the secondary battery can be improved.

Owner:CONTEMPORARY AMPEREX TECH CO

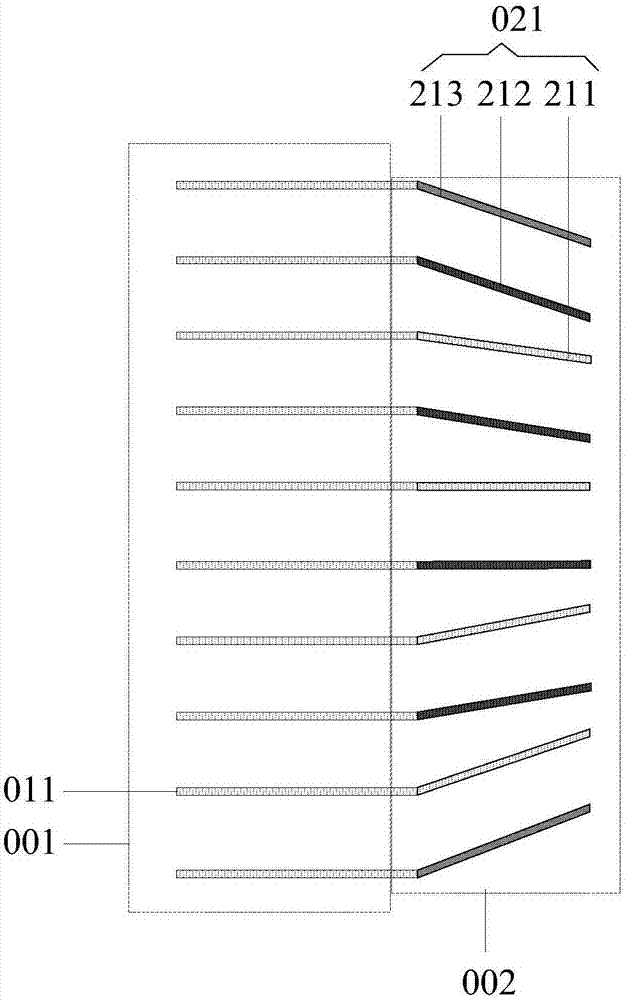

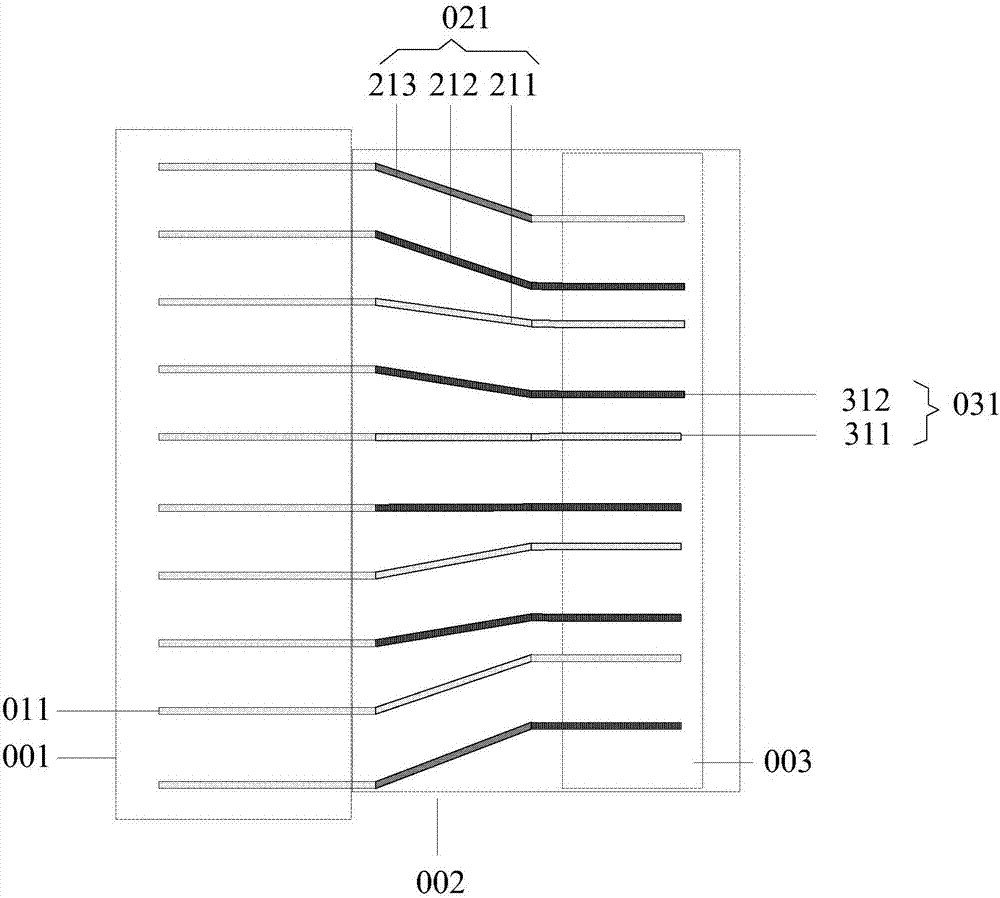

Array substrate, manufacturing method thereof and display device

InactiveCN108732833AWiring Congestion EaseIncrease spacingSolid-state devicesNon-linear opticsDisplay deviceMaterials science

The invention discloses an array substrate, a manufacturing method thereof and a display device, and belongs to the field of display. The array substrate includes a substrate, a first metal layer, a second metal layer, and a third metal layer, wherein the first metal layer, the second metal layer and the third metal layer are disposed on the substrate; the array substrate is divided into a displayarea and a peripheral area; the peripheral area of the array substrate is provided with a plurality of signal line leads, one part of the plurality of signal line leads are located at the first metallayer, another part of the plurality of signal line leads are located in at least one layer of the third metal layer and the second metal layer, the first metal layer includes a shading layer locatedat the display area, the second metal layer comprises a gate layer located at the display area, and the third metal layer includes a source and drain layer located at the display area. In the case where the peripheral area is small, the wiring congestion of the signal line leads is alleviated, the signal line lead pitch is increased, a short circuit risk is lowered, and the signal line leads canbe designed to be thicker due to the reduced wiring congestion, thereby avoiding the open circuit risk of the signal line leads.

Owner:BOE TECH GRP CO LTD +1

Ceramic diaphragm and preparation method therefor

InactiveCN106935778AImprove thermal conductivityReduced risk of short circuitsCell component detailsSecondary cells servicing/maintenanceCeramic coatingHeat conducting

The invention belongs to the technical field of a diaphragm of a lithium ion battery, and particularly relates to a ceramic diaphragm and a preparation method therefor. The ceramic diaphragm comprises a base diaphragm, and a heat-resistant ceramic coating layer which is coated on at least one surface of the base diaphragm, and also comprises a heat-conducting ceramic coating layer which is coated on the surface of the heat-resistant ceramic coating layer and / or the other surface of the base diaphragm. Compared with the prior art, by additionally arranging the heat-conducting ceramic coating layer on the base diaphragm comprising the heat-resistant ceramic coating layer, the heat conducting performance of the ceramic diaphragm is effectively improved; when the battery suffers form partial overheating caused by puncturing, collision, extrusion and the like, the heat-conducting ceramic coating layer can rapidly conduct and scatter the heat on the partial place of the diaphragm to the whole ceramic diaphragm, so that partial heat shrinkage of the ceramic diaphragm can be restrained, and risk of short circuit of the battery can be further lowered.

Owner:东莞市赛普克电子科技有限公司

Array substrate, liquid crystal display panel and touch display device

ActiveCN106647083AImprove manufacturing yieldImprove display qualityNon-linear opticsInput/output processes for data processingLiquid-crystal displayDisplay device

The present invention discloses an array substrate, a liquid crystal display panel and a touch display device. The array substrate comprises: a base substrate, as well as a touch trace layer including a plurality of touch traces, a first insulating layer, touch electrode layer including a plurality of touch electrode blocks in matrix arrangement, a second insulating layer, and a pixel electrode layer including a plurality of pixel electrodes in matrix arrangement and a bridge structure, which are disposed on the base substrate in sequence, wherein the touch traces are electrically connected to the corresponding touch electrode blocks by means of the bridge structure; the bridge structure fills up and runs through first via holes of the second insulating layer that expose the touch electrode blocks and run through second via holes of the second insulating layer and the first insulating layer that expose the traces; and the bridge structure is located between every two adjacent columns of pixel electrodes, and the first via holes and the second via holes that the bridge structure correspondingly fills up are spaced apart by at least one row of pixel electrodes. With the technical solution provided in the present invention, risks of short-circuiting between the bridge structure and the pixel electors are reduced, and the yield of manufacturing of liquid crystal display panels is improved.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

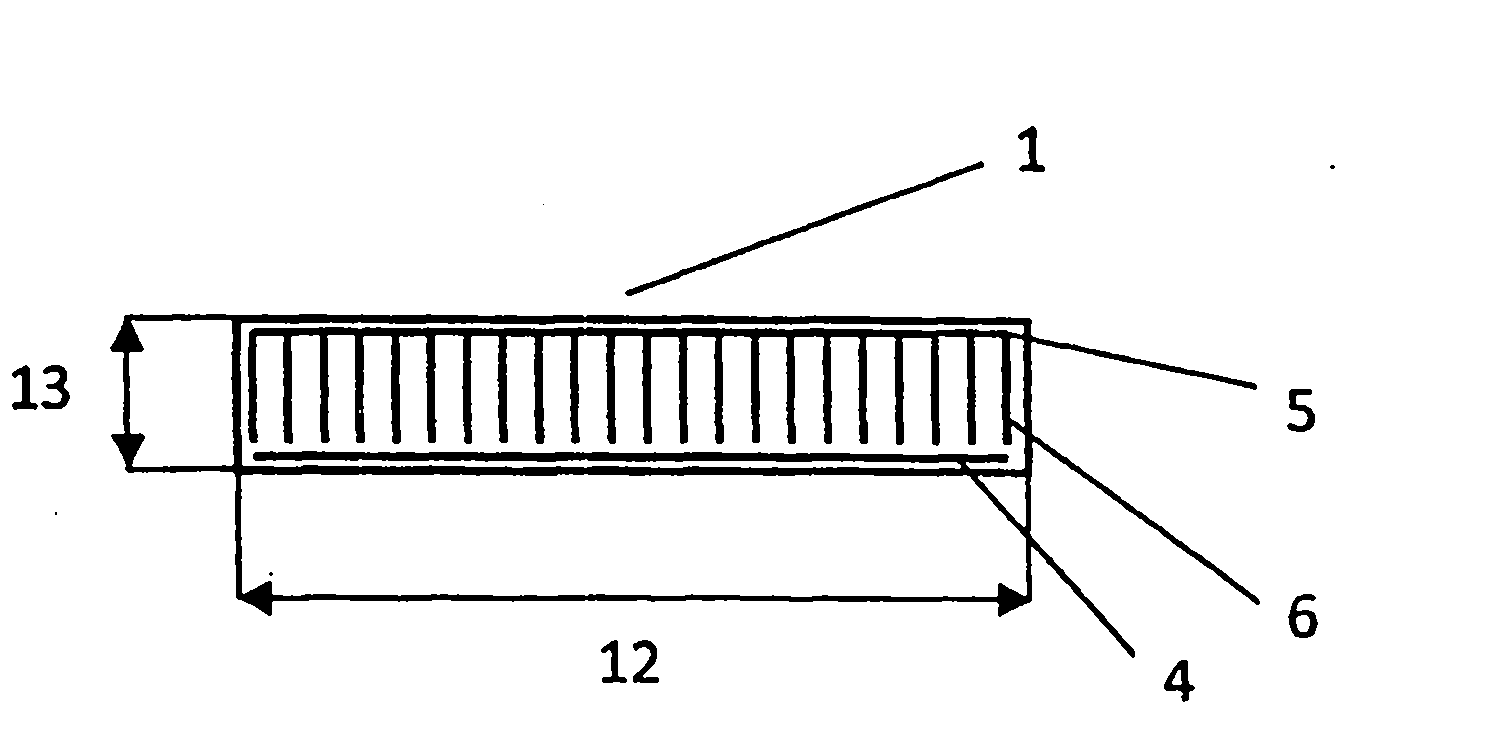

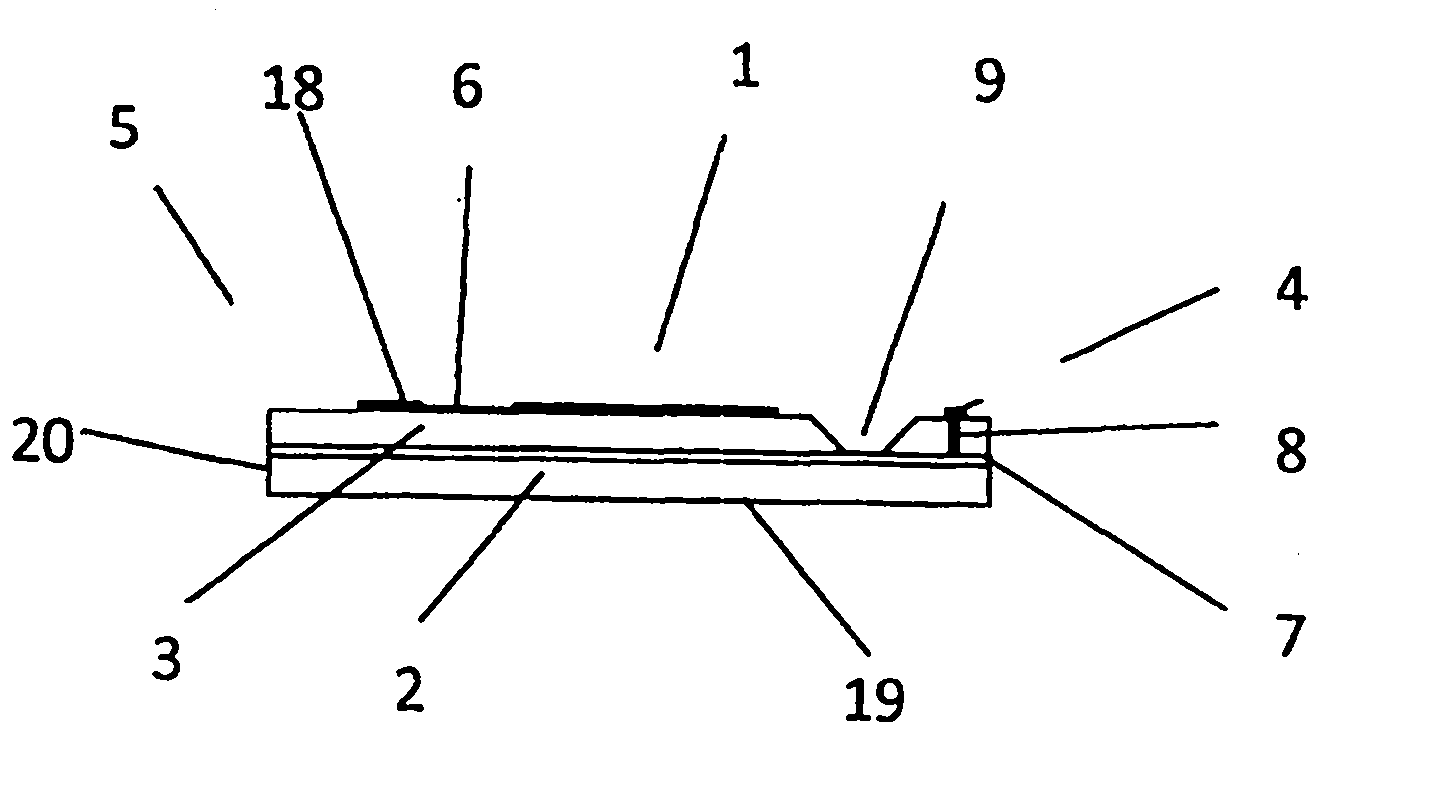

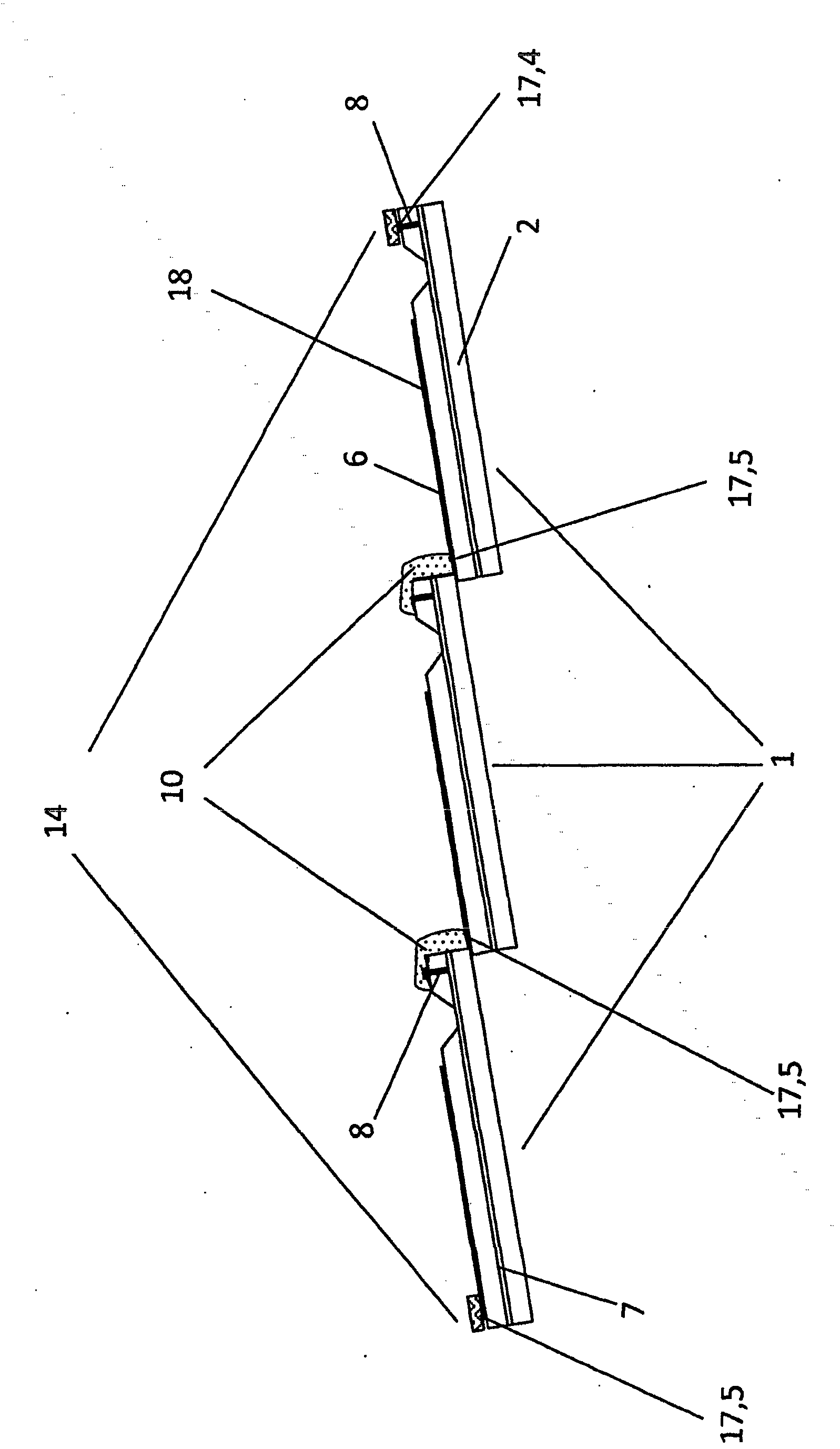

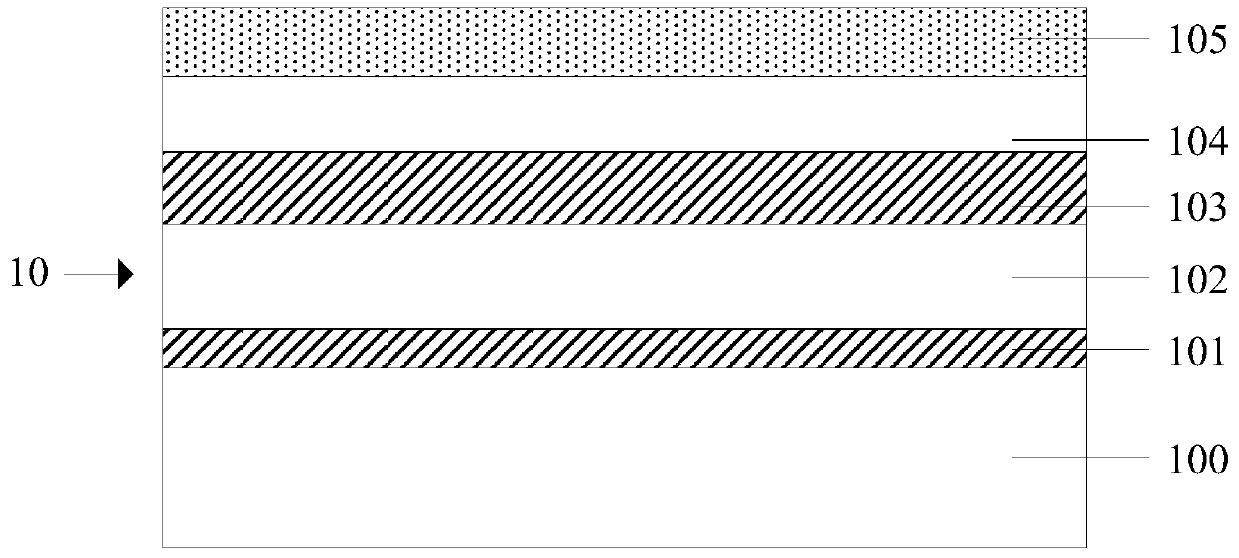

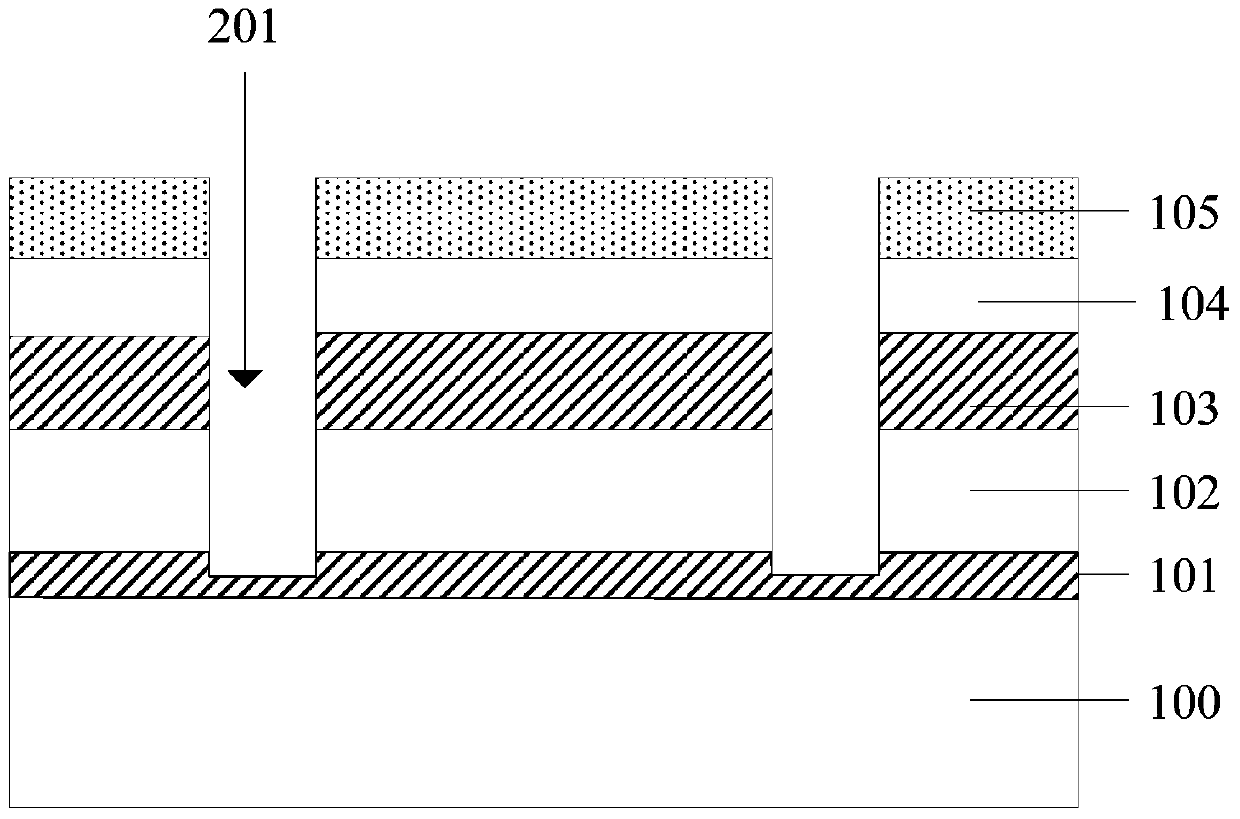

Arrangement and circuit, and method for interconnecting flat solar cells

InactiveCN102714249AReliable and persistent interconnectionReduced risk of short circuitsDiodeEnergy conversion devicesScreen printingEngineering

The invention relates to an arrangement and circuit, and to a method for interconnecting flat rigid or flexible solar cells, the photoelectrically active layers thereof being applied to an insulating substrate material. The solar cells (1) in the arrangement and circuit of flat rigid or flexible solar cells are disposed overlapping in the contact area to one or more adjacent solar cells (1), as is already known as such.; Said solar cells (1) are interconnected to each other directly once or a plurality of times in a novel manner, having a contact material (10) at the overlapping area to each other, using contact material (10) or switching points (22). In the method, an electrically conductive layer is generated on an entire solar cell matrix made of a plurality of overlapping solar cells (1) at individual or, if necessary, selectively at a plurality of (optionally a great many of) switching points (22), by means of screen printing, dispensing, spraying, vaporization, sputtering, or galvanically precipitating. Said layer, or the corresponding number of layers, are then applied pointwise to the corresponding locations so that the back side contact (7) of each of the upper solar cells (1) is connected to the front side contact (17) of the immediately adjacent overlapping solar cell (1).; The contact material (10) can be applied and disposed here as a continuous strand or as individual or a plurality of contacts in one or more switching points (22). The invention can be applied for rigid or flexible solar cells, particularly those produced using thin film technology. Said solar cells can also be individual, discrete solar cells, or also a plurality of so-called monolithically interconnected solar cells on a common substrate material.

Owner:太阳离子股份公司

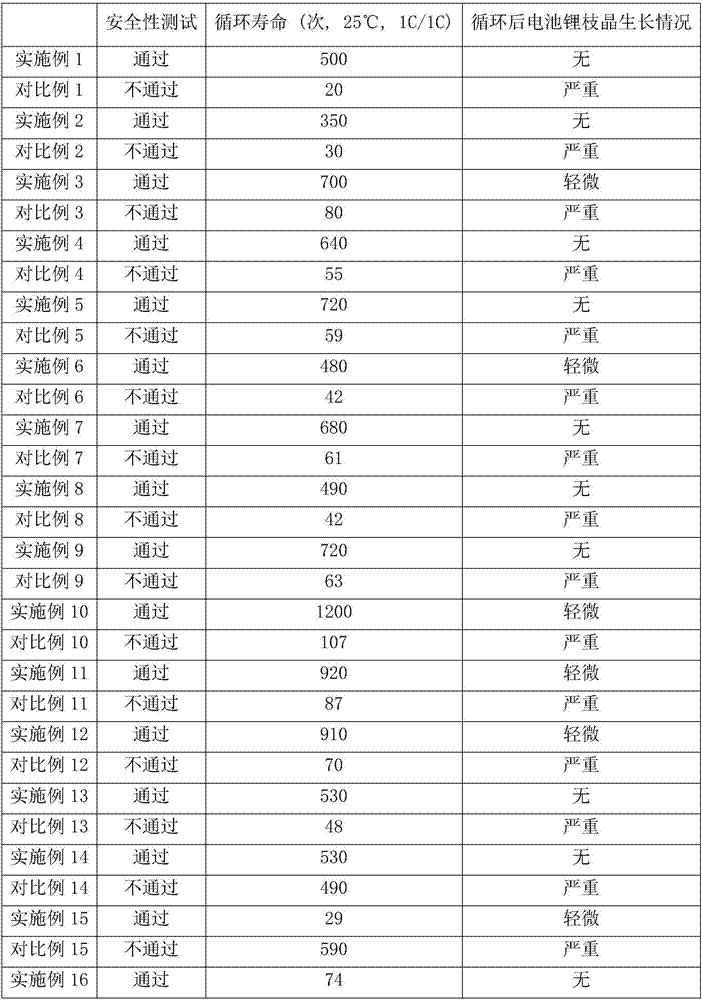

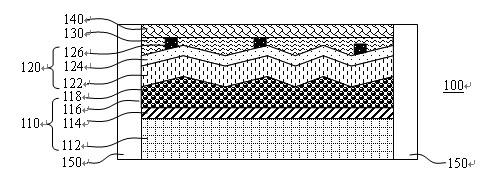

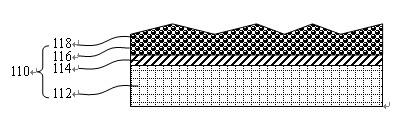

Safety layer and lithium secondary battery

ActiveCN108448160AReduced risk of short circuitsLong cycle lifeFinal product manufactureLi-accumulatorsElectrical batteryEngineering

The invention provides a safety layer and a lithium secondary battery. The safety layer is used for separating a positive electrode sheet and a negative electrode sheet, and comprises at least two layers of electrically insulating ion conducting layers and at least an absorption layer, wherein the absorption layer is positioned between each two adjacent two electrically insulating ion conducting layers, one sides respectively close to the positive electrode sheet and the negative electrode sheet are the electrically insulating ion conducting layers in the safety layer, the absorption layer comprises a substance capable of reversibly deintercalating lithium, and the conductivity of the absorption layer is not less than 10<-1> S / m. According to the present invention, after the safety layer is applied in the lithium secondary battery, the growth of the dendritic lithium can be effectively alleviated, the risk of the short circuit of the lithium secondary battery in various extreme and complicated environments is reduced, the cycle life of the lithium secondary battery is prolonged, and the safety performance of the lithium secondary battery is increased; and the safety layer cannot reduce the energy density of the lithium secondary battery.

Owner:NINGDE AMPEREX TECH

Array substrate and preparation method thereof

InactiveCN104576651ASave wiring spaceReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceInsulation layer

The invention discloses an array substrate and a preparation method thereof. The array substrate comprises a substrate, a buffer layer, a semiconductor pattern layer, a first grid electrode insulation layer, a second grid electrode insulation layer, a first conductive pattern layer, an interlayer insulation layer and a second conductive pattern layer, wherein the substrate comprises a thin-film transistor region and a capacitor region; the buffer layer is formed on the substrate; the semiconductor pattern layer is formed on the buffer layer and comprises a source and drain electrode region and a first electrode; the first grid electrode insulation layer is formed on the semiconductor pattern layer and correspondingly covers regions, except the first electrode, of the thin-film transistor region and the capacitor region; the second grid electrode insulation layer is formed on the first grid electrode insulation layer; the first conductive pattern layer is formed on the second grid electrode insulation layer and comprises a grid electrode and a second electrode; the interlayer insulation layer is formed on the first conductive pattern layer; the second conductive pattern layer is formed on the interlayer insulation layer and comprises a source electrode and a drain electrode which are coupled with the source and drain electrode region as well as a third electrode. With the adoption of the array substrate and the preparation method thereof, the capacitance of a capacitor is increased, film layer structures of the regions except the capacitor region are not changed, the signal line load is effectively decreased, and meanwhile, short-circuit risks of upper and lower film layers of the grid electrode insulation layers are reduced.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

Wafer bonding method and wafer bonding structure

ActiveCN105513983AReduced risk of short circuitsNot easy to short circuitSemiconductor/solid-state device detailsSolid-state devicesEngineeringOxide

The invention provides a wafer bonding method and a wafer bonding structure. The wafer bonding method is characterized in that before the wafer bonding processing, an interlayer dielectric layer is formed on a wafer, and the interlayer dielectric layer comprises a first dielectric layer and an insulation layer, which are formed sequentially; an interconnection structure can be formed in the interlayer dielectric layer, and a part of the interconnection structure is protruded from the surface of the interlayer dielectric layer, and is a bonding end of the interconnection structure; and side walls are formed on the side walls of the bonding end. The wafer bonding method and the wafer bonding structure are advantageous in that the insulation layer is used to completely cover the surface of the interlayer dielectric layer, and the side walls are used to cover the side walls of the bonding end; after the bonding processing of a plurality of wafers, the adjacent bonding ends are provided with the insulation layers and the side walls for the isolation, and the short circuit is not easy to occur; and in addition, under the protection of the side walls, the bonding ends are not exposed in the external environment, and the oxide is not easy to form under the influence of the oxygen and the water vapour, and at the same time, the short circuit risk can be reduced.

Owner:SEMICON MFG INT (SHANGHAI) CORP

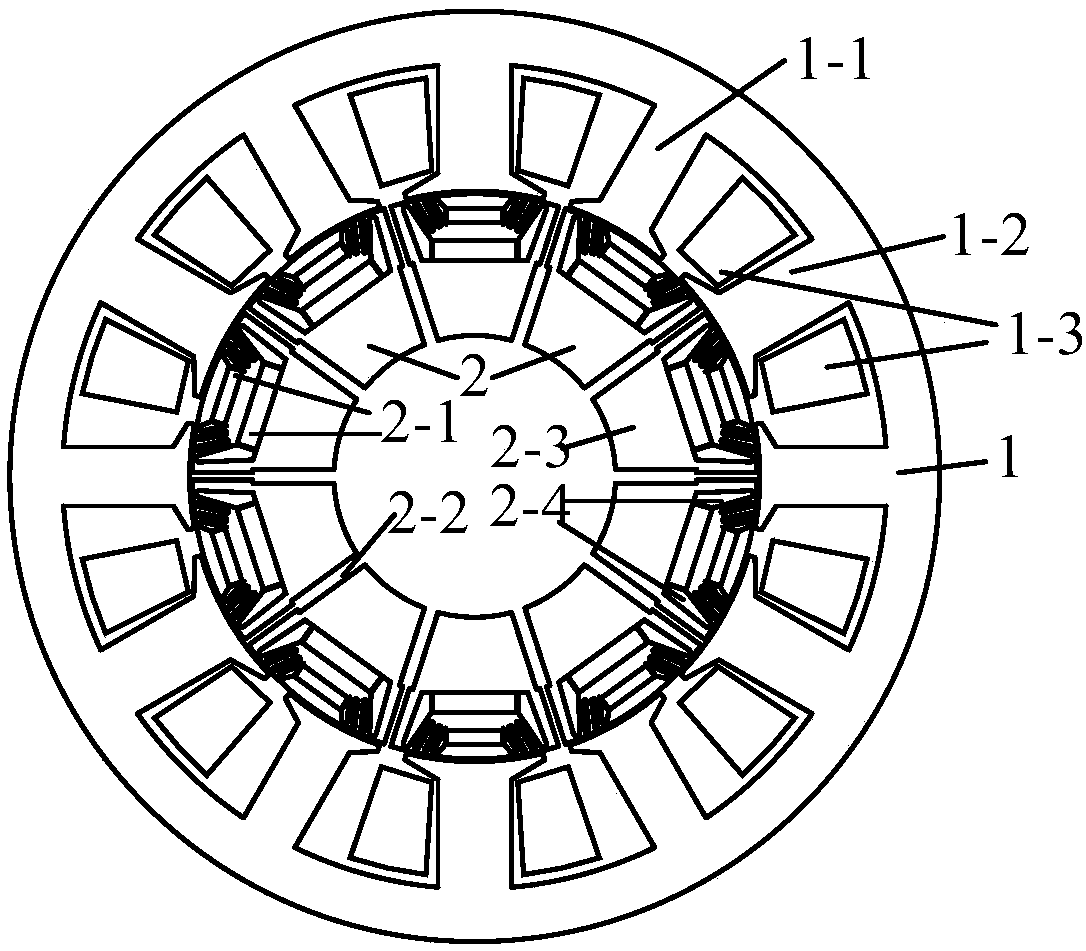

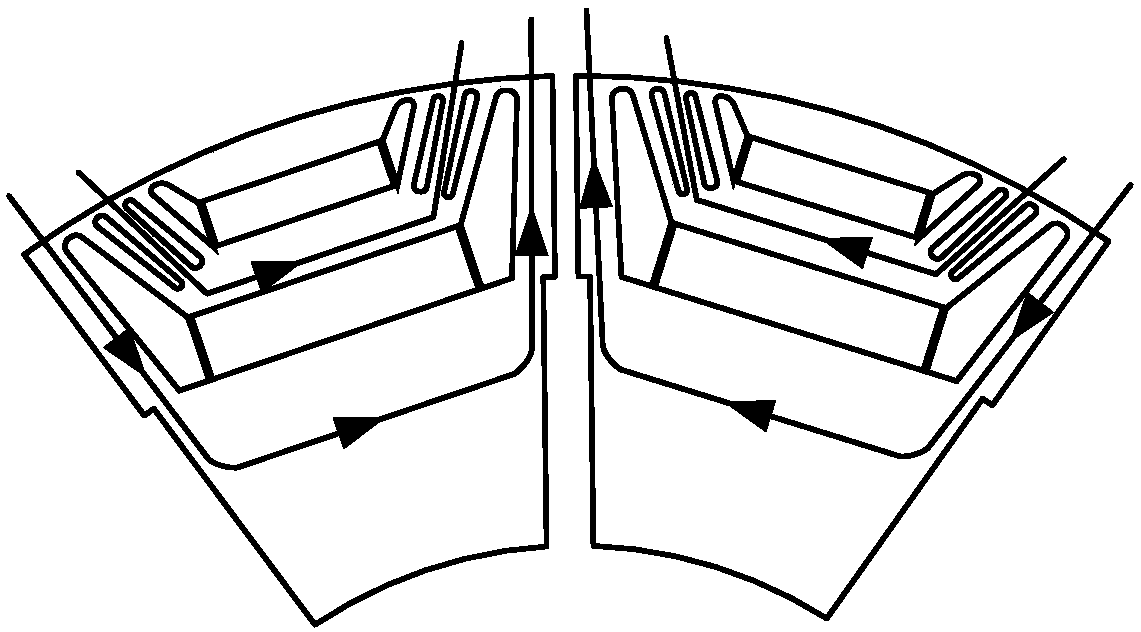

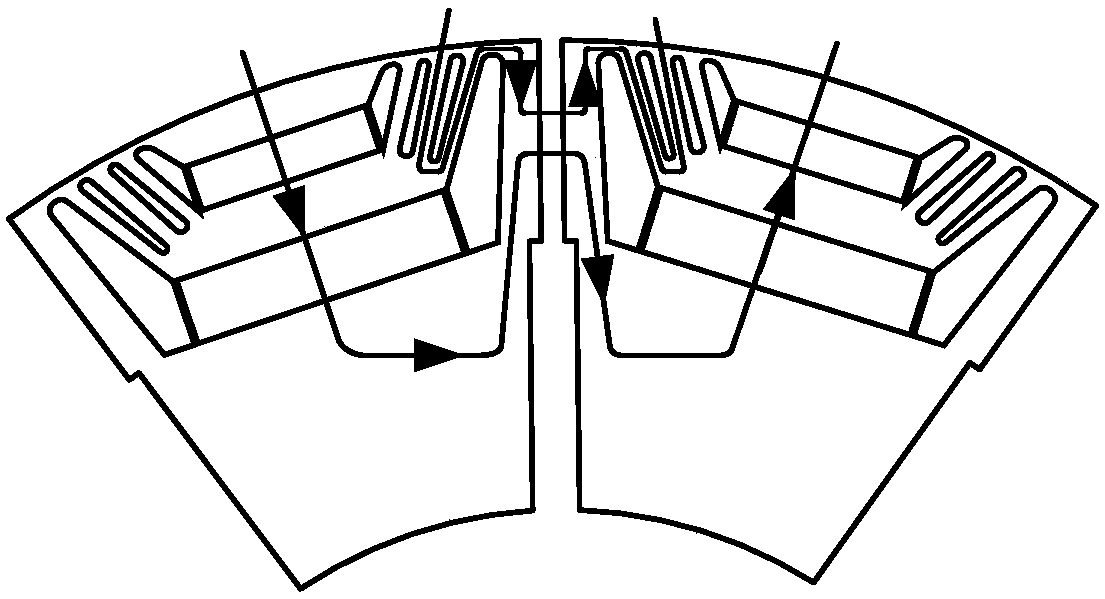

Fractional-slot concentrated winding permanent magnet synchronous motor and design method thereof for improving reluctance torque

InactiveCN108199509ALow failure rateReduce temperature riseMagnetic circuit rotating partsMagnetic circuit stationary partsPermanent magnet synchronous motorMetallic materials

The invention discloses fractional-slot concentrated winding permanent magnet synchronous motor and a design method thereof for improving reluctance torque. The fractional-slot concentrated winding permanent magnet synchronous motor comprises a stator and a rotor, wherein the stator is slotted along the peripheral direction to form fault-tolerant teeth and armature teeth arranged alternately; an armature winding is wound on the armature teeth, the fault-tolerant teeth and the armature teeth are different in widths, and the widths of the armature teeth are wider than those of the fault-tolerantteeth; the rotor consists of a permanent magnet, a rotor core and a magnetic obstacle, the permanent magnet is a double-layer permanent magnet, the rotor core is composed of a plurality of independent units, and during machining, the rotor is wrapped with a non-metal material to form a compact structure. The rotor core is segmented along the axis pole direction of the permanent magnet, and the width of the upper part of the magnetic obstacle during segmentation is narrower than that of the lower part. The permanent magnet synchronous motor has the advantages that the direct-axis inductance can be reduced through the special magnetic obstacle design, the influence on quadrature axis inductance can also be reduced as much as possible, and the subharmonic of the motor is free of obvious inhibition. Therefore, the reluctance torque of the motor can be improved effectively, and the iron loss and eddy-current loss of the motor are reduced.

Owner:JIANGSU UNIV

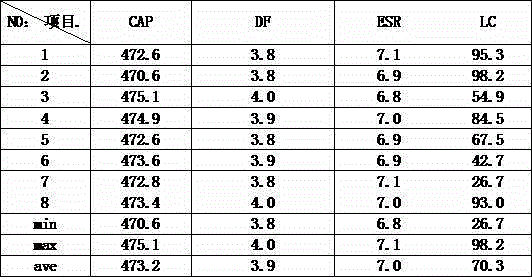

Low-leakage-current winding type solid electrolytic capacitor and production method thereof

InactiveCN105225840AImprove protectionAvoid damageSolid electrolytic capacitorsSelf-healingElectrolysis

The invention discloses a low-leakage-current winding type solid electrolytic capacitor and a production method thereof. The production method comprises steps of element preparation, assembling, and aging. According to the invention, an anode foil and a cathode foil are cut and then are polished, thereby substantially reducing a short-circuit risk because of puncturing a piece of electrolytic paper by burrs and reducing a risk of an increase of leakage currents due to point discharging. On the basis of impregnation of pre treating agents twice, an oxidation film can be protected well, thereby reducing damages on the oxidation film during a polymerization process. Because an oxidizability group is added into an oxidizing agent, the polymer doping effect is realized and an oxygen-containing agent group having oxidability can be decomposed in a high-temperature de-doping mode, so that the damaged oxidation film can be repaired to a certain extent and the self-healing capability of the capacitor can be improved. According to a prepared solid electrolytic capacitor, a leakage current control standard can be set to be larget value that is not larger than 0.05CV or 15 microamps after charging of 2 min under the temperature of 20+ / -5 DEG C.

Owner:HUNAN AIHUA GRP

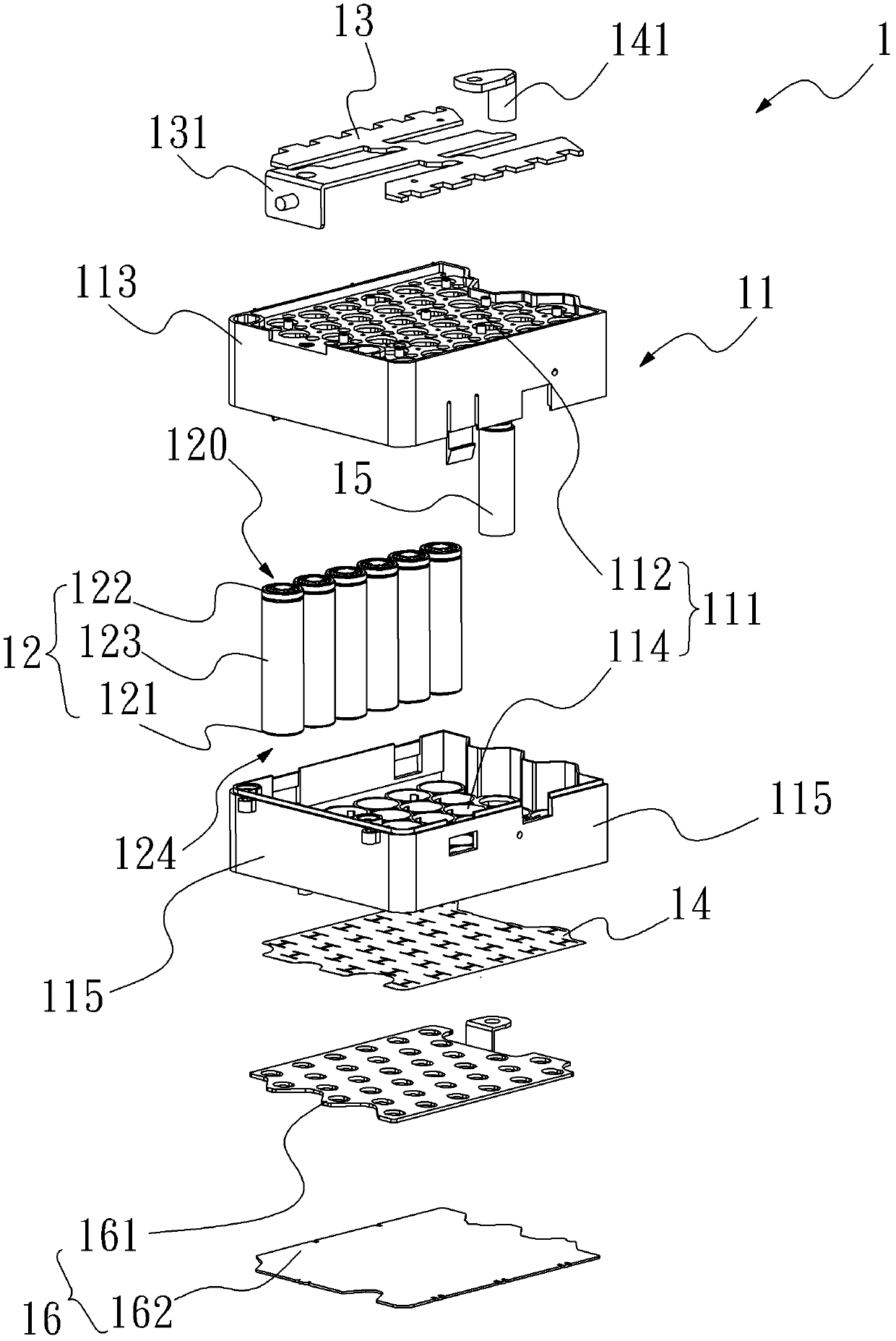

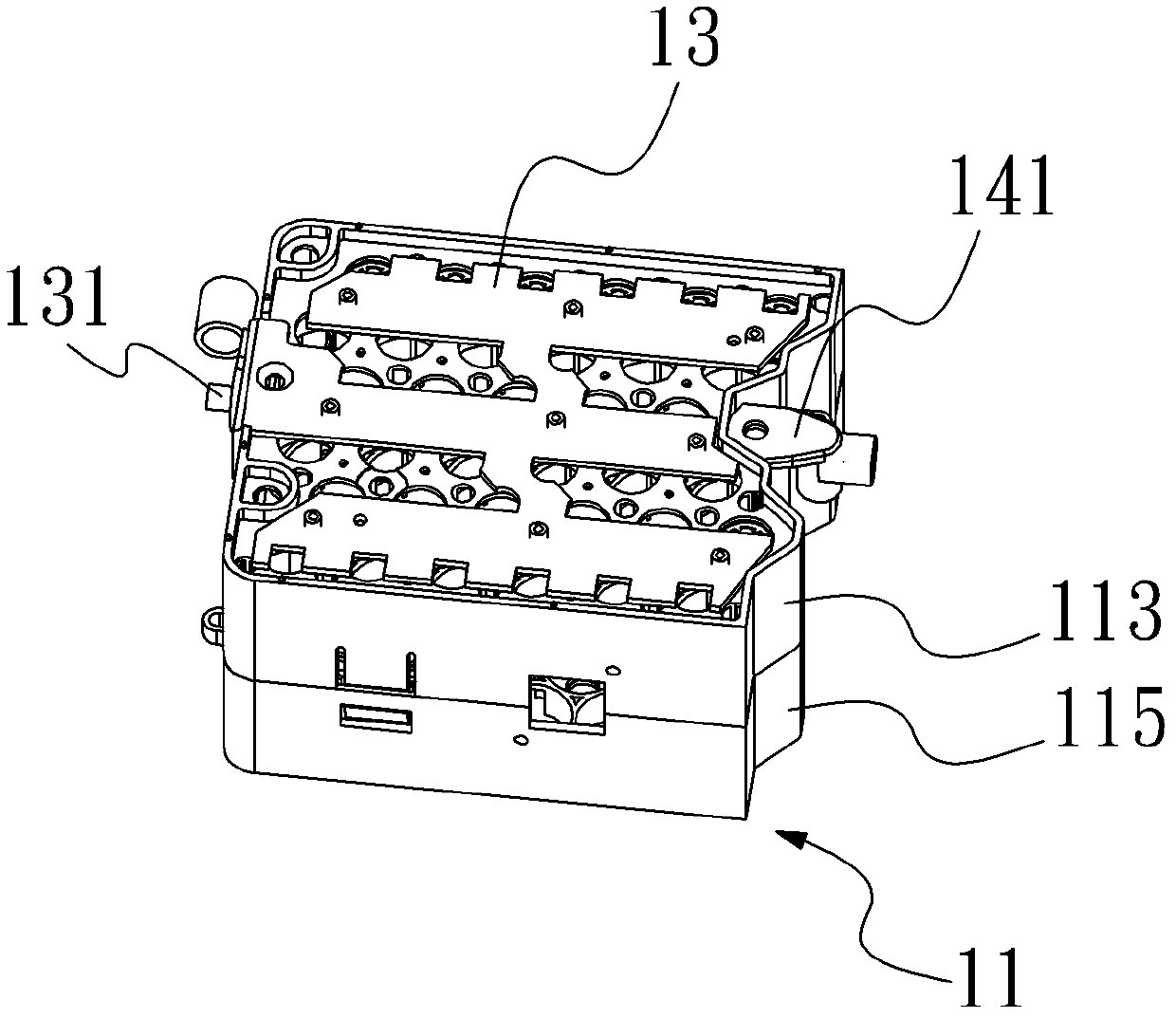

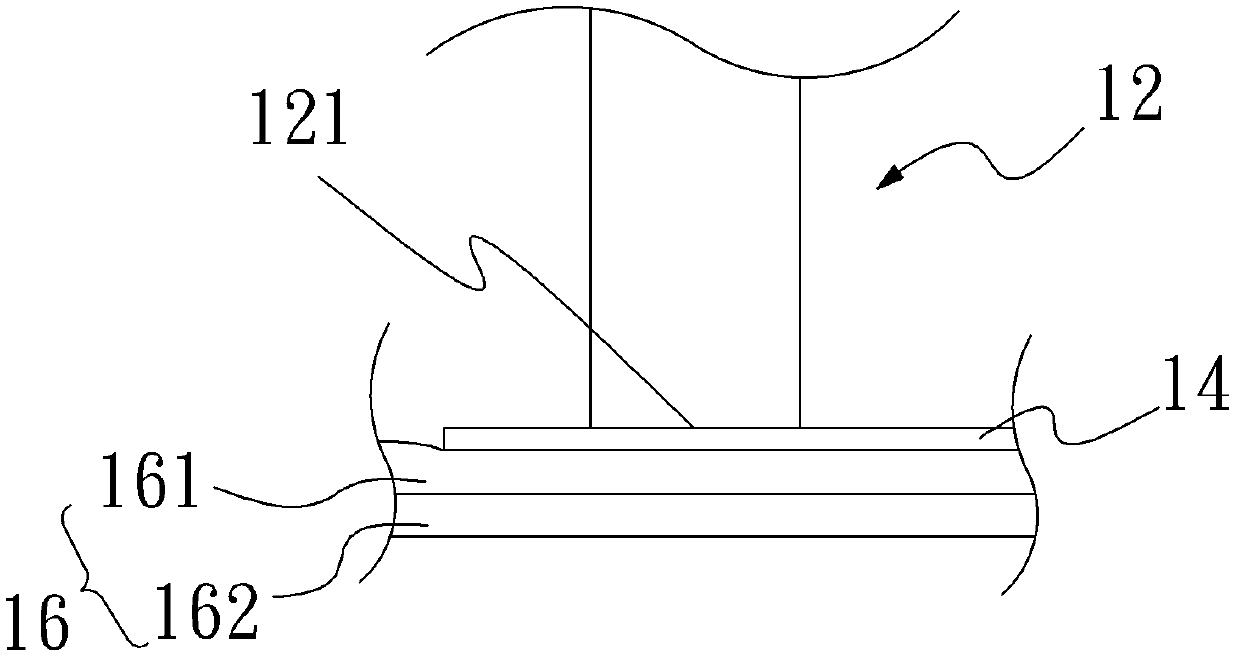

Battery pack with multiple parallel cells and power supply assembly with multiple battery packs connected in series

ActiveCN103378335APoor connectionReduce risk of sheddingFinal product manufactureSecondary cells manufactureElectric capacityFixed frame

The invention relates to a battery pack with multiple parallel cells and a power supply assembly with multiple battery packs connected in series. The battery pack mainly comprises a fixed frame device, the cells, top common electrodes, bottom common electrodes and at least one conductive column, wherein the fixed frame device comprises a plurality of storage grooves, the cells are arranged in the storage grooves, and at least one storage groove is used for installing the conductive column; the top common electrodes and the bottom common electrodes are respectively in conductive contact with the cells and two ends and locked on the upper side surface and the lower side surface of the fixed frame device, the top common electrodes form an electrode, and the bottom common electrodes are conductively connected with one another through the conductive column, are insulated from the top common electrodes and form another electrode. The power supply assembly with high electric capacity is formed by connecting the electrodes of the multiple battery packs in series / parallel.

Owner:阿提瓦公司

Processing method for wrapping side surface of printed-circuit connector product with nickel gold

ActiveCN106132108ANo copper exposureImprove corrosion resistancePrinted circuit aspectsConductive pattern reinforcementResistEngineering

The invention discloses a processing method for wrapping a side surface of a printed-circuit connector product with nickel gold. The processing method comprises the following steps of A, addition of gold-plated leads: adding leads on the corner of a square bonding pad and at a welding ring position of a solder resist covering via hole in a mode of adding the leads on the two sides; B, prevention of gold-plating permeation: adopting processes of using a photosensitive wet film as the base, and performing one-time exposure pattern transferring after photosensitive dry film protection is carried out so as to realize the prevention of gold-plating permeation; and C, performing protection while etching the leads: choosing a Dupont GMP220 thick dry film with the thickness of 2mil, and adopting an alkali etching process so as to prevent circuit corrosion and oxidization caused by attack of liquid medicine on the inlet surface.

Owner:XIAN KING BROTHER CIRCUIT TECH +2

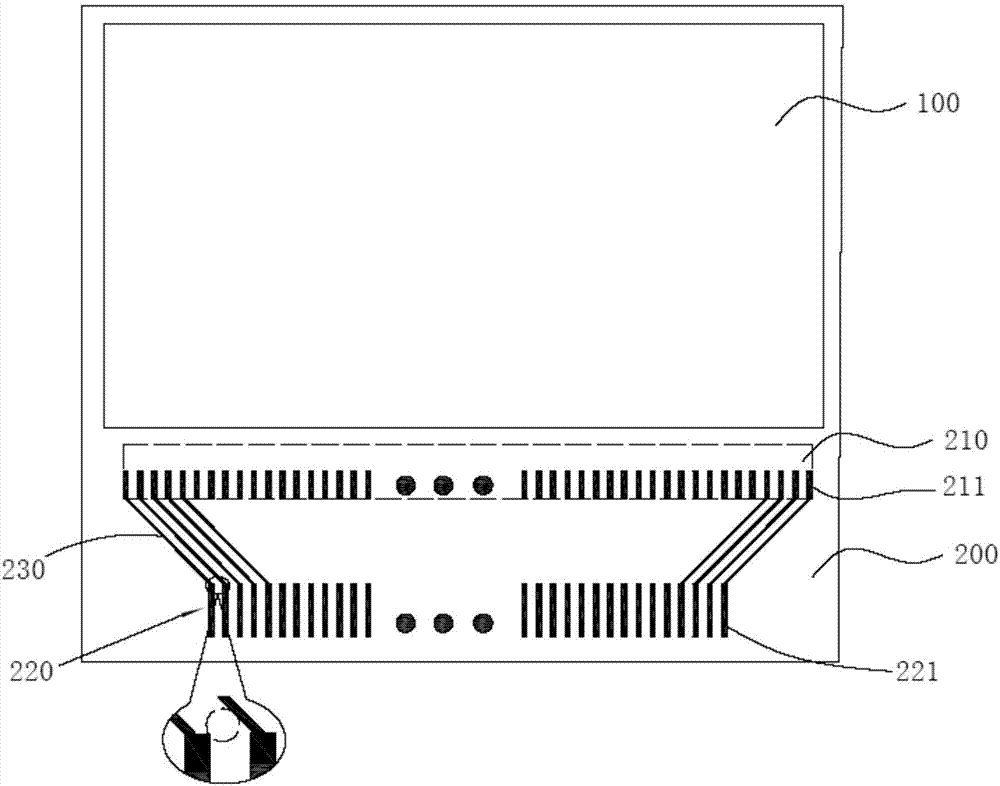

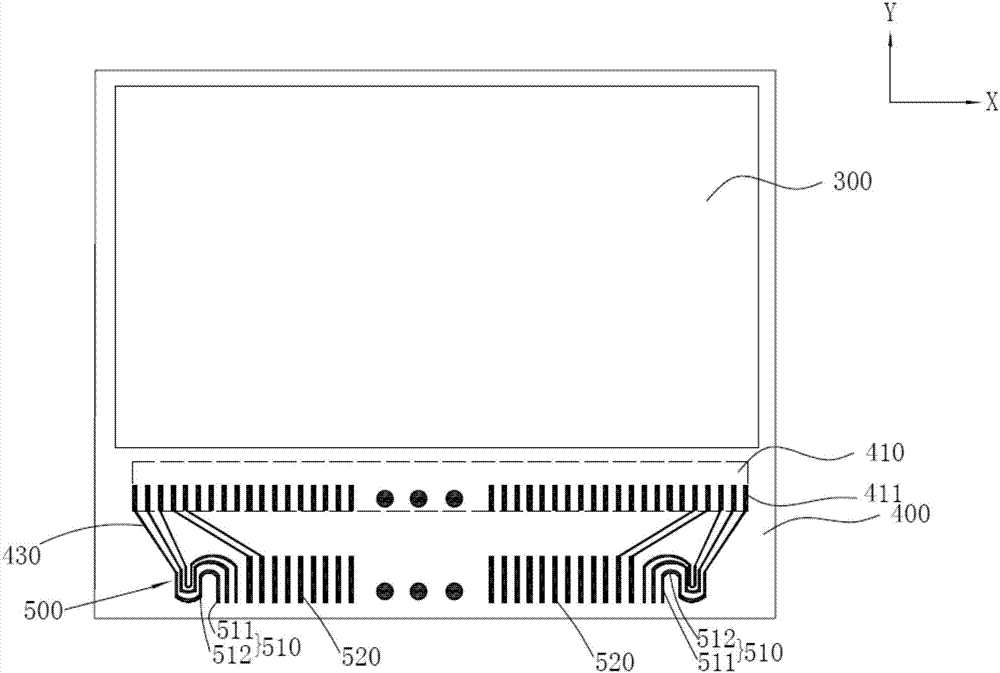

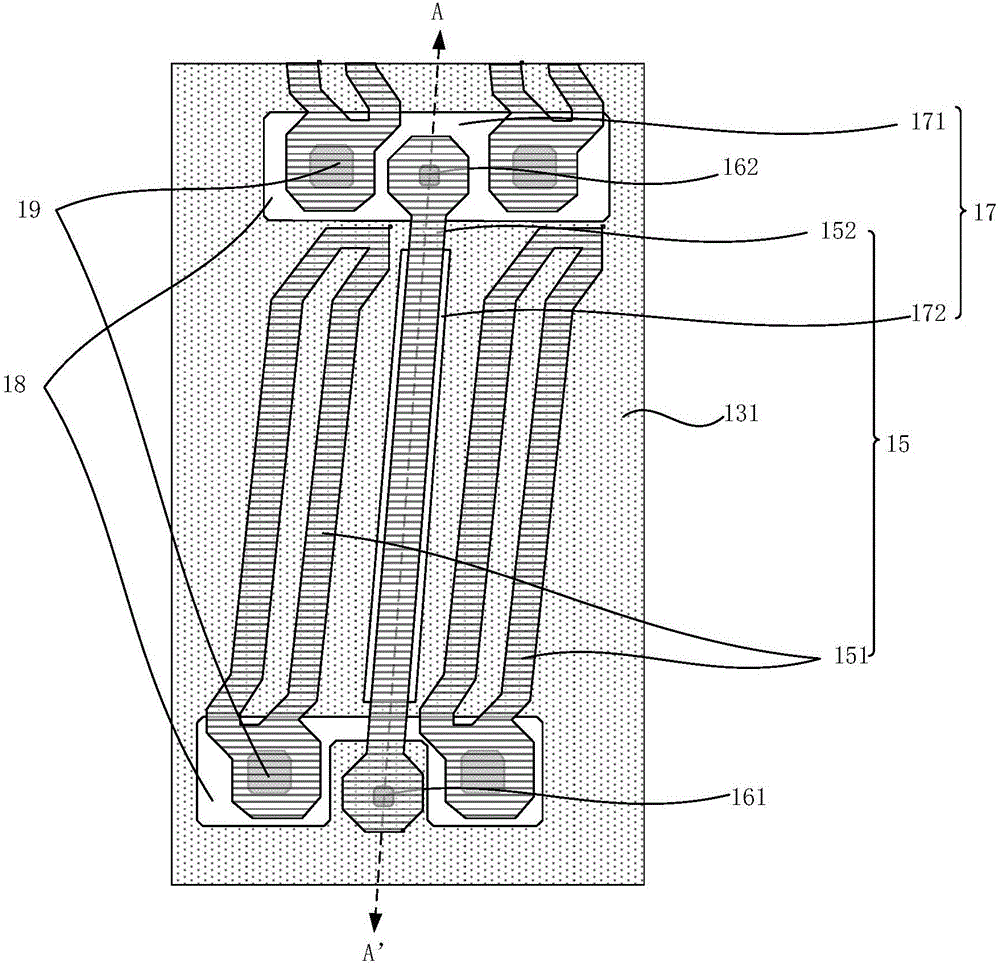

Touch panel, touch display panel and manufacture method of touch panel

InactiveCN103376939AReduced risk of short circuitsInput/output processes for data processingTouch SensesComputer science

The invention discloses a touch panel which comprises a base, a decoration layer, a touch sensing element and at least one first insulation pattern. The base is provided with a light transmitting area and a peripheral area, and the decoration layer is arranged in the peripheral area of the base. The touch sensing element comprises a first patterning transparent sensing layer which is at least arranged in the light transmitting area of the base, wherein the first patterning transparent sensing layer extends into the peripheral area and is partially overlaid with the decoration layer. The insulation pattern is arranged in the peripheral area of the base and positioned between the first patterning transparent sensing layer and the decoration layer, so that the first patterning transparent sensing layer does not contact with the decoration layer.

Owner:WINTEK CHINA TECH LTD +1

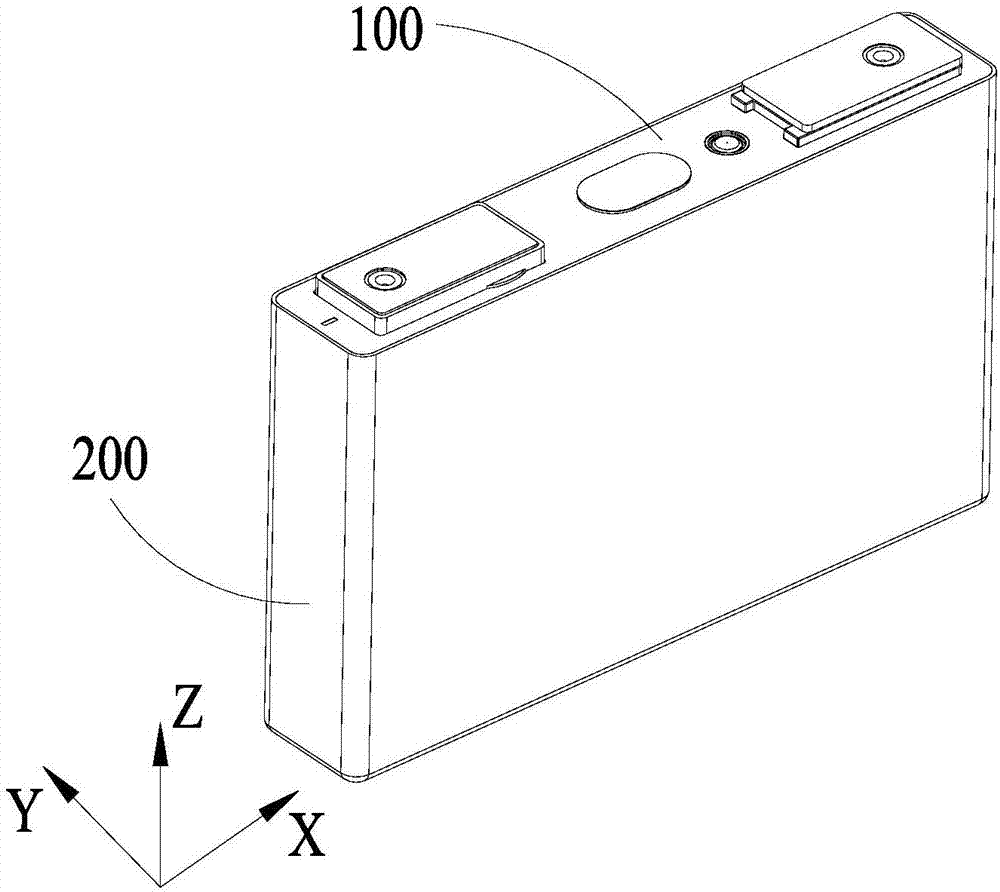

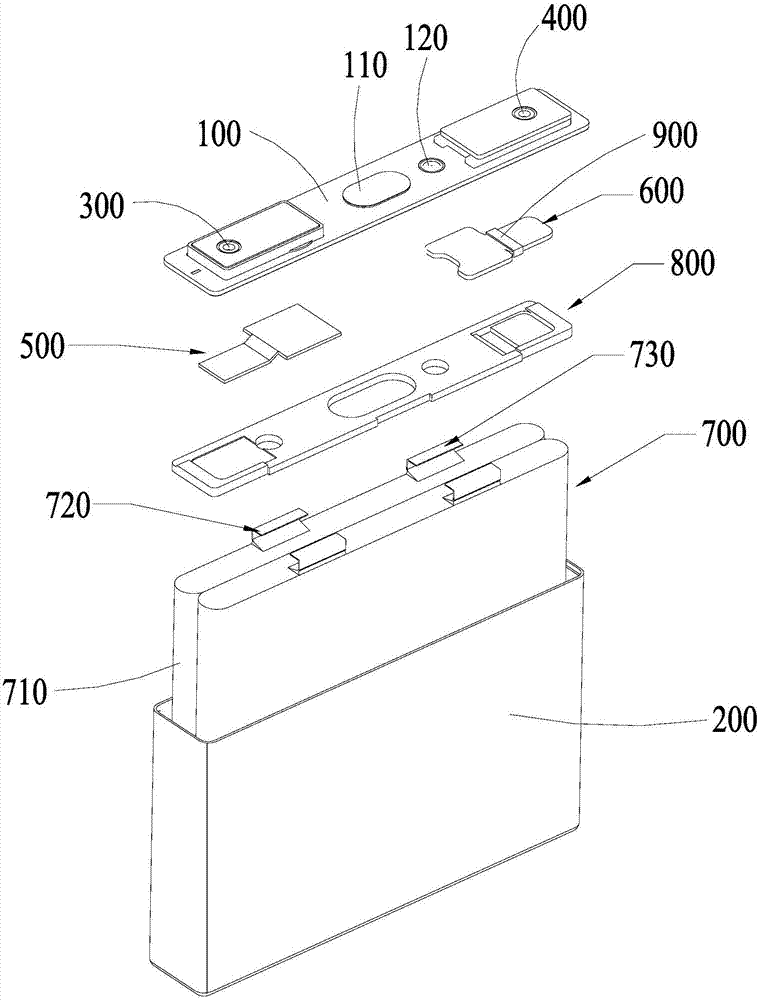

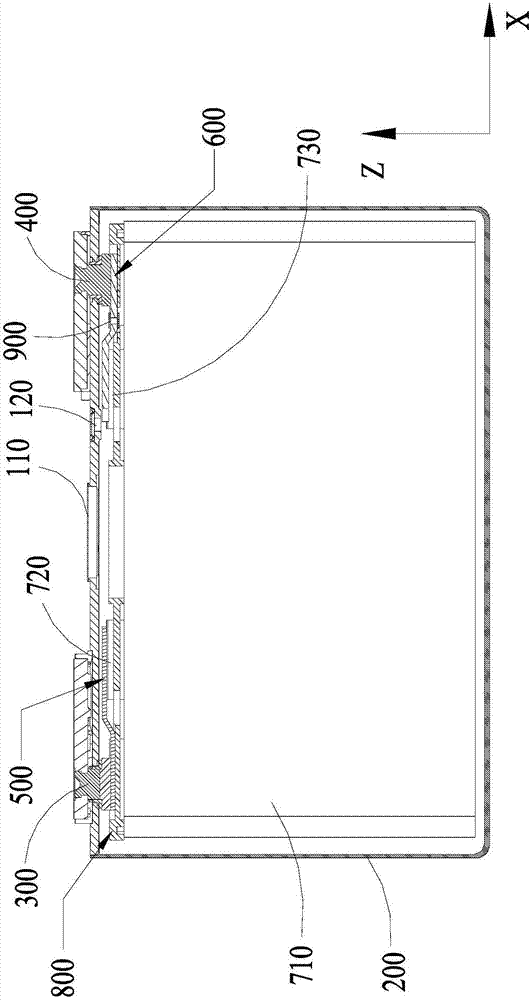

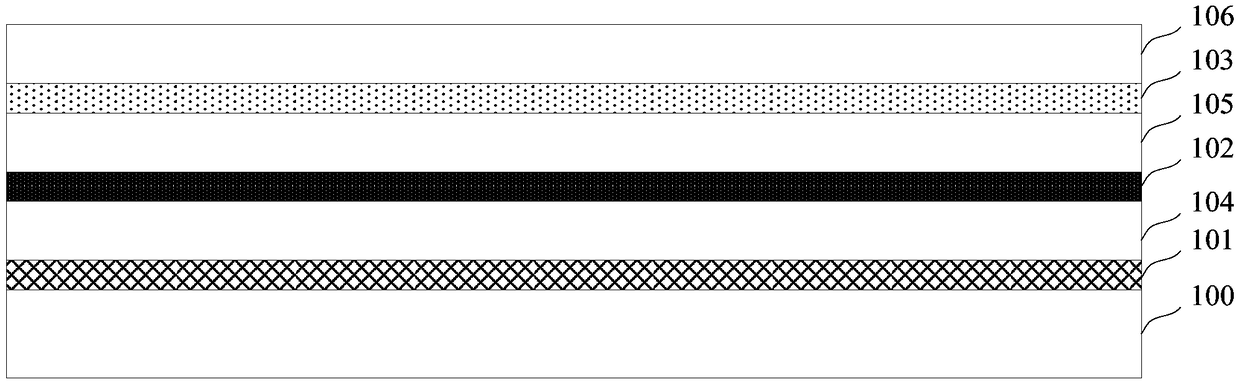

Secondary battery

ActiveCN111326699AReduced risk of short circuitsImprove safety performanceCell electrodesSmall-sized cells cases/jacketsPhysicsElectrical battery

The invention provides a secondary battery, which includes an electrode assembly, a shell and a first electrode terminal, wherein the shell is provided with an accommodating cavity, the electrode assembly is accommodated in the accommodating cavity, and the first electrode terminal is arranged in the shell; the electrode assembly comprises a first pole piece, a second pole piece and a diaphragm, and the diaphragm separates the first pole piece from the second pole piece; the first pole piece comprises a first current collector, a first active substance layer and an insulating layer; the firstcurrent collector comprises a first main body part and a first tab extending from the first main body part, at least part of the surface of the first main body part is coated with the first active substance layer, and the first tab protrudes out of the first main body part and is electrically connected with the first electrode terminal; and the insulating layer is at least partially coated on thesurface of the first tab, and the elastic modulus of the insulating layer is less than that of the first tab.

Owner:CONTEMPORARY AMPEREX TECH CO

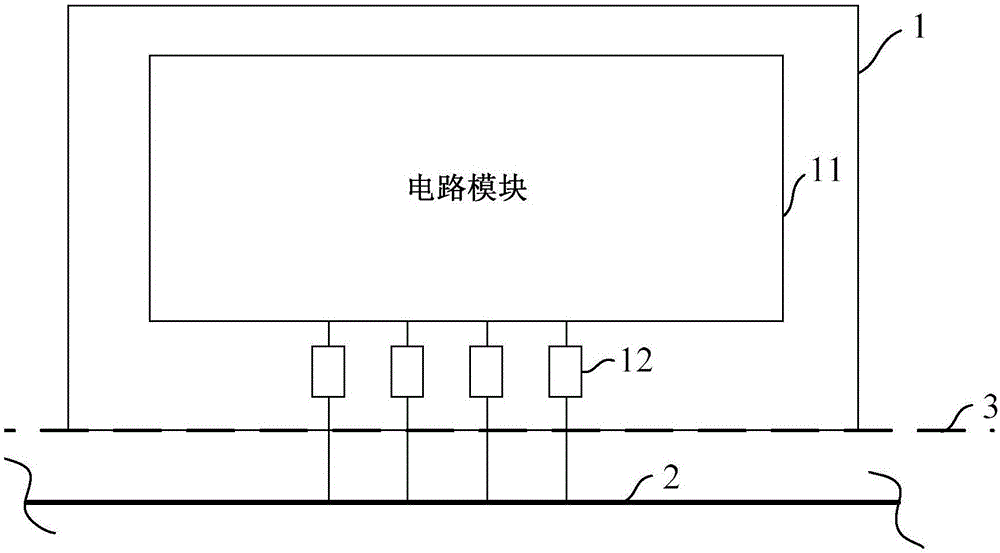

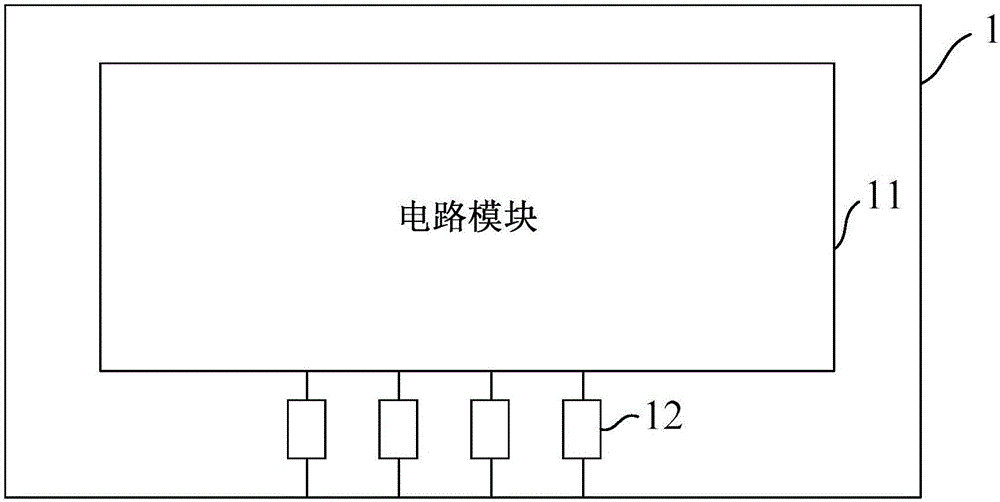

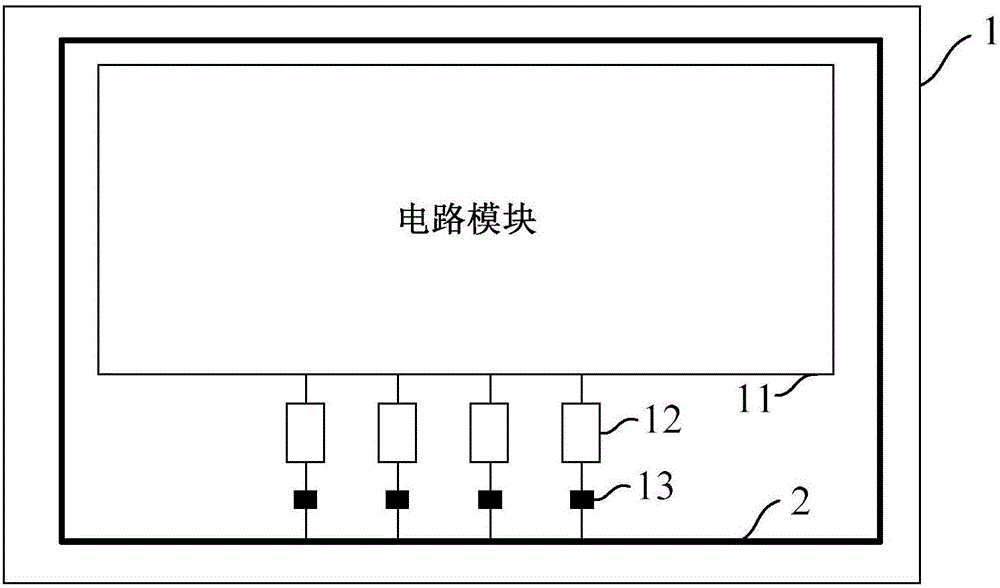

Antistatic protection structure and reliability improving method of semiconductor panel

InactiveCN106057782AImprove reliabilityReduced risk of short circuitsSemiconductor/solid-state device detailsSolid-state devicesElectrical isolationProtection ring

The invention provides an antistatic protection structure and a reliability improving method of a semiconductor panel. The antistatic protection structure comprises an antistatic protection ring, a circuit module and pads, each pad is in short-circuit connection with the antistatic protection ring via a short-circuit line, part, connected with the short-circuit lines, of the antistatic protection ring is positioned at the outer side of a cutting line of the semiconductor panel, and a passivation insulating layer over the short-circuit lines in the semiconductor panel is internally provided with a cut-off window out of which a short-circuit line film layer is exposed. In the manufacture process of the panel, different points of the circuit are kept in the same potential, and static injury is avoided; before completion of the manufacture process of the panel, the short-circuit lines are cut off to disconnect the pads from the antistatic protection ring; and after completion of the manufacture process of the panel, the parts outside the panel of the short-circuit lines are cut to realize dual electrical isolation of the circuit module from the antistatic protection ring. On the premise that a static protection effect is ensured, the reliability of the panel is improved greatly.

Owner:SHANGHAI IRAY TECH

Capacitor structure and manufacturing method thereof

PendingCN110957304AIncreasing the thicknessImprove support stabilityTransistorSemiconductor/solid-state device detailsCapacitanceStructural engineering

The invention provides a capacitor structure and a manufacturing method thereof, and the method comprises the steps: forming an etching stop layer, a lower sacrificial layer, a central supporting layer, a top sacrificial layer, a first supporting layer, and a stress relieving layer on a bottom substrate, wherein the bottom substrate is provided with a contact hole; etching the stress relieving layer based on a first pattern mask to form a stress relieving part; forming a second supporting layer on the first supporting layer and the stress relieving part, wherein the first supporting layer andthe second supporting layer wrap the stress relieving part to form a top supporting layer; etching the top supporting layer based on the second pattern mask to form a primary capacitance hole; forminga lower electrode layer at least on the surface of the inner wall of the primary capacitor hole; etching at least the top supporting layer based on a third pattern mask to form an etching opening; and removing the top sacrificial layer, a portion of the central supporting layer, and the lower sacrificial layer based on the etch opening to form an ultimate capacitance hole. According to the invention, the problem of low stability of the capacitor support layer in the existing capacitor structure is solved.

Owner:CHANGXIN MEMORY TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com