Patents

Literature

77results about How to "Poor connection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

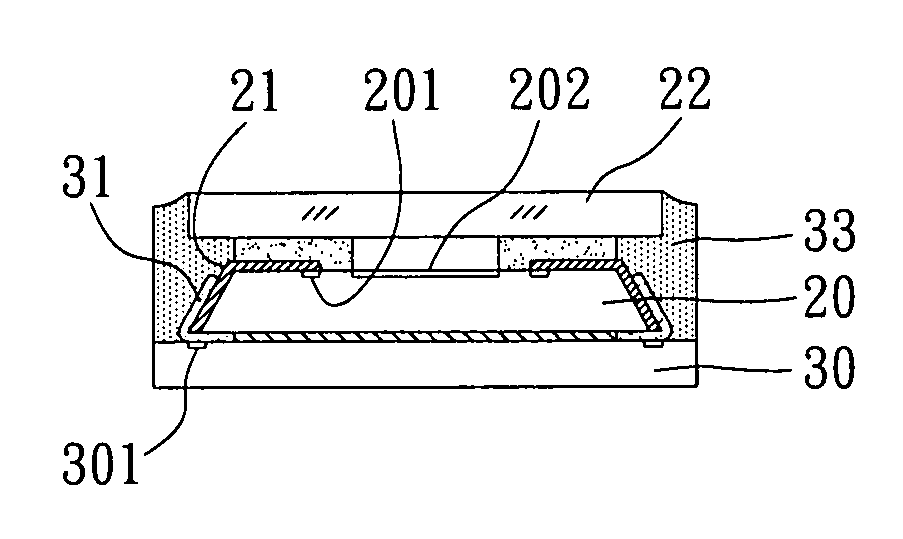

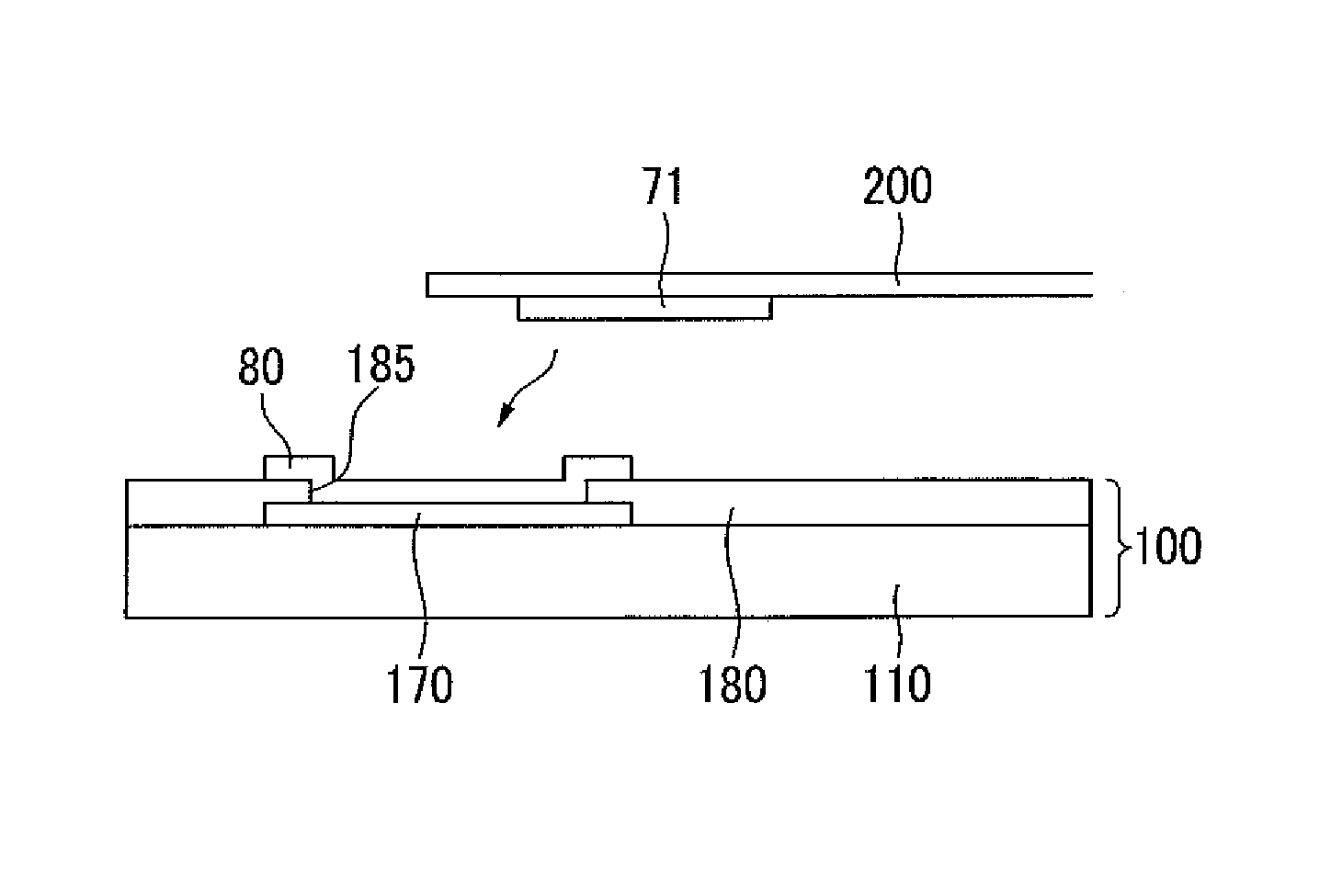

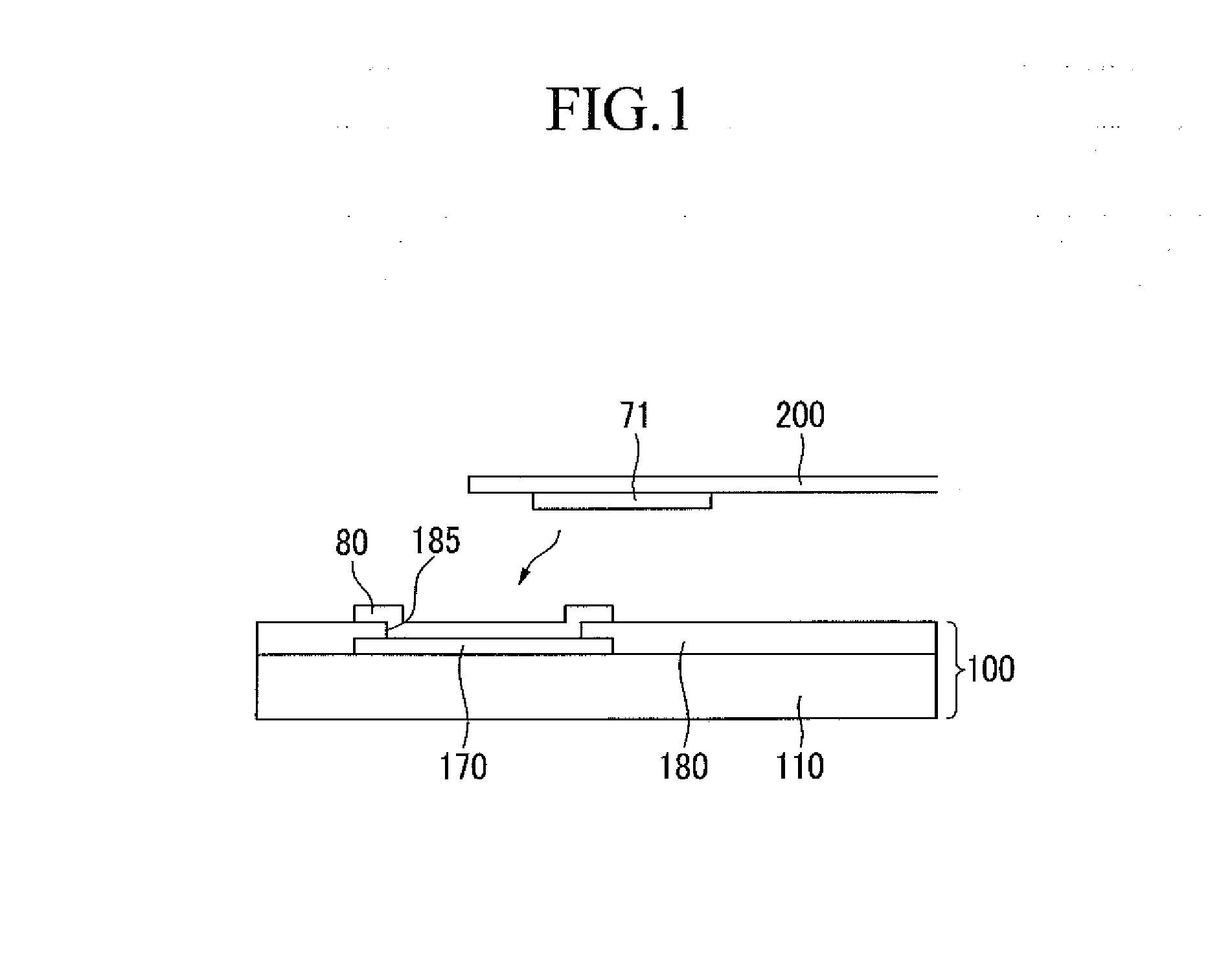

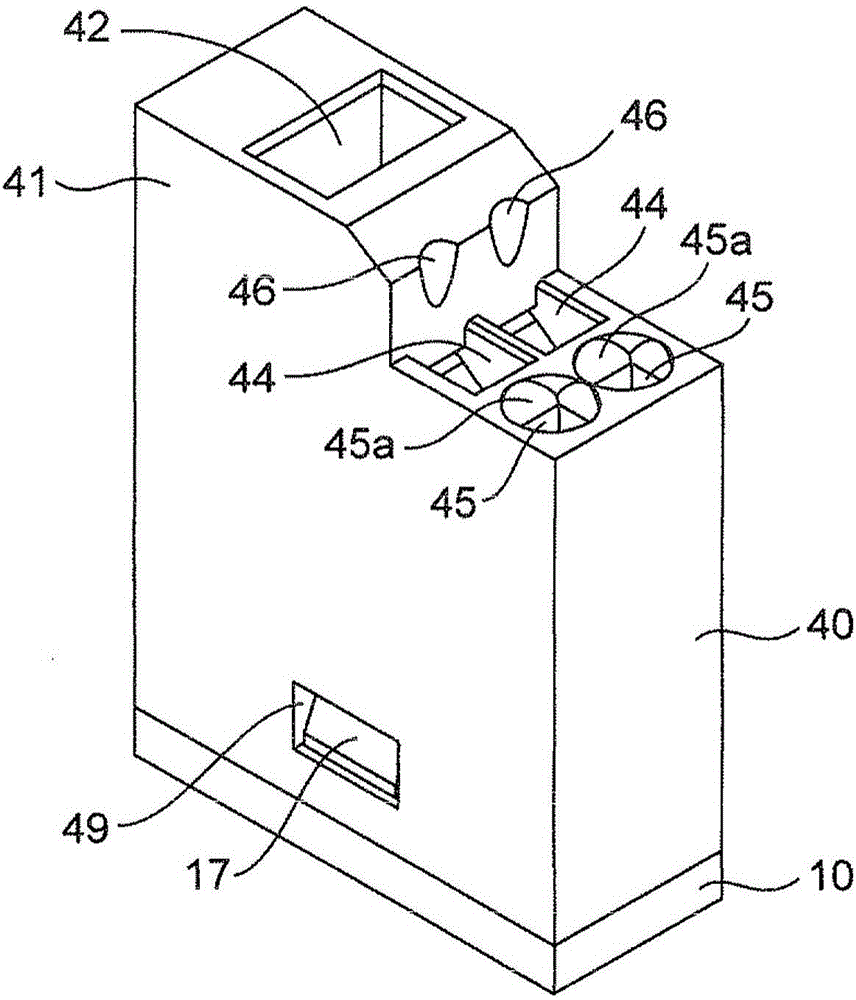

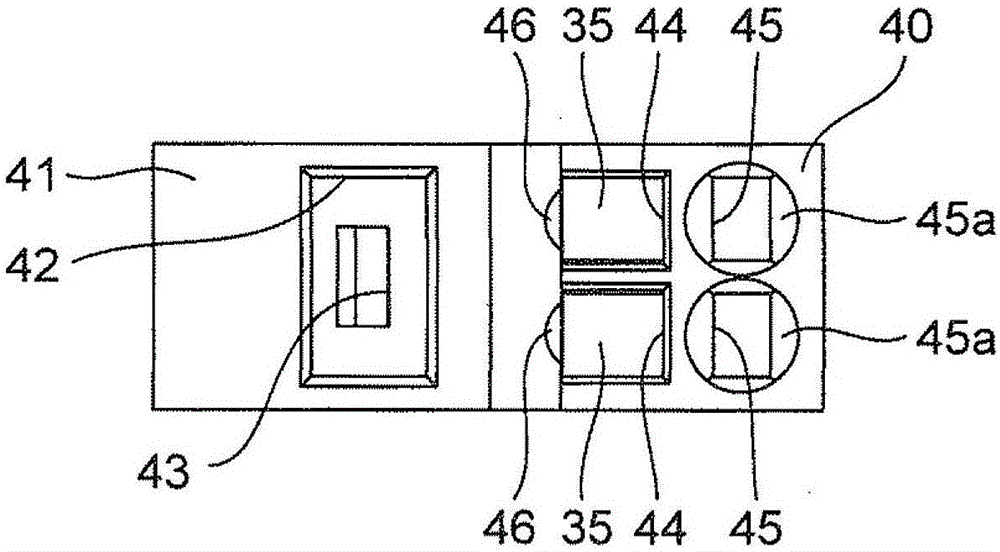

Bonding apparatus and bonding method

InactiveUS20120247664A1Improve reliabilityReduce gapSolid-state devicesLaminationAdhesiveIncrease temperature

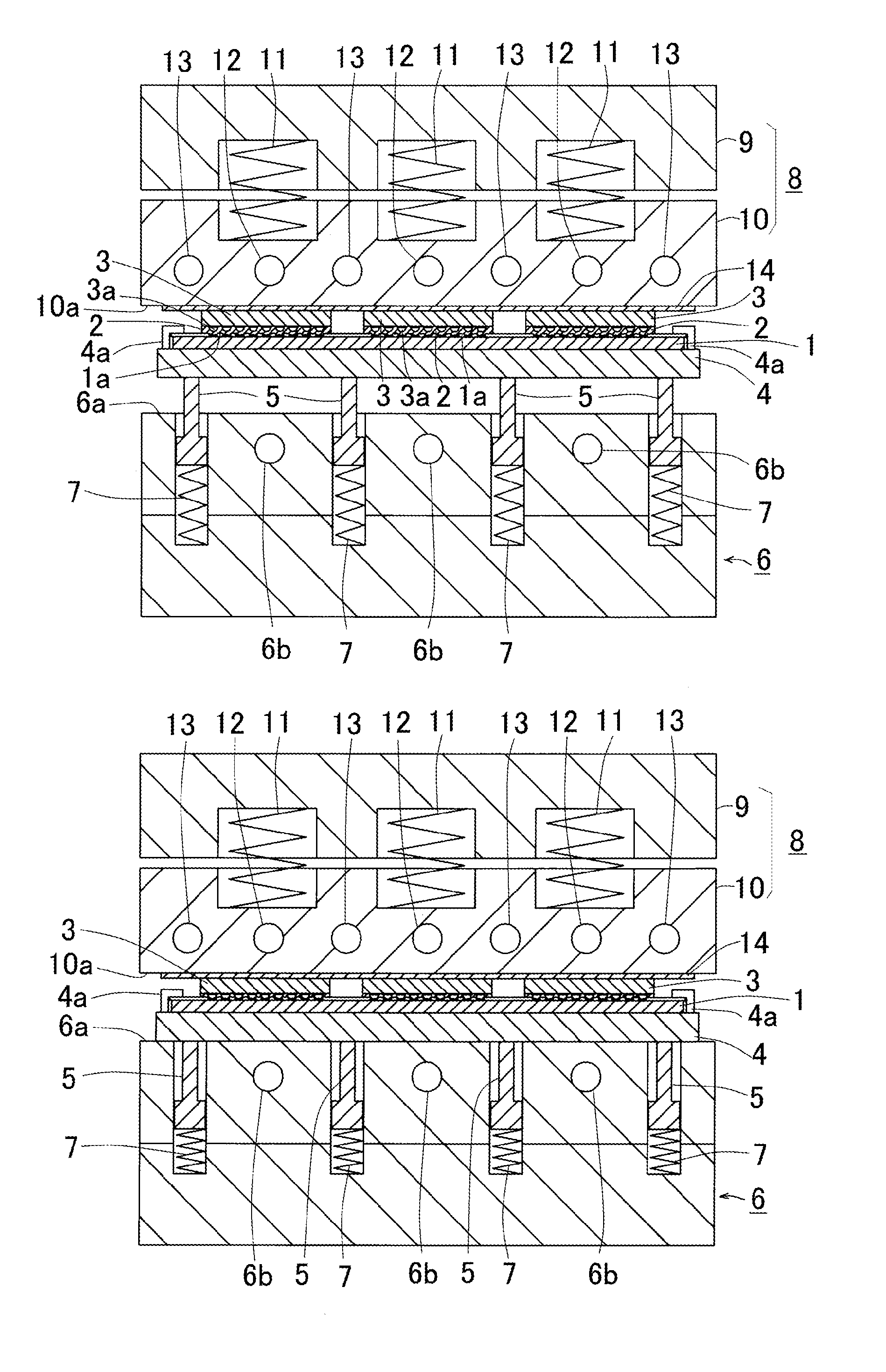

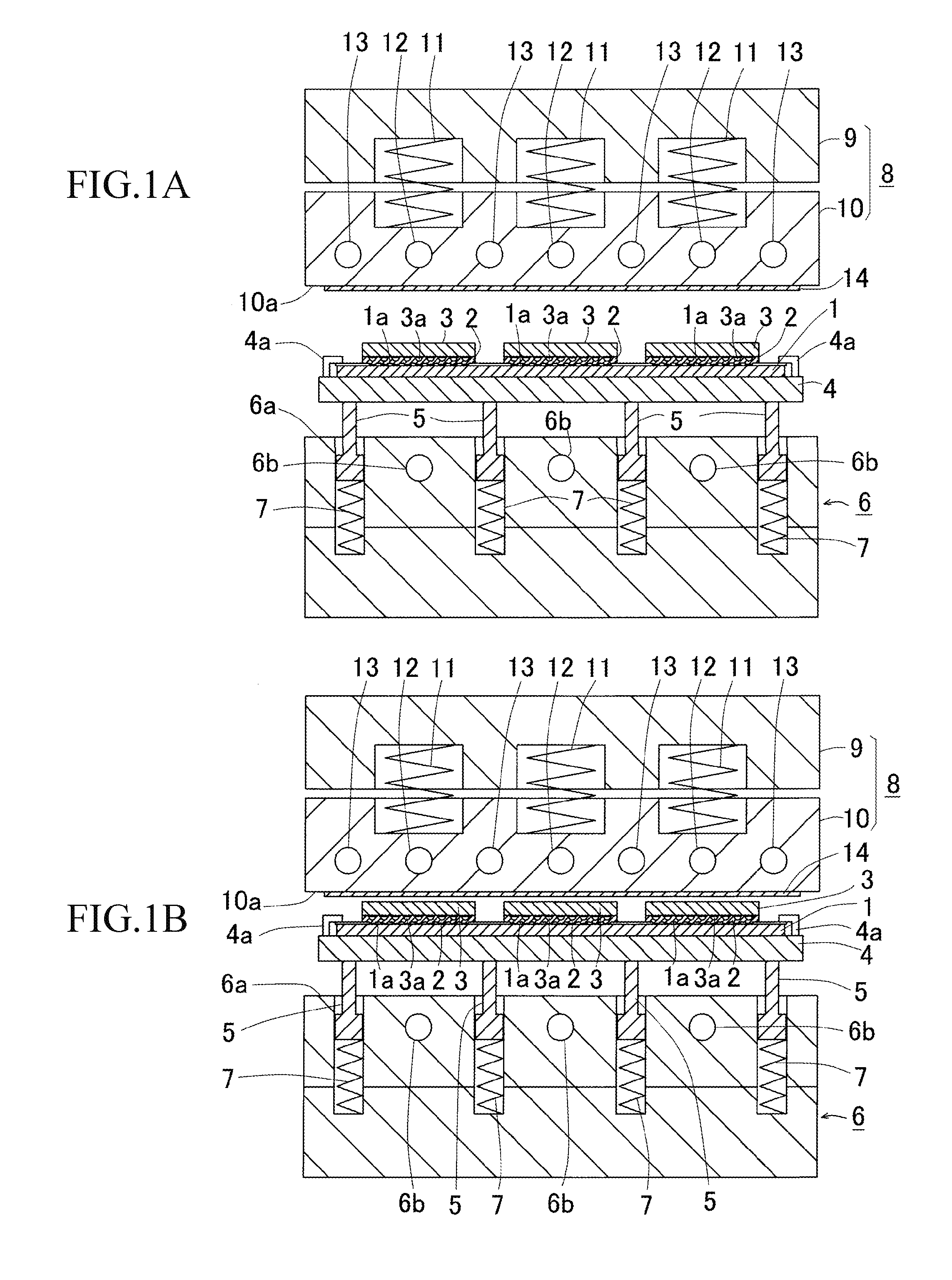

The bonding apparatus is capable of effectively increasing temperature of a substrate and reducing occurrence of position gaps and poor connection in a process of flip-chip-bonding semiconductor devices to the substrate. The bonding apparatus comprises: a supporting unit for supporting the substrate, on which the semiconductor devices have been adhered by a non-conductive; and a heating / pressing unit for heating and pressing the substrate, the heating / pressing unit having a built-in heat source and a clamping face, onto which the substrate supported by the supporting unit is pressed. The substrate supported by the supporting unit is moved toward the clamping face of the heating / pressing unit so as to preheat the substrate and the semiconductor devices by radiation heat. Then, the semiconductor devices are pressed onto the clamping face of the heating / pressing unit so as to cure the non-conductive adhesive and bond bumps of the semiconductor devices to terminal sections of the substrate.

Owner:APIC YAMADA CORP

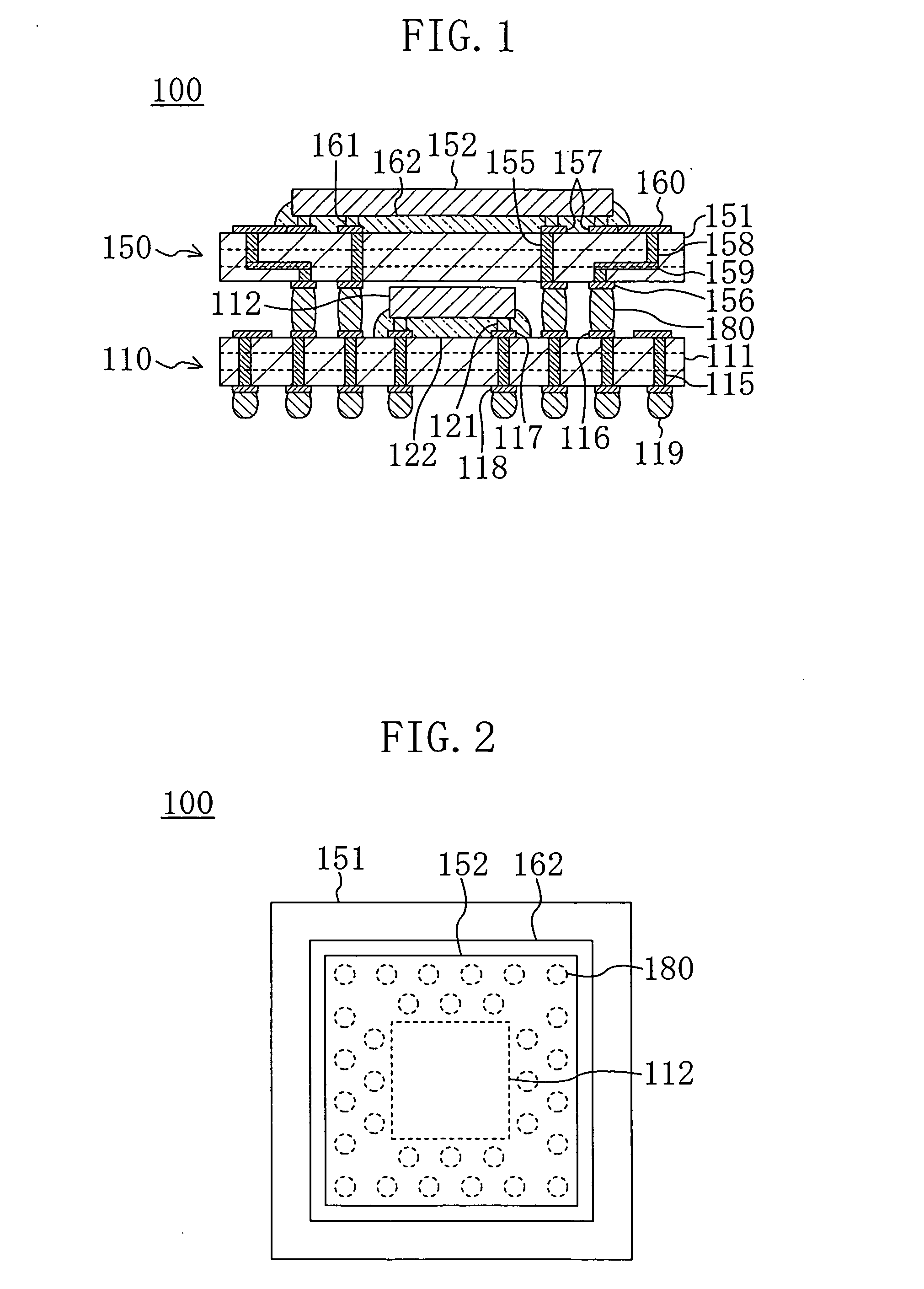

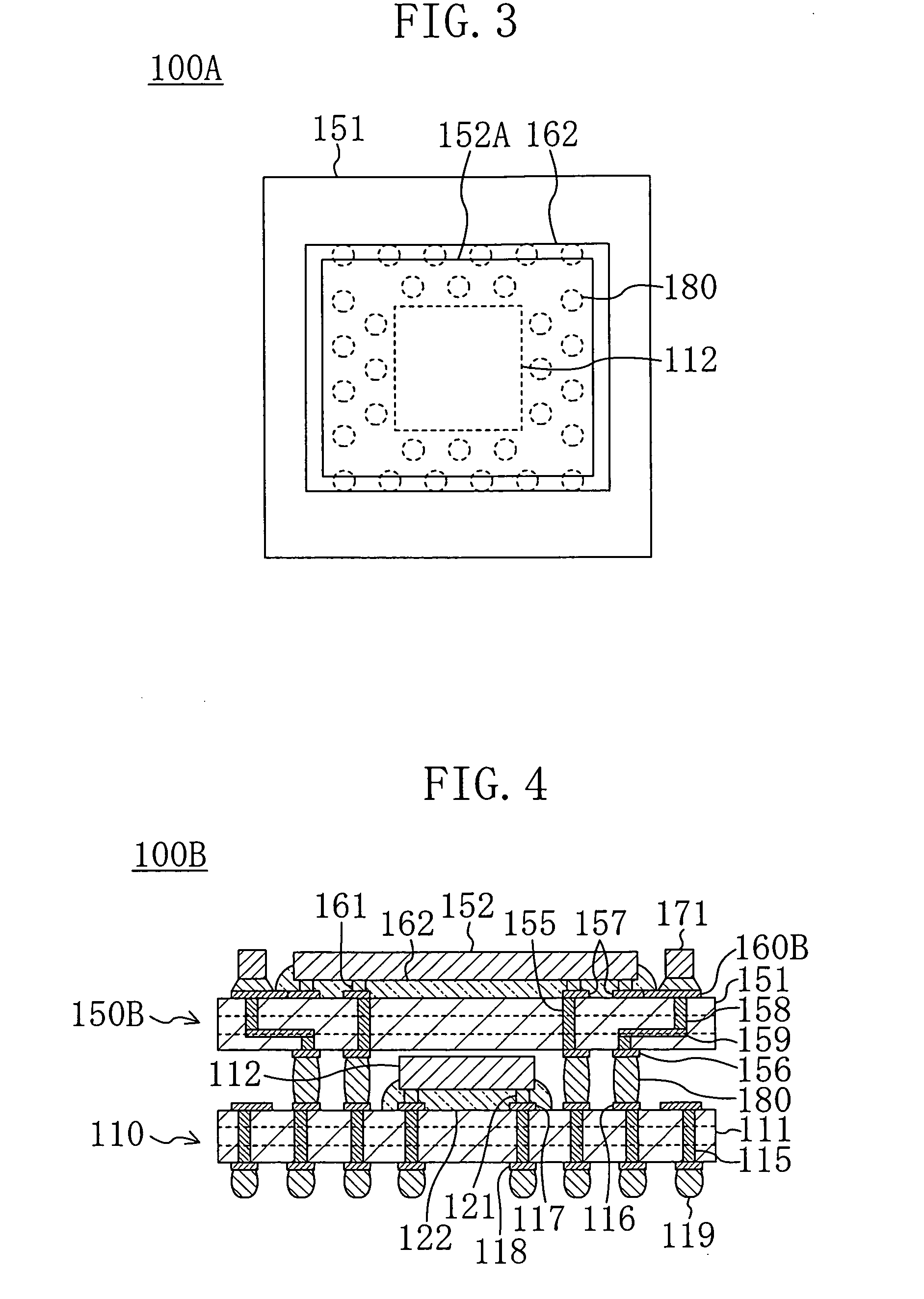

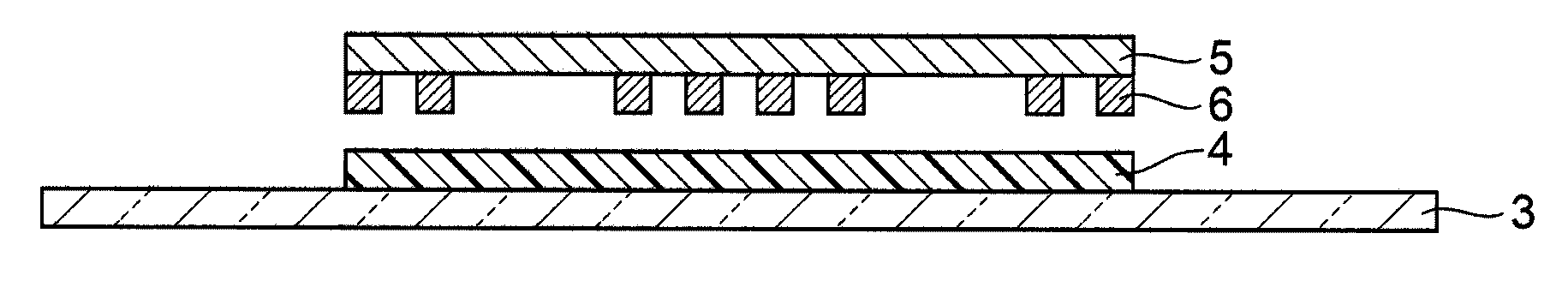

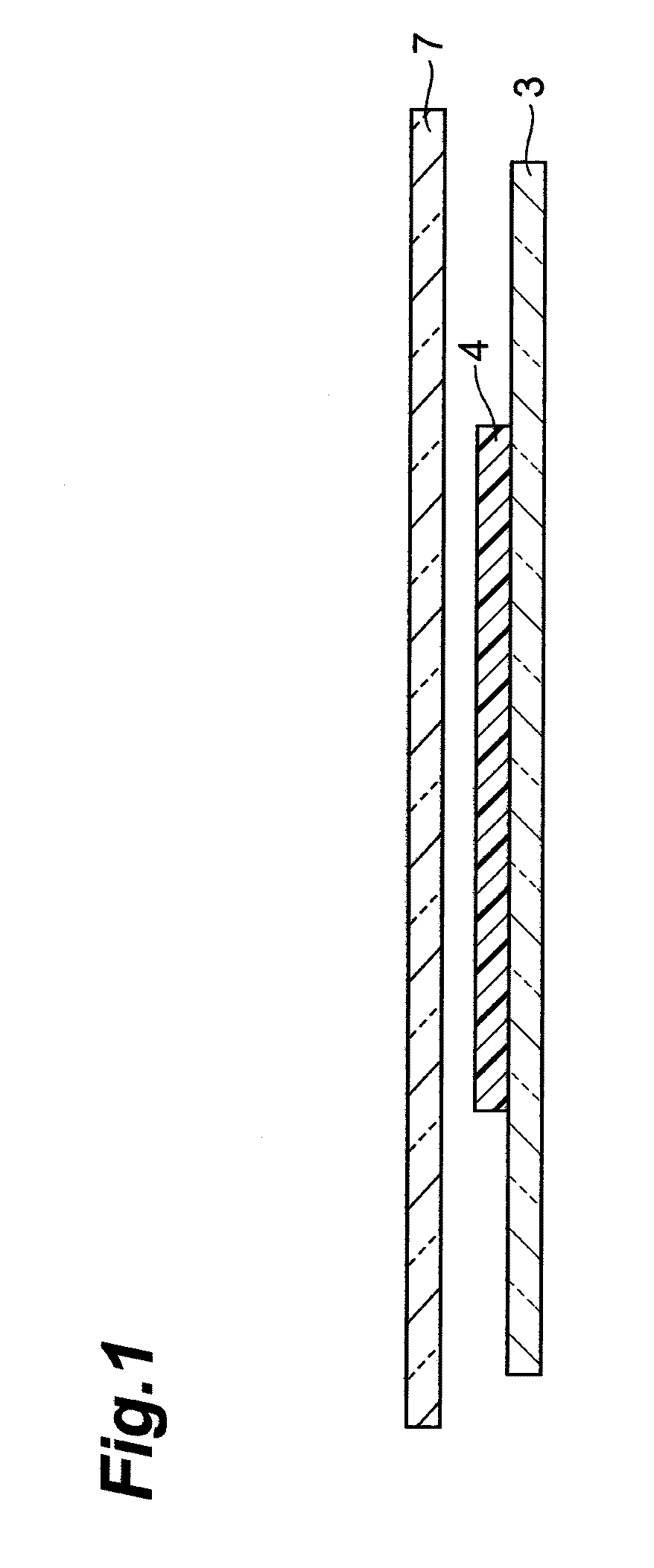

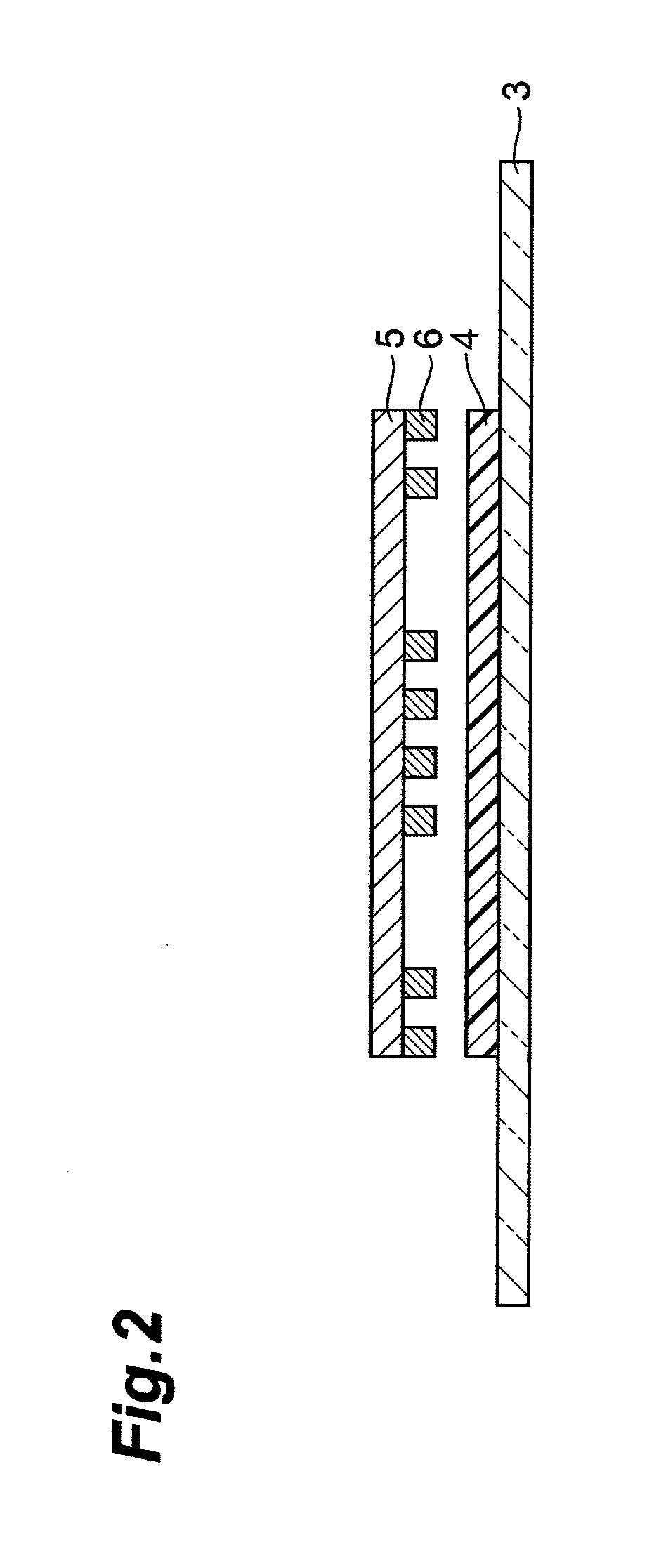

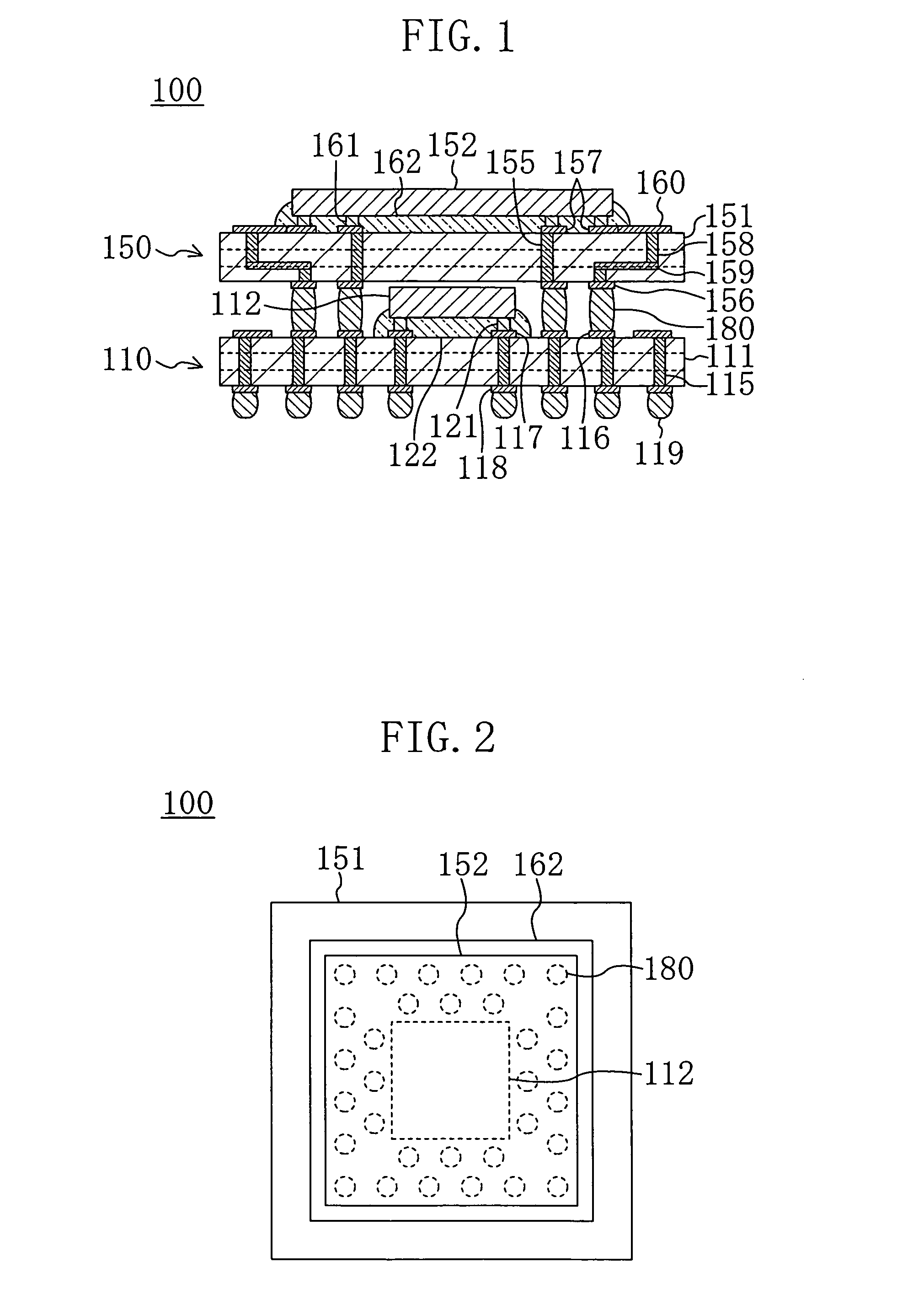

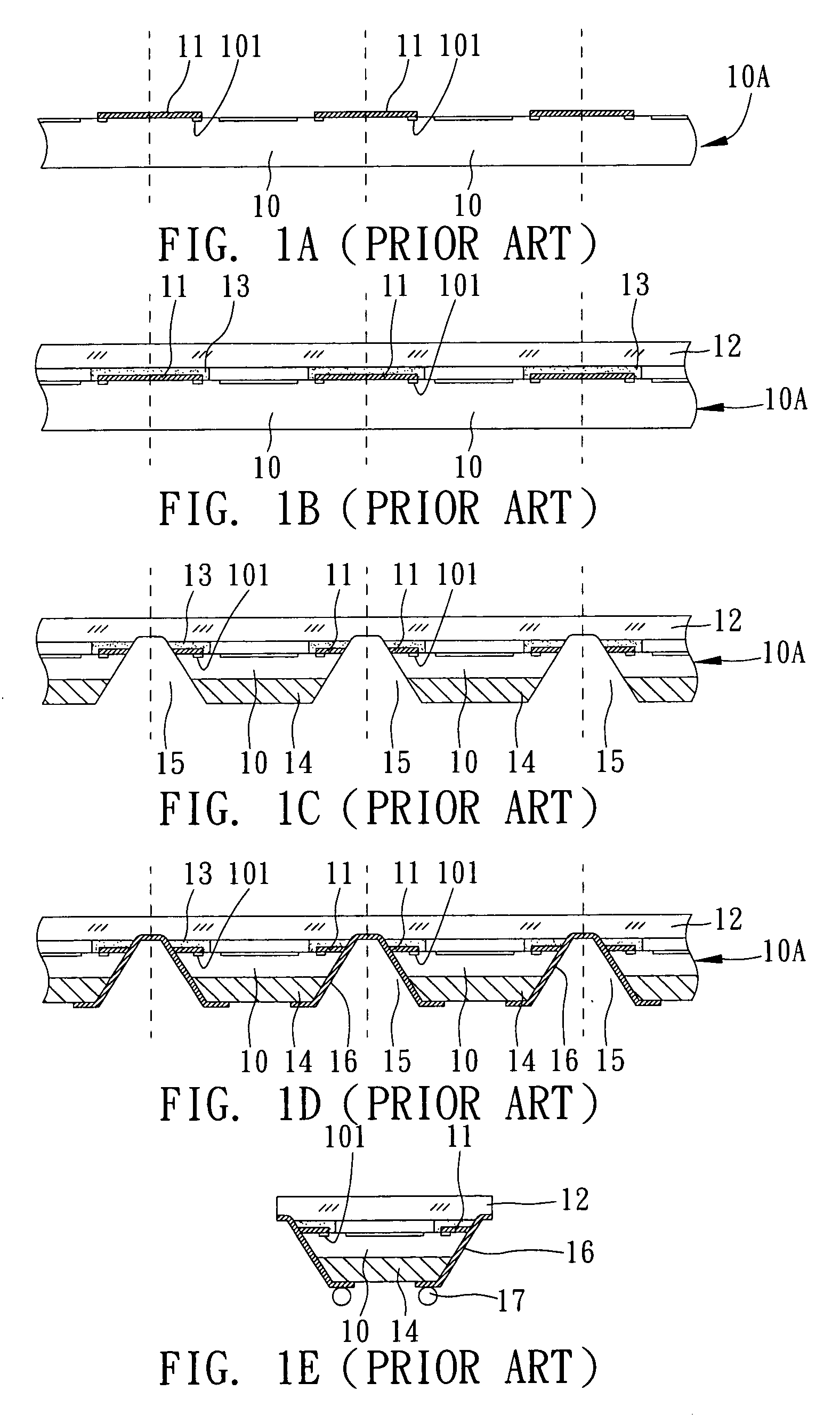

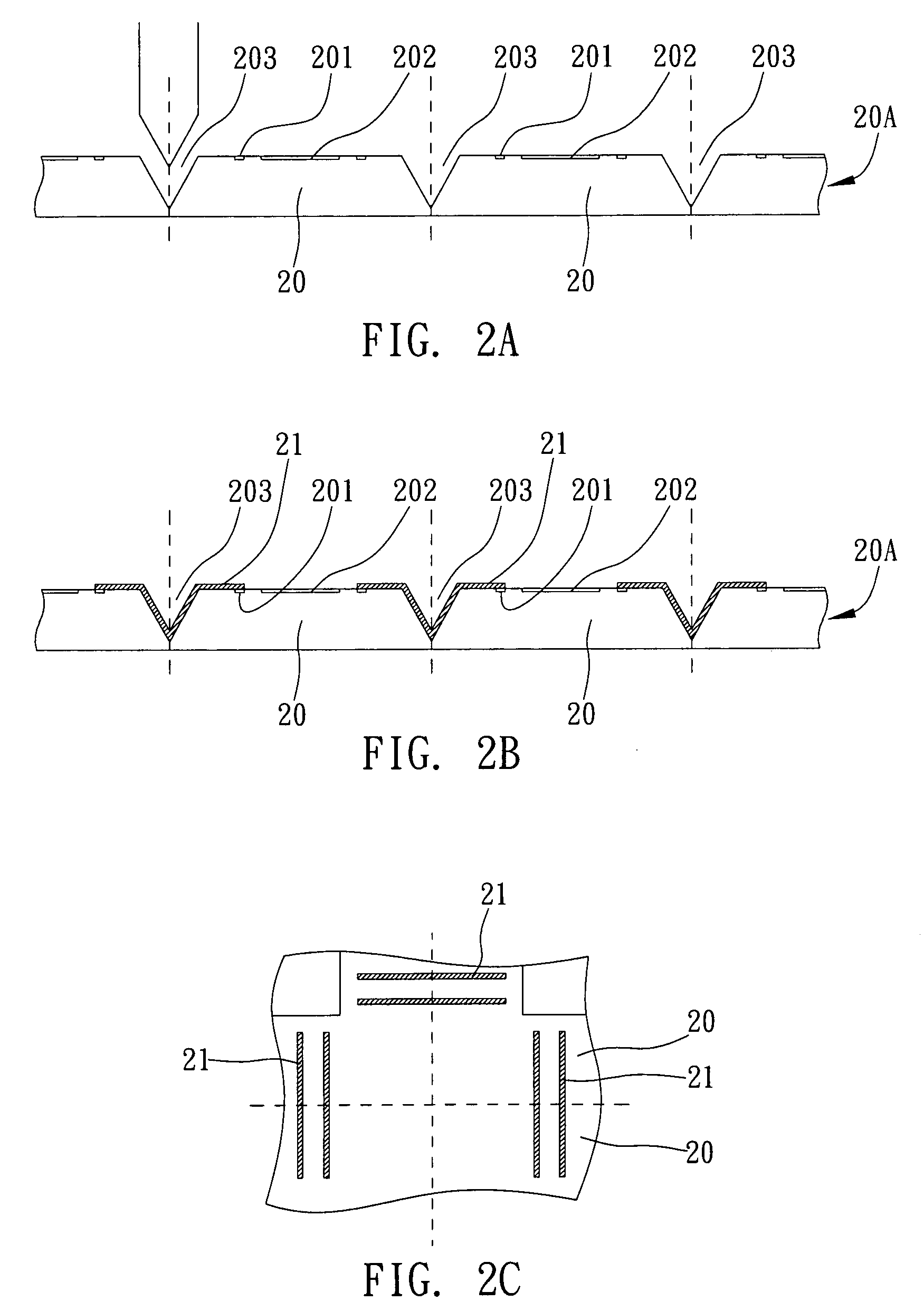

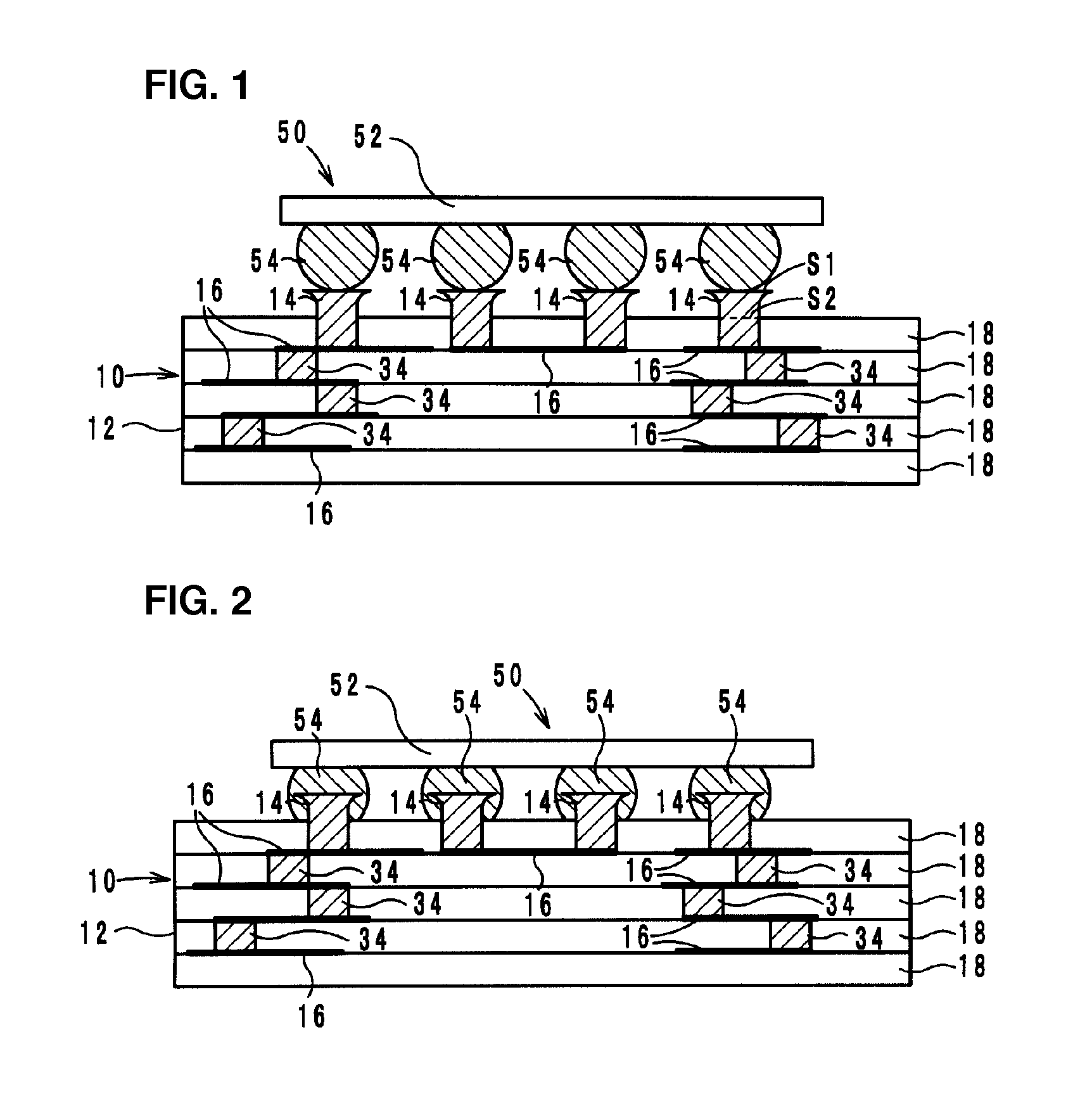

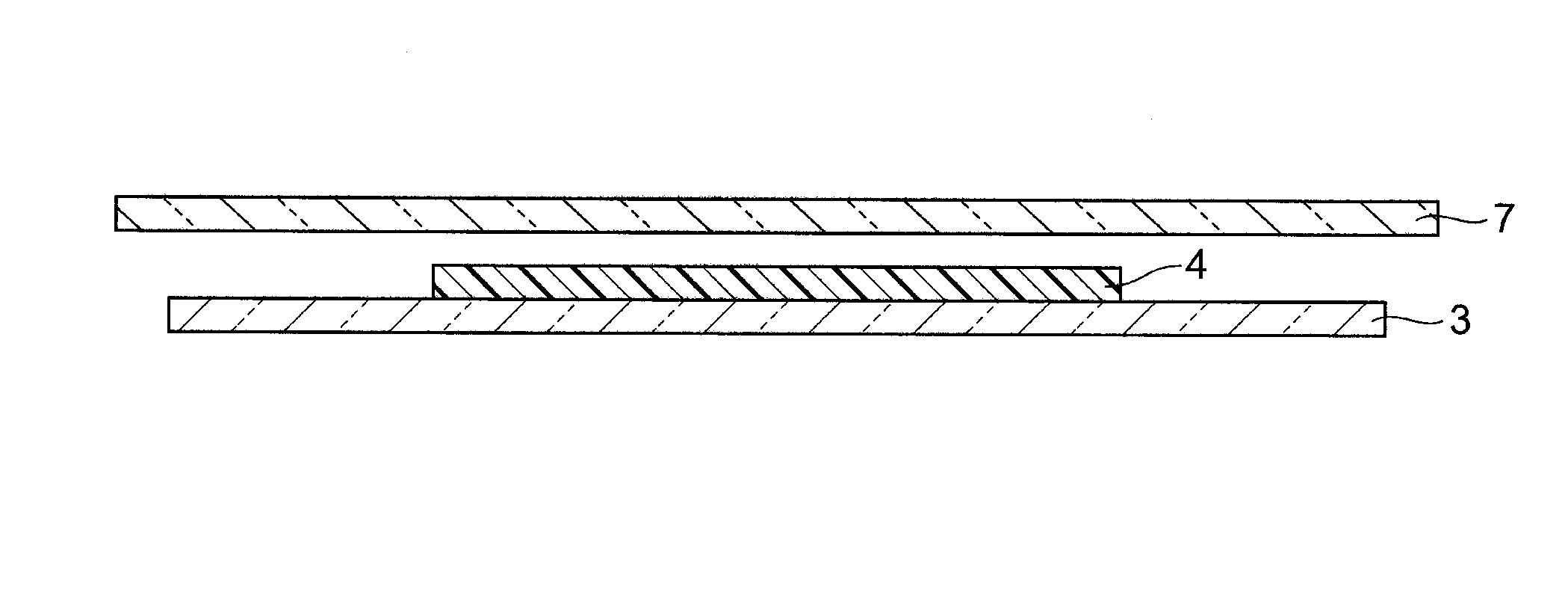

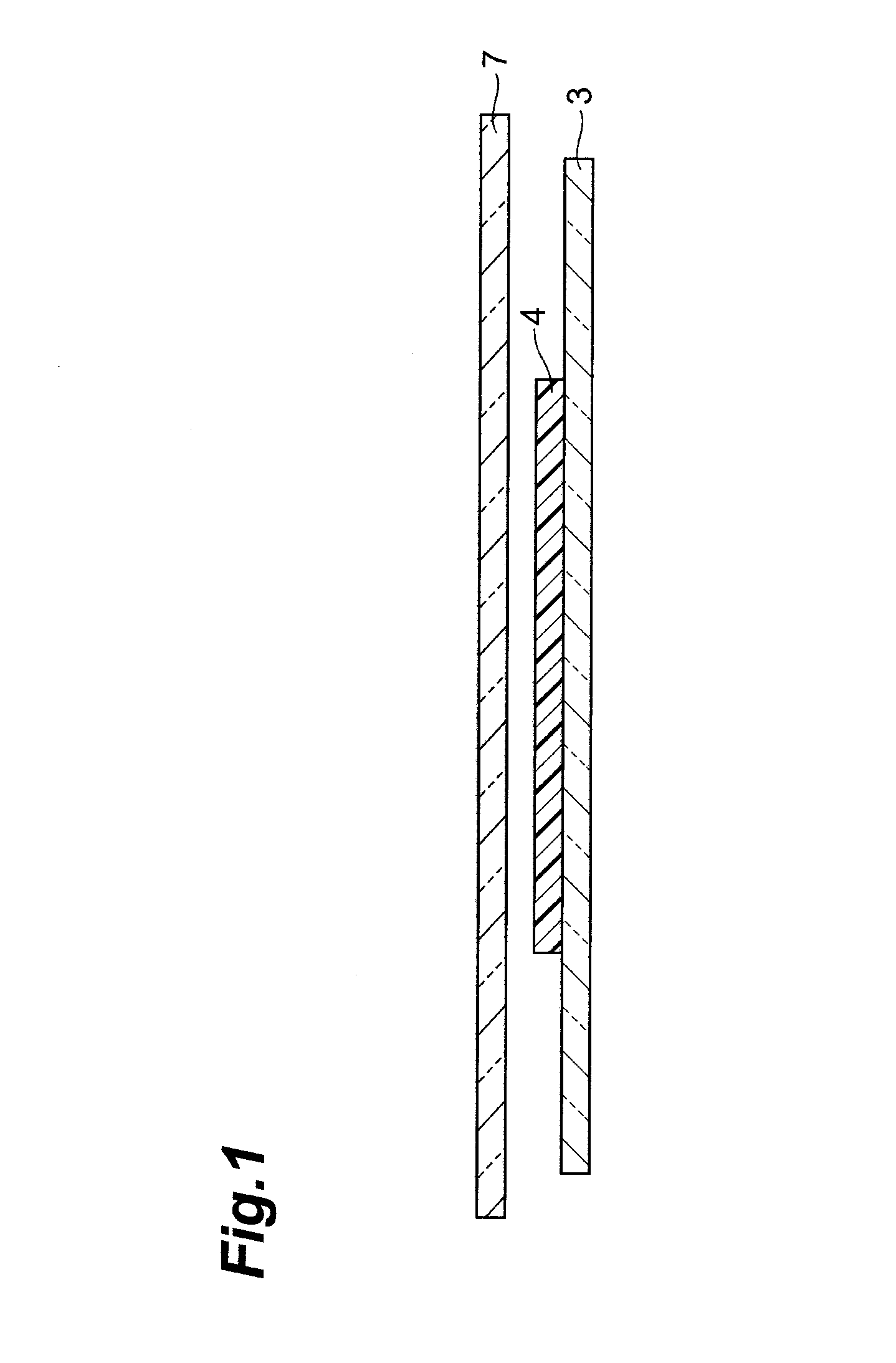

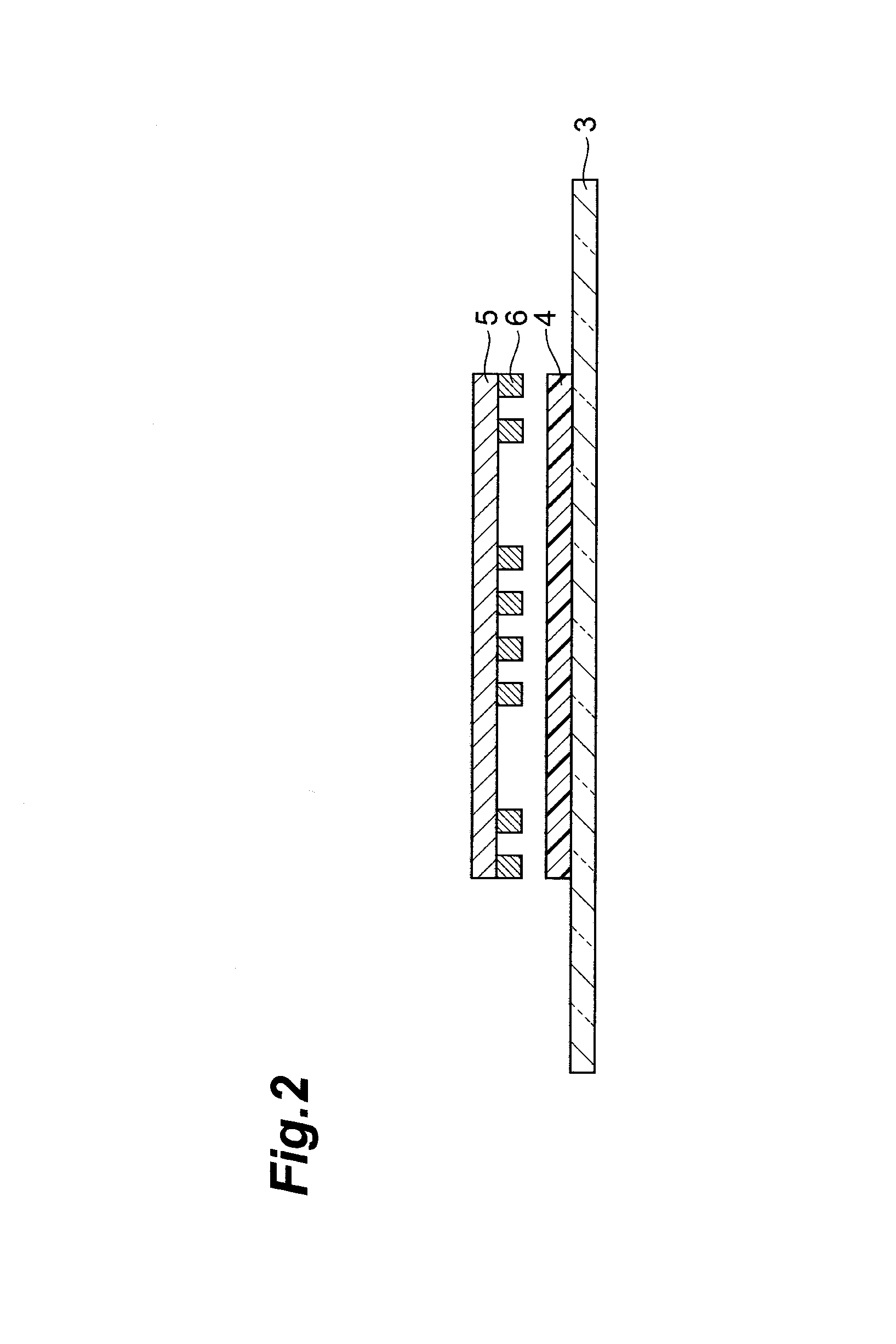

Stacked semiconductor module

ActiveUS20070096334A1Reduce the impactSame coefficientSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A stacked semiconductor module is made by stacking a second semiconductor device having a second semiconductor chip mounted to the top surface of a second semiconductor substrate above the top surface of a first semiconductor device having a first semiconductor chip mounted to a first semiconductor substrate. The top surface of the first semiconductor substrate is provided with a first connection terminal and the bottom surface of the first semiconductor substrate is provided with an external connection terminal. A region of the bottom surface of the second semiconductor substrate lying opposite to the second semiconductor chip is provided with a second connection terminal. A conductive connecting member connects the first connection terminal to the second connection terminal.

Owner:PANASONIC CORP

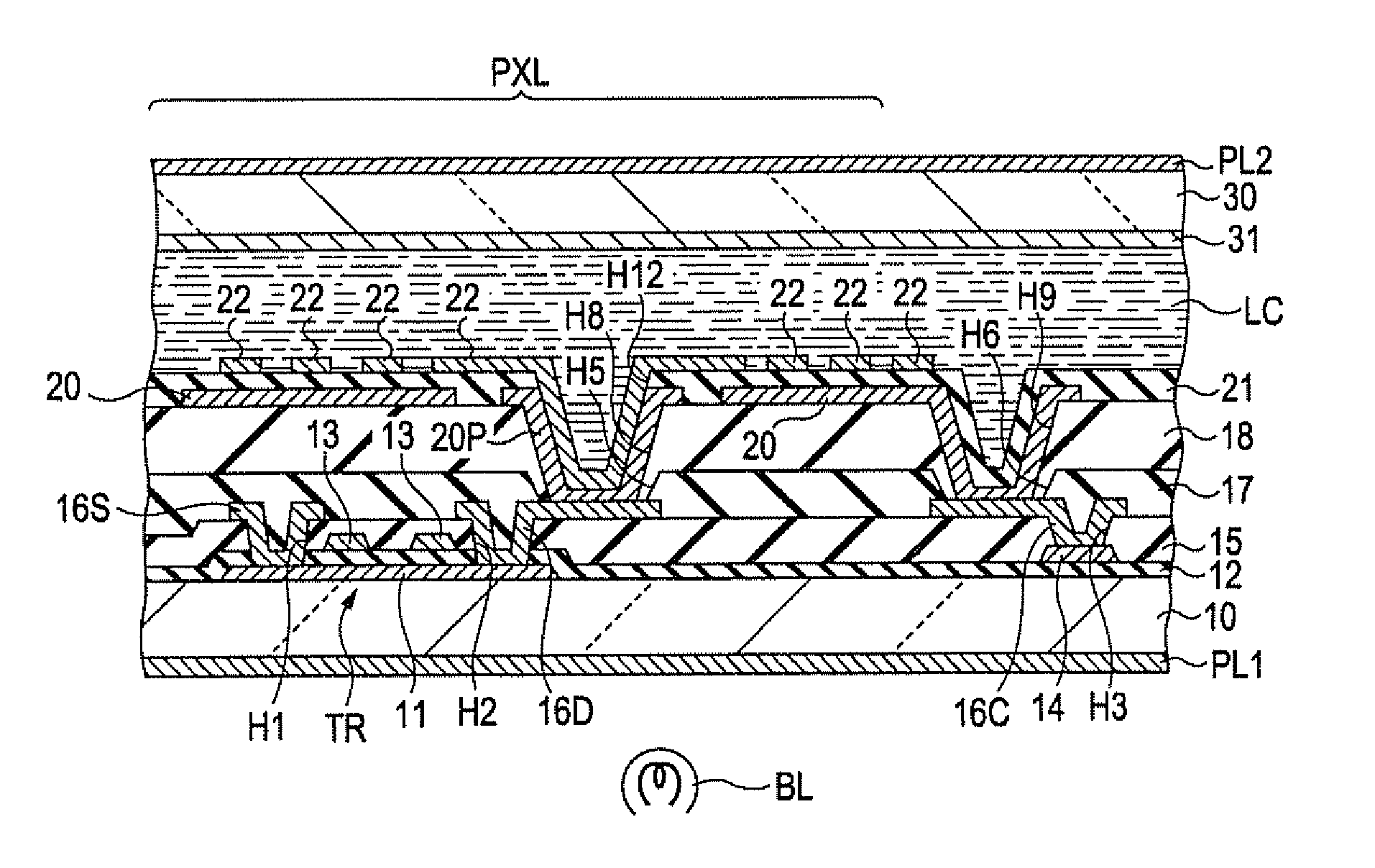

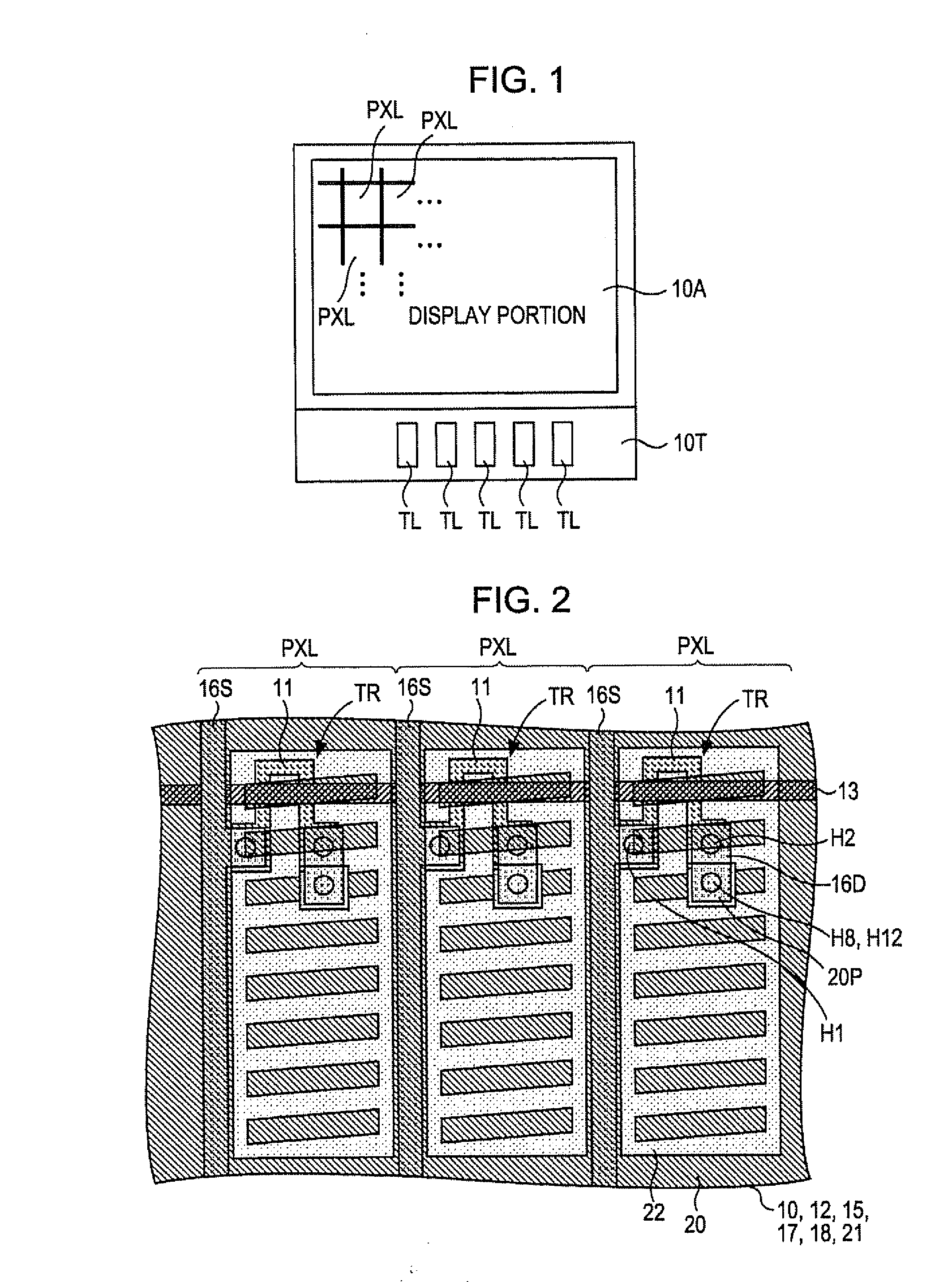

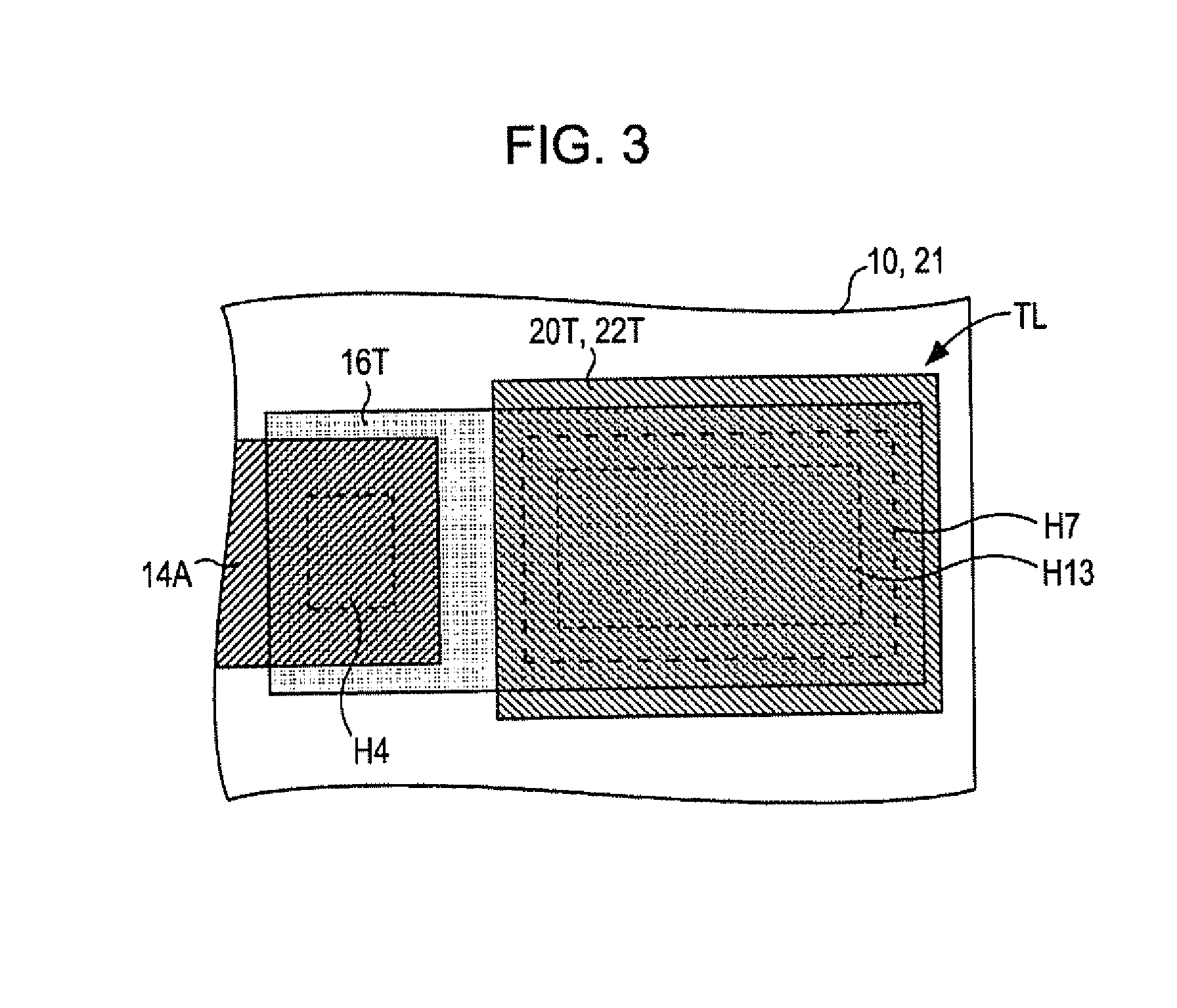

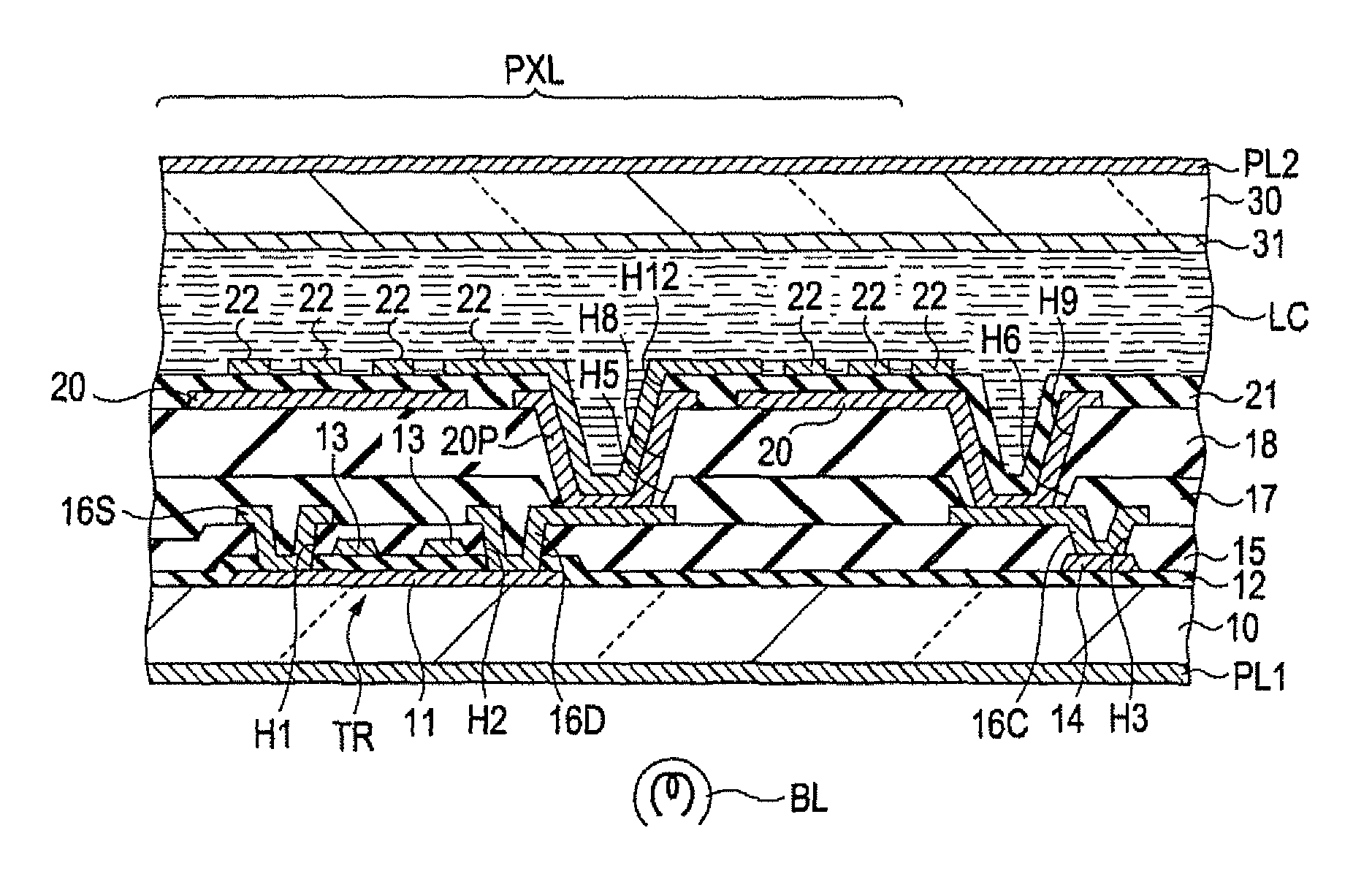

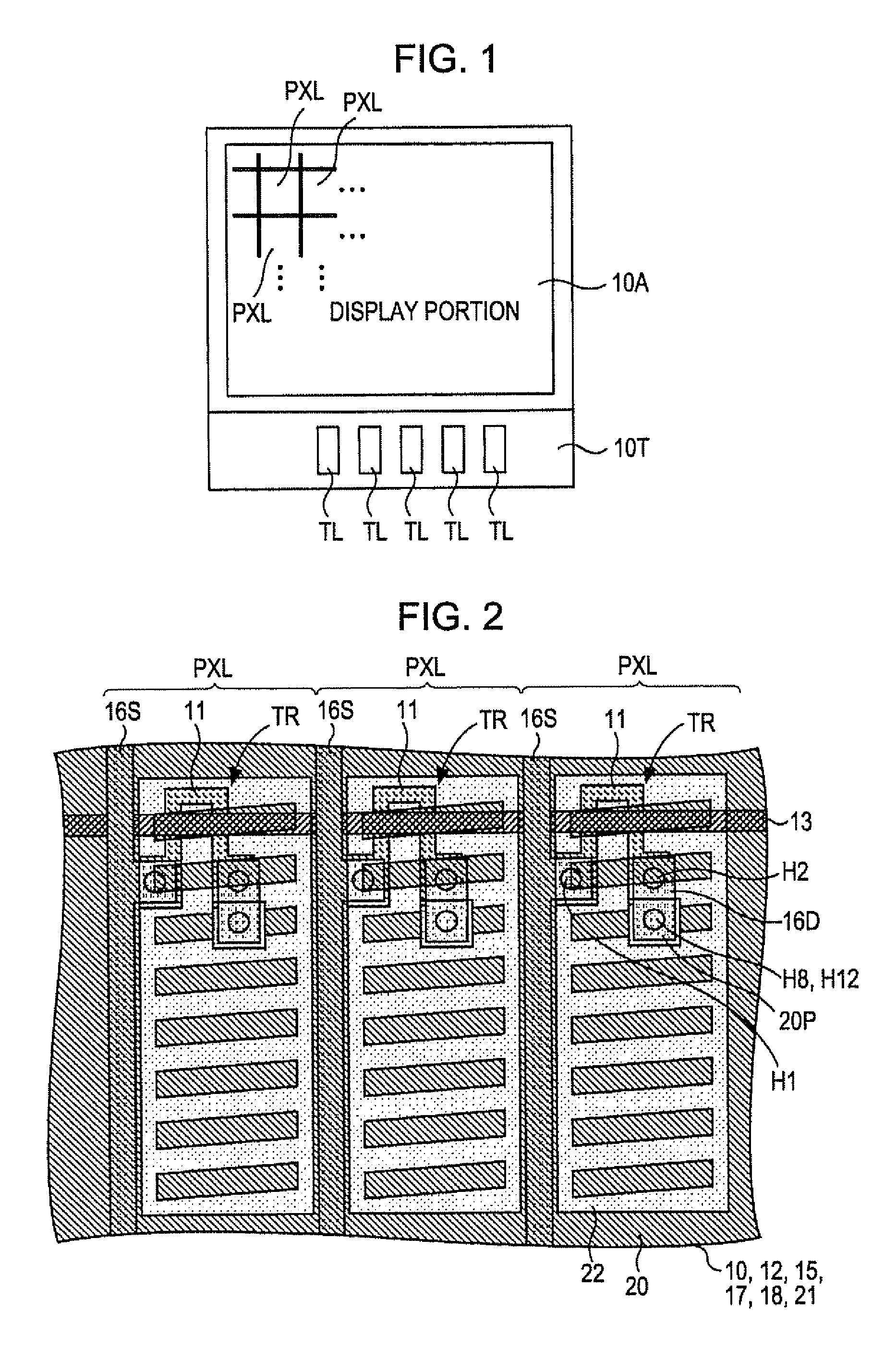

Liquid crystal display device and method of manufacturing the liquid crystal display device

ActiveUS20090027579A1Increase contactDelay foulingNon-linear opticsSemiconductor devicesLiquid-crystal displayEngineering

A liquid crystal display device comprising: a switching element that has a drain electrode and that is arranged on a substrate; a first insulating film that covers the switching element and that has a first opening on the drain electrode; a first etching stopper electrode that is formed in the first opening and that is connected to the drain electrode; a common electrode that is arranged on the first insulating film; a second insulating film that covers the first etching stopper electrode and the common electrode, and that has a second opening on the first etching stopper electrode; and a pixel electrode that is connected through the second opening to the first etching stopper electrode and that extends onto the second insulating film so as to face the common electrode.

Owner:JAPAN DISPLAY WEST

Semiconductor encapsulation adhesive composition, semiconductor encapsulation film-like adhesive, method for producing semiconductor device and semiconductor device

InactiveUS20110291260A1High electronic insulation reliabilityInhibit productionSemiconductor/solid-state device detailsSolid-state devicesEpoxyAntioxidant

A semiconductor encapsulation adhesive composition comprising (a) an epoxy resin, (b) a curing agent and (c) an antioxidant.

Owner:HITACHI CHEM CO LTD

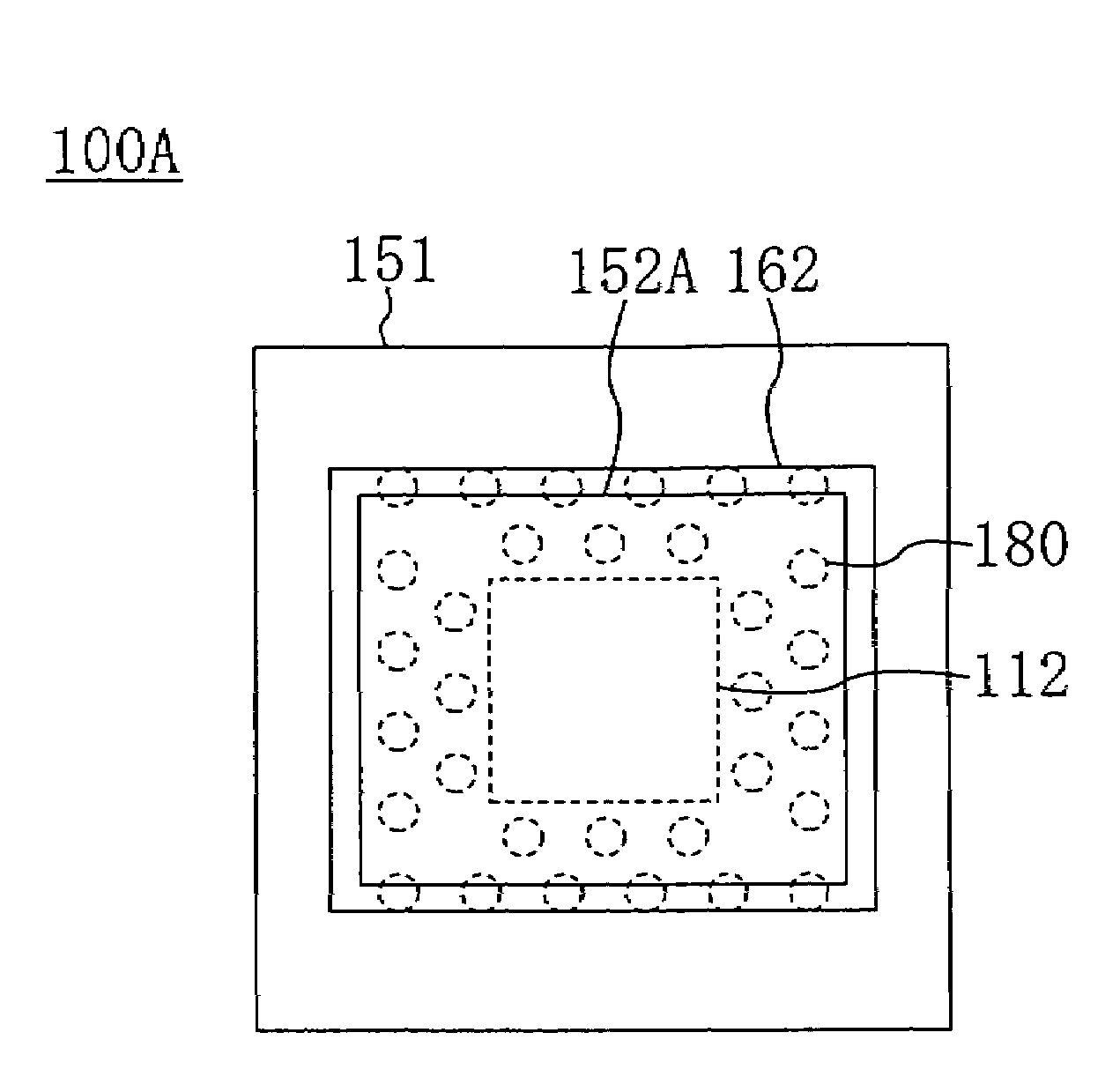

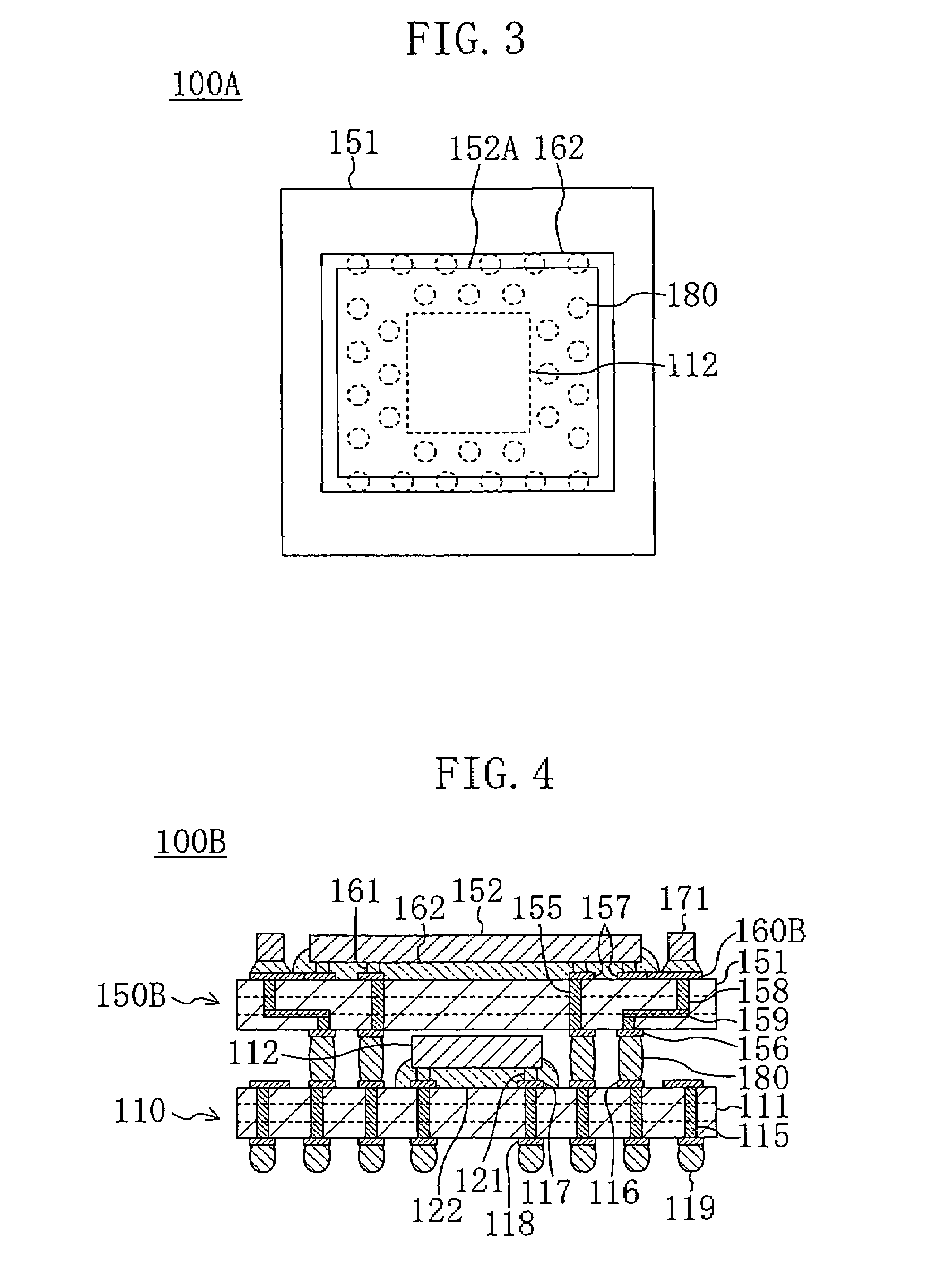

Stacked semiconductor module

ActiveUS7667313B2Poor connectionImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesElectrical conductorSemiconductor chip

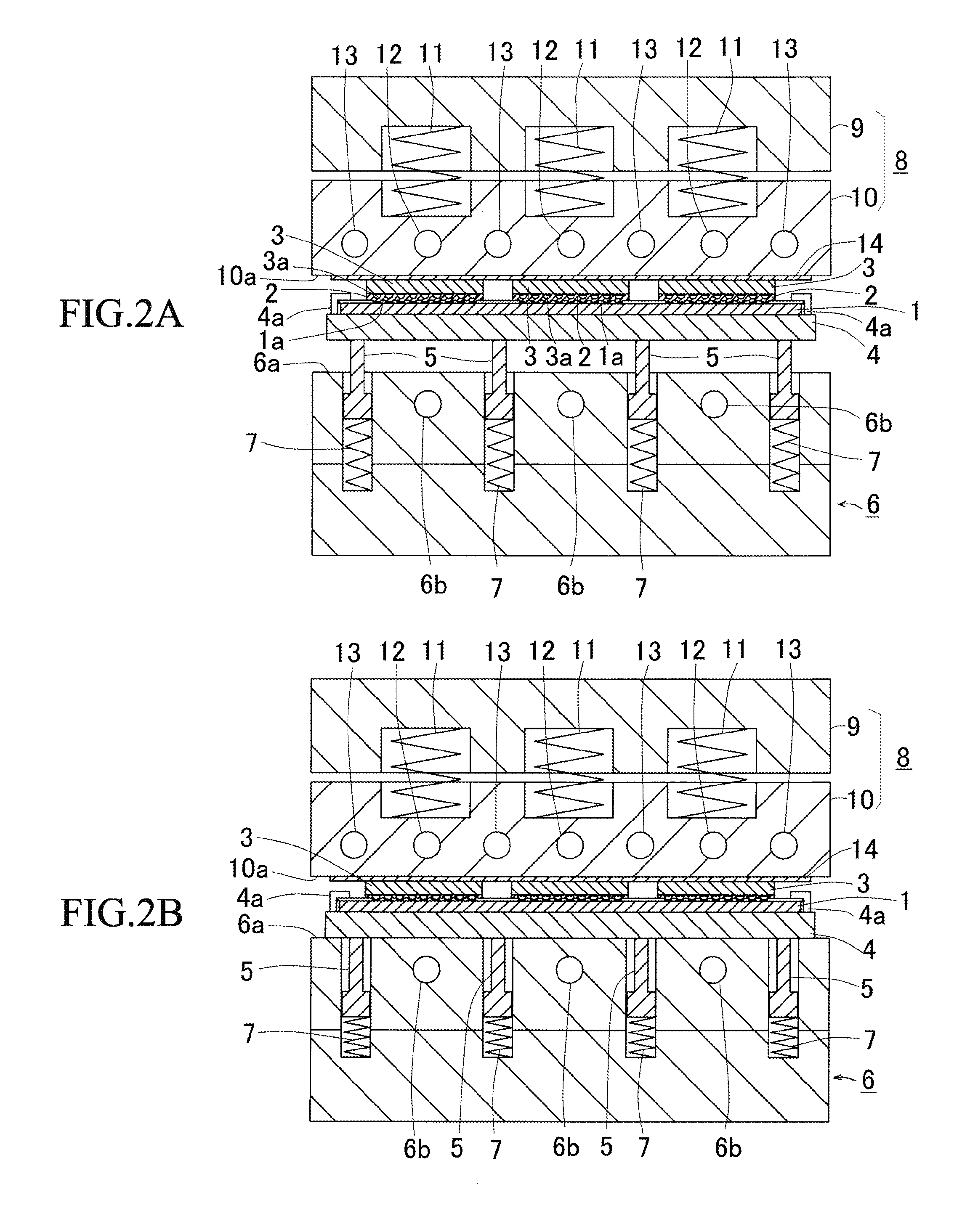

A stacked semiconductor module is made by stacking a second semiconductor device having a second semiconductor chip mounted to the top surface of a second semiconductor substrate above the top surface of a first semiconductor device having a first semiconductor chip mounted to a first semiconductor substrate. The top surface of the first semiconductor substrate is provided with a first connection terminal and the bottom surface of the first semiconductor substrate is provided with an external connection terminal. A region of the bottom surface of the second semiconductor substrate lying opposite to the second semiconductor chip is provided with a second connection terminal. A conductive connecting member connects the first connection terminal to the second connection terminal.

Owner:PANASONIC CORP

Sensor semiconductor device and manufacturing method thereof

InactiveUS20080197438A1Improve reliabilityDifficult to alignSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorActive surface

This invention discloses a sensor semiconductor device and a manufacturing method thereof, including: providing a wafer having a plurality of sensor chips, forming a plurality of grooves between bond pads on active surfaces of the adjacent sensor chips; forming conductive traces in the grooves for electrically connecting the bond pads; mounting a transparent medium on the wafer for covering sensing areas of the sensor chips; thinning the sensor chips from the non-active surfaces down to the grooves, thereby exposing the conductive traces; cutting the wafer to separate the sensor chips; mounting the sensor chips on a substrate module having a plurality of substrates, electrically connecting the conductive traces to the substrates; providing an insulation material on the substrate module and between the sensor chips so as to encapsulate the sensor chips but expose the transparent medium; and cutting the substrate module to separate a plurality of resultant sensor semiconductor devices.

Owner:SILICONWARE PRECISION IND CO LTD

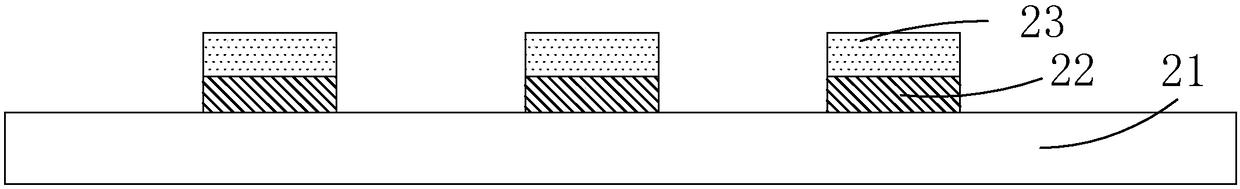

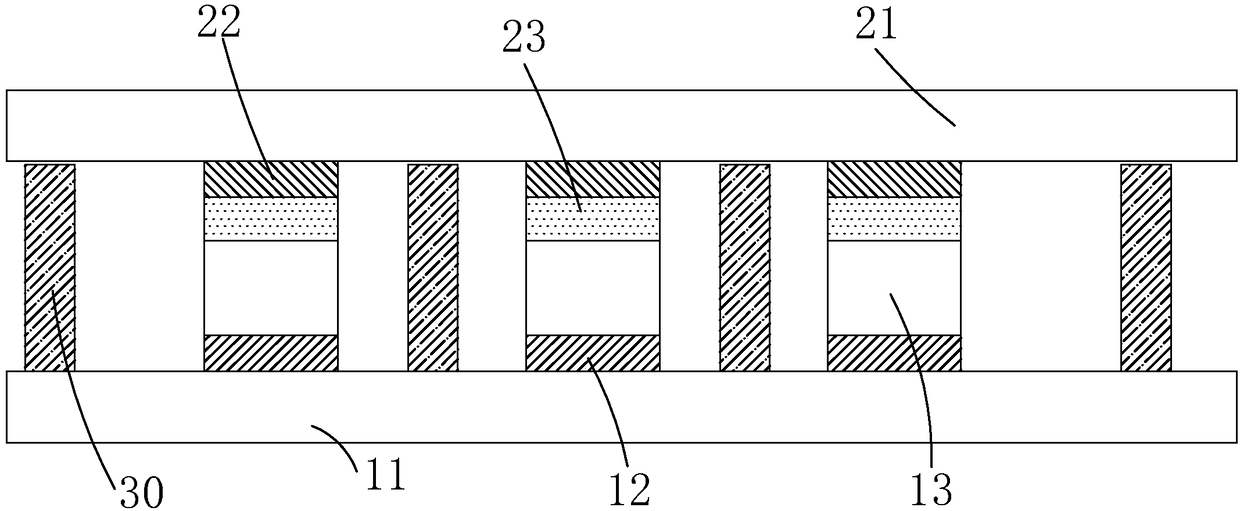

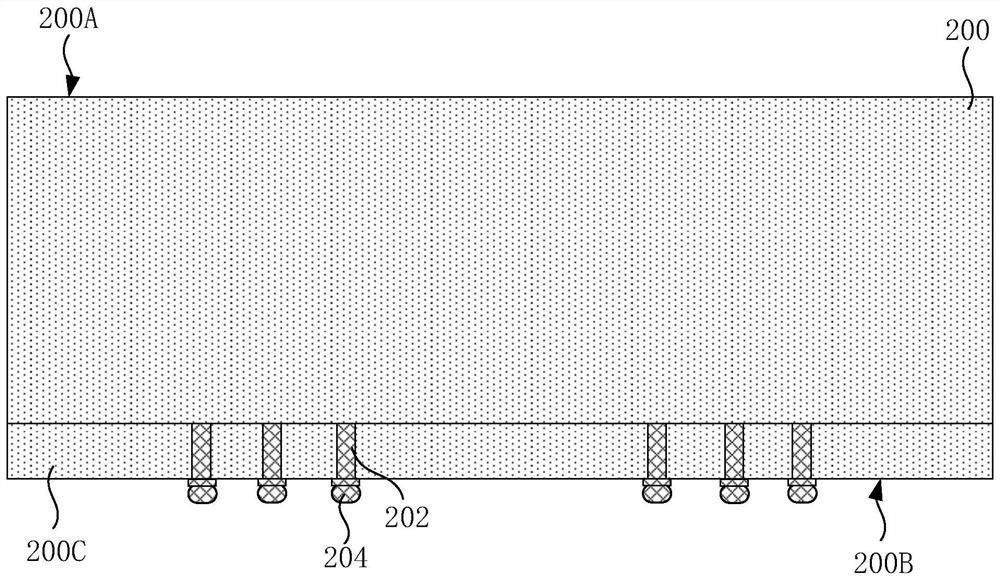

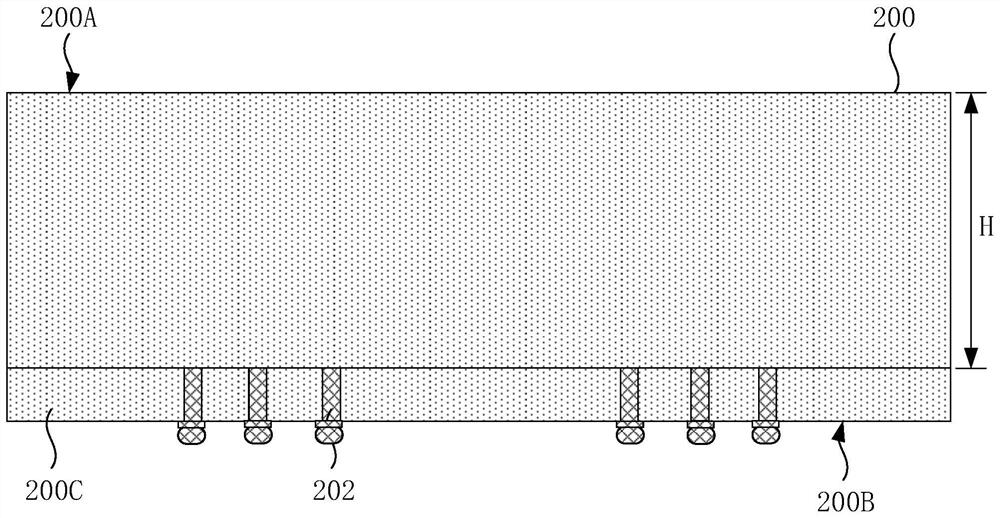

Micro LED display panel manufacturing method and Micro LED display panel

ActiveCN108493154APoor connectionImprove the effect of the groupSolid-state devicesSemiconductor/solid-state device manufacturingLED displayElectrical connection

The invention provides a Micro LED display panel manufacturing method and a Micro LED display panel. The Micro LED display panel manufacturing method is characterized in that, by forming elastic conductive layers on upper pixel electrodes on a package substrate, when the package substrate is paired with a driving substrate, electrical connection between the upper pixel electrodes and upper electrodes of Micro LEDs is realized through the elastic conductive layers; and height difference between the Micro LEDs can be filled by utilizing elasticity of the elastic conductive layers, thereby preventing poor connection between the upper pixel electrodes and the upper electrodes of the Micro LEDs, and improving pairing effect of the Micro LED display panel and process yield of the Micro LED display panel.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

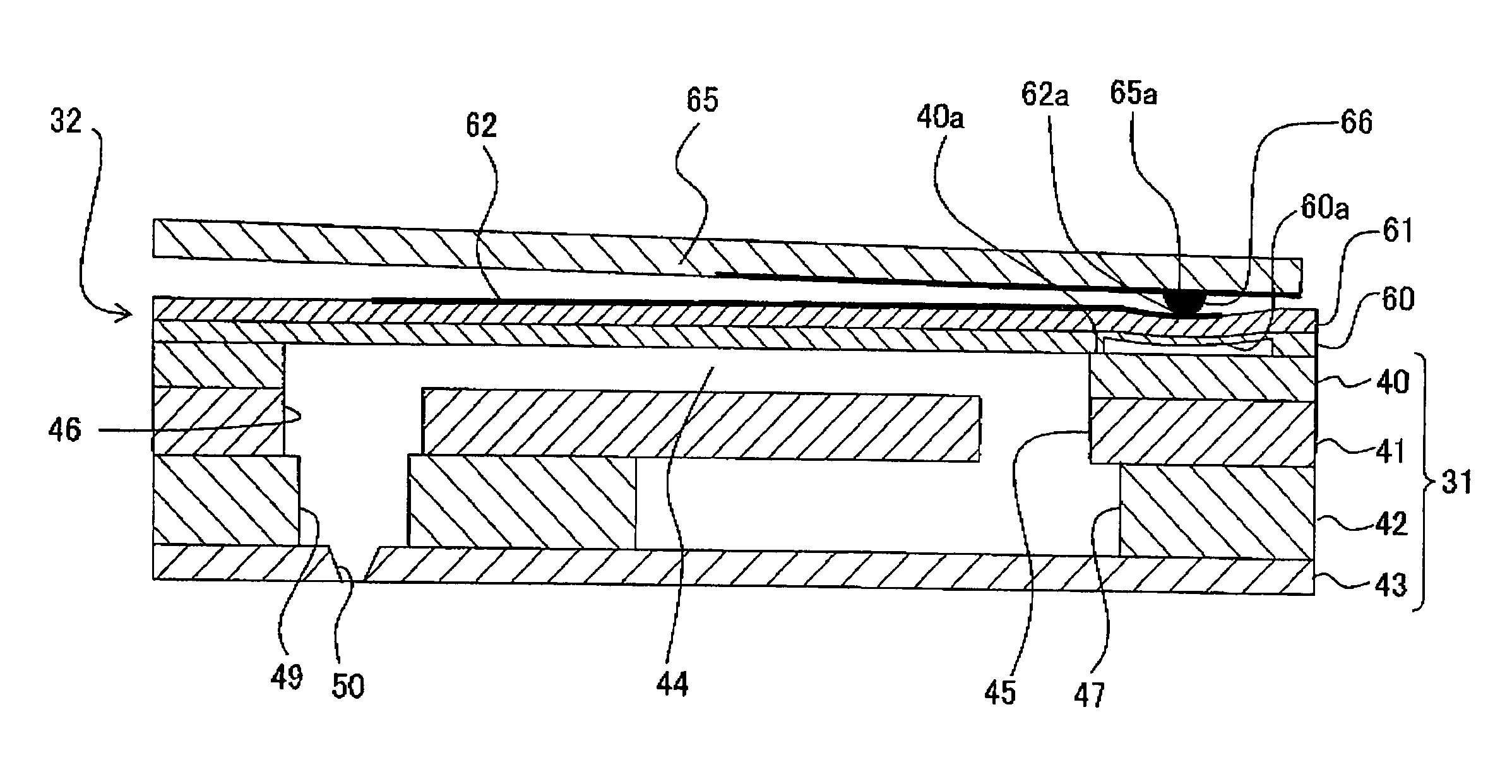

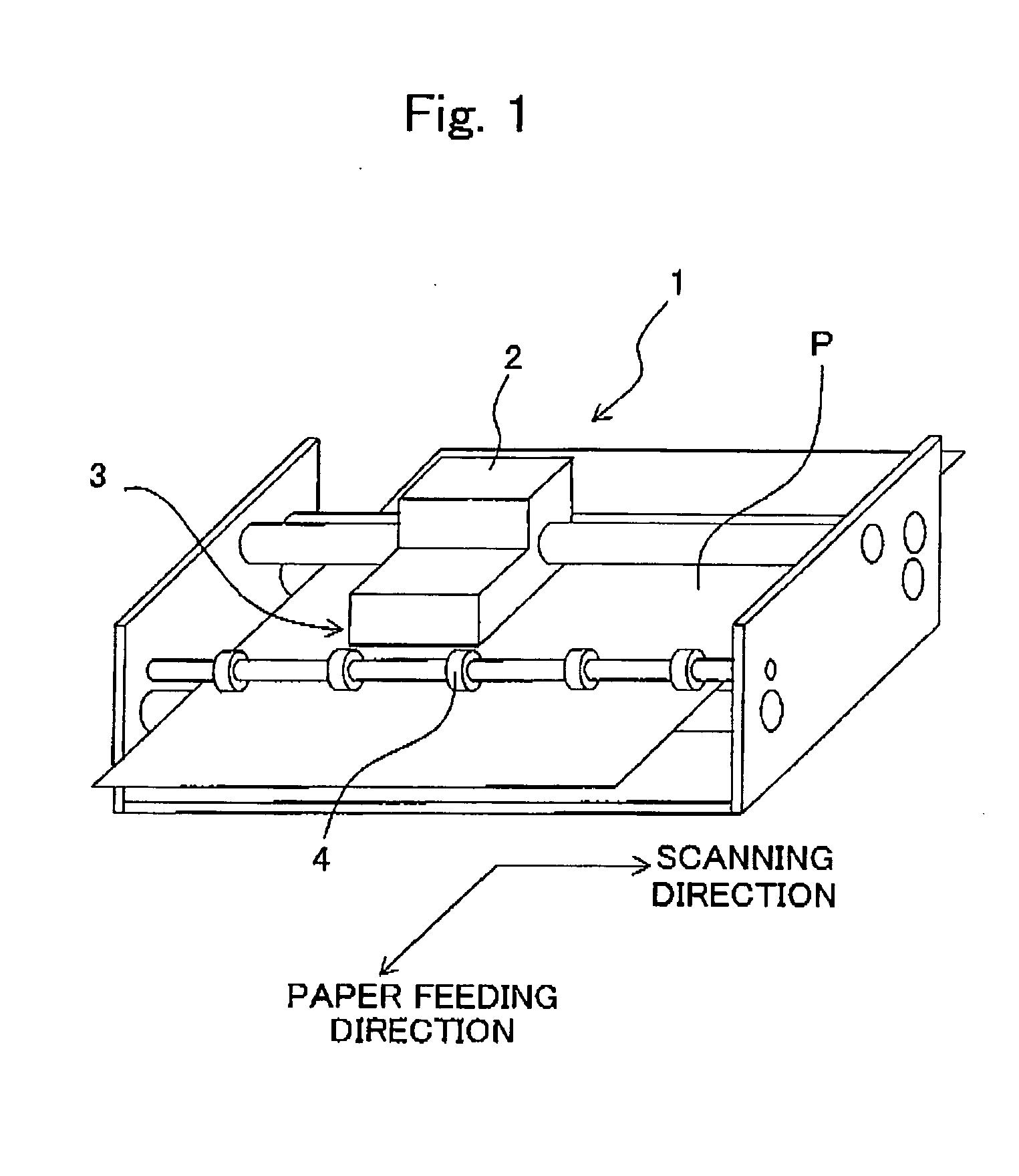

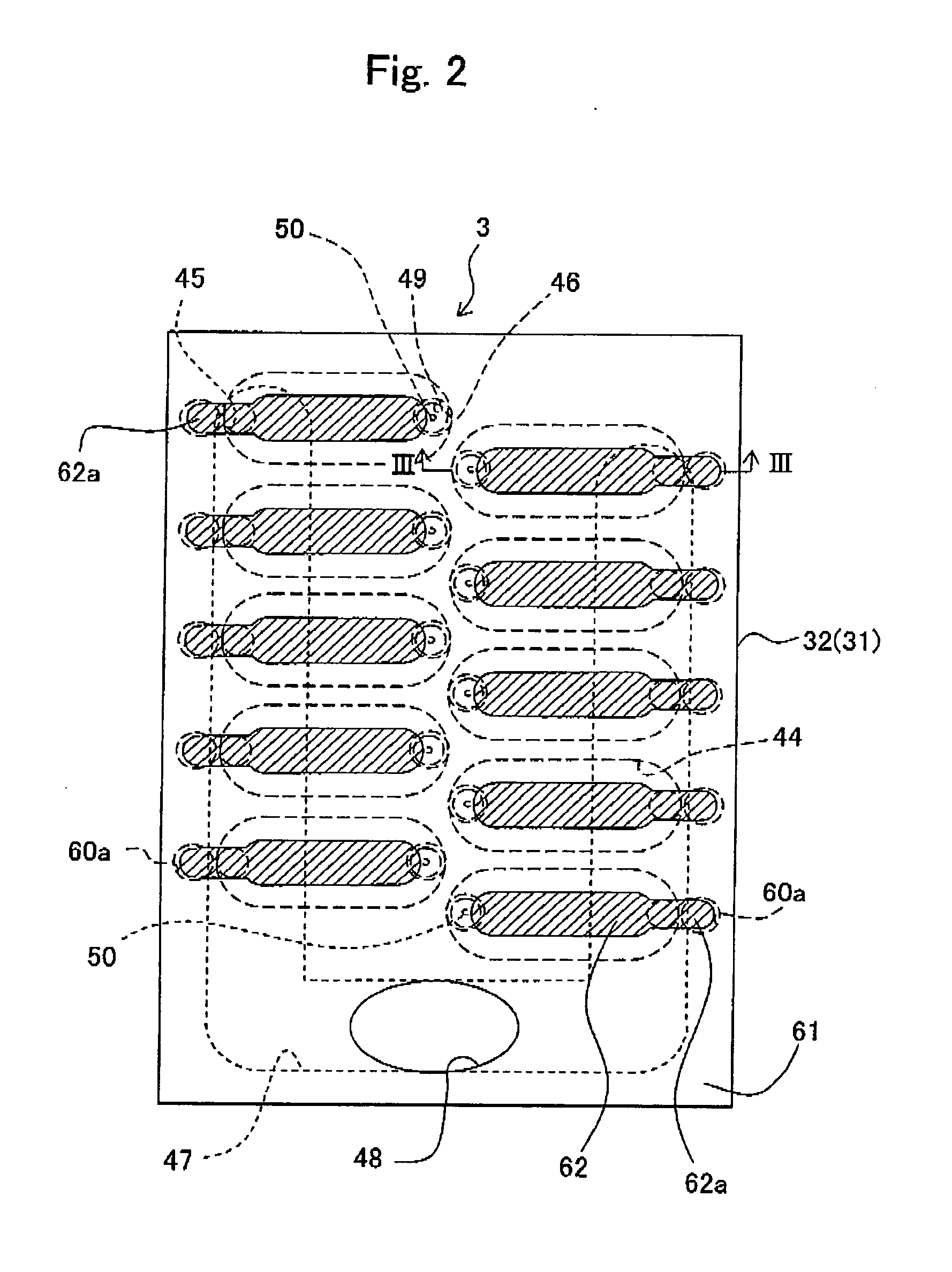

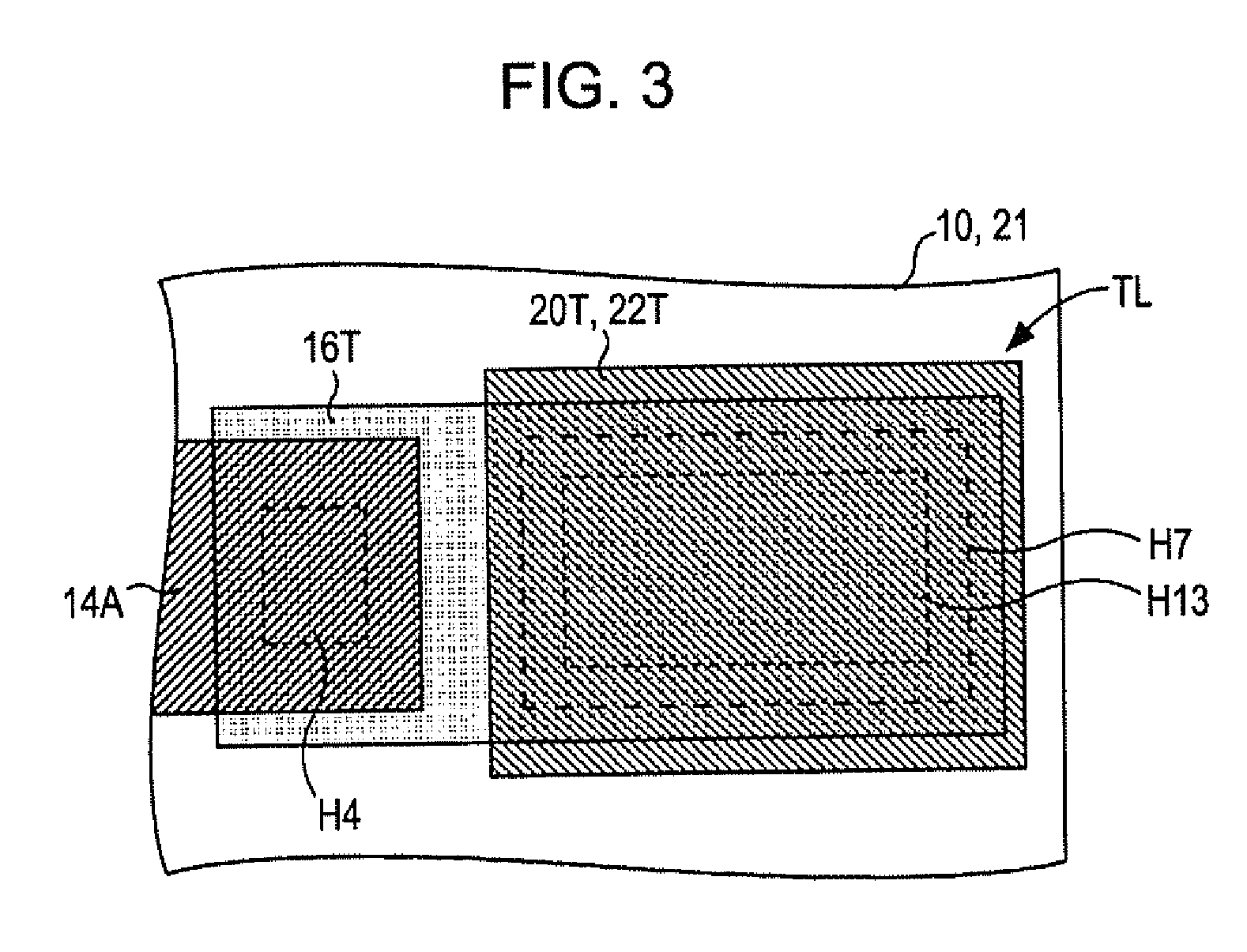

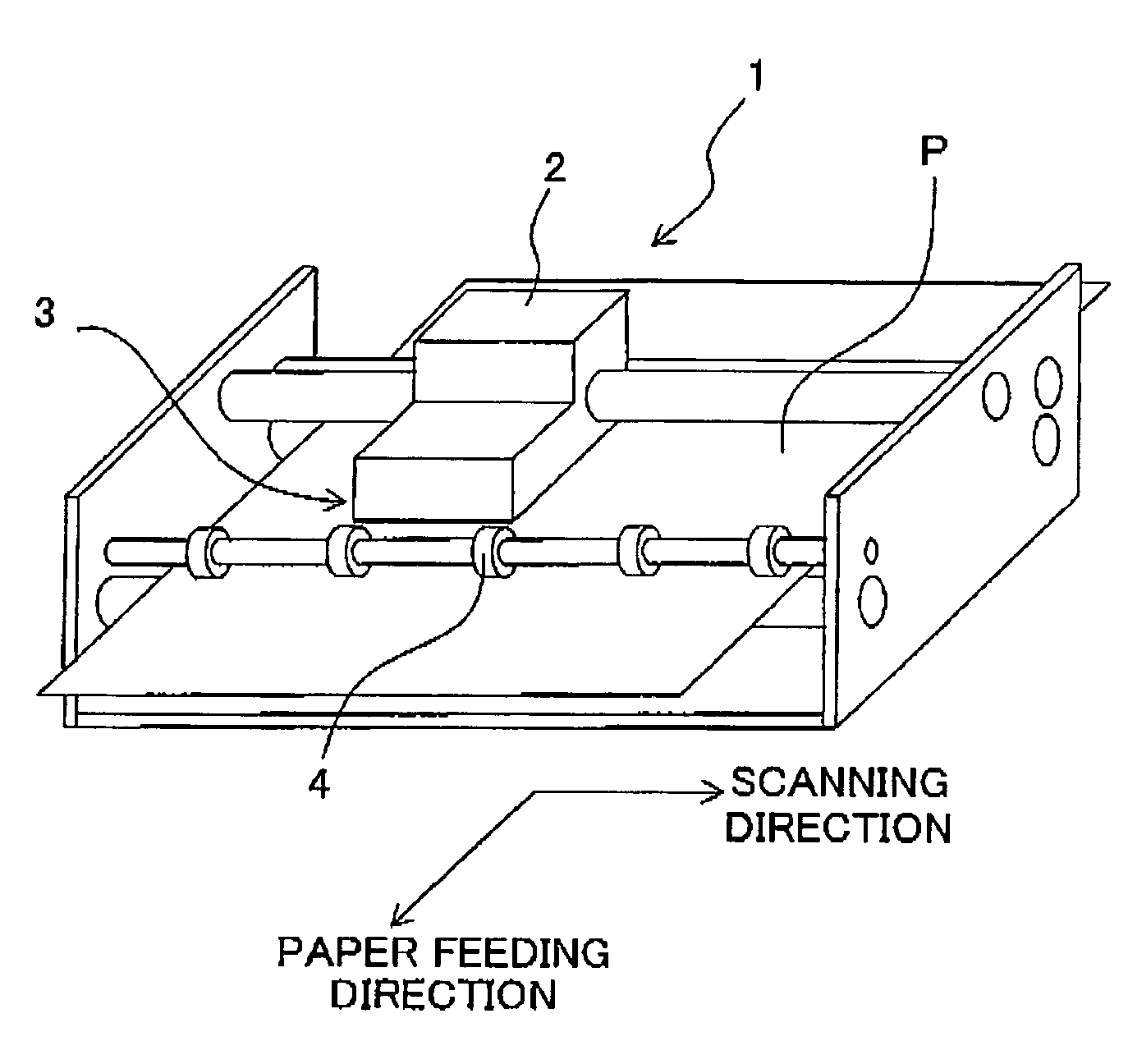

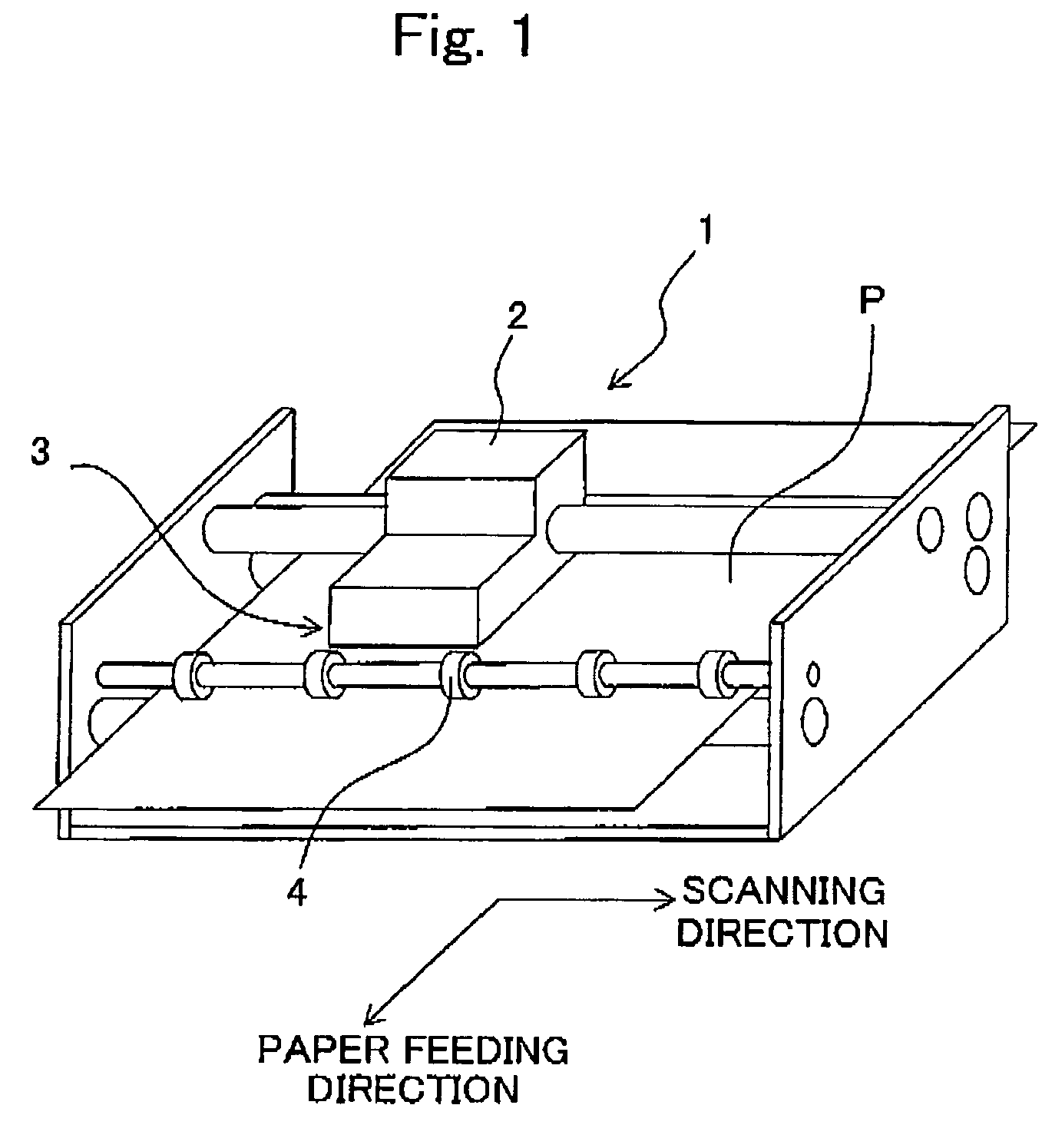

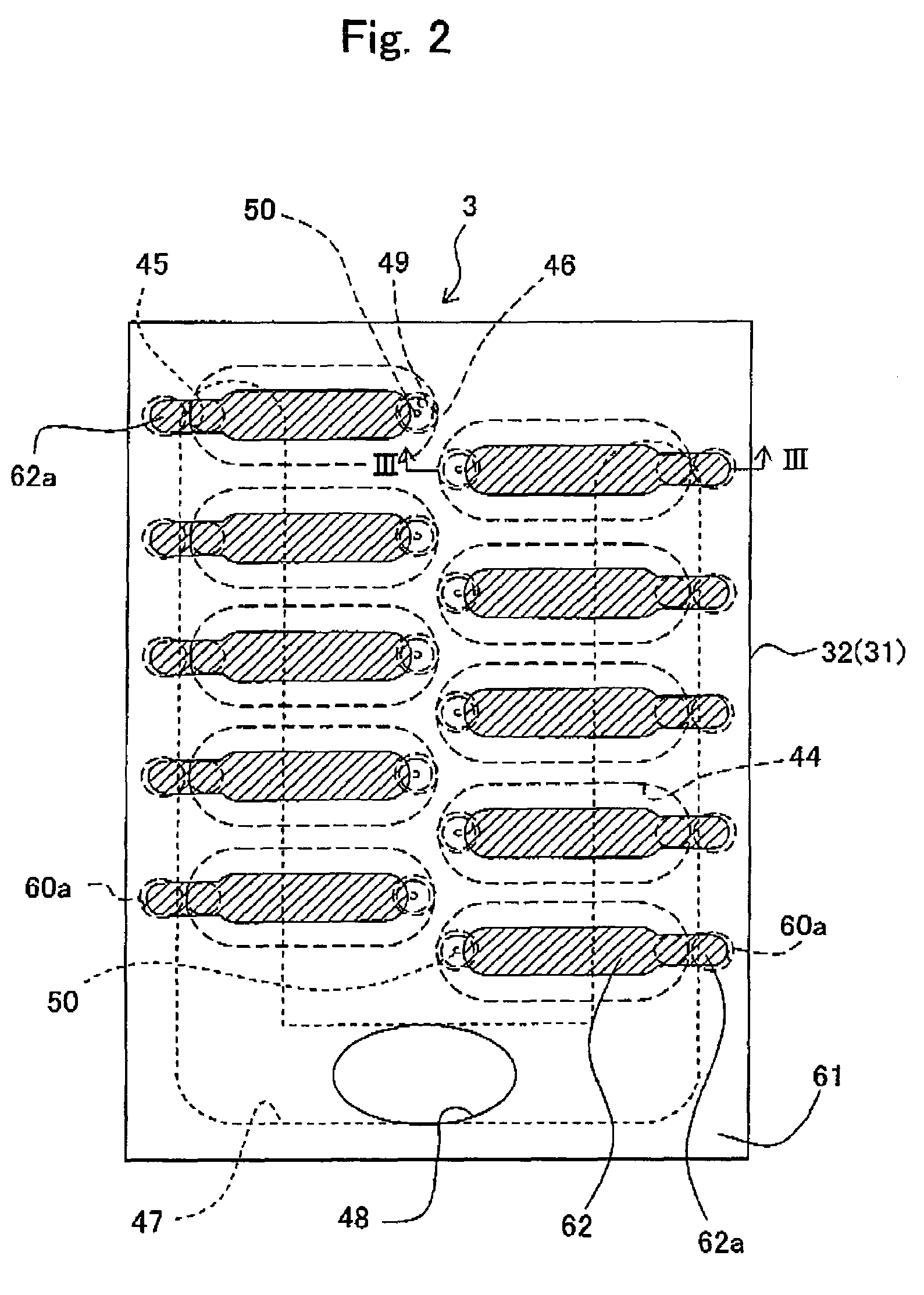

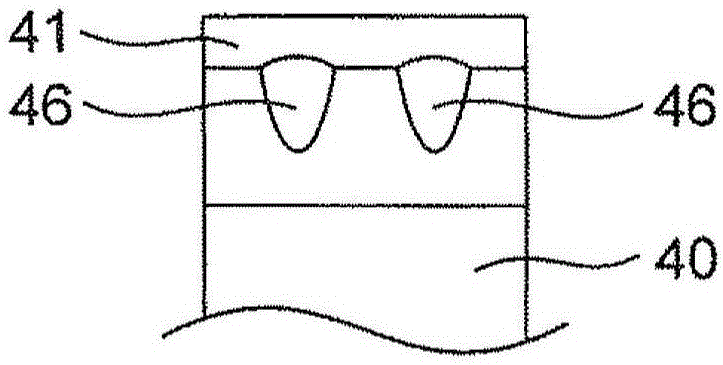

Piezoelectric actuator, method for manufacturing piezoelectric actuator, and liquid transporting apparatus

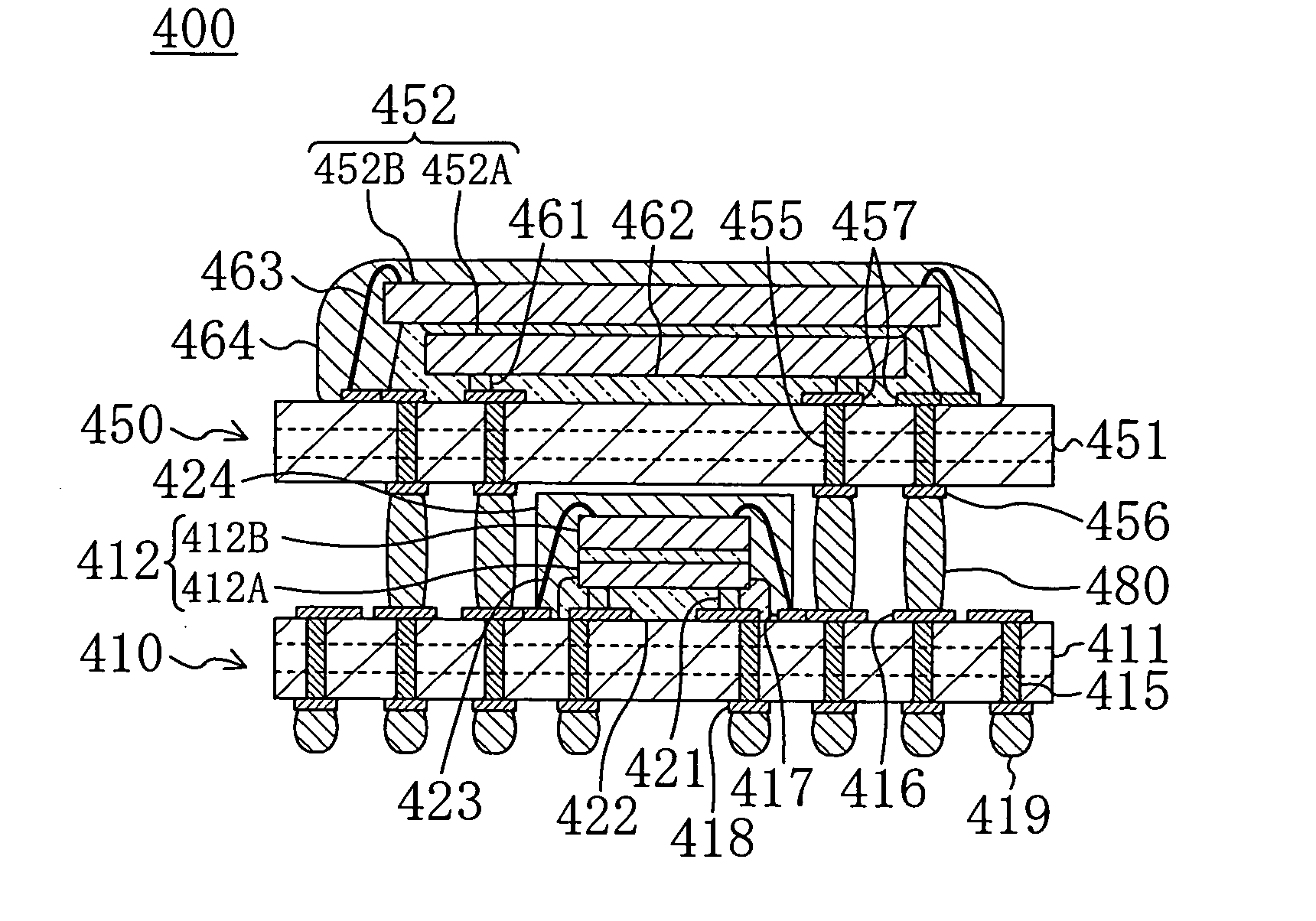

ActiveUS20060103268A1Avoid damageAlleviating concentrated actionPiezoelectric/electrostriction/magnetostriction machinesPrinted circuit aspectsPiezoelectric actuatorsElectrical and Electronics engineering

A piezoelectric actuator includes a supporting member in which pressure chambers are formed, a vibration plate which is joined to a joining section of the supporting member, a piezoelectric layer formed on the vibration plate, and an FPC provided on the piezoelectric layer. A contact section of an electrode formed on the piezoelectric layer and a terminal section of the FPC are electrically connected via a bump formed on the terminal section. A recess is formed on an upper surface of the supporting member right below the bump. While joining the piezoelectric layer and a wire member, any damage of the piezoelectric layer and any poor connection do not occur.

Owner:BROTHER KOGYO KK

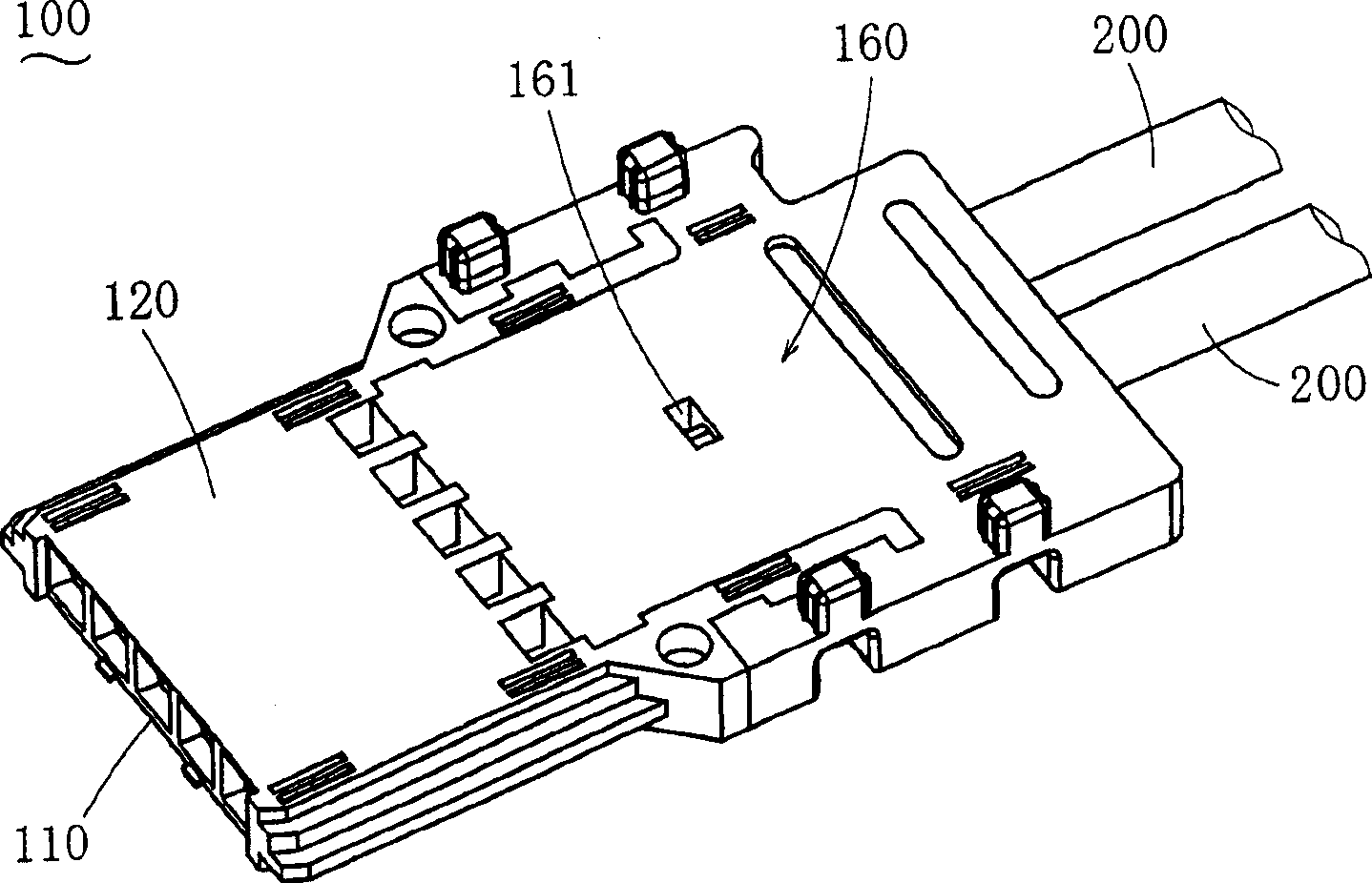

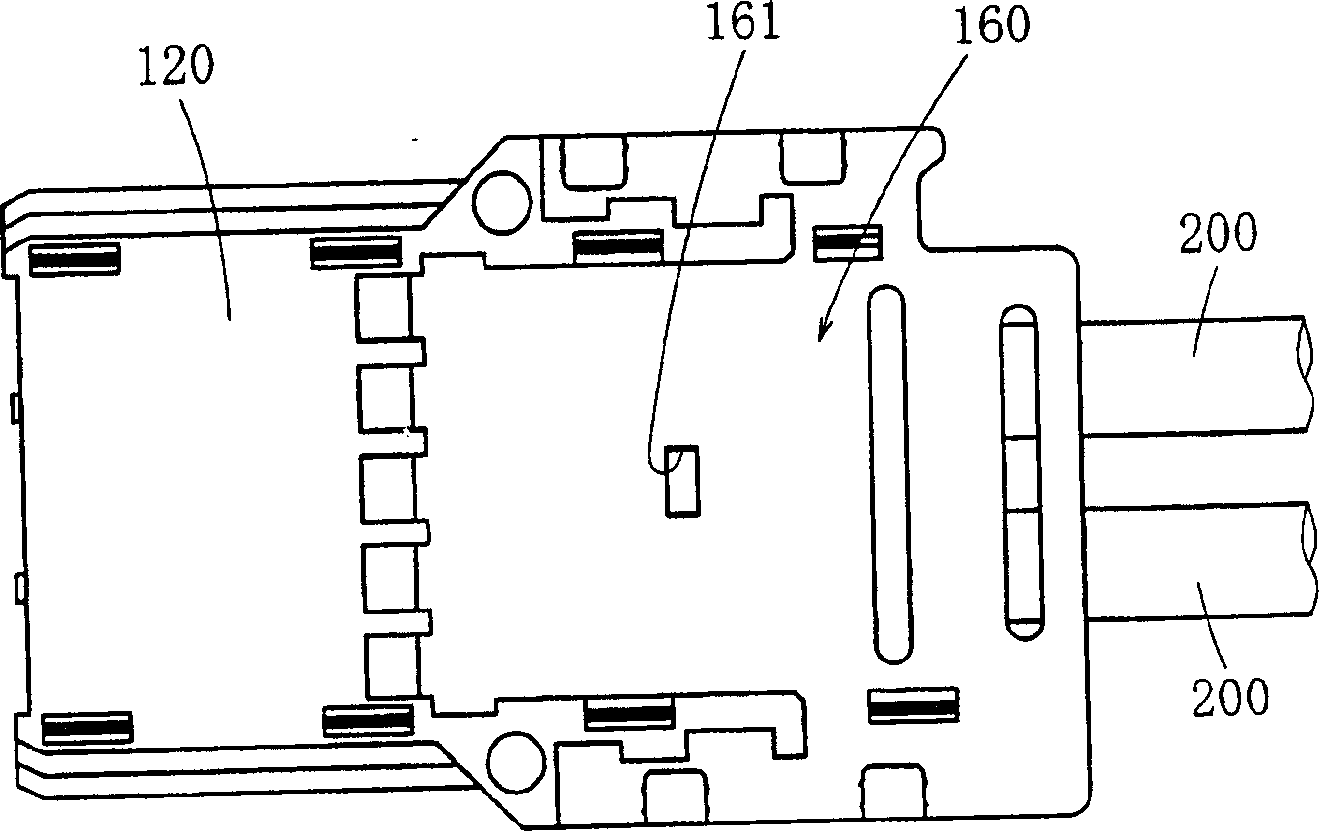

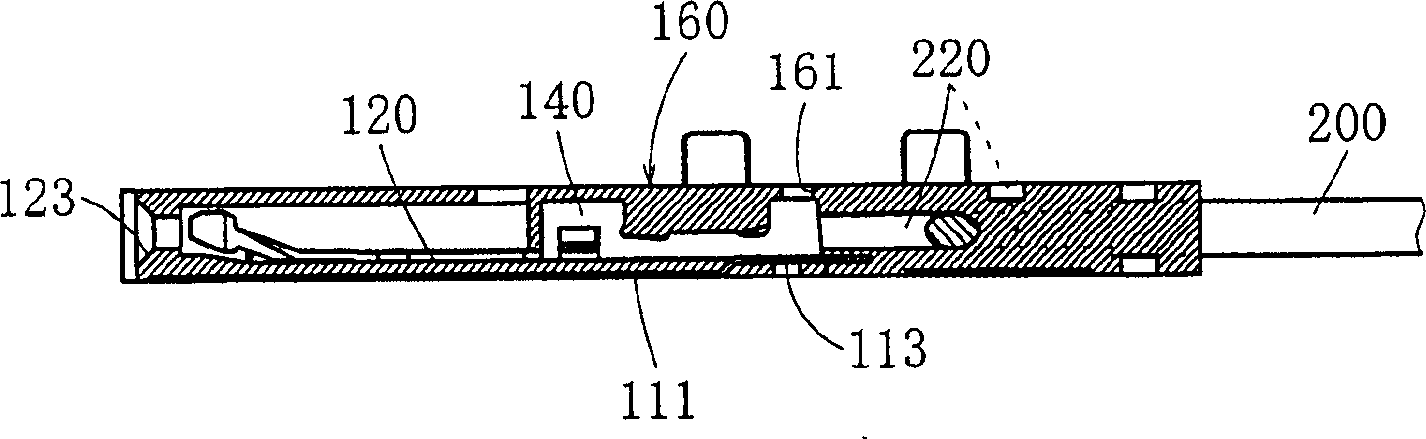

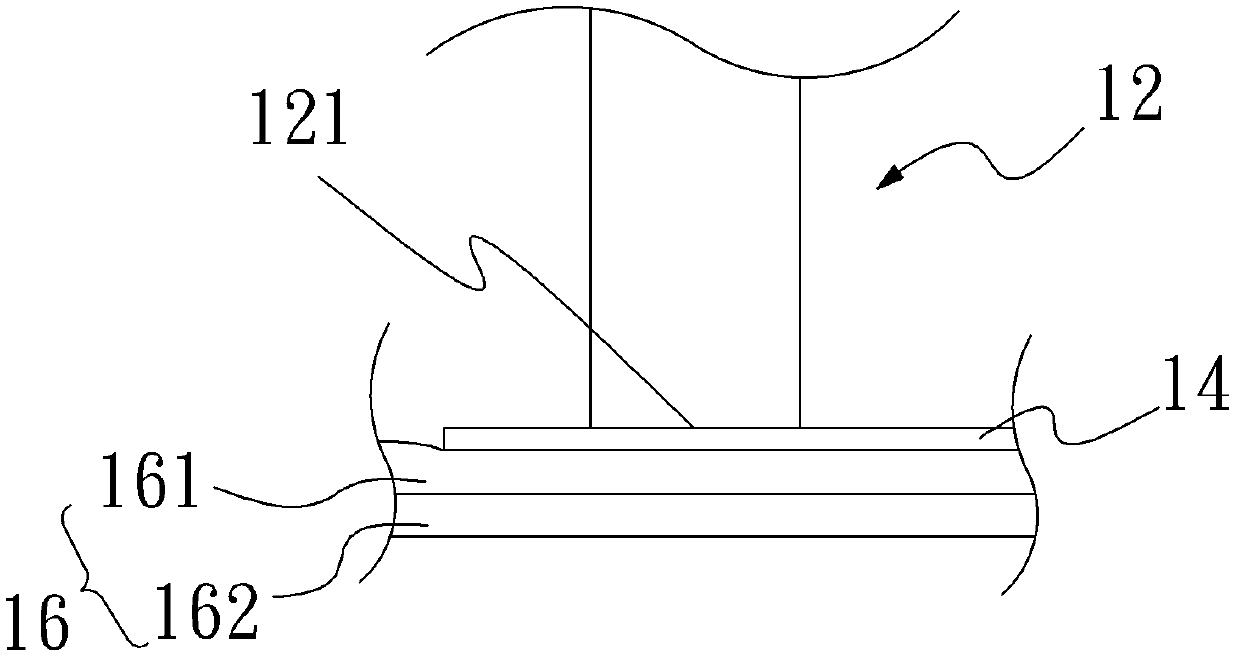

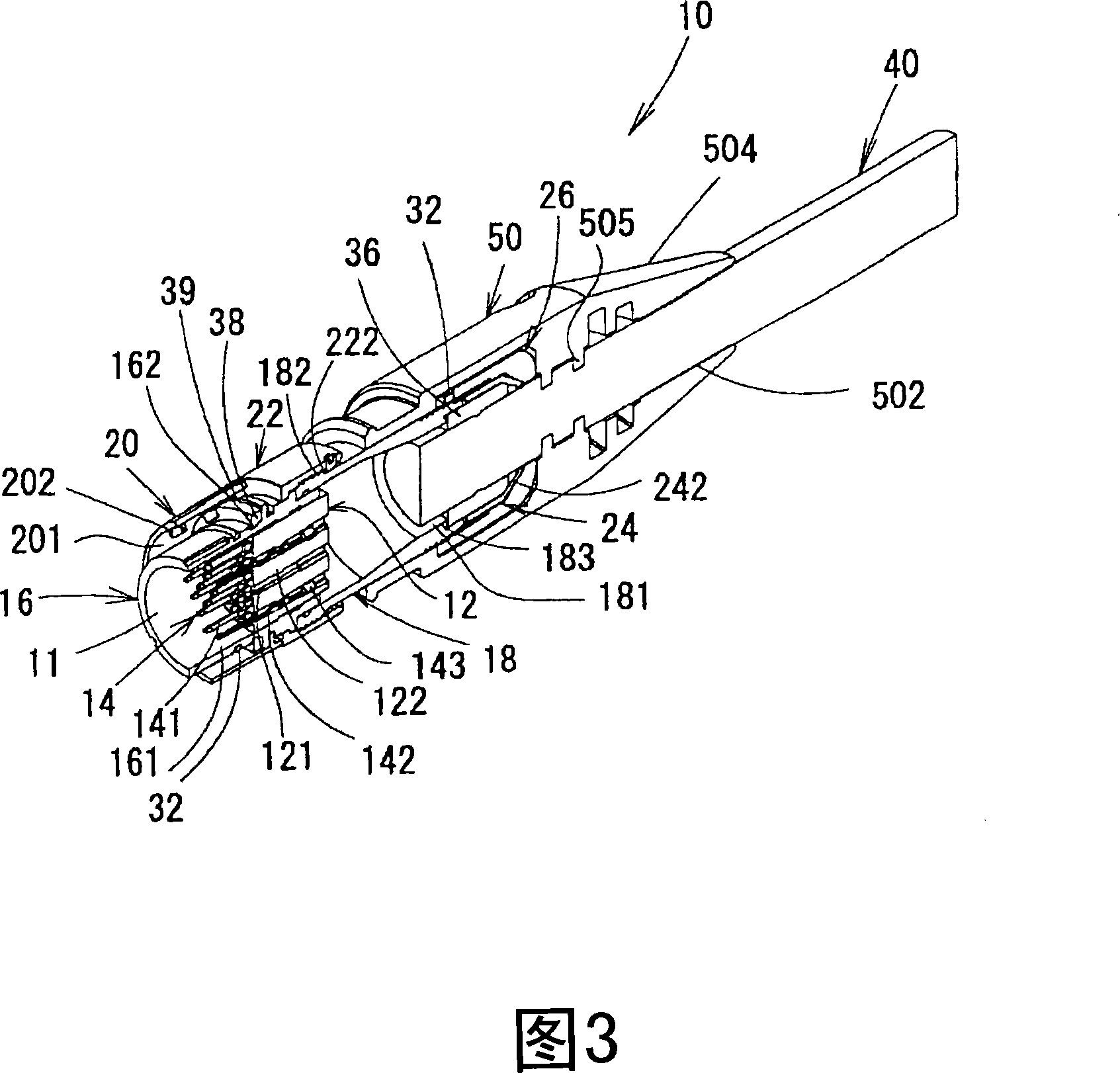

Electric connector of shielding cable, electric connector body and its manufacture

InactiveCN1407668APoor connectionPrevention of poor impedance characteristicsContact member assembly/disassemblyTwo-part coupling devicesElectricityShielded cable

This invention can obtain a stable impedance characteristic by improving reliability of connection of a grounding terminal and an external conductor, to attain improvement in manufacturing and equalization of the impedance characteristic between products by entirely eliminating soldering process, to make thinning available, and to prevent that the grounding terminal and the external conductor cause poor connection by making secondary mold. It is the electric connector 100 used for connection of shield cables 200, which have signal wires 210 and grounding wires 220. The first housing 120 is primarily molded to the external conductor 110, and a support projection 113, which contacts the grounding terminal 140 by projecting to the inner side of the external conductor 110, is formed. At the position, which faces the support projection 113 through the grounding terminal 140 in the second housing 160 which is secondarily molded, a through hole 161, which is made of a core pin 341 that has carried out pressing of the grounding terminal 140 by projecting into the inner direction from a mold 310, is provided.

Owner:JST MFG CO LTD

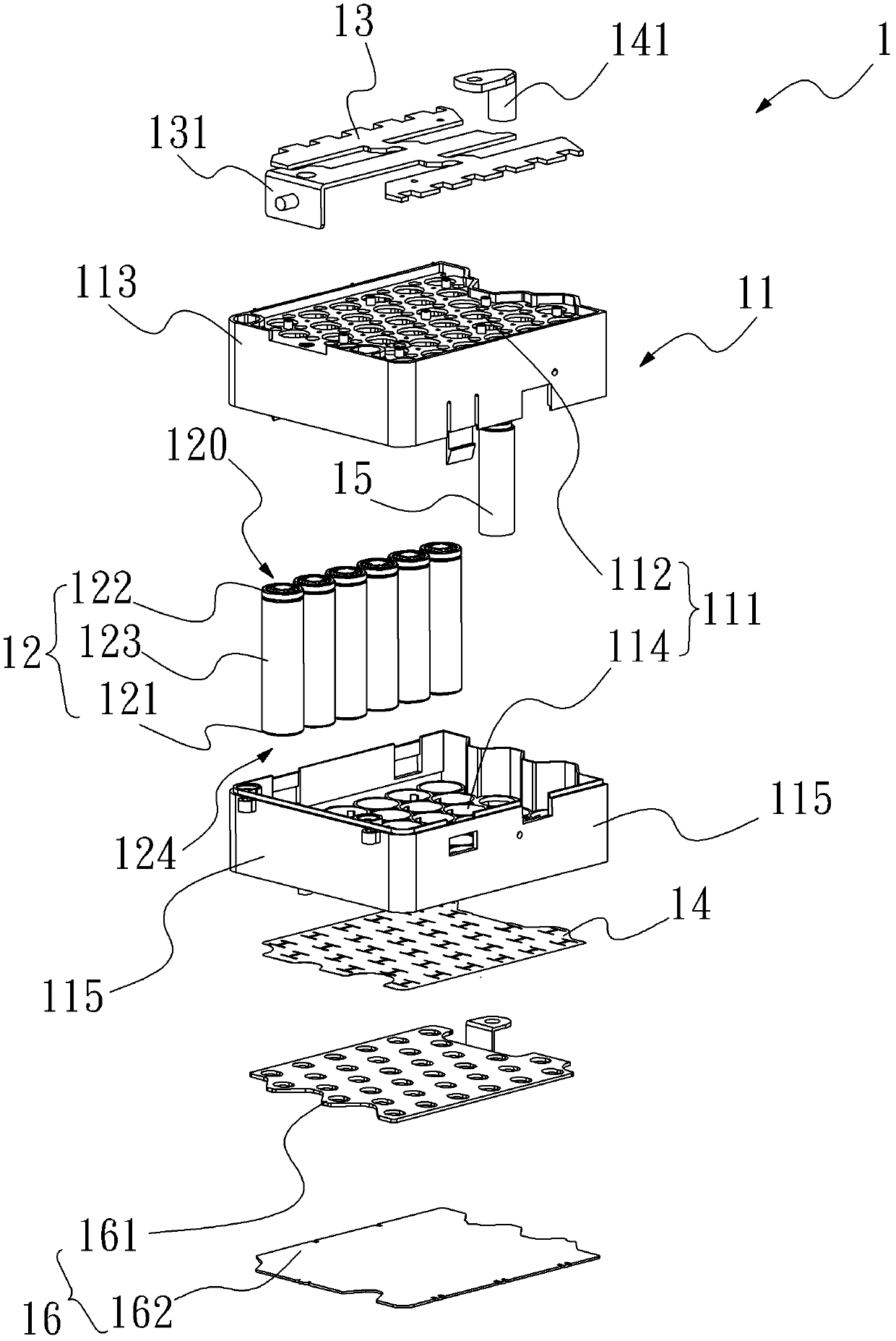

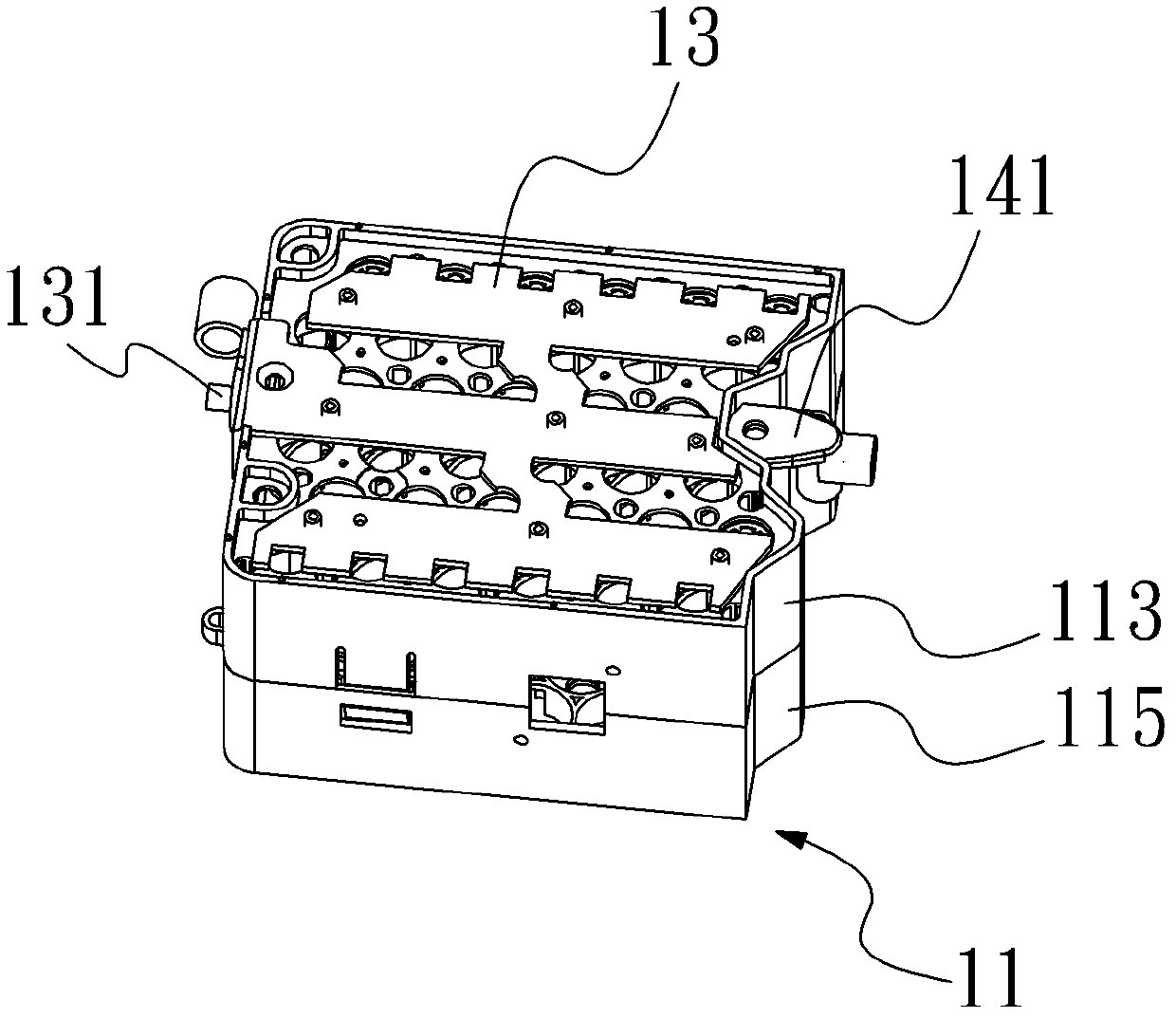

Battery pack with multiple parallel cells and power supply assembly with multiple battery packs connected in series

ActiveCN103378335APoor connectionReduce risk of sheddingFinal product manufactureSecondary cells manufactureElectric capacityFixed frame

The invention relates to a battery pack with multiple parallel cells and a power supply assembly with multiple battery packs connected in series. The battery pack mainly comprises a fixed frame device, the cells, top common electrodes, bottom common electrodes and at least one conductive column, wherein the fixed frame device comprises a plurality of storage grooves, the cells are arranged in the storage grooves, and at least one storage groove is used for installing the conductive column; the top common electrodes and the bottom common electrodes are respectively in conductive contact with the cells and two ends and locked on the upper side surface and the lower side surface of the fixed frame device, the top common electrodes form an electrode, and the bottom common electrodes are conductively connected with one another through the conductive column, are insulated from the top common electrodes and form another electrode. The power supply assembly with high electric capacity is formed by connecting the electrodes of the multiple battery packs in series / parallel.

Owner:阿提瓦公司

Liquid crystal display device having etching stopper electrode and method of manufacturing the liquid crystal display device

ActiveUS7952671B2Increase contactDelay foulingNon-linear opticsSemiconductor devicesLiquid-crystal displayEngineering

A liquid crystal display device comprising: a switching element that has a drain electrode and that is arranged on a substrate; a first insulating film that covers the switching element and that has a first opening on the drain electrode; a first etching stopper electrode that is formed in the first opening and that is connected to the drain electrode; a common electrode that is arranged on the first insulating film; a second insulating film that covers the first etching stopper electrode and the common electrode, and that has a second opening on the first etching stopper electrode; and a pixel electrode that is connected through the second opening to the first etching stopper electrode and that extends onto the second insulating film so as to face the common electrode.

Owner:JAPAN DISPLAY WEST

Laminated ceramic capacitor

ActiveCN1667766APoor connectionImprove yieldMultiple fixed capacitorsFixed capacitor electrodesCeramic capacitorMaterials science

Provided is a laminated ceramic capacitor in which internal electrodes (A1-D1, A2-D2) are buried in layers at intervals in the thickness direction of a ceramic main body (1). The lead-out electrodes (a1-d1, a2-d2) lead out to the side of the ceramic body (1) to constitute a lead-out portion. One end of the dummy electrodes (51-58) is led out to the side in the layer provided with the internal electrodes (A1-D1, A2-D2), and constitutes a lead-out portion. The lead-out portions of the extraction electrodes ( a1 to d1 , a2 to d2 ) of each layer overlap with the lead-out portions of the dummy electrodes ( 51 to 58 ) belonging to other layers in the thickness direction.

Owner:TDK CORP

Piezoelectric actuator, method for manufacturing piezoelectric actuator, and liquid transporting apparatus

ActiveUS7358643B2Avoid damageReduce actionPiezoelectric/electrostriction/magnetostriction machinesPrinted circuit aspectsWire rodPiezoelectric actuators

A piezoelectric actuator includes a supporting member in which pressure chambers are formed, a vibration plate which is joined to a joining section of the supporting member, a piezoelectric layer formed on the vibration plate, and an FPC provided on the piezoelectric layer. A contact section of an electrode formed on the piezoelectric layer and a terminal section of the FPC are electrically connected via a bump formed on the terminal section. A recess is formed on an upper surface of the supporting member right below the bump. While joining the piezoelectric layer and a wire member, any damage of the piezoelectric layer and any poor connection do not occur.

Owner:BROTHER KOGYO KK

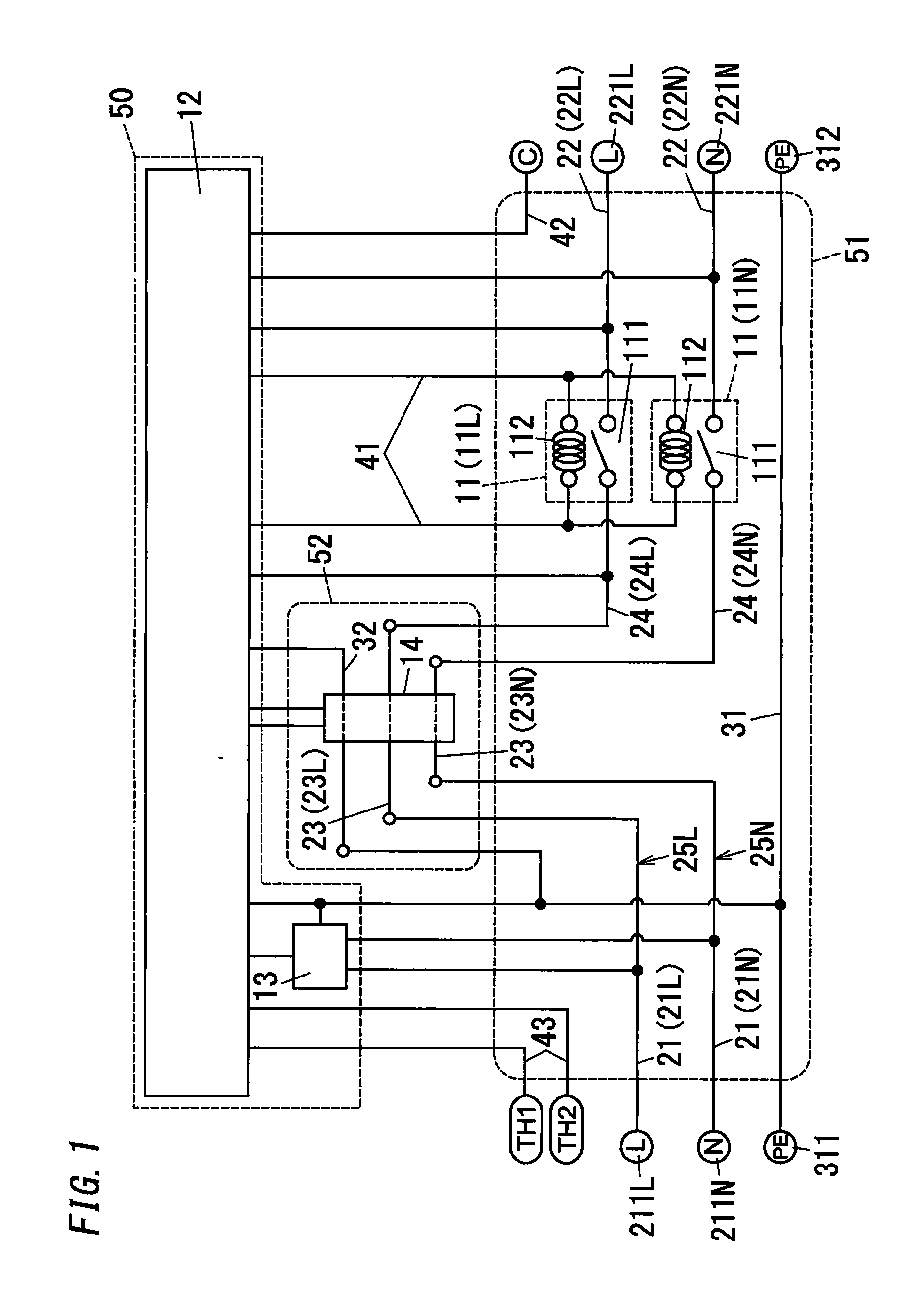

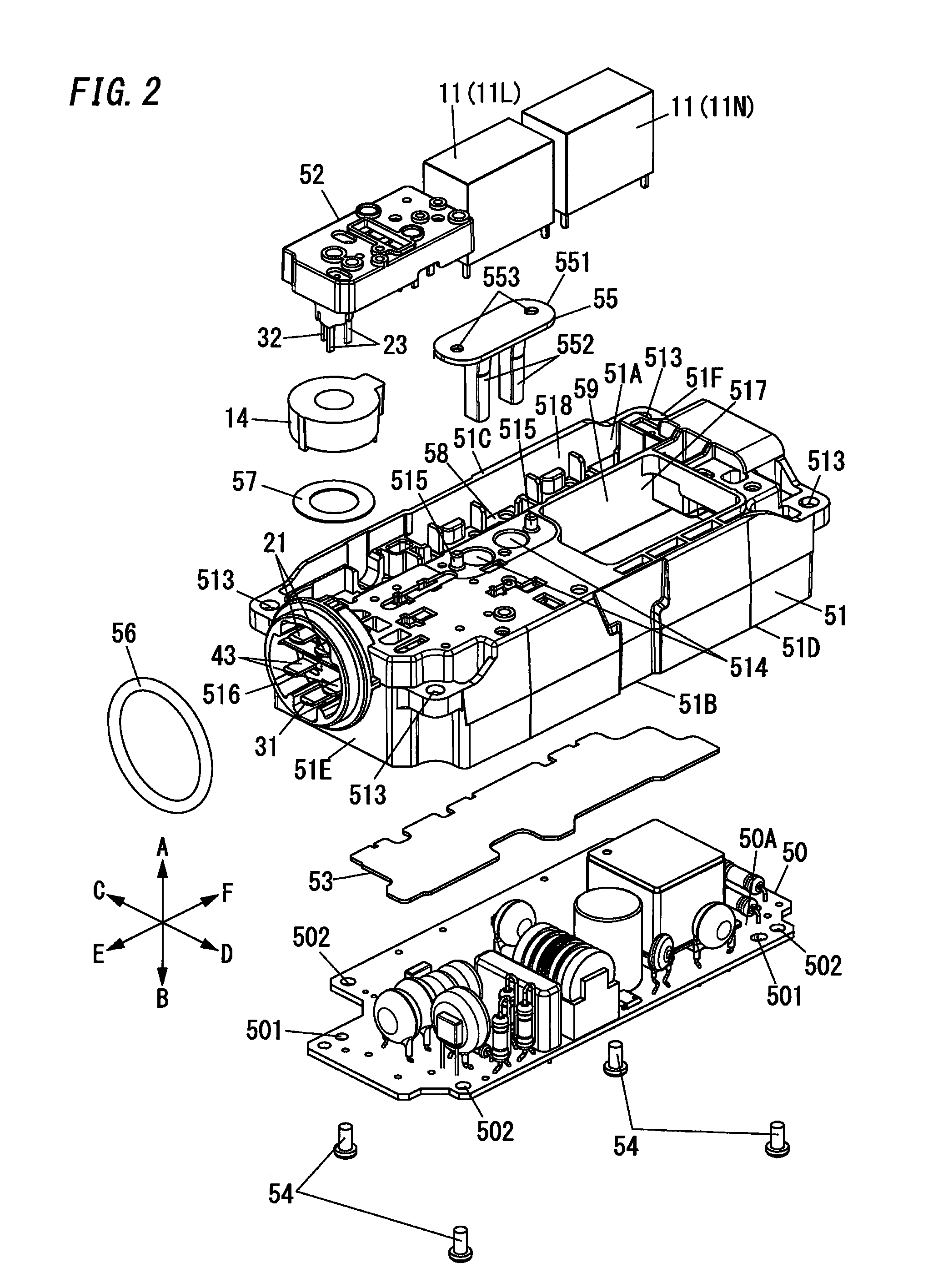

Power supply control device

ActiveUS20140292272A1Poor connectionBatteries circuit arrangementsCharging stationsElectricityElectrical connection

The power supply control device in accordance with the present invention includes: a power reception terminal for receiving power; a power supply terminal for supplying power; a relay configured to make and break an electrical connection between the power reception terminal and the power supply terminal; a control circuit configured to control the relay; a power supply circuit configured to supply power to the control circuit by use of power received via the power reception terminal; and a printed wiring board. The control circuit and the power supply circuit are mounted on the printed wiring board.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

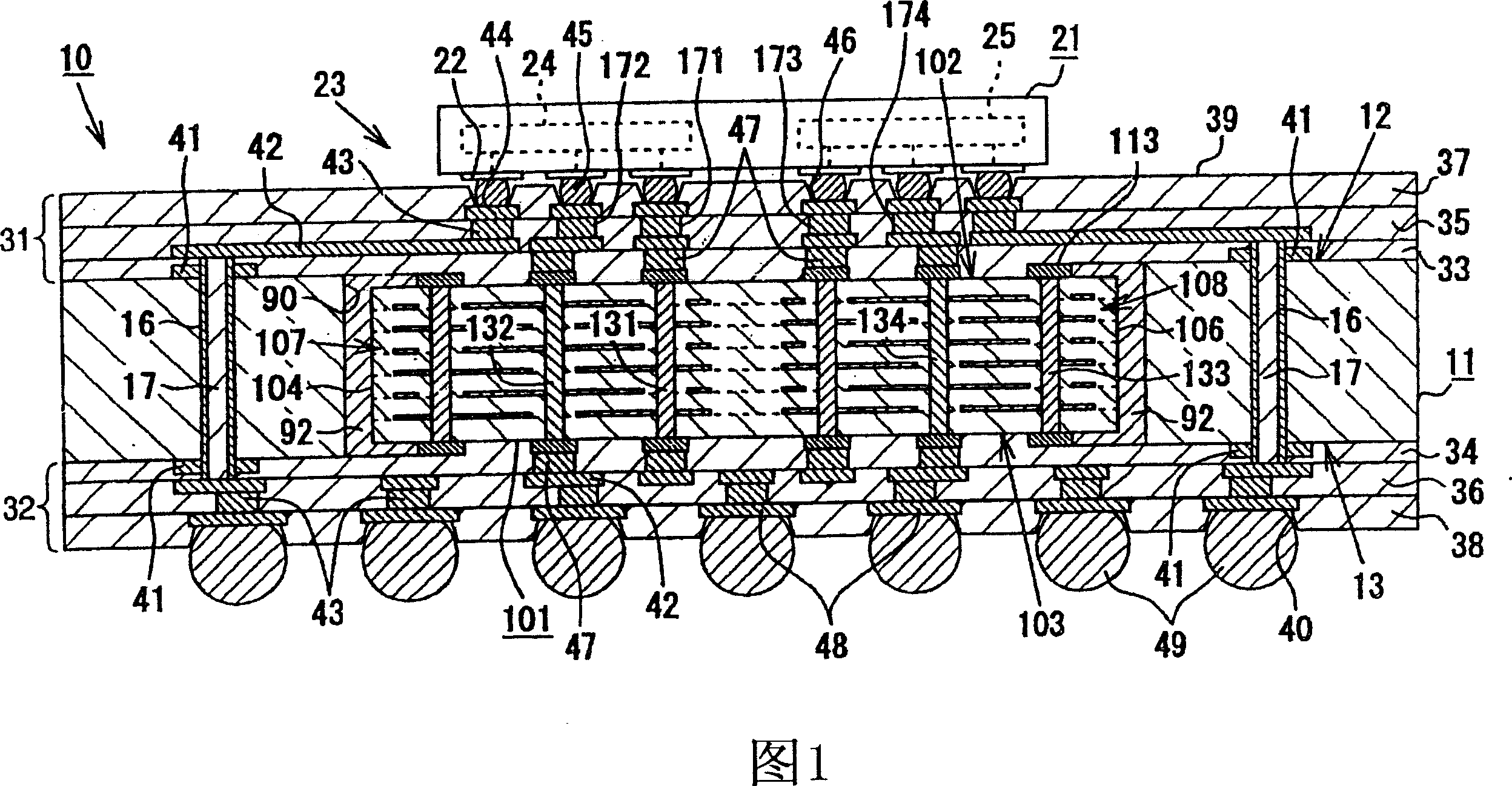

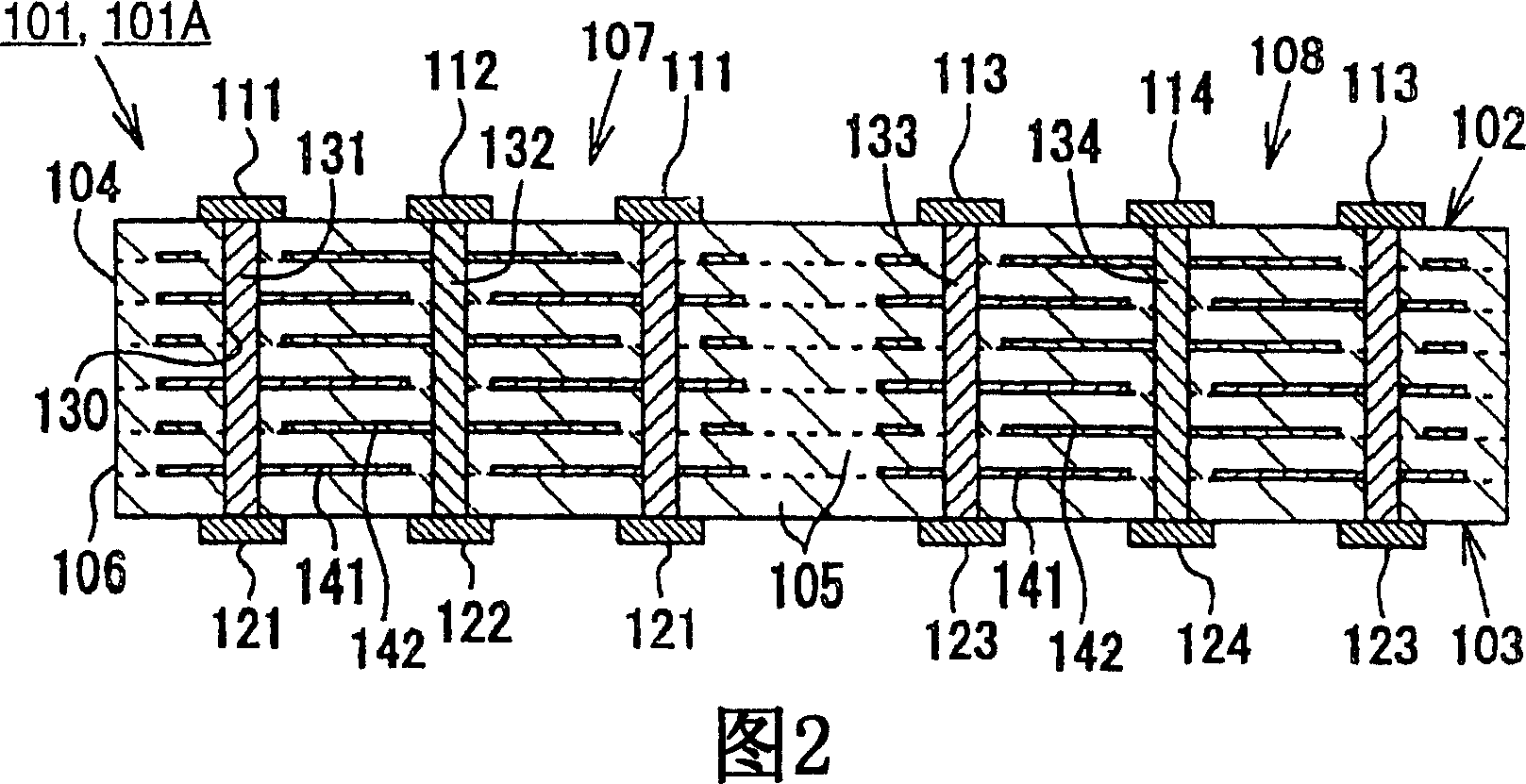

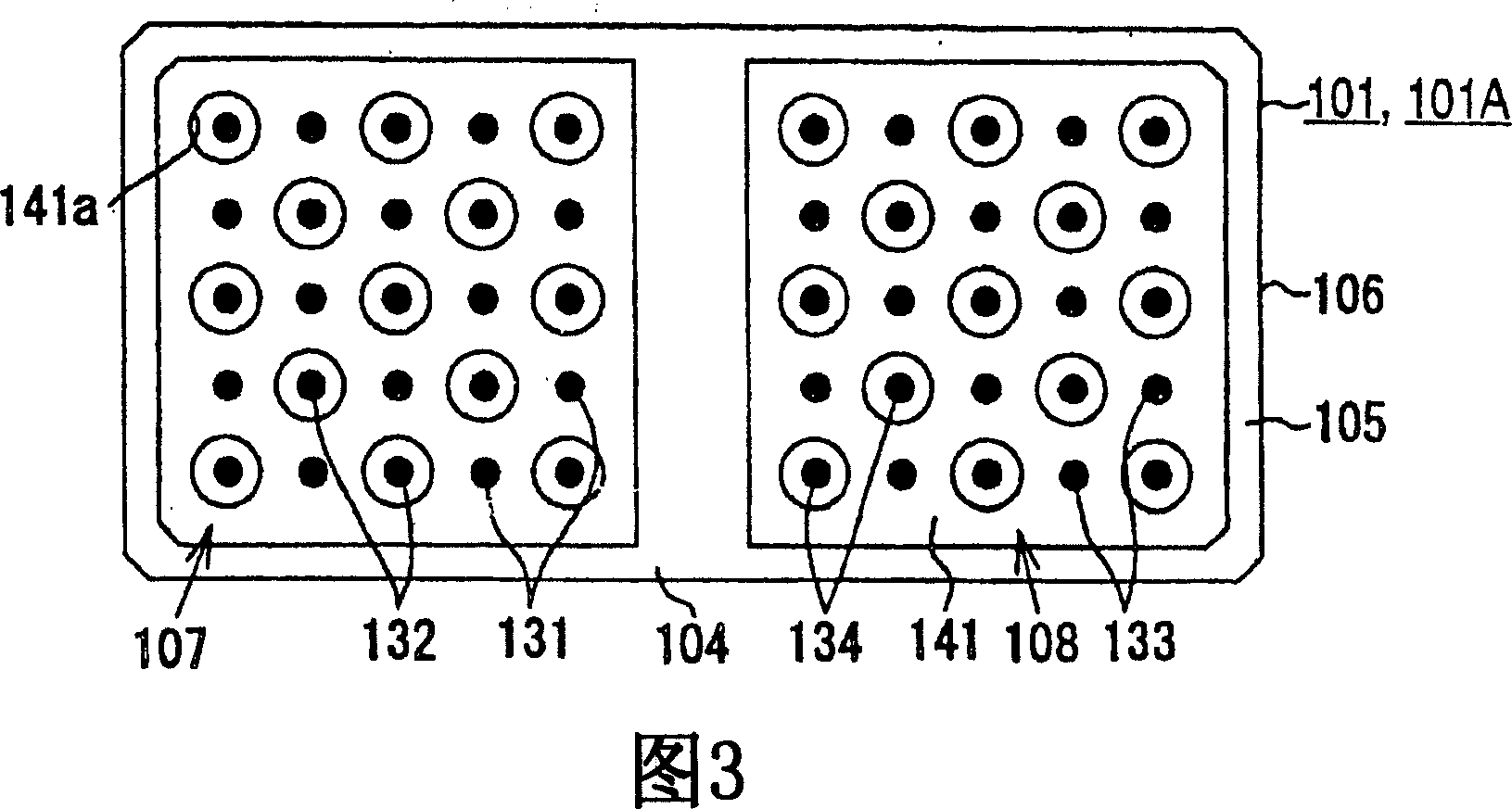

Wiring board and ceramic capacitor

ActiveCN1925721ASimple processAvoid crackingSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorCeramic capacitor

A wiring board which is easily made multifunctional, minisized, and low-costed. And a capacitor comprising the wiring board is also provided. A wiring board comprising: a board core (11) having a coremain surface (12) and a core reverse surface (13); a capacitor (101) having a capacitor main surface (102) and a capacitor reverse surface (103) and having a structure in which first inner electrodelayers (141) and second inner electrode layers (142) are alternately laminated and arranged via a dielectric layer (105), the capacitor (101) being accommodated in the board core (11) in a state in which the core main surface (12) and the capacitor main surface (102) are oriented on a same side; and a wiring laminated portion (31) having a structure in which interlayer insulating layers (33, 35) andconductor layers (42) are alternately laminated on the core main surface (12) and the capacitor main surface (102), wherein an inductor (251) is formed on or in the capacitor (101).

Owner:NGK SPARK PLUG CO LTD

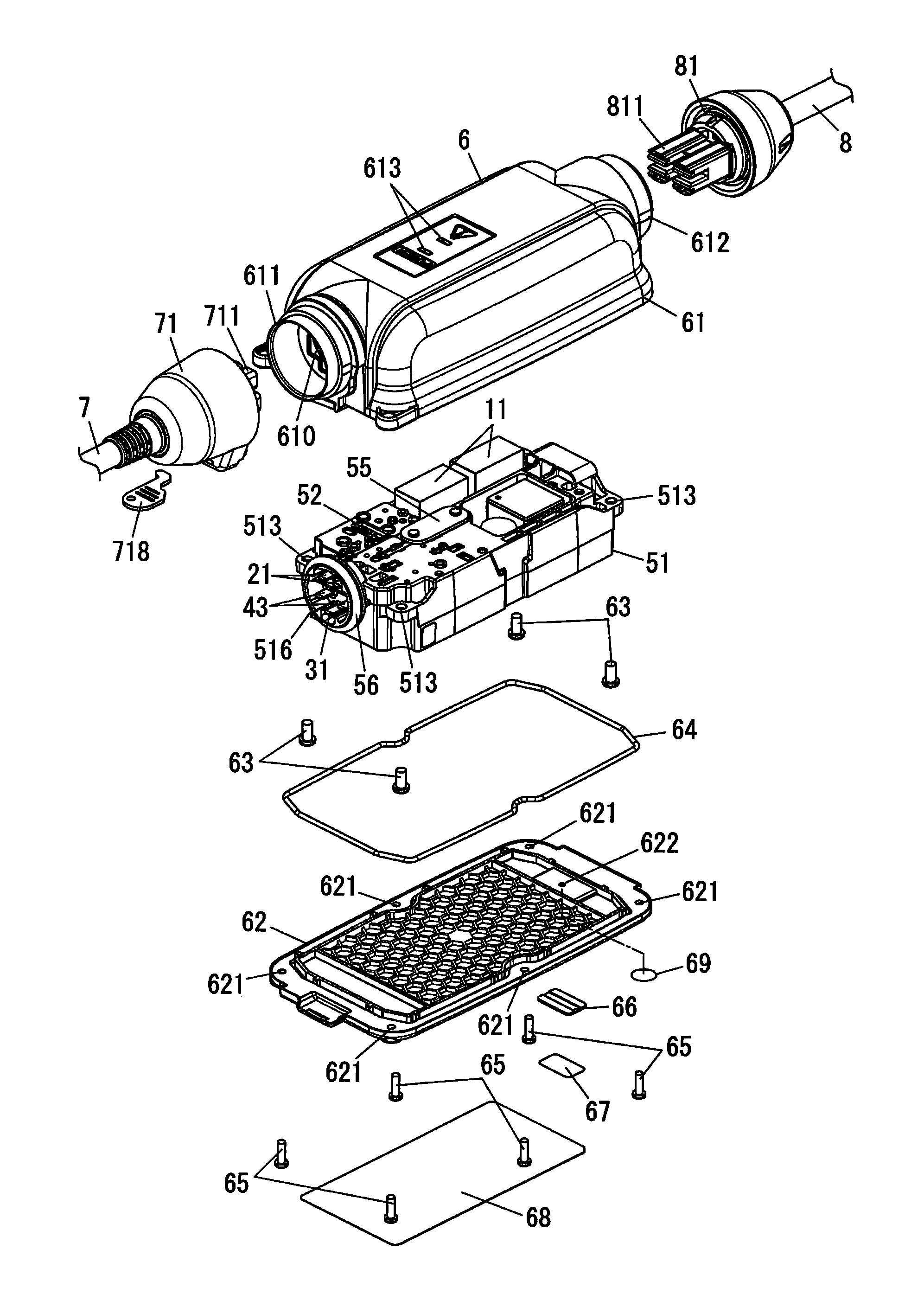

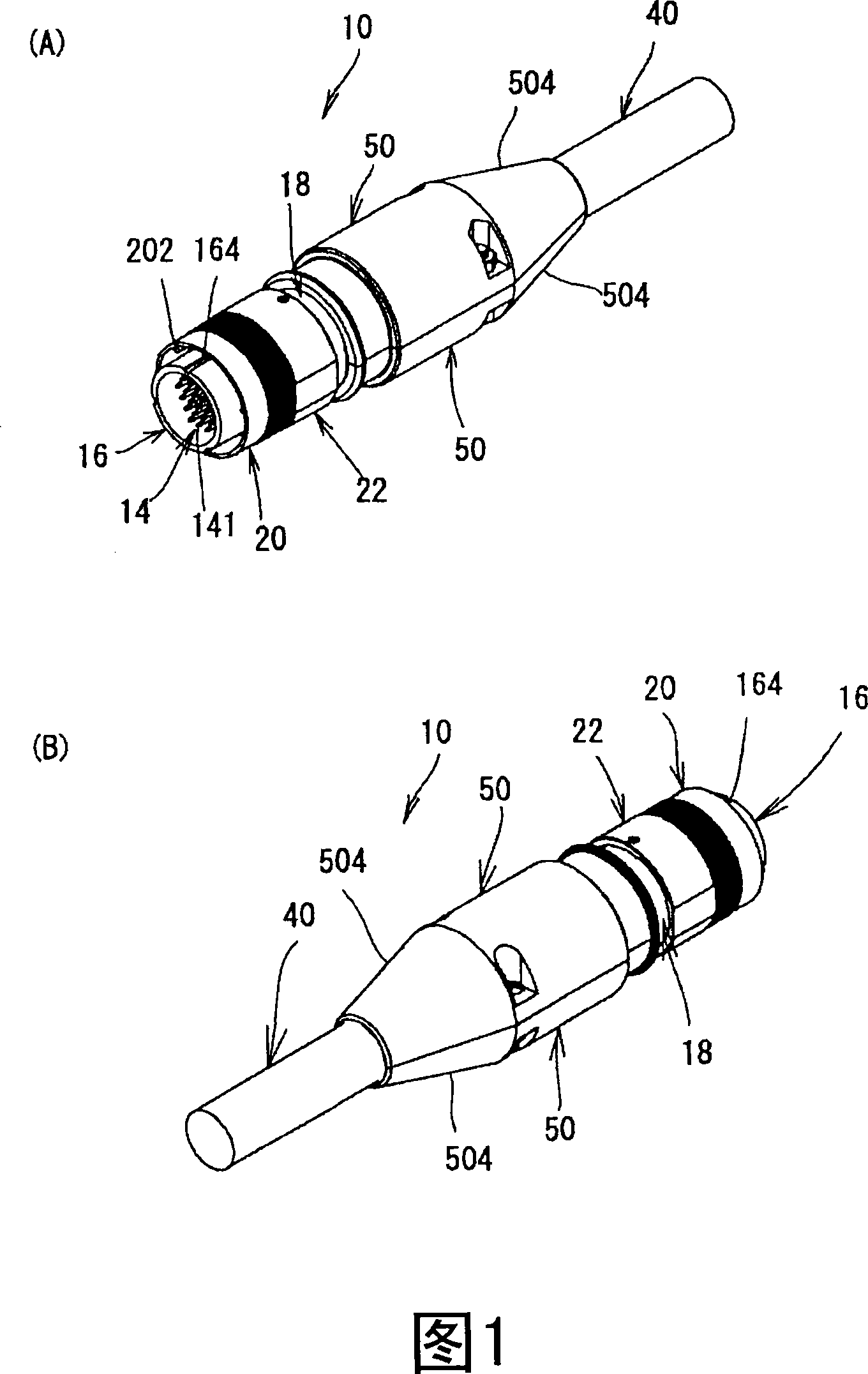

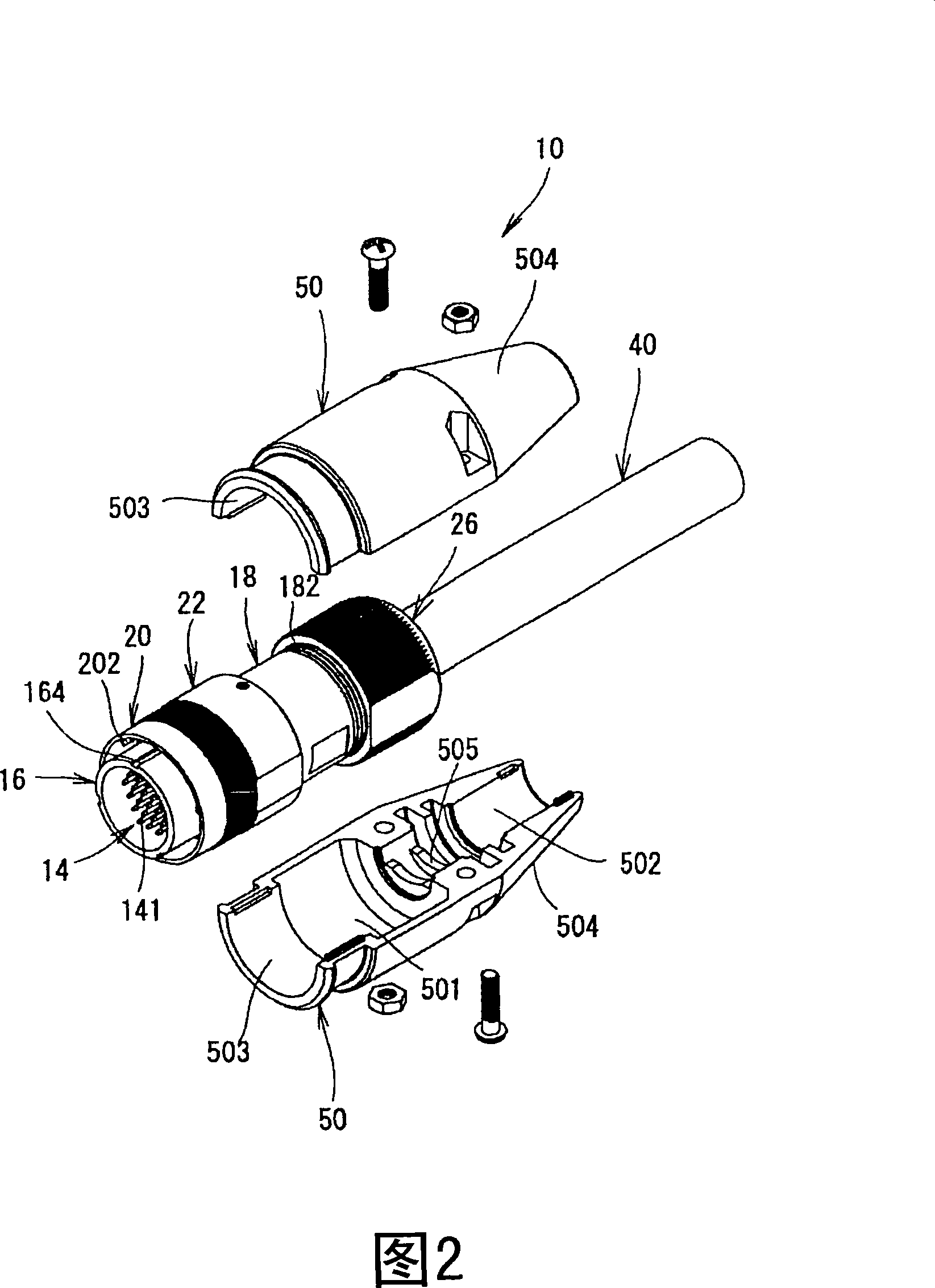

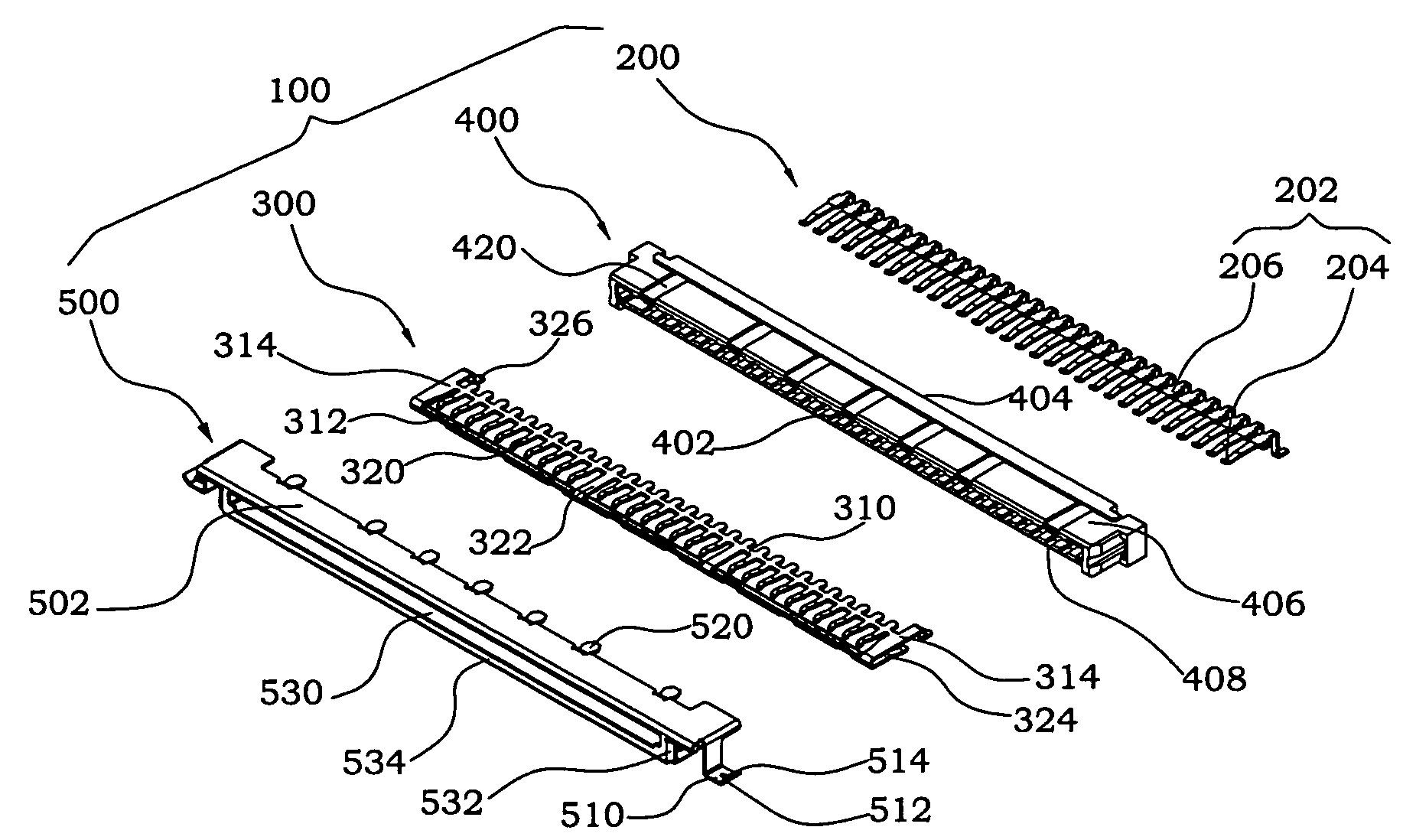

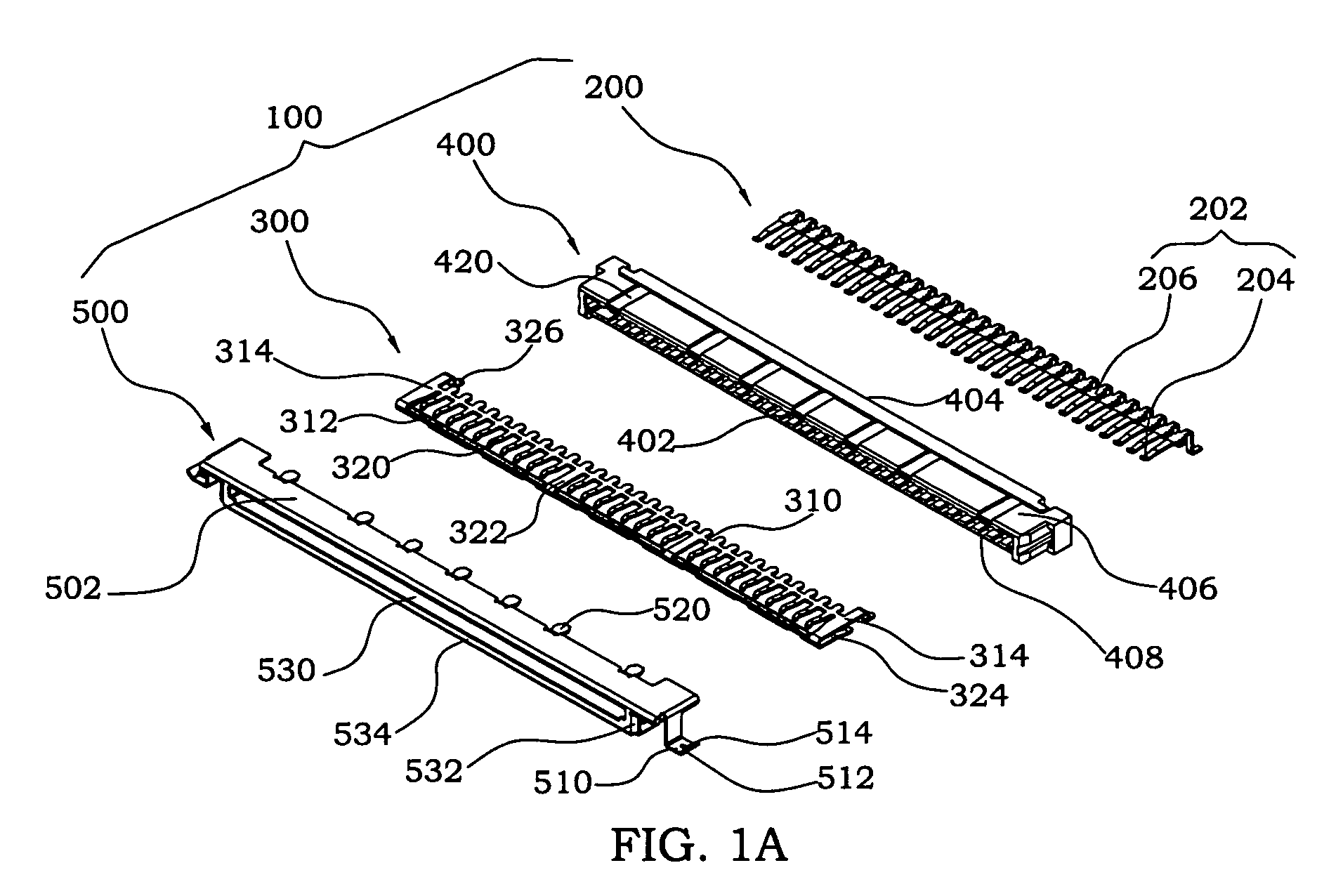

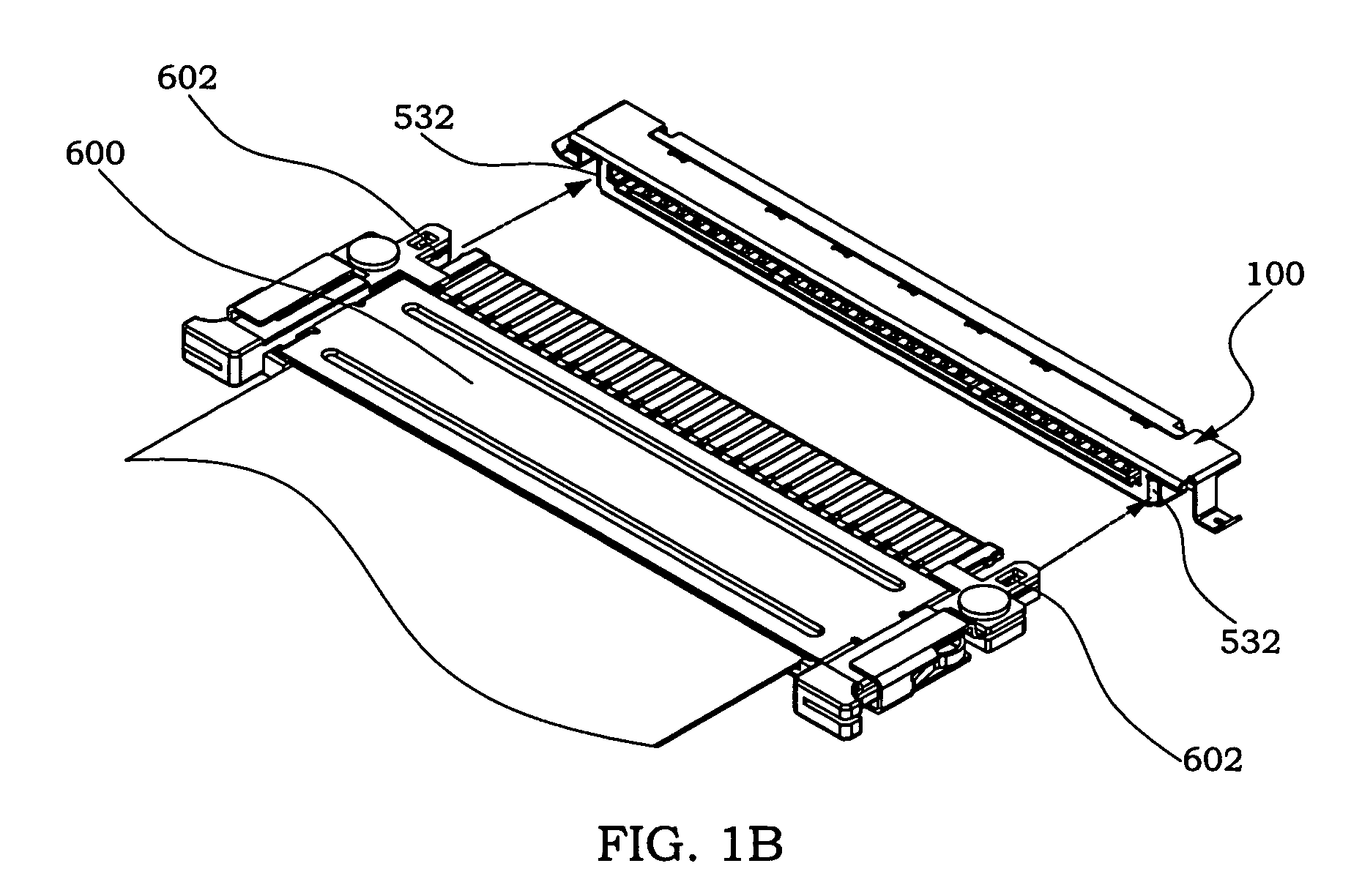

Electric connector

InactiveCN101237093AGood effectImprove retentionRelieving strain on wire connectionCouplingElectrical and Electronics engineering

The invention provides an electric connecter (10) which is hard to hang on the enclosures surrounding the industrial devices and an electronic device when a cable (40) is drew and improves retentiveness of the cable (40) and does not cause poor connection. In the electric connecter having a plurality of contacts (14), insulators (12), plug casings (16), coupling rings (20), rear casings (18), couplings (22), cable clamps (24) and clamp nuts (26), the connecter has a mounting unit (501) having a cable clamp (24), a cable insertion unit (502) where the cable (40) enters and is connected to the mounting unit (501). By arranging a conic section (504) on a periphery of a projection of the cable, or by arranging at least one projection (505) on the cable insertion unit (502) or by arranging both of the conic section (504) and the projection (505), two cover components (50) are mounted on the cable projection side of the mounting mechanism, thus the purpose of the invention can be realized.

Owner:DDK LTD +1

Electrical connector

InactiveUS7261598B1Easy to manufactureSimplify the manufacturing processTwo-part coupling devicesCoupling protective earth/shielding arrangementsMetallic enclosureElectrical connector

An electrical connector includes: a terminal element; a grounding element; an insulating housing; a metal shell enclosing the insulating housing; and two solder terminals extended outward from the metal shell. Wherein the grounding element has at least a supporting rib which is utilized to enhance the structure strength of the grounding element so as to ensure a good grounding effect in limited space. Besides, every one of those solder terminals of the metal shell has a winding portion bended in a tilting angle. Additionally, the metal shell further includes a partner-fitting portion, and two short sides of the peripheral thereof bended backward to form a chamfer-type guiding portion so as to make a corresponding connector connect to the electrical connector smoothly.

Owner:LONGWELL

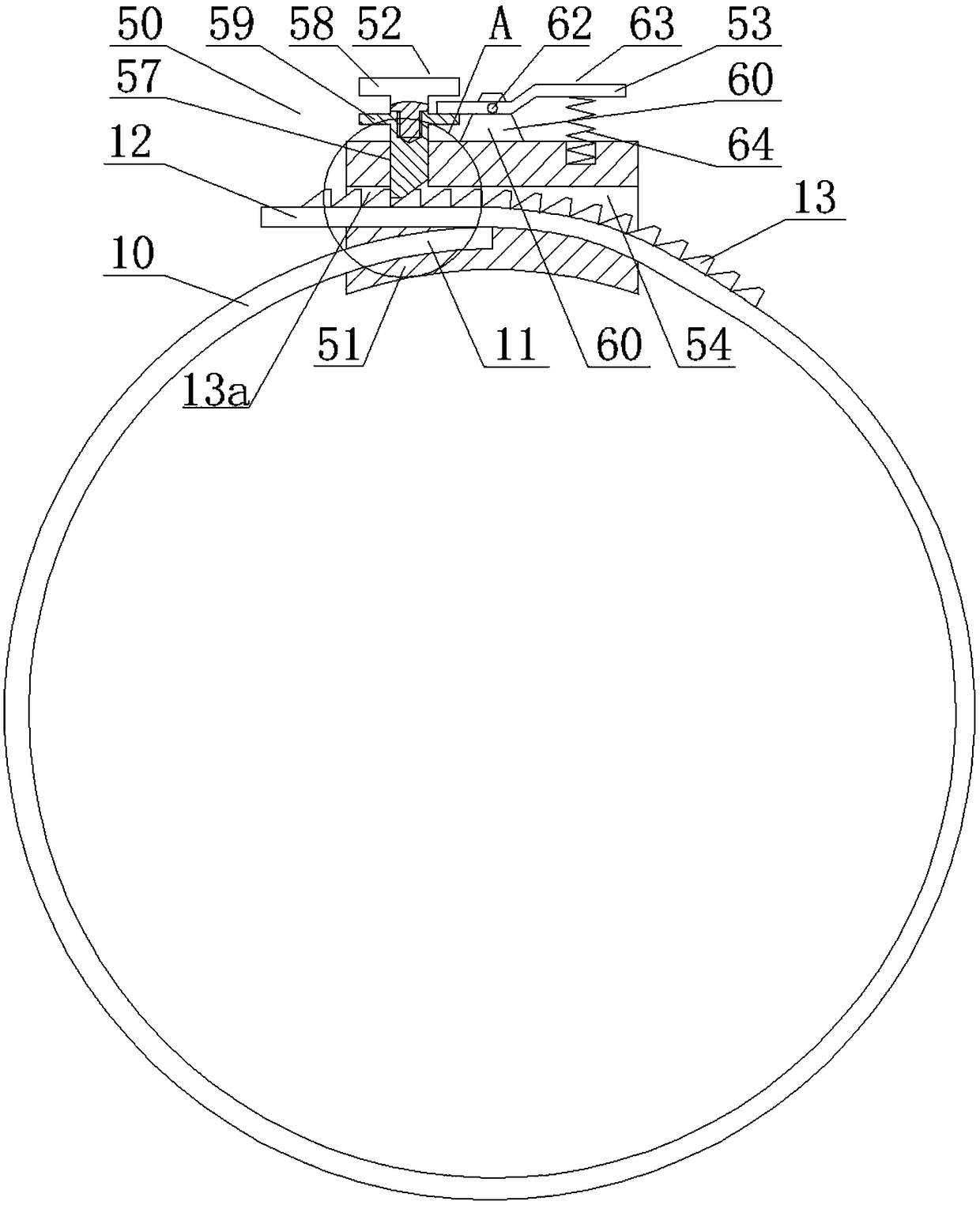

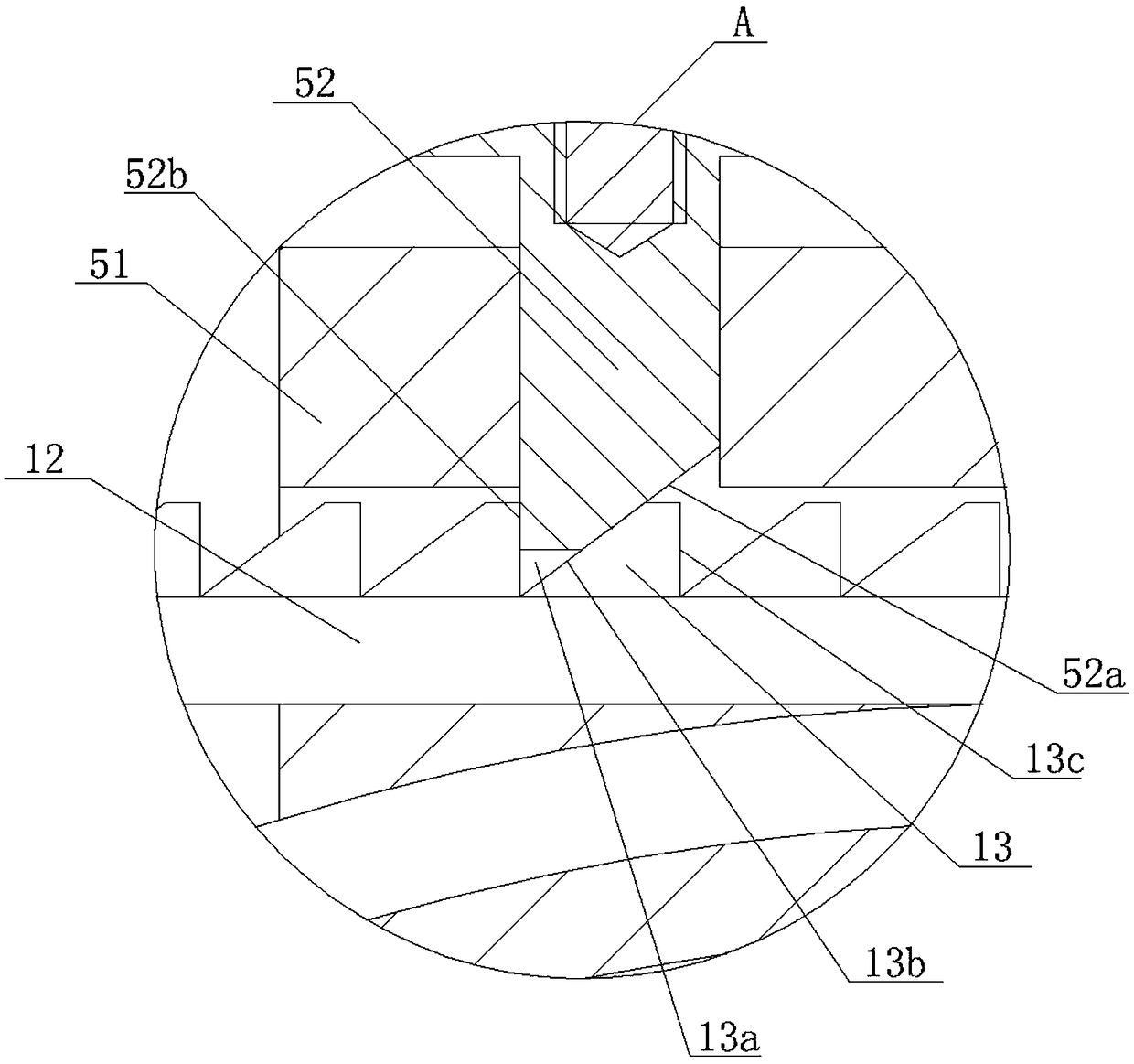

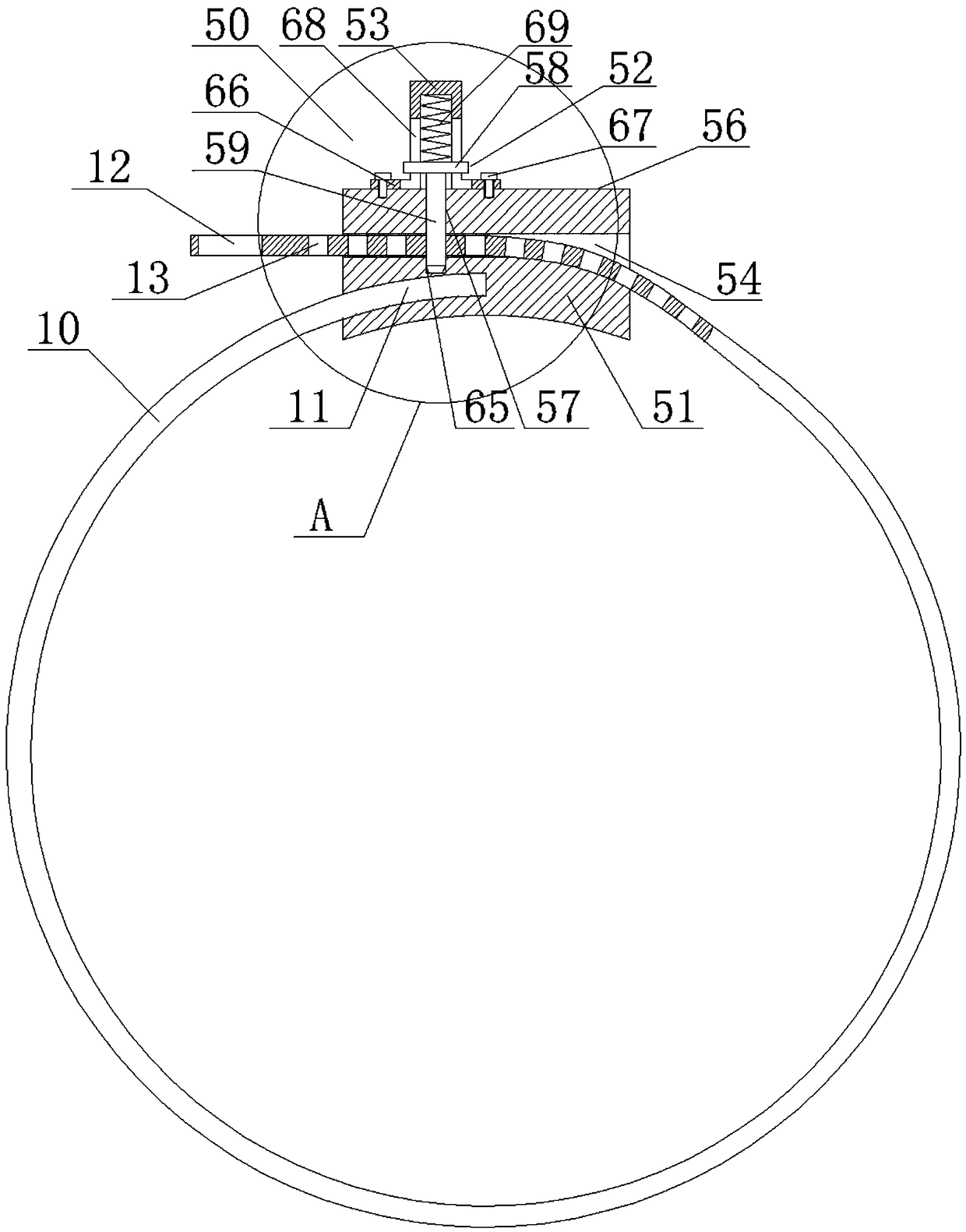

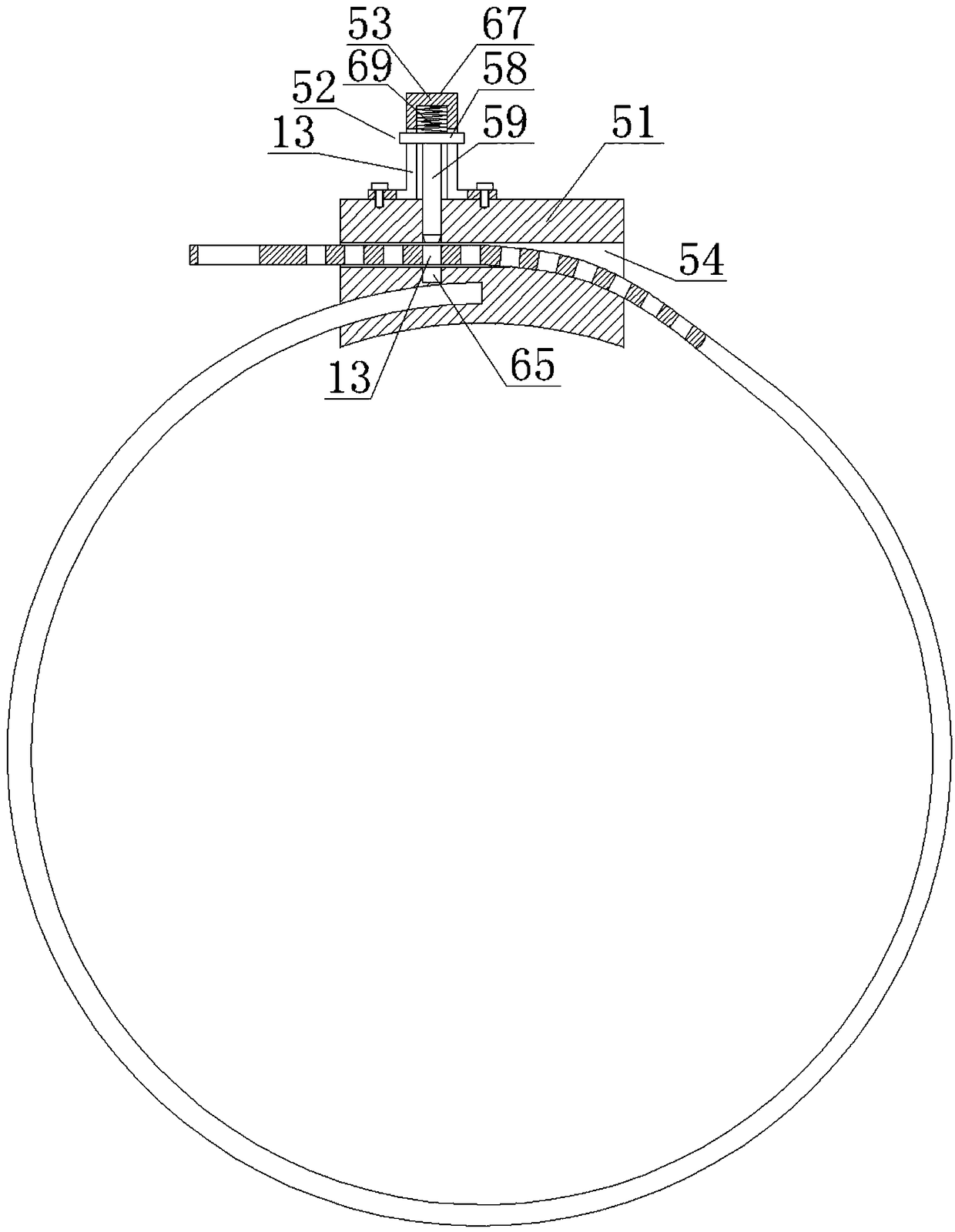

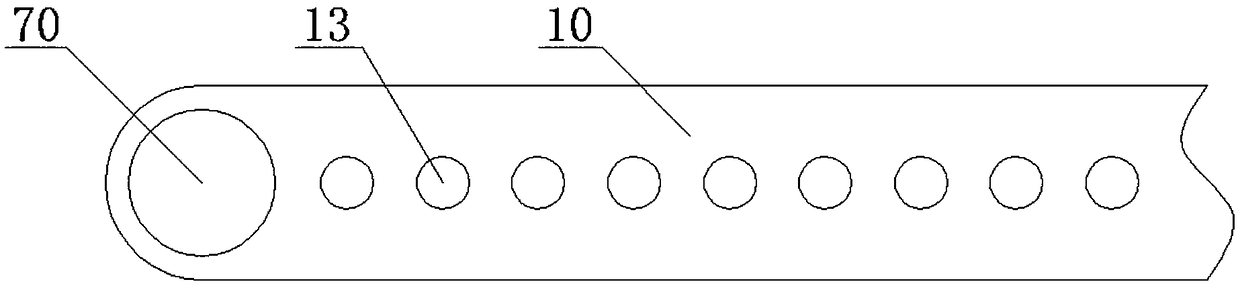

Hose clamp

InactiveCN109058624AImprove reliabilityEasy to operateHose connectionsEngineeringMechanical engineering

The invention discloses a hose clamp. The hose clamp comprises a clamping belt (10) and a locking assembly (50) connected with the clamping belt (10). The locking assembly (50) comprises a lock body (51) and a locking piece (52) slidably connected with the lock body (51) in a matching mode. The clamping belt (10) comprises a movable end (12) penetrating into the lock body (51). The movable end (12) is provided with a plurality of closely arranged stopping parts (13). The locking piece (52) can selectively extend into or out of a groove (13a) formed between two adjacent stopping parts (13). After the locking piece (52) extends into the groove (13a), the movable end (12) can be prevented from moving reversely. According to the hose clamp, through the arrangement of the locking piece and thestopping parts matched with the locking piece, the situation that soft and hard pipes are poor in connection due to thread loosening after vibration or long-term use will not happen, and the reliability is high.

Owner:SUZHOU ANKEN ELECTRONICS TECH

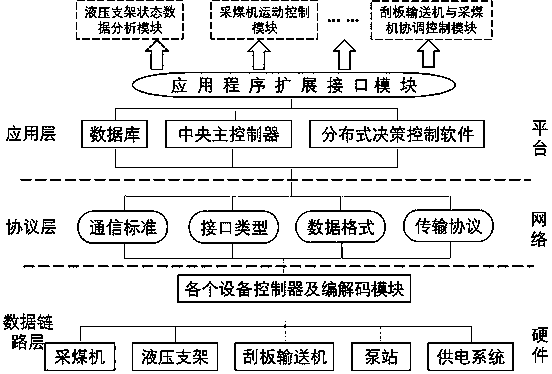

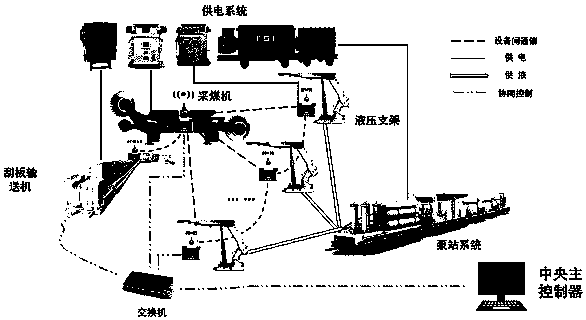

Distributed decision-making control system for underground comprehensively mechanized coal mining face and architecture thereof

ActiveCN108415278ACollaborative operation in real timeRun quicklyProgramme control in sequence/logic controllersData mining softwareDistributed decision

The invention discloses a distributed decision-making control system for an underground comprehensively mechanized coal mining face and architecture thereof so that problems that all devices are not associated of the underground comprehensively mechanized coal mining face of mine and the safe and high-efficiency coordinated operation can not be realized easily can be solved. The existing centralized control mode is changed; each coal mining face device is provided with a standard controller and a standard coding and decoding module that have the unified interfaces and formats. Devices from different manufacturers are connected and all devices make decisions for follow-up actions based on the own state and the states of adjacent devices as well as spatial location information; a distributedcontrol system running at a central main controller is responsible for analyzing, digging, and processing cooperation information between devices to realize coordinated operation of all system devices, so that the real-time performance, accuracy and coordination of the system control are improved effectively. Meanwhile, the distributed control system is provided with an application extension interface to provide a basic platform for developing the upper-layer data mining software and control software, so that the current coal mining face production control system can be changed fundamentally.

Owner:CCTEG COAL MINING RES INST

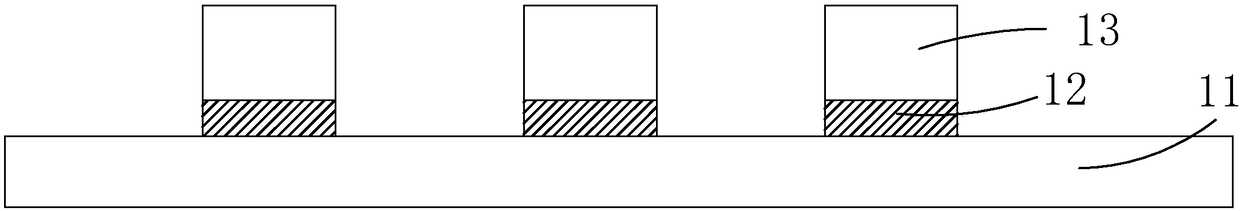

Circuit substrate and circuit substrate manufacturing method

ActiveUS20100147570A1Prevent bad connectionPerformanceFinal product manufactureSemiconductor/solid-state device detailsEngineeringElectronic component

A circuit substrate includes protruding terminals and has a structure that ensures an excellent connection with an electronic component, such as an IC. The circuit substrate on which an IC is to be mounted includes terminals that are to be electrically connected to solder bumps located on the IC. The terminals protrude from the mounting surface of a substrate body on which the IC is to be mounted. The sectional area of the top surface of each of the terminals is about 1.2 times the sectional area of each of the terminals on the mounting surface.

Owner:MURATA MFG CO LTD

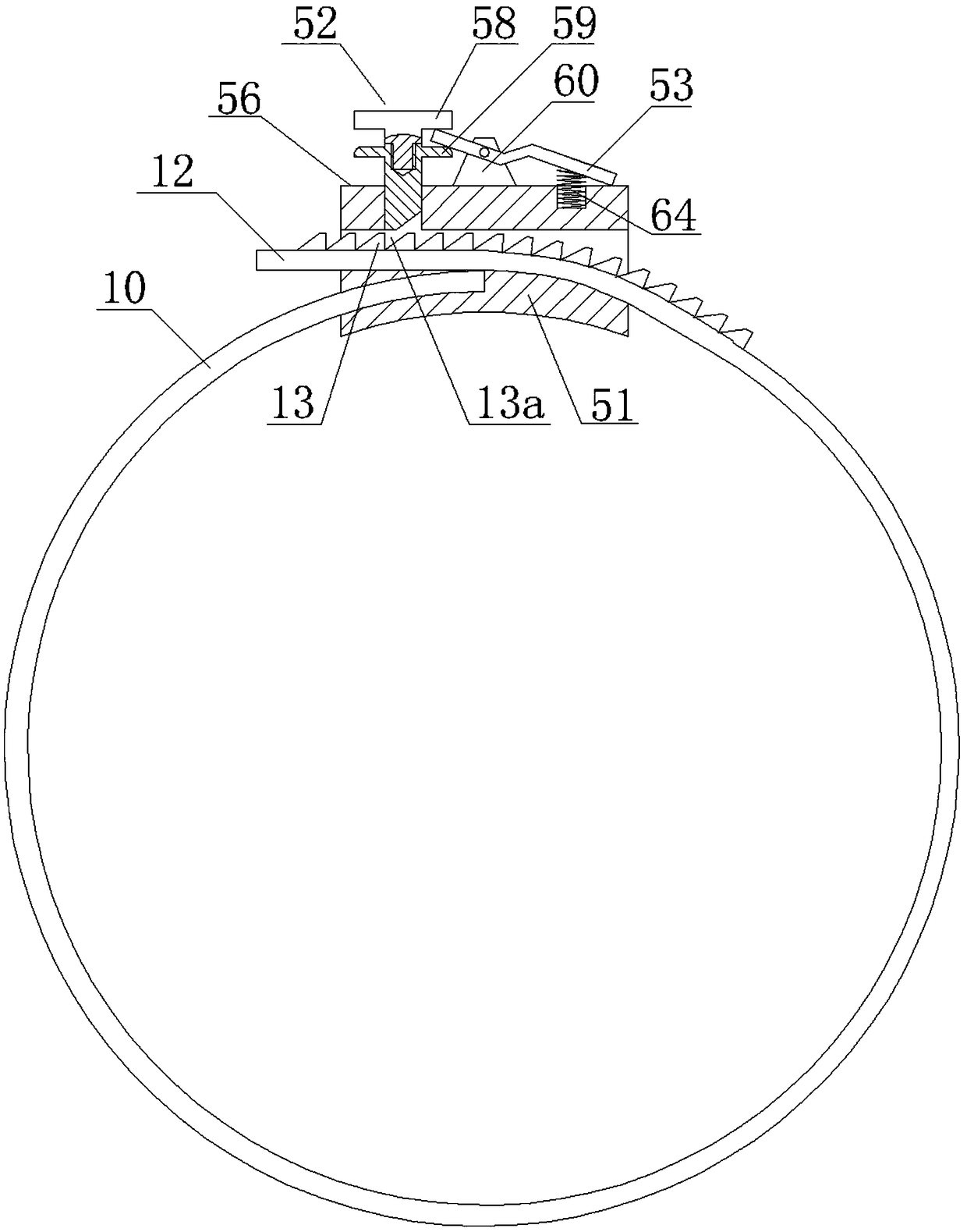

Hose clamp

InactiveCN109140089APoor connectionImprove reliabilityHose connectionsEngineeringMechanical engineering

The invention discloses a hose clamp comprising a strap (10) and a locking assembly (50) connected with the strap (10). The hose clamp is characterized in that the locking assembly (50) comprises a lock body (51) and a locking piece (52) connected with the lock body (51) in sliding and matched manners. The strap (10) comprises a moving end which is arranged in the lock body (51) in a penetrating manner. The moving end (12) is provided with multiple through holes (13). The locking piece (52) selectively extends into or separates from the through holes (13). Through the locking piece and the through holes which are matched with each other, after vibration or long-time use, it is avoided that due to looseness of threads, connection between a hose and a hard pipe is poor, and the hose clamp ishigh in reliability.

Owner:SUZHOU ANKEN ELECTRONICS TECH

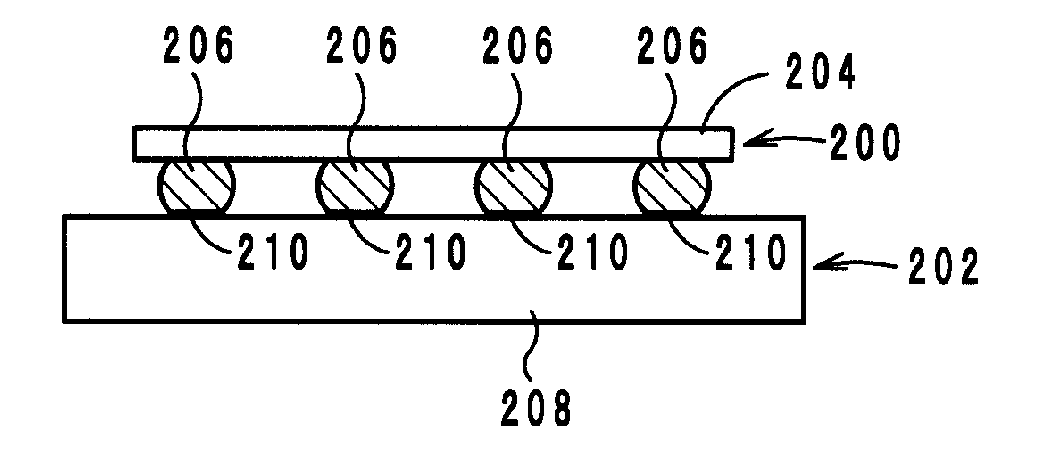

Circuit board and method of mounting electronic component on circuit board

InactiveUS20140144688A1Reliable structurePoor connectionPrinted circuit assemblingFinal product manufactureExposed pointElectronic component

Provided are a circuit board, and a method of mounting an electronic component on the circuit board. The circuit board according to an exemplary embodiment of the present invention includes: a pad pattern including a basic pattern and one or more additional patterns connected to the basic pattern, in which the basic pattern includes a region in which a connection terminal of an electronic component is attached by solder, the one or more additional patterns include regions in which the connection terminal of the electronic component is not attached, and the basic pattern includes an exposed side or an exposed point capable of limiting a mounting position so as to prevent the electronic component from exceeding an alignment margin.

Owner:SAMSUNG DISPLAY CO LTD

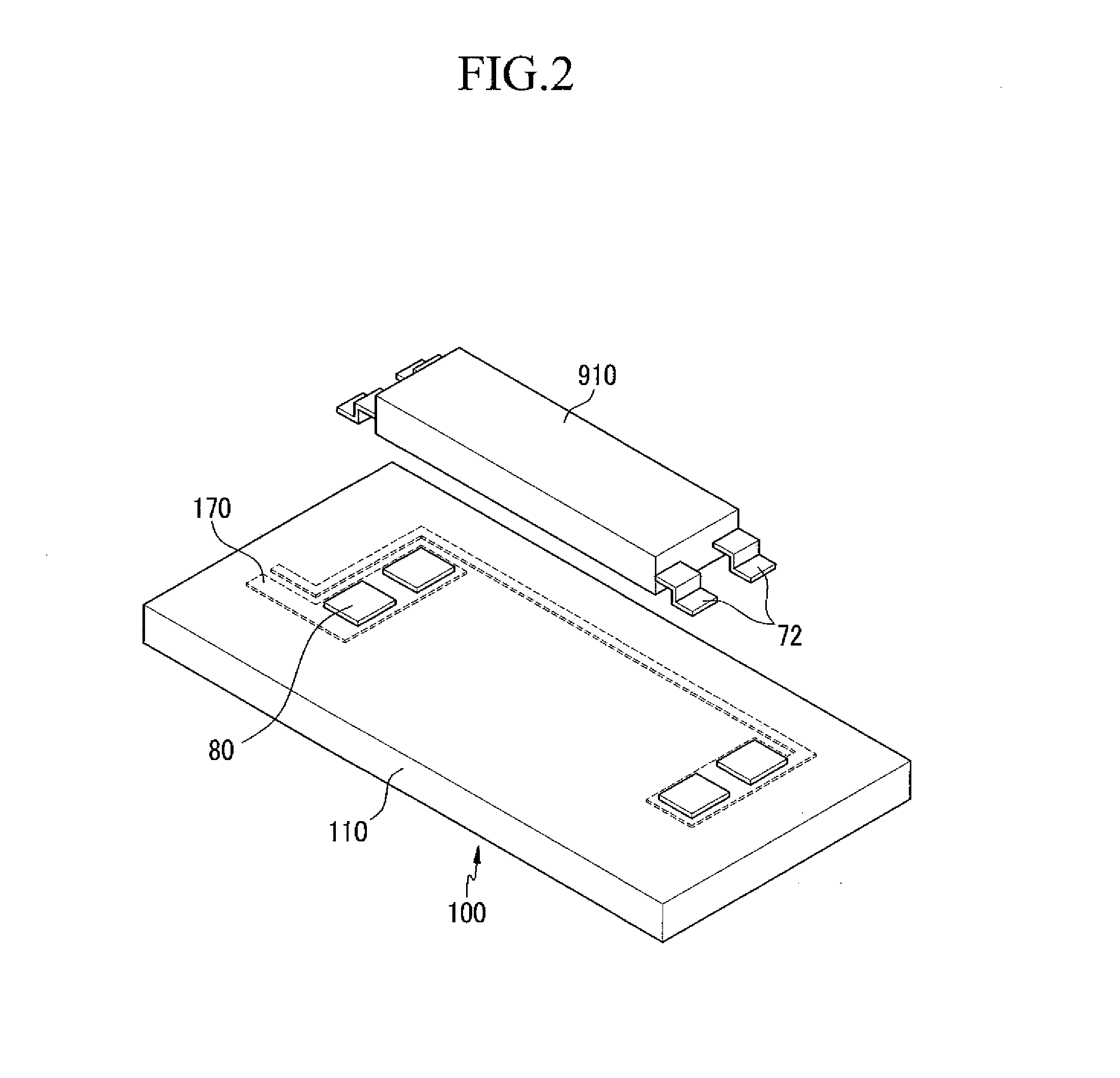

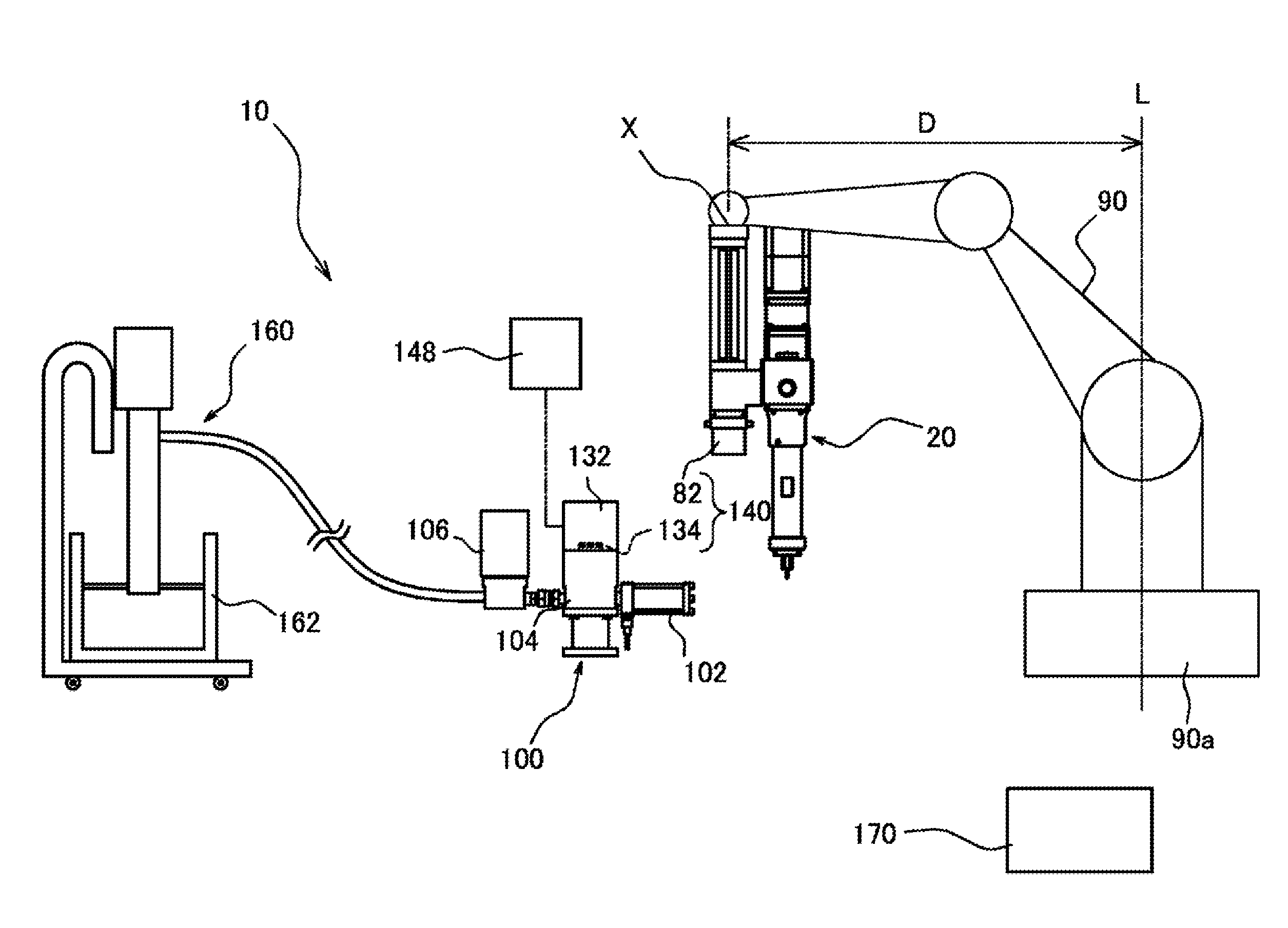

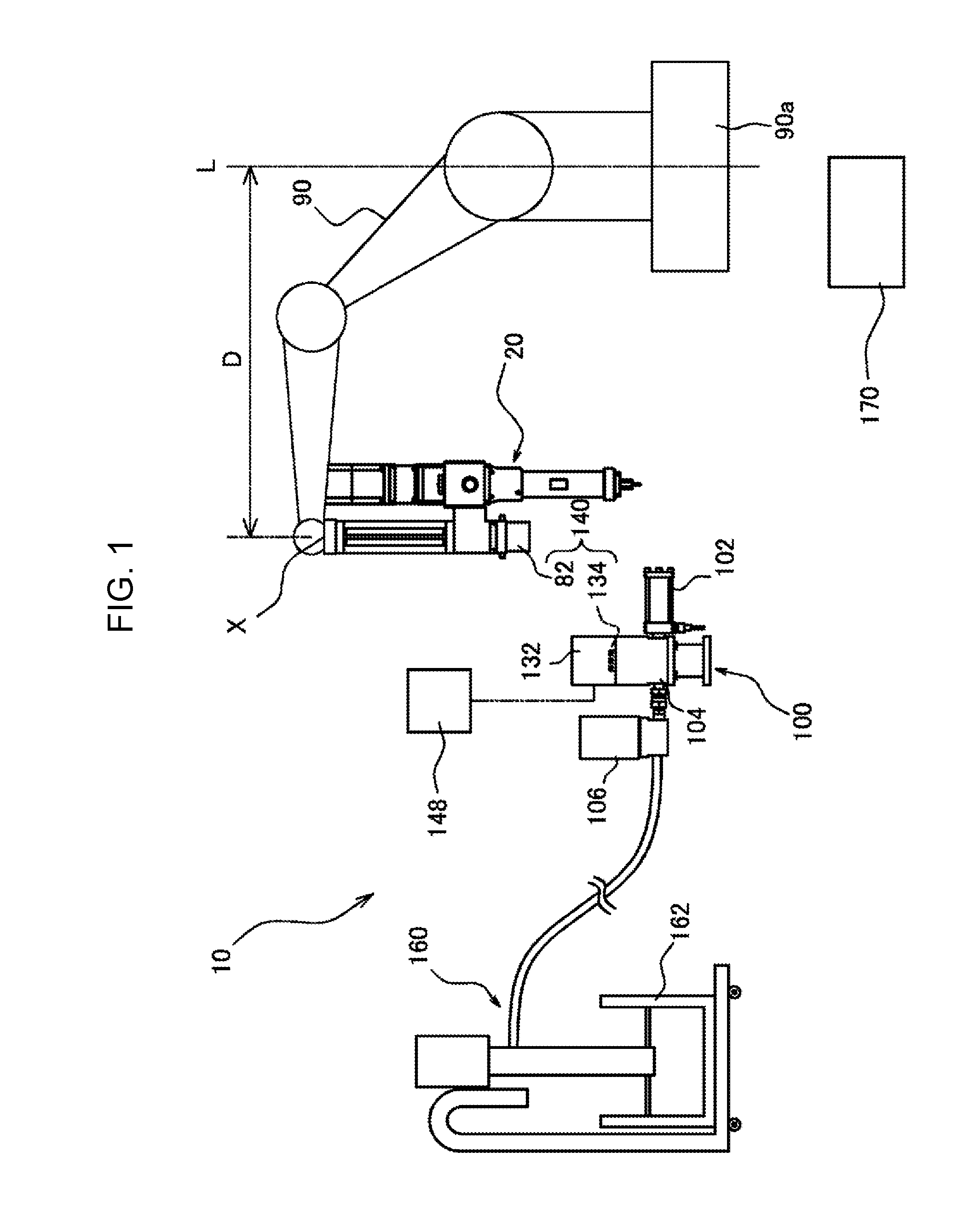

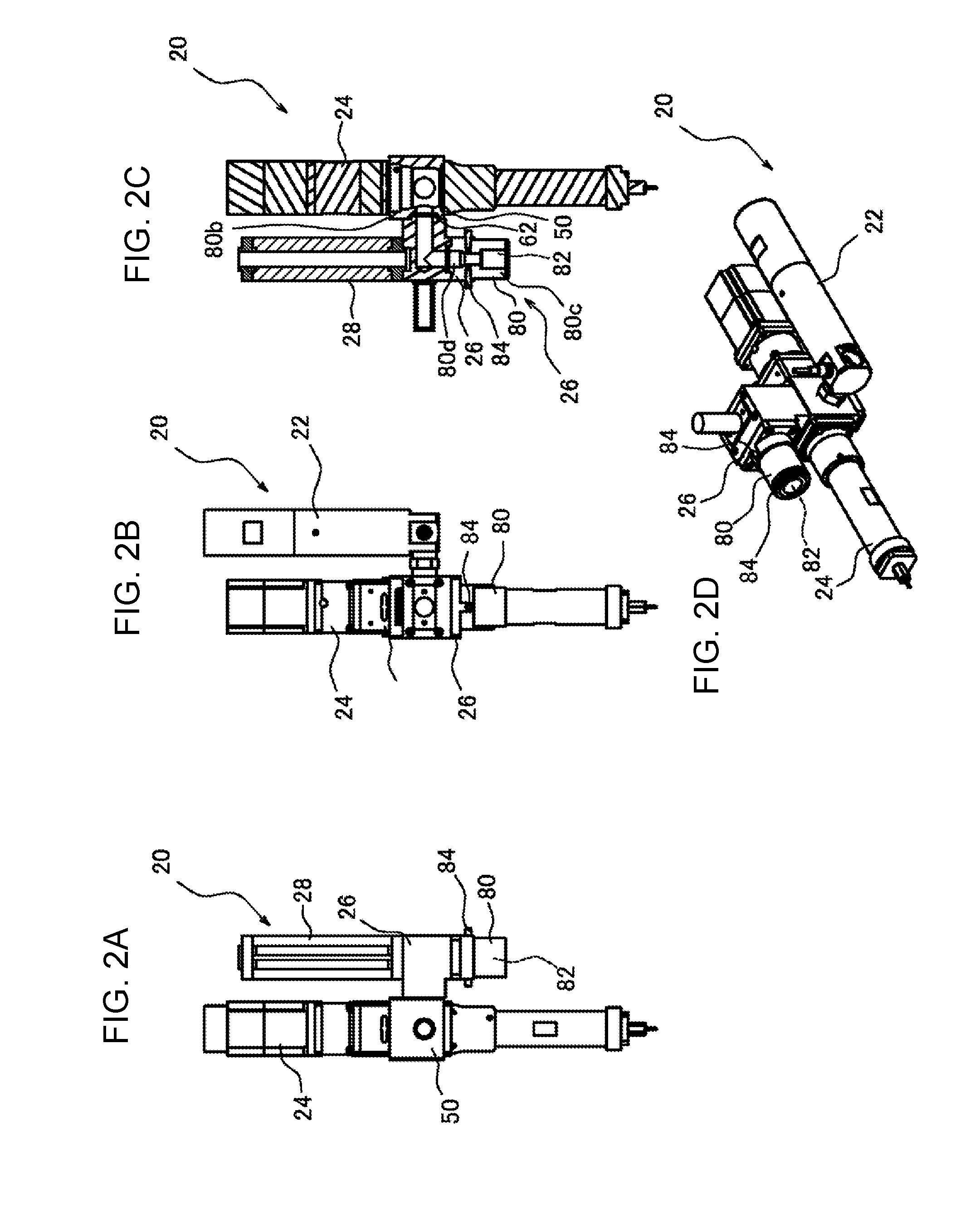

Discharge System

ActiveUS20160279660A1Prevent bad connectionPoor connectionLiquid surface applicatorsSpraying apparatusManipulatorElectrical and Electronics engineering

The purpose is to provide a discharge system that adopts an optimal structure for connecting a discharging device to a refilling device in a substantially aligned fashion by moving the discharging device. A discharge system includes a discharging device, a refilling device, a discharge-side coupler, a refill-side coupler, and a manipulator. The discharge-side coupler is connectable to the refill-side coupler by relatively moving the discharge-side coupler in an axial line N direction of the refill-side coupler and fluid can be refilled from the refilling device side to the discharging device side. A coupling position between the manipulator and the discharging device reaches on the axial line N when connecting the refill-side coupler and the discharge-side coupler.

Owner:HEISHIN ENGINEERING & EQUIPMENT CO LTD

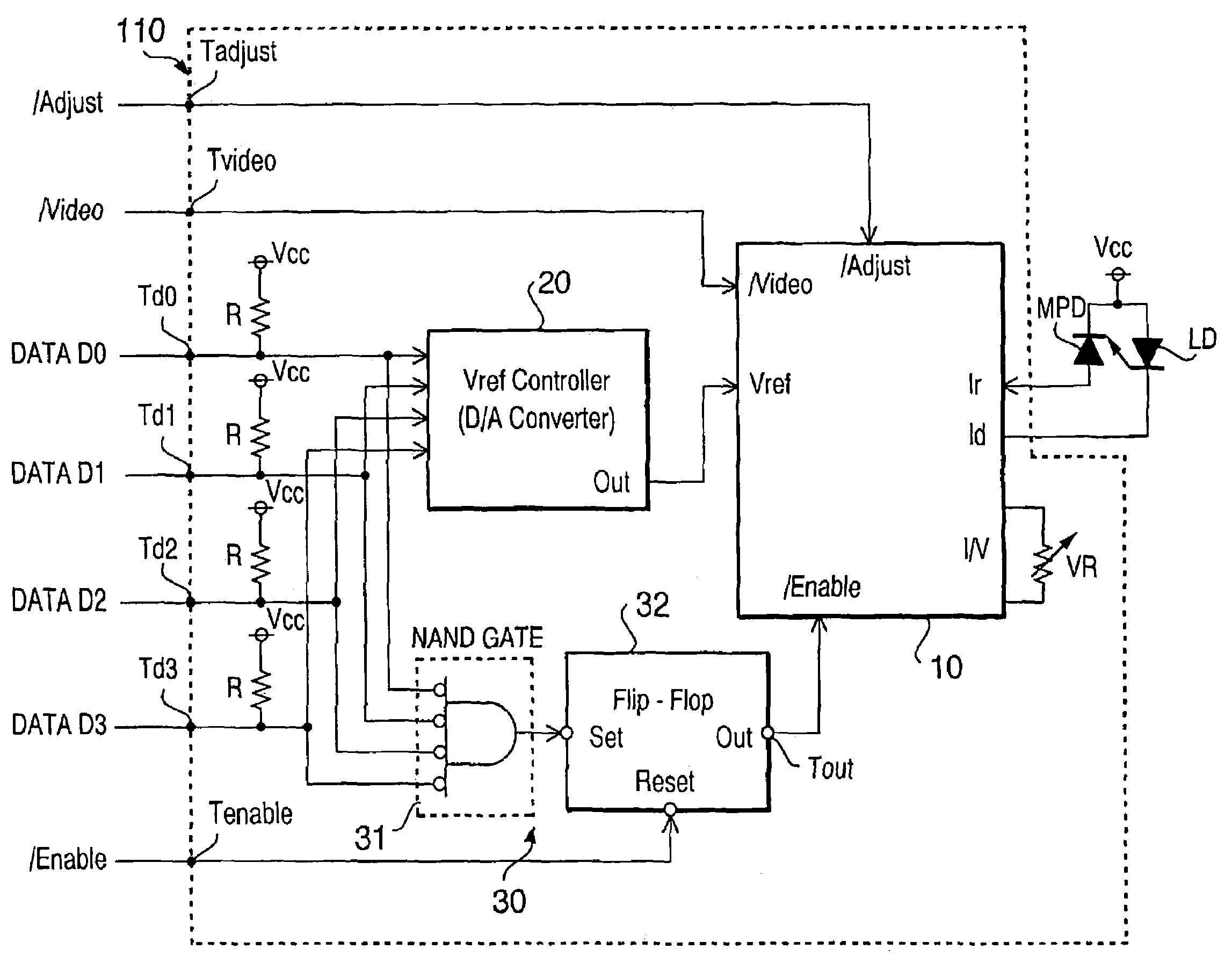

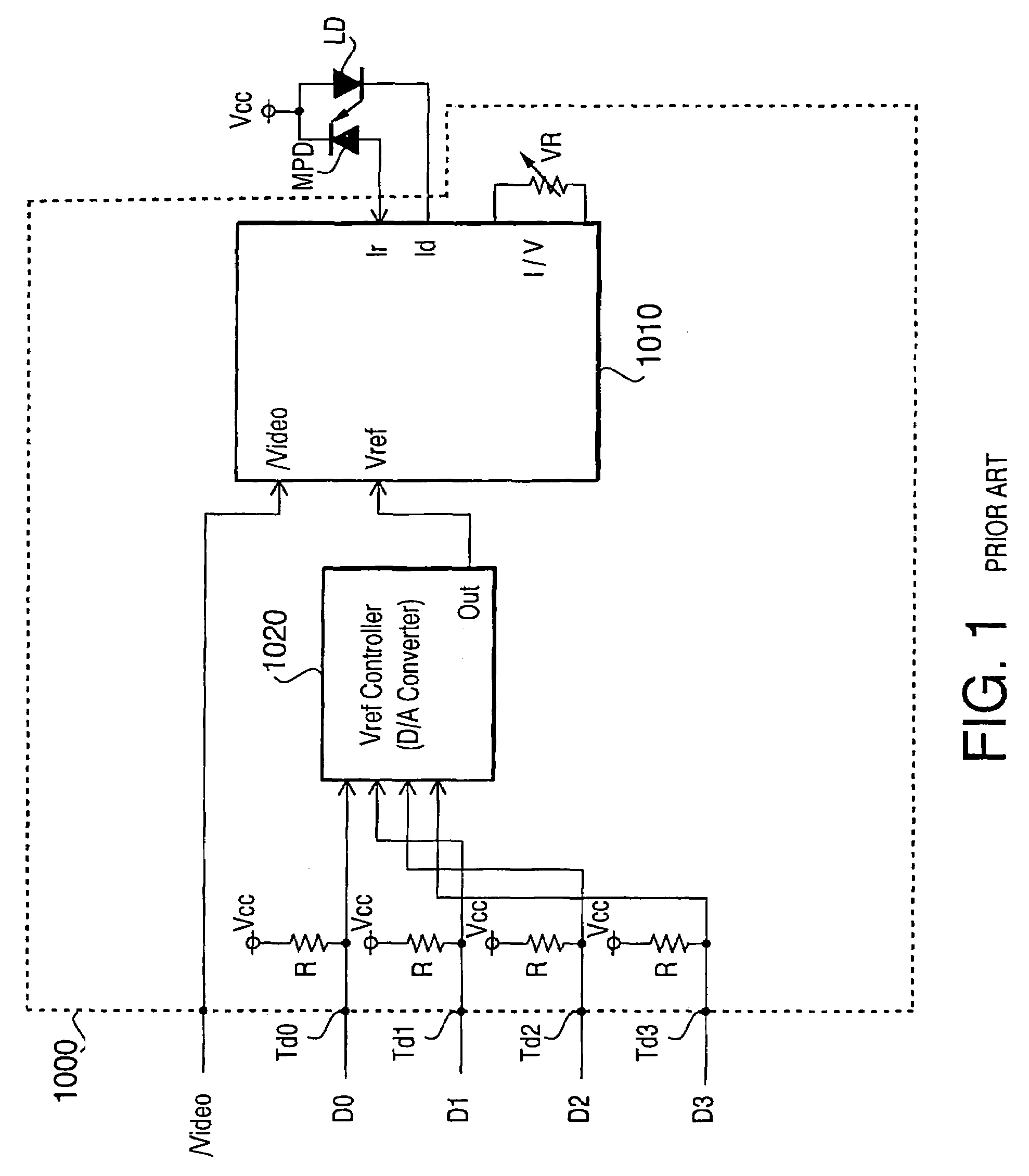

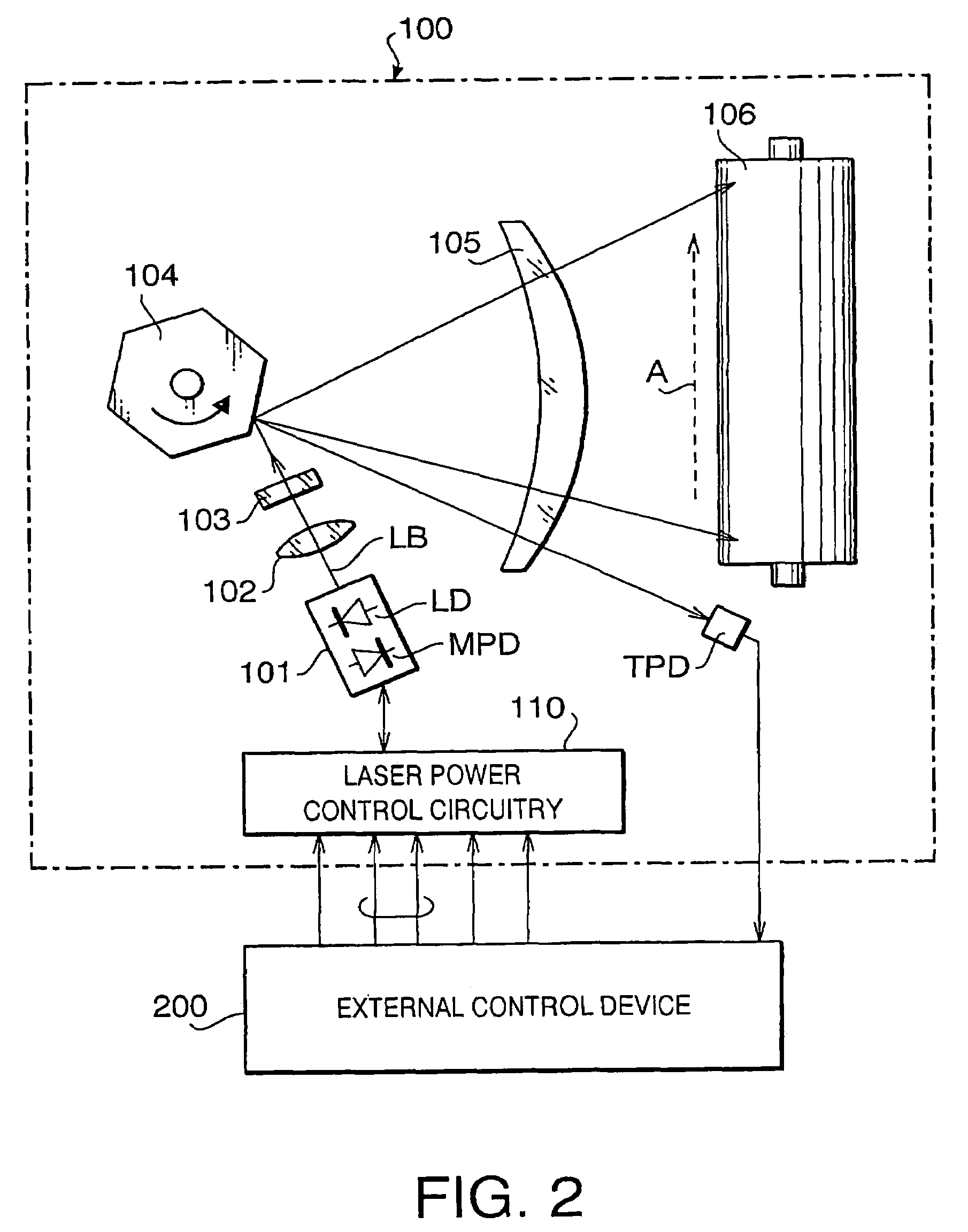

Laser scanning device

InactiveUS7342949B2Poor connectionLaser detailsBeam/ray focussing/reflecting arrangementsDriving currentVoltage generator

A laser scanning device includes a semiconductor laser that emits a laser beam, a laser power detector that detects laser beam power of the semiconductor laser, a reference voltage generator that generates reference voltage for controlling the laser beam power of the semiconductor laser in accordance with a laser power control signal provided from an external device, and a laser driver that compares the reference voltage generated by the reference voltage generator and the laser beam power detected by the laser power detector to control a driving current supplied to the semiconductor laser for emitting the laser beam. The laser scanning device further includes an abnormal condition detector that detects the laser power control signal received by the reference voltage generator. When the detected laser power control signal differs from a predetermined signal, which indicates that the connection between the reference voltage generator and the external device is poor, the abnormal condition detector stops the laser driver from operating.

Owner:ASAHI KOGAKU KOGYO KK

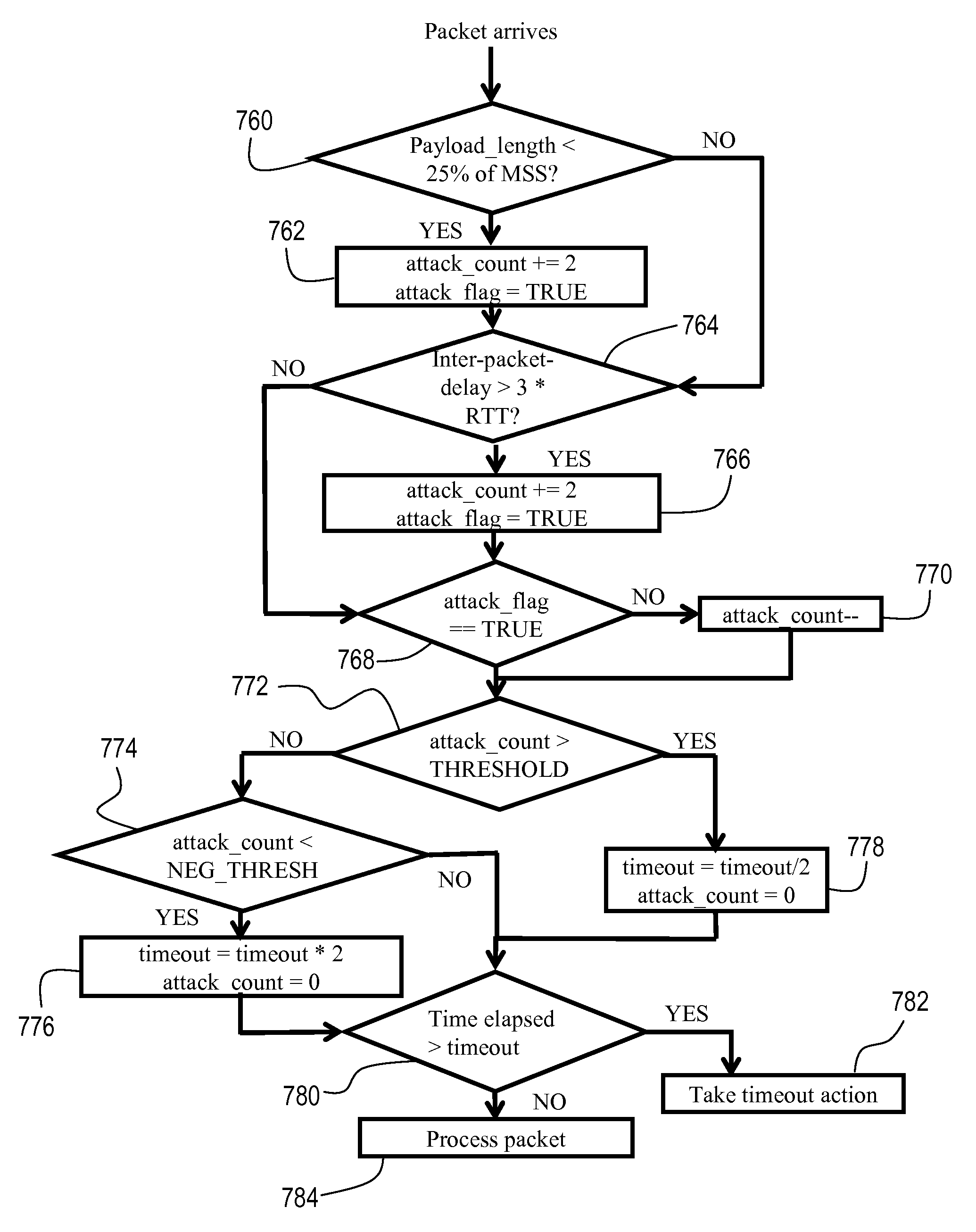

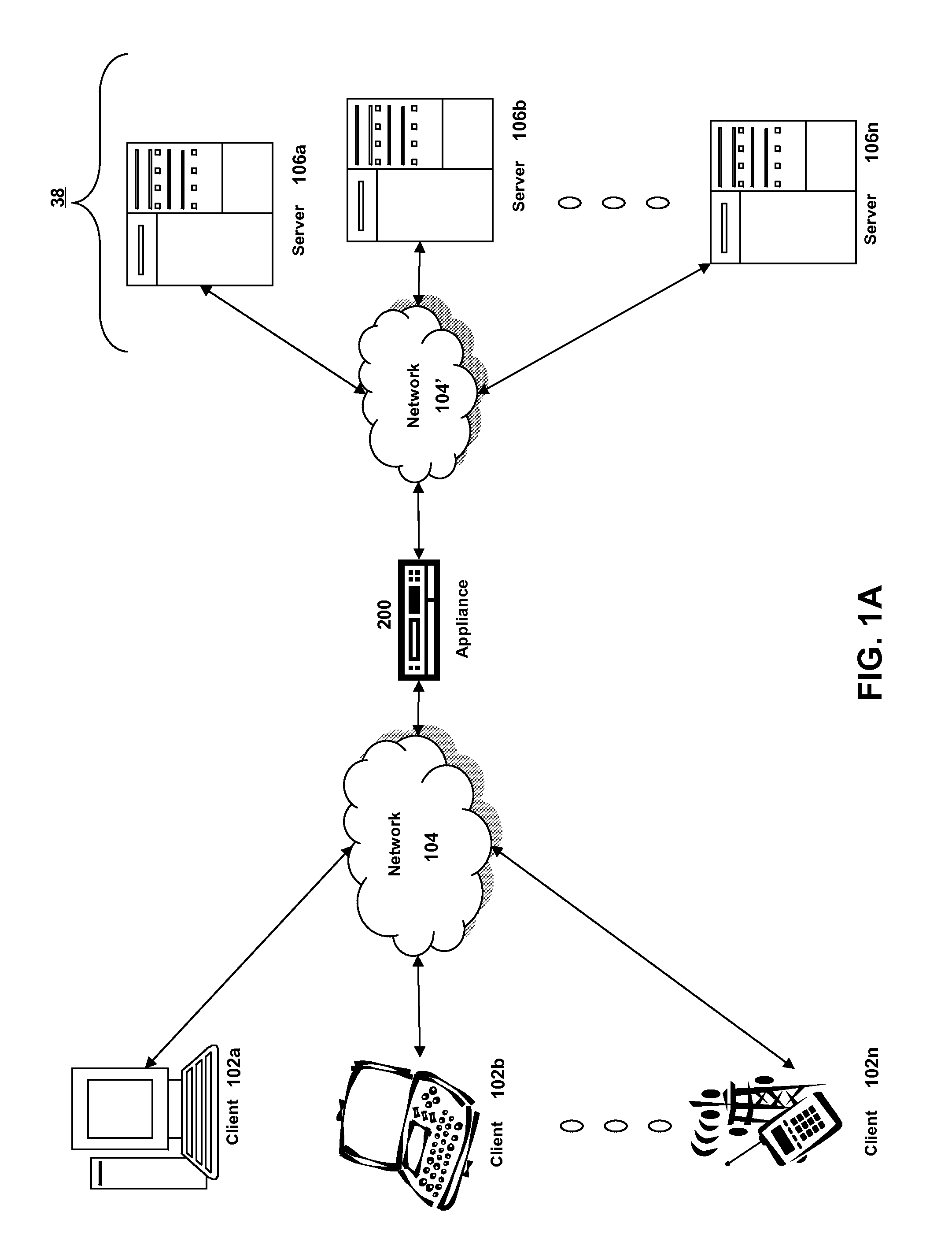

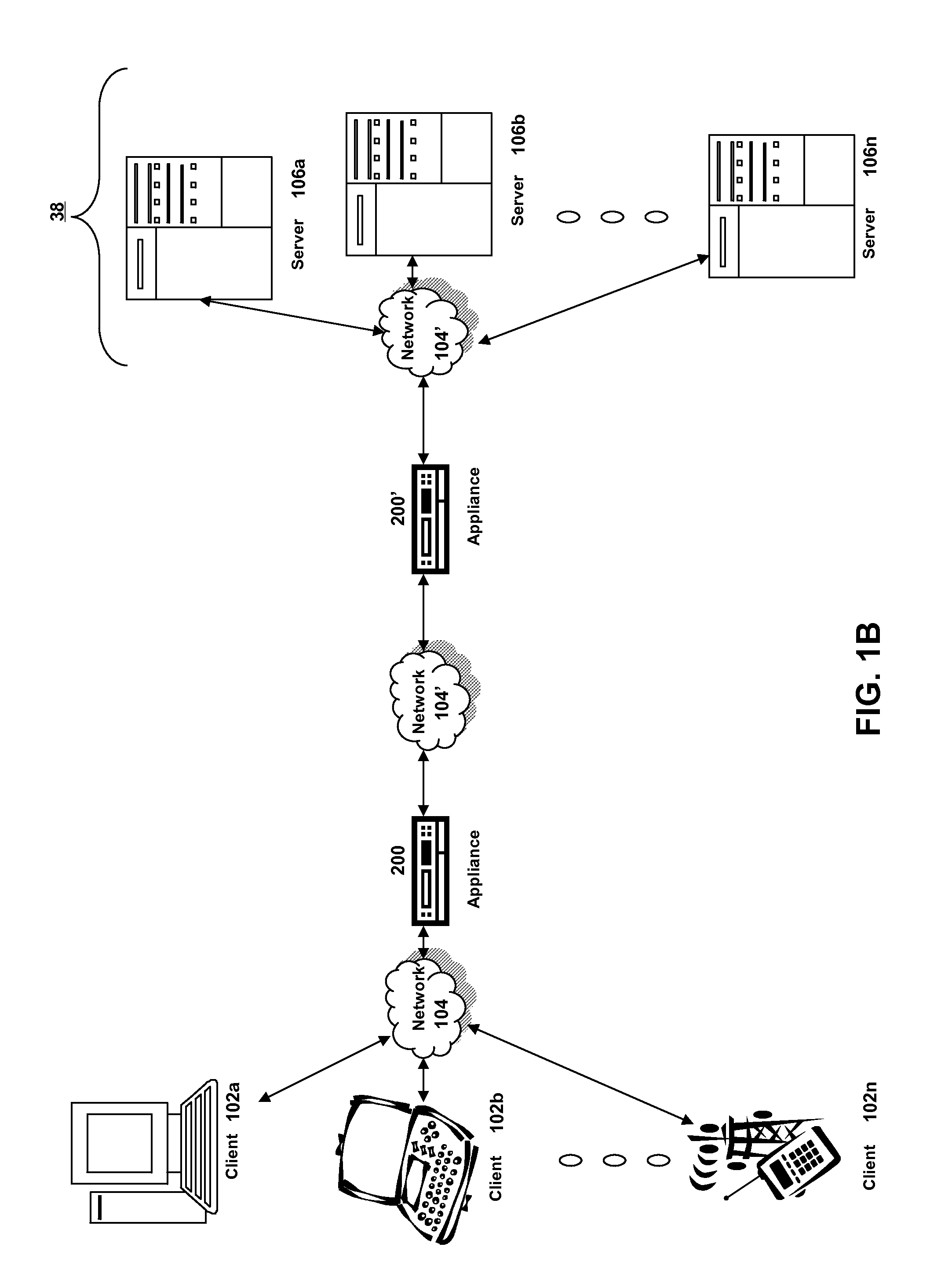

Systems and methods for HTTP-Body DoS attack prevention with adaptive timeout

ActiveUS9055100B2Facilitate mitigating adverse effectKeep for a long timeTransmissionTransport layerClient-side

The present disclosure is directed generally to systems and methods for changing an application layer transaction timeout to prevent Denial of Service attacks. A device intermediary to a client and a server may receive, via a transport layer connection between the device and the client, a packet of an application layer transaction. The device may increment an attack counter for the transport layer connection by a first predetermined amount responsive to a size of the packet being less than a predetermined fraction of a maximum segment size for the transport layer connection. The device may increment the attack counter by a second predetermined amount responsive to an inter-packet-delay between the packet and a previous packet being more than a predetermined multiplier of a round trip time. The device may change a timeout for the application layer transaction responsive to comparing the attack counter to a predetermined threshold.

Owner:CITRIX SYST INC

Socket

ActiveCN106532281ANo bad connection will happenImprove assembly accuracyCoupling device detailsClamped/spring connectionsEngineeringMechanical engineering

There is provided a socket which does not cause connection failure. A socket includes: a base (10); a connection fitting (20) including a bracket (21) and a spring member (30), configured to form pressure springs (35) by dividing the spring member (30) into two in a width direction by a slit (28,34) provided to the spring member (30), and assembled to an upper surface (11) of the base (10); and a case cover (40) configured to fit to the base (10) and to cover the connection fitting (20). The pressure springs (35) of the spring member (30) are pressed and elastically deformed by an operation driver (50) inserted through an operation hole (44) provided to the case cover (40), to sandwich between the bracket (21) and the pressure springs (35) a lead inserted through an insertion hole (45) provided to the case cover (40). Particularly, a guide partition wall (47) configured to engage with the slit (28,34) of the spring member (30) is integrally molded with an inner surface of the case cover (40).

Owner:ORMON CORP

Semiconductor encapsulation adhesive composition, semiconductor encapsulation film-like adhesive, method for producing semiconductor device and semiconductor device

InactiveUS20140015149A1Easy to diffuseEasy to migrateSemiconductor/solid-state device detailsSolid-state devicesEpoxyAdhesive

A semiconductor encapsulation adhesive composition comprising (a) an epoxy resin, (b) a curing agent and (c) an antioxidant.

Owner:HITACHI CHEM CO LTD

Charged-particle beam lens

InactiveUS8710455B2Improve the immunityPoor connectionStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsHigh resistanceSemiconductor

A charged-particle beam lens includes a plate-like anode, a plate-like cathode, and an insulator disposed between the anode and the cathode. The insulator, the anode, and the cathode have a passage portion through which a charged beam is passed. A high-resistance film is formed on an inner side of the insulator, the inner side forming the passage portion, or an outermost side of insulator, and the anode and the cathode are electrically connected together via the high-resistance film. The anode and the high-resistance film, and the cathode and the high-resistance film each contain the same metal or semiconductor element and have different resistant values. This suppresses electric field concentration due to an increase in resistance and poor connection at the interface between the anode and the cathode and the high-resistance film or at the interface between the electroconductive film and the high-resistance film, thus suppressing generation of discharge.

Owner:CANON KK

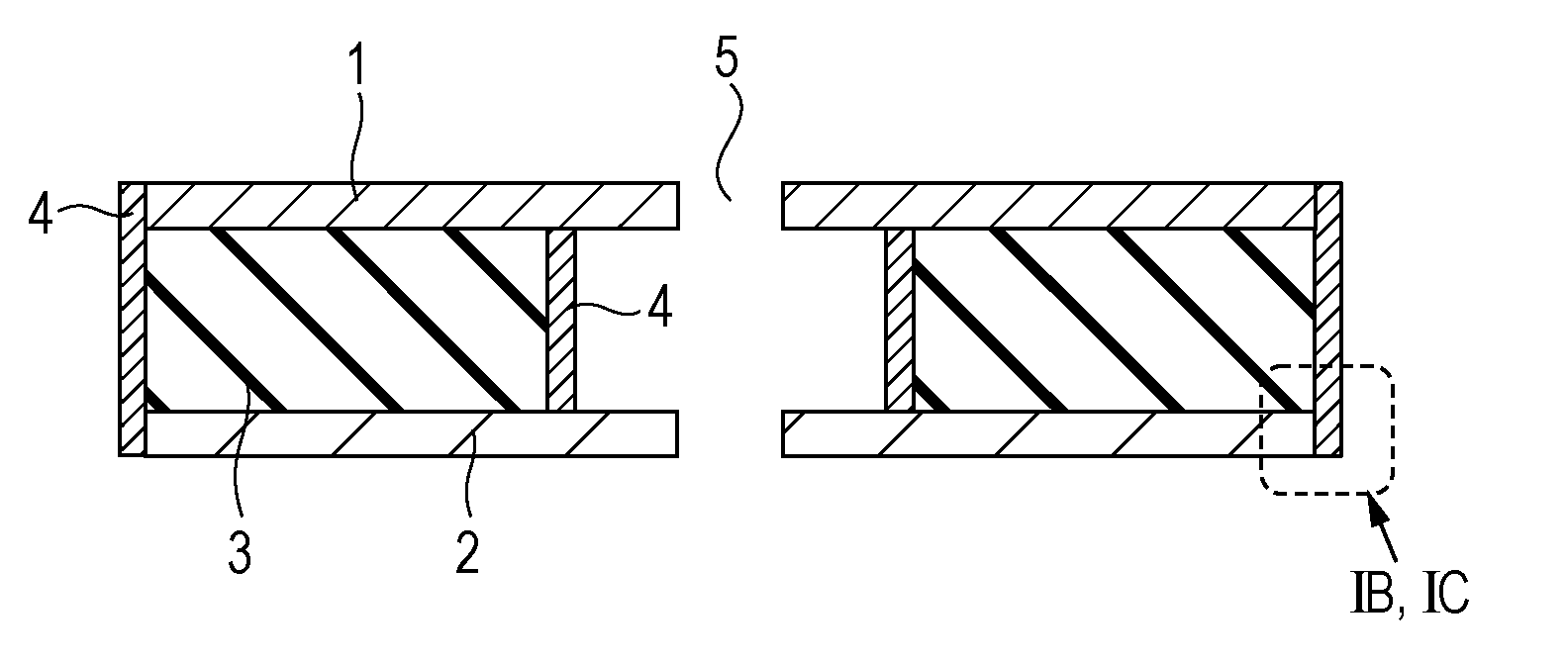

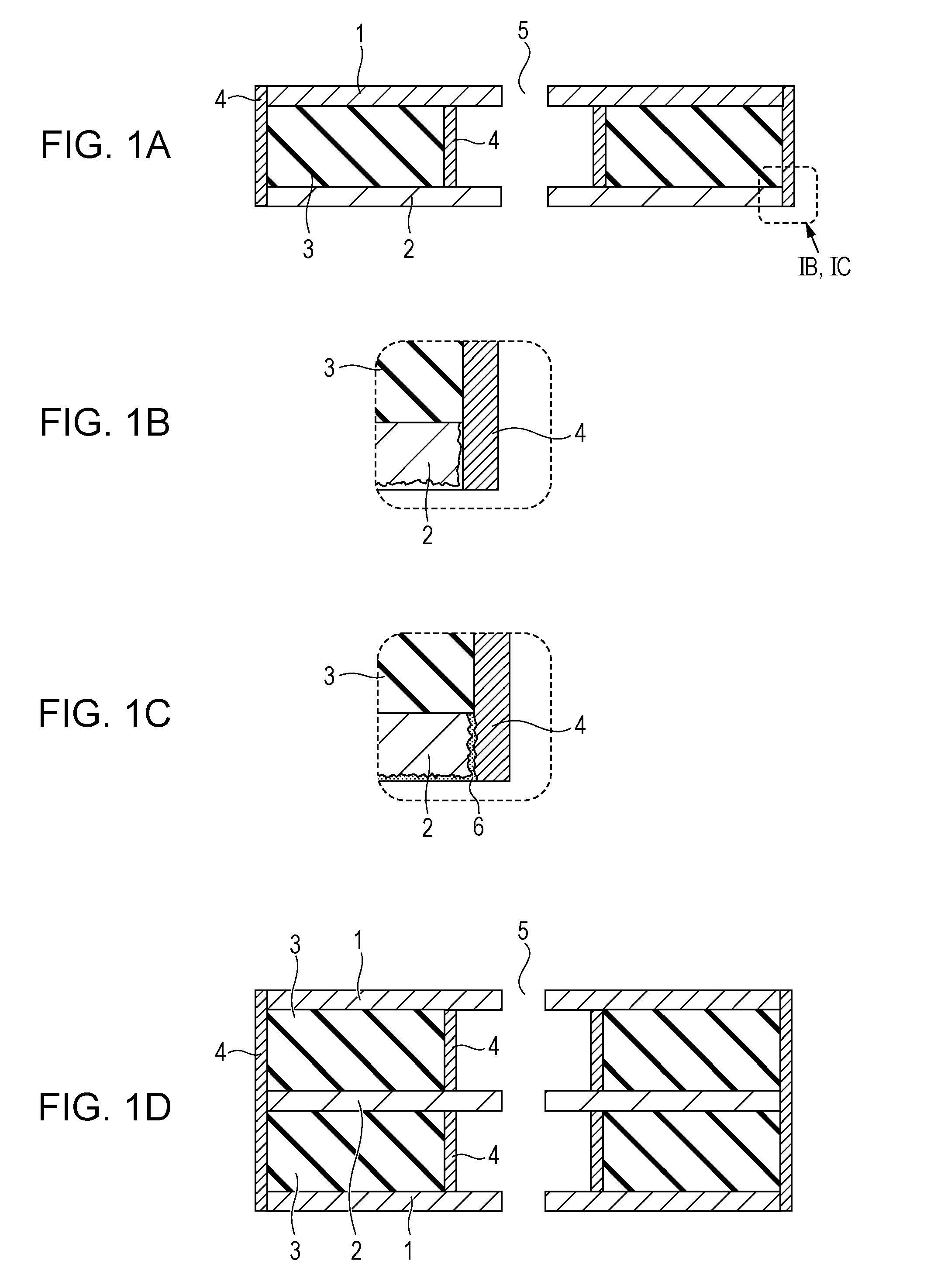

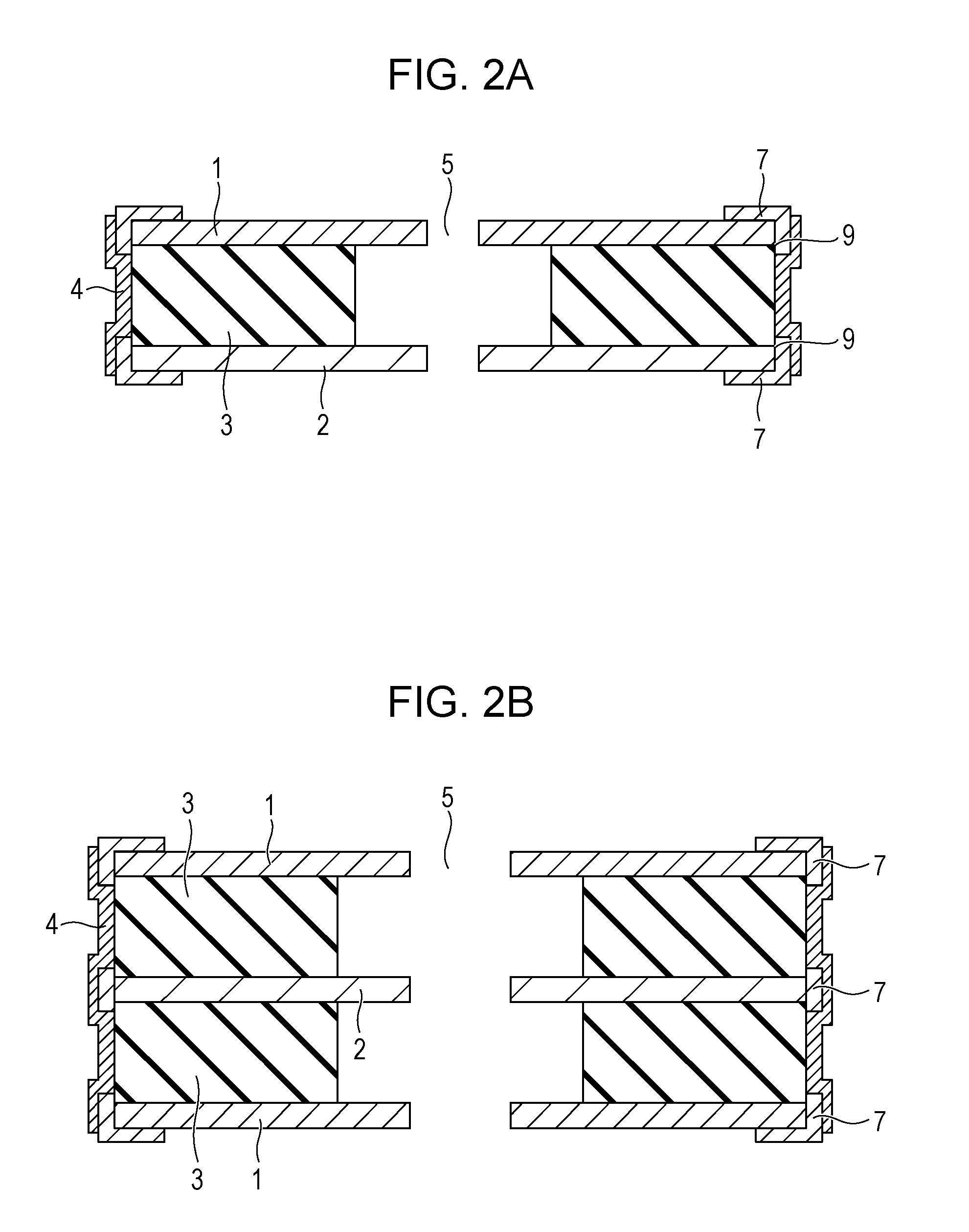

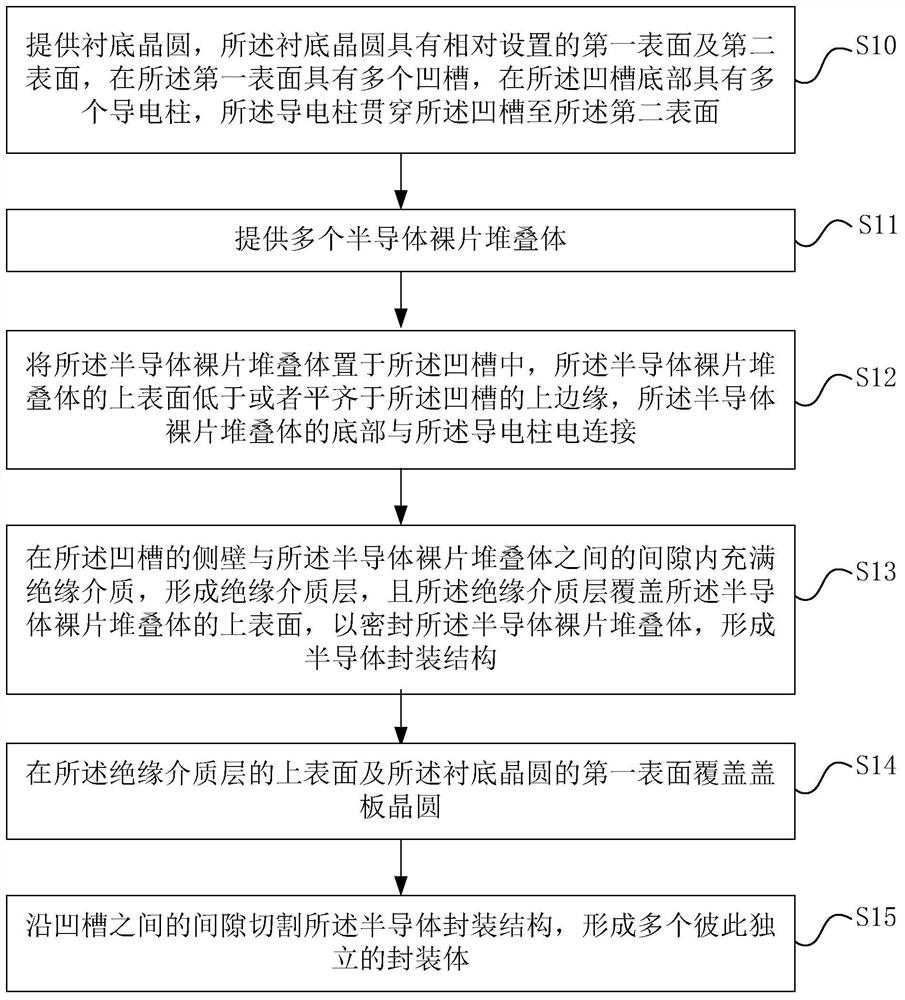

Semiconductor packaging method, semiconductor packaging structure and packaging body

PendingCN112670249AImprove stabilityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectrical connection

The invention provides a semiconductor packaging method, a semiconductor packaging structure and a packaging body. The packaging method comprises the following steps: providing a substrate wafer provided with a first surface and a second surface, wherein the first surface and the second surface are opposite to each other, a plurality of grooves are formed in the first surface, a plurality of conductive columns are arranged at the bottoms of the grooves, and the conductive column penetrates through the bottom of the groove to the second surface; providing a plurality of semiconductor bare chip stacks; placing the semiconductor bare chip stacks in the groove, wherein the upper surface of the semiconductor bare chip stack is lower than or flush with the upper edge of the groove, and the bottom of the semiconductor bare chip stack is electrically connected with the conductive columns; and filling a gap between the side wall of the groove and the semiconductor bare chip stack with an insulating medium to form an insulating medium layer, and covering the upper surface of the semiconductor bare chip stack with the insulating medium layer to seal the semiconductor bare chip stack so as to form the semiconductor packaging structure. The semiconductor packaging structure has the advantages that the formed semiconductor packaging structure is low in packaging height, high in stability, high in reliability and low in warping degree.

Owner:CHANGXIN MEMORY TECH INC

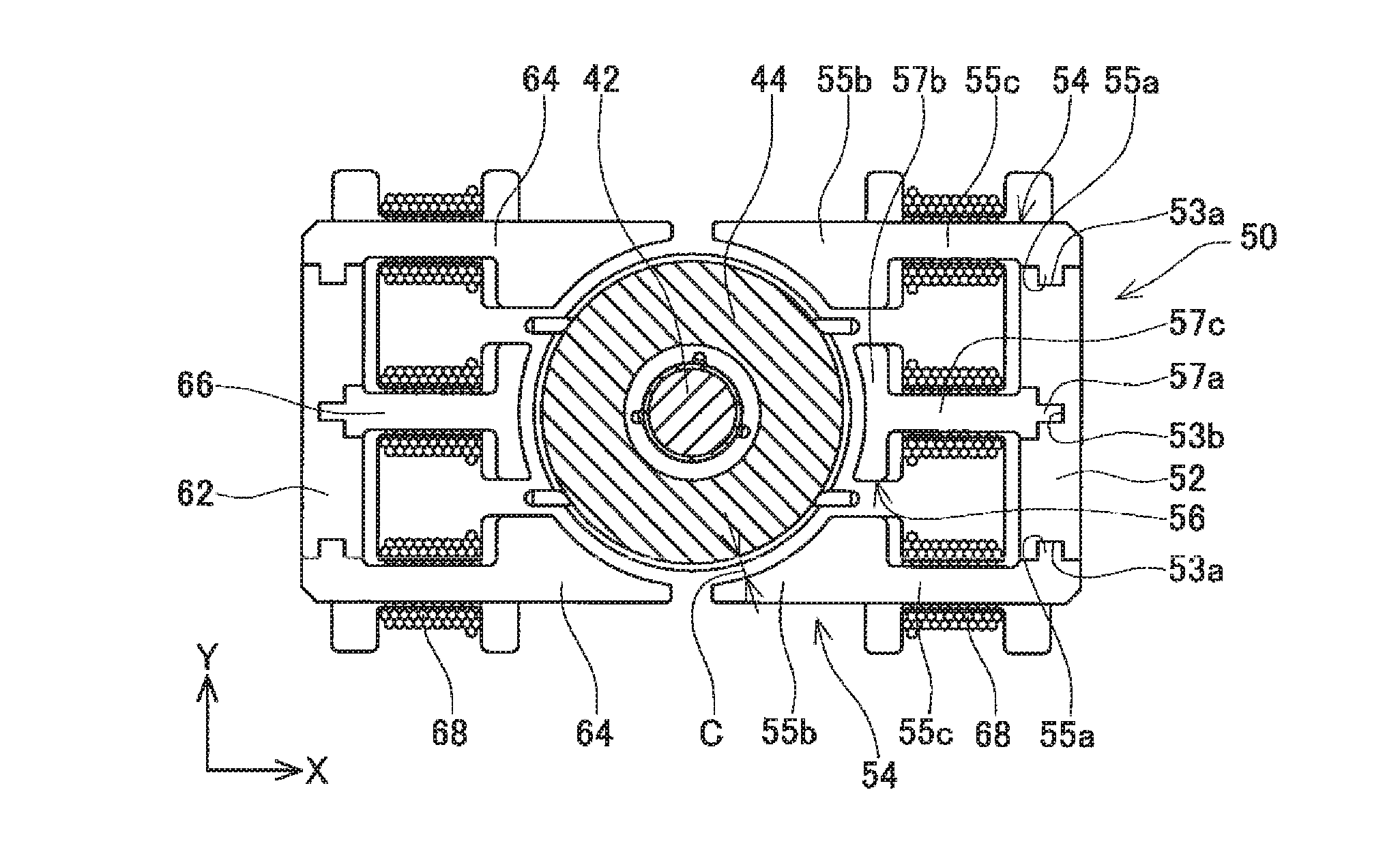

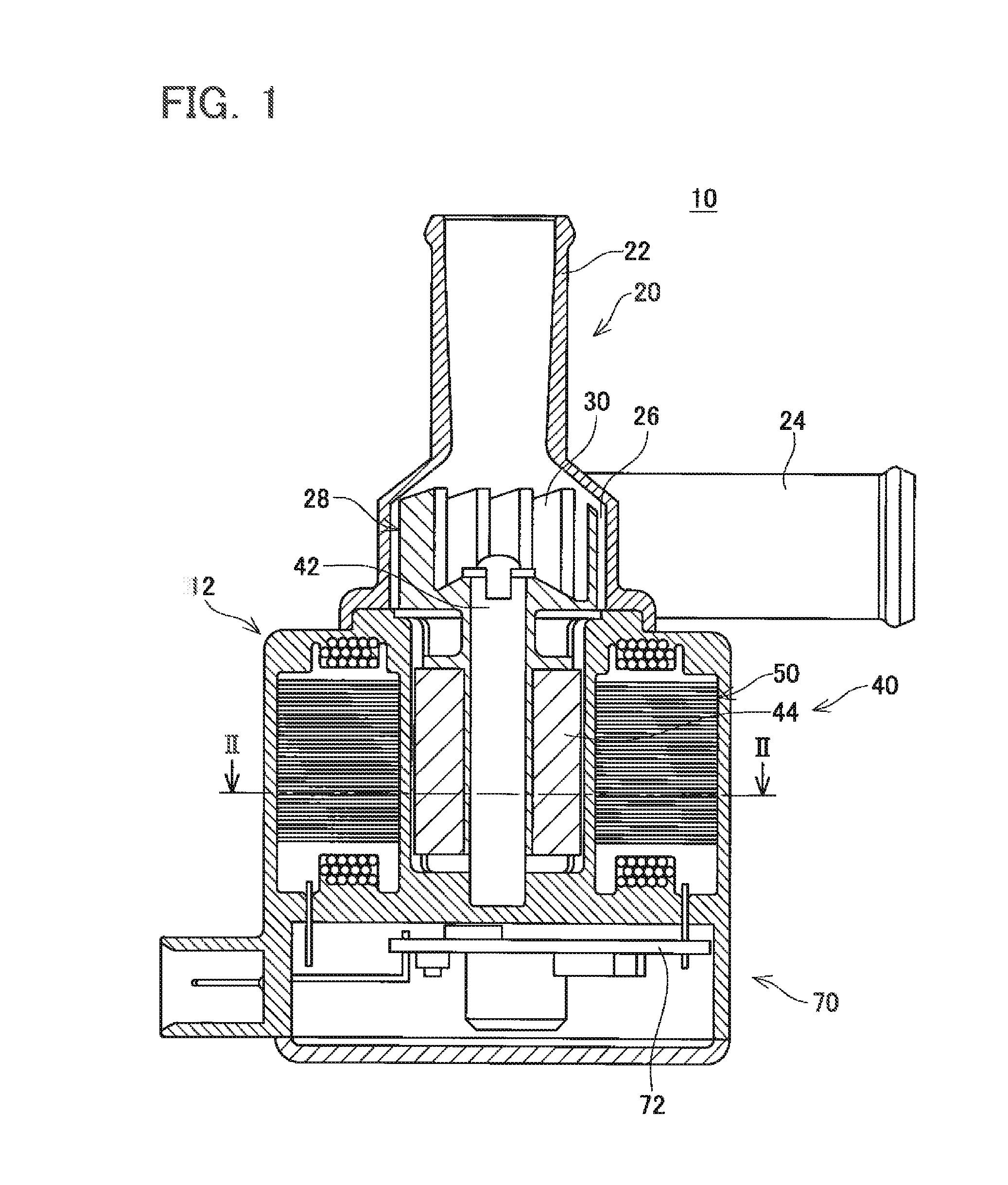

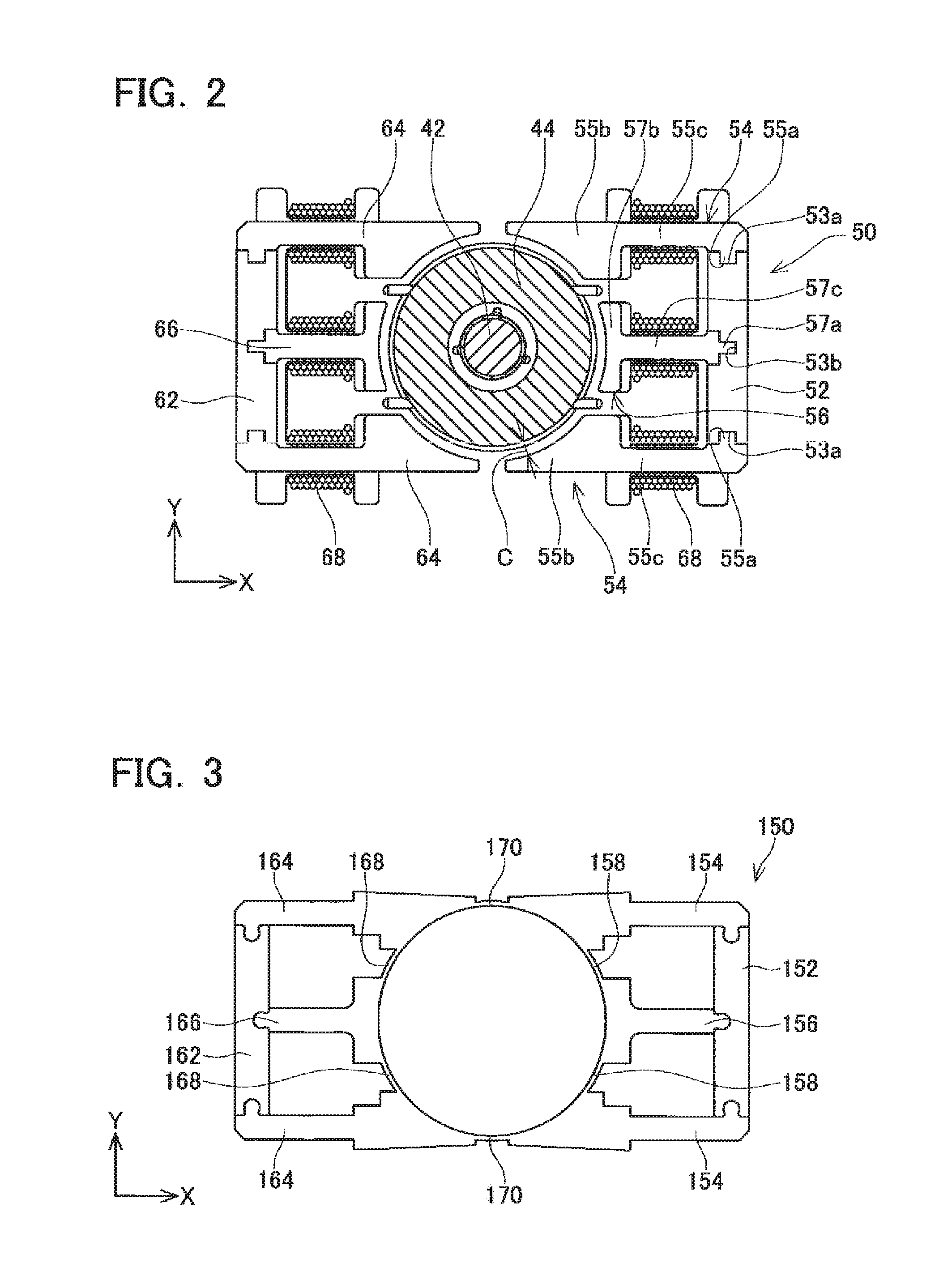

Brushless motor and electric pump

InactiveUS20130089444A1Poor connectionNot consistentWindingsMagnetic circuit stationary partsEngineeringBrushless motors

A brushless motor includes a rotor and a stator. The stator includes yokes and a plurality of teeth. Base ends of the teeth are connected to the yokes, and tip ends of the teeth oppose an outside surface of the rotor with an interval in between. The plurality of teeth include a pair of first teeth connected to both ends of the yokes and second teeth connected to centers of the yokes. The first teeth are connected to the yokes in a first direction, and the second teeth are connected to the yokes in a second direction which is different from the first direction.

Owner:AISAN IND CO LTD