Semiconductor packaging method, semiconductor packaging structure and packaging body

A packaging method and packaging structure technology, which are applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, and semiconductor/solid-state device components, etc., can solve the problem of higher packaging height of electronic components, affecting the structural performance of the package, and the reliability of the package structure. problems such as lowering, to achieve the effect of reducing height, avoiding dislocation, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Specific implementations of the semiconductor packaging method, semiconductor packaging structure, and packaging body provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

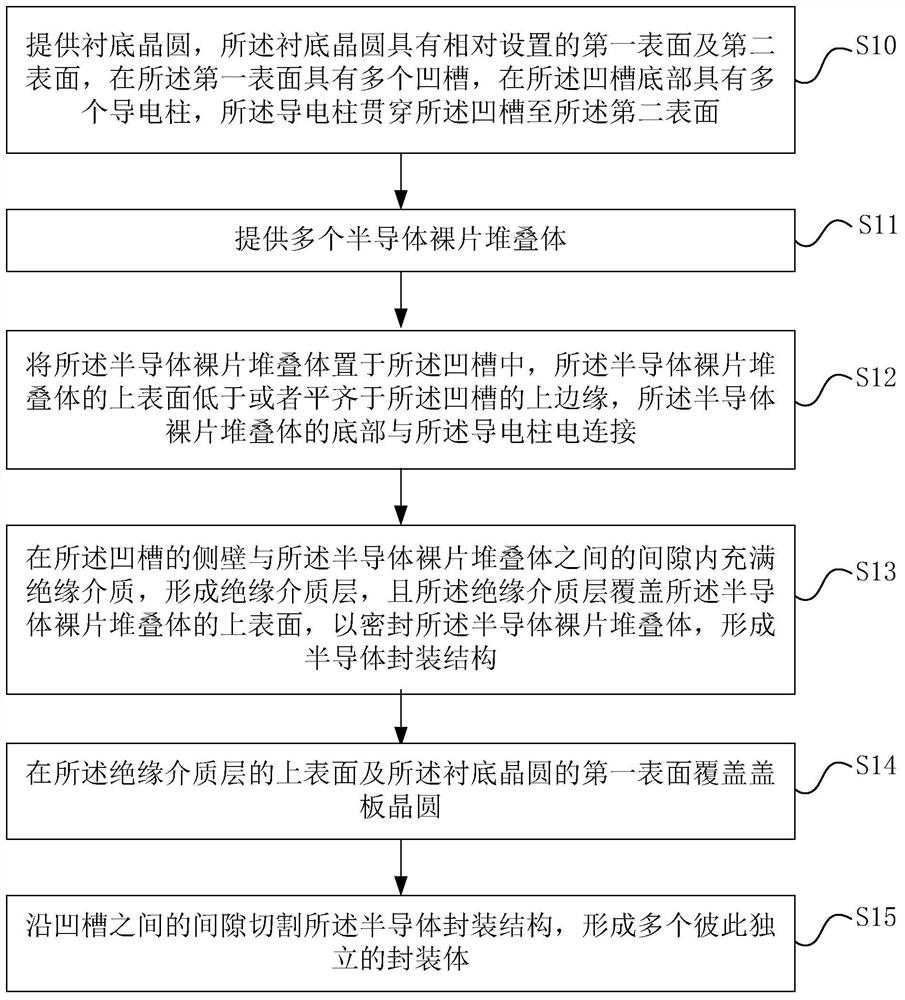

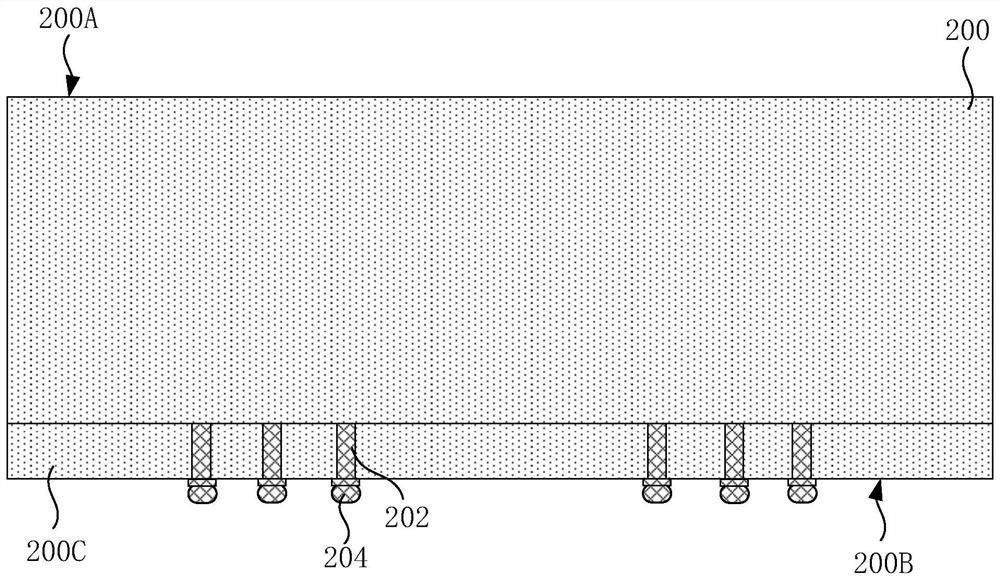

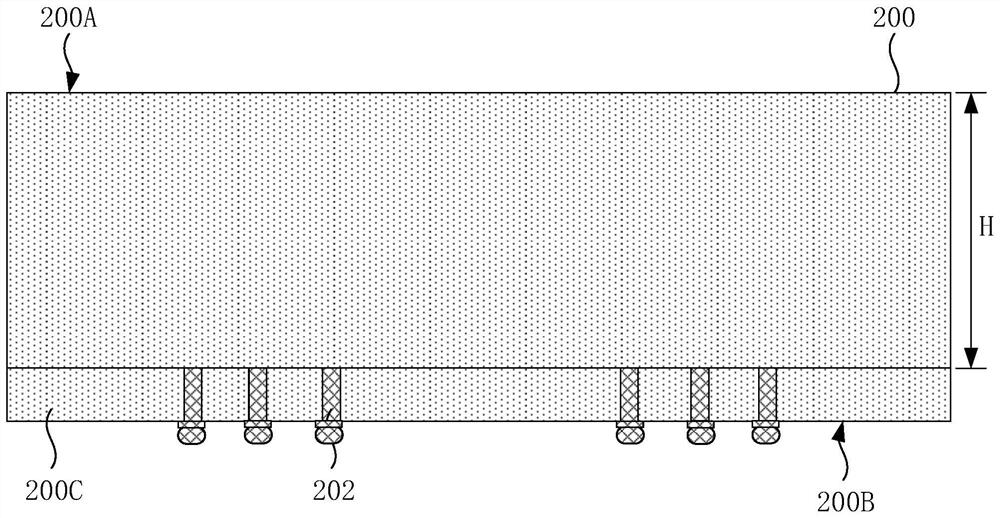

[0033] figure 1 It is a schematic diagram of the steps of a specific embodiment of the semiconductor packaging method of the present invention. see figure 1 , the semiconductor packaging method includes the following steps: step S10, providing a substrate wafer, the substrate wafer has a first surface and a second surface oppositely arranged, there are a plurality of grooves on the first surface, and The bottom of the groove has a plurality of conductive pillars, and the conductive pillars pass through the bottom of the groove to the second surface; step S11, providing a plurality of semiconductor die stacks; step S12, stacking the semiconductor die The body is placed in the groove, the upper surface of the semiconductor die stack is low...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More