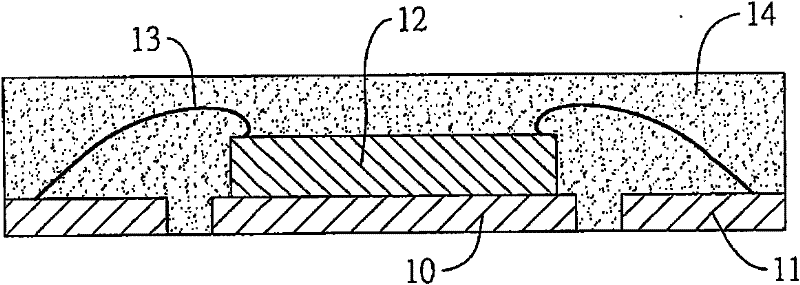

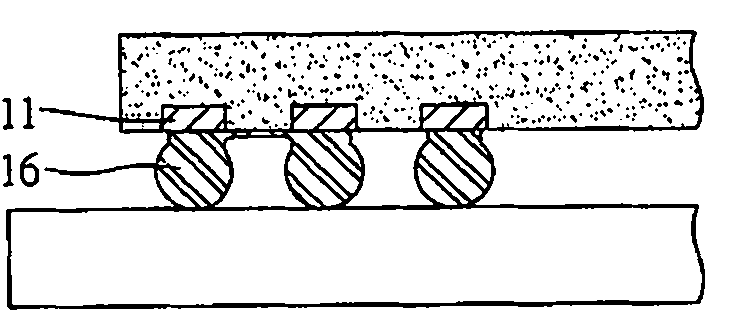

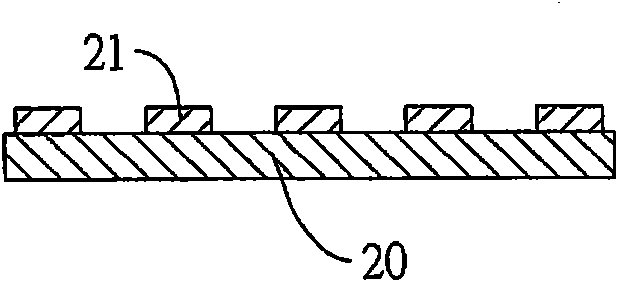

Semiconductor package with electrical connection structure and manufacturing method thereof

An electrical connection and semiconductor technology, applied in the field of packaging structure and its manufacturing method, can solve the problems of increased manufacturing cost, different thermal expansion coefficients, long gold wires 23, etc., to reduce the length of the bonding wire, improve the adhesion strength, and avoid scratching. effect of injury

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] Embodiments of the present invention are described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification.

[0057] It should also be noted that the "top surface" and "bottom surface" described in this specification are not absolute spatial concepts, but change with the spatial relationship of the constituent elements. In the case of semiconductor packages, the "top surface" is the "bottom surface" and the "bottom surface" is the "top surface". Therefore, the use of the term "top surface" and "bottom surface" is to illustrate the connection relationship between the constituent elements in the semiconductor package provided by the present invention, so that the semiconductor package provided by the present invention is within the equivalent range There are reasonable changes and substitutions, but not intended to limit the scope of the prese...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More