Patents

Literature

280results about How to "Good etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

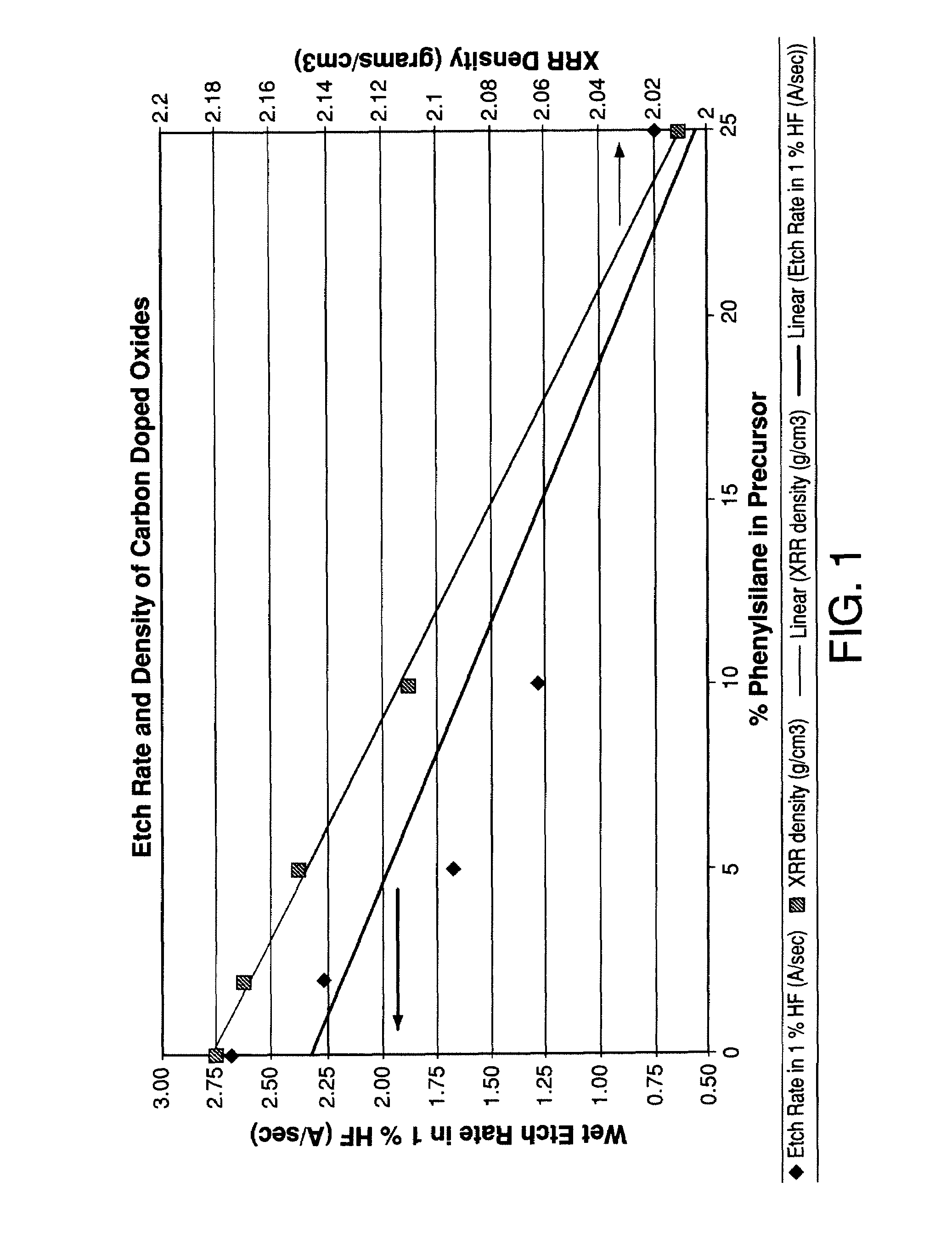

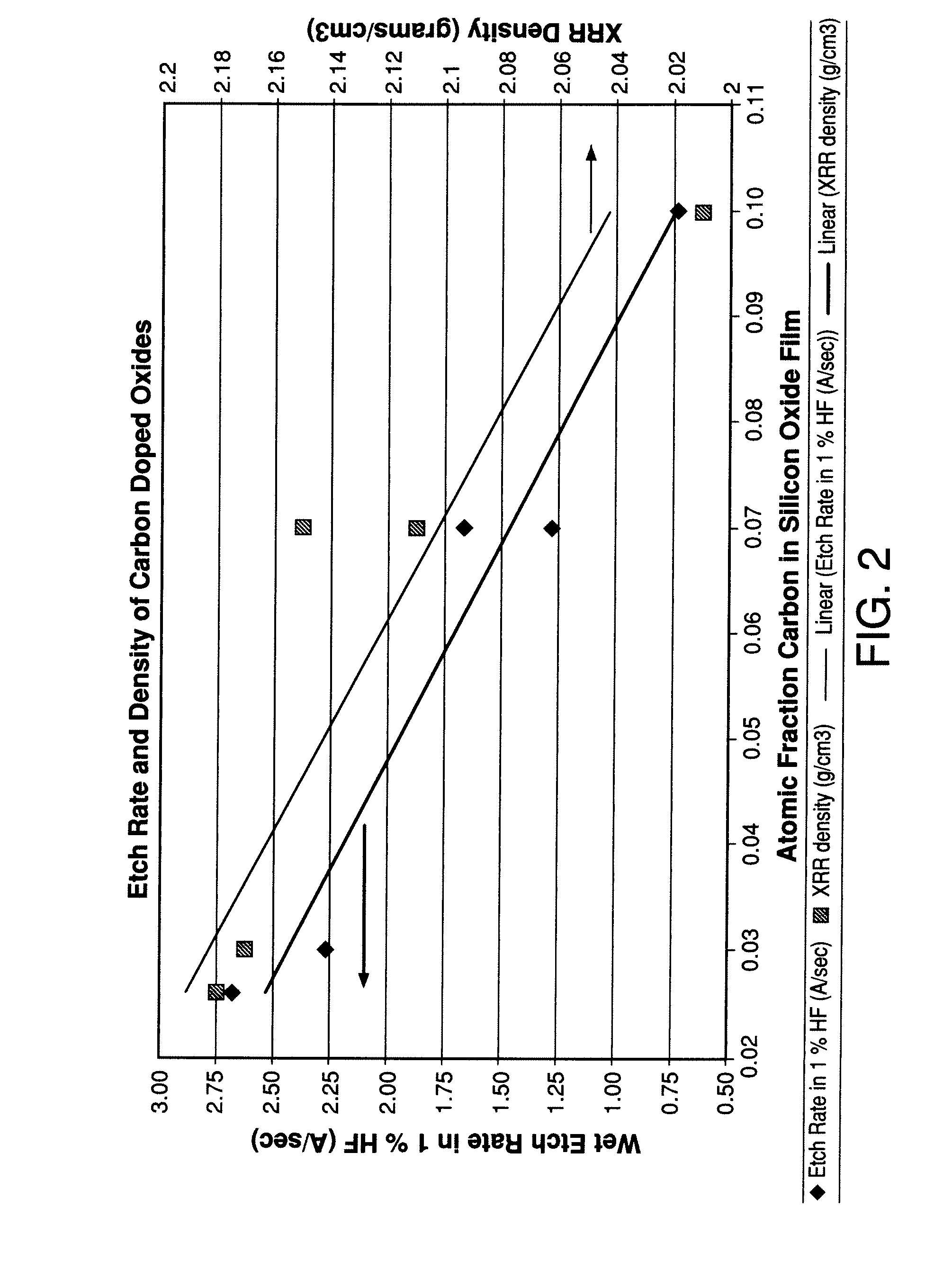

Organosilane compounds for modifying dielectrical properties of silicon oxide and silicon nitride films

InactiveUS20080124946A1Excellent etch resistanceIncreasing flow ratioSemiconductor/solid-state device manufacturingChemical vapor deposition coatingSilicon oxideChemical Modifier

The present invention discloses a process for depositing a carbon containing silicon oxide film, or a carbon containing silicon nitride film having enhanced etch resistance. The process comprises using a silicon containing precursor, a carbon containing precursor and a chemical modifier. The present invention also discloses a process for depositing a silicon oxide film, or silicon nitride film having enhanced etch resistance comprising using an organosilane precursor and a chemical modifier.

Owner:VERSUM MATERIALS US LLC

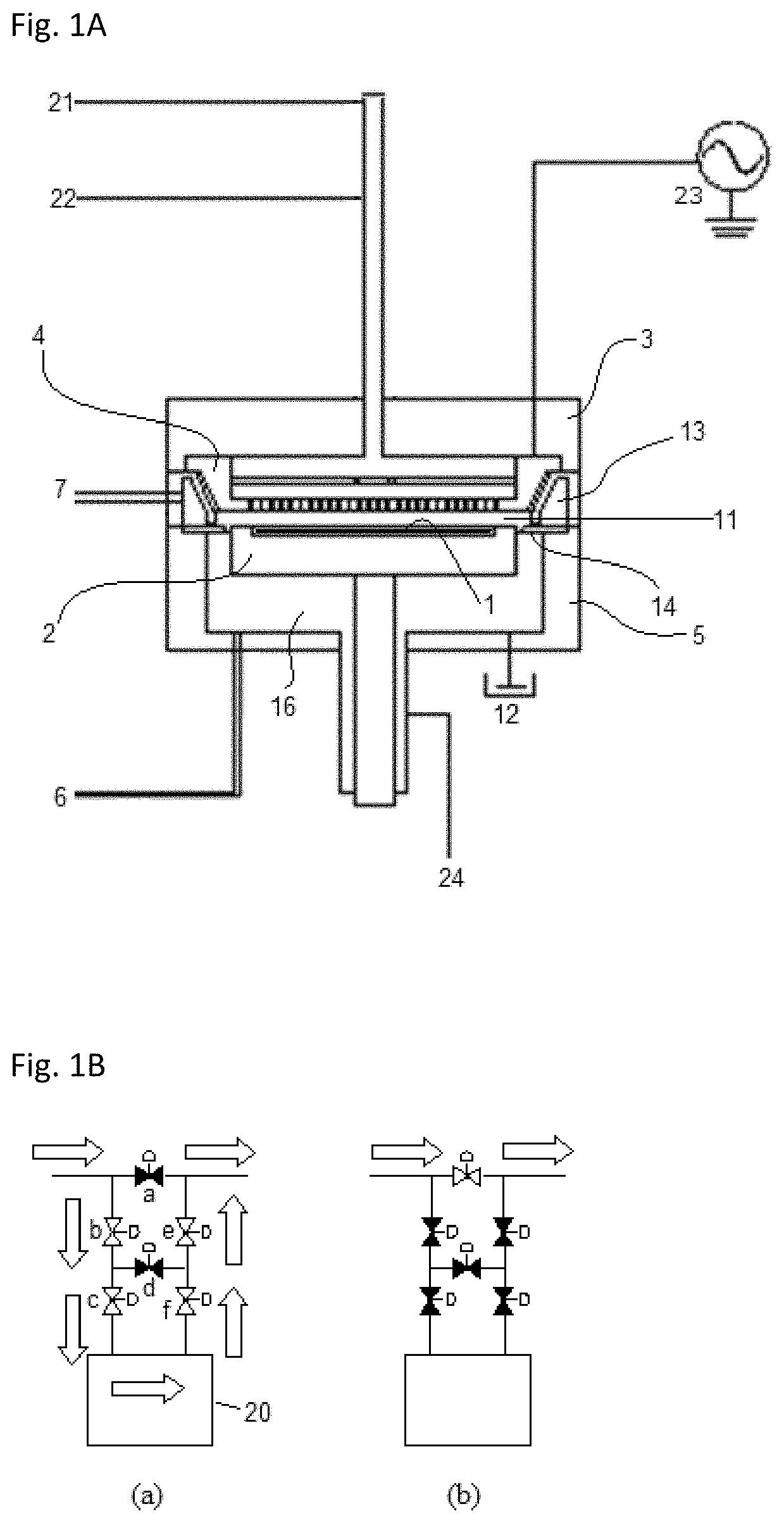

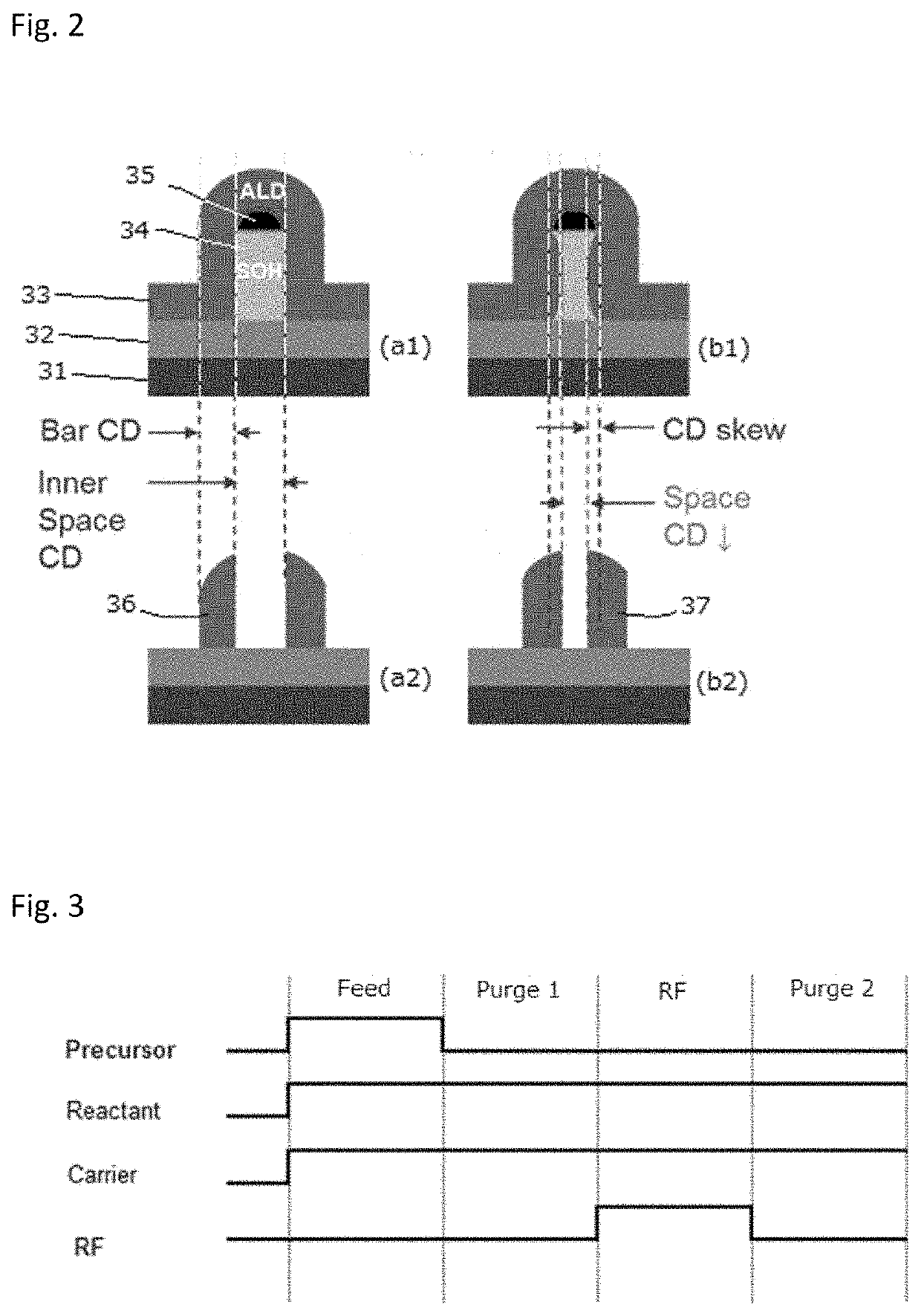

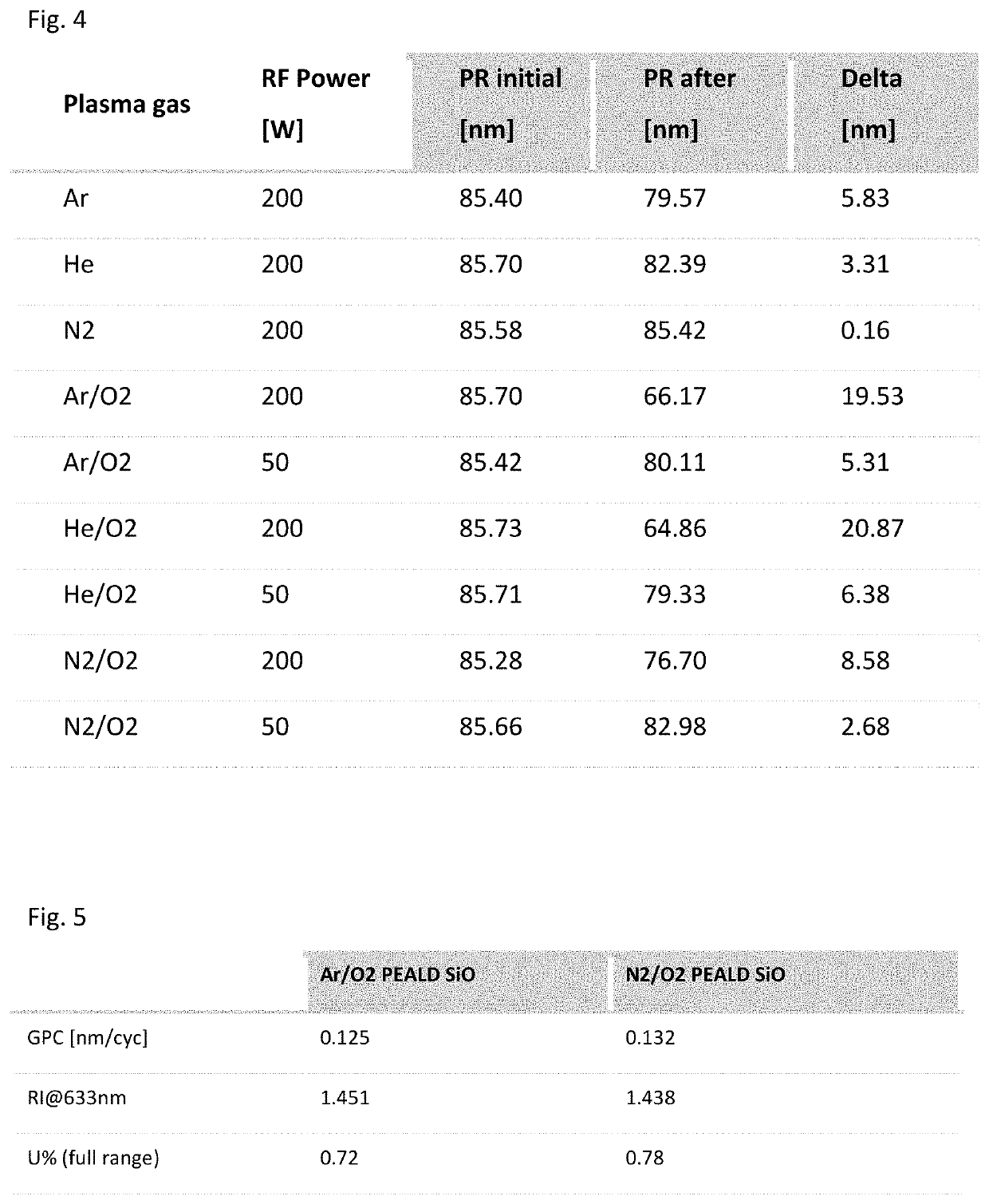

Method for depositing oxide film by peald using nitrogen

InactiveUS20200111669A1Reduce adverse effectsReduce sizeElectric discharge tubesSemiconductor/solid-state device manufacturingNitrogen gasAtomic layer deposition

A method of depositing an oxide film on a template for patterning in semiconductor fabrication, includes: (i) providing a template having patterned structures thereon in a reaction space; and (ii) depositing an oxide film on the template by plasma-enhanced atomic layer deposition (PEALD) using nitrogen gas as a carrier gas and also as a dilution gas, thereby entirely covering with the oxide film an exposed top surface of the template and the patterned structures.

Owner:ASM IP HLDG BV

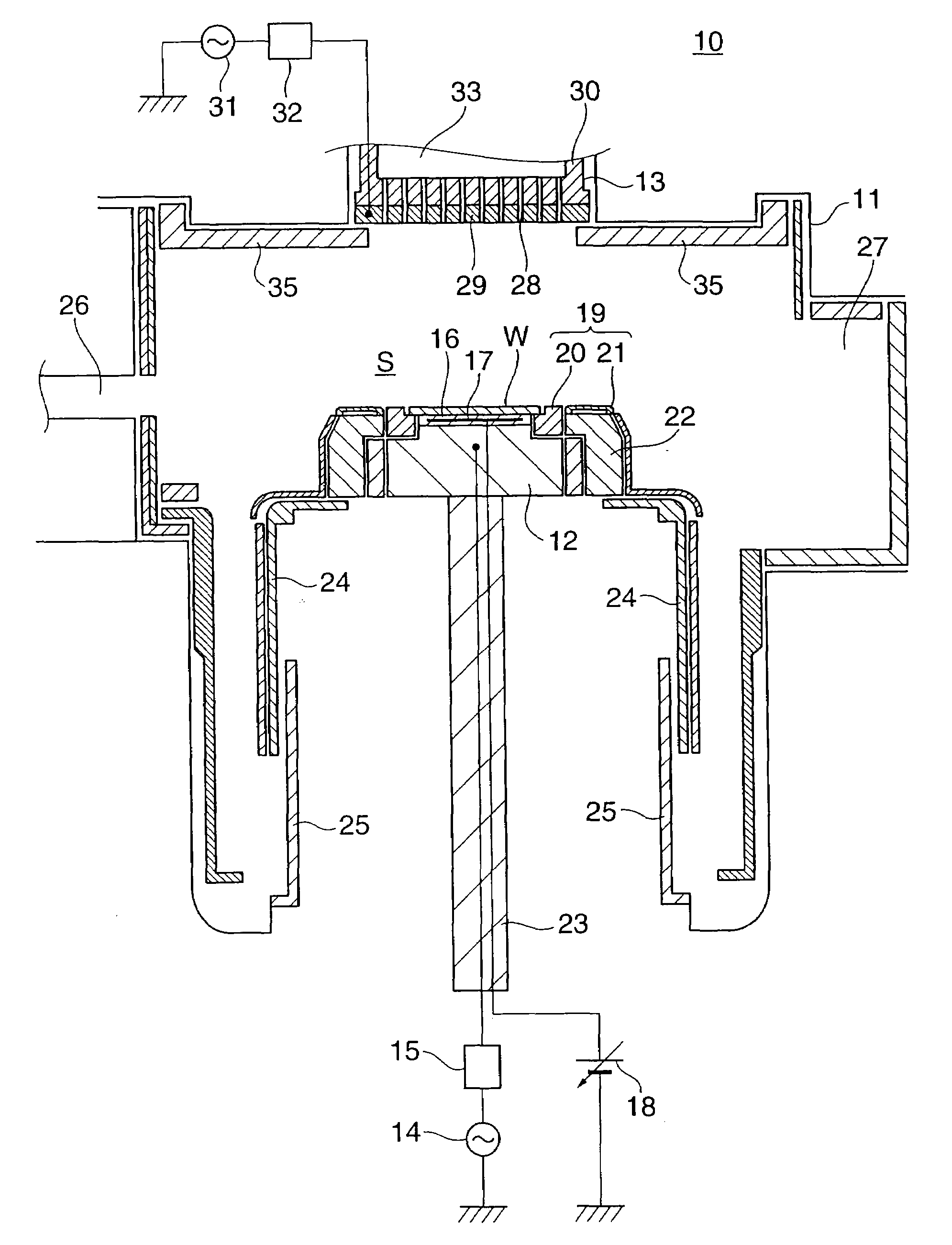

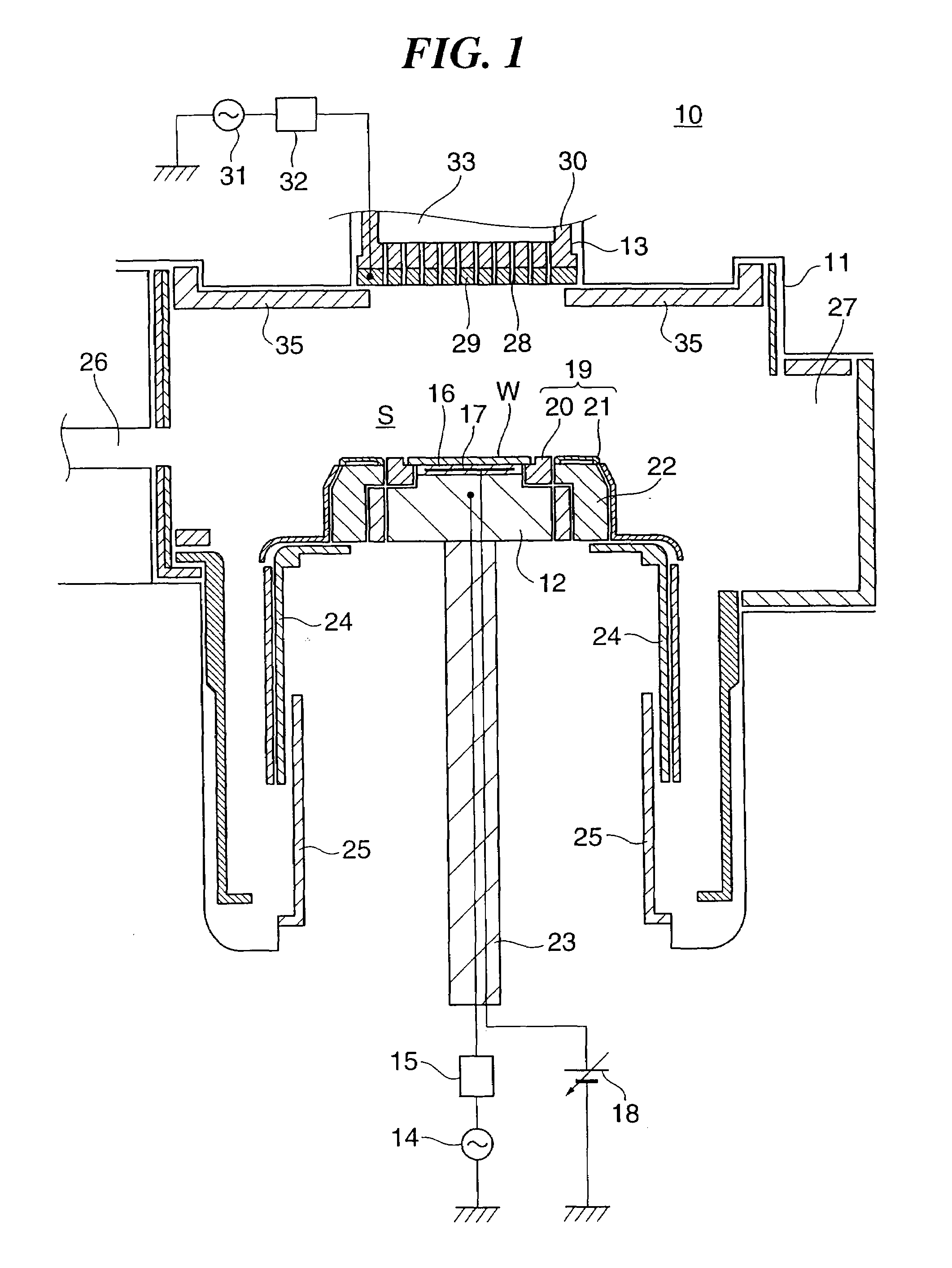

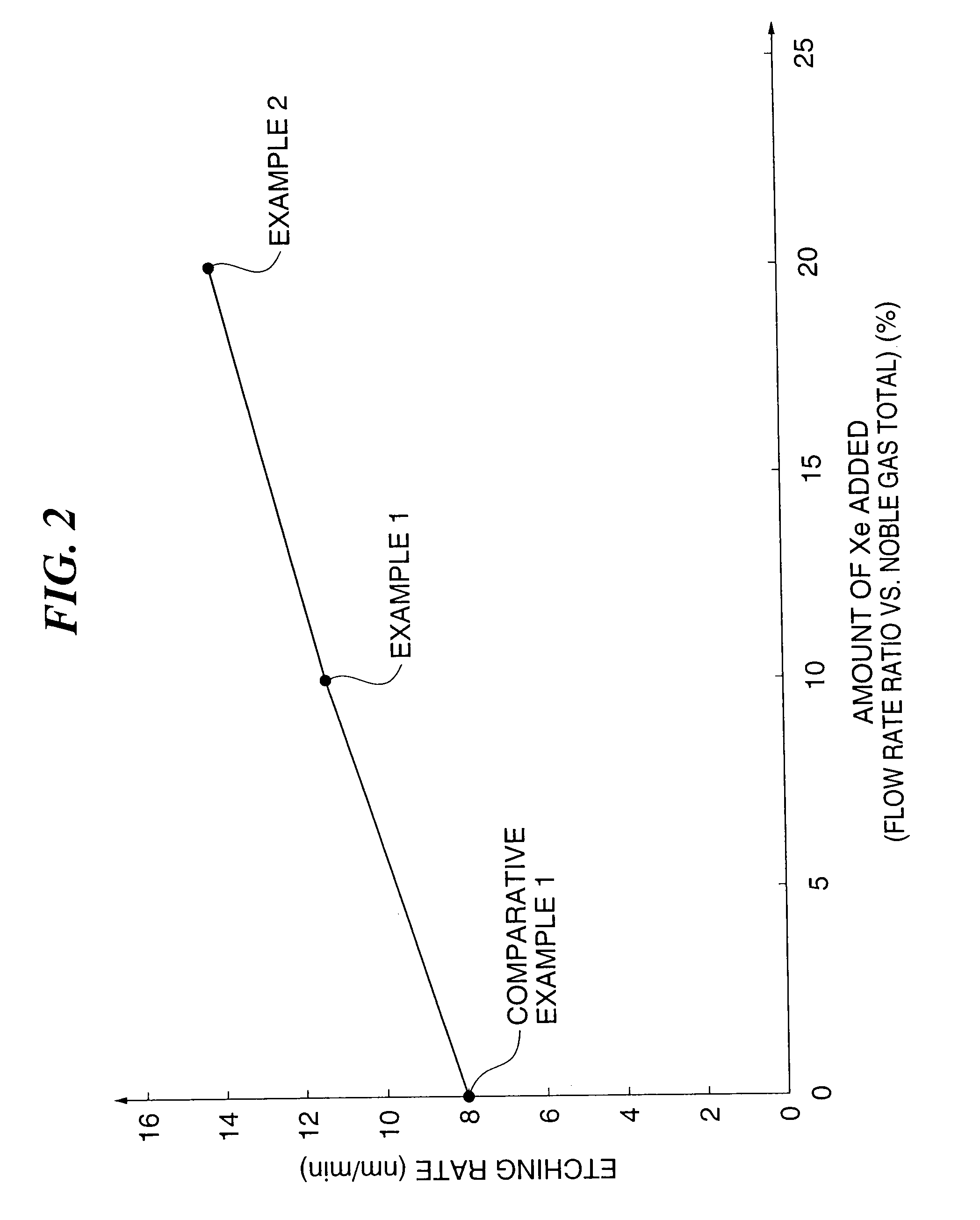

Method of making semiconductor device

InactiveUS20080261404A1Improve controllabilityGood etchingElectric discharge tubesSemiconductor/solid-state device manufacturingNoble gasControllability

A plasma processing method, which enables the etching controllability for a high-dielectric-constant insulating film to be improved. A substrate having a high-dielectric-constant gate insulating film and a hard mask formed thereon is subjected to etching processing using a plasma of a processing gas containing a noble gas and a reducing gas.

Owner:TOKYO ELECTRON LTD

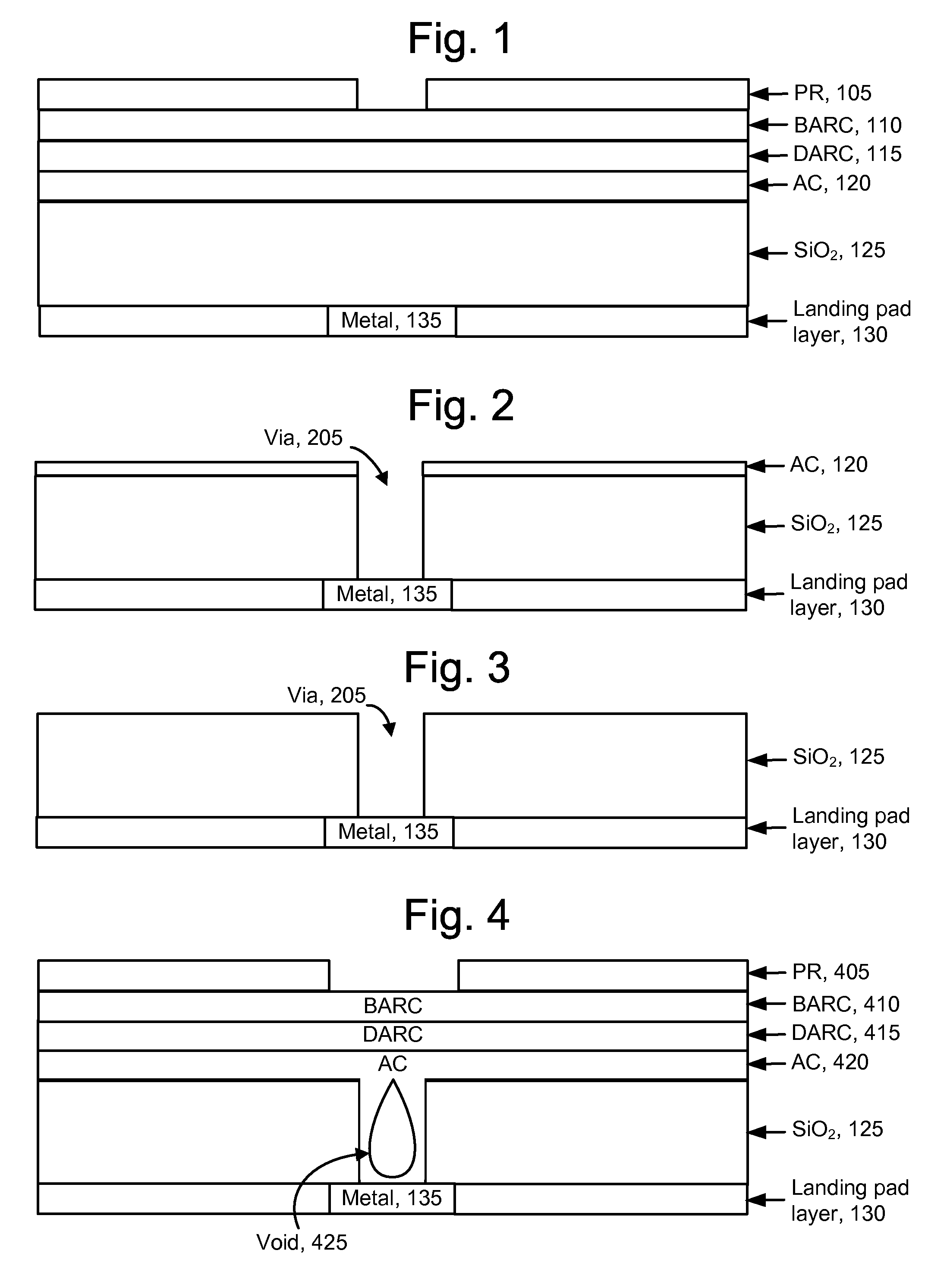

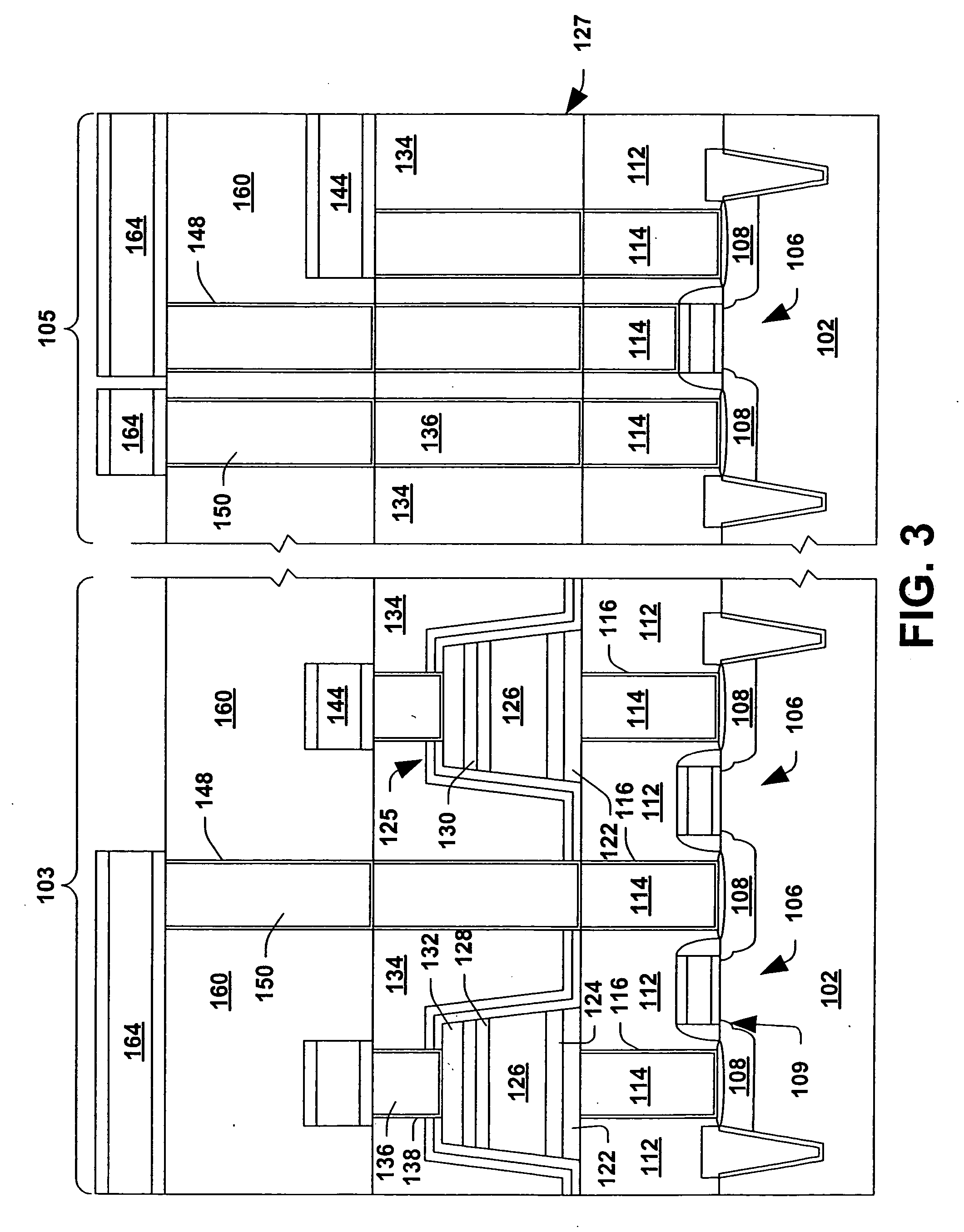

Dual damascene with amorphous carbon for 3D deep via/trench application

ActiveUS20090087979A1Good etchingSolid-state devicesSemiconductor/solid-state device manufacturingBit lineHard mask

A method for fabricating a 3-D monolithic memory device in which a via and trench are etched using an amorphous carbon hard mask. The via extends in multiple levels of the device as a multi-level vertical interconnect. The trench extends laterally, such as to provide a word line or bit line for memory cells, or to provide other routing paths. A dual damascene process can be used in which the via is formed first and the trench is formed second, or the trench is formed first and the via is formed second. The technique is particularly suitable for deep via applications, such as for via depths of greater than 1 μm. A dielectric antireflective coating, optionally with a bottom antireflective coating, can be used to etch an amorphous carbon layer to provide the amorphous carbon hard mask.

Owner:SANDISK CORP +1

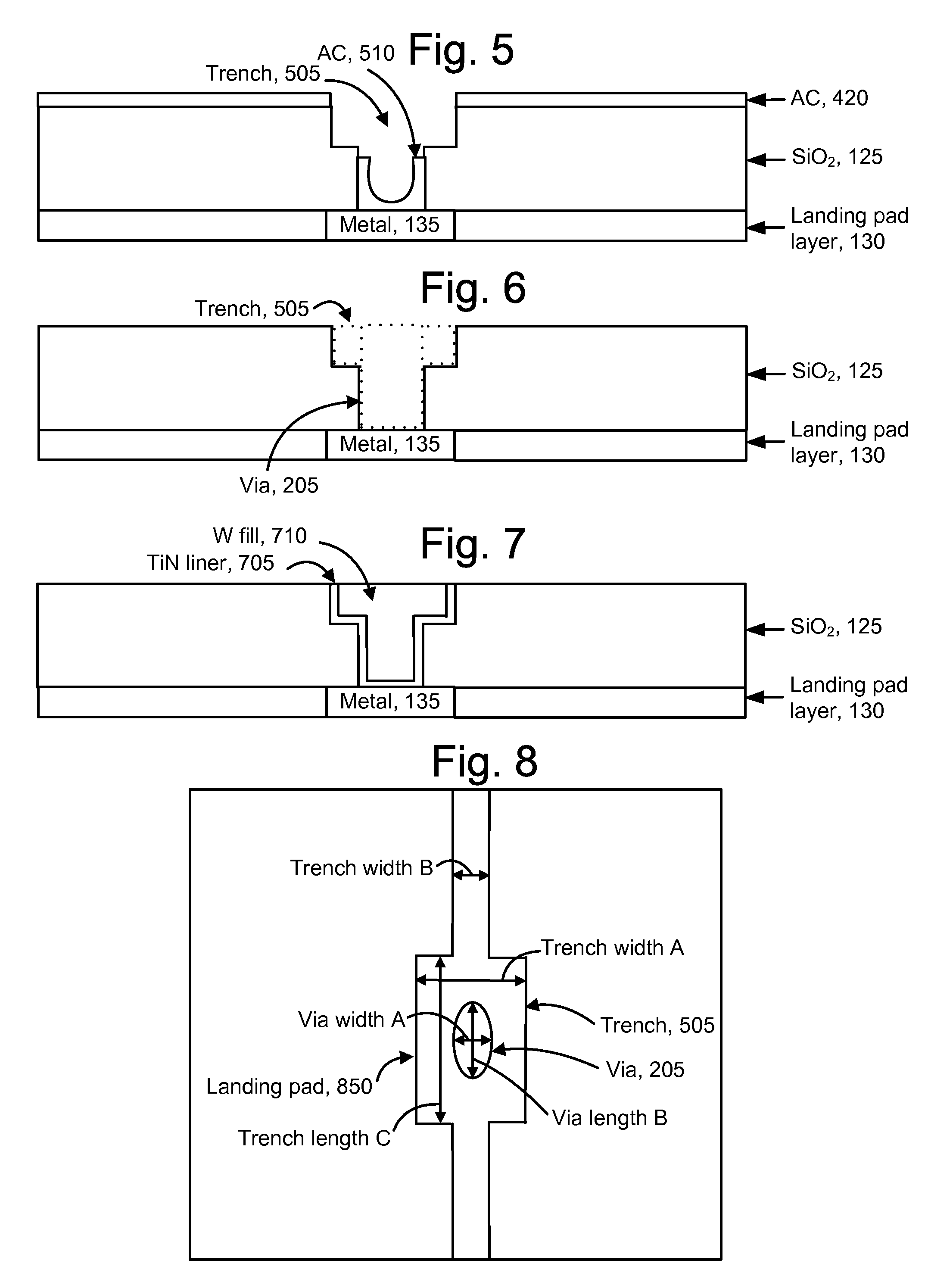

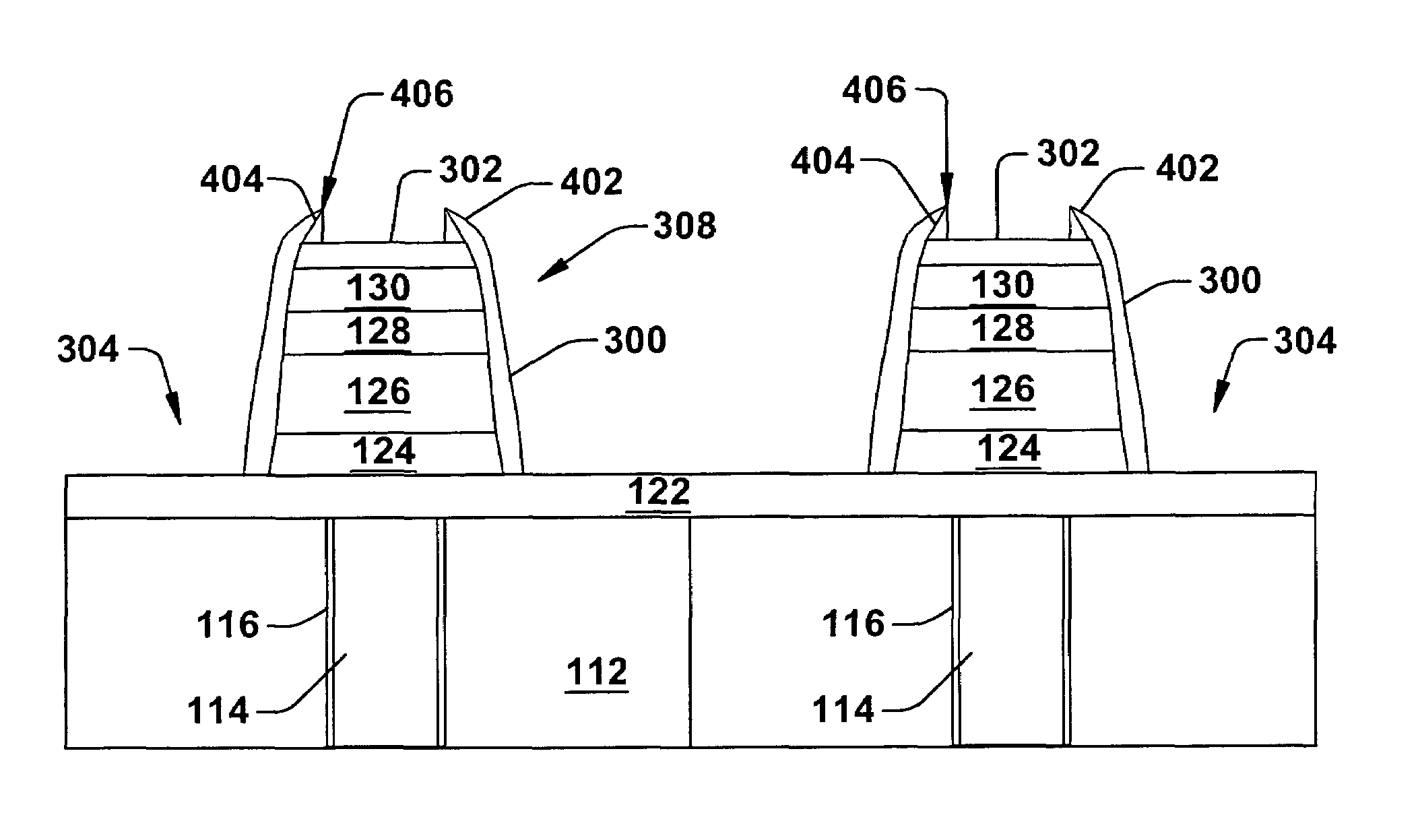

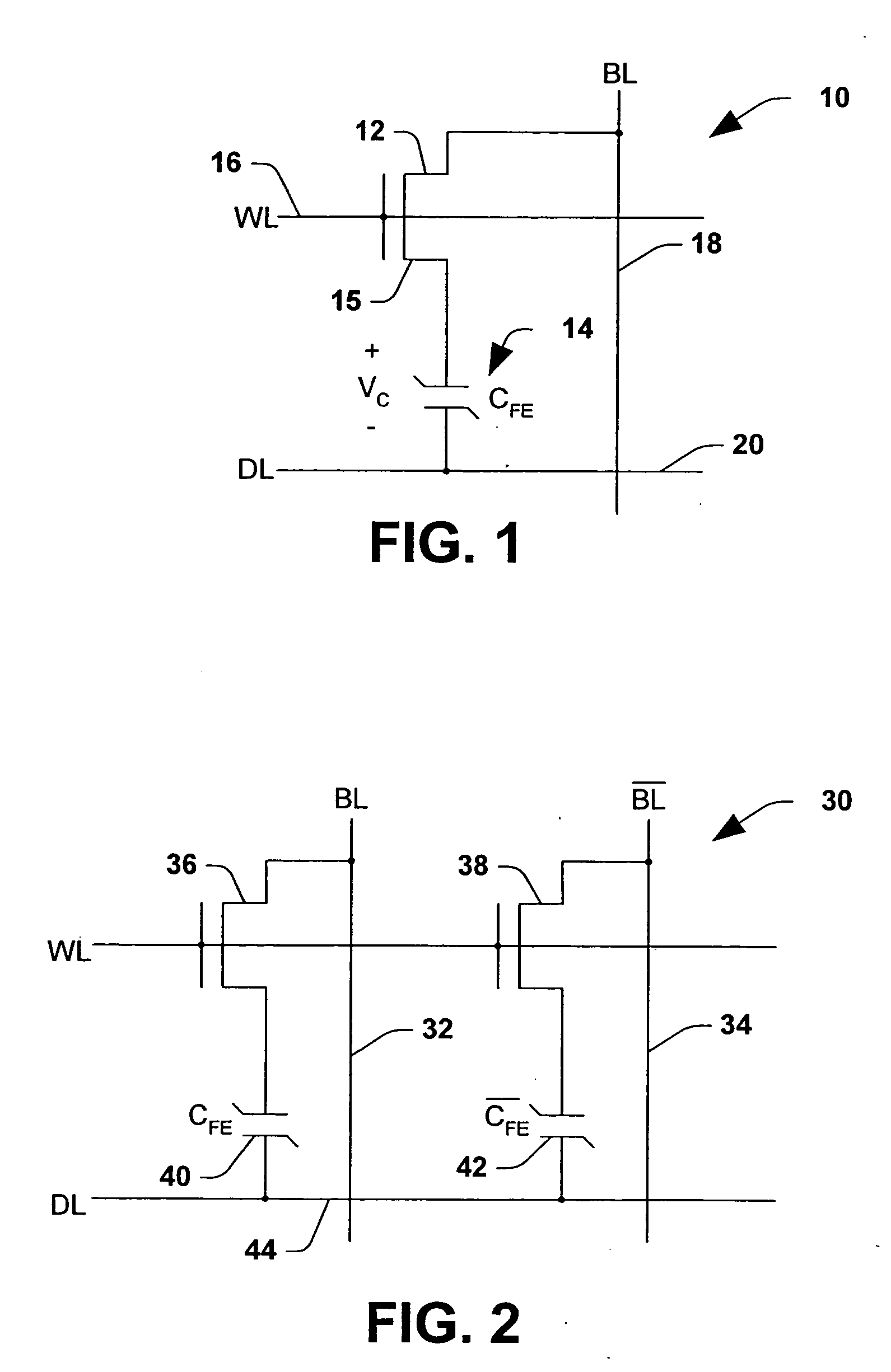

FeRAM capacitor stack etch

InactiveUS7029925B2Sensitive to contaminationCost advantageSolid-state devicesSemiconductor/solid-state device manufacturingConductive materialsEngineering

The present invention is directed to a method of forming an FeRAM integrated circuit, which includes performing a capacitor stack etch to define the FeRAM capacitor. The method comprises etching a PZT ferroelectric layer with a high temperature BCl3 etch which provides substantial selectivity with respect to the hard mask. Alternatively, the PZT ferroelectric layer is etch using a low temperature fluorine component etch chemistry such as CHF3 to provide a non-vertical PZT sidewall profile. Such a profile prevents conductive material associated with a subsequent bottom electrode layer etch from depositing on the PZT sidewall, thereby preventing leakage or a “shorting out” of the resulting FeRAM capacitor.

Owner:TEXAS INSTR INC

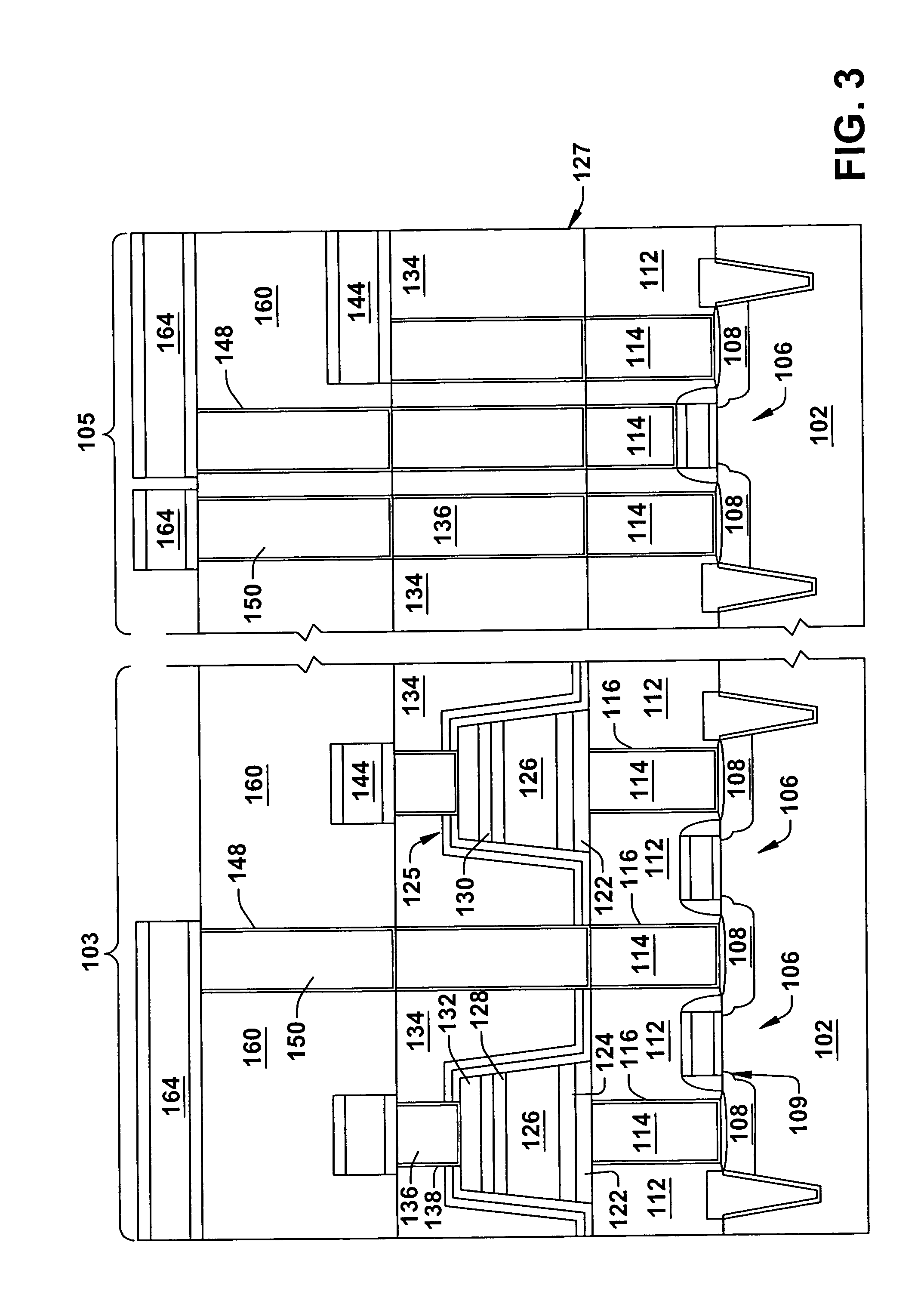

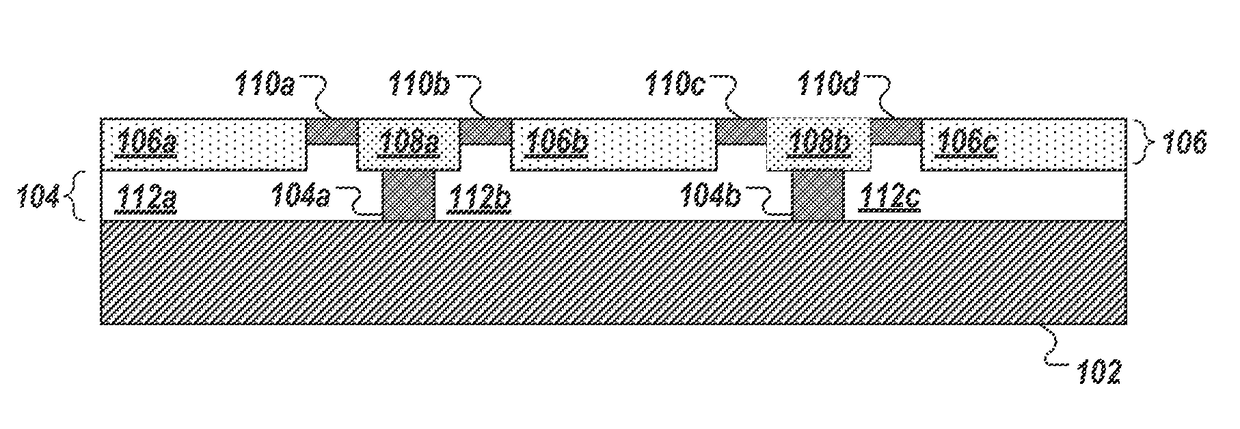

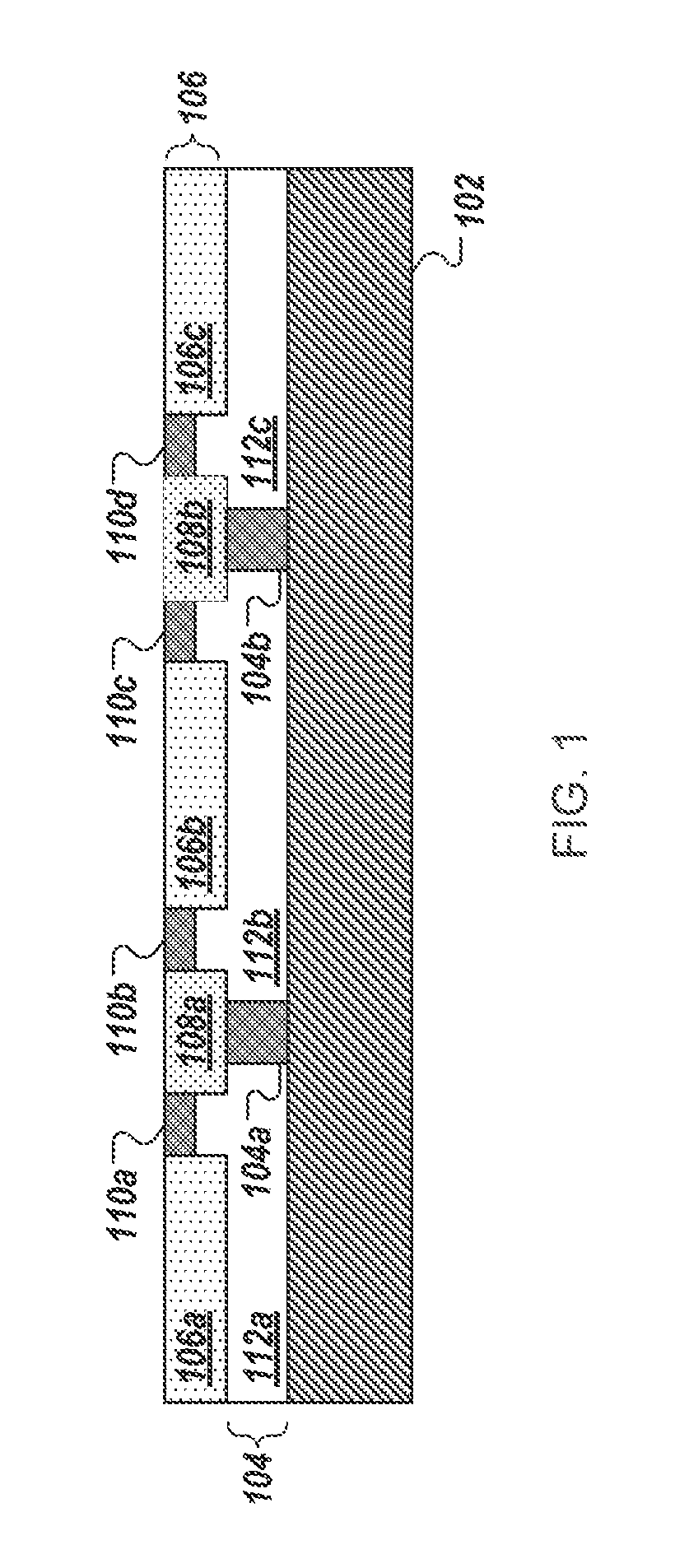

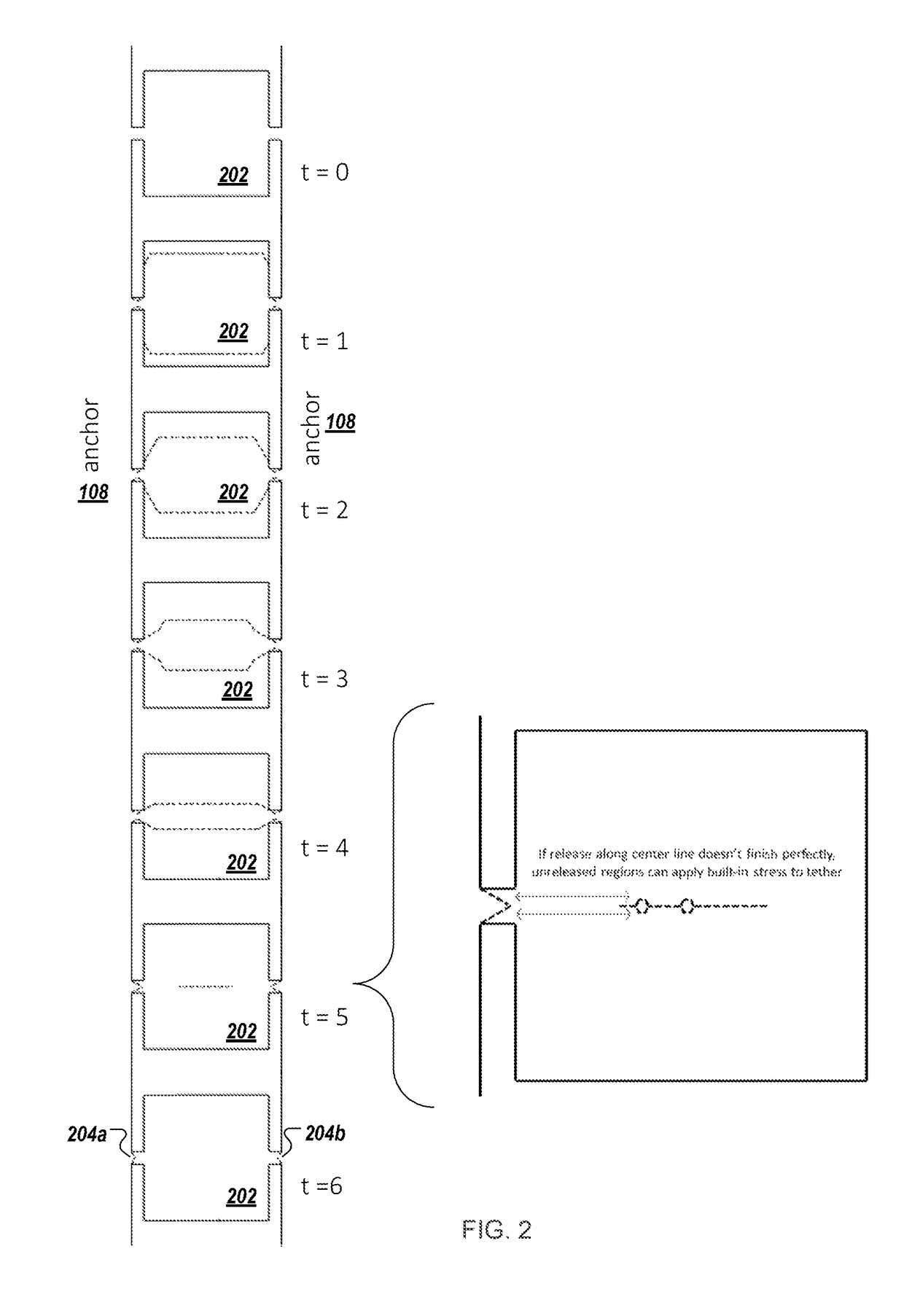

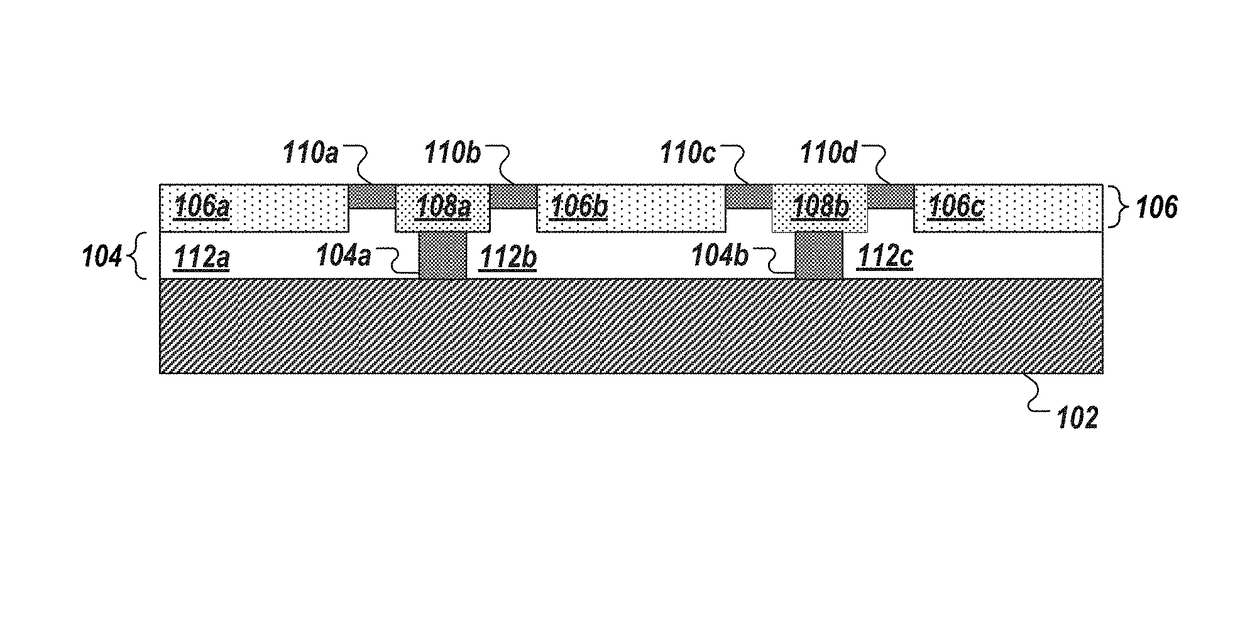

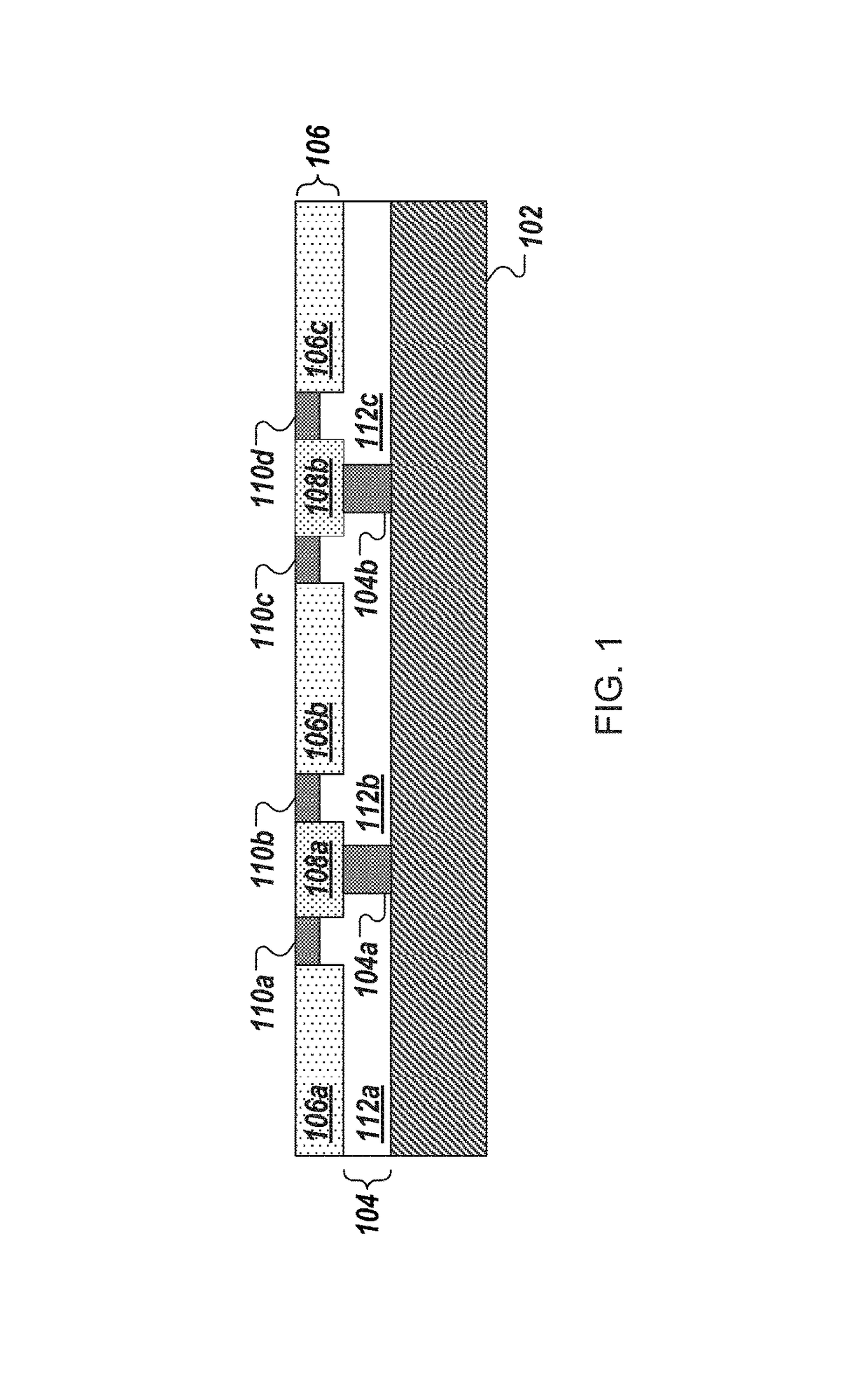

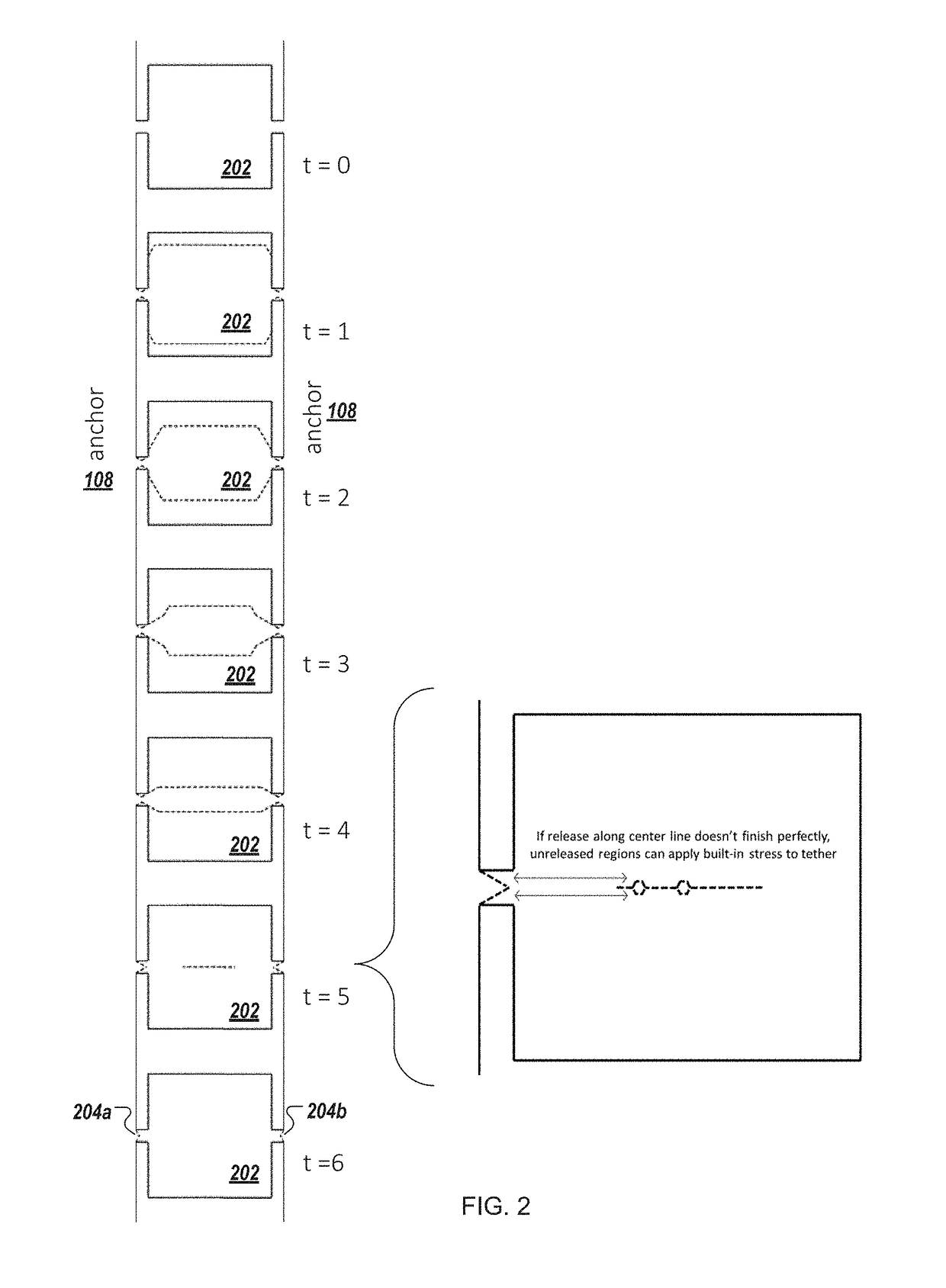

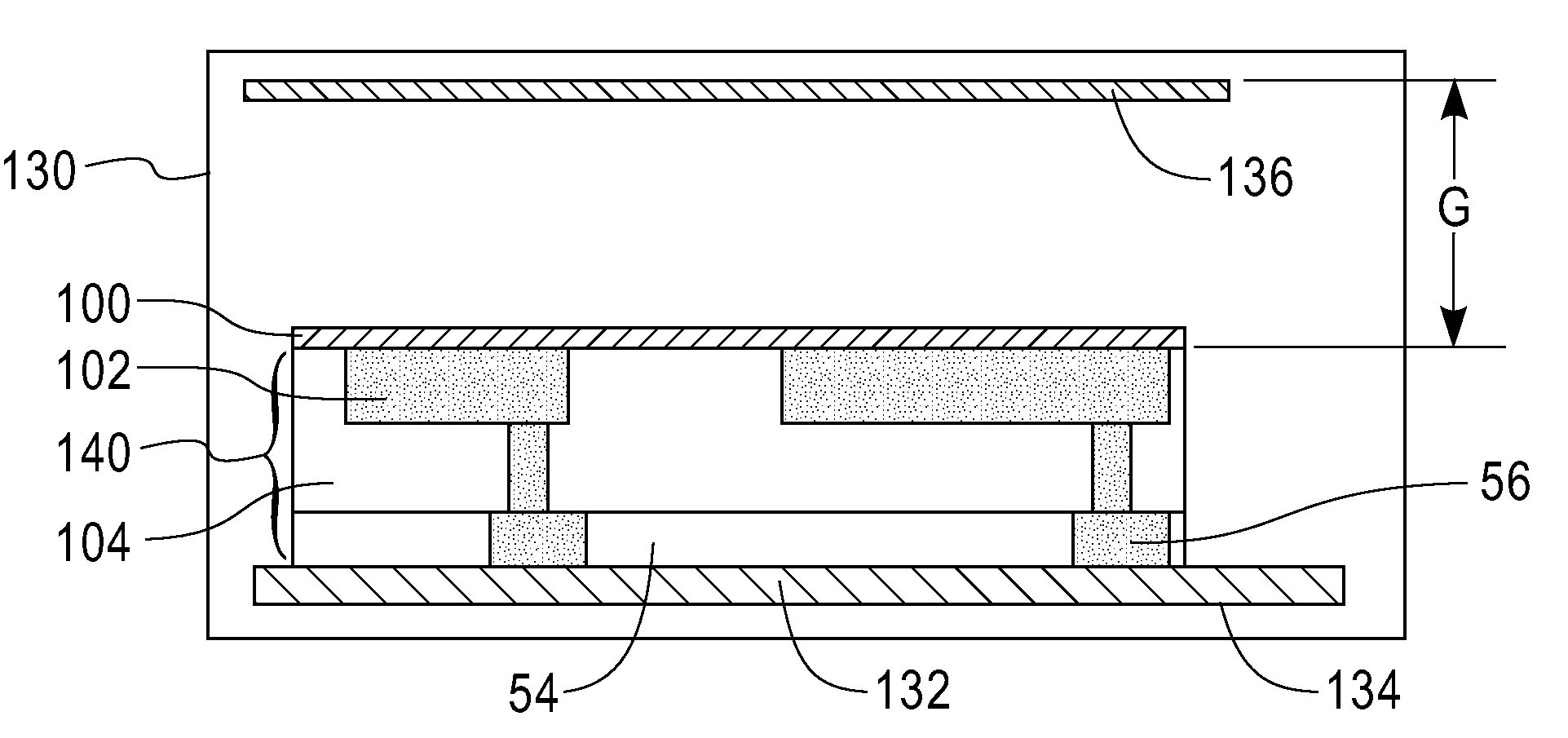

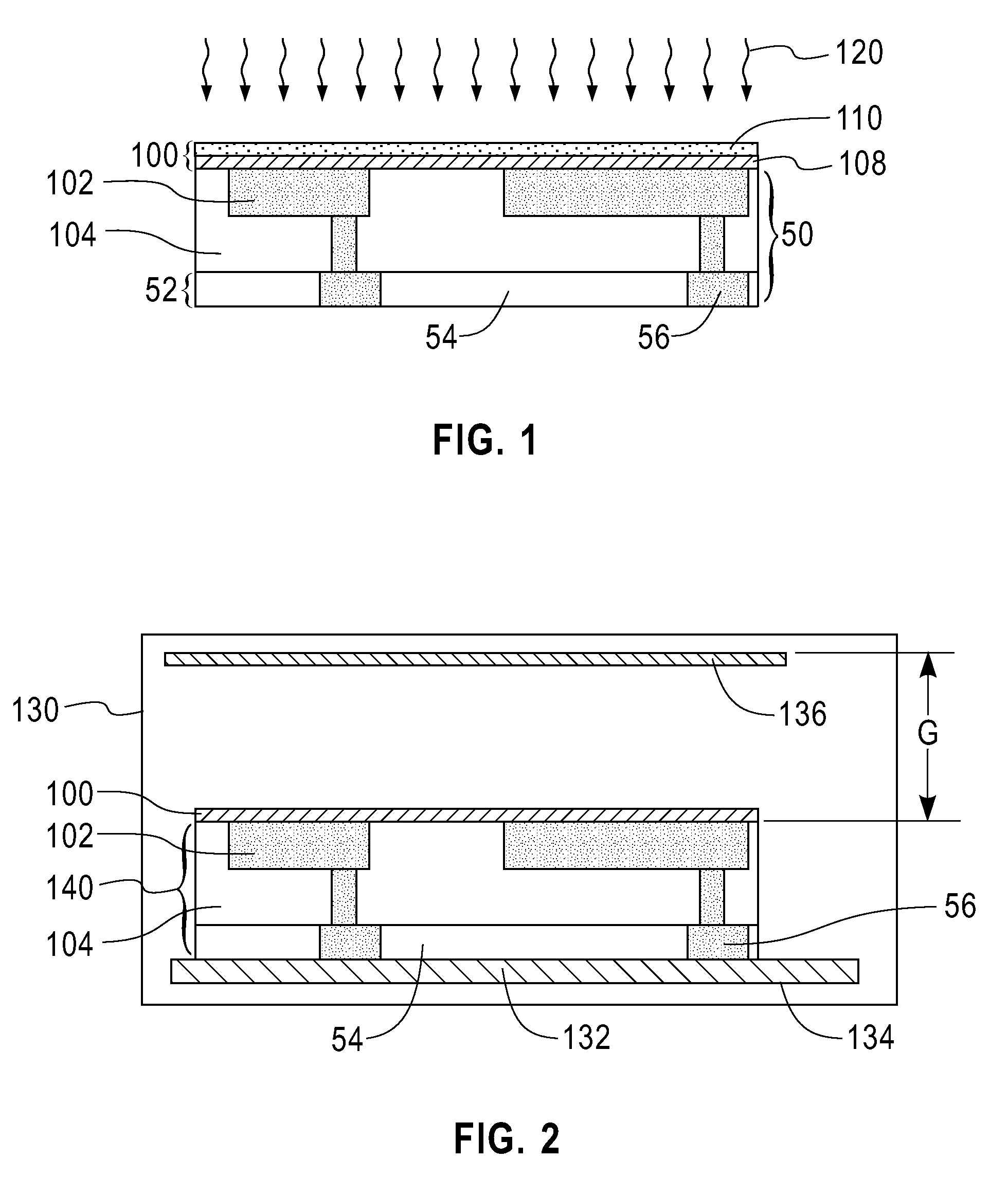

Systems and methods for controlling release of transferable semiconductor structures

ActiveUS9601356B2Good removal effectGood etchingSemiconductor/solid-state device detailsSolid-state devicesControlled releaseMicro devices

The disclosed technology relates generally to methods and systems for controlling the release of micro devices. Prior to transferring micro devices to a destination substrate, a native substrate is formed with micro devices thereon. The micro devices can be distributed over the native substrate and spatially separated from each other by an anchor structure. The anchors are physically connected / secured to the native substrate. Tethers physically secure each micro device to one or more anchors, thereby suspending the micro device above the native substrate. In certain embodiments, single tether designs are used to control the relaxation of built-in stress in releasable structures on a substrate, such as Si (1 1 1). Single tether designs offer, among other things, the added benefit of easier break upon retrieval from native substrate in micro assembly processes. In certain embodiments, narrow tether designs are used to avoid pinning of the undercut etch front.

Owner:X DISPLAY CO TECH LTD

Systems and methods for controlling release of transferable semiconductor structures

ActiveUS9929053B2Good removal effectGood etchingSemiconductor/solid-state device detailsSolid-state devicesControlled releaseSemiconductor structure

The disclosed technology relates generally to methods and systems for controlling the release of micro devices. Prior to transferring micro devices to a destination substrate, a native substrate is formed with micro devices thereon. The micro devices can be distributed over the native substrate and spatially separated from each other by an anchor structure. The anchors are physically connected / secured to the native substrate. Tethers physically secure each micro device to one or more anchors, thereby suspending the micro device above the native substrate. In certain embodiments, single tether designs are used to control the relaxation of built-in stress in releasable structures on a substrate, such as Si (1 0 0). Single tether designs offer, among other things, the added benefit of easier break upon retrieval from native substrate in micro assembly processes. In certain embodiments, narrow tether designs are used to avoid pinning of the undercut etch front.

Owner:X DISPLAY CO TECH LTD

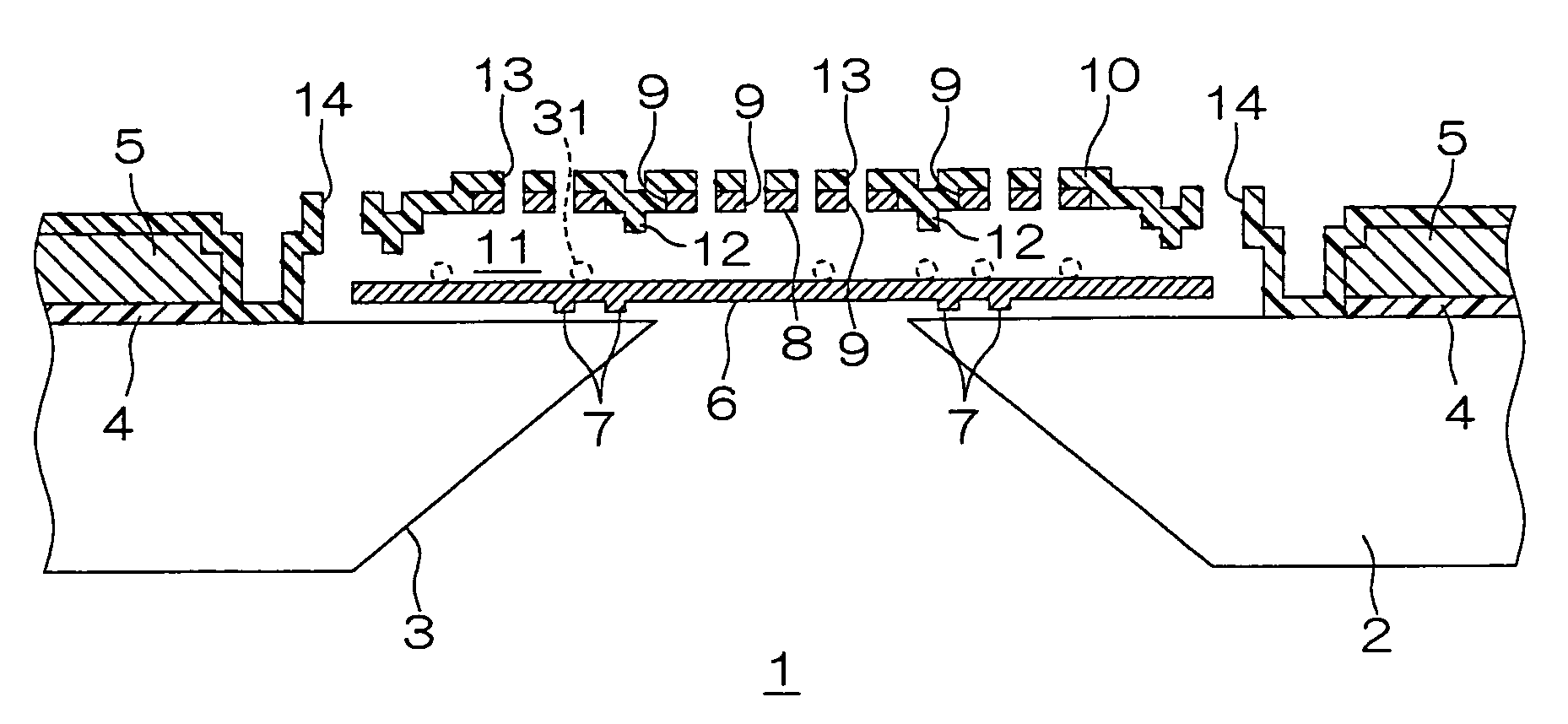

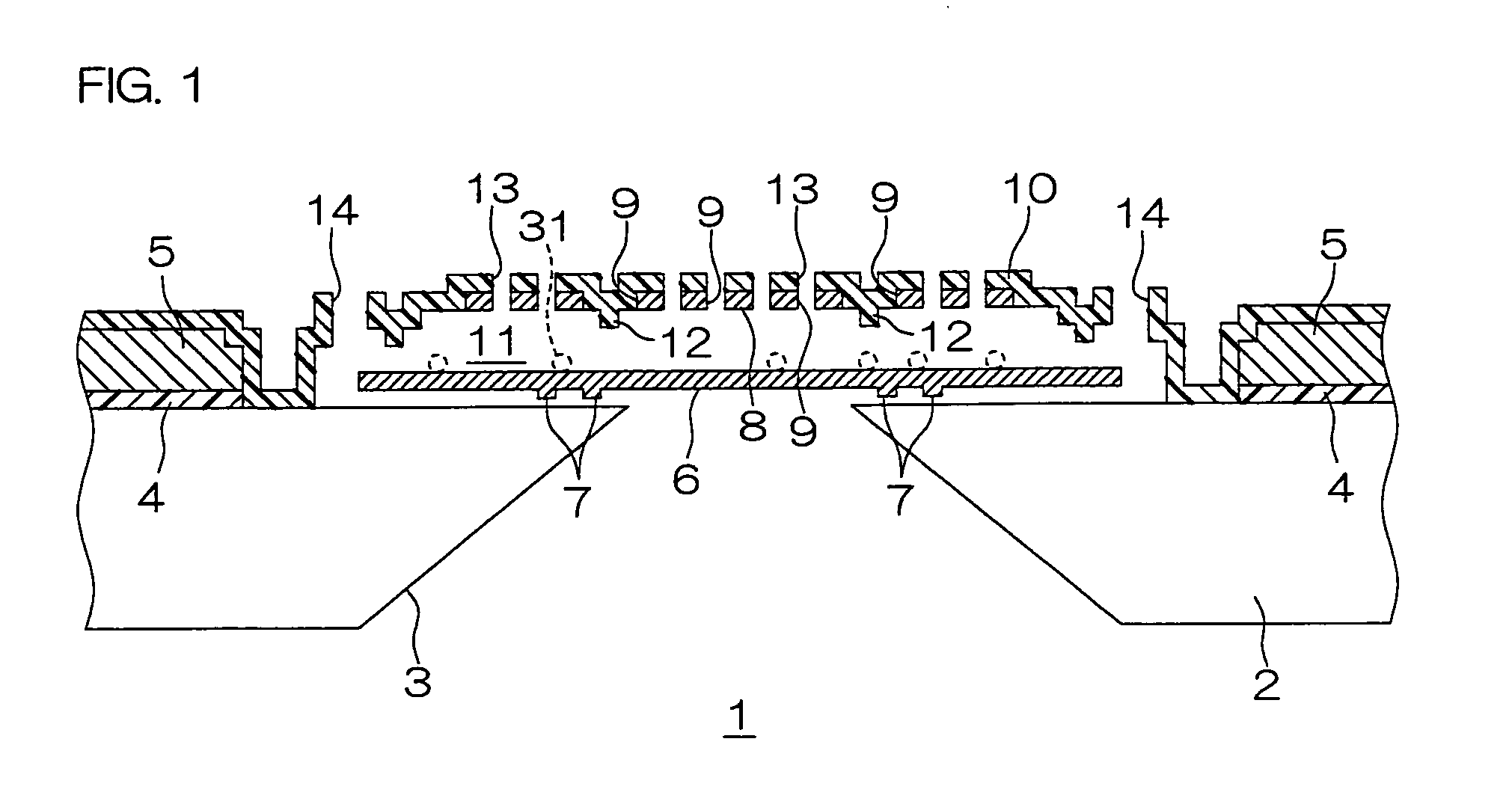

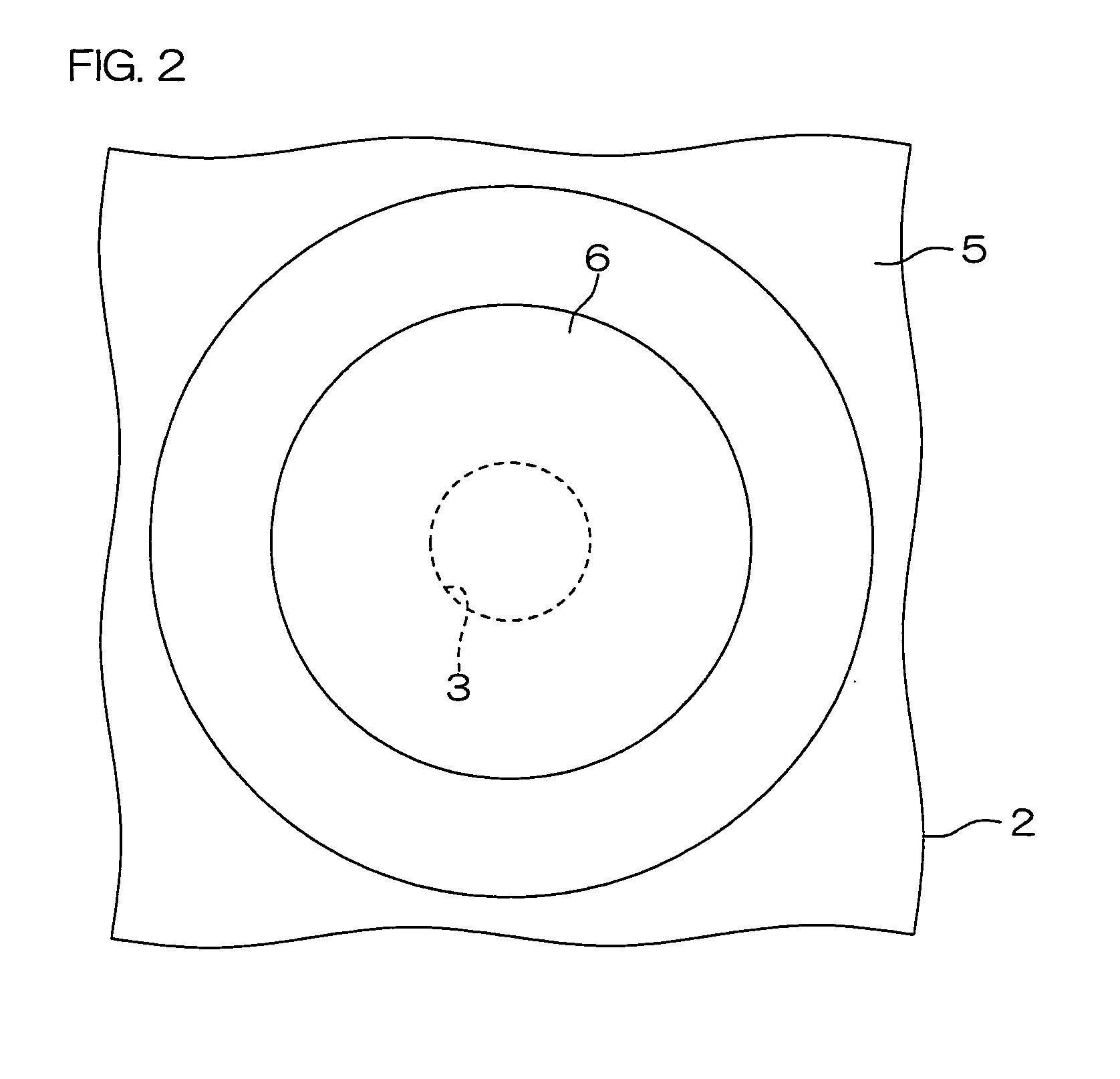

Method of manufacturing MEMS sensor and MEMS sensor

InactiveUS20100096714A1Prevent adhesionPreventing undesired etching of a protective filmAcceleration measurement using interia forcesTransducer detailsMetallic materialsOptoelectronics

A method of manufacturing an MEMS sensor according to the present invention includes the steps of: forming a first sacrificial layer on one surface of a substrate; forming a lower electrode on the first sacrificial layer; forming a second sacrificial layer made of a metallic material on the first sacrificial layer to cover the lower electrode; forming an upper electrode made of a metallic material on the second sacrificial layer; forming a protective film made of a nonmetallic material on the substrate to collectively cover the first sacrificial layer, the second sacrificial layer and the upper electrode; and removing at least the second sacrificial layer by forming a through-hole in the protective film and supplying an etchant to the inner side of the protective film through the through-hole.

Owner:ROHM CO LTD

FeRAM capacitor stack etch

InactiveUS20050054122A1Minimize cell sizeCost advantageSolid-state devicesSemiconductor/solid-state device manufacturingConductive materialsCapacitor

The present invention is directed to a method of forming an FeRAM integrated circuit, which includes performing a capacitor stack etch to define the FeRAM capacitor. The method comprises etching a PZT ferroelectric layer with a high temperature BCl3 etch which provides substantial selectivity with respect to the hard mask. Alternatively, the PZT ferroelectric layer is etch using a low temperature fluorine component etch chemistry such as CHF3 to provide a non-vertical PZT sidewall profile. Such a profile prevents conductive material associated with a subsequent bottom electrode layer etch from depositing on the PZT sidewall, thereby preventing leakage or a “shorting out” of the resulting FeRAM capacitor.

Owner:TEXAS INSTR INC

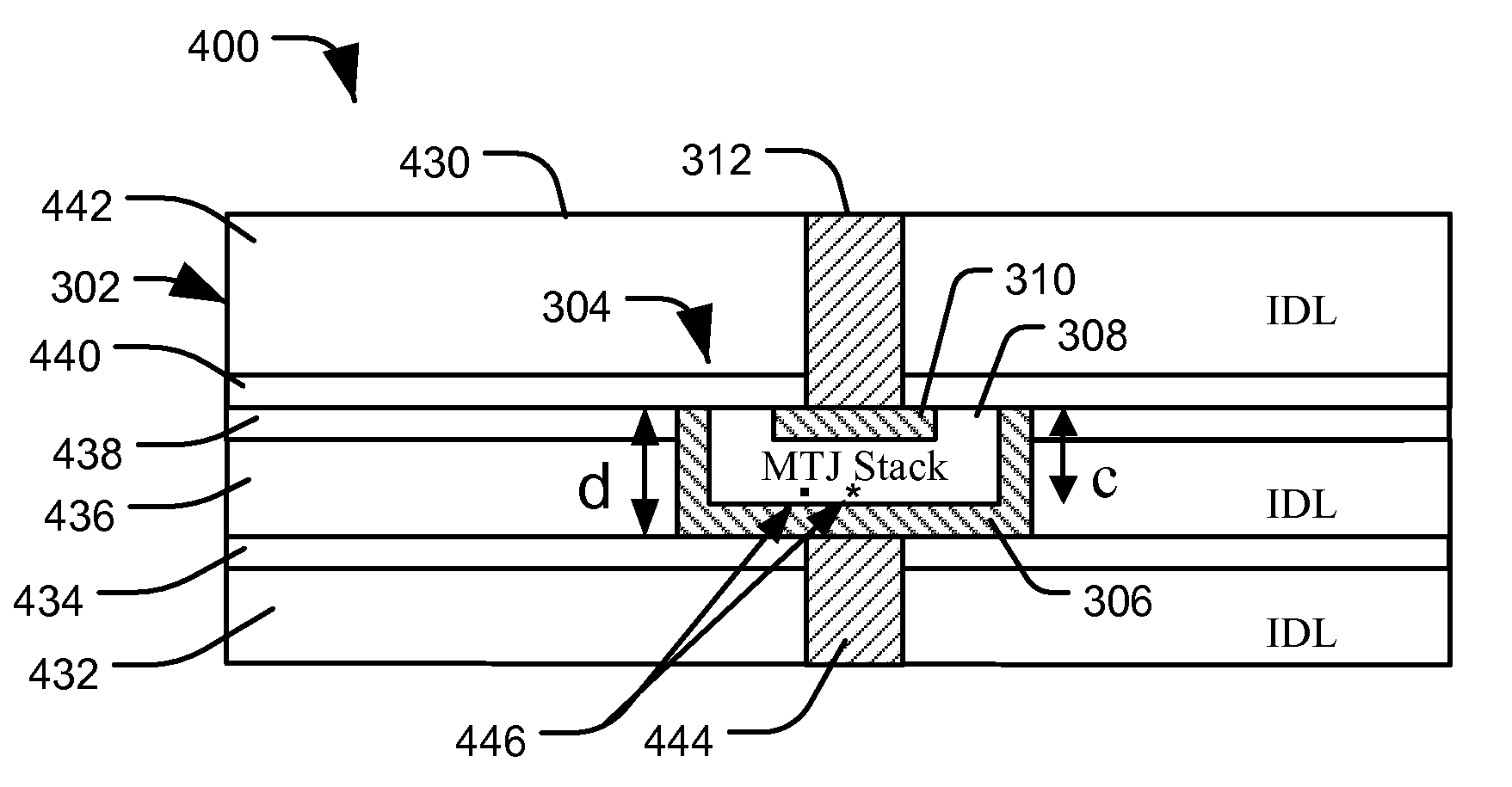

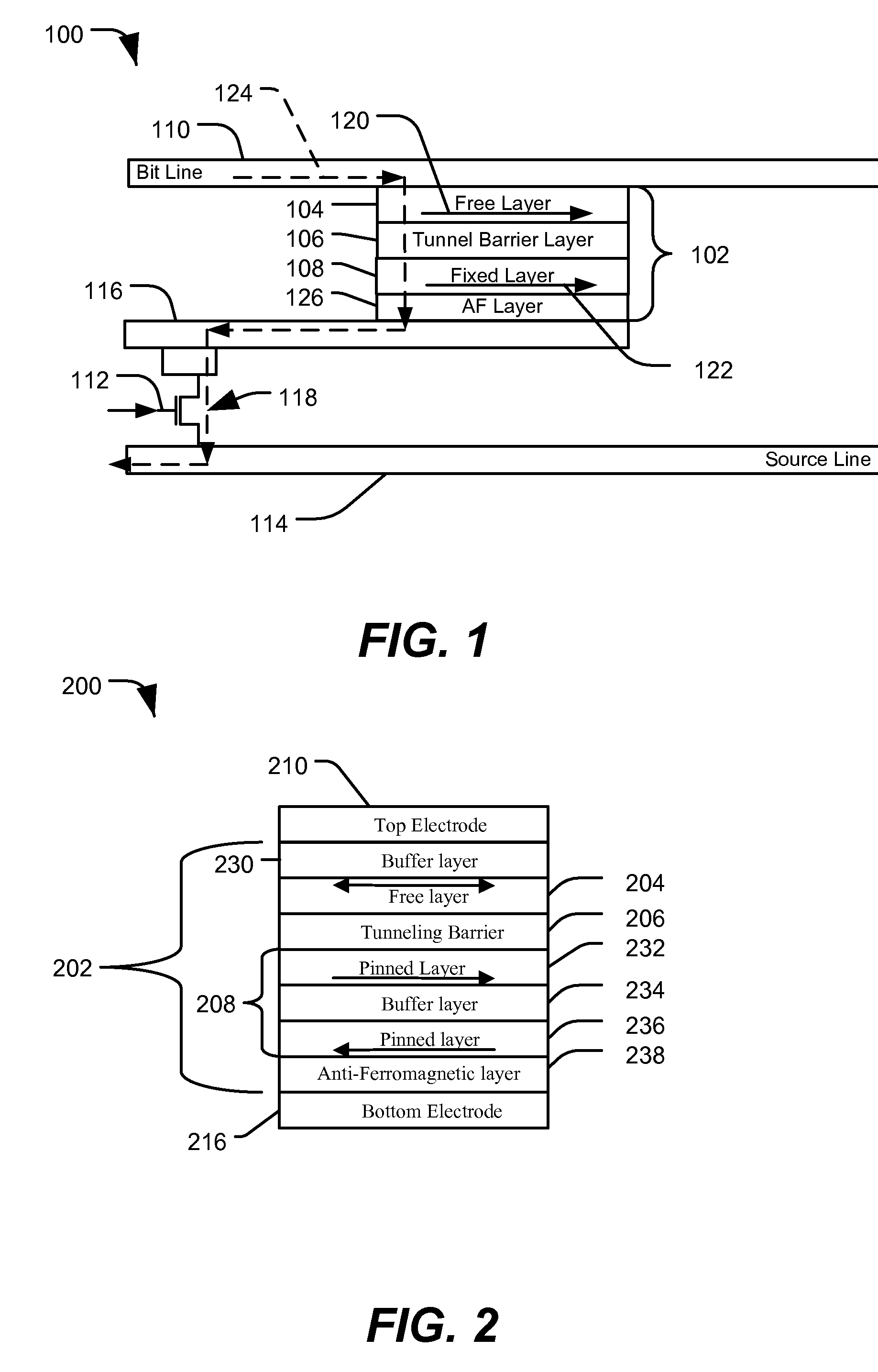

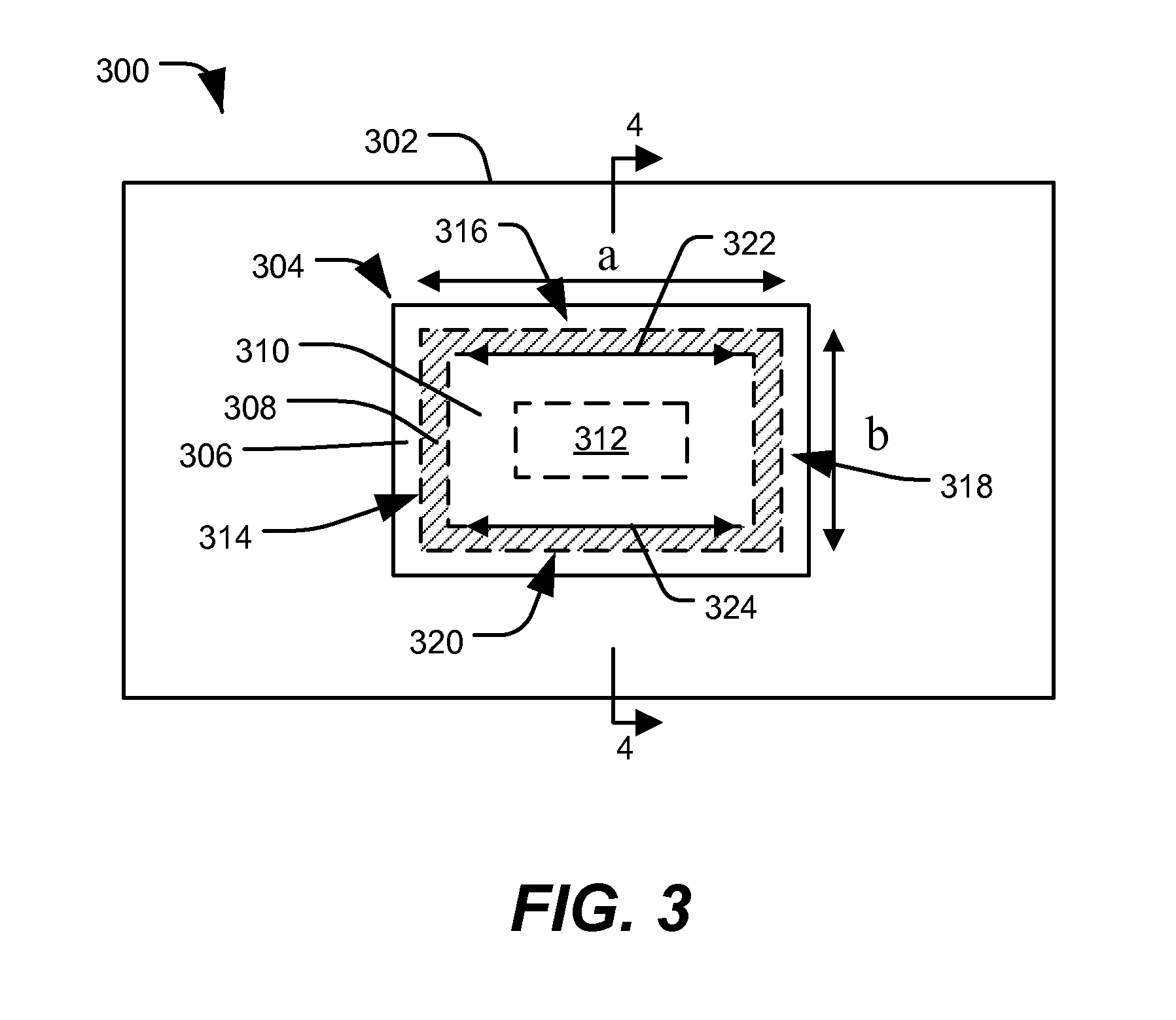

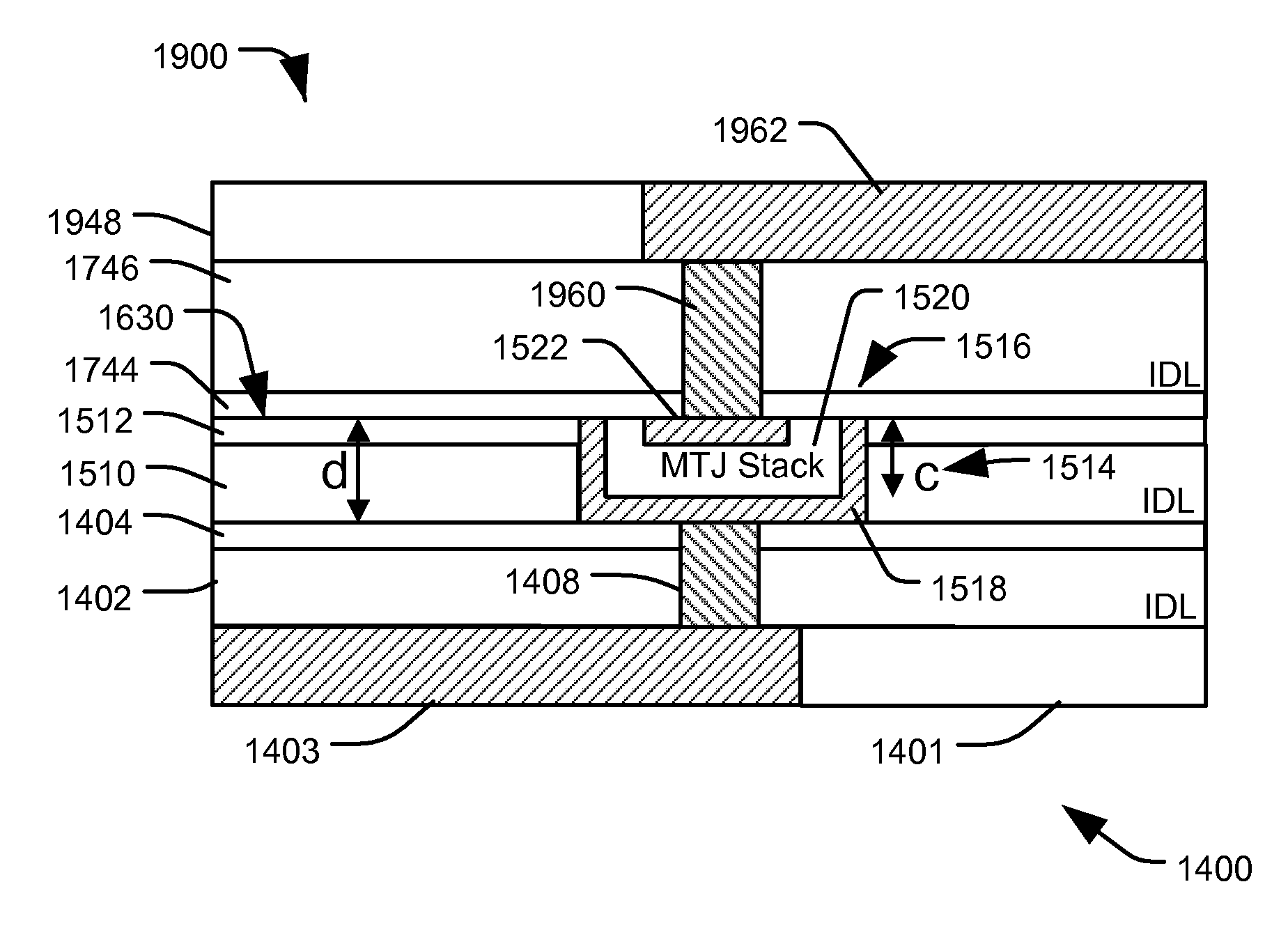

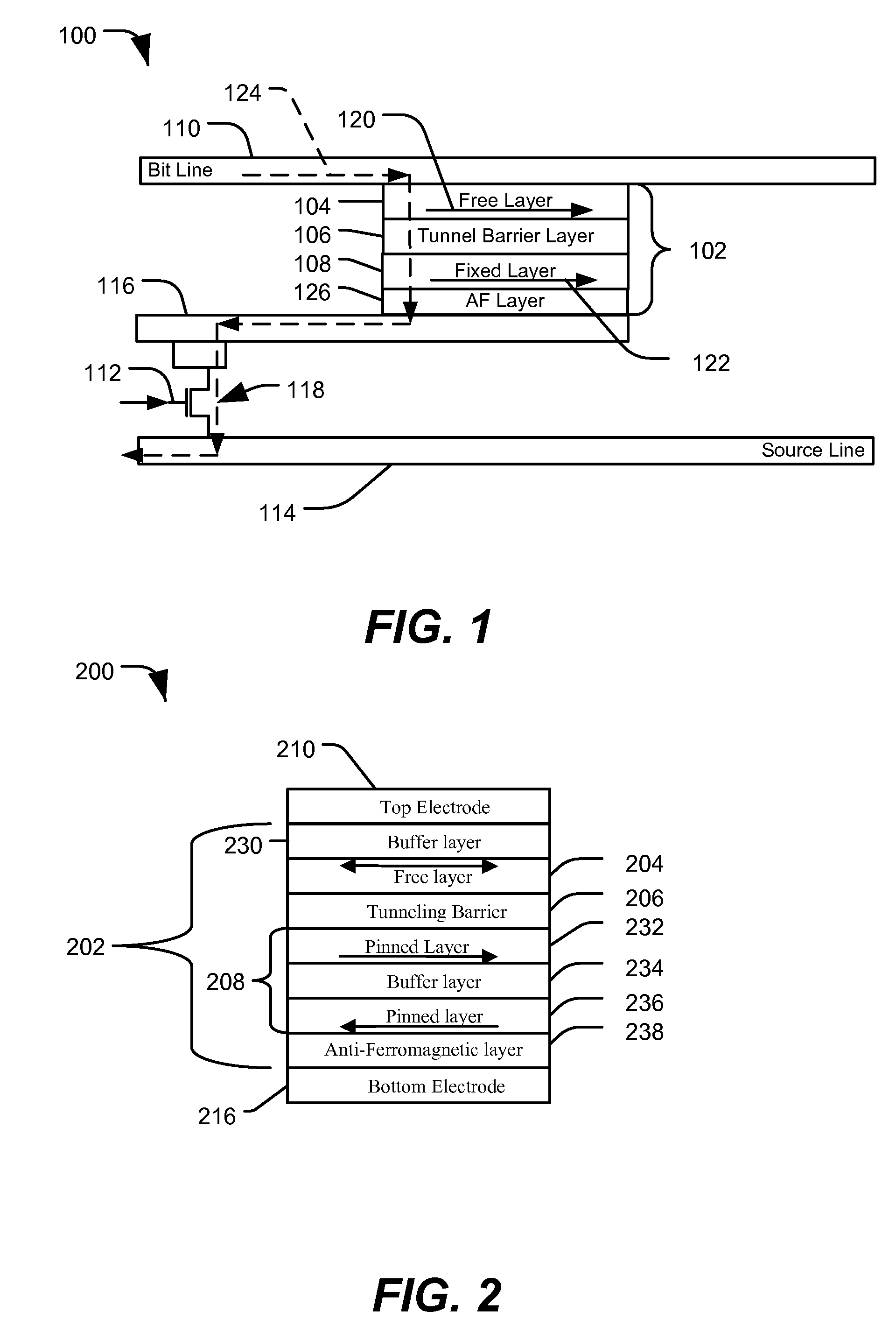

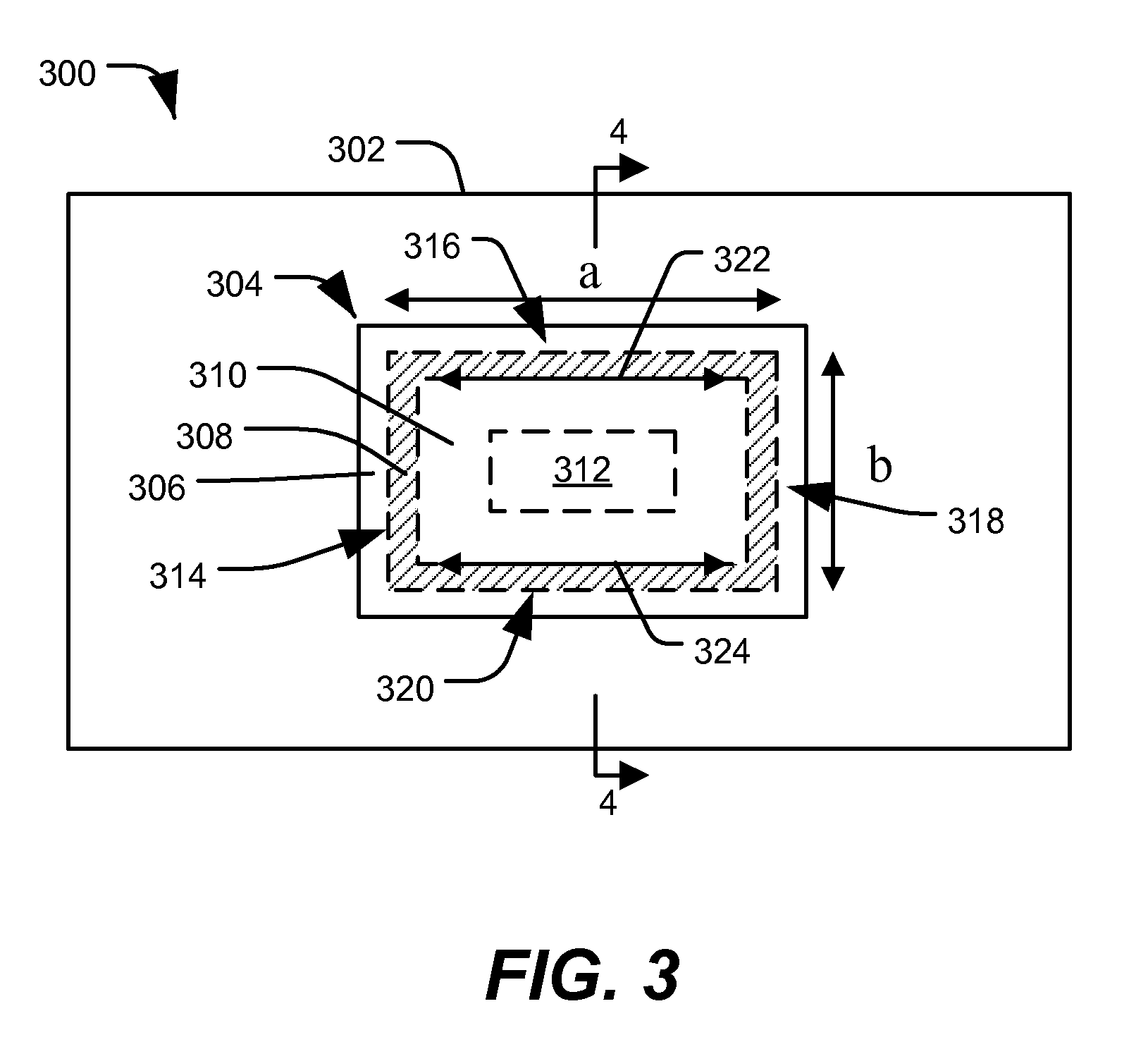

Method of forming a magnetic tunnel junction structure

ActiveUS7579197B1Good etchingIncreased process windowMagnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingEngineeringTunnel junction

In a particular illustrative embodiment, a method of forming a magnetic tunnel junction (MTJ) device is disclosed that includes forming a trench in a substrate. The method further includes depositing a magnetic tunnel junction (MTJ) structure within the trench. The MTJ structure includes a bottom electrode, a fixed layer, a tunnel barrier layer, a free layer, and a top electrode. The method also includes planarizing the MTJ structure. In a particular example, the MTJ structure is planarized using a Chemical Mechanical Planarization (CMP) process.

Owner:QUALCOMM INC

Method of forming a magnetic tunnel junction structure

ActiveUS20090227045A1Good etchingReduce erosionMagnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingEngineeringTunnel junction

In a particular illustrative embodiment, a method of forming a magnetic tunnel junction (MTJ) device is disclosed that includes forming a trench in a substrate. The method further includes depositing a magnetic tunnel junction (MTJ) structure within the trench. The MTJ structure includes a bottom electrode, a fixed layer, a tunnel barrier layer, a free layer, and a top electrode. The method also includes planarizing the MTJ structure. In a particular example, the MTJ structure is planarized using a Chemical Mechanical Planarization (CMP) process.

Owner:QUALCOMM INC

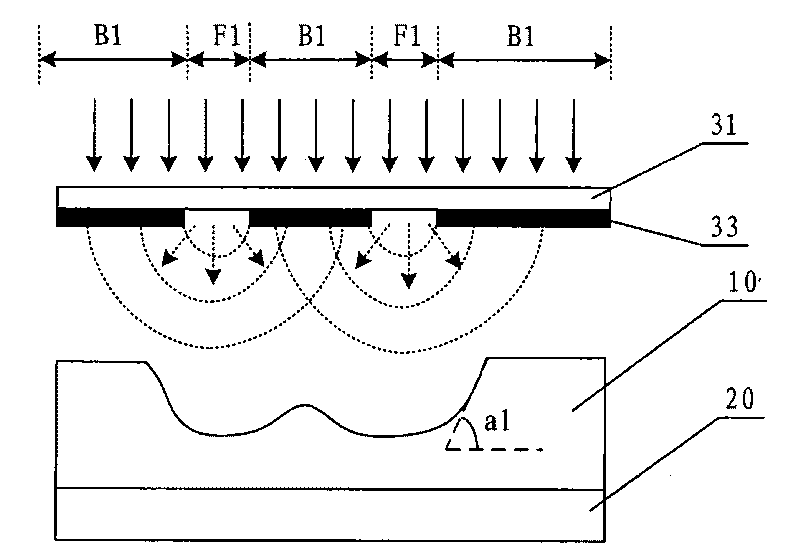

Mask plate and manufacture method thereof

ActiveCN101738846AImprove yield rateImprove electrical performanceSemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentEngineeringPhotoresist

The invention relates to a mask plate and a manufacture method thereof. The mask plate comprises a lightproof region, a fully transparent region and a partial transparent region; the partial transparent region is formed in a such way that a semi-transparent part and a transparent part are alternatively arranged. The invention is a new mask plate manufactured by combining a grey mask plate technique and halftone mask plate technique; the mask plate ensures that the exposure of photoresist at the lower part of the partial nonopaque region is uniform when in use, which is beneficial to forming the smooth surface of a partial maintaining region of the photoresist, thereby facilitating the TFT groove etch and improving the yield of array substrates, at the same time, the obliquity of the photoresist at the edge of the partial maintaining region of the photoresist is increased, thereby the technique can be accurately controlled in the process of forming the TFT groove.

Owner:K TRONICS (SUZHOU) TECH CO LTD +1

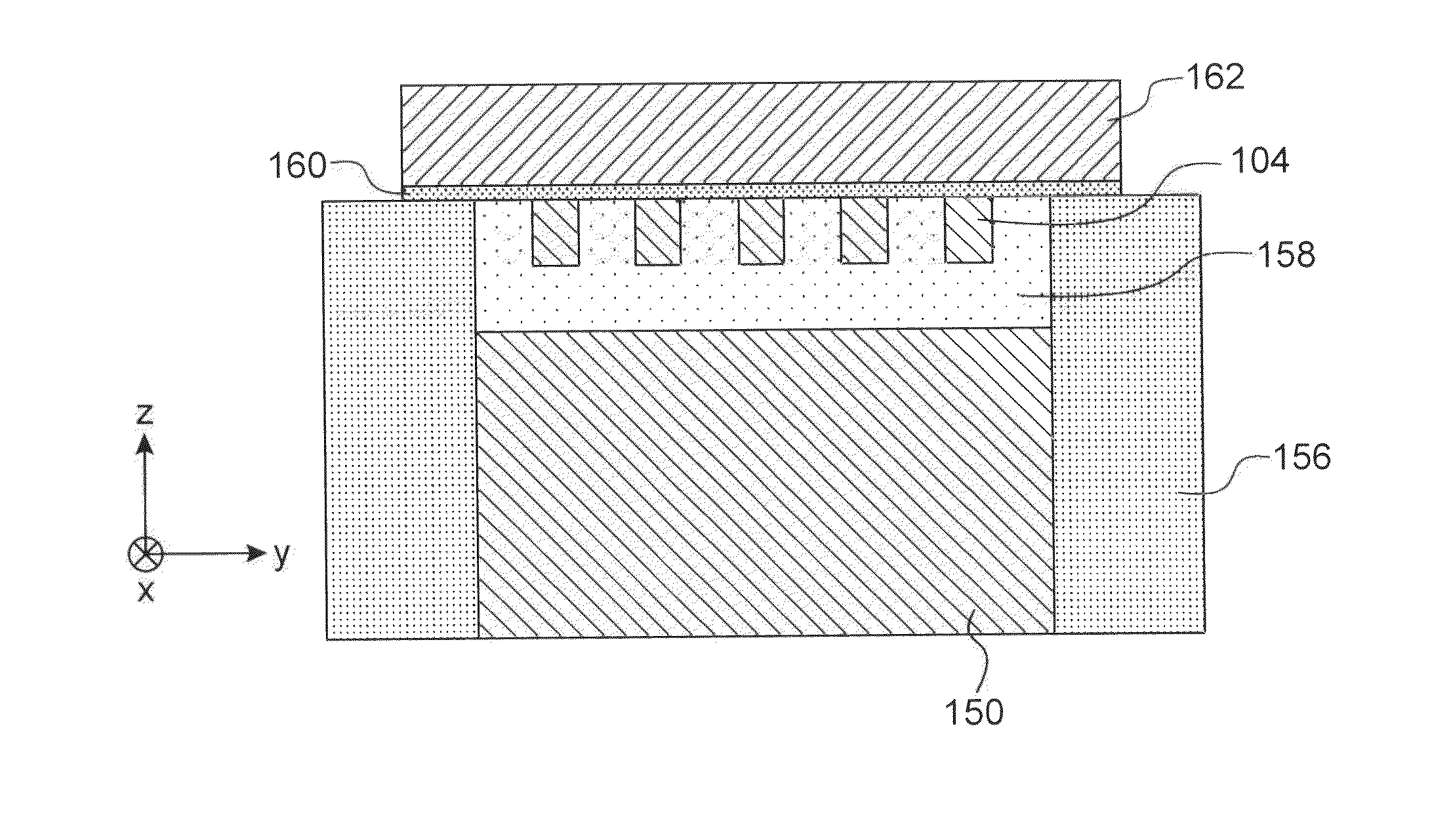

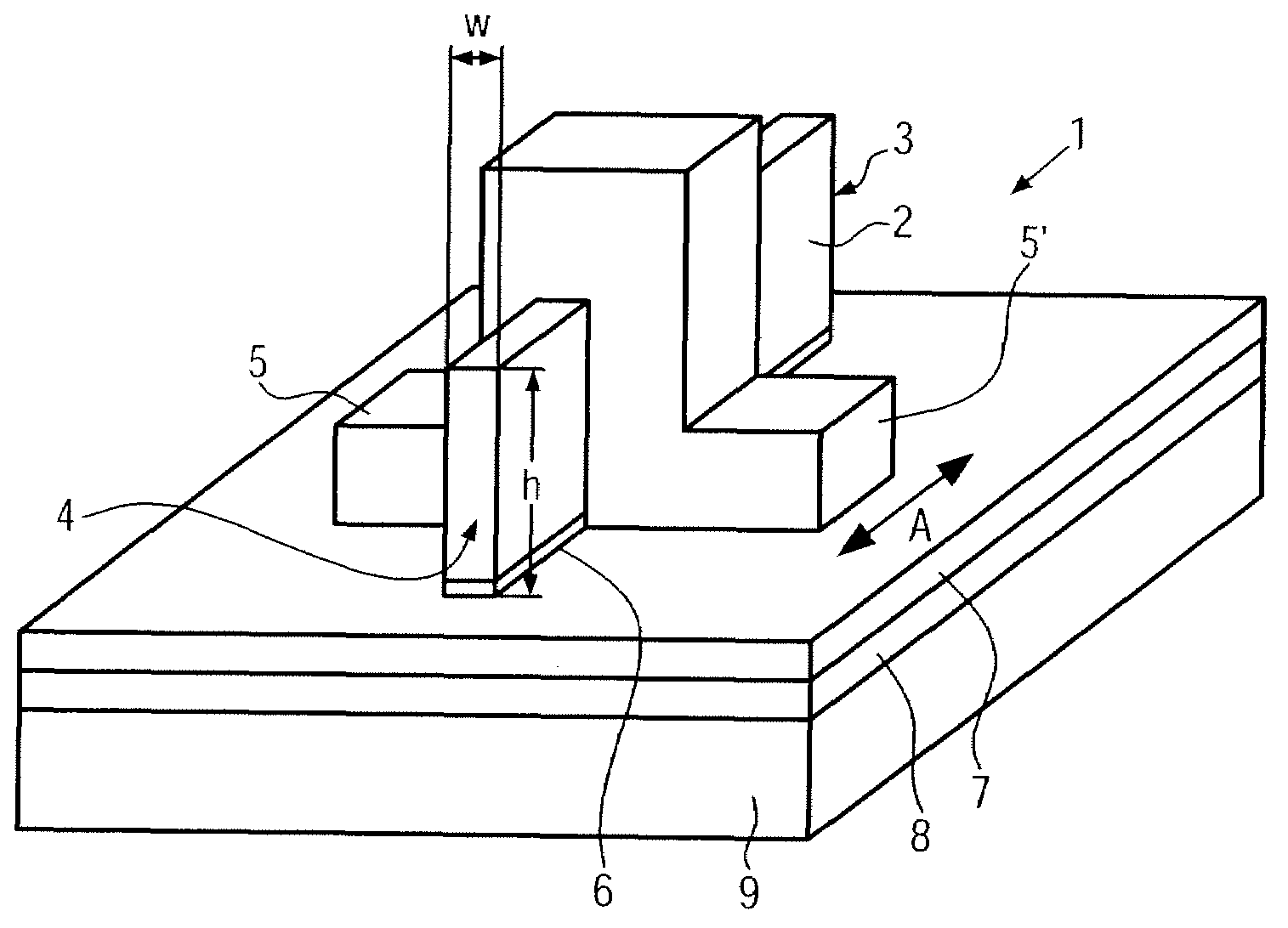

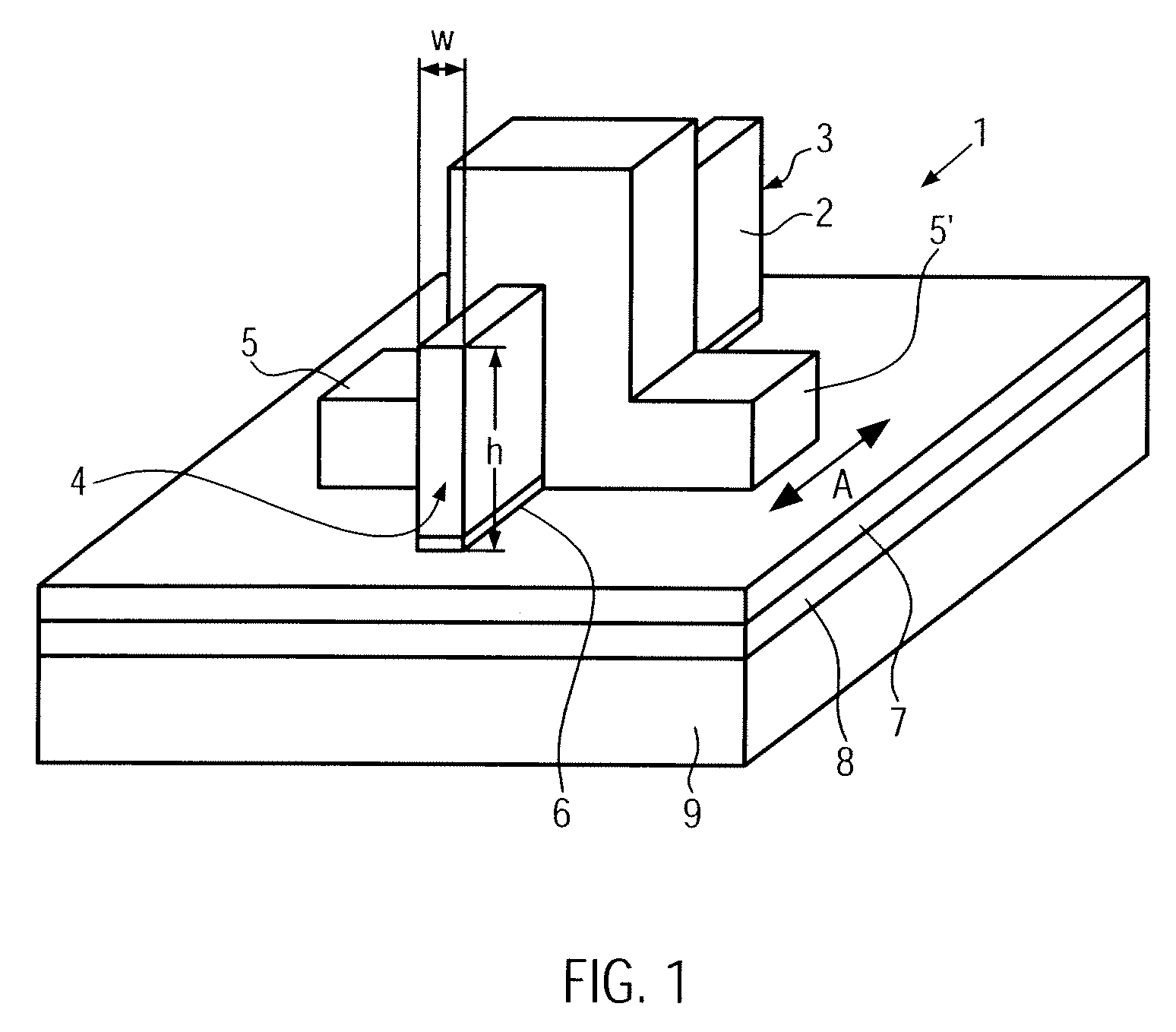

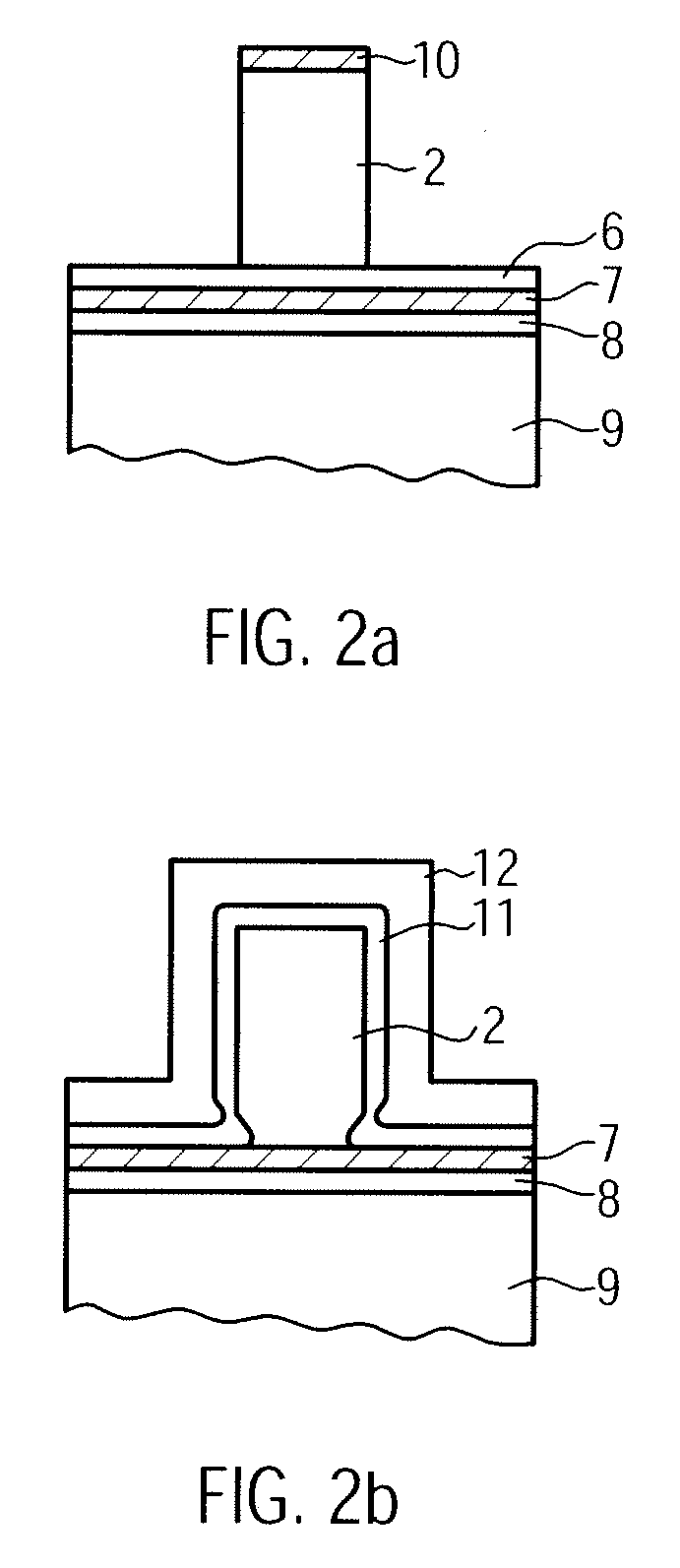

Nanowire semiconductor device partially surrounded by a grating

ActiveUS20150194489A1Easy to carryImprove electrical performanceTransistorNanoinformaticsGate dielectricNanowire

A semiconductor device is provided, including two semiconductor nanowires superimposed one on top of the other or arranged next to one another, spaced one from the other and forming channel regions of the semiconductor device, a dielectric structure entirely filling a space between the nanowires and which is in contact with the nanowires, a gate dielectric and a gate covering a first of the nanowires, sidewalls of the nanowires and sidewalls of the dielectric structure when the nanowires are superimposed one on top of the other, or covering a part of the upper faces of the nanowires and a part of an upper face of the dielectric structure when the nanowires are arranged next to one another, and wherein the dielectric structure comprises a portion of dielectric material with a relative permittivity greater than or equal to 20.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

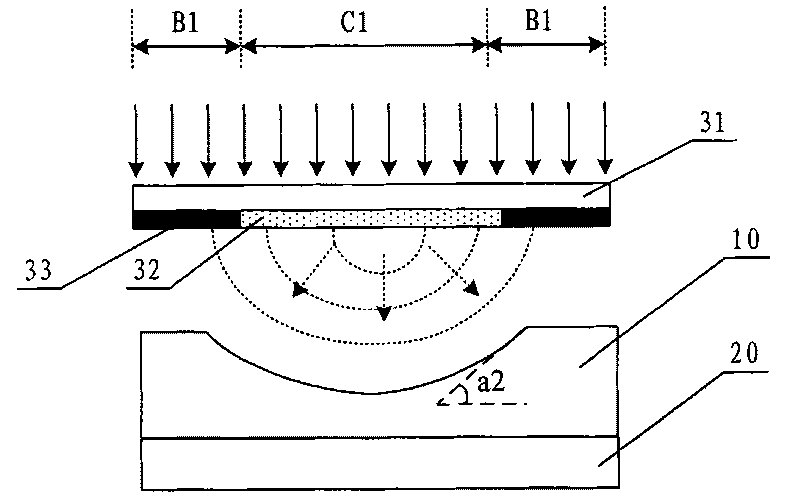

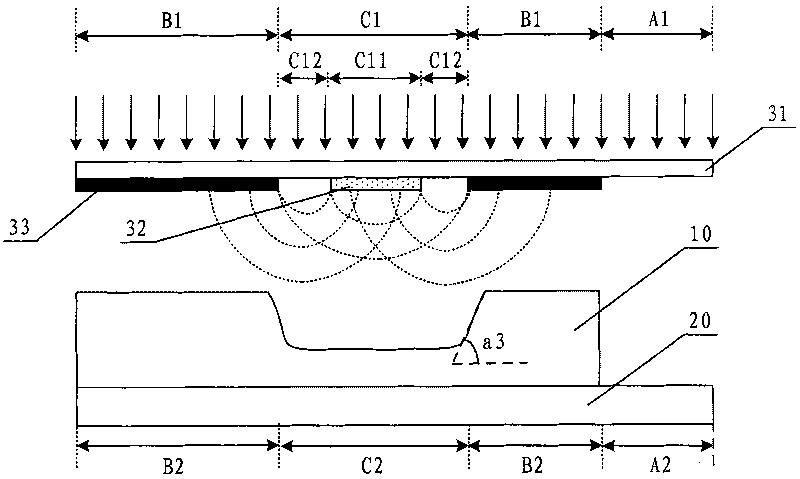

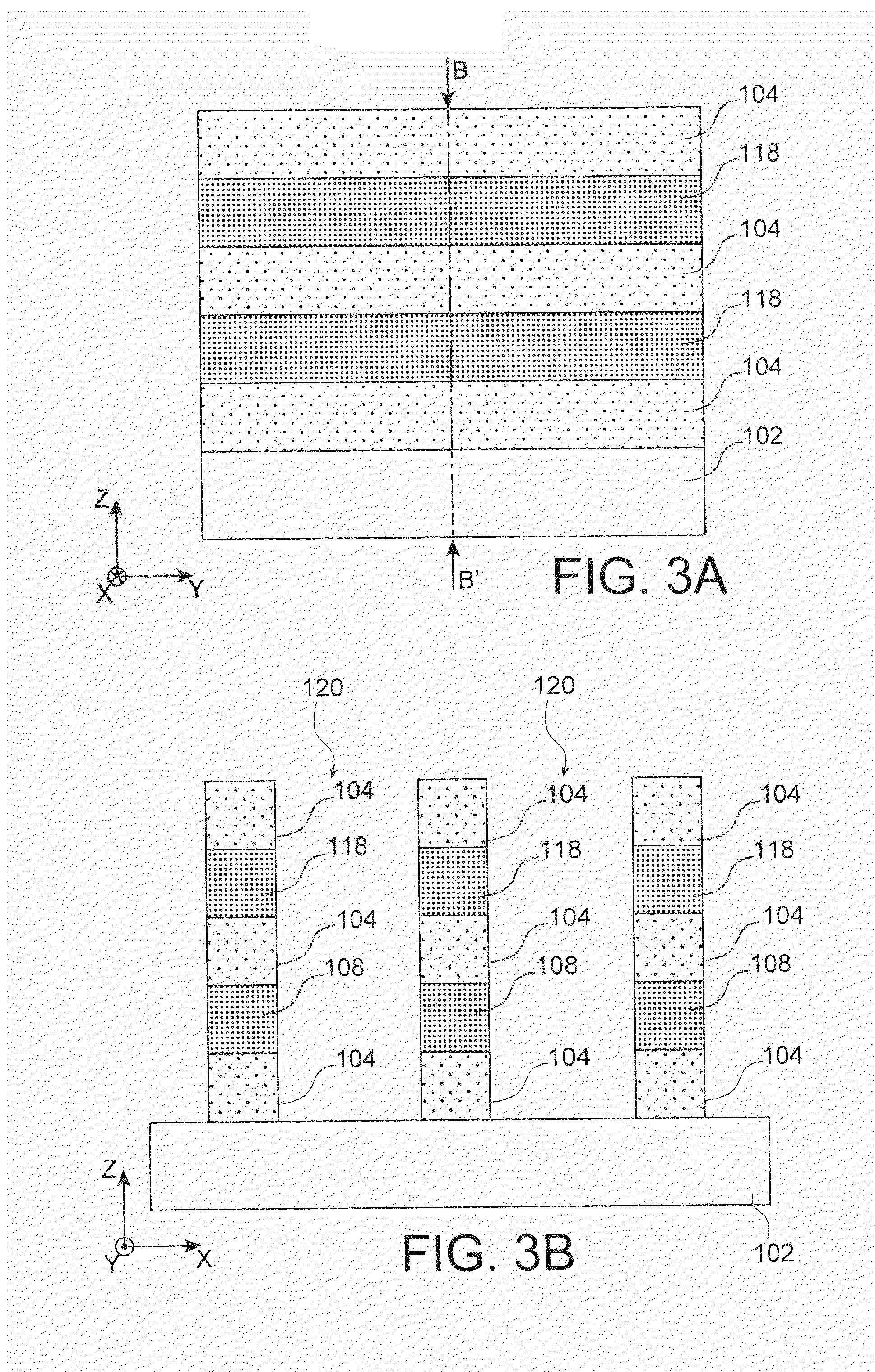

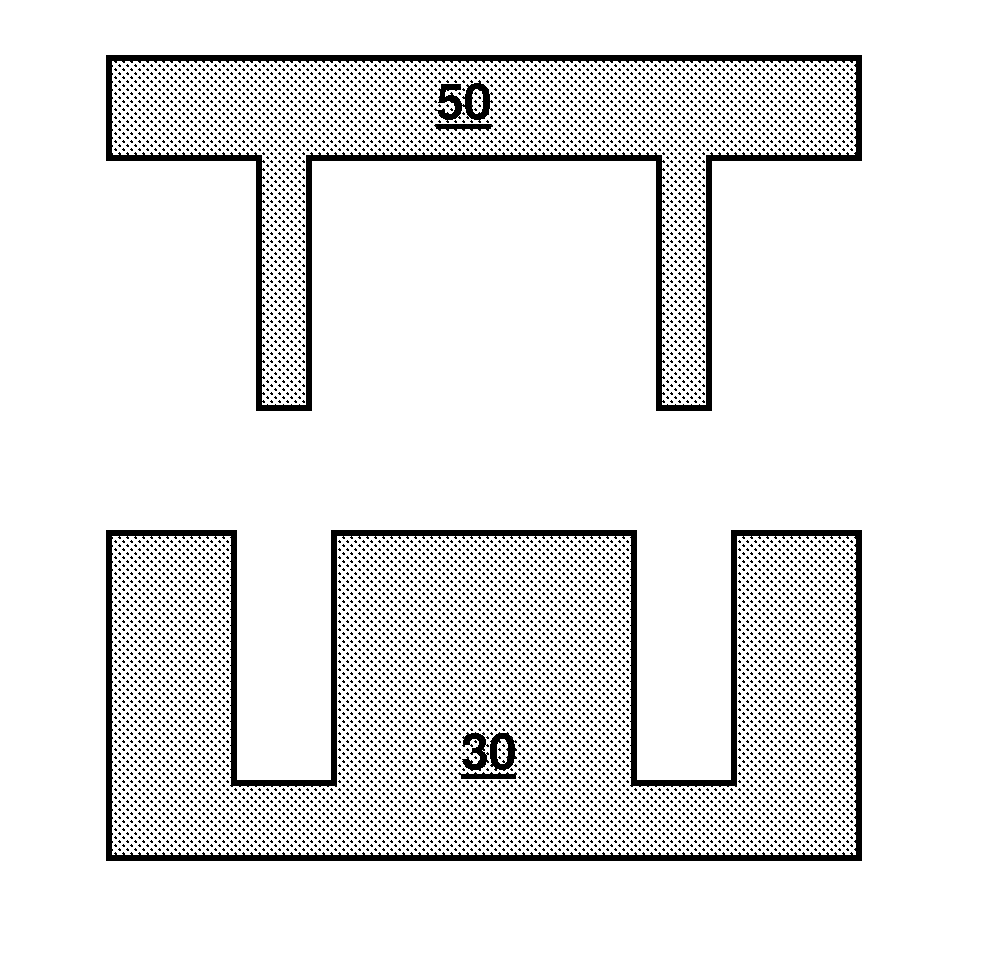

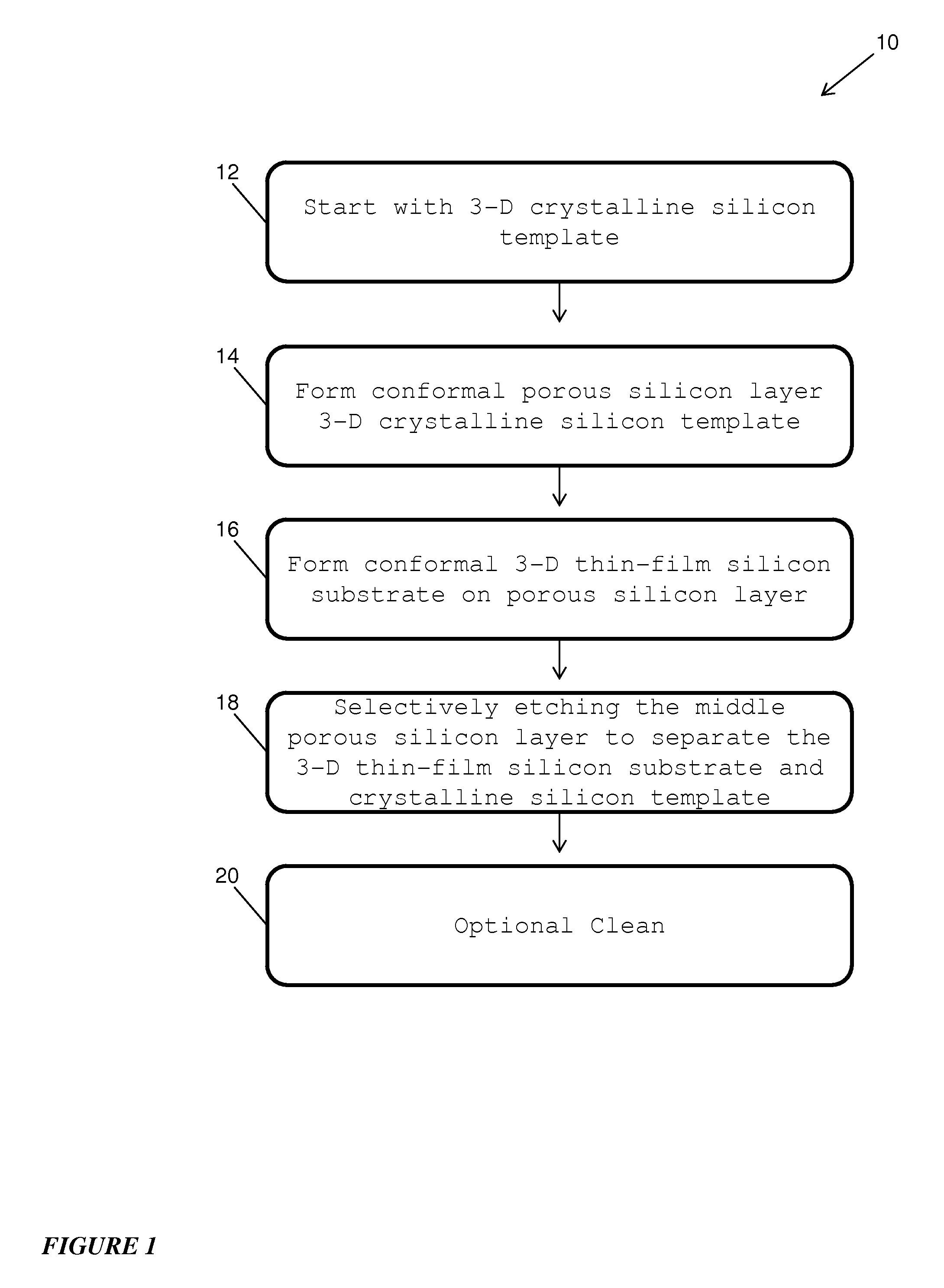

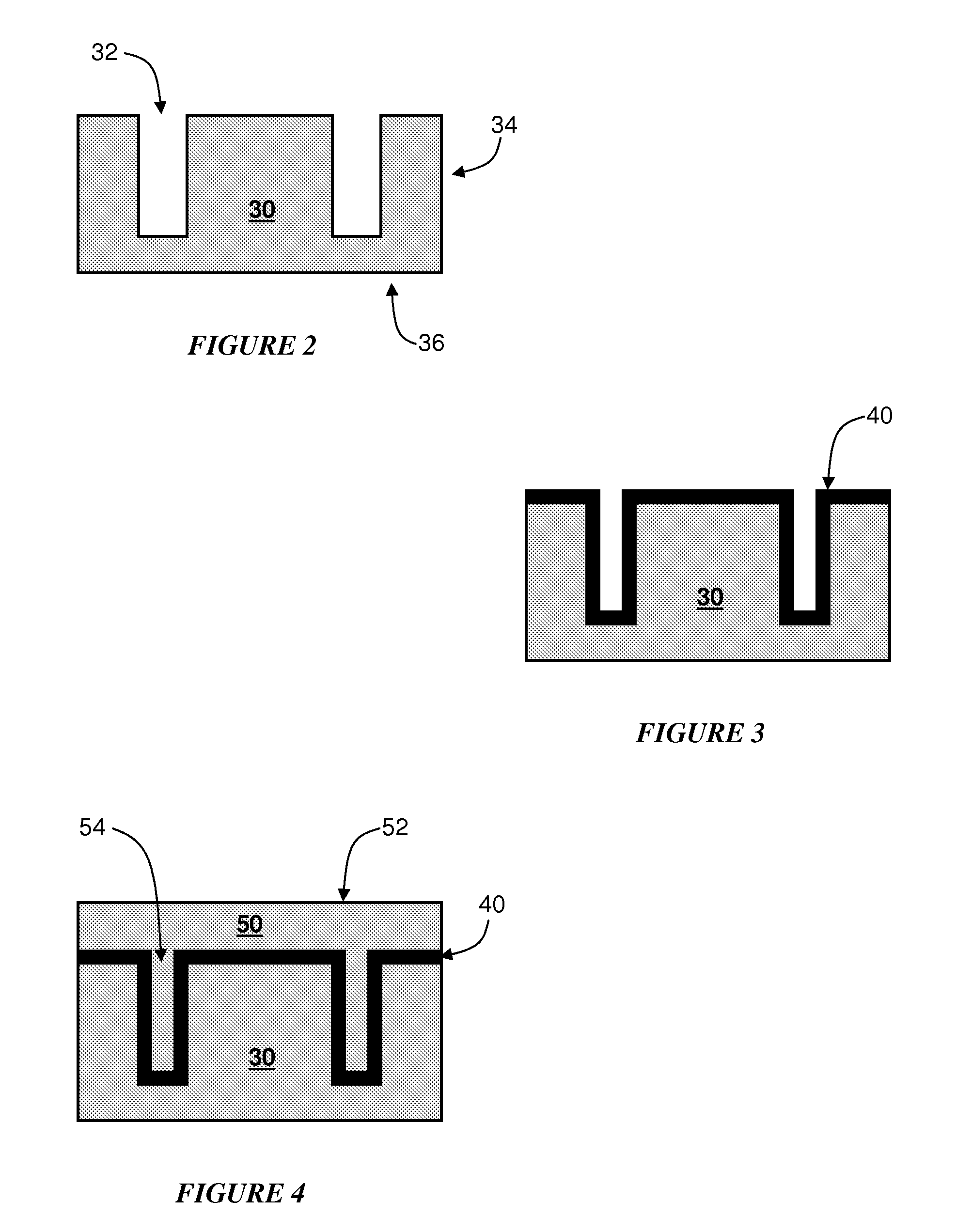

Method For Releasing a Thin-Film Substrate

ActiveUS20100279494A1Easily releaseLow porositySemiconductor/solid-state device manufacturingSemiconductor devicesPorous semiconductorsThin film semiconductors

The present disclosure relates to methods for selectively etching a porous semiconductor layer to separate a thin-film semiconductor substrate (TFSS) having planar or three-dimensional features from a corresponding semiconductor template. The method involves forming a conformal sacrificial porous semiconductor layer on a template. Next, a conformal thin film silicon substrate is formed on top of the porous silicon layer. The middle porous silicon layer is then selectively etched to separate the TFSS and semiconductor template. The disclosed advanced etching chemistries and etching methods achieve selective etching with minimal damage to the TFSS and template.

Owner:BEAMREACH SOLAR INC

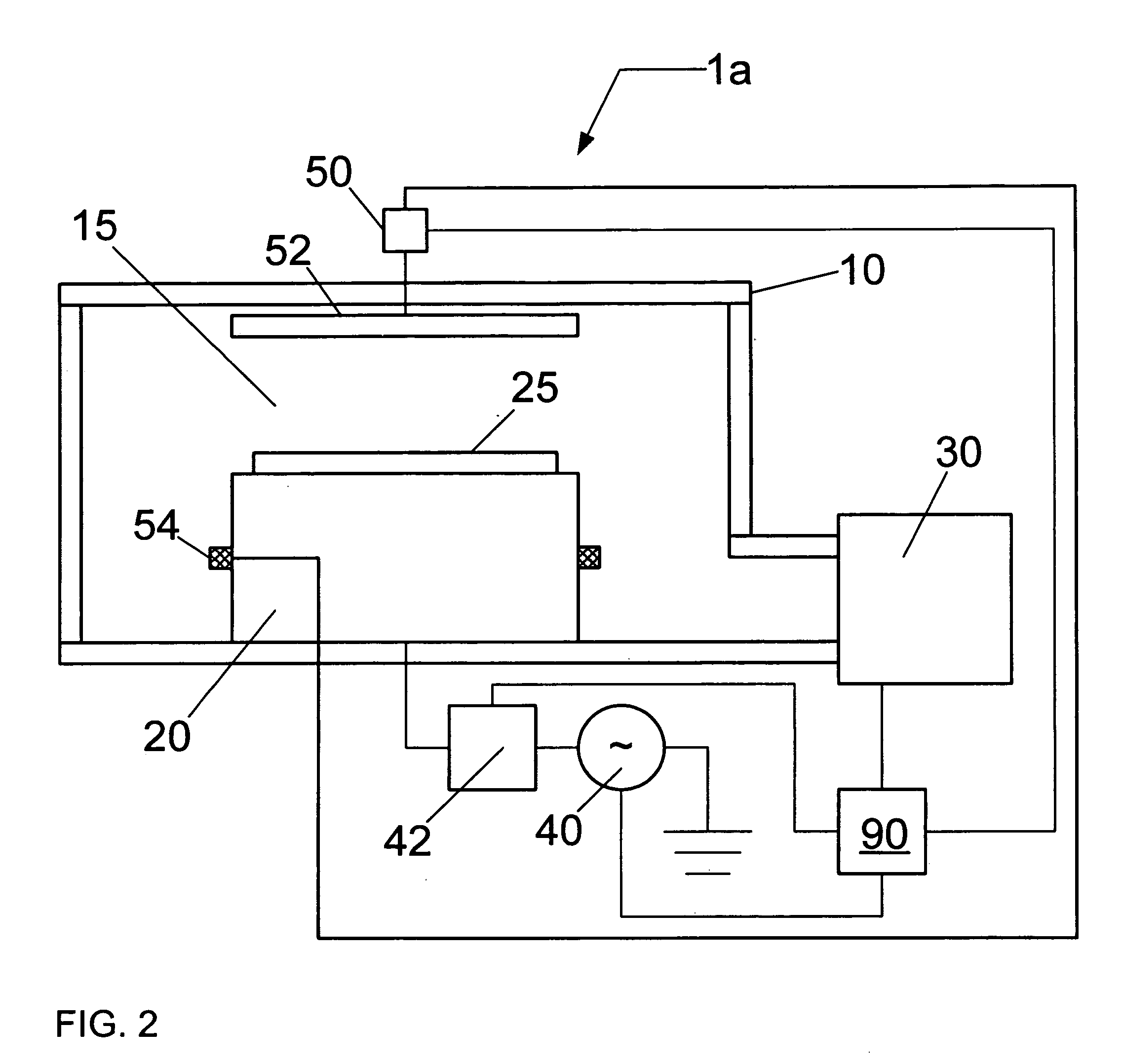

Method and apparatus for detecting endpoint in a dry etching system by monitoring a superimposed DC current

InactiveUS20080026488A1Good etchingFacilitate formation of plasmaSemiconductor/solid-state device testing/measurementElectric discharge tubesElectron temperaturePlasma density

A method and apparatus for detecting the endpoint in a dry plasma etching system comprising a first electrode (e.g., upper electrode) and a second electrode (e.g., lower electrode) upon which a substrate rests is described. A direct current (DC) voltage is applied between the first electrode and a ring electrode surrounding the second electrode, and the DC current is monitored to determine the endpoint of the etching process. The DC current is affected by the impedance of the plasma, and therefore responds to many variations including, for example, the plasma density, electron / ion flux to exposed surfaces, the electron temperature, etc.

Owner:TOKYO ELECTRON LTD +1

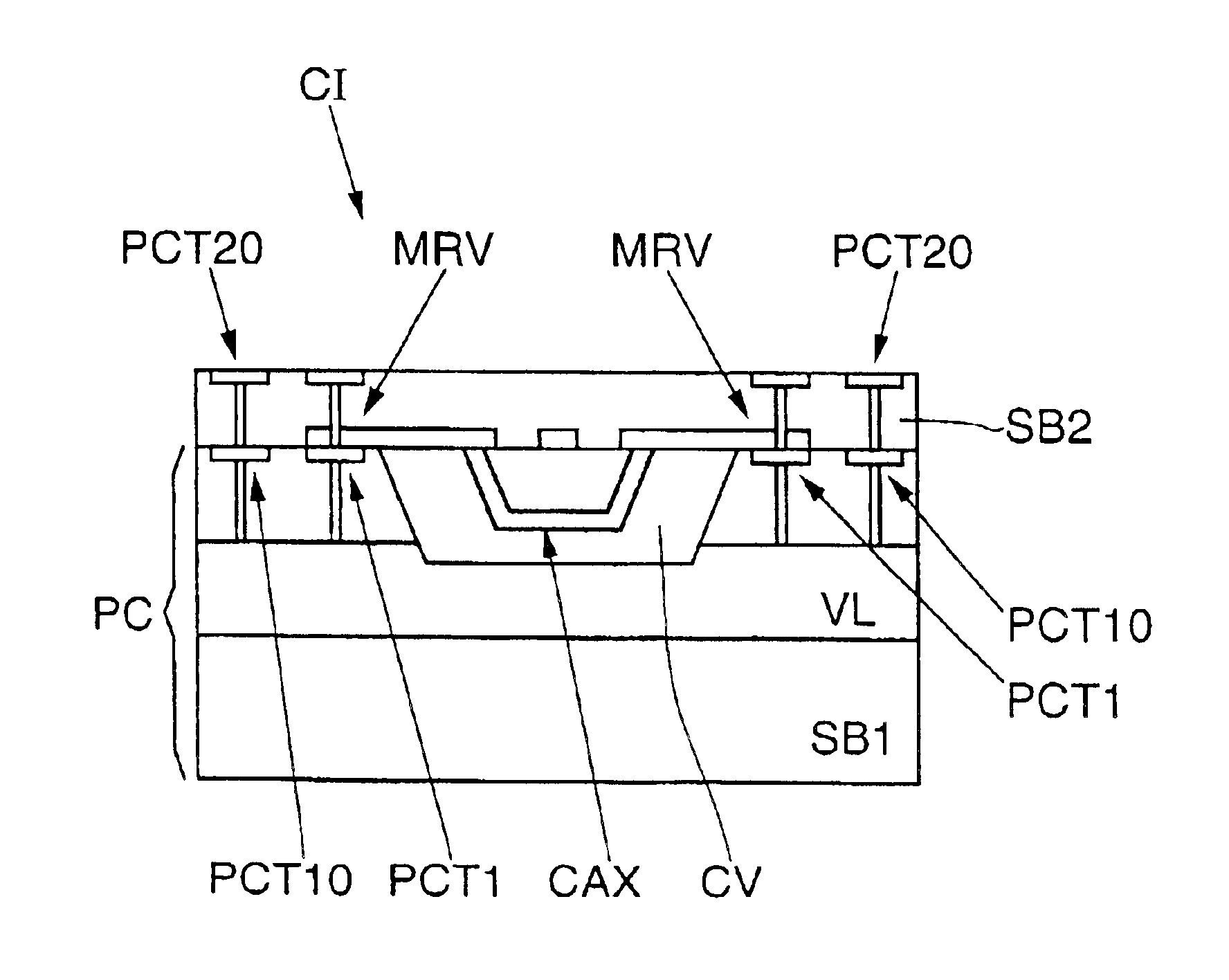

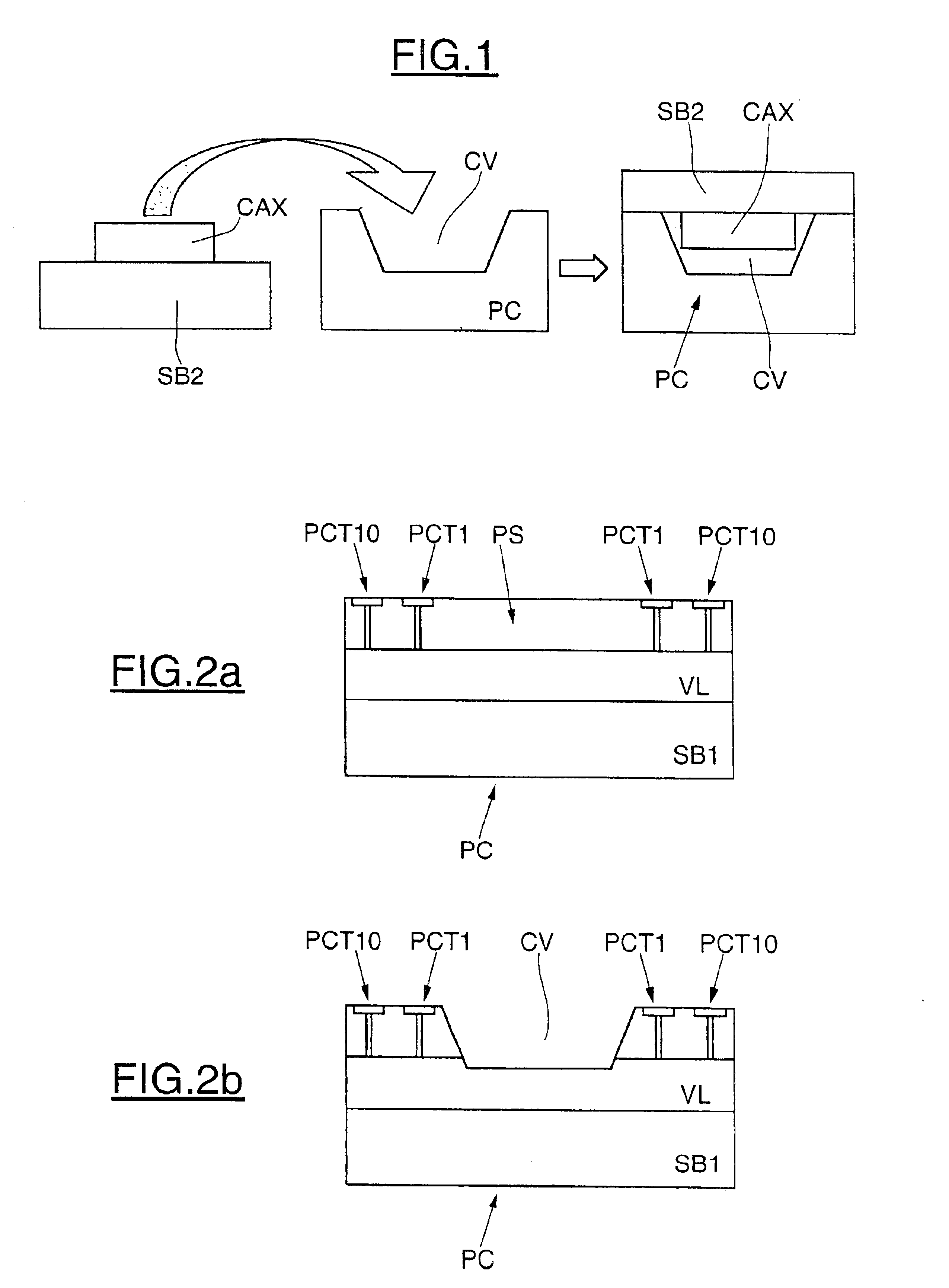

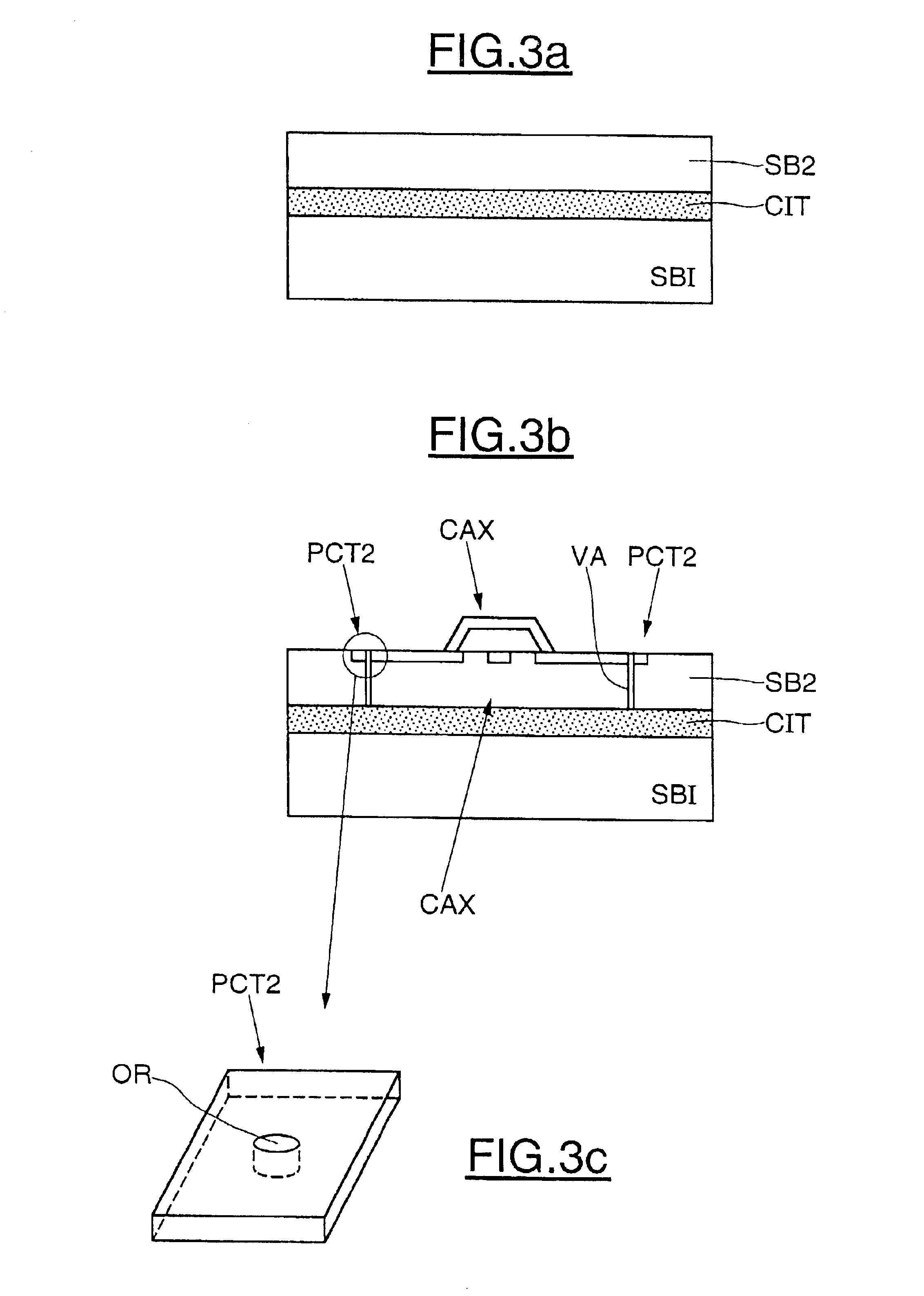

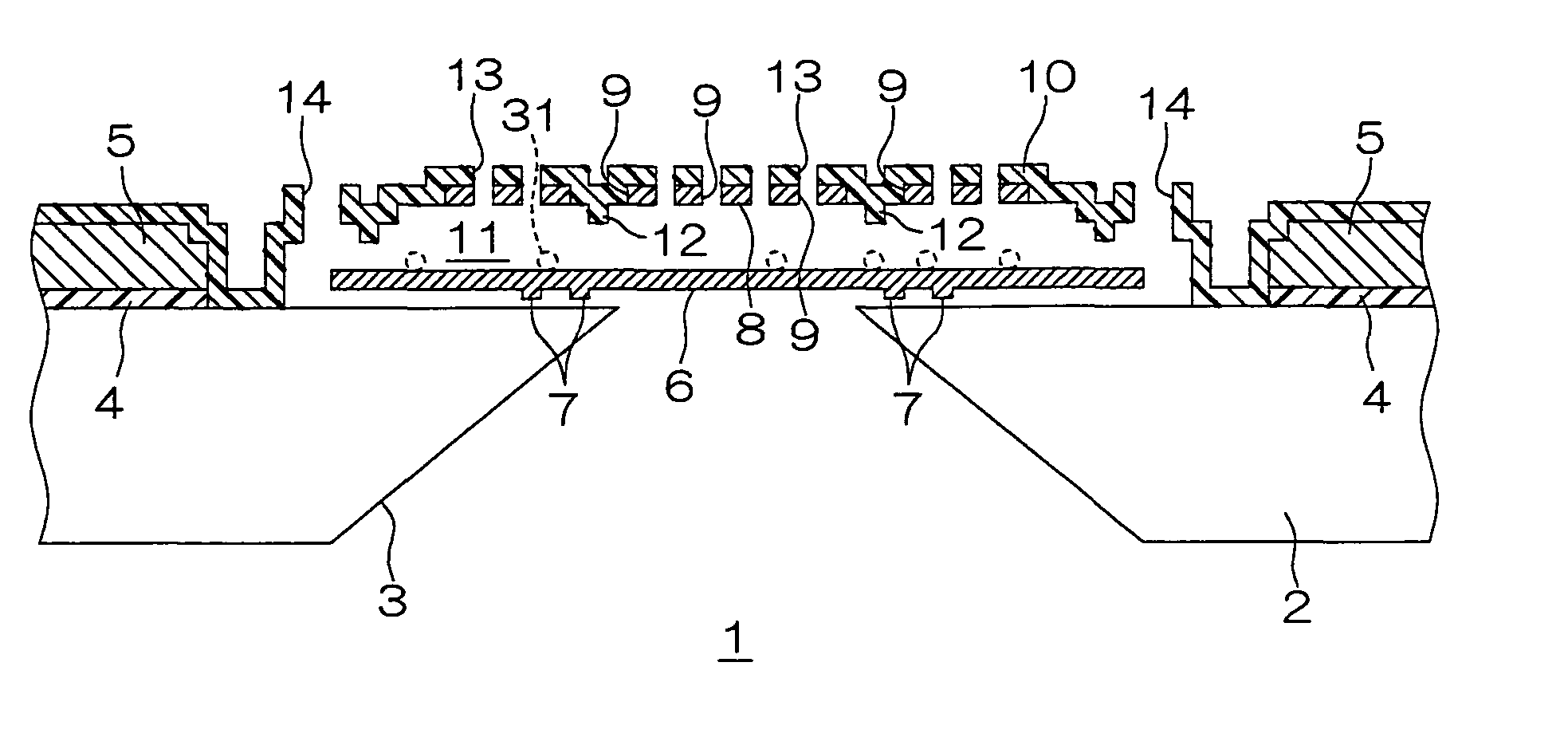

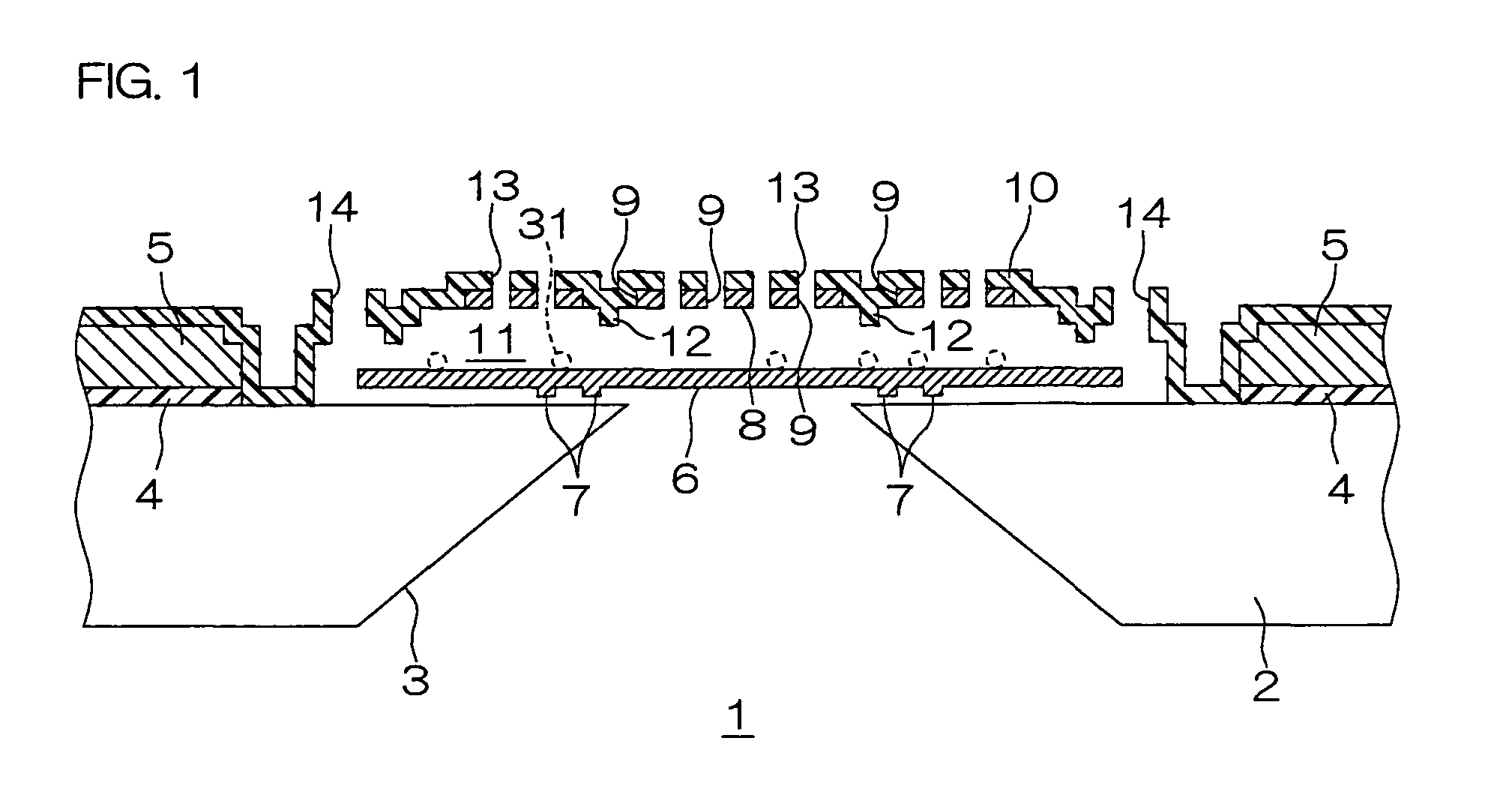

Integrated circuit comprising an auxiliary component, for example a passive component or a microelectromechanical system, placed above an electronic chip, and the corresponding fabrication process

InactiveUS6846690B2ChoiceGood etchingPrecision positioning equipmentSolid-state devicesEngineeringMicroelectromechanical systems

The fabrication of an integrated circuit includes a first phase of producing an electronic chip and a second phase of producing at least one auxiliary component placed above the chip and of producing a protective cover which covers the auxiliary component. The first phase of producing the chip is effected from a first semiconductor substrate and comprises the formation of a cavity lying in a chosen region of the chip and emerging at the upper surface of the chip. The second production phase includes the production of the auxiliary component from a second semiconductor substrate, separate from the first, and then the placement in the cavity of the auxiliary component supported by the second substrate and the mutual adhesion of the second substrate to the upper surface of the chip lying outside the cavity. The second substrate then also forms the protective cover.

Owner:STMICROELECTRONICS SRL

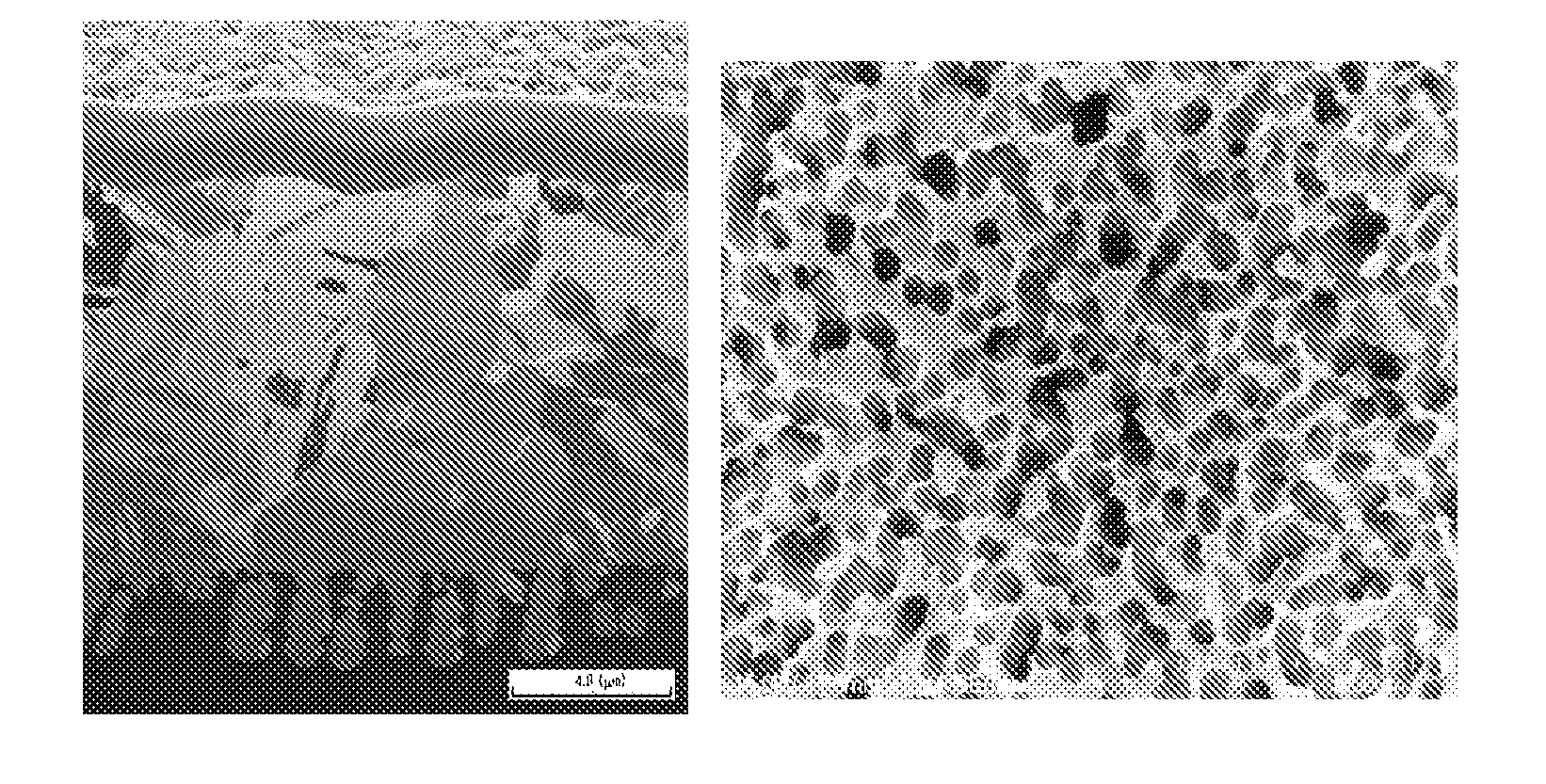

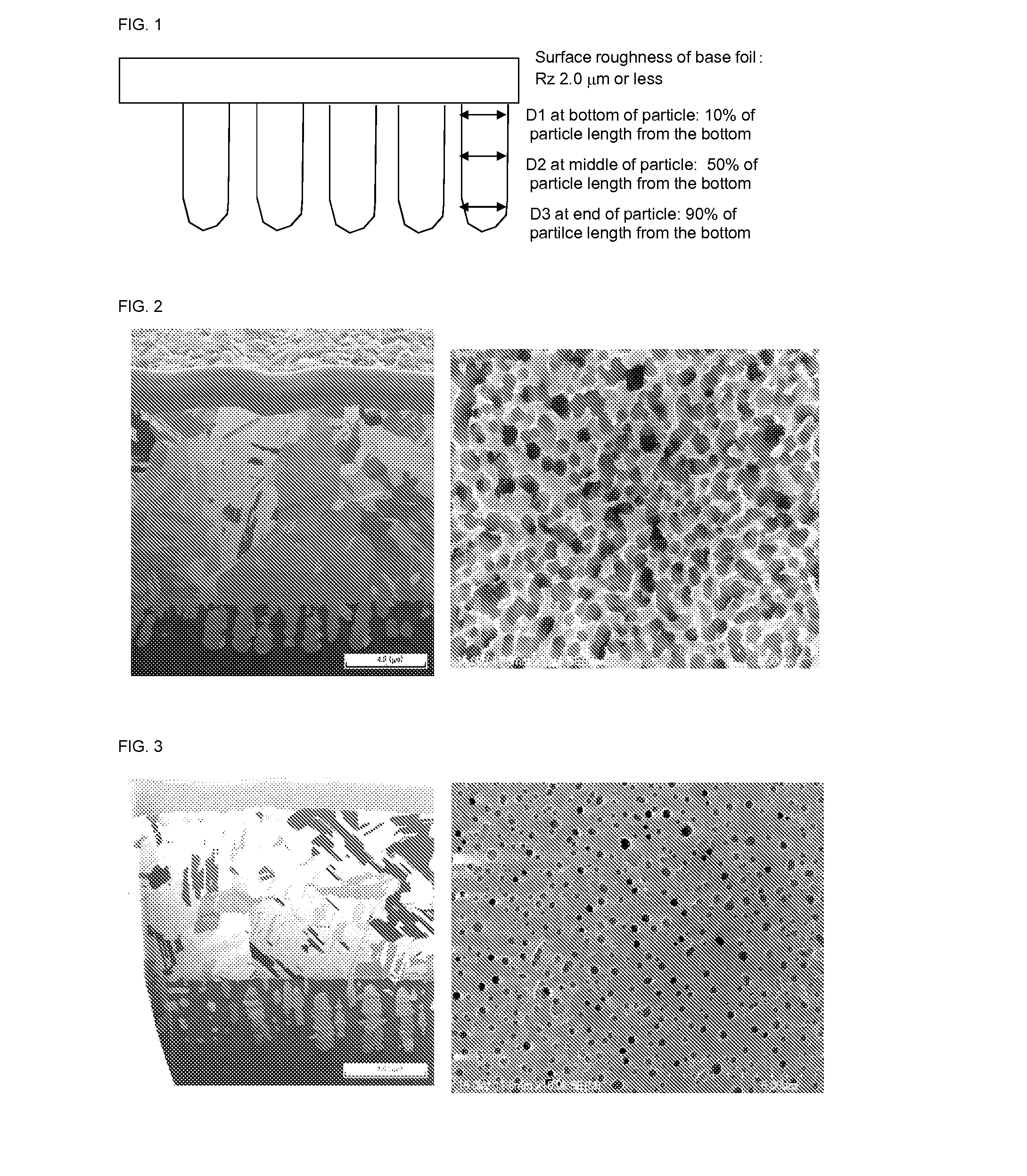

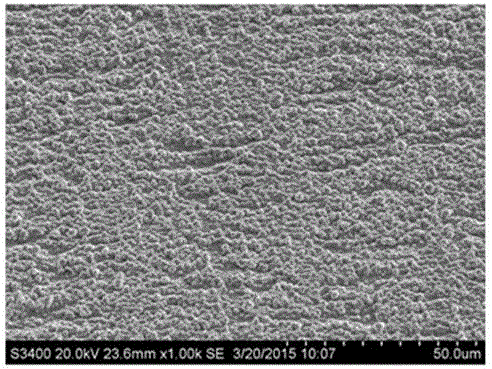

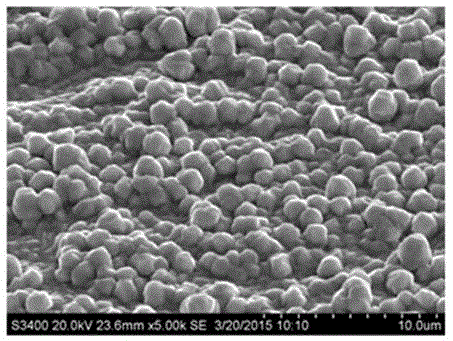

Copper Foil with Carrier, Method of Producing Same, Copper Foil with Carrier for Printed Wiring Board, and Printed Wiring Board

ActiveUS20150047884A1High bonding strengthHigh peel strengthCell electrodesResistor manufactureSemiconductor packageCopper foil

Provided is a copper foil for a printed wiring board including a roughened layer on at least one surface thereof. In the roughened layer, the average diameter D1 at the particle bottom being apart from the bottom of each particle by 10% of the particle length is 0.2 to 1.0 μm, and the ratio L1 / D1 of the particle length L1 to the average diameter D1 at the particle bottom is 15 or less. In the copper foil for printed wiring board, when a copper foil for printed wiring having a roughened layer is laminated to a resin and then the copper layer is removed by etching, the sum of areas of holes accounting for the resin roughened surface having unevenness is 20% or more. The present invention involves the development of a copper foil for a semiconductor package substrate that can avoid circuit erosion without causing deterioration in other properties of the copper foil. In particular, an object of the present invention is to provide a copper foil for a printed wiring board and a method of producing the copper foil, in which the adhesion strength between the copper foil and the resin can be enhanced by improvement of the roughened layer of the copper foil.

Owner:JX NIPPON MINING& METALS CORP

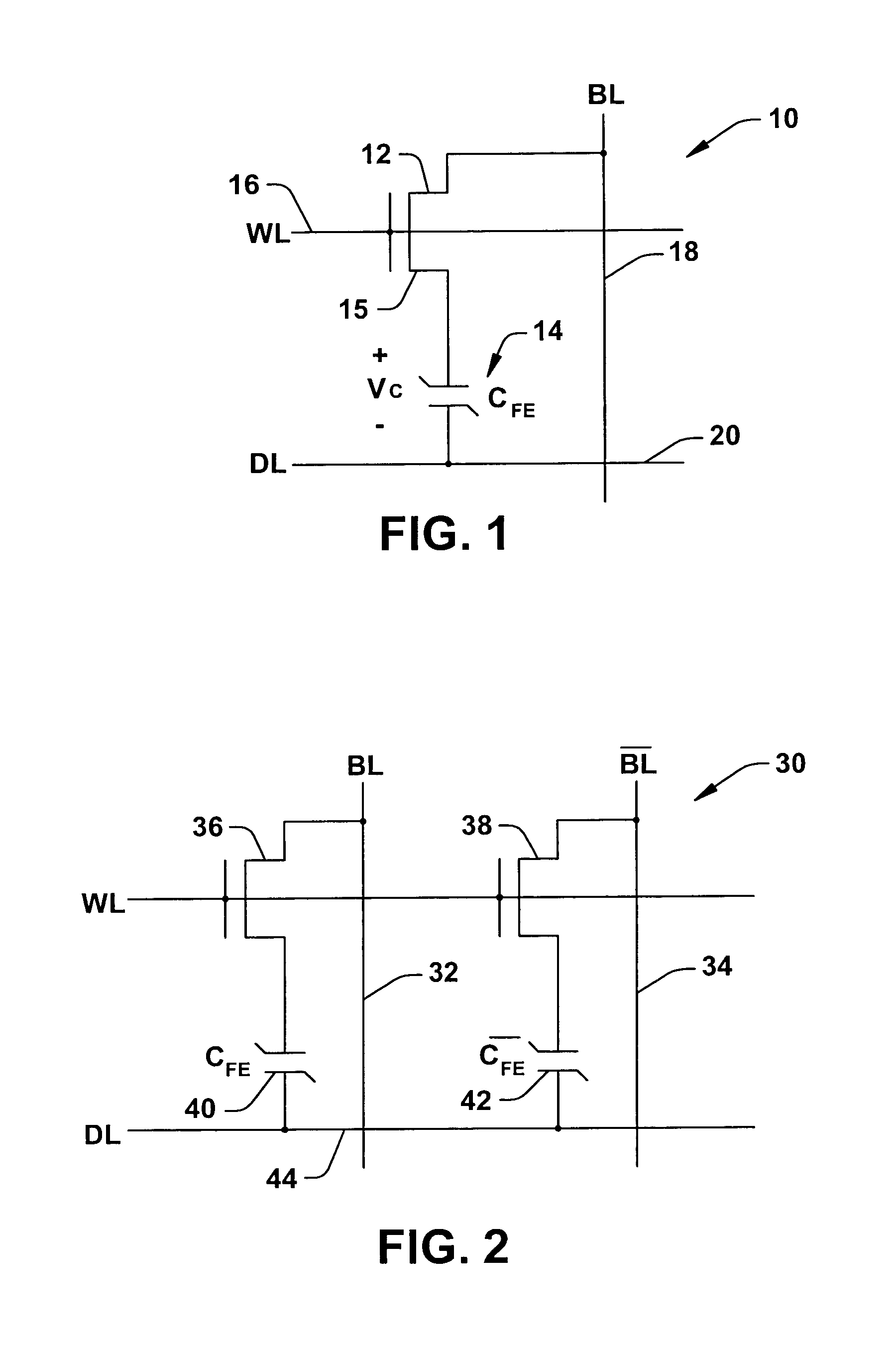

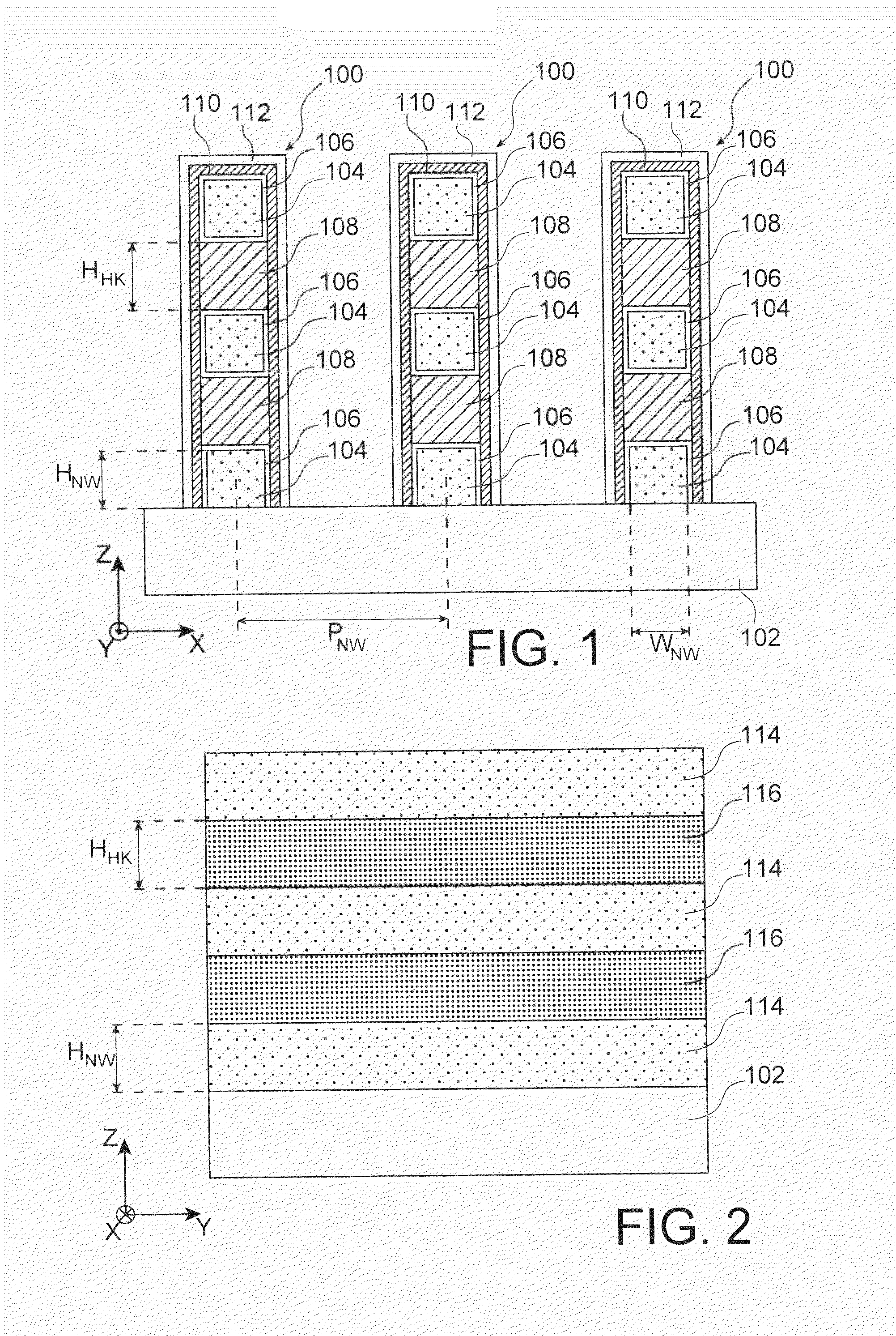

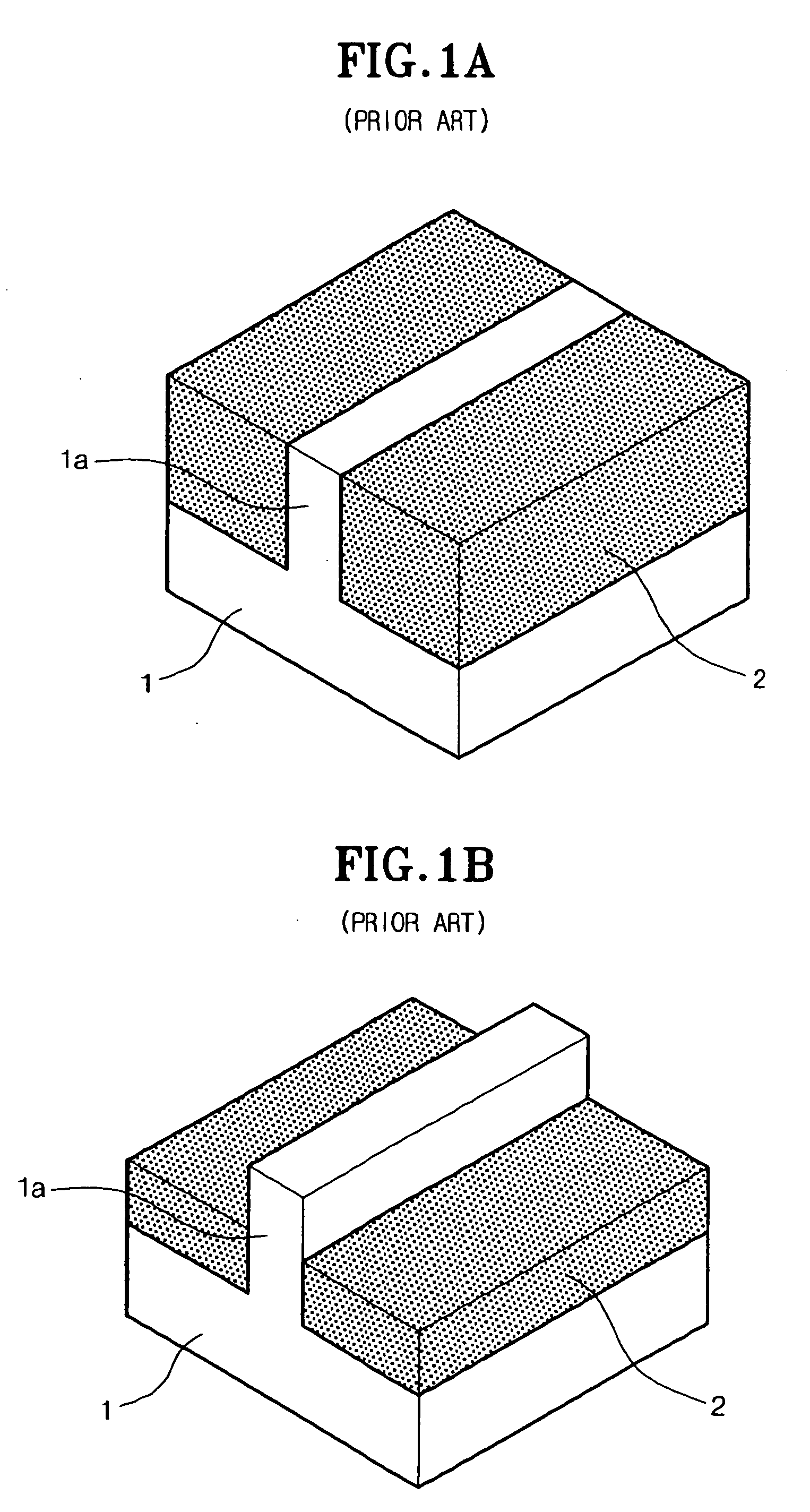

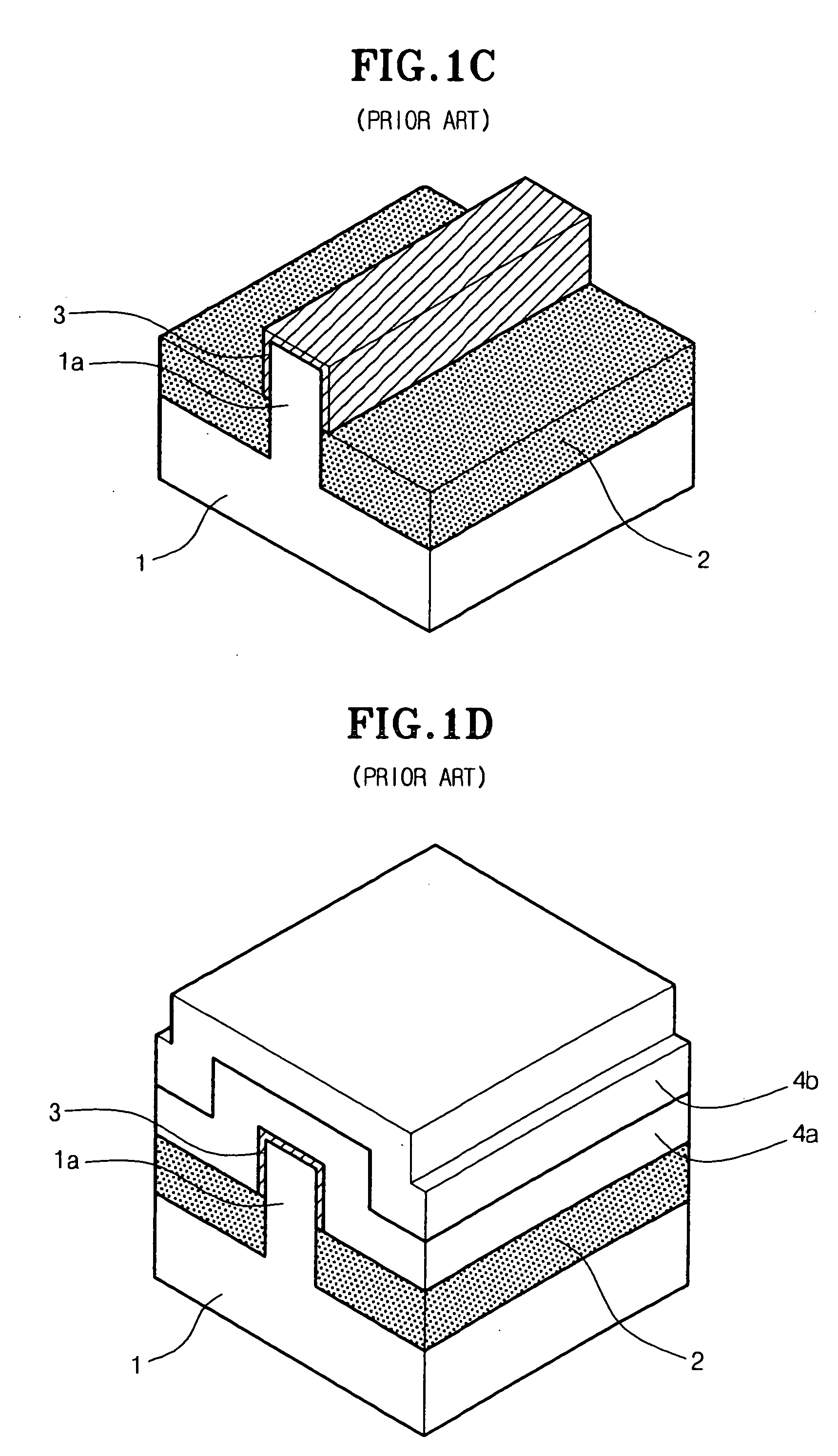

Multiple gate field effect transistor structure and method for fabricating same

InactiveUS20090121288A1Good roundnessGood characteristicSolid-state devicesSemiconductor/solid-state device manufacturingField-effect transistorSilicon oxide

The present invention relates to a Multiple Gate Field Effect Transistor structure and a method for fabricating same. The Multiple Gate Field Effect Transistor structure includes a fin structure made from at least one active semiconductor layer of a silicon on insulator (SOI) structure on a buried insulator of the structure. The Multiple Gate Field Effect Transistor structure also includes an insulator of at least one high-k layer of a material having a dielectric constant that is higher than silicon oxide. This has the advantage that the high-k layer acts as a better etch stop than silicon oxide during formation and cleaning of the fin resulting in a lower recess and undercut effect on the socket of the fin. This leads to a higher stability of the formed fin and enables a smooth finishing of the fin by etching and cleaning steps.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

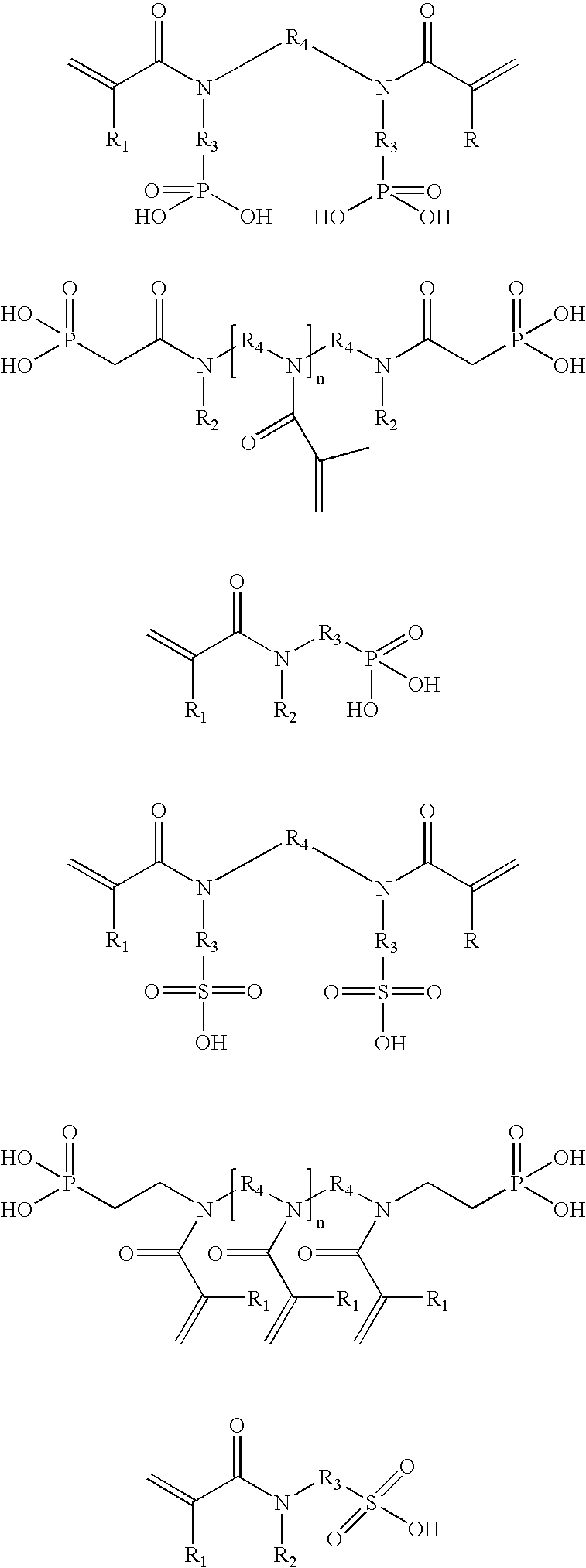

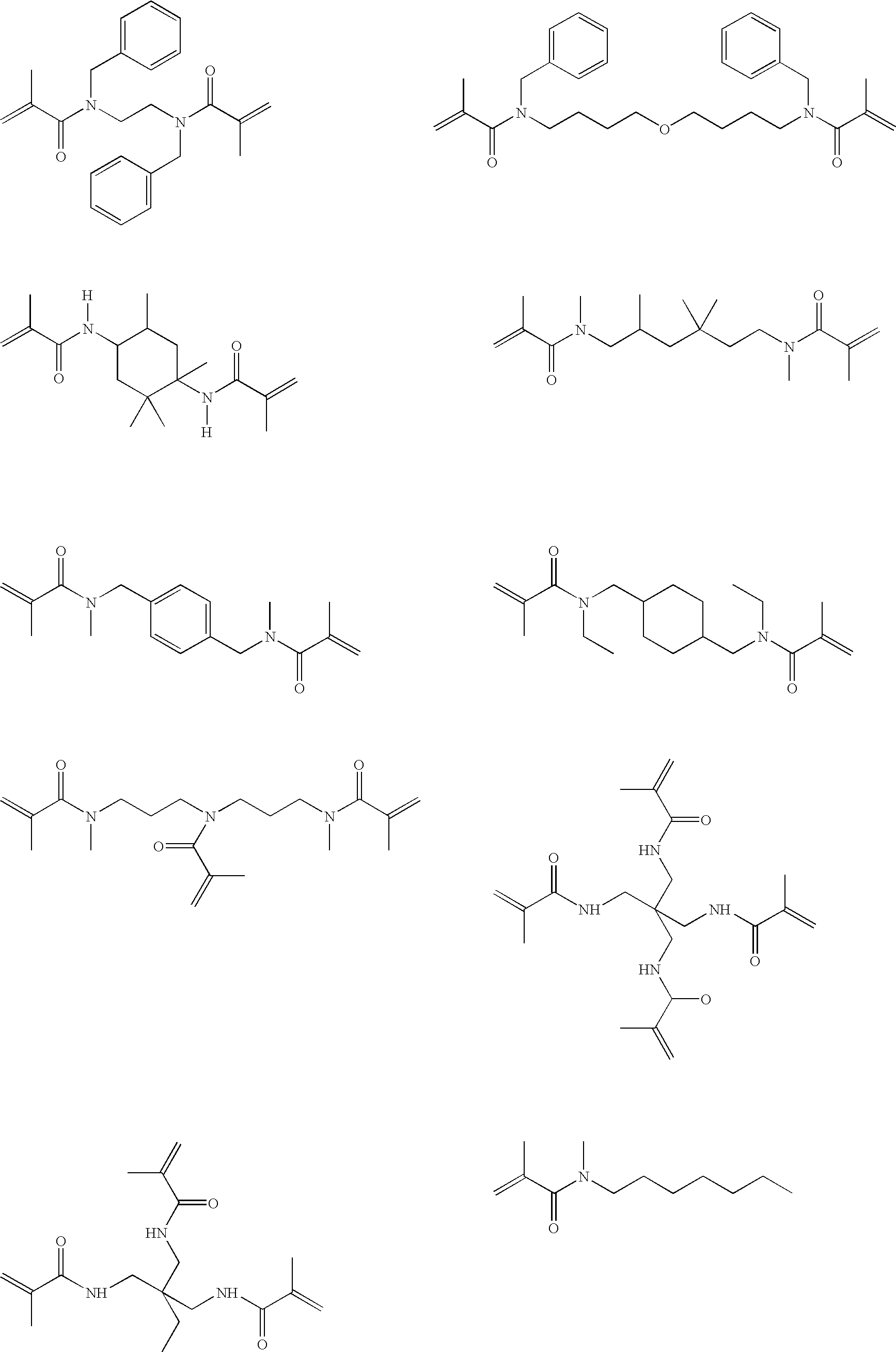

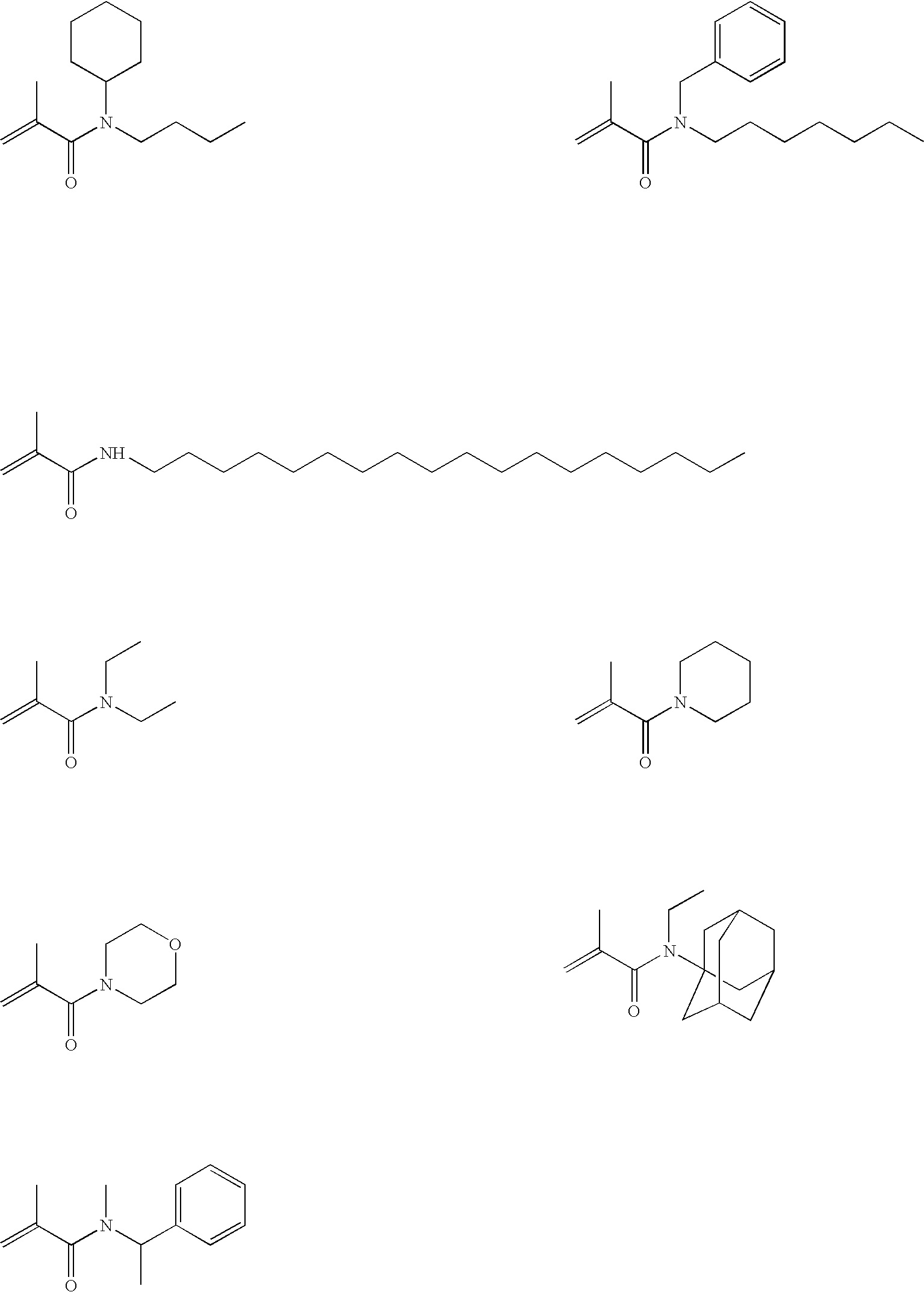

Hydrolysis stable self-etching,self-priming adhesive

InactiveUS20040266906A1Good etchingHigh bonding strengthImpression capsOrganic compound preparationEtchingAdhesive

An aqueous one-pack self-etching and self-priming dental adhesive composition having a pH of at most 2, which comprises: (i) a polymerizable N-substituted alkylacrylic or acrylic acid amide monomer which optionally contains an inorganic acidic moiety selected from a phosphonic acid moiety or a sulfonic acid moiety, and (ii) a curing system.

Owner:KLEE JOACHIM +2

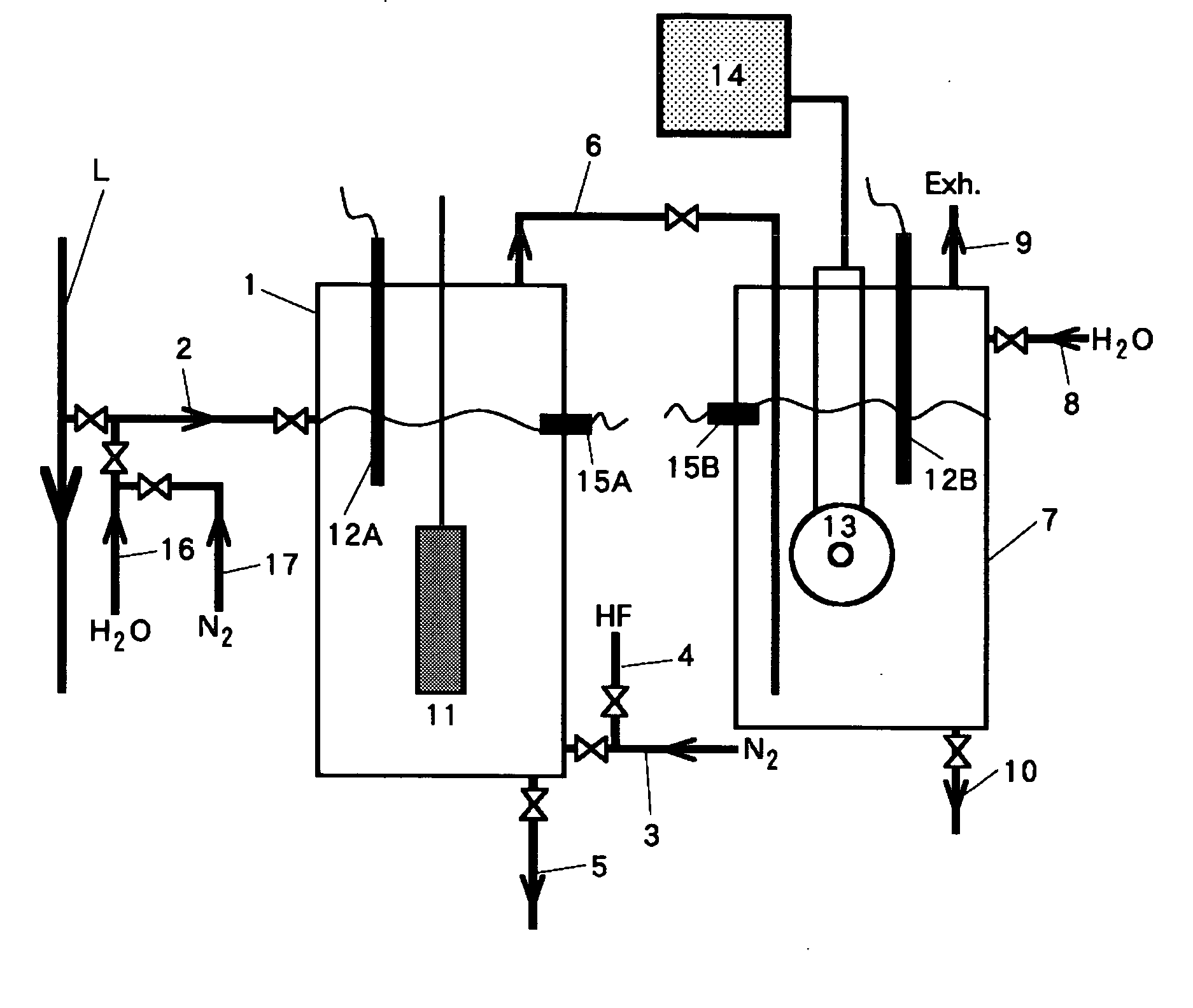

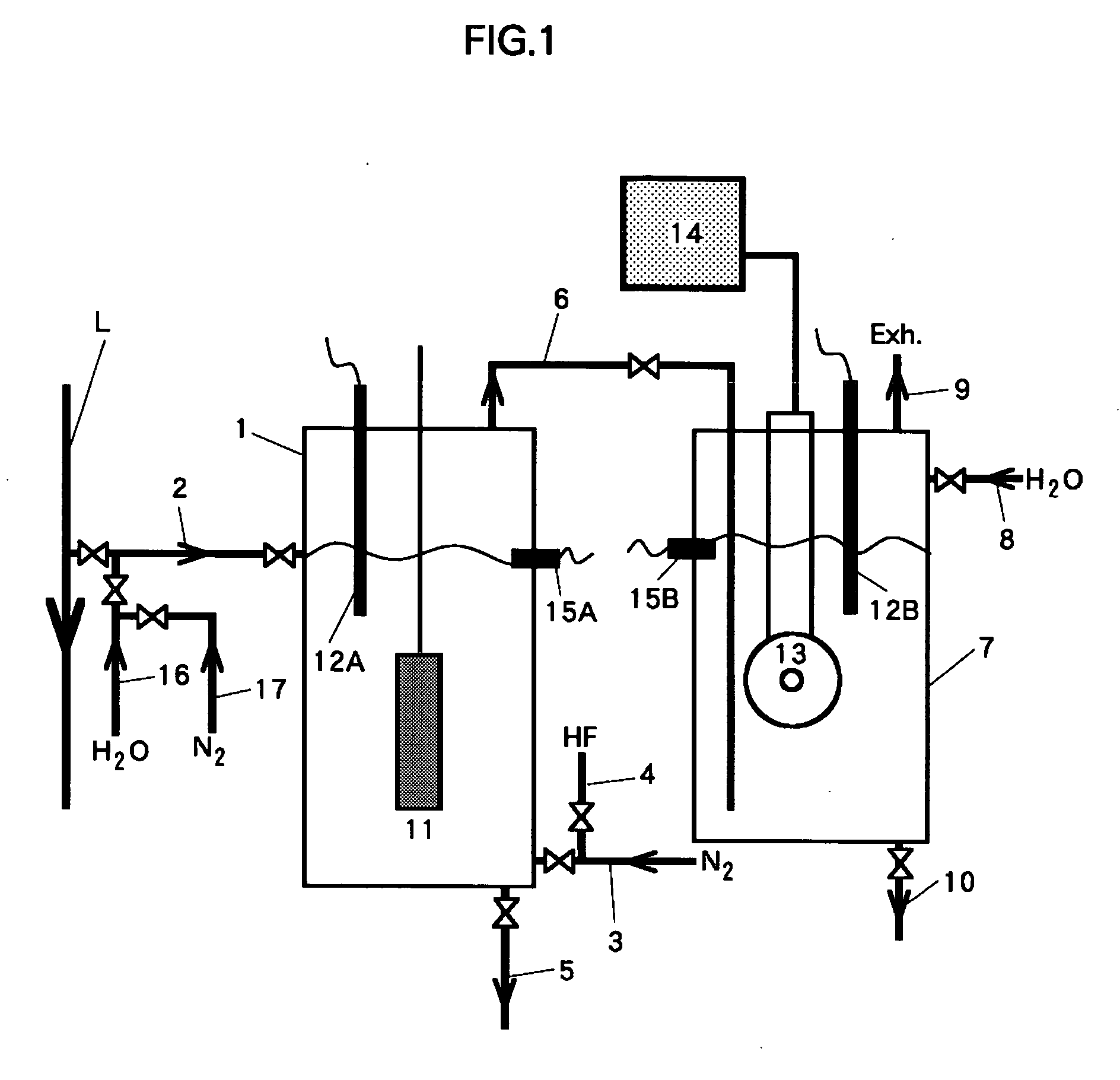

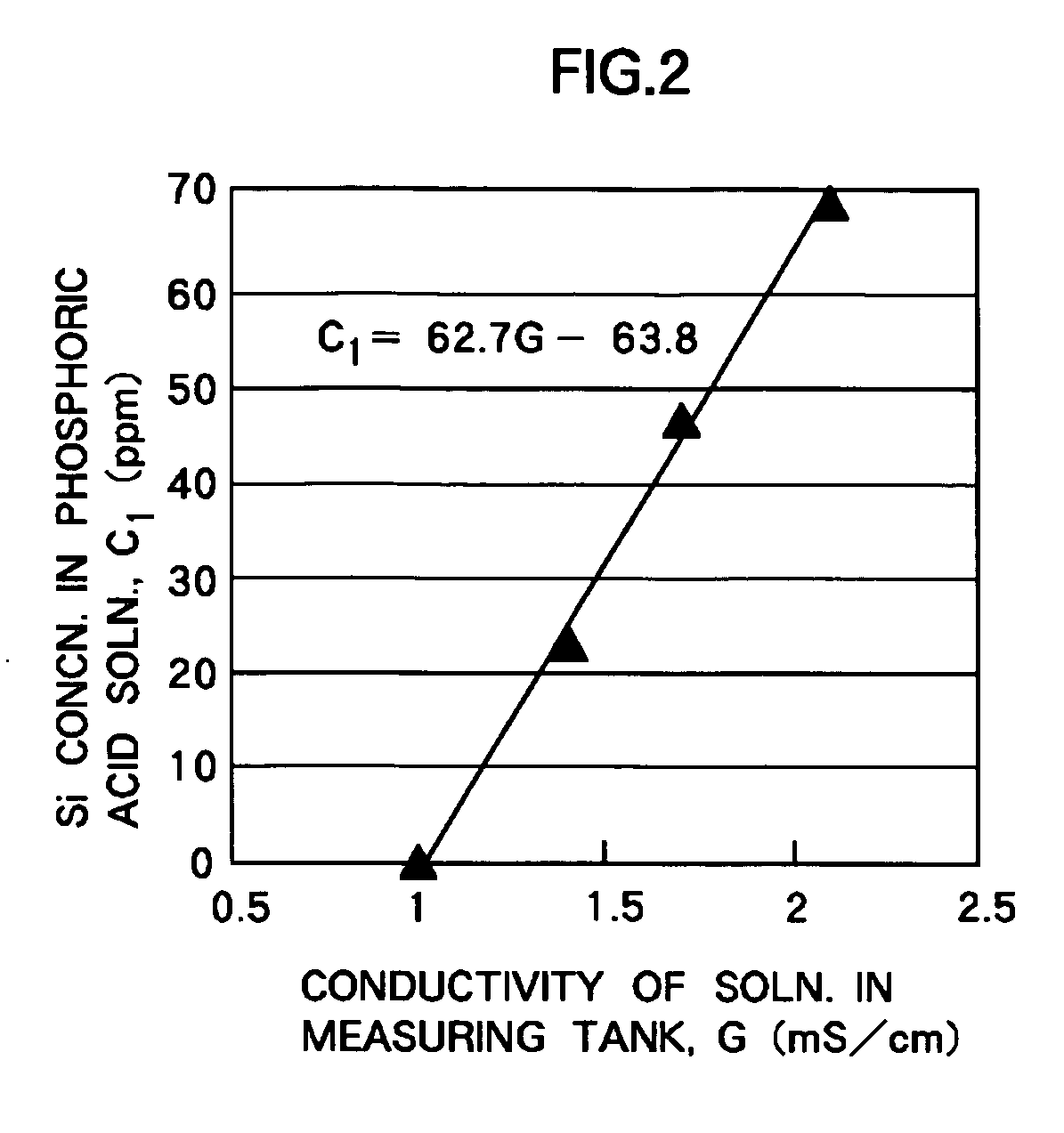

Equipment and method for measuring silicon concentration in phosphoric acid solution

ActiveUS20060263251A1Improve processing performanceReduce amountSemiconductor/solid-state device testing/measurementDecorative surface effectsIonCompound (substance)

Disclosed is equipment for measuring a silicon concentration in a phosphoric acid solution under use as an etching solution during operation of a semiconductor substrate processing system. The equipment is provided with at least a reaction tank and a concentration-measuring tank. The reaction tank includes a reaction unit for adding hydrofluoric acid to a predetermined constant amount of the phosphoric acid solution drawn out of the semiconductor substrate processing system to form a silicon fluoride compound and then causing the silicon fluoride compound to evaporate. The concentration-measuring tank comprises a hydrolysis unit for bubbling the silicon fluoride compound, which has evaporated from the reaction tank, through deionized water to hydrolyze the silicon fluoride compound and a measurement unit for determining a change rate of silicon concentration in the deionized water subsequent to the bubbling. Also disclosed is a method for measuring a silicon concentration in a phosphoric acid solution under recirculation and use as an etching solution in a semiconductor substrate processing system in operation.

Owner:TATSUMO KK

Advanced multilayer dielectric cap with improved mechanical and electrical properties

InactiveUS7737052B2Improve antioxidant capacityImprove mechanical stabilitySemiconductor/solid-state device detailsSolid-state devicesDielectricMechanical stability

A dielectric cap, interconnect structure containing the same and related methods are disclosed. The inventive dielectric cap includes a multilayered dielectric material stack wherein at least one layer of the stack has good oxidation resistance, Cu diffusion and / or substantially higher mechanical stability during a post-deposition curing treatment, and including Si—N bonds at the interface of a conductive material such as, for example, Cu. The dielectric cap exhibits a high compressive stress and high modulus and is still remain compressive stress under post-deposition curing treatments for, for example: copper low k back-end-of-line (BEOL) nanoelectronic devices, leading to less film and device cracking and improved reliability.

Owner:ADVANCED MICRO DEVICES INC +2

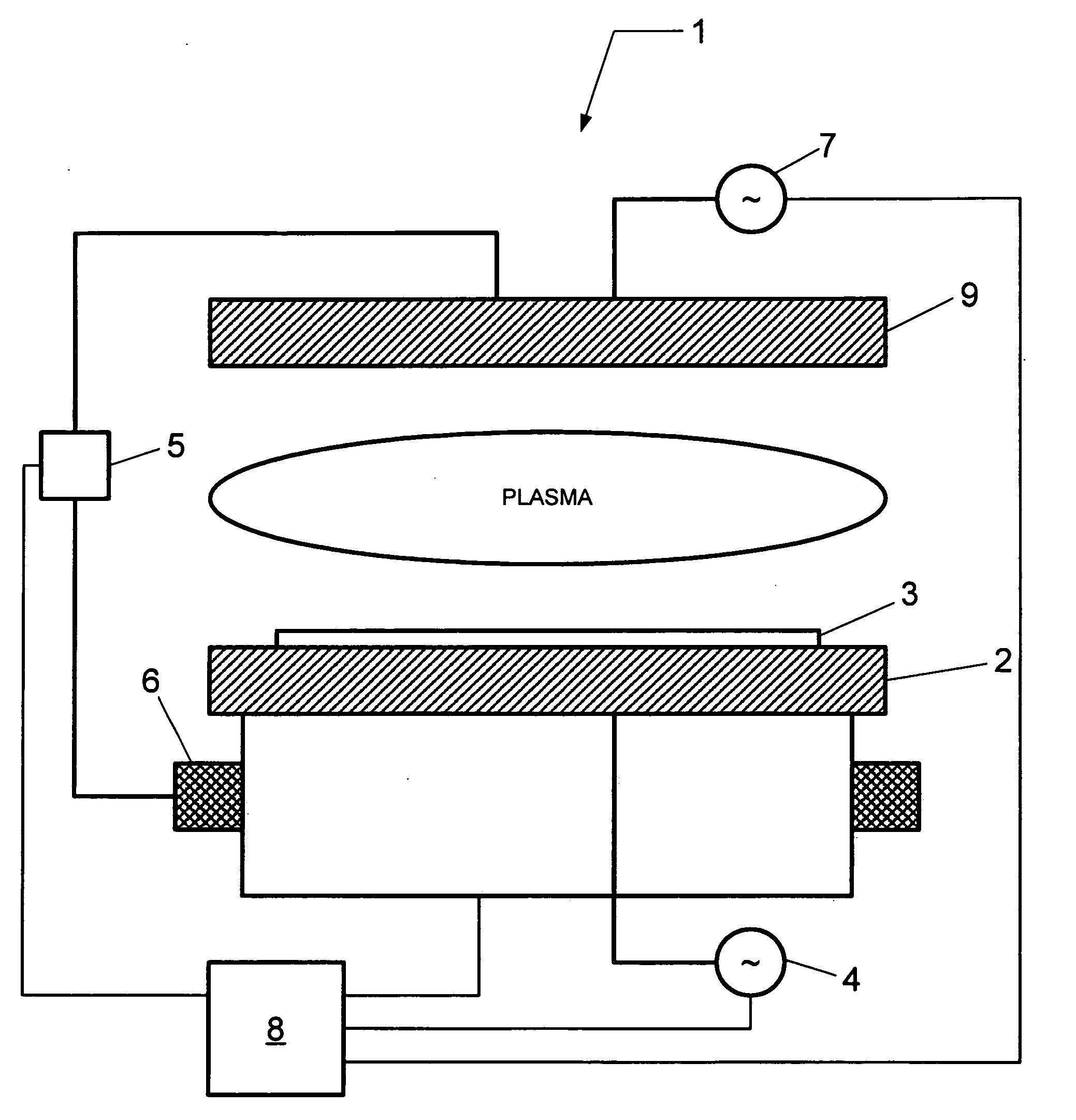

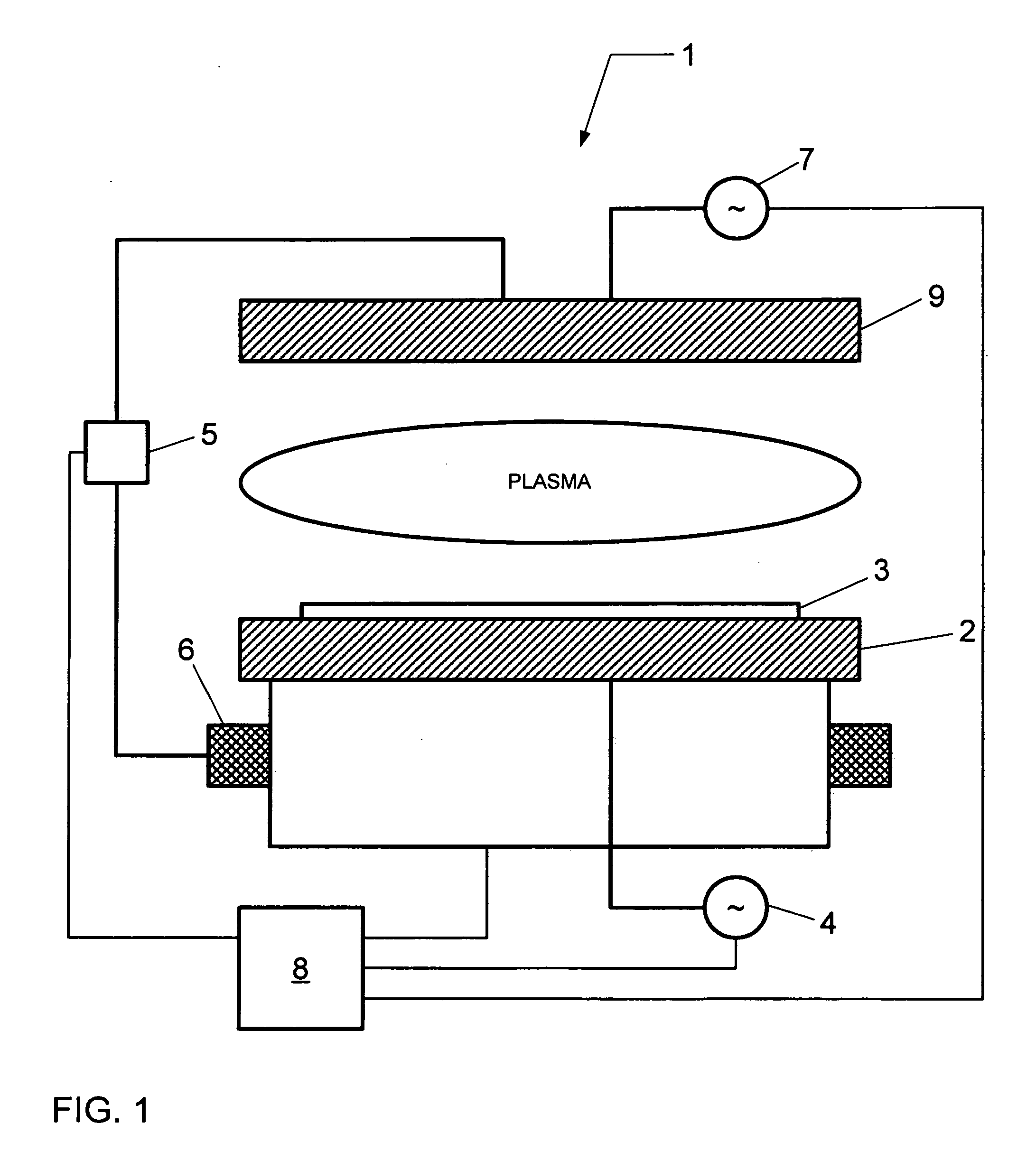

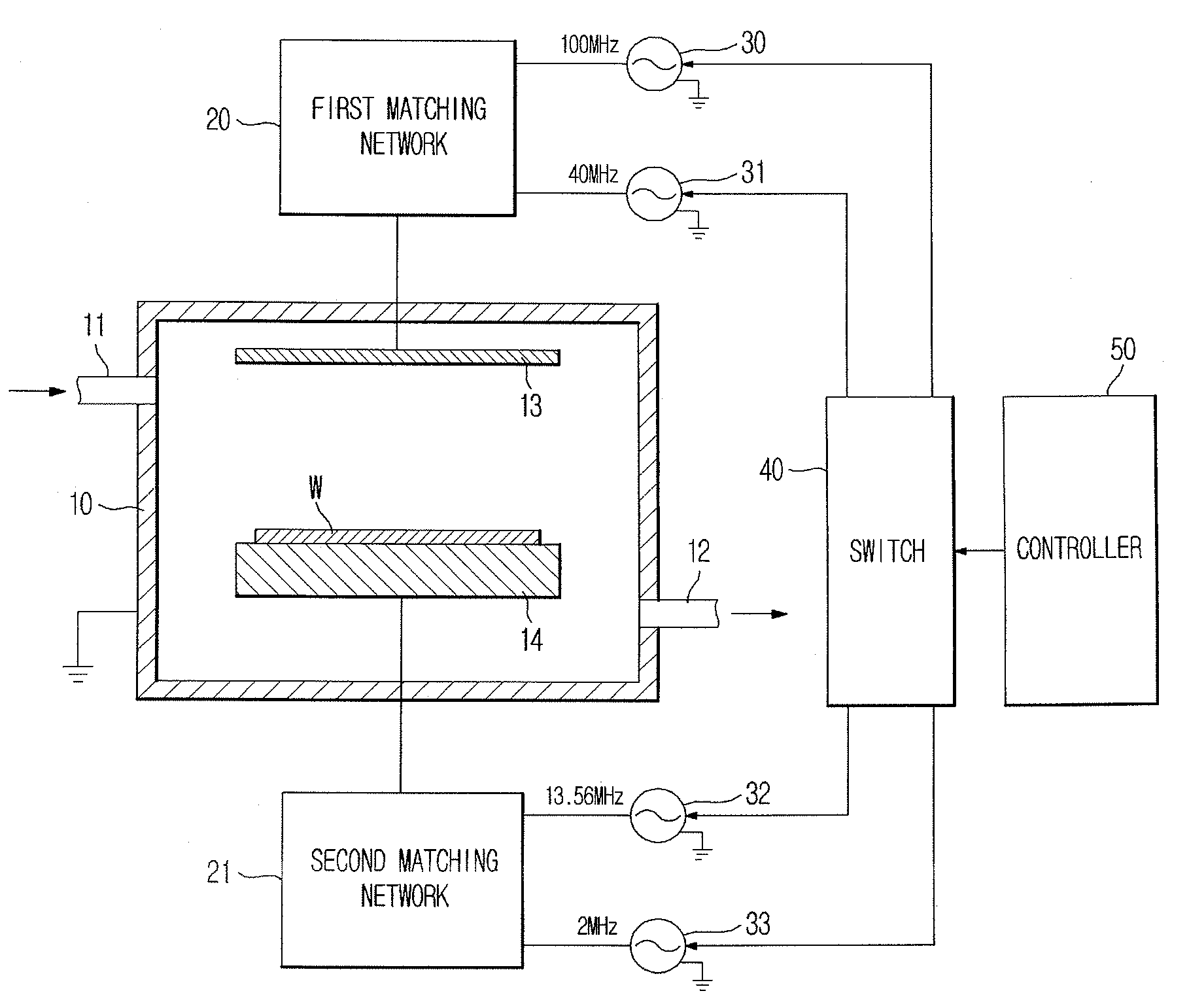

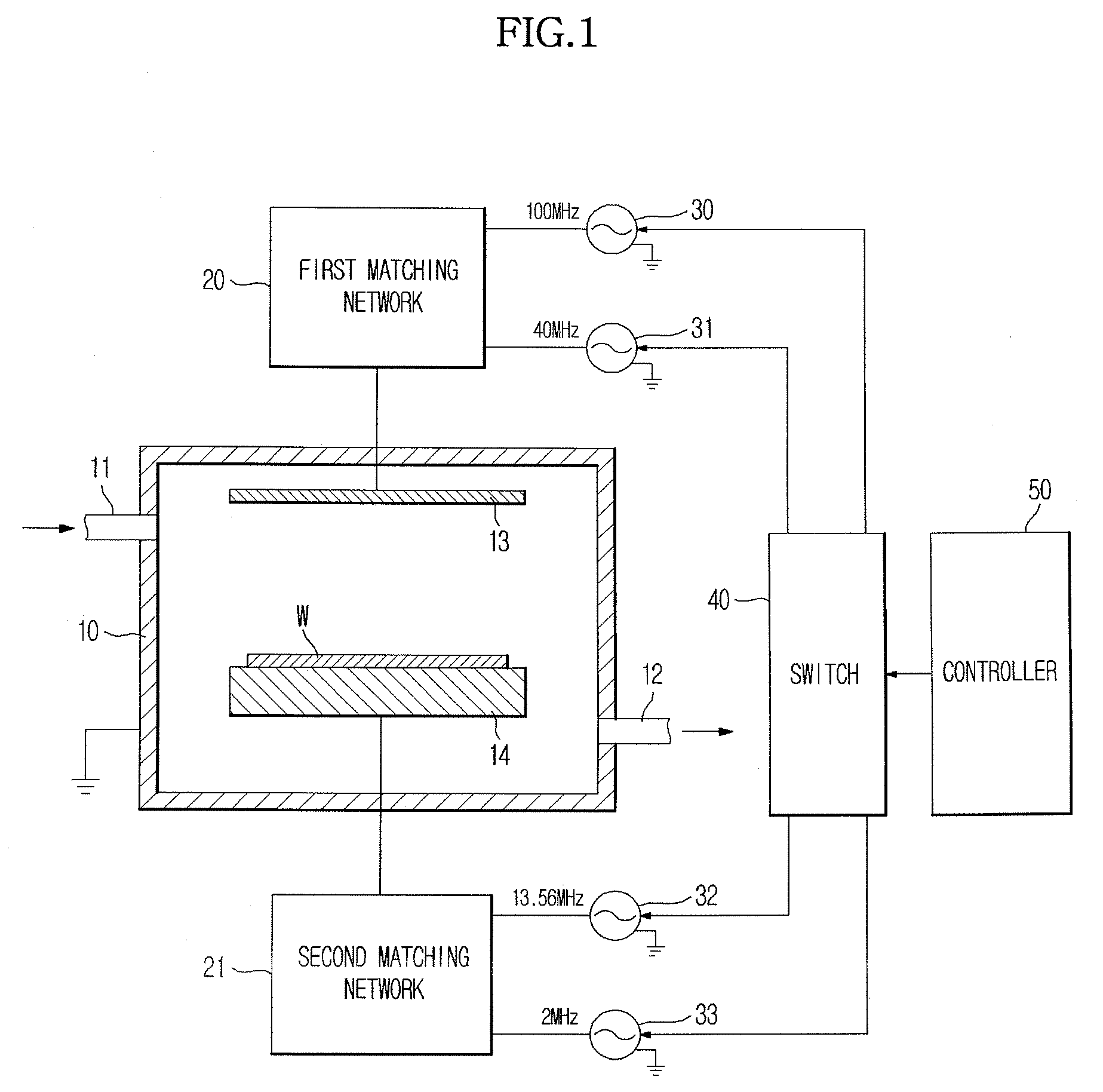

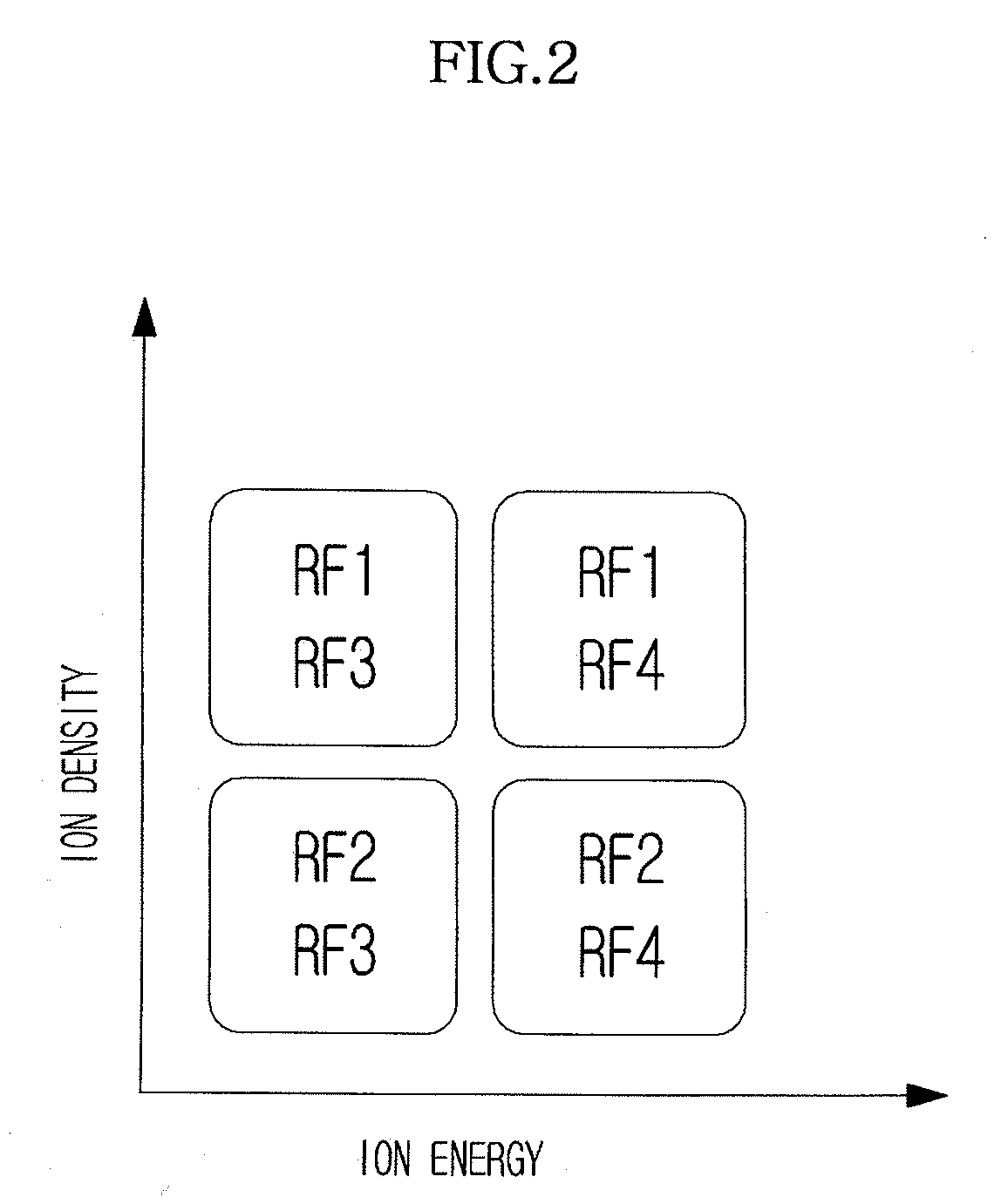

Plasma etching method and apparatus

InactiveUS20080119049A1Good etchingElectric discharge tubesDecorative surface effectsIon densityVolumetric Mass Density

A plasma etching method and apparatus. In the plasma etching apparatus, pluralities of RF power supplies are respectively connected to upper and lower electrode via relevant matching networks to enable generation of various ion densities and ion energies of plasma by individually changing RF powers applied to the upper and lower electrodes through control of the RF power supplies, so that the plasma etching apparatus can perform all processes which includes a process requiring a low ion density and a low ion energy, a process requiring the low ion density and a high ion energy, a process requiring a high ion density and the low ion energy, and a process requiring the high ion density and the high ion energy, thereby realizing various plasma etching processes.

Owner:SAMSUNG ELECTRONICS CO LTD

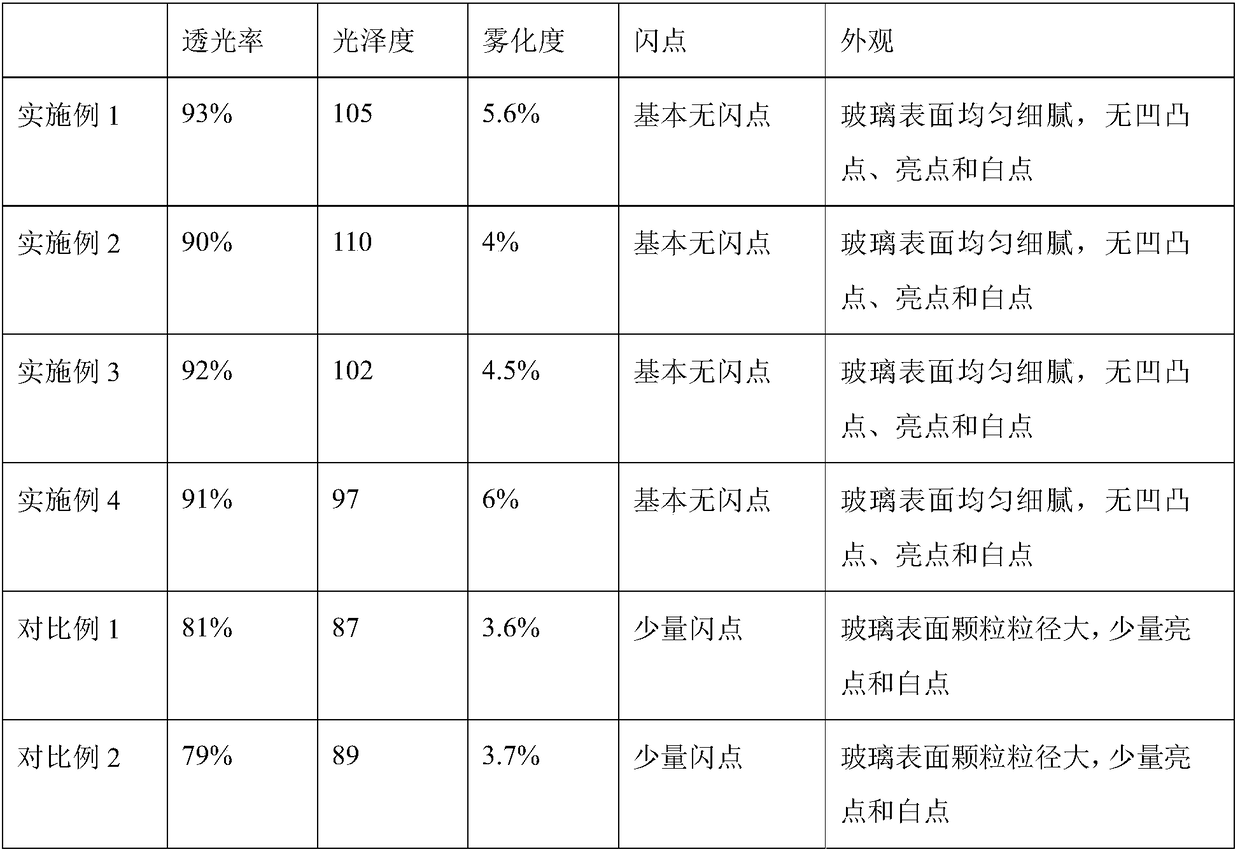

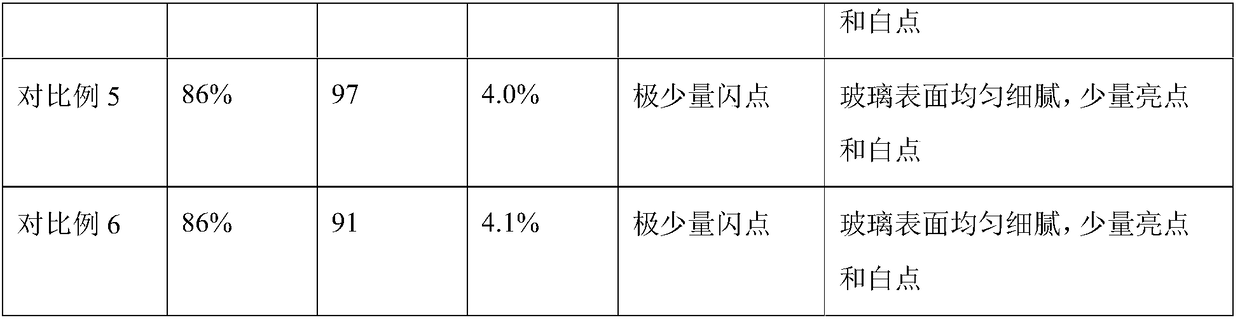

Frosting liquid, preparation method and uses thereof, and anti-glare glass preparation method

The invention relates to a frosting liquid, a preparation method and uses thereof, and an anti-glare glass preparation method, and provides a frosting liquid, which is prepared by mixing the followingraw materials by weight: 10-17 parts of ammonium fluoride, 7-12 parts of sulfuric acid, 3-5 parts of calcium fluoride, 3-5 parts of ammonium sulfate, 15-20 parts of potassium sulfate, and 130-140 parts of water. The invention further provides the an anti-glare glass preparation method, which comprises: (1) placing a glass in a frosting liquid; and (2) introducing a gas into the frosting liquid, and carry out a reaction. According to the present invention, the anti-glare glass prepared by using the frosting liquid through the preparation method has advantages of high light transmittance, highgloss, fine surface particles, uniform particle distribution and the like.

Owner:LENS TECH CHANGSHA

Method of manufacturing MEMS sensor and MEMS sensor

InactiveUS8174085B2Preventing undesired etching of a protective filmHigh selectivityAcceleration measurement using interia forcesTransducer detailsMetallic materialsOptoelectronics

A method of manufacturing an MEMS sensor according to the present invention includes the steps of: forming a first sacrificial layer on one surface of a substrate; forming a lower electrode on the first sacrificial layer; forming a second sacrificial layer made of a metallic material on the first sacrificial layer to cover the lower electrode; forming an upper electrode made of a metallic material on the second sacrificial layer; forming a protective film made of a nonmetallic material on the substrate to collectively cover the first sacrificial layer, the second sacrificial layer and the upper electrode; and removing at least the second sacrificial layer by forming a through-hole in the protective film and supplying an etchant to the inner side of the protective film through the through-hole.

Owner:ROHM CO LTD

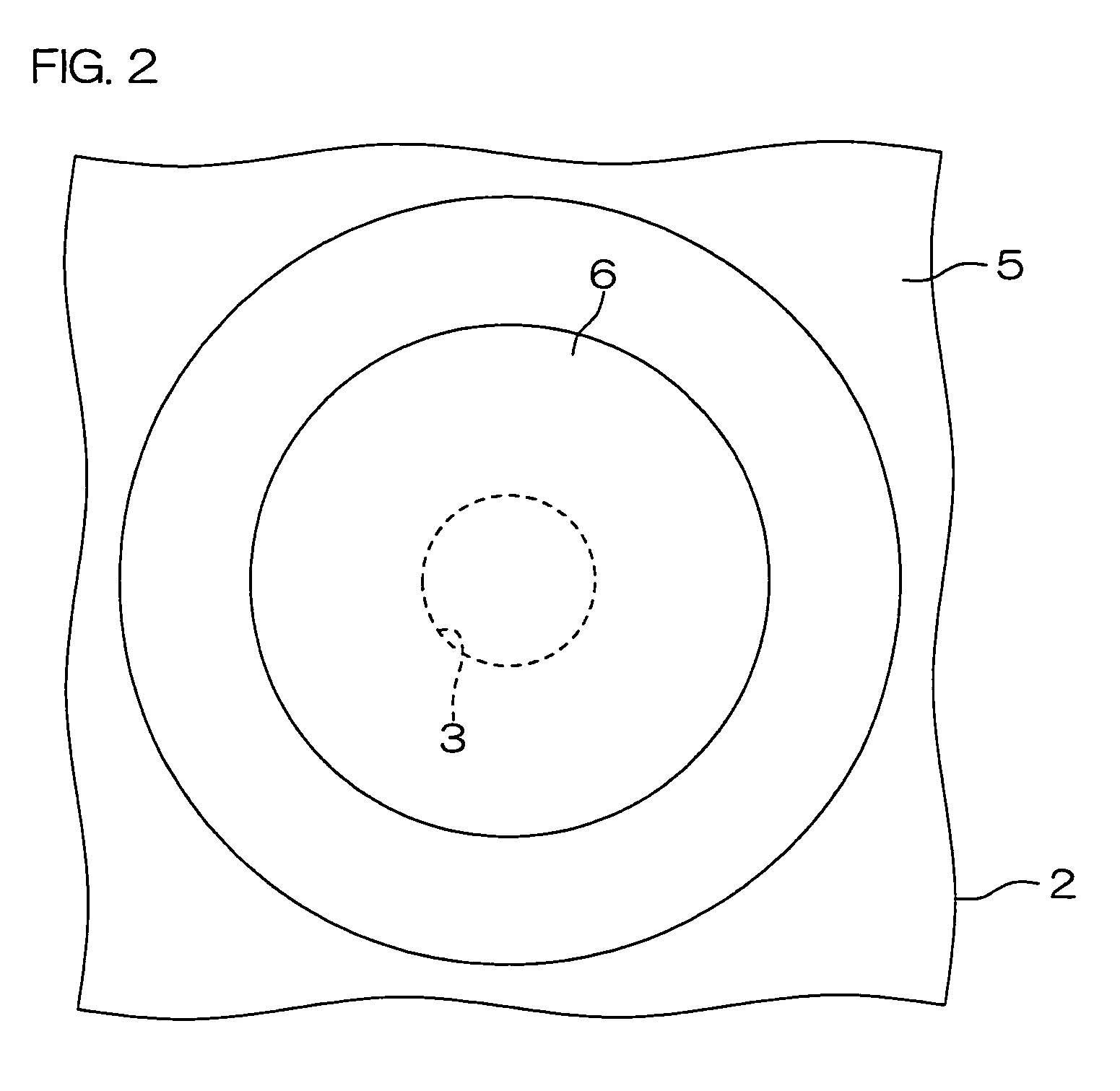

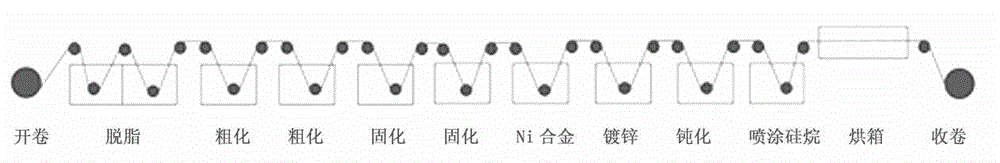

Environmental protection ashing treatment process of calendaring copper foil

ActiveCN104962965AGood corrosion resistanceGood high temperature oxidation resistanceGalvanic depositionAshing

The present invention discloses an environmental protection ashing treatment process of calendaring copper foil. The environmental protection ashing treatment process comprises degreasing washing, roughening electroplating, curing electroplating, nickel alloy electroplating, zinc electroplating, chromate passivation treatment, silane treatment and the like. According to the present invention, after electrochemical degreasing, roughening and curing treatment (roughening and curing can be selected more than two times according to the requirement) Cu grain electrodeposition are performed on the calendaring copper foil, the nano-scale nickel alloy is electrodeposited under the acidic condition, the thin metal zinc layer is electroplated, and finally the chromate passivation treatment is performed and the silane coupling agent is uniformly sprayed on the surface; As, Sb, Cd and other toxic and harmful metals are not added, and the alloy system electrodeposition and other relatively simple processes are used to treat the process; and under the optimization of the process parameters, the environmentally friendly surface treated copper foil with characteristics of good performance, meeting of FPC production requirements, gray appearance of gray, no toxicity and no harm can be obtained.

Owner:LINGBAO JINYUAN ZHAOHUI COPPER

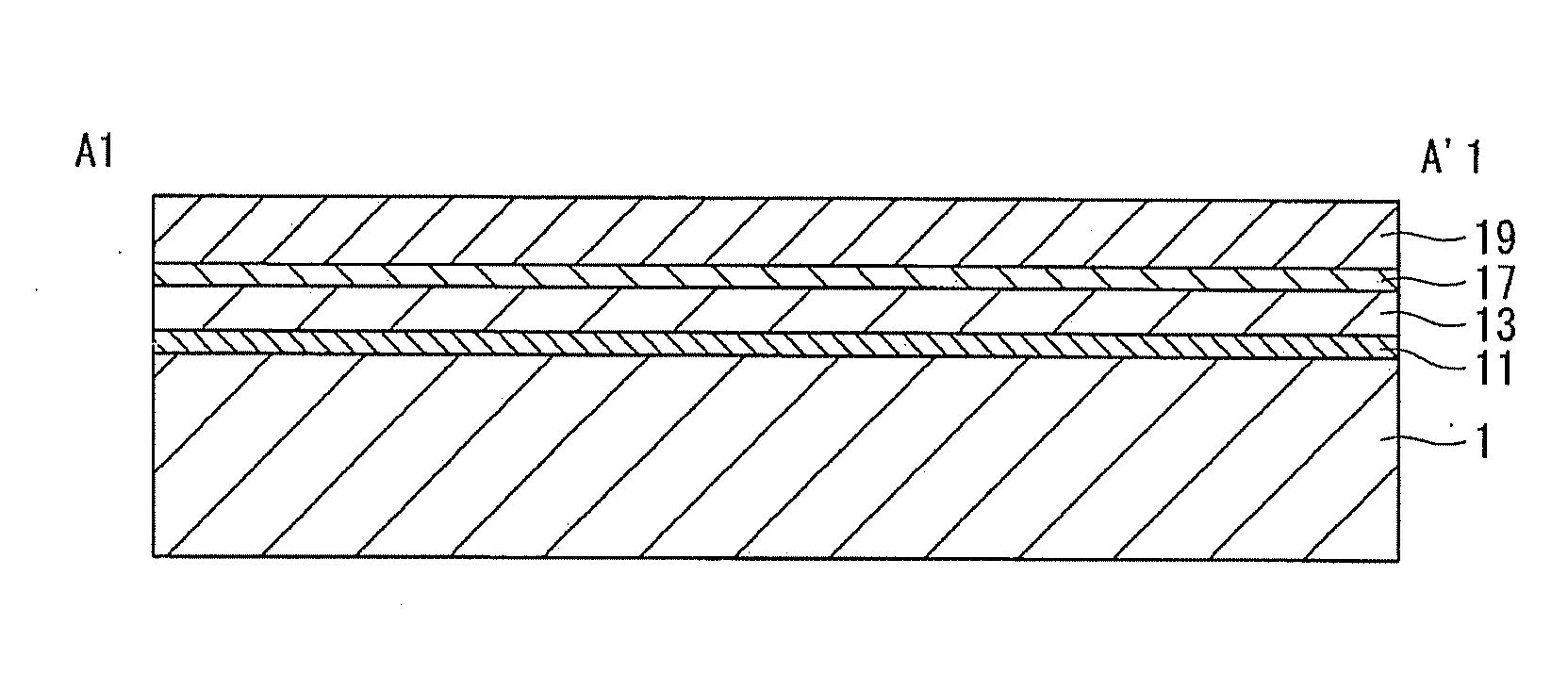

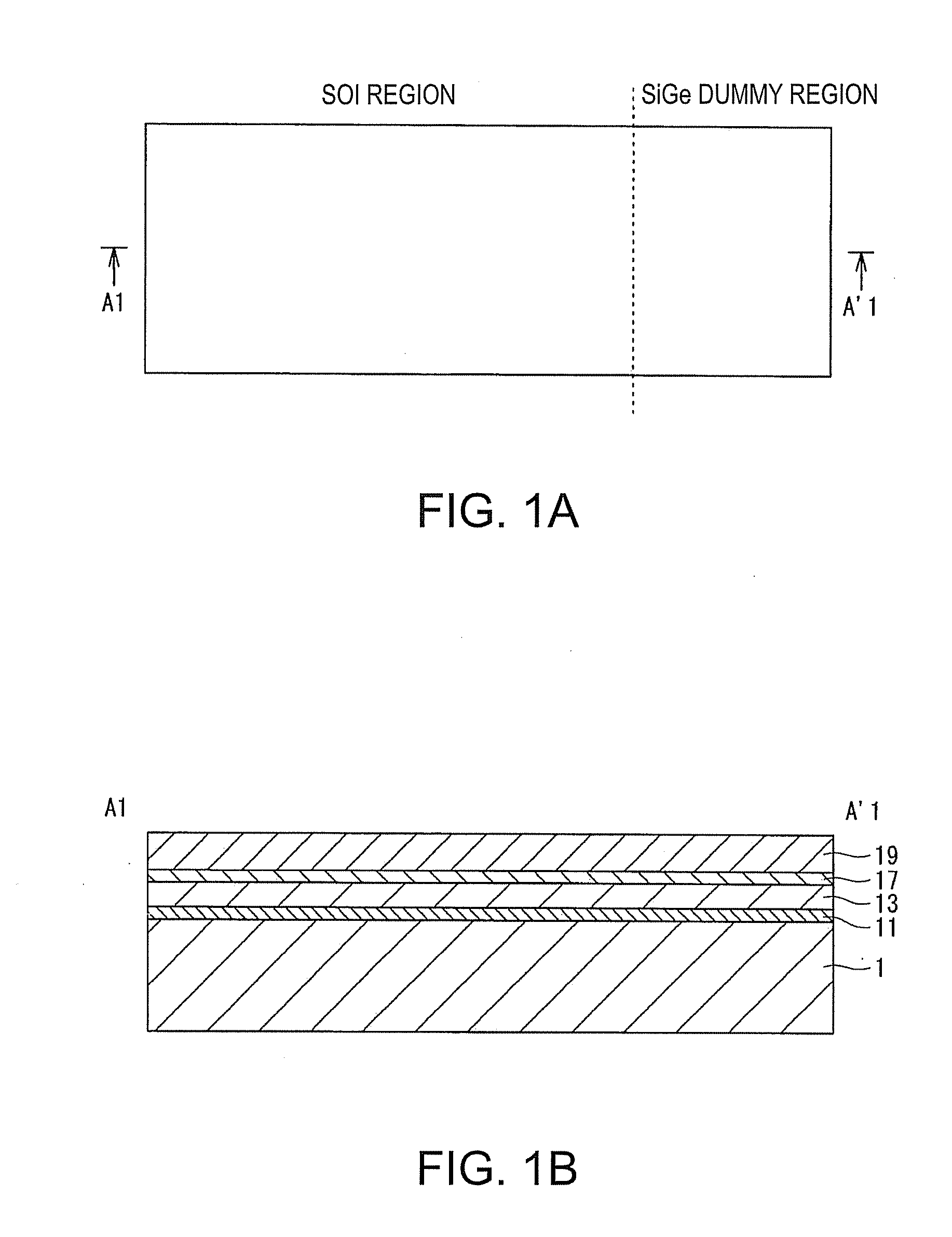

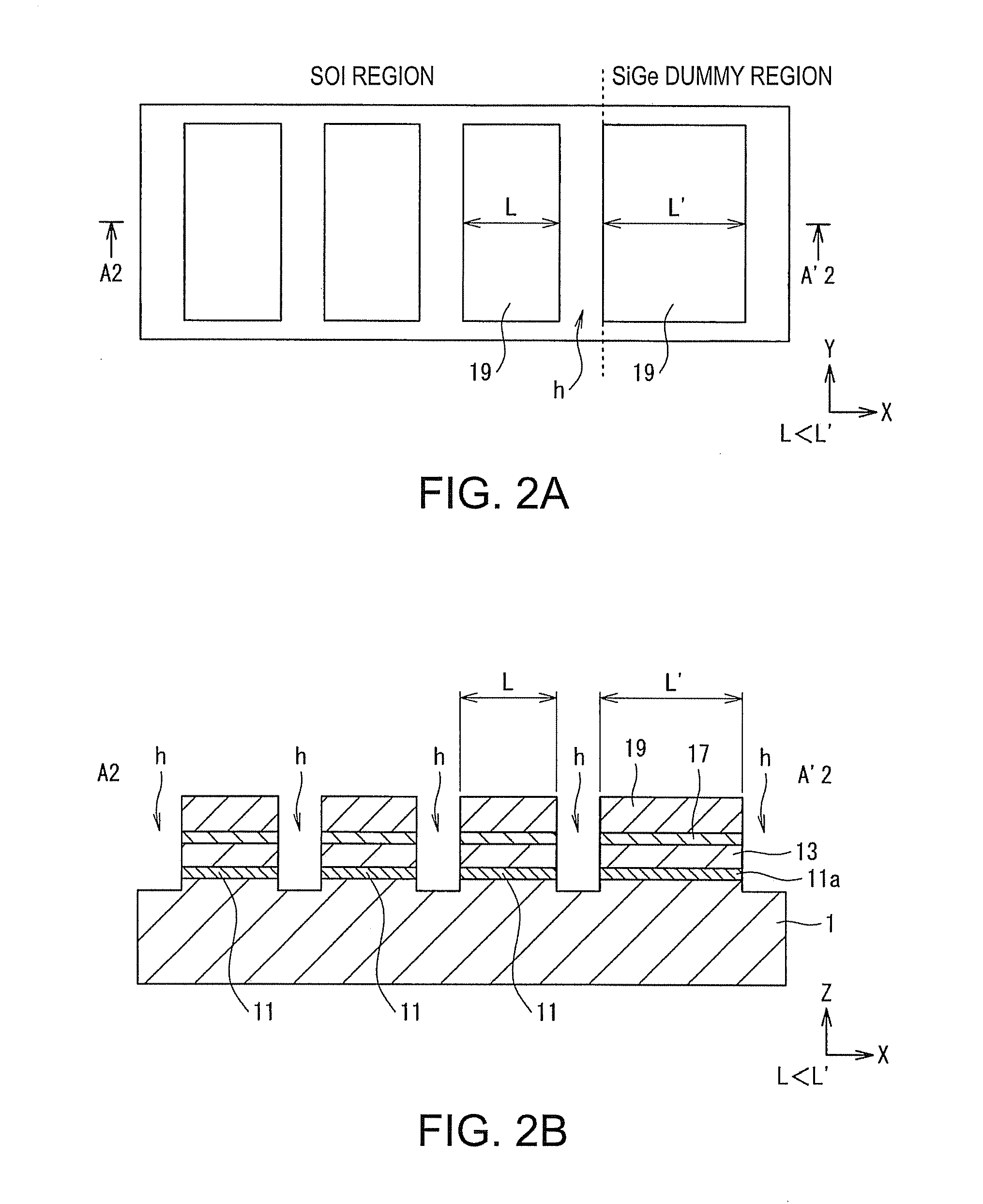

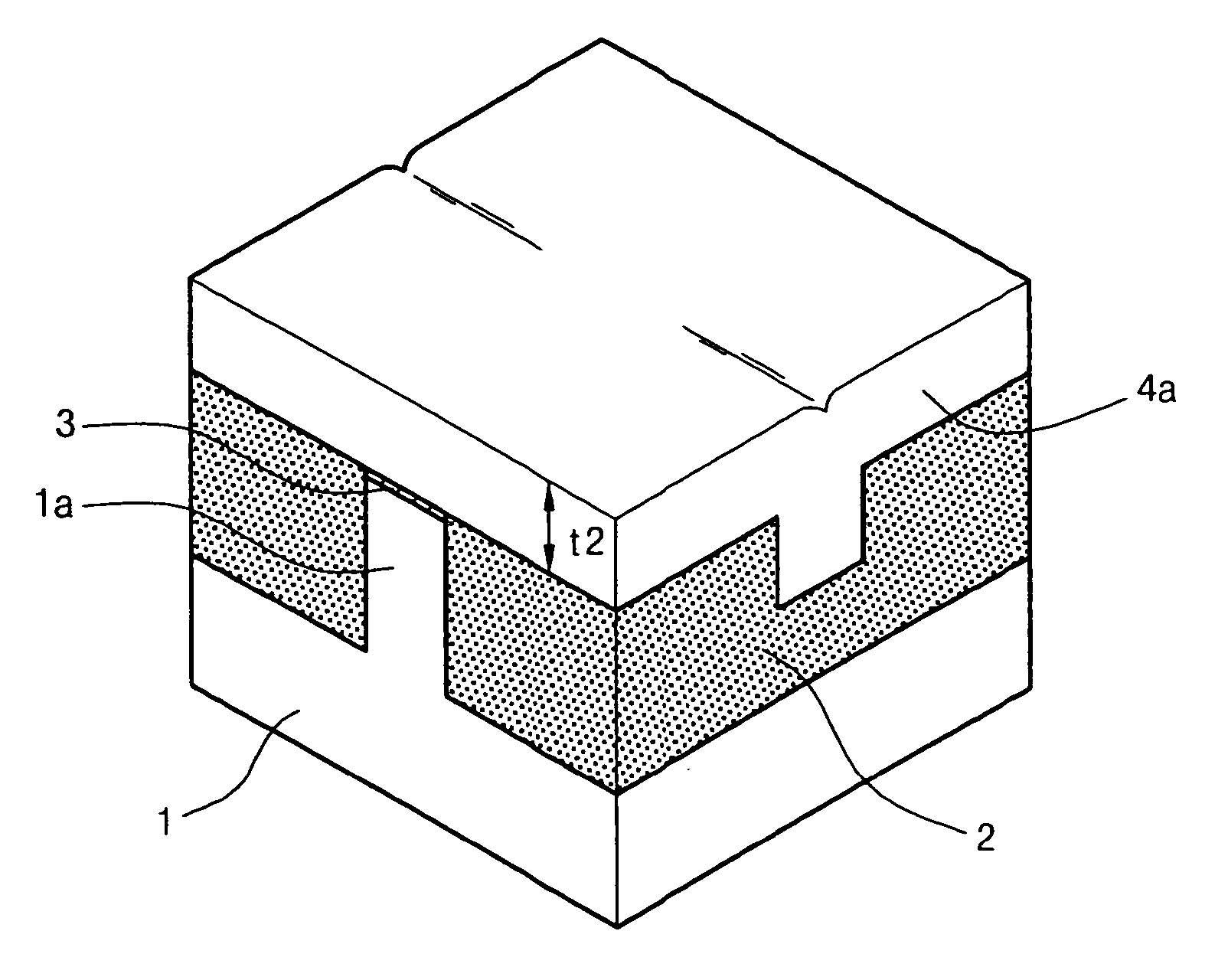

Method for manufacturing semiconductor device

InactiveUS20080194082A1Improve processing yieldElectrically stableSolid-state devicesSemiconductor/solid-state device manufacturingEtchingSemiconductor

A method for manufacturing a semiconductor device, includes: (a) forming a SiGe layer on a Si substrate; (b) forming a Si layer on the SiGe layer; (c) forming a dummy pattern made of SiGe in a dummy region of the Si substrate; and (d) wet-etching and removing the SiGe layer formed under the Si layer. In the step (d), an etchant is kept to contact the dummy pattern from before a complete remove of the SiGe layer to an end of the etching.

Owner:138 EAST LCD ADVANCEMENTS LTD

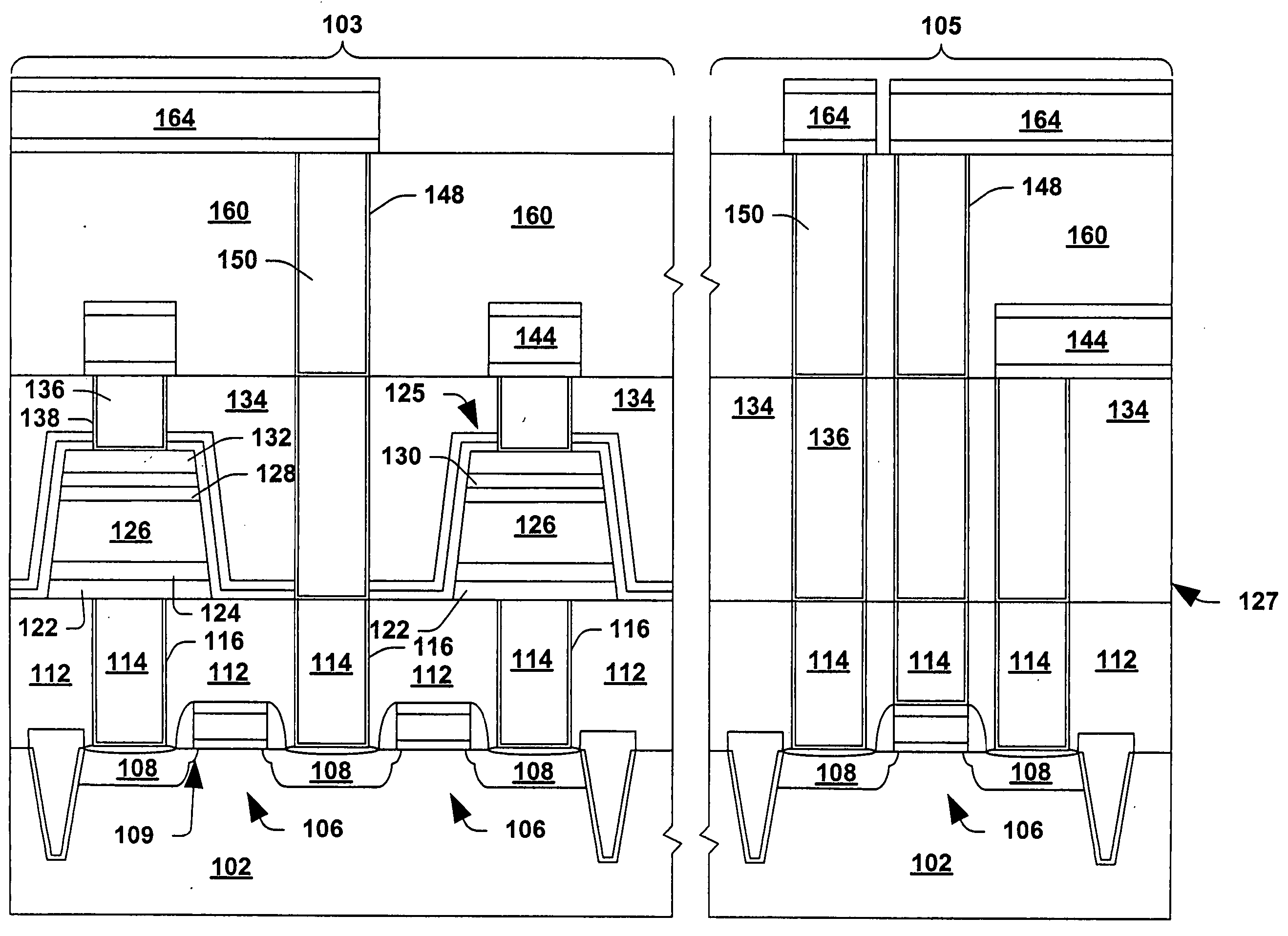

Method of fabricating a transistor having a triple channel in a memory device

ActiveUS20060246671A1Easy to makeGood etchingSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

Disclosed is a method for fabricating a transistor of a memory device capable of preventing voids from being created when forming a low-resistant gate electrode. The method includes the steps of forming an active area by etching a semiconductor substrate, forming a field oxide layer in the semiconductor substrate and forming a recess by etching the field oxide layer. A gate insulation layer is formed along an upper surface of the active area and an exposed portion of the active area. A gate electrode is formed on the field oxide layer such that the gate electrode extends across an upper portion of the active area while being overlapped with a channel area and the recess. The first conductive layer to be patterned has the same thickness, so the low-resistant gate electrode is easily fabricated without forming the voids.

Owner:SK HYNIX INC

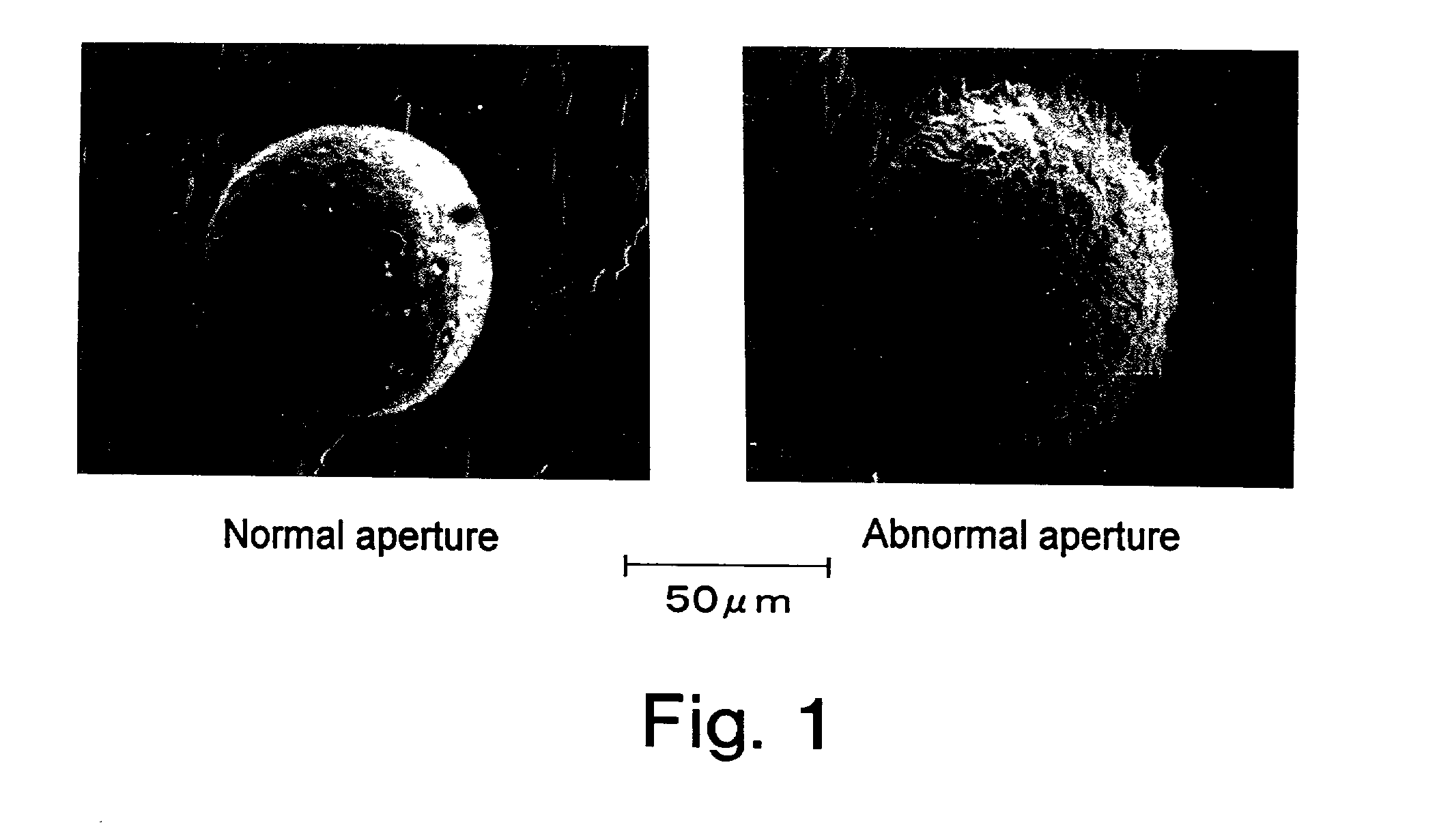

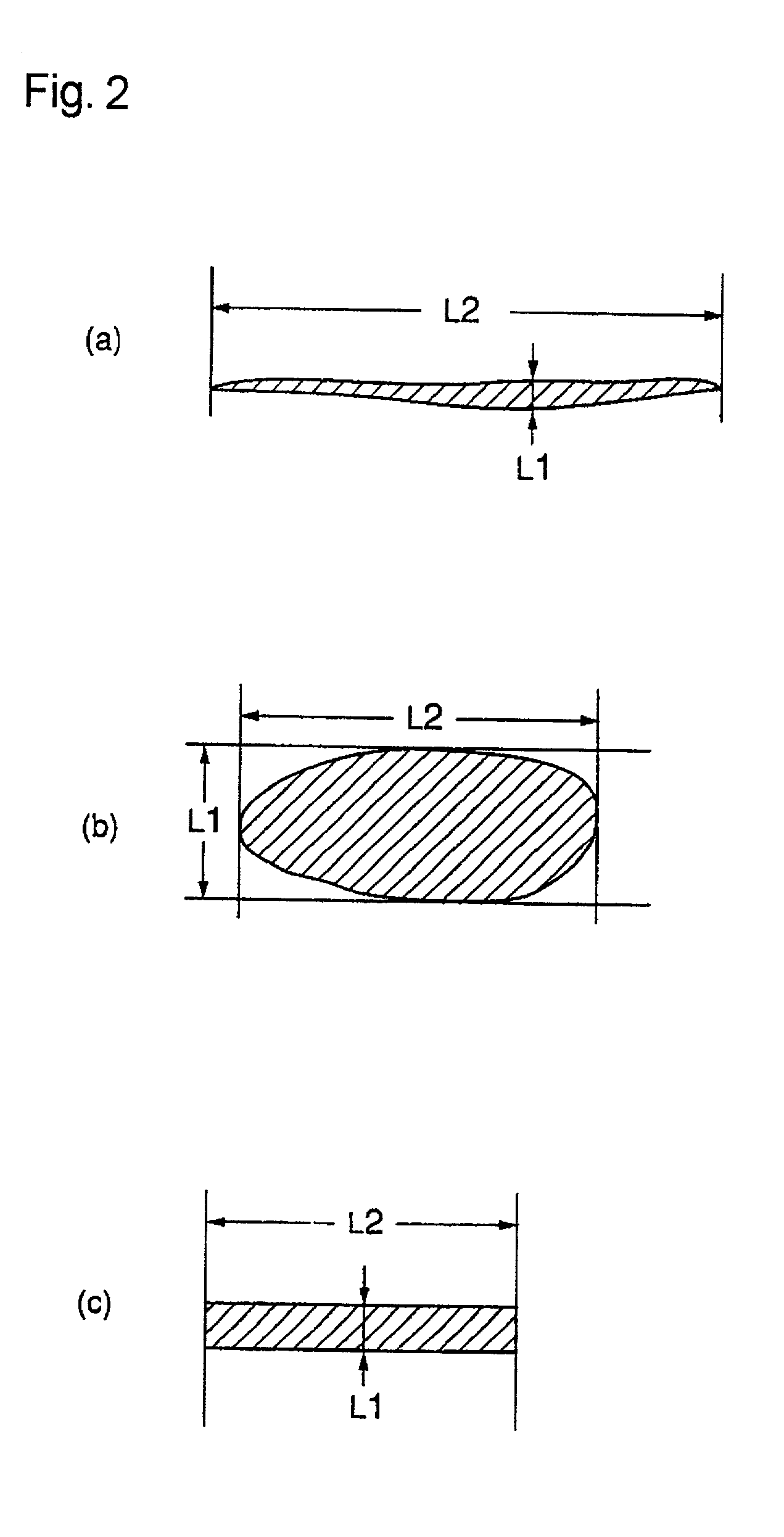

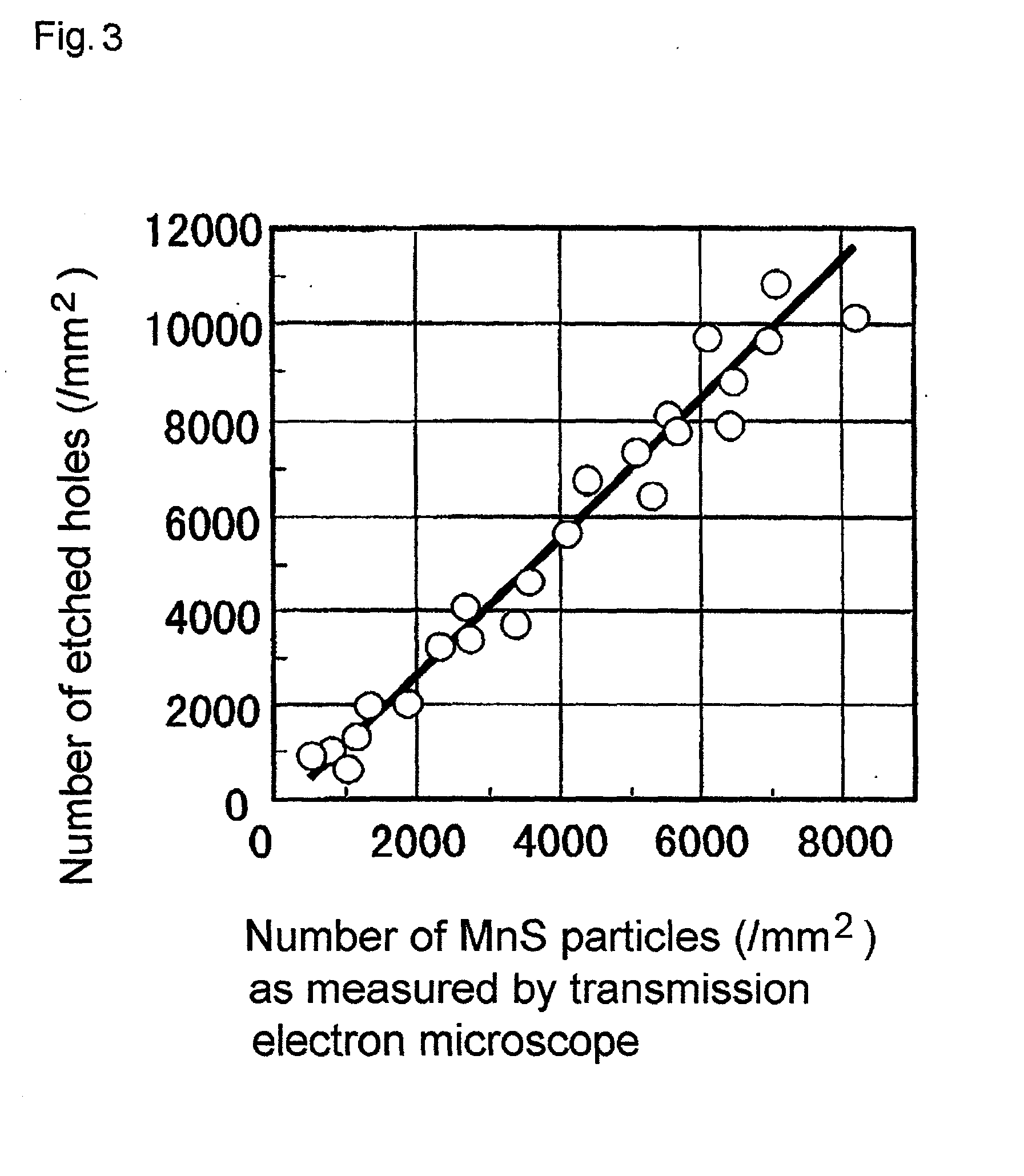

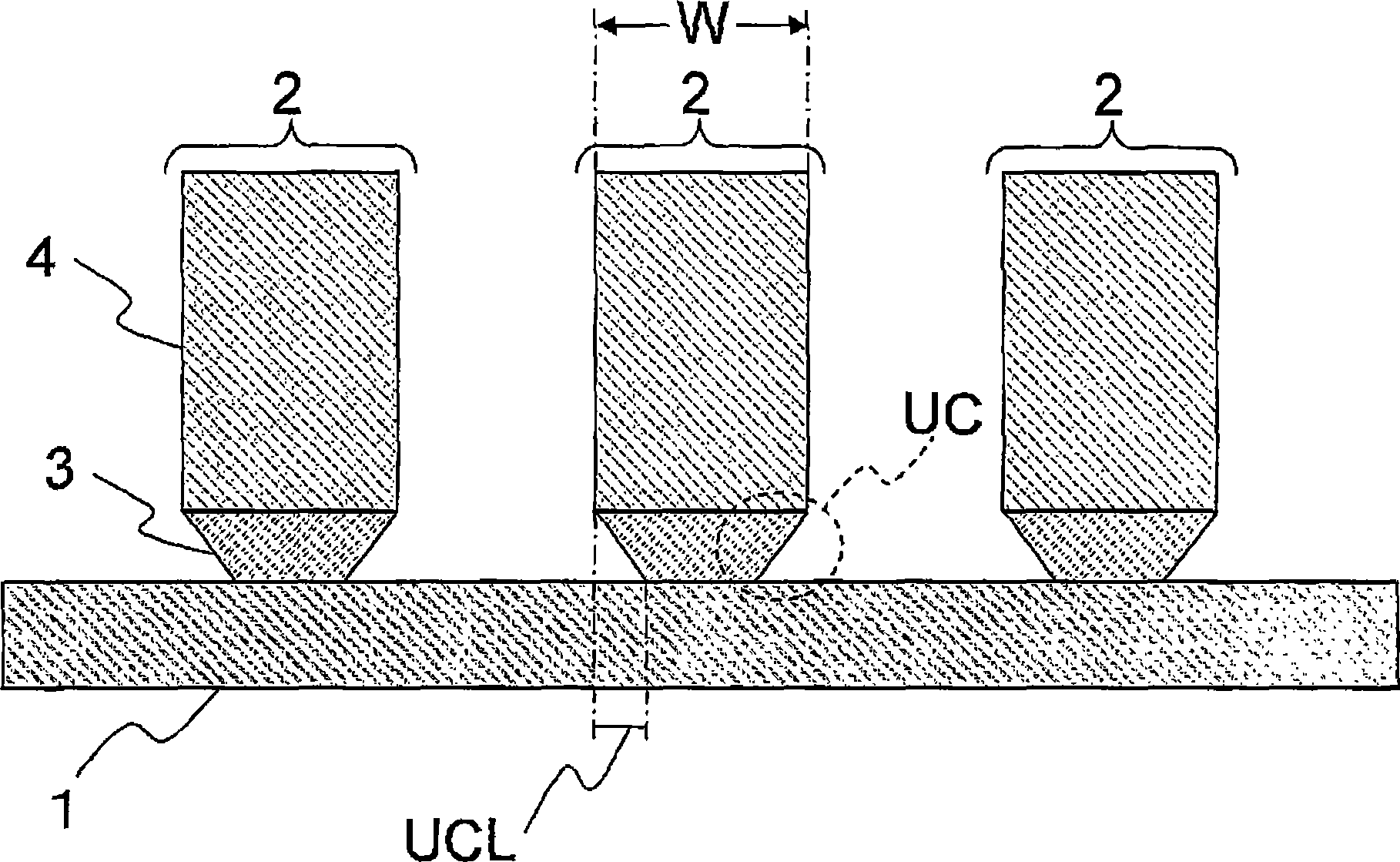

Fe-Ni alloy shadow mask blank with excellent etch perforation properties and method for manufacturing the same

InactiveUS20010047839A1Reduce unevennessNo unevennessCathode ray tubes/electron beam tubesFurnace typesMean diameterReduction ratio

A shadow mask blank of Fe-Ni alloy which exhibits excellent uniformity of diameter of apertures formed by perforation with etching for the passage of electron beams, consisting of 34-38% Ni, 0.05-0.5% Mn, 4-20 ppm S, and the balance Fe and no more than specified limits of C, Si, Al, and P, with MnS inclusions 50-1,000 nm in diameter dispersed at the density of at least 1,500 / mm2 or simply with etched holes 0.5-10 mum in diameter emerging at the density of at least 2,000 / mm2 when the blank is immersed in a 3% nitric acid-ethyl alcohol solution at 20° C. for 30 seconds. A method of manufacturing the blank comprises hot rolling of a slab of the Fe-Ni alloy, cooling, recrystallization annealing, cold rolling, etc. under controlled conditions: e.g., hot rolling the slab at 950-1,250° C. to 2-6 mm thick, cooling the stock in the range of 900-700° C. at the rate of 0.5° C. / second, continuously passing the stock through a heating furnace at 850-1,100° C. for recrystallization annealing to adjust the mean diameter of the recrystallized grains to 5-30 mum, and performing the cold rolling before the final recrystallization annealing at a reduction ratio of 50-85% and the final cold rolling at a reduction ratio of 10-40%.

Owner:JX NIPPON MINING & METALS CO LTD

Developable UV cured hydrofluoric acid-resistant protection glue

ActiveCN104497944AImprove adhesionImprove corrosion resistancePolyureas/polyurethane adhesivesModified epoxy resin adhesivesChemistryPolymer chemistry

The invention discloses a developable UV cured hydrofluoric acid-resistant protection glue, which comprises the following components by mass percentage: 15-75% of main resin, 10-55% of auxiliary resin and 6-30% of active monomer. The developable UV cured hydrofluoric acid-resistant protection glue has excellent gluing capability by comparing with the hydrofluoric acid-resistant protection glue in prior art, and has extremely high bonding intensity and excellent hydrofluoric acid-resistant etching performance.

Owner:惠晶显示科技(苏州)有限公司

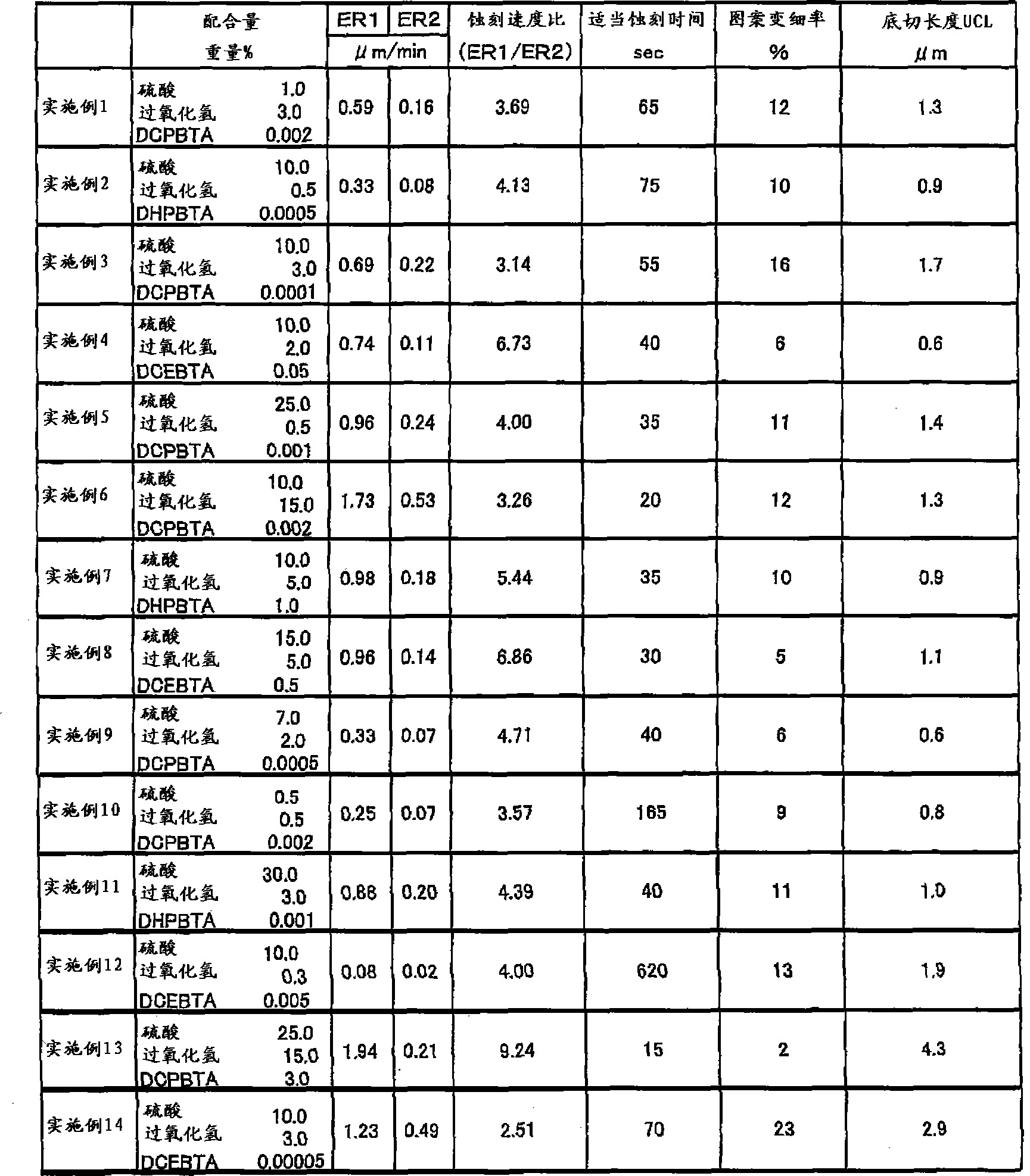

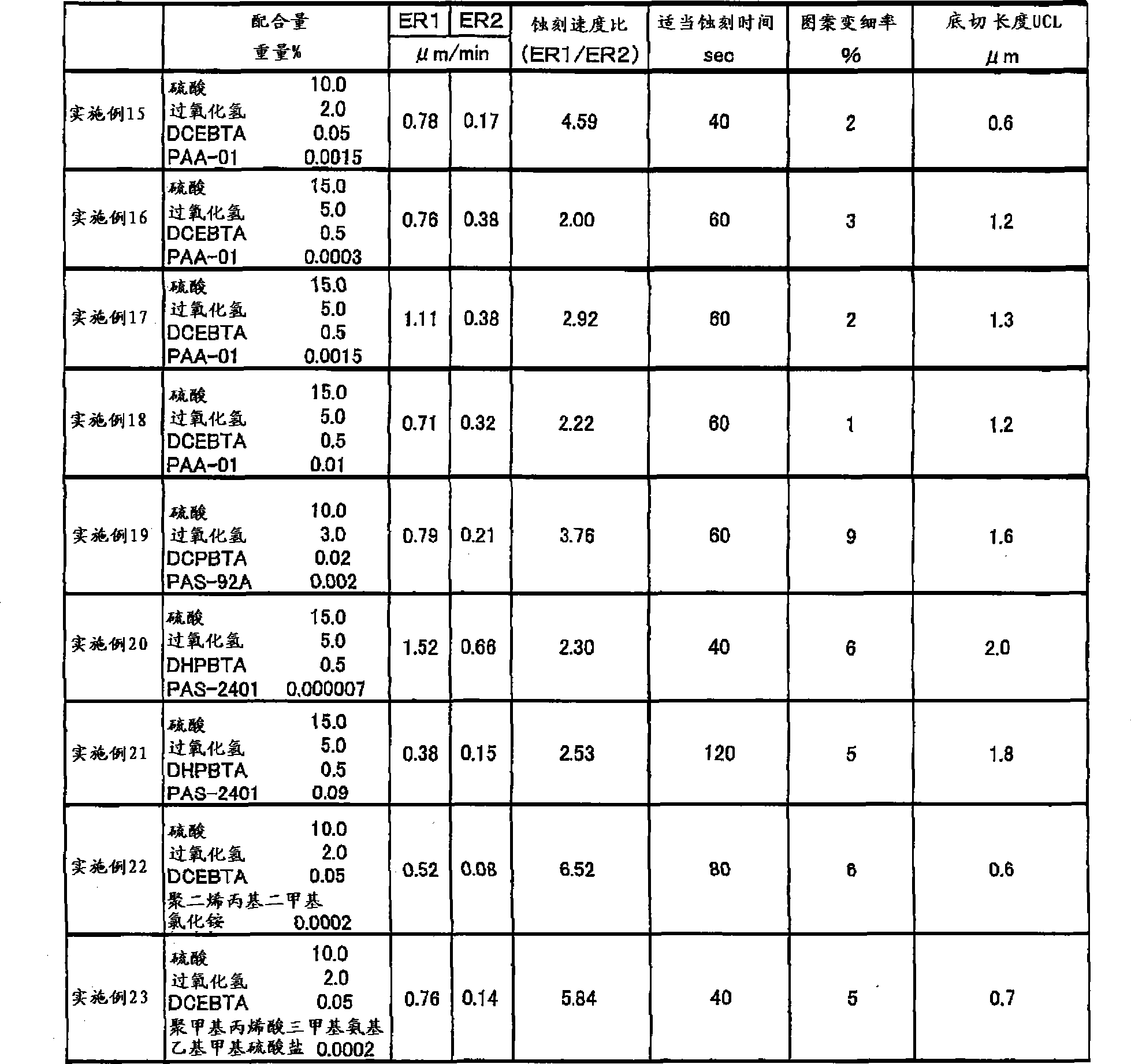

Etchant

ActiveCN101445933AAvoid corrosionGood etchingConductive material chemical/electrolytical removalSurface treatment compositionsNitrogenBenzotriazole

The present invention provides an etchant, capable of preventing dimensional precision of a wiring pattern from reducing when removing a chemical copper plate in a half addition process. A first etchant of the invention is characterized in that it is a copper etchant containing sulphuric acid, hydogen peroxide and water, and containing more than two benzotriazole derivates containing at least oneof carboxyl and dydroxyl in a molecule. A second etchant of the invention is characterized in that it is a copper etchant containing sulphuric acid, hydogen peroxide and water, and containing pyrrolehaving heteroatom of nitrogen atom only in a loop, and polyprotic acid having more than two carboxyl or salts thereof.

Owner:MEC CO LTD