Patents

Literature

64results about How to "Mask saving" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

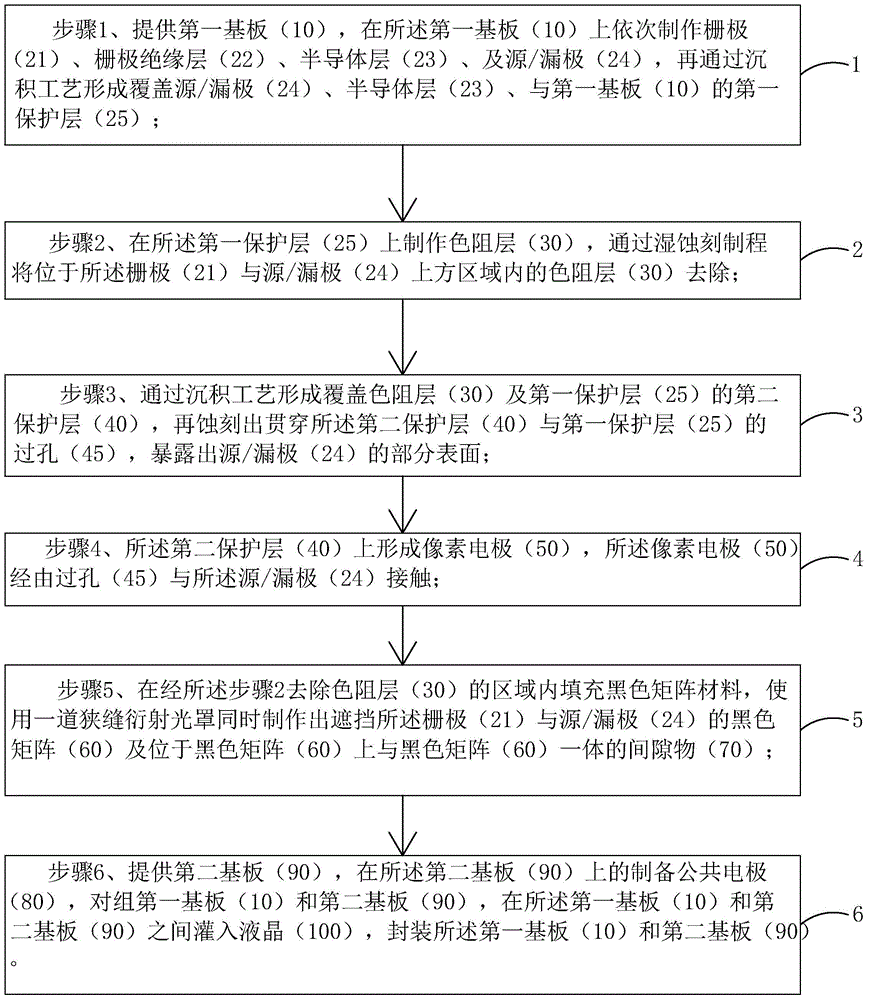

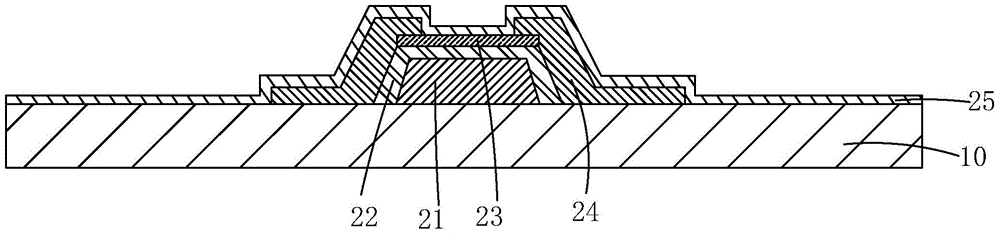

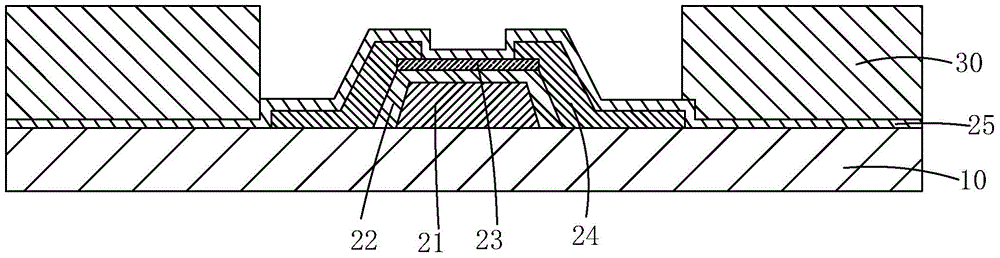

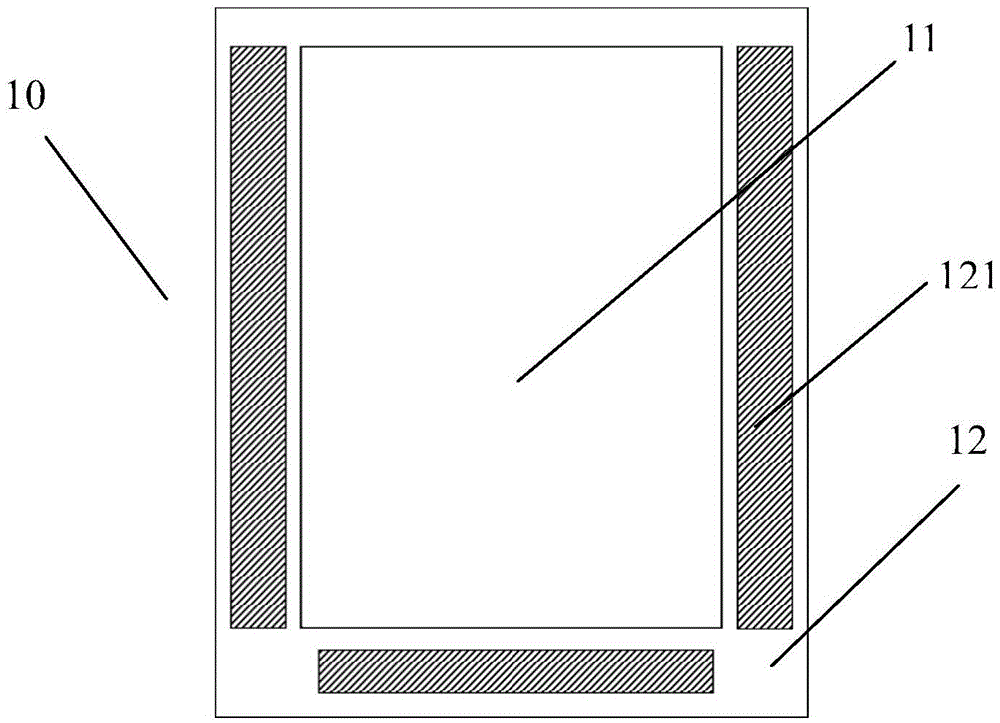

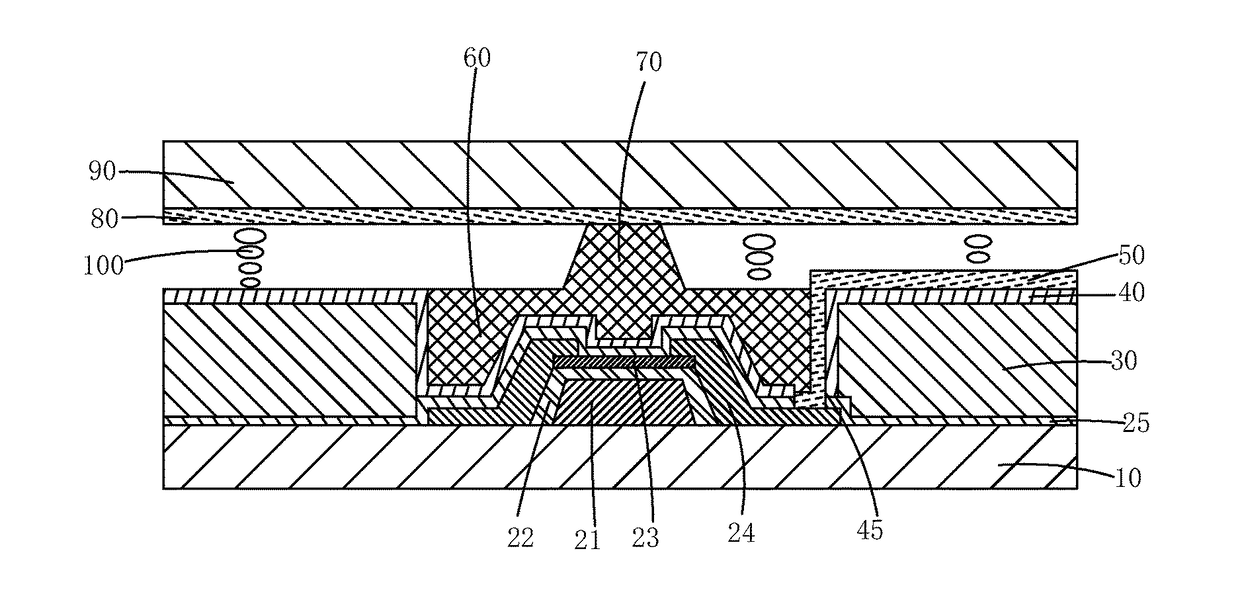

Structure and manufacturing method of array colored film integrated type liquid crystal display panel

ActiveCN104965366AImprove display qualityAchieve connectionNon-linear opticsLiquid-crystal displayEtching

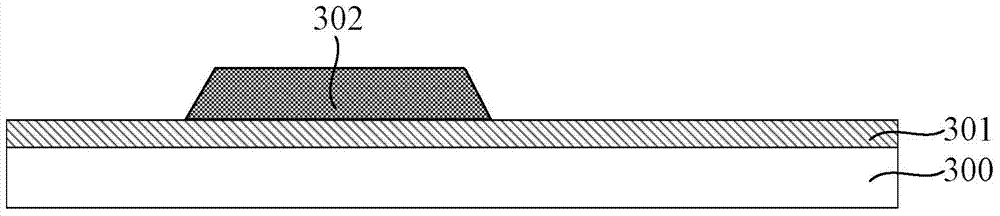

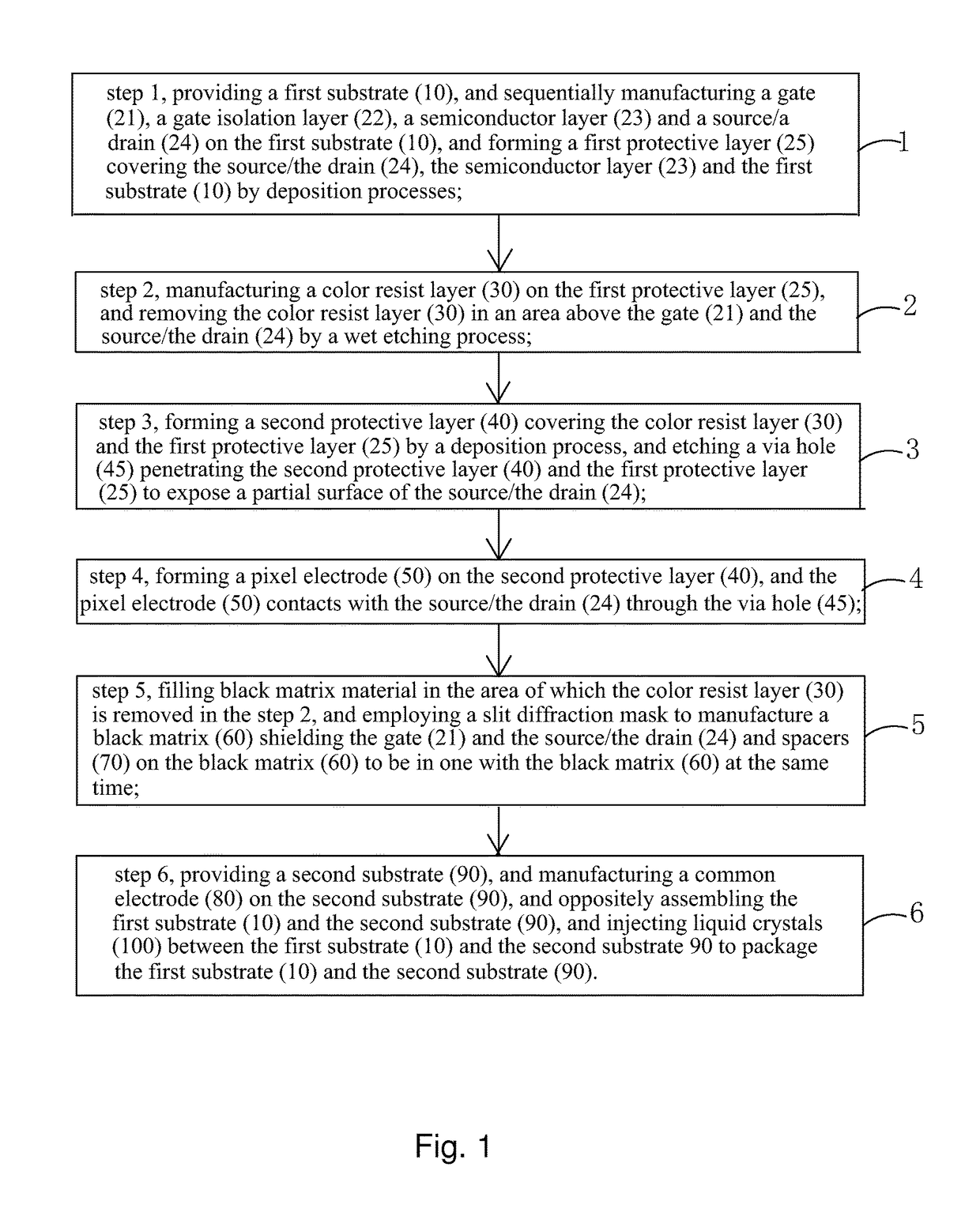

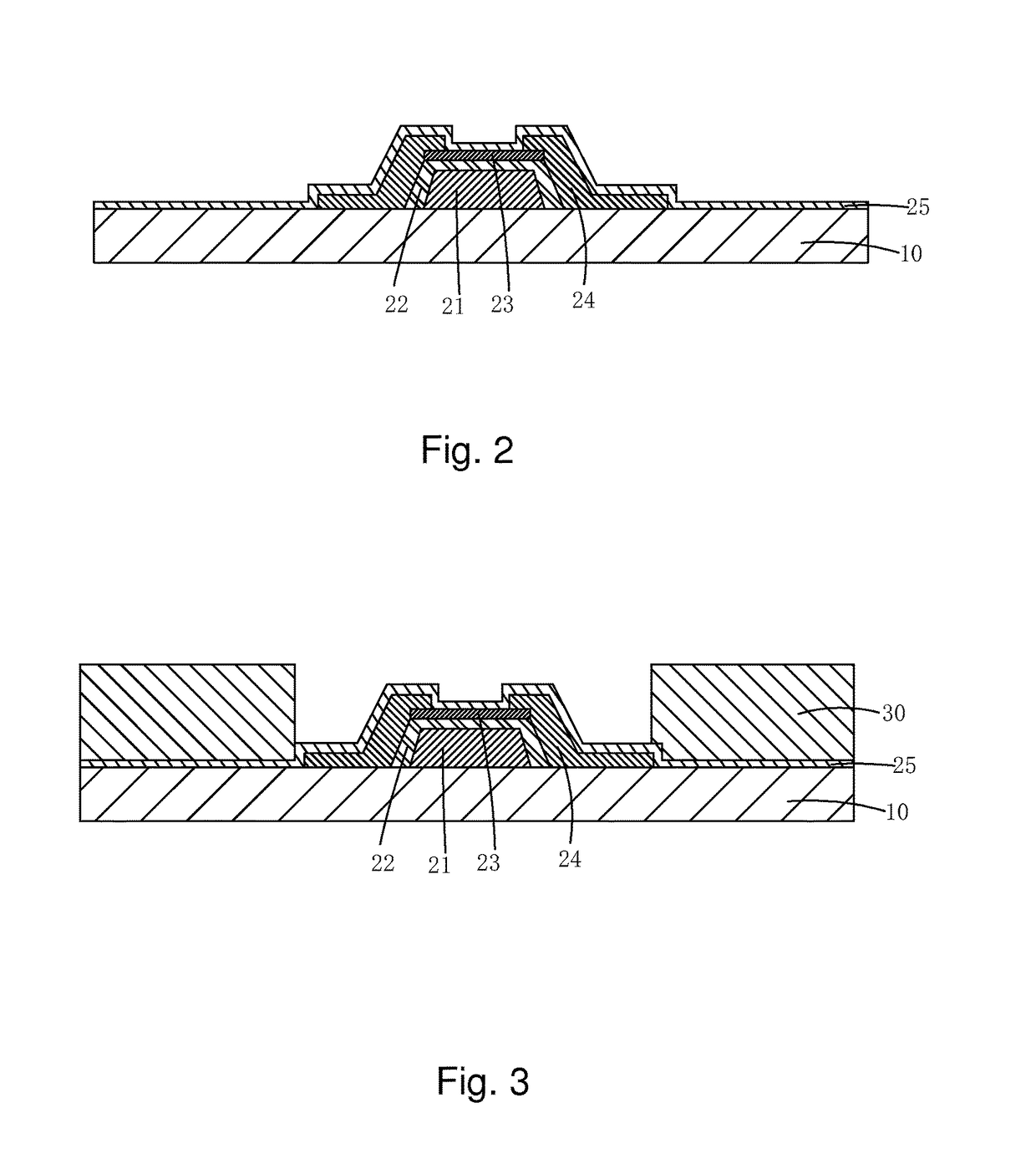

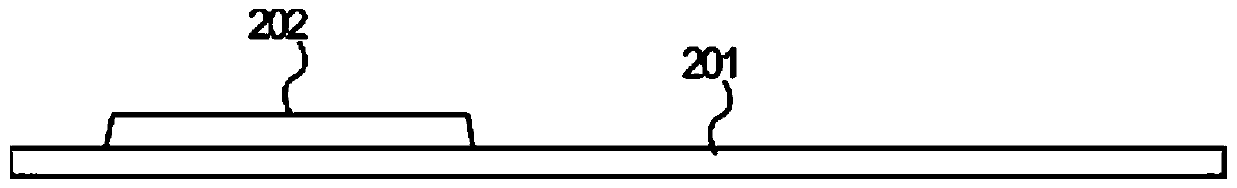

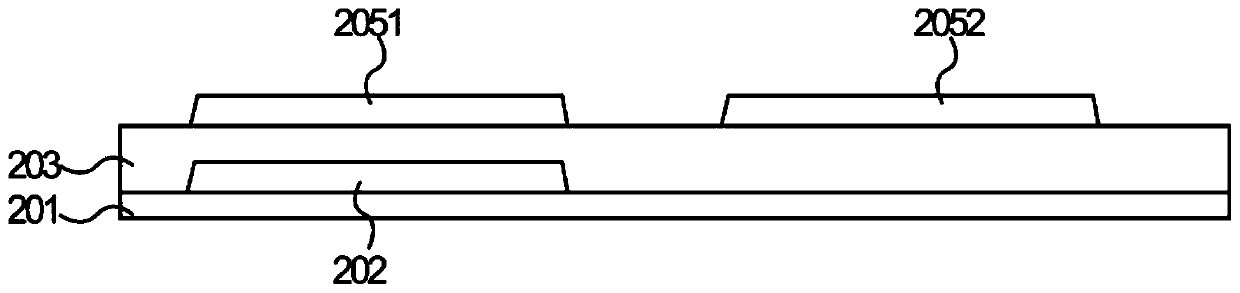

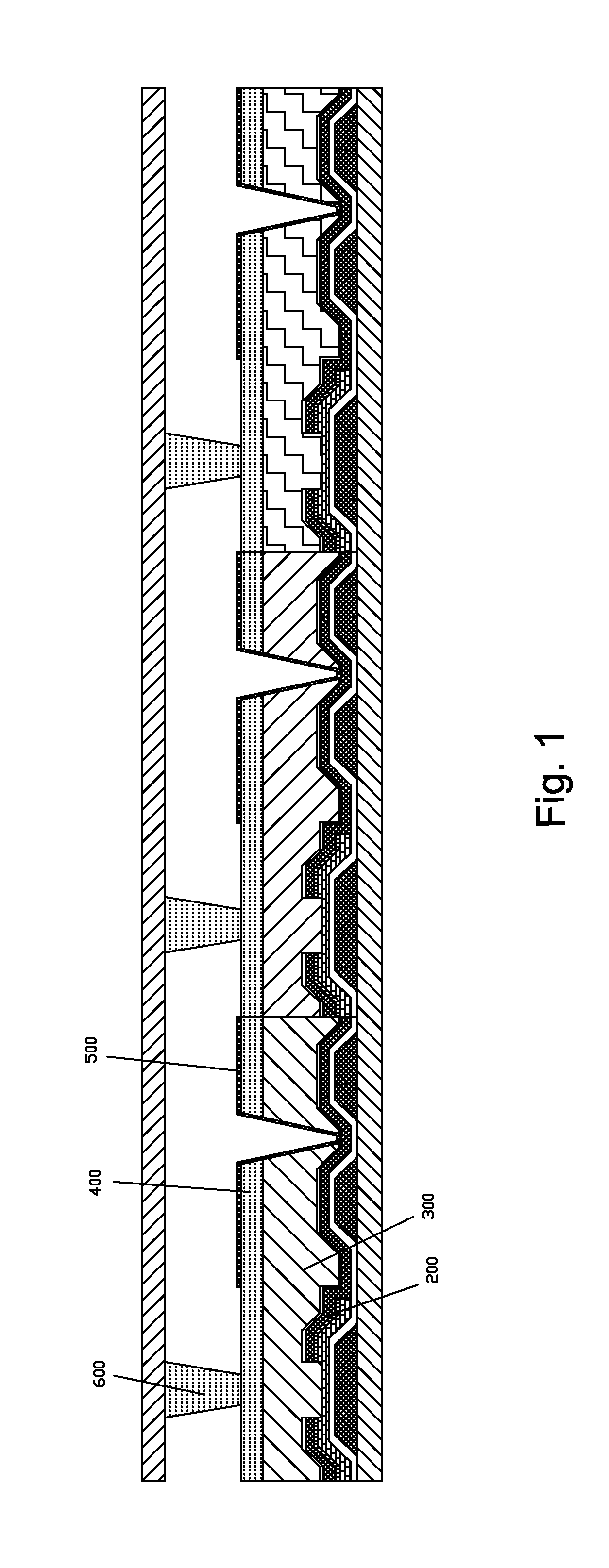

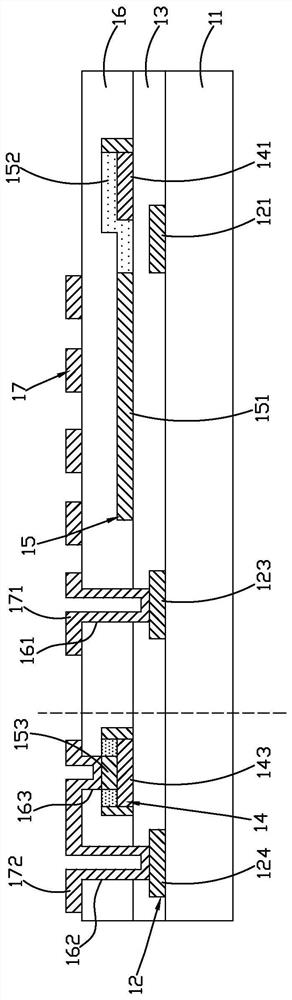

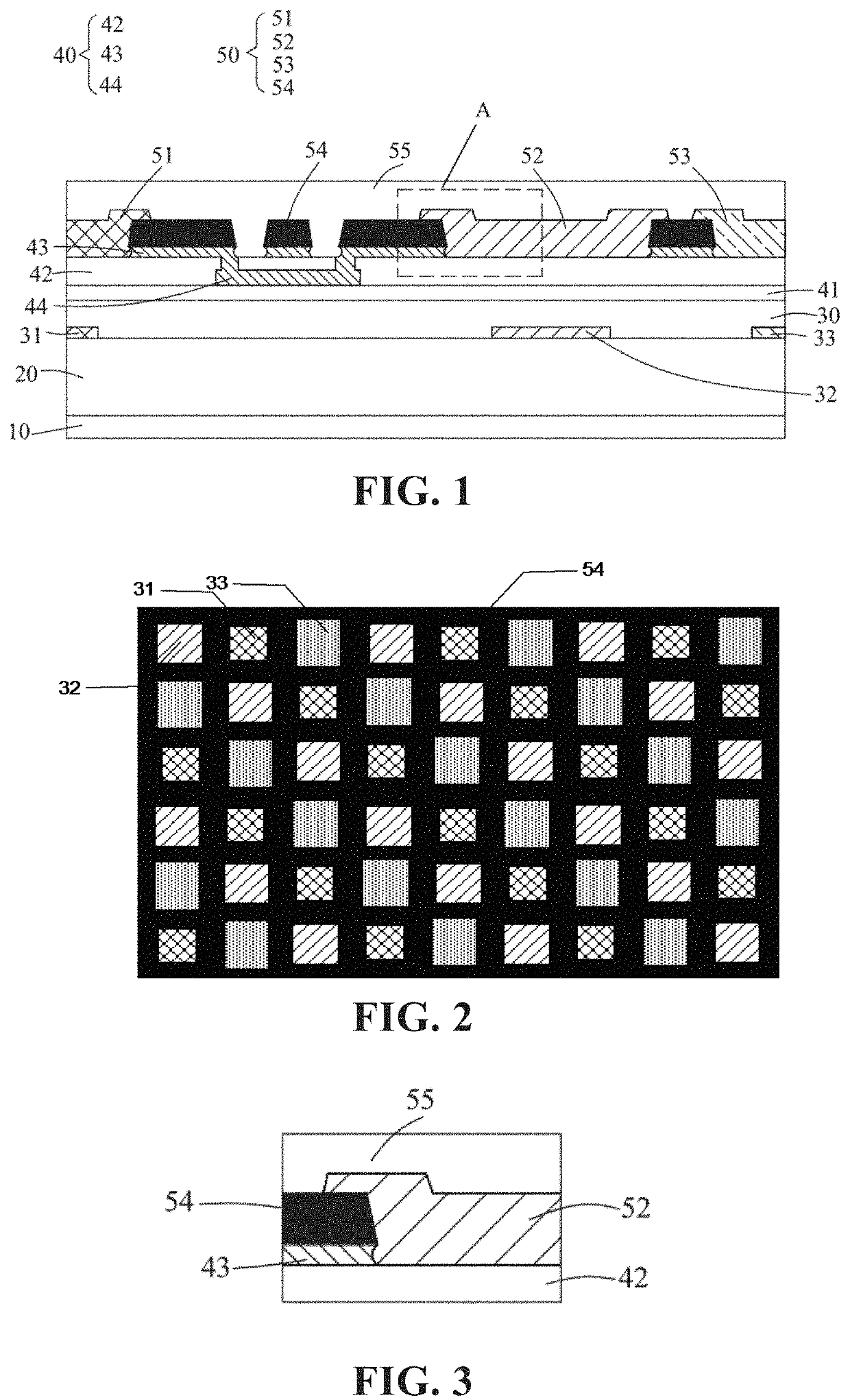

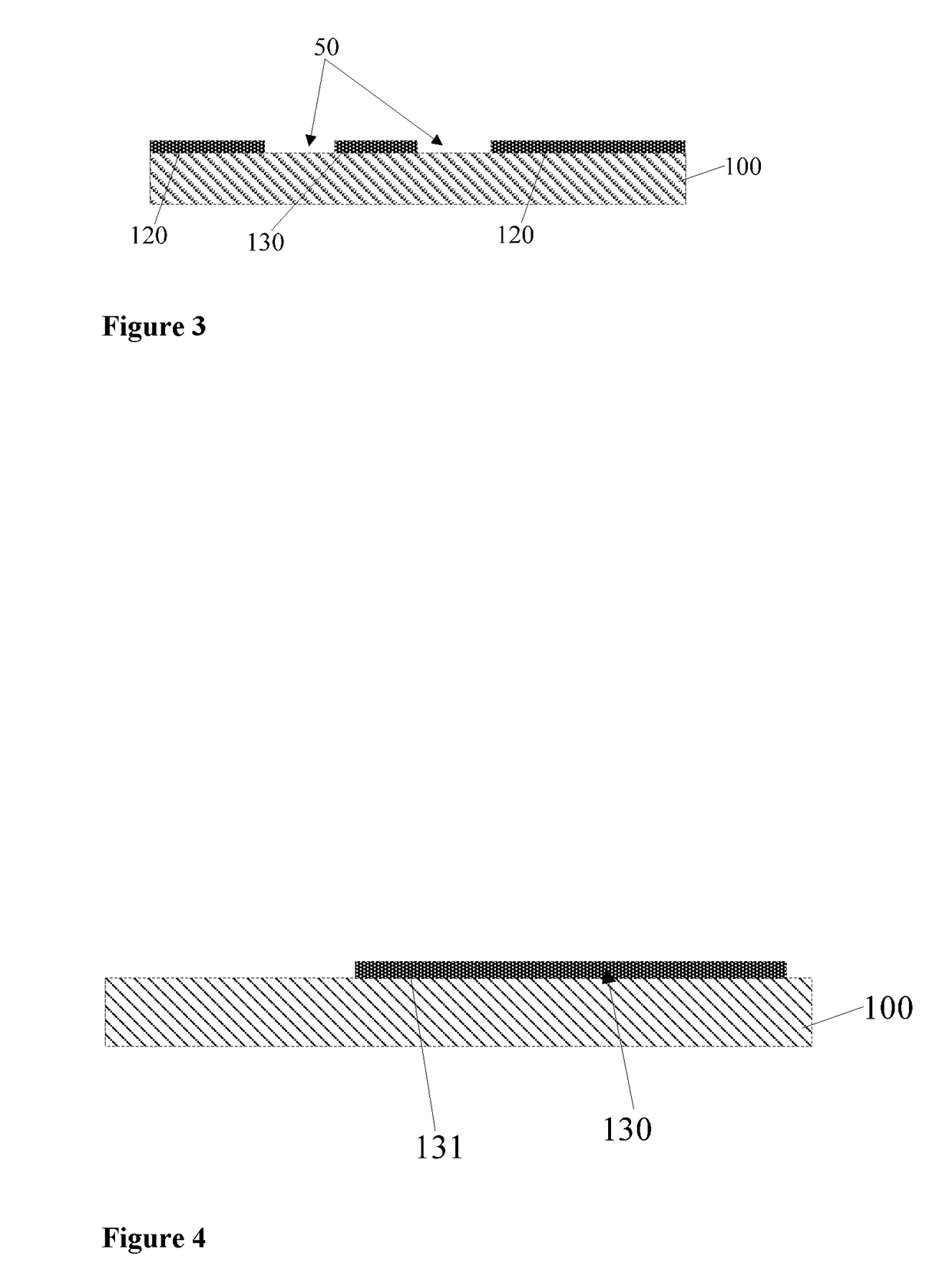

The invention provides a structure and manufacturing method of an array colored film integrated type liquid crystal display panel. The method includes the steps that a color-shielding layer (30) is manufactured on a first protection layer (25), the portions, located above a grid (21) and a source / drain electrode (24), of the color-shielding layer (30) are removed through a wet etching process, and then a second protection layer (40) covering the color-shielding layer (30) and the first protection layer (25) is deposited; a pixel electrode (50) is formed on the second protection layer (40) and penetrates through a via hole (45) of the second protection layer (40) and the first protection layer (25) to be in contact with the source / drain electrode (24); then the region where the color-shielding layer (30) is removed through the wet etching process is filled with black matrix materials, a black matrix (60) and a spacer (70) located on the black matrix (60) and integrated with the black matrix (60) are manufactured at the same time through a slit mask, the aperture opening ratio can be increased, bubbles are avoided, meanwhile the mask is saved, and the production cost is lowered.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

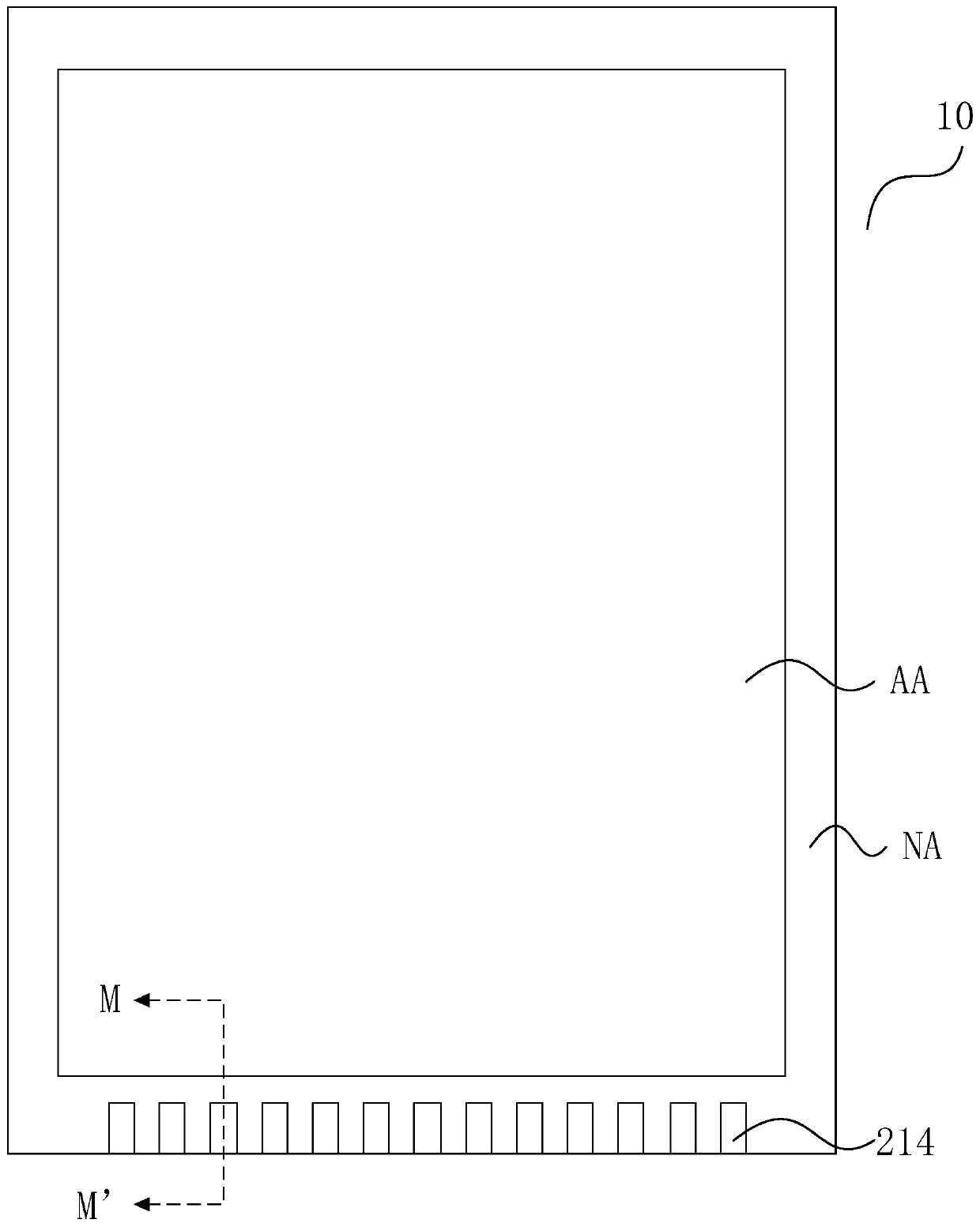

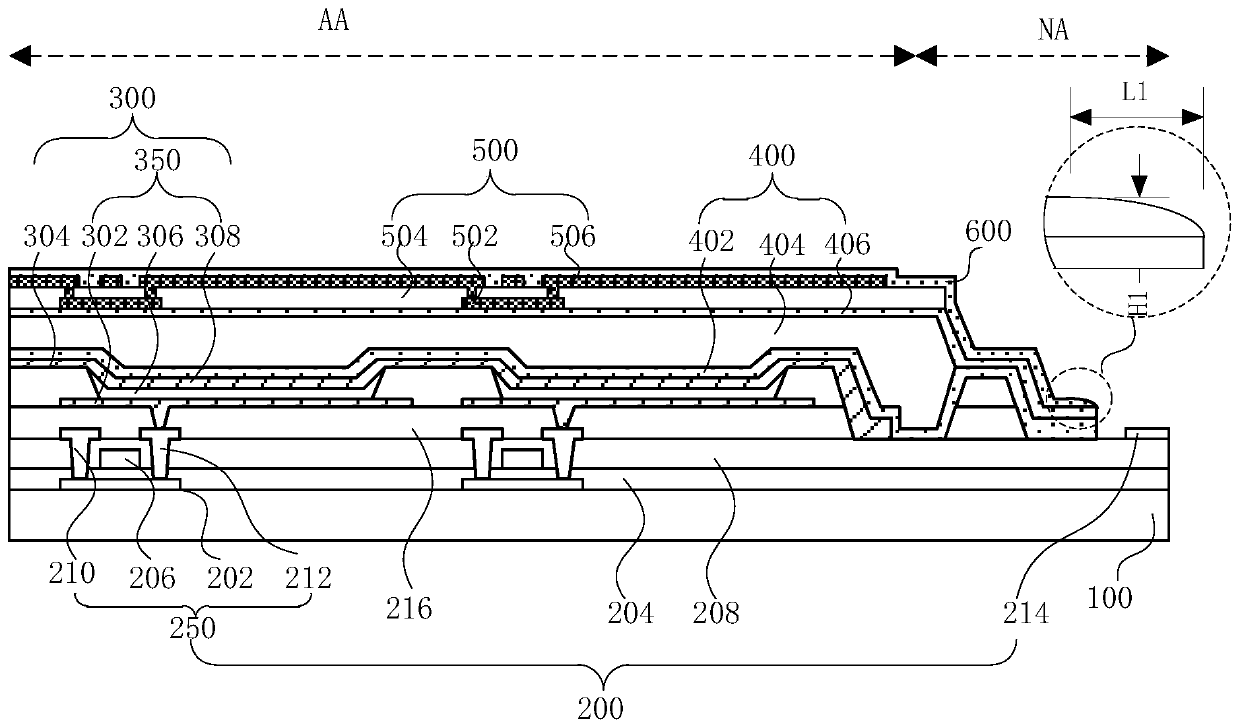

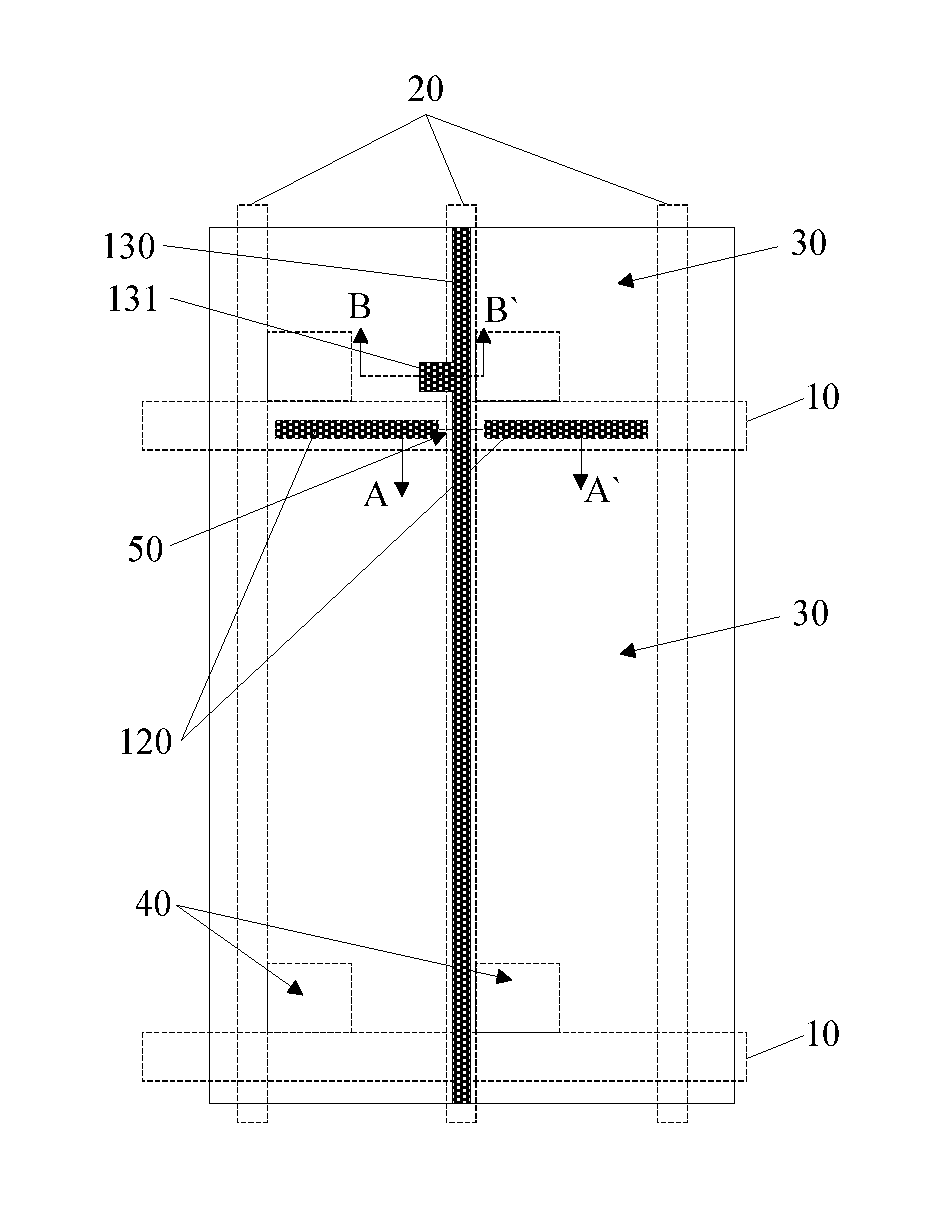

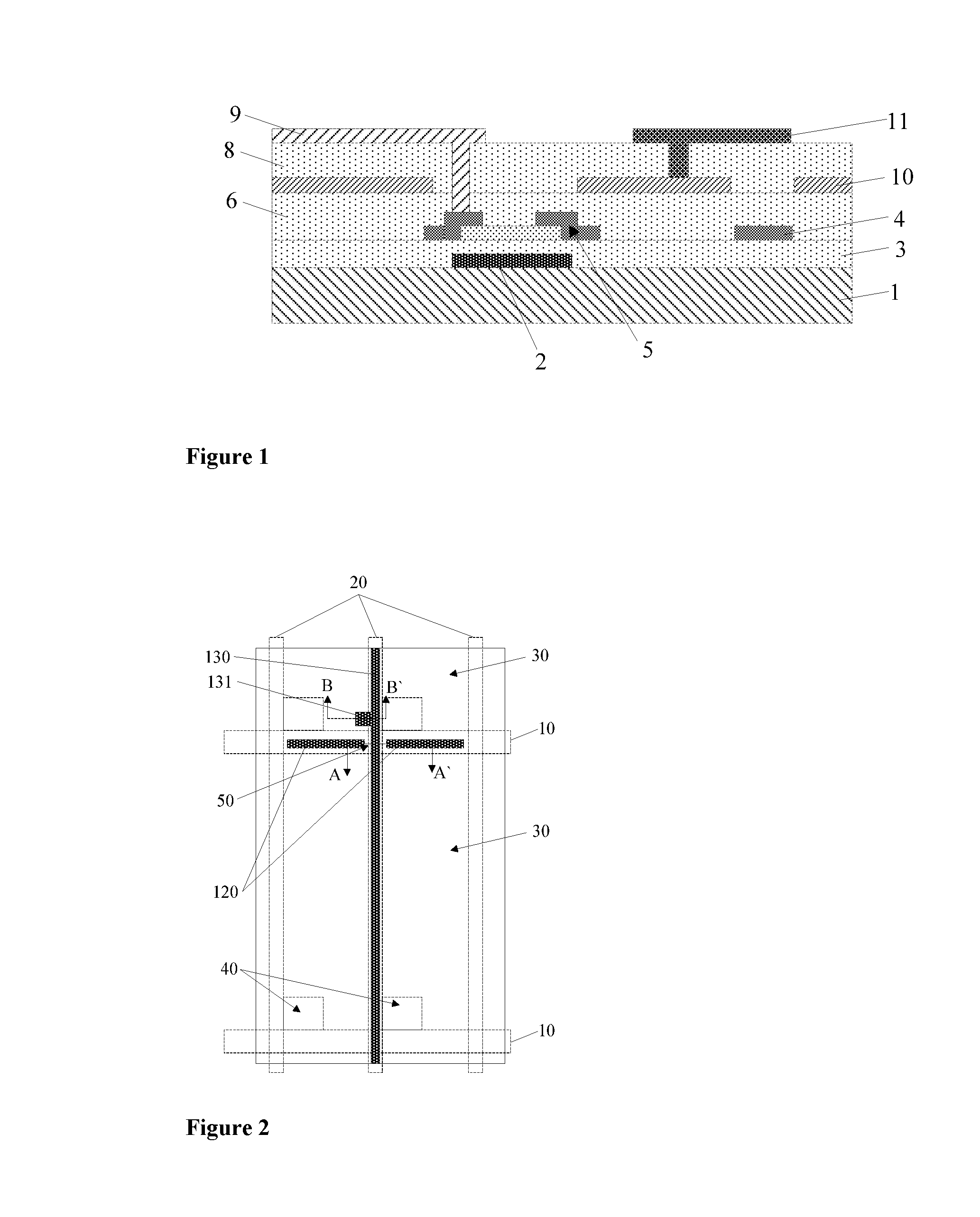

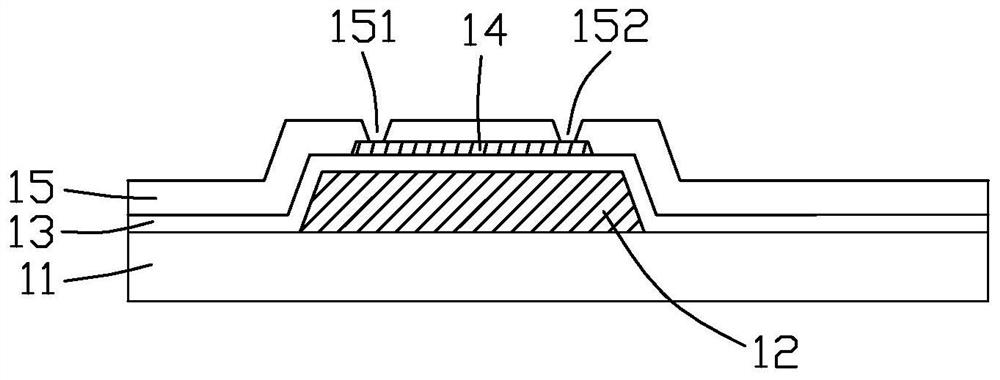

Array substrate, touch screen, touch display device and manufacturing method thereof

ActiveCN105573549AImprove stabilityMask savingStatic indicating devicesSolid-state devicesDisplay deviceAlloy

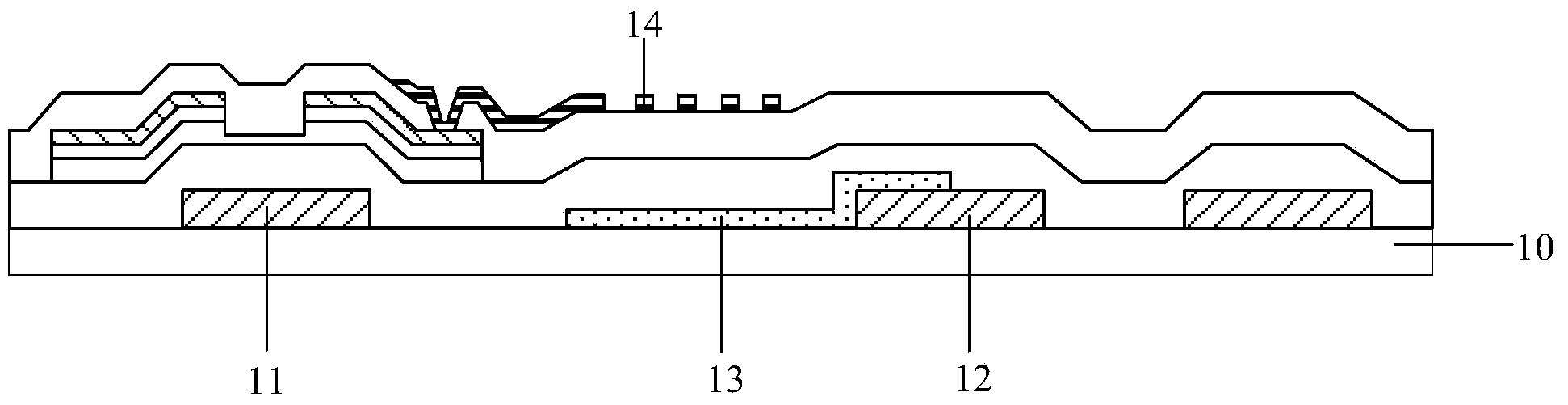

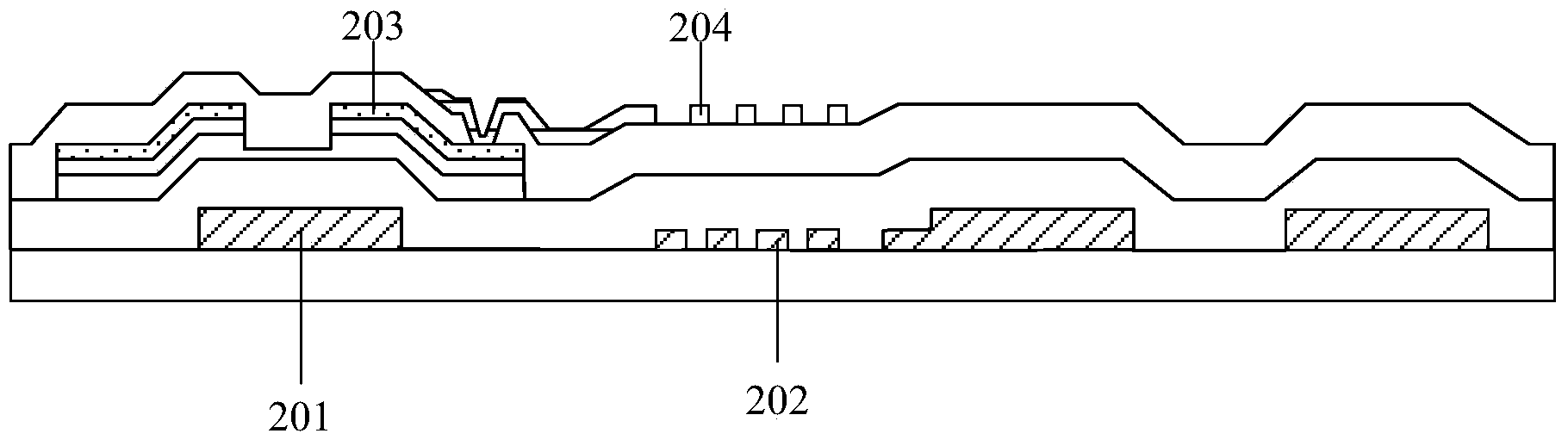

The invention provides an array substrate; a driving transistor of a peripheral driving circuit of the array substrate is a bigrid oxide semiconductor transistor; the top grid of the bigrid oxide semiconductor transistor and a touch lead positioned in a display area are formed in the same layer and made of the same material; and furthermore, the material of the top grid is non-transparent metal or alloy thereof having better conductivity, such as molybdenum, aluminium and copper. On the one hand, the bigrid oxide semiconductor transistor can be formed in the peripheral driving circuit in the event that an extra manufacturing process and a photomask are not increased, such that the purpose of controlling the threshold voltage of the oxide semiconductor transistor is realized; on the other hand, a lightproof metal layer is used as the top grid for covering a semiconductor channel region; and thus, photo-generated current can be reduced, such that influence of illumination on the stability of the oxide semiconductor transistor is avoided.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

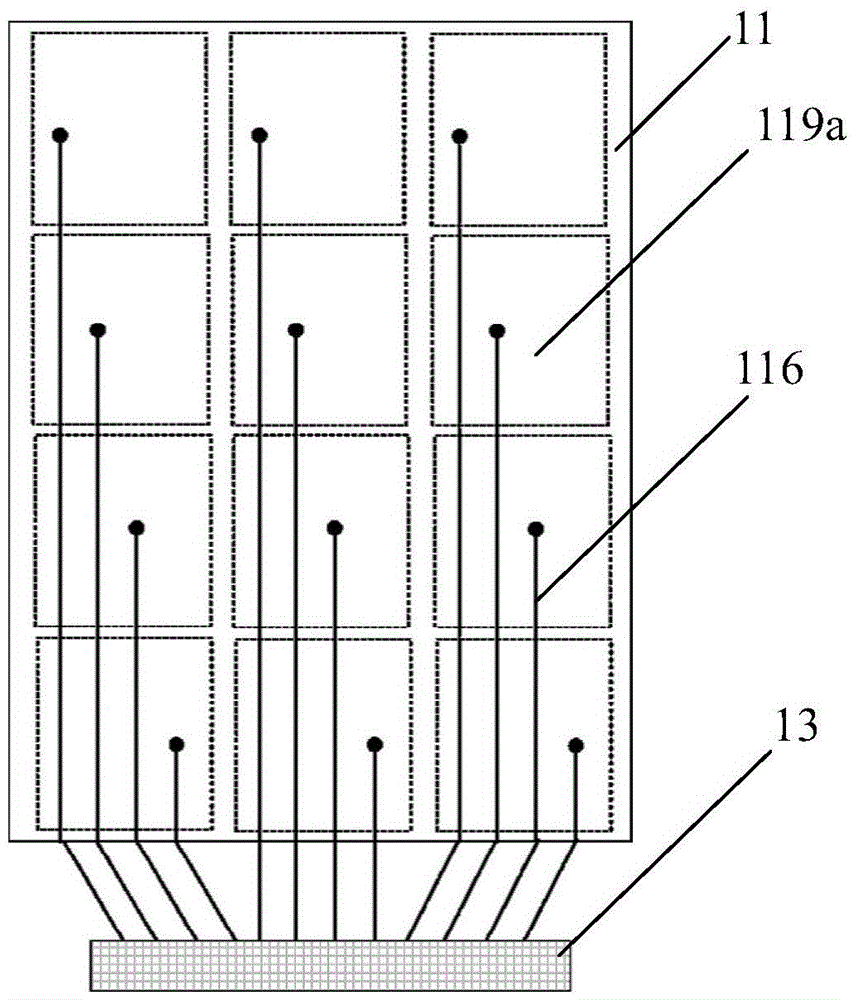

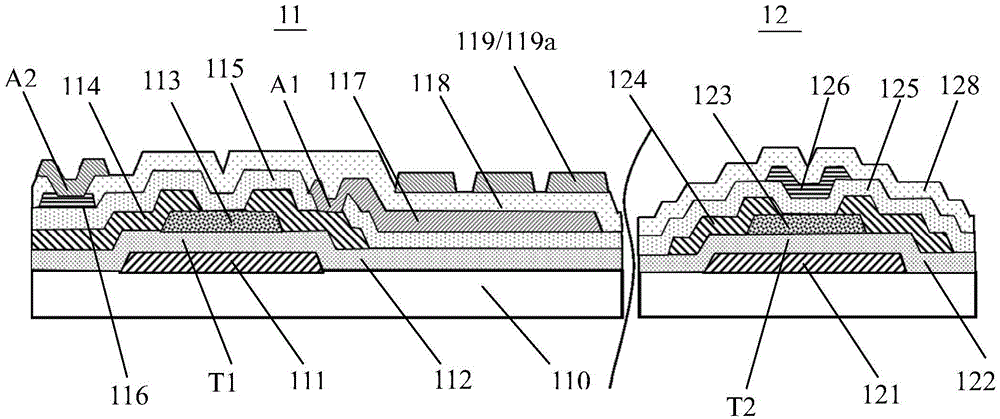

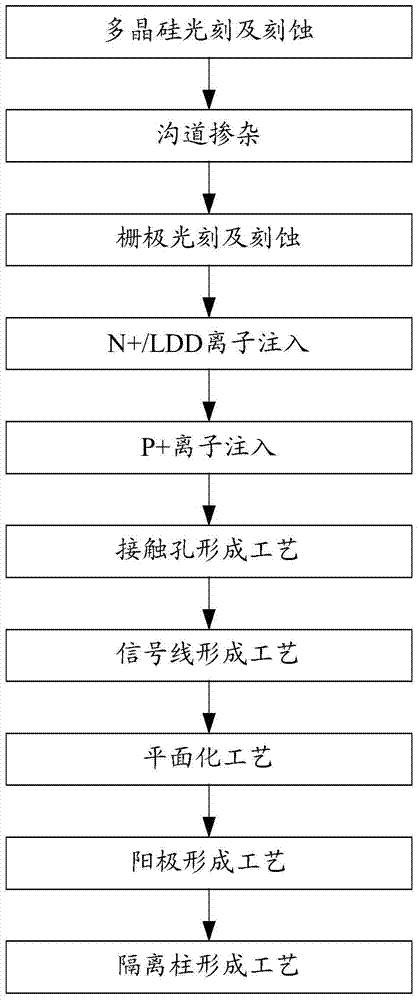

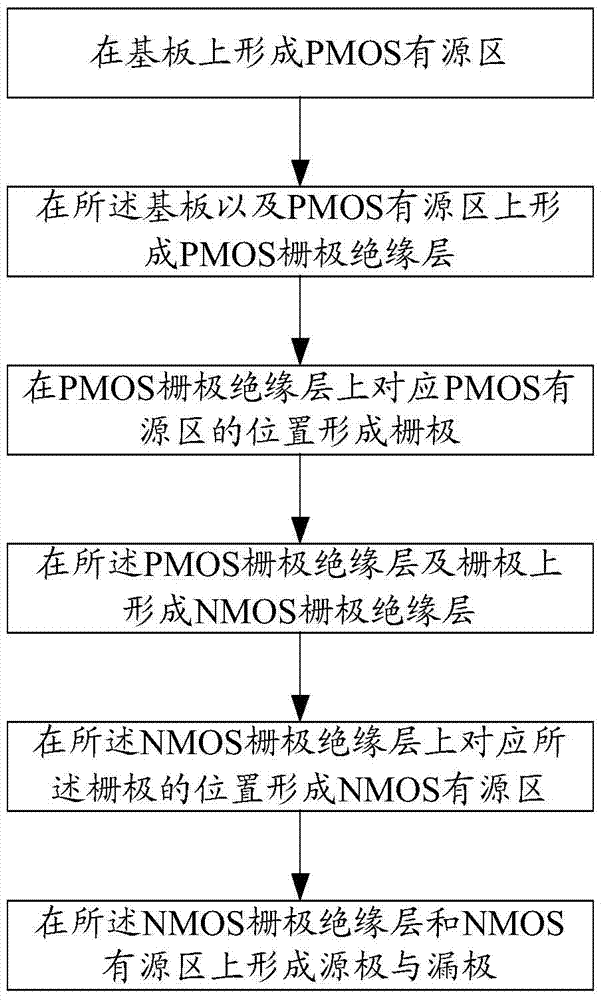

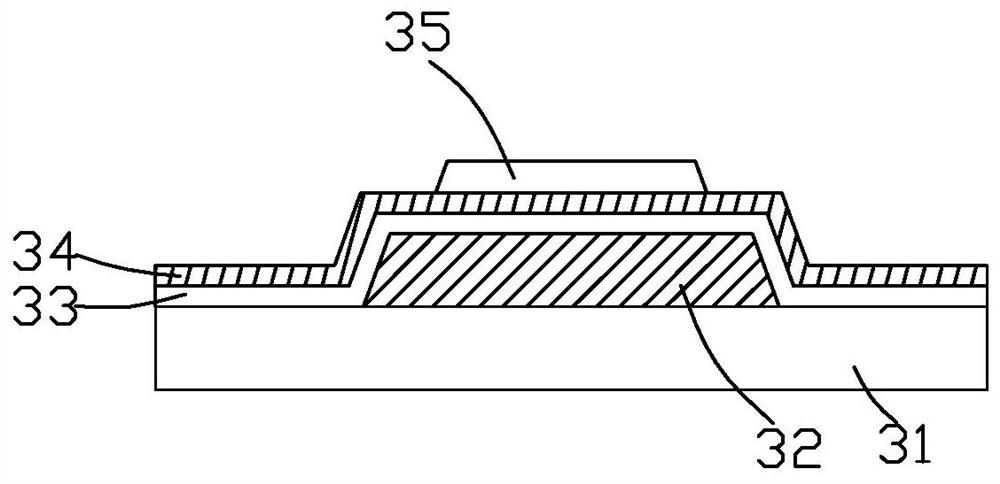

Common-gate stereoscopic CMOS (Complementary Metal-Oxide-Semiconductor Transistor) device, OLED (Organic Light Emitting Diode) device and manufacturing method thereof

InactiveCN104752426AReduced injection processMask savingTransistorSolid-state devicesCMOSEngineering

The invention provides a common-gate stereoscopic CMOS (Complementary Metal-Oxide-Semiconductor Transistor) device, an OLED (Organic Light Emitting Diode) device and a manufacturing method thereof. In the common-gate stereoscopic CMOS device, an NMOS transistor adopts an oxide semiconductor device, a PMOS transistor adopts an LTPS device, the PMOS transistor and the NMOS transistor share a gate, sources and drains of the two are formed through one etching process, the PMOS transistor and the NMOS transistor are arranged in a stacking mode, the occupied area can be effectively reduced, the integration degree of a circuit is improved, and the CMOS device and the LED device manufacturing process is simple and the cost is low.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

Touch control panel and fabrication method thereof

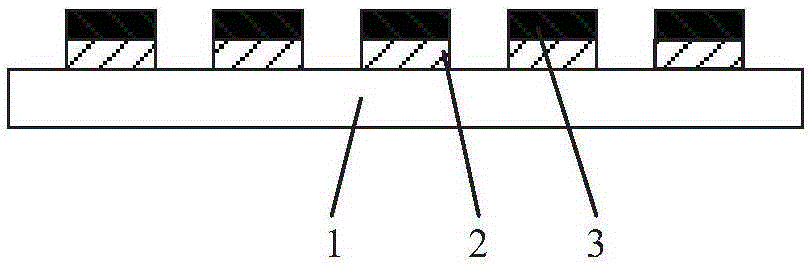

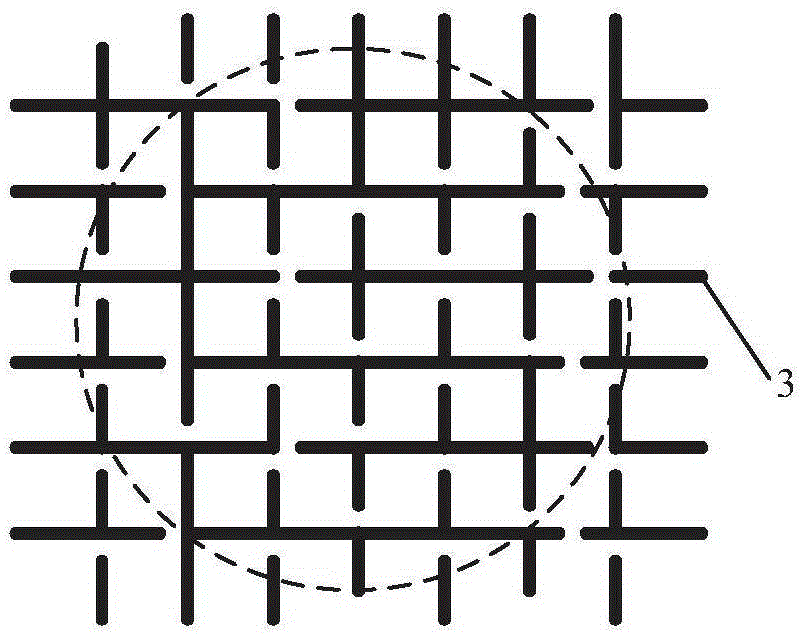

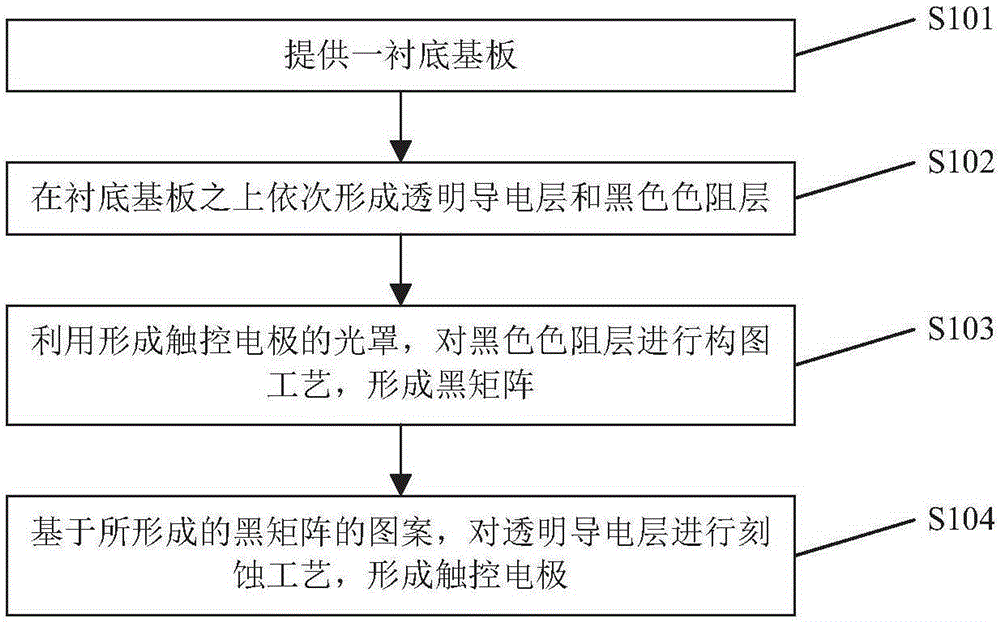

ActiveCN105159514AImprove alignment accuracyIncrease productivityNon-linear opticsInput/output processes for data processingTablet computerDisplay device

The invention disclose a touch control panel and a fabrication method thereof, which belong to the technical field of display and can be used for improving the production efficiency of the touch control panel and reducing the production cost of the control panel. The touch control panel comprises a substrate and also comprises a touch control electrode and a black matrix, wherein the touch control electrode is arranged on the substrate, and the black matrix is arranged on the touch control electrode, has same patterns with the touch control electrode, and is completely coincided with the touch control electrode. The touch control panel can be applicable for display devices with the touch control panel, such as a liquid crystal display television, a liquid crystal displayer, a mobile phone and a tablet computer.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

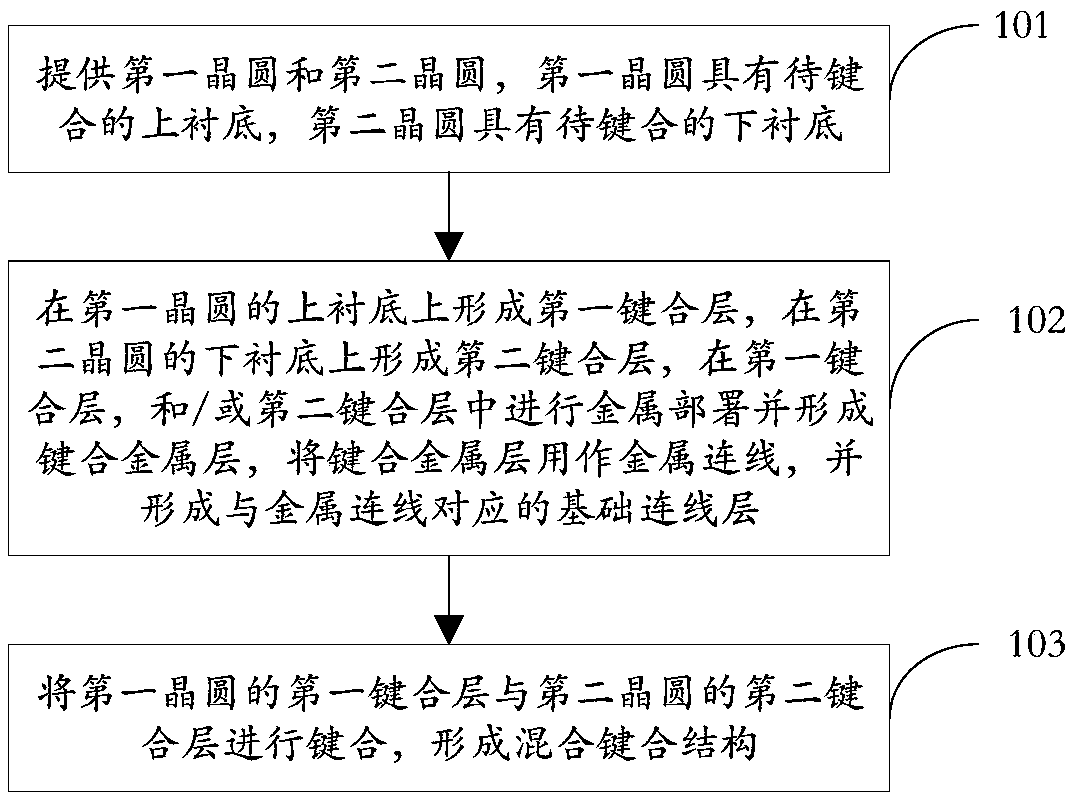

Mixed bonding method having metal wire, and mixed bonding structure

ActiveCN107731667AMask savingReduce processing costsSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductorSemiconductor technology

The invention discloses a mixed bonding method having metal wire, and a mixed bonding structure, which belong to the technical field of semiconductors. The method comprises the steps of providing a first wafer and a second wafer, wherein the first wafer has an upper substrate to be bonded, and the second wafer has a lower substrate to be bonded; forming a first bonding layer on the upper substrateof the first wafer, and forming a second bonding layer on the lower substrate of the second wafer; conducting metal disposition in the first bonding layer and / or the second bonding layer, and forminga bonding metal layer, and using the bonding metal layer as a metal wire, and forming a basic connecting line layer corresponding to the metal wire; conducting bonding on the first bonding layer of the first wafer and on the second bonding layer of the second wafer, and forming a mixed bonding structure. The invention is advantageous in that the present bonding metal layer only used for metal contact is used for the metal wire, and thereby the metal layer is reduced, and one or two layers of optical cover required for the producing of the metal wire can be saved, and technology cost can be reduced.

Owner:YANGTZE MEMORY TECH CO LTD

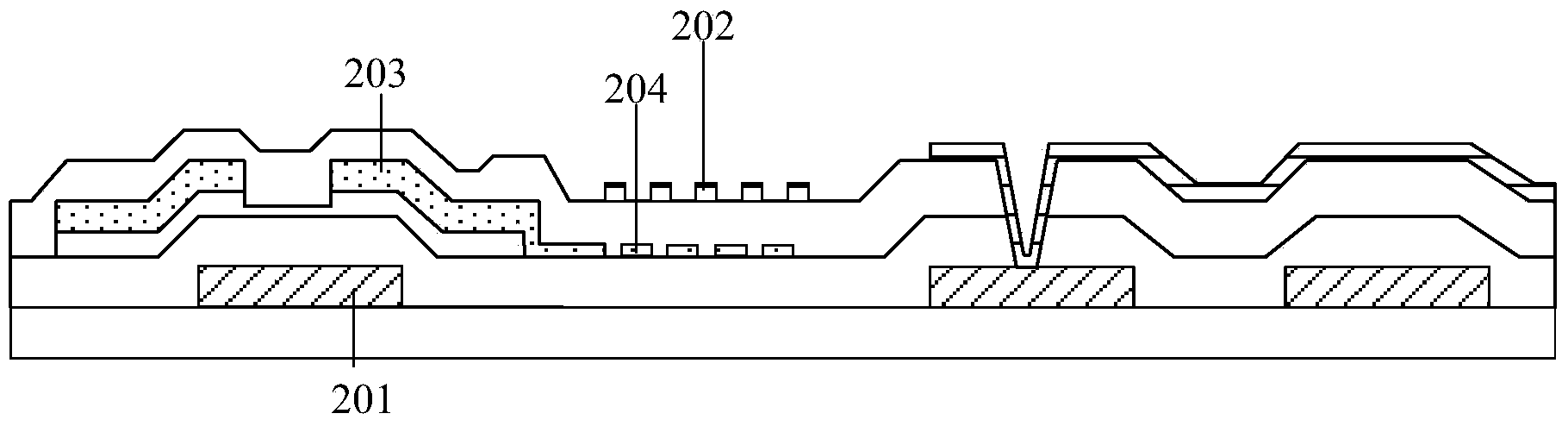

Manufacture method of color filter on array liquid crystal display panel and structure thereof

InactiveUS20170153519A1Increase the aperture ratioAvoid it happening againNon-linear opticsResistEngineering

The present invention provides a manufacture method of a Color Filter On Array liquid crystal display panel and a structure thereof. The method comprises: manufacturing a color resist layer (30) on a first protective layer (25), and removing the color resist layer (30) in an area above the gate (21) and the source / the drain (24), and deposing a second protective layer (40) covering the color resist layer (30) and the first protective layer (25); the pixel electrode (50) is formed on the second protective layer (40), and contacts with the source / the drain (24) through a via hole (45) penetrating the second protective layer (40) and the first protective layer (25); and then, filling black matrix material in the area of which the color resist layer (30) is removed, and employing a slit diffraction mask to manufacture a black matrix (60) and spacers (70) on the black matrix (60).

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Array substrate, display device and array substrate manufacturing method

InactiveCN103779357AReduce thicknessGuaranteed transmittanceSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayDisplay device

The invention discloses an array substrate, a display device and an array substrate manufacturing method, and relates to the liquid crystal display technology. Material of a pixel electrode is the same as that of a source and drain electrode, but the thickness of the pixel electrode is smaller than that of the source and drain electrode, and alternatively material of a public electrode is the same as that of a grid electrode but the thickness of the public electrode is smaller than that of the grid electrode. On the basis of reducing technology difficulty, the transmittance of the array substrate is guaranteed.

Owner:BOE TECH GRP CO LTD

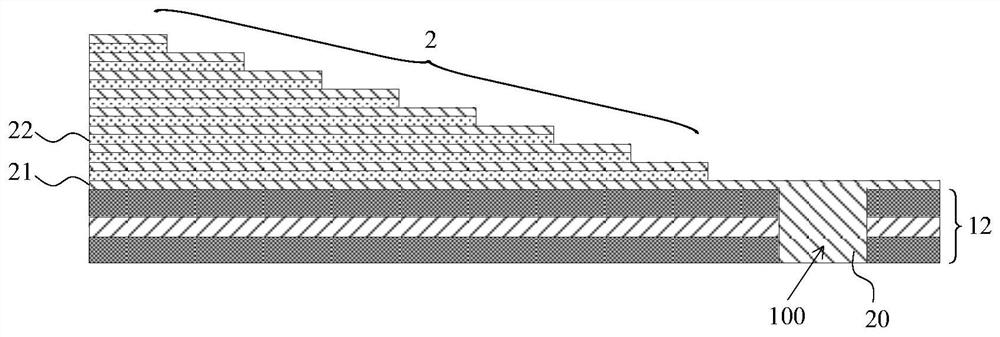

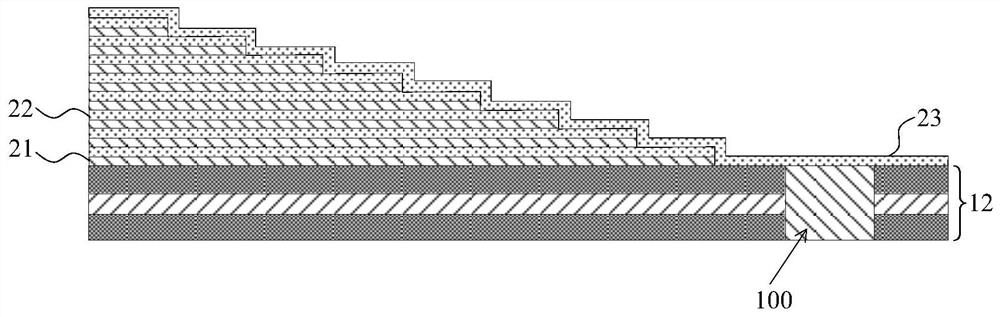

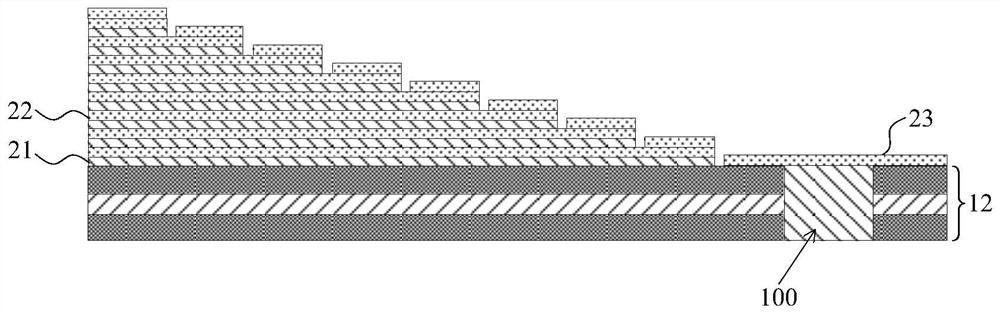

Display device and fabrication method thereof

ActiveCN110061043AMask savingSave etching processSolid-state devicesInput/output processes for data processingEngineeringDisplay device

The invention describes a display device and a fabrication method thereof. The display device comprises a substrate, a driving circuit layer, a light-emitting device layer, a thin film package layer,a touch sensing unit and a protection layer, wherein the driving circuit layer comprises a pin, the pin is arranged at a non-display region, the thin film package layer comprises a first inorganic package layer, the touch sensing unit comprises a touch insulation layer, the projection edges of the first inorganic package layer and the protection layer on the substrate are coincided, or the projection profiles of the first inorganic package layer and the touch insulation layer on the substrate are same, and the projections of the first inorganic package layer and the protection layer / the touchinsulation layer on the substrate does not cover the pin. During the pattering process, the first inorganic package layer and the protection layer / the touch insulation layer employs the same mask, themask and the etching process are saved, the production efficiency is greatly improved, and the cost is reduced.

Owner:WUHAN TIANMA MICRO ELECTRONICS CO LTD

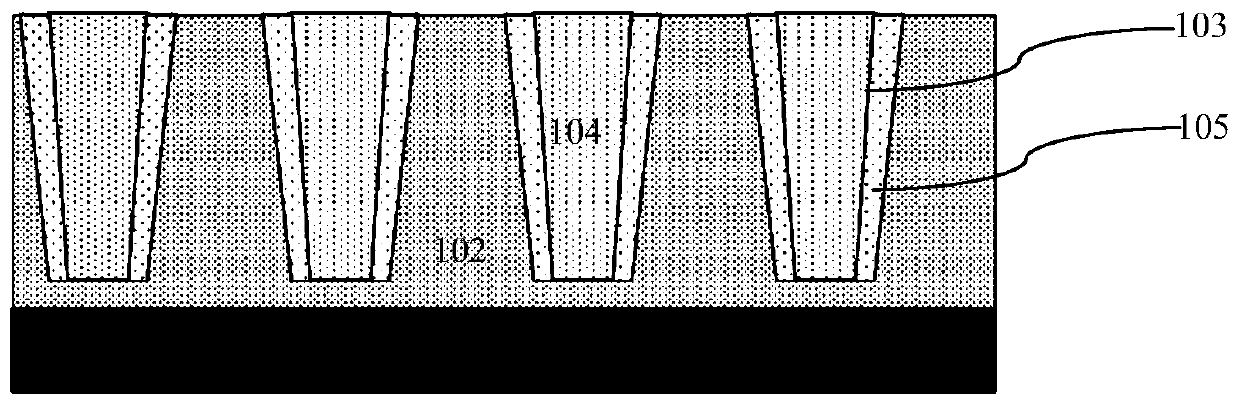

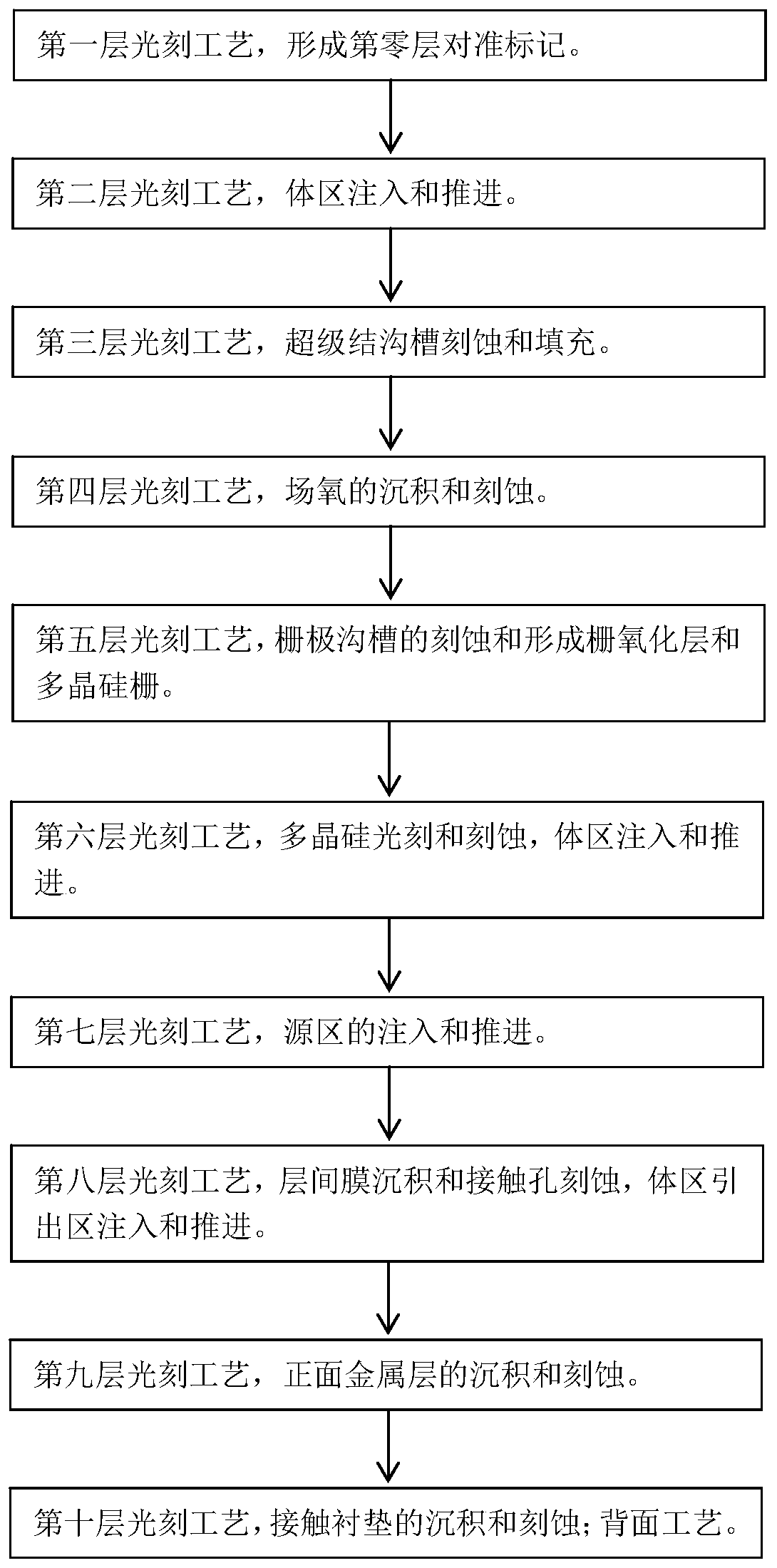

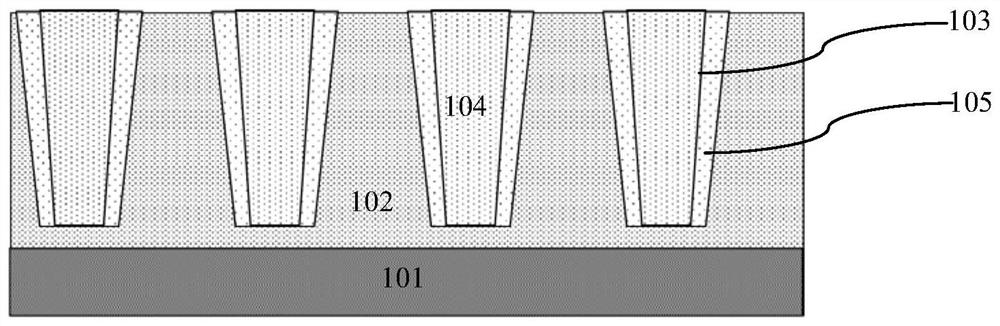

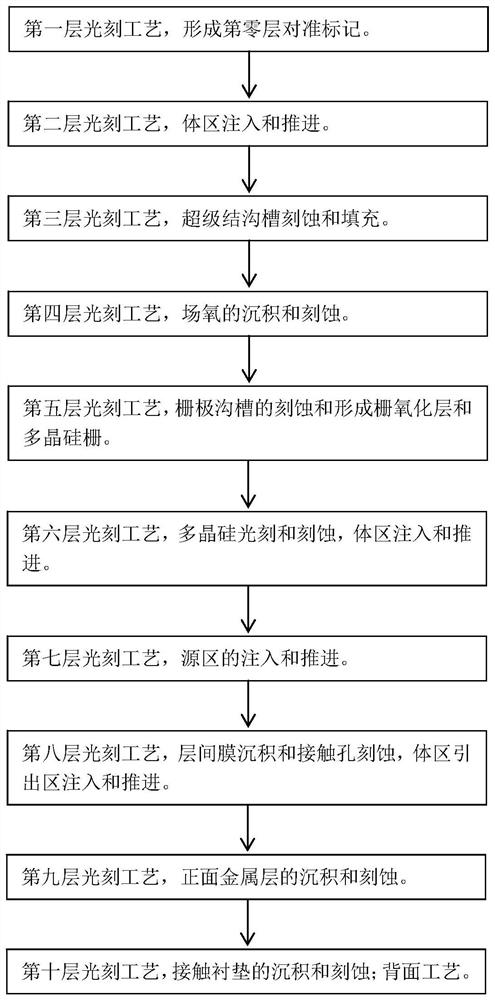

Manufacturing method of super junction device

InactiveCN111540685AReduce interdiffusionReduce processing difficultySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPolysilicon gate

The invention discloses a manufacturing method of a super junction device. The method comprises the following steps: the step 1, forming a gate structure which is a trench gate, filling a gate trenchwith a polysilicon gate in the forming process of the trench gate, then carrying out first planarization to enable the surface of a first epitaxial layer with the trench gate to be a flat surface, andenabling the width of the gate trench at the leading-out position of the gate structure to meet the requirement of forming a contact hole; and the step 2, forming a super junction in the first epitaxial layer with the flat surface on which the trench gate is formed, wherein in the forming process of the super junction, a second epitaxial layer is adopted to fill the super junction trench, and then secondary planarization is performed, so that the surface of the first epitaxial layer with the super junction is a flat surface. According to the invention, the full-flat process can be realized, the trench gate process can be conveniently arranged before the super junction forming process, and the thermal process after the super junction is formed can be reduced, so that the mutual diffusion of impurities of the super junction is reduced, the device performance is improved, a photomask can be saved, and the process cost is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

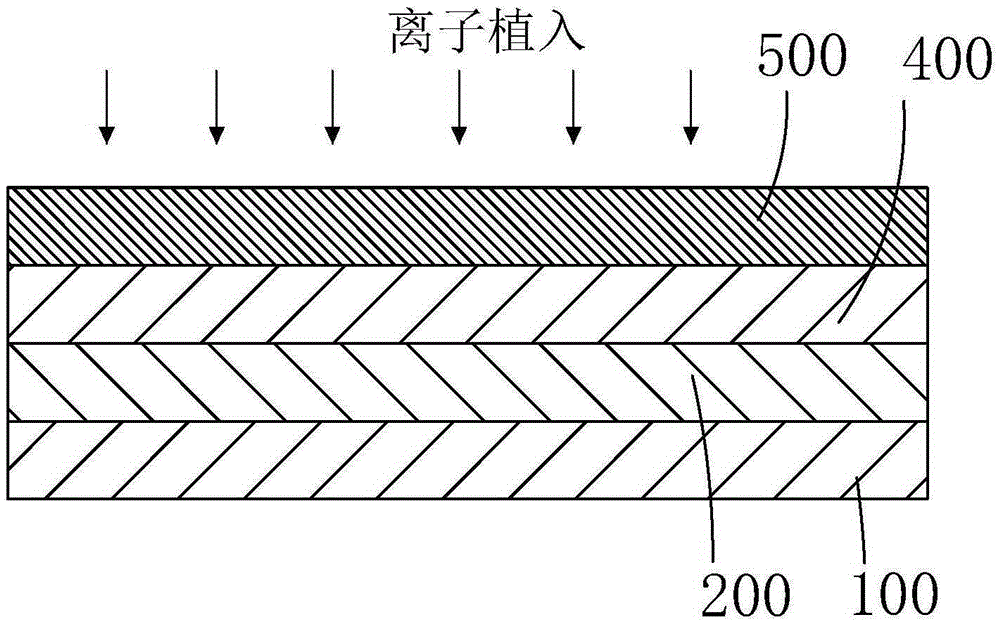

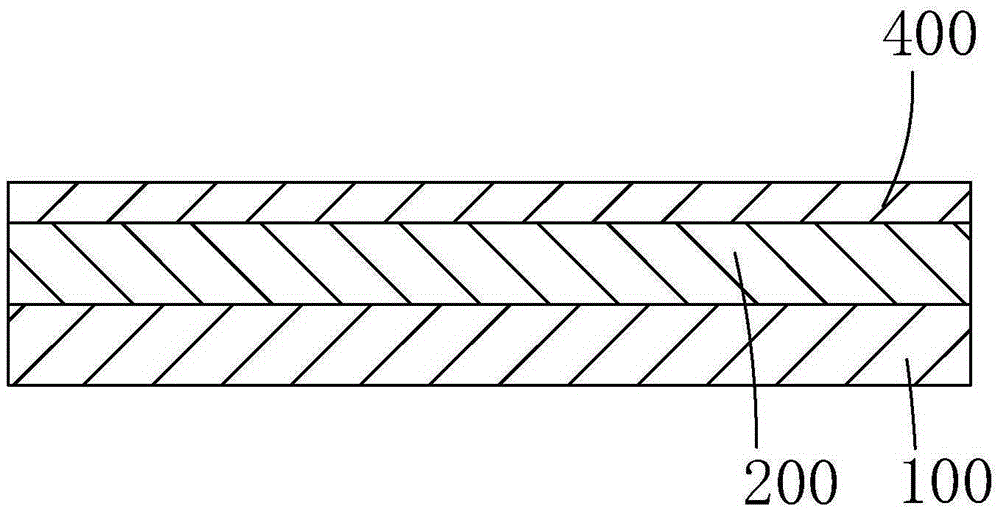

Manufacture method of TFT substrate

ActiveCN105390443AMask savingSimplify the processSolid-state devicesSemiconductor/solid-state device manufacturingPhysicsOptoelectronics

The invention provides a manufacture method of a TFT substrate. After that ion implantation and induced crystallization are carried out on an amorphous silicon layer, it is not required to completely remove an ion induction layer at the surface of an obtained polysilicon layer, instead, only the ion induction layer in a channel region is removed in a half-toning photomask technology, it is not required to carry out ion implantation on a subsequent source / drain electrode contract area again, and a photomask needed by ion implantation again can be saved; source / drain electrodes are prepared under the half-toning photomask, so that a photomask needed by manufacture of the source / drain electrodes can be saved; and the source / drain electrodes are manufactured at first, manufacture of an interlayer insulation layer is omitted, and a photomask needed by manufacture of the interlayer insulation layer is further saved. According to the manufacture method of the TFT substrate, the half-toning photomask technology is used to reduce nine photomasks needed in the prior art to six photomasks, thereby effectively simplifying the process, improving the production efficiency and reducing the production cost.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Polysilicon active layer-containing thin film transistor, manufacturing method thereof and array substrate

InactiveCN102709185AShort manufacturing timeReduce manufacturing costTransistorSolid-state devicesOptoelectronicsActive layer

The invention discloses a method for manufacturing a polysilicon active layer-containing thin film transistor, a manufacturing method thereof and an array substrate. The method comprises the following steps of: depositing an amorphous silicon layer on a substrate; patterning the amorphous silicon layer; forming an active layer which comprises a source region, a drain region and a channel region; forming a gate insulating layer and a gate electrode on the upper part of the channel region; depositing an induced metal layer on the substrate on which the gate electrode is formed; doping impurities into the source region and the drain region in an ion injection way, wherein part of the induced metal is bombarded into the source region and the drain region when ions are injected; removing the induced metal layer; performing heat treatment on the doped active layer, so that impurities are activated, and the active layer is subjected to metal-induced crystallization and metal-induced lateral crystallization under the action of the induced metal; and forming a source electrode and a drain electrode. By the method, the preparation time for a polysilicon thin film transistor (TFT) can be shortened; and the manufacturing cost of the polysilicon TFT can be reduced.

Owner:BOE TECH GRP CO LTD

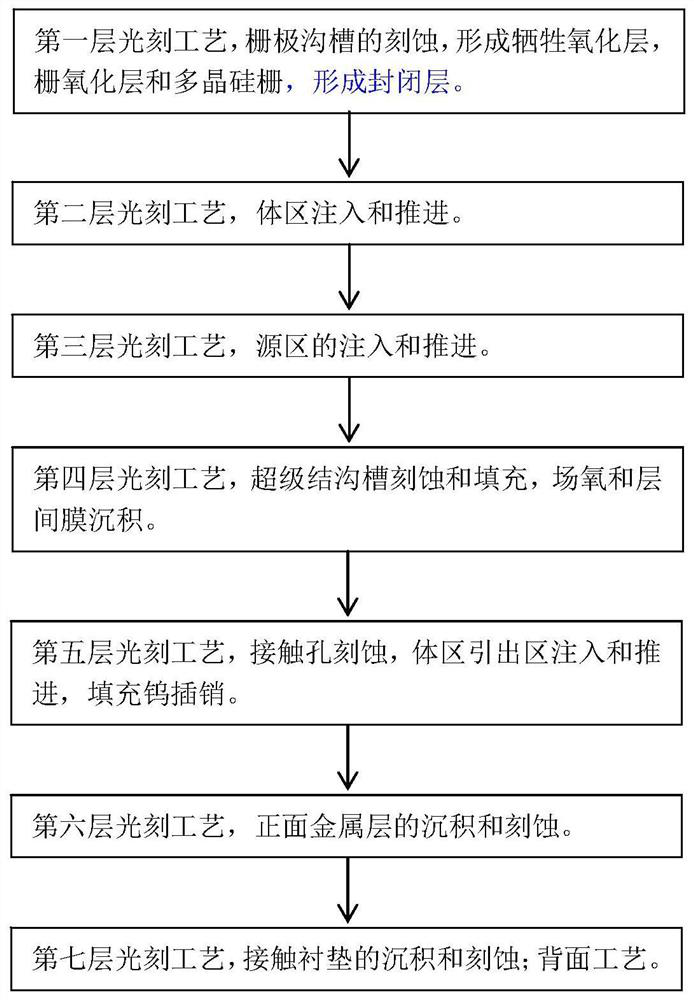

Manufacturing method of super junction device

PendingCN111986997AReduce interdiffusionReduce processing difficultySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingEngineering

The invention discloses a manufacturing method of a super junction device. The manufacturing method comprises the steps: step 1, filling a gate electrode trench with a polysilicon gate and carrying out first planarization to form a gate electrode structure; step 2, etching back the polysilicon gate and forming a sealing layer in a top recess formed by back etching; and step 3, filling the super junction trench with a second epitaxial layer and carrying out secondary planarization to form a super junction. According to the invention, a full-flat process can be realized, the trench gate processcan be conveniently arranged before the super junction forming process, and the thermal process after the super junction is formed can be reduced, so that the mutual diffusion of impurities of the super junction is reduced, the device performance is improved, a photomask can be saved, and the process cost is reduced; and doping and external expansion of the polysilicon gate can be prevented, a gate oxide layer can be protected, and the product quality and reliability can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

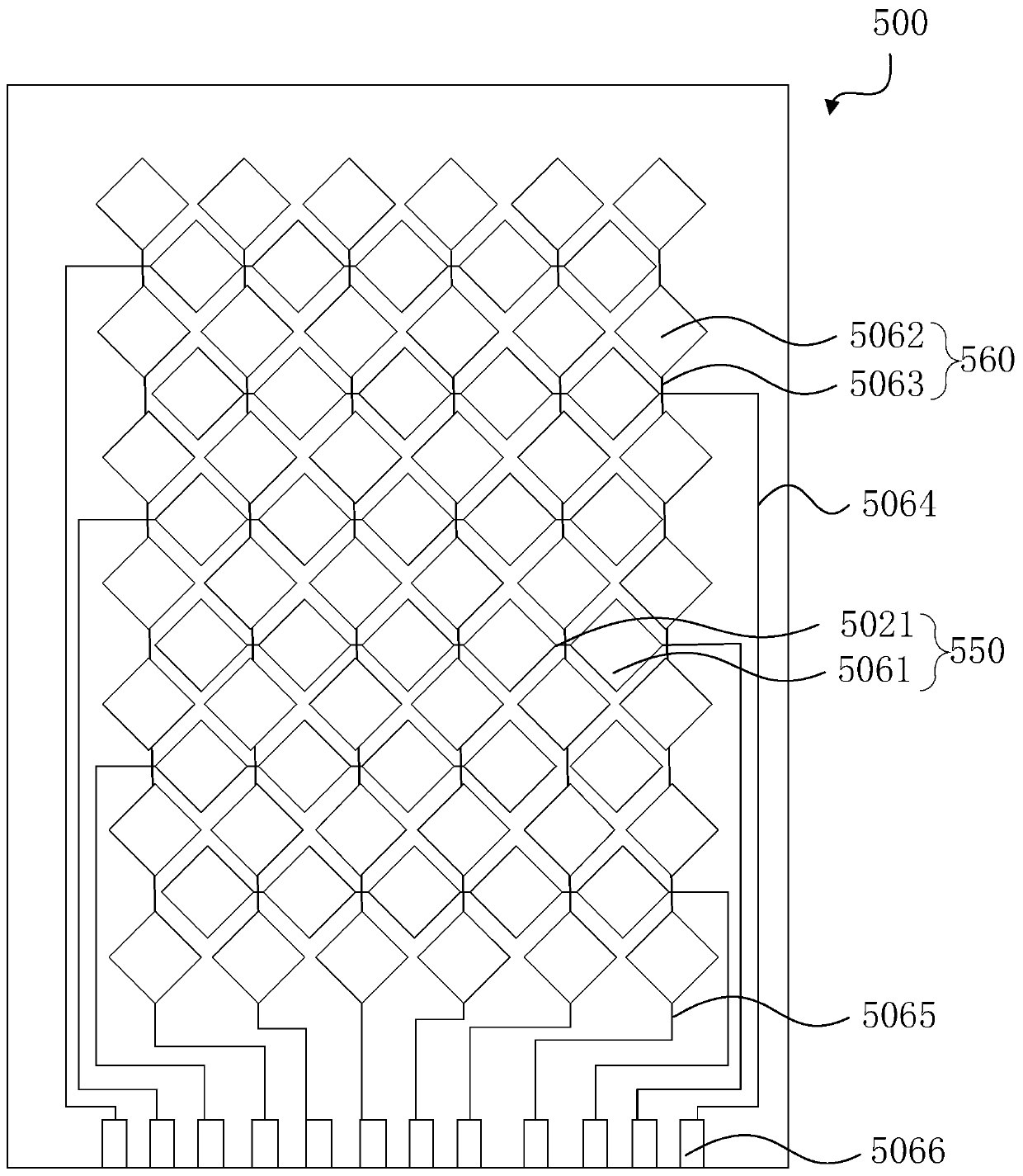

Touch display panel structure, method for forming the same, and touch display device

ActiveUS20160291757A1The process steps are simpleLow costNon-linear opticsInput/output processes for data processingScan lineDisplay device

A touch display panel structure, a method for forming the touch display panel structure, and a touch display device are provided. The touch display panel structure includes: a substrate, scan lines each including a plurality of scan line segments, touch electrode lines each disposed at an interval between adjacent scan line segments; a first dielectric layer and data lines; a second dielectric layer and a first interconnection structure; a first via hole through the first dielectric layer and the second dielectric layer; a third dielectric layer a common electrode layer; a second via hole through the first dielectric layer and the second dielectric layer; and a plurality of third via holes through the third dielectric layer, wherein each touch electrode is connected to a touch electrode line via the second via hole and the third via hole.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1

Display panel and preparation method thereof

InactiveCN111063695AReduce settingsMask savingSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringDielectric layer

The invention provides a display panel. The display panel comprises thin film transistors arranged in an array mode. The source electrodes and the drain electrodes of the thin film transistors comprise electrode layers, and the electrode layers of the source electrodes or the drain electrodes extend to pixel opening areas and can serve as pixel electrodes. Dielectric layers used for arranging thepixel electrodes are reduced. Compared with the prior art, the display panel has the advantages that photomask manufacturing procedures can be reduced, and cost is reduced.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

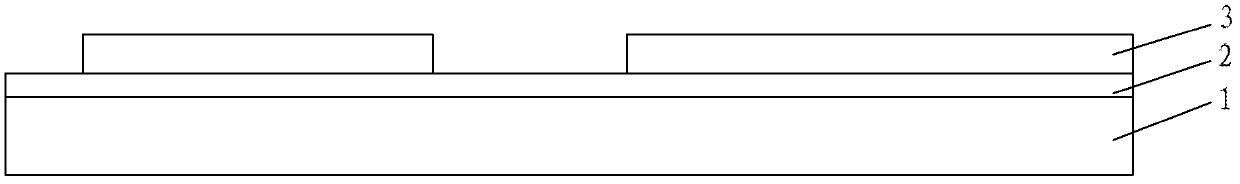

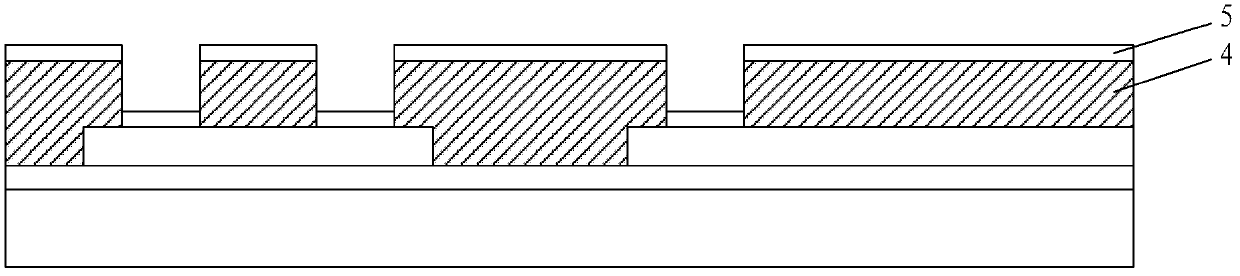

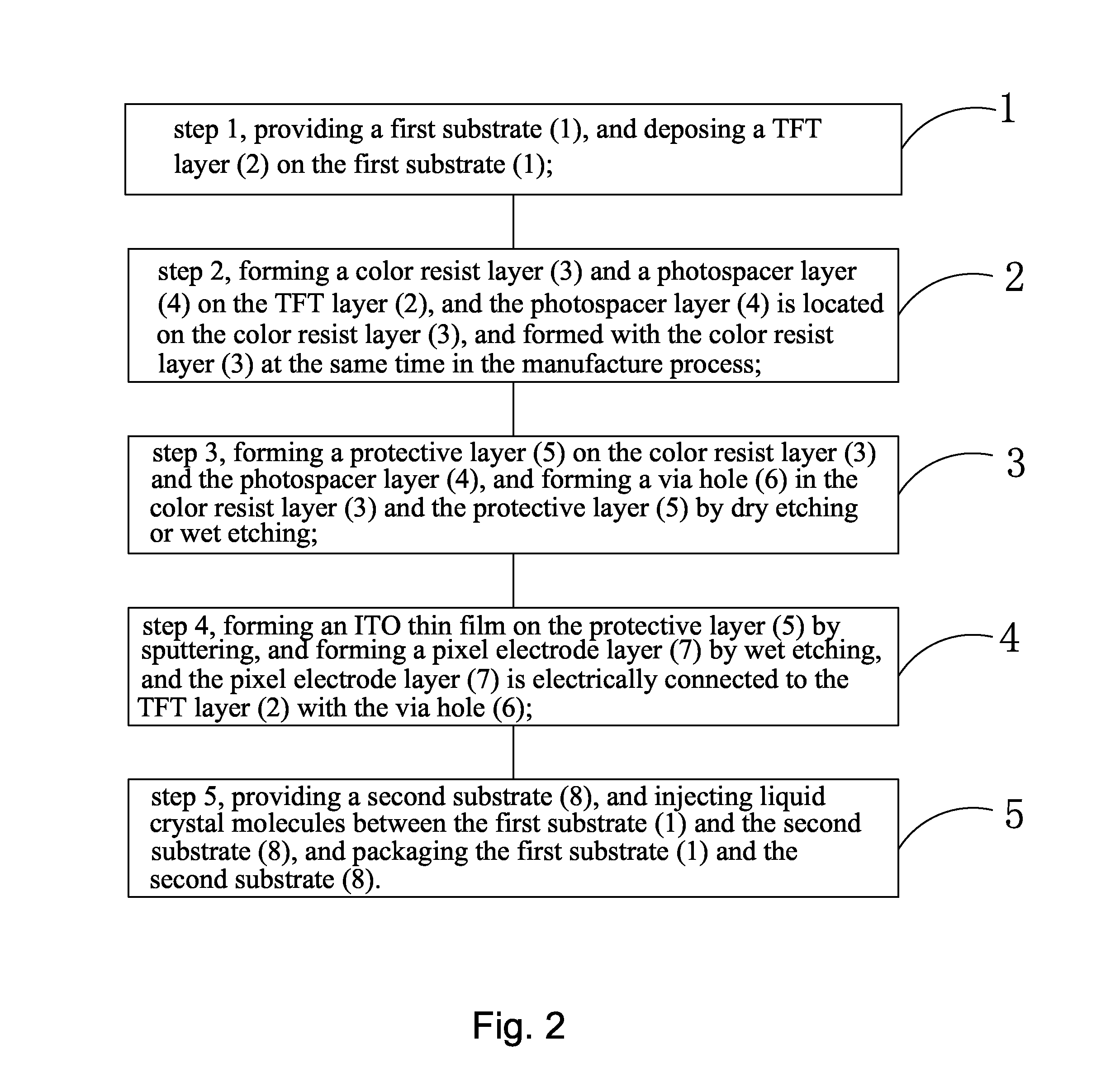

Liquid crystal panel and manufacture method thereof

ActiveUS20160170253A1Reduce probabilityAlignment demandSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLiquid crystal

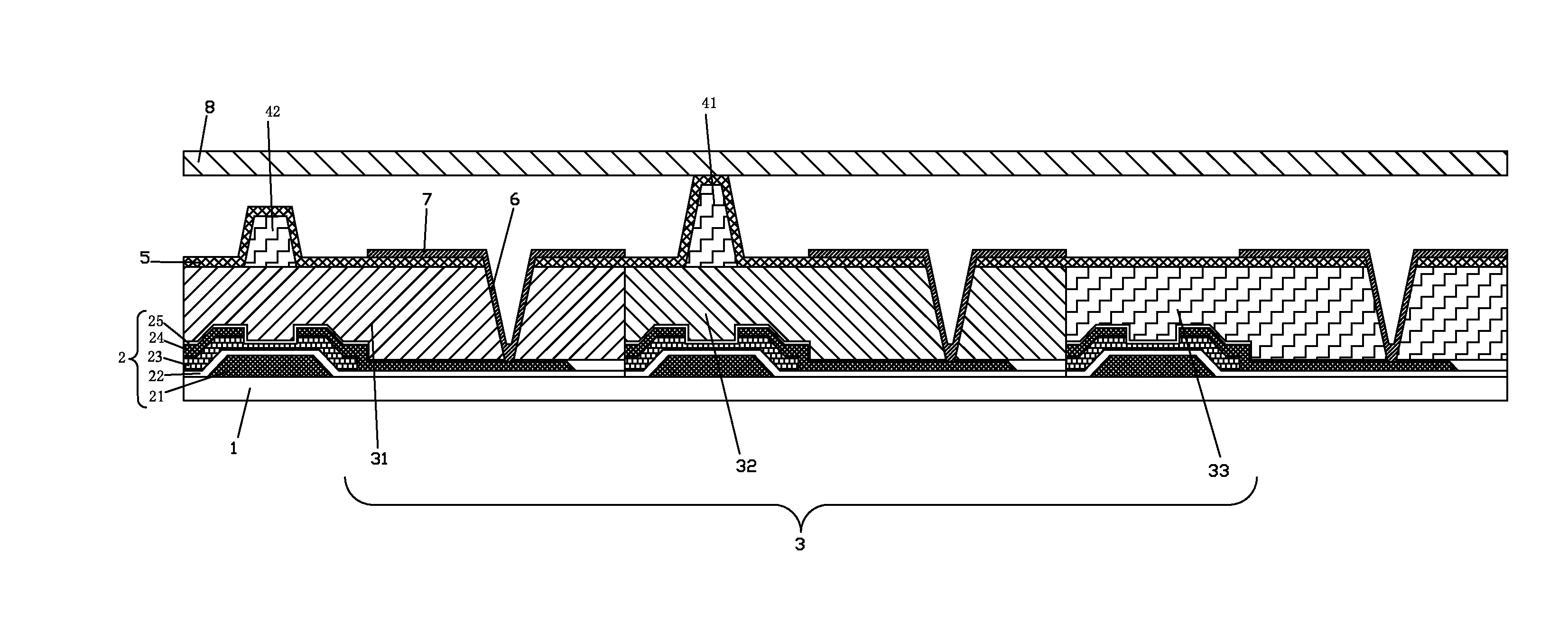

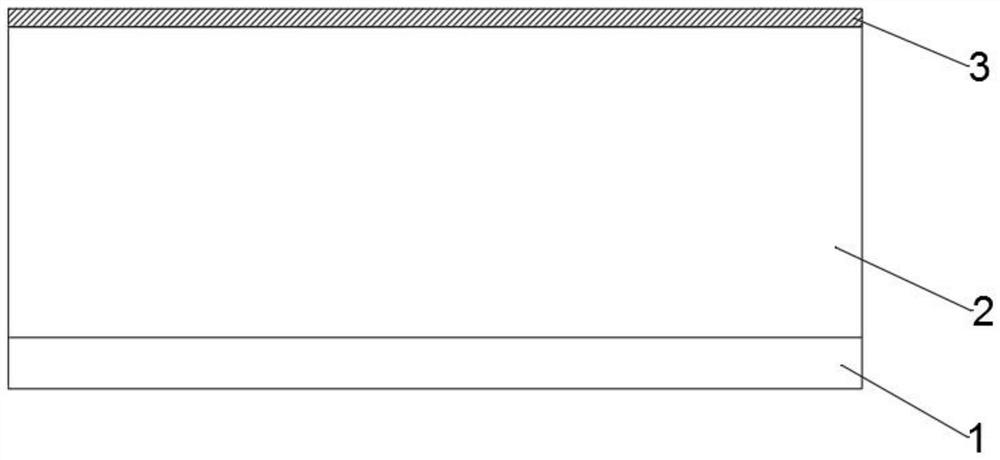

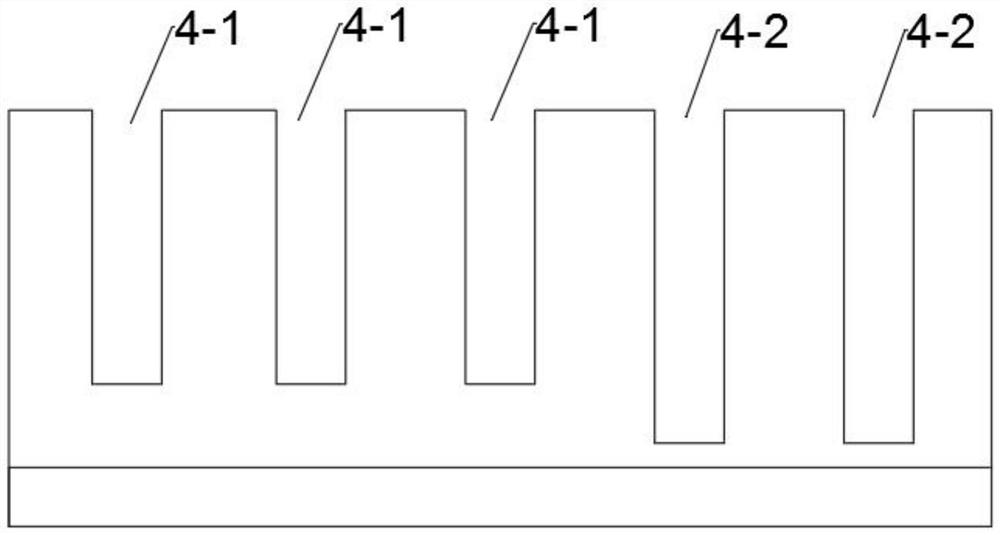

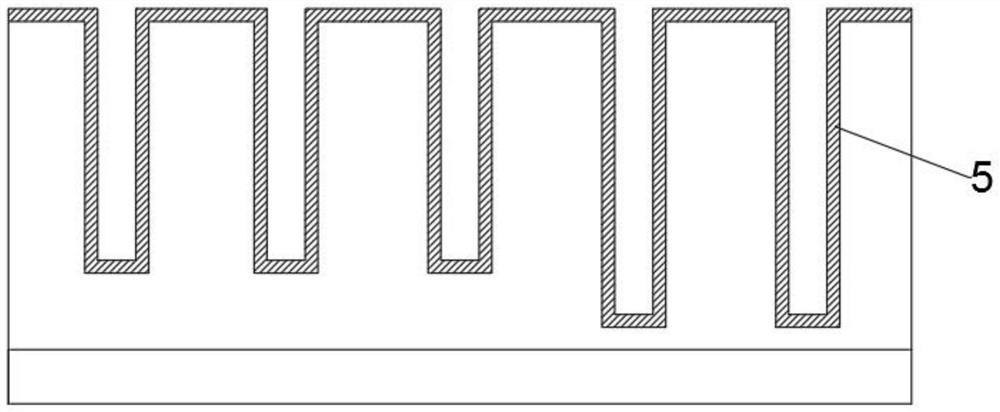

The present invention provides a liquid crystal panel and a manufacture method thereof. The liquid crystal panel comprises: a first substrate (1), a TFT layer (2) located on the first substrate (1), a color resist layer (3) located on the TFT layer (2), a photospacer layer (4) located on the color resist layer (3), a protective layer (5) located on the color resist layer (3) and the photospacer layer (4), a via hole (6) penetrating the color resist layer (3) and the protective layer (5), a pixel electrode layer (7) formed on the protective layer (5) and electrically connected to the TFT layer (2) with the via hole (6) and a second substrate (8) oppositely located to the first substrate (1), and one or more color resist material in the photospacer layer (4) and the color resist layer (3) are the same, and the photospacer layer (4) and the color resist layer (3) are formed at the same time during a manufacture process.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

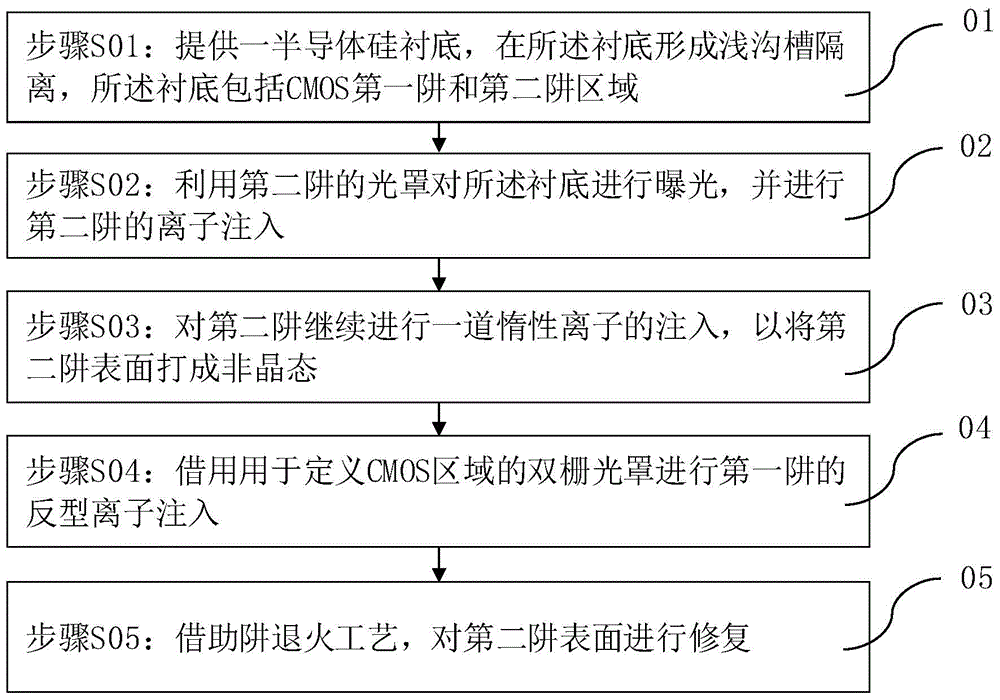

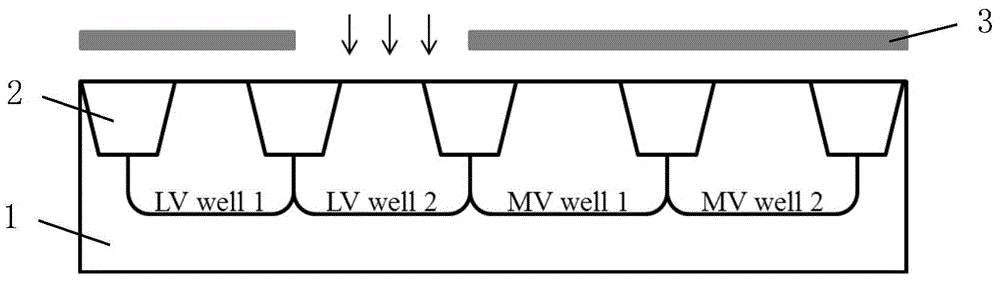

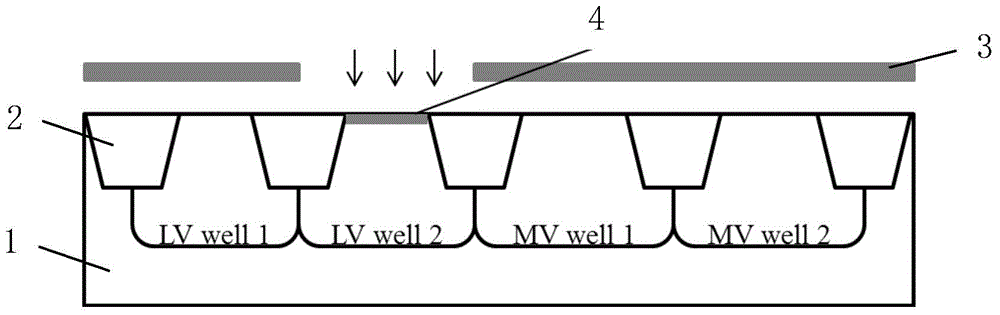

Method of forming CMOS well with mask saved

ActiveCN105070688ALess changes to CMOS processMask savingSemiconductor/solid-state device manufacturingCmos processEnvironmental geology

The invention discloses a method of forming a CMOS well with a mask saved. After exposure and ion implantation on a P-type or an N-type second well are completed, inert ion implantation is further added, the surface of the P-type or the N-type well is in an amorphous state, and implantation of follow-up reversed-type ions can be effectively blocked; then, with the help of a dual-gate mask, implantation on an N-type or a P-type first well is carried out, and as the second well region is protected by the amorphous layer, the second well region is little influenced and the influence can be adjusted back through improving the ion implantation concentration of the second well; and finally, a well annealing process in the traditional technology is used for restoring the amorphous layer on the surface of the second well. The method makes few changes on the CMOS process and is compatible with the traditional technology, the mask can be saved, and the purpose of saving the cost can be finally achieved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Manufacturing method of three-dimensional memory and three-dimensional memory

ActiveCN112185978ASimplify the etch processMask savingSolid-state devicesSemiconductor devicesEtchingEngineering

The invention provides a manufacturing method of a three-dimensional memory and the three-dimensional memory, in the manufacturing method of the three-dimensional memory provided by the invention, after an additional pseudo gate covering layer is deposited on a step structure, only the pseudo gate covering layer on the side wall of the step is removed, and the residual pseudo gate covering layer on a semiconductor layer is not removed, instead, the dielectric layer is directly formed on the residual dummy gate covering layer and is etched and filled to form the metal plug, so that the etchingprocess is simplified, the mask is saved, the production efficiency is improved, and the production cost is reduced; meanwhile, when the contact hole is formed by etching, the etching which originallypasses through the contact hole of the semiconductor layer is changed to stay on the dummy gate covering layer, so that a corresponding etching window is reduced, and the design flexibility of the three-dimensional memory is enhanced.

Owner:YANGTZE MEMORY TECH CO LTD

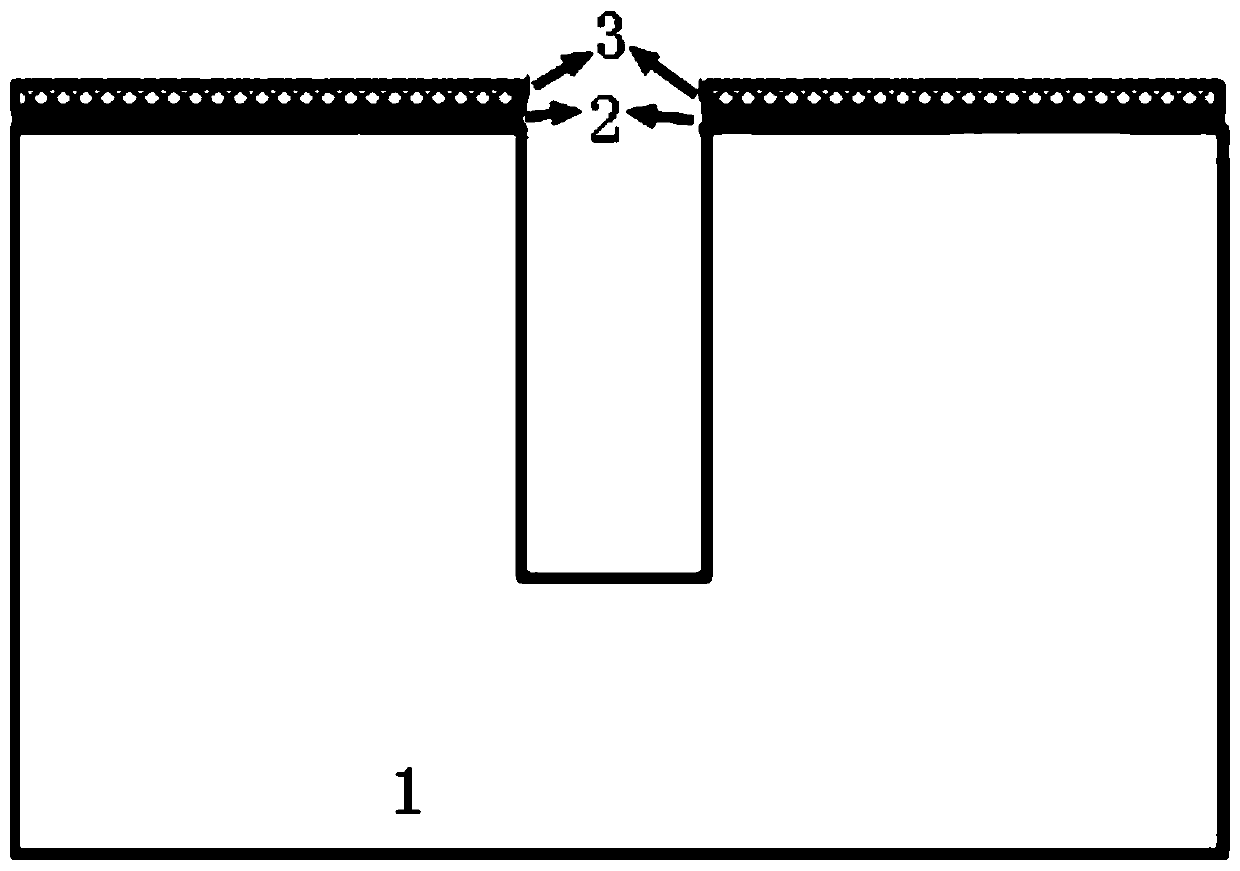

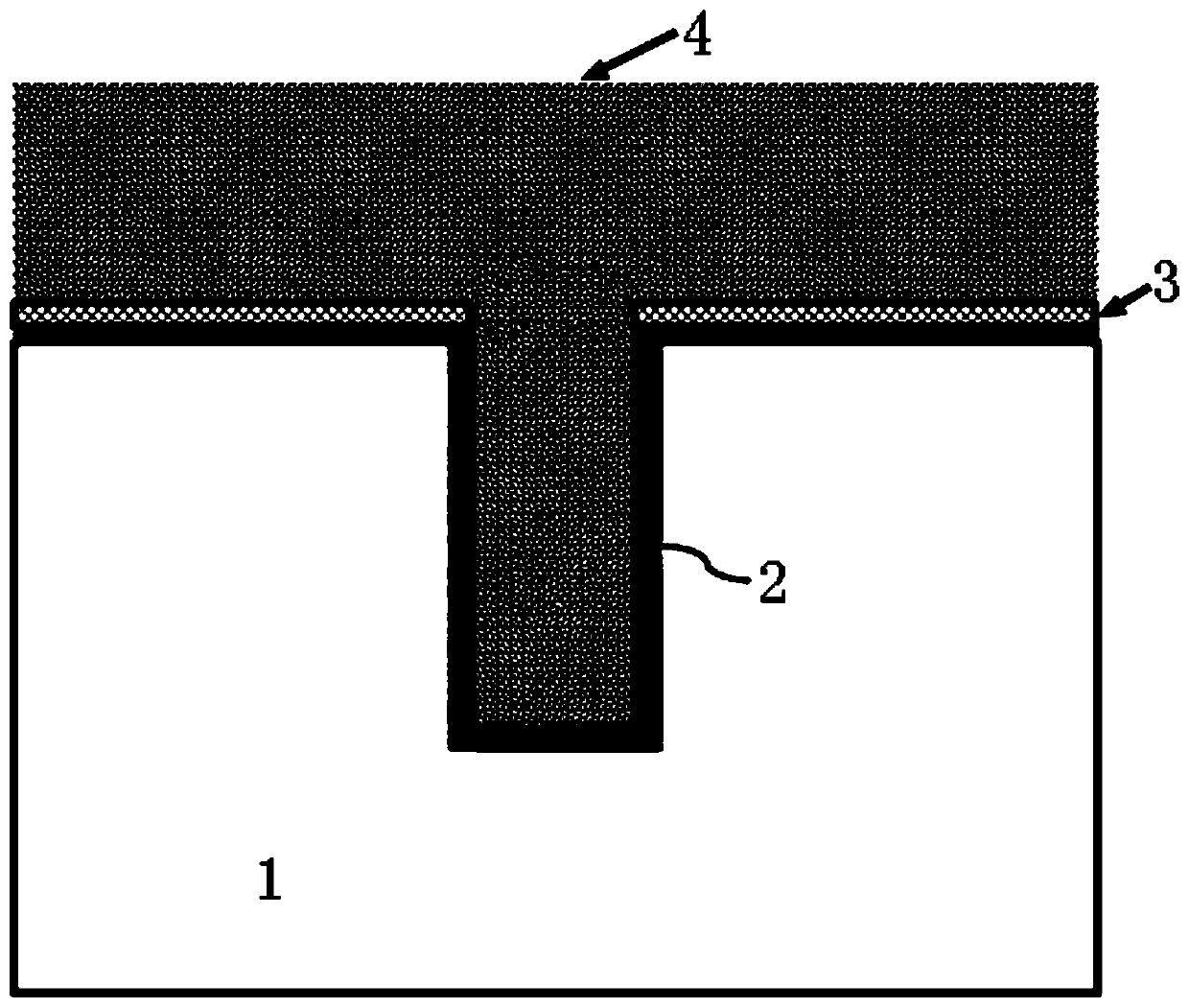

Deep trench isolation technical method

ActiveCN110379765AReduce difficultyLess challengingSemiconductor/solid-state device manufacturingSilicon oxidePhotoresist

The invention discloses a deep trench isolation technical method. The method comprises that a silicon oxide layer and a silicon nitride layer are formed in the surface of a semiconductor substrate successively; a photoresist is defined to etch the silicon oxide layer and the silicon nitride layer, an area to form a deep trench is opened, and the trench of certain depth is formed by etching downwards; a linear oxide layer is formed in the trench, and polycrystalline silicon is filled; polycrystalline silicon is etched back; a furnace tube is oxide to form a silicon oxide layer; the silicon oxide layer and the silicon nitride layer are removed; epitaxial growth is carried out; the silicon oxide layer is formed; polycrystalline silicon is filled; the polycrystalline silicon in the epitaxial surface and the deep trench are etched back; and the silicon oxide layer in the epitaxial surface is removed by etching. According to the technical method, part depth of trench is formed before epitaxial deposition technology, the subsequent trench is formed by using the characteristic of selective growth of the epitaxial deposition technology, the difficulty of dry etching is reduced, challenge totrench pore-filling is reduced, and a zero-layer mask can be omitted.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

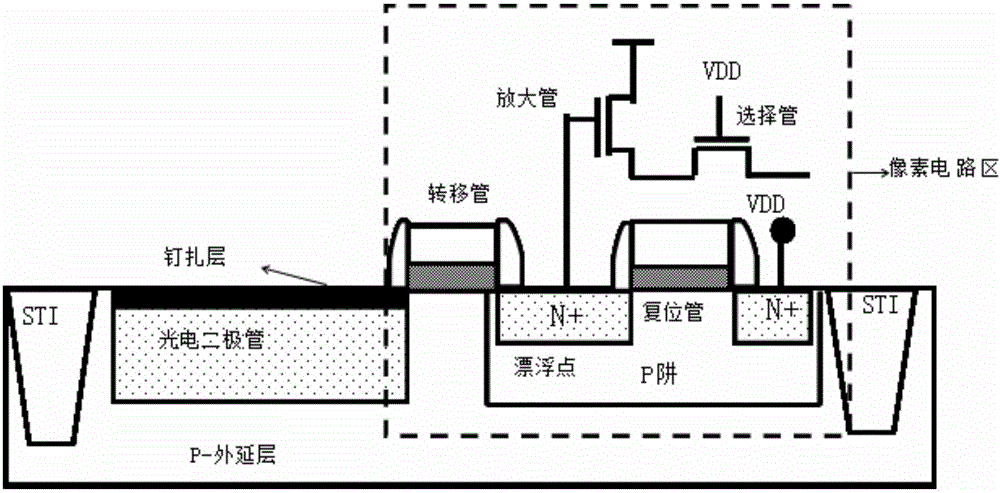

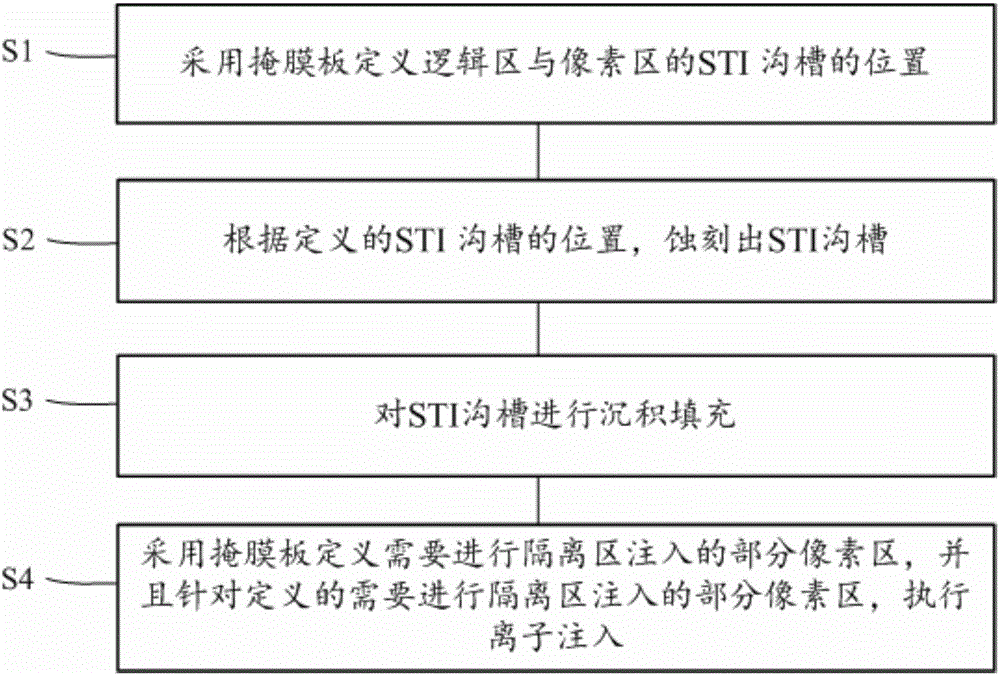

Method for eliminating shallow trench isolation induced dark current of CMOS image sensor

InactiveCN105870004AAvoid bombardment damageAvoid height differenceSolid-state devicesSemiconductor/solid-state device manufacturingCMOSEngineering

The invention provides a method for eliminating shallow trench isolation induced dark current of a CMOS image sensor. The method comprises the step of step 1: defining positions of STI trenches of a logic region and a pixel region through mask plates; step 2: etching the STI trenches according to the defined positions of the STI trenches; step 3: carrying out disposition and filling on the STI trenches; and step 4: defining a part of pixel regions which need to be subjected to isolation region injection by adopting the mask plates, and carrying out ion implantation for the part of the defined pixel regions which need to be subjected to isolation region injection.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

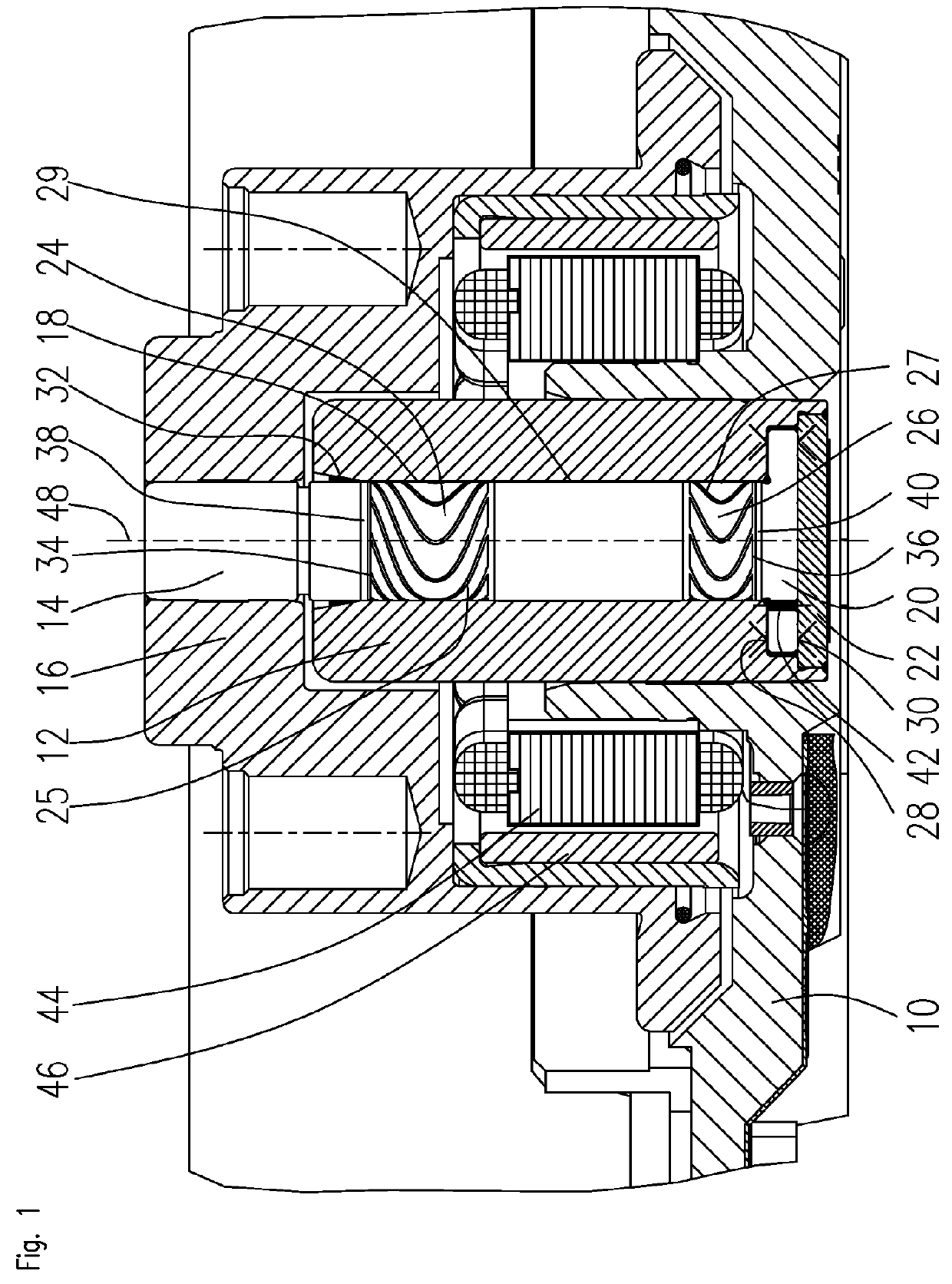

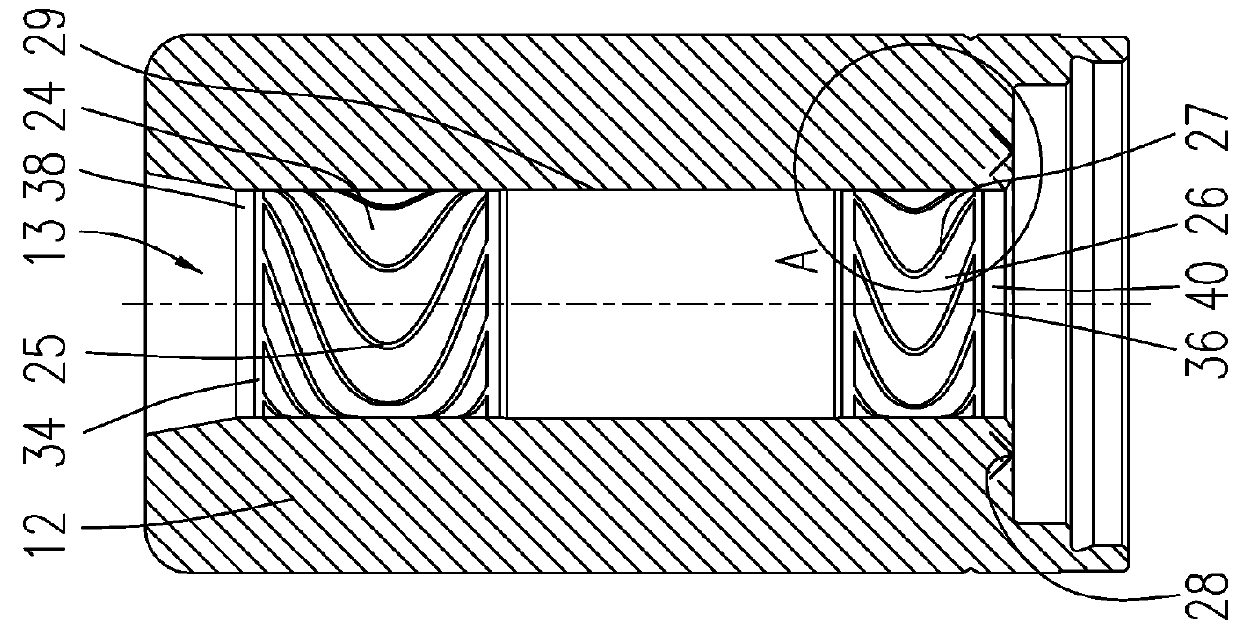

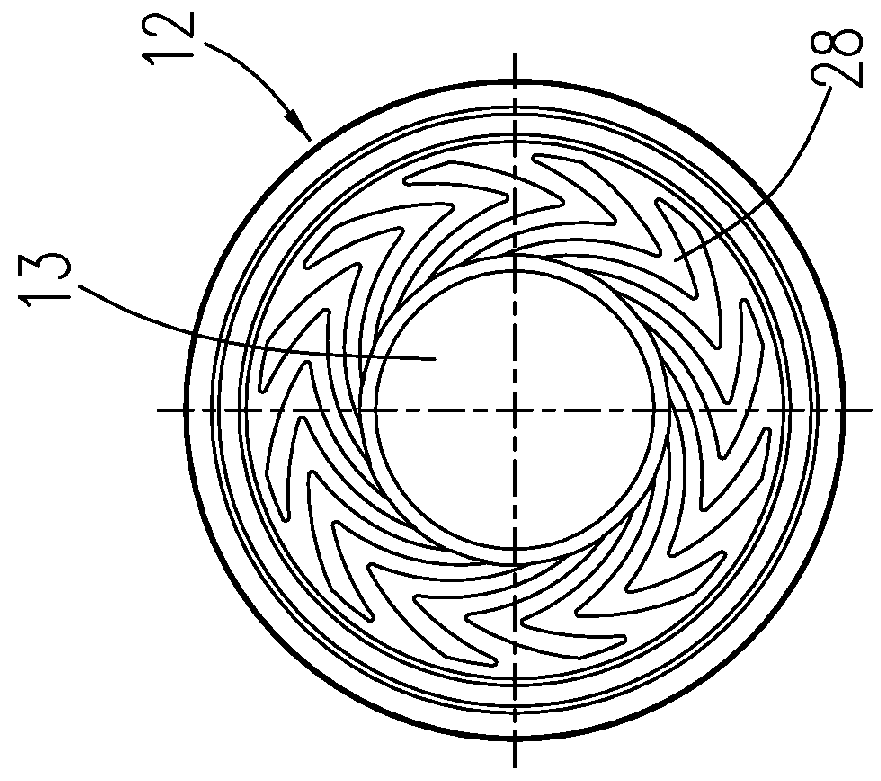

Fluid dynamic bearing

The invention relates to a fluid dynamic bearing system having a stationary bearing component and a moving bearing component, that are separated from one another by a bearing gap filled with a bearing fluid. There are two radial bearing regions separated from one another and marked by radial bearing grooves. A separator region having a larger bearing gap width is disposed between the radial bearing regions. The radial bearing grooves of the two radial bearing regions have inner ends facing each other and outer ends facing away from each other. At least the outer ends of the radial bearing grooves are connected to each other by connecting grooves. According to the invention, wear zones provided especially for this purpose are disposed adjoining the connecting grooves, so as to prevent material wear at other regions of the bearing.

Owner:MINEBEAMITSUMI INC

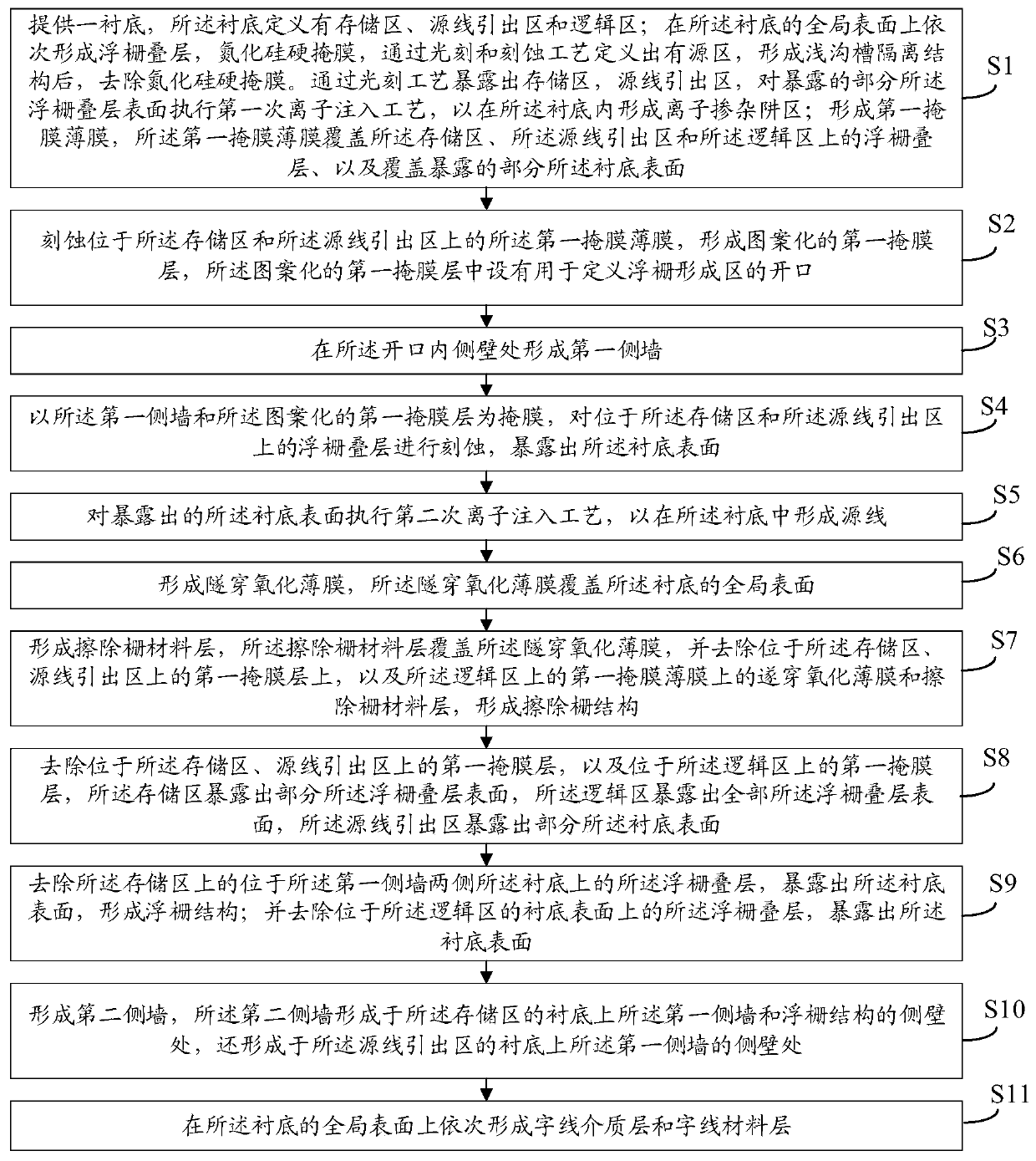

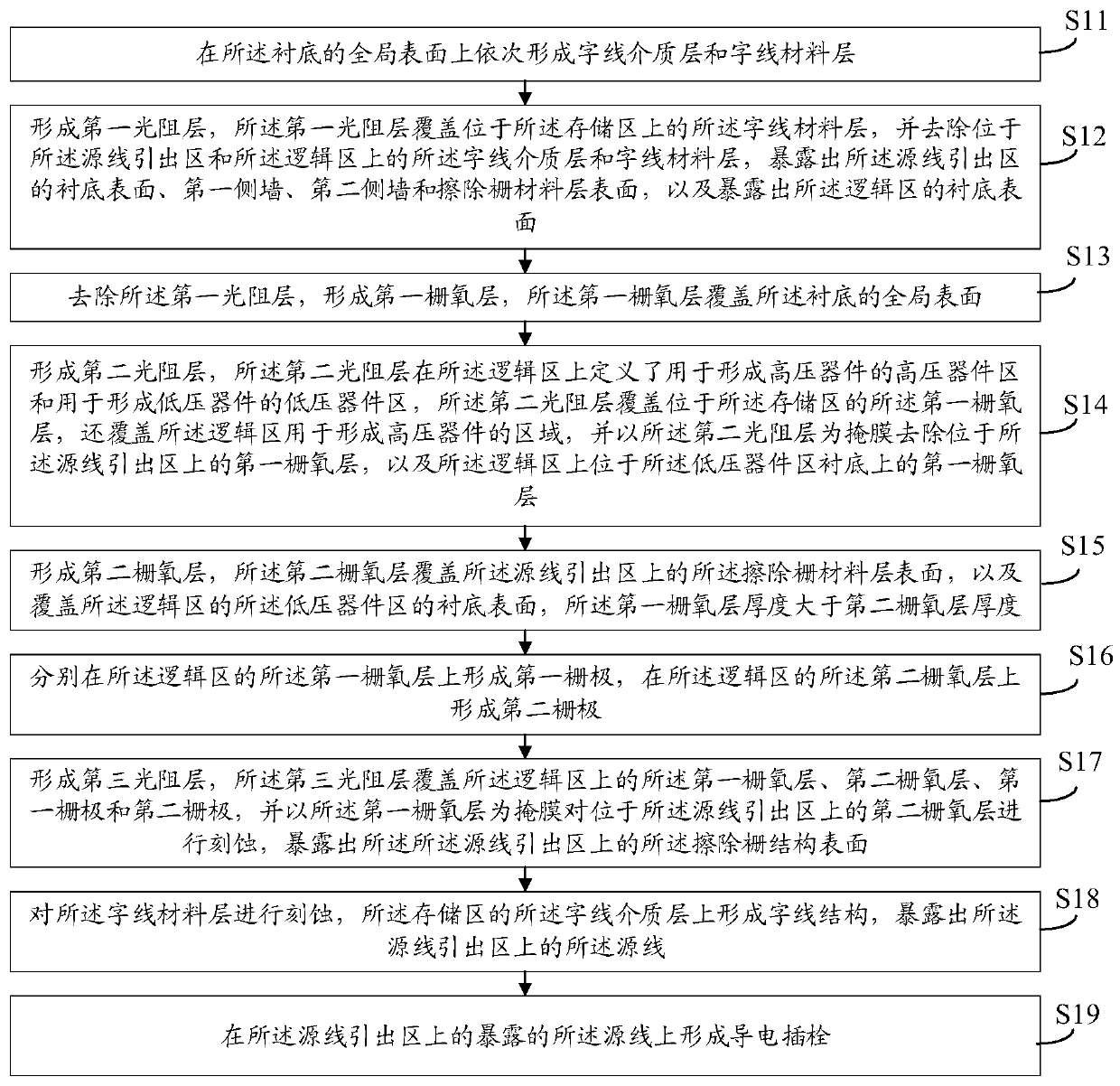

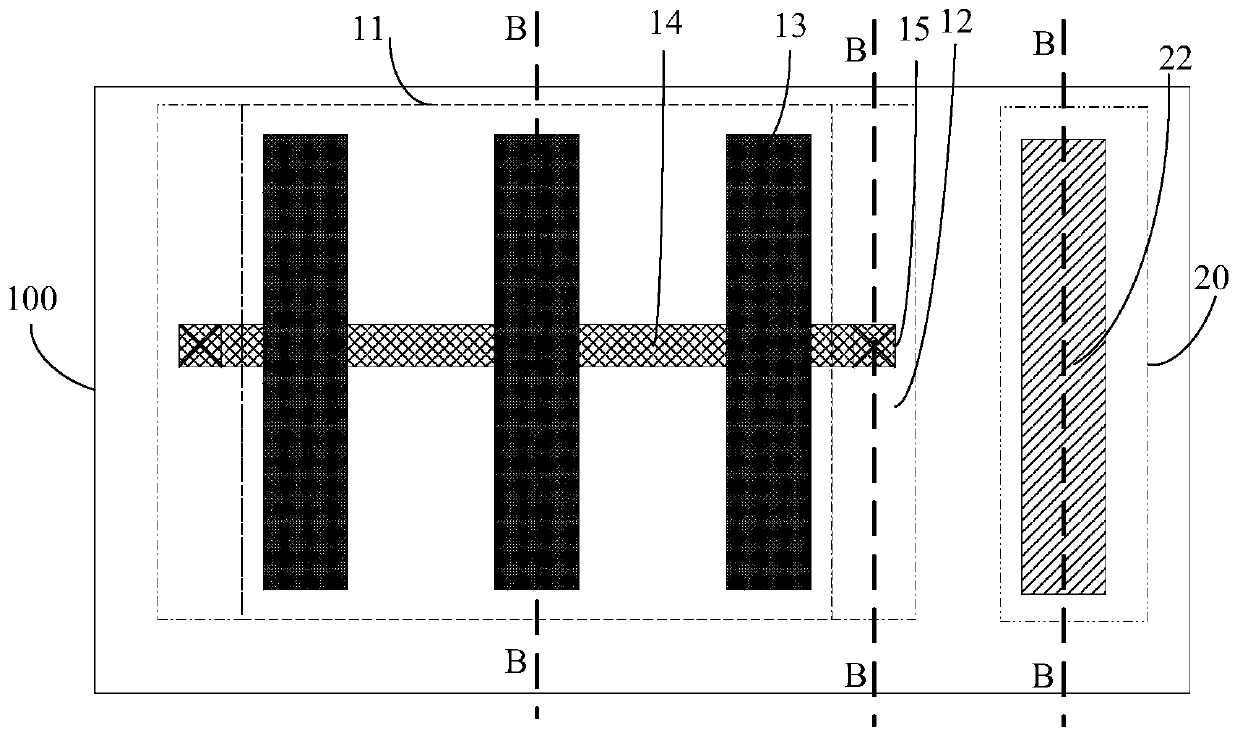

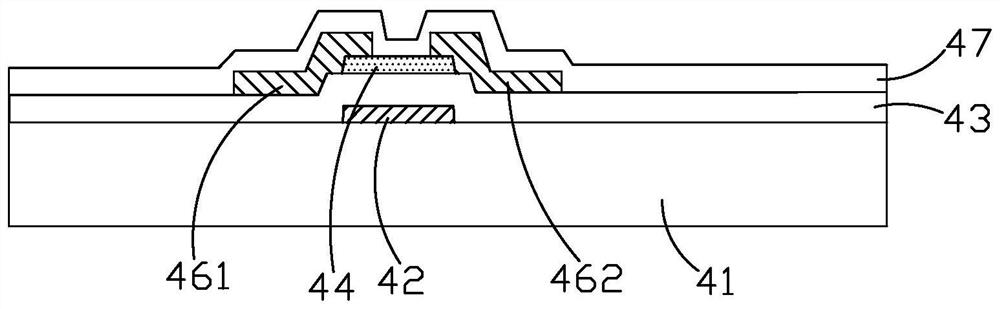

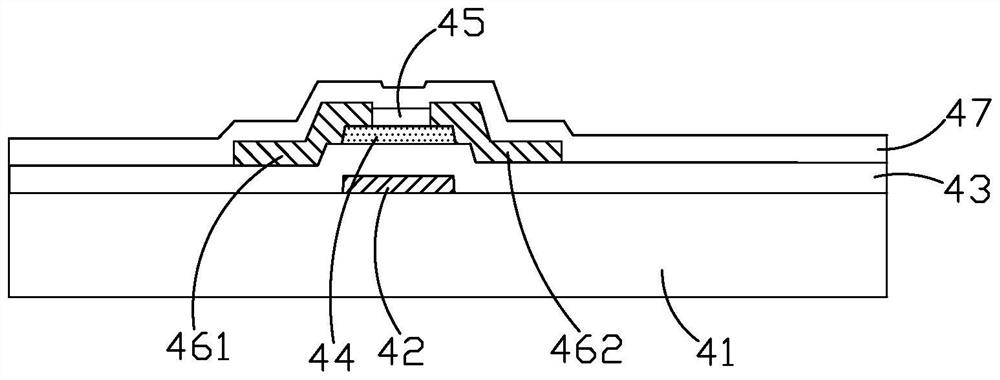

Manufacturing method of embedded flash memory

ActiveCN110164865AMask savingReduce manufacturing costSolid-state devicesSemiconductor devicesLow voltageGate oxide

The invention discloses a manufacturing method of an embedded flash memory. The method comprises the following steps: before forming a low-voltage device and a high-voltage device in a logic region, exposing the source line leading-out position of a source line leading-out region in an etching step of forming a word line in a storage region; during the formation of the grid electrode of the high-voltage device and / or the low-voltage device, by utilizing a protection layer of a first gate oxide layer, removing a first gate oxide layer on an erased gate structure above the source line leading-out position; generating a second gate oxide layer subsequently; utilizing the thickness difference between the first gate oxide layer and the second gate oxide layer, removing the second gate oxide layer and taking the remaining first gate oxide layer as a hard mask; removing one part of the erased gate structure above the source line; removing the remaining erased gate structure during the word line gate etching process and then forming a conductive plug to lead out the source line. In this way, the photoetching step of additionally leading out the source line and a photomask are omitted. Thepurposes of lowering the manufacturing cost of the embedded flash memory and lowering the complexity of the manufacturing process are achieved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

SRAM yield enhancement by read margin improvement

ActiveUS8208316B2Easy to operateIncreases reading marginRead-only memoriesDigital storageBit lineMultiplexer

A sense margin is improved for a read path in a memory array. Embodiments improve the sense margin by using gates with a lower threshold voltage in a read column multiplexer. A cross coupled keeper can further improve the sense margin by increasing a voltage level on a bit line storing a high value, thereby counteracting leakage on the “high” bit line.

Owner:QUALCOMM INC

Array substrate and manufacturing method thereof

PendingCN113725157AHigh light transmittanceSimple preparation processSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorInsulation layer

The invention provides an array substrate and a manufacturing method thereof. The array substrate comprises a substrate; a first metal layer which is formed on the substrate and comprises a grid electrode and a scanning line, wherein the grid electrode is connected with the scanning line; a gate insulating layer which is formed on the substrate and covers the first metal layer; a second metal layer which is formed on the grid electrode insulating layer and comprises a source electrode and a data line, wherein the source electrode is connected with the data line, and the projection of the source electrode and the projection of the grid electrode on the array substrate are aligned or partially overlapped; and a metal oxide semiconductor layer which is formed on the gate insulation layer and comprises a pixel electrode and an active layer, wherein the pixel electrode is subjected to conductor treatment and is connected with the active layer, the active layer is connected with the source electrode, the source electrode is connected with the metal oxide semiconductor layer, and the active layer is correspondingly positioned over the source electrode and the grid electrode.

Owner:KUSN INFOVISION OPTOELECTRONICS

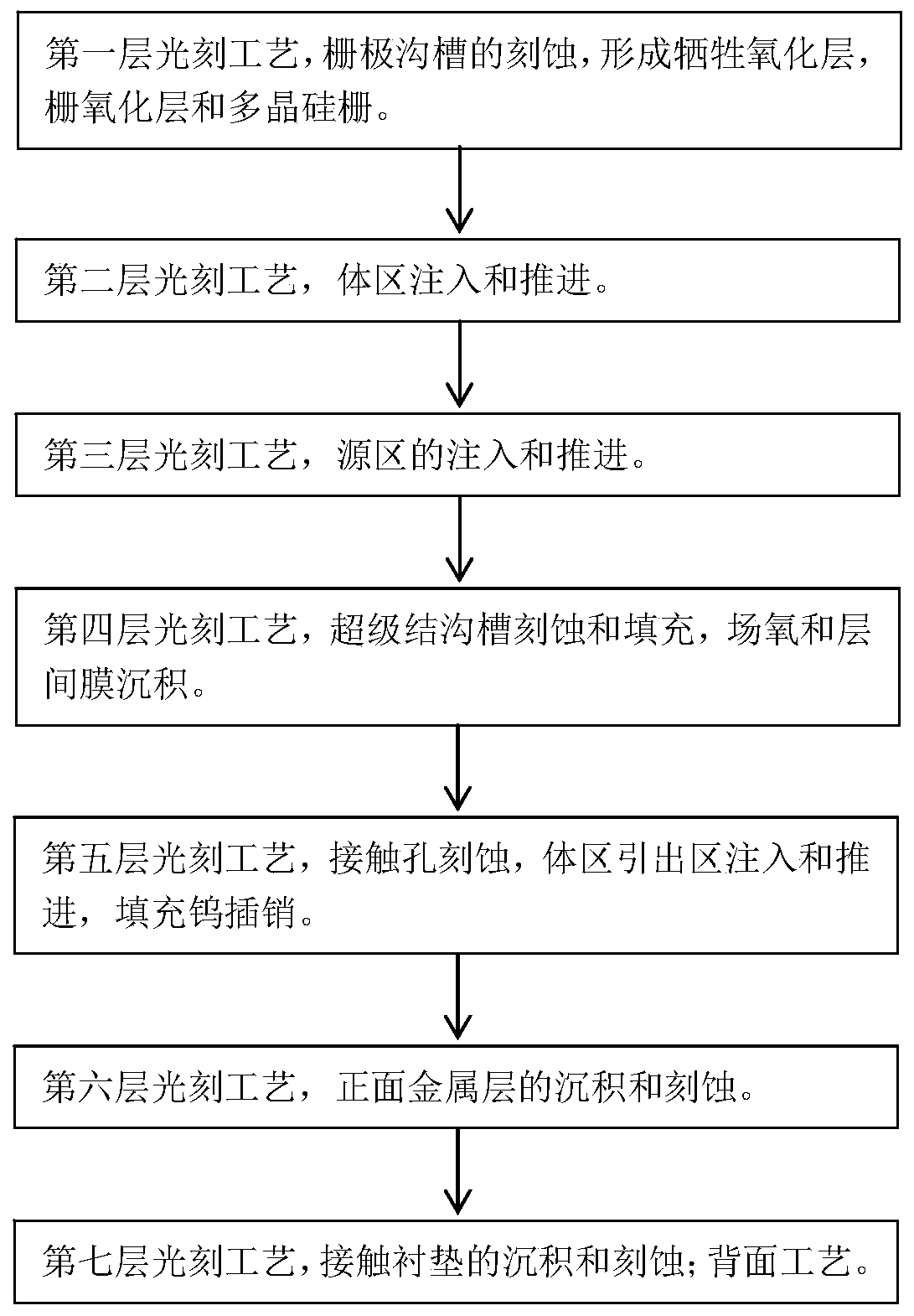

Manufacturing process of SBR (sequencing batch reactor) device capable of realizing charge coupling through three-time masking

PendingCN114864404AMask savingLow costSemiconductor/solid-state device manufacturingSemiconductor devicesSequencing batch reactorThin oxide

The invention discloses a manufacturing process of an SBR (sequencing batch reactor) device for realizing charge coupling through three-time masking. The manufacturing process comprises the following steps: forming a thin oxide layer; forming a body region; forming a thick oxide layer as a first mask; performing photoetching to form a groove; forming a field oxide layer; forming a first polycrystalline silicon; setting a second mask, and etching the first polycrystalline silicon to enable the top of the first polycrystalline silicon to be lower than the surface of the epitaxial layer; injecting source region ions by taking the thick oxide layer between the active region trenches as a mask; depositing to form a first oxide layer; and the first oxide layer is etched downwards in an isotropic manner, so that the epitaxial layer on the surface of the active region is exposed, an active region contact hole is formed in the active region trench, and the active region contact hole extends into the second polycrystalline silicon. According to the manufacturing process, the whole manufacturing process can be completed only through three times of mask, the mask needs to be arranged when the groove is formed, the first polycrystalline silicon is formed and the metal electrode is formed, the mask used when the source region is formed and the body contact region is formed is omitted, and cost is saved.

Owner:捷捷微电(上海)科技有限公司 +1

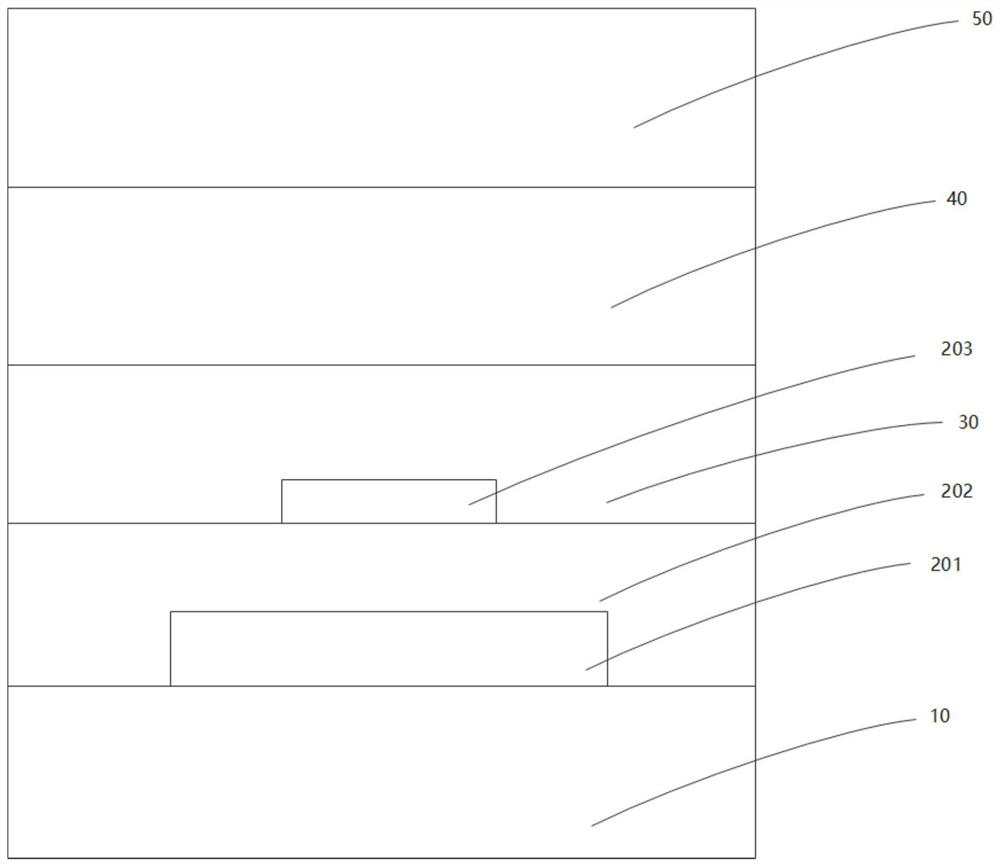

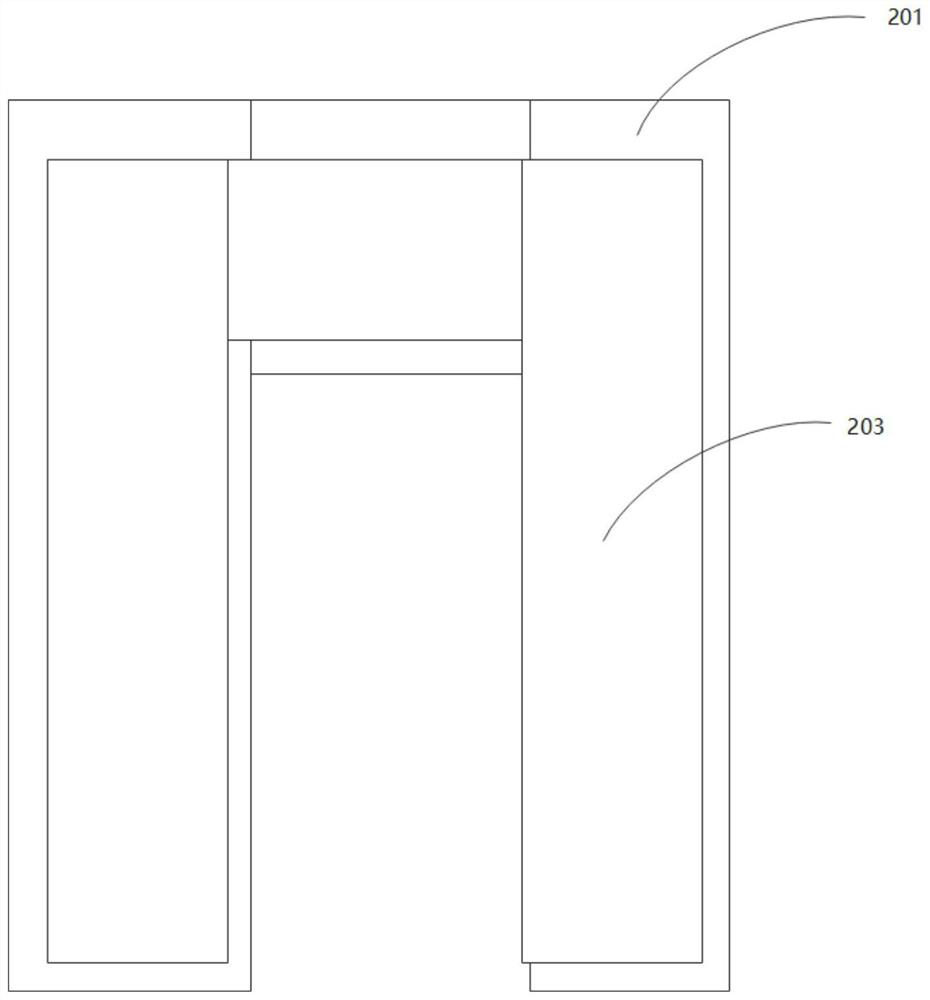

Display panel and method for fabricating same

ActiveUS20220005879A1High light transmittanceReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturingPhysicsLight filter

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

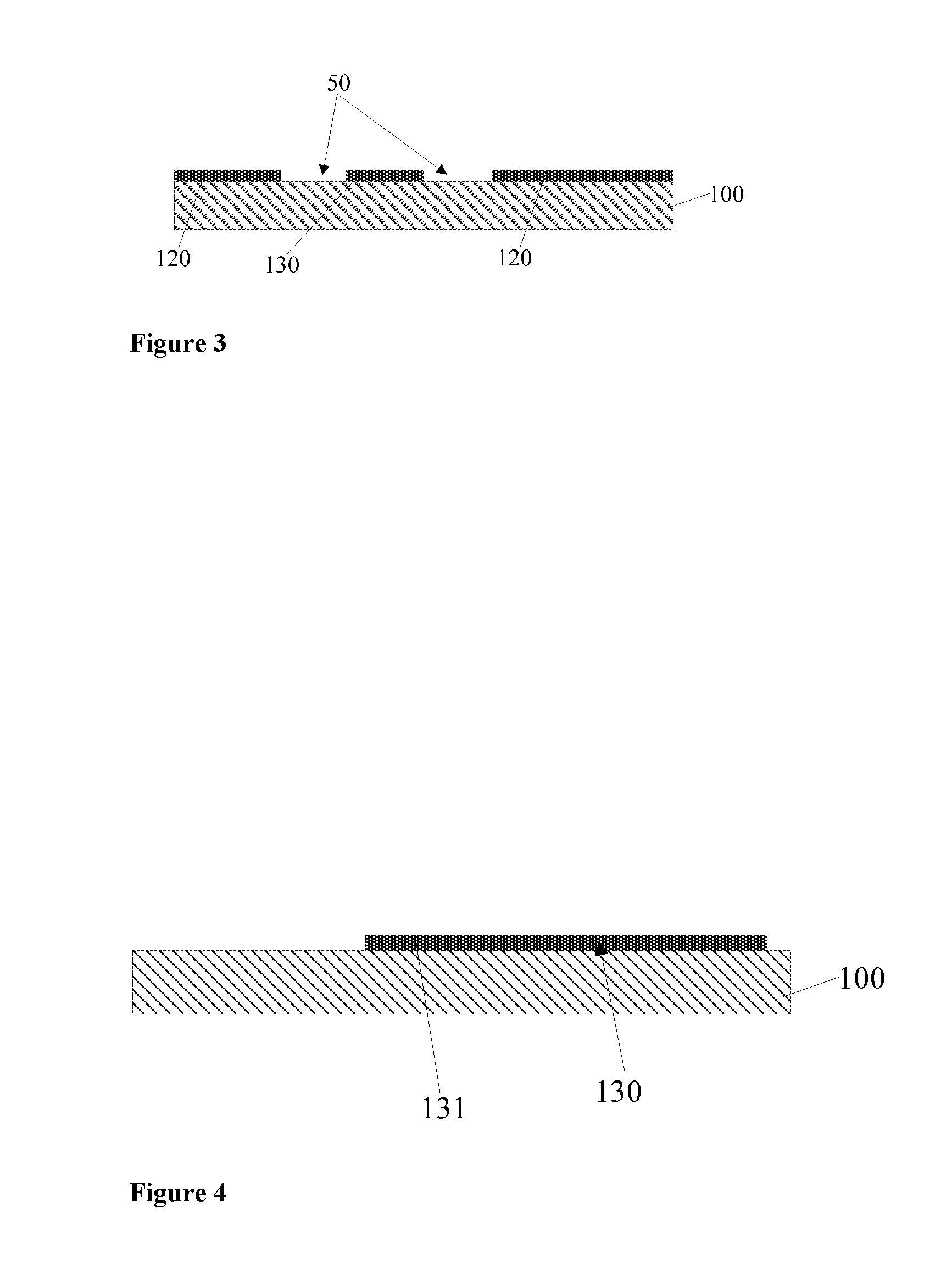

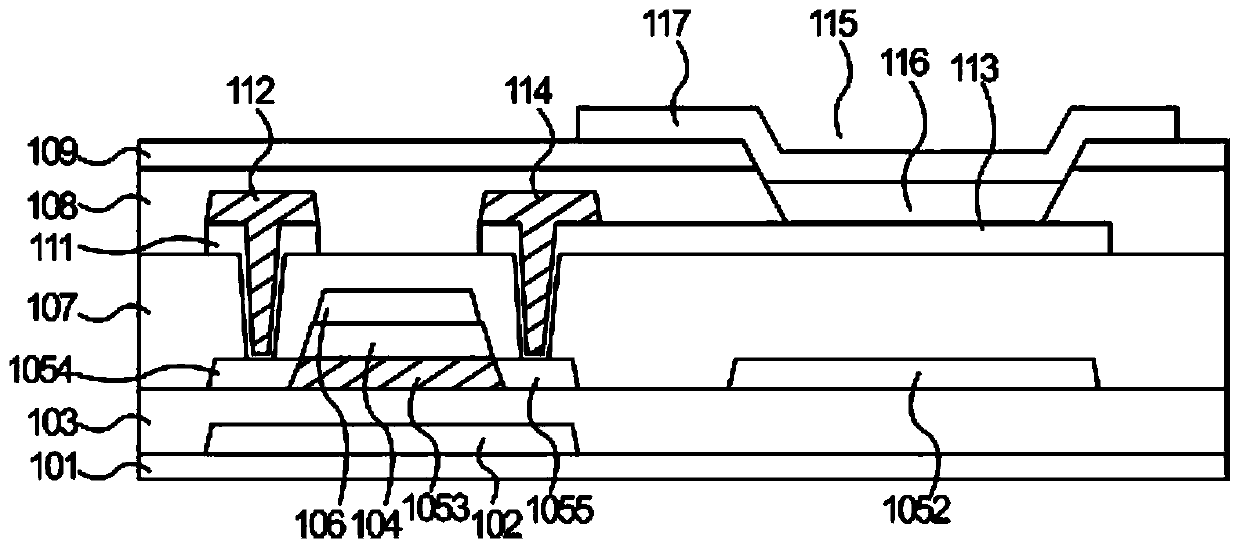

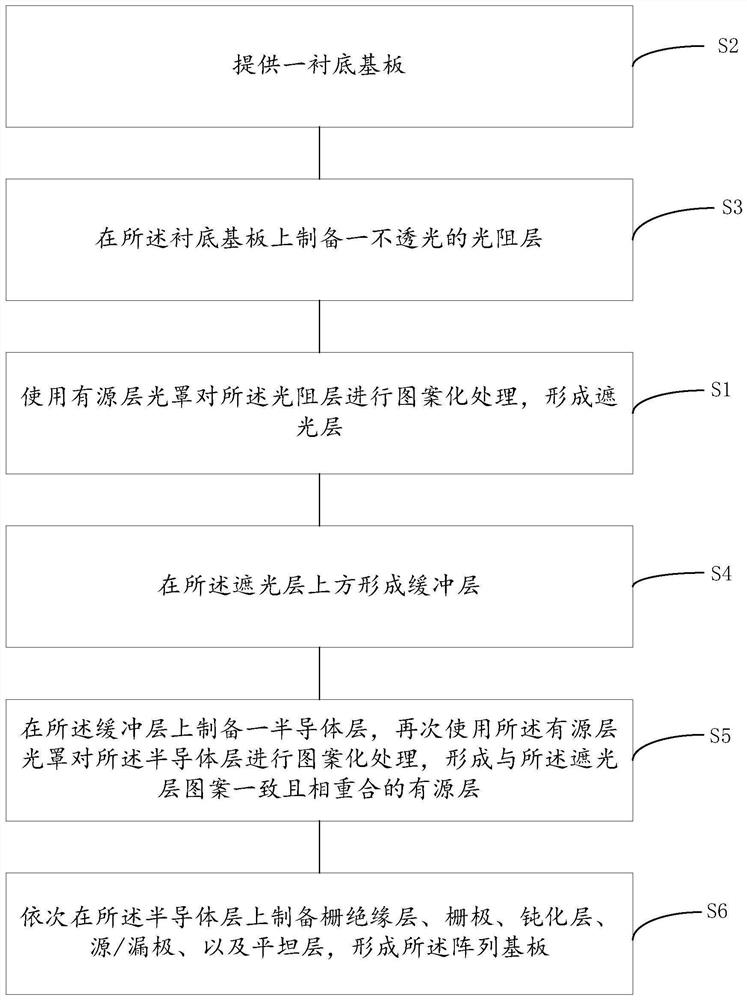

Array substrate preparation method and array substrate

PendingCN111640706AMask savingSolving costly technical issuesSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringActive layer

The embodiment of the invention provides an array substrate preparation method, which comprises the steps of forming a shading layer pattern by adopting an active layer photomask, then forming an active layer pattern by utilizing the active layer photomask, and covering the orthographic projection of the active layer pattern on a substrate by the orthographic projection of the shading layer pattern on the substrate. The shading layer and the active layer share one active layer photomask, so that one shading layer photomask is omitted, and the technical problem that the cost for forming the shading layer of an existing array substrate is high is solved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Thin film transistor array substrate and manufacturing method thereof

PendingCN112951853AReduce productionAvoid corrosionSolid-state devicesSemiconductor/solid-state device manufacturingTransistor arrayThin membrane

The invention discloses a thin film transistor array substrate and a manufacturing method thereof. The method comprises the steps: forming a first photoresist layer on a metal oxide thin film, carrying out exposure and development on the first photoresist layer, keeping the first photoresist layer above a grid electrode to form a first photoresist part, and removing the first photoresist layer at other positions; forming a second metal layer covering the first photoresist part on the metal oxide thin film; forming a second photoresist layer on the second metal layer, exposing and developing the second photoresist layer to form a second photoresist part and a third photoresist part which are separated from each other, and forming an opening between the second photoresist part and the third photoresist part; etching the second metal layer and the metal oxide thin film by using the second photoresist part and the third photoresist part as masks, forming a source electrode and a drain electrode which are spaced from each other after the second metal layer is etched, and forming a metal oxide active layer after the metal oxide thin film is etched; and removing the first photoresist part, the second photoresist part and the third photoresist part.

Owner:KUSN INFOVISION OPTOELECTRONICS

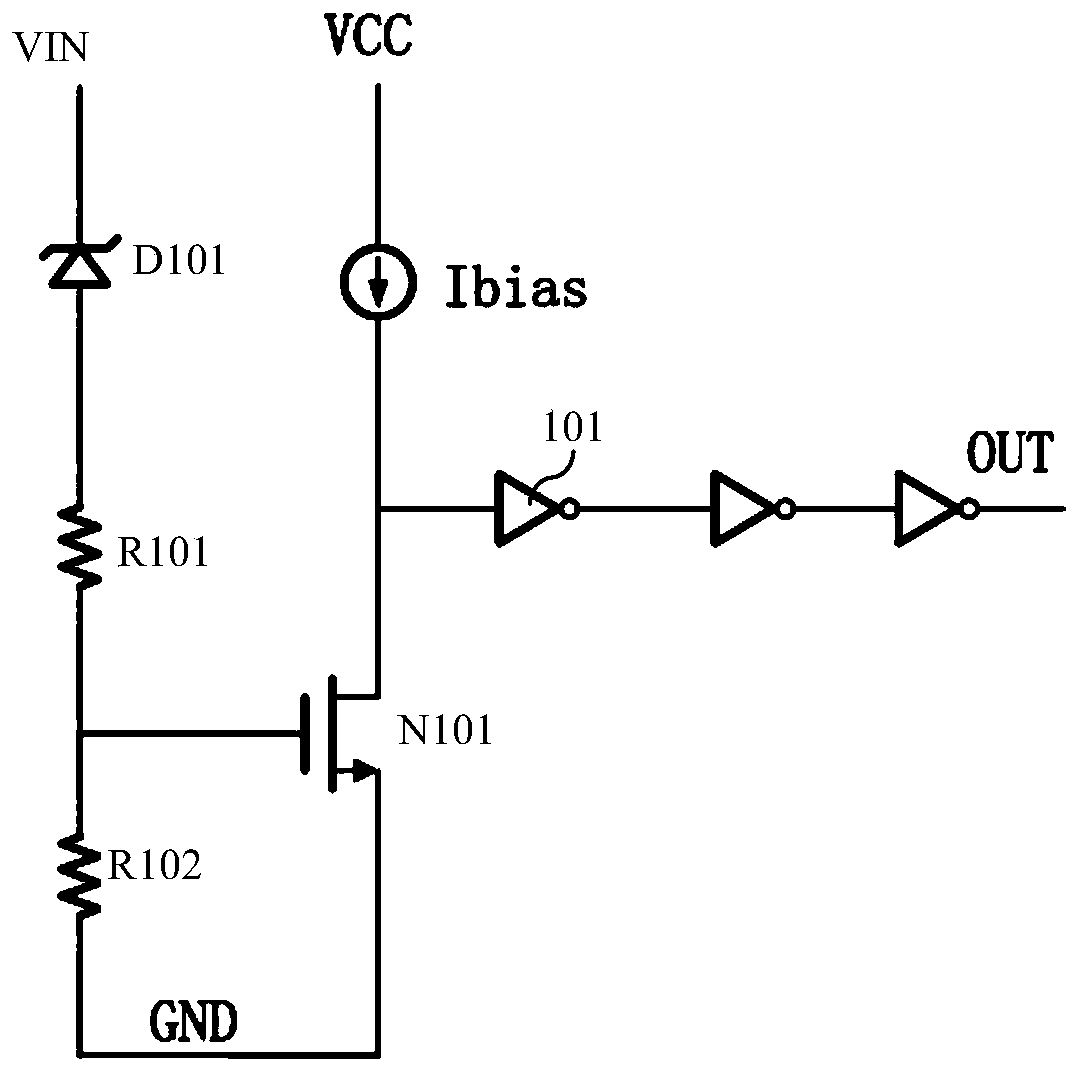

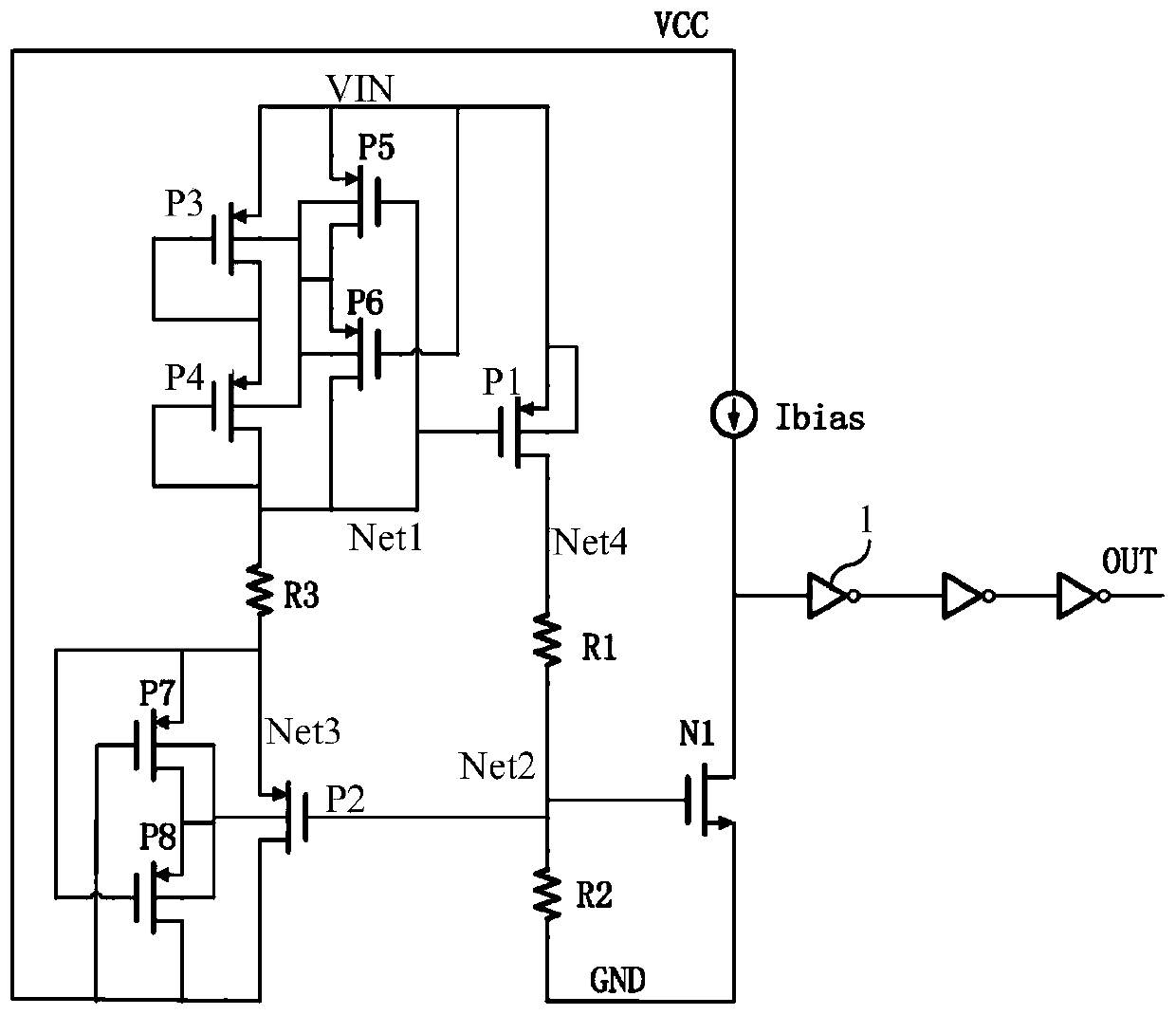

Use the voltage detection circuit on io

ActiveCN107817378BRealize detectionMask savingCurrent/voltage measurementHemt circuitsControl theory

The invention discloses a voltage detection circuit on IO. The voltage detection circuit on IO includes a PMOS transistor serial structure which is formed through serial connection of a plurality of PMOS transistors in a diode connection mode, wherein the PMOS transistor serial structure is connected between an input signal and a first node; the source electrode of the first PMOS transistor is connected with the input signal, and the grid electrode of the first PMOS transistor is connected with the first node; a first resistor and a second resistor are connected in series between the drain electrode of the first PMOS transistor and the ground, and the connection point between the first resistor and the second resistor is the second node which outputs a detection signal; a third resistor isconnected between the first node and the source electrode of the second PMOS transistor, and the drain electrode of the second PMOS transistor is connected with the power supply voltage, and the gridelectrode of the second PMOS transistor is connected with the second node, and the source electrode of the second PMOS transistor is a third node; and each PMOS transistor utilizes the transistor technological structure taking the working voltage as the power supply voltage. The voltage detection circuit on IO is implemented by using the transistor technological structure of the power supply voltage, and does not need Zeners so as to save one layer of photomask to save the cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

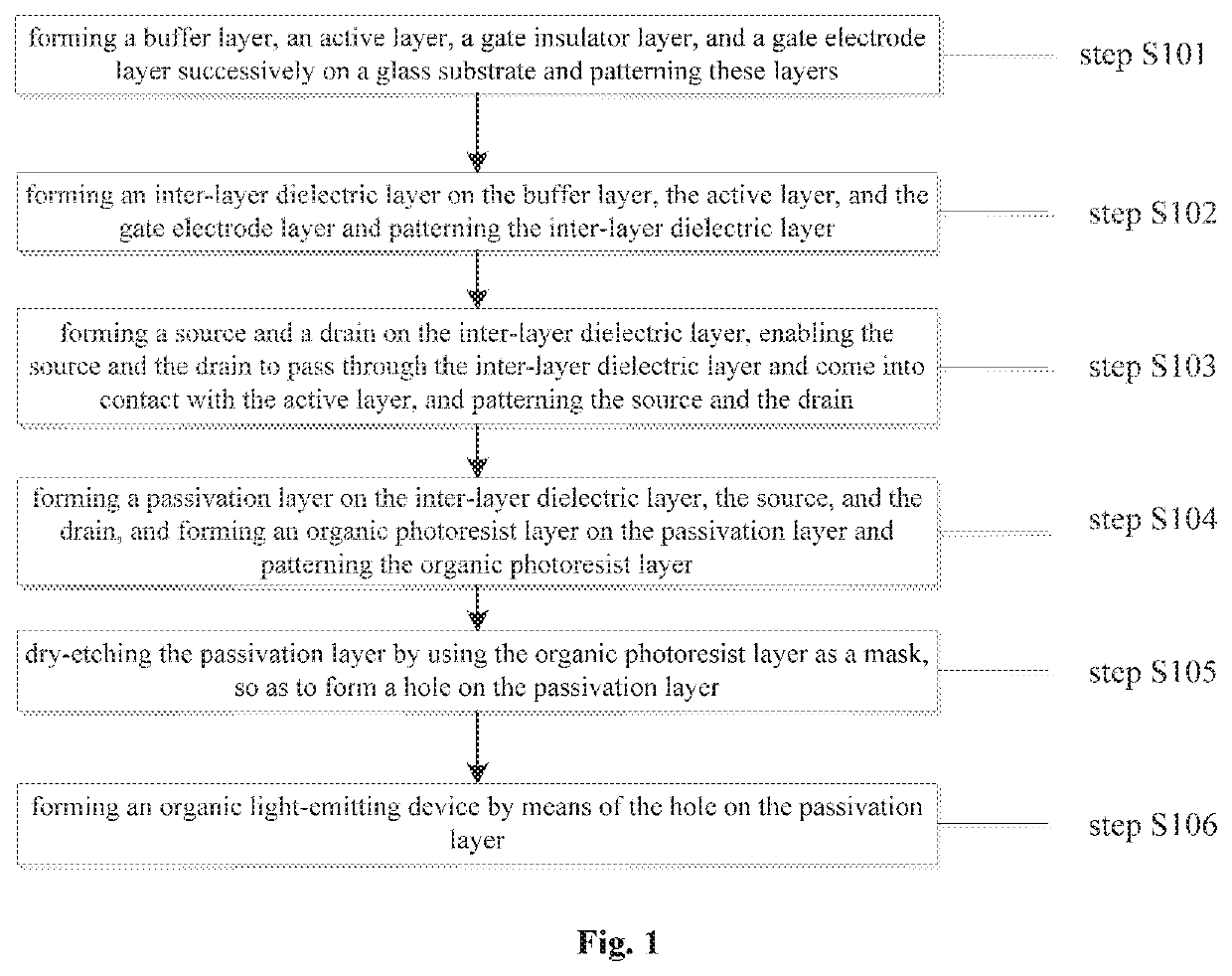

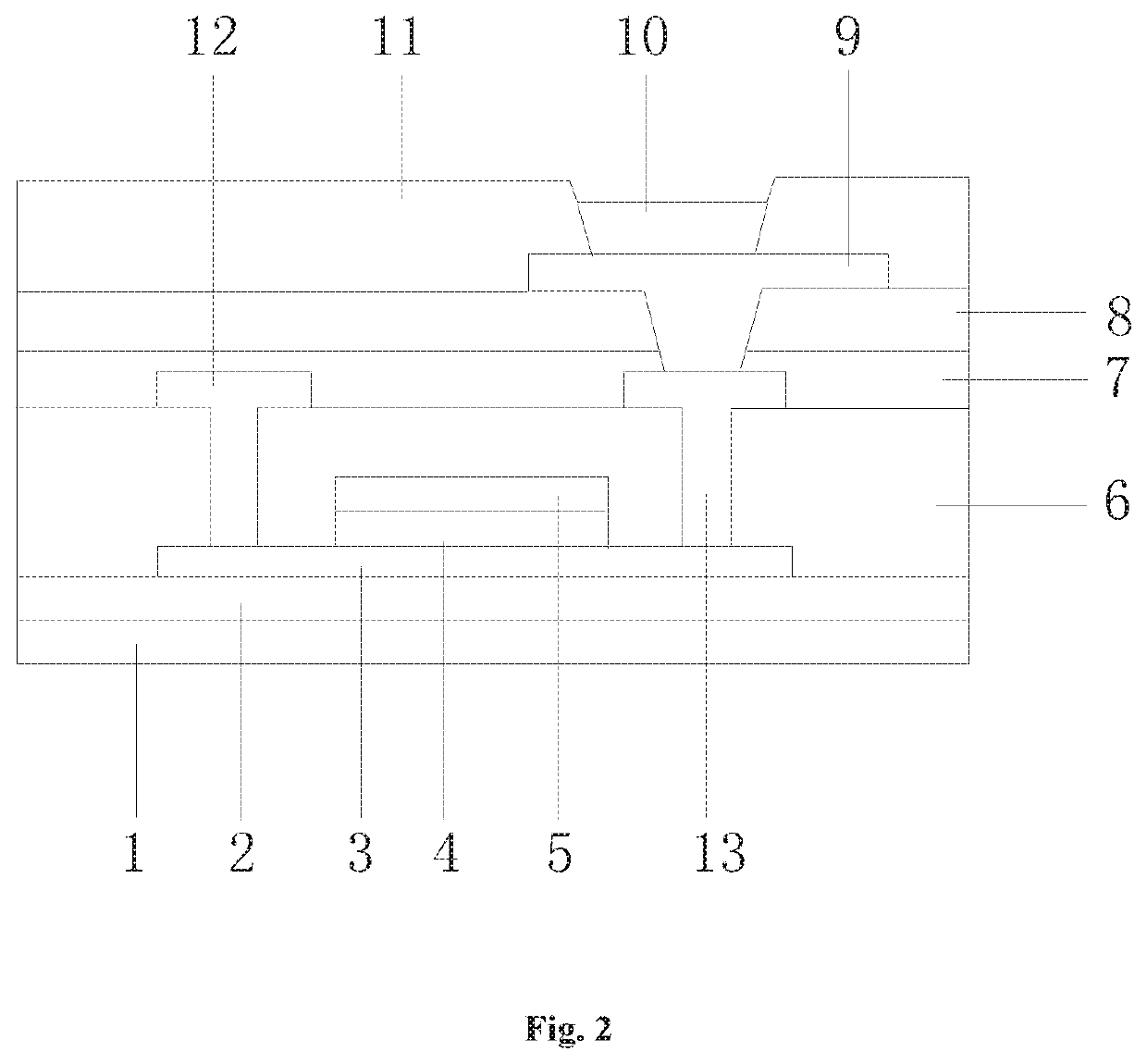

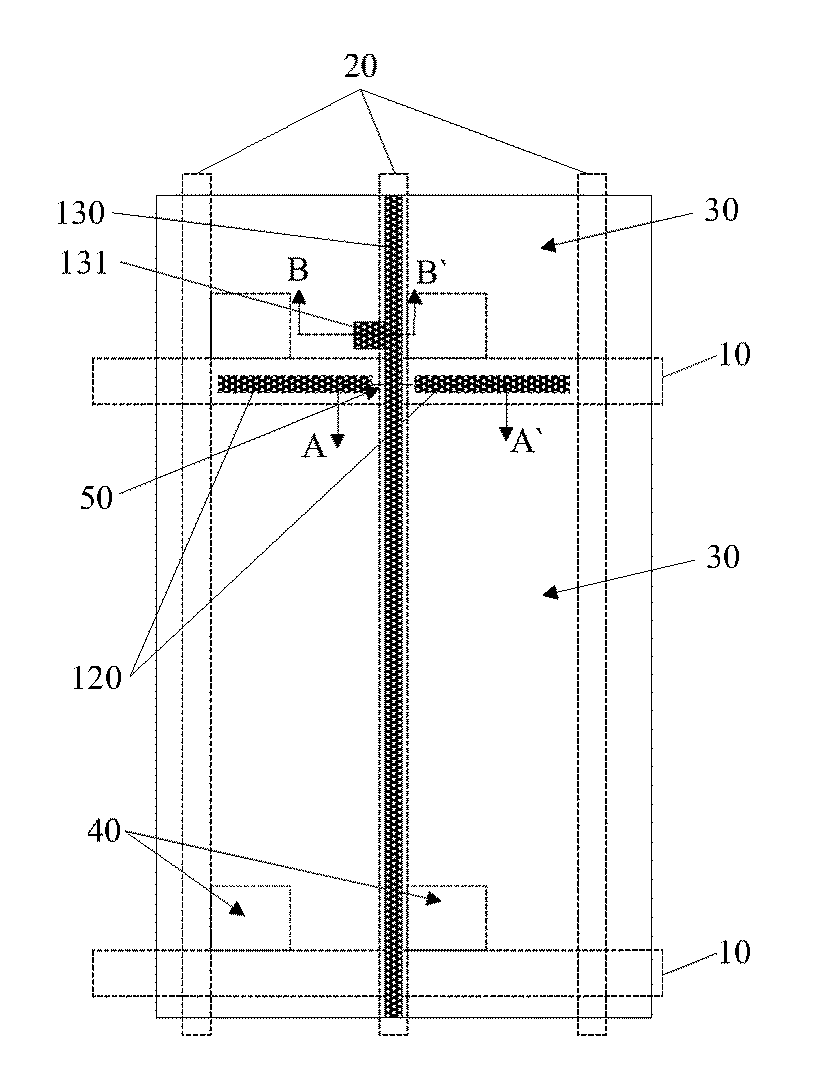

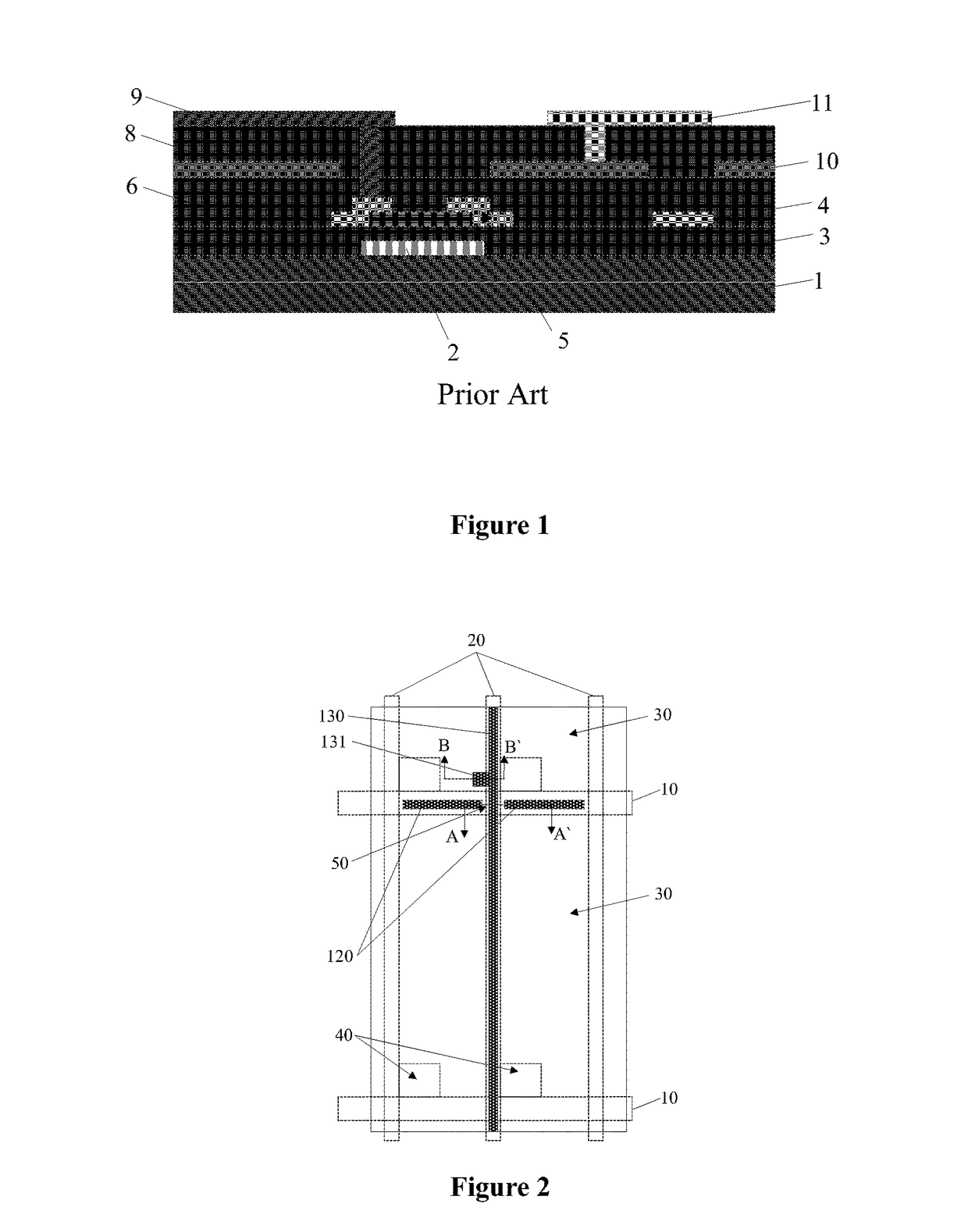

Method for manufacturing thin film transistor, and thin film transistor

ActiveUS20190386030A1Mask savingSimple technologyTransistorSolid-state devicesInter layerLiquid-crystal display

Disclosed is a method for manufacturing a thin film transistor, and a thin film transistor, relating to the technical field of liquid crystal display. The method comprises steps of: forming a buffer layer, an active layer, a gate insulator layer, and a gate electrode layer successively on a glass substrate and patterning these layers; forming an inter-layer dielectric layer on the buffer layer, the active layer, and the gate electrode layer and patterning the inter-layer dielectric layer; forming a source and a drain on the inter-layer dielectric layer, enabling the source and the drain to come into contact with the active layer, and patterning the source and the drain; forming a passivation layer and an organic photoresist layer successively on the inter-layer dielectric layer, the source, and the drain, and patterning the organic photoresist layer; dry-etching the passivation layer by using the organic photoresist layer as a mask, so as to form a hole on the passivation layer; and forming an organic light-emitting device by means of the hole on the passivation layer. The method saves a mask, requires simple techniques, and saves manufacturing costs. Besides, the developer is not able to come into direct contact with exposed aluminum of the source and the drain resulted from etching of the passivation layer. The method thus achieves the aim of improving product characteristics.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Touch display panel structure, method for forming the same, and touch display device

ActiveUS9798405B2Simple manufacturing processThe process steps are simpleNon-linear opticsInput/output processes for data processingScan lineDisplay device

A touch display panel structure, a method for forming the touch display panel structure, and a touch display device are provided. The touch display panel structure includes: a substrate, scan lines each including a plurality of scan line segments, touch electrode lines each disposed at an interval between adjacent scan line segments; a first dielectric layer and data lines; a second dielectric layer and a first interconnection structure; a first via hole through the first dielectric layer and the second dielectric layer; a third dielectric layer a common electrode layer; a second via hole through the first dielectric layer and the second dielectric layer; and a plurality of third via holes through the third dielectric layer, wherein each touch electrode is connected to a touch electrode line via the second via hole and the third via hole.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD +1