Polysilicon active layer-containing thin film transistor, manufacturing method thereof and array substrate

A thin-film transistor and active layer technology, applied in the direction of transistors, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problems of increasing the manufacturing cost of polysilicon TFTs, increasing the preparation time of polysilicon TFTs, and saving masks and photolithography The effect of craft

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0053] figure 2 It is a flowchart of a method for manufacturing a TFT containing a polysilicon active layer according to Embodiment 1 of the present invention. This embodiment is used to form a polysilicon TFT with a top gate structure, refer to figure 2 , including the following steps:

[0054] Step 201: depositing a buffer layer on the substrate, depositing an amorphous silicon layer on the buffer layer, patterning the amorphous silicon layer, and forming an active layer including a source region, a drain region and a channel region;

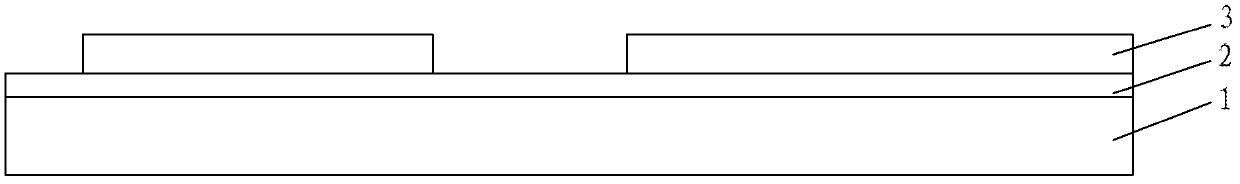

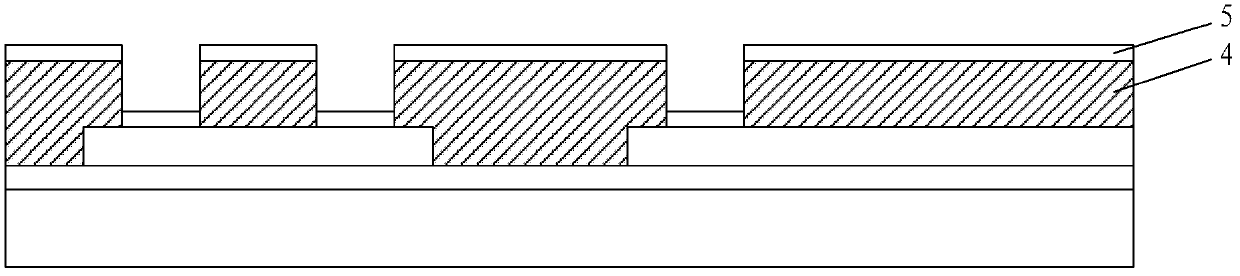

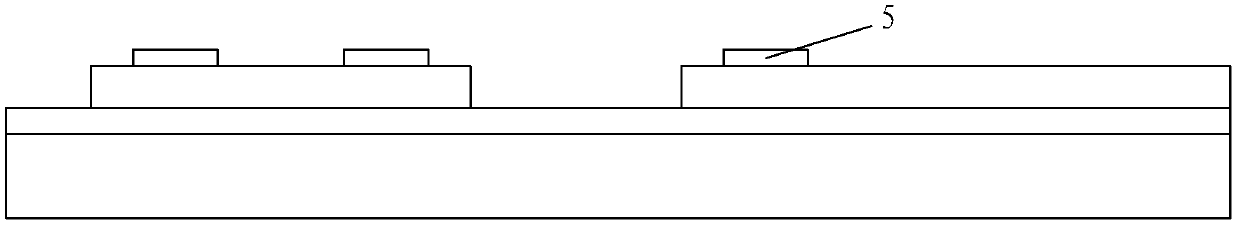

[0055] refer to Figure 3A , first, on a transparent substrate 1 such as glass that has been cleaned in advance, PECVD (plasma enhanced chemical vapor deposition), LPCVD (low pressure chemical vapor deposition), APCVD (atmospheric pressure chemical vapor deposition), ECR-CVD (electron cyclotron resonance chemical vapor deposition) Vapor deposition) or sputtering to form the buffer layer 2 to prevent the impurities contained in the glass f...

Embodiment 2

[0079] Figure 4 It is a flowchart of a method for manufacturing a TFT containing a polysilicon active layer according to Embodiment 2 of the present invention. This embodiment is used to form a polysilicon TFT with a bottom gate structure, refer to Figure 4 , including the following steps:

[0080] Step 401: forming a gate electrode and a gate insulating layer on the substrate;

[0081] First, on a transparent substrate such as glass that has been pre-cleaned, the gate metal layer is deposited by sputtering, thermal evaporation or PECVD, LPCVD, APCVD, ECR-CVD, etc., and then wet etching or dry etching is used. A mask is formed by photolithography, the gate metal layer is etched to form a pattern, and a gate electrode is formed. Finally, a gate insulating layer is deposited on the substrate on which the gate electrode is formed by PECVD, LPCVD, APCVD or ECR-CVD.

[0082] The gate metal layer is made of conductive materials such as metal, metal alloys such as molybdenum, mo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More