Patents

Literature

69 results about "Metal-induced crystallization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

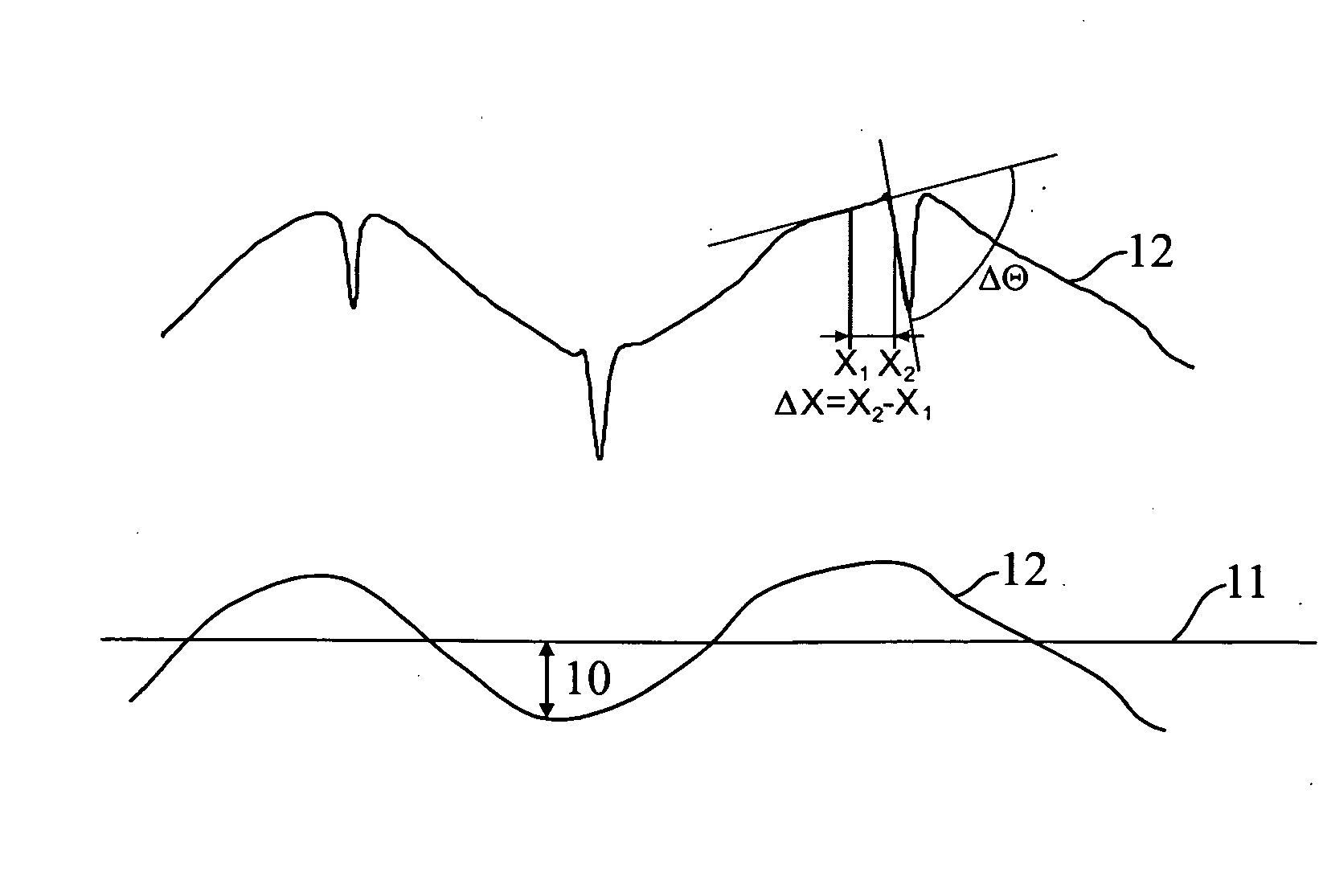

Metal-induced crystallization (MIC) is a method by which amorphous carbon (a-C), amorphous silicon (a-Si), and amorphous germanium (a-Ge) can be turned into their polycrystalline phases at relatively low temperatures.

Low-temperature metal-induced crystallization of silicon-germanium films

Owner:SANDISK TECH LLC

Low temperature production of large-grain polycrystalline semiconductors

InactiveUS7202143B1Final product manufactureSemiconductor/solid-state device manufacturingSolar cellSilicon dioxide

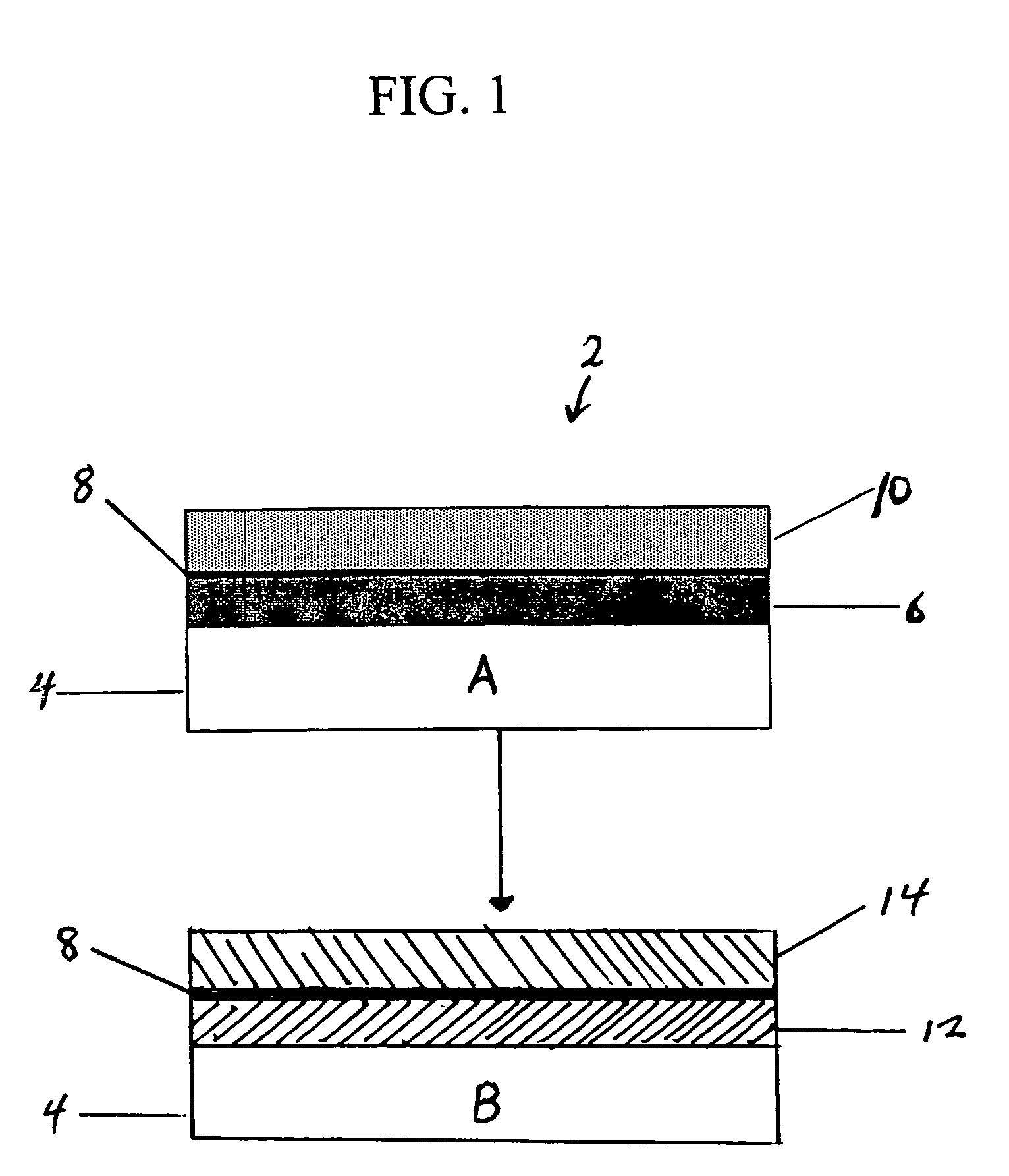

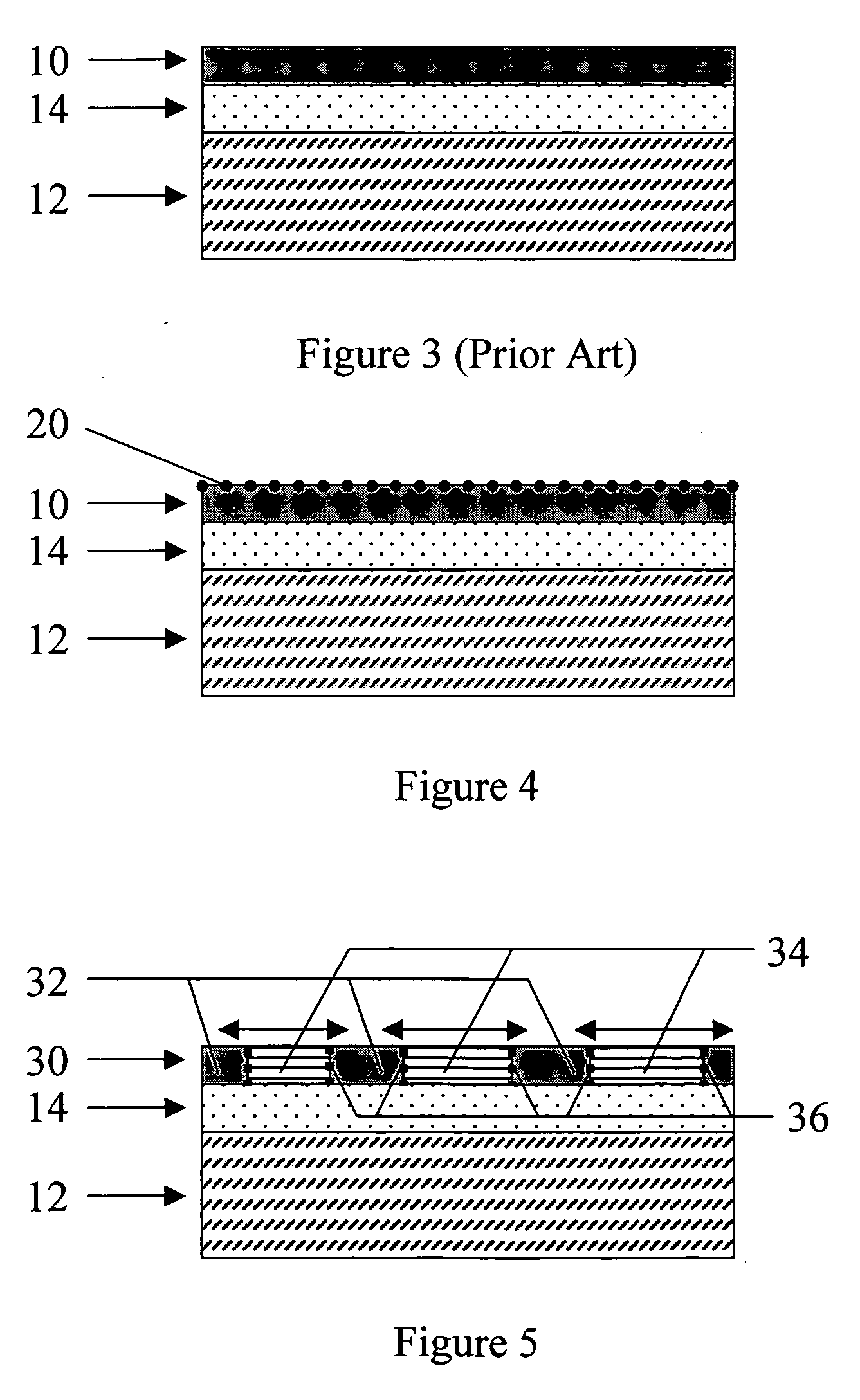

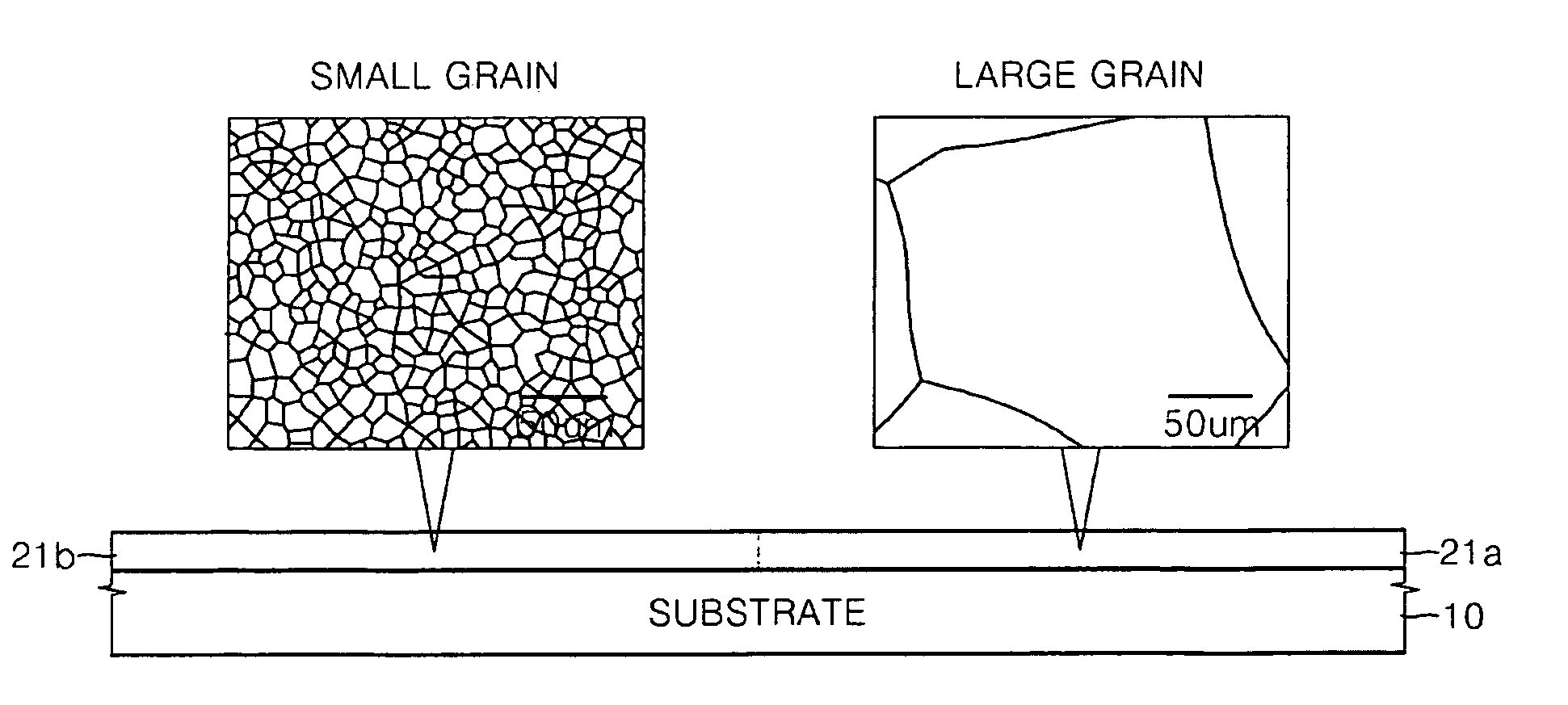

An oxide or nitride layer is provided on an amorphous semiconductor layer prior to performing metal-induced crystallization of the semiconductor layer. The oxide or nitride layer facilitates conversion of the amorphous material into large grain polycrystalline material. Hence, a native silicon dioxide layer provided on hydrogenated amorphous silicon (a-Si:H), followed by deposited Al permits induced crystallization at temperatures far below the solid phase crystallization temperature of a-Si. Solar cells and thin film transistors can be prepared using this method.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ARKANSAS

Method and apparatus for fabricating piezoresistive polysilicon by low-temperature metal induced crystallization

InactiveUS20100102403A1Good piezoresistive propertiesImprove featuresPiezoelectric/electrostrictive device manufacture/assemblyFluid pressure measurement by electric/magnetic elementsRoom temperatureMetal-induced crystallization

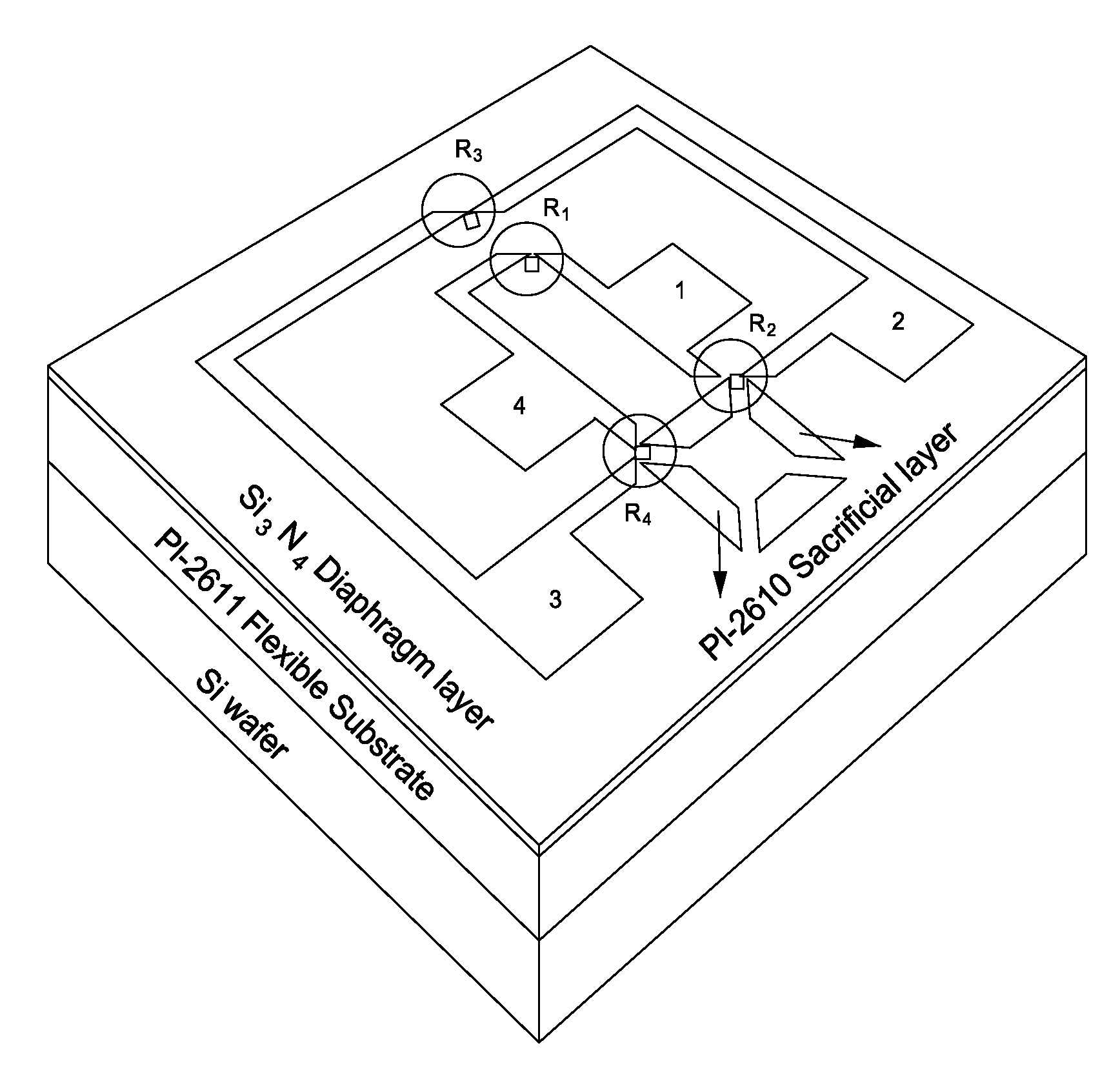

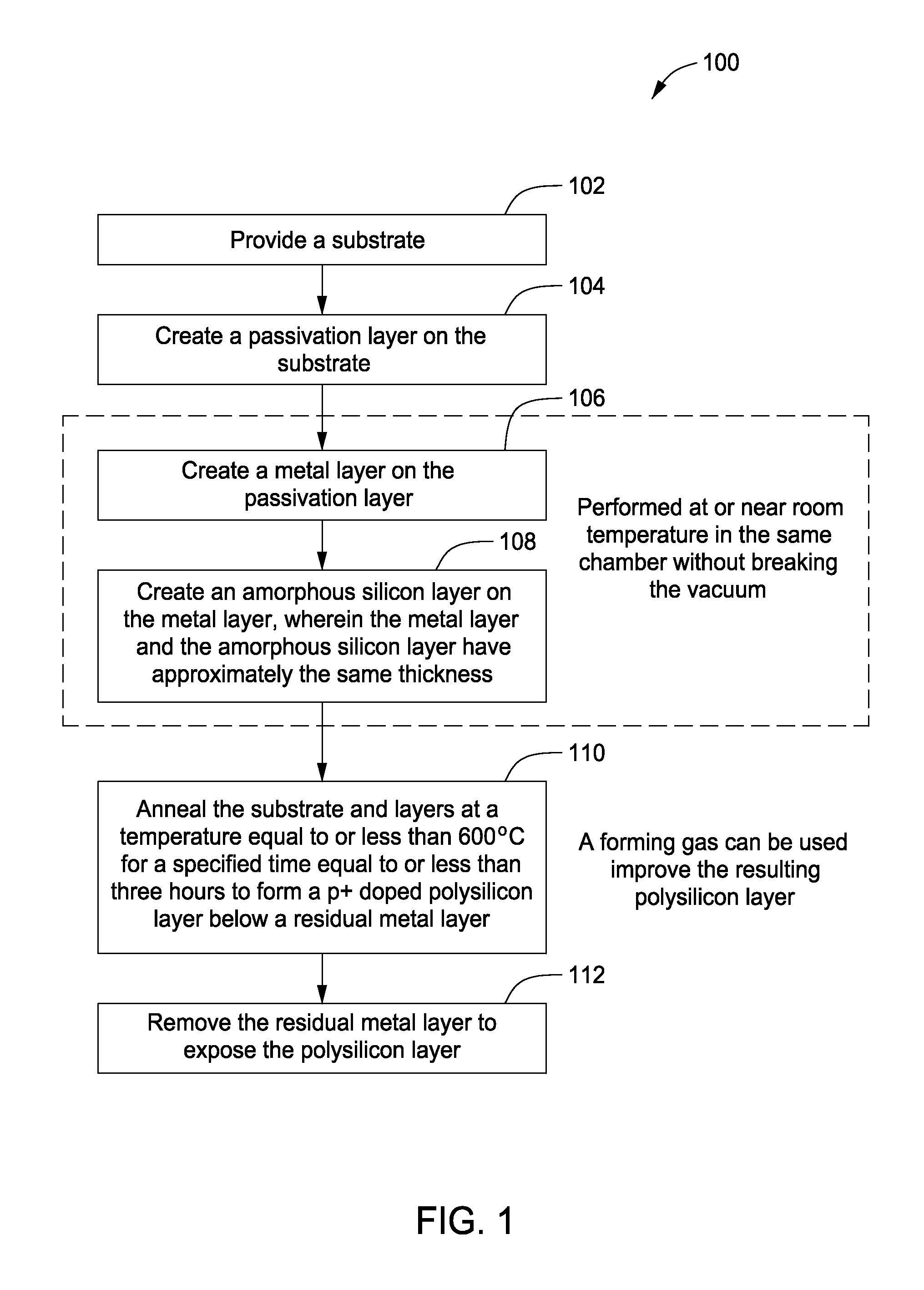

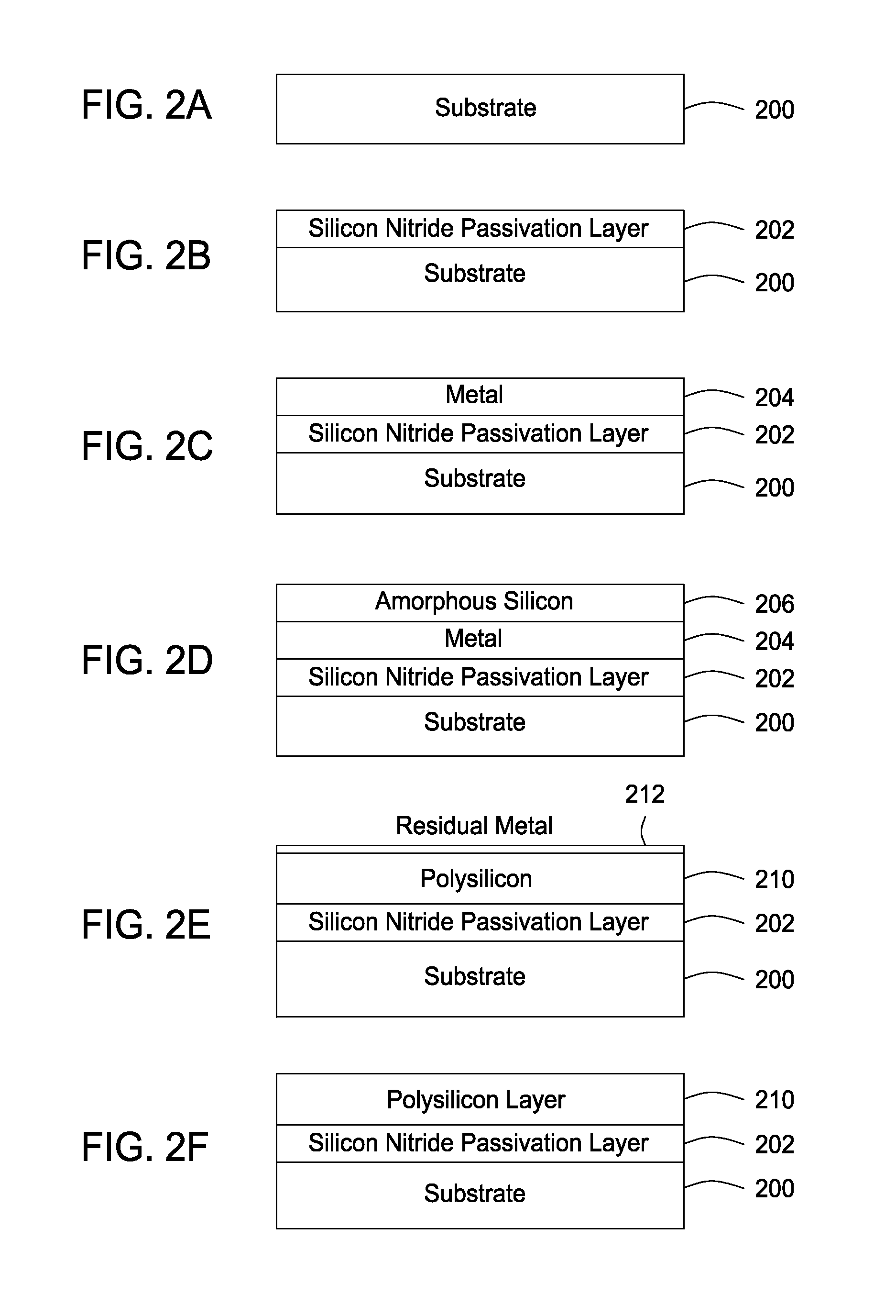

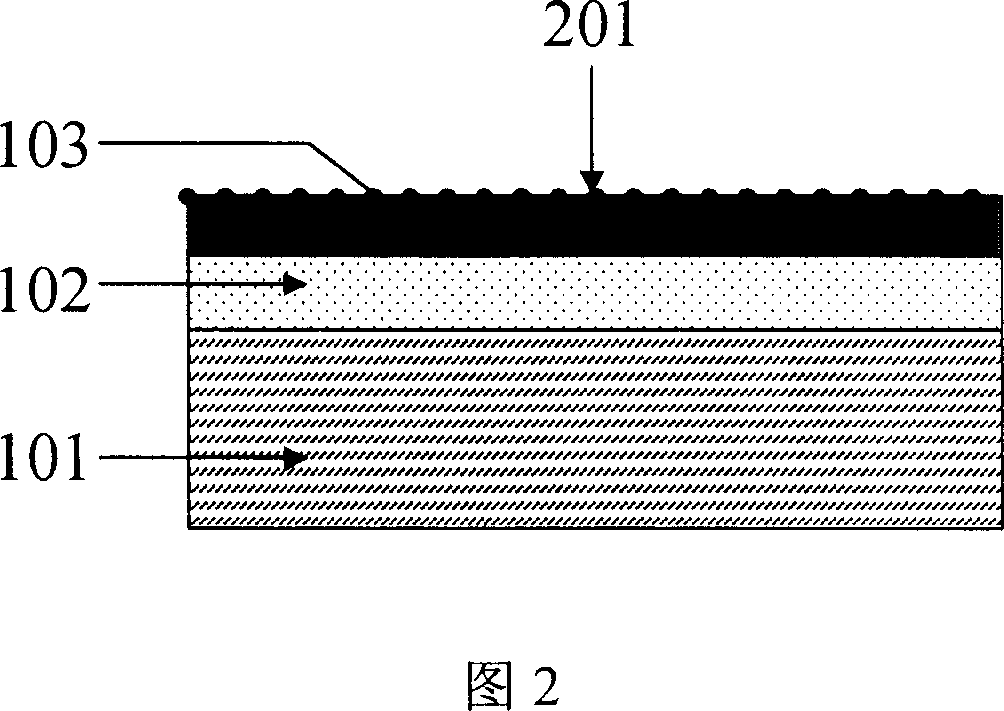

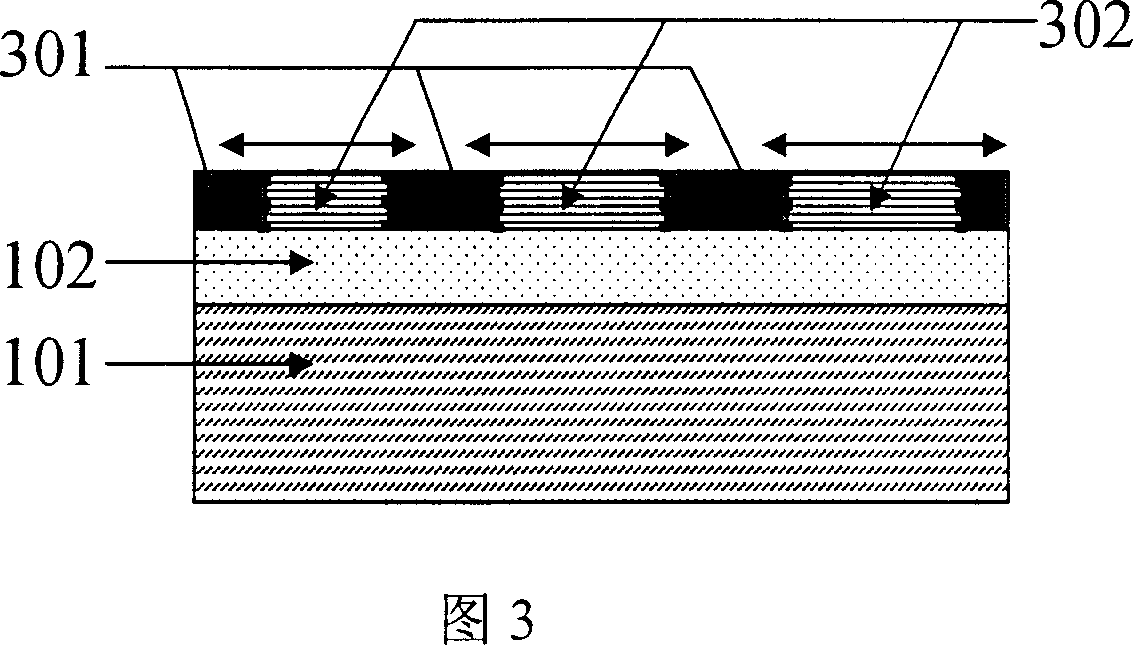

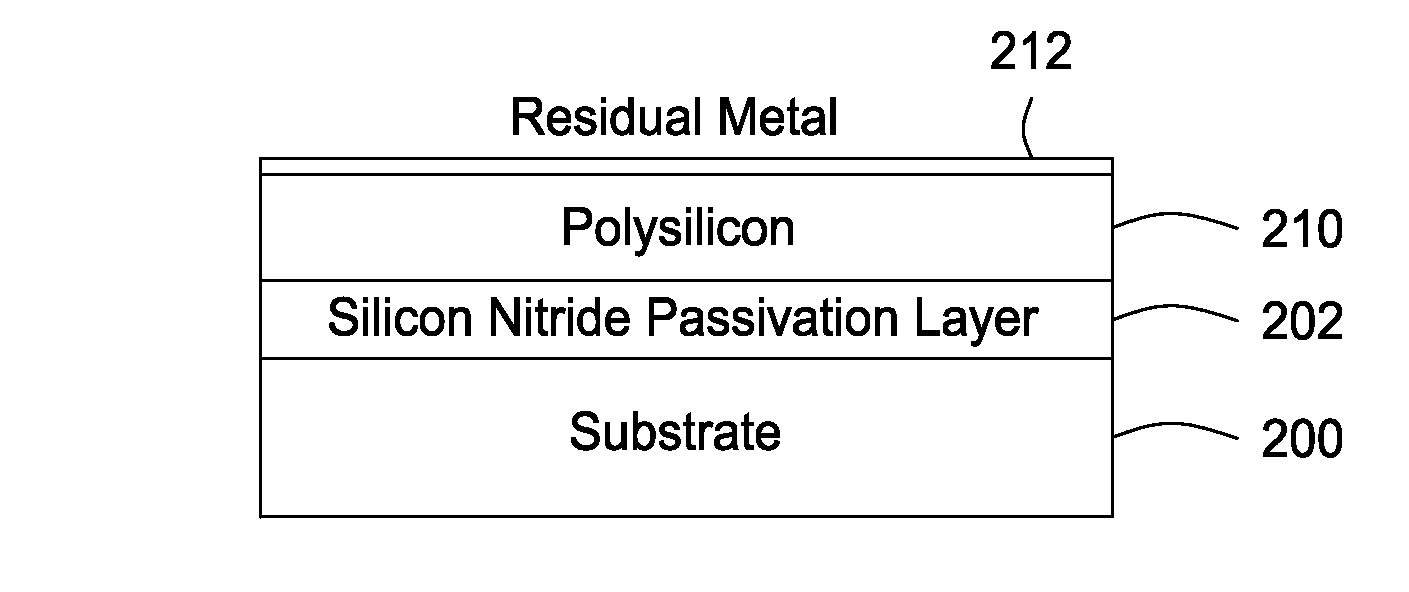

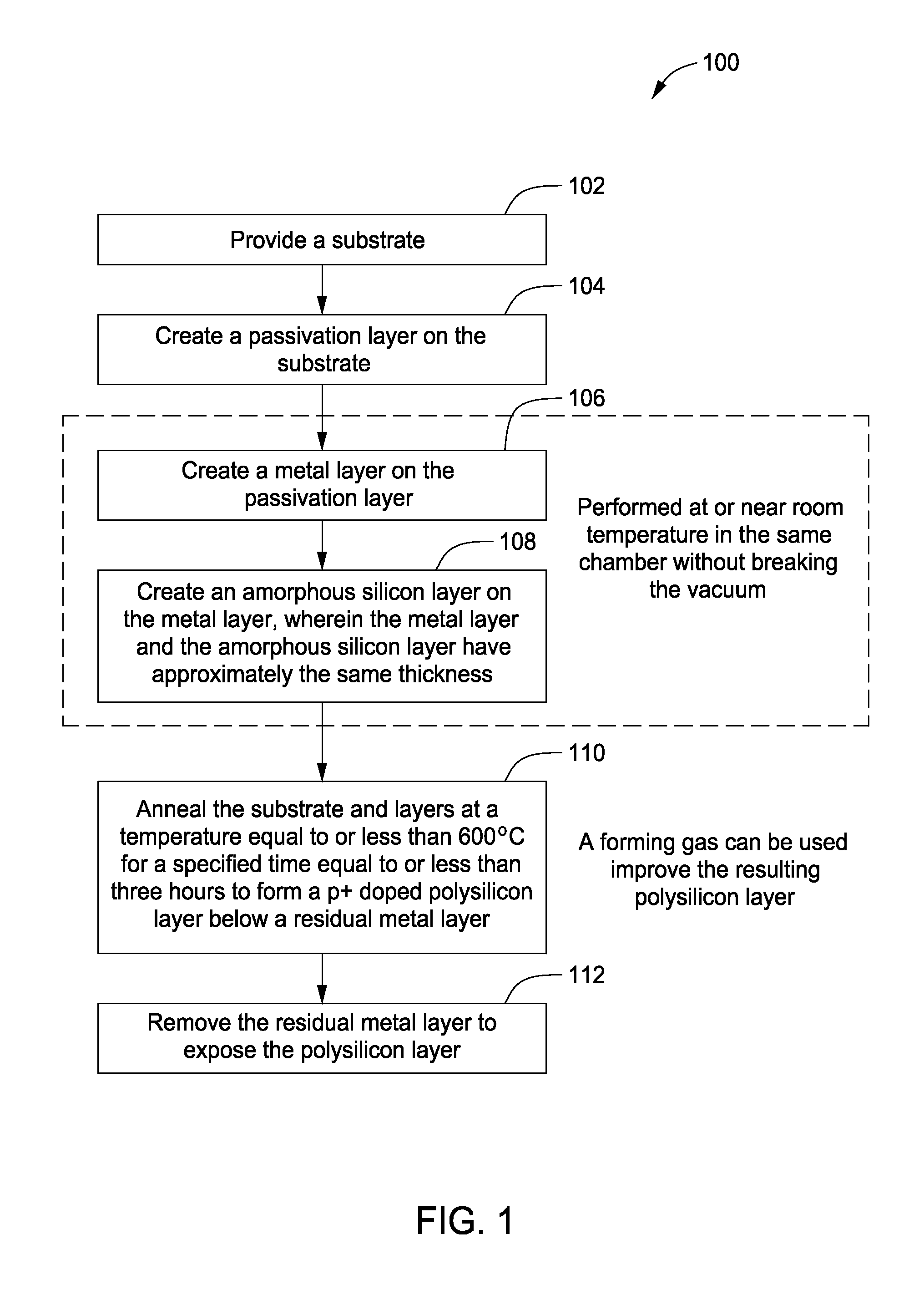

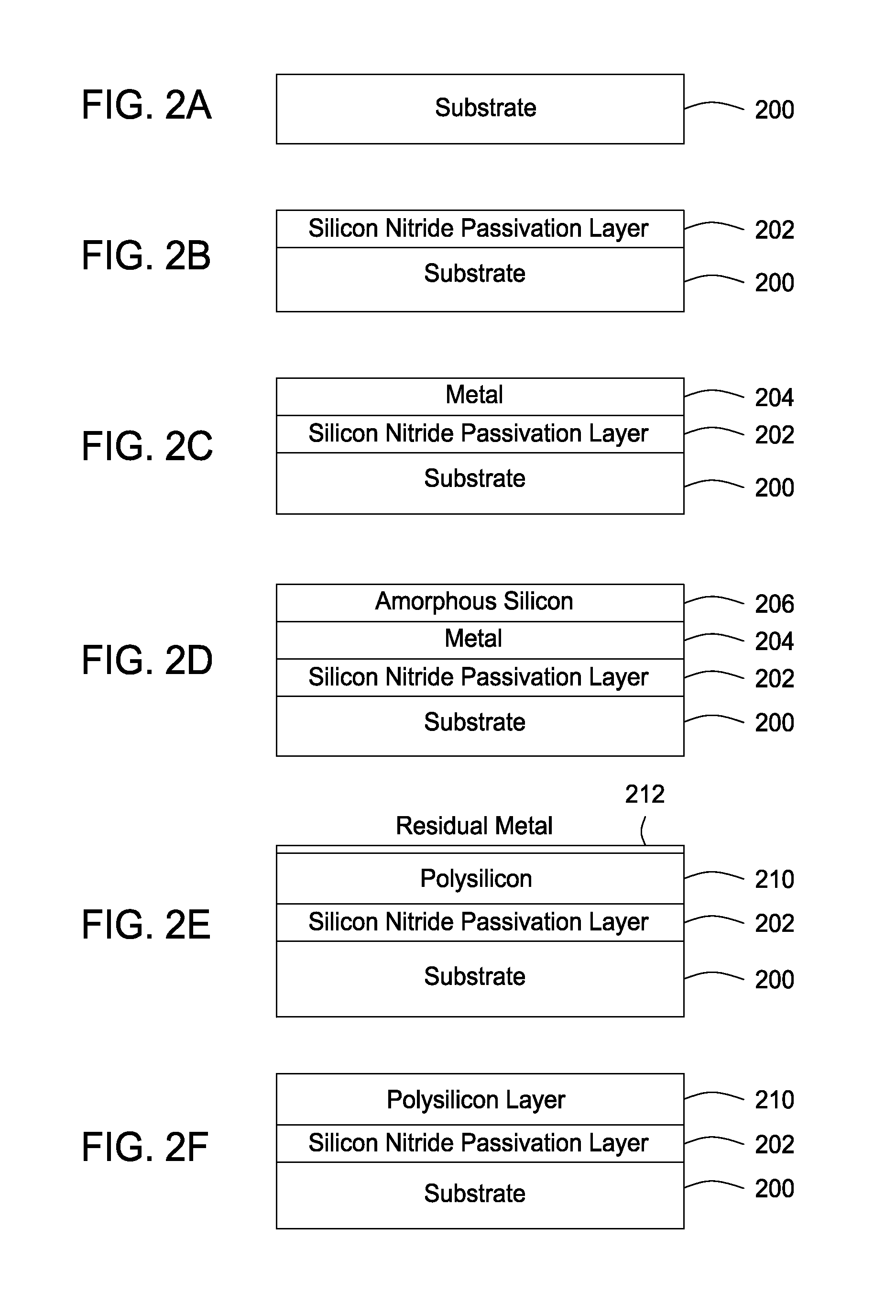

The present invention provides a method and apparatus for fabricating piezoresistive polysilicon on a substrate by low-temperature metal induced crystallization by: (1) providing the substrate having a passivation layer; (2) performing, at or near room temperature in a chamber without breaking a vacuum or near-vacuum within the chamber, the steps of: (a) creating a metal layer on the passivation layer, and (b) creating an amorphous silicon layer on the metal layer, wherein the metal layer and the amorphous silicon layer have approximately the same thickness; (3) annealing the substrate, the passivation layer, the metal layer and the amorphous silicon layer at a temperature equal to or less than 600° C. and a period of time equal to or less than three hours to form a doped polysilicon layer below a residual metal layer; and (4) removing the residual metal layer to expose the doped polysilicon layer.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

Low-temperature metal-induced crystallization of silicon-germanium films

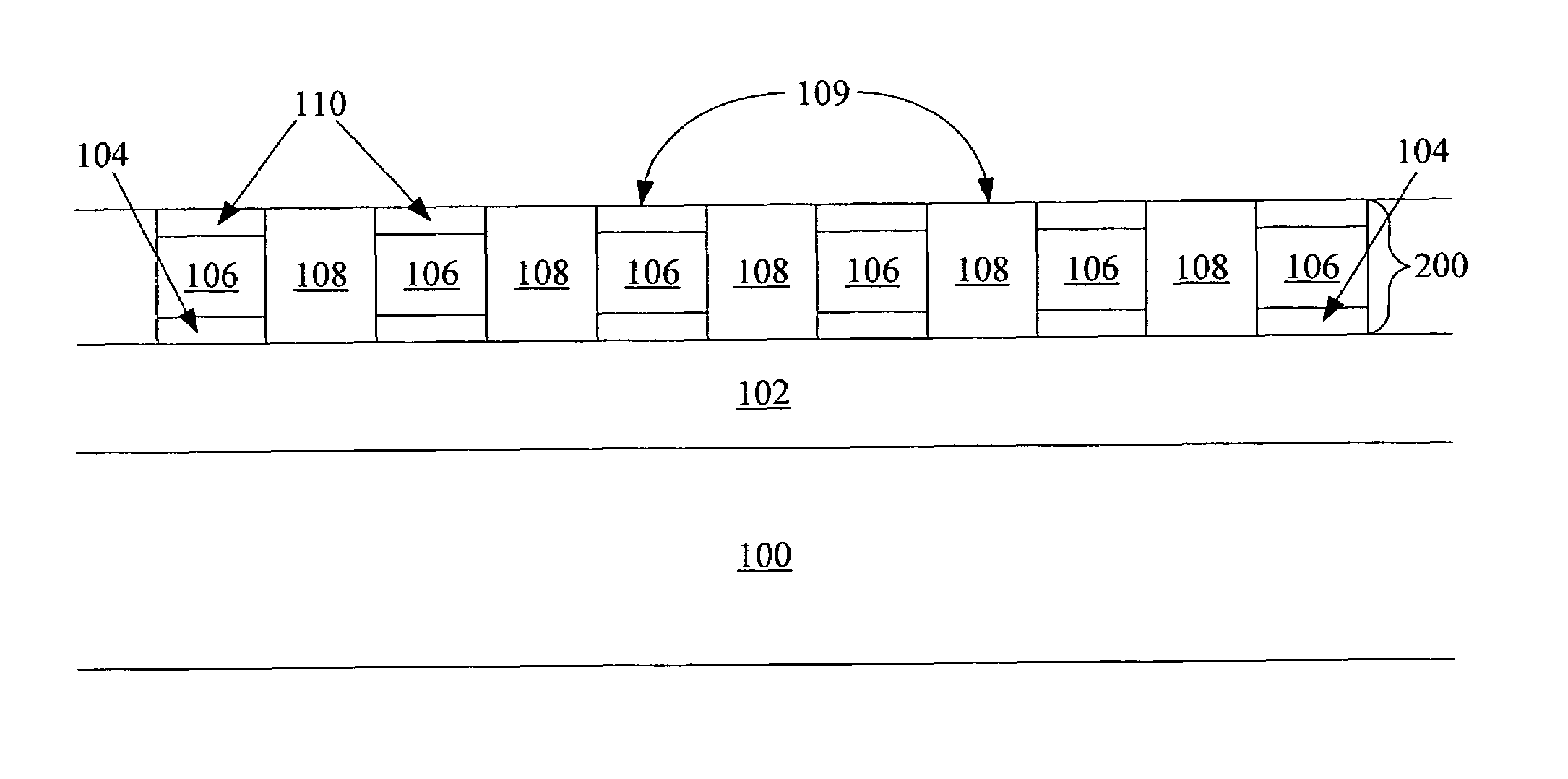

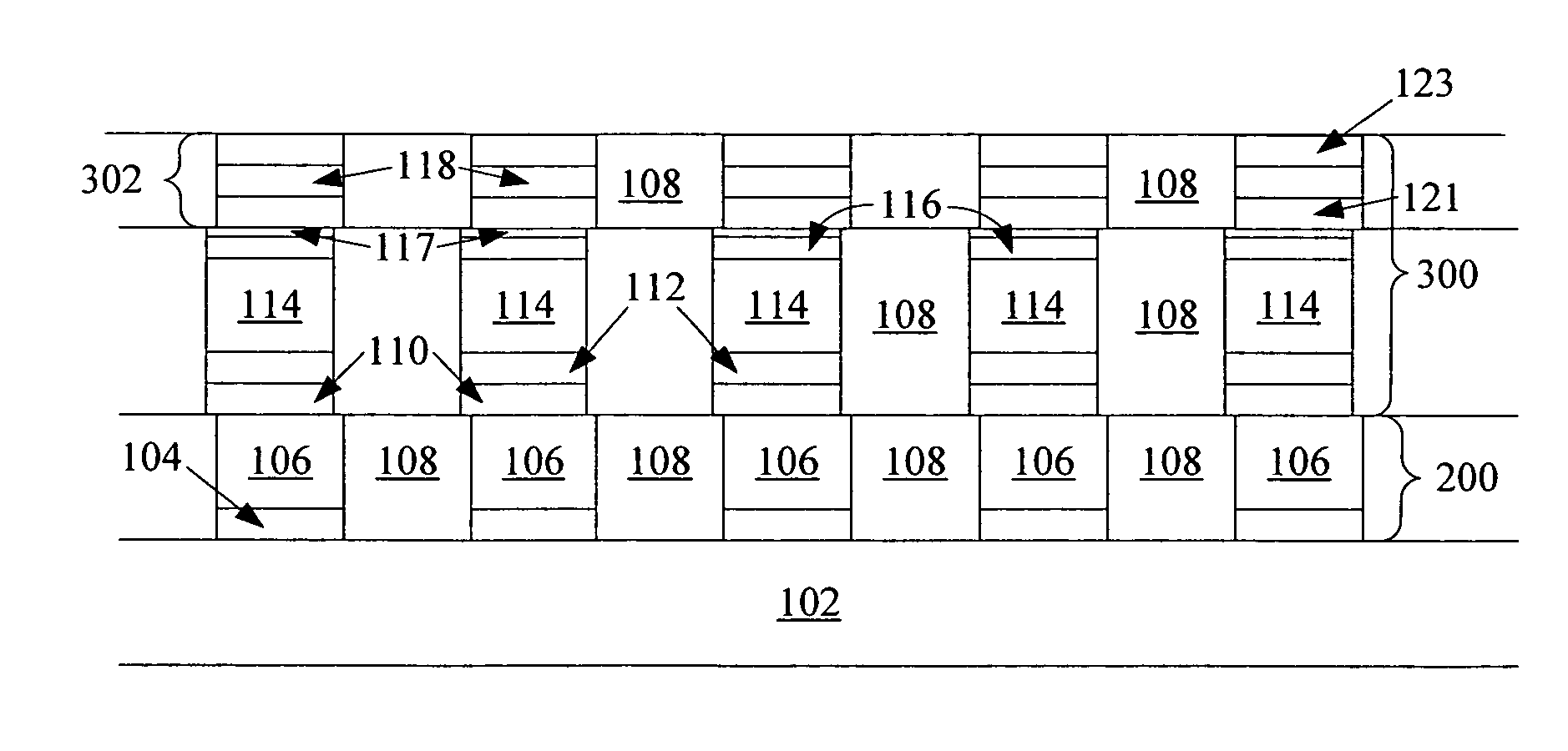

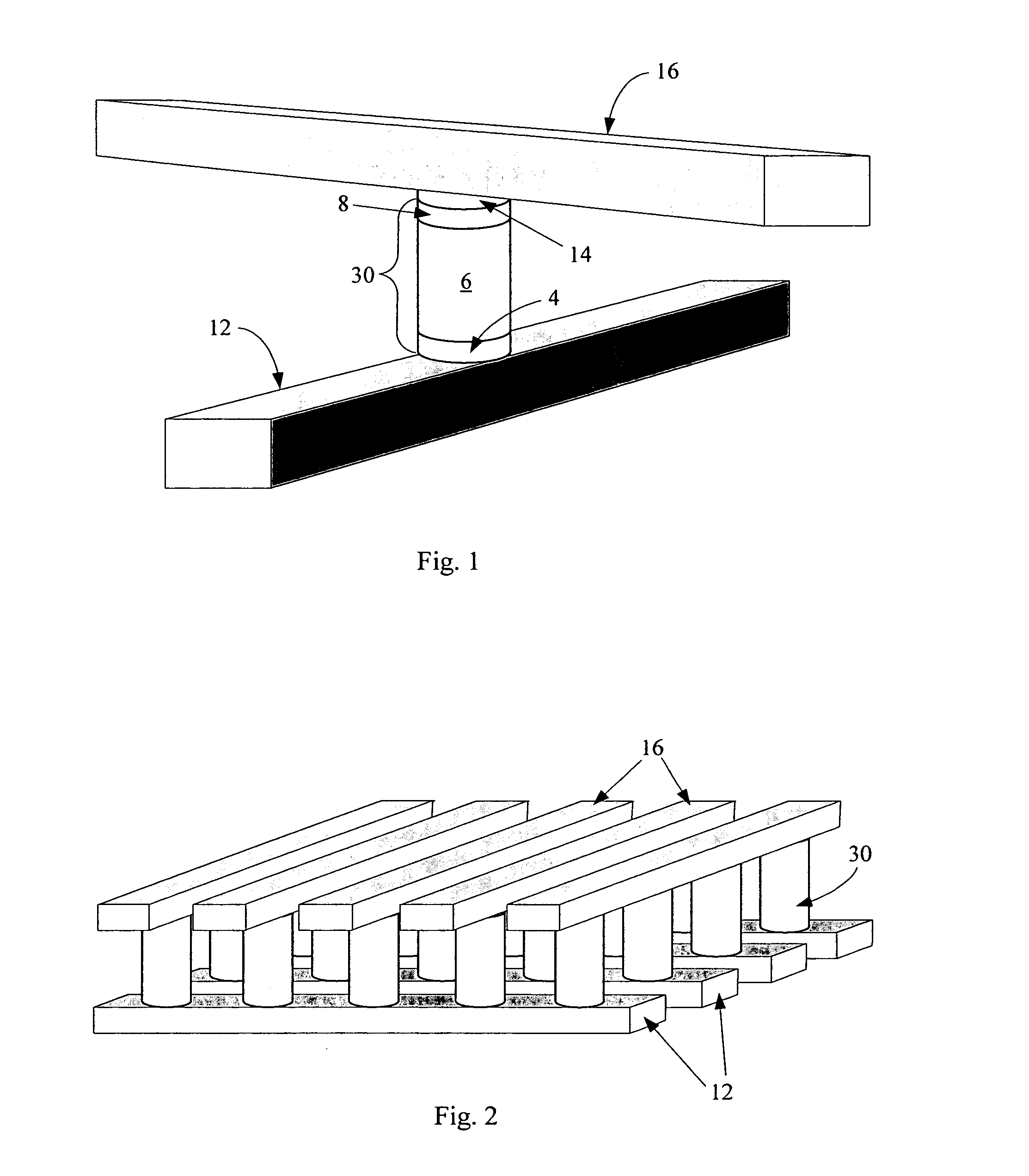

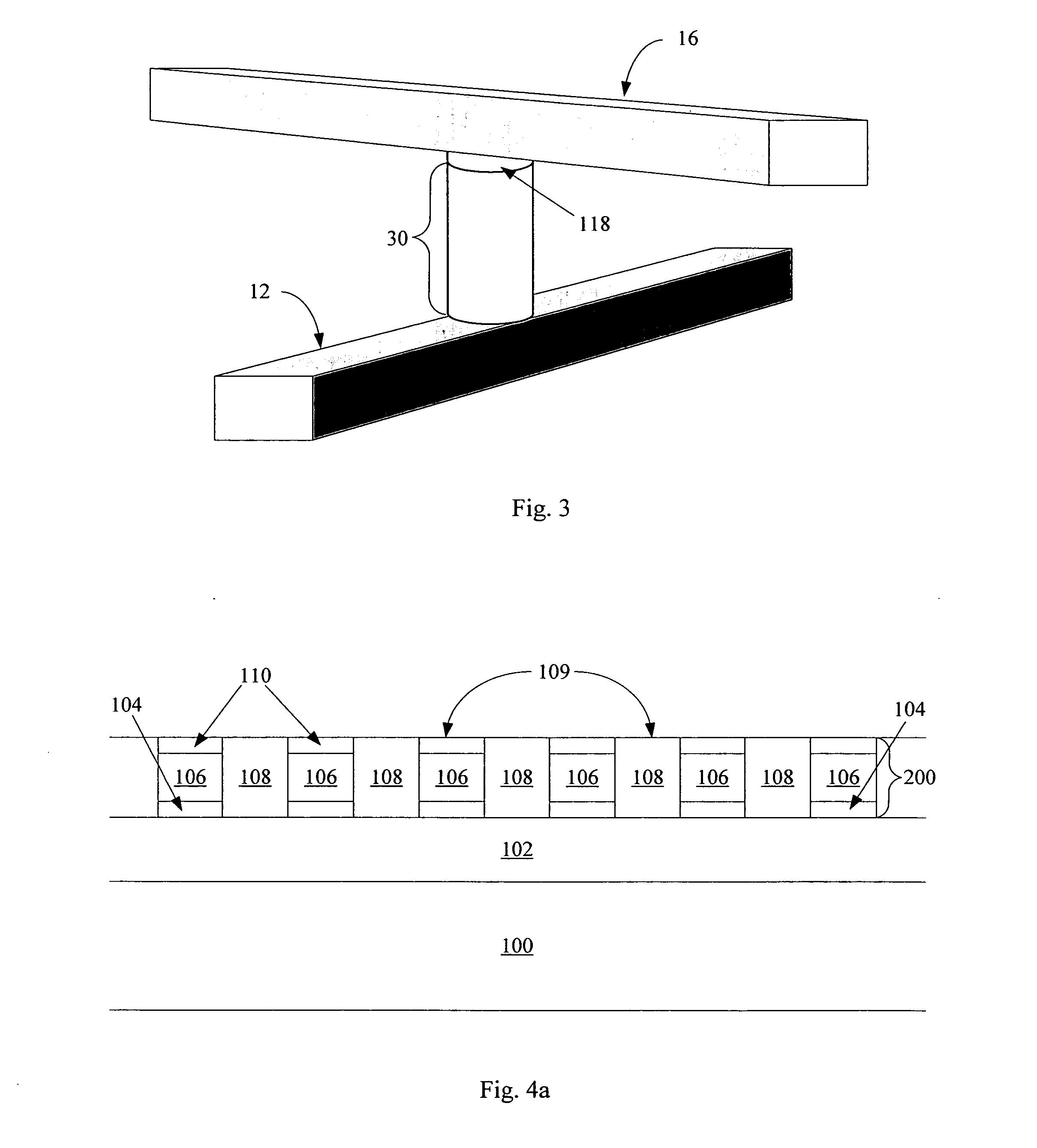

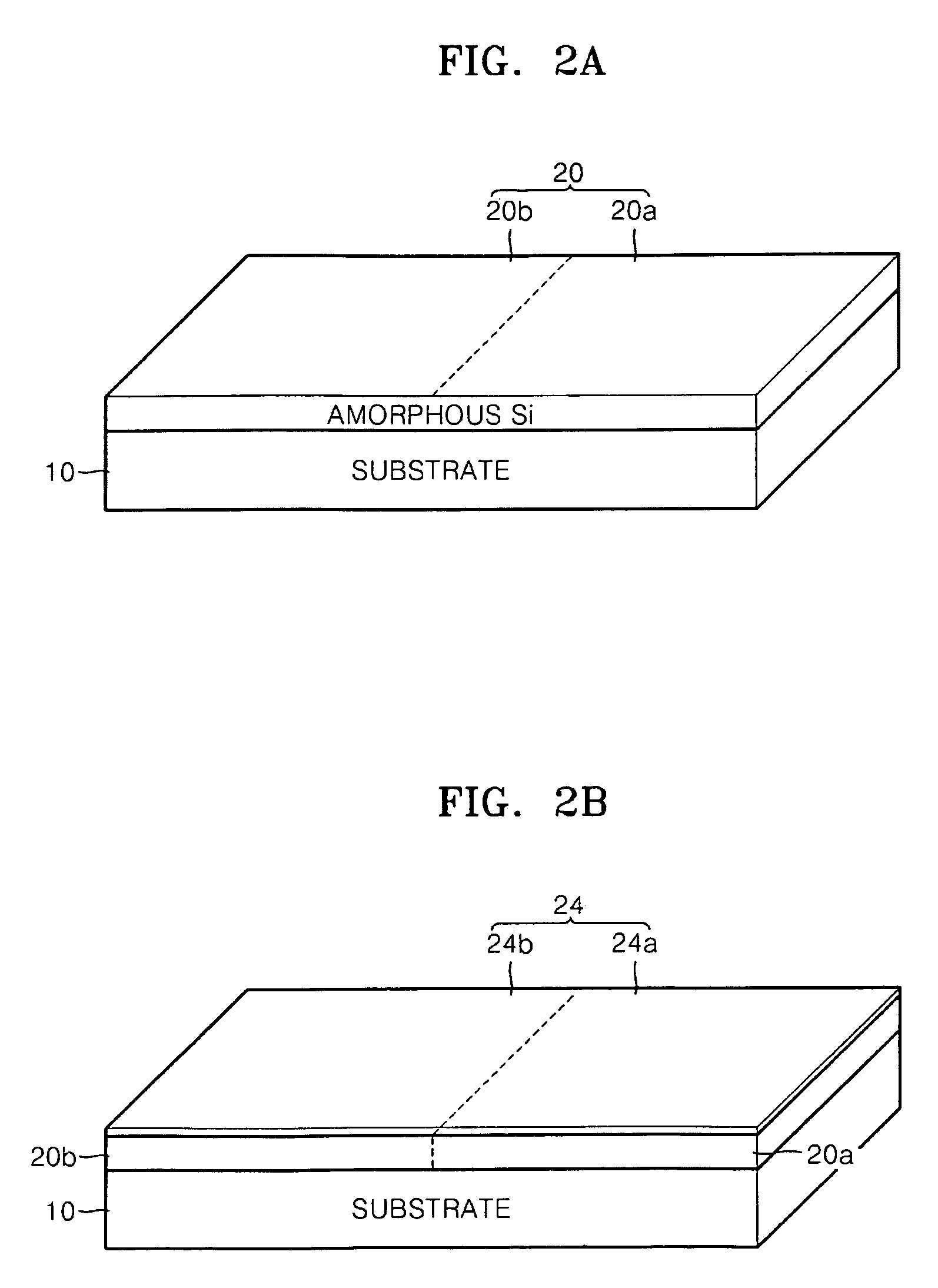

The present invention provides for a low-temperature method to crystallize a silicon-germanium film. Metal-induced crystallization of a deposited silicon film can serve to reduce the temperature required to crystallize the film. Increasing germanium content in a silicon-germanium alloy further decreases crystallization temperature. By using metal-induced crystallization to crystallize a deposited silicon-germanium film, temperature can be reduced substantially. In preferred embodiments, for example in a monolithic three dimensional array of stacked memory levels, reduced temperature allows the use of aluminum metallization. In some embodiments, use of metal-induced crystallization in a vertically oriented silicon-germanium diode having conductive contacts at the top and bottom end is be particularly advantageous, as increased solubility of the metal catalyst in the contact material will reduce the risk of metal contamination of the diode.

Owner:SANDISK TECH LLC

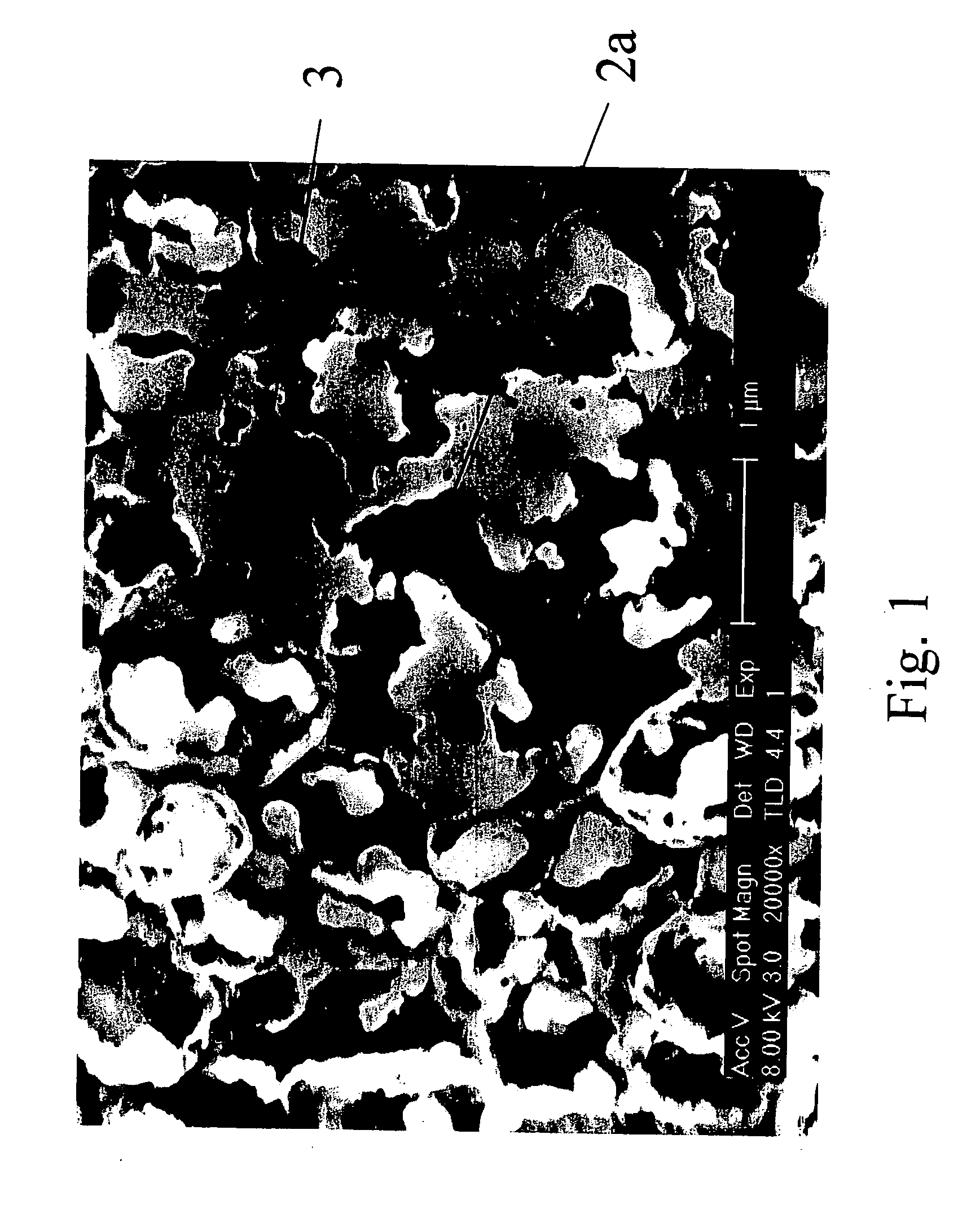

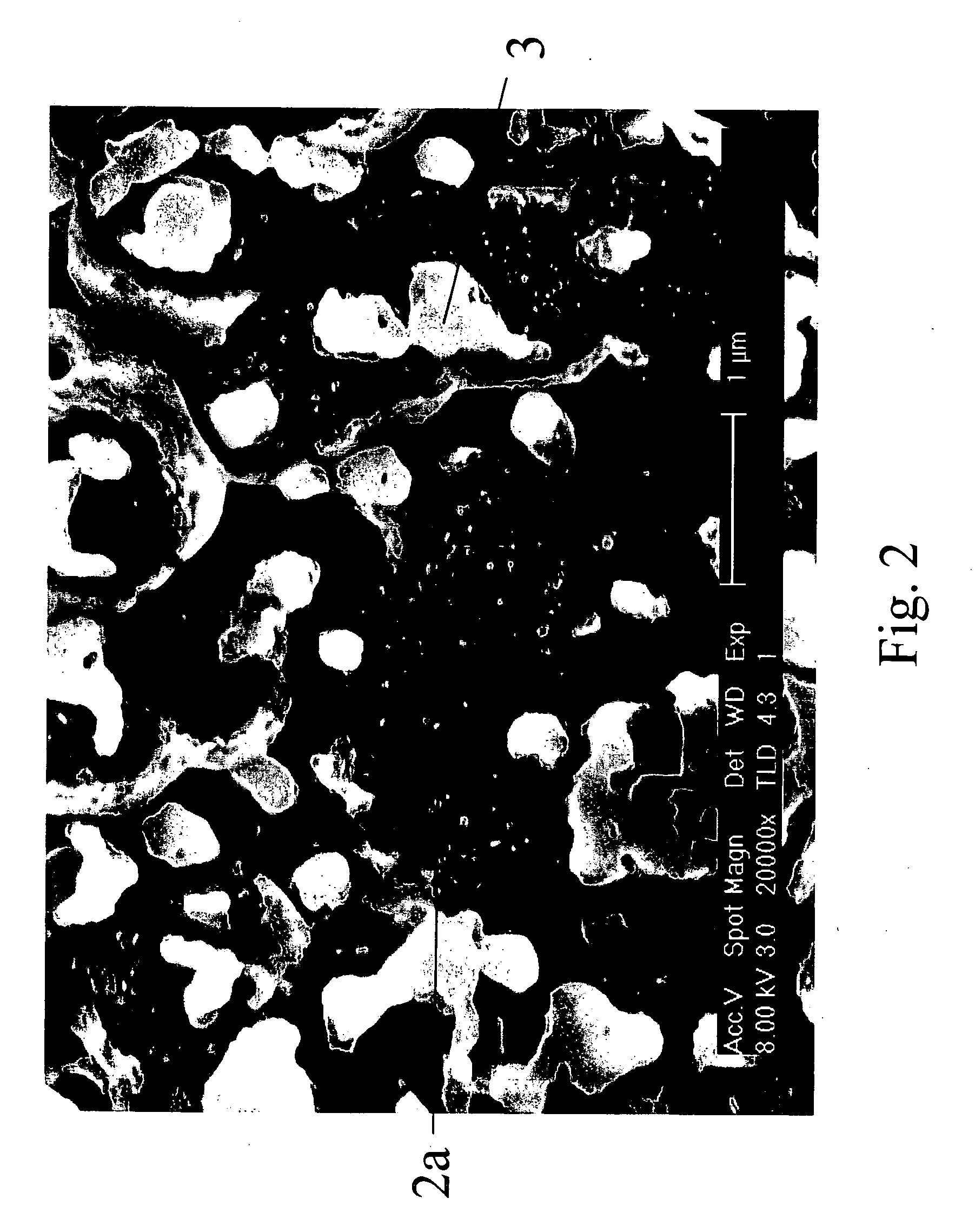

Metal-induced crystallization of amorphous silicon, polycrystalline silicon thin films produced thereby and thin film transistors produced therefrom

ActiveUS20060263957A1Quality improvementResidue reductionSolid-state devicesSemiconductor/solid-state device manufacturingTreatment completedNucleation

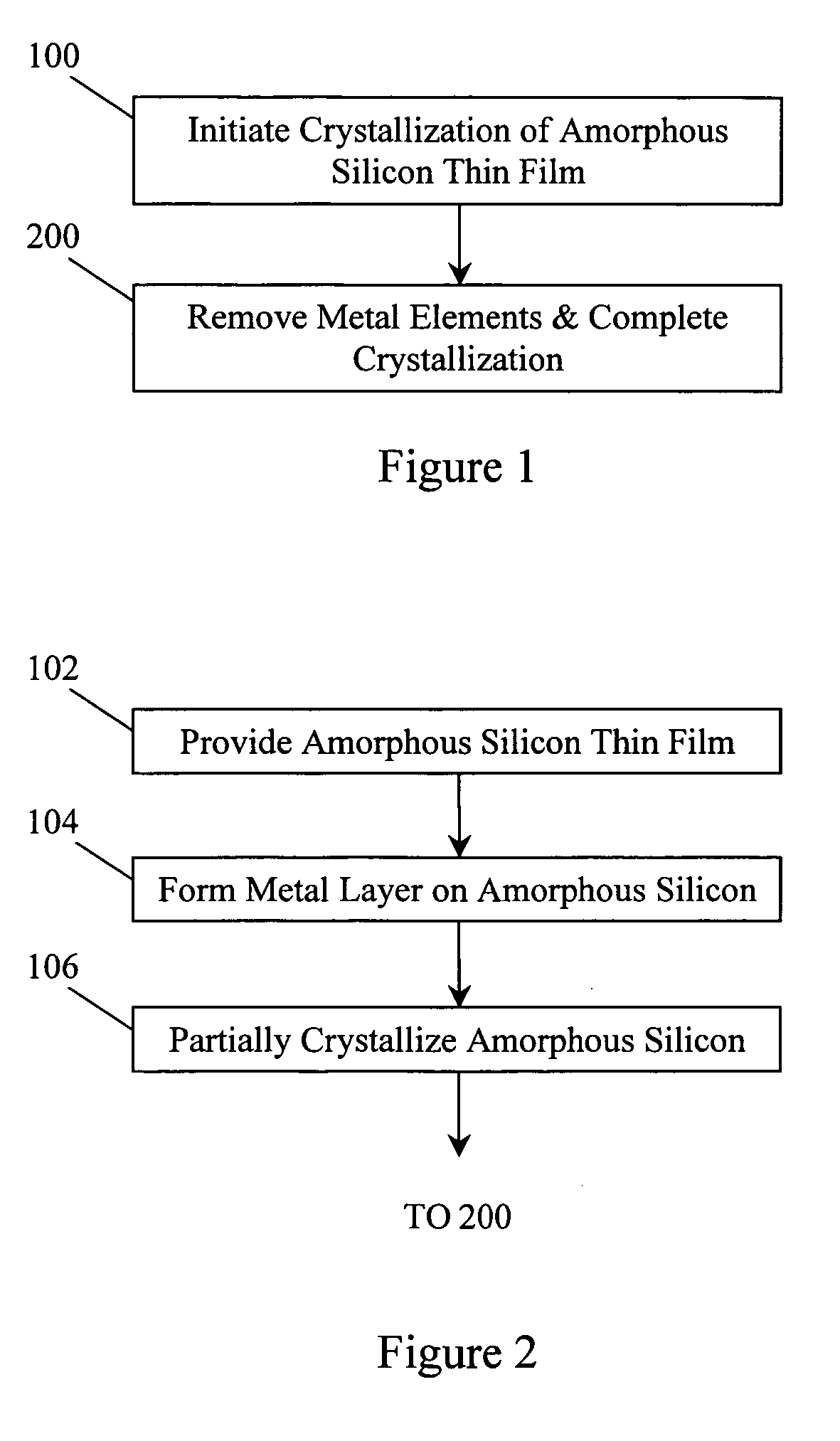

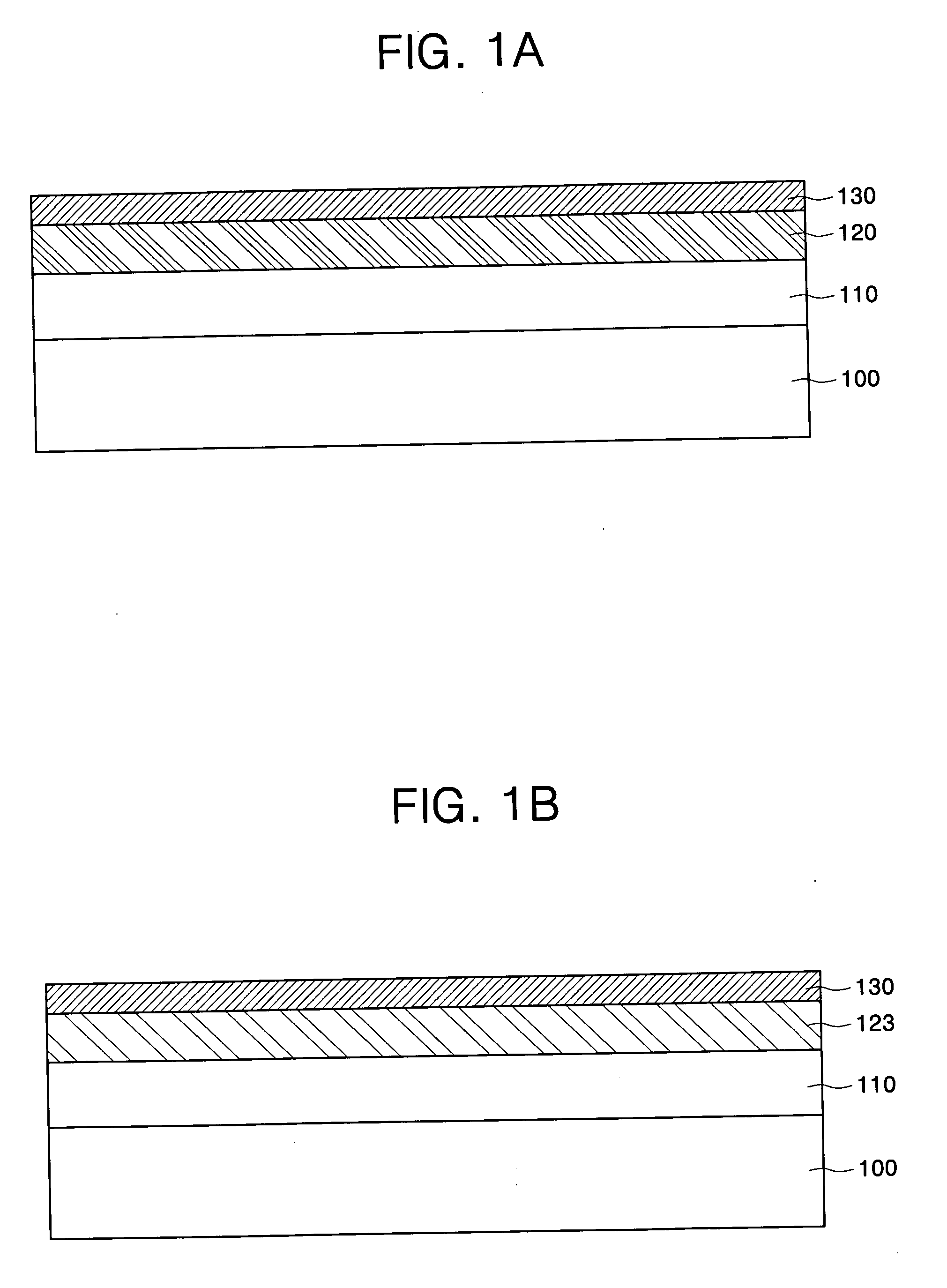

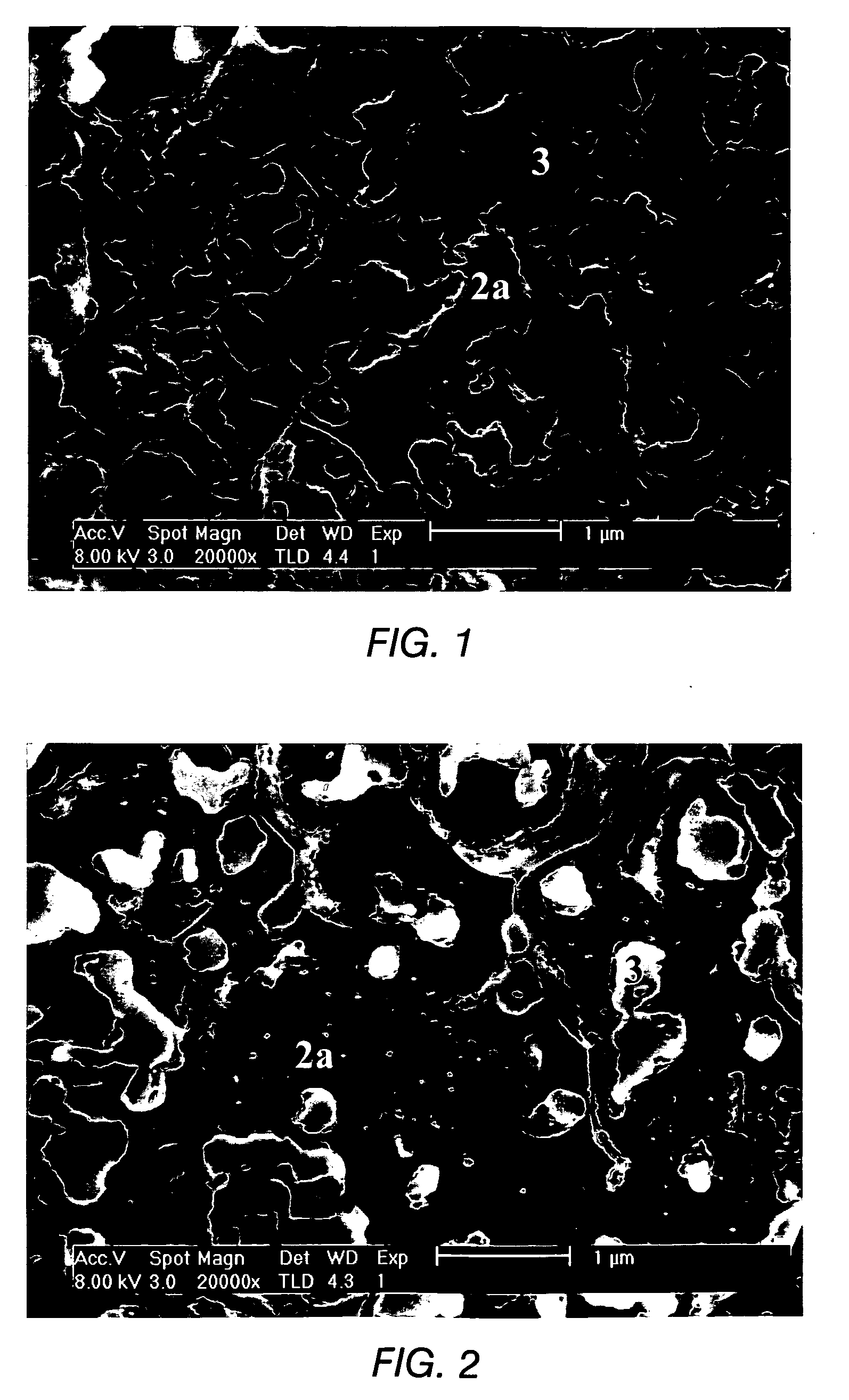

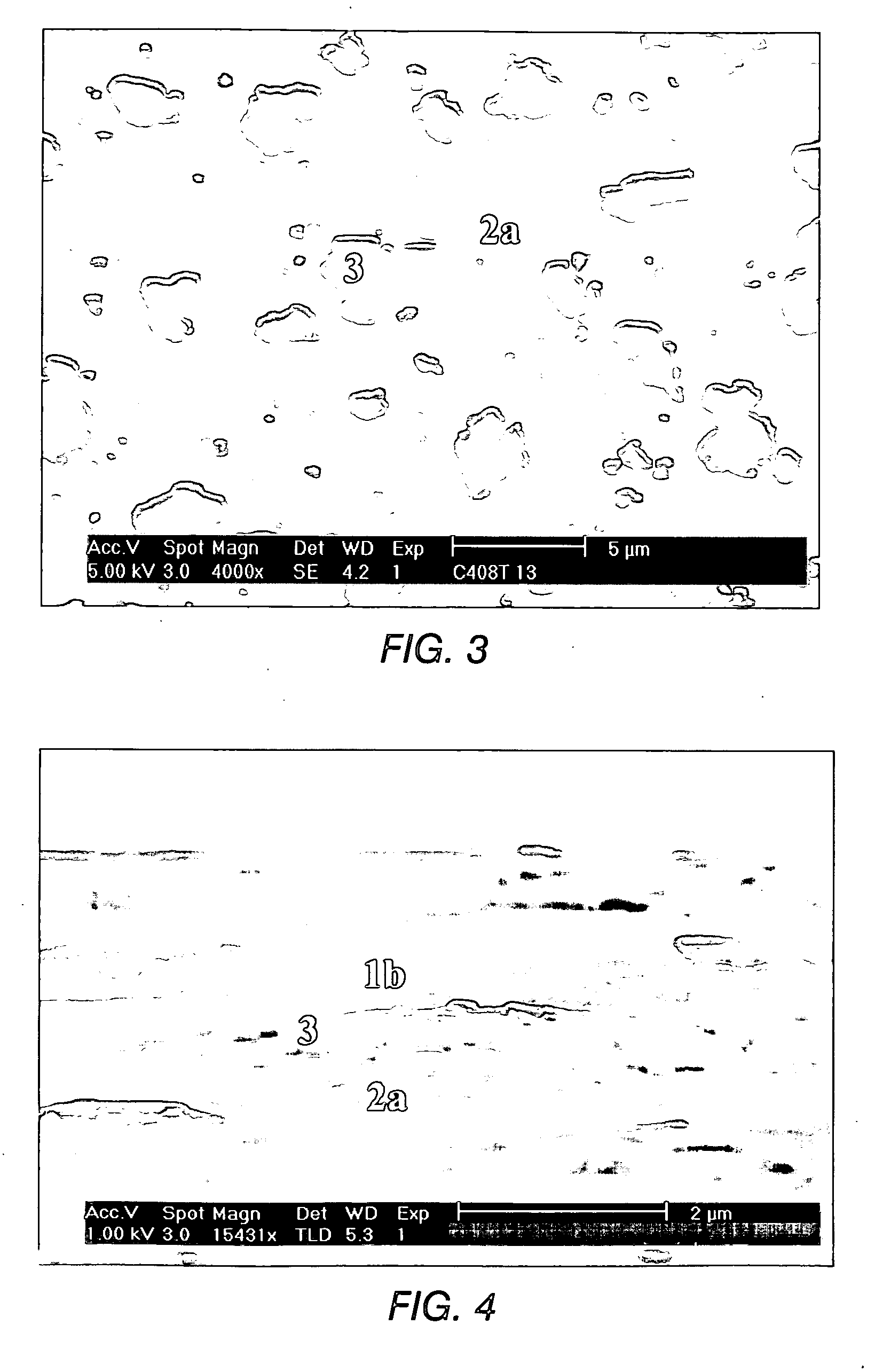

Crystallization-inducing metal elements are introduced onto an amorphous silicon thin film. A first, low-temperature, heat-treatment induces nucleation of metal-induced crystallization (MIC), resulting in the formation of small polycrystalline silicon “islands”. A metal-gettering layer is formed on the resulting partially crystallized thin film. A second, low-temperature, heat-treatment completes the MIC process, whilst gettering metal elements from the partially crystallized thin film. The process results in the desired polycrystalline silicon thin film.

Owner:THE HONG KONG UNIV OF SCI & TECH

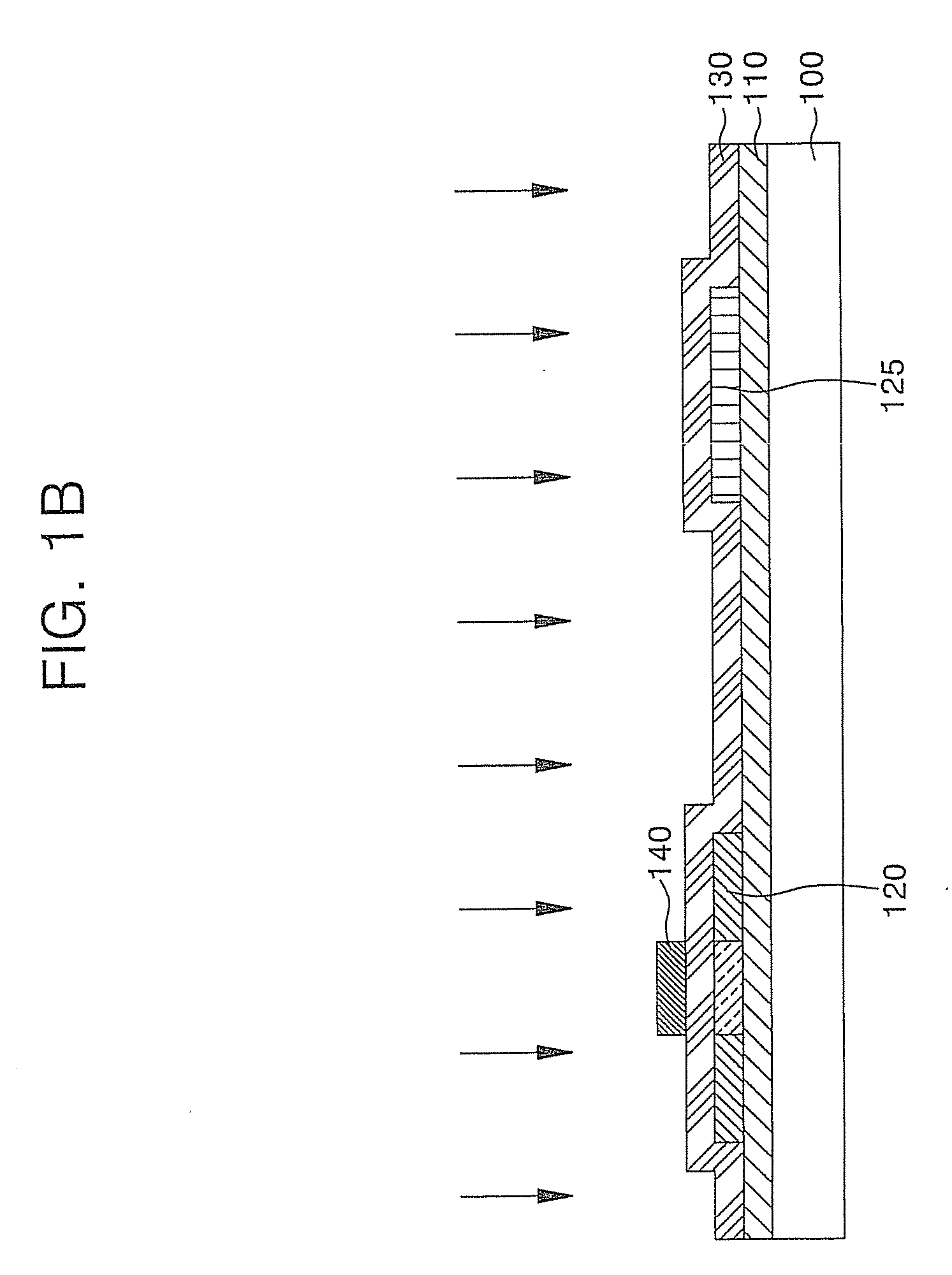

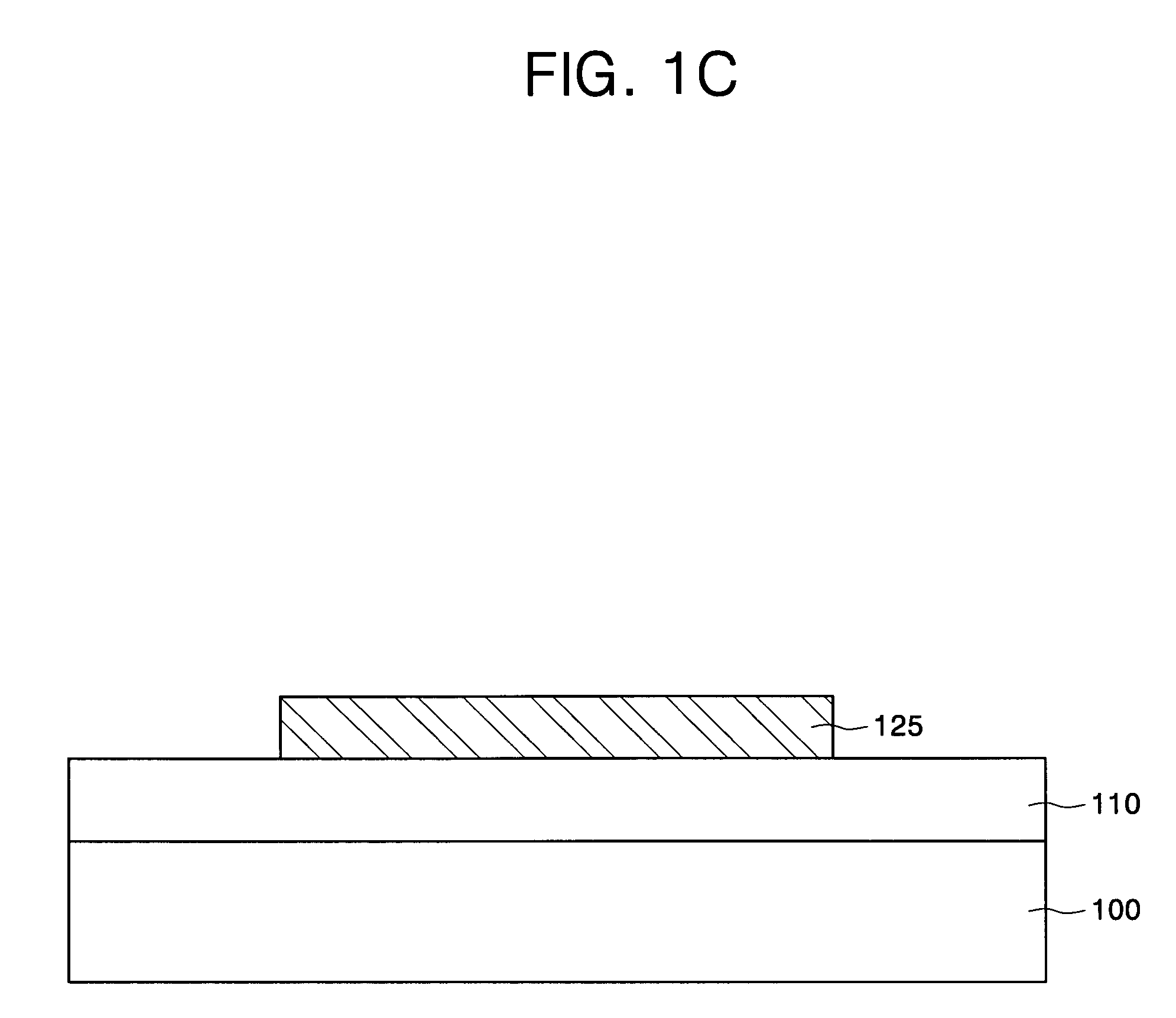

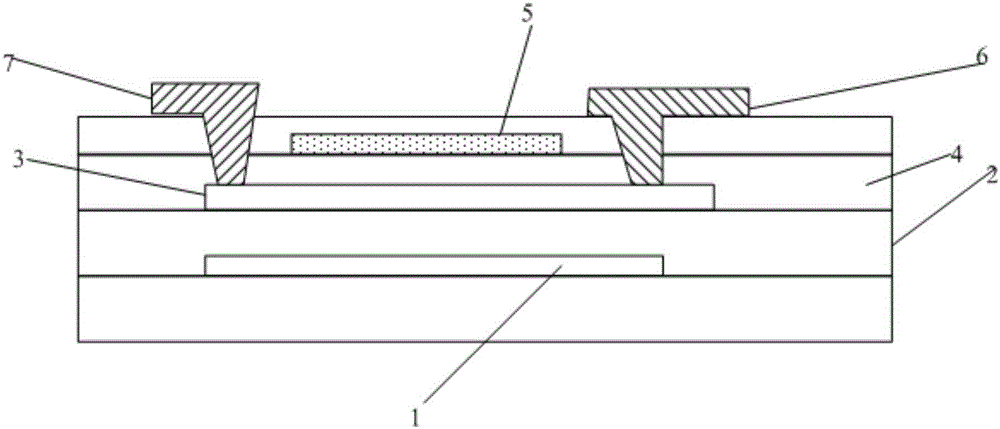

Thin film transistor using a metal induced crystallization process and method for fabricating the same and active matrix flat panel display using the thin film transistor

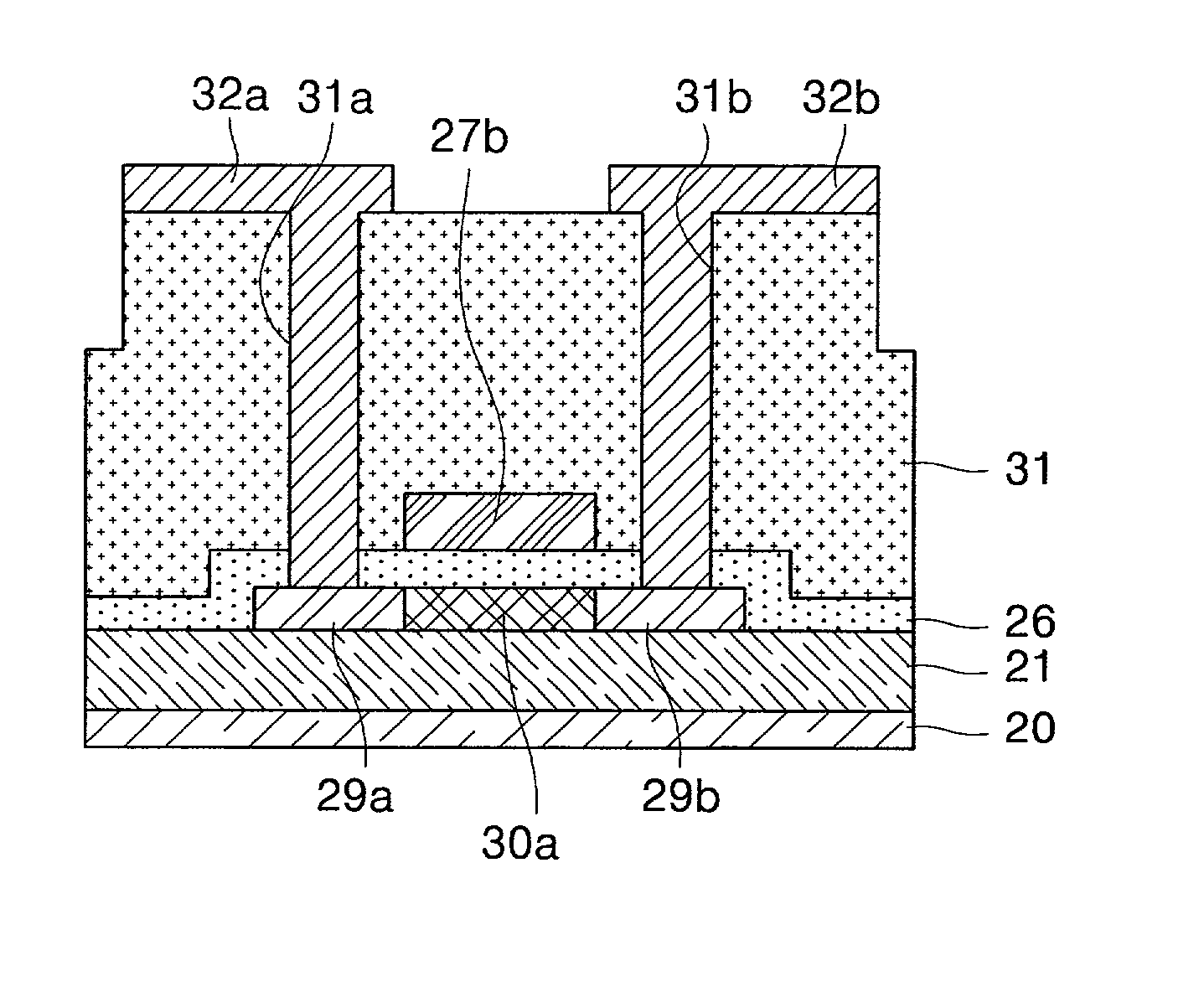

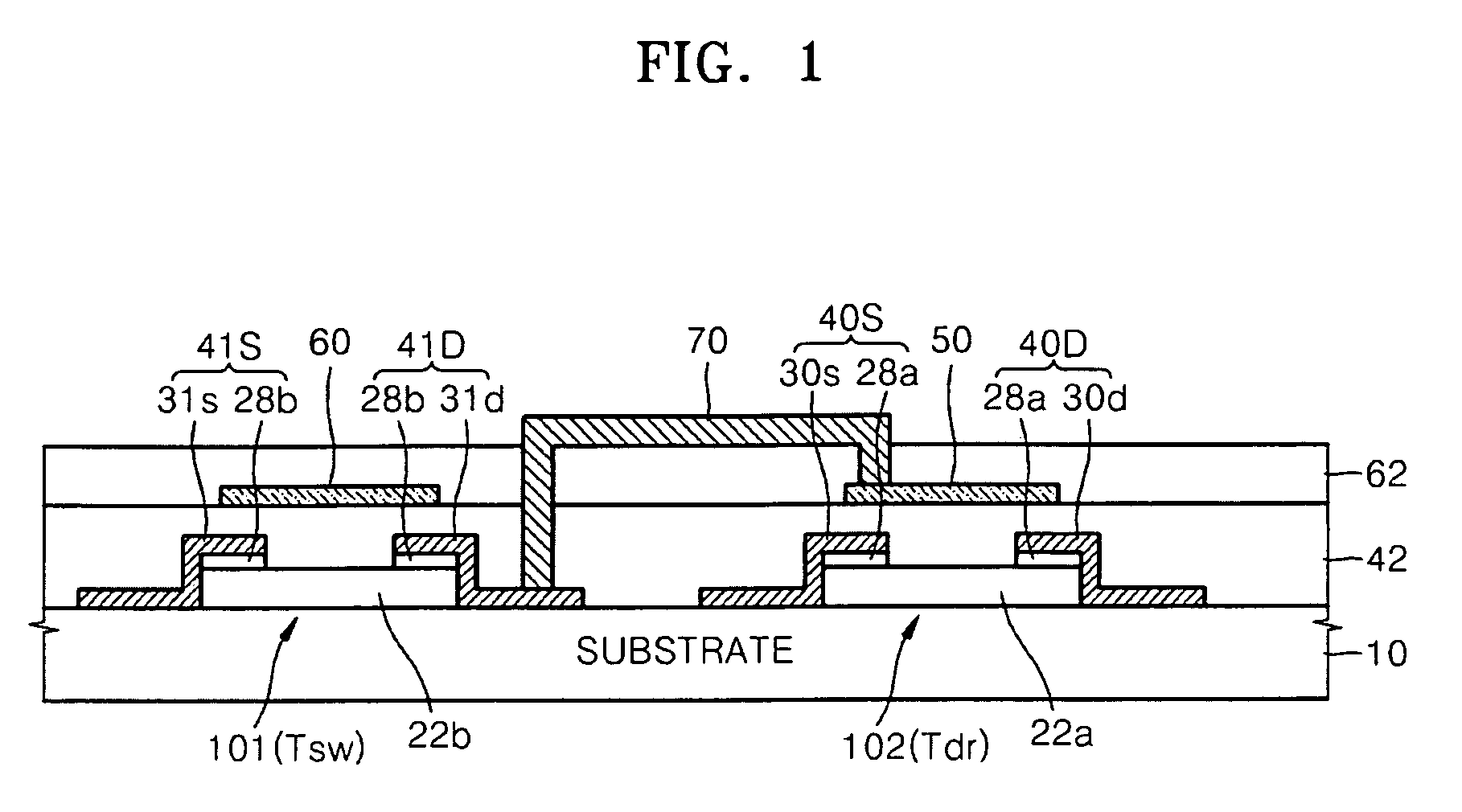

Provided is a thin film transistor that may be manufactured using Metal Induced Crystallization (MIC) and method for fabricating the same. Also provided is an active matrix flat panel display using the thin film transistor, which may be created by forming a crystallization inducing metal layer below a buffer layer and diffusing the crystallization inducing metal layer. The thin film transistor may include a crystallization inducing metal layer formed on an insulating substrate, a buffer layer formed on the crystallization inducing metal layer, and an active layer formed on the buffer layer and including source / drain regions, and including polycrystalline silicon crystallized by the MIC process.

Owner:SAMSUNG DISPLAY CO LTD

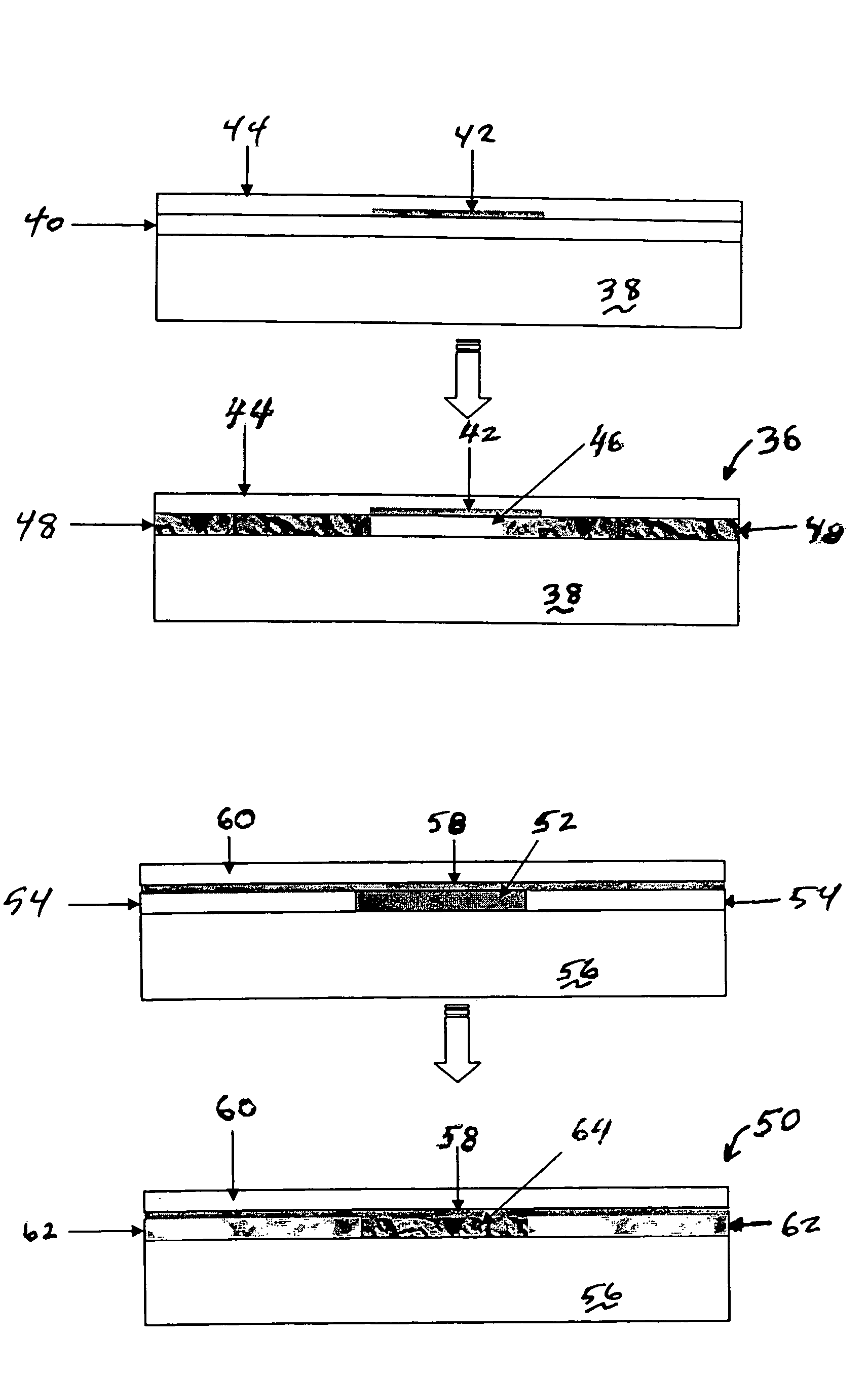

Fabrication method for crystalline semiconductor films on foreign substrates

InactiveUS20060252235A1Minimal timeShorten mining timeFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsMetallurgy

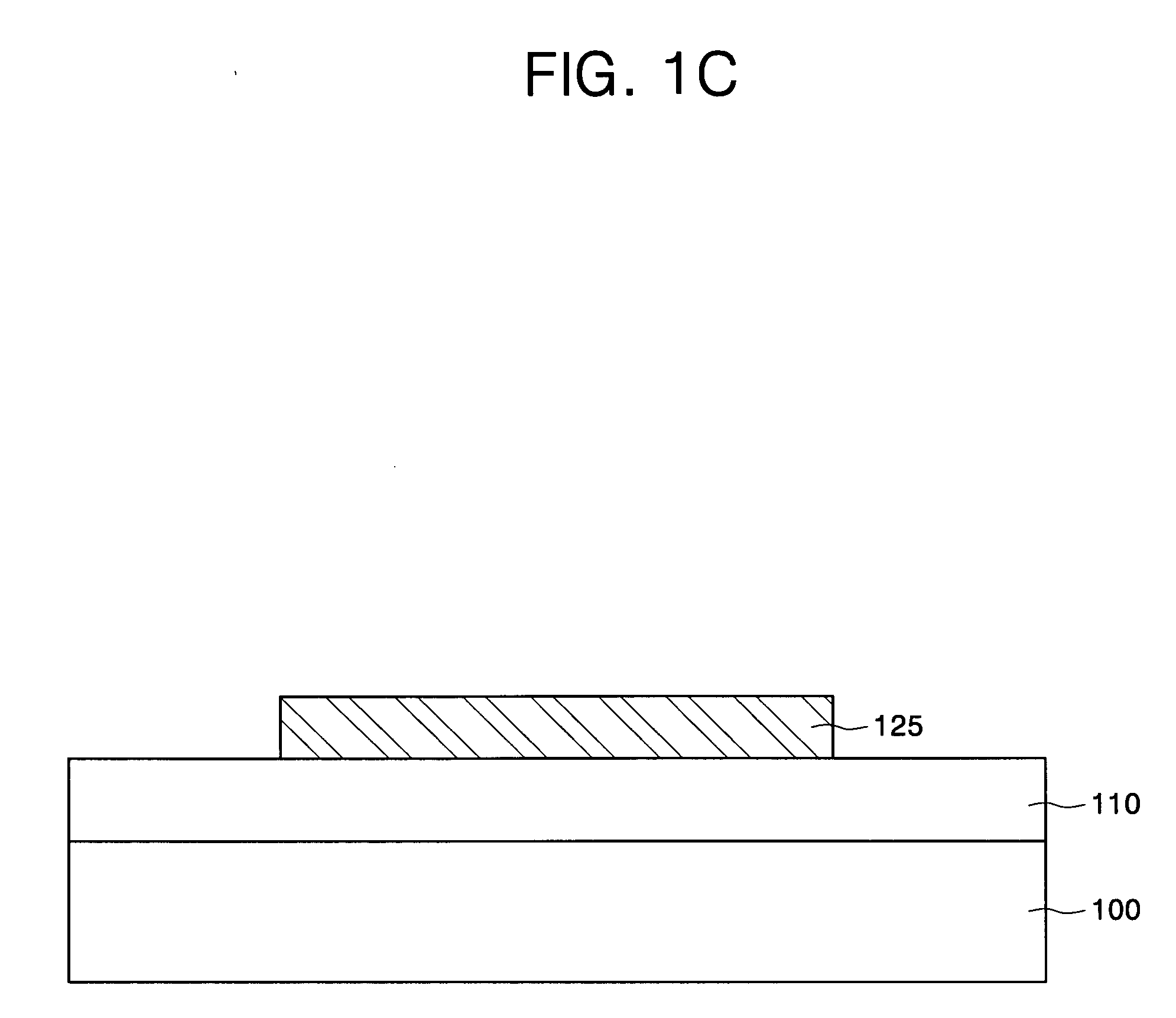

The invention provides a method of forming a polycrystalline semiconductor film on a supporting substrate of foreign material. The method involves depositing a metal film onto the substrate, forming a film of metal oxide and / or hydroxide on a substrate of the metal, and forming a layer of an amorphous semiconductor material over a surface of the metal oxide and / or hydroxide film. The entire sample is then heated to a temperature at which the semiconductor layer is absorbed into the metal layer and deposited as a polycrystalline layer onto the target surface by metal-induced crystallization. The metal is left as an overlayer covering the deposited polycrystalline layer, with semiconductor inclusions in the metal layer. The polycrystalline semiconductor film and the overlayer are generated by porous interfacial metal oxide nd / or hydroxide film. The metal in the overlayer and the interfacial metal oxide and / or hydroxide film are then removed with an etch which underetches the semiconductor inclusions to form freestanding islands. Finally, the freestanding semiconductor “islands” are removed from the surface of the polycrystalline semiconductor layer by a lift-off process.

Owner:NEWSOUTH INNOVATIONS PTY LTD

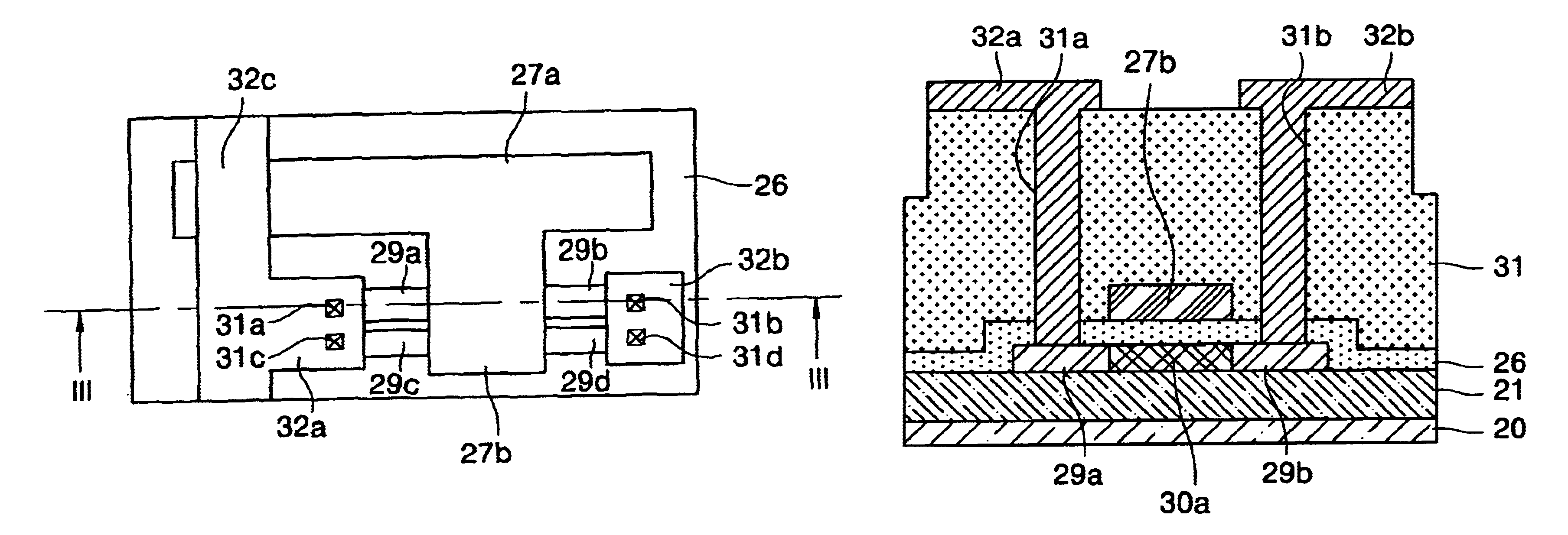

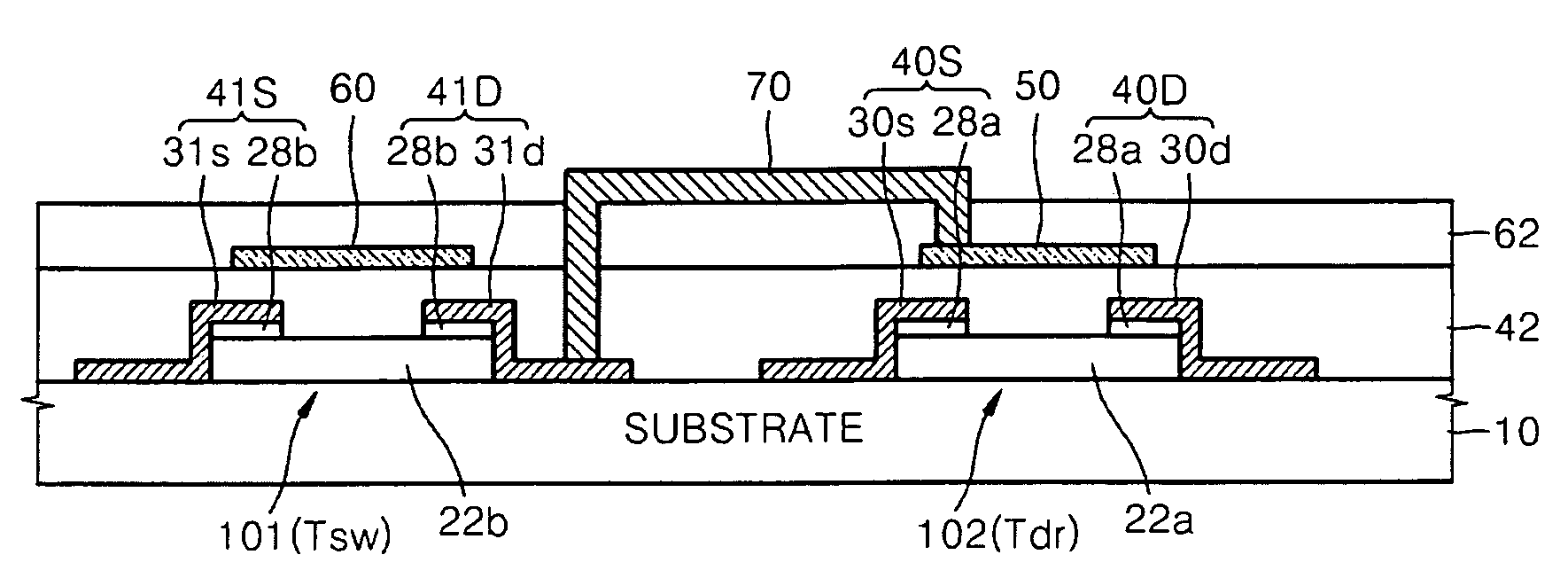

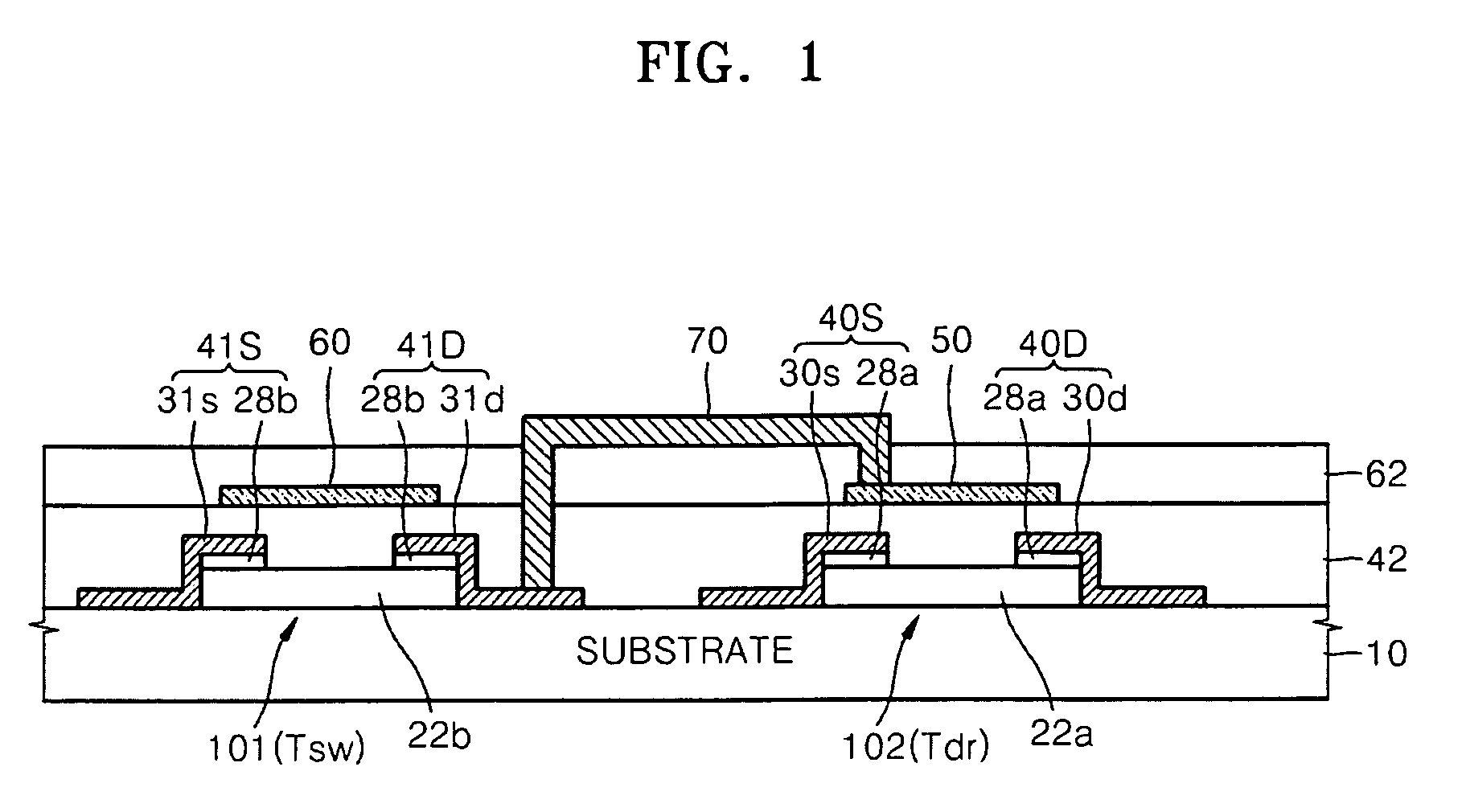

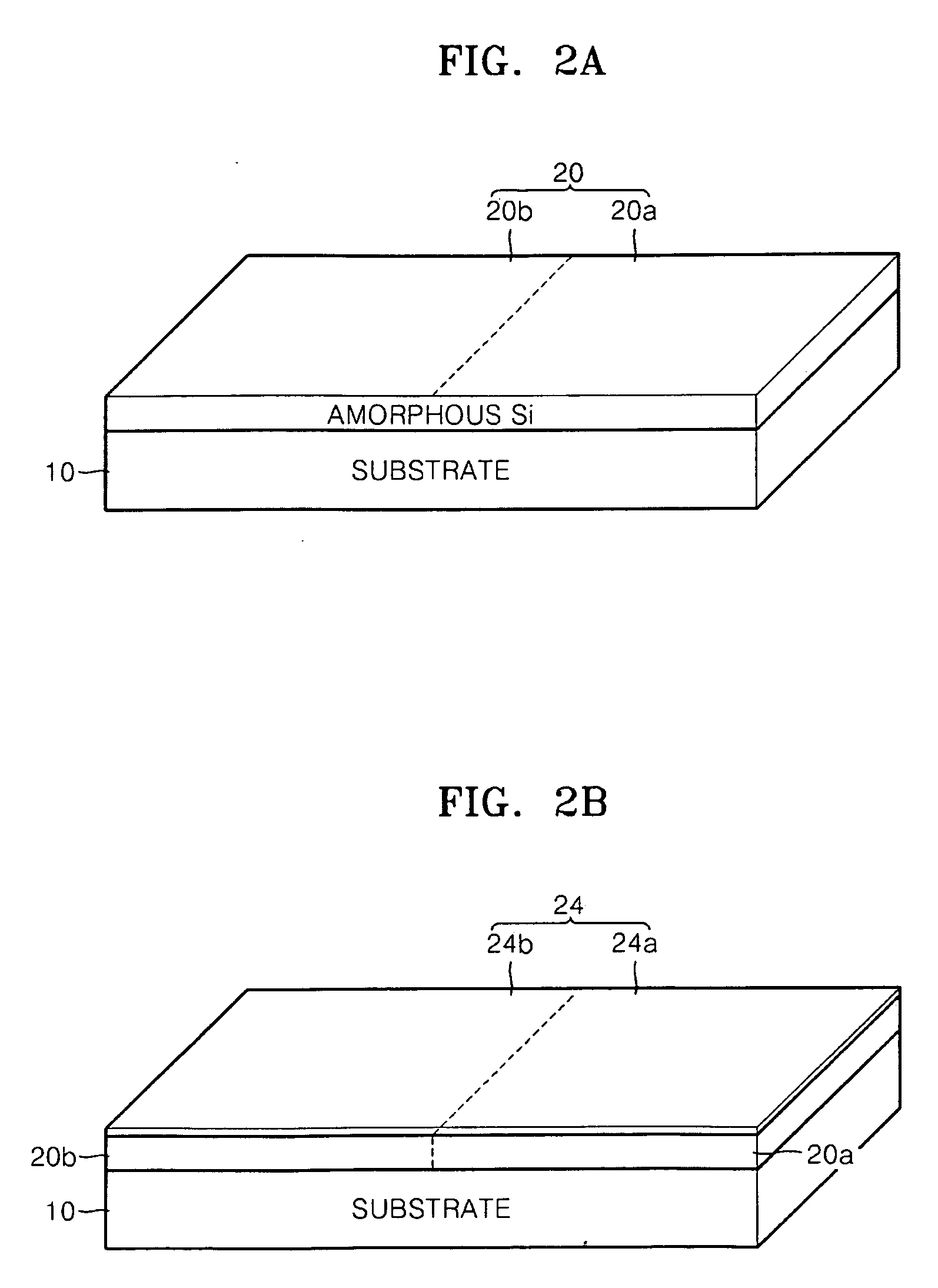

Thin film transistor and method of manufacturing the same

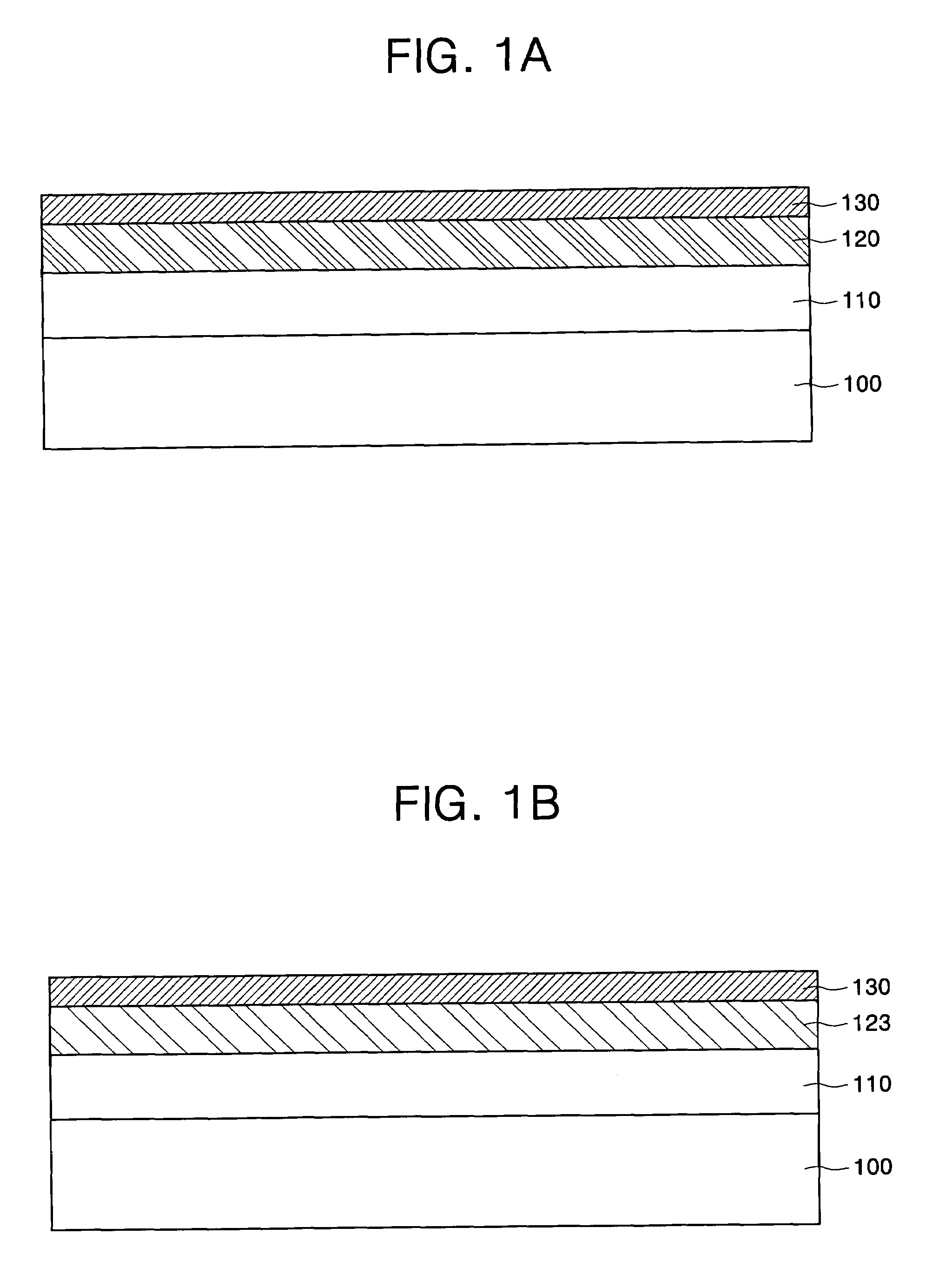

InactiveUS20020146869A1Improve mobilityImprove productivityTransistorSolid-state devicesElectrical conductorMetal-induced crystallization

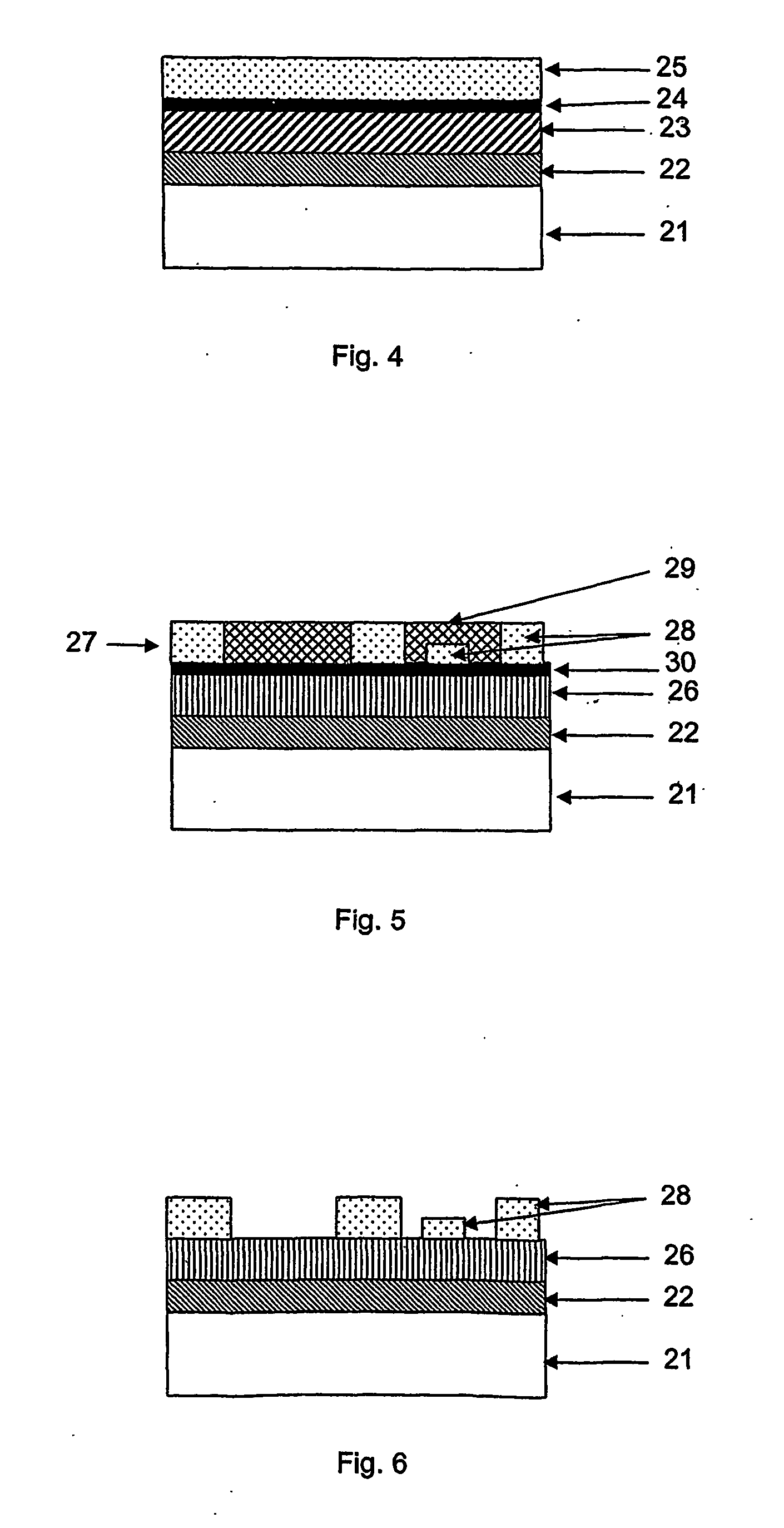

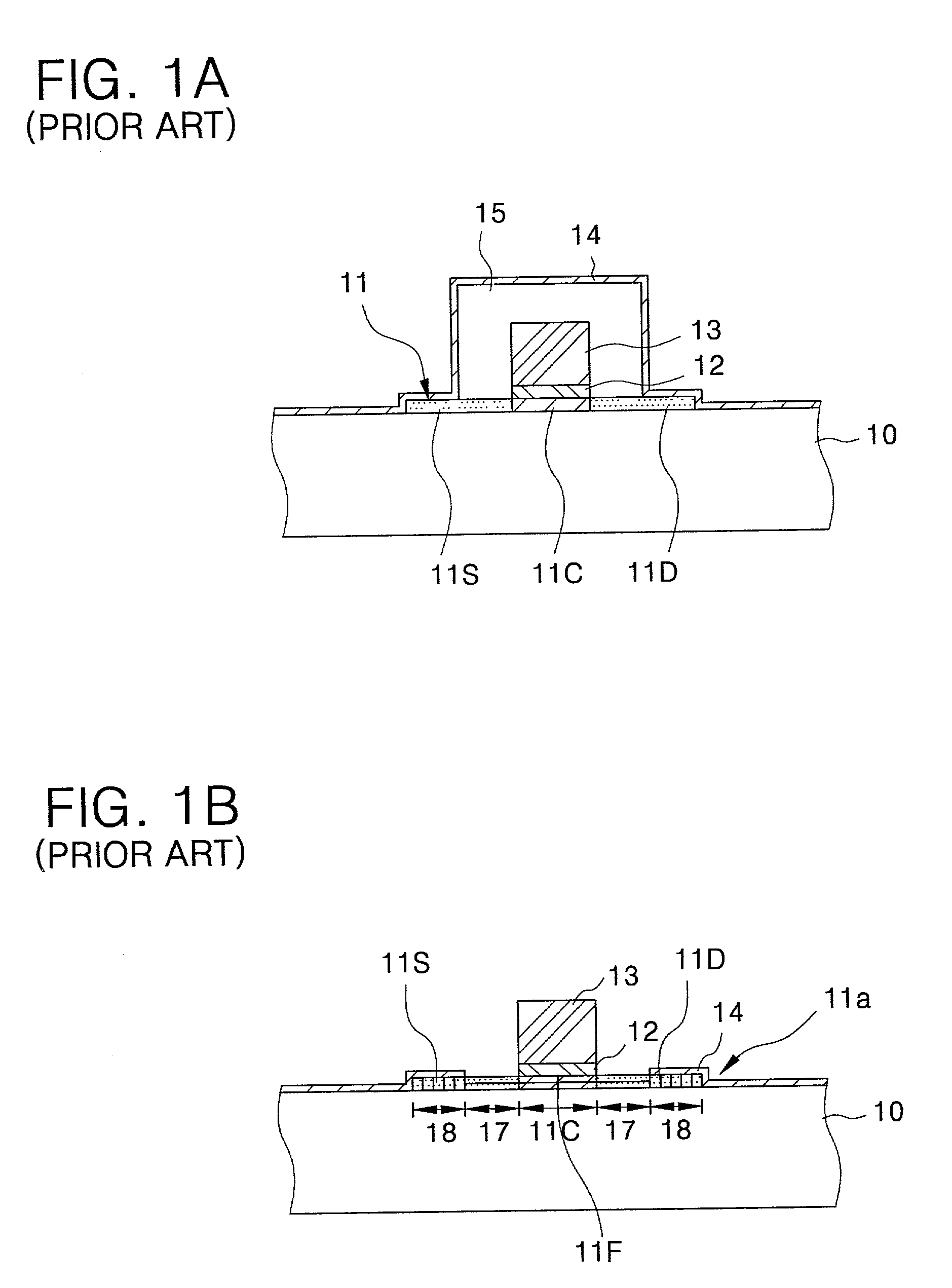

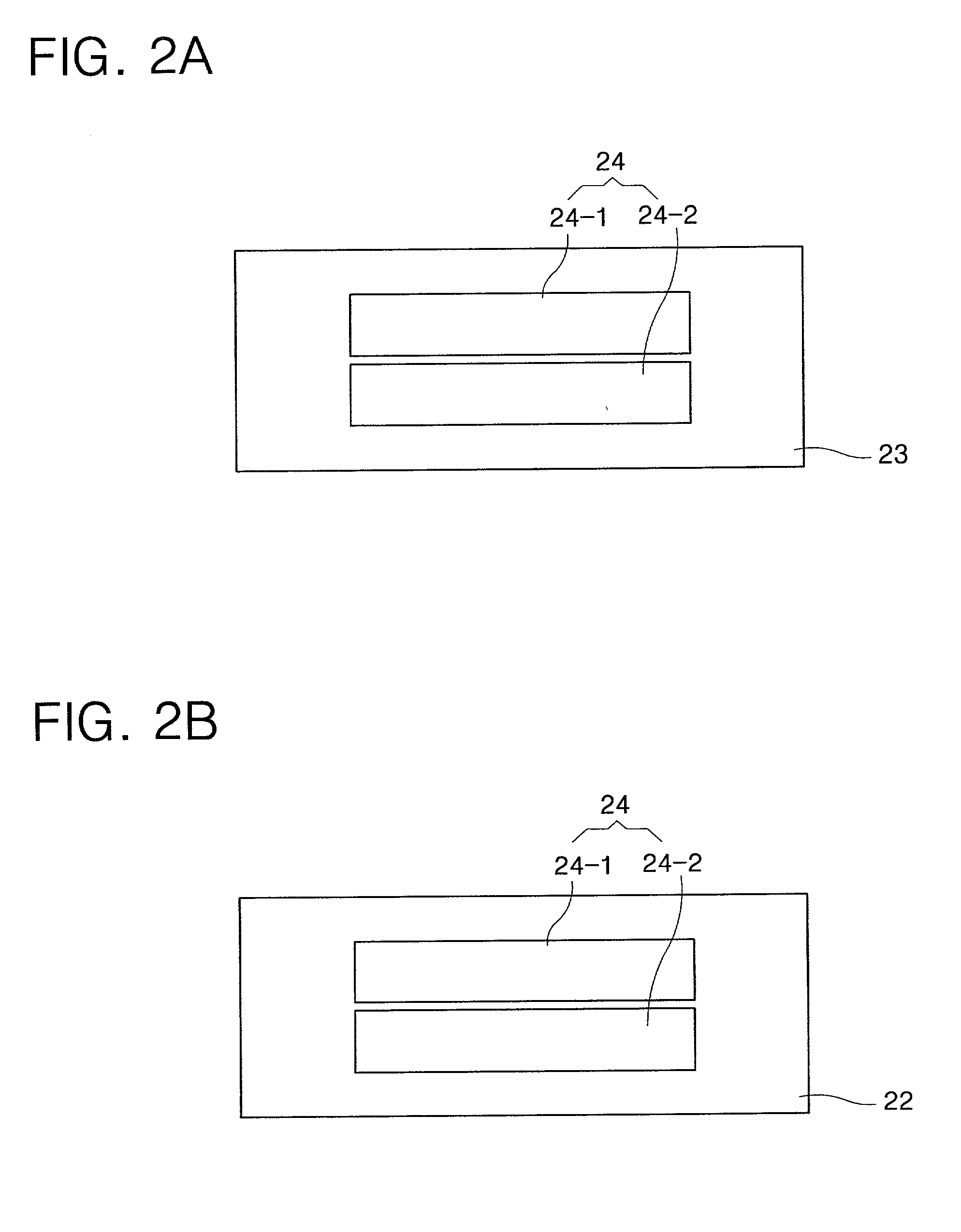

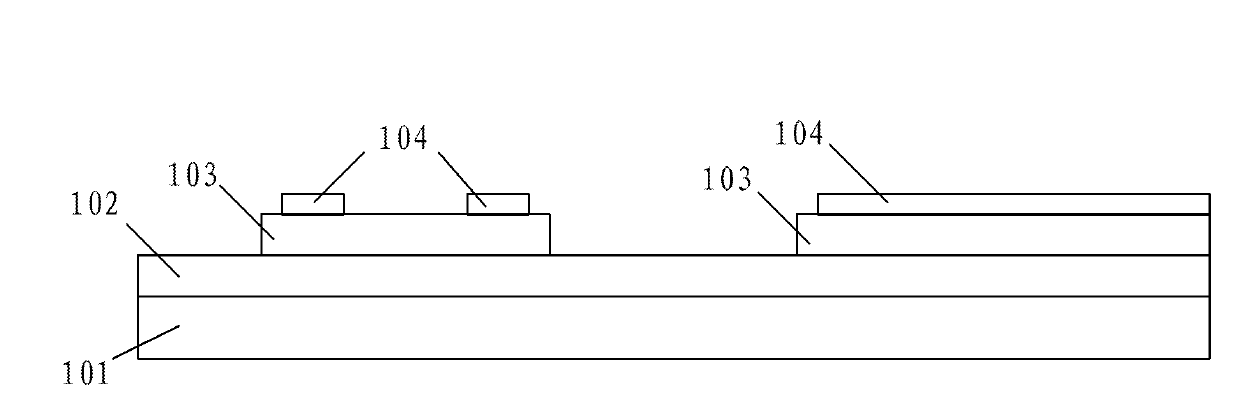

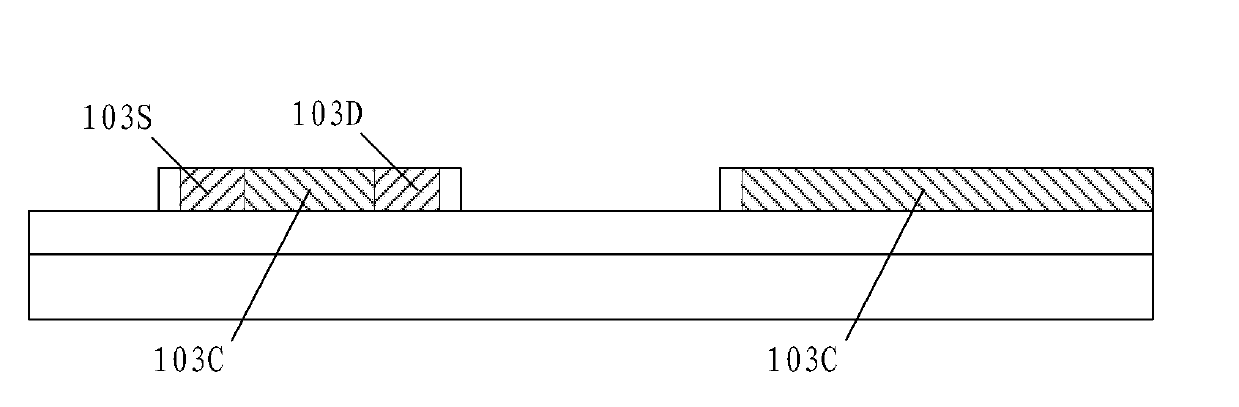

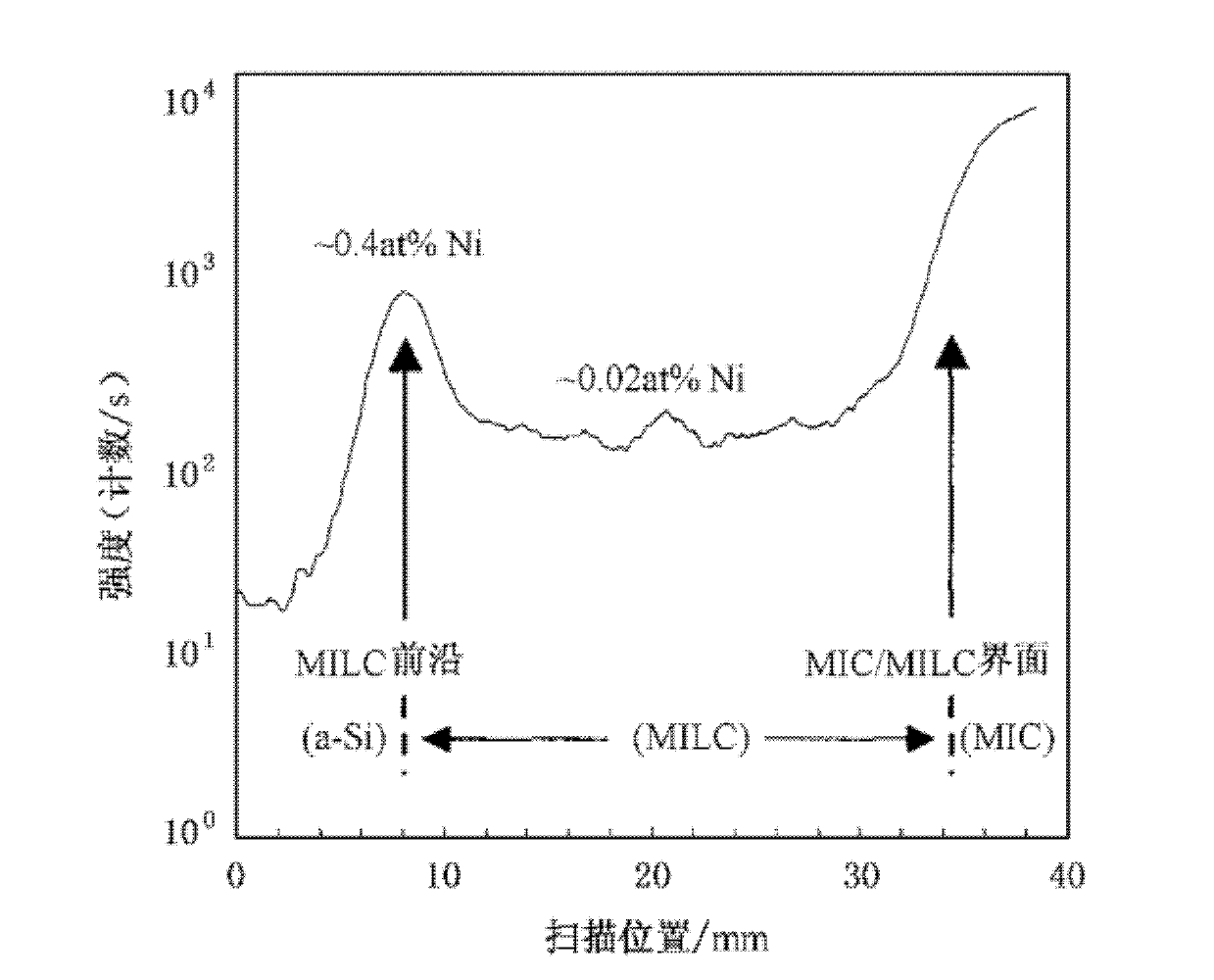

A method of manufacturing a thin film transistor that provides high electric field mobility is disclosed. The method comprising: a) forming an amorphous silicon layer and a blocking layer on an insulating substrate; b) forming a photoresist layer having first and second photoresist patterns on the blocking layer, the first and second photoresist patterns spaced apart from each other; c) etching the blocking layer using the first photoresist pattern as a mask to form first and second blocking patterns; d) reflowing the photoresist layer, so that the first and second photoresist patterns abut on each other to entirely cover the first and second blocking patterns; e) forming a metal layer over the entire surface of the insulating substrate; f) removing the photoresist layer to expose the blocking layer and an offset region between the blocking layer and the metal layer; g) crystallizing the amorphous silicon layer to form a poly silicon layer, wherein a portion of the amorphous silicon layer directly contacting the first metal layer is crystallized through a metal induced crystallization (MIC), and the remaining portion of the amorphous silicon layer is crystallized through a metal induced lateral crystallization (MILC), so that a MILC front exists on a portion of the poly silicon layer between the first and second blocking patterns; h) etching the poly silicon layer using the first and second blocking patterns as a mask to form first and second semiconductor layers and to remove the MILC front; and i) removing the first and second blocking patterns.

Owner:SAMSUNG DISPLAY CO LTD

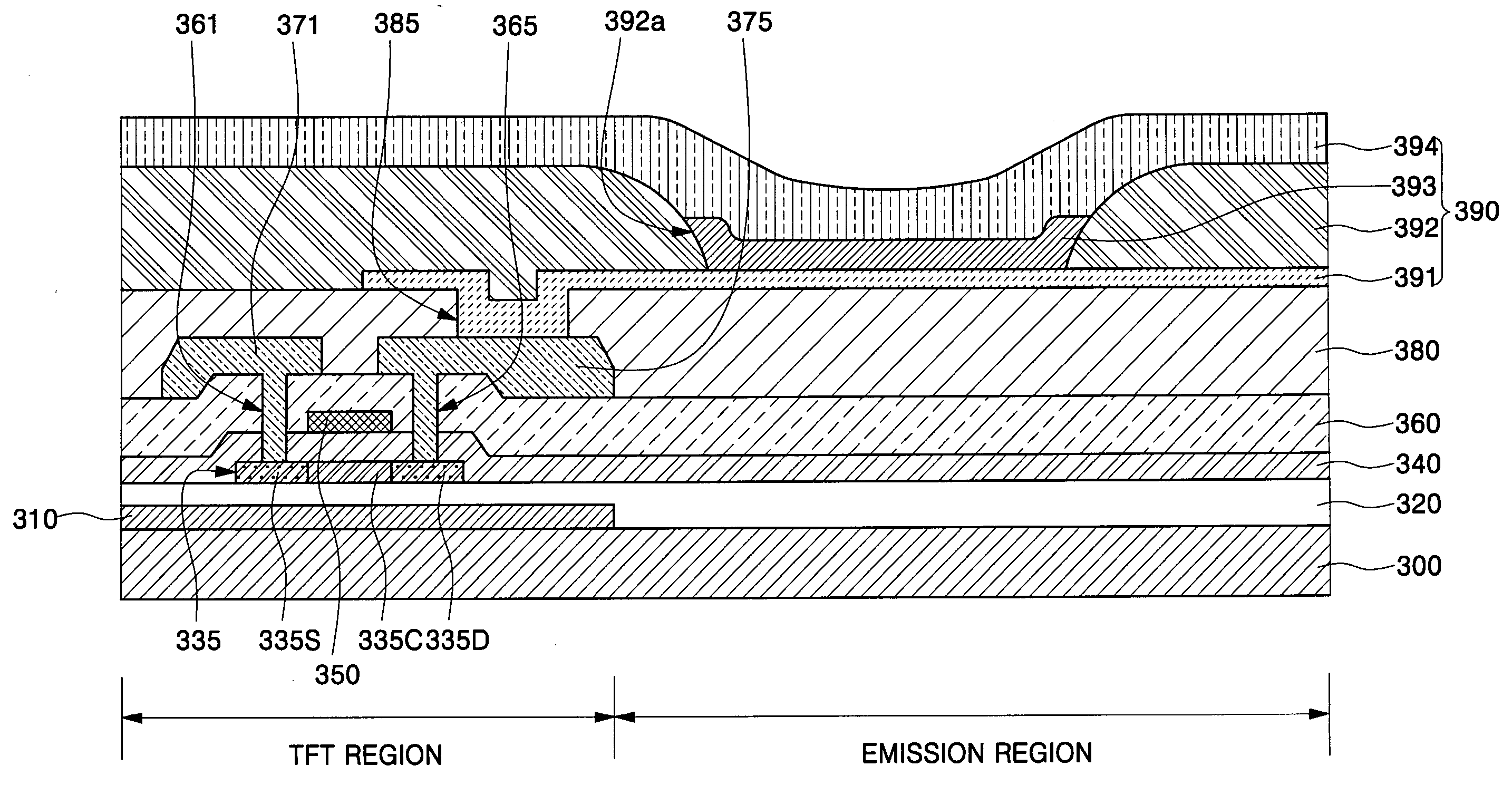

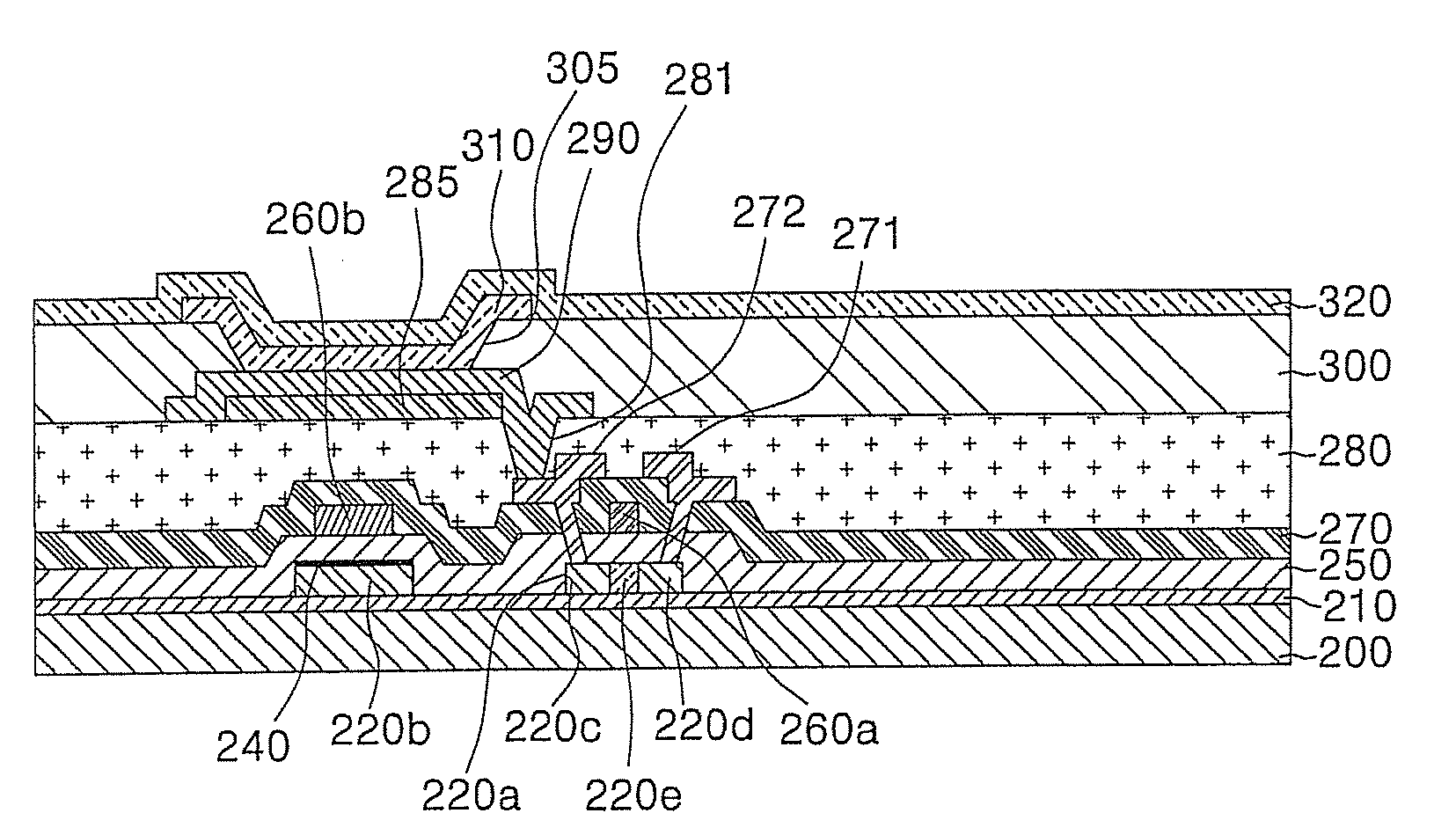

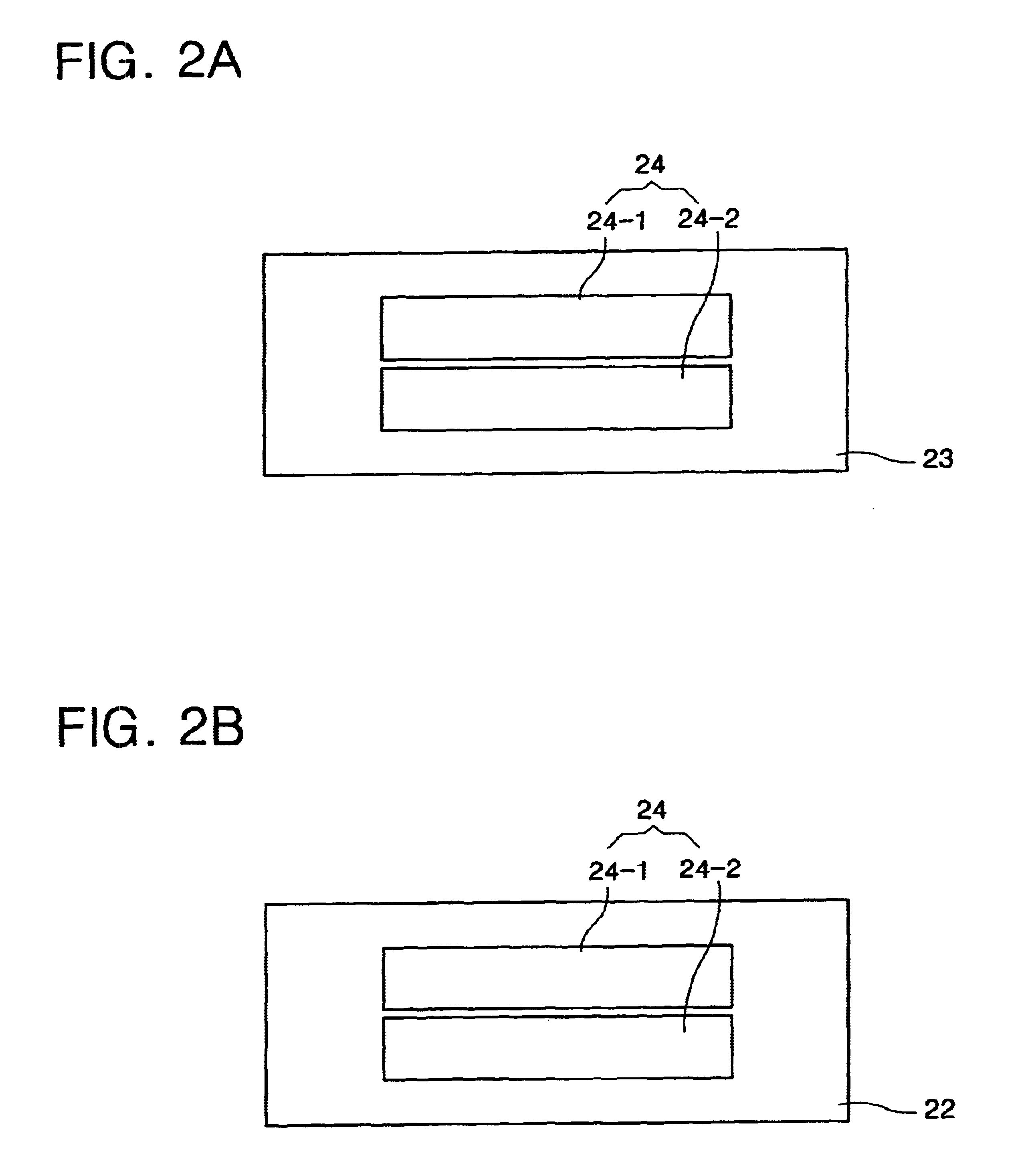

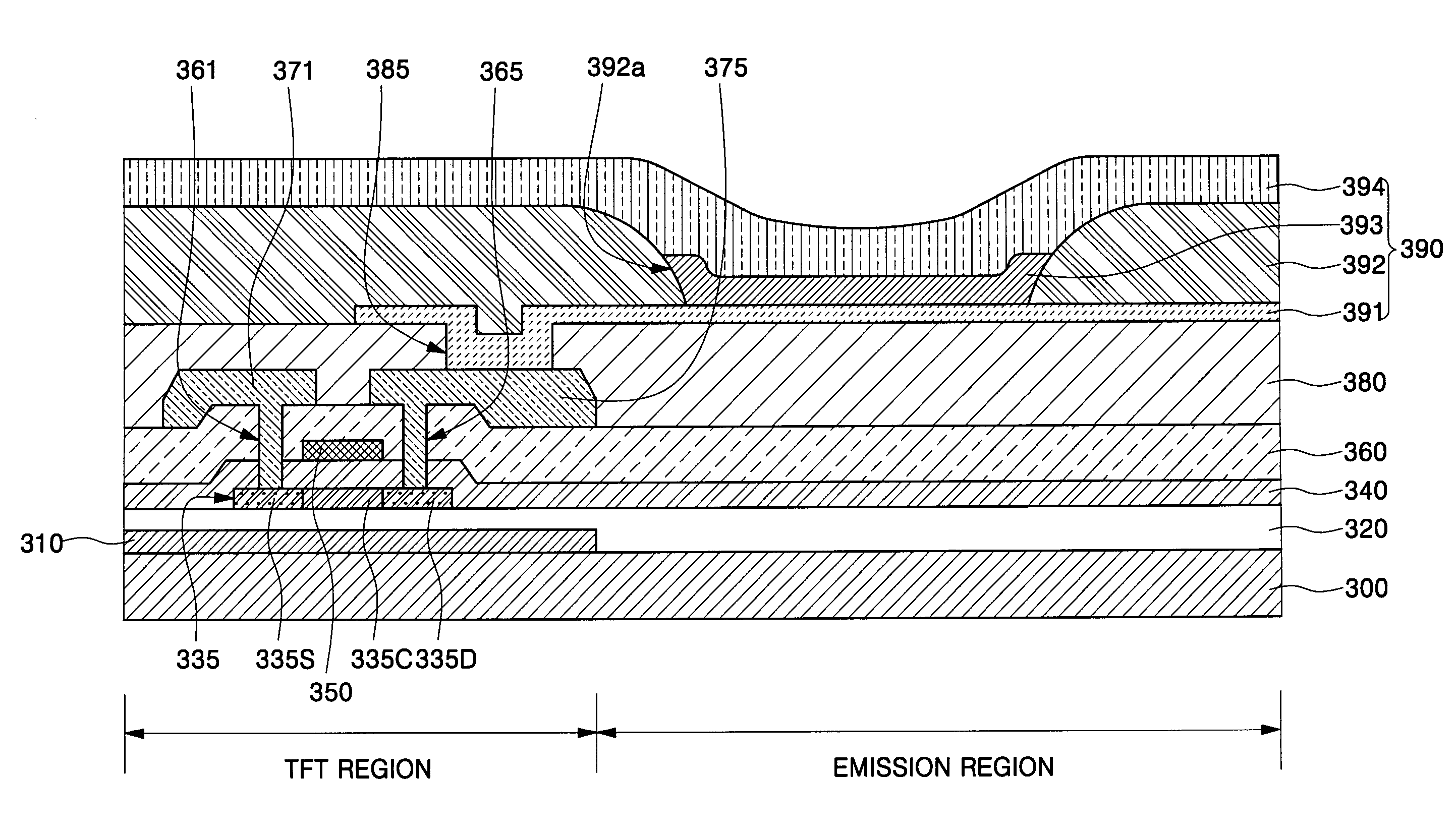

Organic light emitting diode display device and method of manufacturing the same

An organic light emitting diode display device (OLED display device) having uniform electrical characteristics and a method of manufacturing the same. The OLED display device includes: a substrate; a semiconductor layer disposed on the substrate, and including source and drain regions and a channel region formed using metal induced lateral crystallization (MILC); a gate insulating layer for electrically insulating the semiconductor layer; a gate electrode disposed on the gate insulating layer; an interlayer insulating layer for electrically insulating the gate electrode; a thin film transistor (TFT) including source and drain electrodes that are electrically connected to the source and drain regions of the semiconductor layer; a first electrode for a capacitor disposed on a region of the substrate to be spaced apart from the TFT and formed using a metal induced crystallization (MIC); the gate insulating layer for electrically insulating the first capacitor electrode; a second electrode for the capacitor disposed on the gate insulating layer; a planarization layer disposed on the TFT and the capacitor; a first electrode disposed on the planarization layer; a pixel defining layer disposed on the first electrode; an organic layer disposed on the first electrode and the pixel defining layer, and including at least an emission layer; and a second electrode disposed on the organic layer.

Owner:SAMSUNG DISPLAY CO LTD

Thin film transistor and method of manufacturing the same

InactiveUS6706573B2Improve mobilityImprove productivityTransistorSolid-state devicesElectrical conductorMetal-induced crystallization

A method of manufacturing a thin film transistor that provides high electric field mobility is disclosed. The method comprising: a) forming an amorphous silicon layer and a blocking layer on an insulating substrate; b) forming a photoresist layer having first and second photoresist patterns on the blocking layer, the first and second photoresist patterns spaced apart from each other; c) etching the blocking layer using the first photoresist pattern as a mask to form first and second blocking patterns; d) reflowing the photoresist layer, so that the first and second photoresist patterns abut on each other to entirely cover the first and second blocking patterns; e) forming a metal layer over the entire surface of the insulating substrate; f) removing the photoresist layer to expose the blocking layer and an offset region between the blocking layer and the metal layer; g) crystallizing the amorphous silicon layer to form a poly silicon layer, wherein a portion of the amorphous silicon layer directly contacting the first metal layer is crystallized through a metal induced crystallization (MIC), and the remaining portion of the amorphous silicon layer is crystallized through a metal induced lateral crystallization (MILC), so that a MILC front exists on a portion of the poly silicon layer between the first and second blocking patterns; h) etching the poly silicon layer using the first and second blocking patterns as a mask to form first and second semiconductor layers and to remove the MILC front; and i) removing the first and second blocking patterns.

Owner:SAMSUNG DISPLAY CO LTD

Method for manufacturing a crystalline silicon layer

InactiveUS20080268622A1Final product manufactureSemiconductor/solid-state device manufacturingMetal-induced crystallizationCrystalline silicon

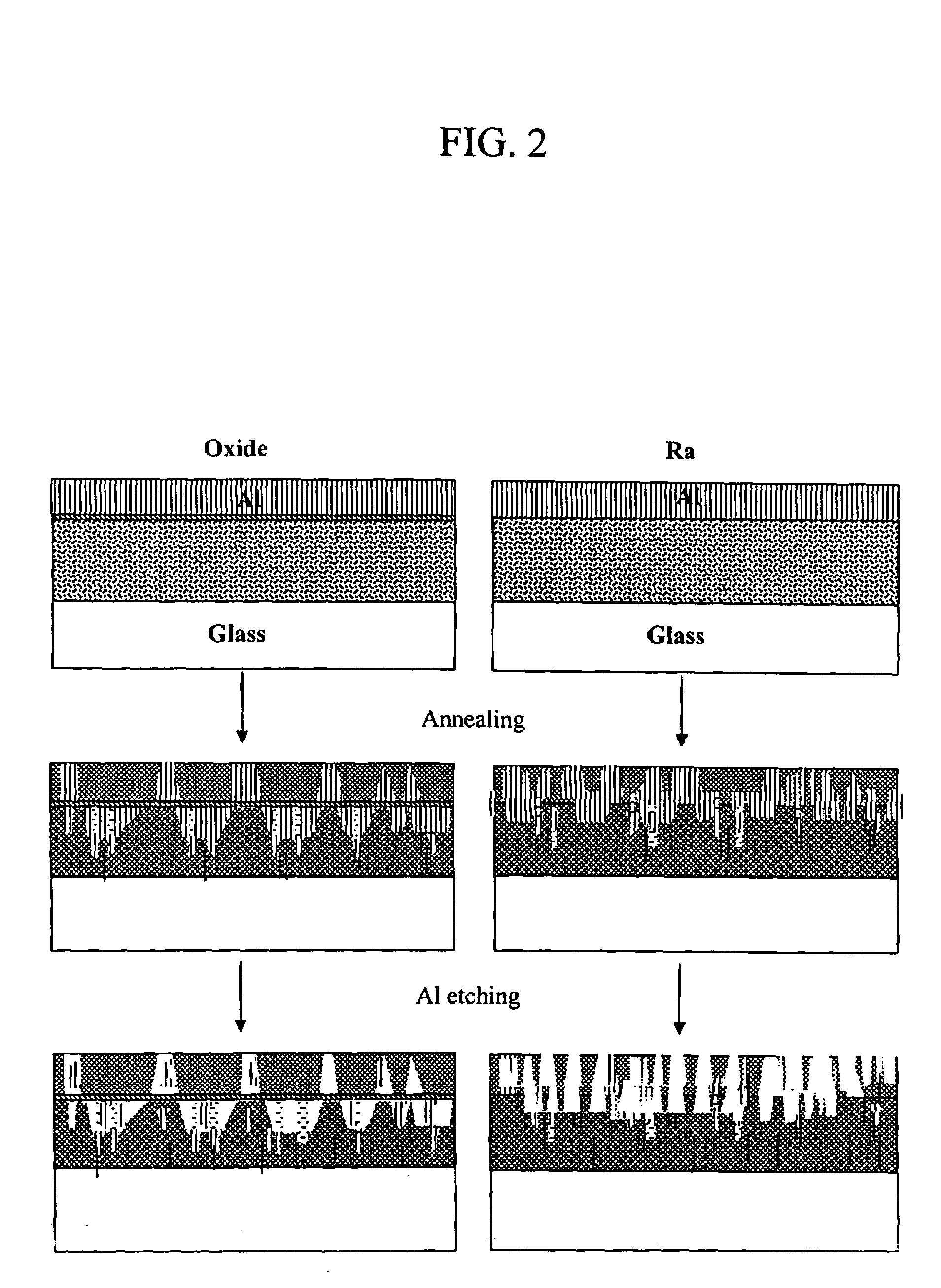

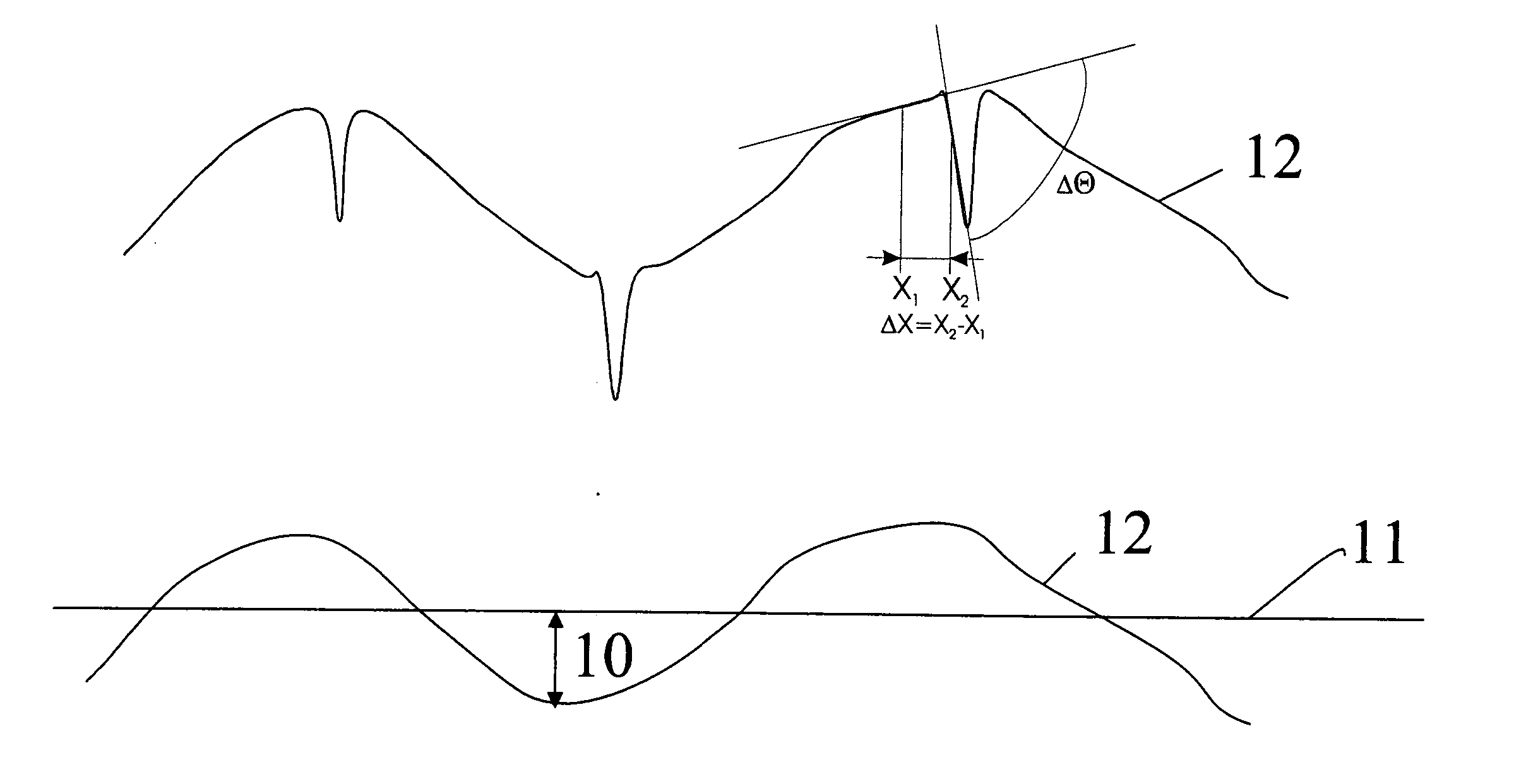

A method of forming a crystalline silicon layer on a microrough face of a substrate by reducing the microroughness of the face and then performing a metal induced crystallization process on the face is disclosed. The method further comprises, after metal induced crystallization and before removing the metal layer, removing silicon islands using the metal layer as a mask.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

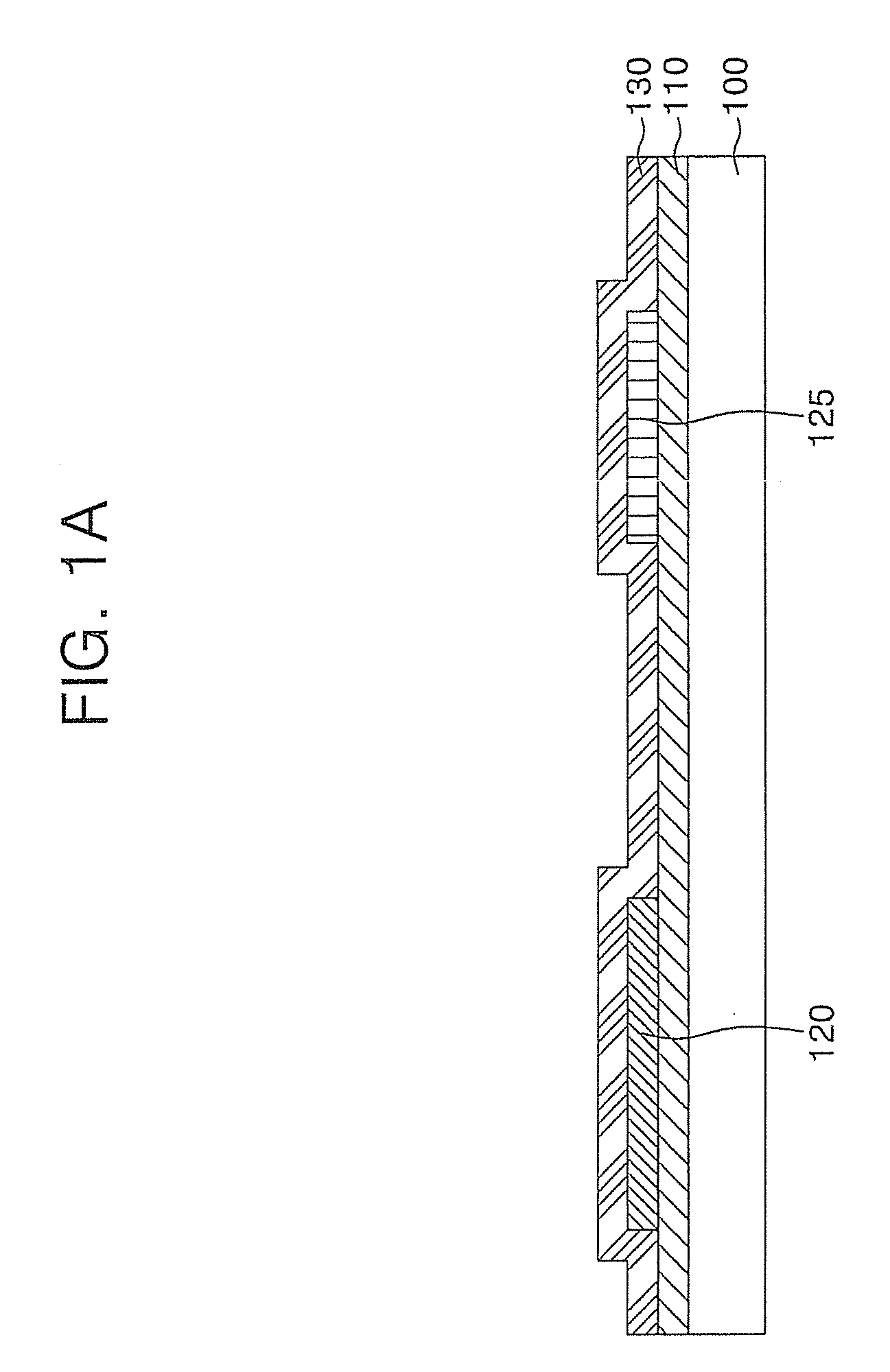

Method of manufacturing driving-device for unit pixel of organic light emitting display

ActiveUS20080153214A1Simple processSimple preparation processSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologySelf-assembled monolayer

Provided is a method of manufacturing a driving-device for a unit pixel of an organic light emitting display having an improved manufacturing process in which the driving device can be manufactured with a smaller number of processes and in simpler processes. The method includes: forming an amorphous silicon layer including a first amorphous region and a second amorphous region disposed on the same plane of a substrate; forming an SAM (self-assembled monolayer) having a hydrophobic property on the first amorphous region; coating an aqueous solution in which nickel particles are dispersed, on the second amorphous region and the SAM, wherein a larger amount of nickel particles than on the SAM are dispersed on the second amorphous region using a hydrophilicity difference between the second amorphous region and the SAM; vaporizing the SAM through an annealing process and simultaneously performing metal induced crystallization in which the nanoparticles are used as a medium, to crystallize the first and second amorphous regions and to form first and second crystallization regions; patterning the first and second crystallization regions to form first and second channel regions; and forming first and second electrodes on the first and second channel regions.

Owner:SAMSUNG ELECTRONICS CO LTD

Thin film transistor using a metal induced crystallization process and method for fabricating the same and active matrix flat panel display using the thin film transistor

Provided is a thin film transistor that may be manufactured using Metal Induced Crystallization (MIC) and method for fabricating the same. Also provided is an active matrix flat panel display using the thin film transistor, which may be created by forming a crystallization inducing metal layer below a buffer layer and diffusing the crystallization inducing metal layer. The thin film transistor may include a crystallization inducing metal layer formed on an insulating substrate, a buffer layer formed on the crystallization inducing metal layer, and an active layer formed on the buffer layer and including source / drain regions, and including polycrystalline silicon crystallized by the MIC process.

Owner:SAMSUNG DISPLAY CO LTD

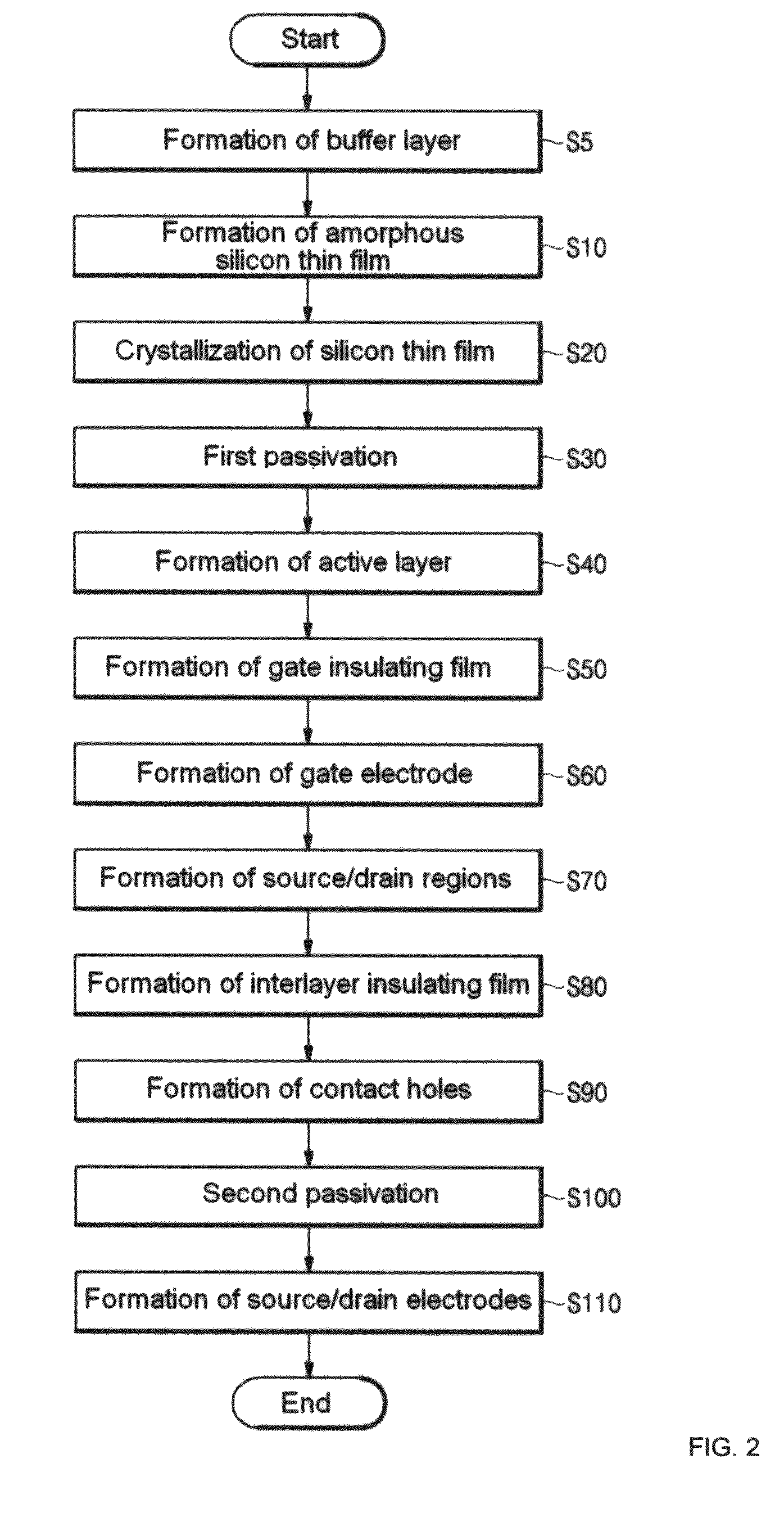

Method for manufacturing thin film transistor

InactiveUS20090170248A1Improve current characteristicsHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingMetal catalystMetal silicide

A method for manufacturing a thin film transistor with improved current characteristics and high electron mobility. According to the method, when an amorphous silicon thin film is crystallized into a polycrystalline silicon thin film by metal-induced crystallization, annealing conditions of the amorphous silicon thin film and the amount of a metal catalyst doped into the amorphous silicon thin film are optimized to reduce the regions of a metal silicide distributed at grain boundaries of the polycrystalline silicon thin film. In addition, oxygen (O2) gas or water (H2O) vapor is supplied to form a passivation film on the surface of the polycrystalline silicon thin film.

Owner:VIATRON TECH INC

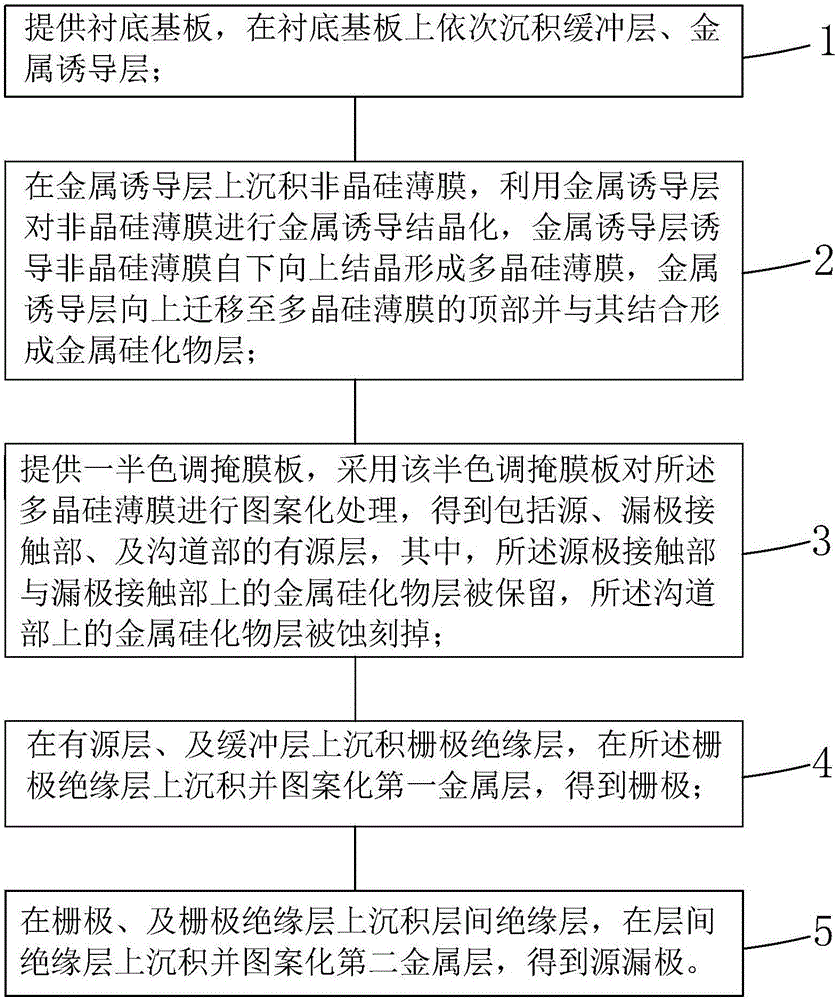

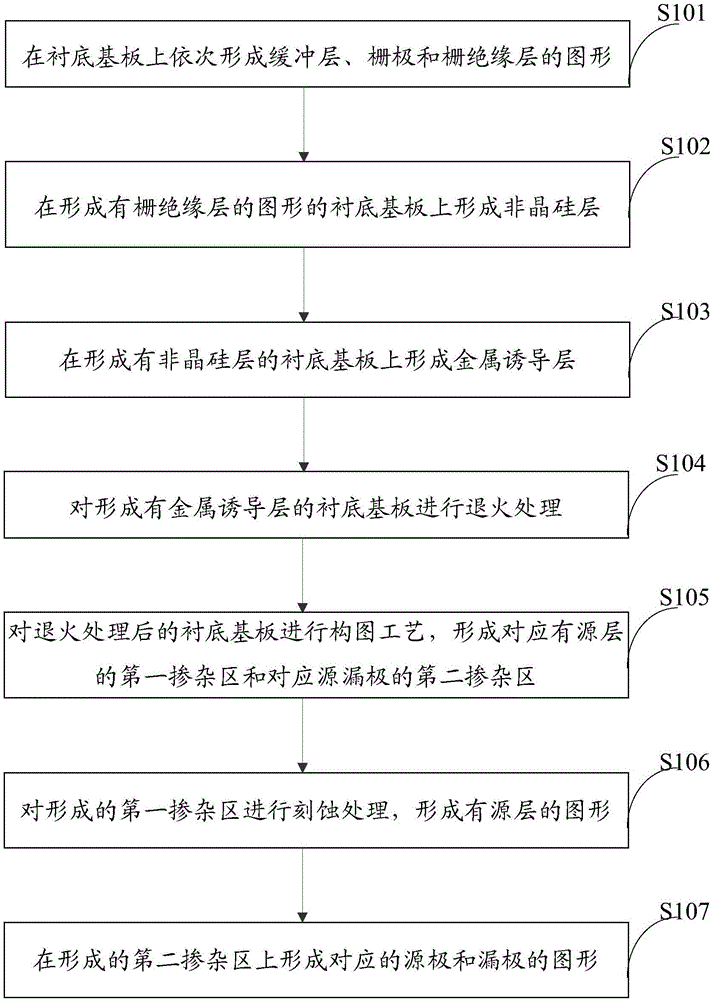

Manufacturing method of LTPS TFT based on metal induced crystallization process

InactiveCN106024639AReduce leakage currentReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesMetal silicideActive layer

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Method for manufacturing a crystalline silicon layer

A method of forming a crystalline silicon layer on a microrough face of a substrate by reducing the microroughness of the face and then performing a metal induced crystallization process on the face is disclosed.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

Thin film transistor and manufacturing method thereof

InactiveCN106601823AGuaranteed electrical performanceExcellent electrical performanceTransistorSolid-state devicesComposition processBottom gate

The invention discloses a thin film transistor and a manufacturing method thereof. Through carrying out annealing treatment on a substrate on which a metal induced layer is formed, metal induced crystallization can be realized for preparing a bottom gate type low-temperature polycrystalline silicon thin film transistor, and a light shield layer adopted in the manufacturing of a top gate type thin film transistor is omitted, thereby saving the manufacturing cost, simplifying the process, and omitting the polycrystalline silicon doping step through metal induced crystallization. In addition, amorphous silicon is converted into the polycrystalline silicon through metal induced crystallization, and the polycrystalline silicon undergoes a composition process to form a first doped region corresponding to an active layer and a second doped region corresponding to a source-drain region, thereby realizing partition of a channel region and the a source-drain region, and ensuring the electrical performance of the thin film transistor. Furthermore, residual metal particles in the channel region due to metal induced crystallization can be removed through etching the first doped region, an off-state current of the device is decreased, the problem of metal particle residual is solved, and the good electrical performance of the device is ensured.

Owner:BOE TECH GRP CO LTD +1

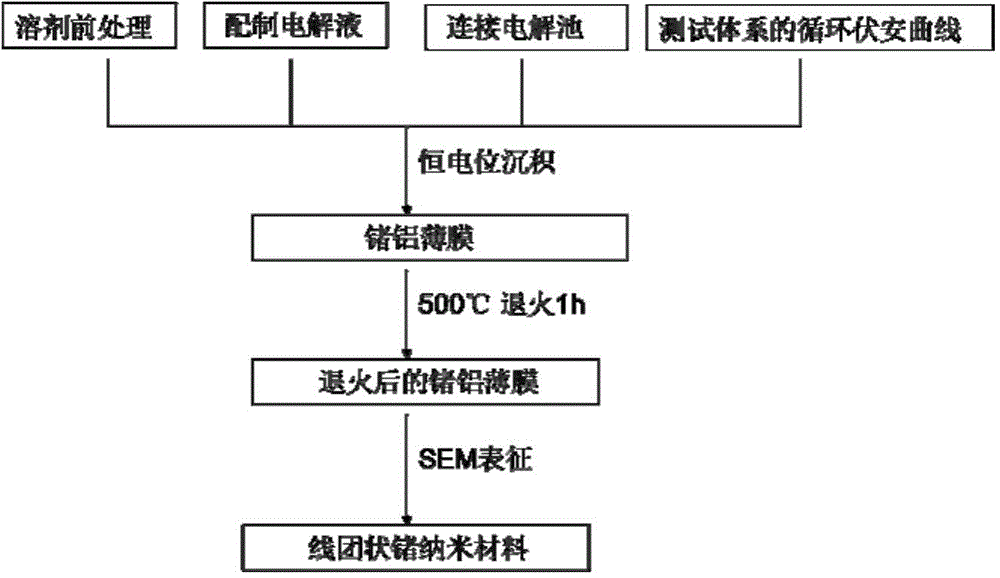

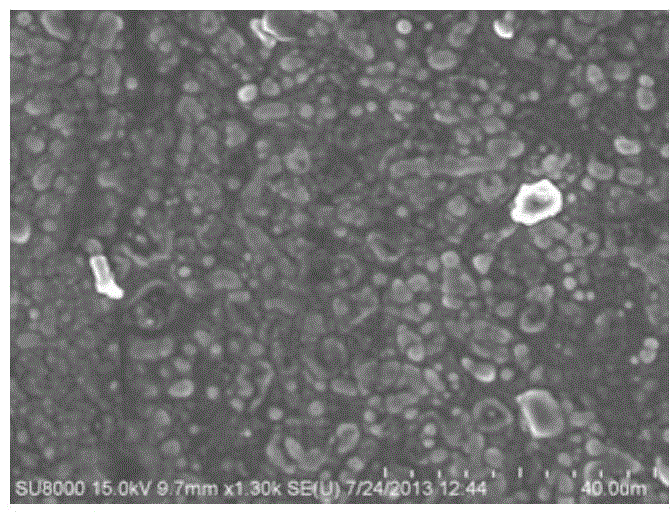

Coiling-type germanium nanomaterial and preparation method thereof

ActiveCN103606683AThe process steps are simpleImproved magnification performanceMaterial nanotechnologyCell electrodesPower batteryElectrical battery

The invention provides a coiling-type germanium nanomaterial and a preparation method thereof. The coiling-type germanium nanomaterial can be used as a negative electrode of a lithium ion battery. According to the preparation method, a metal layer prepared by adopting an ionic liquid electroposition method and a germanium layer are combined, and the coiling-type germanium nanomaterial is prepared by combining with a metal induced crystallization theory. The coiling-type germanium nanomaterial provided by the invention can be used as the negative electrode of the lithium ion battery, so that volume expansion of the germanium-based material can be effectively slowed down; the coiling-type germanium nanomaterial can be used for preparing the lithium ion power battery with high capacity, large multiplying power and long service life.

Owner:HARBIN INST OF TECH

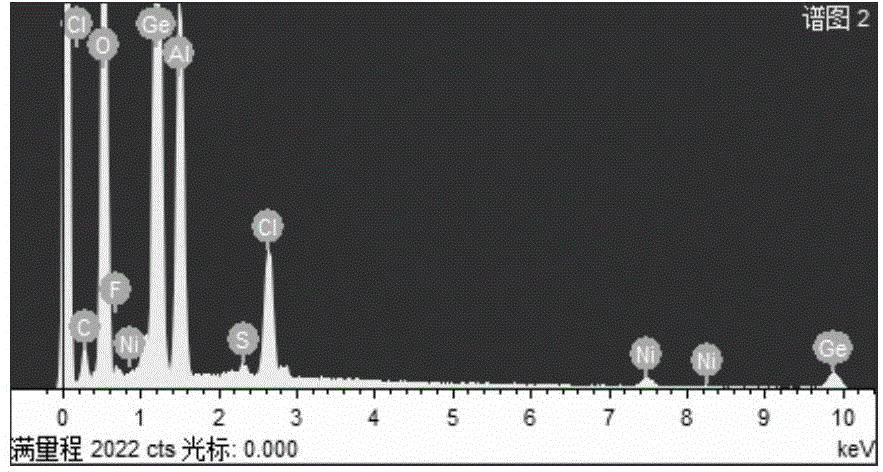

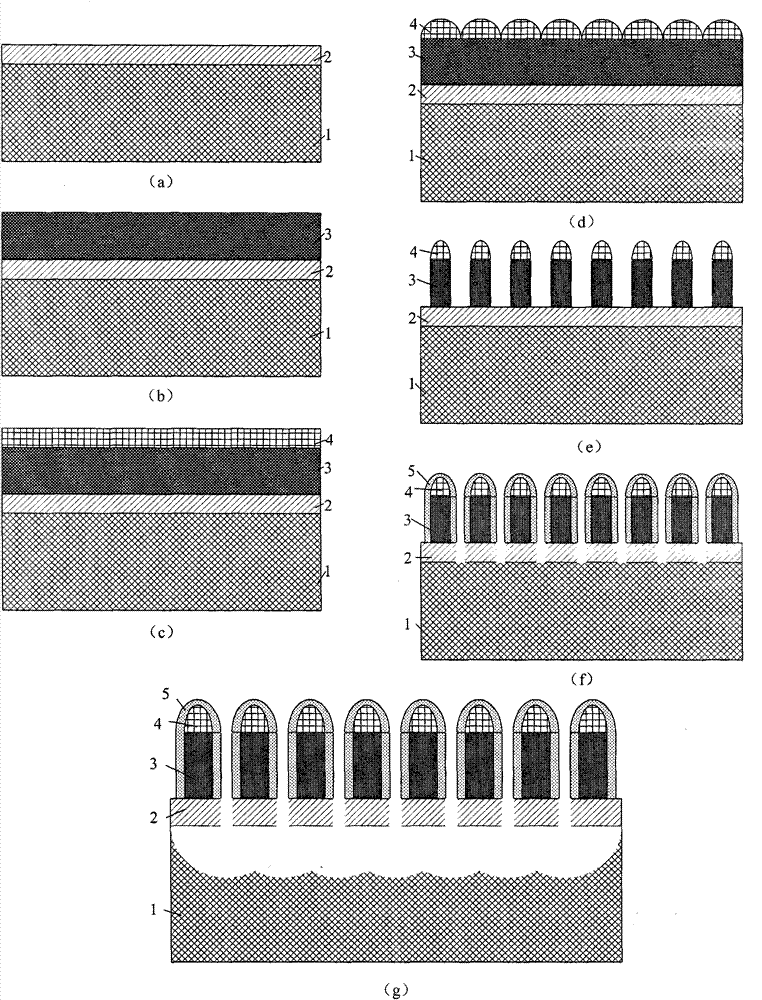

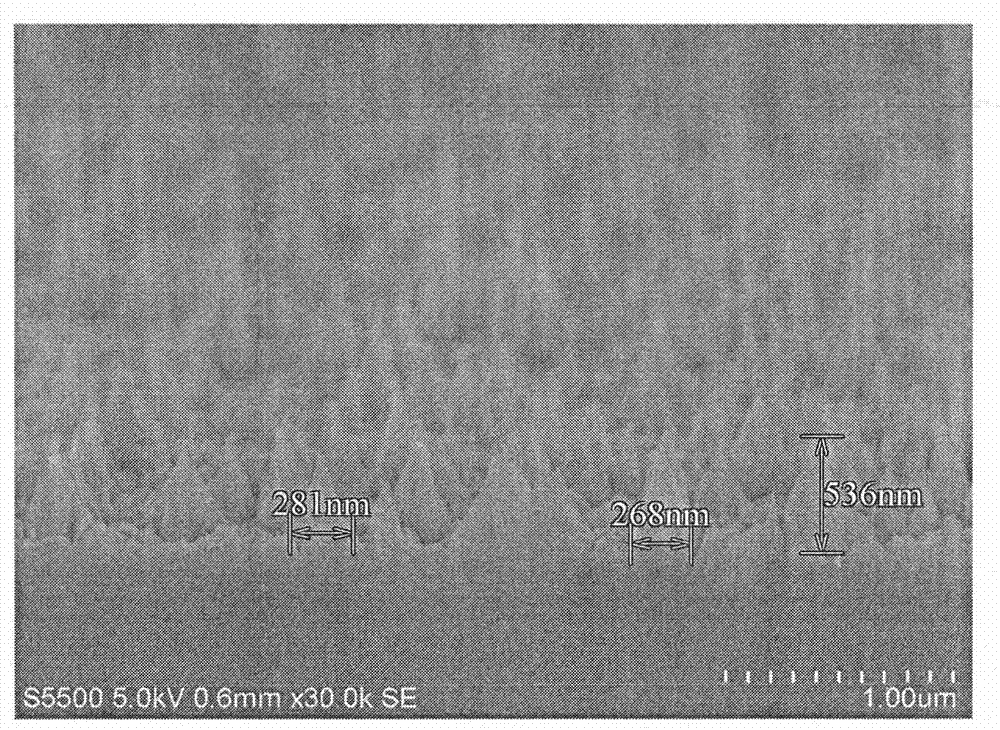

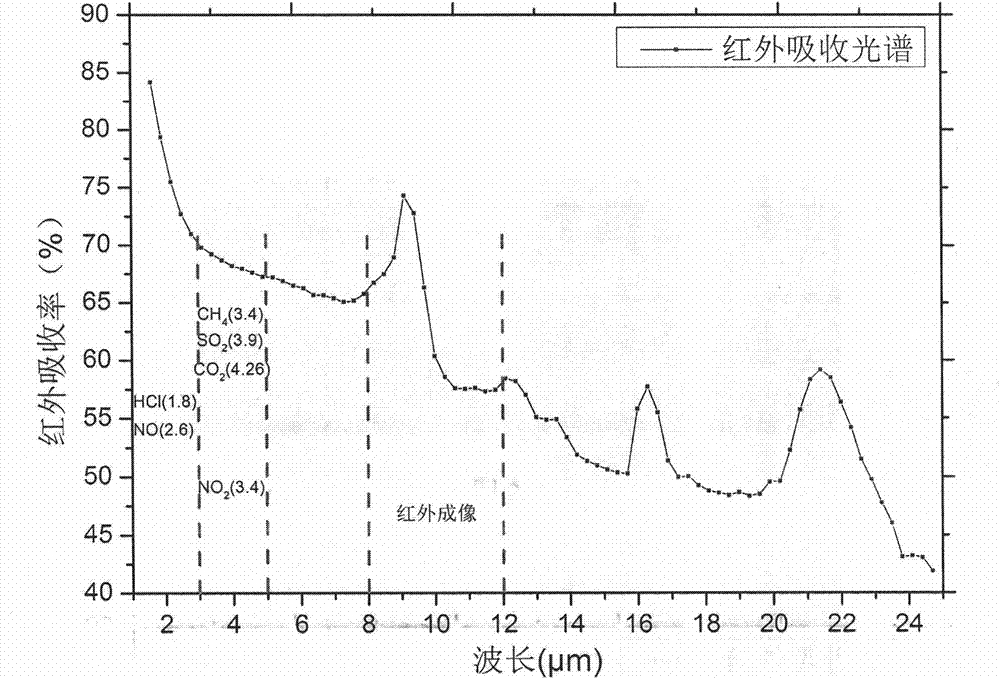

Integratable nanostructure infrared light source

ActiveCN103500788AReduce heat lossReduce structural stressTelevision system detailsImpedence networksManufacturing technologySurface plasmonic resonance

The invention discloses an integratable nanostructure infrared light source. According to the integratable nanostructure infrared light source, the surface of amorphous silicon is subjected to nano-modification processing by using an MEMS / CMOS (Micro-Electro-Mechanical System / Complementary Metal Oxide Semiconductor) process so as to form tapered nanostructures, and then, the tapered nanostructures are subjected to TiN cladding processing; finally, a silicon substrate is subjected to deep silicon etching by using a front XeF2 release technology, and a narrowband infrared light supply is separated from being in contact with the silicon substrate, so that the heat loss during Ohmic heating of silicon wires is reduced, and the operating power of the light source is increased. According to the integratable nanostructure infrared light source, an MEMS / CMOS light source manufacturing technology is adopted, the surface modification for the infrared light source is realized by using a metal-induced crystallization technology so as to obtain the tapered nanostructures, and the tapered nanostructures are subjected to surface TiN cladding processing, so that a surface plasma resonance technology for Si-TiN and TiN-Air is realized; micro cantilevers are formed by adopting a front release technology and support the infrared light source so as to reduce heat loss, and the structure stress is lowered through pre-burying a dielectric layer, namely silicon nitride, below a heating layer.

Owner:ZHONGBEI UNIV

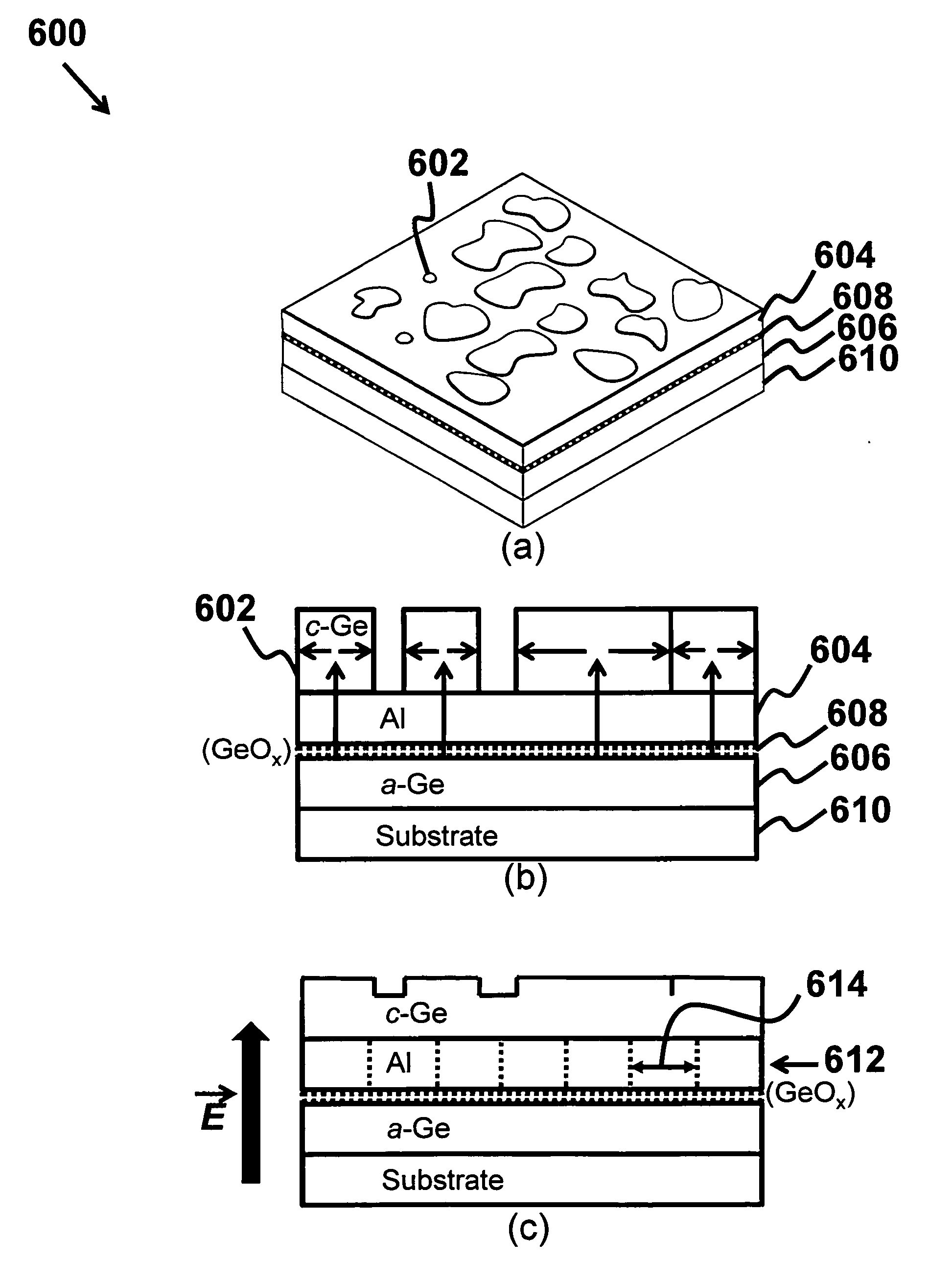

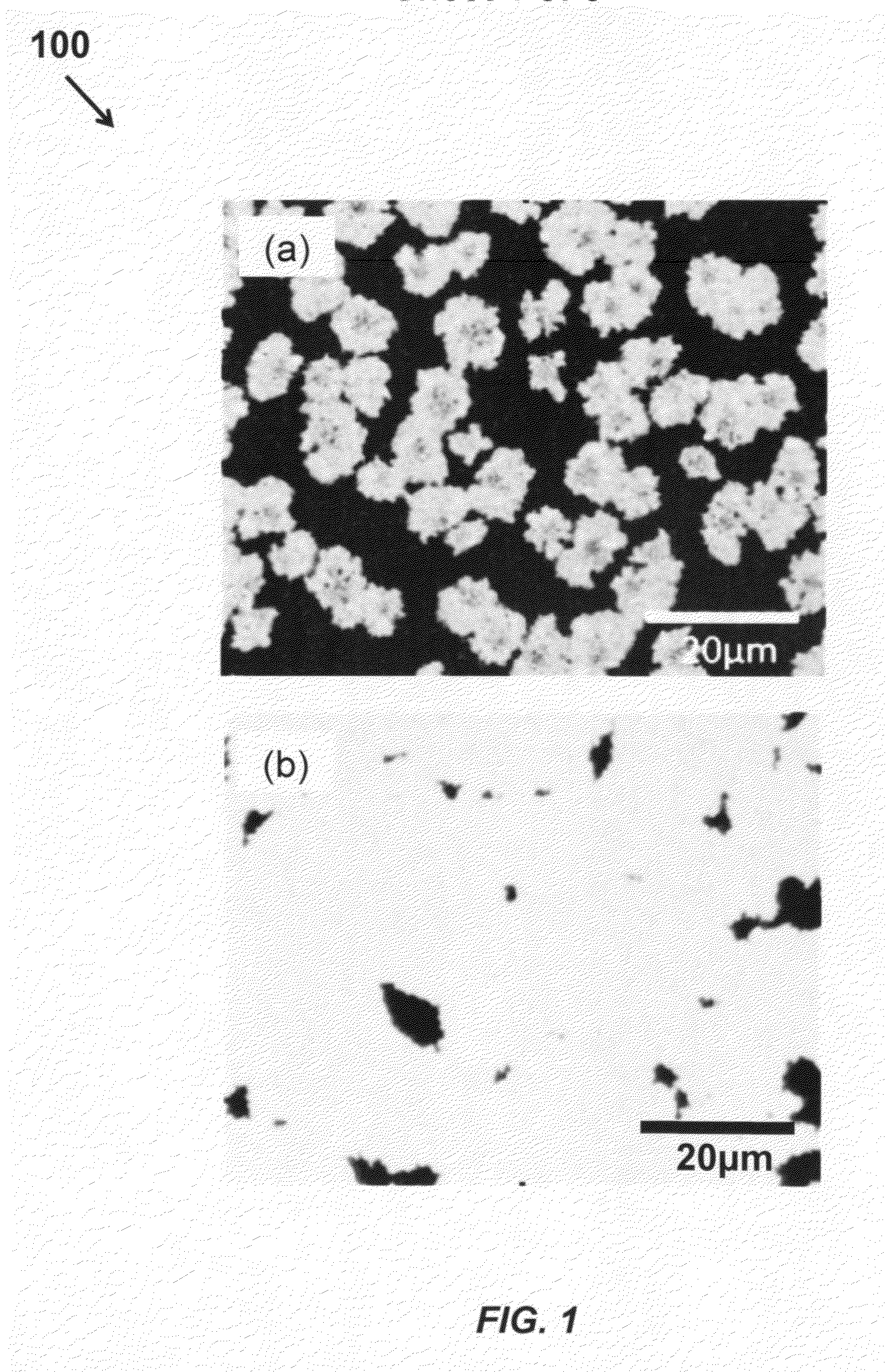

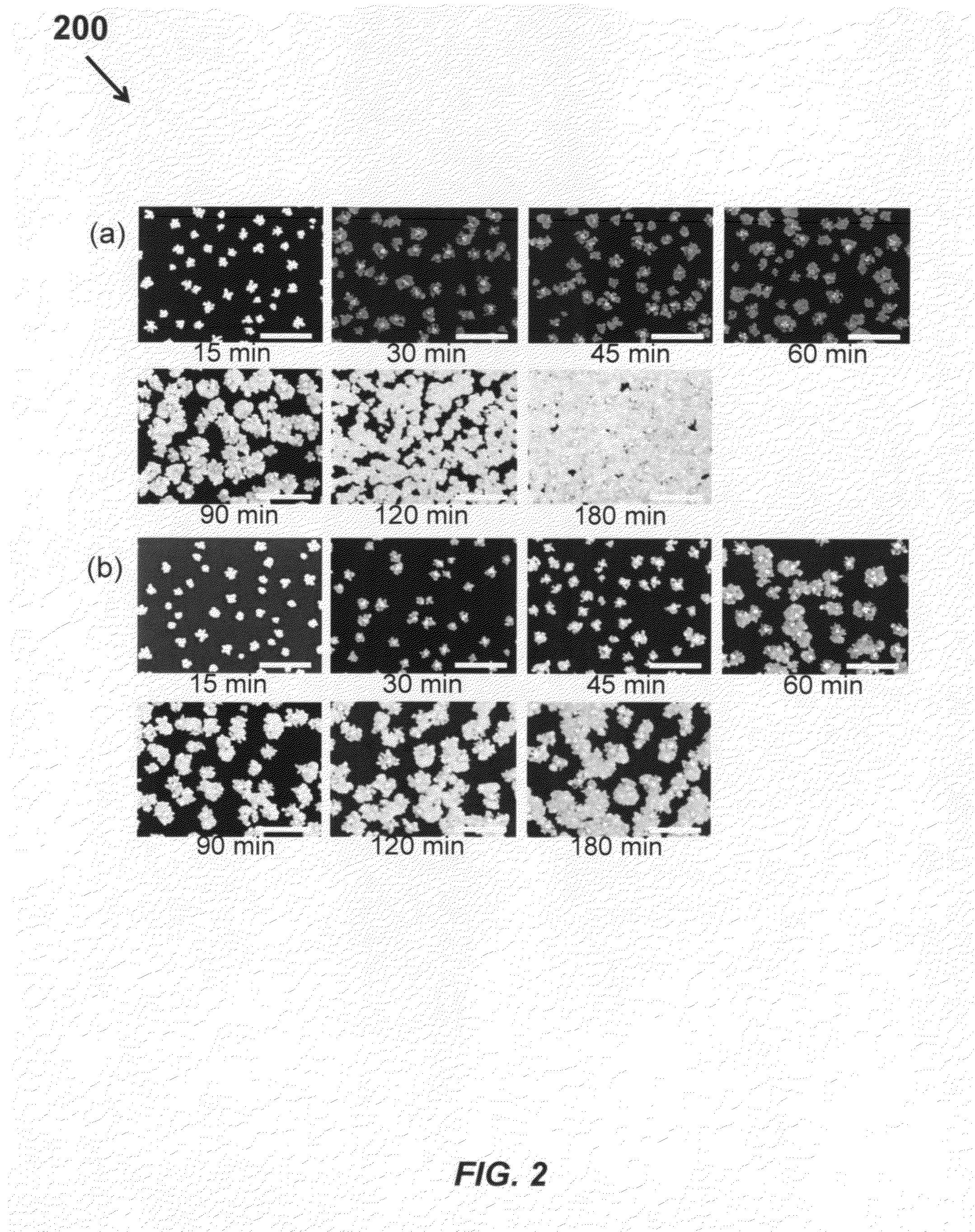

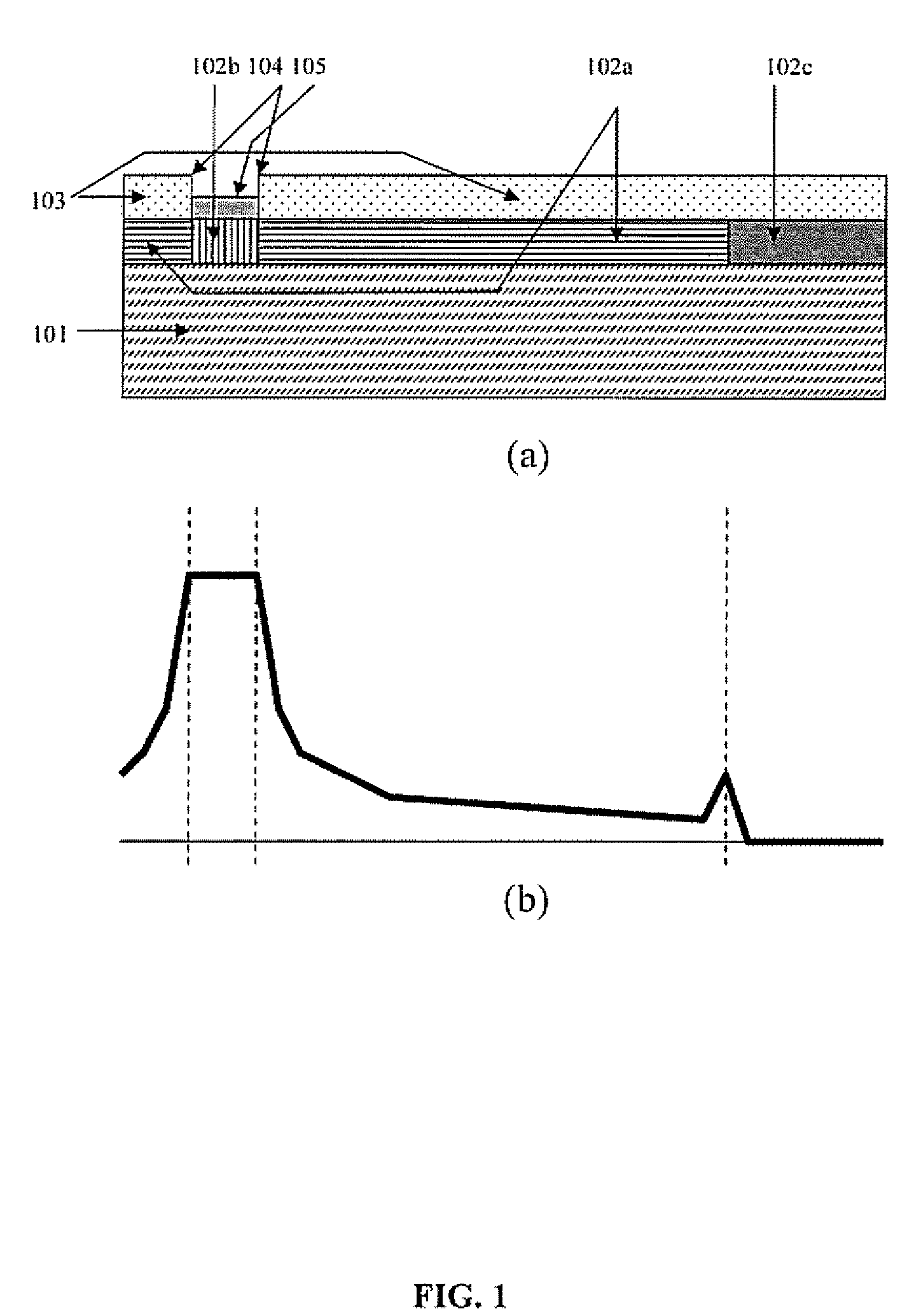

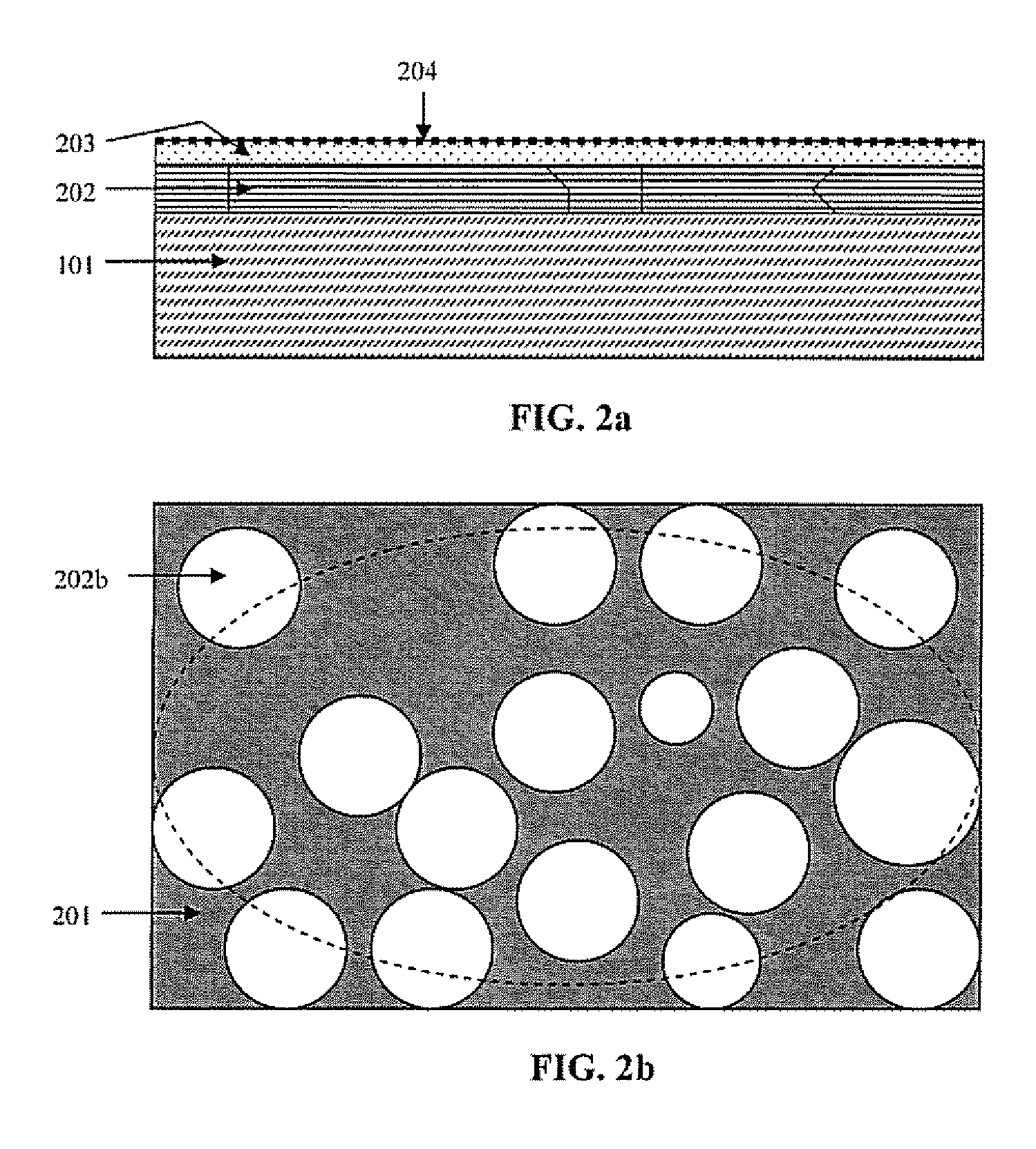

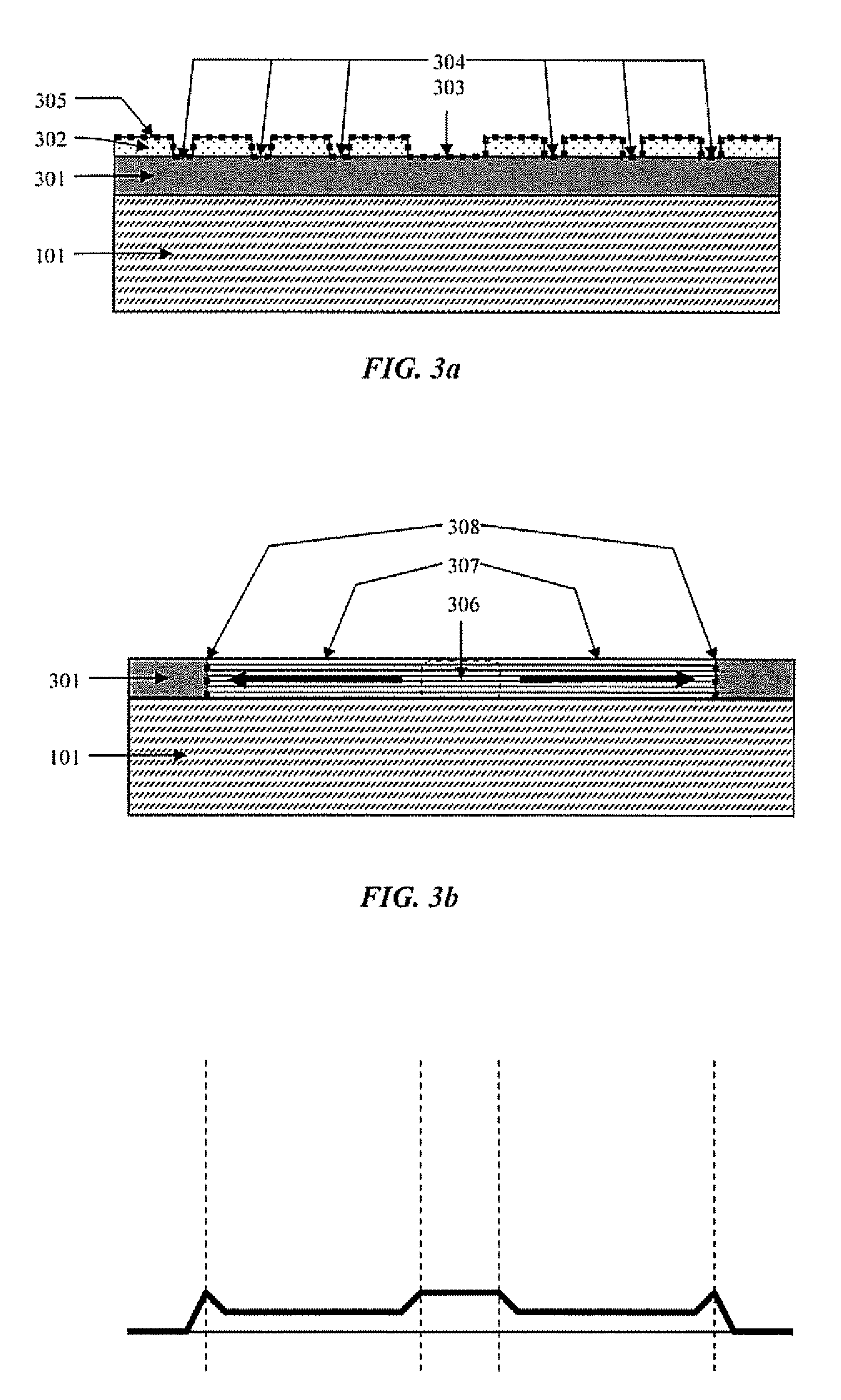

Metal-induced crystallization of continuous semiconductor thin films controlled by a diffusion barrier

ActiveUS20130048985A1Semiconductor/solid-state device manufacturingSemiconductor devicesDiffusion barrierMetal-induced crystallization

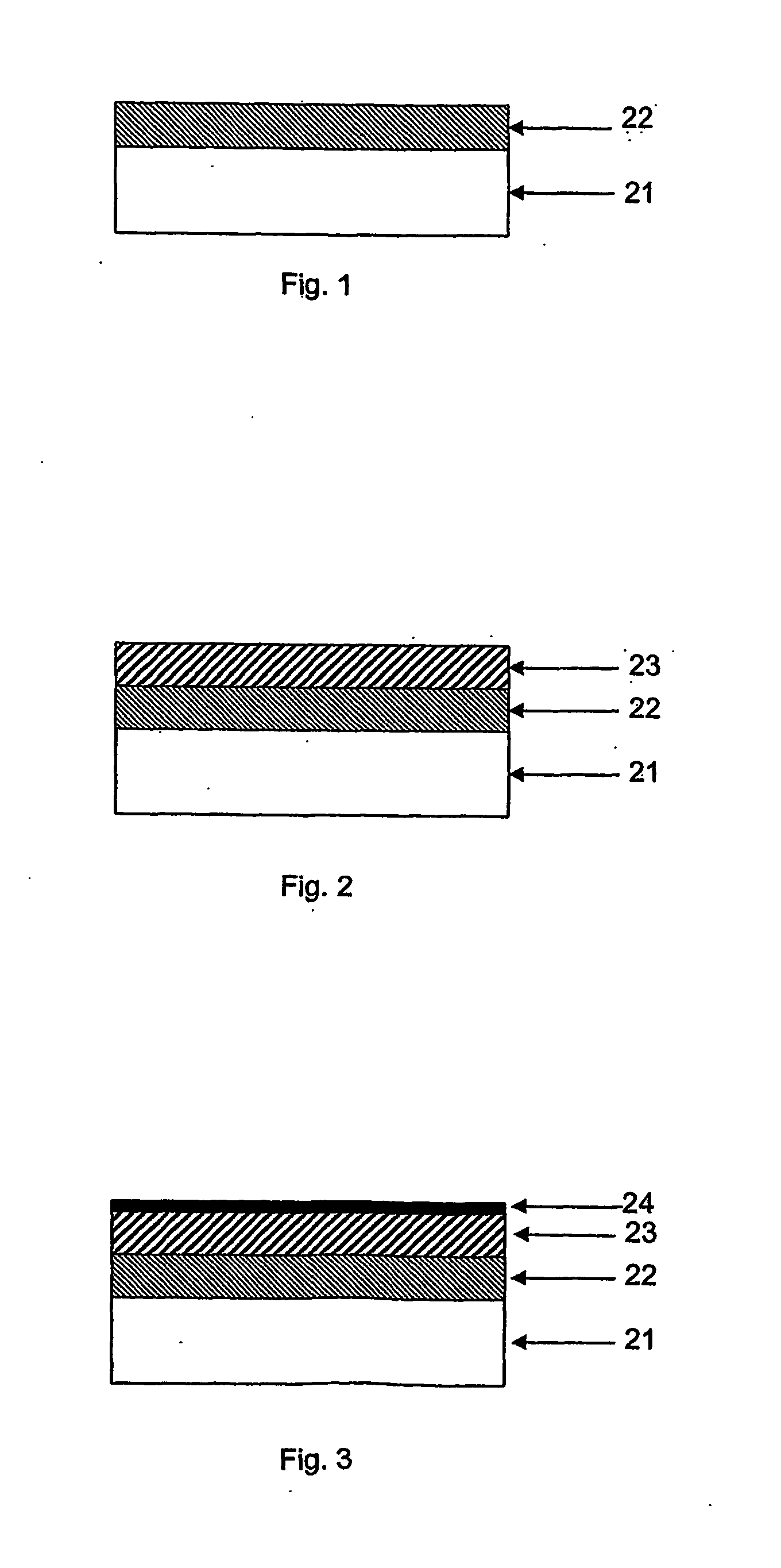

A device and a method of forming a continuous polycrystalline Ge film having crystalline Ge islands is provided that includes depositing an amorphous Ge (a-Ge) layer on a substrate, oxidizing the top surface of the a-Ge layer to form a GeOx layer, depositing a seed layer of Al on the GeOx layer and catalyzing the Al seed layer, where Ge mass transport is generated from the underlying a-Ge layer to the Al seed layer through the GeOx layer by thermal annealing, where a continuous polycrystalline Ge film having crystalline Ge islands is formed on the Al seed layer.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

Metal-induced crystallization of amorphous silicon and metal removal techniques

InactiveCN101064246ASemiconductor/solid-state device manufacturingTreatment completedOptoelectronics

The invention relates to a technology for producing a high quality and large area polycrystalline silicon thin film by amorphous silicon-metal-induced crystallization. Crystallization-inducing metal elements of controllable amound are introduced onto an initial amorphous silicon thin film. A first, low-temperature, heat-treatment induces nucleation of metal-induced crystallization (MIC), resulting in the formation of small polycrystalline silicon''islands''. A metal-gettering layer is formed on the resulting partially crystallized thin film. A second, low-temperature, heat-treatment completes the MIC process to form the desired polycrystalline silicon thin film. while the metal-gettering layer can be removed at randon after crystallization heat-treatment.

Owner:THE HONG KONG UNIV OF SCI & TECH

Method and apparatus for fabricating piezoresistive polysilicon by low-temperature metal induced crystallization

InactiveUS8492238B2Improve featuresPiezoelectric/electrostrictive device manufacture/assemblyFluid pressure measurement by electric/magnetic elementsRoom temperatureMetal-induced crystallization

The present invention provides a method and apparatus for fabricating piezoresistive polysilicon on a substrate by low-temperature metal induced crystallization by: (1) providing the substrate having a passivation layer; (2) performing, at or near room temperature in a chamber without breaking a vacuum or near-vacuum within the chamber, the steps of: (a) creating a metal layer on the passivation layer, and (b) creating an amorphous silicon layer on the metal layer, wherein the metal layer and the amorphous silicon layer have approximately the same thickness; (3) annealing the substrate, the passivation layer, the metal layer and the amorphous silicon layer at a temperature equal to or less than 600° C. and a period of time equal to or less than three hours to form a doped polysilicon layer below a residual metal layer; and (4) removing the residual metal layer to expose the doped polysilicon layer.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

Method of manufacturing driving-device for unit pixel of organic light emitting display

ActiveUS7648866B2Simple processReduce the numberSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing technologySelf-assembled monolayer

Provided is a method of manufacturing a driving-device for a unit pixel of an organic light emitting display having an improved manufacturing process in which the driving device can be manufactured with a smaller number of processes and in simpler processes. The method includes: forming an amorphous silicon layer including a first amorphous region and a second amorphous region disposed on the same plane of a substrate; forming an SAM (self-assembled monolayer) having a hydrophobic property on the first amorphous region; coating an aqueous solution in which nickel particles are dispersed, on the second amorphous region and the SAM, wherein a larger amount of nickel particles than on the SAM are dispersed on the second amorphous region using a hydrophilicity difference between the second amorphous region and the SAM; vaporizing the SAM through an annealing process and simultaneously performing metal induced crystallization in which the nanoparticles are used as a medium, to crystallize the first and second amorphous regions and to form first and second crystallization regions; patterning the first and second crystallization regions to form first and second channel regions; and forming first and second electrodes on the first and second channel regions.

Owner:SAMSUNG ELECTRONICS CO LTD

Polysilicon active layer-containing thin film transistor, manufacturing method thereof and array substrate

ActiveCN102709184AReduce contentReduce leakage currentTransistorSolid-state devicesMetal-induced crystallizationActive layer

The invention discloses a method for manufacturing a polysilicon active layer-containing thin film transistor. The method comprises the following steps of: depositing an amorphous silicon layer on a substrate; patterning the amorphous silicon layer; forming an active layer which comprises a source region, a drain region and a channel region; depositing an induced metal on the source region and the drain region; performing heat treatment on the active layer on which the induced metal is deposited, so that the active layer is subjected to metal-induced crystallization and metal-induced lateral crystallization under the action of the induced metal; doping a first impurity used for collecting the induced metal and a second impurity used for forming a P-channel metal oxide semiconductor (PMOS) or an N-channel metal oxide semiconductor (NMOS) into the source region and the drain region; and performing the heat treatment on the doped active layer, so that the second impurity is activated and the residue induced metal in the channel region is absorbed by the first impurity.

Owner:BOE TECH GRP CO LTD

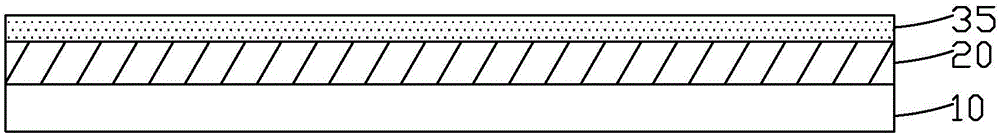

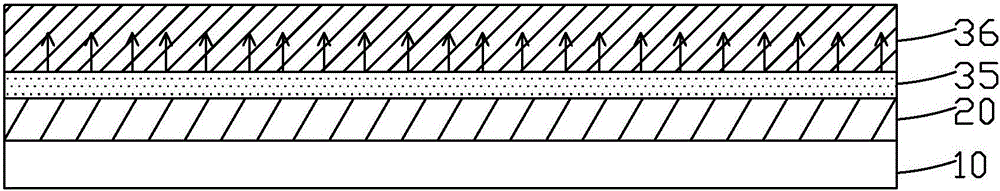

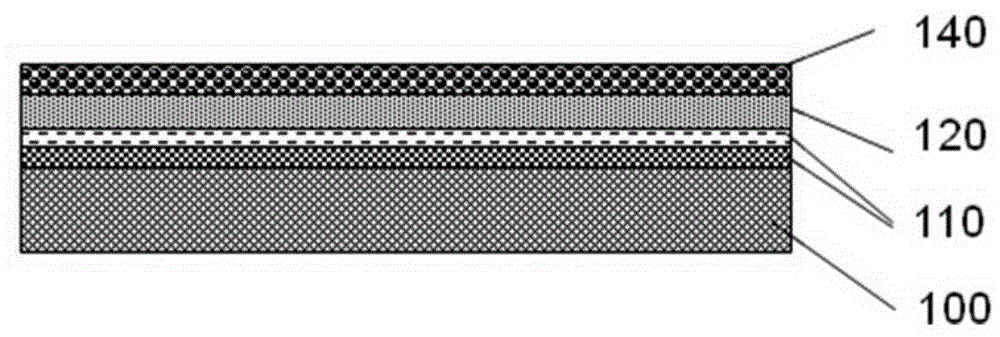

Low temperature polycrystalline silicon film transistor and manufacturing method thereof

ActiveCN104576753AReduce concentrationReduce heavy doping processTransistorSemiconductor/solid-state device manufacturingInsulation layerSurface layer

The invention discloses a lower temperature polycrystalline silicon film transistor and a manufacturing method thereof. The method comprises the following steps: manufacturing a buffer layer on a substrate; manufacturing an amorphous silicon layer on the buffer layer; covering a metal induced layer on the amorphous silicon layer, and performing metal induced crystallization, so as to convert amorphous silicon layer into a polycrystalline silicon layer; schematizing the polycrystalline silicon layer to form a channel region and a source drain region; etching the surface layer, on which metallics remain due to metal induced crystallization, of the channel region; successively forming a gate-insulation layer, a gate, a layer insulation layer and a source drain electrode on the source drain region and the etched channel region. The polycrystalline silicon film transistor and the manufacturing method thereof, disclosed by the invention, realize the individual control of the density of the metallics on the channel region and the source drain region, so that not only is the density of the metallics on the channel region lower, but also the leaked current is reduced; the density of the metallics on the source drain region is higher, the metallics can be used as adulterants so as to reduce the technology of doping again, and besides, contact resistance is decreased; finally, the influence of the metallics remained in an active region on the performance of devices is eliminated.

Owner:CHENGDU VISTAR OPTEOLECTRONICS CO LTD

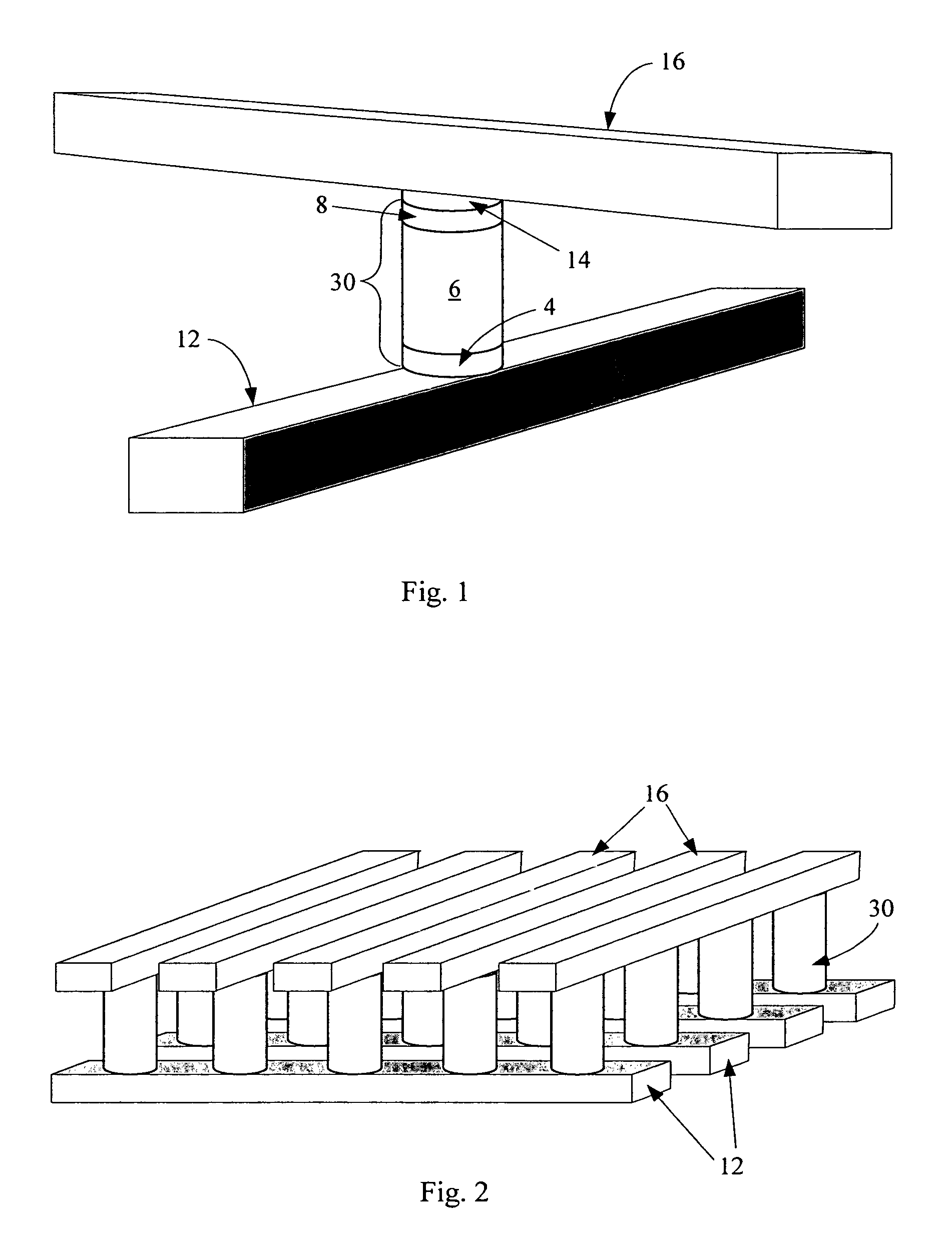

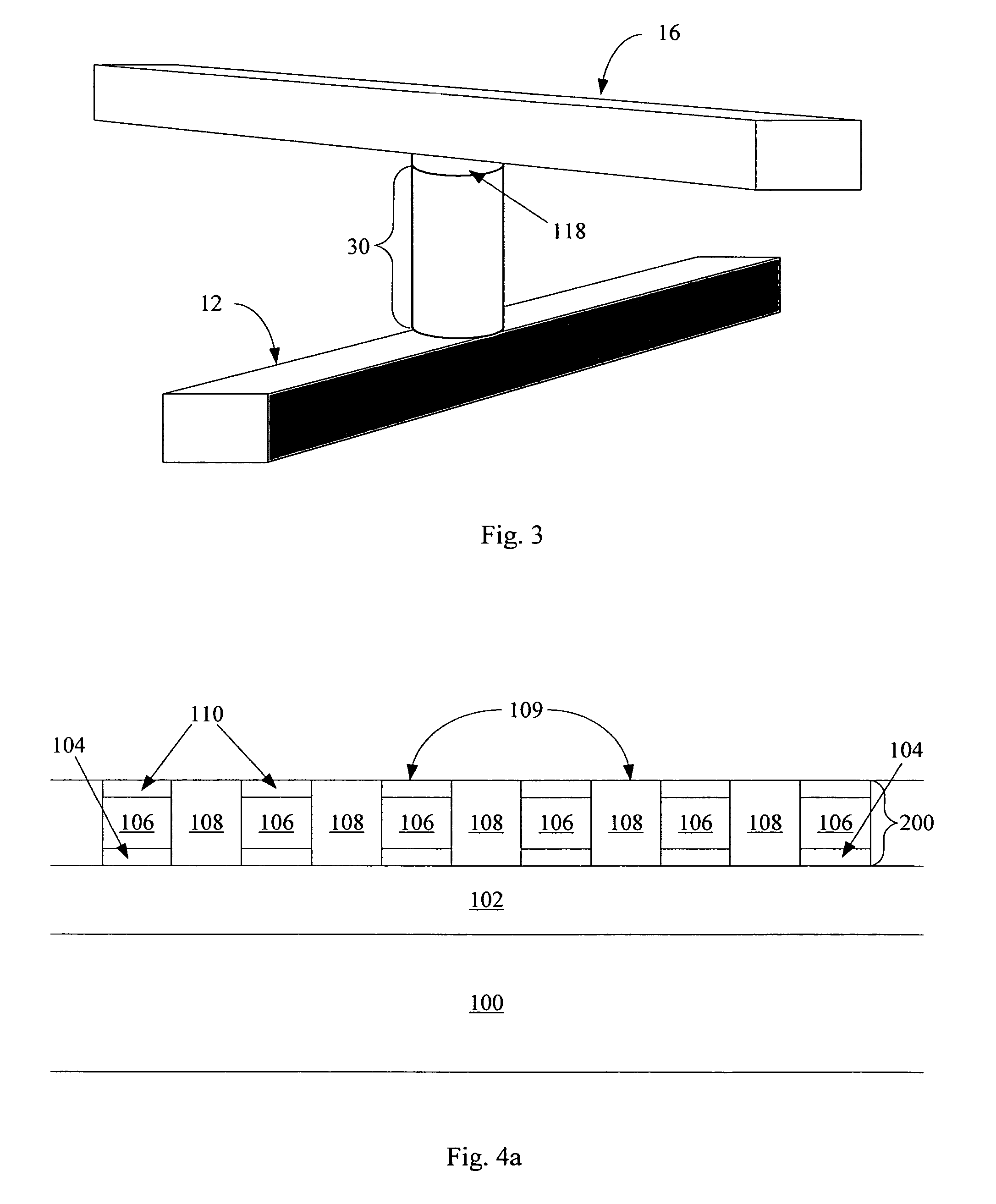

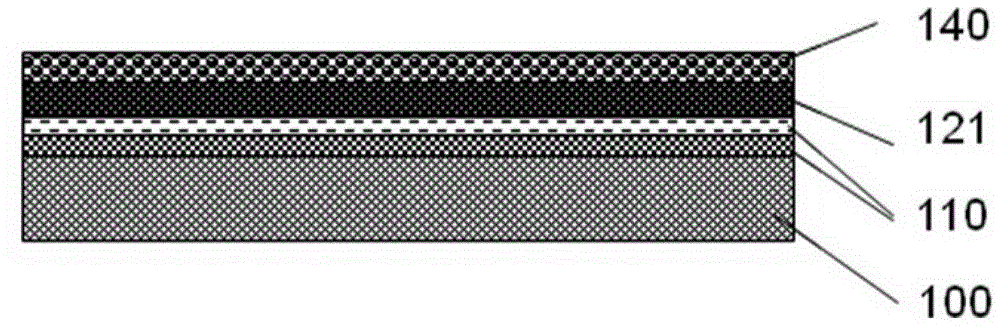

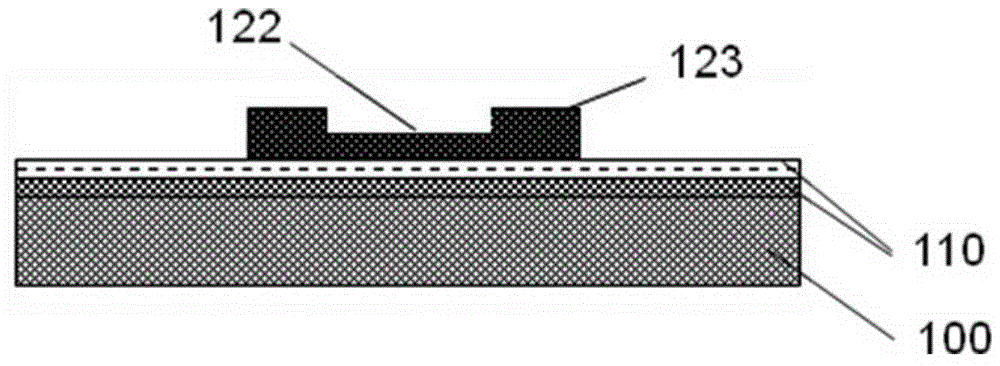

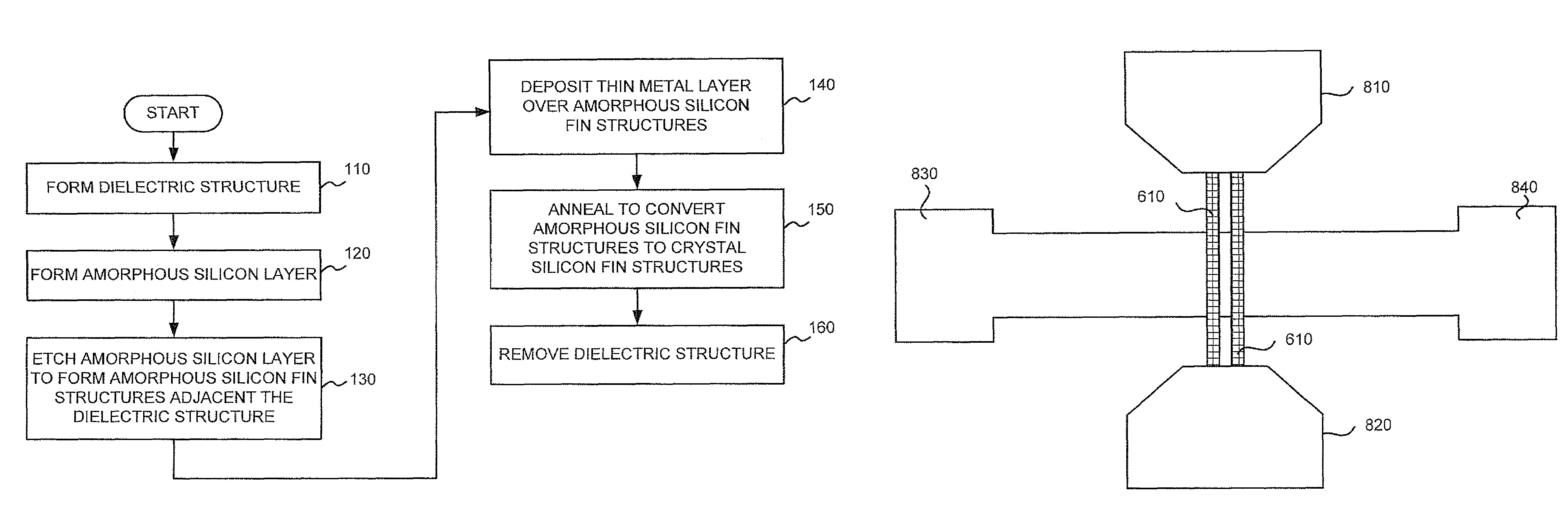

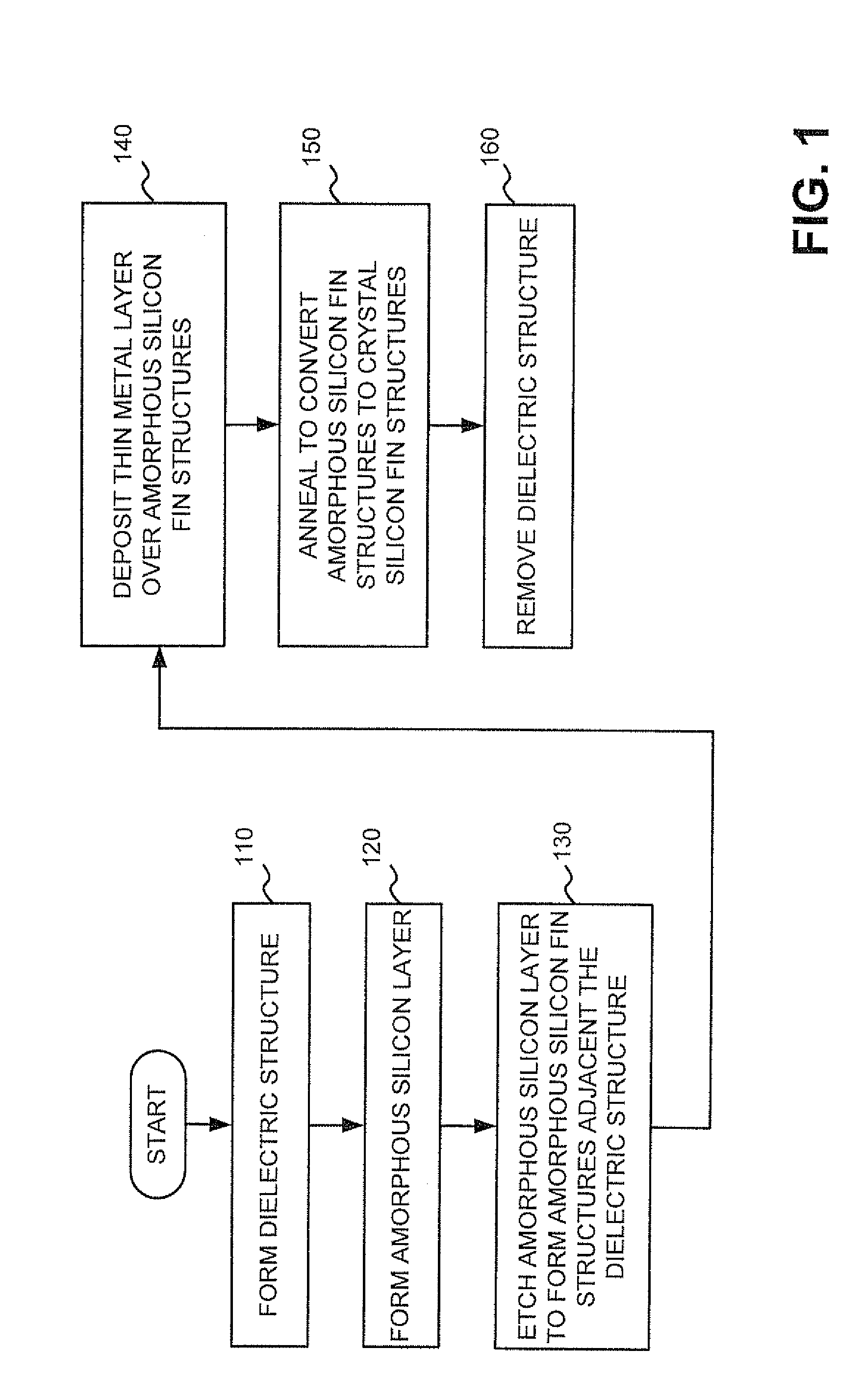

Systems and methods for forming multiple fin structures using metal-induced-crystallization

InactiveUS7498225B1Small spacingEasy to shapeSemiconductor/solid-state device manufacturingSemiconductor devicesMetal-induced crystallizationCrystalline silicon

A method for forming fin structures for a semiconductor device that includes a substrate and a dielectric layer formed on the substrate is provided. The method includes etching the dielectric layer to form a first structure, depositing an amorphous silicon layer over the first structure, and etching the amorphous silicon layer to form second and third fin structures adjacent first and second side surfaces of the first structure. The second and third fin structures may include amorphous silicon material. The method further includes depositing a metal layer on upper surfaces of the second and third fin structures, performing a metal-induced crystallization operation to convert the amorphous silicon material of the second and third fin structures to a crystalline silicon material, and removing the first structure.

Owner:ALSEPHINA INNOVATIONS INC

Method for preparing polycrystalline silicon film by carrying out induced crystallization on amorphous silicon film by using metallic copper under low temperature

InactiveCN102709404AReduce pollutionImprove compatibilityFinal product manufactureChemical vapor deposition coatingOptoelectronicsField-effect transistor

The invention relates to a preparation method of a polycrystalline silicon film, in particular to a method for preparing a polycrystalline silicon film by carrying out induced crystallization on an amorphous silicon film by cycle annealing under low temperature by using catalytic action of metallic copper. The main technical scheme of the invention is as follows: the method comprises the following steps of: growing a substrate / amorphous silicon / silicon dioxide / copper film structure on a glass substrate, then carrying out cycle annealing, putting a sample in corrosive liquid for corroding after first annealing is finished, and carrying out cycle annealing and corroding again, and drying the sample with nitrogen; and finally preparing the polycrystalline silicon film prepared by induced crystallization by copper, wherein the grain size is about 50-200nm. The method disclosed by the invention can ease the problem of serious metal pollution in the traditional MIC (Metal Induced Crystallization) technology and is suitable for the field of thin film field effect transistors and thin-film solar cells.

Owner:SHANGHAI UNIV

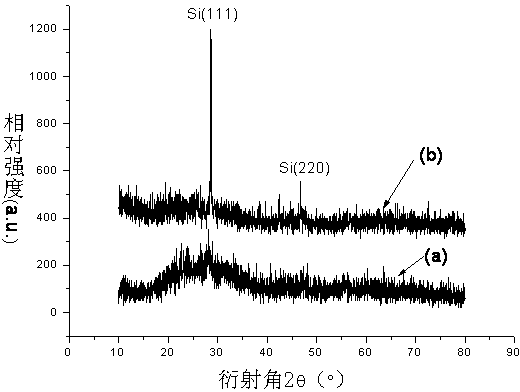

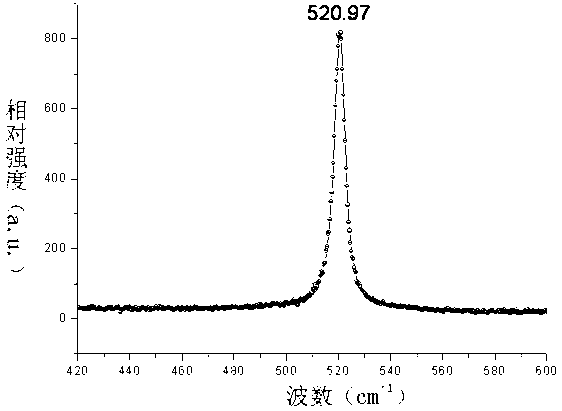

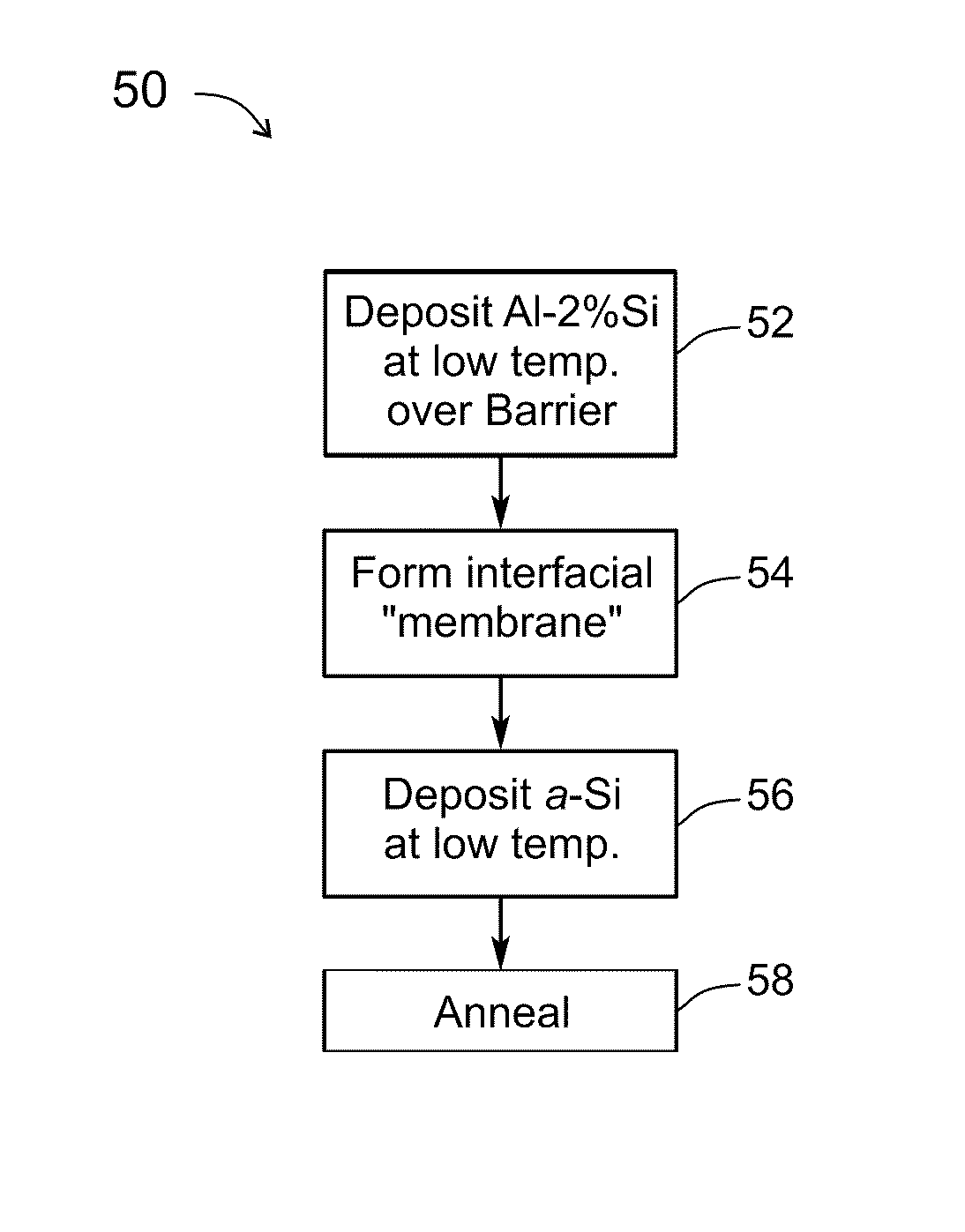

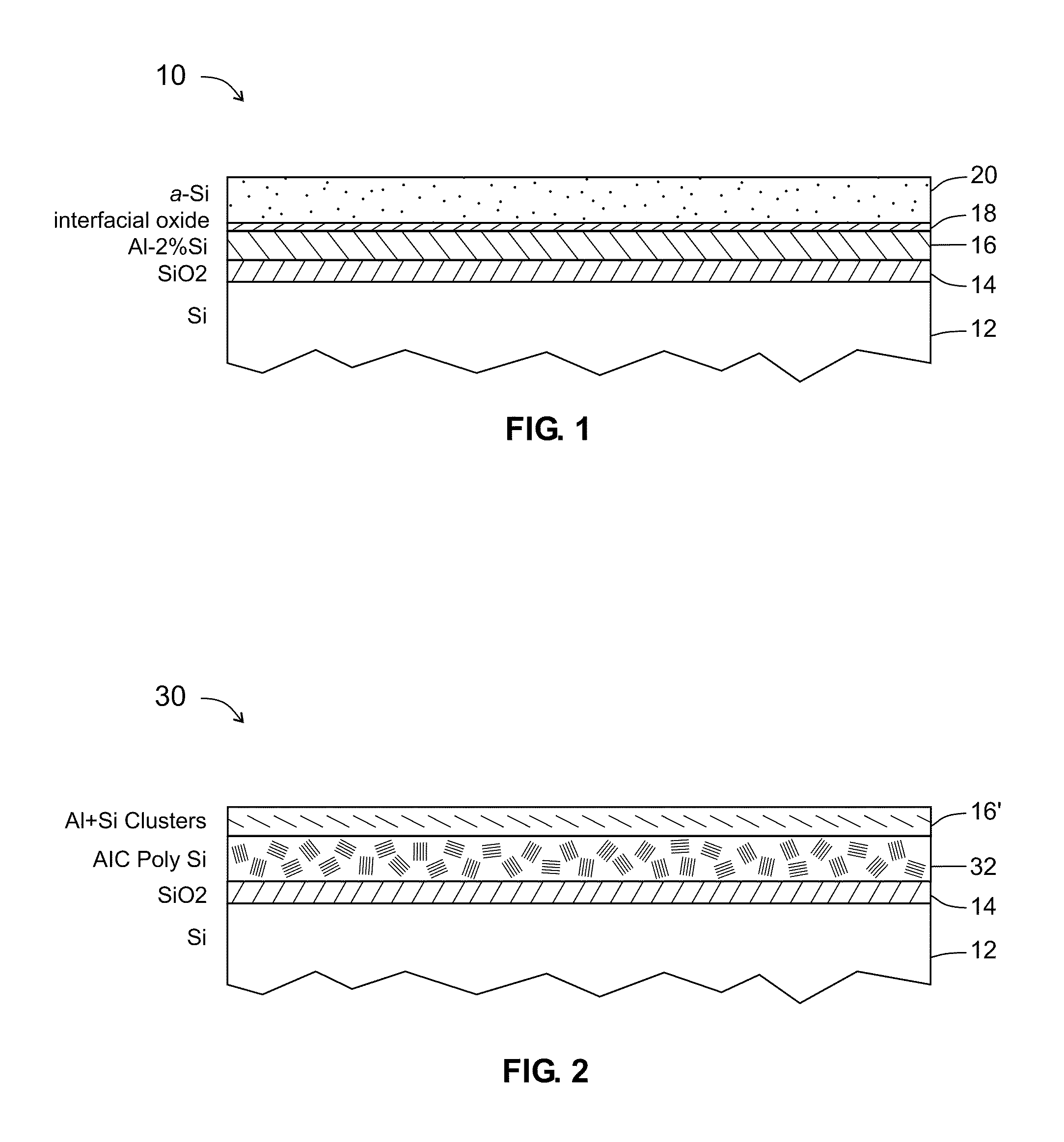

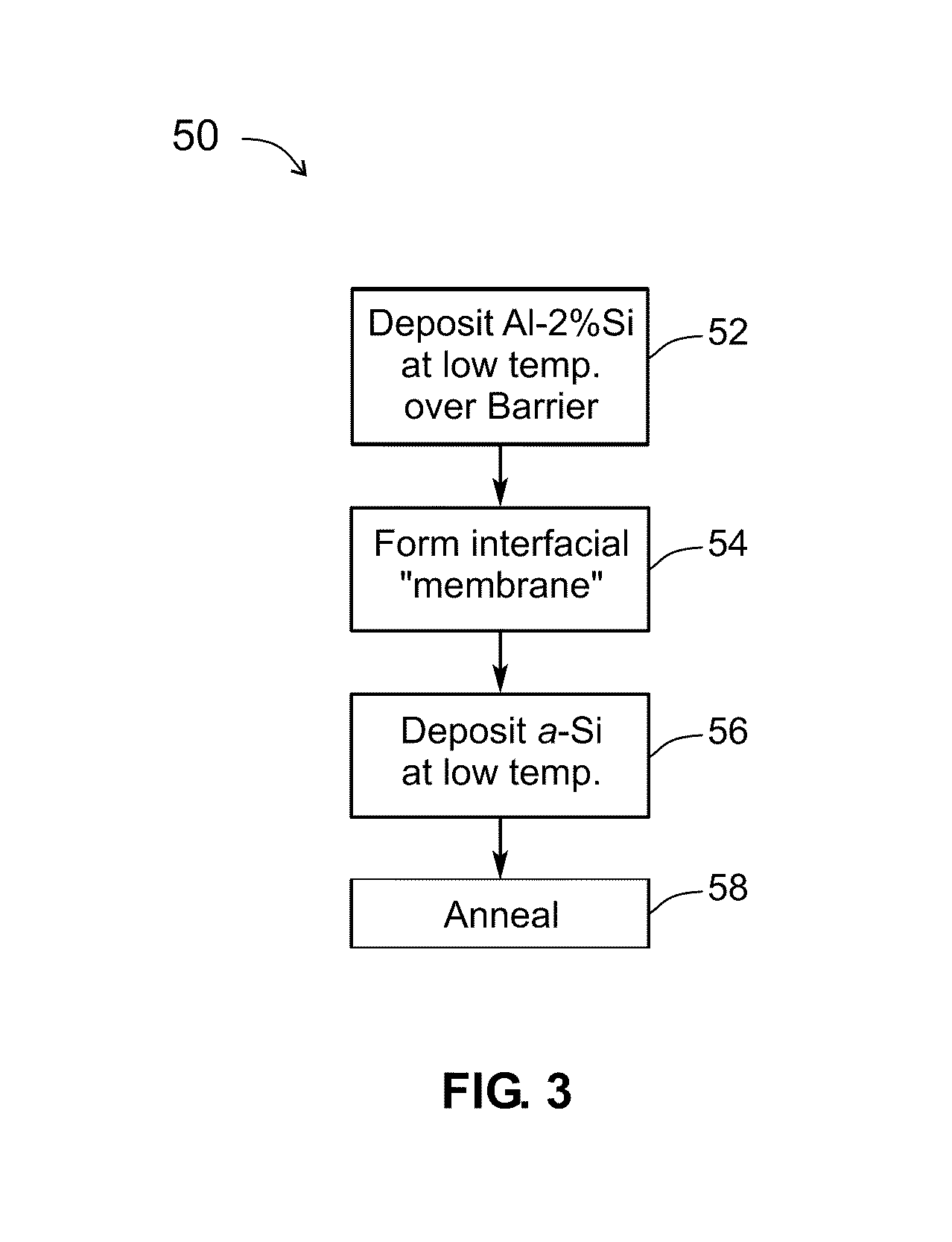

Low-temperature formation of polycrystalline semiconductor films via enhanced metal-induced crystallization

ActiveUS8043943B2Simple materialReduce the temperaturePolycrystalline material growthFrom solid stateSemiconductor materialsMetal-induced crystallization

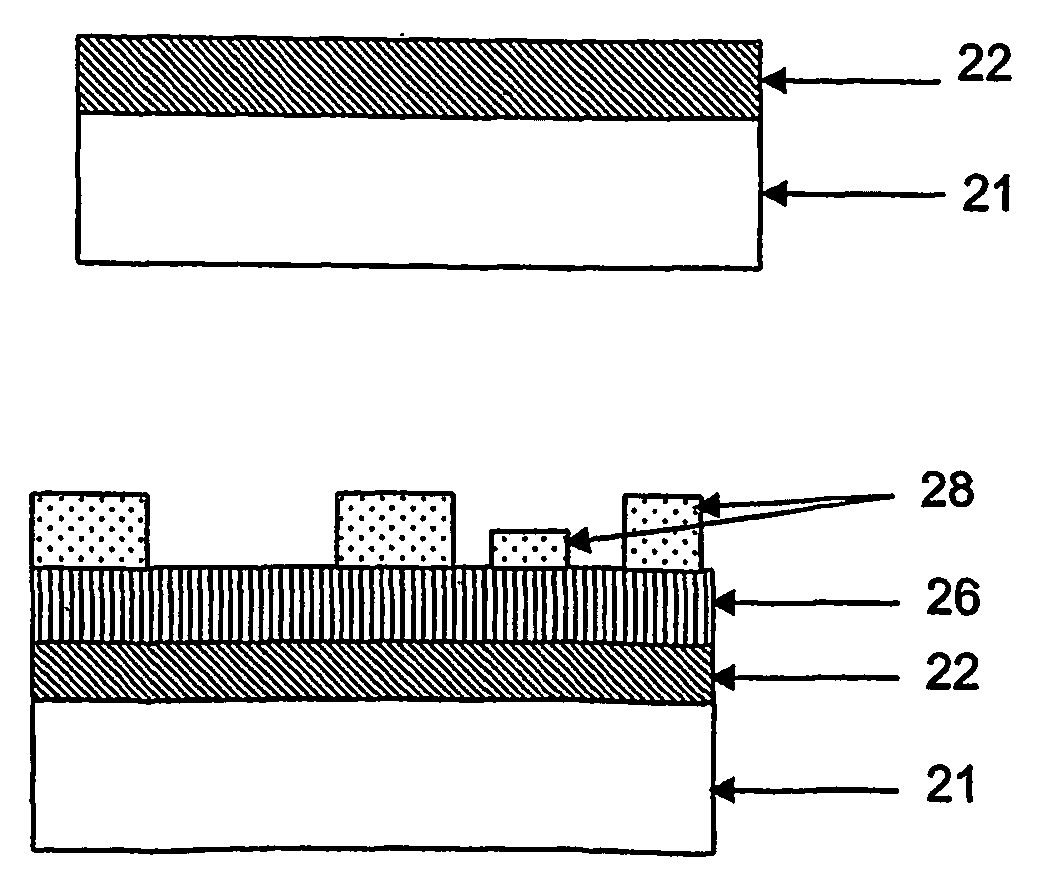

A method for forming polycrystalline semiconductor film from amorphous semiconductor film at reduced temperatures and / or accelerated rates. The inclusion of a small percentage of semiconductor material, such as 2% within the metal layer, reduces the temperatures required for crystallization of the amorphous semiconductor by at least 50° C. in comparison to the use of the metal layer without the small percentage of semiconductor material. During a low temperature isothermal annealing process adjacent Al-2% Si and a-Si films undergo a layer exchange resulting in formation of a continuous polycrystalline silicon film having good physical and electrical properties. Formation of polycrystalline-semiconductor in this manner is suitable for use with low temperature substrates (e.g., glass, plastic) as well as with numerous integrated circuit and MEMs fabrication devices and practices.

Owner:RGT UNIV OF CALIFORNIA

Metal-Induced Crystallization of Amorphous Silicon in Thin Film Transistors

InactiveUS20070212855A1Solid-state devicesSemiconductor/solid-state device manufacturingGas phaseVapor phase

The invention provides a method for forming thin film transistors including a polycrystalline semiconducting film. The method comprises depositing a first layer of amorphous semiconducting thin film on to a substrate; depositing a second layer of thin film on to the first layer of amorphous semiconducting thin film; patterning the second layer or thin film so that the first layer of amorphous semiconducting thin film is exposed at selected locations; exposing the first and second layers of thin film to a nickel containing compound in either a solution or a vapor phase; removing the second layer of thin film; and annealing the first layer of amorphous semiconducting thin film at an elevated temperature so the first layer of amorphous semiconducting thin film converts into a polycrystalline semiconducting thin film.

Owner:THE HONG KONG UNIV OF SCI & TECH

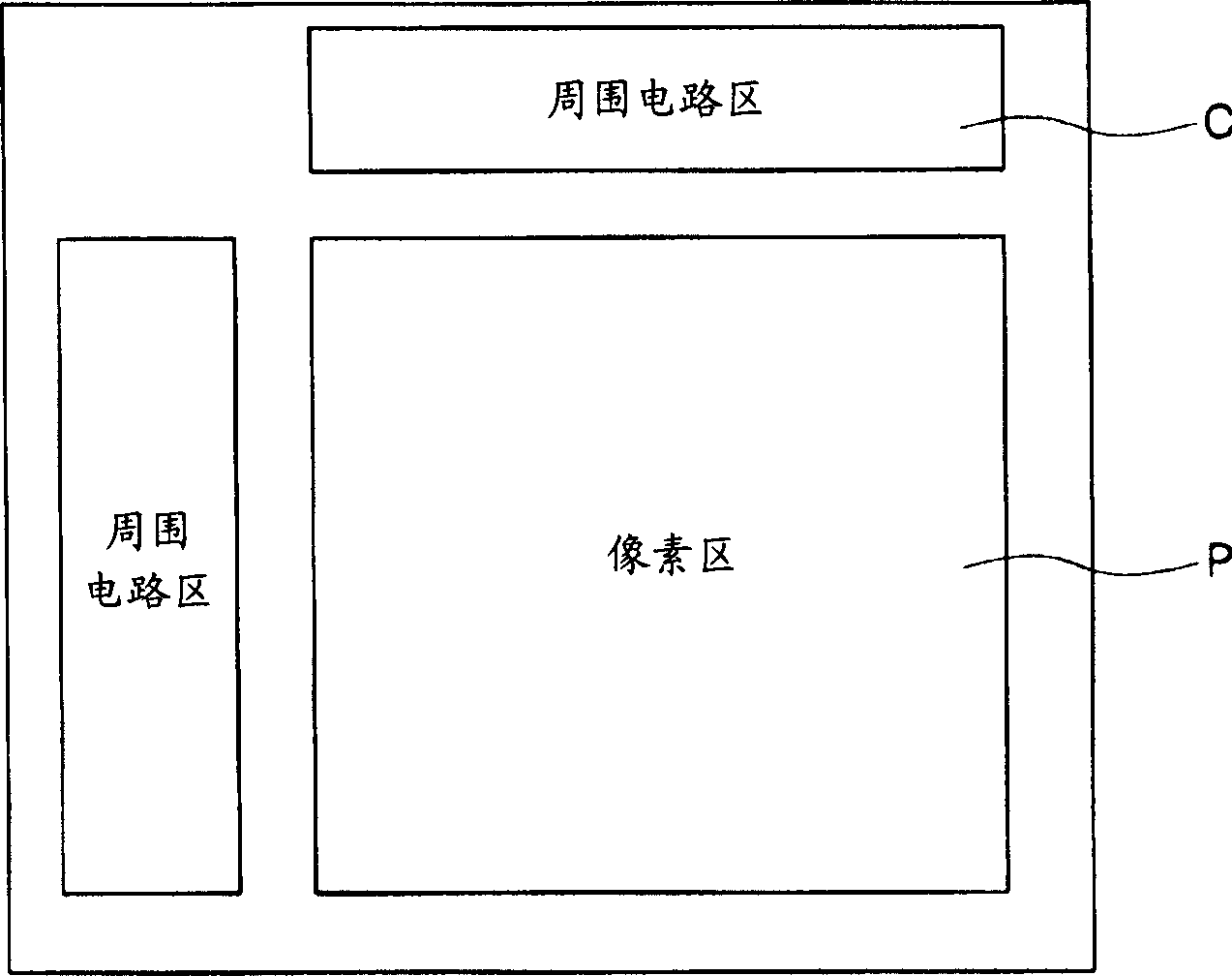

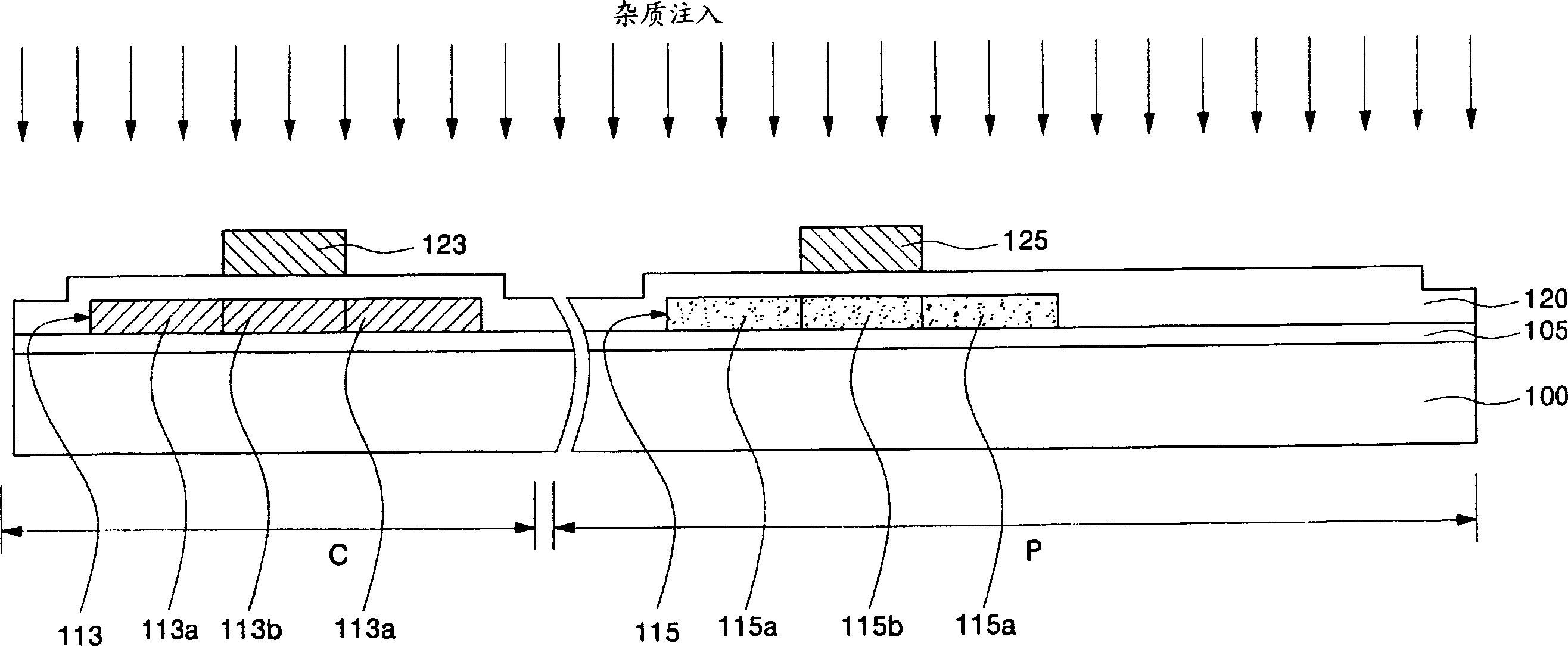

Flat panel display and method for fabricating the same

Disclosed are a flat panel display and a manufacturing method thereof. In a flat panel display, a substrate includes a pixel area having a plurality of unit pixels, and a peripheral circuit area around the pixel area. The peripheral circuit area also includes a driving circuit for driving a plurality of unit pixels. At least one circuit thin film transistor is located in the peripheral circuit region and includes a first semiconductor layer crystallized by a sequential lateral solidification method. At least one pixel thin film transistor is located in the pixel area and includes a second semiconductor layer having a channel region crystallized by one of a metal-induced crystallization method or a metal-induced lateral crystallization method.

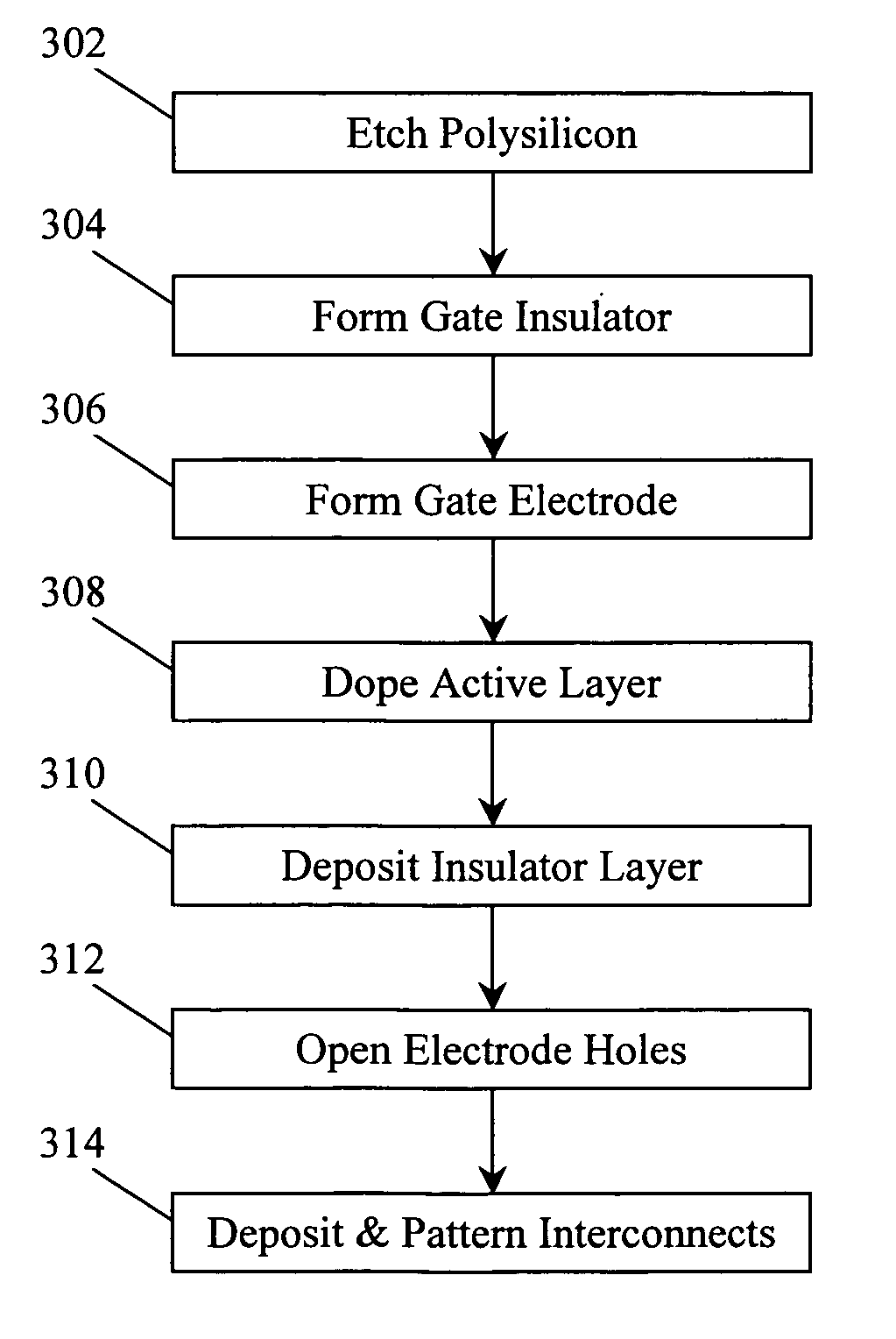

Owner:SAMSUNG DISPLAY CO LTD