Low temperature polycrystalline silicon film transistor and manufacturing method thereof

A technology of thin-film transistors and low-temperature polysilicon, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., and can solve problems such as inability to control by region

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, so that those skilled in the art can better understand the present invention and implement it, but the examples given are not intended to limit the present invention.

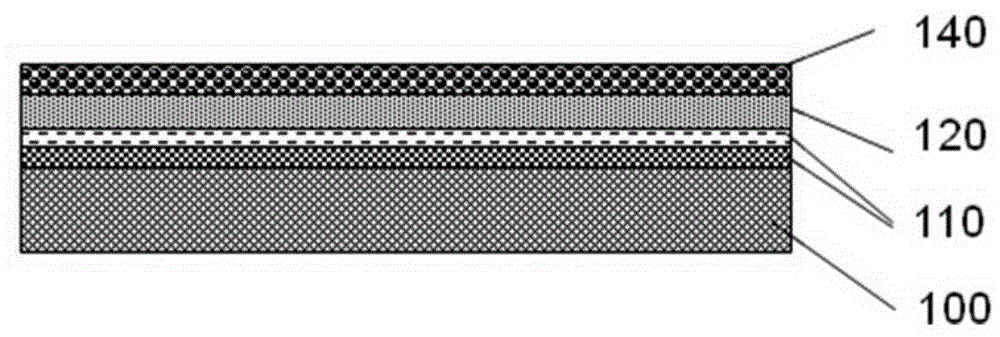

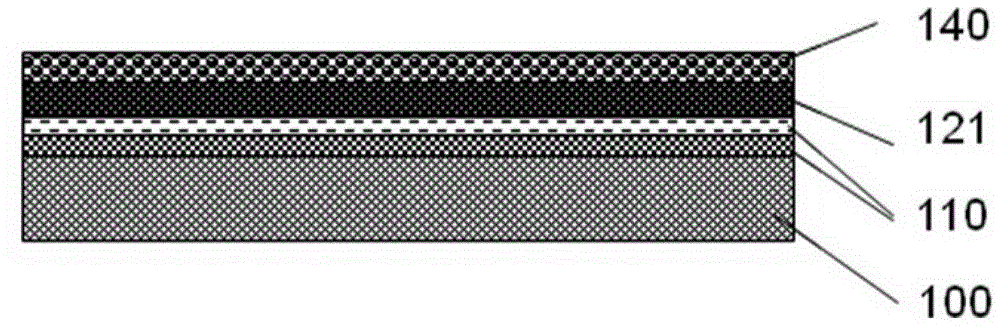

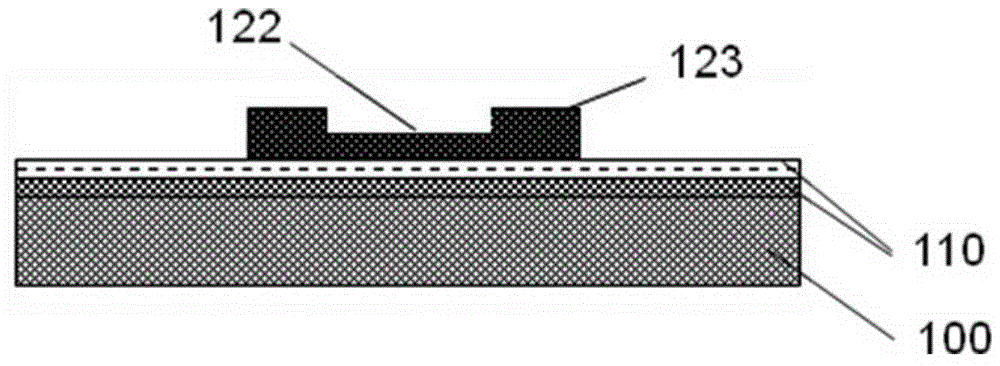

[0025] Such as Figures 1A to 1D A method of manufacturing a low-temperature polysilicon thin film transistor shown, the method comprising:

[0026] In step one, a buffer layer 110 is fabricated on the substrate 100 . The material of the substrate 100 can be glass, quartz, organic polymer, or opaque / reflective material, such as conductive material, wafer, ceramic, or other applicable materials. The buffer layer 110 may adopt a low pressure chemical vapor deposition process or an ion growth chemical vapor deposition process. In a specific embodiment, the buffer layer 110 may be a single layer or a double layer. The single-layer buffer layer 110 may be silicon oxide or silicon ni...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More