Manufacturing method of super junction device

A manufacturing method and super junction technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as reducing device performance, and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

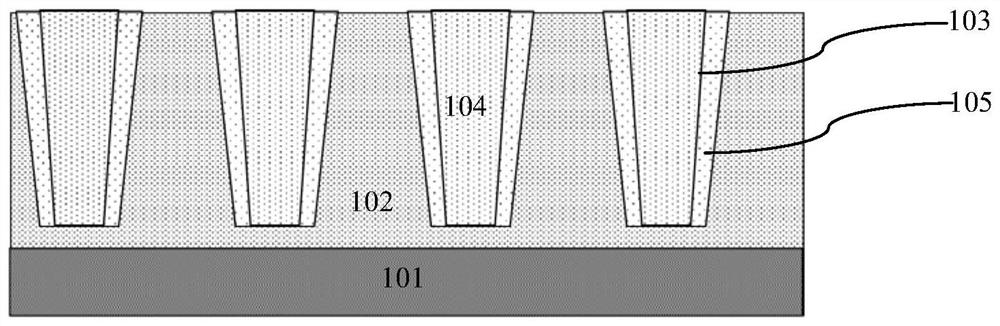

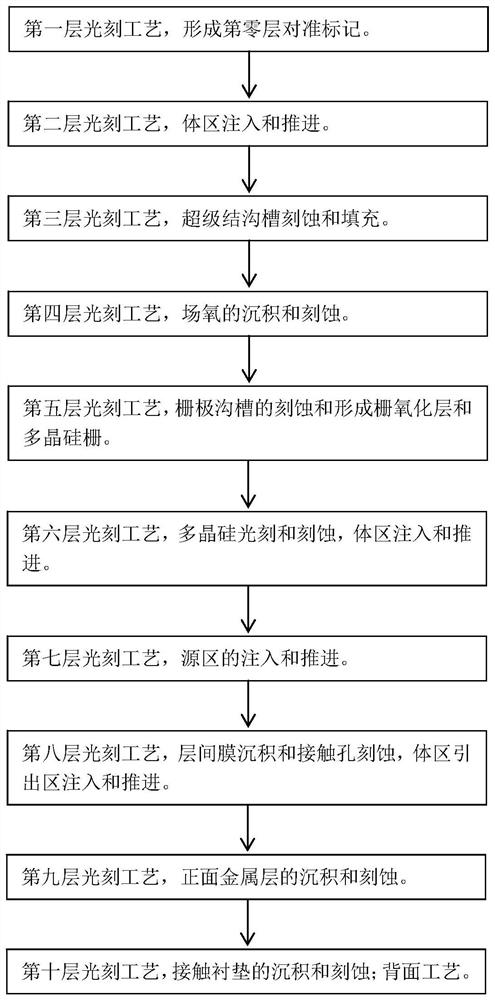

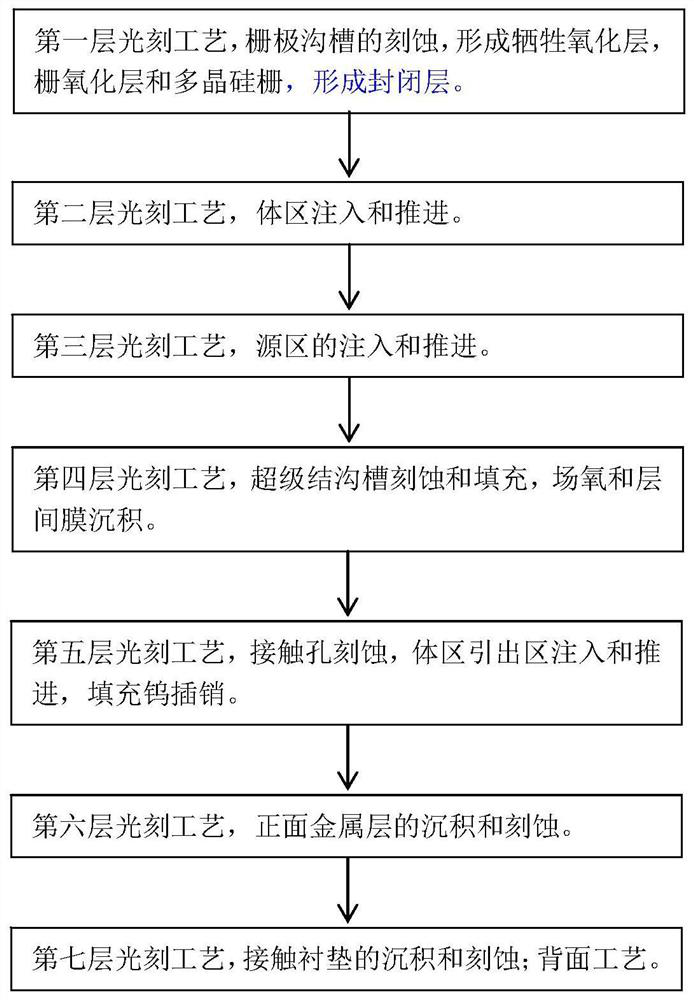

[0097] Such as image 3 Shown is a flowchart of a method for manufacturing a super junction device according to an embodiment of the present invention; image 3 is described according to the lithography process level, a lithography process level includes multiple specific process steps, and a lithography process level only performs the lithography process corresponding to one mask. Such as Figure 4A to Figure 4N Shown is a schematic diagram of the device structure in each step of the manufacturing method of the super junction device in the embodiment of the present invention; the manufacturing method of the super junction device in the embodiment of the present invention includes steps:

[0098] Step 1, forming the gate structure, the gate structure is a trench gate, and the formation process of the trench gate includes:

[0099] A first epitaxial layer 2 with a first conductivity type is provided, and a photolithography process is performed to define a formation region of ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More