Patents

Literature

72results about How to "Increase growth temperature" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

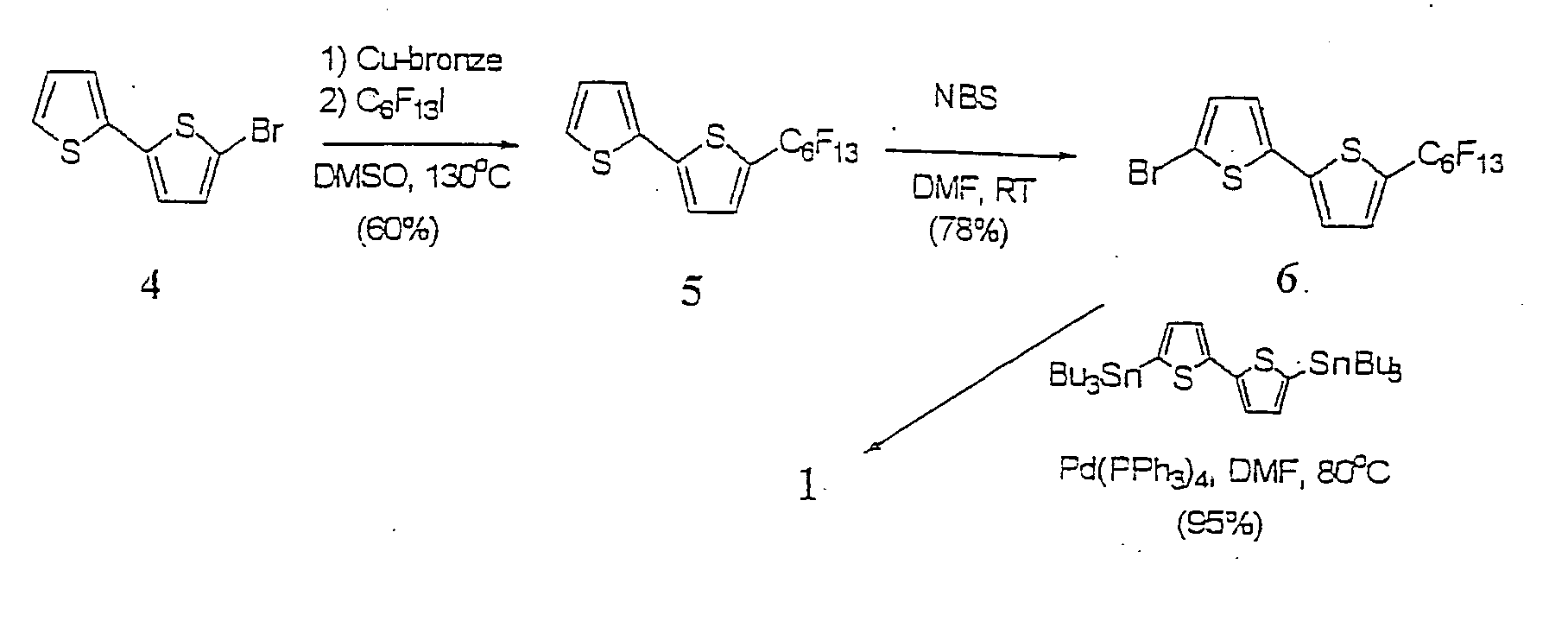

n-Type thiophene semiconductors

InactiveUS6991749B2High yieldHigh purityConductive materialSolid-state devicesThin membraneOrganic semiconductor

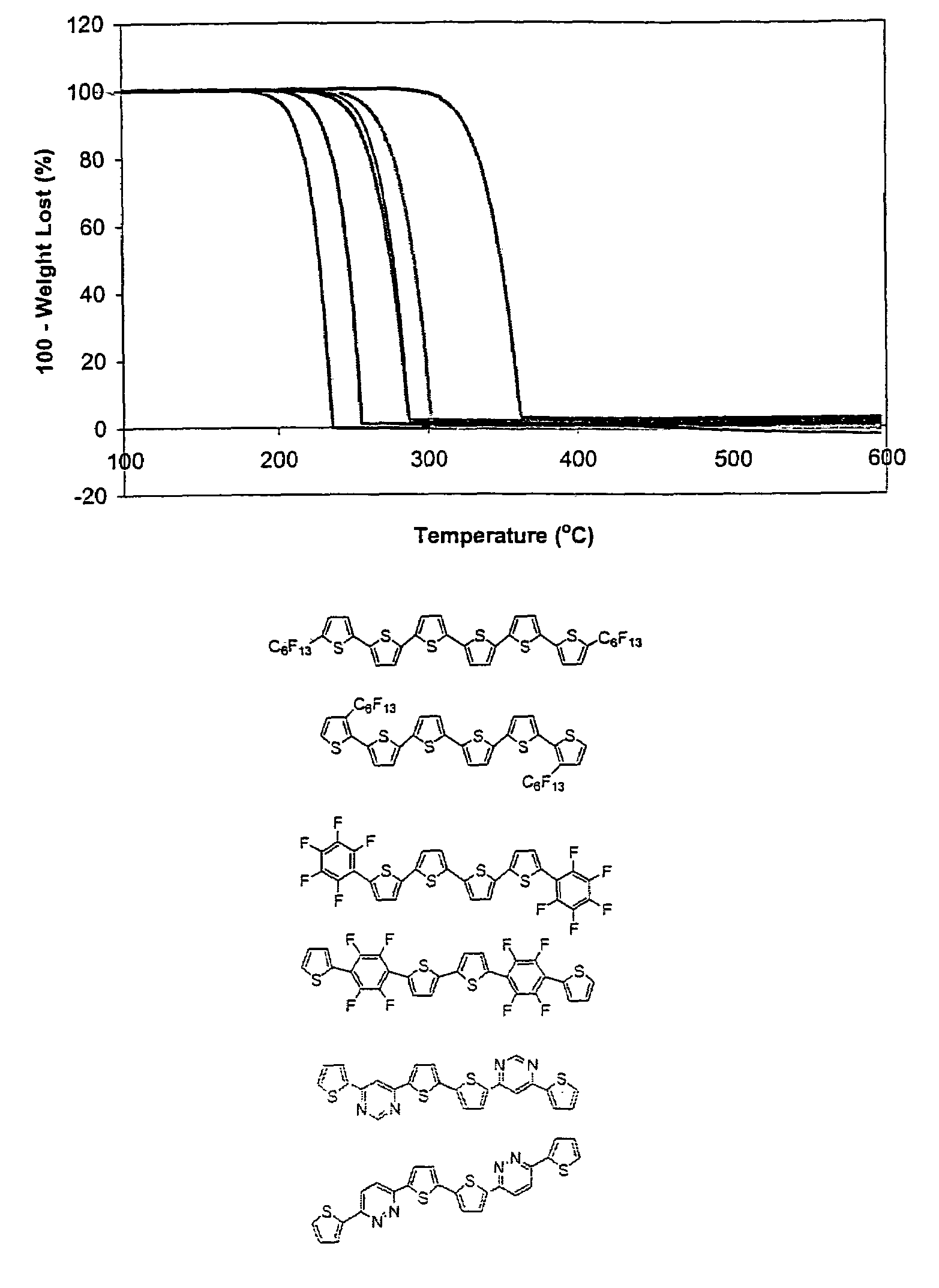

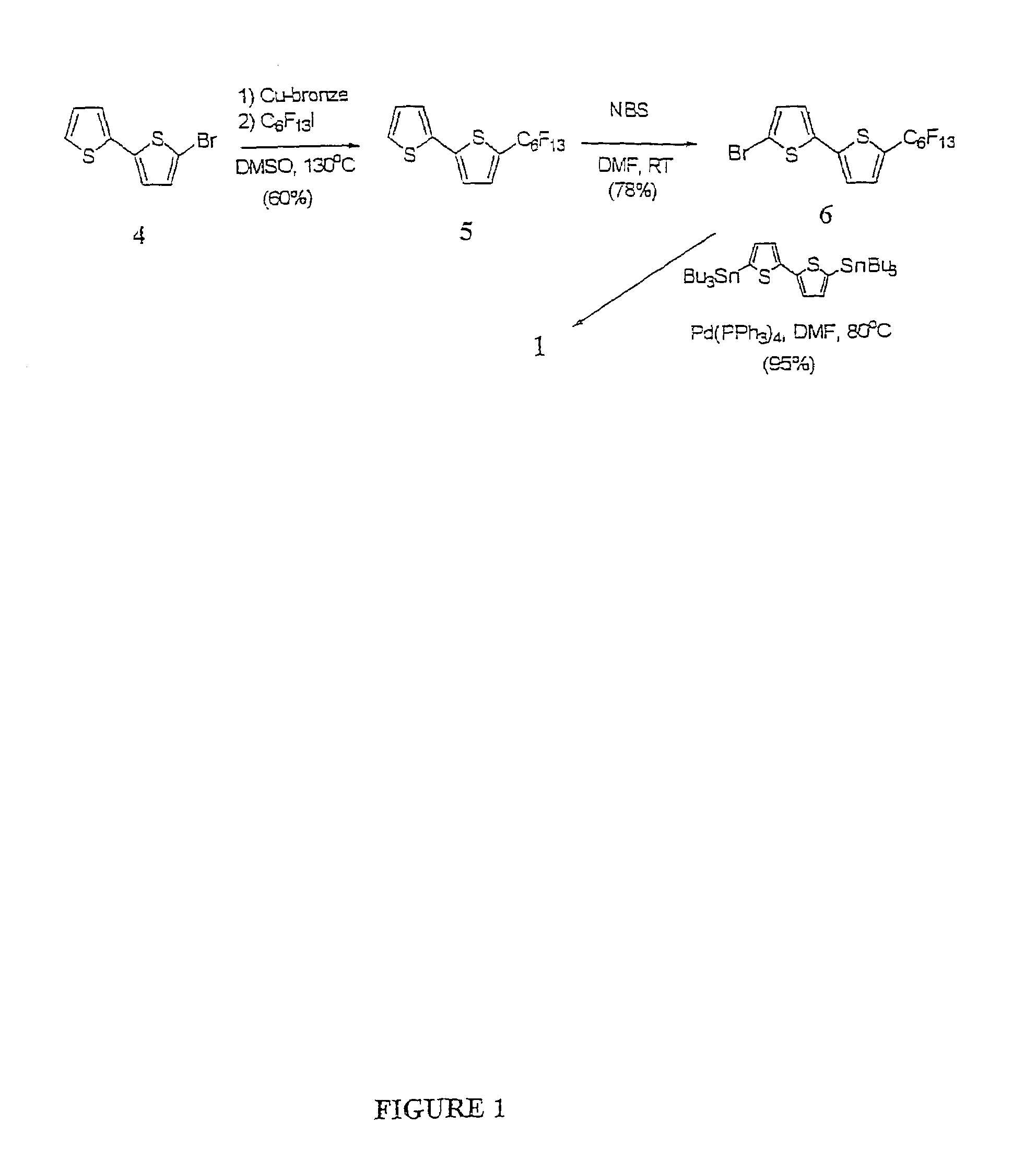

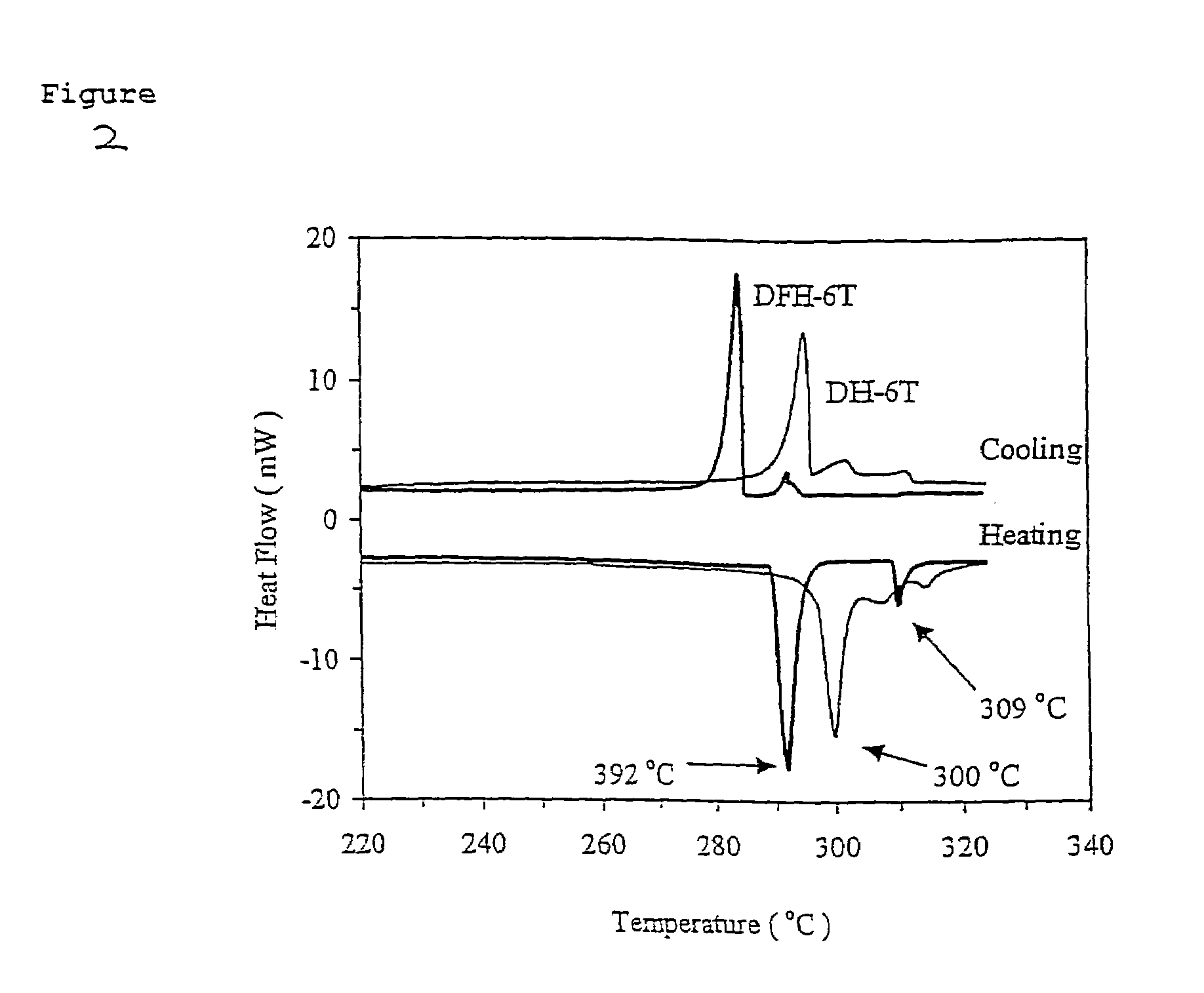

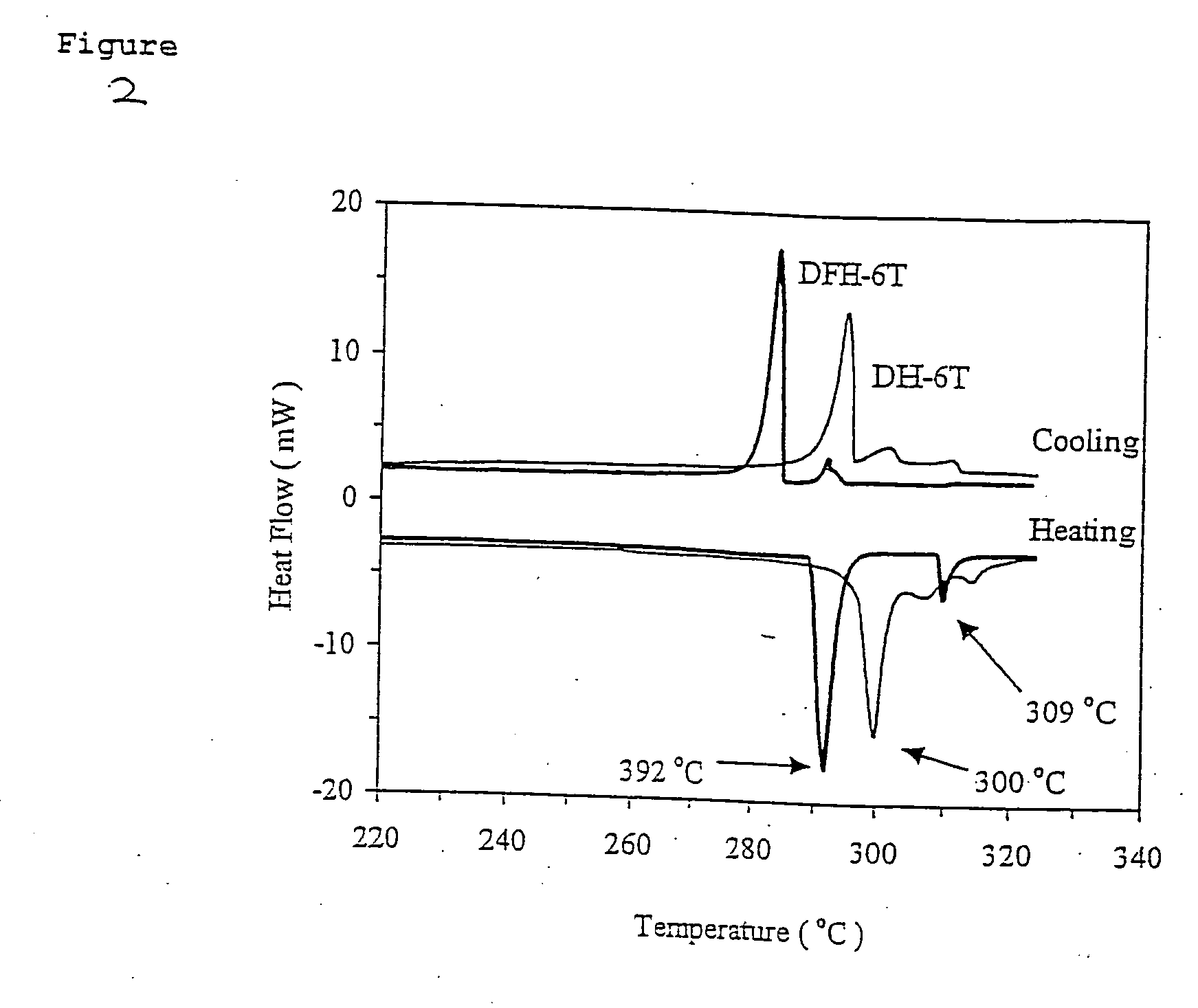

The new fluorocarbon-functionalized and / or heterocycle-modified polythiophenes, in particular, α,ω-diperfluorohexylsexithiophene DFH-6T can be straightforwardly prepared in high yield and purity. Introduction of such modifications to a thiophene core affords enhanced thermal stability and volatility, and increased electron affinity versus the unmodified compositions of the prior art. Evaporated films behave as n-type semiconductors, and can be used to fabricate thin film transistors with FET mobilities ˜0.01 cm2 Vs—some of the highest reported to date for n-type organic semiconductors.

Owner:NORTHWESTERN UNIV

Method for cultivating peonies for oil

ActiveCN103621277AIncrease growth temperatureIncrease the probability of successful pollinationHorticulture methodsPlastic bagIndoor air

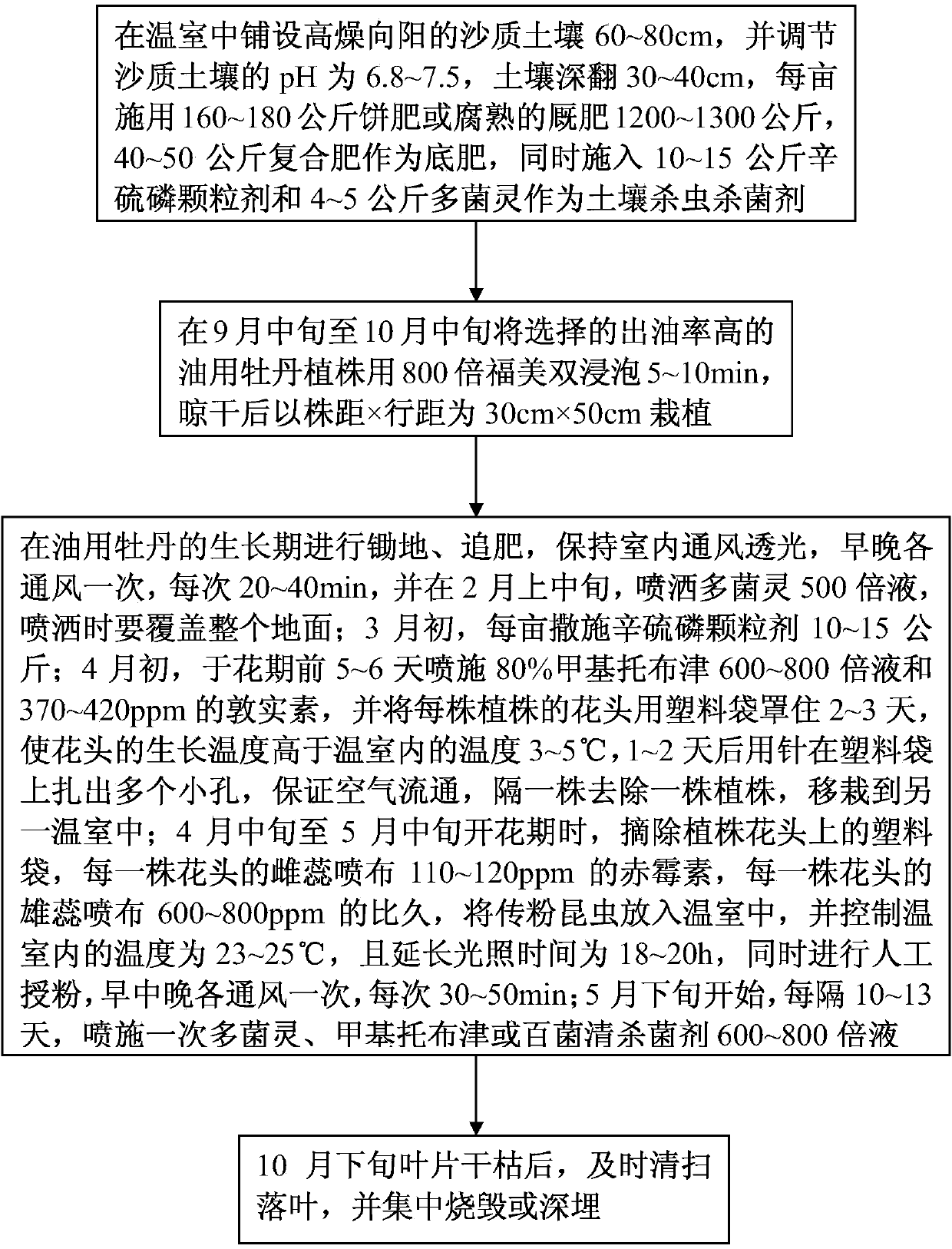

The invention relates to the technical field of flower cultivation, in particular to a method for cultivating peonies for oil. The method comprises the steps that sandy soil is laid in a greenhouse, pH is adjusted, and fertilization and sterilization are carried out; selected peony plants for the oil are planted with row spacing*line spacing of 30cm*50cm; hoeing and topdressing are carried out in the growing period of the peonies for the oil, indoor air ventilation and light transmission are kept, insect killing and sterilization are carried out, chlormequat chloride is sprayed, the flower head of each plant is covered with a plastic bag for 2-3 days, and then a plurality of small holes are pricked in each plastic bag with needles; in the florescence, the plastic bags on the flower heads of the plants are removed, gibberellins and daminozide are sprayed on pistils and stamens respectively, pollinating insects are placed in the greenhouse, temperature, illumination time and ventilation time in the greenhouse are controlled, and meanwhile hand pollination is carried out; fallen leaves are swept away in time, and are burned up or buried deeply in a centralized mode. According to the method, the growing conditions of the peonies for the oil are improved, meanwhile, the pollination success rate in the florescence of the peonies for the oil is increased, and therefore the seed setting rate is improved.

Owner:BEIJING FORESTRY UNIV FOREST SCI CO LTD +1

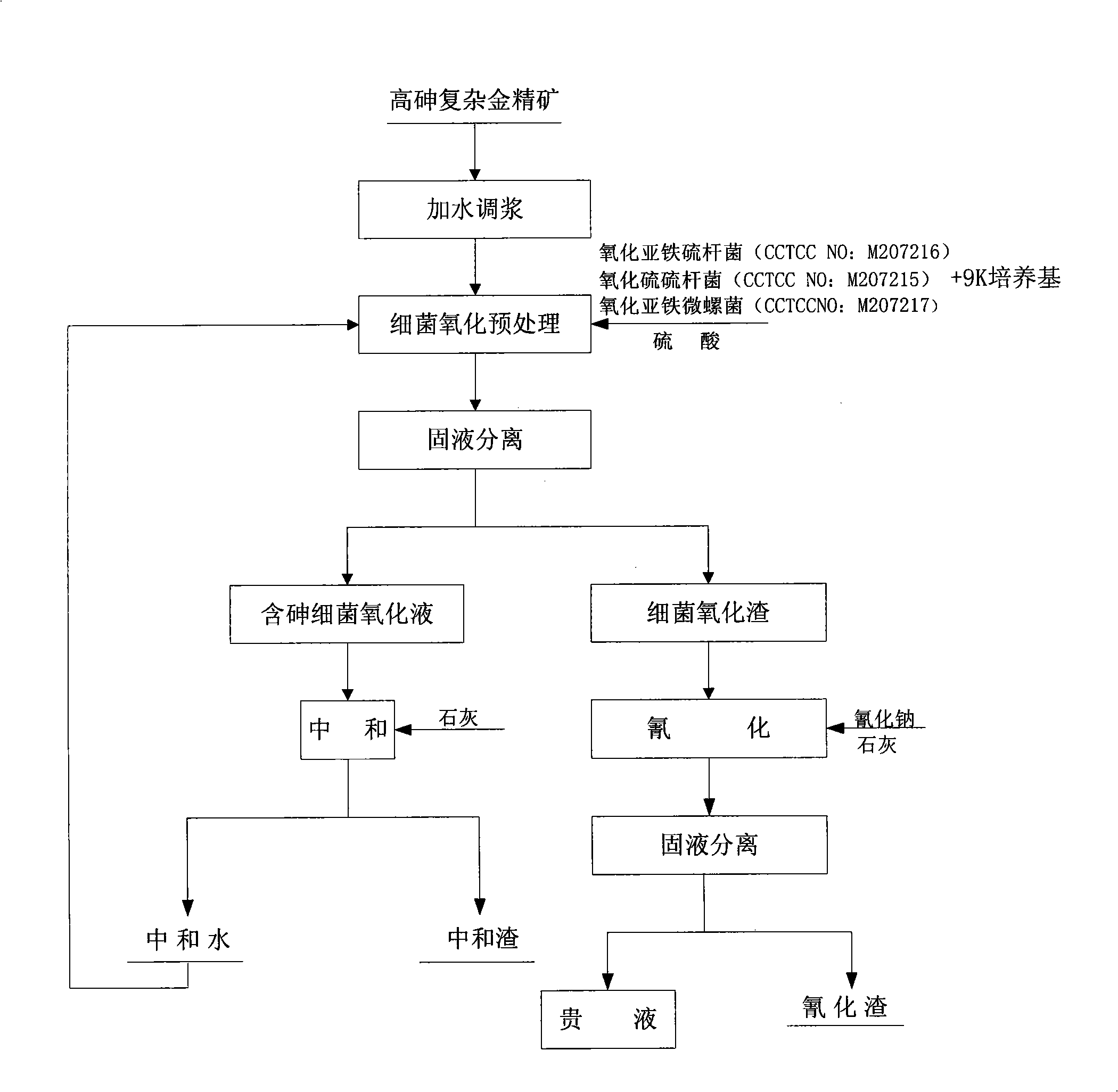

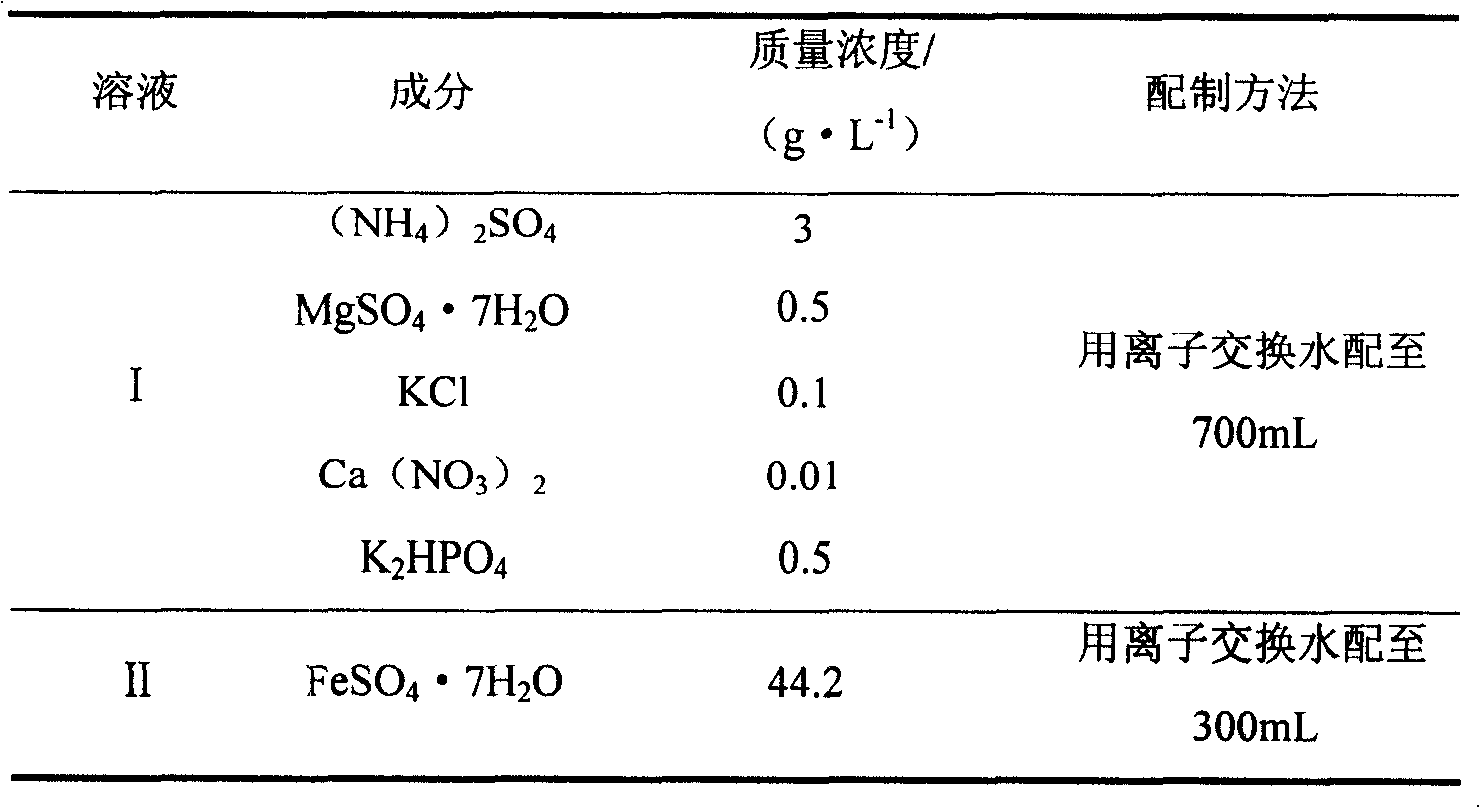

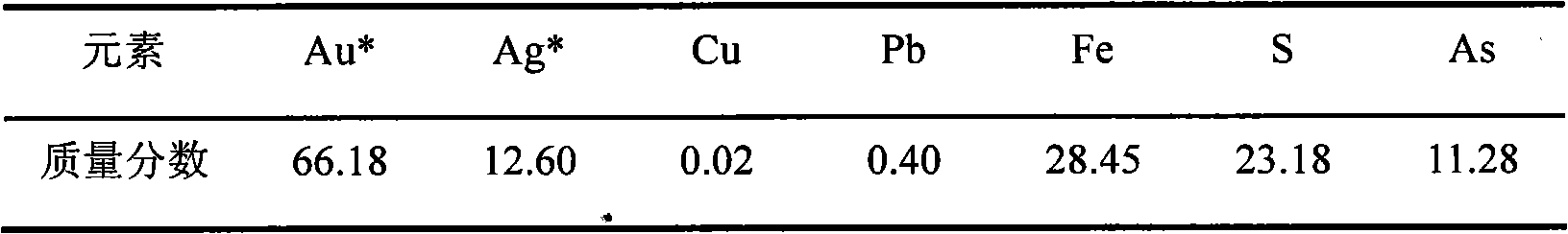

Cyanidation aurum-extracting method for preprocessing high-arsenic complex refractory gold ore by oxidation with arsenic resistant strains

InactiveCN101333599AIncrease growth temperatureStable temperatureProcess efficiency improvementThiobacillus ferrooxidansResistant strain

Disclosed is a cyaniding gold extraction method for pre-treating high-arsenic complex refractory gold ore by arsenic-resistant bacteria oxidation, comprising five steps of arsenic-resistant bacteria culture, flotation concentrate mixing, bacterial oxidation of flotation concentrates, solid-liquid separation and cyaniding gold extraction. The cyaniding gold extraction method adopts specific arsenic-resistant bacteria which are prepared by mixing Thiobacillus ferrooxidans, Thiobacillus thiooxidans and Leptospirillum ferrooxidans, and conducts oxidation pretreatment of high-arsenic complex refractory gold ore. The high-arsenic complex gold ore containing 8 to 20 percent of arsenic can be pretreated, and the arsenic removal rate is 85 to 98 percent. The leaching rate of gold is up to 90 to 95 percent after cyaniding leaching. The cyaniding gold extraction method adopts unique bacteria for leaching ores, greatly saves cooling cost, conducts direct oxidation of high-arsenic complex gold ore containing 8 to 20 percent of arsenic, and has advantages of being widely adaptable, simple in operation, environmentally friendly and remarkably beneficial.

Owner:NORTHEASTERN UNIV

Forming ii-vi core-shell semiconductor nanowires

InactiveUS20110177683A1Many solutionsLow melting pointNanoinformaticsSemiconductor/solid-state device manufacturingNanowireNanoparticle

A method of making II-VI core-shell semiconductor nanowires includes providing a support; depositing a layer including metal alloy nanoparticles on the support; and heating the support and growing II-VI core semiconductor nanowires where the metal alloy nanoparticles act as catalysts and selectively cause localized growth of the core nanowires. The method further includes modifying the growth conditions and shelling the core nanowires to form II-VI core-shell semiconductor nanowires.

Owner:NANOCO TECH LTD

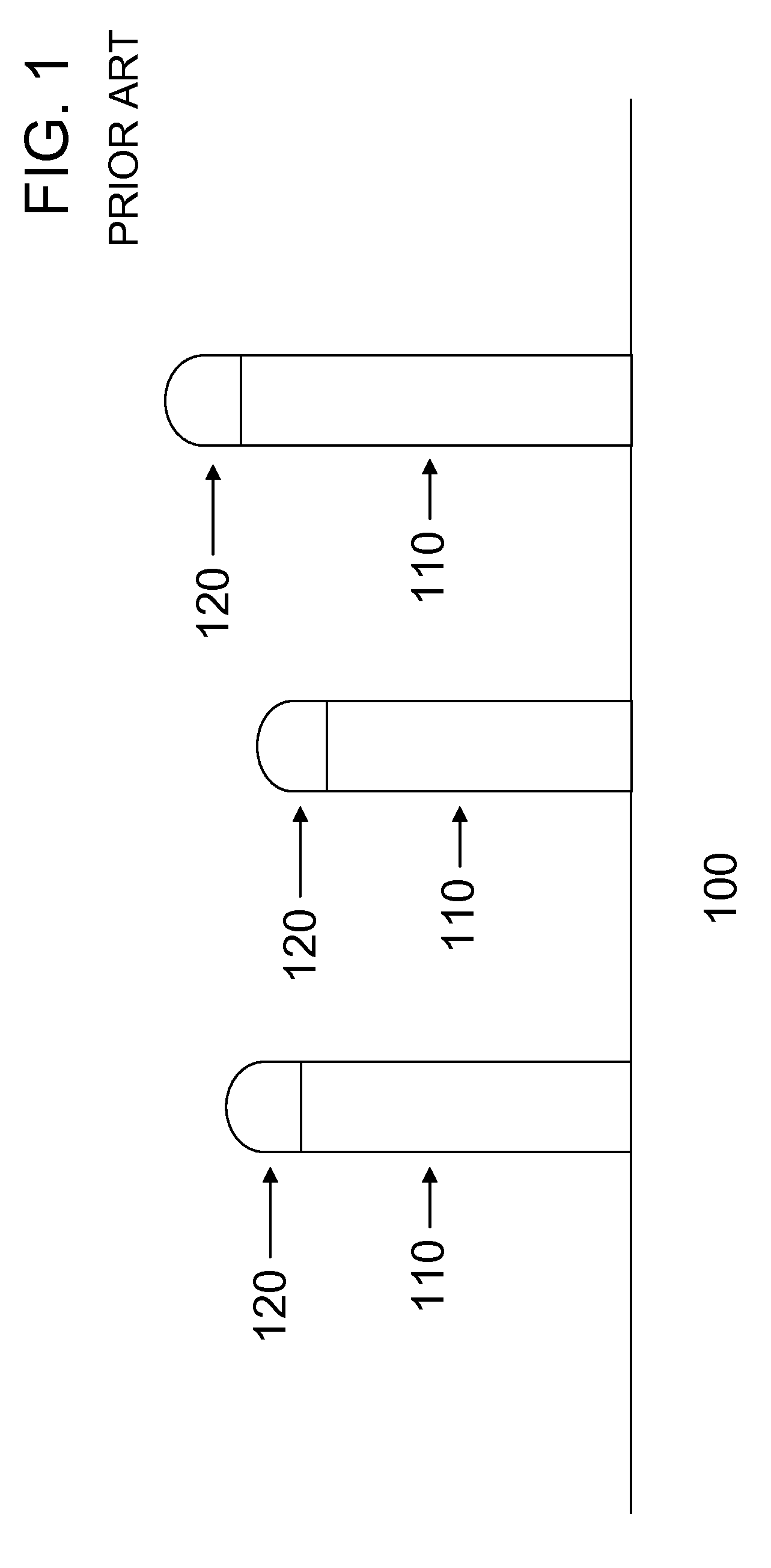

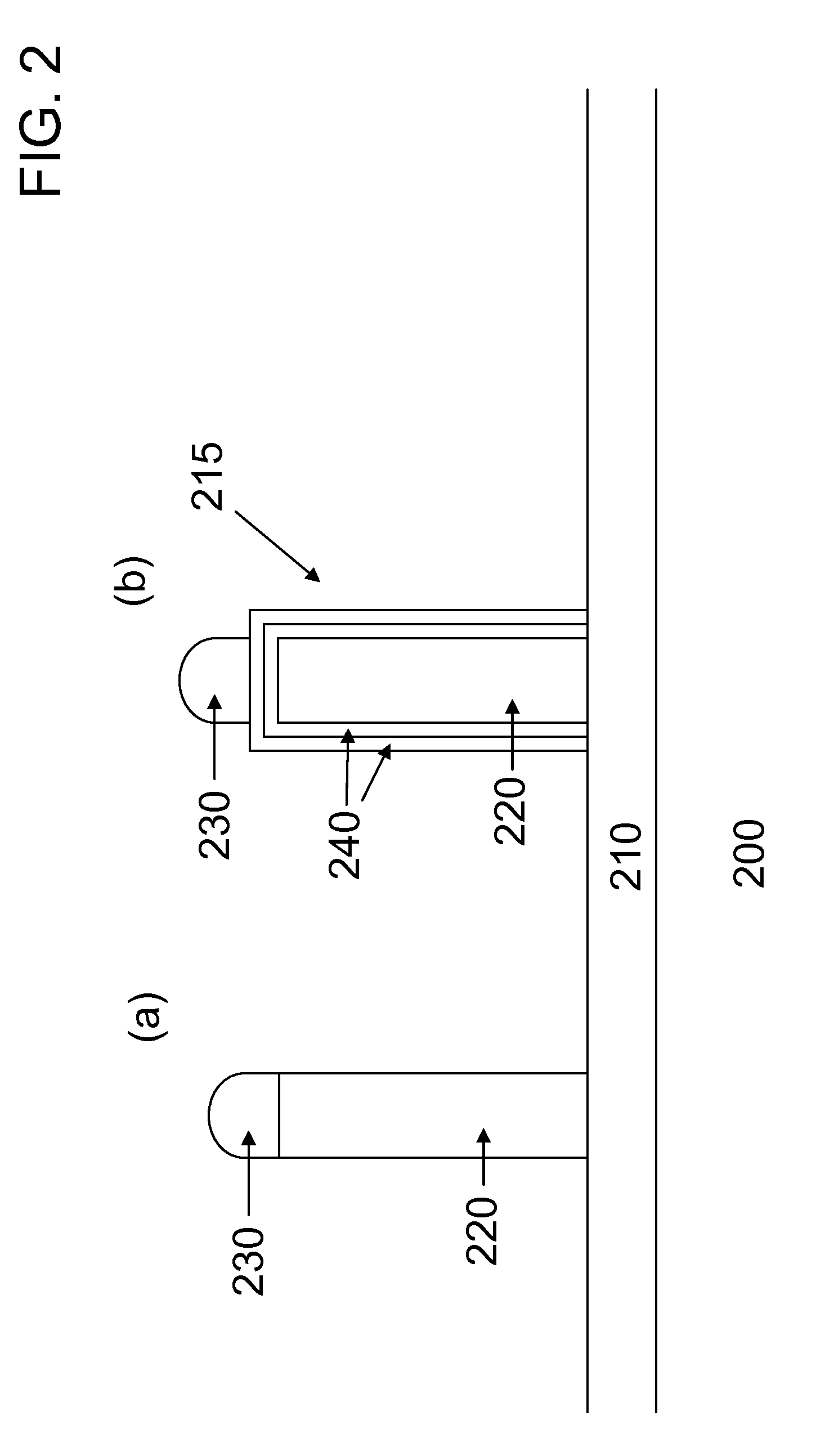

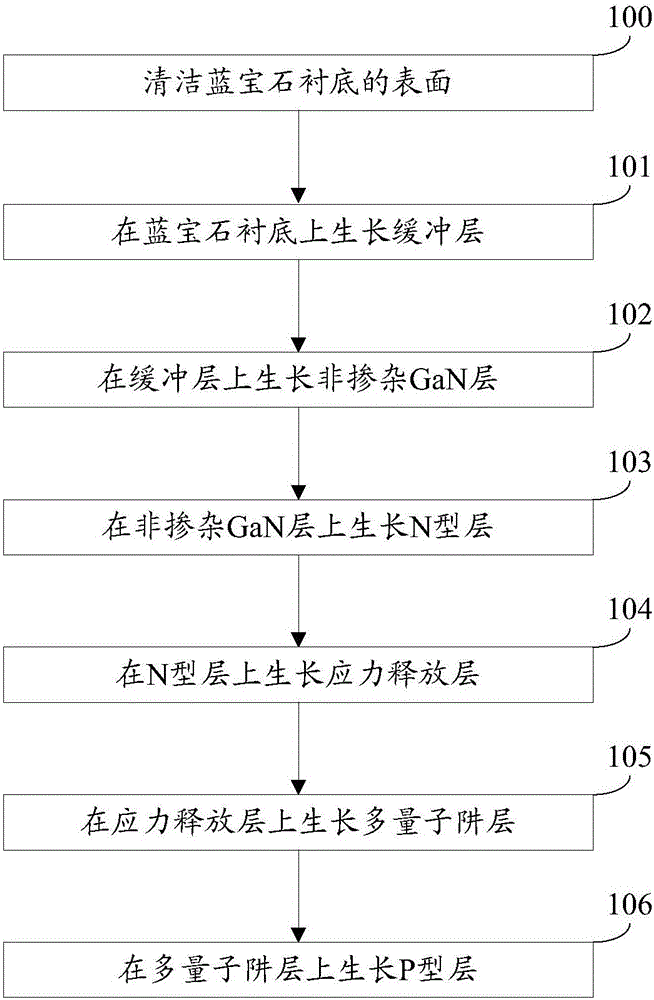

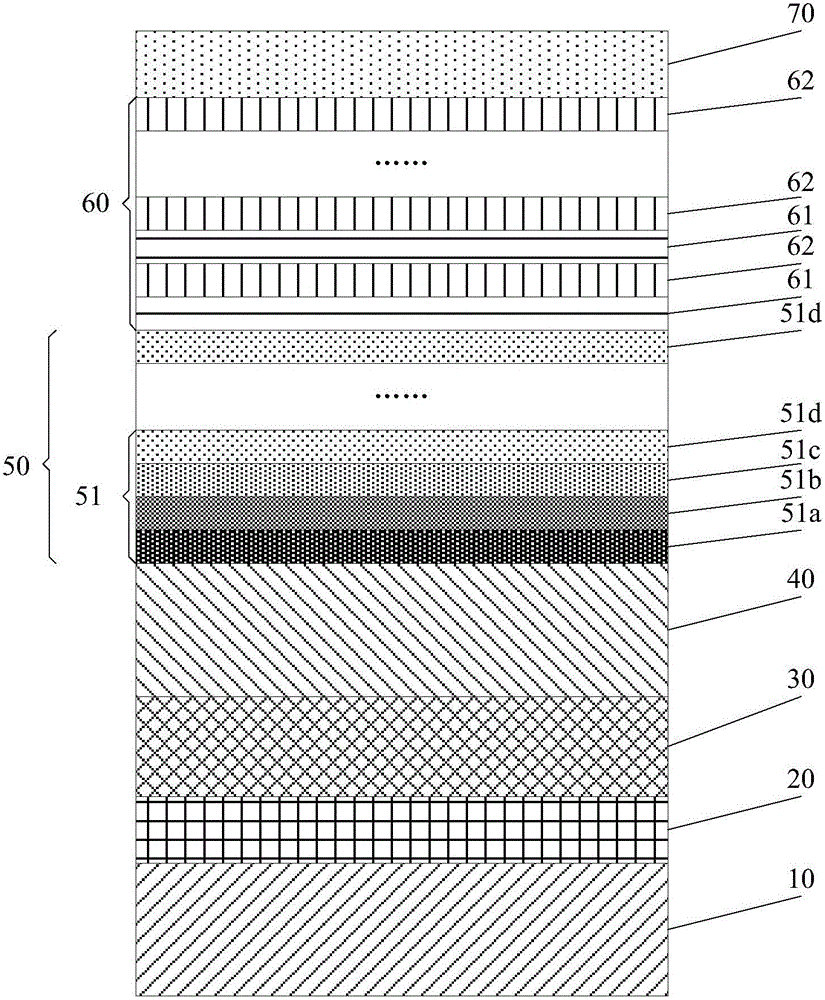

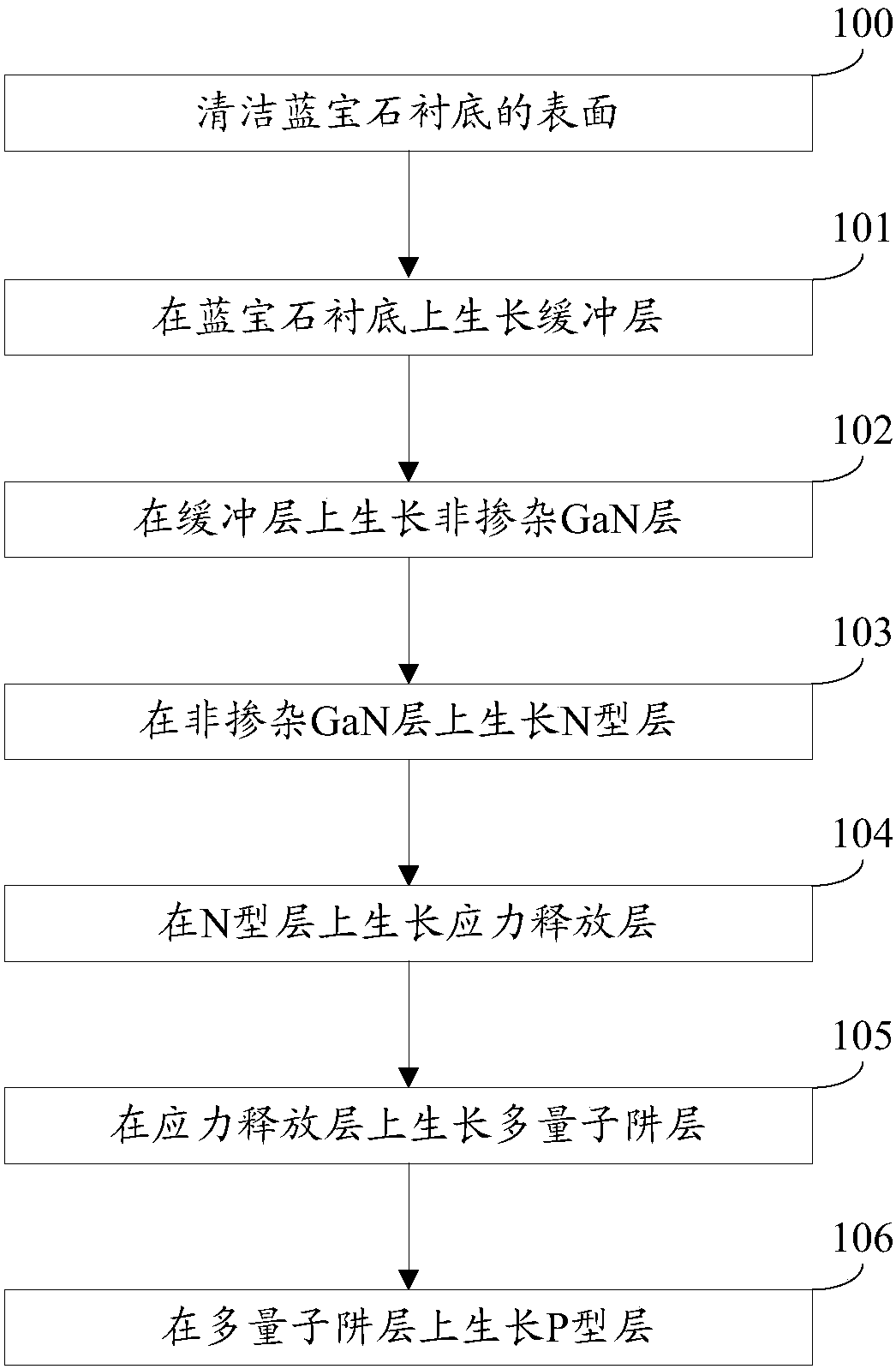

Preparation method for epitaxial wafer of GaN-based light emitting diode

ActiveCN106057988AImprove growth qualityImprove photoelectric performanceSemiconductor devicesLattice mismatchMultiple stress

The invention discloses a preparation method for an epitaxial wafer of a GaN-based light emitting diode, and belongs to the technical field of a semiconductor. The preparation method comprises the steps of laminating a buffer layer, a non-doped GaN layer, an N type layer, a stress release layer, a multi-quantum well layer and a P type layer on a sapphire substrate in sequence, wherein the stress release layer comprises multiple stress release sub-layers, the stress release sub-layers comprise a first sub-layer, a second sub-layer, a third sub-layer and a fourth sub-layer which are laminated in sequence, the first sub-layer is an AIGaN layer, the third sub-layer is an InGaN layer, the second and fourth sub-layers are GaN layers, and the growth temperature of the first sub-layer is higher than that of the third sub-layer. According to the method, a periodic structure is employed in the stress release layer, the relatively low growth temperature is employed in the InGaN layer, thereby facilitating good growth of lattices, the stress generated between the sapphire substrate and the GaN layers due to lattice mismatch can be released, the growth quality of the multi-quantum well layer is improved, and the photoelectric property of the LED is improved.

Owner:HC SEMITEK SUZHOU

Molecular beam epitaxy growth of ternary and quaternary metal chalcogenide films

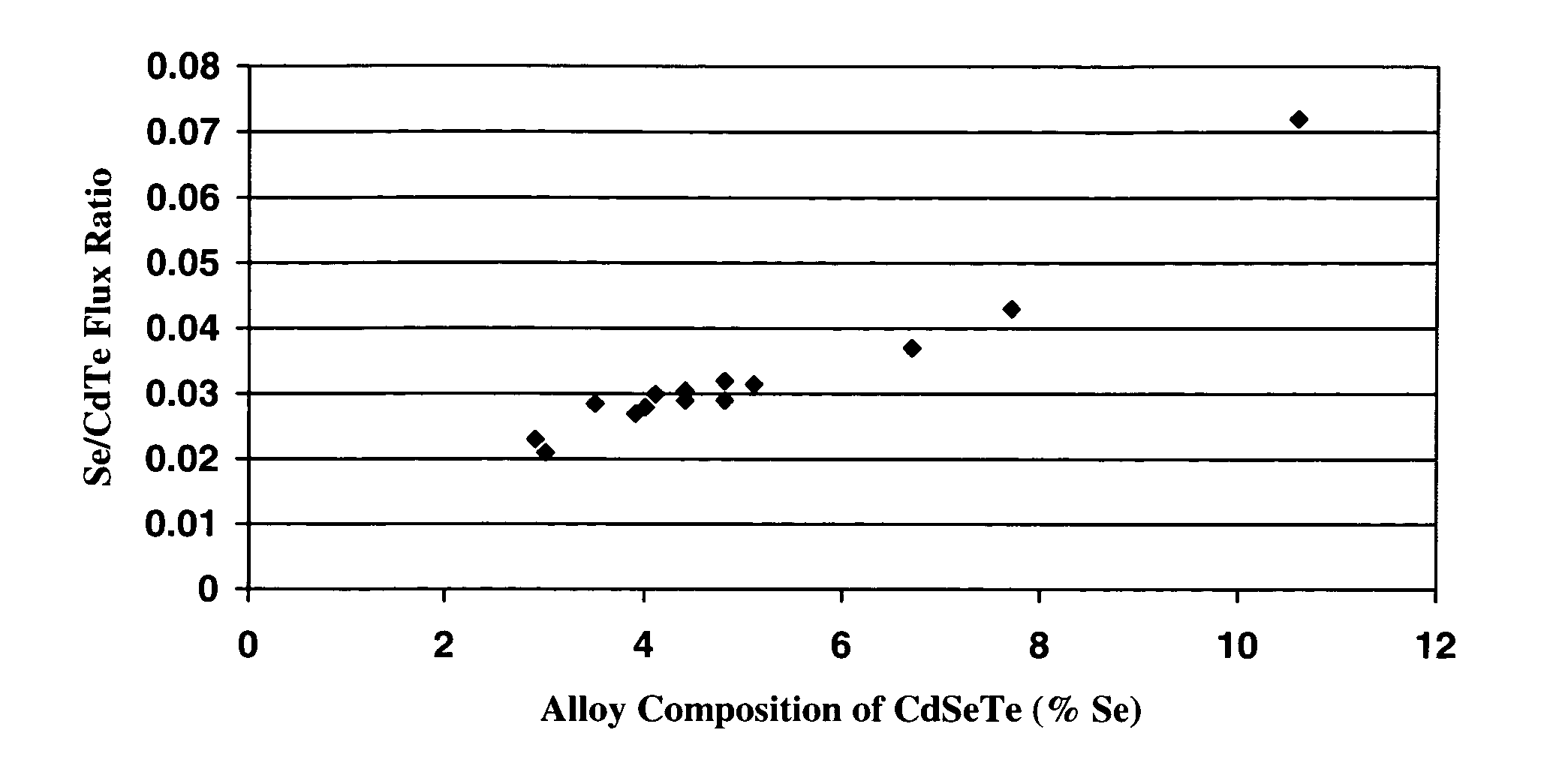

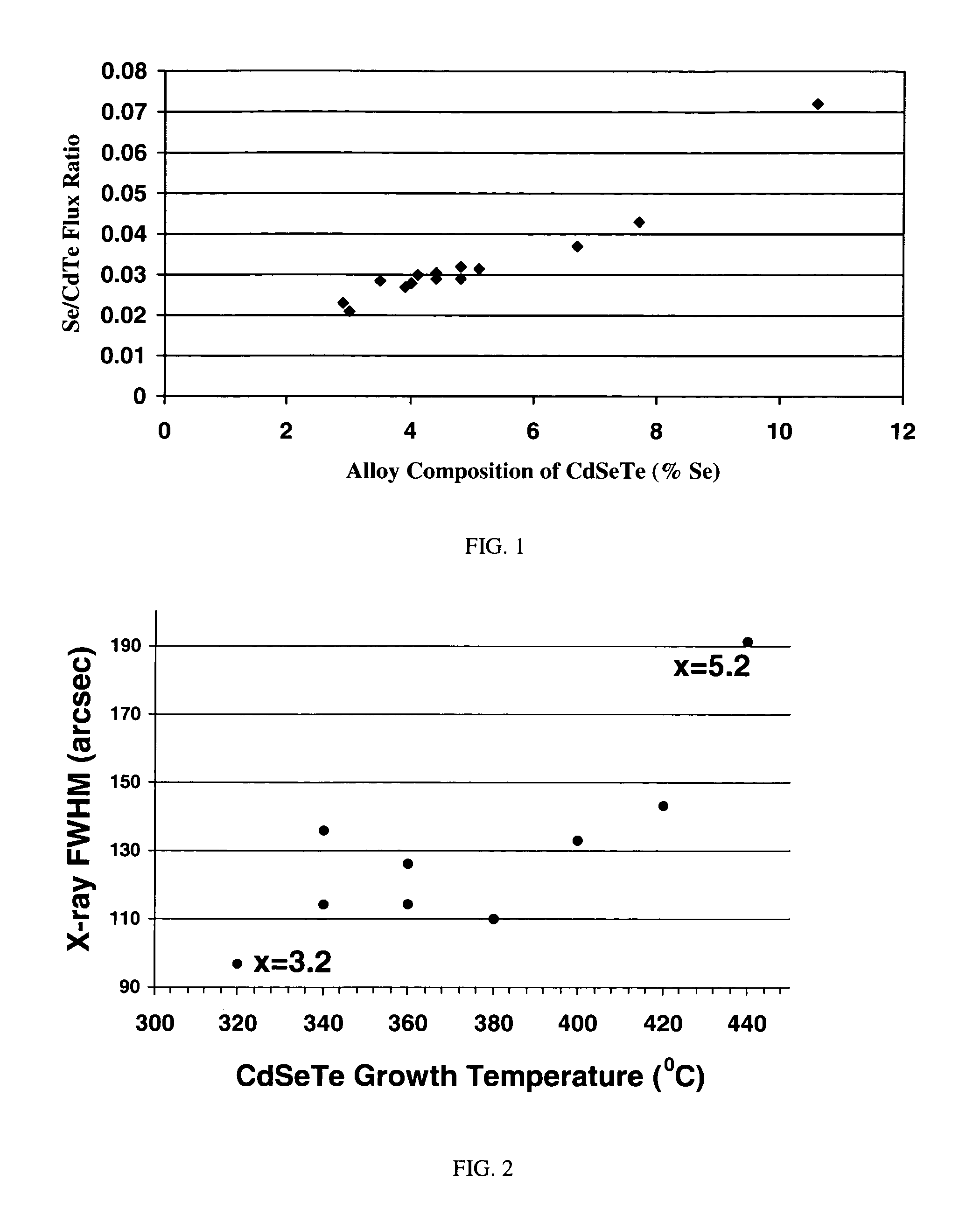

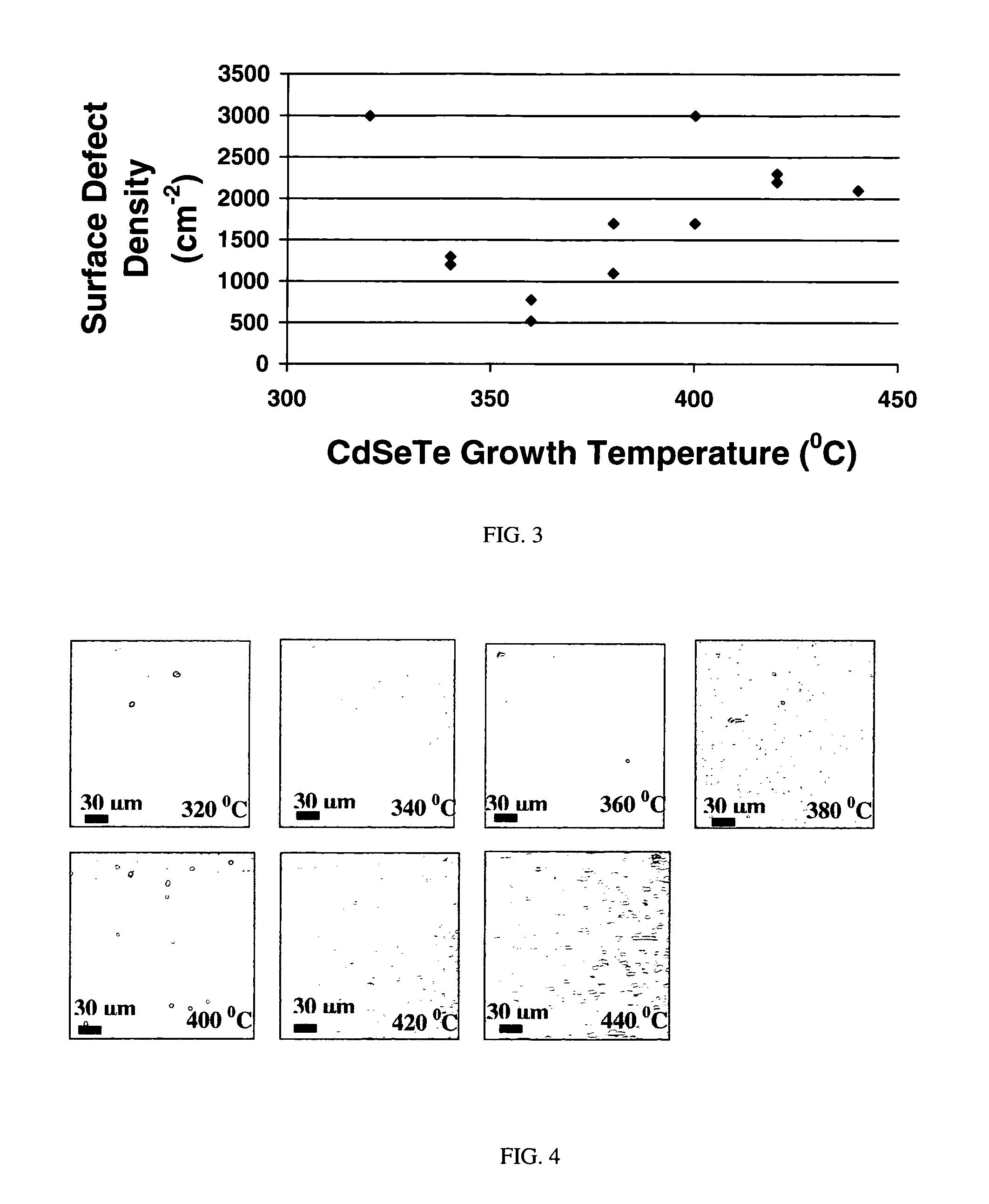

InactiveUS7518207B1Improve surface morphologyReduce surface defect densitySemiconductor/solid-state device manufacturingPhotovoltaic energy generationRocking curveSulfur

The ternary alloy CdSexTe1-x(2 1 1) and the quaternary alloy Cd1-zZnzSexTe1-x have been grown on Si(2 1 1) substrates using molecular beam epitaxy (MBE). The growth of CdSeTe is facilitated using a compound CdTe effusion source and a Se effusion source while the growth of CdZnSeTe is facilitated using a compound CdTe effusion source, a compound ZnTe effusion source, and an elemental Se source. The alloy compositions (x) and (z) of CdSexTe1-x ternary compound and Cd1-zZnzSexTe1-x are controlled through the Se / CdTe and ZnTe / CdTe flux ratios. The rate of Se incorporation is higher than the rate of Te incorporation as growth temperature increases. As-grown CdSeTe with 4% Se and CdZnSeTe with 4% Zn+Se, which is substantially lattice matched to long-wavelength infrared HgCdTe materials, exhibits excellent surface morphology, low surface defect density (less than 500 cm2), and a narrow X-ray rocking curve (a full-width at half maximum of 103 arcsec).

Owner:UNITED STATES OF AMERICA THE AS REPRESENTED BY THE SEC OF THE ARMY

Culture method for chlorella

ActiveCN102311920ASolve the problem of slow growth or even failure to growIncrease concentrationUnicellular algaeMicroorganism based processesChlorellaBioreactor

The invention discloses a culture method for chlorella, which comprises the following contents: the volume of chlorella seed liquid in a bioreactor accounts for 5 to 15 percent of the total volume of a culture medium; a gas containing 5 to 15 volume percent of CO2 is introduced, the volume of introduced gas is 0.1 to 1.0vvm; and the culture temperature is reduced to 0 to 15 DEG C from 25 to 40 DEG C within 0.5 to 10 days, and chlorella is continuously cultured at a constant temperature of 0 to 15 DEG C for 5 to 15 days. The method disclosed by the invention can allow microalgae to grow normally at a low temperature, and the accumulated amount of fat and CO2 utilization rate of microalgae can be increased.

Owner:CHINA PETROLEUM & CHEM CORP +1

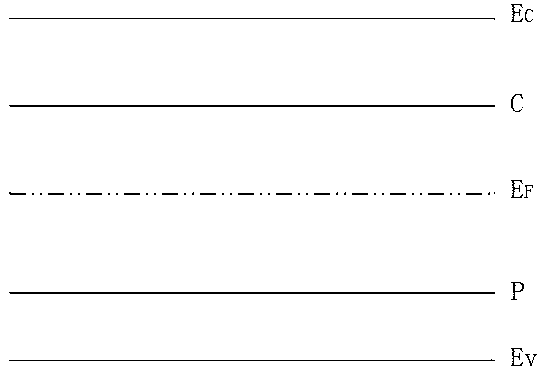

Epitaxial wafer of light-emitting diode and growth method thereof

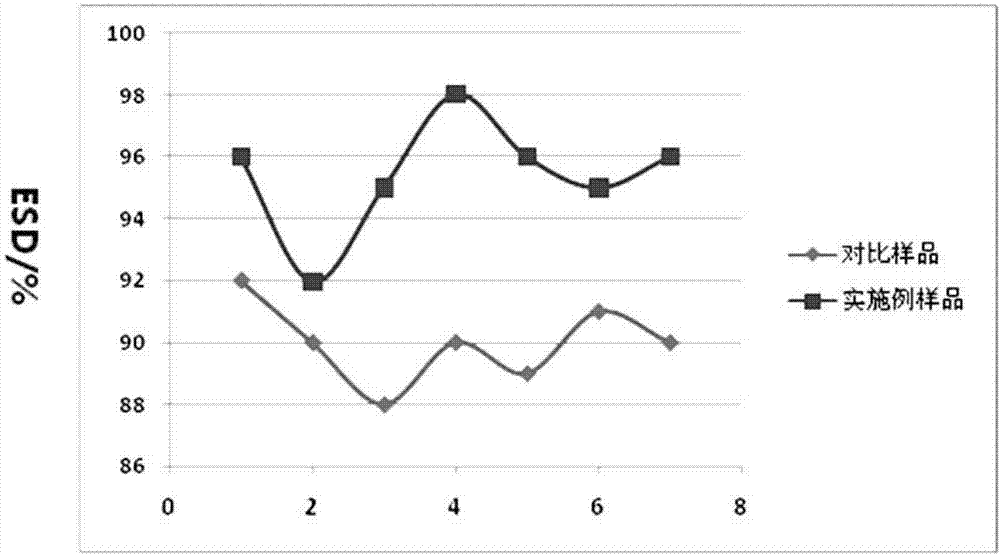

ActiveCN106653970AIncrease growth temperatureImprove internal quantum efficiencySemiconductor devicesDislocationSemiconductor

The invention discloses an epitaxial wafer of a light-emitting diode and a growth method thereof, and belongs to the technical field of semiconductors. The epitaxial wafer comprises a substrate, and a buffer layer, a non-doped GaN layer, an N-type GaN layer, a light-emitting layer and a P-type GaN layer which are laminated on the substrate in turn. Mg is doped in the buffer layer. According to the epitaxial wafer, Mg is doped in the buffer layer, Mg can induce the material of the buffer layer to three-dimensional growth from two-dimensional growth to form three-dimensional island crystal grains with no requirement for the growth mode of low temperature and low pressure of the buffer layer, and the growth temperature of the buffer layer can be increased so that edge dislocation, screw dislocation and other lattice defects can be reduced, the crystal quality of the epitaxial wafer can be enhanced and the internal quantum efficiency and the anti-static capacity of the LED can be enhanced. Besides, the non-doped GaN layer is arranged between the buffer layer and the N-type GaN layer, and the non-doped GaN layer has the effect of separation so as to avoid the influence of the doped Mg in the buffer layer on electron injection light-emitting layer composite luminescence of the N-type GaN layer.

Owner:HC SEMITEK ZHEJIANG CO LTD

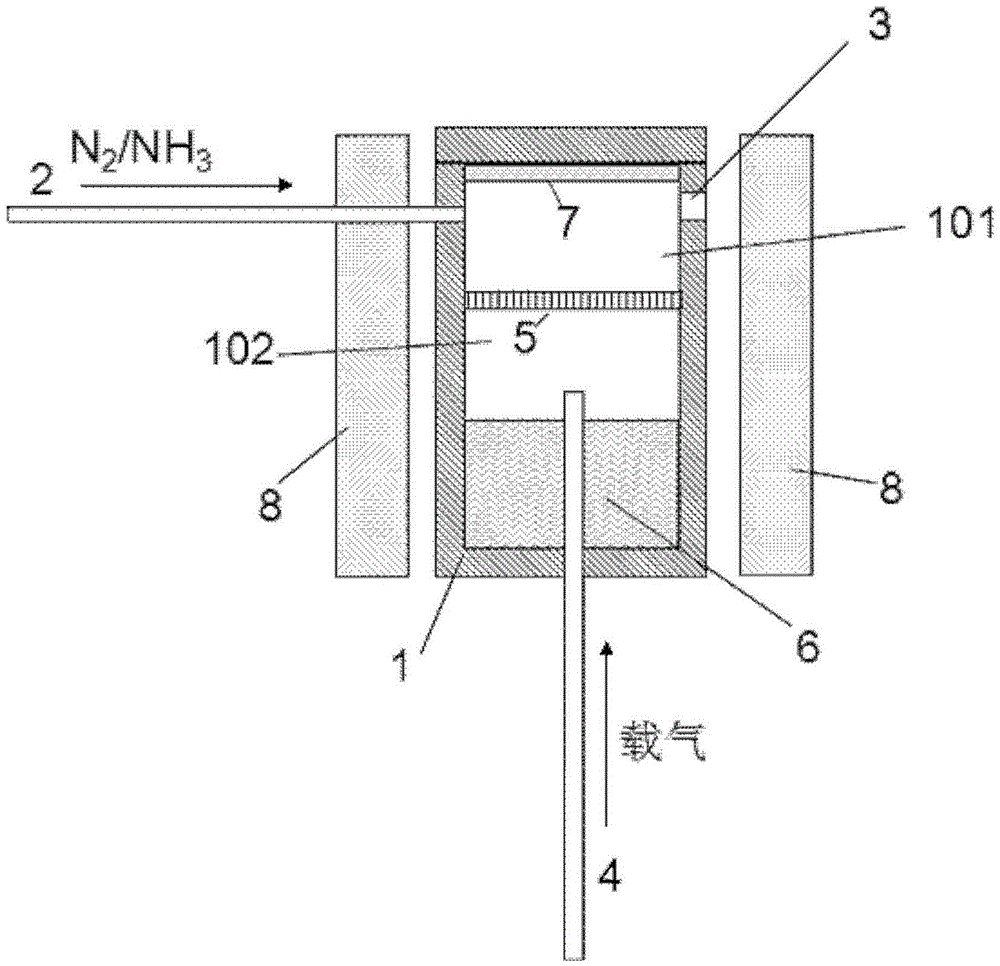

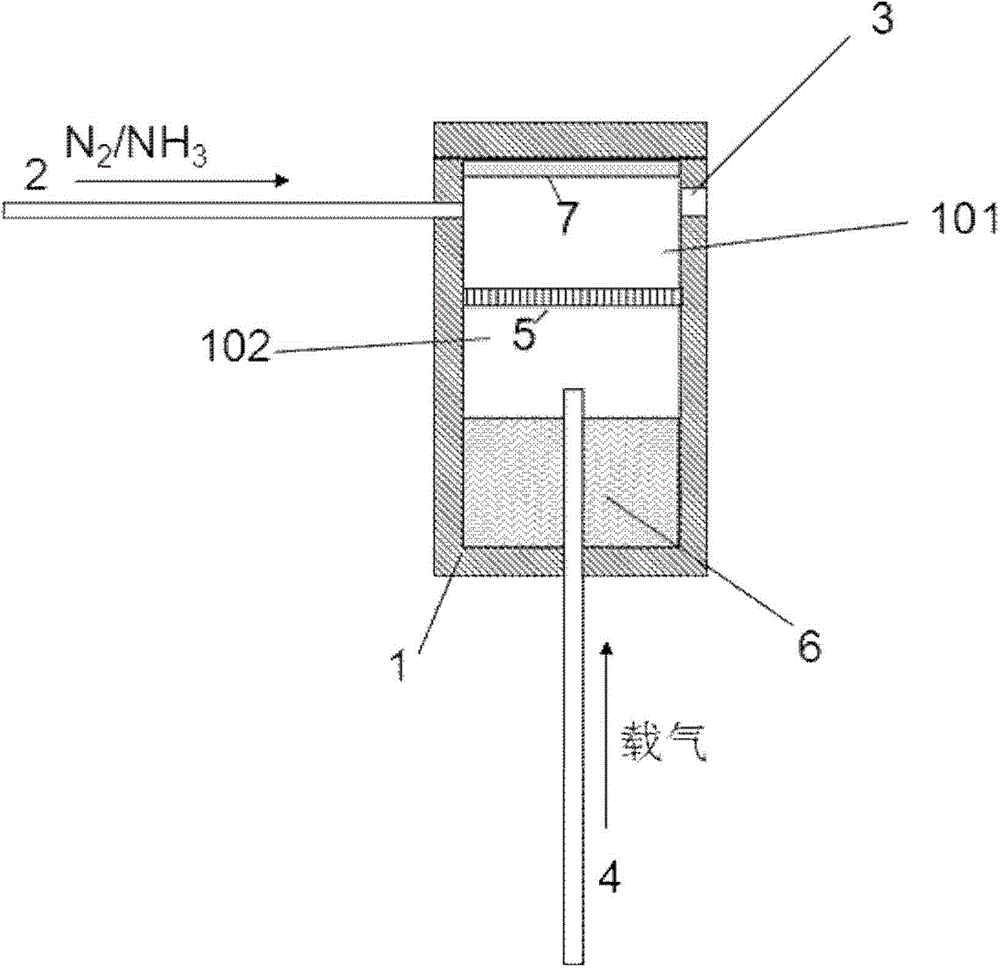

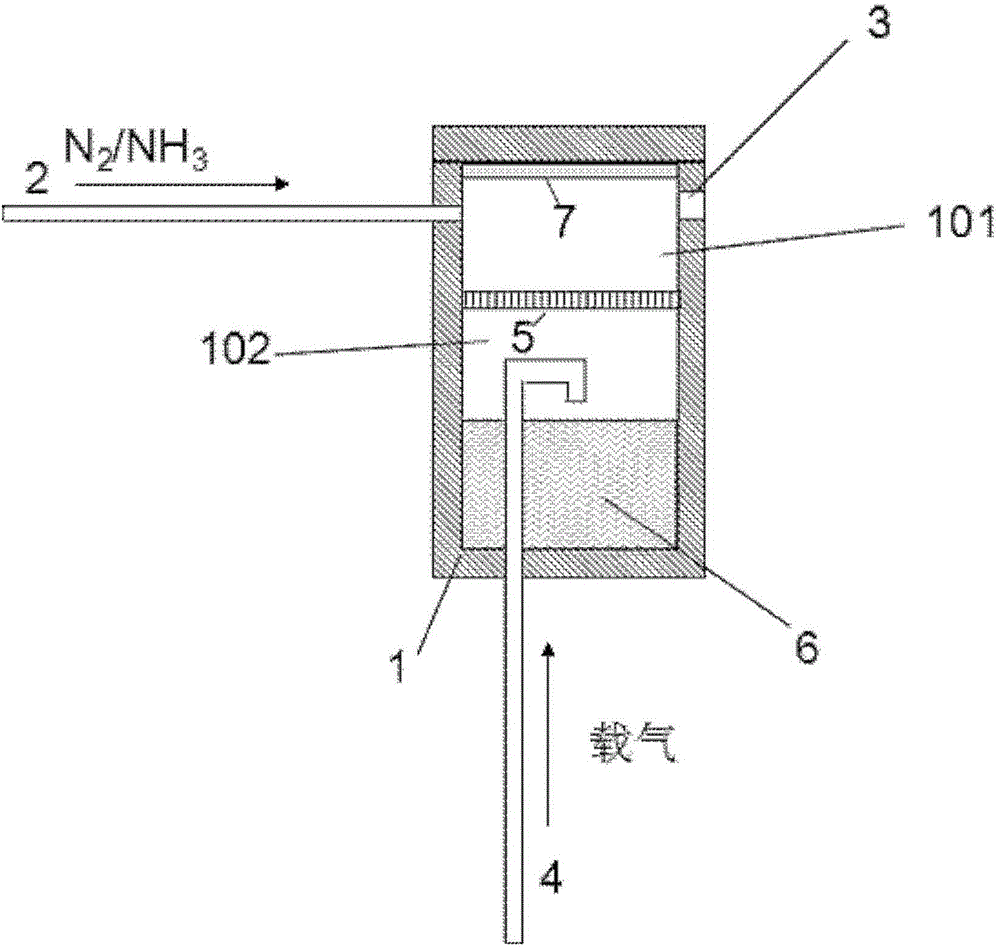

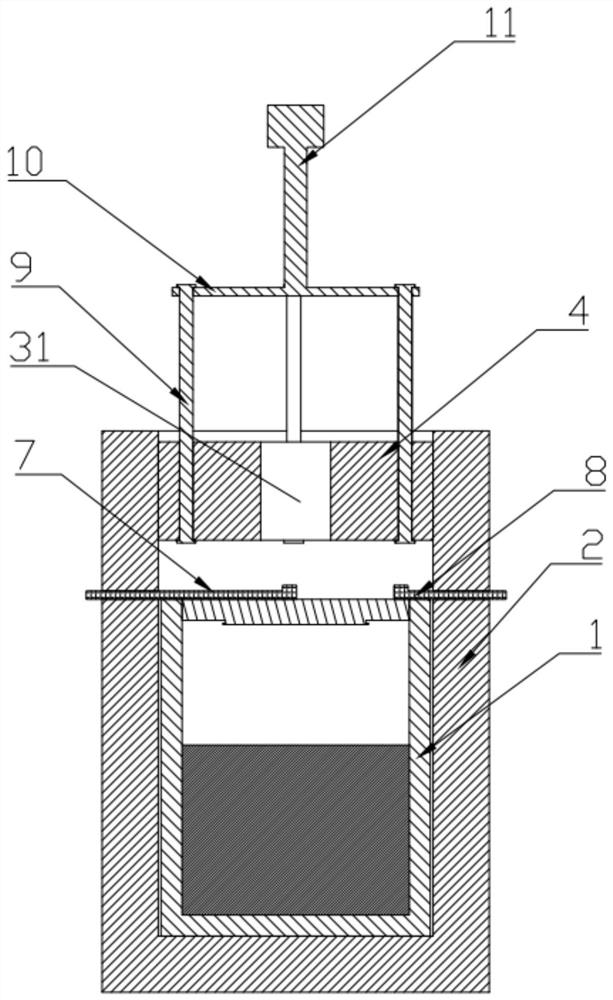

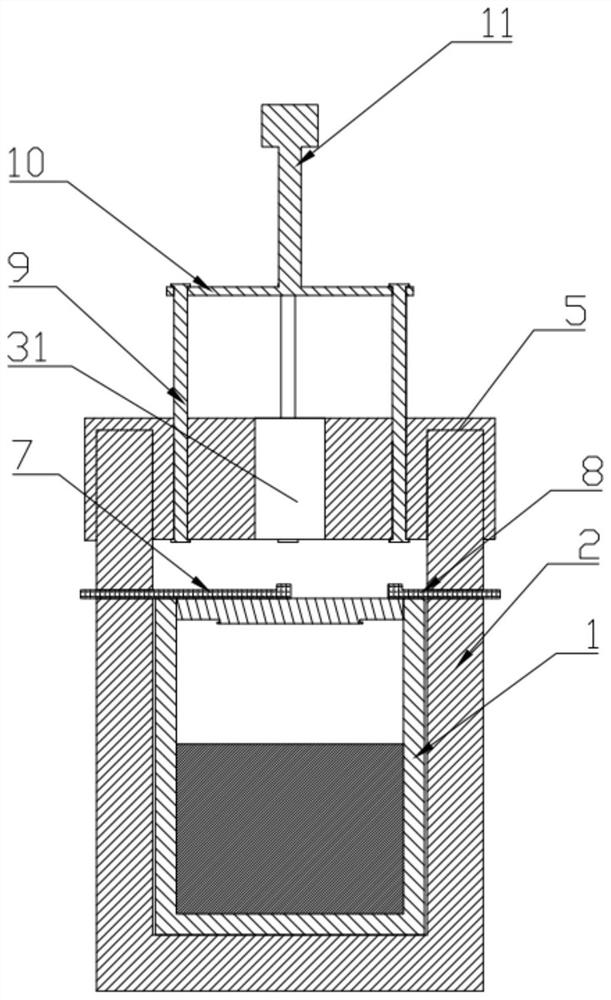

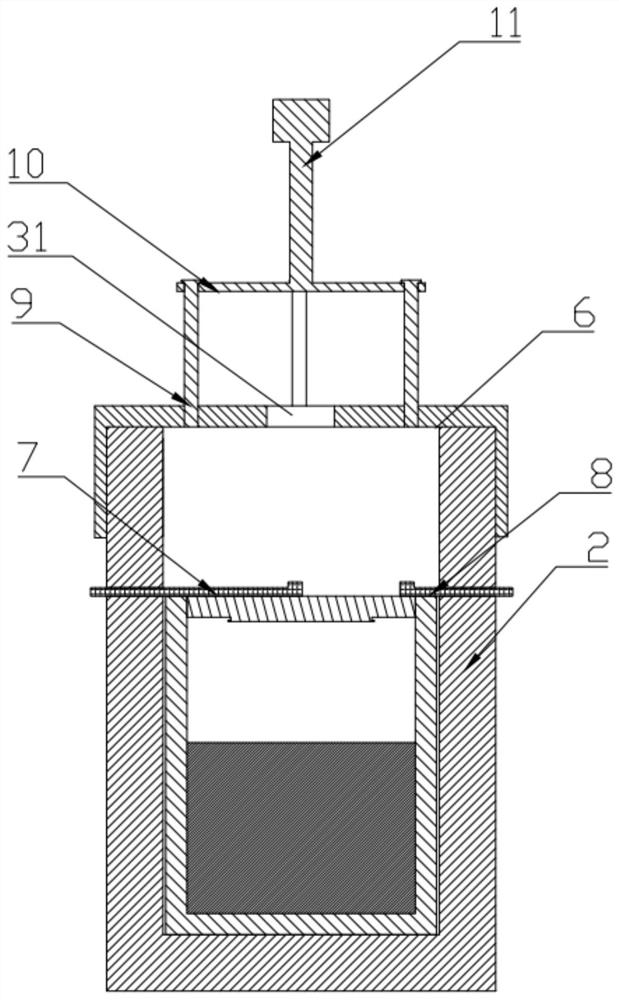

AlN single crystal substrate production apparatus and application method thereof

InactiveCN104878450AAddressing Purity IssuesLess impuritiesPolycrystalline material growthFrom chemically reactive gasesNitrogen gasSeed crystal

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

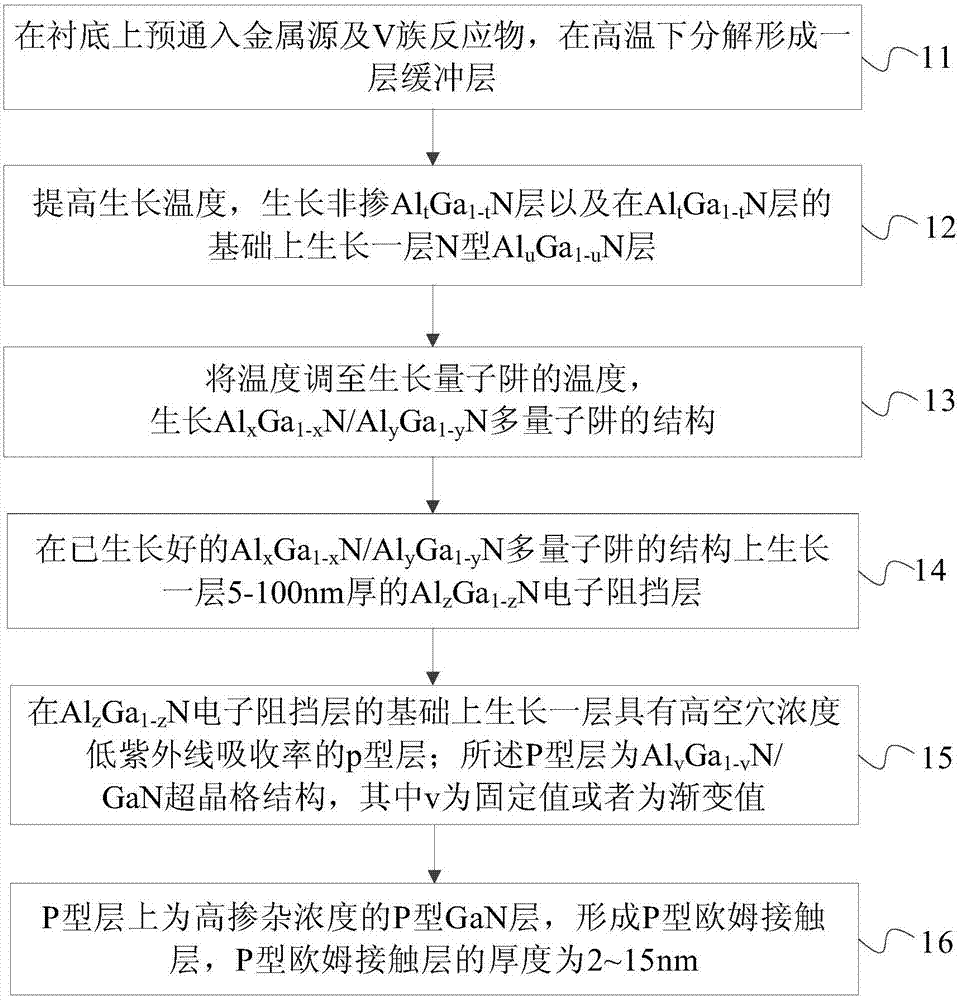

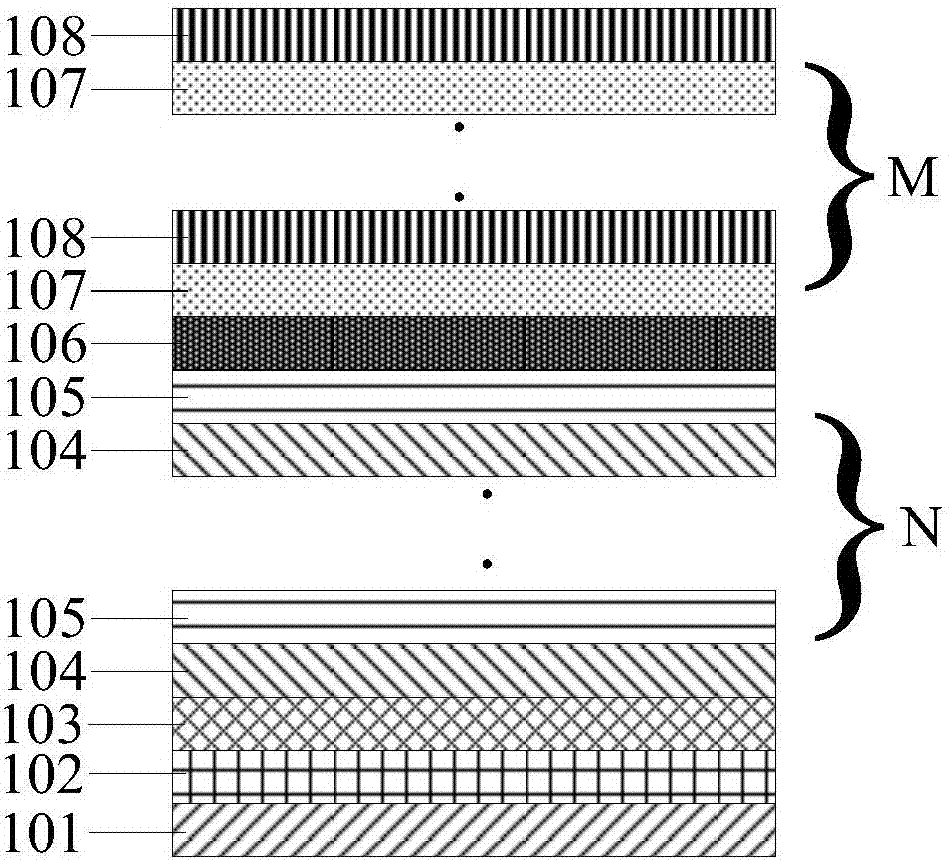

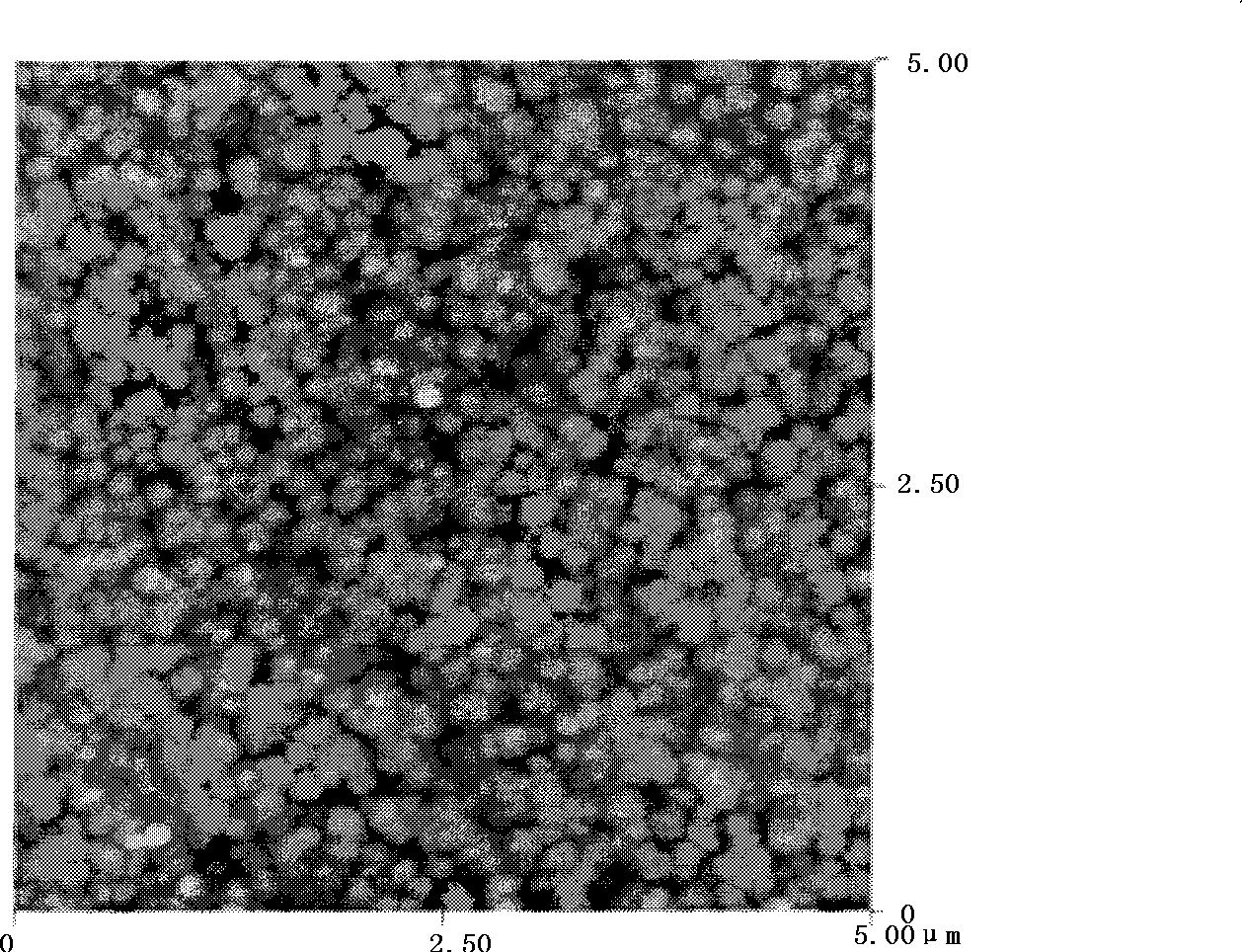

Preparation method of ultraviolet LED and ultraviolet LED

ActiveCN107195742AIncrease growth temperatureImprove performanceSemiconductor devicesOhmic contactQuantum well

The invention provides a preparation method of an ultraviolet LED and the ultraviolet LED. The preparation method comprises the following steps: introducing a metal source and a V-group reactant on a substrate, and decomposing to form a buffer layer under high temperature; increasing growth temperature, growing a non-doped AltGa1-tN layer and growing an N-type AluGa1-uN layer on the basis of the AltGa1-tN layer; adjusting the temperature to be a temperature for growing quantum wells, and growing an AlxGa1-xN / AlyGa1-yN multi-quantum well structure; growing an AlzGa1-zN electron barrier layer with the thickness of 5 to 100 nm on the grown AlxGa1-xN / AlyGa1-yN multi-quantum well structure; growing a P-type layer with high hole concentration and low ultraviolet absorption rate on the basis of the AlzGa1-zN electron barrier layer, wherein the P-type layer is an AlvGa1-vN / GaN superlattice structure, a P-type GaN layer with high dosage concentration is on the P-type layer to form a P-type ohmic contact layer. Through the embodiment of the invention, the absorption of the P-type layer for ultraviolet light emitted by the quantum wells can be effectively reduced, the luminous efficiency of the ultraviolet LED is improved, and the service life of the ultraviolet LED device can be prolonged.

Owner:EPITOP PHOTOELECTRIC TECH

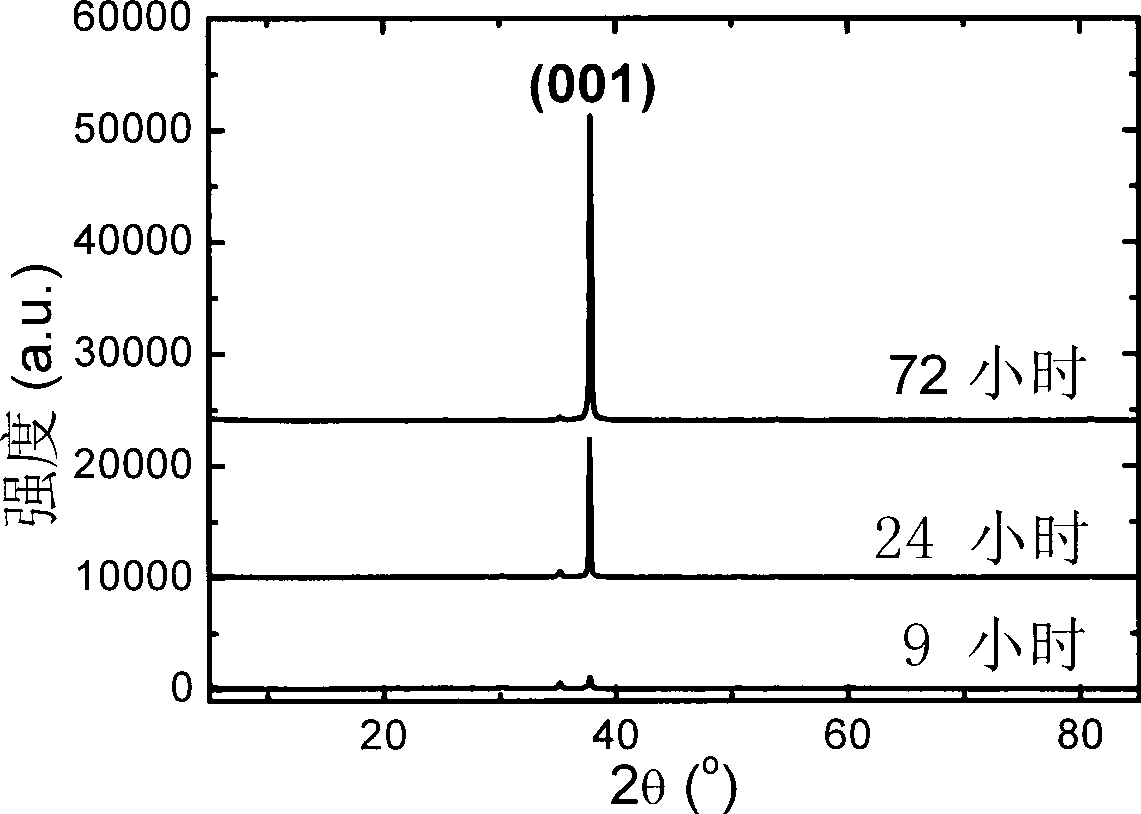

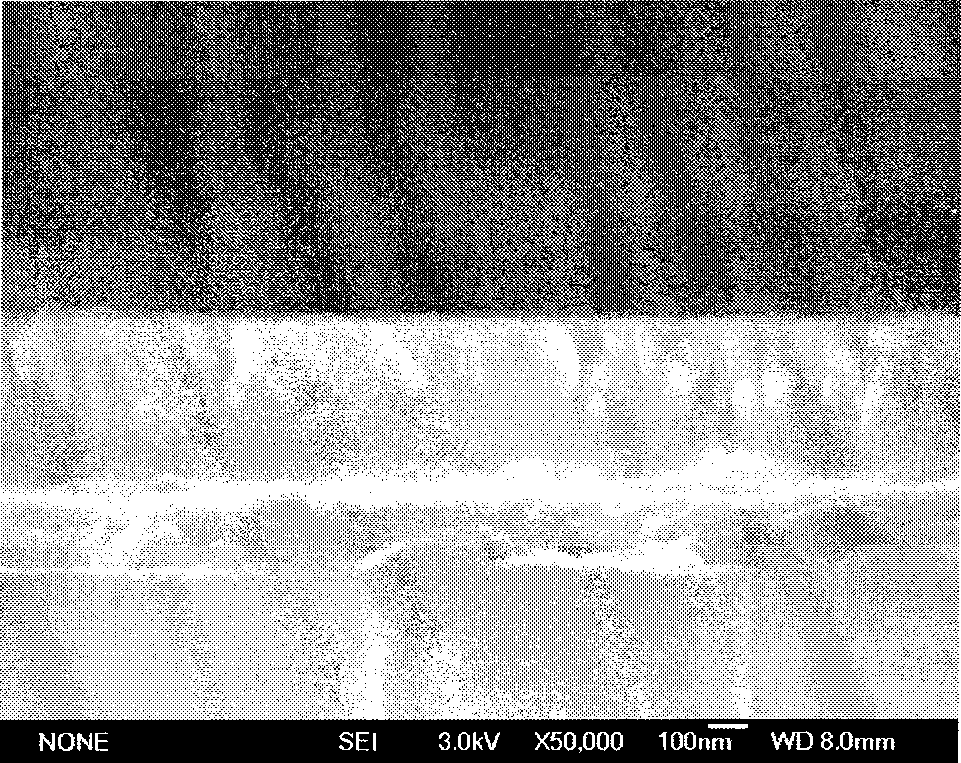

Method for titania film growth in fluorine-based aqueous solution

InactiveCN101439873AHigh densityHigh light transmittanceTitanium dioxideGratingTithonia longiradiata

The invention relates to a method for preparing an anatase titania film with high compactness and high catalytic activity on various matrixes. The method mainly comprises the following steps: firstly, precipitating a titania seed layer with an amorphous form on a matrix; secondly, placing the seed layer in a titanium salt solution which contains a titanium salt stabilizer and has the mol concentration of 0.01 to 0.2mol.L<-1> for growth; and cleaning and drying the grown film to obtain a product. The method improves the compactness of the film and enables the film to have the light transmittance as high as more than 80 percent in the visible light area; and the method also realizes the epitaxial growth of the film in a single c axis direction and greatly improves the crystallinity. In addition, the method adopts a low temperature process and cheap raw material and has little raw material consumption and a simple process, thereby greatly reducing the production cost. The prepared film has potential application prospect in the fields of solar cells, antifog and self-cleaning coating, interference coating, gratings, and microelectronic and electroluminescent devices.

Owner:UNIV OF JINAN

n-Type thiophene semiconductors

InactiveUS20050119440A1High yieldHigh purityConductive materialSolid-state devicesChemistryPolythiophene

The new fluorocarbon-functionalized and / or heterocycle-modified polythiophenes, in particular, α,ω-diperfluorohexylsexithiophene DFH-6T can be straightforwardly prepared in high yield and purity. Introduction of such modifications to a thiophene core affords enhanced thermal stability and volatility, and increased electron affinity versus the unmodified compositions of the prior art. Evaporated films behave as n-type semiconductors, and can be used to fabricate thin film transistors with FET mobilities ˜0.01 cm2 / Vs—some of the highest reported to date for n-type organic semiconductors.

Owner:NORTHWESTERN UNIV

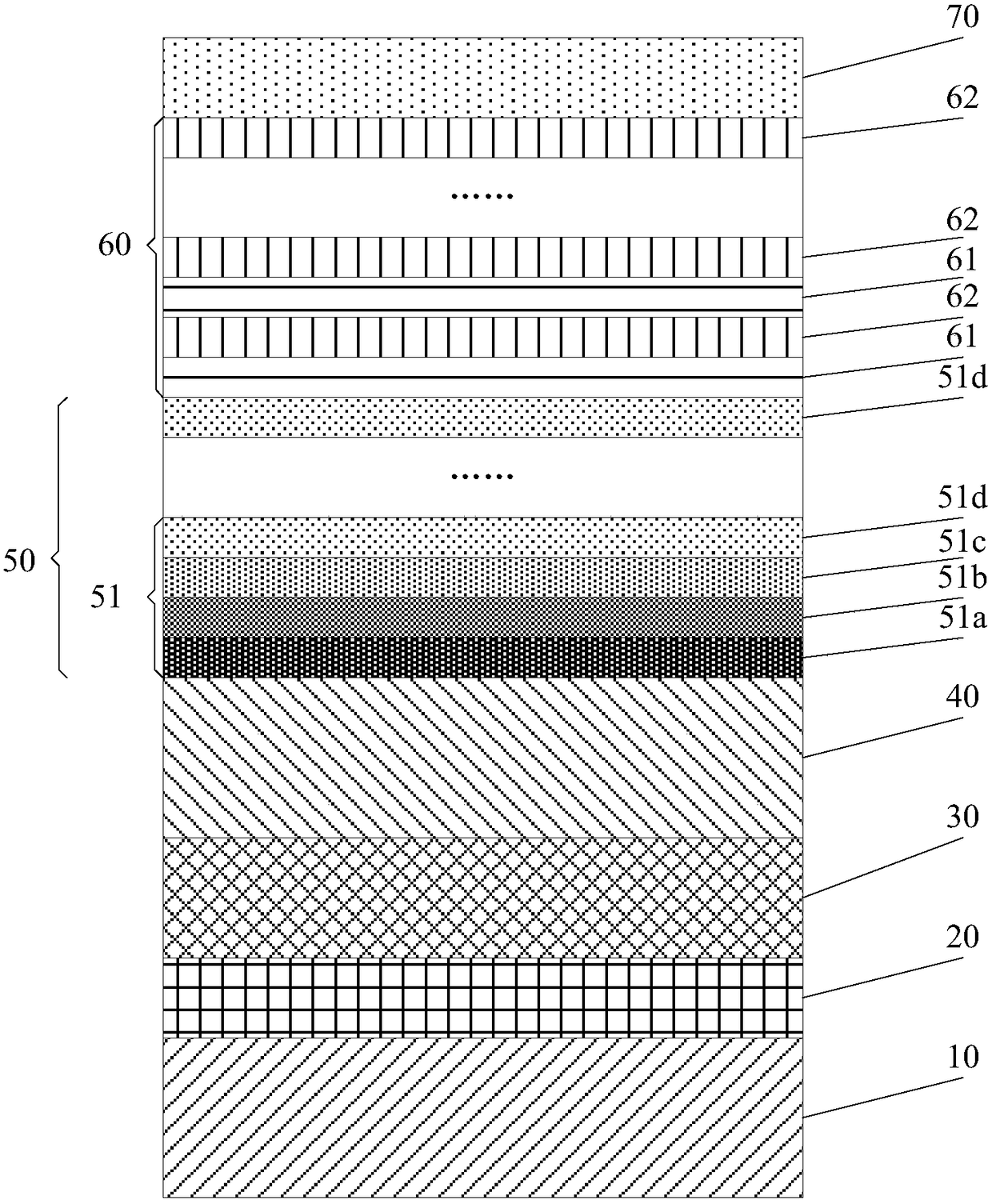

GaN-based light emitting diode epitaxial wafer and manufacturing method therefor

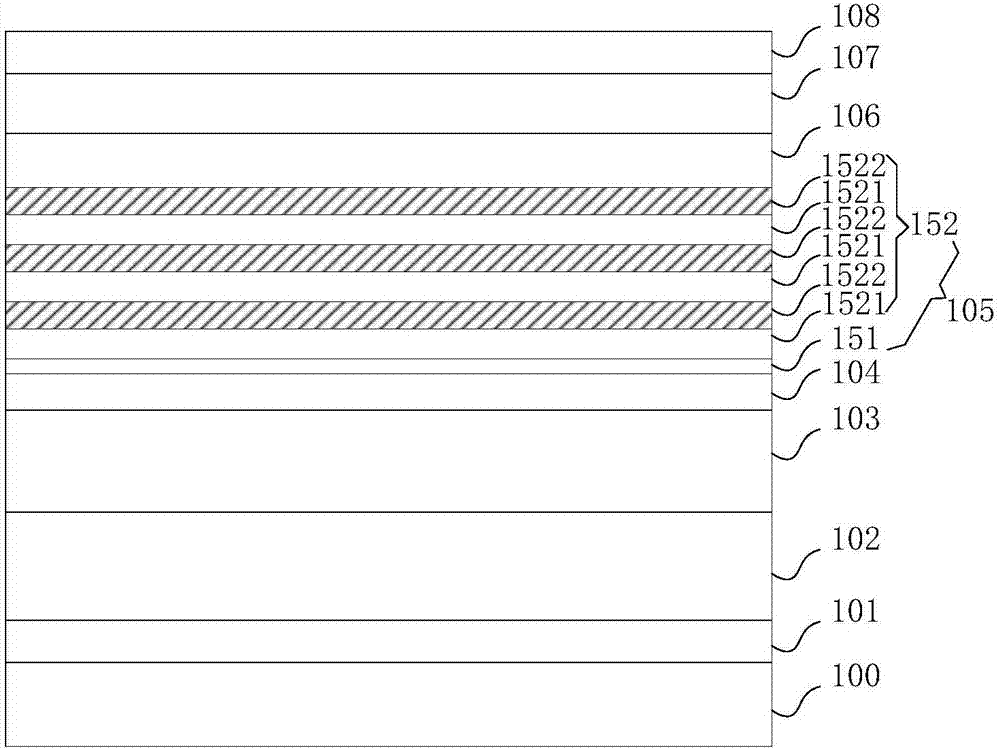

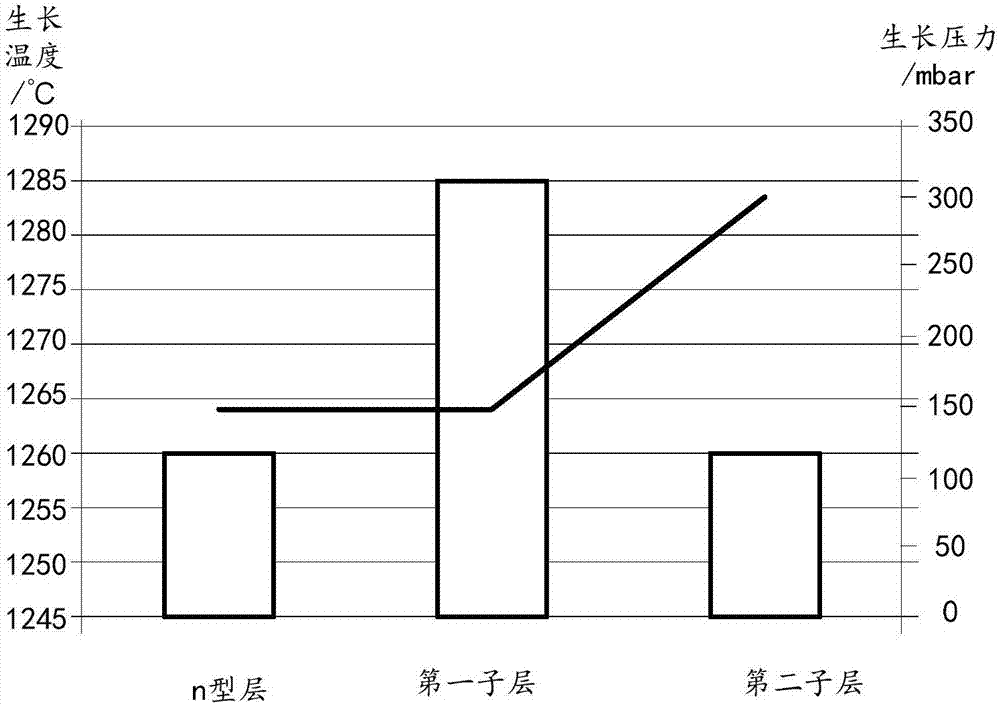

ActiveCN106910801AImprove horizontal scalabilityUniform current distributionSemiconductor devicesMultiple quantumPower flow

The invention discloses a GaN-based light emitting diode epitaxial wafer and a manufacturing method therefor and belongs to the field of light emitting diodes. The GaN-based light emitting diode epitaxial wafer comprises a substrate, a buffer layer, a three-dimensional growth layer, a u-GaN layer, an n type layer, an n type current expansion layer, a stress releasing layer, a multiple quantum well layer and a p type layer; wherein the buffer layer, the three-dimensional growth layer, the u-GaN layer, the n type layer, the n type current expansion layer, the stress releasing layer, the multiple quantum well layer and the p type layer orderly arranged on the substrate in a covering manner; the n type current expansion layer comprises a first sub-layer covering the n type layer and a second sub-layer covering the first sub-layer; the first sub-layer is an AlGaN layer, the second sub-layer is of a superlattice structure formed by a non-Si-doped GaN layer and an Si-doped GaN layer, the first sub-layer is higher than the n type layer and the second sub-layer in terms of growth temperature, and the second sub-layer is greater than the first sub-layer in terms of growth pressure. The GaN-based light emitting diode epitaxial wafer is capable of overcoming defects and improving photoelectric performance.

Owner:HC SEMITEK ZHEJIANG CO LTD

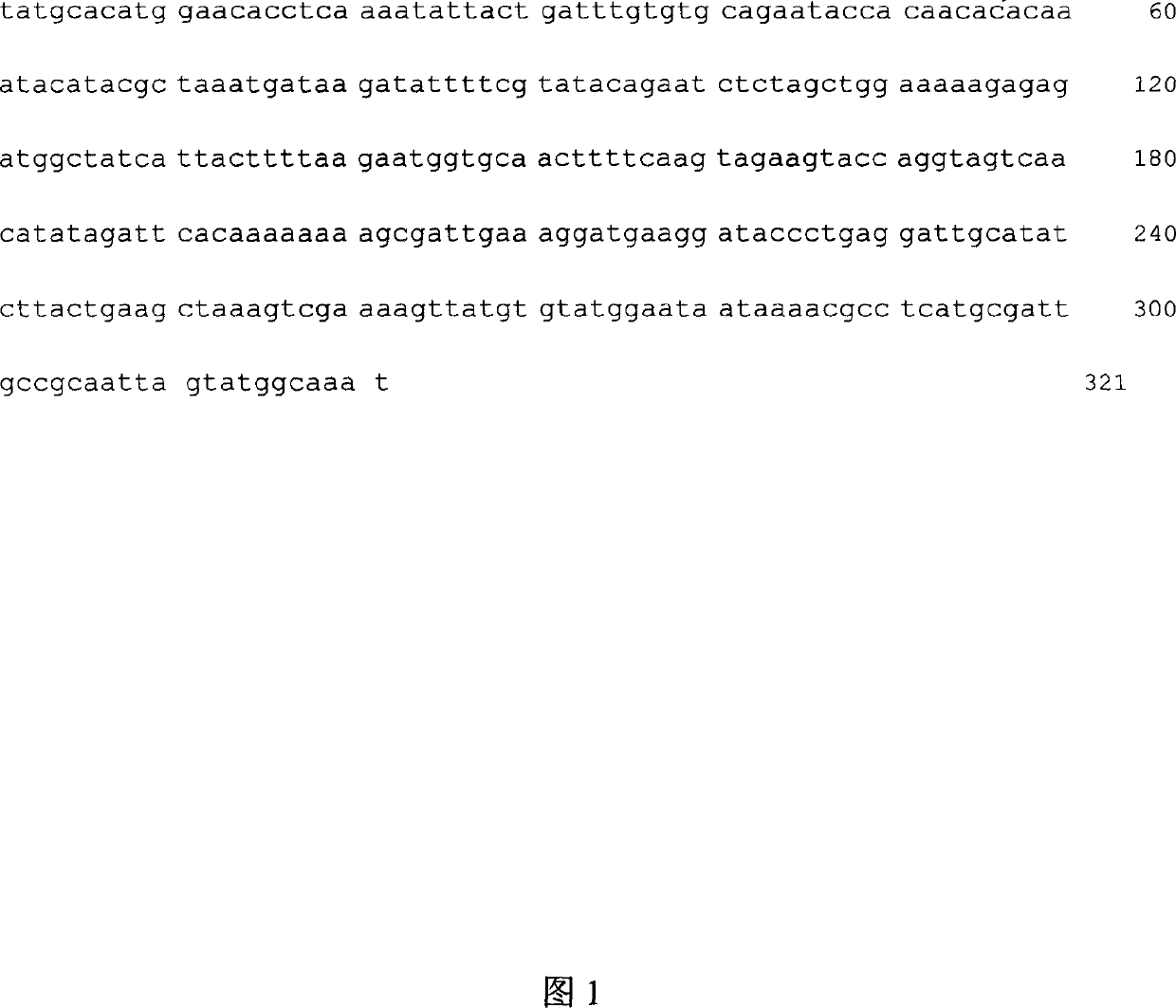

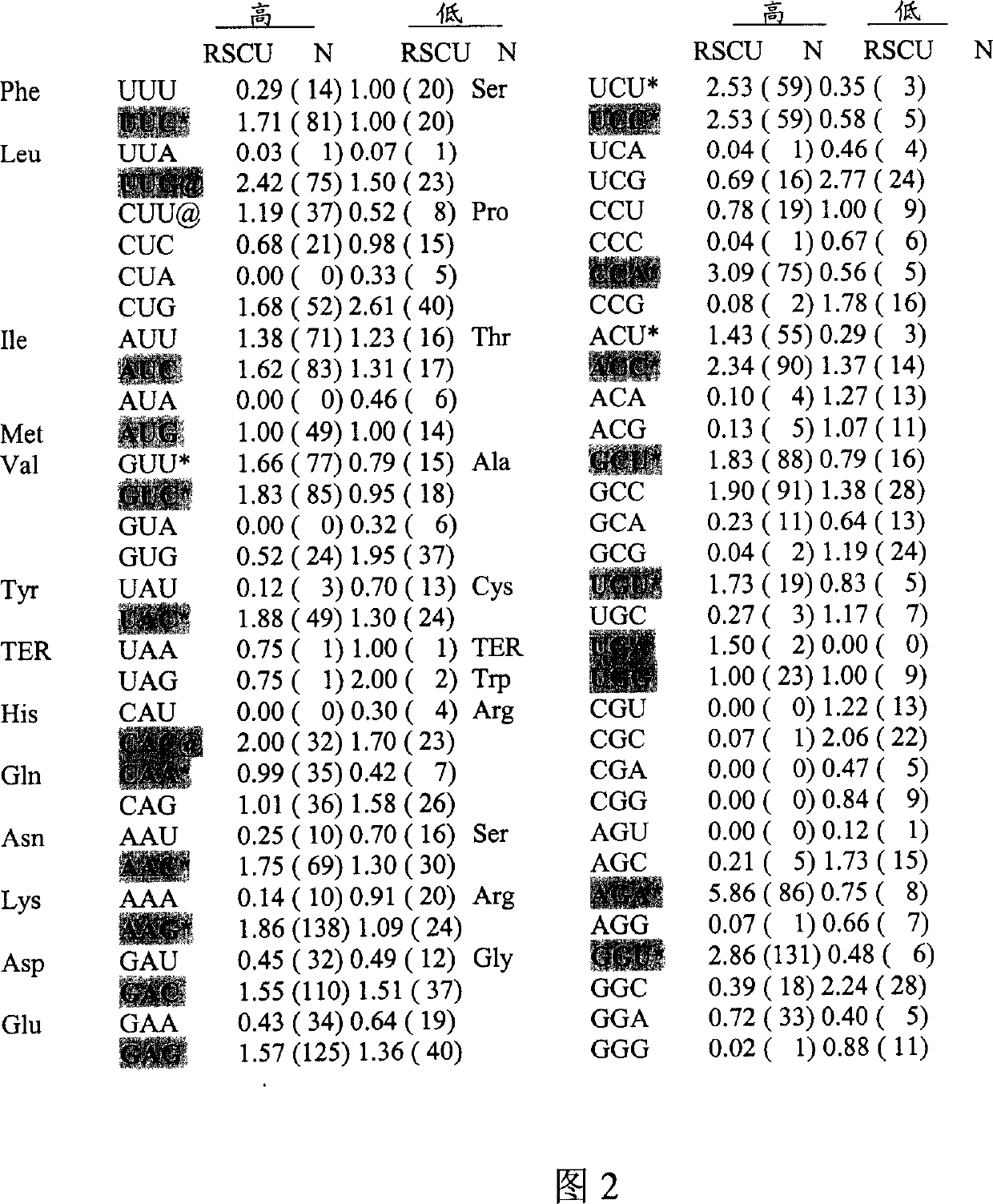

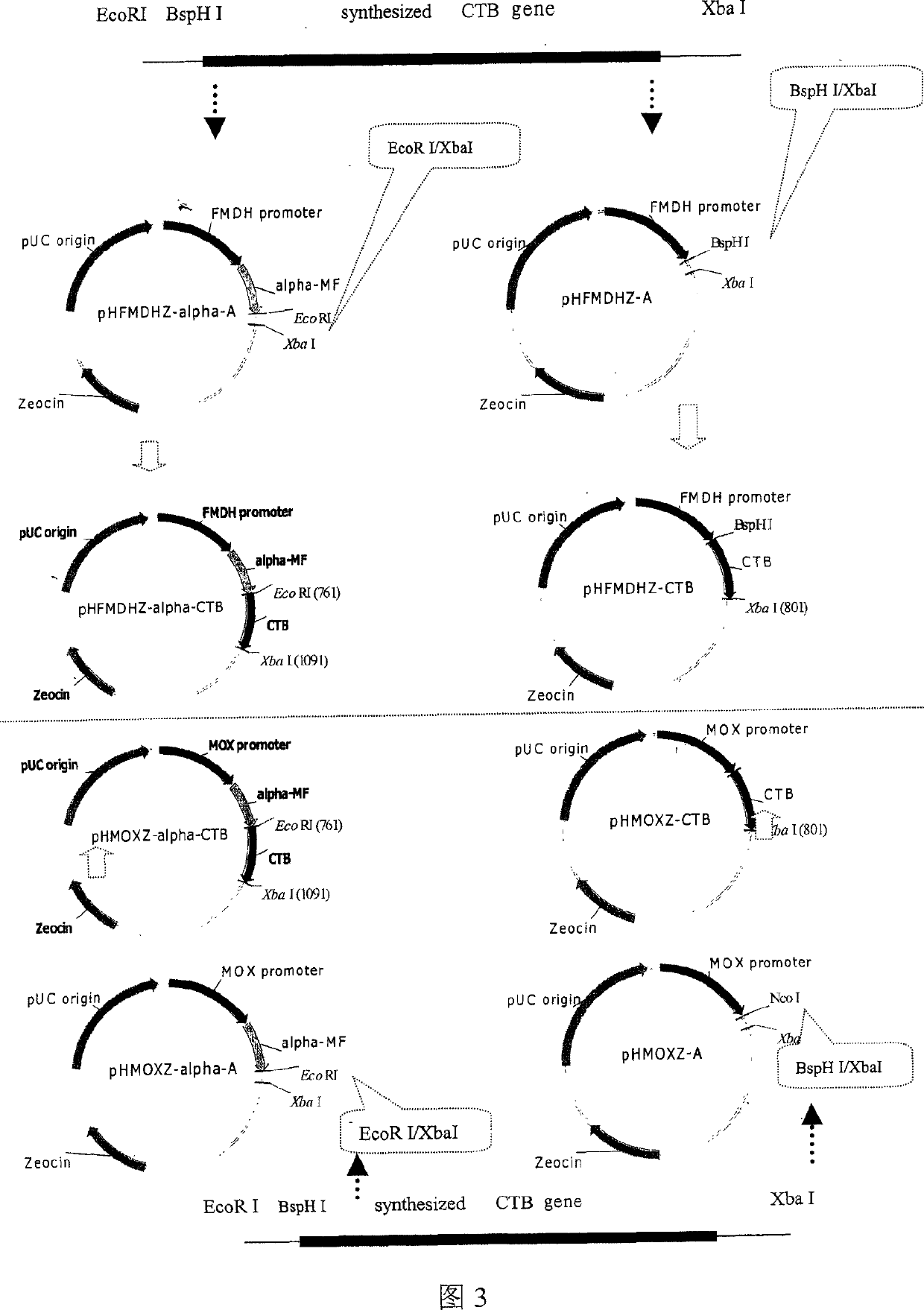

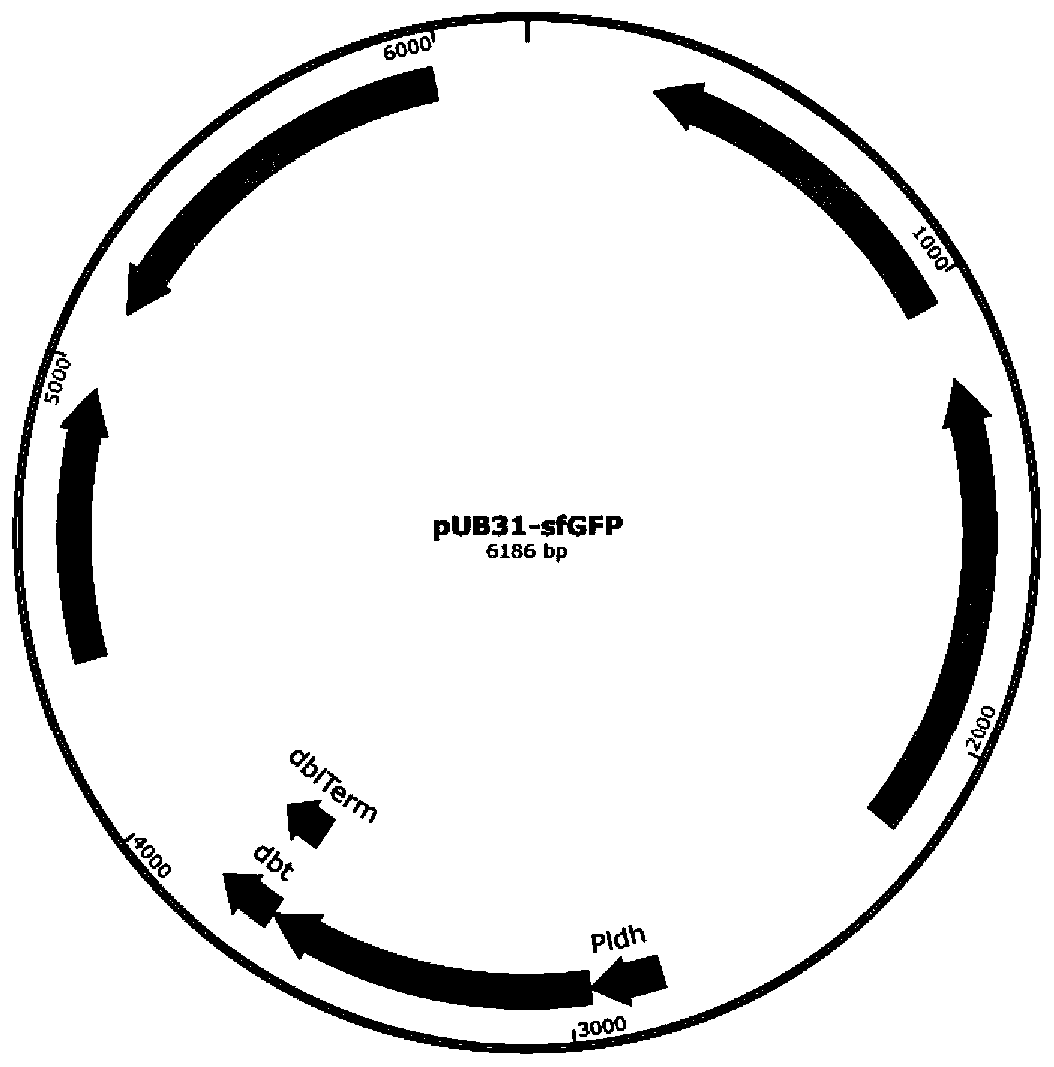

Pleiomorphic saccharomyces hansenii expression recombination cholere toxin B subunit gene and its application

InactiveCN1513995AIncrease growth temperatureFast growth rateFungiDepsipeptidesGenetic engineeringToxin

A polymorphous Hanson yeast expressed recombinant cholera toxin B subunit gene (CTB) is disclosed. In order to increase the expression of CTB in Hanson yeast, the coding gene of CTB is redesigned according to the application method of codon for the high-expression gene of Hanson yeast. The expression product can be used for preventing the diarrhea caused by cholera ribro and as the immune vaccine.

Owner:INST OF MICROBIOLOGY - CHINESE ACAD OF SCI

Method for preparing ultra nanometer diamond coating of ceramic valve core

InactiveCN101830733AIncrease growth temperatureHigh bonding strengthPlug valvesFrictional coefficientThermal expansion

The invention belongs to a method for surface modification of a ceramic valve core, and particularly relates to a method for preparing an ultra nanometer diamond coating, which can improve the overall performance of a ceramic valve core matrix. The method comprises the following steps of: soaking the planar tap ceramic valve core in soaking solution; grinding the surface of the matrix by using diamond micropower suspension; and placing the ceramic valve core in a microwave plasma reaction cavity for growing the ultra nanometer diamond coating. The ultra nanometer diamond coating generated by the method has the advantages of high wear resistance and hardness, small frictional coefficient and thermal expansion coefficient, high self-lubrication, high chemical stability, no toxin and harmlessness and high hydrophobicity; and the ultra nanometer diamond coating can also improve the overall performance of the tap using the ceramic valve core, and the service life of the tap is prolonged by over 10 times. The tap and the oil-gas valve can be used in various mediums for a long time, are always kept tightly sealed and eliminate leakage, and are switched flexibly and light.

Owner:SOUTHWEAT UNIV OF SCI & TECH

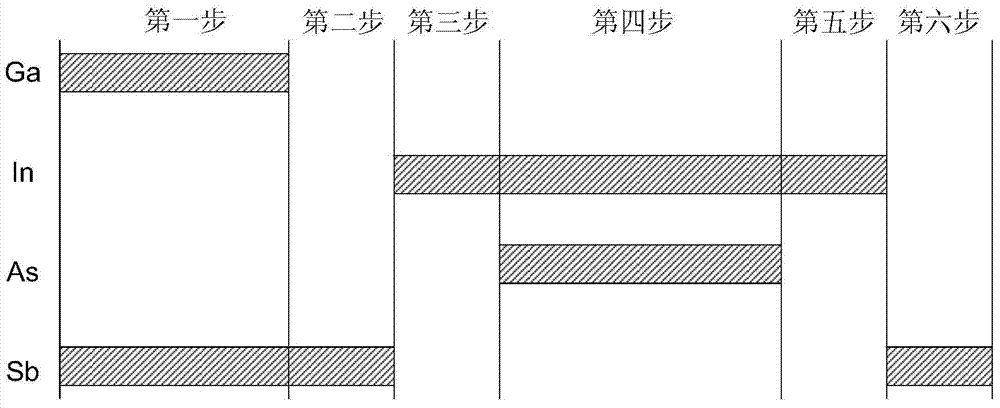

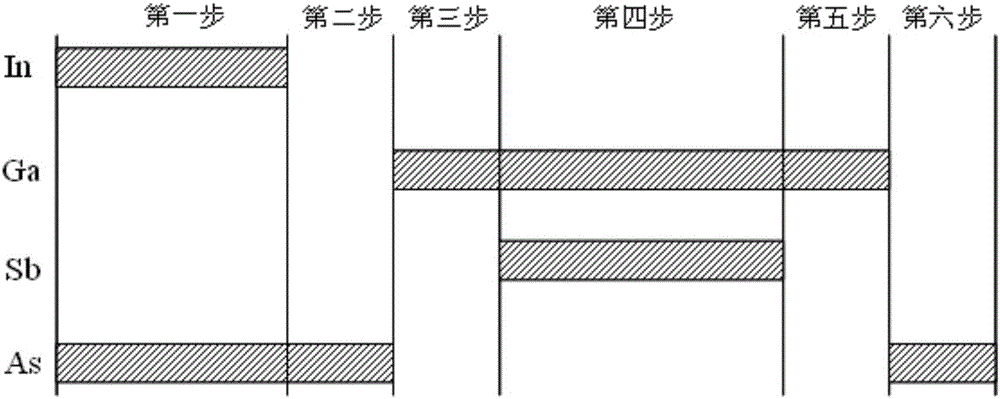

Type-II superlattice structure based on arsenic valve switch and preparation method

ActiveCN103500765AReduce interdiffusionReduce the chance of formationFinal product manufactureNanoopticsInterface layerBinary compound

The invention discloses a type-II superlattice structure based on an arsenic valve switch and a preparation method. Compared with a traditional type-II superlattice structure, the original binary compounds GaSb and InSb are respectively replaced by ternary compounds GaAsSb and InAsSb. The preparation method is characterized in that the As valve is always in an open state in the enter type-II superlattice growth process, the valve position is the same as that during the growth of an InAs layer, and the tertiary compounds GaAsSb and InAsSb are formed because partial As flows out when an GaSb layer and an InSb interface layer grown. The type-II superlattice structure based on the arsenic valve switch and the preparation method have the characteristics that since a common element As exists in all layers, the growth temperature of all layers is enabled to trend to be consistent and the mutual diffusion at the position of interfaces is reduced; under the effect of As atom surfactant, the migration rate of Sb atoms is increased, the forming probability of Sb clusters is reduced, the defects of materials are reduced and the material performance is improved.

Owner:中科爱毕赛思(常州)光电科技有限公司

Preparation method of epitaxial wafer for 8-inch high-power IGBT component

ActiveCN108417483AImprove controllabilityImprove consistencySemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceControllability

The invention discloses a preparation method of an epitaxial wafer for an 8-inch high-power IGBT component. The method includes following steps: preparing a substrate: selecting an 8-inch substrate with a p-doped middle resistance, wherein the resistivity is 3-25 ohm*cm, and a back-sealing structure is in a polycrystalline (Poly) back-sealing mode; HCl polishing: selecting the HCl flow of 1-2 L / min at the temperature lower than 1080 DEG C with the polishing time of 2 minutes, and performing purging with high-flow H2 for 3 minutes after completion of polishing; and epitaxial growth: selecting at least three layers of epitaxial process conditions, wherein a silicon source employs ultra-high-purity trichlorosilane, the epitaxial growth of each layer employs the same growth temperature and growth rate, an epitaxial layer with flat resistivity is grown on a first layer, an intermediate transition layer is grown on an intermediate layer through introduction of a doping source with a variabledoping flow, and a high-resistance epitaxial layer is grown on a final layer. According to the method, the growth of the epitaxial layer of each layer employs the same growth rate and growth temperature so that the controllability of epitaxial parameters of products in a batch production process is facilitated.

Owner:NANJING GUOSHENG ELECTRONICS

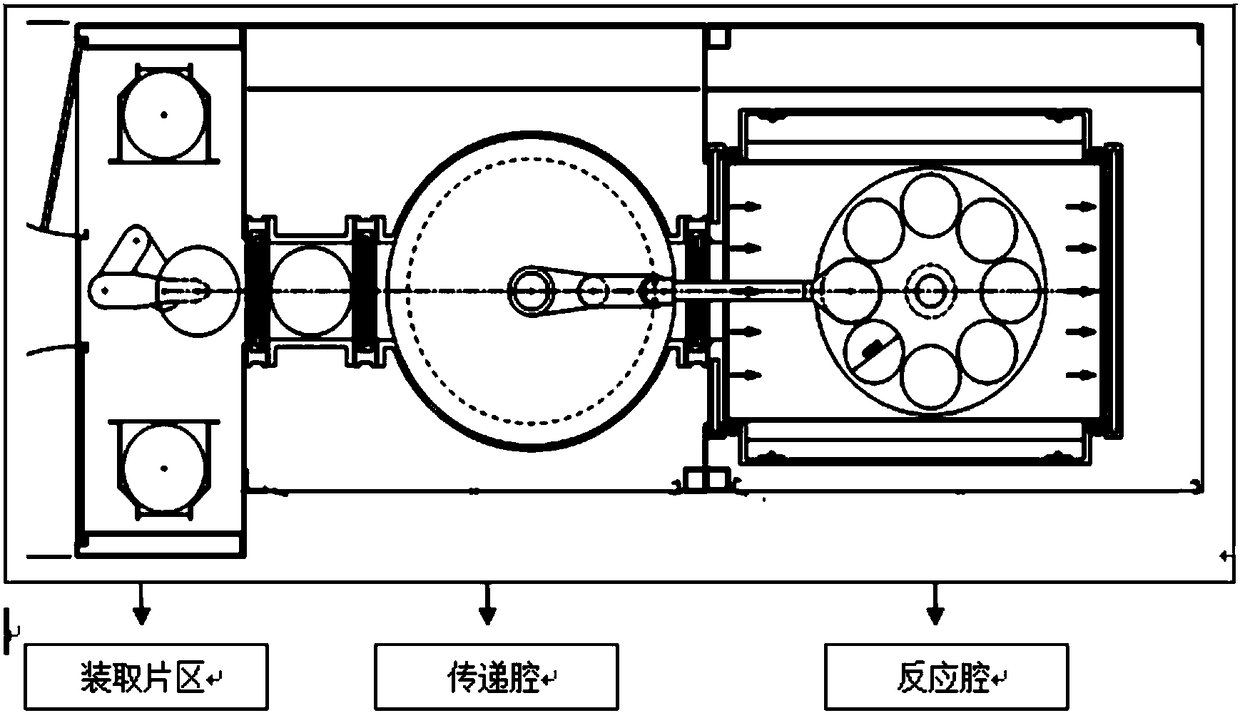

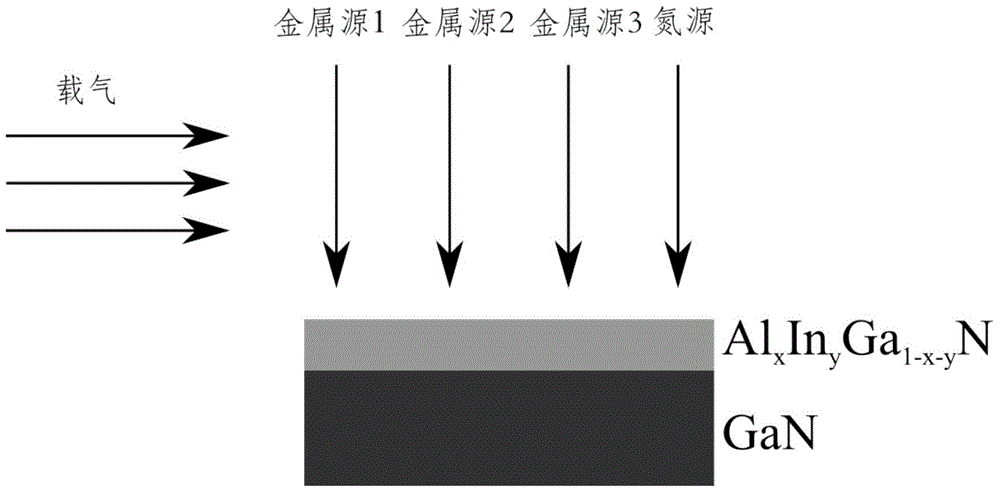

Semiconductor heterostructure, and preparation method and applications thereof

ActiveCN105990106AModerate immiscibilityHigh quality epitaxial growthSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSemiconductor materials

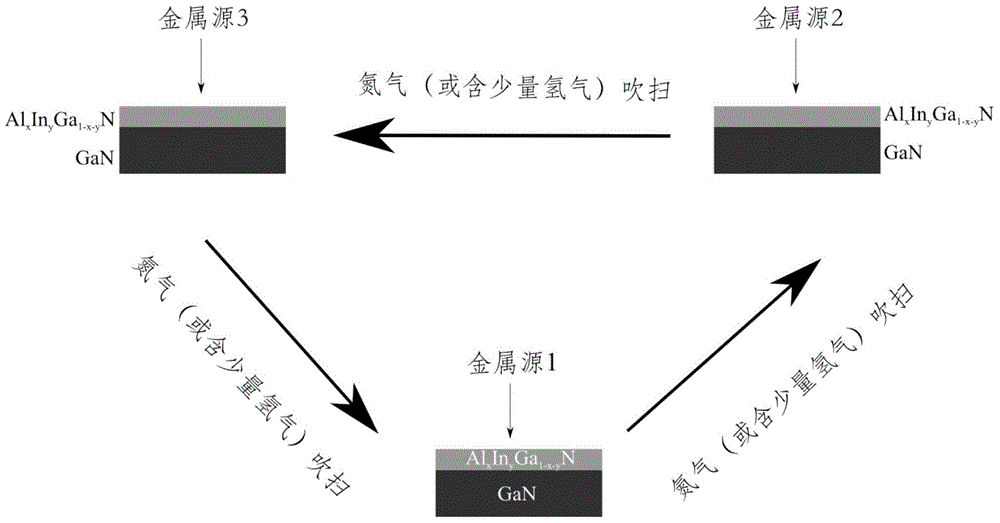

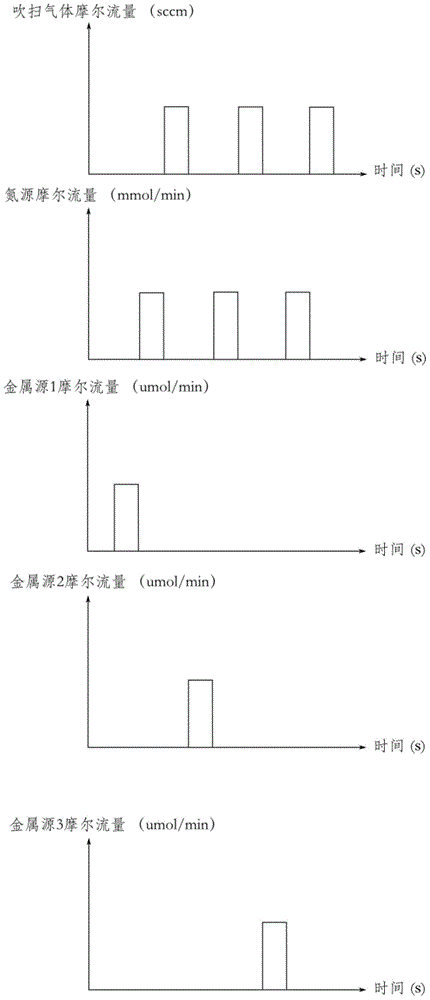

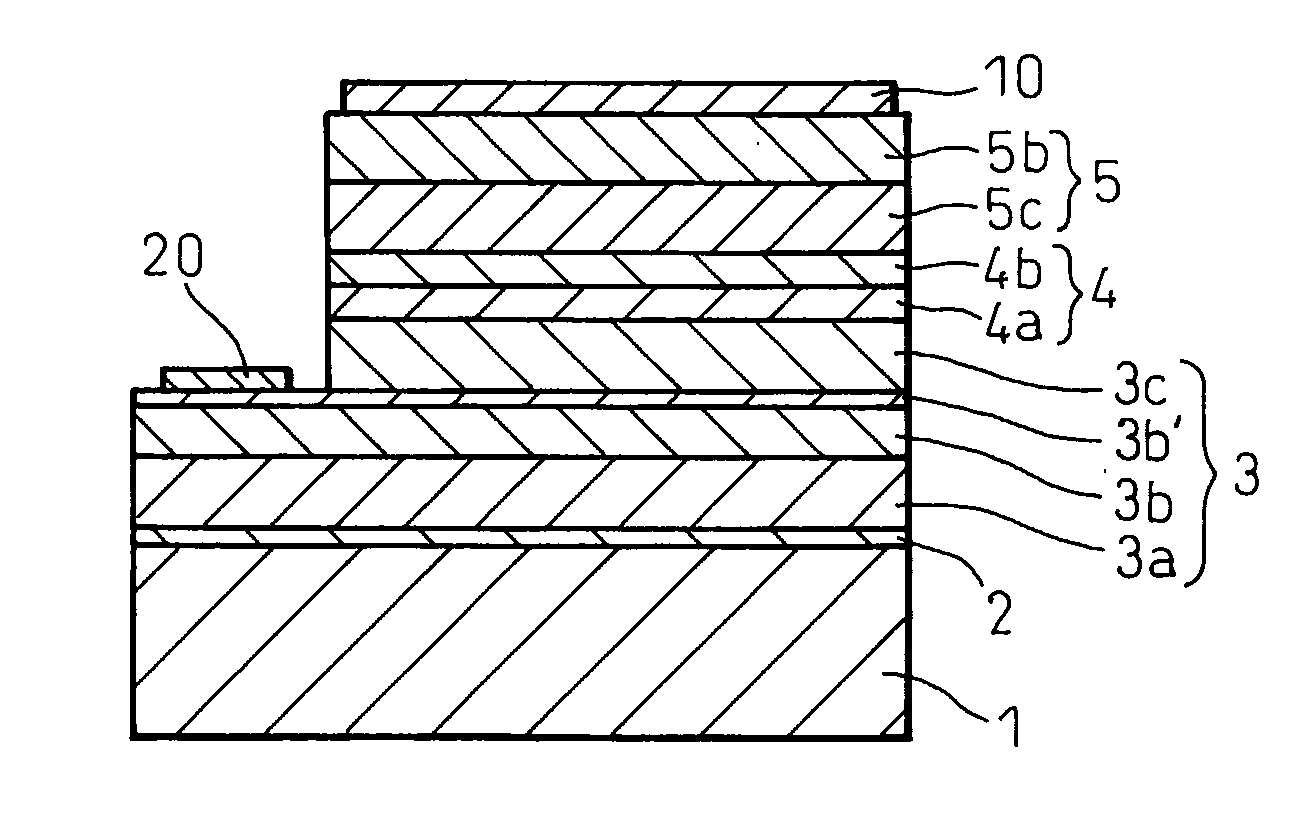

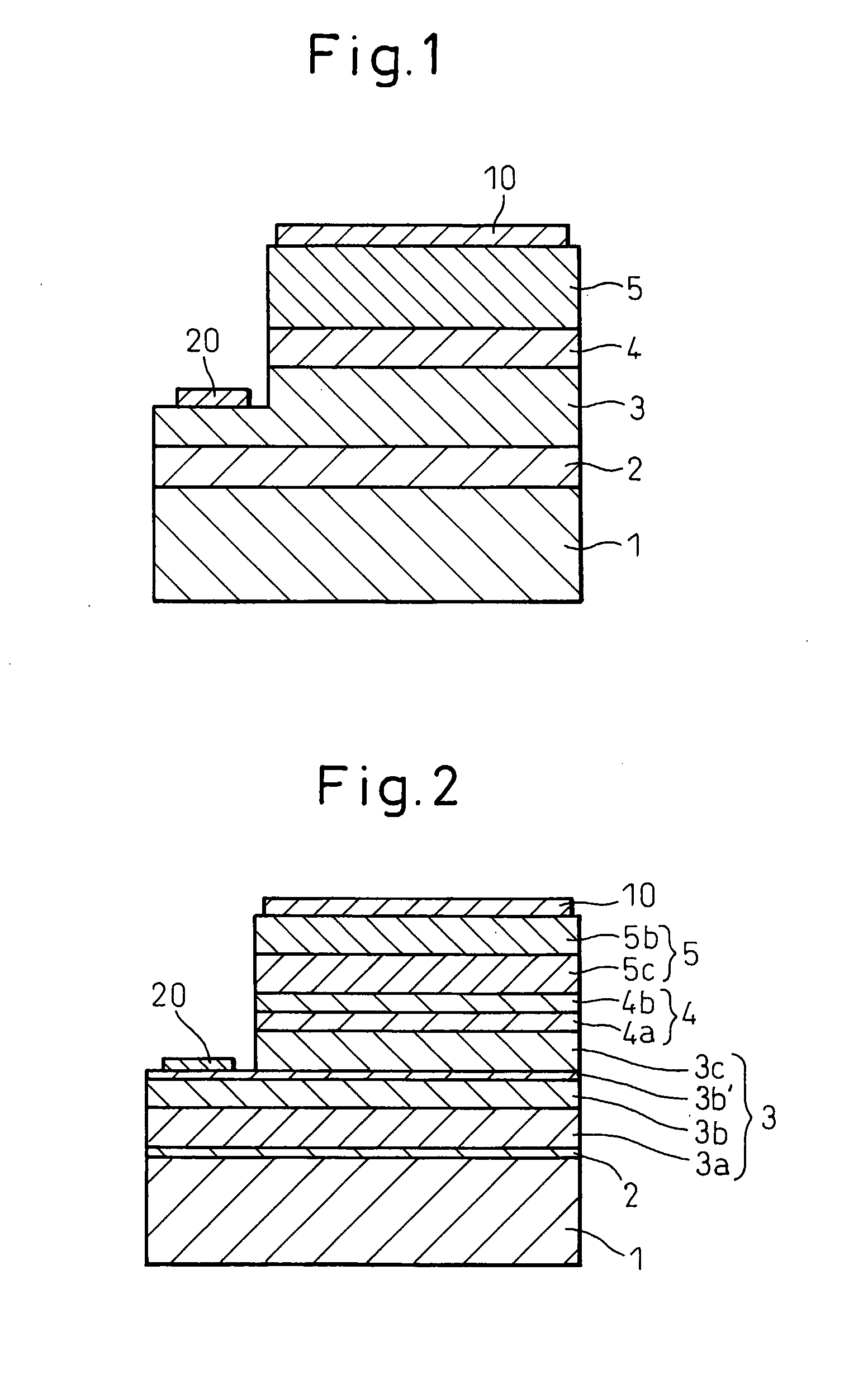

The invention discloses a semiconductor heterostructure, and a preparation method and applications thereof. The semiconductor heterostructure comprises a first semiconductor material and a second semiconductor material. The first semiconductor material and the second semiconductor material are mutually joined to form virtual lattice matching. The first semiconductor material is AlxInyGa1-x-yN, wherein 4.72< / =x / y< / =5.10, 0< / =x< / =1 and 0<y<1. The second semiconductor material is GaN. Preferably, 0.2<(1-x-y)< / =0.6. The preparation method comprises steps: after a GaN layer is formed through growth, an AlxInyGa1-x-yN layer is formed in a mode of introducing an aluminum source, an indium source, a gallium source and a nitrogen source in a reaction chamber of epitaxial growth equipment in a simultaneous and / or pulse means. By using the semiconductor heterostructure of the invention, the production process of a semiconductor device can be effectively simplified, the reliability of the semiconductor device is optimized, and particularly, the reliability problem of devices such as an HEMT due to stress can be eliminated fundamentally, and more ideal spontaneous polarization strength between the barrier layer and the GaN layer can be kept.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

Production Method of Group III Nitride Semiconductor Element

InactiveUS20090140286A1Reduced growth rateReduce the amount requiredSemiconductor/solid-state device manufacturingNanoopticsActive layerNitride semiconductors

An object of the present invention is to provide a production method of a Group III nitride semiconductor element having an excellent electrostatic discharge property and enhanced reliability.In the inventive production method, the Group III nitride semiconductor element has an n-type layer, an active layer and a p-type layer, which comprise a Group III nitride semiconductor, on a substrate in this order, wherein, during or / and after growth of the n-type layer and before growth of the active layer, the growth rate of the semiconductor is reduced.

Owner:SHOWA DENKO KK

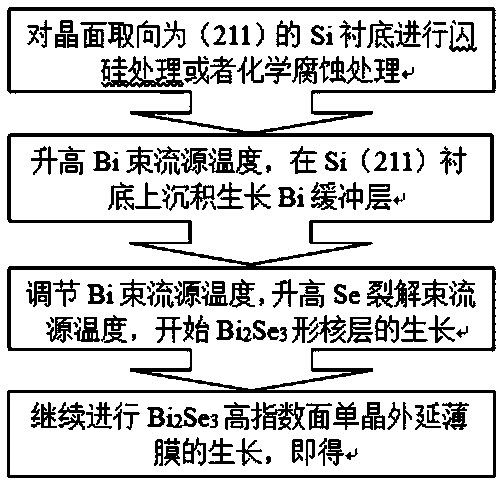

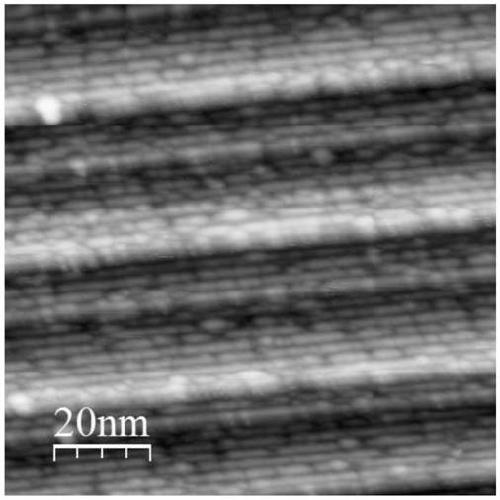

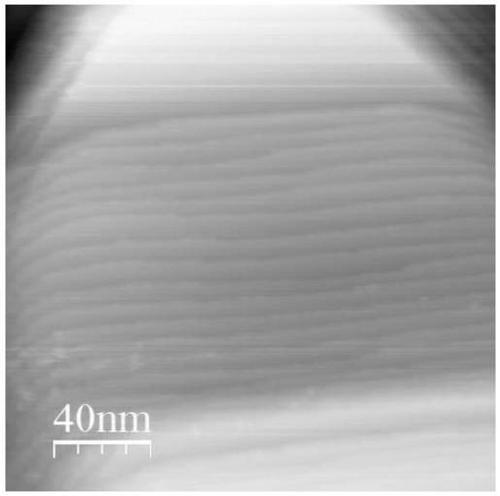

Method for growing bismuth selenide high-index surface single crystal thin film on silicon (211) substrate

InactiveCN109913945ALow priceEasy to makePolycrystalline material growthThermoelectric device manufacture/treatmentBeam sourceSingle crystal

The invention discloses a method for growing a bismuth selenide high-index surface single crystal thin film on a silicon (211) substrate. The method comprises the following steps: 1), performing flashing silicon treatment or chemical etching treatment on a Si substrate having a crystal plane orientation of (211); 2), raising the temperature of a Bi beam source, depositing and growing a Bi buffer layer on the Si (211) substrate prepared in the step 1); 3), after the Bi buffer layer is grown in the step 2), adjusting the temperature of the Bi beam source, raising the temperature of a Se crackingbeam source, and starting to grow a Bi2Se3 nucleation layer; 4): after the growth of the Bi2Se3 nucleation layer is completed in the step 3, continuing to grow a Bi2Se3 high-index surface single crystal epitaxial thin film to obtain the bismuth selenide high-index surface single crystal thin film. According to the method, the Bi ultra-thin single crystal layer is adopted as a buffer layer, the low-temperature Bi2Se3 nucleation layer with a thickness of 3-5 nm is grown on the surface of the Bi buffer layer, then the growth temperature is appropriately increased to grow the Bi2Se3 high-index surface single crystal thin film epitaxial layer, and the Bi2Se3 high-index surface single crystal thin film having a relatively good crystallinity can be obtained.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Forming II-VI core-shell semiconductor nanowires

InactiveUS8377729B2Low melting pointQuality improvementNanoinformaticsSemiconductor/solid-state device manufacturingNanowireNanoparticle

A method of making II-VI core-shell semiconductor nanowires includes providing a support; depositing a layer including metal alloy nanoparticles on the support; and heating the support and growing II-VI core semiconductor nanowires where the metal alloy nanoparticles act as catalysts and selectively cause localized growth of the core nanowires. The method further includes modifying the growth conditions and shelling the core nanowires to form II-VI core-shell semiconductor nanowires.

Owner:NANOCO TECH LTD

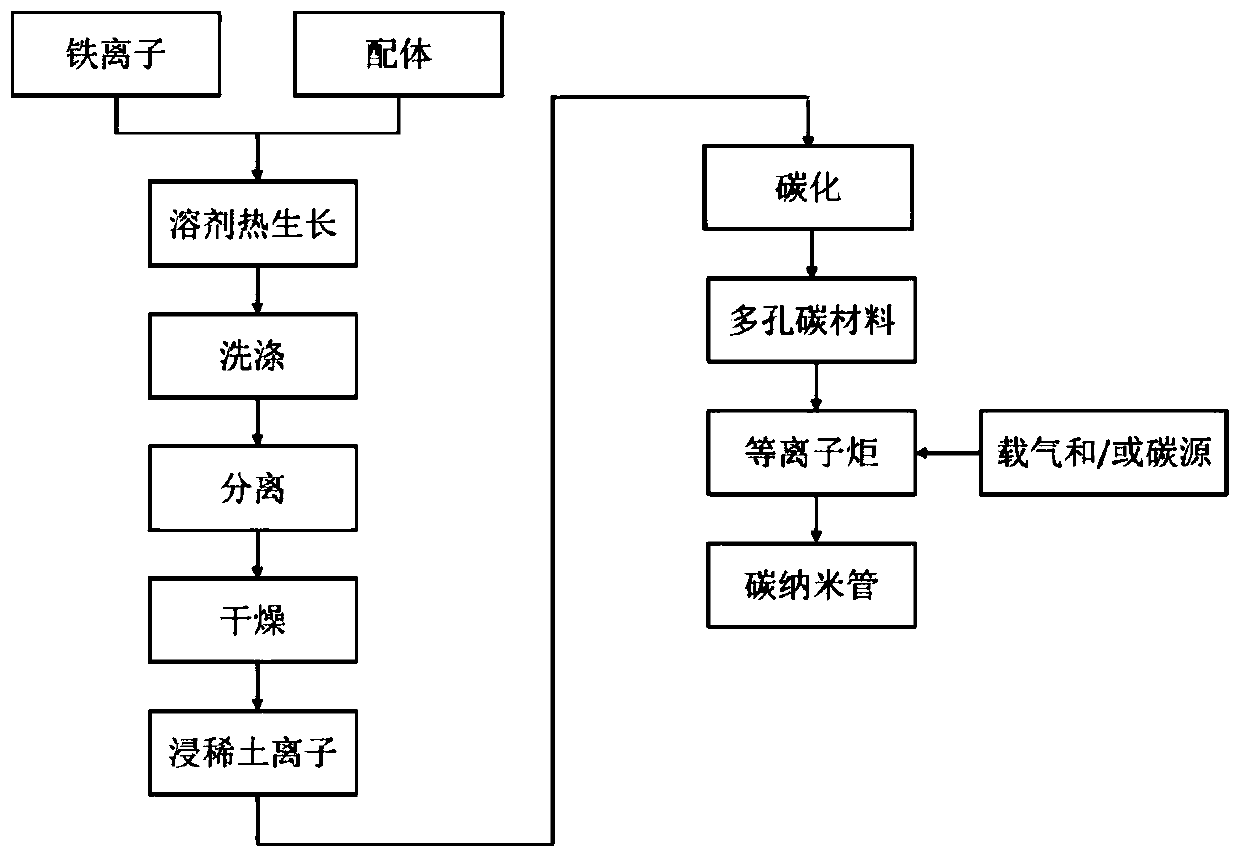

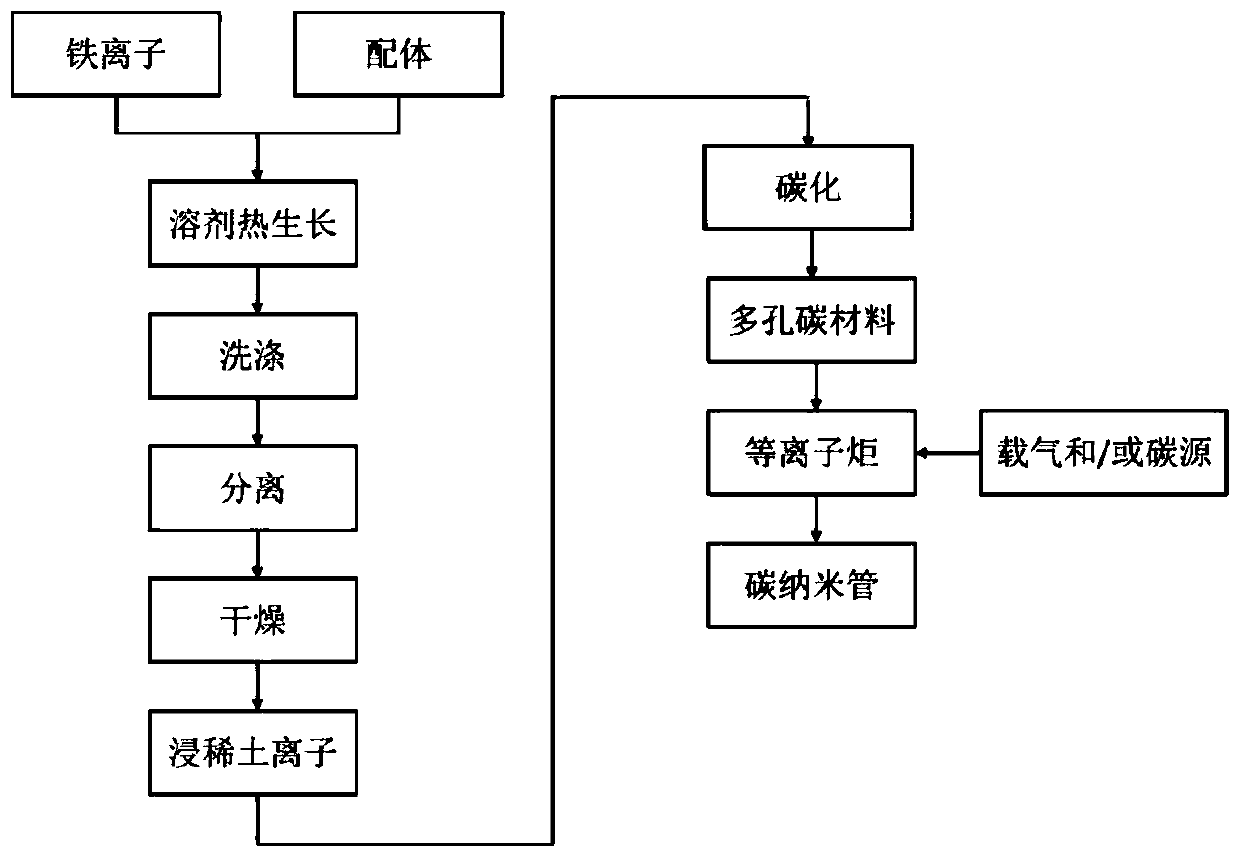

Preparation method of small-tube-diameter carbon nanotubes

ActiveCN109970046AEvenly distributedAvoid uncontrollableMaterial nanotechnologyMulti-walled nanotubesSolid carbonPorous carbon

The invention belongs to the technical field of novel material and relates to a preparation method of small-tube-diameter carbon nanotubes. The method includes generating an iron-containing metal-organic framework compound from iron ions and an organic ligand through a solvothermal process; after separation, washing and drying, soaking the compound in a solution containing rare earth ions and thenperforming carbonization in an inert gas to obtain a porous carbon material loaded with iron; and ejecting the porous carbon material, as a solid carbon source and a catalyst, from a plasma torch byadopting a high-temperature plasma process to gasify the carbon source and catalyst through high temperature so that carbon nanotubes grow during following downstream cooling. The porous carbon material derived from the metal-organic framework compound can enable ultrafine particle uniform distribution of original iron element and the porous carbon facilitates high-temperature gasification, thus providing an ultrafine nanometer catalyst and highly active carbon source for growth of ultrafine carbon nanotubes, and greatly increasing the growth efficiency of the small-tube-diameter carbon nanotubes. The method is an effective means for preparing the small-tube-diameter carbon nanotubes and single-walled carbon nanotubes, and has important practical application value.

Owner:JIANGXI COPPER TECHNOLOGY RESEARCH INSTITUTE CO LTD

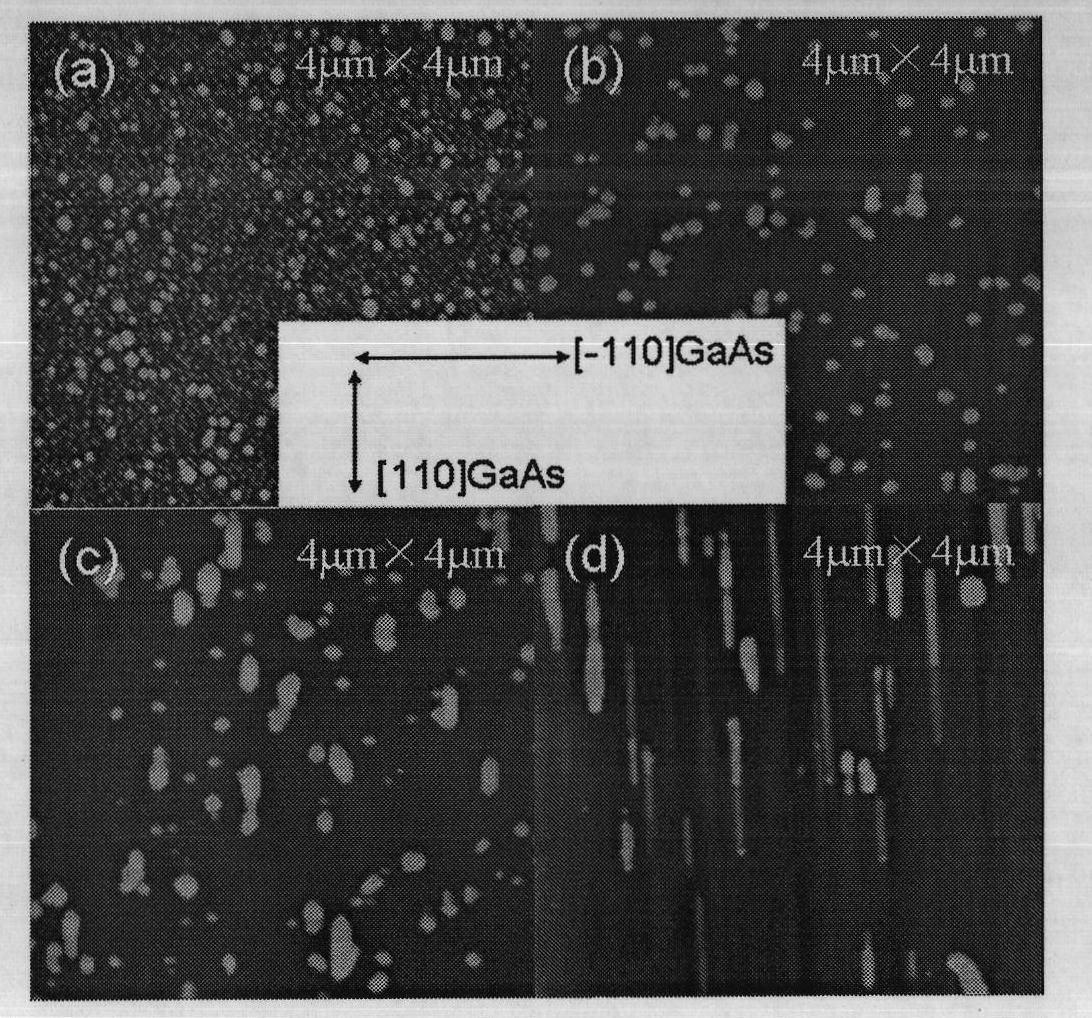

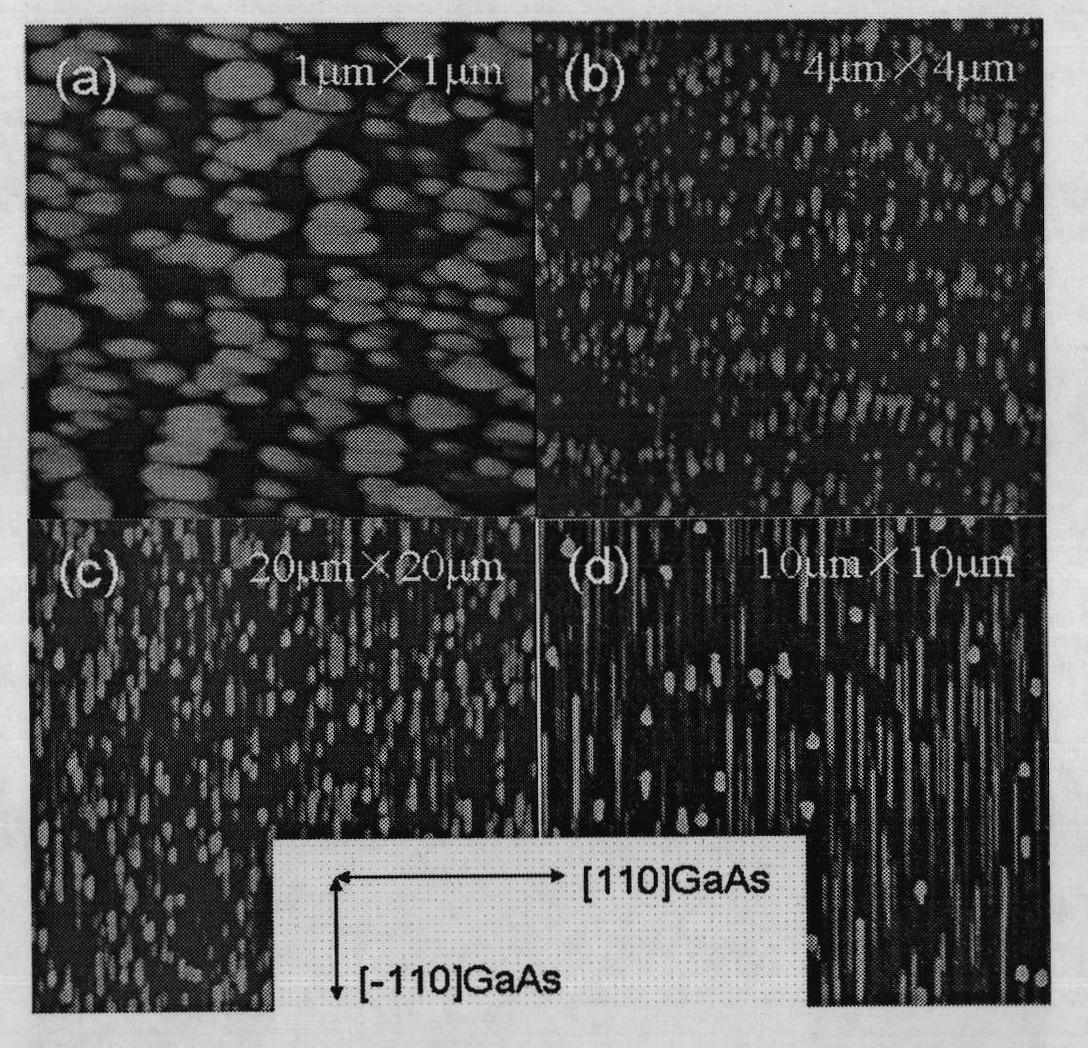

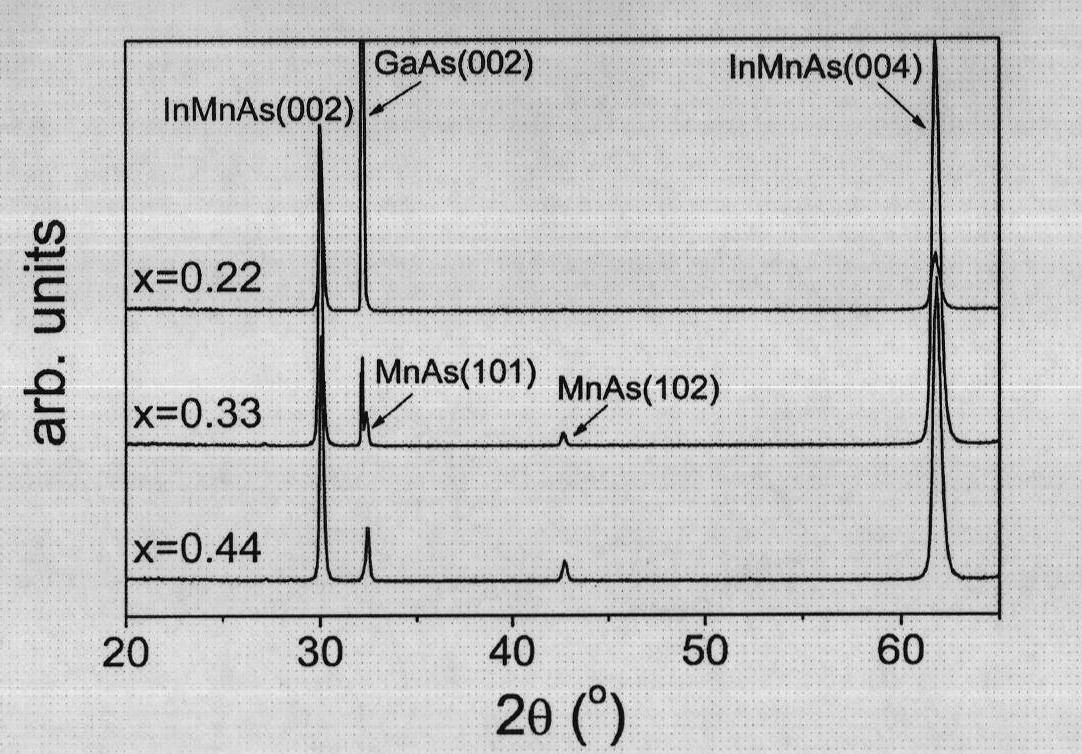

(In, Mn) As nano-wires and preparation method thereof

InactiveCN102477582AAchieve growthRaise the atomic percentagePolycrystalline material growthFrom chemically reactive gasesMagnetic anisotropyCrystal orientation

The invention discloses (In, Mn) As nano-wires and a preparation method thereof. According to the present invention, the nano-wires are aligned along the crystal orientation, the epitaxy of the nano-wires grows on the substrate of the GaAs (001) single crystal, and the nano-wires transversely lie on the surface of the GaAs (001) single crystal; In(1-x)MnxAs (0.3<=x<=0.5) is the nano-wires, the sphalerite structure of the GaAs (001) single crystal is maintained, and the In(1-x)MnxAs is spontaneously aligned along the crystal orientation, such that the In(1-x)MnxAs has the magnetic anisotropy along the orientation, wherein the epitaxy of the In(1-x)MnxAs grows, and the In(1-x)MnxAs transversely lies on the surface of the GaAs (001) single crystal; according to the preparation method for the (In, Mn) As nano-wires, a molecular beam epitaxy technology and equipment are adopted, the GaAs (001) single crystal is adopted as the substrate, the Mn content in the elements of In and Mn is increased to 30-50%, and an intermittent growth way is adopted, such that the (In, Mn) As nano-wires are obtained, wherein the epitaxy of the In(1-x)MnxAs grows, and the nano-wires transversely lie on the surface of the GaAs (001) single crystal, and have the uniaxial anisotropy.

Owner:WUXI NANLIGONG TECH DEV

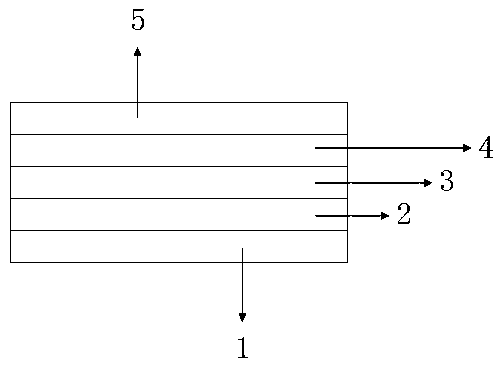

Method for growing silicon carbide crystals by PVT method and device thereof

ActiveCN112981532AReduce the difference in minimum thicknessImprove effective utilizationPolycrystalline material growthFrom condensed vaporsThermal insulationCrucible

The invention provides a method for growing silicon carbide crystals by a PVT method and a device thereof. The method comprises the following steps: (1) an assembling stage; (2) a heating stage: placing the assembled crucible in a furnace body, heating the crucible, and controlling the temperature difference between the temperature of the center of the top end of the crucible and the temperature of the edge of the top end of the crucible to be delta T1; and (3) a crystal growth stage: keeping the temperature of the center of the top end of the crucible unchanged, controlling the thermal insulation cover to move upwards along the side wall of the thermal insulation cylinder, and controlling the temperature difference between the temperature of the center of the top end of the crucible and the temperature of the edge of the top end of the crucible to be reduced to T2, so that the silicon carbide raw material is conveyed to the seed crystal for crystal growth in a gas phase manner. By controlling the heat preservation cover to move upwards, the annular temperature field is more uniform and stable, and the radial temperature gradient is gradually and slowly reduced to delta T2, so that directional quantitative adjustment of the radial temperature gradient is realized, the radial temperature gradient at the seed crystal is gradually reduced, the difference between the minimum thickness of the center and the minimum thickness of the edge of the silicon carbide crystal is reduced, and the effective utilization rate of the silicon carbide crystal with the same weight is increased.

Owner:SICC CO LTD

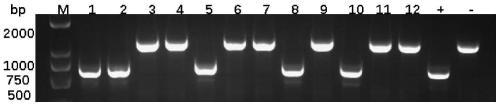

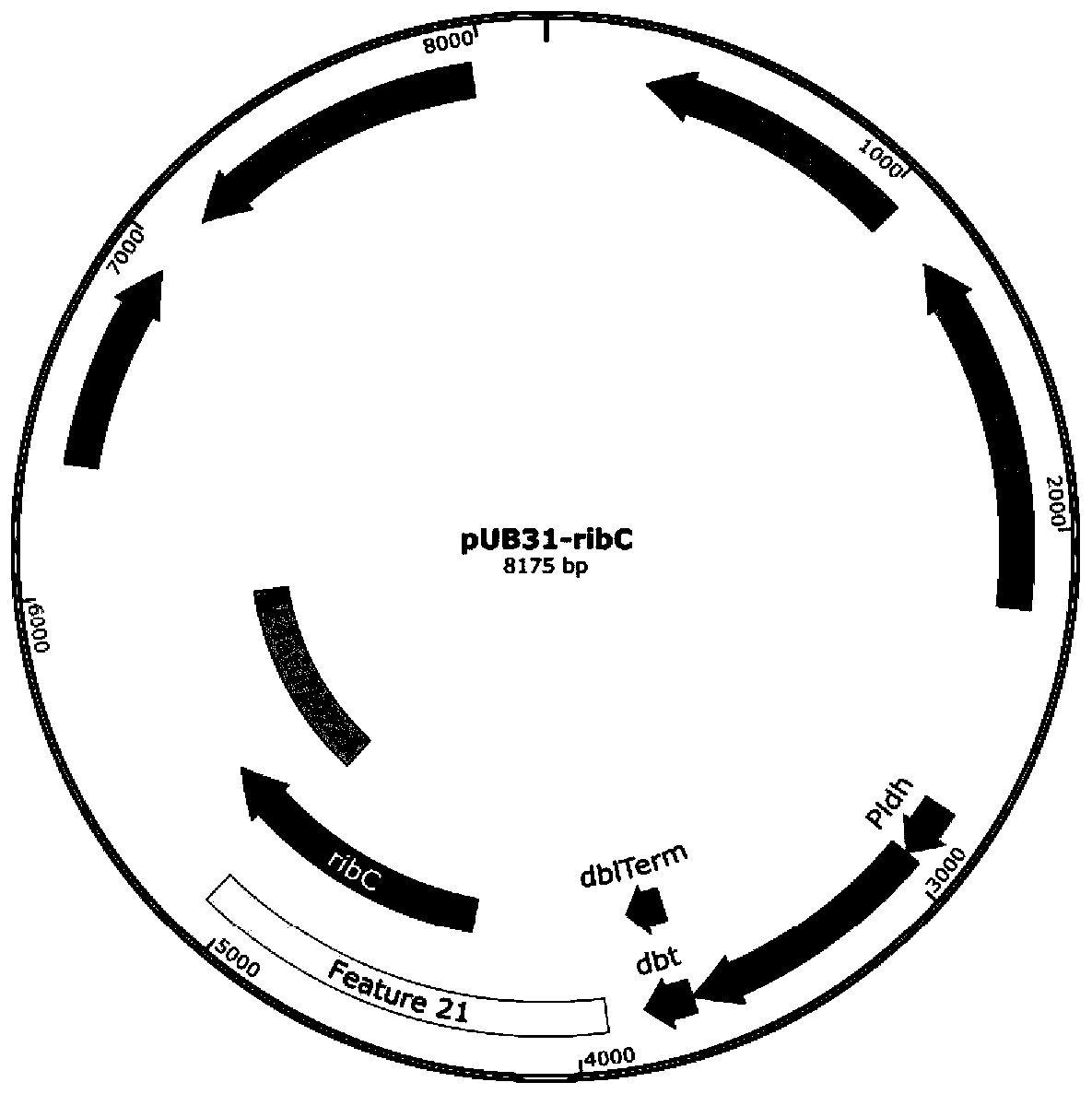

Engineering bacterium of Geobacillusthermoglucosidasius and construction method and application of engineering bacterium

ActiveCN111154705AIncrease growth temperatureTo achieve the purpose of industrial upgradingBacteriaMicroorganism based processesBiotechnologyBacterosira

The invention provides an engineering bacterium of Geobacillusthermoglucosidasius and a construction method and application of the engineering bacterium. The construction method includes: through genetic engineering of Geobacillusthermoglucosidasius, introducing ribC (G199D) point mutation, sequentially knocking out purR, purA, ccpN and ldh genes, and then introducing an expression vector carryinga riboflavin synthesis gene cluster into the transformed engineering bacteria to obtain a series of high-temperature riboflavin-producing geobacillus engineering bacteria. The results show that yieldof riboflavin after fermentation of geobacillus after genetic engineering for 24 h is 520 mg / L; and through mixed fermentation with glucose and xylose for the strain, the yield can reach more than 1g / L. The engineering bacterium has advantages of high growth temperature and short generation time, can utilize an inexpensive carbon source, and can be used for large-scale production of riboflavin at low cost.

Owner:INST OF MICROBIOLOGY - CHINESE ACAD OF SCI +1

Long-wavelength LED epitaxial wafer, chip and preparation method thereof

PendingCN110010731AIncrease brightnessSolve the problem that the photoelectric performance does not match, so a large amount of electronic control space is requiredSemiconductor devicesLong wavelengthGallium nitride

The invention discloses a preparation method of a long-wavelength LED epitaxial wafer. The preparation step comprises a step of placing an epitaxial substrate into an epitaxial growth reaction chamber, and a step of growing a CaN epitaxial layer on the epitaxial substrate, growing a GaN buffer layer on the surface of the epitaxial substrate, growing an n-type Can on the GaN buffer layer, growing aquantum well on the n-type CaN, and growing a p-type CaN on the quantum well, wherein the thickness of the CaN epitaxial barrier is h, the thickness is controlled to be larger than or equal to 0.35 micrometers and smaller than or equal to 6 micrometer. The electrical performance of an LED prepared by a gallium-nitride-based long-wavelength LED epitaxial wafer prepared by the invention is consistent with the electrical performance of a blue-green CaN-based LED.

Owner:东莞市中晶半导体科技有限公司

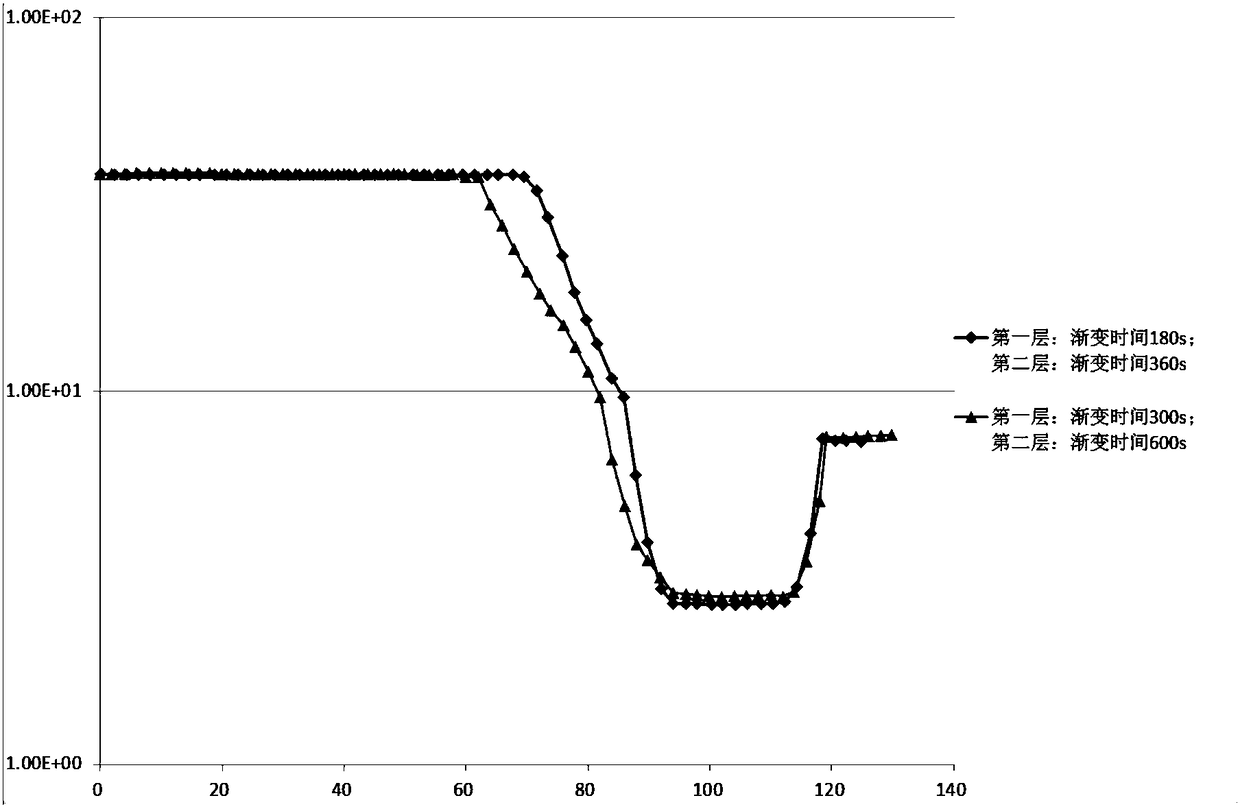

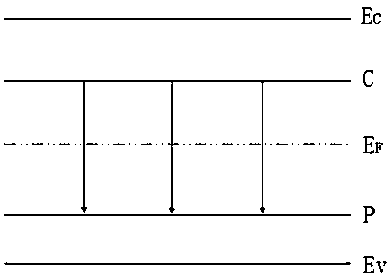

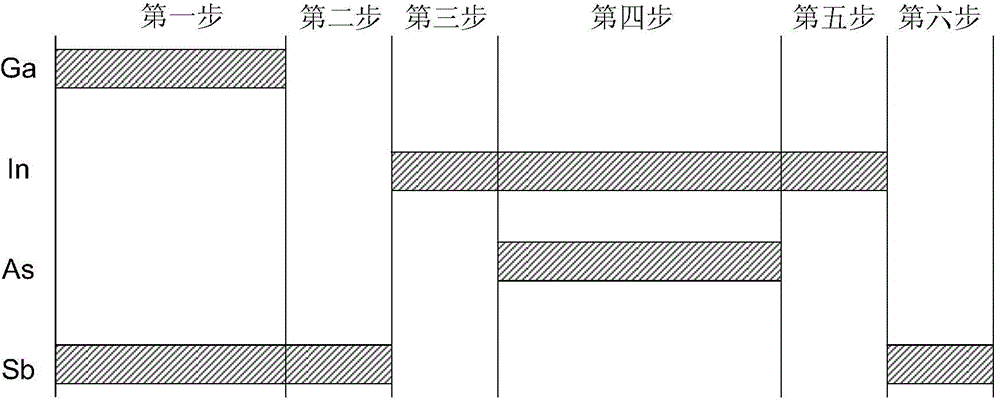

Type-II superlattice structure based on indium arsenide and preparation method

InactiveCN105789355AIncrease growth temperatureIncrease the diffusion lengthFinal product manufactureSemiconductor devicesMaterial defectAluminium arsenide

The invention discloses a type-II superlattice structure based on indium arsenide and a preparation method. The type-II superlattice structure based on indium arsenide comprises an InAs layer, a GaAs layer, a GaAsxSb1-xlayer and a GaAs layer from bottom to top, and is characterized in that: (1) an original GaSb substrate is replaced with an InAs substrate, so that the growth temperature of superlattices is substantially increased, and the increasement of the growth temperature is conductive to increasing a diffusion length of surface atoms, thereby being more conductive to the two-dimensional growth of materials and the reduction of material defect density; (2) an As valve is always in an open state during the whole growth process of type-II superlattices, so that a GaAsSb ternary compound is formed due to the outflow of partial As when growing a GaSb layer, growth temperature of the layers tends to be uniform due to the existence of the common element As in the layers, and the counterdiffusion at interfaces is reduced; (3) variation of thickness of the InAs layer has small influence on mismatching of the InAs-based type-II superlattices, the growth difficulty of long waves materials, particularly extremely-long-wave materials, is extremely reduced, and the performance and quality of the materials can be more easily improved.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Type II superlattice structure and preparation method based on arsenic valve switch

ActiveCN103500765BReduce interdiffusionReduce the chance of formationFinal product manufactureNanoopticsInterface layerBinary compound

Owner:中科爱毕赛思(常州)光电科技有限公司

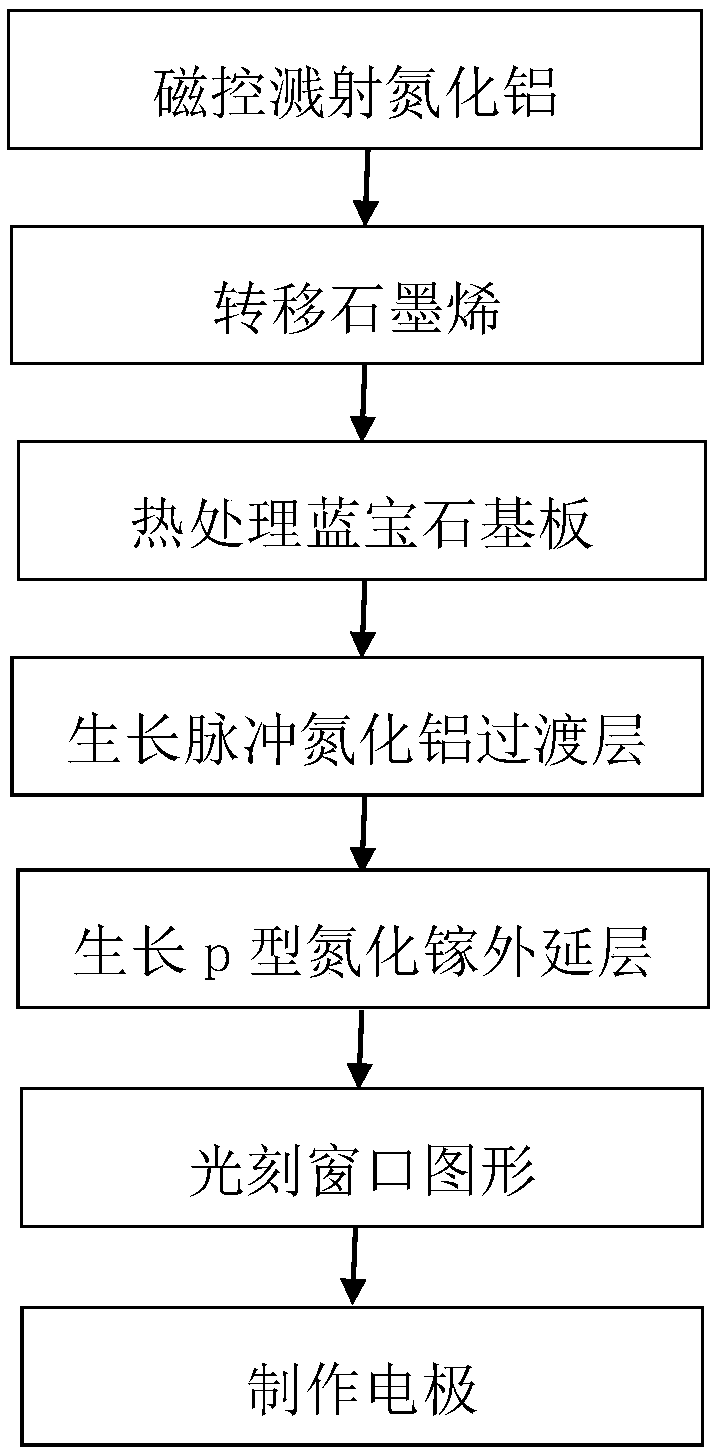

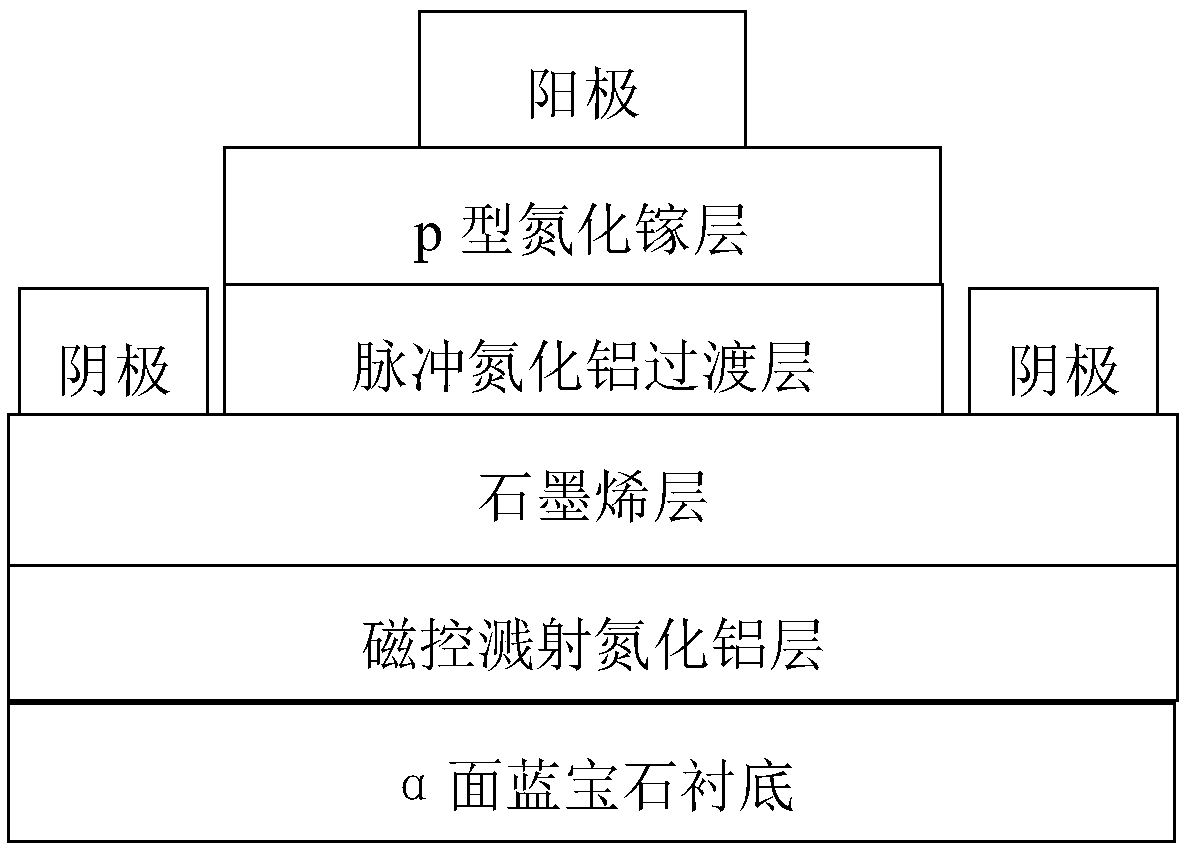

Method for preparing gallium-nitride-based photoelectric detector based on graphene insertion layer structure

InactiveCN108878588AQuality improvementIncrease growth temperatureFinal product manufactureSemiconductor devicesCvd grapheneCopper substrate

The invention discloses a method for preparing a gallium-nitride-based photoelectric detector based on a graphene insertion layer. The method is mainly used for solving the problems that in the priorart, a nitride material epitaxially grown on a copper substrate is poor in quality and is not provided with a transition layer. The method comprises the preparation steps that a magnetron sputtering aluminum nitride thin film is arranged on an alpha-surface sapphire substrate; graphene is transferred to the magnetron sputtering aluminum nitride thin film, and a sapphire substrate covered with thegraphene is obtained and heated; a pulsed aluminum nitride transition layer is grown on the heated sapphire substrate; a low-temperature gallium nitride layer is grown on the transition layer to obtain a gallium nitride substrate; and a window graph is photoetched on the gallium nitride substrate, and an electrode is manufactured. Magnetron sputtering aluminum nitride and the pulsed aluminum nitride transition layer are adopted, the graphene serves as the insertion layer, thus gallium nitride can grow on the substrate with the large lattice mismatch constant, the quality of the gallium-nitride-based photoelectric detector is improved, and the method can be used for manufacturing gallium-nitride-based photoelectric devices.

Owner:XIDIAN UNIV

A kind of preparation method of epitaxial wafer of gan-based light-emitting diode

ActiveCN106057988BIncrease growth temperaturePromote growthSemiconductor devicesQuantum wellLattice mismatch

The invention discloses a preparation method for an epitaxial wafer of a GaN-based light emitting diode, and belongs to the technical field of a semiconductor. The preparation method comprises the steps of laminating a buffer layer, a non-doped GaN layer, an N type layer, a stress release layer, a multi-quantum well layer and a P type layer on a sapphire substrate in sequence, wherein the stress release layer comprises multiple stress release sub-layers, the stress release sub-layers comprise a first sub-layer, a second sub-layer, a third sub-layer and a fourth sub-layer which are laminated in sequence, the first sub-layer is an AIGaN layer, the third sub-layer is an InGaN layer, the second and fourth sub-layers are GaN layers, and the growth temperature of the first sub-layer is higher than that of the third sub-layer. According to the method, a periodic structure is employed in the stress release layer, the relatively low growth temperature is employed in the InGaN layer, thereby facilitating good growth of lattices, the stress generated between the sapphire substrate and the GaN layers due to lattice mismatch can be released, the growth quality of the multi-quantum well layer is improved, and the photoelectric property of the LED is improved.

Owner:HC SEMITEK SUZHOU