Patents

Literature

65results about How to "Reduce interdiffusion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

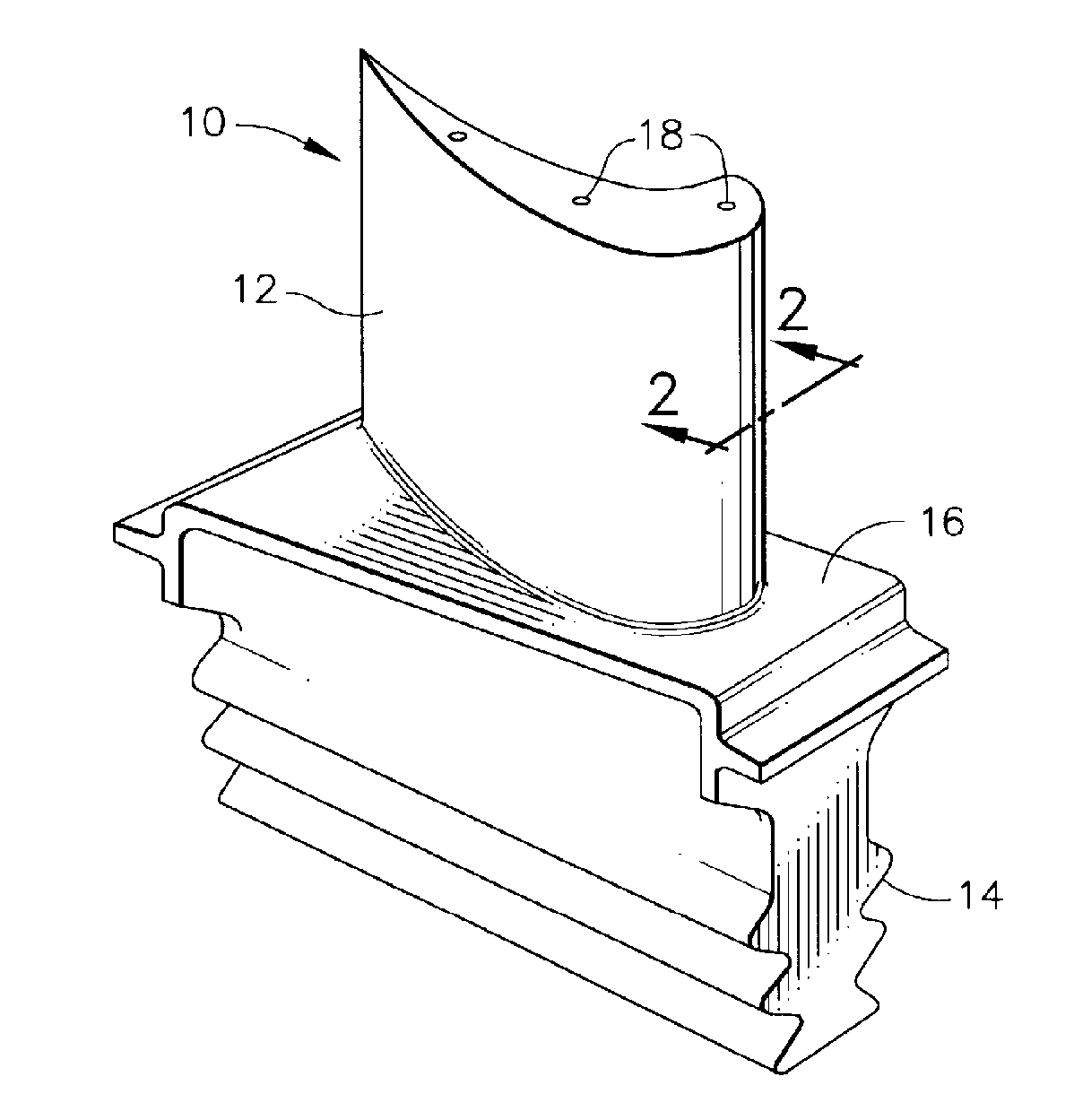

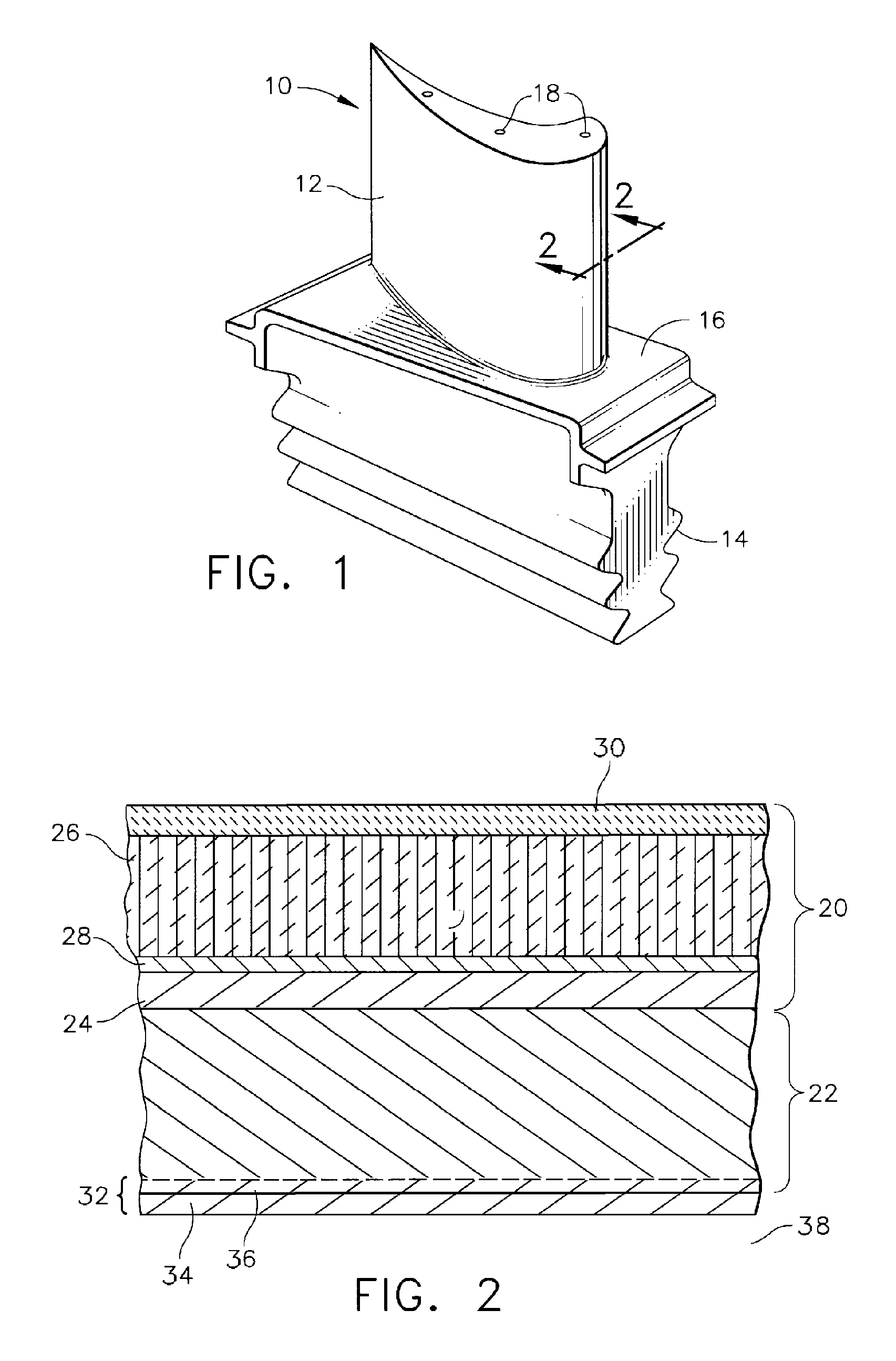

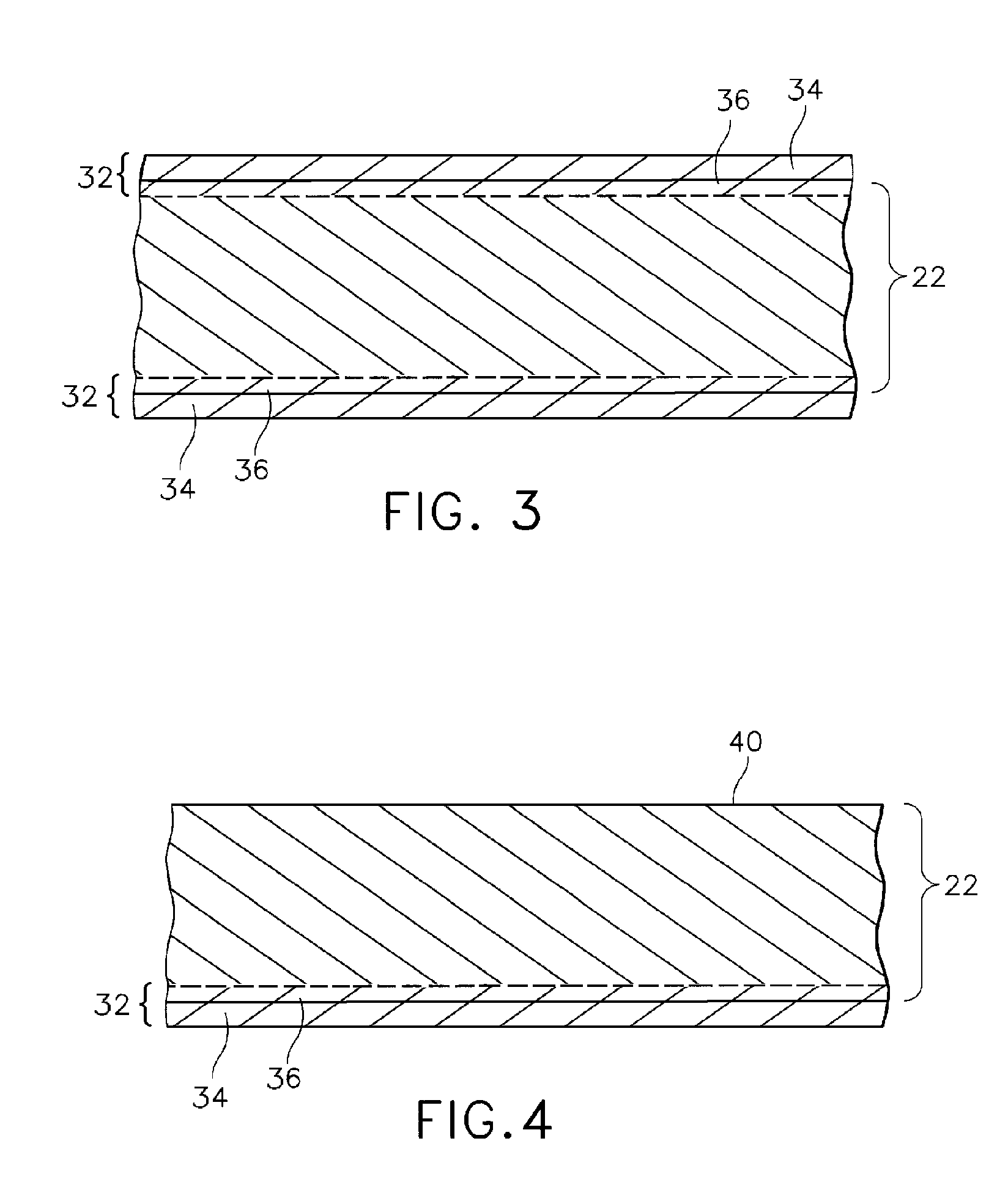

Process for inhibiting SRZ formation and coating system therefor

InactiveUS20050118334A1Reduce morbidityIncrease contentLiquid surface applicatorsBlade accessoriesCoating systemReaction zone

A process for reducing the incidence of a secondary reaction zone (SRZ) in alloys prone to SRZ formation, particularly superalloys that have a high refractory element content. The process finds use with articles having a wall region that defines external and internal surfaces on the exterior and within the article, respectively. Diffusion coatings are formed on the internal and external surfaces of the article, with at least the diffusion coating on the external surface comprising an additive layer and a diffusion zone that is beneath the additive layer and extends into the wall region. The additive layer and at least a portion of the diffusion zone of the external diffusion coating is then removed to define an exposed surface region on the exterior of the article. An overlay coating is then deposited on the exposed surface region.

Owner:GENERAL ELECTRIC CO

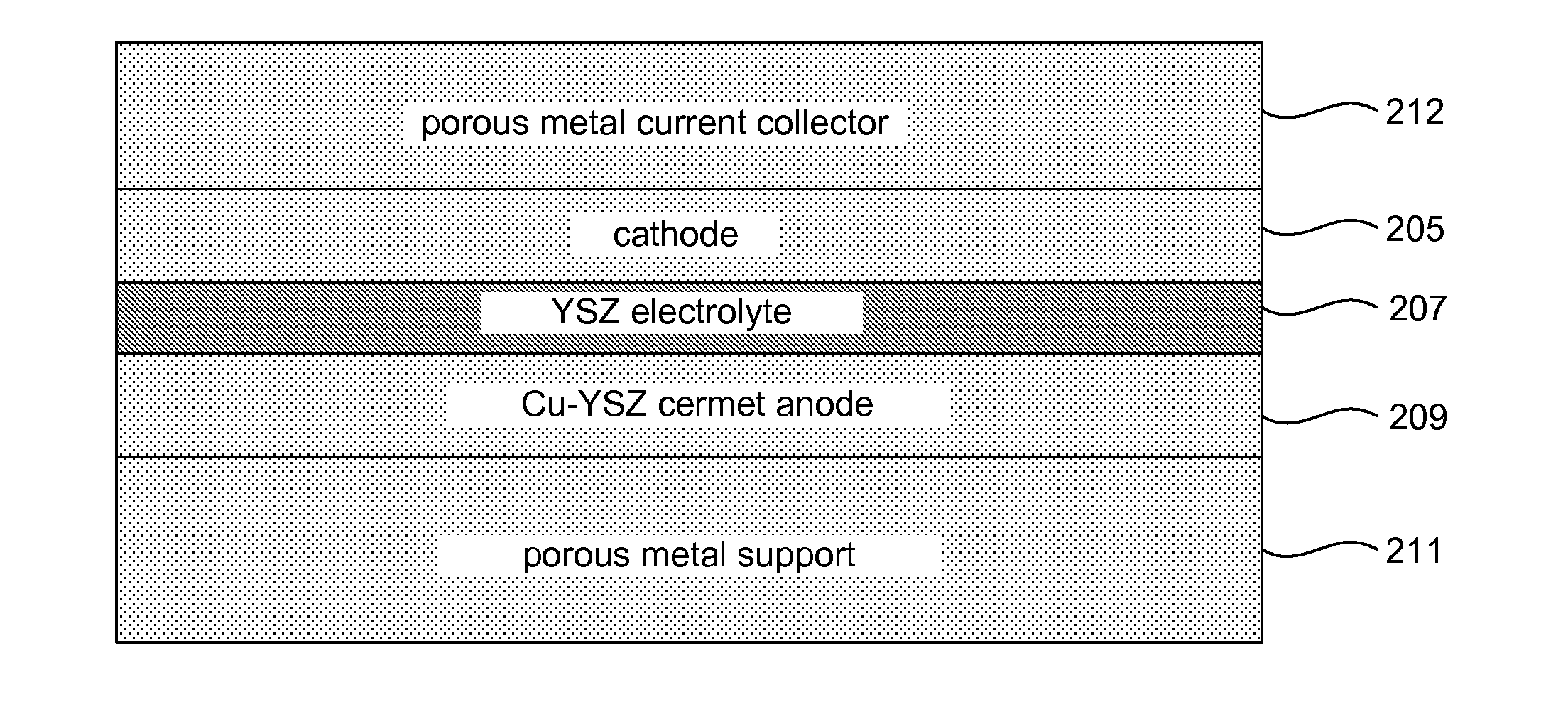

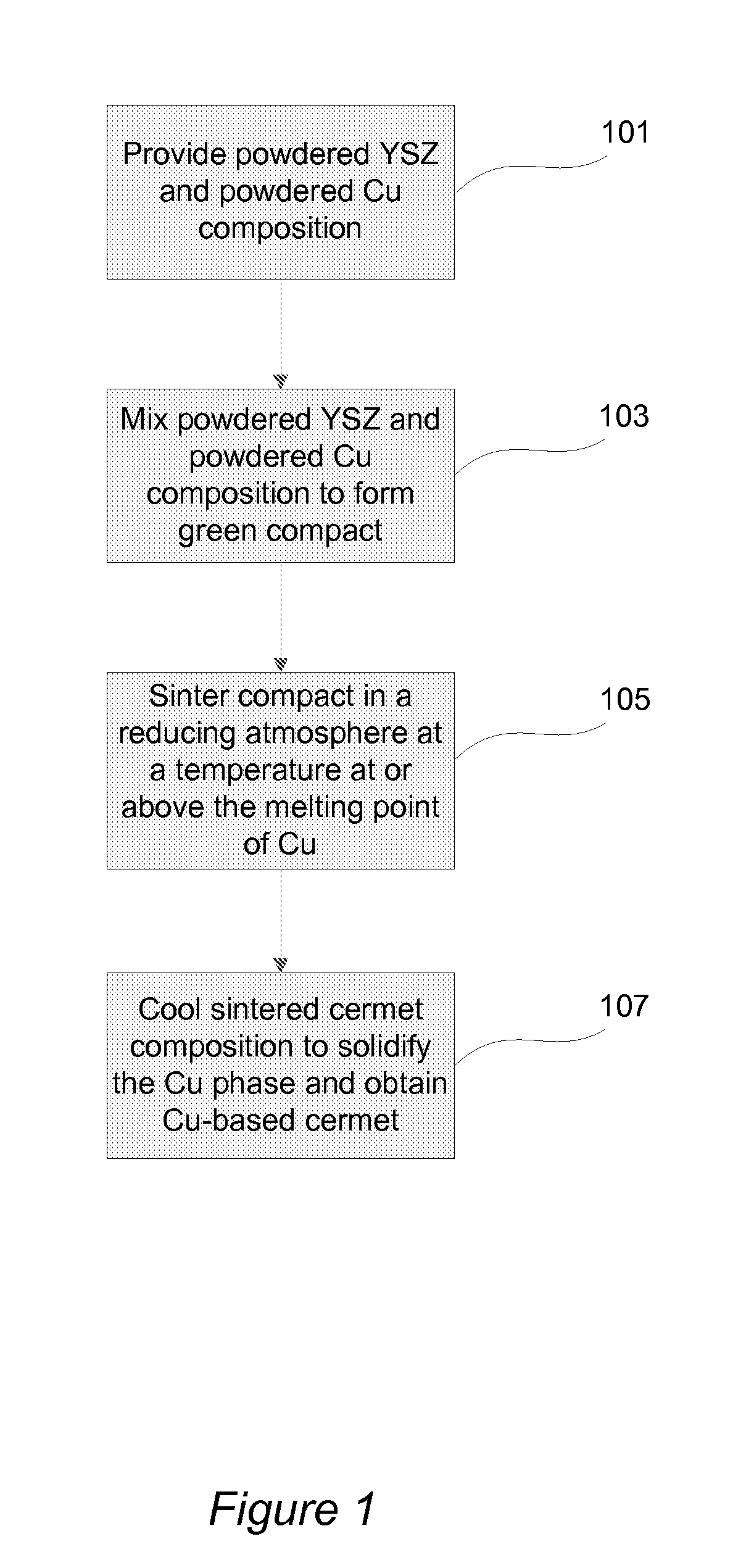

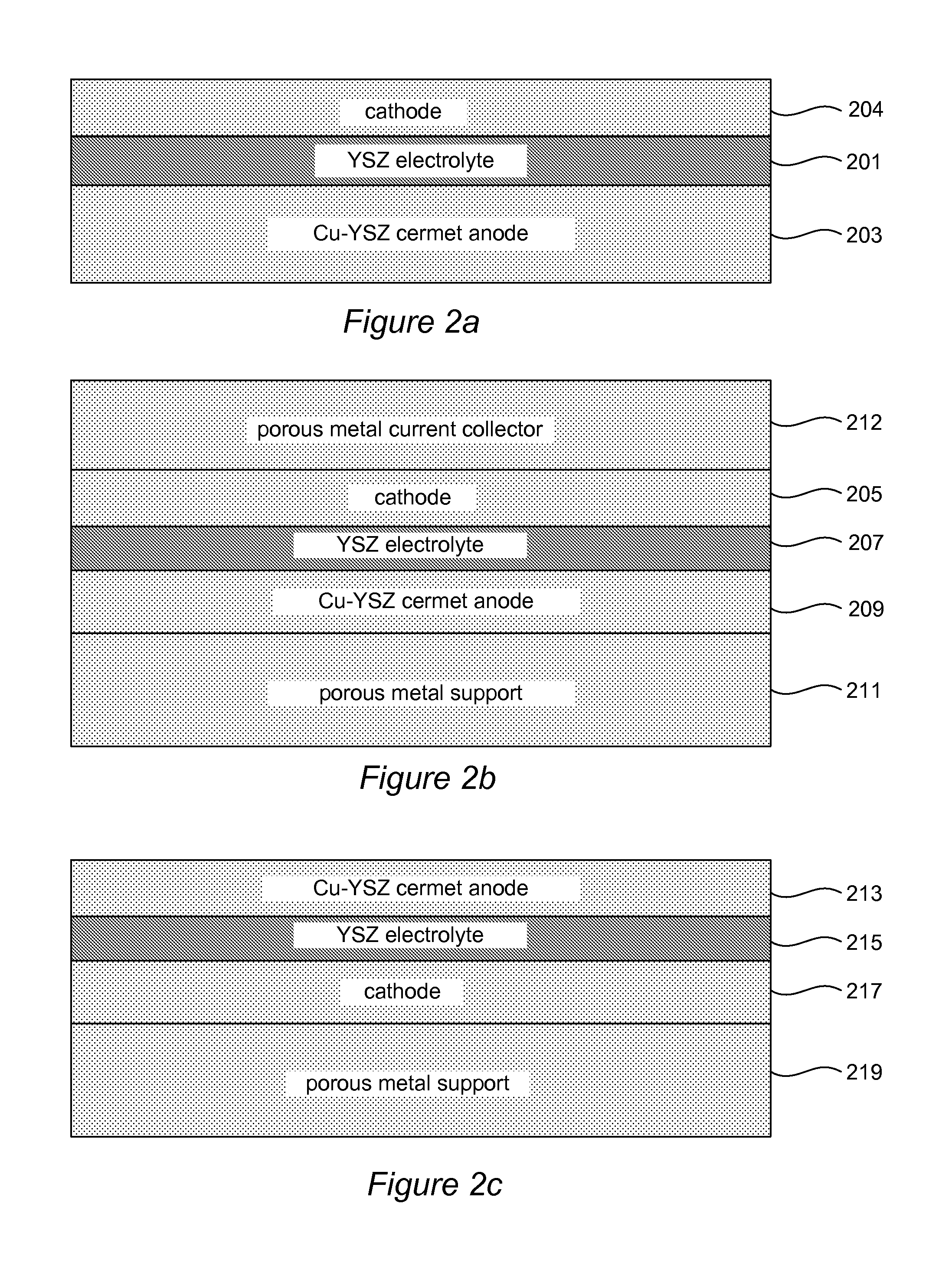

Cu-based cermet for high-temperature fuel cell

InactiveUS20110053041A1Reduce interdiffusionCell electrodesFinal product manufactureHydrogenFuel cells

Copper-based cermets and methods of preparing them are provided. The Cu-based cermets have interpenetrating networks of copper alloy and stabilized zirconia that are in intimate contact and display high electronic connectivity through the copper alloy phase. In certain embodiments, methods of preparing the cermets involving sintering a mixture of ceramic and copper-based powders in a reducing atmosphere at a temperature above the melting point of the copper or copper alloy are provided. Also provided are electrochemical structures having the Cu-based cermet, e.g., as an anode structure or a barrier layer between an anode and a metal support. Applications of the cermet compositions and structures include use in high-operating-temperature electrochemical devices, including solid oxide fuel cells, hydrogen generators, electrochemical flow reactors, etc.

Owner:RGT UNIV OF CALIFORNIA

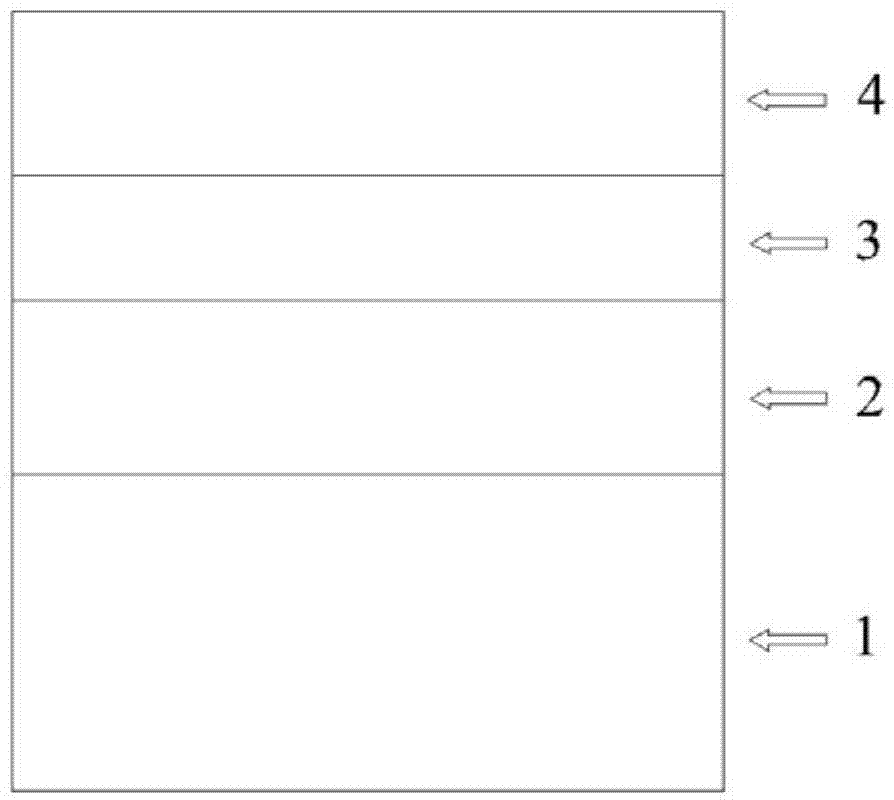

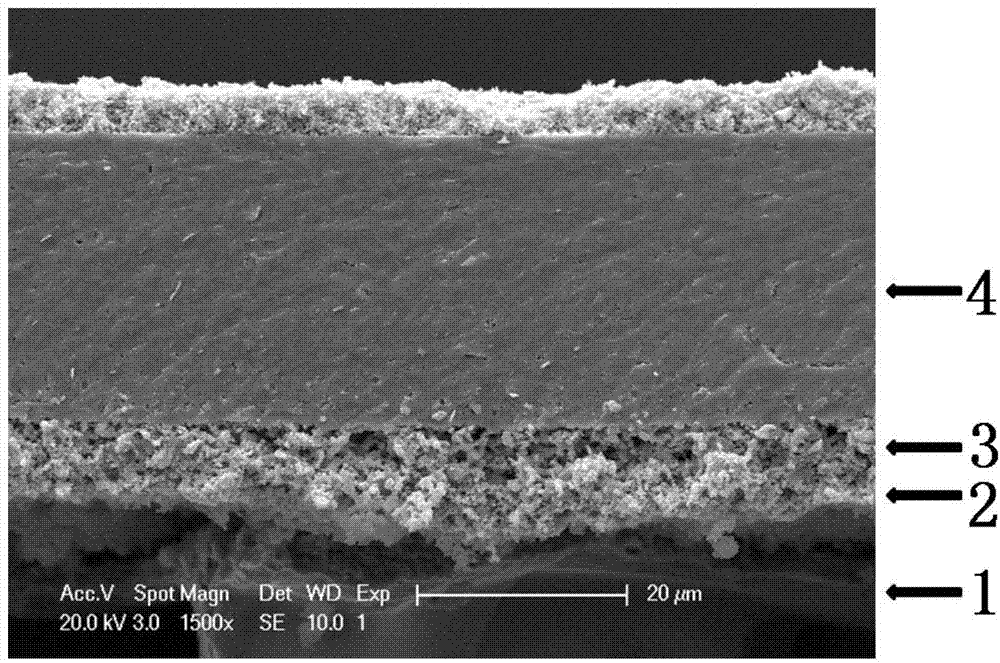

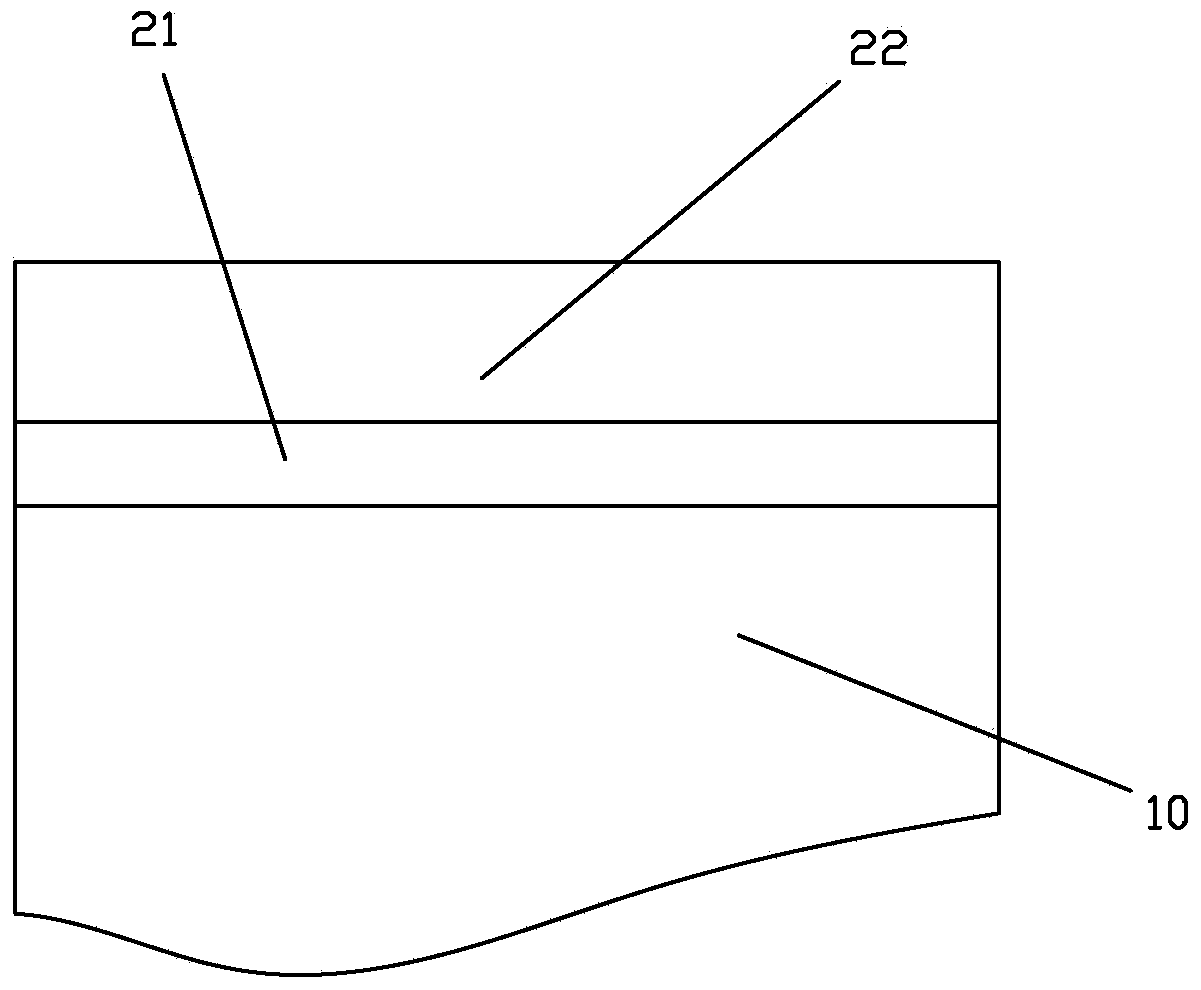

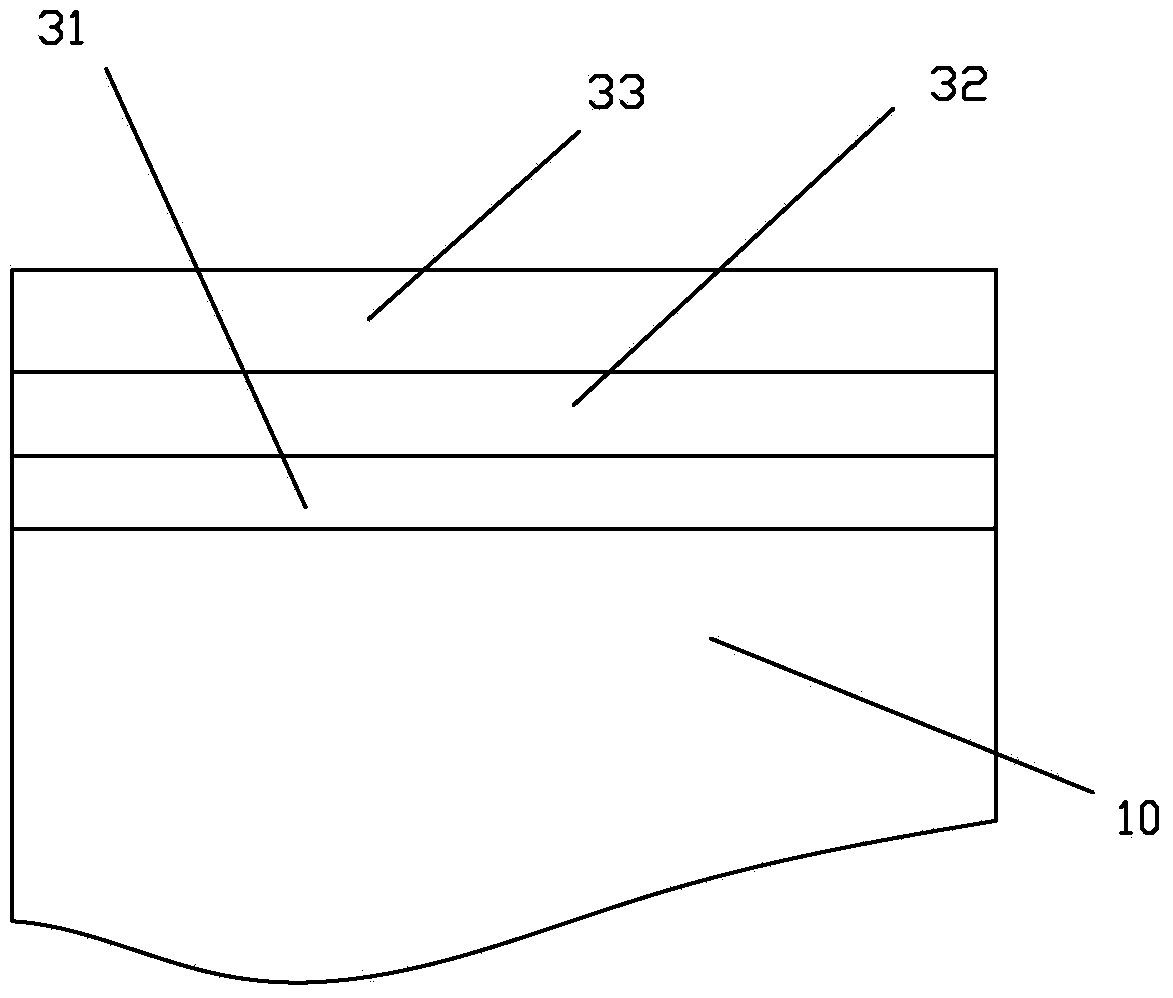

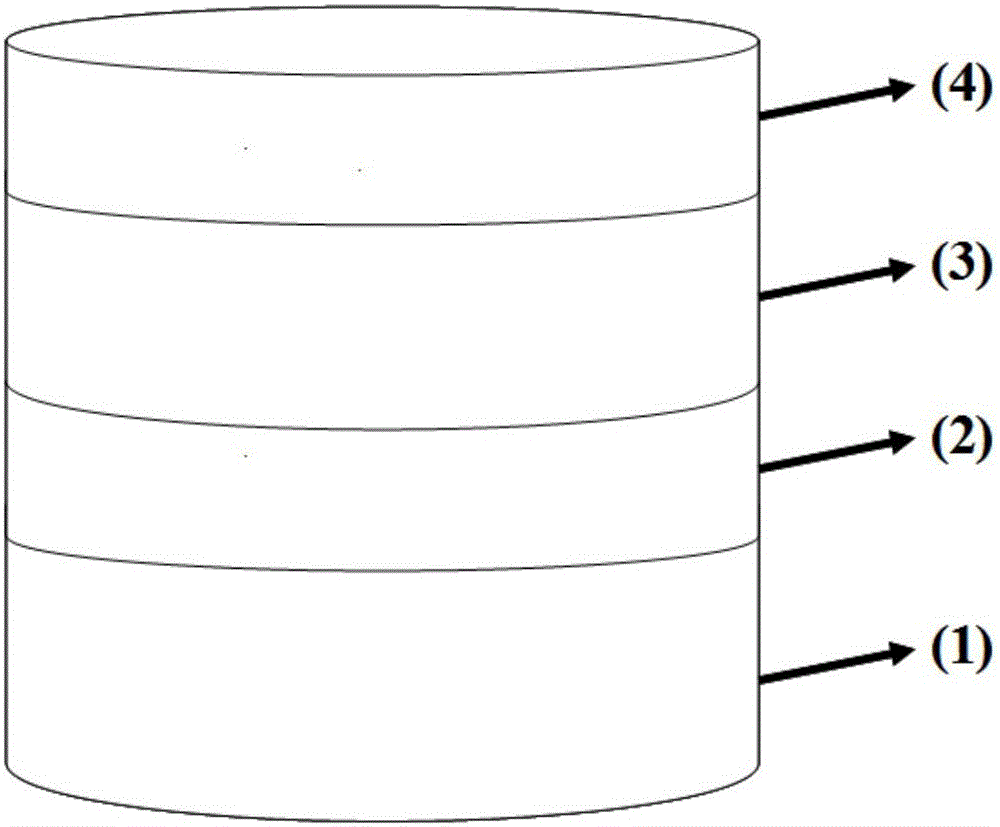

Metal support half-cell of solid oxide fuel cell and preparation method thereof

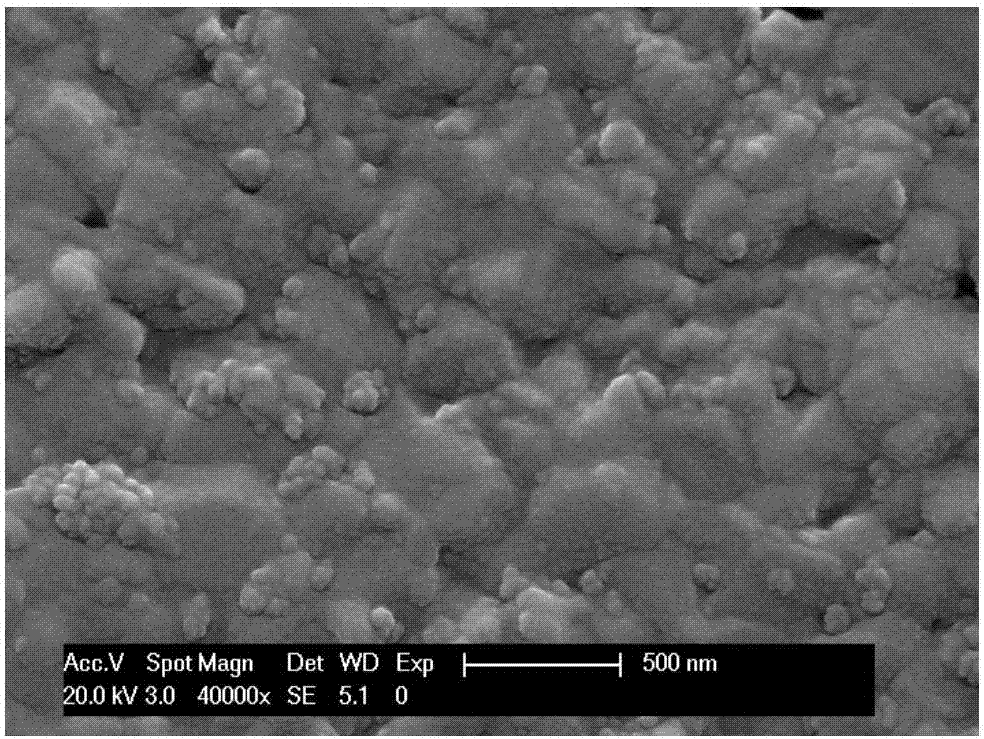

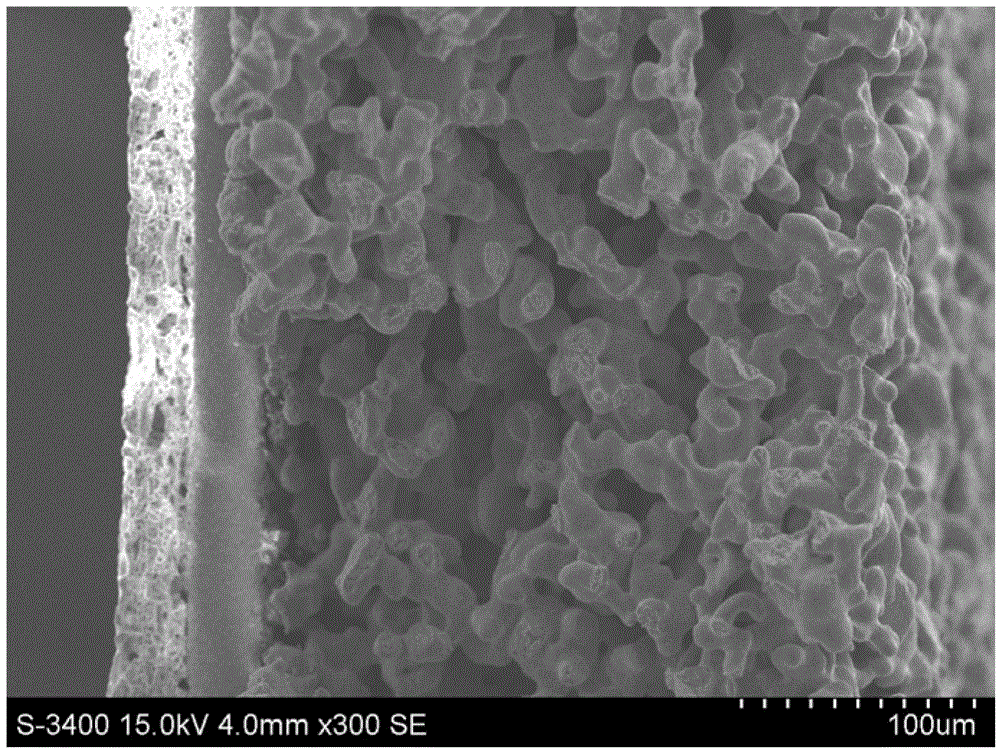

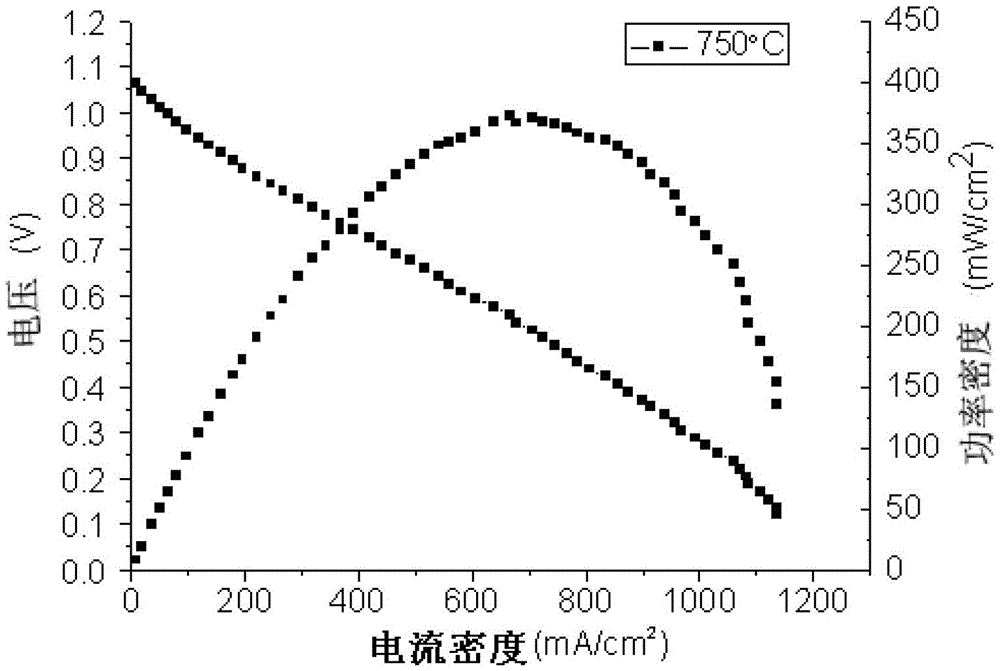

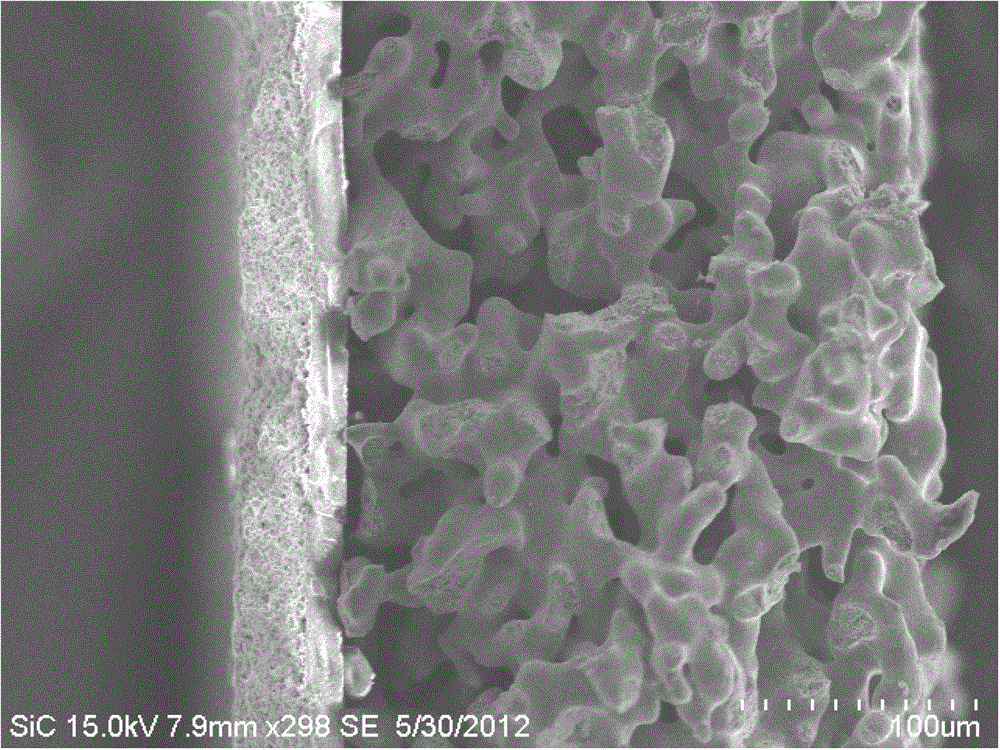

ActiveCN103928693AAvoid direct contactReduce interdiffusionCell electrodesSolid electrolyte fuel cellsFuel cellsMixed oxide

The invention discloses a metal support half-cell of a solid oxide fuel cell and a preparation method thereof. The half-cell comprises a porous metal supporting layer thick membrane, a porous cermet gradient transition layer film, a porous anode layer and a compact electrolyte layer film from down to up. The porous gradient transition layer composed of a mixed oxide and a oxide with a fluorite structuring can avoid the direct contact of the porous metal supporting layer and the porous anode layer, and the mutual diffusion of Fe / Cr elements in the metal supporting layer and Ni element in the porous anode layer can be reduced under high temperature sintering condition. The mixed oxide is reduced to an alloy under the work condition of the cell; a high anode active material is formed at a side interface of the anode, a high conductivity composite material which takes the alloy as a main phase is formed on the side interface of a metal support body, so that higher conductivity is presented, ohmic resistance is reduced, electrocatalytic activity is not reduced, long-term stability for operation of the cell can be ensured, and good combination of the porous metal supporting layer and the porous anode layer can be simultaneously realized.

Owner:中弗(无锡)新能源有限公司

Method for preparing flat-plate type metal-support solid oxide fuel cell

InactiveCN102881930AImprove performanceImprove long-term stabilityFinal product manufactureCell electrodesOperabilitySurface-active agents

The invention discloses a method for preparing a flat-plate type metal-support solid oxide fuel cell. The method comprises the following steps of: firstly respectively preparing three layers of biscuits such as a porous metal support layer, a compact electrolyte layer and a porous cathode precursor layer, then superimposing from bottom to top in sequence for carrying out hot pressing, then carrying out high-temperature common sintering, using a surface active agent to carry out surface treatment on the porous metal support layer, finally immersing a salt solution of an active cathode material in the porous cathode precursor layer, and performing heat treatment, so as to obtain a cathode of the cell; and immersing a salt solution of an active anode material in the porous metal support layer, performing the heat treatment, so as to obtain an anode of the cell. The method has the advantages that the cost is low, the operability is strong, the batched and continuous production is convenient; and according to the prepared cell, the combination among all the layers is close, the thickness, the porosity and the like of all the function layers can be controlled, the cathode and the anode of the cell are prepared by immersion, the performance of the cell is high, the stability is good, the service life of an electric pile can be guaranteed, the cost of a system is reduced and the application prospect is very good.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

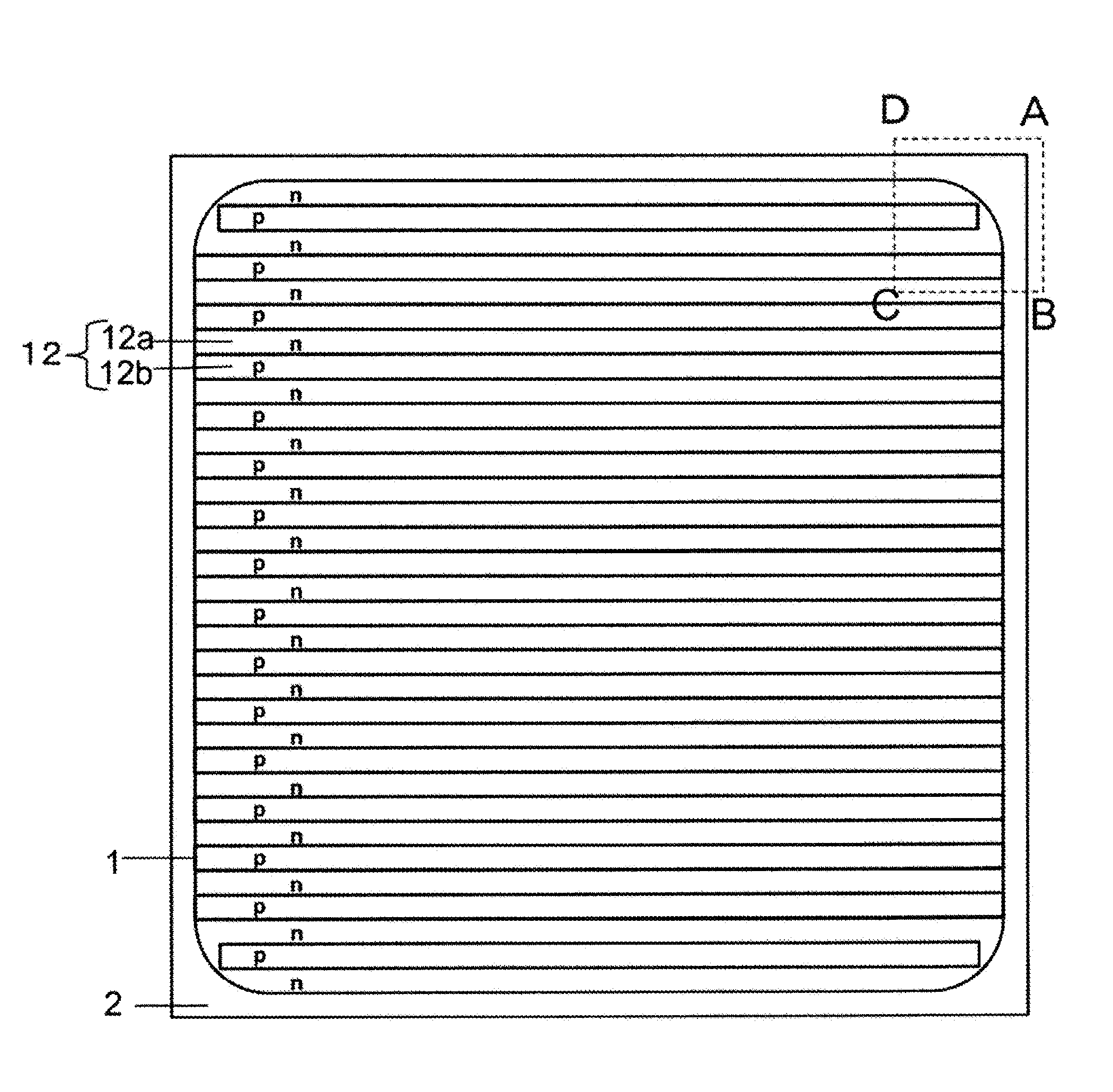

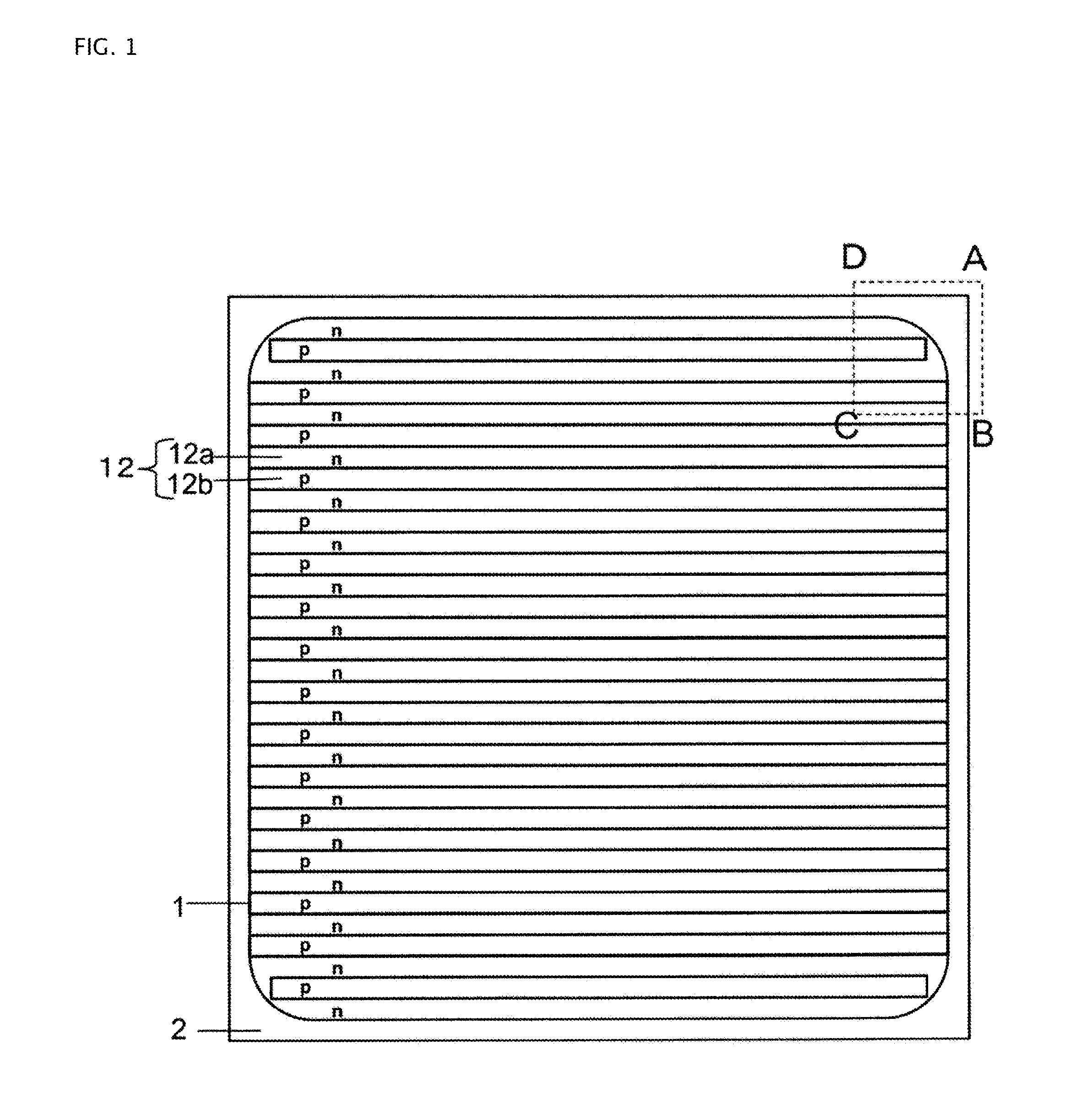

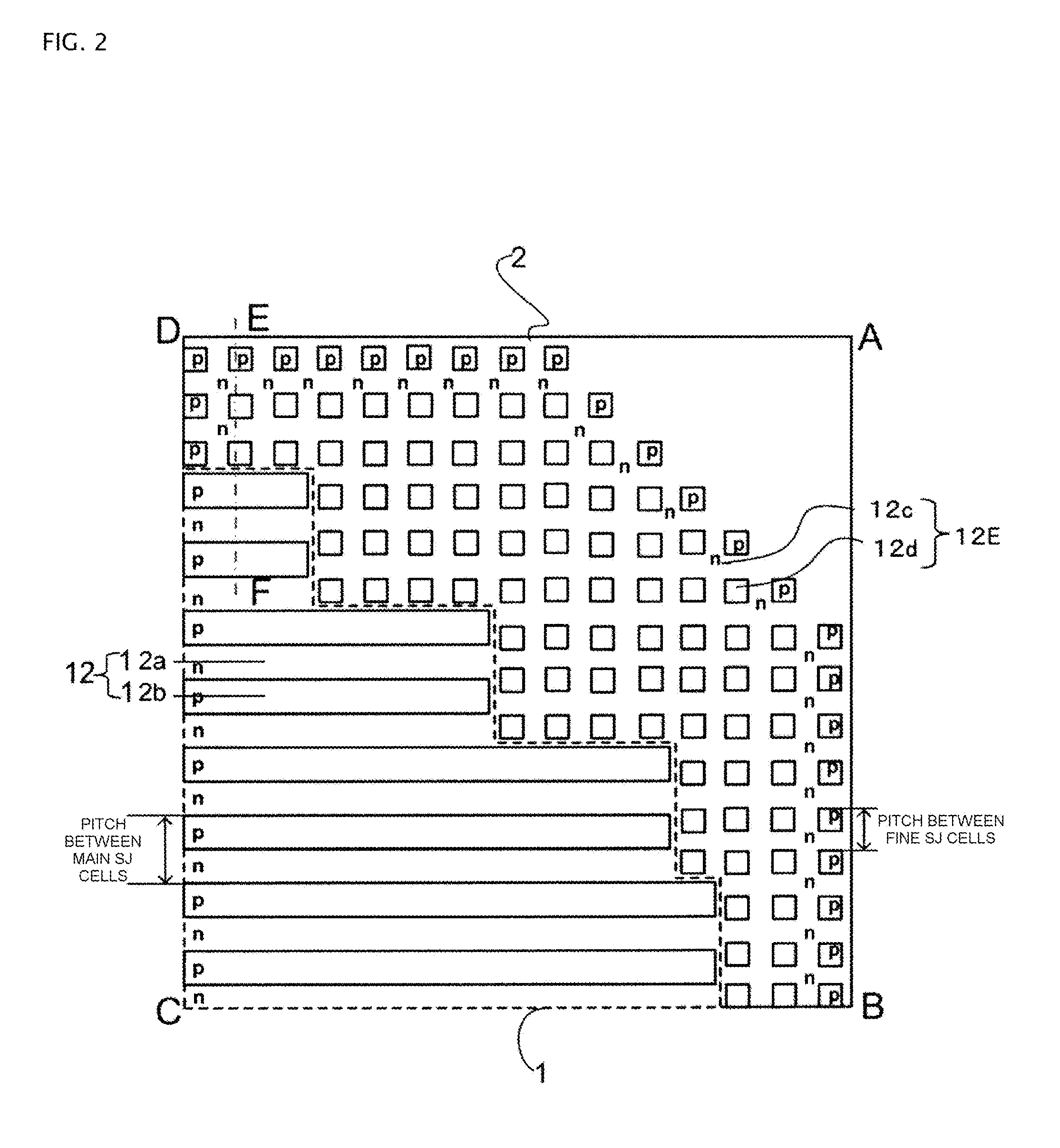

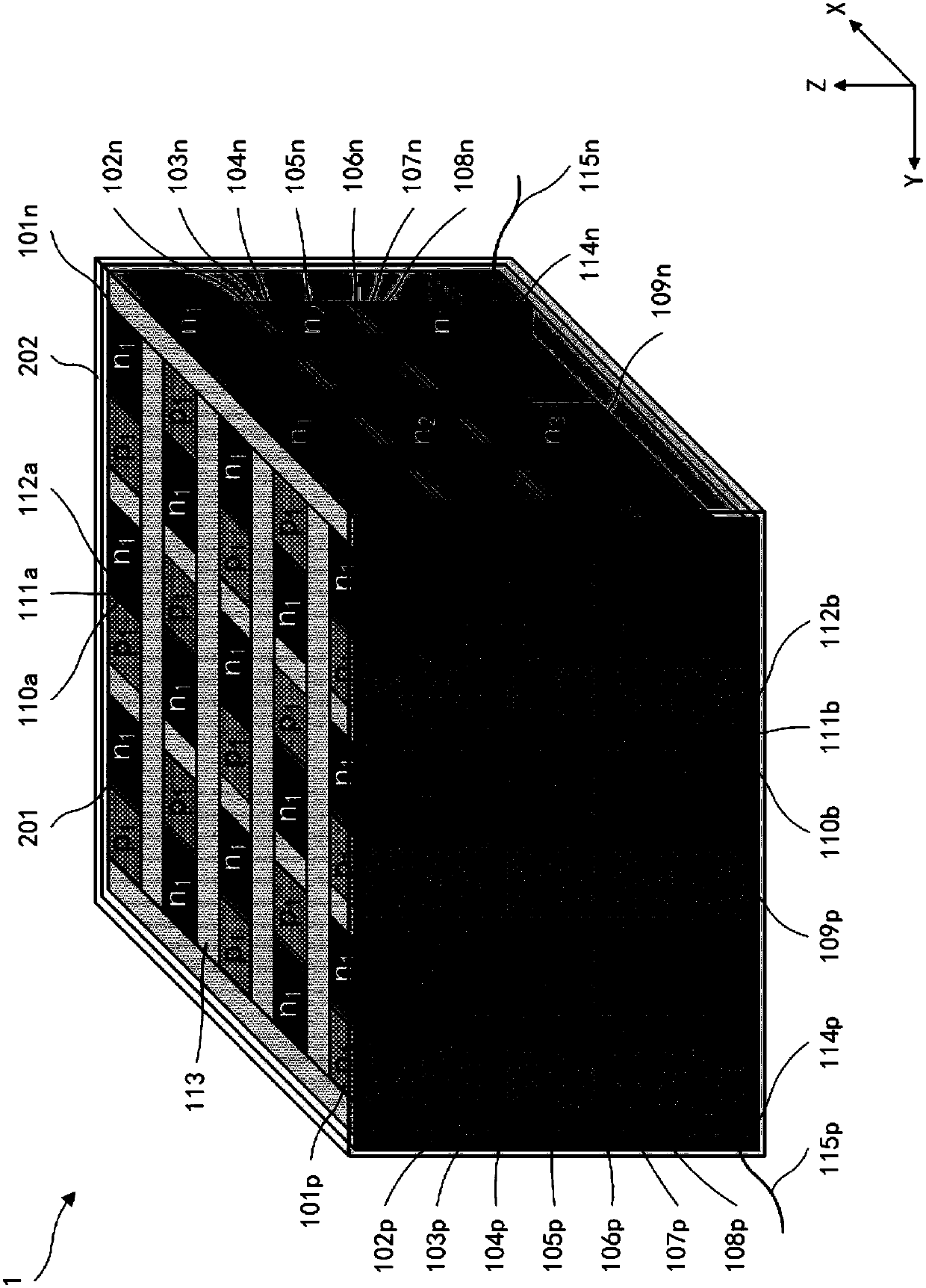

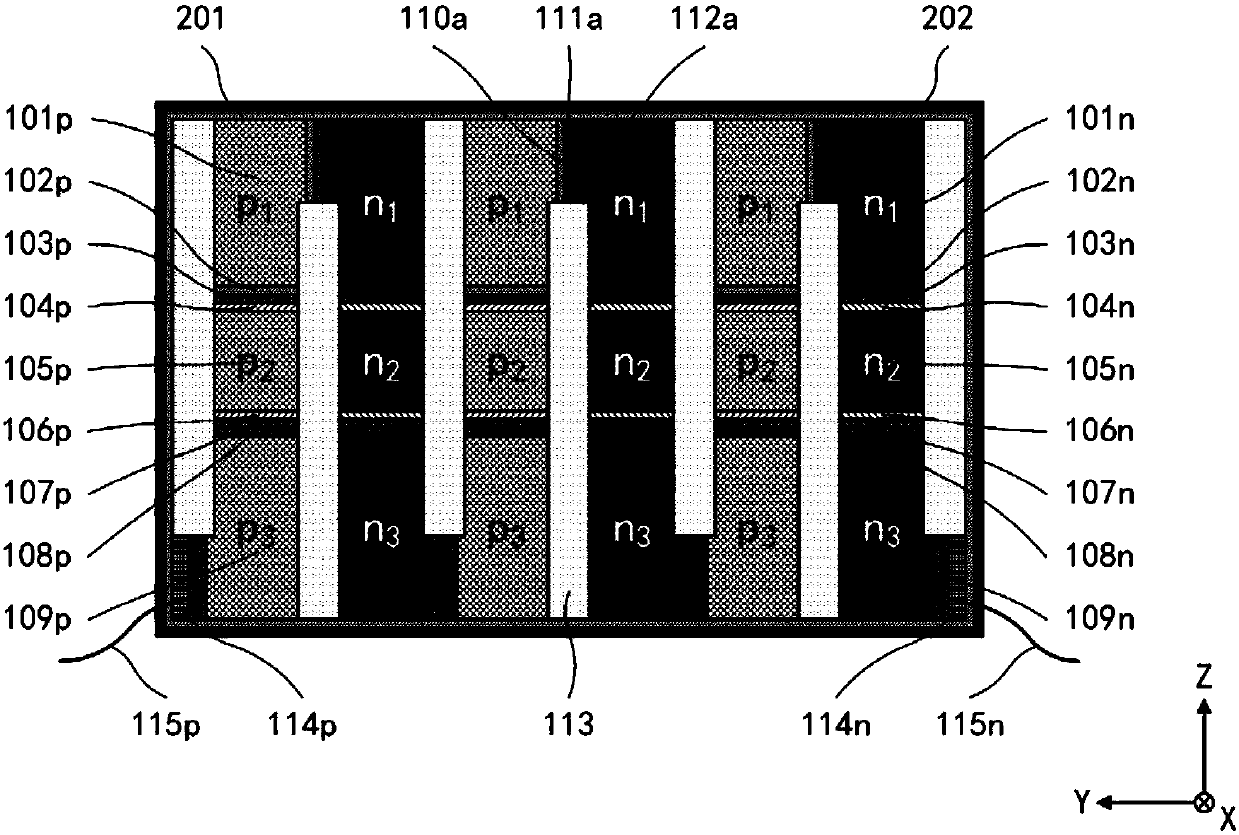

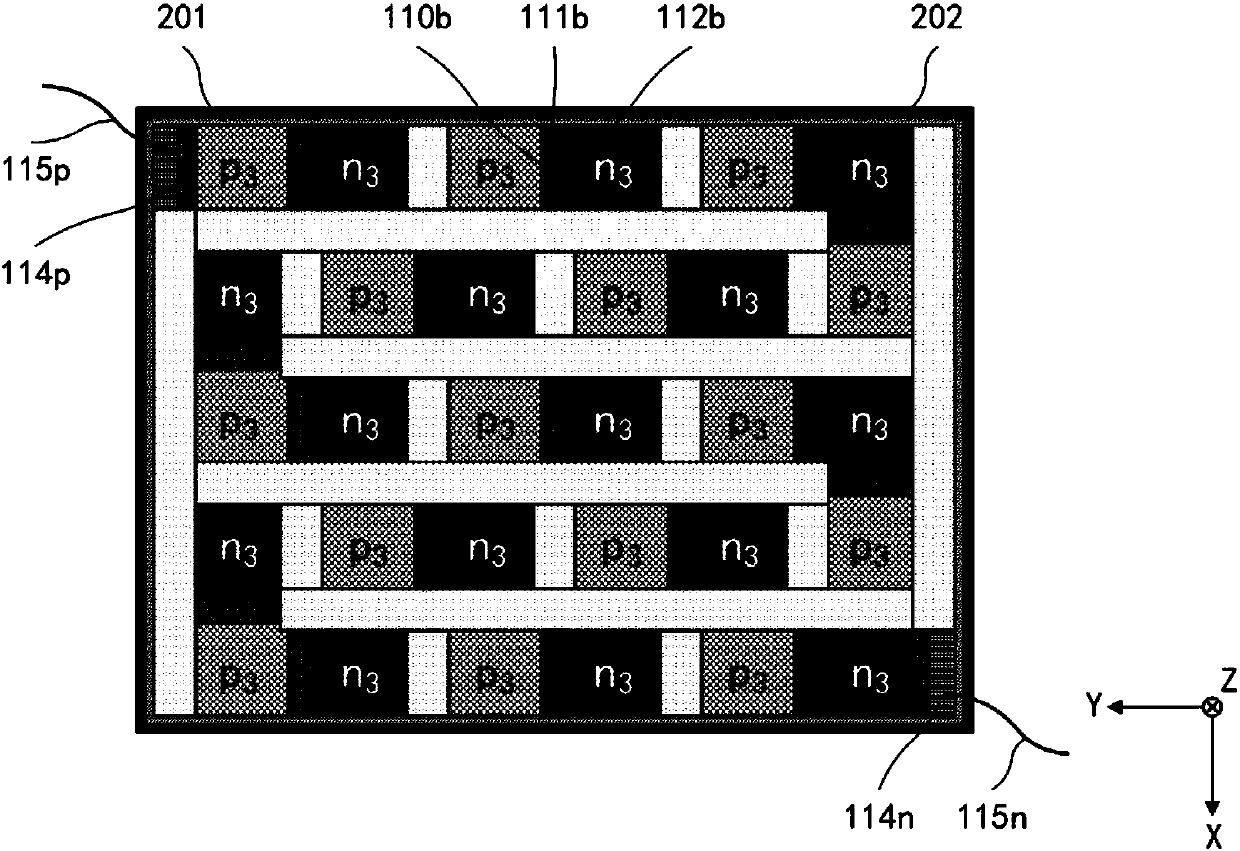

High breakdown voltage semiconductor device

ActiveUS20140035002A1Reduce mutual diffusionReduce Process VariationsSemiconductor devicesDevice materialSemiconductor

Semiconductor regions are alternately arranged in a parallel pn layer in which an n-type region and a p-type region are alternately arranged parallel to the main surface of a semiconductor substrate. Pitch between n drift region and p partition region of a second parallel pn layer in an edge termination region is two thirds of pitch between n drift region and p partition region of a first parallel pn layer in an active region. At boundaries between main SJ cells and fine SJ cells at four corners of the semiconductor substrate having rectangular shape in plan view, ends of two pitches of main SJ cells face the ends of three pitches of fine SJ cells. In this way, it is possible to reduce the influence of a process variation and thus reduce mutual diffusion between n drift region and p partition region of the fine SJ cell.

Owner:FUJI ELECTRIC CO LTD

Miniature PVD coat miller cutter for PCB, and making method thereof

InactiveCN103737092AReduce coefficient of frictionAnti-oxidation temperature is highMilling cuttersVacuum evaporation coatingMilling cutterWear resistant

The invention discloses a miniature PVD coat miller cutter for PCB, and a making method thereof. The miniature PVD coat miller cutter for PCB comprises a substrate and one or more layers of a hard and wear-resistant coat deposited on the substrate through a physical vapor deposition process; the hard and wear-resistant coat is an MeCxNyOz coat, Me is one or more of Al, Cr, Ti, Zr, Si, Hf, Nb, Ni, W, Ta, B, V, Y and Cu, and x+y+z is 1; and the total thickness of the one or more layers of the coat on the substrate is 0.1-10mum. The substrate is made by using a cemented carbide material, a ceramet material, a ceramic material, a cubic boron nitride based material or a high-speed steel material. By improving the structure of the PVD coat in the invention, a processing problem that printed circuit boards are difficult to process is overcome, and a problem that the service life of a common miniature milling cutter is short is prolonged.

Owner:XIAMEN GOLDEN EGRET SPECIAL ALLOY

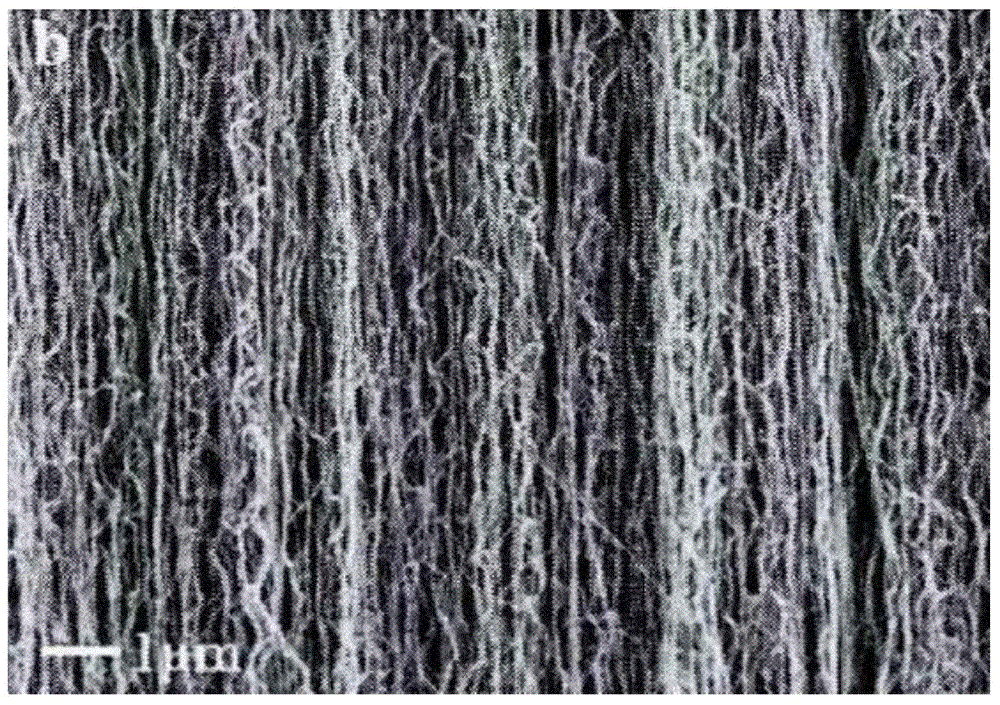

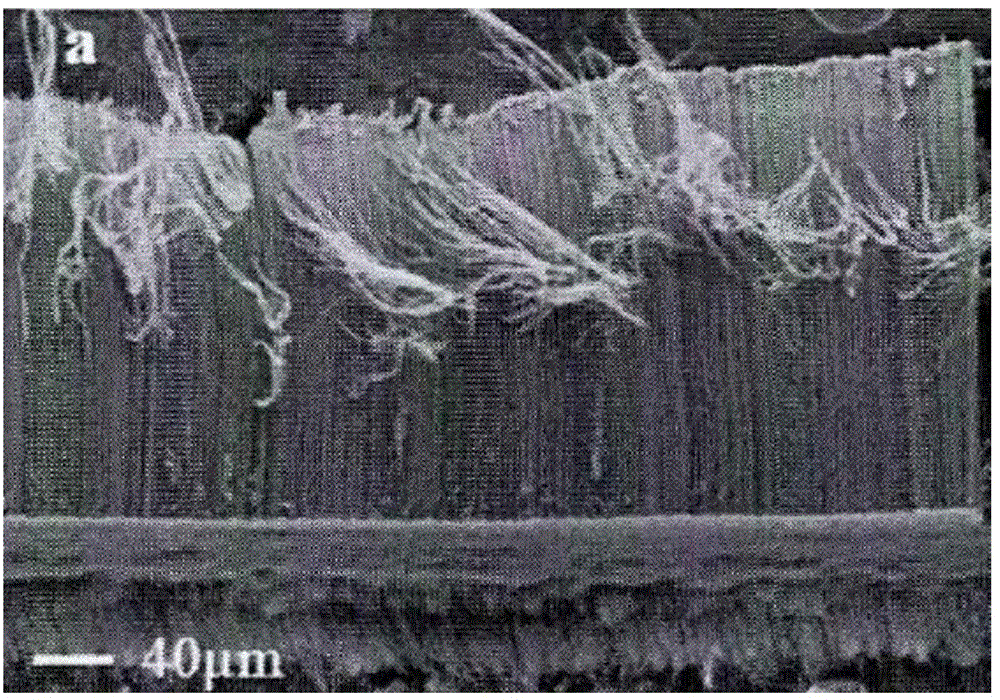

Method for directly growing carbon nano tube array on fiber substrate

ActiveCN104310372AIncrease coverageReduce interdiffusionMaterial nanotechnologyPre treatmentCarbon nanotube

The invention provides a method for directly growing a carbon nano tube array on a fiber substrate. The method comprises the following steps: (1) pre-treating the fiber substrate; (2) attaching a catalyst precursor on the surface of the substrate obtained in the step 1, wherein the catalyst comprises transitional metal elements such as Fe, Co, Ni, Cu, Au, Pt, Mo or Ag; (3) putting the substrate obtained in the step (2) in a reaction furnace, heating the substrate to a first temperature and maintaining for a preset time, and introducing inert gas to remove organic matters in the catalyst precursor; (4) heating to a second temperature and maintaining for a preset time, continuously introducing inert gas, introducing mixed gas of reductive gas and carbon source gas, maintaining the pressure in the reaction furnace, and growing high-density carbon nano tubes on the surface of the substrate; and (5) after reaction, stopping introduction of the reductive gas and carbon source gas, and continuously introducing inert gas till the temperature is reduced to room temperature.

Owner:4MICRO TECH COMPANY

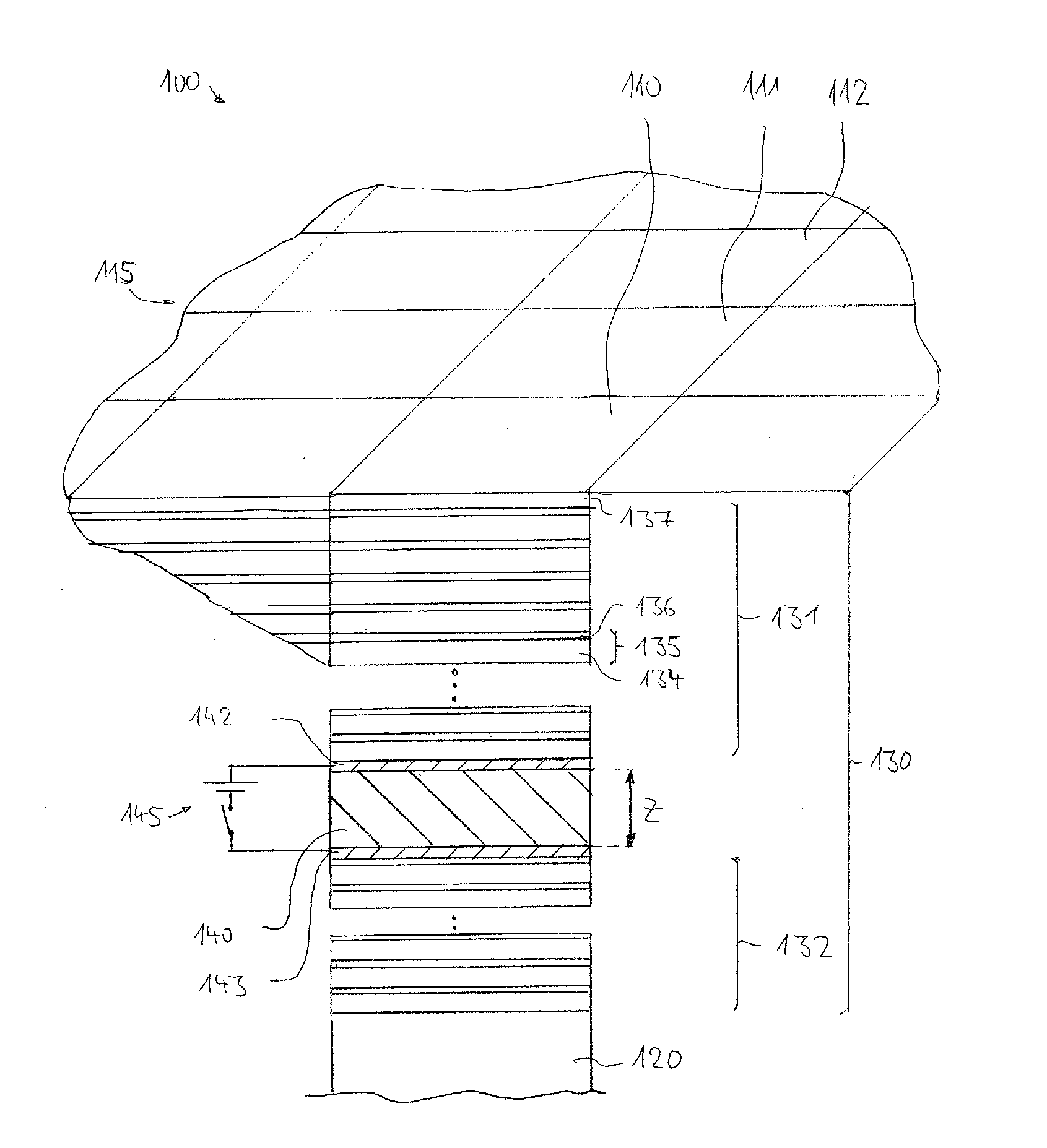

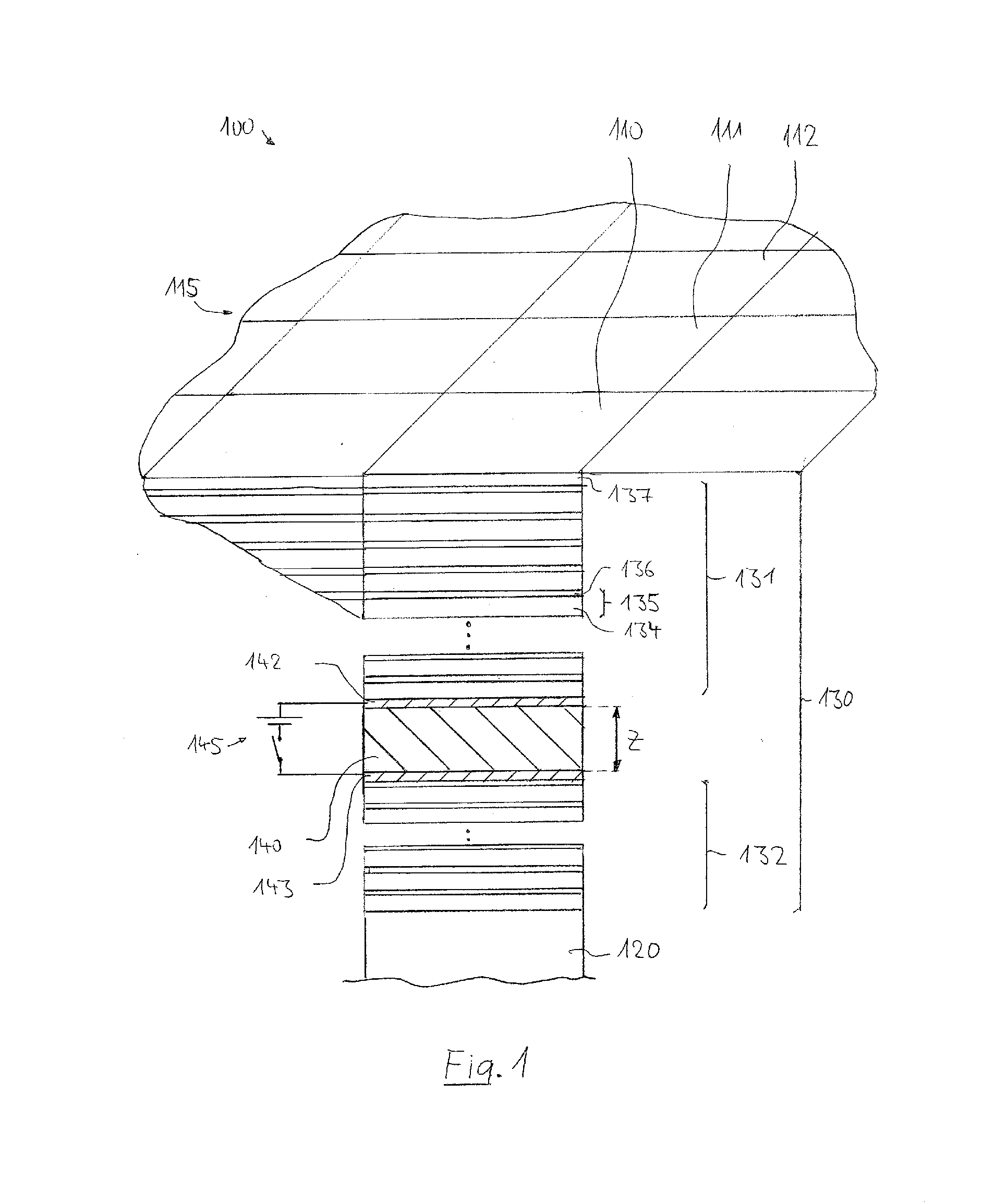

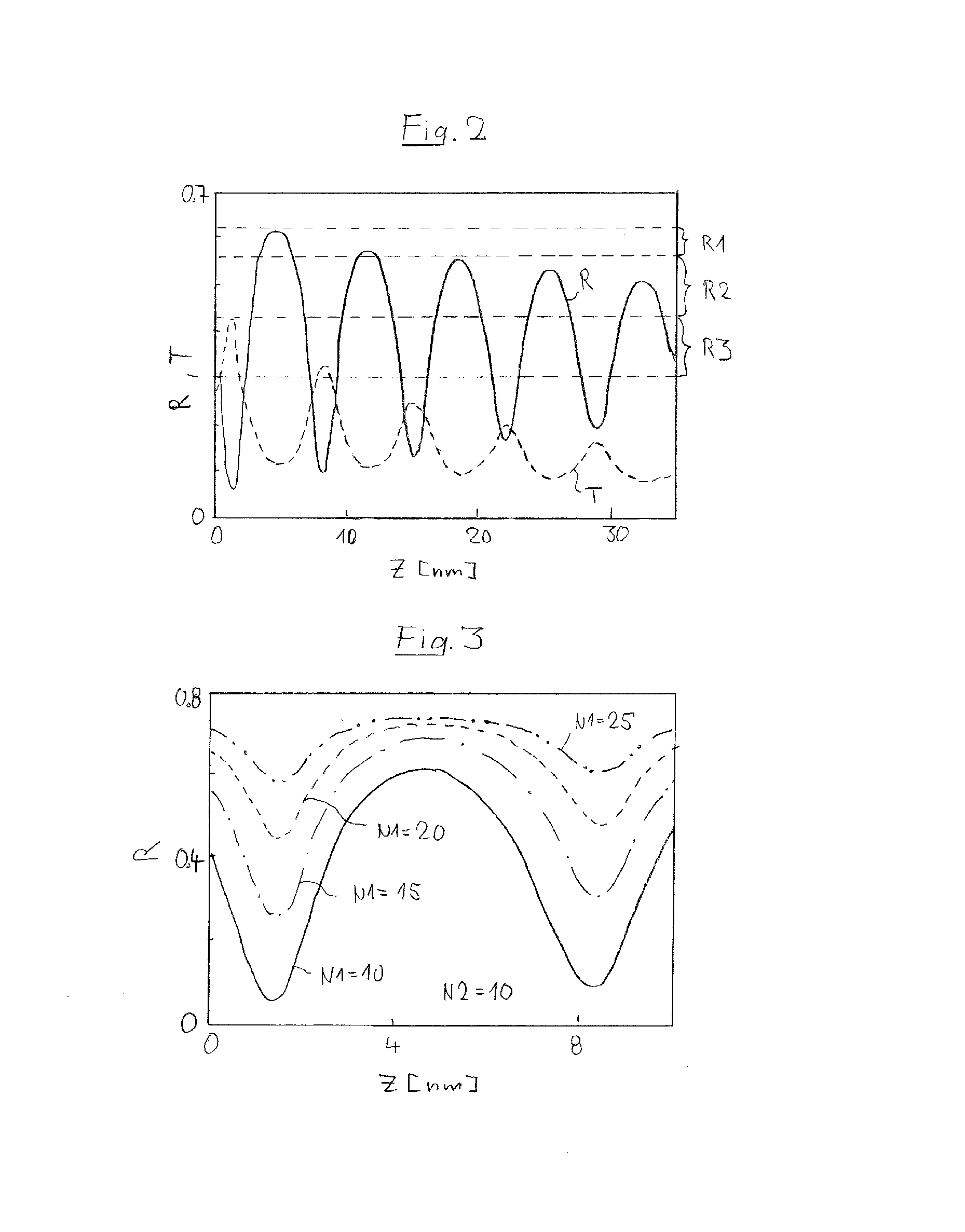

Euv-mirror arrangement, optical system with euv-mirror arrangement and associated operating method

ActiveUS20140285783A1Little surface roughnessHigh piezoelectric coefficientMirrorsNanoinformaticsExtreme ultravioletElectric field

An EUV mirror arrangement (100) has a multiplicity of mirror elements (110, 111, 112) which are arranged alongside one another and jointly form a mirror surface of the mirror arrangement. Each mirror element has a substrate (120) and a multilayer arrangement (130) applied on the substrate and having a reflective effect with respect to radiation from the extreme ultraviolet range (EUV), said multilayer arrangement comprising a multiplicity of layer pairs (135) having alternate layers composed of a high refractive index layer material and a low refractive index layer material. The multilayer arrangement has an active layer (140) arranged between a radiation entrance surface and the substrate and consisting of a piezoelectrically active layer material, the layer thickness (z) of which active layer can be altered by the action of an electric field. For each active layer provision is made of an electrode arrangement for generating an electric field acting on the active layer.

Owner:CARL ZEISS SMT GMBH

High-performance thermoelectric device and ultrafast fabrication method thereof

ActiveCN107946452AImprove electrical output performanceImprove job stabilityThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentThermoelectric materialsEnergy conversion efficiency

The invention discloses a high-performance thermoelectric device and an ultrafast fabrication method thereof. In the high-performance thermoelectric device, a segmented structure is employed to perform optimal matching of a thermoelectric material and a temperature difference environment, a blocking layer and a buffer stress layer are employed to reduce interface element migration and longitudinalcontact thermal expansion stress and improve bonding strength, a phonon scattering layer and a negative thermal expansion buffer layer are embedded to fix a thermoelectric leg so as to improve internal thermal resistance and horizontal thermal matching performance of the high-performance thermoelectric device, internal package and external package are employed to prevent the thermoelectric material from being oxidized and sublimed and improve external collision-resistant capability, the technical bottlenecks of low energy conversion efficiency, small specific power, poor thermal stability, poor collision performance, complicated fabrication process and the like of a traditional thermoelectric device are effectively broken through, meanwhile, the thermal stability and the mechanical structural performance of the high-performance thermoelectric device are improved to a great extent, long-term and excellent electrical output performance is guaranteed, and the working environment is expanded.

Owner:深圳热电新能源科技有限公司

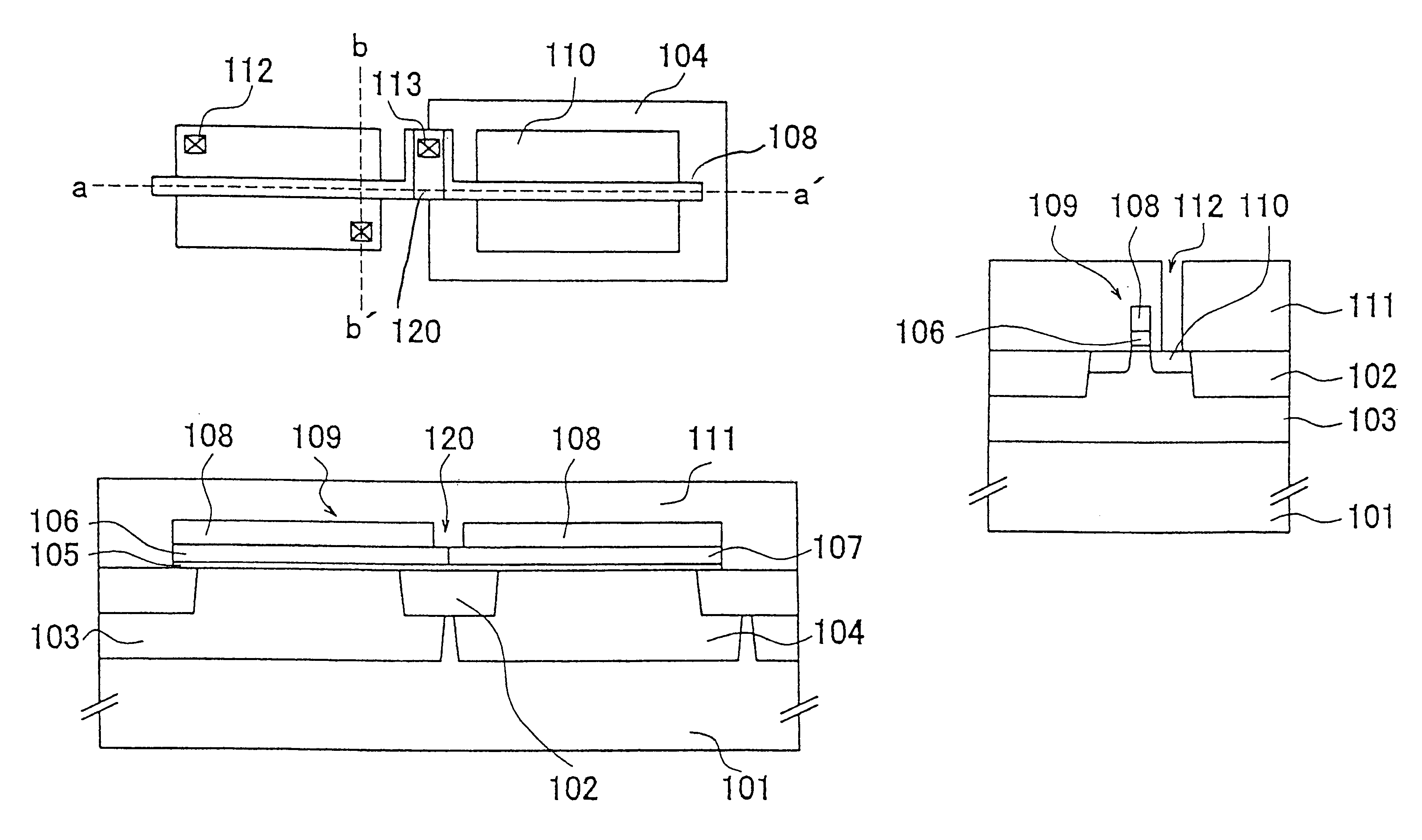

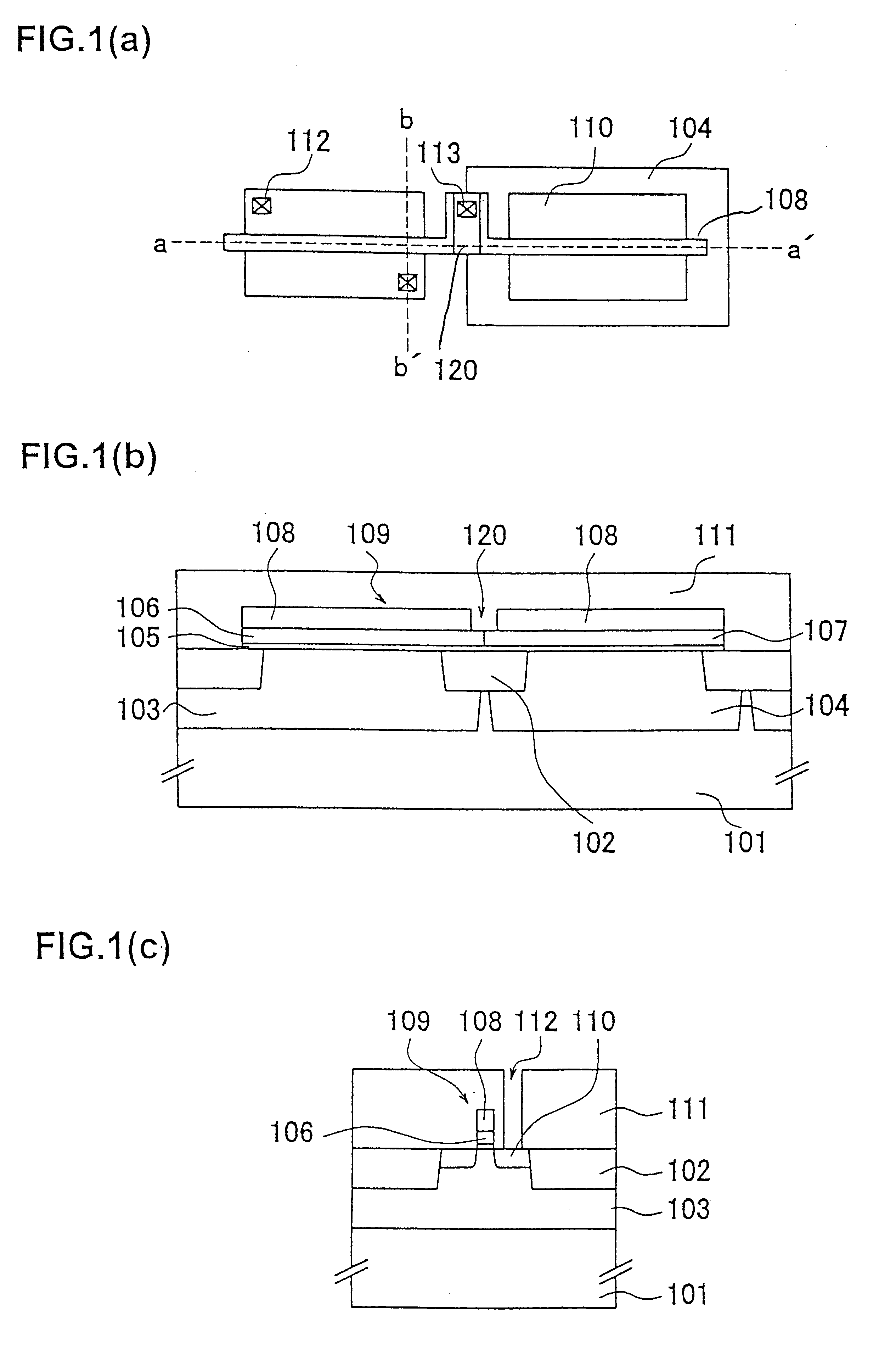

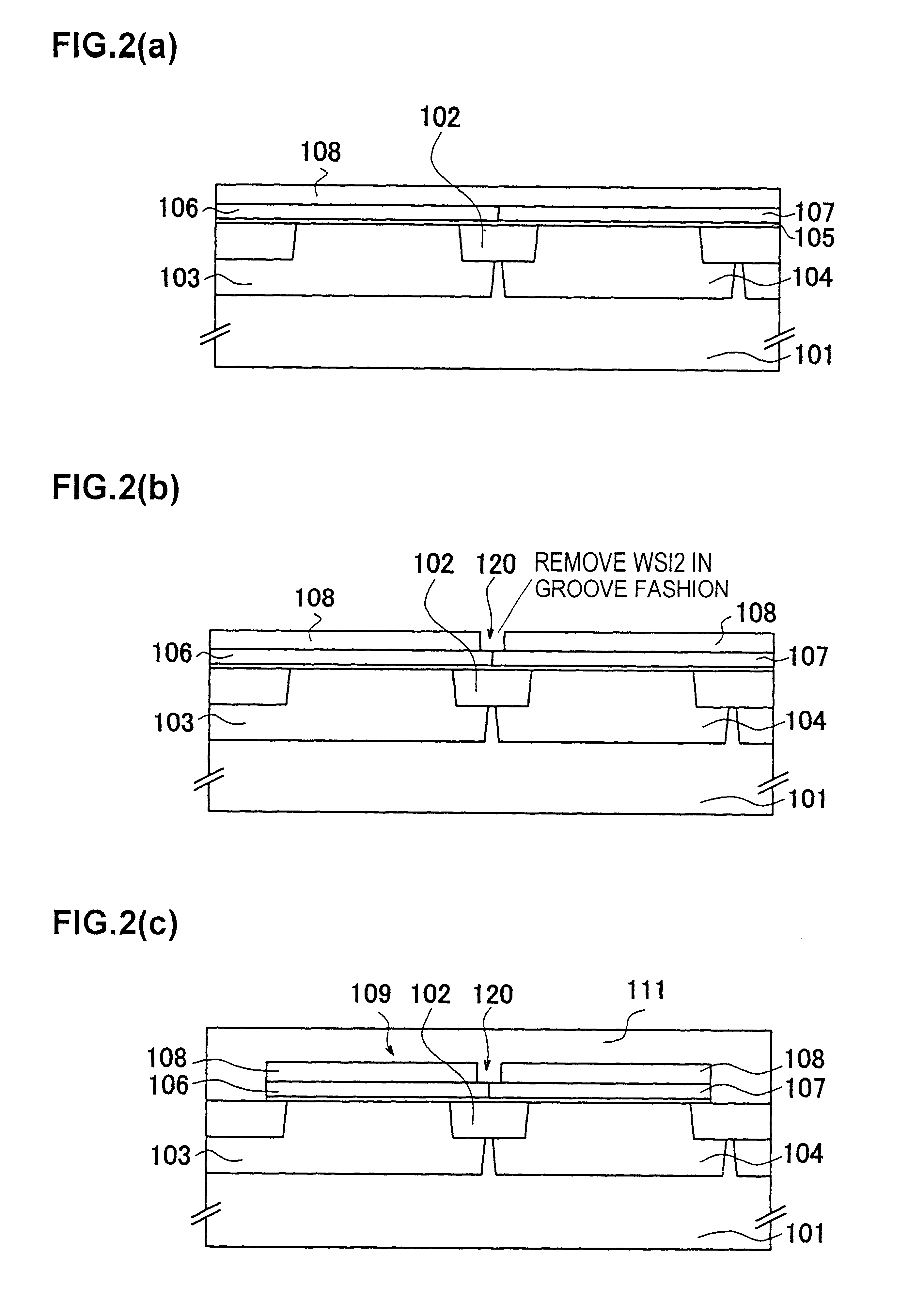

Dual-gate CMOS semiconductor device manufacturing method

InactiveUS6602746B2Reduce interdiffusionTransistorSemiconductor/solid-state device detailsCMOSSemiconductor

A manufacturing method for a dual-gate CMOS semiconductor device that suppresses mutual diffusion of P type impurities and N type impurities in a gate electrode. An NMOS part and a PMOS part are formed on a semiconductor substrate. A polycrystalline silicon layer is formed on the NMOS part and the PMOS part, and consists of an N type impurity containing polycrystalline silicon layer and a P type impurity containing polycrystalline silicon layer. A first conductive layer is formed on the polycrystalline silicon layer so as to include a groove region, in which the first conductive layer is not formed, on a predetermined region including a boundary between the N type impurity containing polycrystalline silicon layer and the P type impurity containing polycrystalline silicon layer.

Owner:LAPIS SEMICON CO LTD

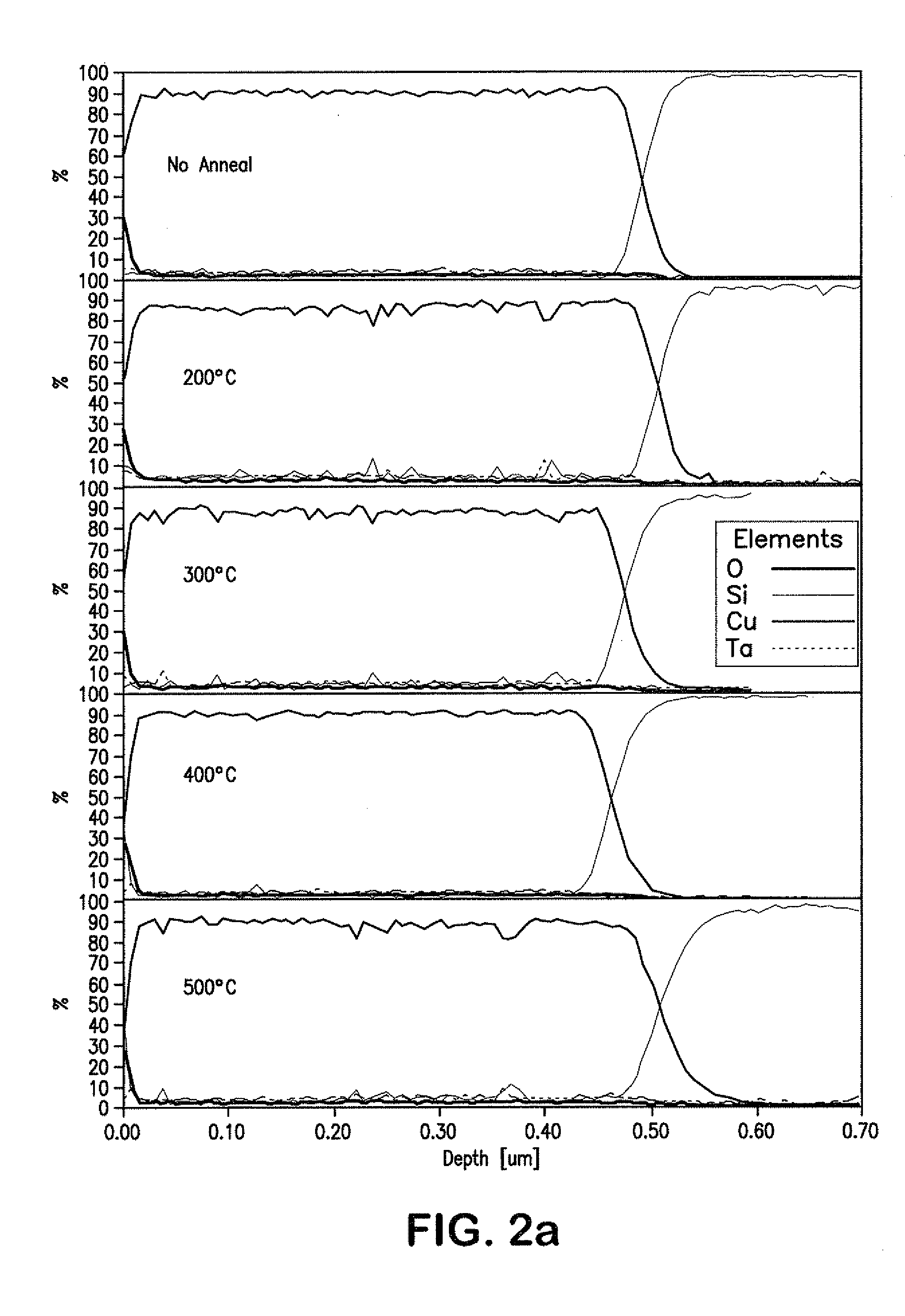

Refractory metal-doped sputtering targets, thin films prepared therewith and electronic device elements containing such films

Metallic materials consisting essentially of a conductive metal matrix, preferably copper, and a refractory dopant component selected from the group consisting of tantalum, chromium, rhodium, ruthenium, iridium, osmium, platinum, rhenium, niobium, hafnium and mixtures thereof, preferably in an amount of about 0.1 to 6% by weight based on the metallic material, alloys of such materials, sputtering targets containing the same, methods of making such targets, their use in forming thin films and electronic components containing such thin films.

Owner:GLAS TRUST +1

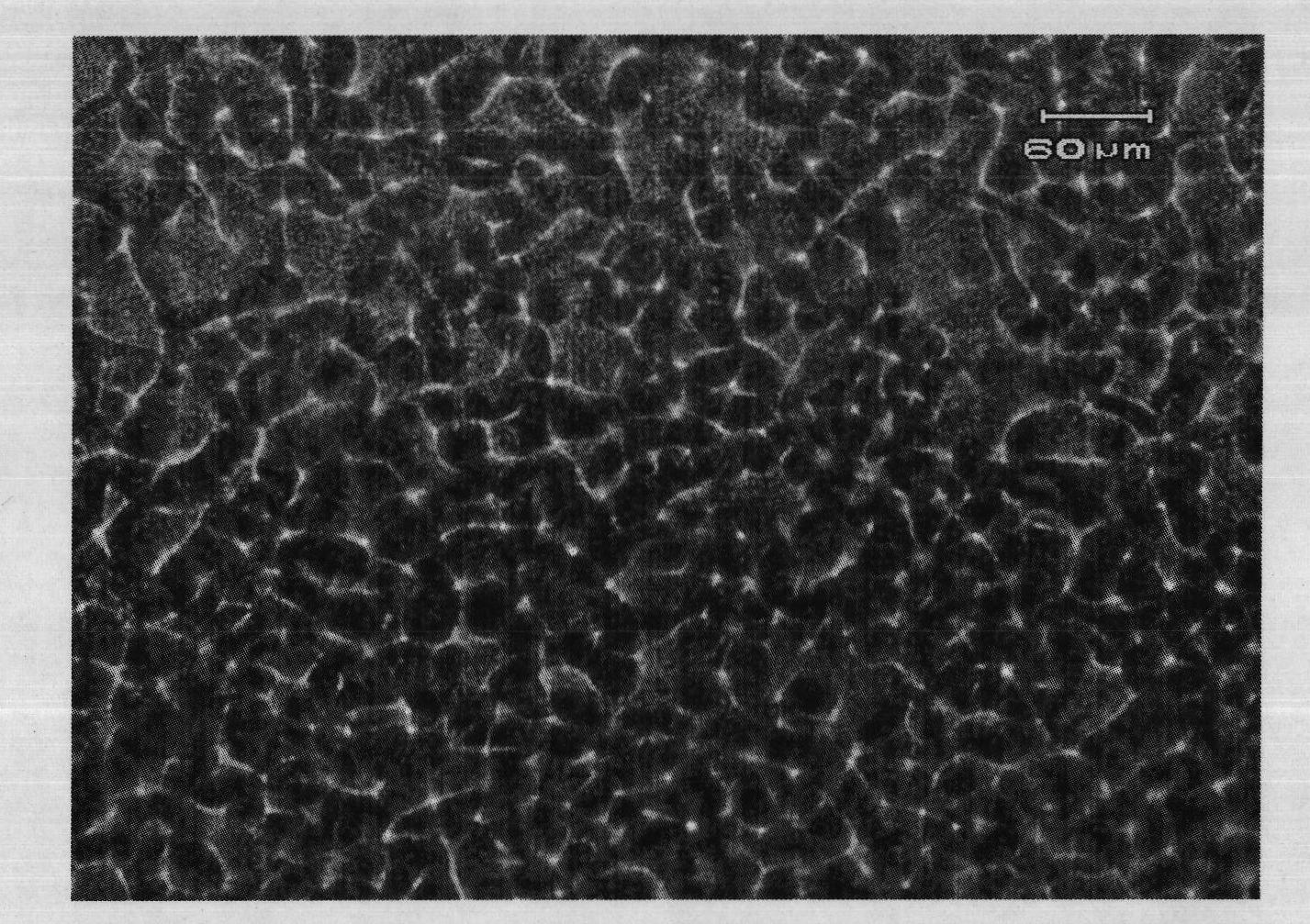

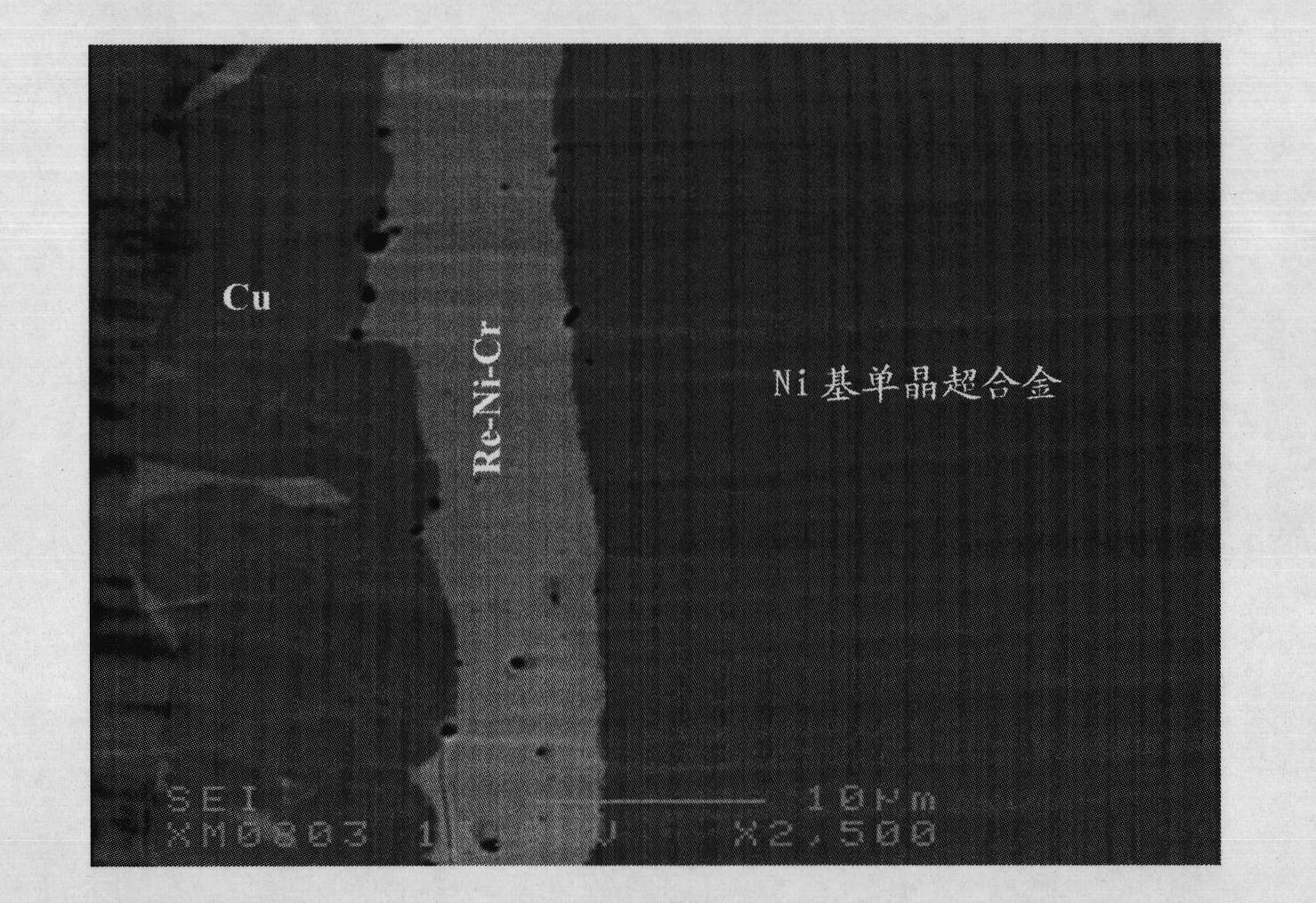

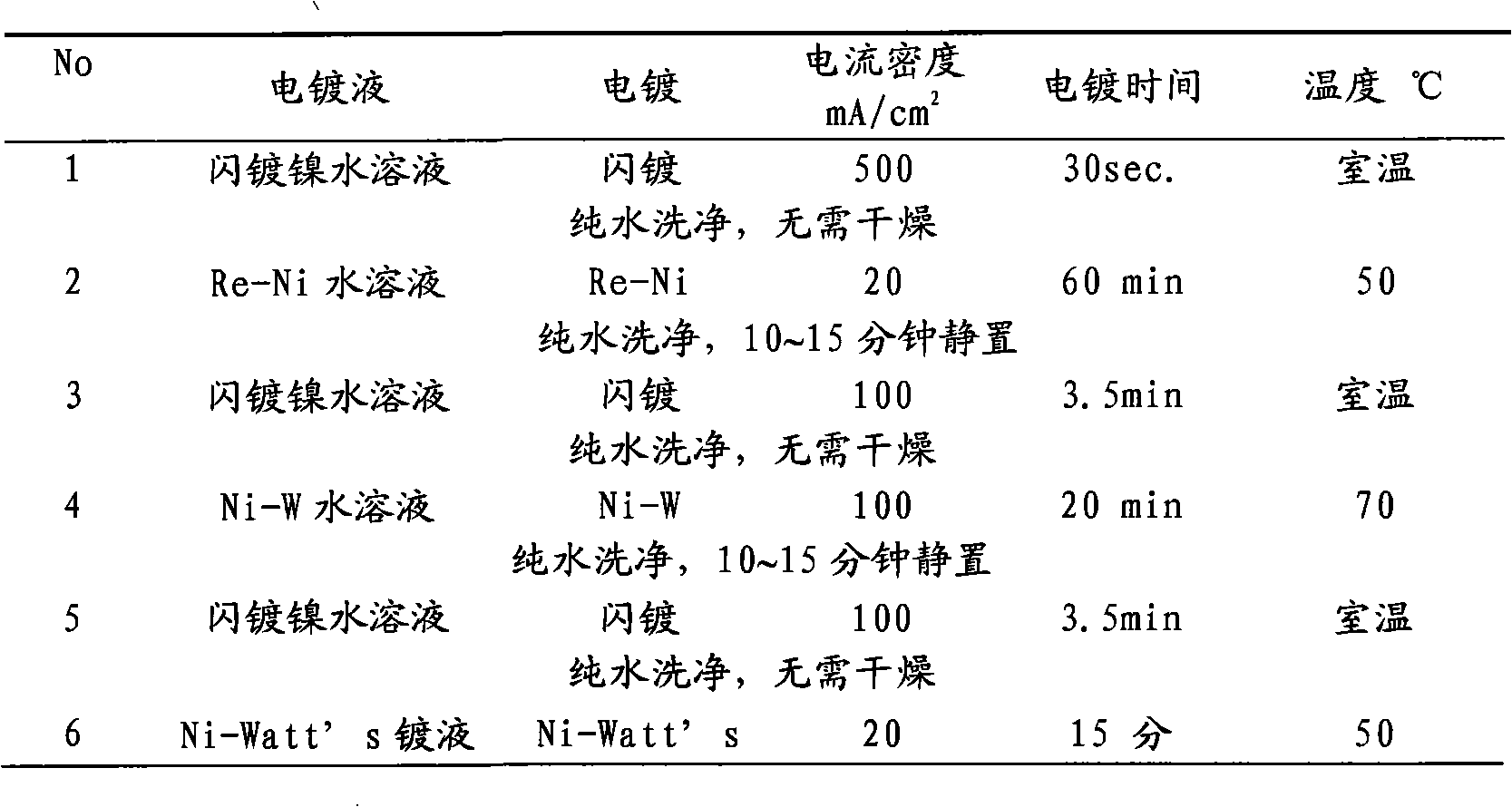

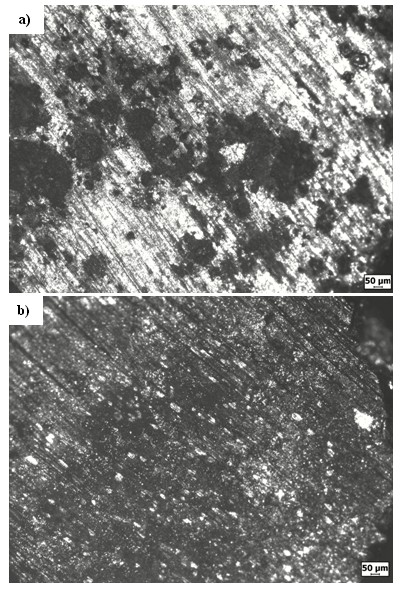

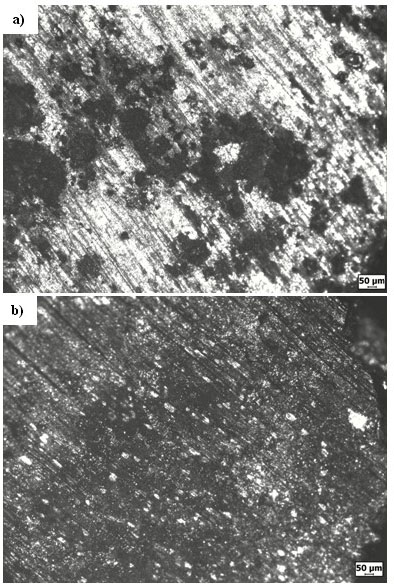

Bonding layer material having Re-Ni-Cr alloy diffusion barrier layer and preparation method thereof

InactiveCN101914774AImprove stabilityReduce interdiffusionSolid state diffusion coatingNi cr alloyDiffusion barrier

The invention discloses a bonding layer material having a Re-Ni-Cr alloy diffusion barrier layer and a preparation method thereof. The Re-Ni-Cr alloy diffusion barrier layer is coated on a matrix material, wherein the matrix material is a Ni, Al, Ti, Fe or Nb-based alloy material, and the Re-Cr-Ni alloy diffusion barrier layer comprises the following elements in percentage by mass: 20-65% of Re, 30-50% of Cr and 5-30% of Ni. The preparation method comprises the step of forming the Re-Cr-Ni alloy diffusion barrier layer material on a matrix high-temperature super alloy by electroplating. The bonding layer material having a Re-Ni-Cr alloy diffusion barrier layer has smooth and uniformly distributed surface coating, can remain stable under high-temperature conditions, can prevent alloy elements in the matrix from outward diffusion and prevents oxygen in the air from inward diffusion to the alloy matrix.

Owner:SHANGHAI INST OF TECH

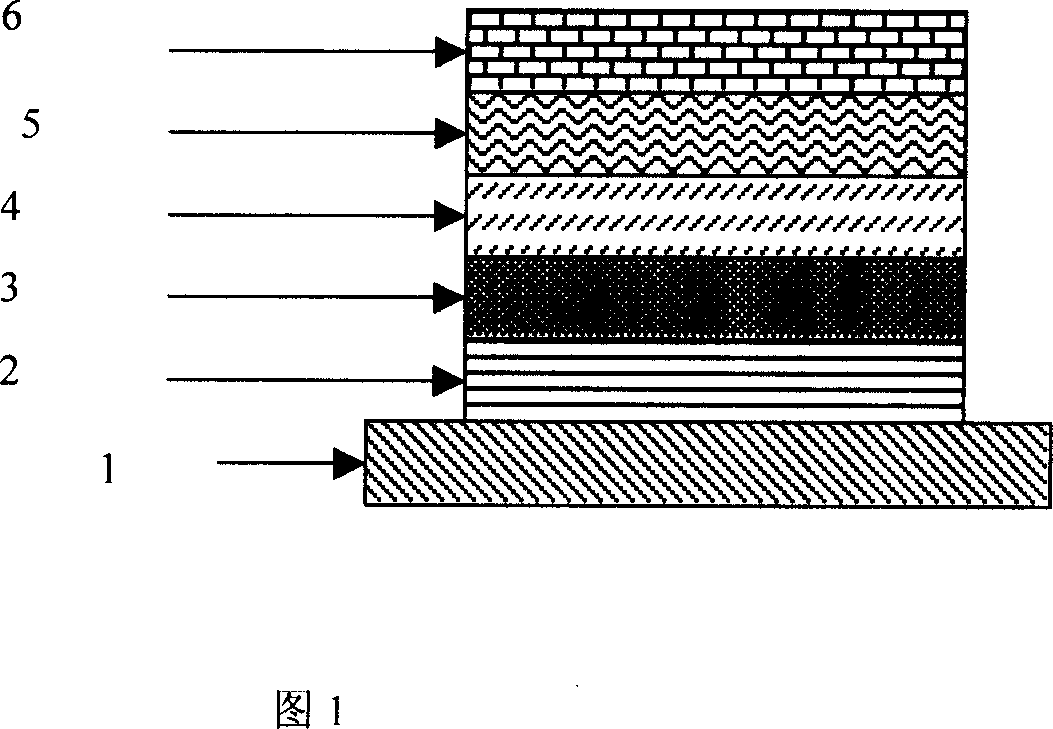

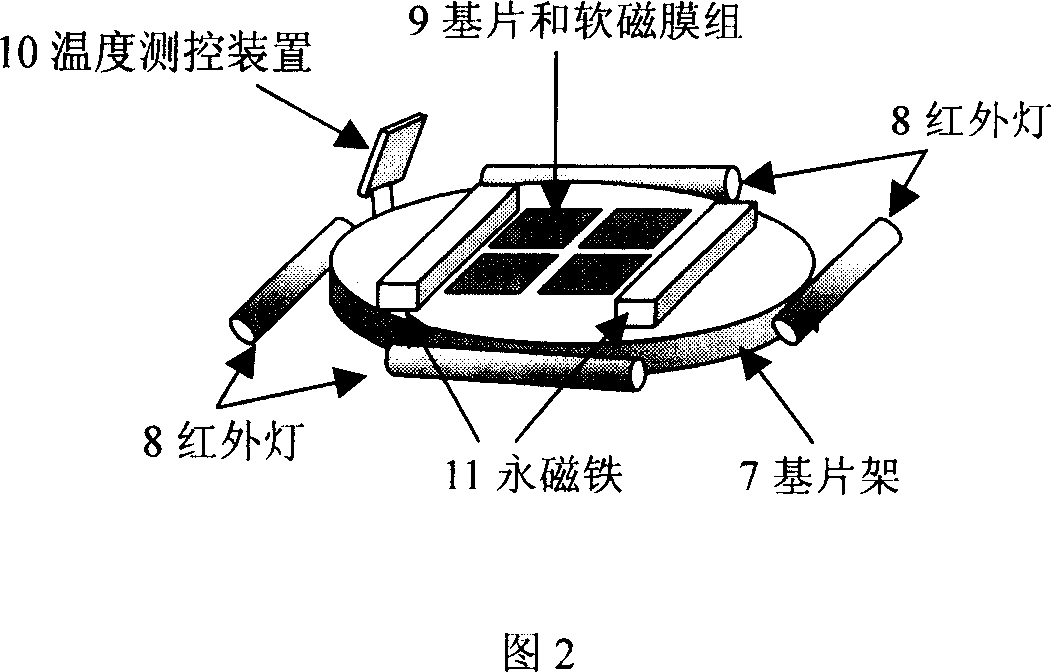

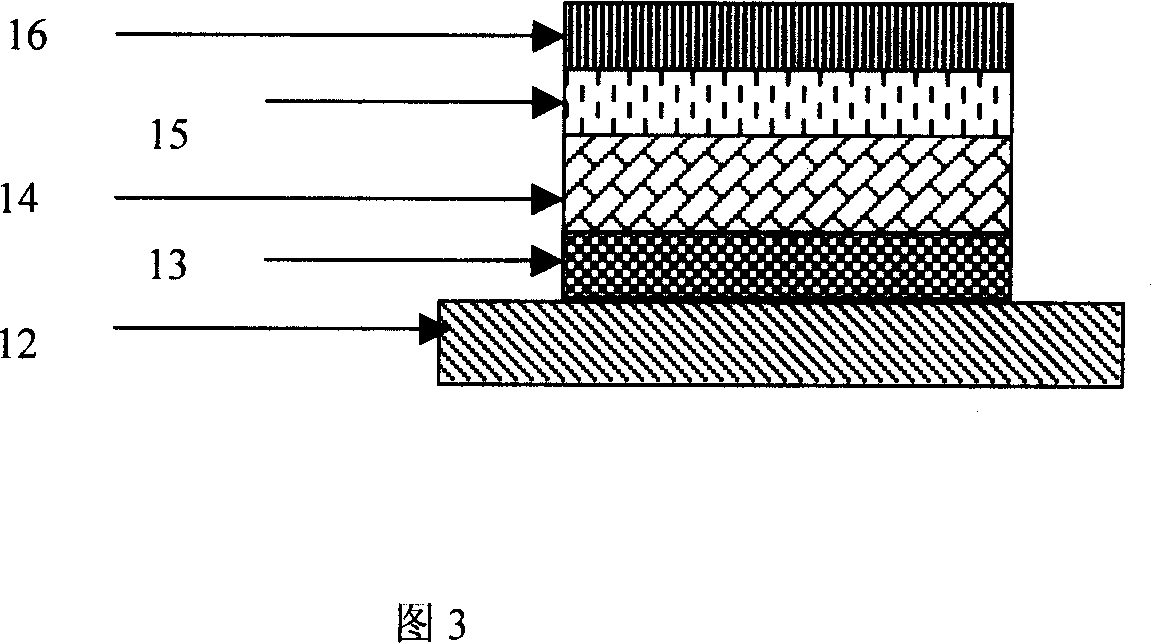

Magnetic sandwich material based on nanocrystalline soft magnetic thin film and its preparing method

InactiveCN1921003AStable single domain stateExcellent turning characteristicsManufacture of flux-sensitive headsDigital storageDirect current magnetron sputteringTotal thickness

The invention relates to a magnetic sandwich material based on nanometer crystal soft magnetic film and relative production, wherein said material is formed by separating two iron magnetic layers with one non-magnetic metal layer; it is characterized in that: one iron magnetic layer is nanometer crystal magnetic film while another one is multi-crystal magnetic film, whose total thickness is 10nm. The inventive material is prepared by direct-current magnetic-control splash method, with four-target splash device, and it on-site quickly anneals the material on the substrate support of four-target splash device, while the material has small interlayer couple, better magnetic resistance effect, and better thermal stability.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

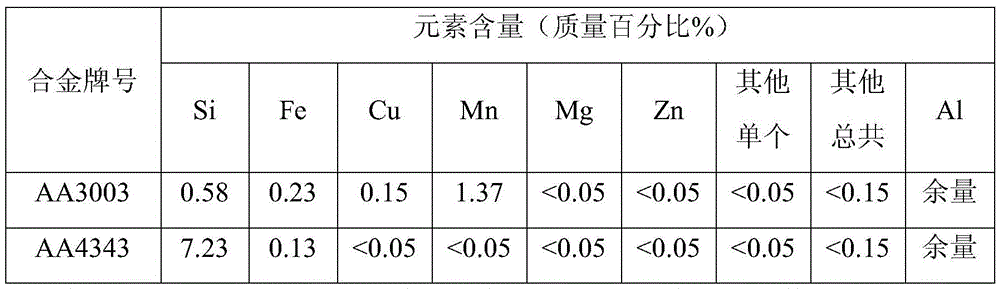

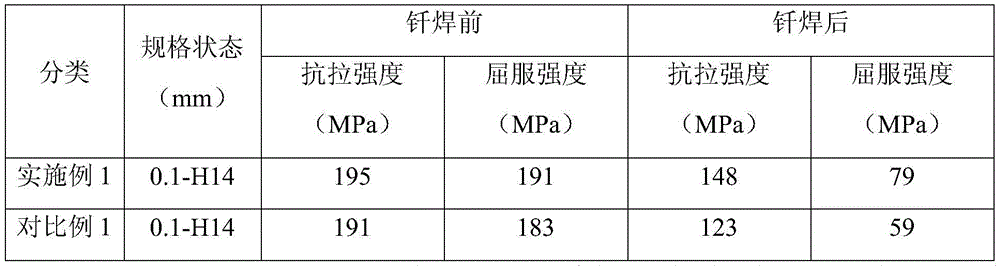

Preparation method of aluminum alloy brazing composite foil for automotive condenser fin

ActiveCN105666052ALow heating temperatureHigh strengthVehicle componentsGrain structureHeating temperature

The invention discloses a preparation method of aluminum alloy brazing composite foil for an automotive condenser fin and belongs to the technical field of aluminum alloy calendaring. The preparation method specifically comprises the steps of preparation of Al-Mn alloy of a core layer, preparation of Al-Si alloy of a brazing cladding layer, and composite rolling according to the Al-Si / Al-Mn / Al-Si combination. According to the preparation method, the low-temperature hot rolling technique is adopted, and no grain refiner is added, so that original grains of the core Al-Mn alloy of the composite foil are made large, and a large long-strip-shaped grain structure can be formed after rolling deformation; a high-angle grain boundary exists so that the number of medium channels through which main elements of the alloy of the brazing cladding layer diffuse and penetrate towards the core alloy after welding can be reduced, and accordingly mutual diffusion of alloy elements is reduced, the strength of the composite foil after brazing is improved, and the probability of collapse of materials is lowered. Meanwhile, the heating temperature of a cast ingot is low, the heating time is short, energy consumption is reduced, and good economic benefits and social benefits are achieved.

Owner:长沙众兴新材料科技有限公司

Method for preparing NdFeB/SmCo5 composite permanent magnet doped with PrCu alloy by adopting thermal deformation method

InactiveCN106298136AReduce interdiffusionWeaken the exchange coupling effectInorganic material magnetismInductances/transformers/magnets manufactureMagnetic phaseThermal deformation

The invention relates to a method for preparing an NdFeB / SmCo5 composite permanent magnet doped with PrCu alloy by adopting a thermal deformation method and belongs to the technical field of magnetic materials. The ratio of the weight of PrCu alloy powder for doping to the weight of total powder is 2-15 weight percent. The deformation quantity of the composite magnet is 60-90 percent. The SPS technology thermal deformation method is adopted for preparing the NdFeB / SmCo5 thermal deformation composite rare earth permanent magnet doped with the PrCu alloy; in the process of thermal deformation, as a boundary phase, a PrCu phase can isolate two hard magnetic phases, so that the mutual diffusion is reduced, an exchange coupling effect between the two phases is weakened, and the coercive force is improved; in the process of thermal deformation, after being liquefied, the PrCu phase is diffused at a crystal boundary and can also coordinate the thermal deformation of the two phases to promote the thermal deformation of the two phases; the obtained nanocrystalline NdFeB / SmCo5 composite magnet doped with the PrCu alloy has good magnetic property, thermal stability, corrosion resistance and mechanical property.

Owner:BEIJING UNIV OF TECH

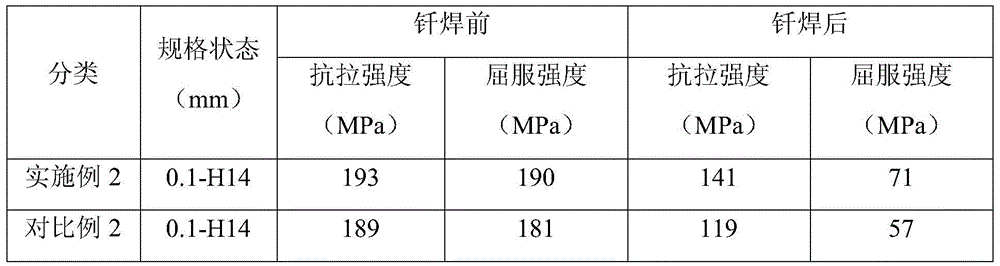

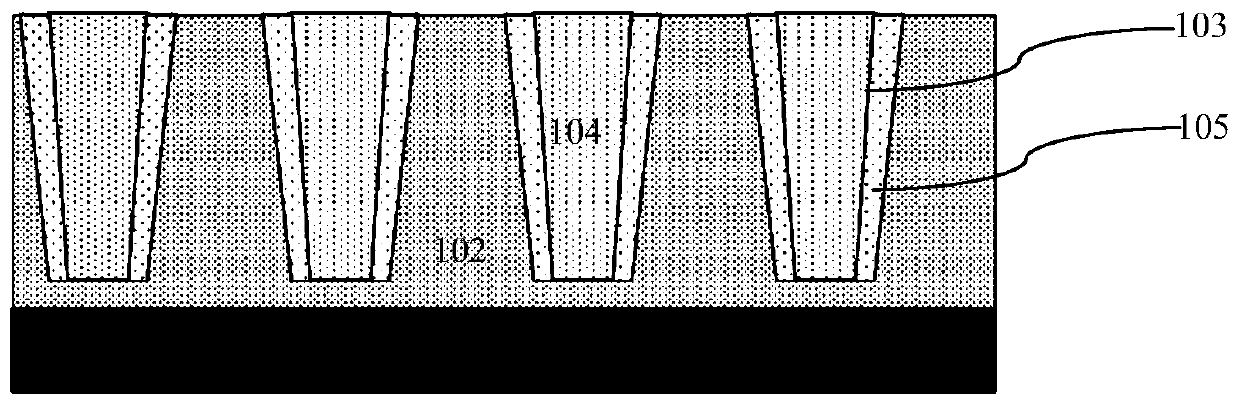

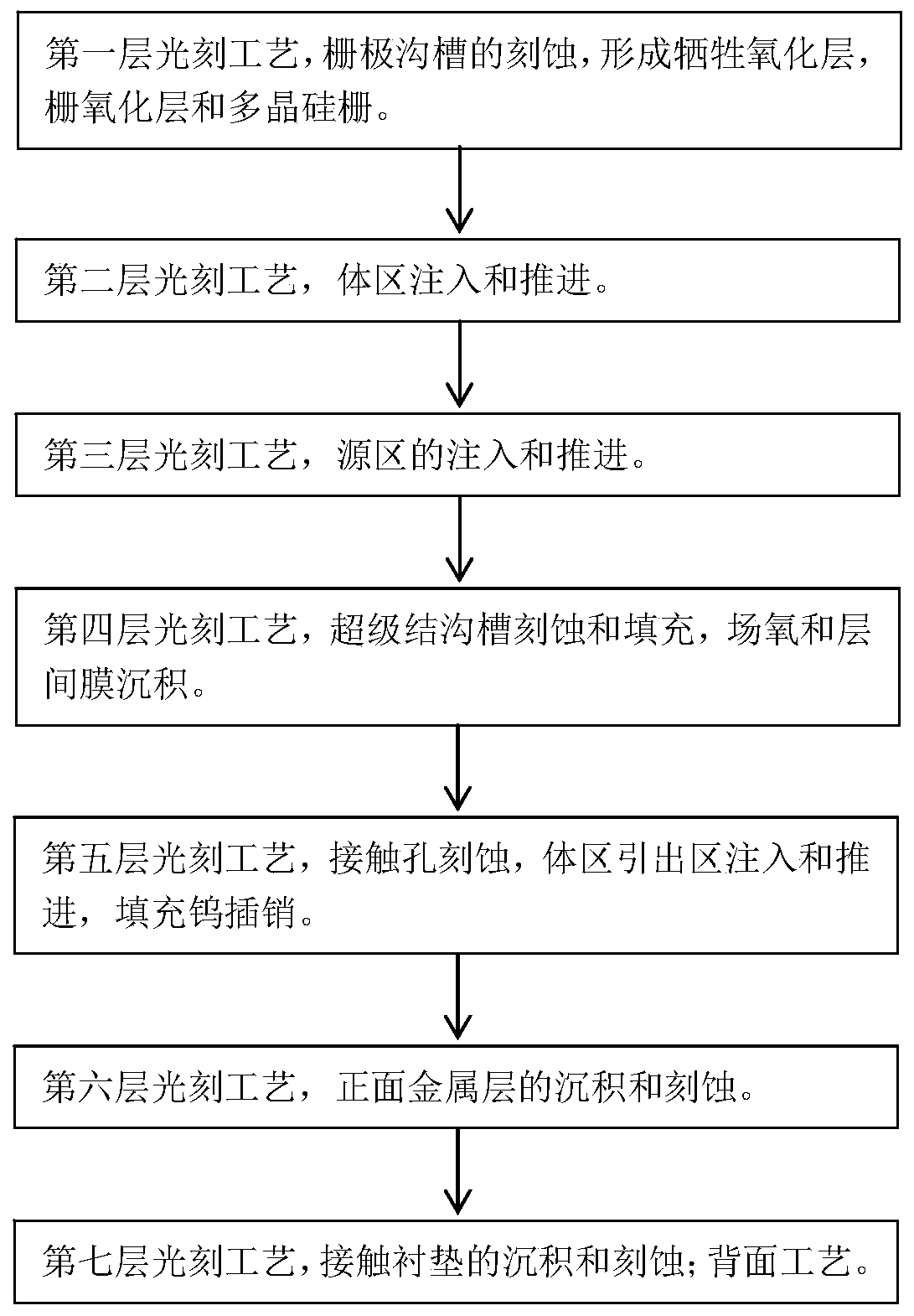

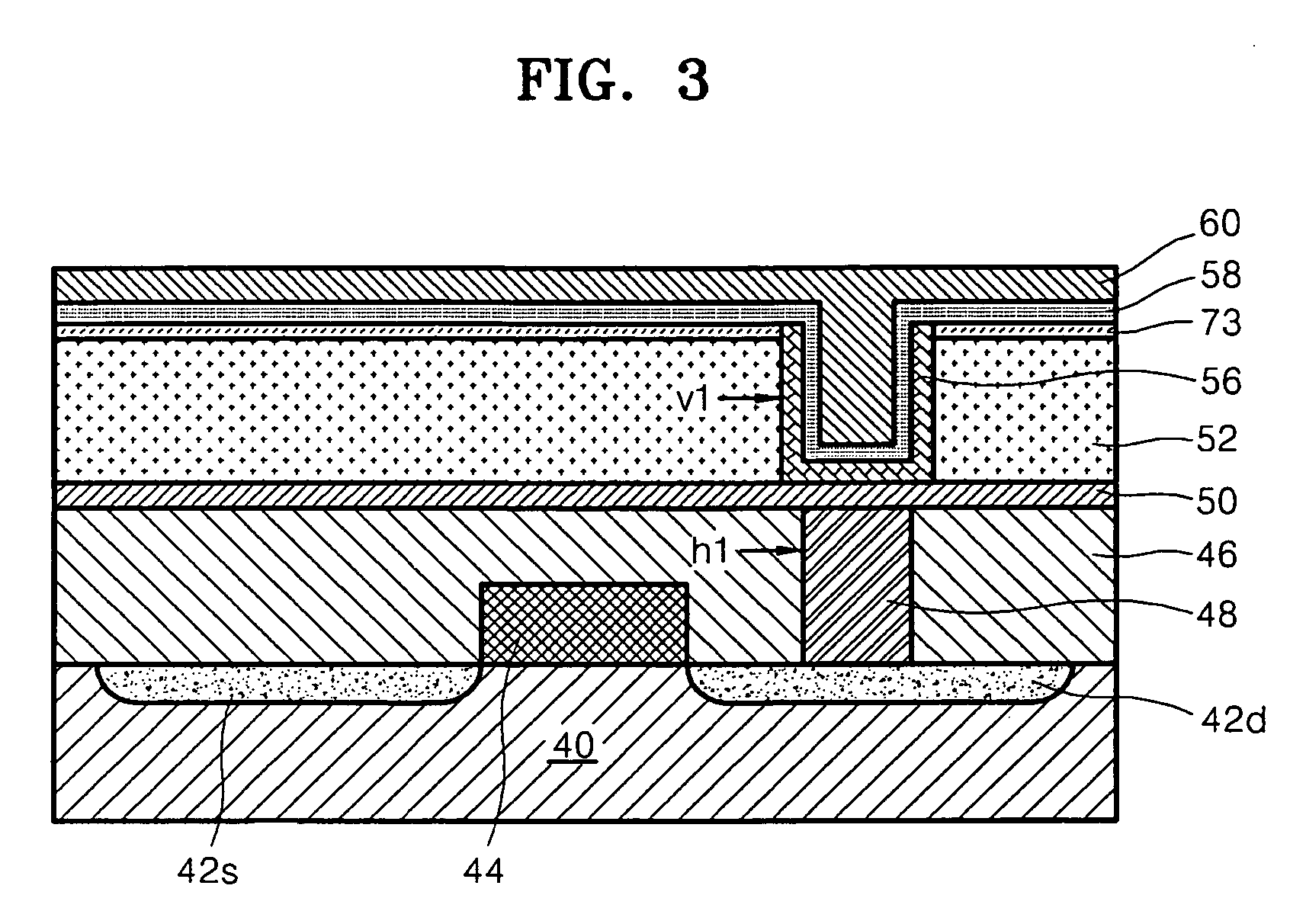

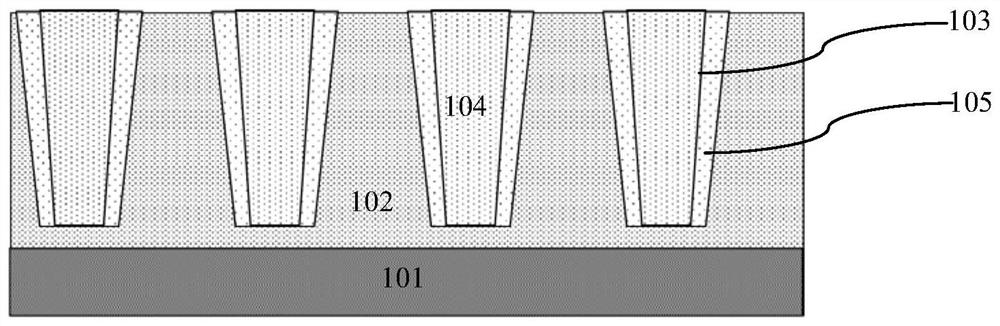

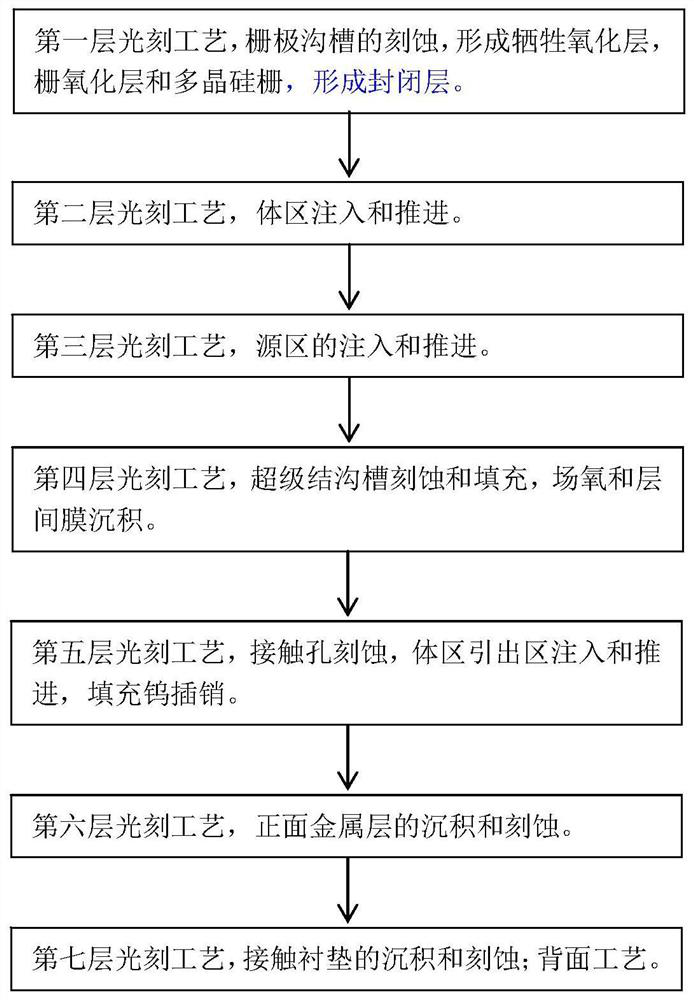

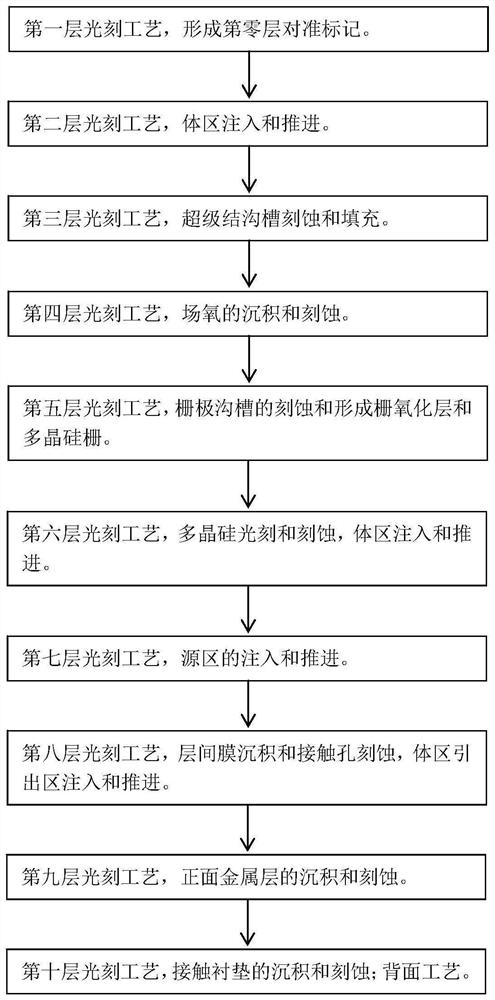

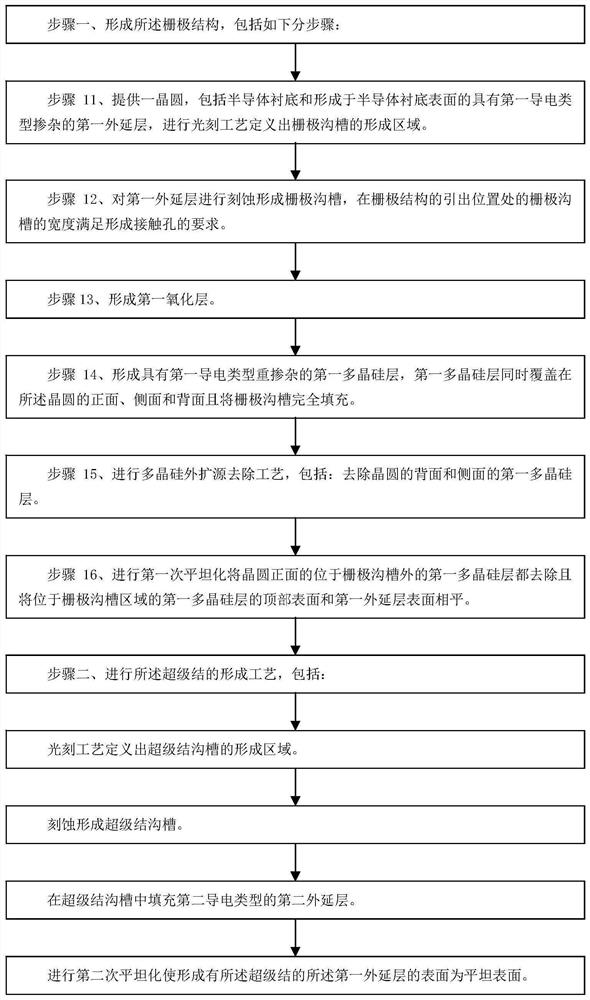

Manufacturing method of super junction device

InactiveCN111540685AReduce interdiffusionReduce processing difficultySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPolysilicon gate

The invention discloses a manufacturing method of a super junction device. The method comprises the following steps: the step 1, forming a gate structure which is a trench gate, filling a gate trenchwith a polysilicon gate in the forming process of the trench gate, then carrying out first planarization to enable the surface of a first epitaxial layer with the trench gate to be a flat surface, andenabling the width of the gate trench at the leading-out position of the gate structure to meet the requirement of forming a contact hole; and the step 2, forming a super junction in the first epitaxial layer with the flat surface on which the trench gate is formed, wherein in the forming process of the super junction, a second epitaxial layer is adopted to fill the super junction trench, and then secondary planarization is performed, so that the surface of the first epitaxial layer with the super junction is a flat surface. According to the invention, the full-flat process can be realized, the trench gate process can be conveniently arranged before the super junction forming process, and the thermal process after the super junction is formed can be reduced, so that the mutual diffusion of impurities of the super junction is reduced, the device performance is improved, a photomask can be saved, and the process cost is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

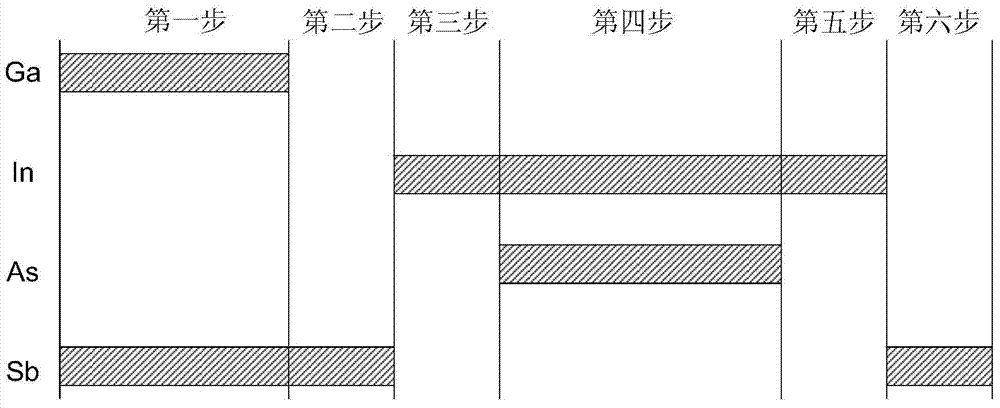

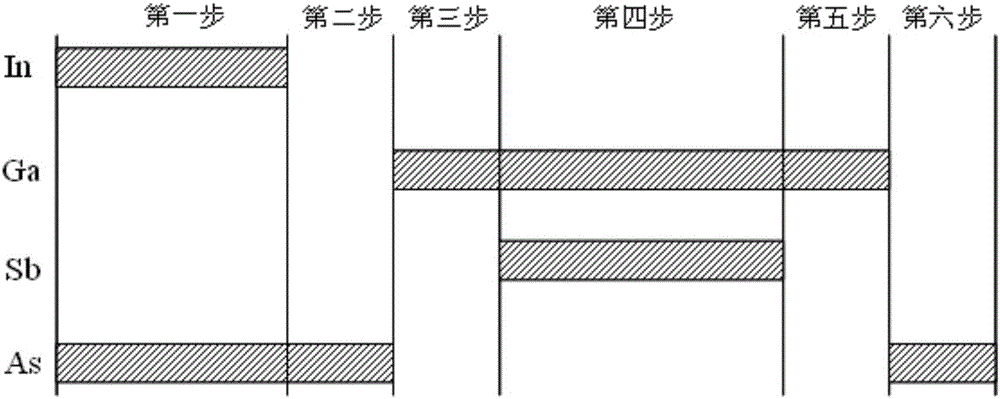

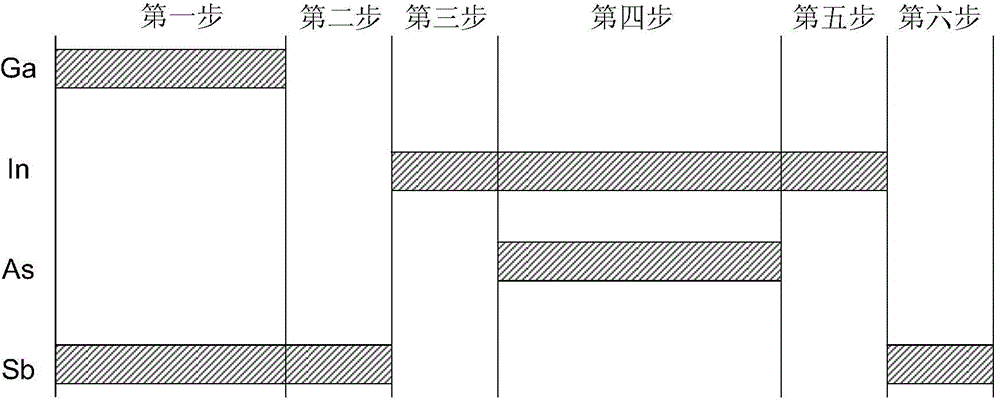

Type-II superlattice structure based on arsenic valve switch and preparation method

ActiveCN103500765AReduce interdiffusionReduce the chance of formationFinal product manufactureNanoopticsInterface layerBinary compound

The invention discloses a type-II superlattice structure based on an arsenic valve switch and a preparation method. Compared with a traditional type-II superlattice structure, the original binary compounds GaSb and InSb are respectively replaced by ternary compounds GaAsSb and InAsSb. The preparation method is characterized in that the As valve is always in an open state in the enter type-II superlattice growth process, the valve position is the same as that during the growth of an InAs layer, and the tertiary compounds GaAsSb and InAsSb are formed because partial As flows out when an GaSb layer and an InSb interface layer grown. The type-II superlattice structure based on the arsenic valve switch and the preparation method have the characteristics that since a common element As exists in all layers, the growth temperature of all layers is enabled to trend to be consistent and the mutual diffusion at the position of interfaces is reduced; under the effect of As atom surfactant, the migration rate of Sb atoms is increased, the forming probability of Sb clusters is reduced, the defects of materials are reduced and the material performance is improved.

Owner:中科爱毕赛思(常州)光电科技有限公司

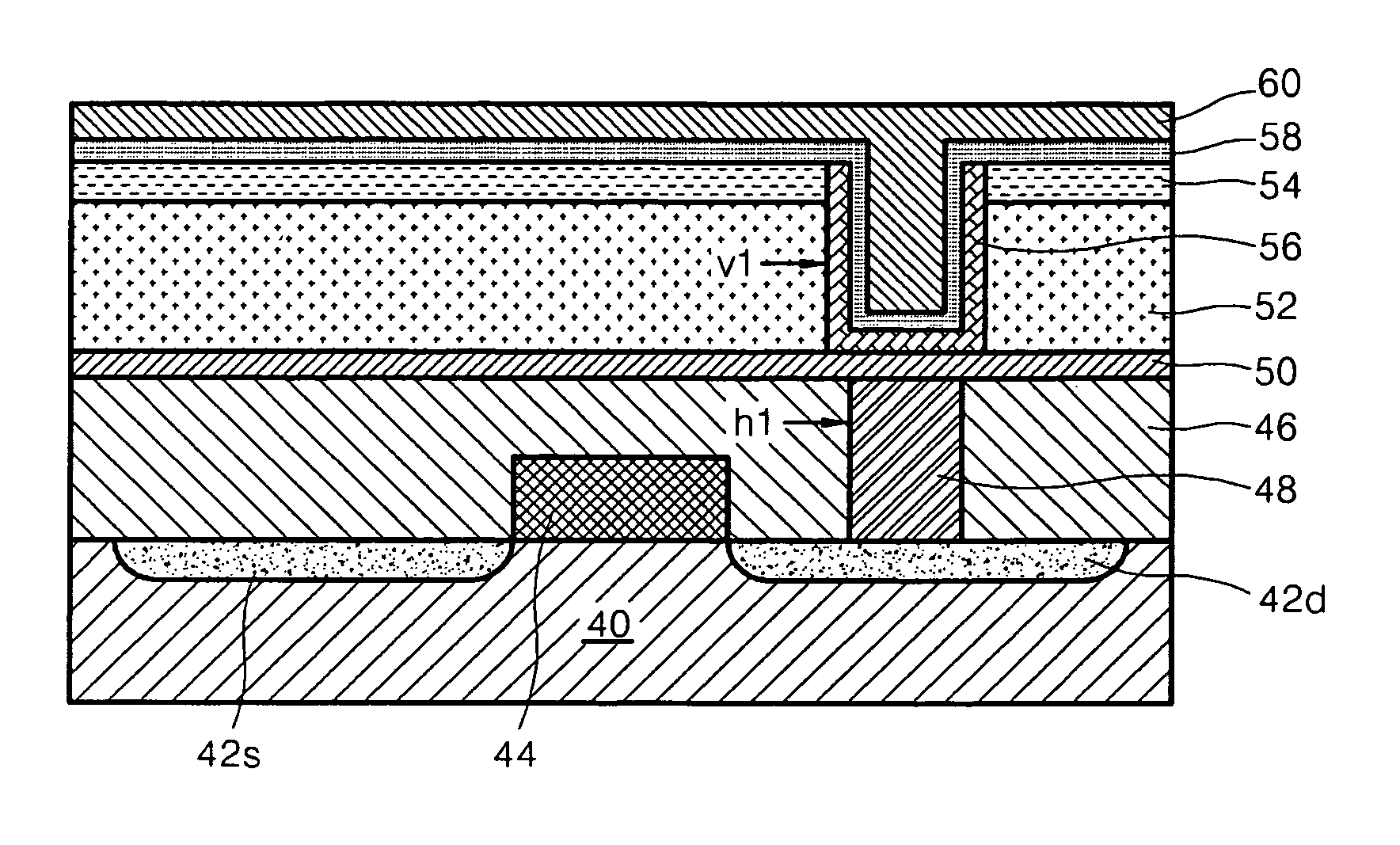

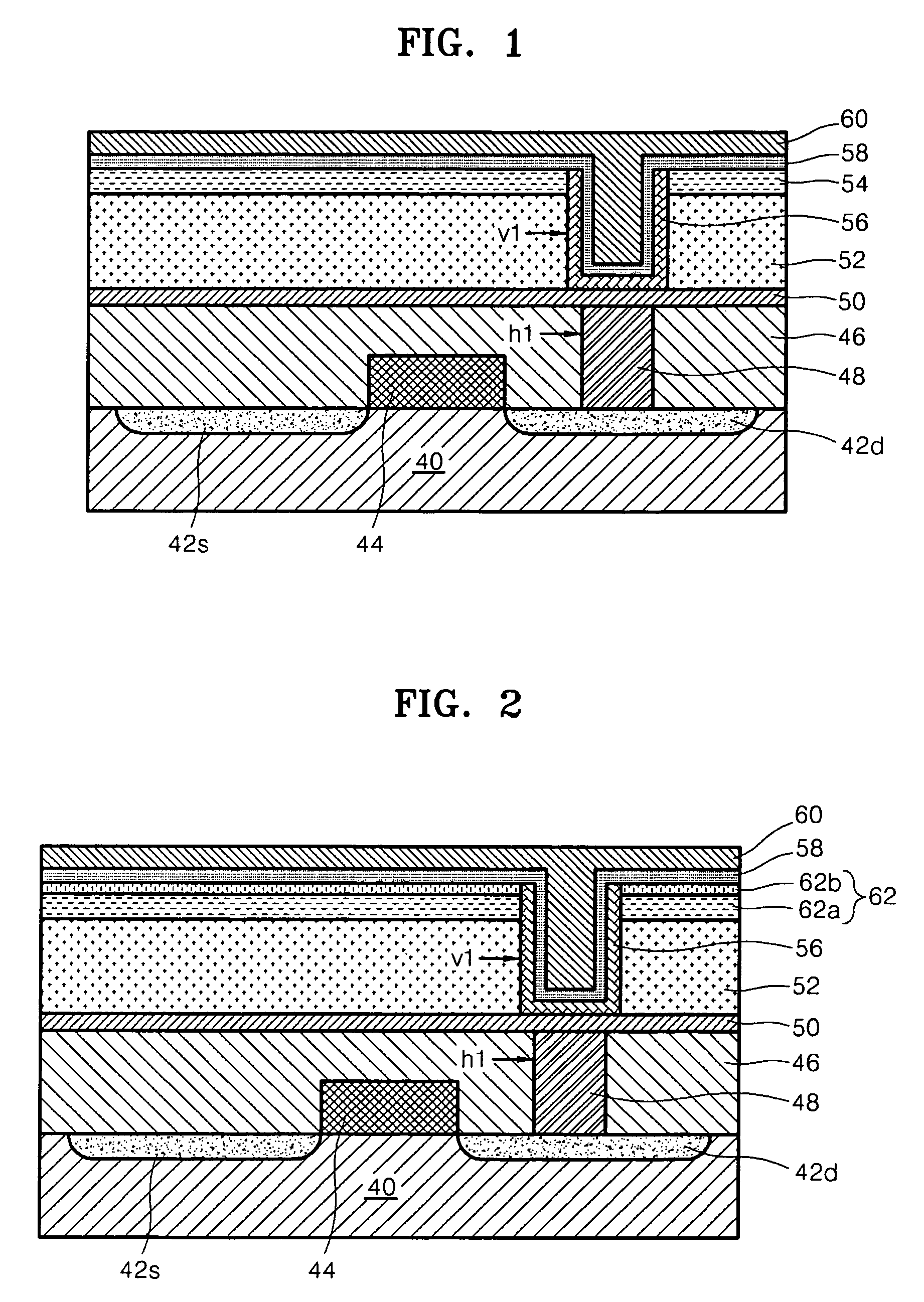

Ferroelectric capacitor having three-dimensional structure, nonvolatile memory device having the same and method of fabricating the same

InactiveUS7910967B2Reduce interdiffusionSemiconductor/solid-state device detailsSolid-state devicesCrystal structureDiffusion barrier

A ferroelectric capacitor having a three-dimensional structure, a nonvolatile memory device having the same, and a method of fabricating the same are provided. The ferroelectric capacitor may include a trench-type lower electrode, at least one layer formed around the lower electrode, a ferroelectric layer (PZT layer) formed on the lower electrode and the at least one layer and an upper electrode formed on the ferroelectric layer. The at least one layer may be at least one insulating interlayer and the at least one layer may also be at least one diffusion barrier layer. The at least one layer may be formed of an insulating material excluding SiO2 or may have a perovskite crystal structure excluding Pb.

Owner:SAMSUNG ELECTRONICS CO LTD

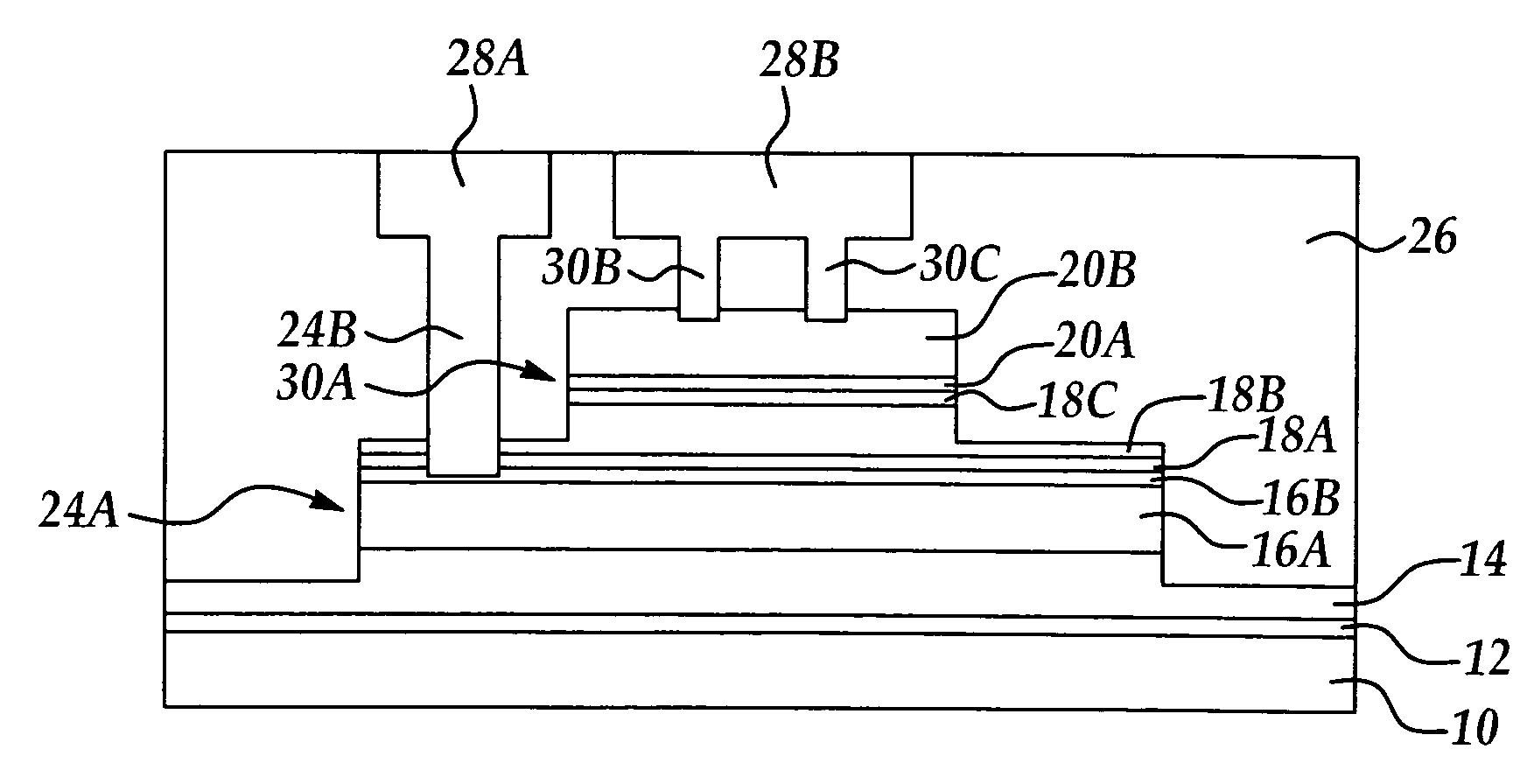

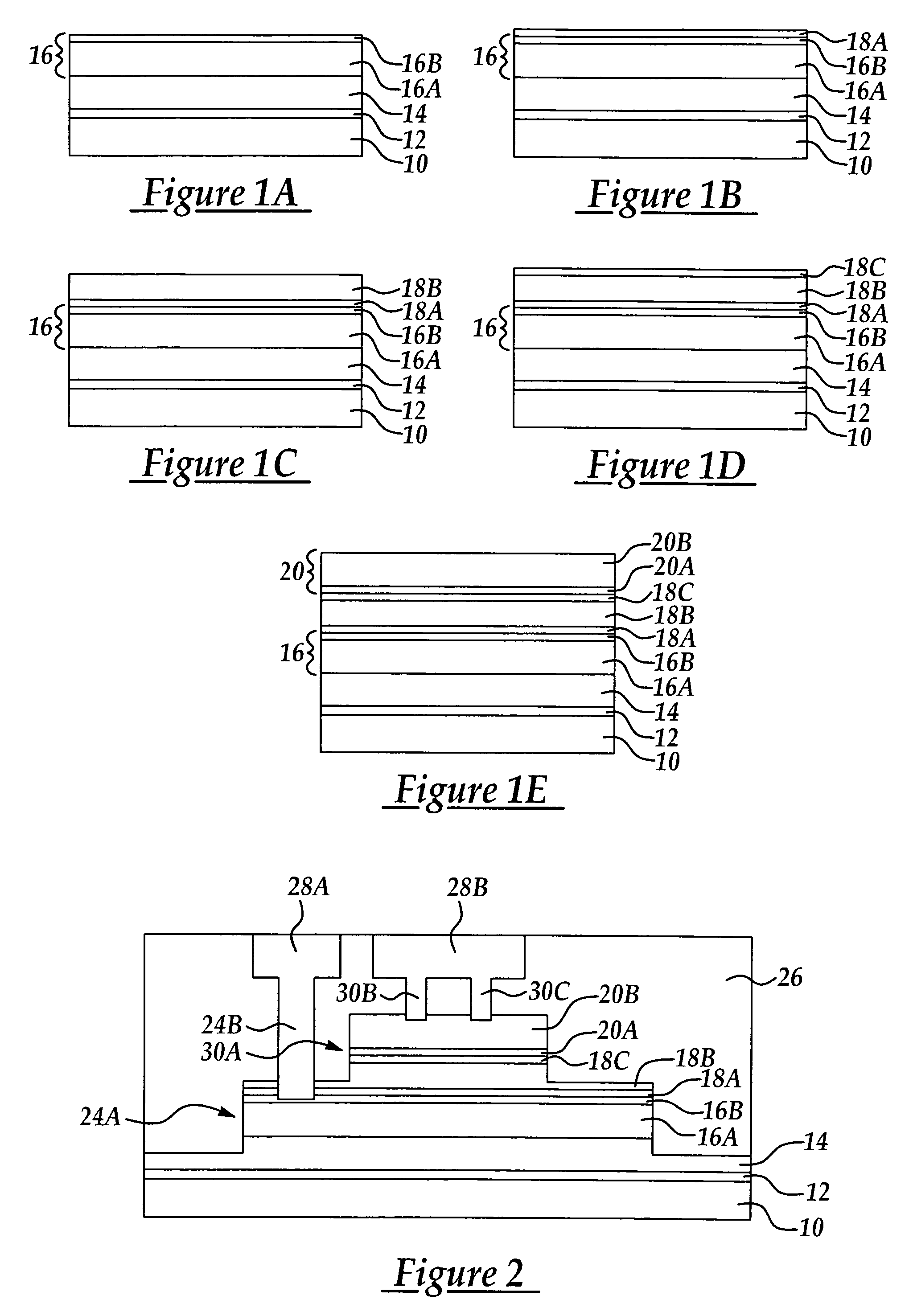

Manufacturing method of super junction device

PendingCN111986997AReduce interdiffusionReduce processing difficultySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingEngineering

The invention discloses a manufacturing method of a super junction device. The manufacturing method comprises the steps: step 1, filling a gate electrode trench with a polysilicon gate and carrying out first planarization to form a gate electrode structure; step 2, etching back the polysilicon gate and forming a sealing layer in a top recess formed by back etching; and step 3, filling the super junction trench with a second epitaxial layer and carrying out secondary planarization to form a super junction. According to the invention, a full-flat process can be realized, the trench gate processcan be conveniently arranged before the super junction forming process, and the thermal process after the super junction is formed can be reduced, so that the mutual diffusion of impurities of the super junction is reduced, the device performance is improved, a photomask can be saved, and the process cost is reduced; and doping and external expansion of the polysilicon gate can be prevented, a gate oxide layer can be protected, and the product quality and reliability can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

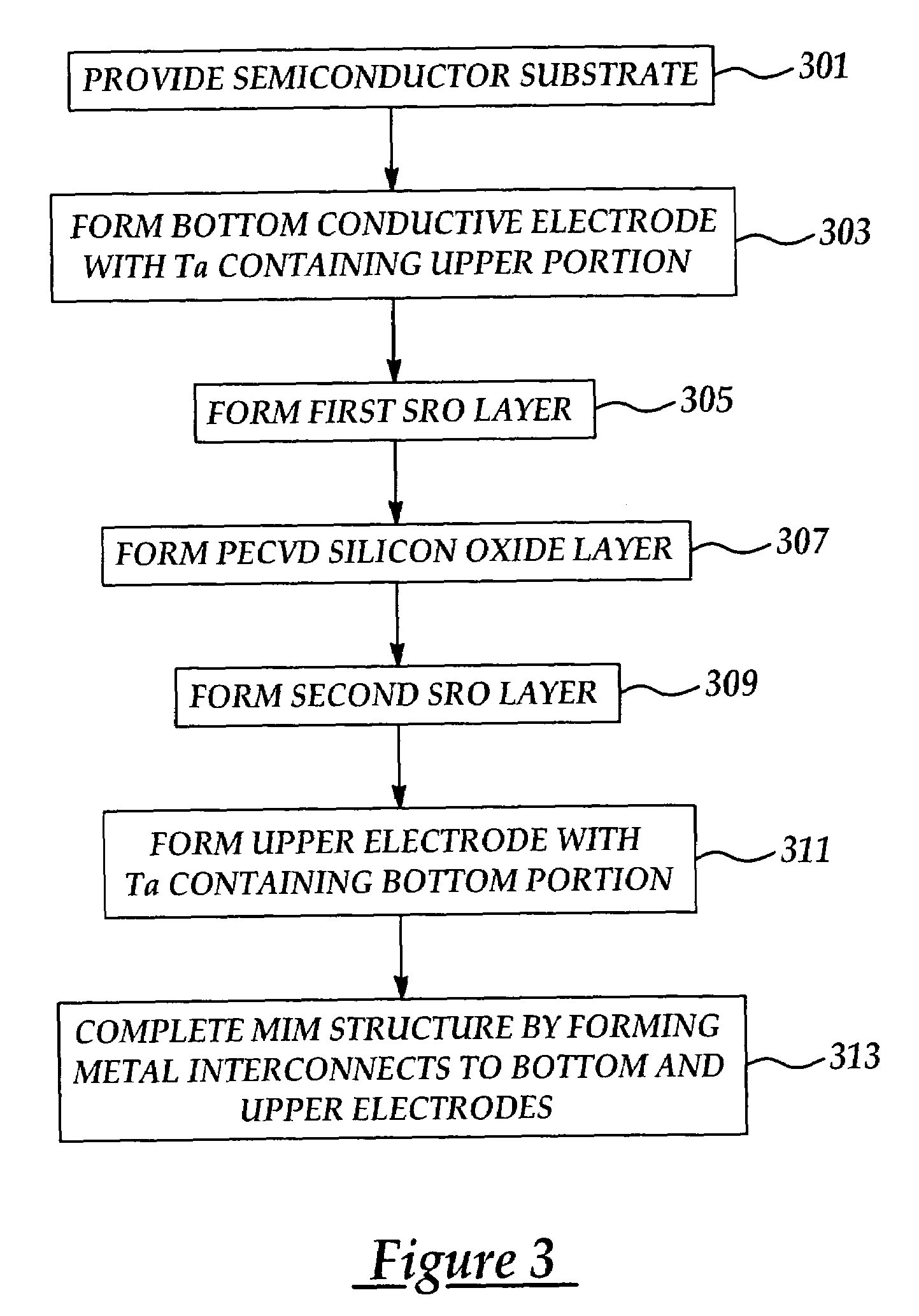

MIM structure and fabrication process with improved capacitance reliability

InactiveUS7205634B2Reduce interdiffusionIncrease capacitanceTransistorSolid-state devicesMetal-insulator-metalCapacitance

An MIM structure and method for forming the same the method including forming a bottom conductive electrode overlying a semiconducting substrate; forming a first protection layer on the conductive electrode; forming a dielectric layer on the first protection layer; and, forming an upper conductive electrode on the dielectric layer to form a metal-insulator-metal (MIM) structure.

Owner:TAIWAN SEMICON MFG CO LTD

A diamond film flat field emission cathode and method for making same

InactiveCN1567506AImplement injectionReduce compoundingDischarge tube/lamp detailsCold cathode manufactureElectron injectionMetal silicide

The invention belongs to a diamond film planar field emission cathode applied to plate display and its making method. It includes: a substrate, where a measuring metal electrode is deposited on one surface of the substrate and a measuring lead wire is connected with them; there is a diamond film layer on the other surface of the substrate; a metal silicide transition layer is situated between the substrate and diamond film layer. Its making method includes: firstly making a metal silicide transition layer on one surface of the substrate; then adopting various traditional methods to grow a diamond film on the metal silicide, because it is difficult in directly growing diamond film on the metal silicide, normally nucleating at bias voltage and then growing the diamond film; adopting spurting or depositing process to deposit 300-1000 nm thick Au electrode on the other surface of the substrate. The metal silicide transition layer provides two interface barriers tunneled by electron resonance, thus realizing high-density electron injection. And the making method is easy to spread.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

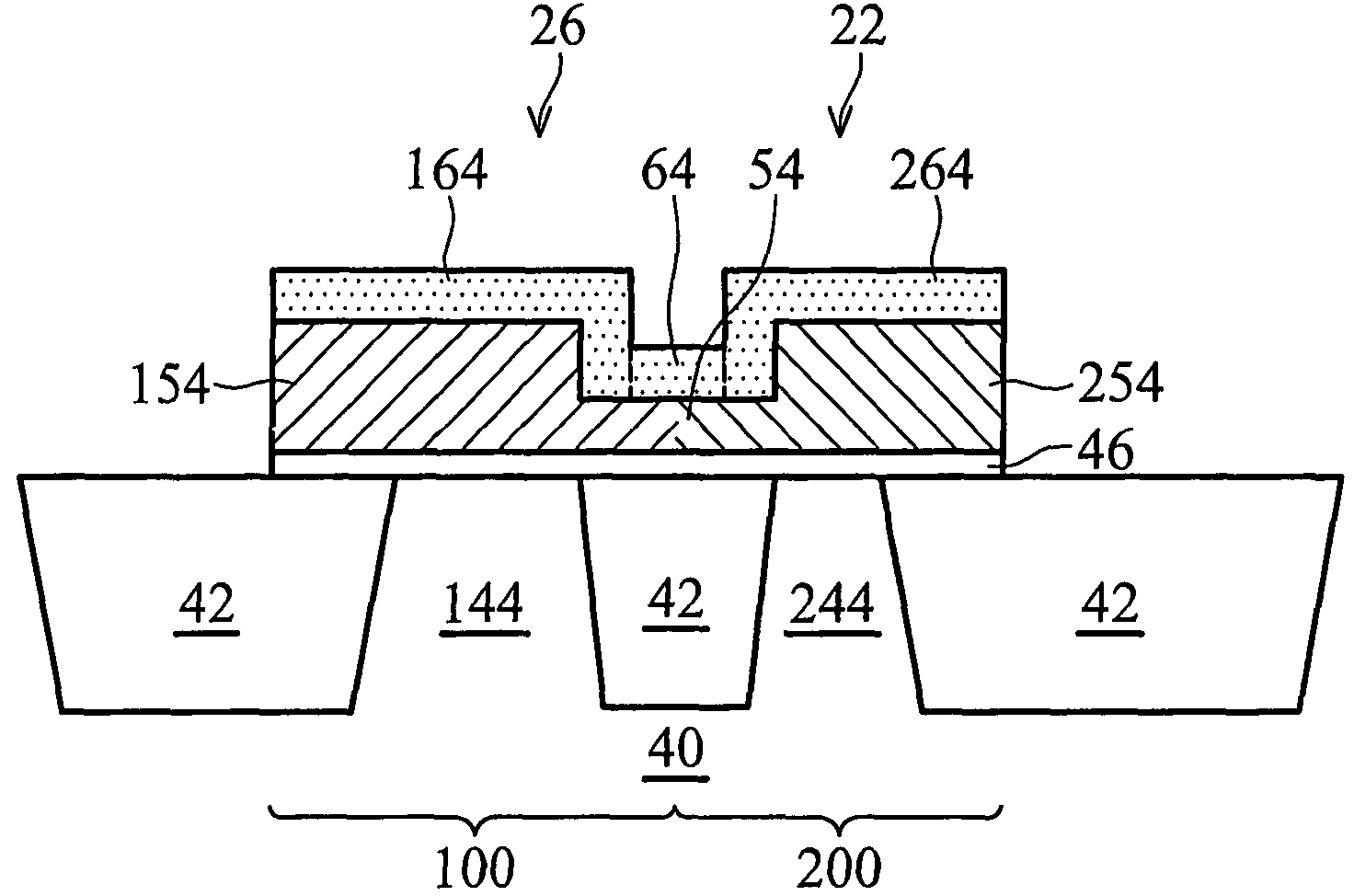

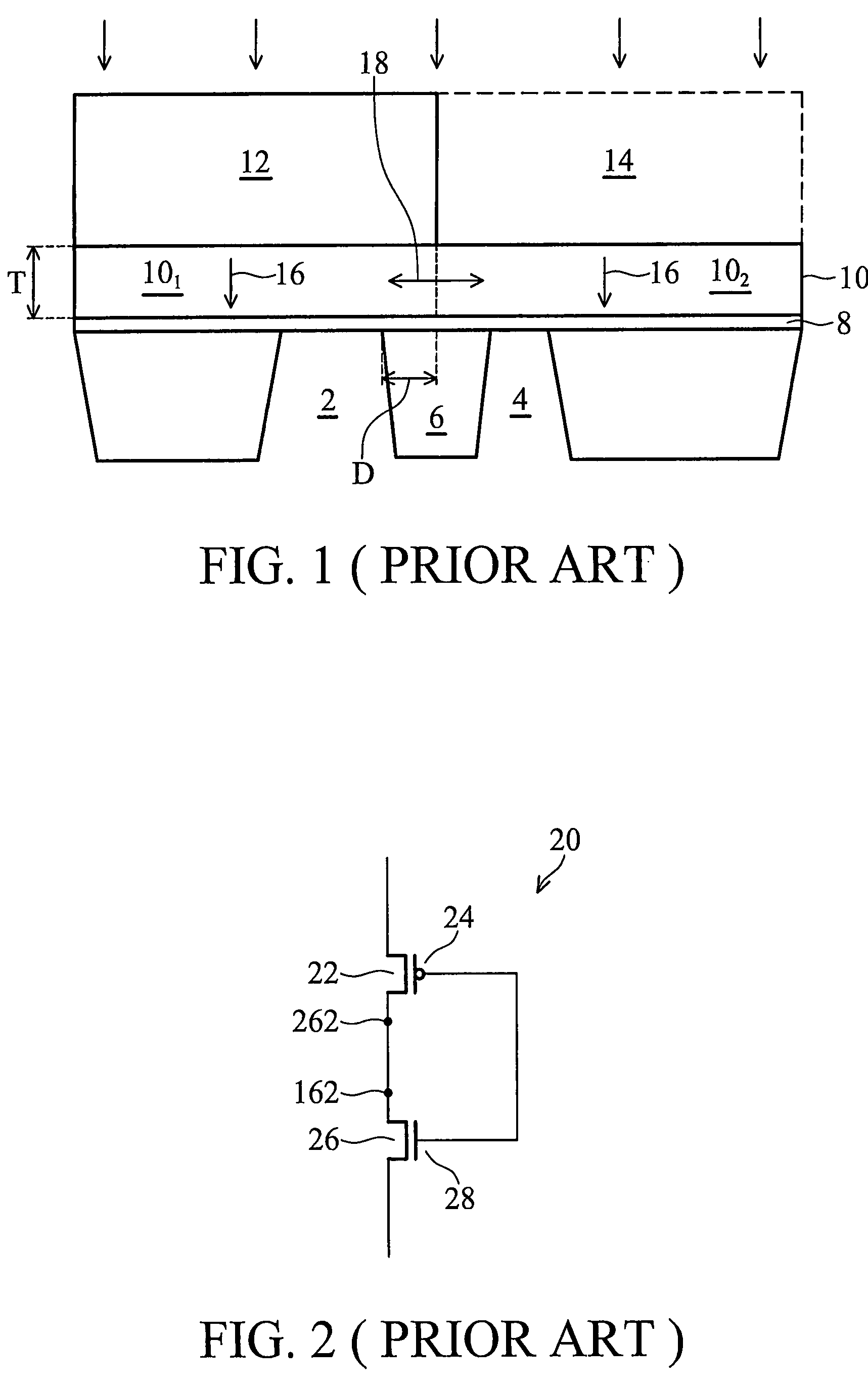

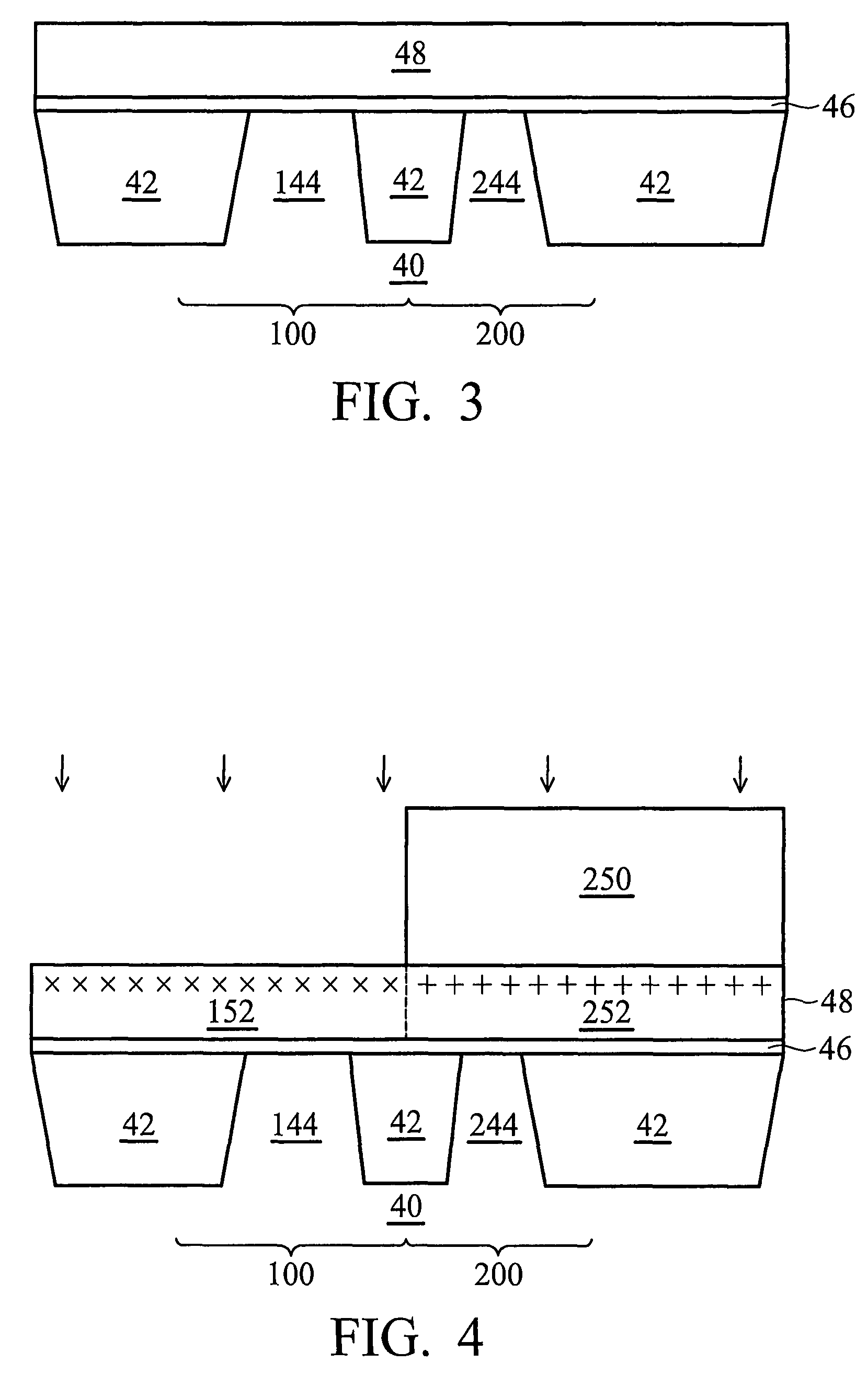

Gate strip with reduced thickness

ActiveUS7812400B2Reduce interdiffusionEasy to controlSemiconductor/solid-state device detailsSolid-state devicesGate dielectricSemiconductor structure

A semiconductor structure with reduced inter-diffusion is provided. The semiconductor structure includes a semiconductor substrate; a first well region in the semiconductor substrate; a second well region in the semiconductor substrate; an insulating region between and adjoining the first and the second well regions; a gate dielectric layer on the first and the second well regions; and a gate electrode strip on the gate dielectric and extending from over the first well region to over the second well region. The gate electrode strip includes a first portion over the first well region, a second portion over the second well region, and a third portion over the insulating region. A thickness of the third portion is substantially less than the thicknesses of the first and the second portions.

Owner:TAIWAN SEMICON MFG CO LTD

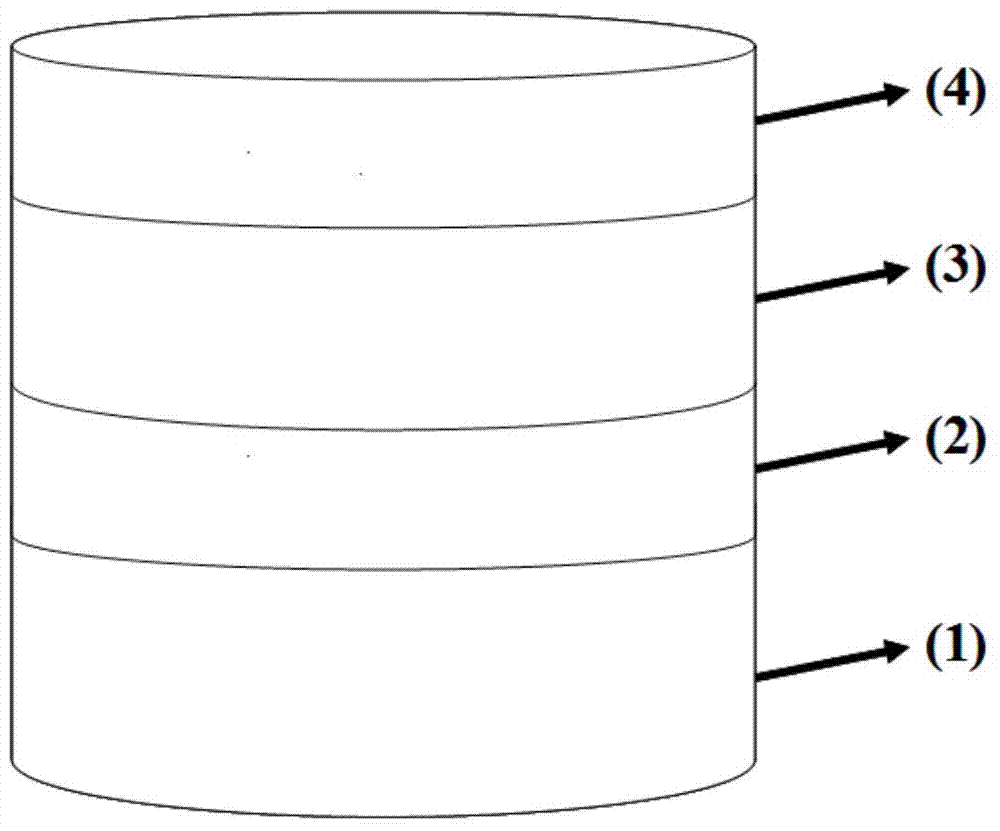

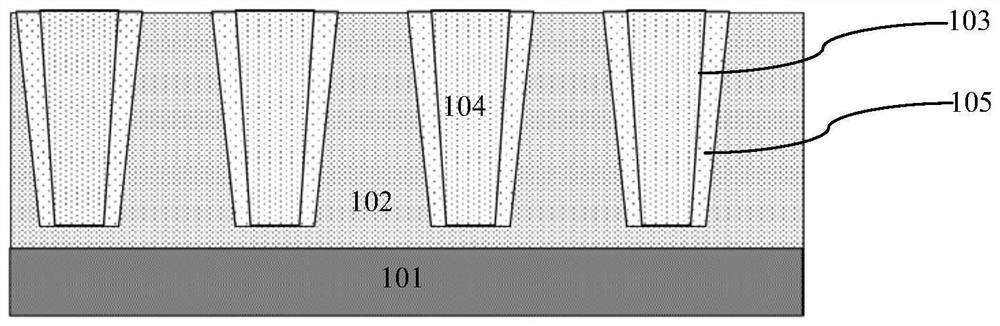

Manufacturing method of super junction device

ActiveCN112002643AMinimize the effect of interdiffusionReduce interdiffusionFinal product manufactureSemiconductor/solid-state device manufacturingTrench gateCondensed matter physics

The invention discloses a manufacturing method of a super junction device, which comprises the steps of 1, forming a gate structure, specifically, forming a gate trench, a first oxide layer and a first polycrystalline silicon layer, removing the first polycrystalline silicon layer on the side surface and the back surface of a wafer, and carrying out primary planarization to remove the first polycrystalline silicon layer on the front surface of the wafer outside the gate trench; and 2, forming a super junction in the first epitaxial layer with the flat surface on which the trench gate is formed, wherein in the forming process of the super junction, a second epitaxial layer is adopted to fill the super junction trench, and then secondary planarization is performed so as to enable the surfaceof the first epitaxial layer with the super junction to be a flat surface. According to the invention, the full-flat process can be realized, the trench gate process can be conveniently arranged before the super junction forming process, and the thermal process after the super junction is formed can be reduced, so that the mutual diffusion of impurities of the super junction is reduced, the device performance is improved, a photomask can be saved, and the process cost is reduced; and the influence of polycrystalline silicon residues on the charge balance of the super junction can be prevented.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

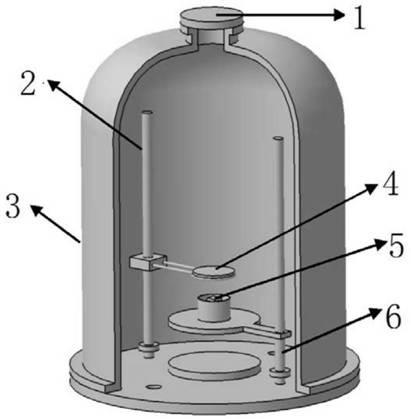

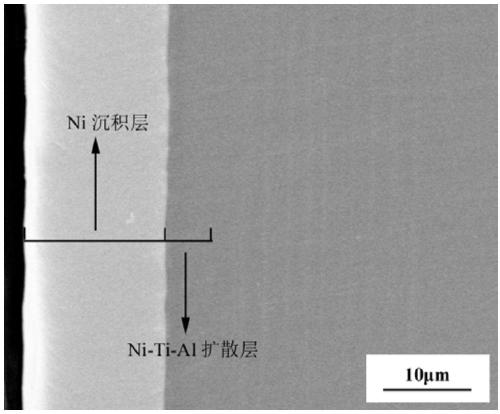

Surface treatment method for improving welding properties of Si3N4 ceramic and gamma-TiAl alloy

ActiveCN109161865AImprove welding effectSolve welding difficultiesVacuum evaporation coatingSputtering coatingGlow plasmaNickel alloy

The invention discloses a surface treatment method for improving the welding properties of Si3N4 ceramic and gamma-TiAl alloy. The method comprises the following steps: (1), preparing nickel alloy layer on the surface of the gamma-TiAl alloy from a Ni-Ti alloy target material by adopting a double glow plasma surface metallurgy method, wherein the nickel alloy layer comprises a nickel deposition layer and an inter-diffused layer; (2), injecting Ti ions on the surface of the Si3N4 ceramic through an ion injection method, so as to treat the surface of the Si3N4 ceramic; and (3), welding the gamma-TiAl alloy treated through the double glow plasma surface metallurgy method in the first step and the Si3N4 ceramic subjected to surface treatment in the second step in vacuum diffusion welding equipment. According to the method, the nickel alloy layer is prepared on the surface of the gamma-TiAl alloy, the Ti ions are injected to the surface of the Si3N4 ceramic through the ion injection method,and the vacuum diffusion welding between the Si3N4 ceramic and the gamma-TiAl alloy can be directly realized. The method is high in efficiency, and can greatly improve the application of vacuum diffusion welding to the welding technology of the Si3N4 ceramic and the gamma-TiAl alloy.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

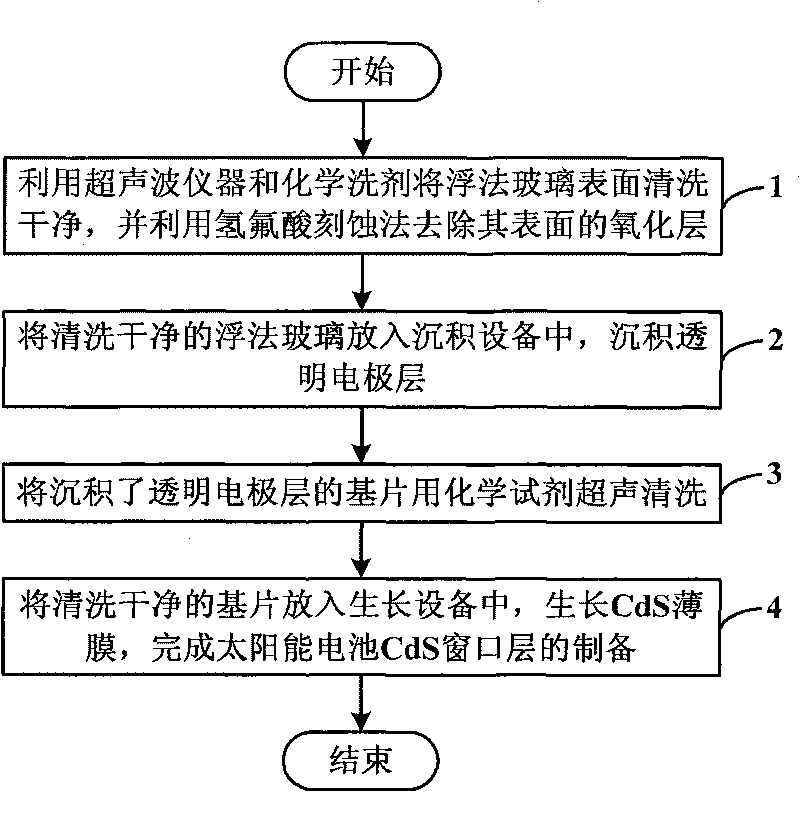

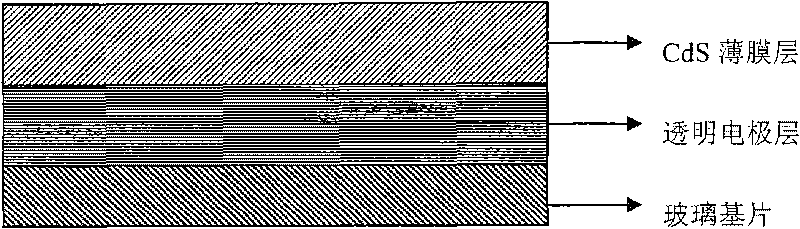

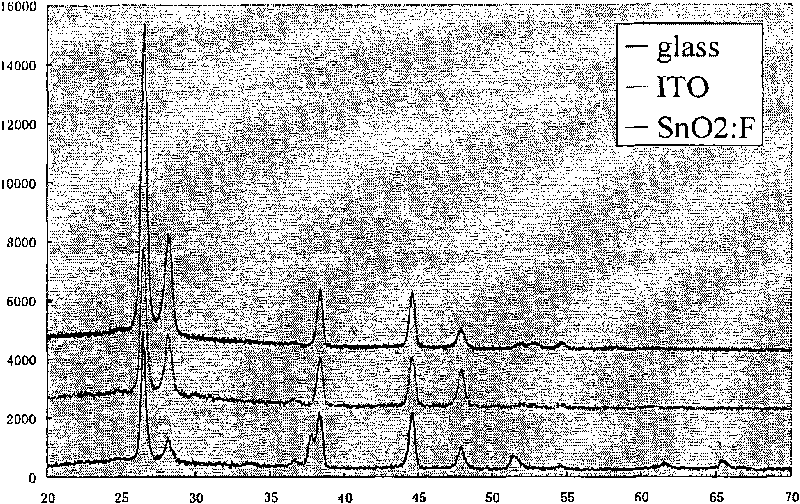

Method for preparing CdS film used for window layer of solar battery

InactiveCN101740665ADoes not affect transmittanceDoes not interfere with absorption issuesFinal product manufactureSemiconductor devicesCleansing AgentsSolar battery

The invention belongs to the technical field of the preparation of film solar batteries and discloses a method for preparing a CdS film used for a window layer of a solar battery. The method comprises the following steps of: 1, cleaning the surface of float glass by an ultrasonoscope and a chemical cleaning agent, and removing an oxide layer on the surface of the float glass by a hydrofluoric acid etching method; 2, putting the well cleaned float glass in deposition equipment to deposit a transparent electrode layer; 3, ultrasonically cleaning a substrate on which the transparent electrode layer is deposited by a chemical agent; and 4, putting the well cleaned substrate in growth equipment to grow the CdS film, and completing the preparation of the CdS window layer of the solar battery. The method has the advantages of improving performance of the device, using the CdS film to prepare solar batteries and other optical devices which are big in area and low in cost, reducing an impurity concentration of the CdS film and enhancing the quality of the CdS film.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Type-II superlattice structure based on indium arsenide and preparation method

InactiveCN105789355AIncrease growth temperatureIncrease the diffusion lengthFinal product manufactureSemiconductor devicesMaterial defectAluminium arsenide

The invention discloses a type-II superlattice structure based on indium arsenide and a preparation method. The type-II superlattice structure based on indium arsenide comprises an InAs layer, a GaAs layer, a GaAsxSb1-xlayer and a GaAs layer from bottom to top, and is characterized in that: (1) an original GaSb substrate is replaced with an InAs substrate, so that the growth temperature of superlattices is substantially increased, and the increasement of the growth temperature is conductive to increasing a diffusion length of surface atoms, thereby being more conductive to the two-dimensional growth of materials and the reduction of material defect density; (2) an As valve is always in an open state during the whole growth process of type-II superlattices, so that a GaAsSb ternary compound is formed due to the outflow of partial As when growing a GaSb layer, growth temperature of the layers tends to be uniform due to the existence of the common element As in the layers, and the counterdiffusion at interfaces is reduced; (3) variation of thickness of the InAs layer has small influence on mismatching of the InAs-based type-II superlattices, the growth difficulty of long waves materials, particularly extremely-long-wave materials, is extremely reduced, and the performance and quality of the materials can be more easily improved.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Novel platinum-iridium-based ultrahigh-temperature multi-component alloy bonding layer capable of being used at temperature of 1300 DEG C or above, and preparation method thereof

PendingCN114000086AReduce interdiffusionHigh temperature strengthMolten spray coatingRare-earth elementIridium

The invention discloses a novel platinum-iridium-based ultrahigh-temperature multi-component alloy bonding layer capable of being used at a temperature of 1300 DEG C or above, and a preparation method thereof, and relates to the technical field of thermal barrier coatings. According to a technical scheme, the novel platinum-iridium-based ultrahigh-temperature multi-component alloy bonding layer is characterized by comprising, by mass, 6.8%-9.2% of Ir, 0.0%-21.0% of Al, 0.0%-6.0% of Cr, 0.0%-4.0% of Ru, 2.0%-4.0% of Hf, 0.0%-4.0% of Zr, 0.0%-3.0% of Ta, 0.0%-9.0% of Ni, 0.0%-5.0% of Co and 0.0%-1.0% of a rare earth element, with the balance being Pt, wherein the rare earth element is one or more selected from Y, Ce, La and Th. The novel platinum-iridium-based ultrahigh-temperature multi-component alloy bonding layer can be applied as a thermal barrier coating bonding layer for hot-end components in aerospace equipment, particularly to high-temperature components such as of blades, spray pipes, nozzles, throat liners and inner combustion chamber walls of various ultrahigh-temperature engines like aero-engines, rocket engines and large gas turbines, and can prolong the service life of the high-temperature components.

Owner:KUNMING UNIV OF SCI & TECH

Type II superlattice structure and preparation method based on arsenic valve switch

ActiveCN103500765BReduce interdiffusionReduce the chance of formationFinal product manufactureNanoopticsInterface layerBinary compound

Owner:中科爱毕赛思(常州)光电科技有限公司

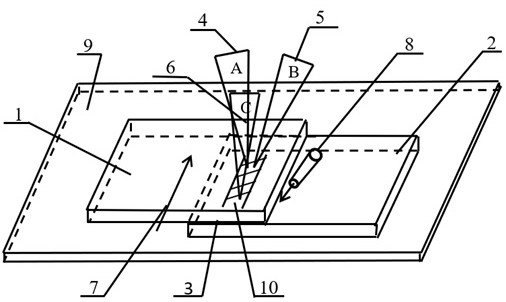

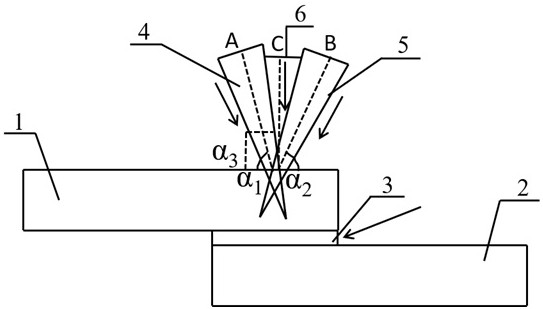

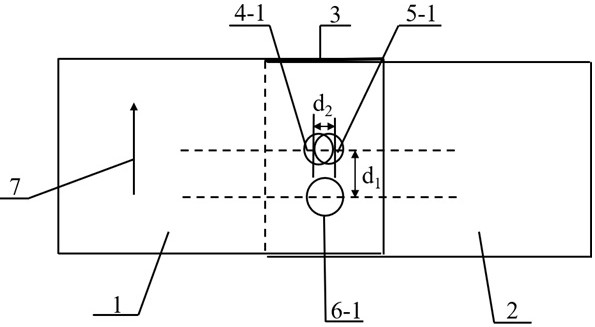

Steel-aluminum alloy laser welding method adopting nickel-based high-entropy alloy intermediate layer

PendingCN114406469AReduce thicknessReduce interdiffusionWelding/soldering/cutting articlesLaser beam welding apparatusMolten stateMetal foil

The invention relates to a steel-aluminum alloy laser welding method adopting a nickel-based high-entropy alloy intermediate layer, and belongs to the technical field of dissimilar material welding. And a nickel-based high-entropy alloy metal foil is used as a middle layer material. The high entropy effect and the high thermal resistance effect of the nickel-based high-entropy alloy metal foil control that no intermetallic compound is generated in a weld fusion area, and the intermetallic compound is only generated at the interface of the fusion area and the aluminum alloy. And by adding the nickel element and the silicon element, generation of Fe-Al intermetallic compounds at the interface is reduced, a Ni-Al-Si phase with better toughness is generated, the metallurgical reaction at the interface is improved, and then the mechanical property of the joint is improved. Laser beams A, B and C are adopted for simultaneous welding, the connecting area of the interface of the steel plate and the aluminum alloy plate is increased, and it is ensured that aluminum in the molten state fully wets and spreads the interface. The anti-shearing strength of a lap joint is improved; and meanwhile, the defects such as cracks and air holes are avoided.

Owner:JILIN UNIV

Method for increasing service life of aluminium alloy spot-welding electrode

InactiveCN102441731AAvoid arcingAvoid direct contactResistance welding apparatusGraphiteSpot welding

The invention relates to a spot-welding electrode, in particular to a method for increasing the service life of an aluminium alloy spot-welding electrode, which is characterized by comprising the following steps of: grinding a part of an aluminium alloy plate to be welded to be contacted with the electrode and coating graphite-engine oil paint on the part, enabling the electrode to contact with the aluminium alloy plate to be welded with the movement speed of 1-100 mm / s, clamping the aluminium alloy plate to be welded between the spot-welding electrodes, carrying out spot welding by electrifying, and replacing another point to be welded after completing, thus, repeating above operations, wherein the spot-welding electrode can be ensured to have longer service life.

Owner:JIANGSU UNIV