Manufacturing method of super junction device

A manufacturing method and super junction technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as reducing device performance, and achieve the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

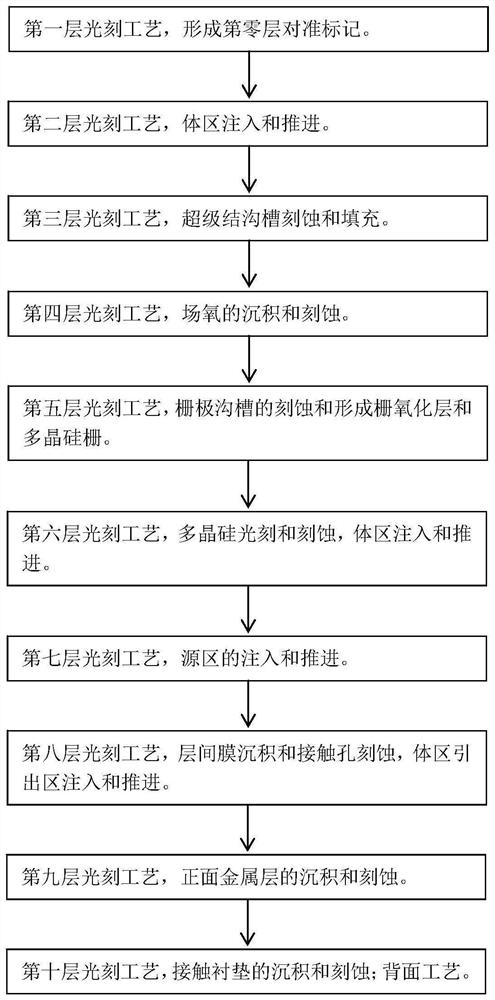

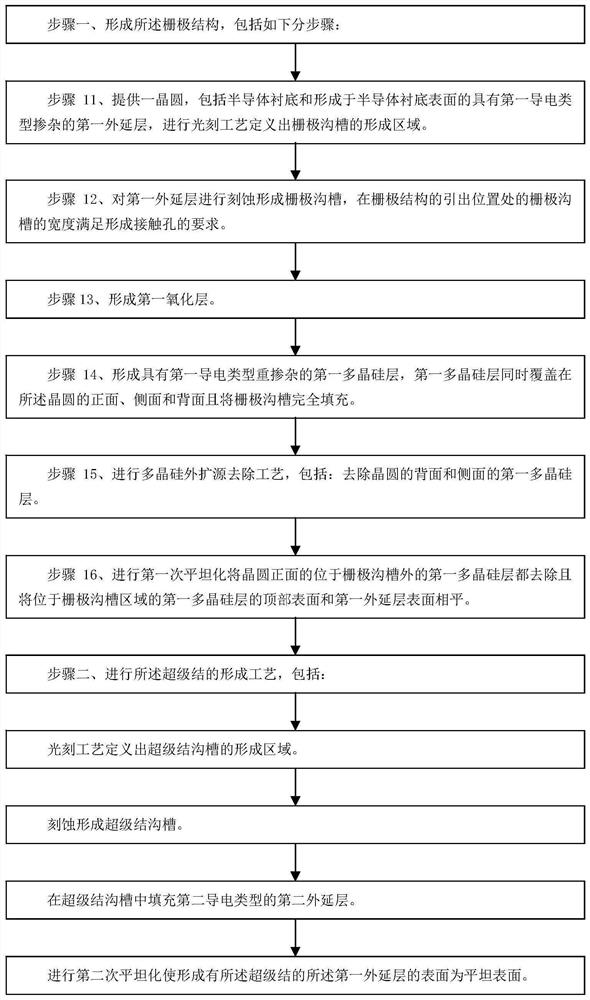

[0108] The manufacturing method of the super junction device of the embodiment of the present invention:

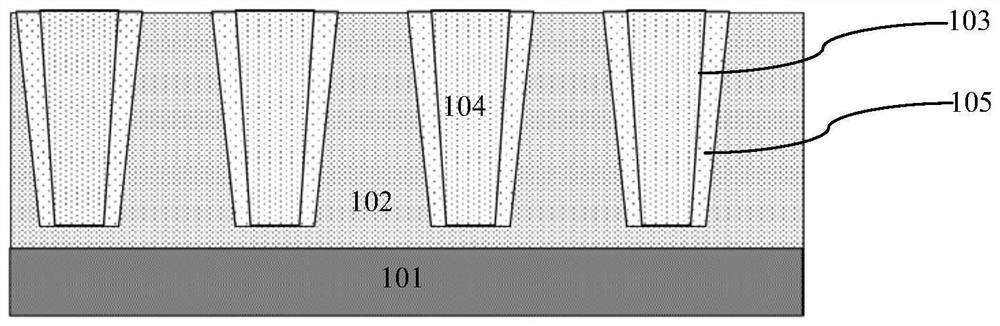

[0109] In the manufacturing method of the super junction device in the embodiment of the present invention, the super junction device includes a super junction, and the structure schematic diagram of the super junction device please refer to Figure 5Q As shown, in the device unit area, the device front unit structure of the super junction device is formed on the super junction; the device front unit structure includes a gate structure, a body region 5 of the second conductivity type, a first conductivity type heavily doped impurity source region 6, field oxygen 8, interlayer film 9, contact hole 10, front metal layer 11; the super junction is formed by alternating columns of the first conductivity type and the second conductivity type, and one of the first conductivity type A column of a conductivity type and an adjacent column of the second conductivity type form a supe...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More