Method of forming CMOS well with mask saved

A photomask and substrate technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to achieve the effect of saving photomasks, saving costs, and less CMOS process changes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The specific embodiment of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0025] It should be noted that, in the following specific embodiments, when describing the embodiments of the present invention in detail, in order to clearly show the structure of the present invention for the convenience of description, the structures in the drawings are not drawn according to the general scale, and are drawn Partial magnification, deformation and simplification are included, therefore, it should be avoided to be interpreted as a limitation of the present invention.

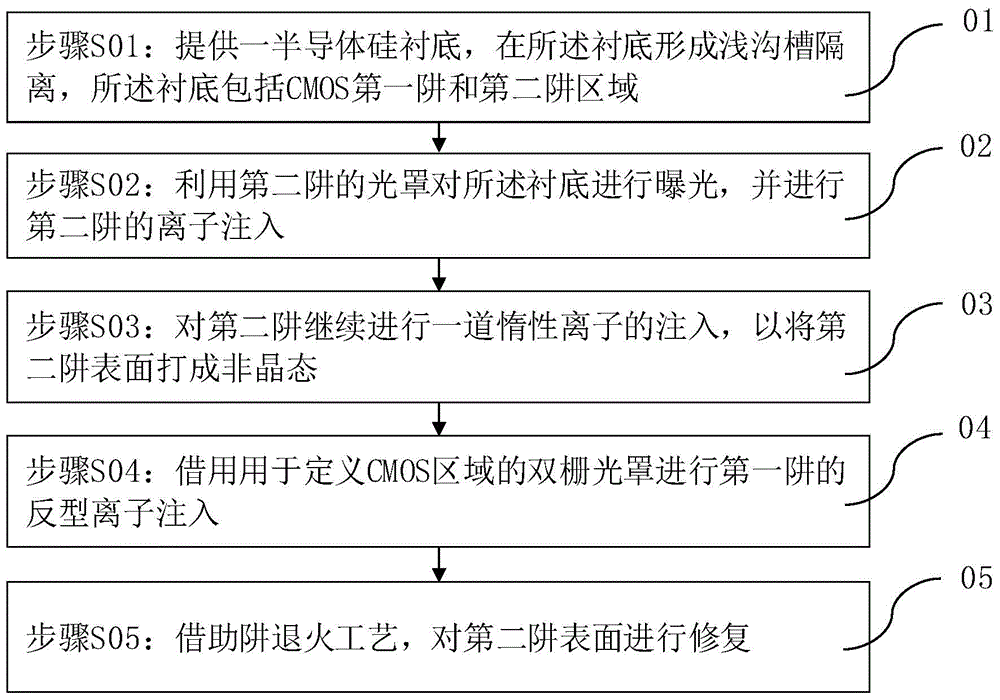

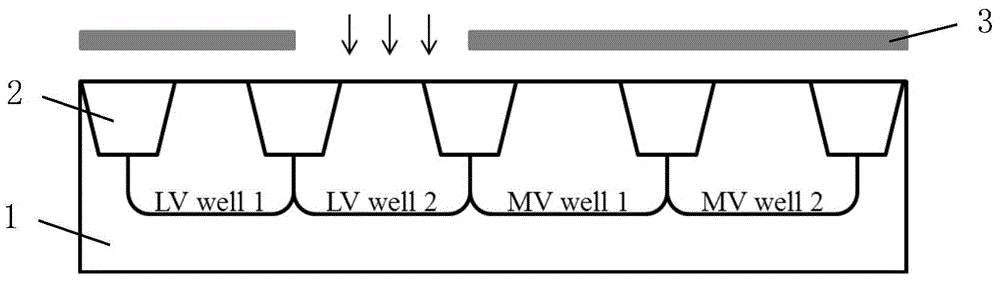

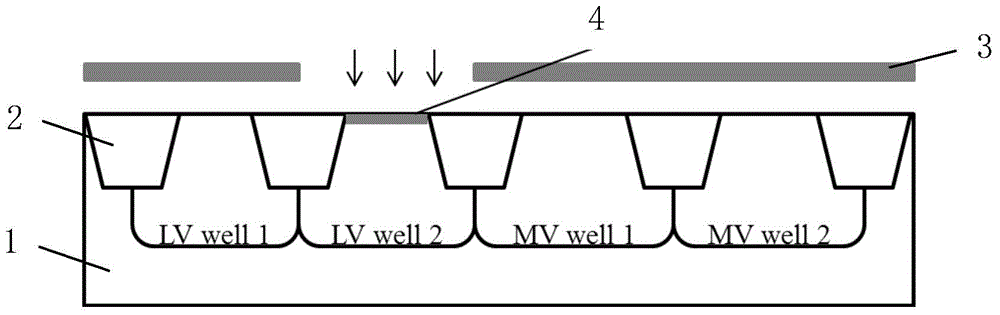

[0026] In the following specific embodiments of the present invention, please refer to figure 1 , figure 1 It is a flow chart of a CMOS well forming method that saves photomasks in the present invention; at the same time, please refer to Figure 2 to Figure 5 , Figure 2 to Figure 5 is an embodiment of the present invention according to figure 1 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More