Digital-to-analog converter with sectional capacitor array structure

A digital-to-analog converter, array structure technology, applied in digital-to-analog converter, analog-to-digital conversion, code conversion and other directions, can solve the problems of gain error, deterioration, mismatch, etc., to improve NDL and IDL, eliminate capacitance loss. Matching and eliminating the effect of gain error

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the technical problems, technical solutions and beneficial effects to be solved by the present invention clearer and clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

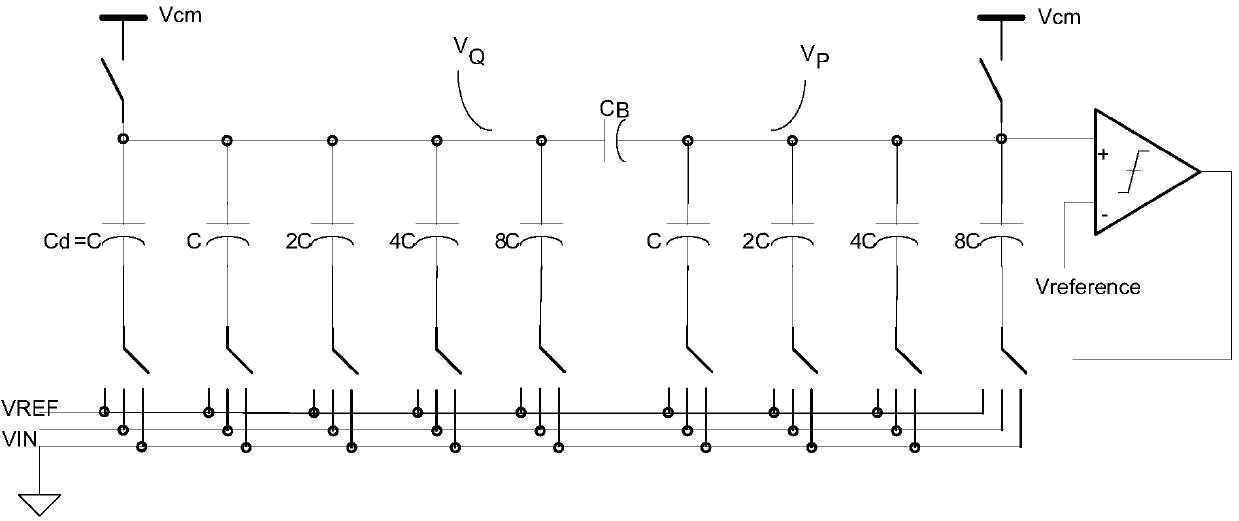

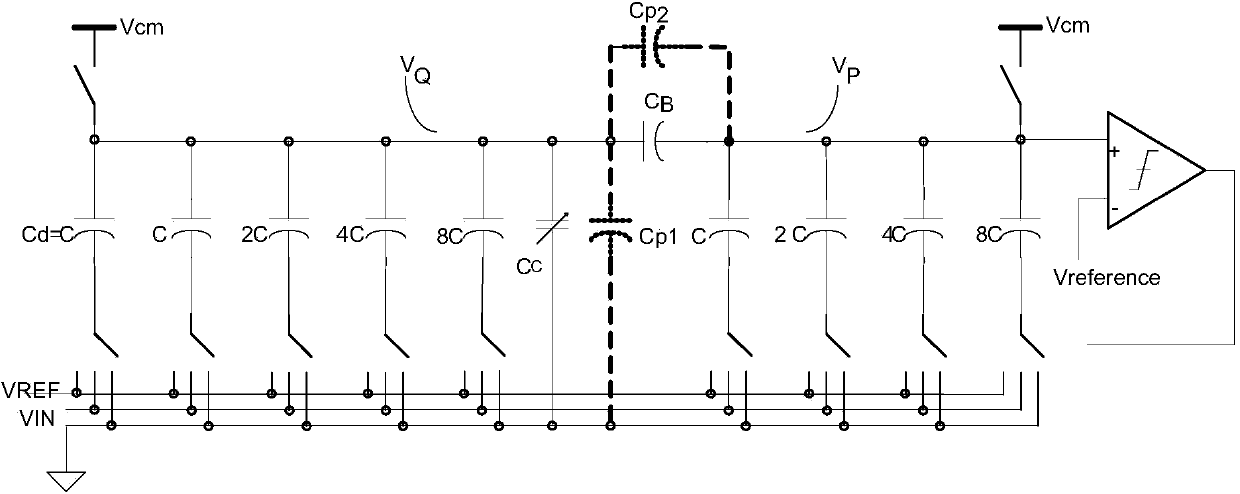

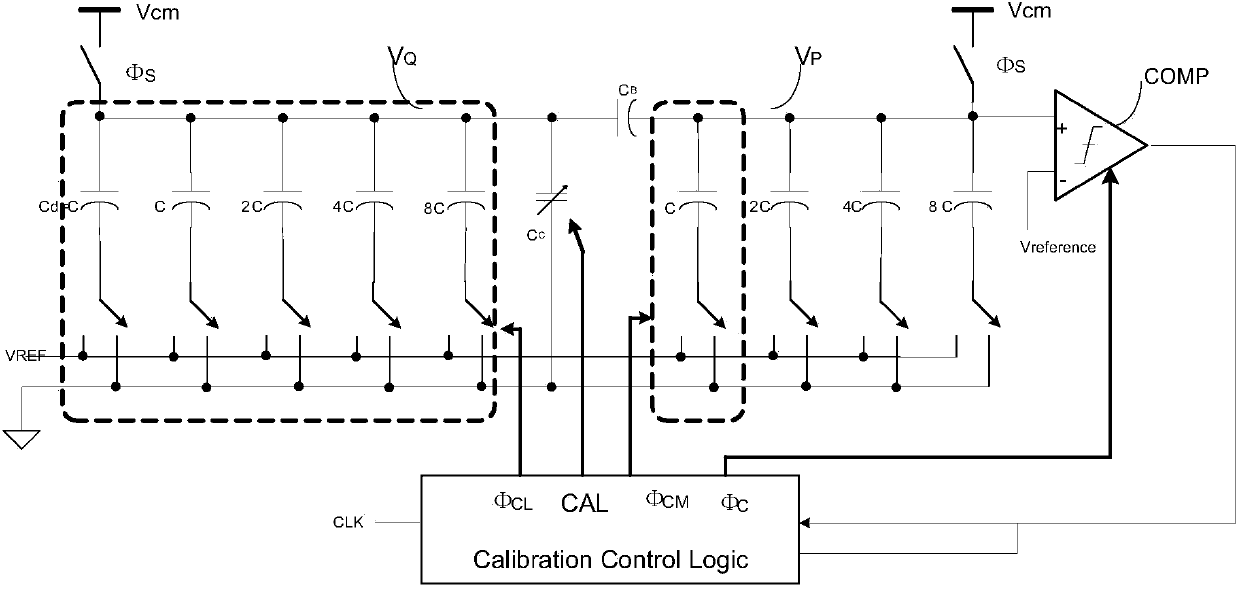

[0021] Such as figure 2 Schematic diagram of the DAC correction principle of the segmented charge redistribution capacitor array provided by the embodiment of the present invention, in the figure:

[0022] Capacitance C B For bridging capacitors, connect the left and right capacitor sub-arrays respectively. Wherein, the subarray on the left corresponds to quantization bits with lower weights, and the subarray on the right corresponds to quantization bits with higher conversion weights. C d is the matching capacitance of the minimum weight bit capac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More